Patents

Literature

933results about How to "Reduce storage capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

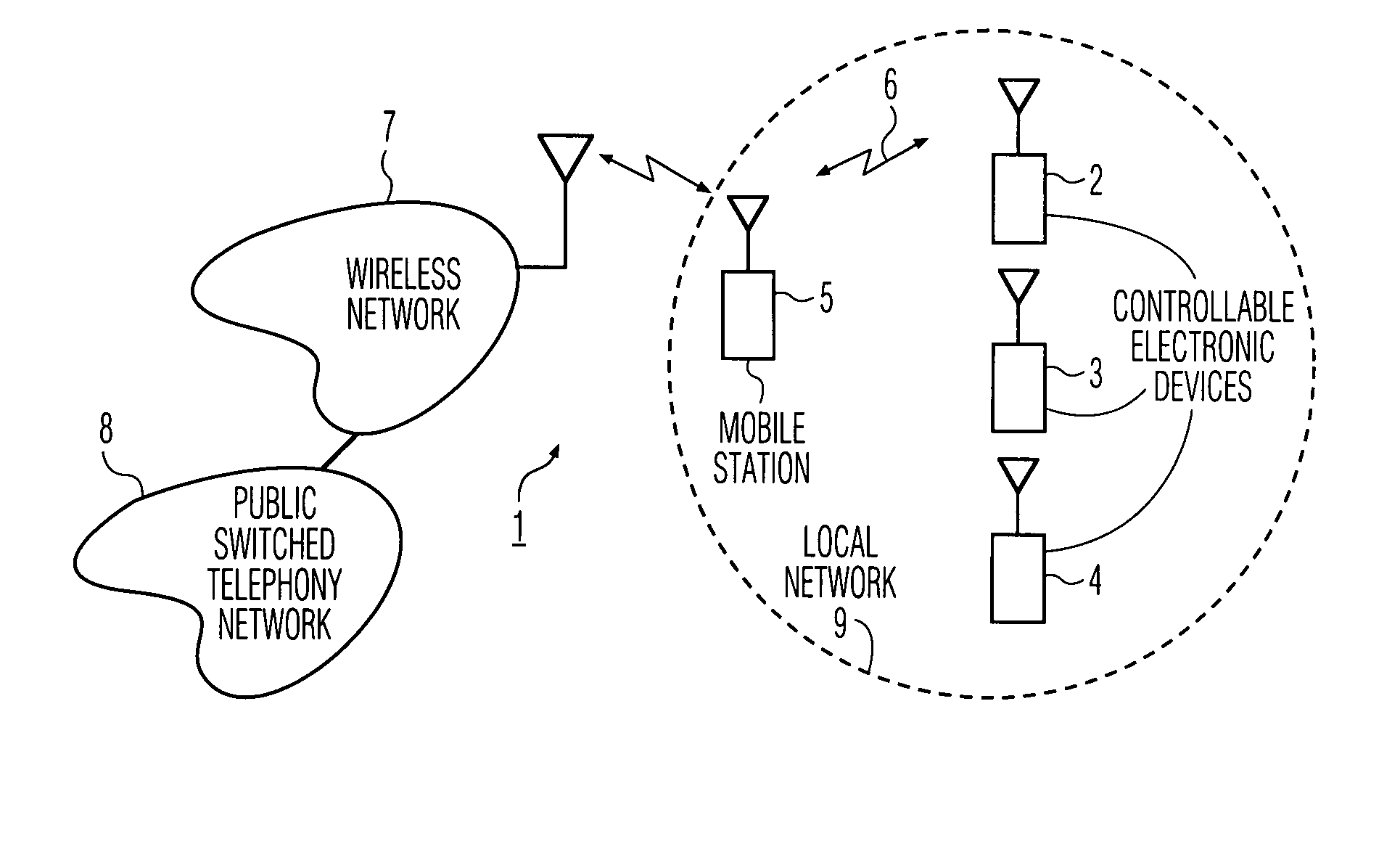

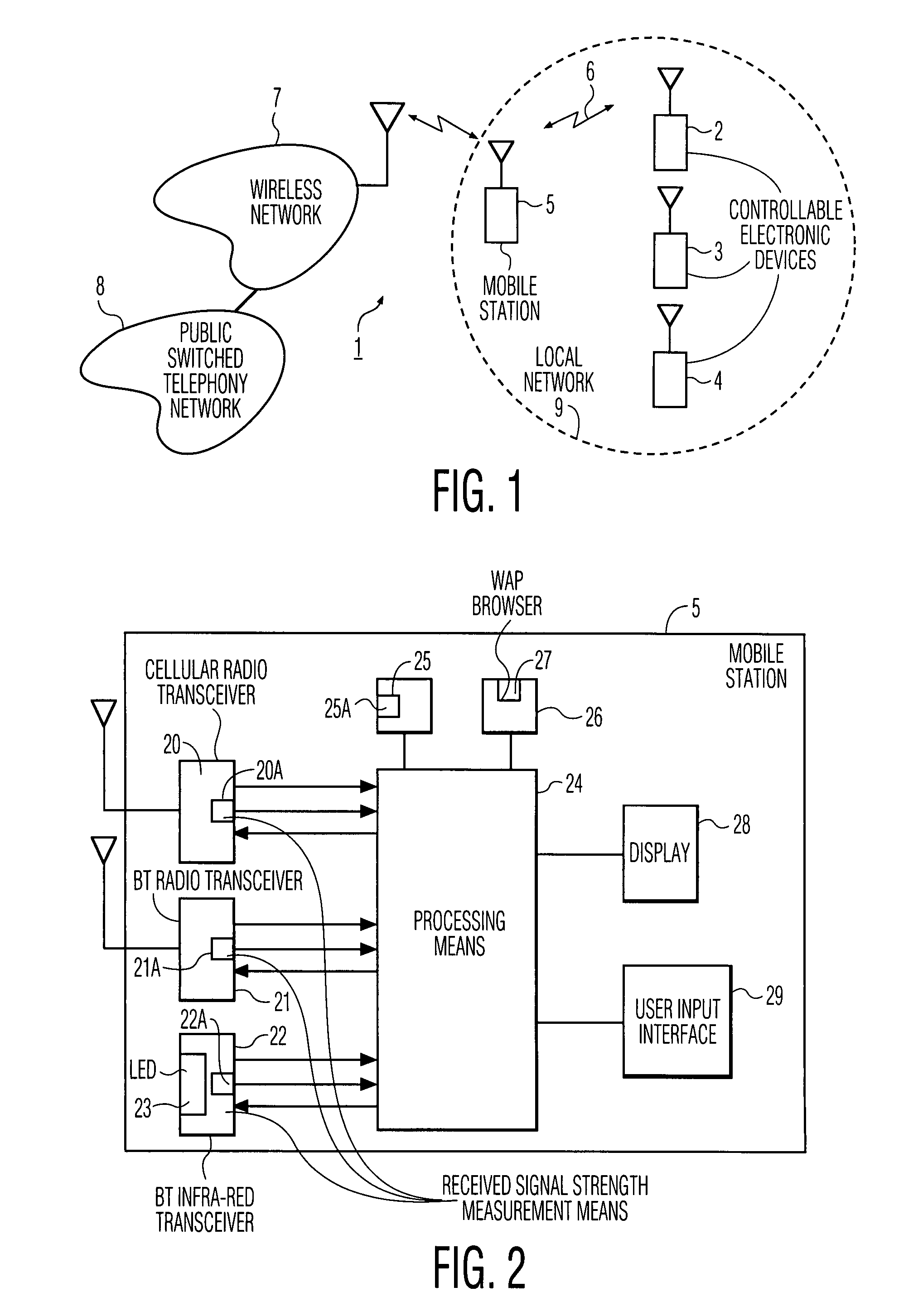

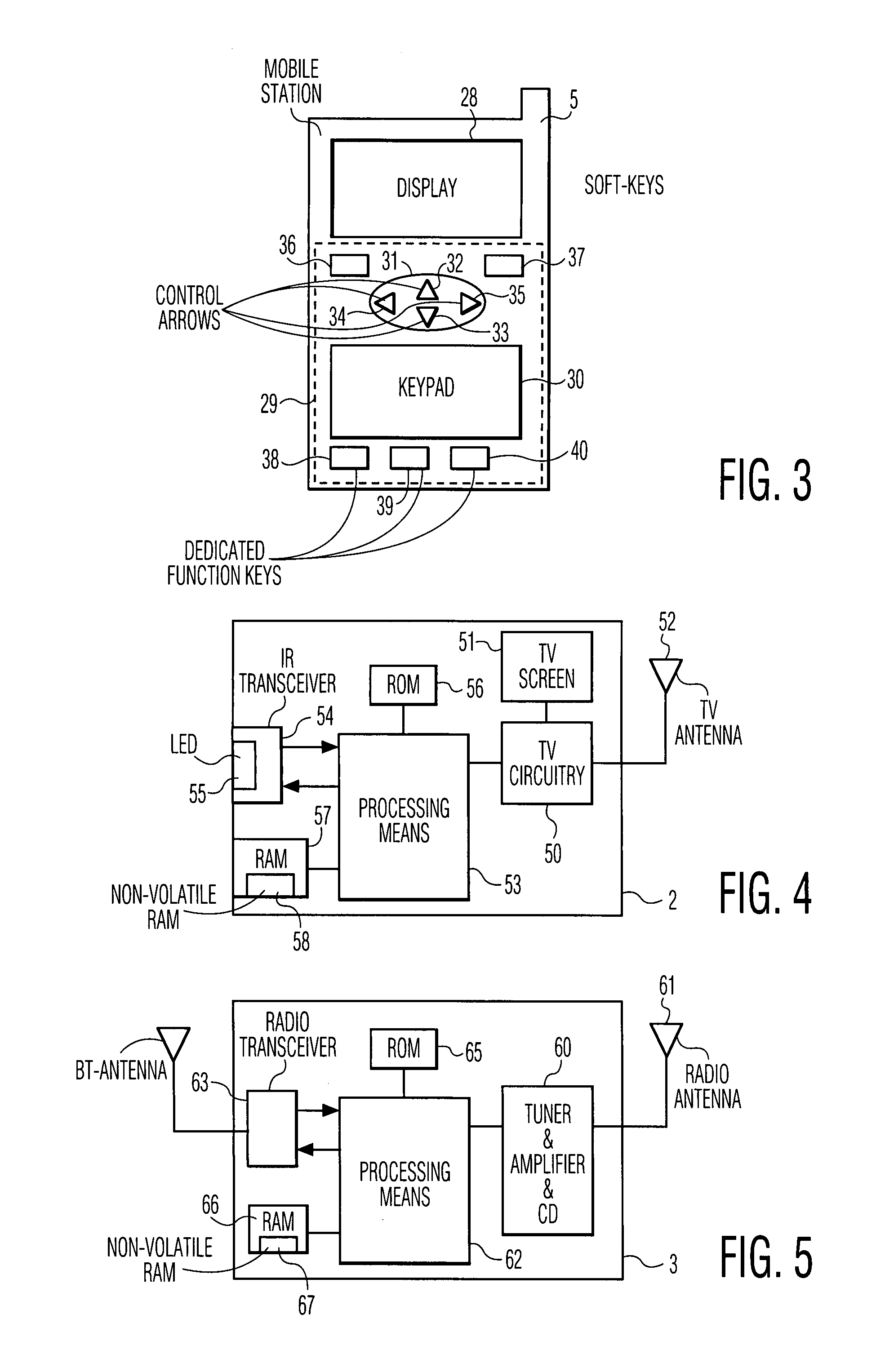

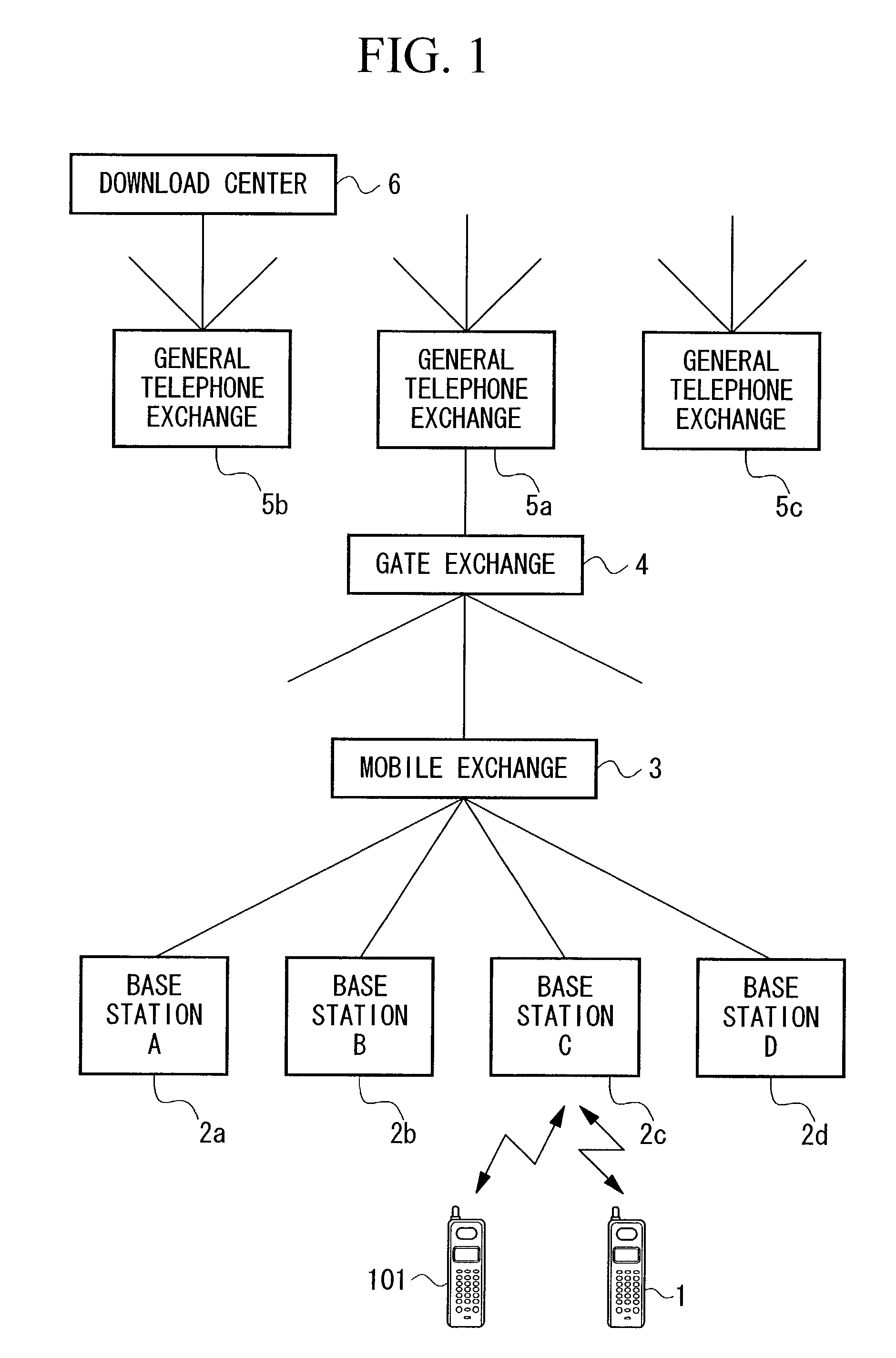

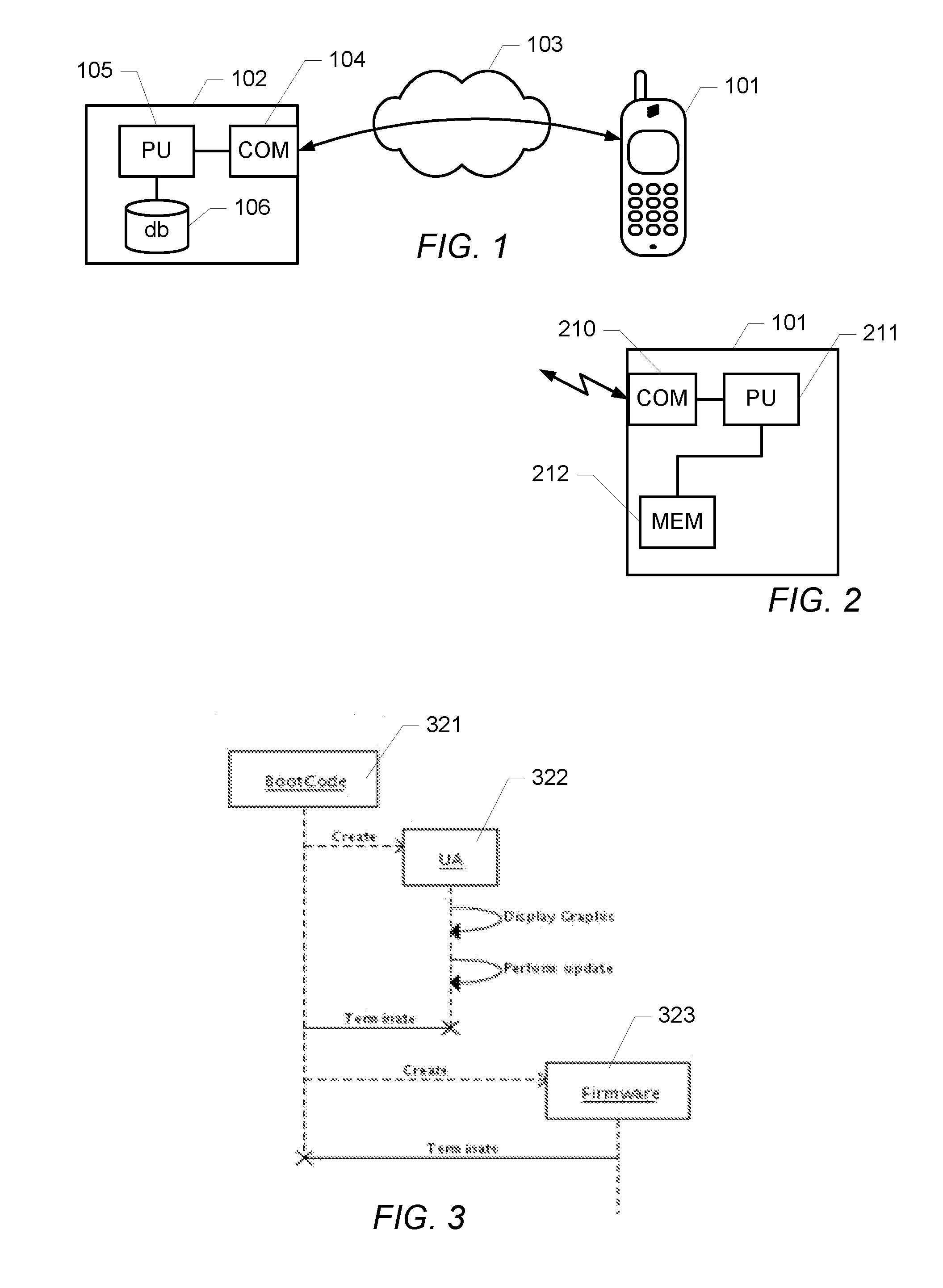

Remote control of an electronic device through downloading of a control interface of the electronic device in a mobile station

InactiveUS7894474B1Easy to operateReduce storage capacityElectric signal transmission systemsTelemetry/telecontrol selection arrangementsTelecommunications linkCommunications system

A wireless communication system includes a number of controllable electronic devices and a mobile station for communication with one of the controllable electronic devices through a short-range wireless communication link, when in-range with the one controllable electronic device. The mobile station includes a display screen and a browser. The mobile station and the one controllable electronic device form a client-server pair. Through the short-range wireless communication link, the client requests the server to download a control interface stored at the server. Upon downloading, a browser is used to navigate through control menu pages included in the control interface, and to post control parameter settings to the server. In the server, a program runs to interpret received control parameter settings, to invoke a control action in accordance with the received control parameter settings, and to instruct the client what to do next.

Owner:HOME CONTROL SINGAPORE

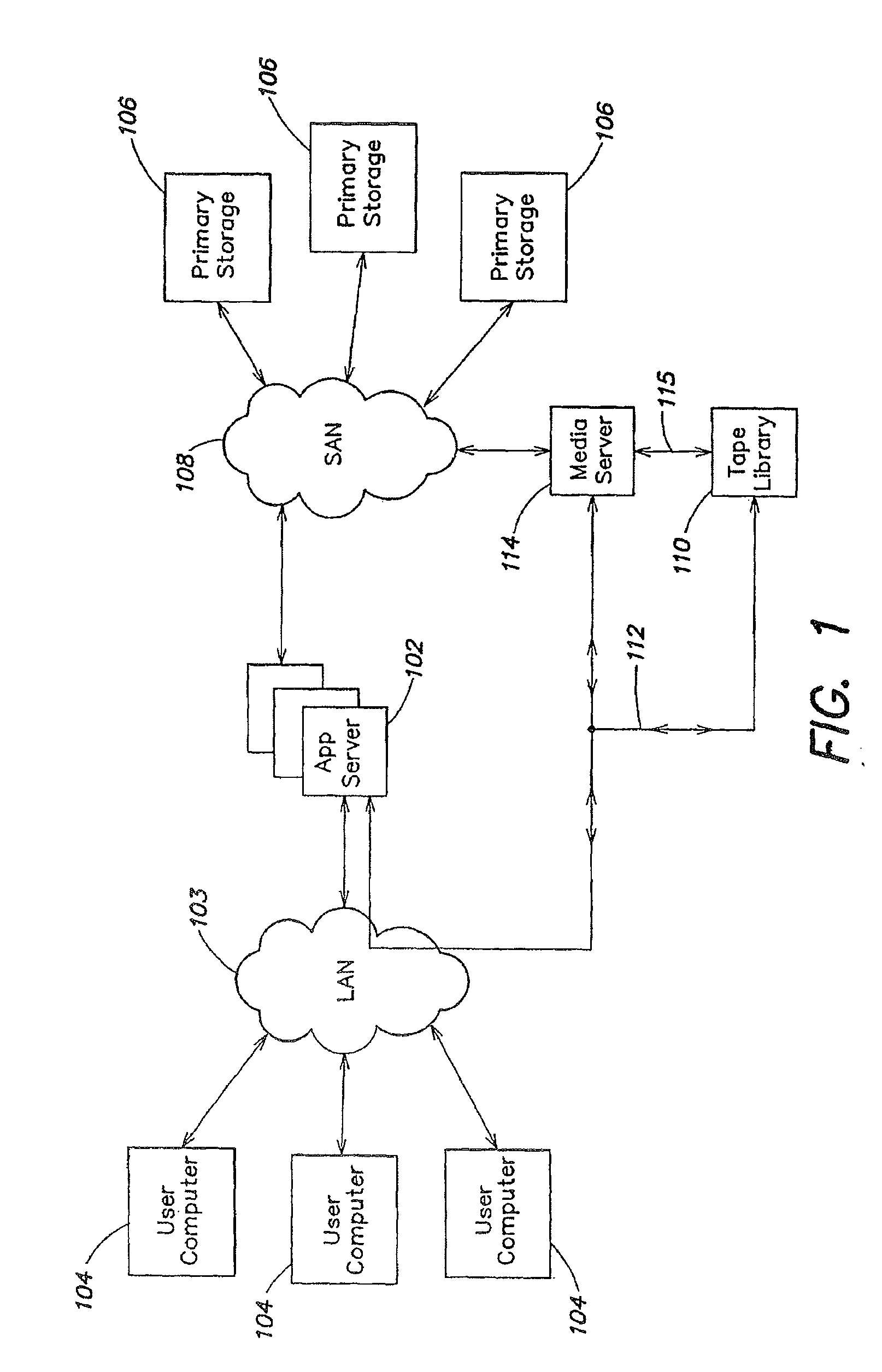

Scalable de-duplication mechanism

ActiveUS20090182789A1Improve efficacyImprove scalabilityDigital data processing detailsError detection/correctionProtocol ApplicationData deduplication

A method for removing redundant data from a backup storage system is presented. In one example, the method may include receiving the application layer data object, selecting a de-duplication domain from a plurality of de-duplication domains based at least in part on a data object characteristic associated with the de-duplication domain, determining that the application layer data object has the characteristic and directing the application layer data object to the de-duplication domain.

Owner:HITACHI VANTARA LLC

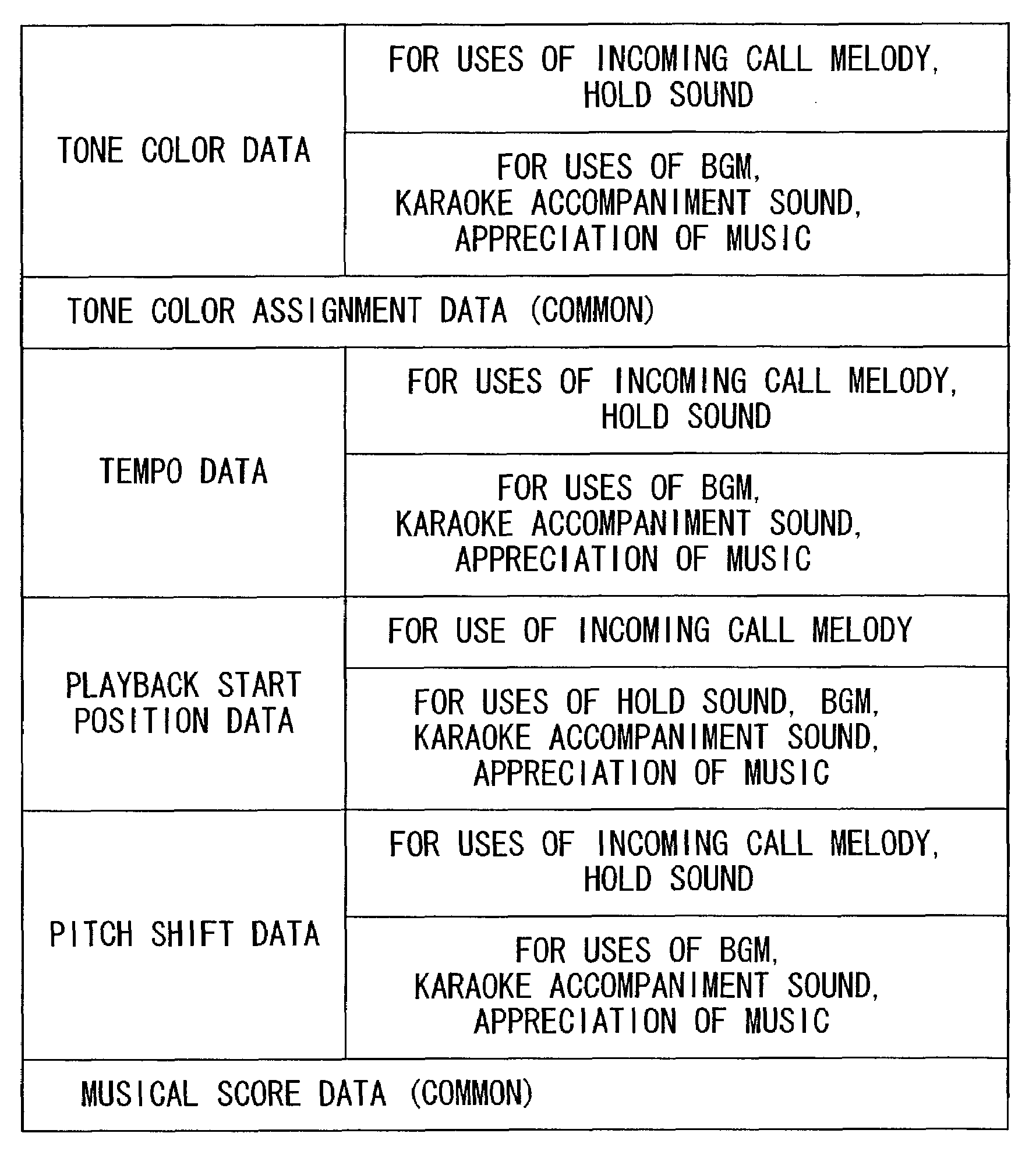

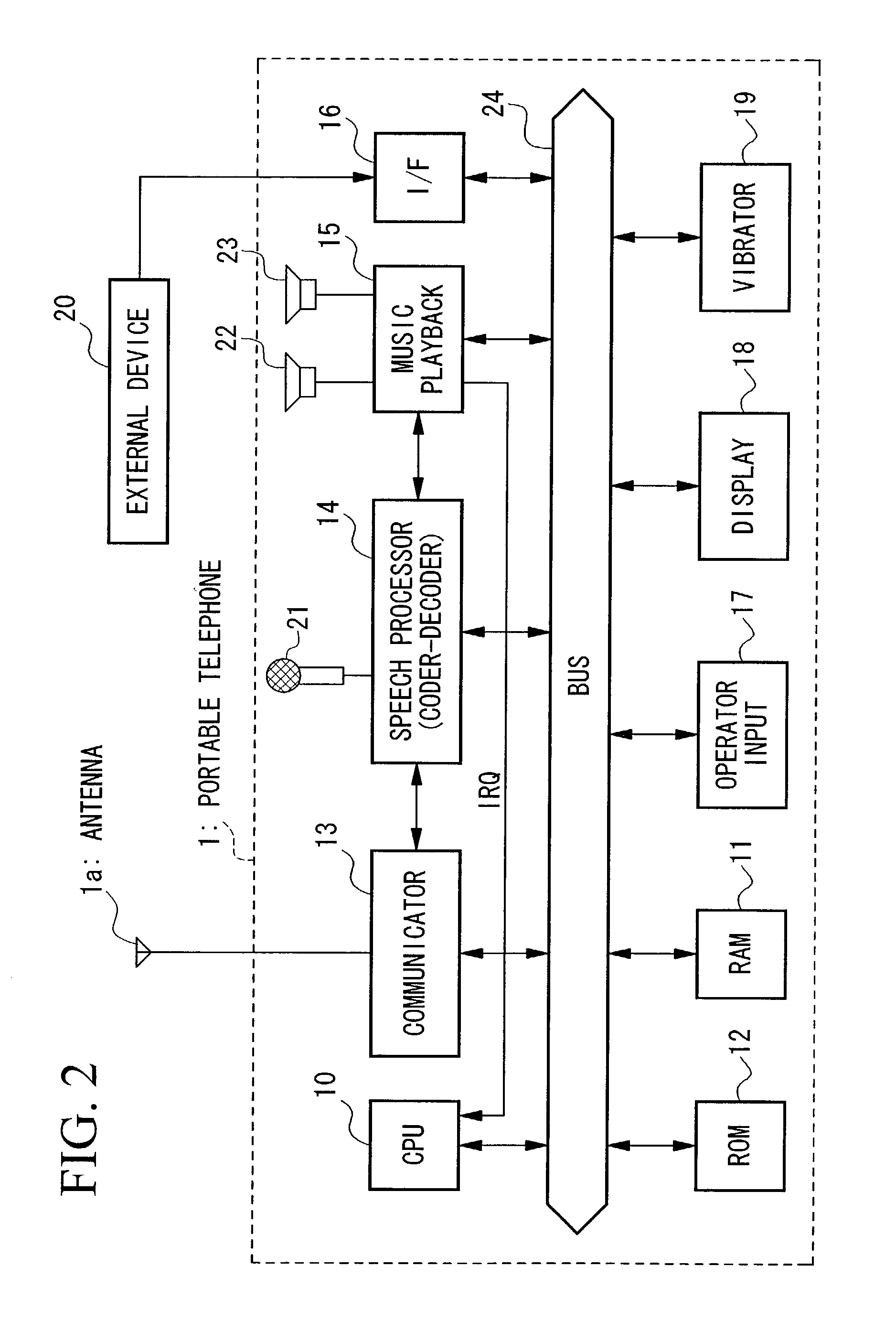

Telephone terminal

InactiveUS7076052B2Reduce storage capacityElectrophonic musical instrumentsSubstation speech amplifiersTelephone terminalComputer terminal

A telephone terminal device such as a portable telephone performs music playback processes with respect to use-specified music data in which tempos, tone colors, and pitches are specifically processed to suit different uses while tone color assignment and musical score are commonly shared among different uses, or common-use music data that are partially modified to suit a specific use in reproduction such as production of incoming call melody sound, hold sound, background music (BGM) during conversation in progress, karaoke accompaniment sound, and music for appreciation.

Owner:YAMAHA CORP

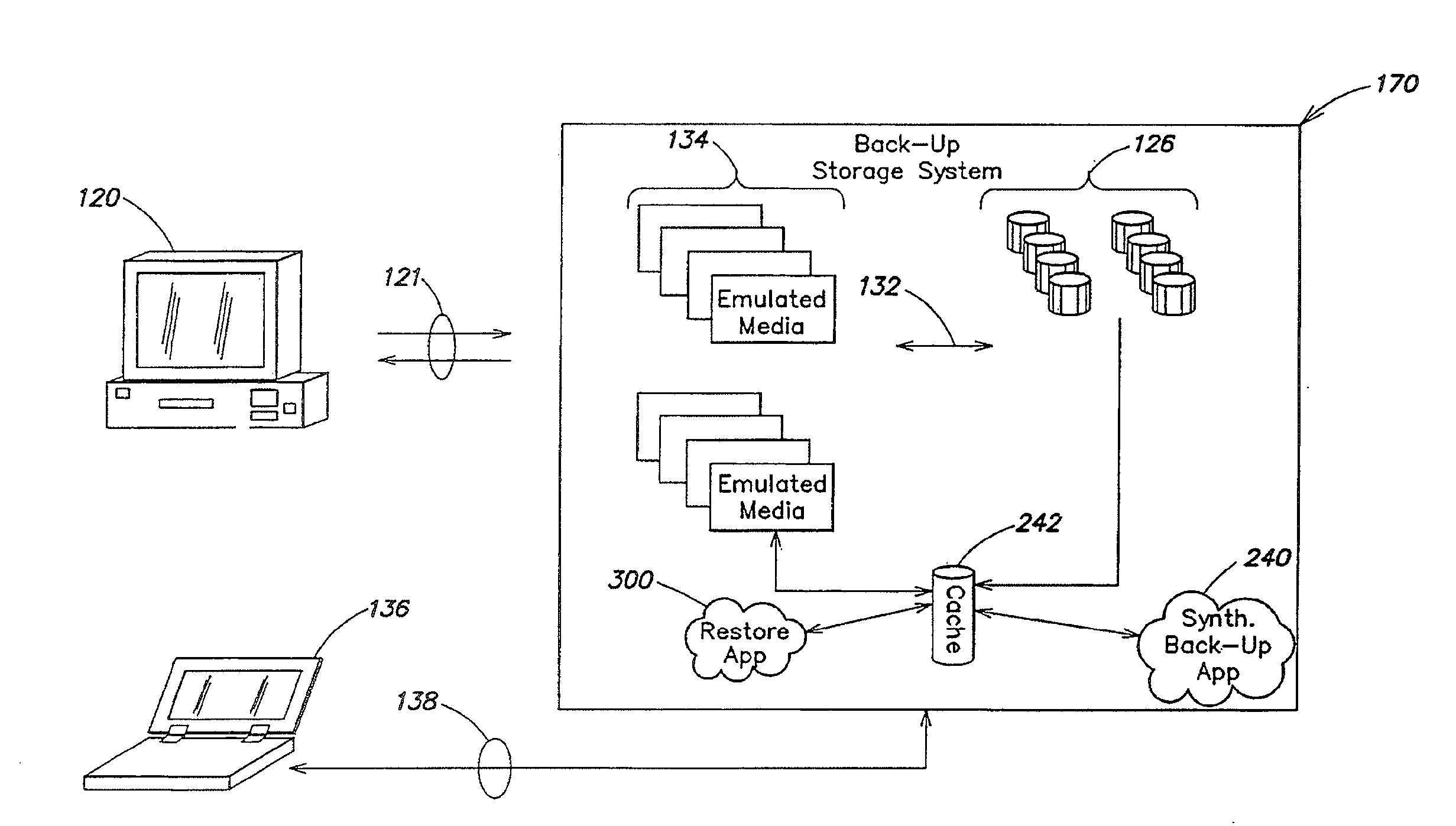

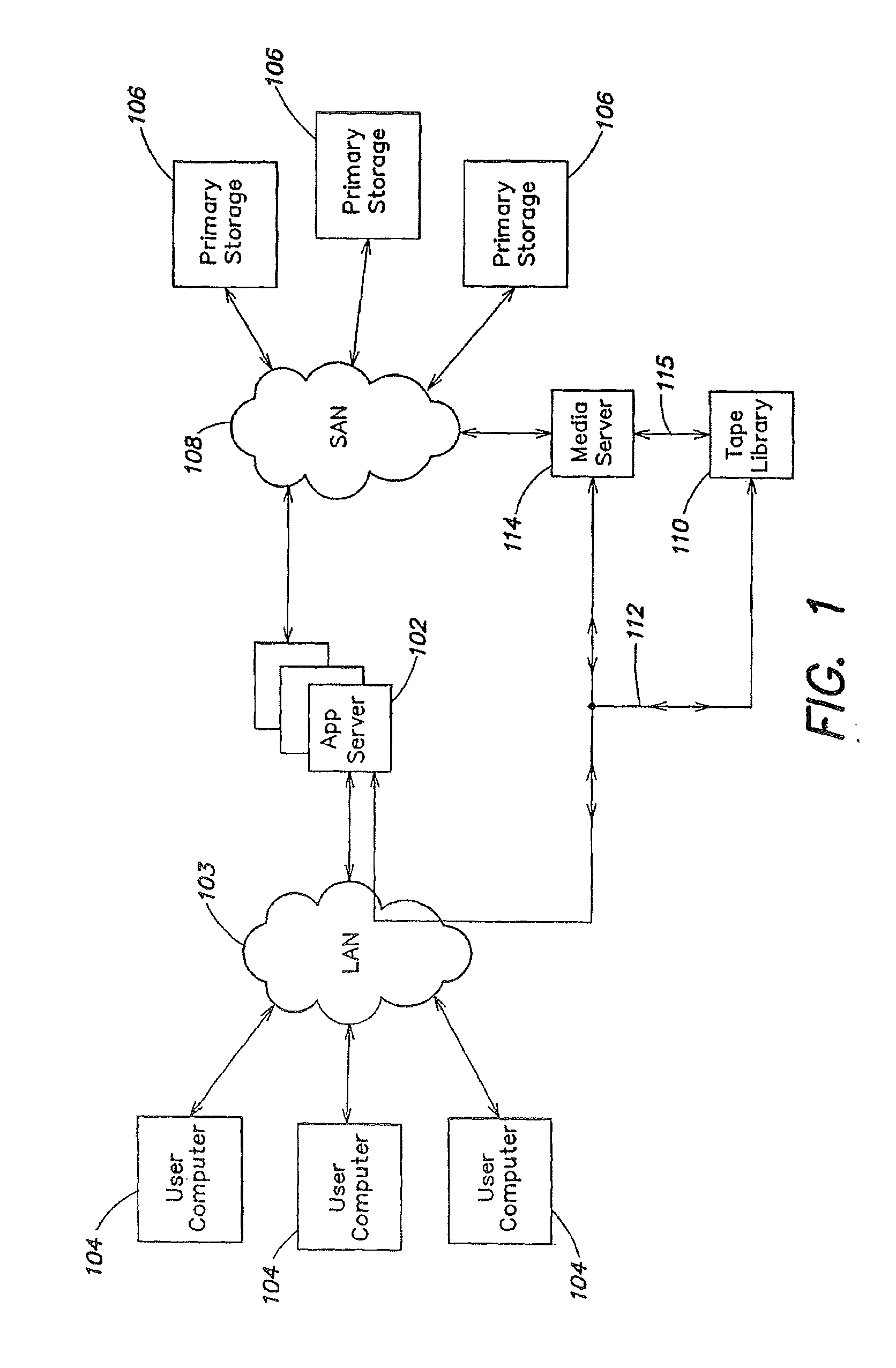

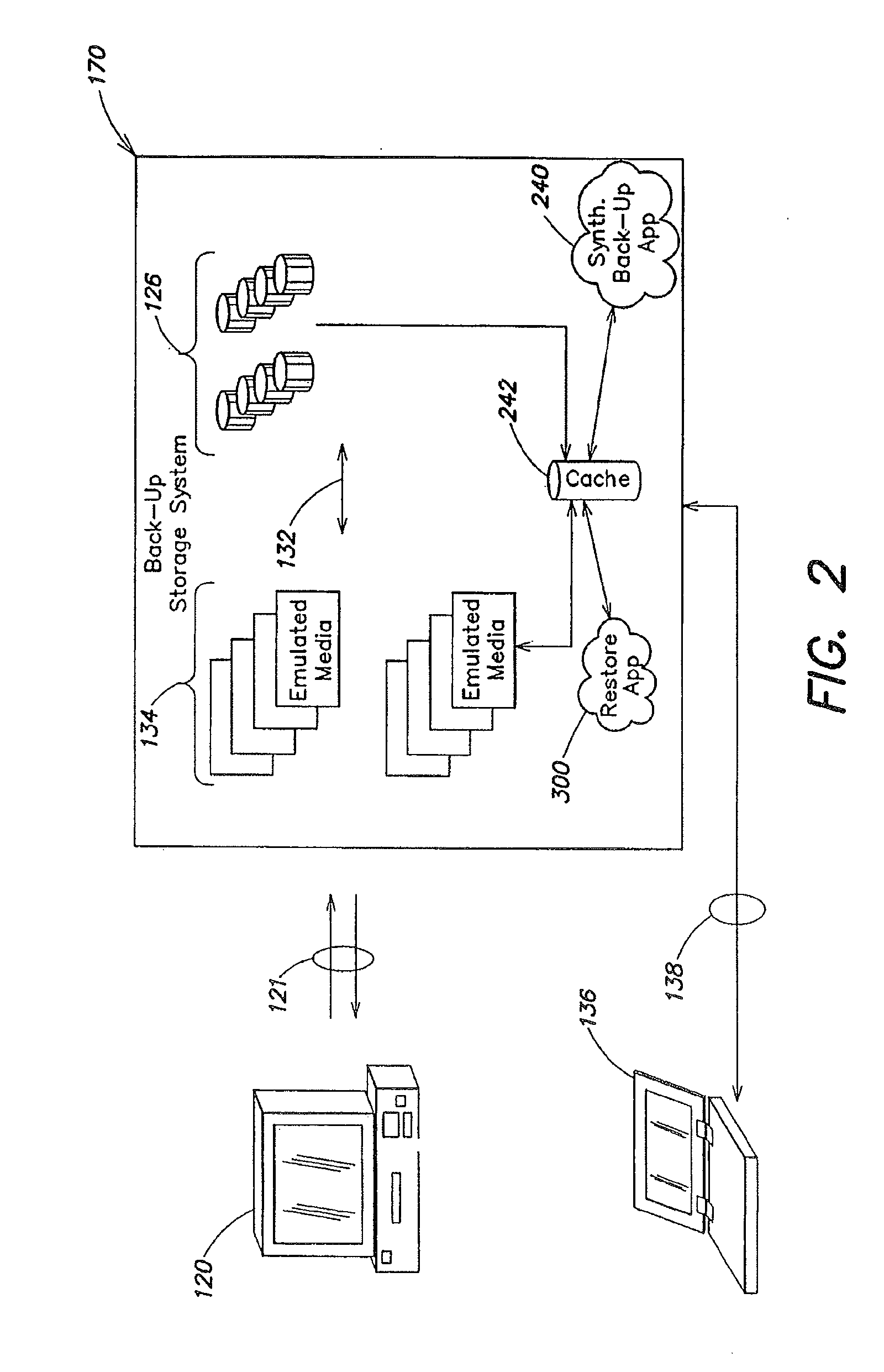

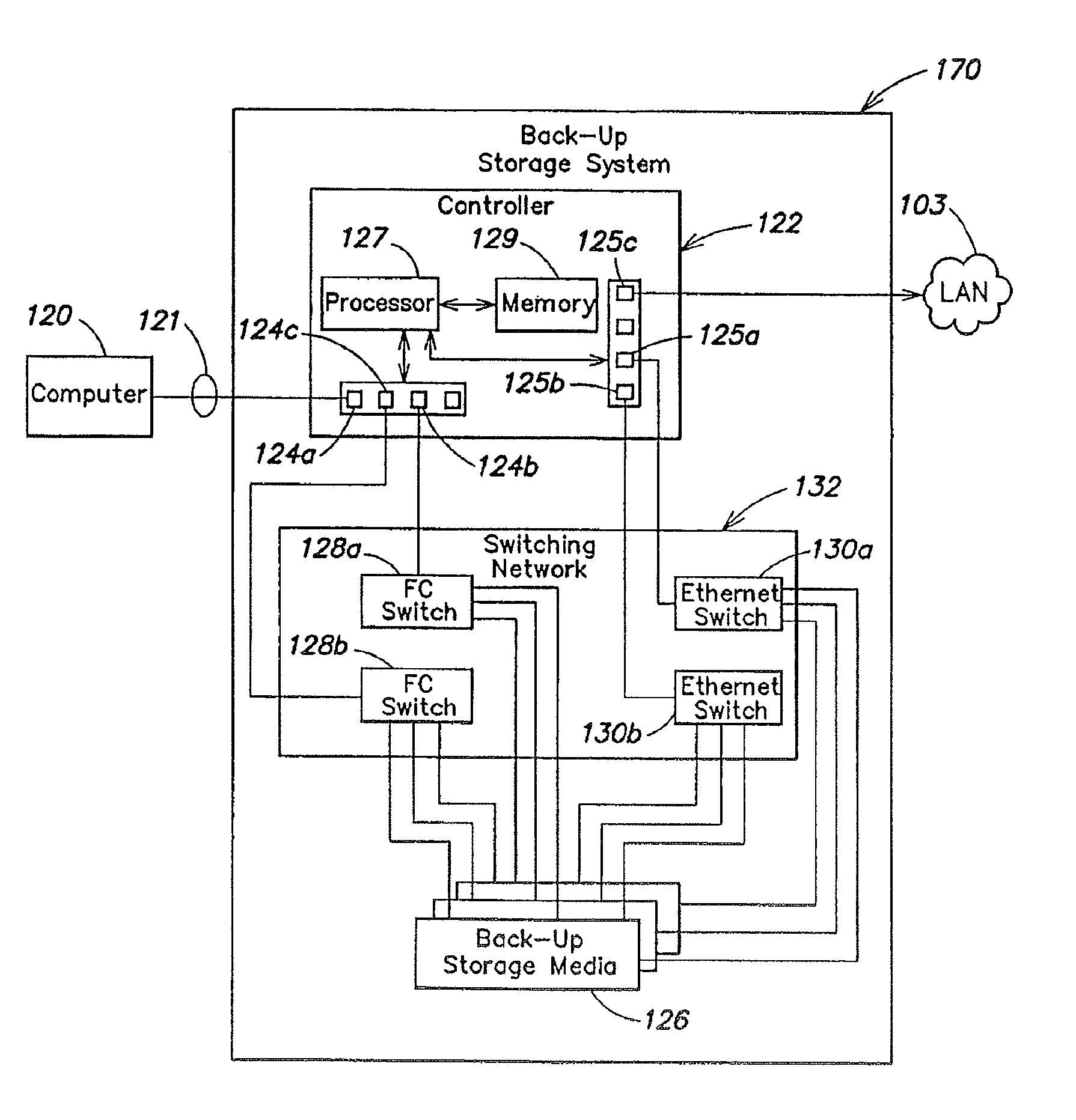

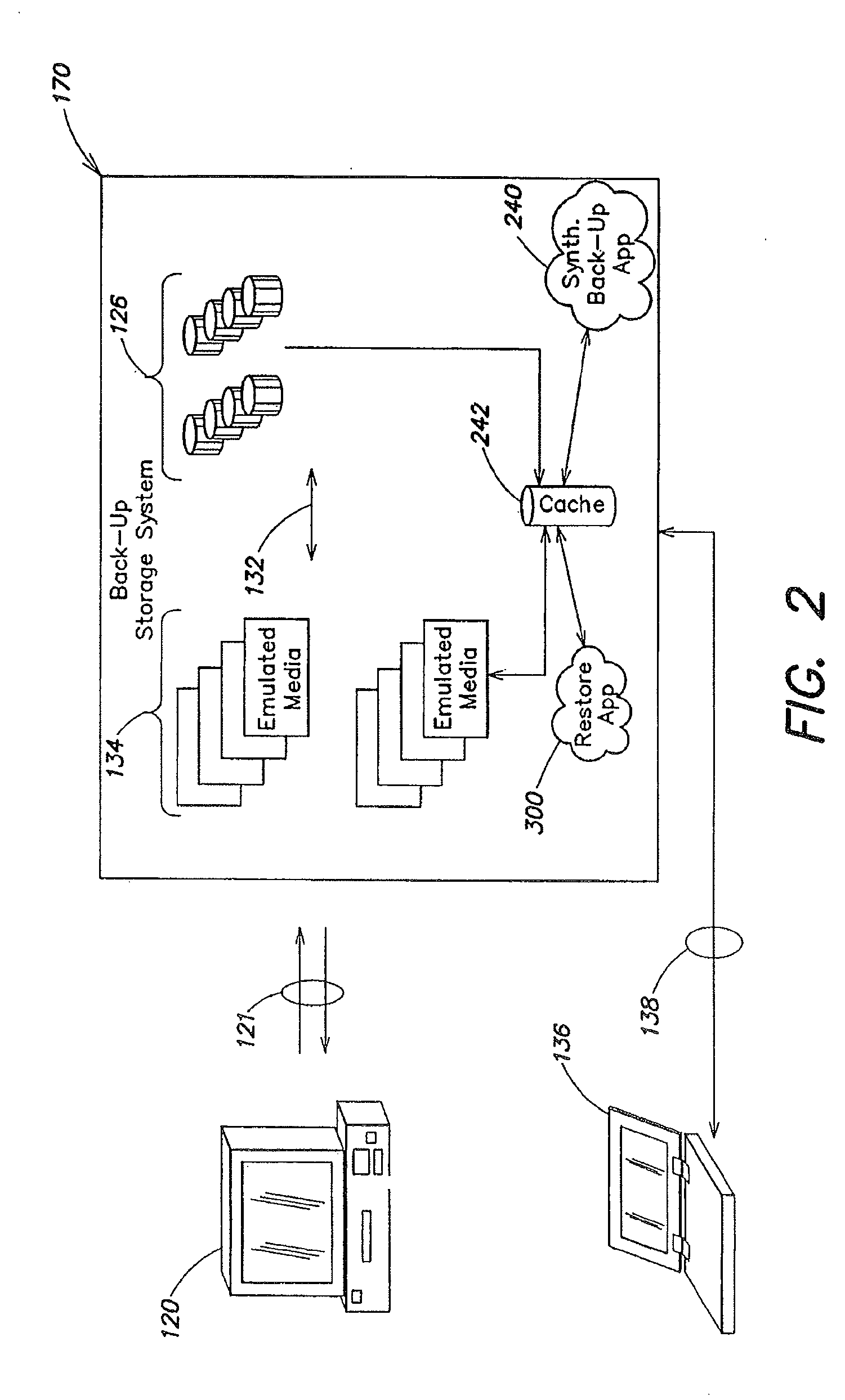

Emulated storage system

ActiveUS20080016131A1Good flexibilityReduce storage capacityMemory loss protectionError detection/correctionDatabaseData objects

A method for removing redundant data from a backup storage system is presented. In one example, the method may include identifying a first back-up data object, identifying a second back-up data object, detecting a first portion of the first back-up data object that is a copy of a second portion of the second back-up data object, and replacing the second portion with a pointer to the first portion.

Owner:HITACHI VANTARA LLC

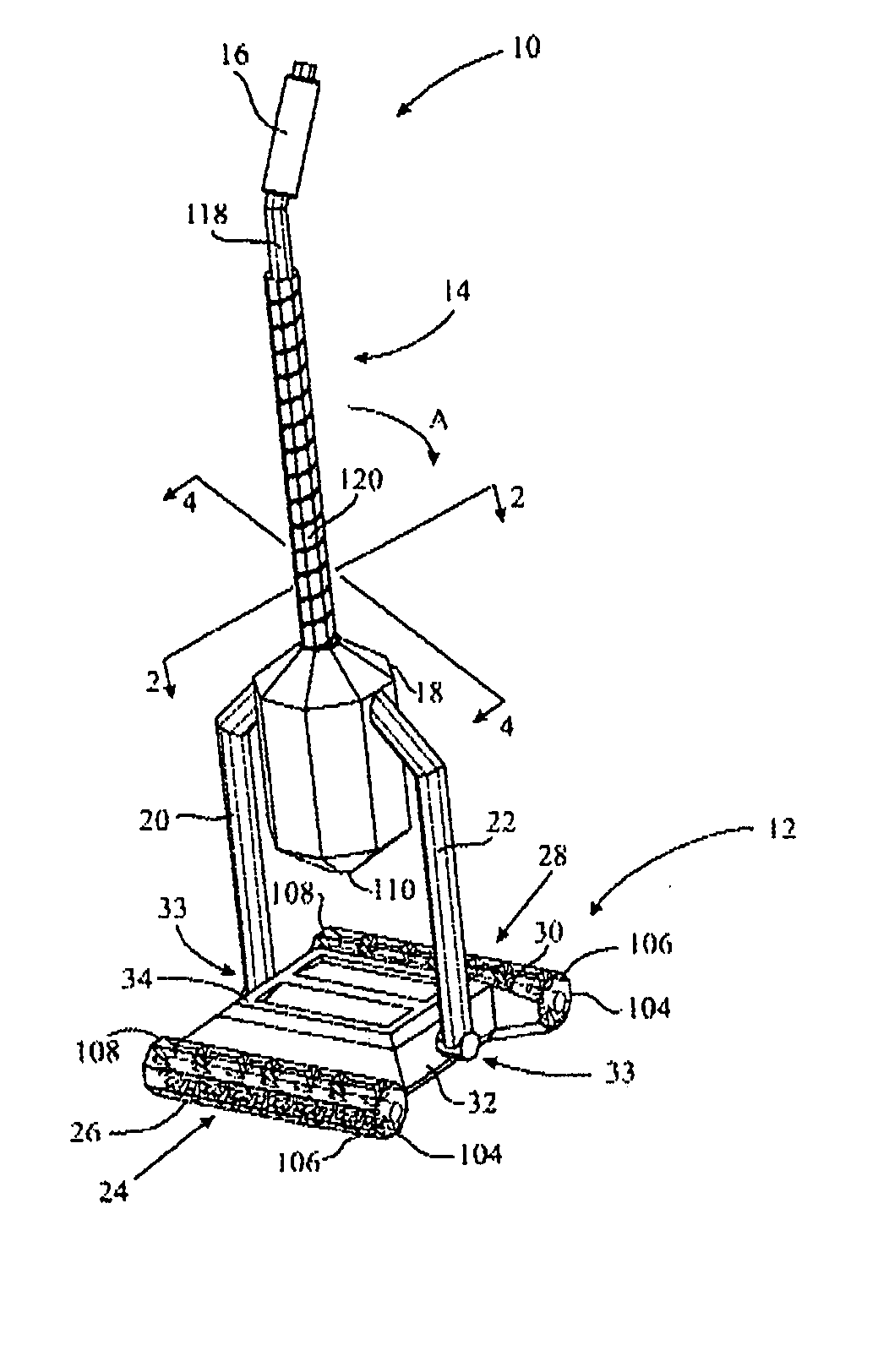

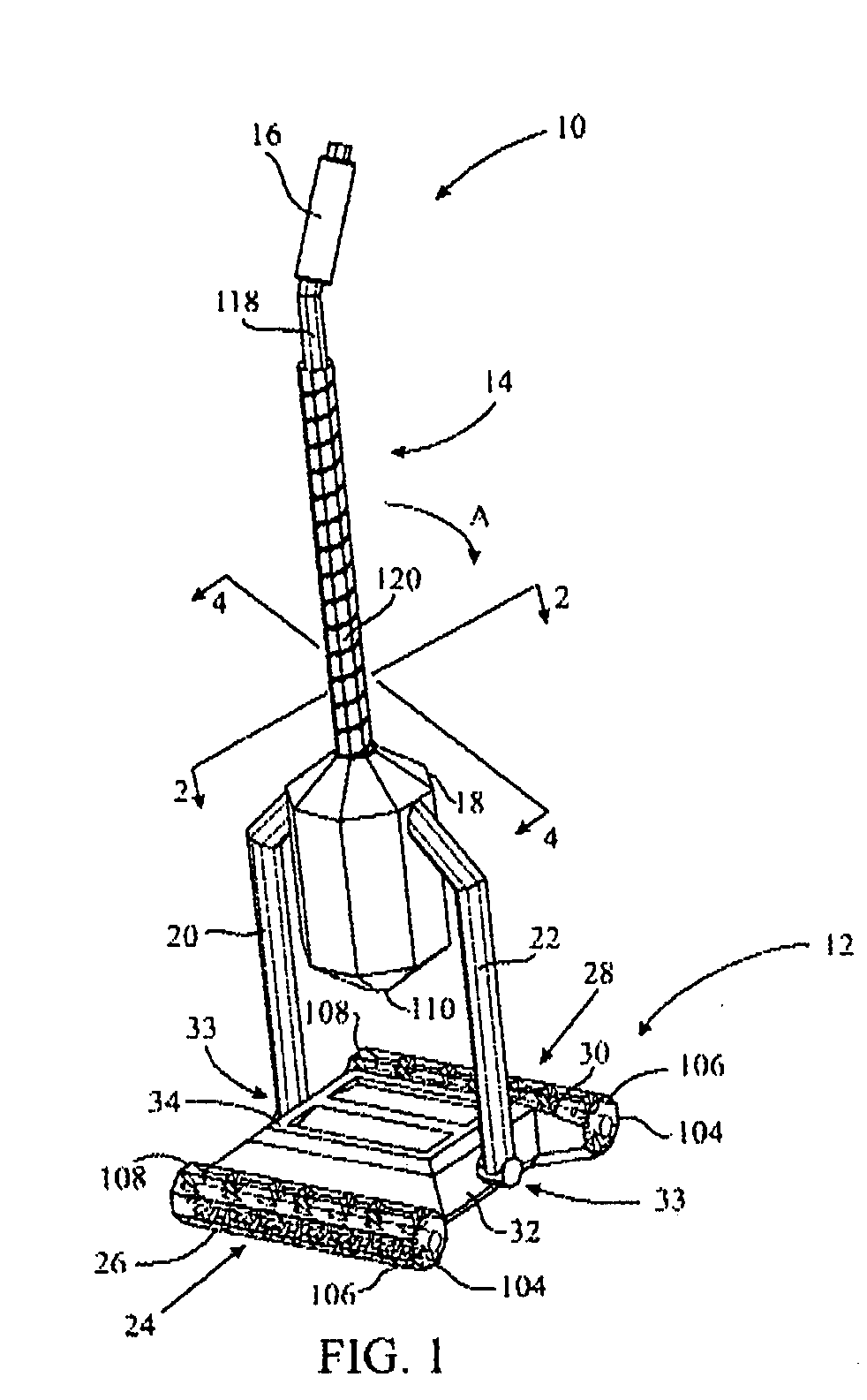

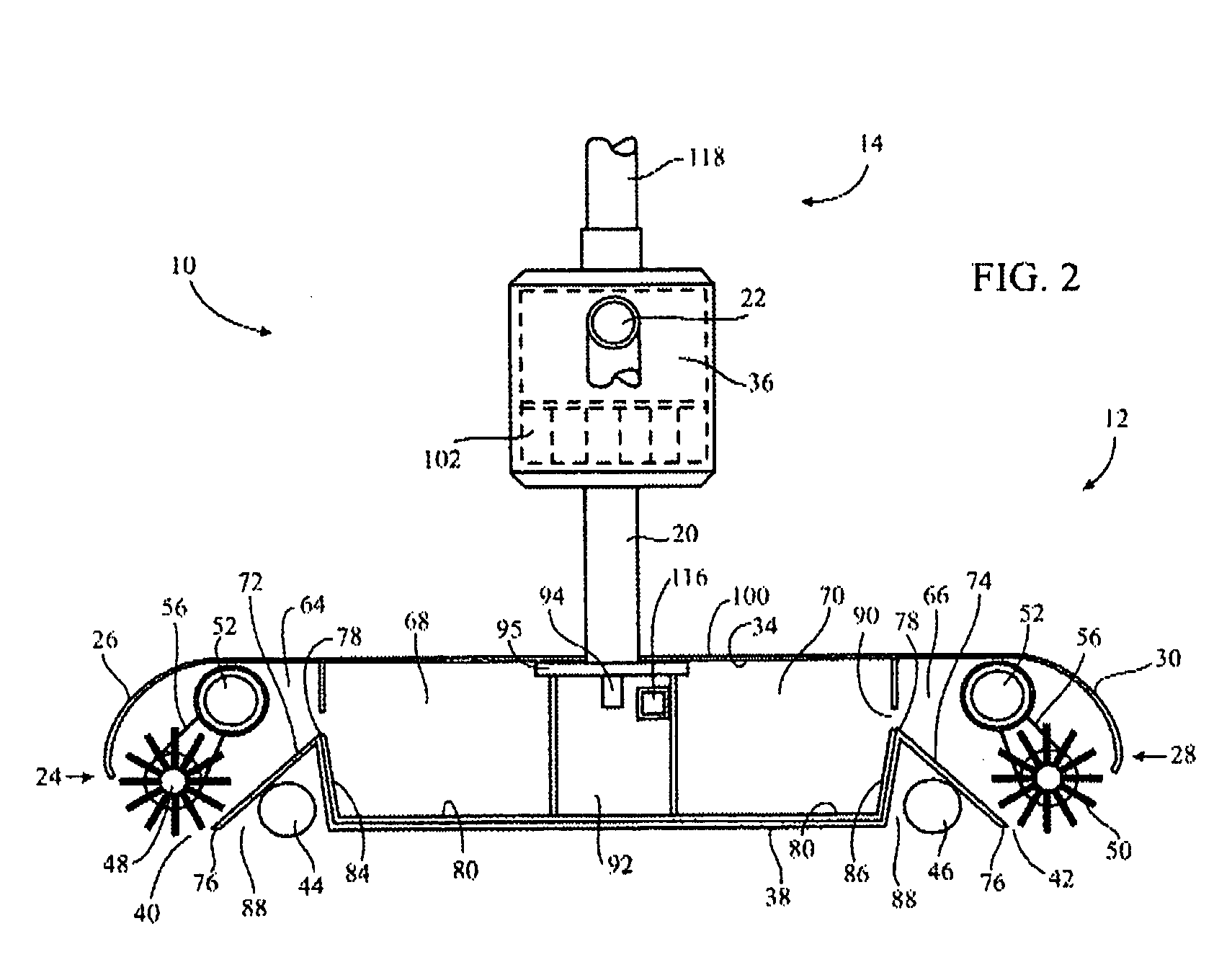

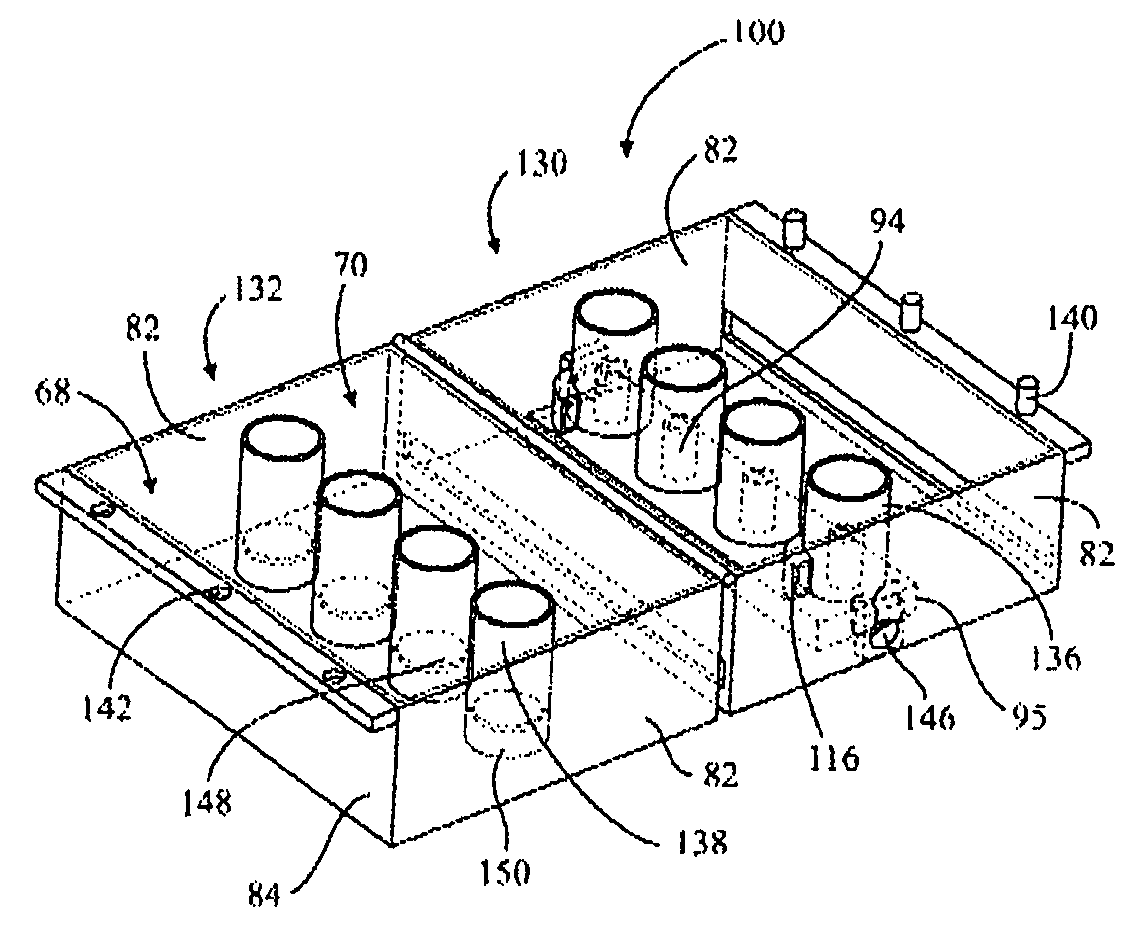

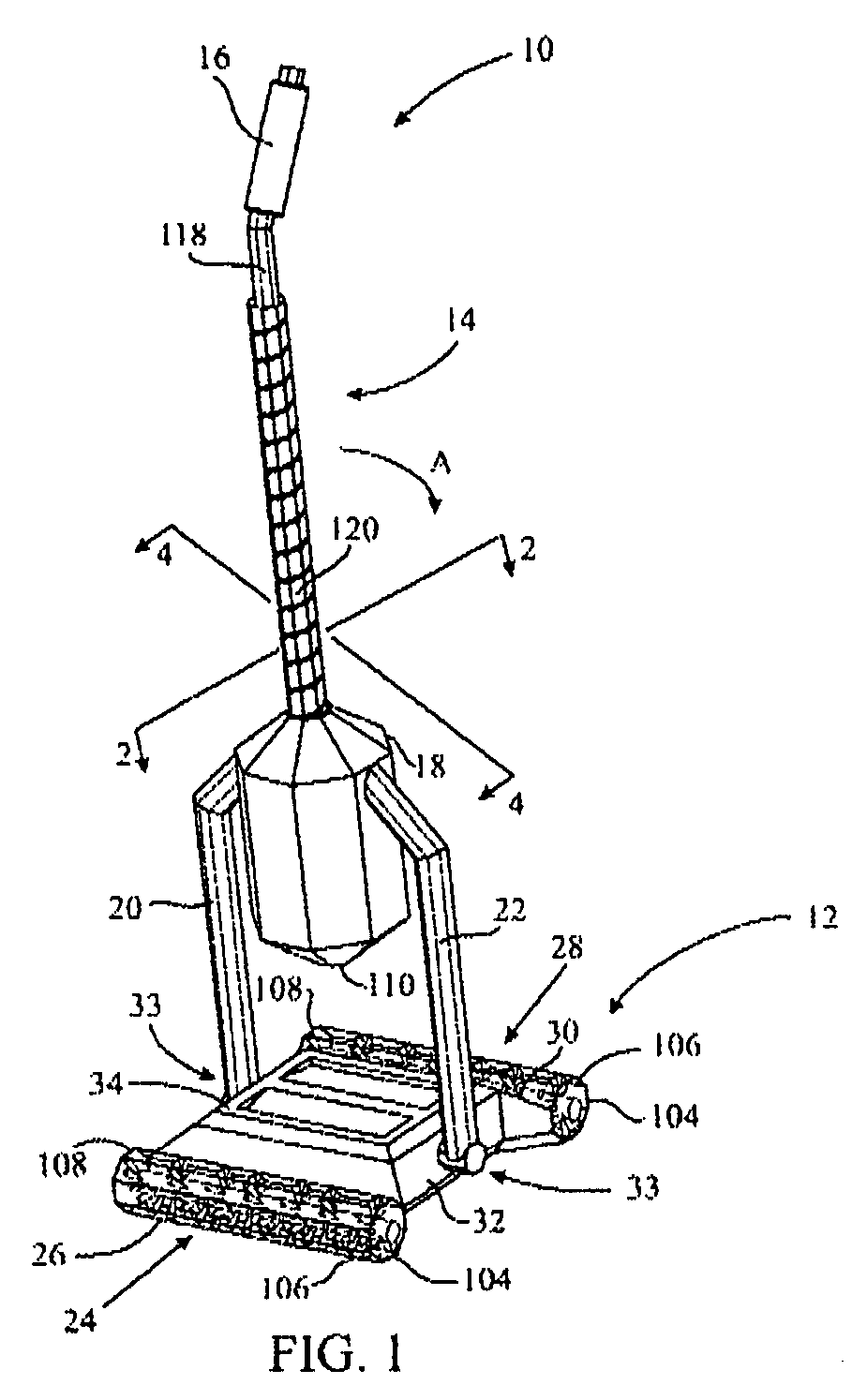

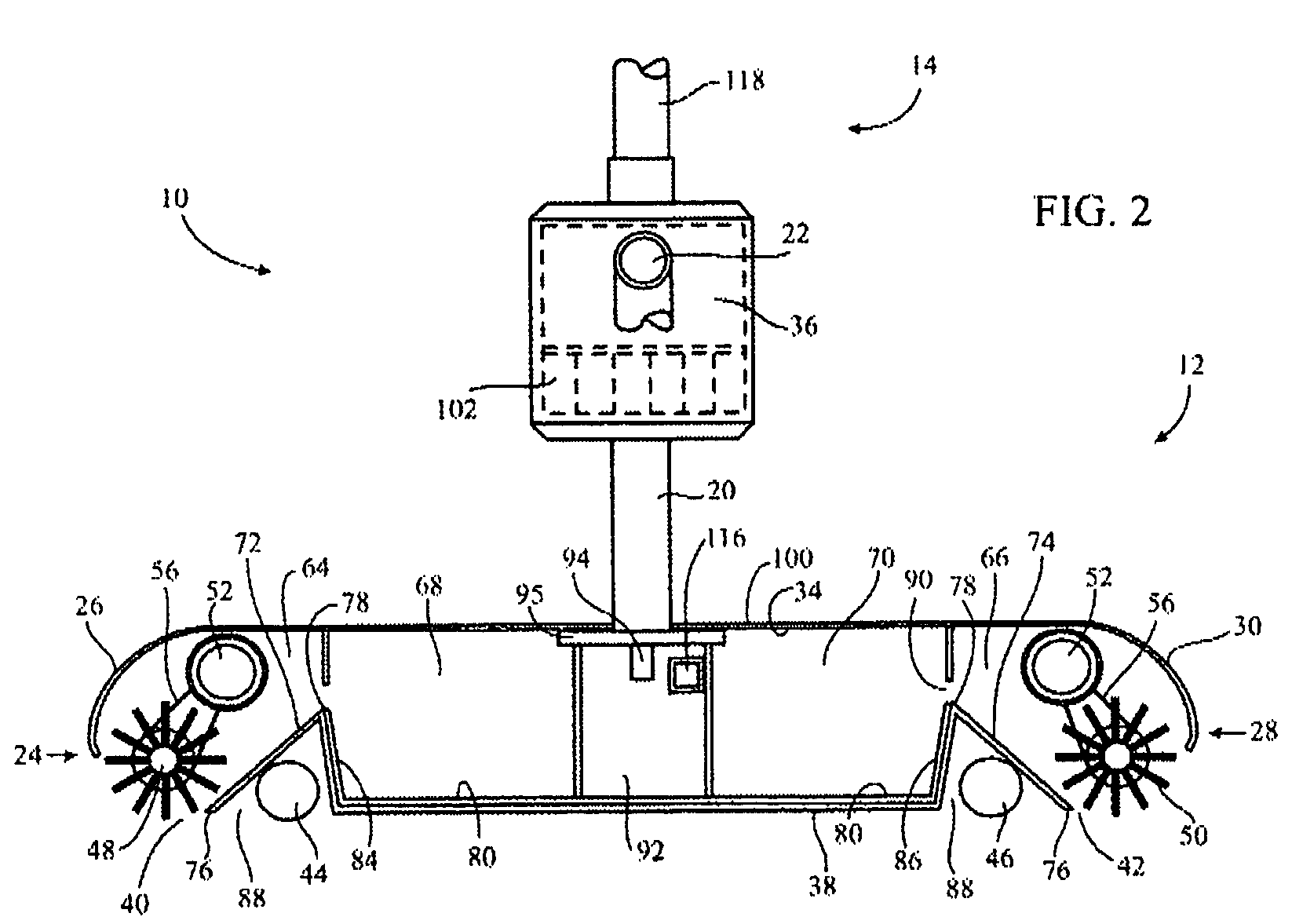

Dirt container for a surface cleaning apparatus and method of use

InactiveUS20050115409A1Efficient removalReduce the amount requiredCombination devicesAuxillary pretreatmentSurface cleaningEngineering

A dirt container for a surface cleaning apparatus is constructed from an air impermeable material and exterior walls of sufficient rigidity to maintain the shape of the dirt container. The dirt container may be supplied in a disassembled condition and assembled by a consumer prior to use.

Owner:POLAR LIGHT

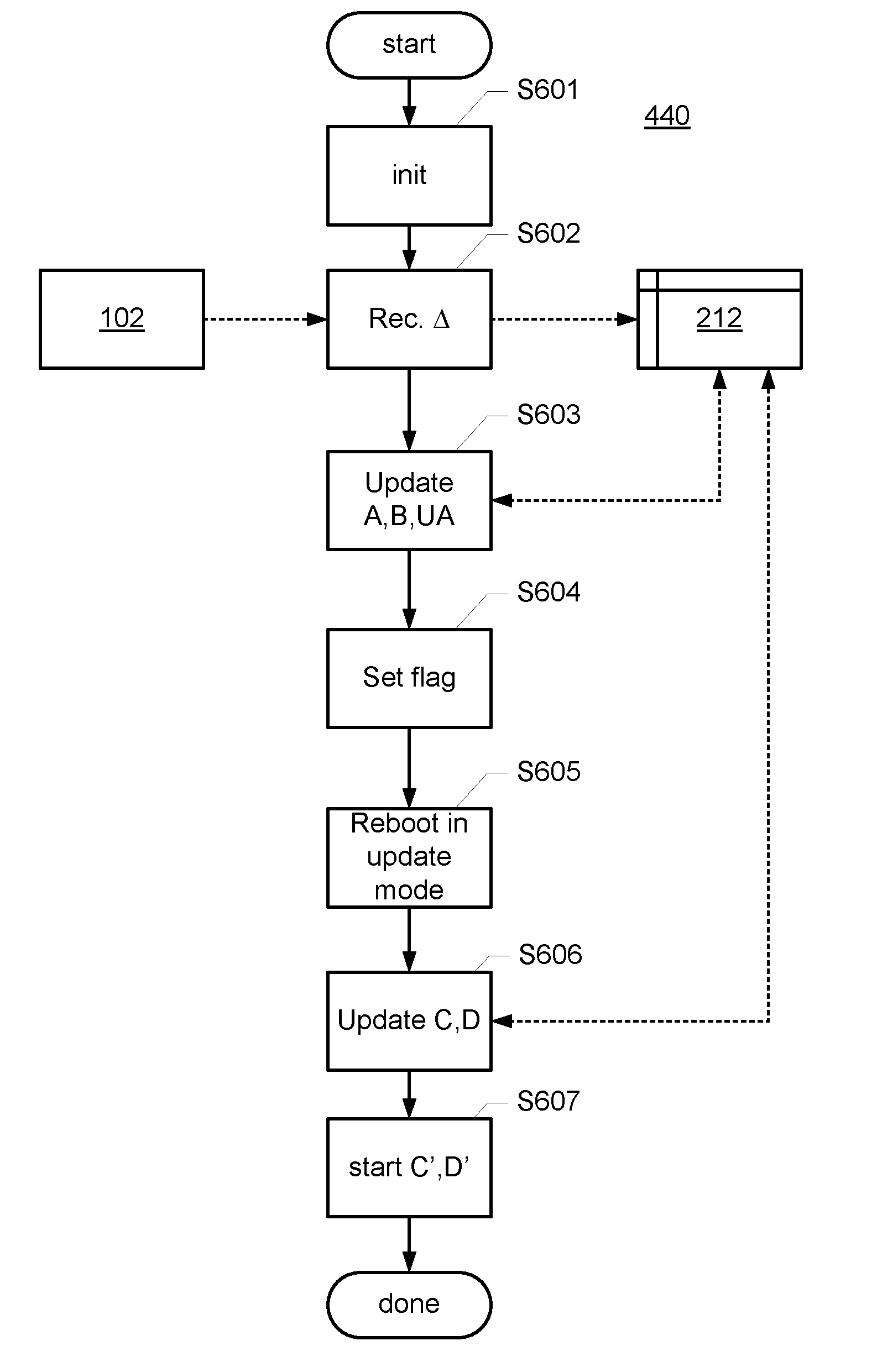

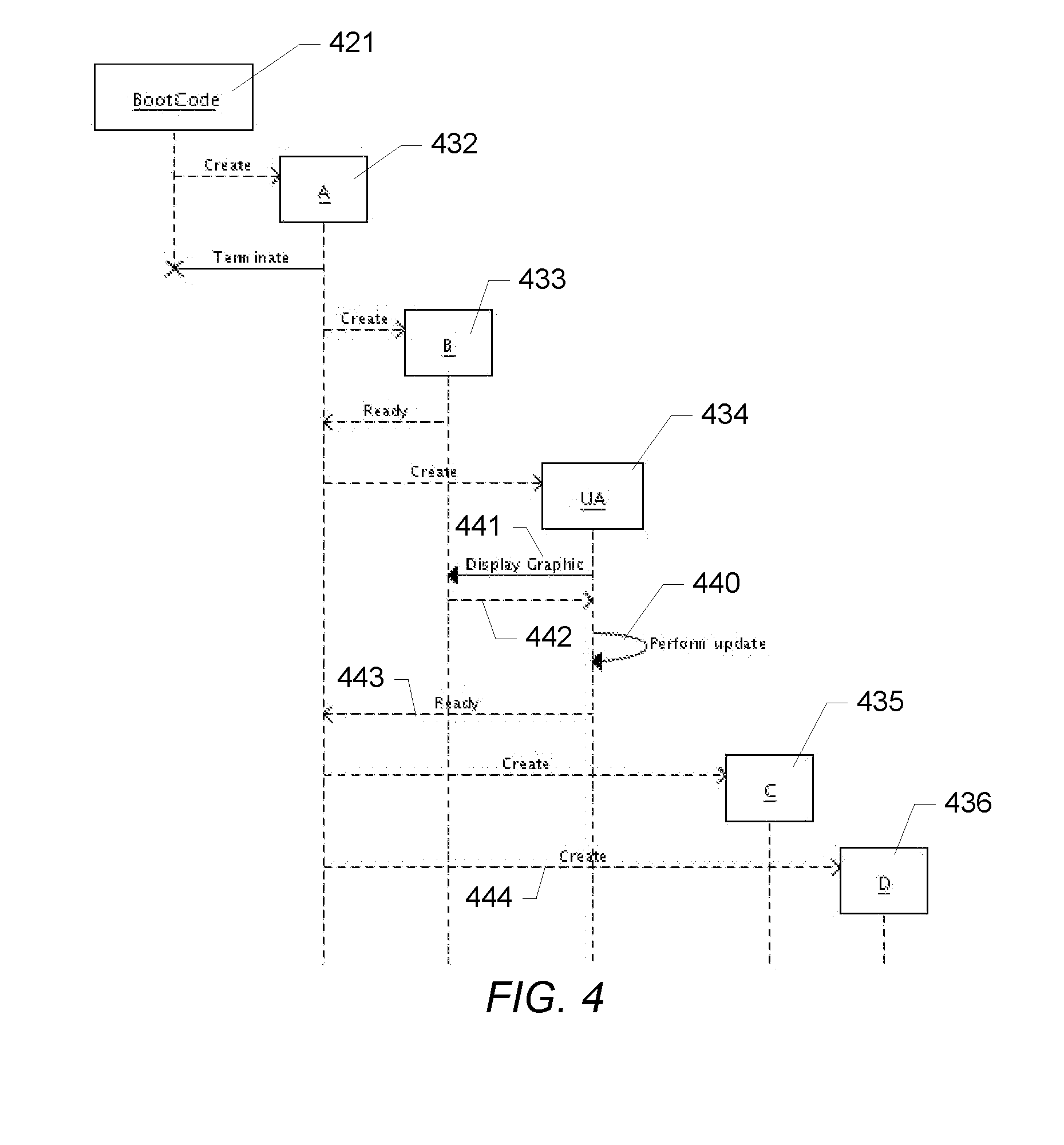

Updating Firmware of an Electronic Device

InactiveUS20100325622A1Reduce storage capacityMore fail-safeSoftware engineeringDigital computer detailsComputer engineeringSoftware

Disclosed is a method for updating software of an electronic device from a current to an updated version. A first set of load modules of the software is required for operating the electronic device in an update mode. The method comprises: receiving and storing incremental update instructions, executing a first set of update instructions so as to update the stored current version of the first set of load modules with the generated updated version of the first set of load modules; booting the electronic device in said update mode in which only the updated version of the first set of load modules is executed; and executing a stored second set of update instructions so as to perform an in-place update of the rest of the load modules.

Owner:IDTP HLDG

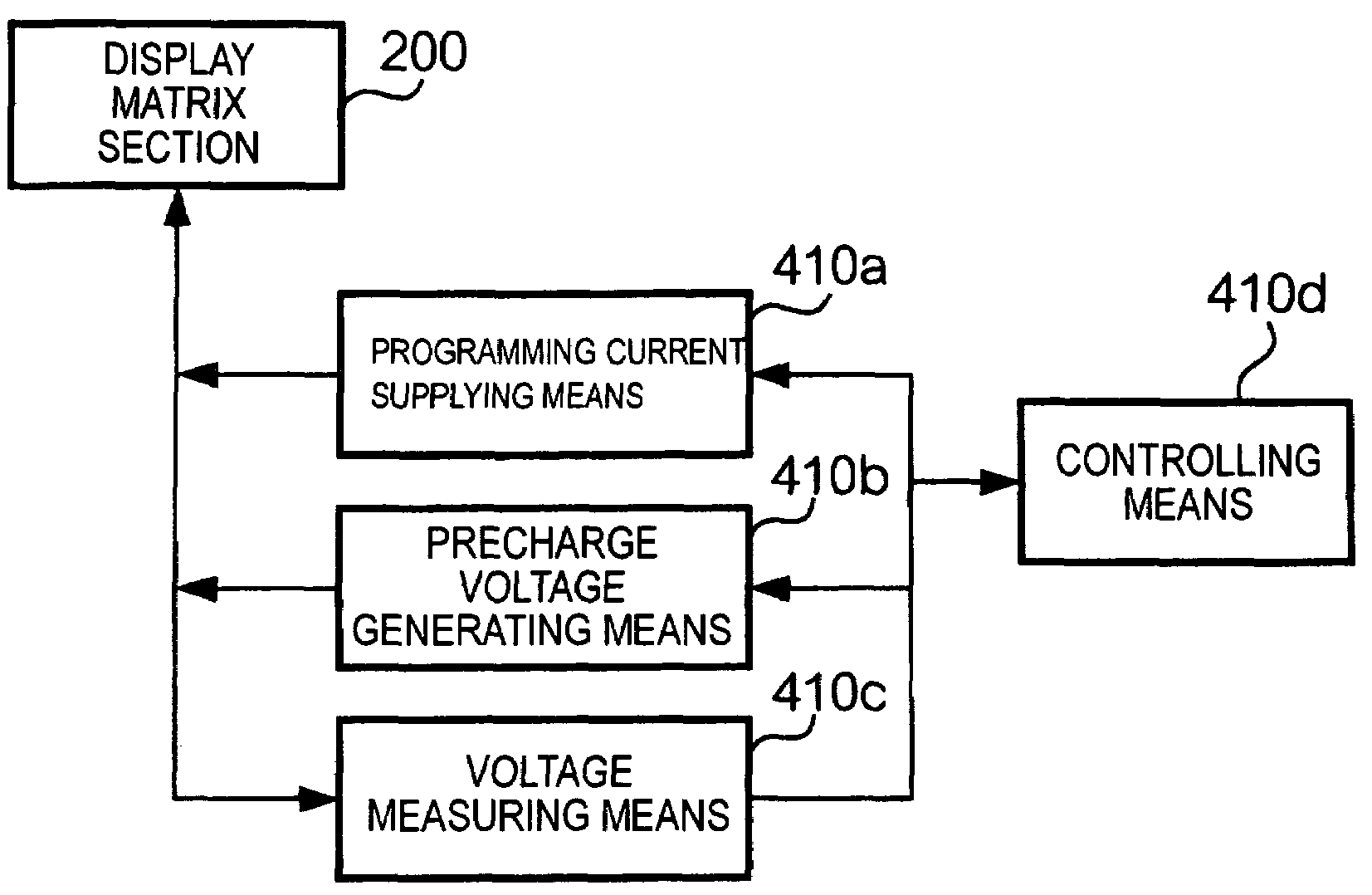

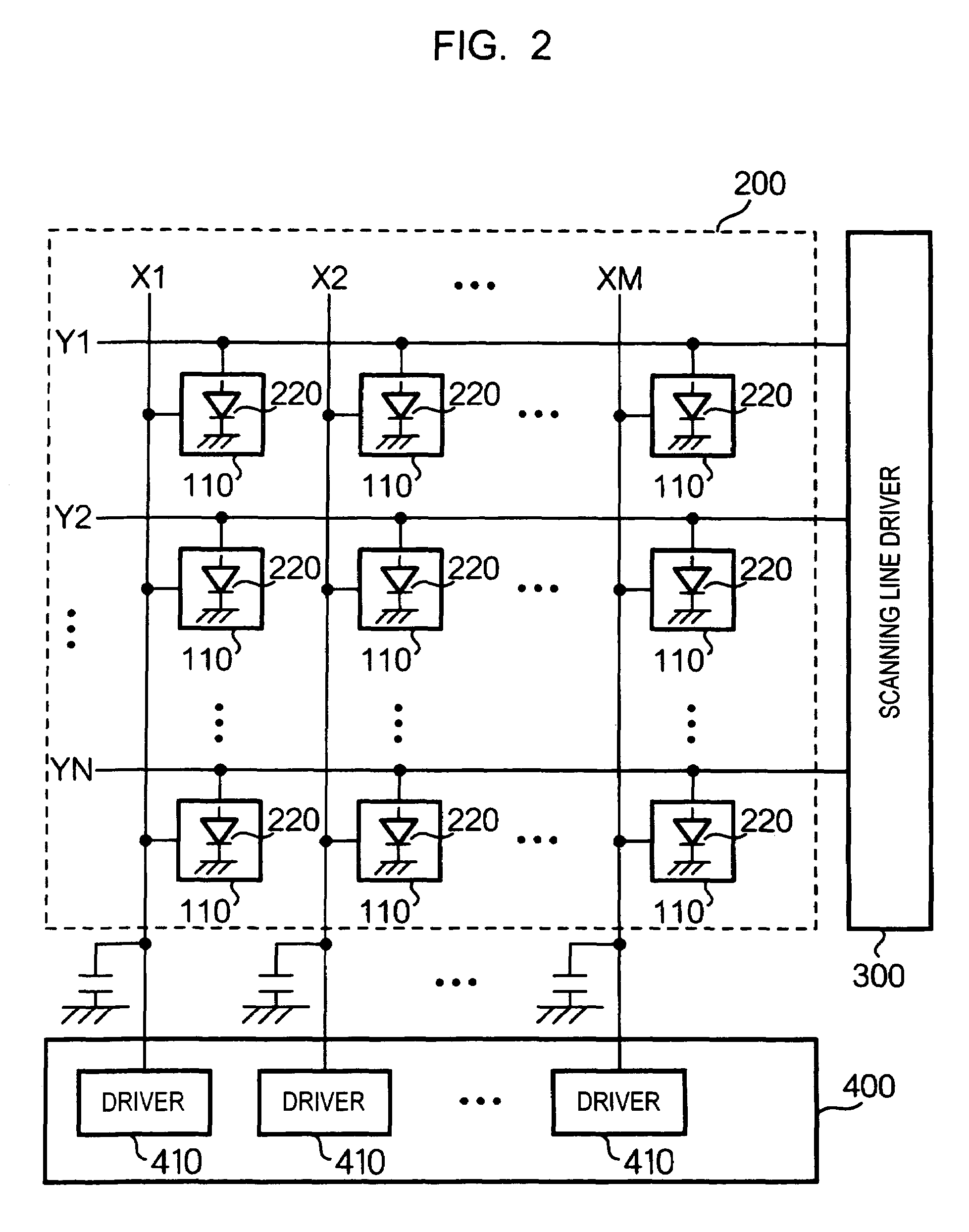

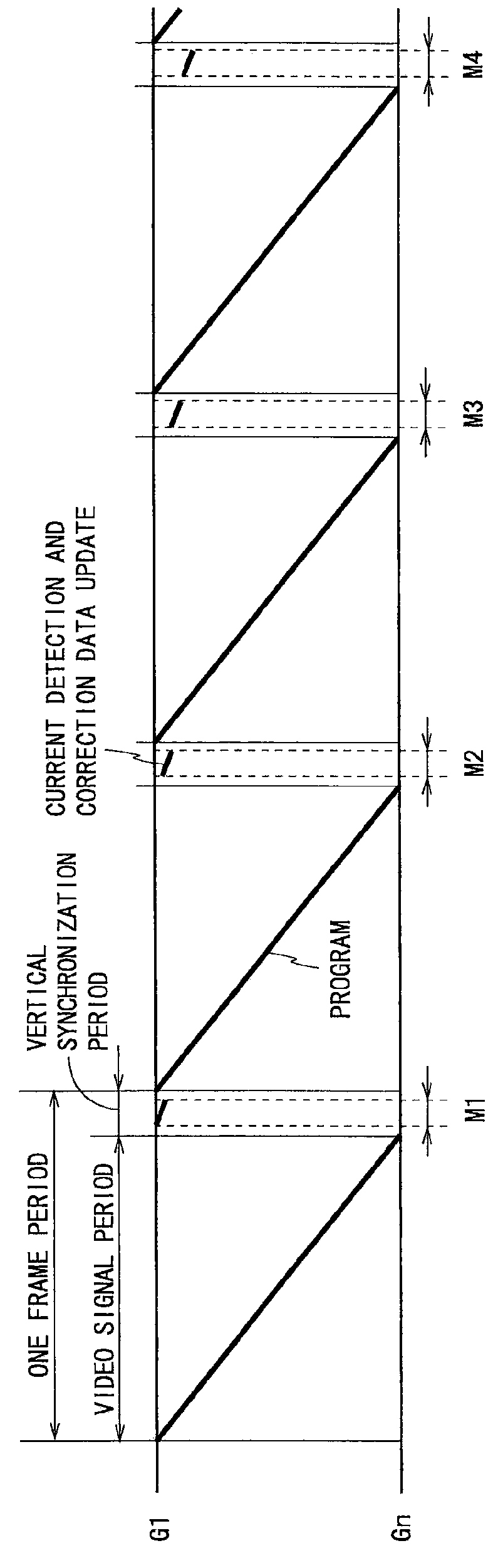

Display apparatus and method of driving the same

InactiveUS7576718B2InhibitionOptimize timingElectroluminescent light sourcesSolid-state devicesLight emissionThreshold voltage

To provide a technology for preventing effect of precharging from becoming nonuniform when the threshold voltage of a driving transistor included in a current drive type pixel circuit is nonuniform. In the technology, before setting the internal state of each of current drive type pixel circuits, provided to corresponded to intersections of a plurality of data lines and a plurality of scanning lines, in accordance with light emission grayscales, precharge voltages as voltages to be applied to the data lines are specified. A predetermined current is supplied to the current drive type pixel circuits via the data lines. A precharge voltage is specified in accordance with voltages appearing in the data lines after the predetermined current is supplied.

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

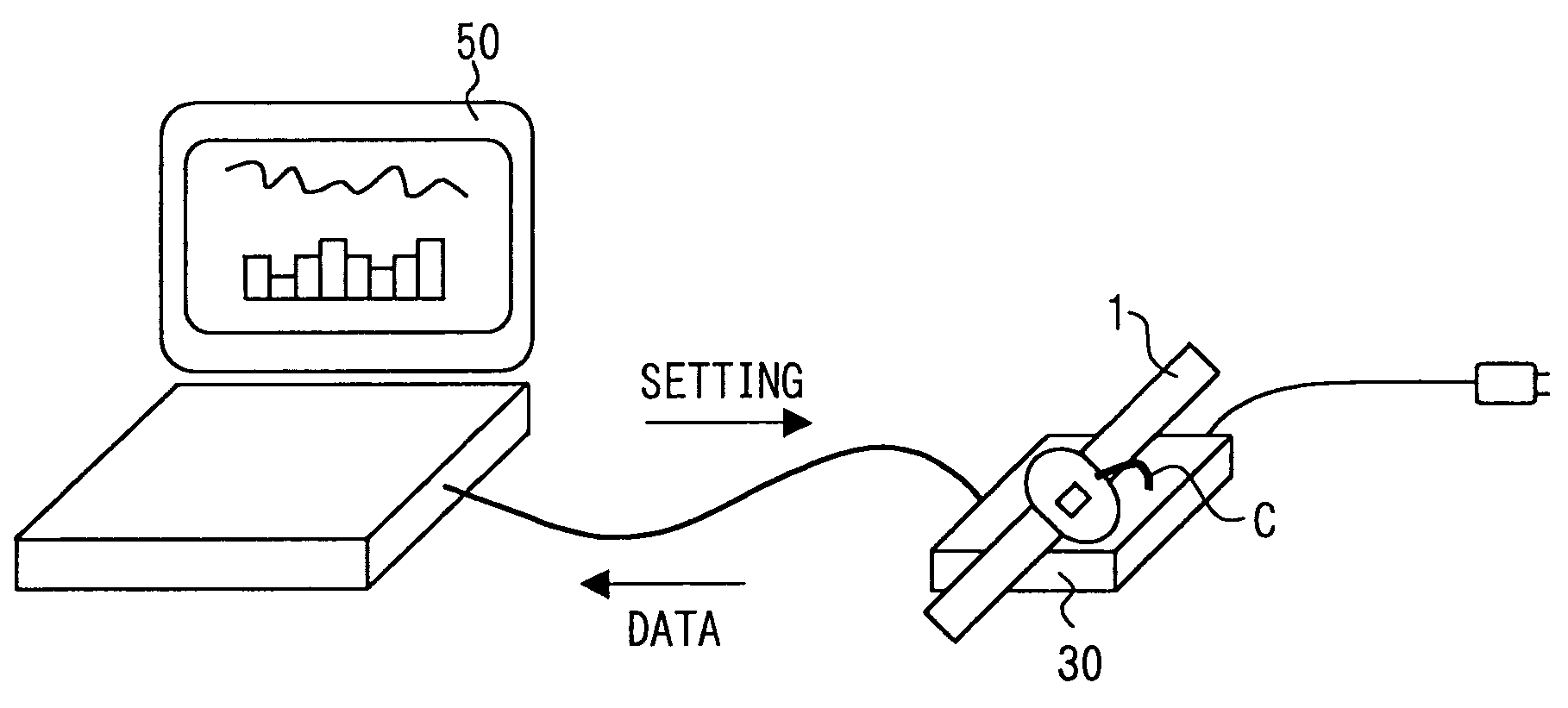

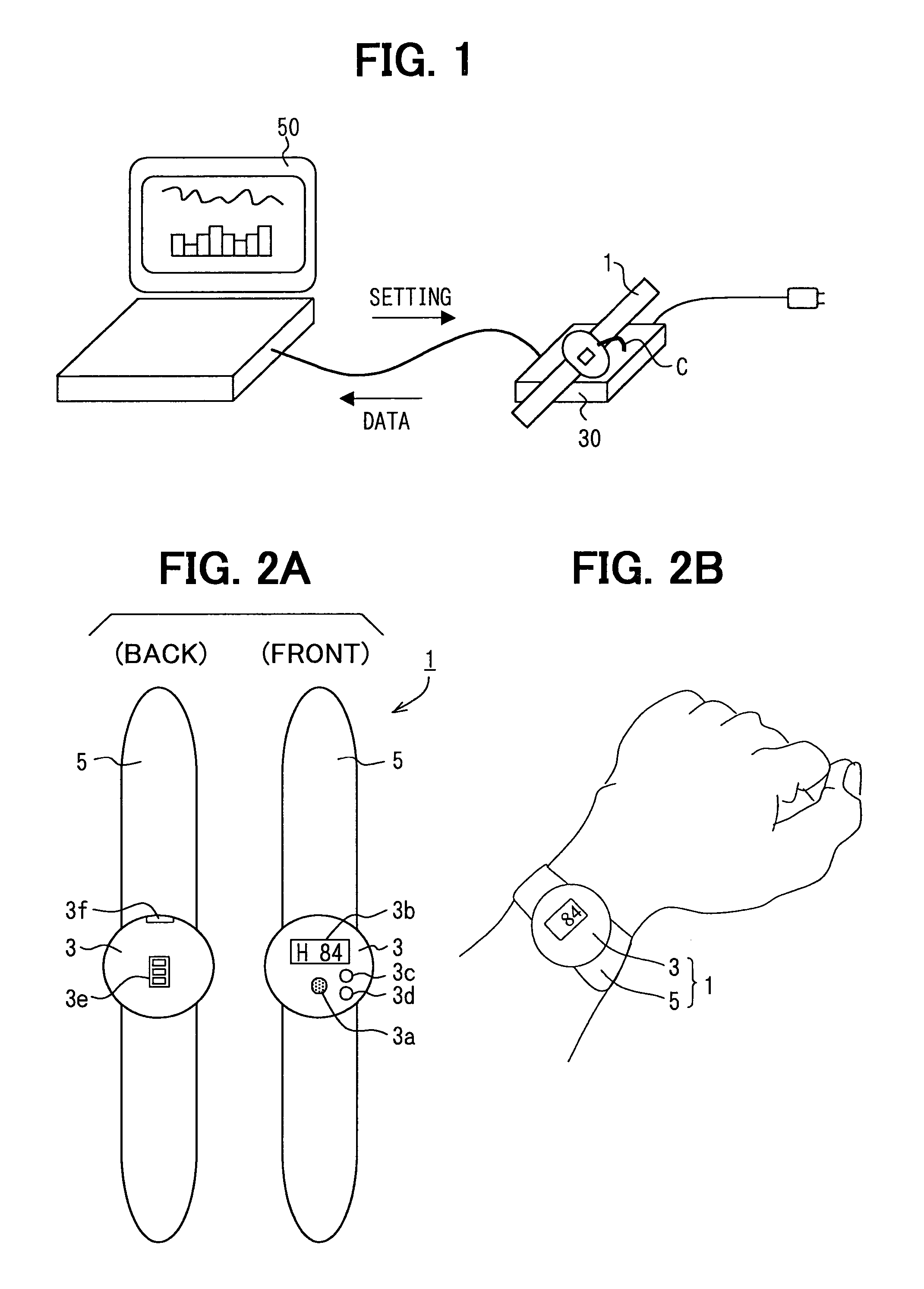

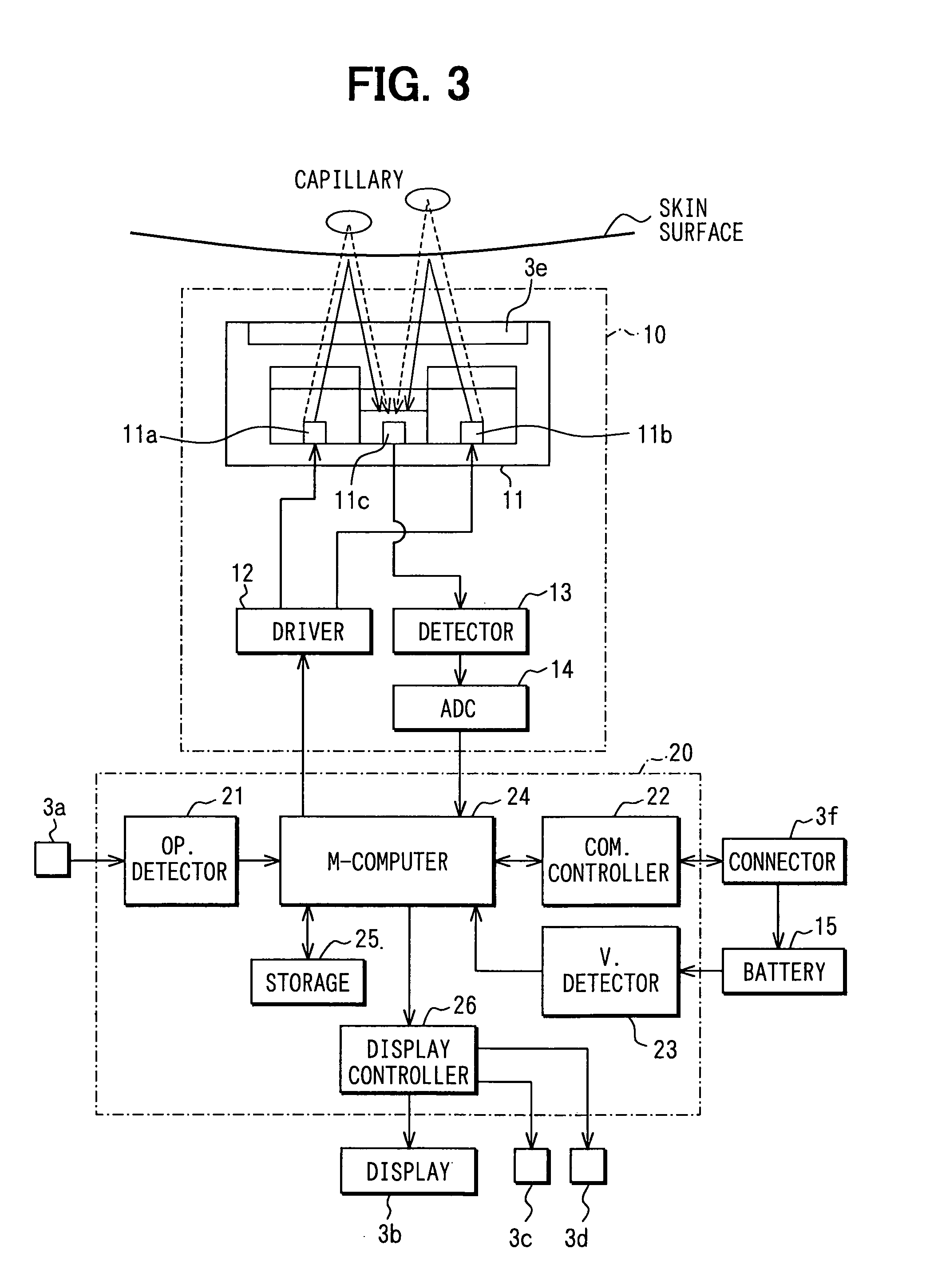

Portable biological information monitor apparatus and information management apparatus

In a portable biological information monitor apparatus, a pulse wave detection signal obtained by light emission from a green LED and a body motion detection signal obtained by light emission from an infrared LED are detected as biological information. This biological information is analyzed to compute various barometers. In a wake normal mode of a set generation mode, body motion and pulse are calculated as wake evaluation barometers for evaluation of a test subject's status in wake. In a wake steady state motion mode, body motion, pulse, and pitch are calculated as motion evaluation barometers for evaluation of the test subject's status in steady state motion. In a sleep mode, body motion, pulse, and autonomic nervous function are calculated as sleep evaluation barometers for evaluation of the test subject's status in sleep. Necessary barometers are thereby generated regardless of the test subject's action using the portable monitor apparatus alone.

Owner:DENSO CORP

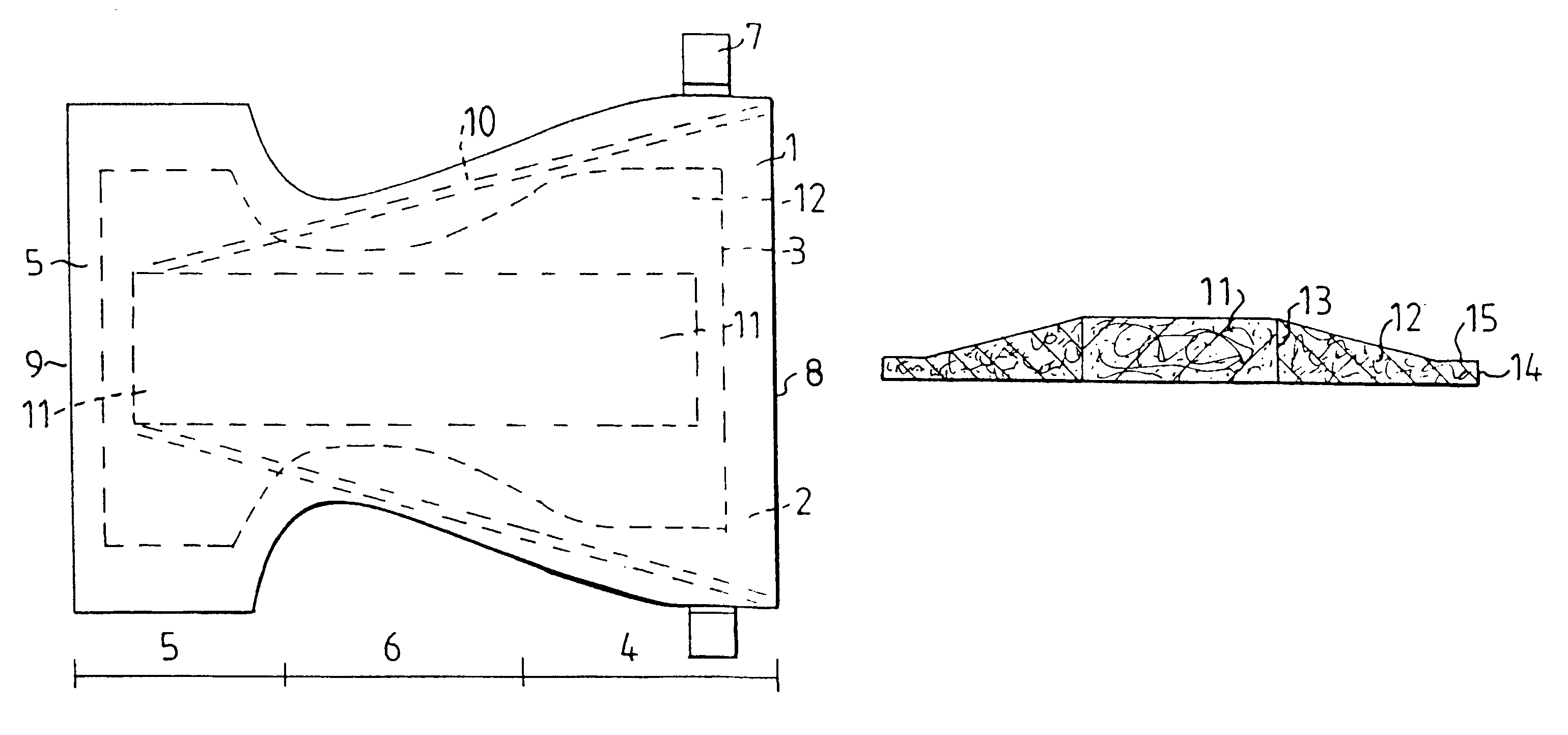

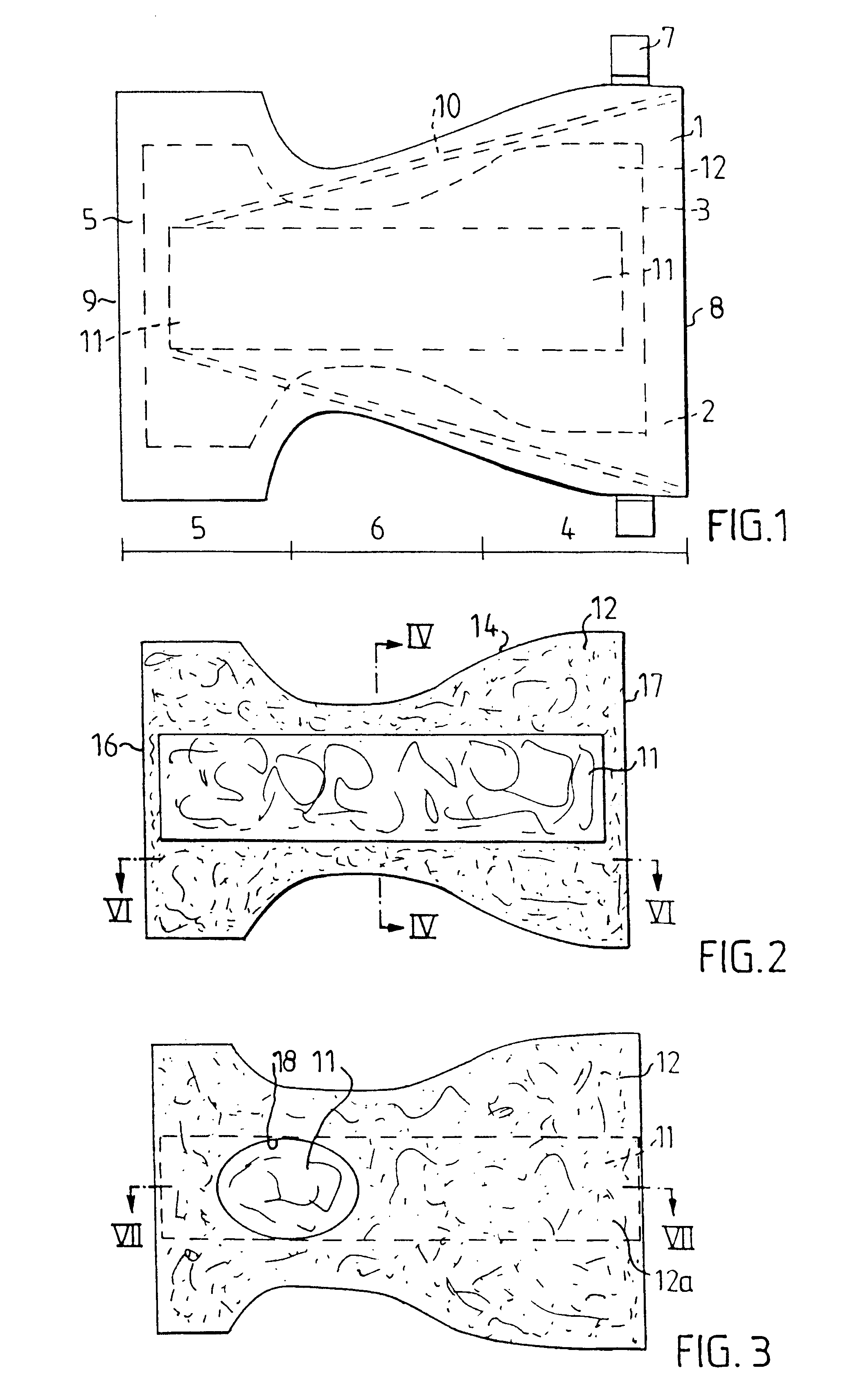

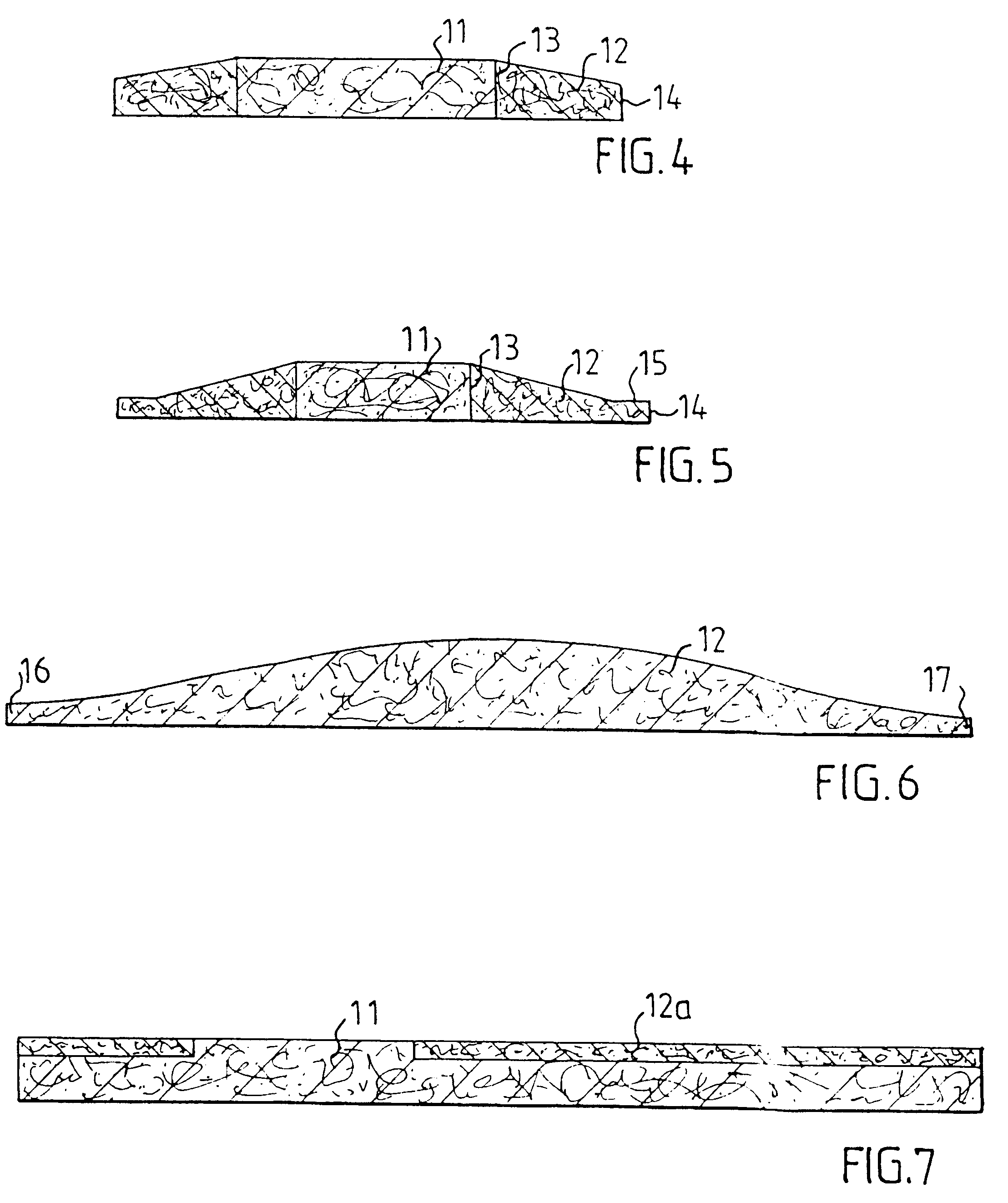

Absorbent structure that has a high degree of utilization

InactiveUS6441268B1Improve acquisitionImprove storage propertiesLayered productsBaby linensVolumetric Mass DensityBiomedical engineering

An absorbent structure in an absorbent article, such as a diaper, an incontinence guard, a sanitary napkin or like article. The structure includes a liquid-acquisition and liquid-dispersing core of high bulk, porous material. The core is in liquid communication with a liquid storage part that surrounds the core at least along its longitudinally extending side-edges and which has a mean pore size that is smaller than the mean pore size of the high bulk, porous core. The density of the liquid storage part increases in a direction out towards the longitudinally extending side-edges of the absorbant structure.

Owner:SCA HYGIENE PROD AB

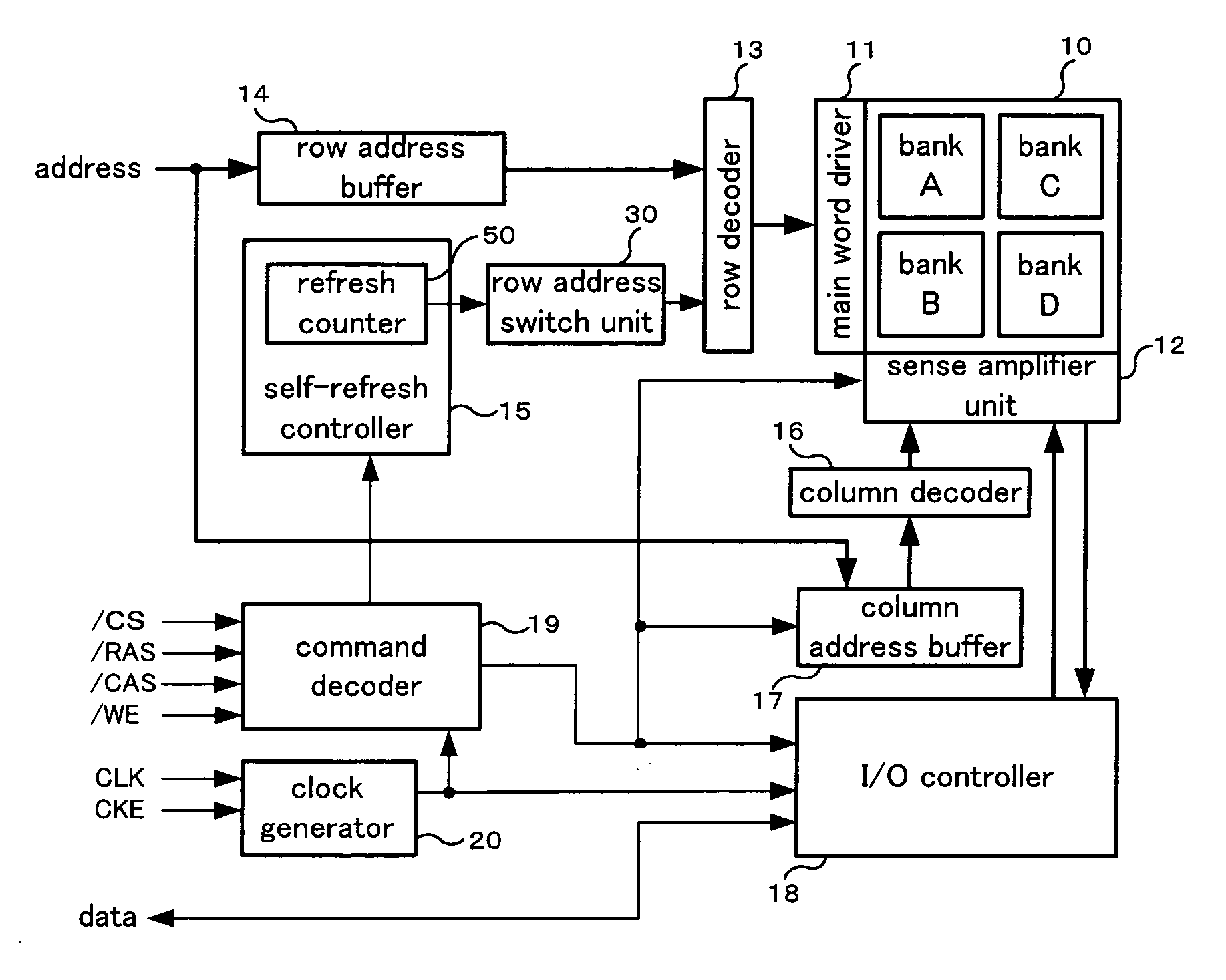

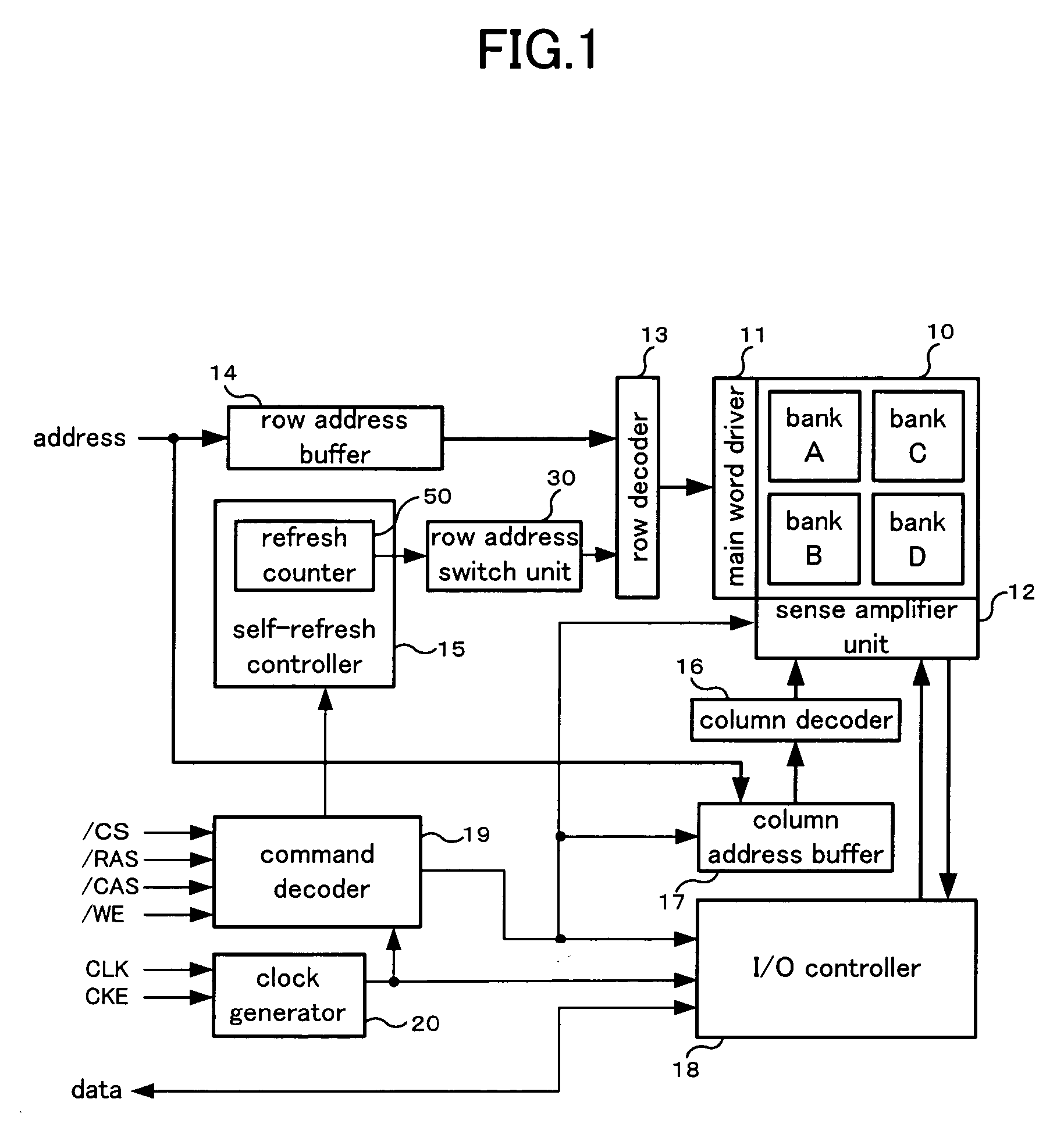

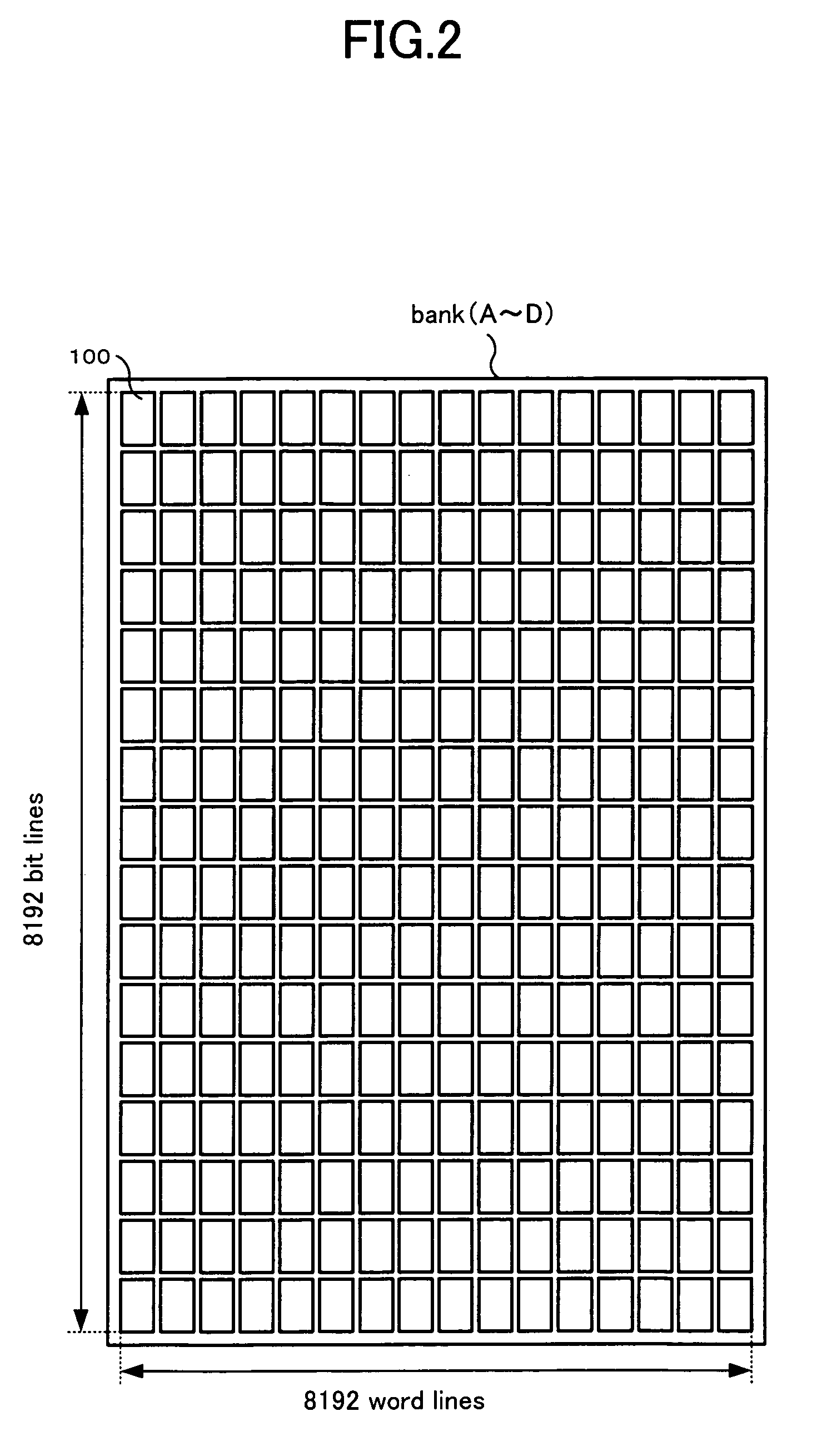

Refresh control method of a semiconductor memory device and semiconductor memory device

A refresh control method of a semiconductor memory device which controls a self-refresh operation to hold data in a memory array having a plurality of memory cells disposed at intersections of word lines corresponding to row addresses and bit lines corresponding to column addresses, comprising: a step for dividing the memory array into a holding area used as a copy source which includes memory cells on a predetermined number of word lines, and a copy area used as a copy destination which includes memory cells on word lines to which entire data of the holding area is to be copied, a step for executing copy operation in which data of each memory cell of the holding area is copied to one or more memory cells in the copy area on the same bit line or the same pair of bit lines before executing the self-refresh operation, and a step for executing the self-refresh operation in which a row address of the holding area is designated and a corresponding word line is selected and driven, and at the same time, one or more word lines in the copy area corresponding to the selected word line are selected and driven.

Owner:PS4 LUXCO SARL

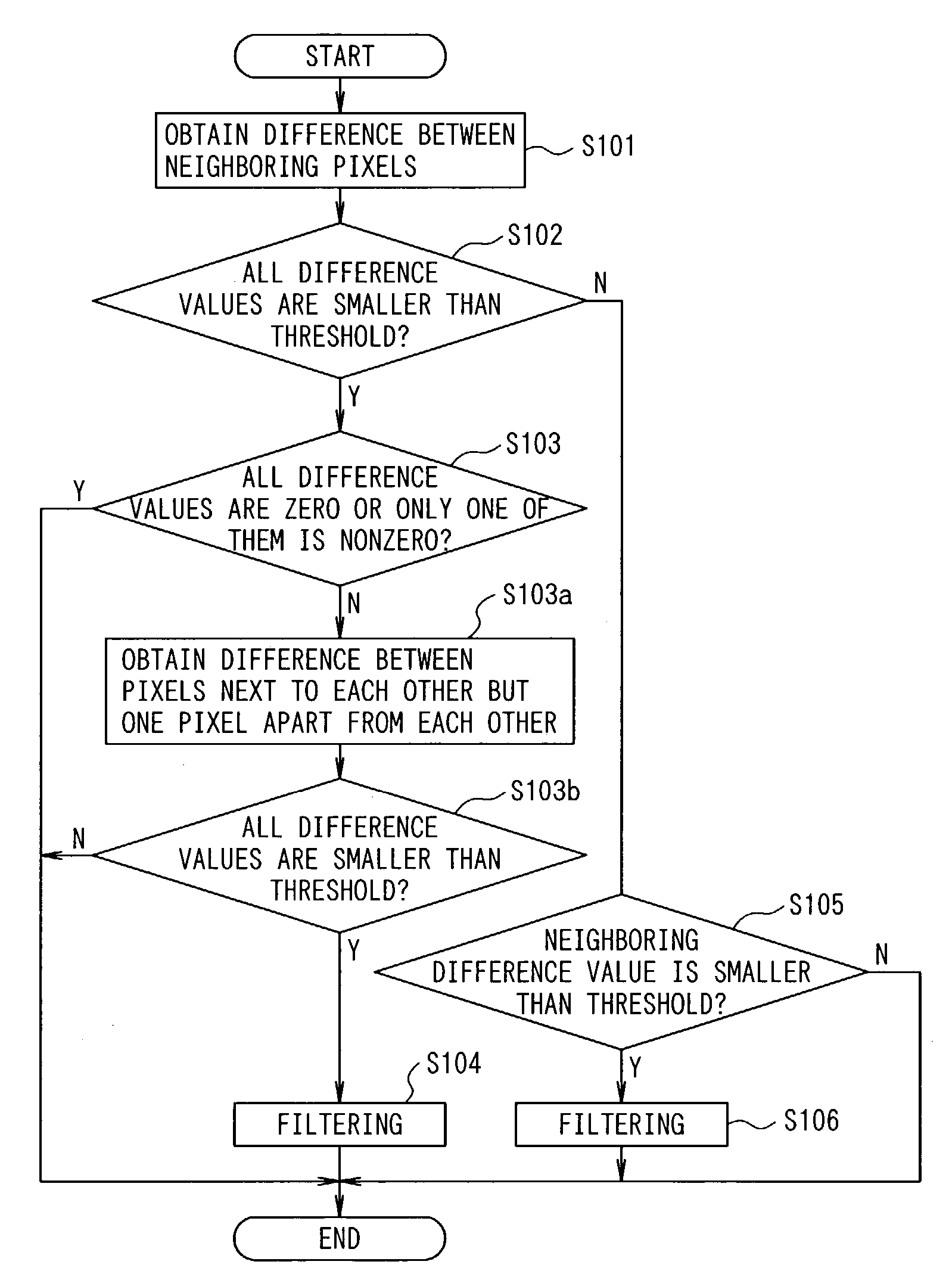

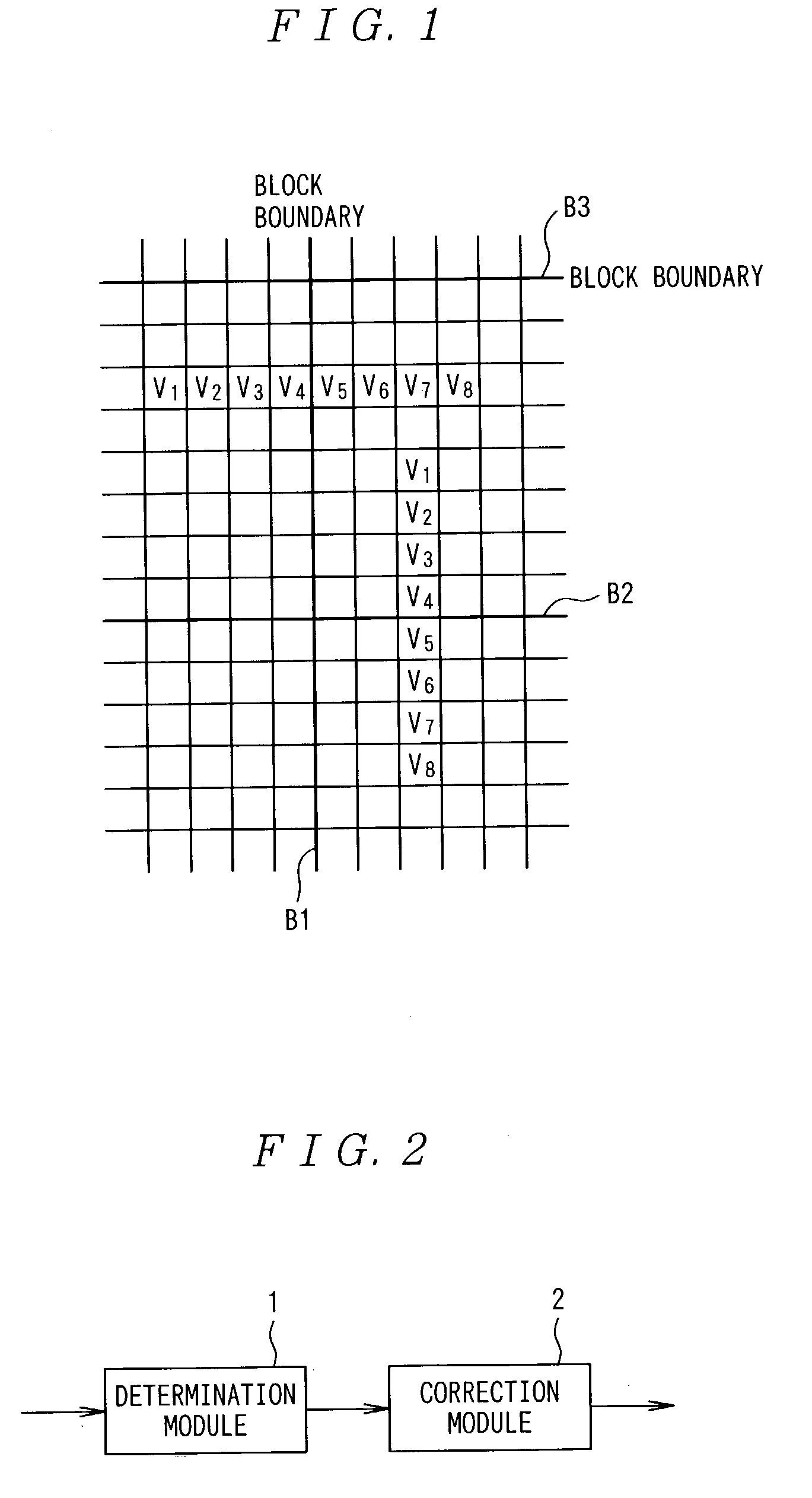

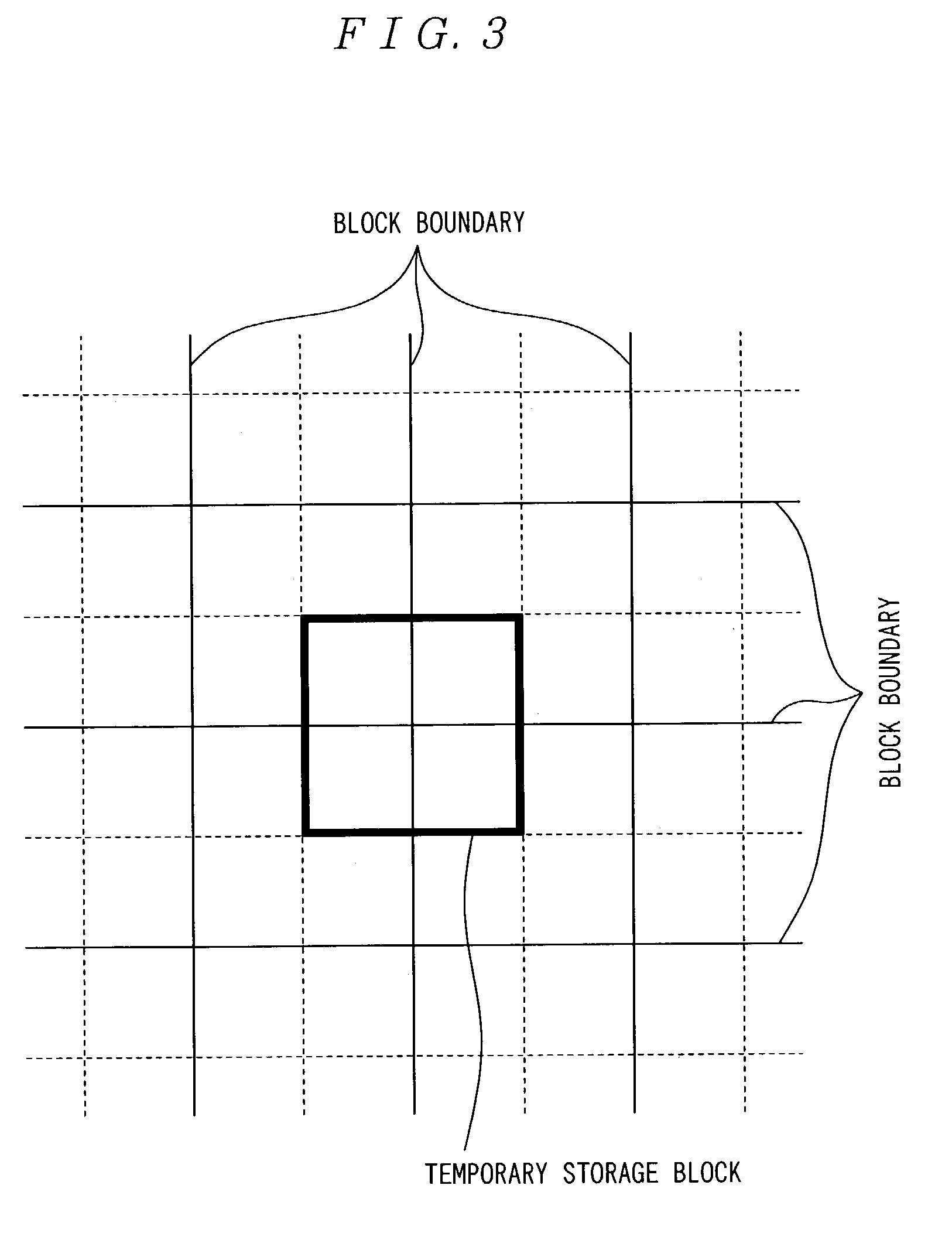

Image processing system, image processing method, and image processing program

ActiveUS7054503B2Easy to processReducing mosquito noiseImage enhancementCharacter and pattern recognitionImaging processingDiscrete cosine transform

In the present invention, 2N pixels (having signal levels V1 through V8), including a boundary pixel, that consist of N pixels on each side of a boundary and run orthogonally to the boundary are referenced to determine whether correction should be performed or not. If it is determined that the correction should be performed, the boundary pixel and M pixels on each side of the boundary pixel are used to perform the correction. In an image processing system for performing filtering on pixels belonging to a block, which is a unit of discrete cosine transform in image compression, the maximum value of differences between neighboring pixels in at least half, including a pixel of interest, of all the pixels composing a block to be processed is obtained. Differences between neighboring pixels in 2N pixels, including the pixel of interest, that run orthogonally to the boundary between blocks and consist of N pixels on each side of the boundary are calculated. The differences calculated are compared with a threshold corresponding to the maximum value to determine whether filtering should be performed. If it is determined that filtering should be performed, the pixel of interest and M pixels on each side of the pixel of interest are used to perform filtering. N is a positive integer and M is a positive integer smaller than N.

Owner:GK BRIDGE 1

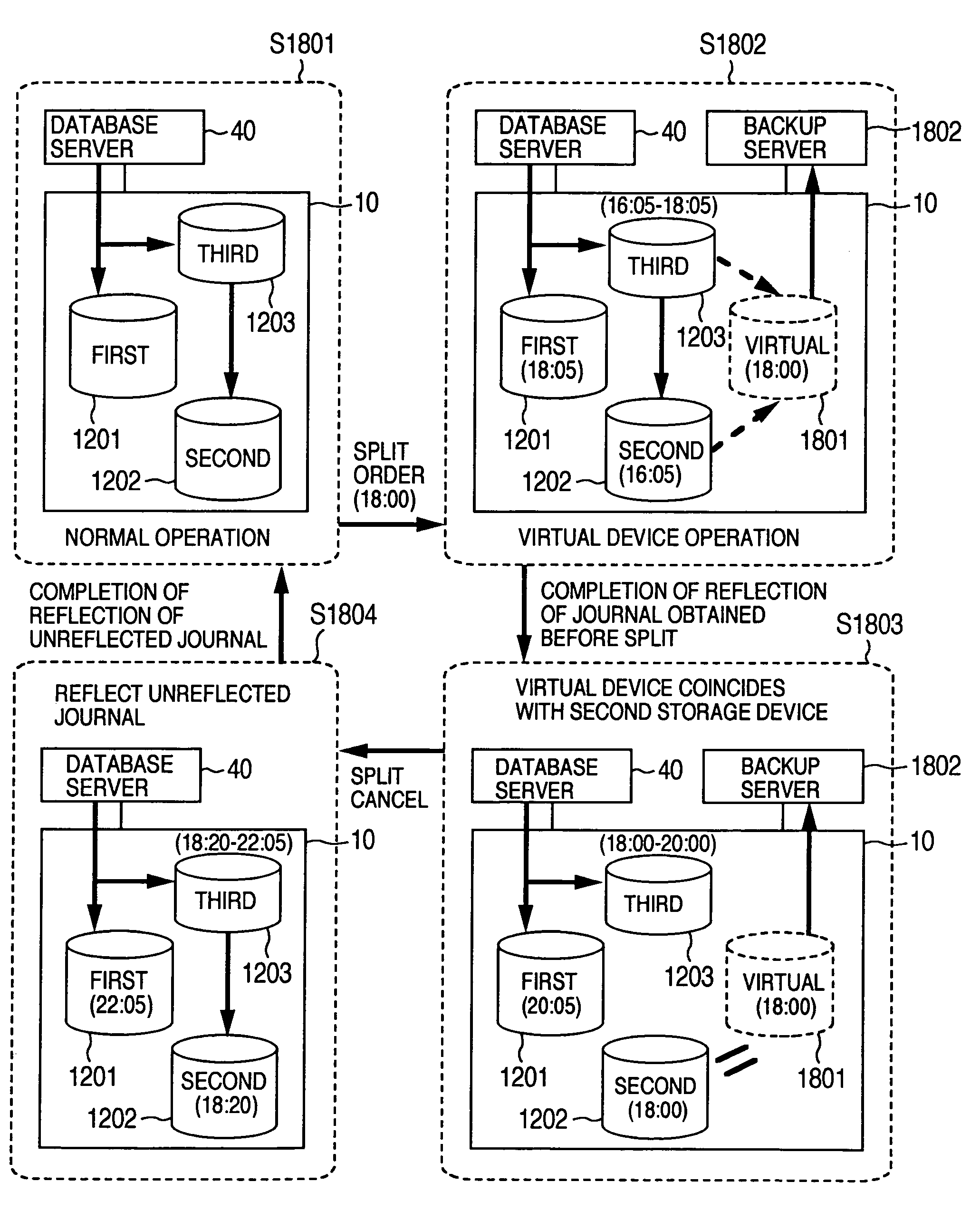

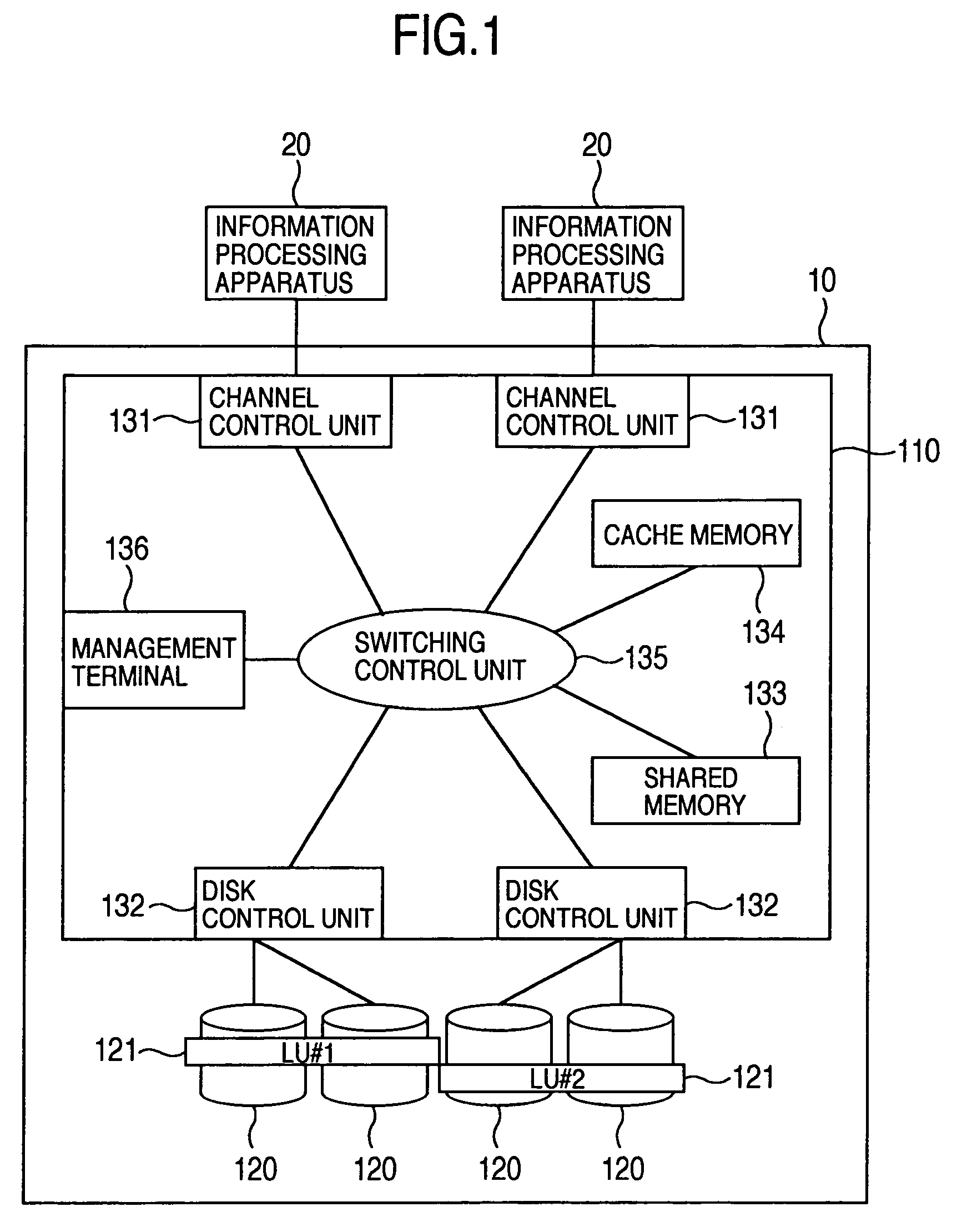

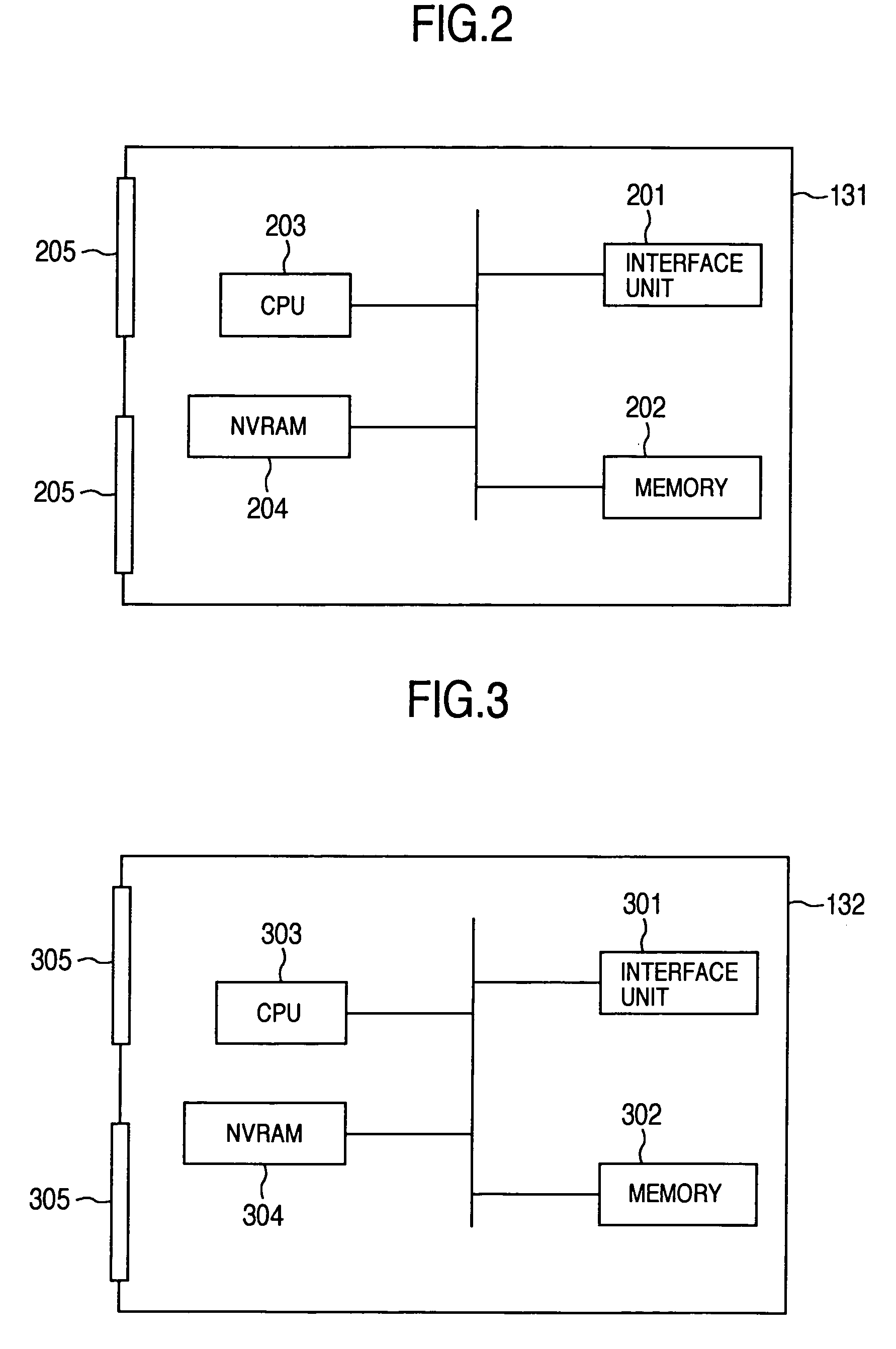

Disk array apparatus and disk array apparatus control method

InactiveUS7017003B2Reduce storage capacityPromote recoveryInput/output to record carriersMemory loss protectionRenewal timeDisk array

A journal write unit writes journal data into a third storage device. The journal data includes an identifier of a logical volume in a first storage device into which data has been written, information of a location in which the data is stored in the logical volume, update time which is current time acquired from a timing mechanism, and the data. A second write unit refers to update time of the journal data stored in the third storage device, selects journal data for which a difference between current time acquired from the timing mechanism and the update time is longer than a detection time stored in the third storage device, and writes the data into a place indicated by the location information, in a logical volume in the second storage device in the order of update time in the selected journal data.

Owner:HITACHI LTD

Dirt container for a surface cleaning apparatus and method of use

InactiveUS7329294B2Reduce storage capacityLower the volumeCombination devicesAuxillary pretreatmentSurface cleaningEngineering

A dirt container for a surface cleaning apparatus is constructed from an air impermeable material and exterior walls of sufficient rigidity to maintain the shape of the dirt container. The dirt container may be supplied in a disassembled condition and assembled by a consumer prior to use.

Owner:POLAR LIGHT

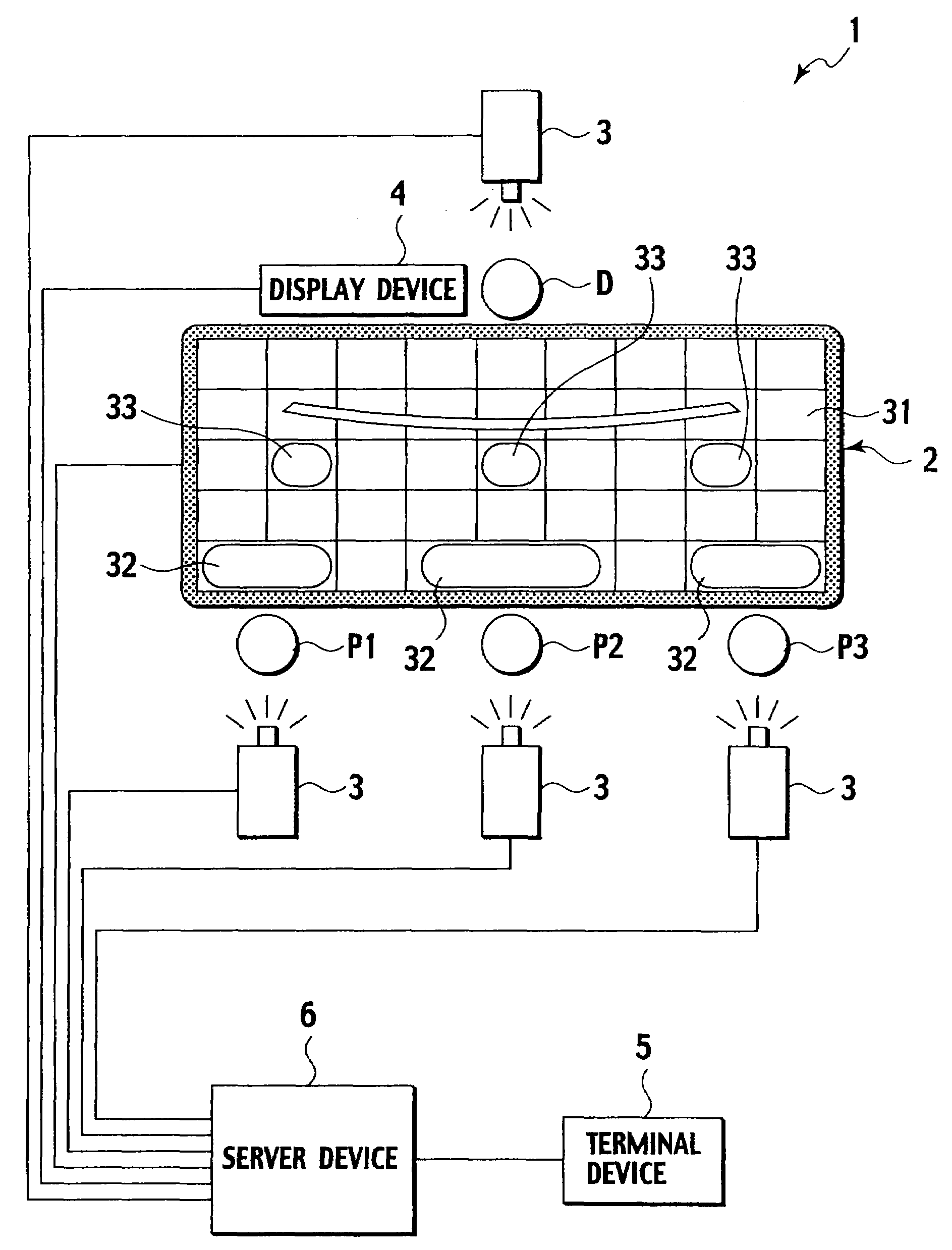

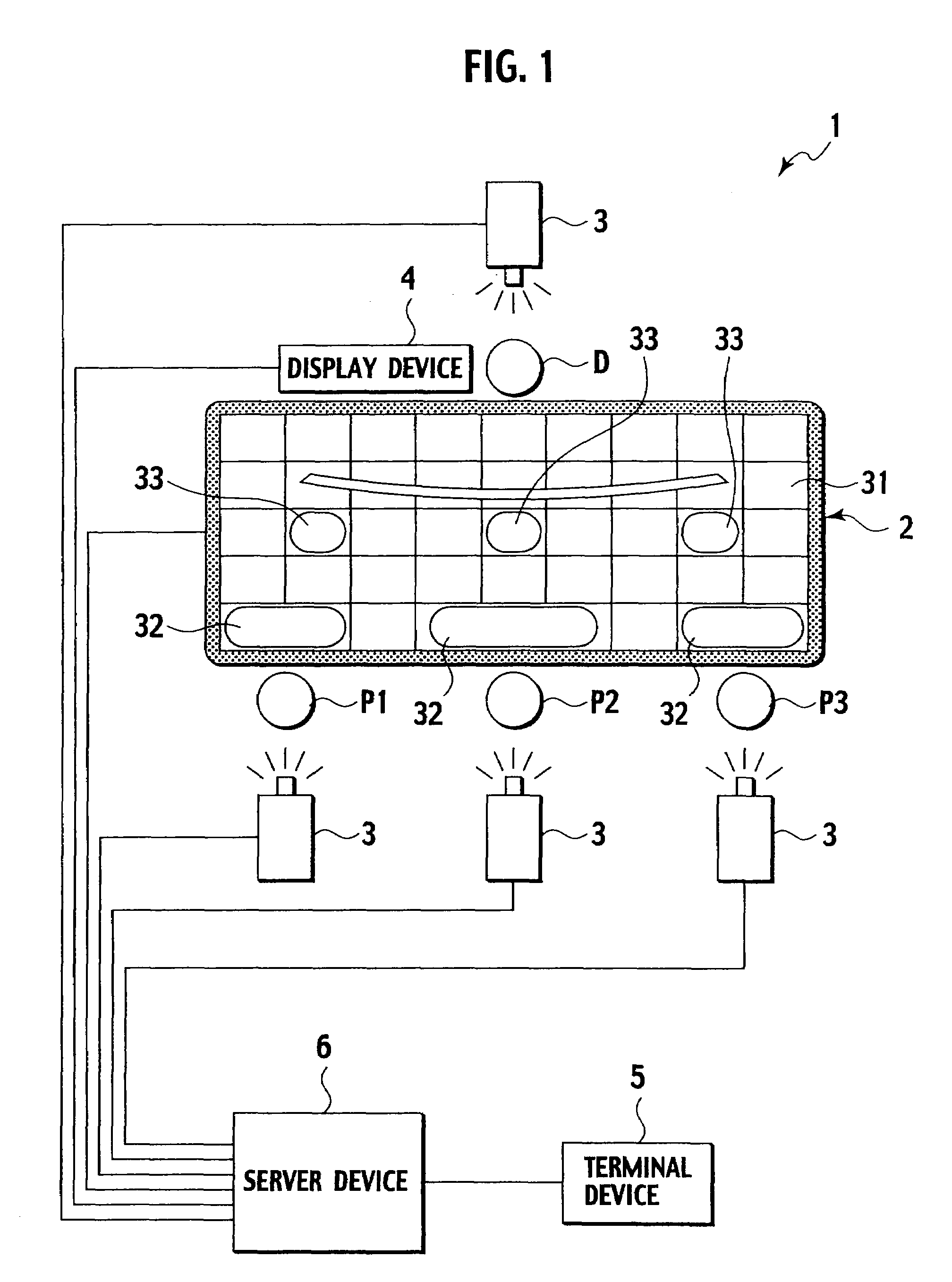

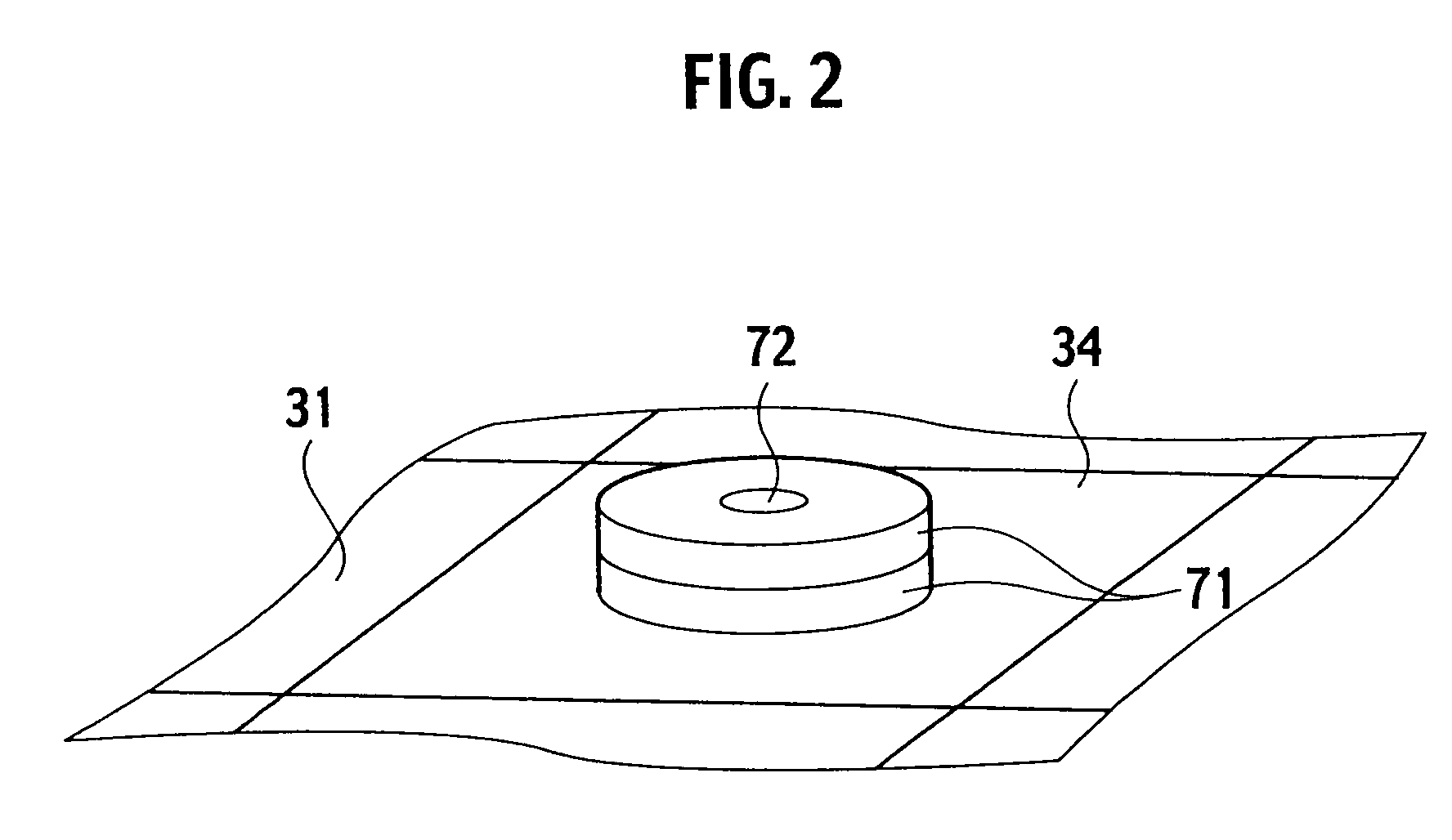

Game judgment system

ActiveUS20090233699A1Reduce storage capacityEliminate needCard gamesRoulette gamesServer applianceWireless

A server device uses cameras to capture the images of cards dealt to players and a dealer. The server device automatically judges the game win / lose result of the players and the dealer and the dividends of the players through image recognition based on the card images from the cameras. The server device reads information from the wireless IC tags provided on game chips to judge the dividends of the players. The server device compares between the two dividends of a player to judge whether or not the dividends are inconsistent. If the dividends are inconsistent, the server device notifies the dealer and a casino hotel manager that the dividends are inconsistent.

Owner:UNIVERSAL ENTERTAINMENT CORP

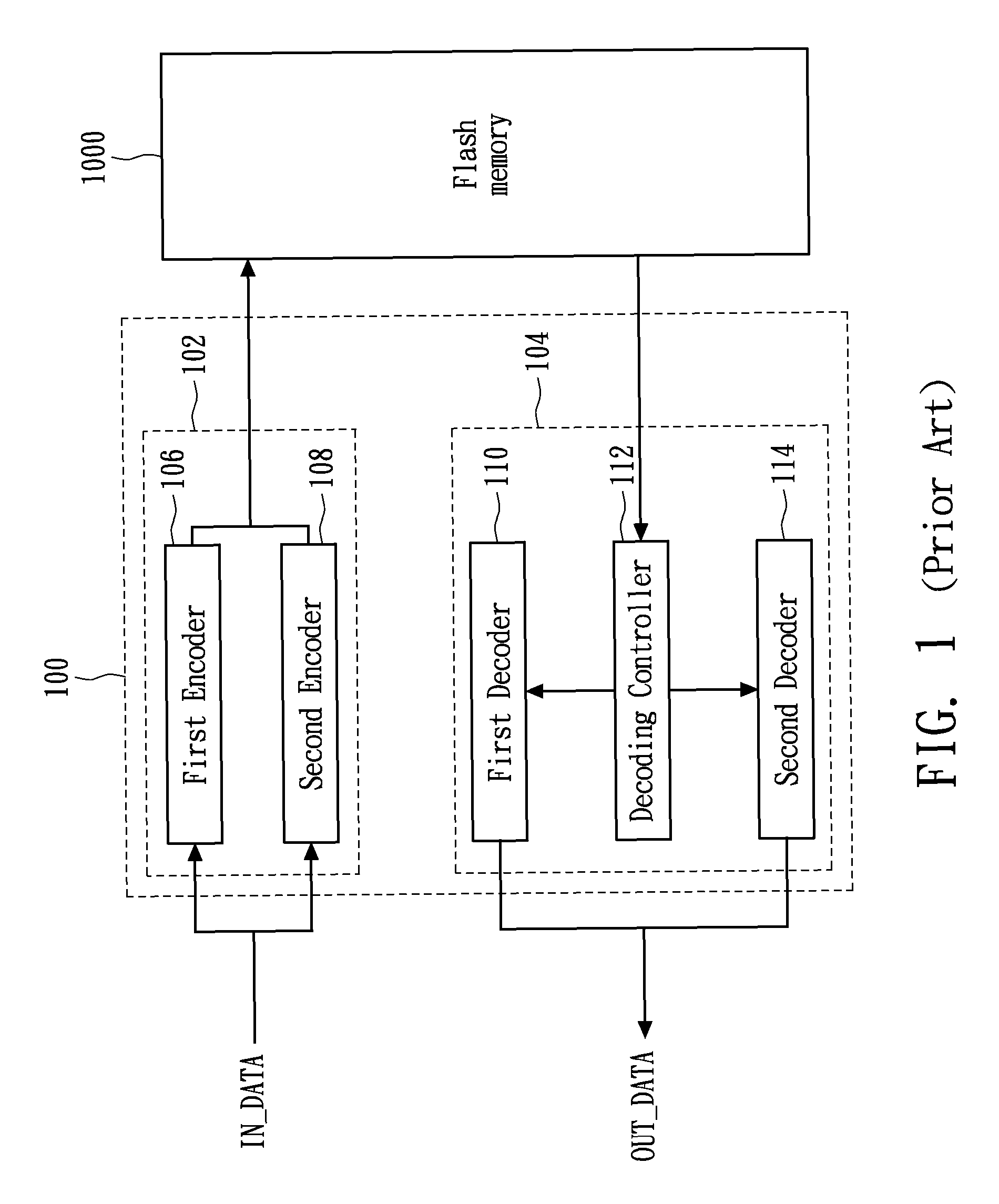

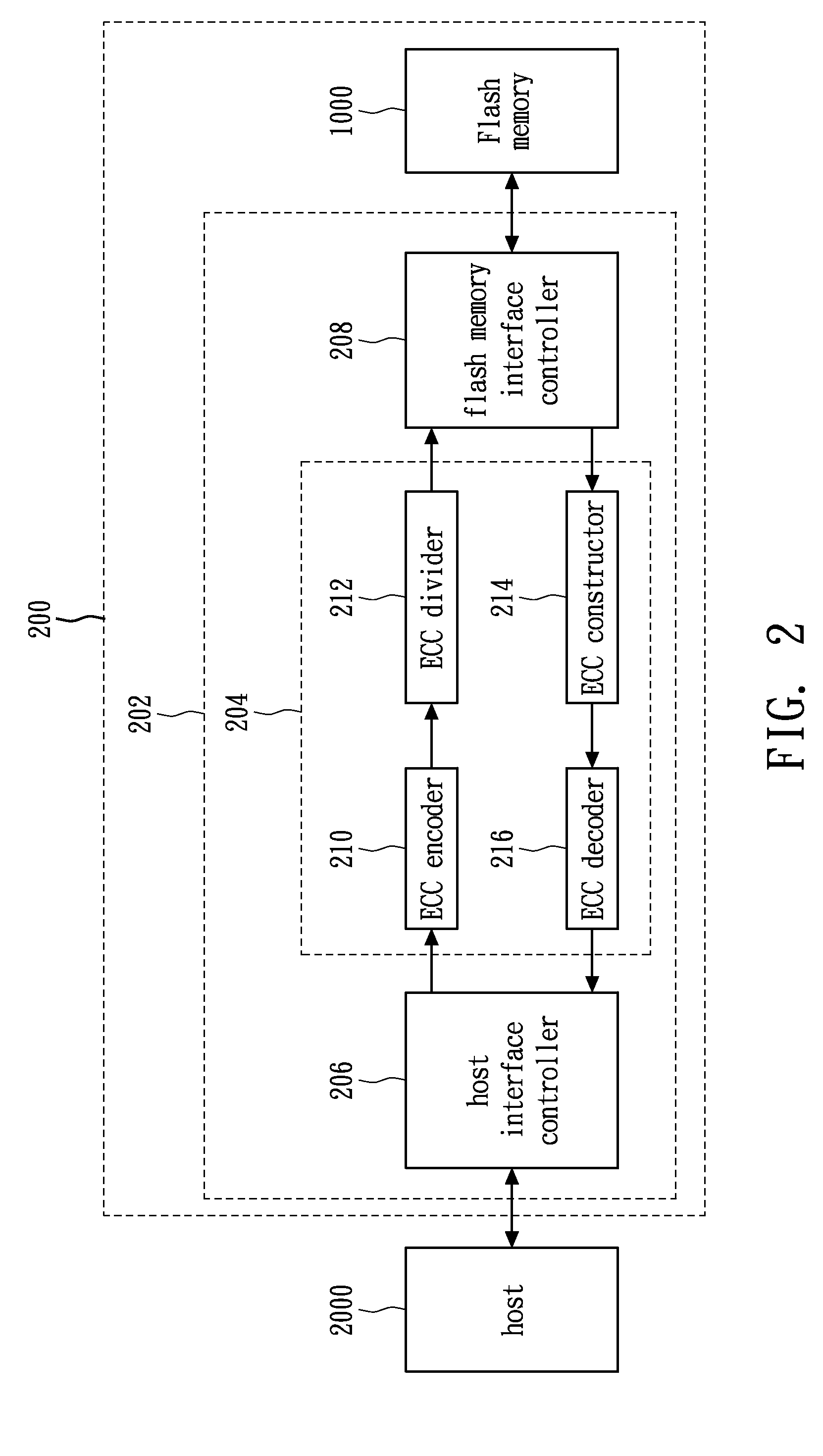

Methods and systems of a flash memory controller and an error correction code (ECC) controller using variable-length segmented ECC data

ActiveUS8473815B2Extended service lifeReduce storage capacityError detection/correctionStatic storageFlash memory controllerVariable length

An ECC controller comprises an ECC encoder, an ECC divider, an ECC constructor and an ECC decoder. The ECC encoder is configured to generate ECC data with different lengths in response to information data to be stored into a flash memory. The ECC divider is configured to divide each ECC datum generated by the ECC encoder into one or more ECC segments according to the length of the ECC datum. The ECC constructor is configured to generate an ECC datum by combining one or more ECC segments for each information datum read from the flash memory. The ECC decoder is configured to correct the errors of the information data read from the flash memory device by using the ECC data generated by the ECC constructor.

Owner:IND TECH RES INST

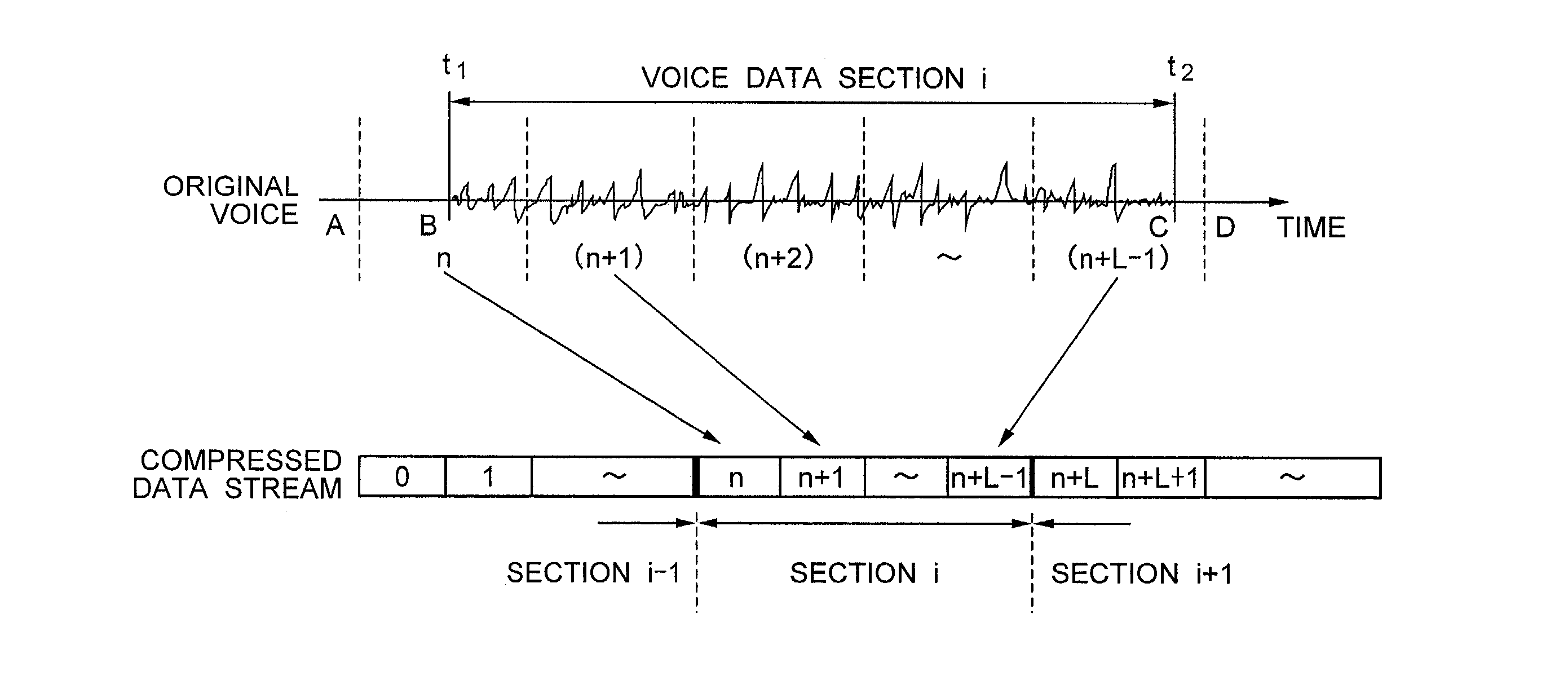

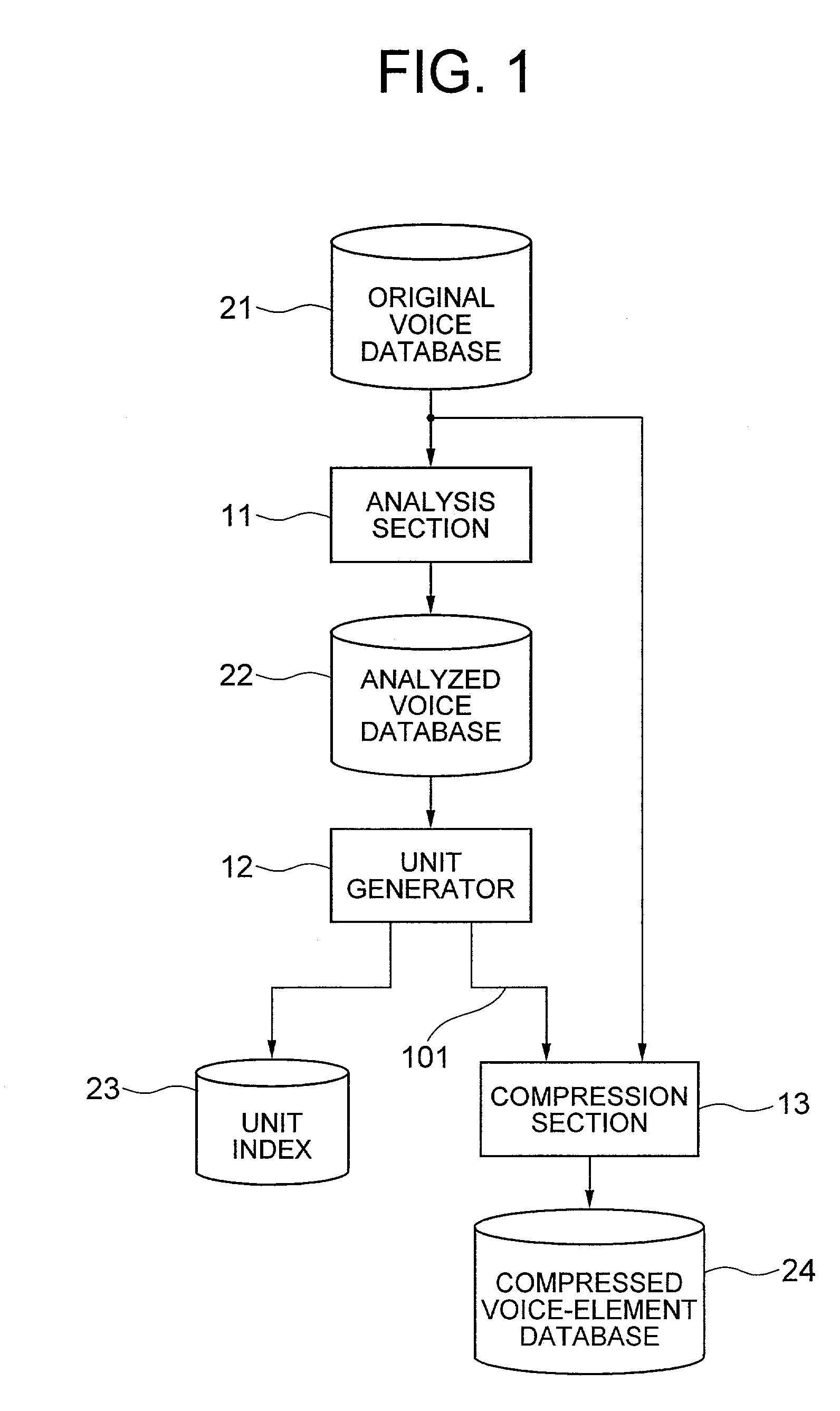

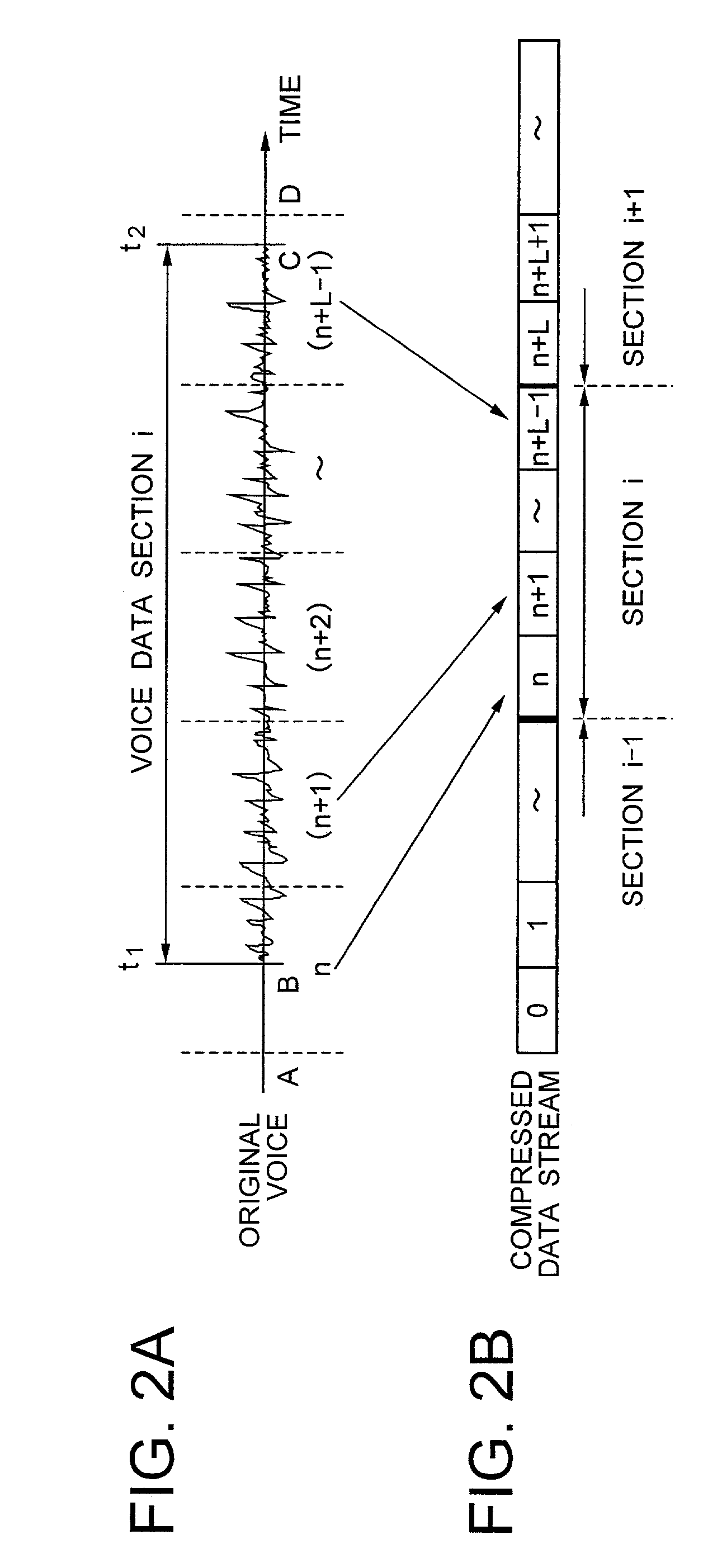

Method for synthesizing a voice waveform which includes compressing voice-element data in a fixed length scheme and expanding compressed voice-element data of voice data sections

A method for synthesizing a voice waveform includes compressing voice-element data in a fixed length scheme that uses data from a preceding or succeeding frame. The compressed voice-element data of each voice section is expanded, and the preceding or succeeding frame of the expanded voice-element data is discarded. The remaining voice-element data is synthesized after discarding portions of the expanded voice-element data.

Owner:NEC CORP

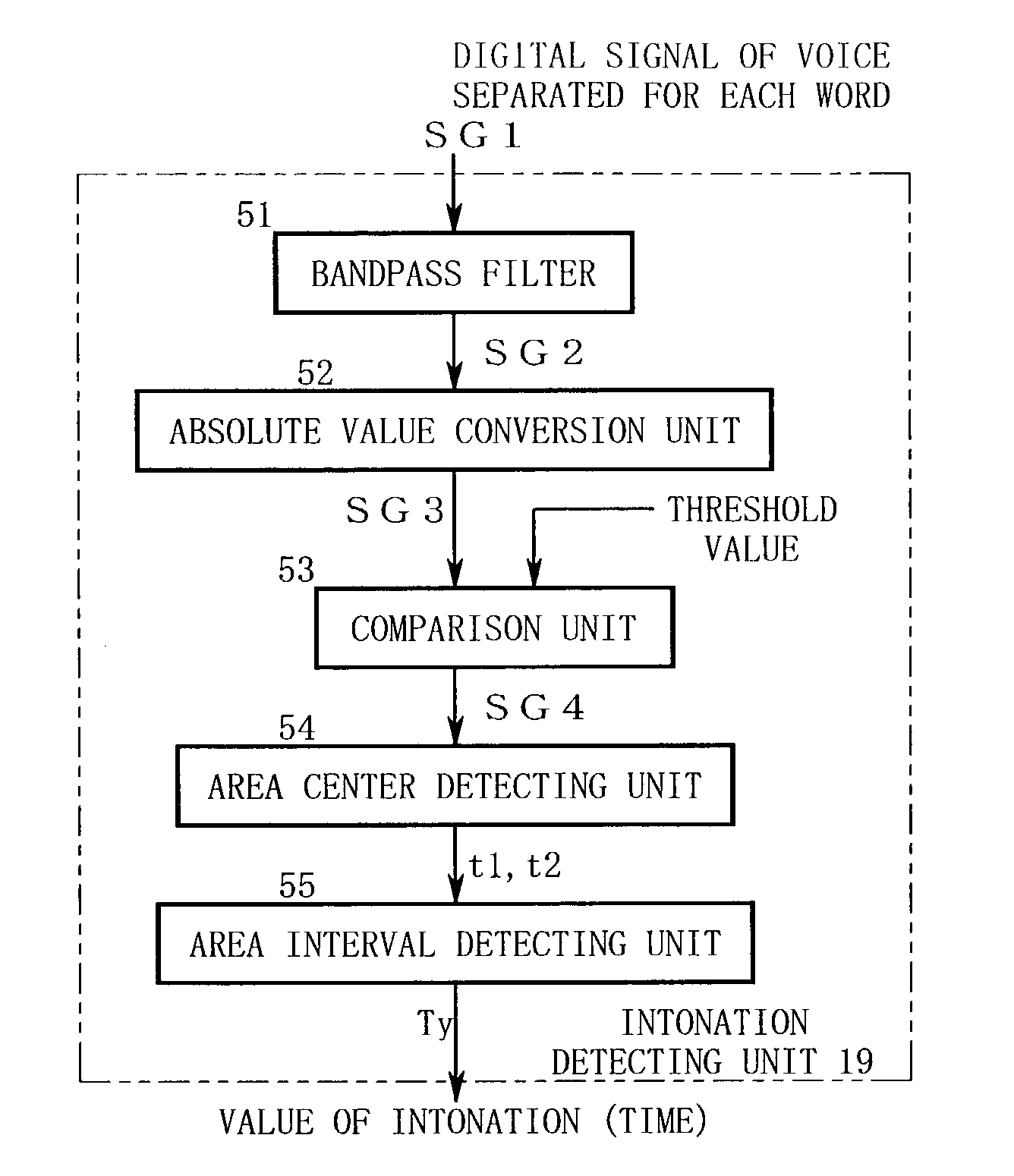

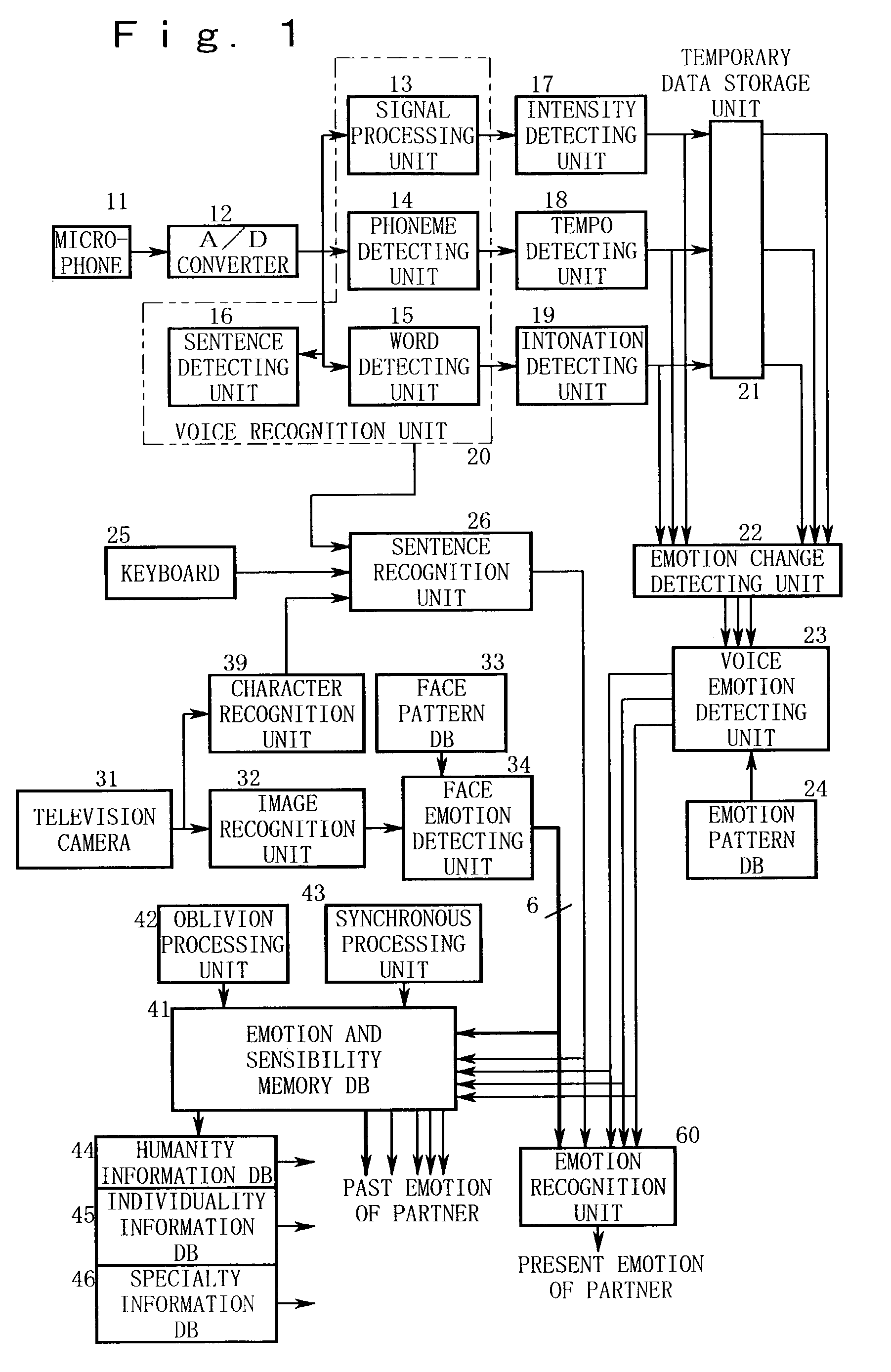

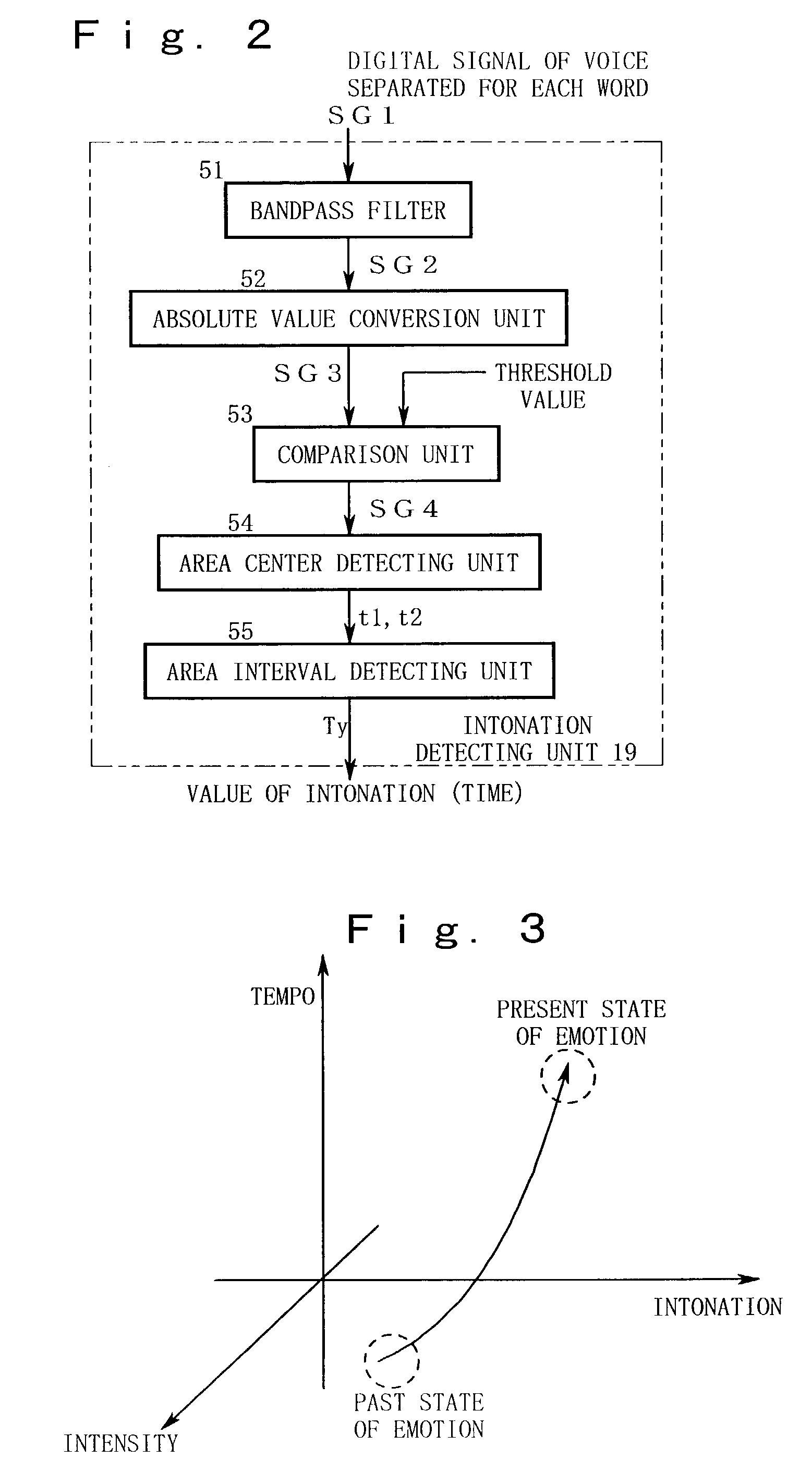

Emotion recognizing method, sensibility creating method, device, and software

ActiveUS7340393B2Reduce system capacityEnhanced informationIndoor gamesDigital computer detailsPattern recognitionSadness

An object of the invention is to provide an emotion detecting method capable of detecting emotion of a human accurately, and provide sensibility generating method capable of outputting sensibility akin to that of a human. An intensity, a tempo, and intonation in each word of a voice are detected based on an inputted voice signal, amounts of change are obtained for the detected contents, respectively, and signals expressing each states of emotion of anger, sadness, and pleasure are generated based on the amounts of change. A partner's emotion or situation information is inputted, and thus instinctive motivation information is generated. Moreover, emotion information including basic emotion parameters of pleasure, anger, and sadness is generated, which is controlled based on the individuality information.

Owner:AGI INC

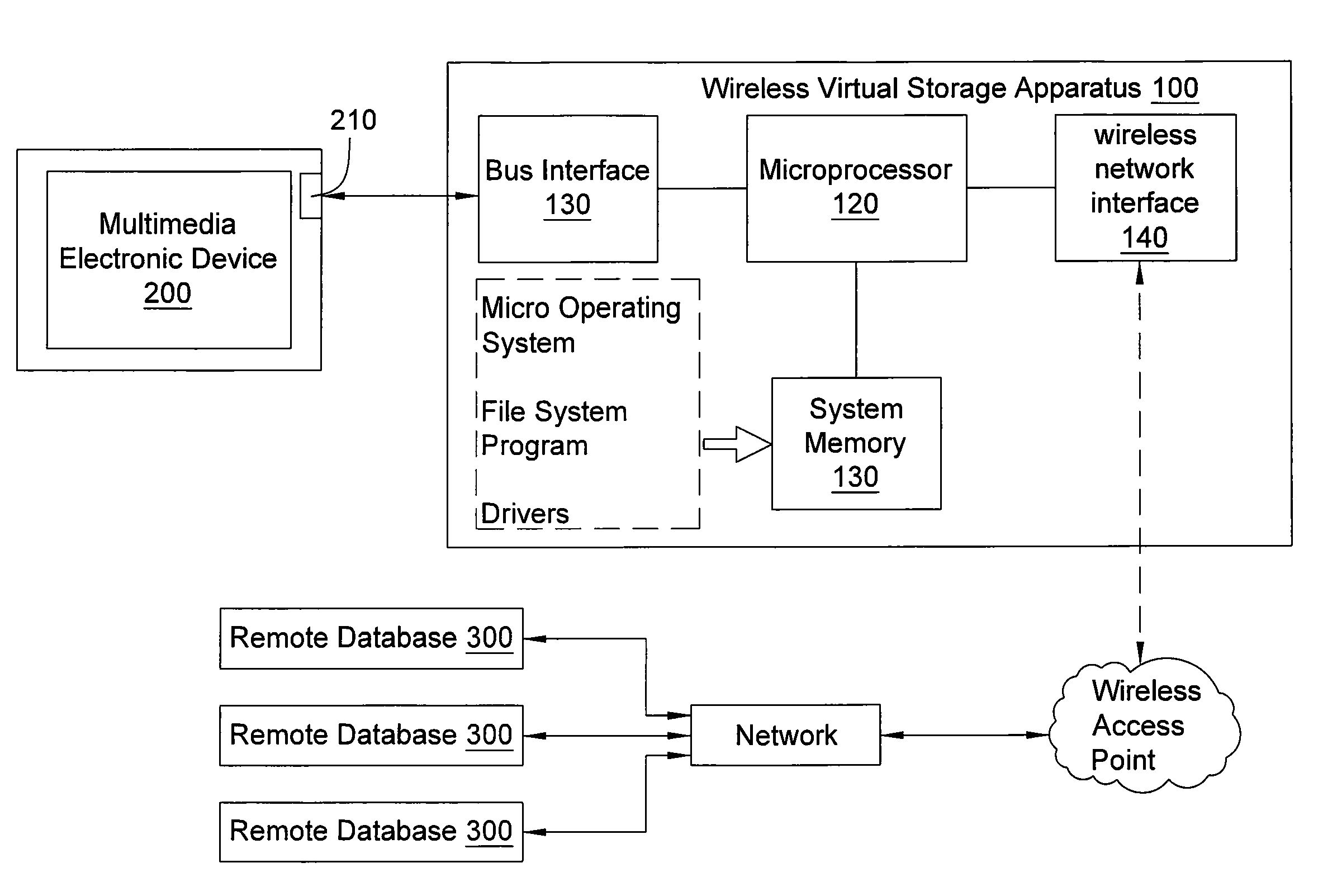

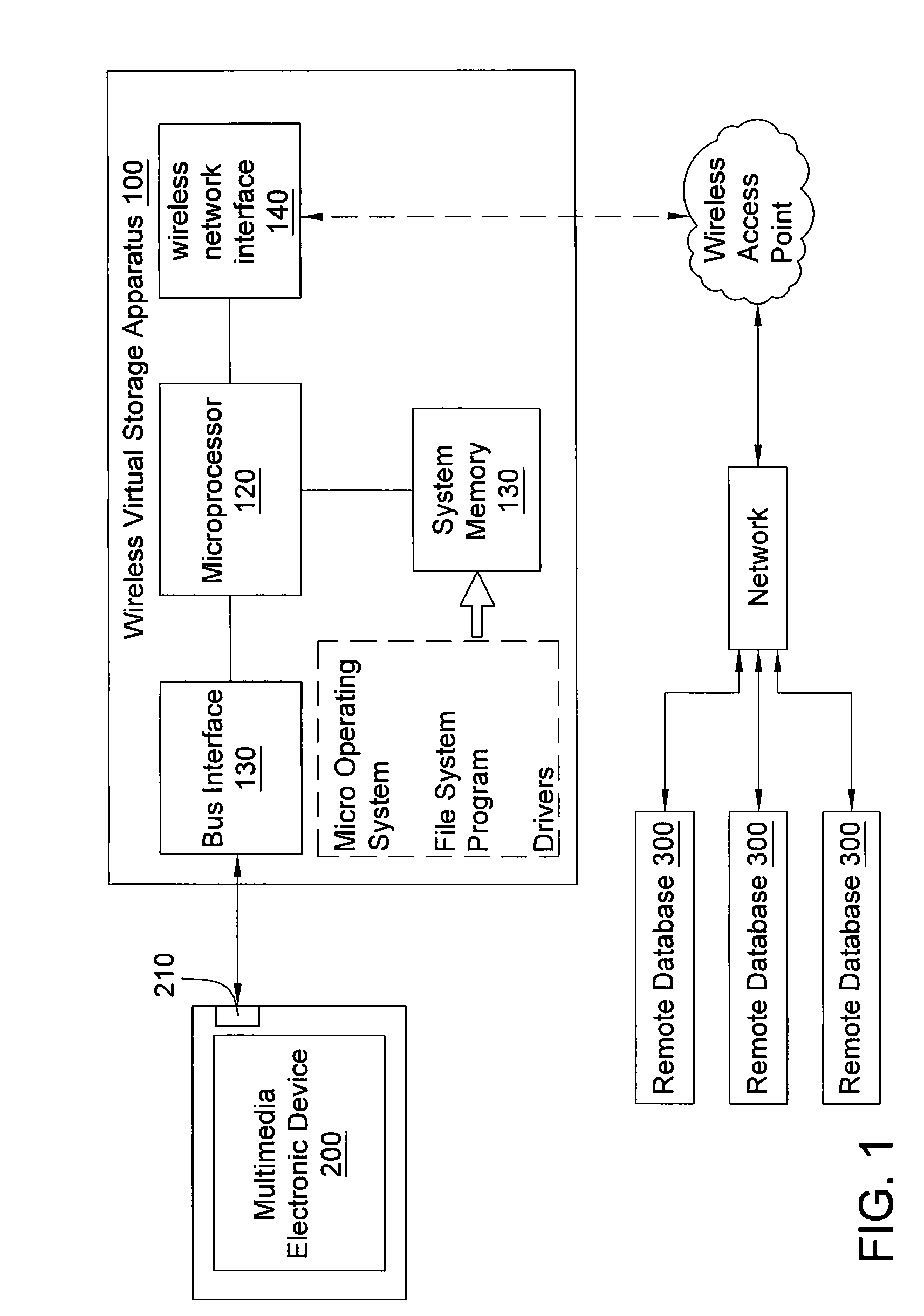

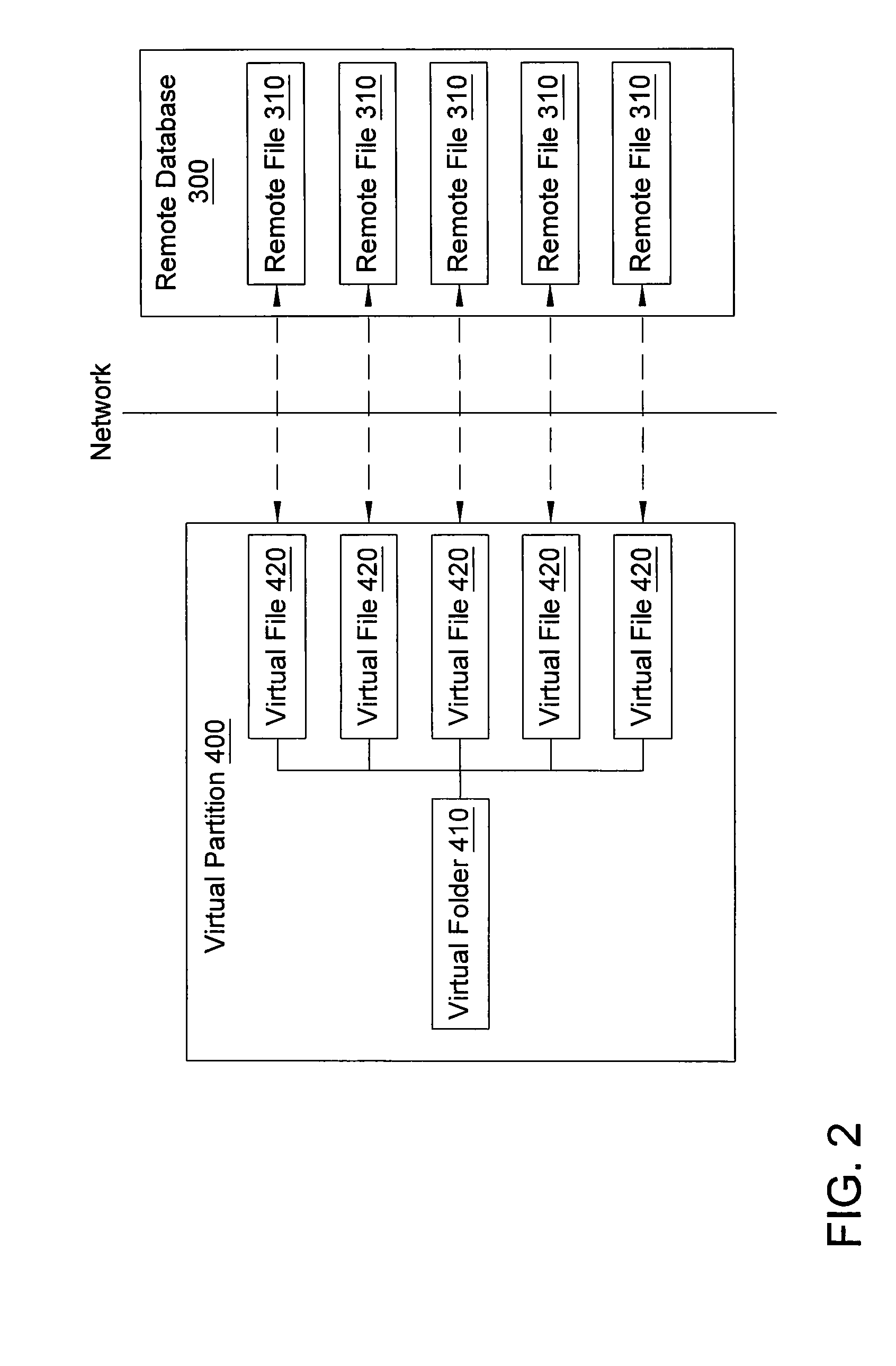

Wireless virtual storage apparatus and remote file accessing method

InactiveUS20090300020A1Reduce storage capacityReduce capacityDigital data information retrievalDigital data processing detailsFile systemRemovable media

A wireless virtual storage apparatus and a remote file accessing method are utilized for a multimedia electronic device accessing remote files in a remote database. The apparatus includes a wireless network interface, microprocessor, and bus interface. The microprocessor runs a file system program, so as to create a virtual partition. Then the processor connects to a removable storage media reader of the multimedia electronic device via the bus interface, and the virtual partition is mounted by the multimedia electronic device. The microprocessor logs in the remote database via the wireless network interface, and creates virtual files in the virtual partition corresponding to the remote files. When the multimedia electronic device accessing the virtual files, the microprocessor loads the remote files from the remote database and changes the accessing path of the multimedia electronic device to the loaded remote files.

Owner:Z-COM INC

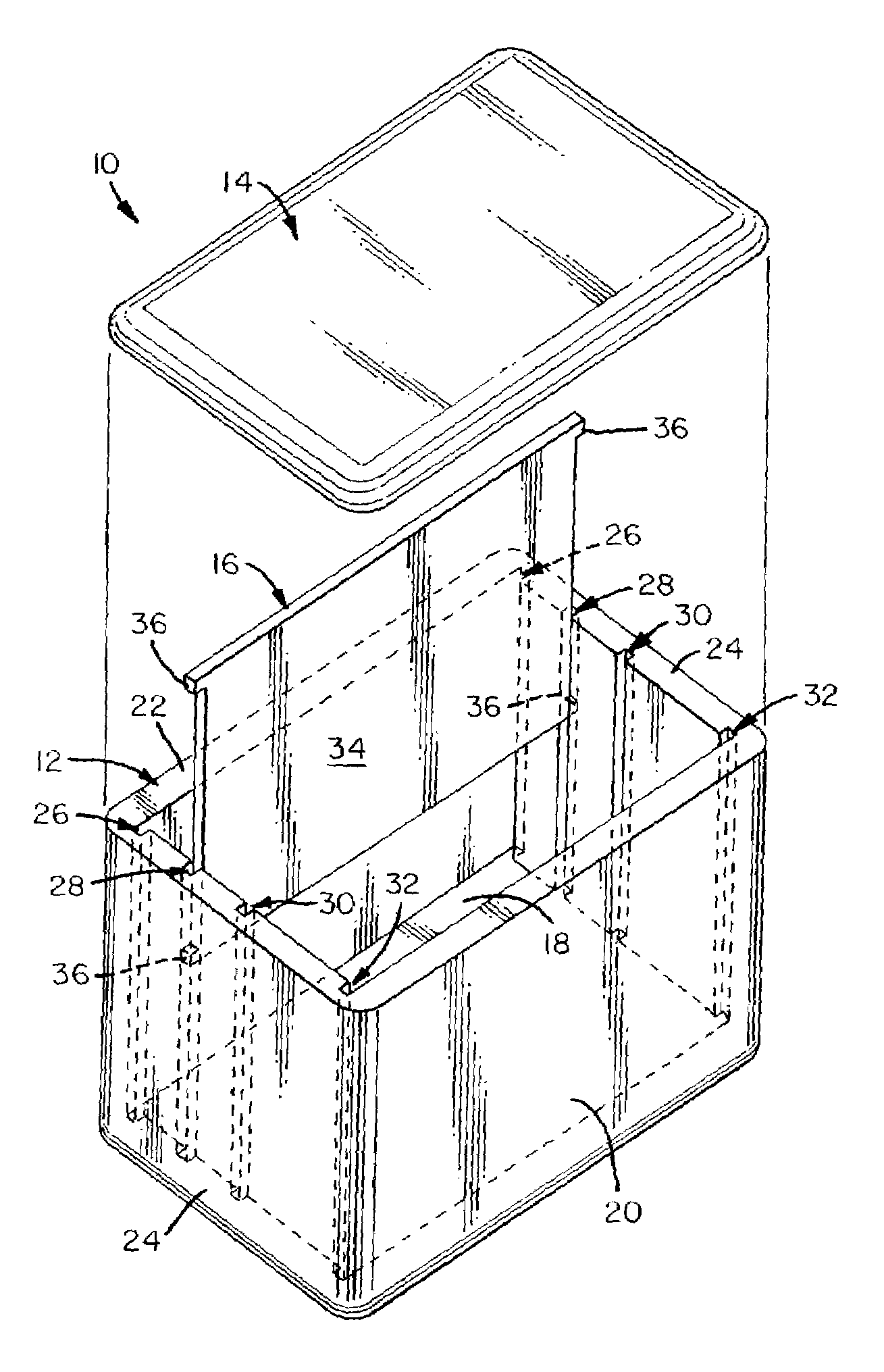

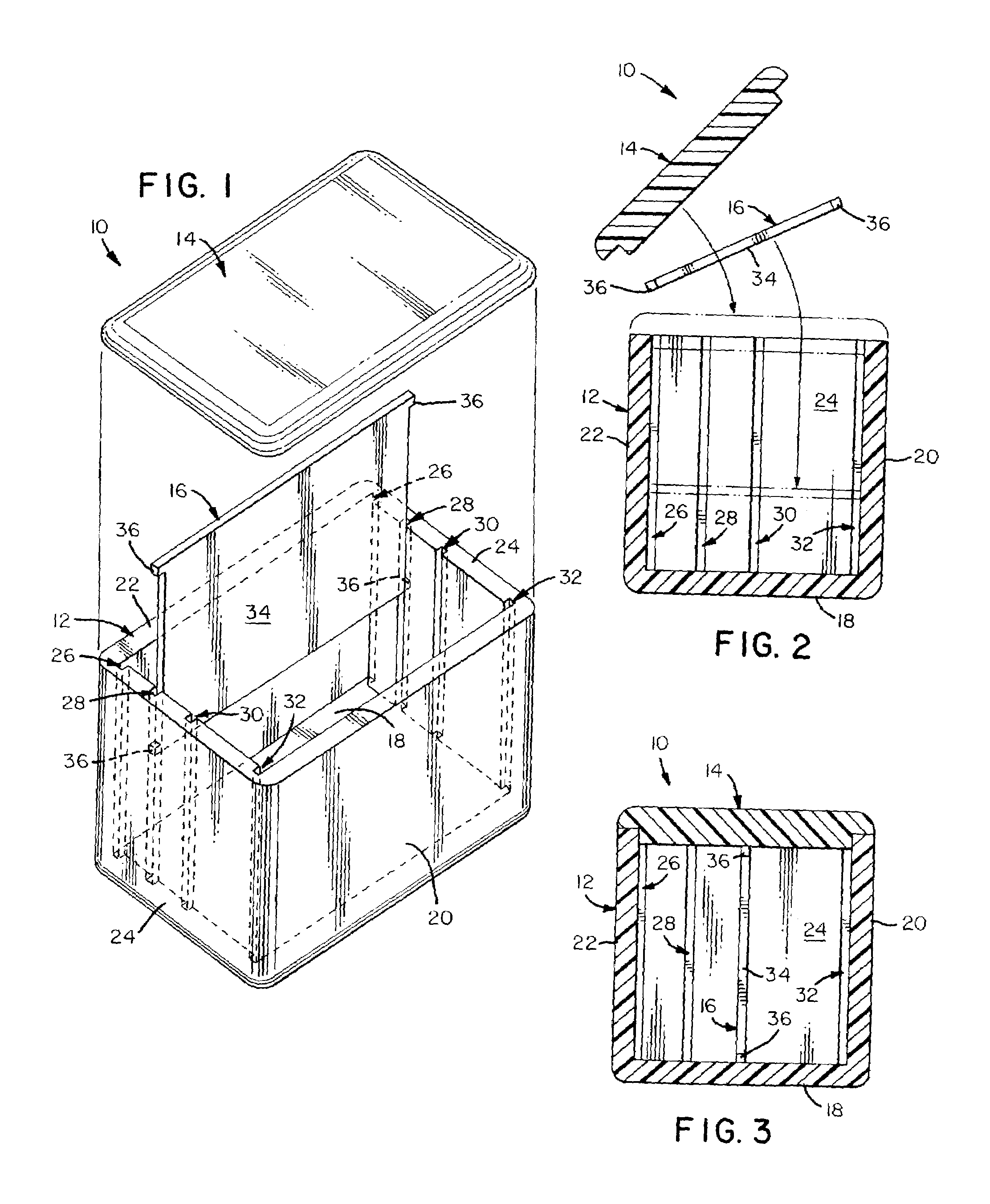

Partitioned ice chest

InactiveUS6966450B2Improve insulation qualityReduce storage capacityDomestic cooling apparatusLighting and heating apparatusMechanical engineeringEngineering

Owner:ASKEW STACY W

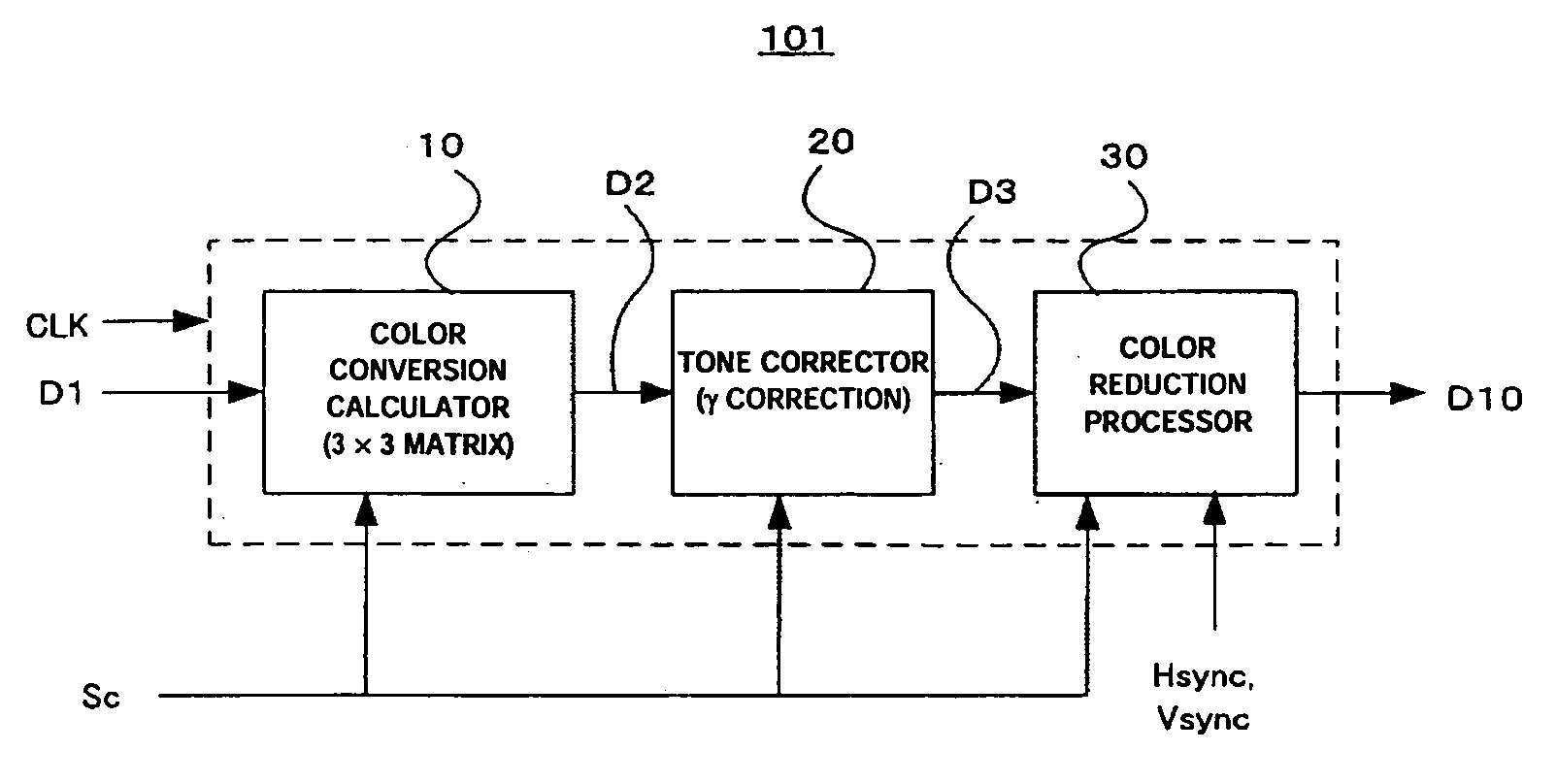

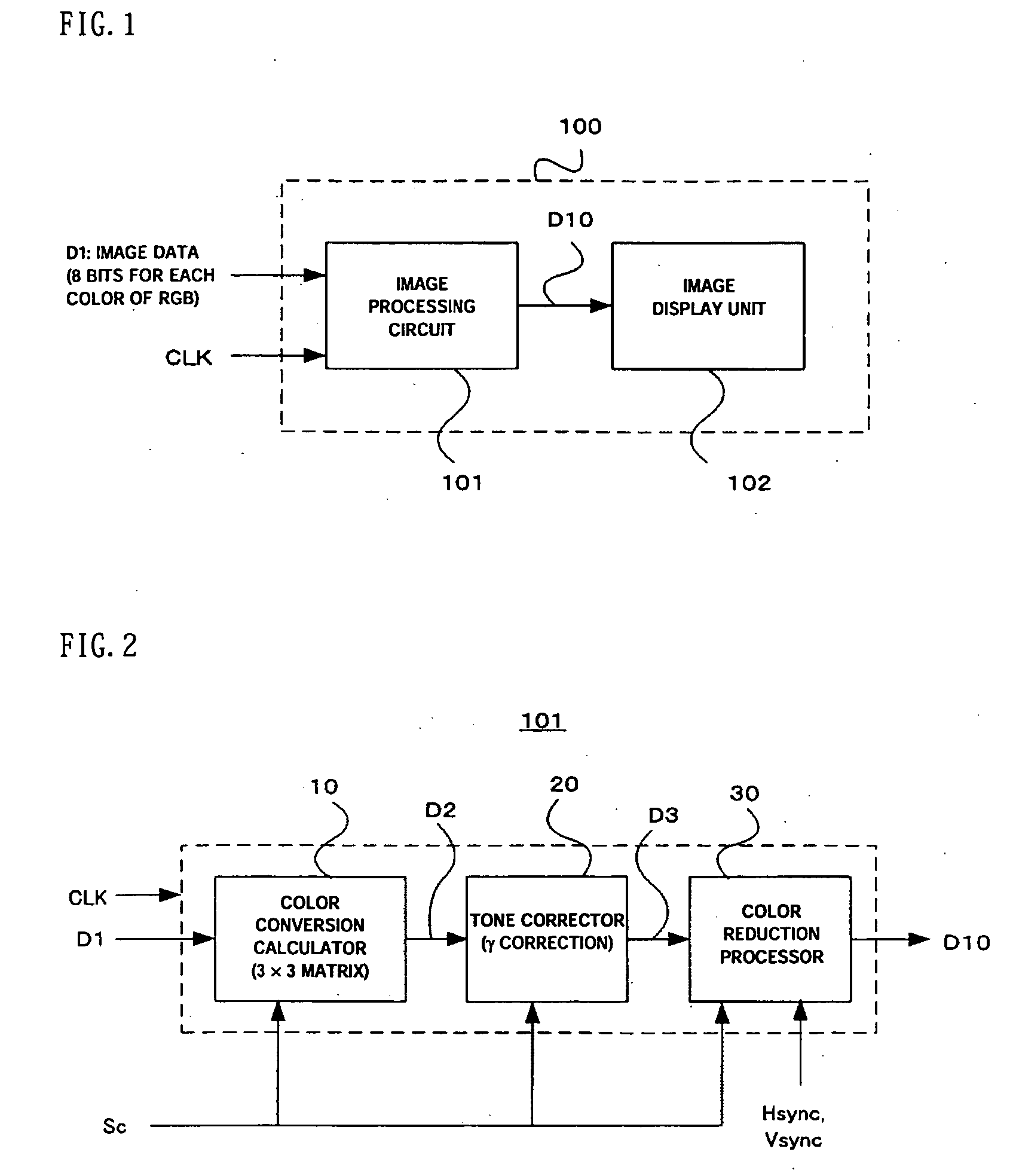

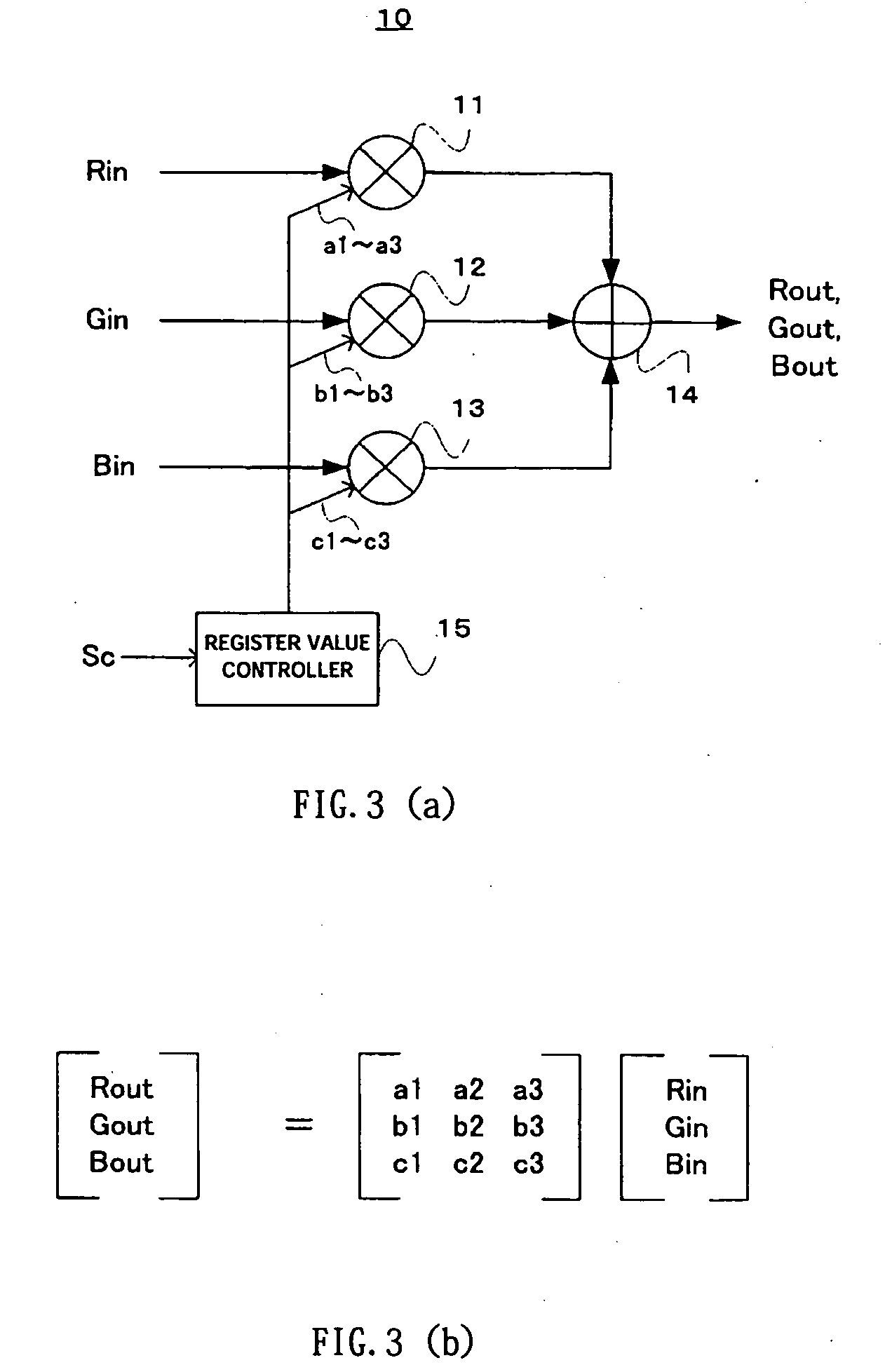

Image processing circuit, image display apparatus, and image processing method

ActiveUS20050111046A1Reduce storage capacityIncrease clock frequencyImage enhancementTelevision system detailsColor correctionImaging data

Aspects of the invention can provide an image processing circuit for gray scale correction, an image display apparatus, and an image processing method that allow reduction in the storage capacity needed for storing correction characteristics data without increasing clock rate in relation to interpolation processing of correction characteristics. A exemplary image processing circuit according to the invention can be applied, for example, to color correction or gamma correction of color image data. Gray scale correction characteristics data for a number of gray scale levels that is less than the number of gray scale levels of input image data can be stored in first and second lookup table storing units. Considering a gray scale value of a pixel that is being considered for gray scale correction processing as an input gray scale value, the first and second lookup-table storing units are referred to, obtaining an output gray scale value corresponding to the input gray scale value and an output gray scale value corresponding to an adjacent input gray scale value. An adjacent gray scale value refers to a gray scale value that is higher by one or lower by one than another input gray scale value. Then, output gray scale values between these two adjacent output gray scale values can be calculated by linear interpolation, obtaining output values for all input gray scale values. Subsequently, gray scale correction can be performed for each pixel of input image data, outputting corrected image data.

Owner:BOE TECH GRP CO LTD

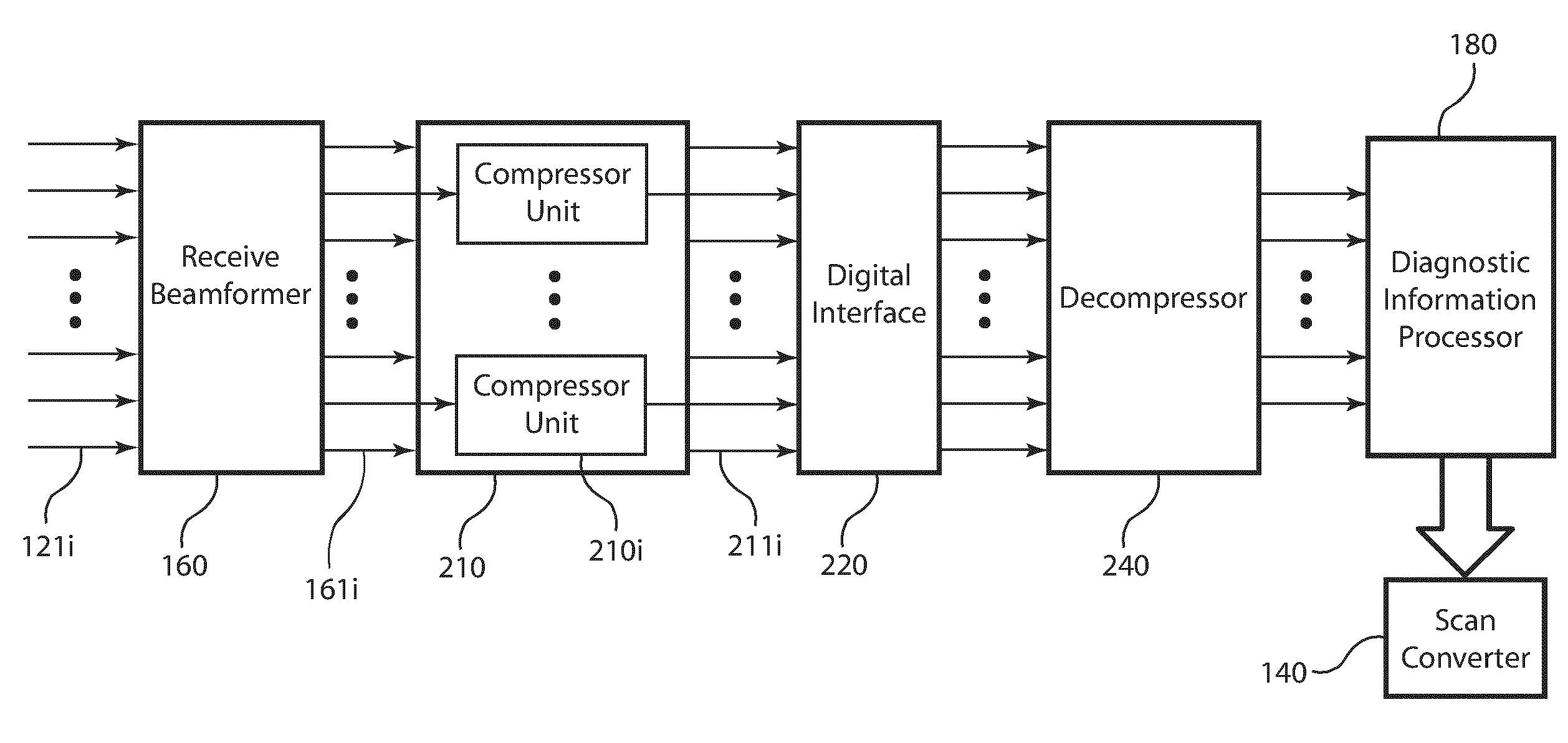

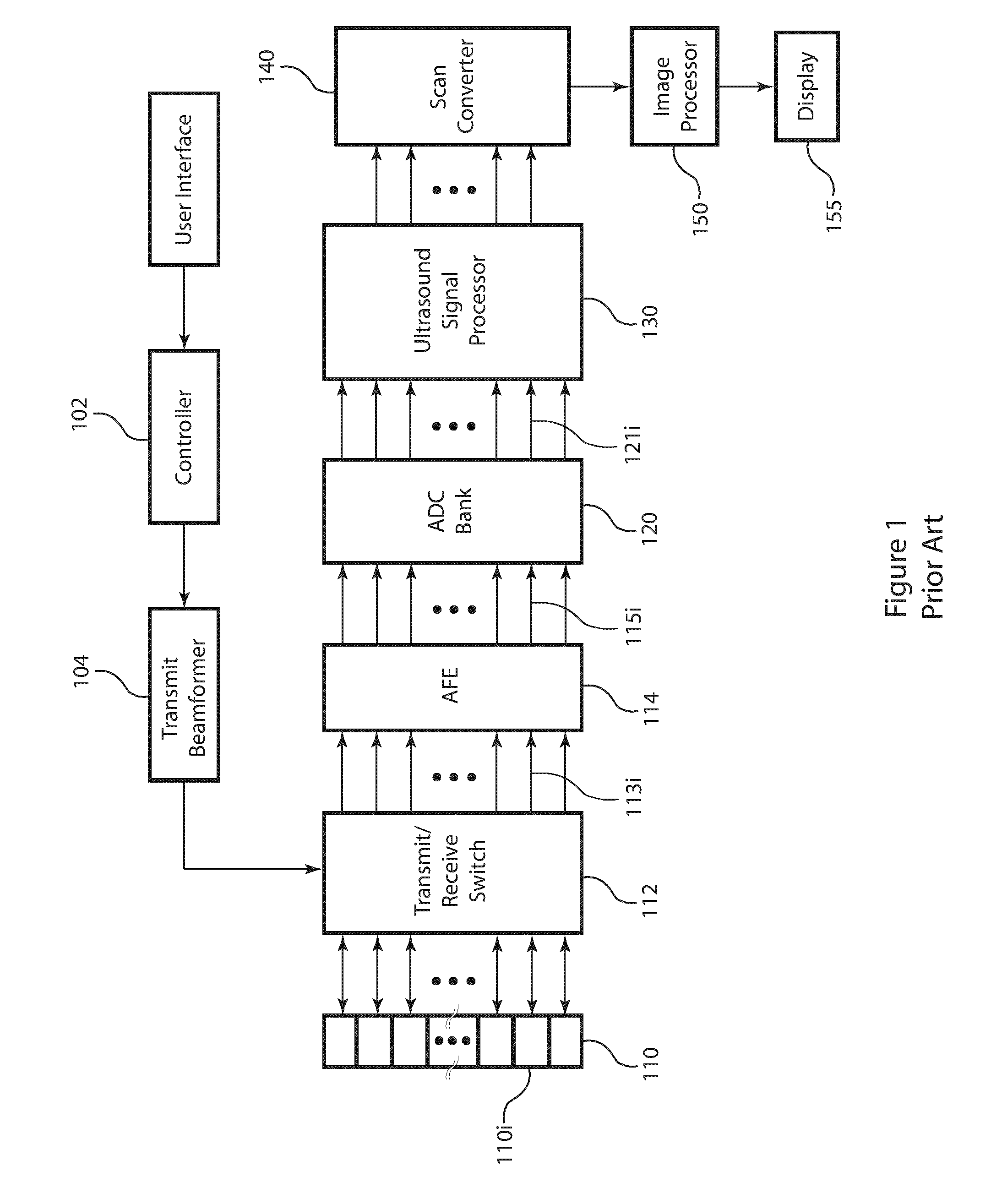

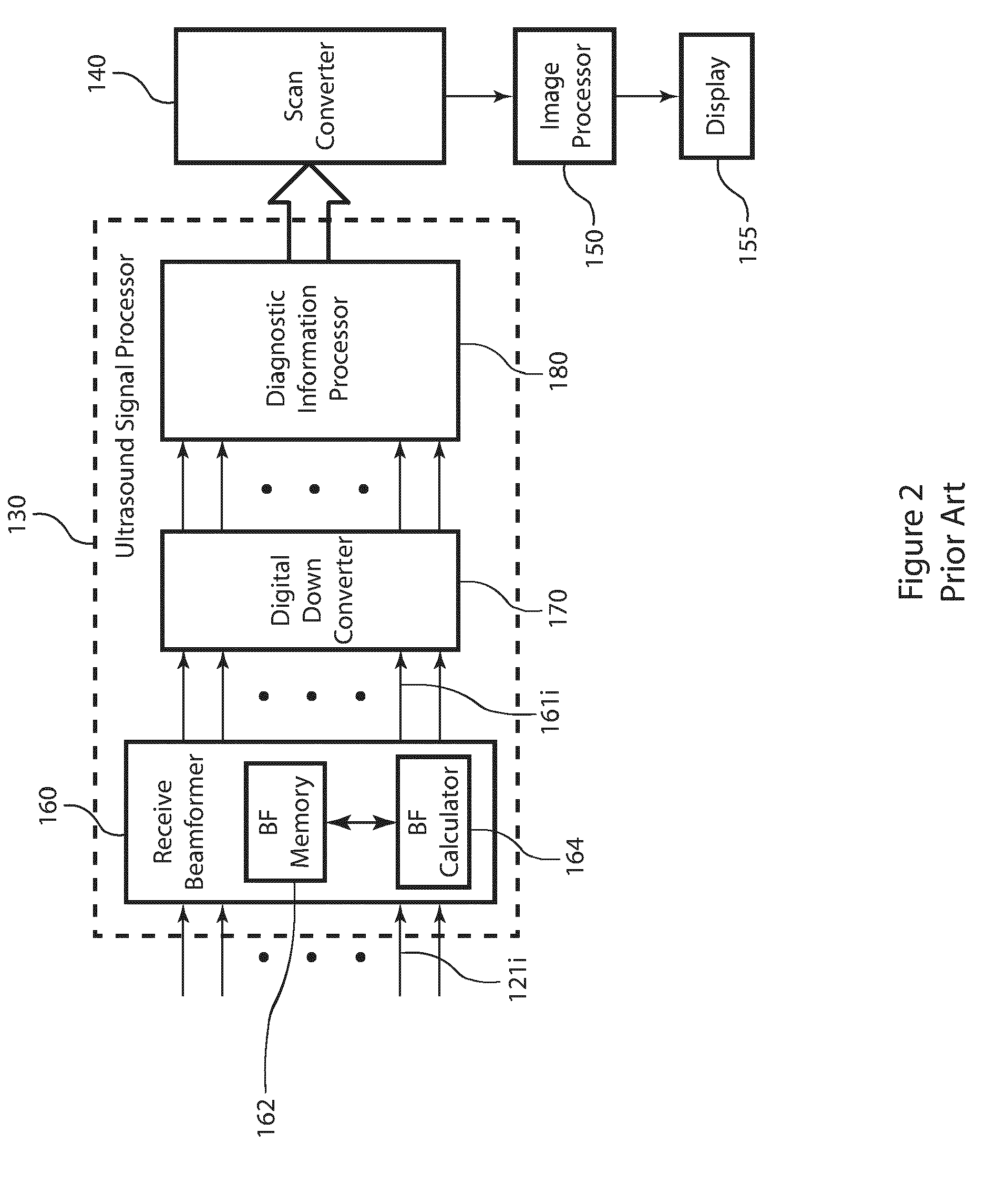

Post-beamforming compression in ultrasound systems

InactiveUS20100331689A1Efficient storageReduce storage capacityWave based measurement systemsBlood flow measurement devicesUltrasound imagingScan conversion

In an ultrasound imaging system that applies a beamformer to received ultrasound signal samples to form one or more beams represented by arrays of beamformed samples, a method and an apparatus compress each array of beamformed samples independently of the other arrays to form compressed beams. A plurality of analog to digital converters sample multiple analog ultrasound signals produced by a transducer array to provide multiple streams of ultrasound signal samples to the beamformer. The compressed beams are transferred via a digital interface to a signal processor. At the signal processor, the compressed beams are decompressed to form decompressed beams. The signal processor further processes the decompressed beams for diagnostic imaging, such as for B-mode and Doppler imaging, and scan conversion to prepare the resulting ultrasound image for display. This abstract does not limit the scope of the invention as described in the claims.

Owner:ALTERA CORP

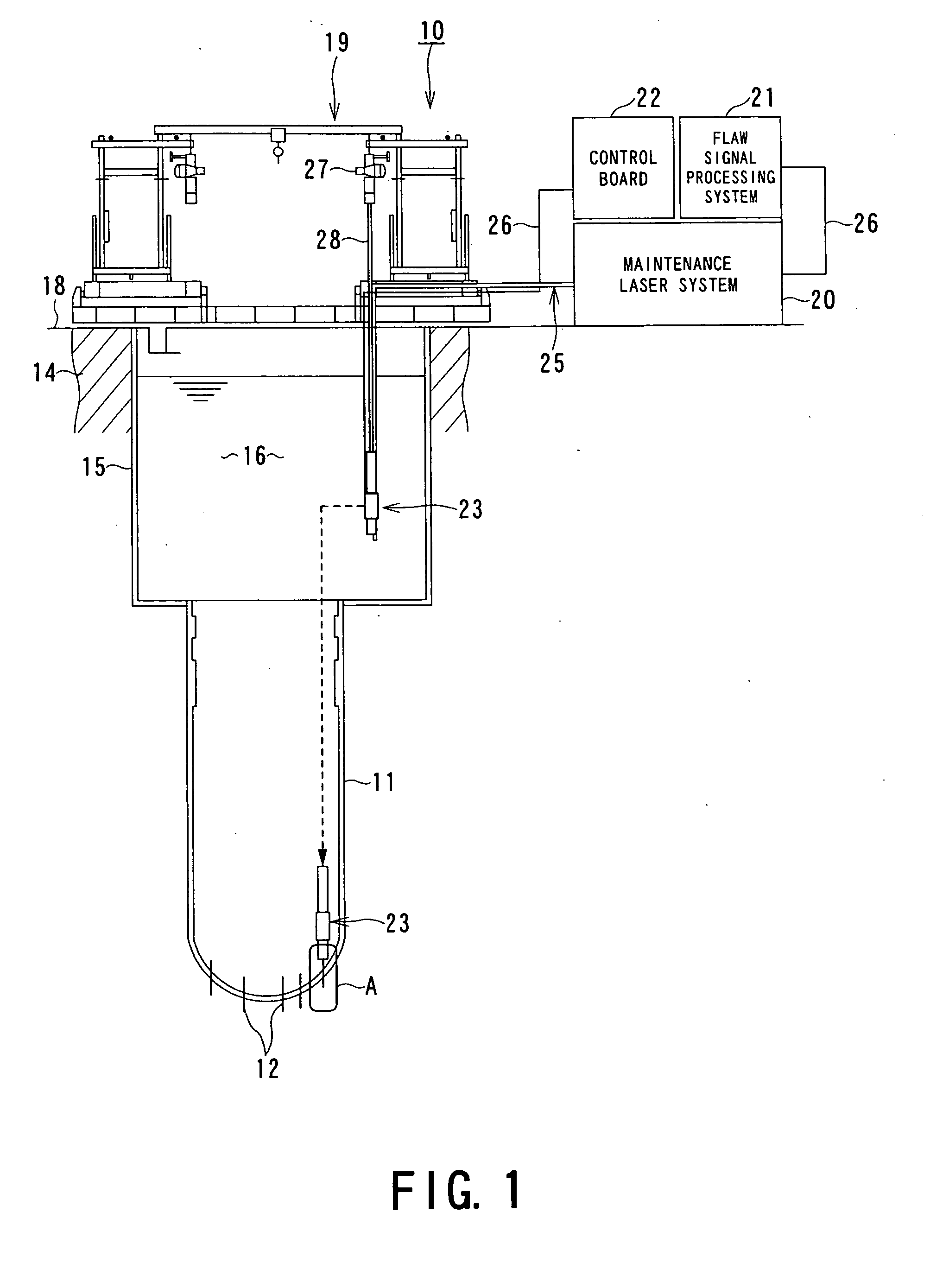

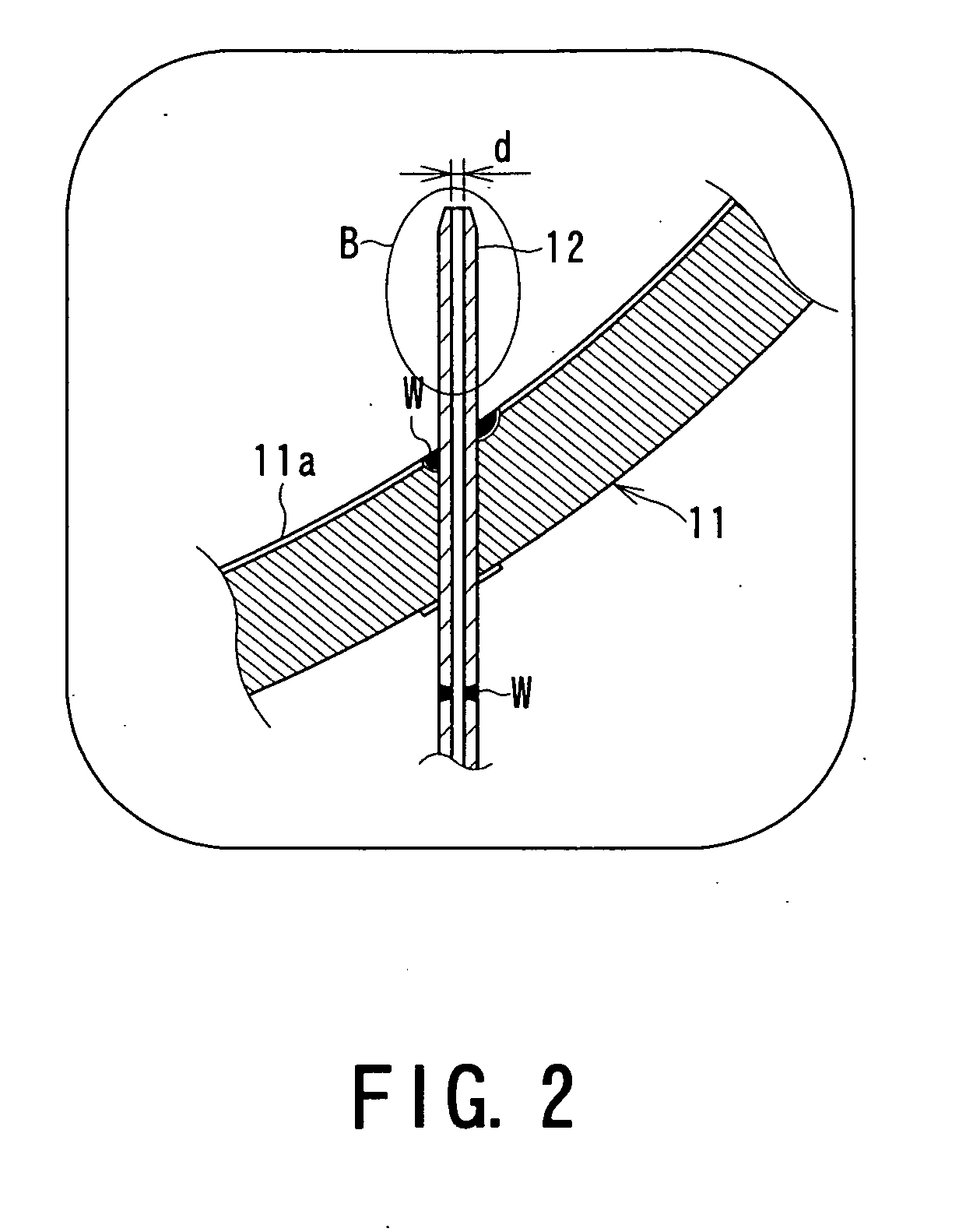

Laser-based maintenance apparatus

ActiveUS20070157730A1Shorten the timeEfficient and effectiveAnalysing solids using sonic/ultrasonic/infrasonic wavesNuclear energy generationOptoelectronicsLaser light

A laser maintenance apparatus is provided with a laser system including a laser light source and an optical system and emitting a laser light, a light transmitting device for generating the laser light emitted from the laser system, and a laser irradiation device for irradiating the laser light generated by the light transmitting device to an object portion. The laser system includes an element for changing an irradiation condition of the laser light.

Owner:KK TOSHIBA

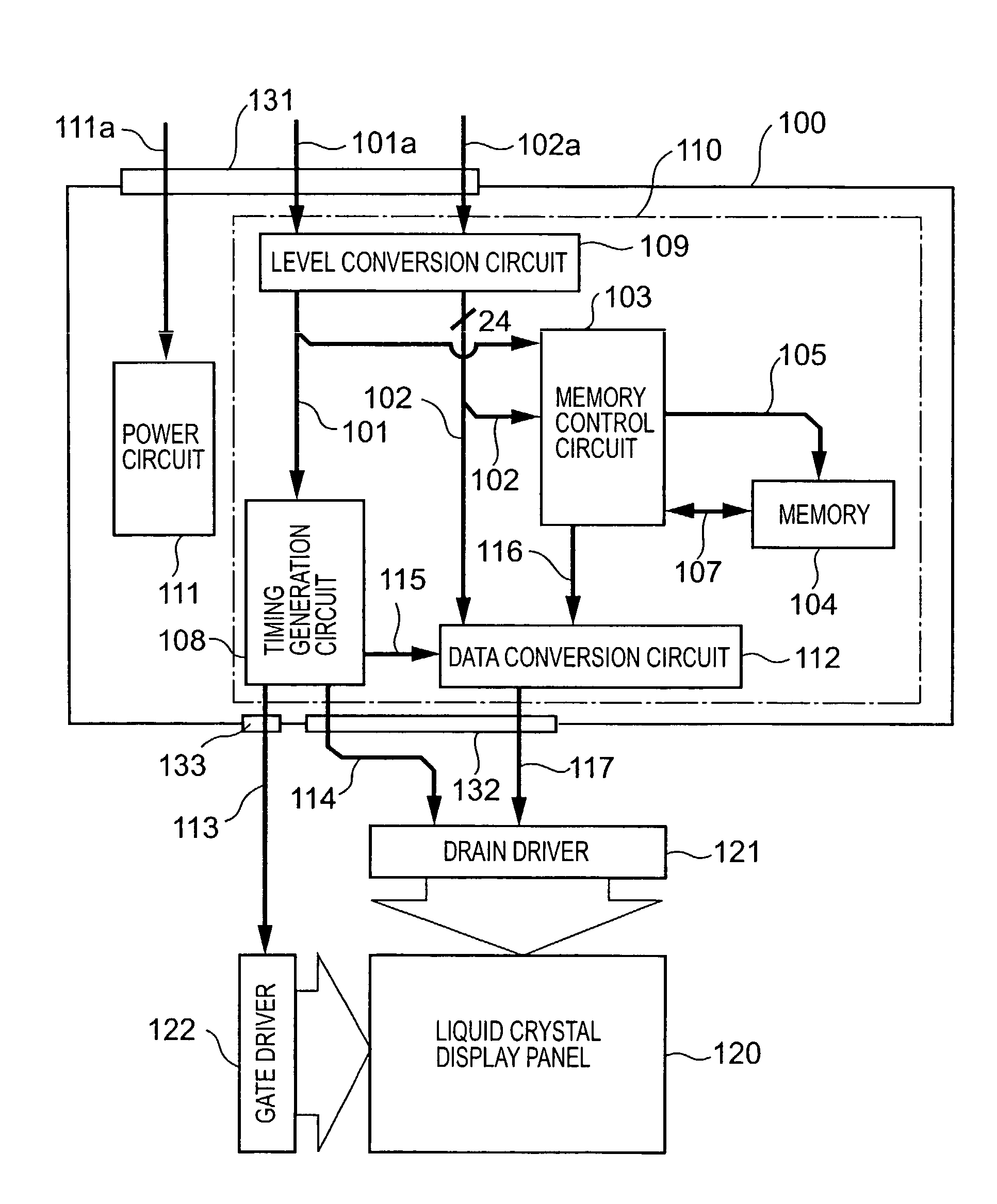

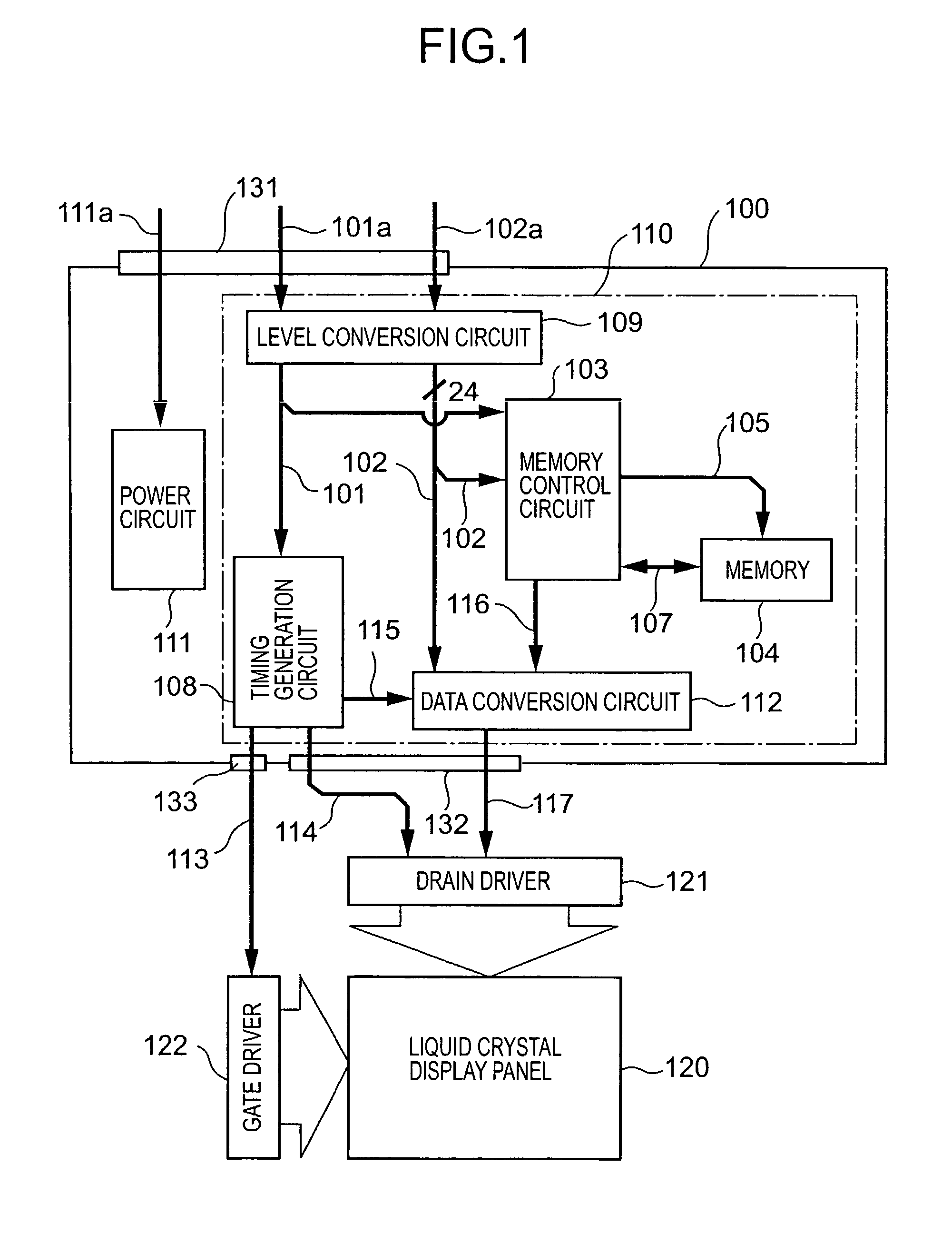

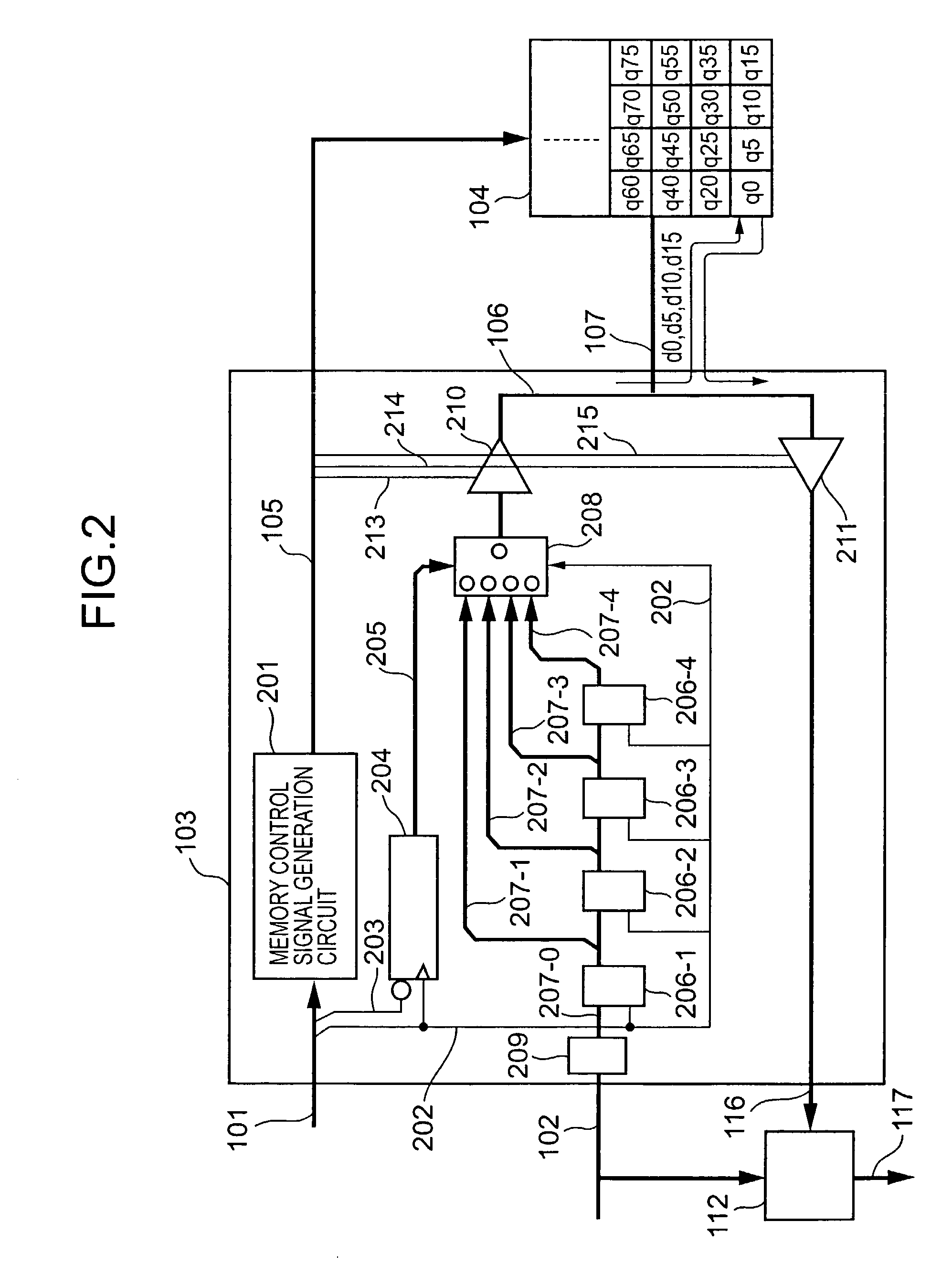

Display controller and display device provided therewith

InactiveUS7164415B2Improve display qualityLow costTelevision system detailsCathode-ray tube indicatorsDisplay deviceData signal

The present invention can realize better display of a dynamic image, and in addition, can make storage capacity of a memory smaller. A data conversion circuit 112 compares display data 102 of an n-th frame from the outside and display data 116 of the (n−1)-th frame stored in the memory 104, to generate a driving data signal 117 to deliver to a driver. Each time when a memory control circuit 103 reads display data q0, q5, q10, q15 corresponding to 20 pixels out of the display data 116 of the (n−1)-th frame, the memory control circuit 103 compresses display data d0–d19 of 20 pixels out of the display data 102 of the n-th frame from the outside to generated d0, d5, d10, d15, and stores the generated data into the same area where the display data q0, q5, q10, q15 of the display data of the (n−1)-th frame have been stored.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

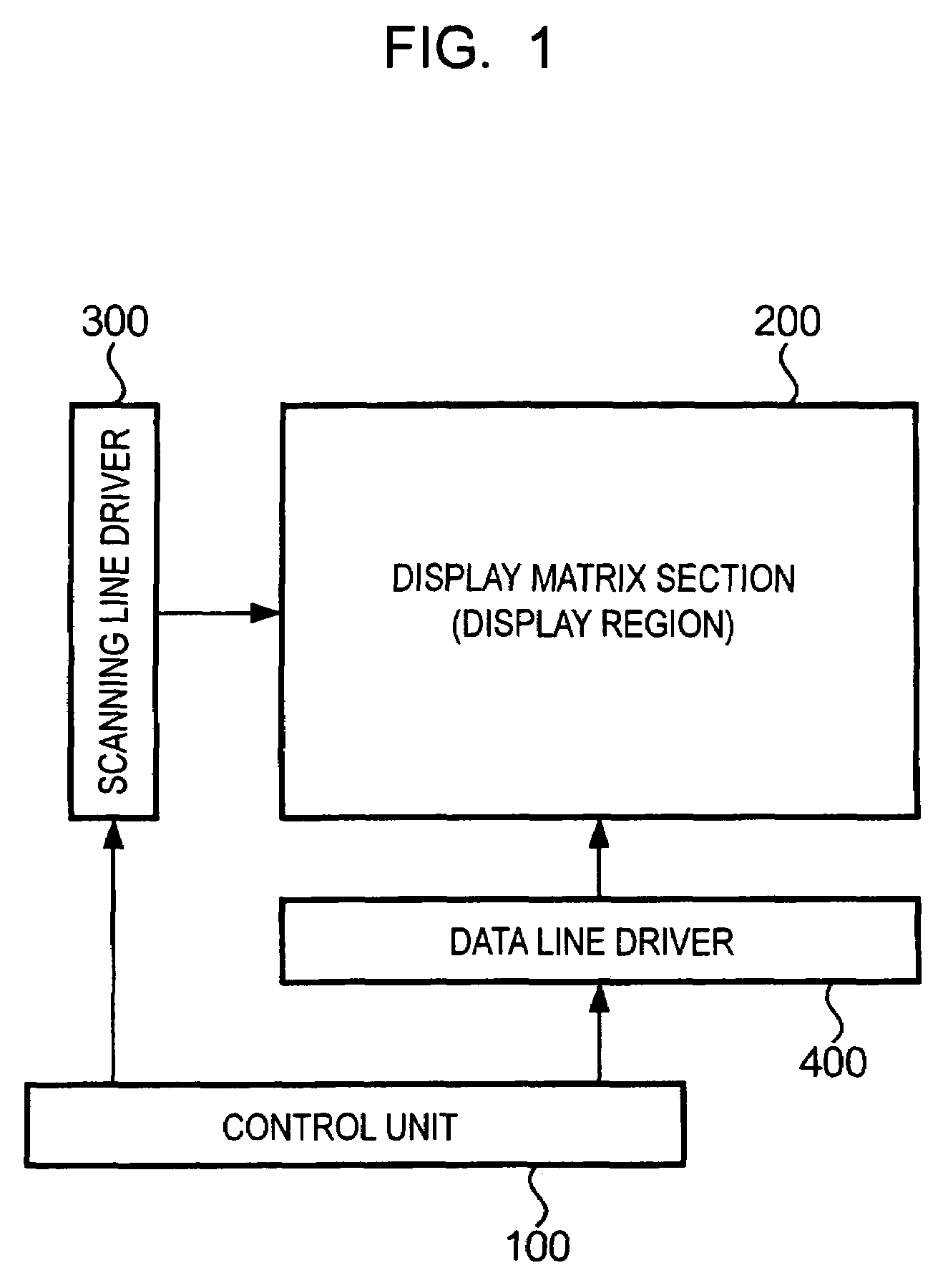

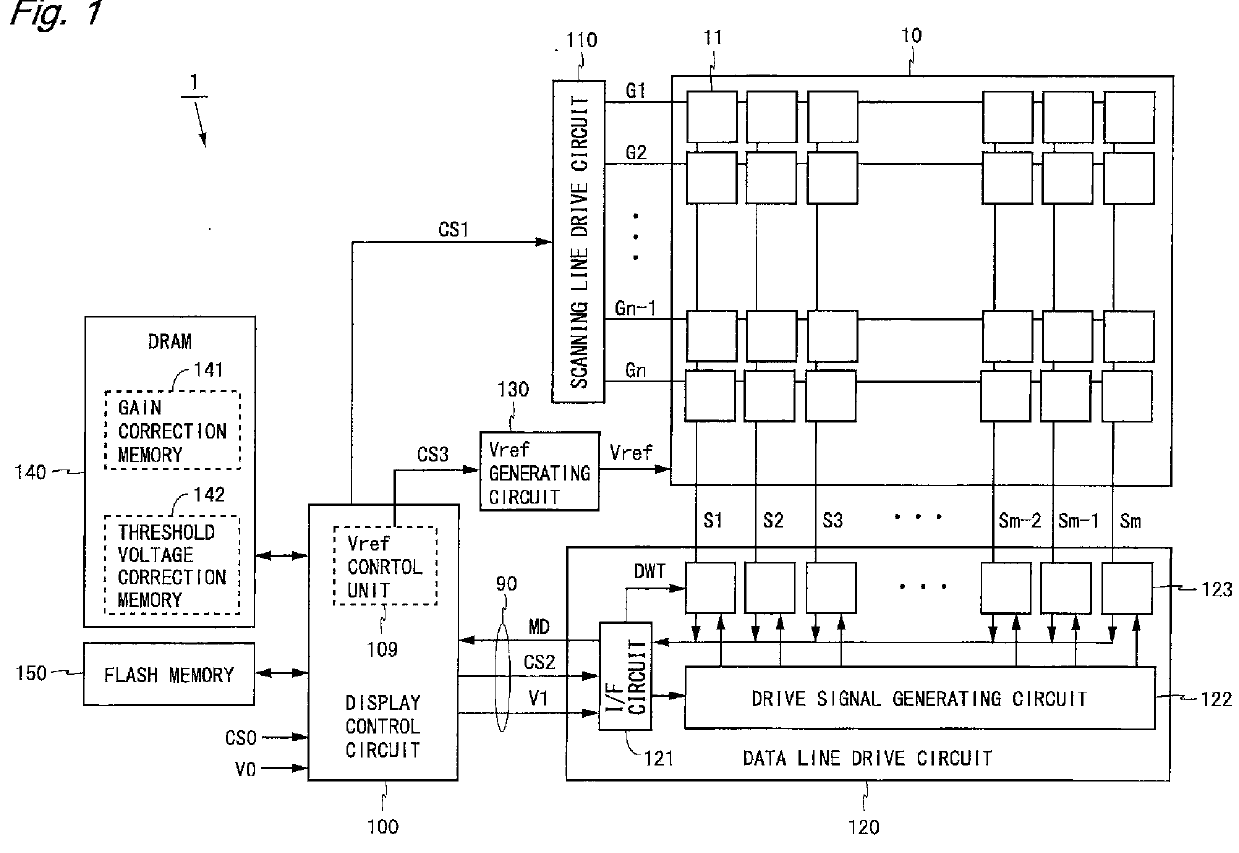

Display device and drive current detection method for same

ActiveUS20160055791A1Improve accuracyAvoid changeCathode-ray tube indicatorsInput/output processes for data processingDriving currentDisplay device

A data line drive circuit provides a voltage according to a detection voltage and to a reference voltage, between the gate and source of a drive transistor in a pixel circuit, and detects a drive current having passed through the drive transistor and outputted external to the pixel circuit. A threshold voltage correction memory stores, for each pixel circuit, data representing a threshold voltage of the drive transistor. A display control circuit controls the reference voltage based on the data stored in the threshold voltage correction memory. By this, even if the threshold voltage of the drive transistor is changed, the drive current can be detected with a high accuracy. The threshold voltage correction memory may store, for each pixel circuit, data representing a difference between the threshold voltage of the drive transistor and the reference voltage.

Owner:SHARP KK

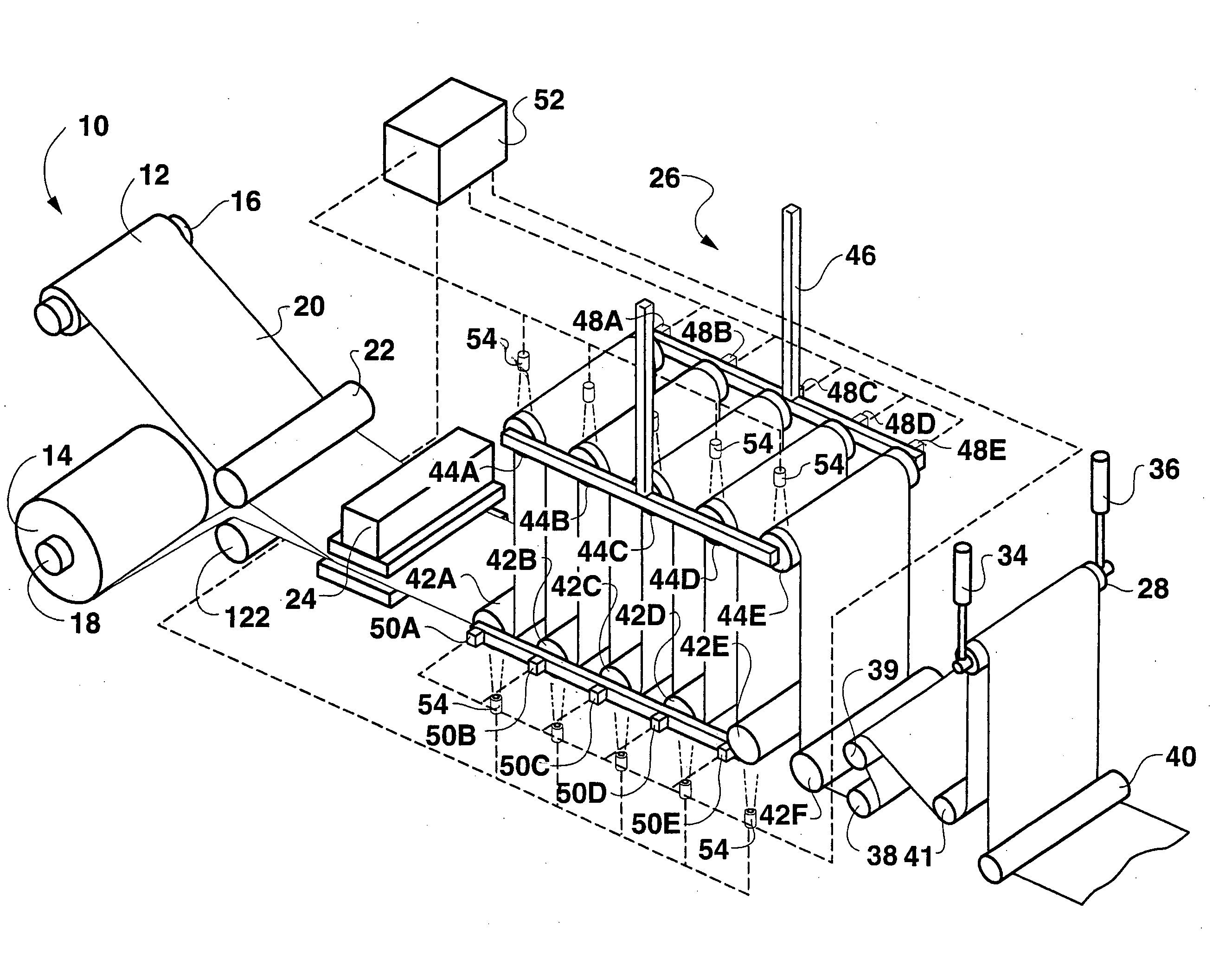

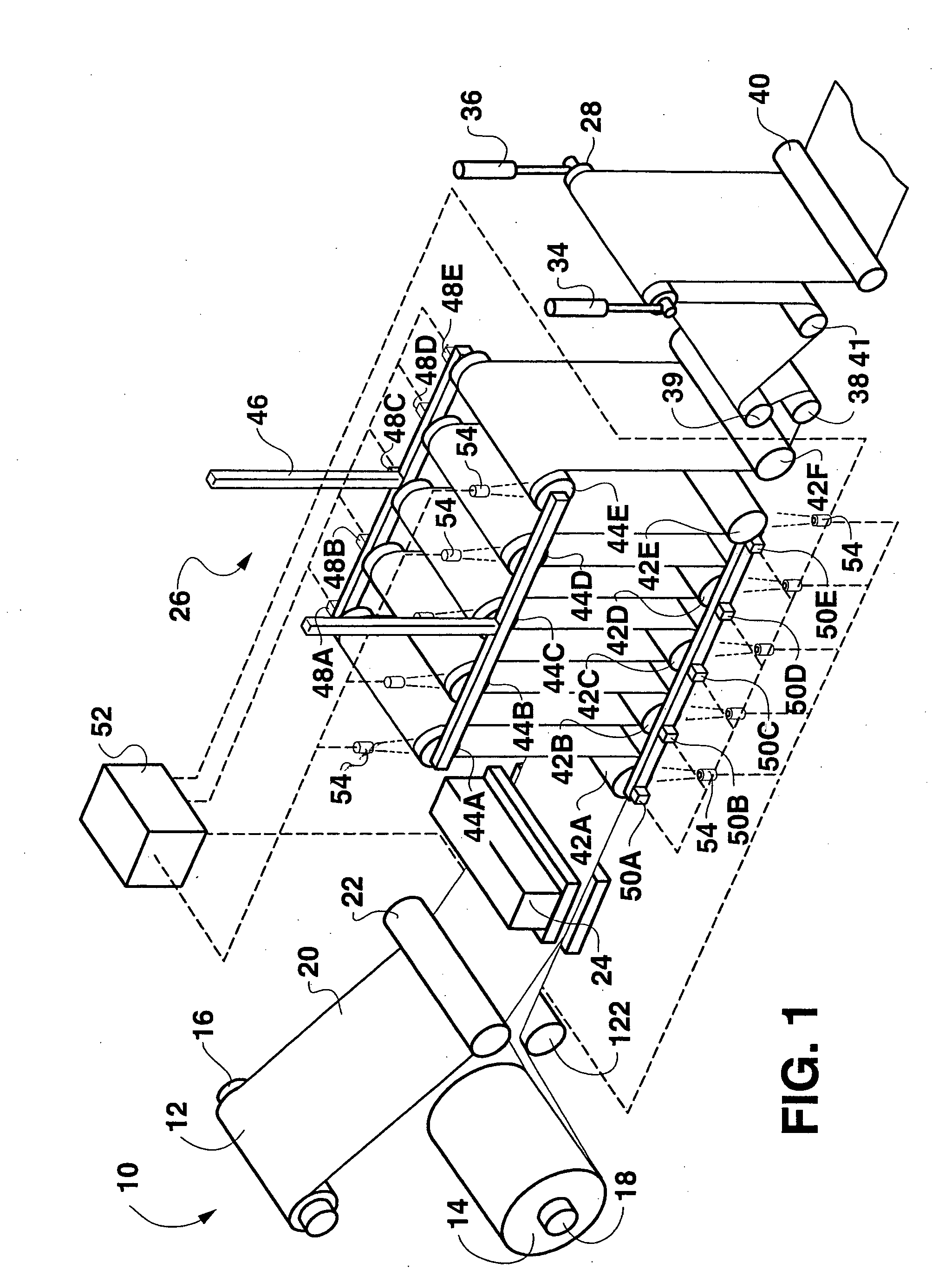

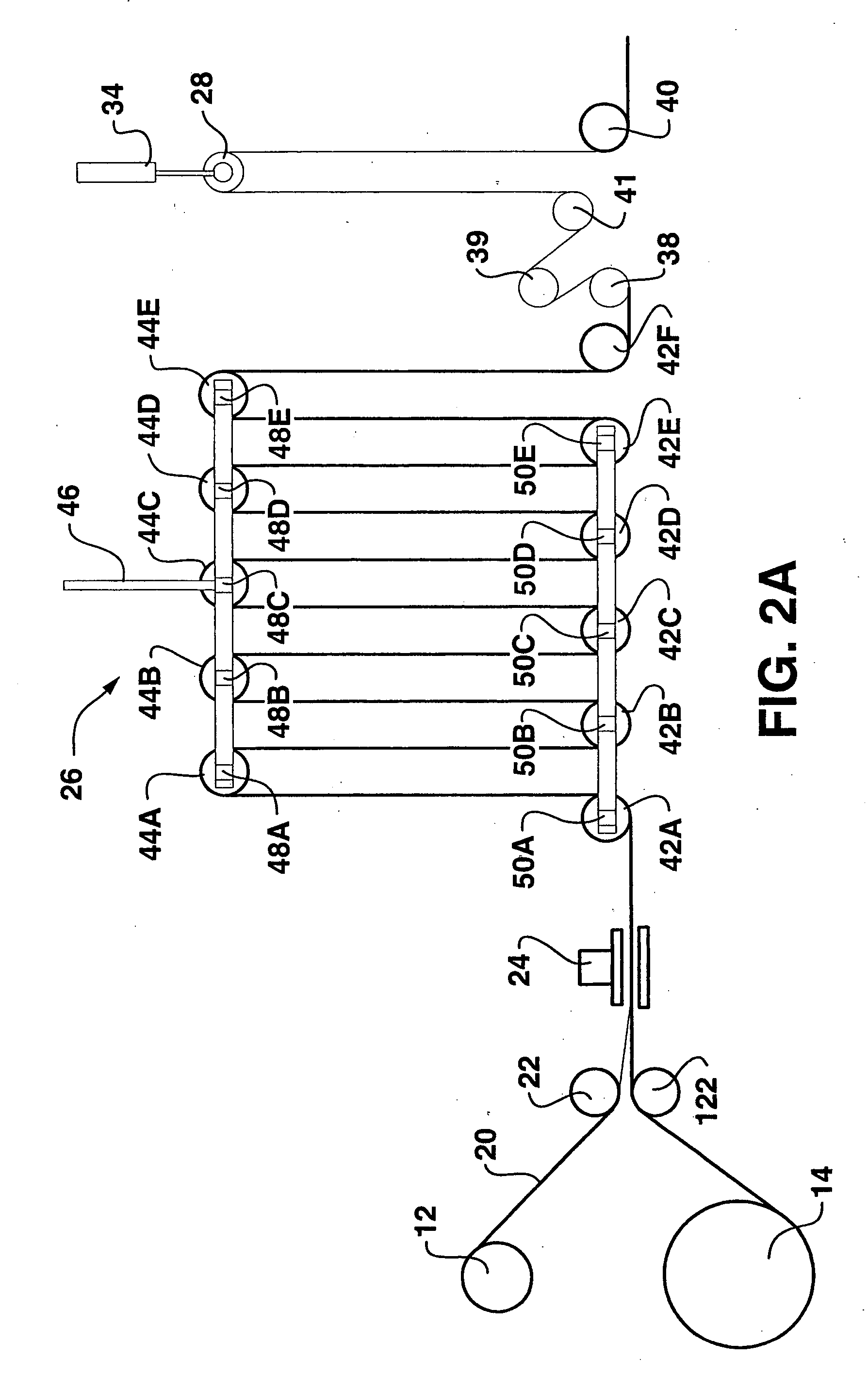

System and process for controlling the deceleration and acceleration rates of a sheet material in forming absorbent articles

ActiveUS20050139713A1Reduce tensionReduce probabilityFilament handlingRecord information storageEngineeringAcceleration rate

A system and process for unwinding materials in forming absorbent articles is described. The system includes an unwind device in association with a festoon. The festoon is for accumulating a determined length of material. The amount of material contained in the festoon is increased or decreased depending upon the rate at which a roll of material is unwound in relation to the rate at which the first material is fed into a downstream process. In order to minimize the capacity of the festoon and in order to minimize tension swings in the festoon, the festoon includes a plurality of drive devices associated with selected guide rolls contained in the festoon. The drive devices can accelerate and / or decelerate the guide rolls in response to rate increases or decreases occurring at the unwind device in relation to the downstream process speed. In one embodiment, each of the guide rolls is controlled independently of the remaining guide rolls in the festoon.

Owner:KIMBERLY-CLARK WORLDWIDE INC

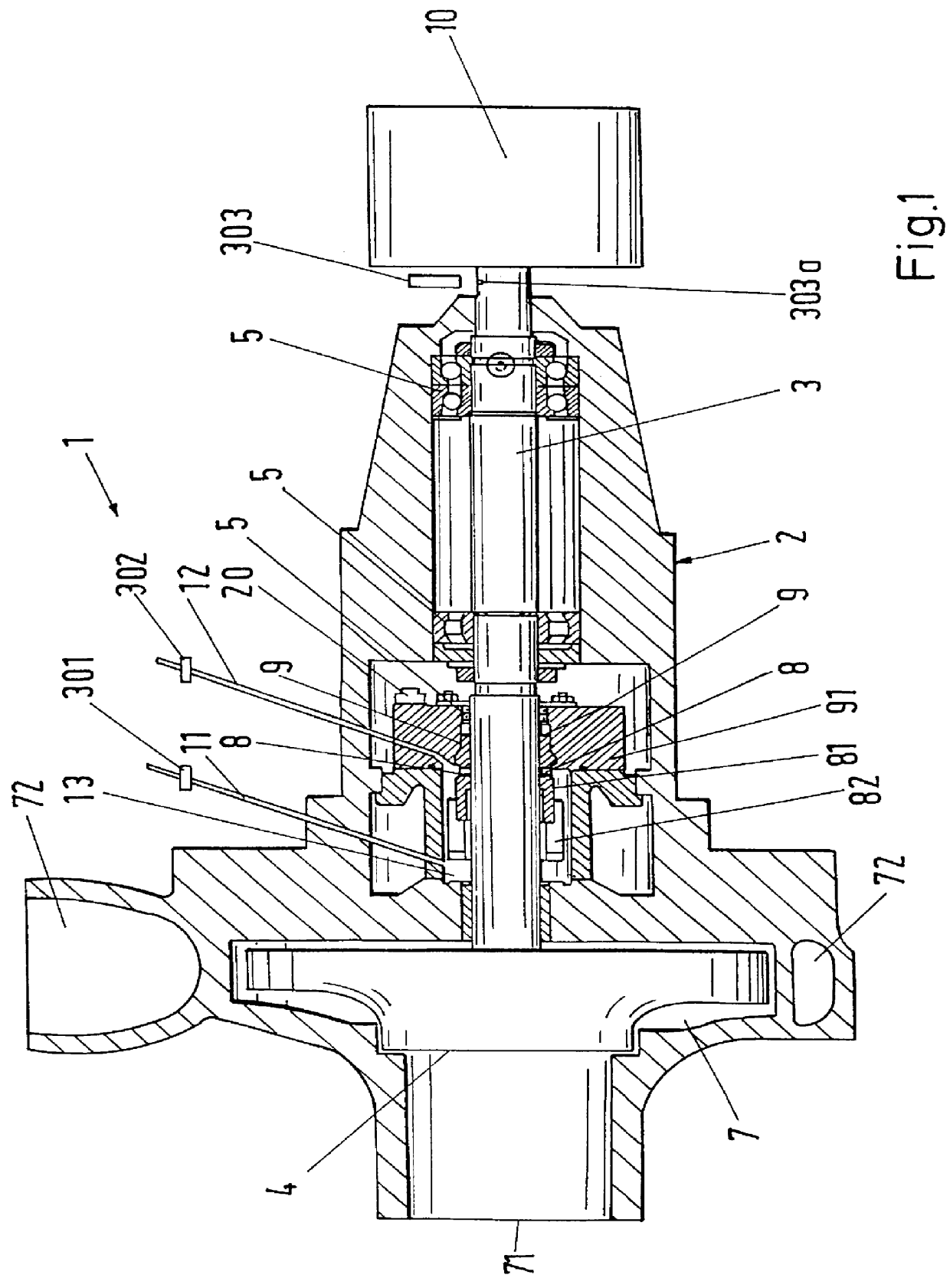

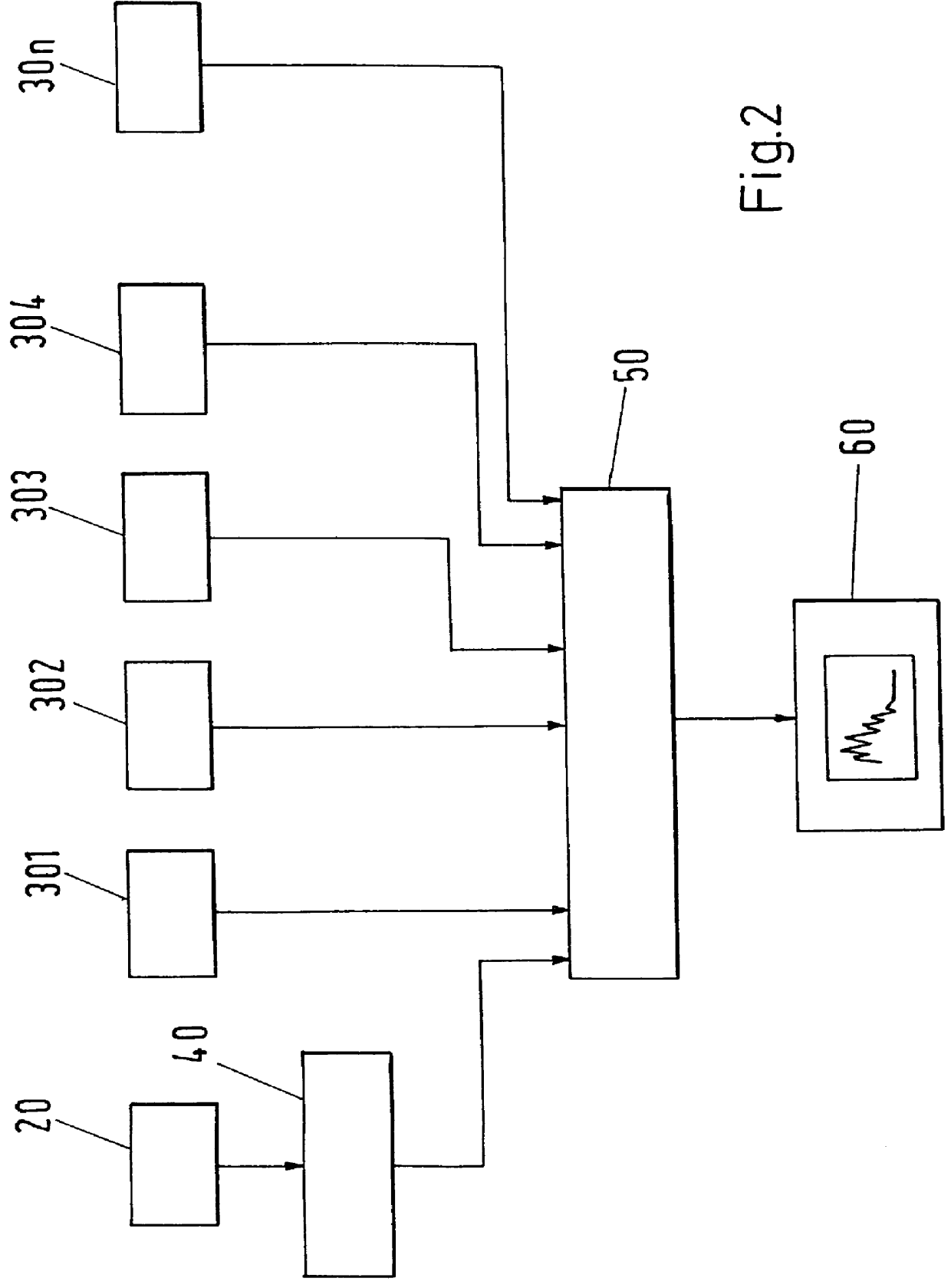

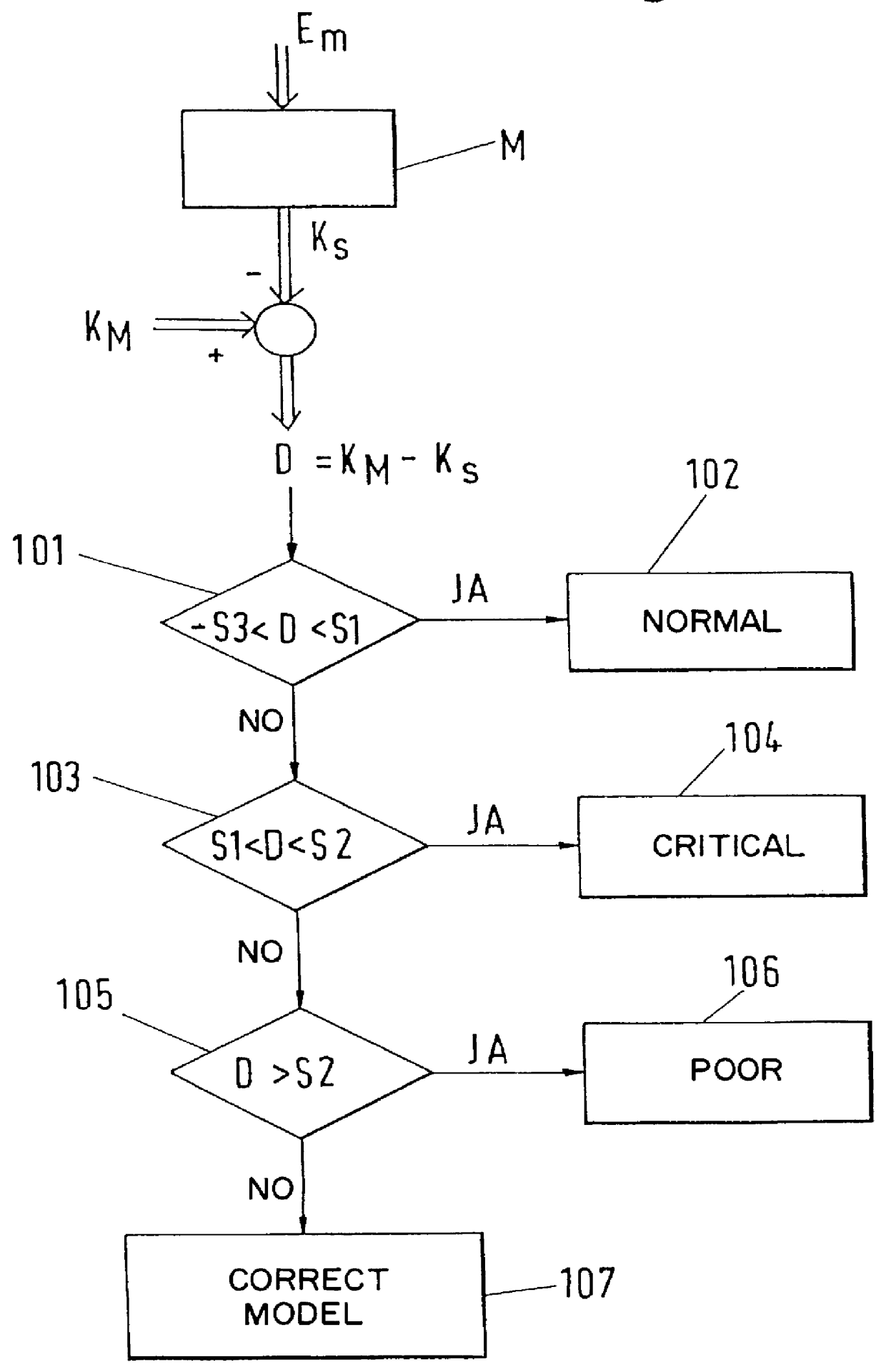

Method for monitoring the condition of a mechanical seal

InactiveUS6065345ALow costEconomical and simpleVibration measurement in solidsMachine part testingEngineeringSound emission

In a method for monitoring the condition of a mechanical seal in an apparatus provided with a rotating part, in particular in a pump which has a rotating shaft for the forwarding of a fluid, the sound emission of the seal is continually measured at discrete times in the operating state of the apparatus and at least one statistical characteristic value is won from the acoustic signals. The analog acoustic signals are converted prior to the determination of the statistical characteristic value into analog demodulated signals, the maximum frequency of which is less than about 50 kHz.

Owner:SULZER PUMPEN

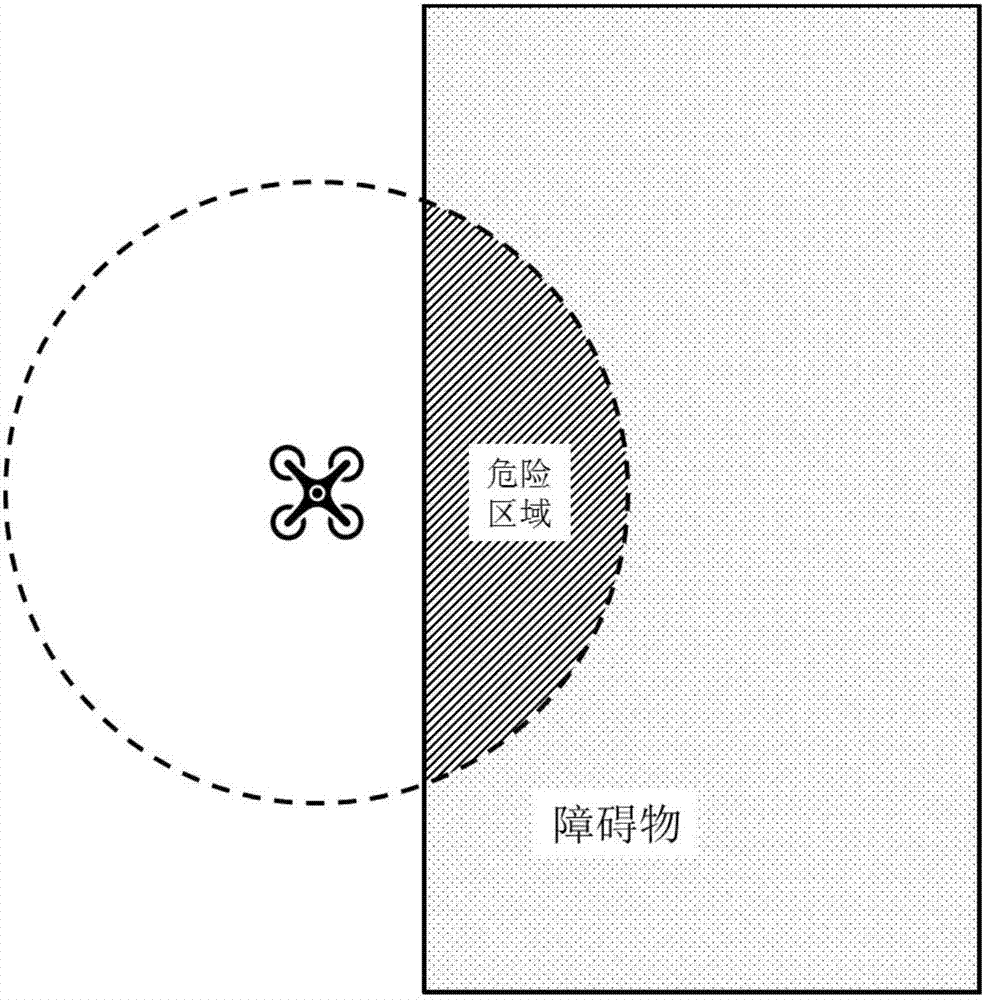

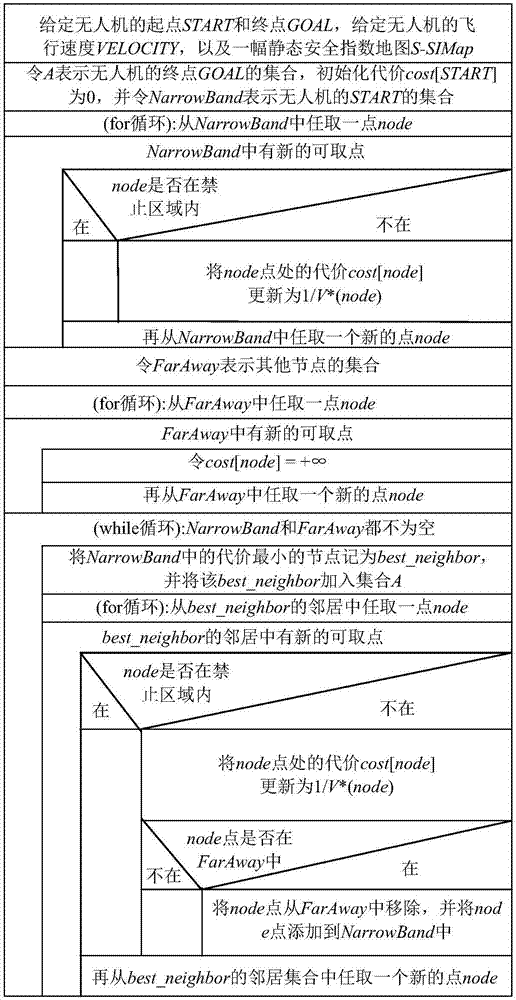

Multi-target route planning and united searching method of drone in urban low-altitude environment

ActiveCN106970648AReduce storage capacityLower requirementRemote controlled aircraftTarget-seeking controlUncrewed vehiclePath cost

The invention provides a multi-target route planning and united searching method of a drone in an urban low-altitude environment, and belongs to the technical field of drone route planning. The method comprises steps of firstly, based on a static-state known obstacle, constructing a static-state safe index map, and based on an obstacle which is actively detected by the drone in a flight process and is not marked in a geographical map, constructing a dynamic state safe index map on an airborne platform; and then, based on offline searching and online searching, solving and optimizing a multi-target route planning problem of flight time and flight safety of the drone in an united manner. According to the invention, a path costing little from a start point to a termination point is planned in an offline manner; when an unknown obstacle is detected, a changed flight track is planned in an online manner through online searching, so a dynamic obstacle is avoided; and there is a quite small searching space in the online searching, so a safe route can be planned again from the drone rapidly, so requirements on real-time planning of routes for drones are met.

Owner:BEIHANG UNIV

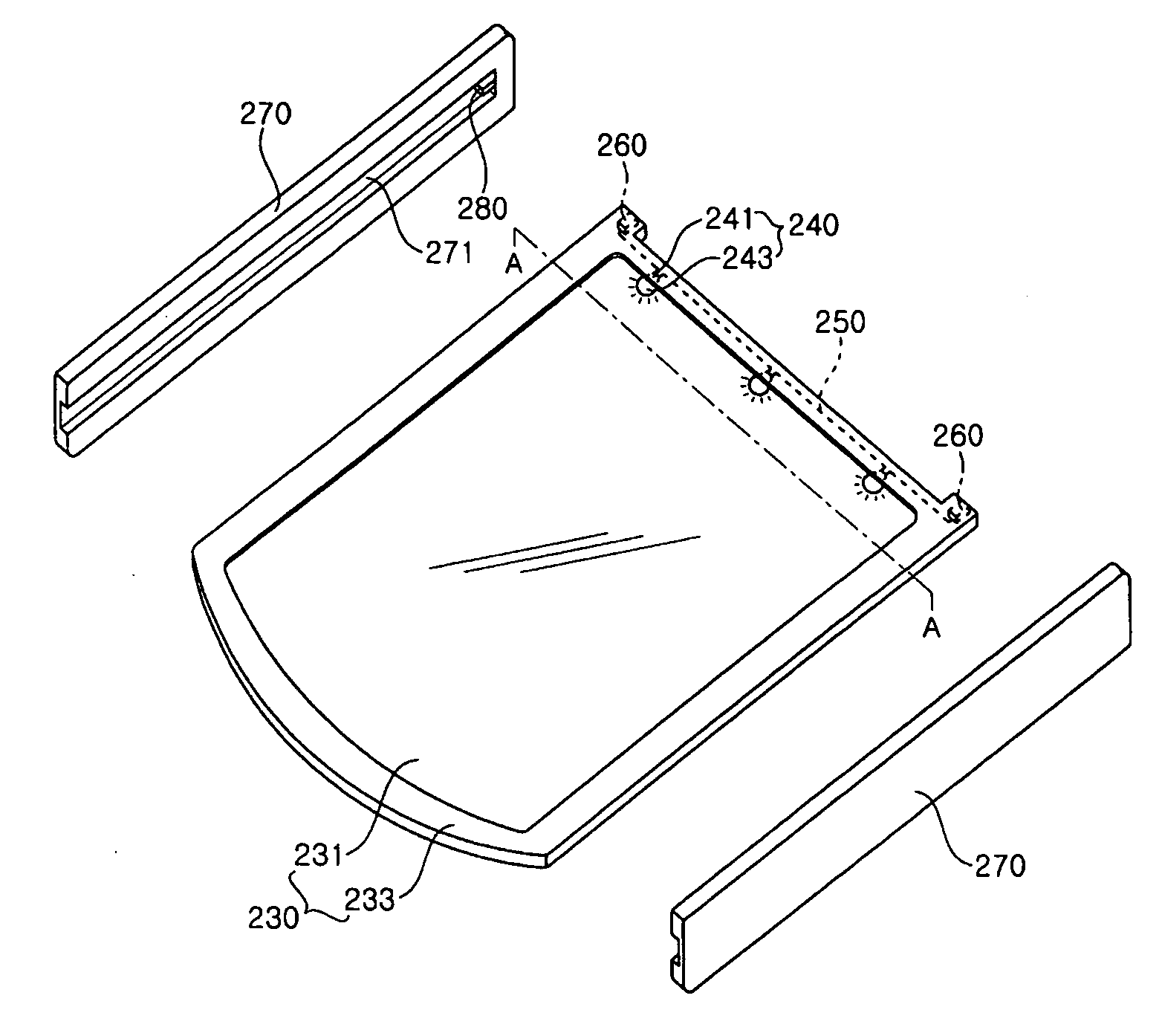

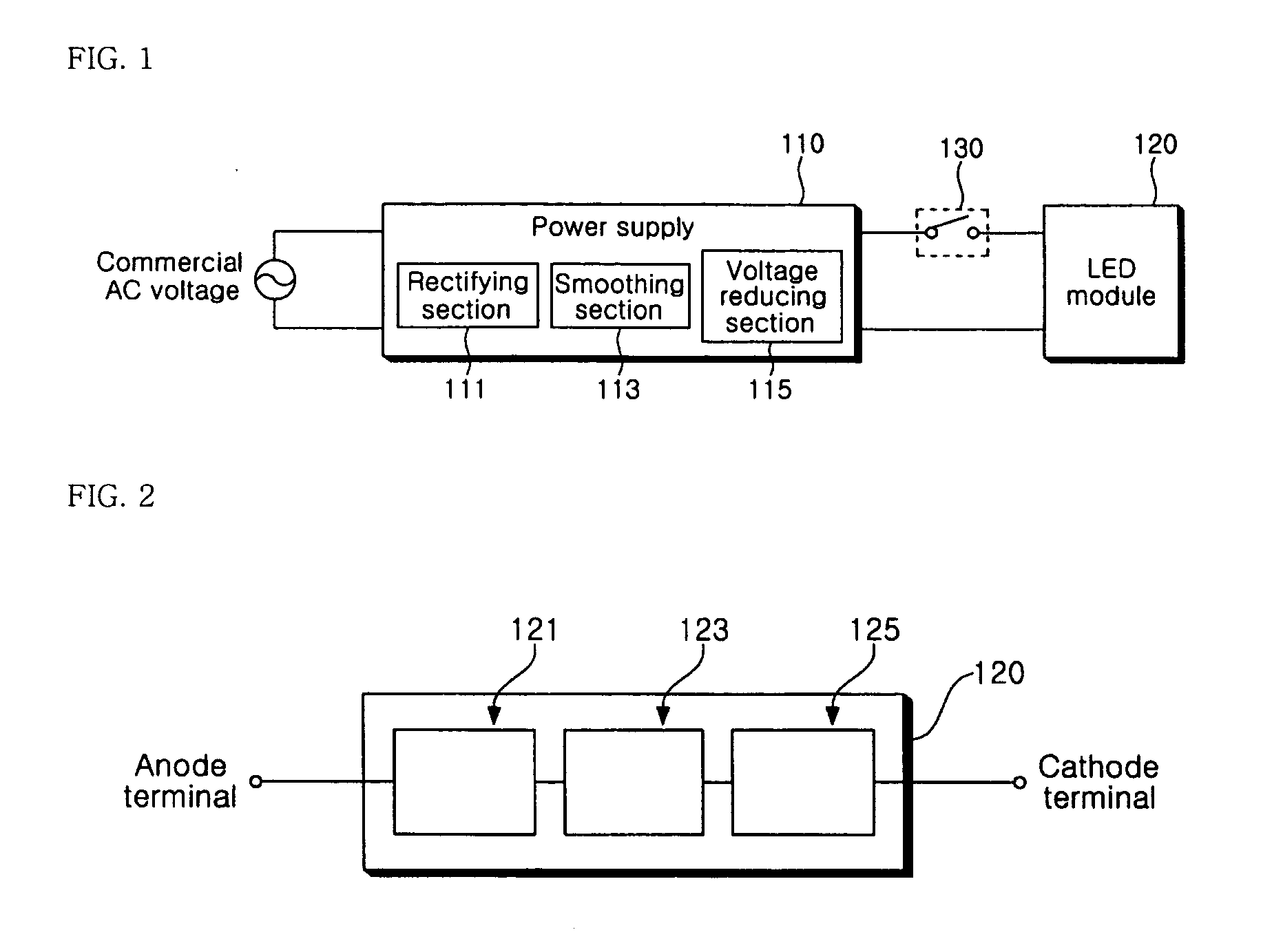

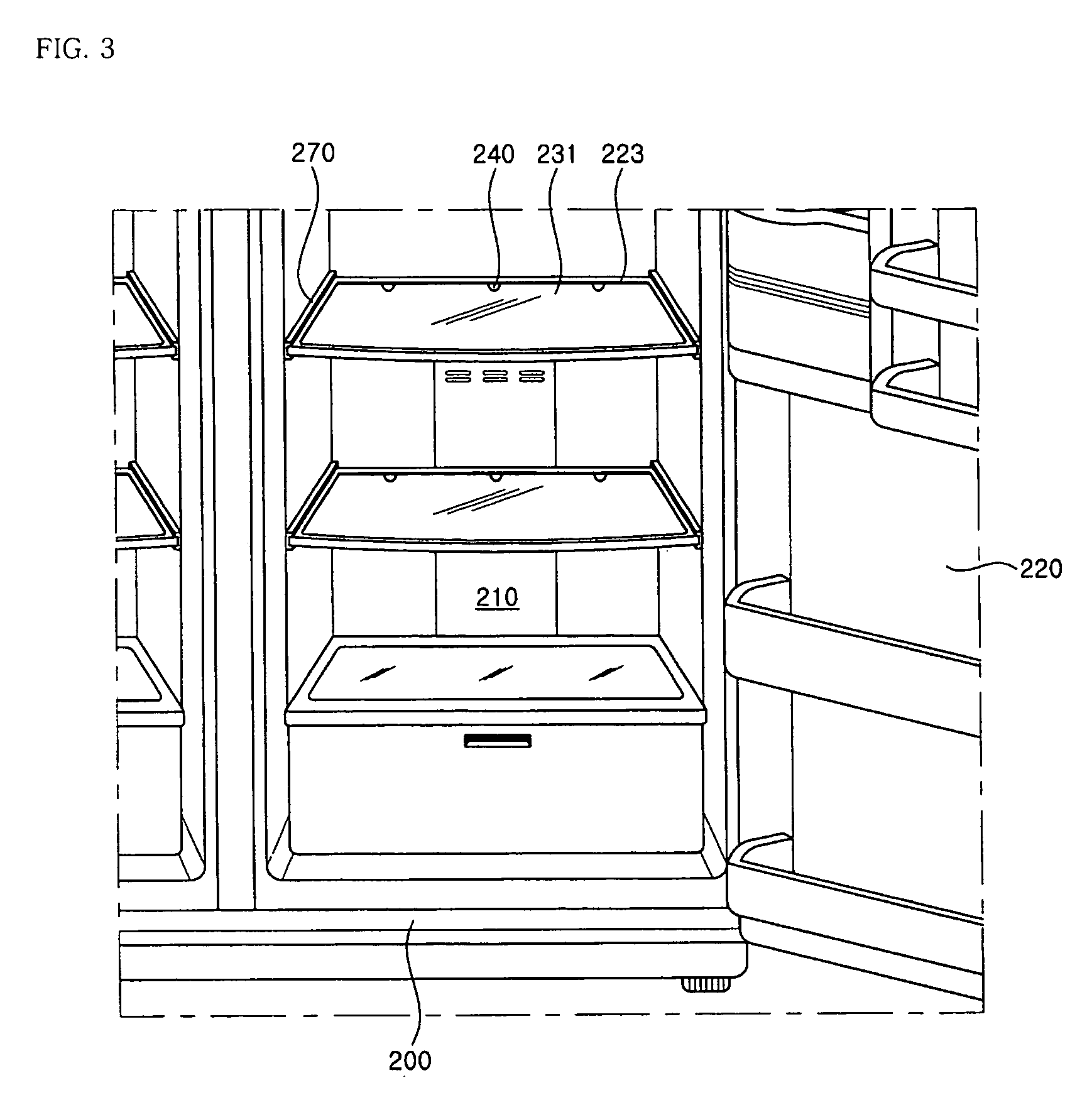

Illumination device for refrigerator

ActiveUS20070127229A1Efficient illuminationLow efficiencyMechanical apparatusDomestic lightingEngineeringLight-emitting diode

A light source for a refrigerator includes a power supply and a light emitting diode (LED) module. A light emitting portion of the LED module may be located in the interior of a rear end of a shelf plate.

Owner:LG ELECTRONICS INC

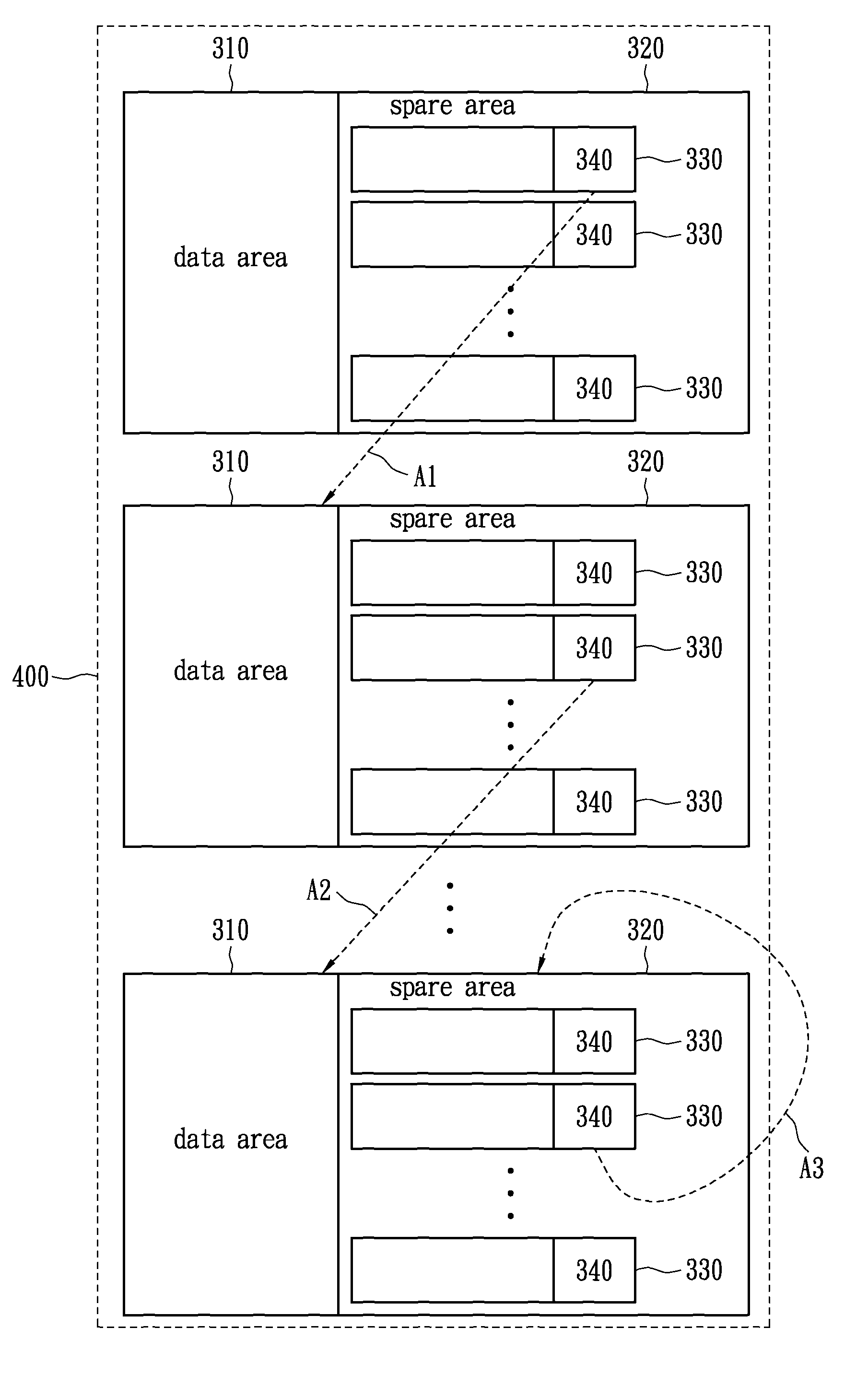

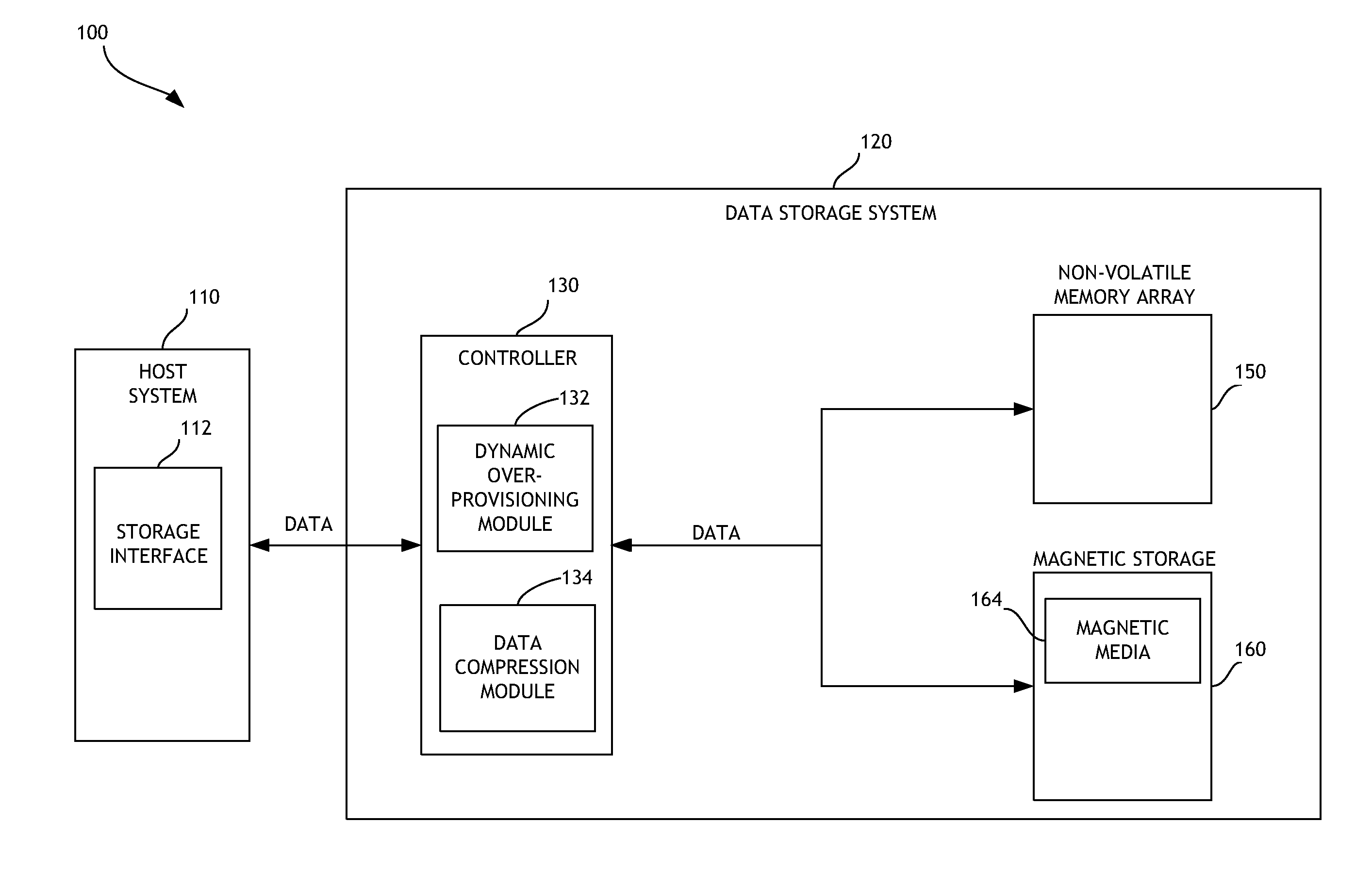

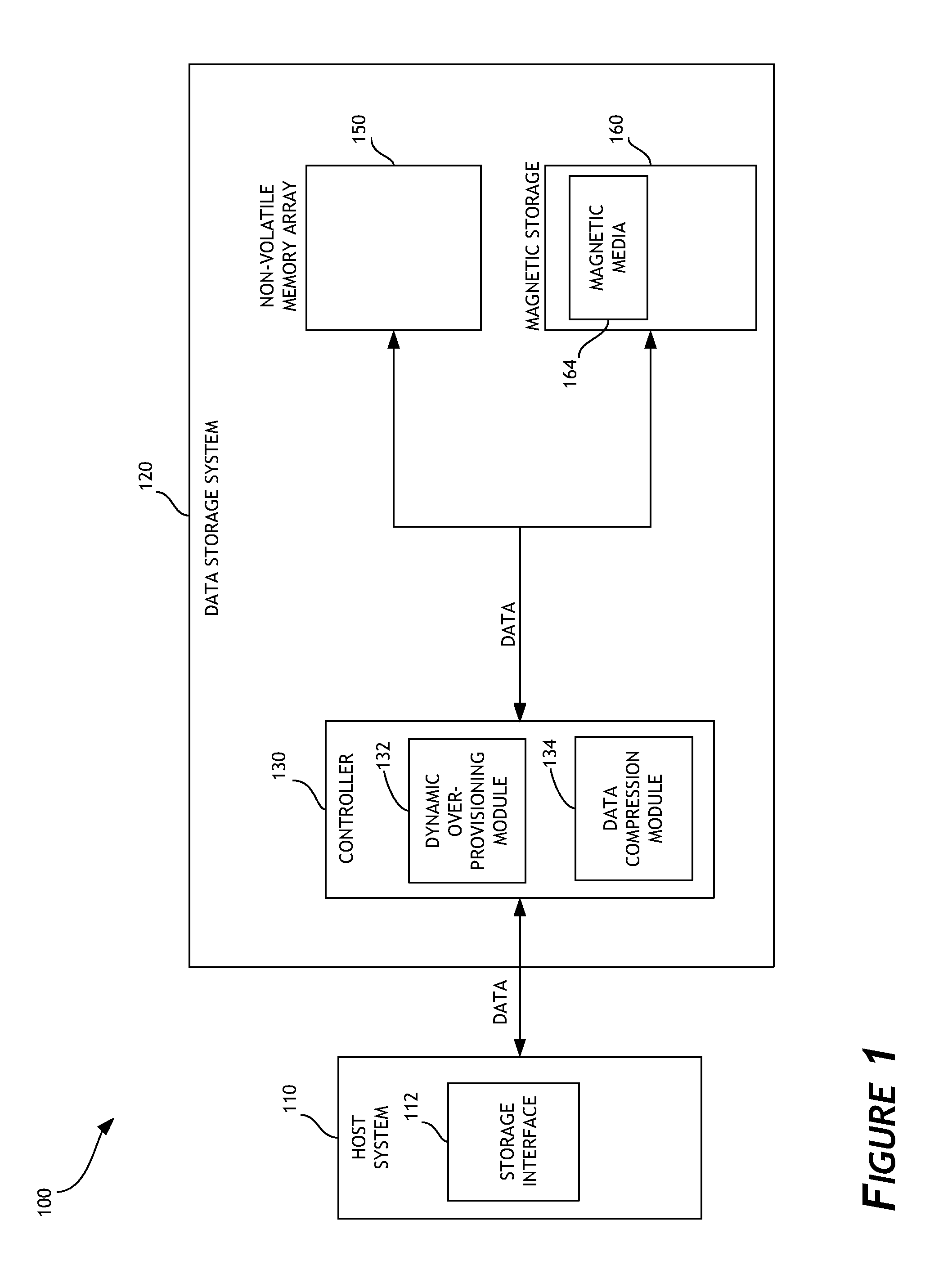

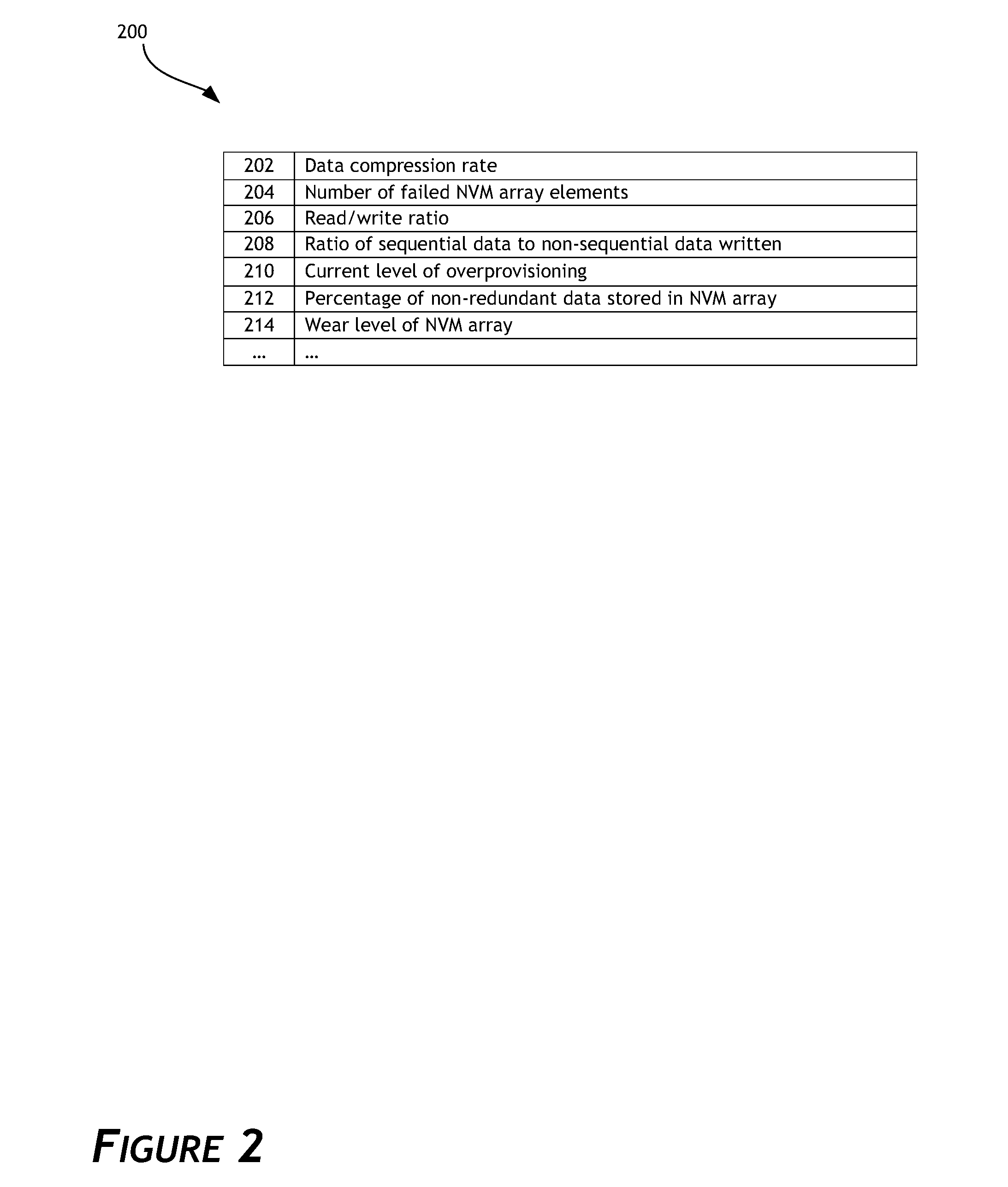

Dynamic overprovisioning for data storage systems

ActiveUS20140181369A1Improve efficiencyIncreased longevityMemory architecture accessing/allocationMemory adressing/allocation/relocationWrite amplificationCache hit rate

Disclosed embodiments are directed to systems and methods for dynamic overprovisioning for data storage systems. In one embodiment, a data storage system can reserve a portion of memory, such as non-volatile solid-state memory, for overprovisioning. Depending on various overprovisioning factors, recovered storage space due to compressing user data can be allocated for storing user data and / or overprovisioning. Utilizing the disclosed dynamic overprovisioning systems and methods can result is more efficient utilization of cache memory, reduction of write amplification, increase in a cache hit rate, and the like. Improved data storage system performance and increased endurance and longevity can thereby be attained.

Owner:WESTERN DIGITAL TECH INC

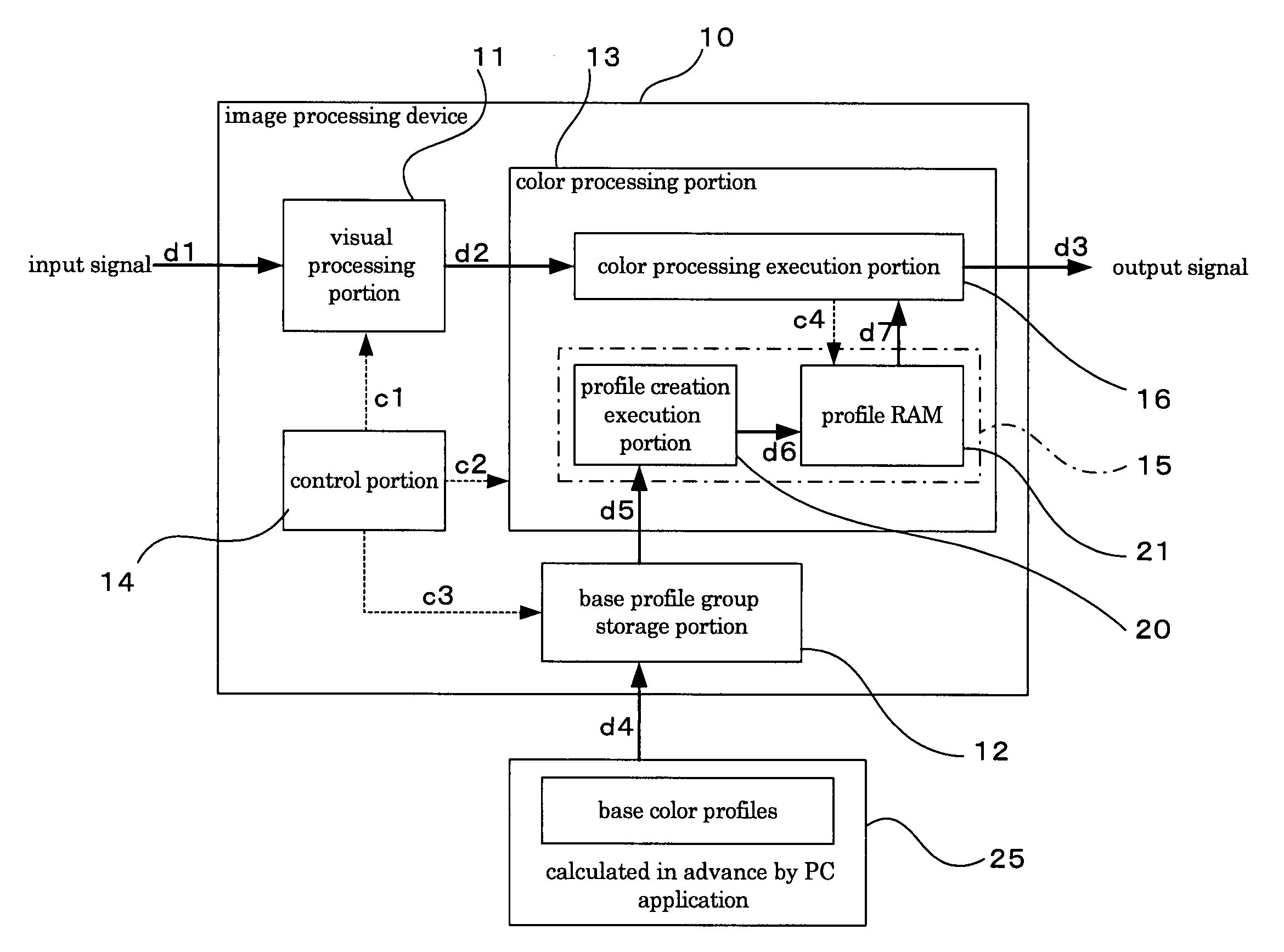

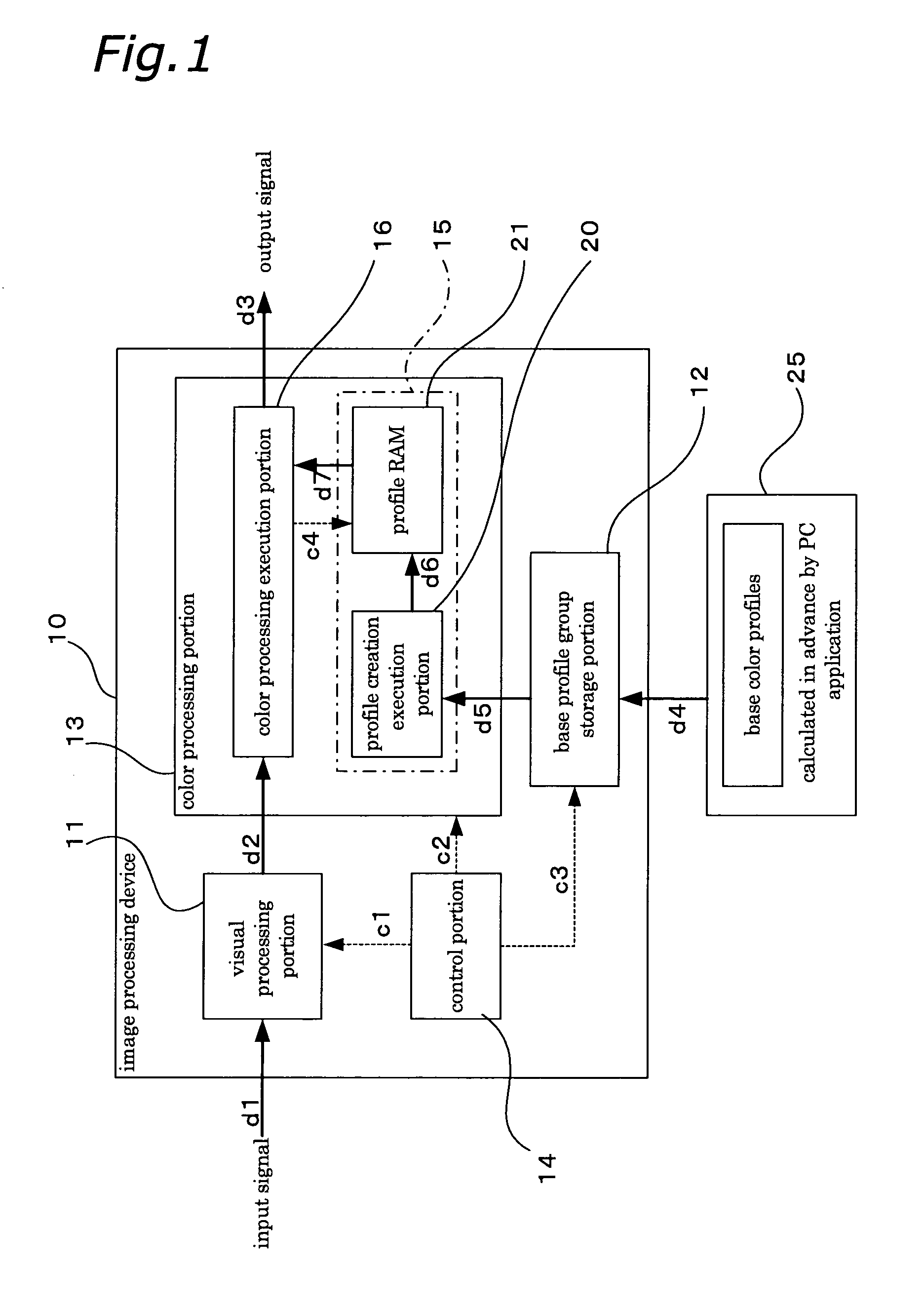

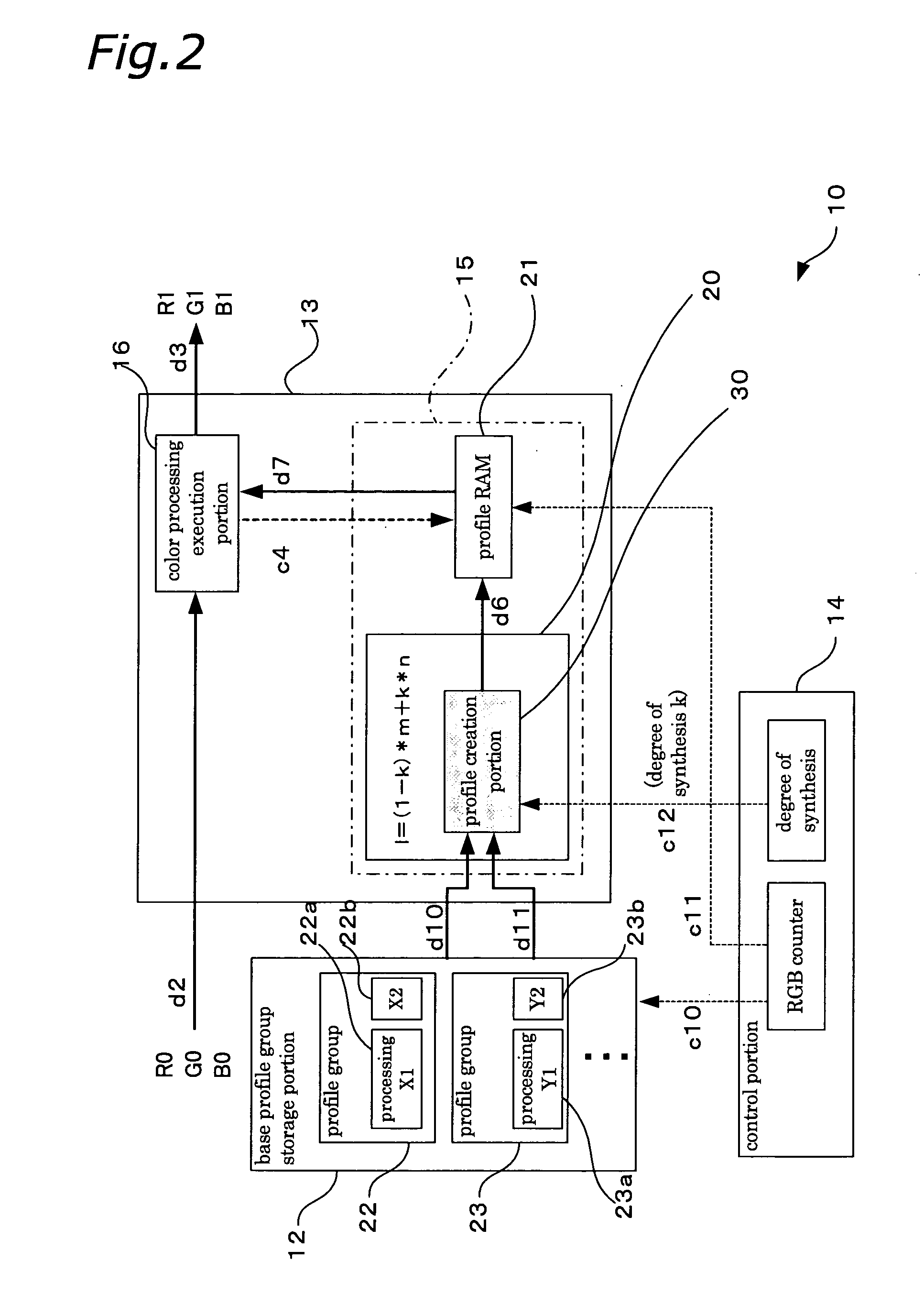

Image processing device, image processing method, and image processing program

InactiveUS20070165048A1Reduce storage capacityDegree of processing of the various color processing operations can be adjusted freelyImage enhancementImage analysisImaging processingColor transformation

The present invention provides an image processing device with which the storage capacity for storing lookup tables can be reduced while allowing the degree to which various color processing operations are performed to be freely adjusted. The image processing device 10 performs color processing of an image signal d2, and is provided with a profile creation portion 15 and a color processing execution portion 16. The profile creation portion 15 creates a new color transformation profile that achieves a predetermined color processing to a predetermined degree of processing based on a plurality of base color transformation profiles that achieve the predetermined color processing to different degrees of processing. The color processing execution portion 16 executes color processing of the image signal d2 based on the new color transformation profile that has been created.

Owner:PANASONIC CORP