Patents

Literature

283results about How to "Increase clock frequency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

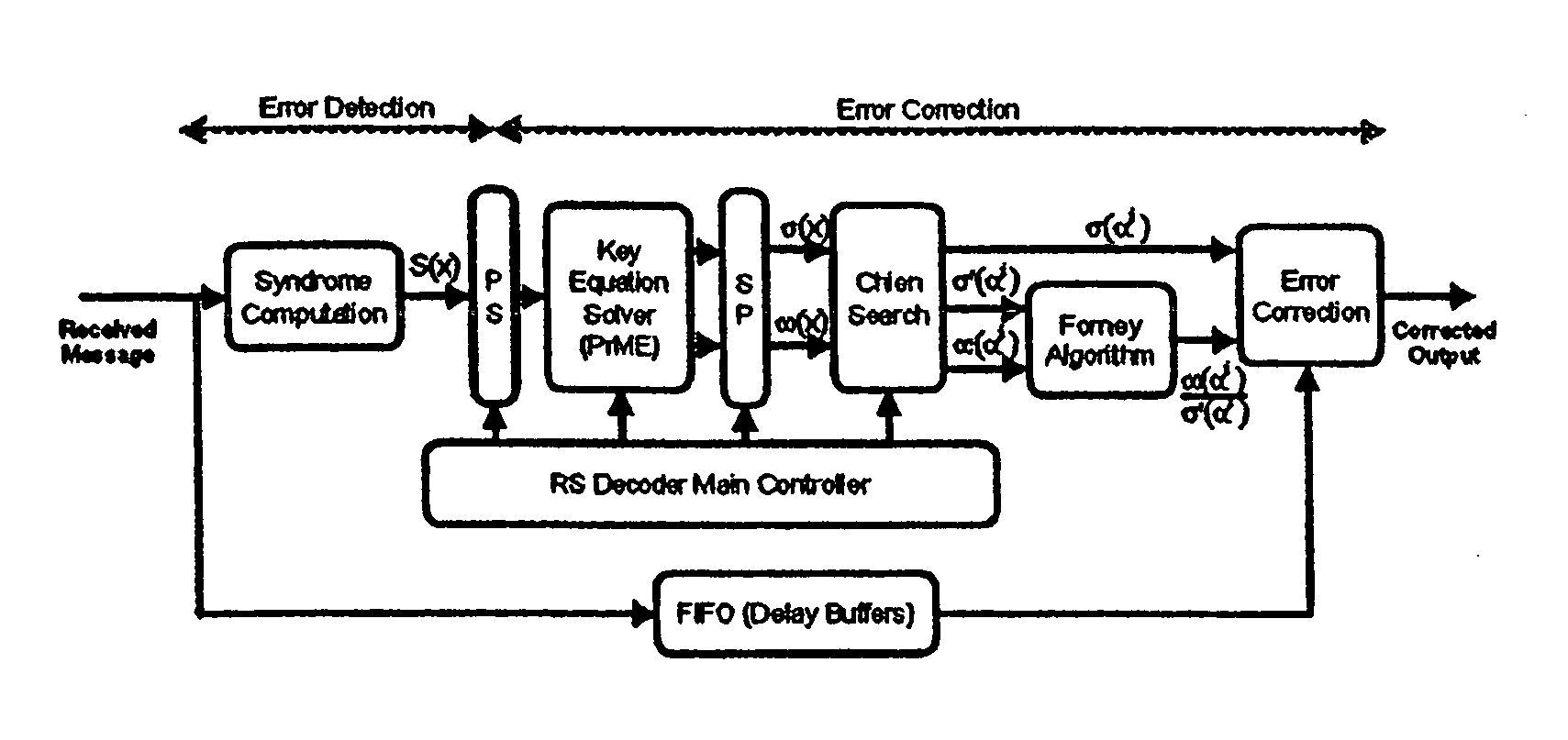

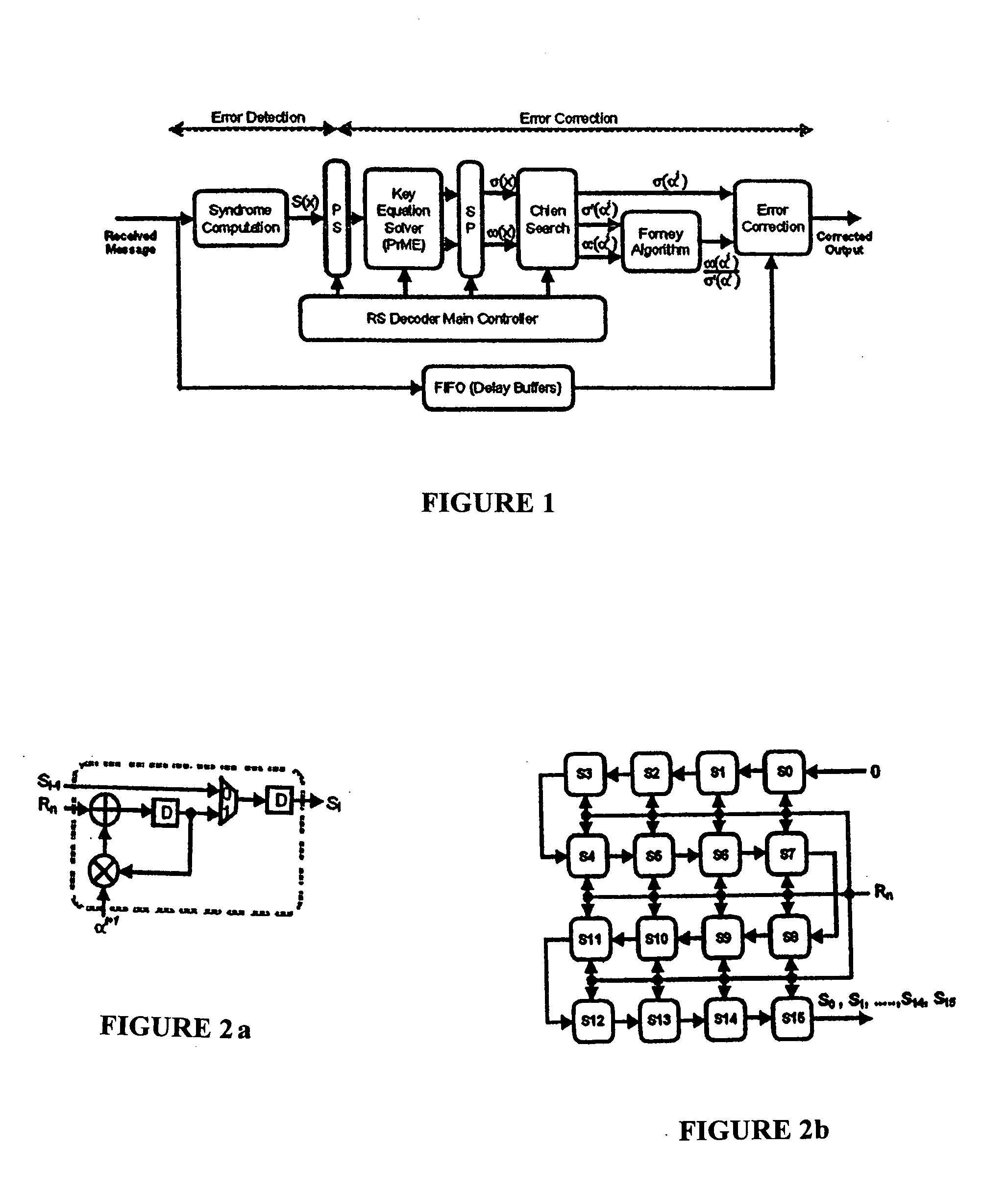

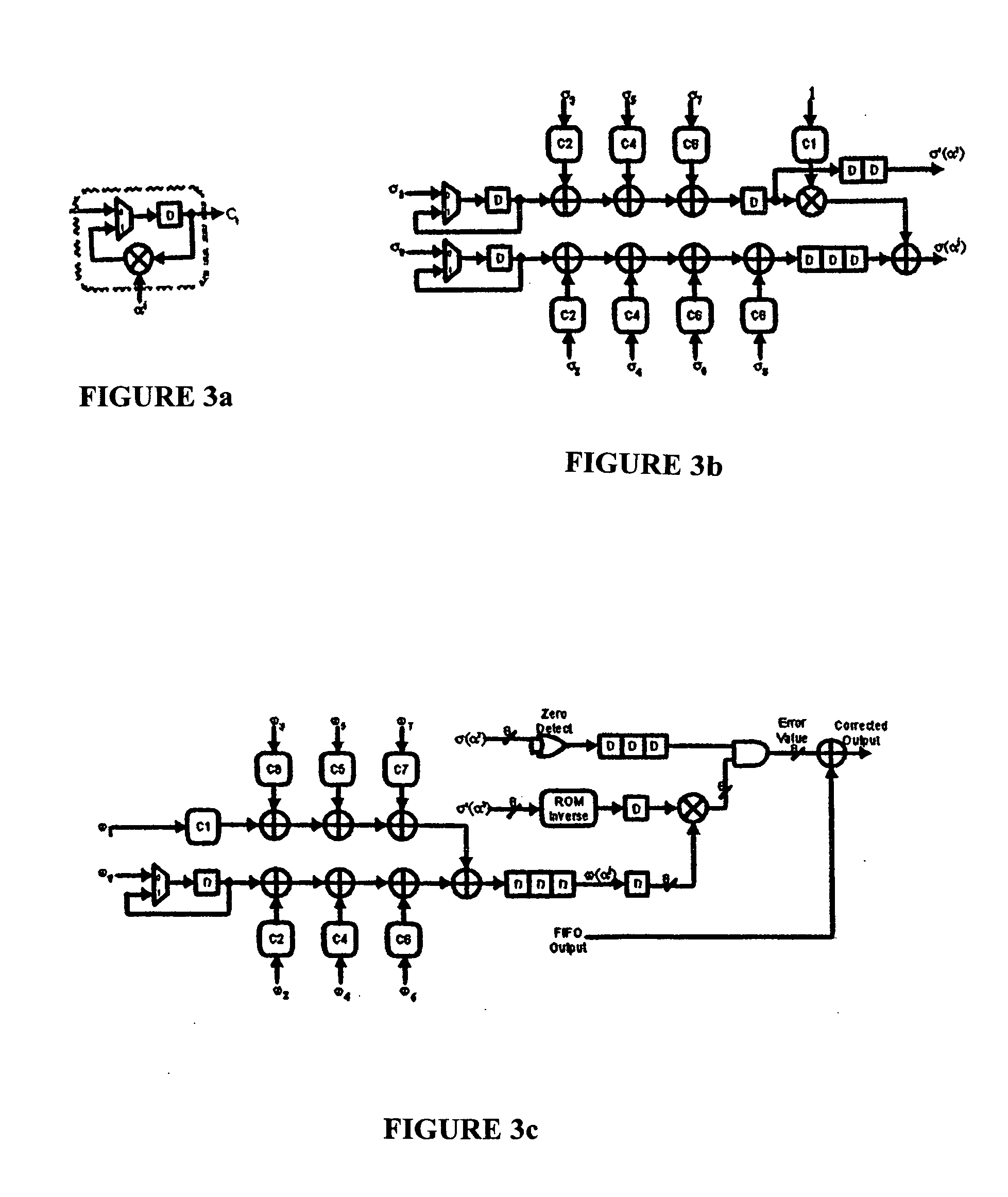

Reed-solomon decoder systems for high speed communication and data storage applications

InactiveUS20060059409A1Effective and reliable error correction functionalityReduce complexityCode conversionCoding detailsModem deviceHigh rate

A high-speed, low-complexity Reed-Solomon (RS) decoder architecture using a novel pipelined recursive Modified Euclidean (PrME) algorithm block for very high-speed optical communications is provided. The RS decoder features a low-complexity Key Equation Solver using a PrME algorithm block. The recursive structure enables the low-complexity PrME algorithm block to be implemented. Pipelining and parallelizing allow the inputs to be received at very high fiber optic rates, and outputs to be delivered at correspondingly high rates with minimum delay. An 80-Gb / s RS decoder architecture using 0.13-μm CMOS technology in a supply voltage of 1.2 V is disclosed that features a core gate count of 393 K and operates at a clock rate of 625 MHz. The RS decoder has a wide range of applications, including fiber optic telecommunication applications, hard drive or disk controller applications, computational storage system applications, CD or DVD controller applications, fiber optic systems, router systems, wireless communication systems, cellular telephone systems, microwave link systems, satellite communication systems, digital television systems, networking systems, high-speed modems and the like.

Owner:UNIV OF CONNECTICUT

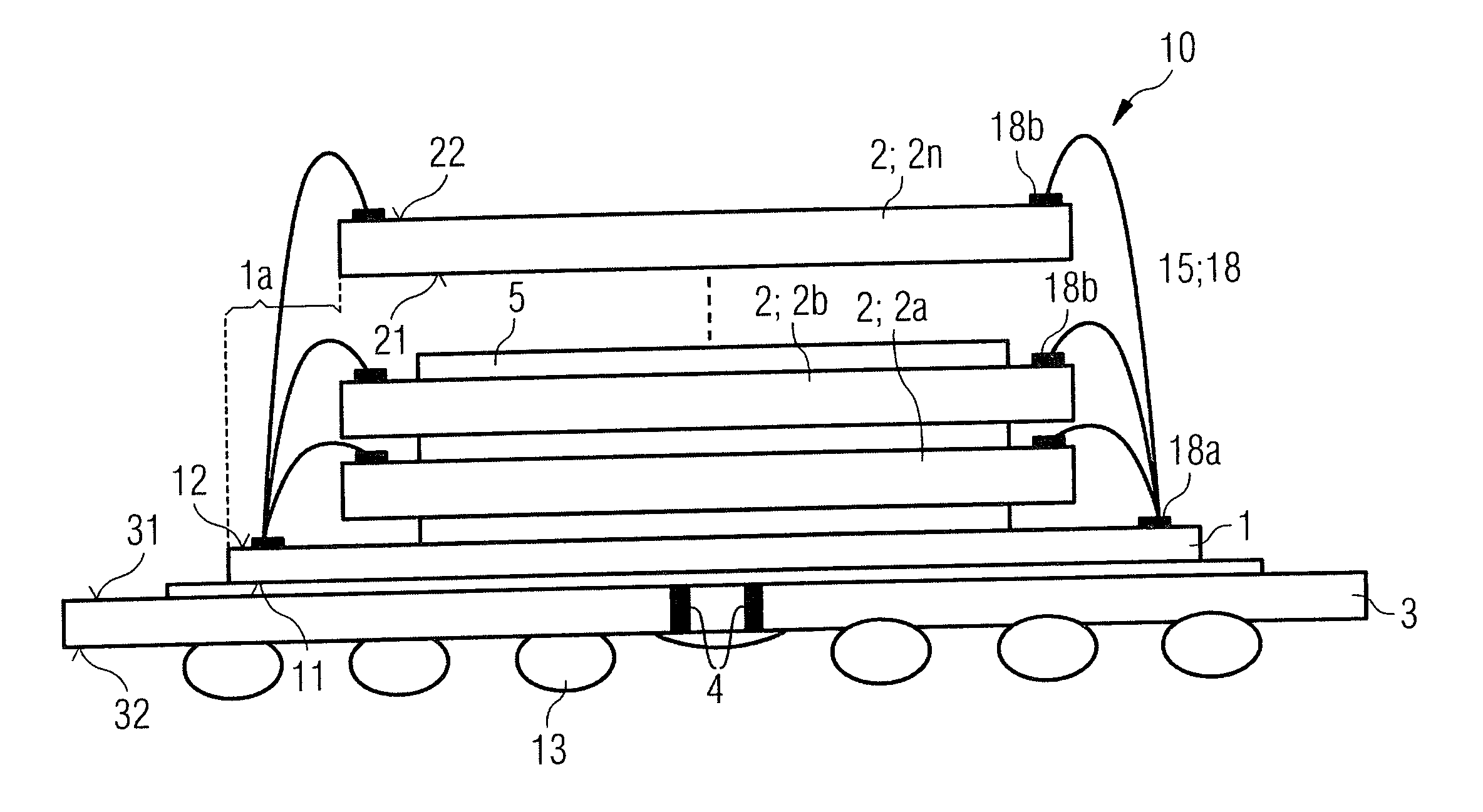

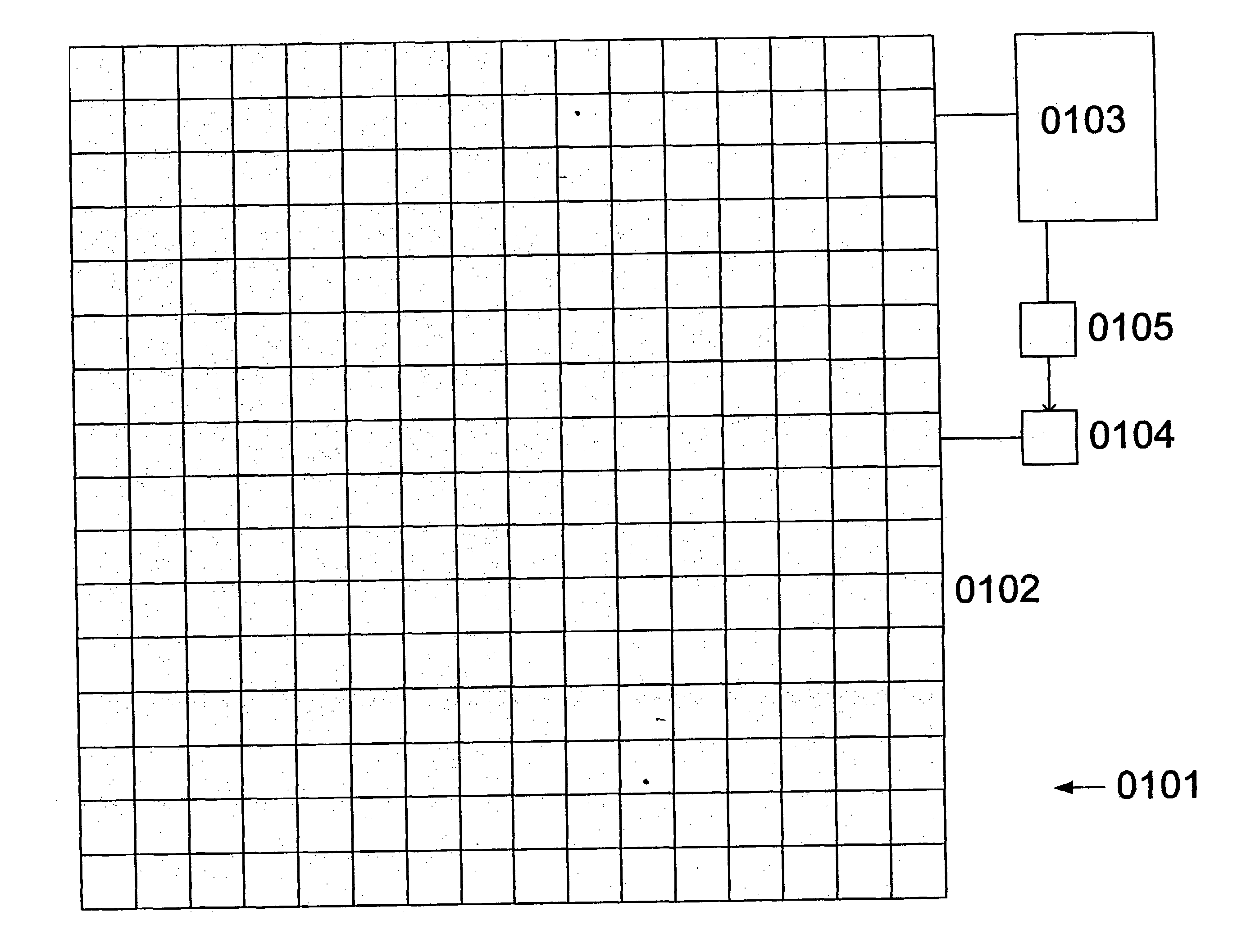

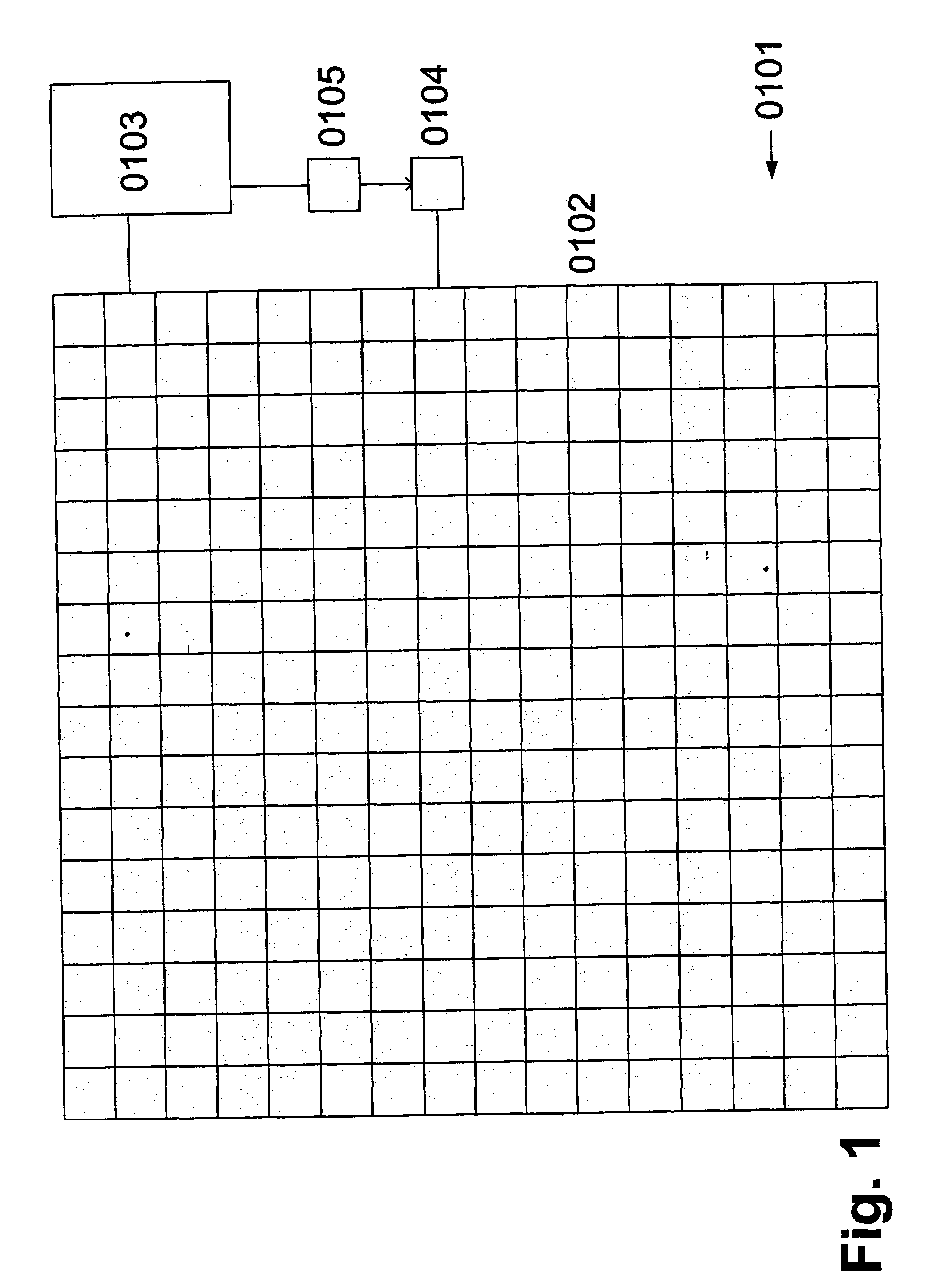

Semiconductor product and method for forming a semiconductor product

InactiveUS20070109831A1Increase storage capacityIncrease the number ofSolid-state devicesStatic storageMemory bankSemiconductor chip

A semiconductor product includes a first semiconductor chip that includes input / output circuitry enabling transfer of data from memory banks of the semiconductor product to an external electronic device and / or from an external electronic device to the memory banks of the semiconductor product. A number of second semiconductor chips are stacked on and electrically coupled to the first semiconductor chip. The second semiconductor chips are stacked on one another. Each second semiconductor chip of the plurality of second semiconductor chips comprises at least one of the memory banks of the semiconductor product. The memory banks of the second semiconductor chips are accessible by the input / output circuitry arranged on the first semiconductor chip.

Owner:INFINEON TECH AG

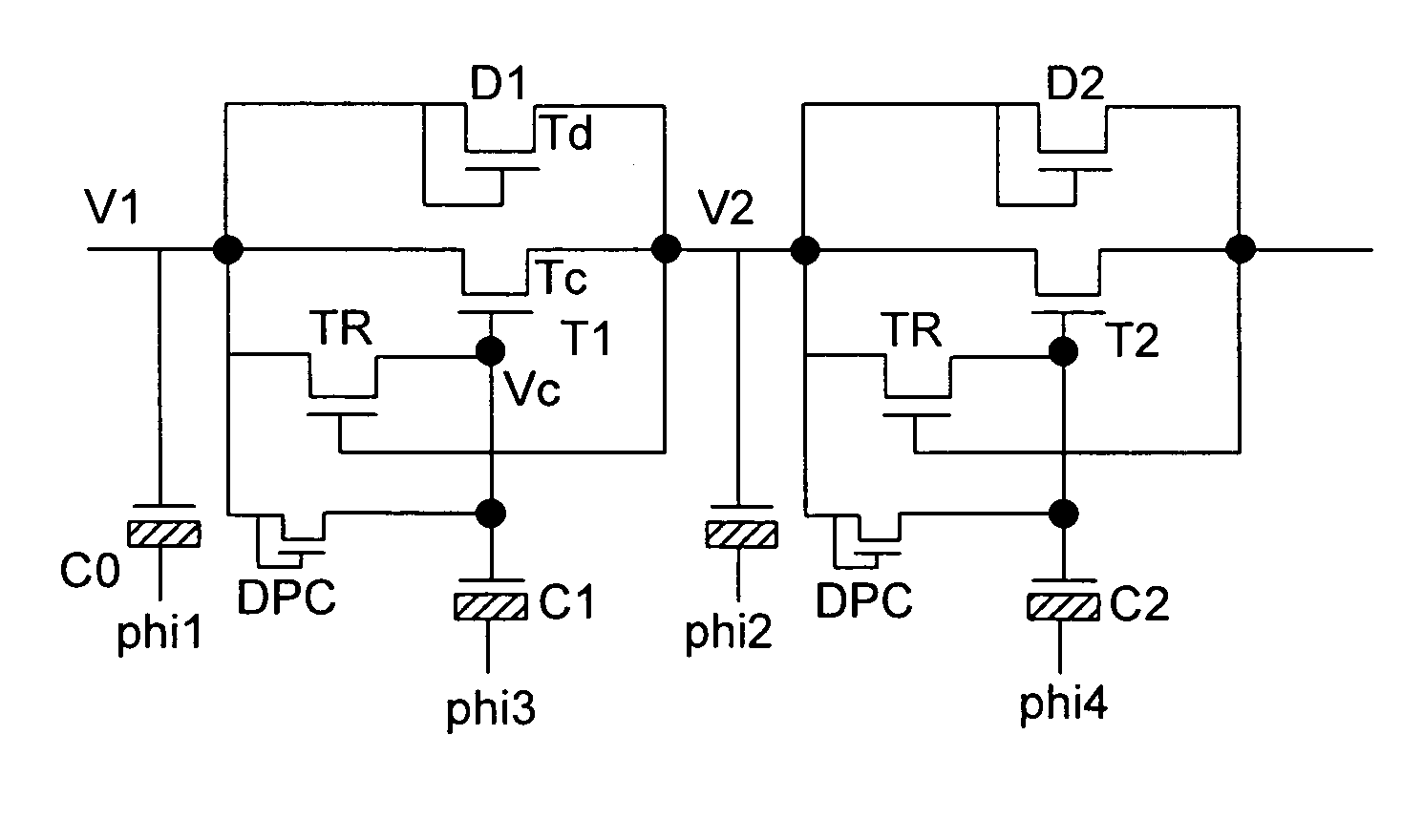

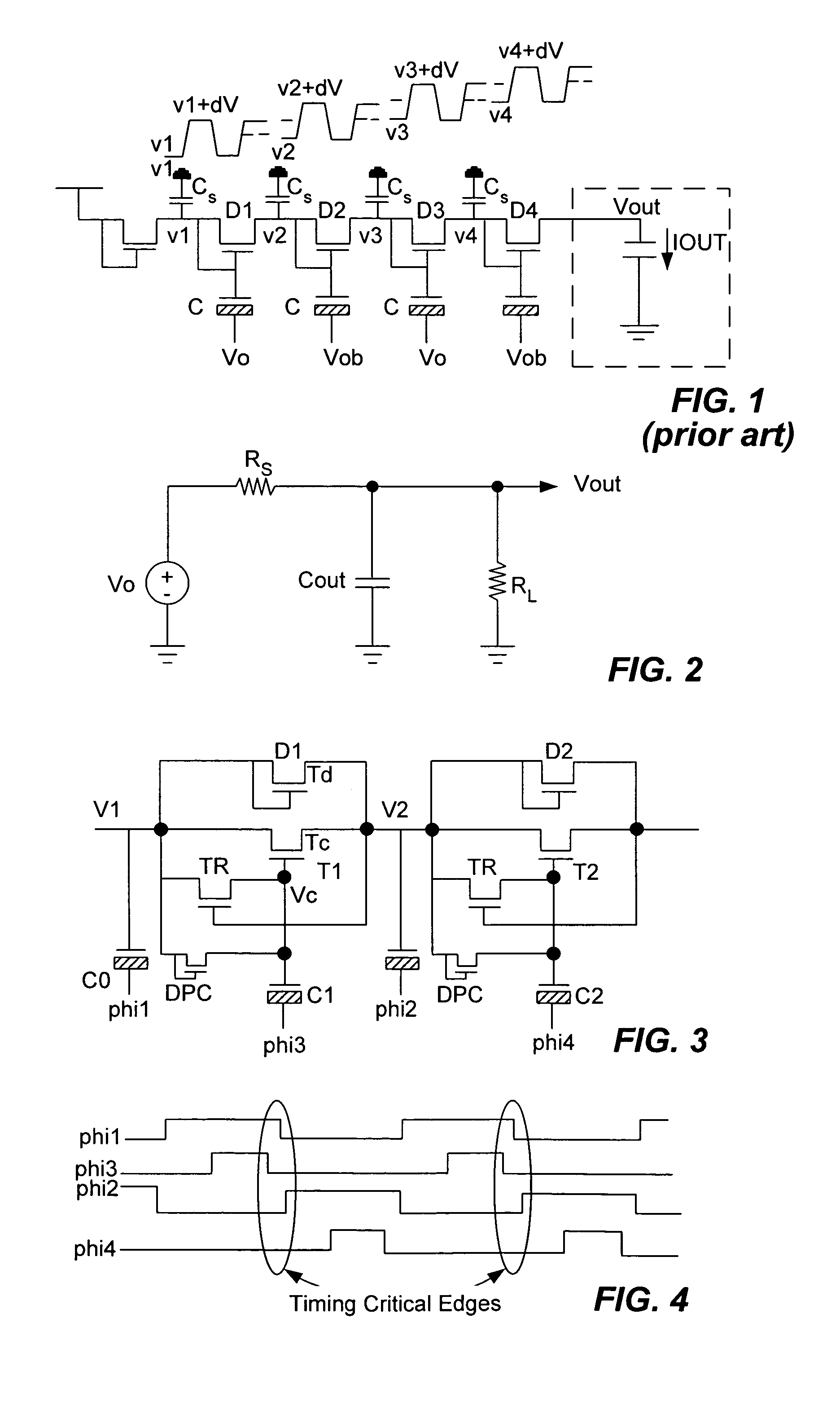

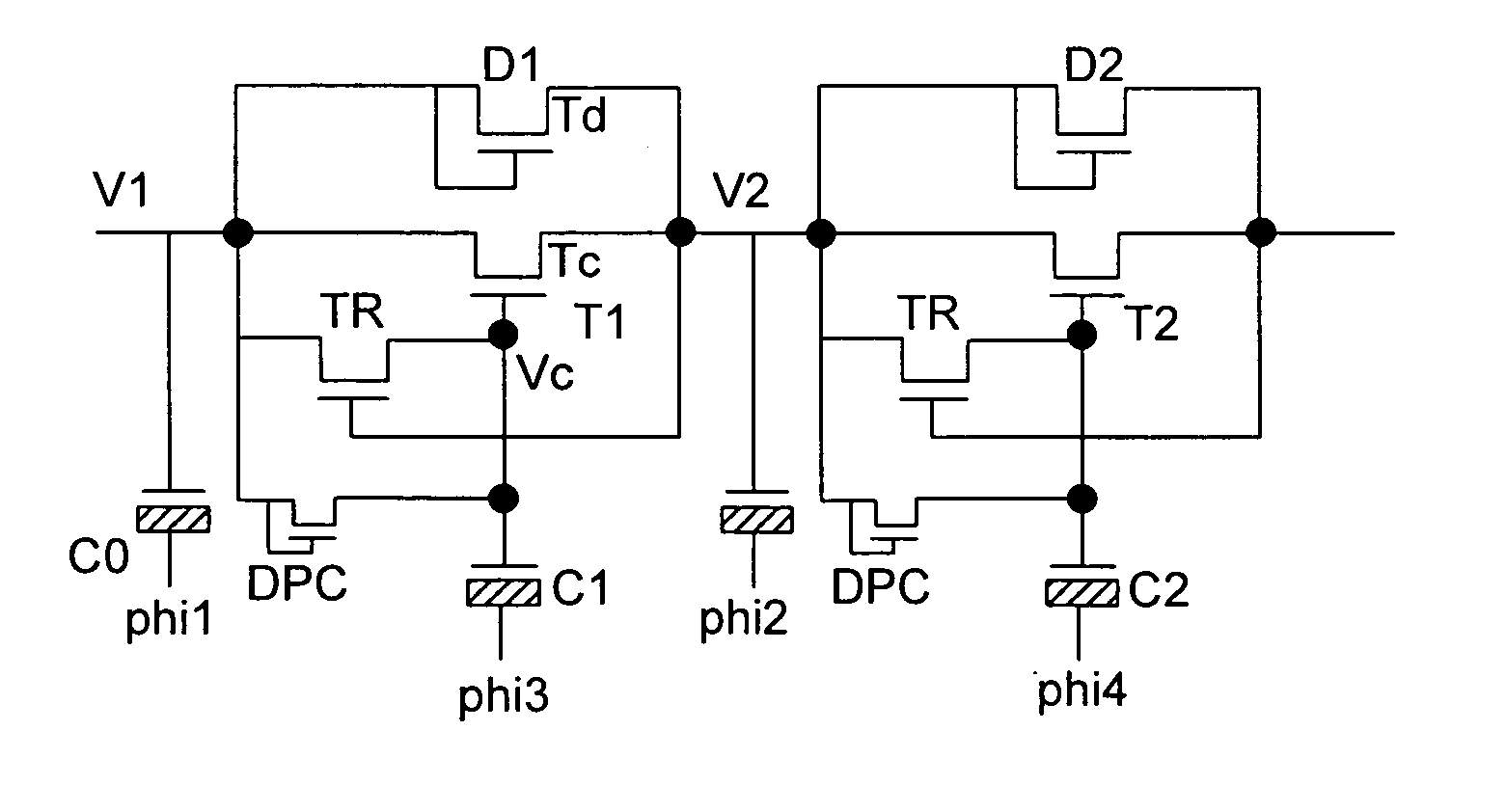

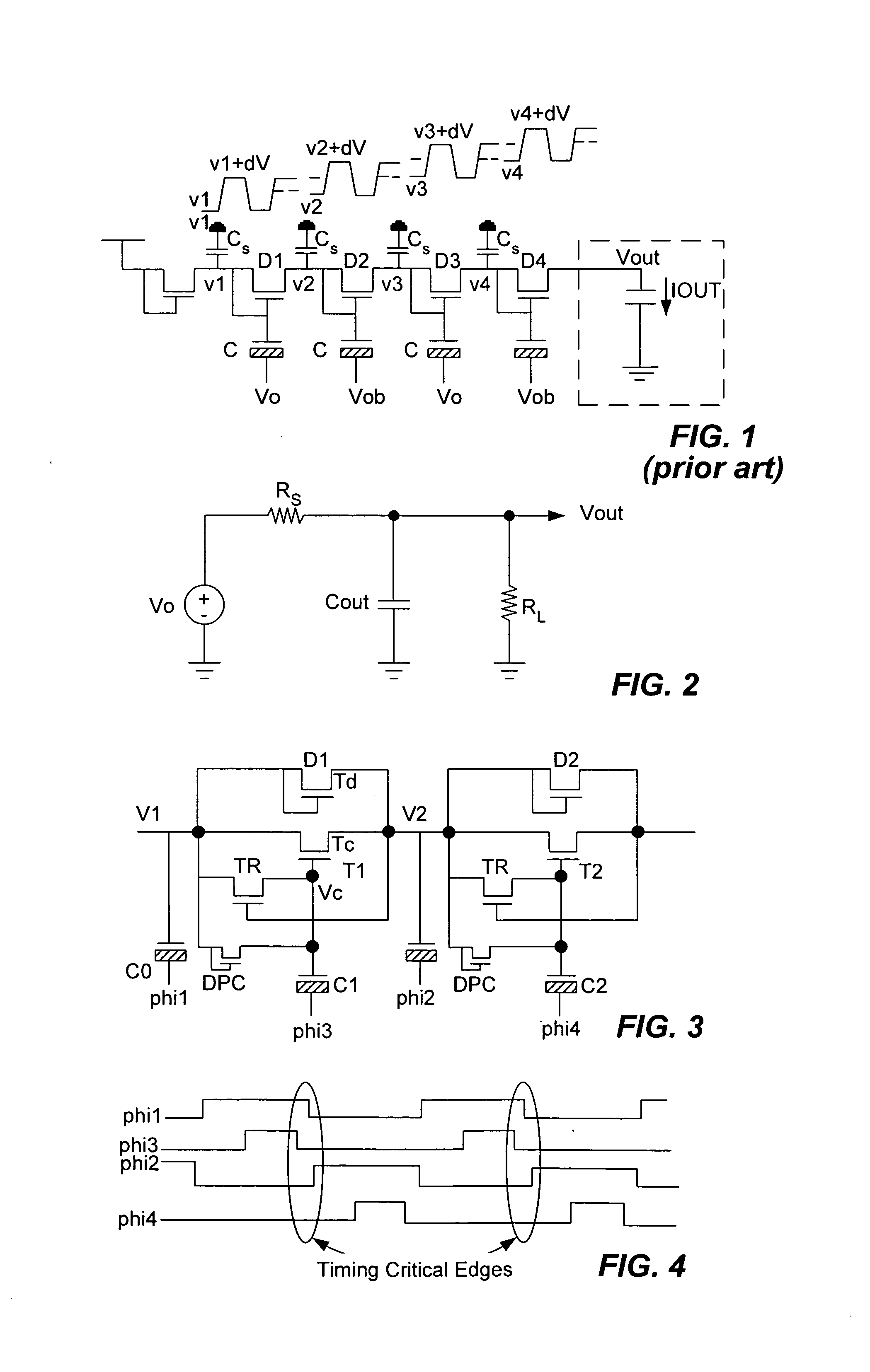

Four phase charge pump operable without phase overlap with improved efficiency

ActiveUS7030683B2Increase conductanceIncrease clock frequencyApparatus without intermediate ac conversionElectric variable regulationRecovery periodPre-charge

In a Dickson type charge pump in which a plurality of serially connected diodes sequentially respond to anti-phase 50 / 50 clock cross over or overlapped (φ1, φ2), efficiency of the charge pump is increased by providing with each diode a charge transfer transistor in parallel therewith between two adjacent nodes, and driving the charge transfer transistor to conduction during a time when the parallel diode is conducting thereby transferring any residual trapped charge at one node through the charge transfer transistor to the next node. Operating frequency can be increased by providing a pre-charge diode coupling an input node to the gate of the charge transfer transistor to facilitate conductance of the charge transfer transistor, and by coupling the control terminal of the charge transfer transistor to an input node in response to charge on an output node to thereby equalize charge on the control terminal and on the input node during a recovery period.

Owner:SANDISK TECH LLC

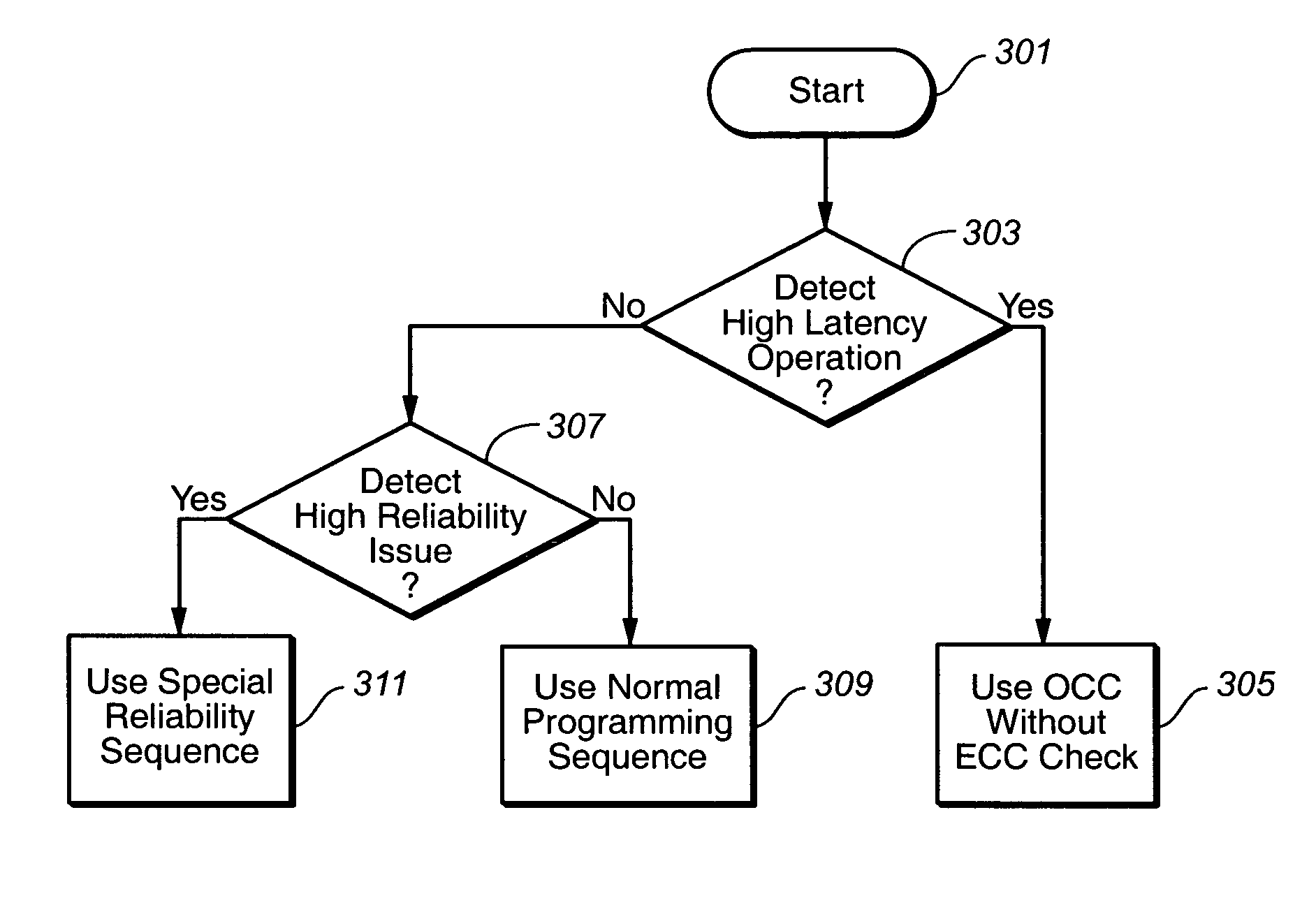

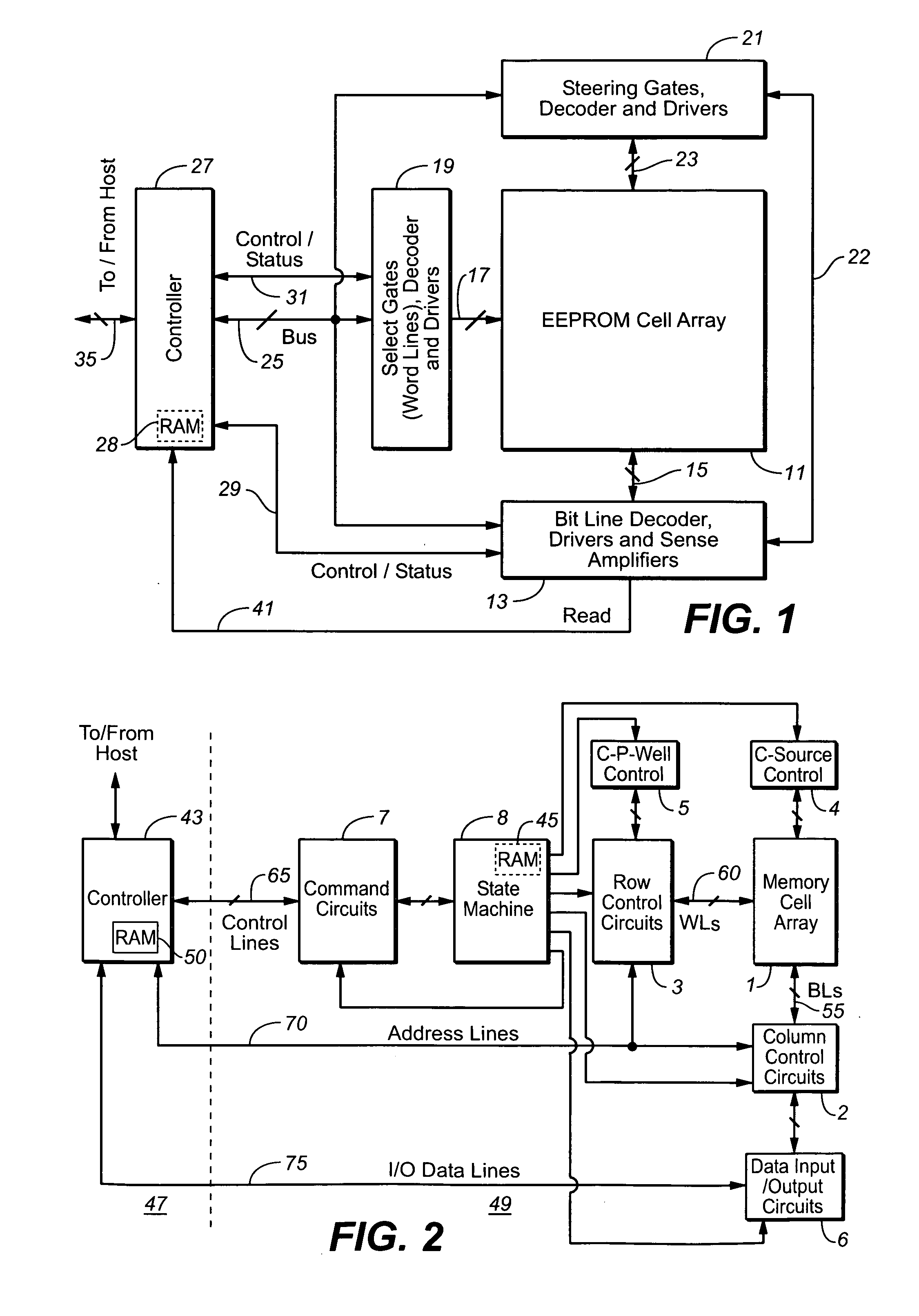

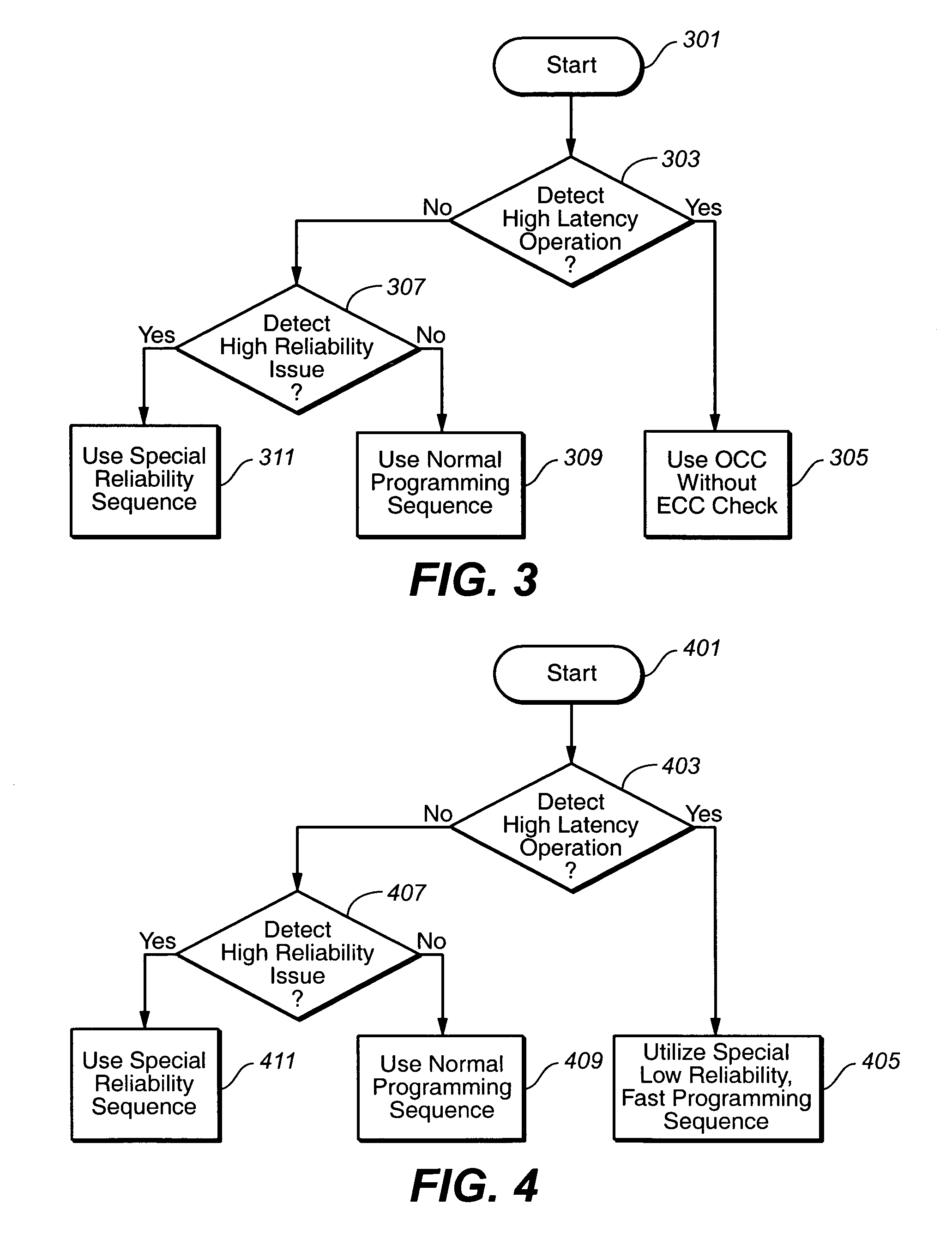

Situation sensitive memory performance

ActiveUS20070033581A1Avoid timeoutImprove programming speedEnergy efficient ICTVolume/mass flow measurementTerm memoryComputer science

The present invention presents a non-volatile memory system that adapts its performance to one or more system related situation. If a situation occurs where the memory will require more than the allotted time for completing an operation, the memory can switch from its normal operating mode to a high performance mode in order to complete the operation quickly enough. Conversely, if a situation arises where reliability could be an issue (such as partial page programming), the controller could switch to a high reliability mode. In either case, once the trigging system situation has returned to normal, the memory reverts to the normal operation. The detection of such situations can be used both for programming and data relocation operations. An exemplary embodiment is based on firmware programmable performance.

Owner:SANDISK TECH LLC

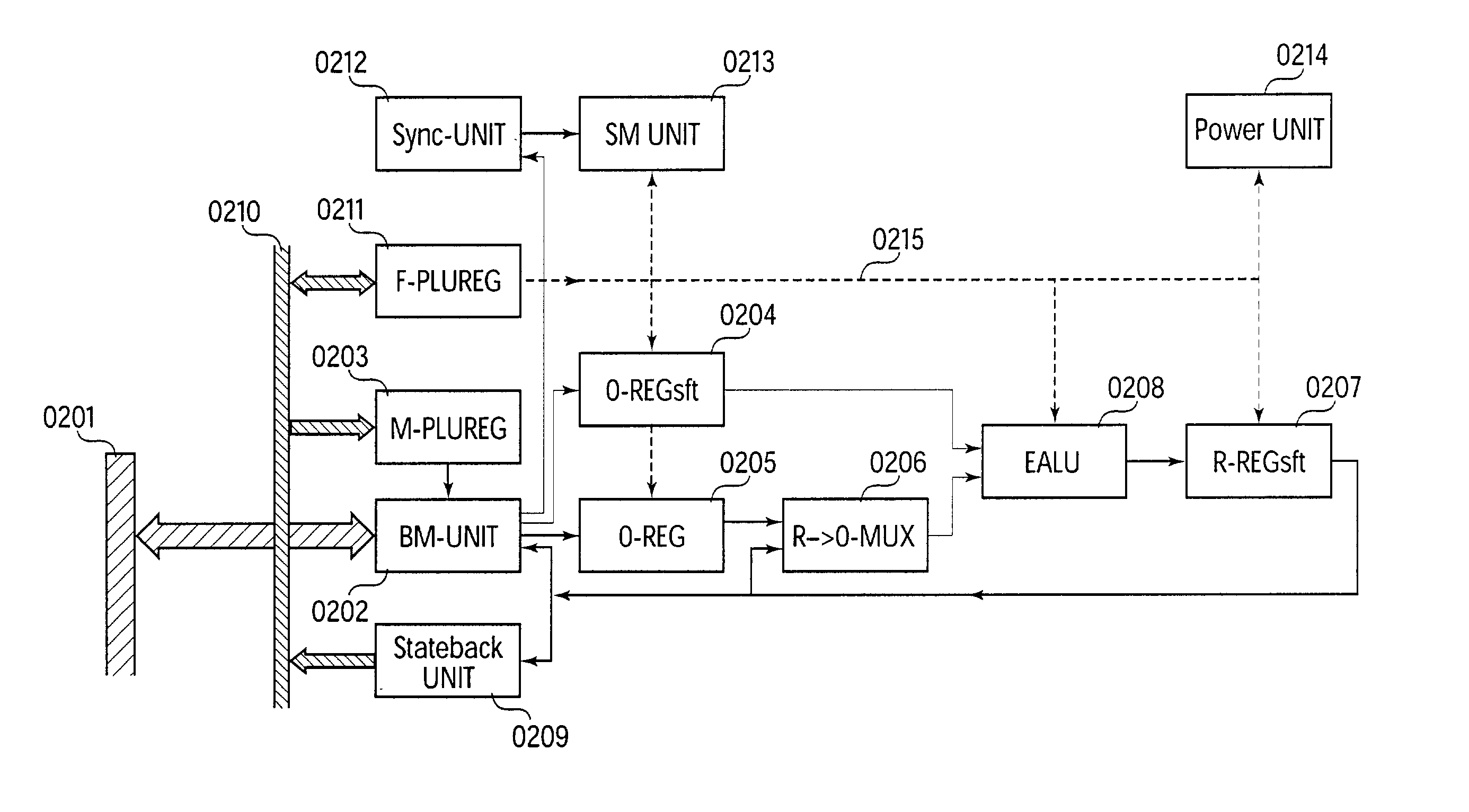

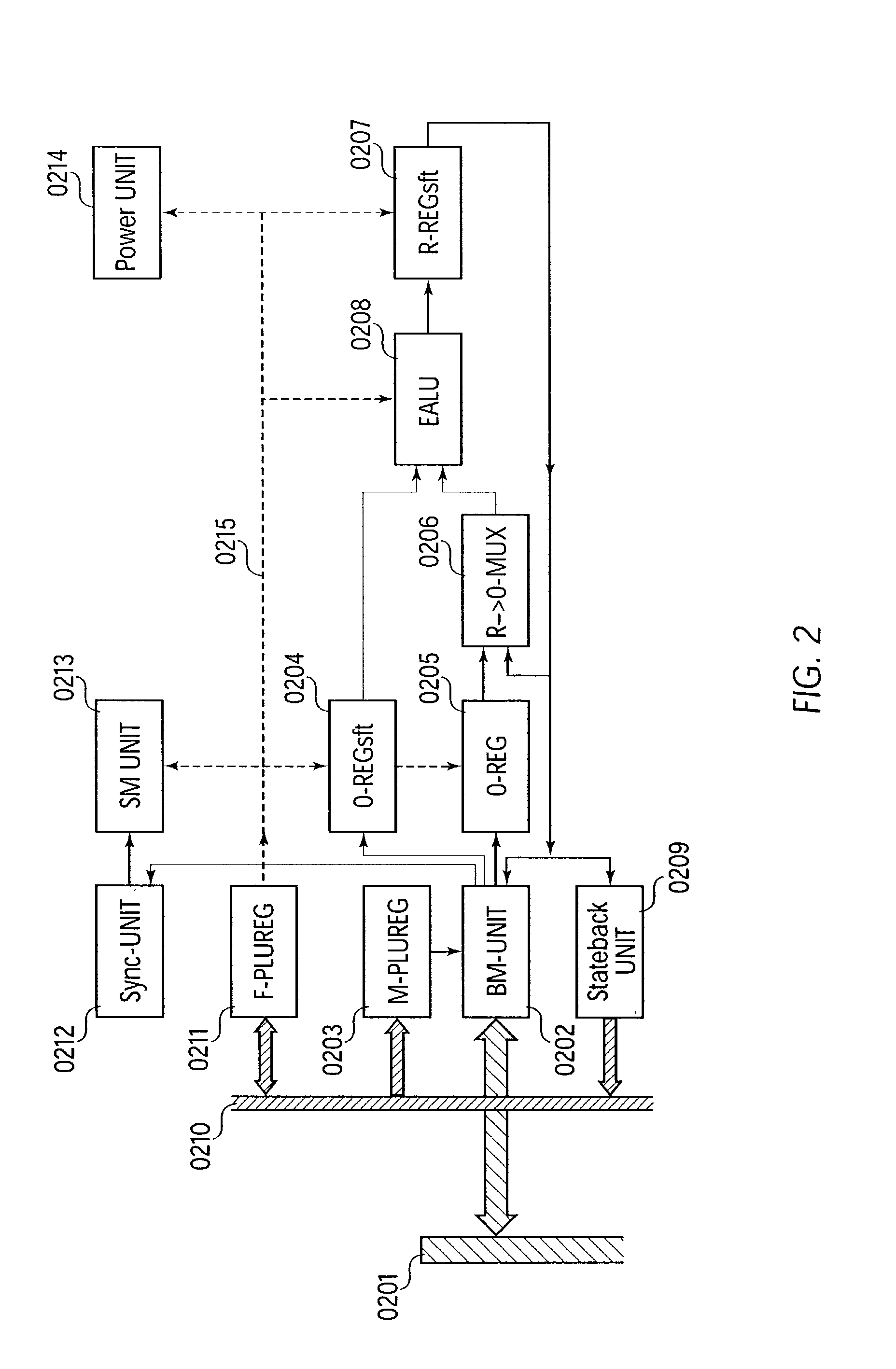

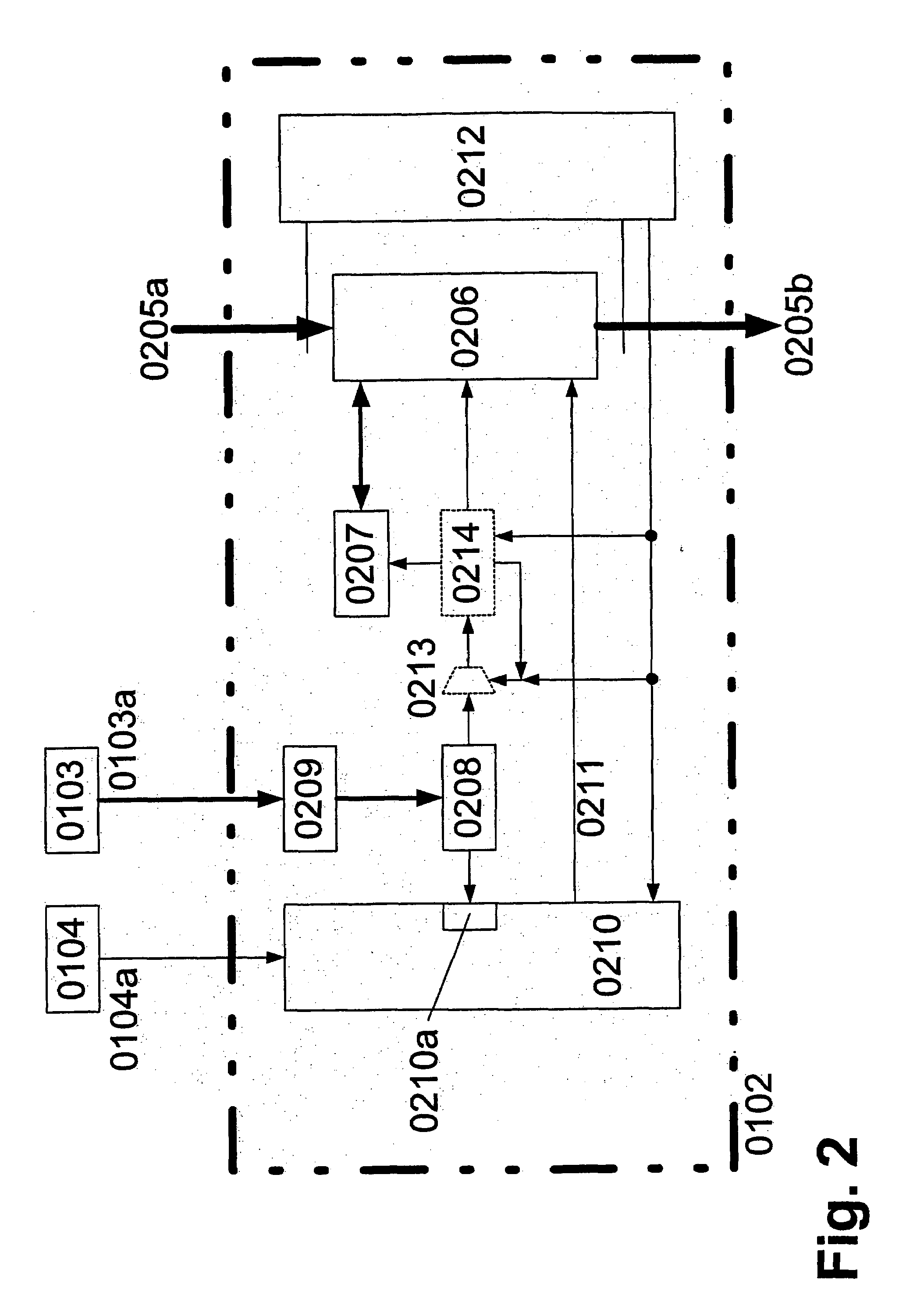

Unit for processing numeric and logic operations for use in central processing units (CPUS), multiprocessor systems, data-flow processors (DSPS), systolic processors and field programmable gate arrays (FPGAS)

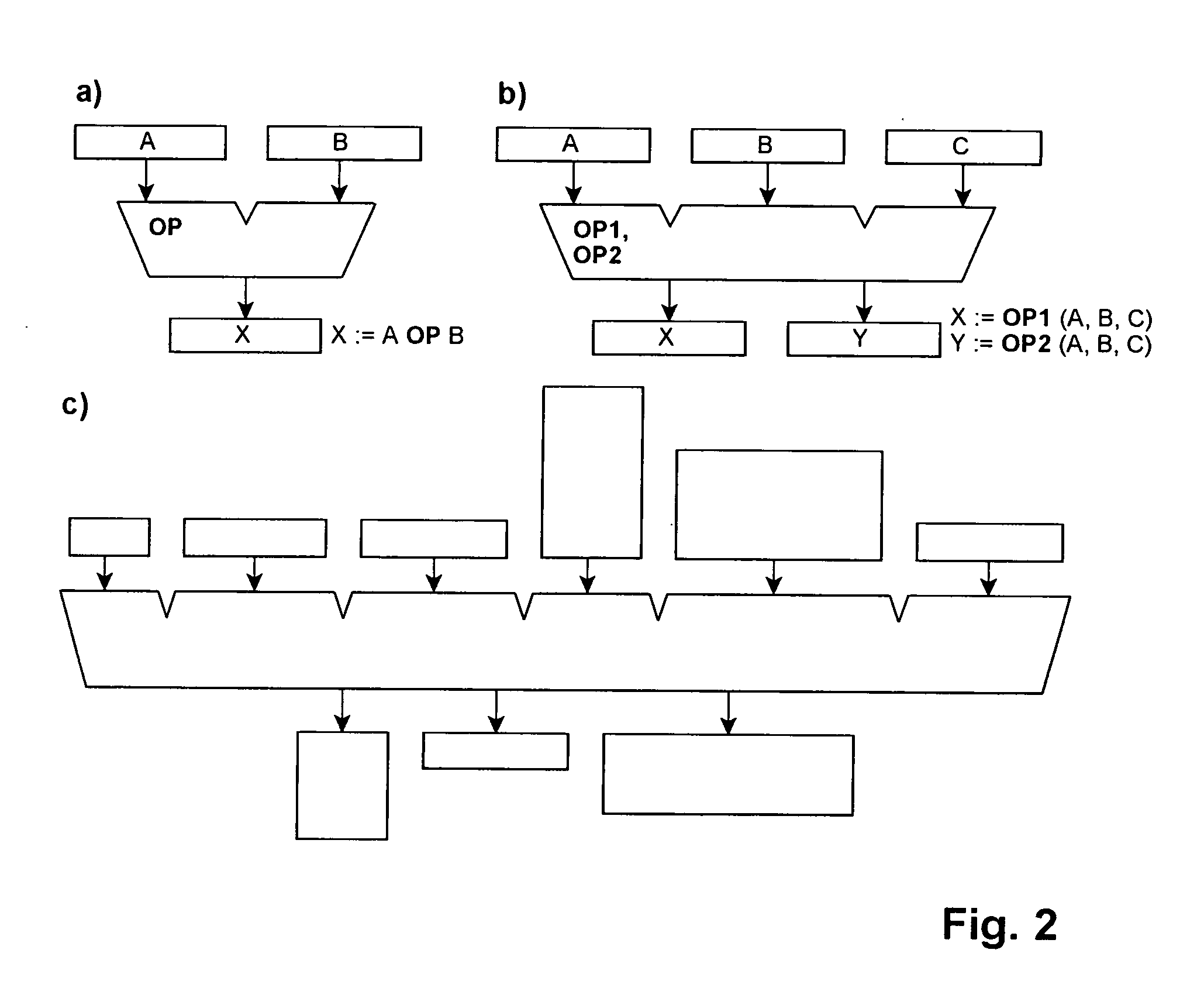

InactiveUS20030056085A1The process is convenient and fastSimplifies (re)configurationEnergy efficient ICTMultiple digital computer combinationsBus masteringBroadcasting

An expanded arithmetic and logic unit (EALU) with special extra functions is integrated into a configurable unit for performing data processing operations. The EALU is configured by a function register, which greatly reduces the volume of data required for configuration. The cell can be cascaded freely over a bus system, the EALU being decoupled from the bus system over input and output registers. The output registers are connected to the input of the EALU to permit serial operations. A bus control unit is responsible for the connection to the bus, which it connects according to the bus register. The unit is designed so that distribution of data to multiple receivers (broadcasting) is possible. A synchronization circuit controls the data exchange between multiple cells over the bus system. The EALU, the synchronization circuit, the bus control unit, and registers are designed so that a cell can be reconfigured on site independently of the cells surrounding it. A power-saving mode which shuts down the cell can be configured through the function register; clock rate dividers which reduce the working frequency can also be set.

Owner:PACT +1

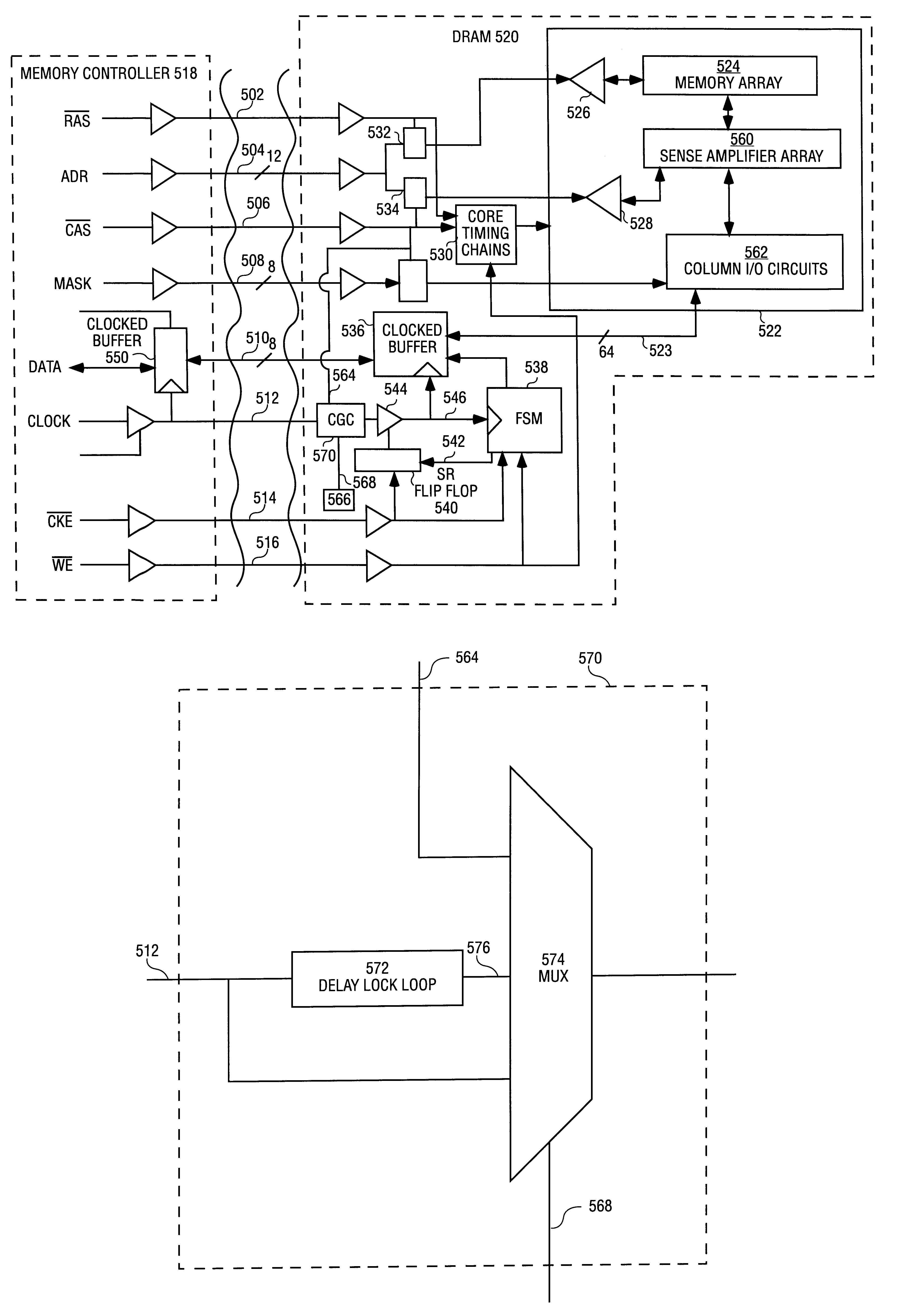

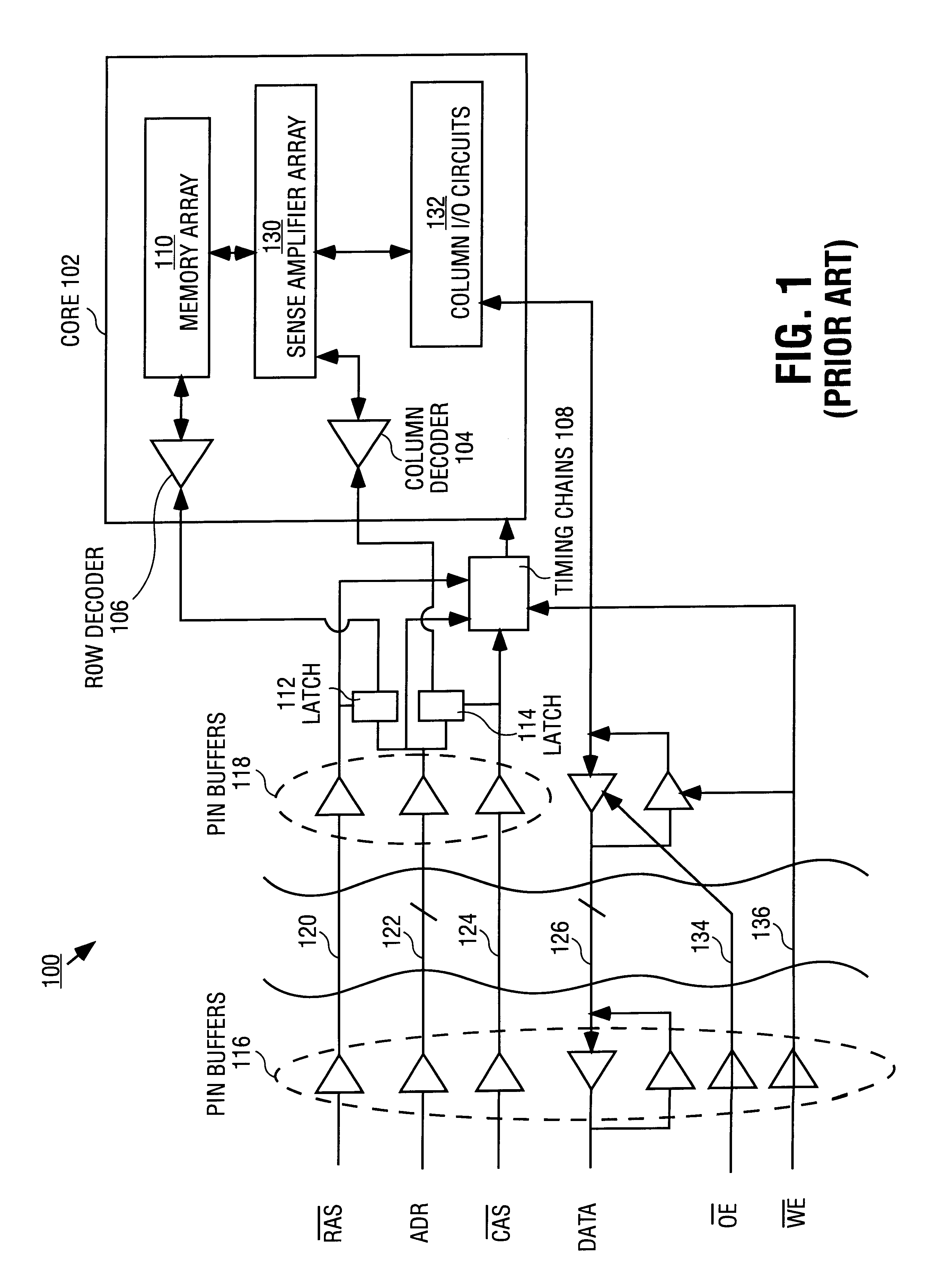

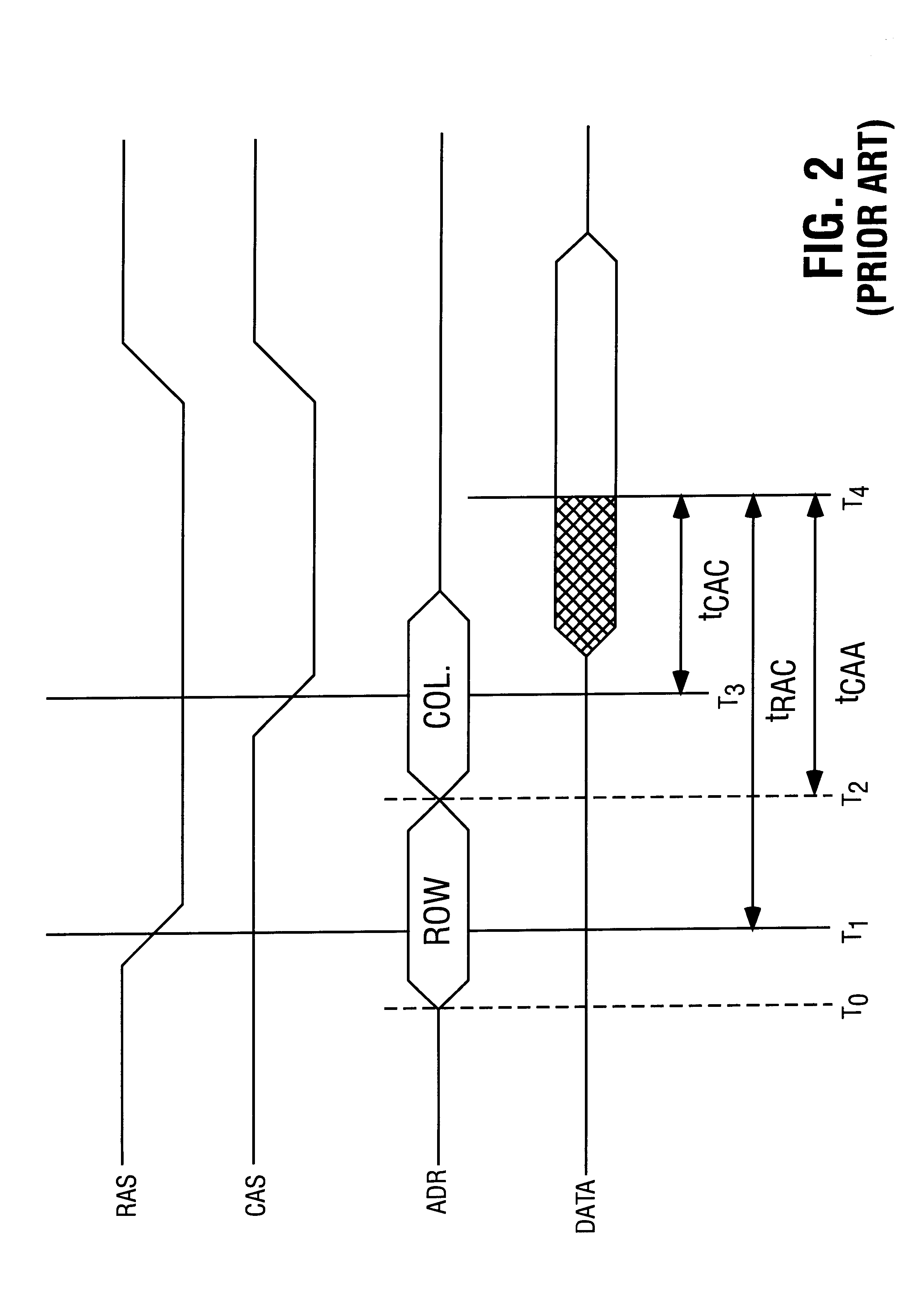

Asynchronous request/synchronous data dynamic random access memory

InactiveUS6209071B1Improve balanceReducing latency and power requirementEnergy efficient ICTDigital storagePower modeAsynchronous circuit

A method and system for transferring information within a computer system is provided. The system includes a memory device that has a lower power mode in which data transfer circuitry is not driven by a clock signal, and a higher power mode in which data transfer circuitry is driven by a clock signal. The system further includes a memory controller that sends control signals to the memory device to initiate a data transfer transaction. The memory device receives the control signals asynchronously, and assumes the second mode in response to one of the control signals. While the memory device is in the second mode, the memory controller sends a control signal to identify a particular clock cycle. The memory device synchronously transfers the data. The memory device determines when to begin the data transfer based on the identified clock cycle and the type of data transfer that has been specified.

Owner:RAMBUS INC

Method for information processing

InactiveUS20060259744A1Improve executionAddress decoding is simplifiedDigital computer detailsSpecific program execution arrangementsResource poolOperating system

In a method for program-controlled information processing, resources for information processing form a resource pool. Suitable resources are selected from the resource pool and connections between the selected resources are configured. Parameters are supplied to the selected resources and information processing operations are initiated in the selected resources. Data are transported between the selected resources and results are assigned. Connections that are no longer needed are disconnected between the selected resources. The selected resources that are no longer needed are returned to the resource pool.

Owner:MATTHES WOLFGANG

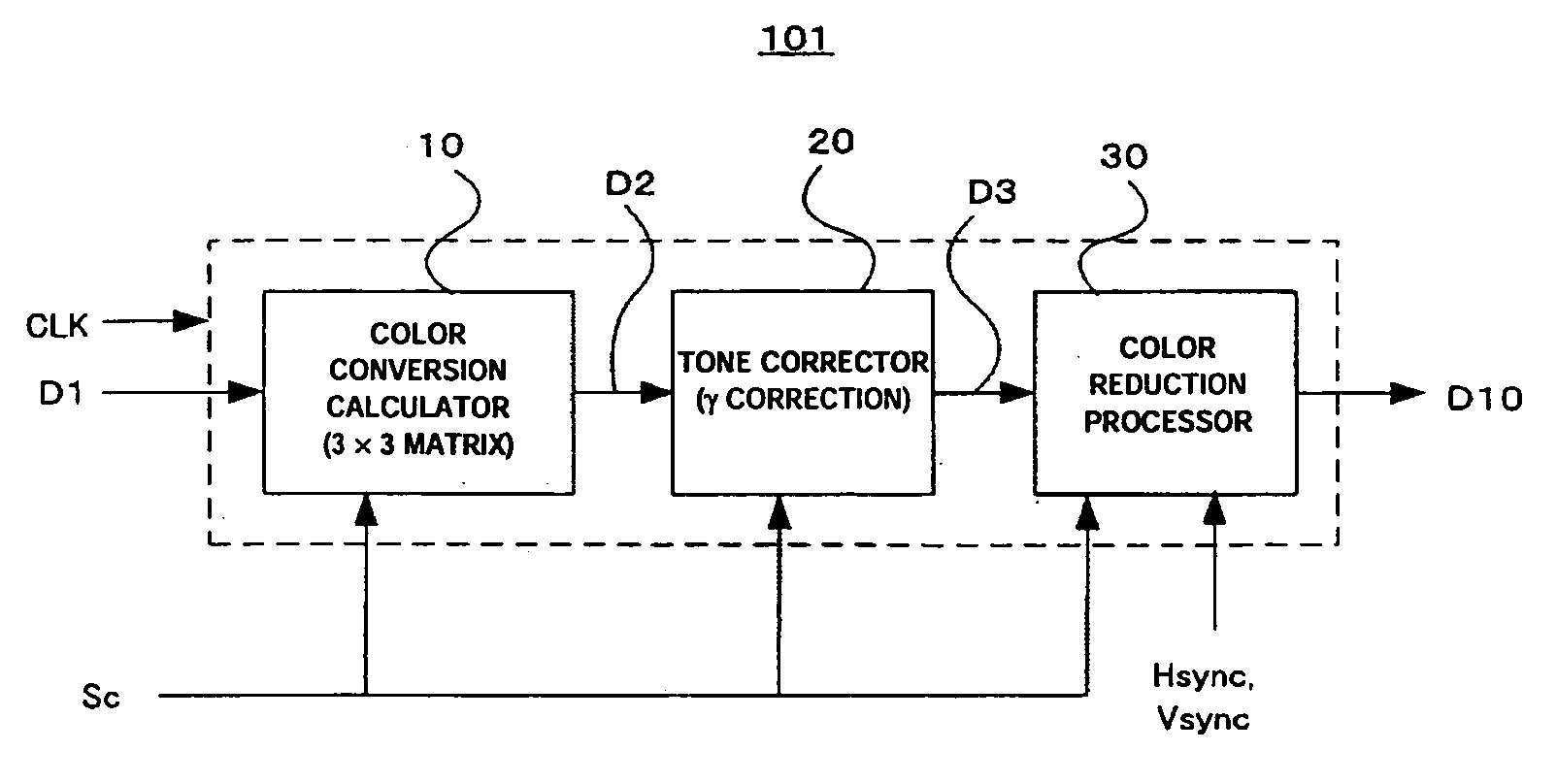

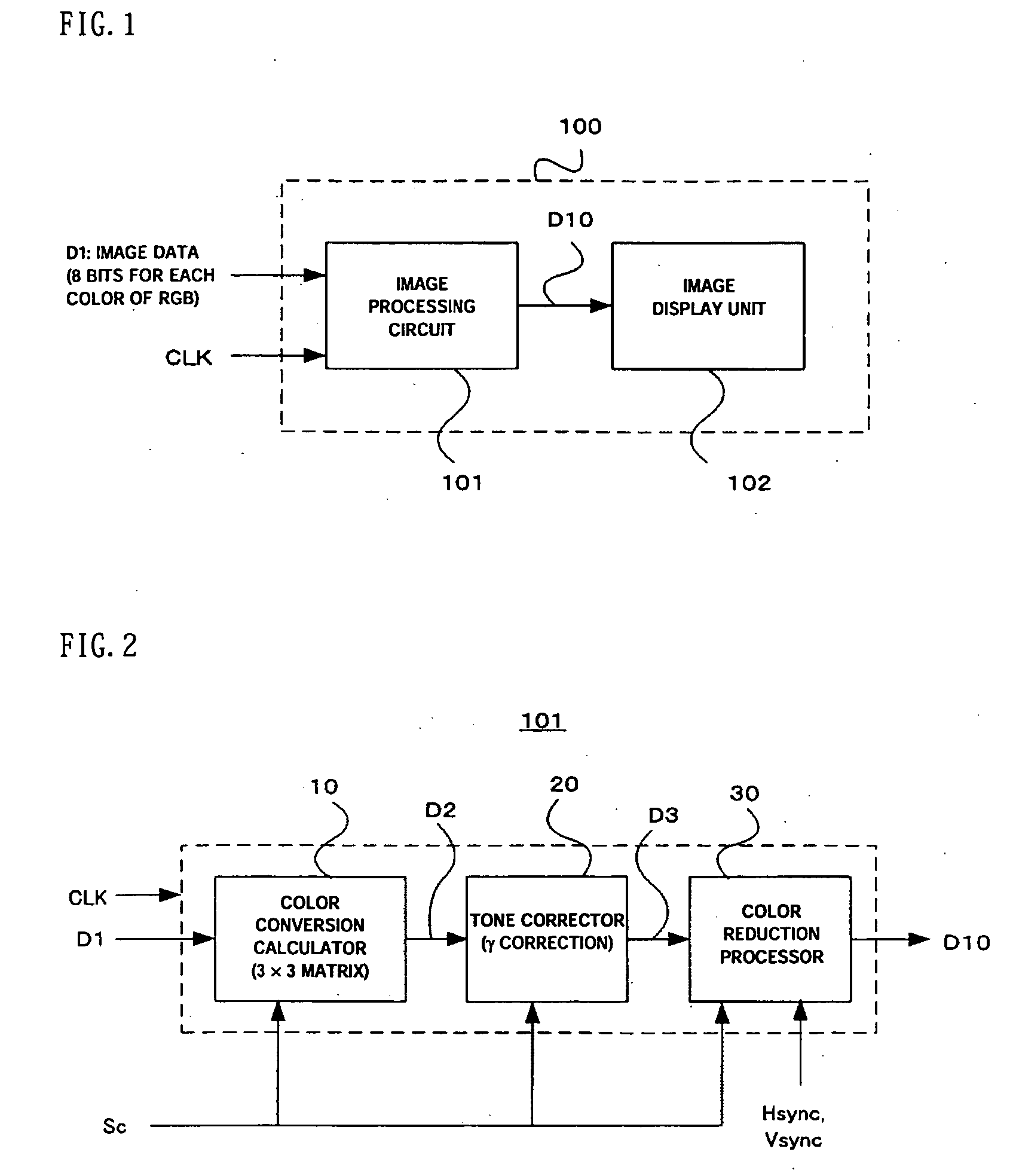

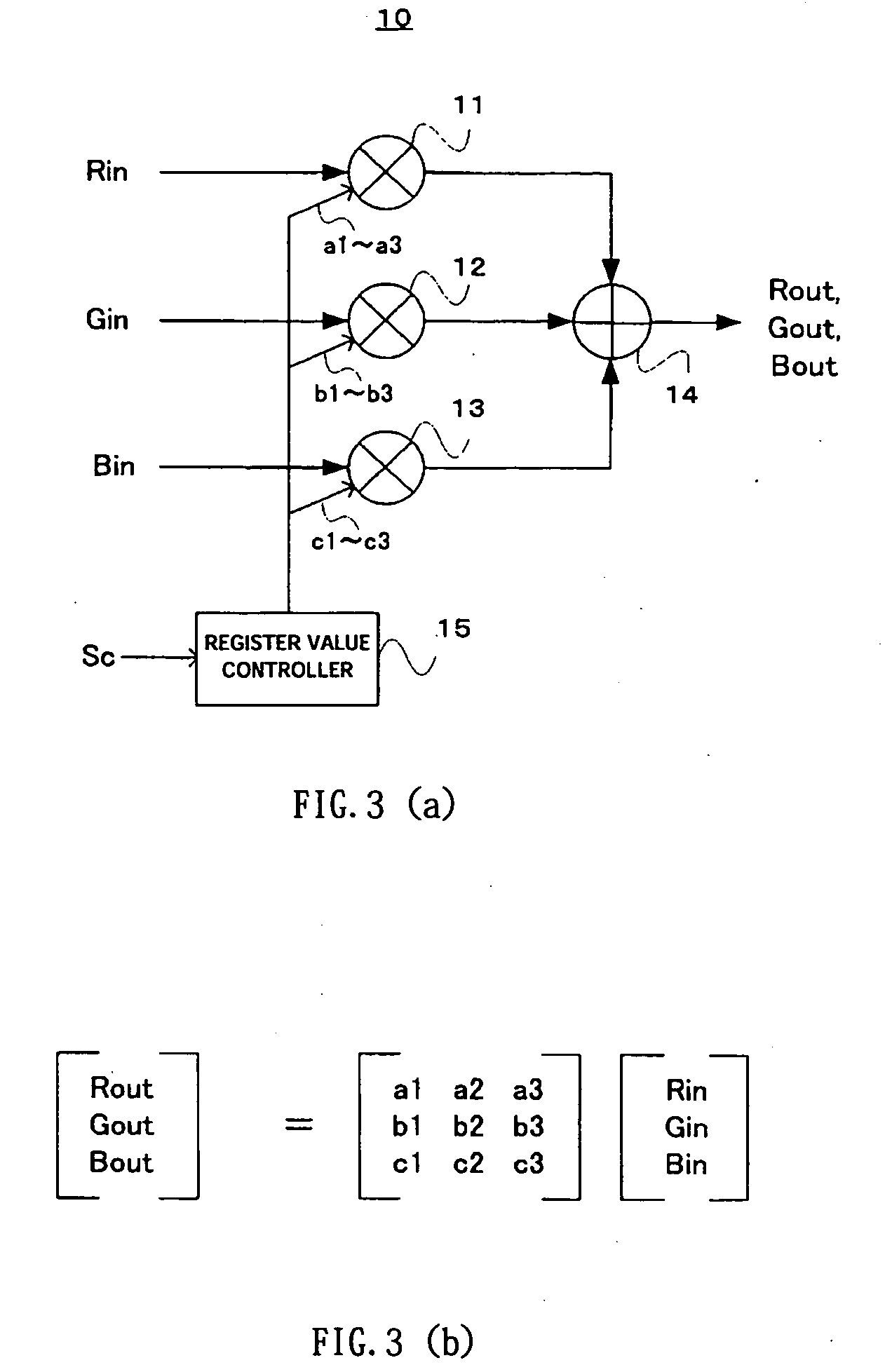

Image processing circuit, image display apparatus, and image processing method

ActiveUS20050111046A1Reduce storage capacityIncrease clock frequencyImage enhancementTelevision system detailsColor correctionImaging data

Aspects of the invention can provide an image processing circuit for gray scale correction, an image display apparatus, and an image processing method that allow reduction in the storage capacity needed for storing correction characteristics data without increasing clock rate in relation to interpolation processing of correction characteristics. A exemplary image processing circuit according to the invention can be applied, for example, to color correction or gamma correction of color image data. Gray scale correction characteristics data for a number of gray scale levels that is less than the number of gray scale levels of input image data can be stored in first and second lookup table storing units. Considering a gray scale value of a pixel that is being considered for gray scale correction processing as an input gray scale value, the first and second lookup-table storing units are referred to, obtaining an output gray scale value corresponding to the input gray scale value and an output gray scale value corresponding to an adjacent input gray scale value. An adjacent gray scale value refers to a gray scale value that is higher by one or lower by one than another input gray scale value. Then, output gray scale values between these two adjacent output gray scale values can be calculated by linear interpolation, obtaining output values for all input gray scale values. Subsequently, gray scale correction can be performed for each pixel of input image data, outputting corrected image data.

Owner:BOE TECH GRP CO LTD

Four phase charge pump operable without phase overlap with improved efficiency

ActiveUS20050248386A1Facilitates conductanceIncrease clock frequencyApparatus without intermediate ac conversionElectric variable regulationCross overRecovery period

In a Dickson type charge pump in which a plurality of serially connected diodes sequentially respond to anti-phase 50 / 50 clock cross over or overlapped (φ1, φ2), efficiency of the charge pump is increased by providing with each diode a charge transfer transistor in parallel therewith between two adjacent nodes, and driving the charge transfer transistor to conduction during a time when the parallel diode is conducting thereby transferring any residual trapped charge at one node through the charge transfer transistor to the next node. Operating frequency can be increased by providing a pre-charge diode coupling an input node to the gate of the charge transfer transistor to facilitate conductance of the charge transfer transistor, and by coupling the control terminal of the charge transfer transistor to an input node in response to charge on an output node to thereby equalize charge on the control terminal and on the input node during a recovery period.

Owner:SANDISK TECH LLC

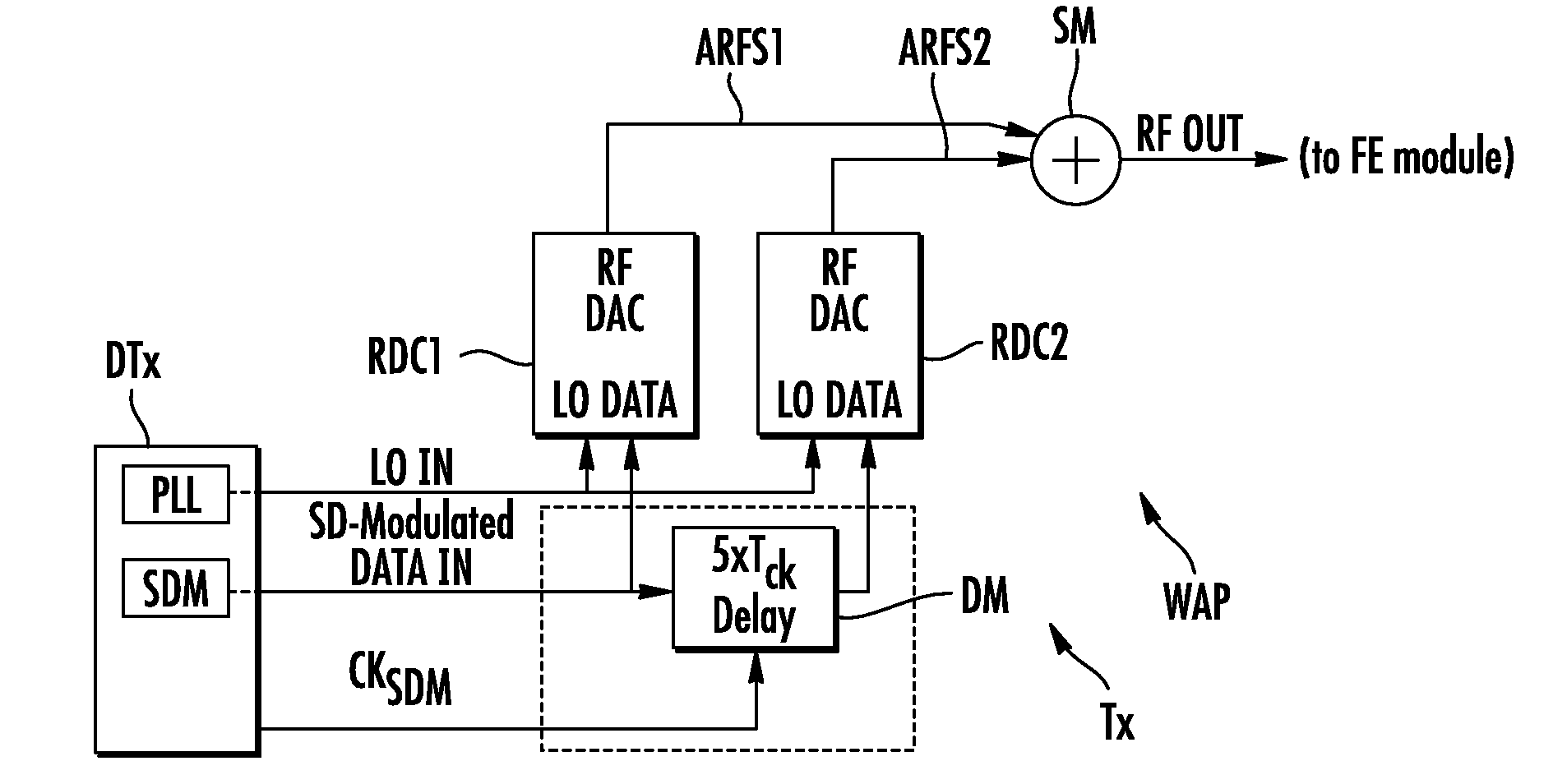

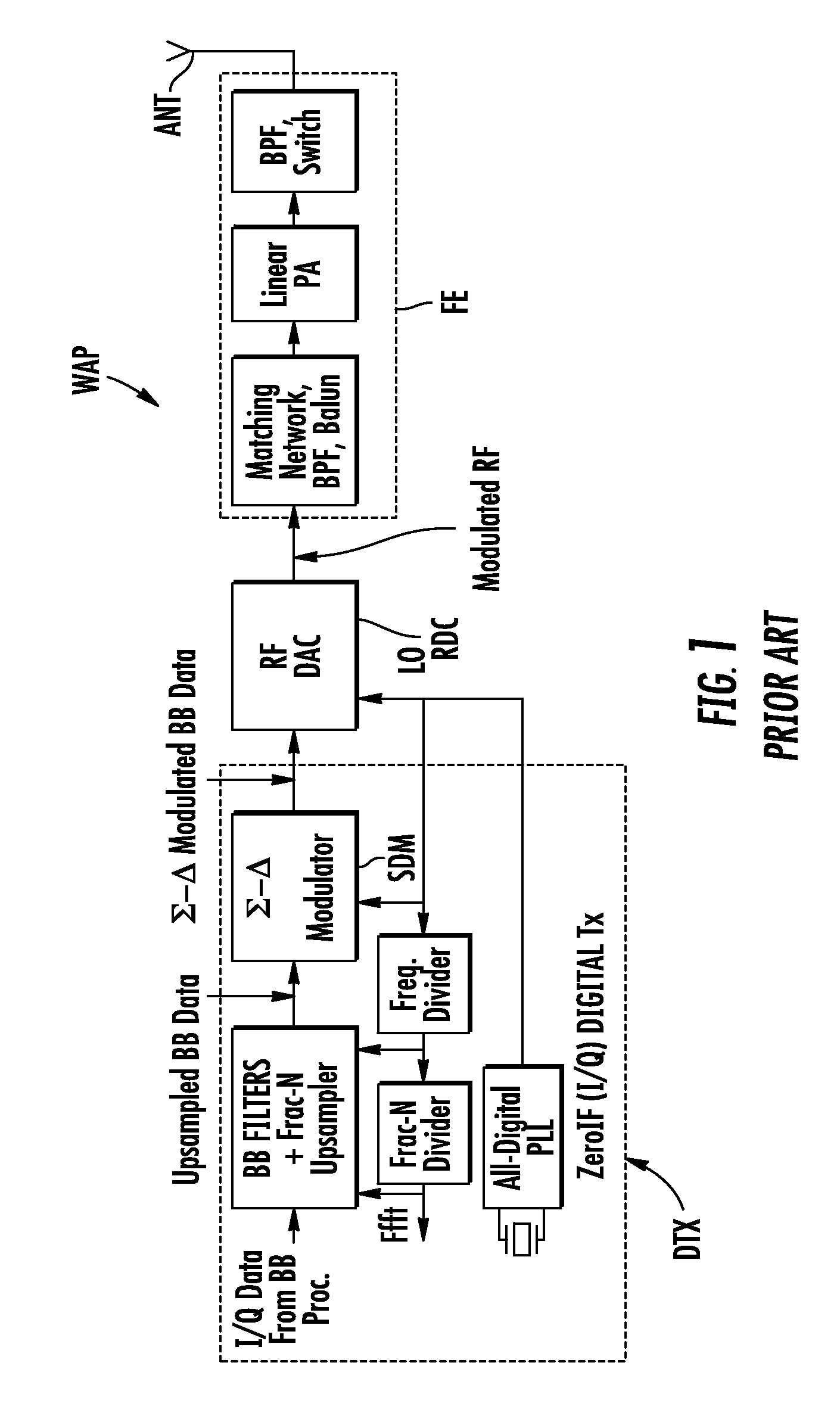

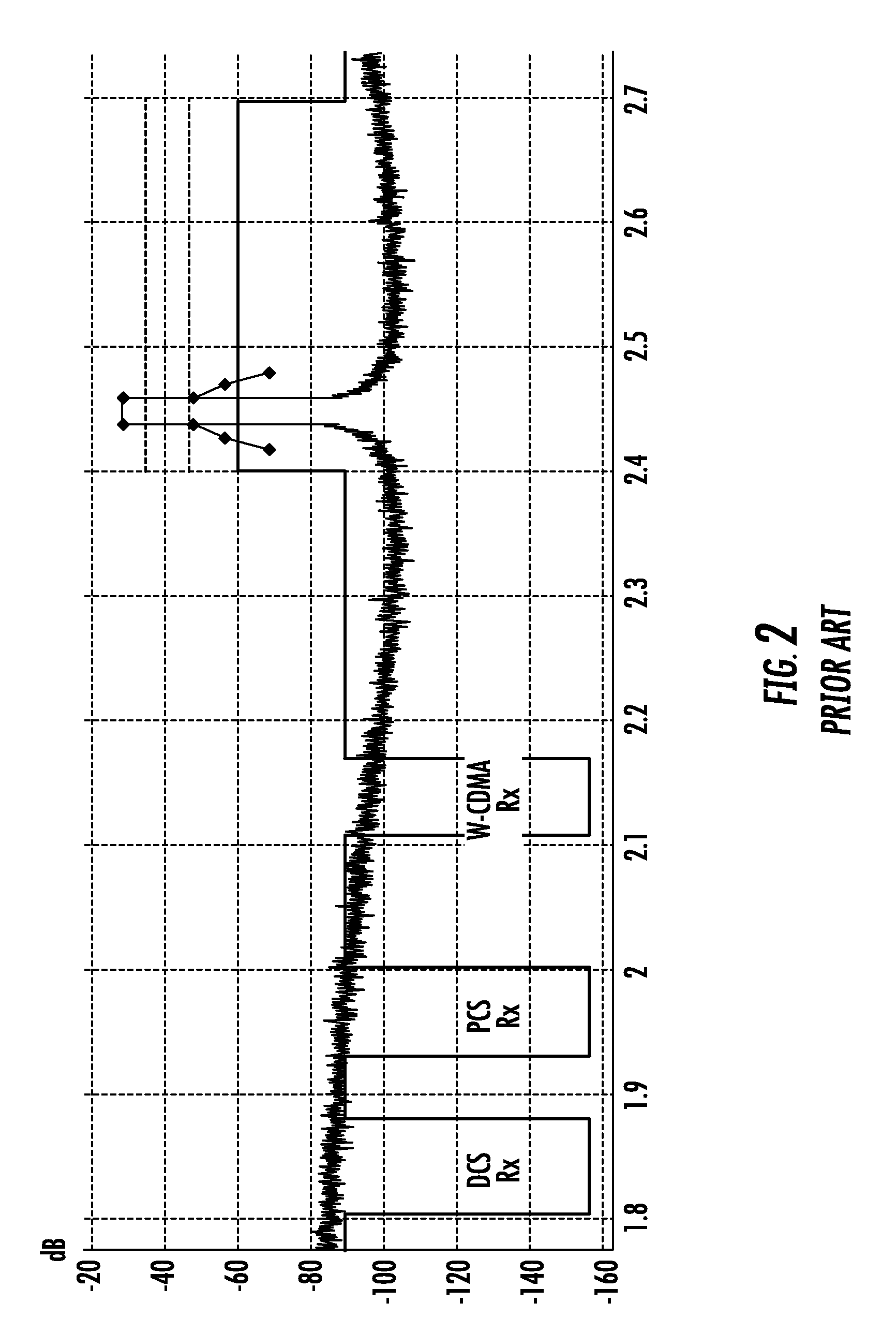

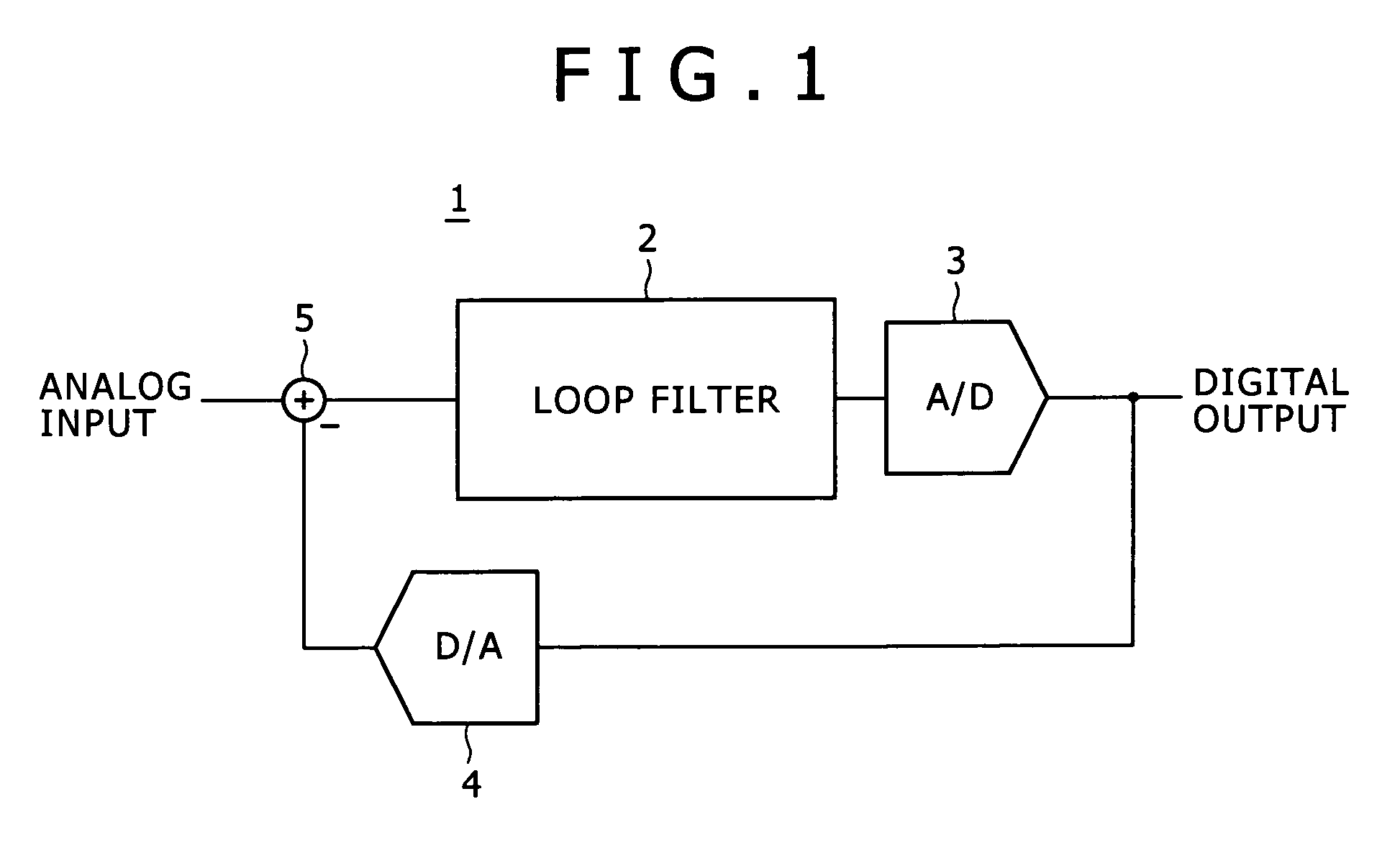

Method for notch filtering a digital signal, and corresponding electronic device

ActiveUS20090082006A1Reduce quantization noiseMore power consumptionElectric signal transmission systemsDigital technique networkDigital dataAnalog signal

An electronic device, includes sigma-delta modulation circuit to operate with a clock signal and having output circuitry to deliver a digital data signal. First circuitry delivers a radiofrequency transposition signal. A notch filter includes radiofrequency digital-to-analog conversion blocks, having first input circuitry coupled to the output circuitry. Second input circuitry receives the radiofrequency transposition signal. Second output circuitry delivers a radiofrequency analog signal. Digital delay circuitry is controlled by the clock signal and includes a delay block between the two first input circuits. The frequency of a notch of the notch filter is related to the value of the delay from the delay block. Summation circuitry sums the radiofrequency signals.

Owner:ST ERICSSON SA

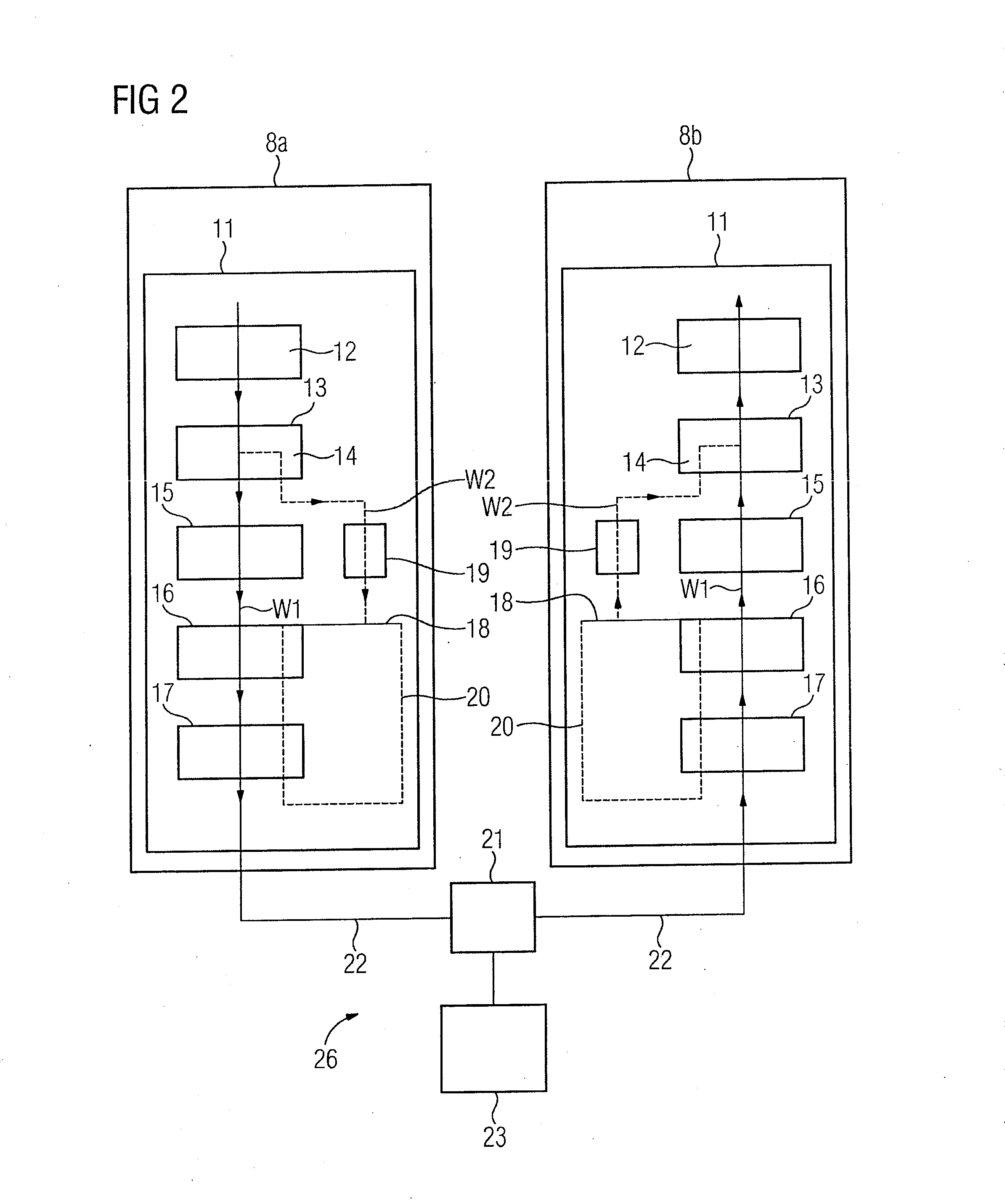

Method and Apparatus for Interchanging Data, and Network

InactiveUS20130070788A1Highly integratedHigh degreeTime-division multiplexTransmissionComputer hardwareNetwork Communication Protocols

A method for interchanging data between two devices in a network which utilizes a communication protocol with an interface based on the OPC-UA standard to interchange the data, wherein the communication protocol comprises an interface based on the stream reservation protocol standard or an interface based on the multiple stream registration protocol standard in accordance with IEEE standard 802.1Qat, such that the data is interchangeable between the two devices using both interfaces in a prescribed period of time.

Owner:SIEMENS AG

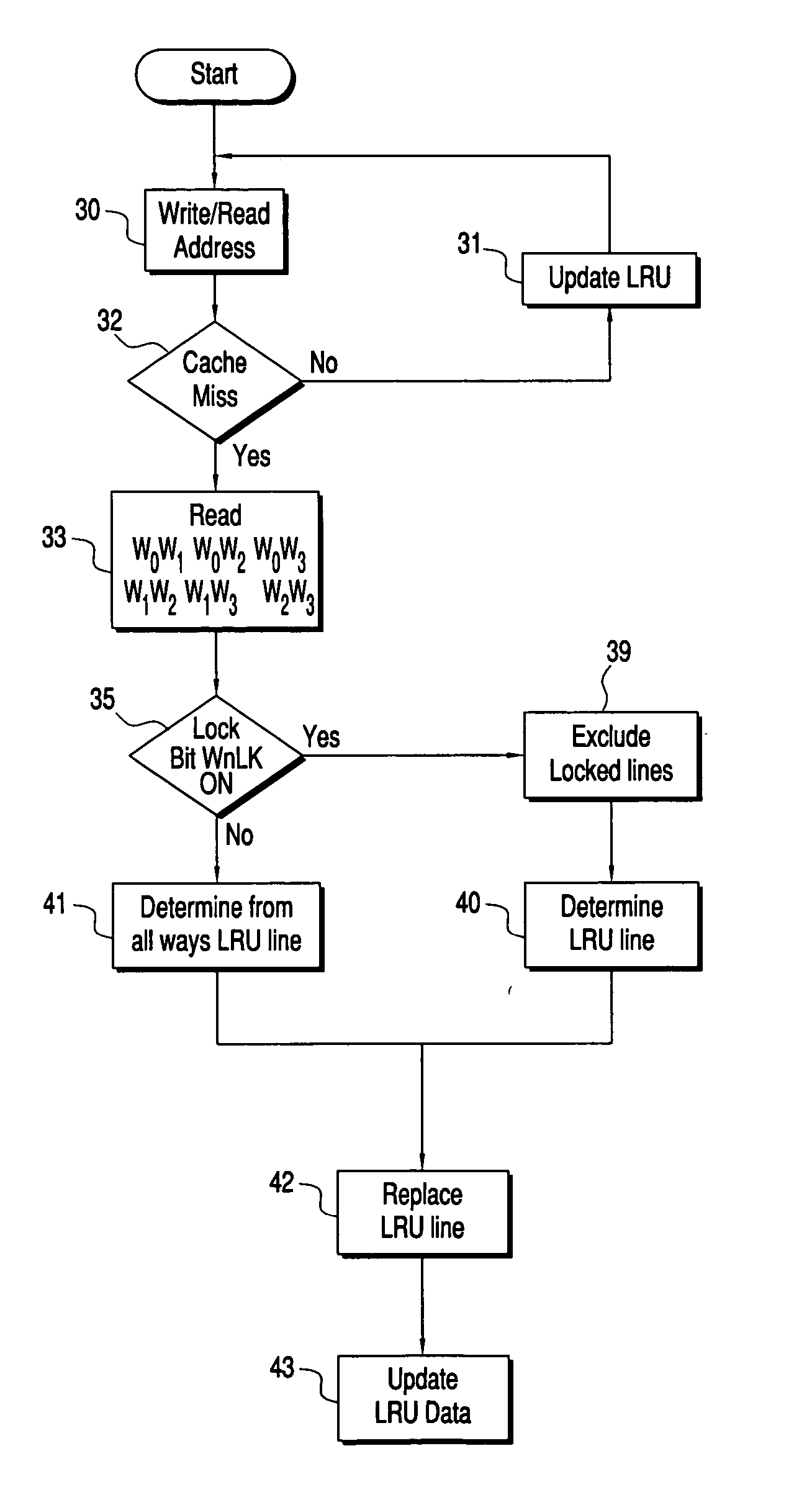

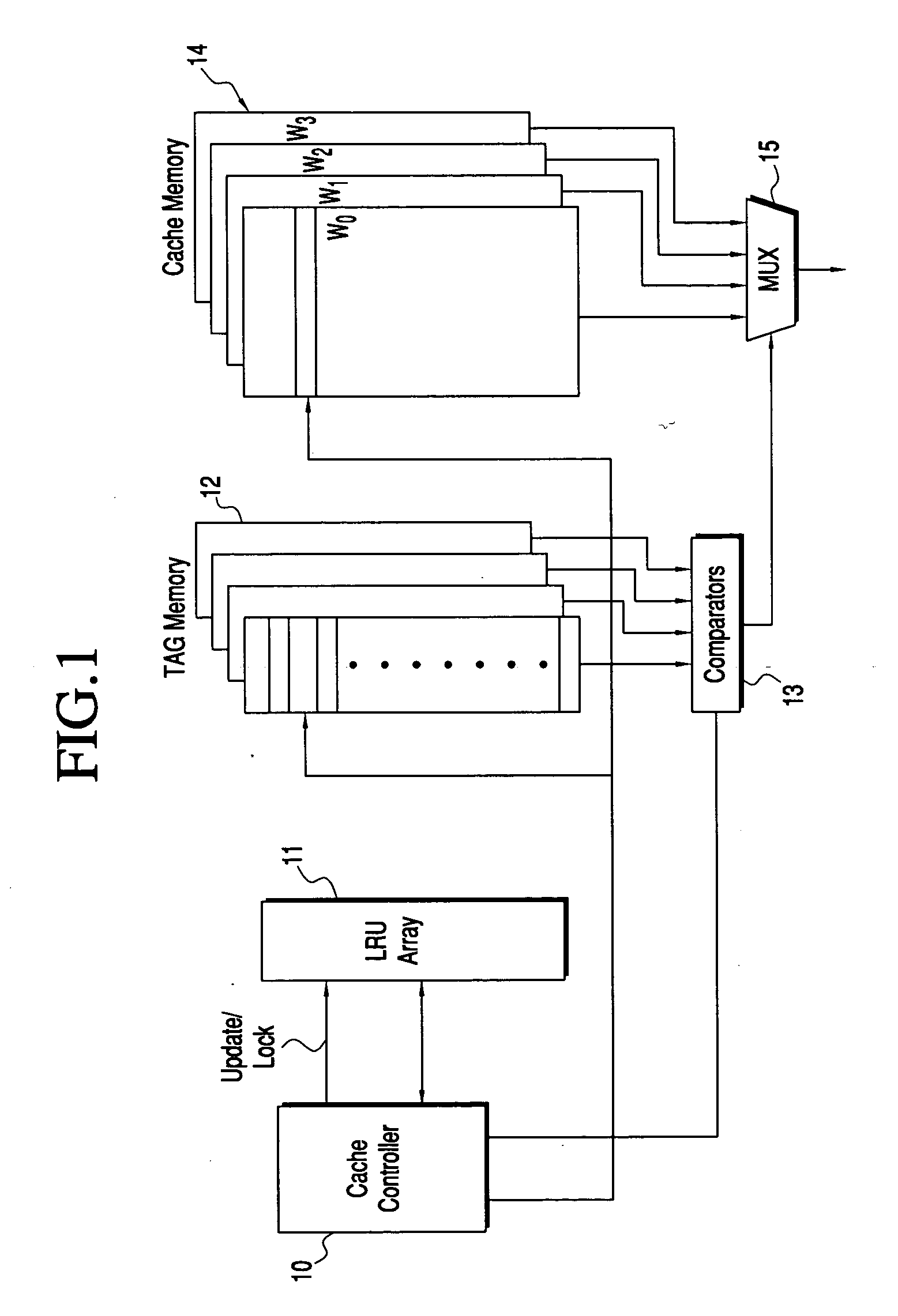

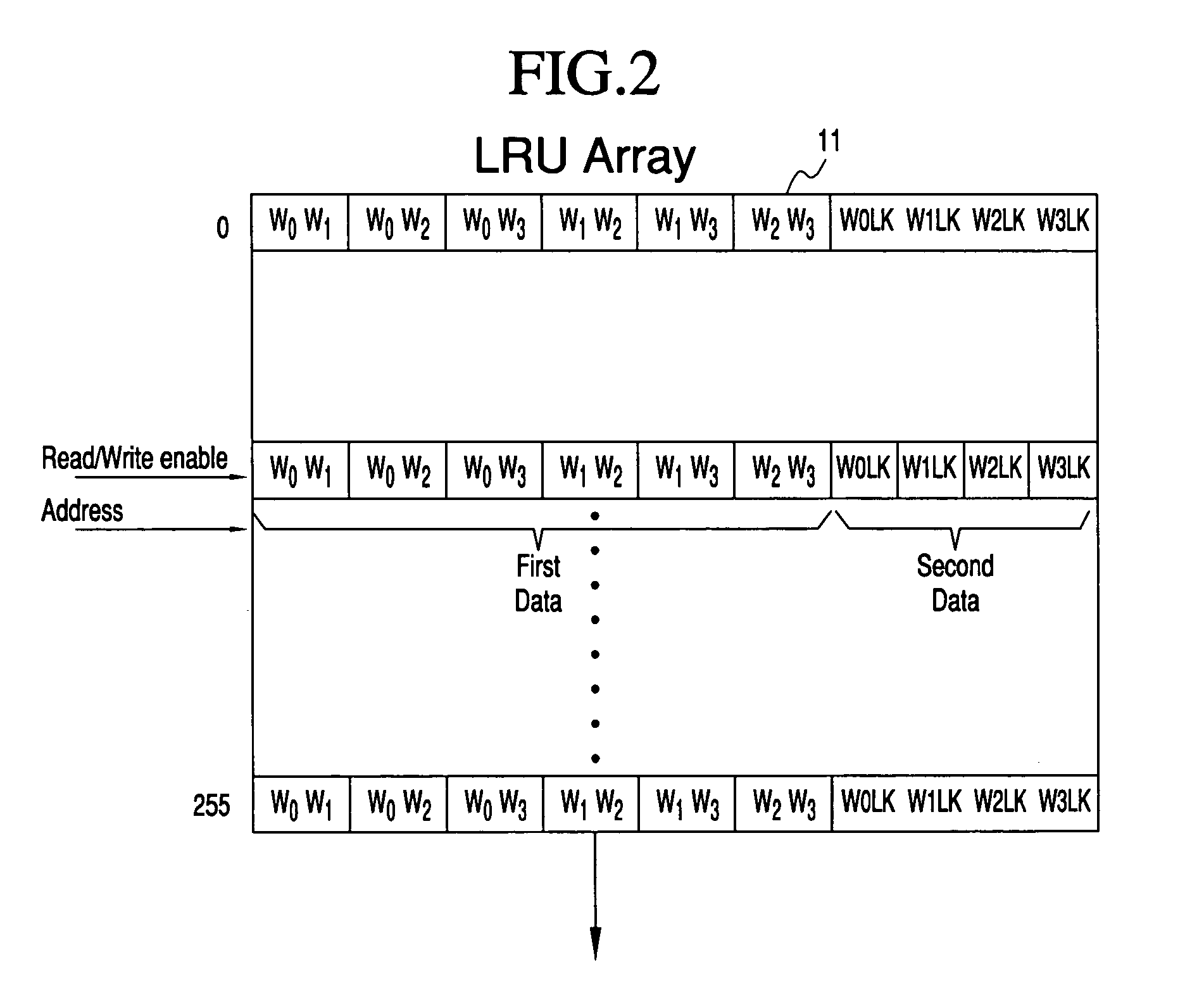

Method for software controllable dynamically lockable cache line replacement system

InactiveUS20060036811A1Shorten access timeSpeed up access timeMemory systemsParallel computingAccess line

An LRU array and method for tracking the accessing of lines of an associative cache. The most recently accessed lines of the cache are identified in the table, and cache lines can be blocked from being replaced. The LRU array contains a data array having a row of data representing each line of the associative cache, having a common address portion. A first set of data for the cache line identifies the relative age of the cache line for each way with respect to every other way. A second set of data identifies whether a line of one of the ways is not to be replaced. For cache line replacement, the cache controller will select the least recently accessed line using contents of the LRU array, considering the value of the first set of data, as well as the value of the second set of data indicating whether or not a way is locked. Updates to the LRU occur after each pre-fetch or fetch of a line or when it replaces another line in the cache memory.

Owner:GOOGLE LLC

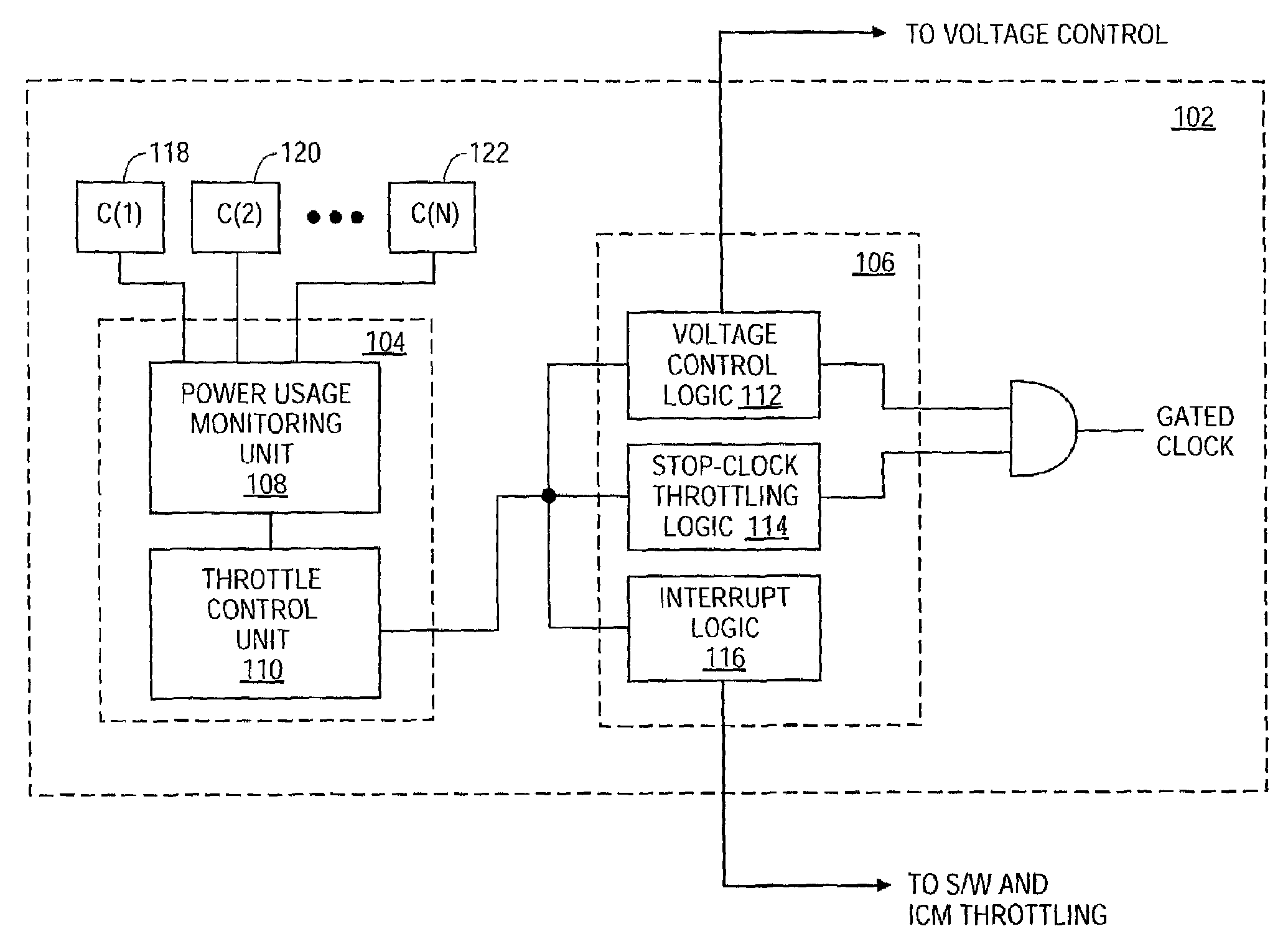

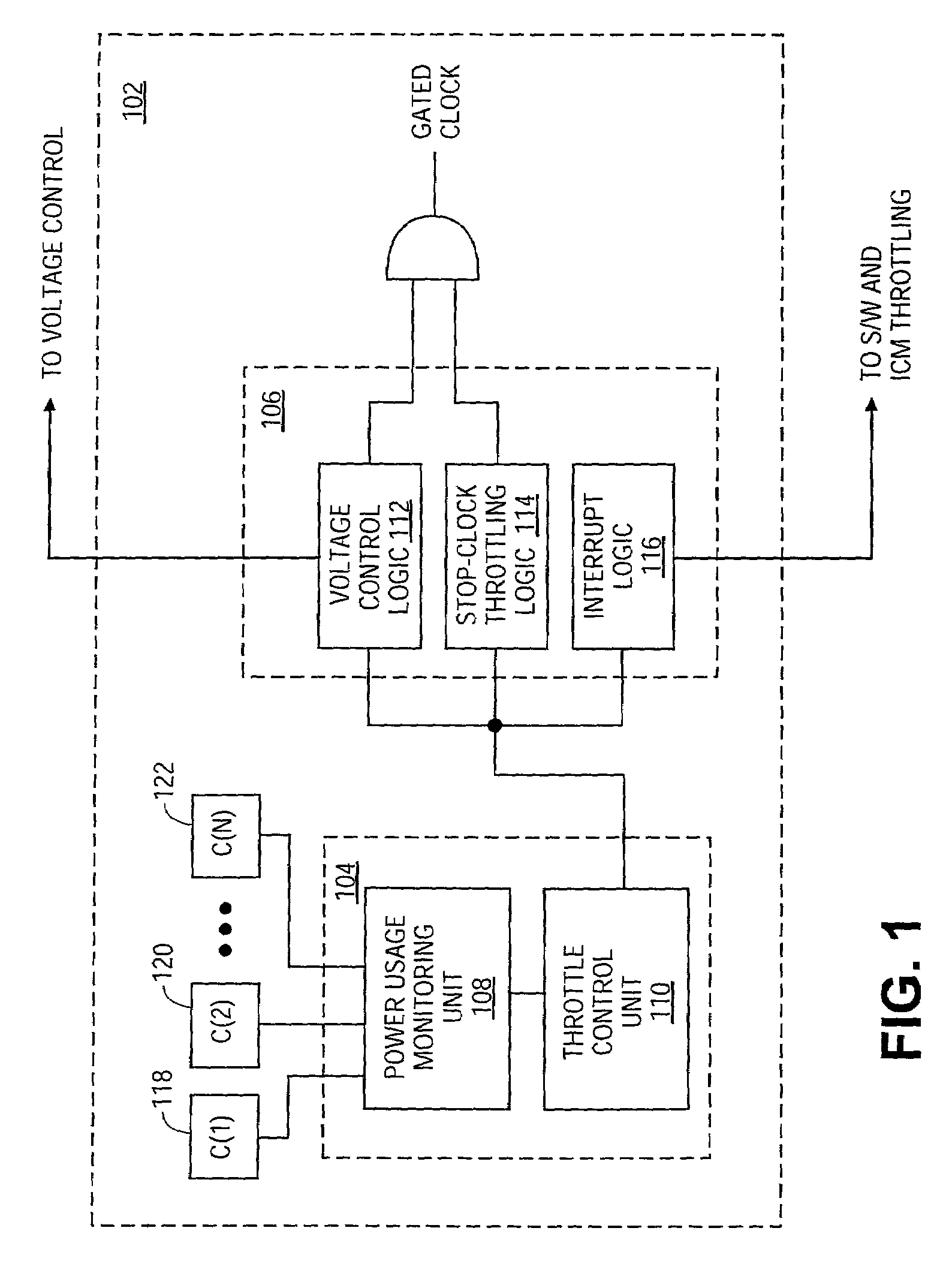

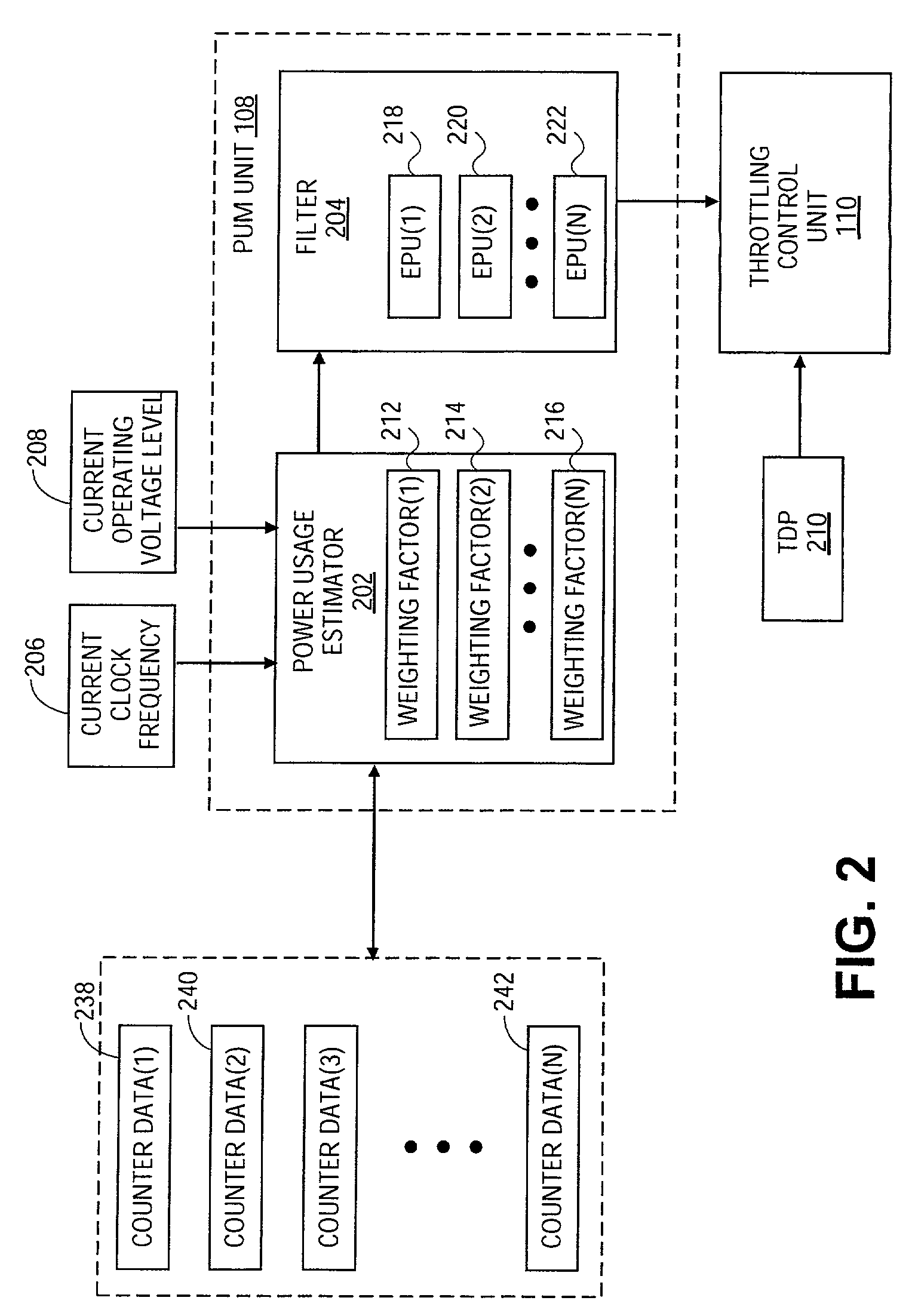

Deterministic power-estimation for thermal control

InactiveUS7096145B2Improve performanceHigh voltage levelThermometer detailsEnergy efficient ICTJunction temperaturePower usage

A system is described that includes a microprocessor and a thermal control subsystem. The microprocessor includes execution resources to support processing of instructions and consumes power. The microprocessor also includes at least one throttling mechanism to reduce the amount of heat generated by the microprocessor. The thermal control subsystem is configured to estimate an amount of power used by the microprocessor and to control the throttling mechanism based on the estimated amount of current power usage to ensure that junction temperature will not exceed the maximum allowed temperature.

Owner:RAKUTEN GRP INC

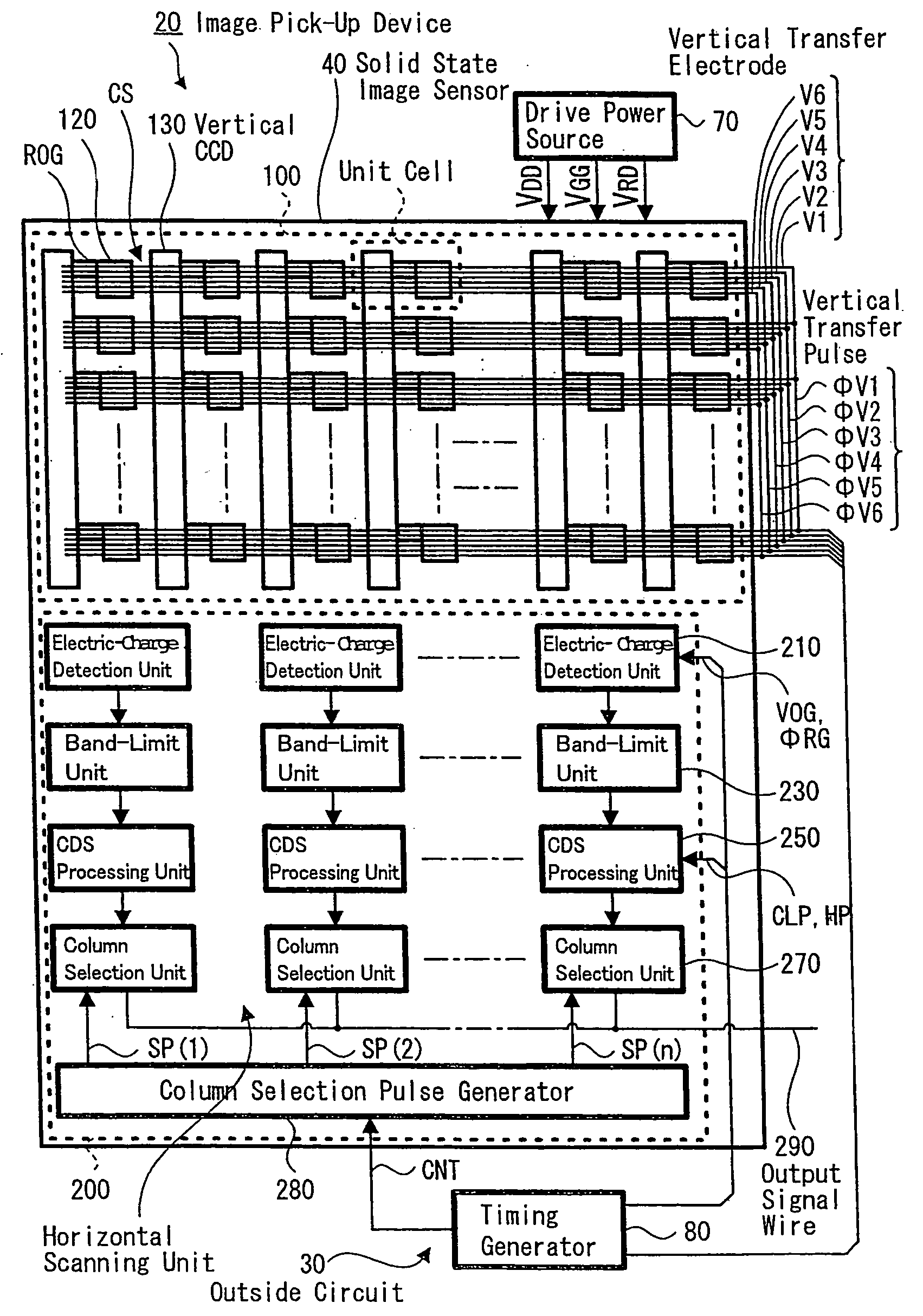

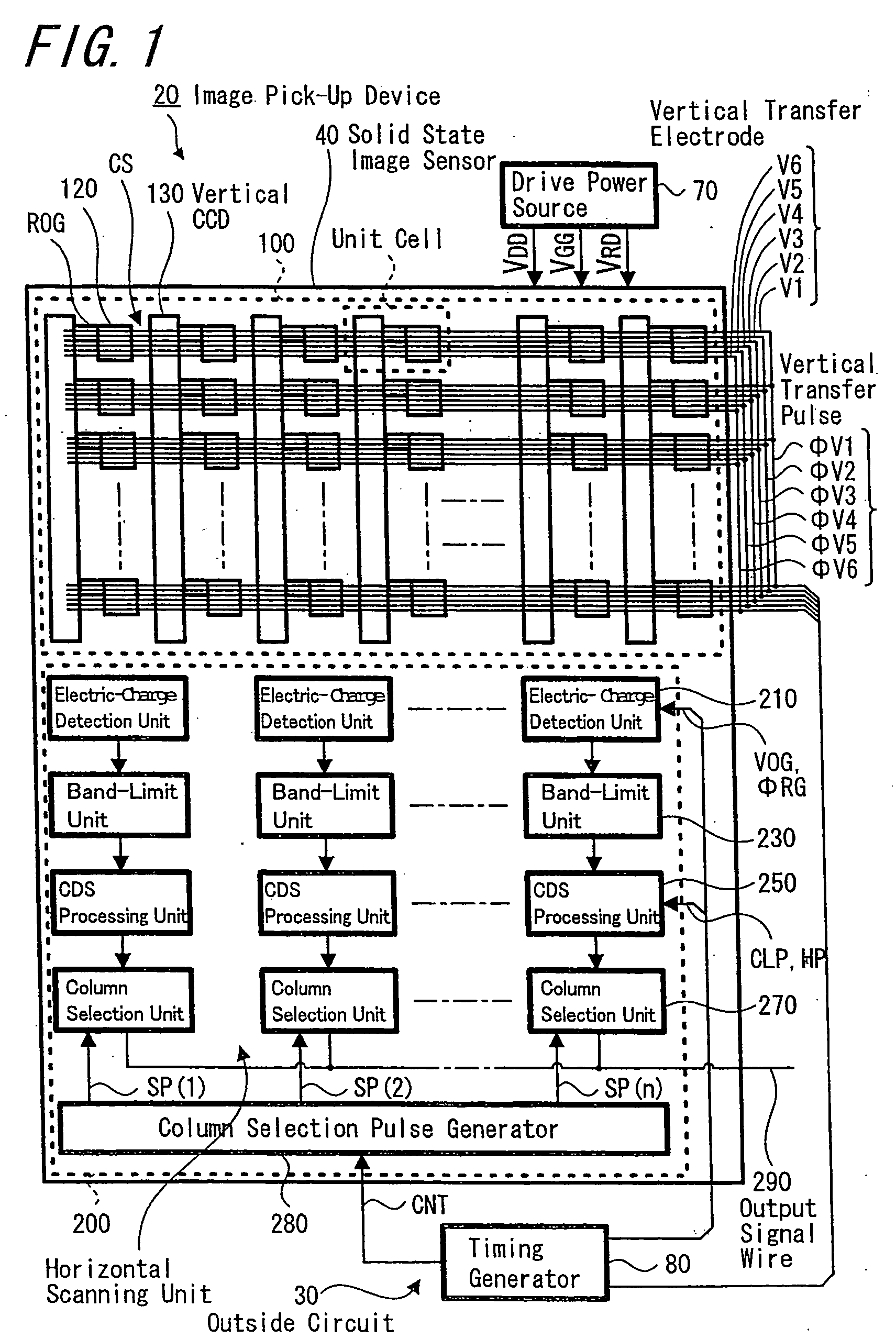

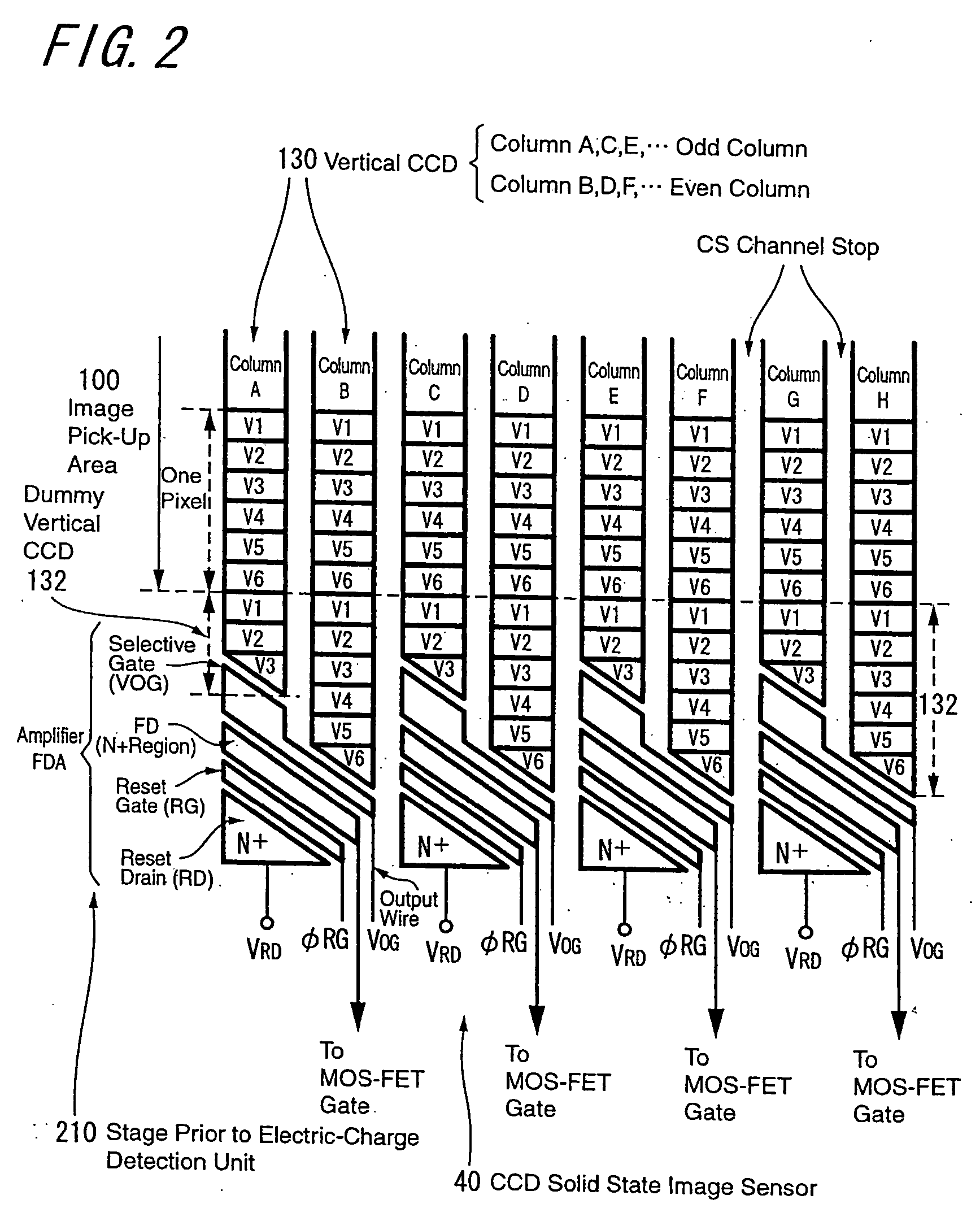

Solid-state imaging device, method for driving dolid-state imaging device, imaging method, and imager

InactiveUS20050224842A1Increase clock frequencyHigh sensitivityTelevision system detailsSolid-state devicesCharge detectionSolid-state

The present invention relates to a CCD solid state image sensor of a scanning read-out type and to a drive method thereof as well as an image pick-up method and the image pick-up device, particularly in which a plurality of vertical CCD columns can be assigned to one electric-charge detection unit with the small number of wiring. In the present invention, adjacent columns of the vertical CCDs are assigned to one electric-charge detection unit. Further, the stages of the voltage transfer between the vertical CCD column and a voltage detection unit is made different; the electrode arrangement is devised; or the drive timing is adjusted. Accordingly, the phase of electric-charge transfer with respect to the plurality of adjacent vertical CCD columns, when the horizontal electric-charge at the same position in the direction of the row obtained by the photo-conductive units is made to reach the electric-charge detection unit, becomes different.

Owner:SONY CORP

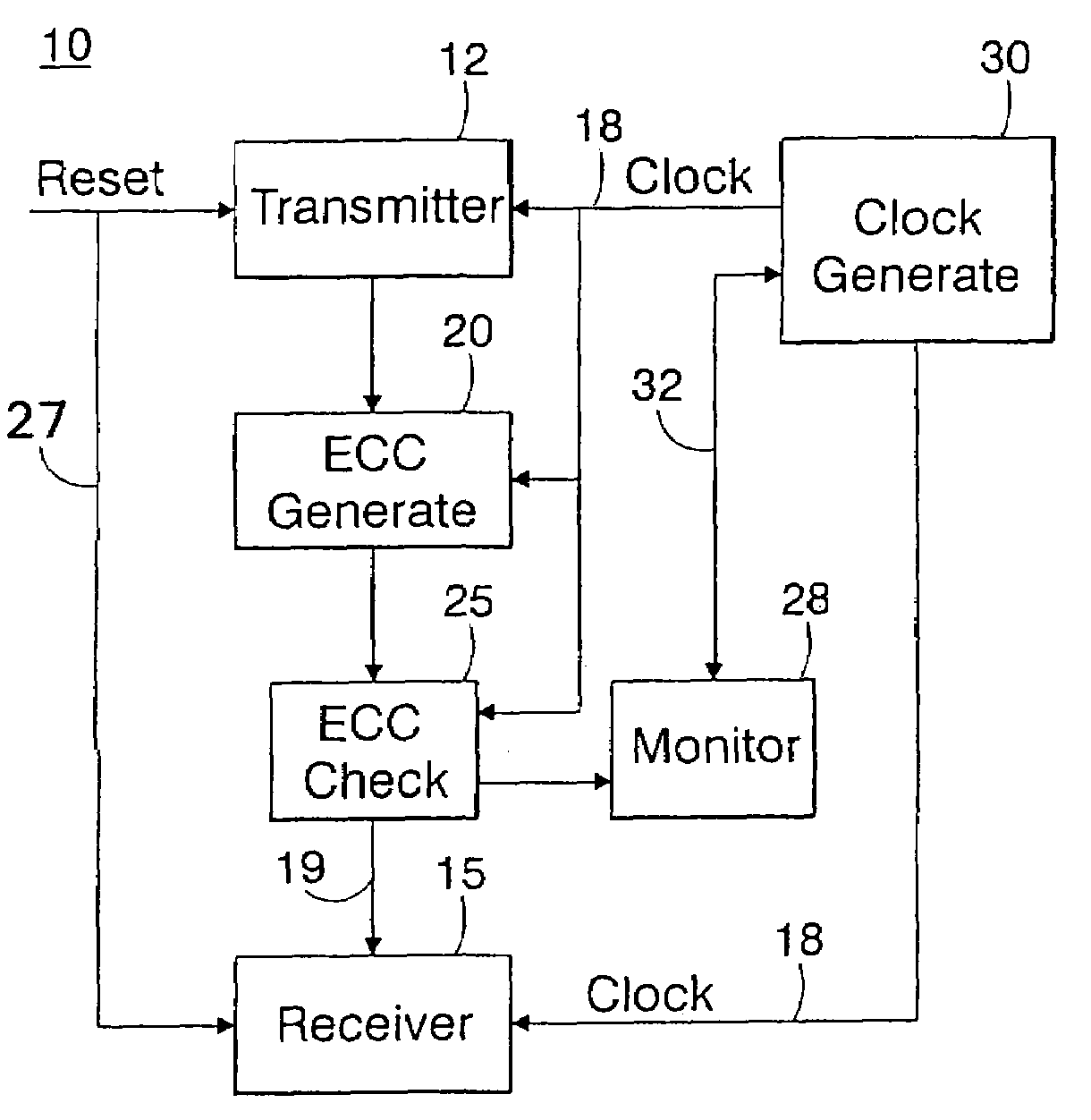

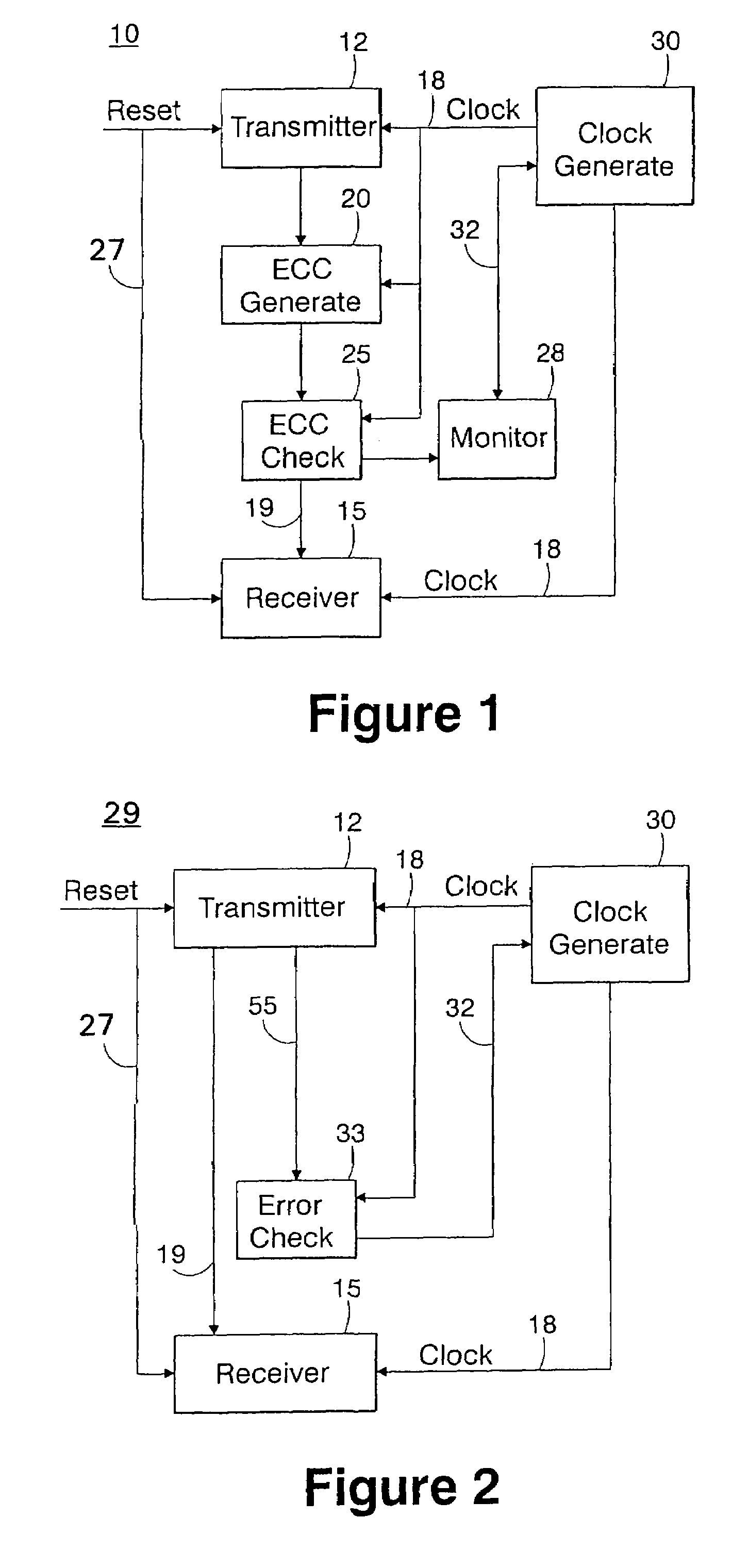

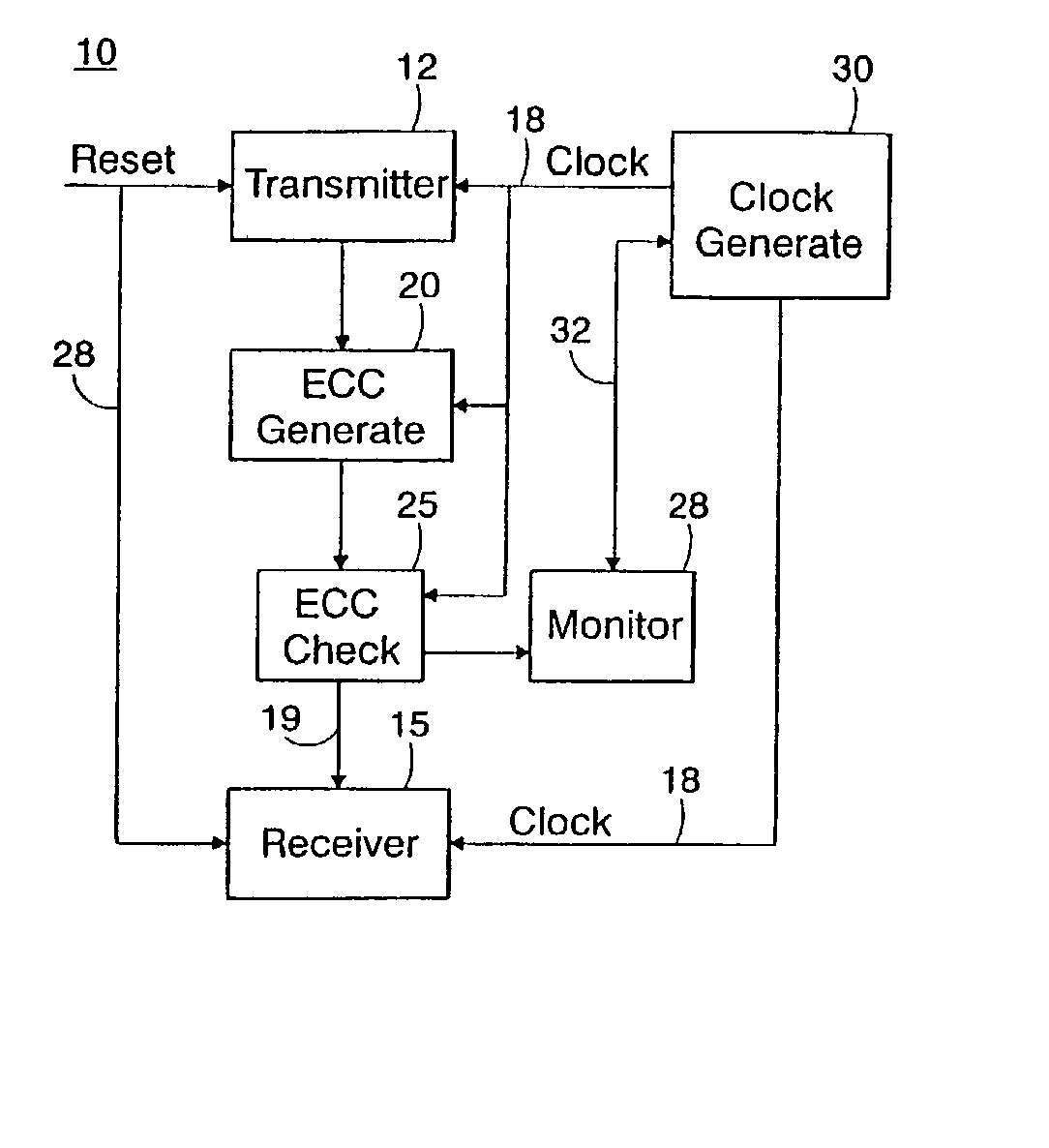

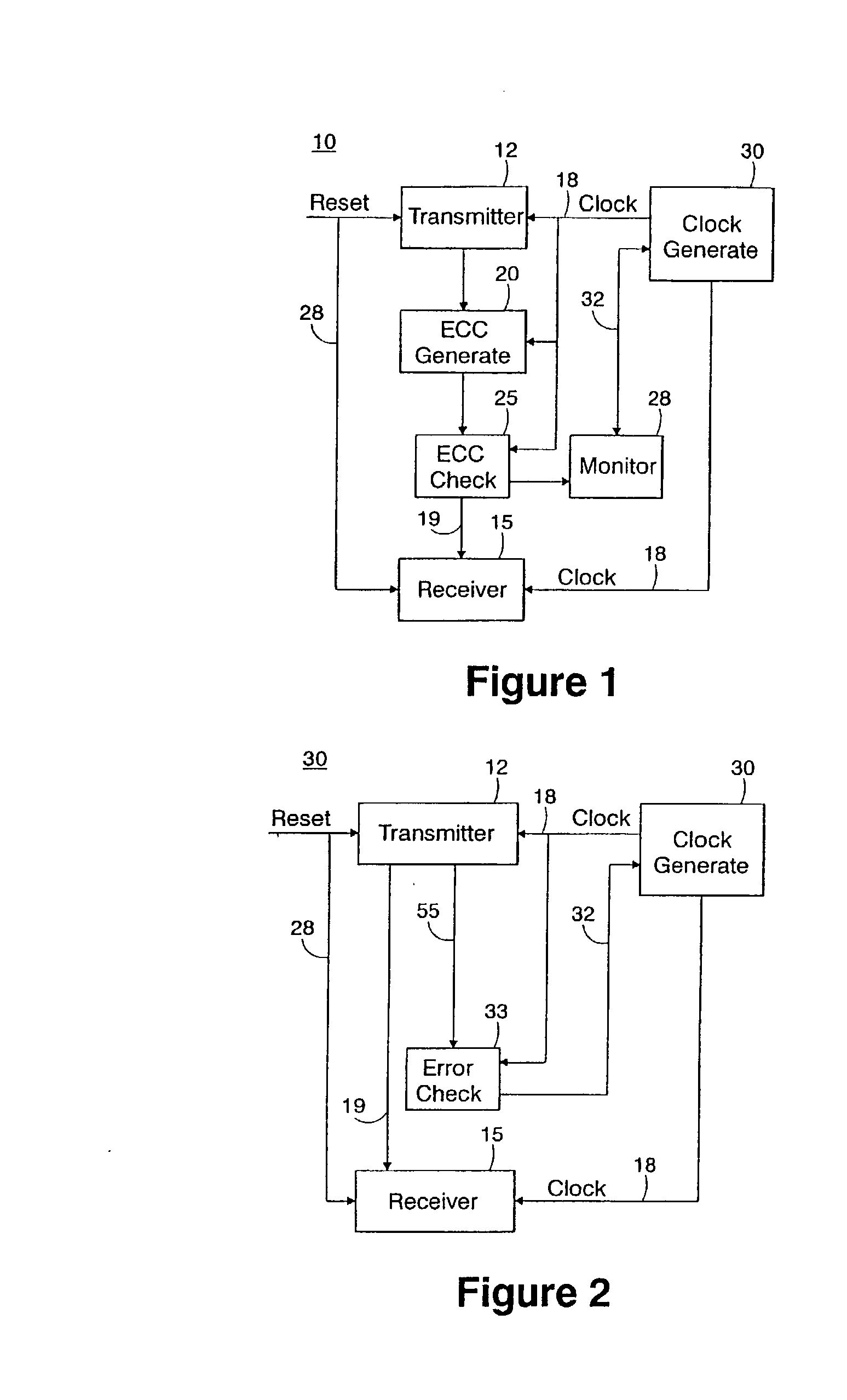

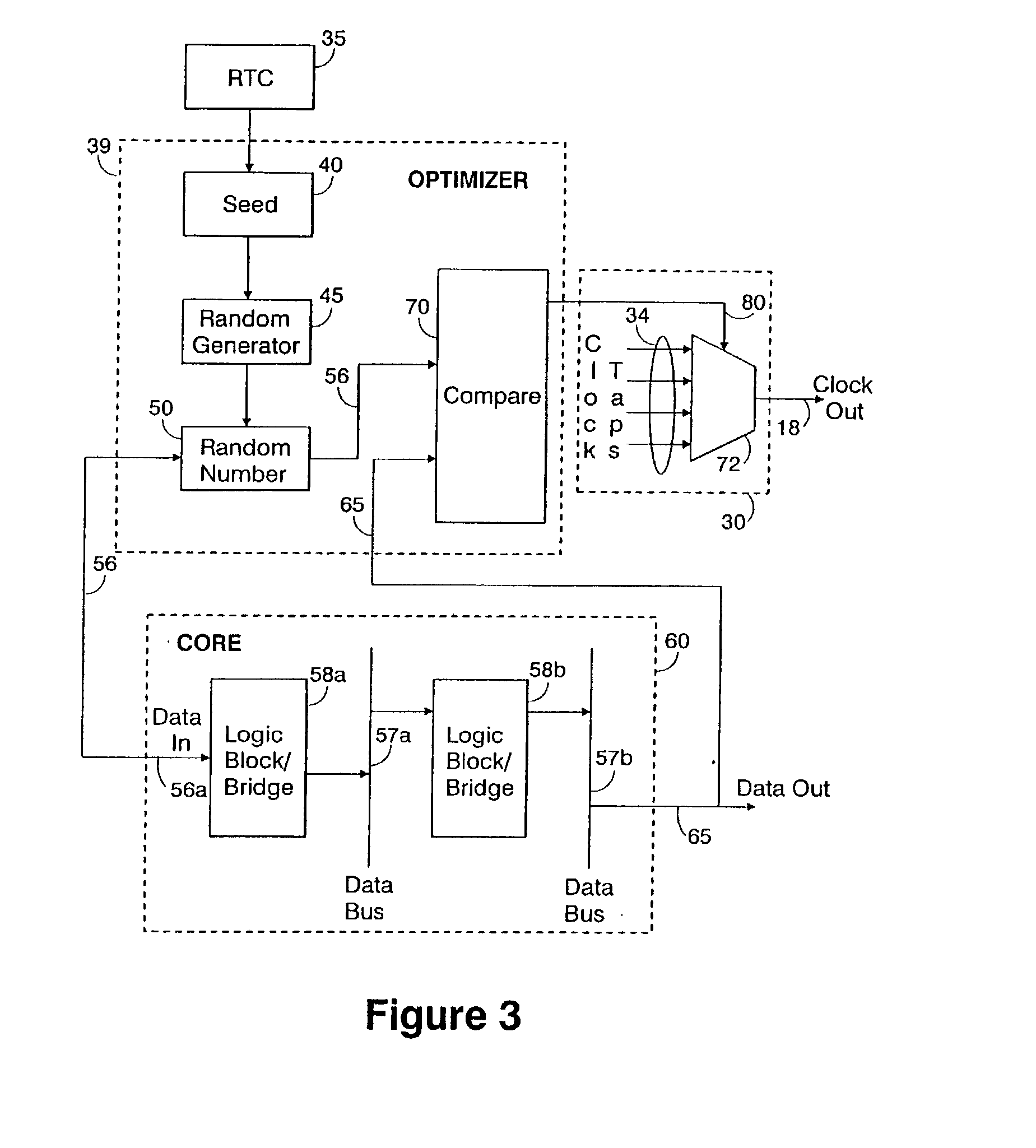

System and method for correcting timing signals in integrated circuits

InactiveUS7085993B2Increase clock frequencyData representation error detection/correctionRecording carrier detailsData signalIntegrated circuit layout

A system and method for dynamically altering a clock speed of a clock signal used for timing of data signal transmissions and receptions within an integrated circuit (IC) device. The system includes a clock generator circuit for providing a clock signal used for timing of data signal transmission and reception within the IC; a monitoring circuit for receiving data transmissions generated at different clock speeds and detecting when a data transmission fail point is achieved at a particular clock speed; and, a device for adjusting the clock speed according to a maximum speed allowed for the IC that avoids the data transmission fail point.

Owner:INT BUSINESS MASCH CORP

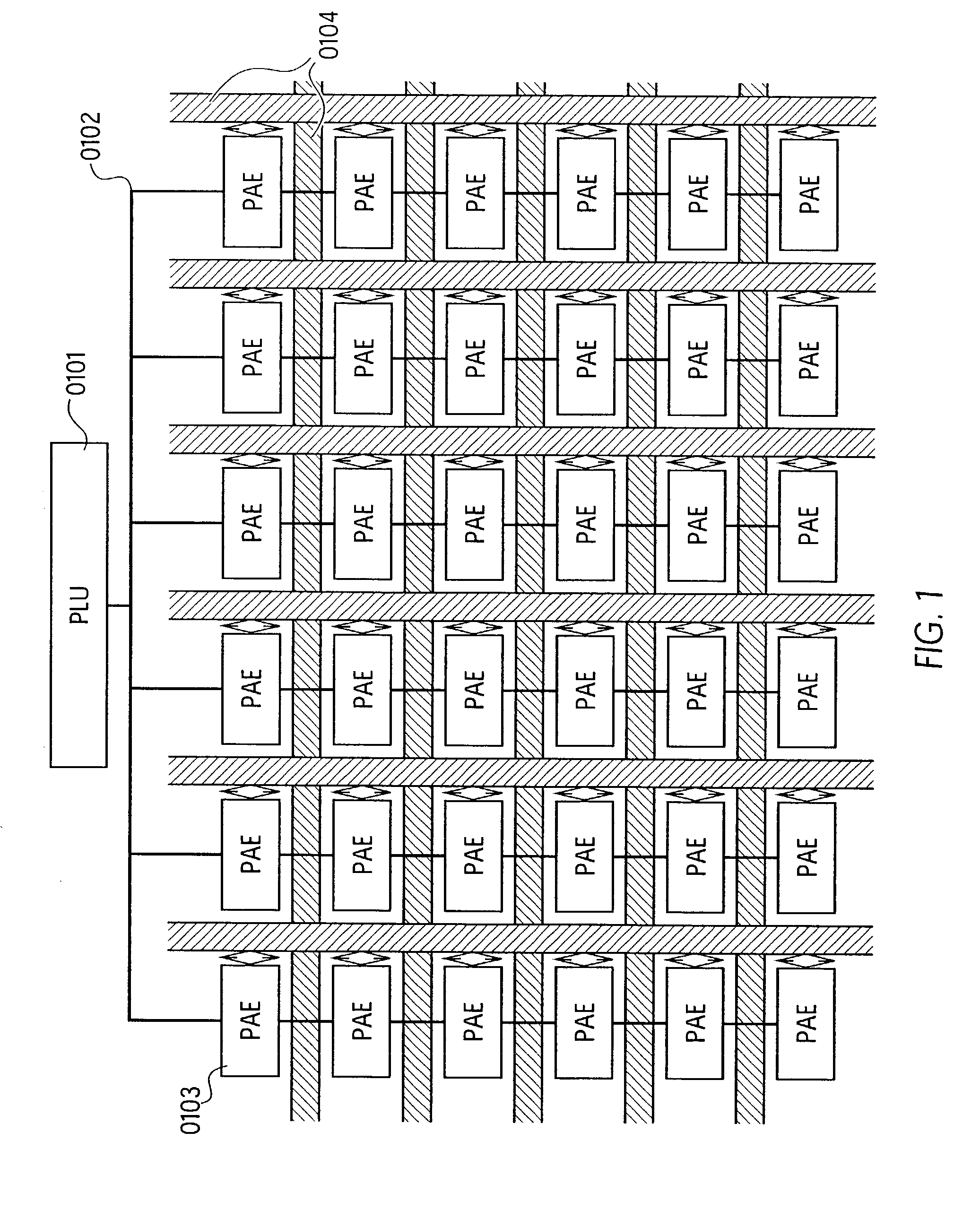

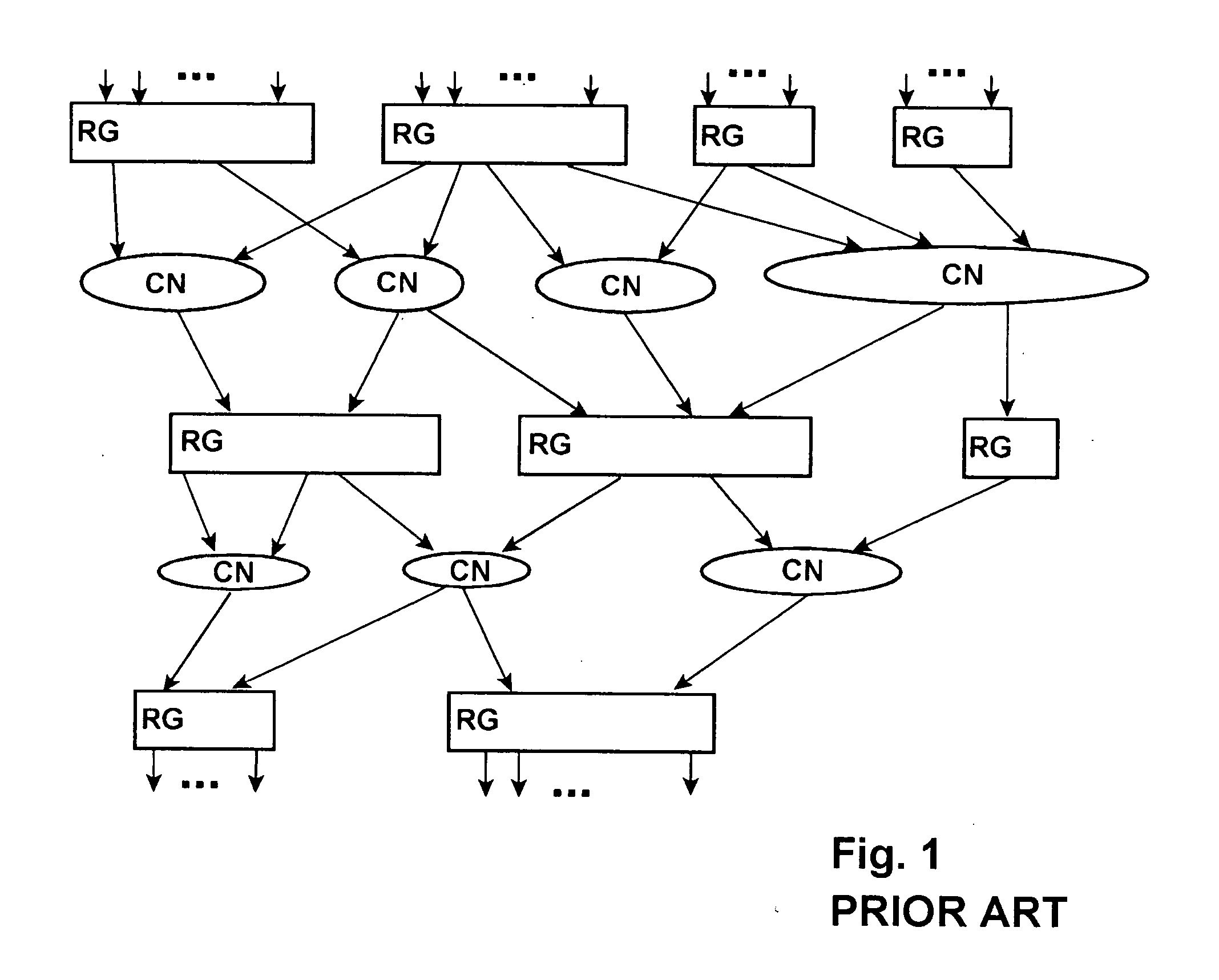

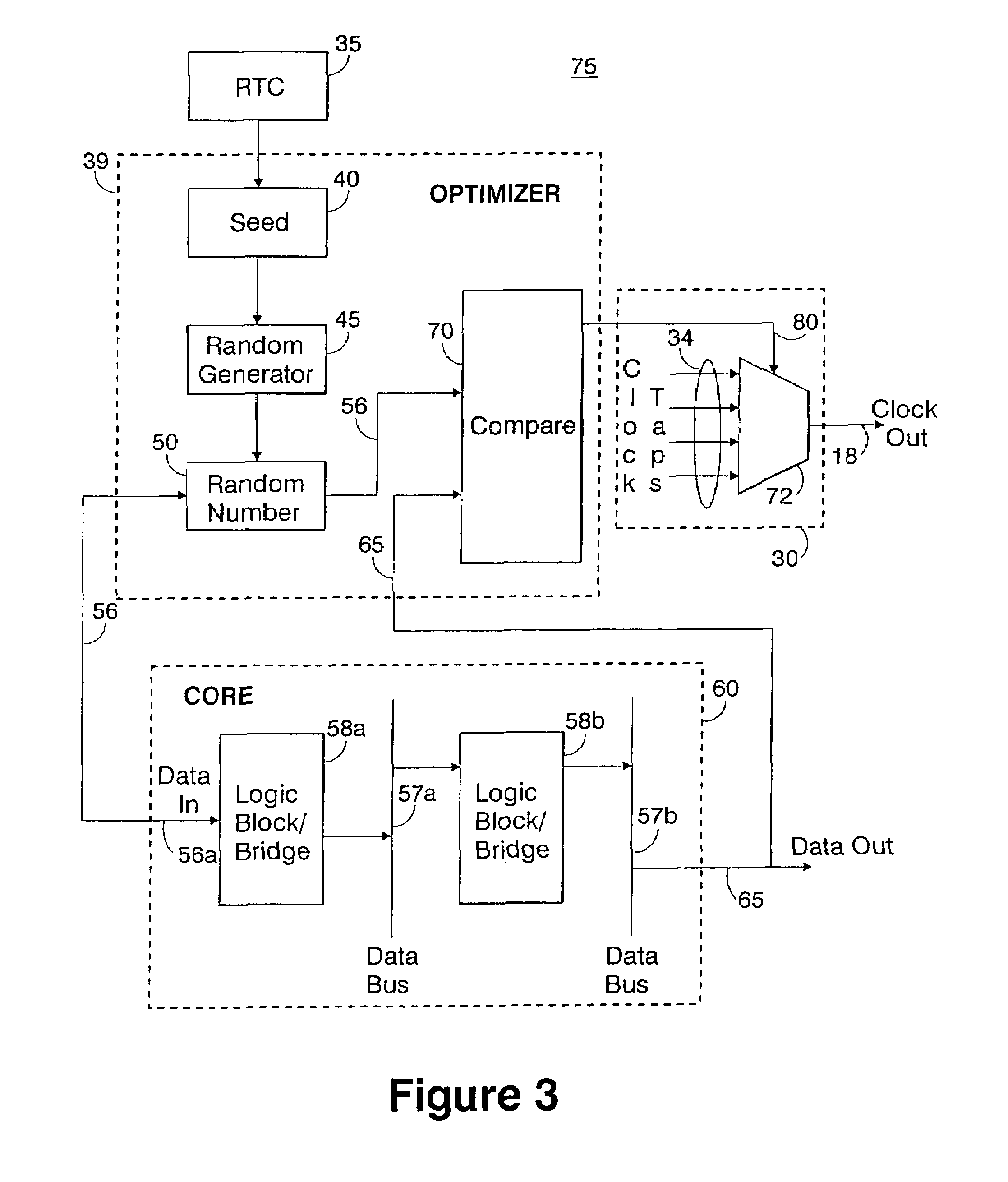

Methods and devices for treating and processing data

InactiveUS7444531B2Reduce power consumptionSimple technologyEnergy efficient ICTVolume/mass flow measurementLogic cellData processing

A data processing unit having a field of clocked logic cells (PAEs) which is operable in different configuration states and a clock preselecting means for preselecting logic cell clocking. The clock preselecting means is designed in such a way that, depending on the state, a first clock is preselected at least at a first cell (PAE) and an additional clock is preselected at least at an additional cell.

Owner:SCIENTIA SOL MENTIS AG

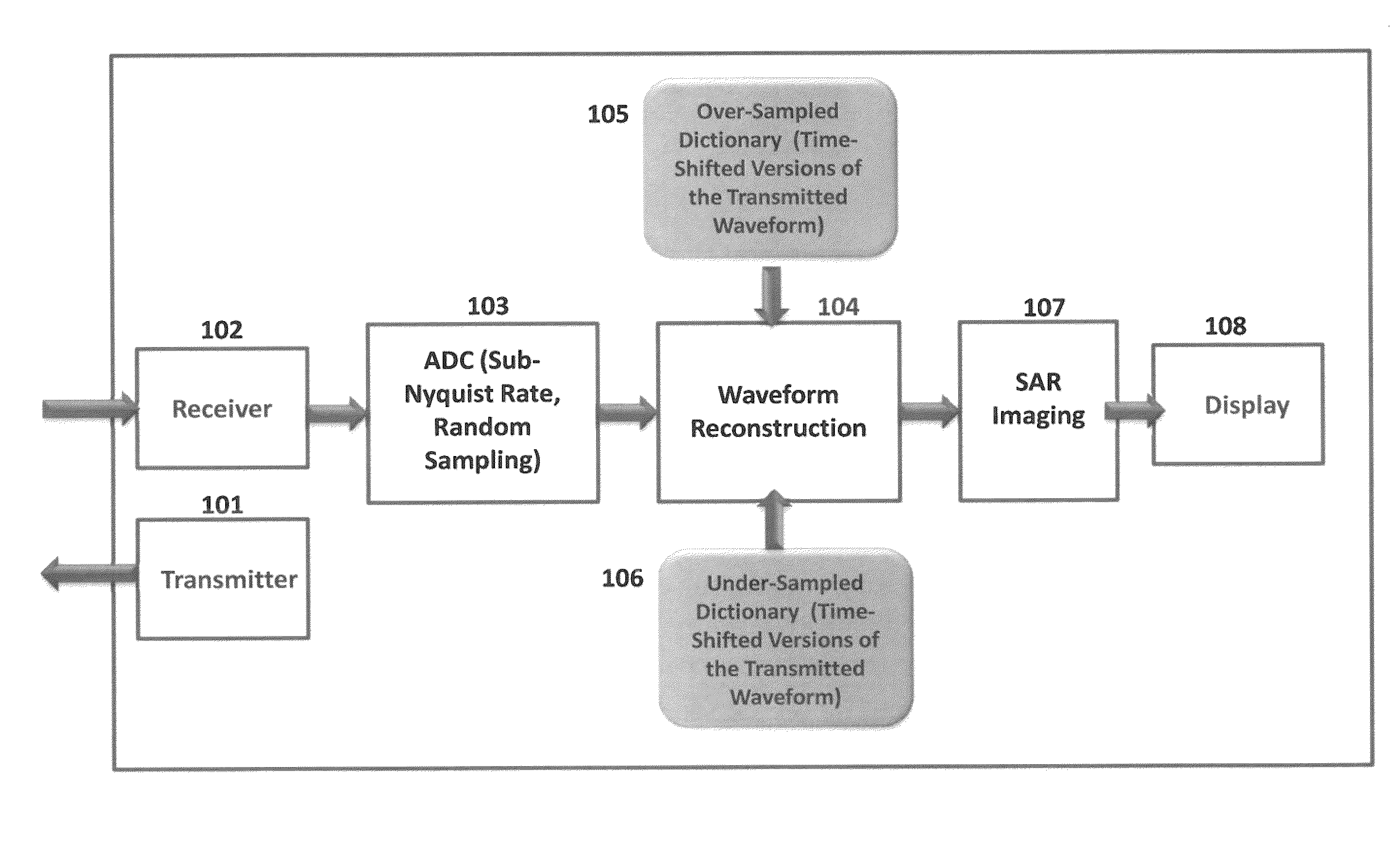

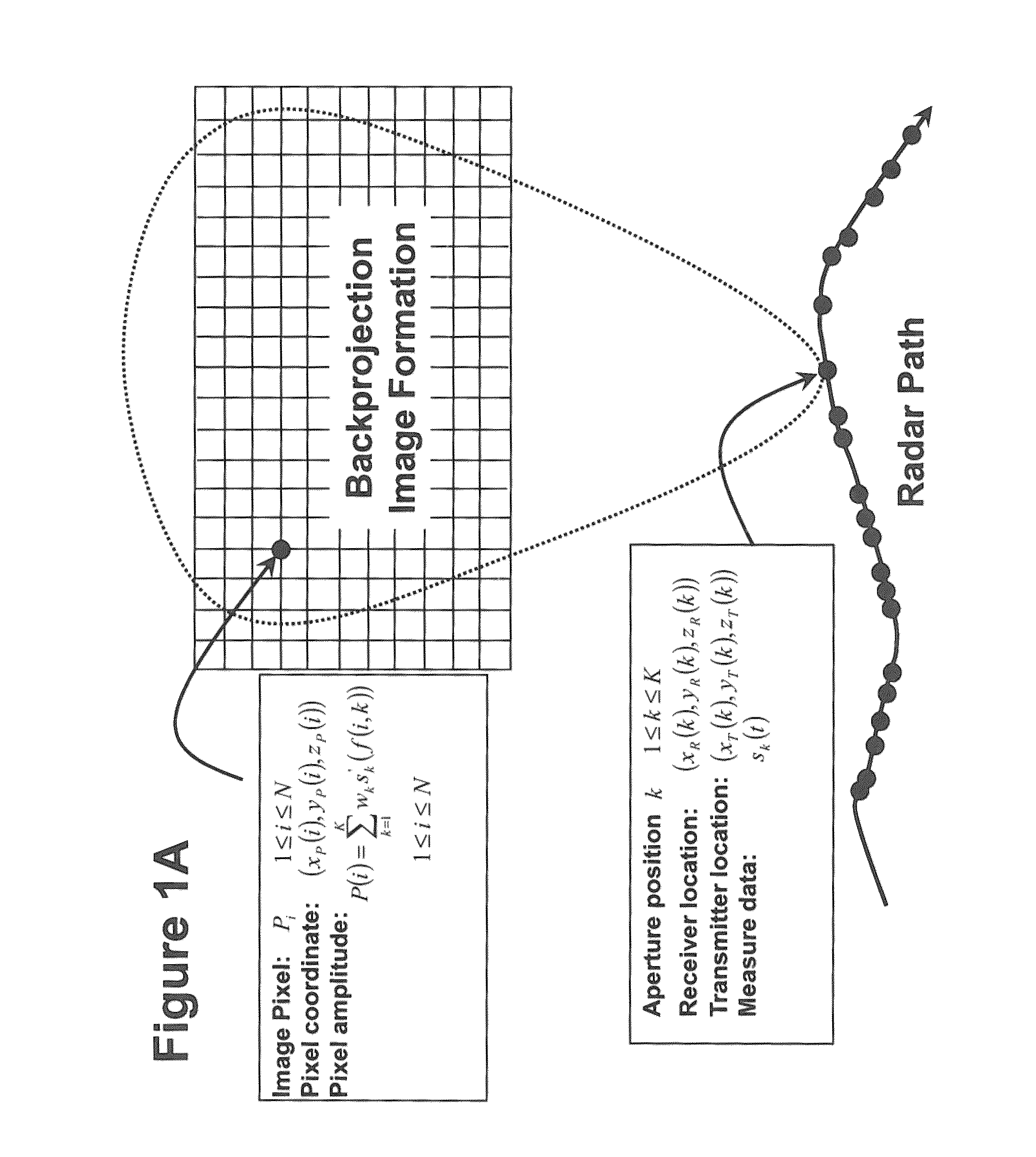

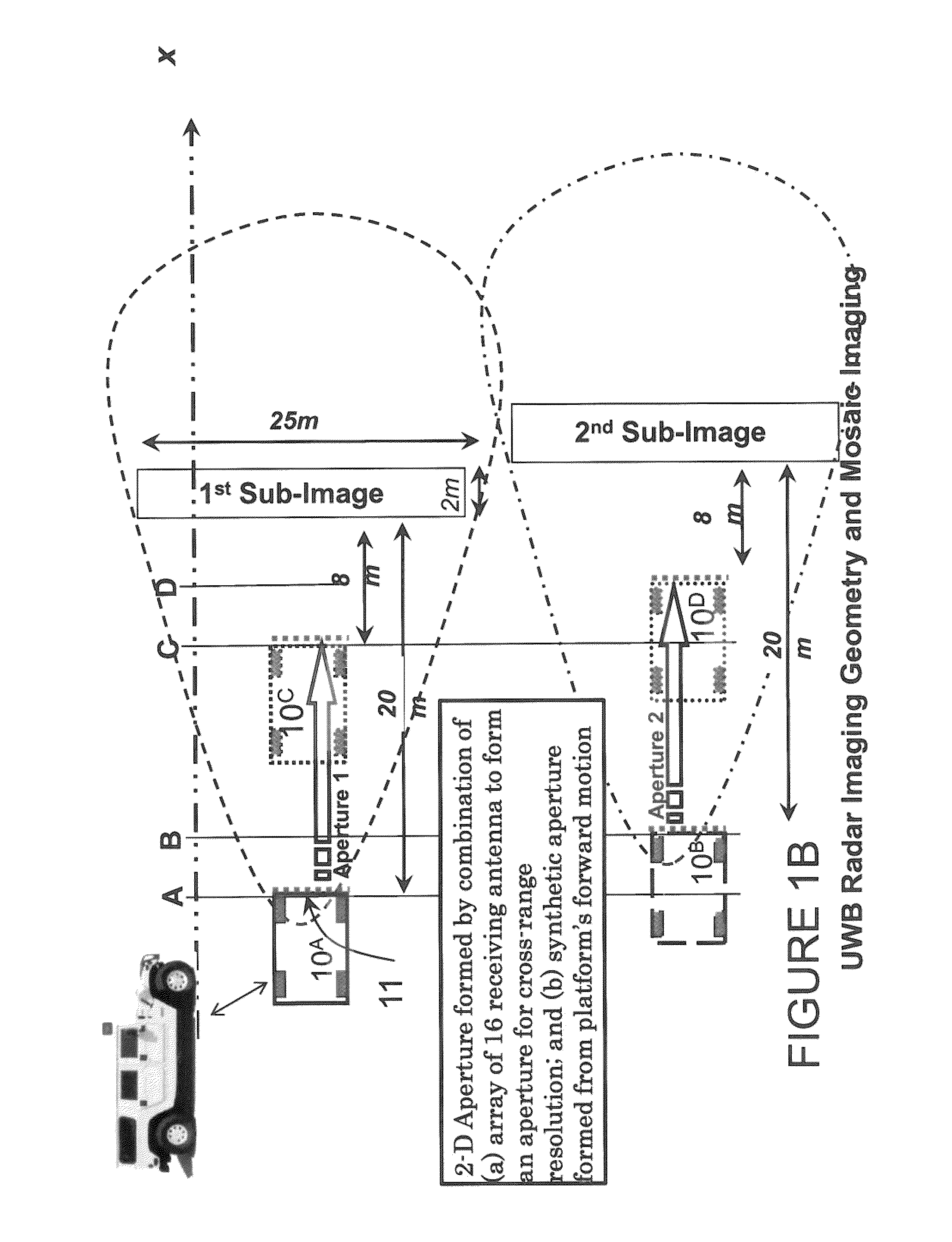

Apparatus and method for sampling and reconstruction of wide bandwidth signals below Nyquist rate

InactiveUS8861588B2Reduction in size and weight and power and costIncrease clock frequencyElectric signal transmission systemsModulated-carrier systemsWave shapeData signal

A method and system of reconstructing data signals from one of incomplete measurements comprising a receiver for receiving data signals, an ADC system operatively connected to the receiver that digitizes the received data signal at a slower rate than the Nyquist rate to obtain sparse measurements; first and second dictionaries comprising a plurality of time shifted responses recovered from the data signal; the first dictionary comprising time shifted versions of the previously observed data signals which are sampled at or above the Nyquist minimum sample rate; the second dictionary comprising time shifted versions are sampled below the Nyquist minimum, and at least one processor for reconstruction of the waveform signals by transforming the sub-Nyquist digitized output using the first and second dictionaries to produce the data signal.

Owner:ARMY US SEC THE THE

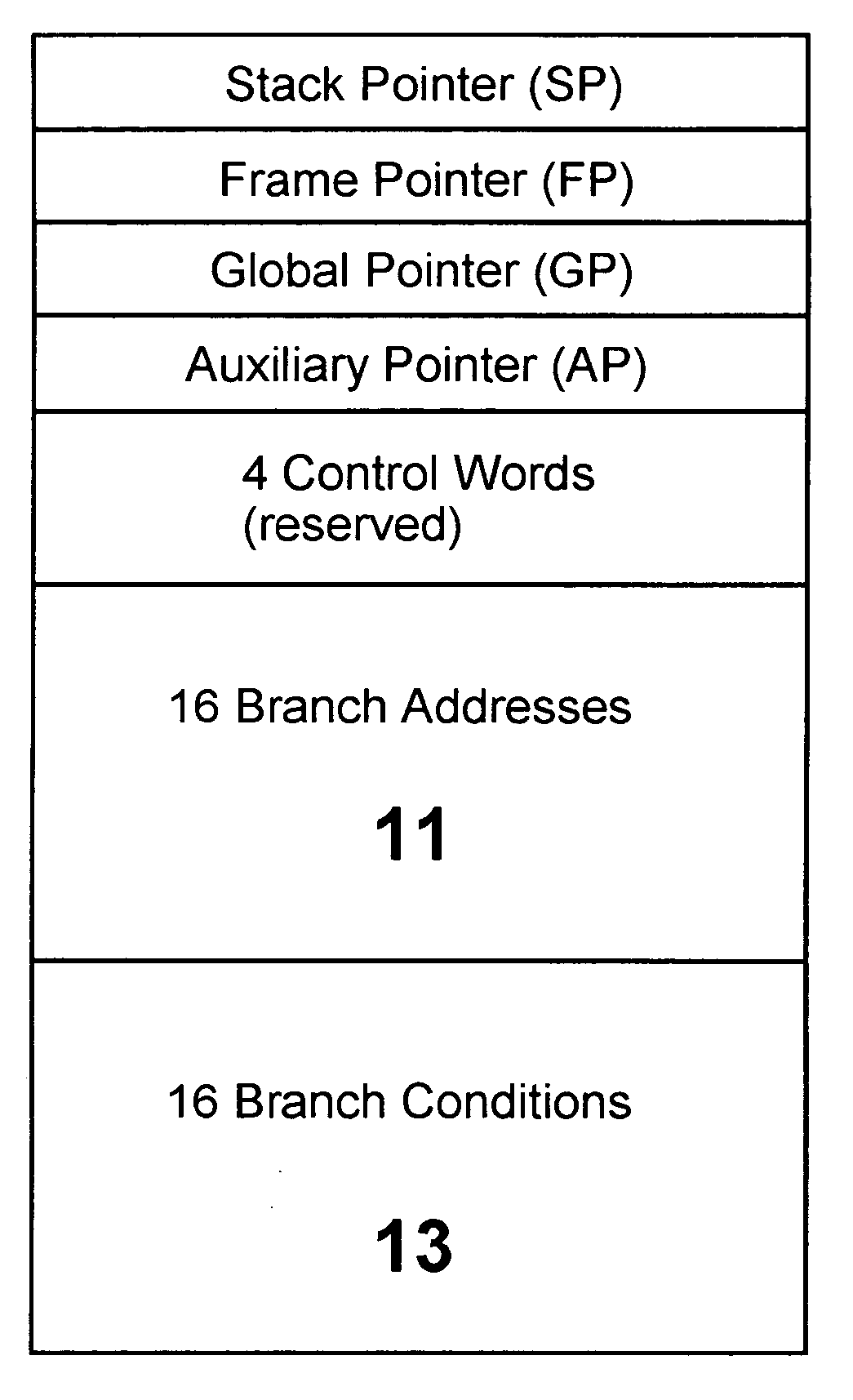

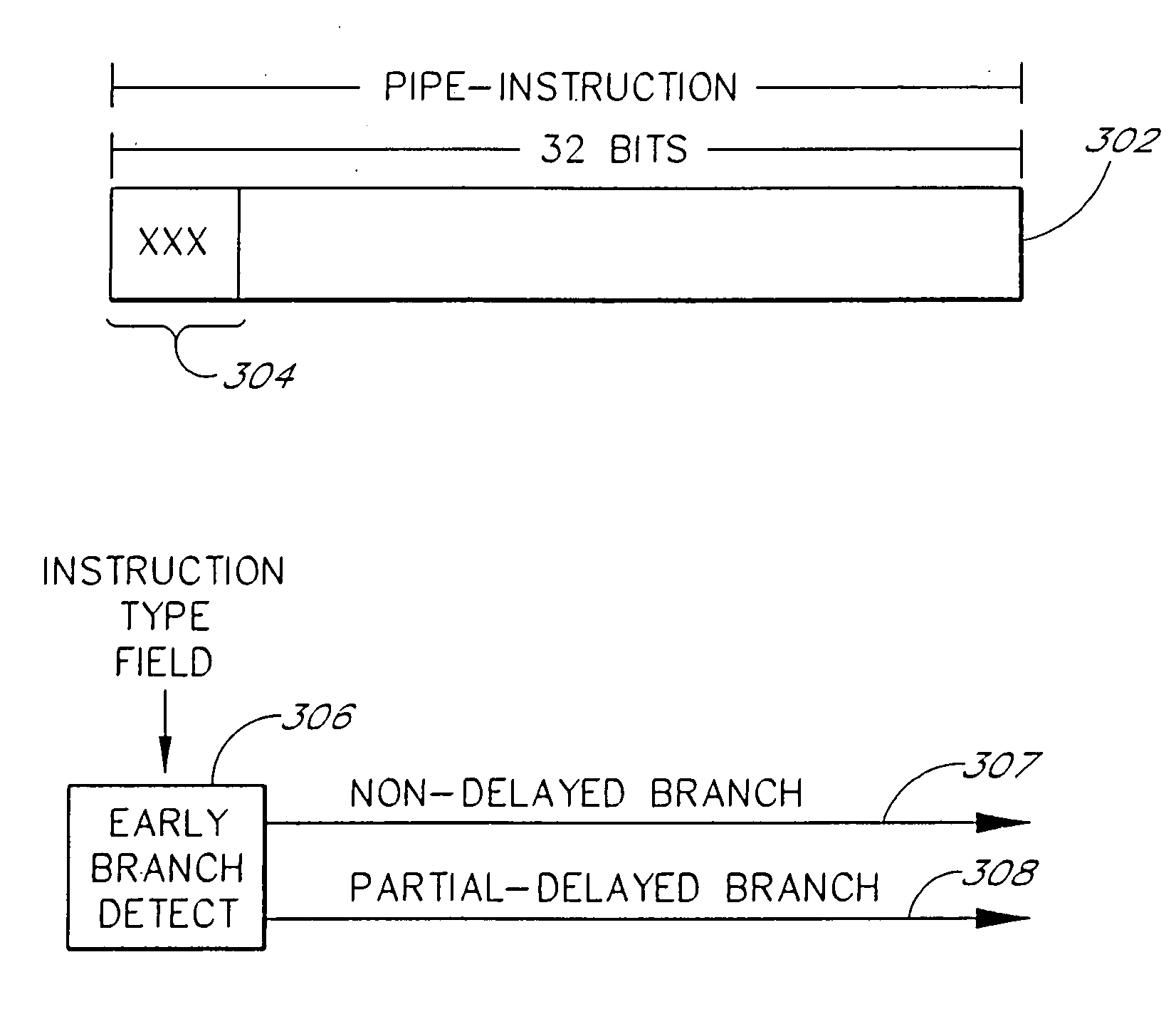

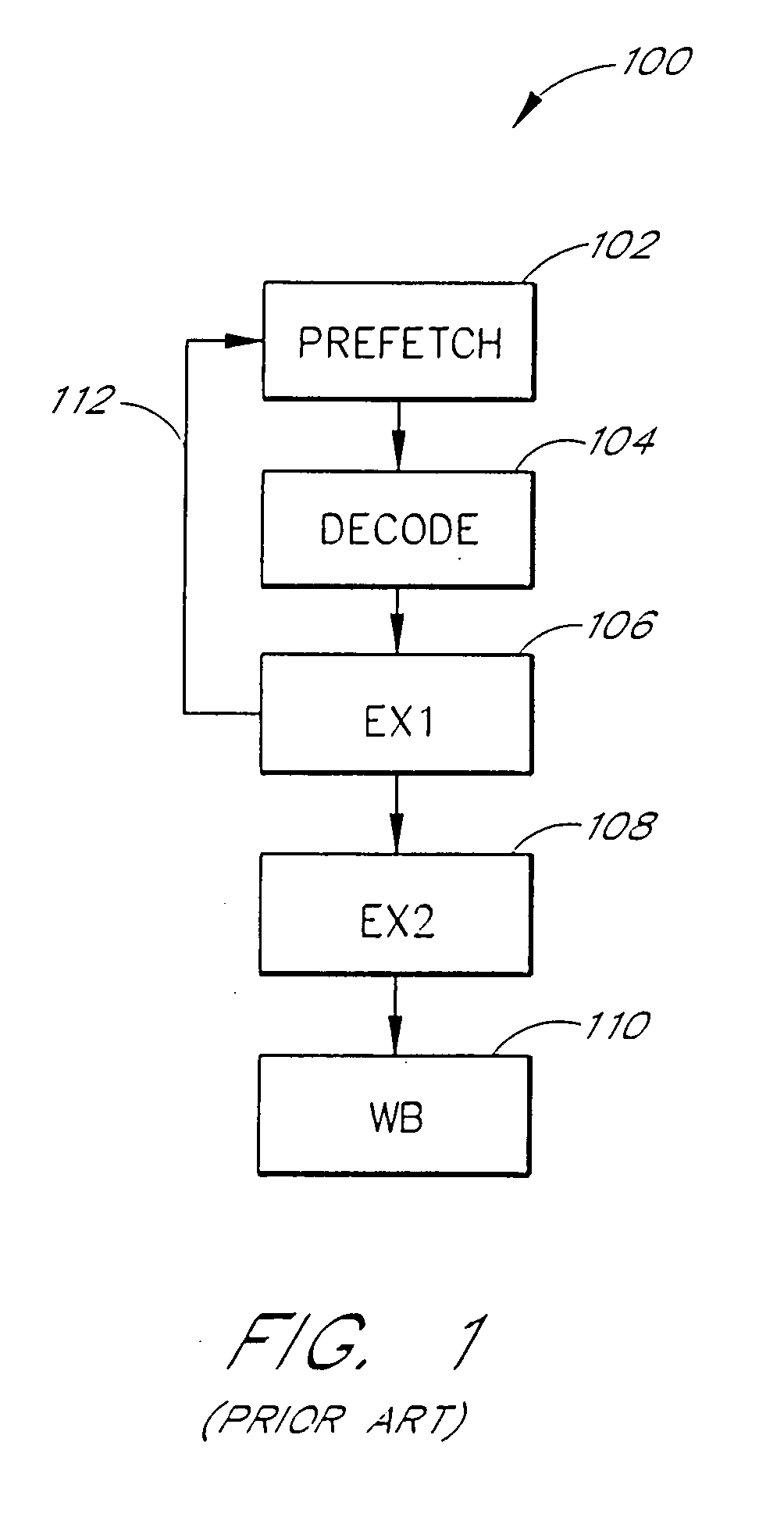

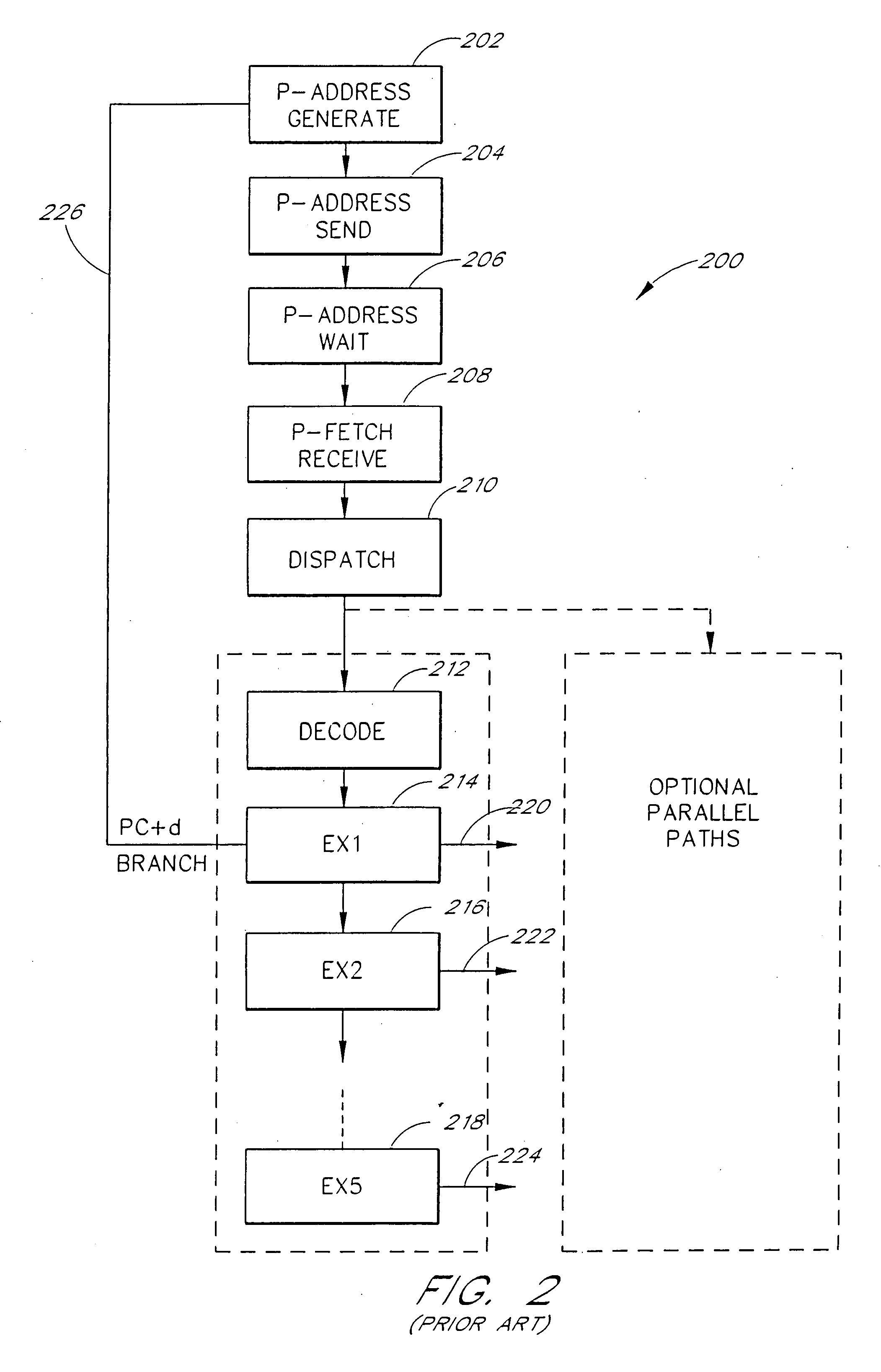

Method and apparatus for high performance branching in pipelined microsystems

InactiveUS20070174599A1Reduces or eliminates pipeline stallsEasy to operateMemory adressing/allocation/relocationDigital computer detailsParallel computingAssessment data

A pipelined processor includes a branch acceleration technique which is based on an improved branch cache. The improved branch cache minimizes or eliminates delays caused by branch instructions, especially data-dependent unpredictable branches. In pipelined and multiply pipelined machines, branches can potentially cause the pipeline to stall because the branch alters the instruction flow, leaving the prefetch buffer and first pipeline stages with discarded instructions. This has the effect of reducing system performance by making the branch instruction appear to require multiple cycles to execute. The improved branch cache differs from conventional branch caches. In particular, the improved cache is not used for branch prediction, but rather, the improved branch cache avoids stalls by providing data that will be inserted into the pipeline stages that would otherwise have stalled when a branch is taken. Special architectural features and control structures are supplied to minimize the amount of information that must be cached by recognizing that only selected types of branches should be cached and by making use of available cycles that would otherwise be wasted. The improved branch cache supplies the missing information to the pipeline in the place of the discarded instructions, completely eliminating the pipeline stall. This technique accelerates performance, especially in real-time code that must evaluate data-dependent conditions and branch accordingly.

Owner:ROUND ROCK RES LLC

System and method for correcting timing signals in integrated circuits

InactiveUS20040019844A1Increase clock frequencyData representation error detection/correctionRecording carrier detailsData signalIntegrated circuit layout

A system and method for dynamically altering a clock speed of a clock signal used for timing of data signal transmissions and receptions within an integrated circuit (IC) device. The system includes a clock generator circuit for providing a clock signal used for timing of data signal transmission and reception within the IC; a monitoring circuit for receiving data transmissions generated at different clock speeds and detecting when a data transmission fail point is achieved at a particular clock speed; and, a device for adjusting the clock speed according to a maximum speed allowed for the IC that avoids the data transmission fail point.

Owner:IBM CORP

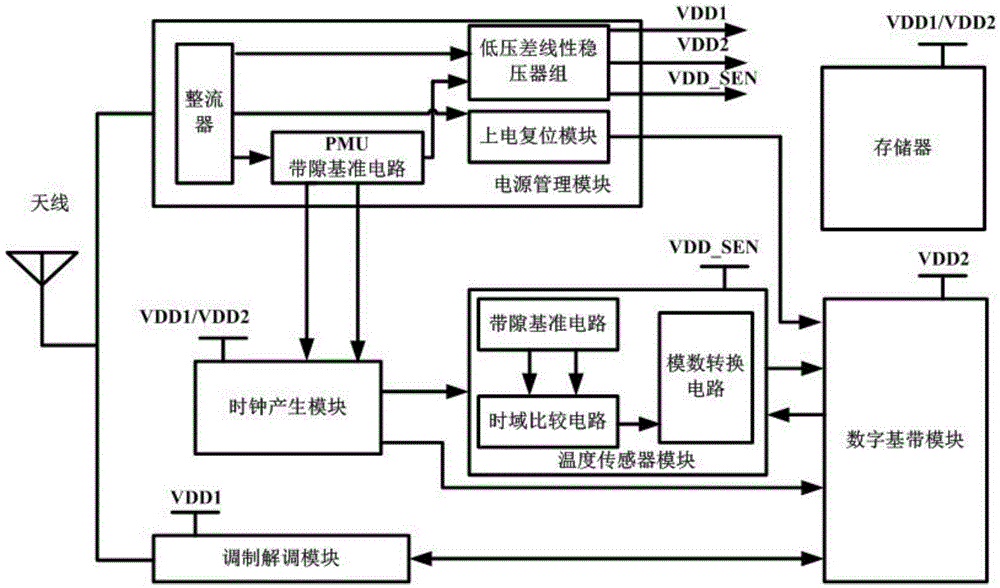

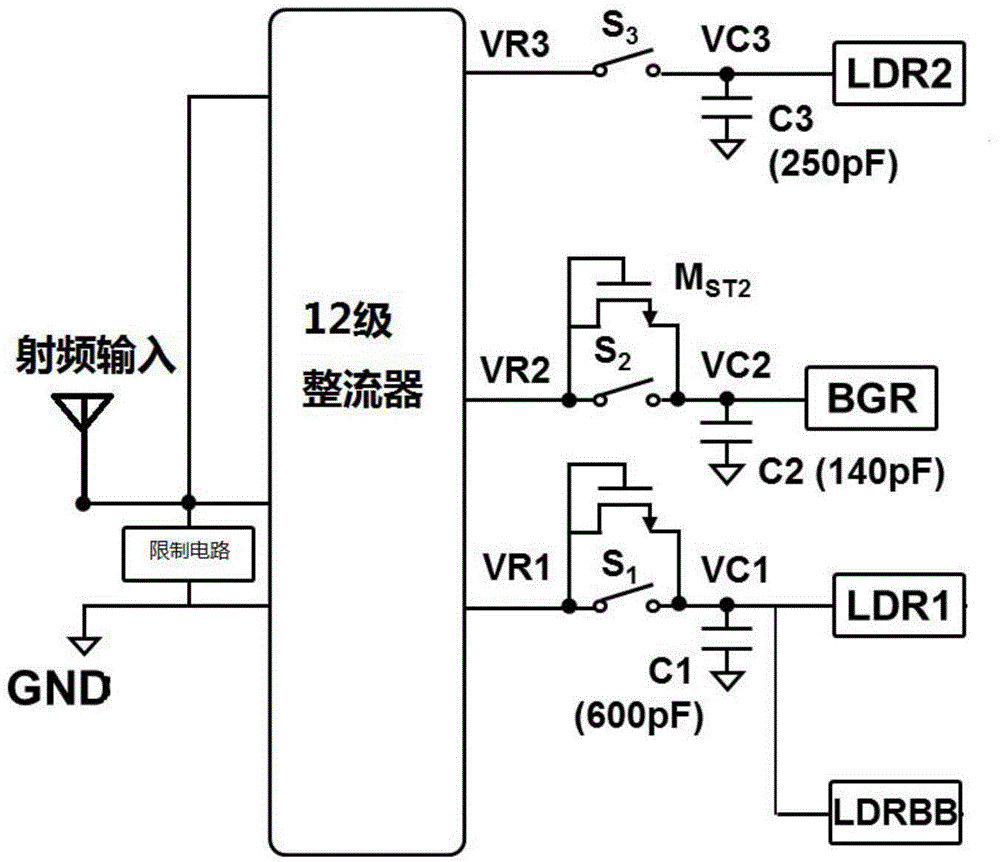

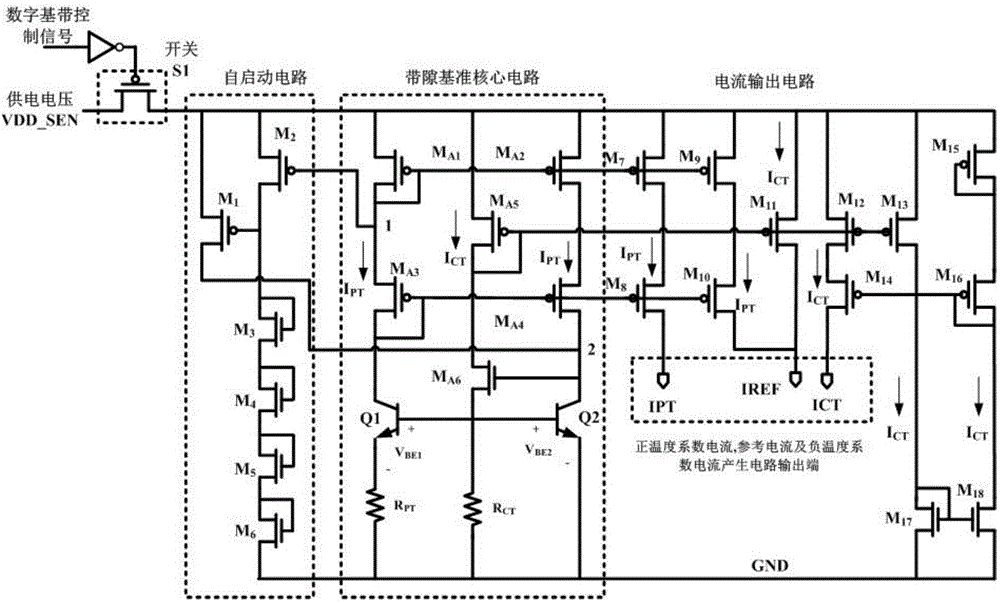

Passive ultrahigh-frequency ultralow-power consumption RFID chip with built-in temperature sensor

ActiveCN104156757AReduce sensitivityImprove conversion efficiencyThermometers using electric/magnetic elementsUsing electrical meansError processingComputer module

The invention discloses a passive ultrahigh-frequency ultralow-power consumption RFID chip with a built-in temperature sensor. The chip comprises a power management module, a modulation-demodulation module, a clock generation module, a digital base-band module, a temperature sensor module and a memory. By low-power consumption treatment processing of the passive ultrahigh-frequency RFID chip with the built-in temperature sensor, the sensitivity and the read-write distance of the RFID chip with the built-in temperature sensor are improved. In addition, the built-in temperature sensor is subjected to high-precision and low-error processing, and thus a more stable and more accurate temperature measurement value can be obtained, thereby providing more reliable temperature data.

Owner:赵犁

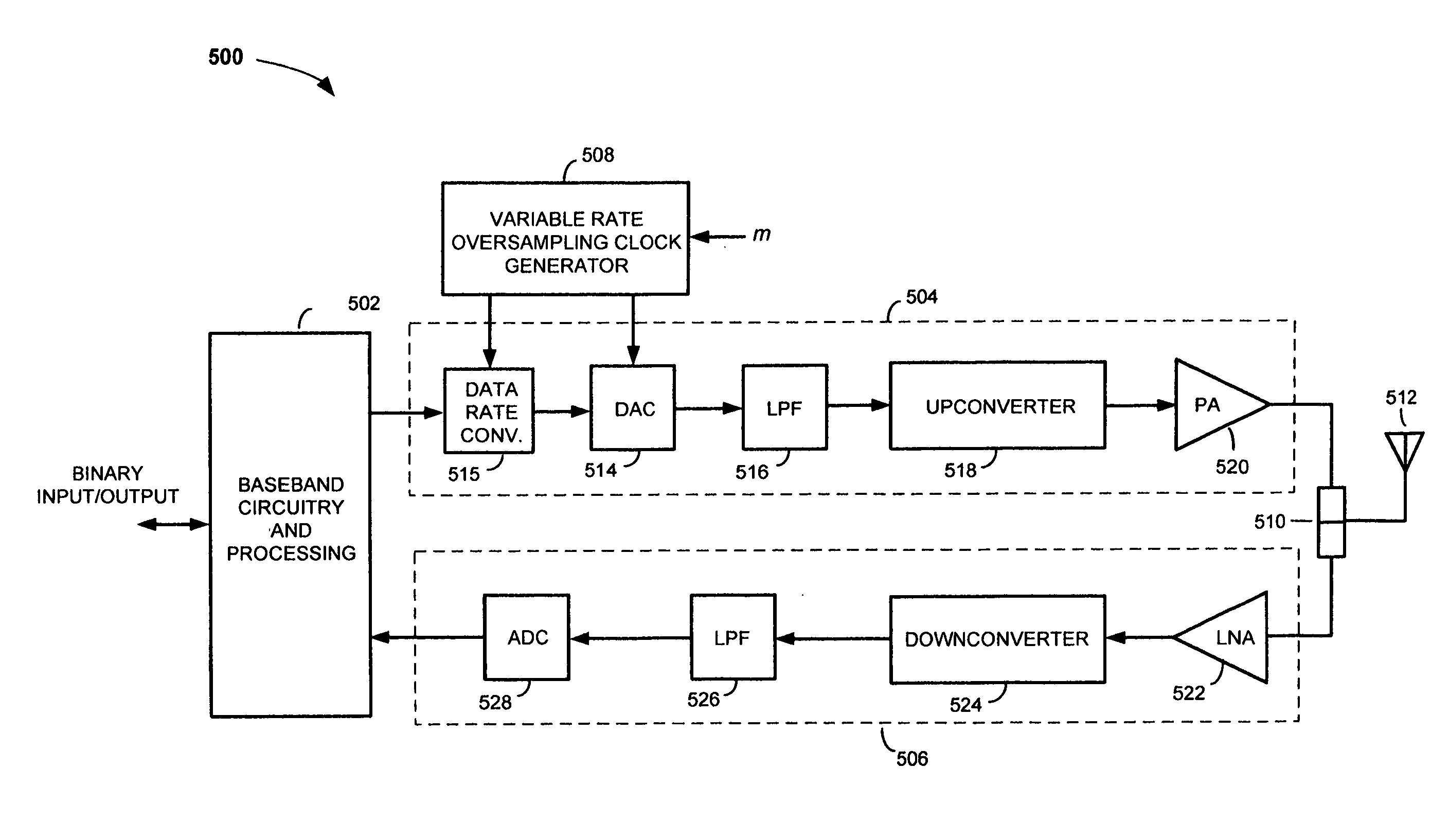

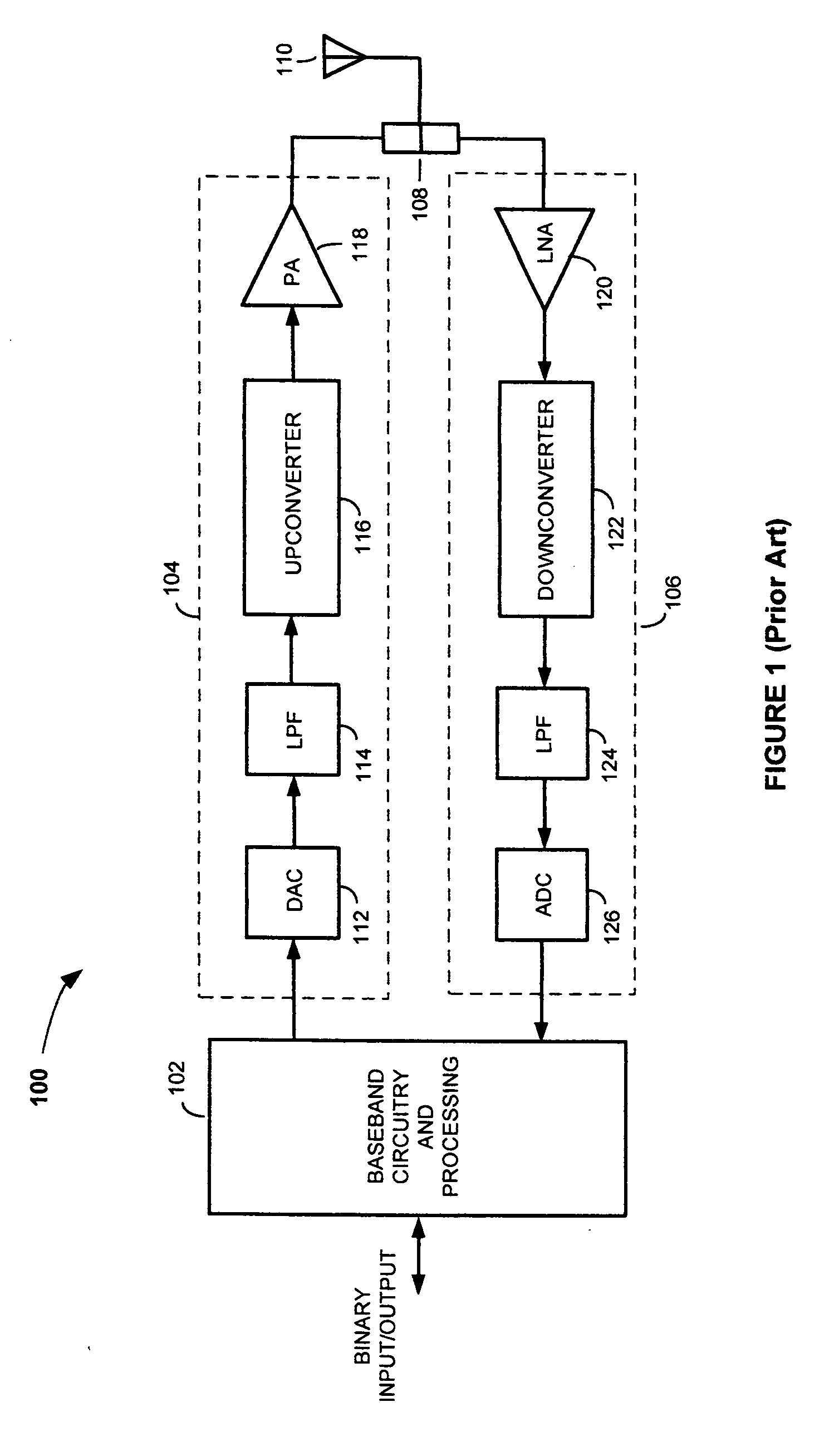

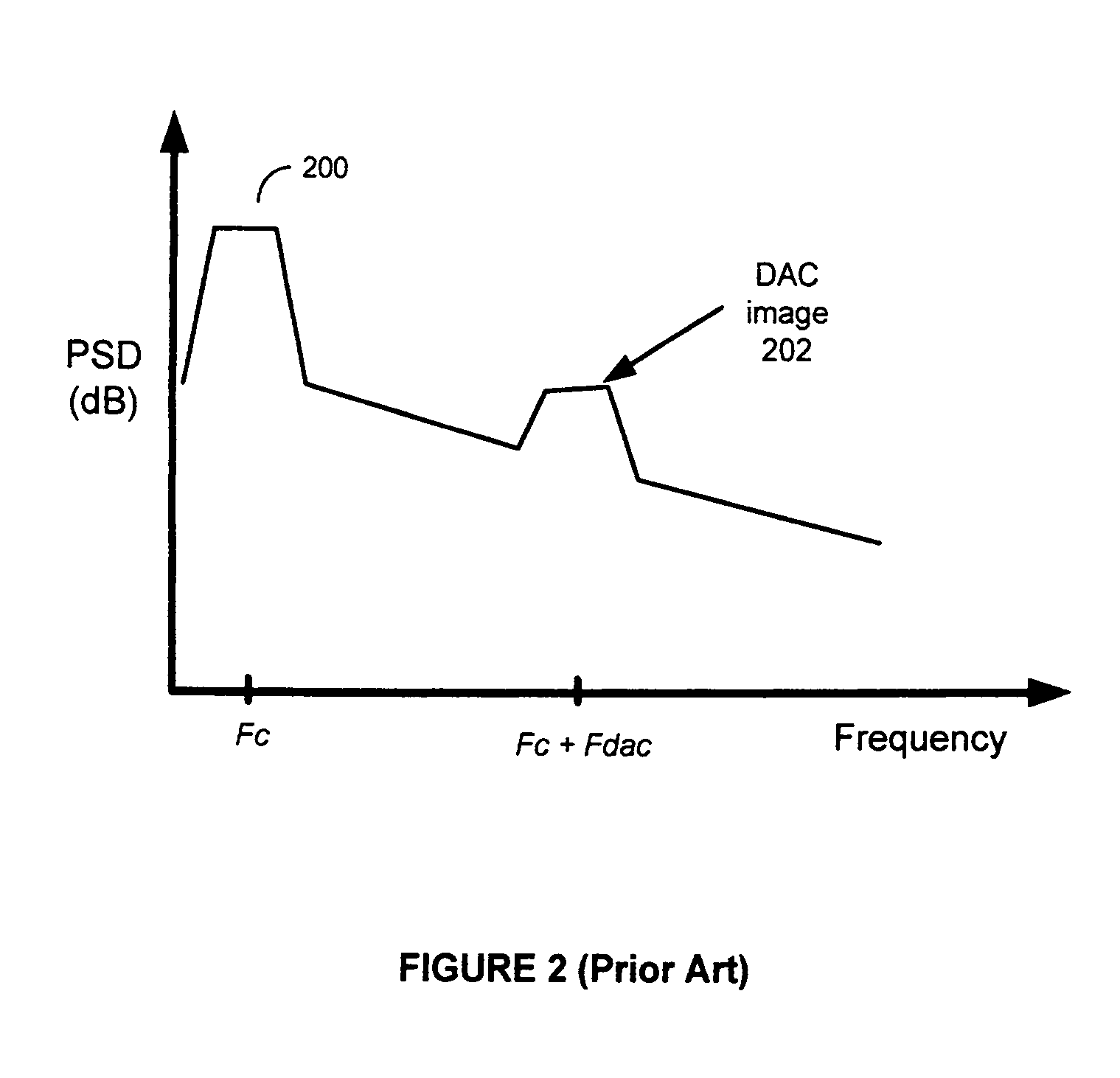

Methods and apparatus for reducing the effects of DAC images in radio frequency transceivers

InactiveUS20080219331A1Reduce the impactGreat signal attenuationAnalogue conversionDuplex signal operationTransceiverLow-pass filter

Methods and apparatus for reducing the effects of digital-to-analog converter (DAC) images and transmission spurious effects in a receive frequency band of a radio frequency (RF) transceiver. A transceiver apparatus includes a transmitter portion having a DAC, a receiver portion configured to receive RF signals in a receive frequency band, and a variable rate clock generator. The variable rate clock generator is used to provide an oversampling clock for the DAC. The rate of the oversampling clock is adjustable and is selected so that an upconverted version of a DAC image created by the DAC is steered away from frequencies within the receive frequency band. A notch-effect low-pass filter (NELPF) may also, or alternatively, be used in the transceiver to reduce transmission spurious effects in the receive frequency band.

Owner:PANASONIC CORP

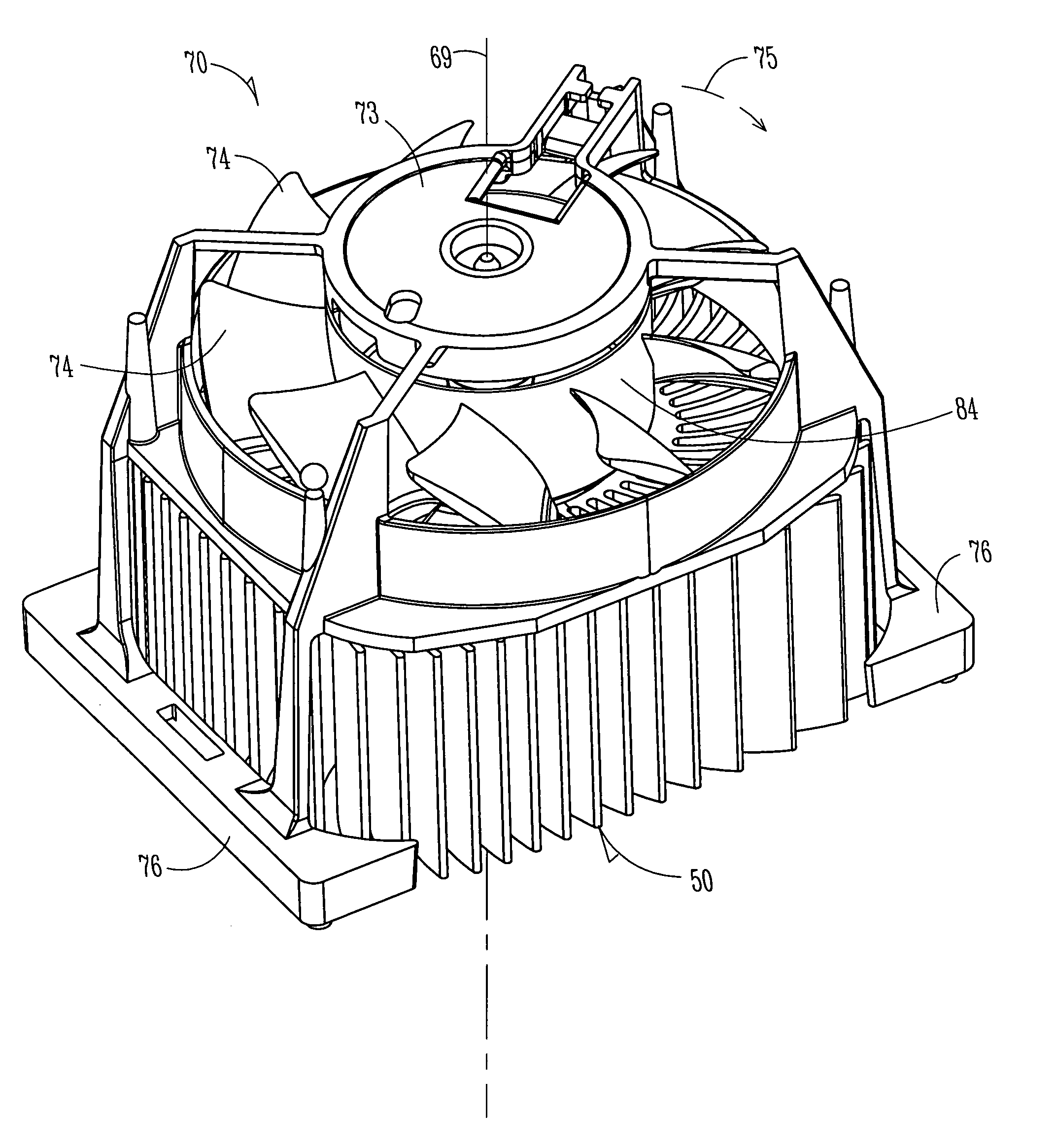

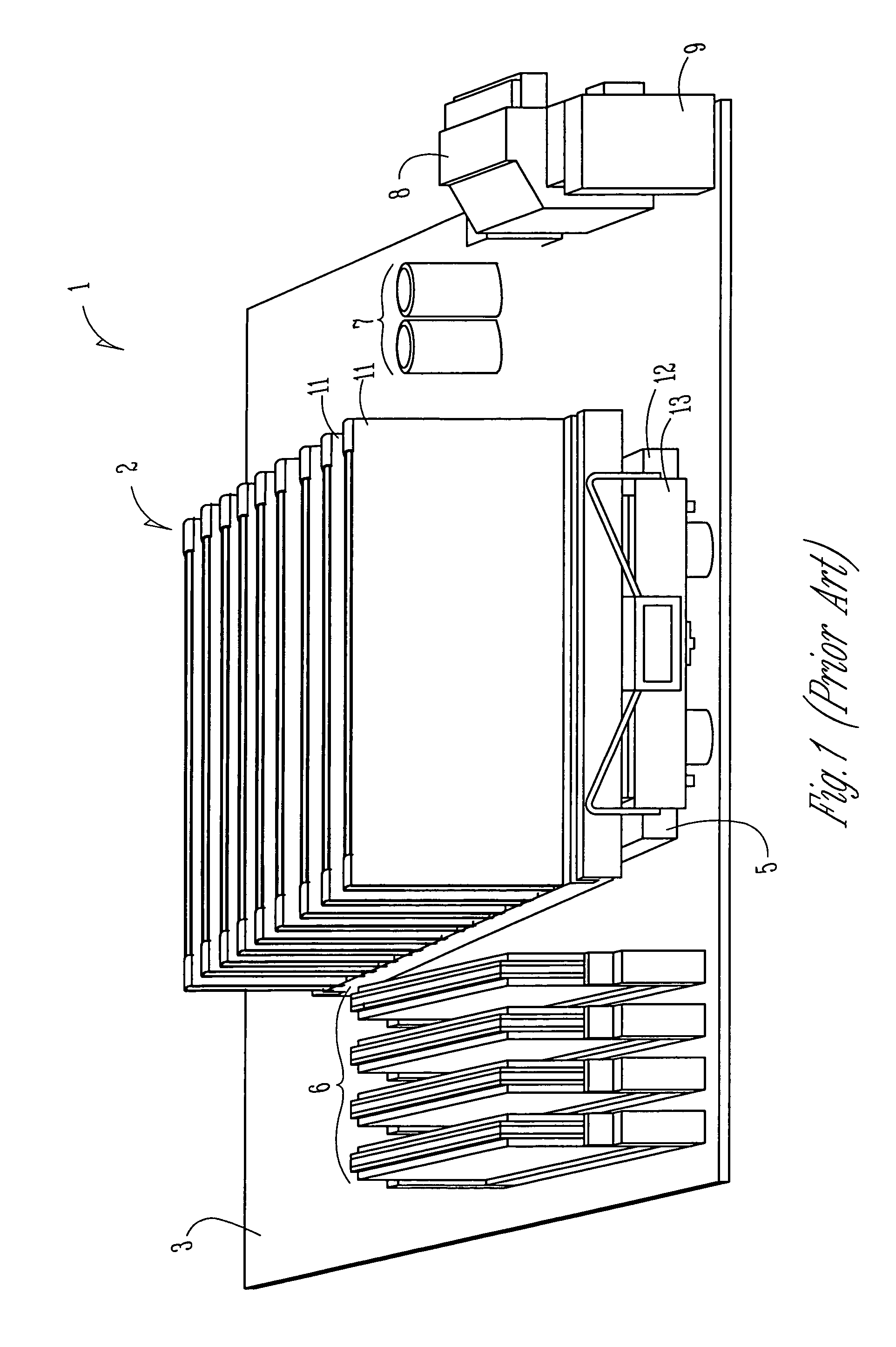

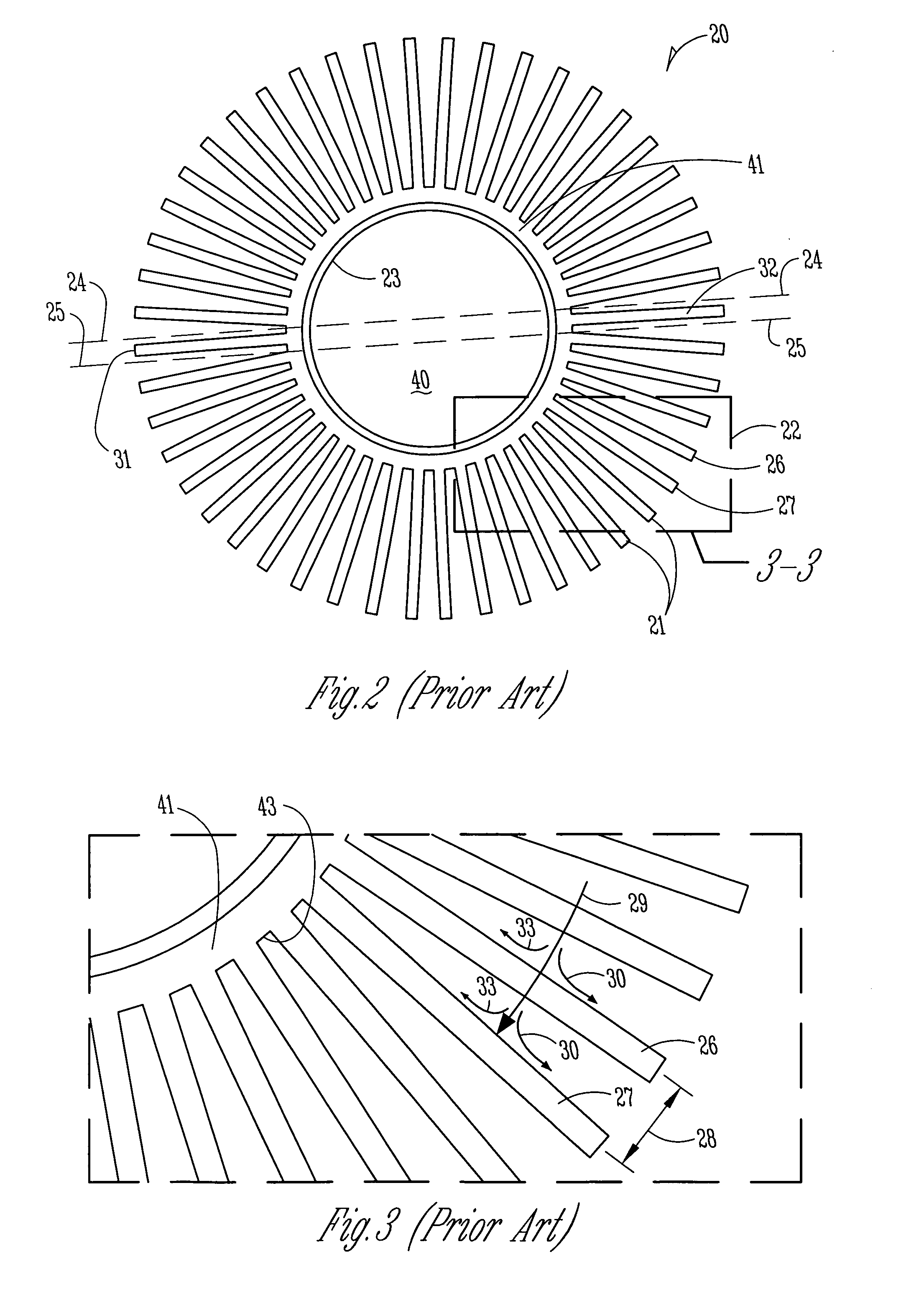

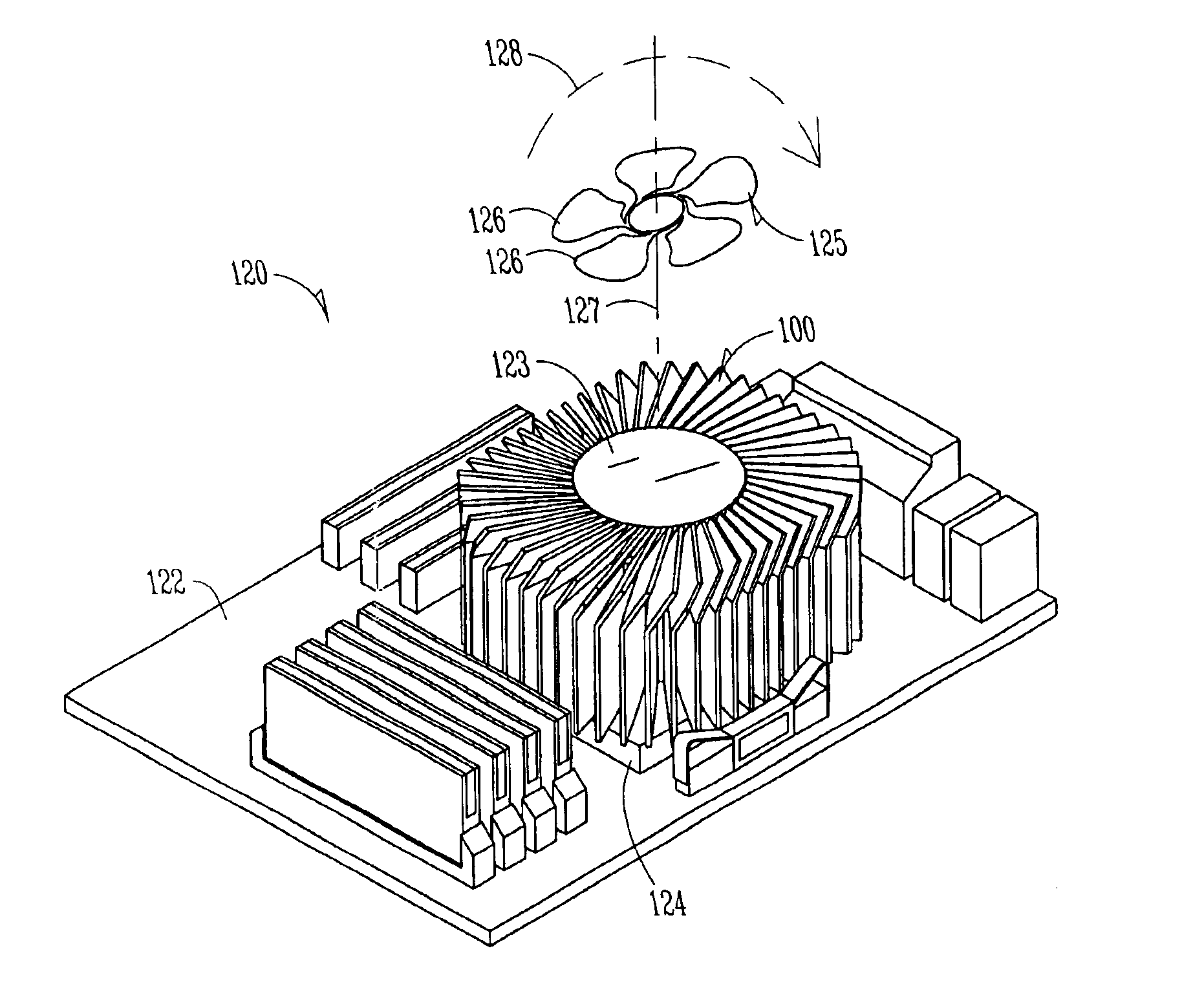

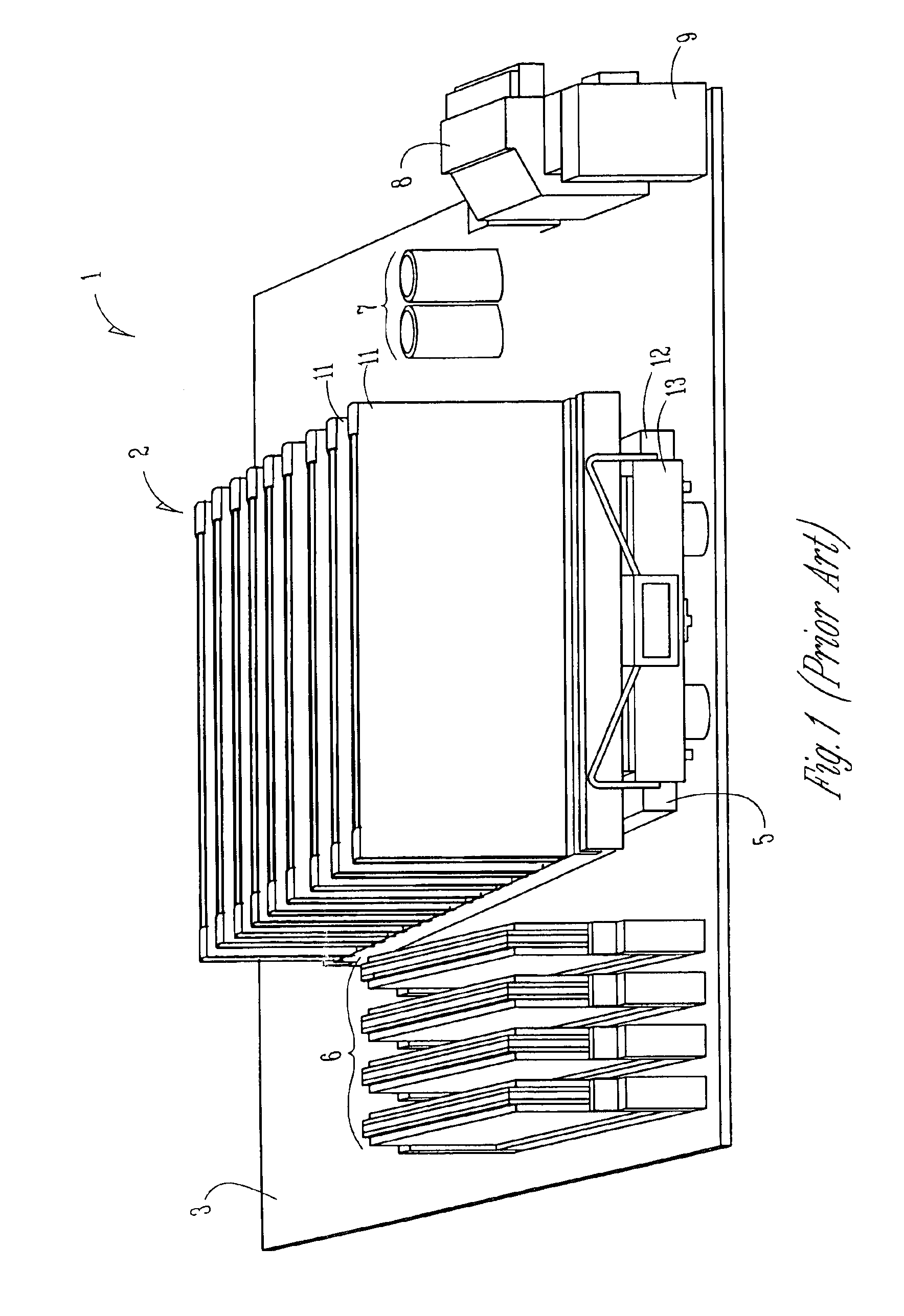

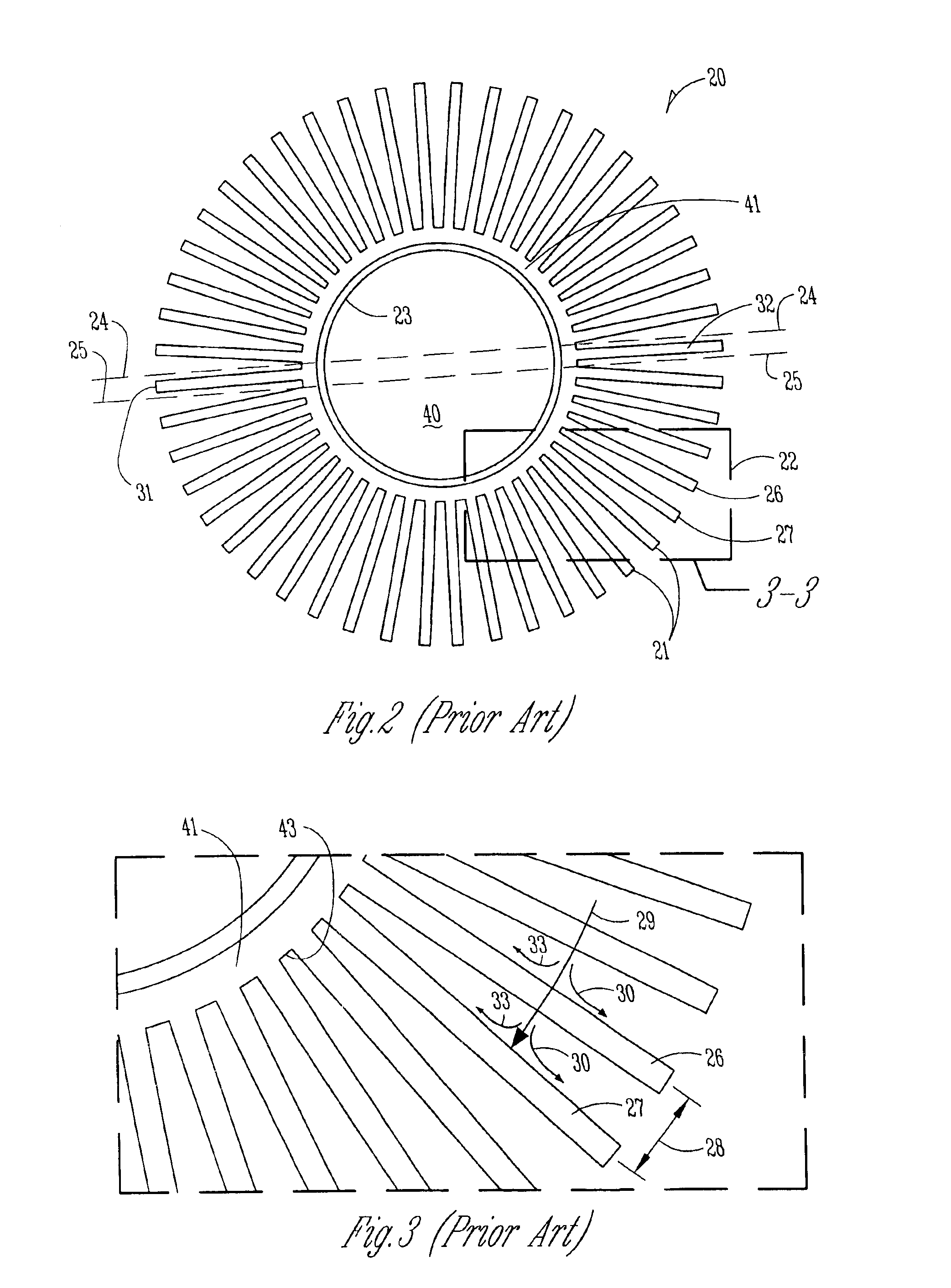

Electronic assemblies with high capacity curved and bent fin heat sinks and associated methods

InactiveUS20050280992A1Improve power densityMinimizes problemSemiconductor/solid-state device detailsSolid-state devicesElectronic systemsElectronic assemblies

An electronic assembly comprising one or more high performance integrated circuits includes at least one high capacity heat sink. The heat sink, which comprises a number of fins projecting substantially radially from a core, is structured to capture air from a fan and to direct the air to optimize heat transfer from the heat sink. The heat sink fins can be formed in different shapes. In one embodiment, the fins are curved. In another embodiment, the fins are bent. In yet another embodiment, the fins are curved and bent. Methods of fabricating heat sinks and electronic assemblies, as well as application of the heat sink to an electronic assembly and to an electronic system, are also described.

Owner:INTEL CORP

Electronic assemblies with high capacity bent fin heat sinks

InactiveUS7120020B2Improve power densityMinimizes problemSemiconductor/solid-state device detailsSolid-state devicesElectronic systemsElectronic assemblies

An electronic assembly comprising one or more high performance integrated circuits includes at least one high capacity heat sink. The heat sink, which comprises a number of fins projecting substantially radially from a core, is structured to capture air from a fan and to direct the air to optimize heat transfer from the heat sink. The heat sink fins can be formed in different shapes. In one embodiment, the fins are curved. In another embodiment, the fins are bent. In yet another embodiment, the fins are curved and bent. Methods of fabricating heat sinks and electronic assemblies, as well as application of the heat sink to an electronic assembly and to an electronic system, are also described.

Owner:INTEL CORP

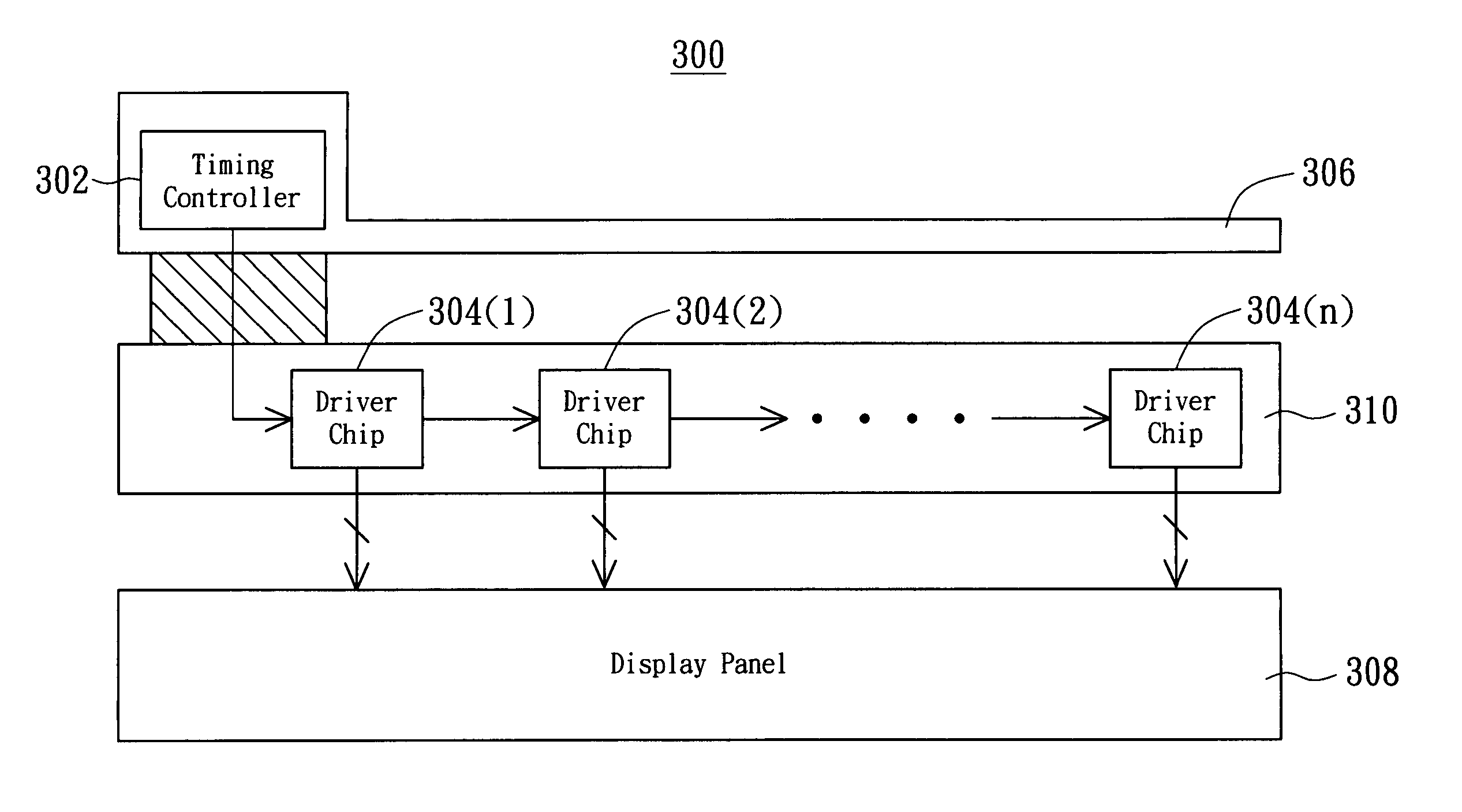

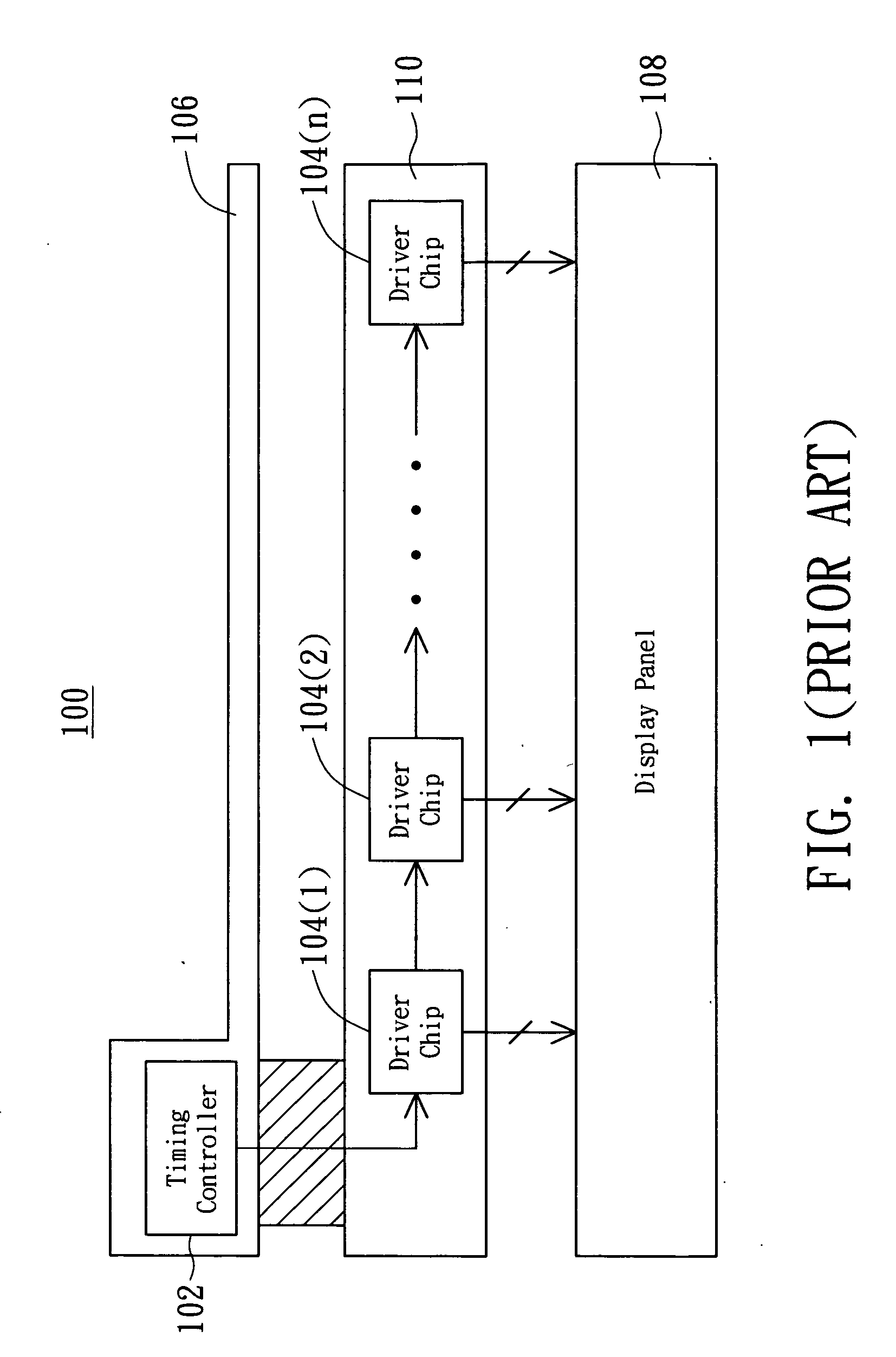

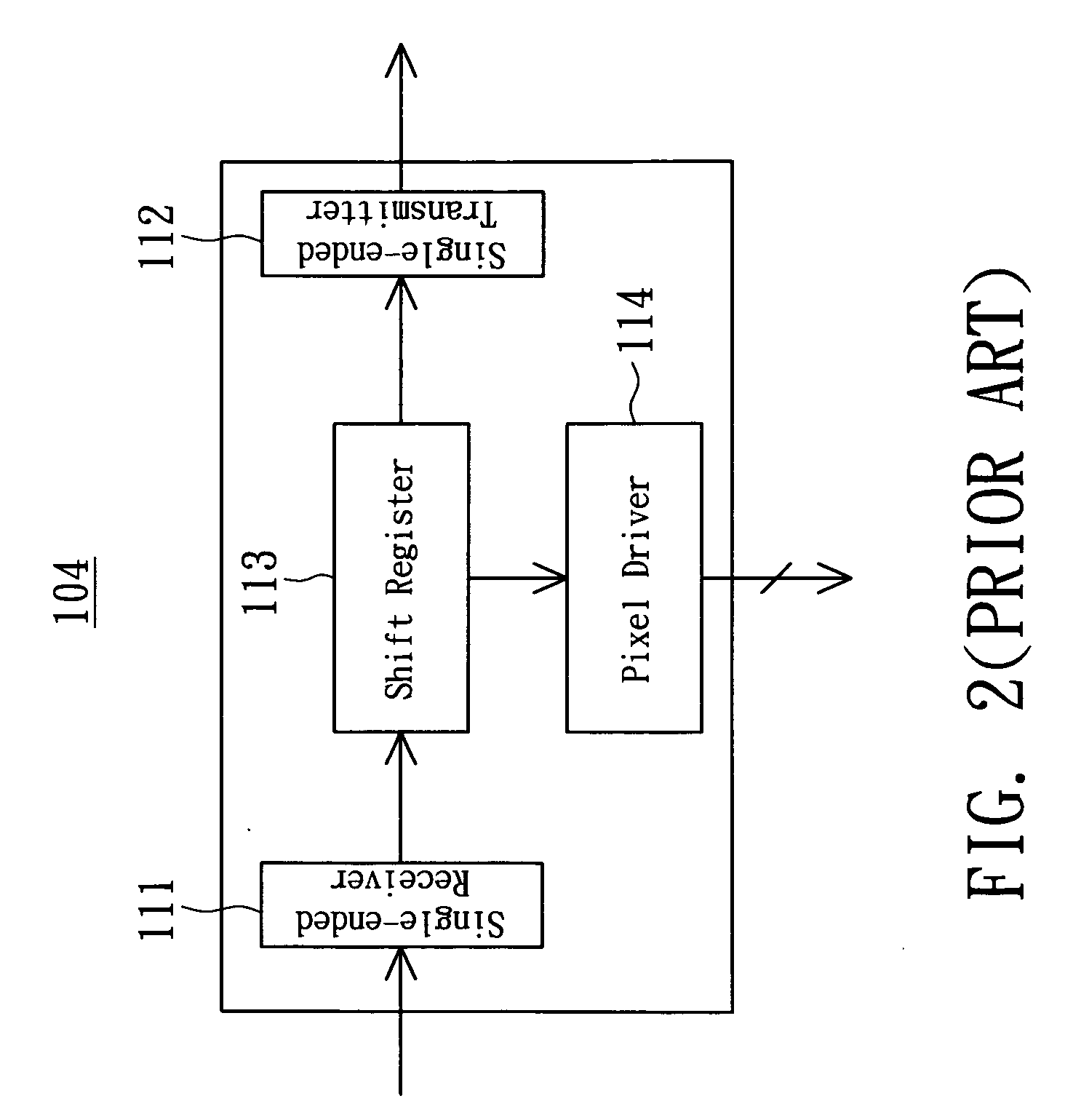

Liquid crystal display, driver chip and driving method thereof

ActiveUS20060012550A1Avoid signal attenuationIncrease clock frequencyCathode-ray tube indicatorsInput/output processes for data processingShift registerLiquid-crystal display

A liquid crystal display and the driving method thereof. The LCD includes a timing controller, a plurality of driver chips and a display panel. The driver chips are cascaded together for driving the display panel to display frames. A driver chip includes a differential receiver, a single-ended receiver, a shift register, a differential transmitter, a single-ended transmitter and a pixel driver. The driver chip receives a pixel signal and drives the display panel according to the pixel signal, and outputs the pixel signal to the next driver chip.

Owner:OPTRONIC SCI LLC

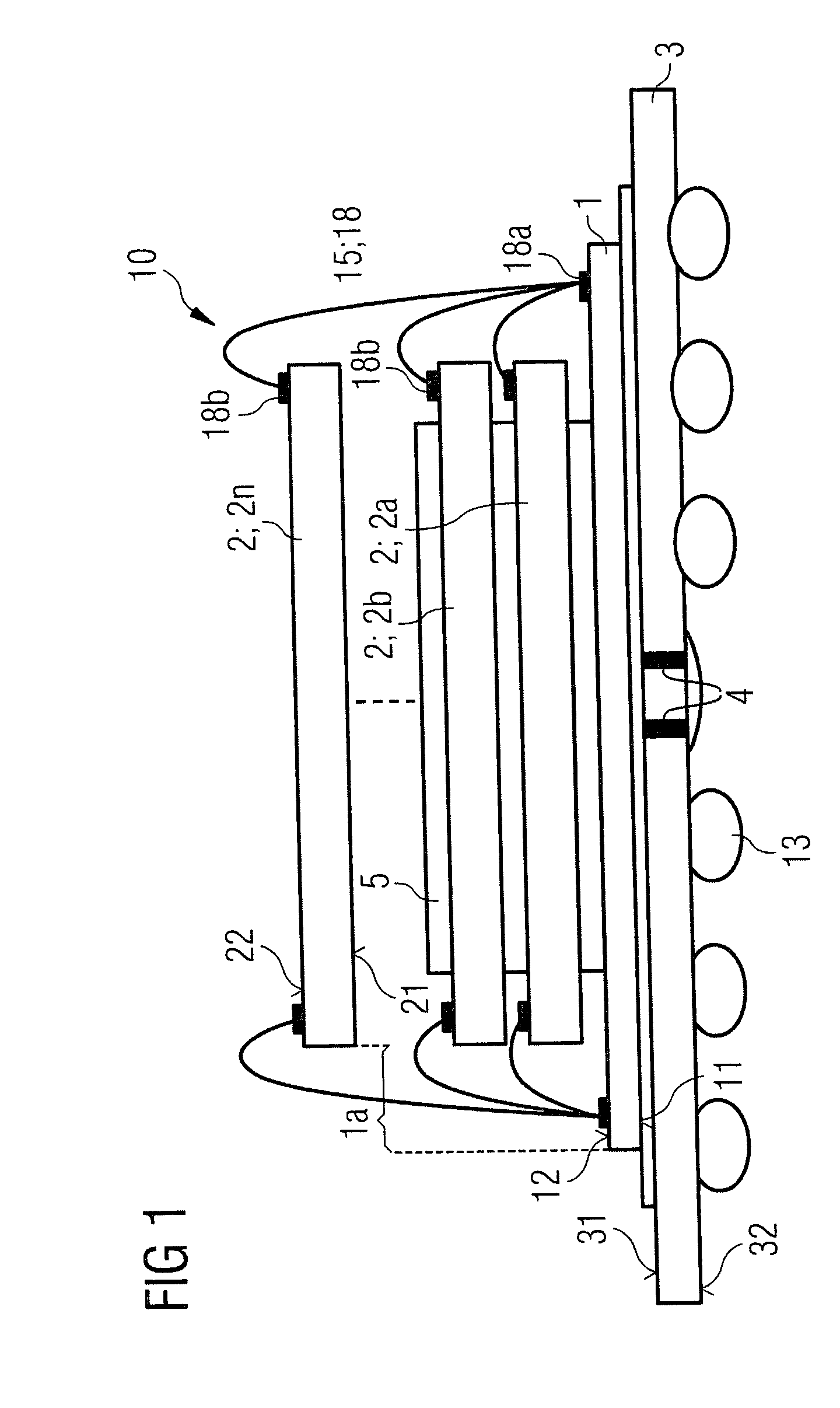

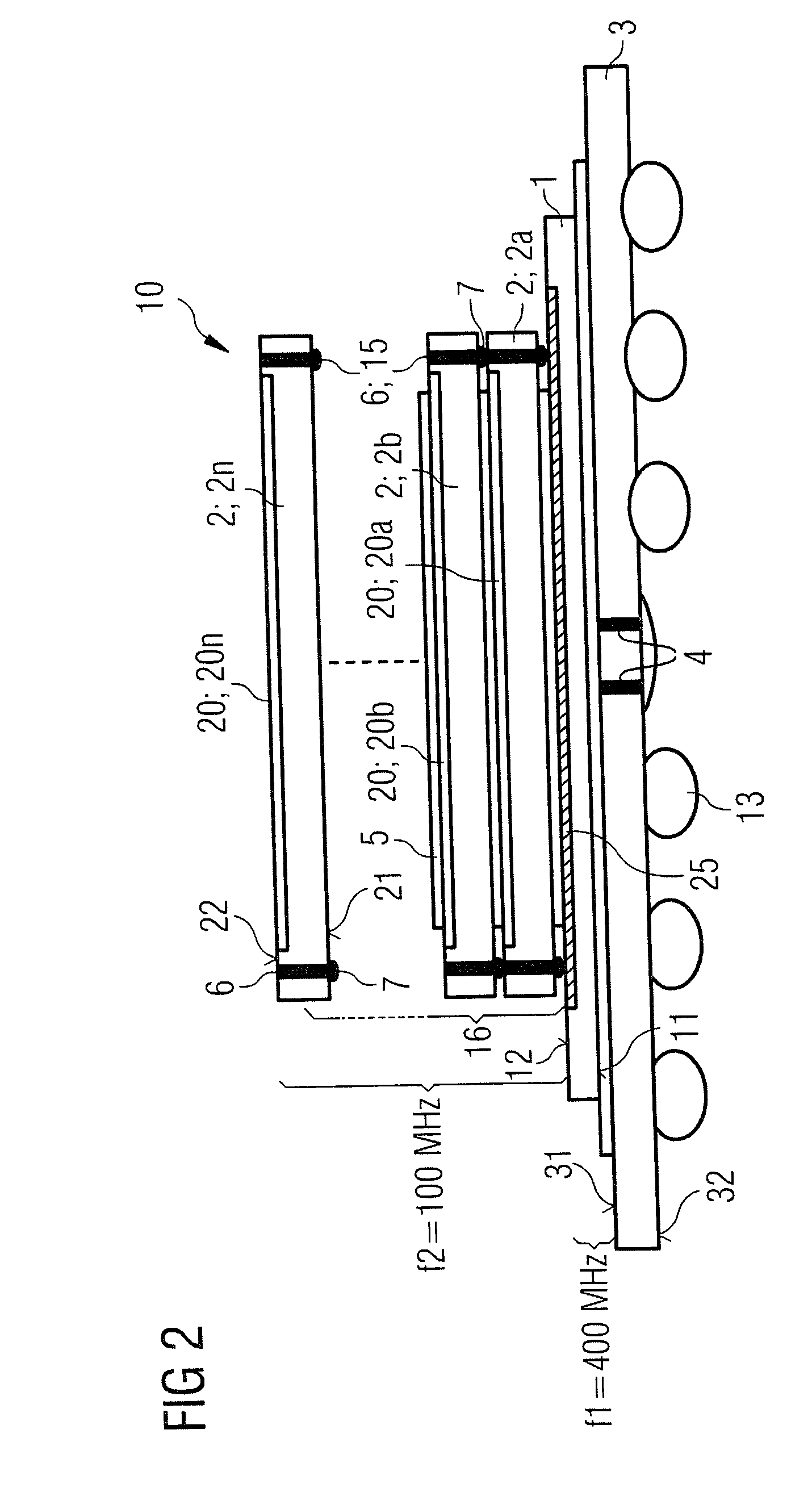

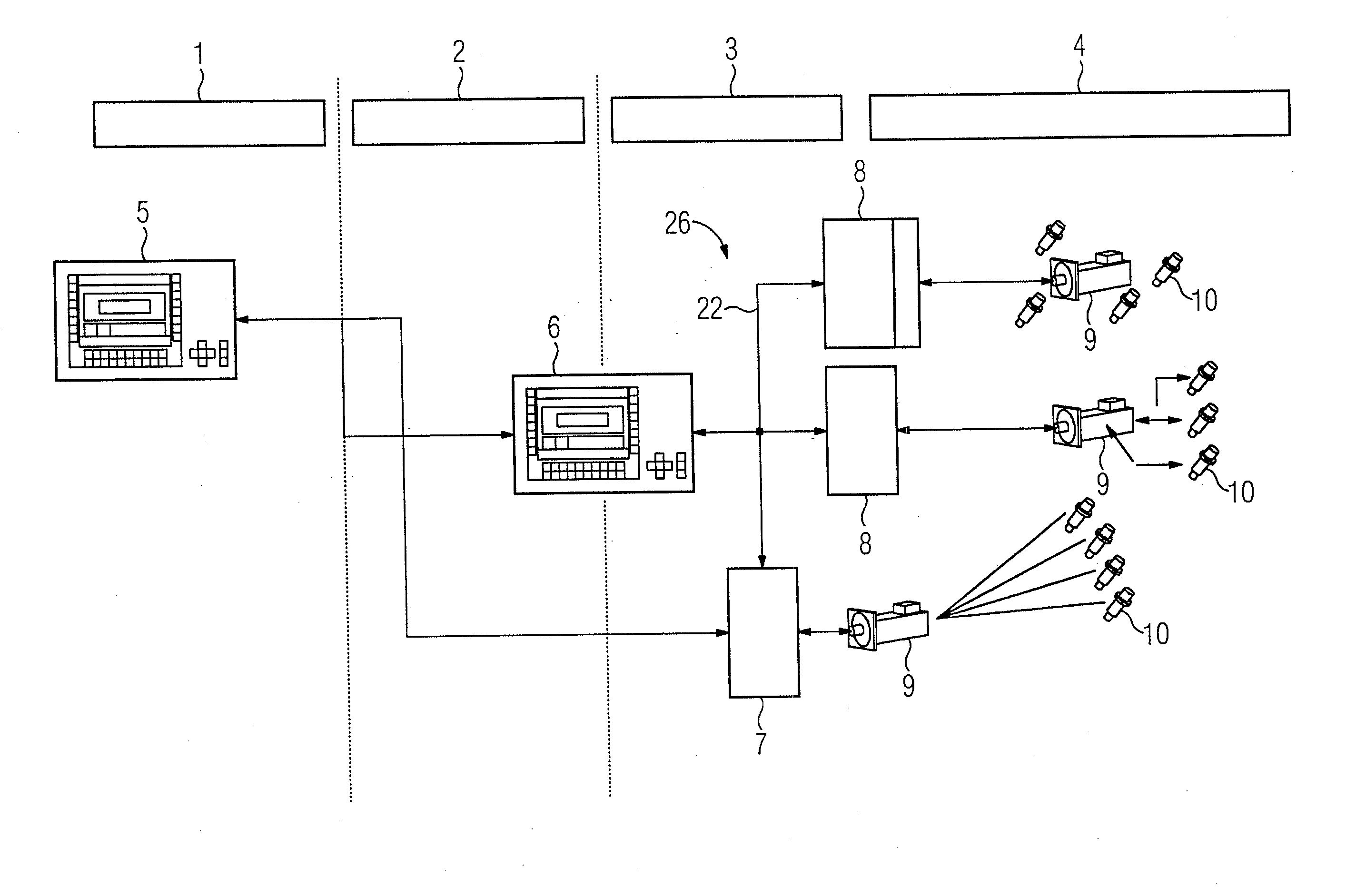

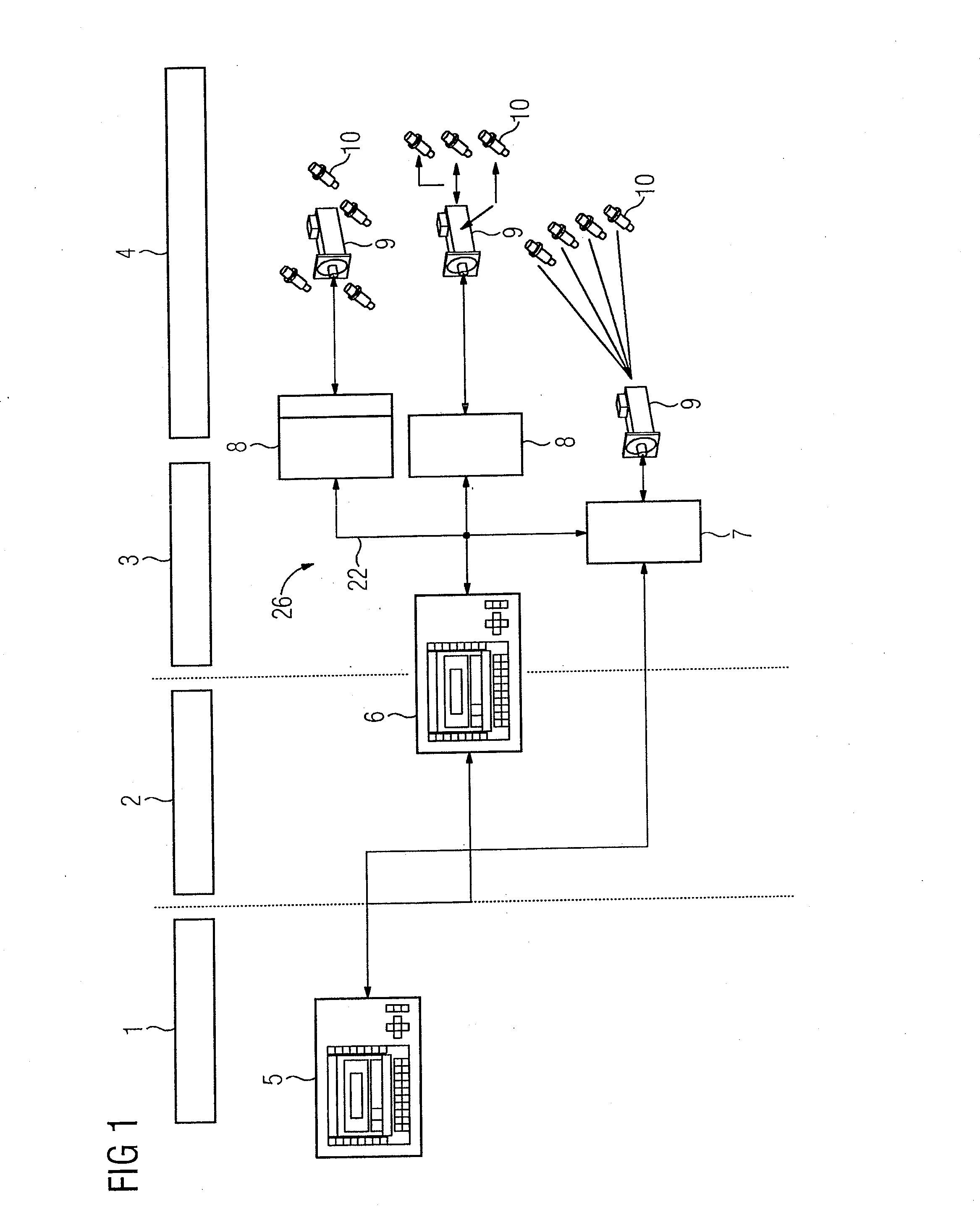

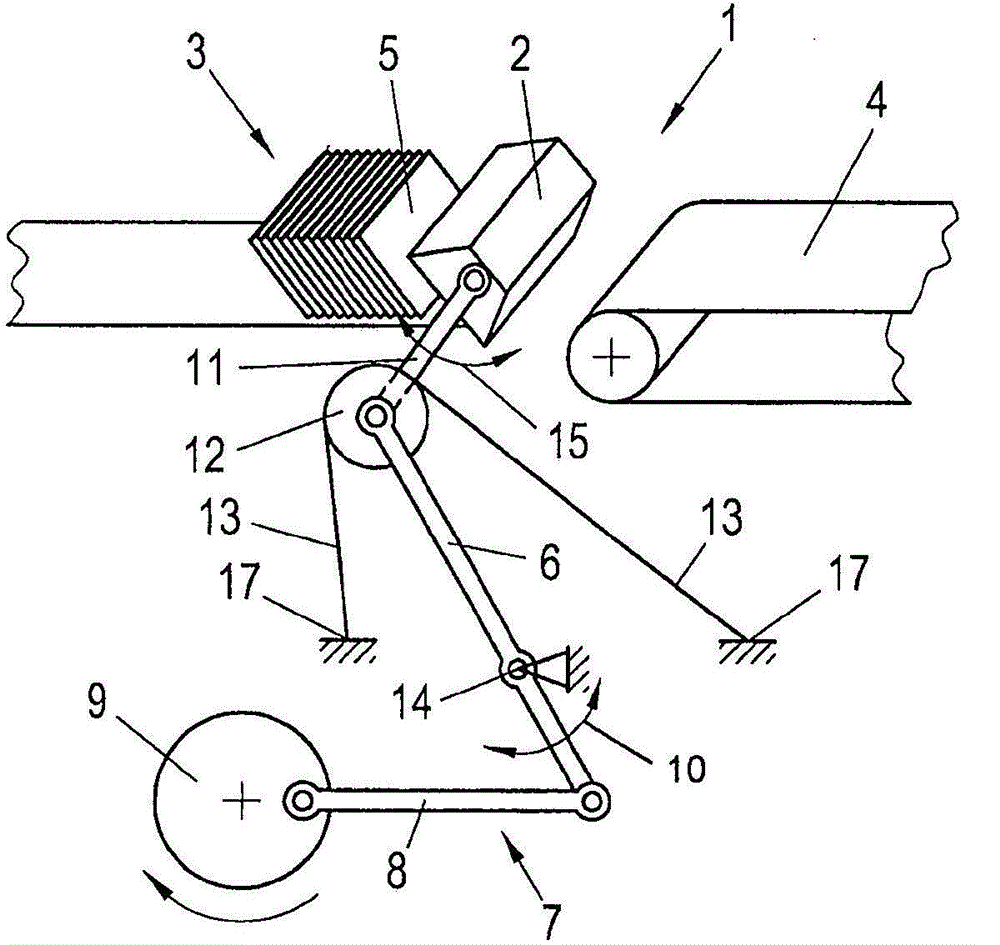

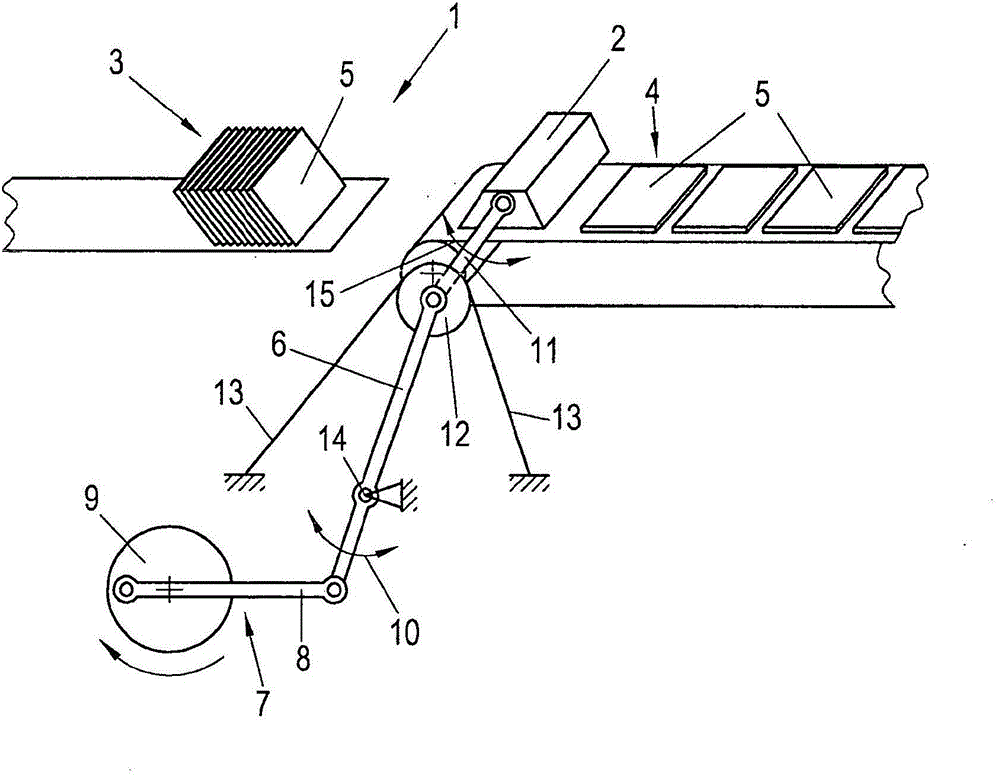

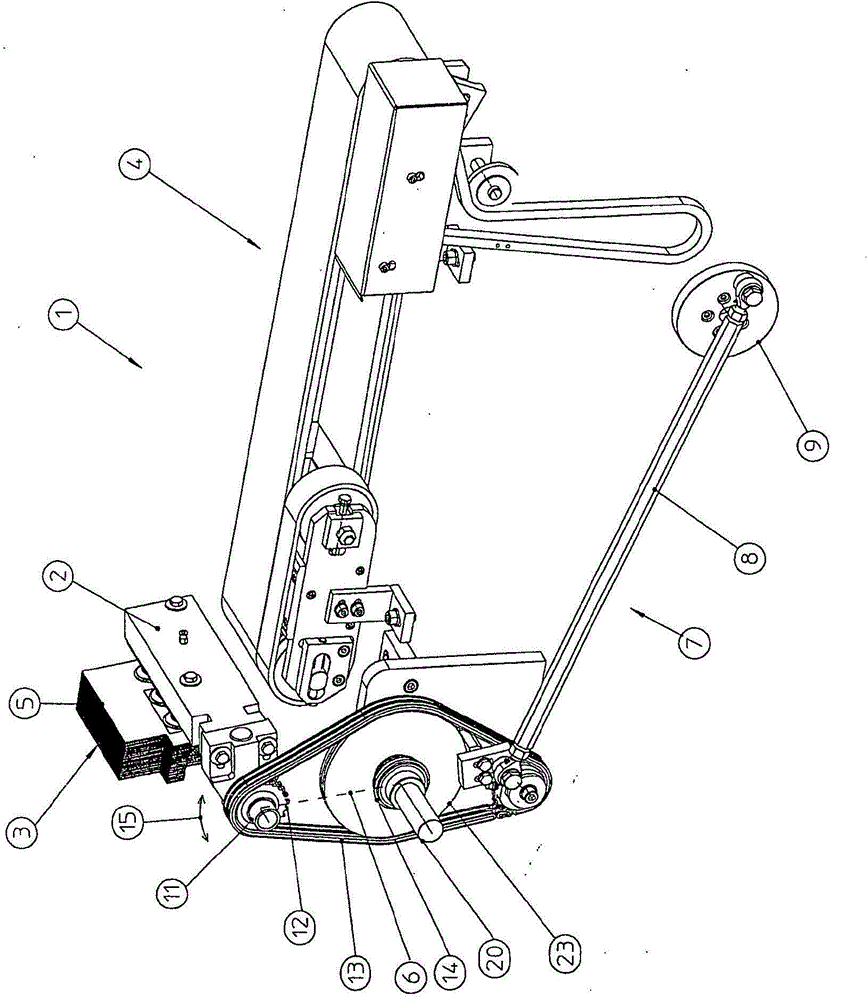

Device for handling plate-shaped objects

ActiveCN104470836AIncrease clock frequencyReduced torque demandConveyor partsEngineeringMechanical engineering

Owner:ROSENDAHL NEXTROM

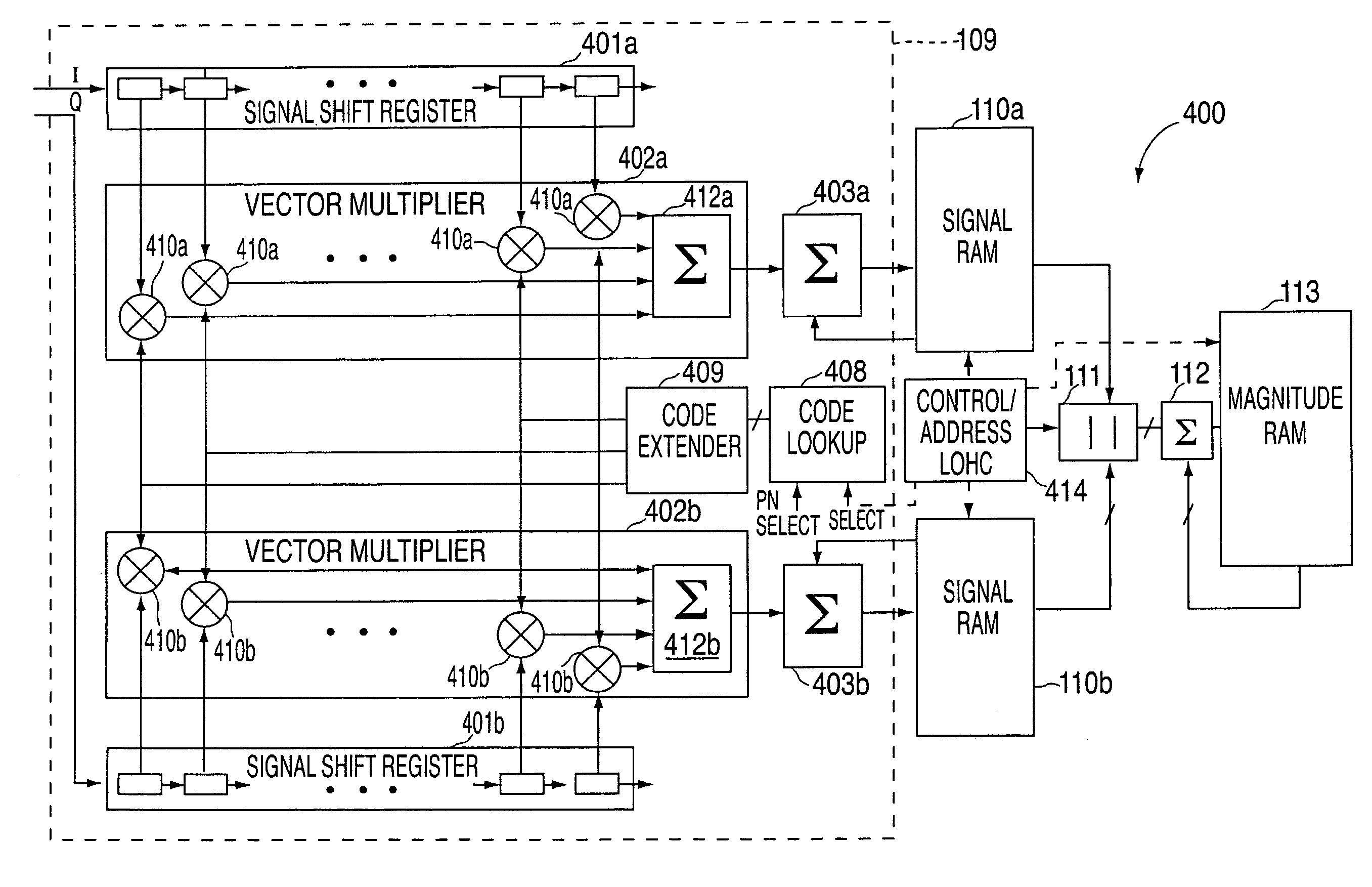

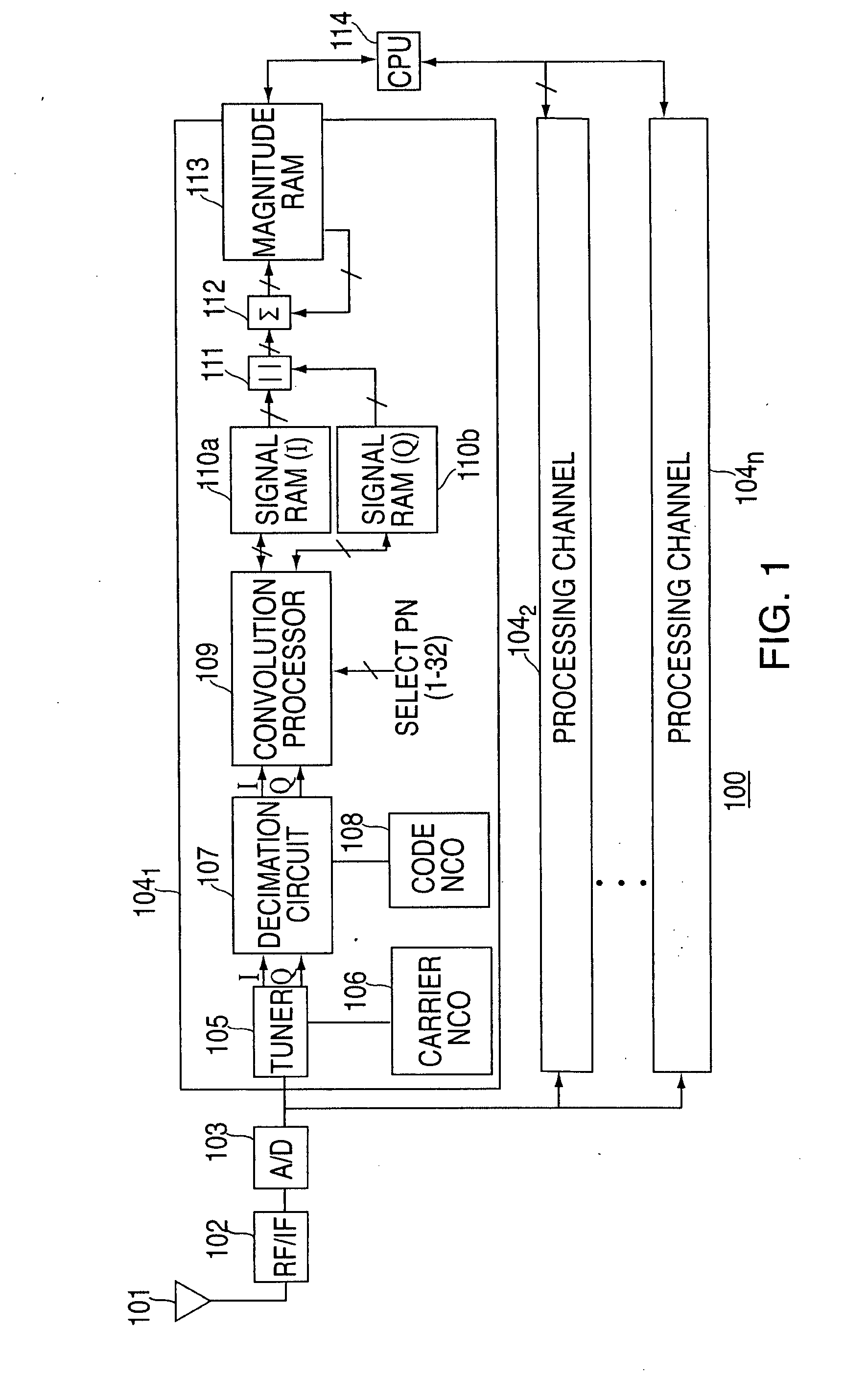

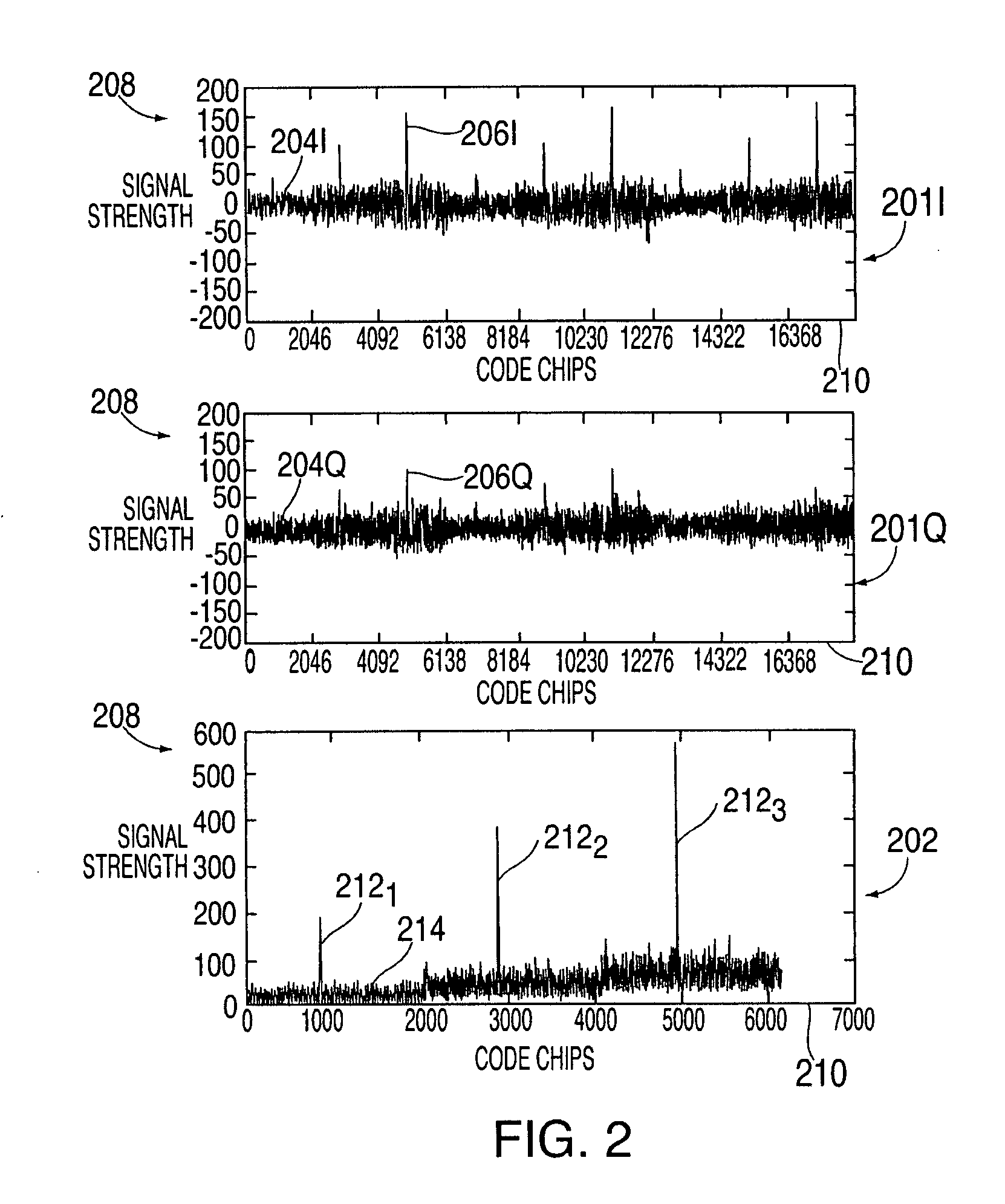

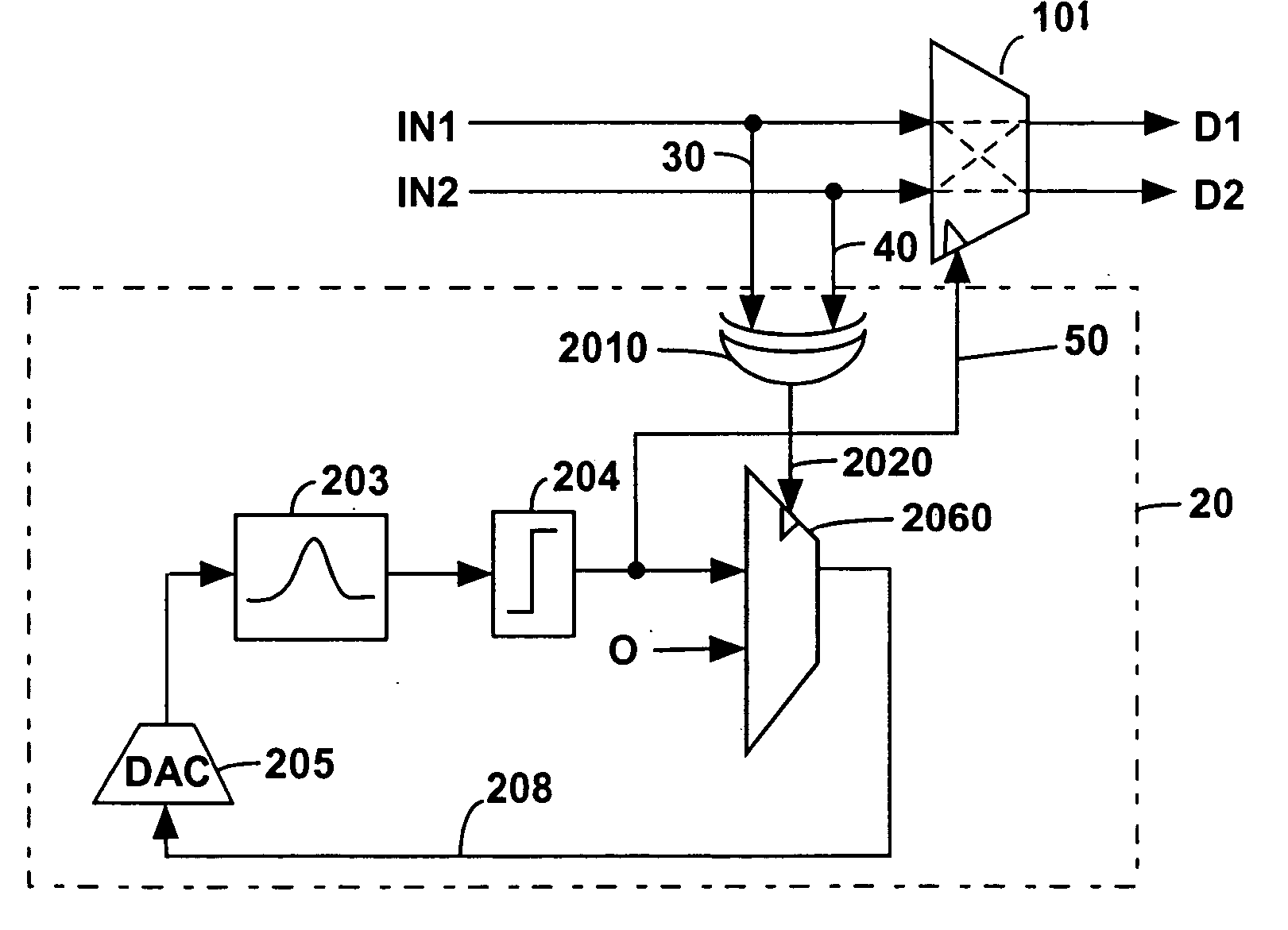

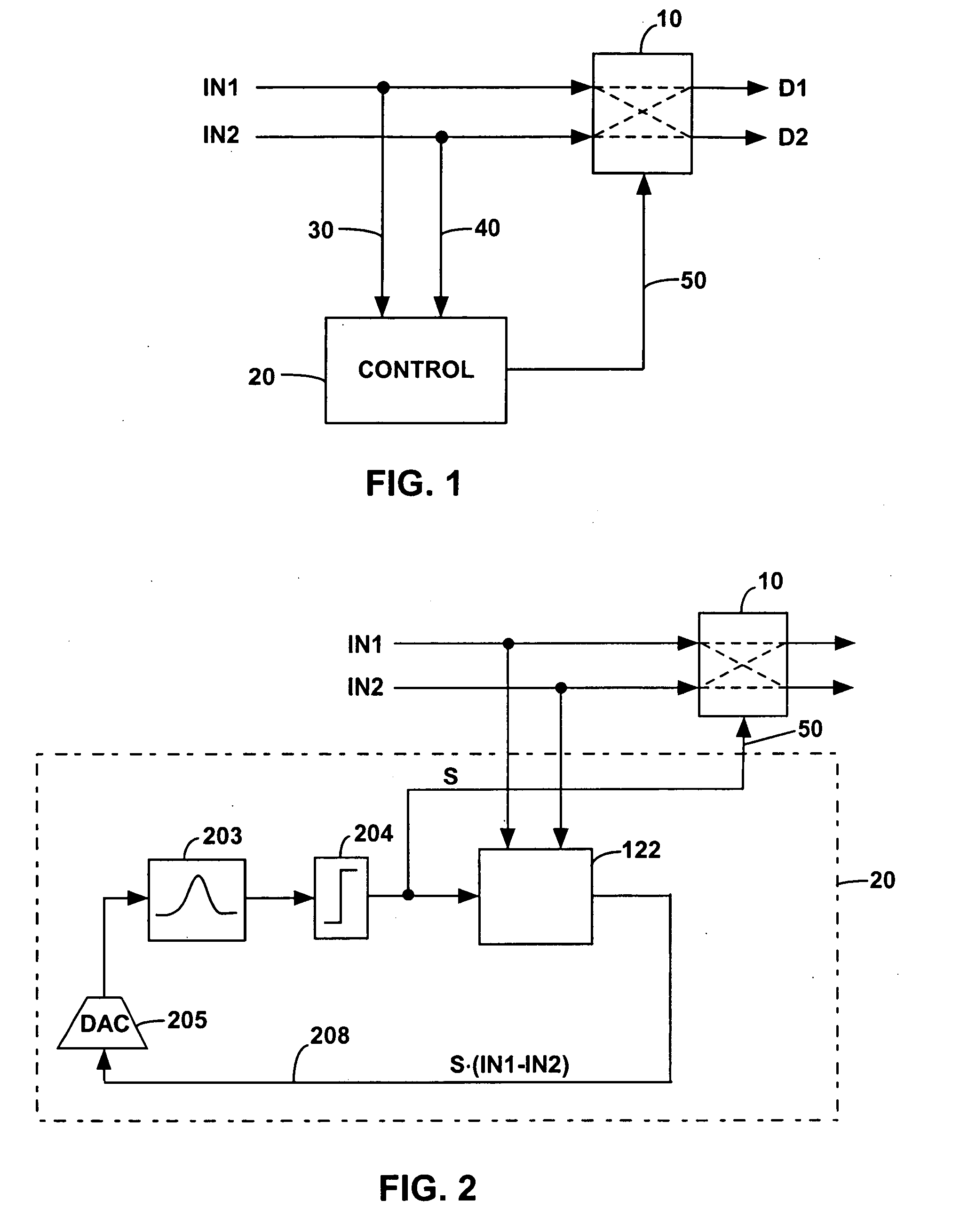

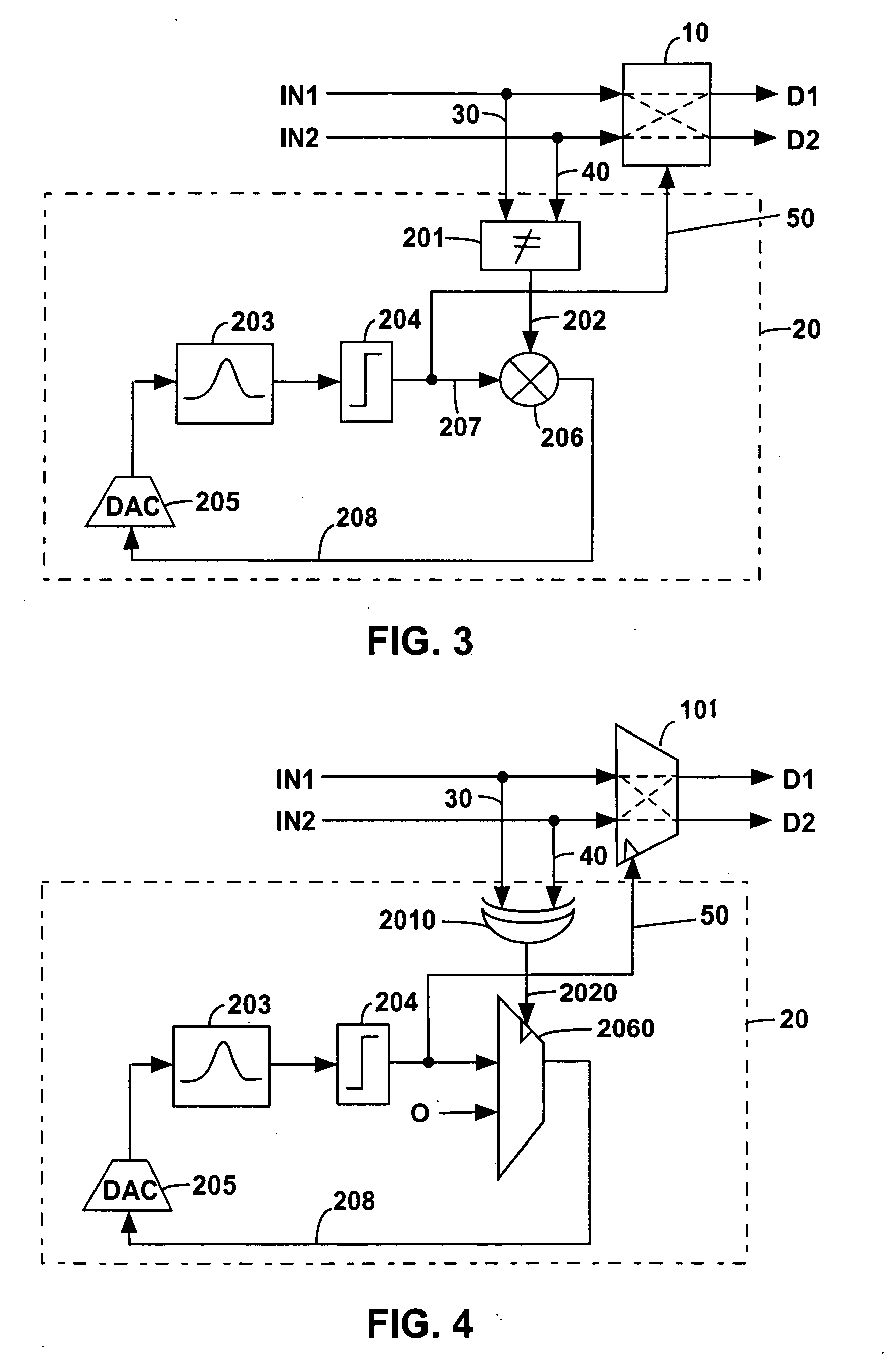

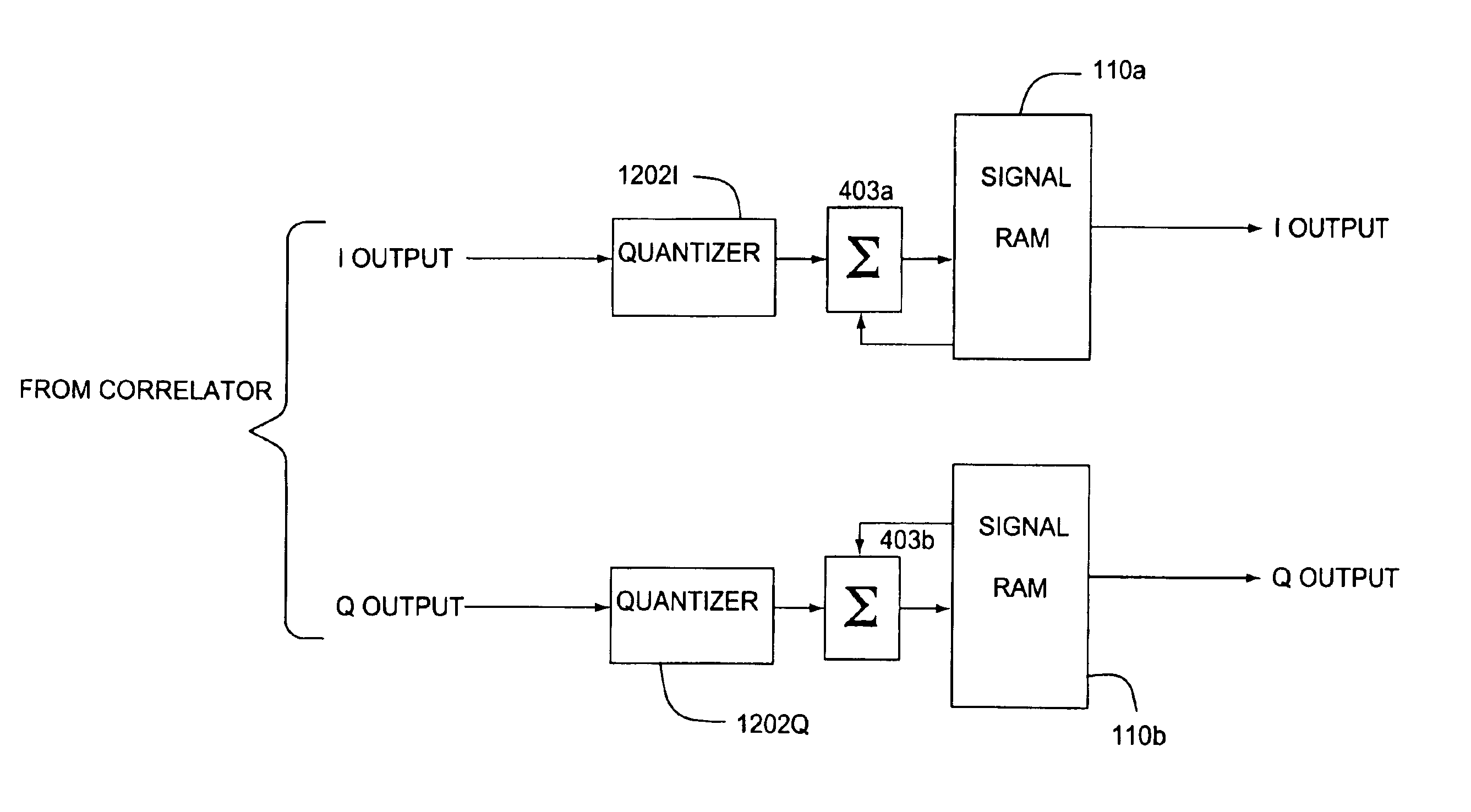

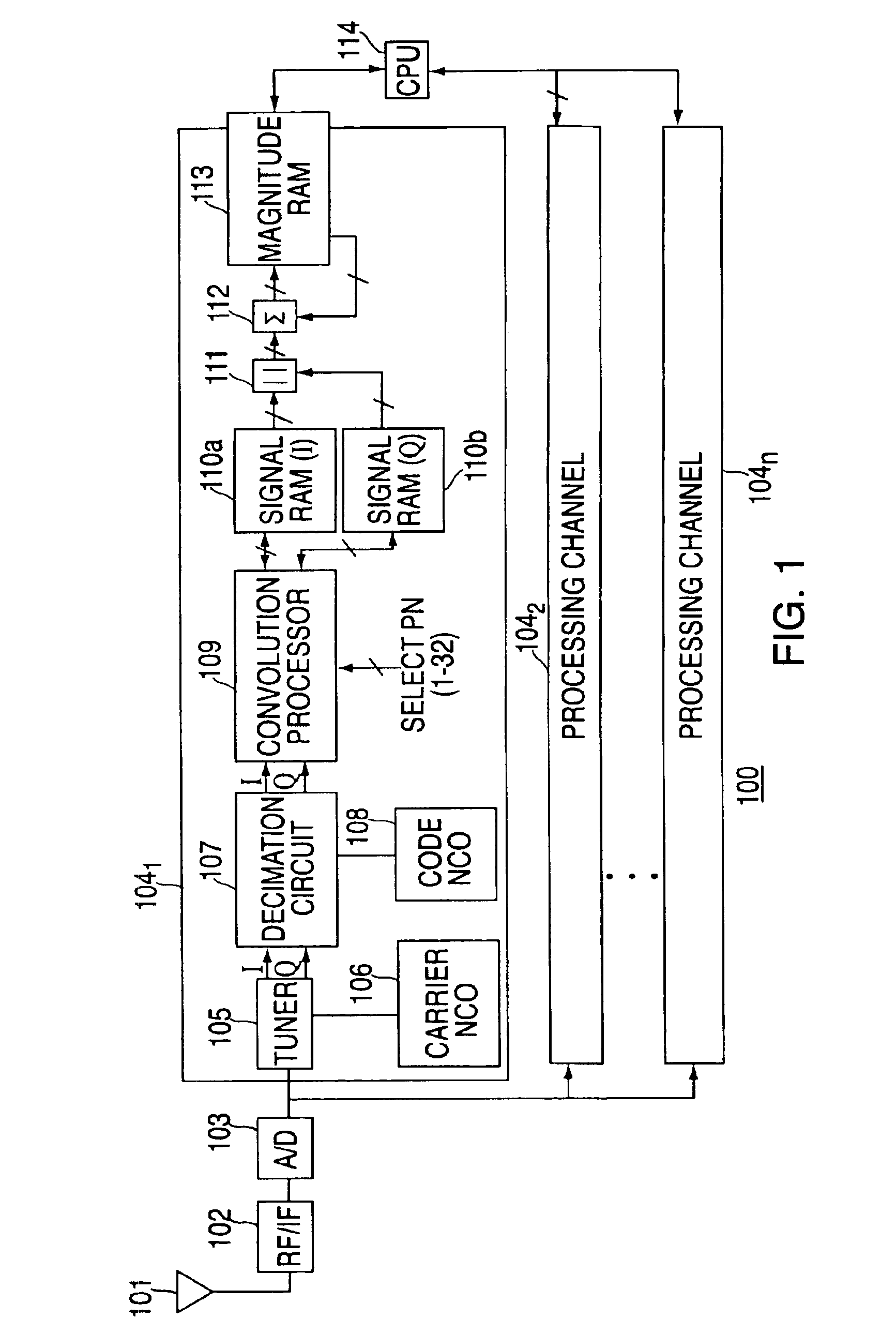

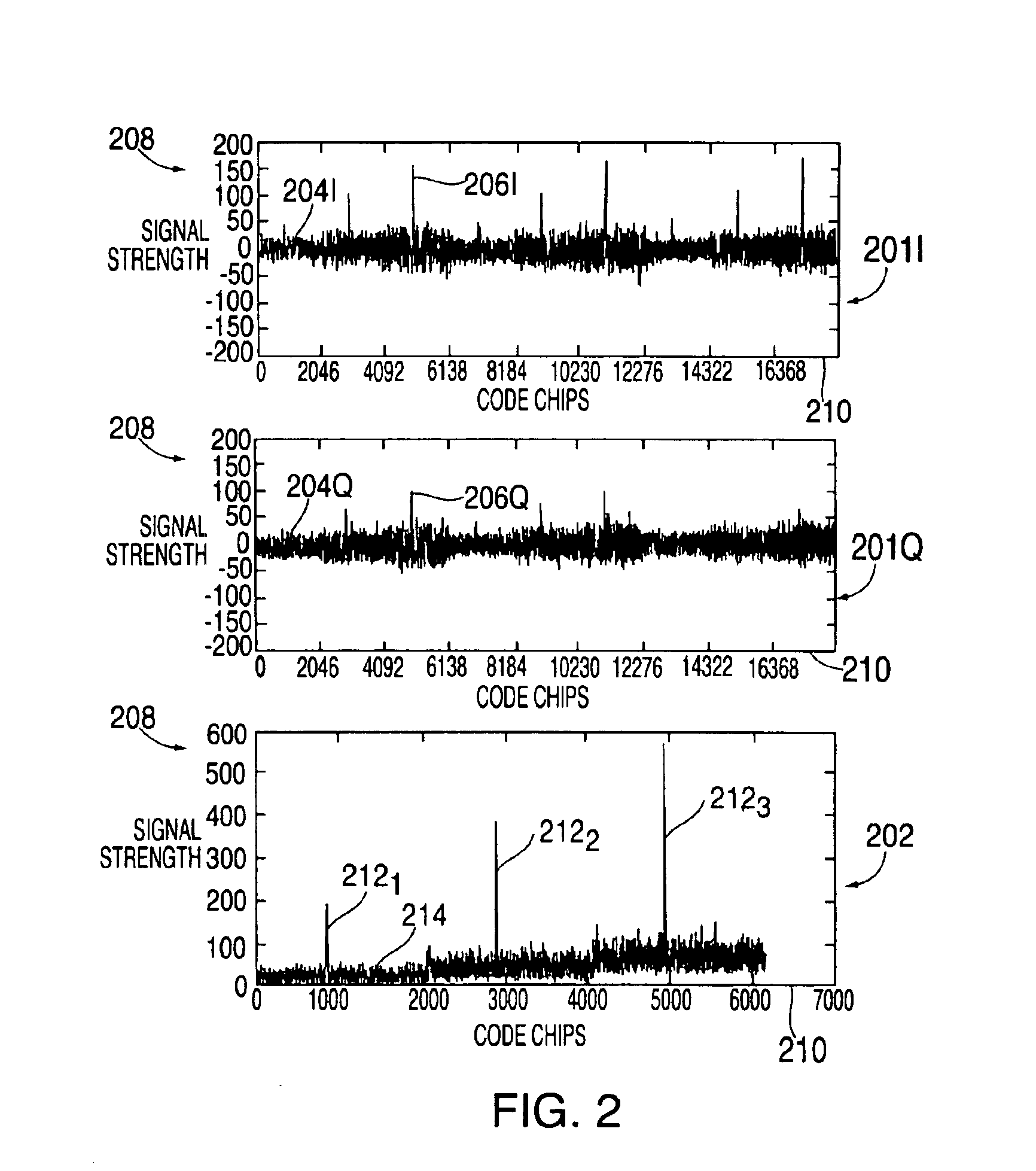

Method and apparatus for performing signal correlation

InactiveUS20070160121A1Efficient retrievalSimple lookup tableBeacon systems using radio wavesPosition fixationSignal correlationSatellite

A method of computing a correlation between a pseudorandom reference code and a satellite signal is provided. The method comprises receiving a satellite signal having a repeating code modulated thereon, wherein the satellite signal comprises a pseudorange; correlating the satellite signal with less than an entire length of the pseudorandom reference code with a portion of the satellite signal to produce a correlation over a period less than a period of the repeating code; and processing the correlation to form values representative of magnitude or power of the correlation to produce an energy signal.

Owner:AVAGO TECH INT SALES PTE LTD

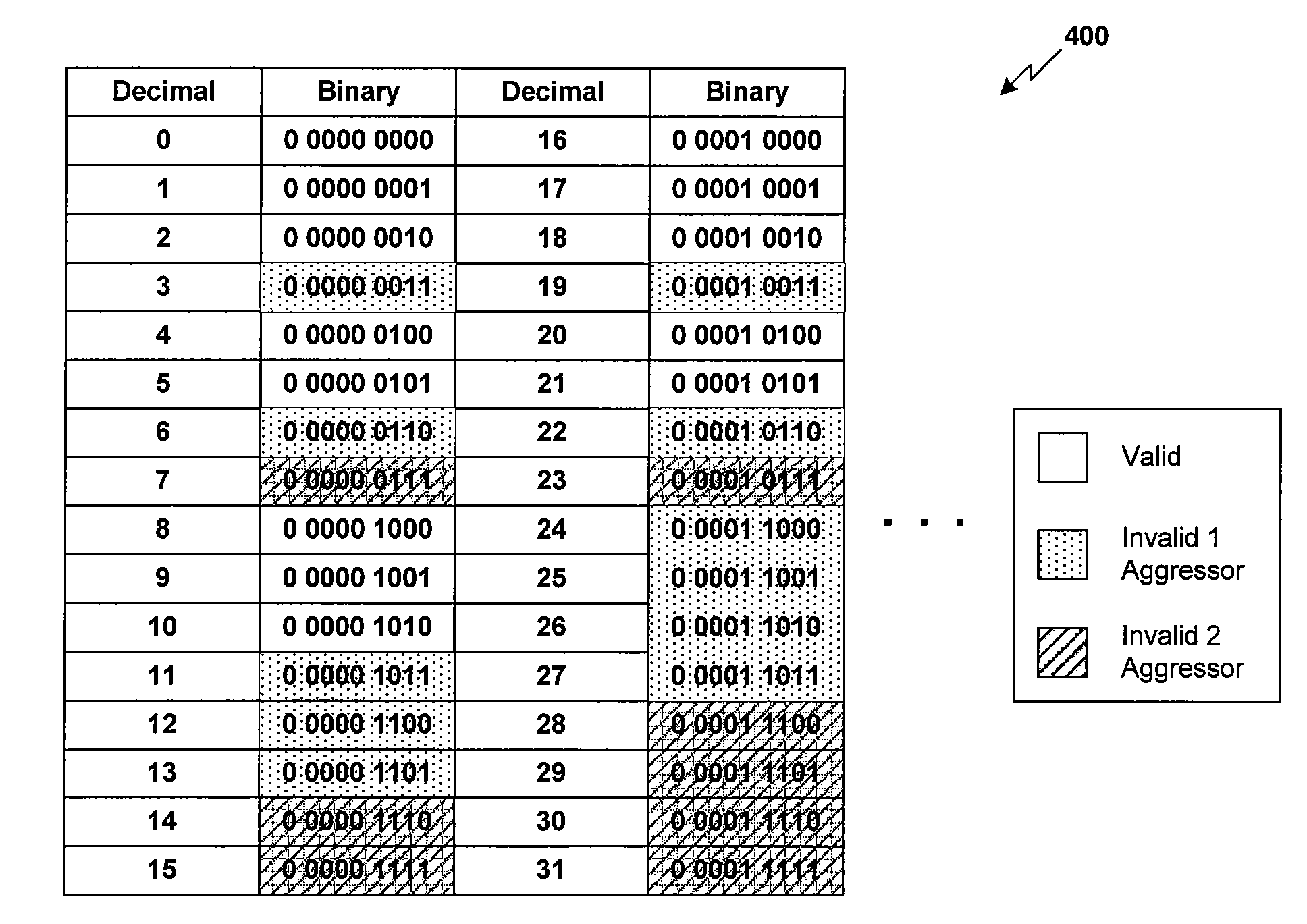

8b/9b decoding for reducing crosstalk on a high speed parallel bus

ActiveUS20130266047A1Increase clock frequencyImprove signal integrityChannel dividing arrangementsError preventionTheoretical computer scienceCrosstalk

Systems and methods for encoding a data word using an 8b / 9b encoding scheme that eliminates two-aggressor crosstalk are disclosed. The 8b / 9b encoding scheme enables a data word that can be subdivided into portions of eight bits or less to be encoded using code words having one extra bit than the corresponding portion of the data word. Each of the valid code words does not include any three consecutive bits having a logic level of logic-high (i.e., ‘1’), and represent transition vectors for consecutive symbols transmitted over the high speed parallel bus. An encoder and corresponding decoder are disclosed for implementing the 8b / 9b encoding scheme. In one embodiment, the encoder / decoder implements a modified Fibonacci sequence algorithm. In another embodiment, the encoder / decoder implements a look-up table. In some embodiments, data words may be less than eight bits wide.

Owner:NVIDIA CORP

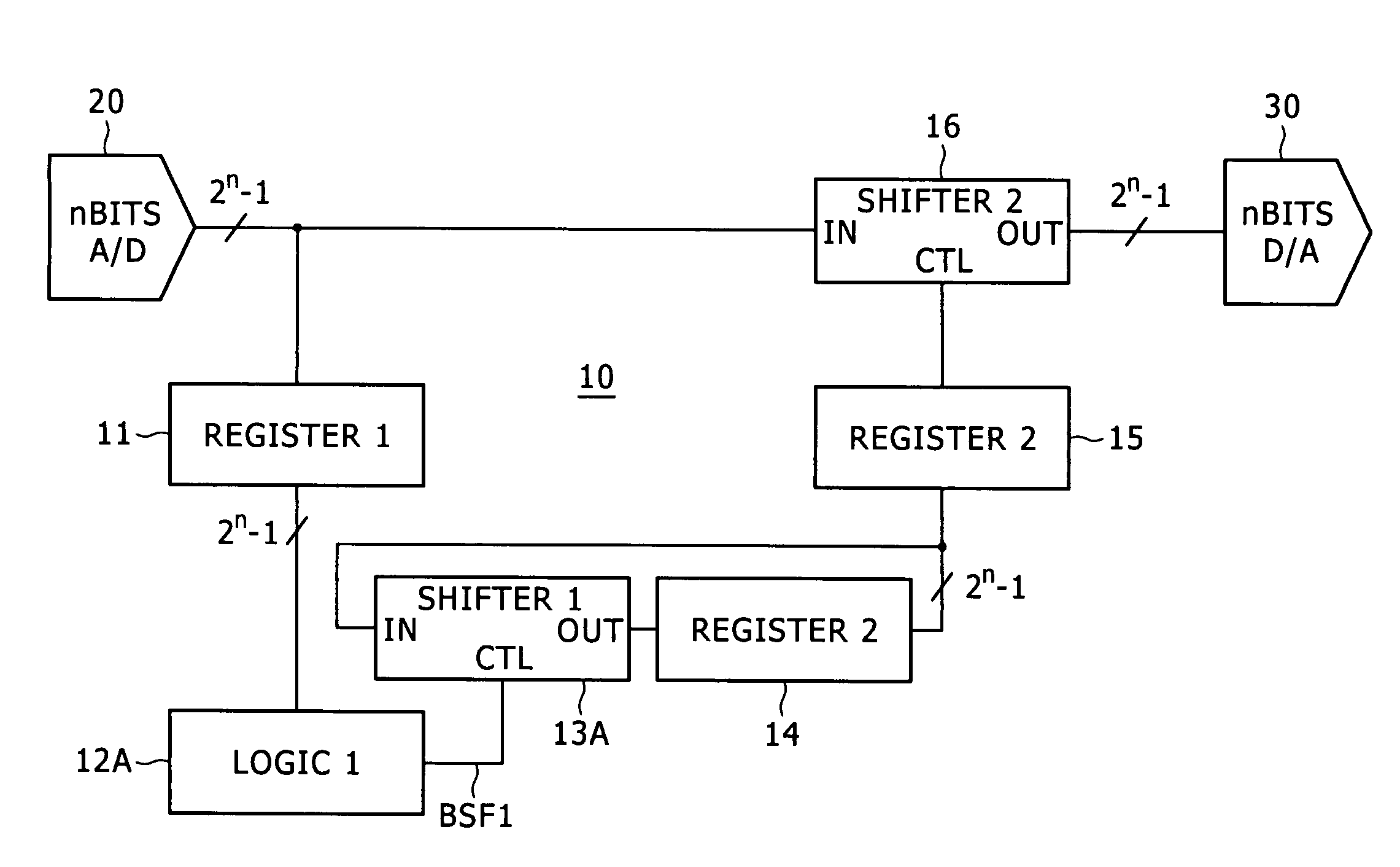

Linearity enhancement circuit, ΣΔ A/D converter, and reception apparatus

InactiveUS8144046B2Increase clock frequencyIncrease the number of digitsElectric signal transmission systemsAnalogue conversionProcessor registerBuck converter

A linearity enhancement circuit is disclosed which includes: a first shift amount creation block creating a first shift amount in keeping with the immediately preceding output code of an n-bit A / D converter; a first shifter circuit bit-shifting input code data by the first shift amount that has been supplied, the first shifter circuit further outputting the bit-shifted input code data; a register storing the output of the first shifter circuit in order to output the stored data as the input code data to the first shifter circuit thereby forming a loop circuit in conjunction with the first shifter circuit, the register further outputting the stored code data as a second shift amount; and a second shifter circuit bit-shifting the output code of the A / D converter by the second shift amount that has been supplied, the second shifter circuit further outputting the bit-shifted output code to an n-bit D / A converter.

Owner:SONY CORP

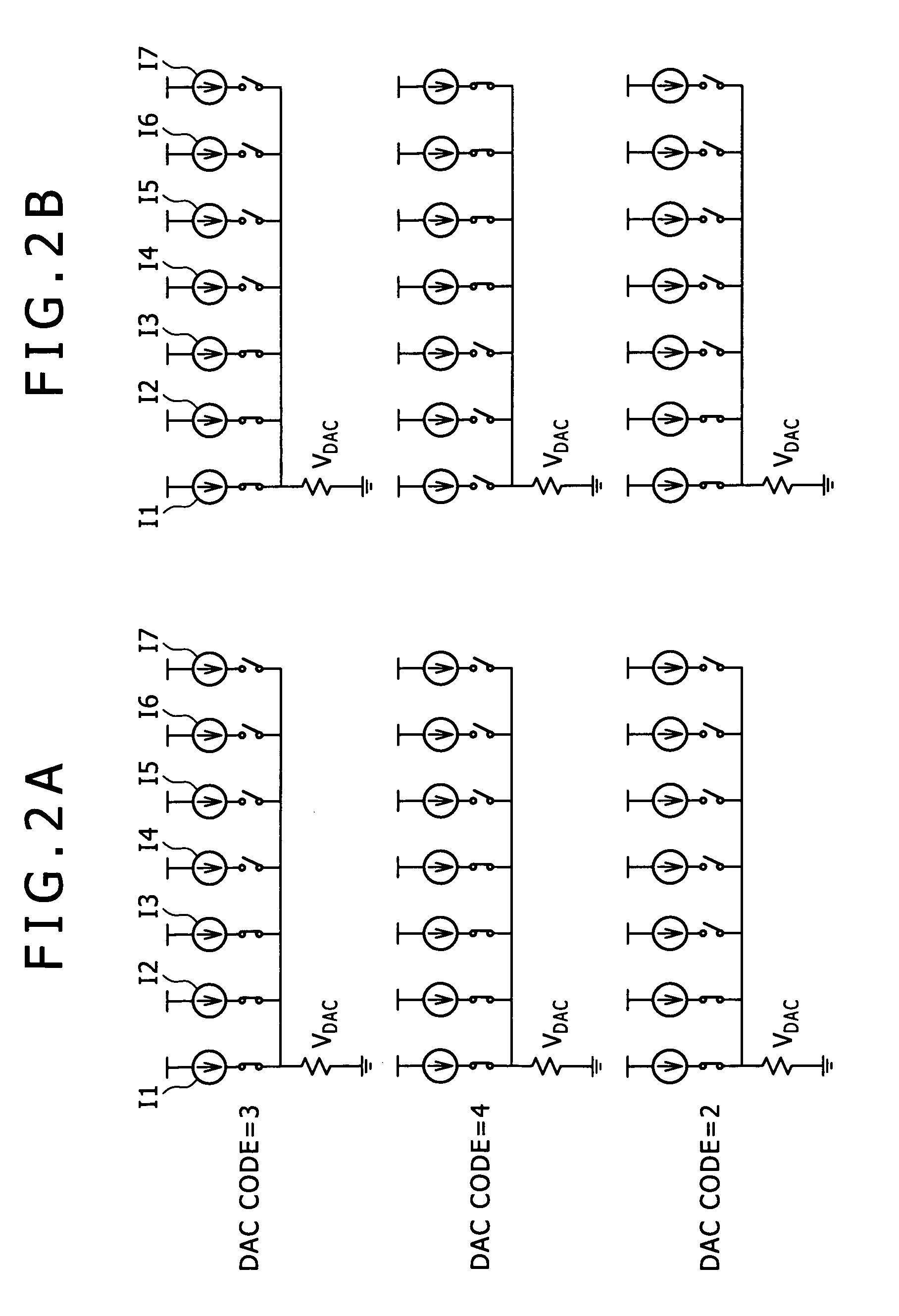

Switching arrangement and DAC mismatch shaper using the same

ActiveUS20050168365A1Increase clock frequencyElectric signal transmission systemsDifferential modulationFrequency spectrumEngineering

A digital-to-analog converter (DAC) error mismatch shaper. The shaper comprises a switching arrangement with a delta-sigma modulator having analog signal processing components. The analog signal processing components allow the spectral behavior of the shaper to be controlled. The switching arrangement comprises a control circuit. The control circuit is a tunable, pipelined control circuit.

Owner:HRL LAB

Method and apparatus for performing signal correlation

InactiveUS6891880B2Reduce circuit complexityEfficient retrievalTime-division multiplexAmplitude-modulated carrier systemsCircuit complexitySignal correlation

A method and apparatus for computing a convolution between an input GPS signal and a C / A code reference by generating the convolution result in real time without storing unprocessed signal samples. The apparatus comprises a vector multiplier running at high speed to achieve the same result as a vector multiplier sized to process an entire epoch. Additionally, the input samples to, and the output samples of, the vector multiplier can be quantized to reduced circuit complexity.

Owner:AVAGO TECH INT SALES PTE LTD