Patents

Literature

126results about How to "Increase the number of digits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

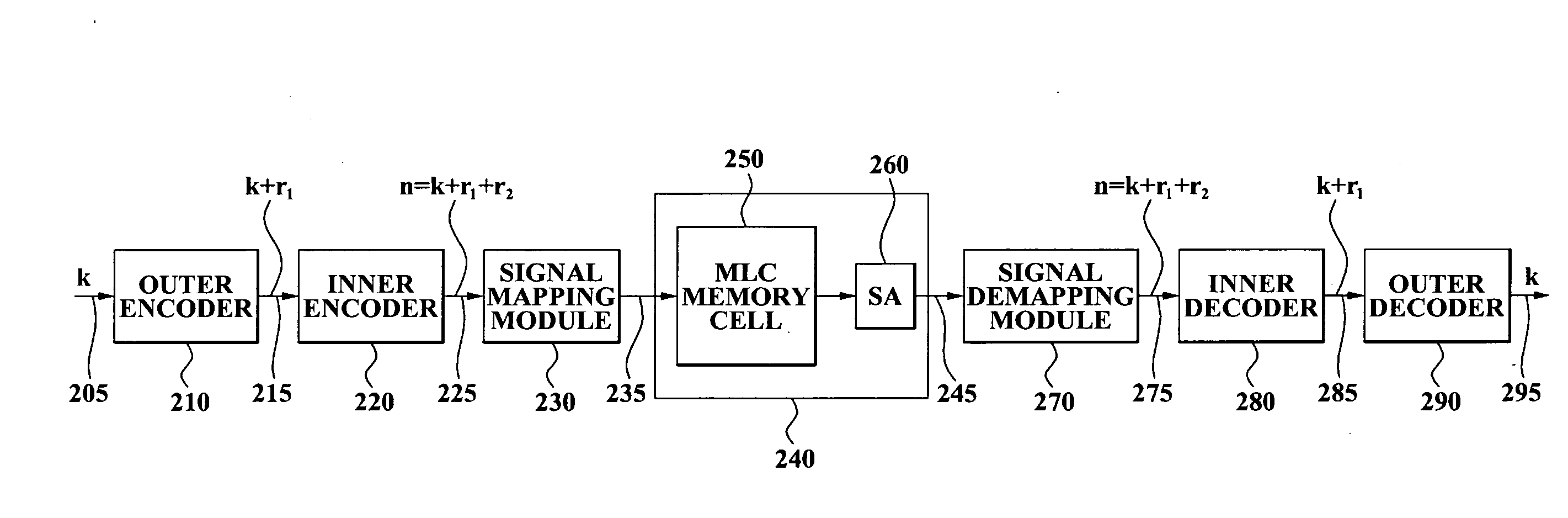

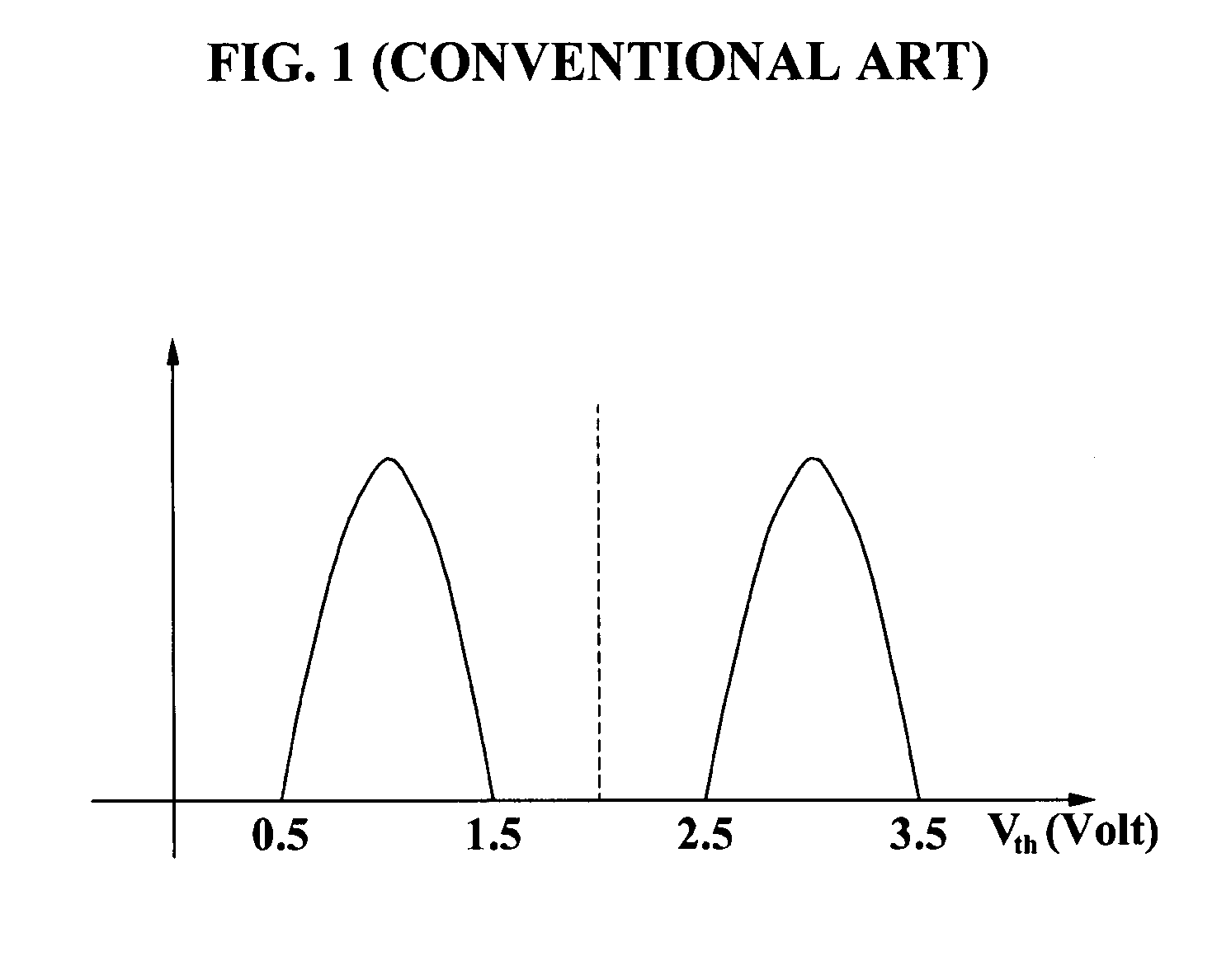

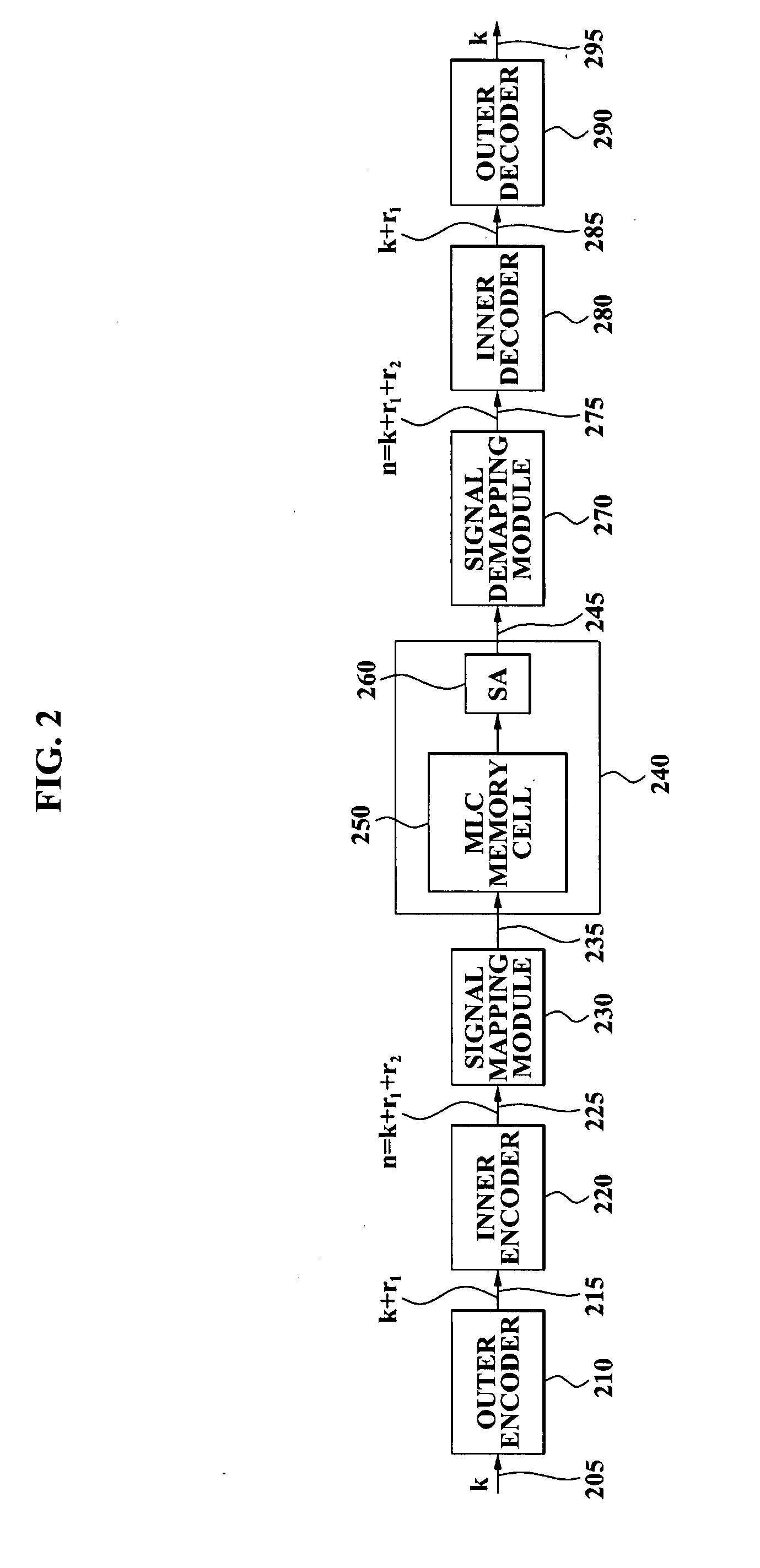

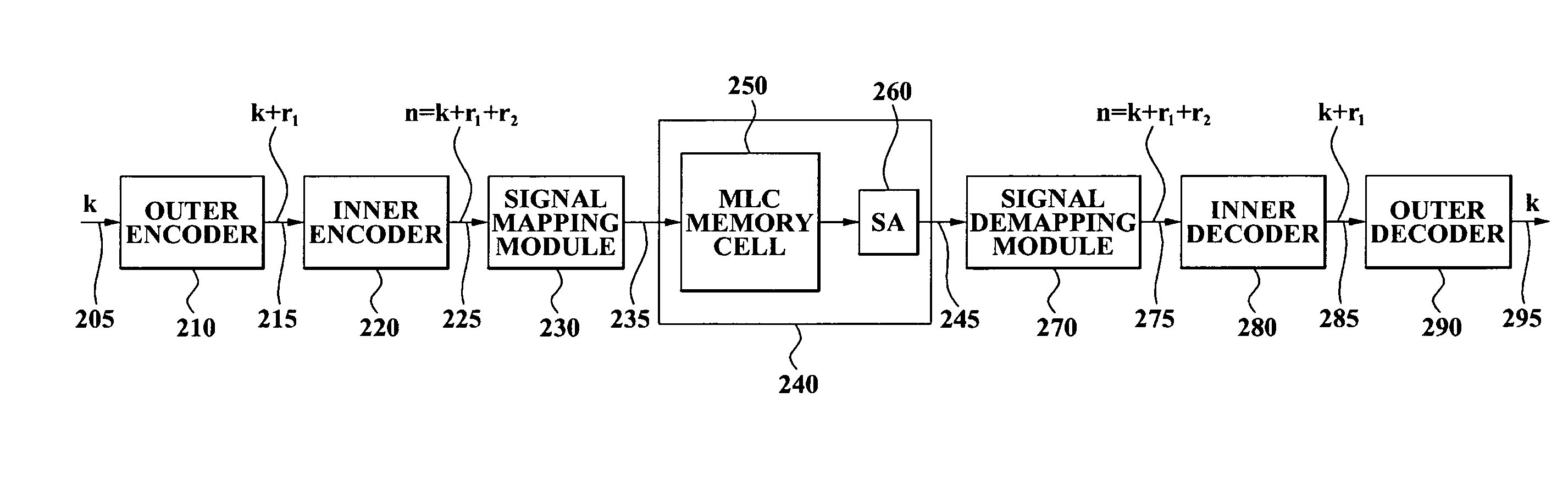

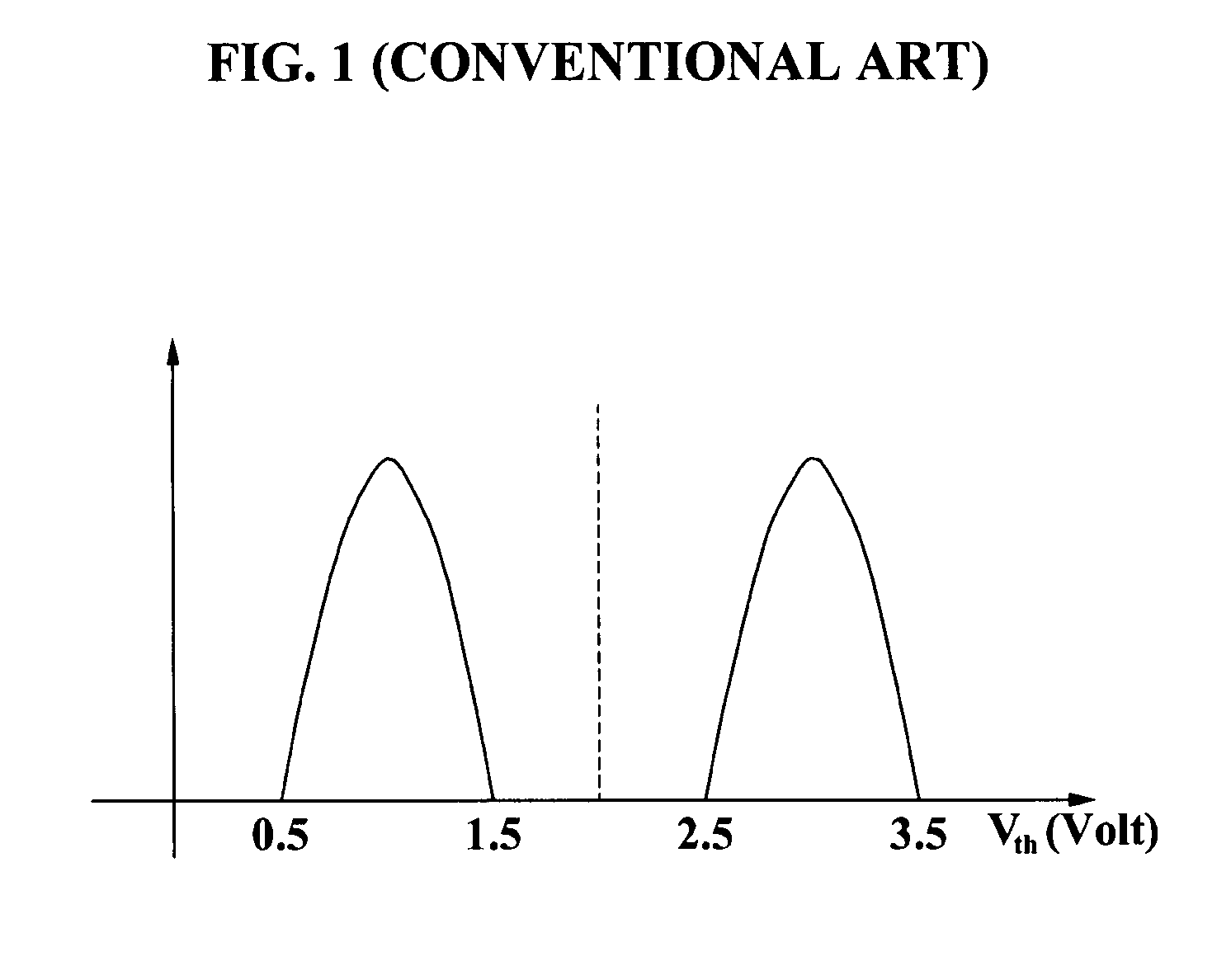

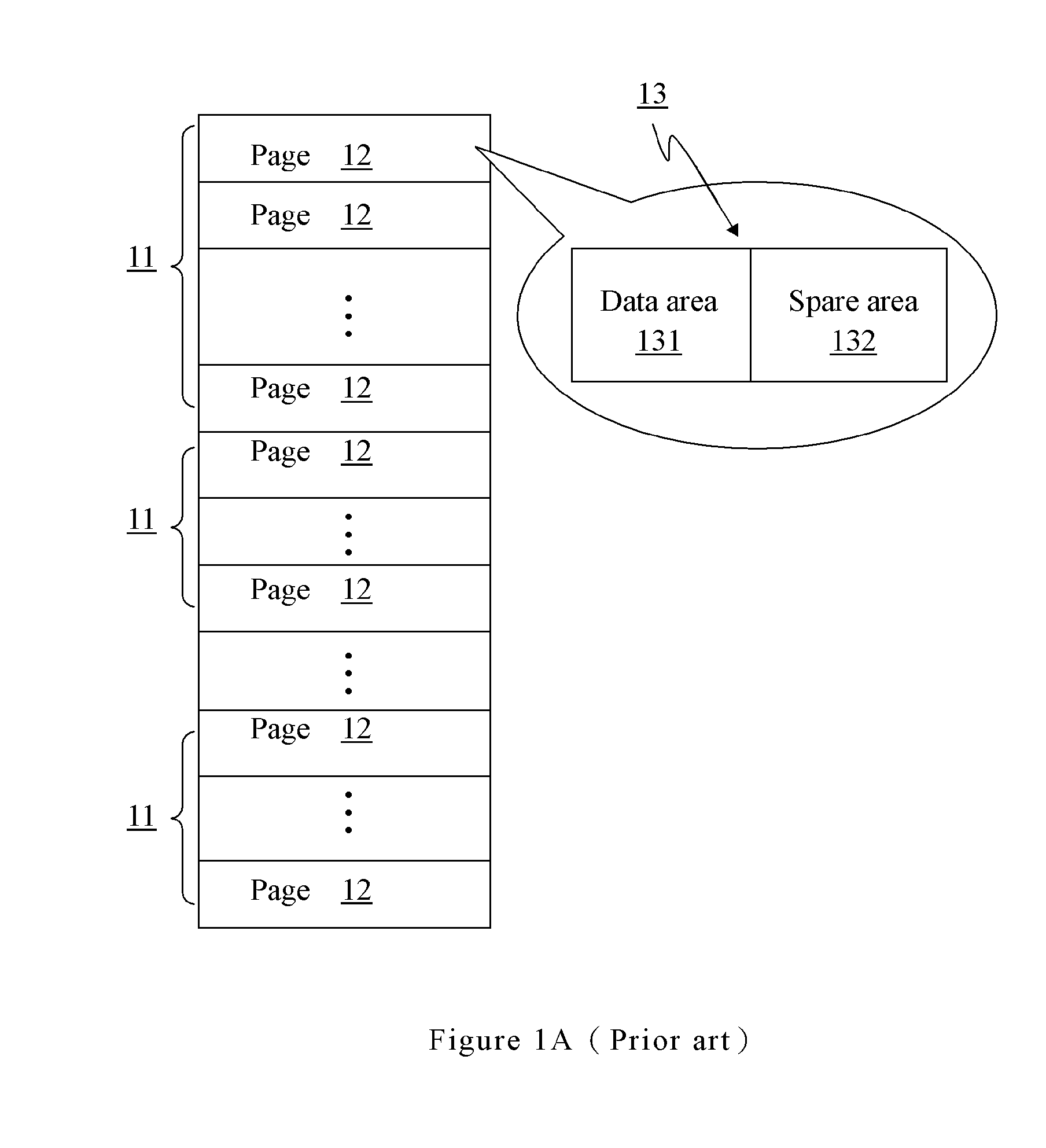

Multi-level cell memory device and method thereof

ActiveUS20080137414A1Increase stabilityIncrease in numberRead-only memoriesDigital storageCell memoryStorage cell

A Multi-Level Cell (MLC) memory device and method thereof are provided. The example MLC memory device may be configured to perform data operations, and may include an MLC memory cell, a first coding device performing a first coding function, the first coding function being one of an encoding function and a decoding function, a second coding device performing a second coding function, the second coding function being one of an encoding function and a decoding function and a signal module configured to perform at least one of instructing the MLC memory cell to store data output by the second coding device if the first and second coding functions are encoding functions, and generating a demapped bit stream based on data retrieved from the MLC memory cell if the first and second coding functions are decoding functions.

Owner:SAMSUNG ELECTRONICS CO LTD

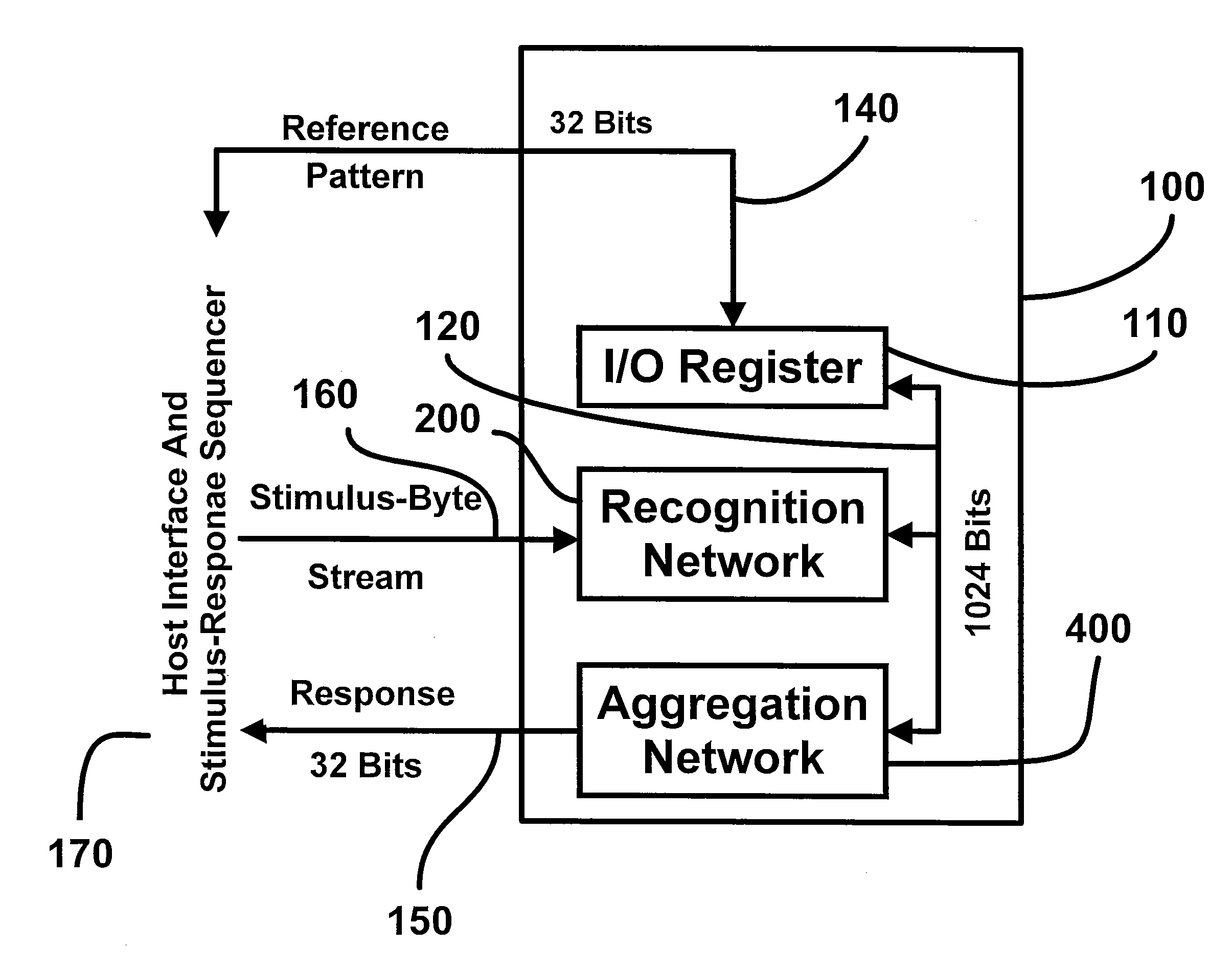

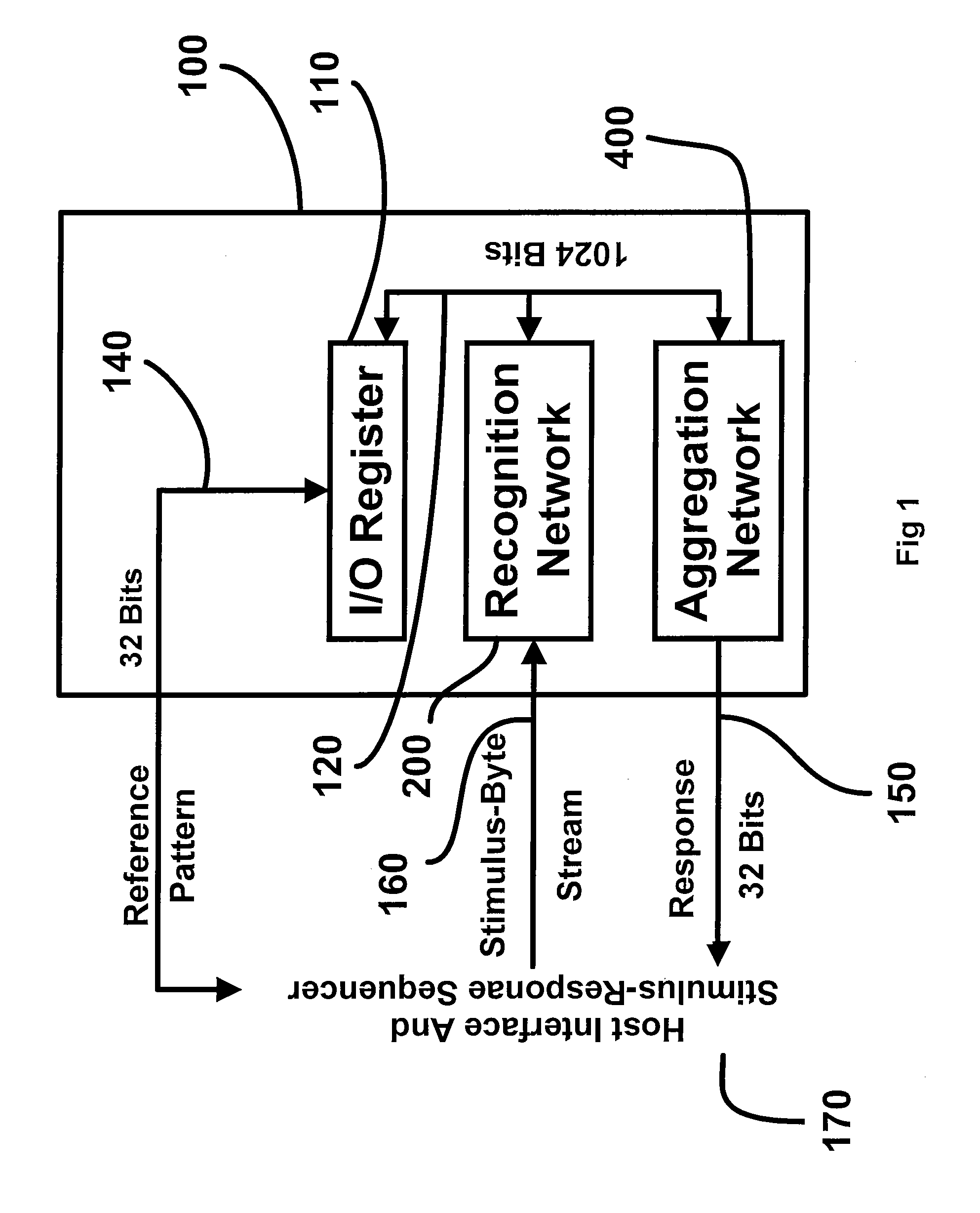

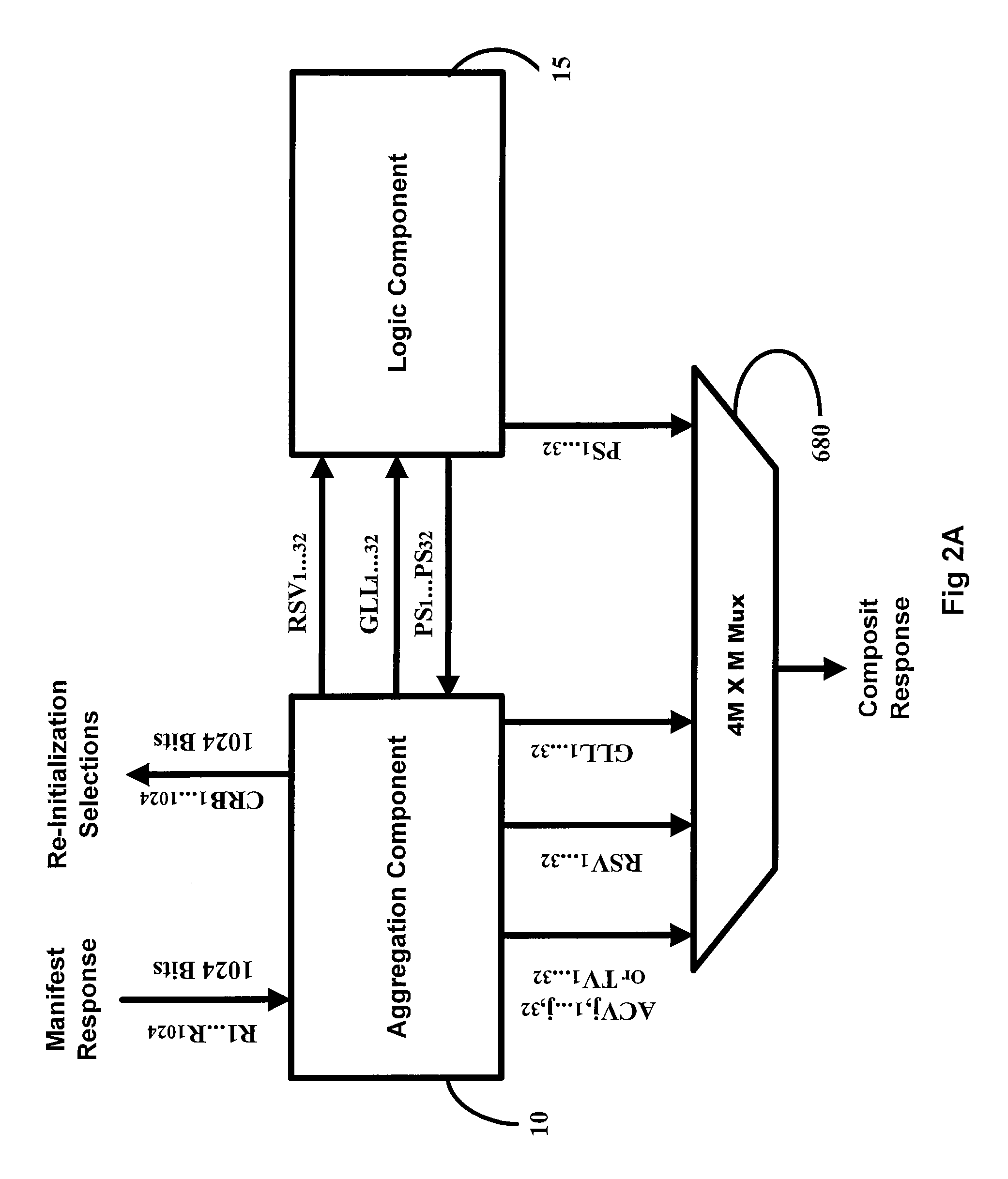

GPSTP with enhanced aggregation functionality

ActiveUS8065249B1Increase the number of digitsDigital computer detailsCharacter and pattern recognitionGeneral purposeTheoretical computer science

A general purpose set theoretic processor is enhanced 1) by providing multi-function counters in stead of down-counters, 2) by internalizing the composite Boolean Logic function by introducing a two stage (two matrix) programmable composite Boolean Logic functionality wherein the first stage yields logical products of selected aggregation logic responses (or their complements) and the second stage yields logical sums of selected sets of those logical products, and 3) by providing internal selective re-initialization by means of a re-initialization routing matrix functionality that directs logical sums of Composite Boolean Logic sums of products to selected GPSTP cells to be re-initialized.

Owner:HARRIS CURTIS L +1

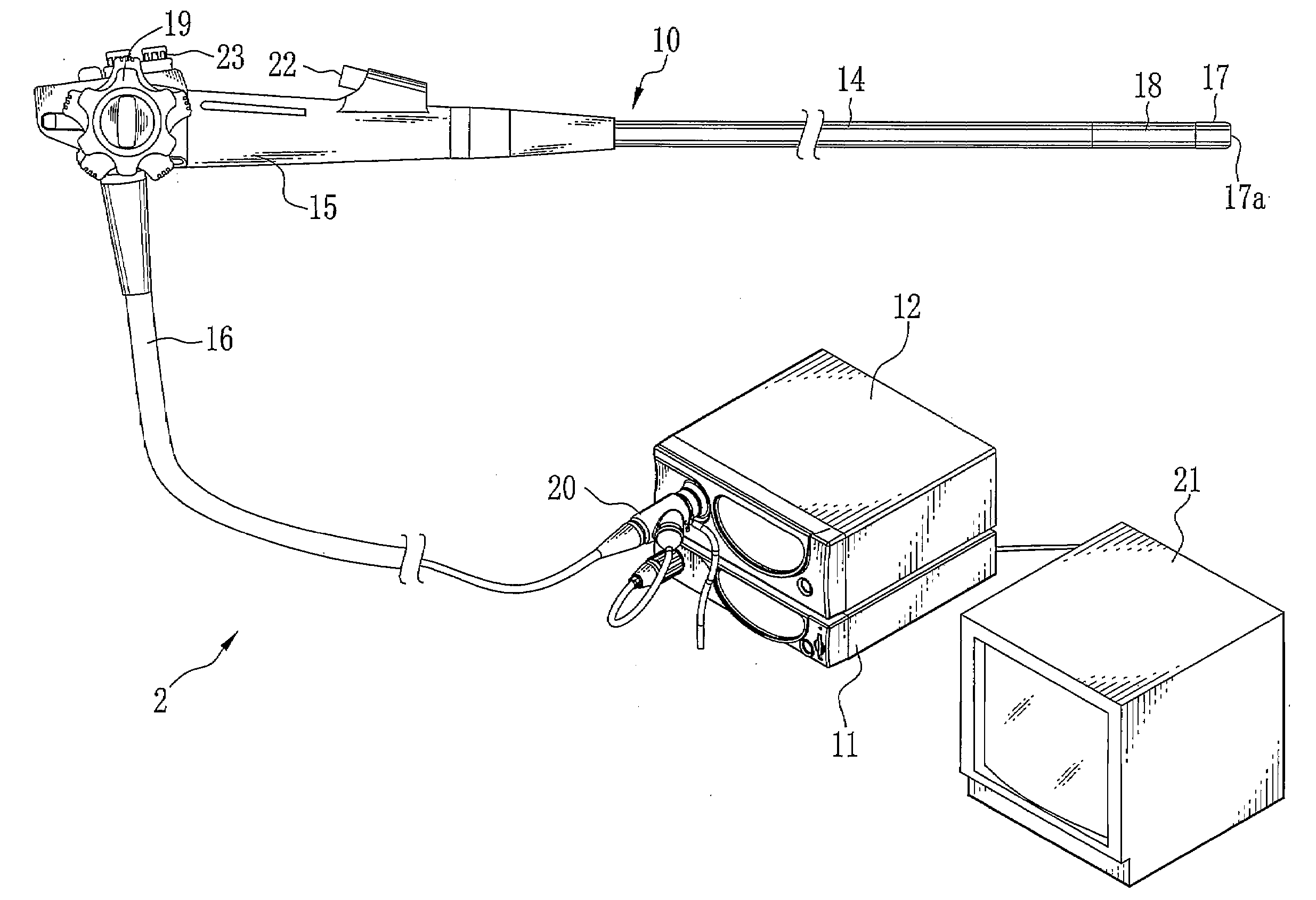

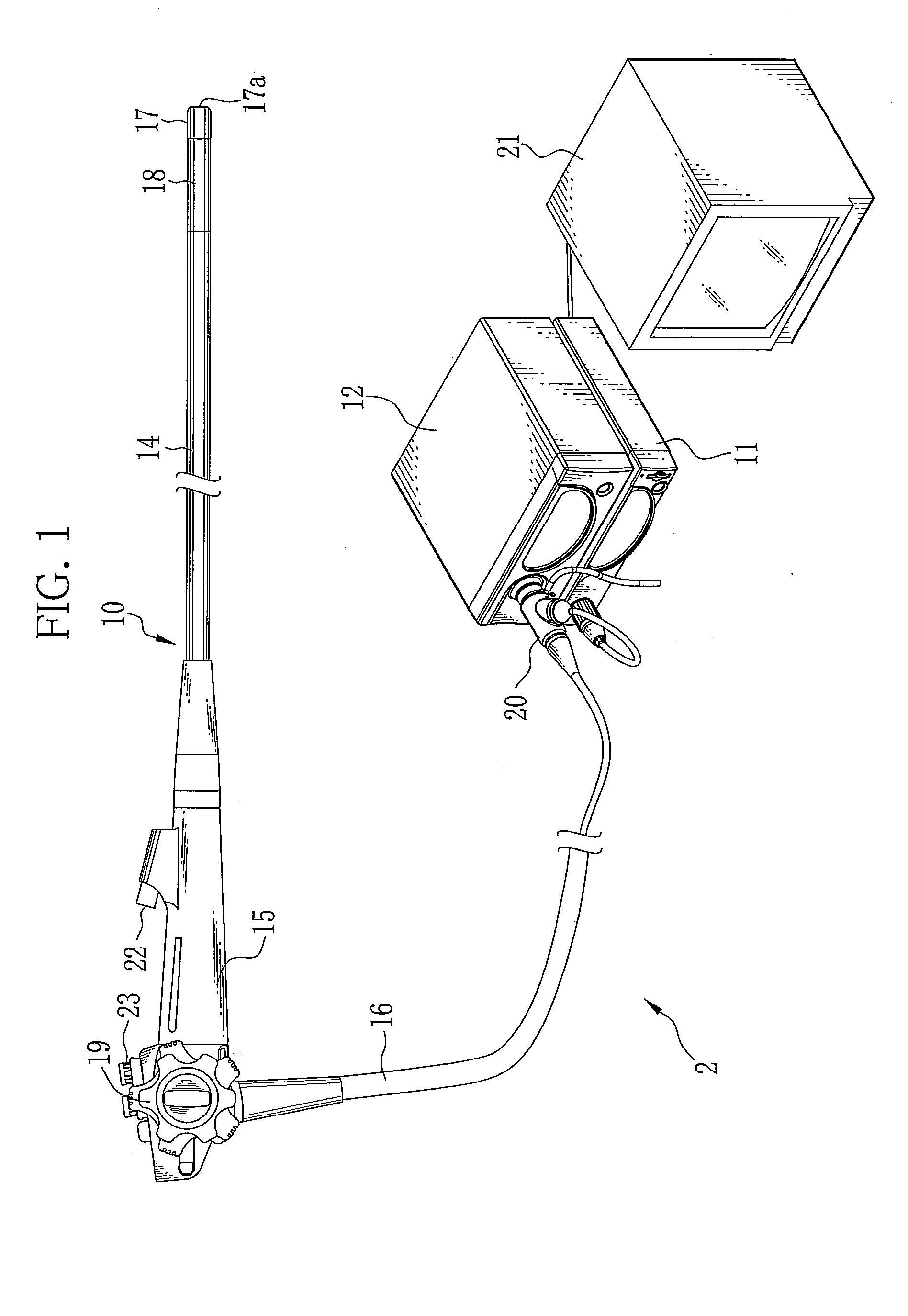

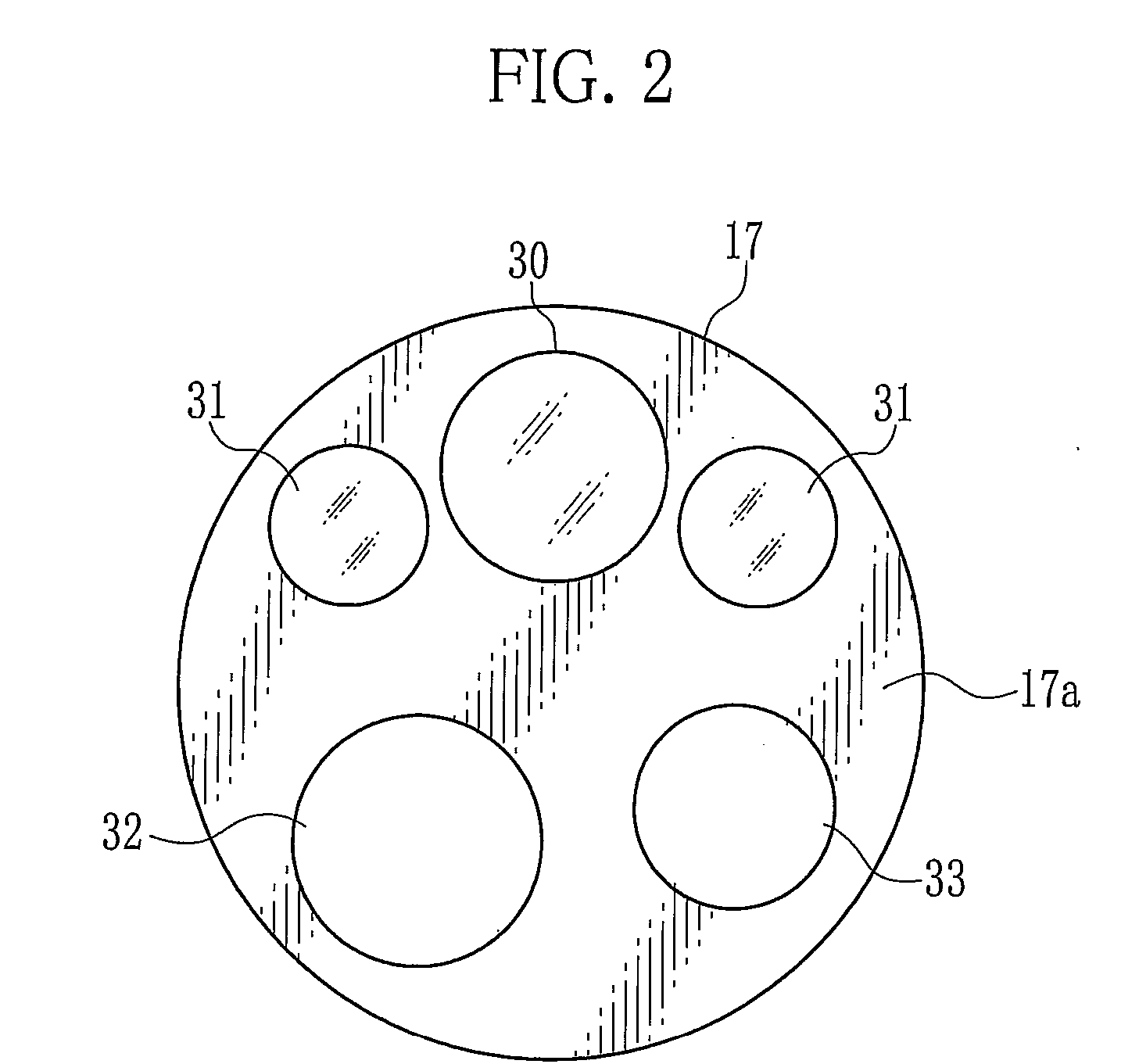

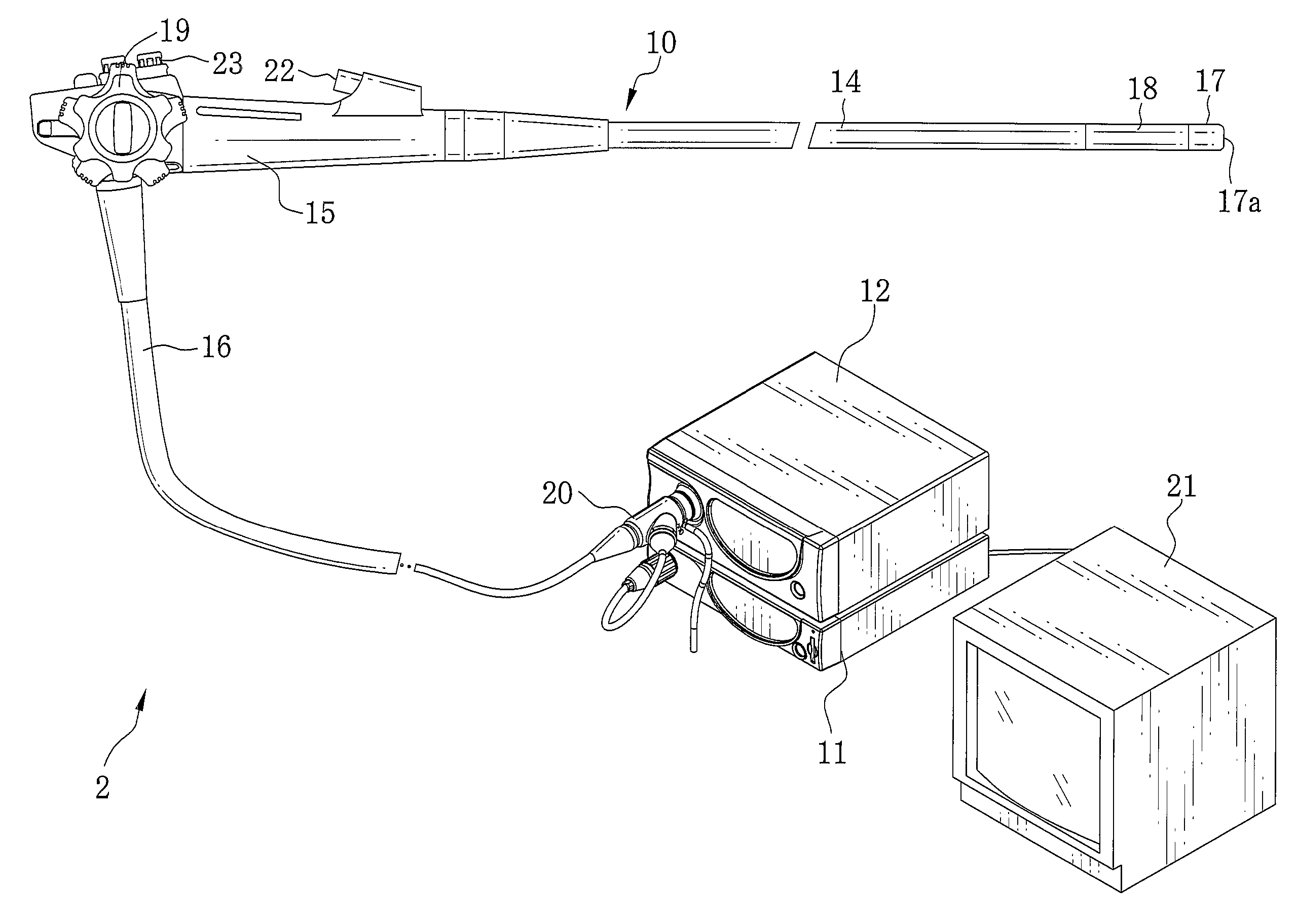

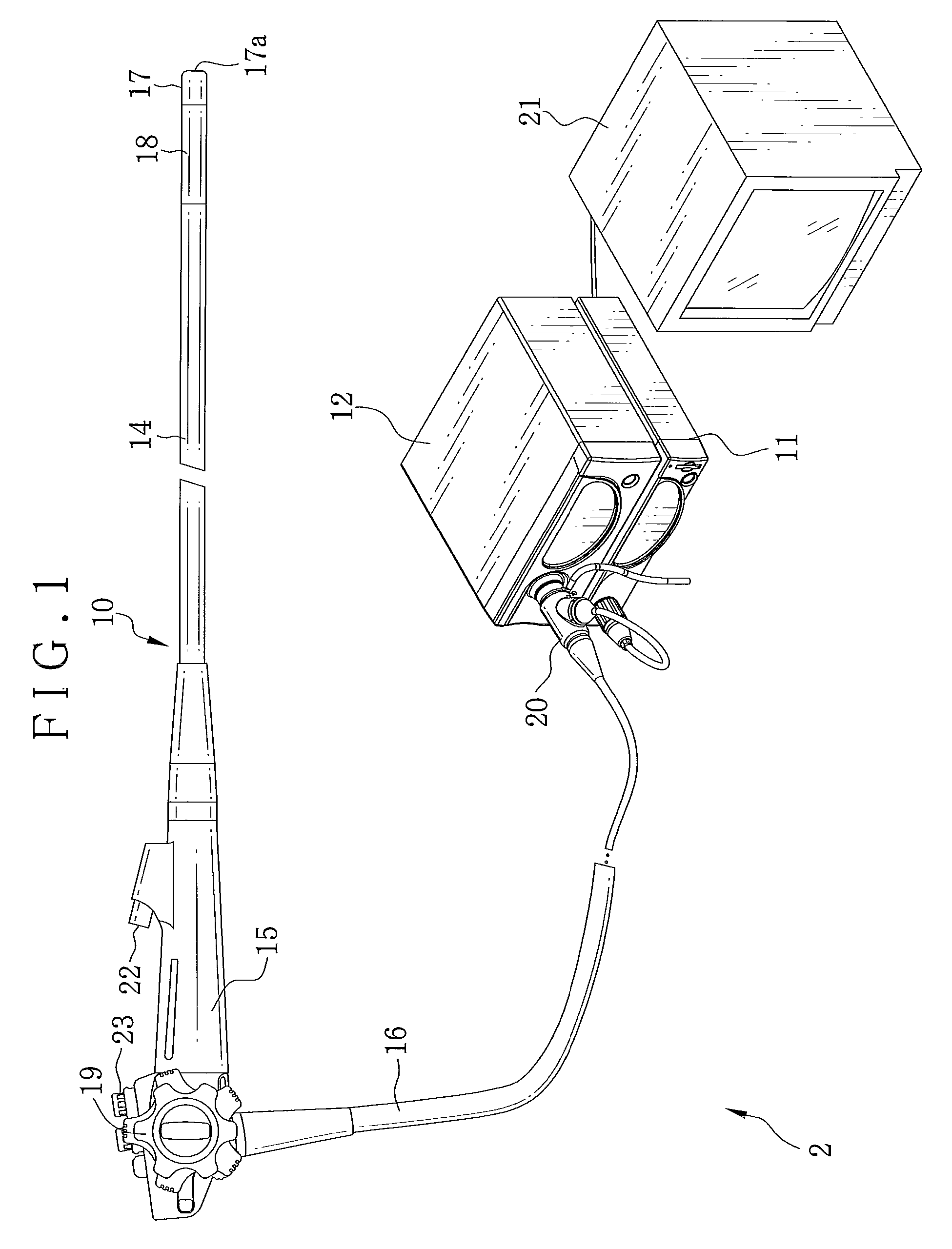

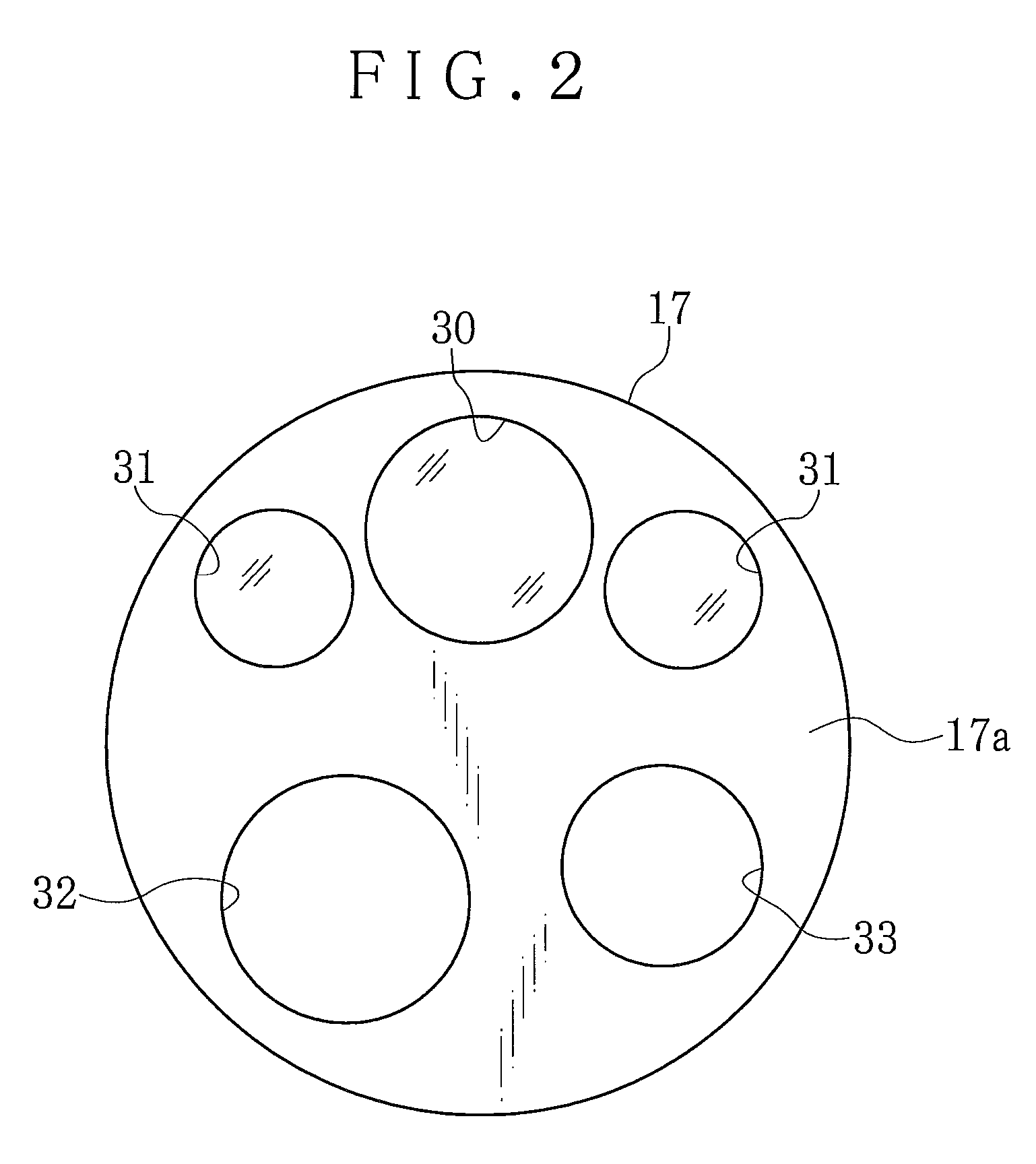

Electronic communication system and endoscope system

InactiveUS20090216080A1High-speed and stable serial transmissionIncrease the number of digitsTelevision system detailsSurgeryElectronic communicationControl data

An external control device includes a reference clock generating circuit for generating a reference clock, a CPU for generating control data, and a signal superimposing circuit for serially transmitting an external clock signal, composed of the reference clock signal and the control data superimposed thereon, to an electronic device through a signal line. The electronic device includes a PLL circuit for generating an internal clock signal synchronized with a frequency of the external clock signal serially transmitted from the external control device, and a control data extracting circuit for extracting the control data from the external clock signal based on the internal clock signal.

Owner:FUJIFILM CORP

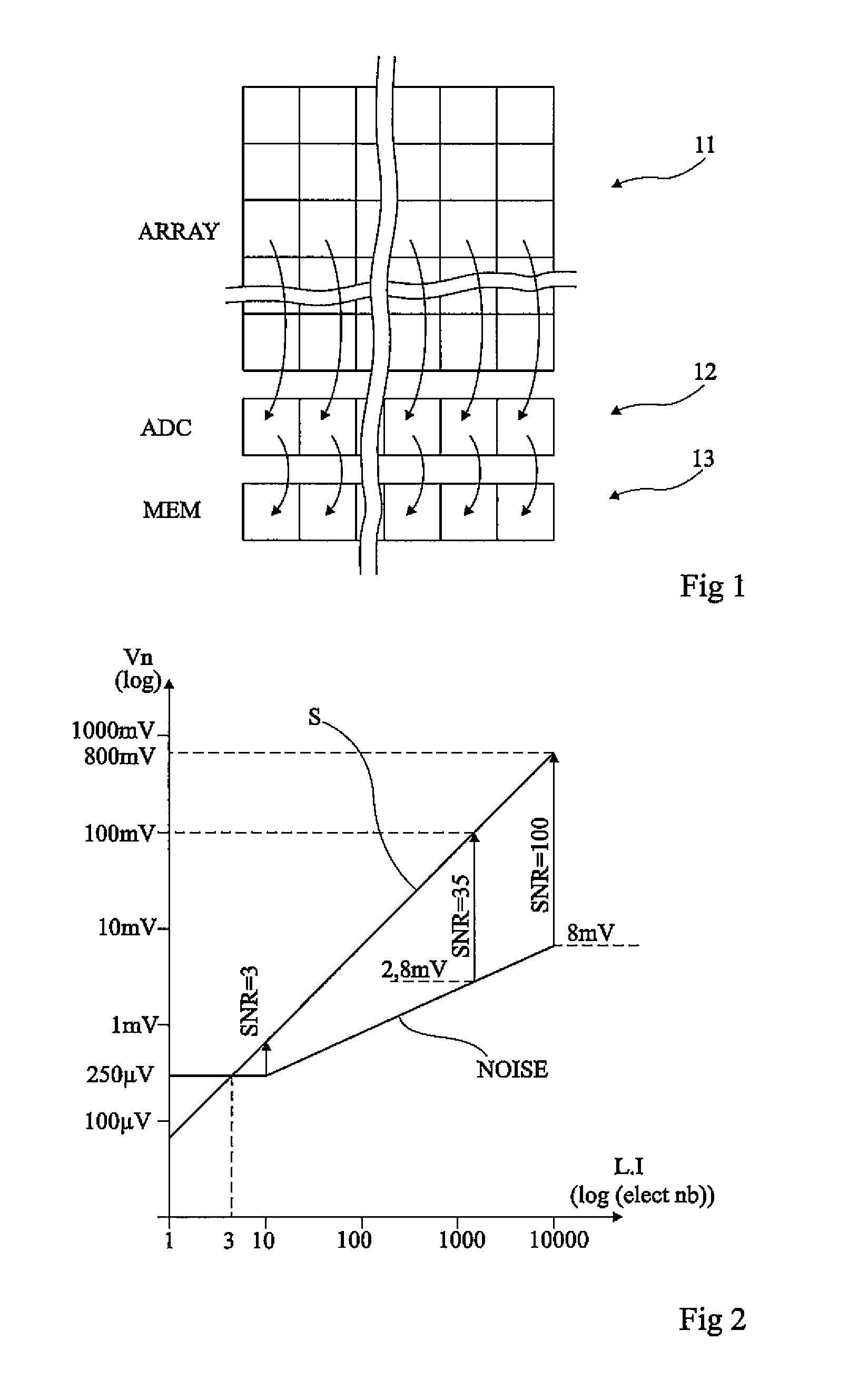

Image pickup system and endoscope system

InactiveUS20090213212A1Increase the number of digitsIncrease speedTelevision system detailsTelevision system scanning detailsCMOSSolid-state

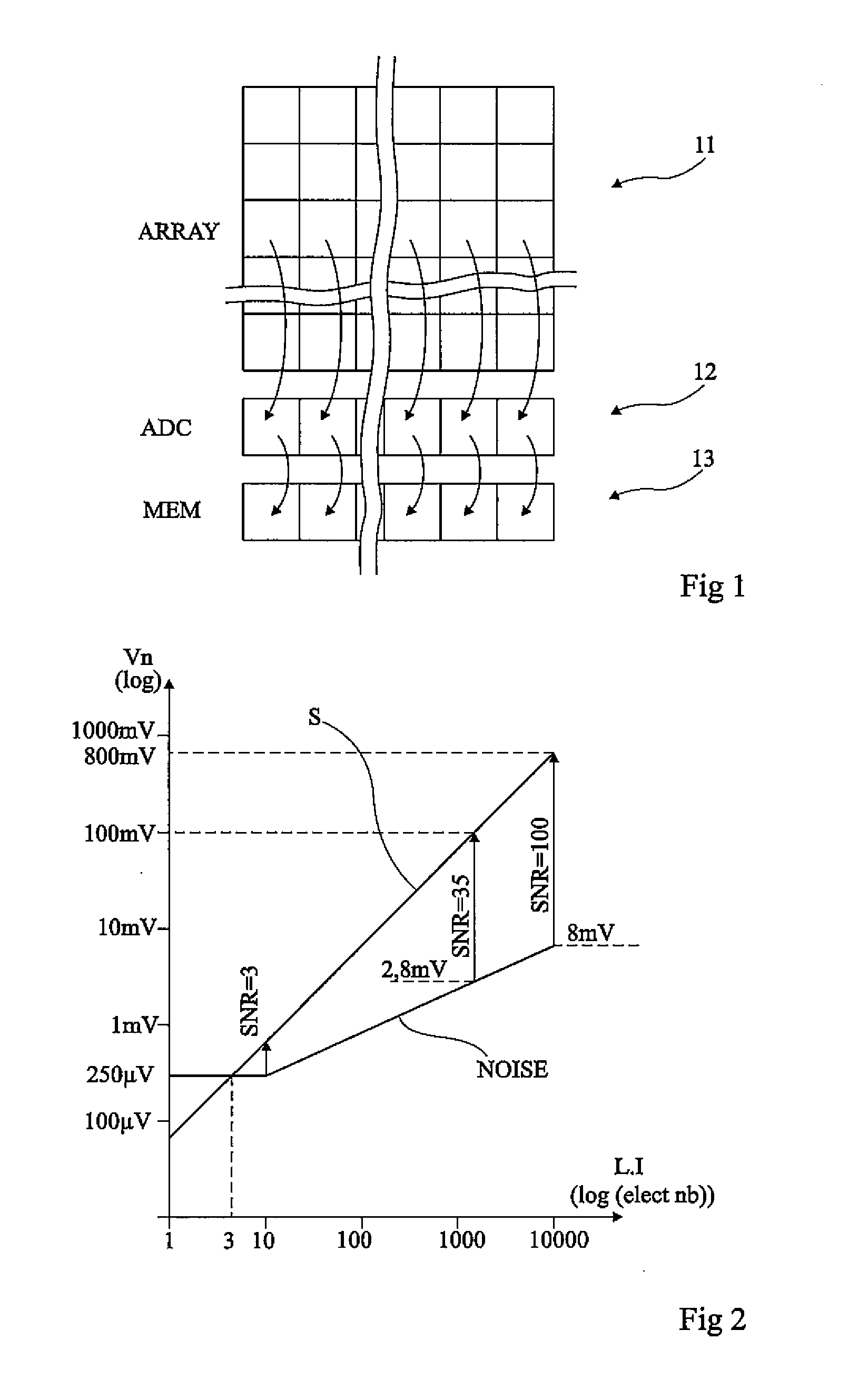

An image pickup system includes an image pickup unit having a solid-state image pickup device, for example, CMOS. A processor controls the image pickup device and receives an image signal from the image pickup unit with a signal line in serial transmission. The processor includes a clock and data recovery circuit for deriving a clock signal from the image signal input by the signal line, and for producing a data signal synchronized with the clock signal in phase synchronization. There is a signal processing unit for signal processing according to the data signal and the clock signal produced by the clock and data recovery circuit. Preferably, the image pickup unit includes an A / D converter for digitally converting the image signal from the image pickup device into parallel data of bits of a predetermined number.

Owner:FUJIFILM CORP

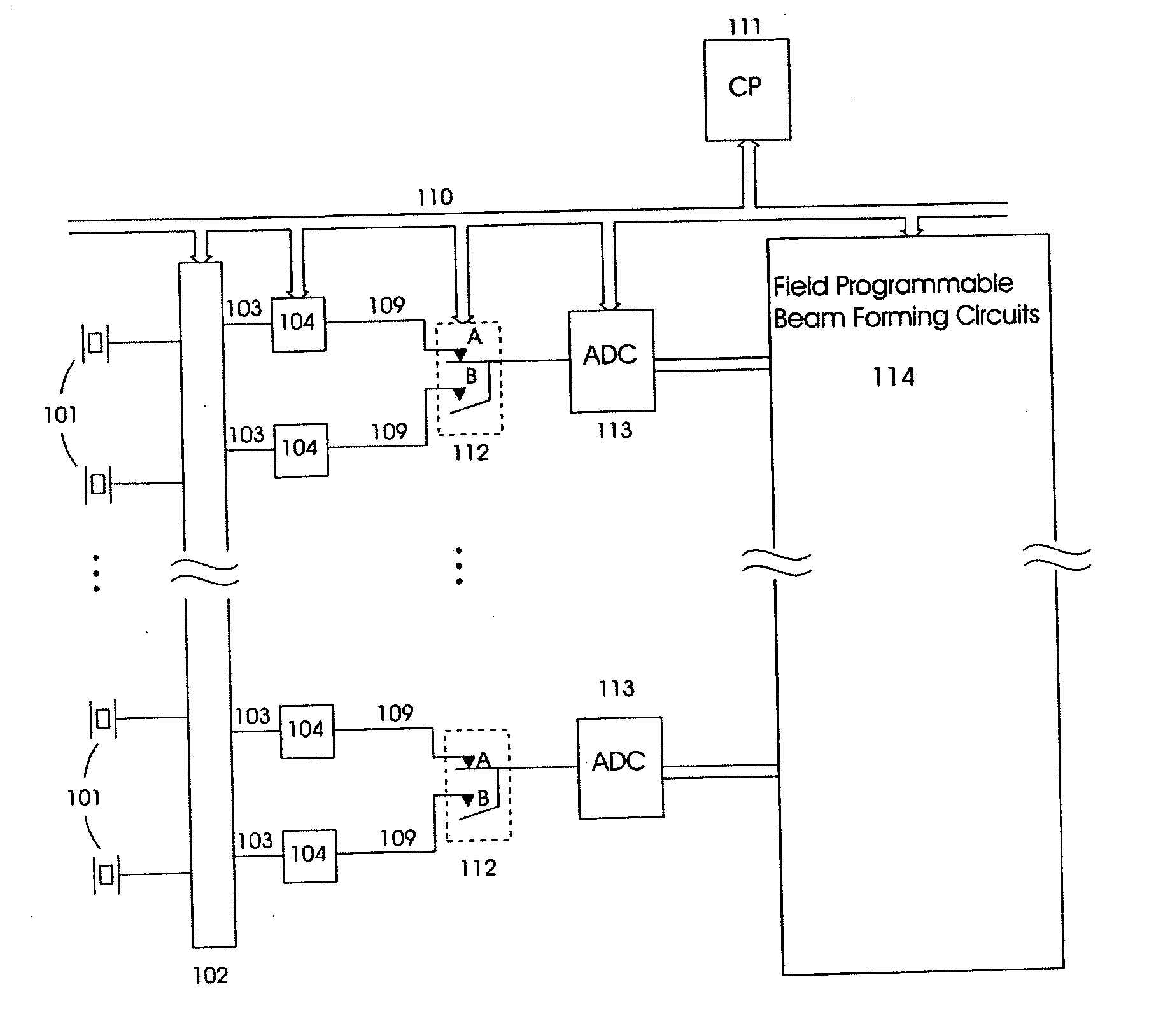

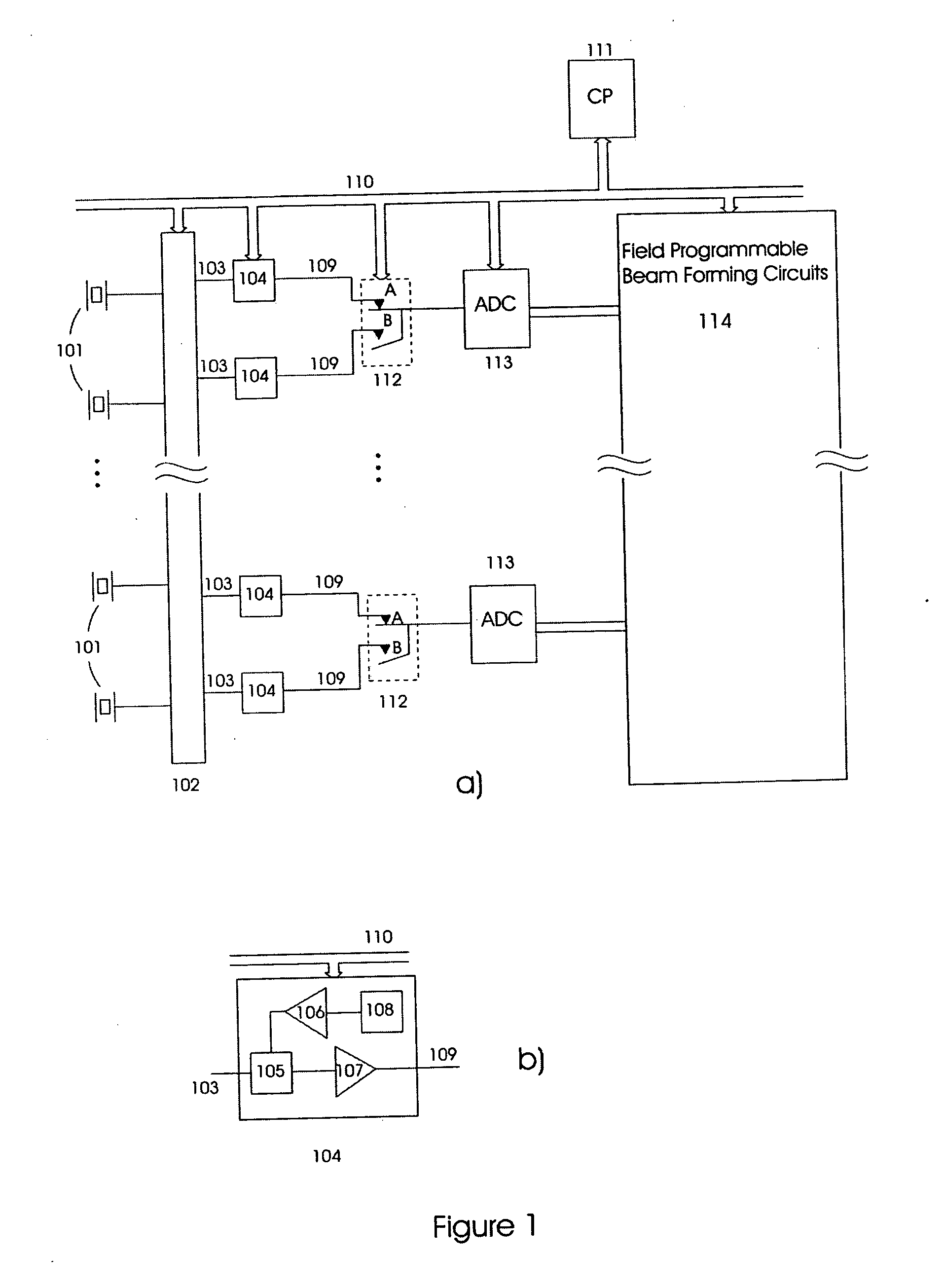

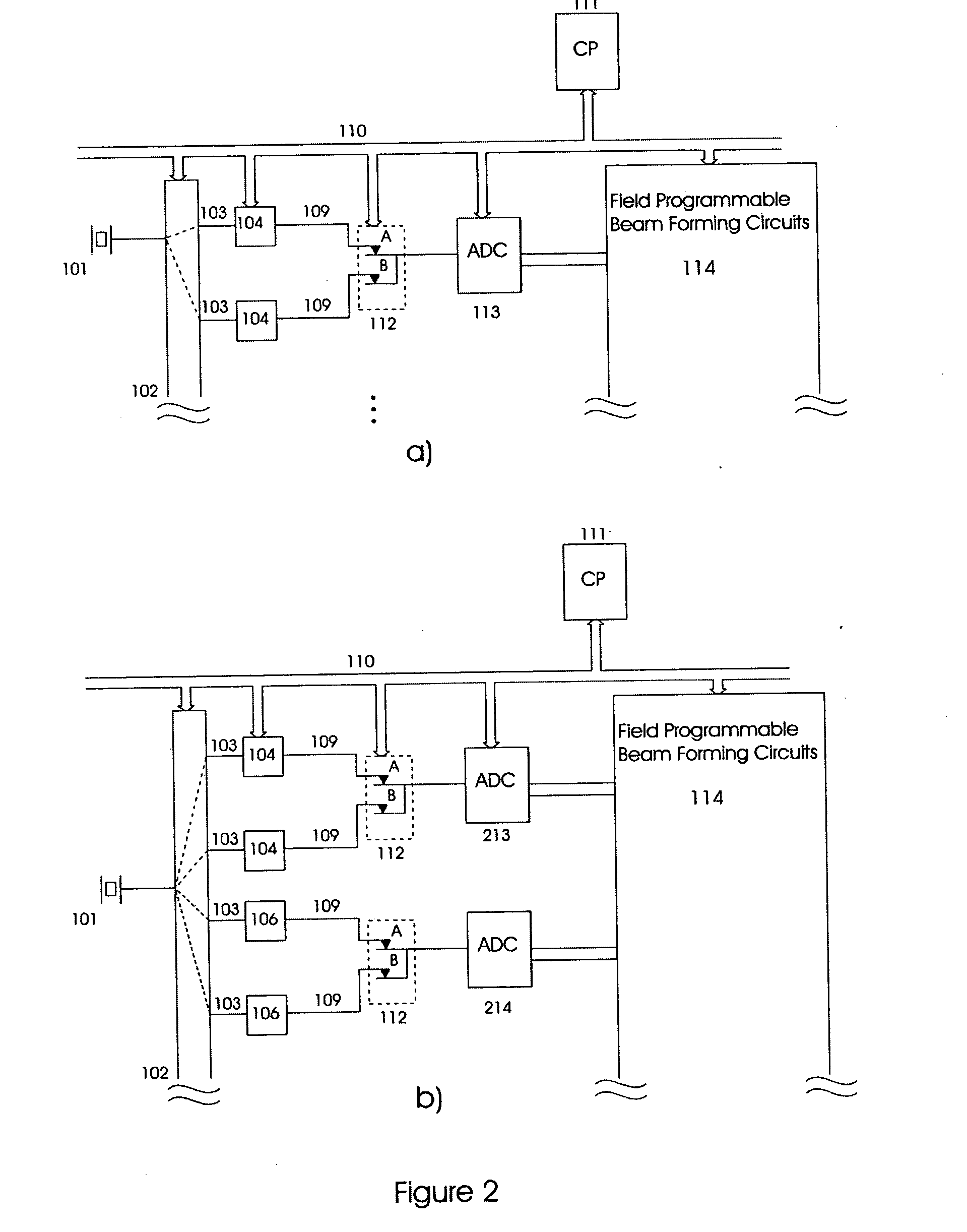

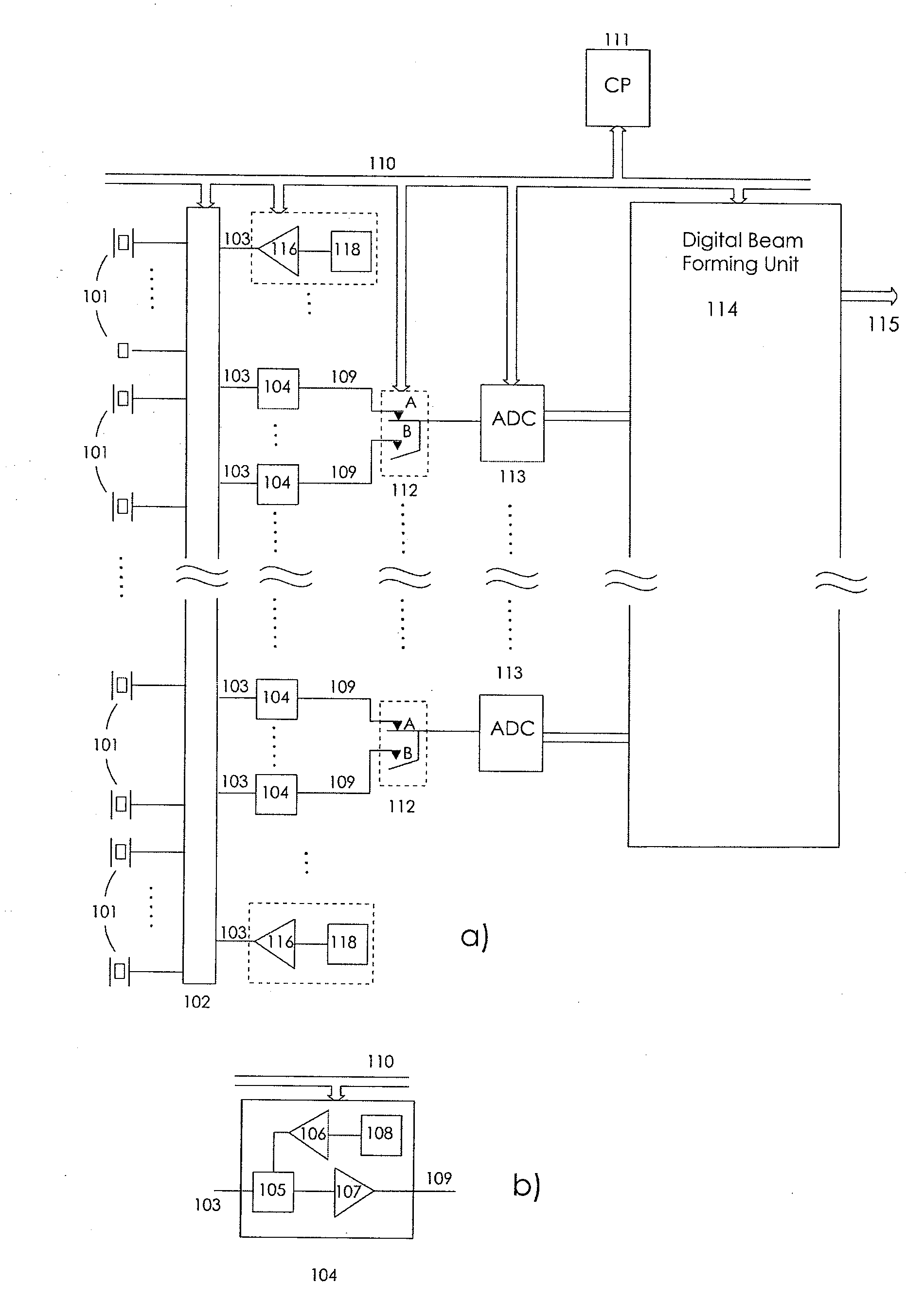

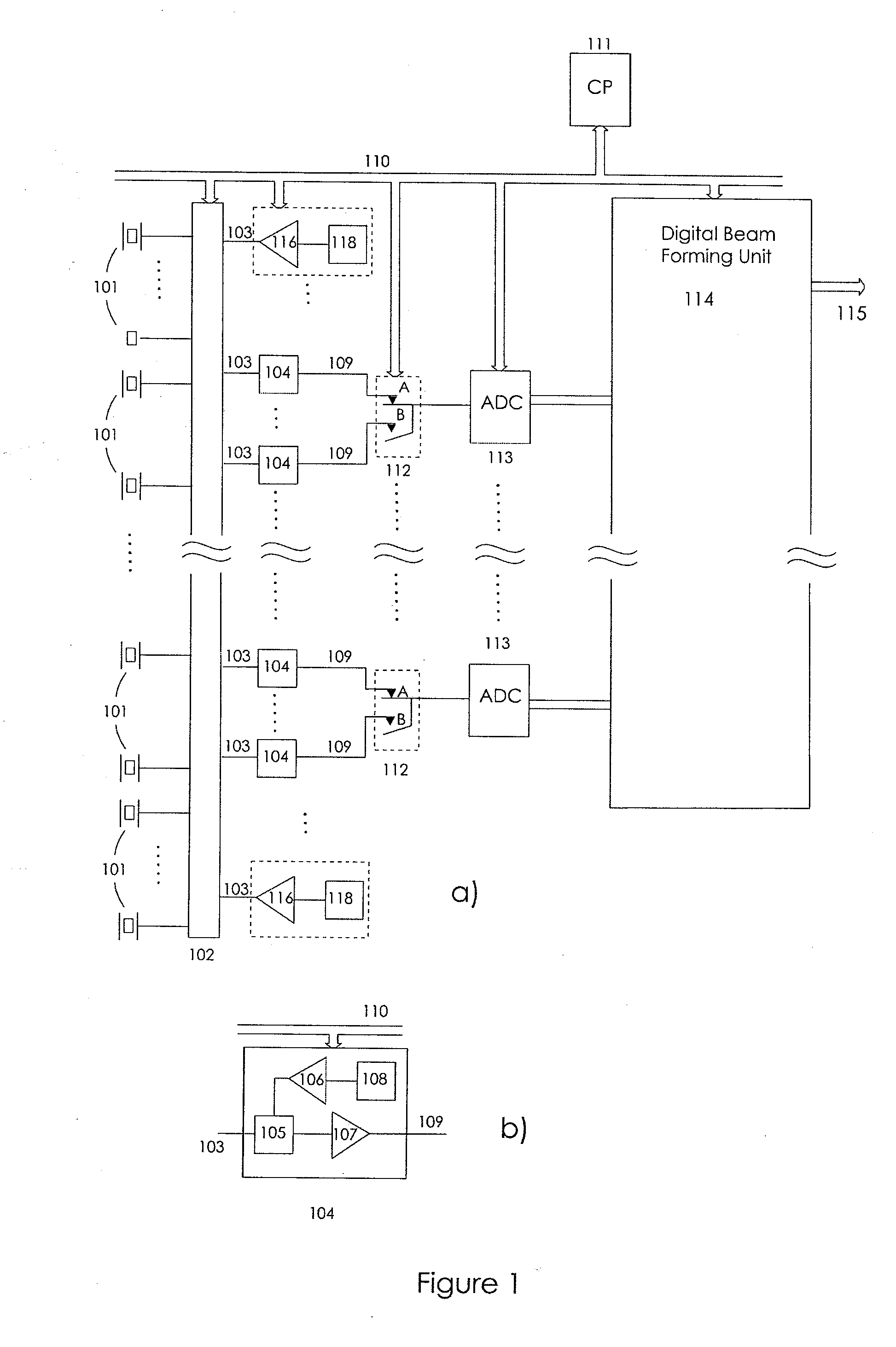

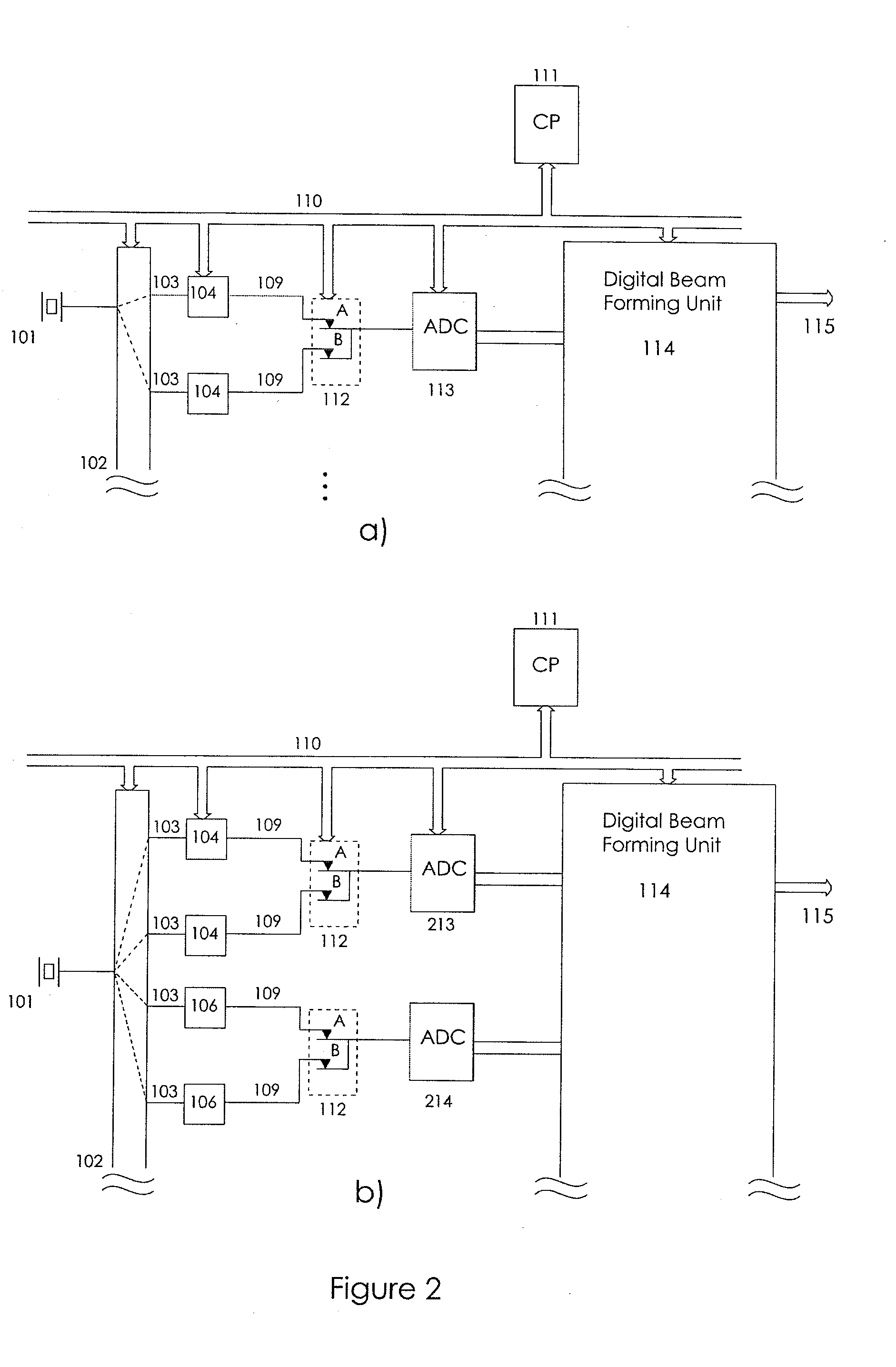

Digital ultrasound beam former with flexible channel and frequency range reconfiguration

InactiveUS20050203402A1Reduced sampling rate requirementsImprove dynamic rangeWave based measurement systemsBlood flow measurement devicesElectrical resistance and conductanceUltrasound imaging

A digital ultrasound beam former for ultrasound imaging, that can be configured by a control processor to process the signals from ultrasound transducer arrays with variable number of elements at variable sampling frequencies, where the lowest sampling frequency allows for the highest number of array elements. The maximal number of array elements is reduced in the inverse proportion to the sampling frequency. Parallel coupling of transmit / receive circuits for each element allow adaption of the receive Noise Figure and transmit drive capabilities to variations in the electrical impedance of the array elements.

Owner:ANGELSEN BJORN A J +1

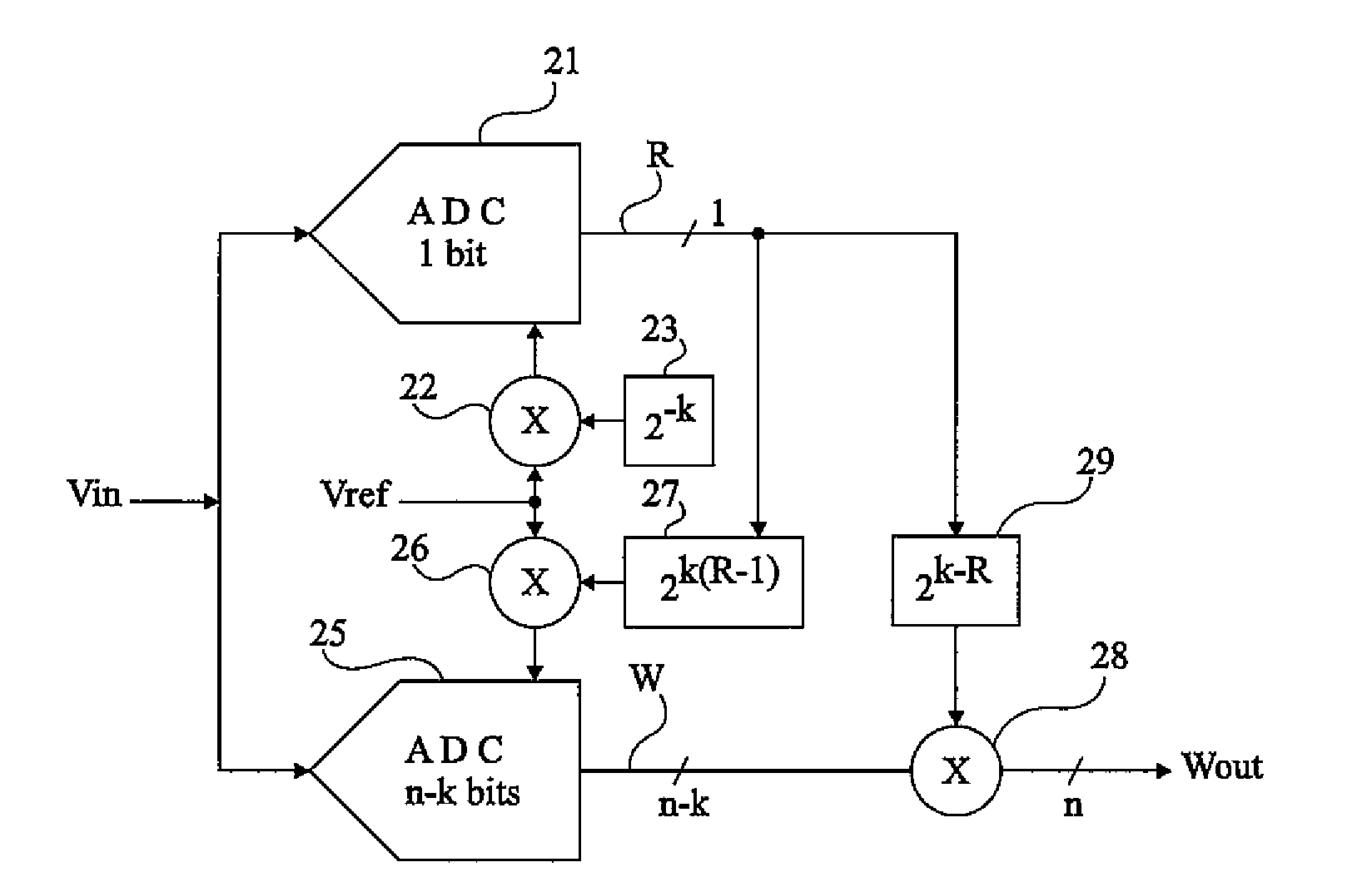

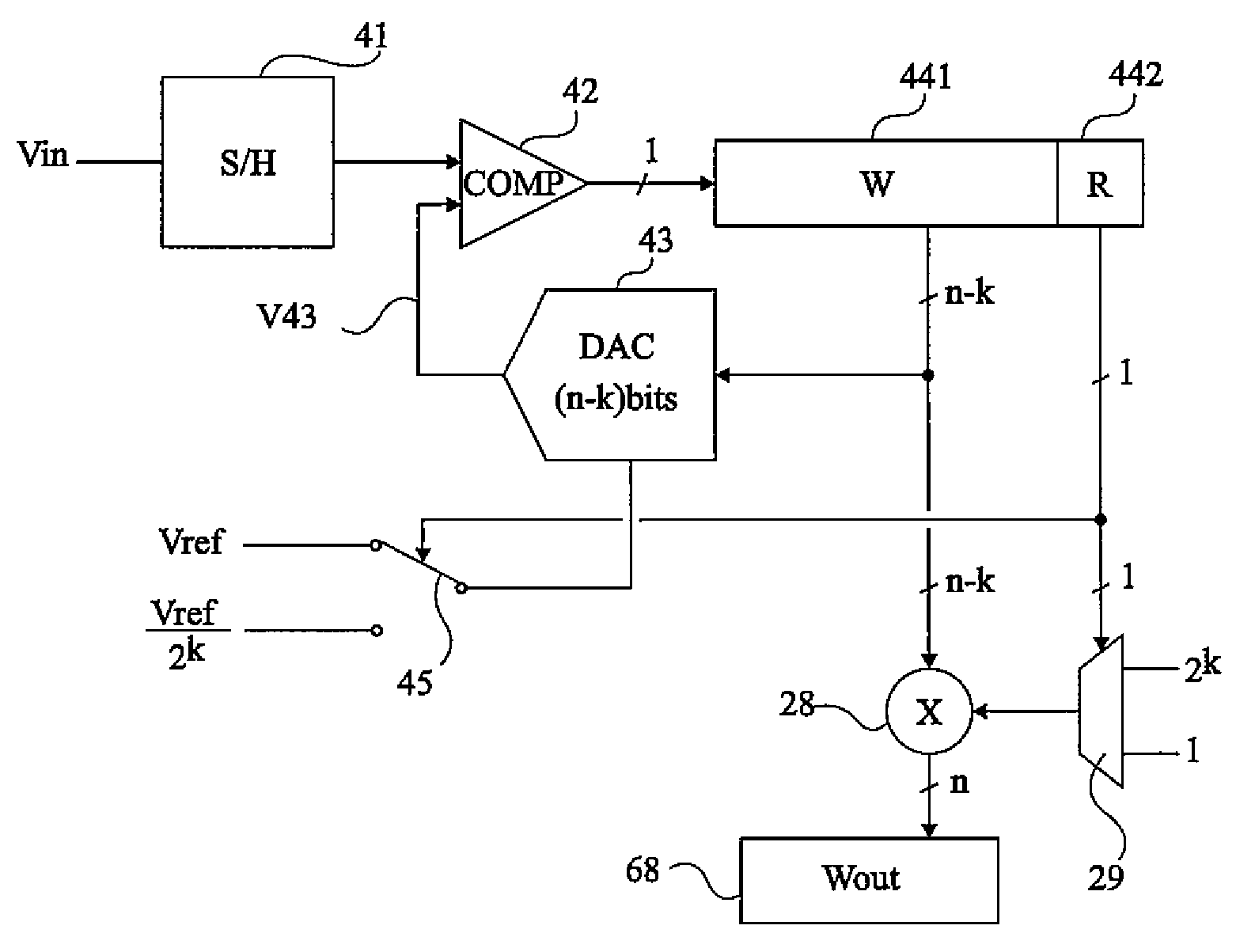

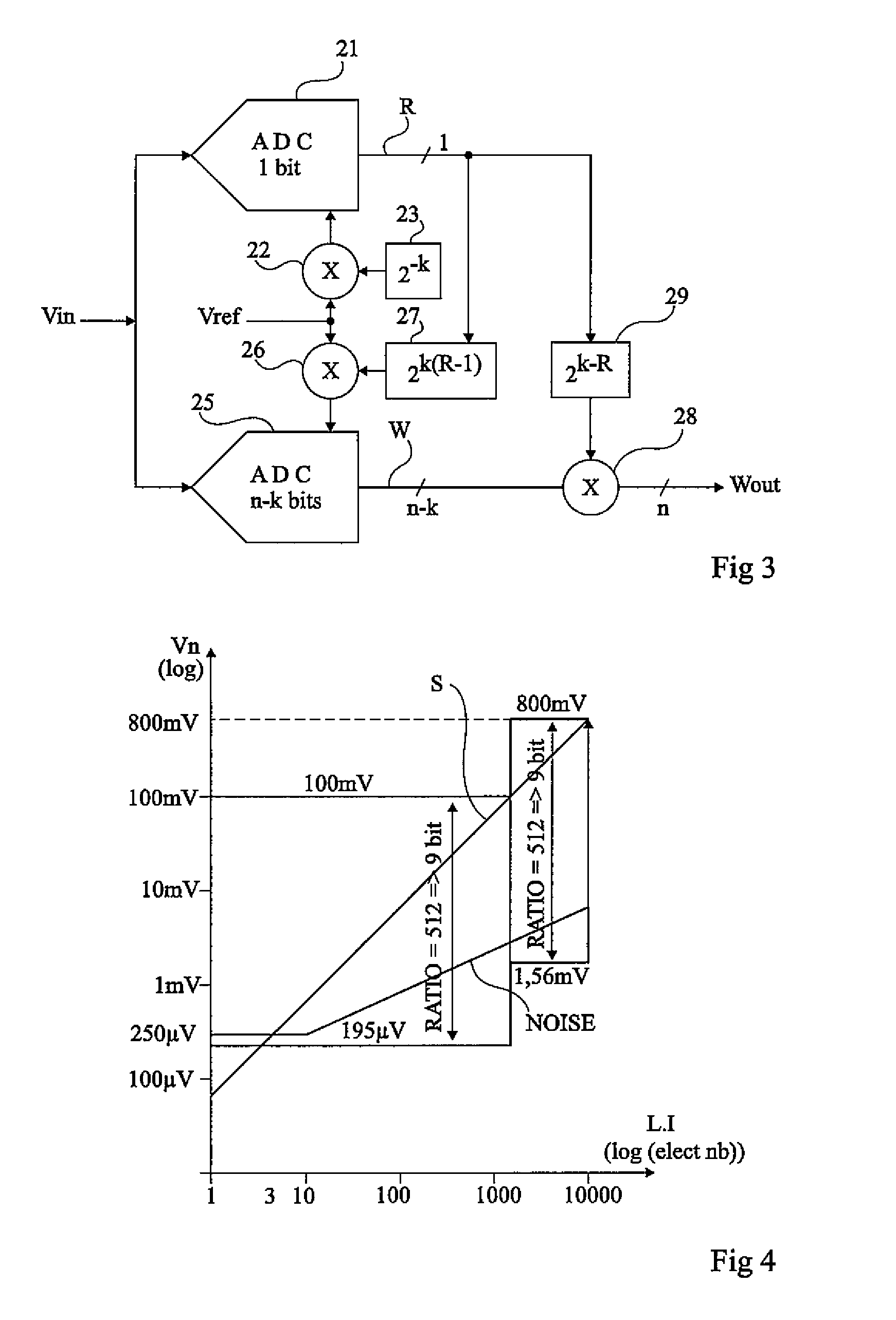

Analog-to-digital converter

ActiveUS20100039306A1Increase the number of digitsWithout complexityElectric signal transmission systemsAnalogue-digital convertersLeast significant bitA d converter

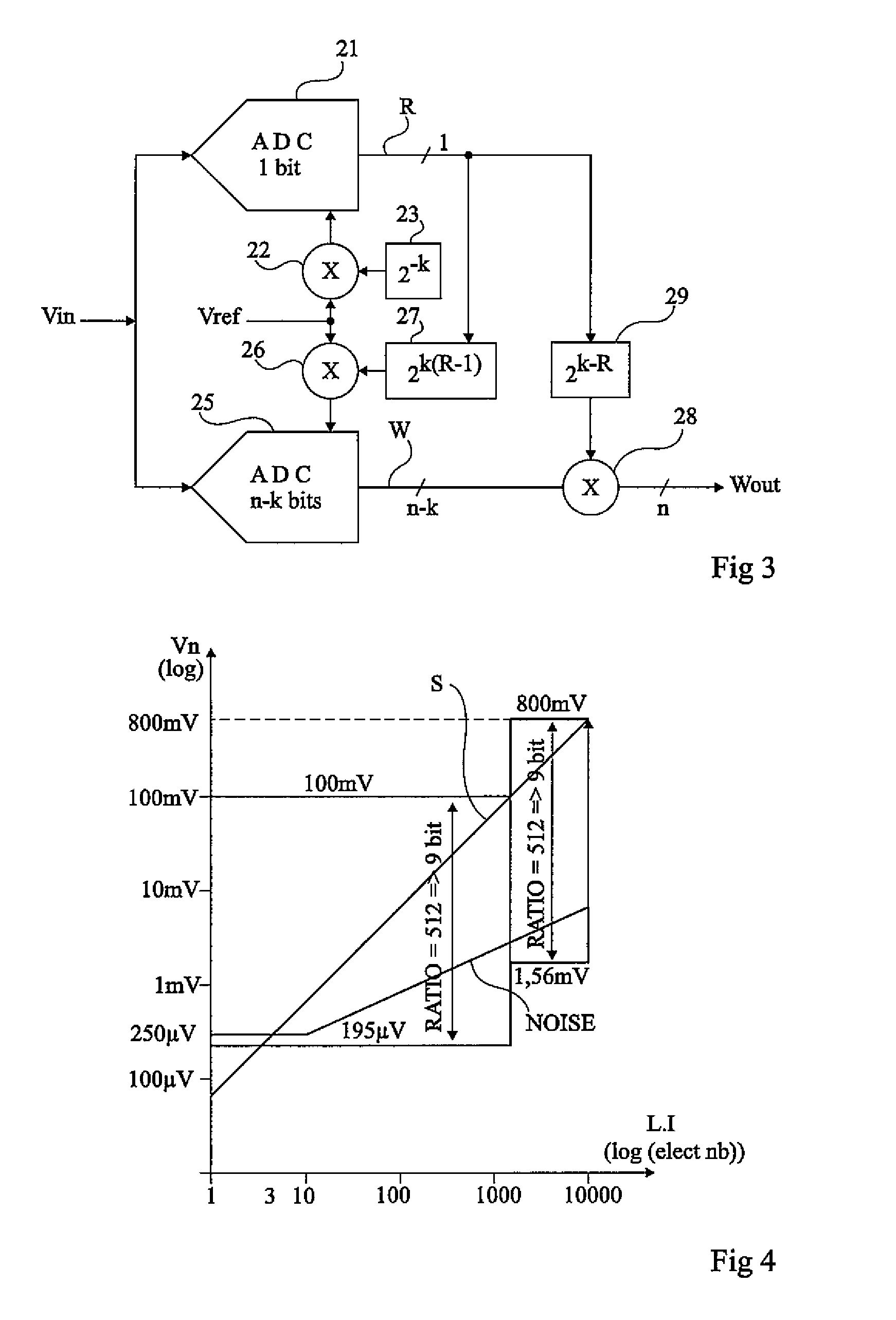

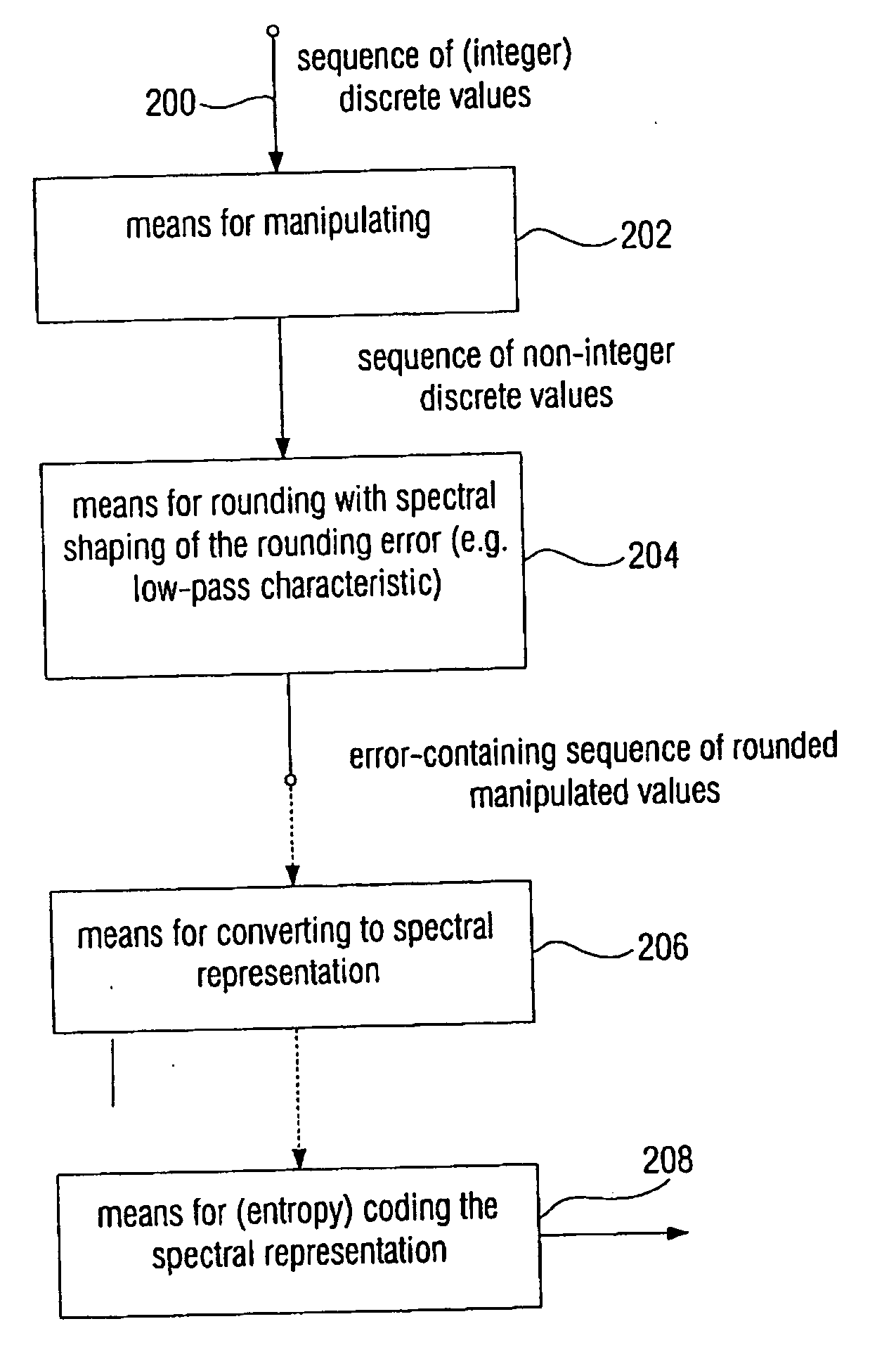

A method of analog-to-digital conversion over n bits of an analog signal, including the steps of: comparing the amplitude of the analog signal with a threshold representing the amplitude of the full-scale analog signal divided by 2k, where k is an integer smaller than n; performing an analog-to-digital conversion of the analog signal over n-k bits to obtain the n-k most significant bits of a binary word over n bits if the result of the comparison step indicates that the amplitude of the input signal is greater than the threshold, and the n-k least significant bits of this binary word otherwise. An analog-to-digital converter and its application to image sensors.

Owner:STMICROELECTRONICS SRL

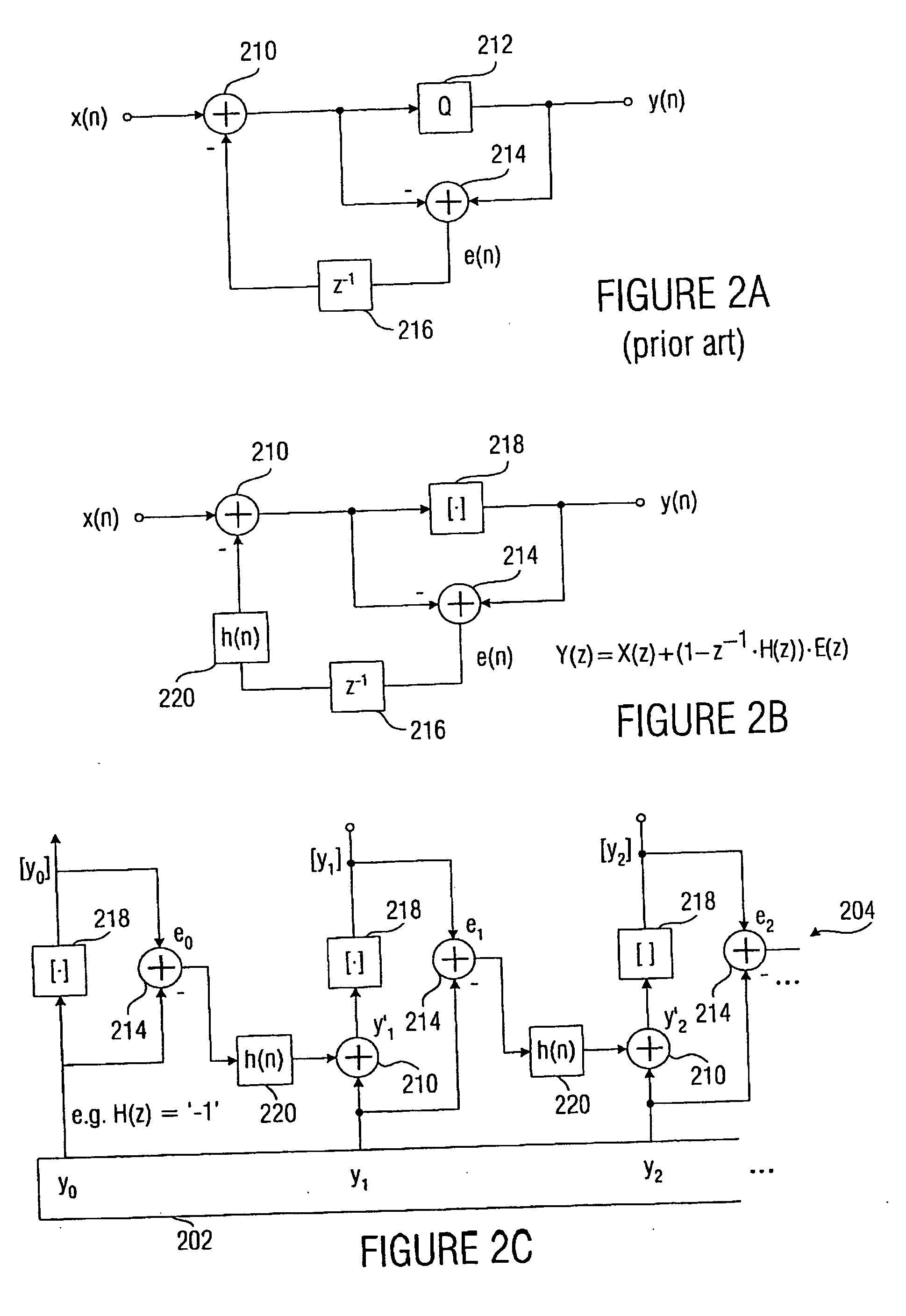

Device and method for processing a signal having a sequence of discrete values

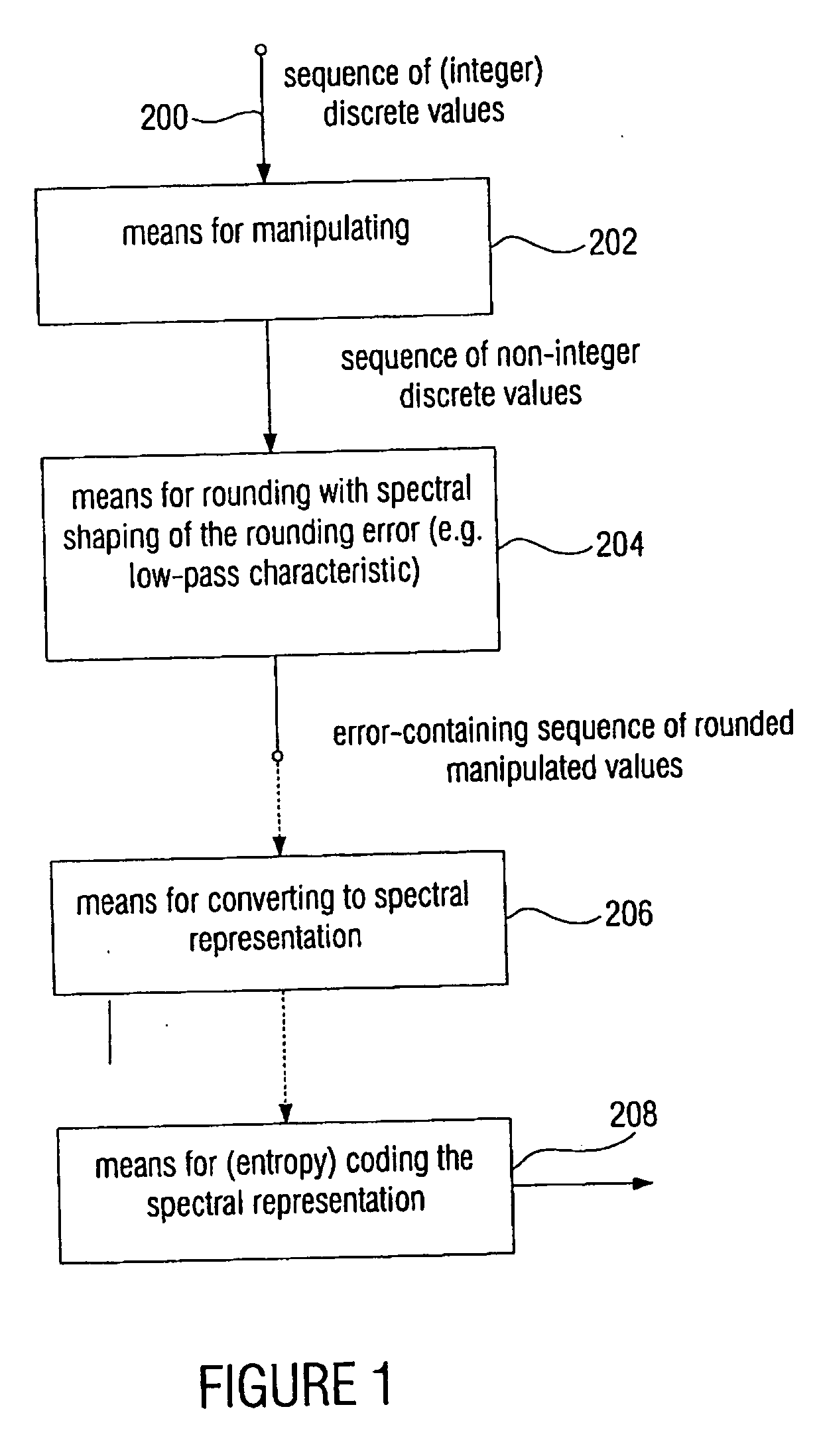

ActiveUS20060210180A1Few rounding errorIncrease the number ofSpeech analysisCharacter and pattern recognitionLossless codingFrequency spectrum

When processing a signal having a sequence of discrete values, wherein there is a first frequency range, in which the signal has a high energy, and wherein there is a second frequency range, in which the signal has a low energy, the sequence of discrete values is first manipulated to obtain a sequence of manipulated values, so that at least one of the manipulated values is non-integer. Then the sequence of manipulated values is rounded to obtain a sequence of manipulated values. The rounding is formed to effect a spectral shaping of a generated rounding error so that a spectrally shaped rounding error has a higher energy in the first frequency range than in the second frequency range. By spectrally shaping the rounding error so that the rounding error does not have any energy either in the storage areas where there is no signal energy, an especially efficient coding is obtained particularly in connection with a lossless coding context.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

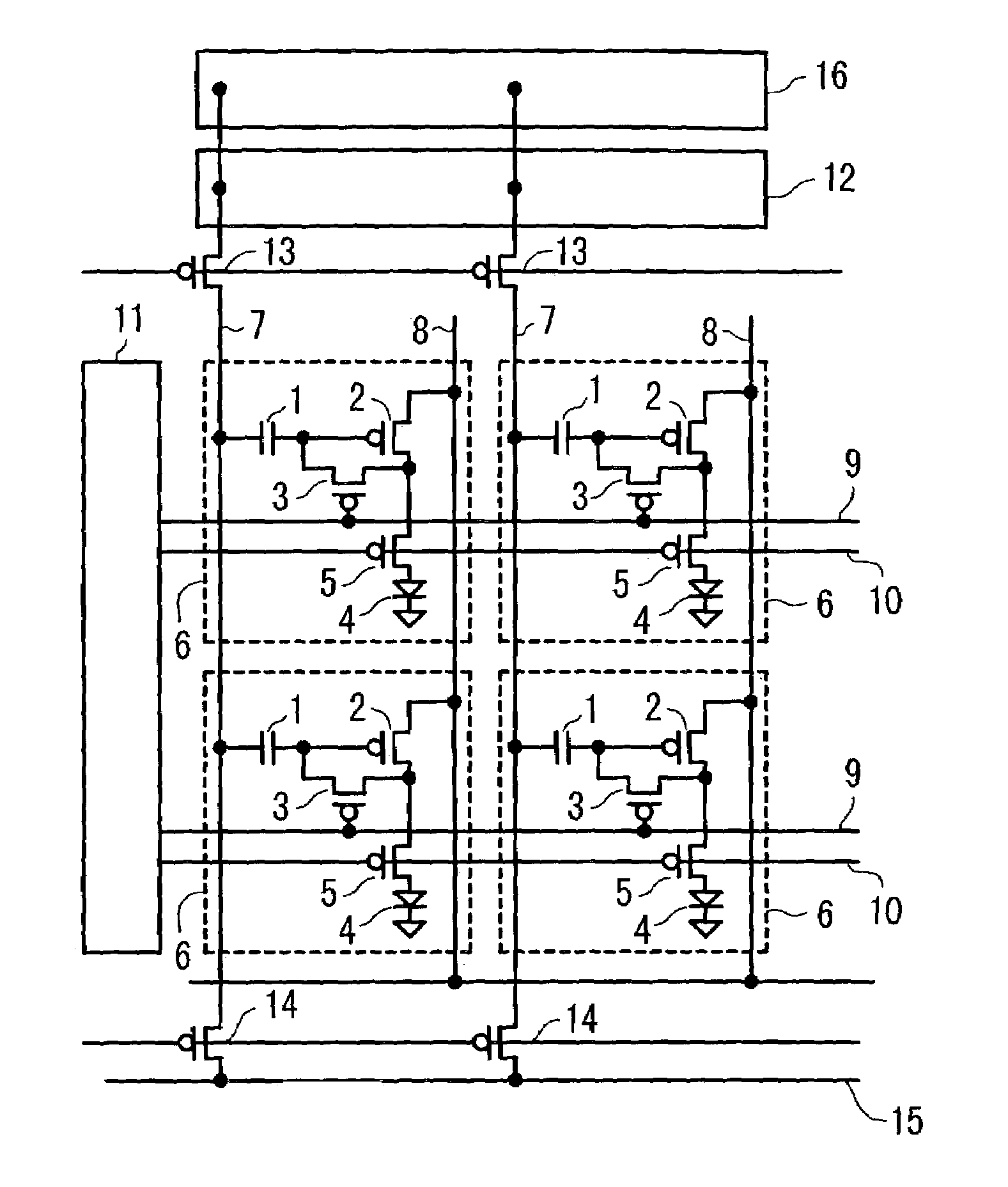

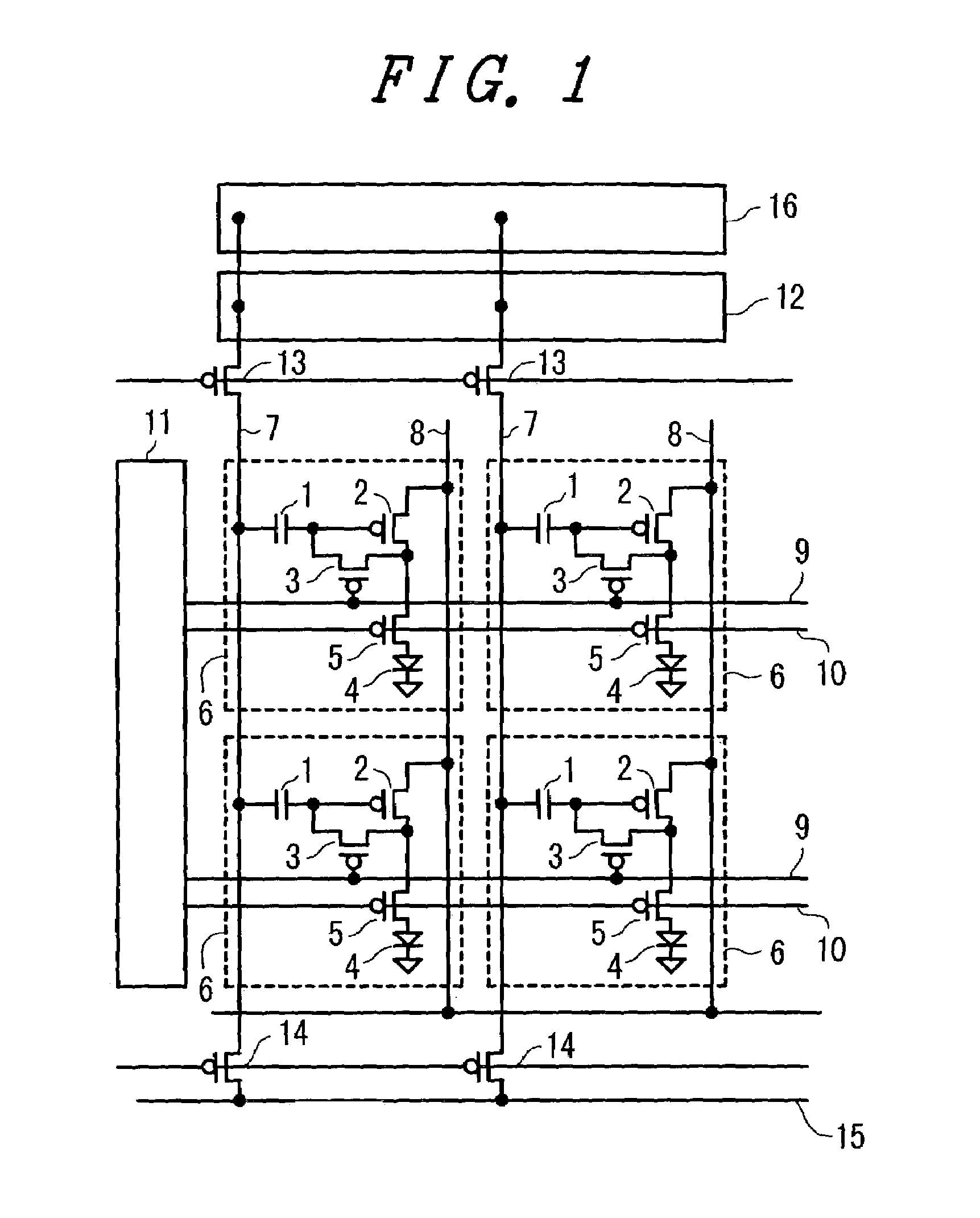

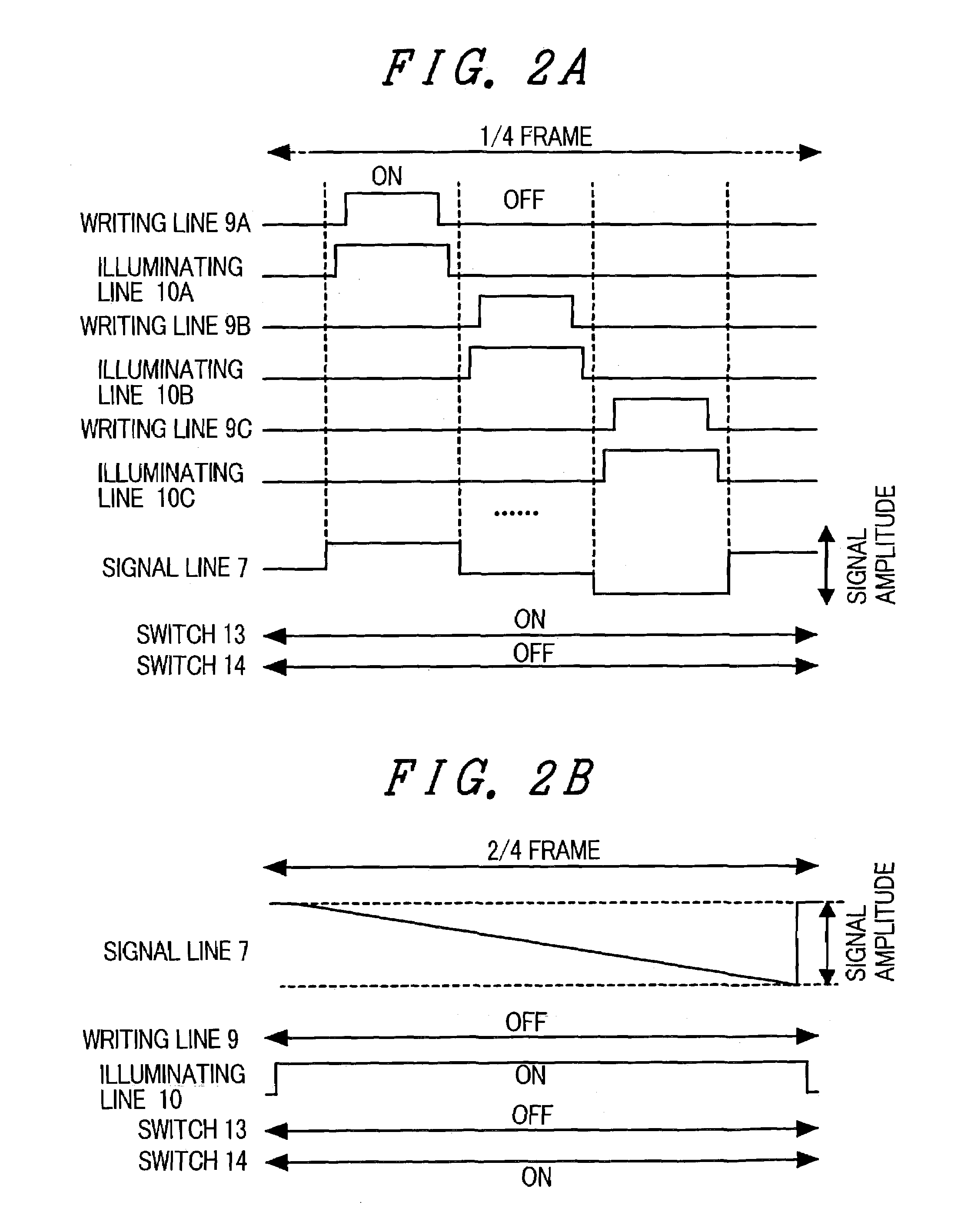

Image display

InactiveUS7286105B2Increase the number of digitsAvoid problemsSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceAnalog signal

The present invention provides an image display capable of performing high-precision multi-gradation display while avoiding problems of a subtle noise and increase in a drive frequency. Display signal data of one frame is constructed by a plurality of sub frames of, for example, four sub frames 1 / 4 to 4 / 4. The 1 / 4 frame is set as an address period of an analog signal, the 2 / 4 frame is set as an analog gradation display period, the 3 / 4 frame is set as an address period of a digital signal, and the 4 / 4 frame is set as a digital gradation light emission period. The image display is constructed in such a manner that, in the analog gradation display period, an OLED device in a pixel emits light of time according to an analog signal voltage stored in a storage capacitor in the pixel by an analog drive signal circuit and, in the digital gradation display period, a binary light emitting operation of light emission and non light emission is performed according to a digital signal voltage stored in the storage capacitor by a digital signal driving circuit.

Owner:SAMSUNG DISPLAY CO LTD +1

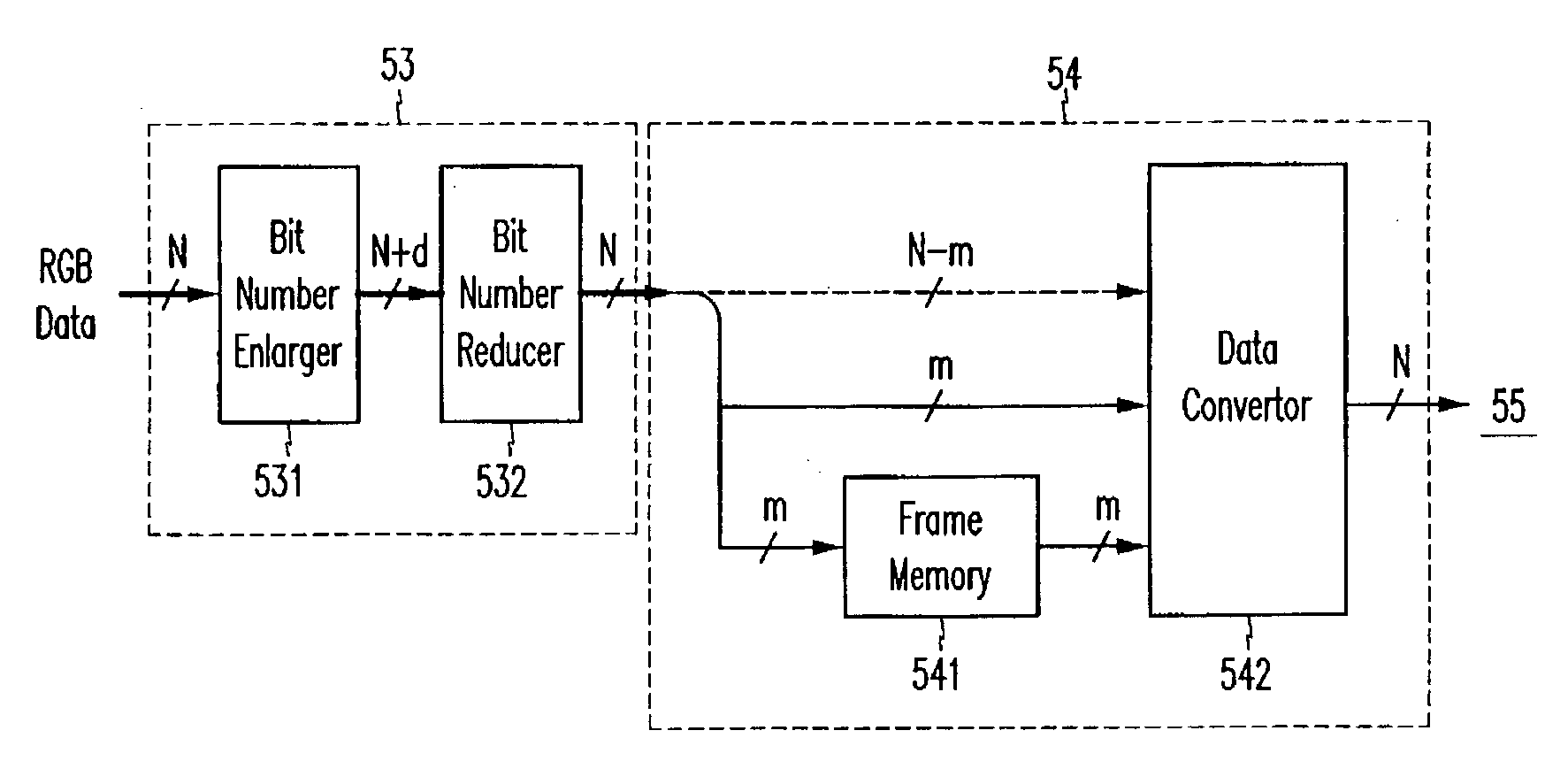

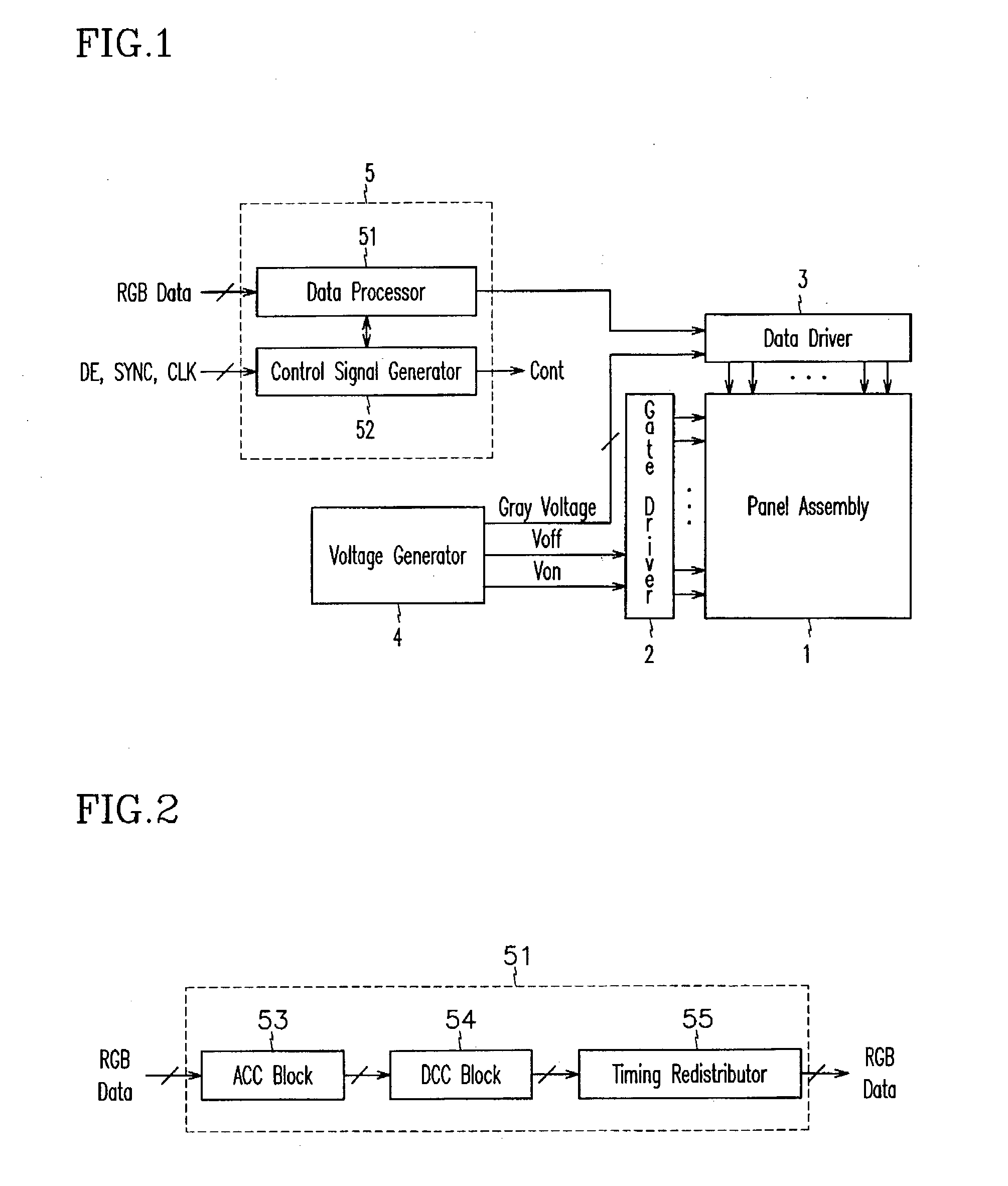

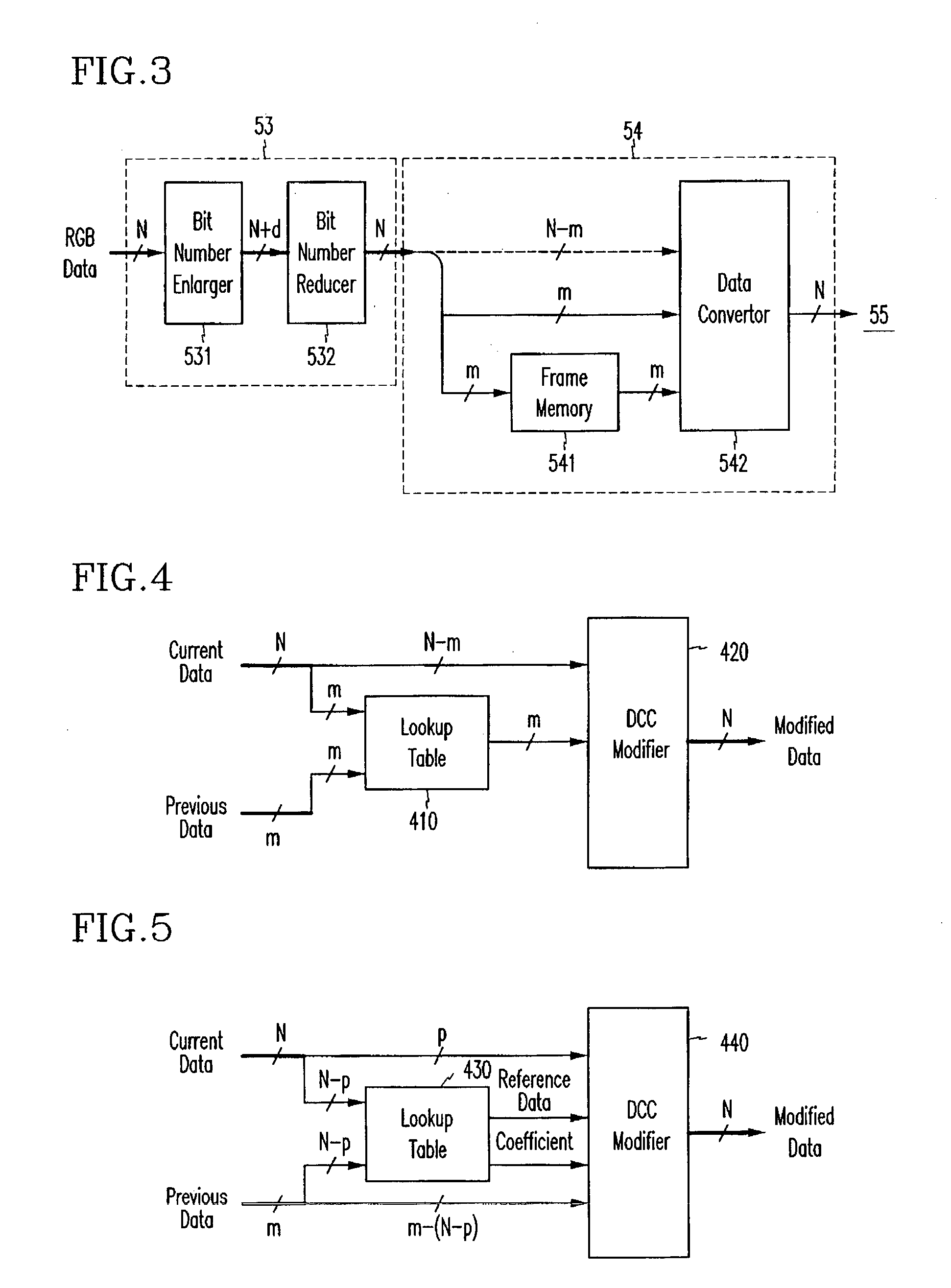

Liquid crystal display

ActiveUS7148868B2Reduce digitsIncrease the number of digitsTelevision system detailsDigital computer detailsCapacitanceLiquid-crystal display

A liquid crystal display is provided, which includes: a liquid crystal panel assembly including a plurality of pixels connected to a plurality of gate lines and a plurality of data lines; a signal controller for processing image data, the signal controller including a dynamic capacitance capture (“DCC”) block for modifying image data assigned to the pixels by selectively performing DCC on the image data based on the difference between the image data of a current frame (“current data”) and the image data of a previous frame (“previous data”); a gate driver for sequentially applying a gate-on voltage to the gate lines of the liquid crystal panel assembly; and a data driver selecting data voltages among a plurality of gray voltages in response to the modified image data from the signal controller and applies the data voltages to the data lines of the liquid crystal panel assembly.

Owner:SAMSUNG DISPLAY CO LTD

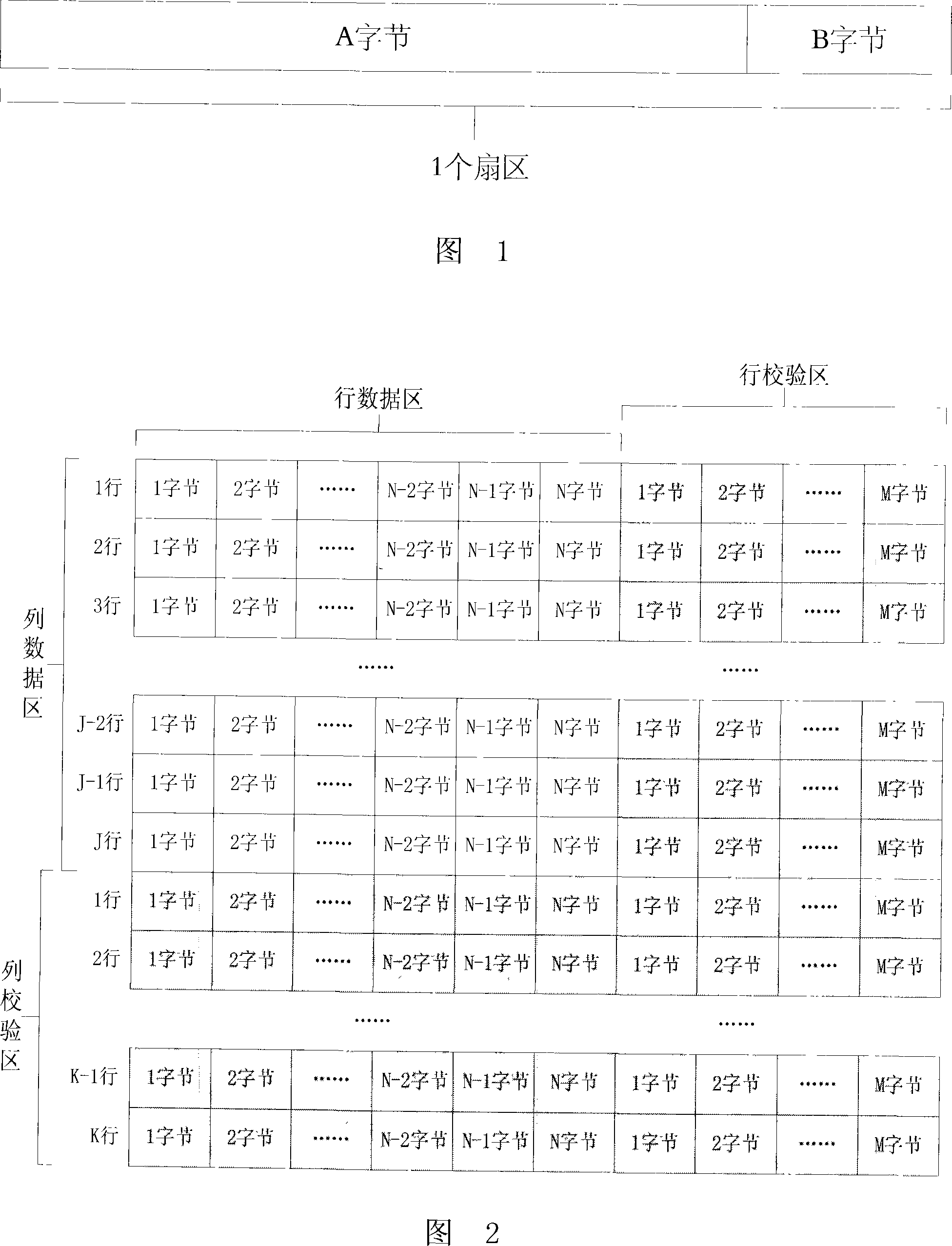

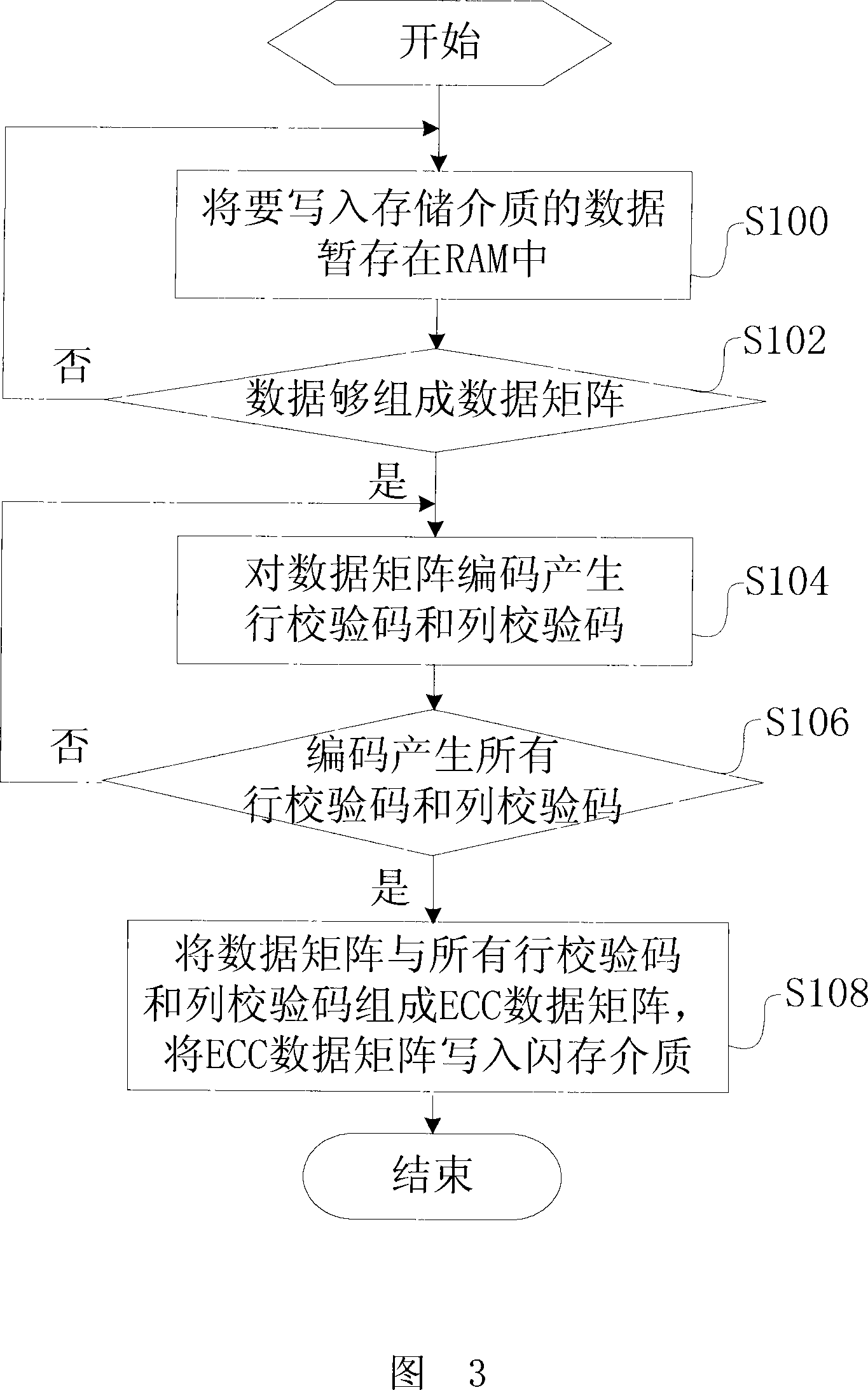

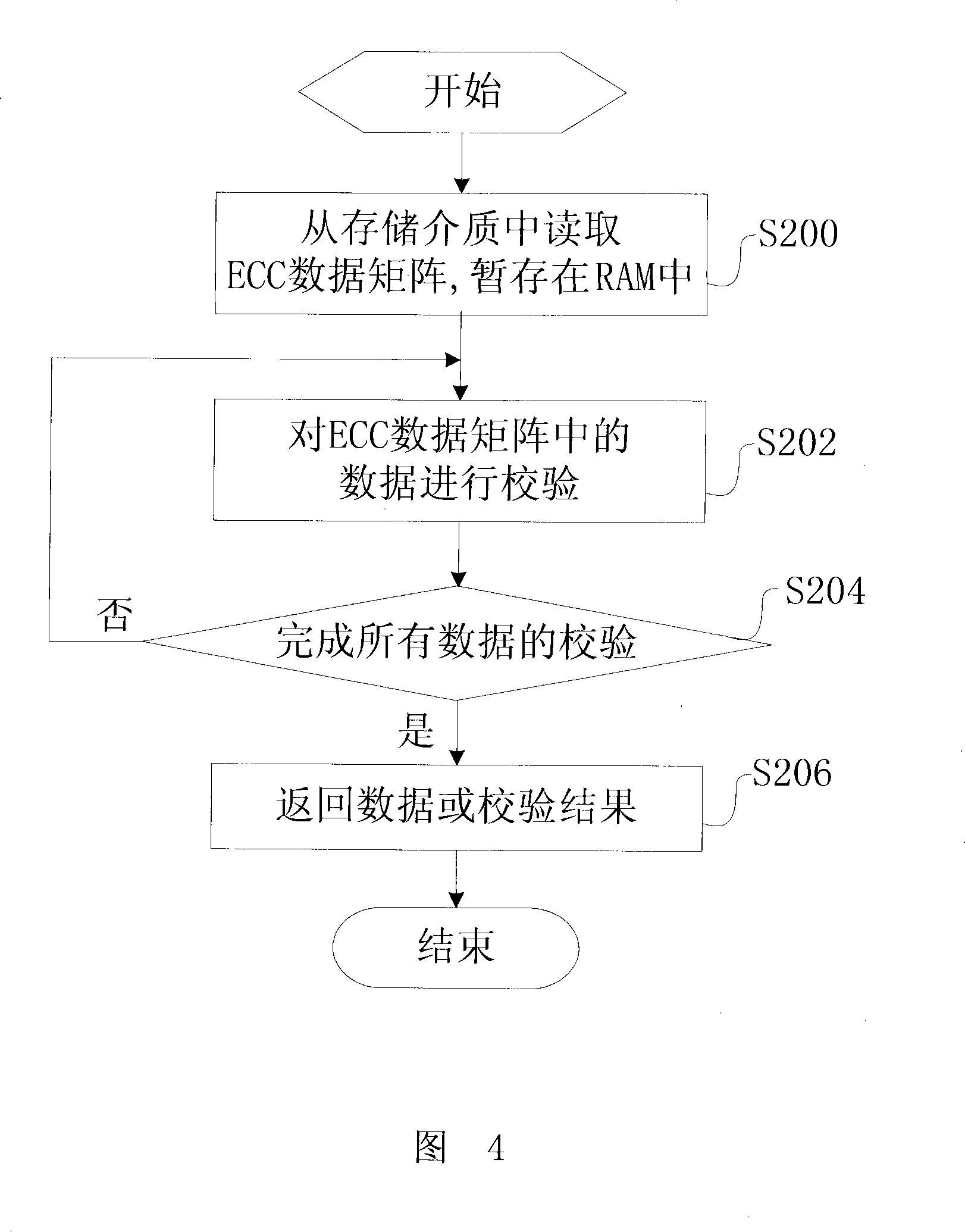

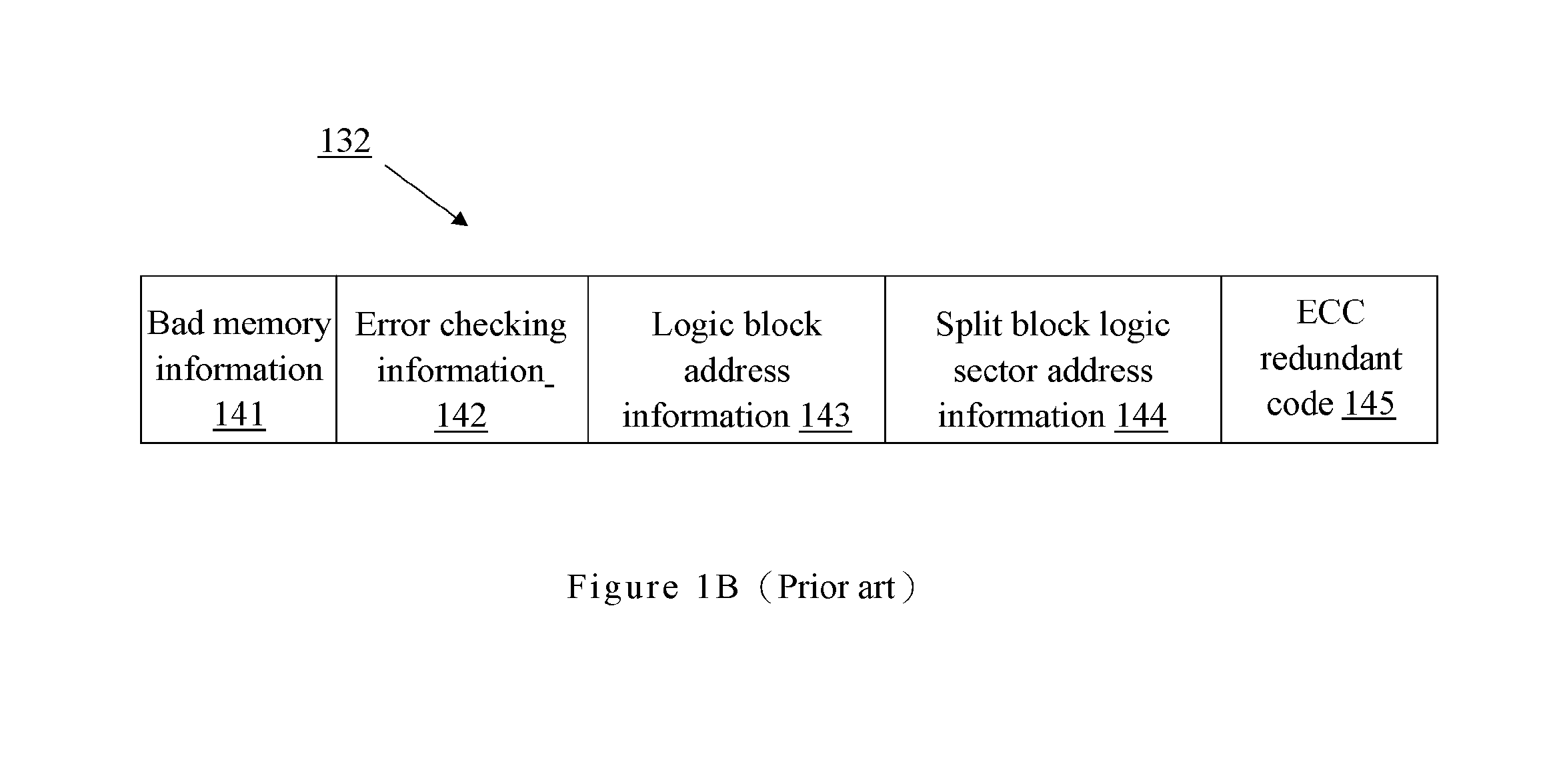

Data verification method for storage medium

ActiveCN101183565AIncrease the number of digitsIncrease profitStatic storageData operationsSource Data Verification

The invention provides a data verification method in a storage medium, comprising: organizing an ECC data matrix; encoding the data to generate a row check code and a column check code; when performing data operations on the ECC data matrix, using the row check code and column The check code checks the data. The present invention has stronger error correction capability than the single row check, can correct more byte errors, can increase the number of check data, allows more error bits in the storage medium, and can be well Correct these errors. The invention can better support MLC and 4LC type storage media, and achieve the purpose of prolonging the service life of the storage medium, improving the utilization rate of the storage medium and reducing the system cost.

Owner:SLICONGO MICROELECTRONICS INC

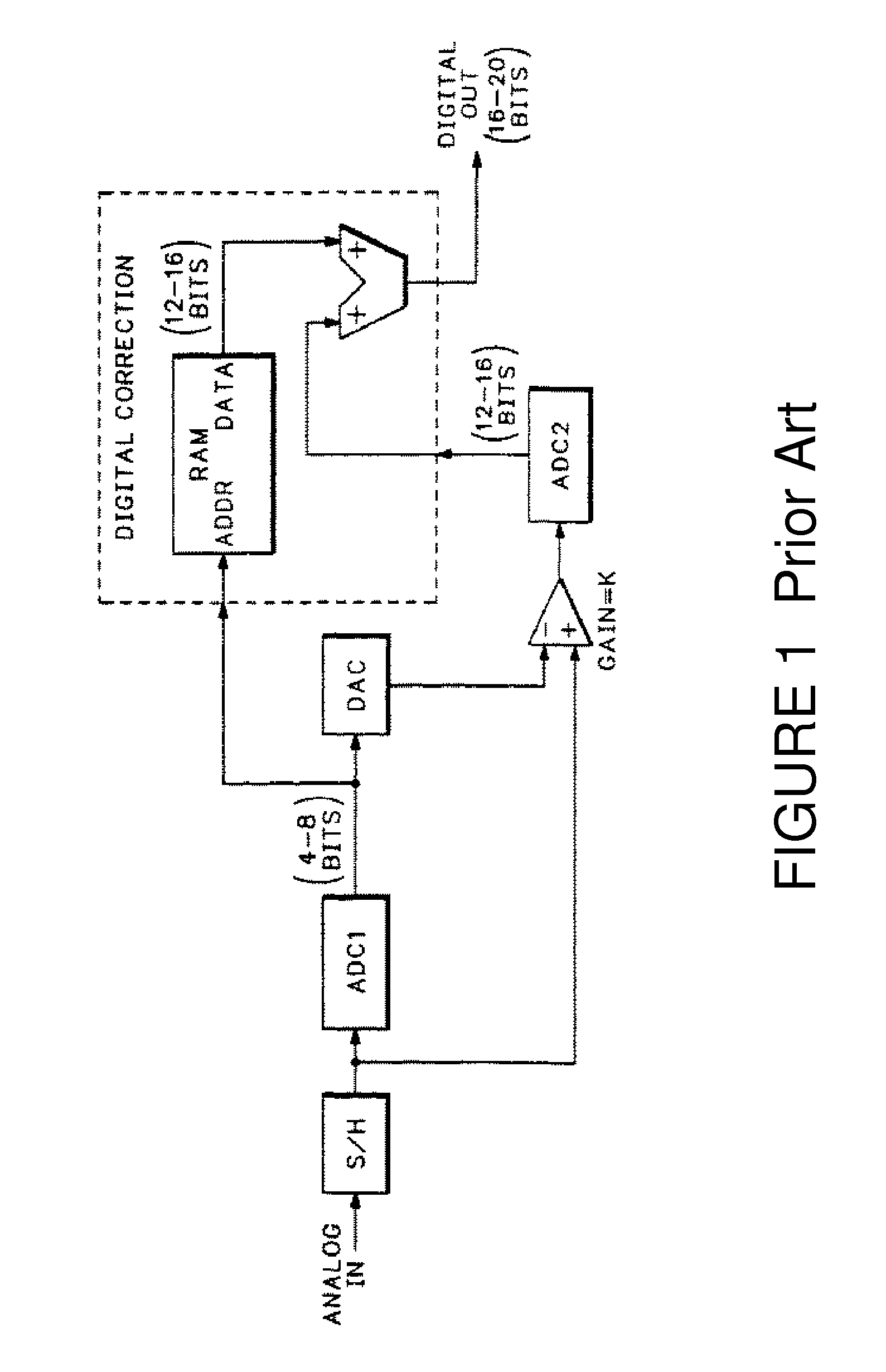

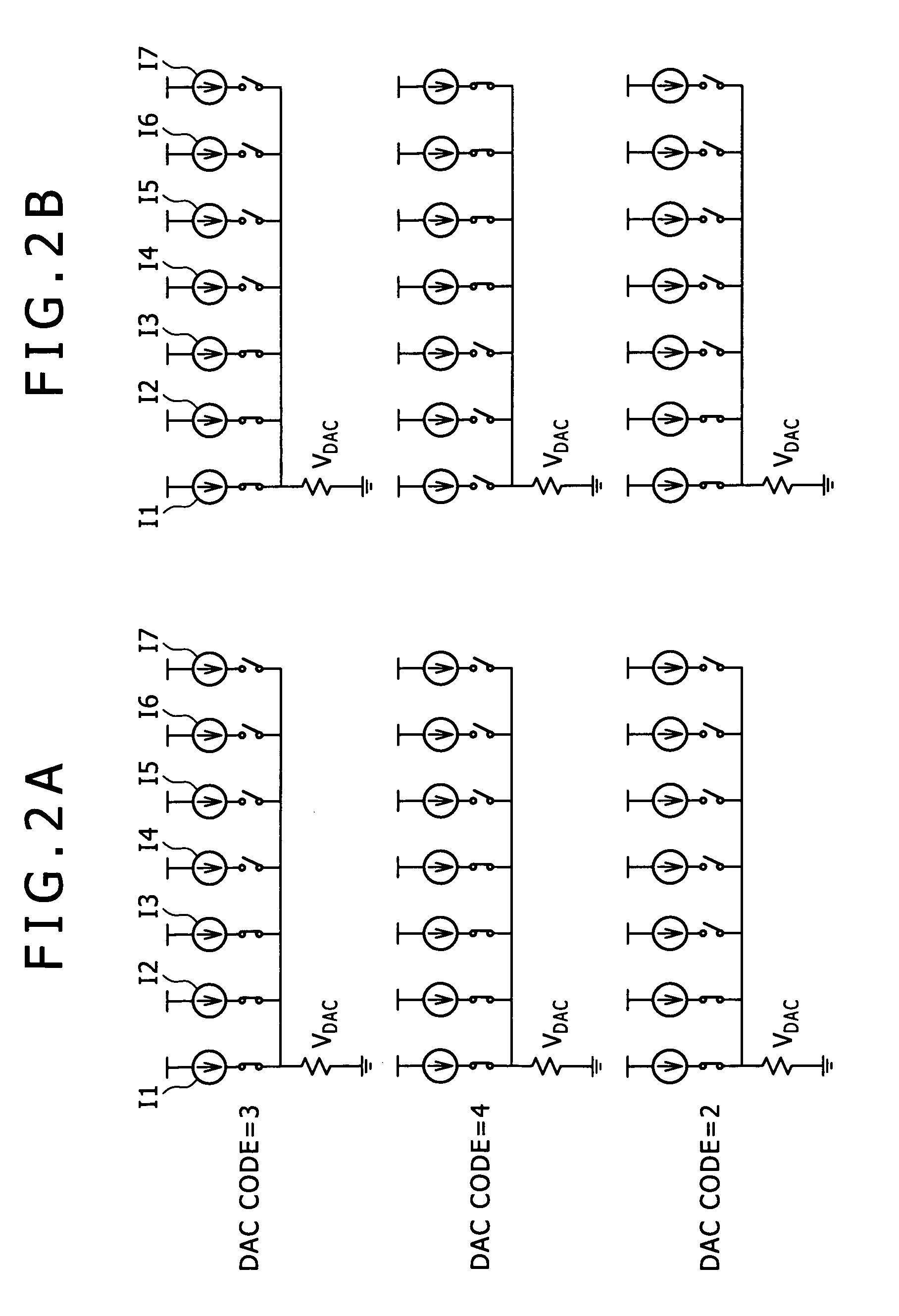

Superconductor analog to digital converter

ActiveUS8188901B1Increase the number of effective digitsAttenuation bandwidthElectric signal transmission systemsDelta modulationDigital down converterAudio power amplifier

Superconductor analog-to-digital converters (ADC) offer high sensitivity and large dynamic range. One approach to increasing the dynamic range further is with a subranging architecture, whereby the output of a coarse ADC is converted back to analog and subtracted from the input signal, and the residue signal fed to a fine ADC for generation of additional significant bits. This also requires a high-gain broadband linear amplifier, which is not generally available within superconductor technology. In a preferred embodiment, a distributed digital fluxon amplifier is presented, which also integrates the functions of integration, filtering, and flux subtraction. A subranging ADC design provides two ADCs connected with the fluxon amplifier and subtractor circuitry that would provide a dynamic range extension by about 30-35 dB.

Owner:HYPRES

Digital Ultrasound Beam Former with Flexible Channel and Frequency Range Reconfiguration

InactiveUS20090240152A1Improve dynamic rangeReduced sampling rate requirementsHeart/pulse rate measurement devicesInfrasonic diagnosticsUltrasound imagingSonification

A digital ultrasound beam former for ultrasound imaging, that can be configured by a control processor to process the signals from ultrasound transducer arrays with variable number of elements at variable sampling frequencies, where the lowest sampling frequency allows for the highest number of array elements. The maximal number of array elements is reduced in the inverse proportion to the sampling frequency. The beam former can be operated both in a RF-sampling mode and a quadrature mode. Parallel coupling of transmit / receive circuits for each element allow adaption of the receive Noise Figure and transmit drive capabilities to variations in the electrical impedance of the array elements.

Owner:SURF TECH AS

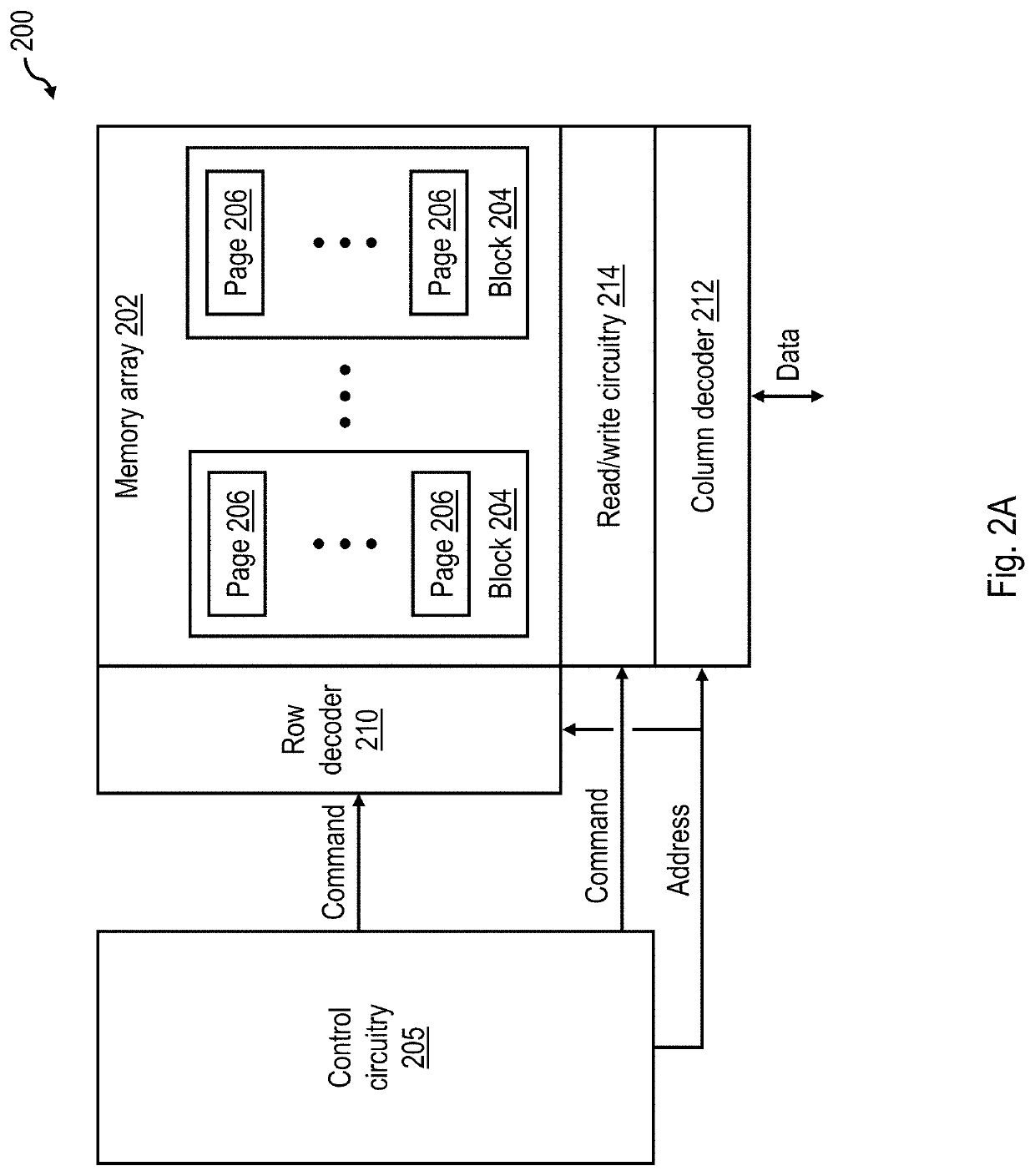

Multi-level cell memory device and method thereof

ActiveUS7962831B2Improve stabilityIncrease the number of digitsRead-only memoriesDigital storageData operationsMulti-level cell

A Multi-Level Cell (MLC) memory device and method thereof are provided. The example MLC memory device may be configured to perform data operations, and may include an MLC memory cell, a first coding device performing a first coding function, the first coding function being one of an encoding function and a decoding function, a second coding device performing a second coding function, the second coding function being one of an encoding function and a decoding function and a signal module configured to perform at least one of instructing the MLC memory cell to store data output by the second coding device if the first and second coding functions are encoding functions, and generating a demapped bit stream based on data retrieved from the MLC memory cell if the first and second coding functions are decoding functions.

Owner:SAMSUNG ELECTRONICS CO LTD

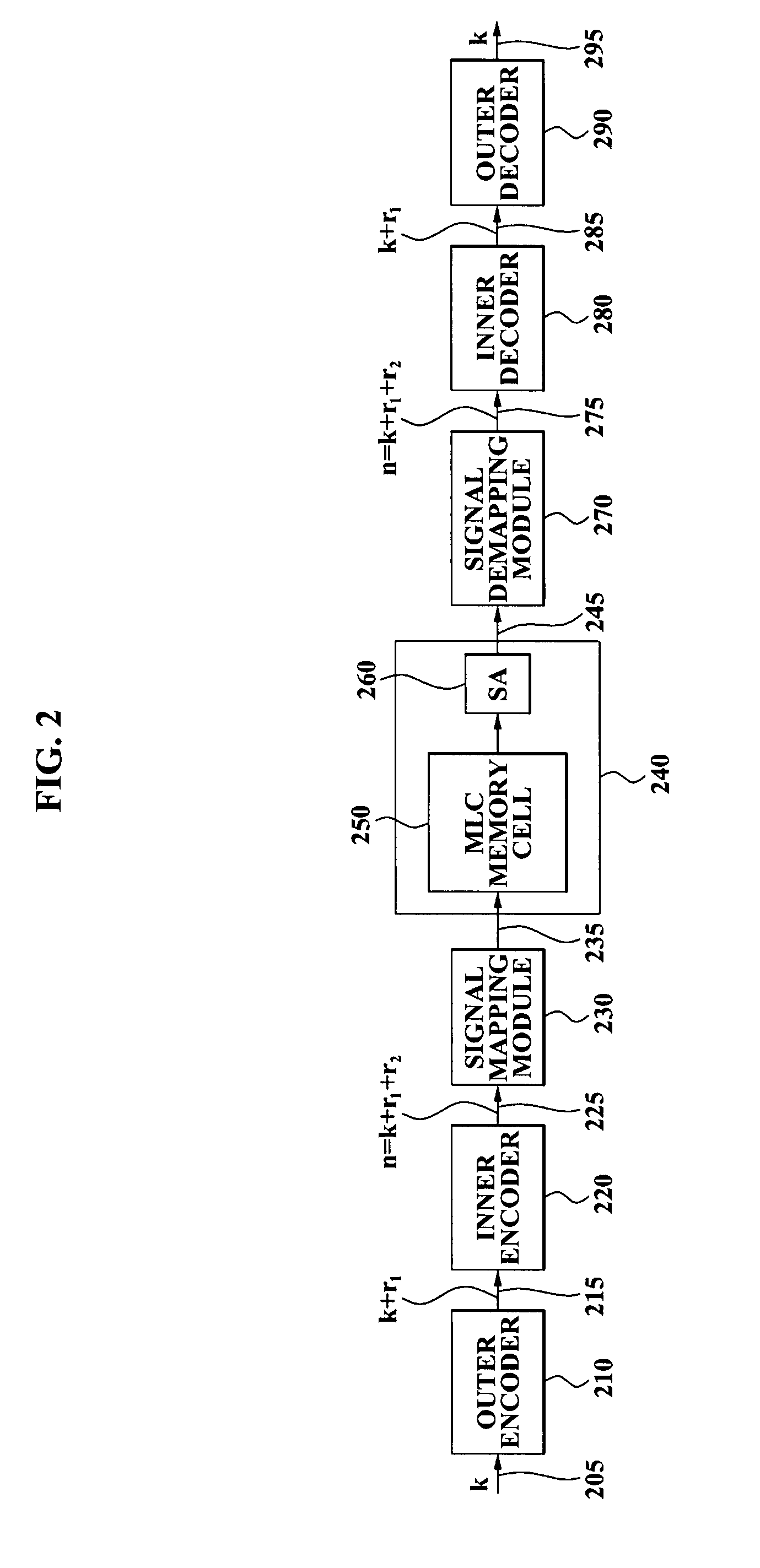

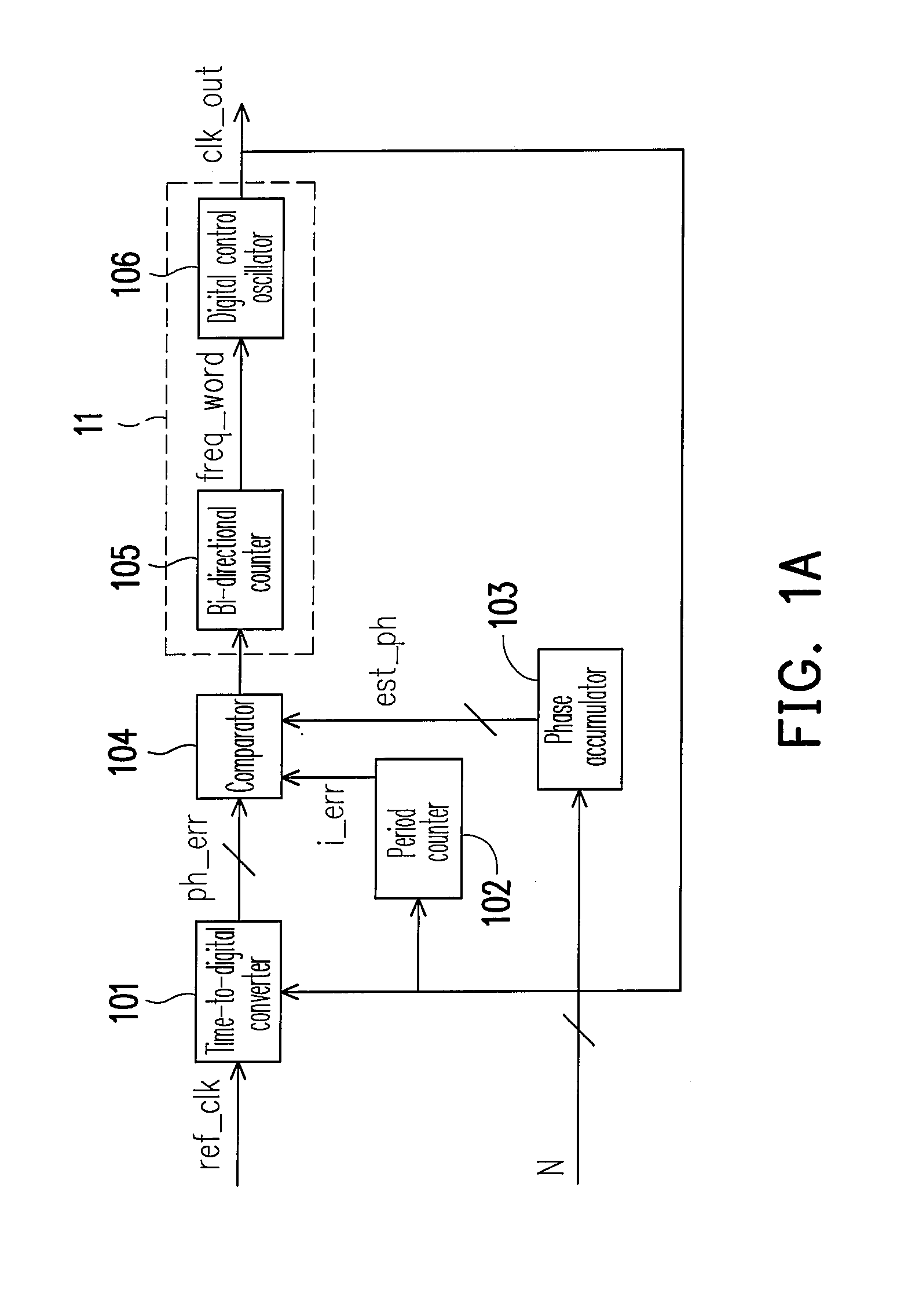

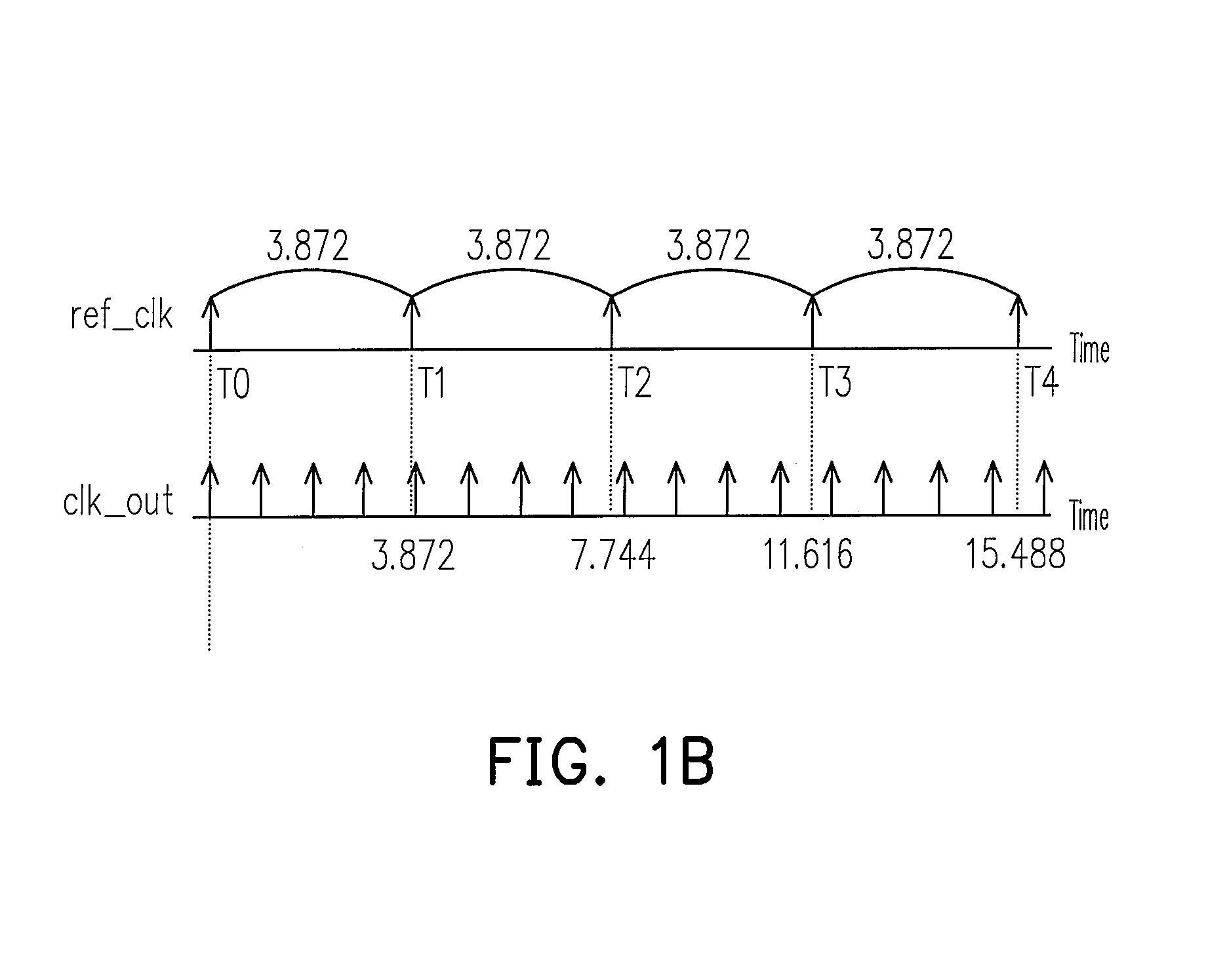

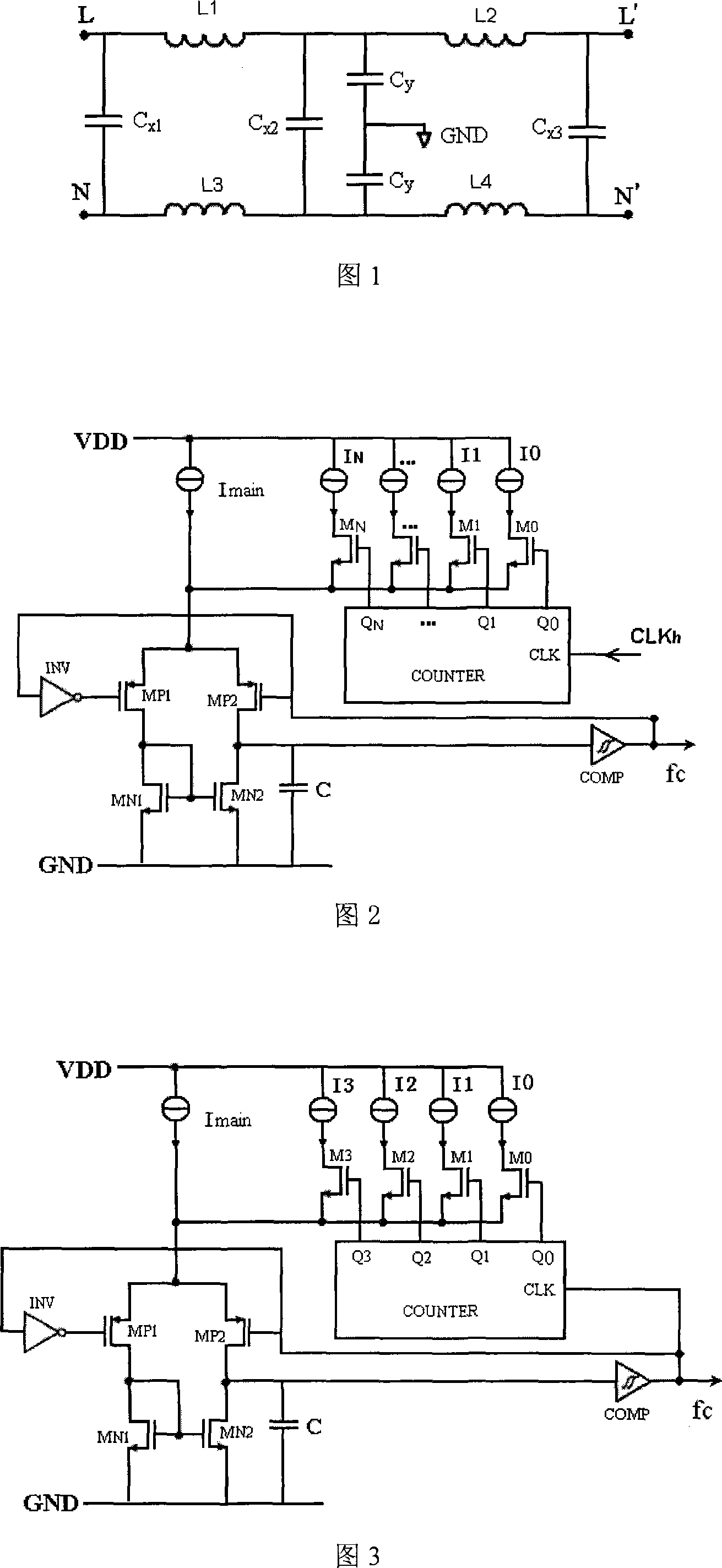

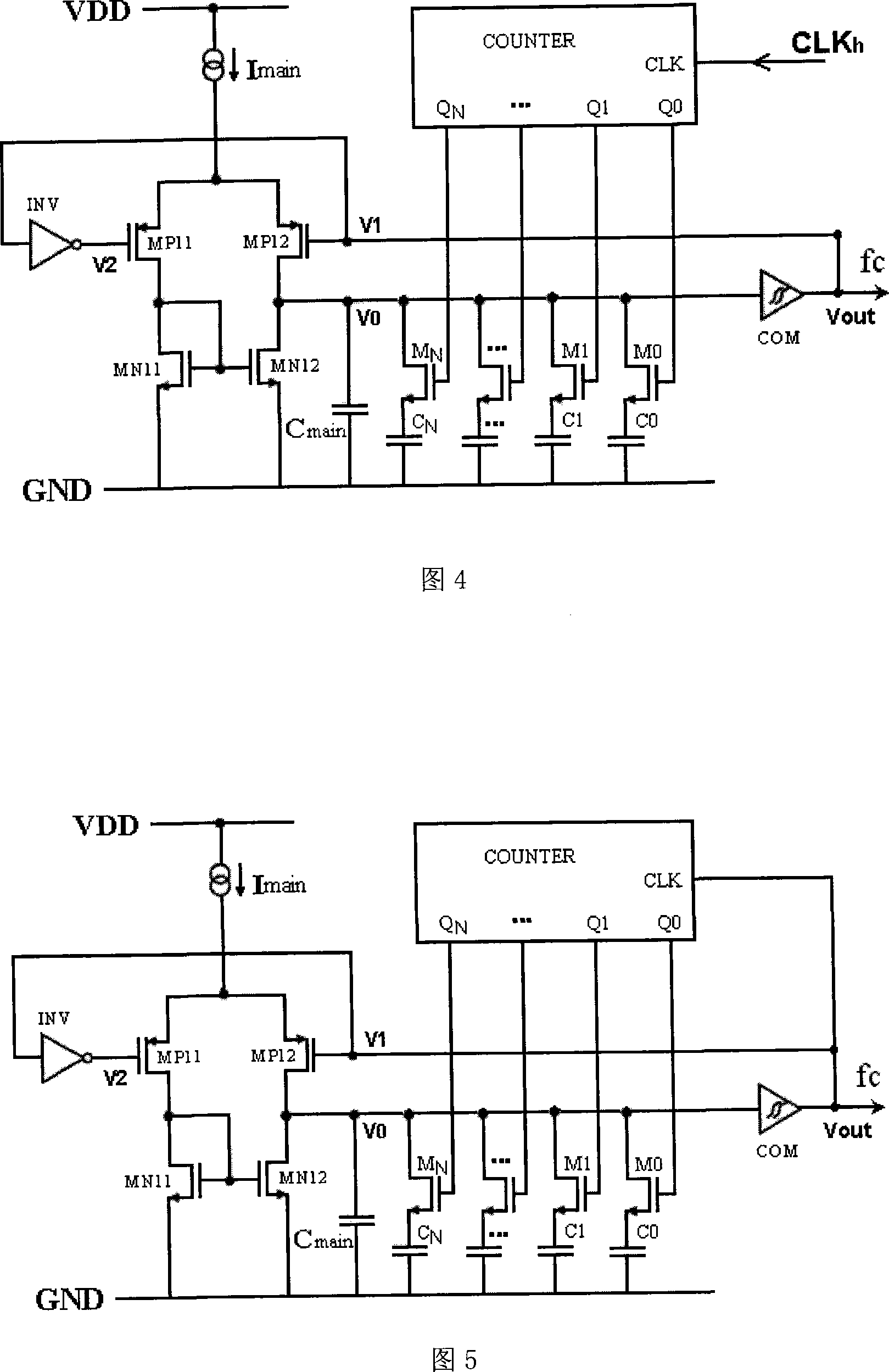

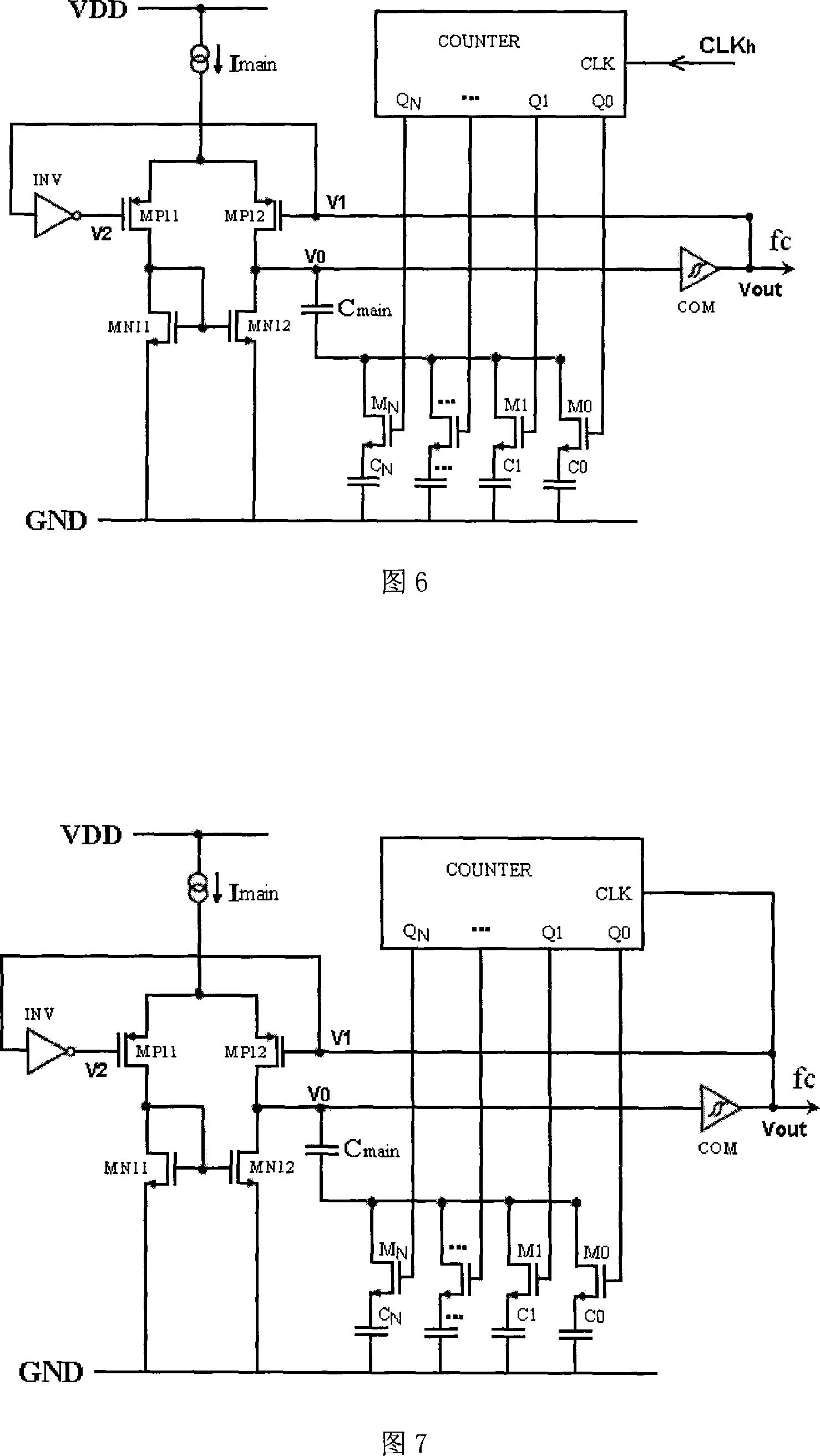

Phase lock loop and digital control oscillator thereof

InactiveUS20070291173A1Rapid responseIncrease the number of digitsPulse automatic controlEngineeringDigital controlled oscillator

A phase lock loop including a time-to-digital converter, a period counter, a phase accumulator, a comparator, and an output unit is disclosed. The time-to-digital converter outputs a detected phase error based on the timing difference between a reference clock signal and an output clock signal. The period counter increases a first accumulative value in each period of the output clock signal. The phase accumulator increases a second accumulative value in each period of the reference clock signal and outputs the second accumulative value as an estimative phase error between the reference clock signal and the output clock signal in next period. The comparator outputs a frequency correction signal according to the detected phase error, the first accumulative value, and the estimative phase error. The output unit provides the output clock signal and adjusts its frequency according to the frequency correction signal.

Owner:NOVATEK MICROELECTRONICS CORP

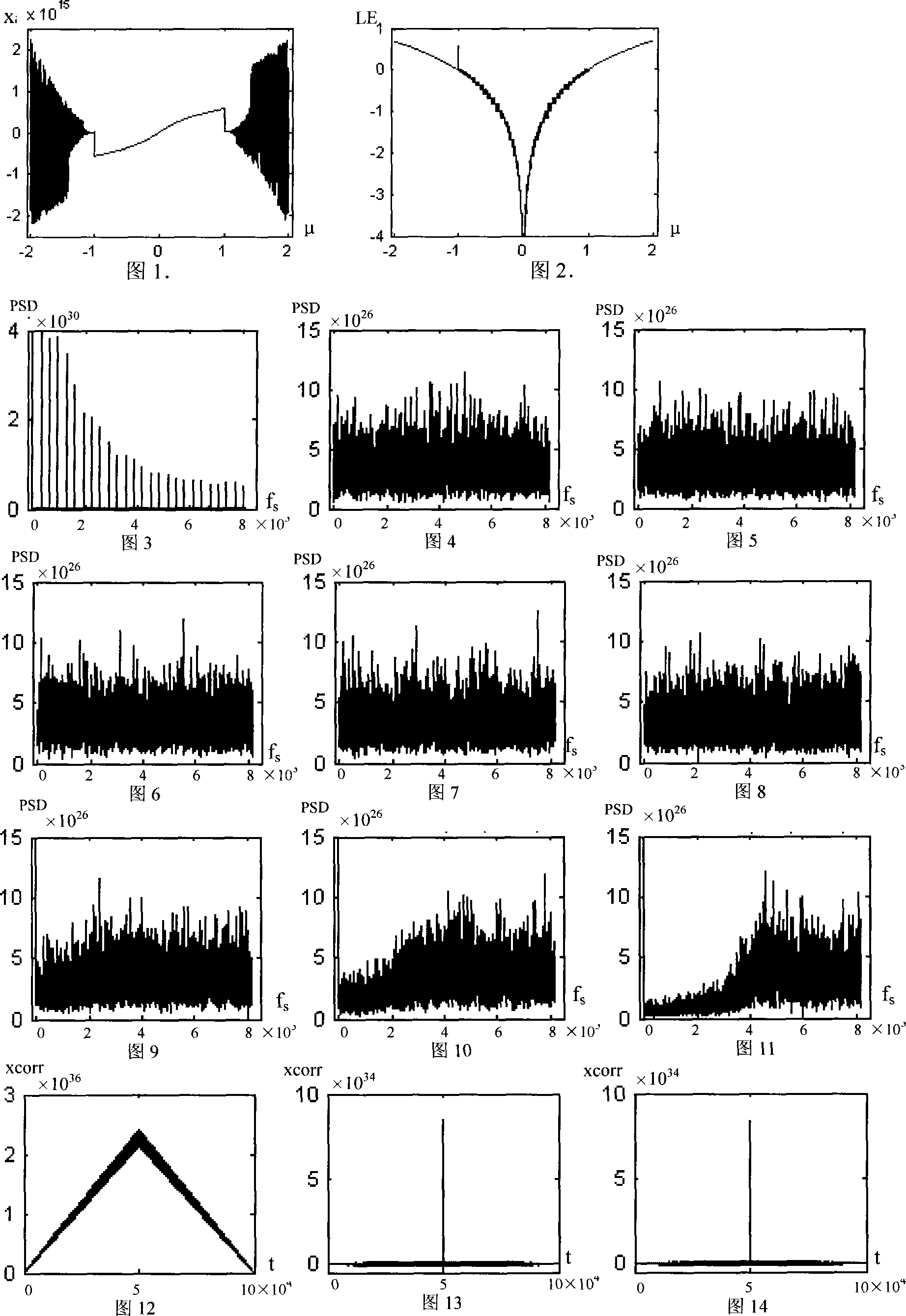

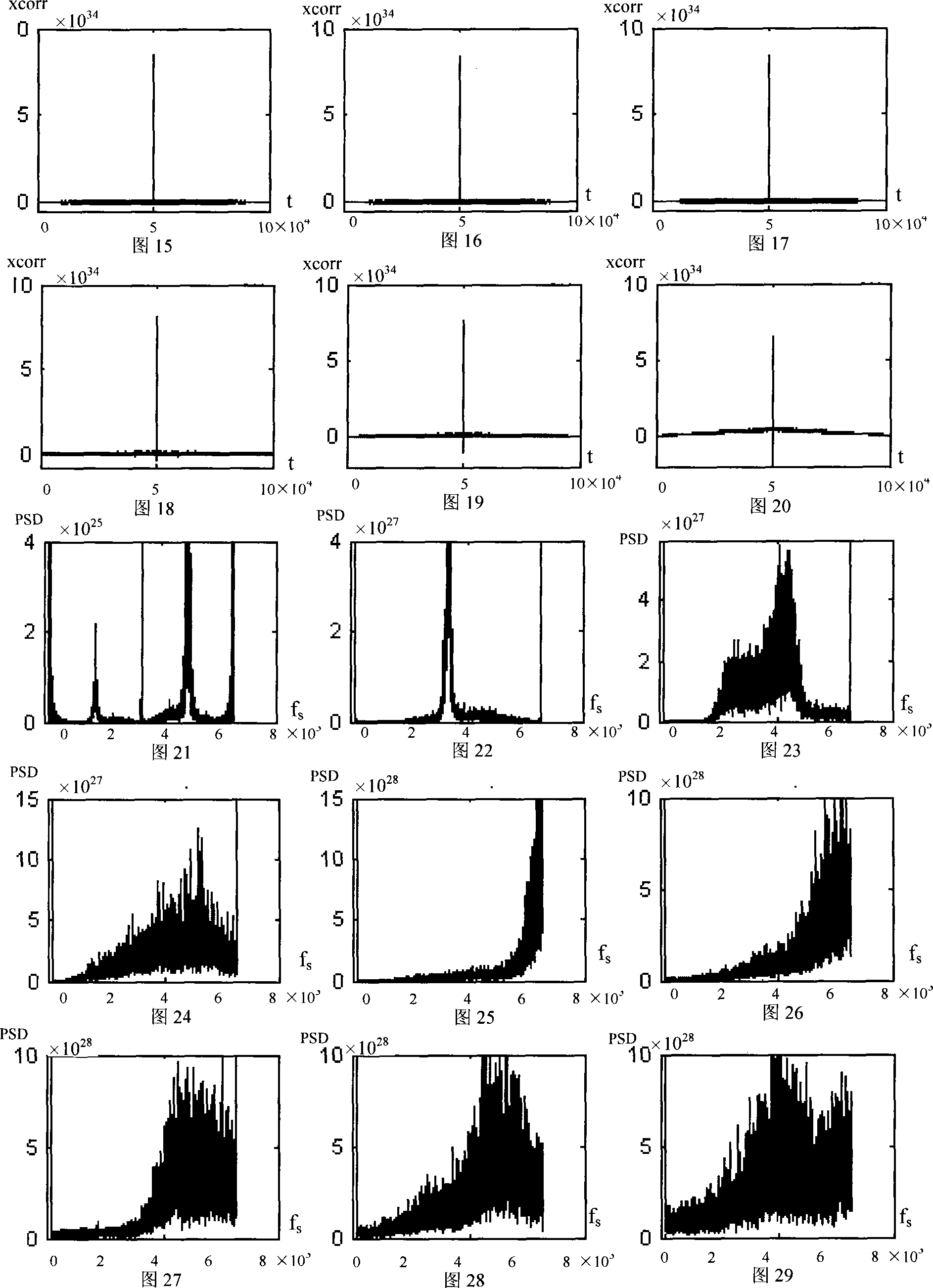

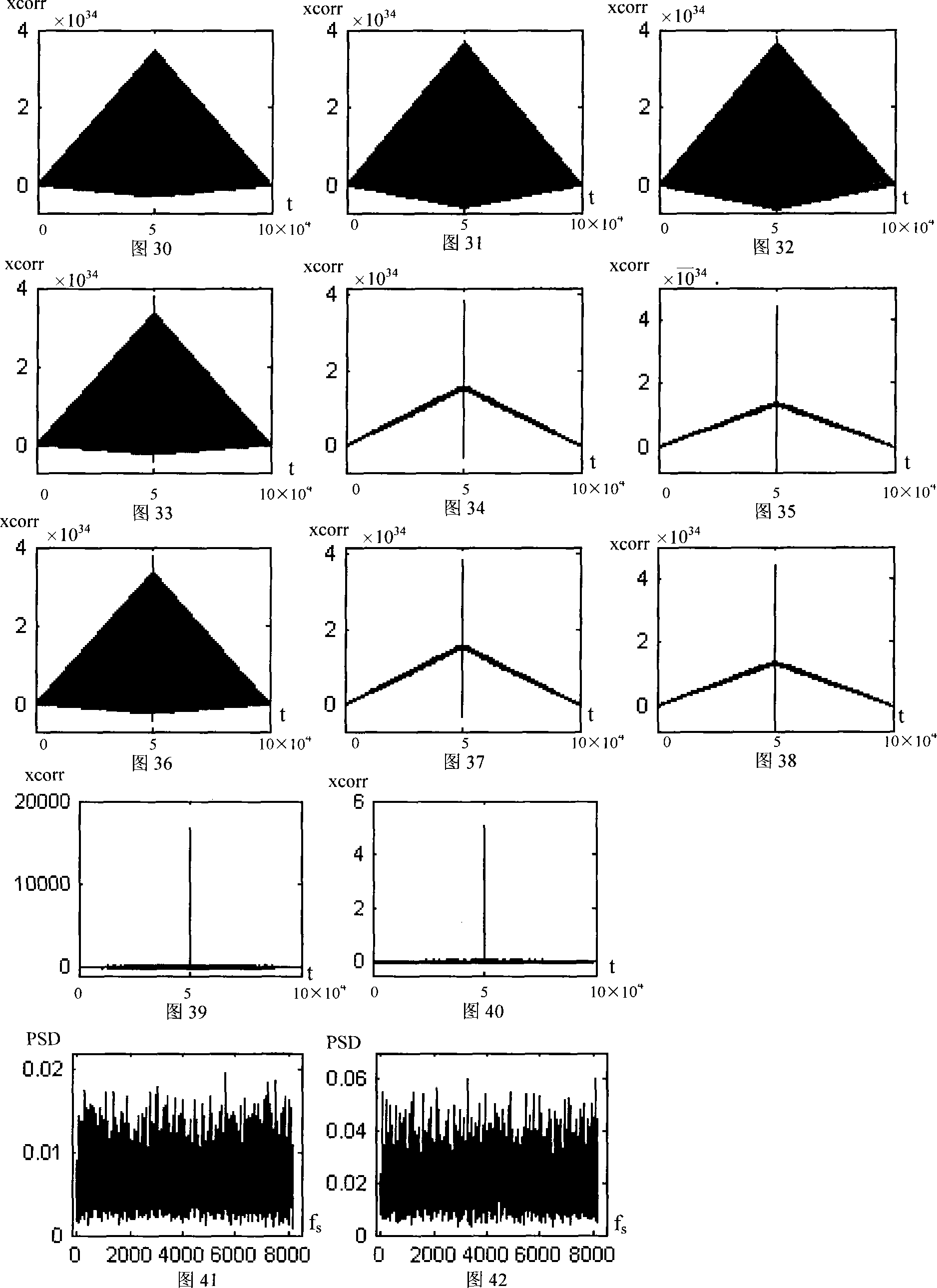

Chaotic sequence generation method and sequence generator of high speed high-precision chaotic function

InactiveCN101222318AGood statistical propertiesOvercome short cycle responseSecuring communicationComplex mathematical operationsPlaintextMultiplexer

The invention discloses a chaotic sequence generation method and a sequence generator for high-speed high-accuracy chaotic functions. An initial key circuit stores the initial value of a chaotic latch unit, a u value key circuit stores a sequence ui value; each cp chaotic function finishes one-time interactive operation: a bitwise conversion circuit outputs a bitwise XOR to the chaotic latch unit, the bitwise XOR is used to realize a subtraction operation N minus one and minus the absolute value of xi and so on; a shift data selector takes the ui as an address code of the data selector, the data is shifted with a plurality of bits toward right, then the subtraction is used to realize a multiplication that the ui is multiplied by the data; the subtraction result is stored into the chaotic latch unit at the rising edge of the cp, each cp generates a 160-bit chaotic output; the randomness is good due to the existence of an initial key and a u value key; the precision is far greater than that of the double type, the cycle of the cp can reach 90ns, the encryption of a 128-bit plaintext needs 1.7us; the invention can be realized by using FPGAs, GPLDs and ASICs and so on, and is used in the network security technical field, particularly in the wireless networks and the wireless sensor networks.

Owner:HEILONGJIANG UNIV

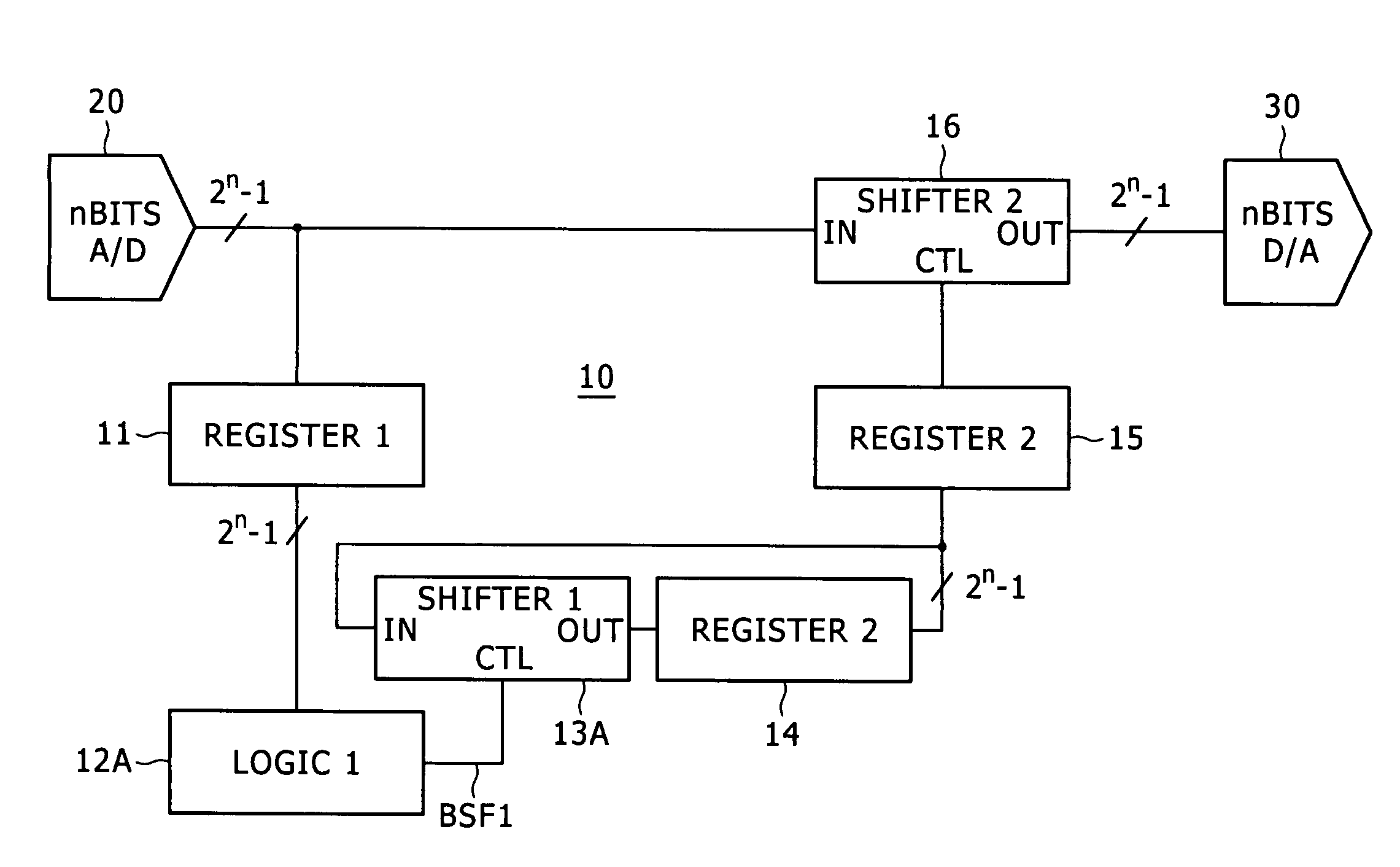

Linearity enhancement circuit, ΣΔ A/D converter, and reception apparatus

InactiveUS8144046B2Increase clock frequencyIncrease the number of digitsElectric signal transmission systemsAnalogue conversionProcessor registerBuck converter

A linearity enhancement circuit is disclosed which includes: a first shift amount creation block creating a first shift amount in keeping with the immediately preceding output code of an n-bit A / D converter; a first shifter circuit bit-shifting input code data by the first shift amount that has been supplied, the first shifter circuit further outputting the bit-shifted input code data; a register storing the output of the first shifter circuit in order to output the stored data as the input code data to the first shifter circuit thereby forming a loop circuit in conjunction with the first shifter circuit, the register further outputting the stored code data as a second shift amount; and a second shifter circuit bit-shifting the output code of the A / D converter by the second shift amount that has been supplied, the second shifter circuit further outputting the bit-shifted output code to an n-bit D / A converter.

Owner:SONY CORP

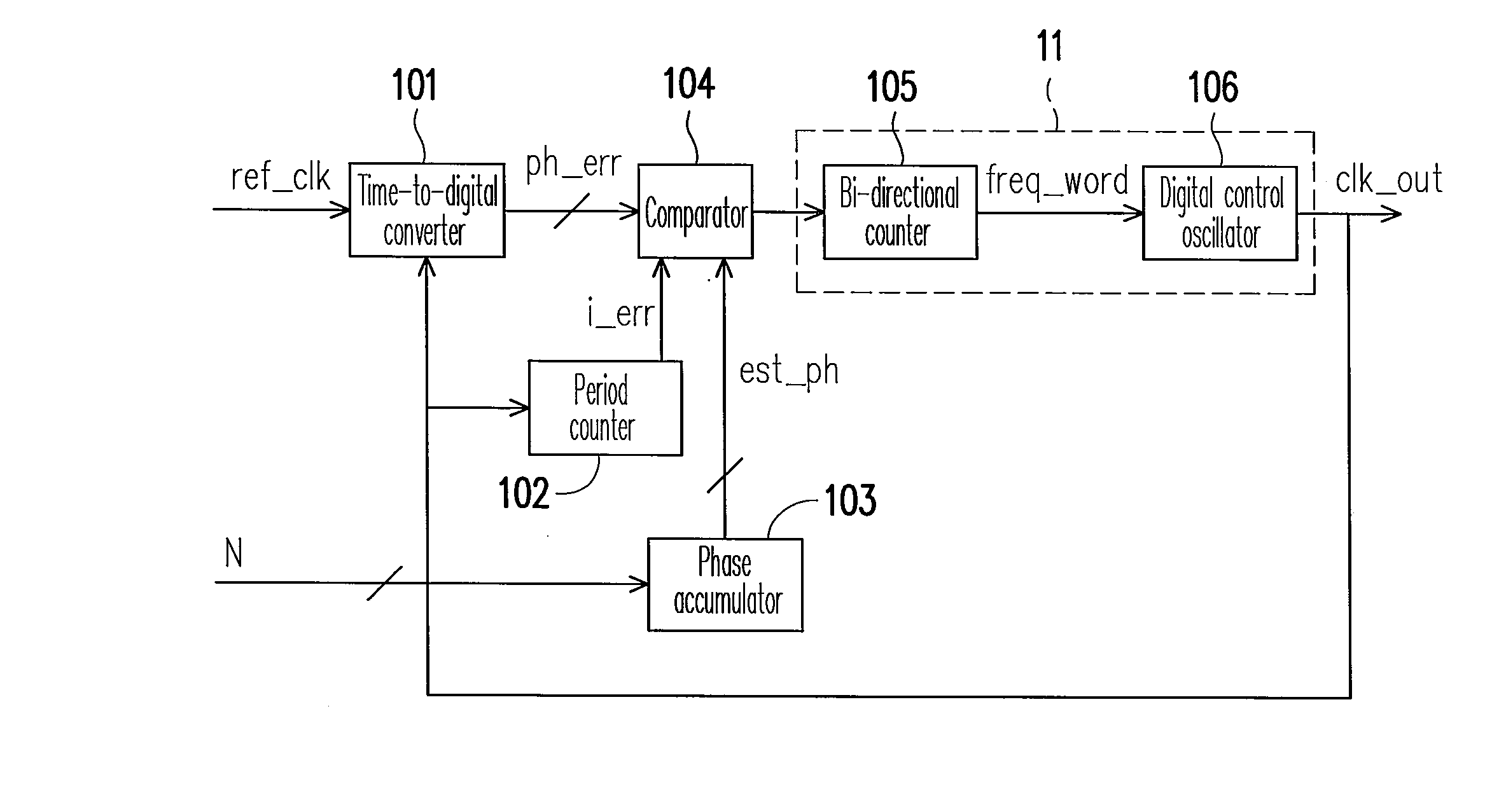

State-dependent read voltage threshold adaptation for nonvolatile memory

ActiveUS20190043588A1Increase the number of digitsQuick upgradeRead-only memoriesDigital storageState dependentOperating system

A controller adapts the read voltage thresholds of a memory unit in a non-volatile memory. In one embodiment, the controller determines, based on statistics for a memory unit of the non-volatile memory, an operating state of the memory unit from among a plurality of possible operating states and adapts at least one read voltage threshold for a memory cell in the memory unit based on the determined operating state.

Owner:IBM CORP

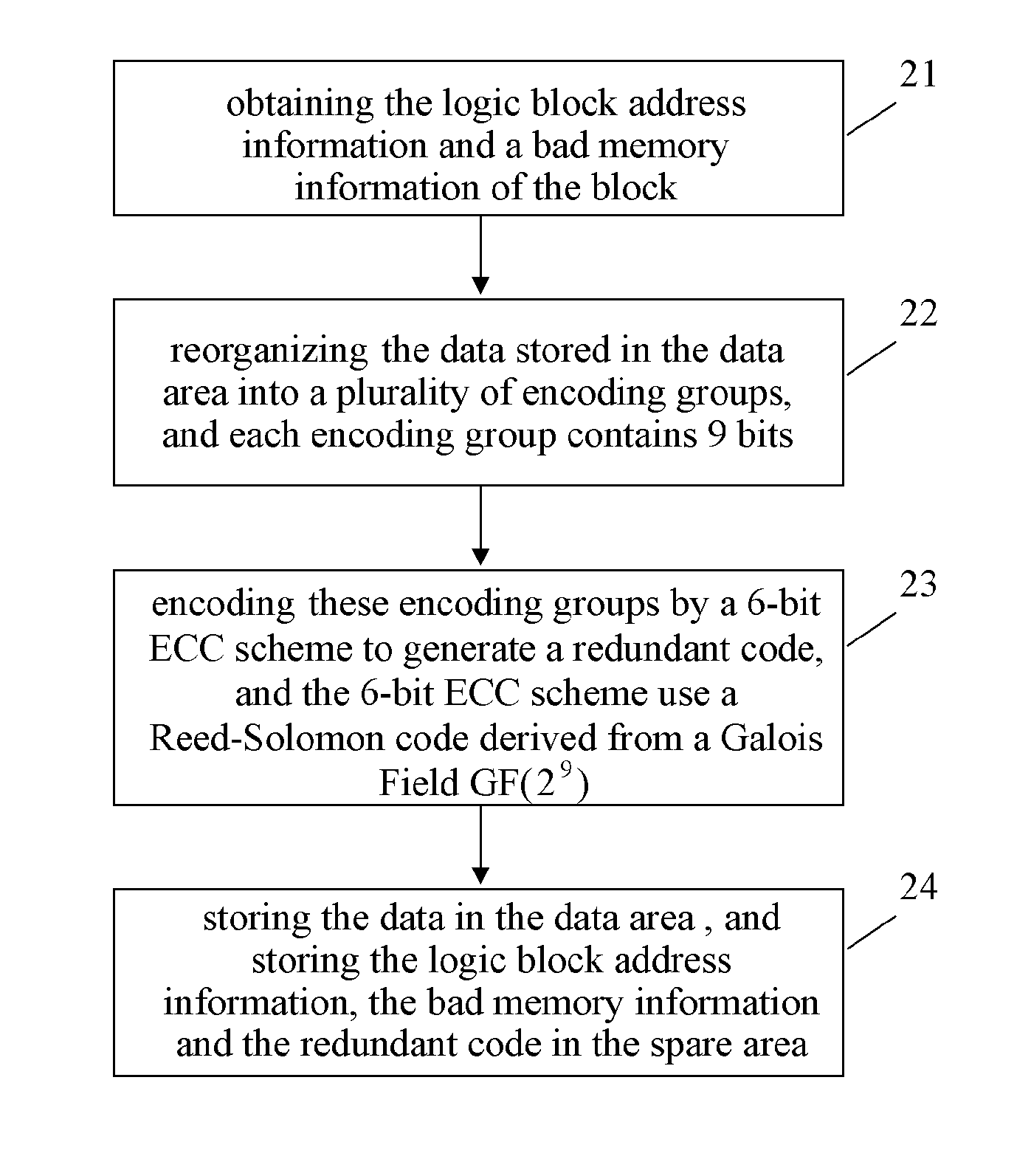

Data Writing Method For Flash Memory and Error Correction Encoding/Decoding Method Thereof

ActiveUS20080294965A1Good data protecting mechanismImprove data securityCode conversionError correction/detection using block codesByteDecoding methods

A data writing method for flash memory and an error correction encoding / decoding method thereof are disclosed. In an embodiment of the data writing method, a 6-bit ECC scheme using a Reed-Solomon code derived from a Galois Field GF (29) is used to encode a data for generating a redundant which requires smaller storing space. In an embodiment of the error correction encoding / decoding method, an erase checking value corresponding to the status where all the bytes of data area and parameter storing area are “0xff” is provided to improve the security of stored data.

Owner:REALTEK SEMICON CORP

Analog-to-digital converter

ActiveUS7982652B2Increase the number of digitsWithout complexityElectric signal transmission systemsAnalogue-digital convertersDigital down converterLeast significant bit

Owner:STMICROELECTRONICS SRL

Capacity controlled numerical frequency modulation circuit

InactiveCN101197531AIncrease the areaIncrease the number of digitsFrequency selective two-port networksPower conversion systemsCapacitanceFrequency spectrum

The invention relates to a capacity control digital frequency adjusting circuit which belongs to the frequency adjusting technology in the electronic technology field. The invention comprises a capacitance charge-discharge circuit and a variable capacitance circuit. In the variable capacitance circuit, the switching on-off of the switch tube is controlled by the output signal of the counter and thus the total capacitance value of the charge-discharge capacitance; therefore, the dither output of frequency can be achieved, the frequency spectrum of the former higher harmonic is extended to a new frequency range which lowers the frequency spectrum amplitude and thus the electromagnetic interference of the switch power supply is reduced. Compared with flow control digital frequency adjusting circuit, the invention can achieve the dither function of frequency much better and lower the peak value of the switch frequency higher harmonic frequency spectrum and thus inhibit electromagnetic interference, besides, the chip area is reduced greatly, the production costs are reduced efficiently and thus the invention can be applied widely in the switch power supply chip field.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

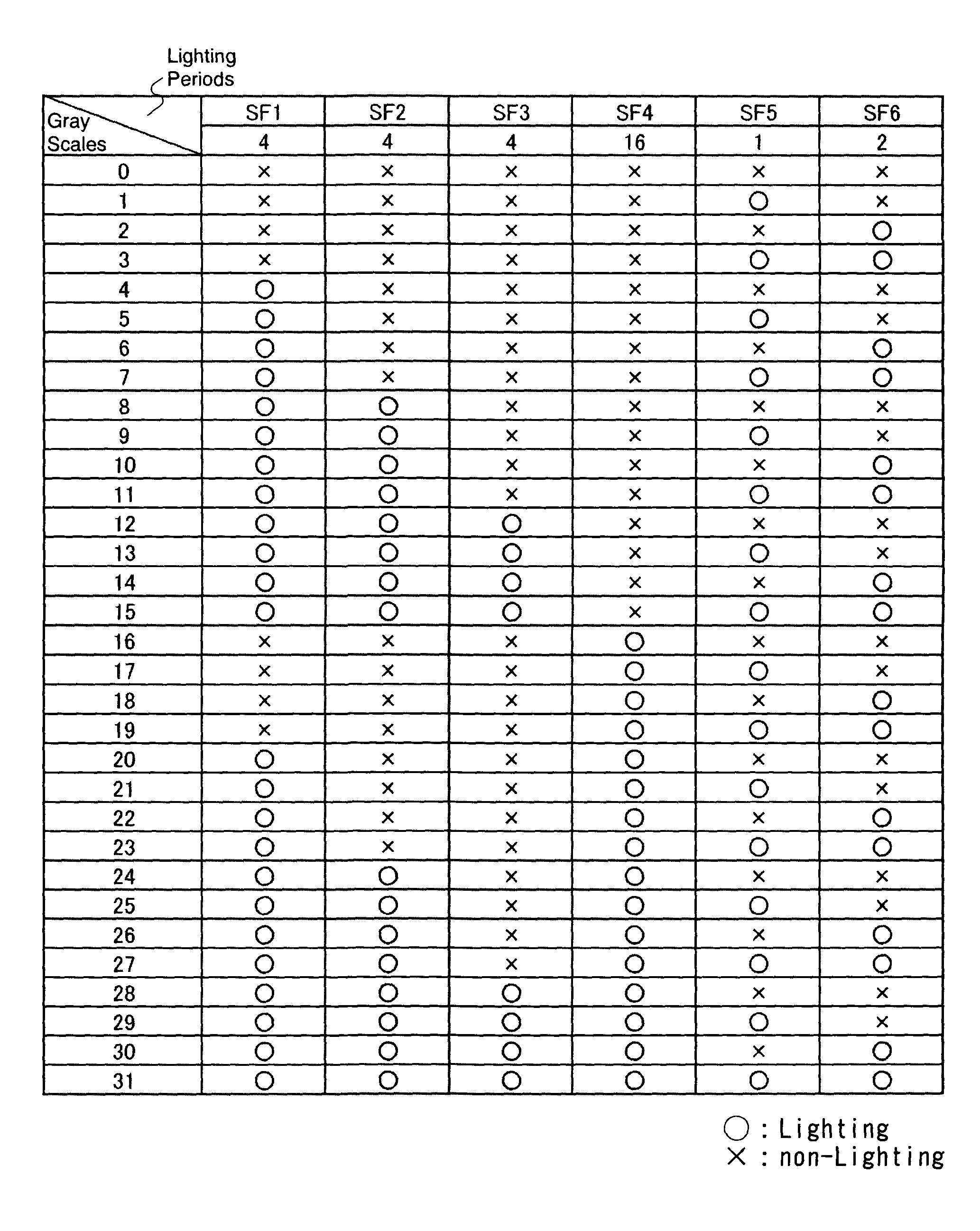

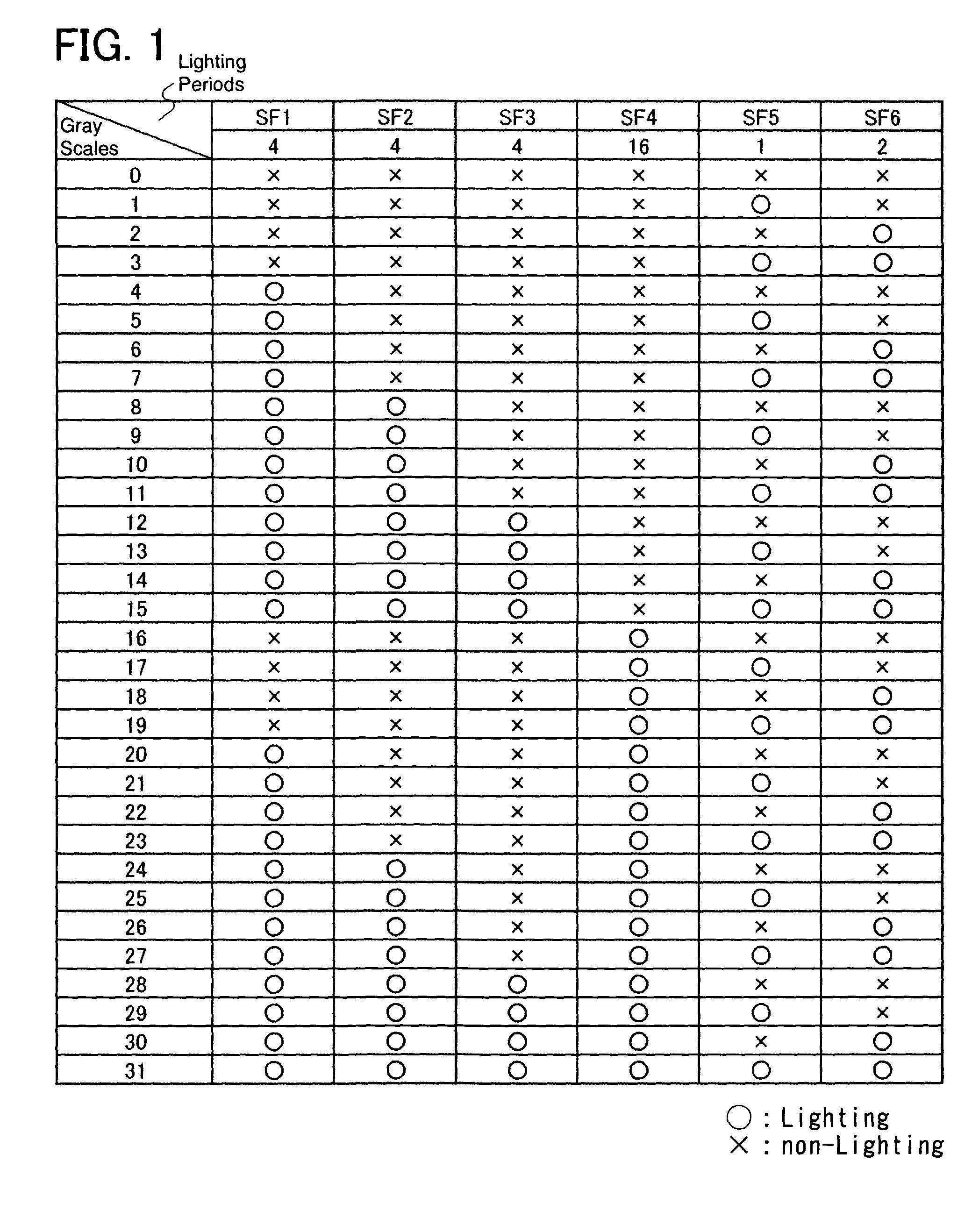

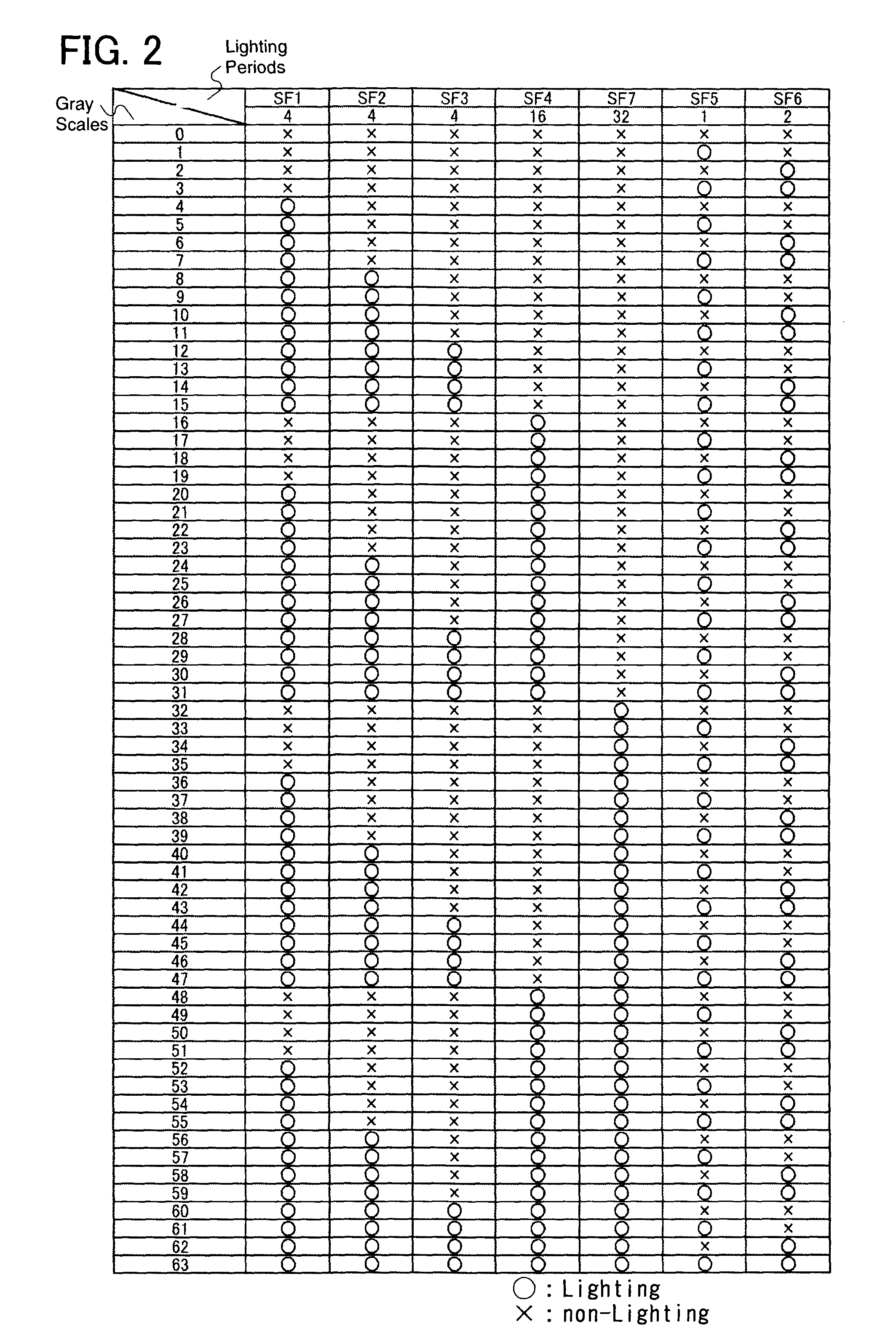

Driving method of display device

InactiveUS20070171241A1Efficiently displayedSmall weightElectrical apparatusElectroluminescent light sourcesDisplay deviceComputer science

It is an object to provide a driving method of a display device capable of reducing pseudo contours while increase in the number of sub-frames is suppressed as much as possible. In a driving method of a display device where one frame is divided into a plurality of sub-frames to display a gray scale, the plurality of sub-frames has a plurality of middle-order sub-frames each of which has a middle-degree weighting and is used for an overlapping time gray scale method, at least one high-order sub-frame which has a larger weighting than that of the middle-order sub-frame and is used for a binary code time gray scale method, and at least one low-order sub-frame which has a smaller weighting than that of the middle-order sub-frame and is used for a binary code time gray scale method.

Owner:SEMICON ENERGY LAB CO LTD

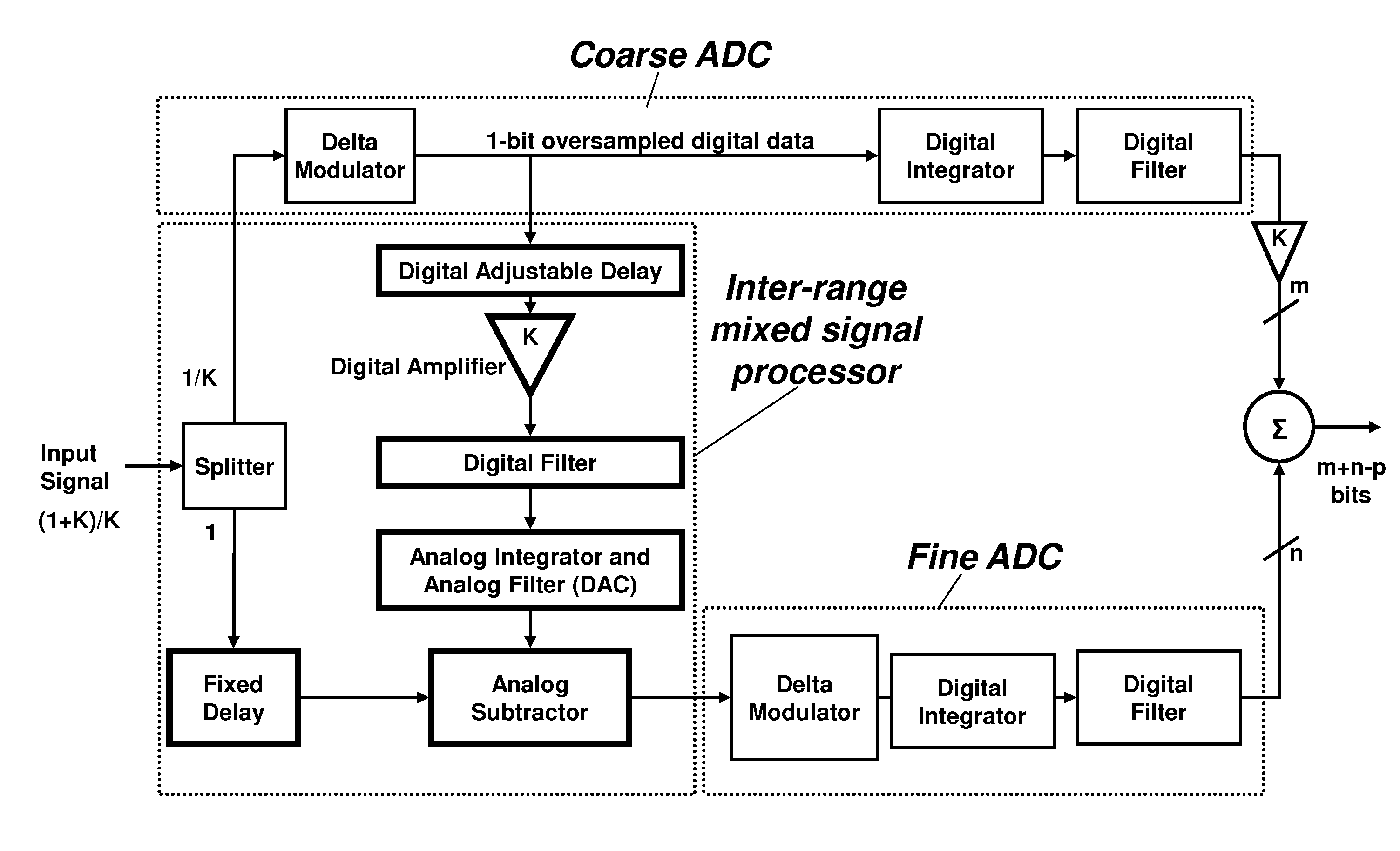

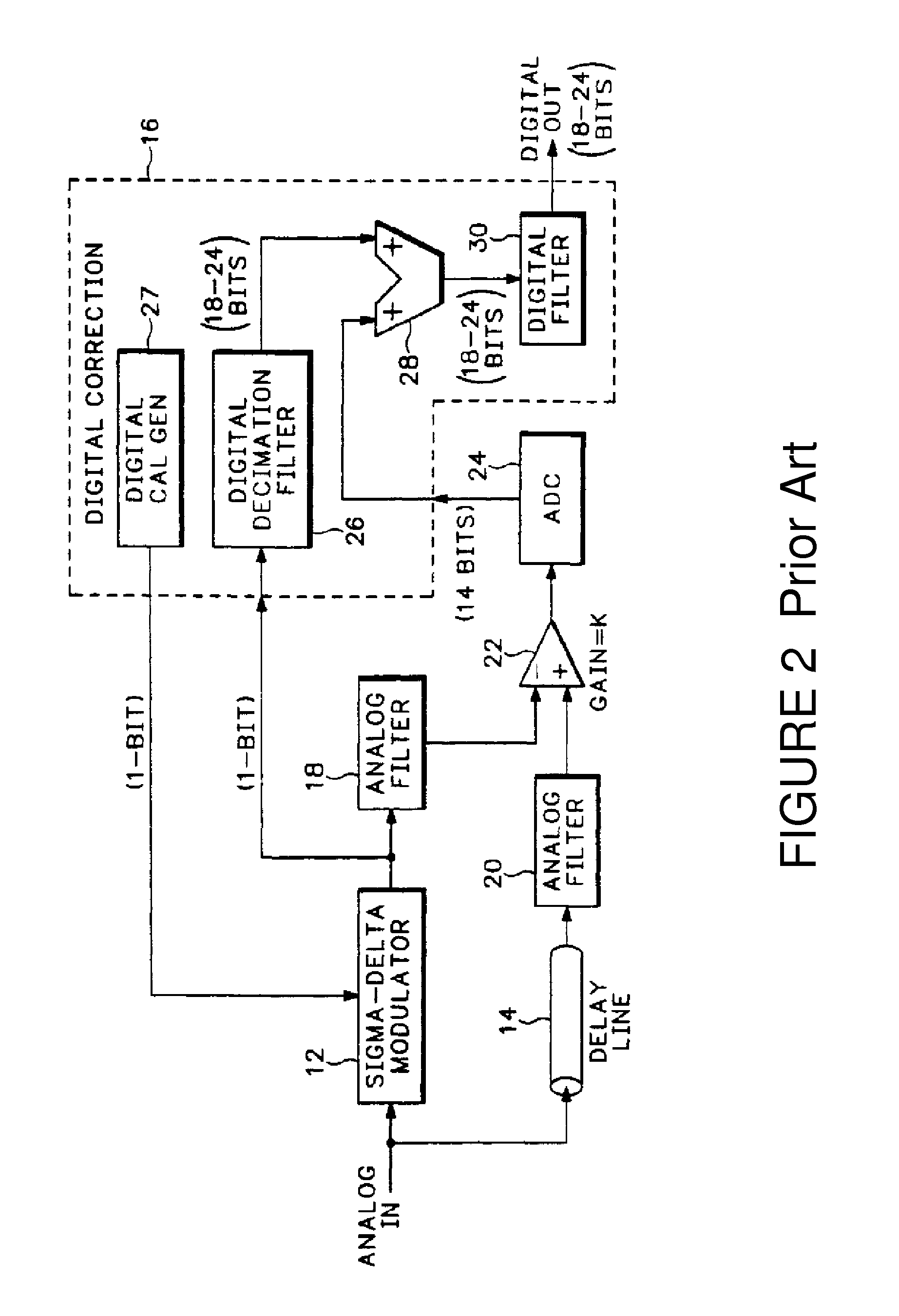

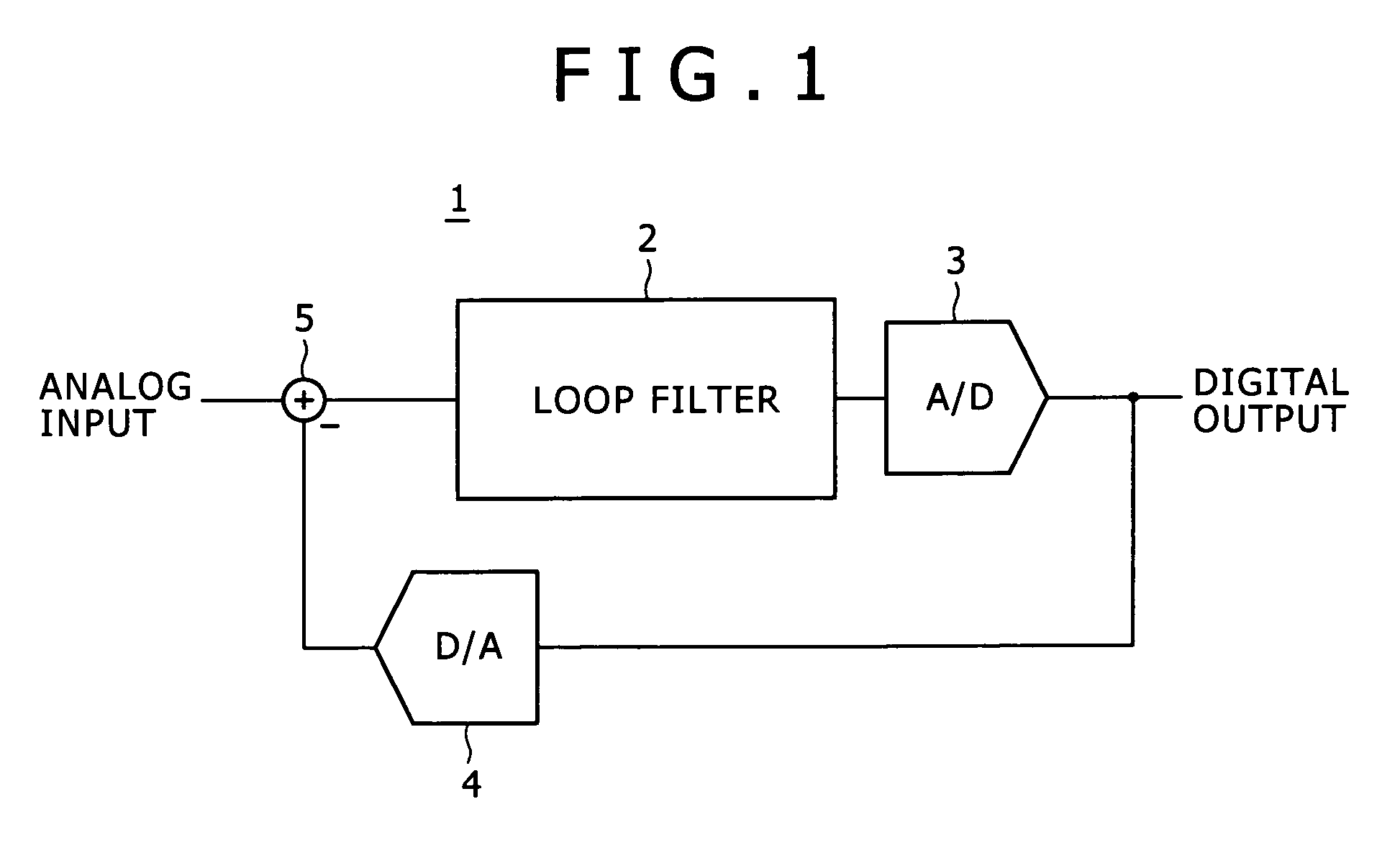

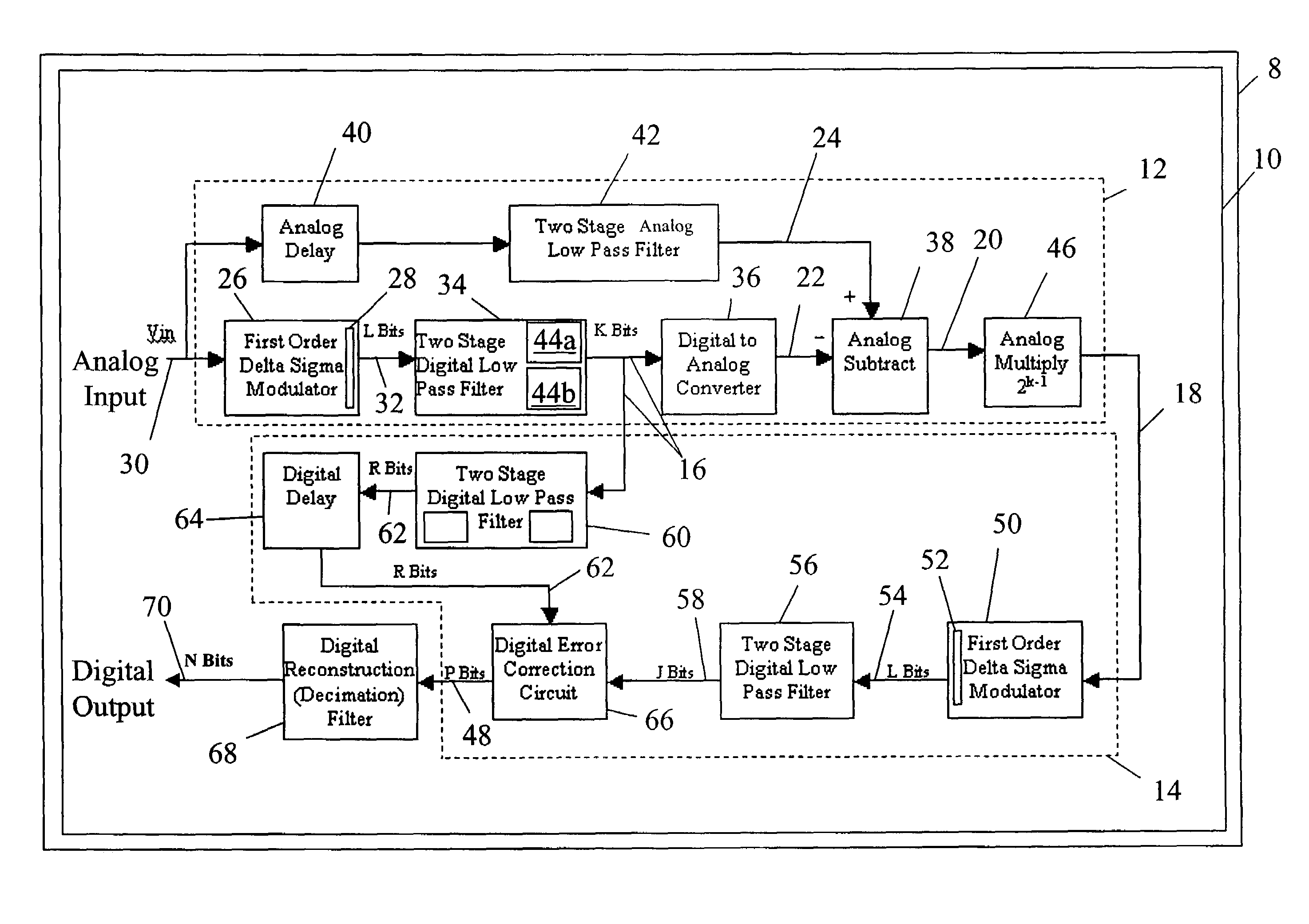

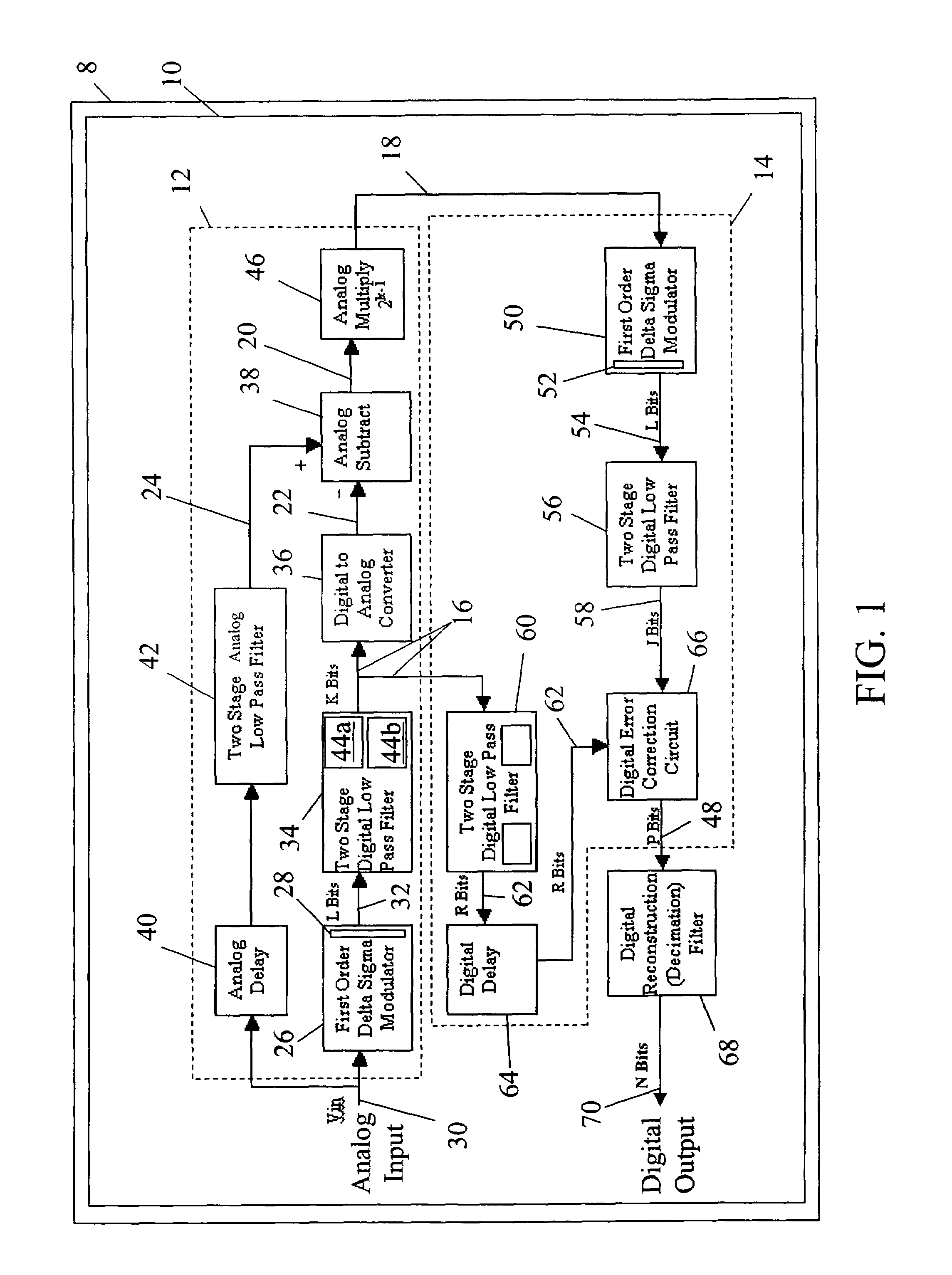

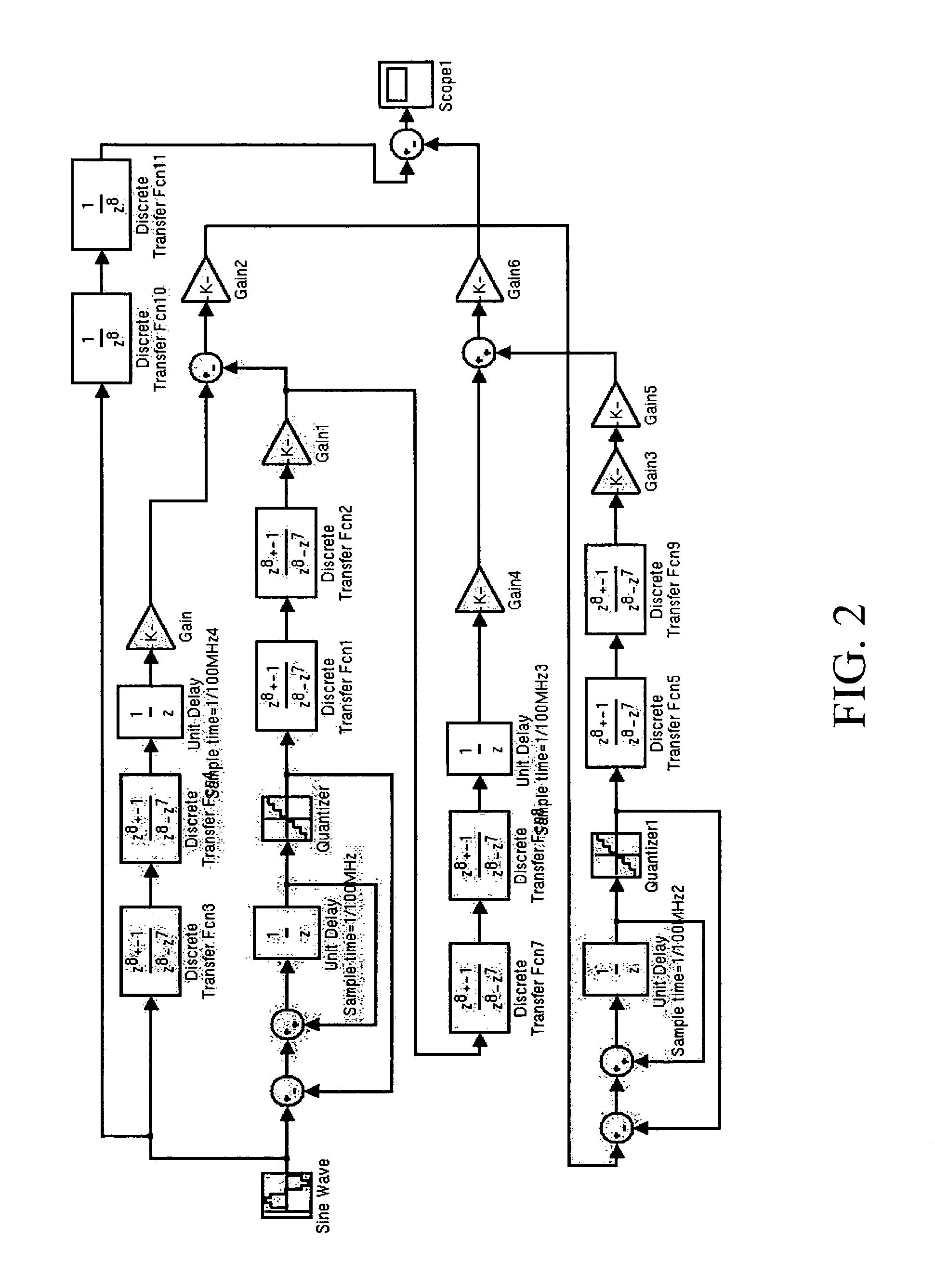

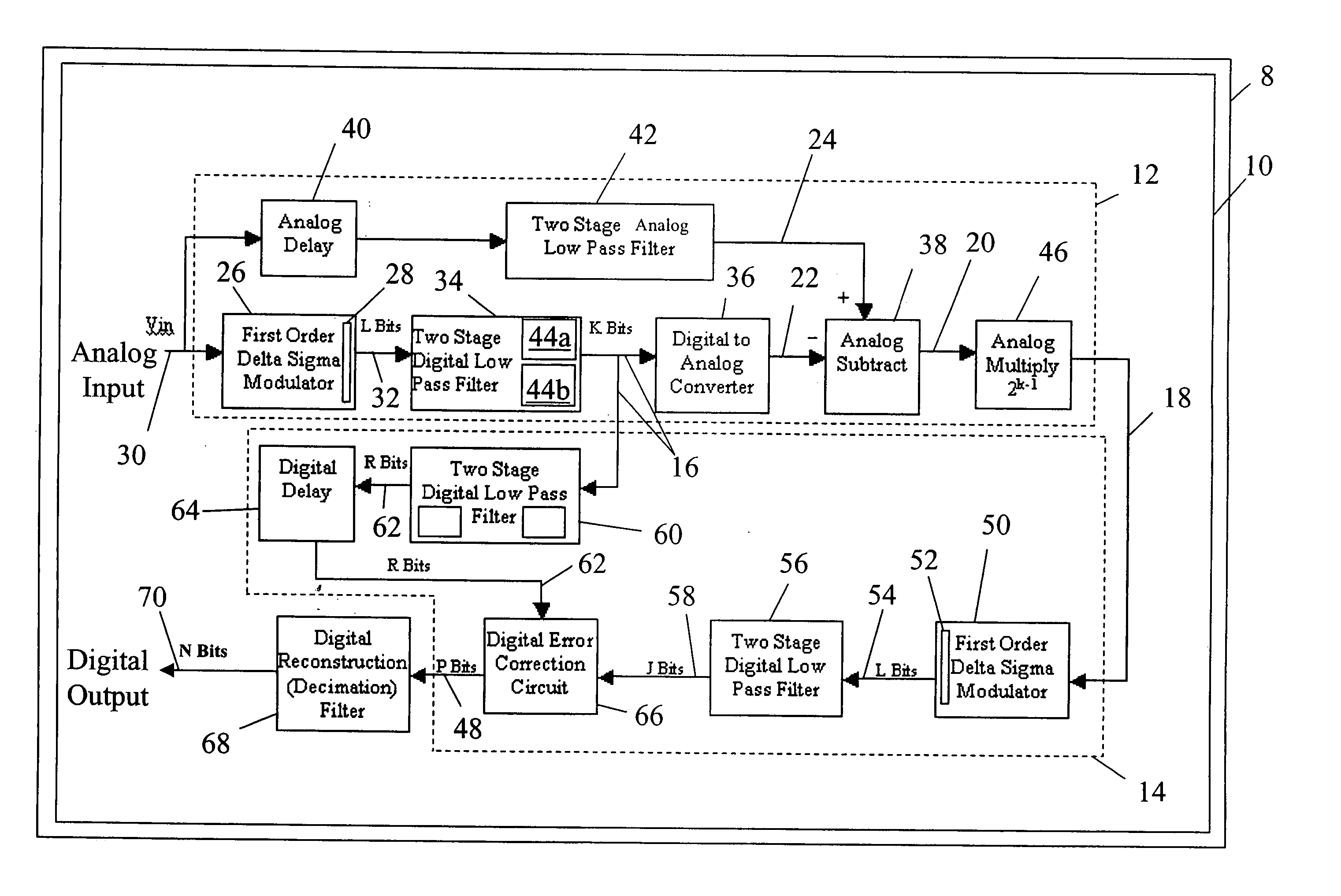

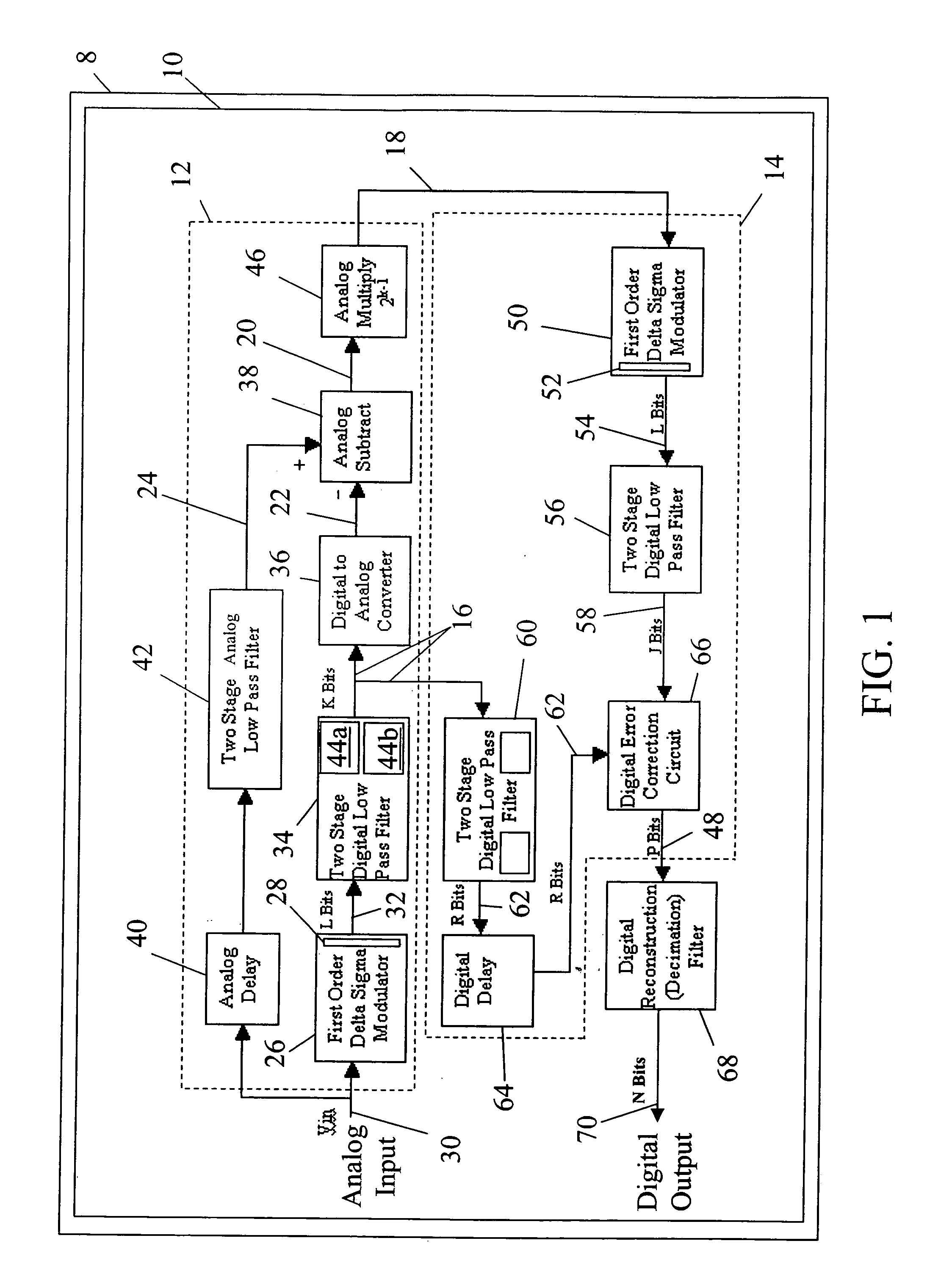

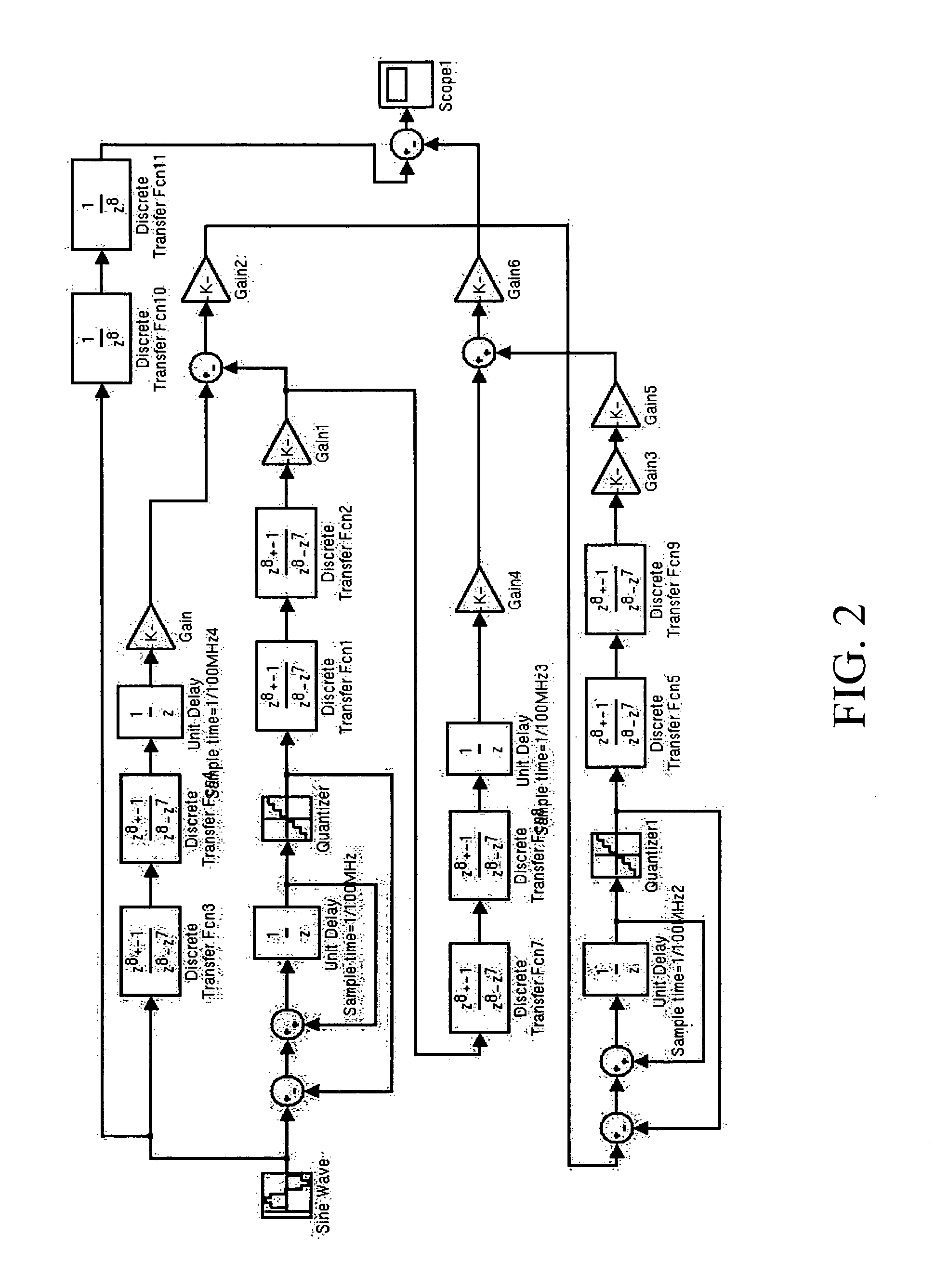

Pipelined delta sigma modulator analog to digital converter

InactiveUS7034730B2Suitable performanceHigh resolution performanceElectric signal transmission systemsDelta modulationDigital down converterEngineering

A pipelined delta-sigma modulator (PDSM) analog to digital converter (ADC) architecture is disclosed where each stage of the pipelined ADC includes a delta sigma modulator with a digital low pass filter and a corresponding analog low pass filter that precisely matches the digital low pass filter. An error signal is generated at each stage based on the difference of the low pass filtered analog input and the low pass filtered digital output of the delta sigma modulator (after converting to an analog signal). The digital outputs of each stage are passed through the appropriate low pass filter stages so all digital signals have been subjected to the same filtering prior to combining in a digital error correction circuit. The present invention also uses a compensation filter to correct any errors in the pass band caused by the low pass filtering and to help reject unwanted noise outside the pass band.

Owner:WRIGHT STATE UNIVERSITY

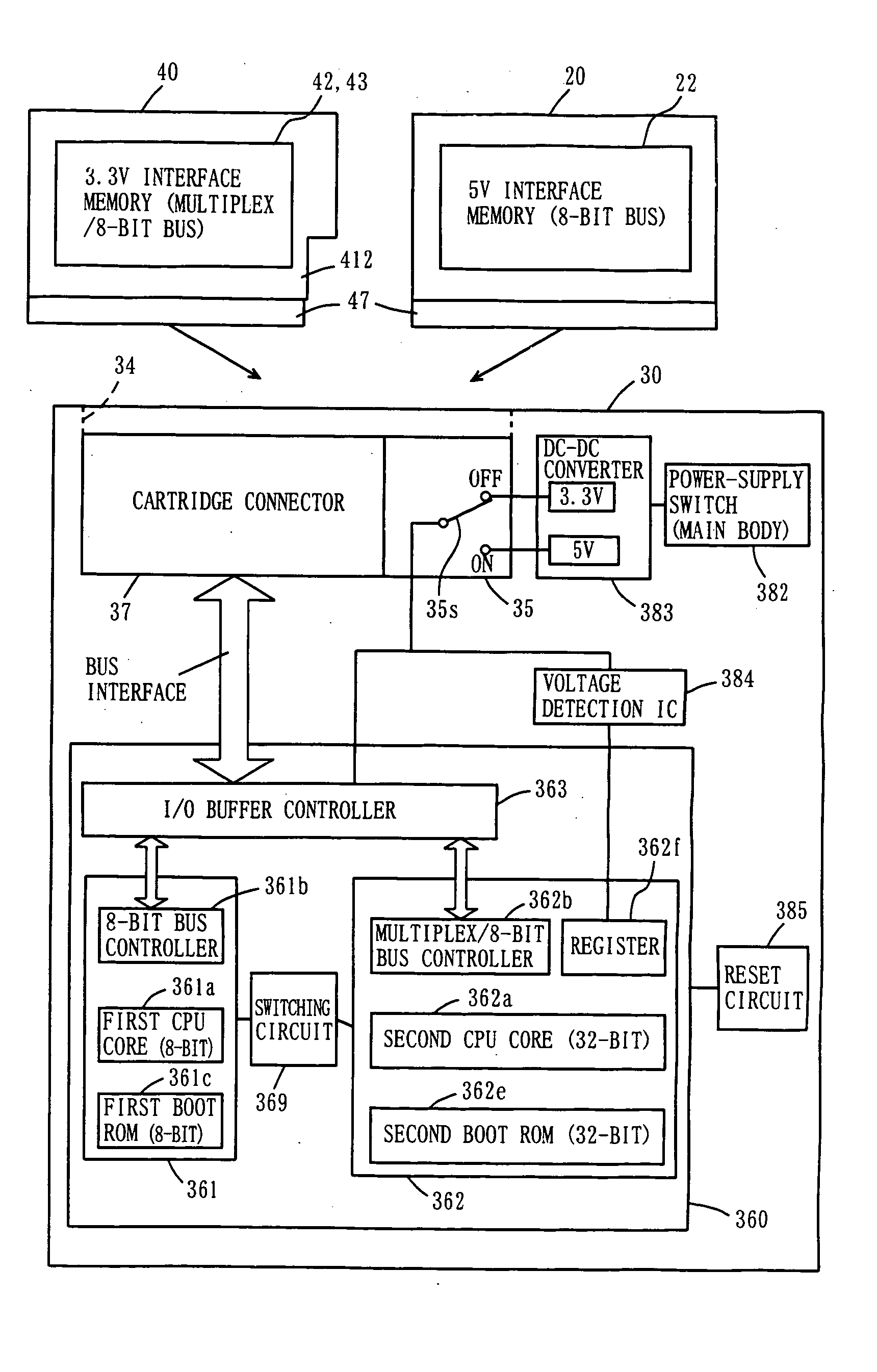

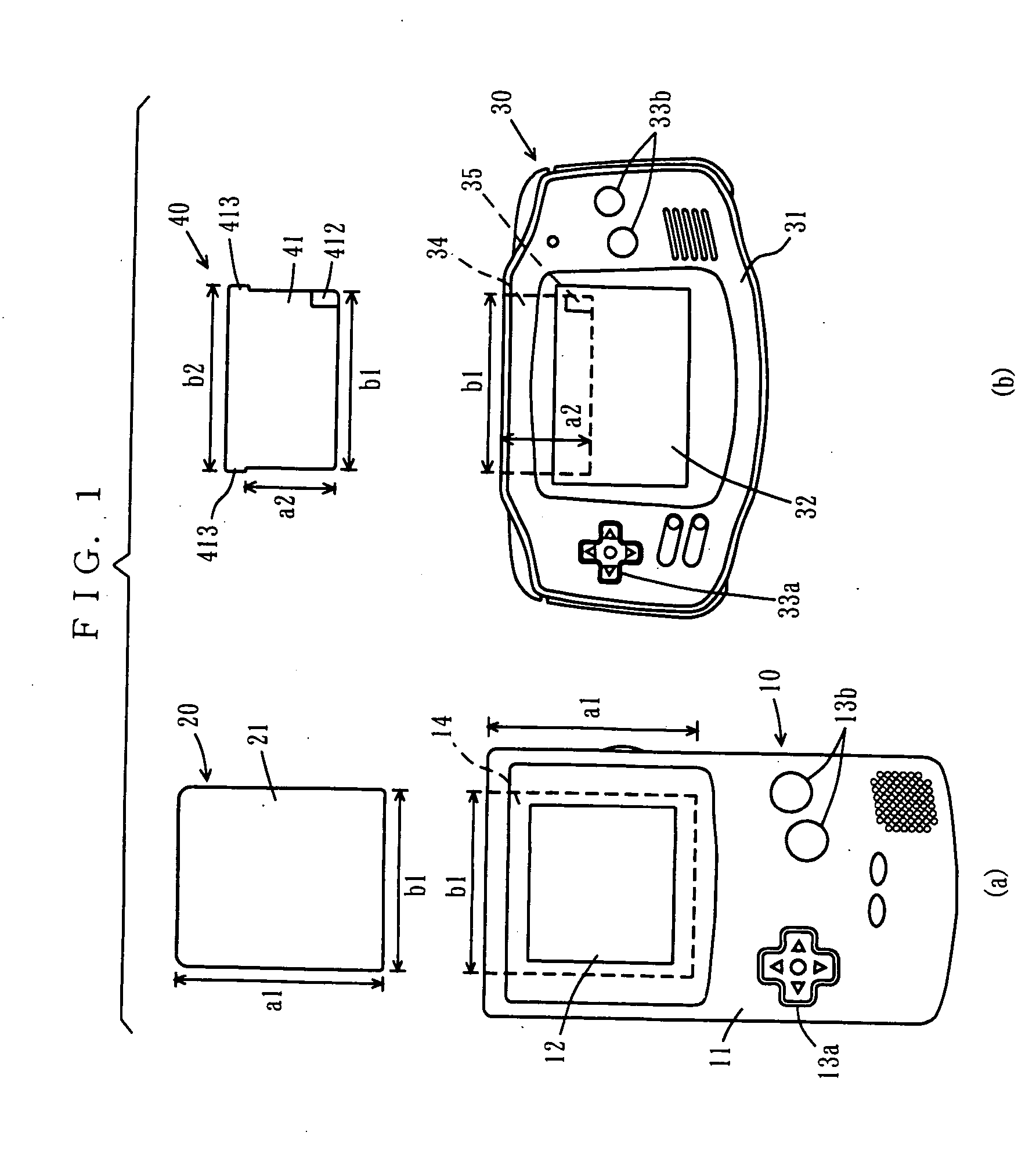

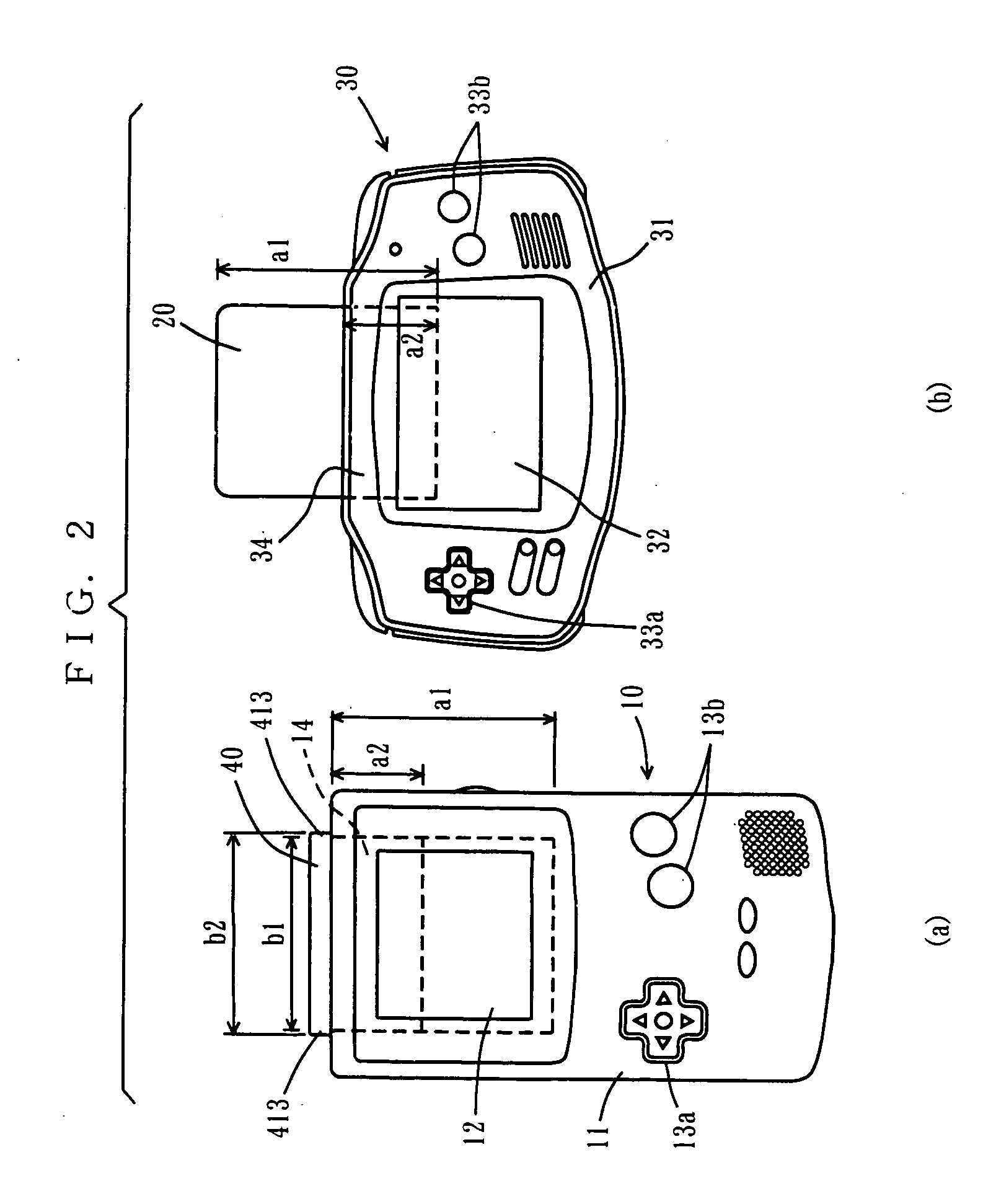

Information processing device and peripheral devices used therewith

InactiveUS20040268042A1Increase the number of digitsMemory loss protectionUnauthorized memory use protectionInformation processingComputer hardware

An information processing device such as a game machine is selectively connectable to different peripheral devices such as memory devices. The peripheral devices may be provided with characteristics for distinguishing one from another. The information processing device carries out operations based on the peripheral device connected thereto The information processing device may also access memories which store data having different data widths.

Owner:NINTENDO CO LTD

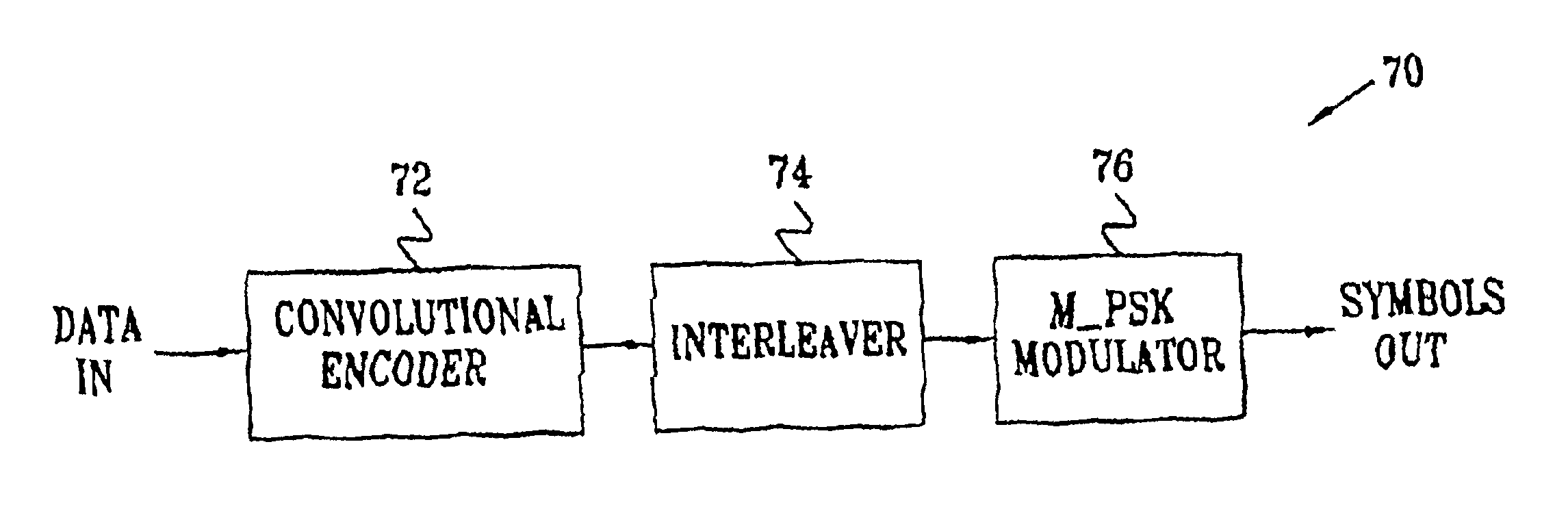

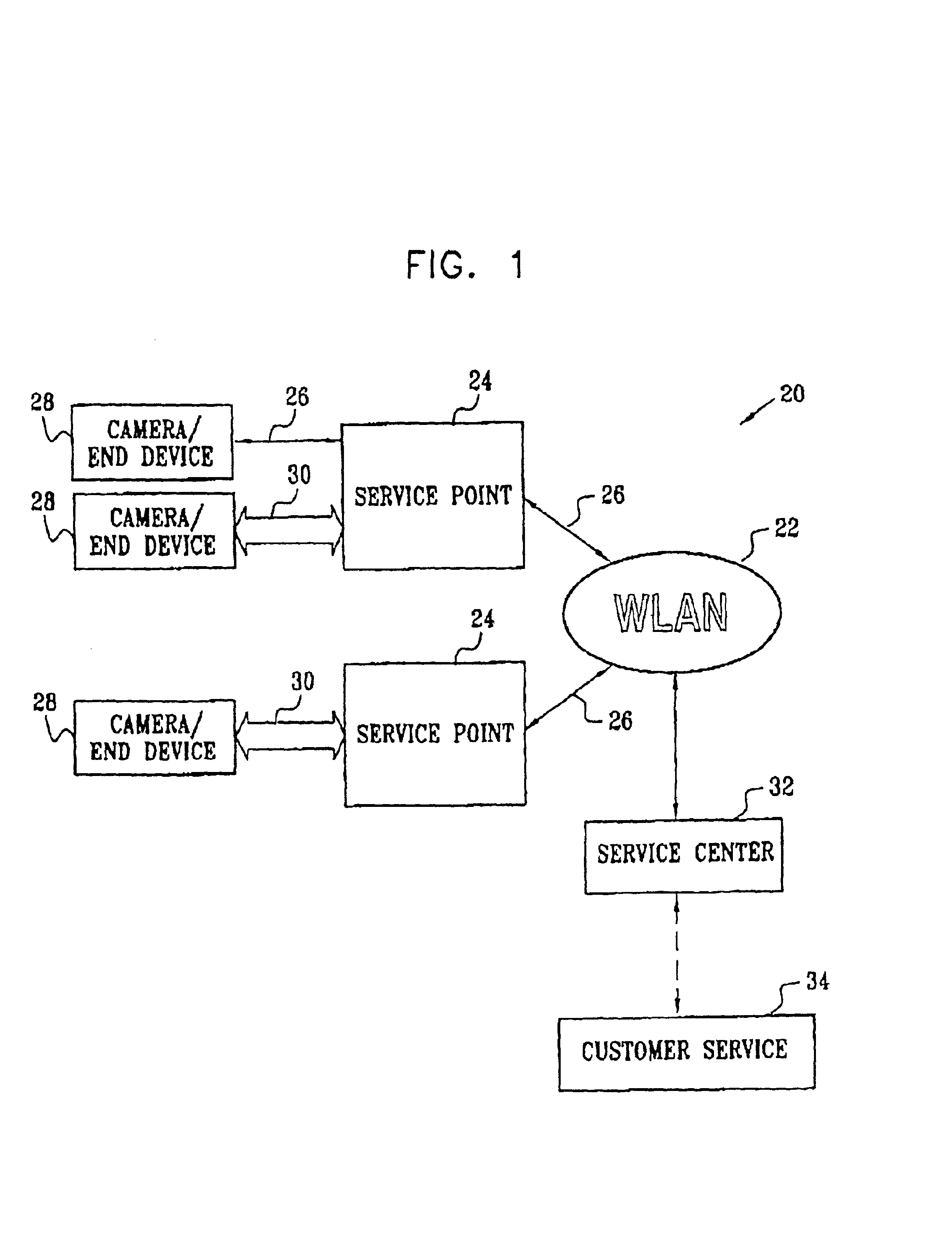

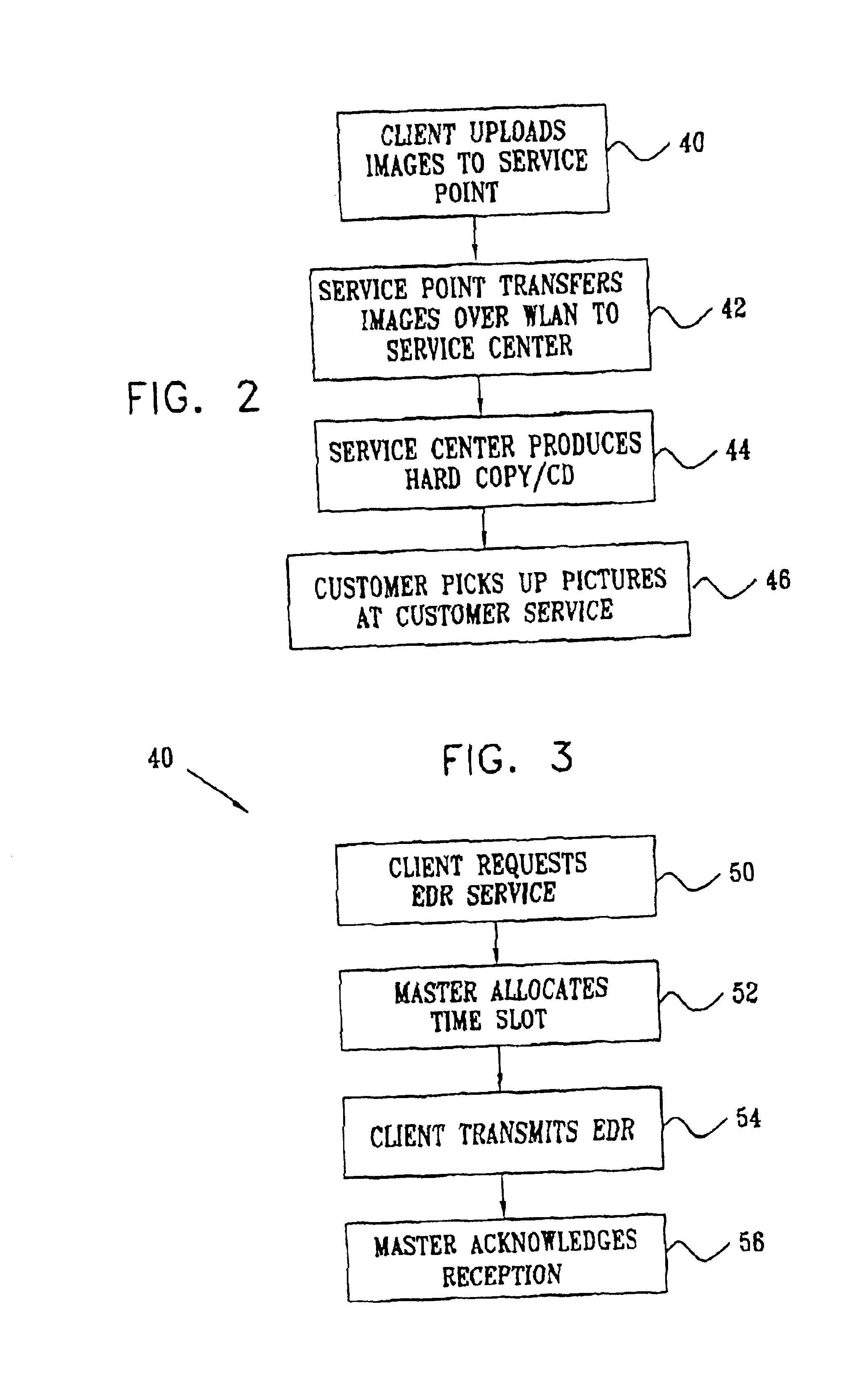

Wireless network with enhanced data rate

InactiveUS6928123B2High data rateReduce impactNetwork traffic/resource managementCode conversionDigital dataTheoretical computer science

Owner:INTEL CORP

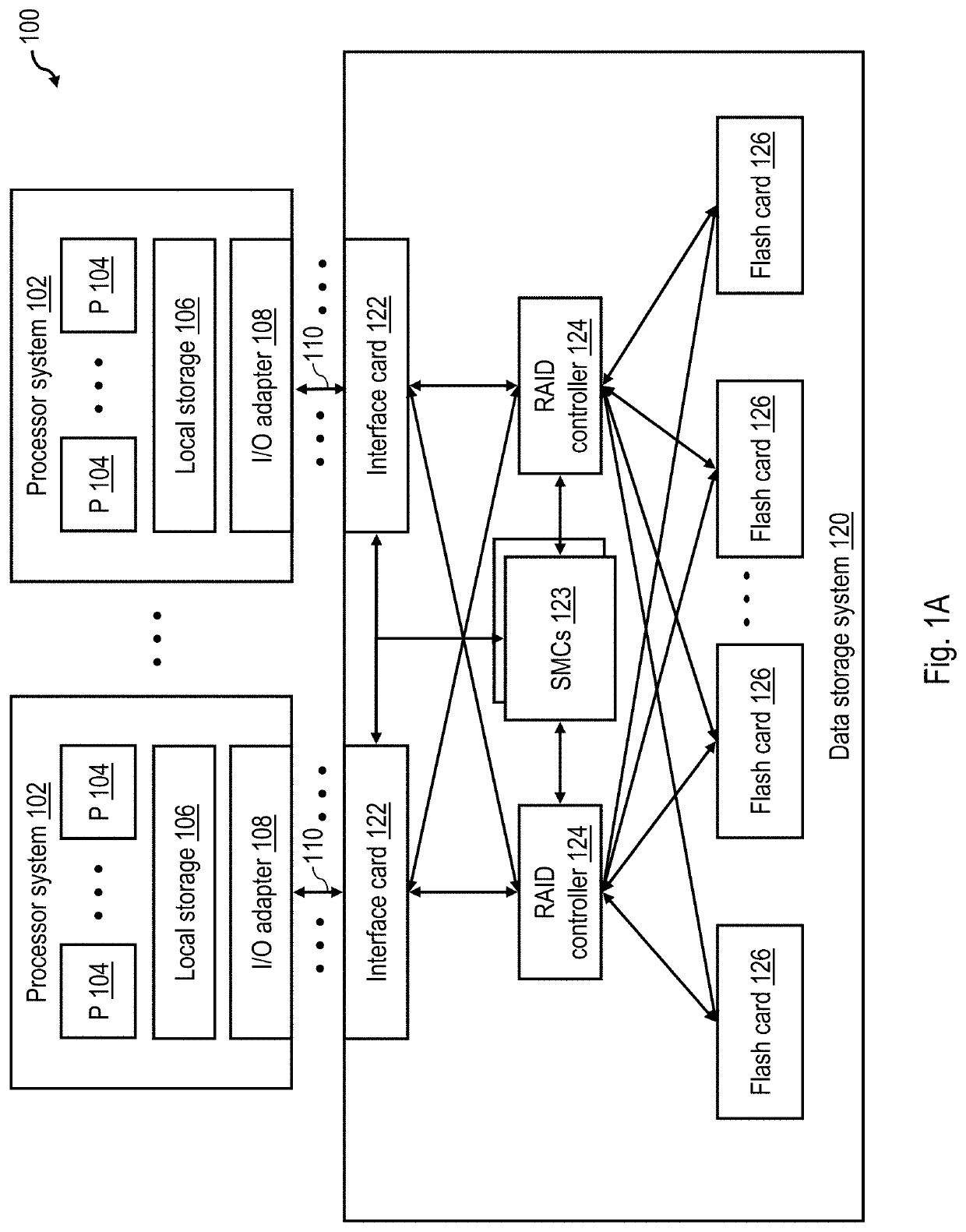

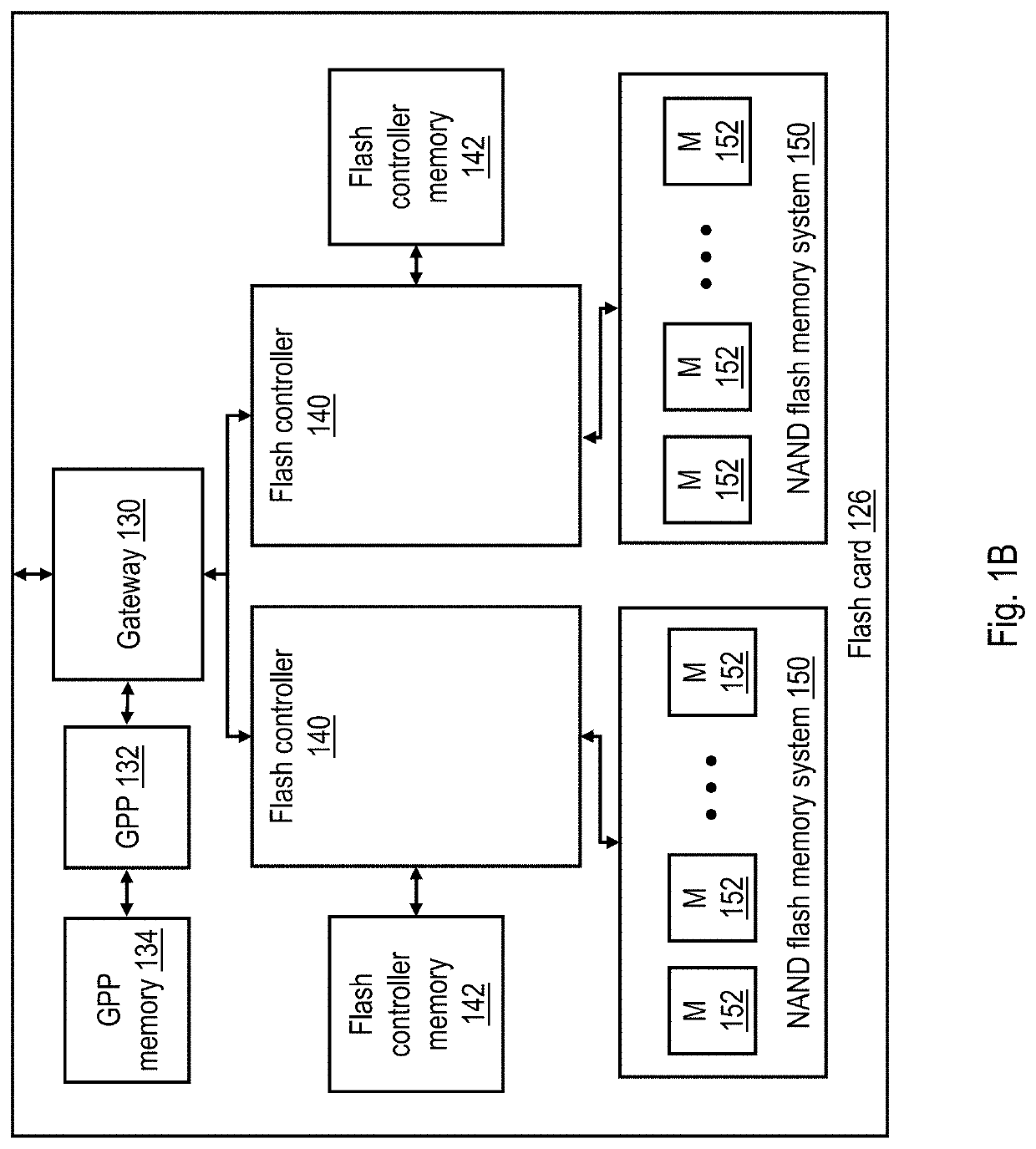

Garbage collection in non-volatile memory that fully programs dependent layers in a target block

ActiveUS20200257621A1Improve bit error rateDecrease over-provisioningMemory architecture accessing/allocationInput/output to record carriersComputer architectureInvalid Data

A non-volatile memory includes a plurality of blocks of physical memory, including a target block and at least one source block containing at least some valid data and some invalid data. Responsive to determining to perform garbage collection for the non-volatile memory, the controller transfers valid data from the at least one source block to the target block. The controller ends garbage collection on the at least one source block with at least some valid data present in the at least one source block and all interfaces of the target block closed at the boundary of independent layers. In at least some embodiments, the target block may be configured to store more bits per cell than the at least one source block.

Owner:IBM CORP

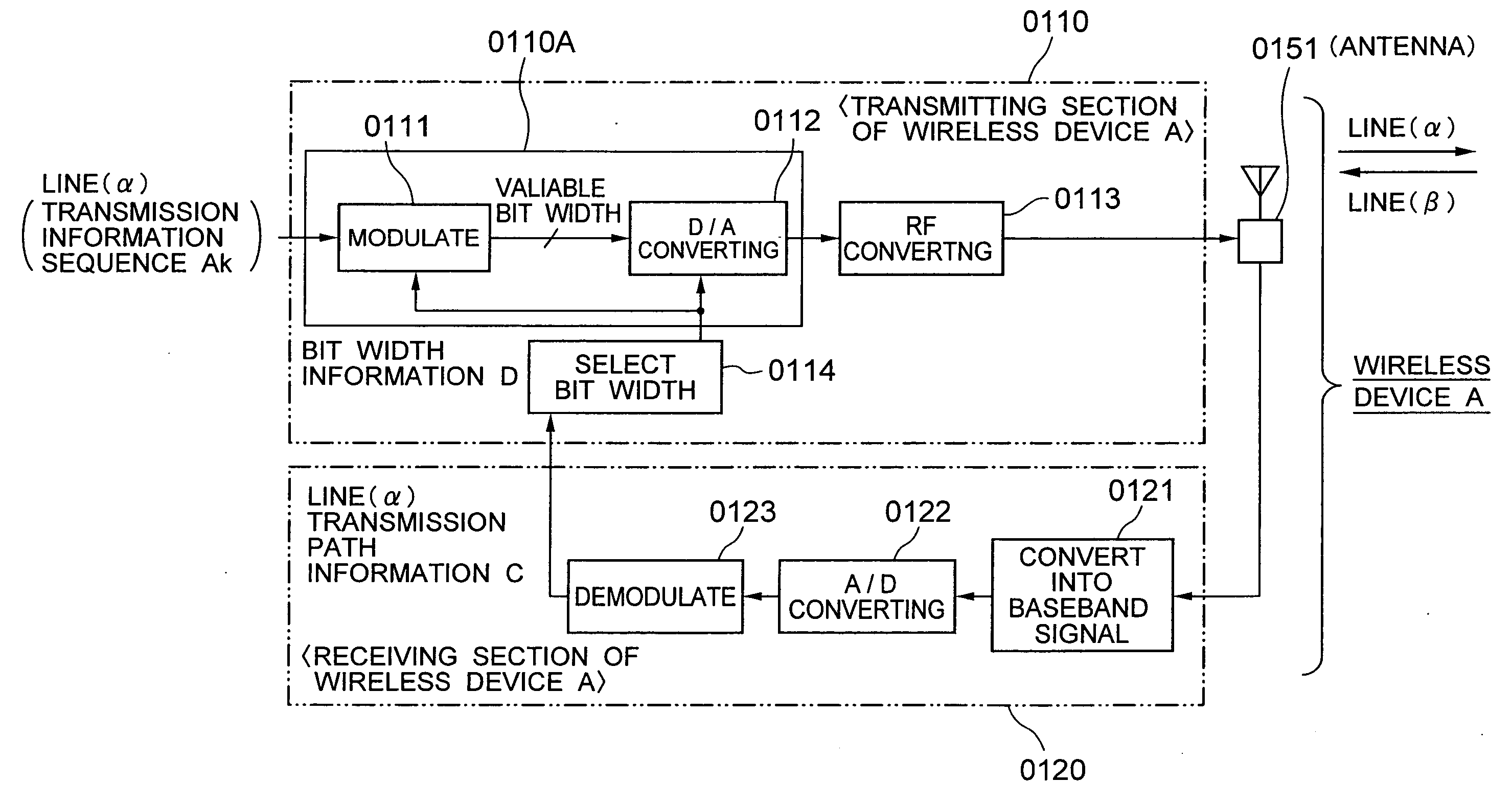

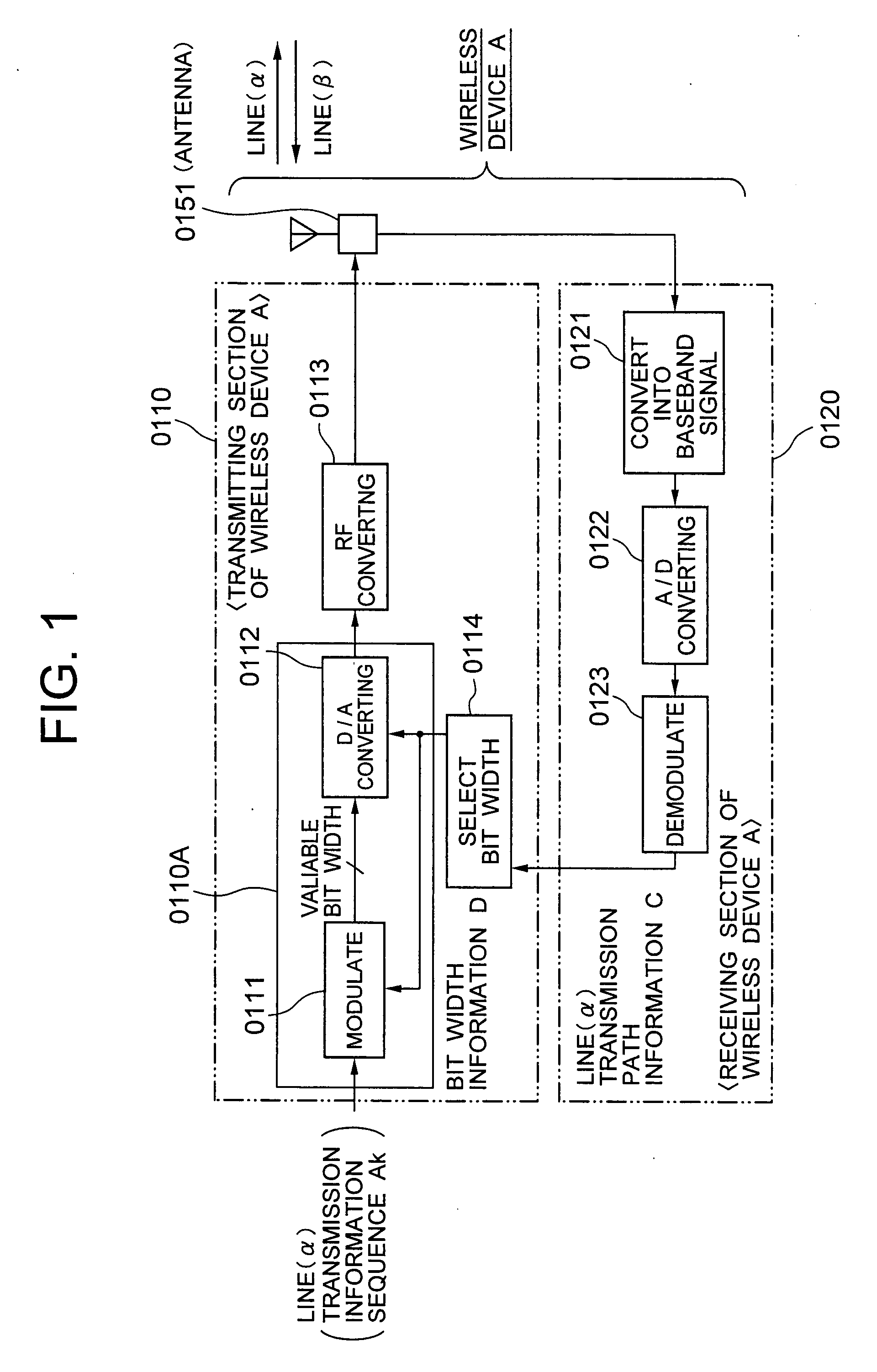

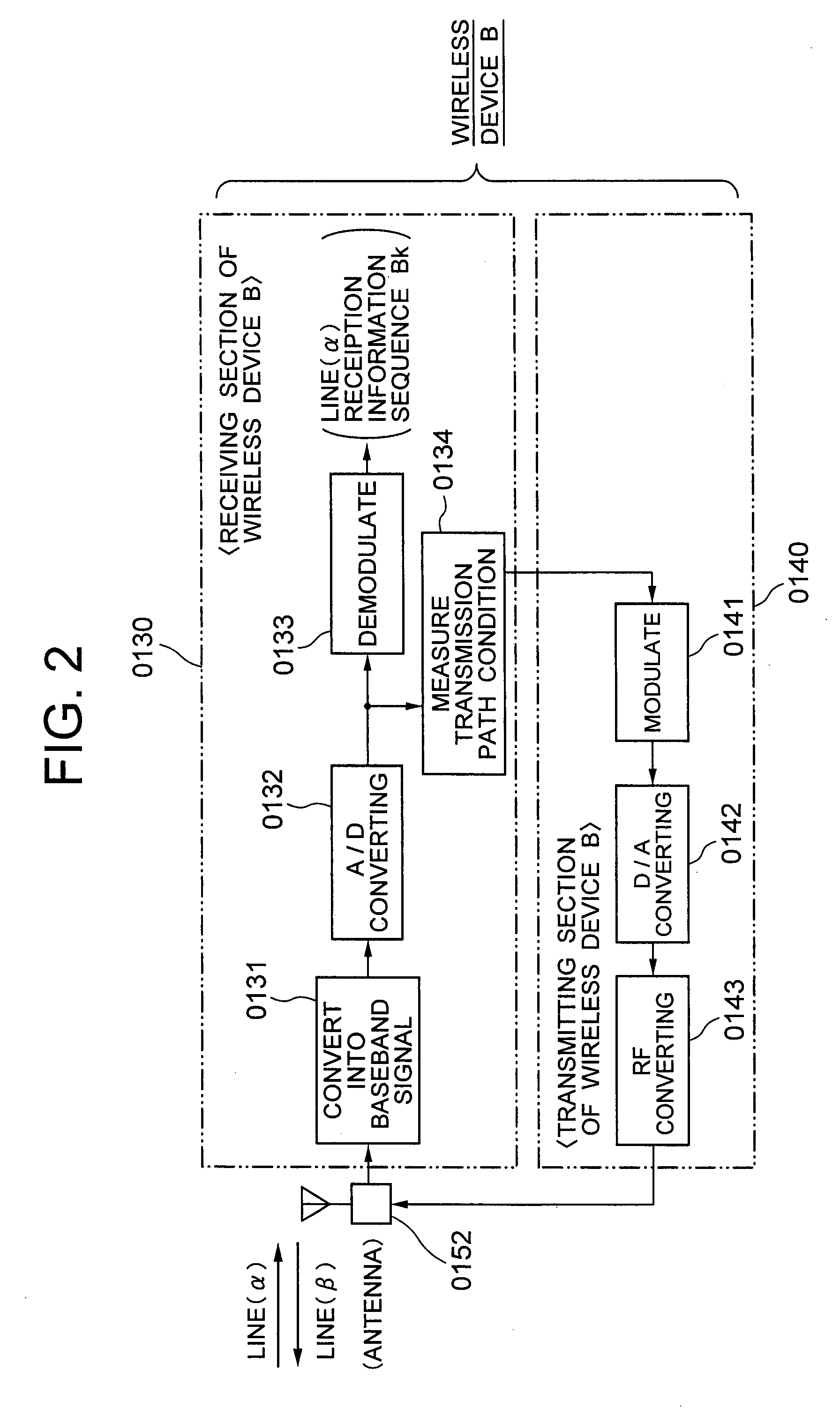

Wireless communication system, wireless communication method, and signal processing program therefor

InactiveUS20070218863A1Increase the number of digitsAddressing slow performanceEnergy efficient ICTPower managementDigital signal processingCommunications system

To achieve a wireless communication apparatus capable of lowering power consumption for a digital signal processing of a transmitter in response to a transmission path condition.A wireless communication system performs communication by digital transmission or analog transmission of a signal processed by a digital signal processing unit in a transmitting section on a transmission side toward a reception side through a line, wherein a transmission path condition of the line is measured on the reception side, the transmission path condition is transmitted to the transmission side using a reverse line with respect to the above described line, and a bit width for signal processing of digital signal processing units such as a modulating unit and a digital / analog converting unit is varied by a bit width selecting unit in response to the transmission path condition of the line notified by the reverse line on the transmission side.

Owner:NEC CORP

Pipelined delta sigma modulator analog to digital converter

InactiveUS20050083220A1High resolutionReduces accuracy requirementElectric signal transmission systemsDelta modulationGreek letter sigmaEngineering

A pipelined delta-sigma modulator (PDSM) analog to digital converter (ADC) architecture is disclosed where each stage of the pipelined ADC includes a delta sigma modulator with a digital low pass filter and a corresponding analog low pass filter that precisely matches the digital low pass filter. An error signal is generated at each stage based on the difference of the low pass filtered analog input and the low pass filtered digital output of the delta sigma modulator (after converting to an analog signal). The digital outputs of each stage are passed through the appropriate low pass filter stages so all digital signals have been subjected to the same filtering prior to combining in a digital error correction circuit. The present invention also uses a compensation filter to correct any errors in the pass band caused by the low pass filtering and to help reject unwanted noise outside the pass band.

Owner:WRIGHT STATE UNIVERSITY

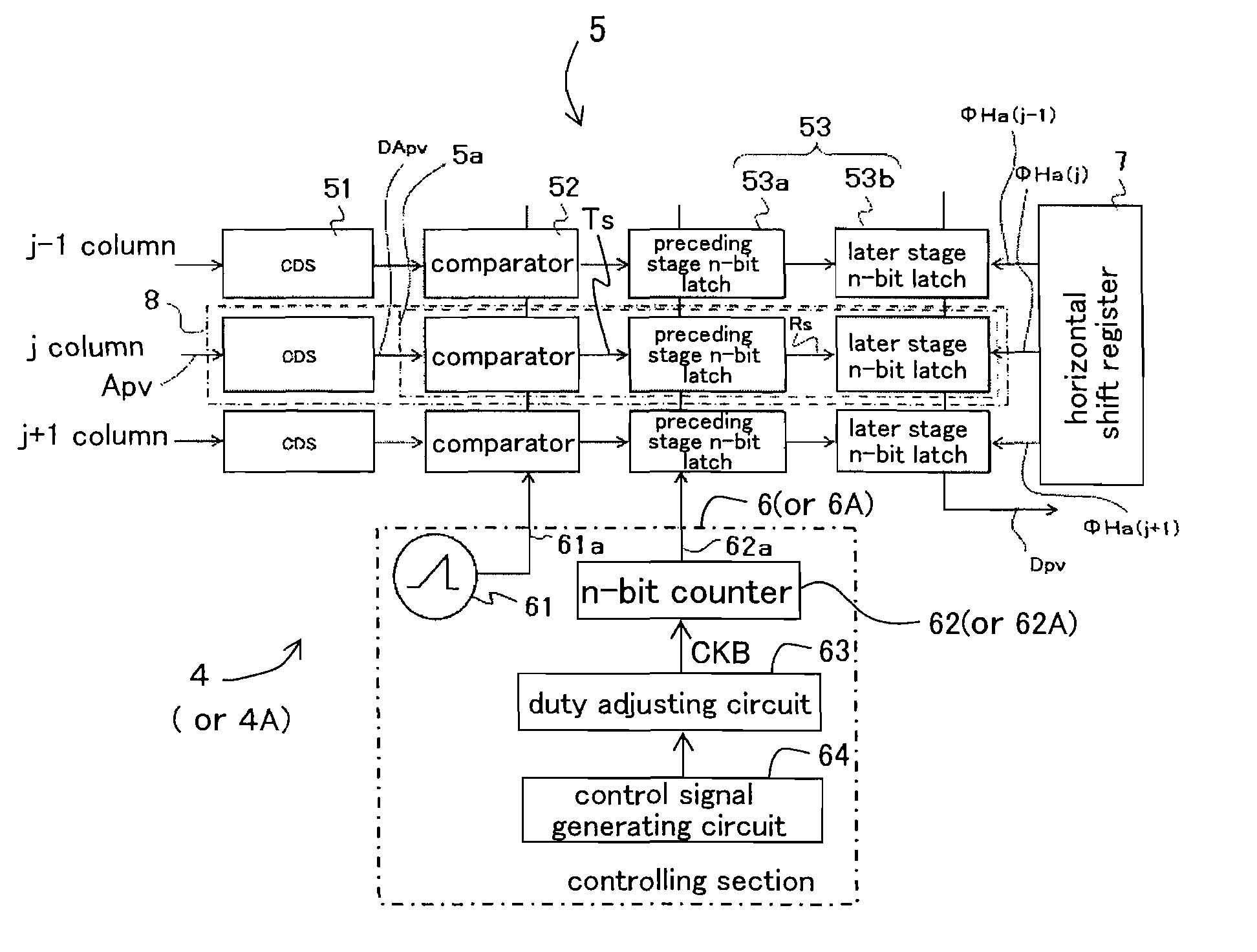

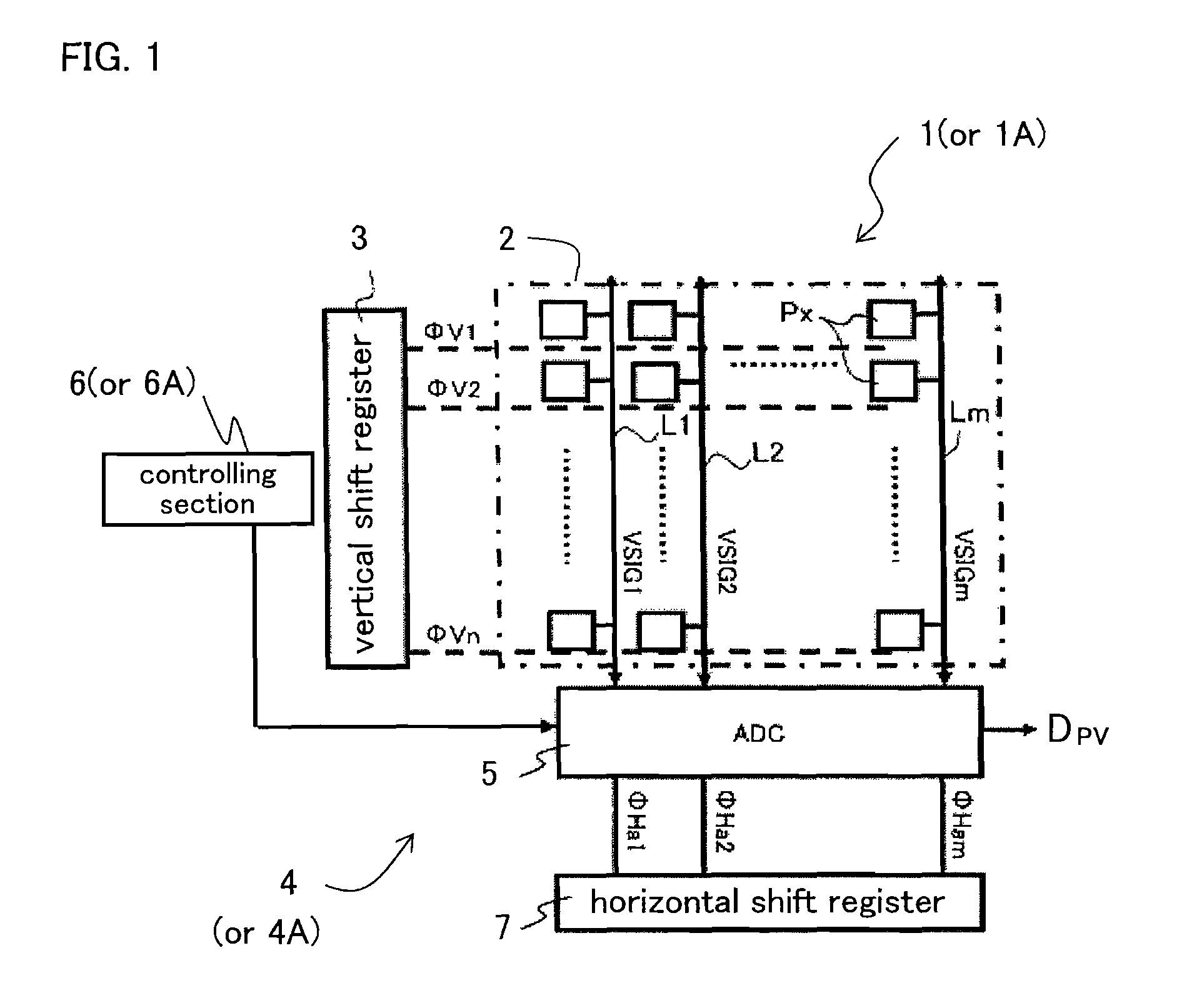

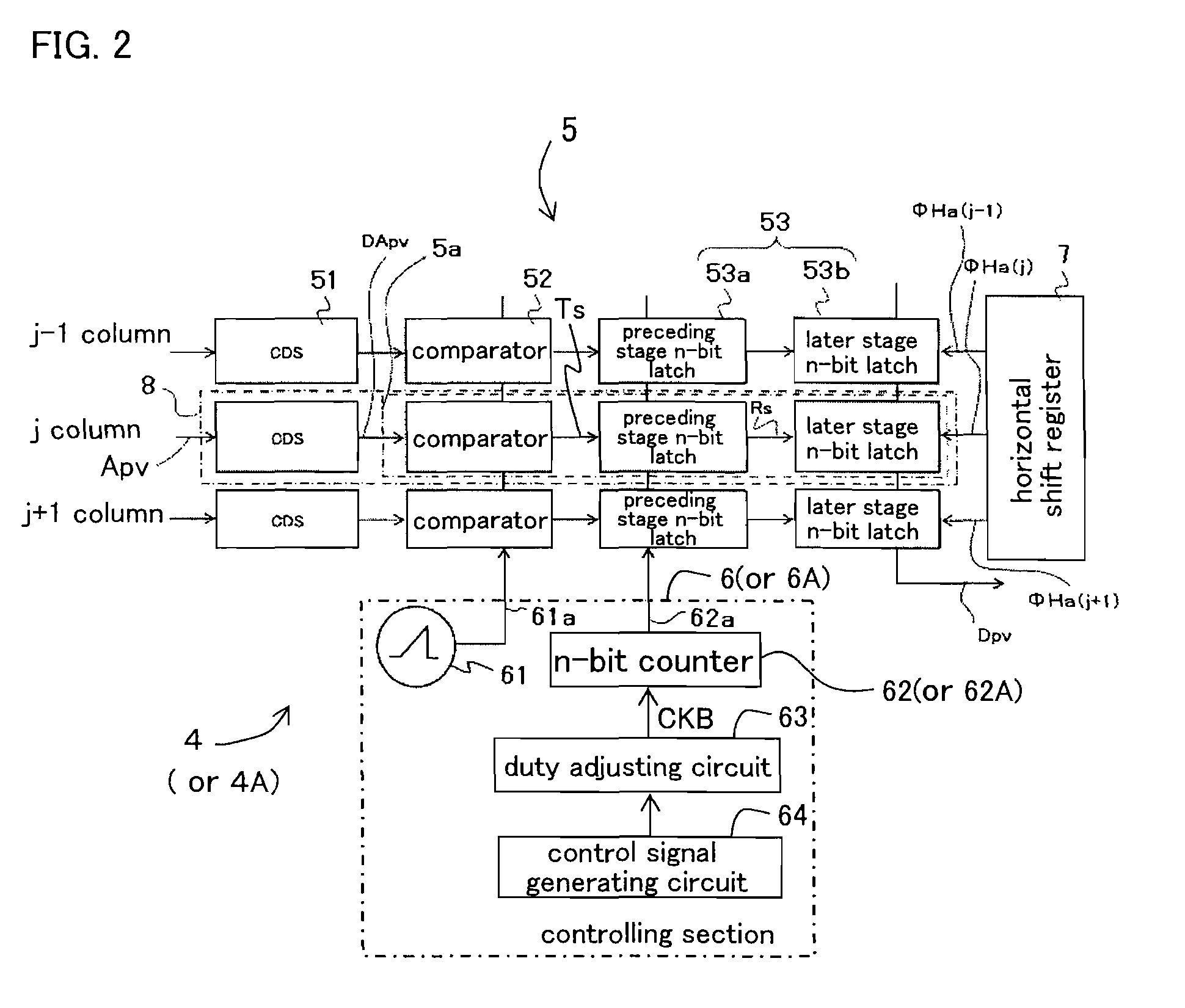

A/D conversion apparatus using gray code counter, solid-state image capturing apparatus and electronic information device

ActiveUS8421891B2Suppressing increase in area occupancyIncreased power consumptionTelevision system detailsElectric signal transmission systemsLeast significant bitAnalog signal

An A / D conversion apparatus according to the present invention for comparing a reference signal with an analog signal, and when the reference signal matches with the analog signal, outputting a corresponding digital value, is provided, and the A / D conversion apparatus includes a gray code counter for generating the digital value from a reference clock or a reverse clock of the reference clock, and uses a gray code, in which a most significant bit to a second least significant bit of the digital value is a count value of the gray code counter and a least significant bit of the digital value is generated from the reference clock or the reverse clock thereof and defined as a least significant bit of the gray code counter.

Owner:SHARP KK

State-dependent read voltage threshold adaptation for nonvolatile memory

ActiveUS10236067B2Increase the number of digitsQuick upgradeRead-only memoriesDigital storageOperating systemNon-volatile memory

A controller adapts the read voltage thresholds of a memory unit in a non-volatile memory. In one embodiment, the controller determines, based on statistics for a memory unit of the non-volatile memory, an operating state of the memory unit from among a plurality of possible operating states and adapts at least one read voltage threshold for a memory cell in the memory unit based on the determined operating state.

Owner:INT BUSINESS MASCH CORP

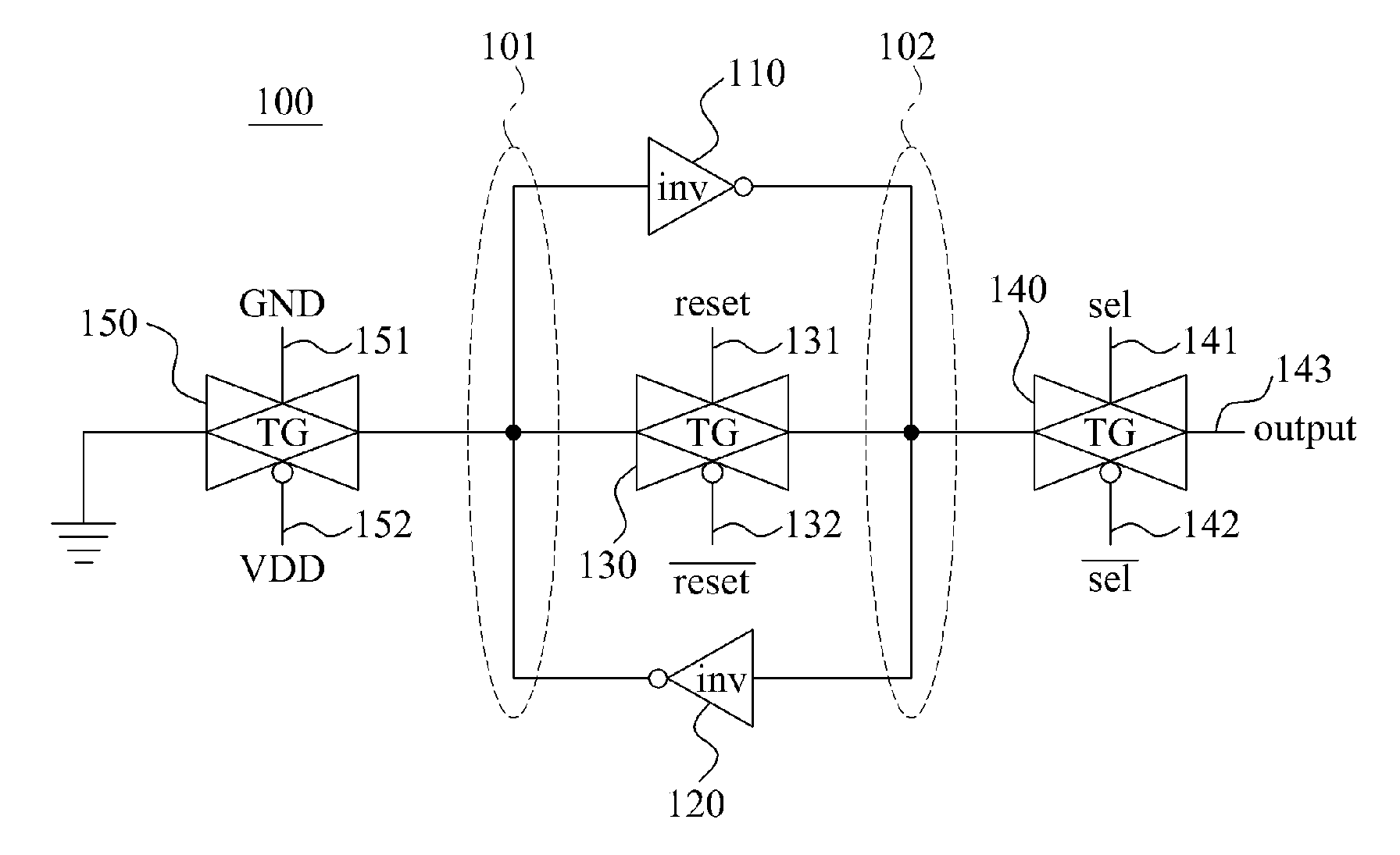

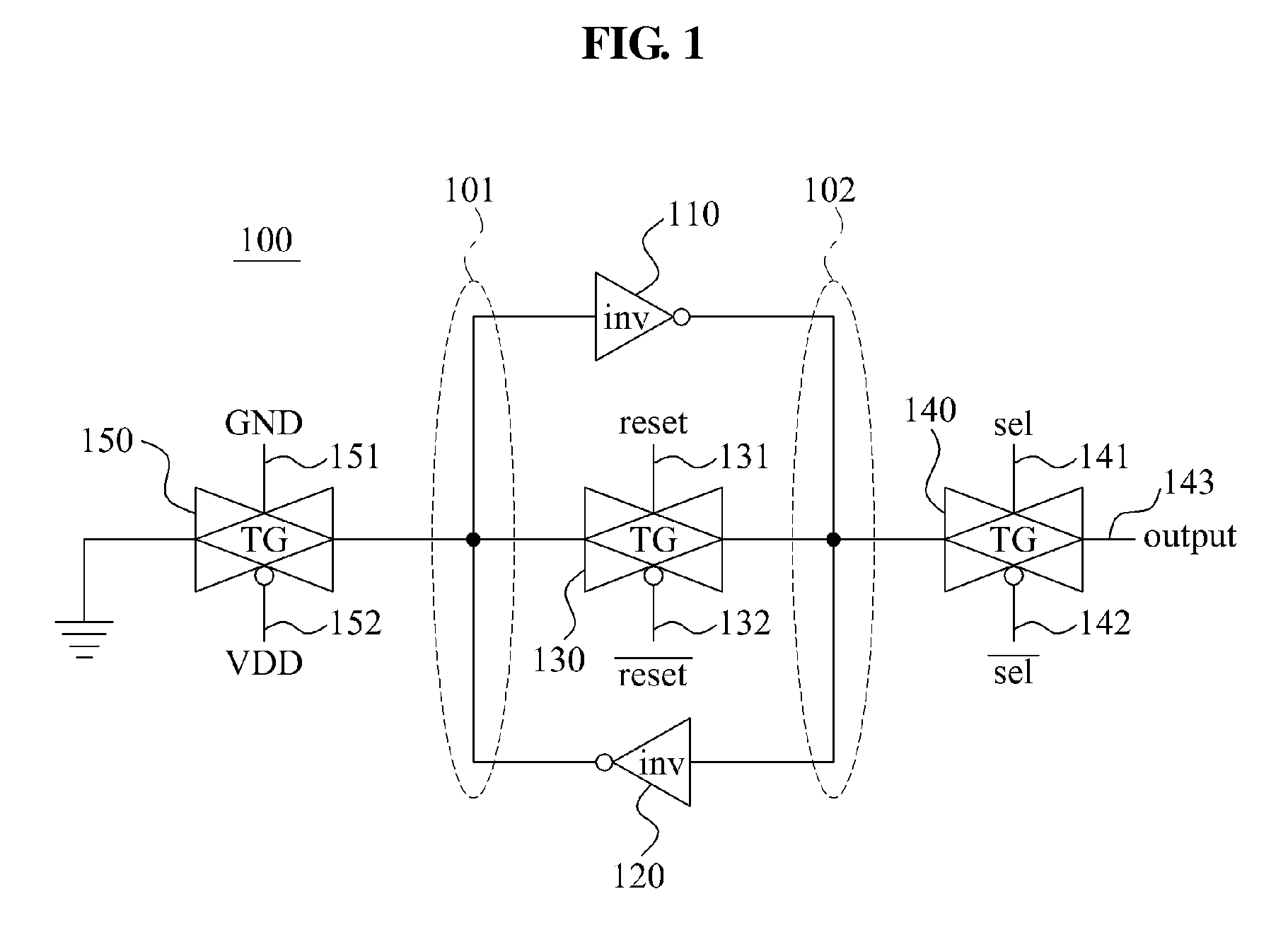

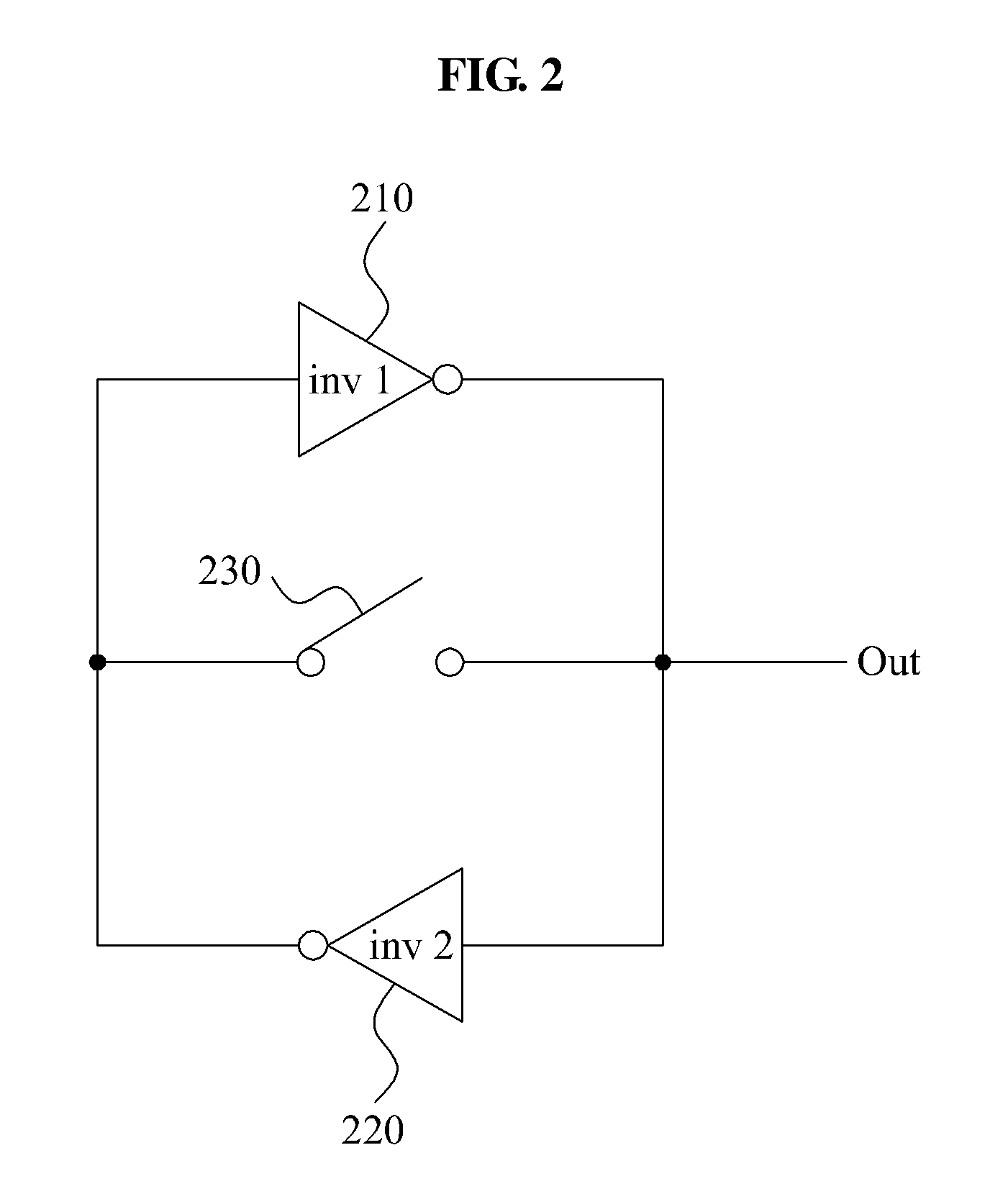

Semiconductor chip and method for generating digital value using process variation

ActiveUS20120037711A1Low costSimple circuit structureDigital data processing detailsCoding/ciphering apparatusIdentification keySemiconductor chip

Provided is a semiconductor chip to generate an identification key. The semiconductor chip may include a first inverter having a first logic threshold, a second inverter having a second logic threshold, and a first switch. The first switch may include a first terminal and a second terminal, and may short or open a connection between the first terminal and the second terminal according to an first input voltage value. An input terminal of the first inverter, an output terminal, and the first terminal of the first switch may be connected to a first node. An output terminal of the first inverter, an input terminal of the second inverter, and the second terminal of the first switch may be connected to a second node.

Owner:ICTK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com