Patents

Literature

1440results about "Frequency selective two-port networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

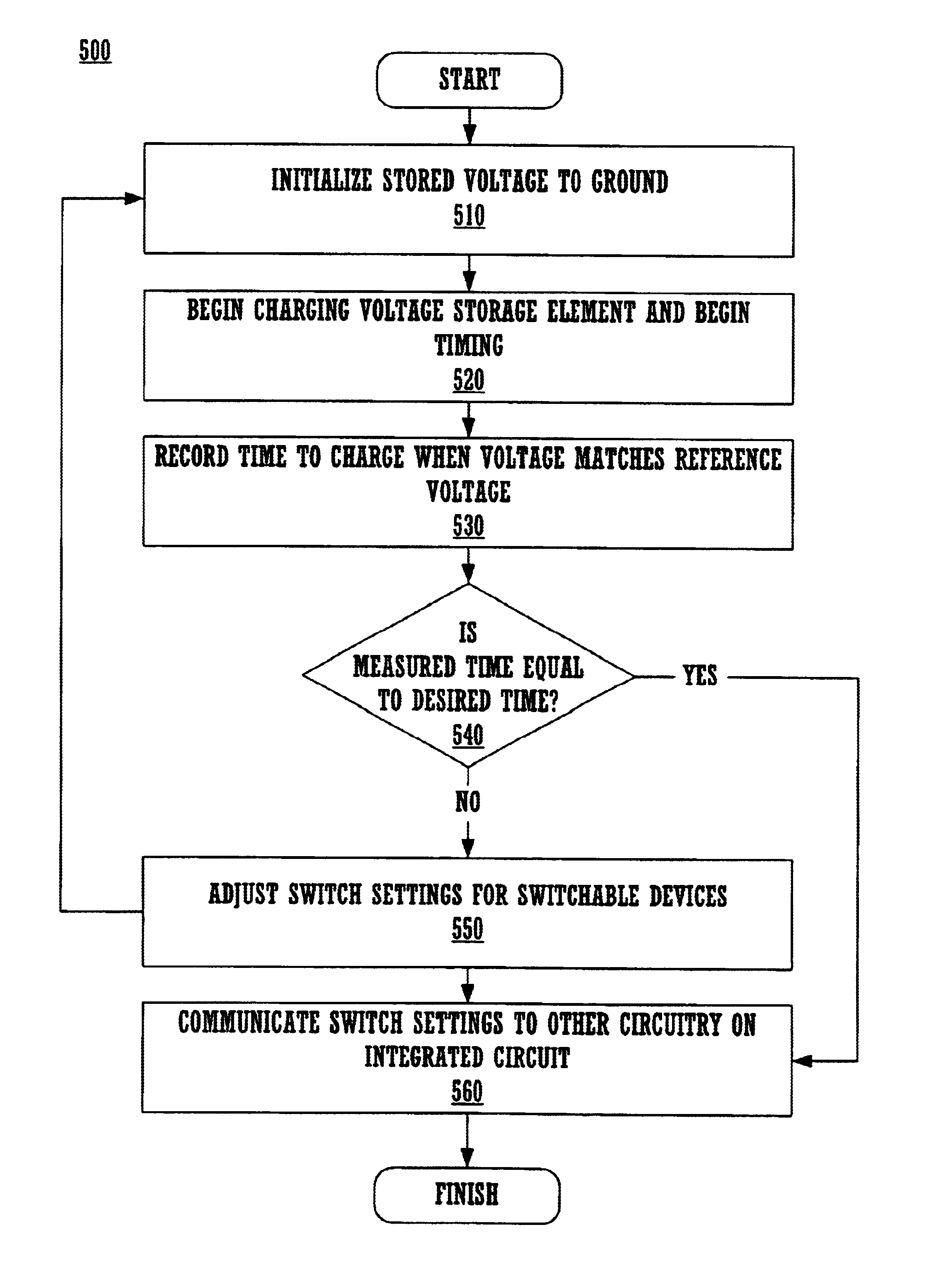

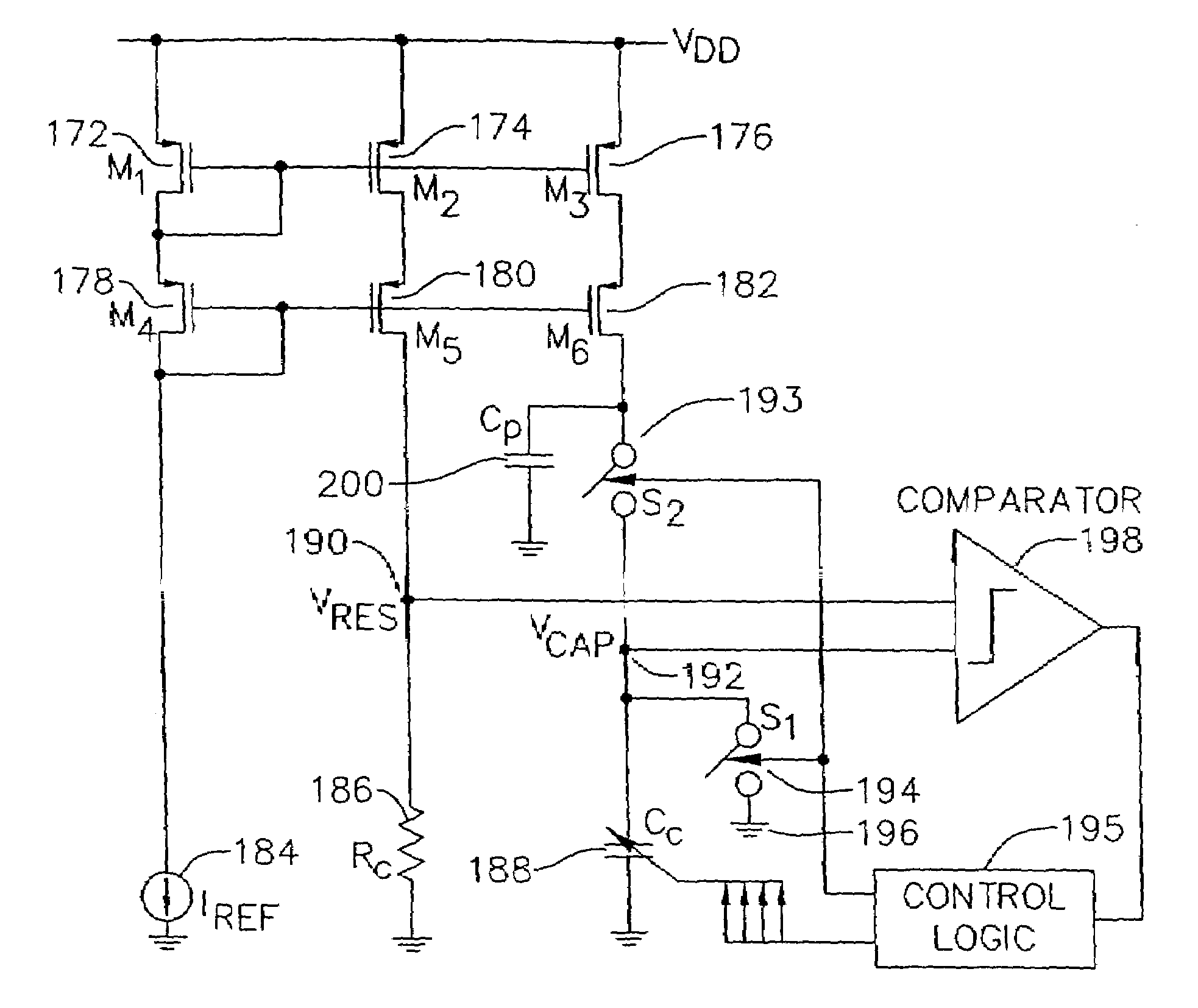

Calibration of integrated circuit time constants

InactiveUS6842710B1Computing operations for integral formationComputing operations for integration/differentiationRC time constantVoltage reference

A method and system for calibrating a time constant within an integrated circuit. A voltage storage element is charged, and the time required to achieve a reference voltage on the storage element is measured. The measured time is compared to a desired time. It necessary, an adjustable impedance is modified to change the charging time, and the cycle may be repeated until the charging time matches the desired time. In this novel manner, an actual RC time constant, as rendered in a particular integrated circuit, is measured and potentially adjusted to match a desired time constant. Advantageously, configuration information of the adjustable impedance may be communicated to other circuitry within the integrated circuit to enable such circuitry to implement the same RC time constant in analog signal processing. Consequently, embodiments of the present invention overcome incidences of wide tolerance in passive components implemented in integrated circuits. Beneficially, no external test equipment is required.

Owner:TAMIRAS PER PTE LTD LLC

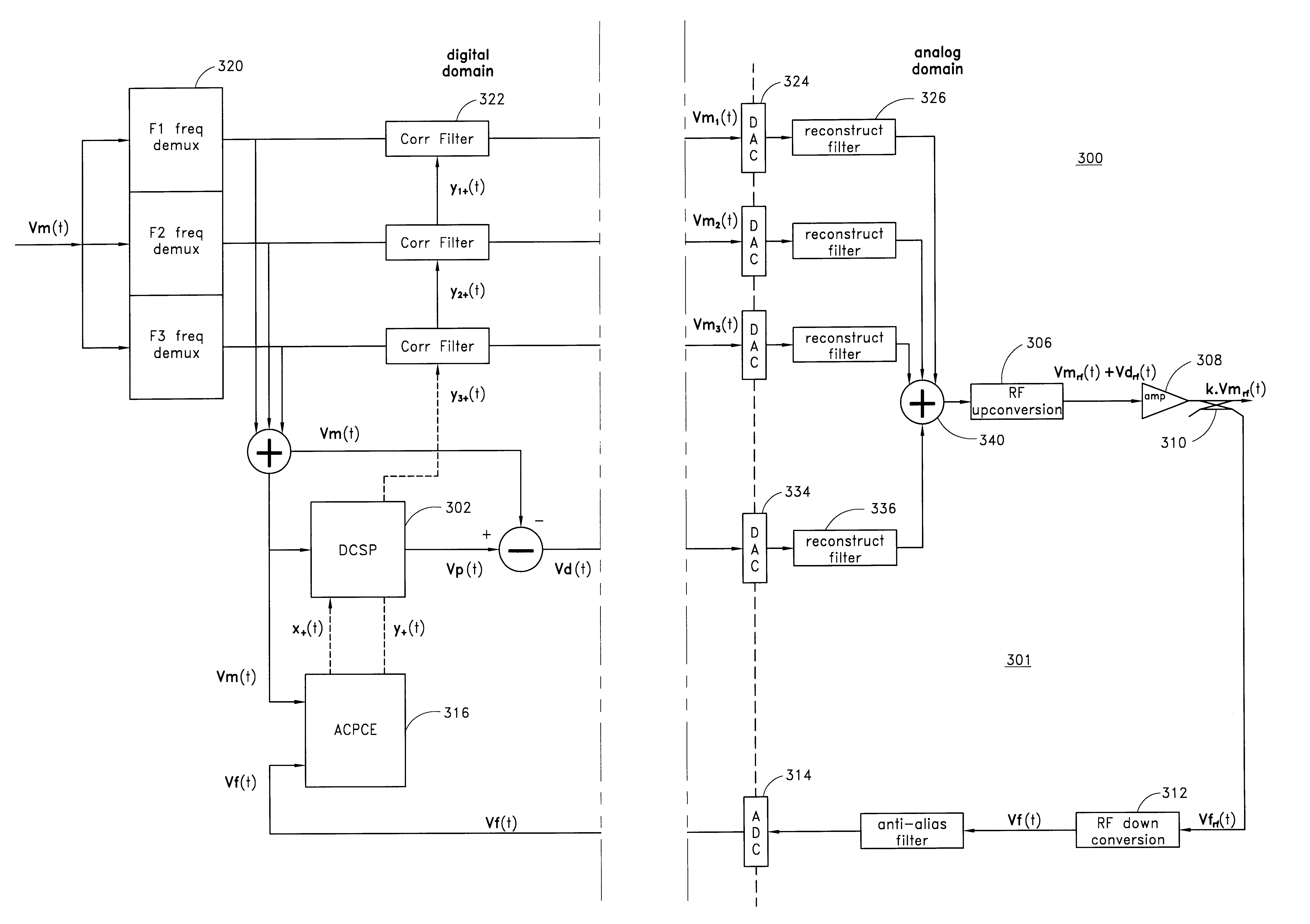

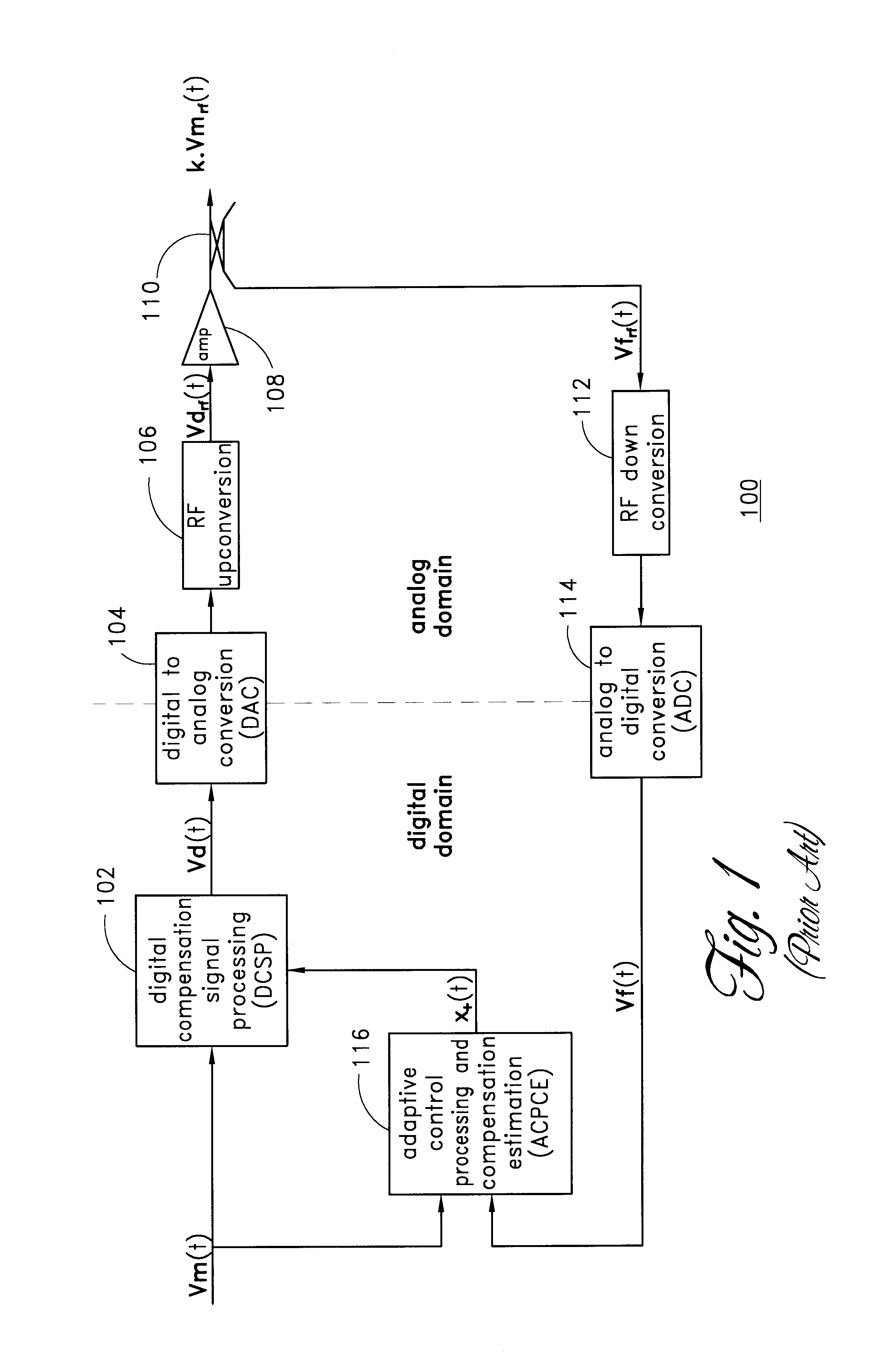

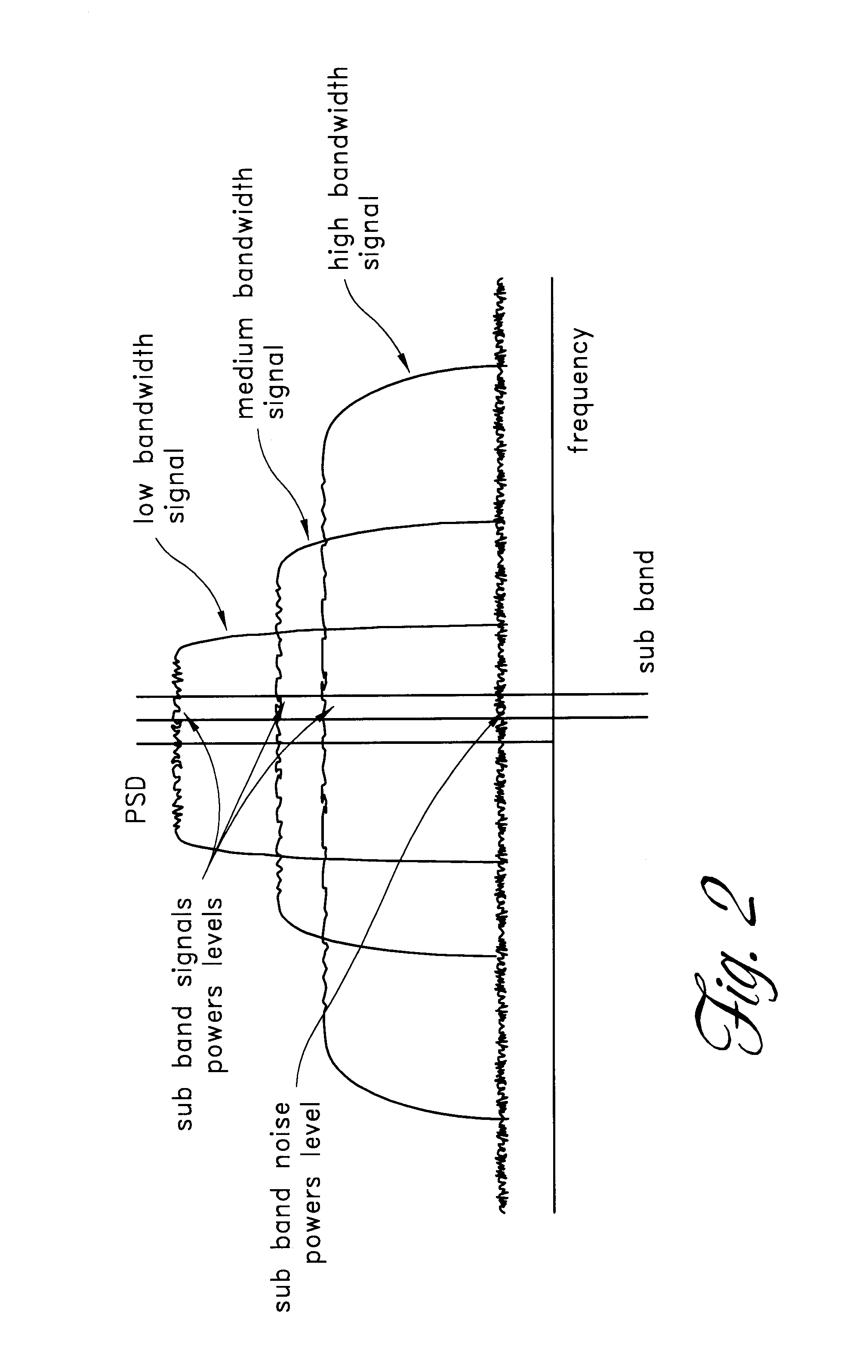

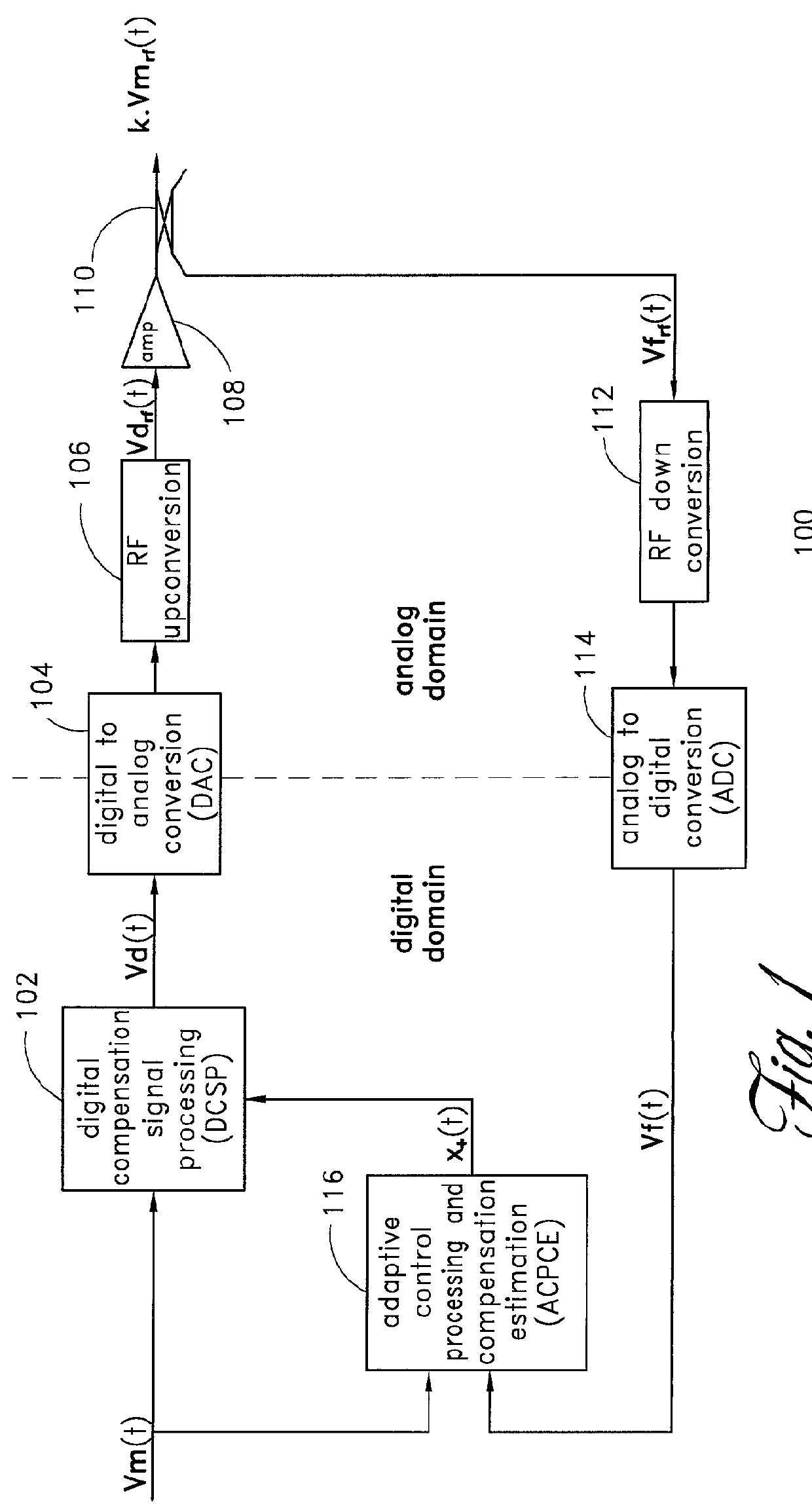

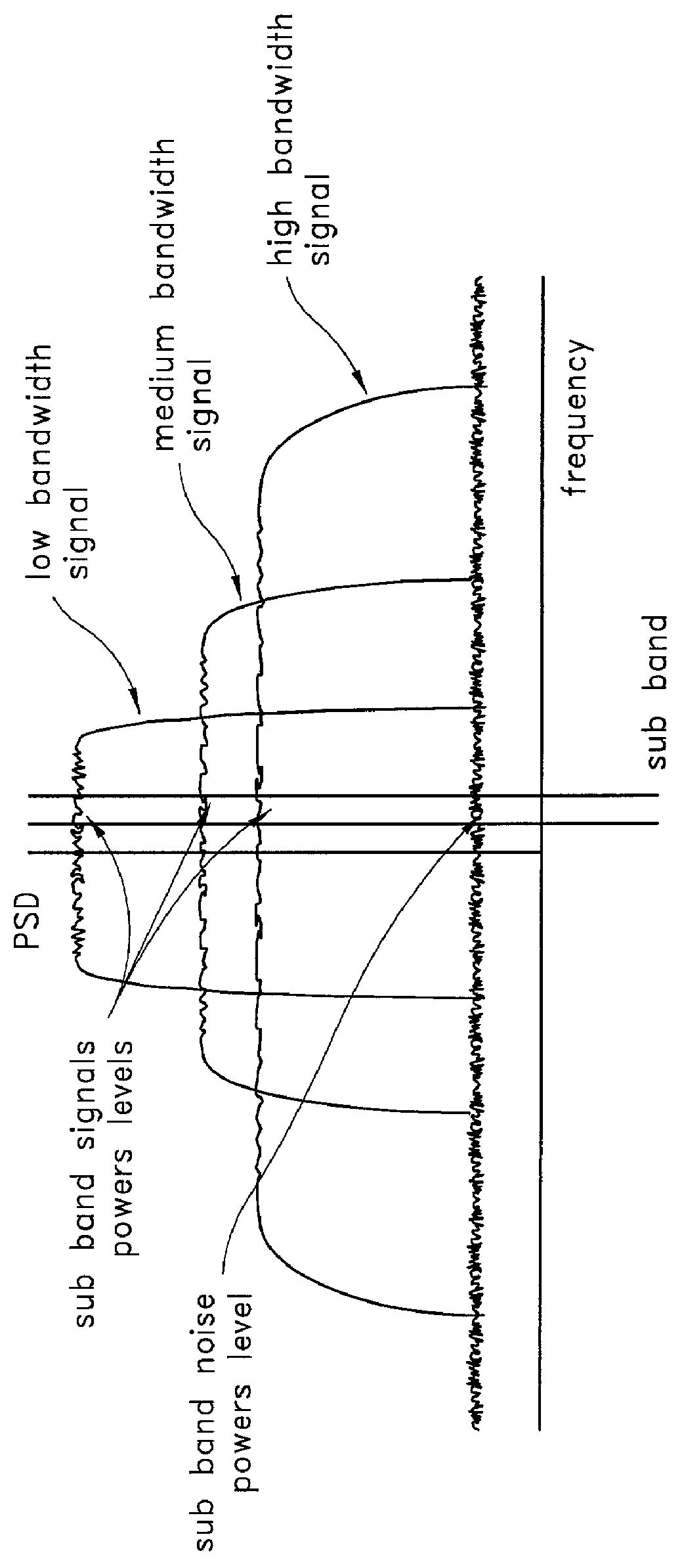

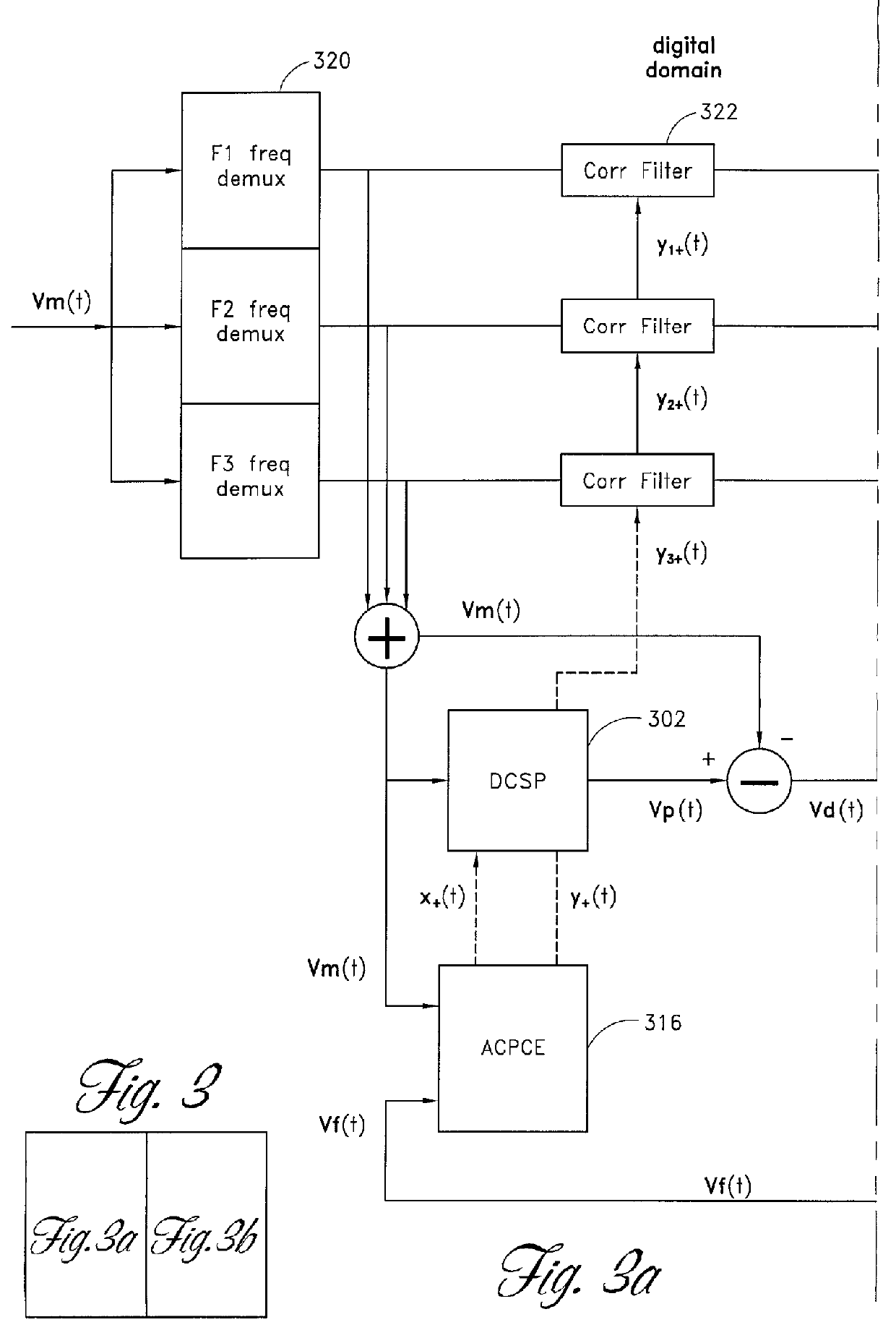

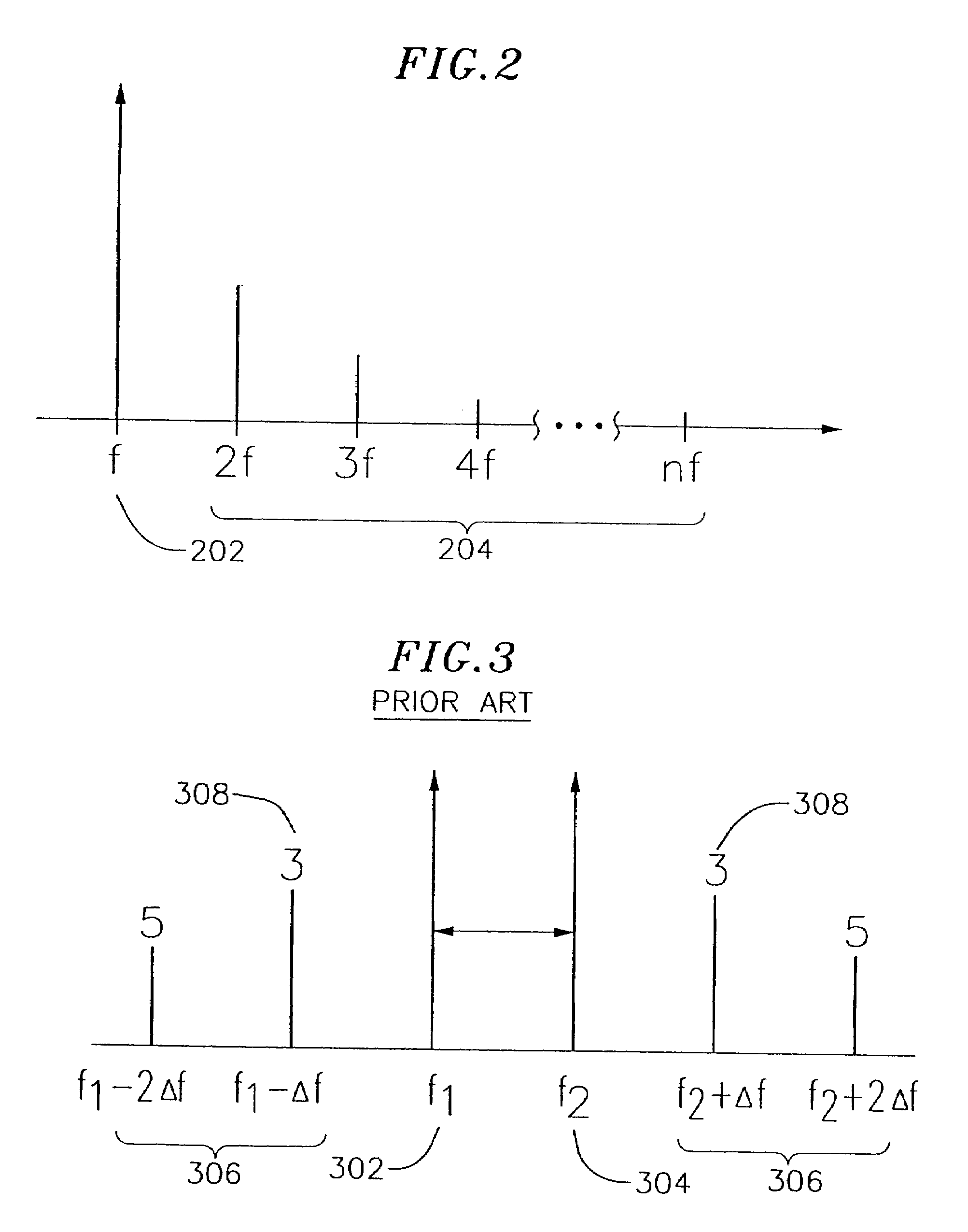

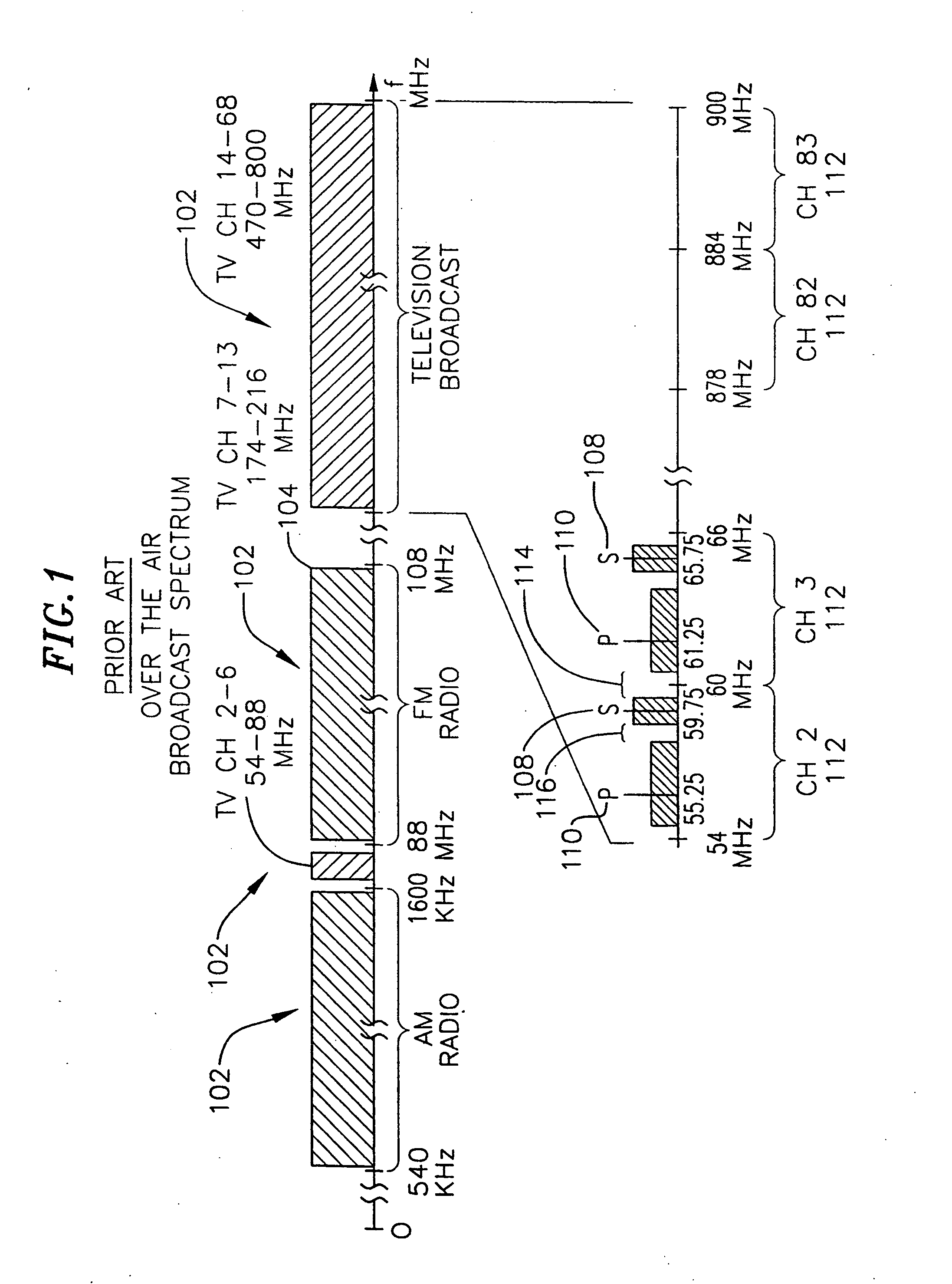

Low noise wideband digital predistortion amplifier

InactiveUS6570444B2Low bandwidthReduce total powerAmplifier modifications to reduce non-linear distortionElectric signal transmission systemsLow noiseSignal-to-noise ratio (imaging)

A digital predistortion amplifier design compensates for non-linear amplification of an input signal using predistortion techniques. The design provides a reduced noise floor by using separate digital to analog converters (DAC) to separately convert the input signal and an error correction signal. Furthermore, the input signal can be separated into two or more subbands of narrower bandwidth. Each of the subbands are converted to analog using a separate DAC. By reducing the power and / or bandwidth to be handled by any one DAC, the available levels of quantization of the DAC are applied to a lower power signal and therefore the signal to noise ratio resulting from the conversion process is improved. In addition, each digital subband is passed through a correction filter, which is driven by an adaptive control processing and compensation estimator to compensate for relative gain, phase, and delay inconsistencies between the different subbands.

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

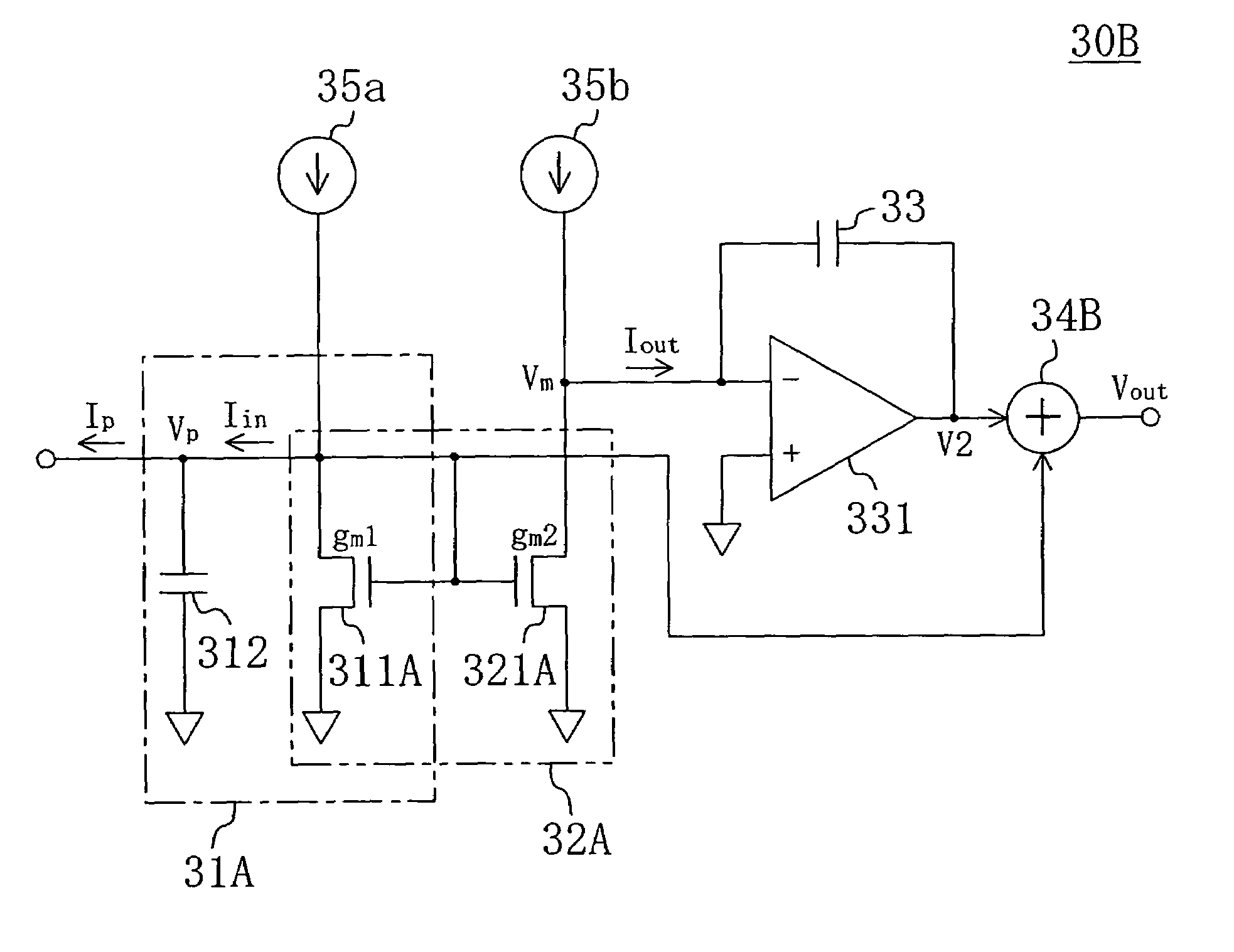

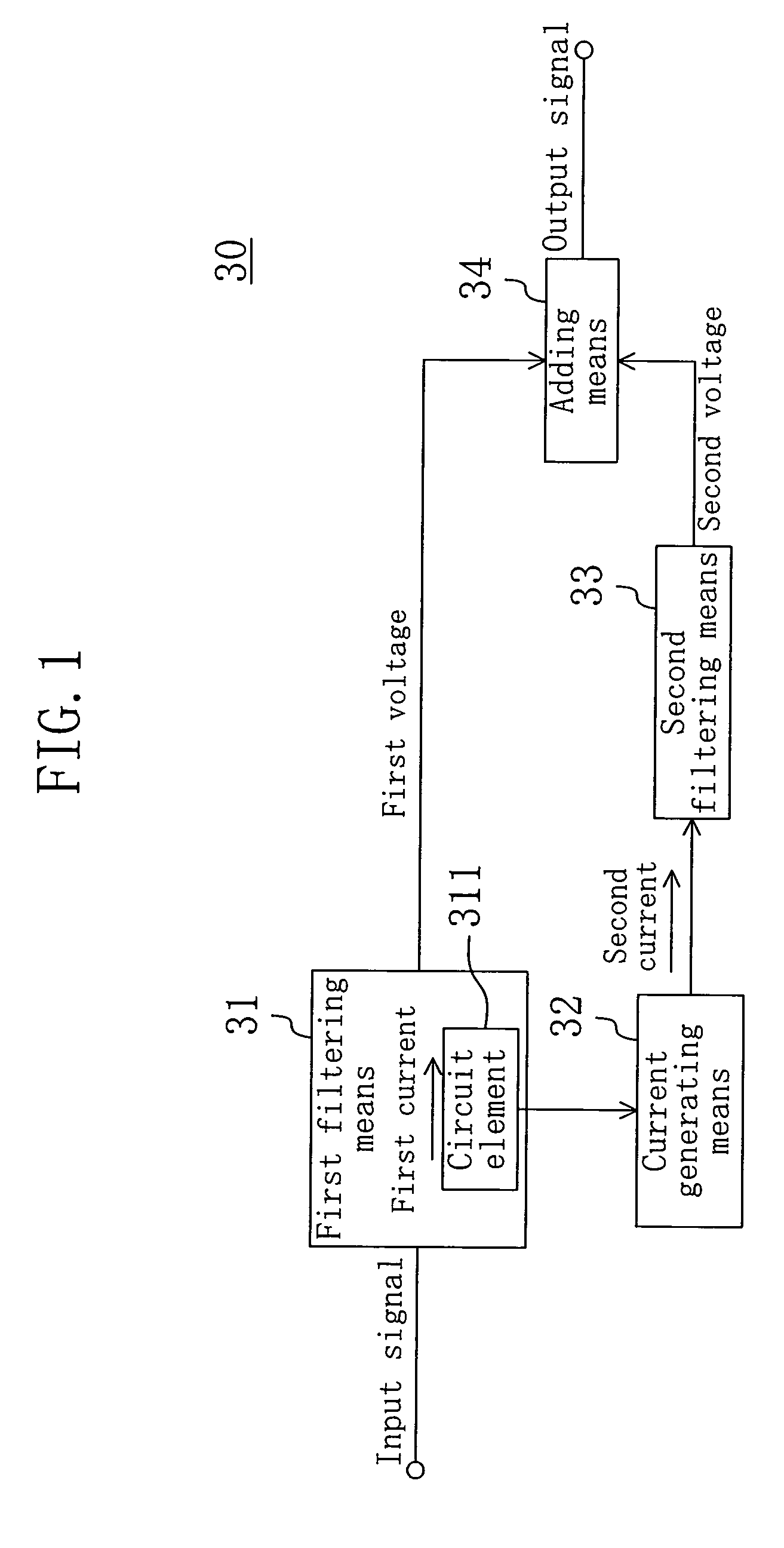

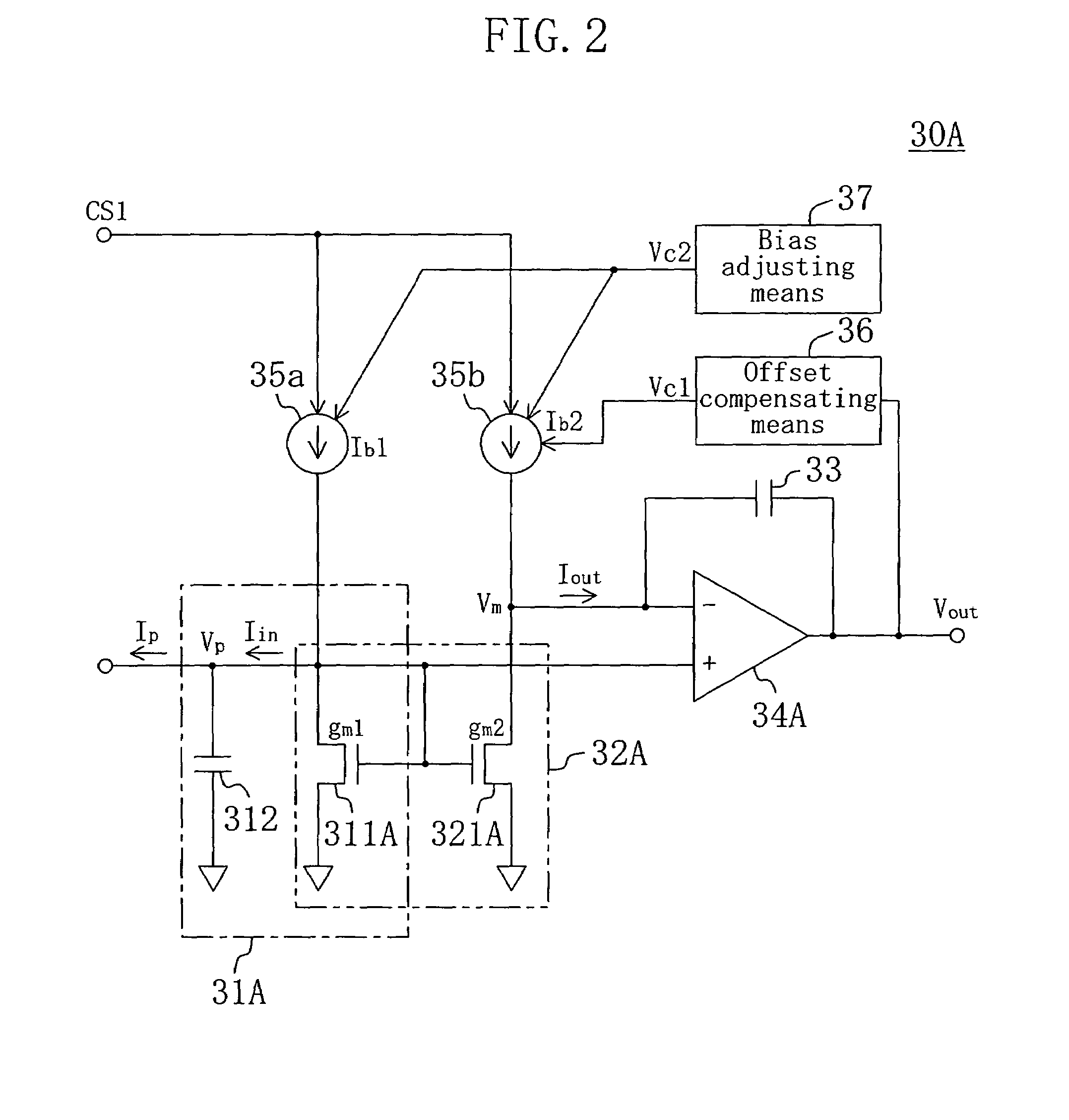

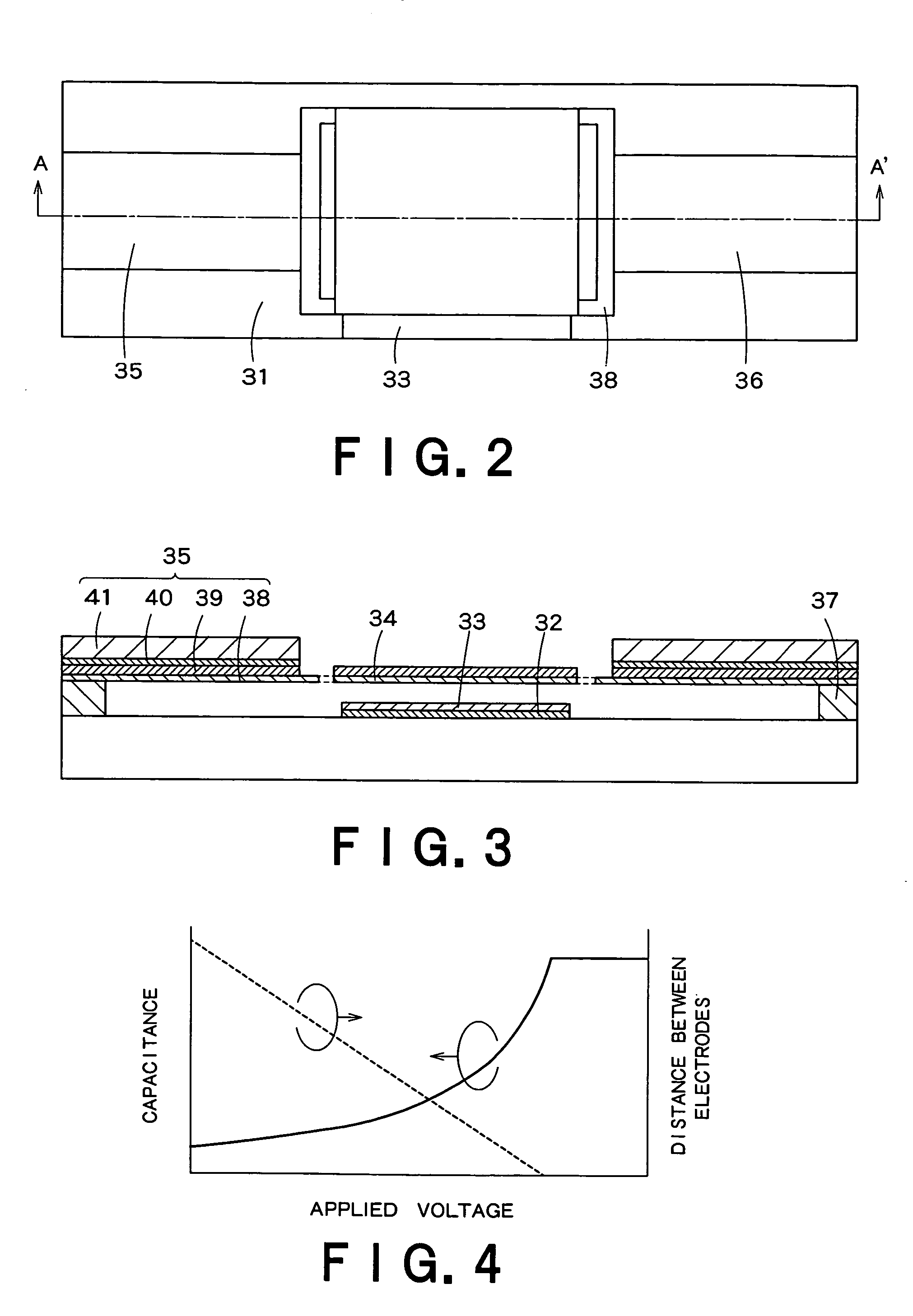

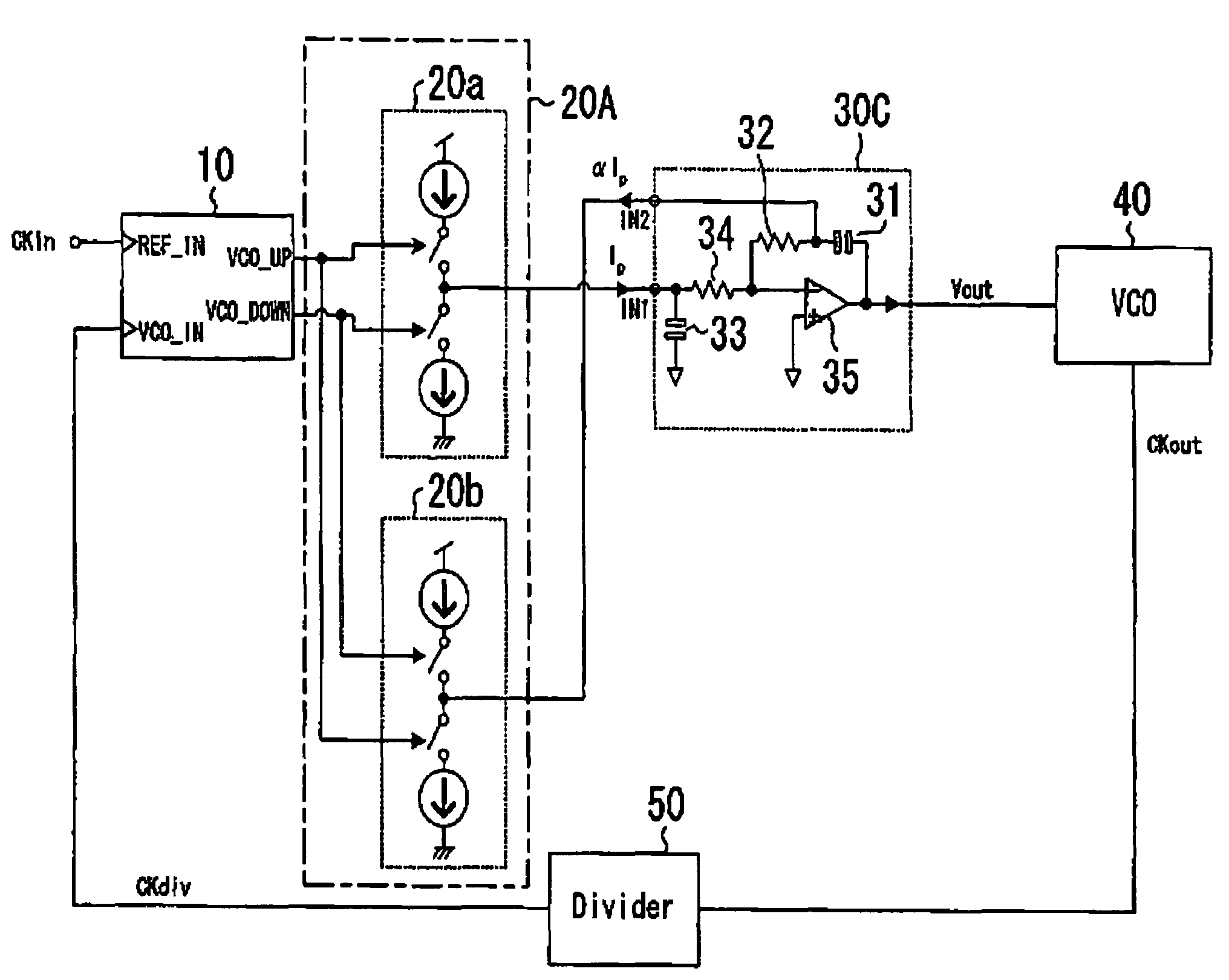

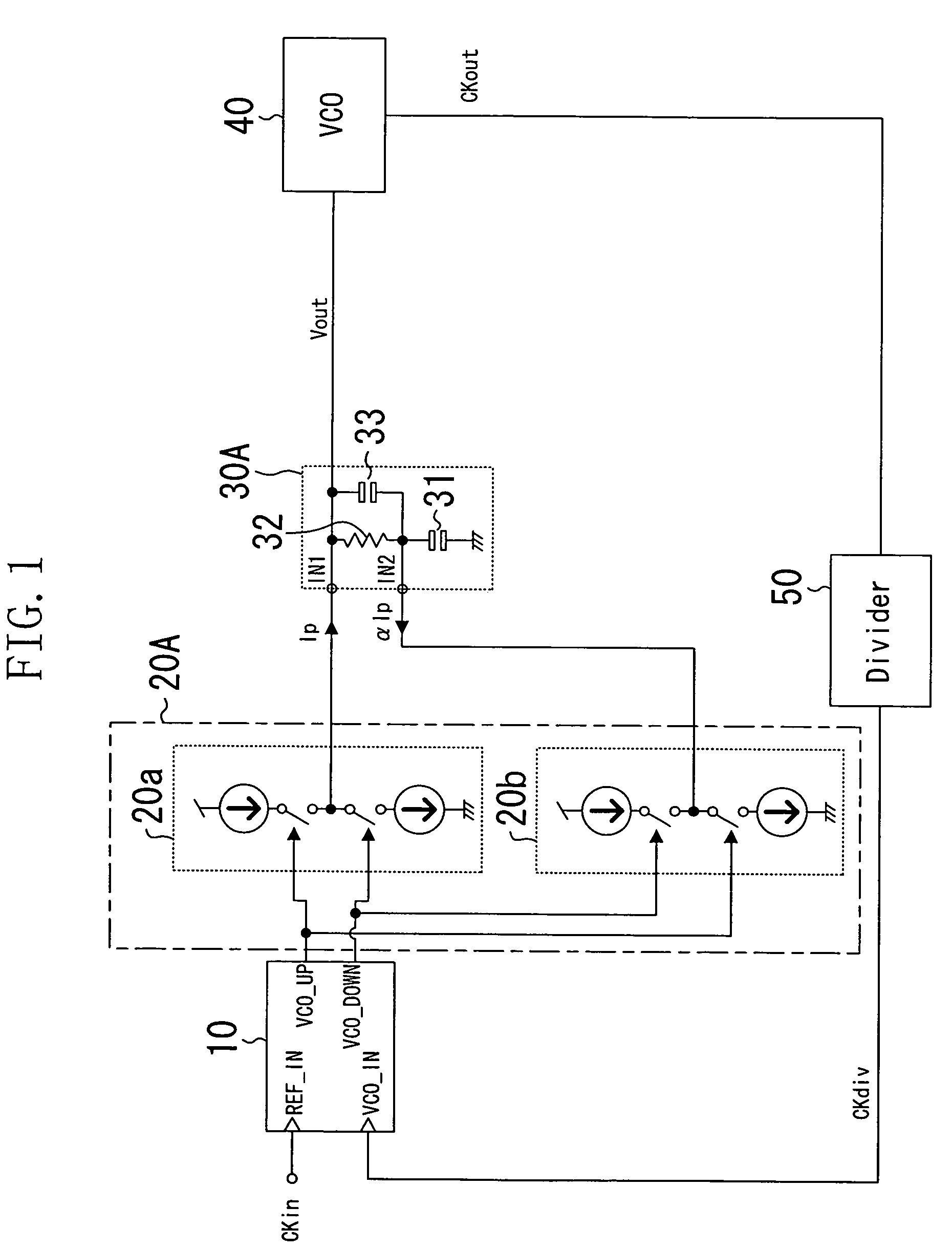

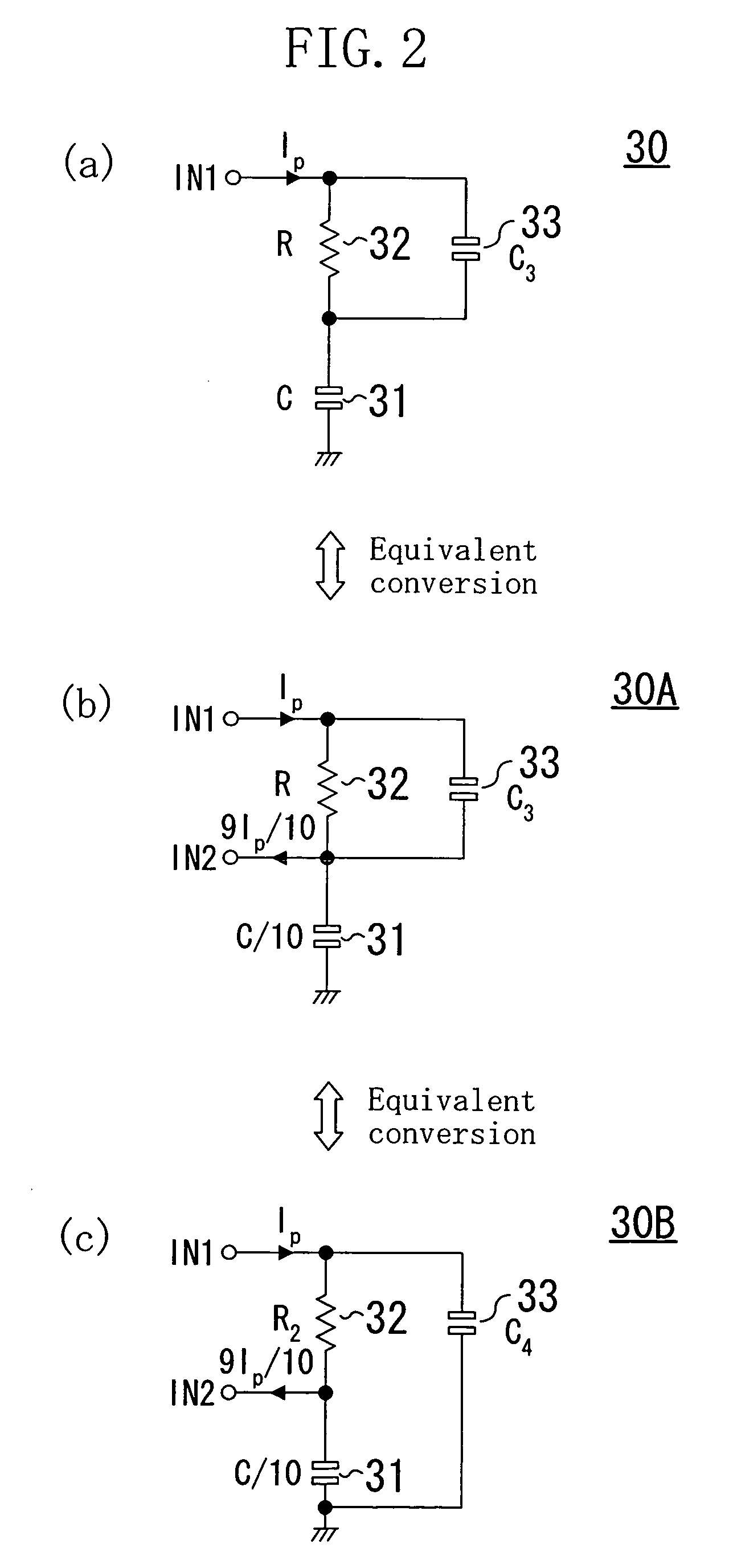

Low-pass filter for a PLL, phase-locked loop and semiconductor integrated circuit

InactiveUS7030688B2Reduce circuit sizeReduce circuit areaPulse automatic controlOscillations generatorsLoop filterBand-pass filter

The invention provides a low-pass filter suitably used as a loop filter for a PLL or a DLL that has a filtering characteristic equivalent to that of a conventional one and can be realized in a smaller circuit area. The low-pass filter includes first filtering means (31) for accepting, as an input, an input signal to the low-pass filter and outputting a first voltage; a circuit element (311) included in the first filtering means (31) for allowing a first current to flow in accordance with the first voltage; current generating means (32) for generating a second current at a given rate to the first current; second filtering means (33) for accepting, as an input, the second current and outputting a second voltage; and adding means (34) for adding the first voltage and the second voltage and outputting an output signal of the low-pass filter, in which the second current is set to be smaller than the first current.

Owner:PANASONIC CORP

Low noise wideband digital predistortion amplifier

InactiveUS20010054974A1Amplifier modifications to reduce non-linear distortionElectric signal transmission systemsLow noiseSignal-to-noise ratio (imaging)

A digital predistortion amplifier design compensates for non-linear amplification of an input signal using predistortion techniques. The design provides a reduced noise floor by using separate digital to analog converters (DAC) to separately convert the input signal and an error correction signal. Furthermore, the input signal can be separated into two or more subbands of narrower bandwidth. Each of the subbands are converted to analog using a separate DAC. By reducing the power and / or bandwidth to be handled by any one DAC, the available levels of quantization of the DAC are applied to a lower power signal and therefore the signal to noise ratio resulting from the conversion process is improved. In addition, each digital subband is passed through a correction filter, which is driven by an adaptive control processing and compensation estimator to compensate for relative gain, phase, and delay inconsistencies between the different subbands.

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

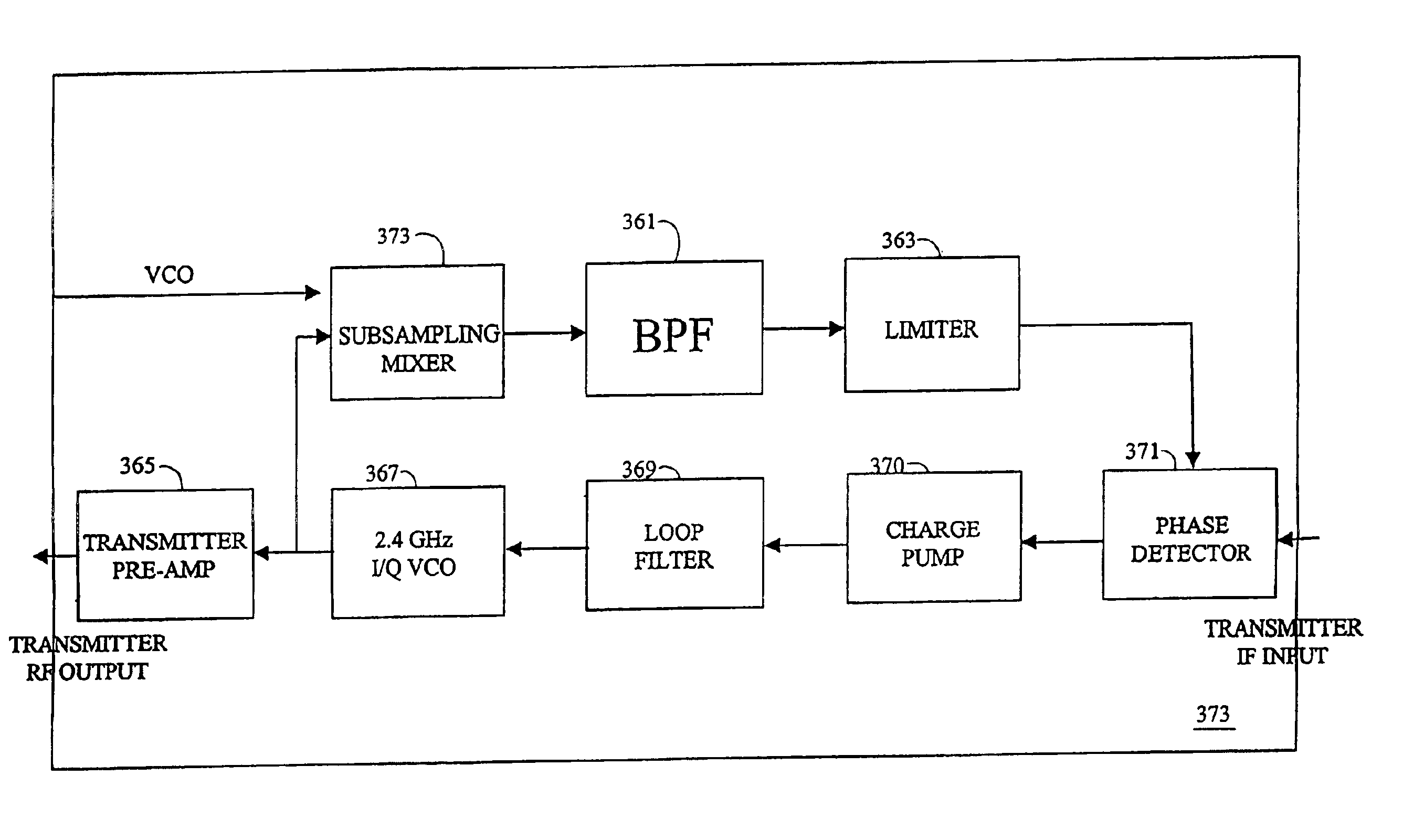

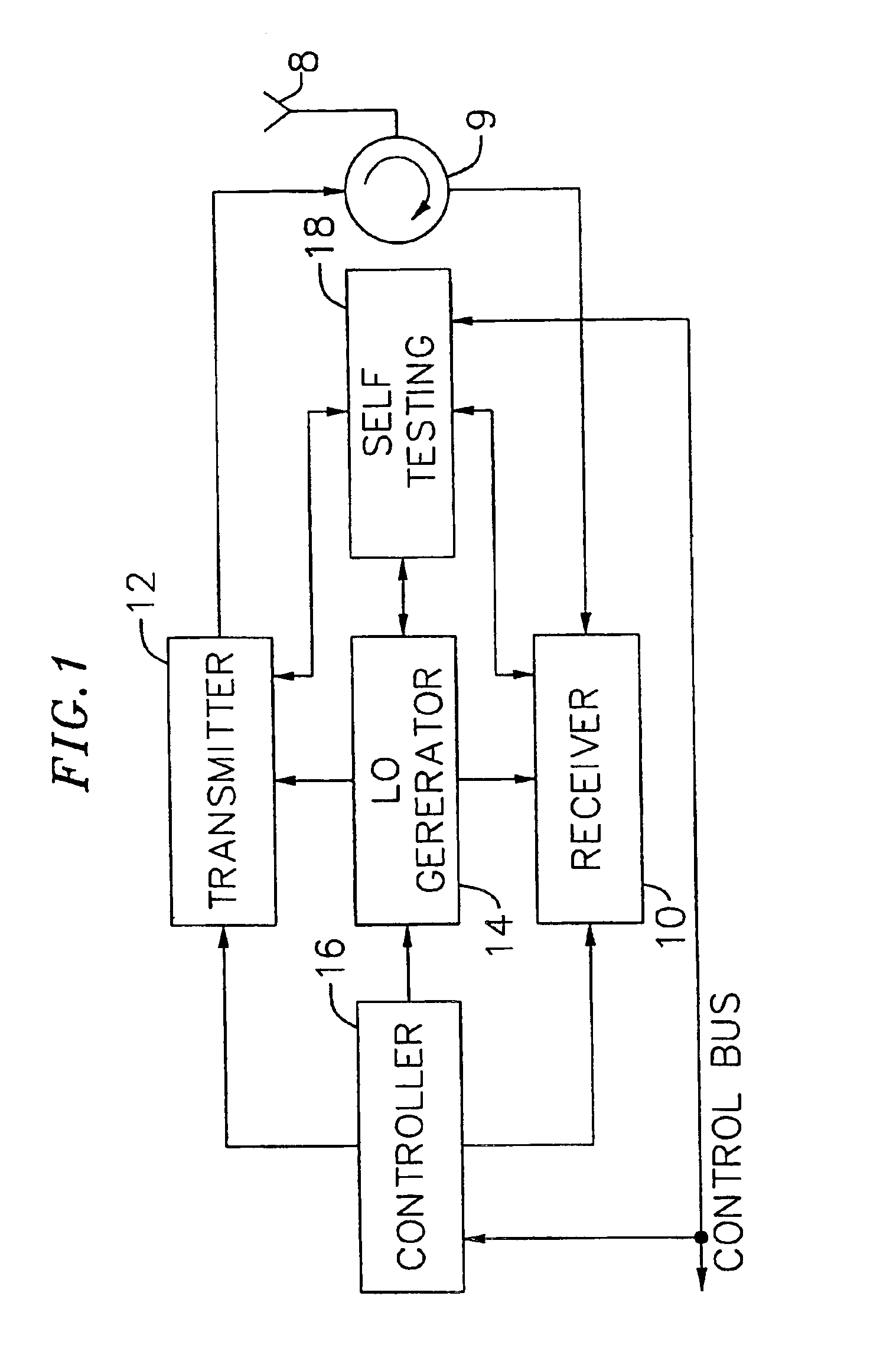

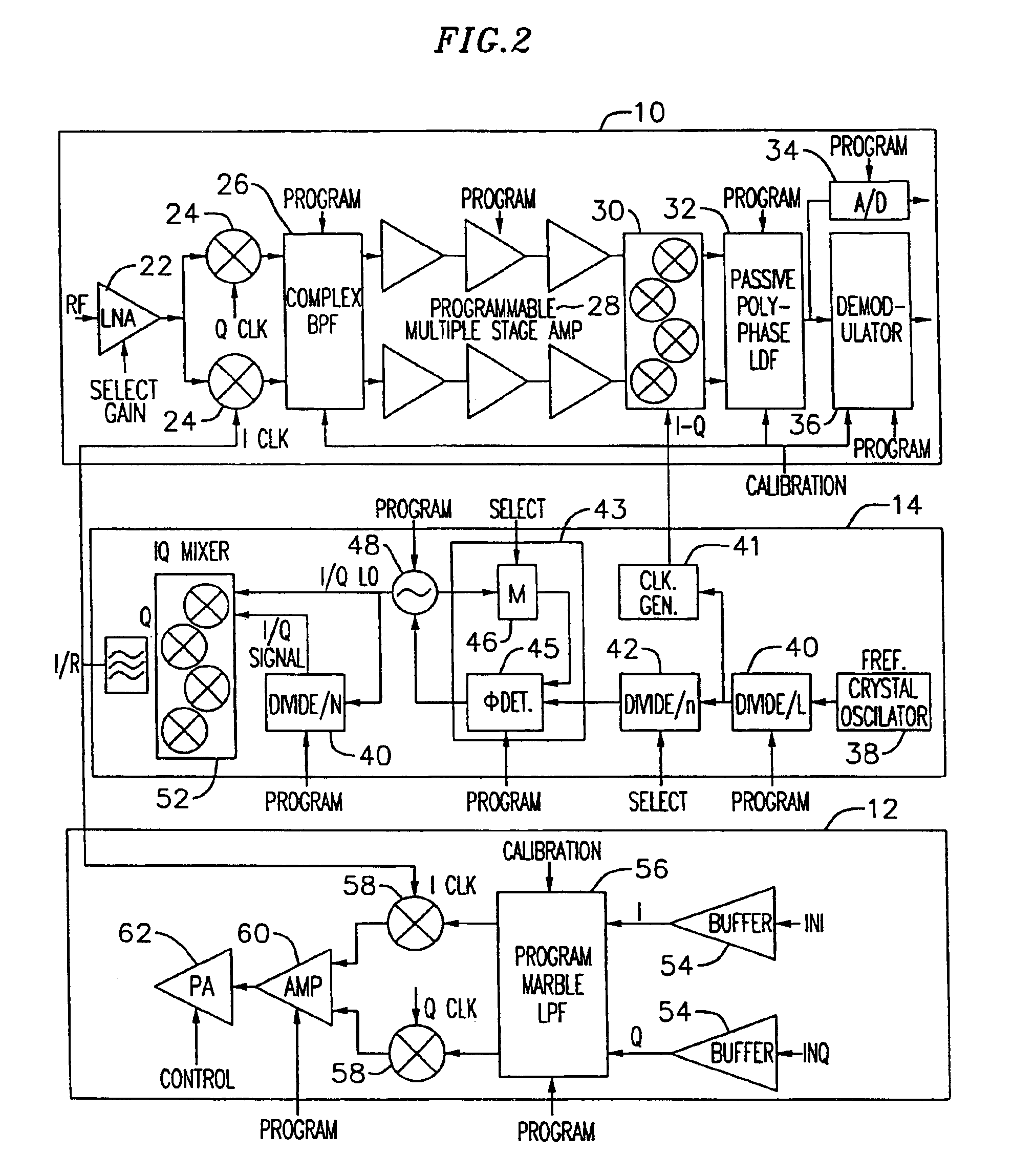

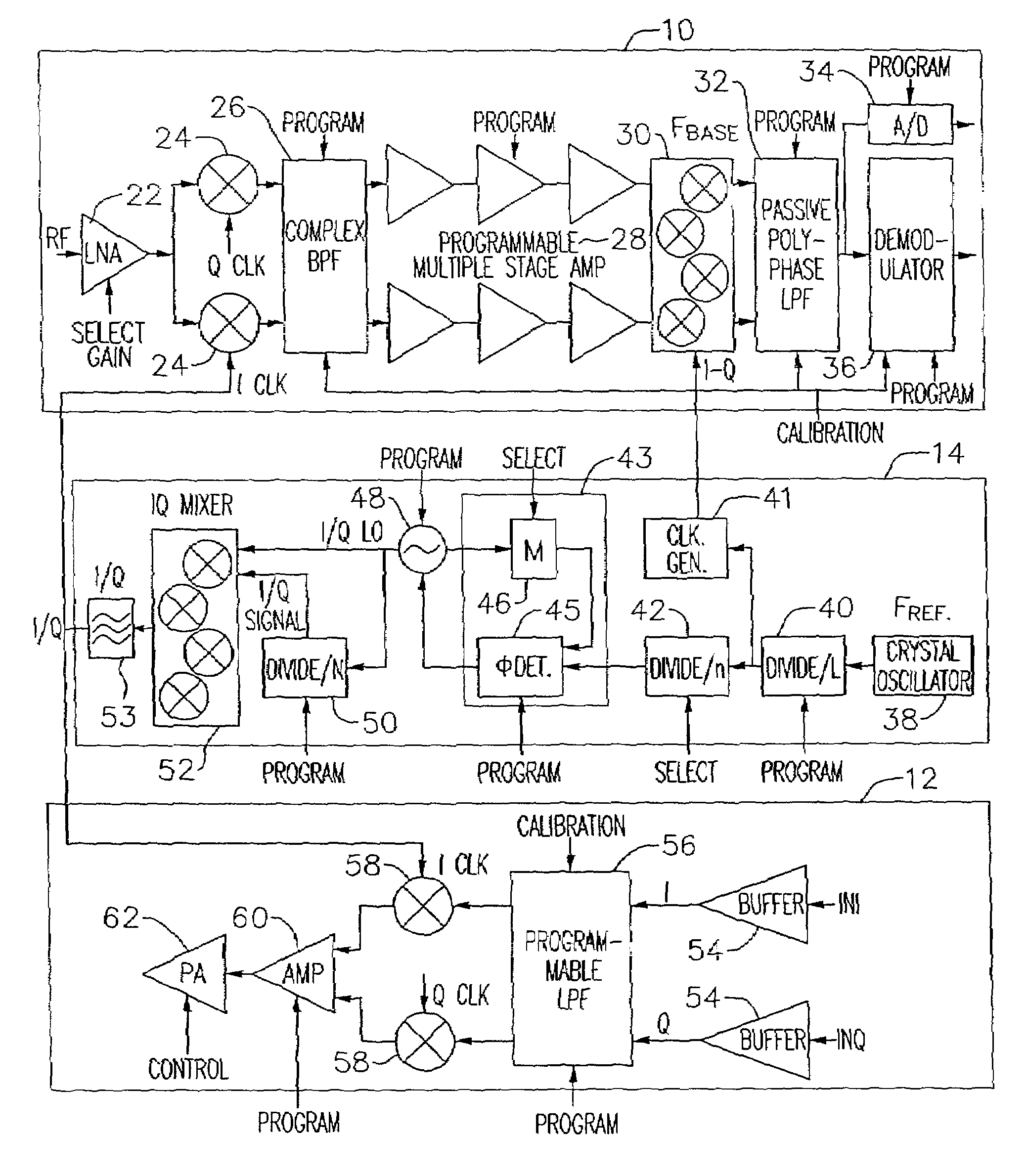

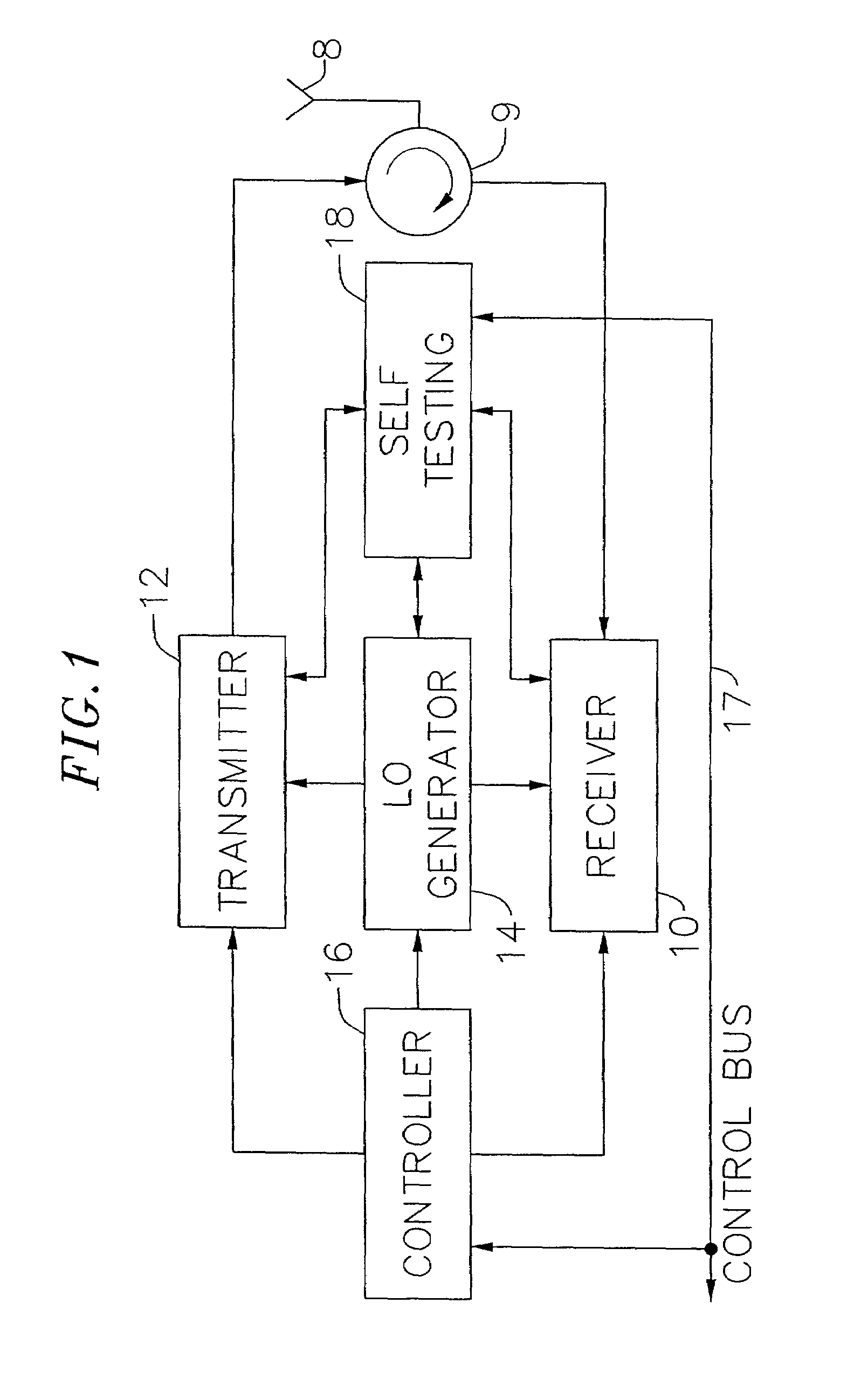

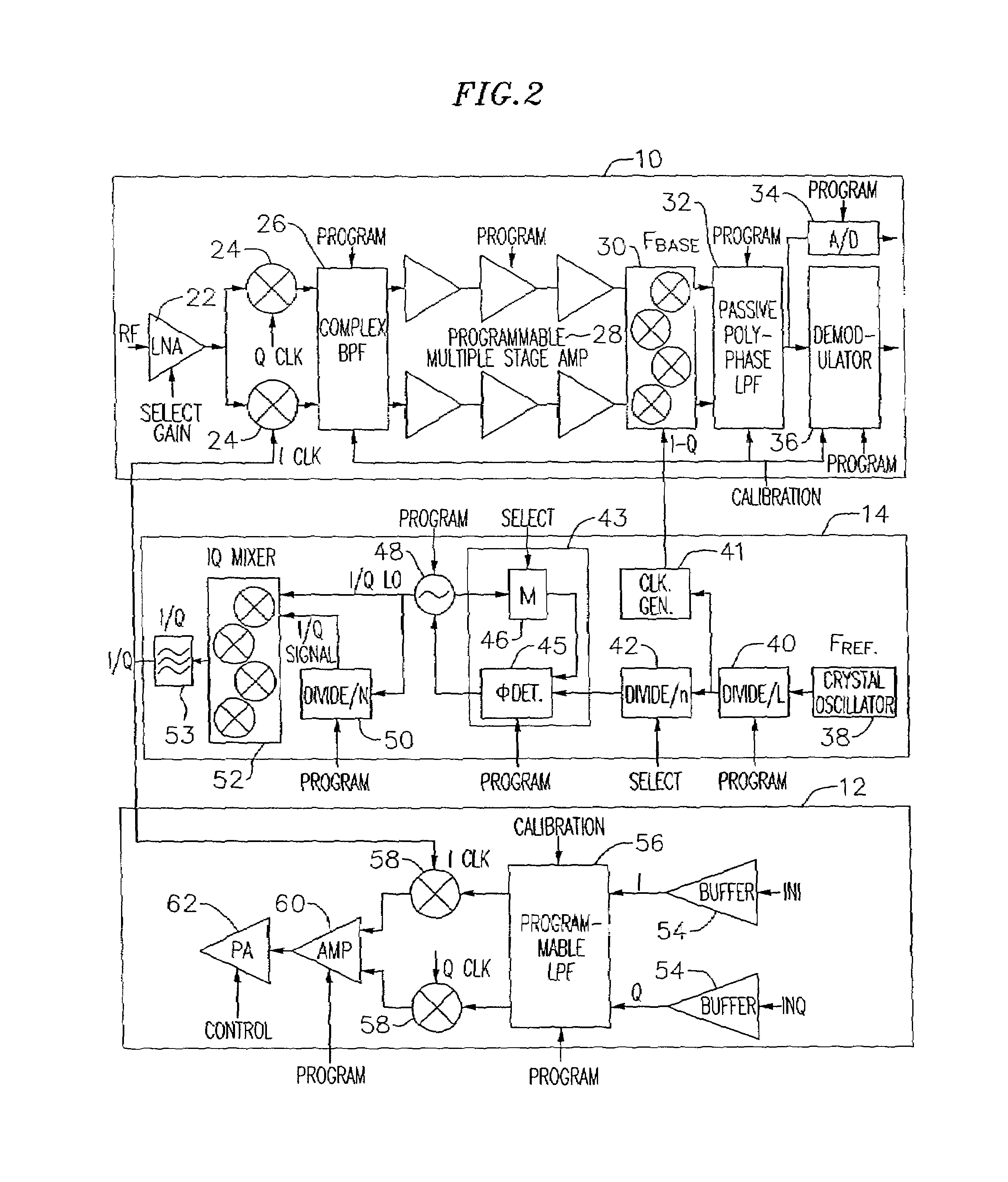

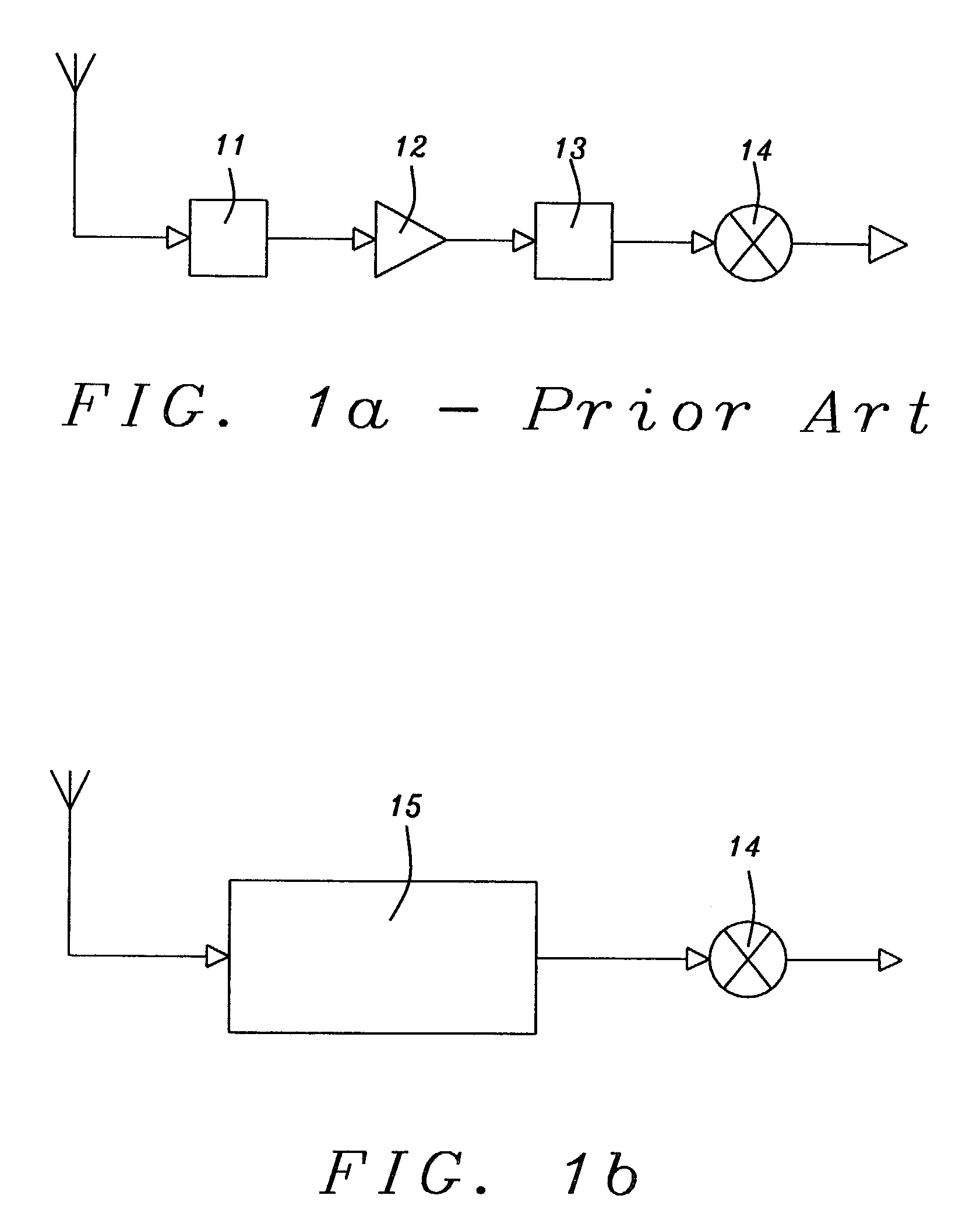

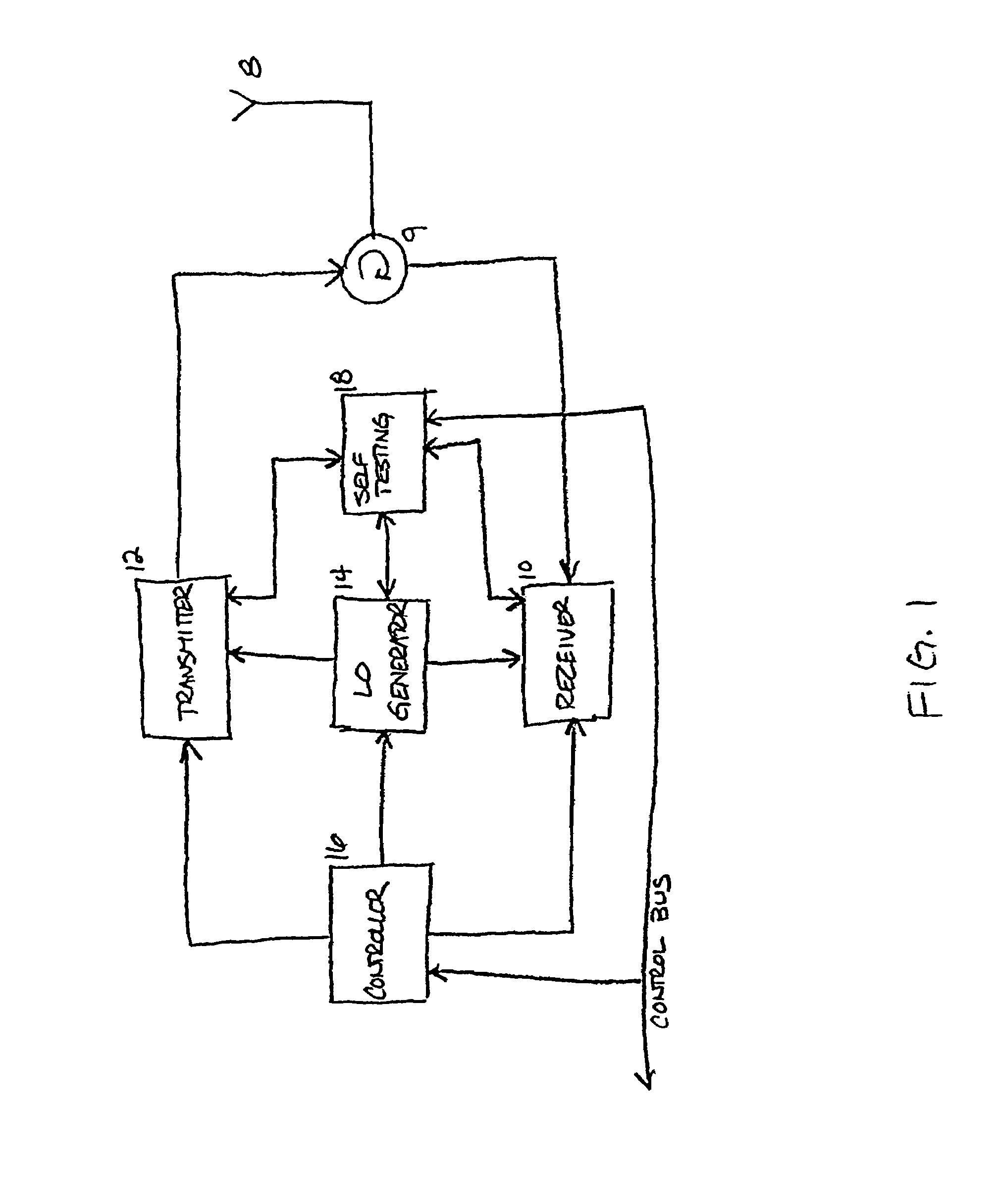

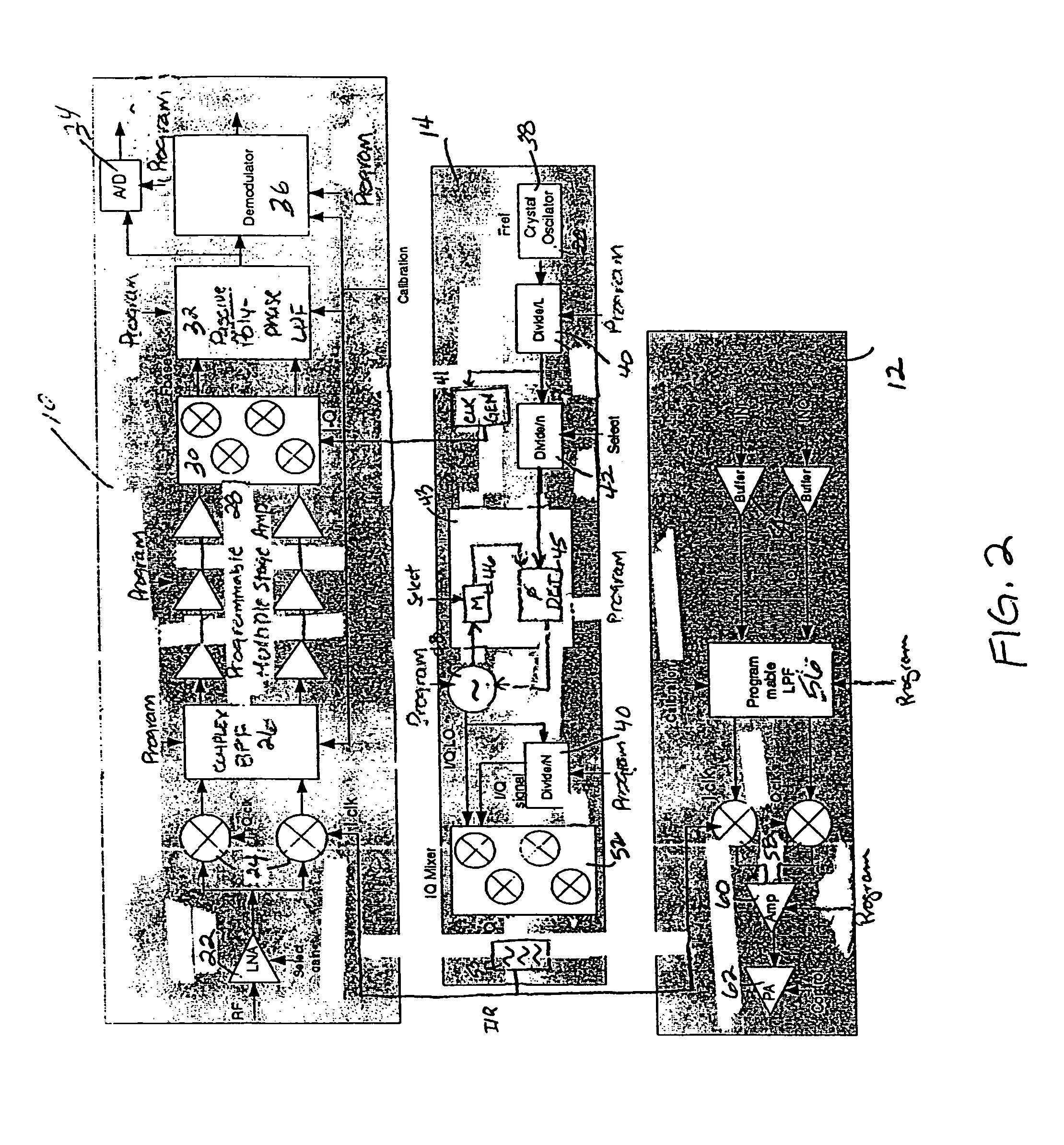

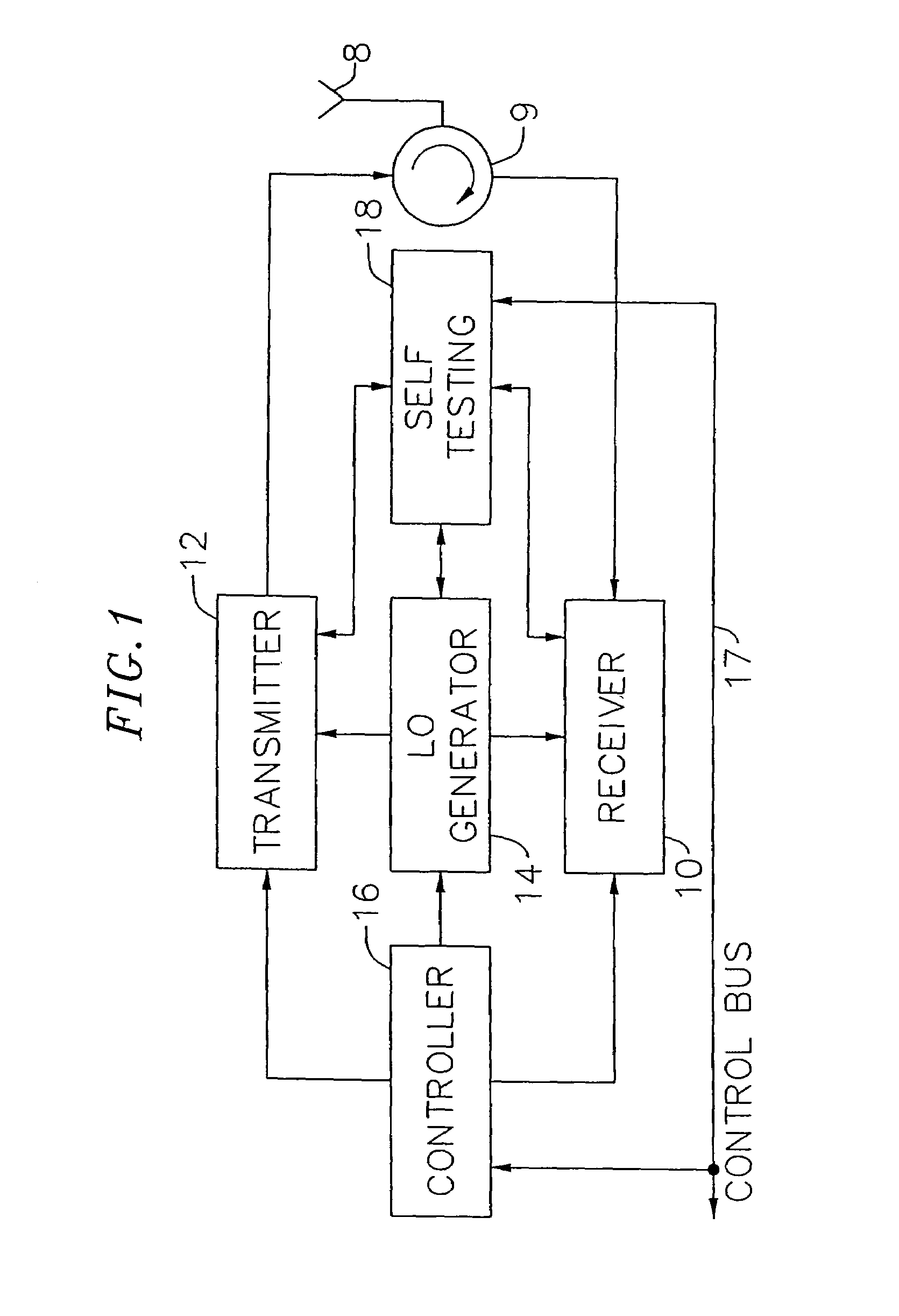

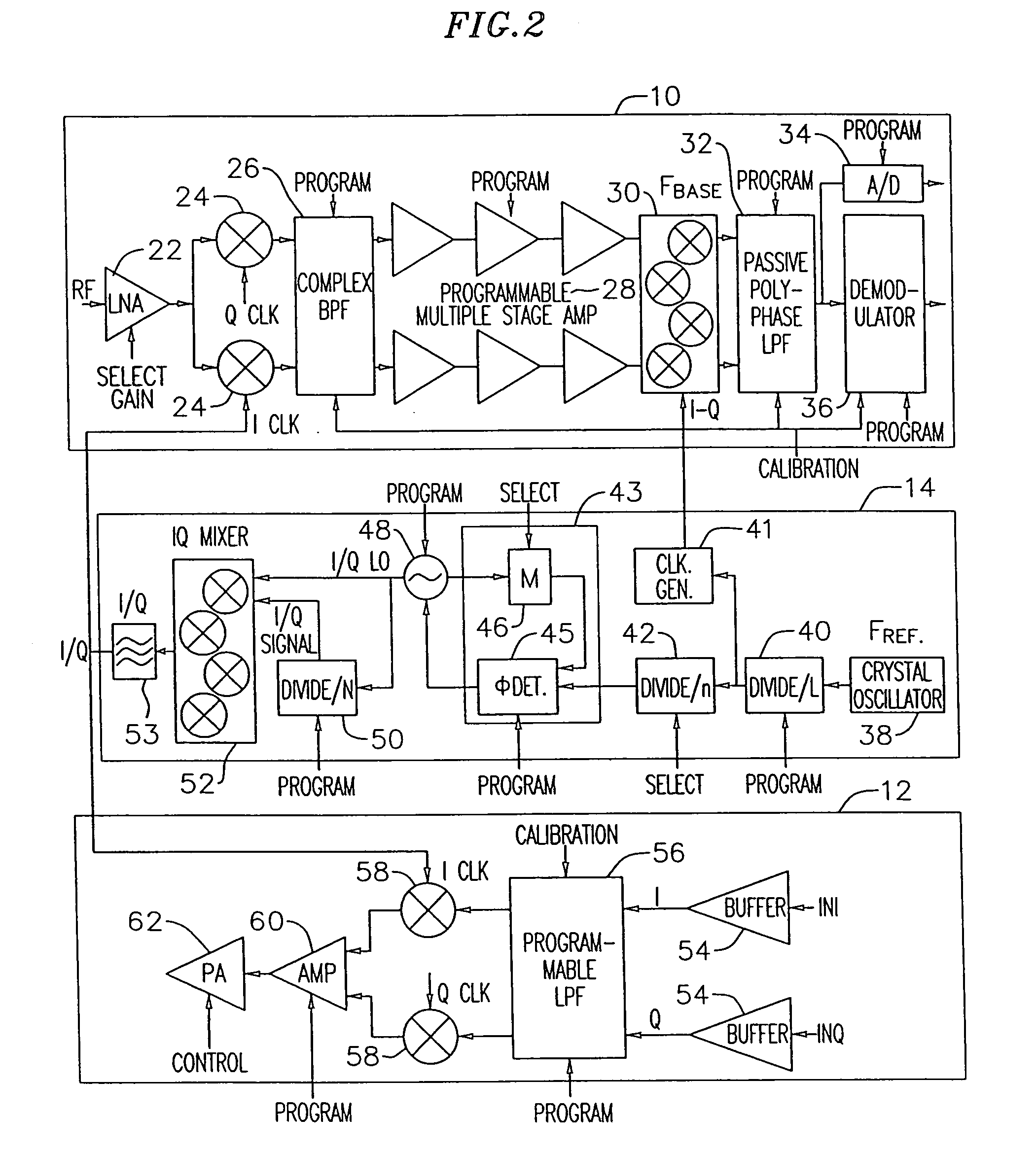

Adaptive radio transceiver with offset PLL with subsampling mixers

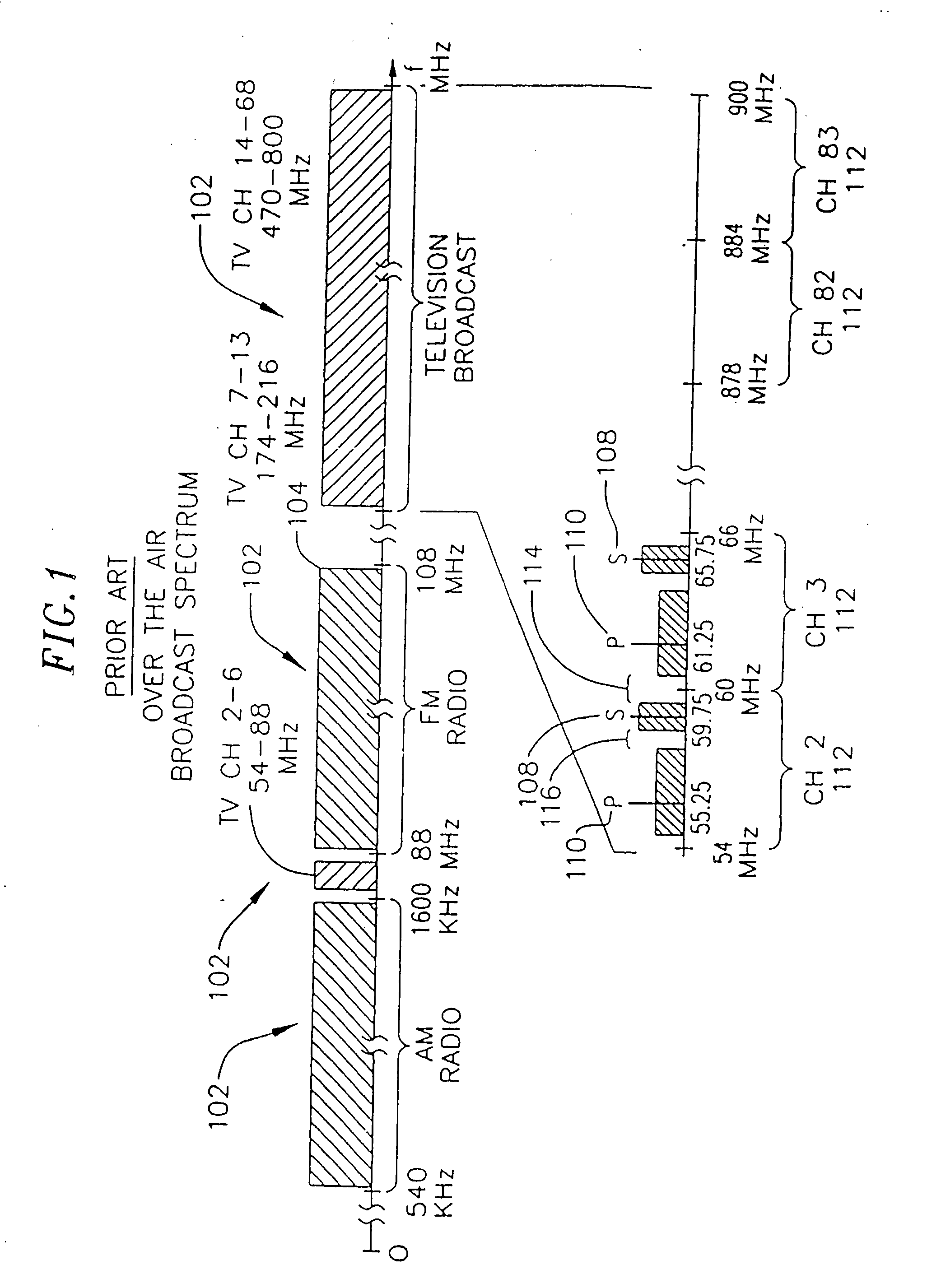

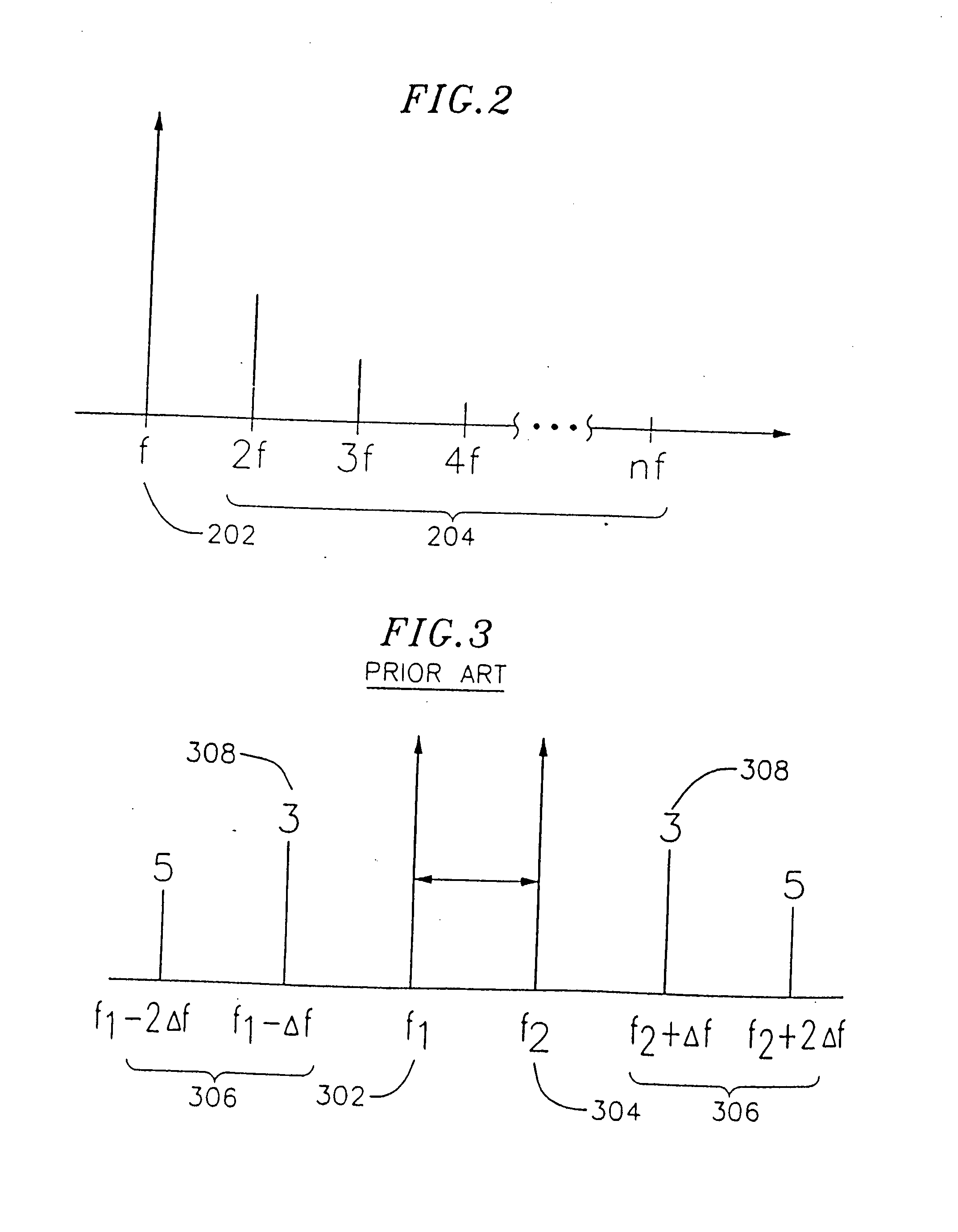

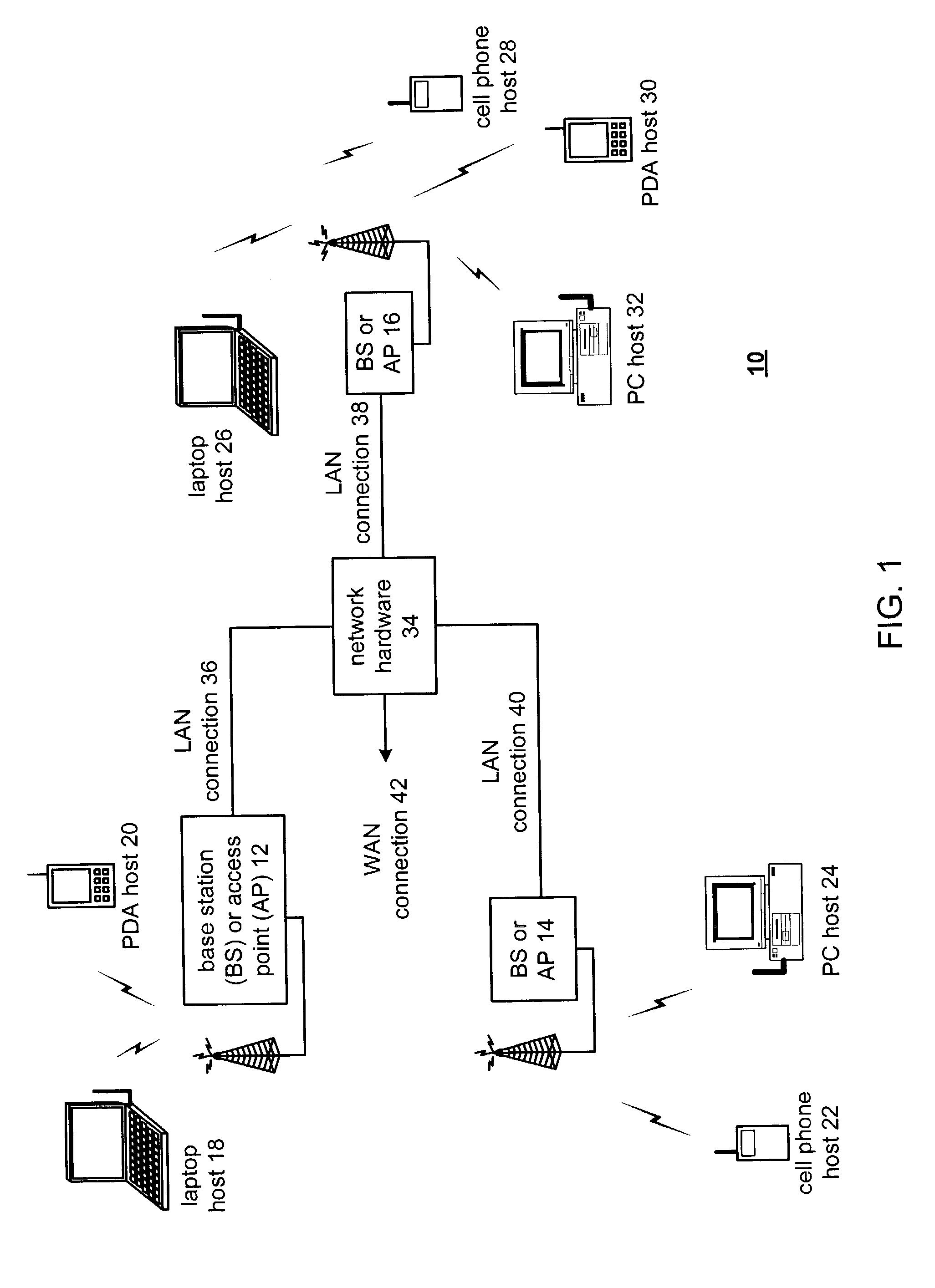

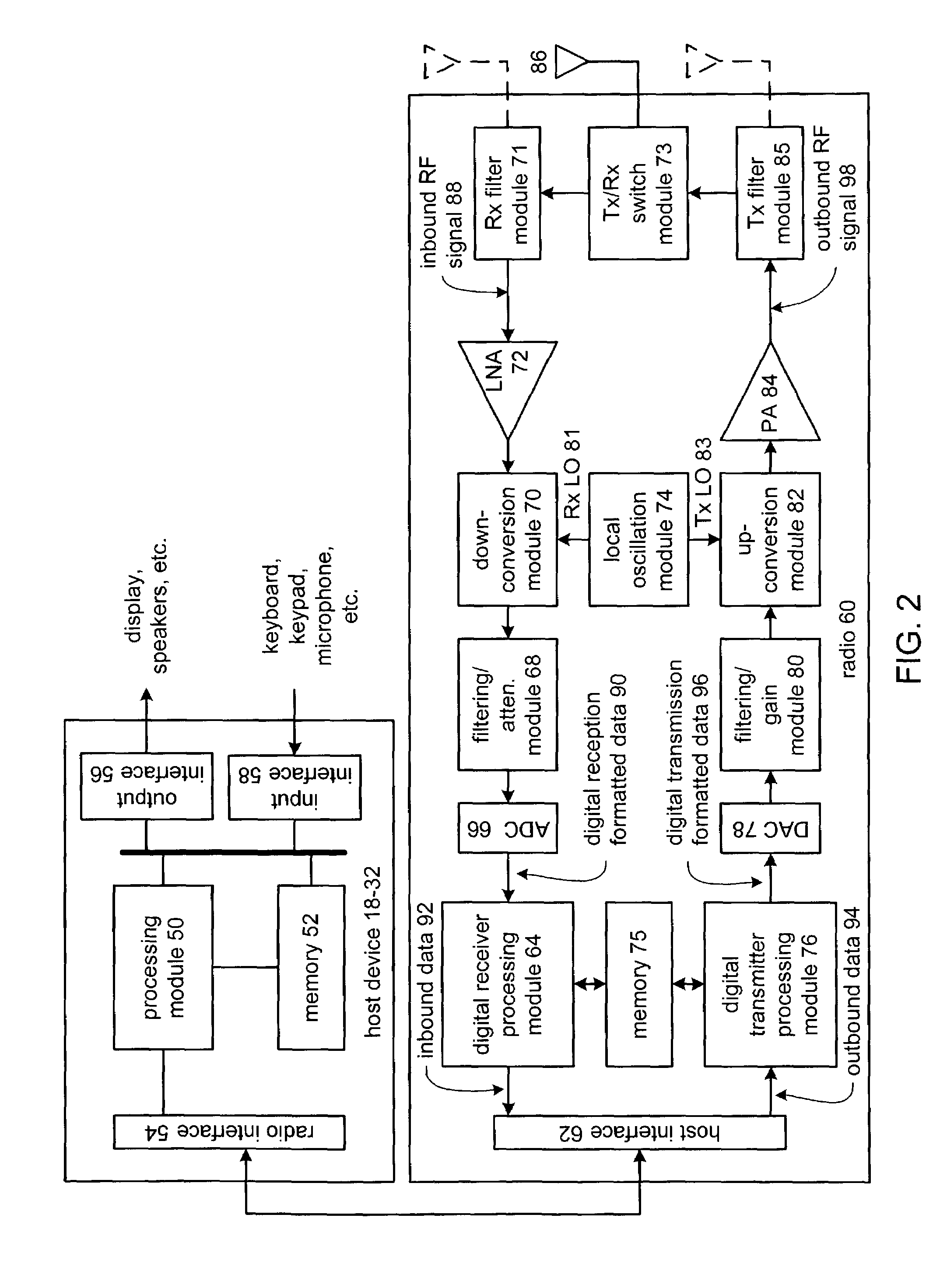

InactiveUS20050186930A1Minimize adverse effectsReduce power consumptionTransmitters monitoringResonant long antennasTransceiverAdaptive programming

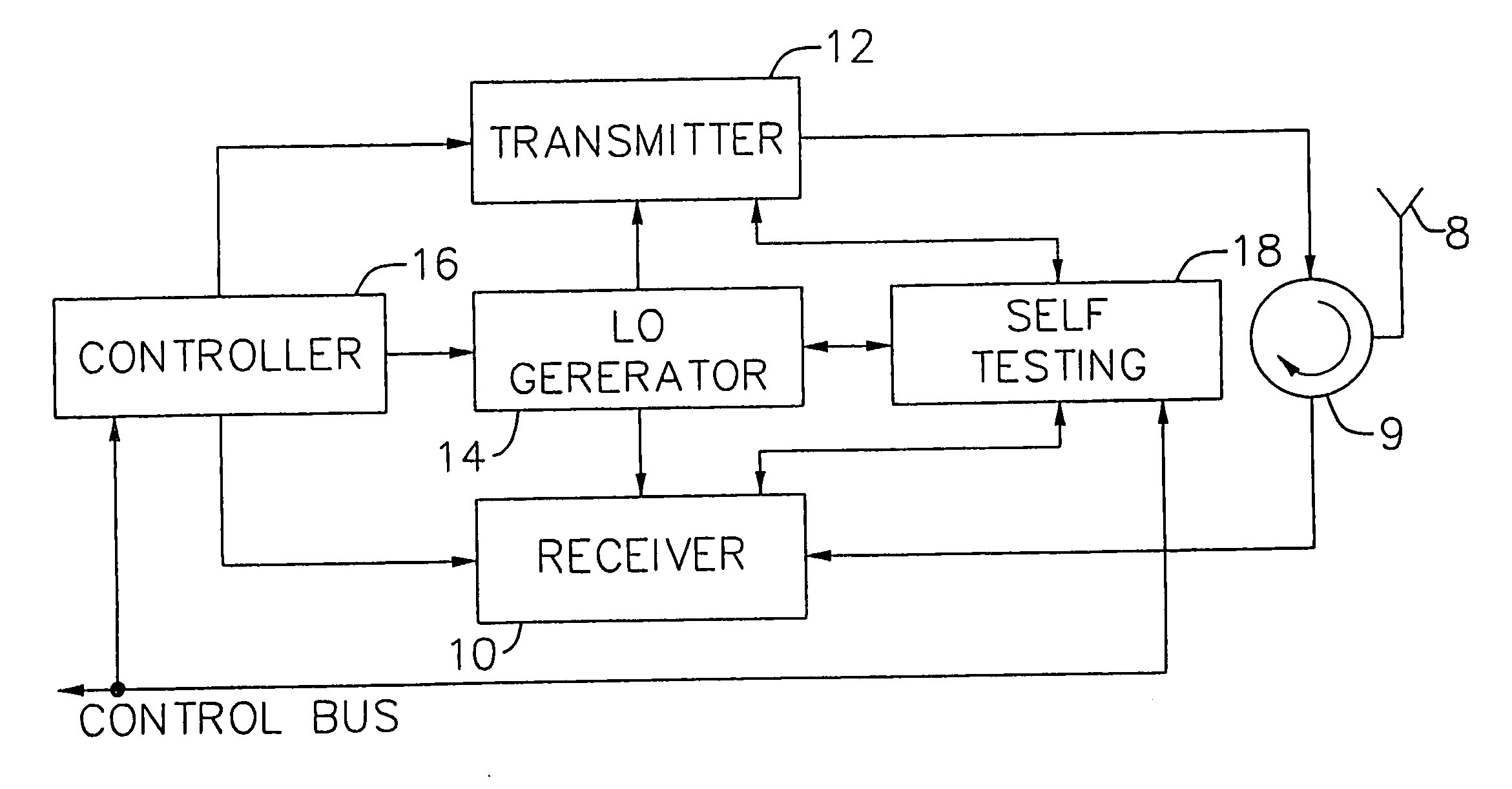

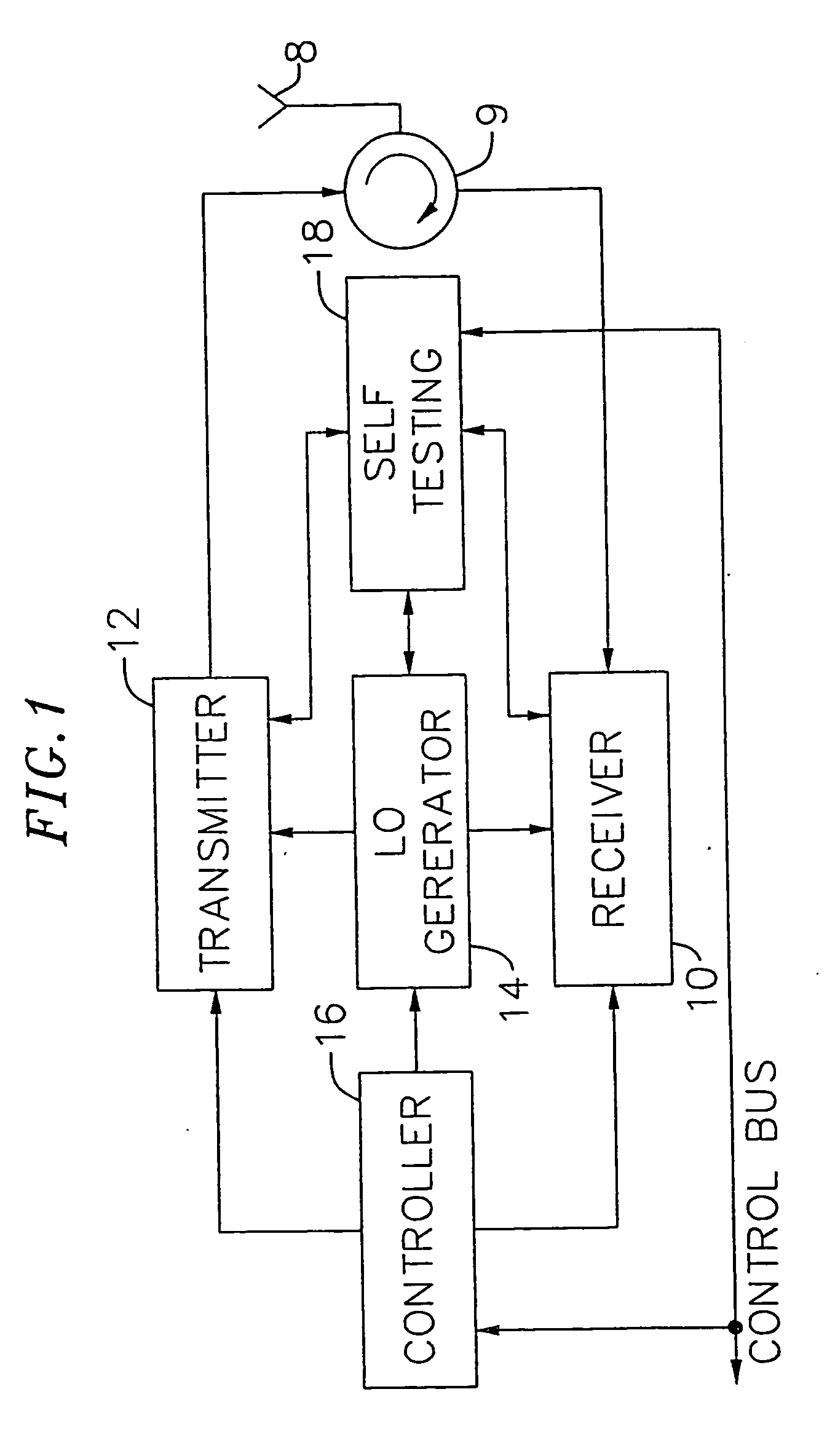

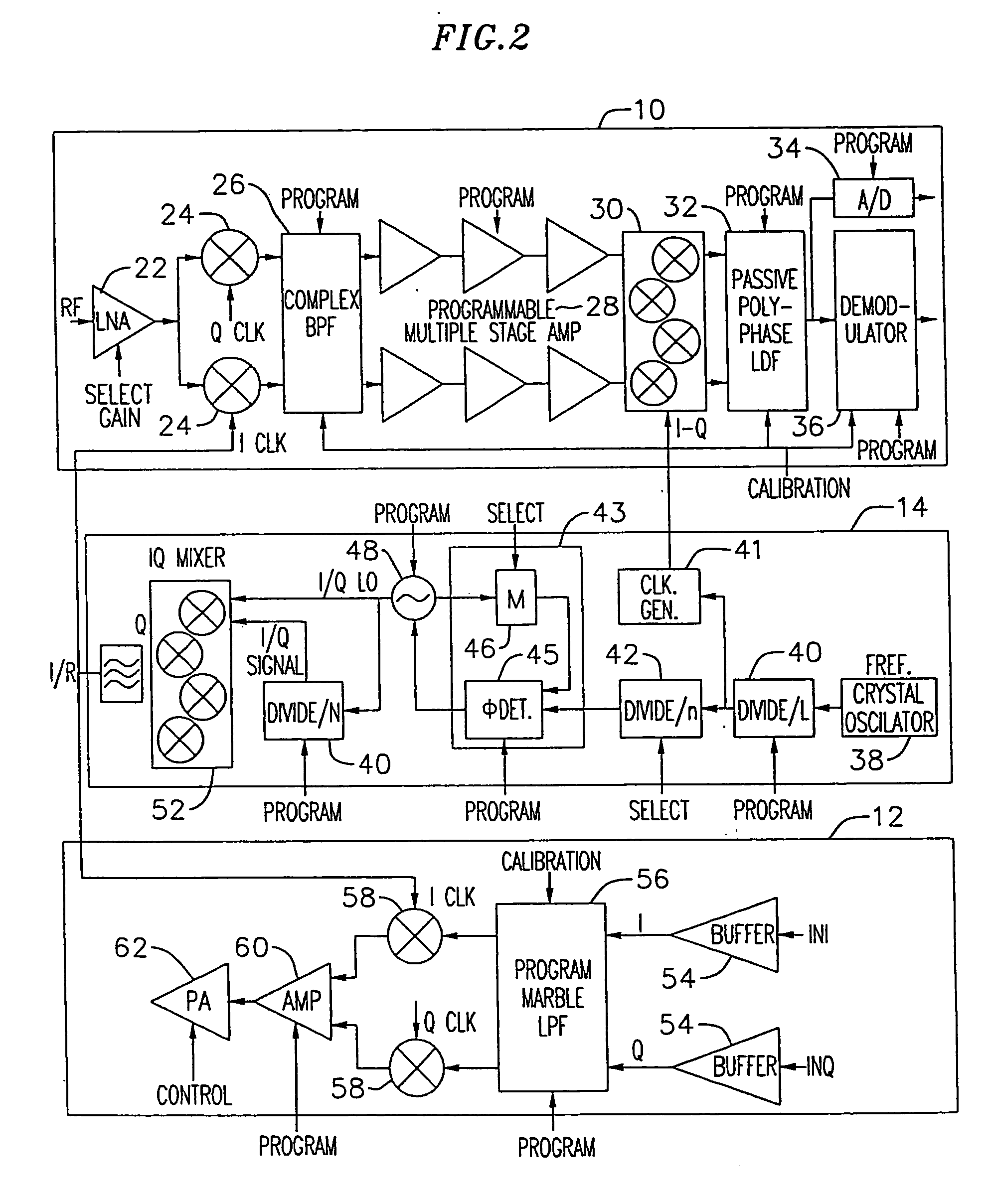

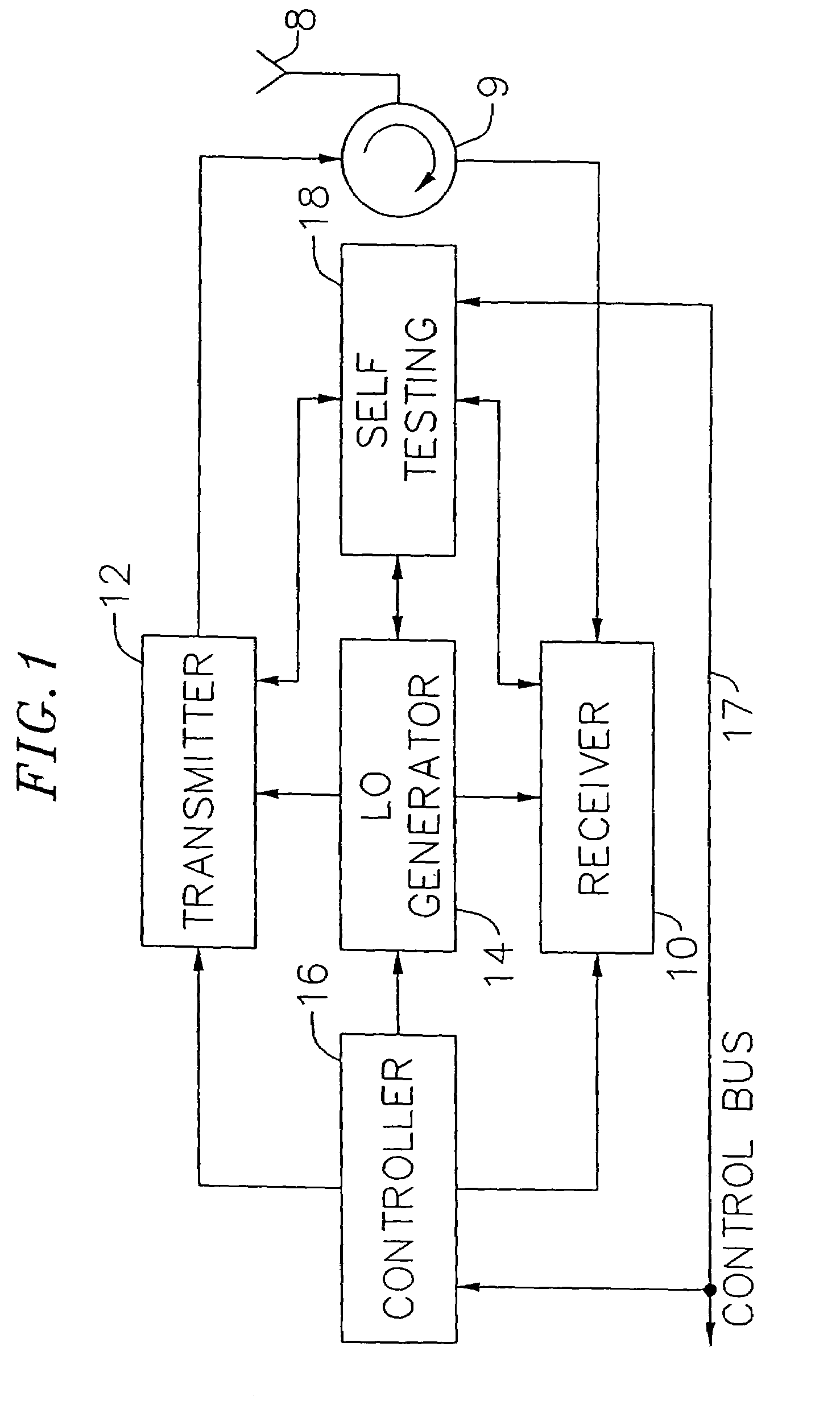

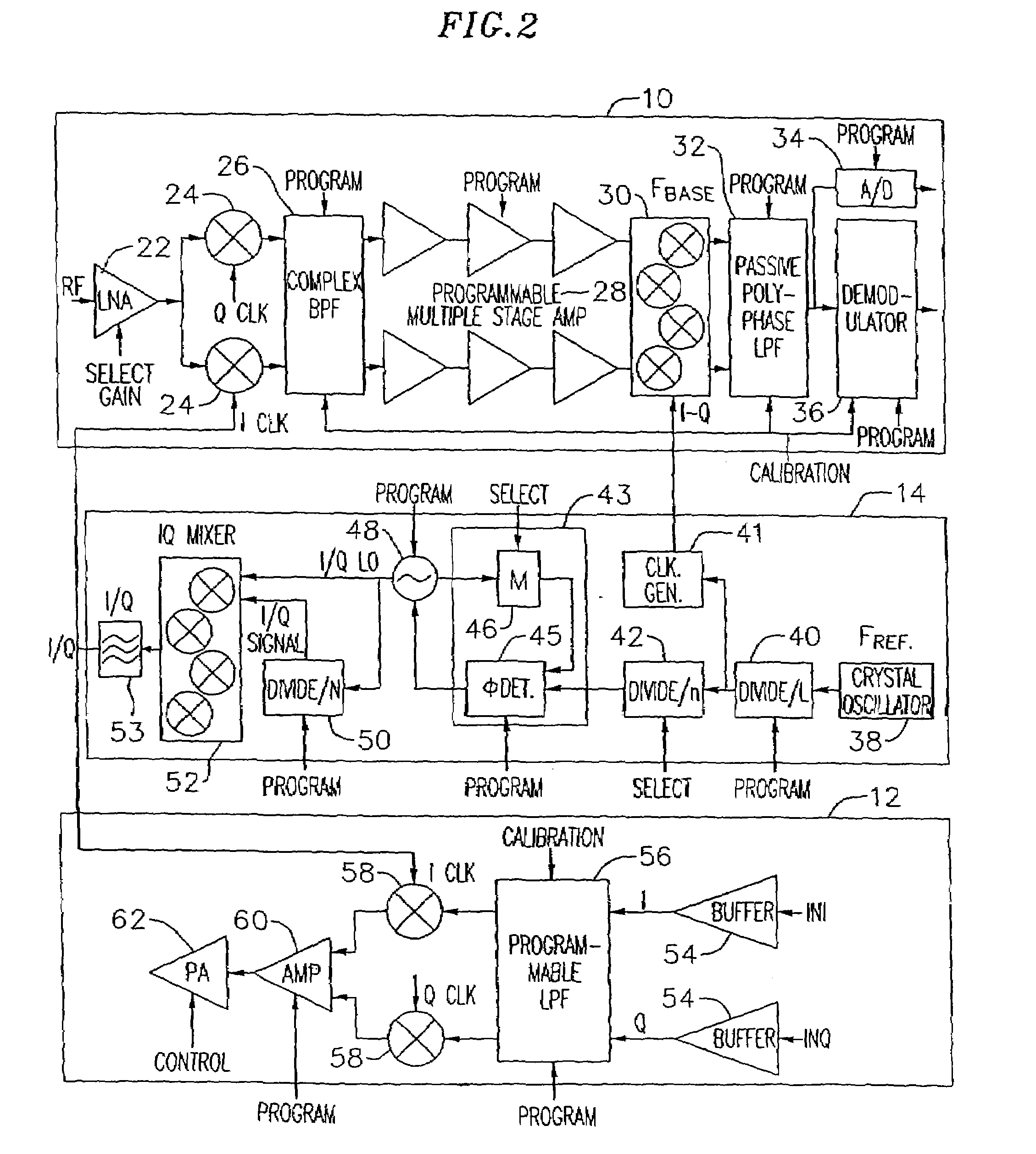

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

Multi-track integrated spiral inductor

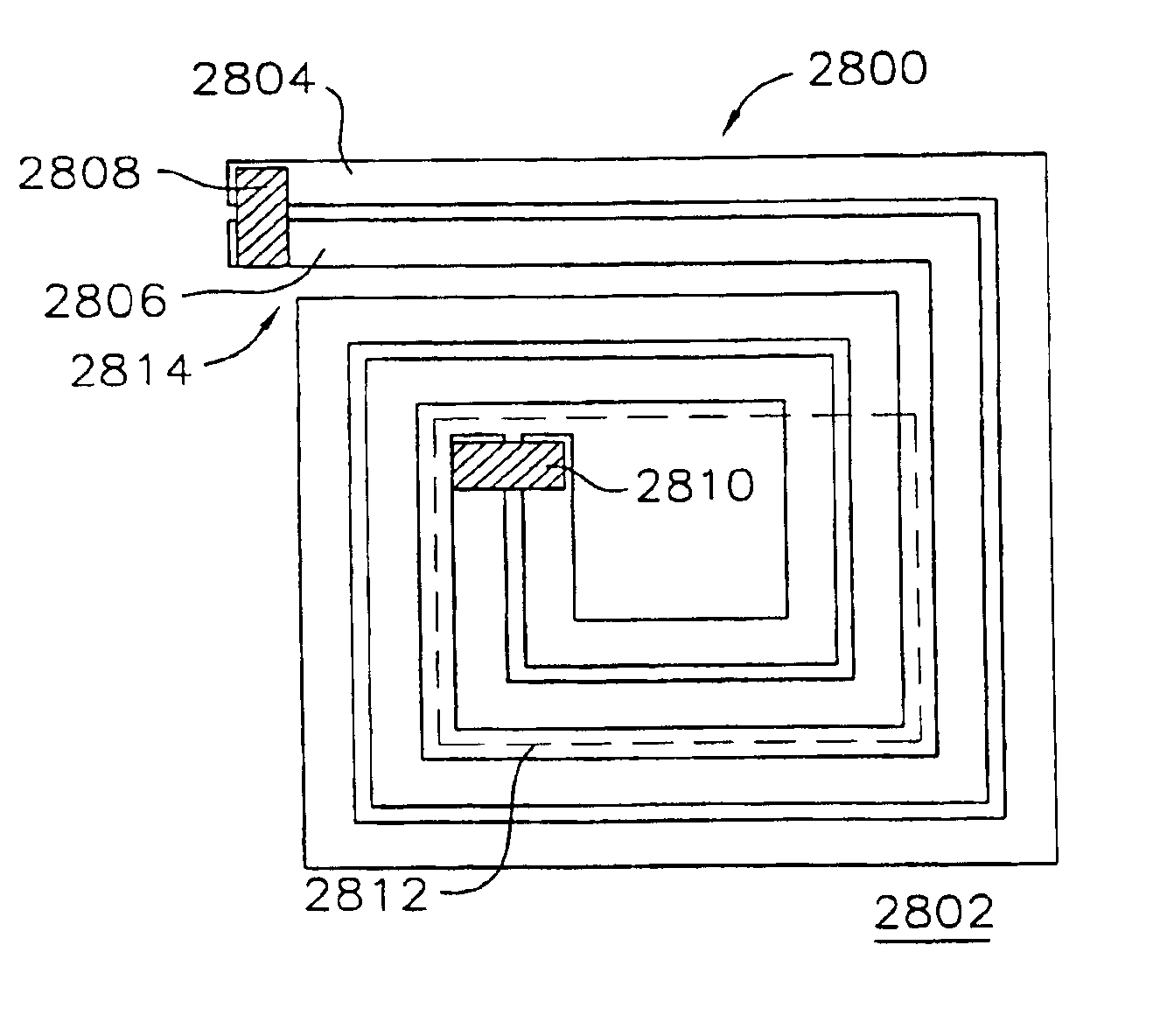

InactiveUS6885275B1Resonant circuit detailsSemiconductor/solid-state device detailsSpiral inductorEngineering

An integrated circuit inductor includes a spiral pattern disposed upon a substrate. The track of the spiral is divided into multiple tracks to form a multi-track inductor. The individual tracks are disposed side by side and in different layers. Tracks that are aligned vertically are coupled by feed throughs, or vias. Multiple vias are used along the length of each of the multiple tracks. Tracks disposed in the same layer are joined together at their beginning, and at their termination. A patterned shield is fabricated from conductive fingers of n+ salicided material that is separated by non conducting polysilicon that fills the gaps between the fingers. The conductive fingers are coupled together in groups, which are in turn tied to a single point ground. In tying the groups together, a gap in the conducting path is provided to prevent ground loop currents. The shield is disposed between the multi-track inductor and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

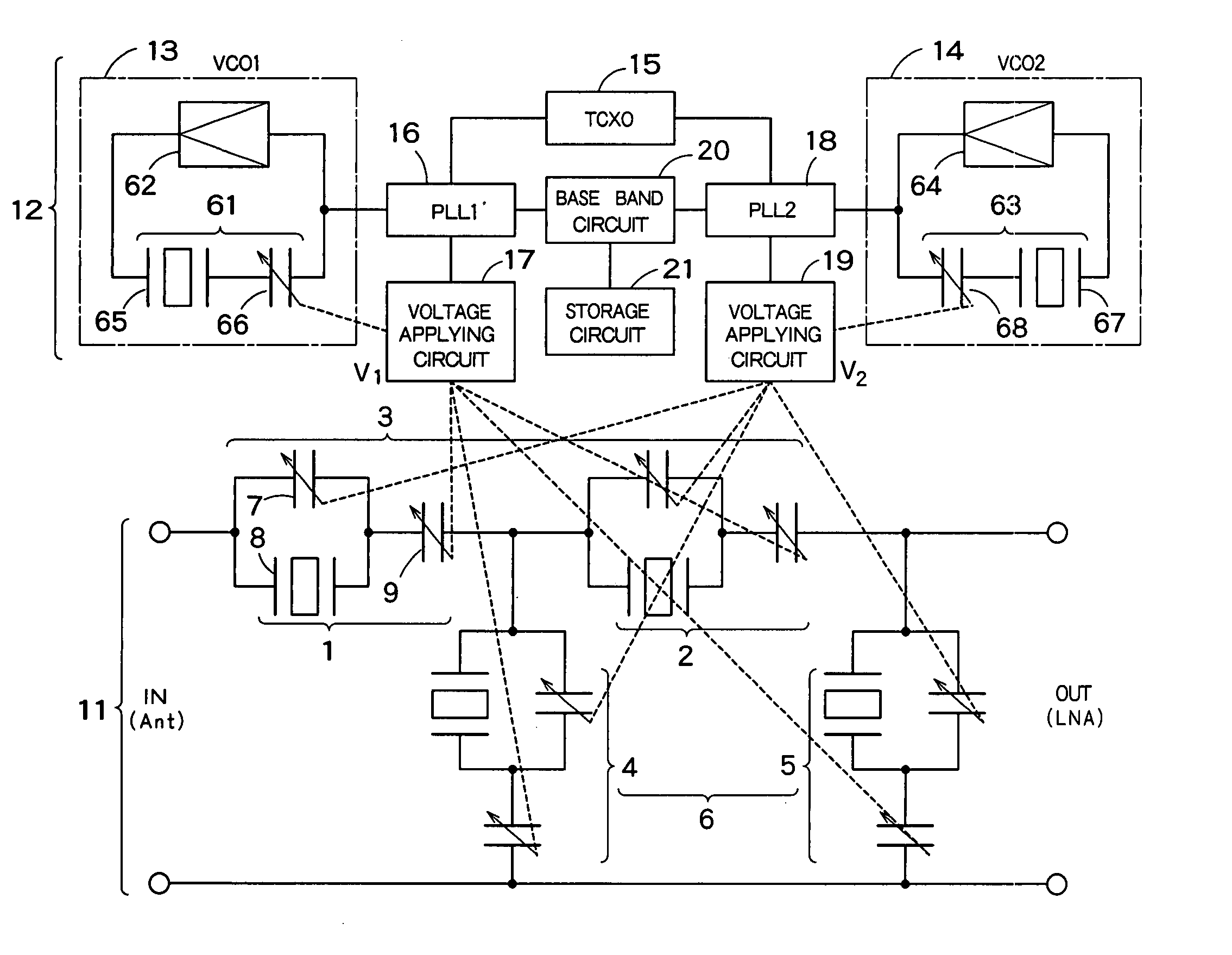

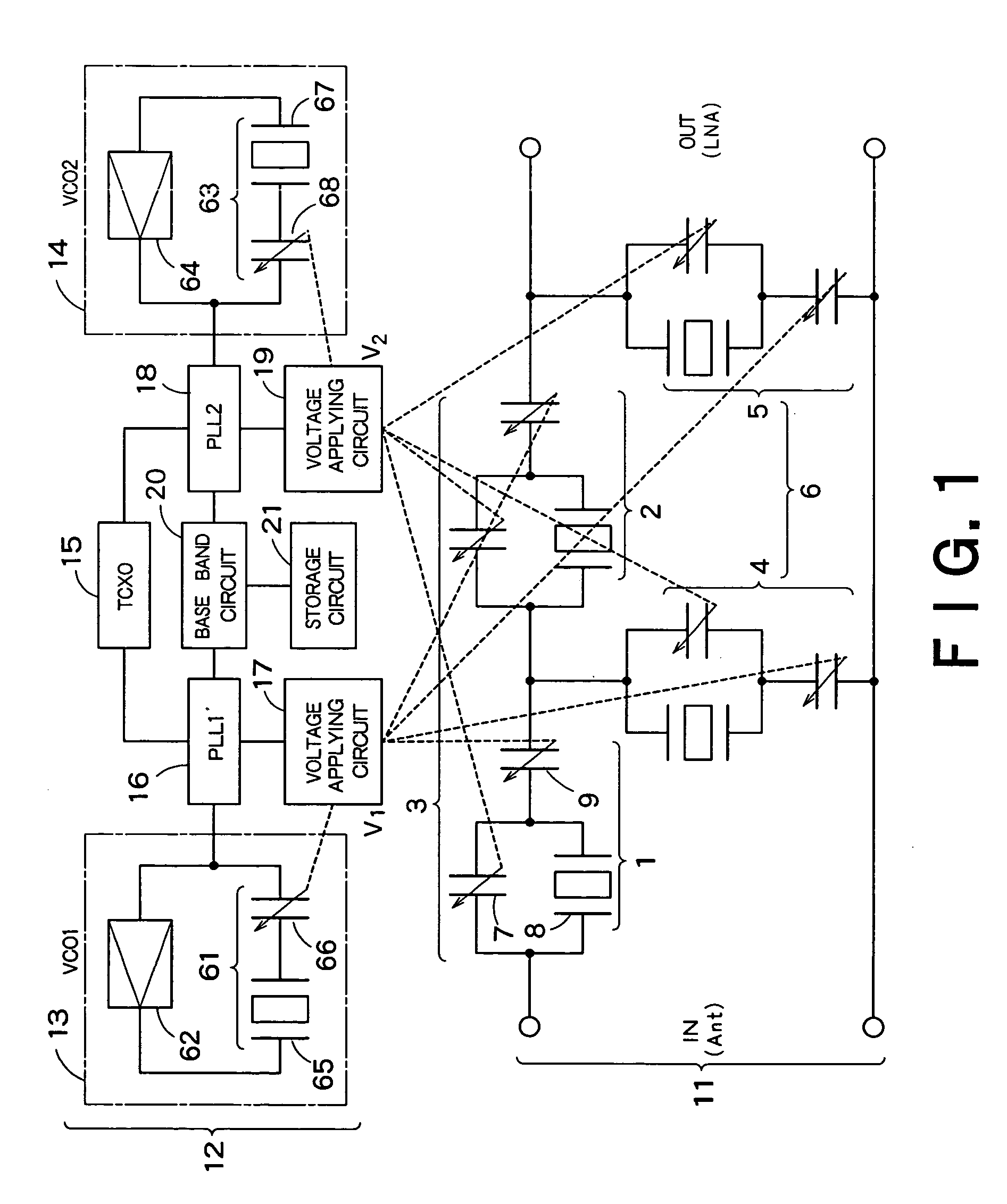

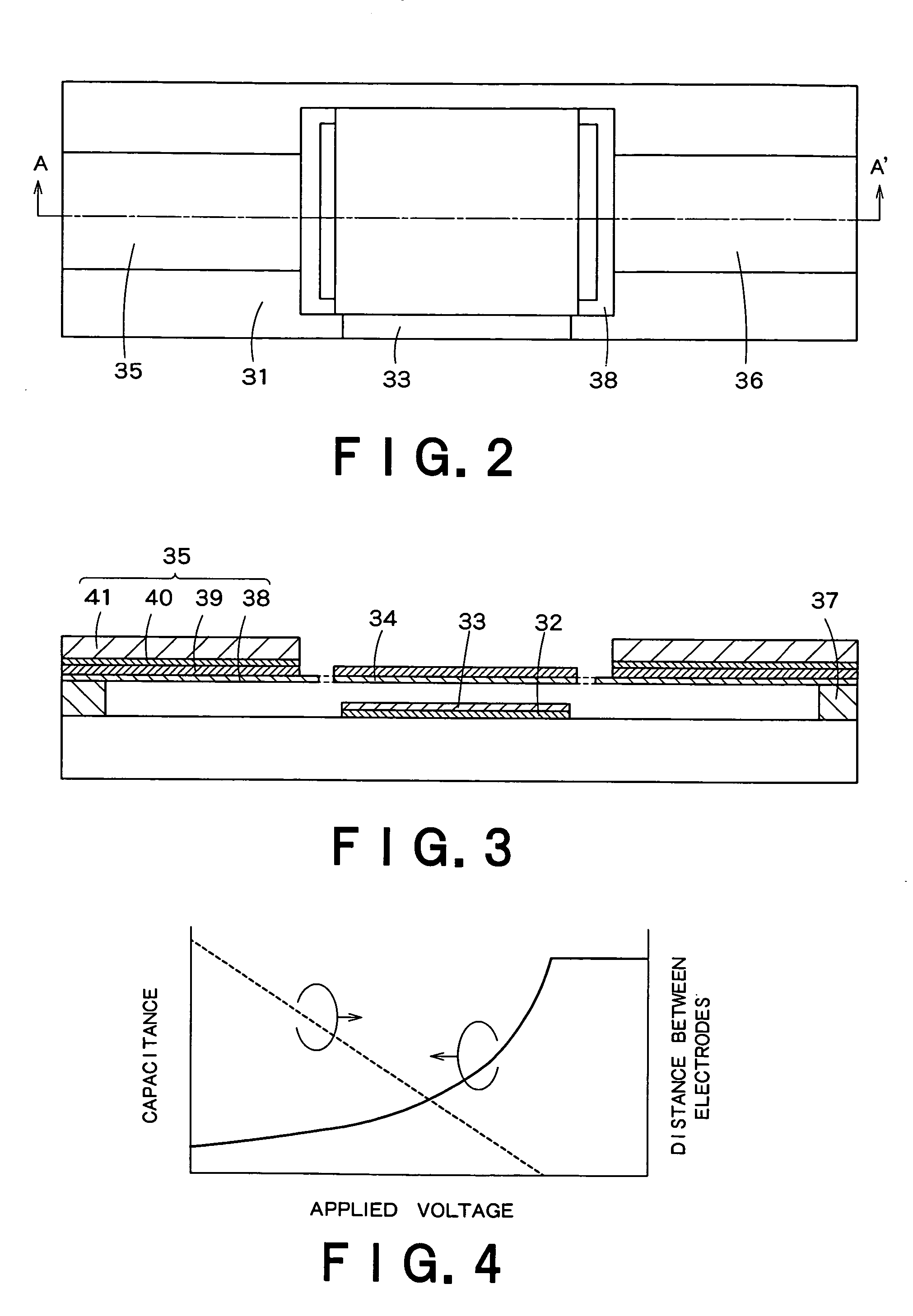

Tunable filter and portable telephone

InactiveUS20050212612A1Low insertion lossImprove reliabilityMultiple-port networksTransmission control/equlisationCapacitanceEngineering

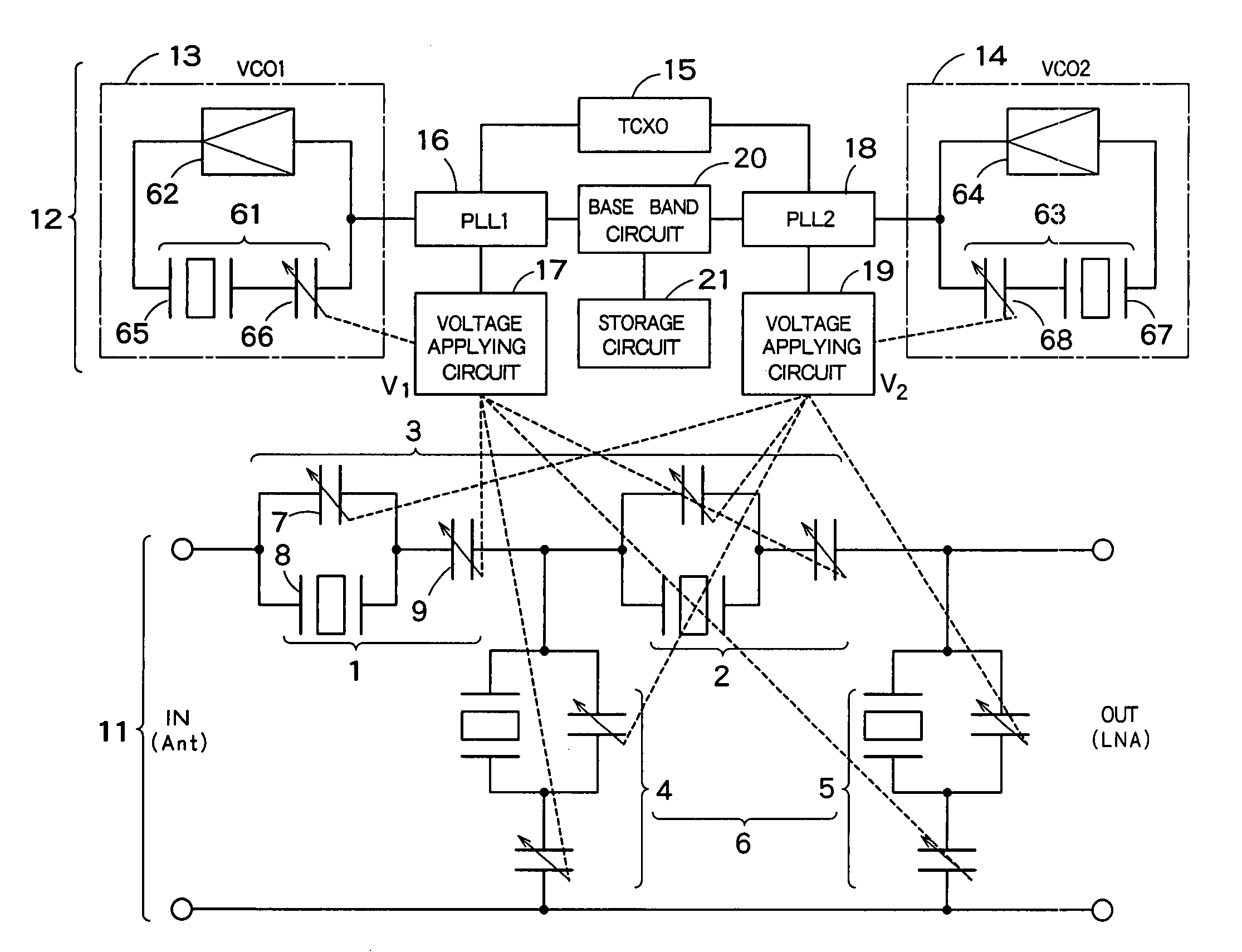

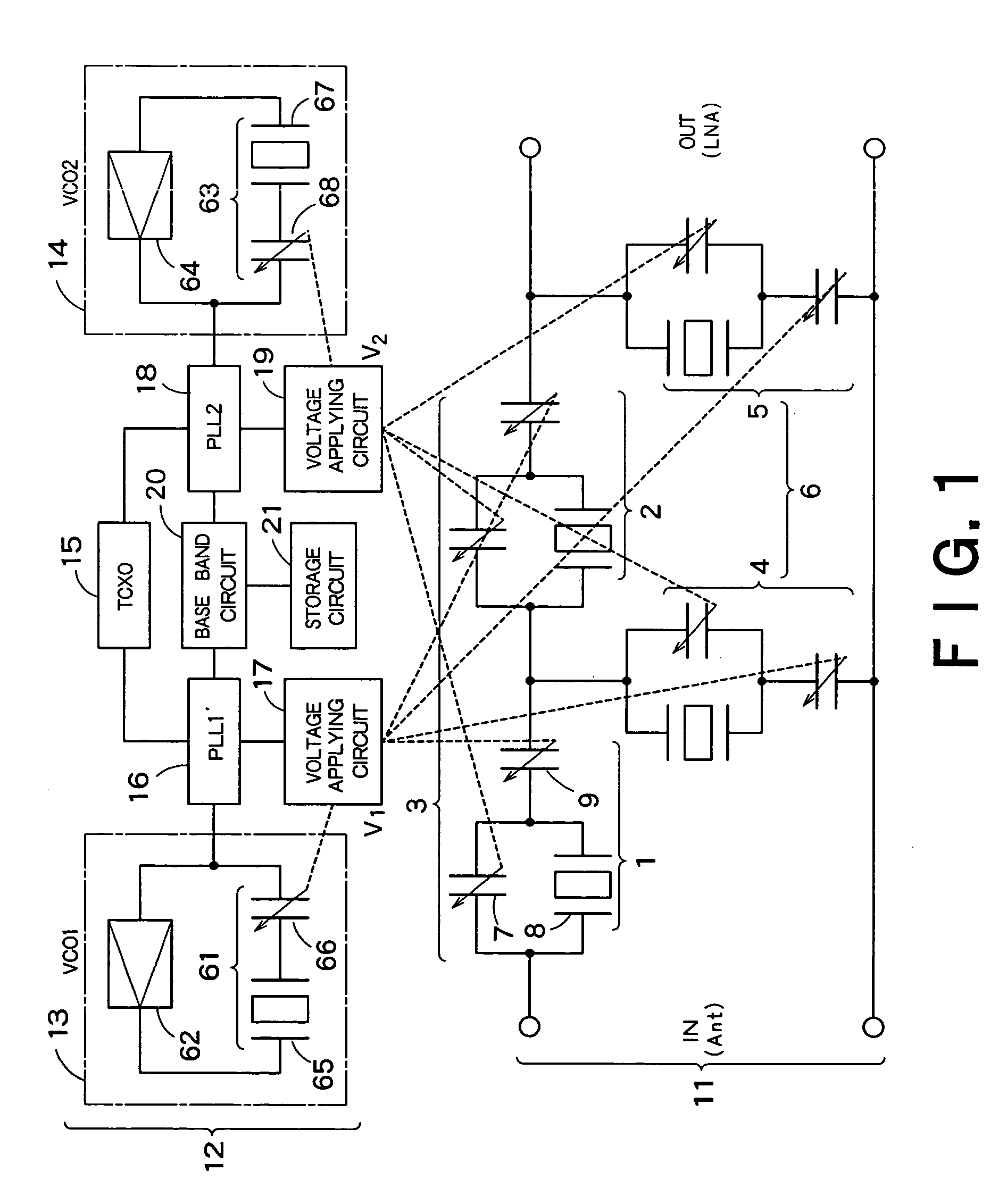

A tunable filter has a plurality of variable capacitors and a plurality of inductor elements, each being formed on a common substrate, a filter circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a monitor circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a detecting circuit which detects a prescribed circuit constant of the monitor circuit, a storage which stores information relating to a reference circuit constant of the monitor circuit, and a capacitance control circuit which controls capacitance of the variable capacitors in the monitor circuit and capacitance of the variable capacitors in the filter circuit, based on a result detected by the detecting circuit and information stored in the storage.

Owner:KK TOSHIBA

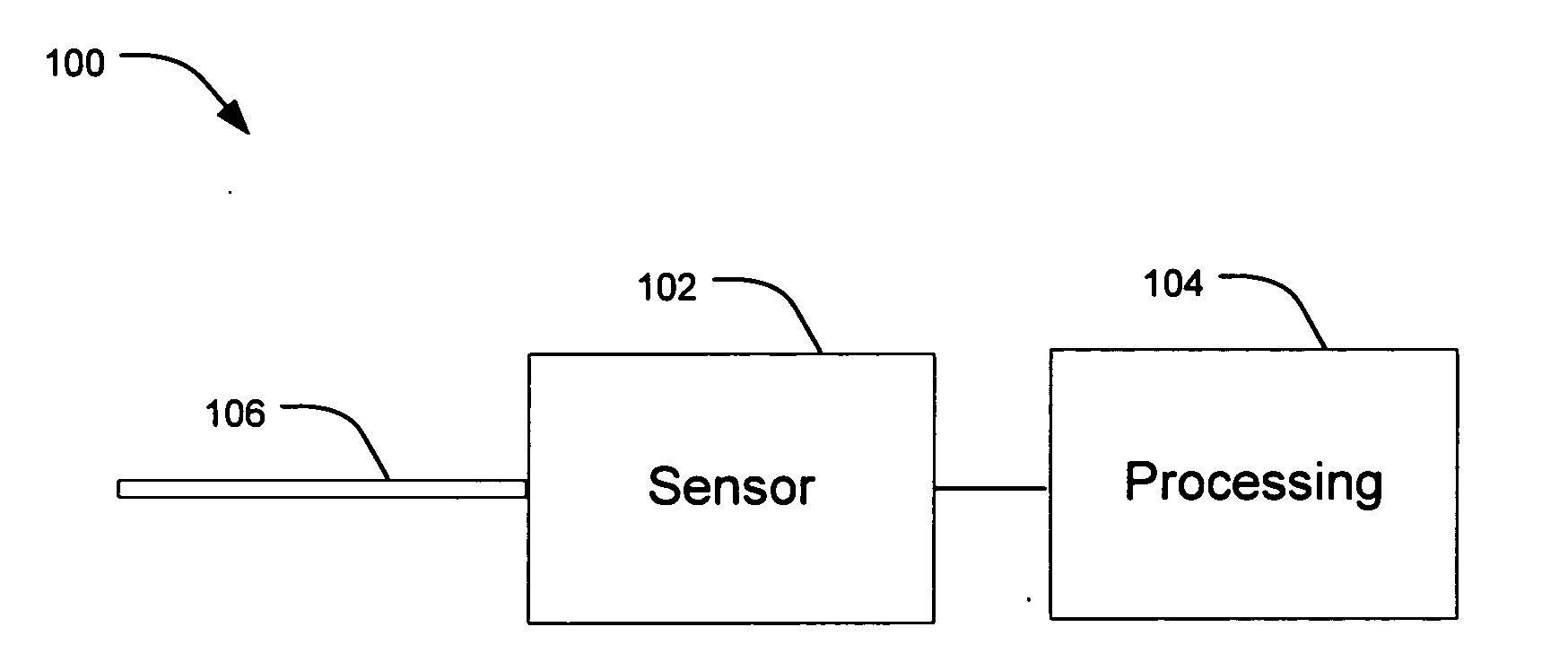

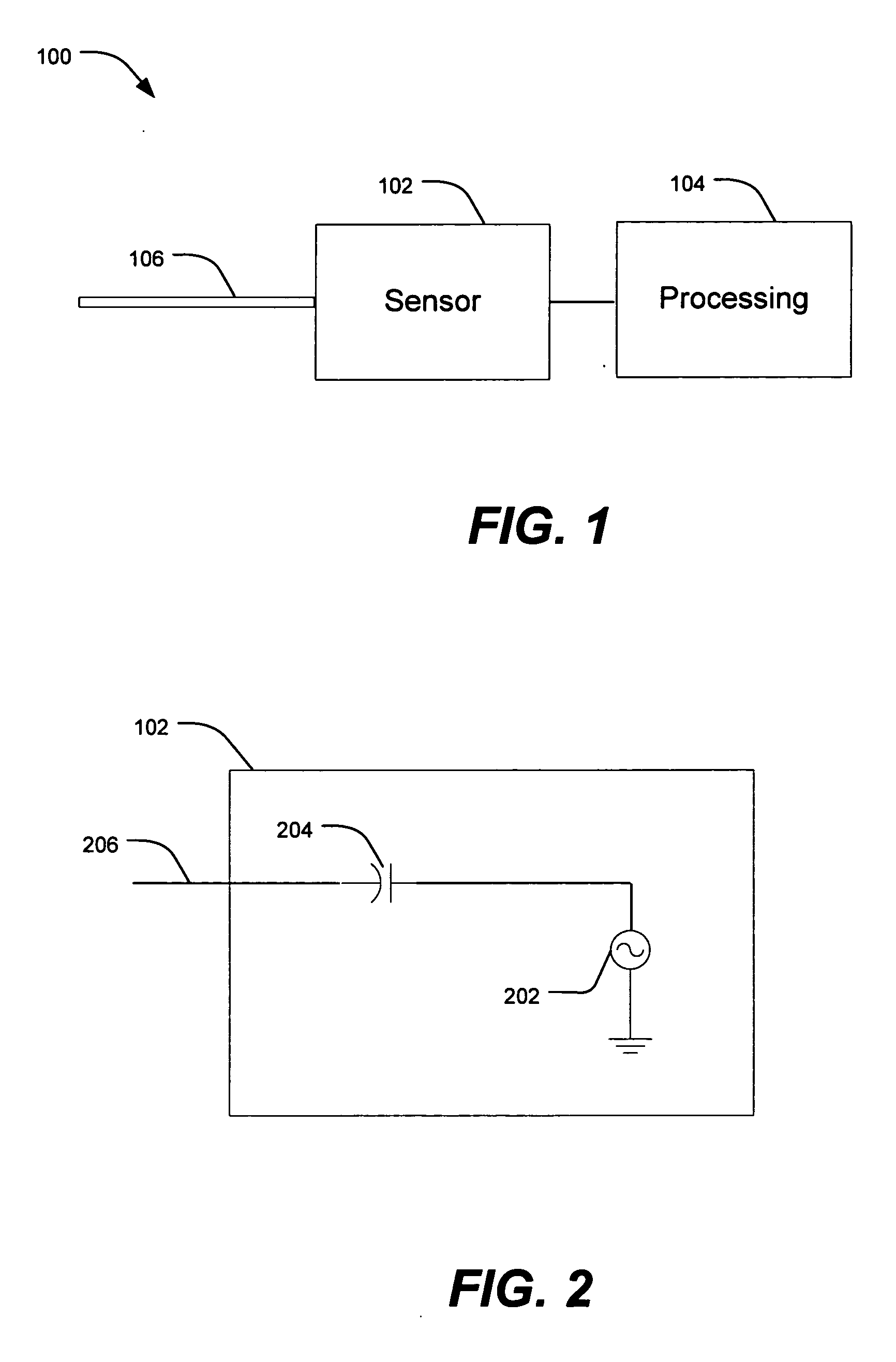

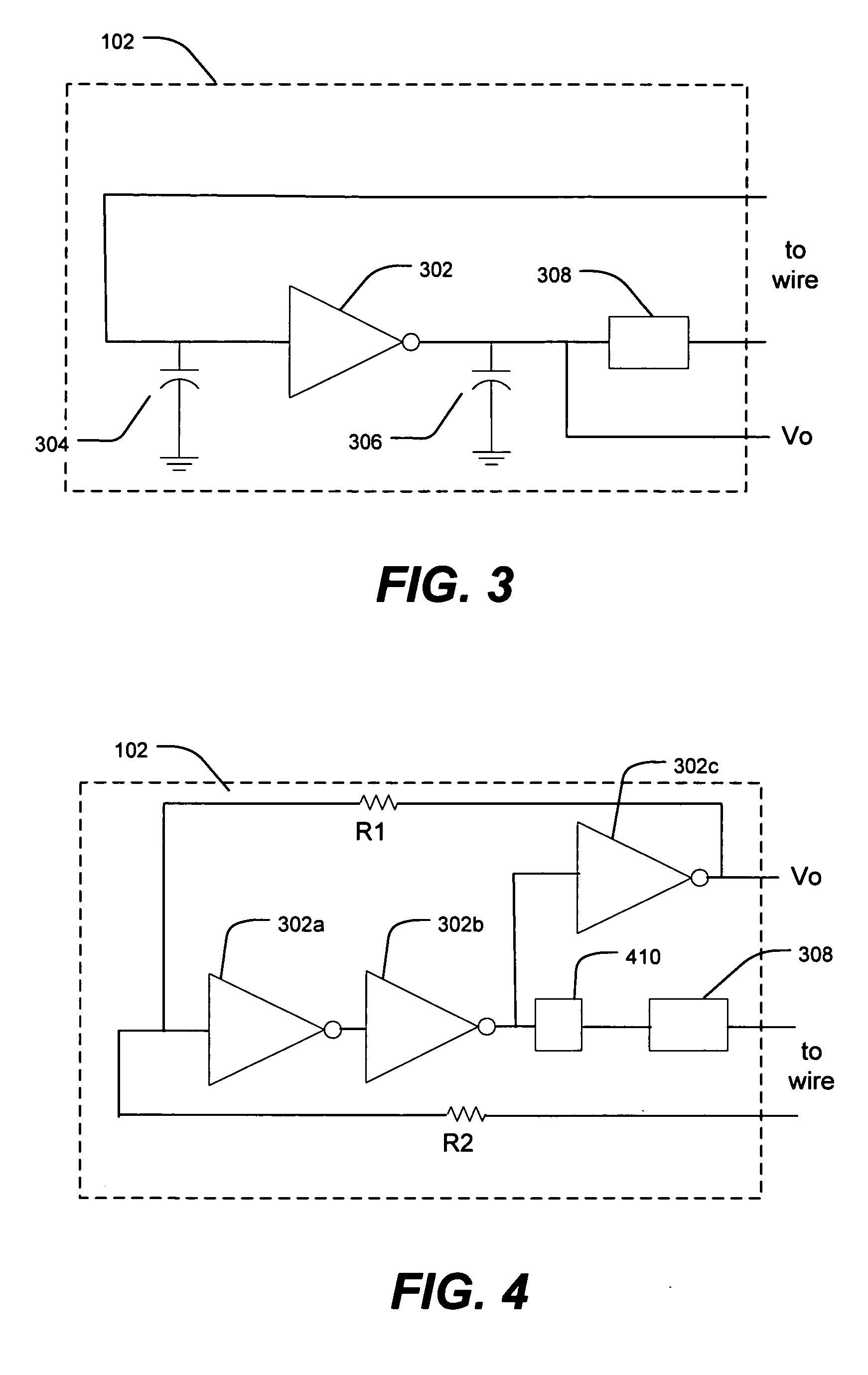

Device and method for detecting anomolies in a wire and related sensing methods

ActiveUS20060061368A1Multiple-port networksSparking plugsElectrical and Electronics engineeringShort circuit

Owner:UNIV OF UTAH RES FOUND

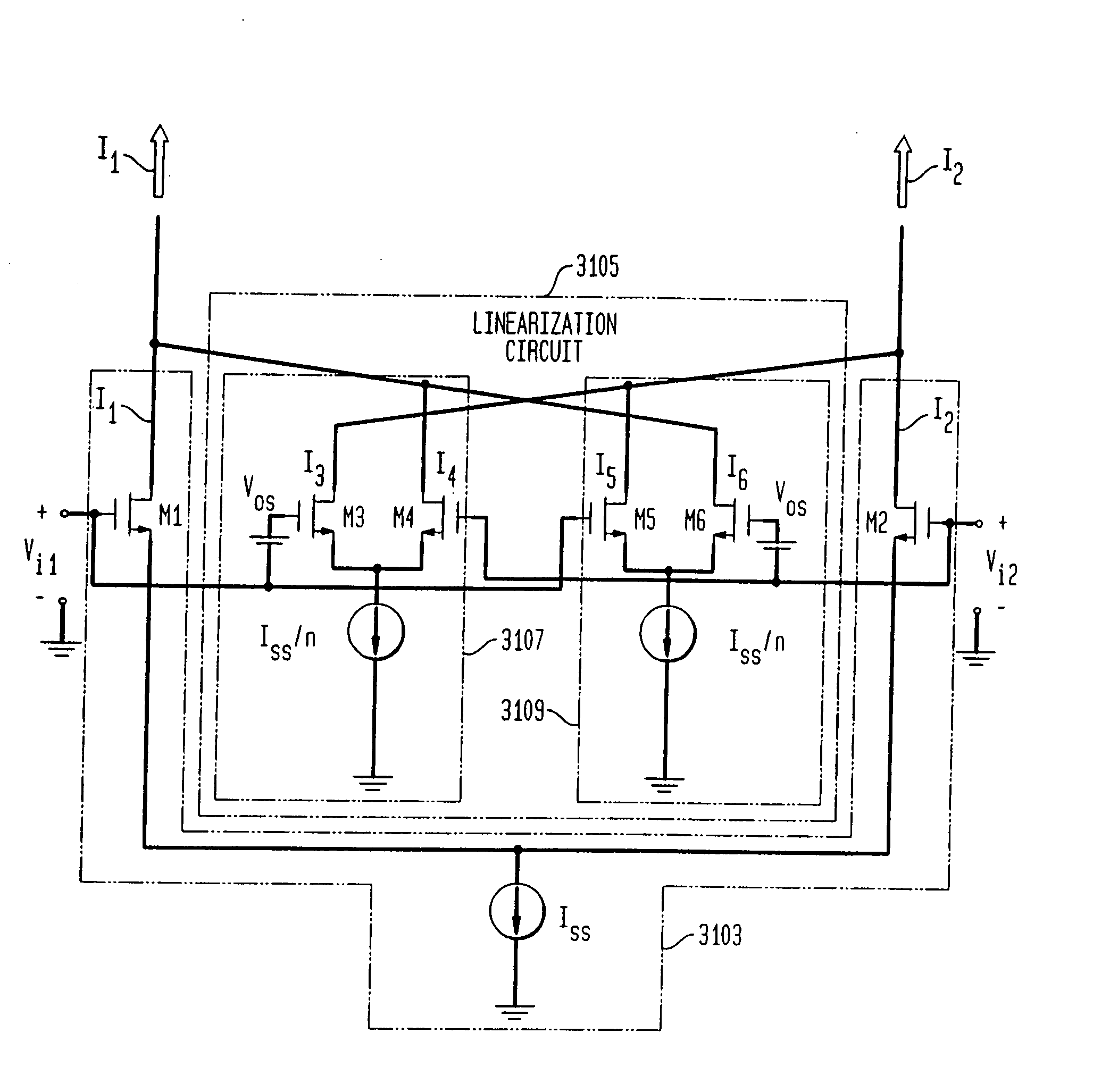

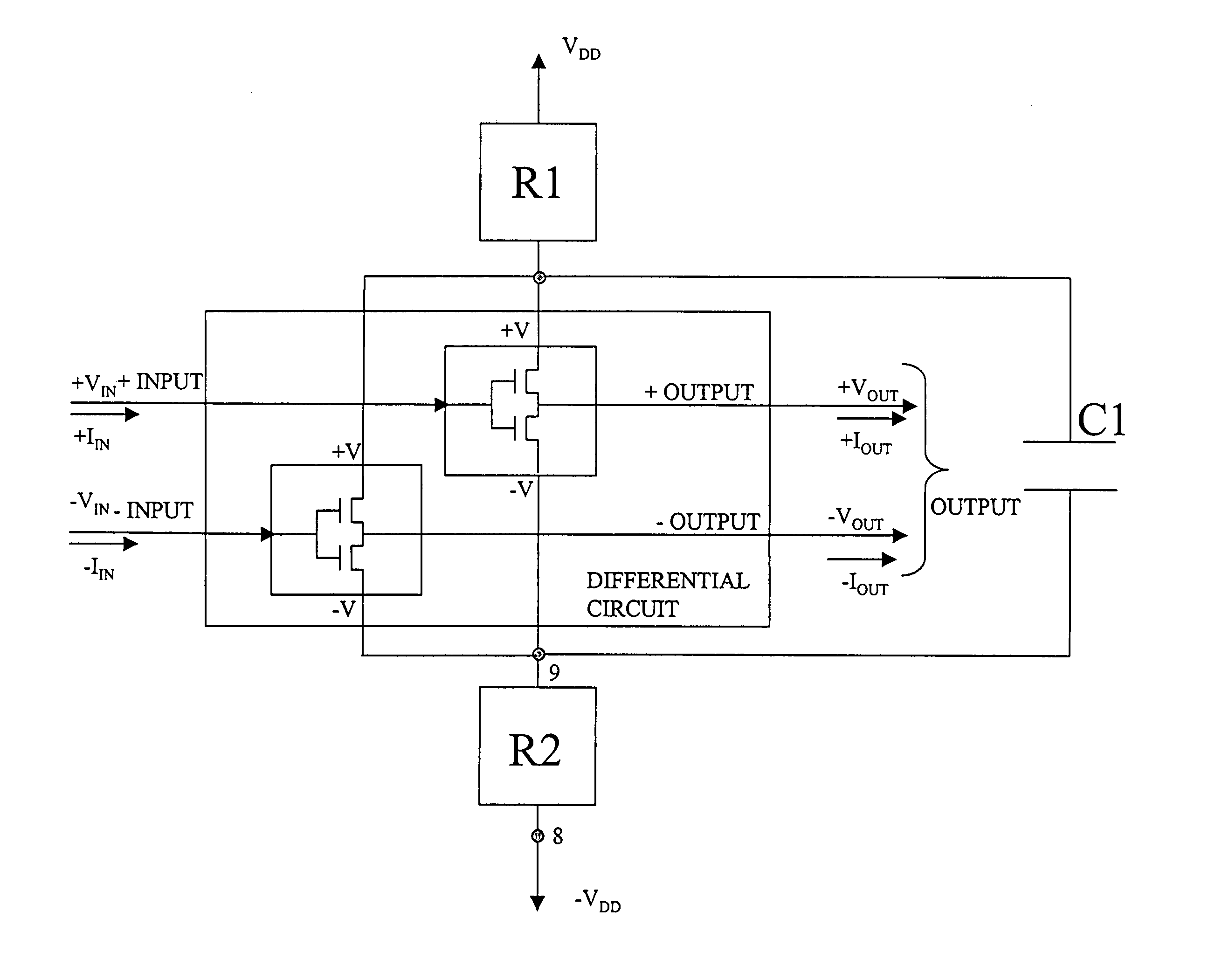

Low-voltage transconductance amplifier/filters

InactiveUS6704560B1Amplifier modifications to reduce non-linear distortionDifferential amplifiersAudio power amplifierLow voltage

Wireless communications devices must handle a wide range of useful signal levels and must also cope with large interfering signals of nearby frequencies. They often use transconductance amplifiers / filters as building blocks as such amplifier / filters exhibit good characteristics of both amplification and filtering. The transconductance cells described make use of feedbacks which involve no signal conversions. As the result, the cells have high linearity and yet can operate at low voltage.

Owner:SKYWORKS SOLUTIONS INC

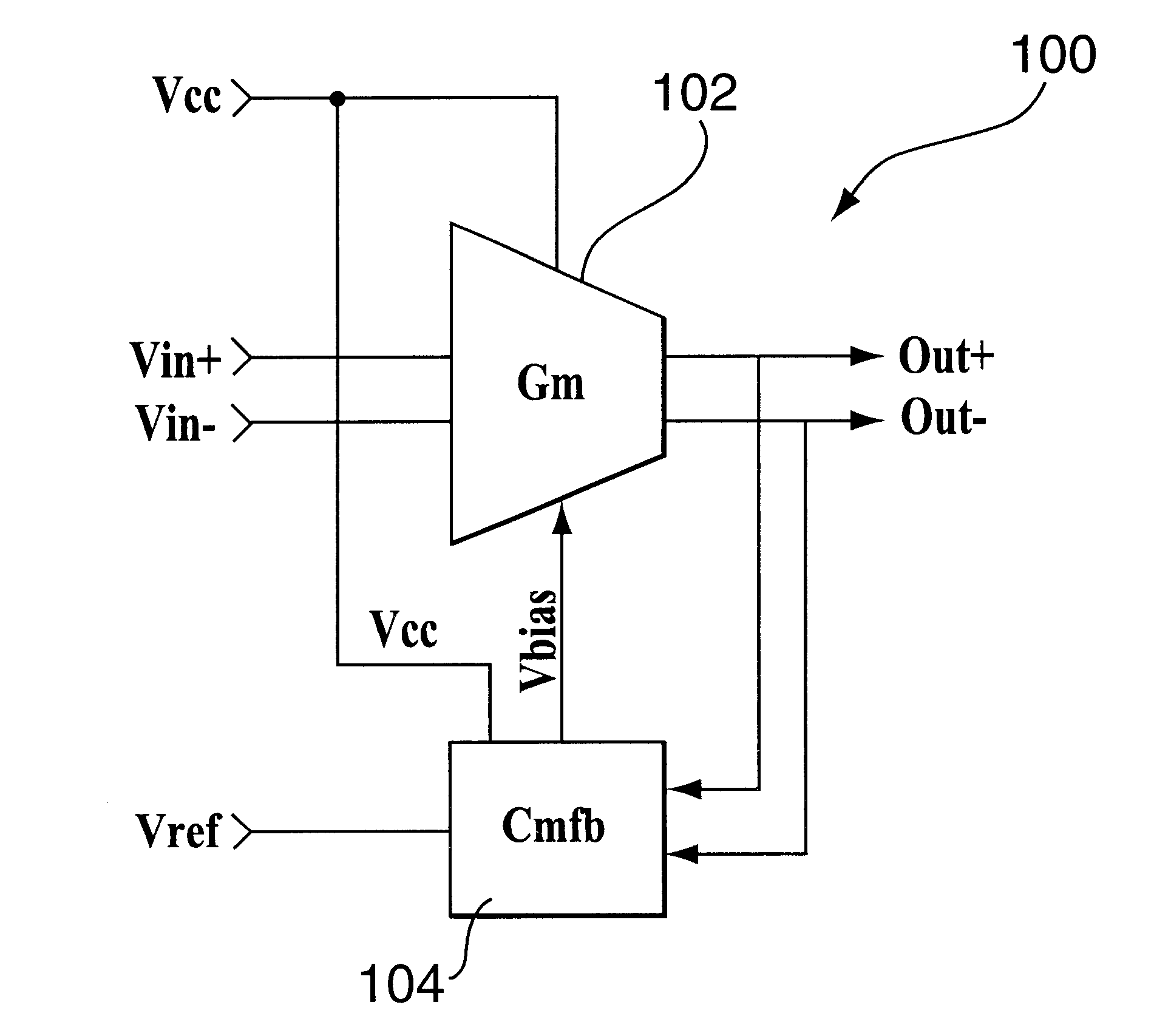

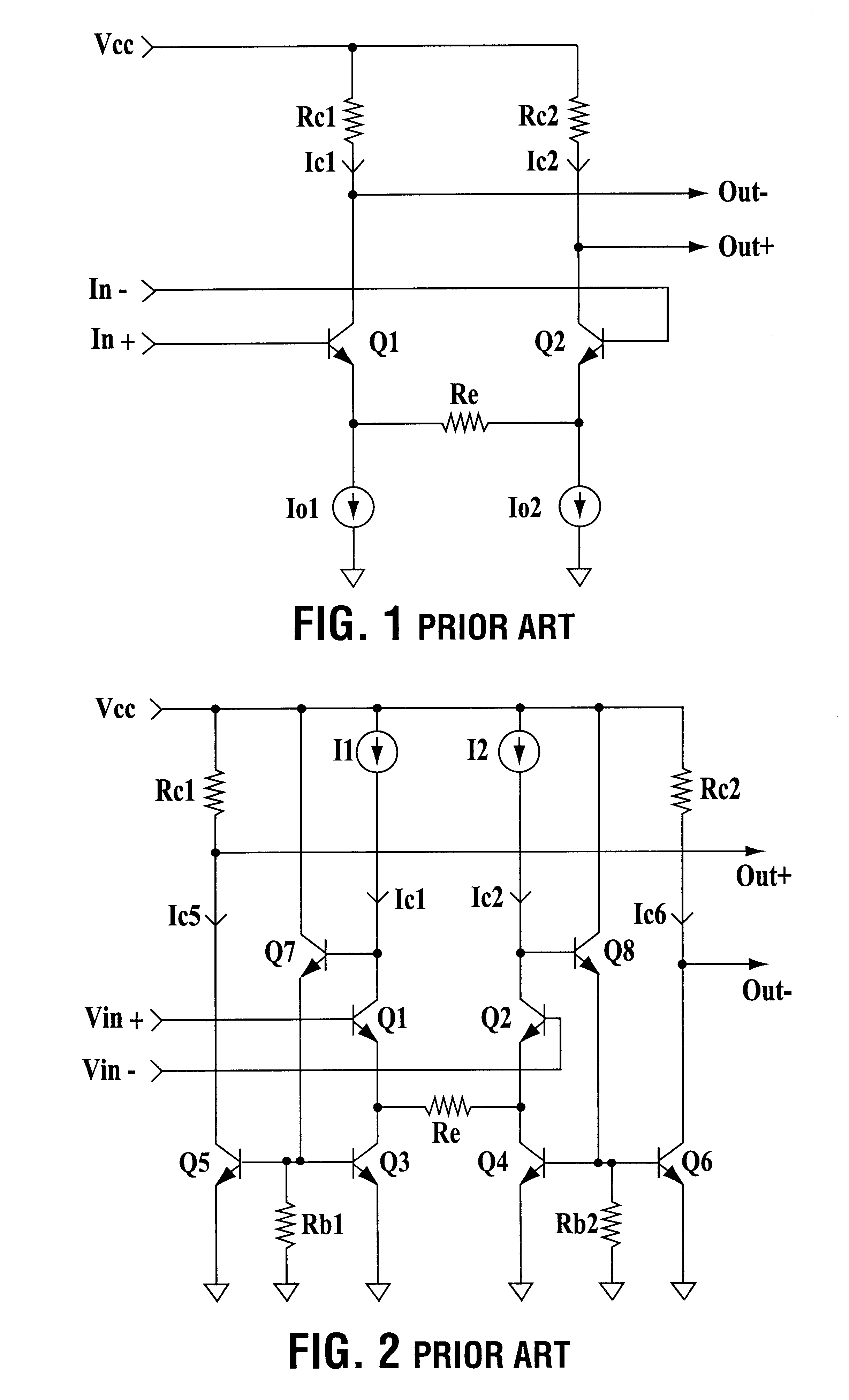

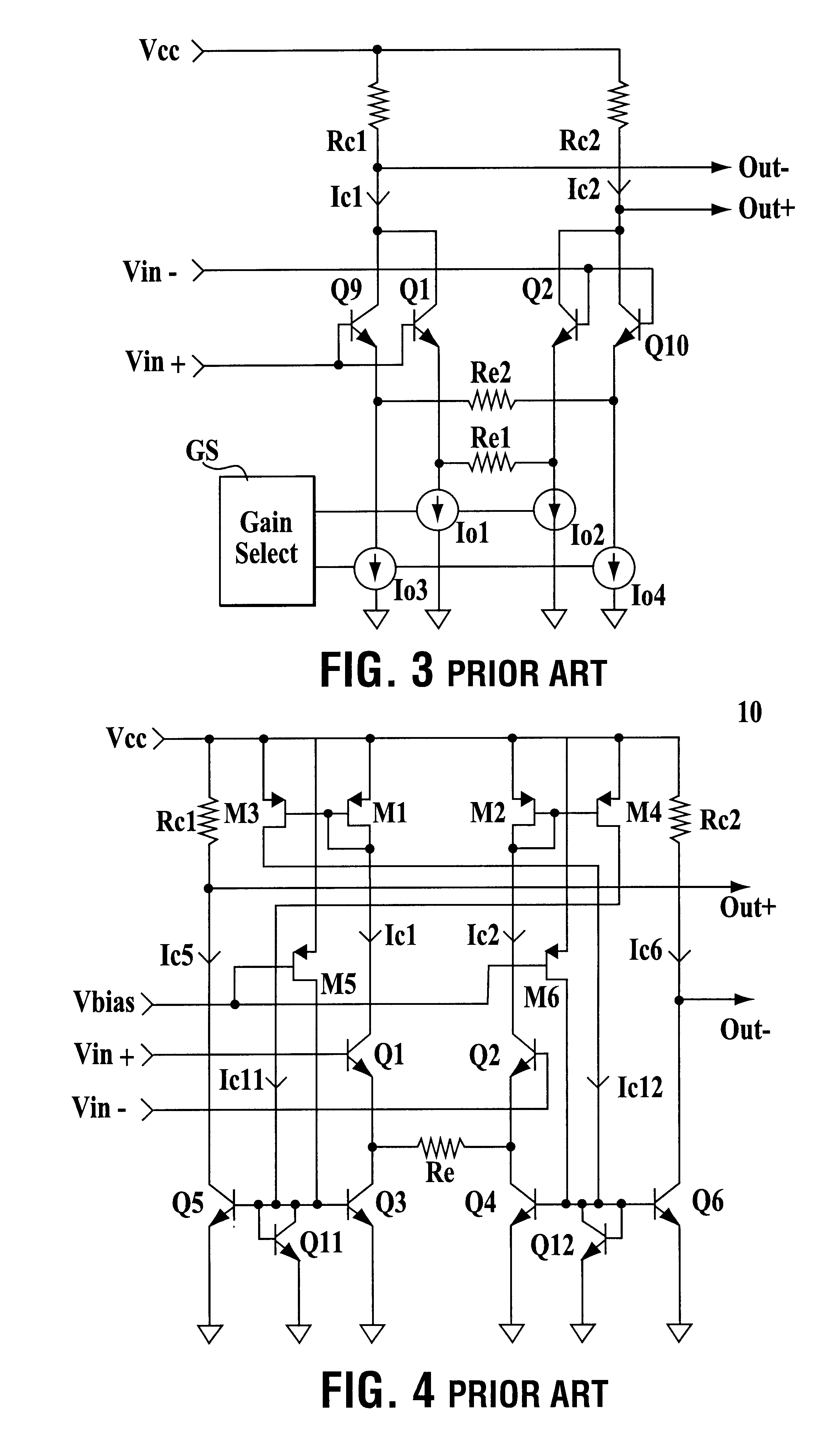

System and method for linearizing a CMOS differential pair

InactiveUS20080036536A1Multiple-port networksSemiconductor/solid-state device detailsShunt DeviceFilter tuning

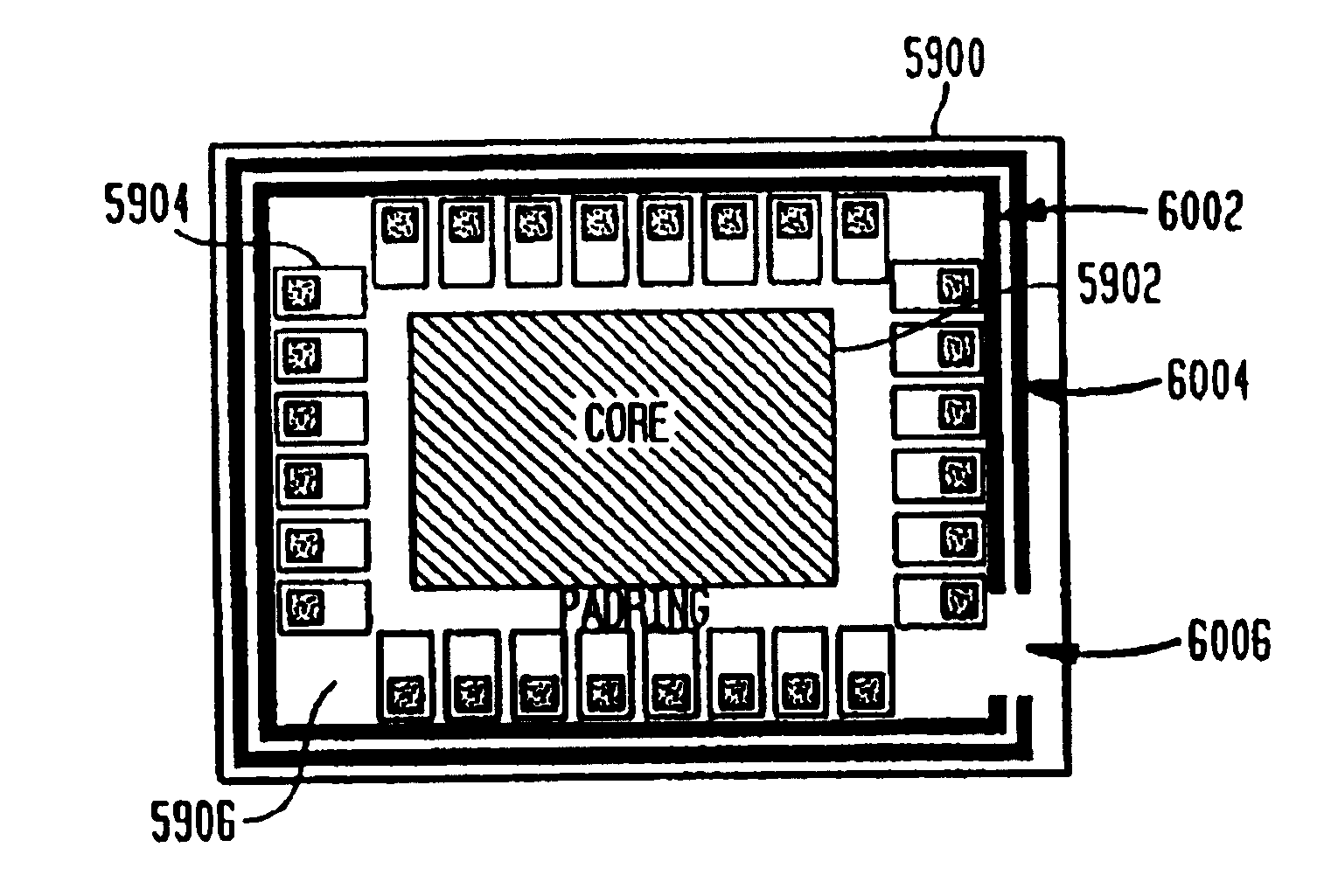

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

Adaptive radio transceiver with offset PLL with subsampling mixers

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Adaptive radio transceiver with a local oscillator

InactiveUS7031668B2Increase data rateIncrease costTransmitters monitoringResonant circuit tuningTransceiverAdaptive programming

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

Low-pass filter, feedback system, and semiconductor integrated circuit

InactiveUS7078948B2Reduce circuit areaSmall sizeFluid heatersMultiple-port networksCircuit complexityCapacitance

In a low-pass filter which is preferably used as a loop filter in a PLL or DLL, filter characteristics which are the same as those of a conventional low-pass filter are realized without causing collateral problems, such as an increase in the circuit area, the circuit complexity, or the resistance value, which may be caused due to size reduction of a capacitive element in the conventional low-pass filter. Thus, in a loop filter including a capacitive element and a resistive element which are connected in series, the first input terminal is provided at the side including the resistive element, and the second input terminal is provided at a connection point of the capacitive element and the resistive element. The first input terminal is supplied with the first electric current. On the other hand, the second electric current, which is a part of the first electric current supplied to the first input terminal, is extracted from the second input terminal, so that the electric current flowing into the capacitive element is smaller than the electric current flowing through the resistive element.

Owner:PANASONIC CORP

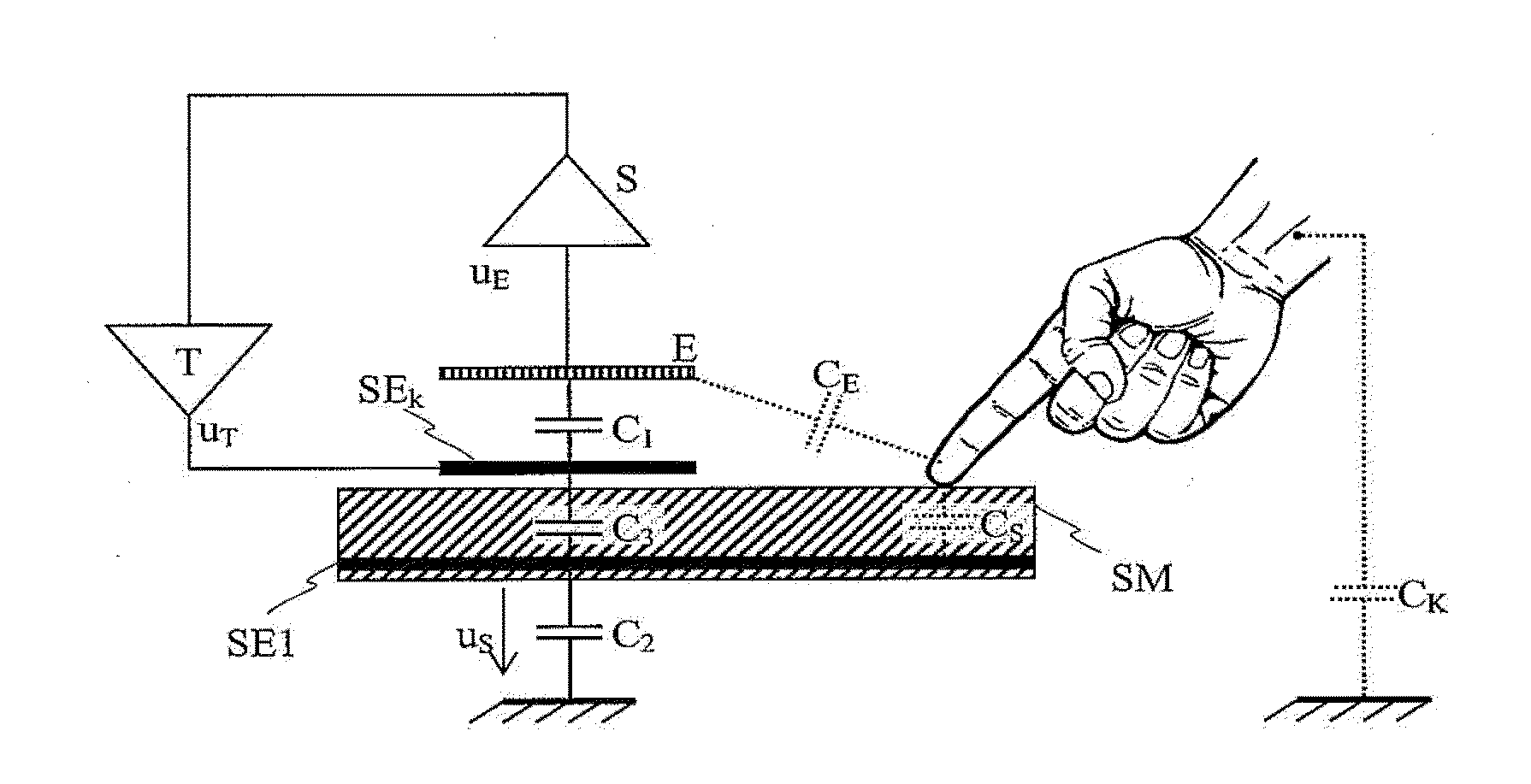

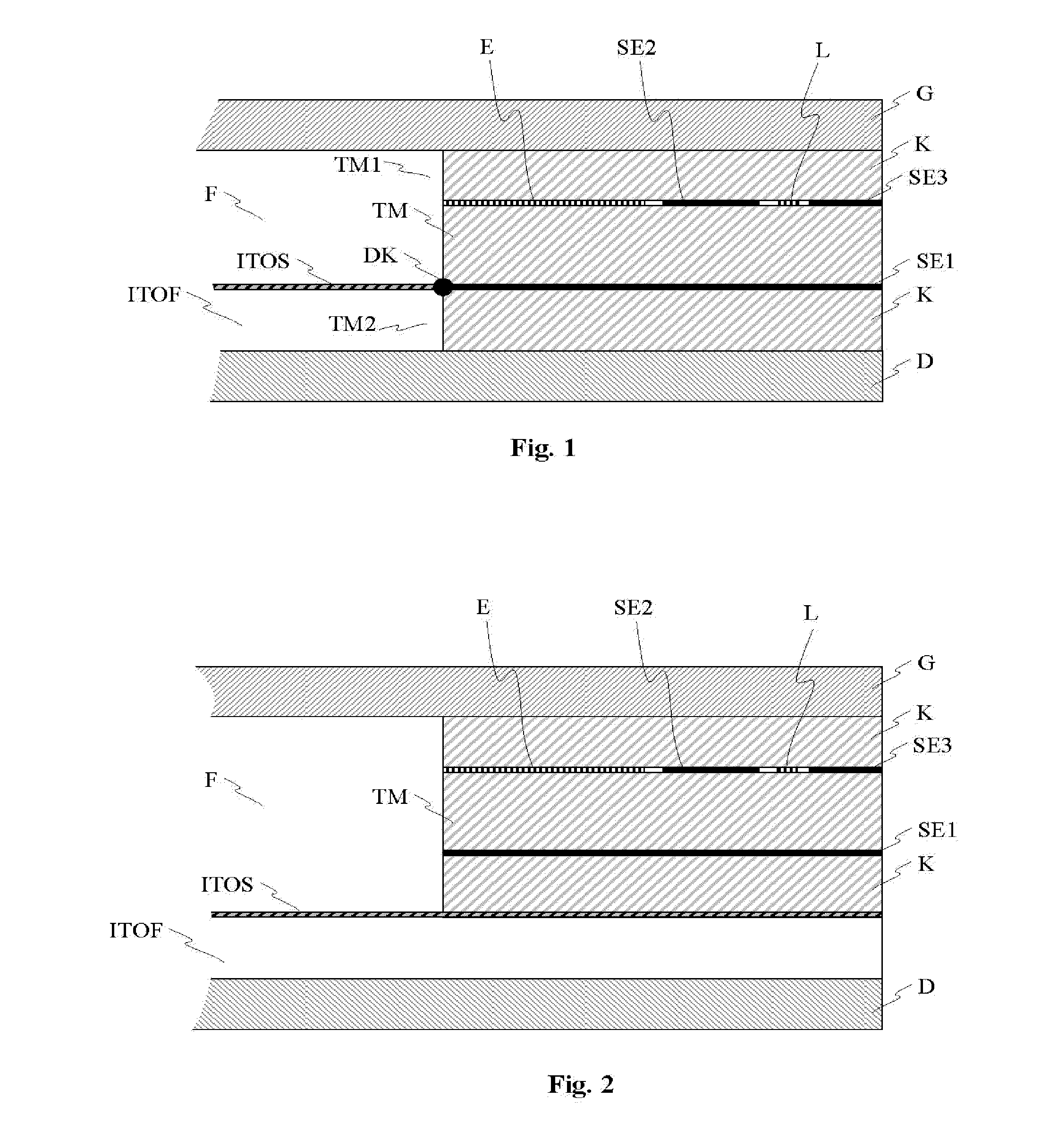

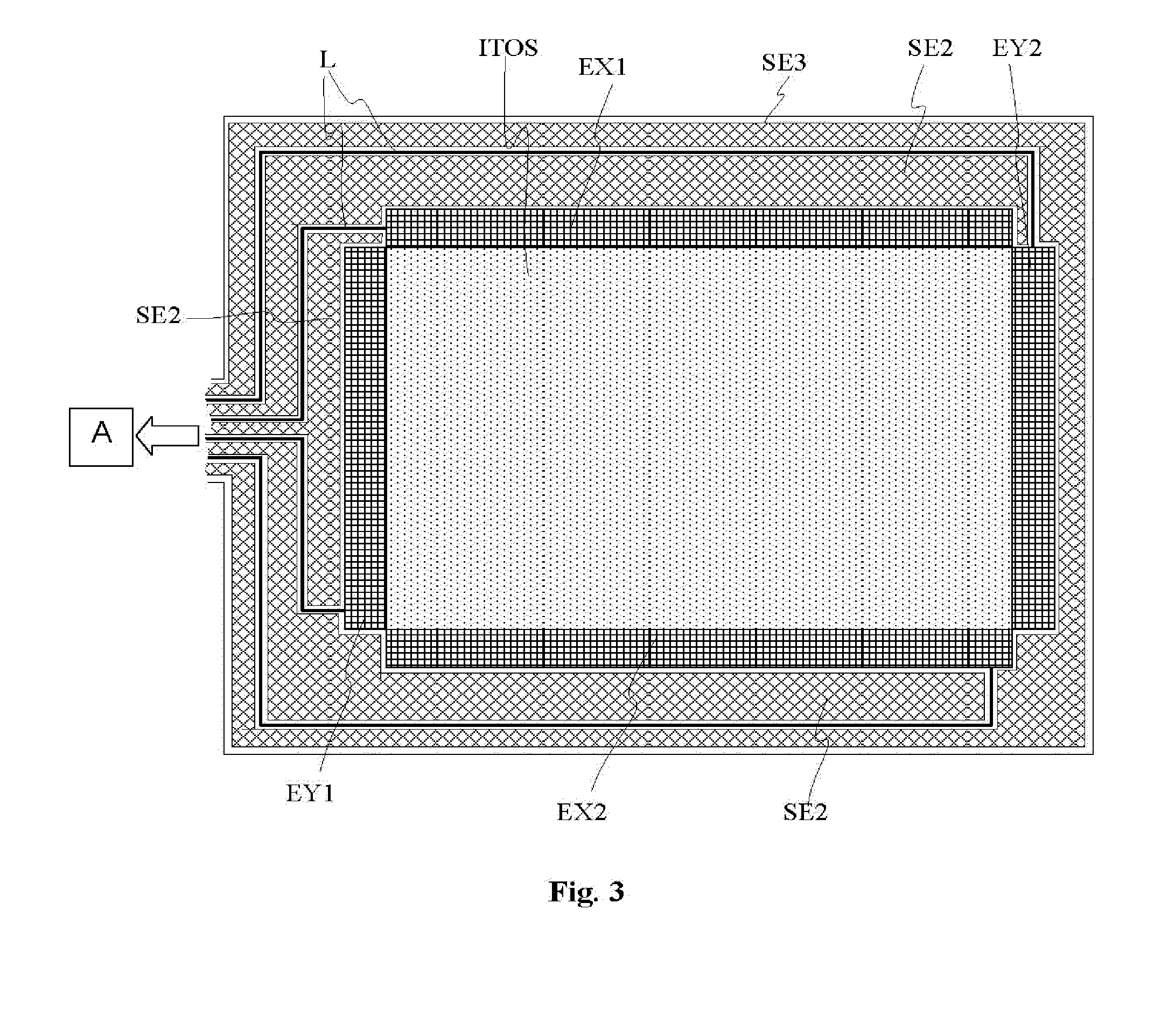

Electrode arrangement for display device

ActiveUS20120081328A1High sensitivityReduce impactMultiple-port networksPrinted circuit assemblingDisplay deviceEngineering

The invention provides an electrode arrangement for a capacitive sensor device and for a capacitive sensor, respectively, for detecting a position and / or an approach of an object, which comprises a sensor electrode and a first shield electrode, wherein the sensor electrode is arranged on a first side of a substantially flat substrate with a first side and a second side, and wherein the first shield electrode is arranged on the second side of the substrate and serves for shielding the alternating electric field emitted by the sensor electrode from ground. There is also provided a foil with an electrode arrangement according to the invention as well as a method for the production of a display arrangement with an electrode arrangement according to the invention.

Owner:MICROCHIP TECH GERMANY II

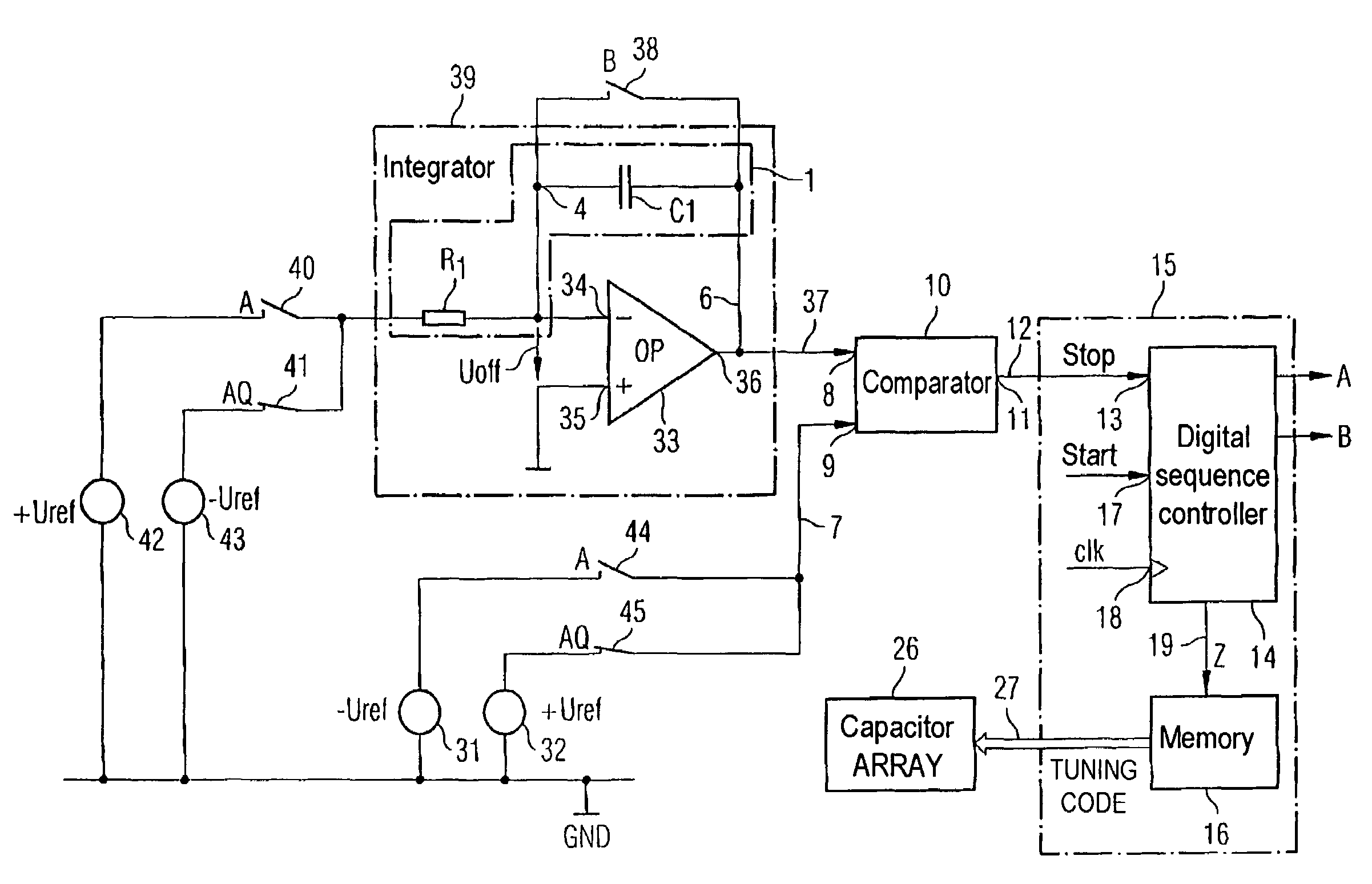

Tuning circuit for a filter

ActiveUS7002404B2Space minimizationImprove accuracyMultiple-port networksTransmission control/equlisationCapacitanceRC time constant

The invention relates to a tuning circuit for tuning a filter stage, which has an RC element (1) with an RC time constant (τ), with the RC time constant (τ) being the product of the resistance of a resistor (R1) in the RC element (1) and the capacitance of a capacitor (C1), which is connected in series with the resistor (R1), in the RC element (1), having a comparator (10) for comparison of the voltage which is produced at the potential node (4) between the resistor (R1) and the capacitor (C1), with a reference ground voltage; and having a controller (15) which varies the charge on the capacitor (C1) in the RC element (1) until the comparator (10) indicates that the voltage which is produced at the potential node (4) is equal to the reference ground voltage, with the controller (15) switching a capacitor array (26) as a function of the charge variation time, which capacitor array (26) is connected in parallel with the capacitor (C1) in the RC element (1), in order to compensate for any discrepancy between the RC time constant (τ) of the RC element (1) and a nominal value.

Owner:MAXLINEAR INC

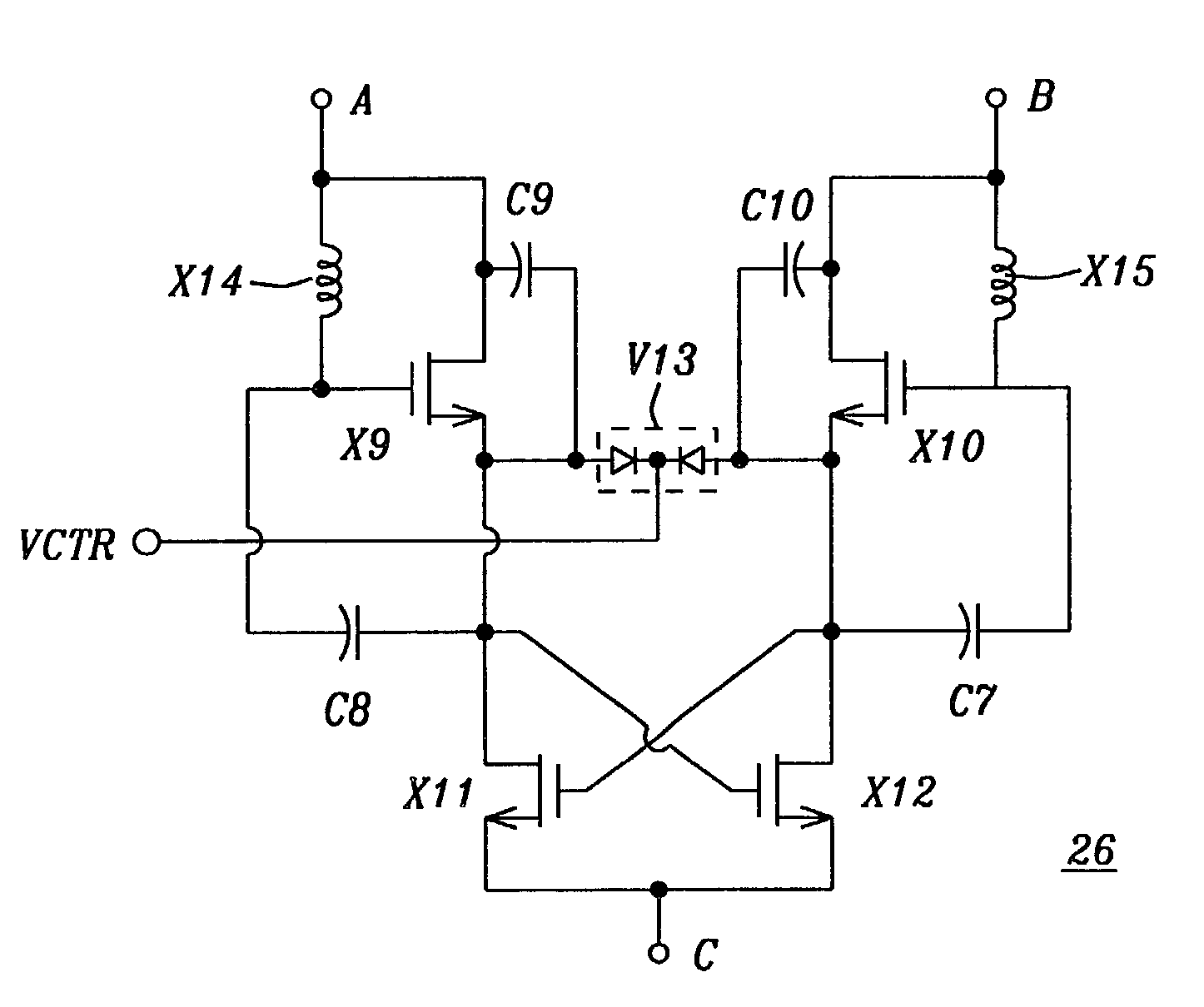

Wideband monolithic tunable high-Q notch filter for image rejection in RF application

InactiveUS6990327B2Good image rejectionWide tunable rangeMultiple-port networksTransmissionEngineeringInductor

A notch filter with a high Q factor, which is integrated with a first and a second cascoded LNA, is totally contained on an integrated chip. The notch filter, comprising two Q-enhancement circuits, is coupled to the second differential LNA. The two Q-enhancement circuits are combined to generate sufficient negative impedance to compensate for the loss in the on-chip low Q inductors. To improve the image rejection of the notch filter in a wide frequency band, the notch filter uses an automatic current tuning circuit which consists of an analog multiplier and fixed and voltage controlled current sources. Furthermore, by modifying the connection and location of the tunable varactor, another wideband tunable notch filter is implemented. The notch filter can be applied in all current wireless receiver systems.

Owner:AGENCY FOR SCI TECH & RES

Adaptive radio transceiver with calibration

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

Tunable filter and portable telephone

InactiveUS7135940B2Good reproducibility and reliabilityLow insertion lossMultiple-port networksTransmission control/equlisationCapacitanceInductor

A tunable filter has a plurality of variable capacitors and a plurality of inductor elements, each being formed on a common substrate, a filter circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a monitor circuit formed by using at least a portion of the plurality of variable capacitors and a portion of the plurality of inductor elements, a detecting circuit which detects a prescribed circuit constant of the monitor circuit, a storage which stores information relating to a reference circuit constant of the monitor circuit, and a capacitance control circuit which controls capacitance of the variable capacitors in the monitor circuit and capacitance of the variable capacitors in the filter circuit, based on a result detected by the detecting circuit and information stored in the storage.

Owner:KK TOSHIBA

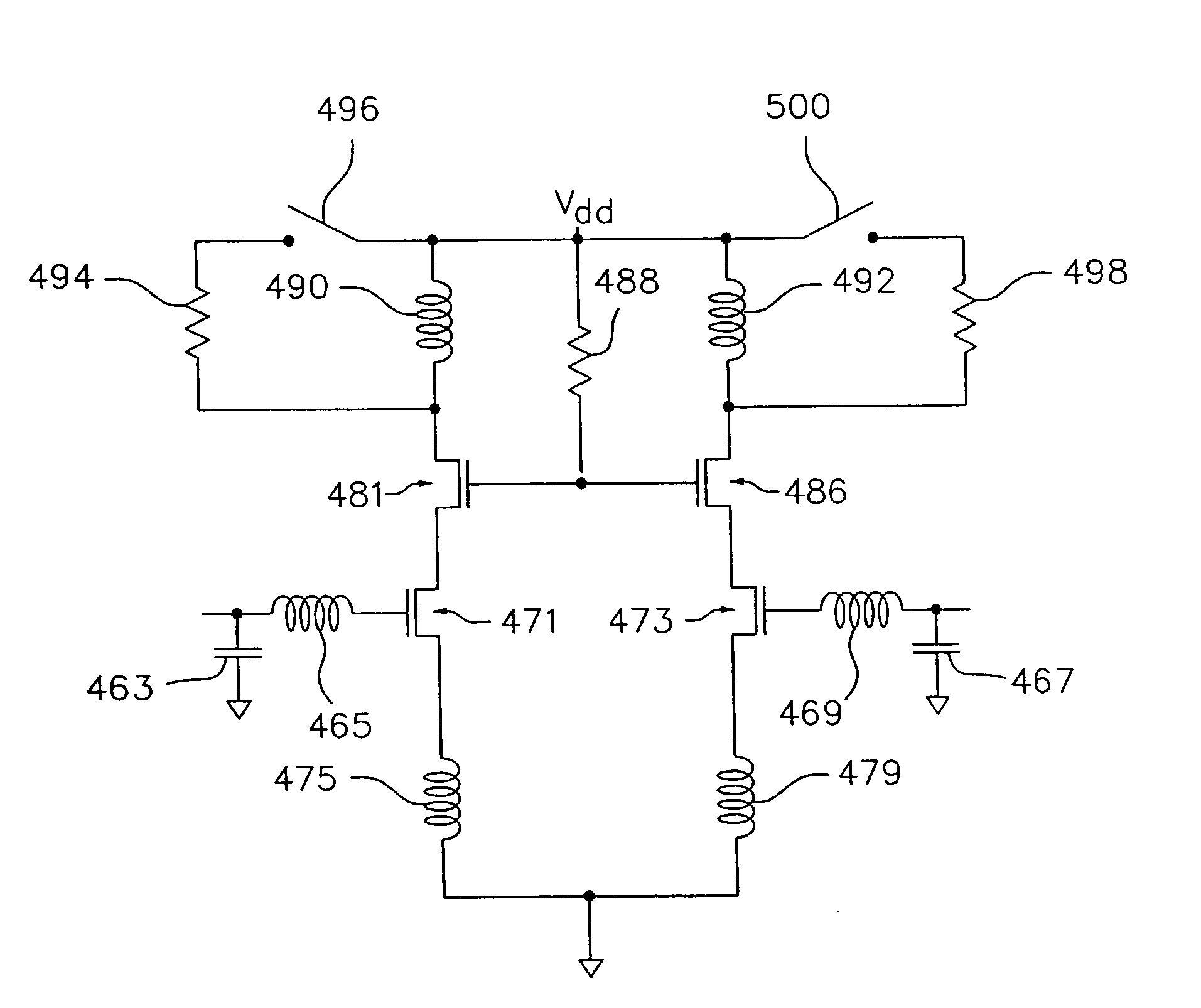

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS7019598B2Angle modulation by variable impedenceResonant circuit detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

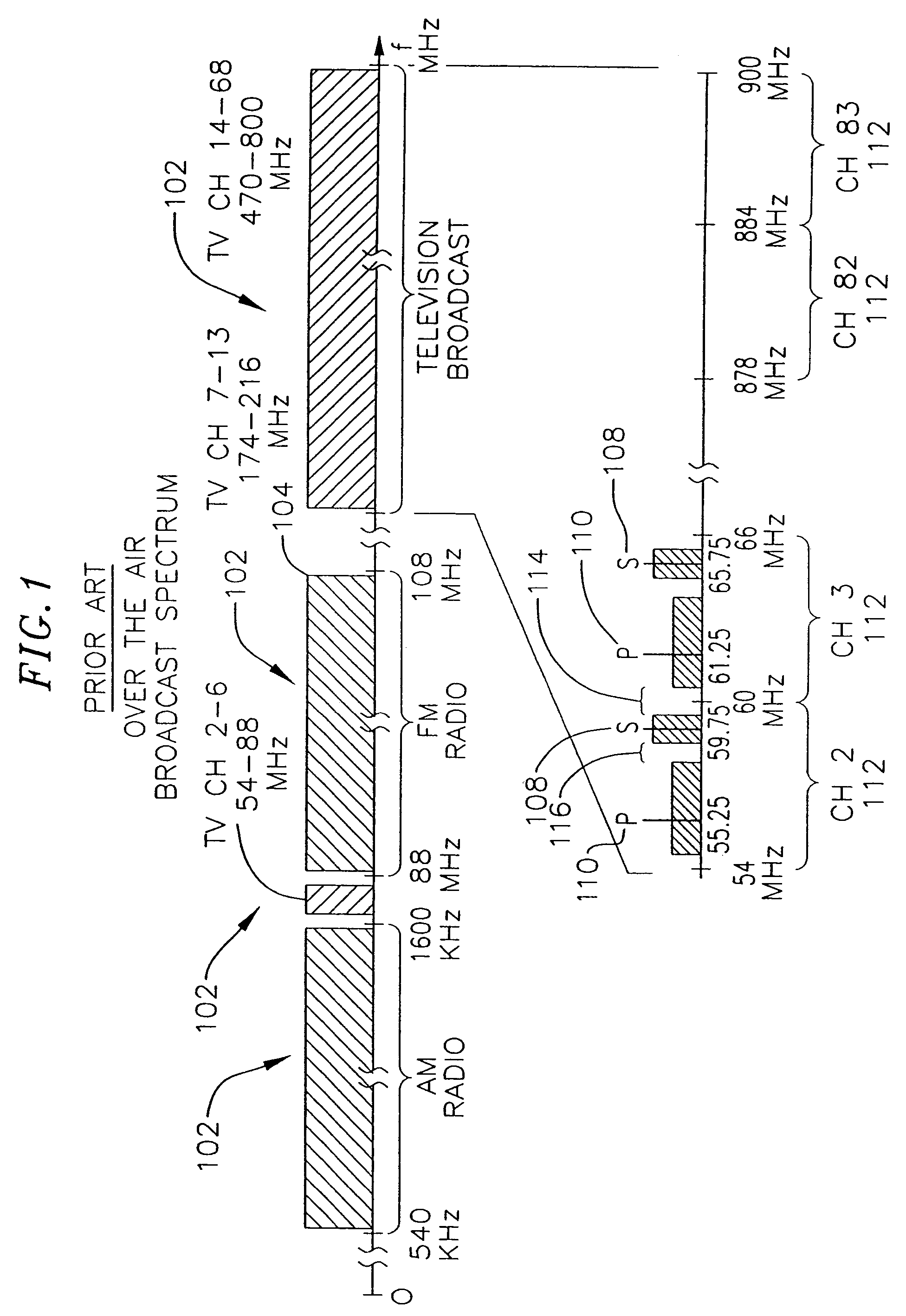

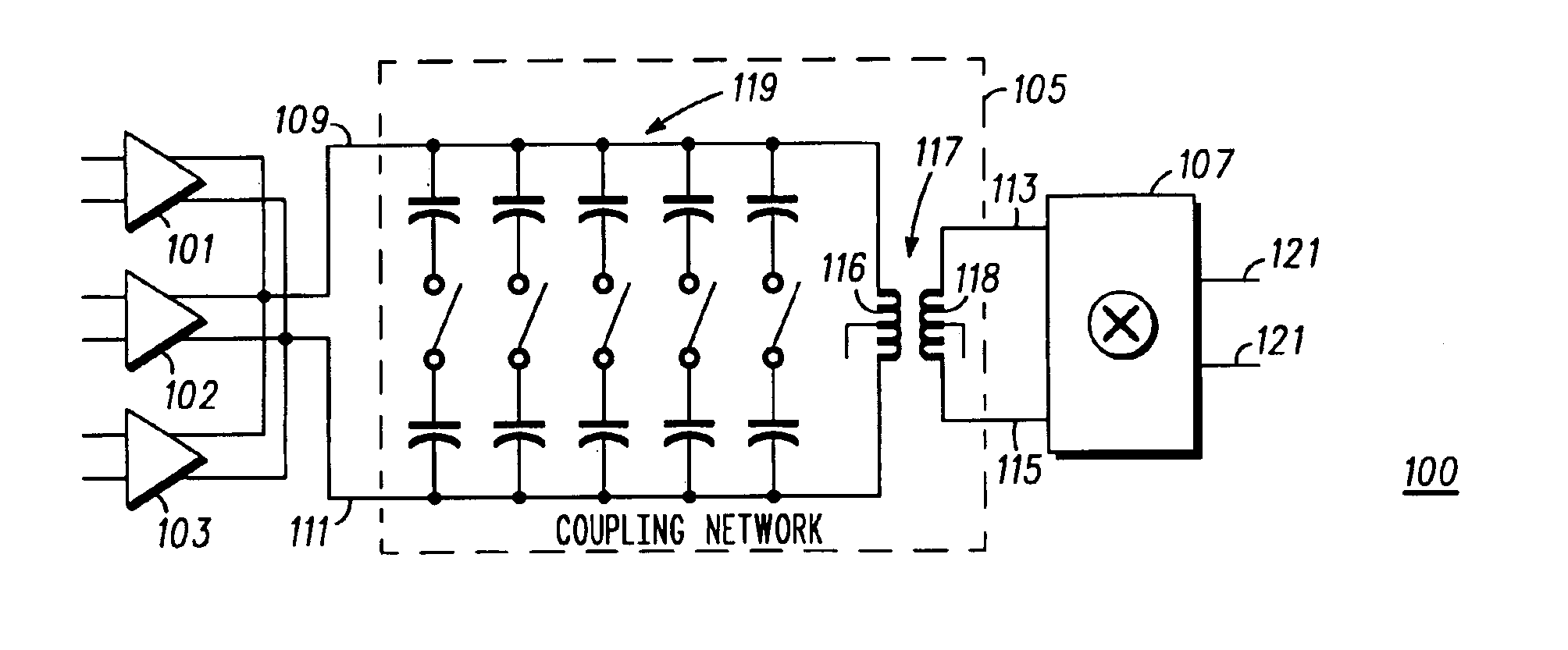

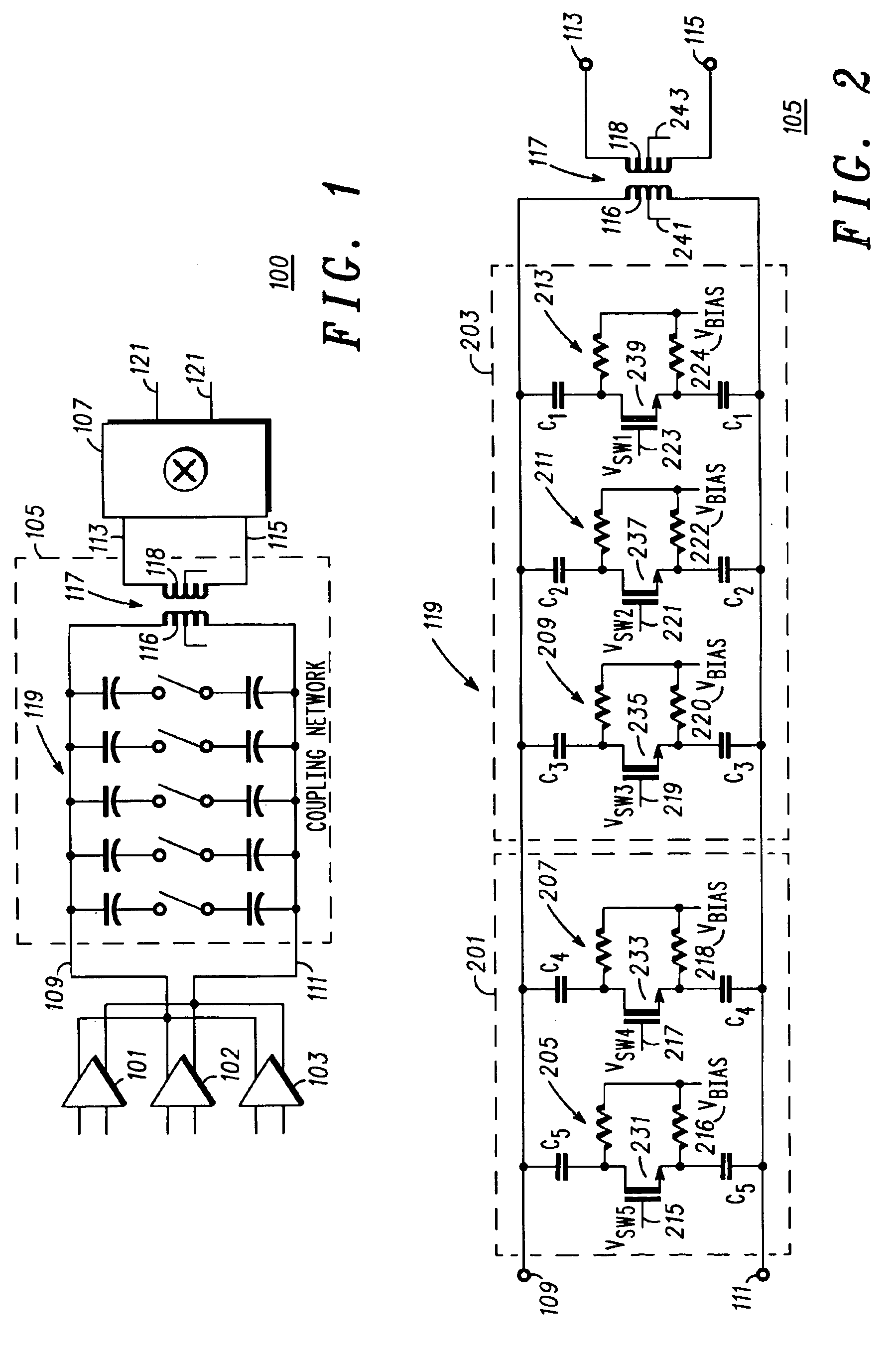

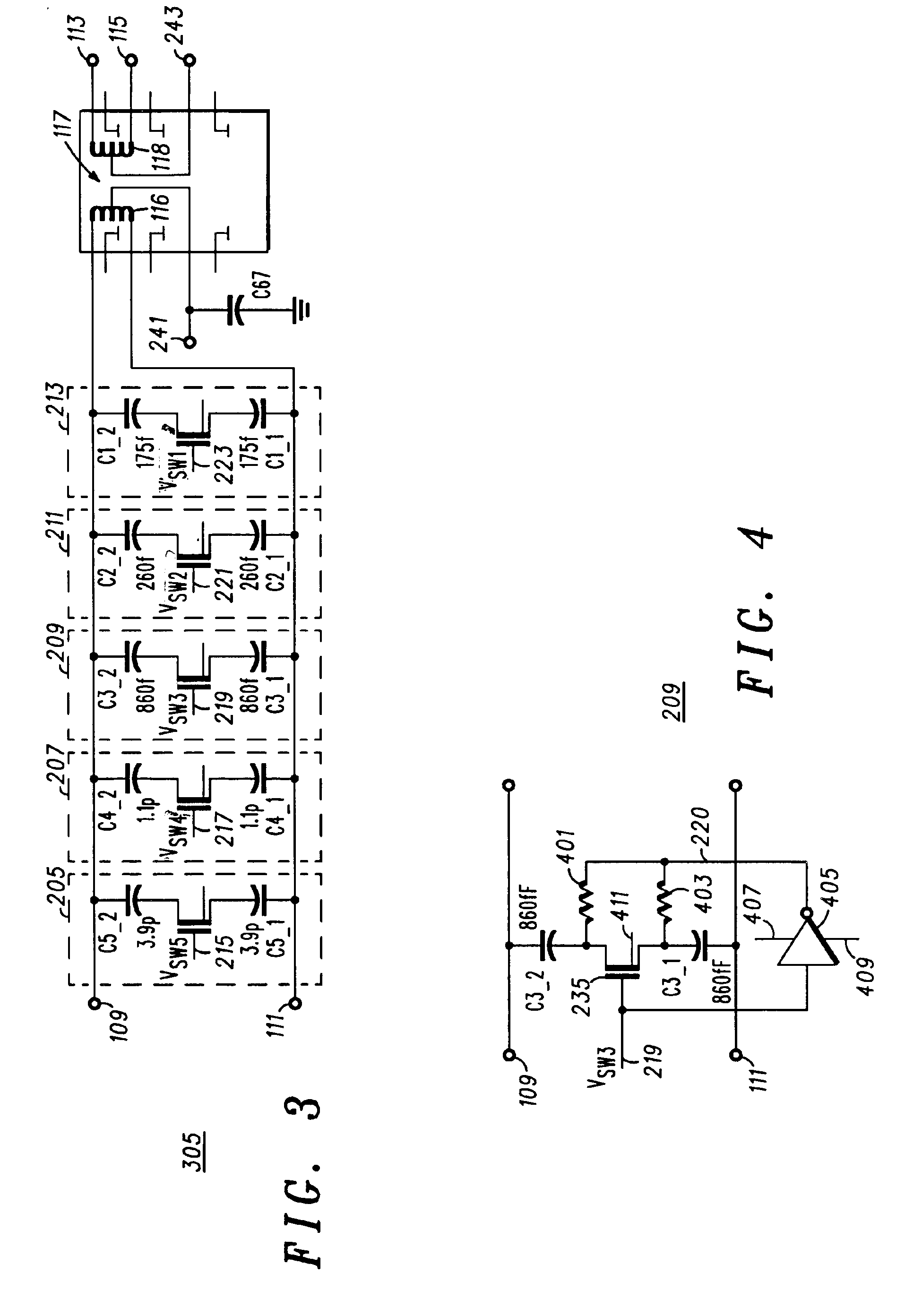

Integrated frequency selectable resonant coupling network and method thereof

InactiveUS6889036B2Reduce noiseDiscontnuous tuning with seperate pretuned circuitsTransmissionCouplingConductor Coil

An integrated center frequency selectable resonant coupling network suited for use in an integrated circuit is disclosed. The network includes an integrated coupling transformer having a secondary winding for coupling to a load and a primary winding for coupling to a source; a first integrated capacitive circuit controllably coupled across one of the primary and secondary windings and when so coupled operable to resonate with the integrated coupling transformer at a frequency in a first frequency band; and a second integrated capacitive circuit coupled across a second one of the primary and the secondary windings that is operable to resonate with the integrated coupling transformer at a frequency in a second frequency band. The method is in an IC and includes providing and coupling an input signal within alternatively a first frequency band and a second frequency band to a primary winding of an integrated coupling transformer; controlling an integrated switched capacitor network, coupled to the transformer, to provide a coupling network that is alternatively and respectively resonant at a first and second frequency within the first and second frequency band thus selectively providing an output signal at a secondary winding of the transformer; and down converting the output signal.

Owner:APPLE INC

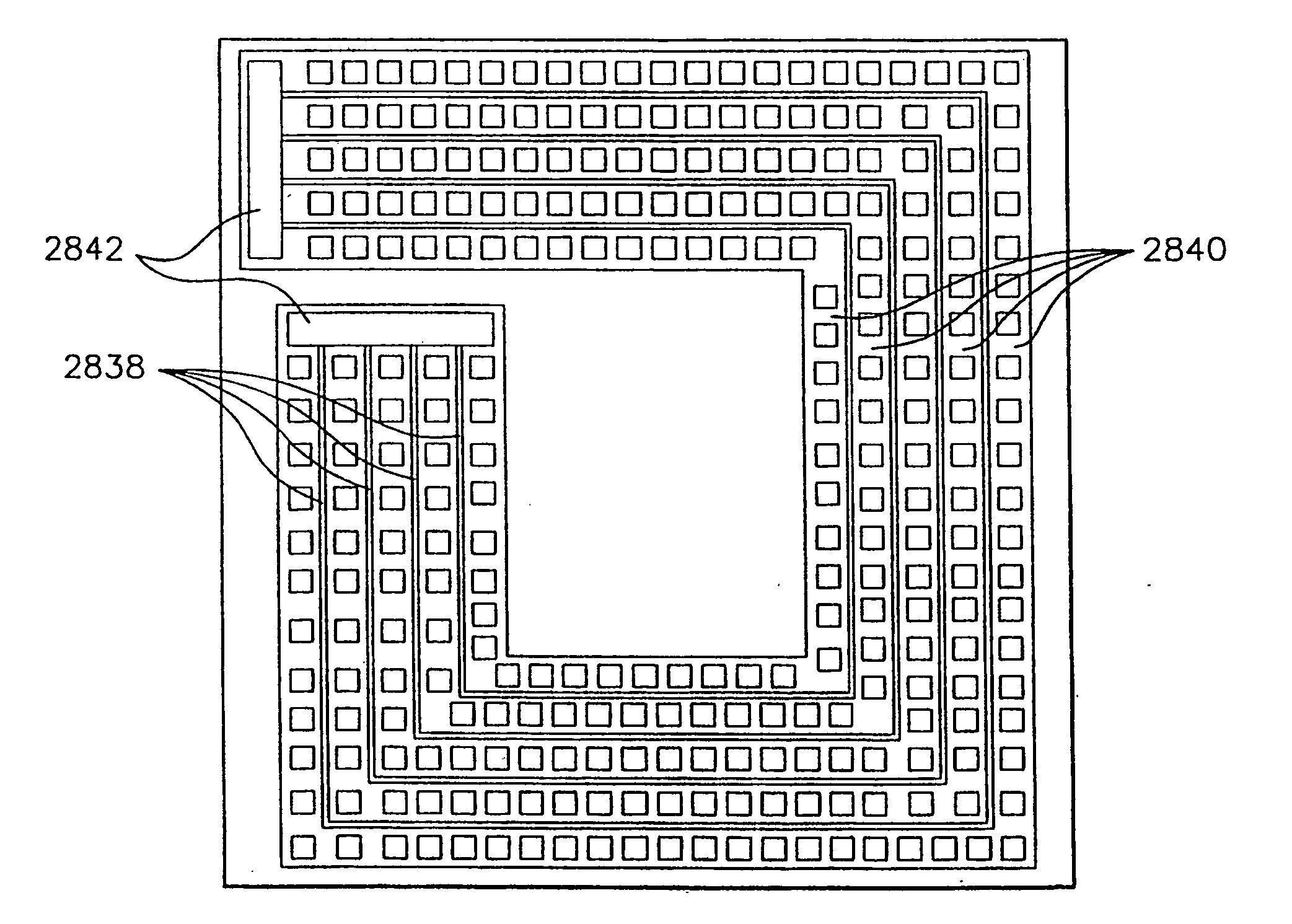

Integrated spiral inductor

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

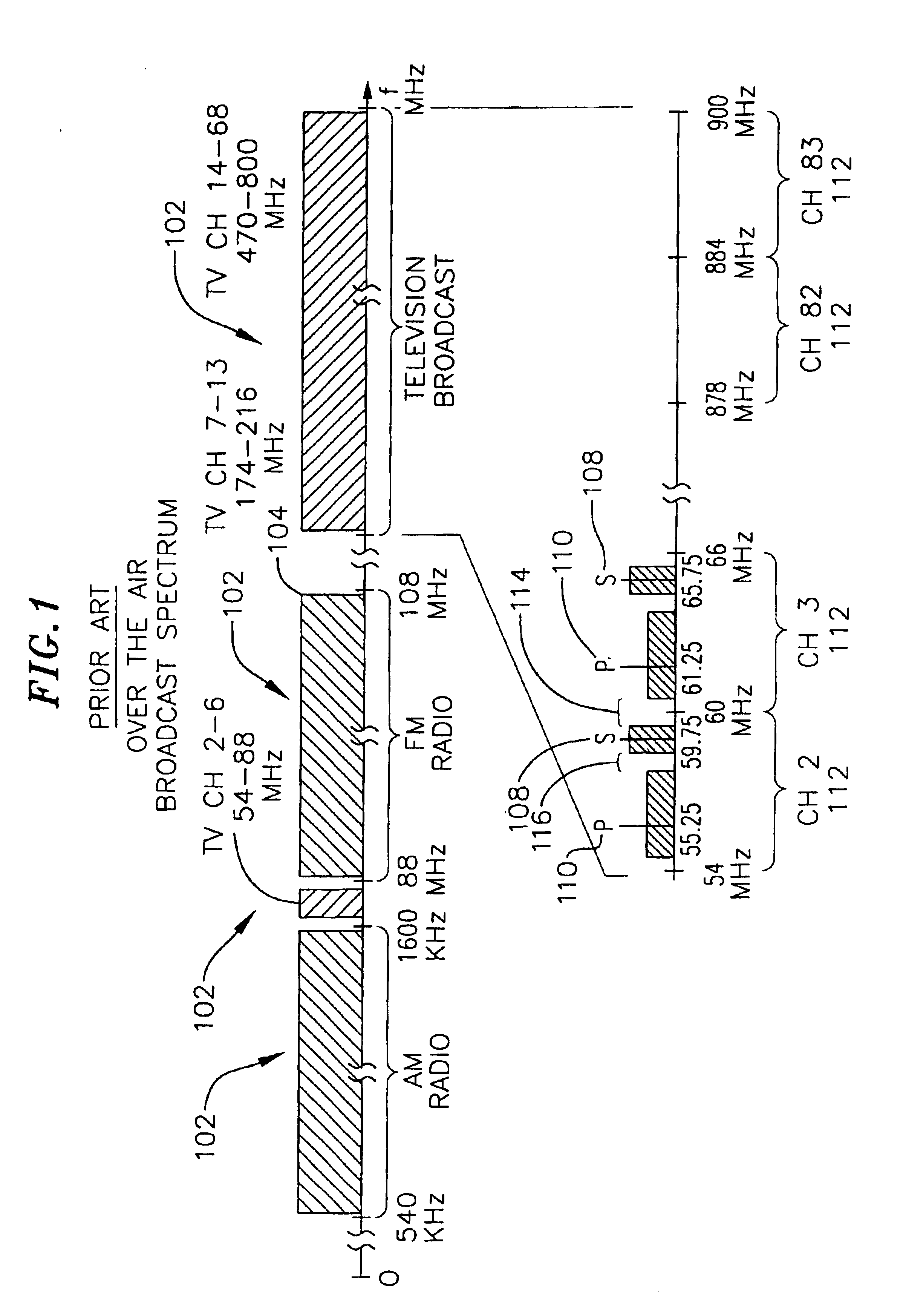

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

Controlling Q-factor of filters

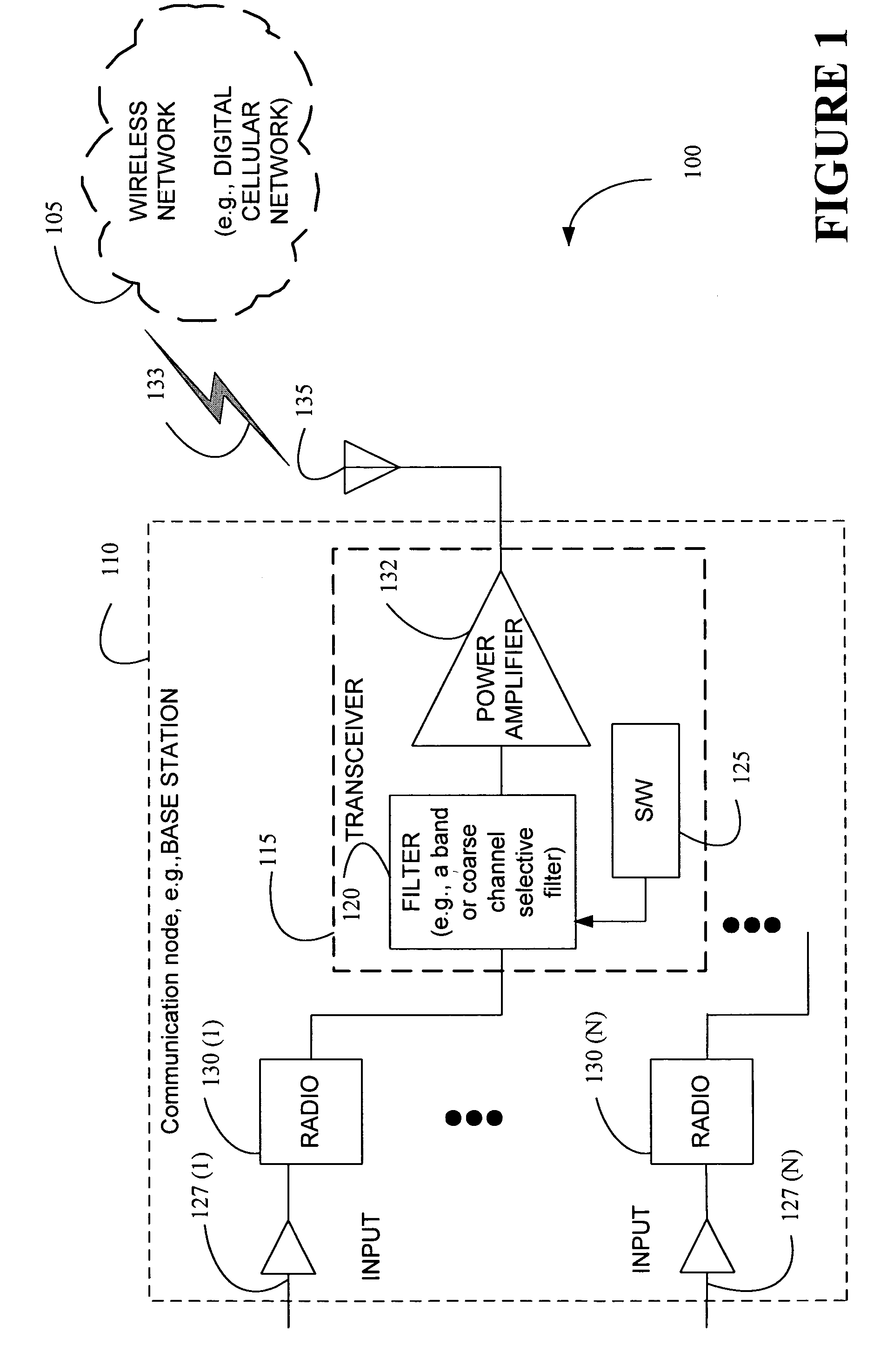

The present invention provides a method and an apparatus for controlling a Q-factor for a filter. The method comprises stabilizing an active feedback to provide a variable feedback in a filter, varying the active feedback based on an input signal to the filter, and producing a desired Q-factor for the filter at a first frequency band, in response to the variable feedback. The method further comprises reconfiguring a center frequency and a bandwidth of the filter based on a channel bandwidth of the input signal to the filter to adjust the Q-factor for the filter in response to a second frequency band different than the first frequency band. By reconfiguring a center frequency and a bandwidth of a filter, the Q-factor for the filter, such as a flexible or reconfigurable filter, may be controlled across a multiplicity of frequency band signals. Using software, for example, a common signal path may be provided for the multiplicity of frequency band signals within a frequency agile radio of a base station by tuning the radio based on a variable feedback through realization of a negative parallel resistance. Thus, tuneability of the Q-factor may provide frequency agile radios that include flexible or reconfigurable filters in a base station to serve different frequency bands without changing hardware. In this way, significant savings associated with frequency agility may be obtained.

Owner:WSOU INVESTMENTS LLC +1

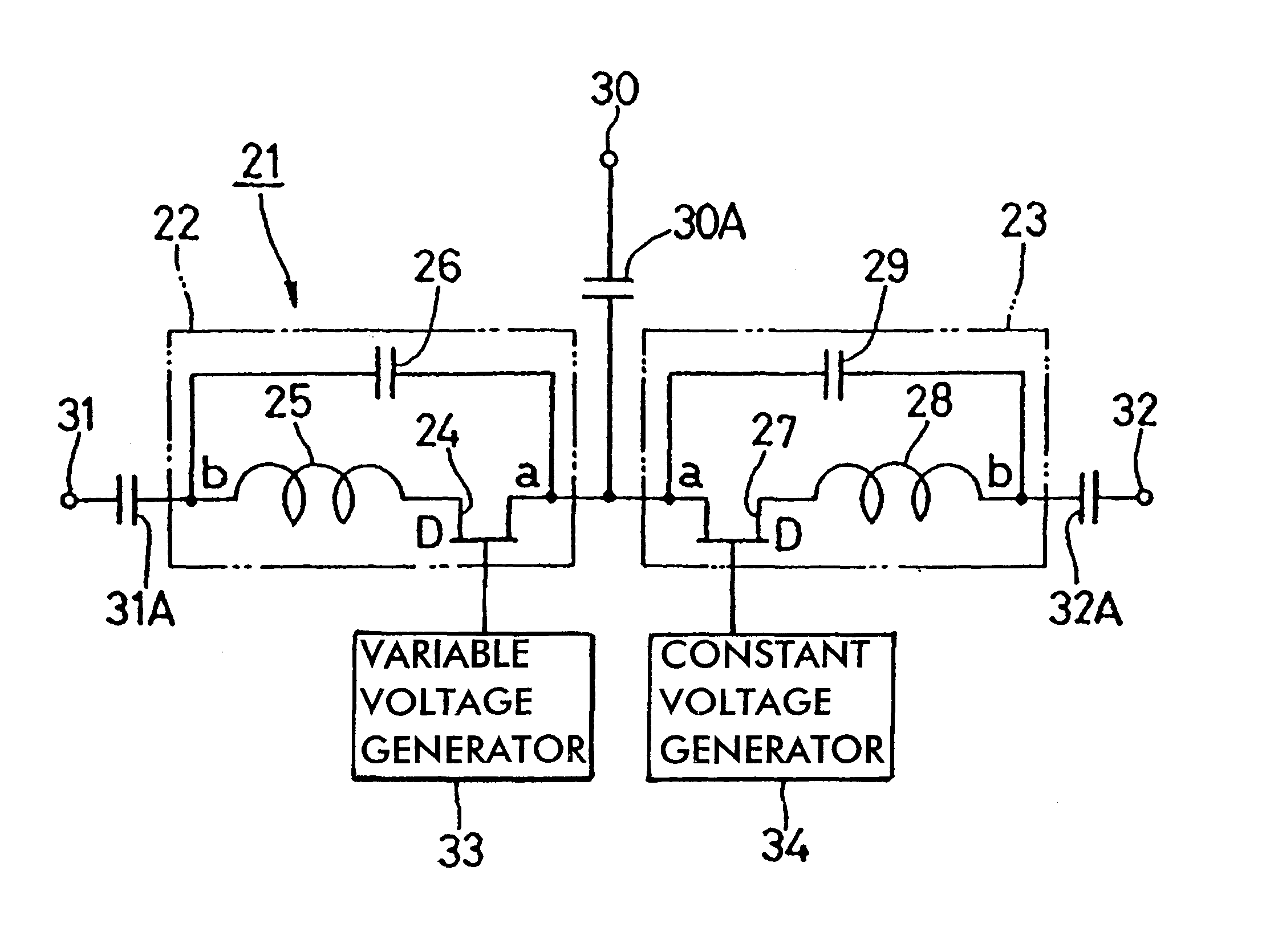

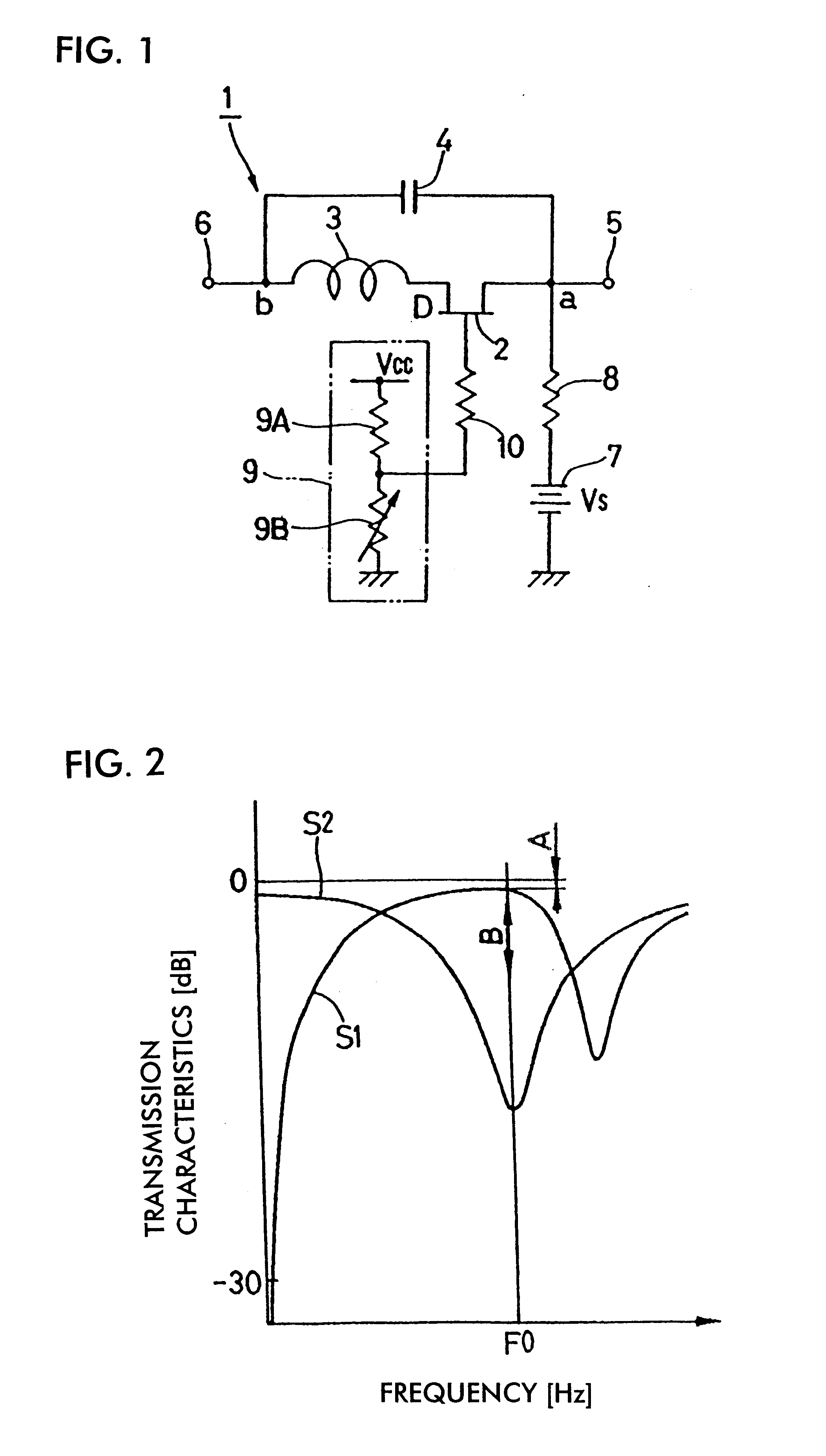

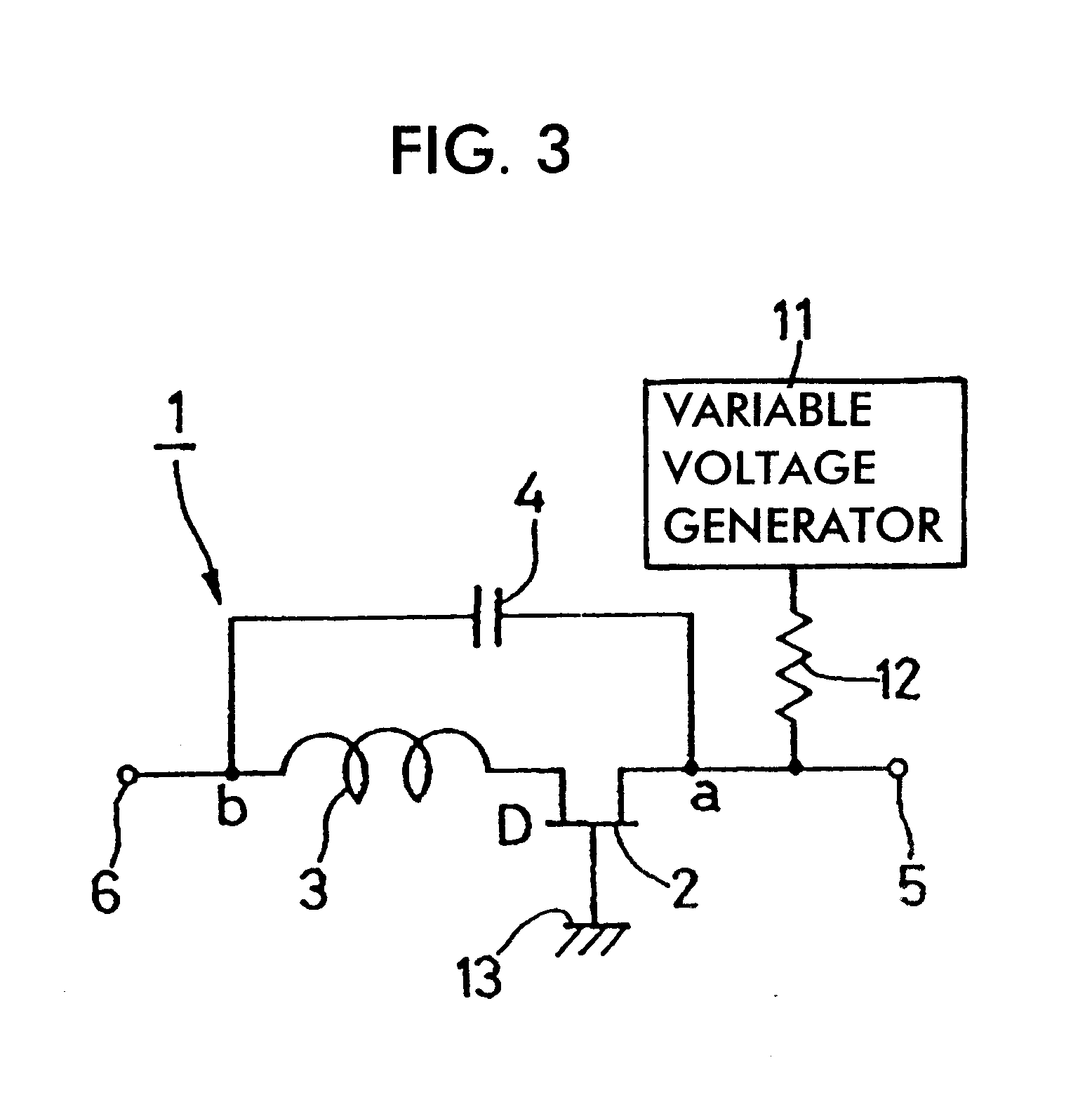

Variable attenuator

InactiveUS6720850B2Improve isolationIncrease rangeMultiple-port networksPulse automatic controlCapacitanceUltrasound attenuation

A resonance type SPST switch is formed by connecting an inductive element in series with the drain of an FET, and then by connecting a capacitive element in parallel with the series connection of the FET and the inductive element. A constant-voltage source for feeding a voltage Vs is connected to the source of the FET, and a variable-voltage generator for switching the FET between an on state and a state in the vicinity of pinchoff is connected to the gate of the FET. When the variable-voltage generator feeds a voltage Valpha in the vicinity of a pinchoff voltage to the gate of the FET, the SPST switch is closed while the amount of attenuation between first and second terminals is variably set. The resulting variable attenuator is thus compact in size, allows a large amount of attenuation to be set, and involves low manufacturing costs.

Owner:MURATA MFG CO LTD

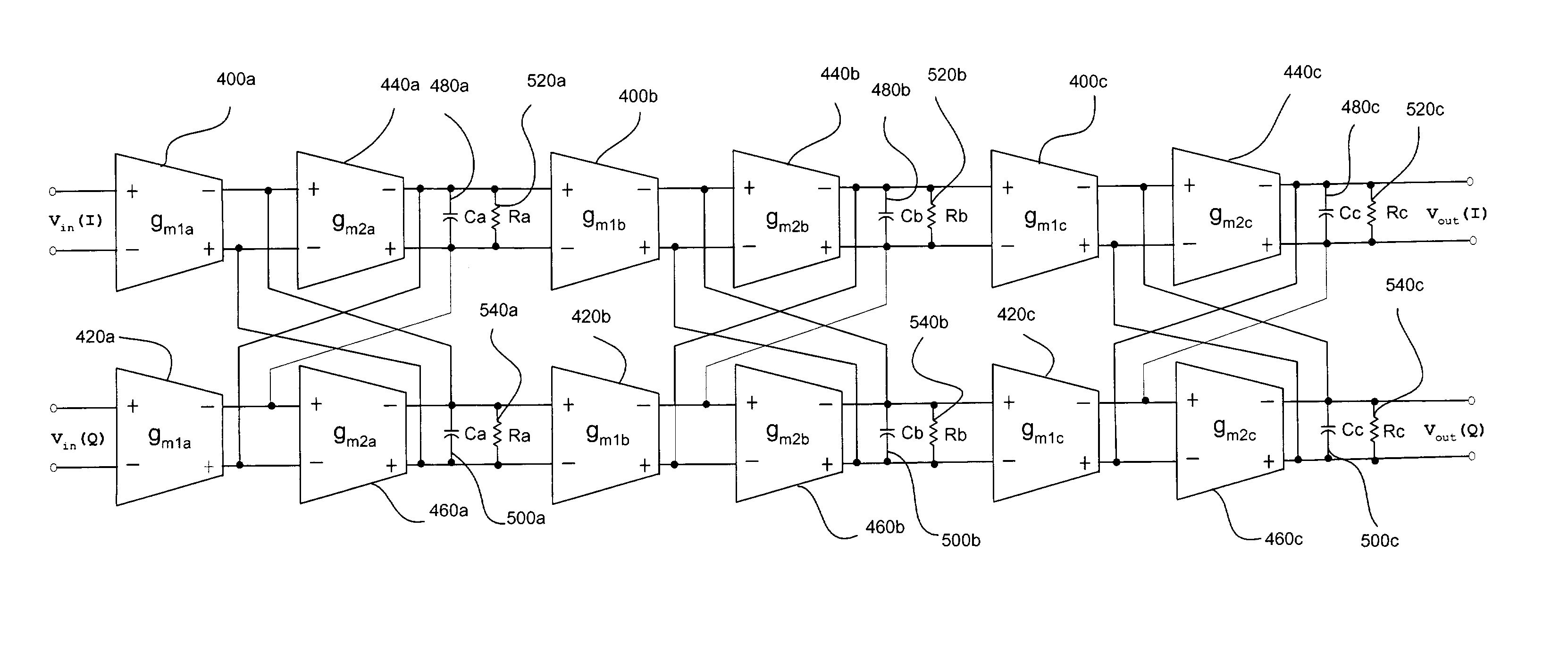

Transconductance/C complex band-pass filter

ActiveUS7002403B2Guaranteed smooth progressPulse automatic controlRadio transmissionTransceiverAudio power amplifier

A complex filter such as the channel select filter in a radio transceiver is implemented using a transconductance / C topology to benefit from the ability to tune such filters and thereby stabilize the output transfer function of the filter over variations in temperature, power supply voltage and process. The topology is based on an active R / C biquadratic topology to achieve the additional benefit of independently controlled stages. The problem created by the R in the output impedance is can be overcome by separately tuning the R value along with the transconductance / C ratio, by implementing the R as a transconductance amplifier having common mode feedback, or by implementing the transconductance amplifiers of the topology using Nauta transconductors, and unbalancing the common mode circuit of the Nauta transconductor to achieve a differential resistance that can be used to implement the R in the output impedance.

Owner:AVAGO TECH INT SALES PTE LTD

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

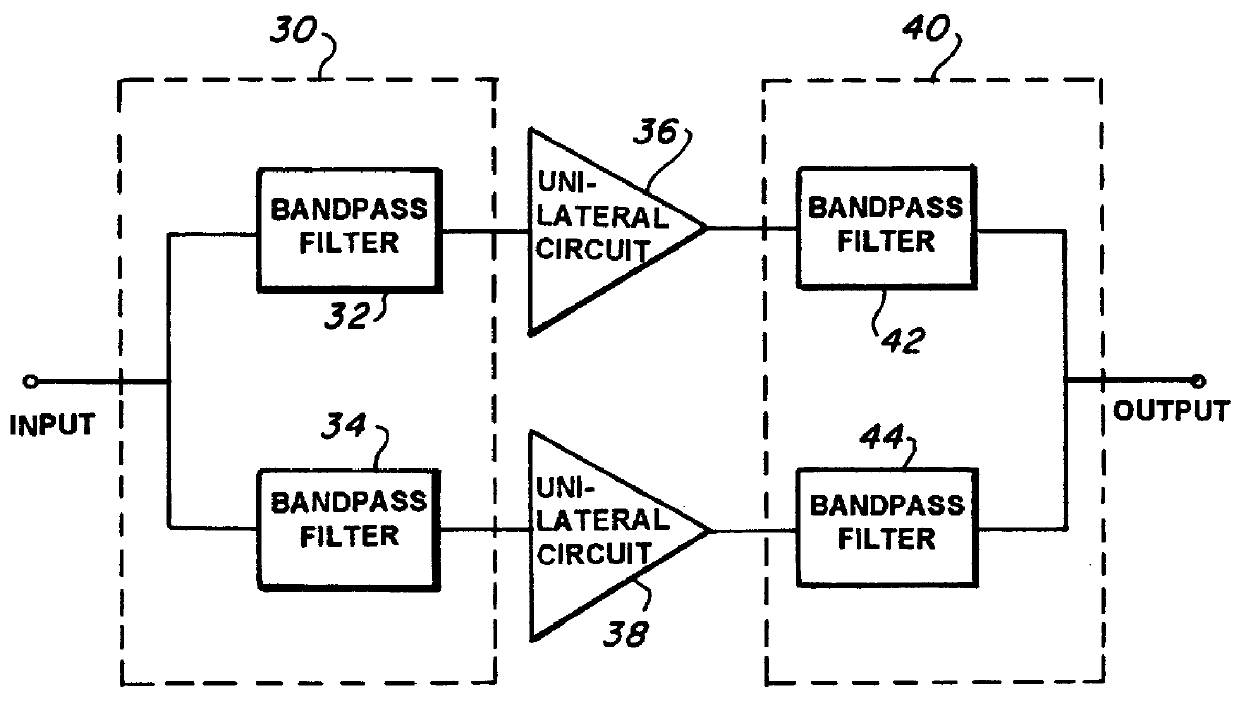

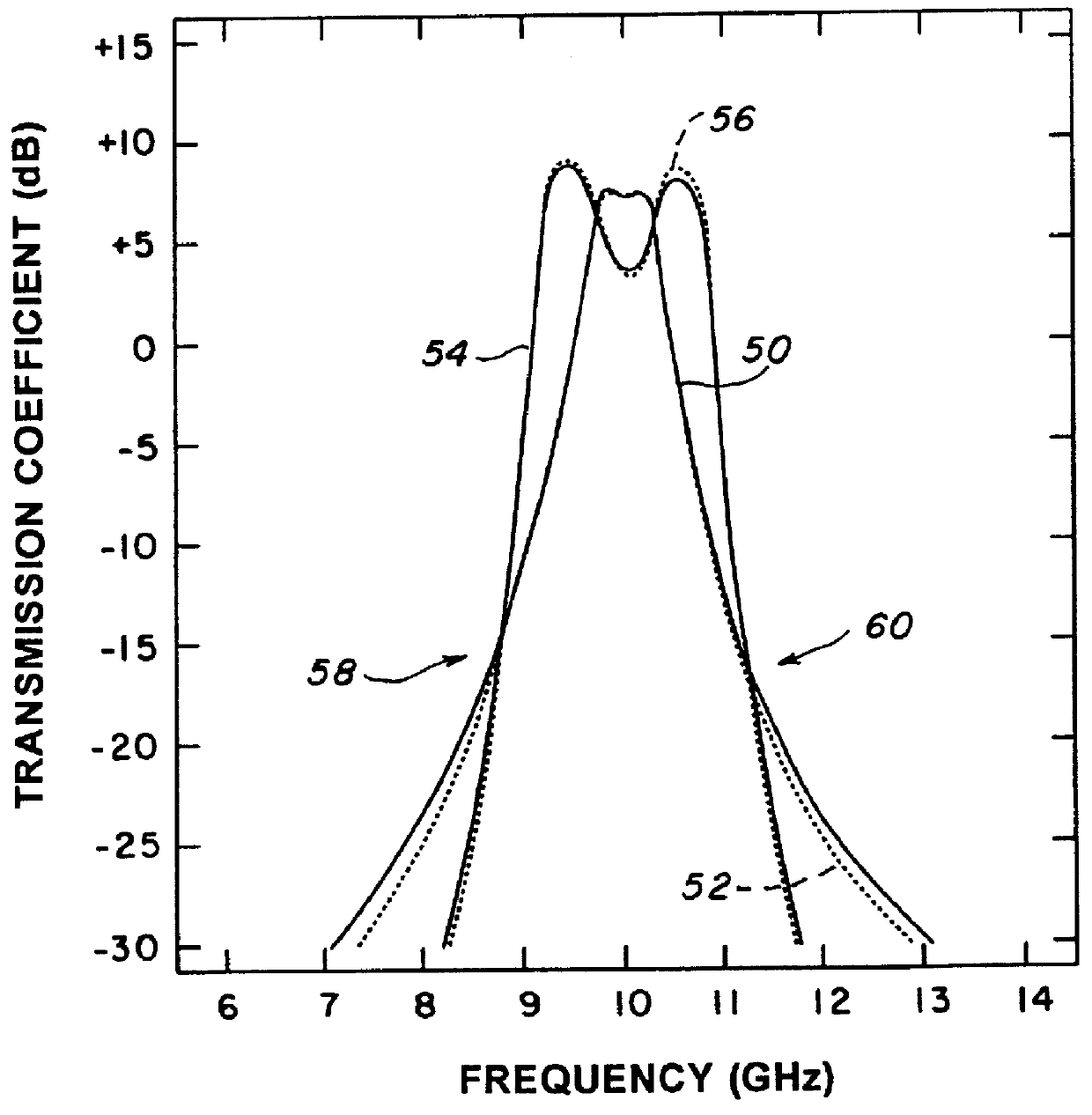

Microwave channelized bandpass filter having two channels

InactiveUS6107898AMultiple-port networksAmplifiers wit coupling networksBandpass filteringPhase splitter

A channelized active bandpass filter having only two branches which provide respective frequency-selective feed-forward signal paths. The two signal paths have overlapping frequency response bands such that the combination of the two paths provides a composite filter with a bandpass response. The two branches may be provided with bandpass transfer characteristics of different orders and shapes, such as a second-order response and a fourth-order response. Two-way signal splitting and combining to define the two channels may be performed with in-phase splitters and combiners, for example, or diplexer circuits, each composed of two bandpass filters with different characteristics but overlapping frequency responses and preferably approximately equal center frequencies. Combinations of the two splitting and combining arrangements are also usable.

Owner:THE GOVERNMENT OF THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SEC OF THE NAVY NAVAL RES LAB WASHINGTON

Adaptive radio transceiver with noise suppression

InactiveUS6975838B1Suppress noiseTransmitters monitoringResonant long antennasTransceiverAdaptive programming

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

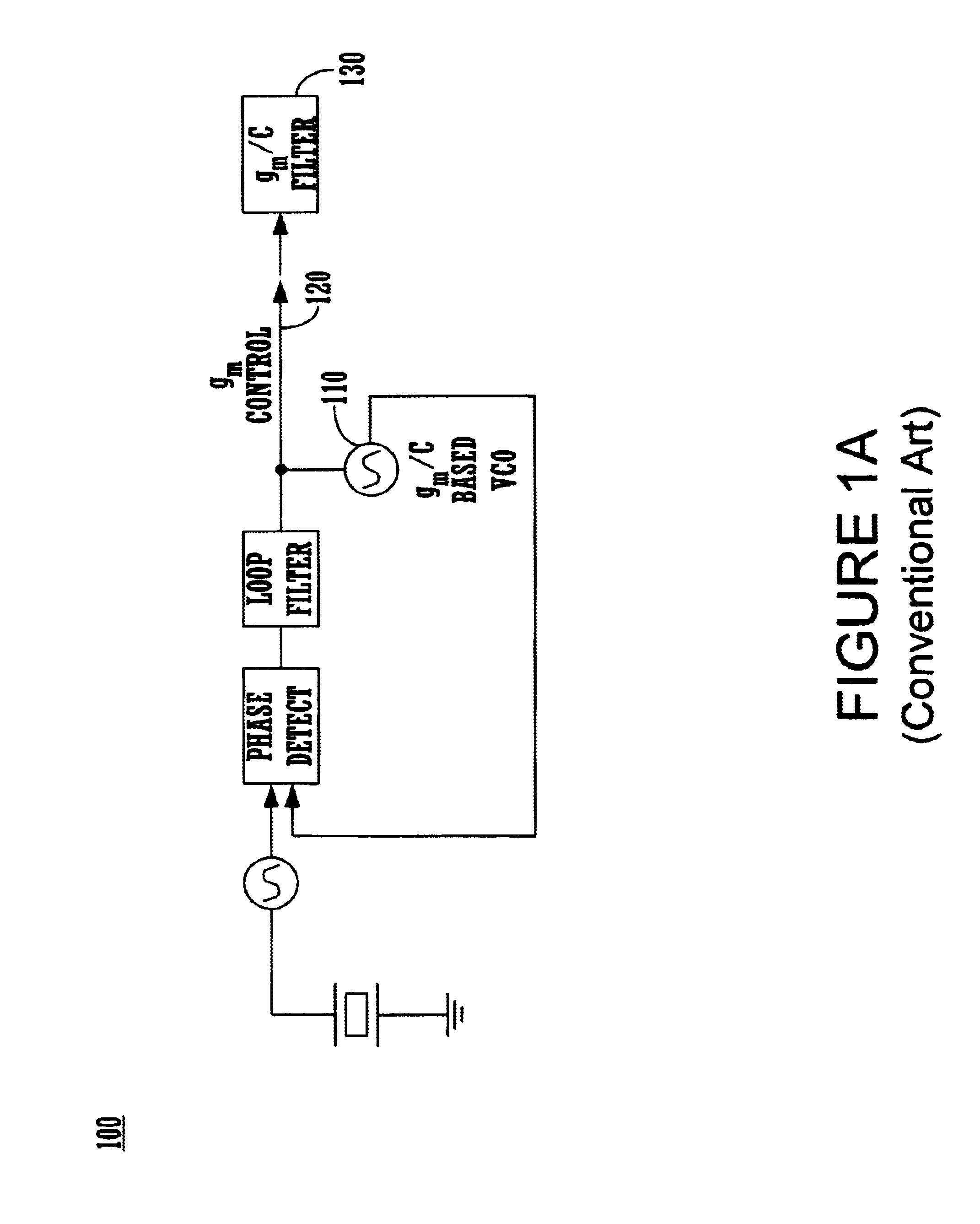

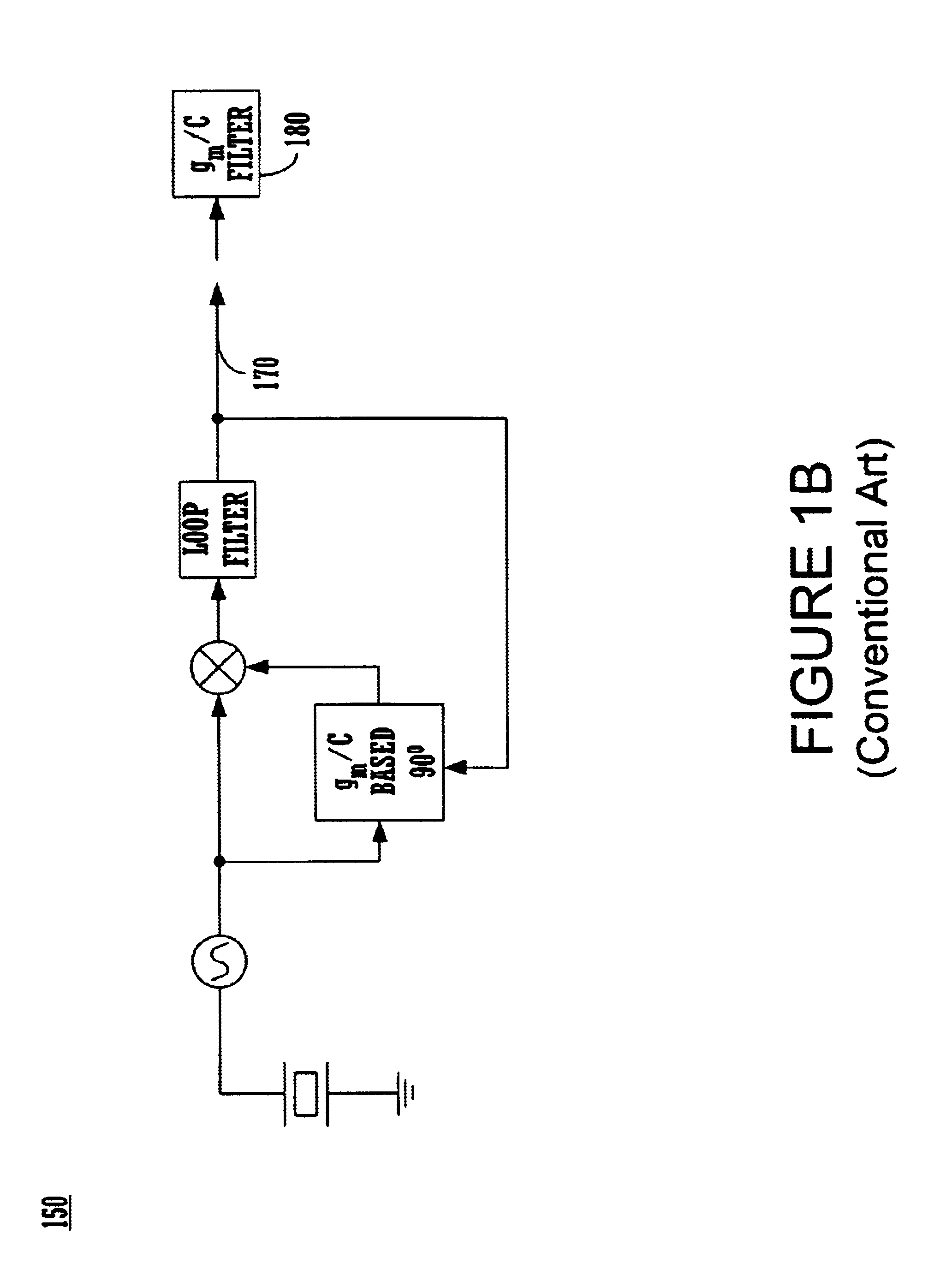

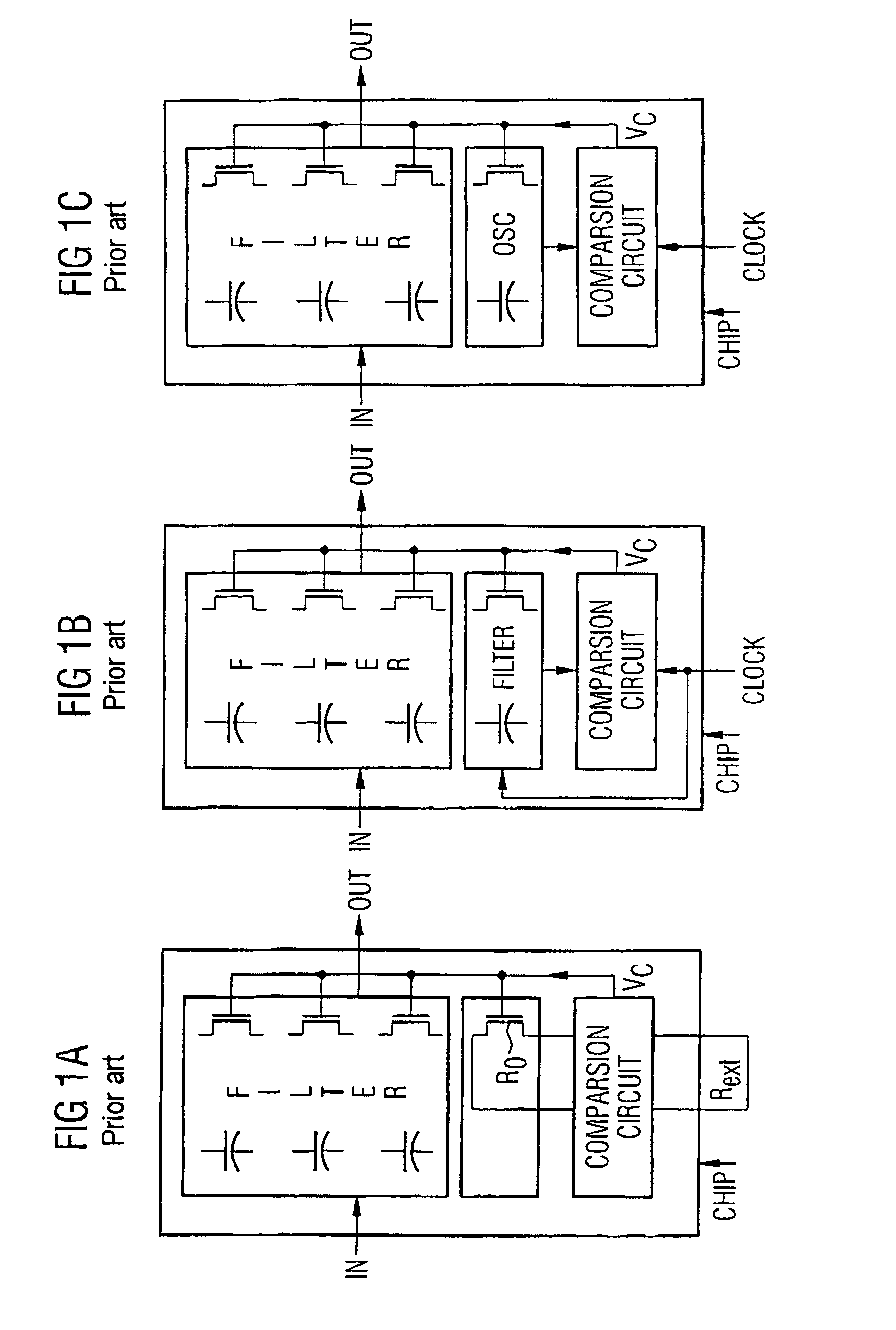

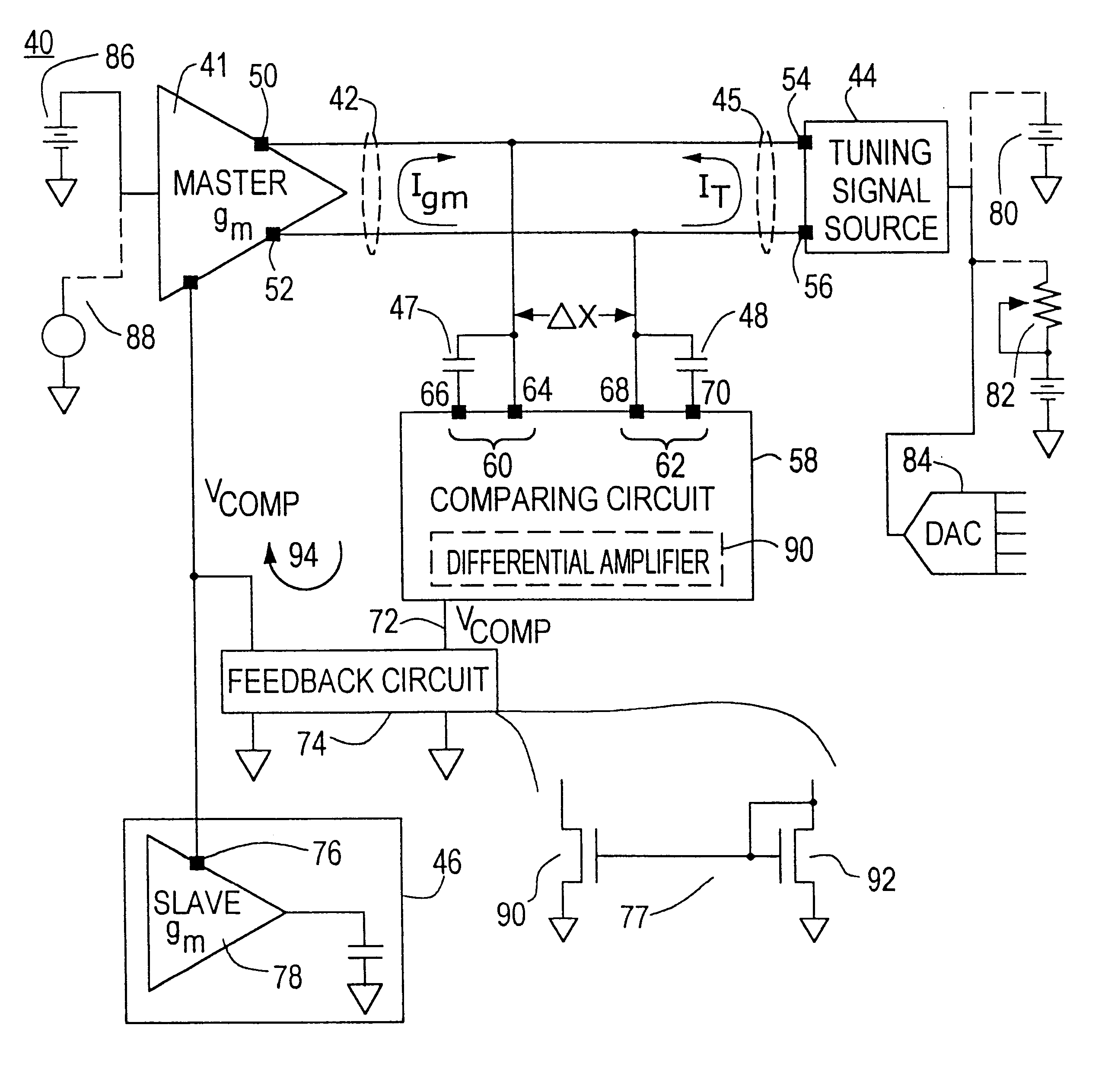

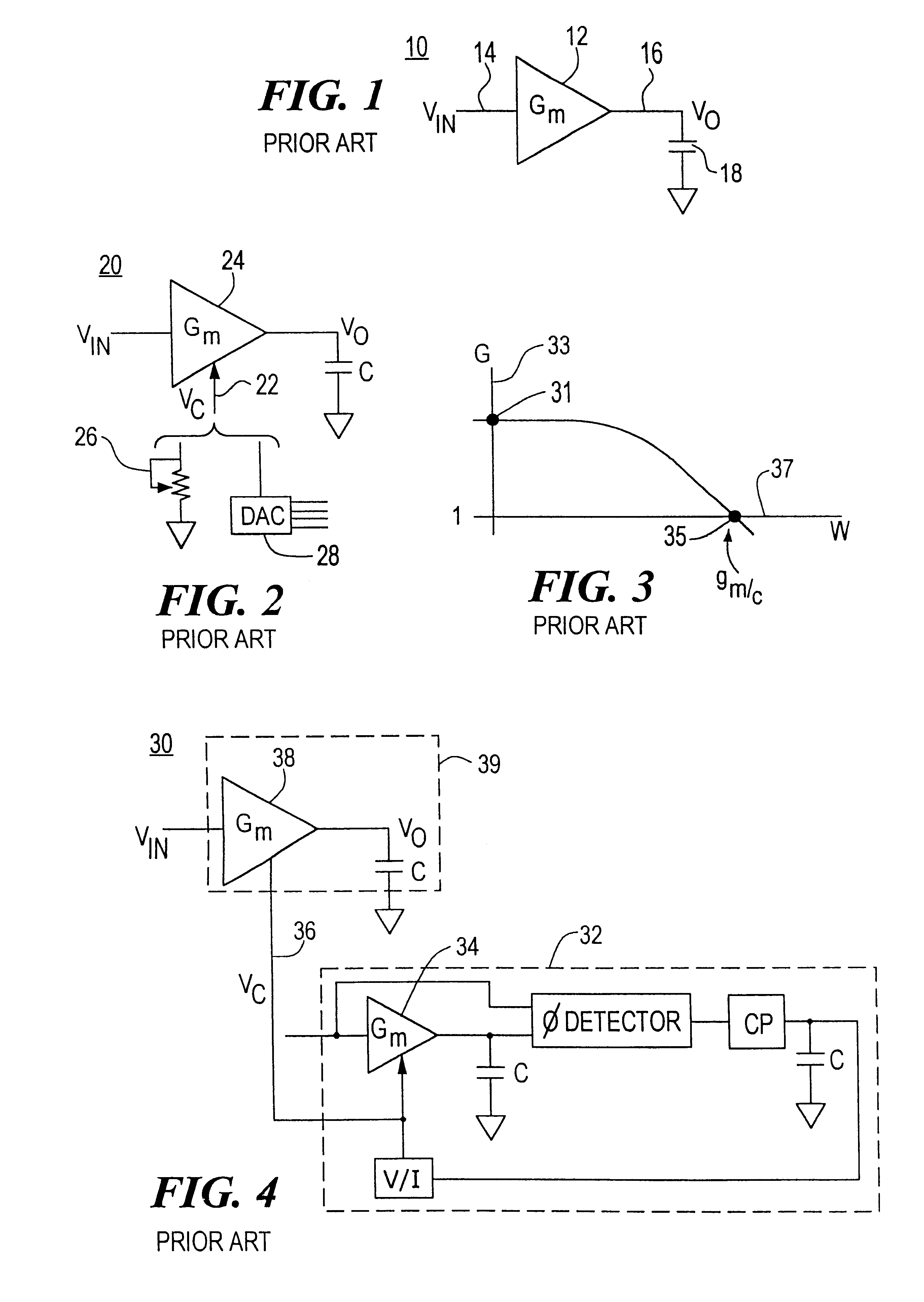

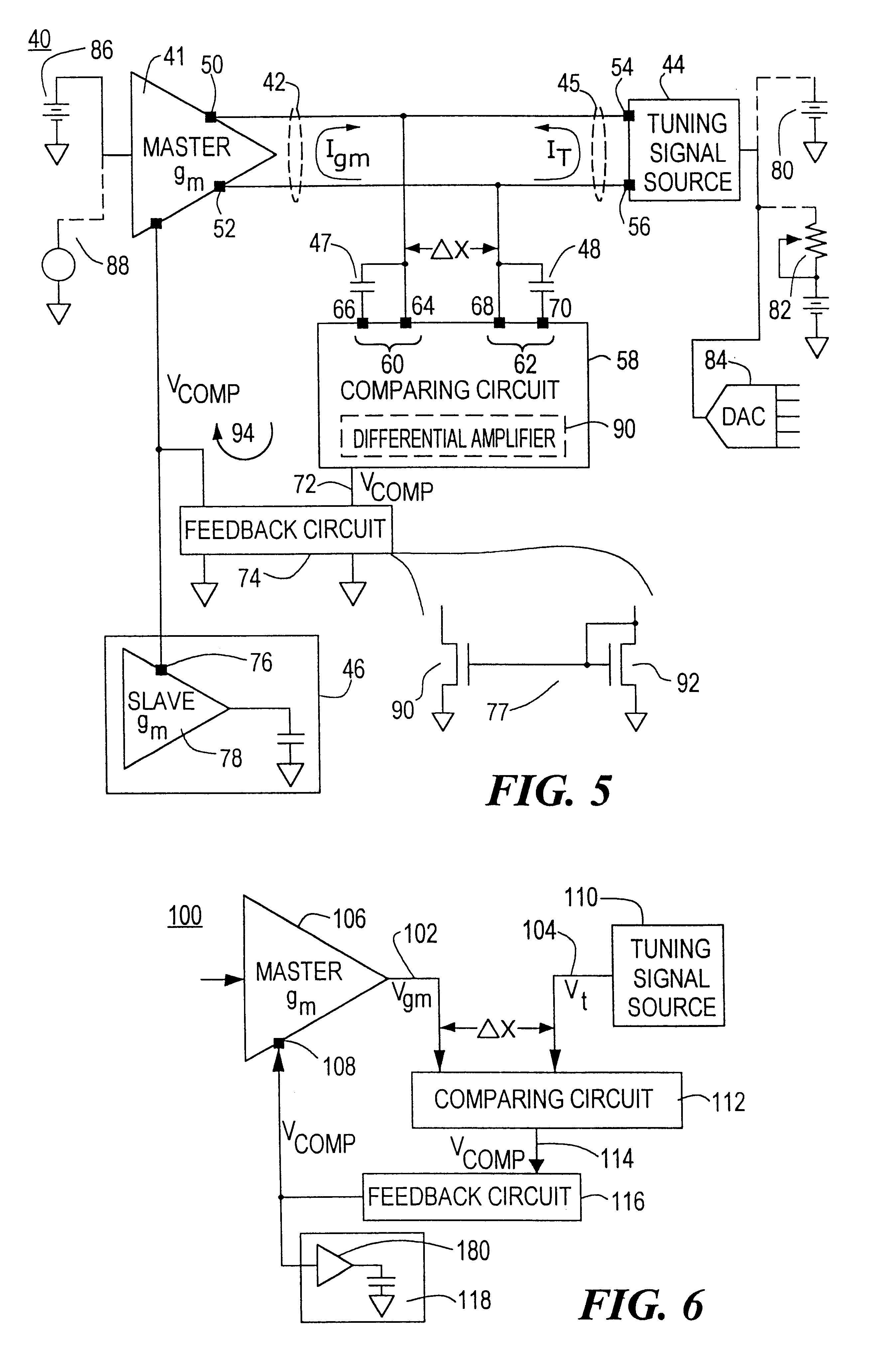

Transconductance filter control system

InactiveUS6172569B1Increase power consumptionIncrease in sizeContinuous tuning detailsGain controlAudio power amplifierControl system

A transconductance filter control system for compensating for drift in transconductance of a slave transconductance amplifier in a continuous time transconductance filter including: a master transconductance amplifier having an output which is a function of its transconductance and a control input for controlling the transconductance of the master transconductance amplifier; a tuning signal source for providing a tuning signal representative of a preselected characteristic of the transconductance filter; a comparing circuit, responsive to any deviation from a predetermined difference between the tuning signal and the output of the master transconductance amplifier, representative of a deviation of the transconductance of the master transconductance amplifier, for providing a compensation signal; and a circuit for applying the compensation signal to the control input of the master transconductance amplifier and to the control input of the slave transconductance amplifier in the transconductance filter to adjust the transconductance of both the master and slave transconductance amplifiers and restore the predetermined difference between the tuning signal and the output of the master transconductance amplifier.

Owner:ANALOG DEVICES INC +1

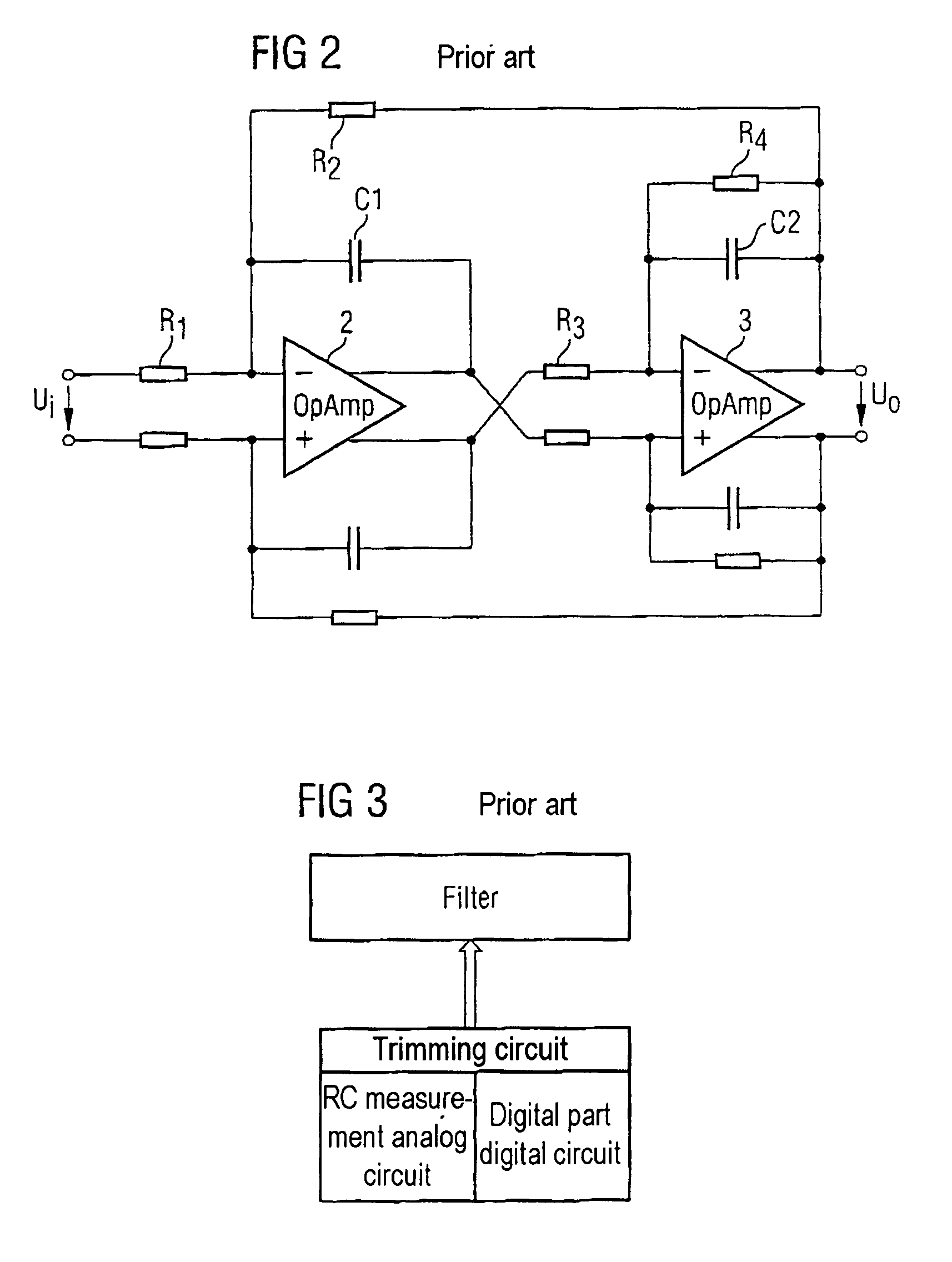

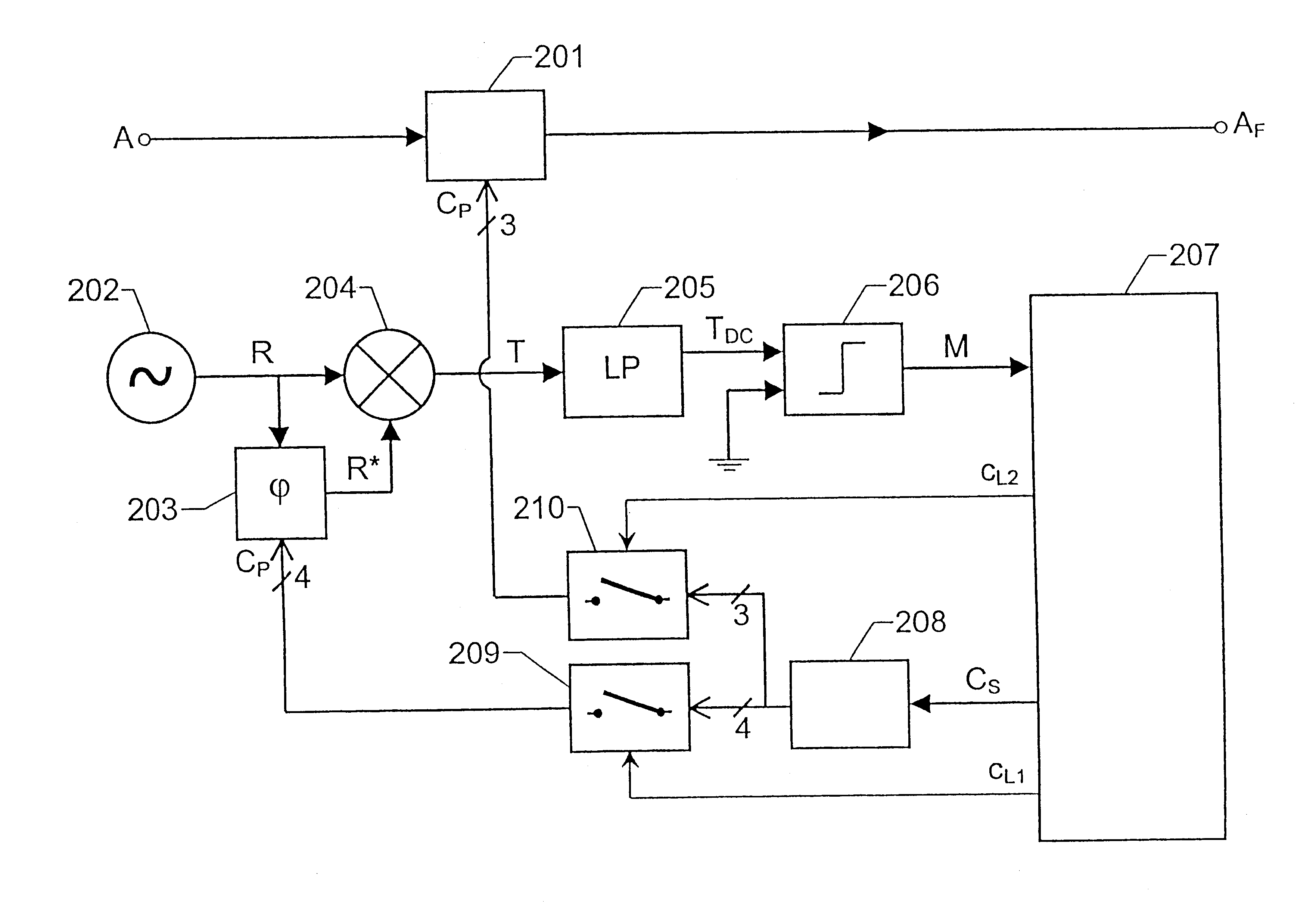

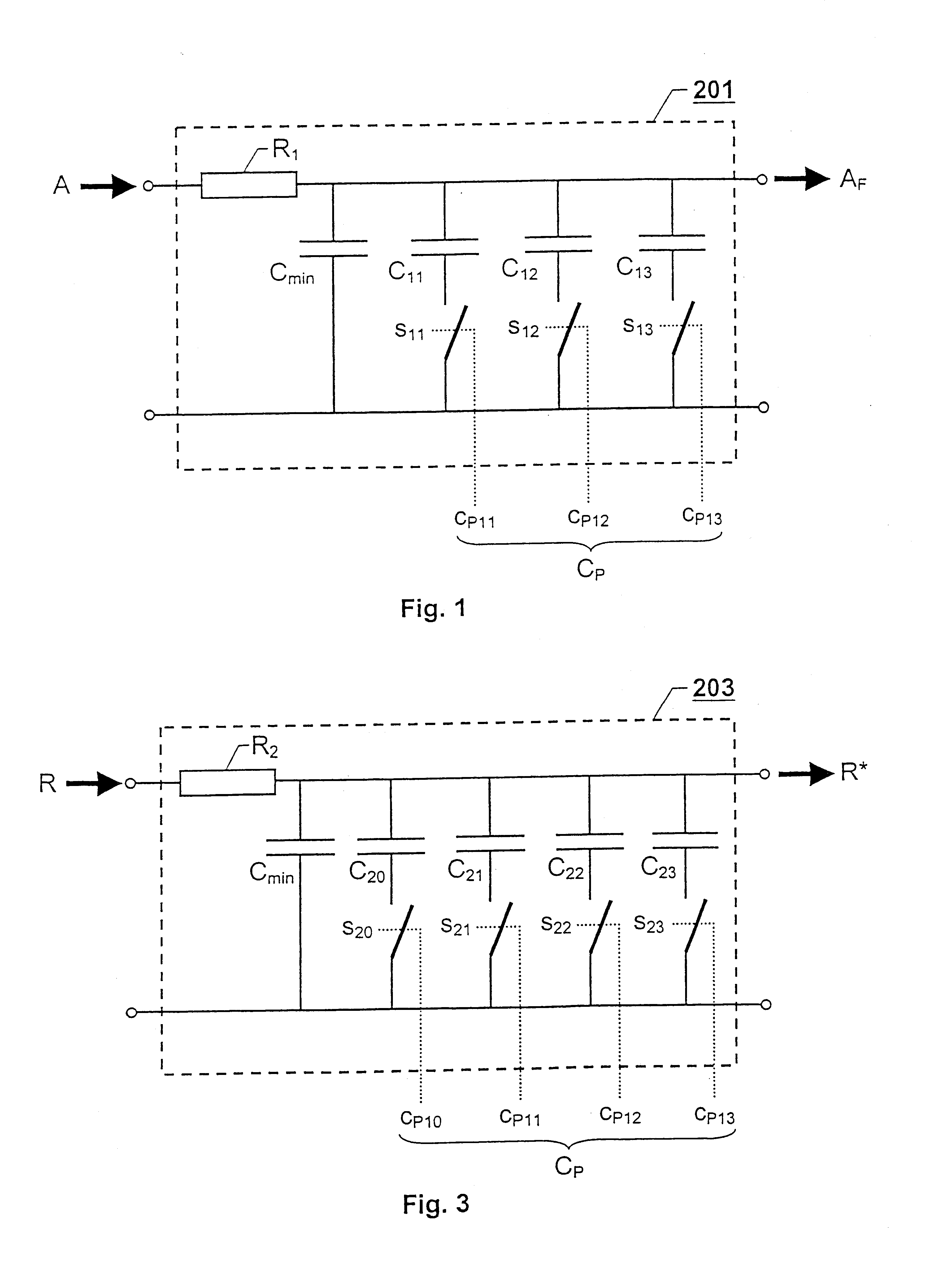

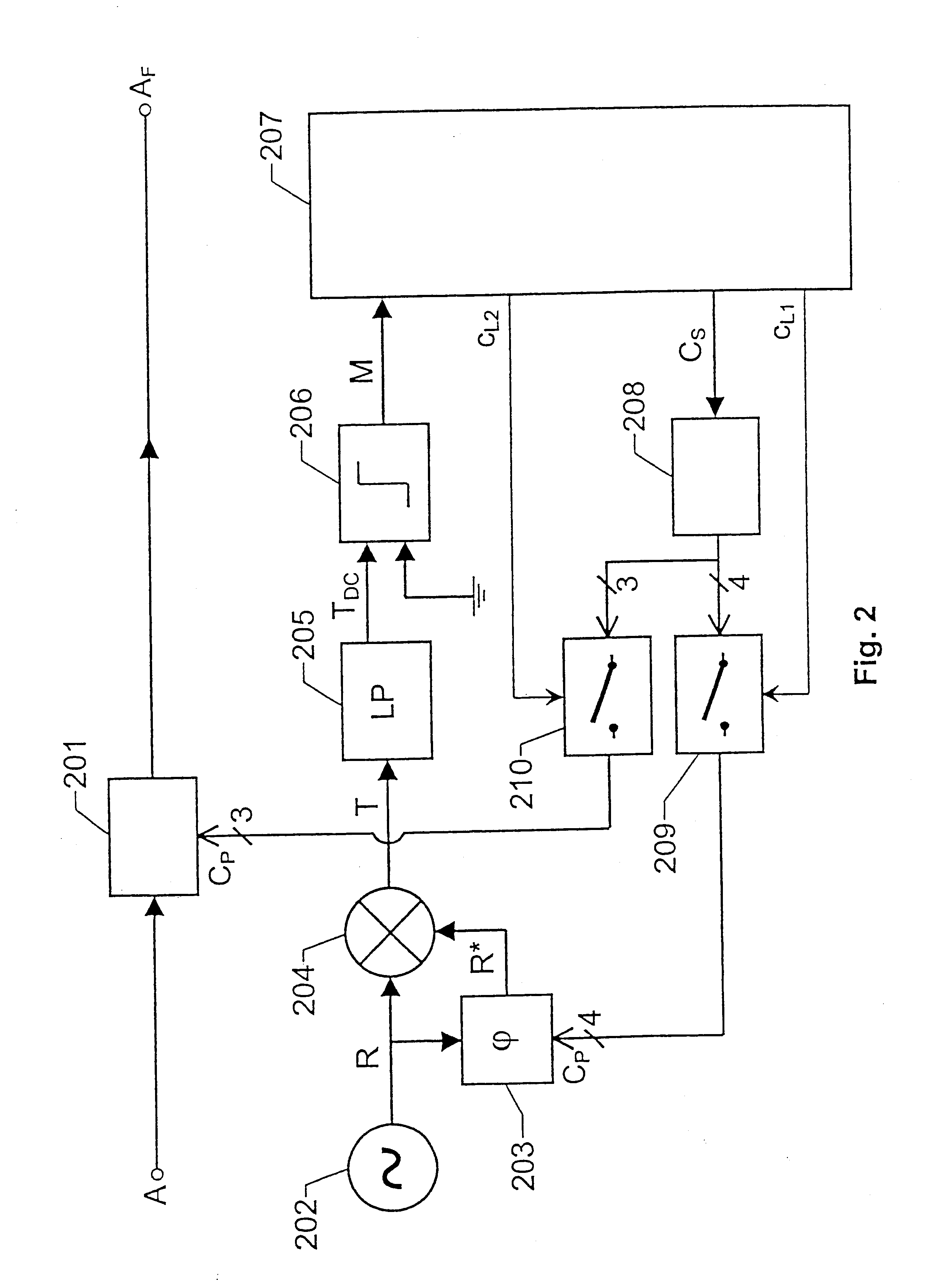

Filter trimming

InactiveUS6686809B2Multiple-port networksTransmission control/equlisationDigital signal processingPhase difference

The invention relates to trimming of analogue filters (201) in integrated circuits by means of an automatic adjusting circuit. A local oscillator (202) in the automatic adjusting circuit provides a periodic reference signal (R) to an adjustable phase shifter (203), which on basis thereof, produces a periodic phase shifted signal (R*). A phase detector (204) receives both the periodic reference signal (R) and the phase shifted period signal (R*) and produces a test signal (T) in response to a phase difference between the periodic reference signal (R) and the periodic phase shifted signal (R8). A lowpass filter (205) receives the test signal (T) and generates a level signal (TDC) relative a reference level, e.g. representing a zero voltage. A digital signal processor (207) produces a primary control signal (CS), having a serial format, on basis of the observation signal (M). A serial-to-parallel converter (208) converts the primary control signal (CS) into a control signal (CP) having a parallel signal format. The control signal (CP) influences a magnitude of at least one component value in the adjustable phase shift between the periodic reference signal (R) and the periodic phase shifted signal (R*) attains a calibrated value being as close as possible to a desired value. A latch (210) forwards at least one signal element of the control signal (CP) for setting of at least one component value in the analogue filter (201) in accordance with a setting of at least one component value in the adjustable phase shifter (203) which produces the calibrated value.

Owner:NAT SEMICON CORP

Adaptive radio transceiver with a power amplifier

InactiveUS7113744B1Increase data rateIncrease costTransmitters monitoringResonant long antennasTransceiverAdaptive programming

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

Popular searches

Resistance/reactance/impedence Electronic circuit testing Digital differential analysers Frequency selective two-port networks Special data processing applications Tunable filters Amplifier modifications to reduce noise influence Amplifier modifications to reduce temperature/voltage variation Secret communication Transmitter/receiver shaping networks