Patents

Literature

134 results about "Filter tuning" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

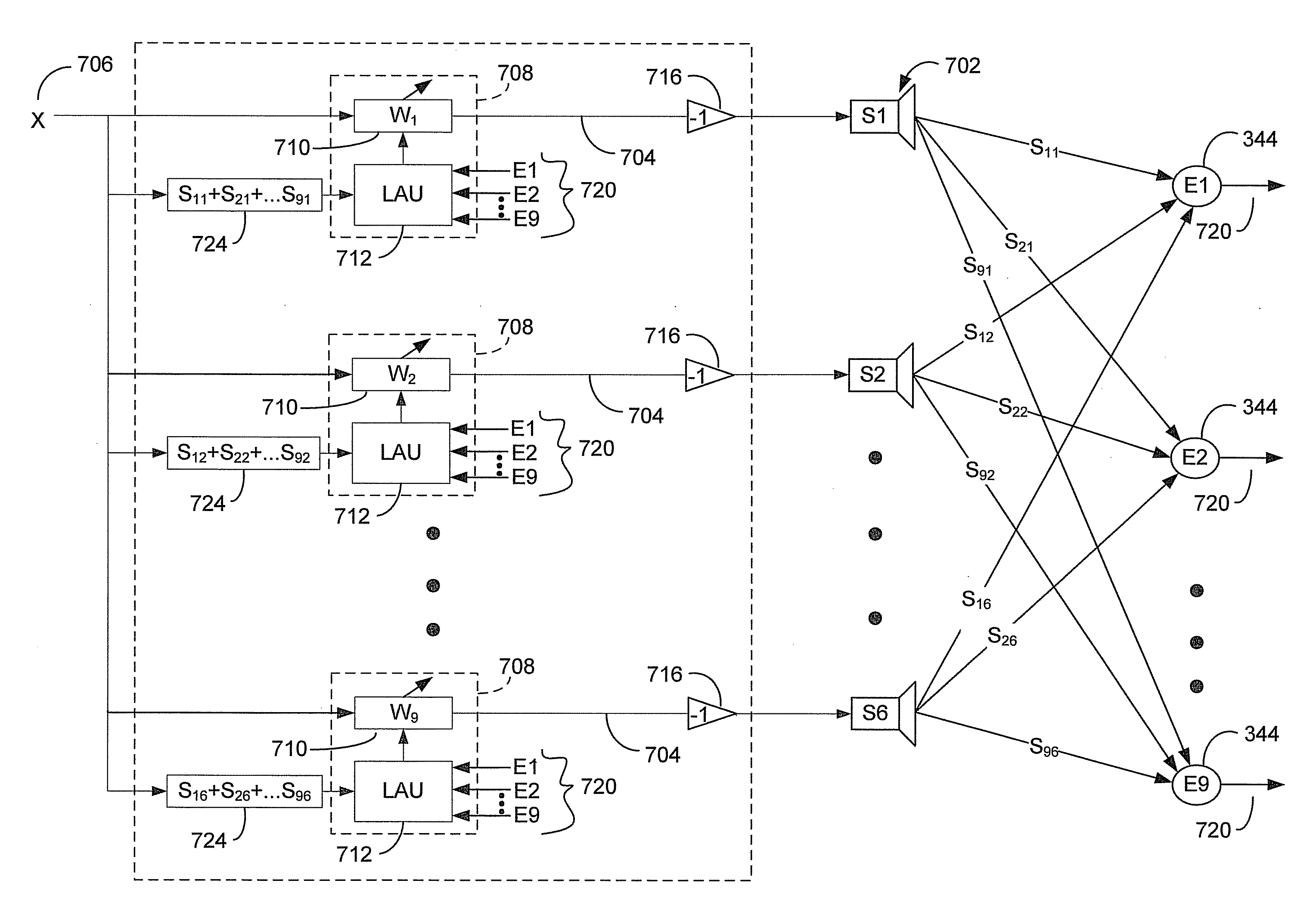

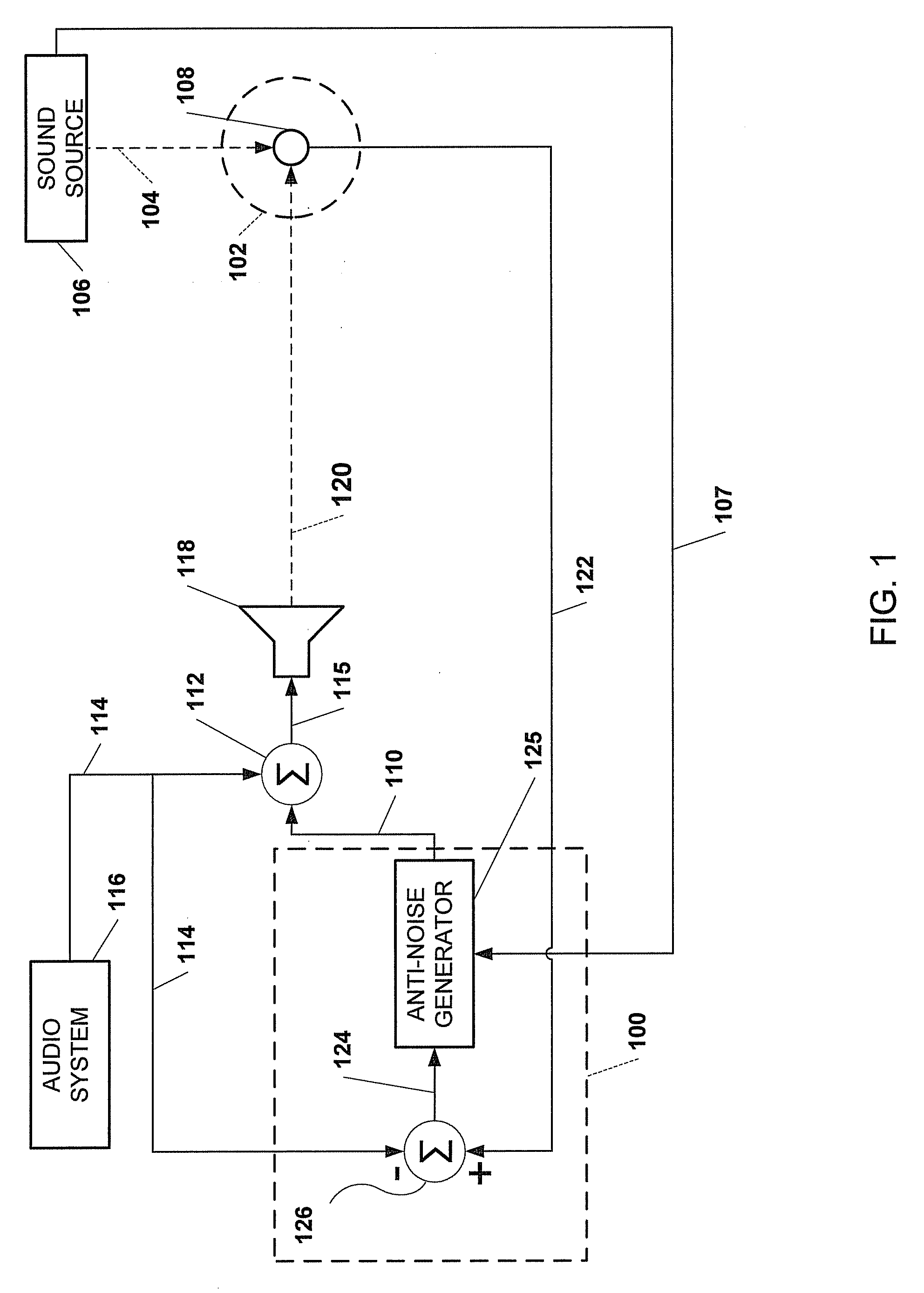

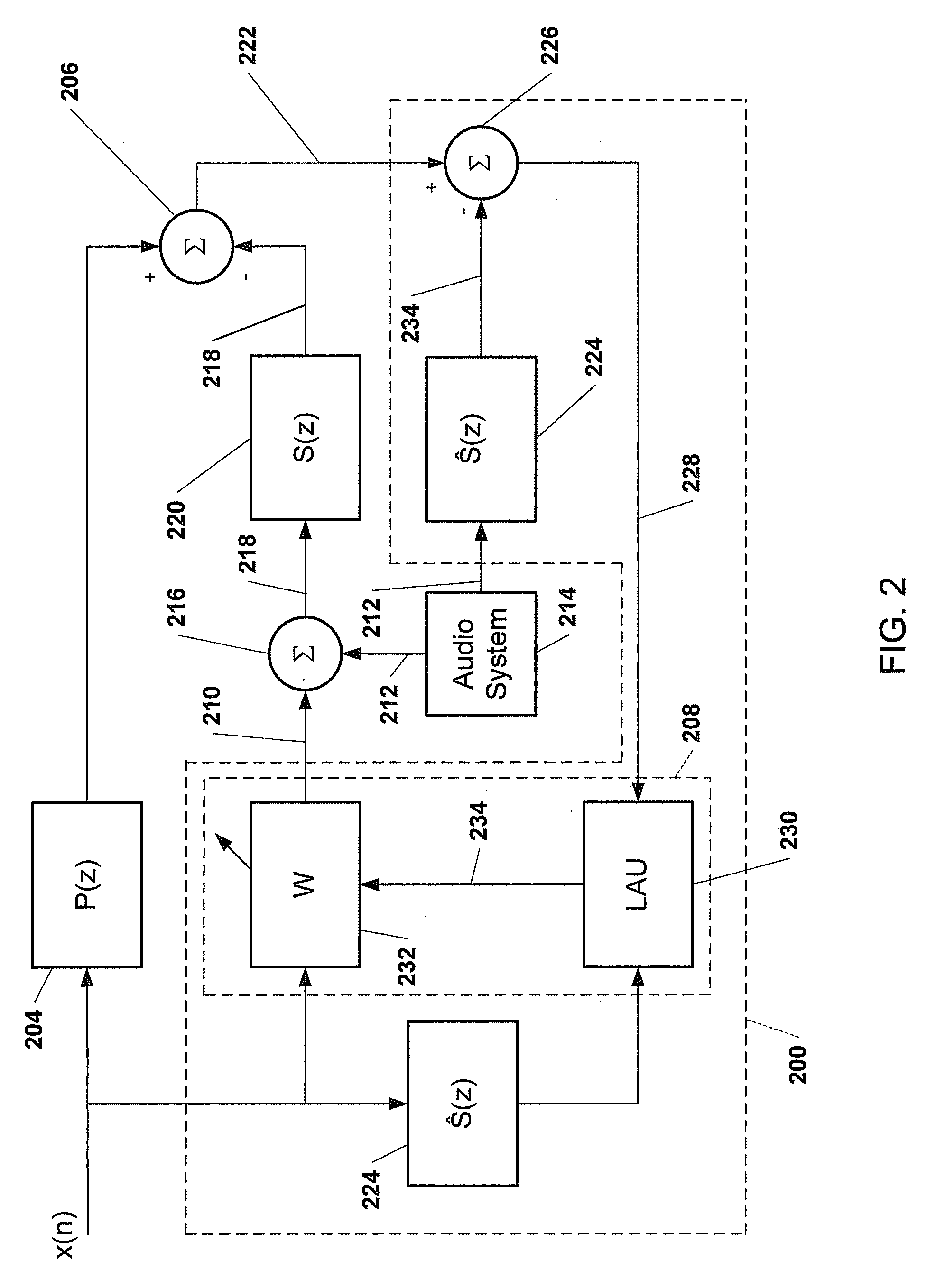

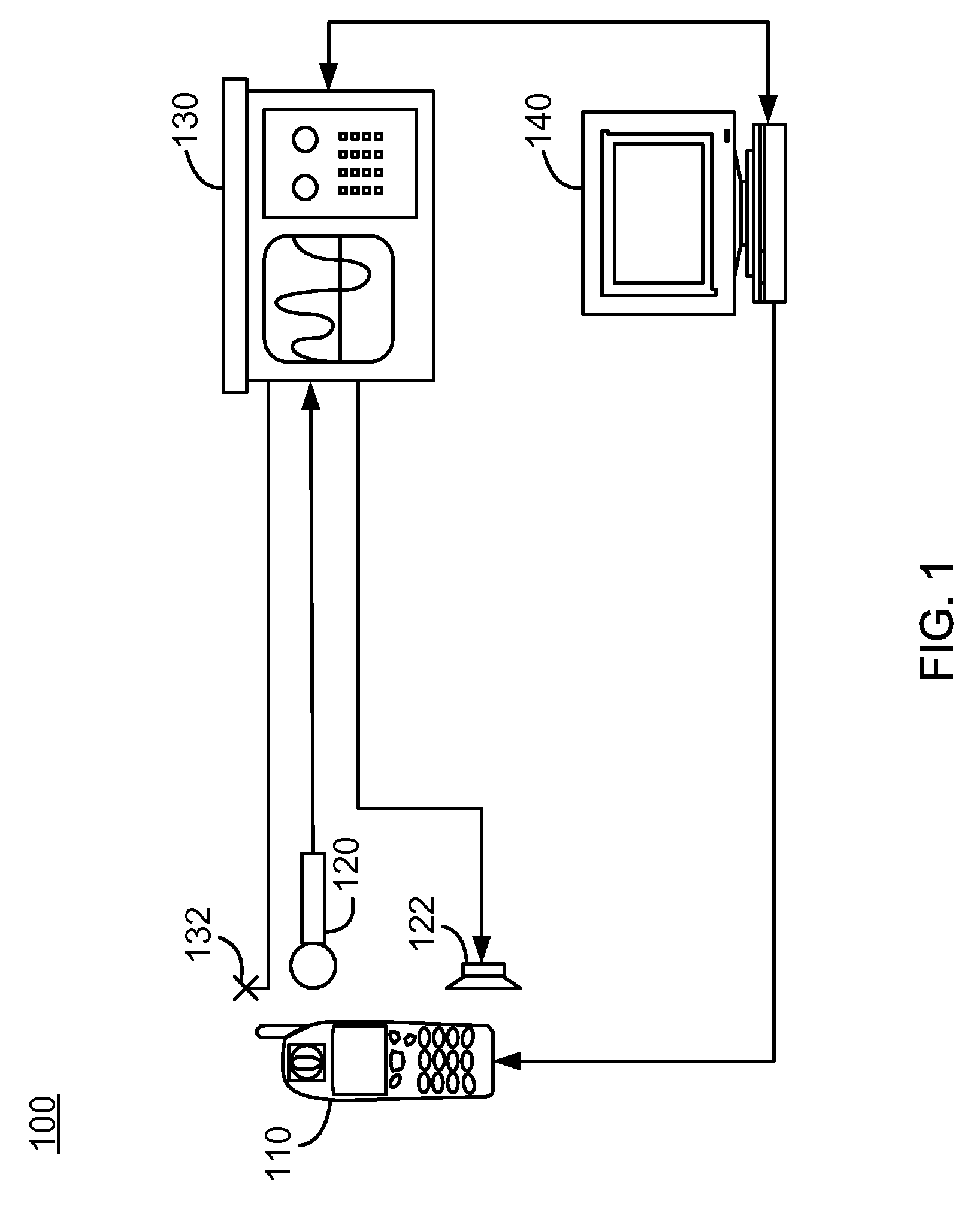

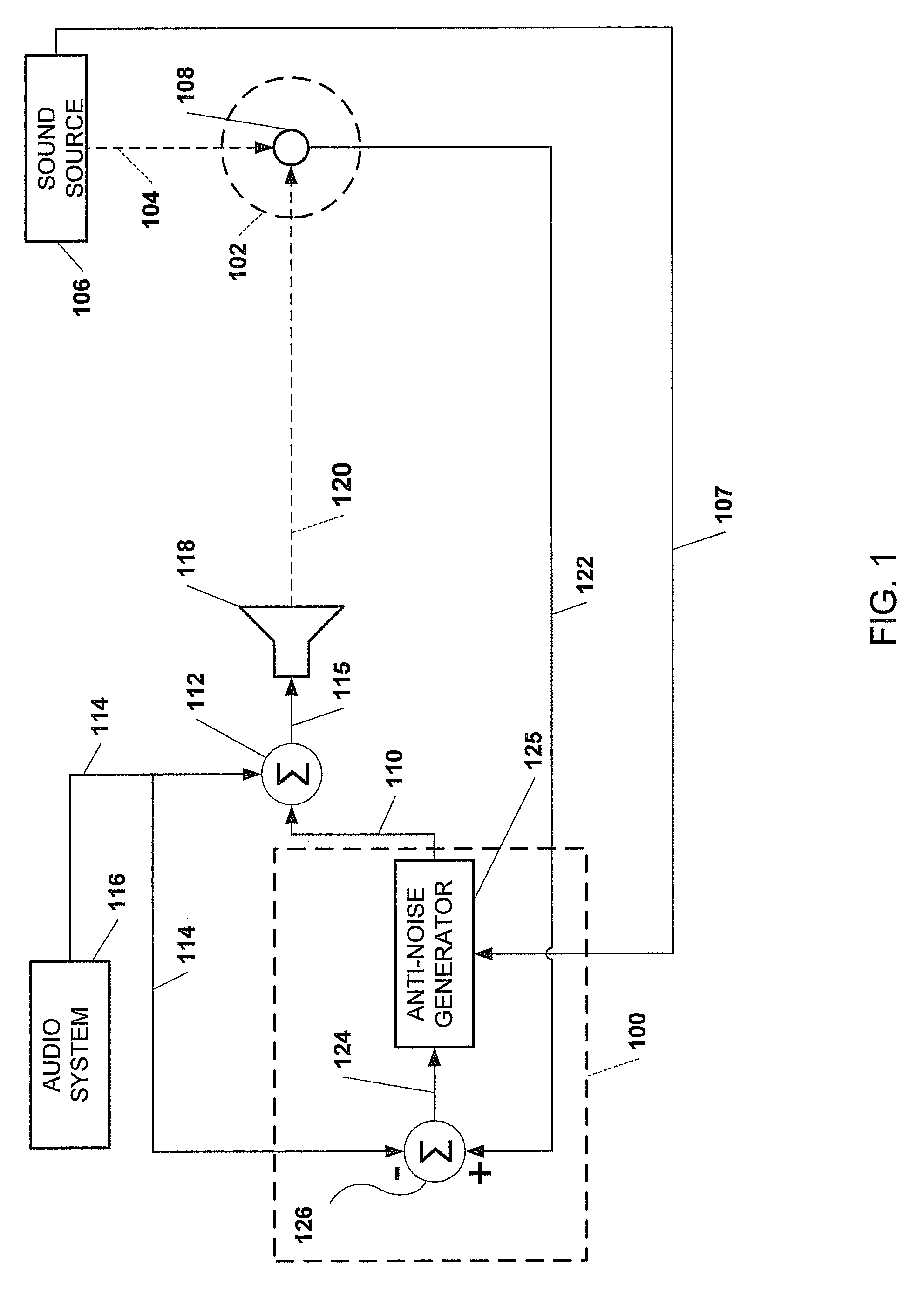

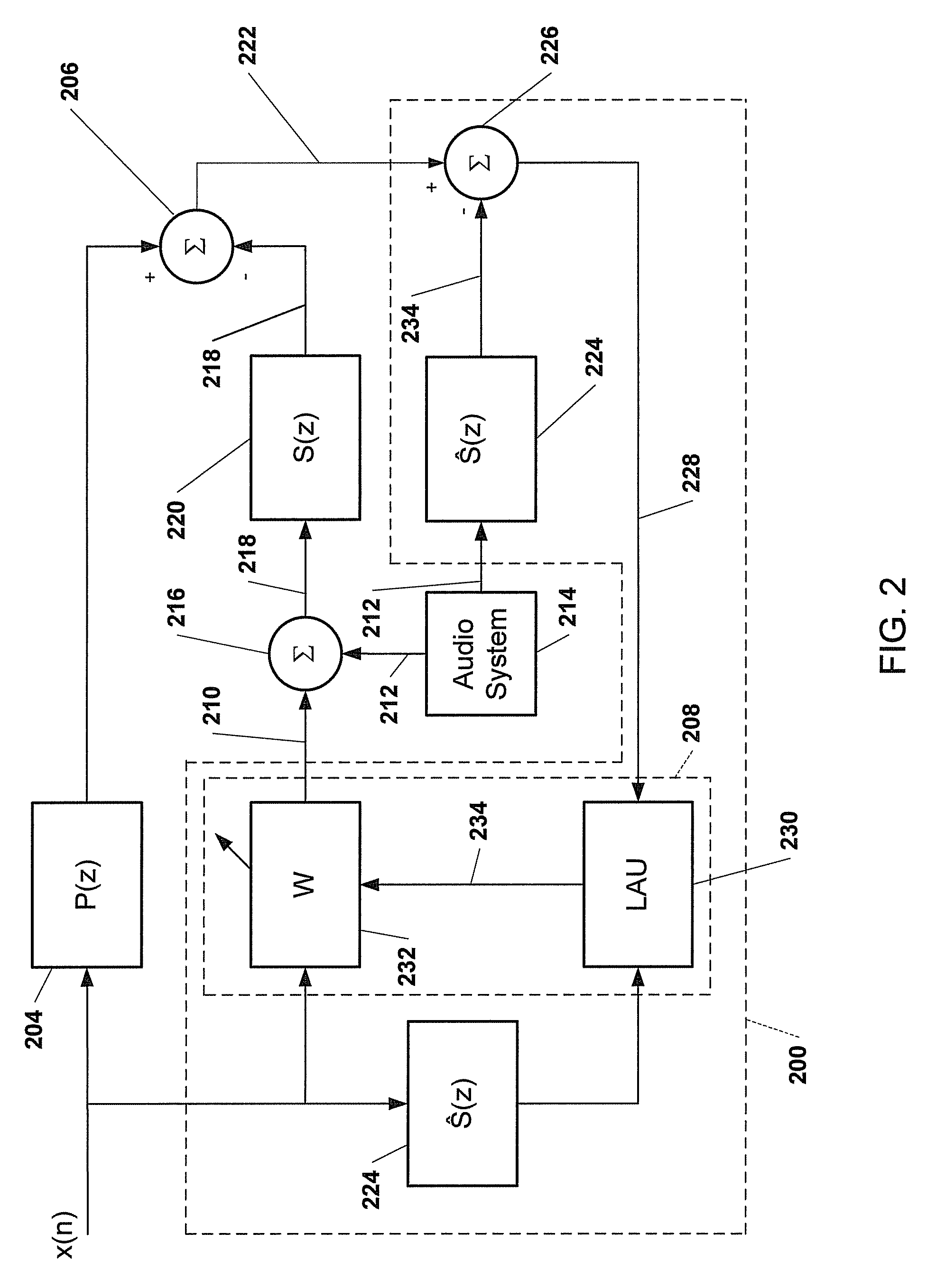

Quiet zone control system

An active noise control system generates an anti-noise signal to drive a speaker to produce sound waves to destructively interfere with an undesired sound in a quiet zone. The anti-noise signal is generated with an adaptive filter having filter coefficients. The coefficients of the adaptive filter may be adjusted based on a first filter adjustment from a first listening region, and a second filter adjustment from a second listening region. A first weighting factor may be applied to the first filter adjustment, and a second weighting factor may be applied to the second filter adjustment. The first and second weighting factors may dictate the location and size of the quiet zone as being outside or partially within at least one of the first listening region and the second listening region.

Owner:HARMAN INT IND INC

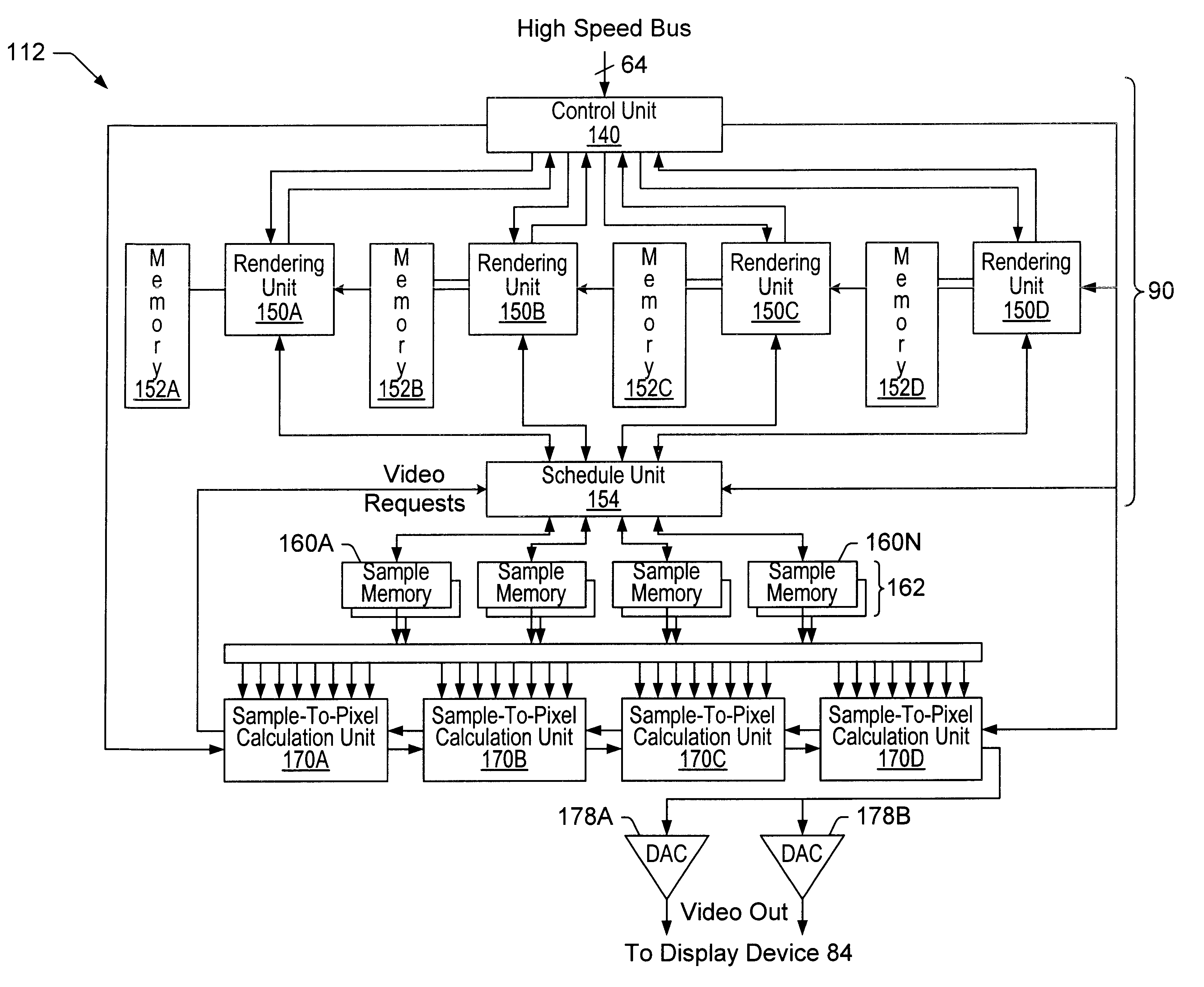

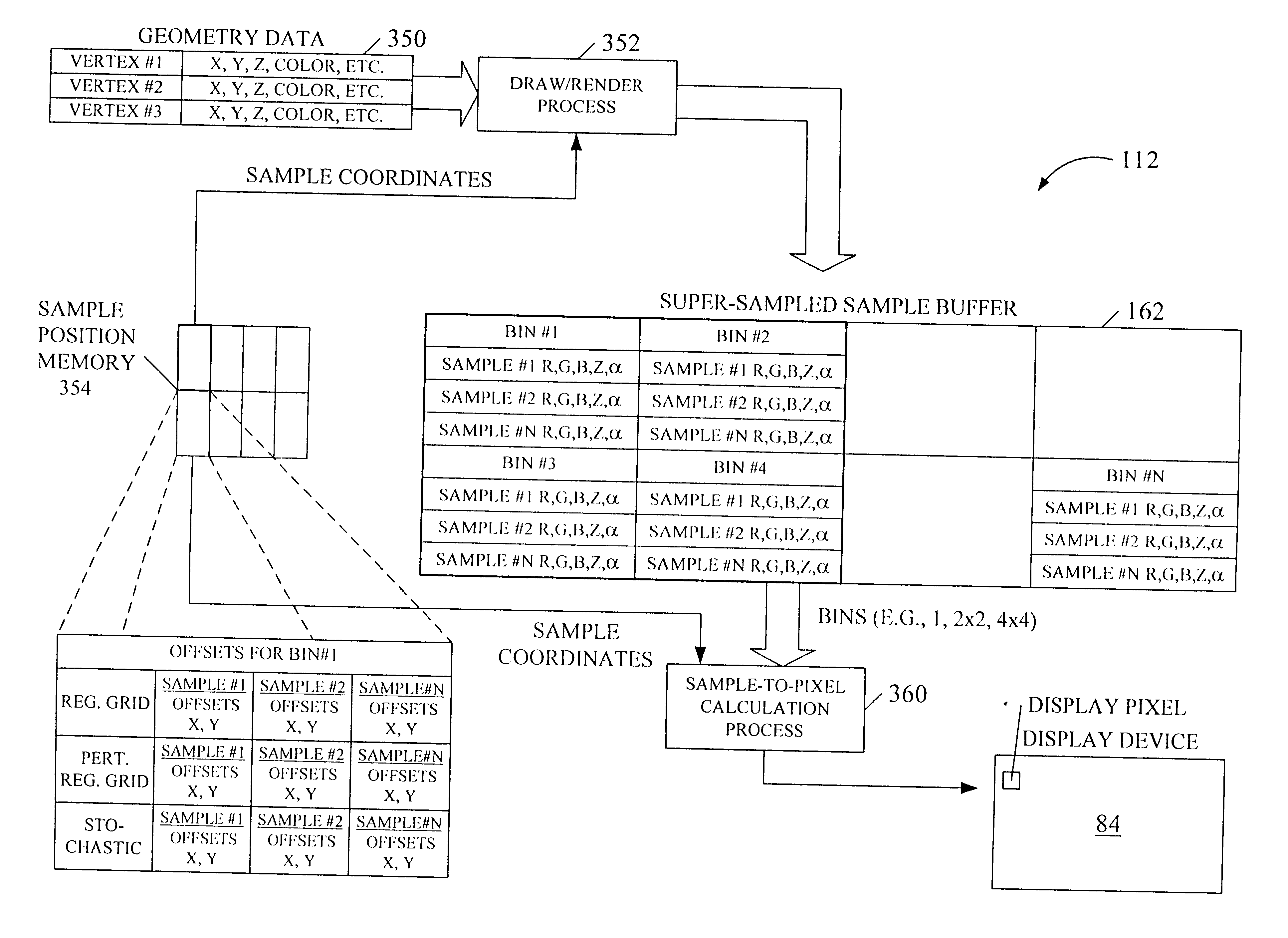

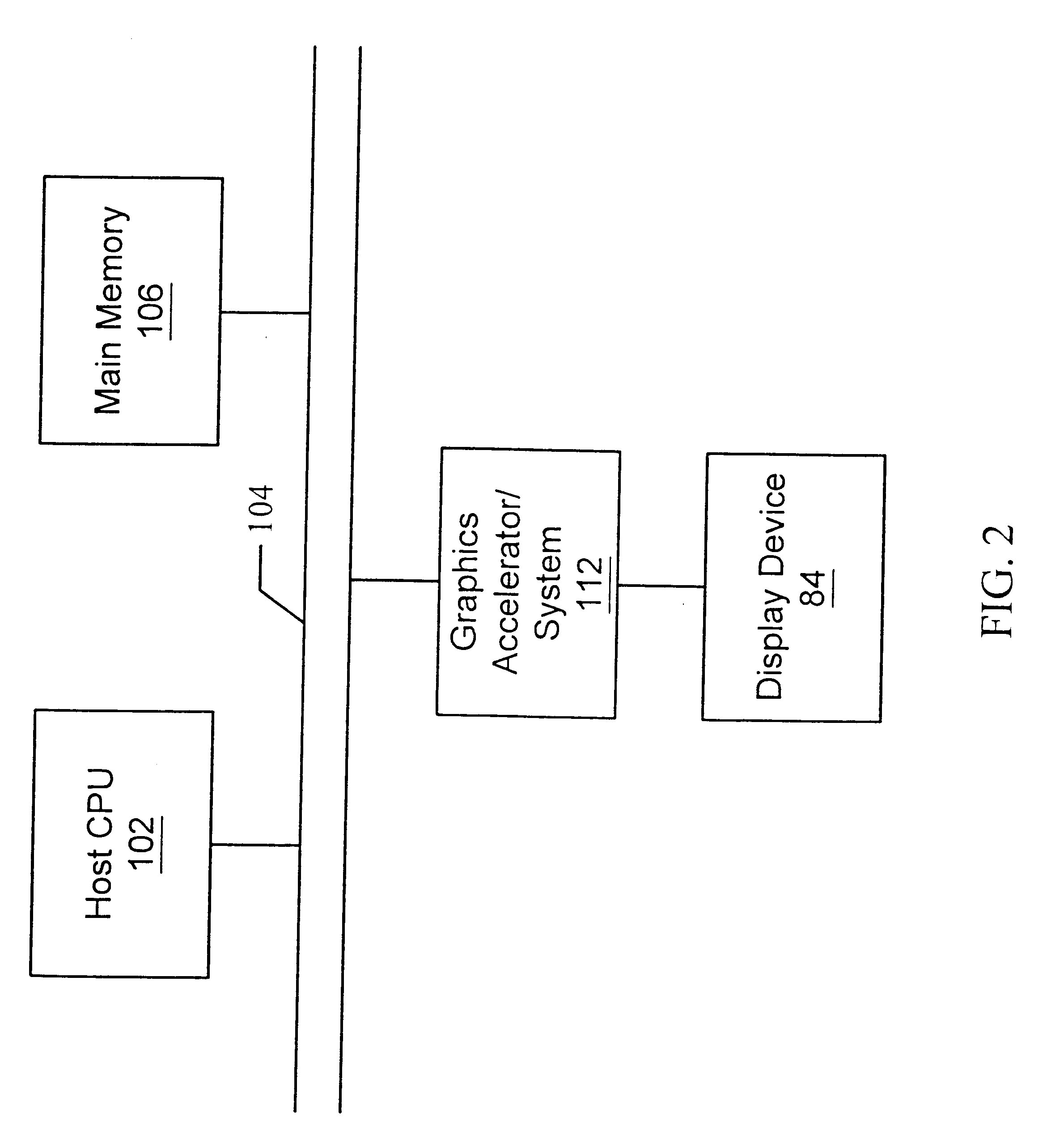

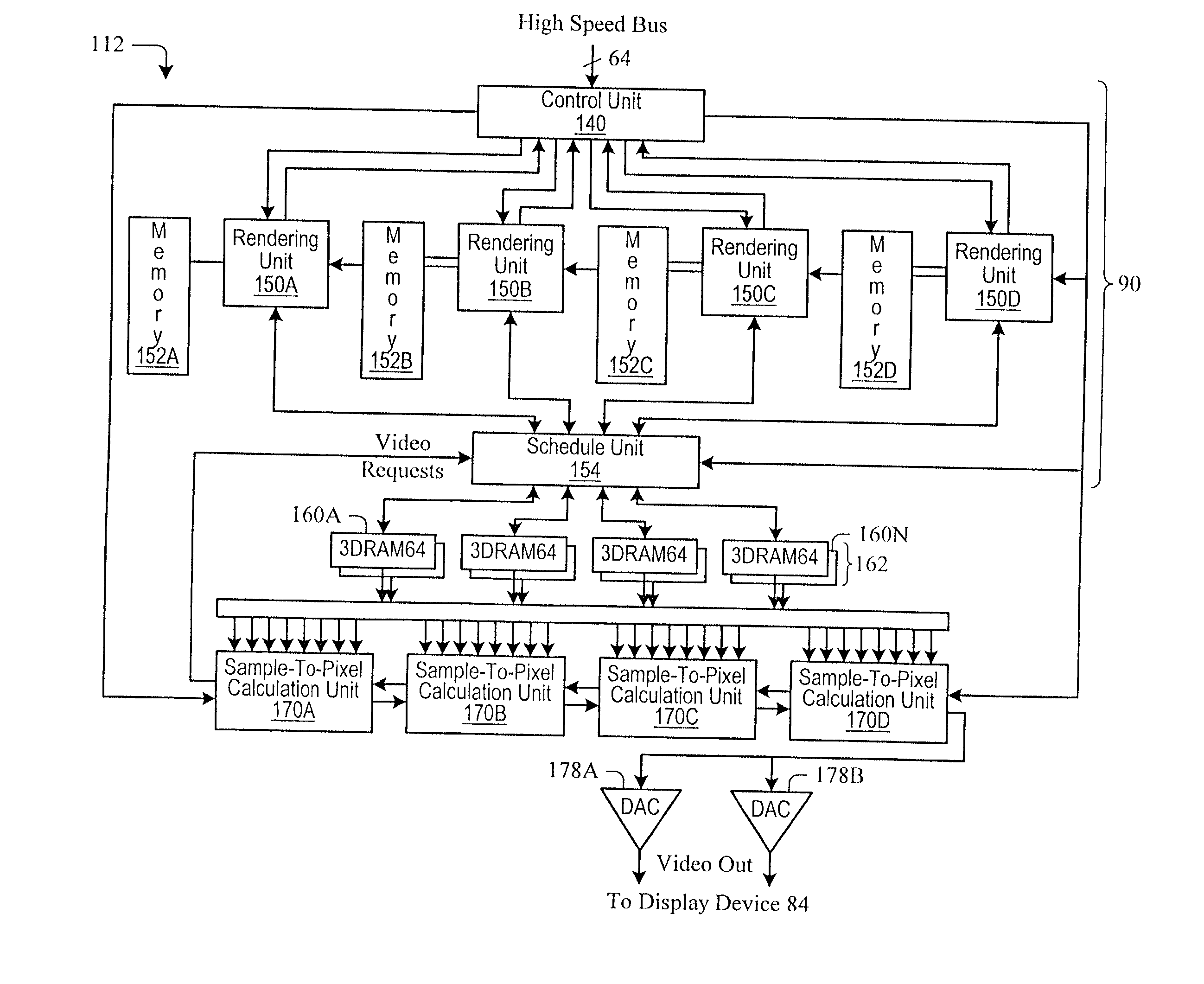

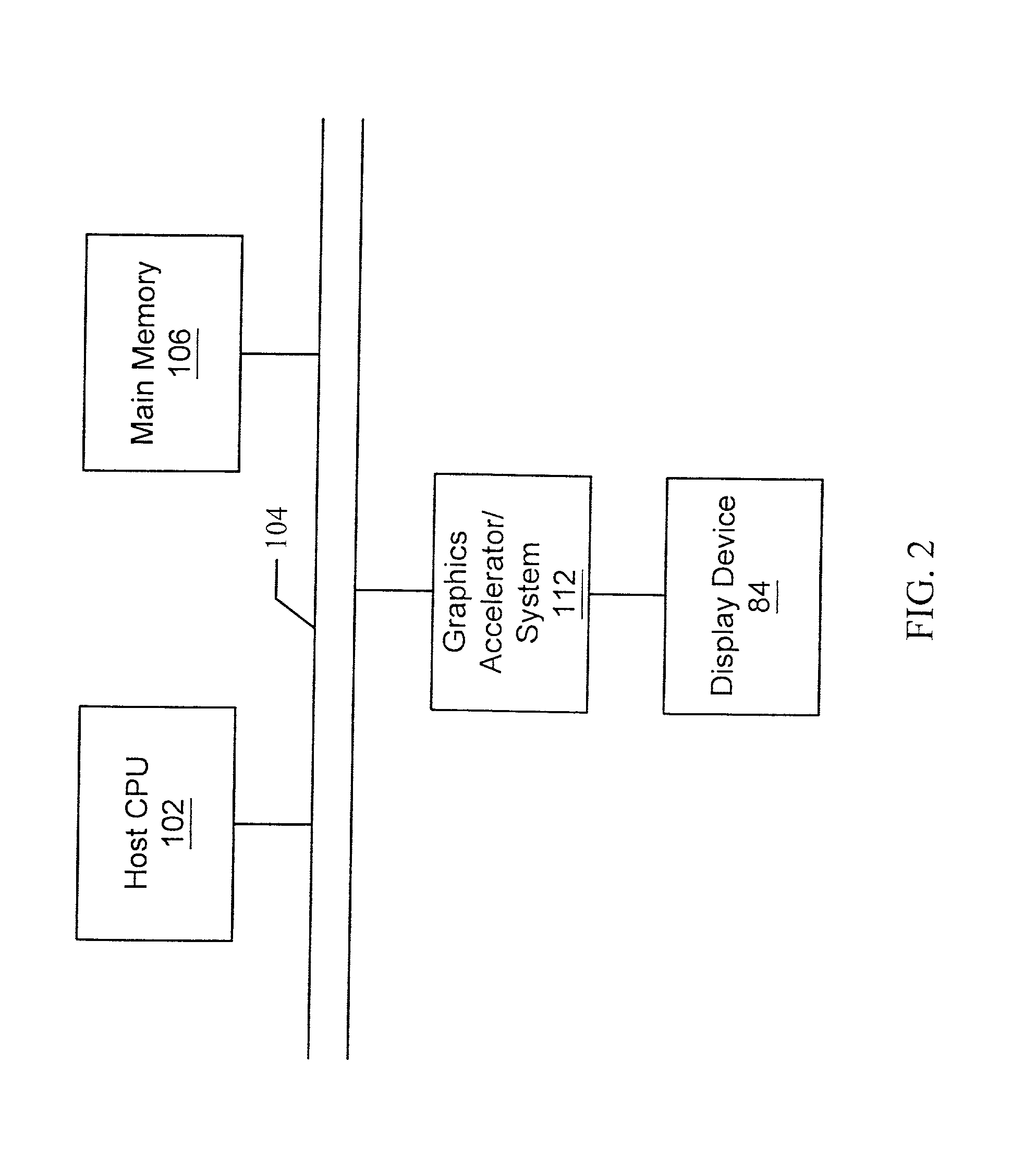

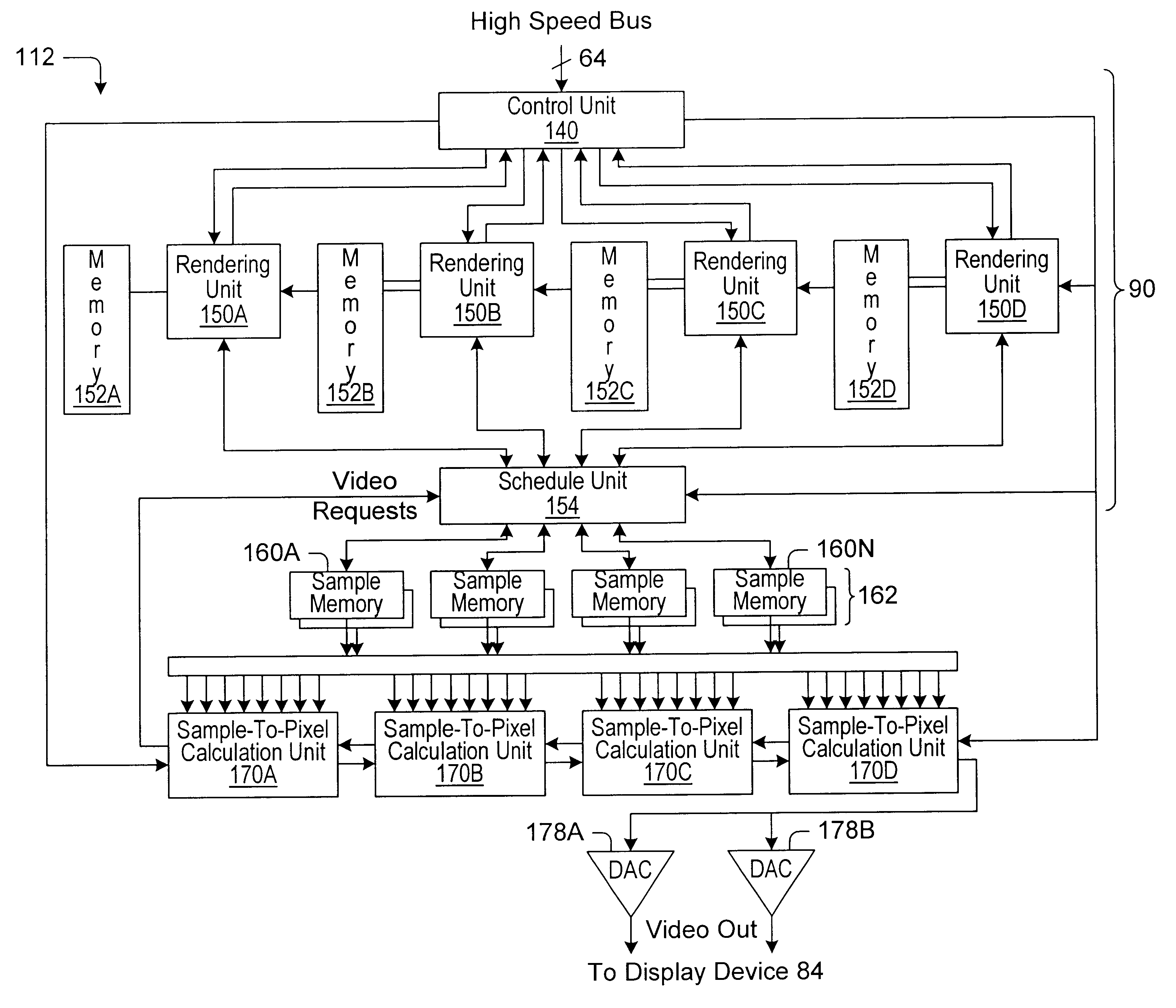

Graphics system having a super-sampled sample buffer with generation of output pixels using selective adjustment of filtering for reduced artifacts

A computer graphics system that utilizes a super-sampled sample buffer and a programmable sample-to-pixel calculation unit for refreshing the display, wherein the graphics system may adjust filtering to reduce artifacts or implement display effects. In one embodiment, the graphics system may have a graphics processor, a super-sampled sample buffer, and a sample-to-pixel calculation unit. The graphics processor renders a plurality of samples and stores them into a sample buffer. The sample-to-pixel calculation unit reads the samples from the super-sampled sample buffer and filters or convolves the samples into respective output pixels which are then provided to refresh the display. The sample-to-pixel calculation unit may selectively adjust the filtering of stored samples to reduce artifacts, e.g., is operable to selectively adjust the filtering of stored samples in neighboring frames to reduce artifacts between the neighboring frames. The filter adjustment may be applied where the sample-to-pixel calculation unit generates output pixels at the same rate as the graphics processor rendering samples to the sample buffer, or at a different (e.g., higher) rate than the render rate. The sample-to-pixel calculation unit is operable to adjust filtering of stored samples to implement a display effect, such as panning, zooming, rotation, or moving scenes, among others. The sample-to-pixel calculation unit may also selectively adjust the filtering of stored samples on a fractional-pixel boundary.

Owner:ORACLE INT CORP

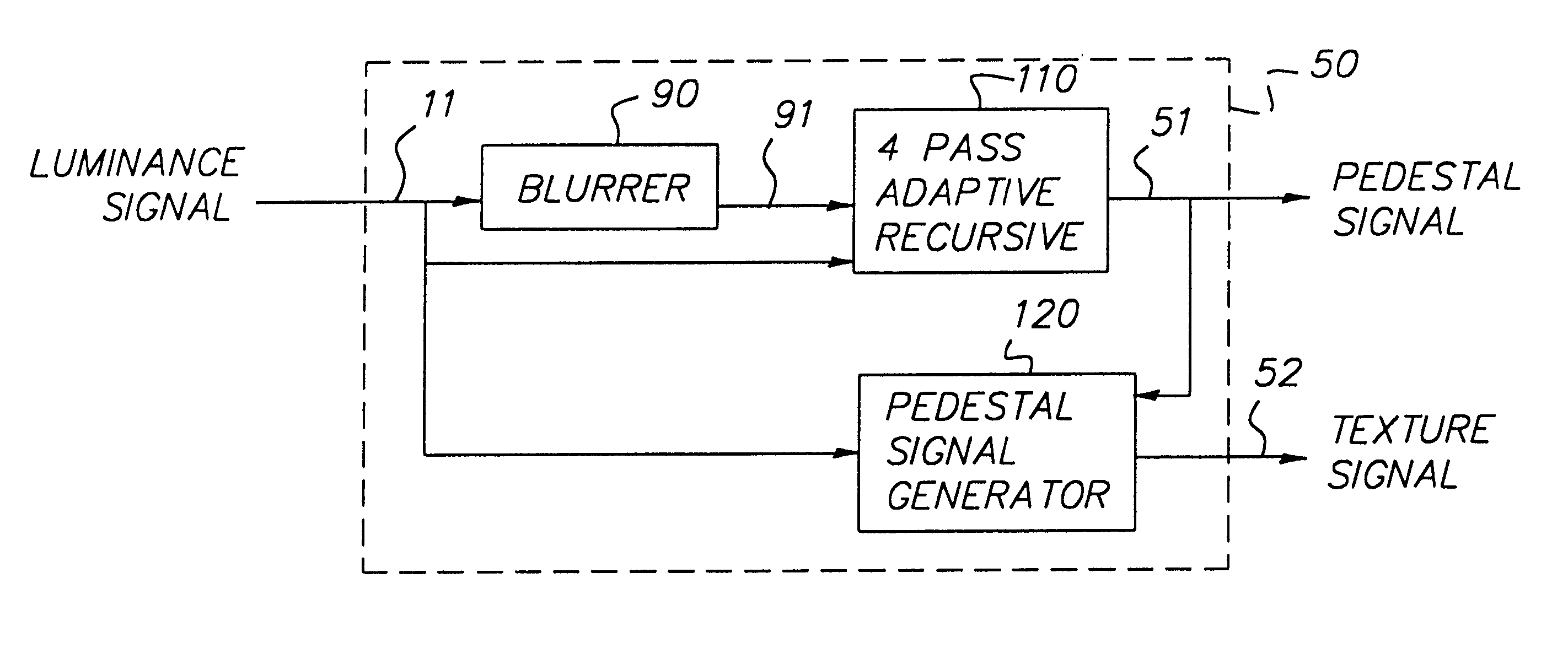

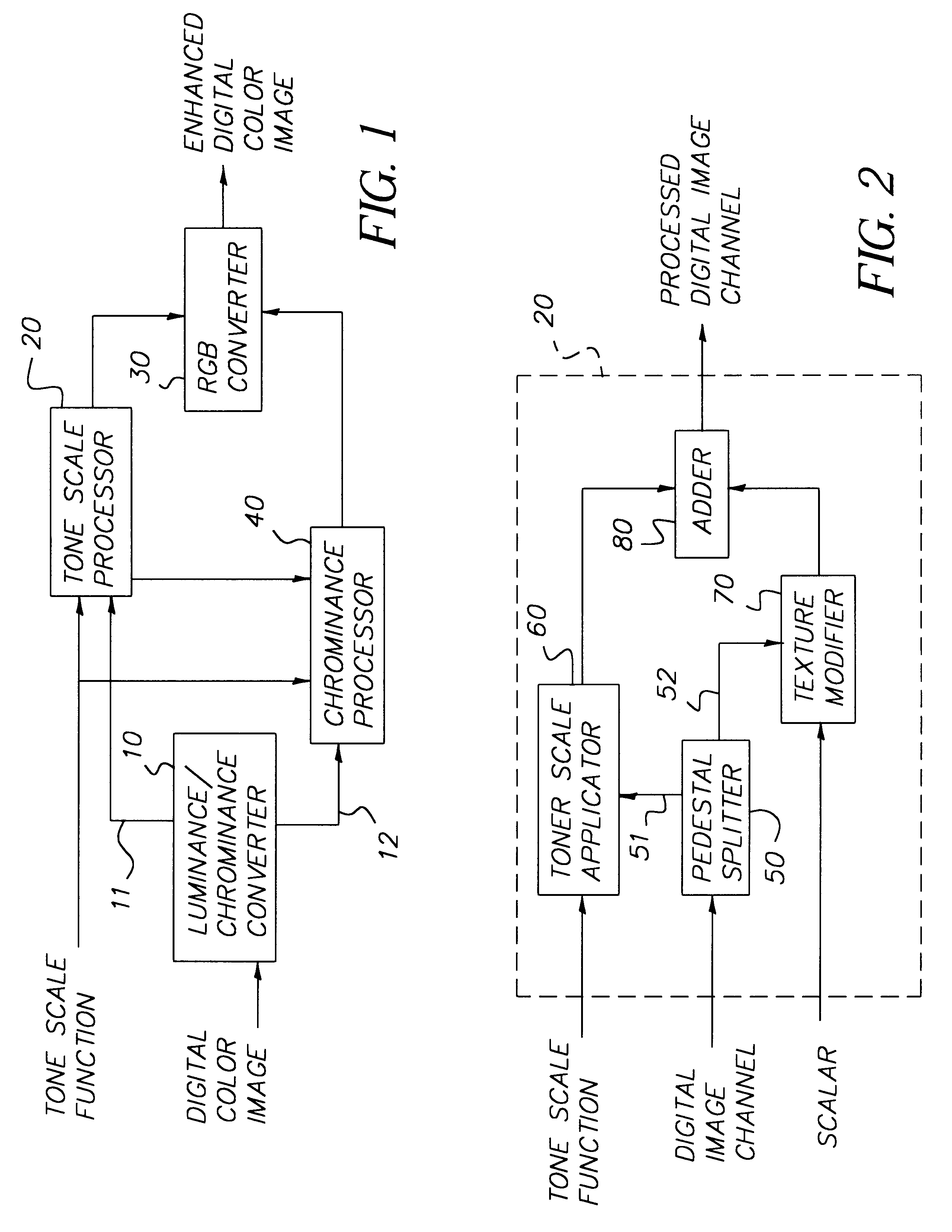

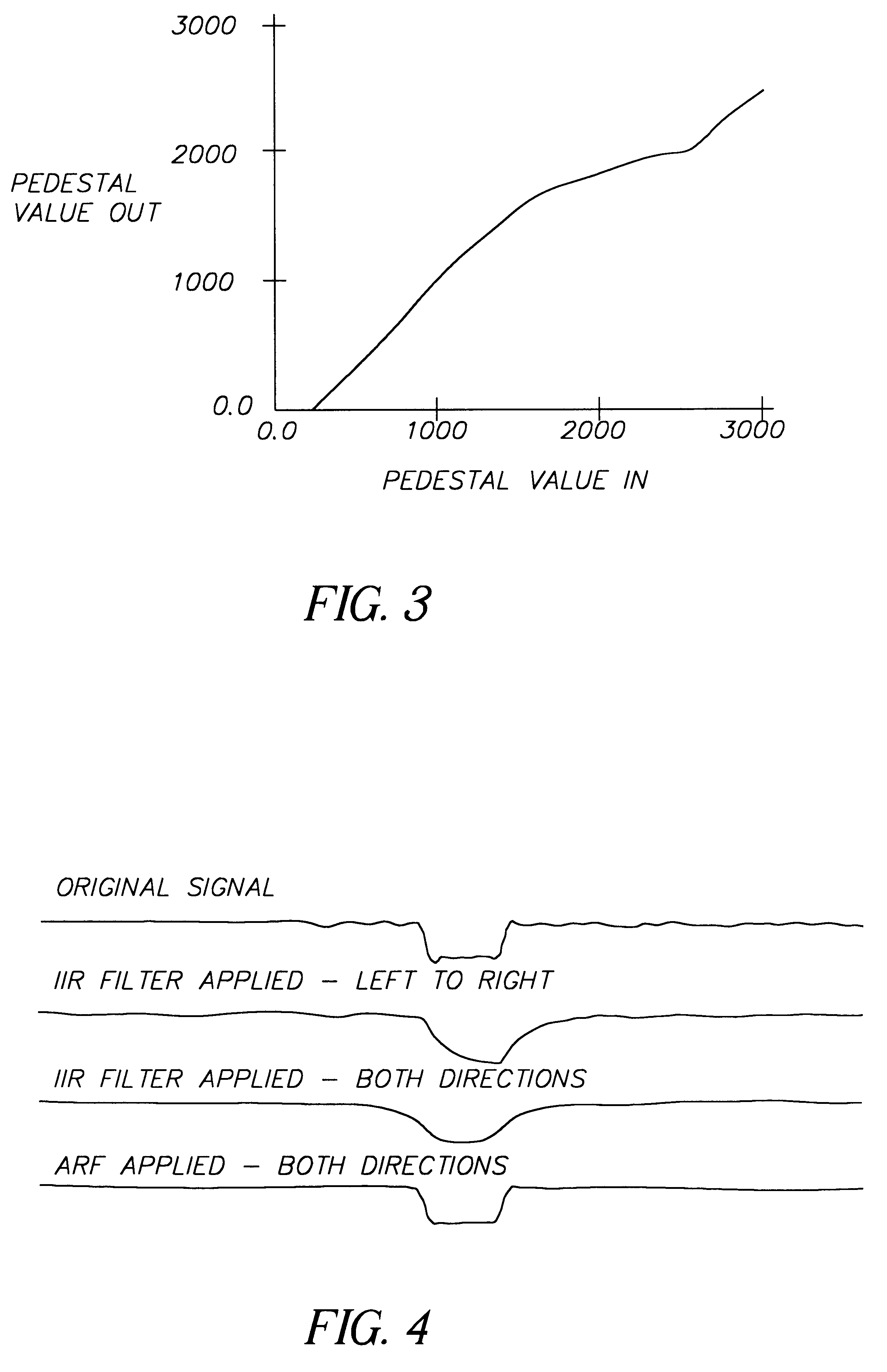

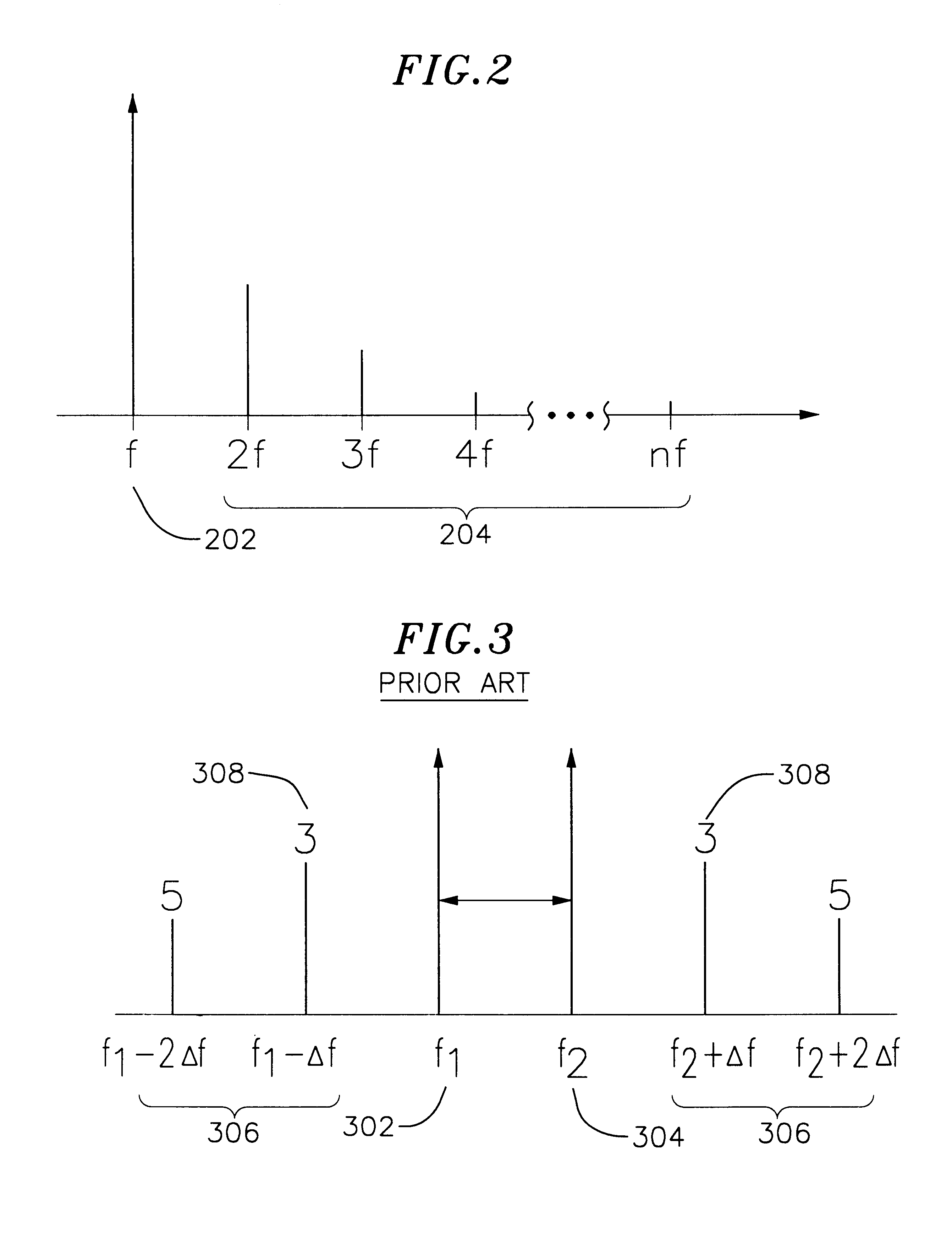

Adjusting the contrast of a digital image with an adaptive recursive filter

InactiveUS6728416B1Fast processingAvoid artifactsTelevision system detailsImage enhancementFilter tuningDigital image

A method and structure for adjusting the contrast of a digital image includes inputting an image, dividing the image into a pedestal signal and a texture signal, applying a tone scale function to the pedestal signal to produce a modified pedestal signal, and adding the texture signal to the modified pedestal signal to produce a processed digital image channel. The dividing filters a pixel of the image using weighting that is dependent upon coefficients of neighboring pixels adjacent the pixel. The filtering blurs the pedestal signal such that flat areas of the image are blurred more that discontinuities in the image.

Owner:MONUMENT PEAK VENTURES LLC

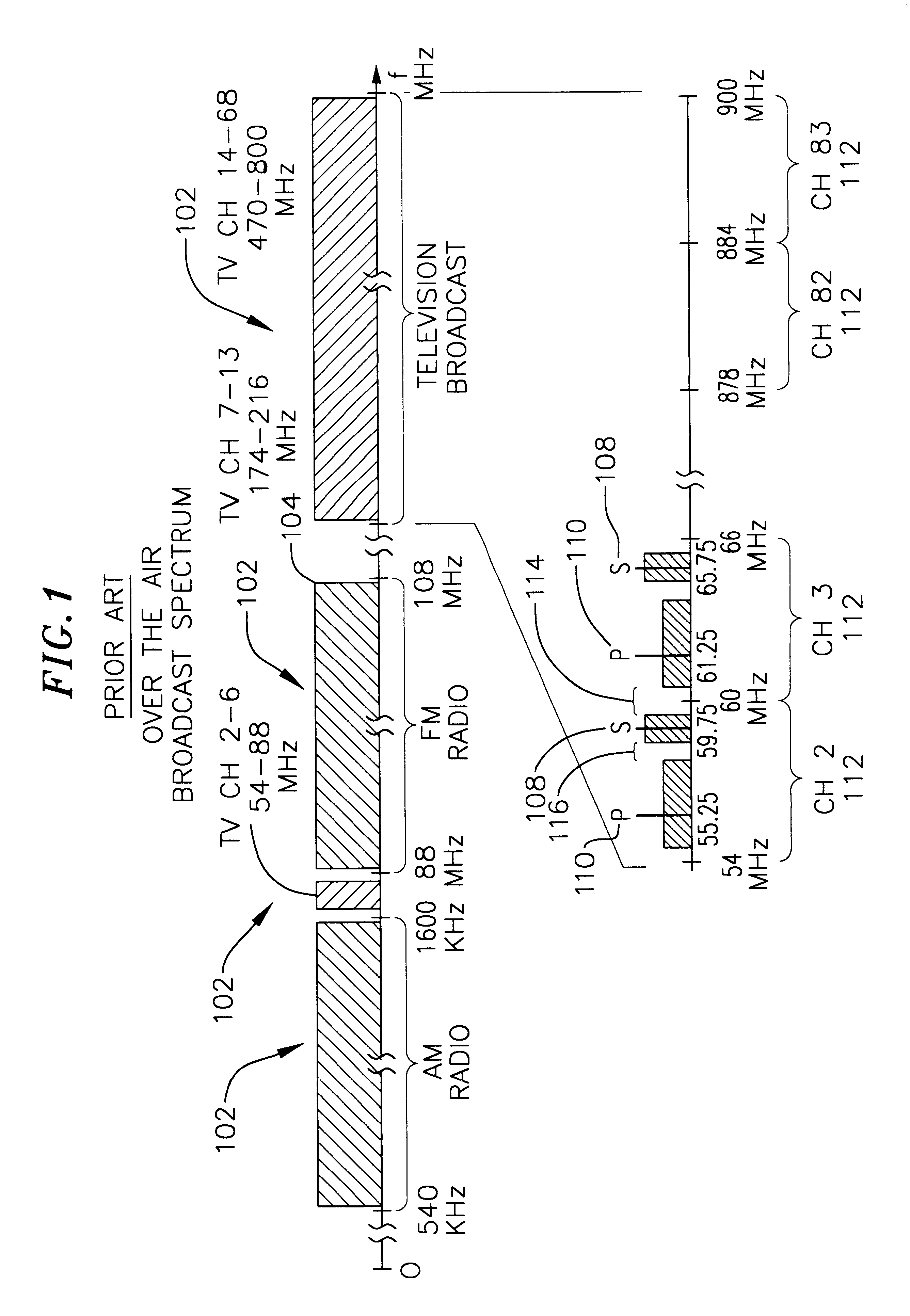

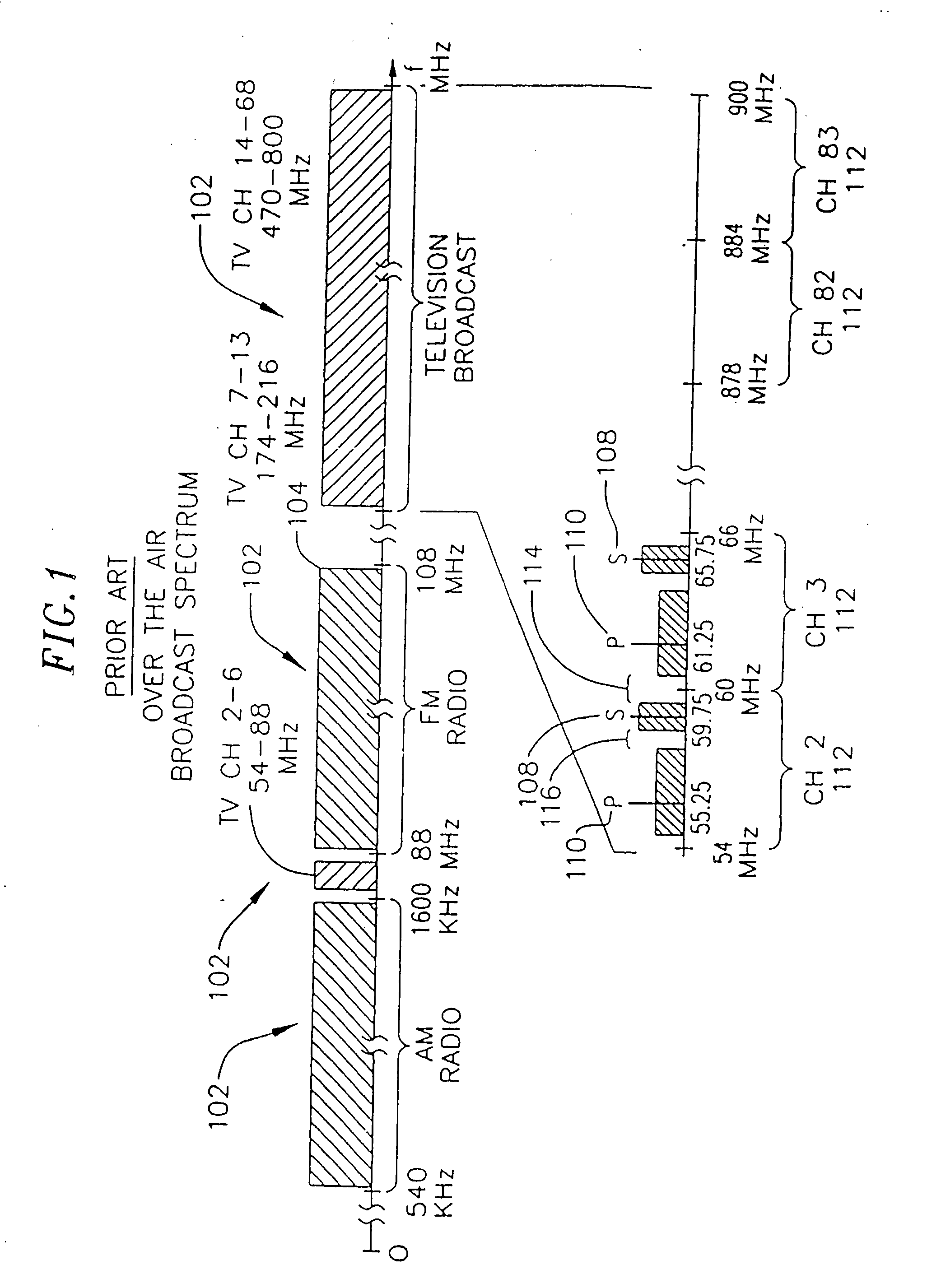

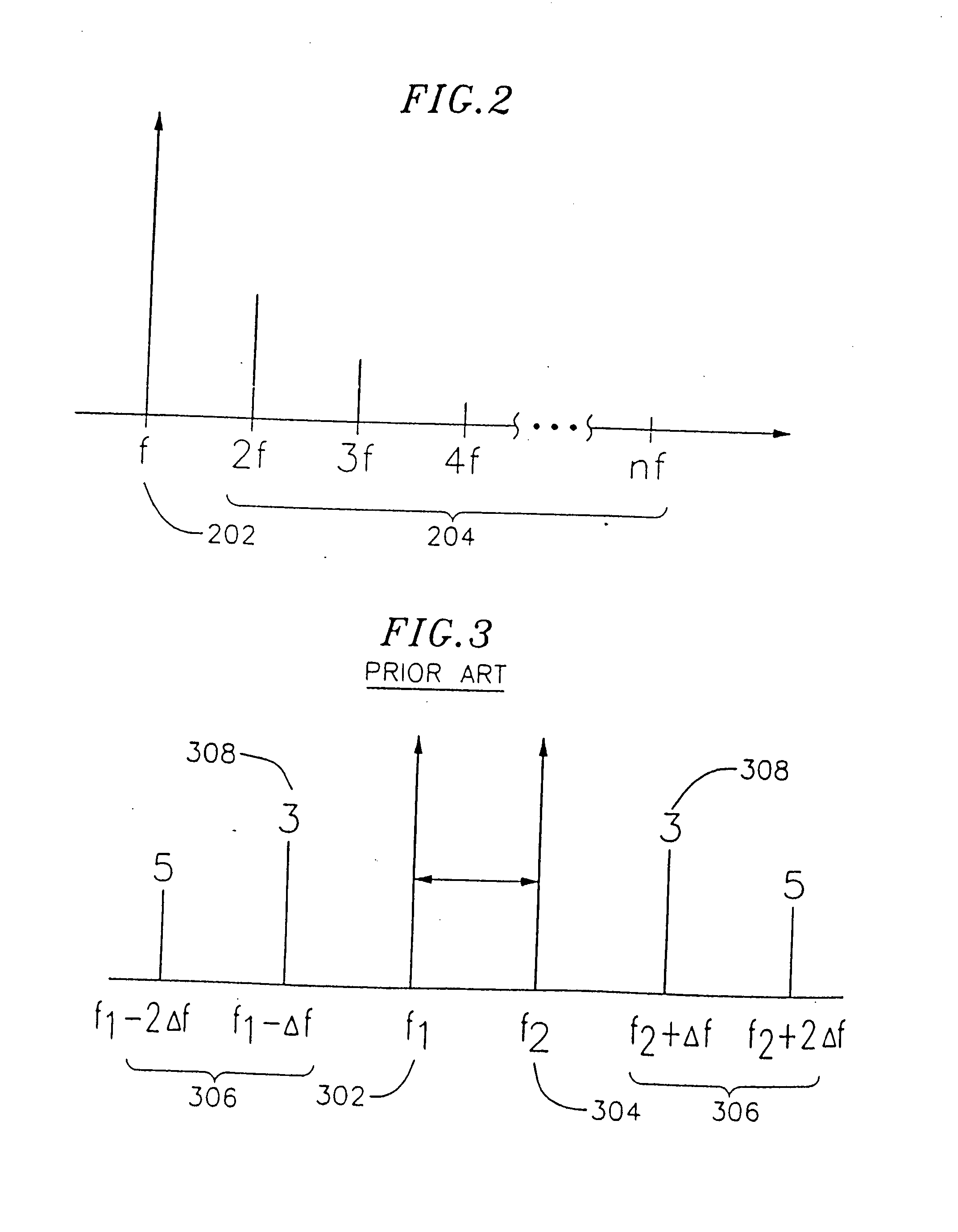

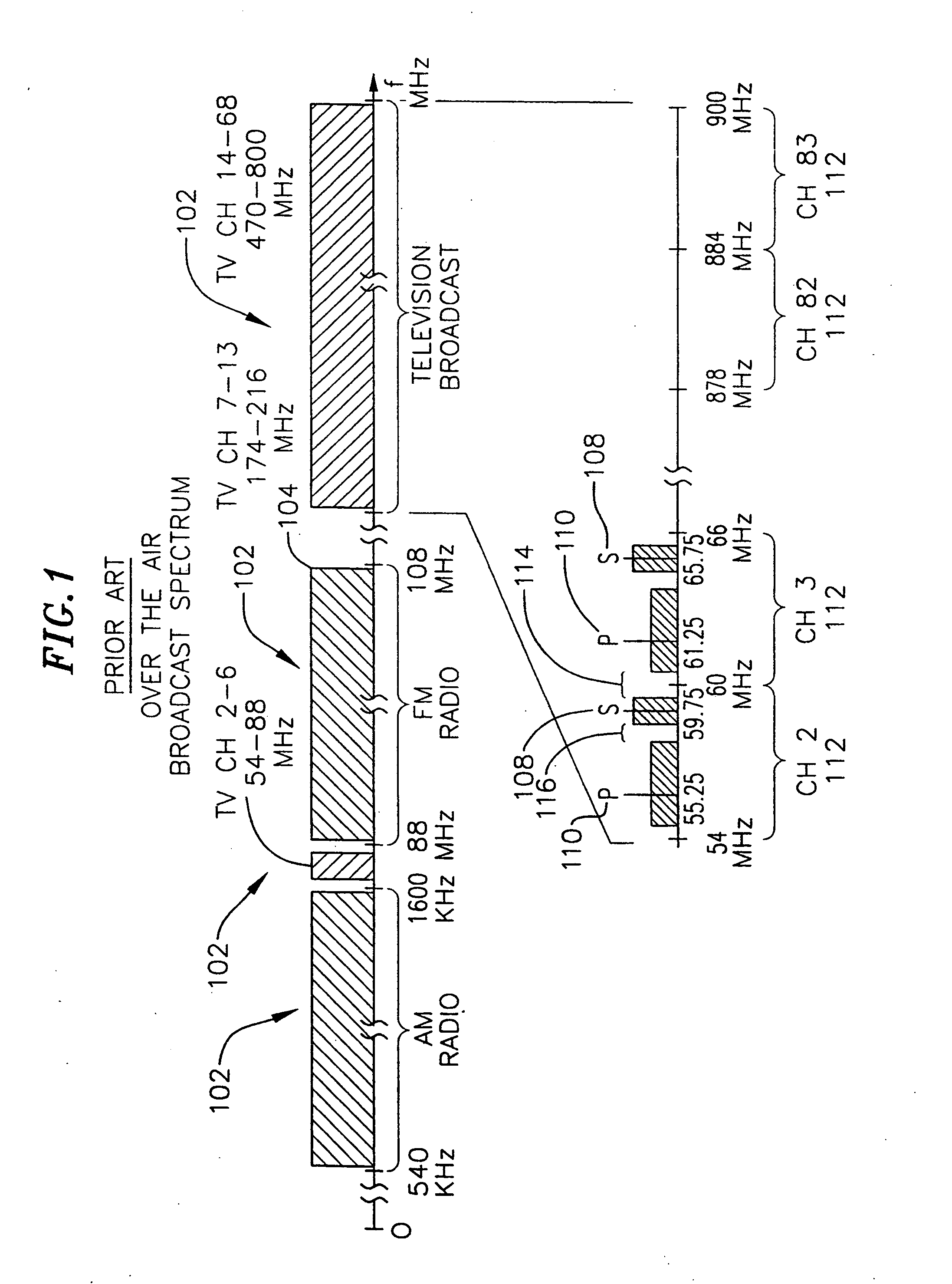

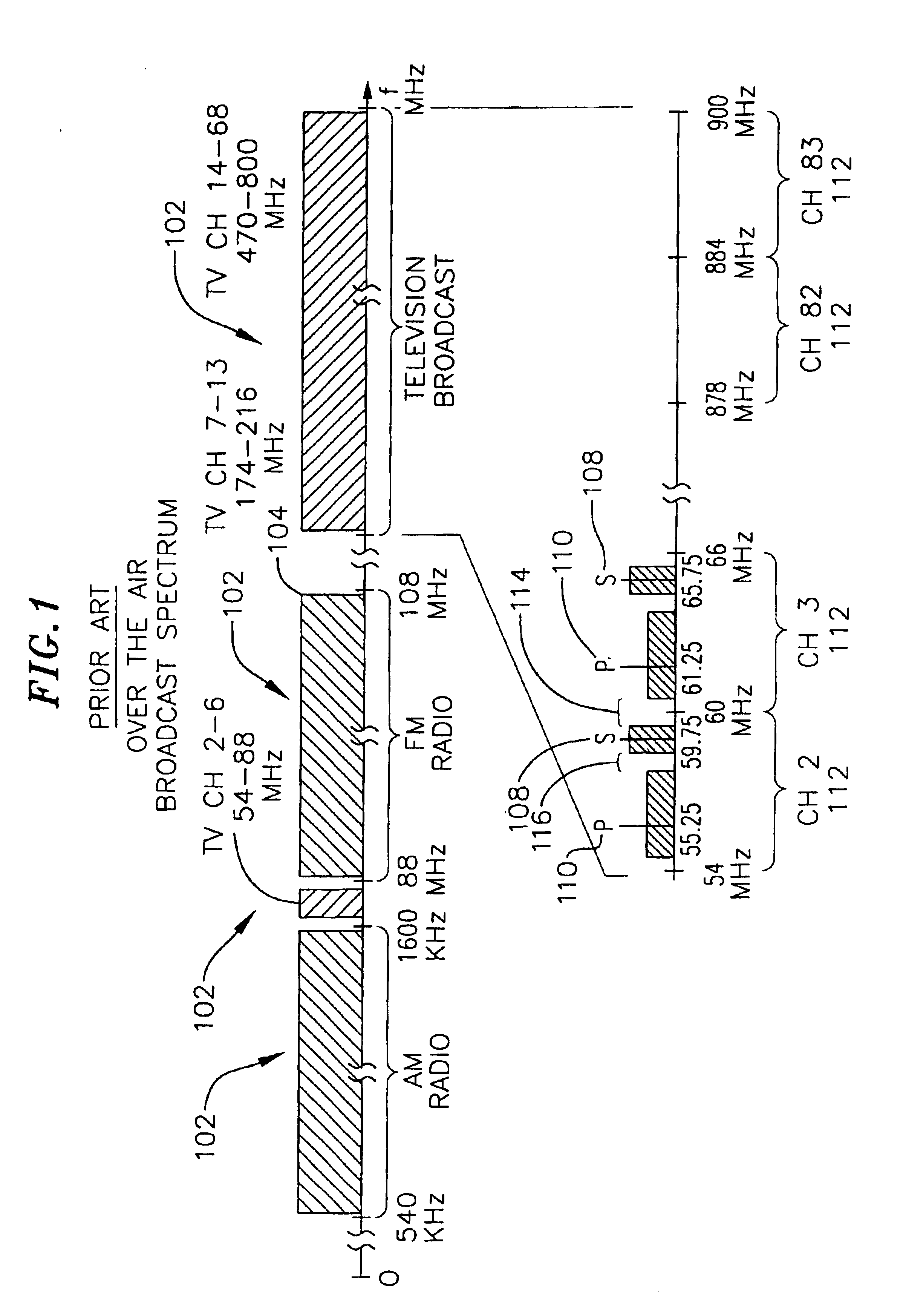

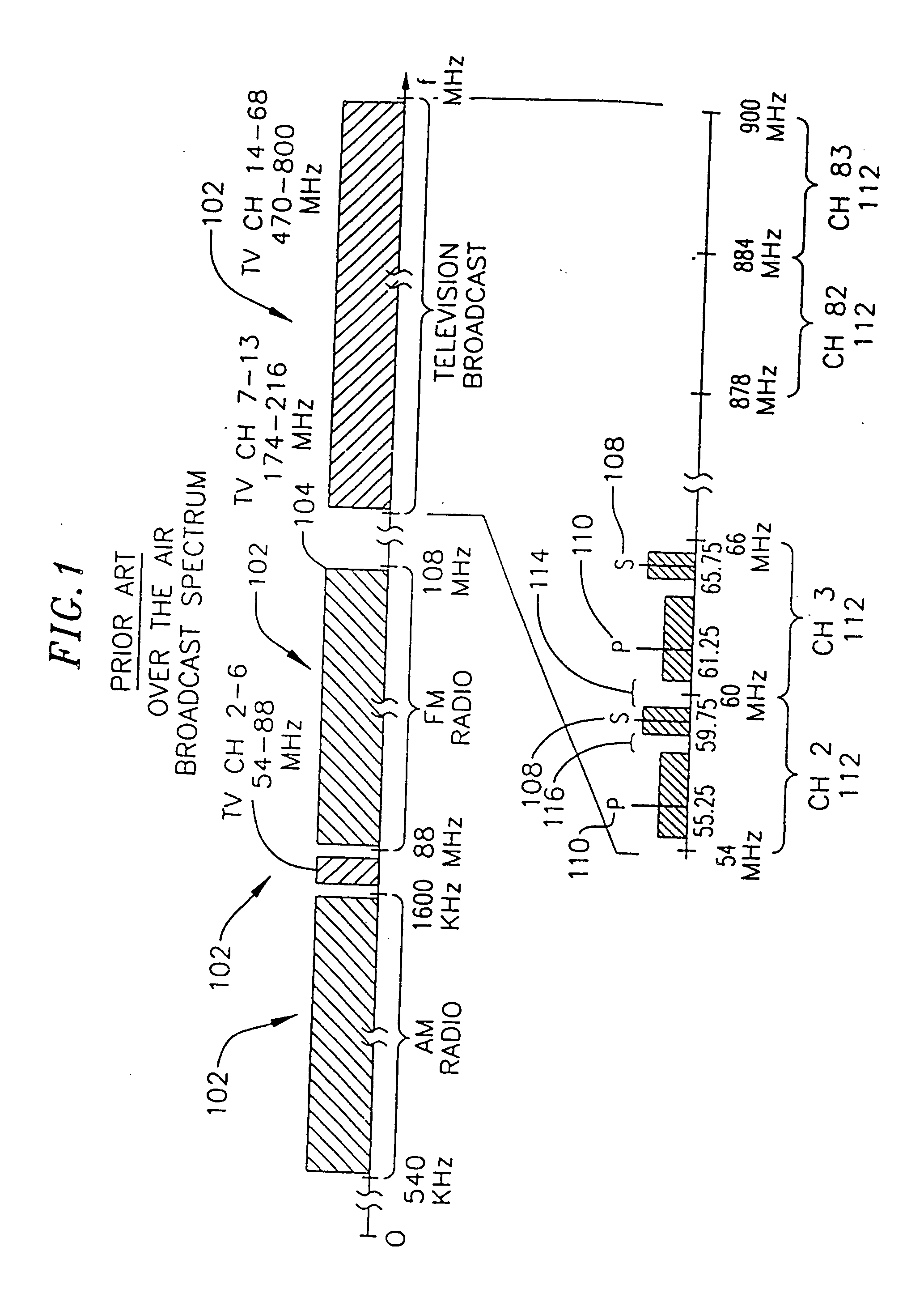

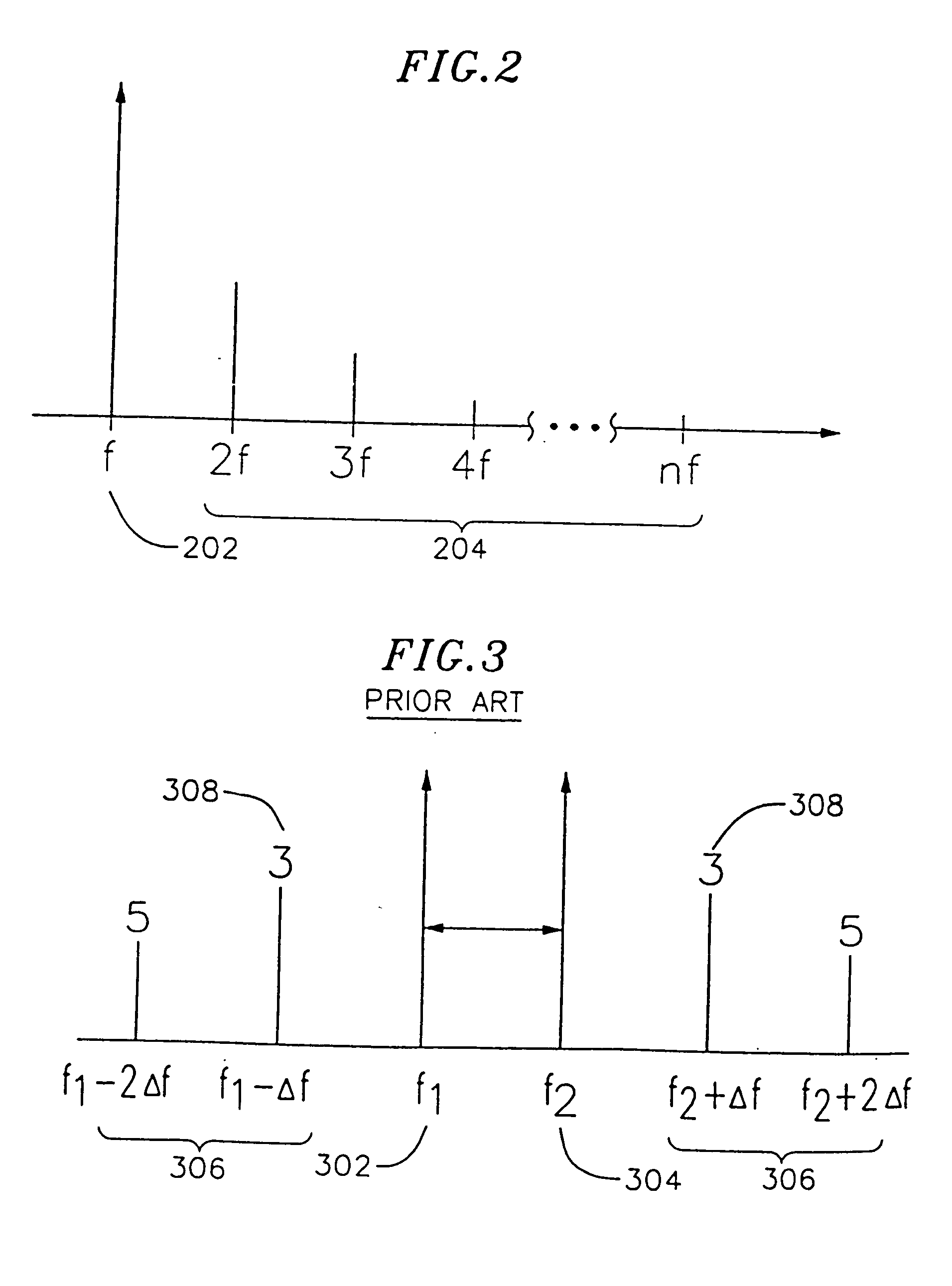

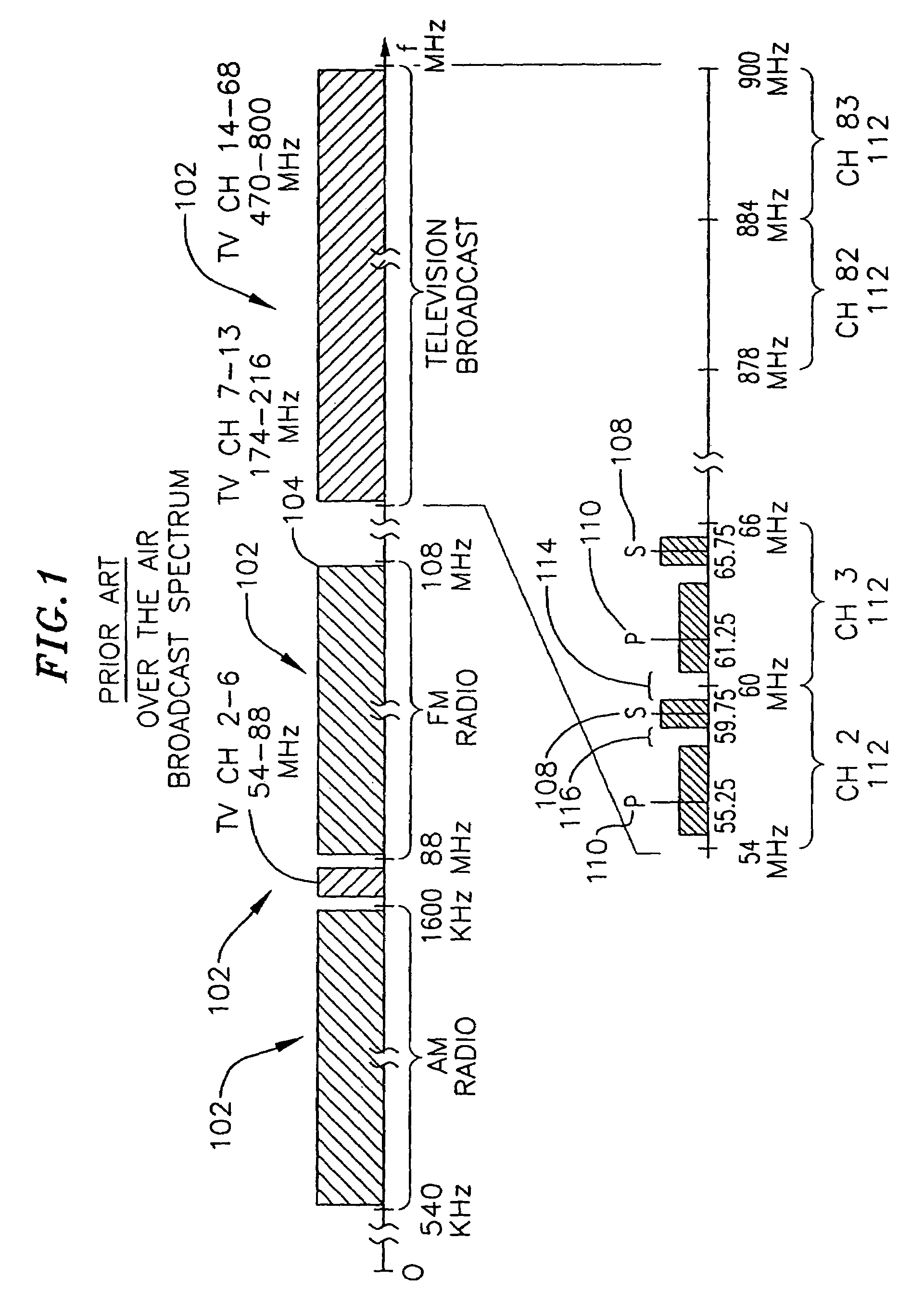

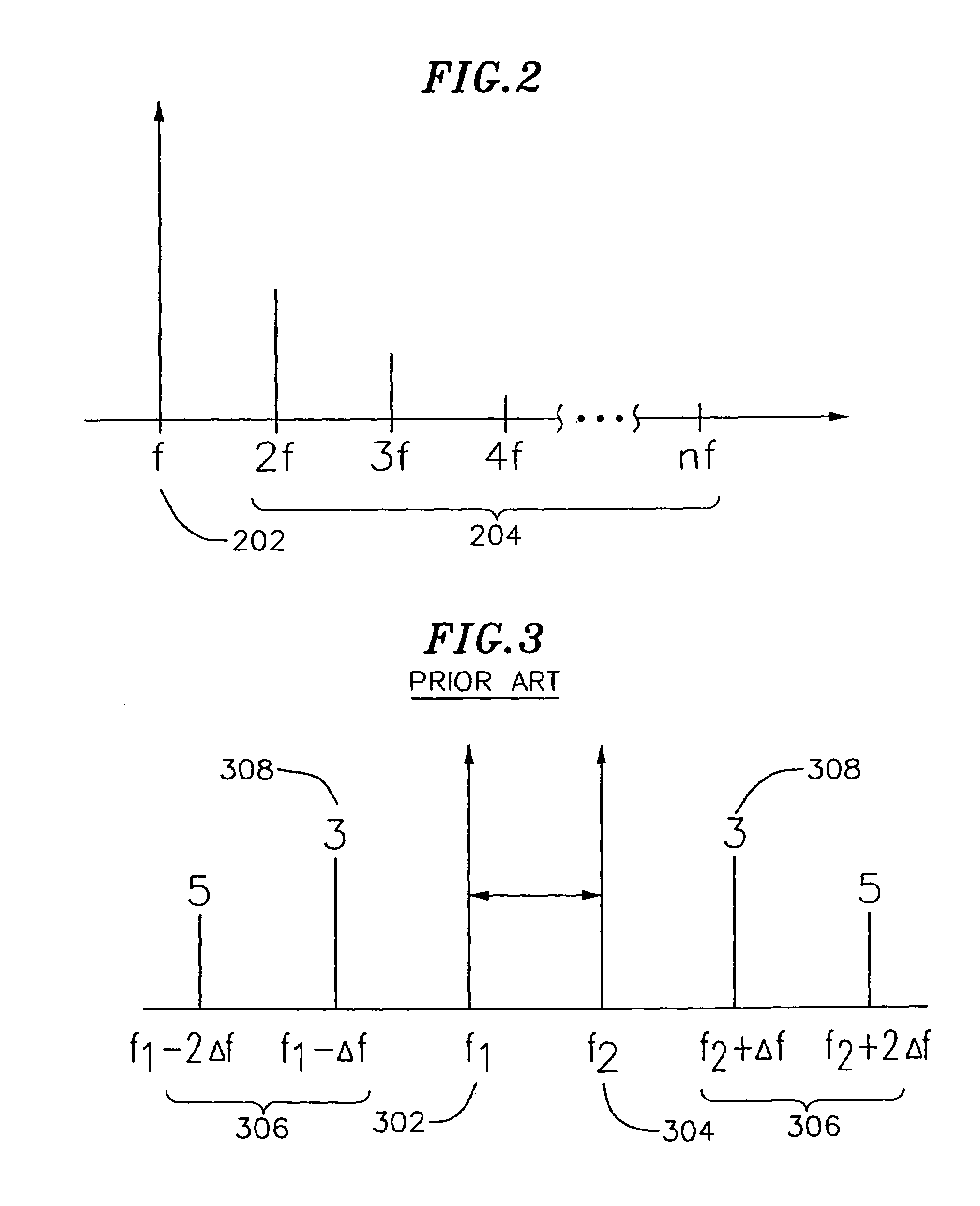

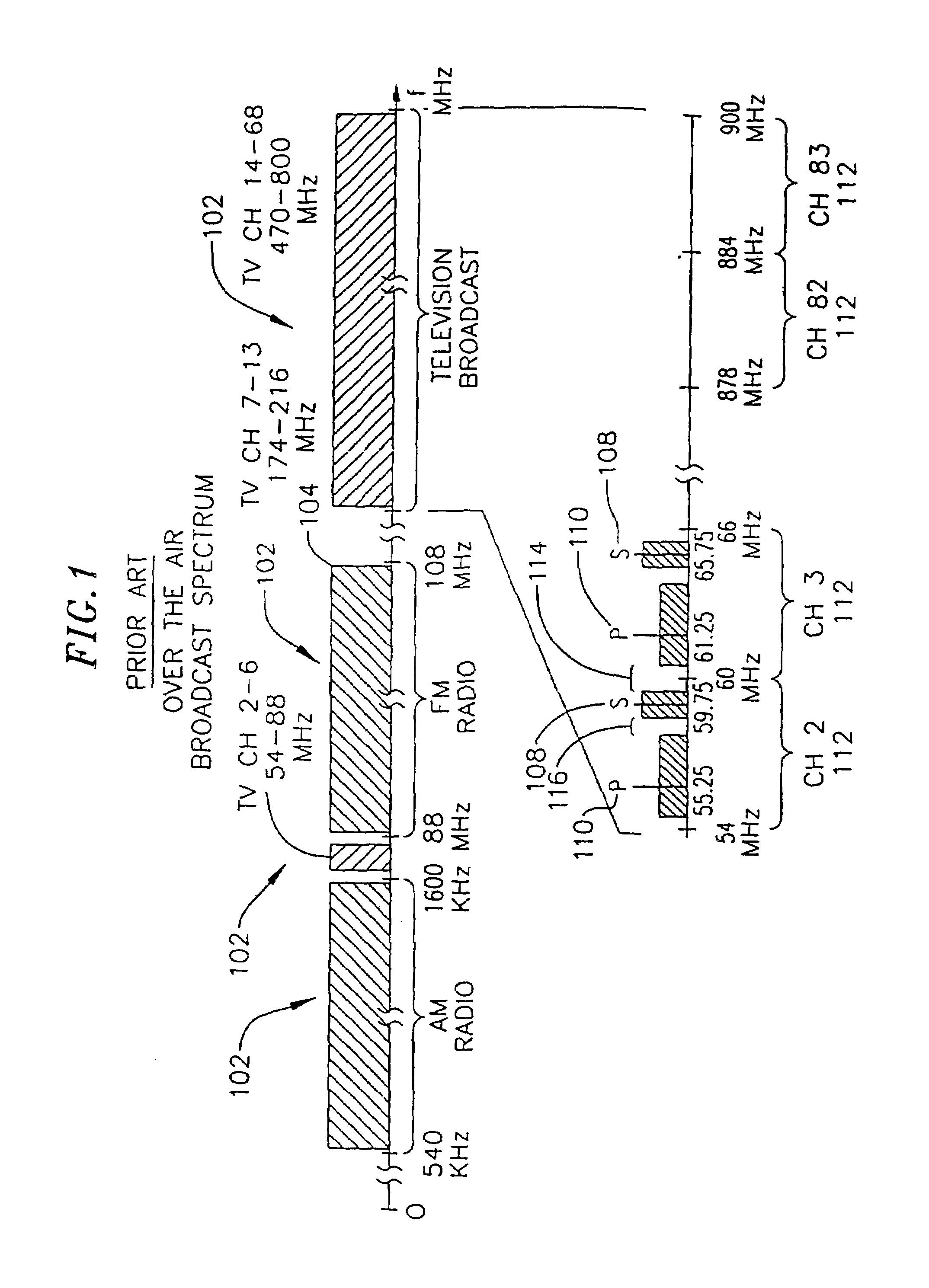

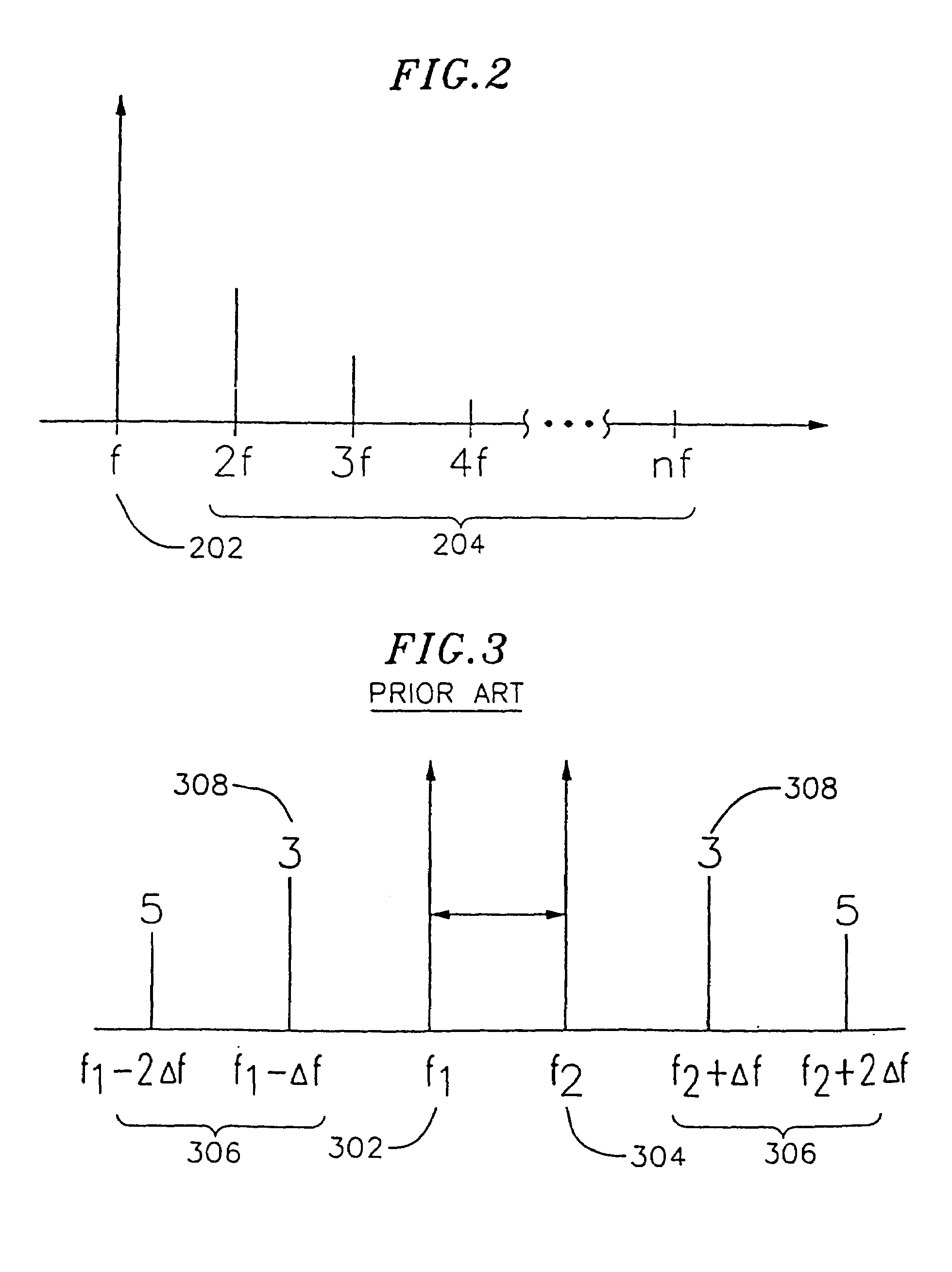

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

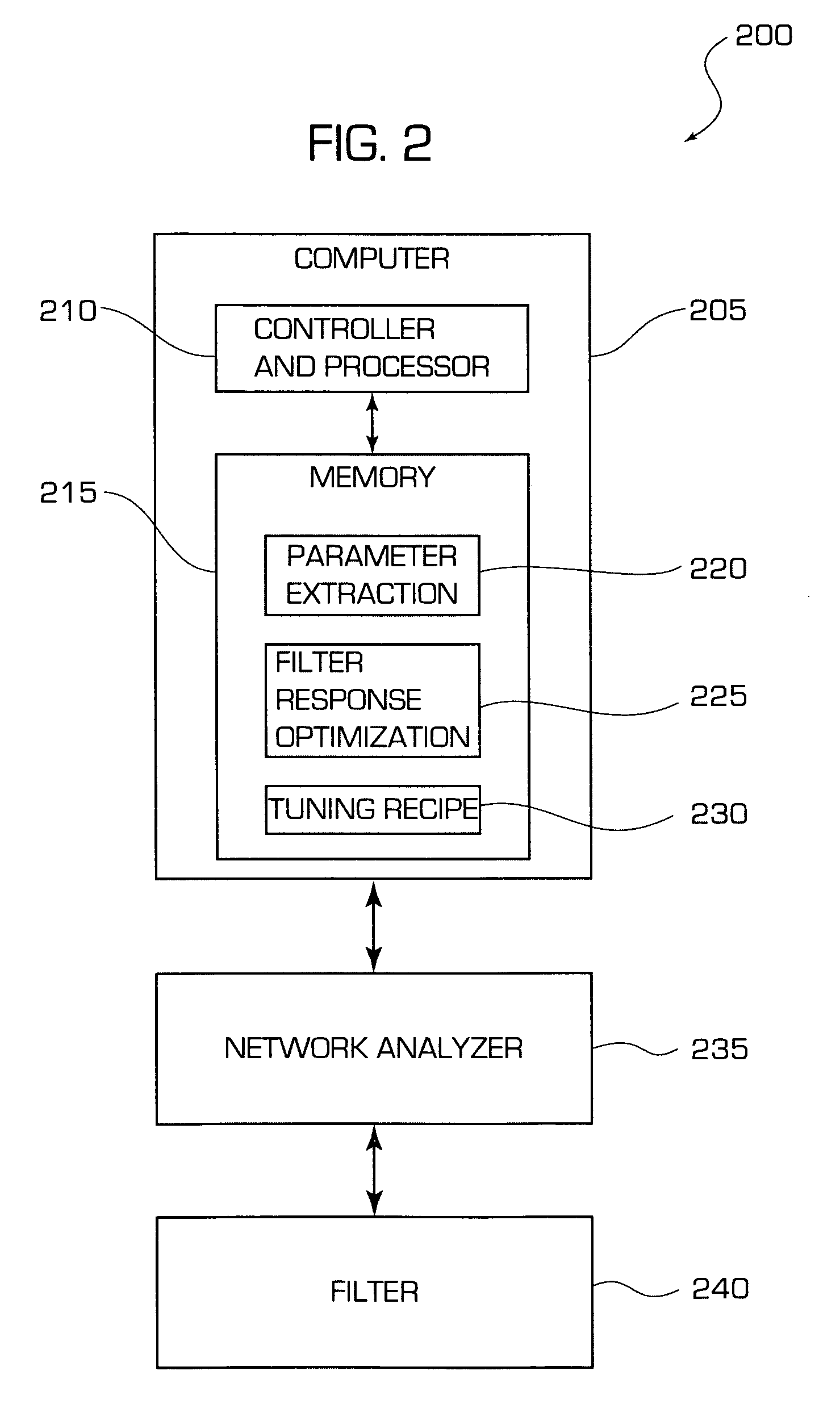

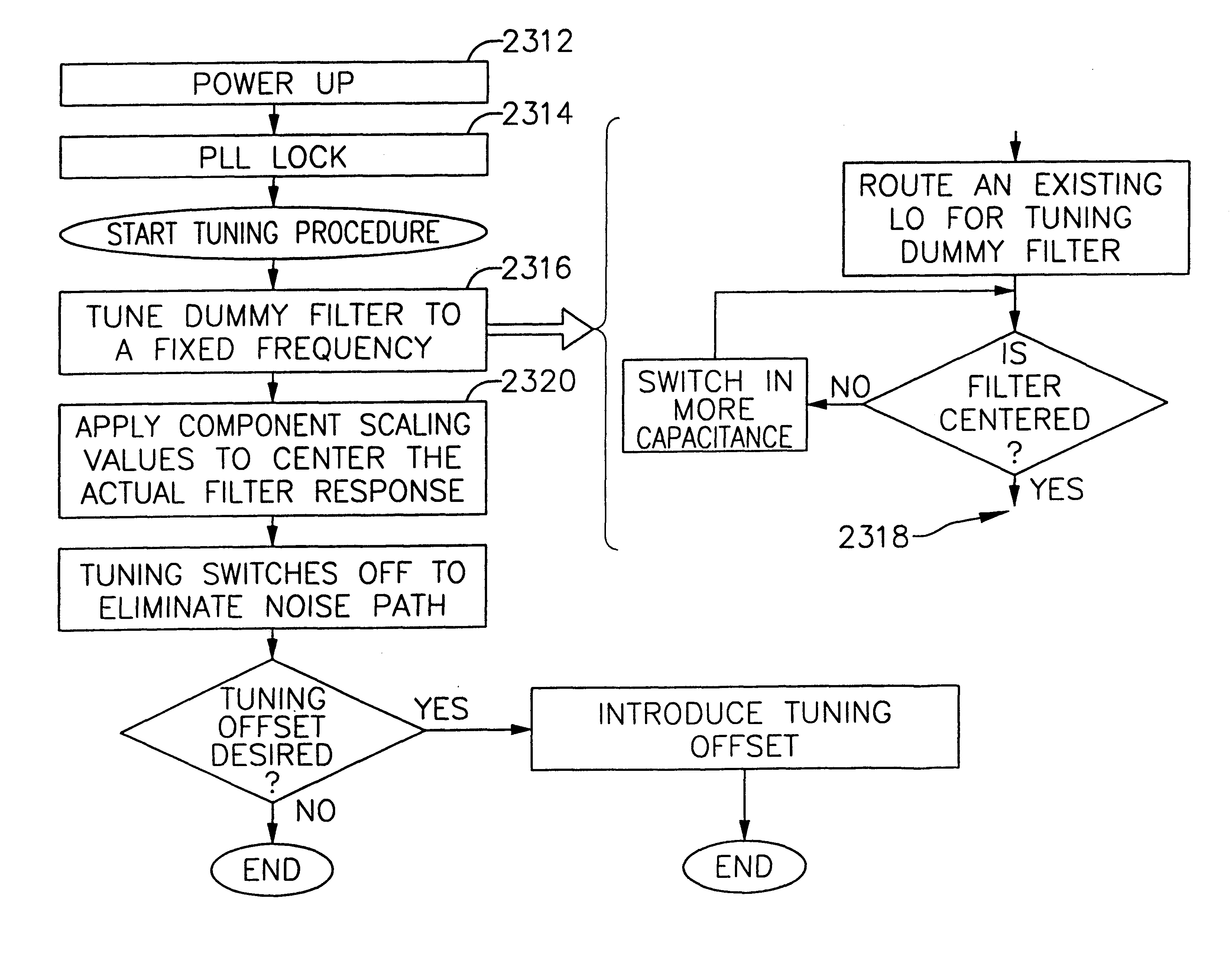

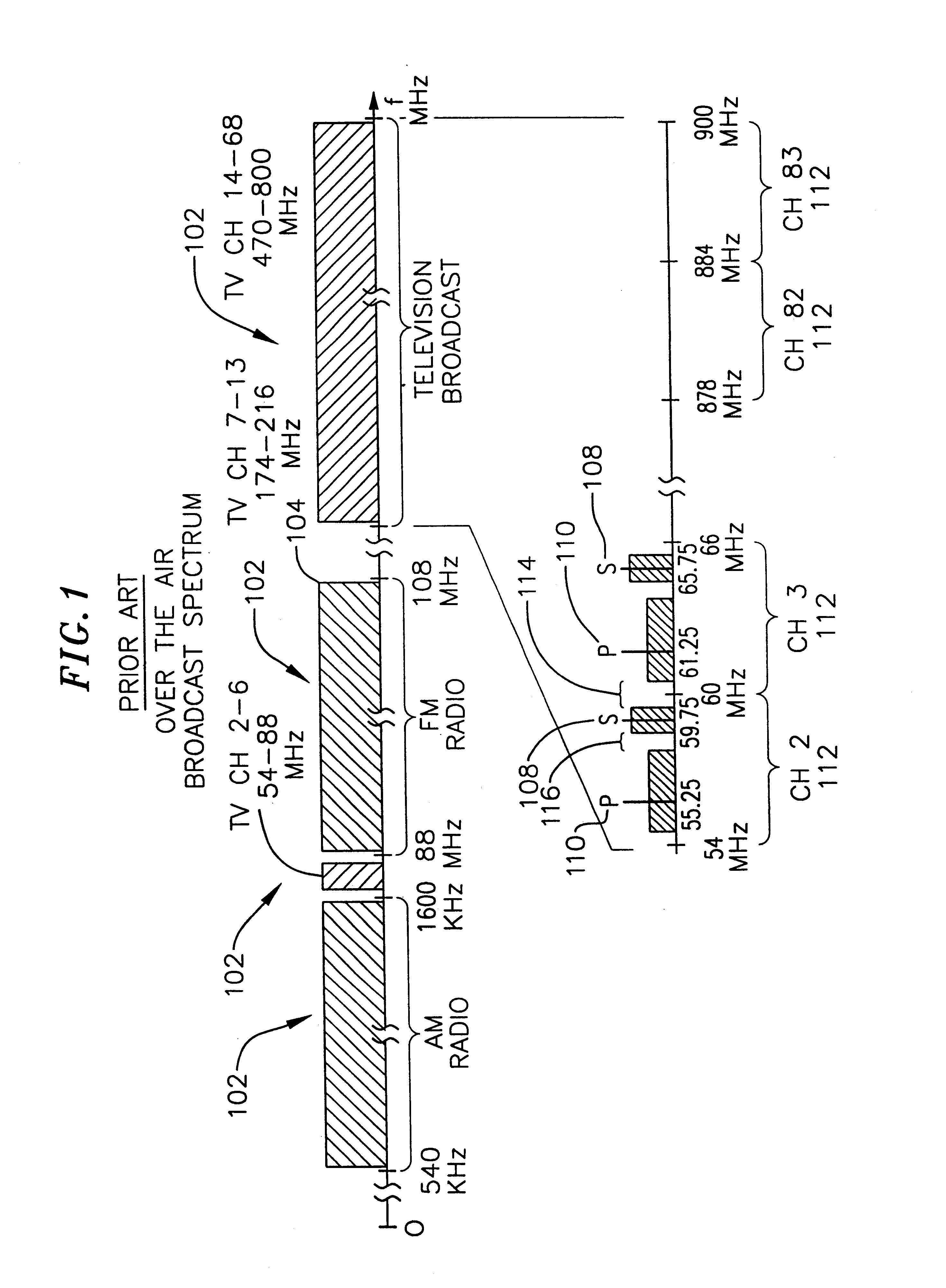

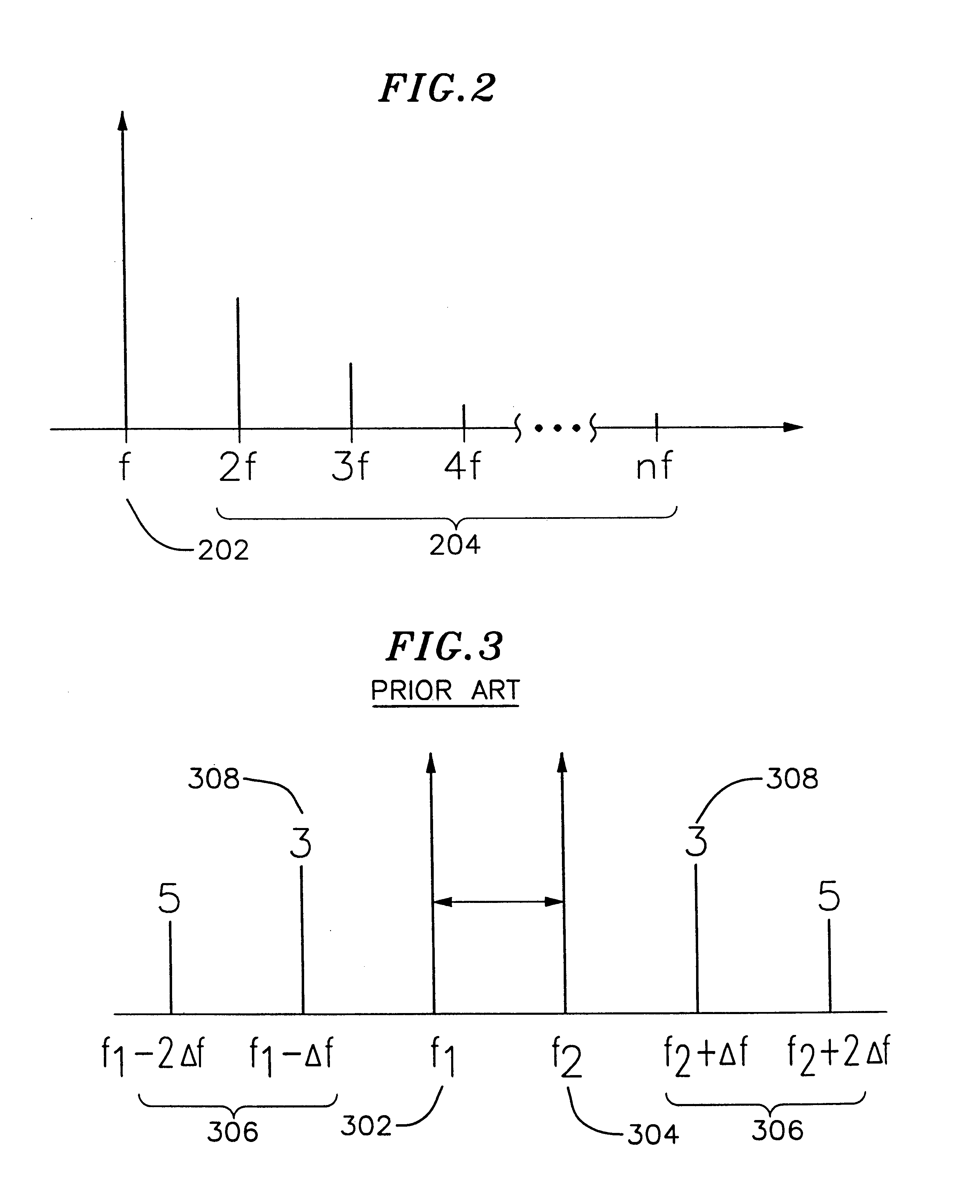

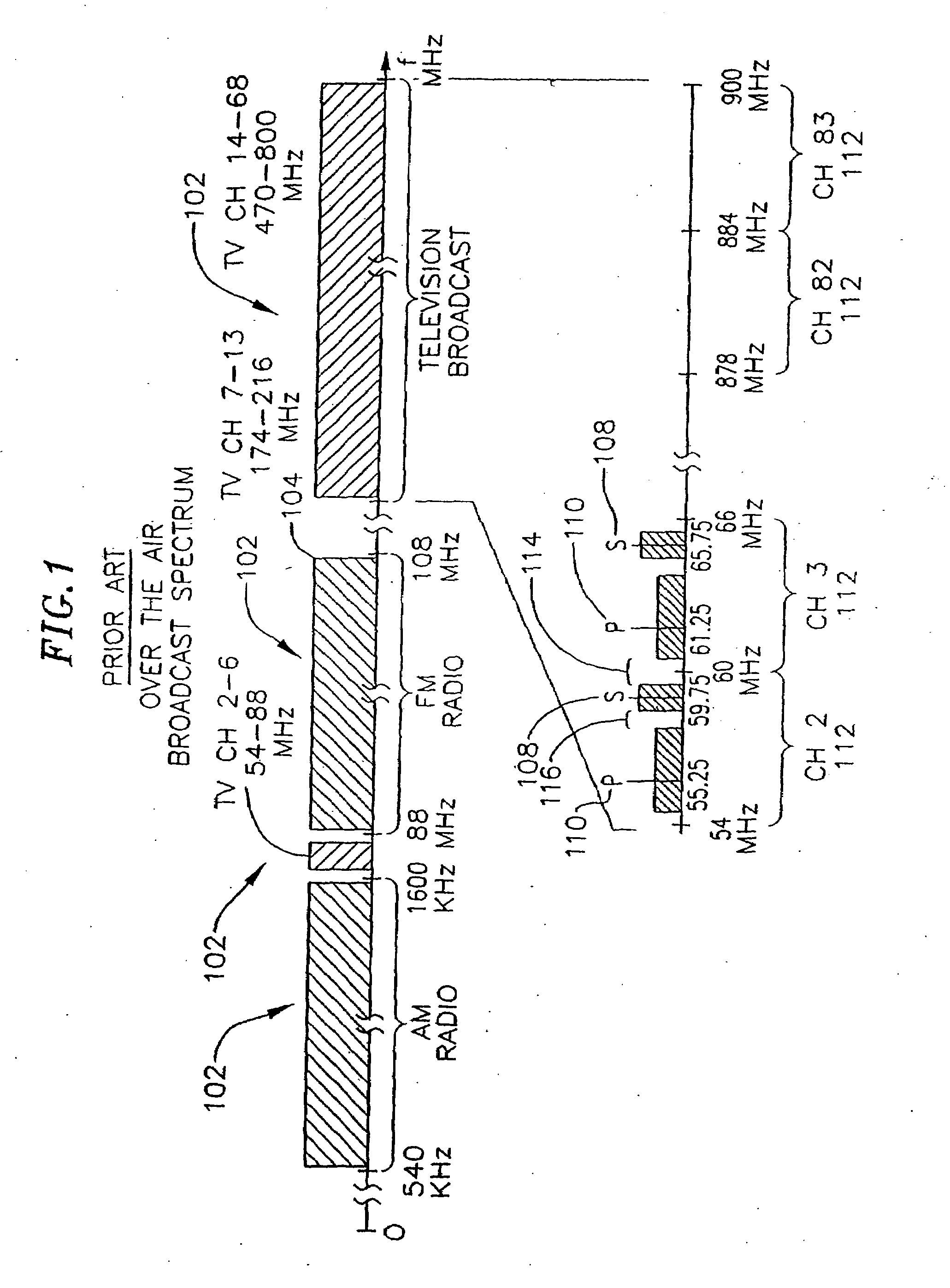

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

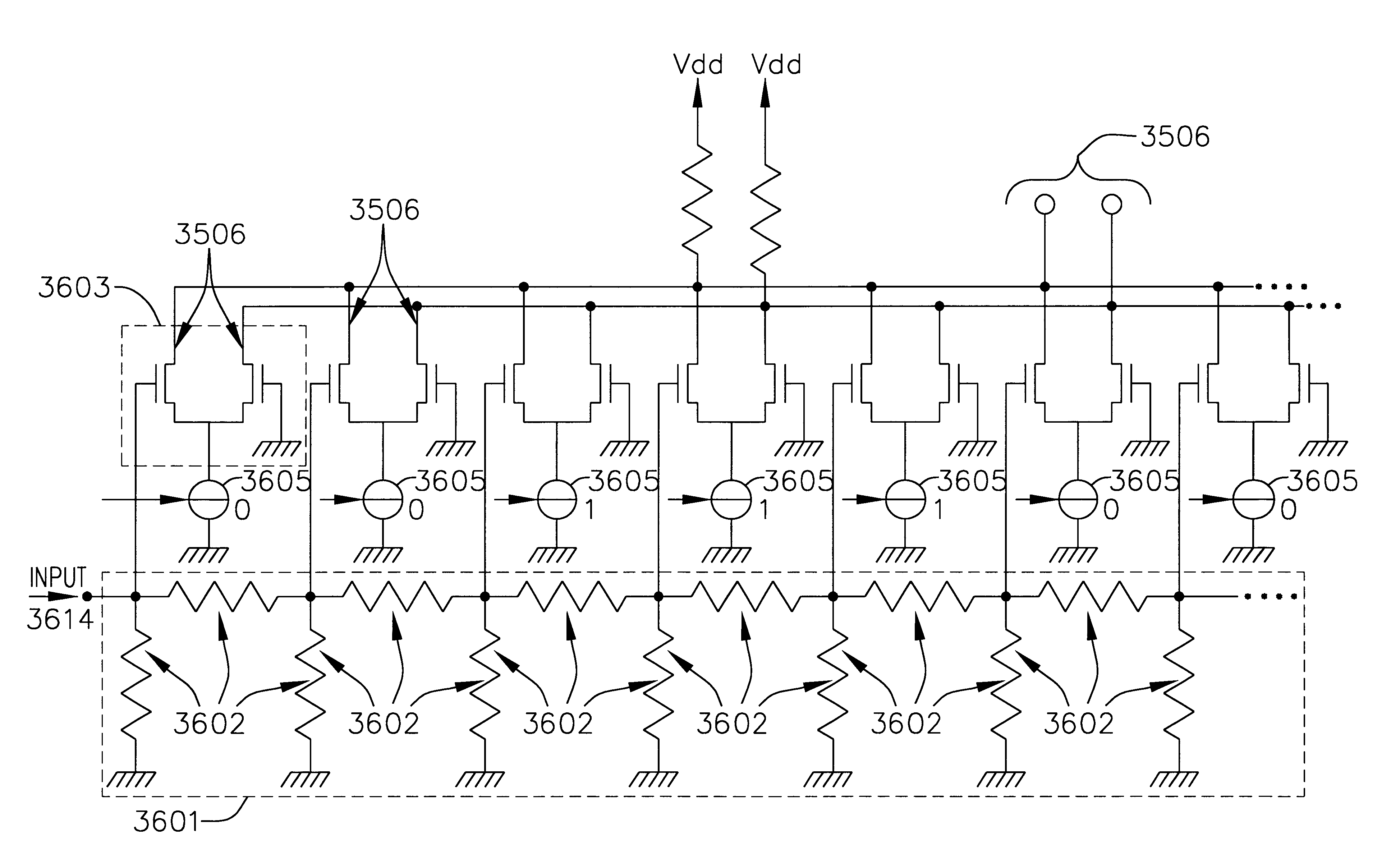

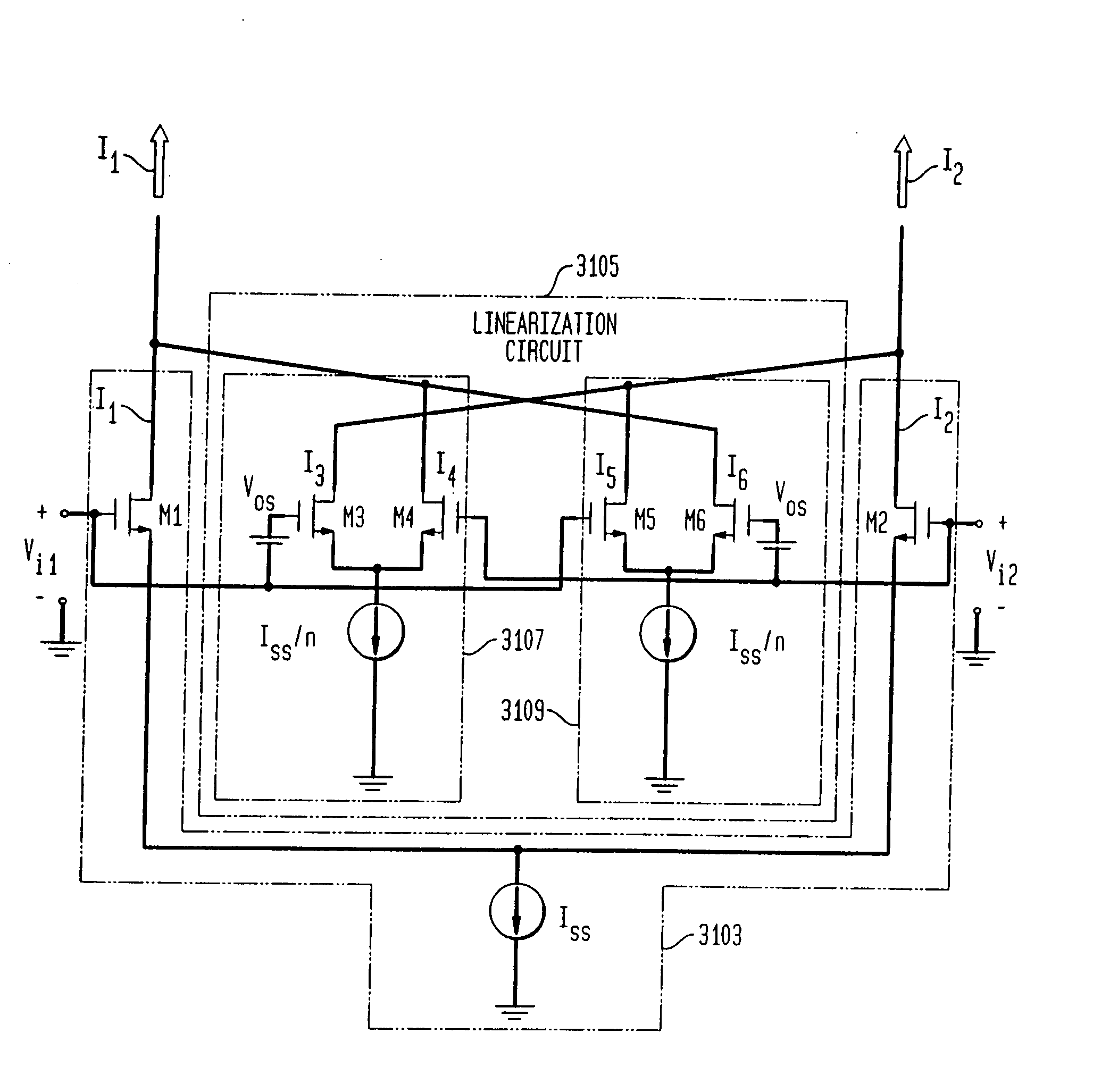

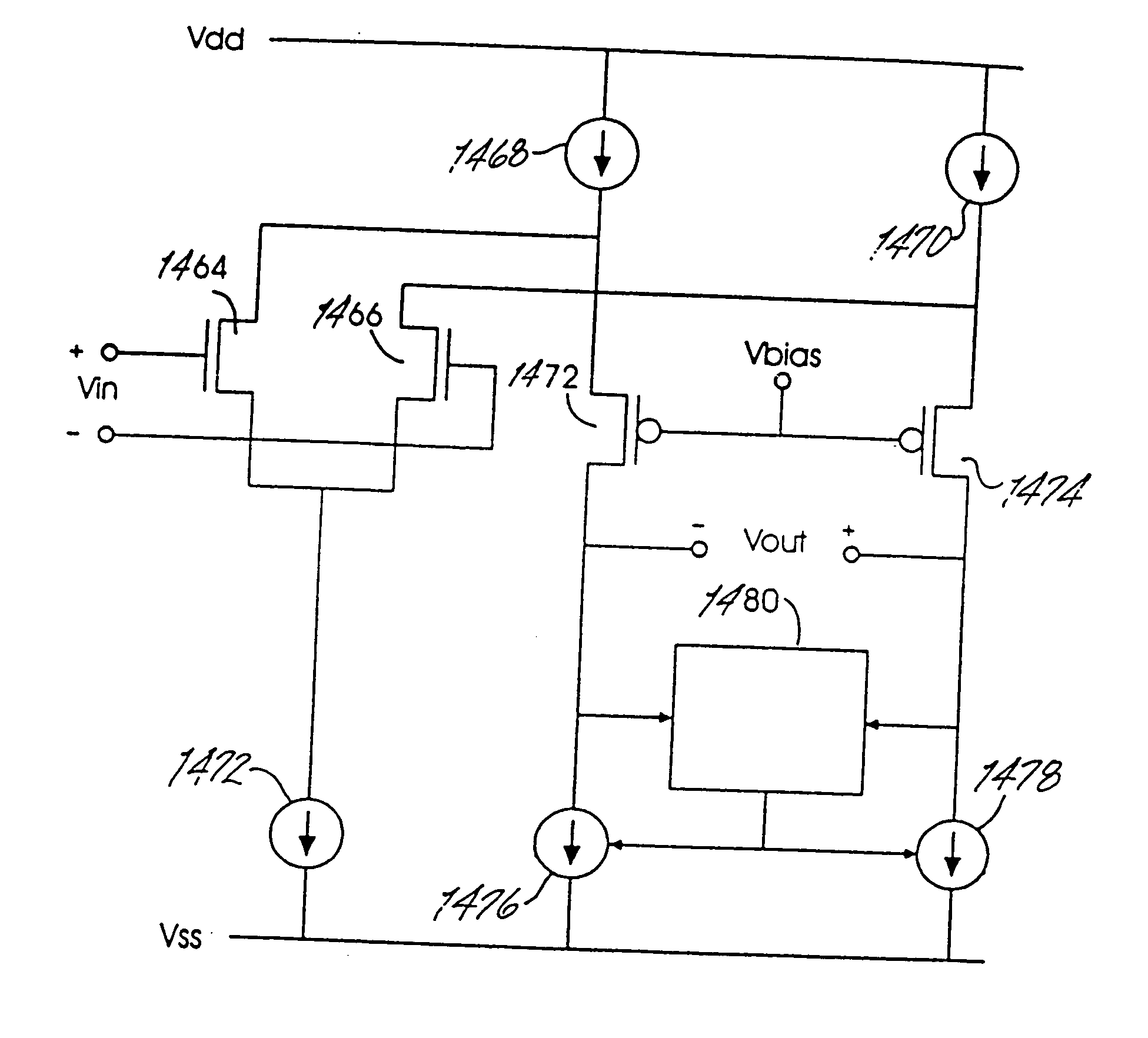

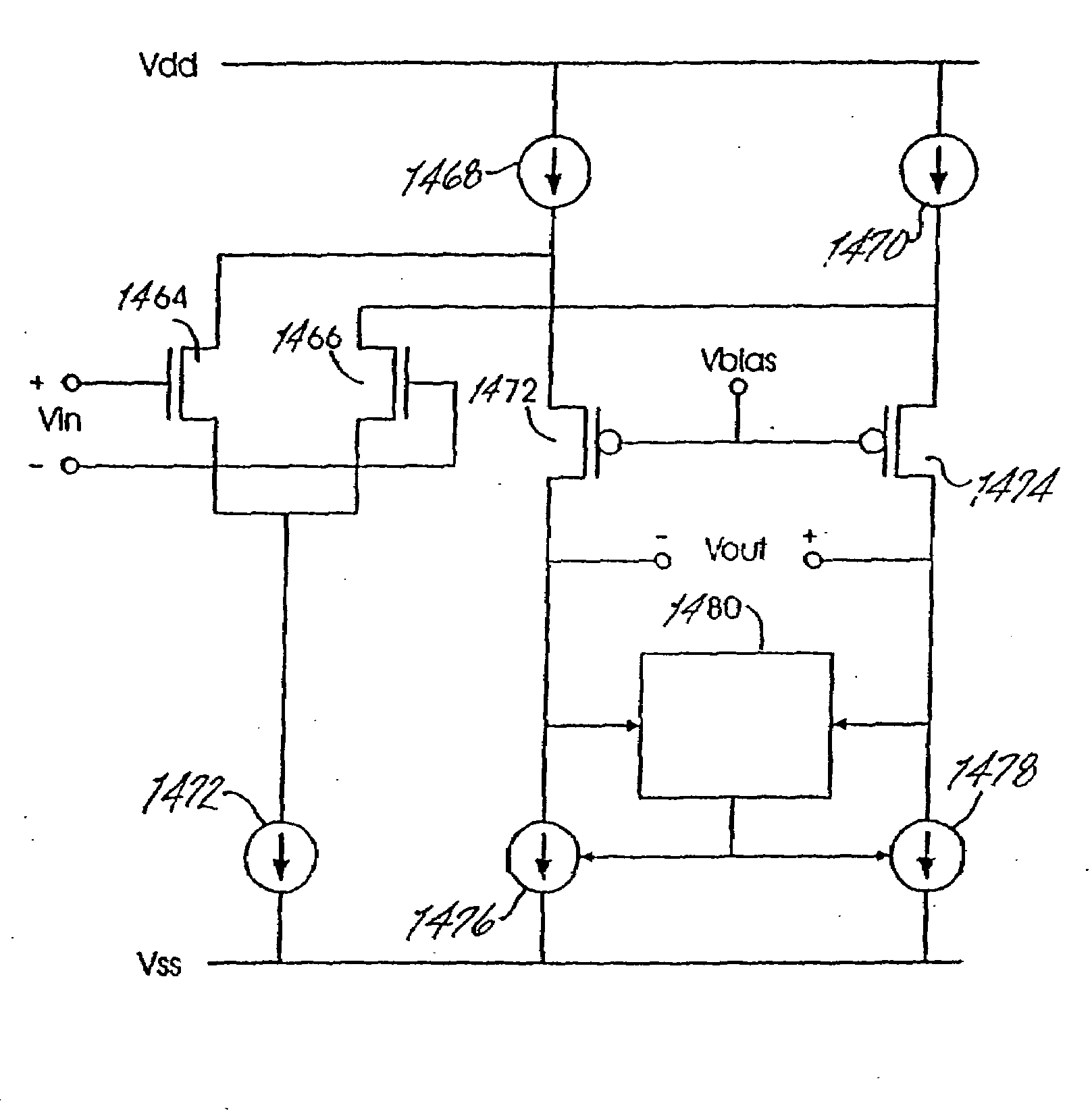

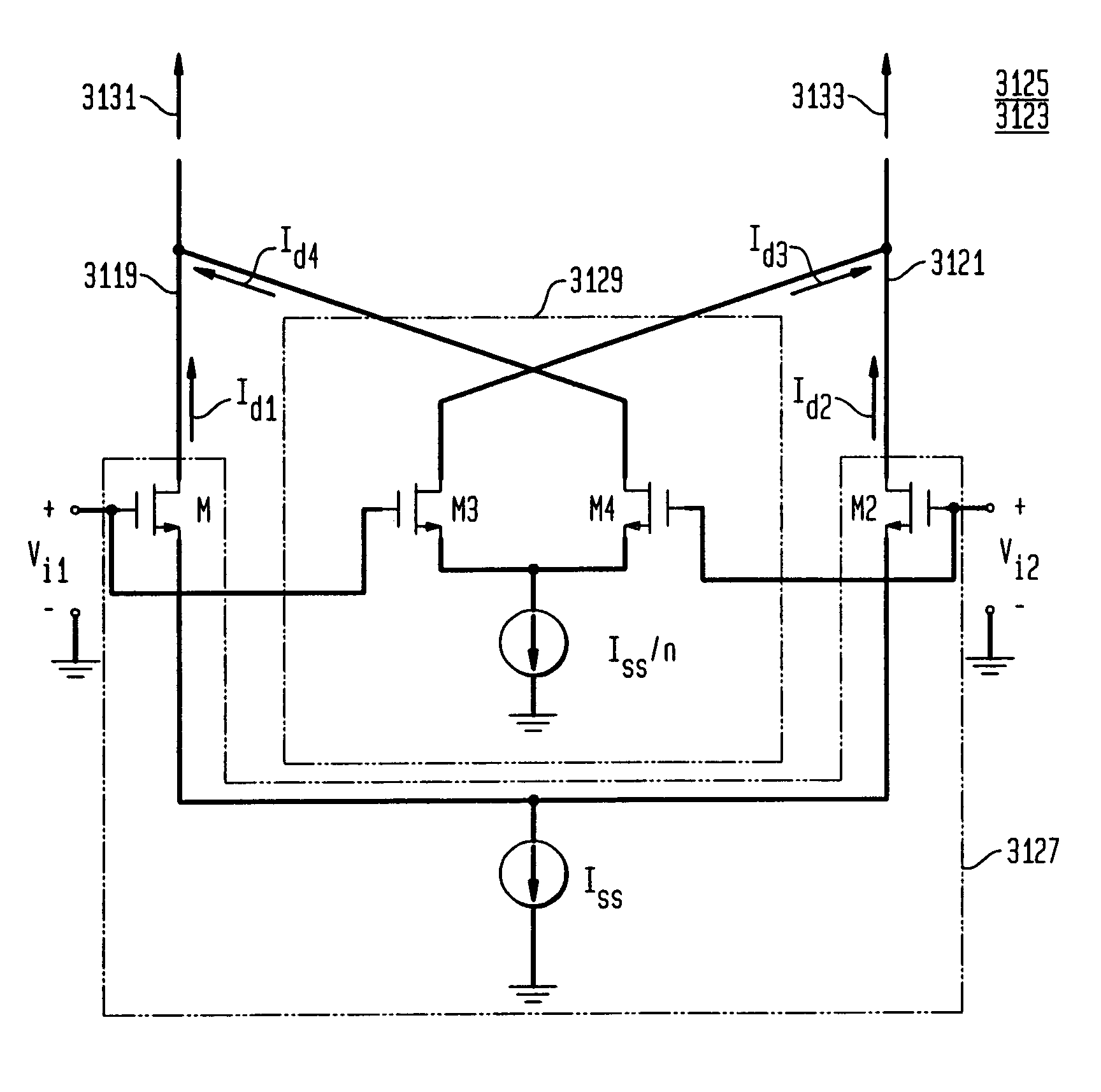

System and method for linearizing a CMOS differential pair

InactiveUS20080036536A1Multiple-port networksSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

Dynamically adjusting a sample-to-pixel filter in response to user input and/or sensor input

InactiveUS6850236B2LevelAvoid flickeringDrawing from basic elementsCathode-ray tube indicatorsGraphicsFilter tuning

Owner:ORACLE INT CORP

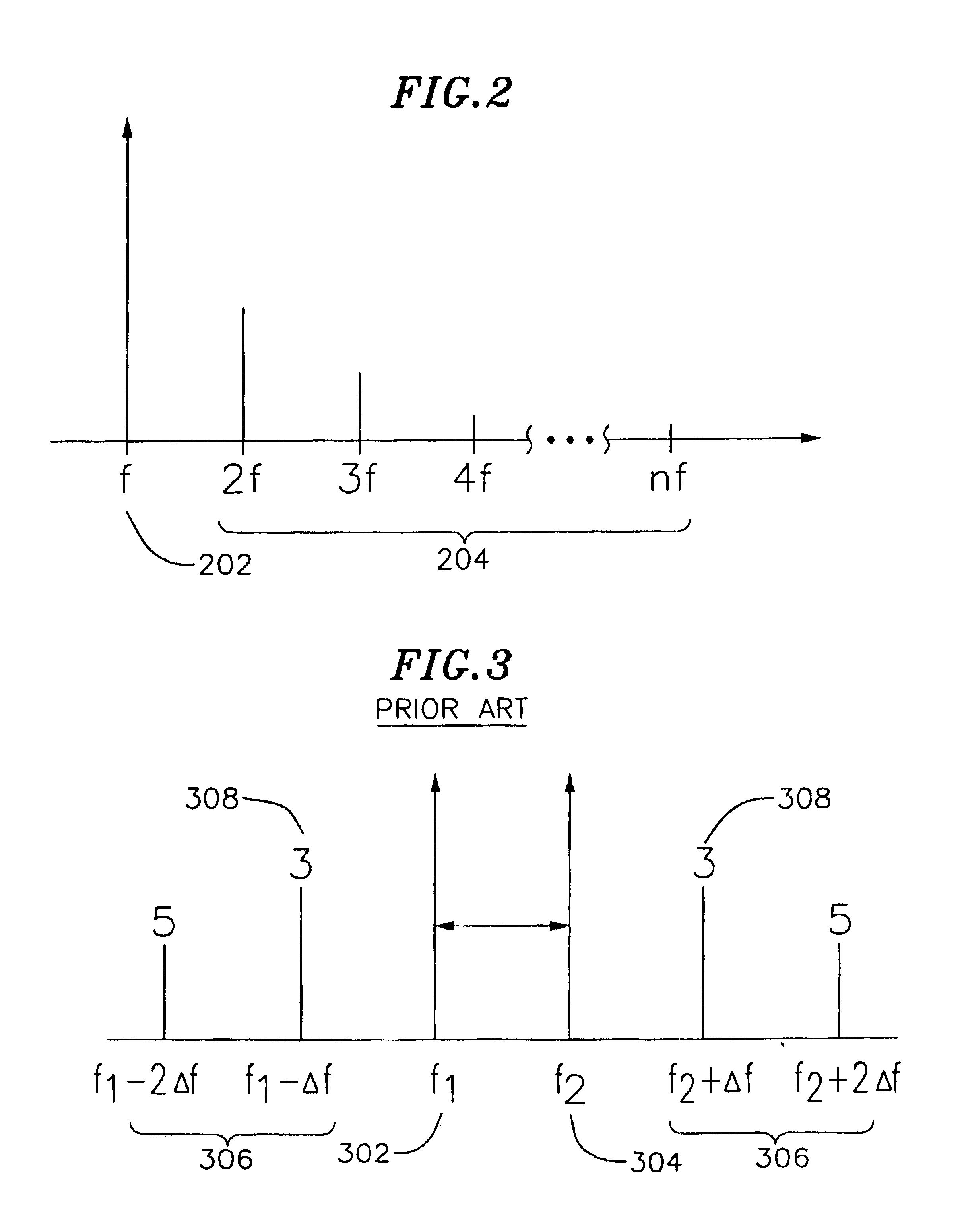

Interference Reduction Techniques in Haptic Systems

InactiveUS20180304310A1Input/output for user-computer interactionMechanical vibrations separationTransducerCarrier signal

As control points in haptic systems move around, the phase offsets for each transducer change at discrete points in time. These are each expressed as a phase offset combined with a monochromatic carrier frequency. To prevent sharp frequency changes, an algorithm that maintains smooth transitions is used. Further, non-idealities in the implementation of haptic array modulation can create spurs in the frequency response of audio output from the array. Adjusting the signal carrier frequency and the signal modulating frequency may substantially reduce audio noise via a notch filter centered at an interpolation frequency.

Owner:ULTRAHAPTICS IP LTD

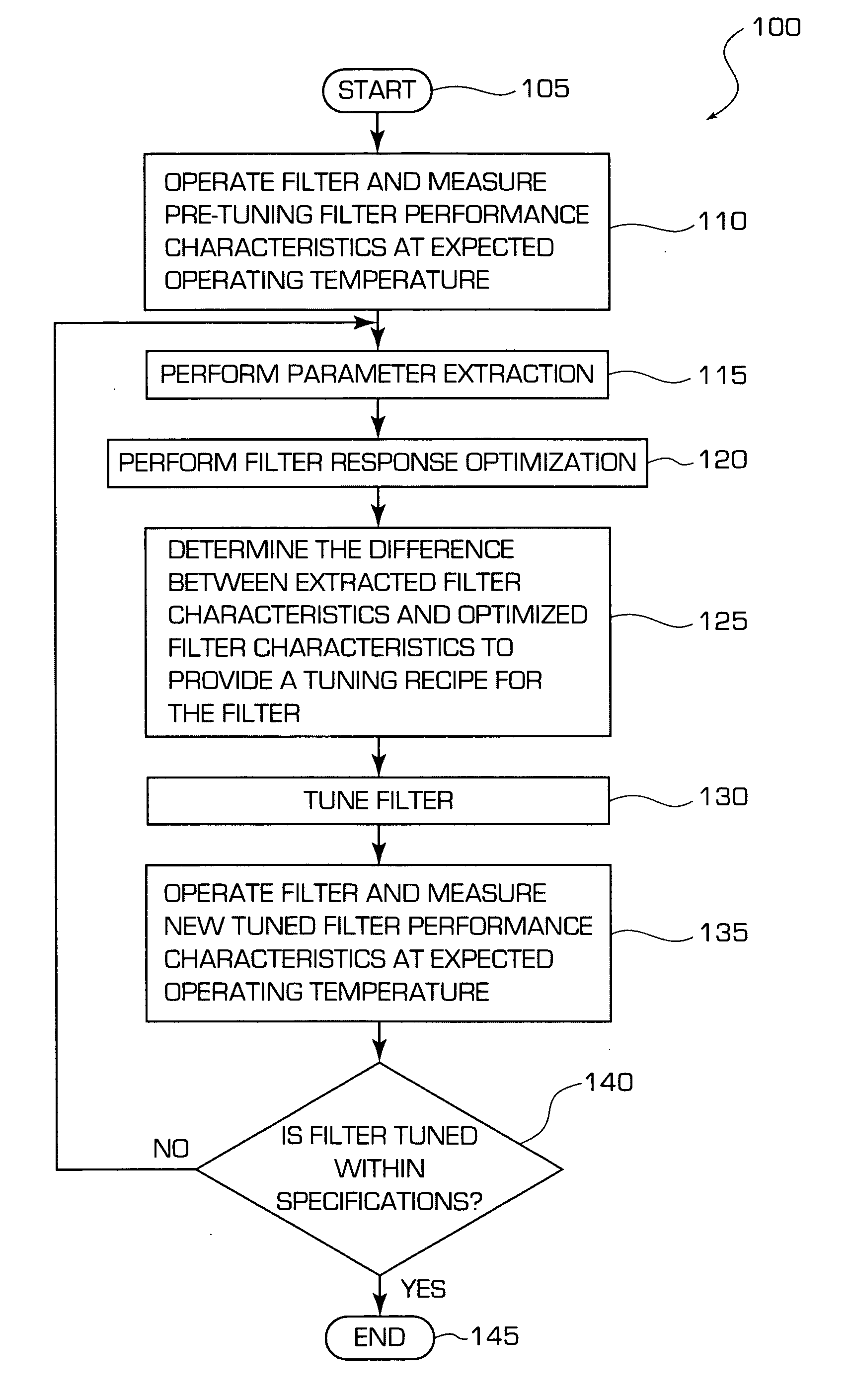

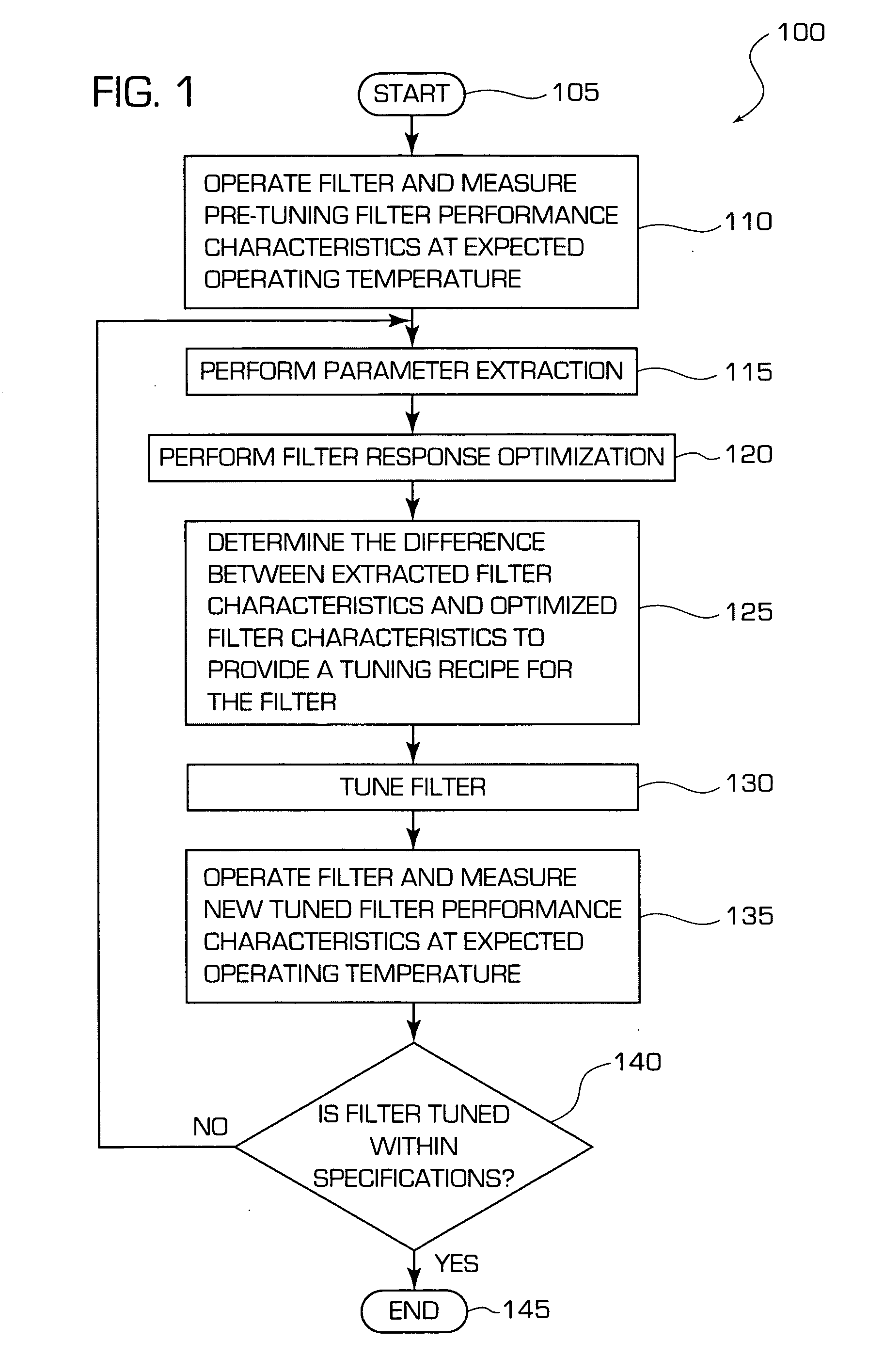

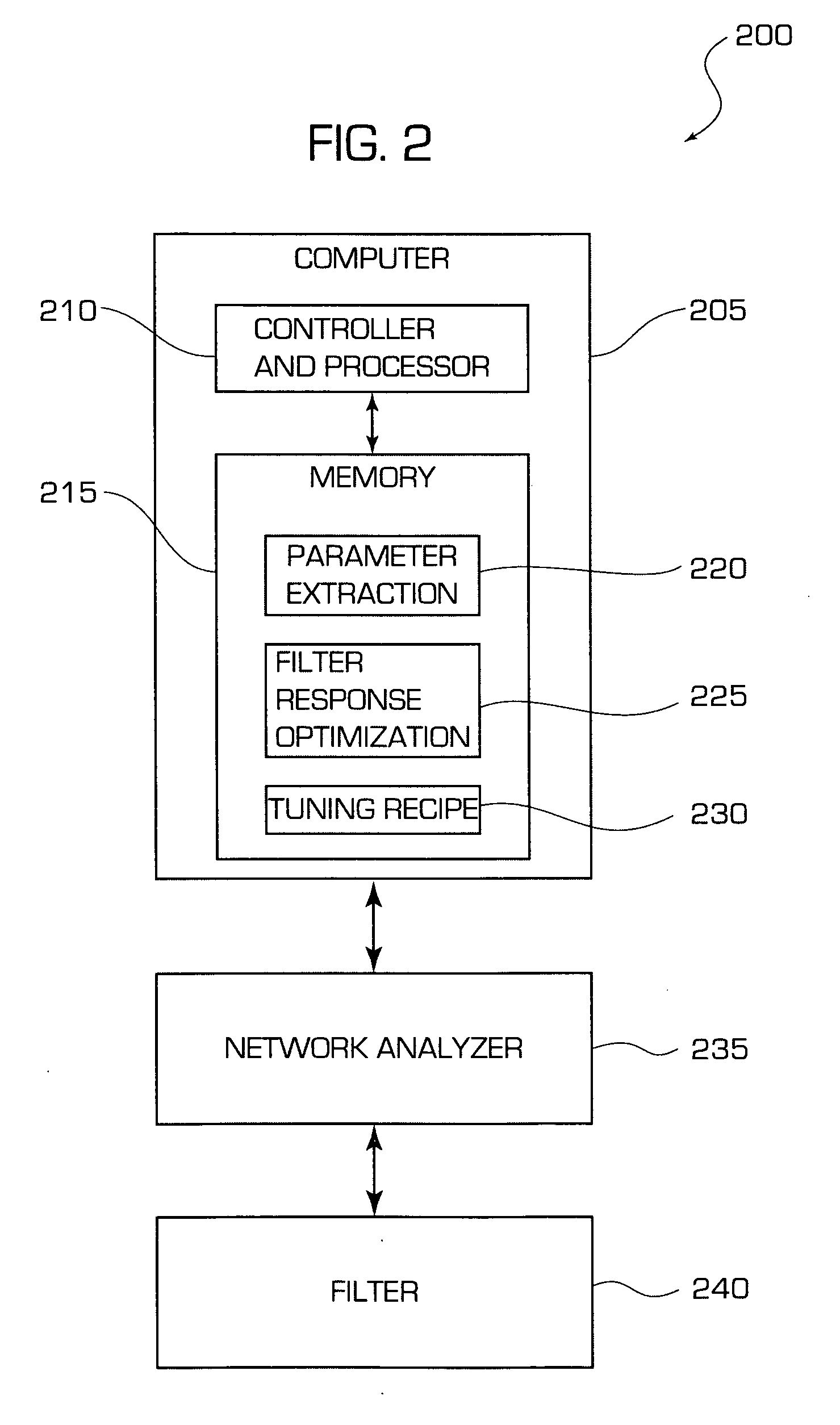

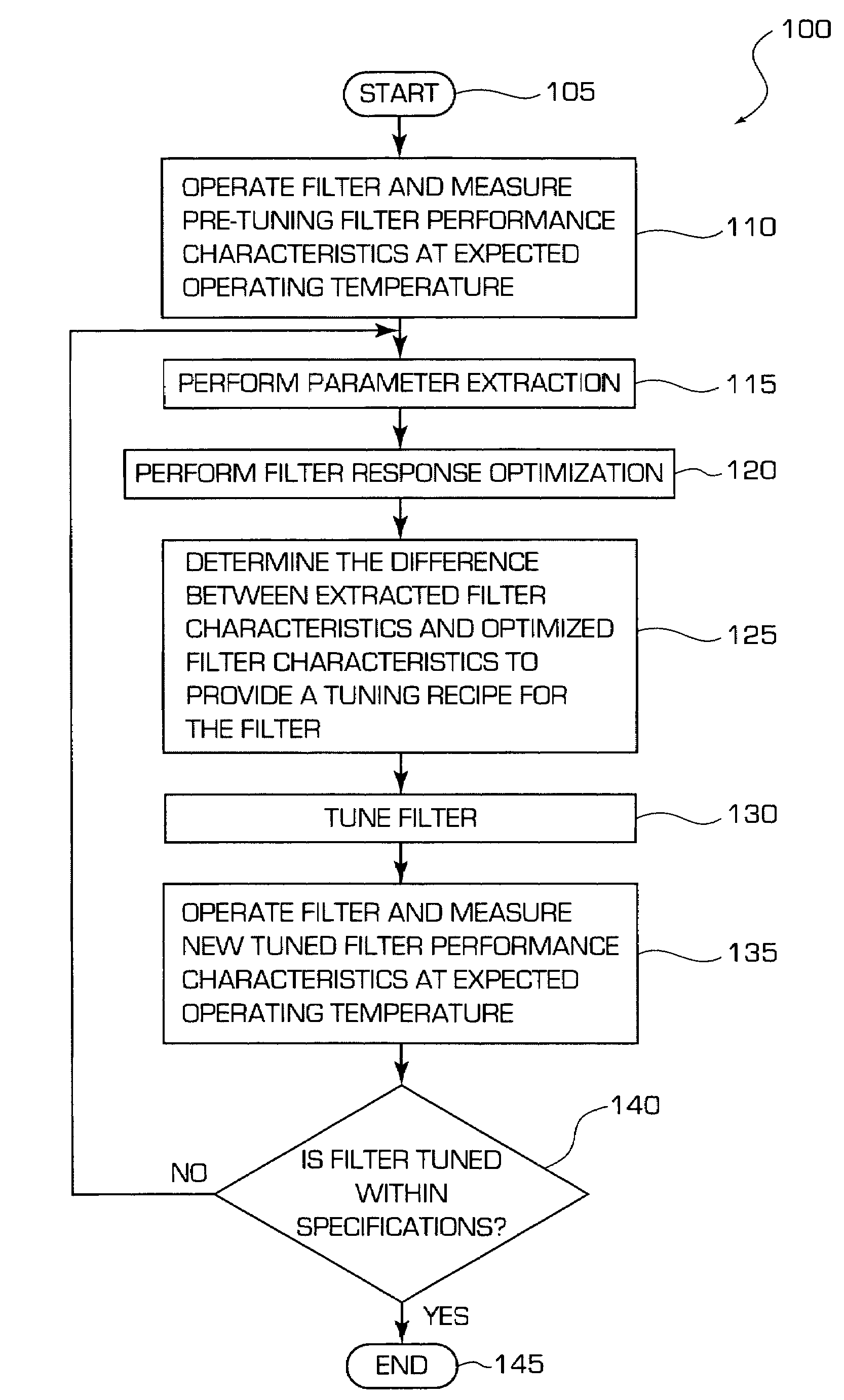

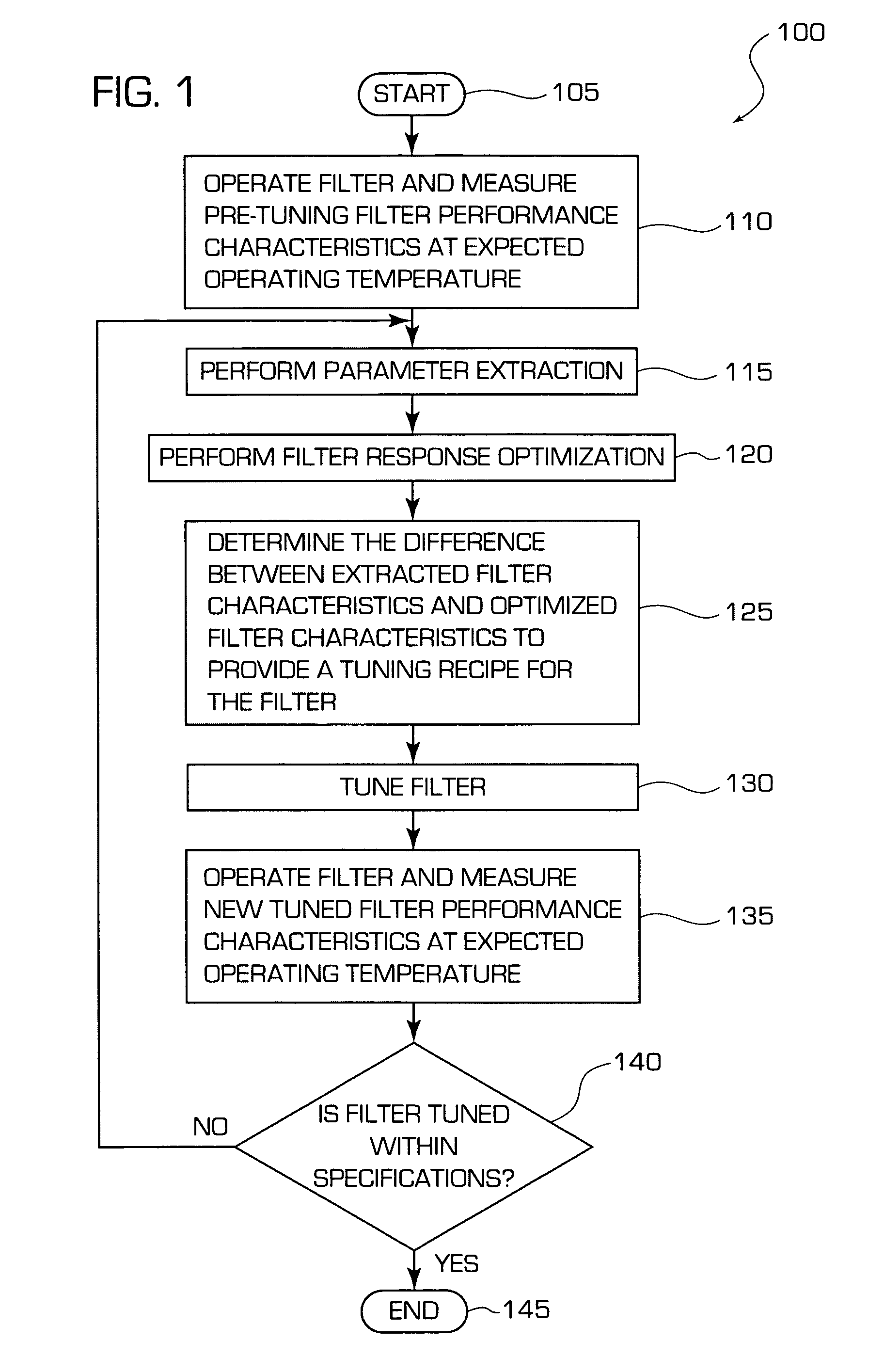

Systems and methods for tuning filters

InactiveUS20060202775A1Reduce sensitivityError in sensitivityTransmission control/equlisationSignal/carrier strength dependant limiting amplitudeFir filter designTrim tab

Methods, systems and apparatus for filter design, analysis and adjustment are provided. Various embodiments may include, for example, methods, systems and apparatus for electric signal filter tuning. Embodiments may also include design techniques for planar electric signal (e.g., RF signals) filter tuning. In at least an embodiment of the present invention a technique for filter tuning is provided which may include parameter extraction, optimization and tuning recipes techniques that may require only a single permanent filter tuning. In at least another embodiment a system and method of filter design, analysis and adjustment according to the present invention includes use of tuning that may be set using a mechanical scribing tool or a laser trimming device. In at least one other embodiment, a filter tuning technique may be provided and include providing trimming tabs on a resonator edge that may be disconnected or trimmed for filter tuning.

Owner:SUPERCONDUCTOR TECHNOLOGIES INC

Integrated spiral inductor

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

Dynamically adjusting a sample-to-pixel filter in response to user input and/or sensor input

A graphics system capable of super-sampling and performing real-time convolution. The graphics system may comprise a graphics processor, a sample buffer, and a sample-to-pixel calculation unit. The graphics processor receives graphics data and generates a plurality of samples for each of a plurality of frames. The sample buffer stores the samples. The sample-to-pixel calculation unit is operable to generate output pixels by filtering the rendered samples using a filter. A display device then receives and displays the output pixels. A user may observe the displayed image and adjust properties of the filter according to the user's personal visual preferences. A display-monitoring device may be configured to capture the displayed image. The graphics system may then analyze the captured image and, in response to the captured image, perform filter adjustments.

Owner:ORACLE INT CORP

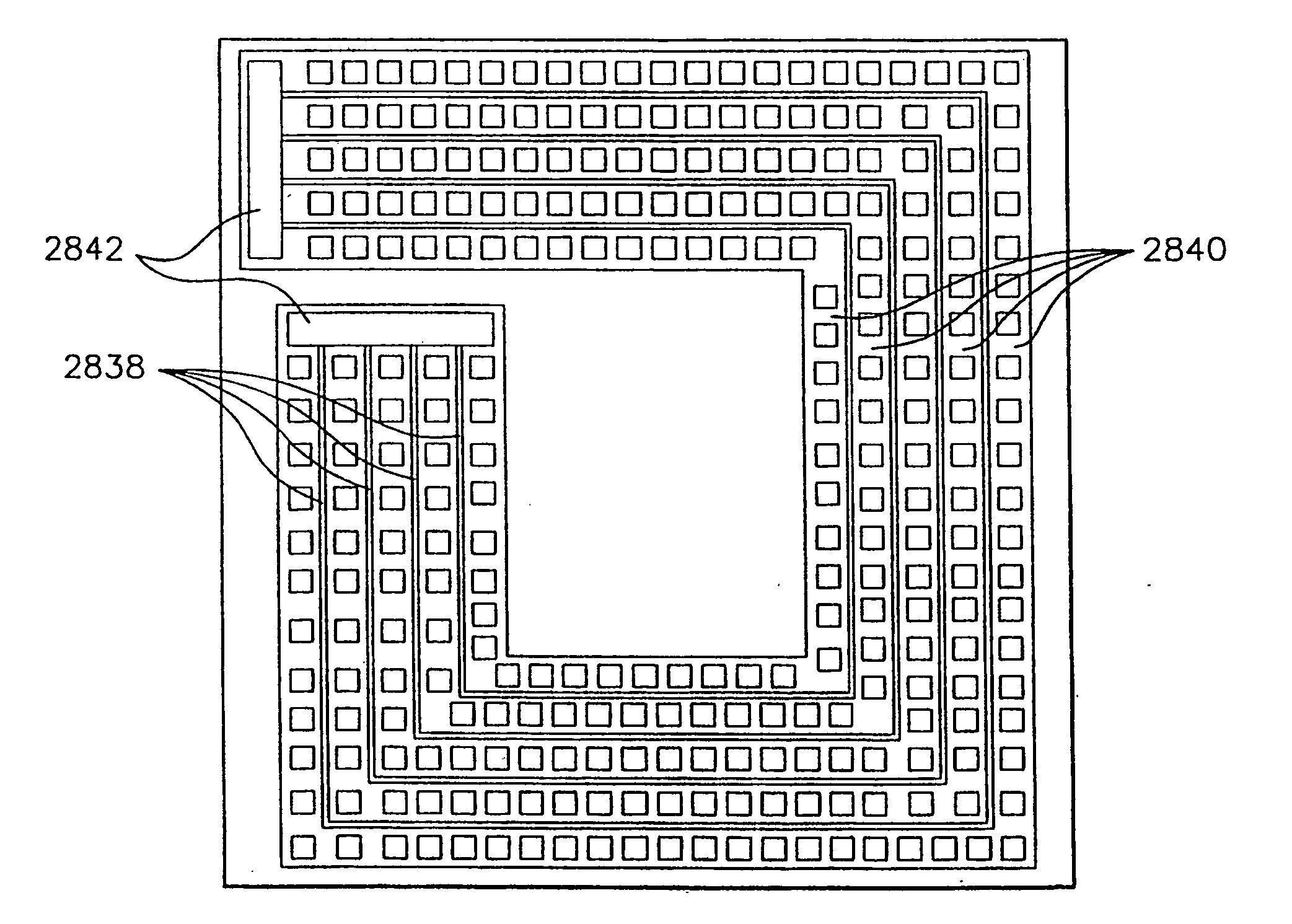

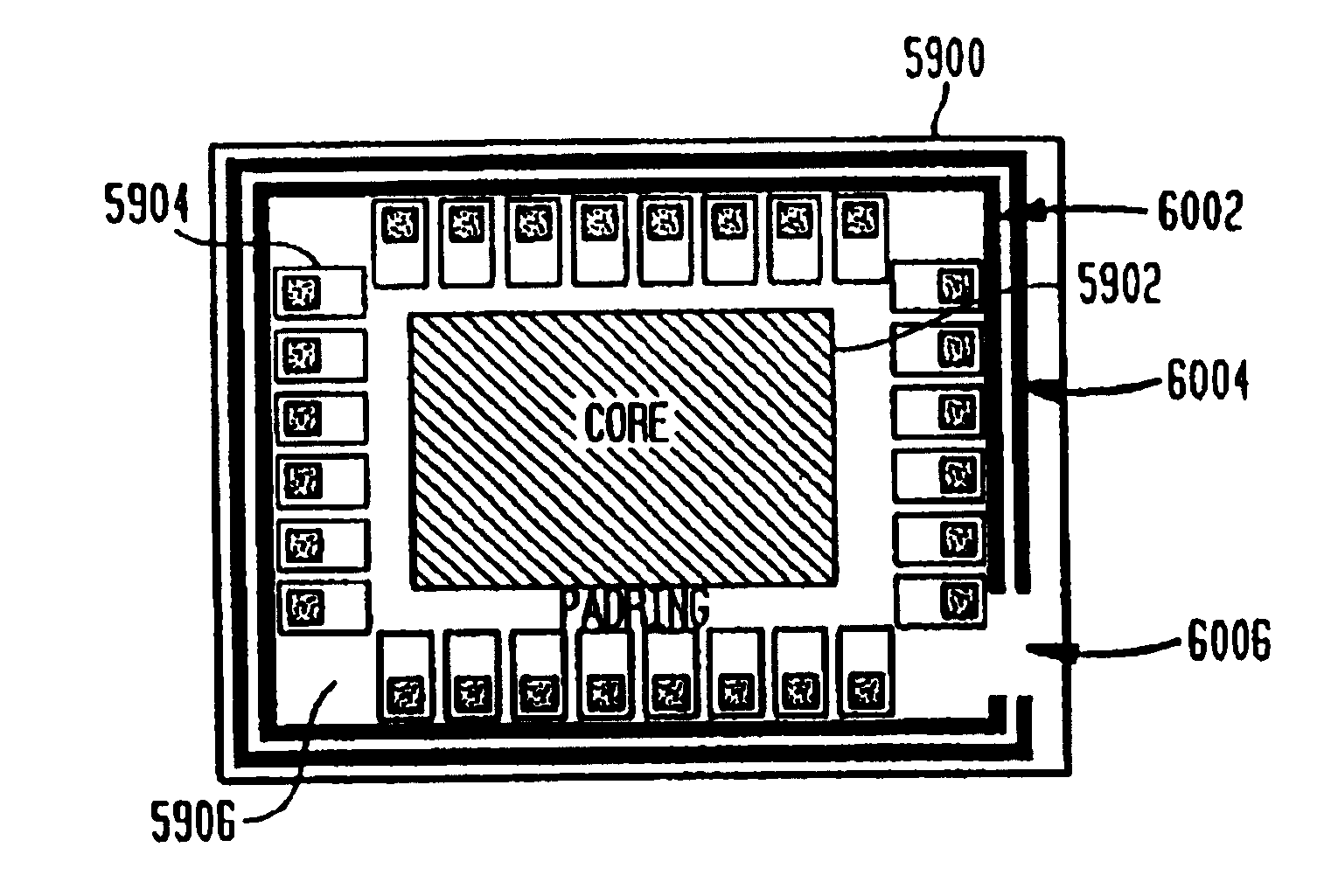

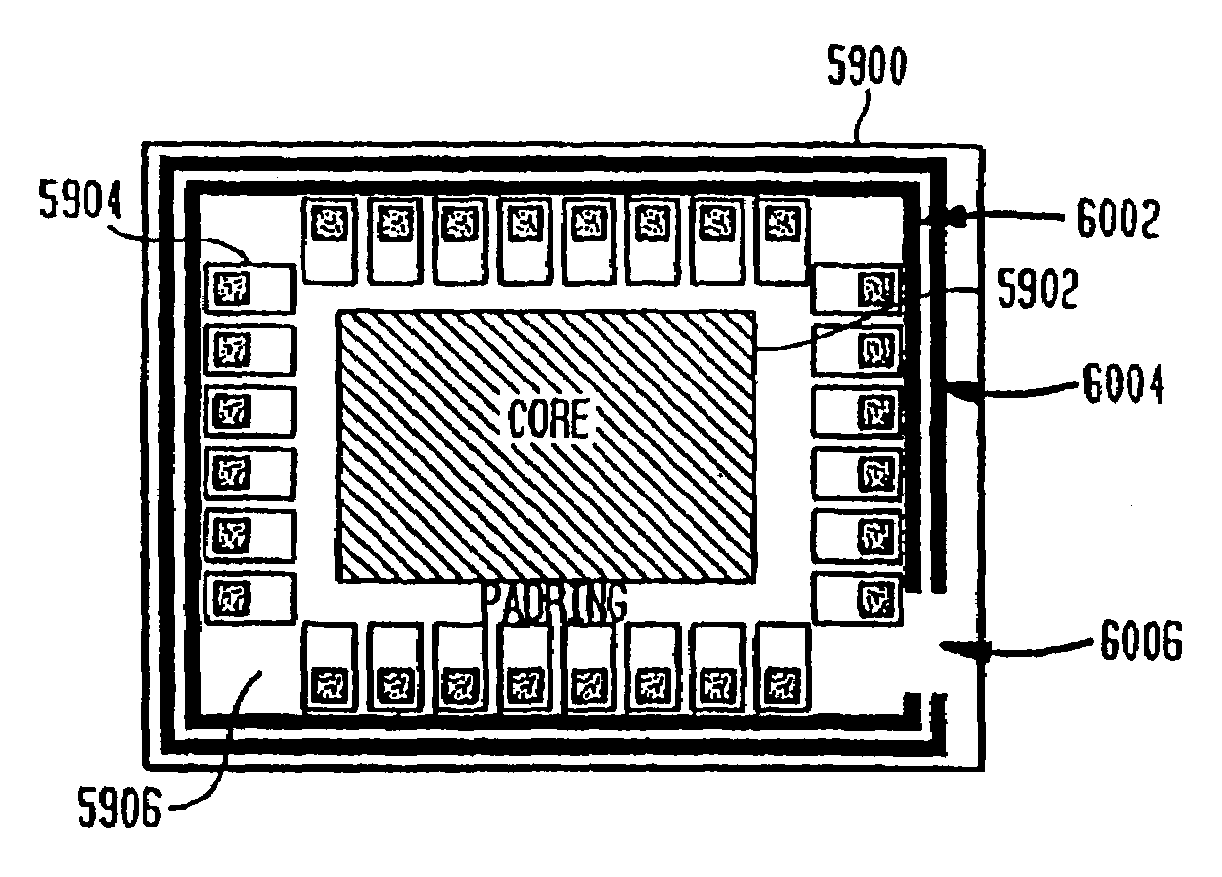

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Graphics system having a super-sampled sample buffer with generation of output pixels using selective adjustment of filtering for implementation of display effects

A computer graphics system that utilizes a super-sampled sample buffer and a programmable sample-to-pixel calculation unit for refreshing the display, wherein the graphics system may adjust filtering to reduce artifacts or implement display effects. In one embodiment, the graphics system may have a graphics processor, a super-sampled sample buffer, and a sample-to-pixel calculation unit. The graphics processor renders a plurality of samples and stores them into a sample buffer. The sample-to-pixel calculation unit reads the samples from the super-sampled sample buffer and filters or convolves the samples into respective output pixels which are then provided to refresh the display. The sample-to-pixel calculation unit may selectively adjust the filtering of stored samples to reduce artifacts, e.g., is operable to selectively adjust the filtering of stored samples in neighboring frames to reduce artifacts between the neighboring frames. The filter adjustment may be applied where the sample-to-pixel calculation unit generates output pixels at the same rate as the graphics processor rendering samples to the sample buffer, or at a different (e.g., higher) rate than the render rate. The sample-to-pixel calculation unit is operable to adjust filtering of stored samples to implement a display effect, such as panning, zooming, rotation, or moving scenes, among others. The sample-to-pixel calculation unit may also selectively adjust the filtering of stored samples on a fractional-pixel boundary.

Owner:ORACLE INT CORP

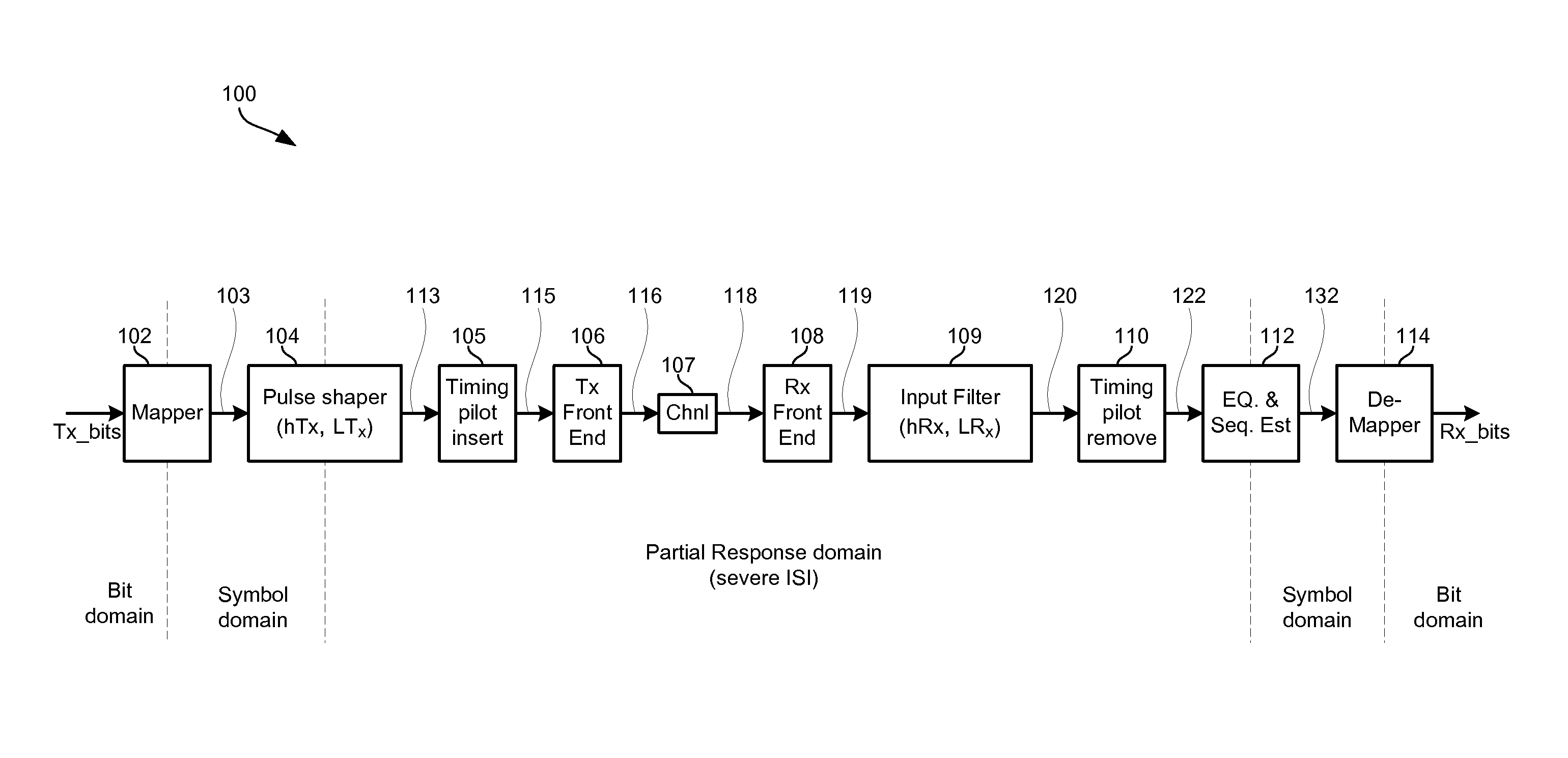

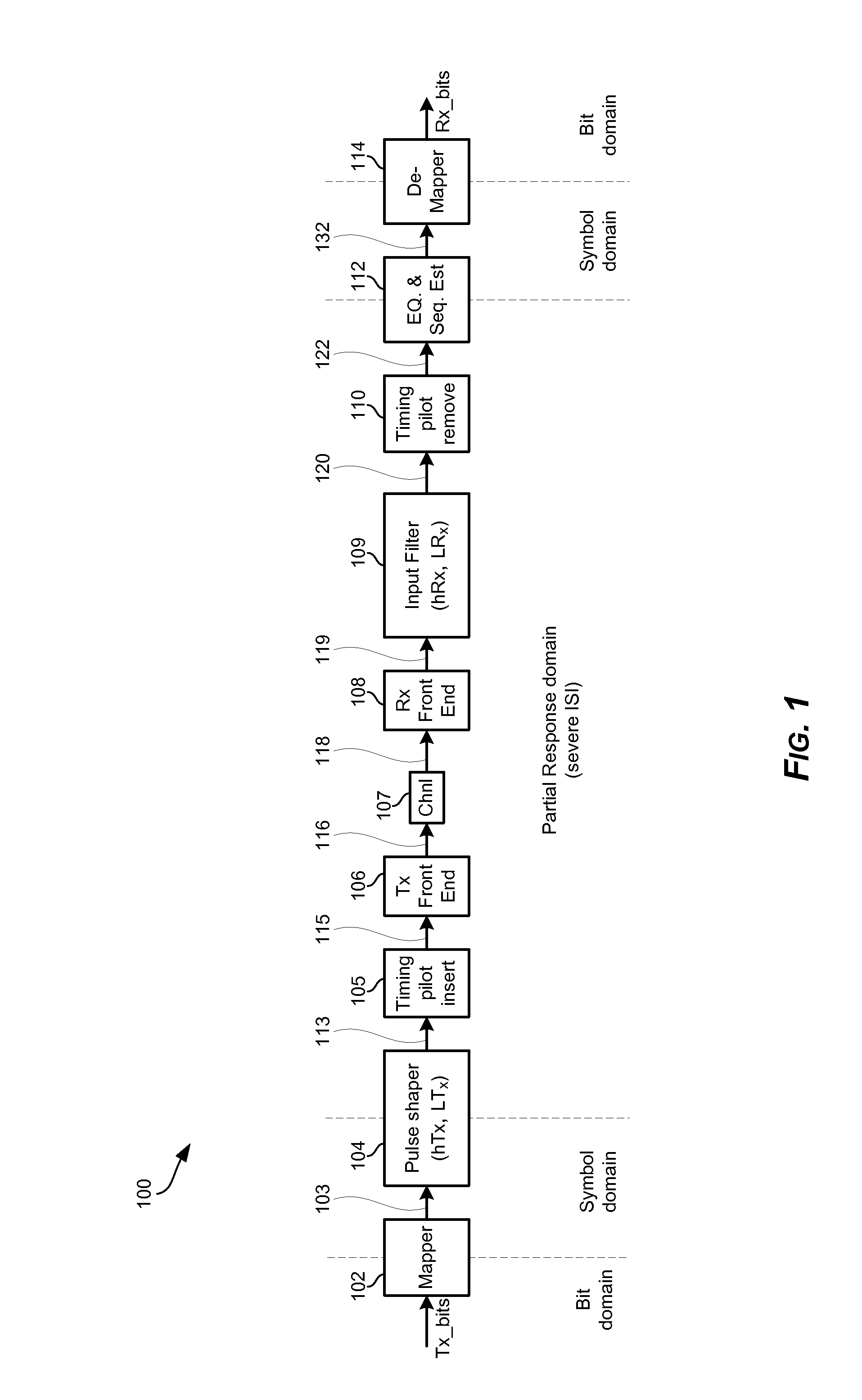

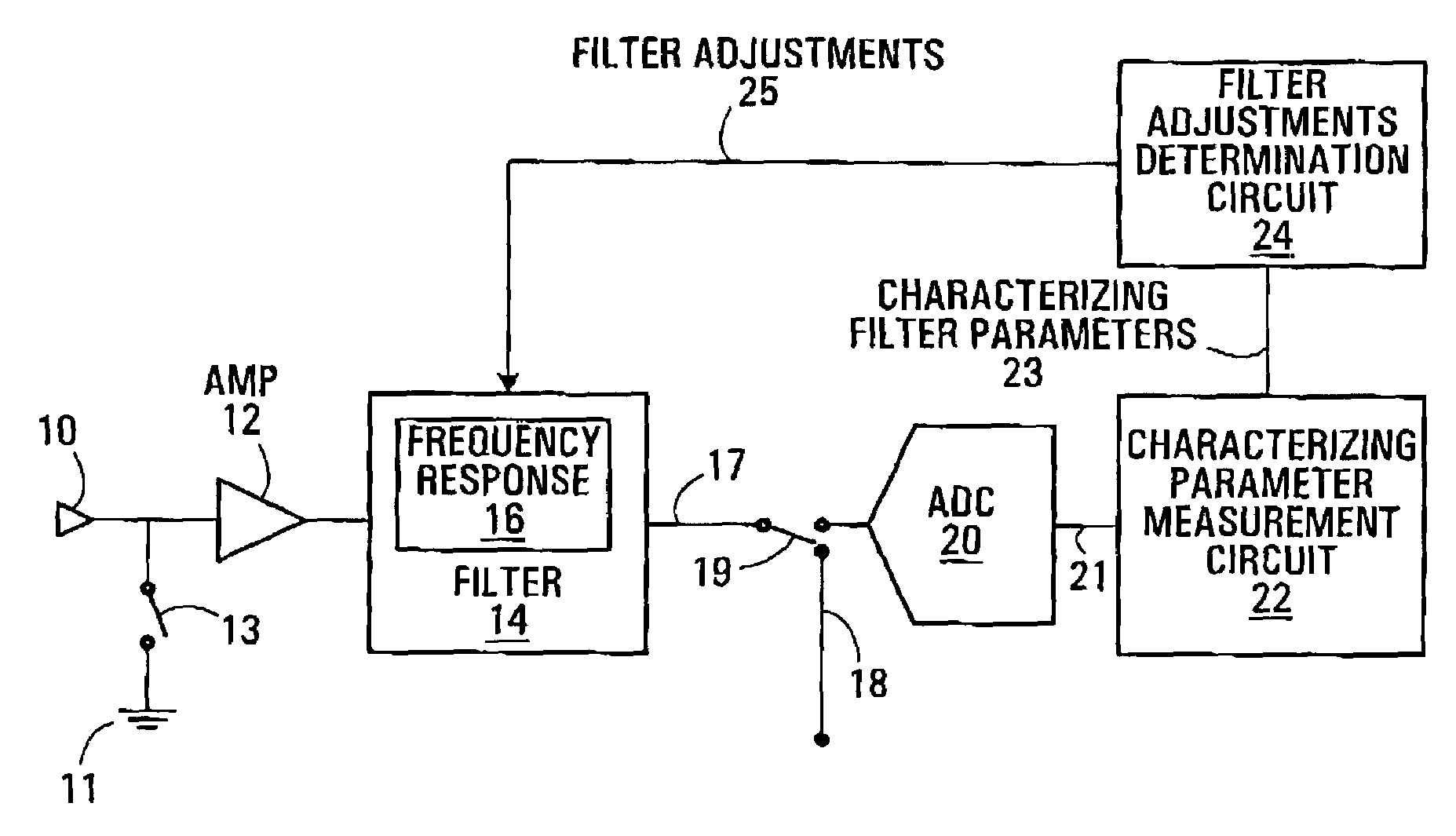

Dynamic Filter Adjustment for Highly-Spectrally-Efficient Communications

ActiveUS20140146911A1Forward error control useTransmission noise suppressionFilter tuningEngineering

A method and system for dynamic configuring of one or both of a transmitter pulse-shaping filter and a receiver pulse-shaping filter to generate a total partial response that incorporates a predetermined amount of inter-symbol interference (ISI). The predetermined amount of ISI is determined based on an estimation process during extraction of data from an output of the receiver pulse-shaping filter, such that performance of total partial-response-based communication matches or surpasses performance of communication incorporating filtering based on no or near-zero ISI. The reconfiguring may comprise obtaining data relating to changes affecting one or more of: the pulse-shaping filtering, and a channel and / or an interface used in the communication of data based on the total partial response, and adjusting the filter configuration, such as by determining a new optimized filtering configuration or changes to existing configurations (e.g., by applying a filtering optimization process).

Owner:AVAGO TECH INT SALES PTE LTD

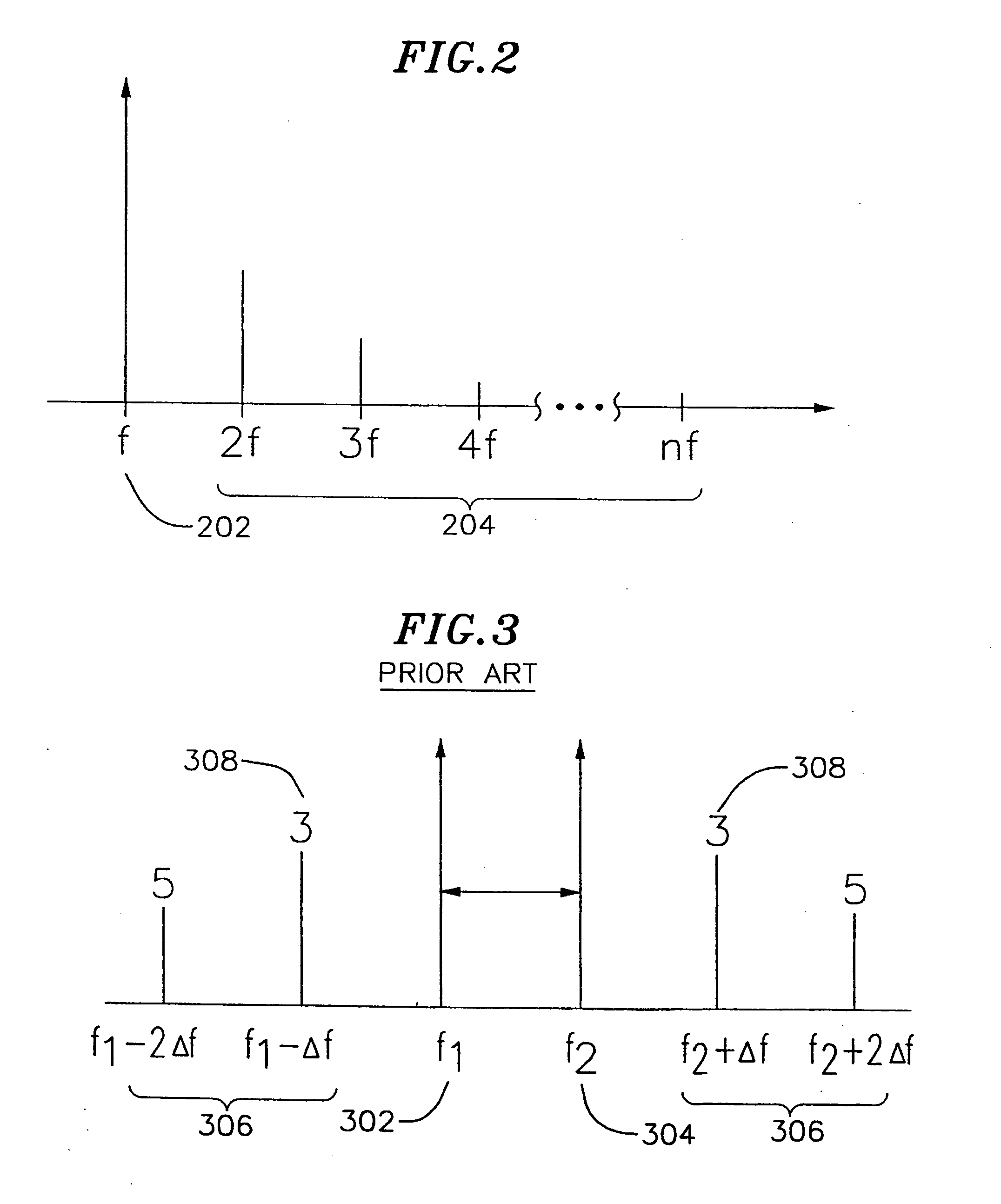

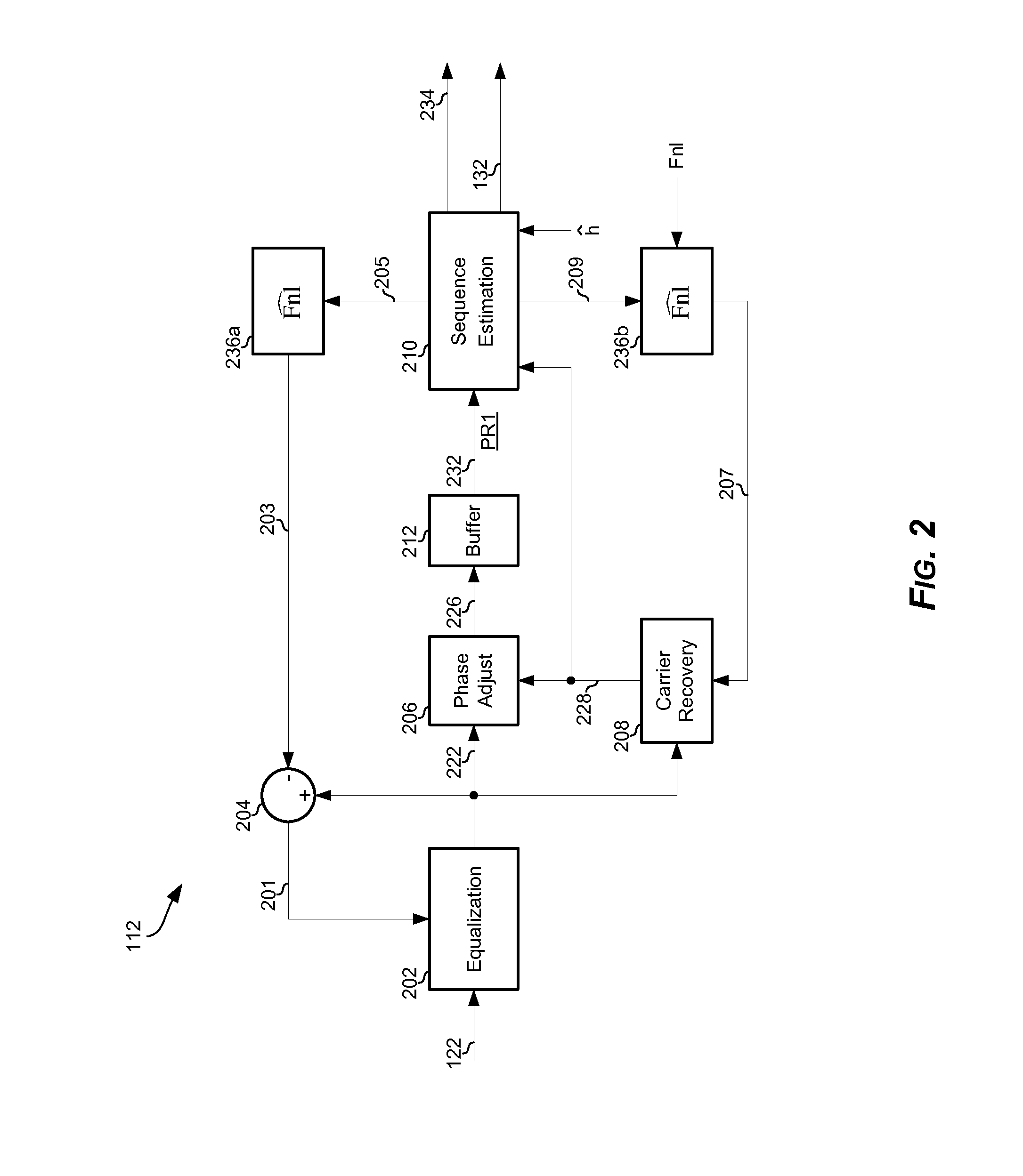

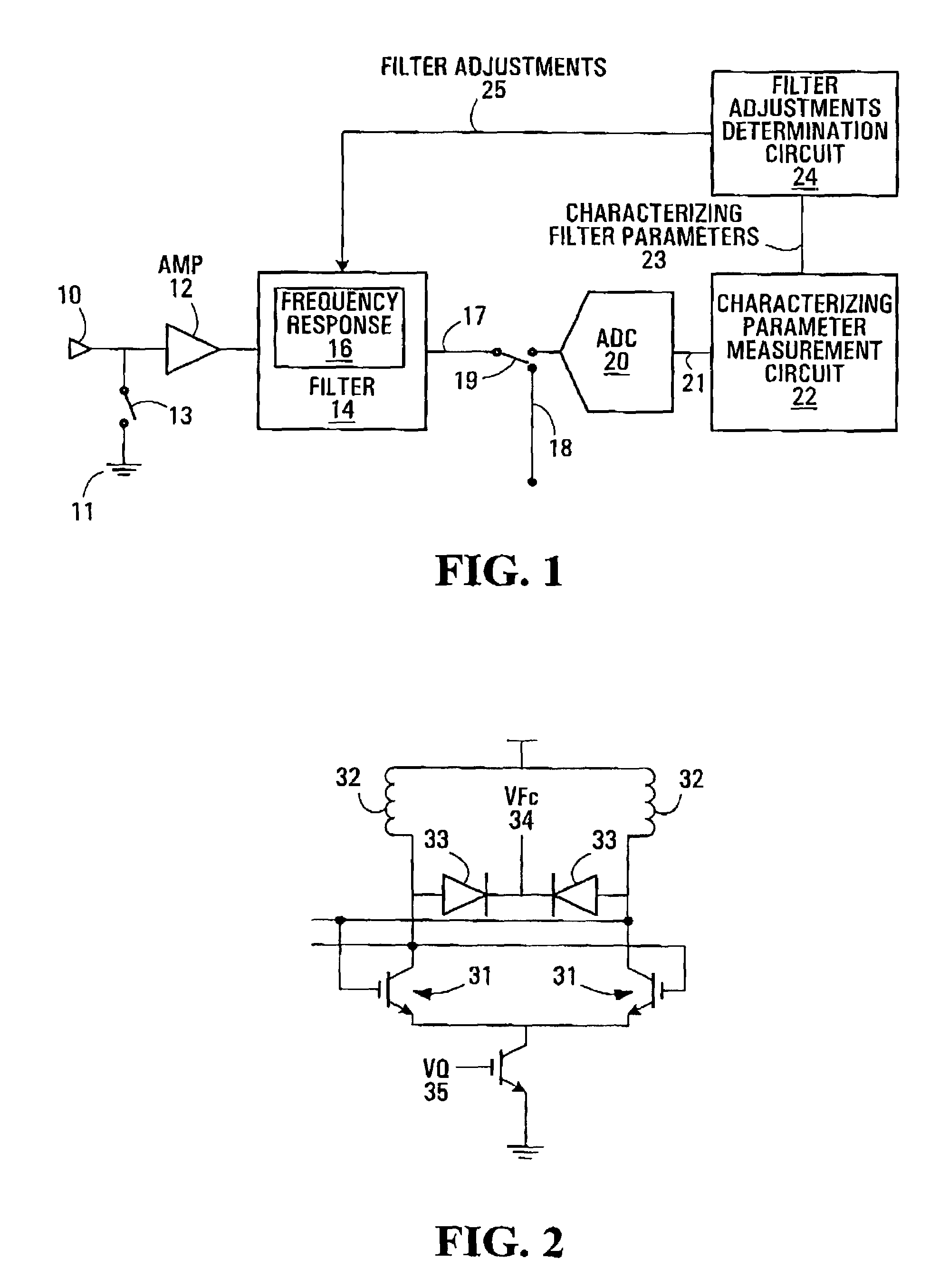

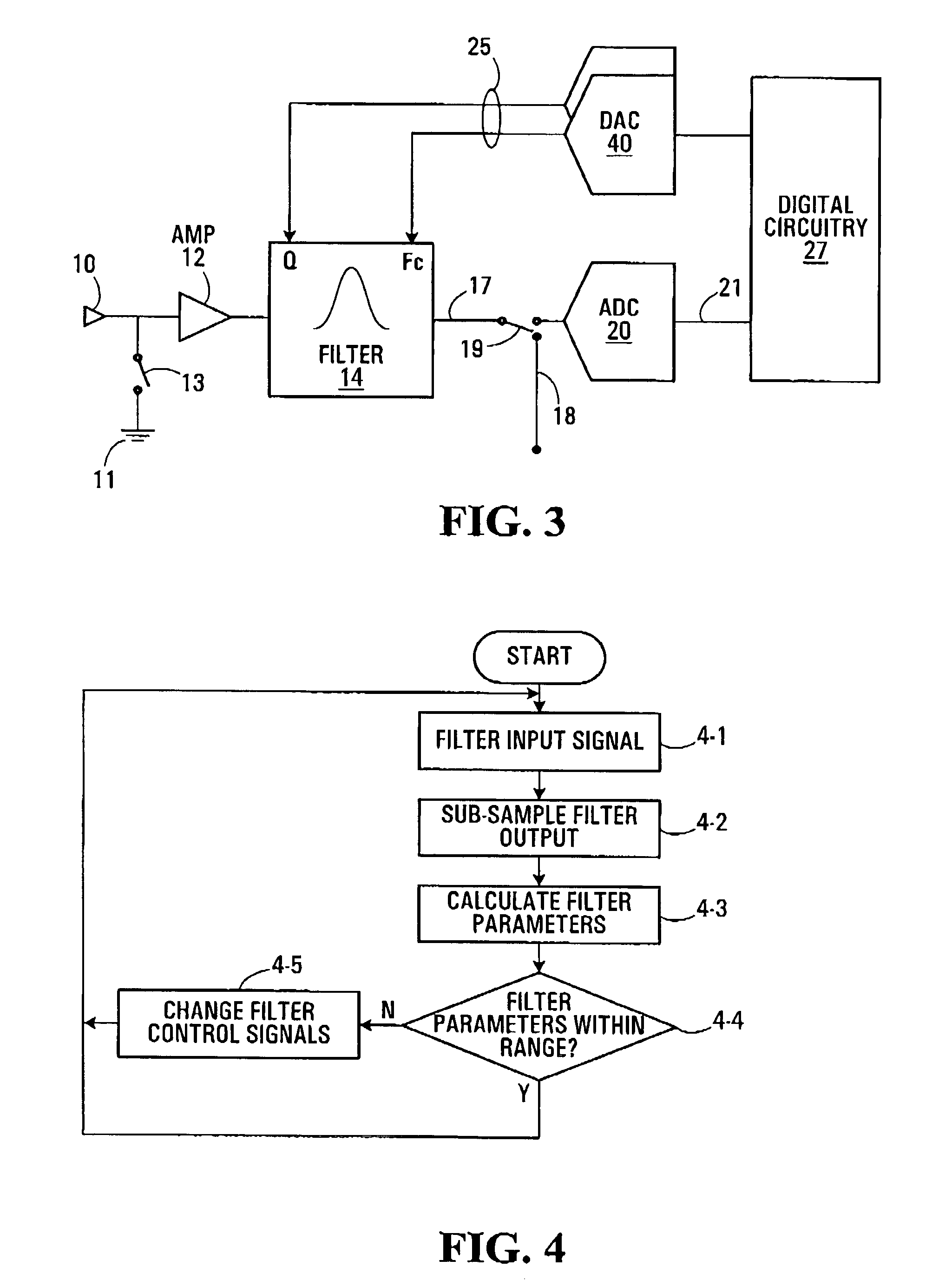

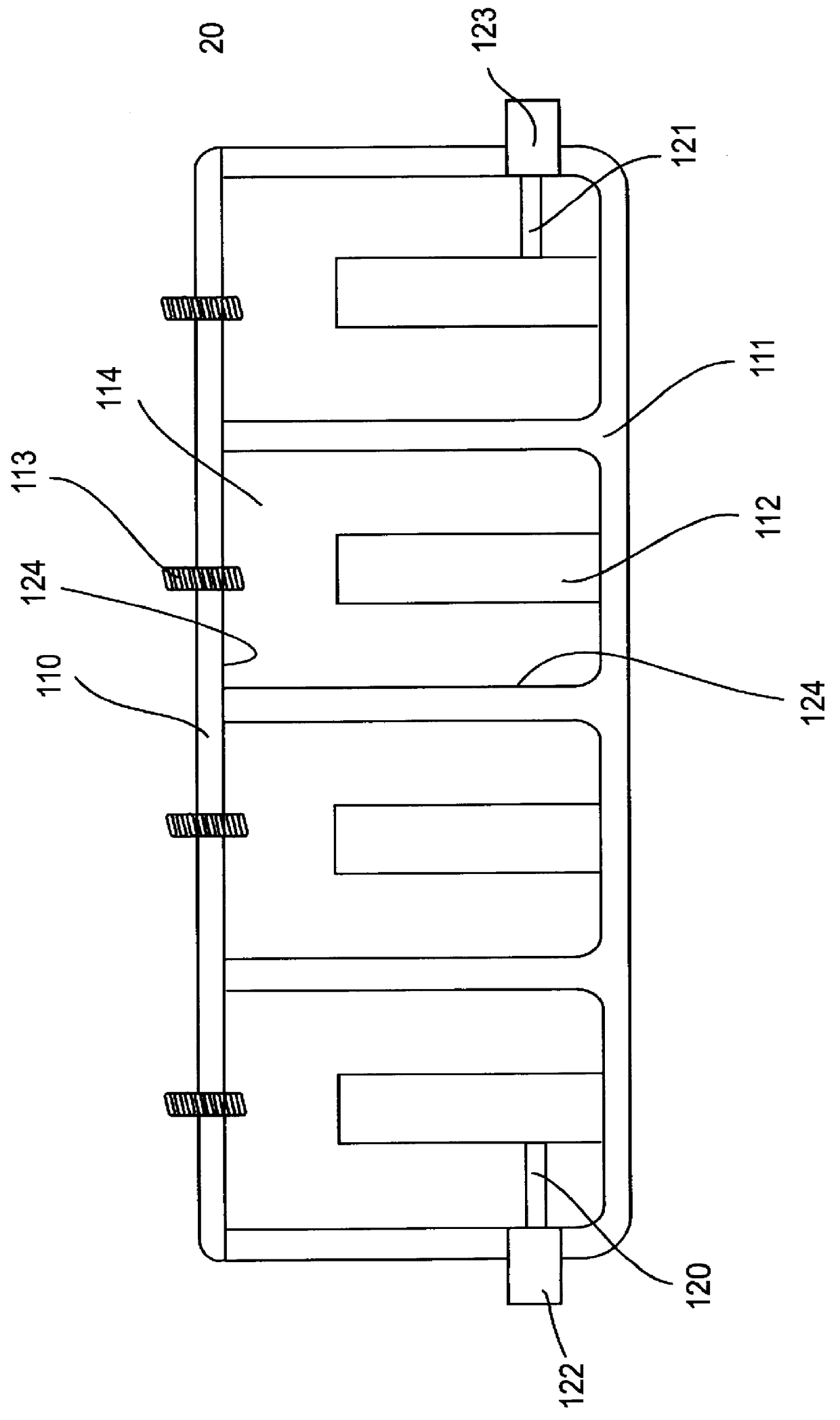

Directly tuned filter and method of directly tuning a filter

ActiveUS6983136B2Eliminate needImprove data transfer rateAnalogue adaptive filtersTransmission monitoringFilter tuningDigital analog converter

A Method for filter tuning using direct digital sub-sampling is provided. The tuning is accomplished in the digital domain by determining the filter characteristics from the shape of the transfer function. The input signal (1) is passed through the filter (3) and is then sub-sampled by and Analog-to-digital Converter (ADC) (5). The sub-sampled signal (6) is then processed in the digital domain using a digital circuit (7) that is used to determine the center frequency (Fc) and Quality factor (Q) and / or other important filter parameters. The Fc, Q and / or other important filter parameters are then adjusted by generating digital control signals (8) that can be converted to analog signals (10) using Digital-to-analog Converters (DACs) (9).

Owner:SMSC HLDG

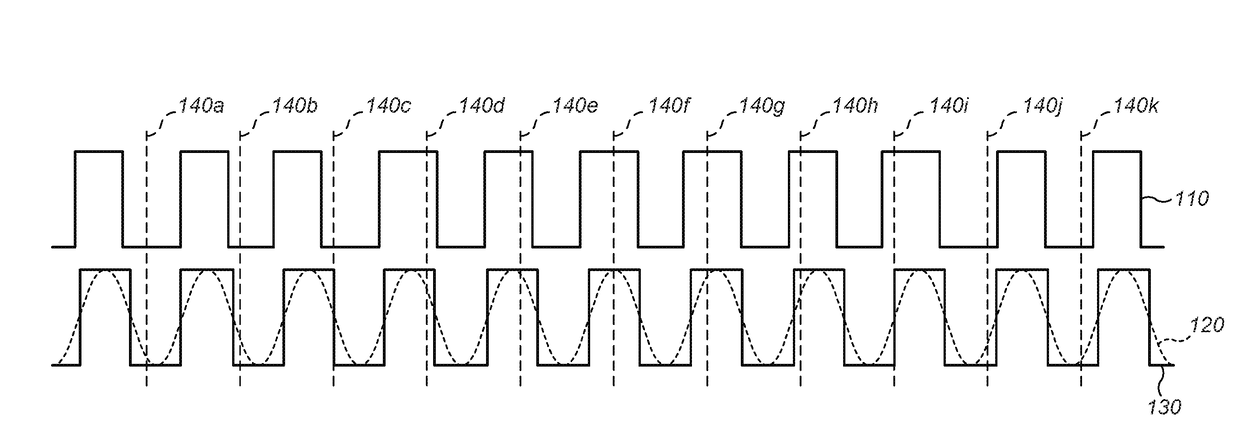

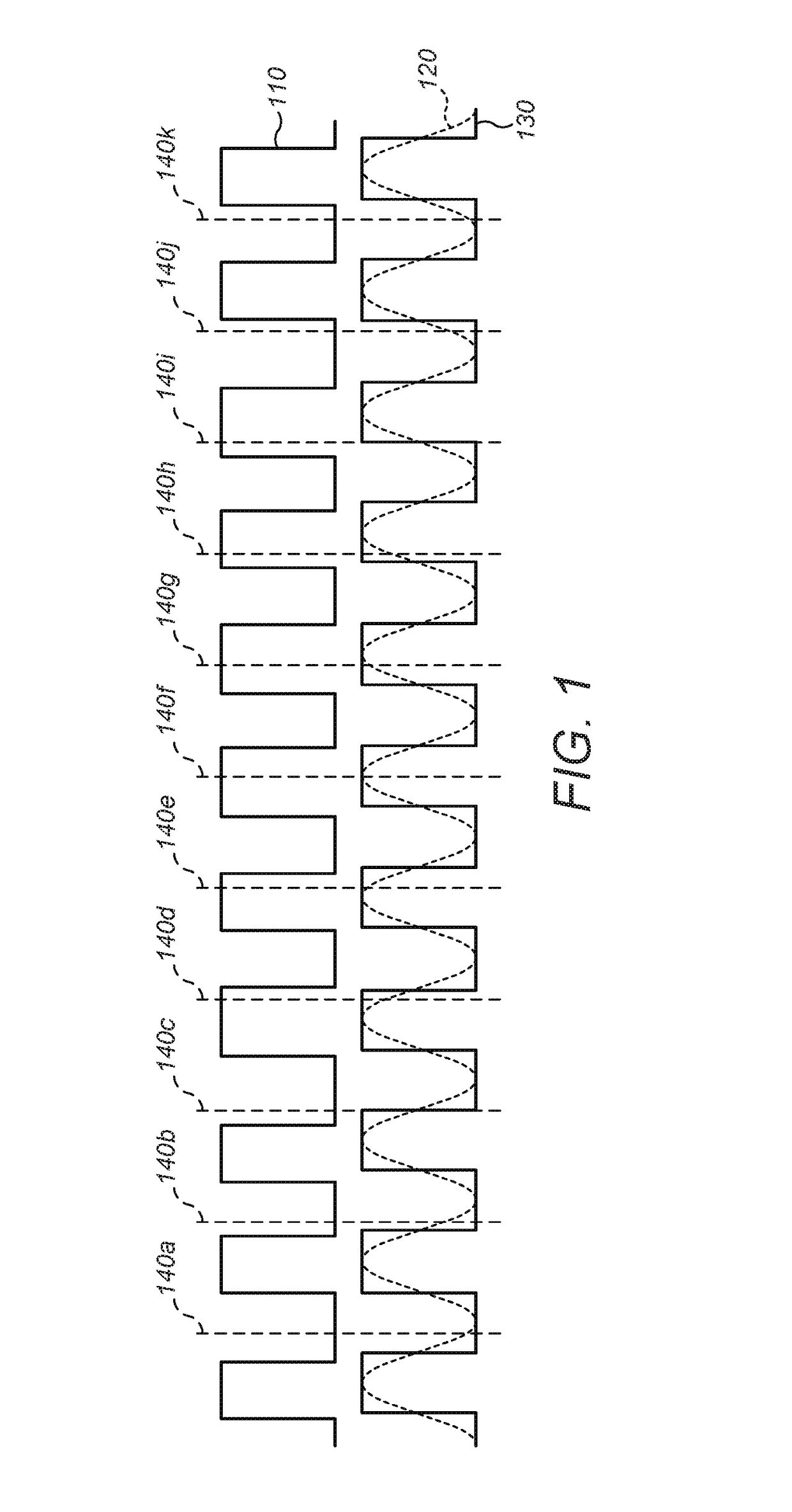

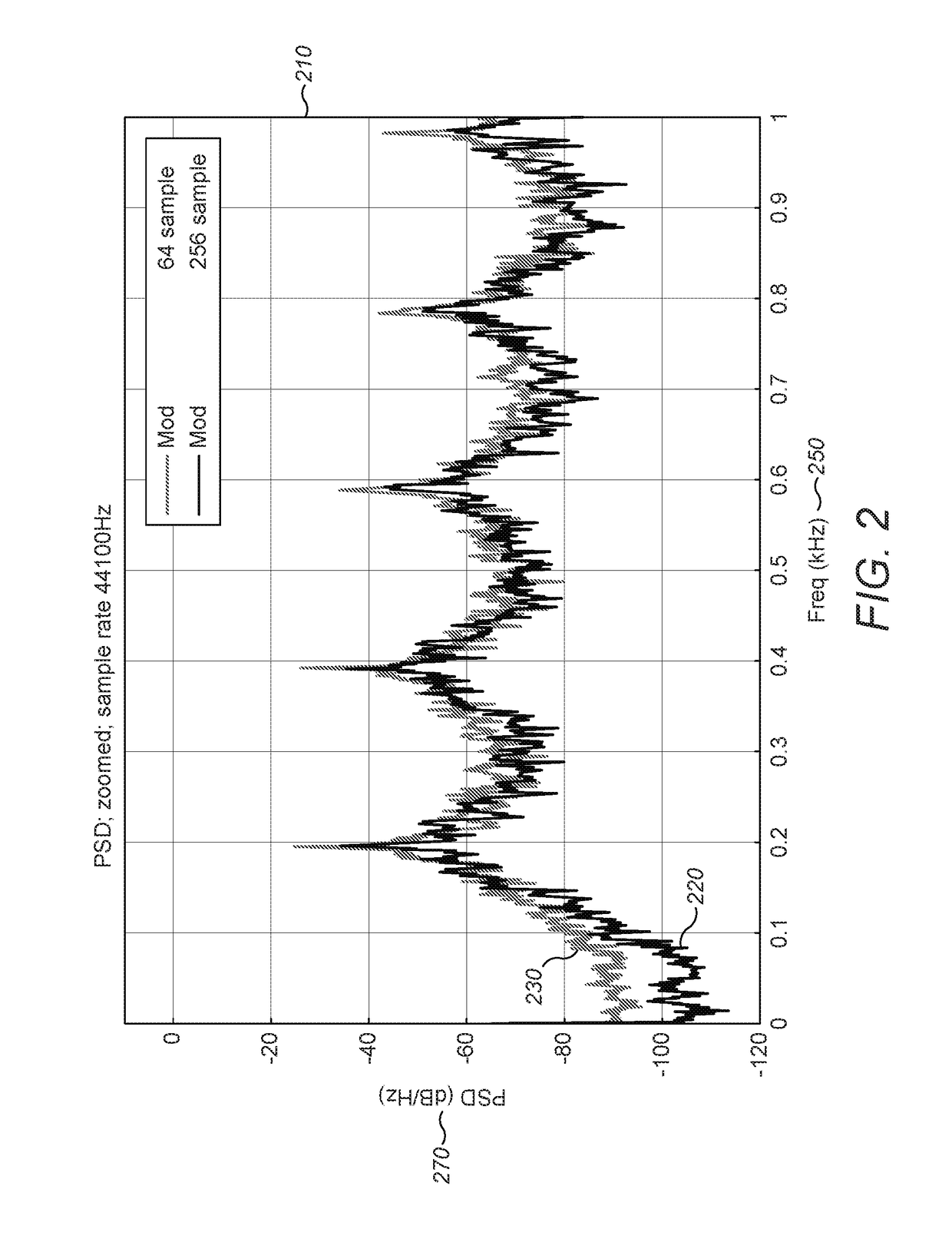

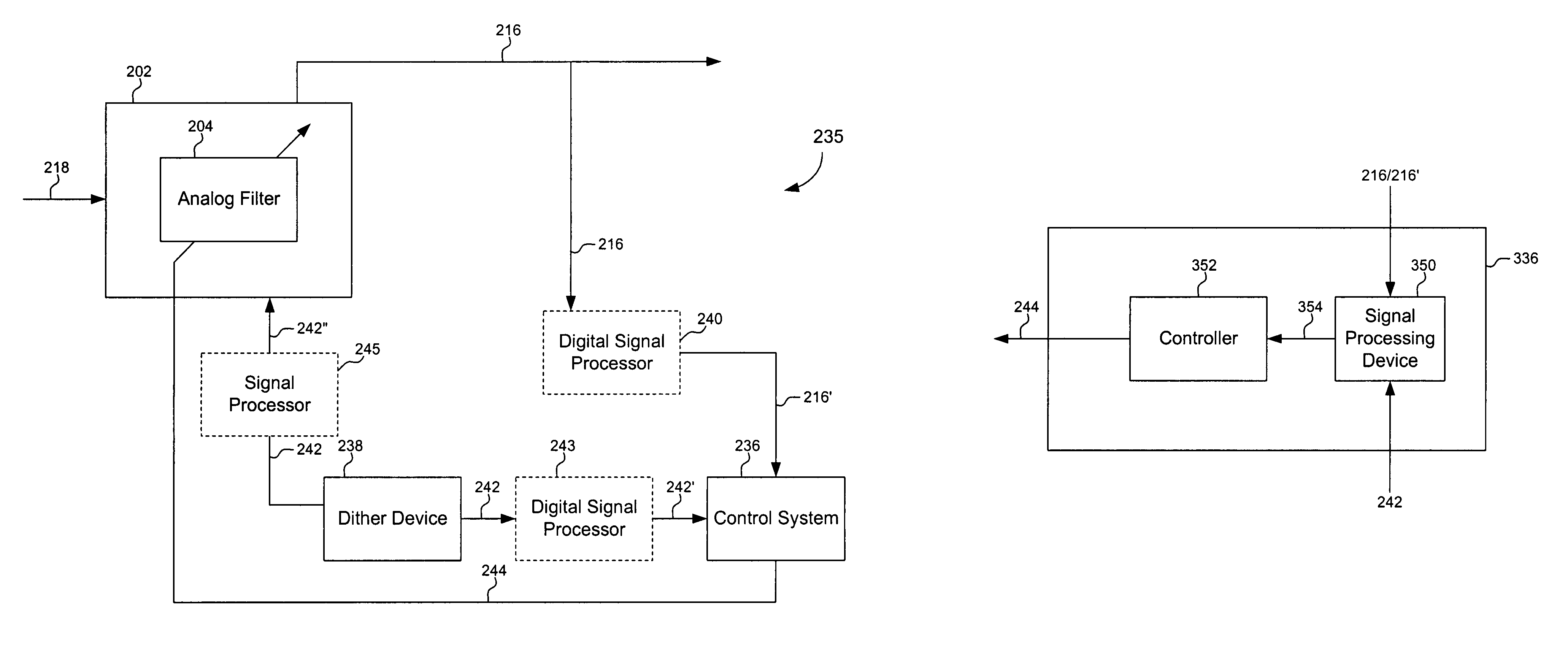

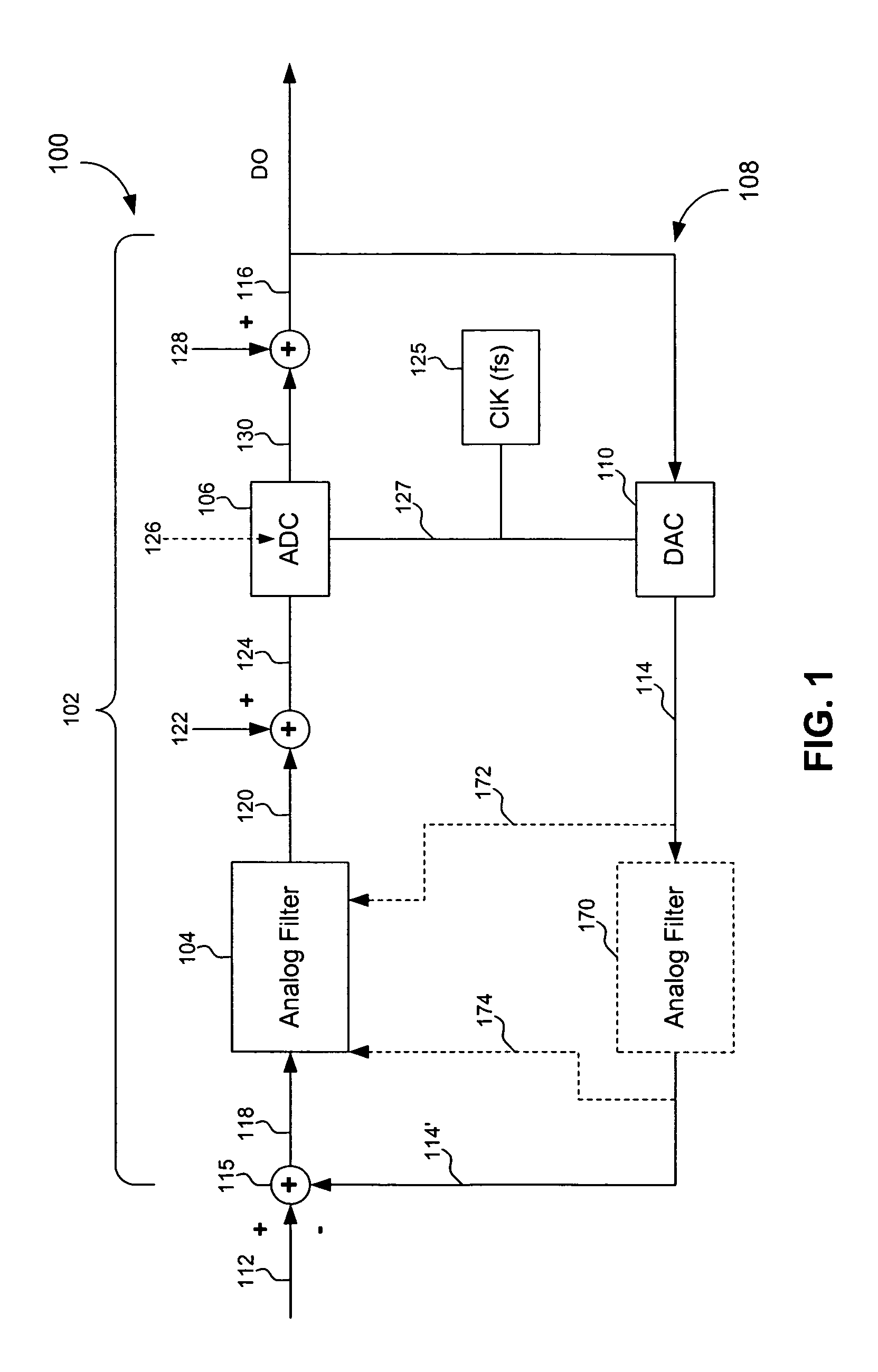

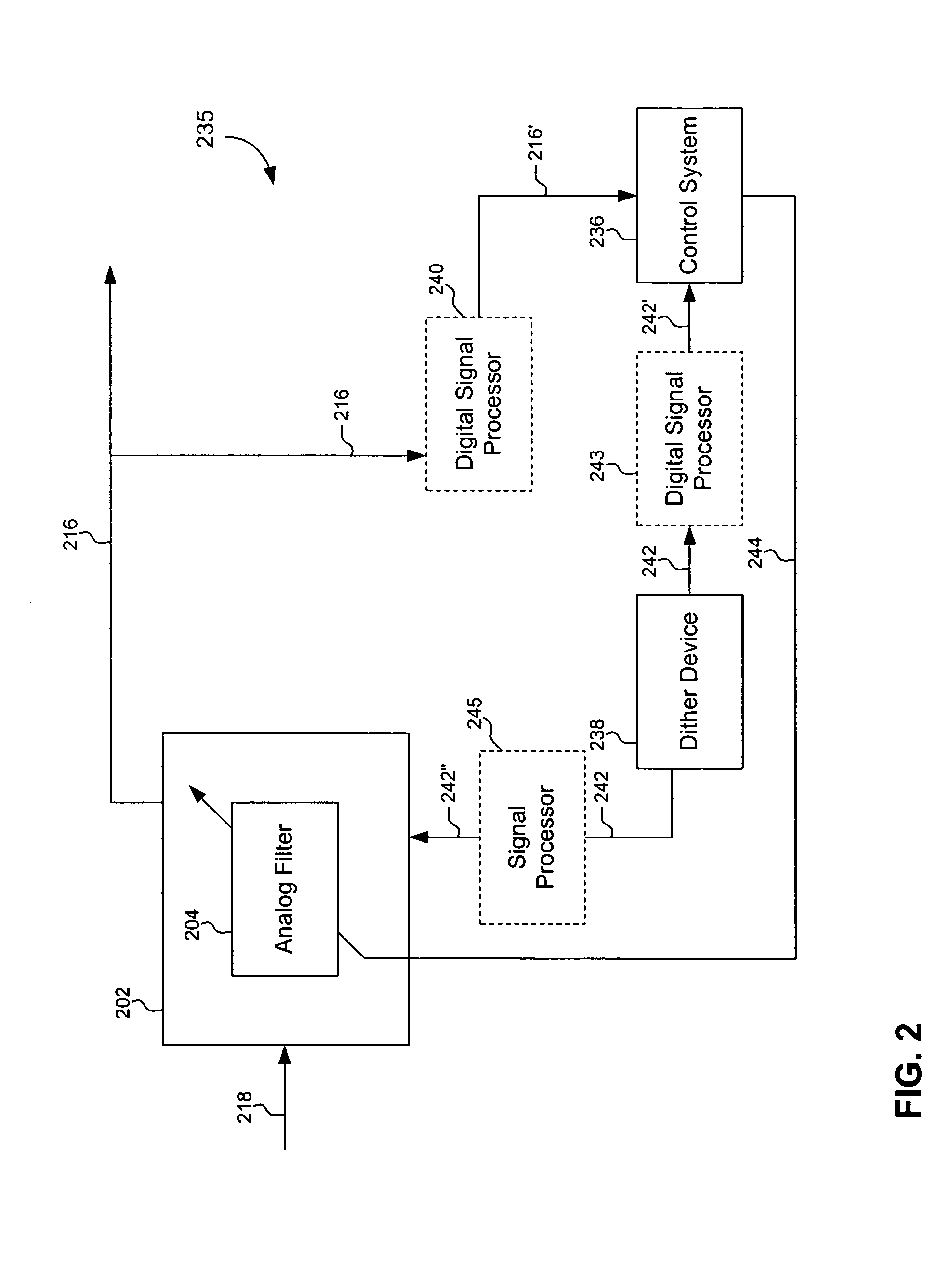

System and method using dither to tune a filter

A system and method is used to tune filters, for example, analog filters in a sigma-delta modulator ADC. A known dither signal is used, for example a digital dither signal. Through adding of the dither to the modulator loop, the digital output of the sigma delta modulator ADC contains a filtered version of the digital dither. This signal can be used to reveal characteristics of the modulator-loop, including characteristics of a continuous-time filter in the modulator. Therefore, using the known digital dither signal and the output signal of the modulator, the continuous-time loop filter can be tuned. The tuning can be done in multiple ways, for example, by using standard LMS adaptive filter techniques to estimate the actual response of the continuous-time loopfilter and adjust the continuous-time loopfilter to the desired response.

Owner:AVAGO TECH INT SALES PTE LTD

System and method for linearizing a CMOS differential pair

InactiveUS20050258901A1Resonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programable attenuation and a programable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

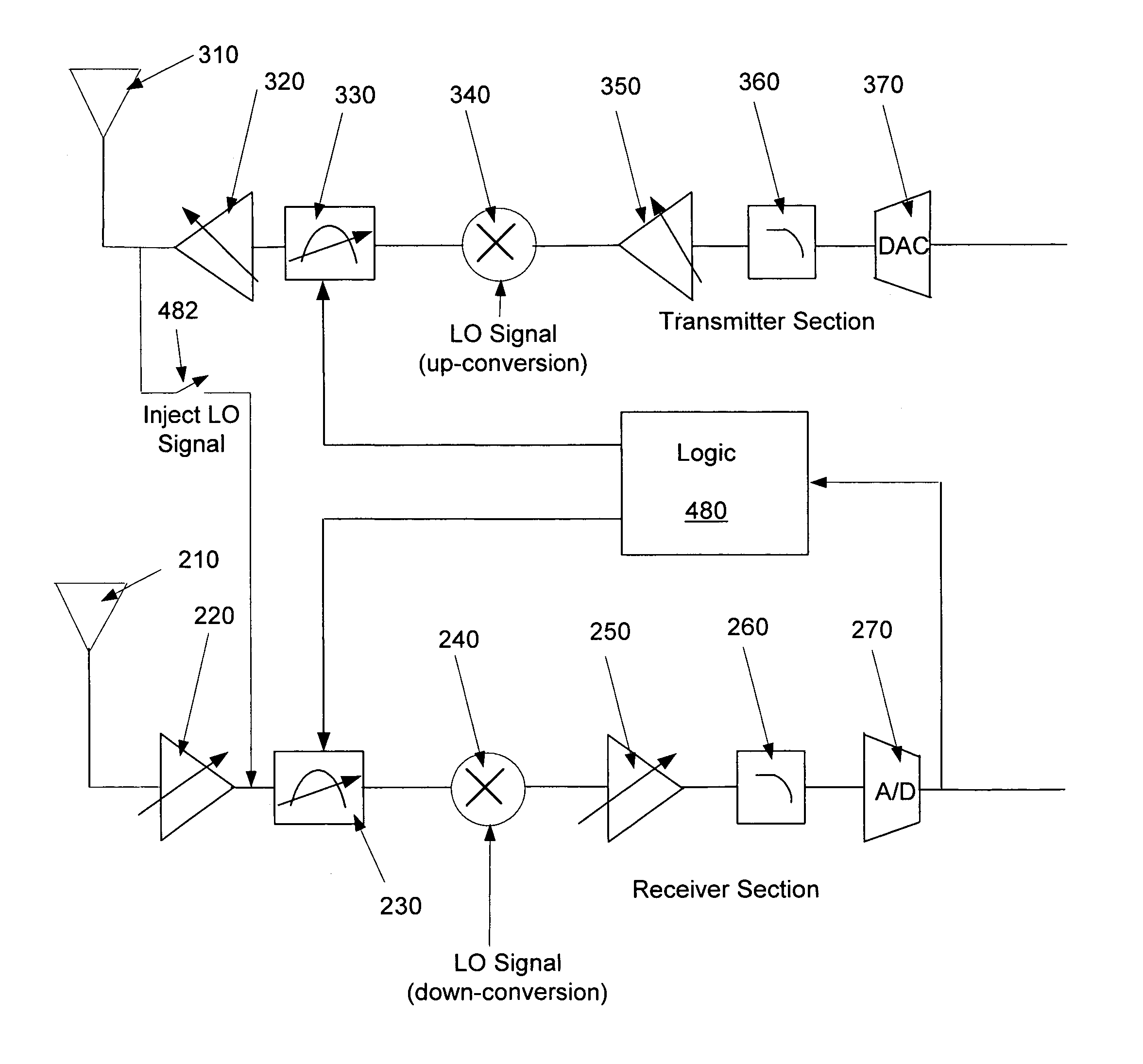

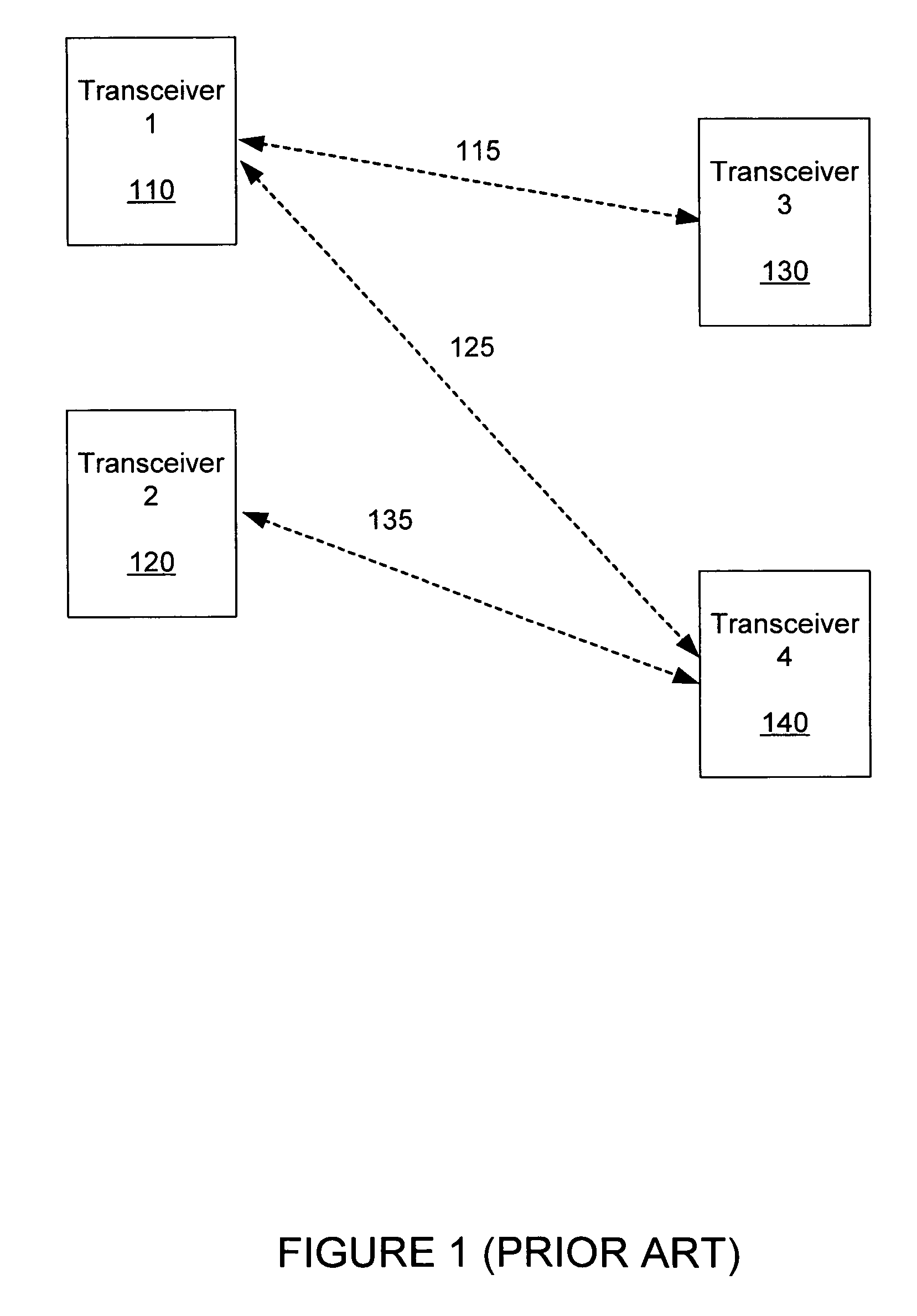

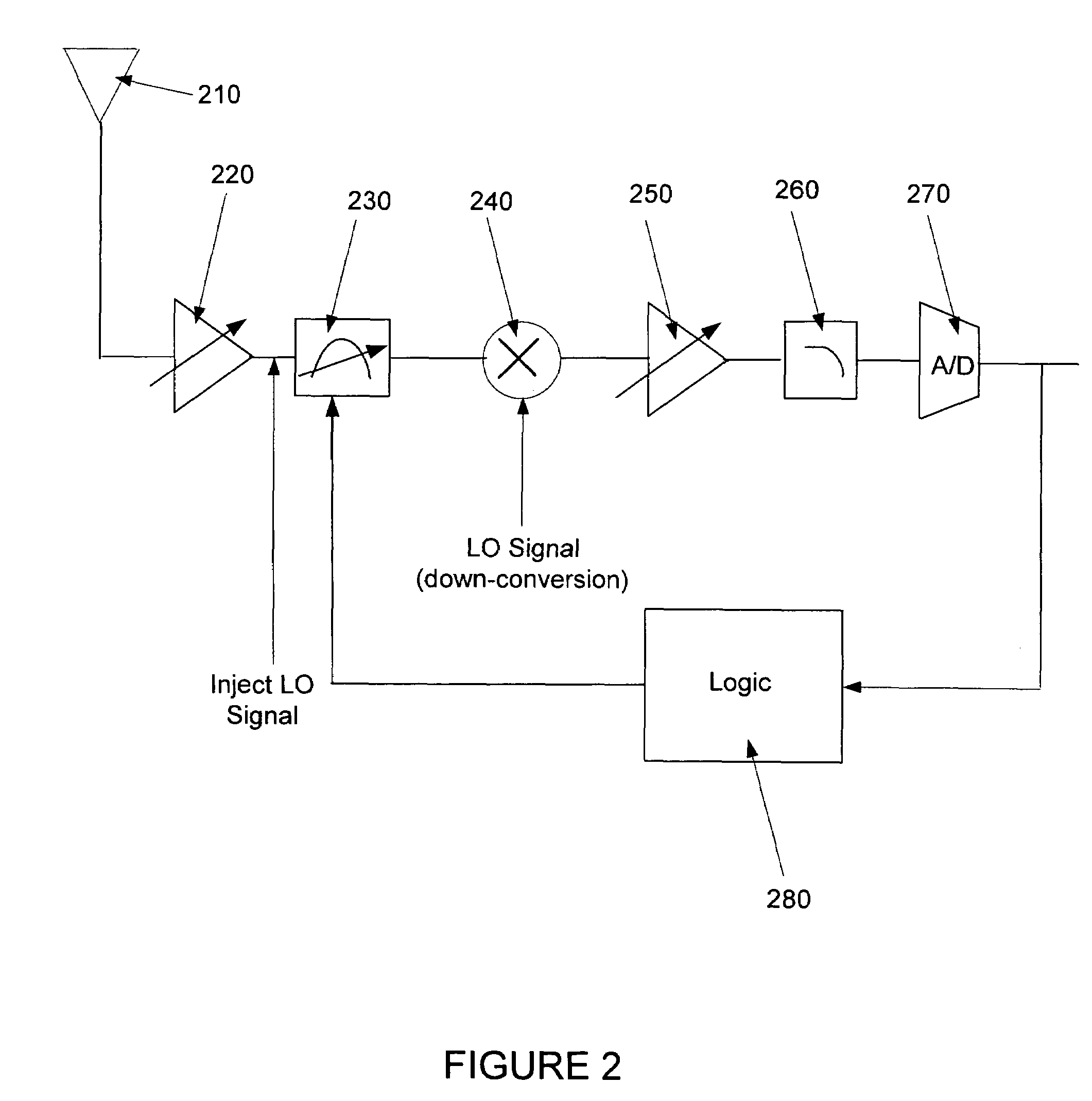

Method and apparatus for calibrating filtering of a transceiver

A method and apparatus of calibrating filtering of receive and transmit signals is disclosed. The method of calibrating filtering of a received signal includes injecting an LO signal. The injected LO signal is filtered by a tunable filter. The filtered signal is frequency down-converted with an equivalent LO signal. The frequency down-converted signal is sampled while tuning the filtering. A desired filter tuning is determined based upon the samples and a frequency of the LO signal. The method of calibrating filtering of a transmit signal includes injecting an LO signal to a transmitter. The LO signal is filtered by a tunable filter. The filtered signal is frequency down-converted with an equivalent LO signal. The frequency down-converted signal is sampled while tuning the filter. A desired filter tuning is determined based upon the samples and a frequency of the LO signal.

Owner:NOVANTA INC

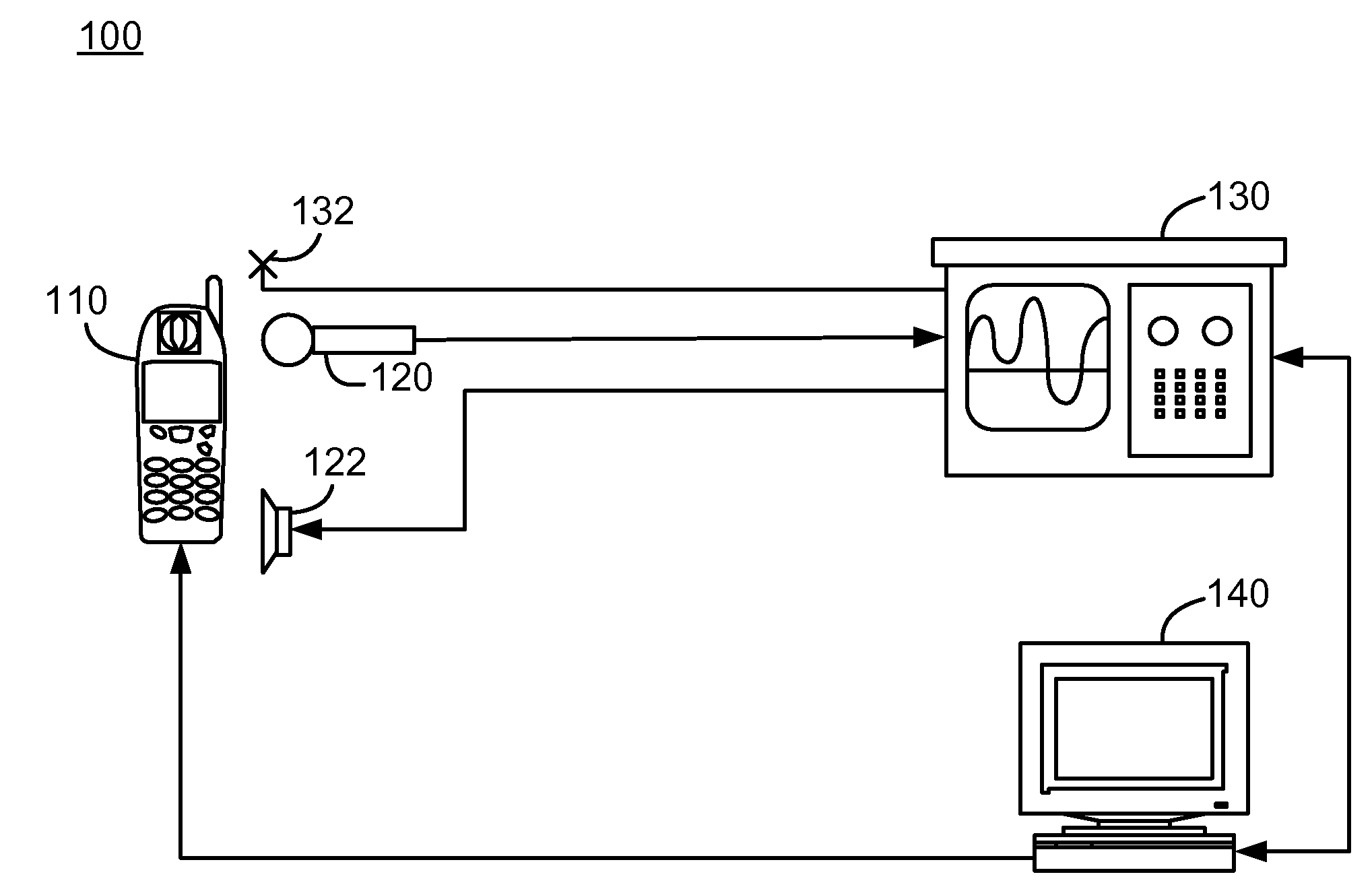

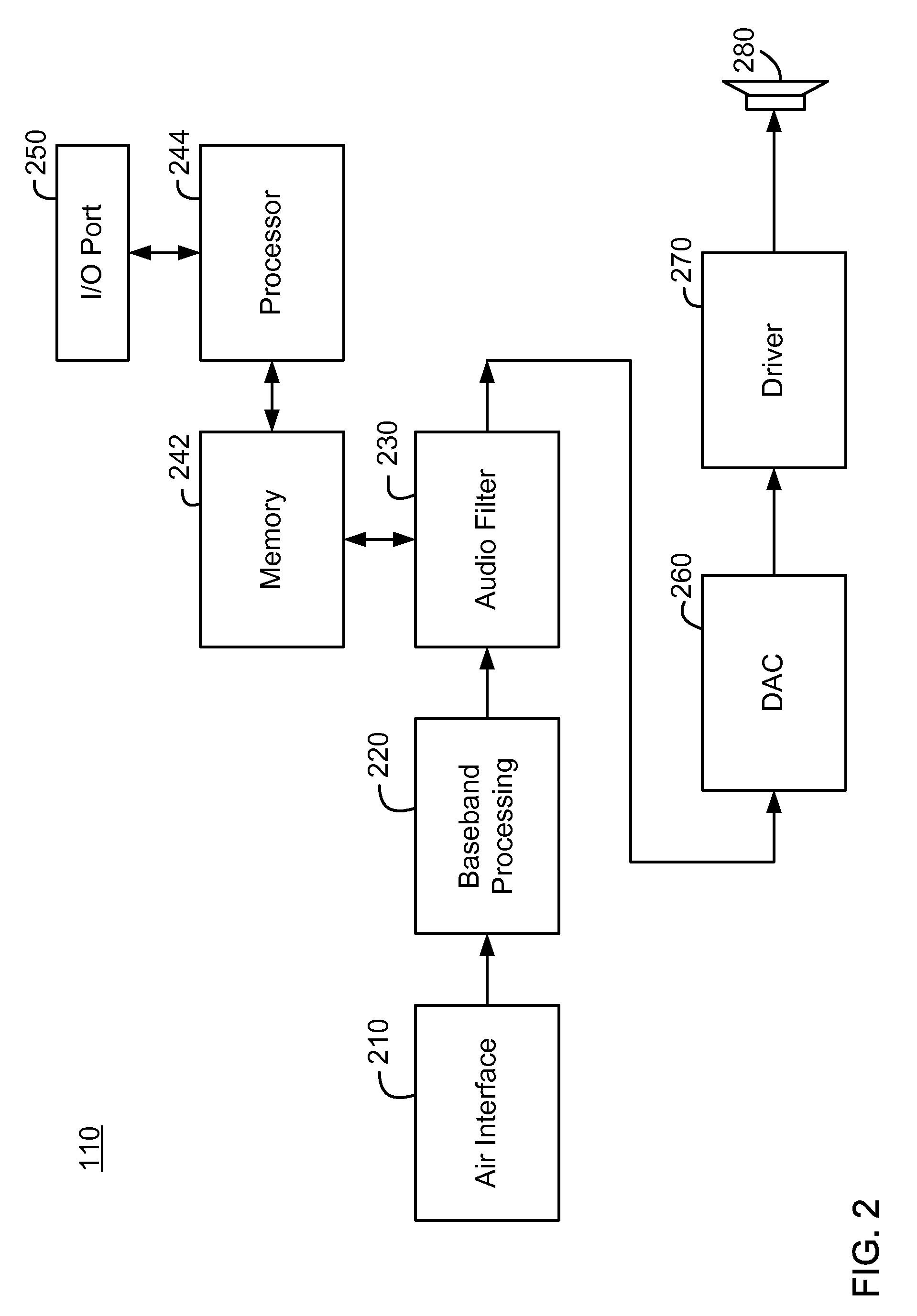

Method and apparatus for audio path filter tuning

InactiveUS20080292113A1Digital signal tone/bandwidth controlTransducer casings/cabinets/supportsFilter tuningDigital filter

Methods and apparatus for tuning the audio path response of an audio device are described herein. The audio output of an audio device is captured and monitored over a predetermined frequency band. The frequency response of the captured audio output can be compared to one or more predetermined limits defining an acceptable frequency response. One or more dynamically configurable bands can be defined, and one or more parameters affecting the response within each configurable band can be adjusted. A simulated frequency response is produced and filter coefficients for a corresponding filter within the audio path are determined. The filter coefficients can be loaded to a digital filter within the audio path to modify the actual frequency response produced by the audio device.

Owner:QUALCOMM INC

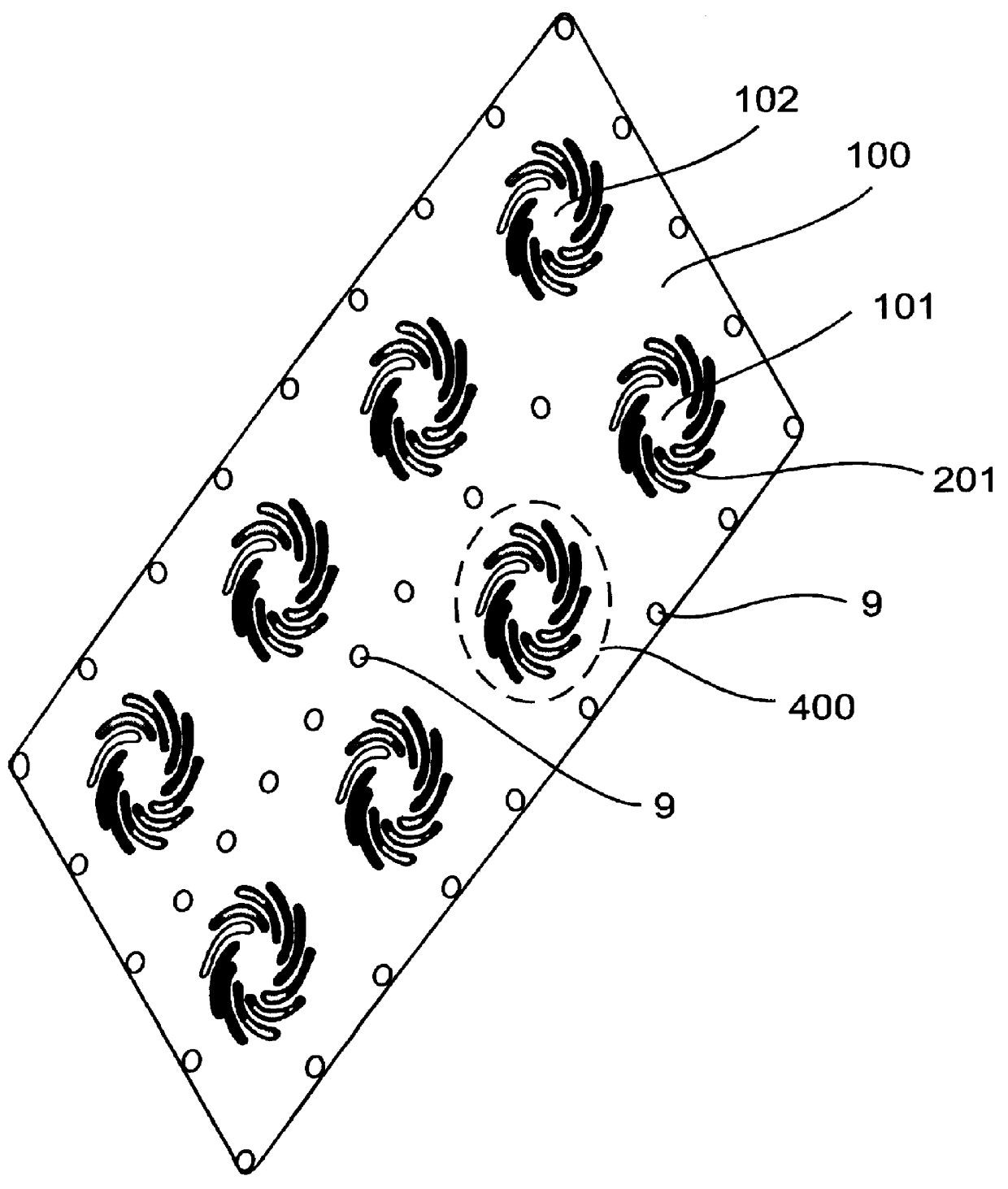

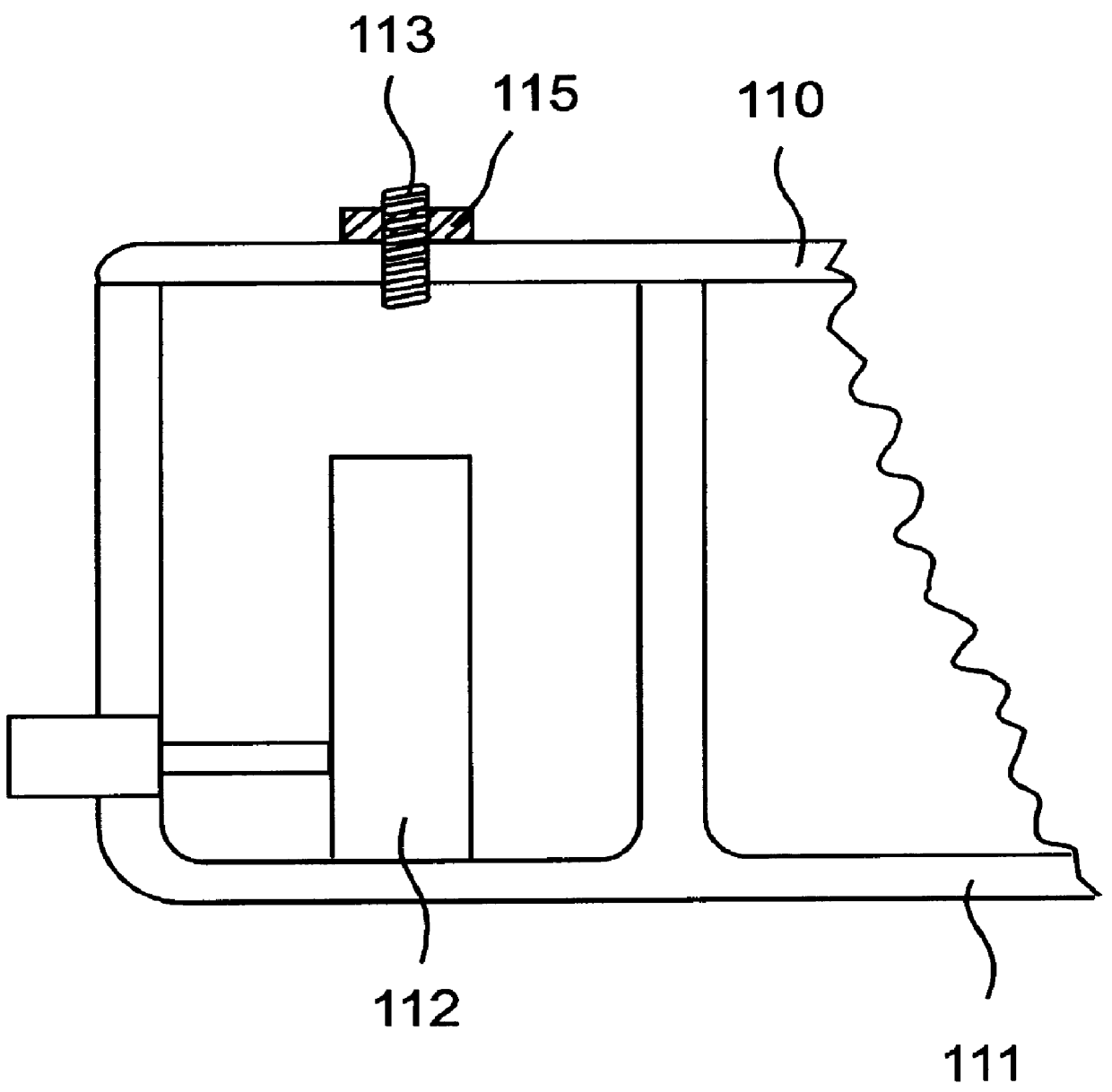

Filter tuning device and tuning plate including a number of such devices

InactiveUS6111484ARisk minimizationMinimizes electromagnetic radiationResonatorsWaveguidesFilter tuningEngineering

The present invention relates to a tuning device in radio filter equipment for mobile telephony in which one or more cavities in the equipment should be tuned to the right frequency. The invention also relates to a tuning plate including a number of such tuning devices. The tuning device preferably includes regular or square formed depressed parts in the tuning plate. The depressed part converges each to a square formed central plate which is provided with an elevation or bulb. By turning a tuning screw on the equipment a force is developed on the plate and the surrounding depressed parts. This implies that the tuning can be made automatically, more secure and with less risk for intermodulation.

Owner:TELEFON AB LM ERICSSON (PUBL)

System and method for ESD protection

InactiveUS7115952B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

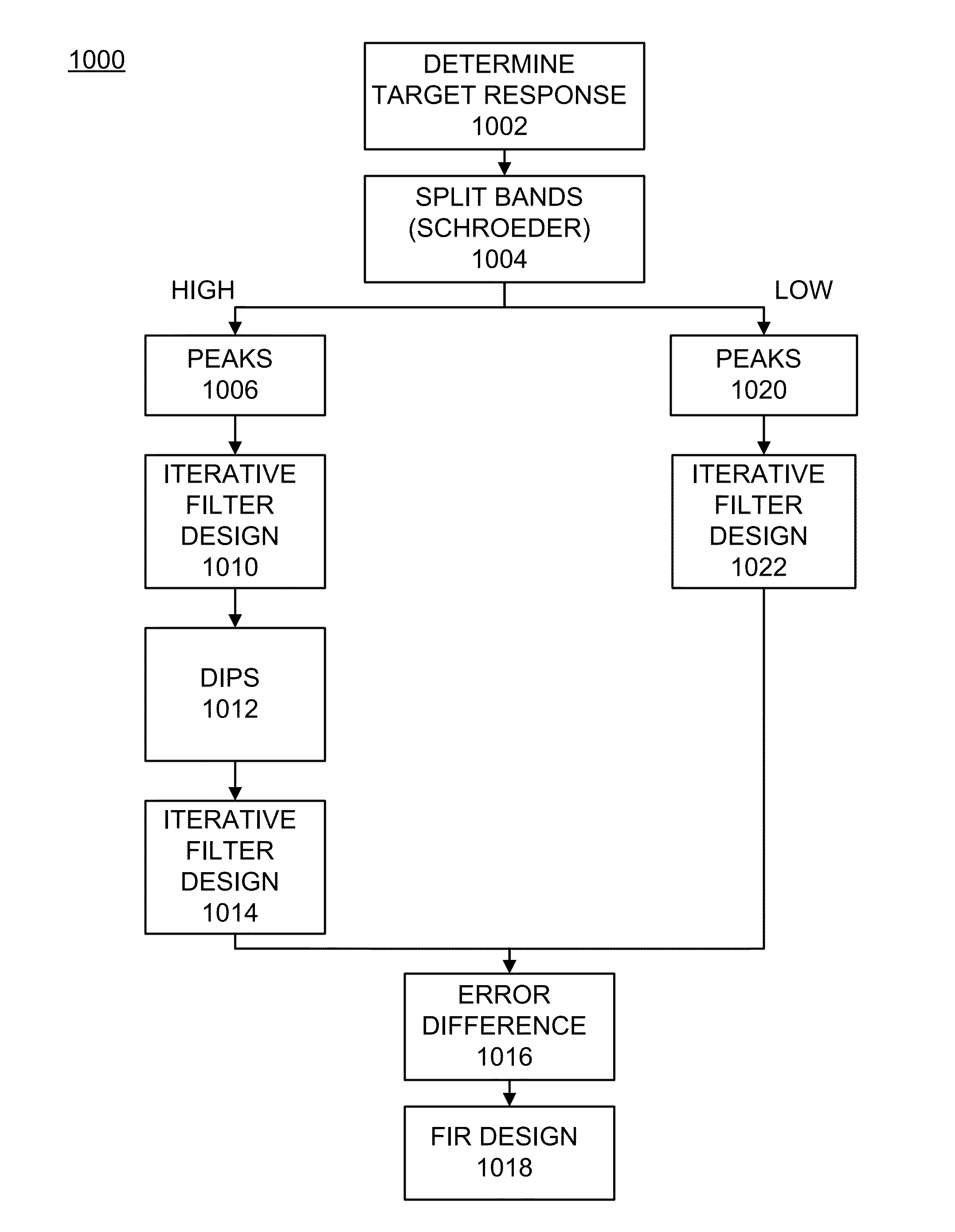

Systems and Methods for Tuning Filters

InactiveUS7482890B2Reduce sensitivityError in sensitivityTransmission control/equlisationAutomatic frequency controlFir filter designFilter tuning

Methods, systems and apparatus for filter design, analysis and adjustment are provided. Various embodiments may include, for example, methods, systems and apparatus for electric signal filter tuning. Embodiments may also include design techniques for planar electric signal (e.g., RF signals) filter tuning. In at least an embodiment of the present invention a technique for filter tuning is provided which may include parameter extraction, optimization and tuning recipes techniques that may require only a single permanent filter tuning. In at least another embodiment a system and method of filter design, analysis and adjustment according to the present invention includes use of tuning that may be set using a mechanical scribing tool or a laser trimming device. In at least one other embodiment, a filter tuning technique may be provided and include providing trimming tabs on a resonator edge that may be disconnected or trimmed for filter tuning.

Owner:SUPERCONDUCTOR TECHNOLOGIES INC

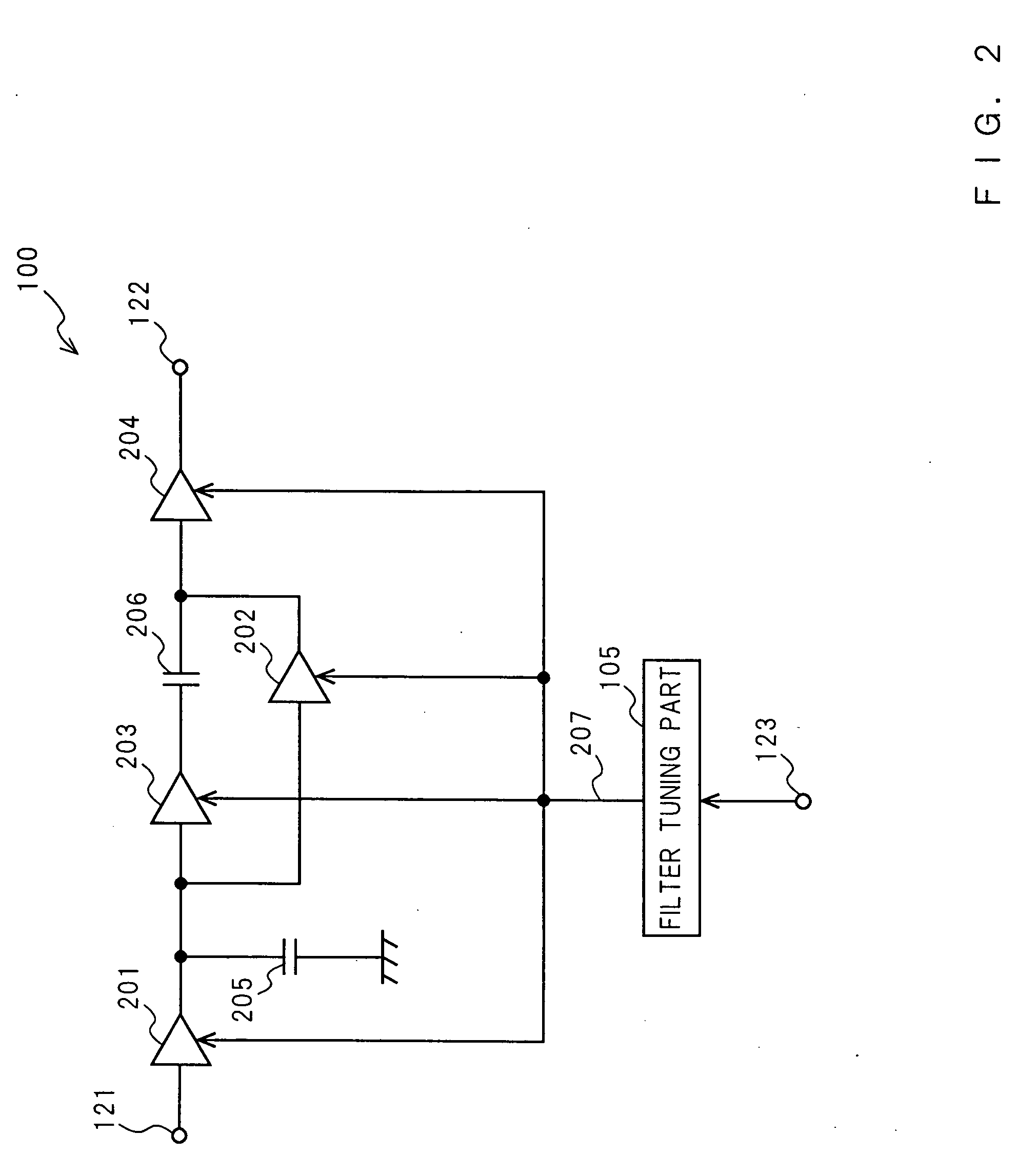

System and method for on-chip filter tuning

InactiveUS6865381B2Low selectivityMultiple-port active networksSolid-state devicesCapacitanceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH INT SALES PTE LTD

System and method for ESD protection

InactiveUS20080174925A1Reduce areaReduce capacitanceContinuous tuning detailsPulse automatic controlCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

Quiet zone control system

An active noise control system generates an anti-noise signal to drive a speaker to produce sound waves to destructively interfere with an undesired sound in a quiet zone. The anti-noise signal is generated with an adaptive filter having filter coefficients. The coefficients of the adaptive filter may be adjusted based on a first filter adjustment from a first listening region, and a second filter adjustment from a second listening region. A first weighting factor may be applied to the first filter adjustment, and a second weighting factor may be applied to the second filter adjustment. The first and second weighting factors may dictate the location and size of the quiet zone as being outside or partially within at least one of the first listening region and the second listening region.

Owner:HARMAN INT IND INC

Demodulation and timing synchronization combined method for GFSK (Gauss Frequency Shift Key)

InactiveCN102170414ASimplify complexityReduce overheadSynchronisation arrangementFrequency-modulated carrier systemsLoop filterFilter tuning

The invention relates to a demodulation and timing synchronization combined method for a GFSK (Gauss Frequency Shift Key). In the invention, an oversampling signal is used as an input of a demodulation and synchronization loop; after a phase of the sampling signal is adjusted by an interpolation filter, conjugate multiplication is carried out on the sampling signal by every two continuous sampling values to obtain a phase difference; and the phase difference is used as an input of timing error detection. With a difference between front and back phase values as a direction of error adjustment,a middle phase value of every three continuously calculated phase values is used as a size of the error adjustment. A timing error is fed back to the interpolation filter after passing through a loopfilter, and a new sampling value is adjusted again and again. By using the invention, the realization complicatedness of hardware is simplified and the use of a square error detection algorithm is avoided under an oversampling situation; and the demodulation and timing synchronization combined method for the GFSK, provided by the invention, has the advantages of small hardware cost and good timing detection performance.

Owner:浙江瑞讯微电子有限公司

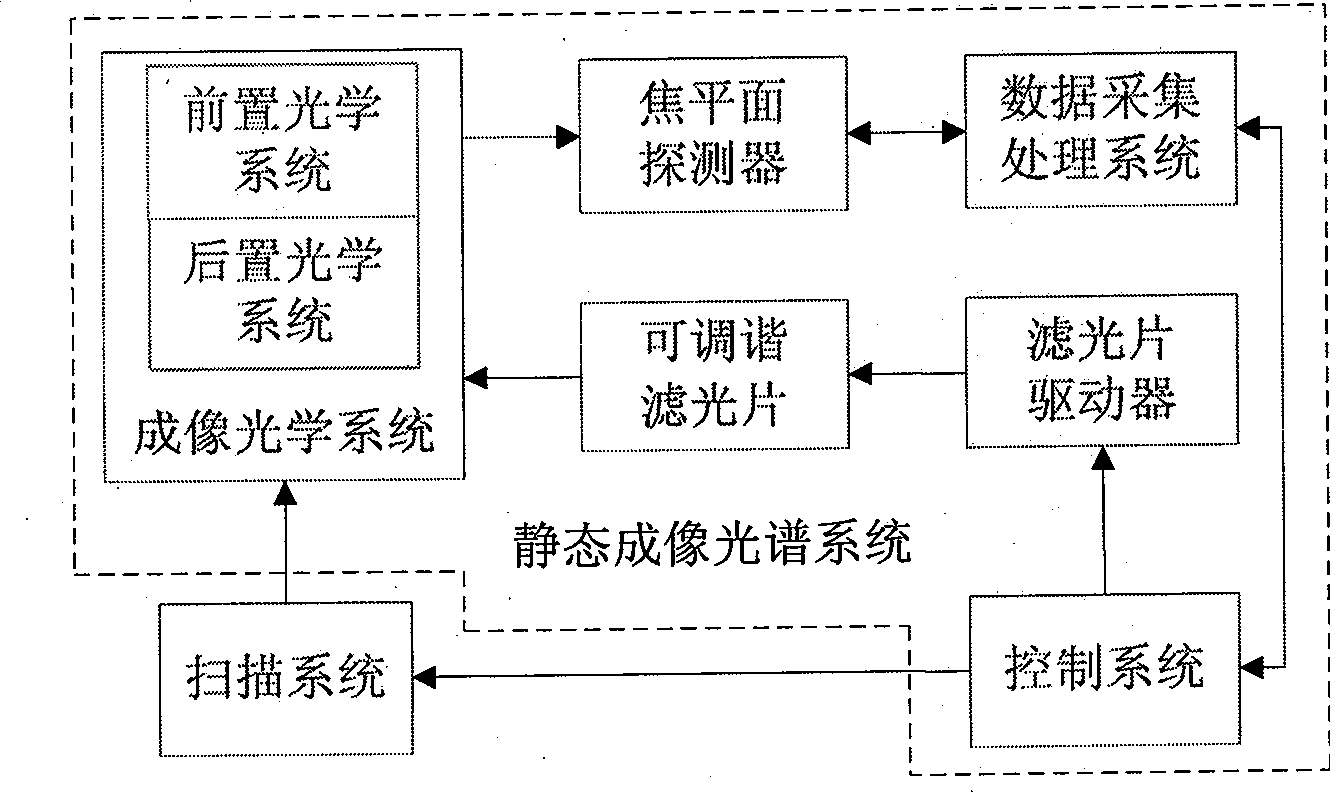

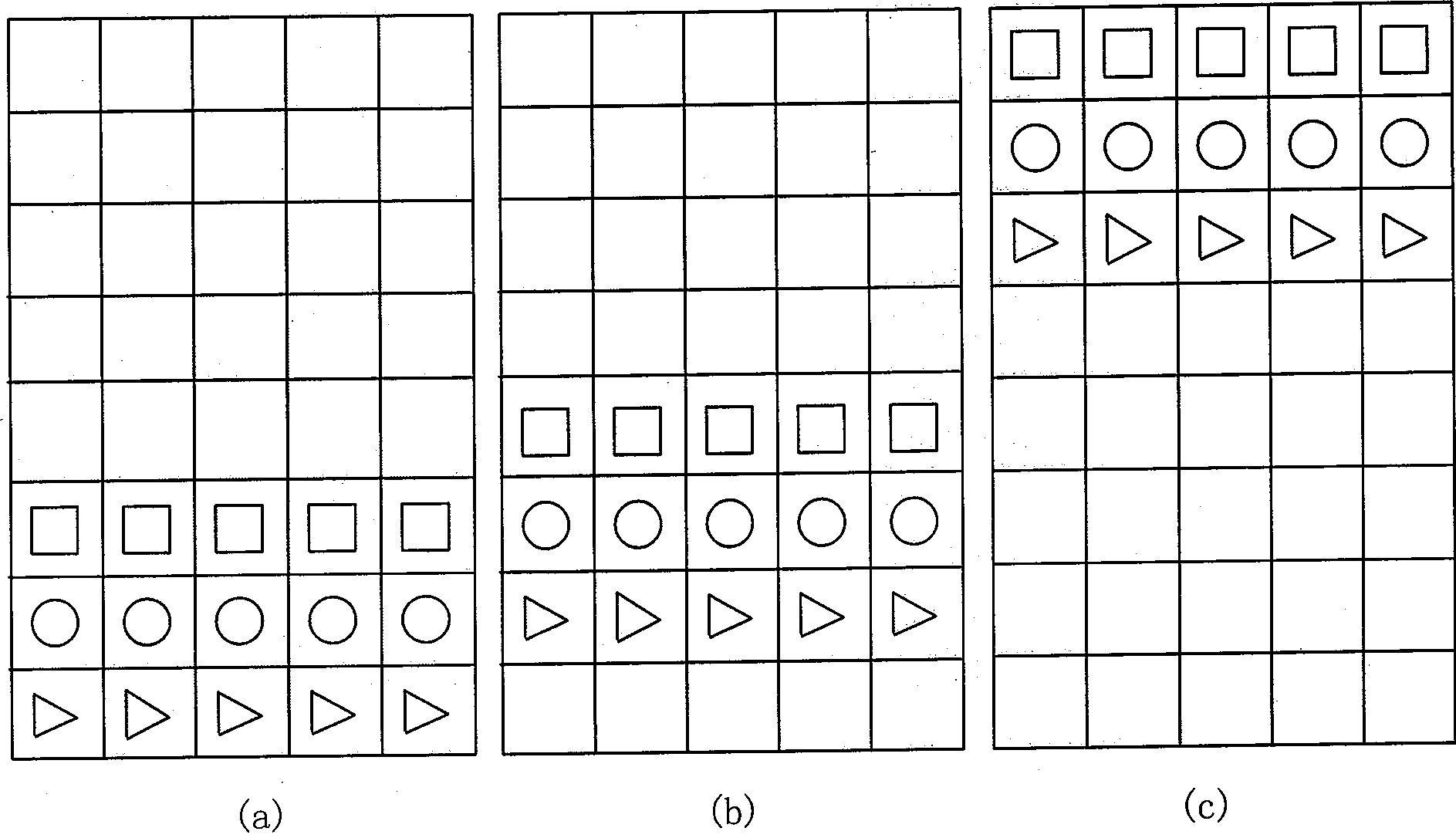

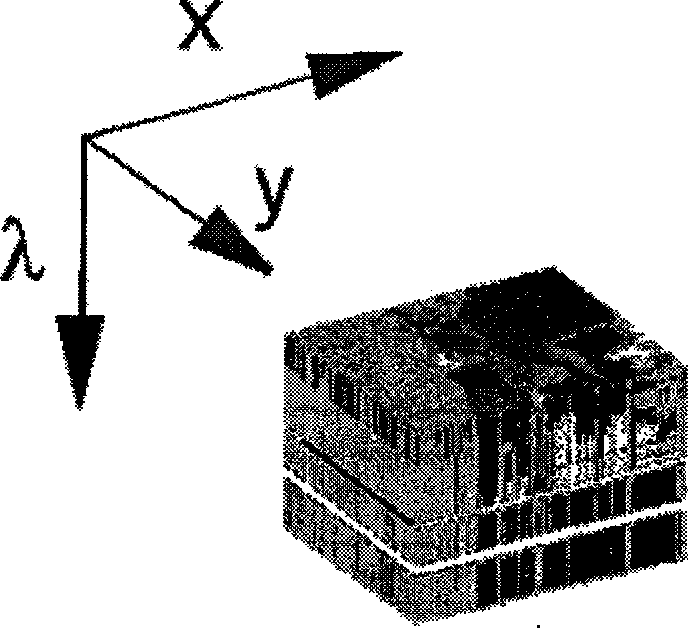

Color filter tuning type window scanning optical spectrum imaging system and method

InactiveCN101504316AHigh spectral resolutionMeet job requirementsSpectrum investigationSpectrum generationFilter tuningLight energy

The invention relates to a tuning window-scanning spectral imaging system for a light filter and a tuning window-scanning spectral imaging method for the light filter, and belongs to the field of spectral imaging. The invention is to add a scanning system into a tuning static spectral imaging system for the light filter to make the tuning window-scanning spectral imaging system capable of performing dynamic window-scanning imaging. Moreover, the invention adopts a data acquisition processing system which is matched with the scanning system to make the tuning window-scanning spectral imaging system be capable of completing data processing in the mode of window scanning and output correct spectral cubical result. The invention has high utilization rate of light energy, high spectral resolution and flexible and adjustable service band of spectrums, has both the image signal-to-noise ratio and the spectrum signal-to-noise ratio easy to reach high level, can only be operated in interested wavebands, reduces the data quantity, increases the regulating range of the integral time, can improve the detection level of weak signals, and is suitable to be widely applied in the fields of agricultural production, resource exploration, environmental monitoring, disaster prevention and reduction, substance identification, public safety and the like.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Audio signal correction and calibration for a room environment

ActiveUS20140161281A1Piezoelectric/electrostrictive resonant transducersHigh frequency amplifiersSignal correctionFilter tuning

Disclosed are an apparatus and method of processing an audio signal to optimize audio for a room environment. One example method of operation may include recording the audio signal generated within a particular room environment and processing the audio signal to create an original frequency response based on the audio signal. The method may also include identifying a target sub-region of the frequency response which has a predetermined area percentage of a total area under a curve generated by the frequency response, determining whether the target sub-region is a narrow energy region, creating a filter to adjust the frequency response, and applying the filter to the audio signal.

Owner:HARMAN PROFESSIONAL INC

Automatic tuning apparatus for filter and communication instrument

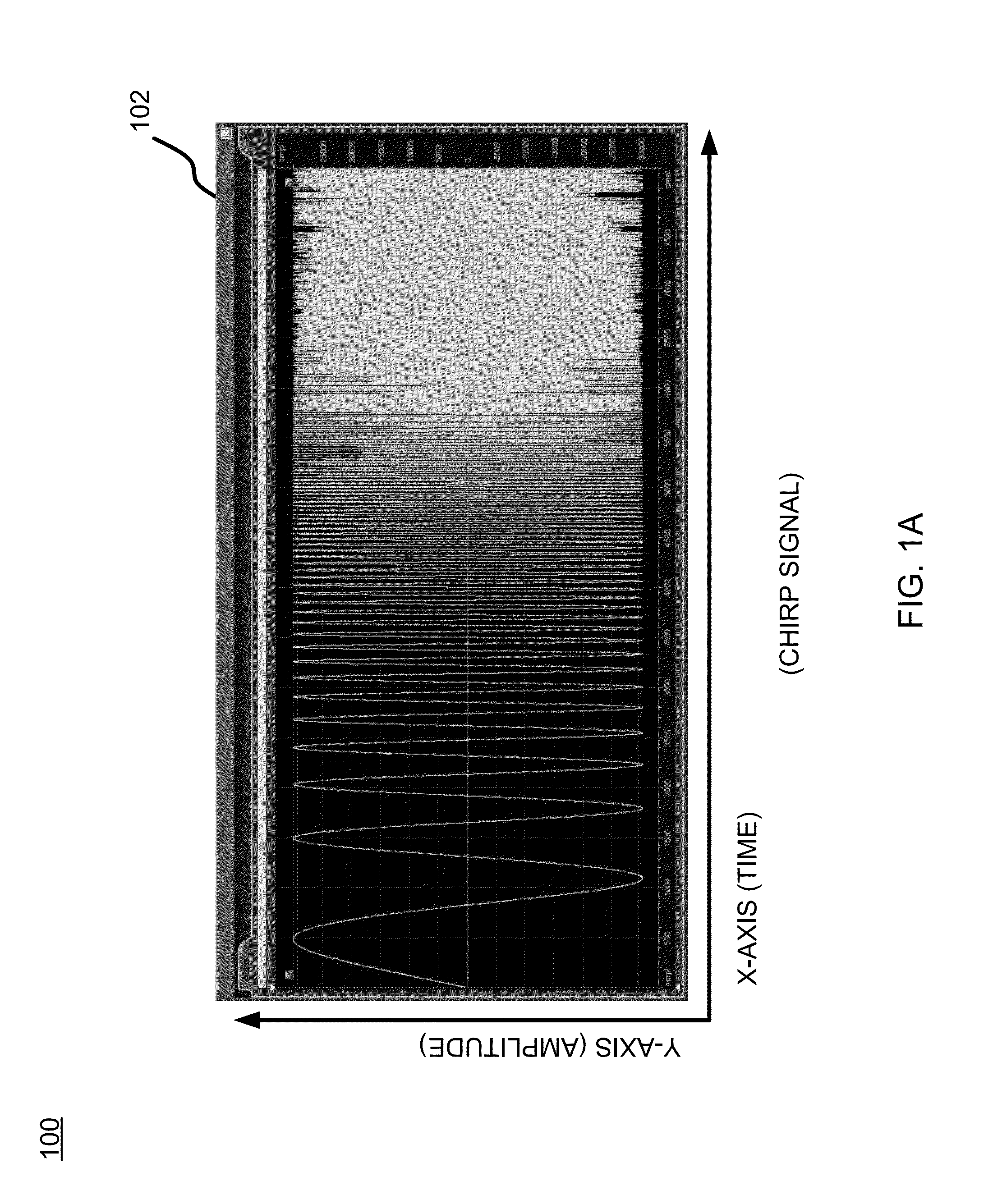

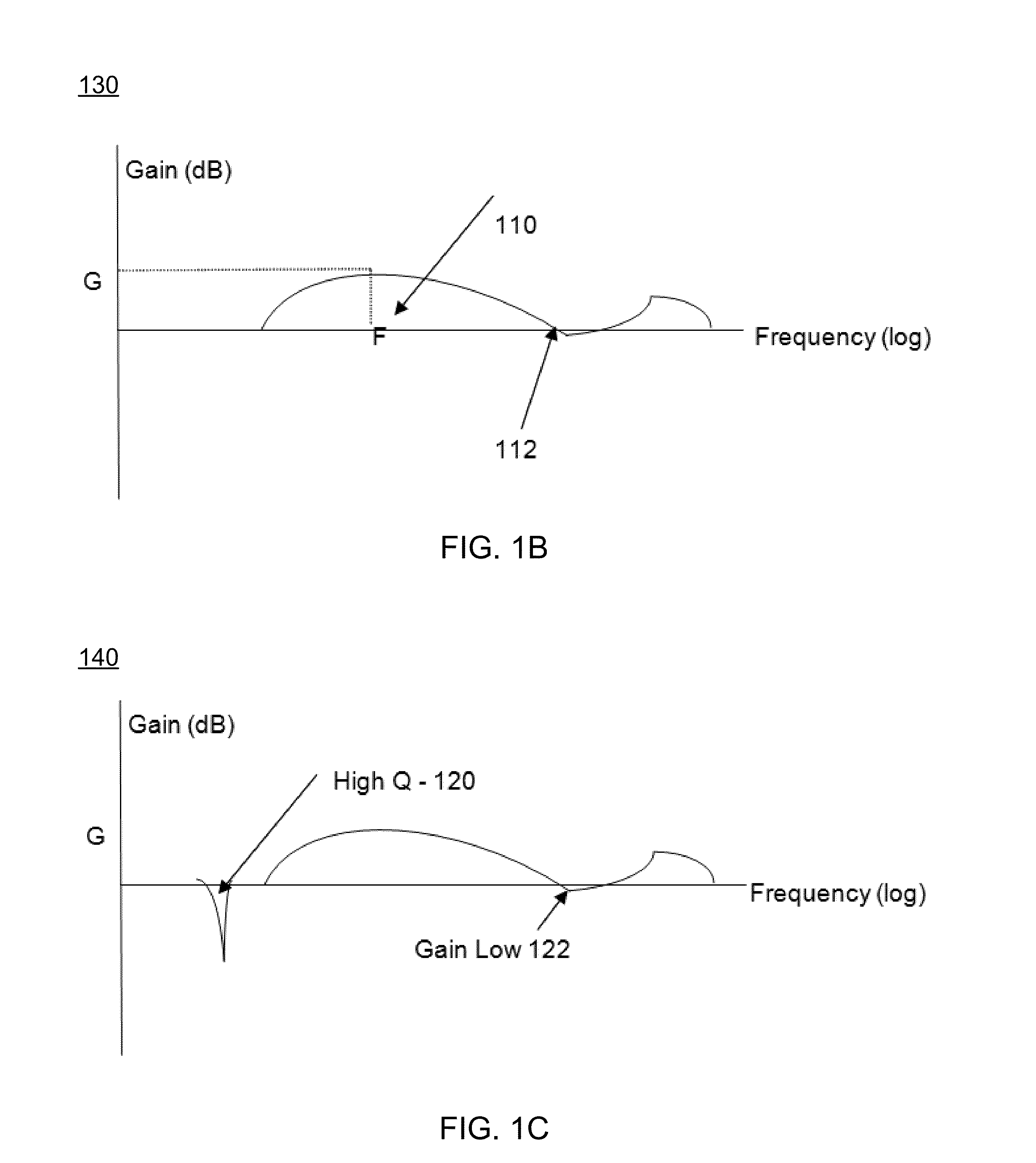

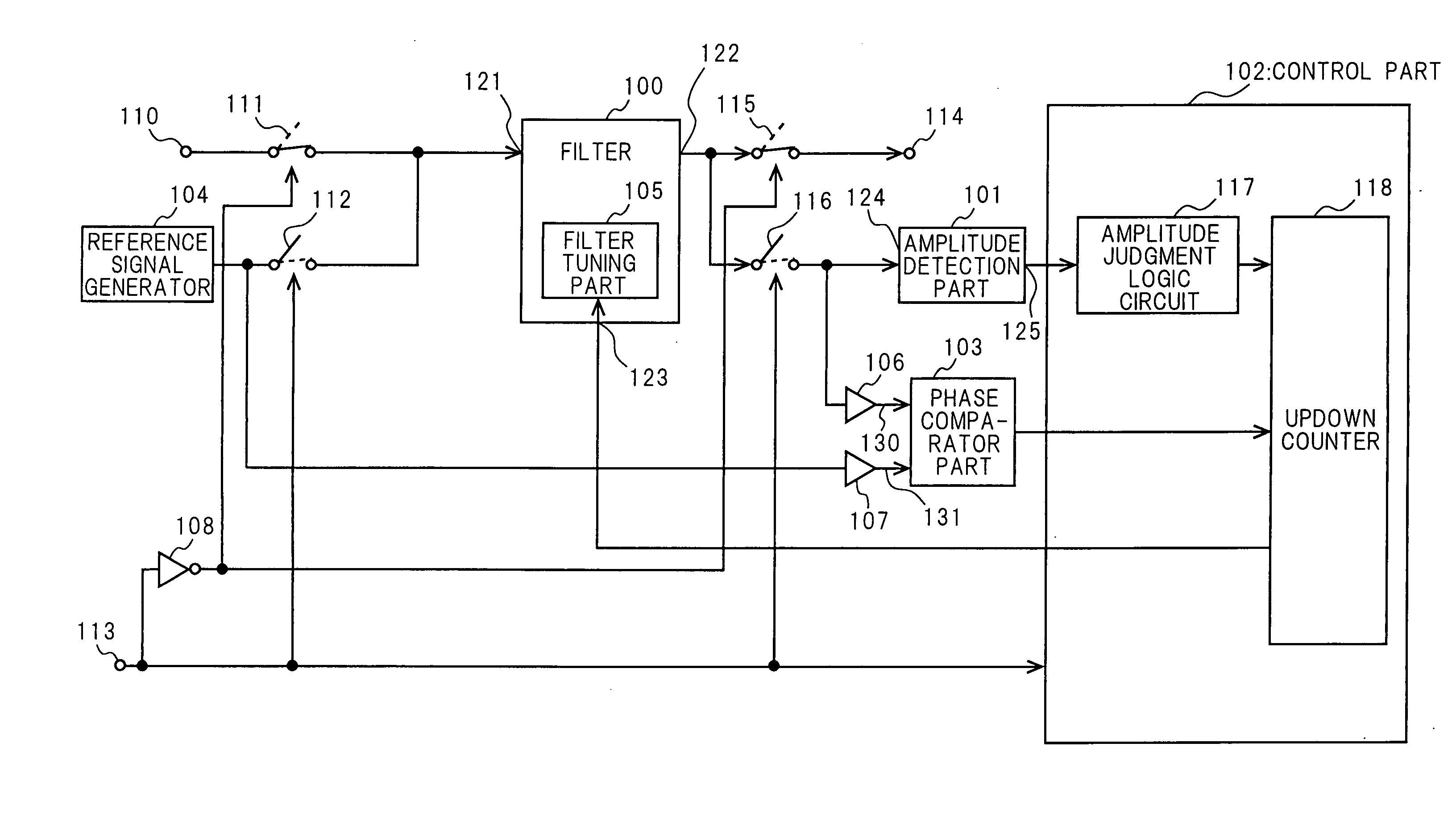

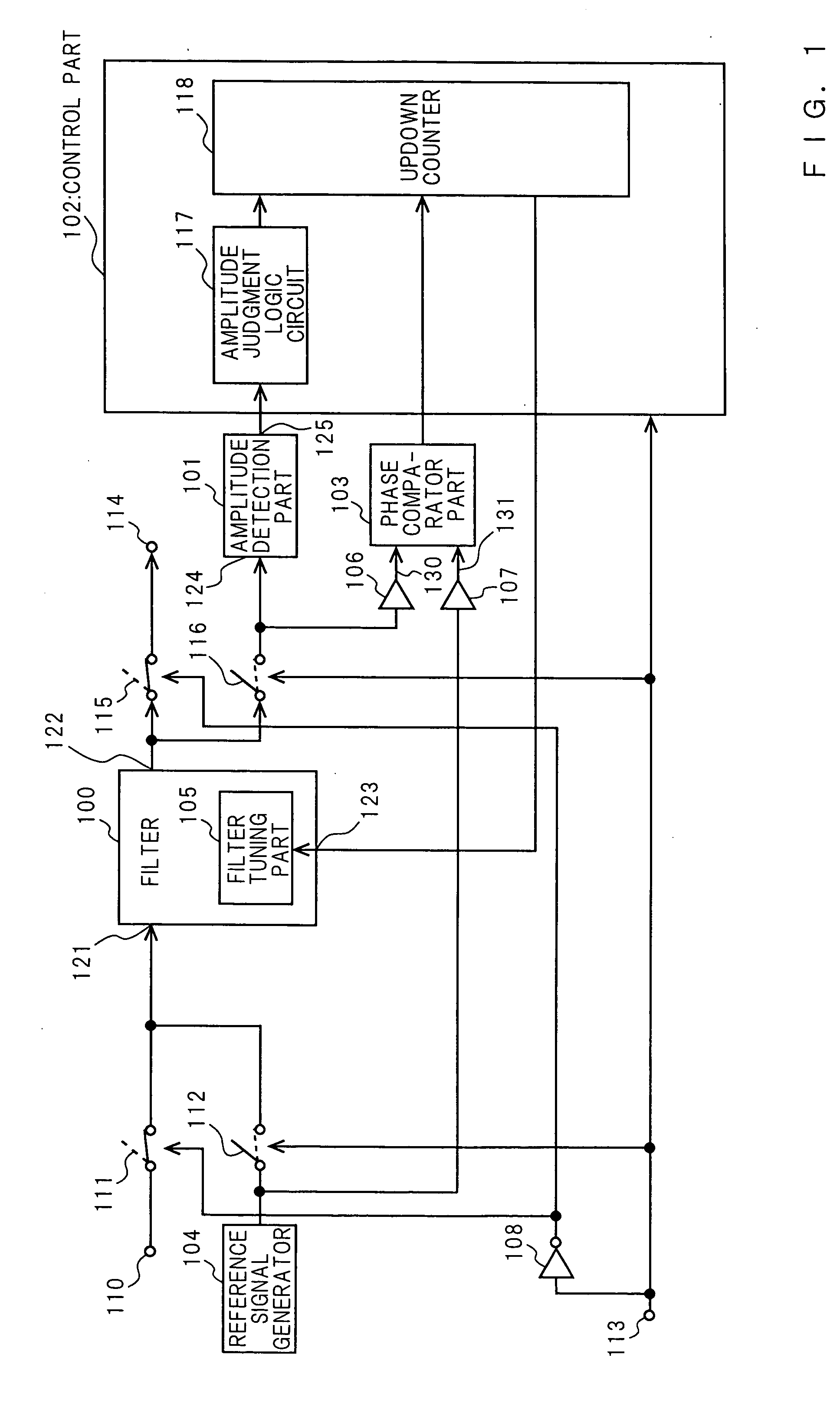

InactiveUS20050148309A1Small sizeReduce weightMultiple-port networksTransmission control/equlisationFilter tuningPhase difference

Purposes to offer an automatic tuning apparatus for filter which enables an accurate tuning to be attained and is small size and low power consumption and a communication instrument using the above. The automatic tuning apparatus for filter of the present invention has an input terminal; a reference signal generator, a filter having a control terminal through which a control signal for controlling its filter characteristic is inputted, an output terminal from which the signal inputted from the input terminal and passed through the filter is outputted; an amplitude detection part to which the output signal of the filter is inputted and which detects its amplitude; a phase comparator part detecting the phase difference between the signal before its passing through the filter and the signal after passing through the filter; and a control part in which, during the filter tuning, by letting the reference signal inputted to the filter and inputting successively a plural number of control signals to the control terminal of the filter, thereby a value of the control signal to be used during the normal operation time is determined based on respective amplitudes detected by the amplitude detection part and respective phase differences detected by the phase comparator part.

Owner:COLLABO INNOVATIONS INC

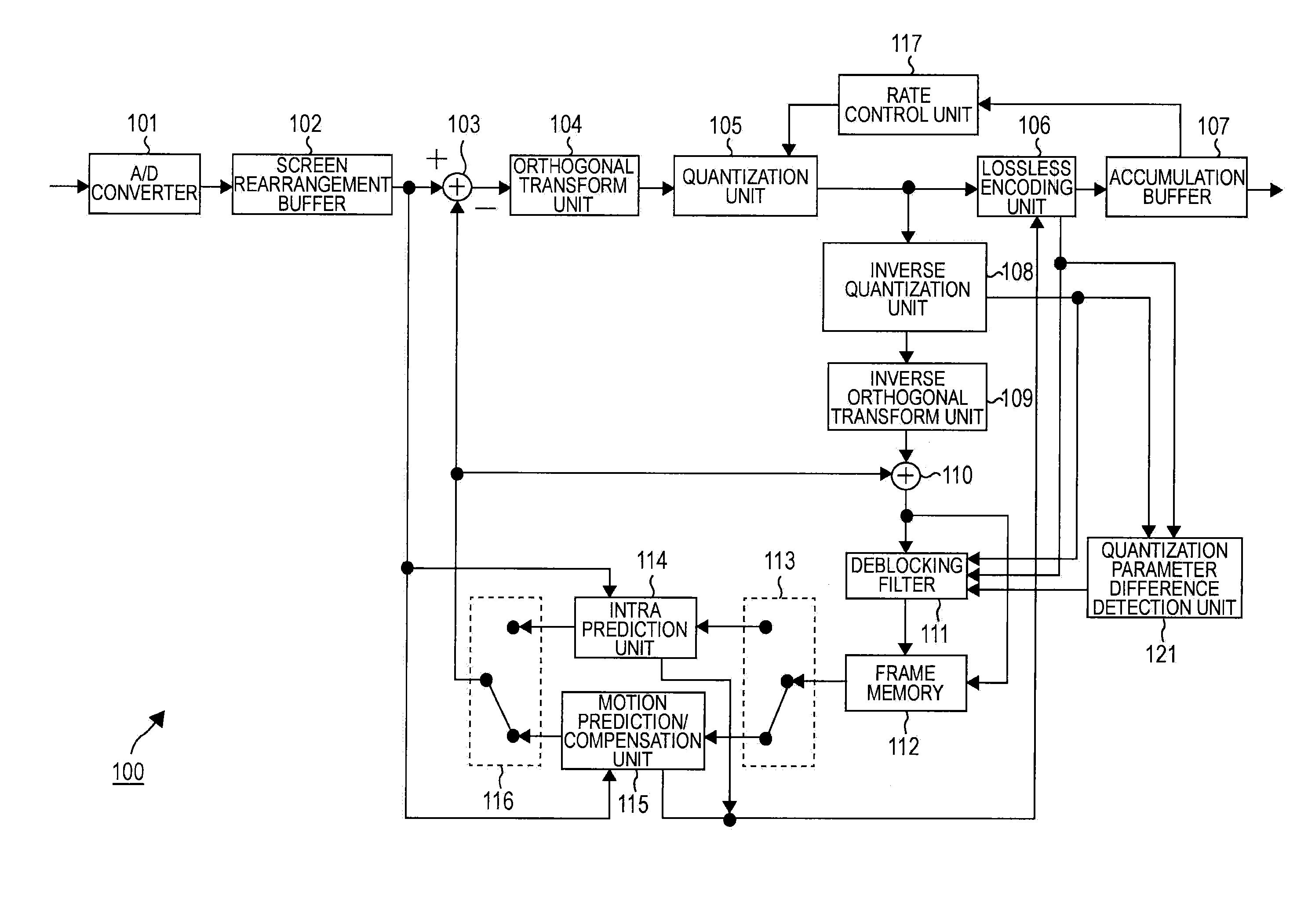

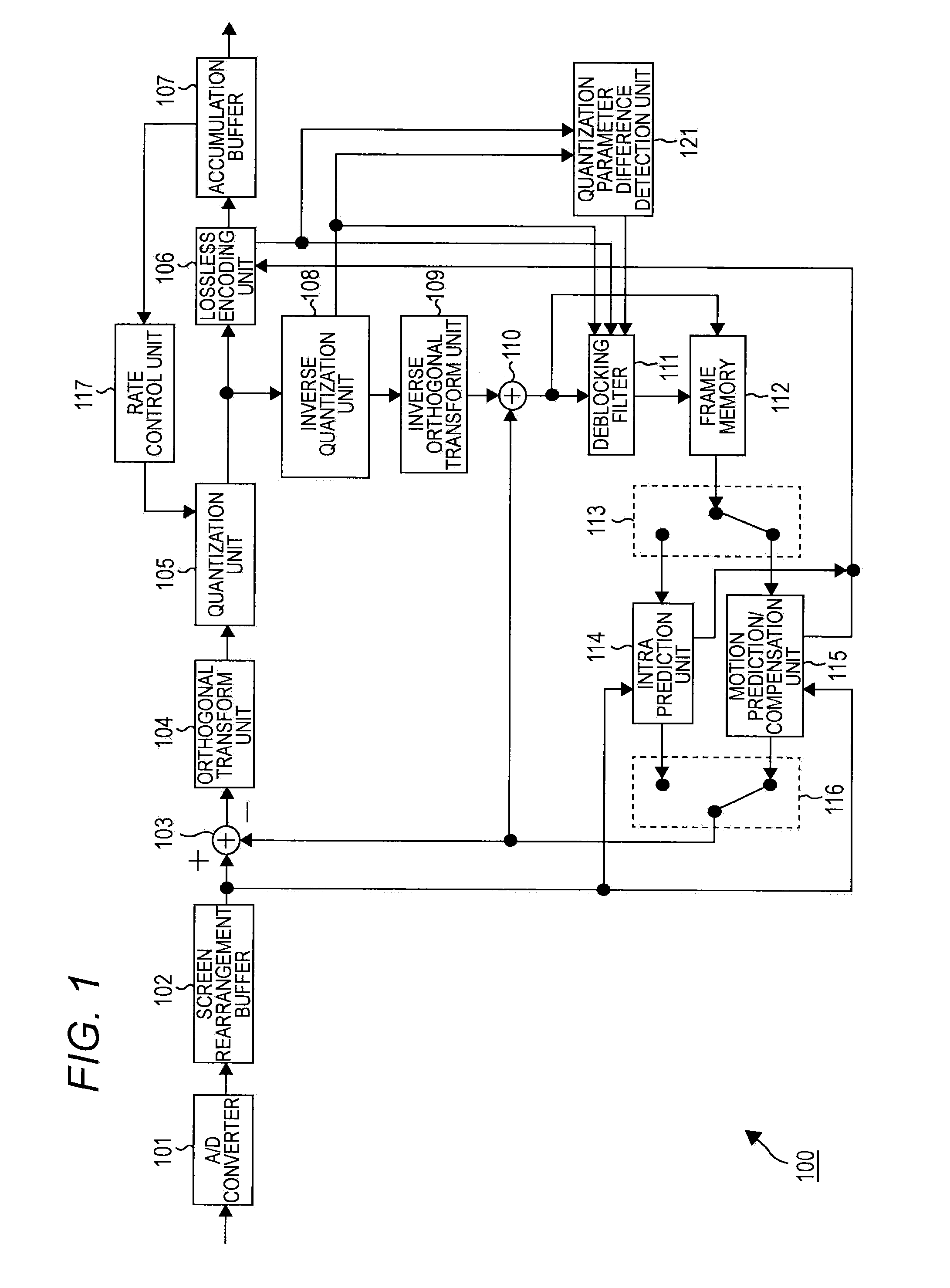

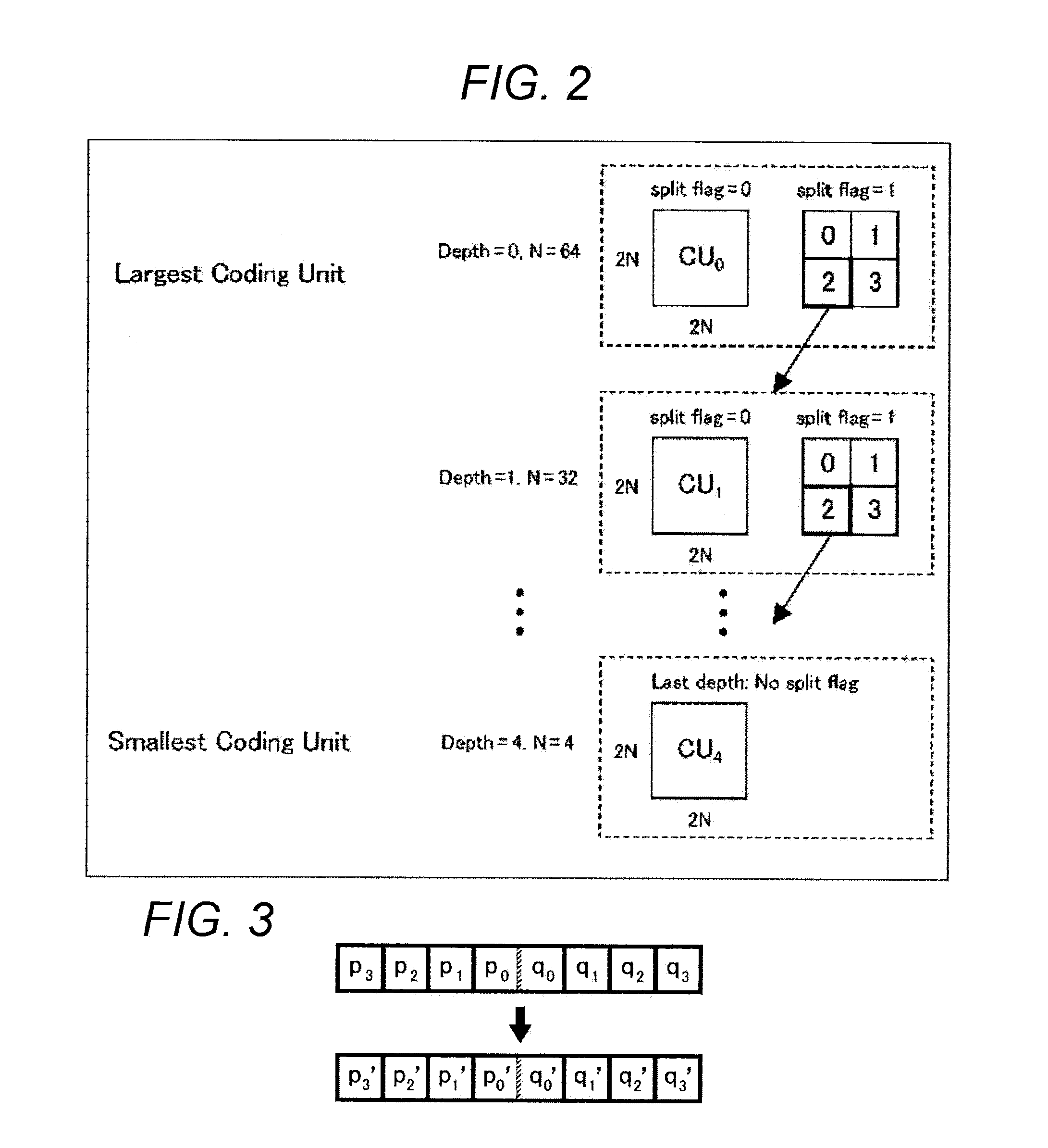

Image processing device and method

ActiveUS20140050413A1Prevent removalCharacter and pattern recognitionImage codingFilter tuningImaging processing

The present technique relates to image processing devices and methods for enabling more appropriate removals of block distortions. When the difference between the quantization parameter QPc of a current region C and the quantization parameter QPN of a neighboring region N is determined to be larger than a predetermined threshold value, a deblocking filter adjusts the deblocking filtering operation so that stronger filtering is performed on a boundary between the current region and the neighboring region. This disclosure can be applied to image processing devices, for example.

Owner:SONY CORP

System and method for linearizing a CMOS differential pair

InactiveUS7276970B2Resonant circuit detailsSemiconductor/solid-state device detailsLocal oscillator signalFilter tuning

Owner:AVAGO TECH INT SALES PTE LTD