Patents

Literature

270 results about "Analog multiplier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronics, an analog multiplier is a device which takes two analog signals and produces an output which is their product. Such circuits can be used to implement related functions such as squares (apply same signal to both inputs), and square roots.

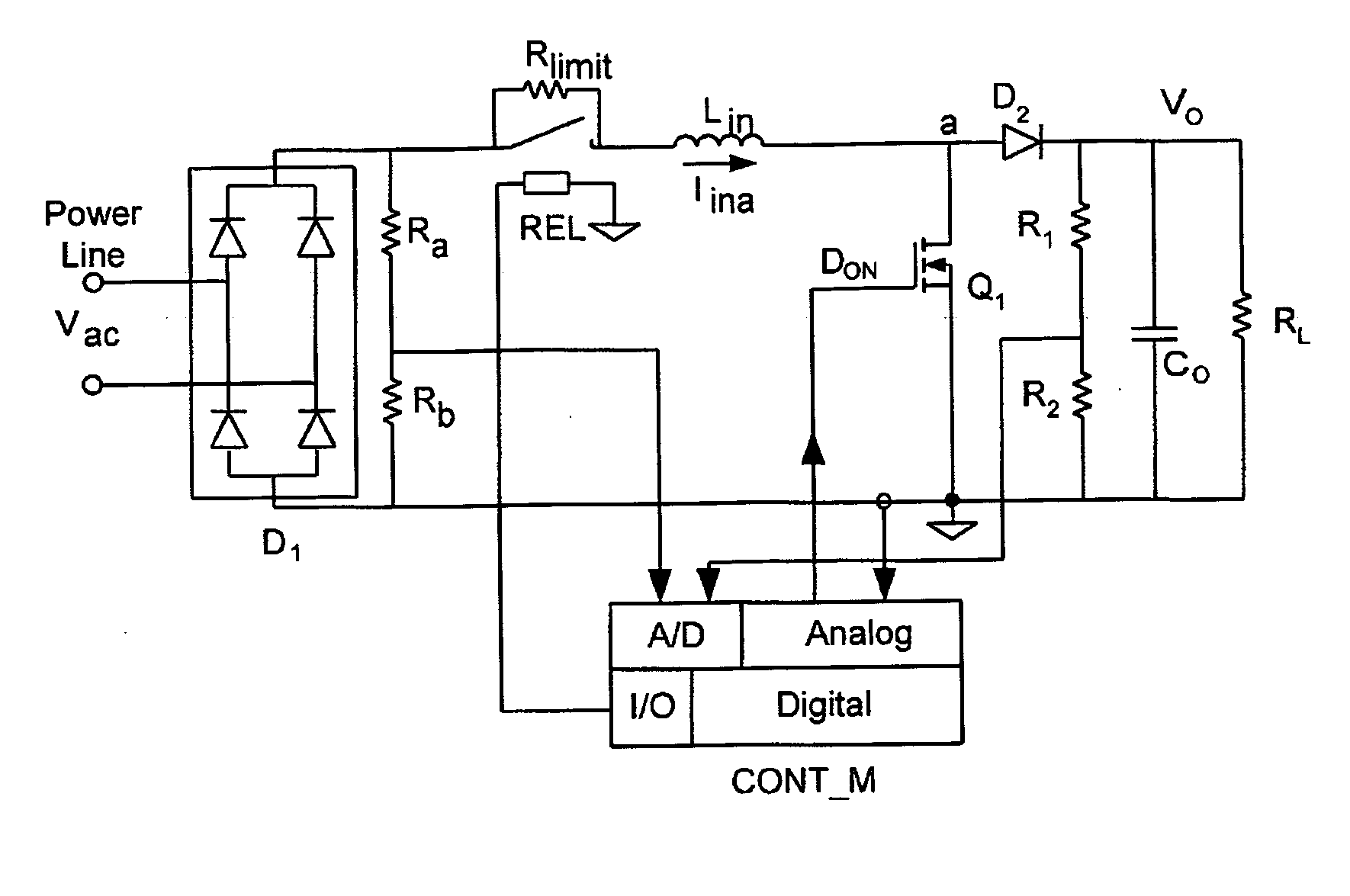

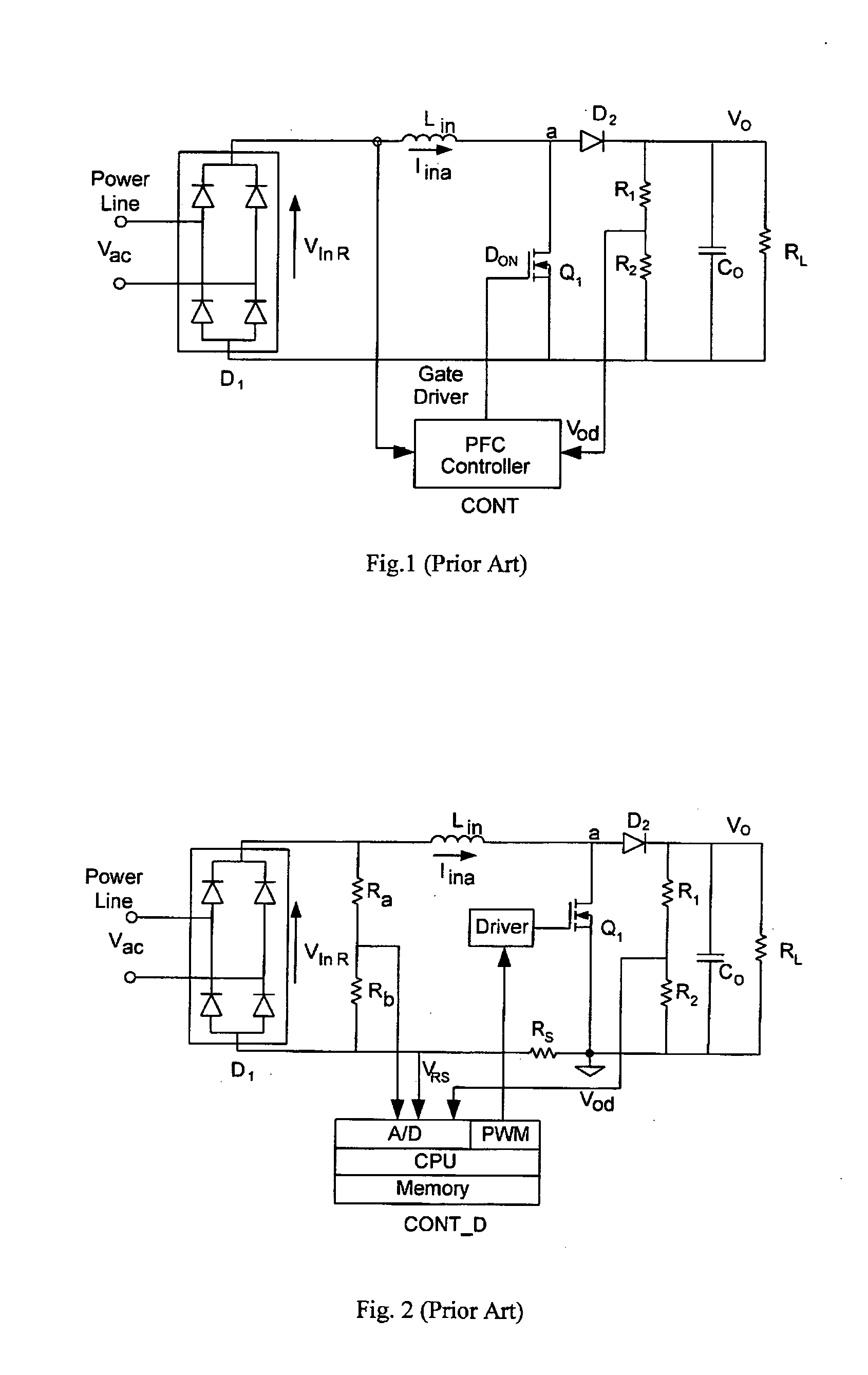

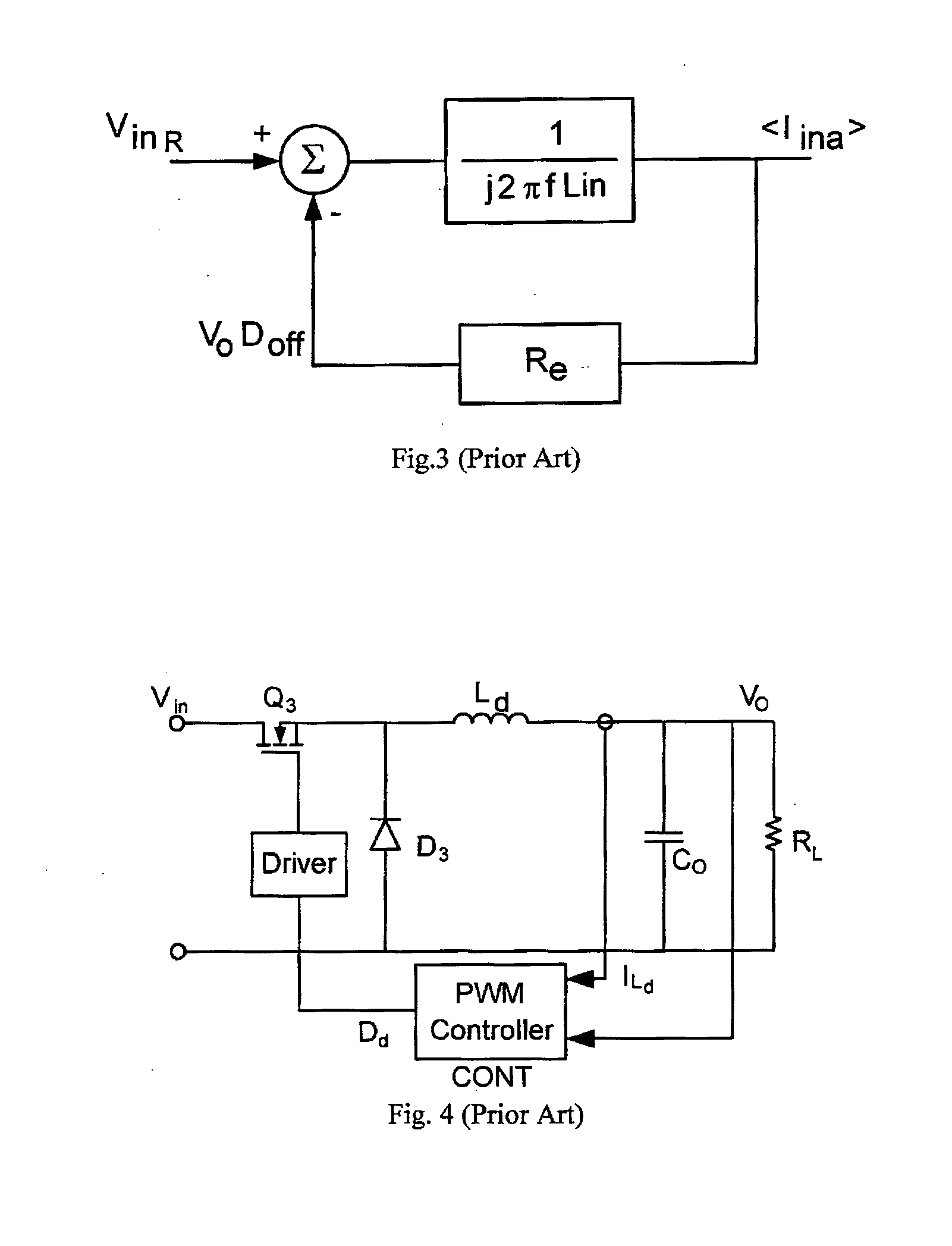

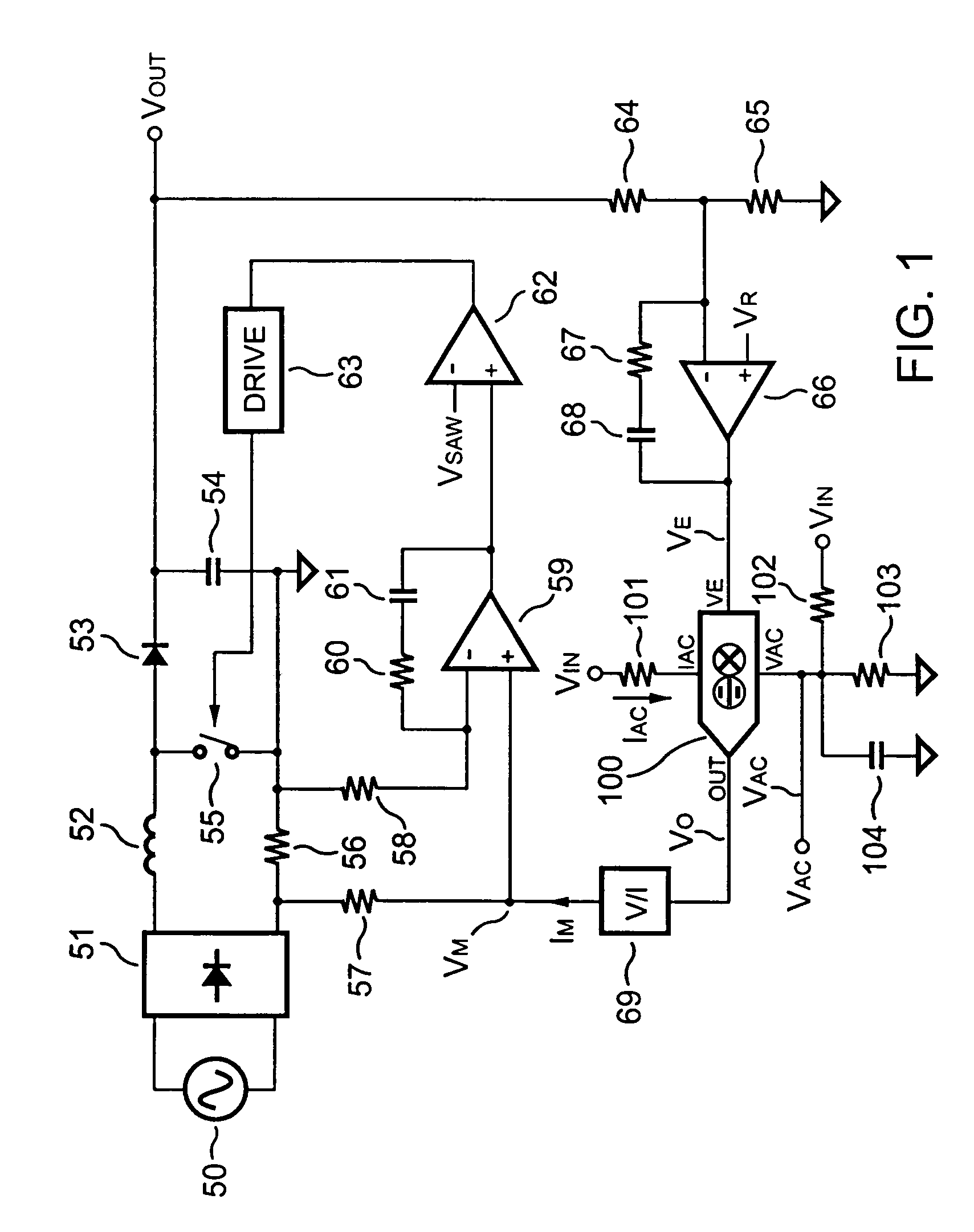

Method and control circuitry for improved-performance switch-mode converters

InactiveUS20060022648A1Relatively large bandwidthEasy constructionEfficient power electronics conversionElectric variable regulationElectricityPower factor

A system and method for supplying power to a load and for controlling the power factor presented to the power line. Output voltage is controlled by a digital, outer, control loop, and inner, analog, control loop causes the input current to be substantially proportional to the input voltage at any particular point in the power line cycle. Thus, the system presents a load to the power line that appears to be purely resistive. The use of an analog multiplier is not required, nor is sampling of input voltage. Limiting of inrush current provides for brown-out protection and soft-start.

Owner:GREEN POWER TECH LTD

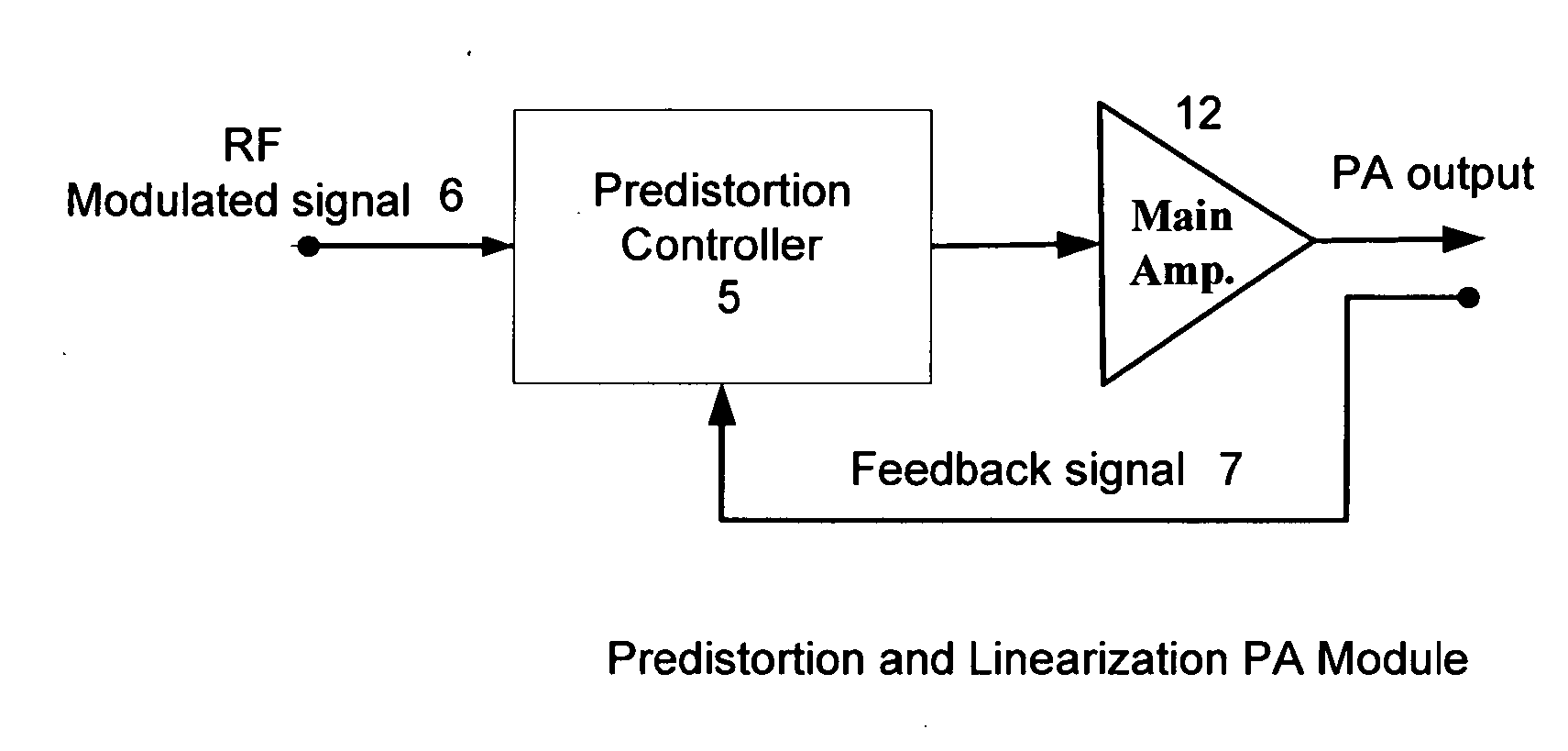

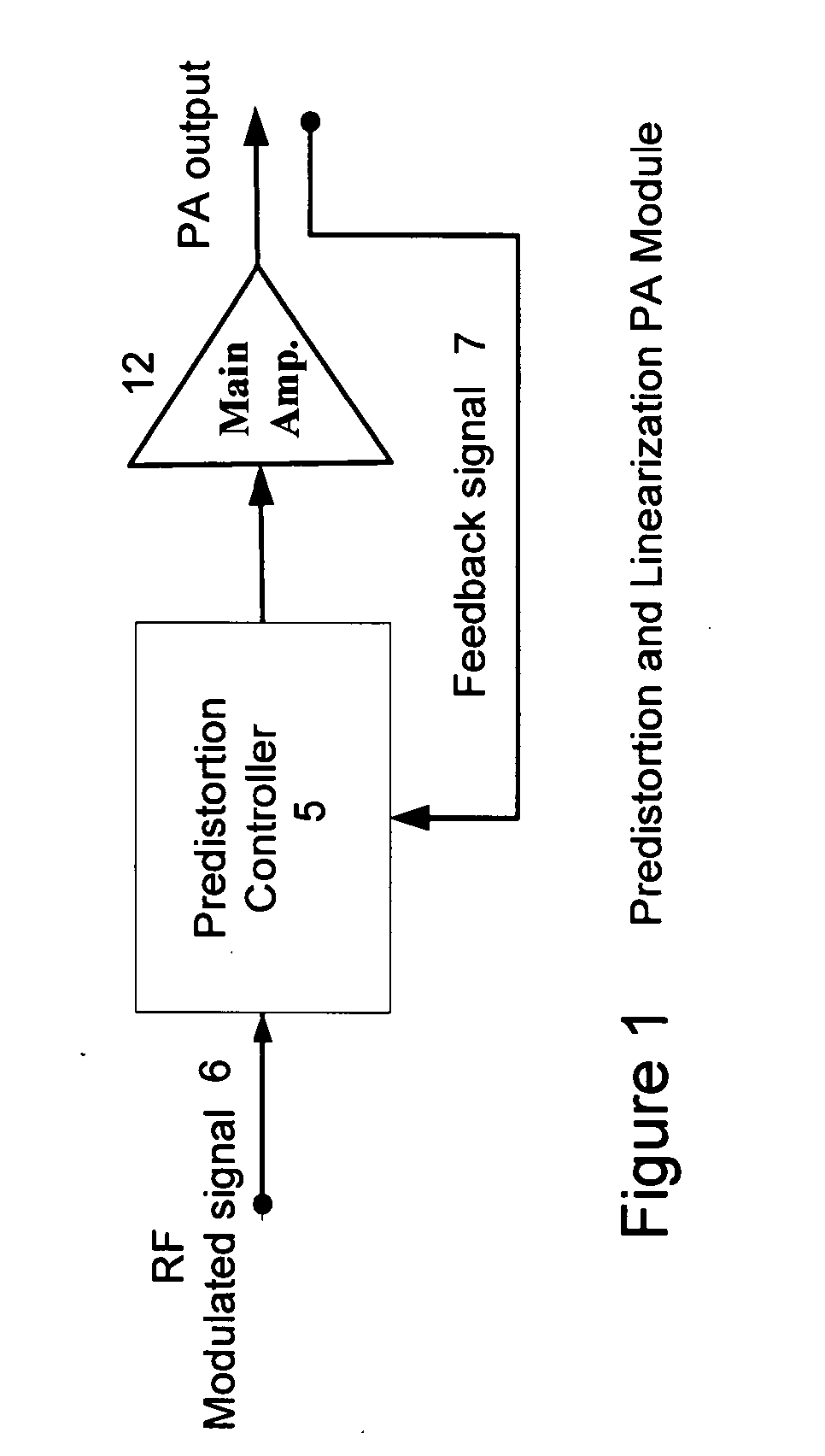

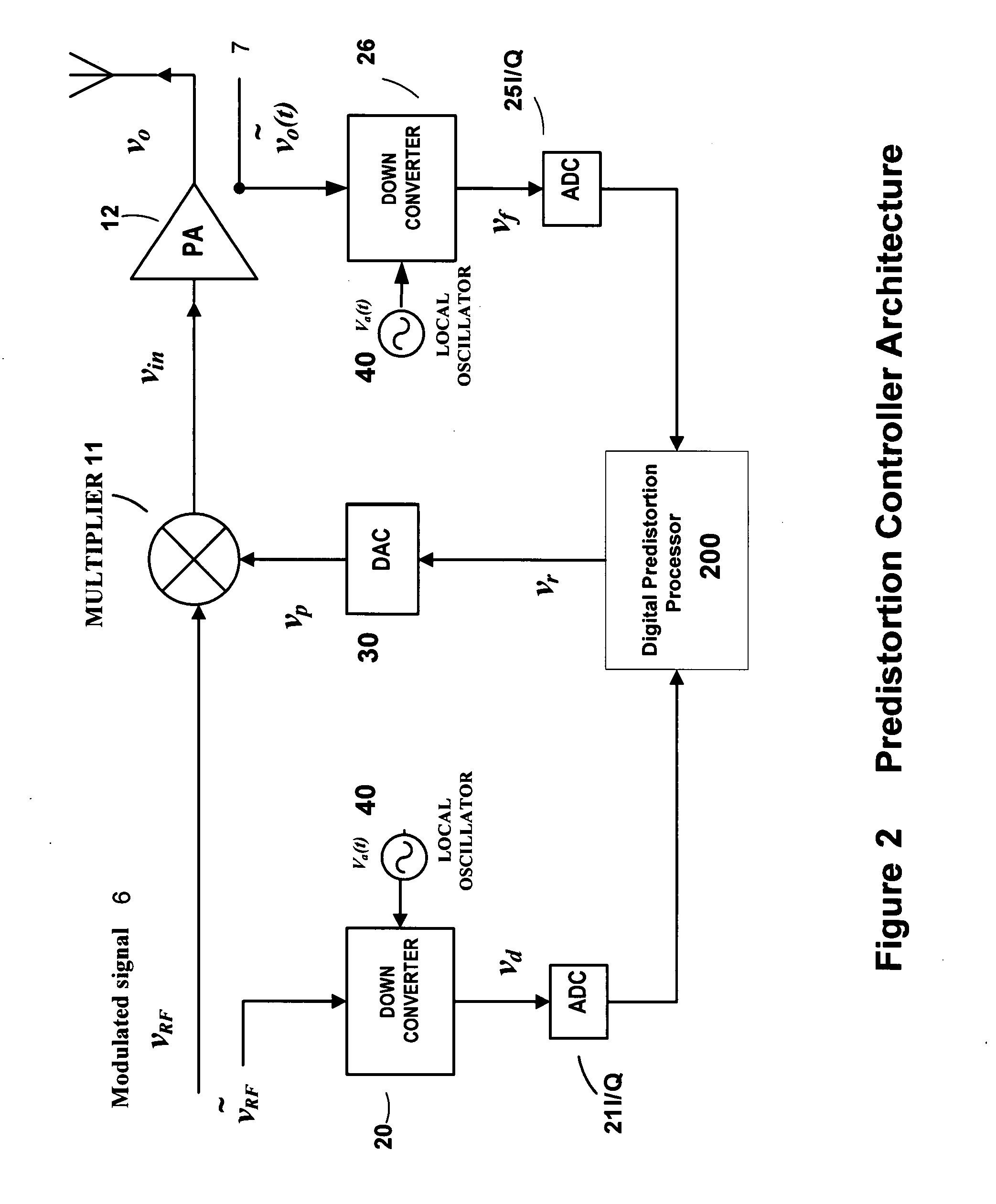

High efficiency linearization power amplifier for wireless communication

ActiveUS20070241812A1Improve efficiencyImprove linearityEnergy efficient ICTAmplifier details to increase power/efficiencyFrequency changerControl signal

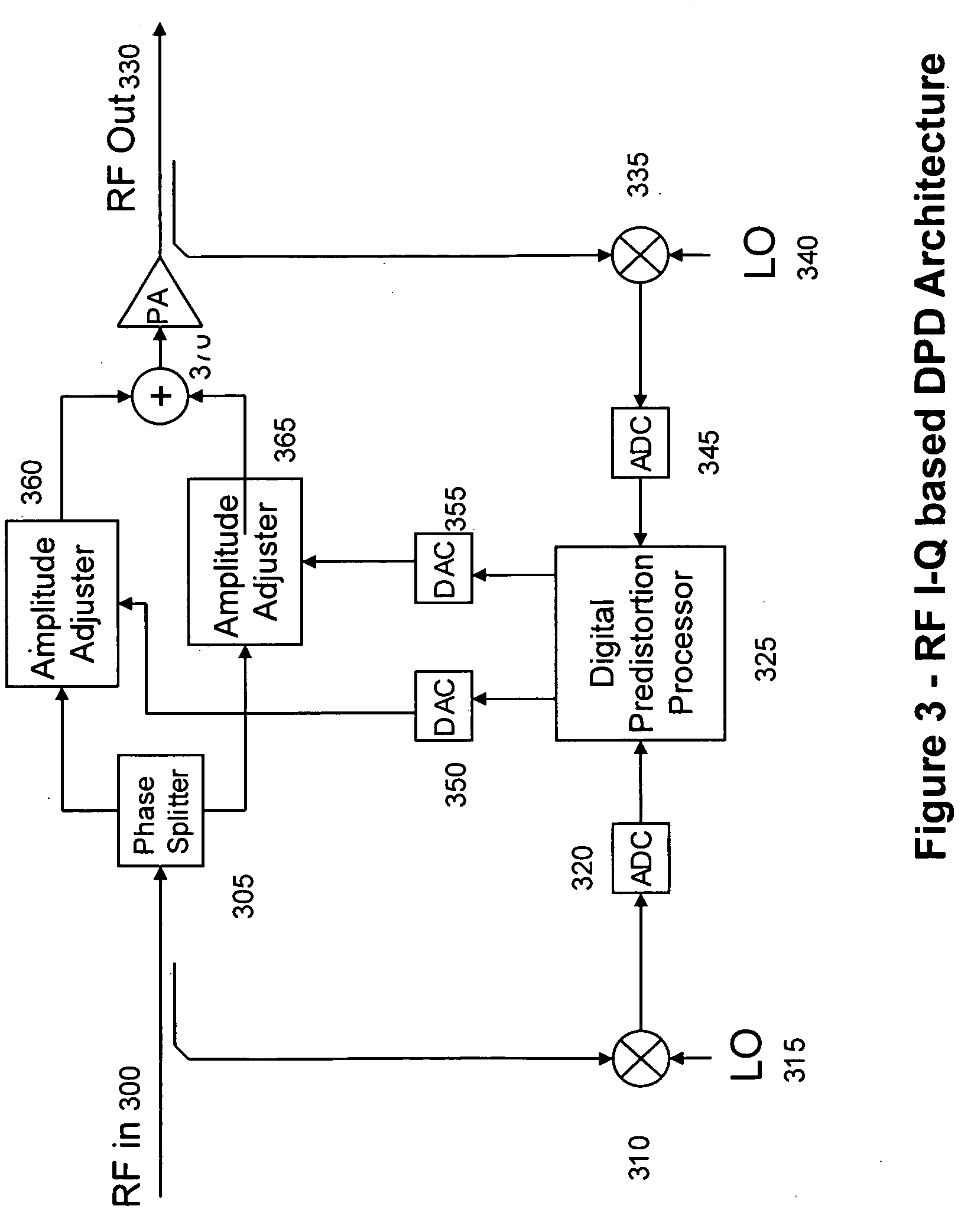

An embodiment of the invention uses a predistortion correction signal to combination the modulated RF signal by an analog multiplier for linearization of power amplifiers having nonlinear characteristics such as those used in wireless RF transmitters. A predistortion controller comprises a plurality of down converters for retrieving both the ideal non-distorted information and the feedback distorted information, together with pre-stored digitally-indexed predistortion information stored, for example, in a look-up table. The digitally-indexed information models nonlinear characteristics of the high power amplifier, and is stored prior to processing of pre-compensation in the power amplifier. When the predistortion information is combined with the modulated RF signal in the analog multiplier, the result is a substantially linear information transmission from the power amplifier. In an embodiment of the system, the modulated RF input signal and the feedback signal from PA output are down-converted, respectively, by analog devices, such as mixers, after which the analog intermediate frequency (IF) signals are digitized by analog-to-digital converters for digital predistortion correction processing, followed by predistortion processing performed by, for example, a DSP or FPGA chip to generate a digital correction control signal, which is then converted to an analog signal by a digital-to-analog converter, followed by combining the analog correction signal with the RF modulated input signal to yield the input to the power amplifier.

Owner:DALI WIRELESS

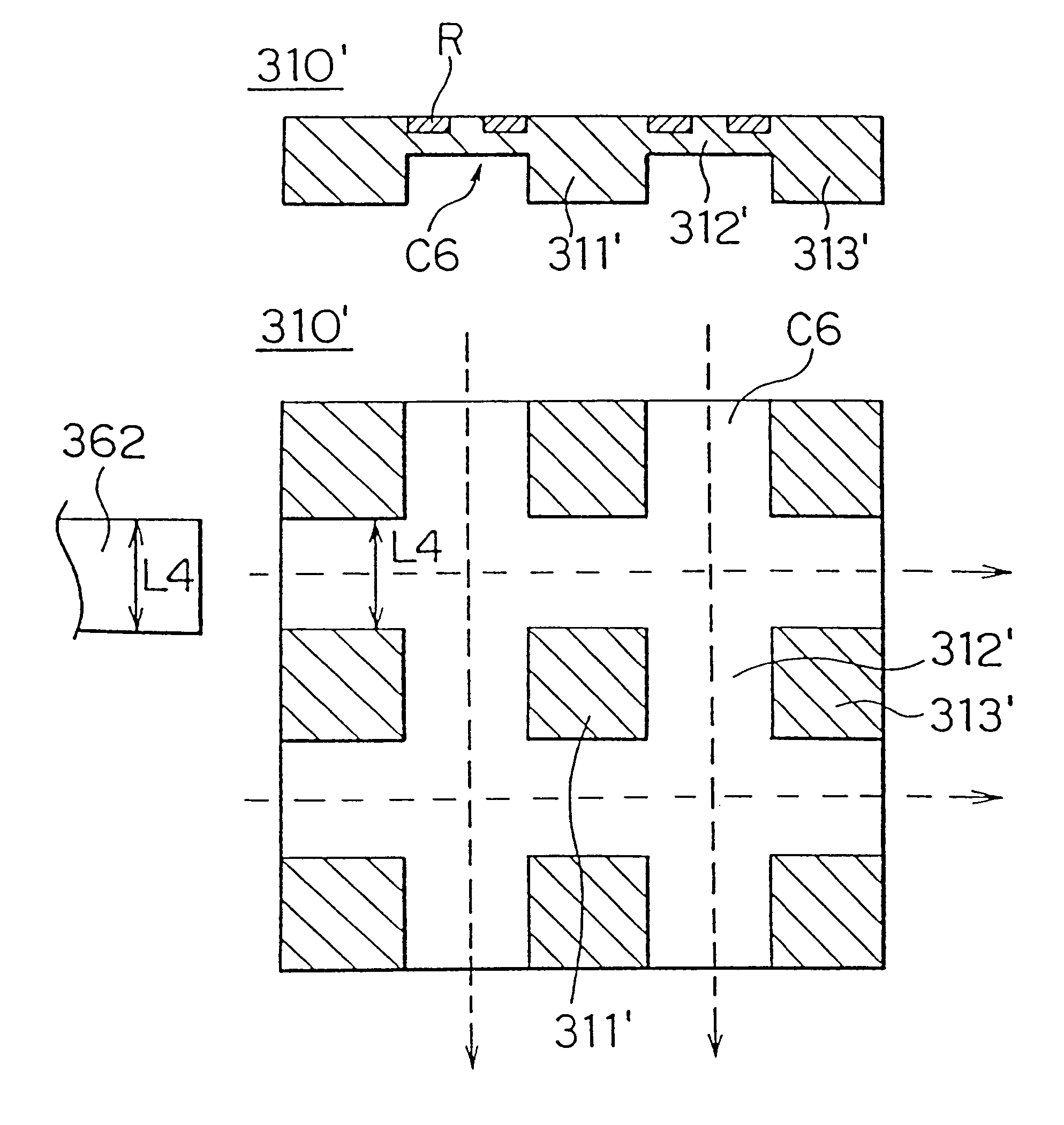

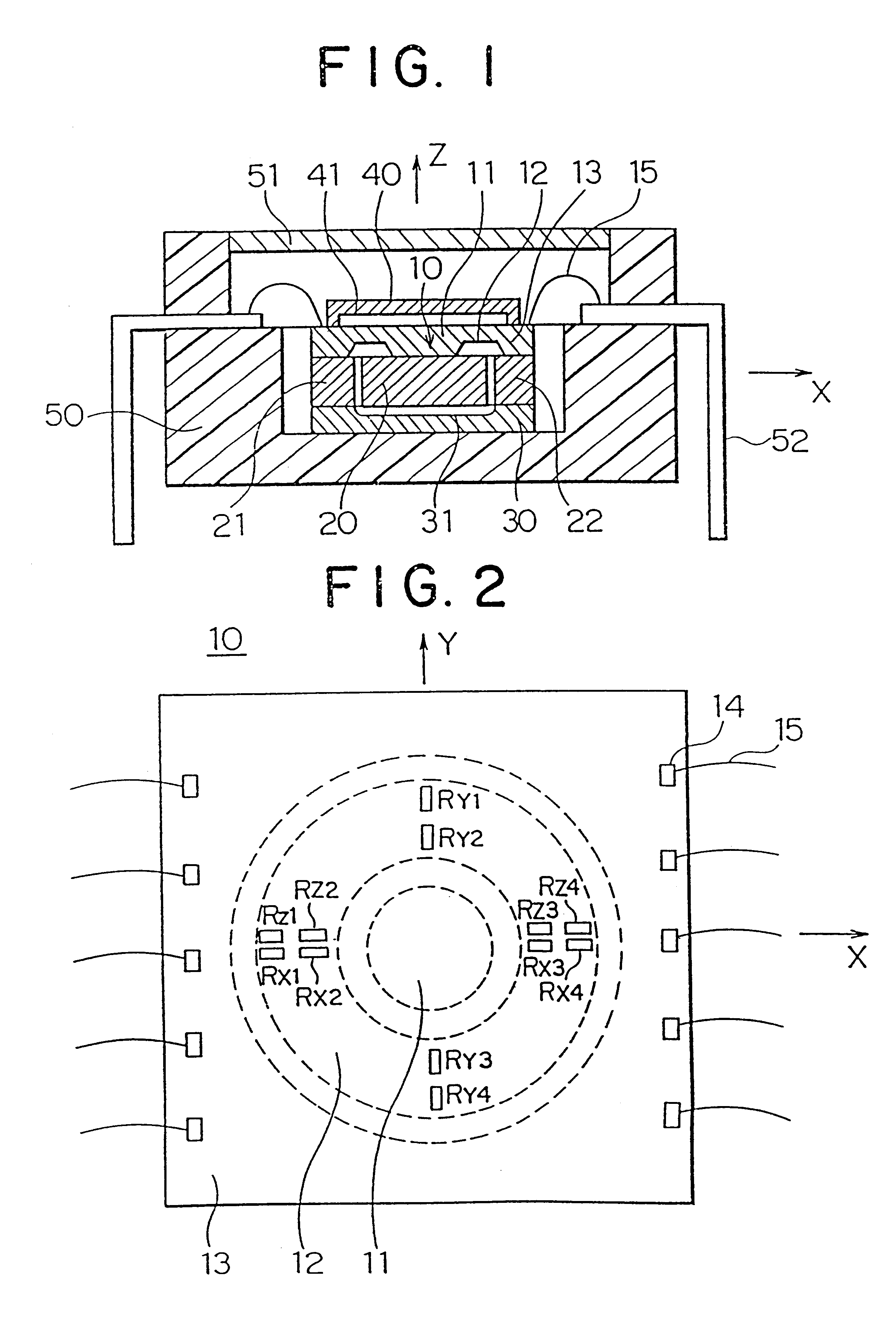

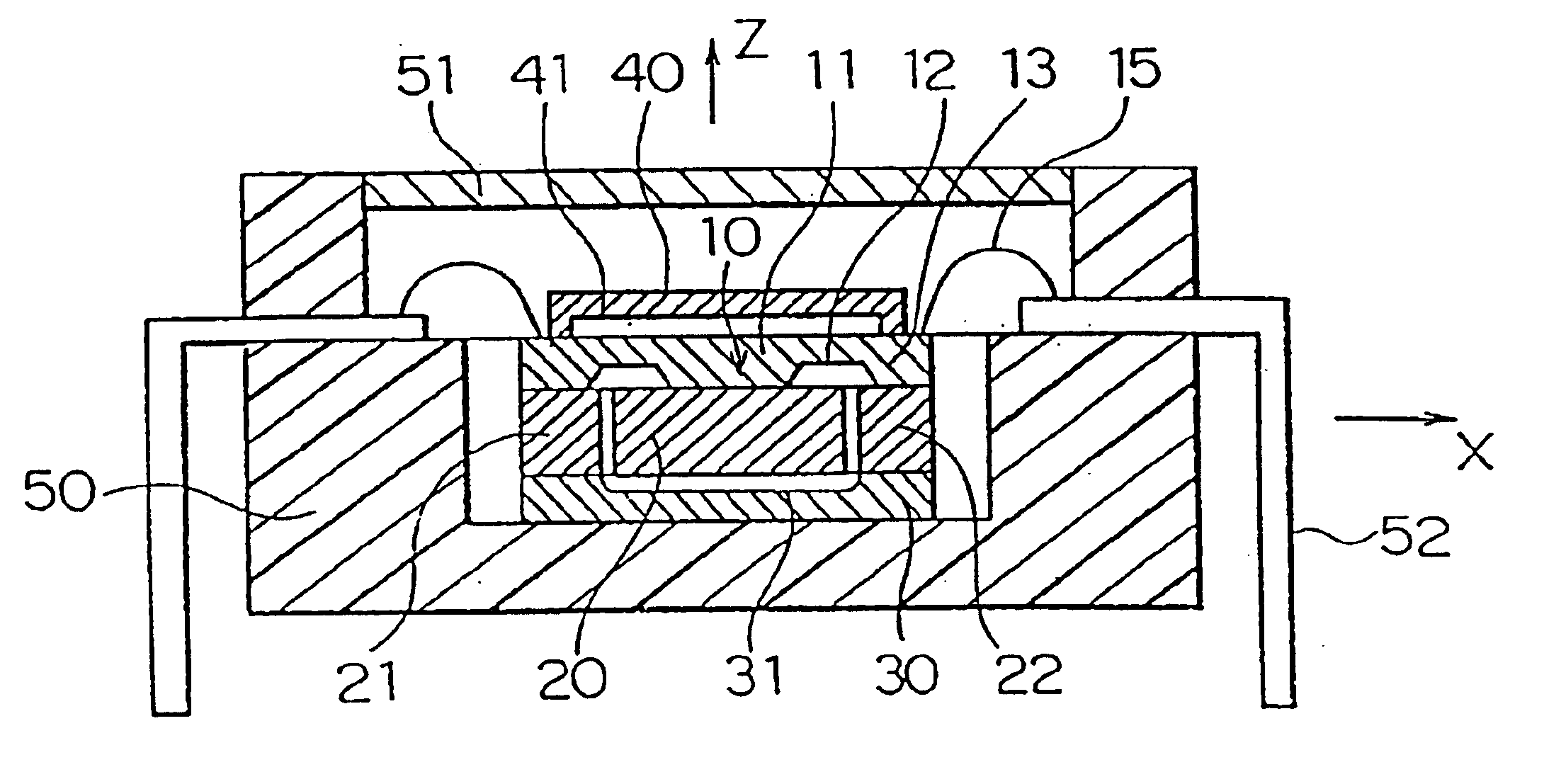

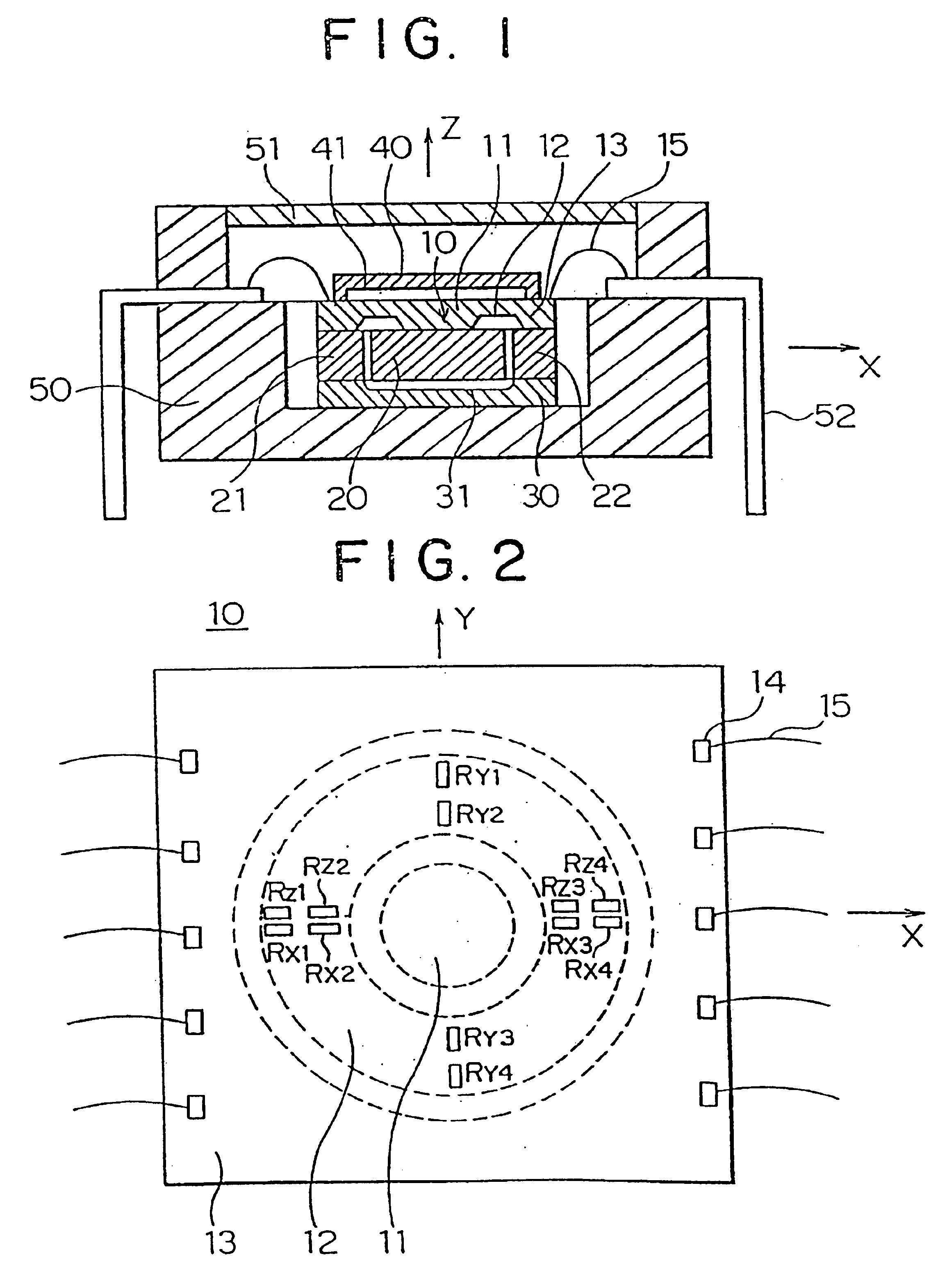

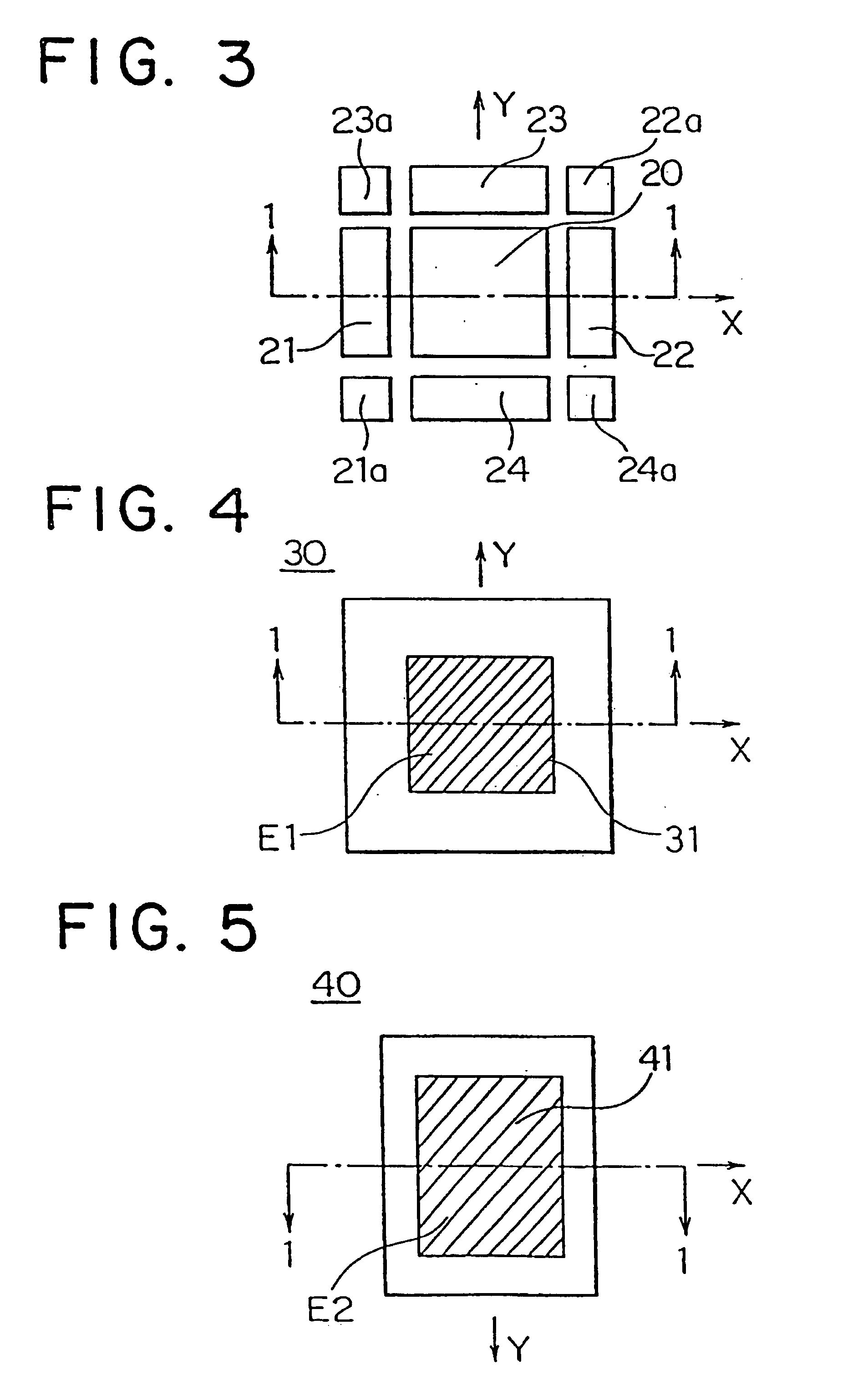

Method of manufacturing a sensor detecting a physical action as an applied force

InactiveUS6185814B1Low costSimple circuit configurationAcceleration measurement using interia forcesForce measurement using piezo-resistive materialsSignal processing circuitsSemiconductor chip

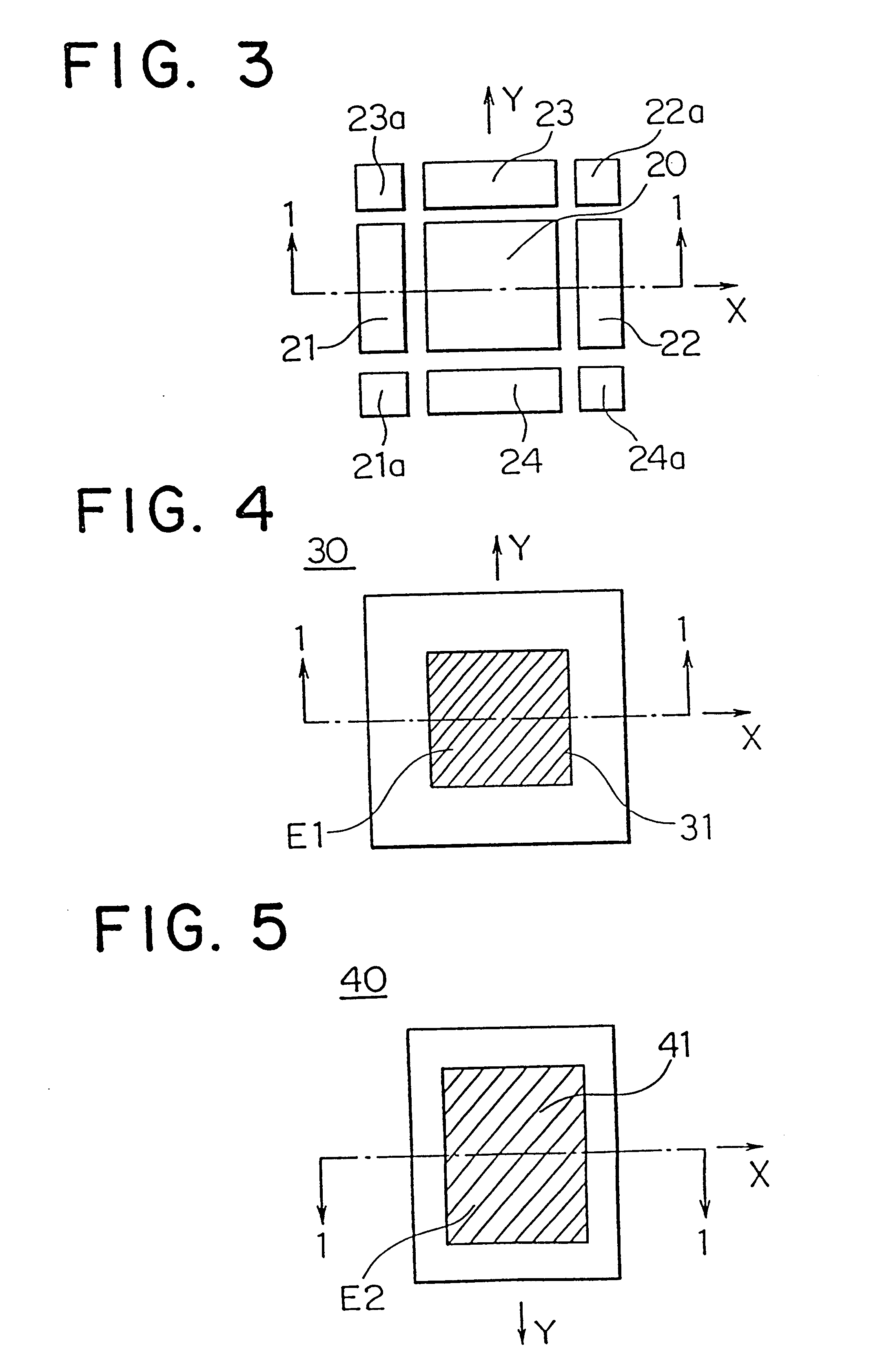

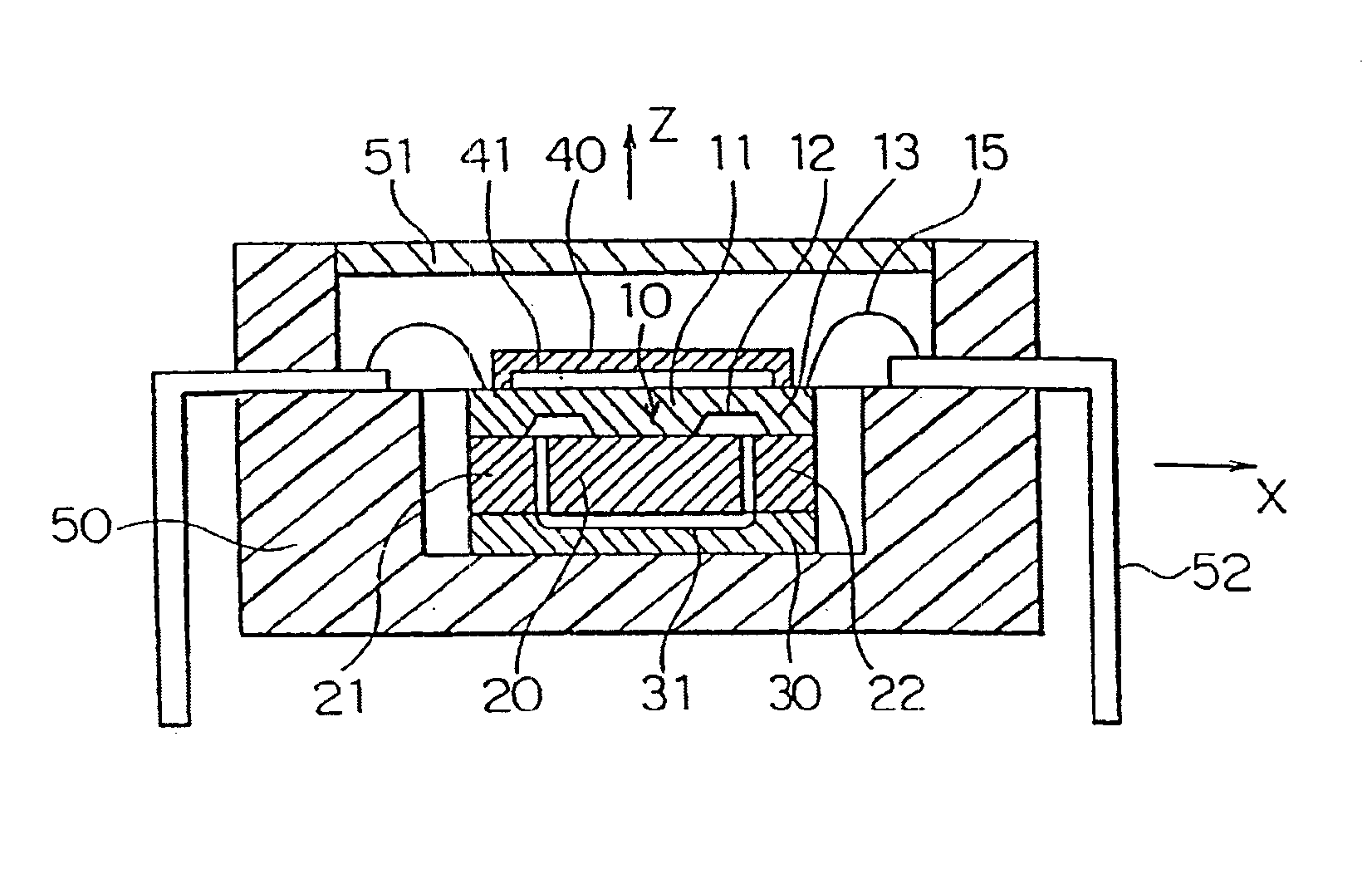

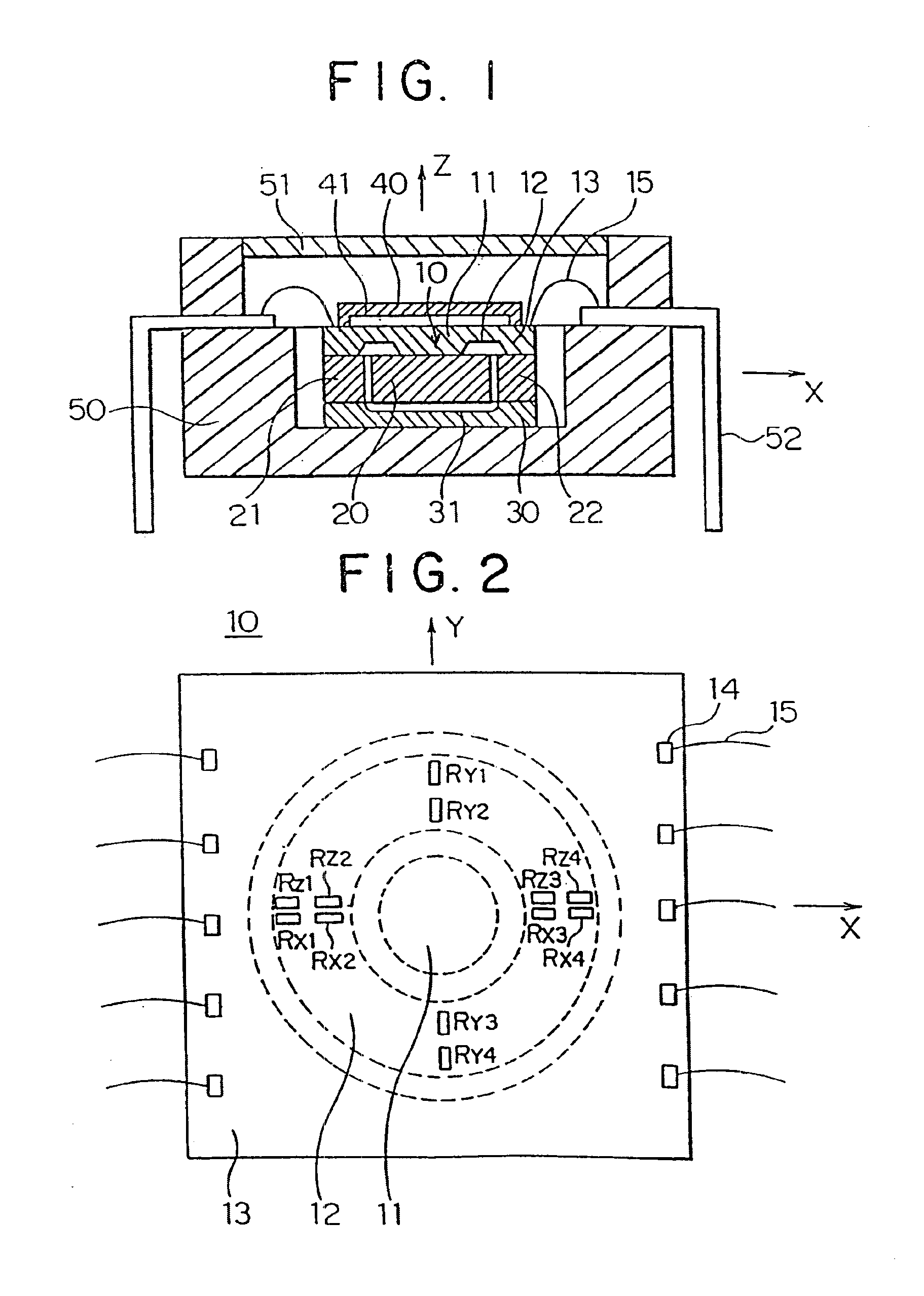

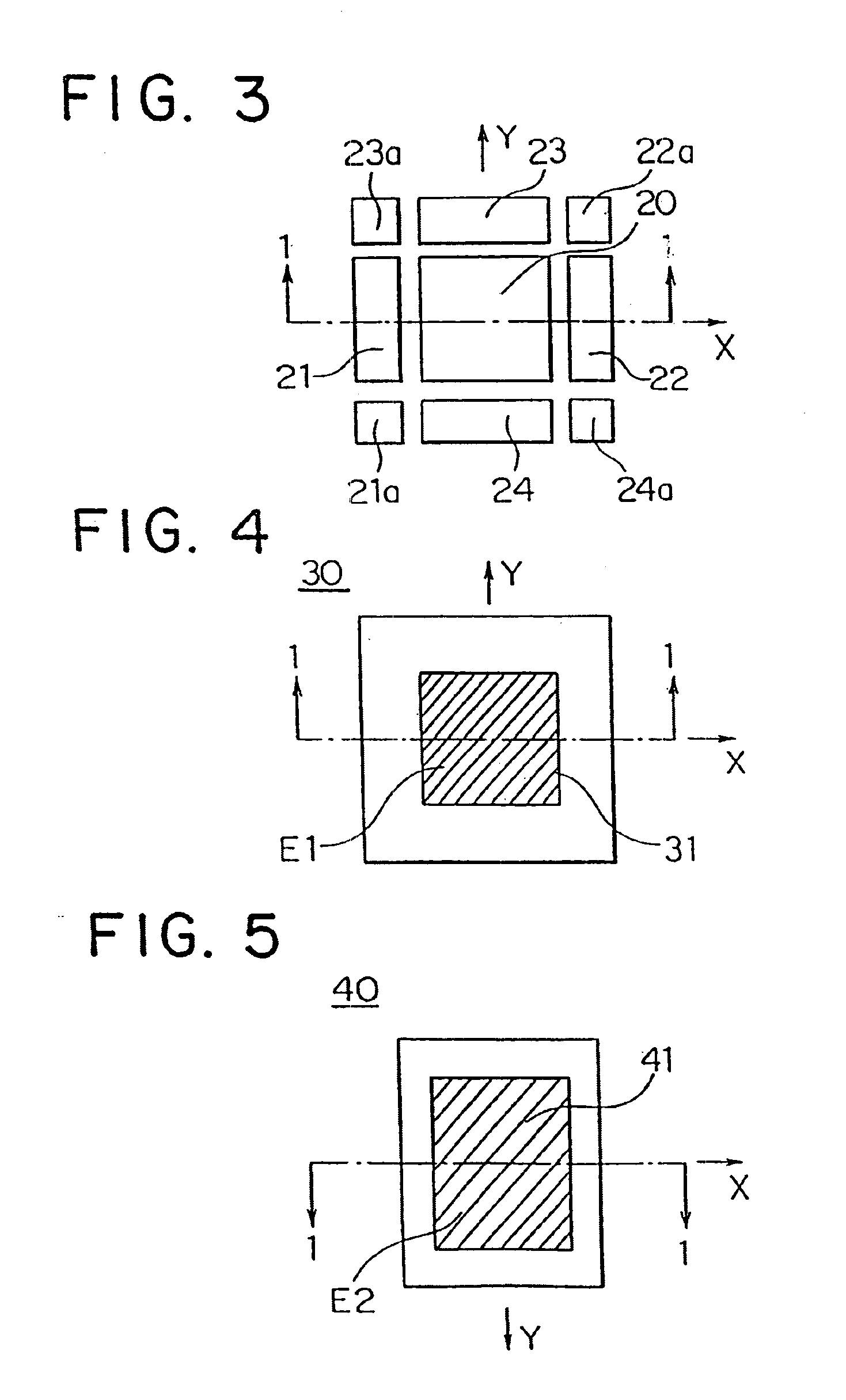

A sensor comprises a semiconductor pellet (10) including a working portion (11) adapted to undergo action of a force, a fixed portion (13) fixed on the sensor body, and a flexible portion (13) having flexibility formed therebetween, a working body (20) for transmitting an exterted force to the working portion, and detector means (60-63) for transforming a mechanical deformation produced in the semiconductor pellet to an electric signal to thereby detect a force exerted on the working body as an electric signal. A signal processing circuit is applied to the sensor. This circuit uses analog multipliers (101-109) and analog adders / subtracters (111-113), and has a function to cancel interference produced in different directions. Within the sensor, two portions (E3, E4-E8) located at positions opposite to each other and producing a displacement therebetween by action of a force are determined. By exerting a coulomb force between both the portions, the test of the sensor is carried out. Further, a pedestal (21, 22) is provided around the working body (20). The working body and the pedestal are located with a predetermined gap or spacing therebetween. A displacement of the working body is caused to limitatively fall within a predetermined range corresponding to the spacing. The working body and the pedestal are provided by cutting a same common substrate (350, 350')

Owner:OKADA KAZUHIRO

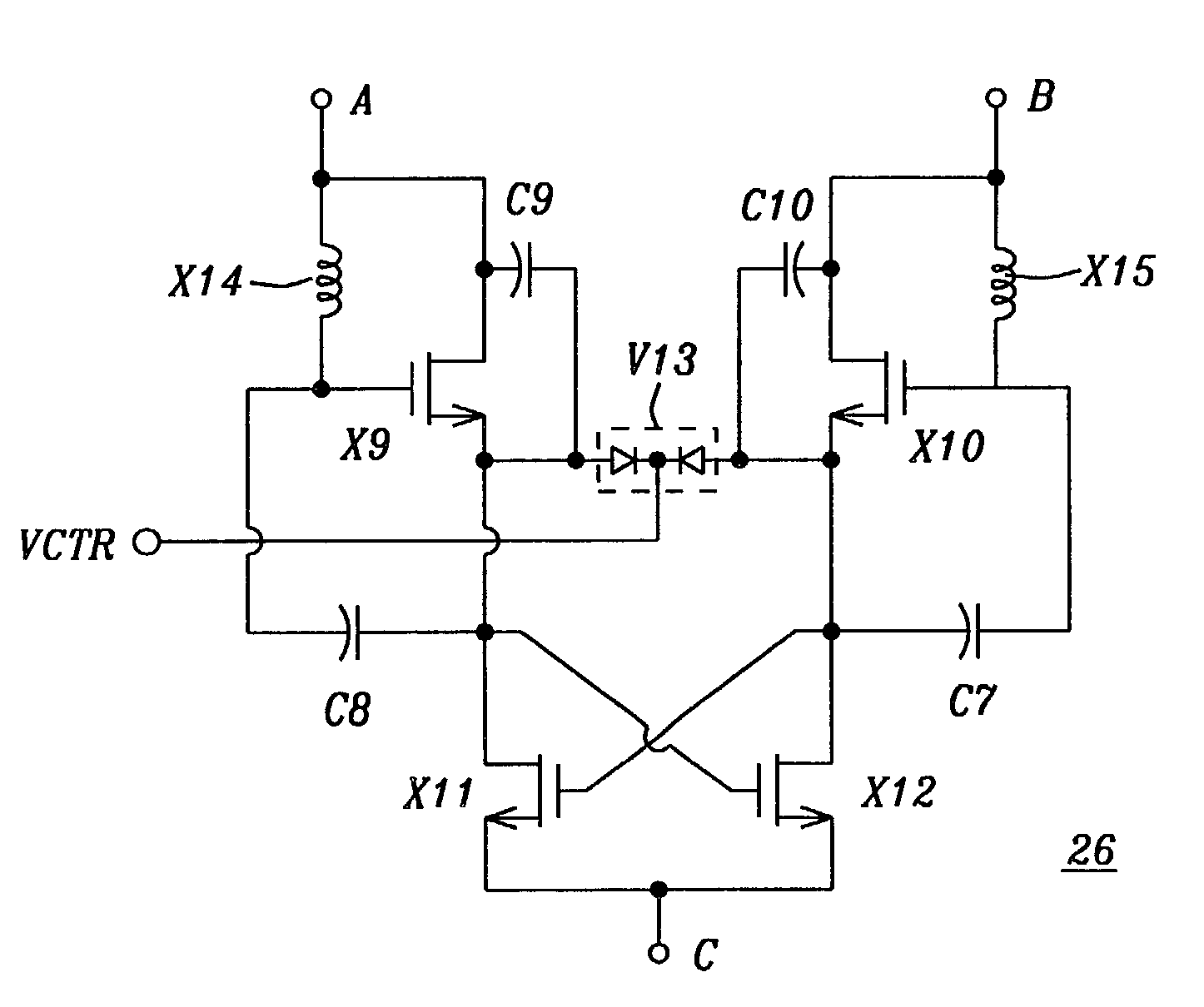

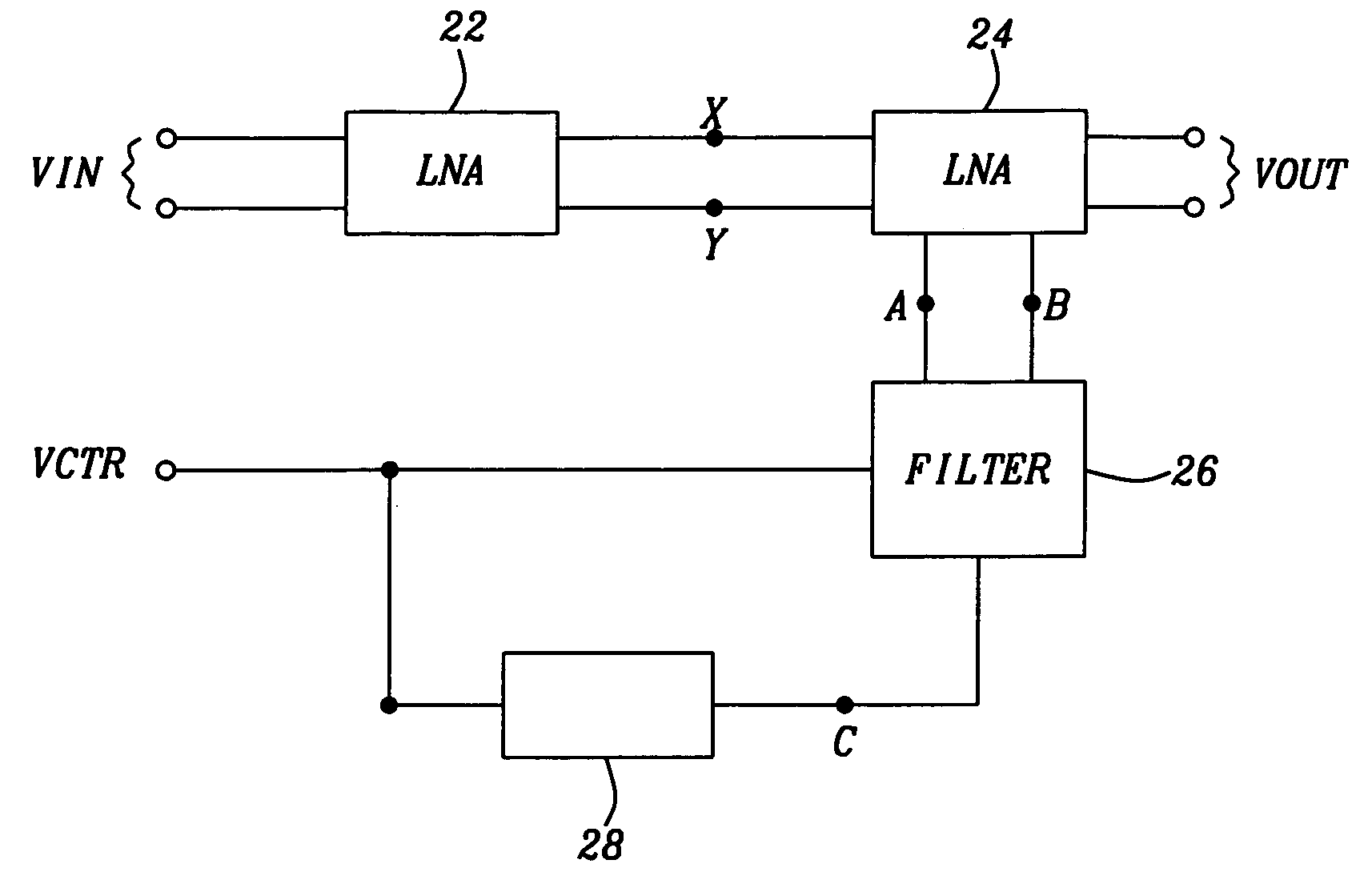

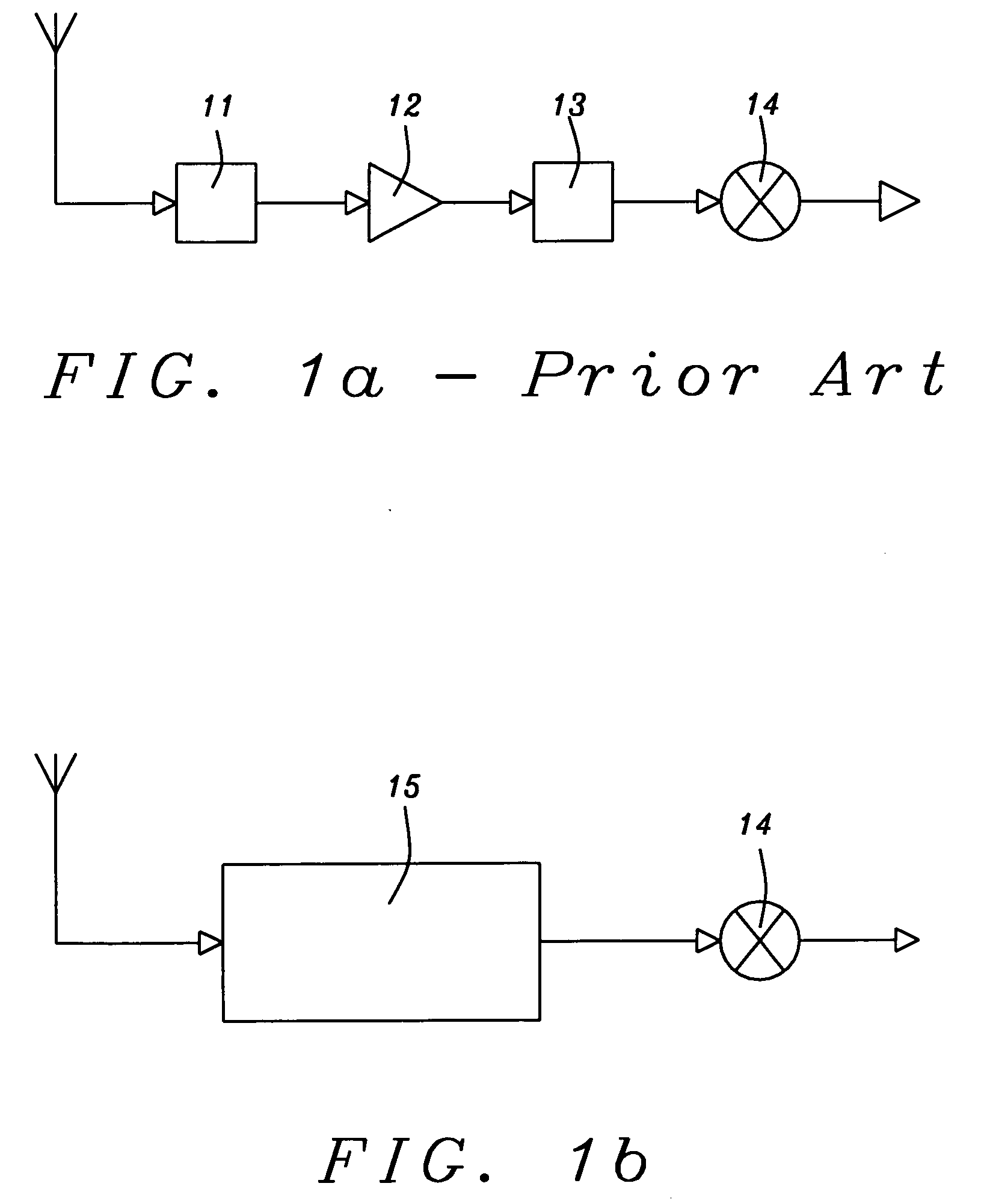

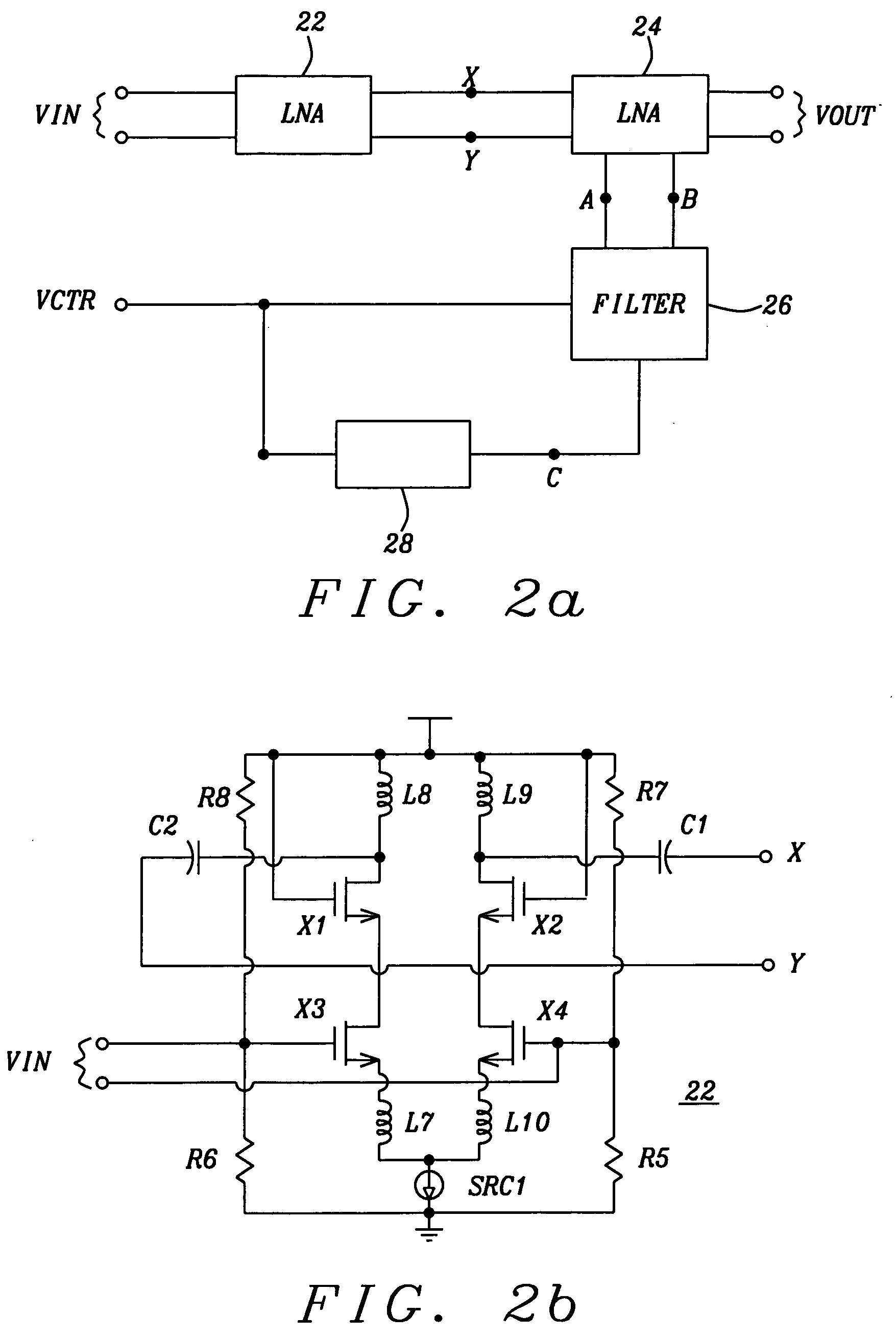

Wideband monolithic tunable high-Q notch filter for image rejection in RF application

InactiveUS6990327B2Good image rejectionWide tunable rangeMultiple-port networksTransmissionEngineeringInductor

A notch filter with a high Q factor, which is integrated with a first and a second cascoded LNA, is totally contained on an integrated chip. The notch filter, comprising two Q-enhancement circuits, is coupled to the second differential LNA. The two Q-enhancement circuits are combined to generate sufficient negative impedance to compensate for the loss in the on-chip low Q inductors. To improve the image rejection of the notch filter in a wide frequency band, the notch filter uses an automatic current tuning circuit which consists of an analog multiplier and fixed and voltage controlled current sources. Furthermore, by modifying the connection and location of the tunable varactor, another wideband tunable notch filter is implemented. The notch filter can be applied in all current wireless receiver systems.

Owner:AGENCY FOR SCI TECH & RES

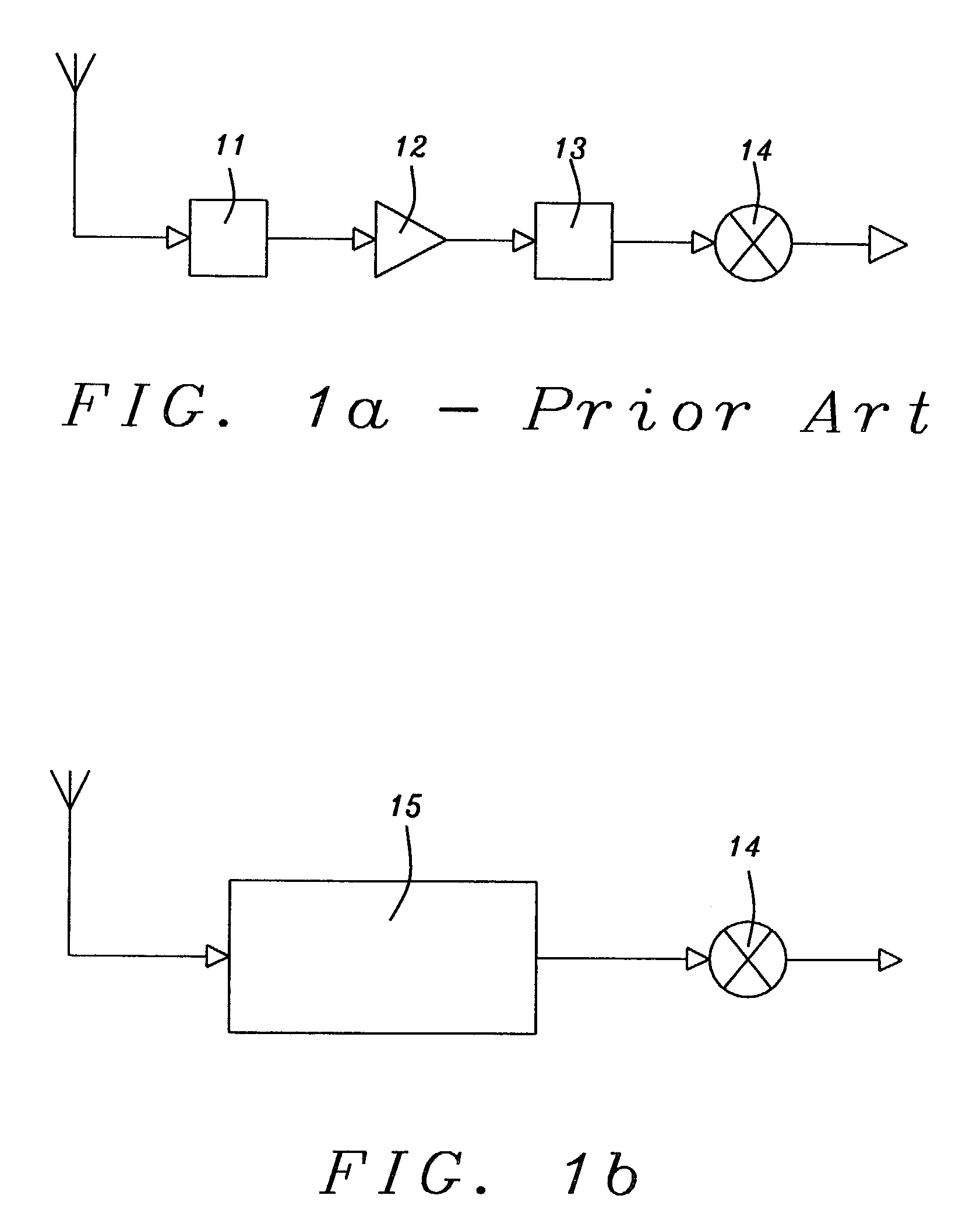

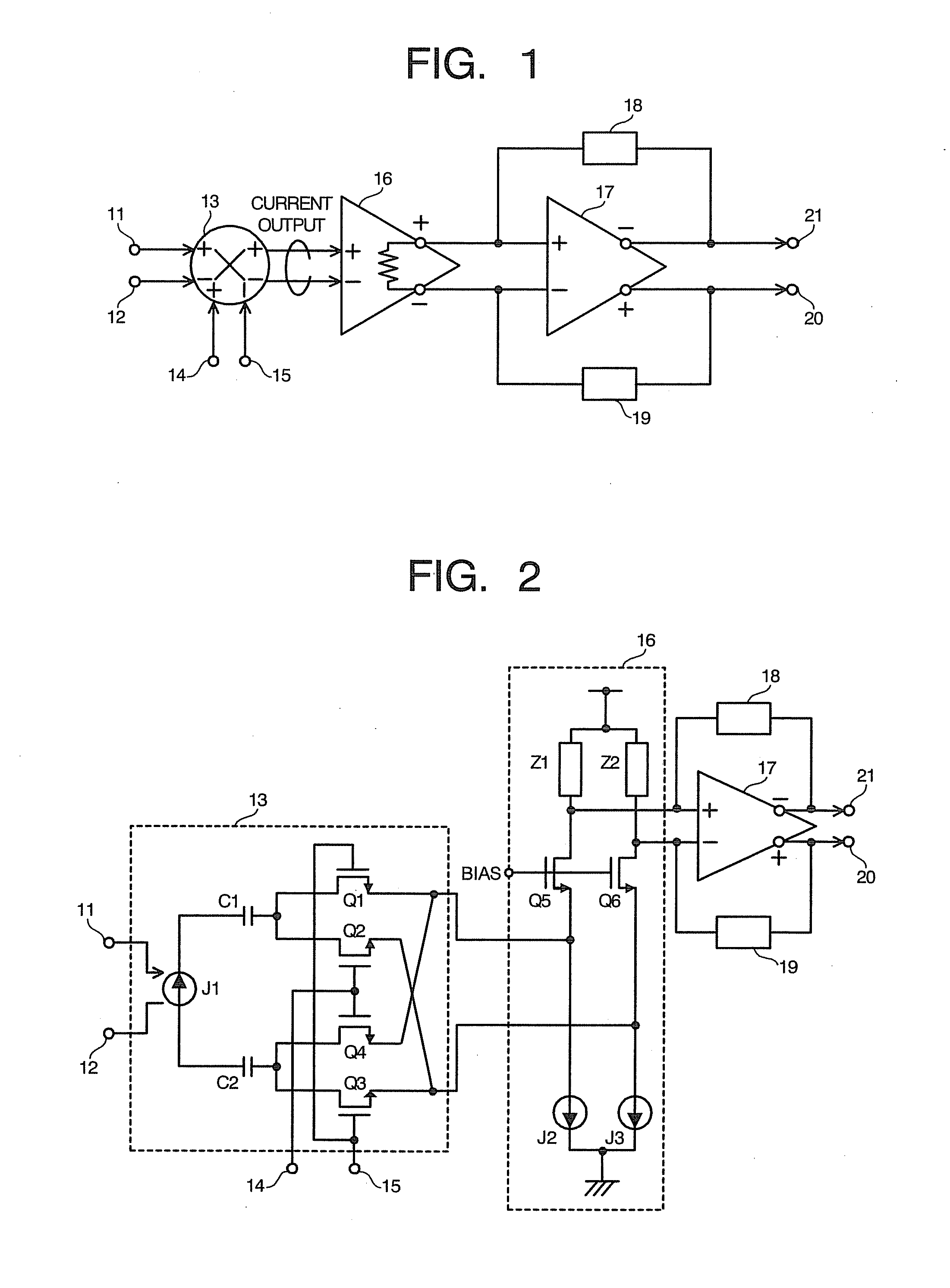

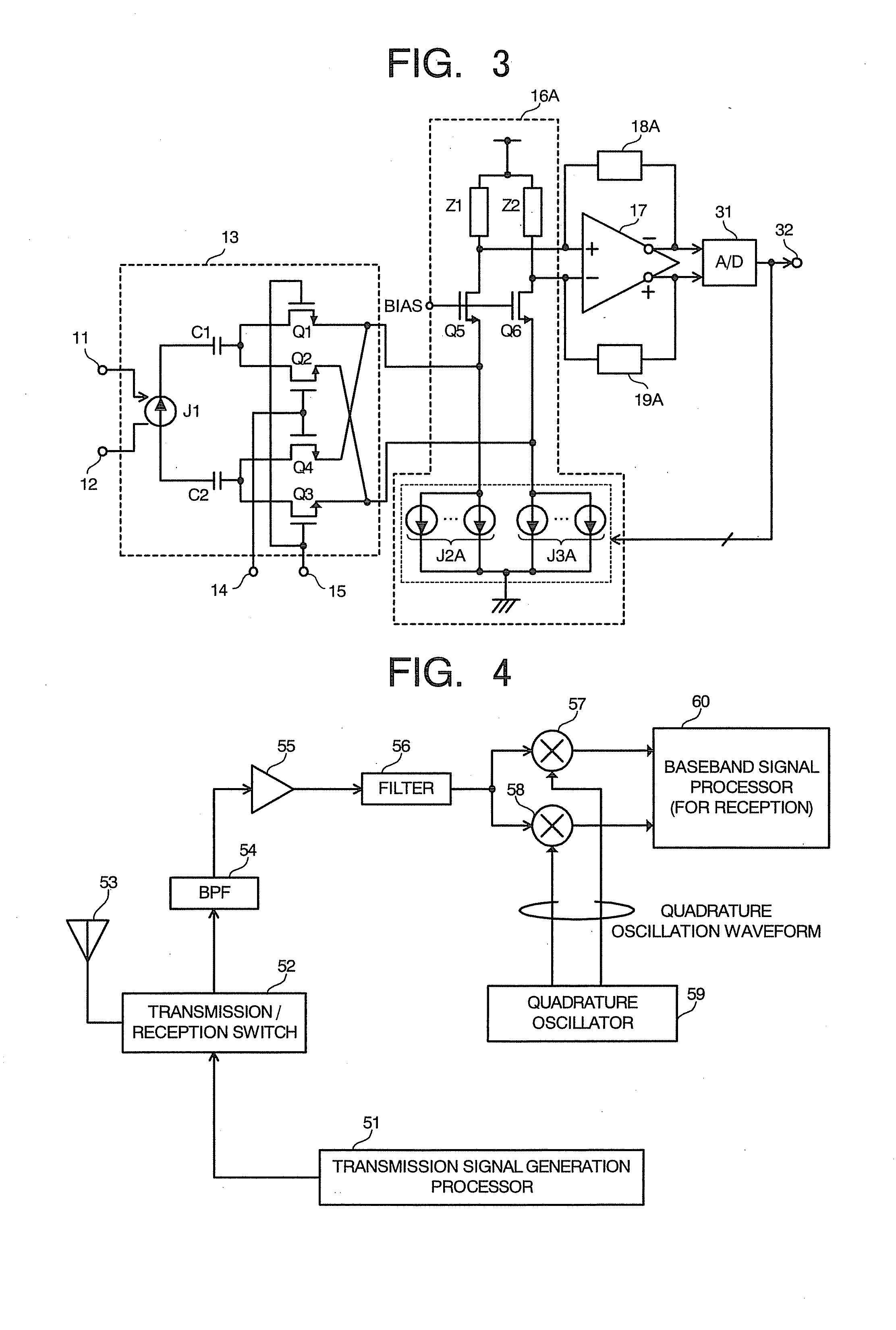

Frequency converter, radio receiver

InactiveUS20080233906A1Easy to solveIncrease valueOscillations generatorsMulti-frequency-changing modulation transferenceVoltage converterFrequency changer

Disclosed is a frequency converter including: a passive type analog multiplier configured to output a multiplication result in a current; a buffer outputting a buffering current by buffering the current of the multiplication result; and a current-voltage converter current-voltage converting the buffering current. Alternately, disclosed is a frequency converter including: a passive type analog multiplier configured to output a multiplication result in a current; a buffer outputting a buffering current by buffering the current of the multiplication result; and an integrator integrating the buffering current to output a voltage.

Owner:KK TOSHIBA

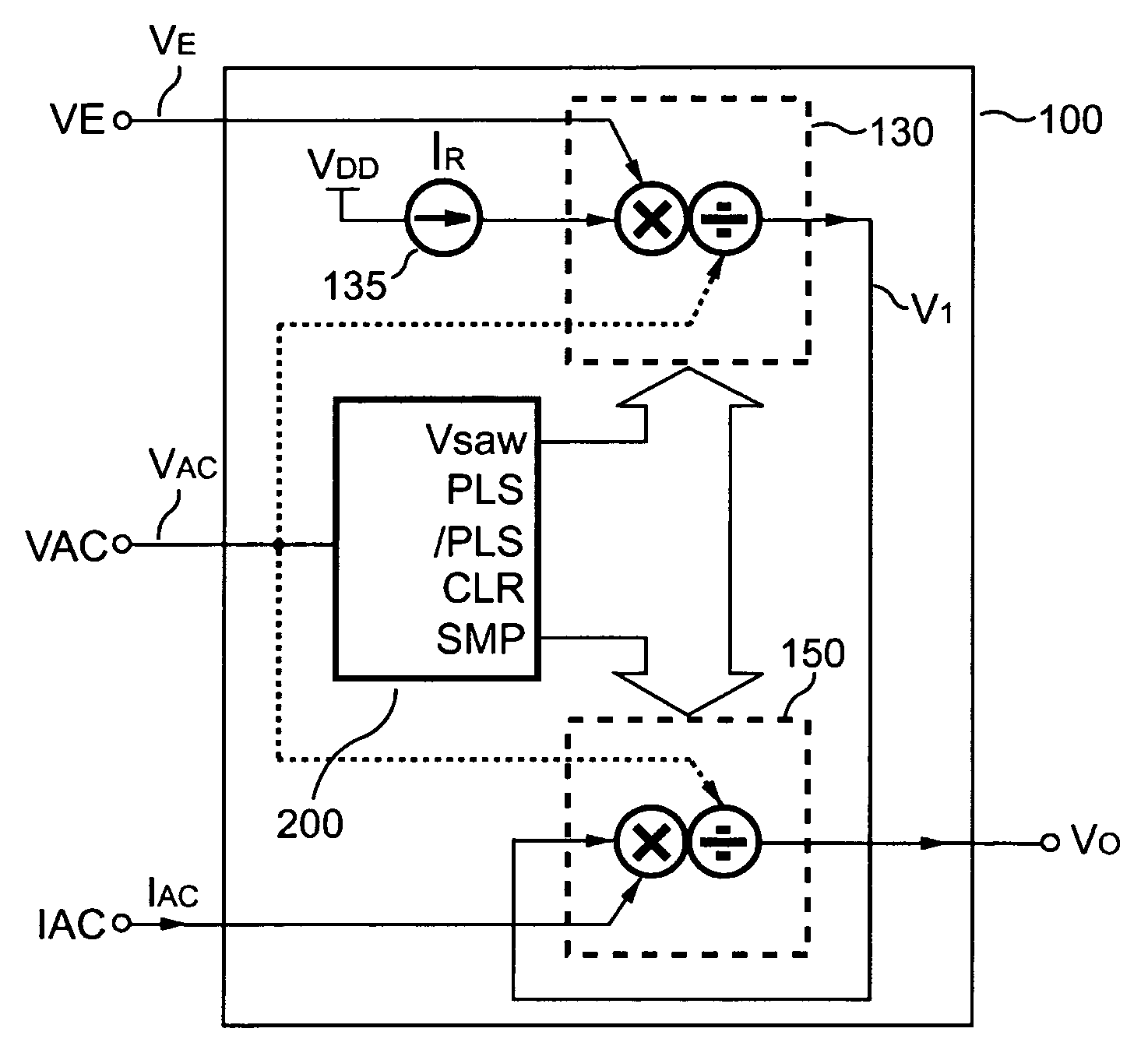

Multiplier-divider circuit for a PFC controller

ActiveUS7057440B2Small die-sizeLow costAc-dc conversion without reversalComputations using contact-making devicesCMOSAnalog multiplier

The present invention introduces an integrated analog multiplier-divider circuit. The multiplier-divider block according to the present invention is ideal for use in the power factor correction (PFC) controllers of many switch-mode power supplies. The analog multiplier-divider according to the present invention is built with CMOS devices. Because of this, it has many advantages over prior-art multiplier-dividers. One important advantage is that the die-size and the cost can be reduced. Another important advantage of the multiplier-divider according to the present invention is substantially reduced temperature dependence.

Owner:SEMICON COMPONENTS IND LLC

Apparatus for detecting a physical quantity acting as an external force and method for testing and manufacturing this apparatus

InactiveUS6894482B2Low costSimple circuit configurationAcceleration measurement using interia forcesElectrical testingSignal processing circuitsSemiconductor chip

A sensor comprises a semiconductor pellet (10) including a working portion (11) adapted to undergo action of a force, a fixed portion (13) fixed on the sensor body, and a flexible portion (13) having flexibility formed therebetween, a working body (20) for transmitting an exterted force to the working portion, and detector means (60-63) for transforming a mechanical deformation produced in the semiconductor pellet to an electric signal to thereby detect a force exerted on the working body as an electric signal. A signal processing circuit is applied to the sensor. This circuit uses analog multipliers (101-109) and analog adders / subtracters (111-113), and has a function to cancel interference produced in different directions. Within the sensor, two portions (E3, E4-E8) located at positions opposite to each other and producing a displacement therebetween by action of a force are determined. By exerting a coulomb force between both the portions, the test of the sensor is carried out. Further, a pedestal (21, 22) is provided around the working body (20). The working body and the pedestal are located with a predetermined gap or spacing therebetween. A displacement of the working body is caused to limitatively fall within a predetermined range corresponding to the spacing. The working body and the pedestal are provided by cutting a same common substrate (350, 350′).

Owner:WAKO CO LTD

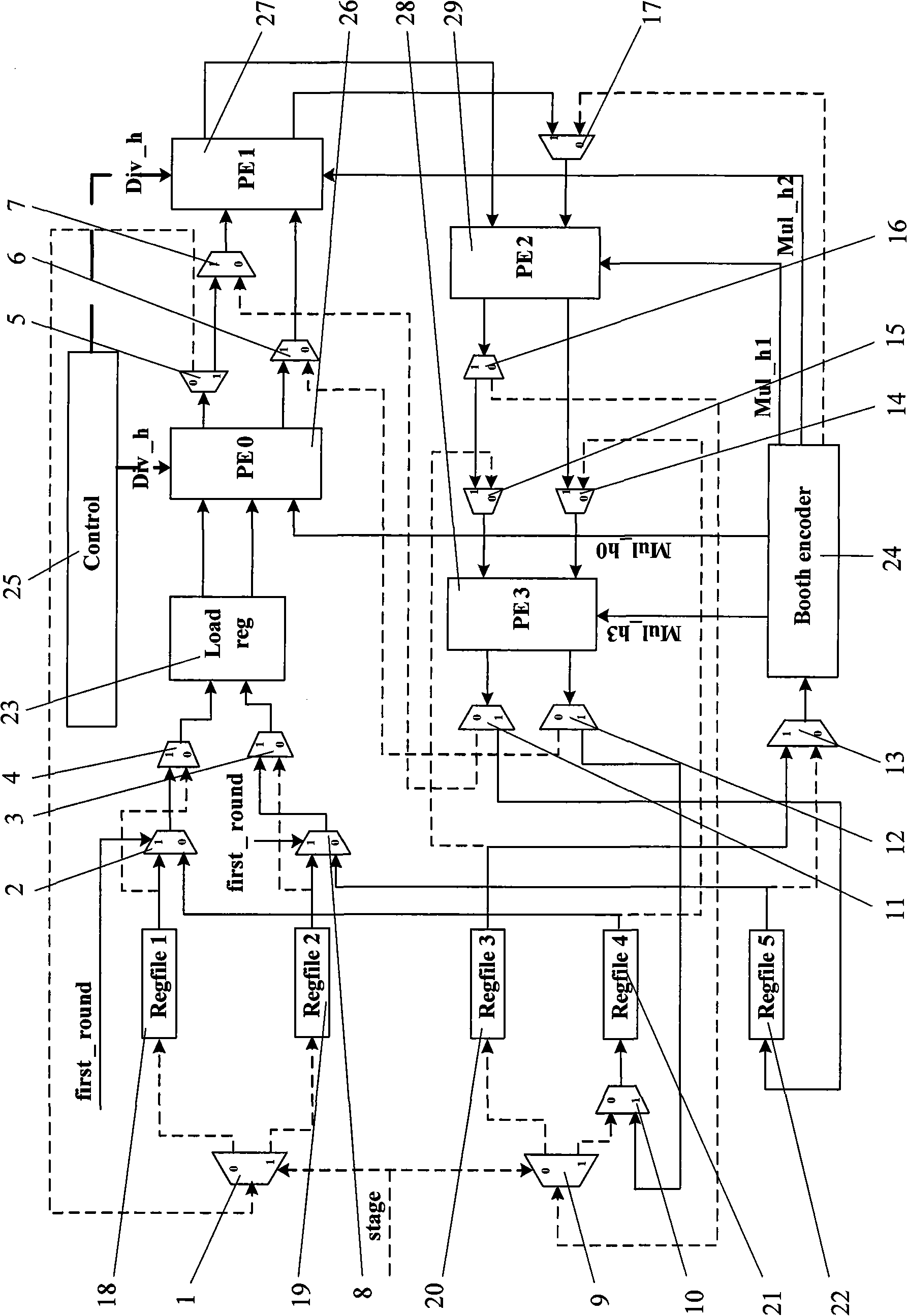

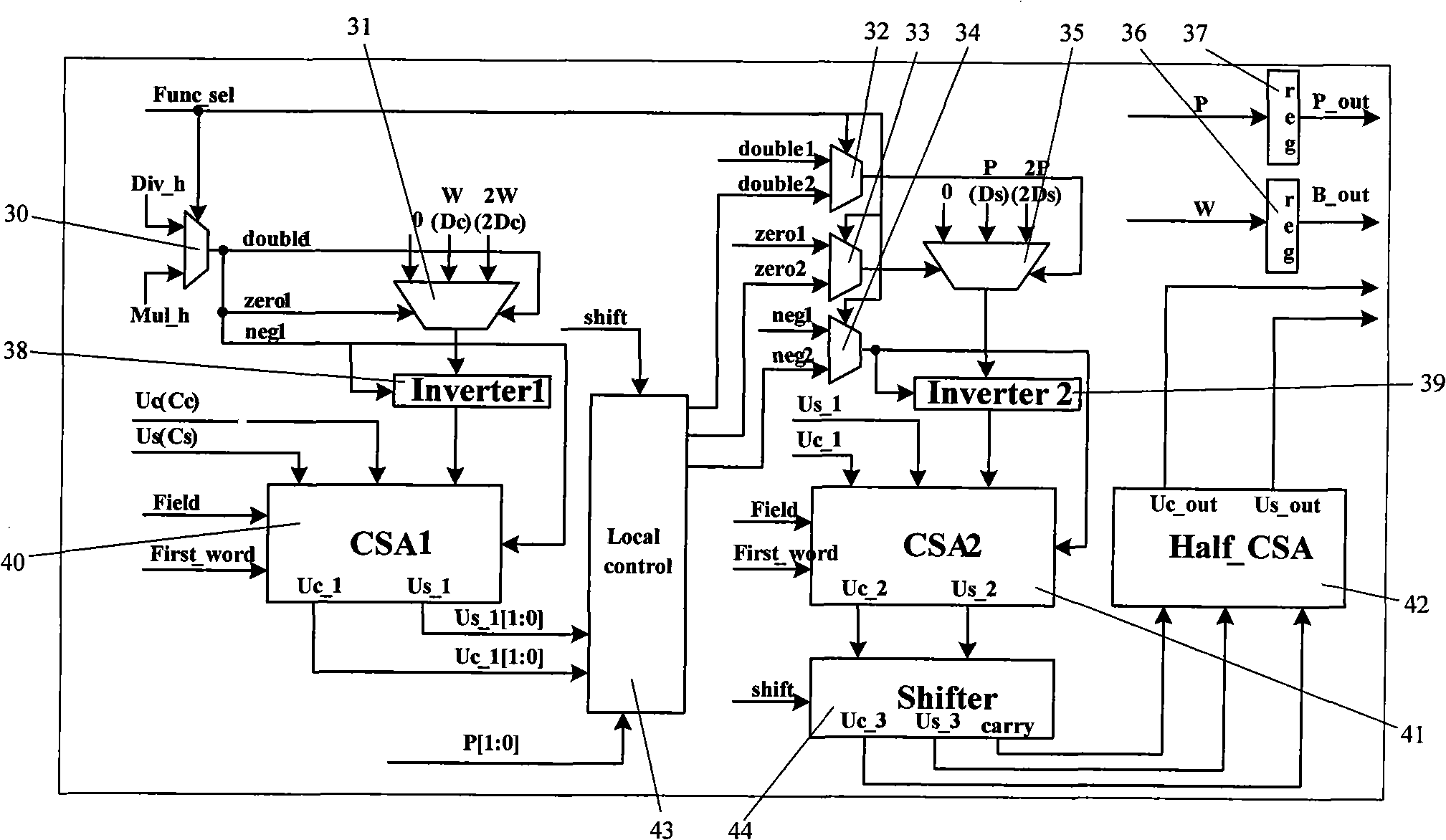

Analog multiplier/divider applicable to prime field and polynomial field

InactiveCN102122241AHigh speedReduce areaComputation using non-contact making devicesExtensibilityByte

The invention relates to a dual-field analog multiplier / divider which is suitable for an ECC (Elliptic Curve Cypher) algorithm required in high-speed network application and portable mobile equipment application. The analog multiplier / divider comprises four PE operating units, 5 register files (Regfile), a Booth encoding unit, an input register (Load file), a control module (control) and 17 multi-path selectors. The analog multiplier / divider changes the connection of the four PE operating units and the reading position of data through the 17 multi-path selectors so as to complete analog multiplying or analog dividing, has expandability, can support 480-bit analog multiplying / dividing operations maximally, and shares hardware units for multiplying / dividing operations so as to reduce the area of the hardware; and in the algorithm, addition and subtraction and shift operation of long operands are carried out by the unit of byte, therefore, the convergence rate of the algorithm is greatly accelerated, and further the operating speed is multiplied.

Owner:FUDAN UNIV

Method of testing a sensor

InactiveUS6864677B1Low costSimple circuit configurationAcceleration measurement using interia forcesWave based measurement systemsSignal processing circuitsSemiconductor chip

A sensor comprises a semiconductor pellet (10) including a working portion (11) adapted to undergo action of a force, a fixed portion (13) fixed on the sensor body, and a flexible portion (13) having flexibility formed therebetween, a working body (20) for transmitting an exterted force to the working portion, and detector means (60-63) for transforming a mechanical deformation produced in the semiconductor pellet to an electric signal to thereby detect a force exerted on the working body as an electric signal. A signal processing circuit is applied to the sensor. This circuit uses analog multipliers (101-109) and analog adders / subtracters (111-113), and has a function to cancel interference produced in different directions. Within the sensor, two portions (E3, E4-E8) located at positions opposite to each other and producing a displacement therebetween by action of a force are determined. By exerting a coulomb force between both the portions, the test of the sensor is carried out. Further, a pedestal (21, 22) is provided around the working body (20). The working body and the pedestal are located with a predetermined gap or spacing therebetween. A displacement of the working body is caused to limitatively fall within a predetermined range corresponding to the spacing. The working body and the pedestal are provided by cutting a same common substrate (350, 350).

Owner:WAKO CO LTD

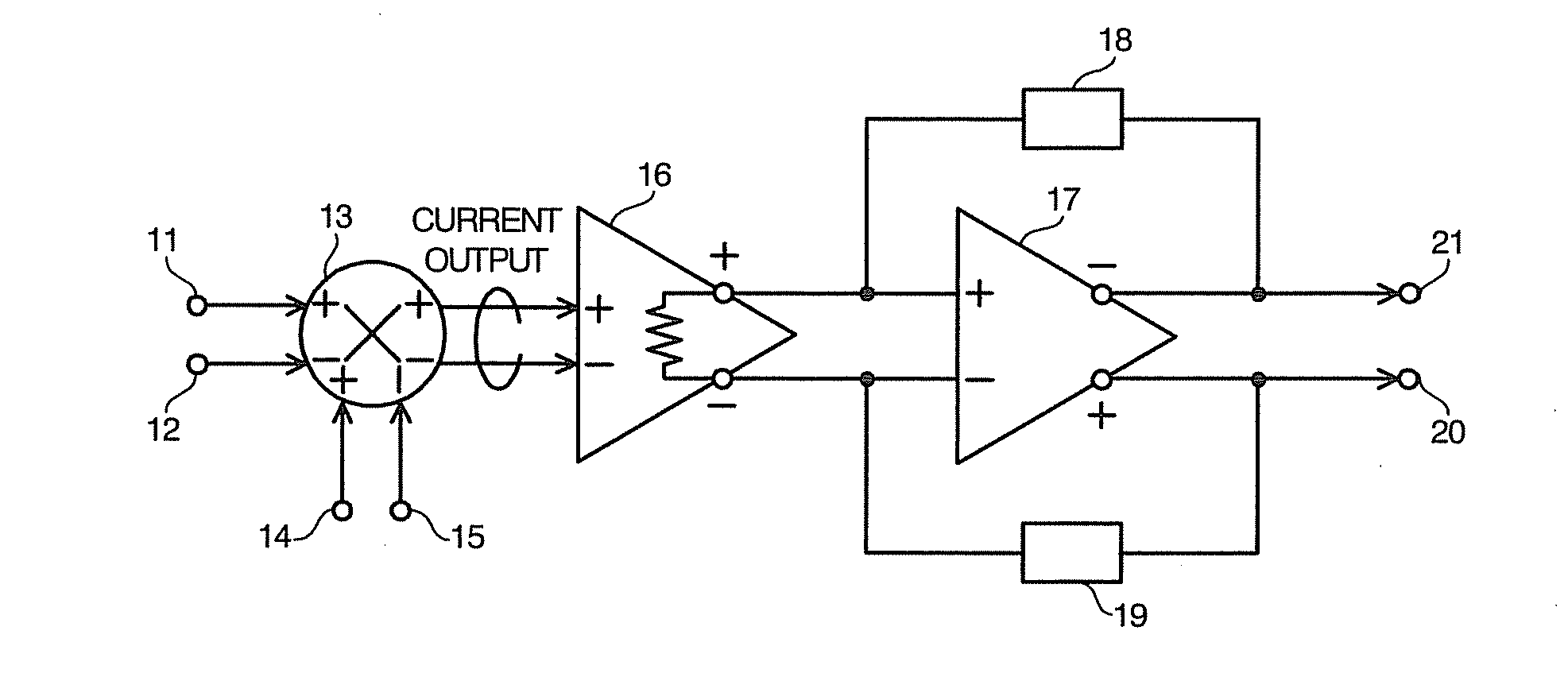

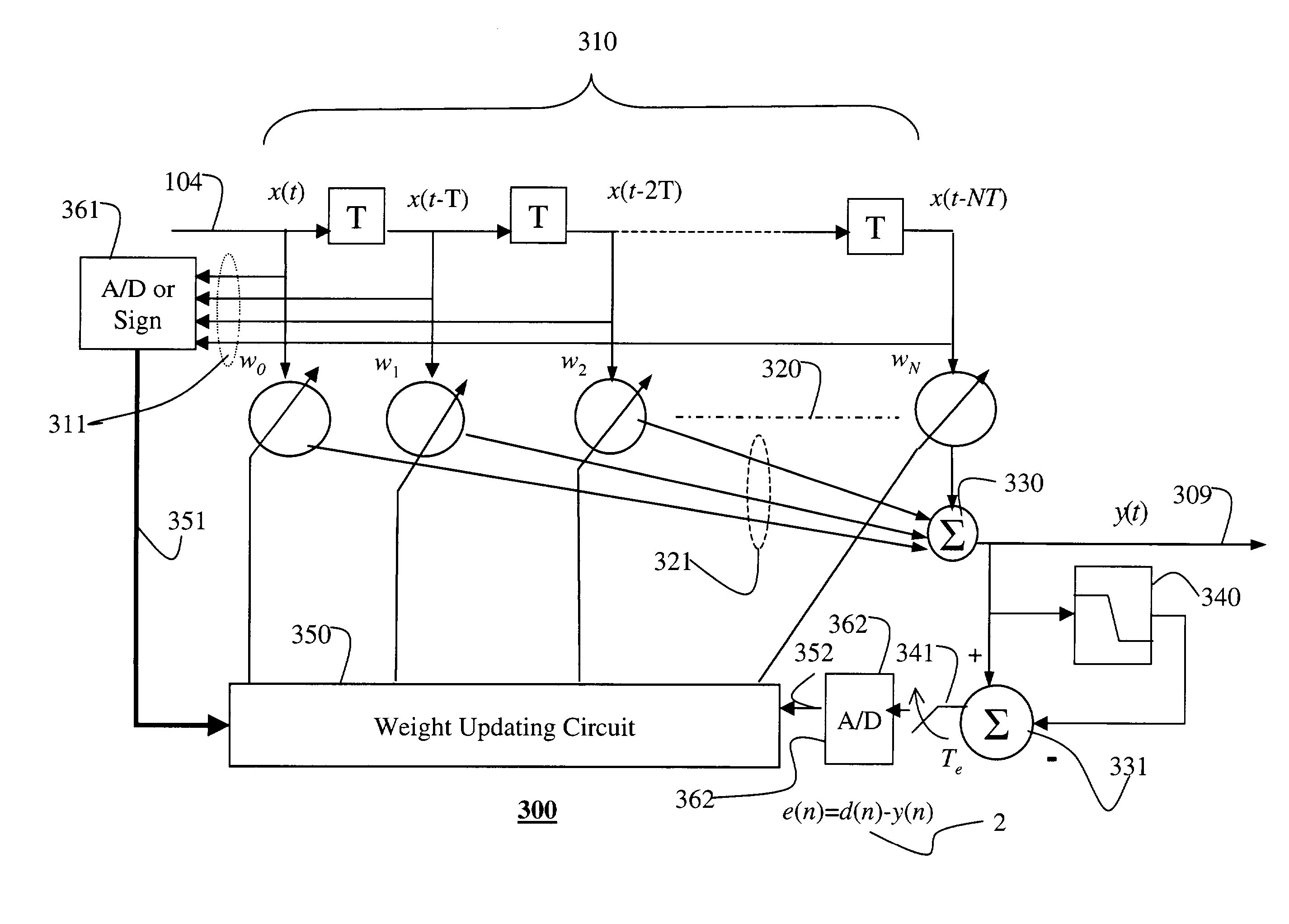

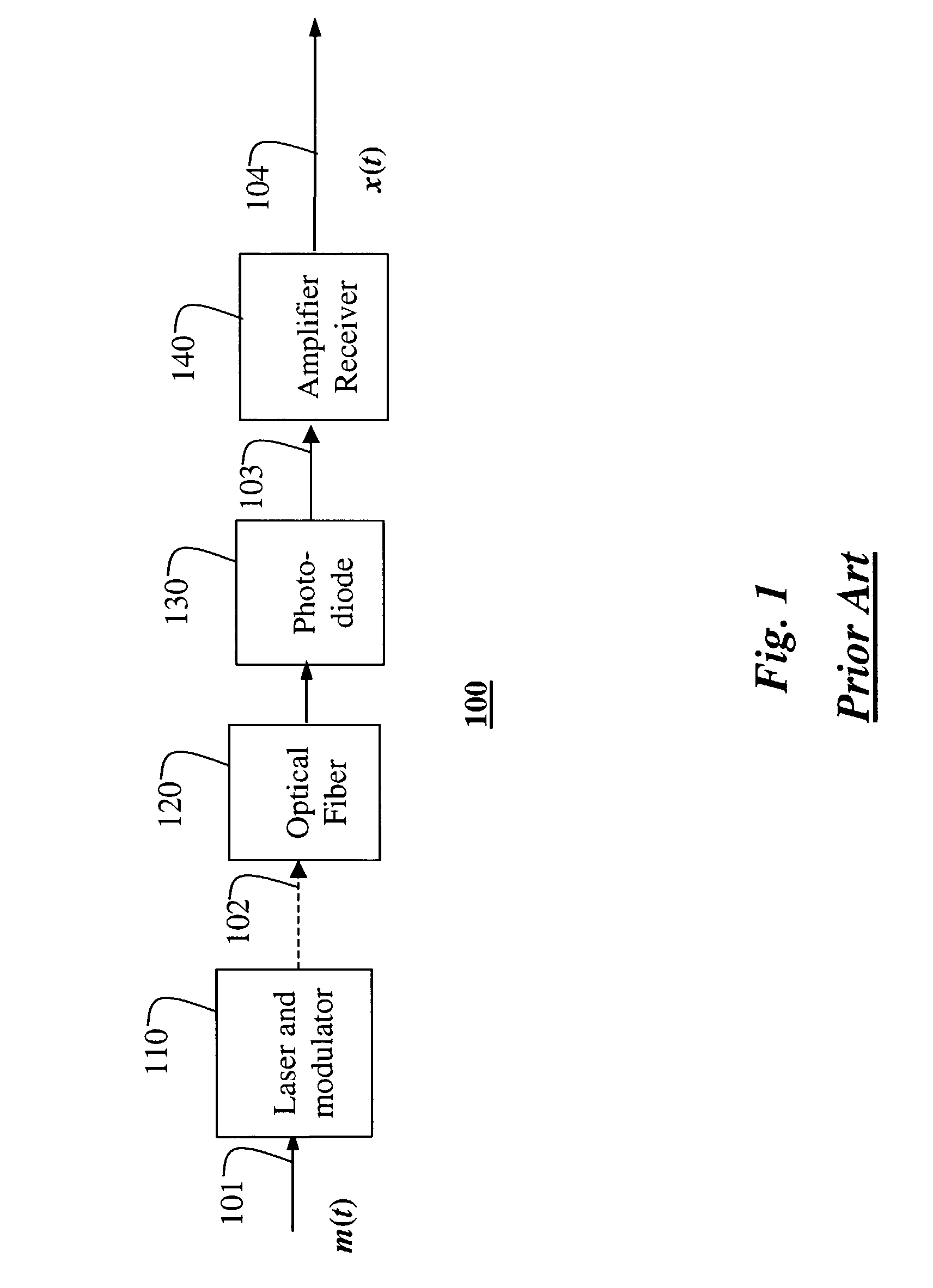

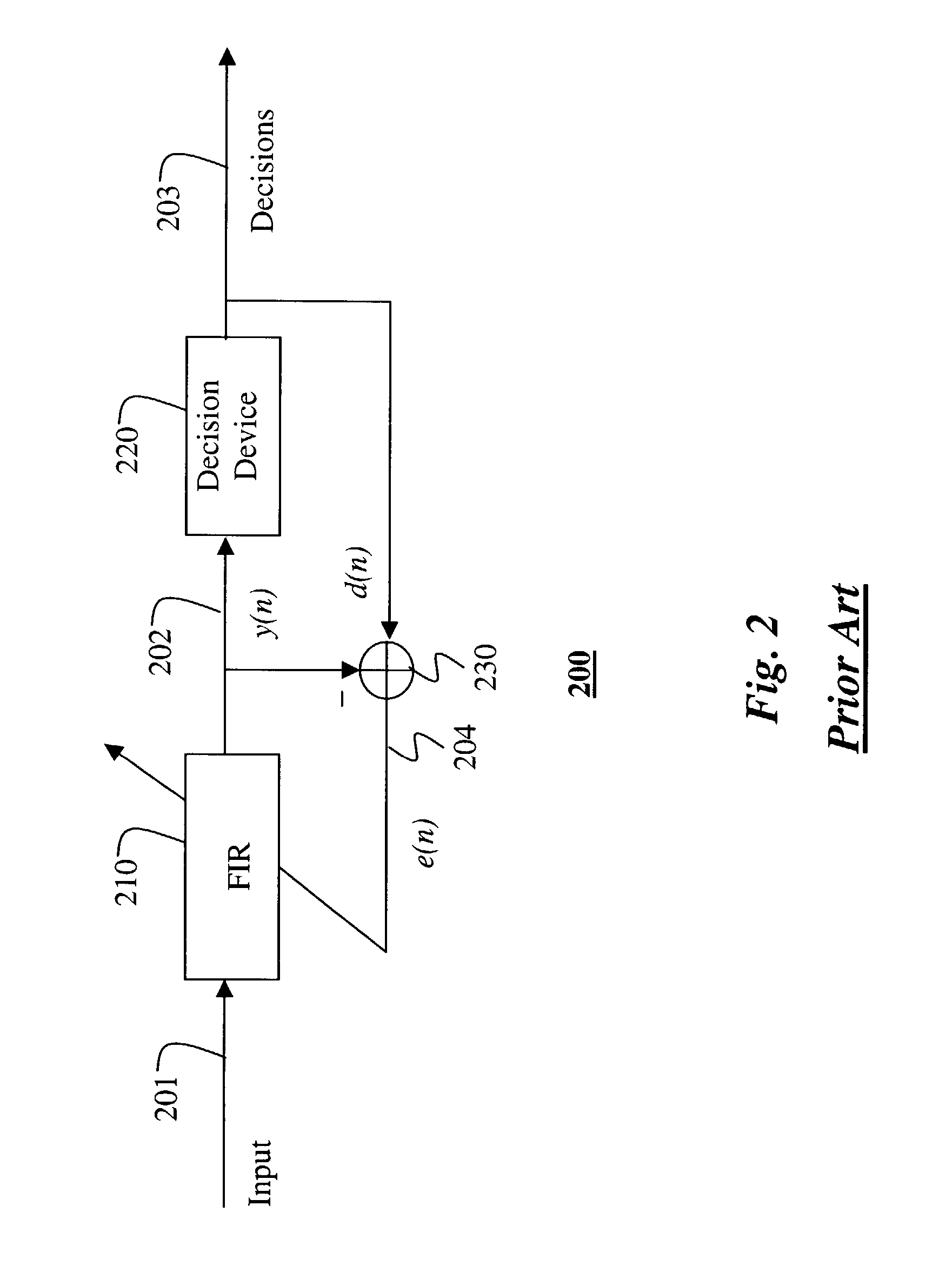

Hybrid adaptive equalizer for optical communications systems

InactiveUS7023912B2Reduce Intersymbol InterferenceEliminate needMultiple-port networksTransmission control/equlisationCommunications systemAnalog delay line

A method equalizes a received signal in an optical communications system. The received signal is passed through an analog delay line where it is tapped to generate a set of delayed copies of the received signal. In a set of analog multipliers, each delayed copy of the received signal is multiplied by a corresponding weight to generate a set of weighted signals that are then summed to produce an output signal. The output signal is thresholded and subtracted from the output signal to produce an error signal, which is periodically sampled. In a digital weight updating circuit, the weights are produced from digitized versions of the sampled error signal and samples of the delayed copies of the received signal.

Owner:MITSUBISHI ELECTRIC RES LAB INC

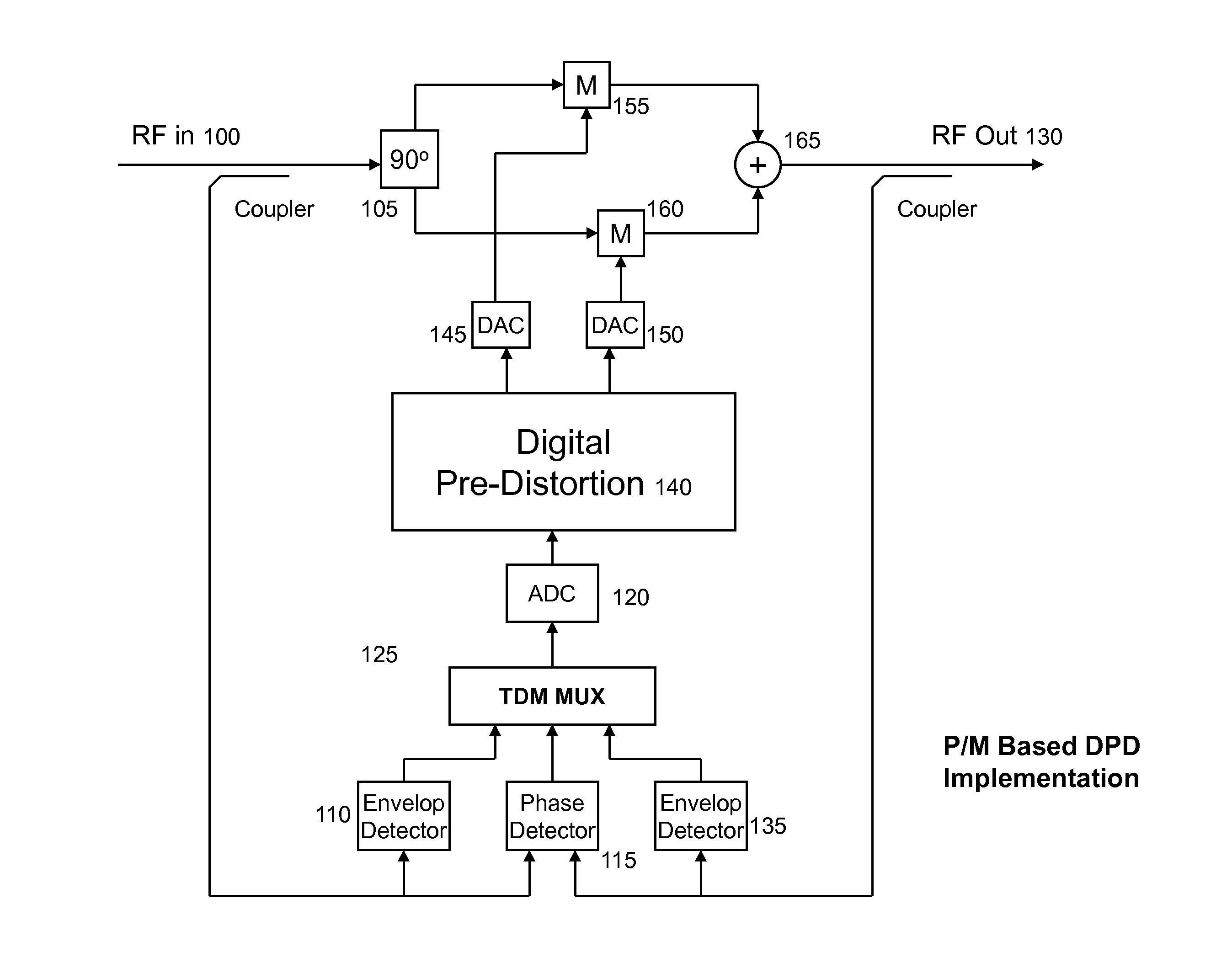

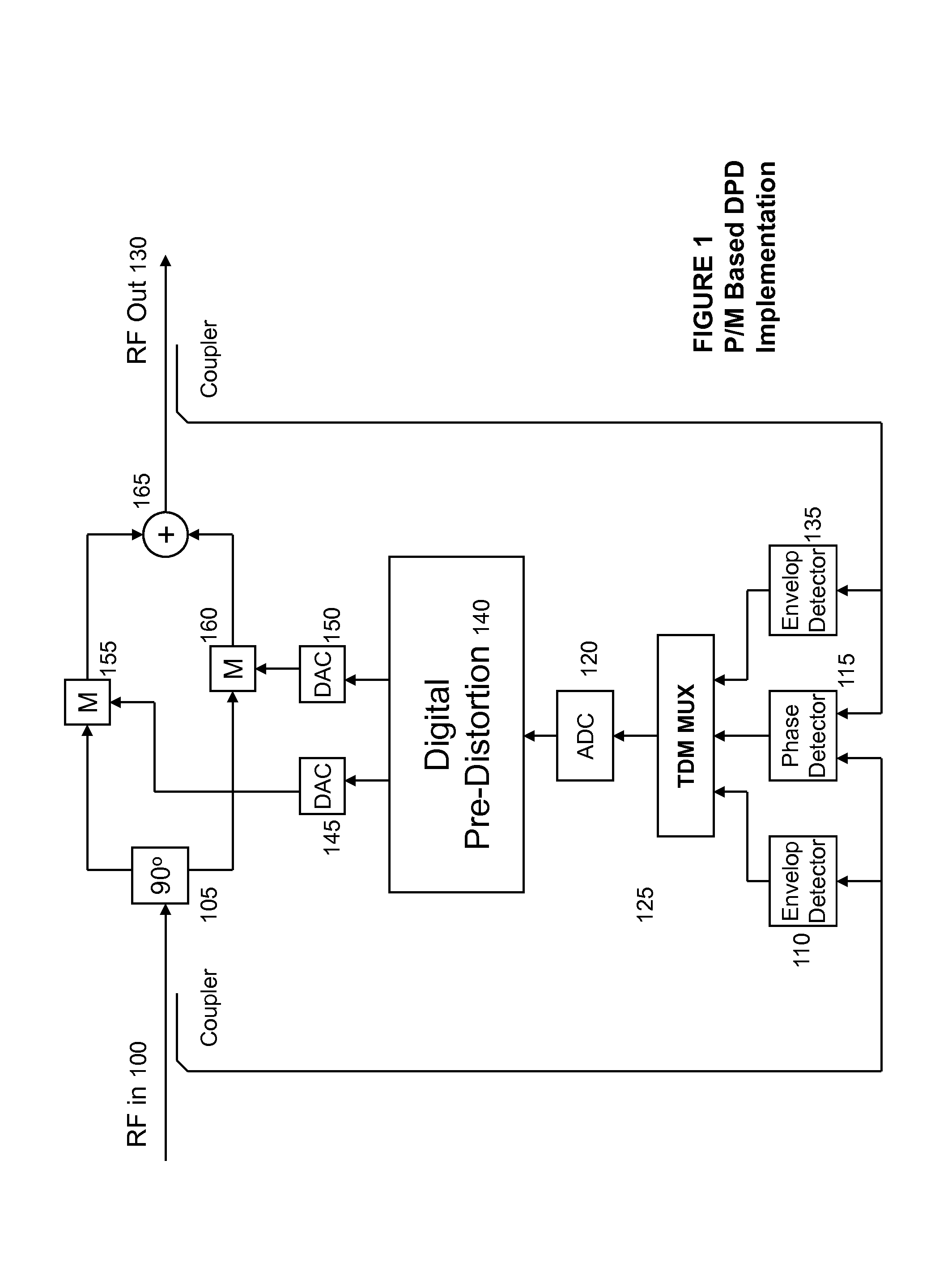

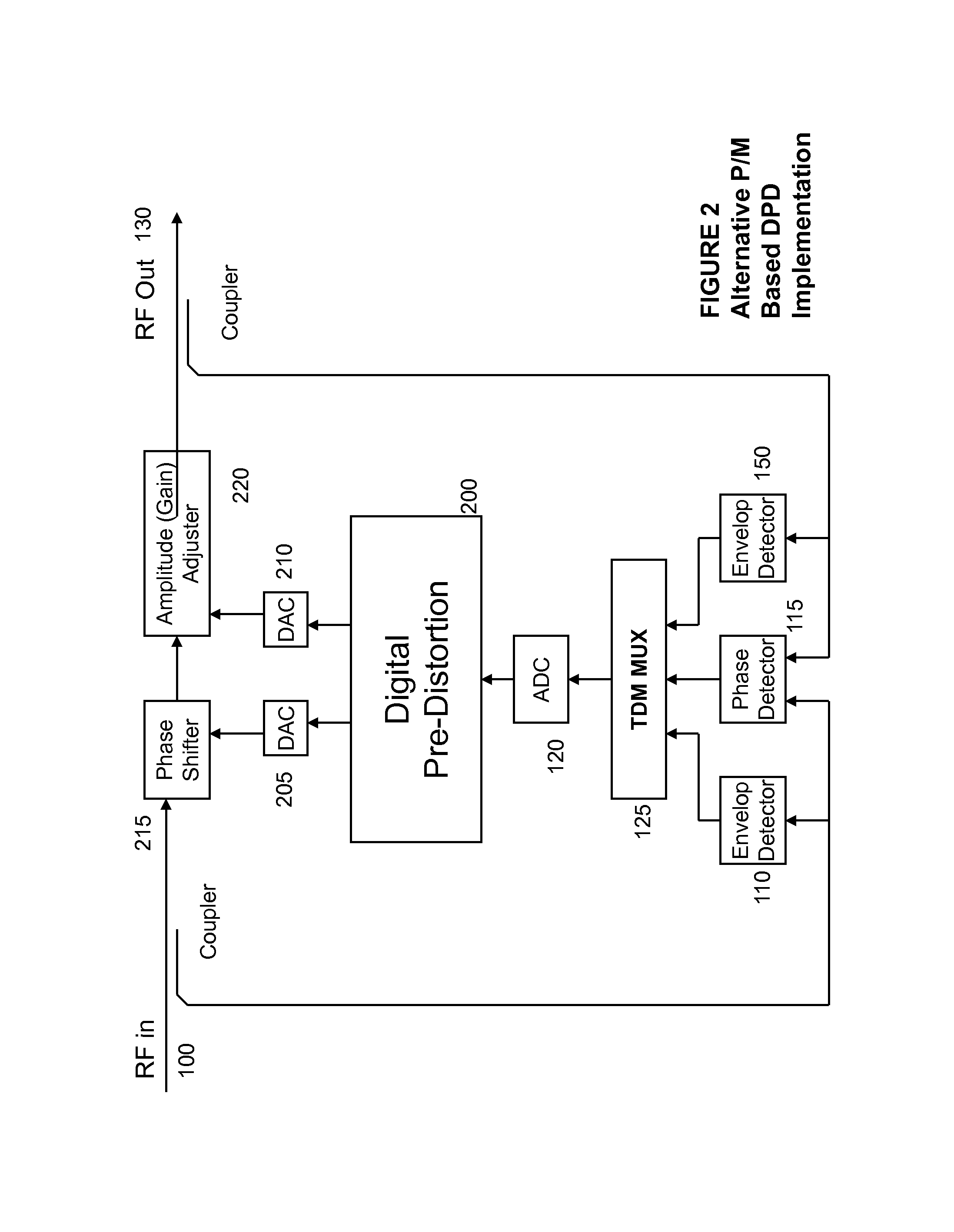

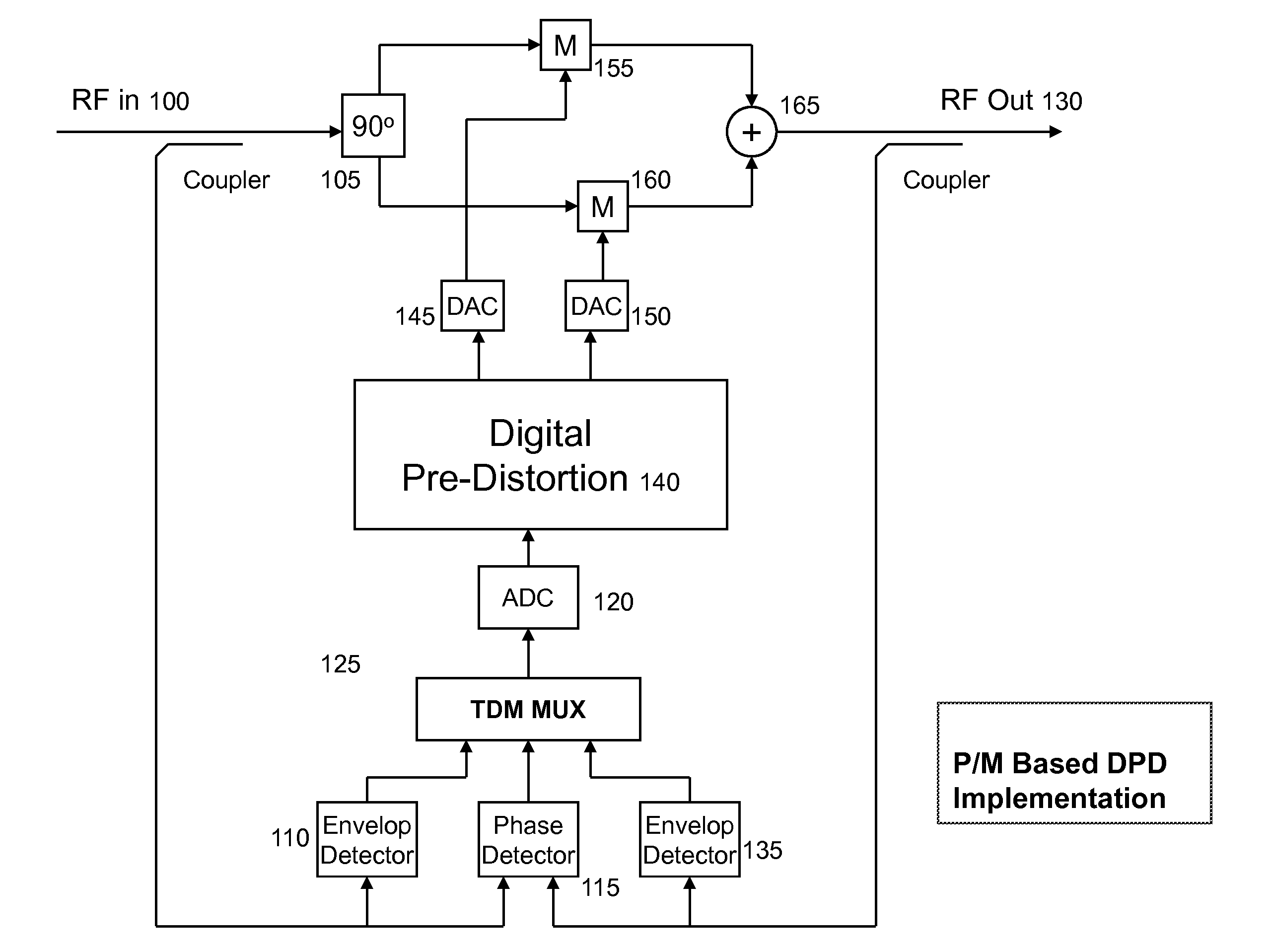

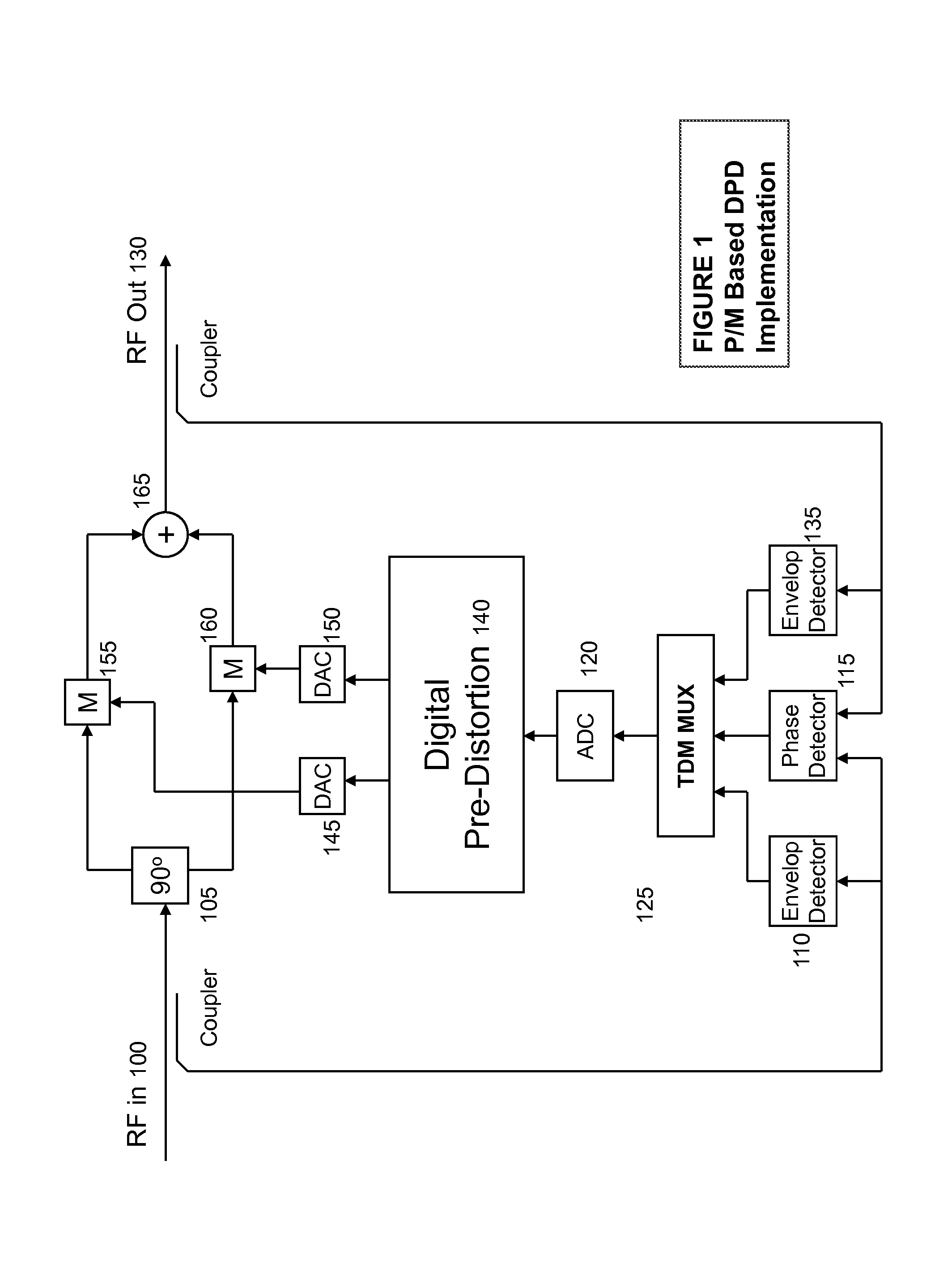

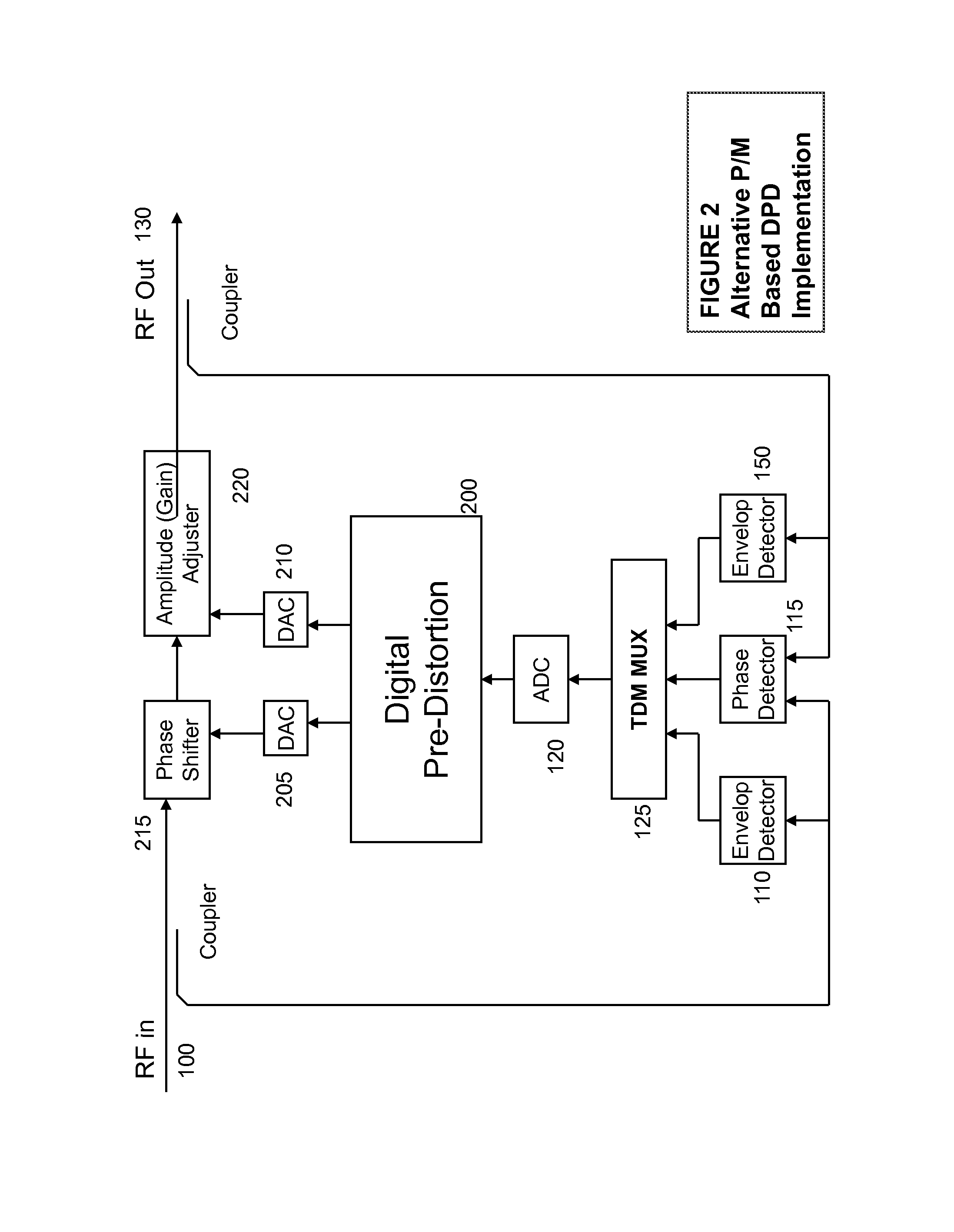

Power amplifier predistortion methods and apparatus using envelope and phase detector

ActiveUS8224266B2Resonant long antennasAmplifier modifications to reduce noise influenceLow noiseCarrier signal

An embodiment of the invention is a predistortion approach to linearize a power amplifier without frequency conversion of the RF signals by using envelope and phase detectors to detect the error to be corrected, and then one or more analog multiplier(s) and a DSP-based processor. For the analog embodiment, the inherent nature of the analog circuitries allows digital predistortion processing structured directly at the RF band, and enables a single power amplifier to support multi-modulation schemes, multi-carriers and multi-channels. As a result, the predistortion architecture is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems. The wireless system performance can be improved and upgraded just by using the new PA module rather than change or rebuild new subsystem in existing base station. The analog embodiment can also mix and match its analog multipliers with other analog components such as phase splitters, phase shifters, attenuators, filters, couplers, mixers, low-noise amplifiers, buffers, envelope detectors, and etc., to provide additional features.

Owner:DALI SYST LTD

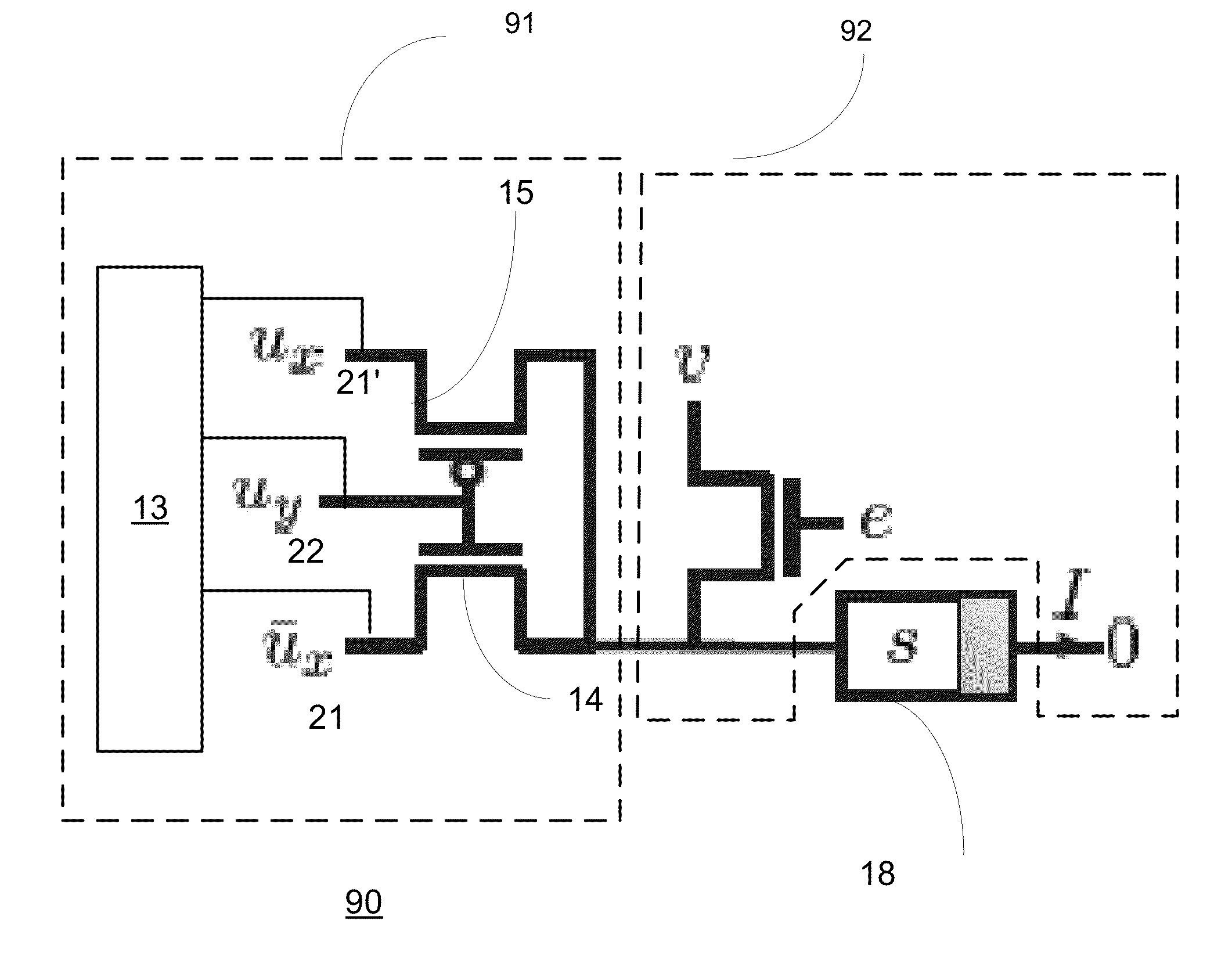

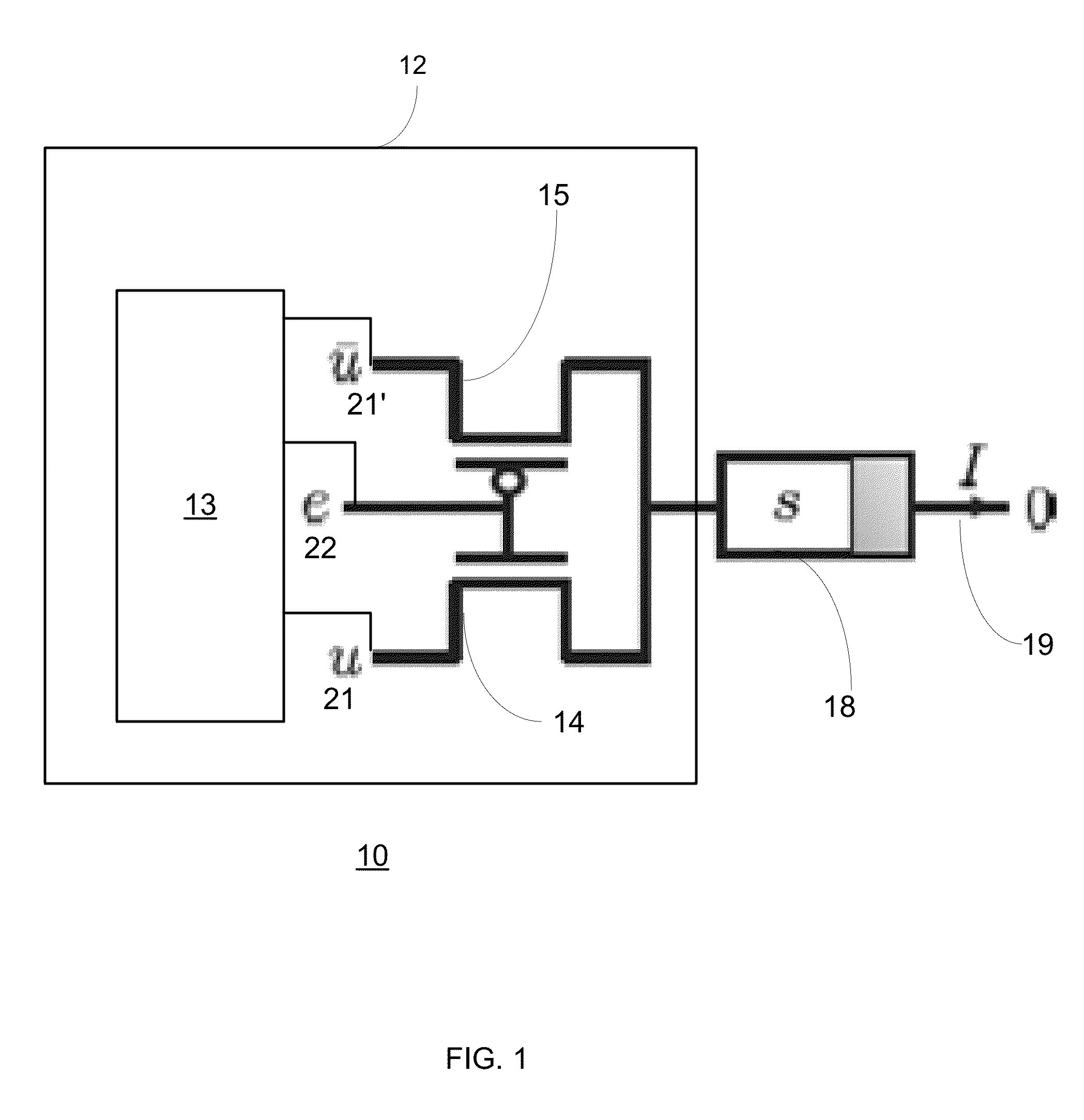

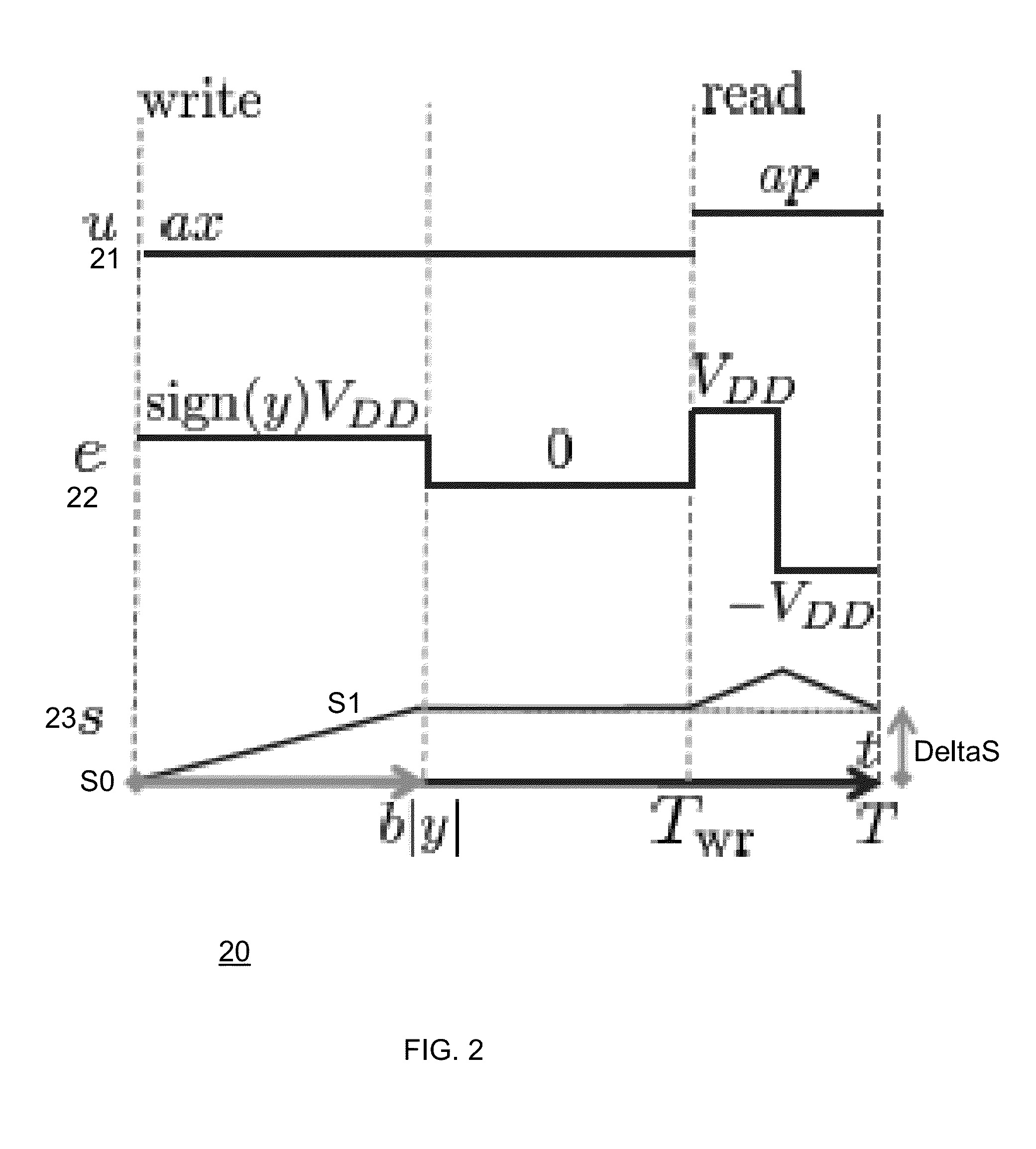

Analog multiplier using a memristive device and method for implemening hebbian learning rules using memrisor arrays

ActiveUS20140289179A1Digital computer detailsComputing operations for multiplication/divisionBinary multiplierAlgorithm

A device, comprising: an array of cells, wherein the cells are arranged in columns and rows; wherein each cell comprises a memristive device; an interfacing circuit that is coupled to each cell of the array of cells; wherein the interfacing circuit is arranged to: receive or generate first variables and second variables; generate memristive device input signals that once provided to memristive devices of the array will cause a change in a state variable of each of the memristive devices of the cells of the array, wherein the change in the state variable of each of the memristive devices of the cells of array reflects a product of one of the first variables and one of the second variables; provide the memristive device input signals to memristive devices of the array; and receive output signals that are a function of at least products of the first variables and the second variables;

Owner:TECHNION RES & DEV FOUND LTD

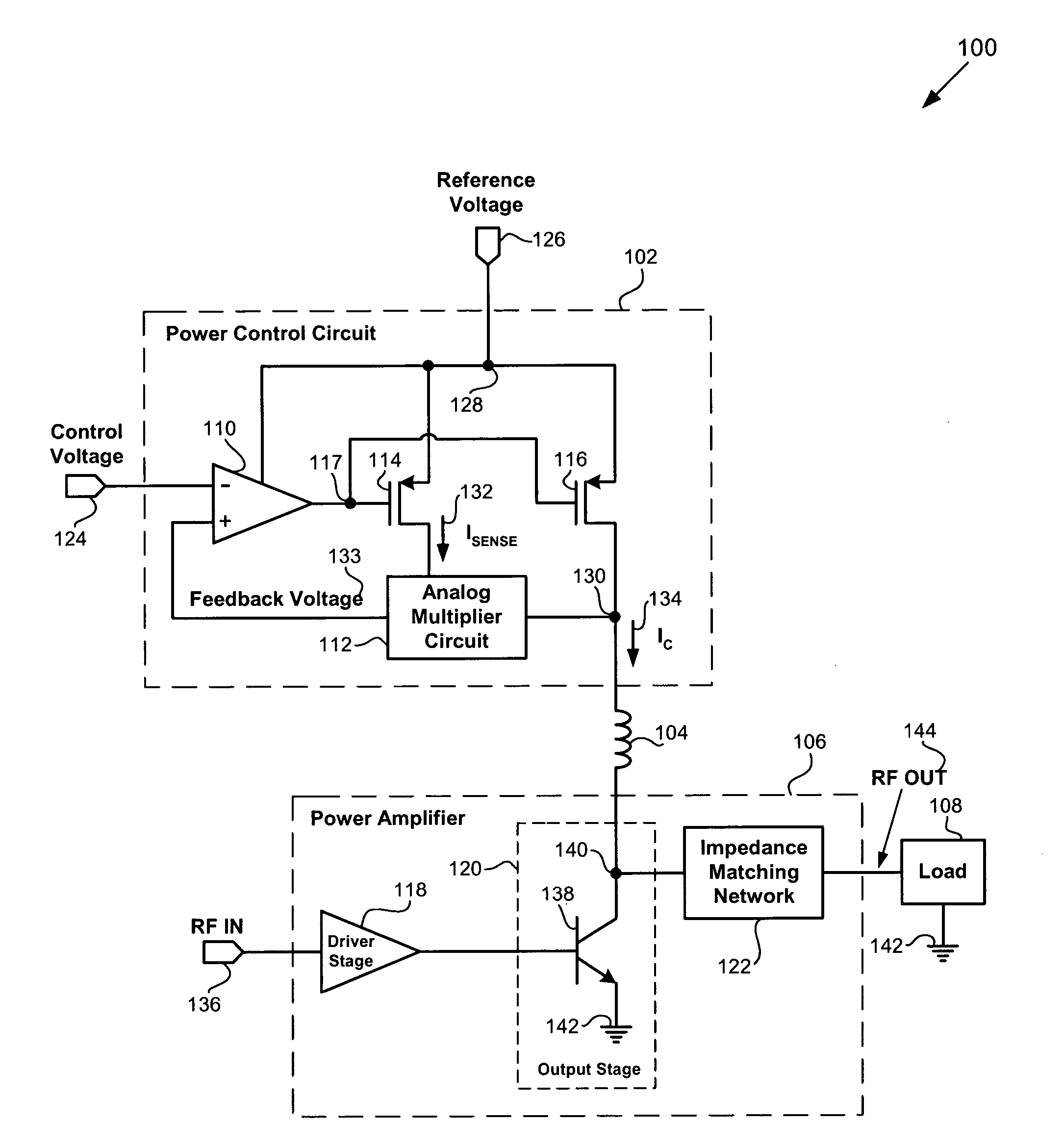

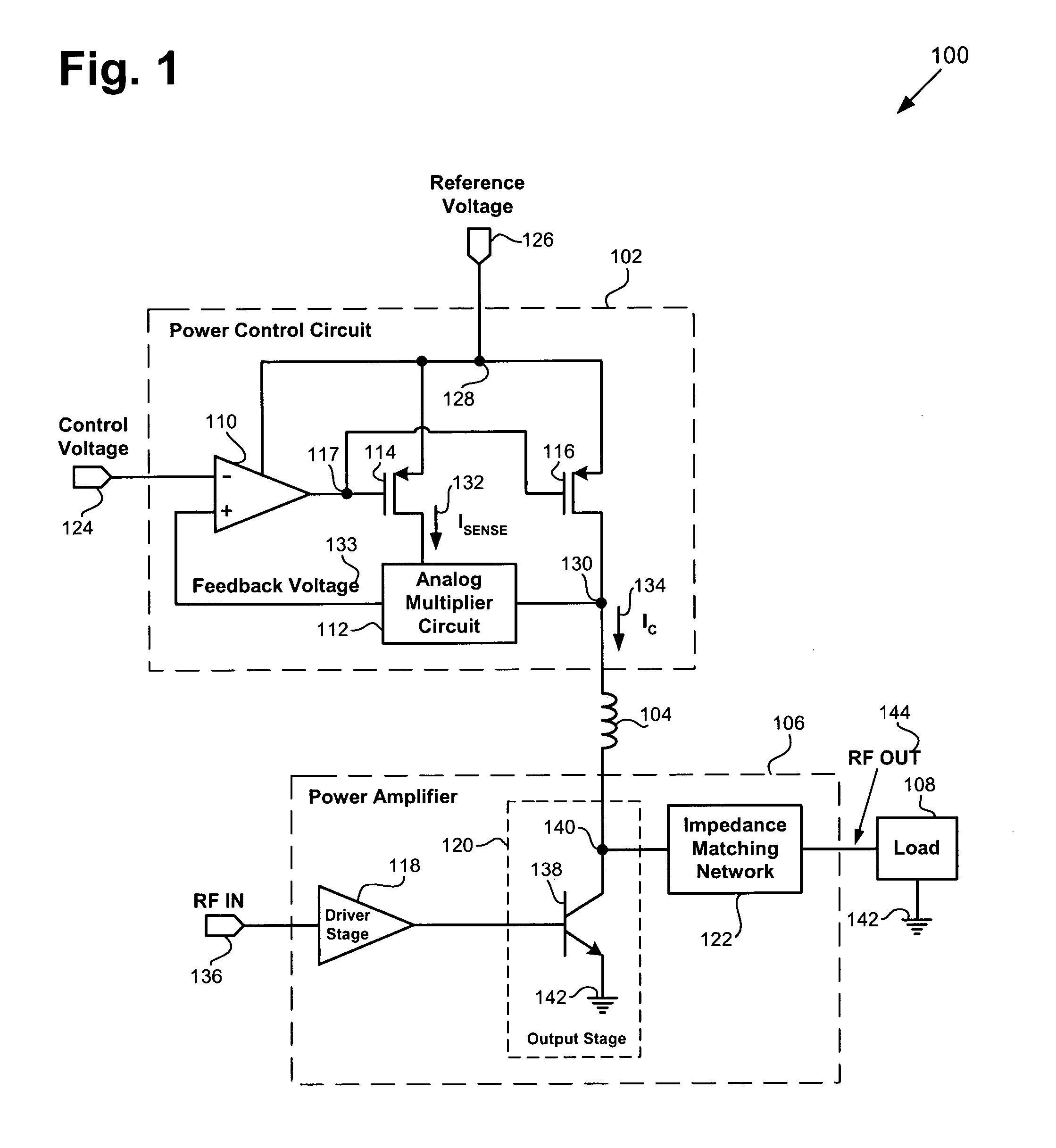

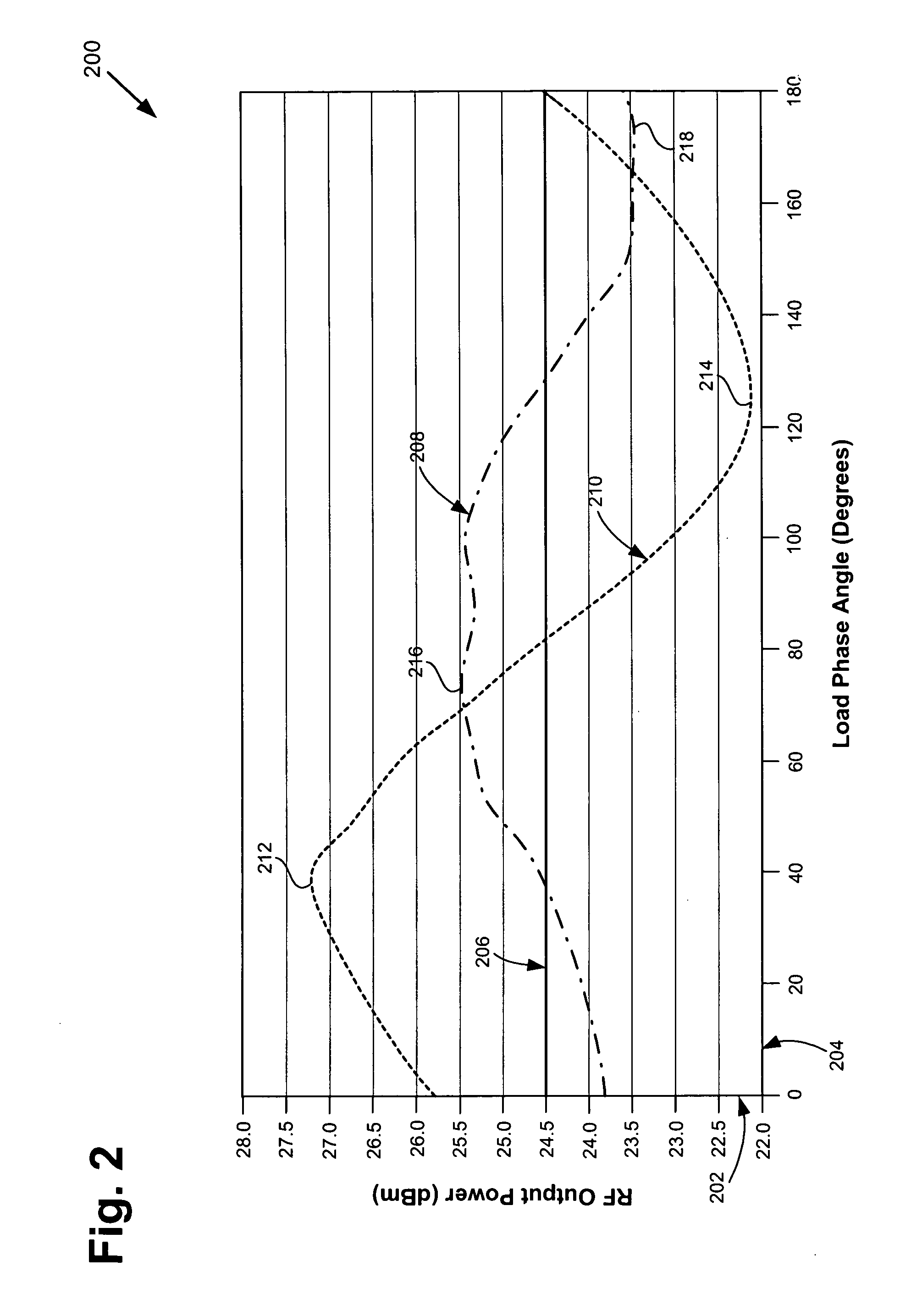

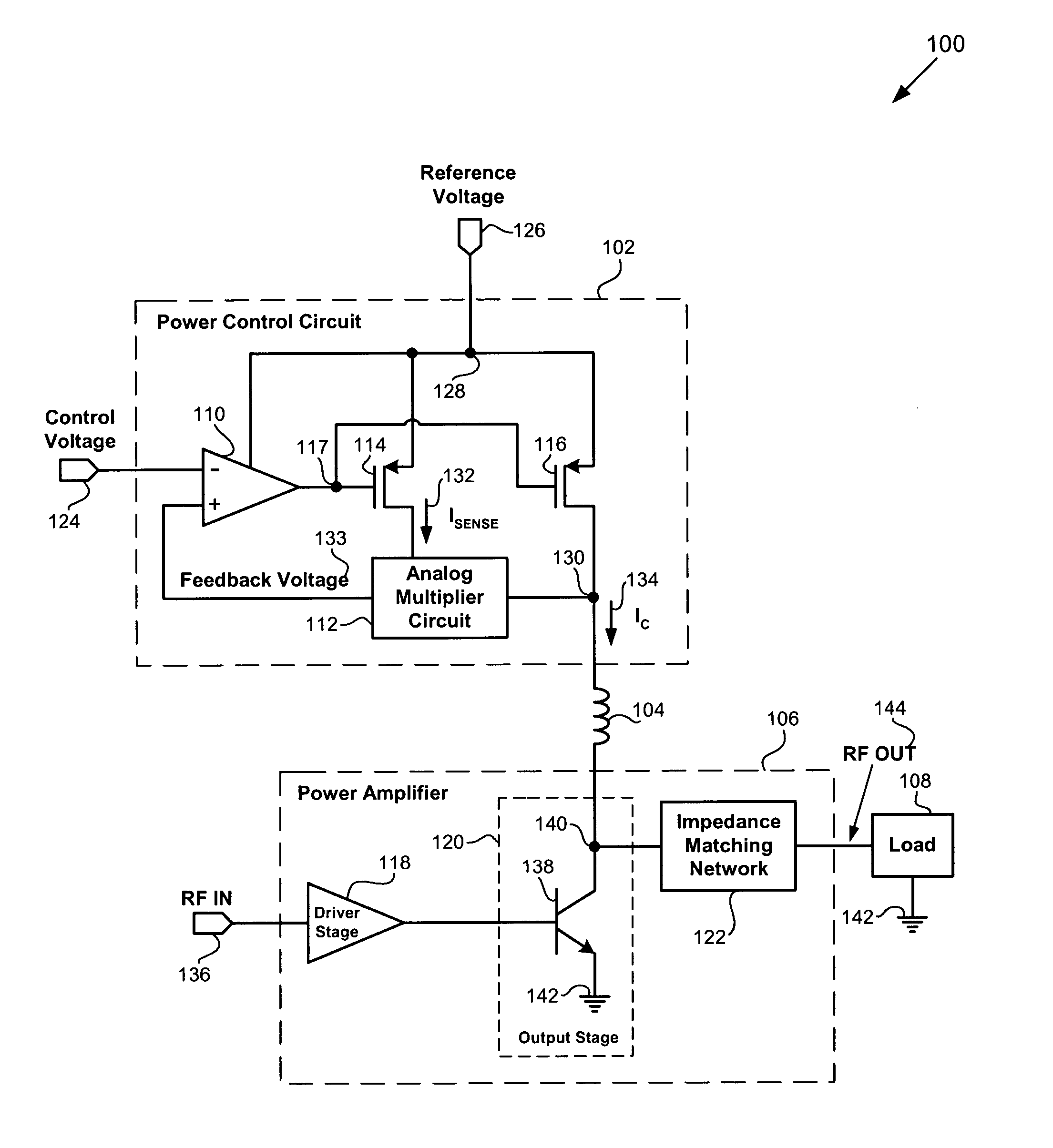

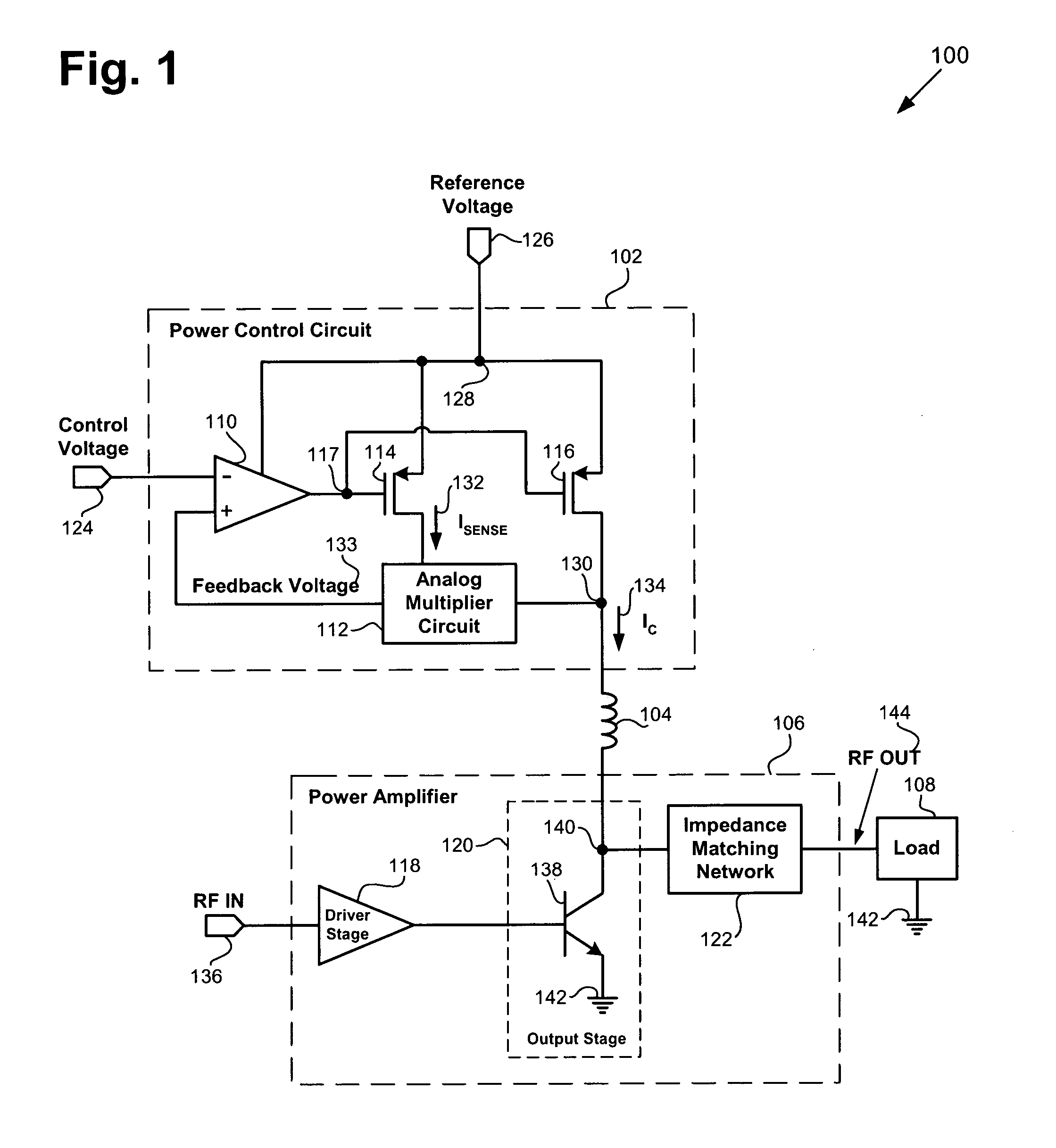

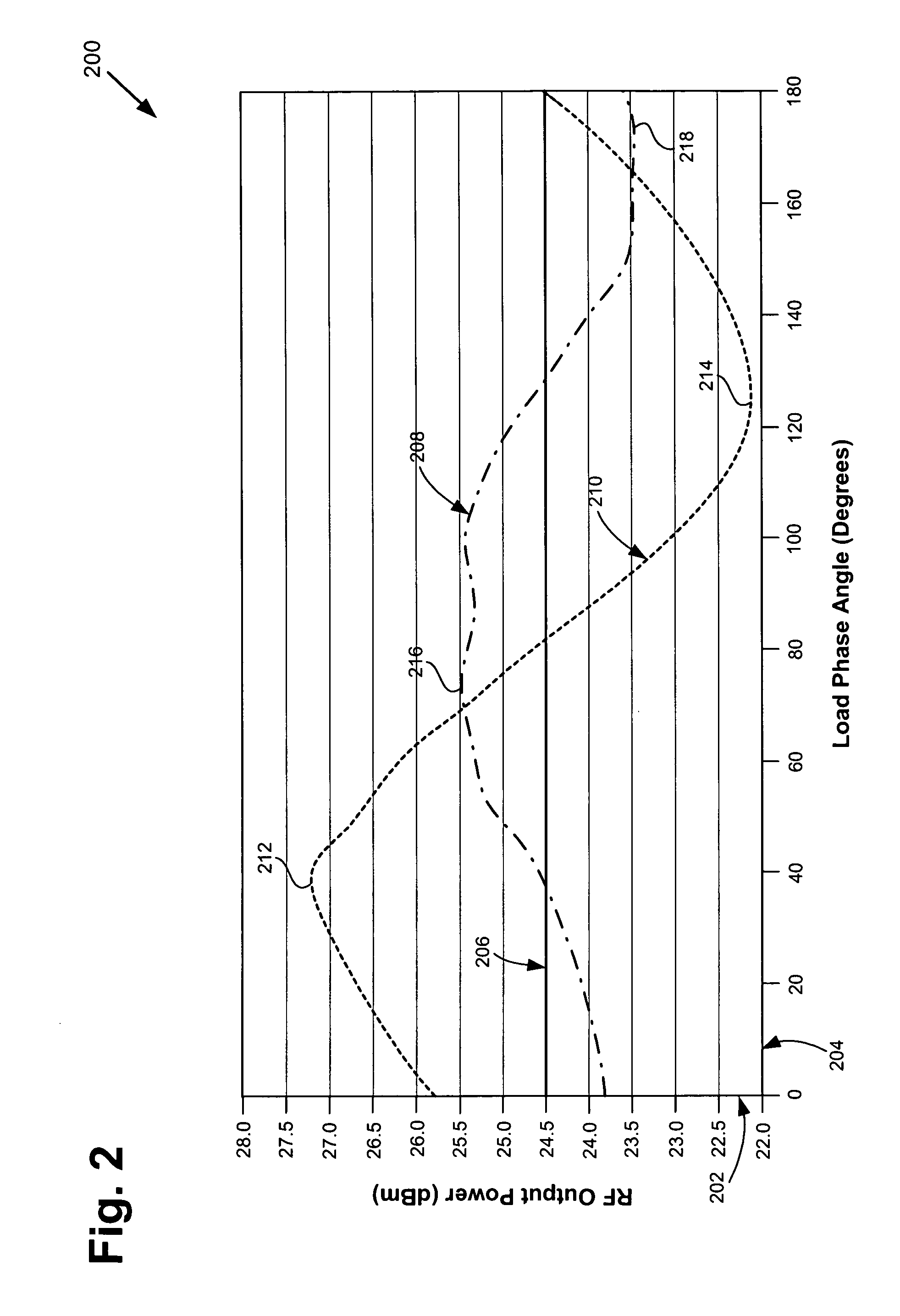

Power control circuit for accurate control of power amplifier output power

According to an exemplary embodiment, an amplification module includes a power control circuit. The amplification module further includes a power amplifier coupled to the power control circuit and configured to draw a supply current and receive a supply voltage from the power control circuit. The power control circuit is configured to control a DC power provided to the power amplifier by controlling a product of a sense current, which is a mirror current of the supply current, and the supply voltage. The power control circuit includes a feedback voltage that corresponds to the product of the sense current and the supply voltage. The power control circuit further includes an analog multiplier circuit configured to receive the sense current and the supply voltage and generate the feedback voltage. The power control circuit further includes a differential error amplifier configured to compare the feedback voltage to a control voltage.

Owner:SKYWORKS SOLUTIONS INC

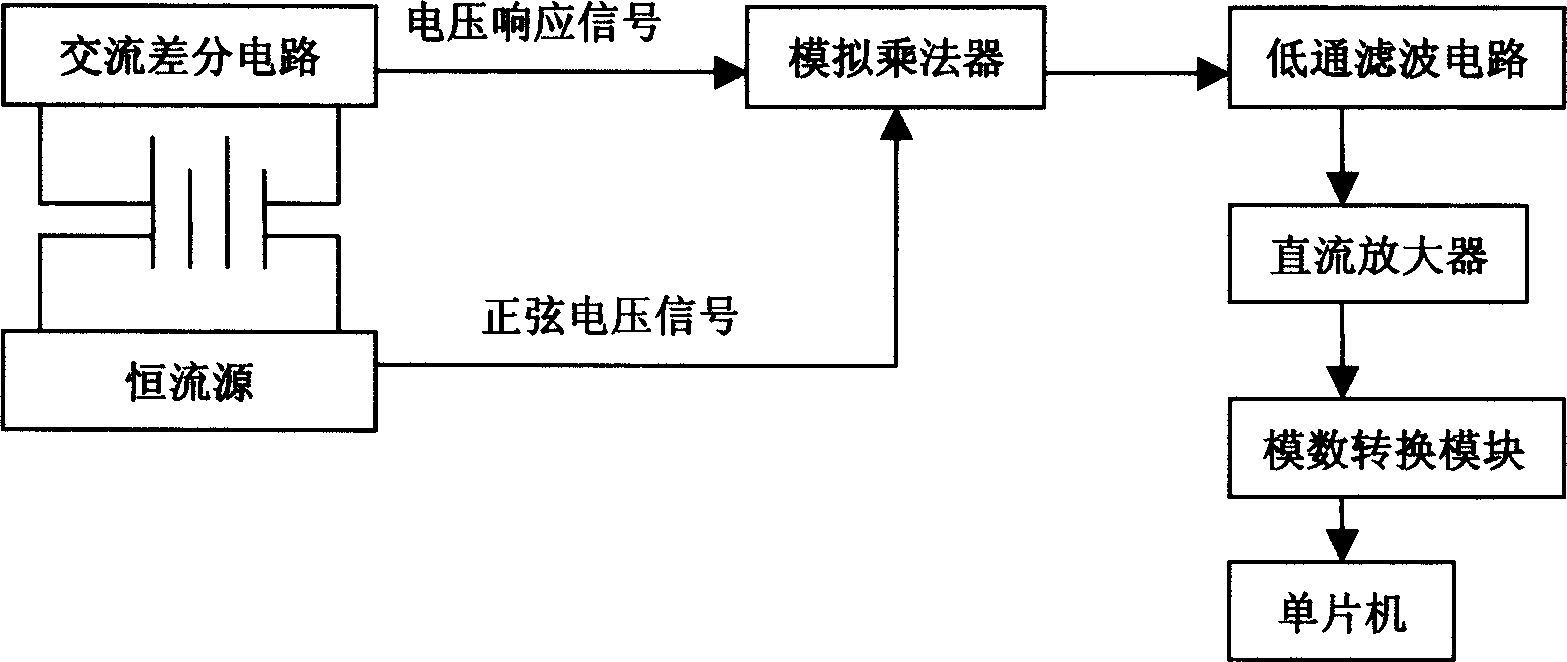

Method for measuring internal resistance of storage battery

InactiveCN1763551ASimplify complexityResistance/reactance/impedenceElectrical testingLow-pass filterInternal resistance

The invention discloses an accumulator internal resistance measuring method, which comprises the following steps: first, preparing four terminals with two for measuring and other two for supplying alternating current actuation current signal; second, letting pressure response signal of accumulator multiplied by the sine pressure signal of constant alternating current source in the analog multiplier; third, transforming the alternating current signal output of analog multiplier into direct current signal through low-pass filter circuit; forth, sending the magnified direct current signal into the modular transformation mode.

Owner:ZHUHAI TITANS TECH

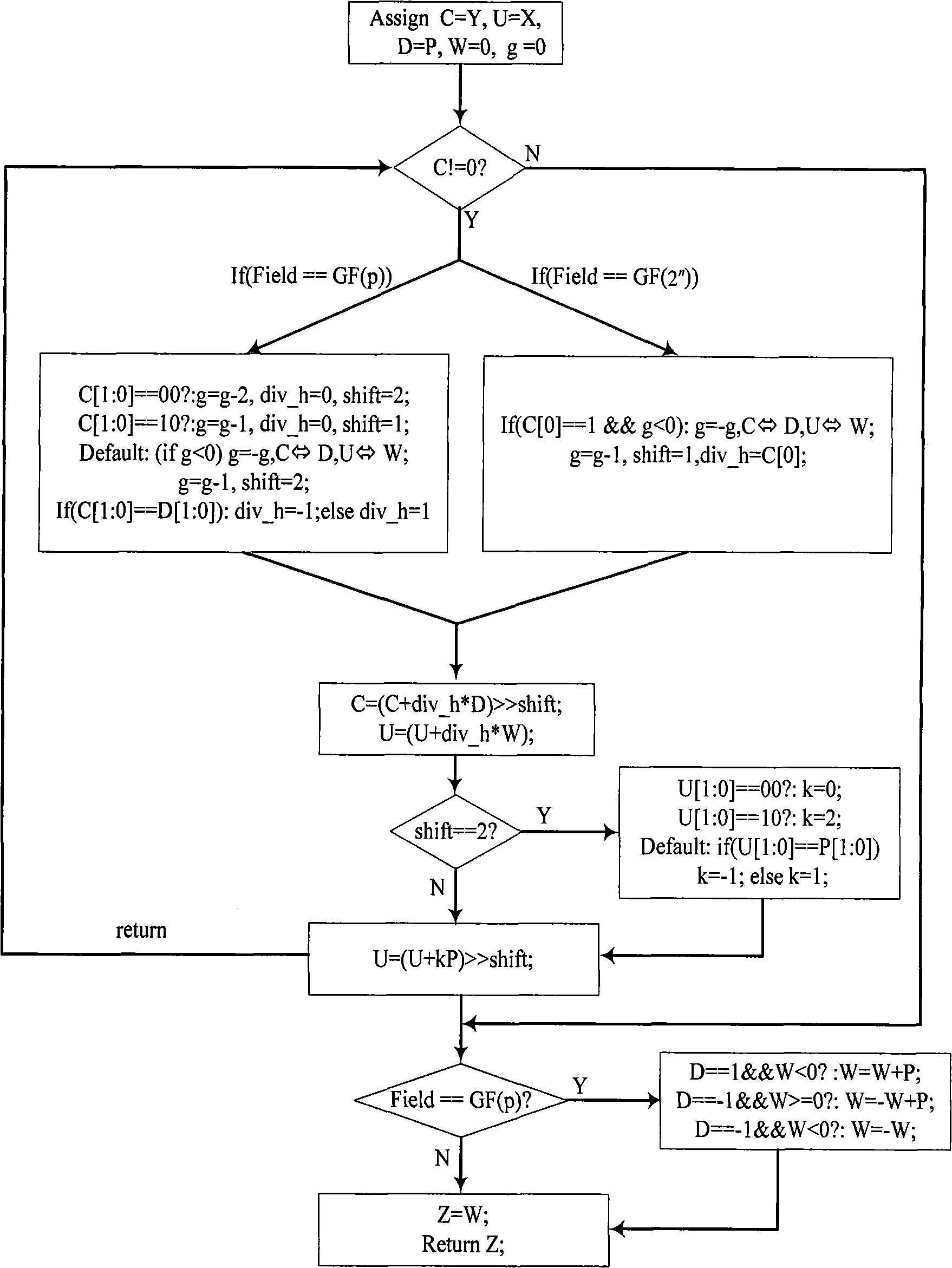

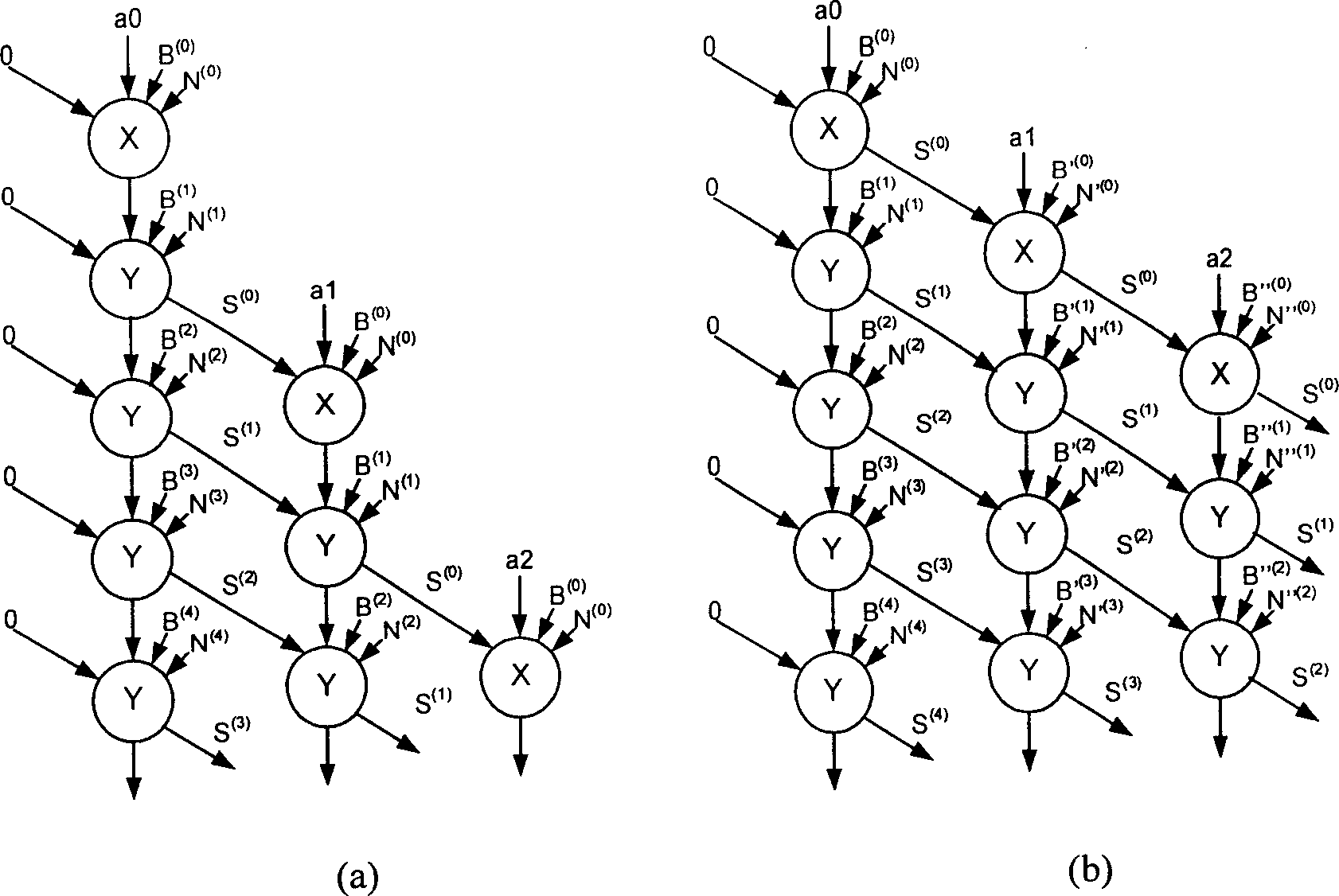

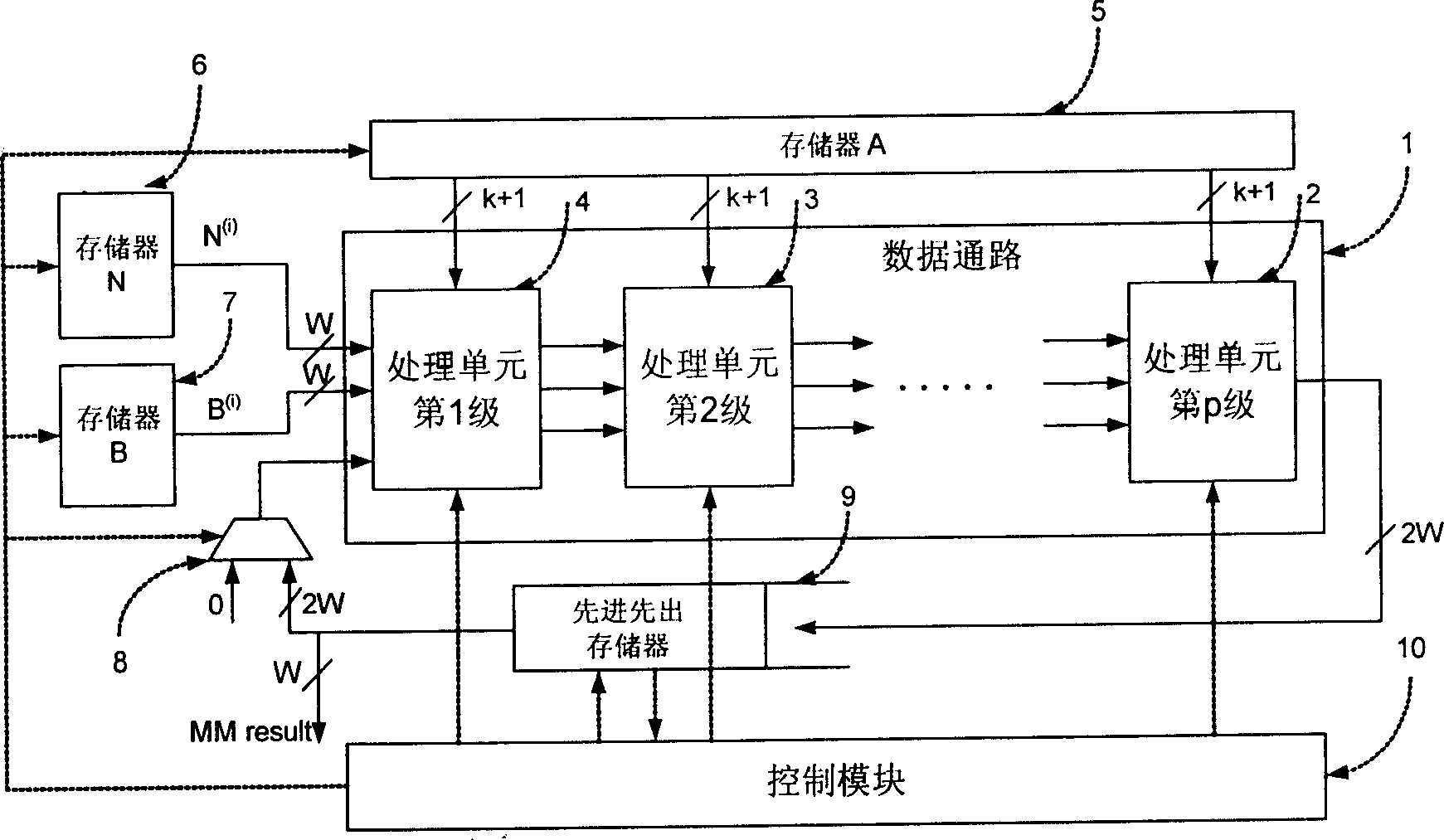

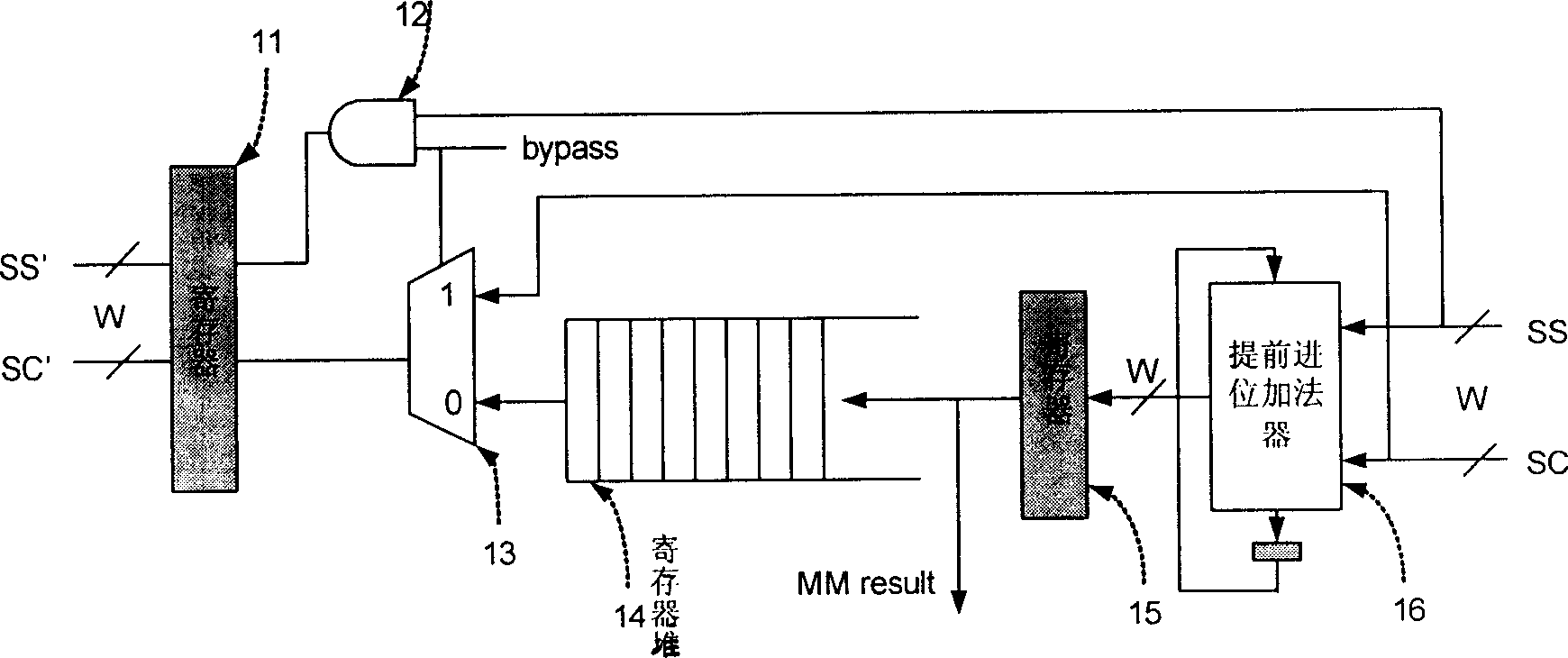

Extensible high-radix Montgomery's modular multiplication algorithm and circuit structure thereof

InactiveCN1731345AHigh speedReduce overheadComputations using residue arithmeticMontgomery reductionAnalog multiplier

The invention relates to an extended high base Montgomery analog multiplying algorithm and the circuit structure in the field of integrated circuit technology. It improves multiply characters high base Montgomery analog multiplying algorithm, wherein each step dose left shift operation to the batch N and the multiplicand B but not to the result S so that the delay between the two data path lines can de reduced from two clock weeks to one clock week. The circuit structure comprises: three storages used to store A, B and N operation numbers, a line type data path module which is formed by first stage to p stage processing units, a control module used to control the entire analog multiplier computing course and first-in first-out storage.

Owner:上海微科集成电路有限公司 +1

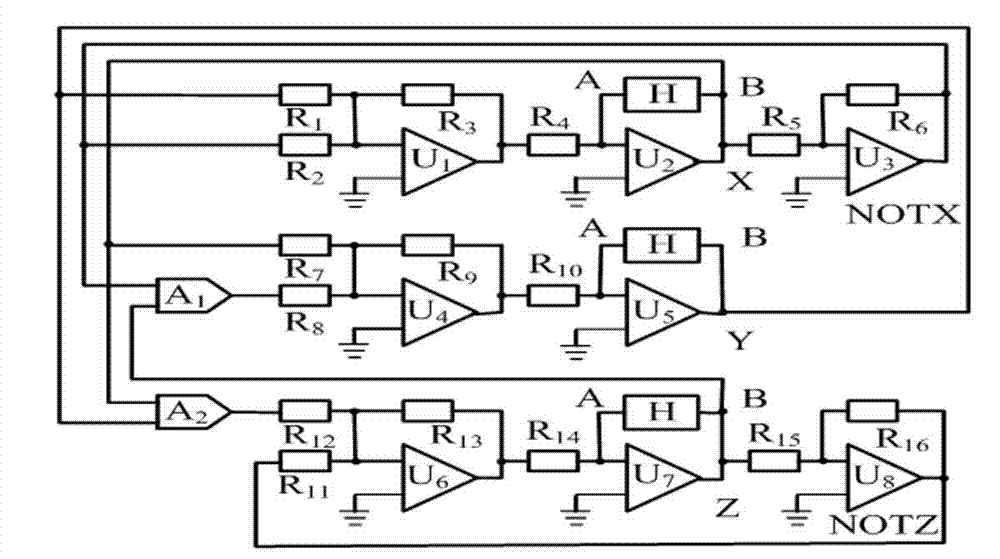

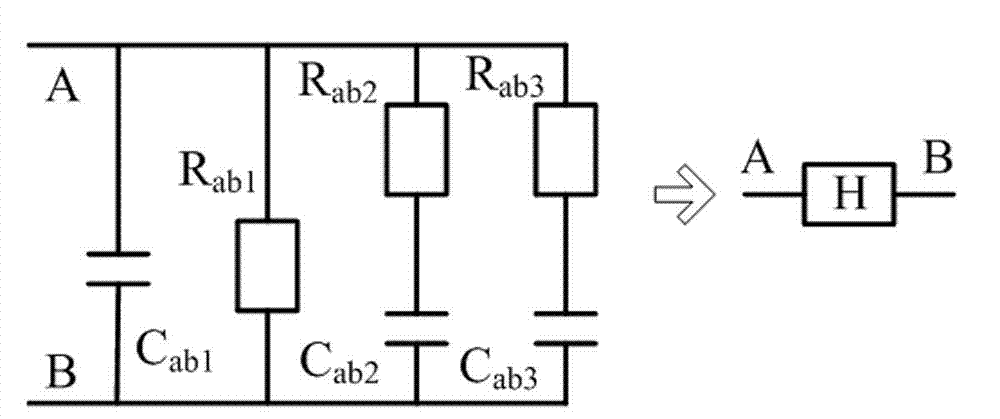

Novel fractional order chaotic circuit

The invention discloses a novel fractional order chaotic circuit which comprises two analog multipliers, eight calculation amplifiers, resistors and capacitors. According to the novel fractional order chaotic circuit, oscillograms of X, Y and Z output ends can be observed on an ordinary oscilloscope, and X-Y, X-Z and Y-Z phase diagrams can also be observed. The novel fractional order chaotic circuit is based on an integer order chaotic system, the fractional order calculus theory and a fractional order unit circuit are applied, a frequency domain approximation method based on a bode diagram is adopted, a fractional order chaotic system is realized, and the understand of people on the fractional order chaotic system and the integer order chaotic system is deepened. The novel fractional order chaotic circuit is applicable to chaotic science, experiment teaching and demonstration, science popularization and experiment demonstration and the like in colleges.

Owner:HEFEI UNIV OF TECH

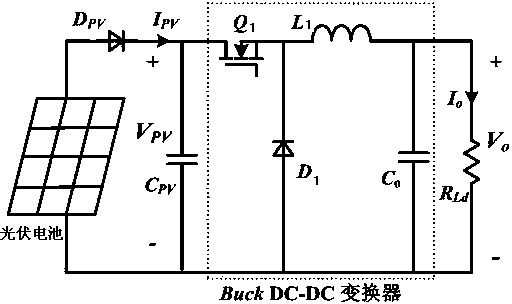

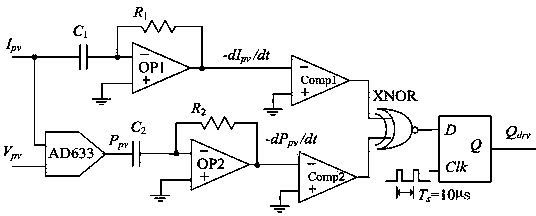

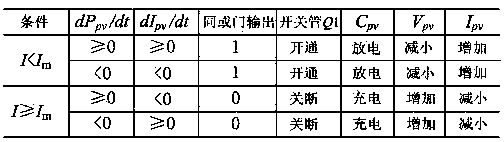

Analogy control circuit capable of achieving photovoltaic cell maximum power point tracing

InactiveCN103440019ARealize MPPTPhotovoltaic energy generationElectric variable regulationCapacitanceDifferentiator

The invention discloses an analogy control circuit capable of achieving photovoltaic cell maximum power point tracing, and belongs to the technical field of power electronic application. The analogy control circuit comprises an analogy multiplier, two differentiators, two comparators, an XNOR and a D trigger. According to the analogy control circuit, based on a perturbation and observation method, the change rate of output currents of a photovoltaic cell and the change rate of the output power of the photovoltaic cell are compared, the simple and practical analogy control circuit is used, the output currents and voltages of the photovoltaic cell only need to be sampled, charging-discharging of output end capacitance of the photovoltaic cell is controlled based on on / off, the output currents (or voltages) of the photovoltaic cell are made to achieve maximum power point currents (or voltages), and the maximum power point tracing in the real sense is achieved. The analogy control circuit capable of achieving photovoltaic cell maximum power point tracing is applied to a solar photovoltaic power generating system, and has good engineering application value.

Owner:JIANGSU UNIV

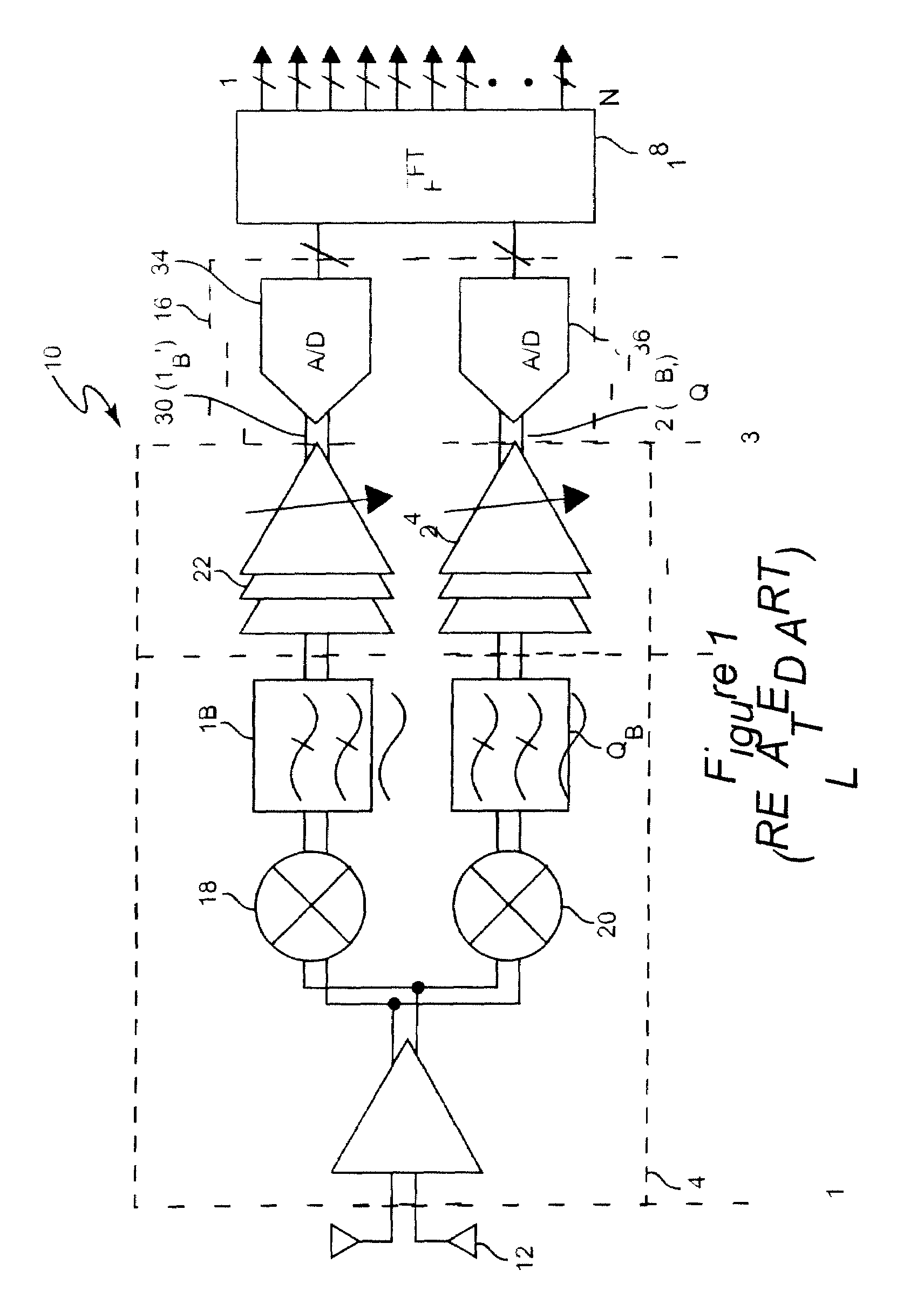

Analog fourier transform channelizer and OFDM receiver

Owner:VIRGINIA TECH INTPROP INC

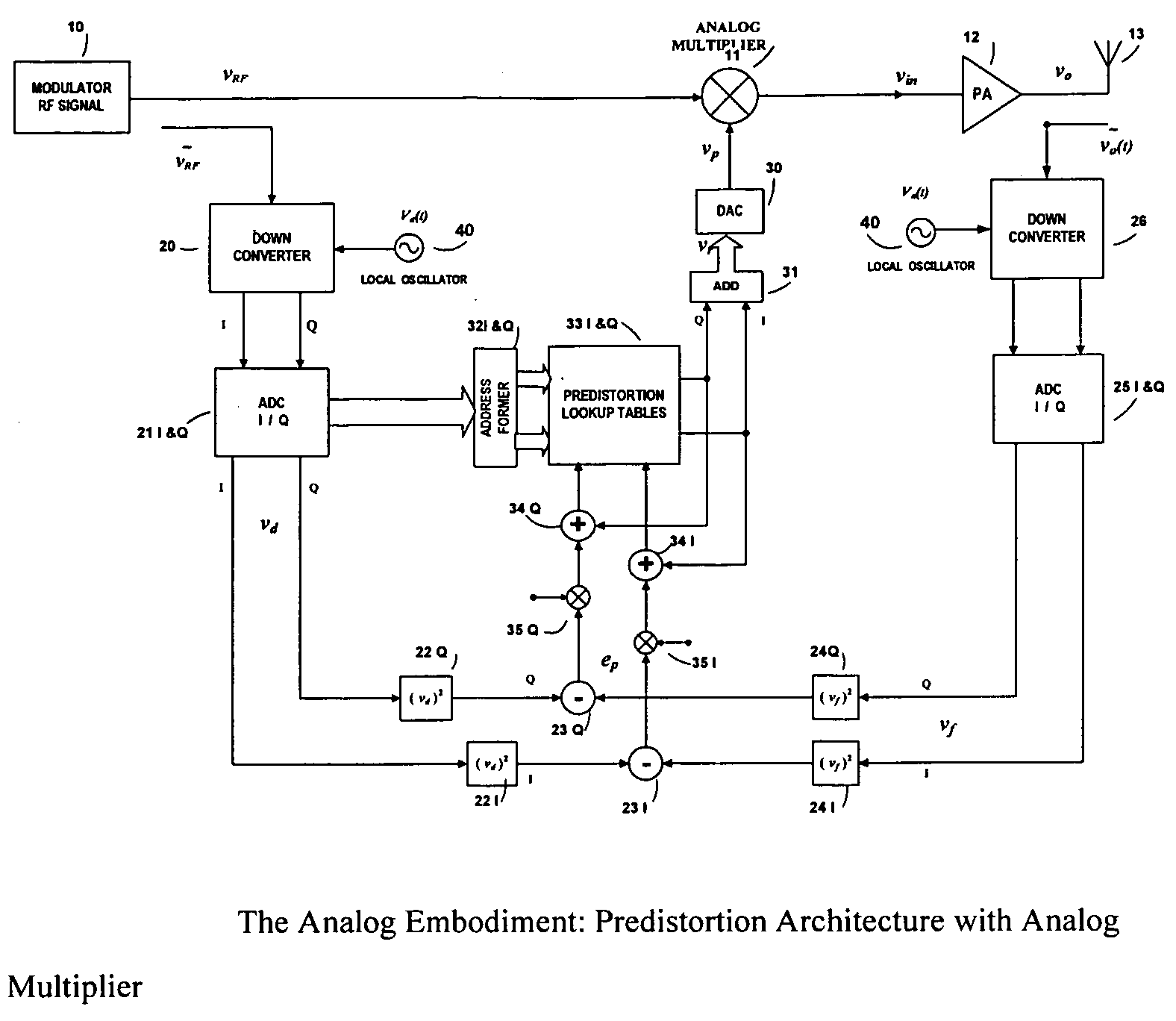

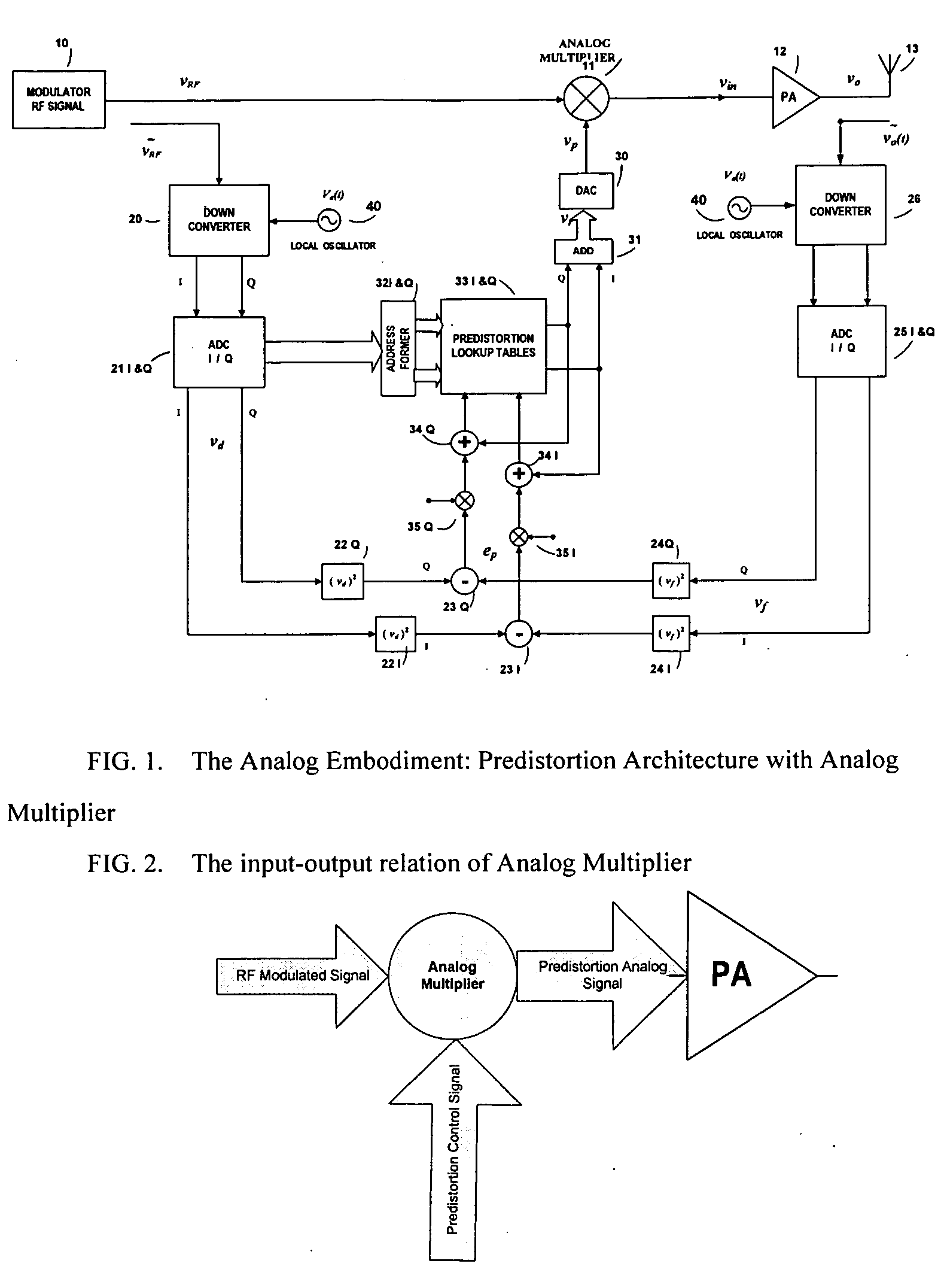

Power amplifier predistortion methods and apparatus using envelope and phase detector

ActiveUS20090096521A1Reduce power consumptionReduce speedResonant long antennasAmplifier modifications to reduce noise influenceLow noiseCarrier signal

An embodiment of the invention is a predistortion approach to linearize a power amplifier without frequency conversion of the RF signals by using envelope and phase detectors to detect the error to be corrected, and then one or more analog multiplier(s) and a DSP-based processor. For the analog embodiment, the inherent nature of the analog circuitries allows digital predistortion processing structured directly at the RF band, and enables a single power amplifier to support multi-modulation schemes, multi-carriers and multi-channels. As a result, the predistortion architecture is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems. The wireless system performance can be improved and upgraded just by using the new PA module rather than change or rebuild new subsystem in existing base station. The analog embodiment can also mix and match its analog multipliers with other analog components such as phase splitters, phase shifters, attenuators, filters, couplers, mixers, low-noise amplifiers, buffers, envelope detectors, and etc., to provide additional features.

Owner:DALI SYST LTD

Power control circuit for accurate control of power amplifier output power

According to an exemplary embodiment, an amplification module includes a power control circuit. The amplification module further includes a power amplifier coupled to the power control circuit and configured to draw a supply current and receive a supply voltage from the power control circuit. The power control circuit is configured to control a DC power provided to the power amplifier by controlling a product of a sense current, which is a mirror current of the supply current, and the supply voltage. The power control circuit includes a feedback voltage that corresponds to the product of the sense current and the supply voltage. The power control circuit further includes an analog multiplier circuit configured to receive the sense current and the supply voltage and generate the feedback voltage. The power control circuit further includes a differential error amplifier configured to compare the feedback voltage to a control voltage.

Owner:SKYWORKS SOLUTIONS INC

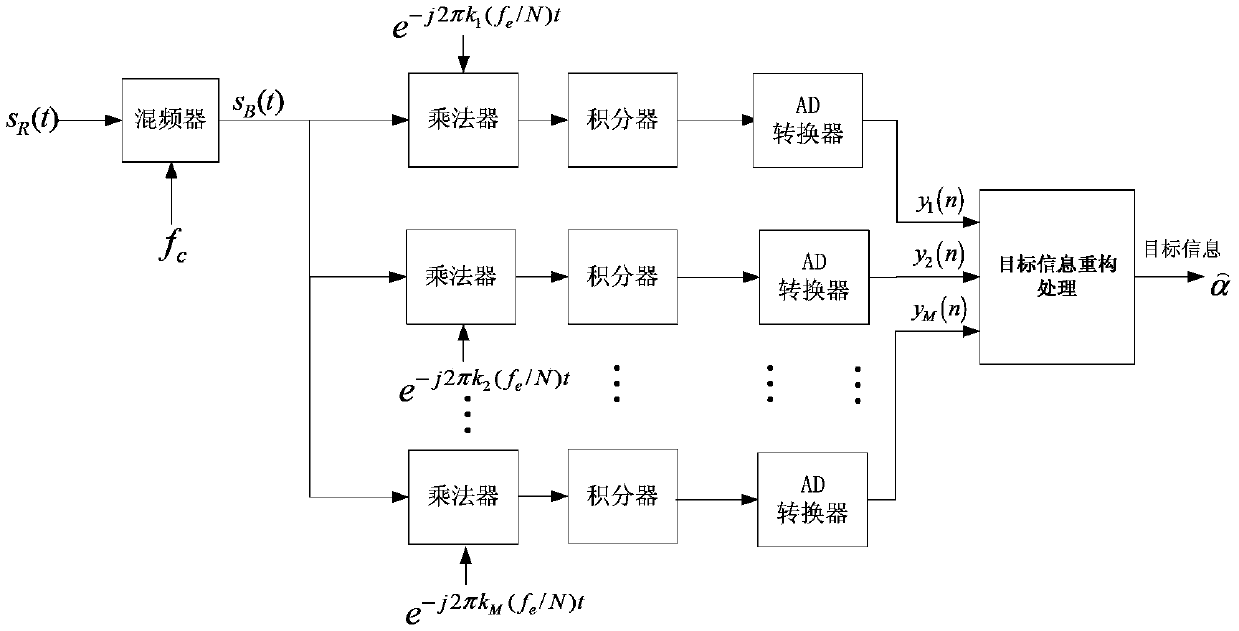

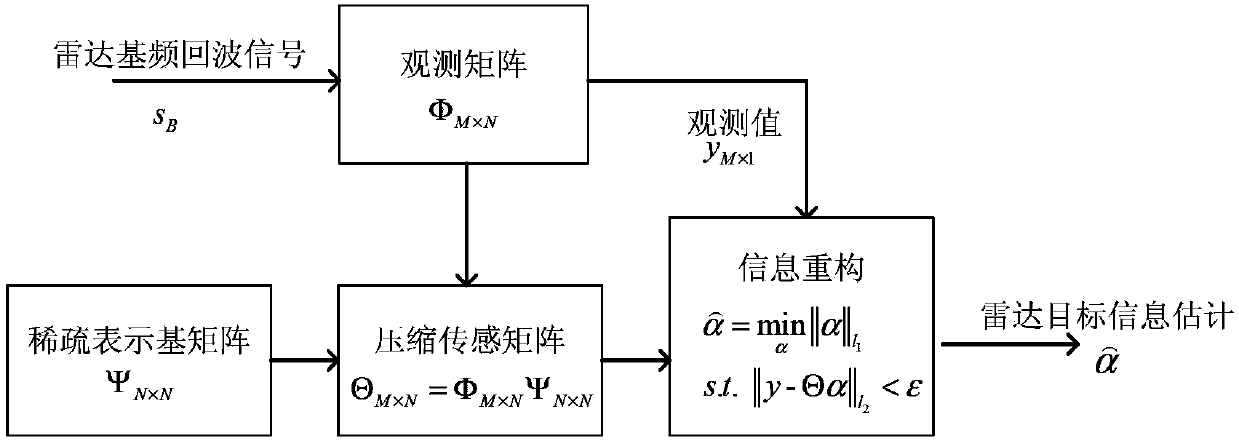

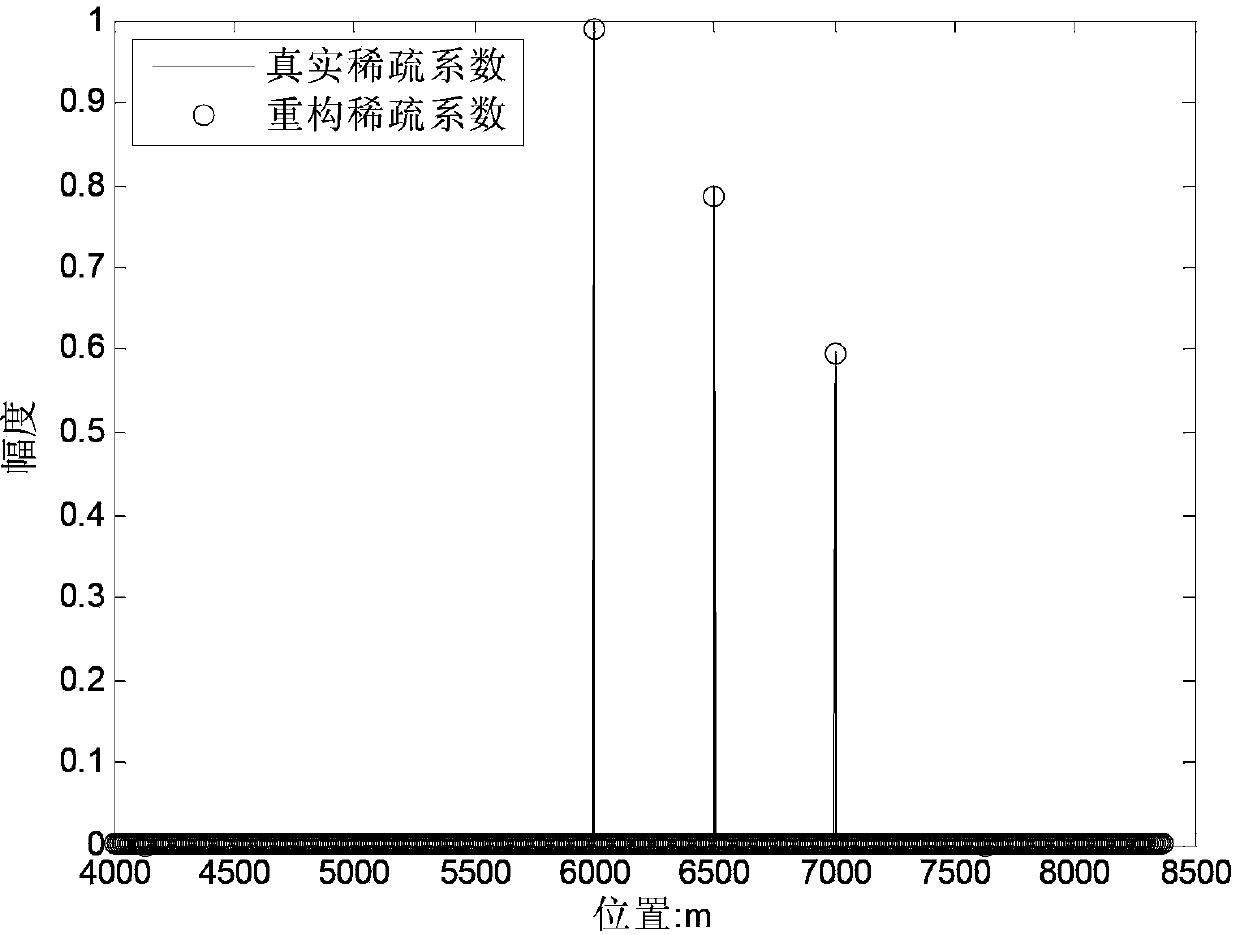

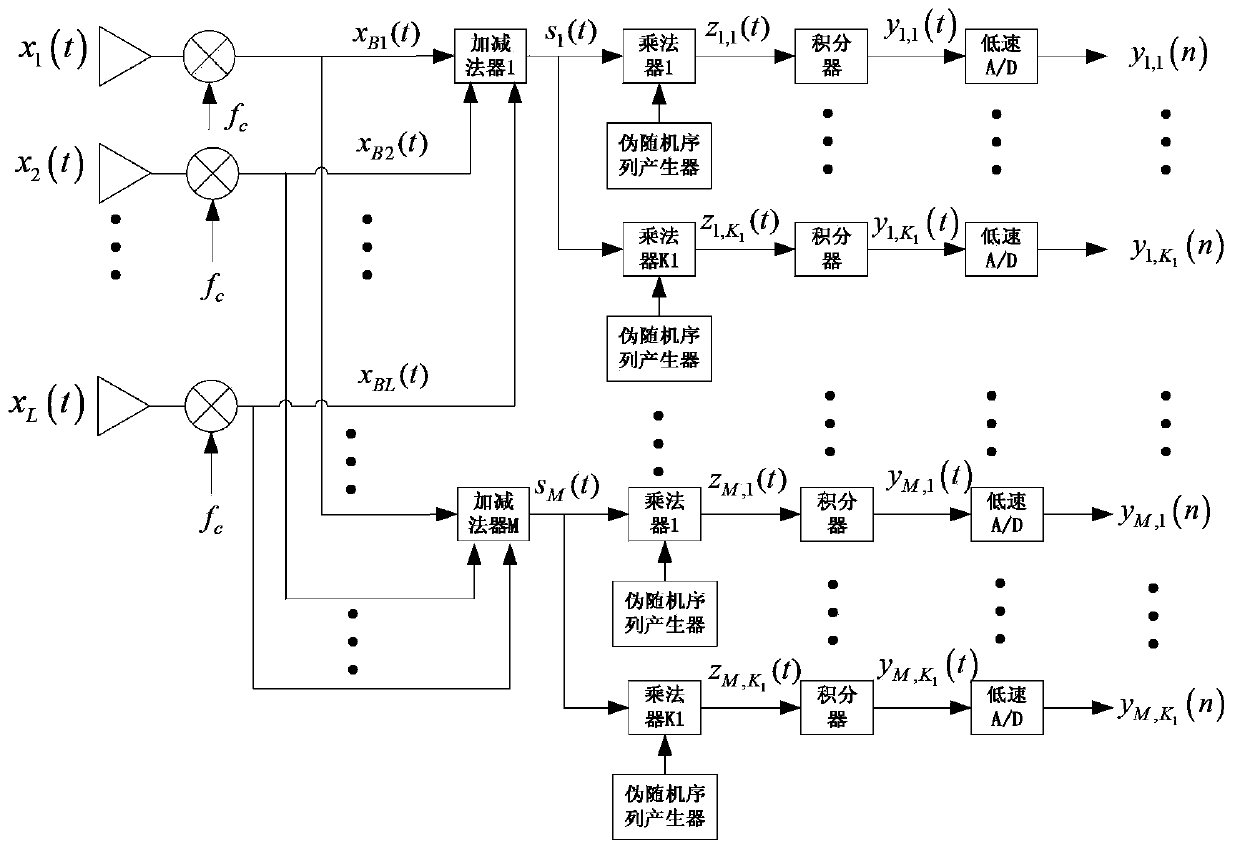

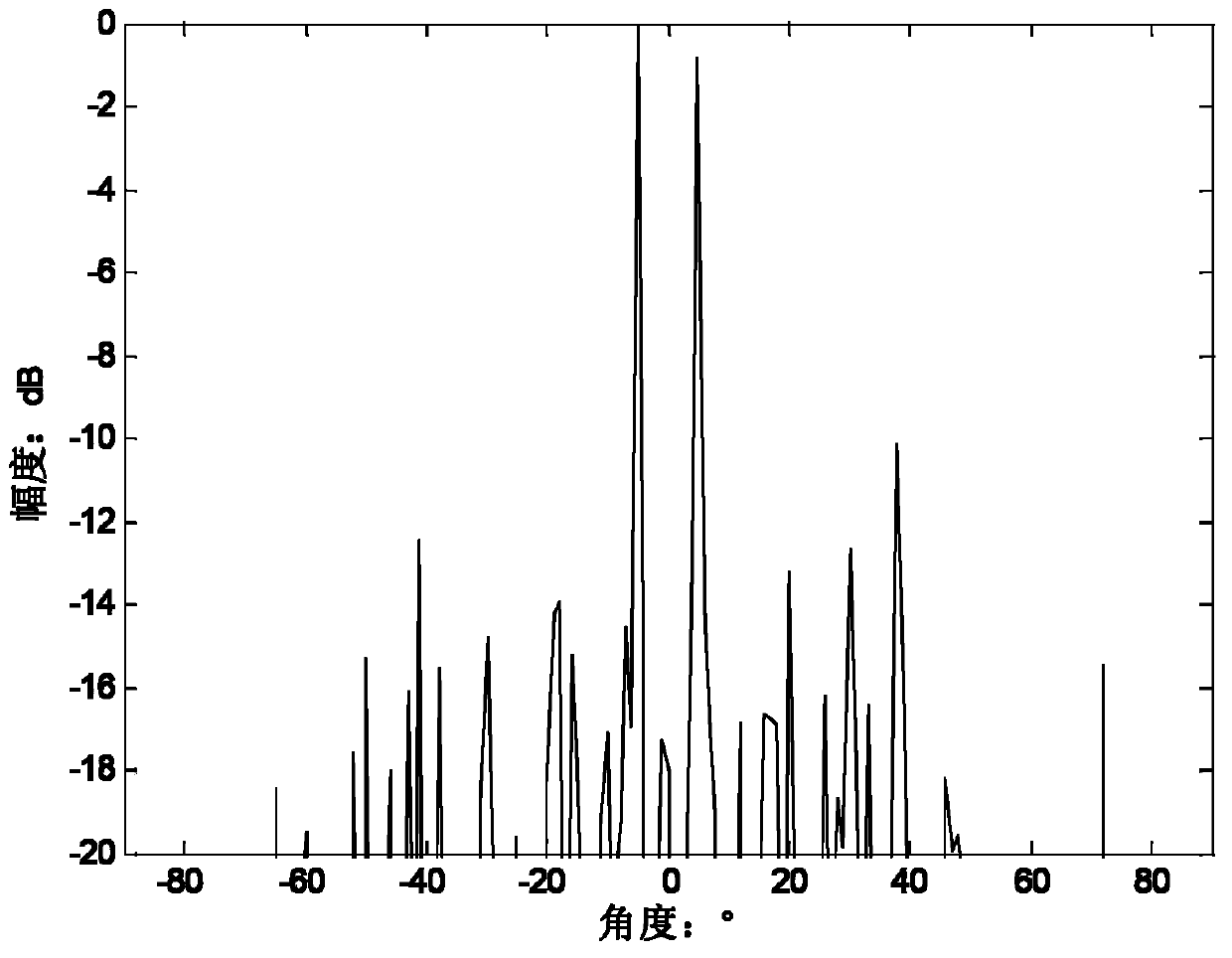

Multichannel random harmonic modulation sampling radar receiver and method thereof

InactiveCN103389492ADownsamplingSolving Digitized Sampling ChallengesWave based measurement systemsLow speedIntegrator

The invention discloses a multichannel random harmonic modulation sampling radar receiver and a method thereof. The multichannel random harmonic modulation sampling radar receiver comprises a frequency mixer, M analog multipliers, M integrators, M low-speed AD convertors and a target information reconstruction processing module, wherein the frequency mixer is connected with the M analog multipliers; each analog multiplier is connected with one integrator; each integrator is connected with one AD convertor; data collected by the AD convertors are input into the target information reconstruction processing module; and the target information reconstruction processing module achieves the purpose of radar target information estimation through three steps, namely, measurement matrix construction, radar sparse representation matrix construction and reconstruction of radar information. The difficult problem of ultra wide band radar system digital sampling is solved; and a signal reconstruction effect is guaranteed, and the realizing difficulty and the cost of signal hardware modulation are effectively reduced at the same time.

Owner:XIDIAN UNIV

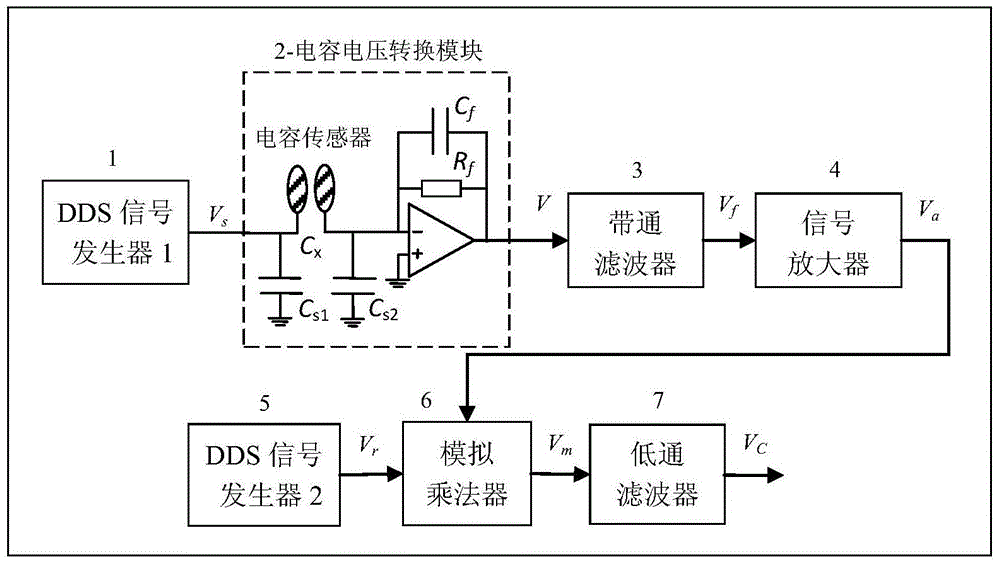

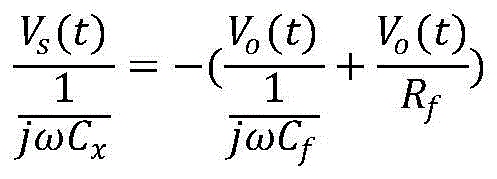

Electrostatic interference preventing capacitance measuring circuit and method

ActiveCN104597328AResolve interferenceDoes not cause measurement biasResistance/reactance/impedenceMaterial capacitancePhase differenceLow-pass filter

The invention discloses electrostatic interference preventing capacitance measuring circuit and method. The measuring circuit comprises a first signal generator, a second signal generator, a capacitance and voltage conversion module, a band-pass filter, a signal amplifier, an analog multiplier and a low-pass filter; the capacitance and voltage conversion module comprises a capacitance sensor, and a converting module for converting the capacitance detected by the capacitance sensor into voltage; the first signal generator is connected with an exciting electrode of the capacitance sensor; the band-pass filter, the signal amplifier, the analog multiplier and the low-pass filter are sequentially connected in series with the output end of the conversion module; the second signal generator is connected to another signal input port of the analog multiplier; an output signal of the second signal generator has the same frequency with the output siganl of the first signal generator, and the phase difference of the two output signals is zero. Compared with the prior art, the circuit has the advantages that the problem of particle charge interference during charge injection, zero drifting and air and solid flowing as the measuring objects can be overcome, and therefore, measurement deviation can be avoided.

Owner:SOUTHEAST UNIV

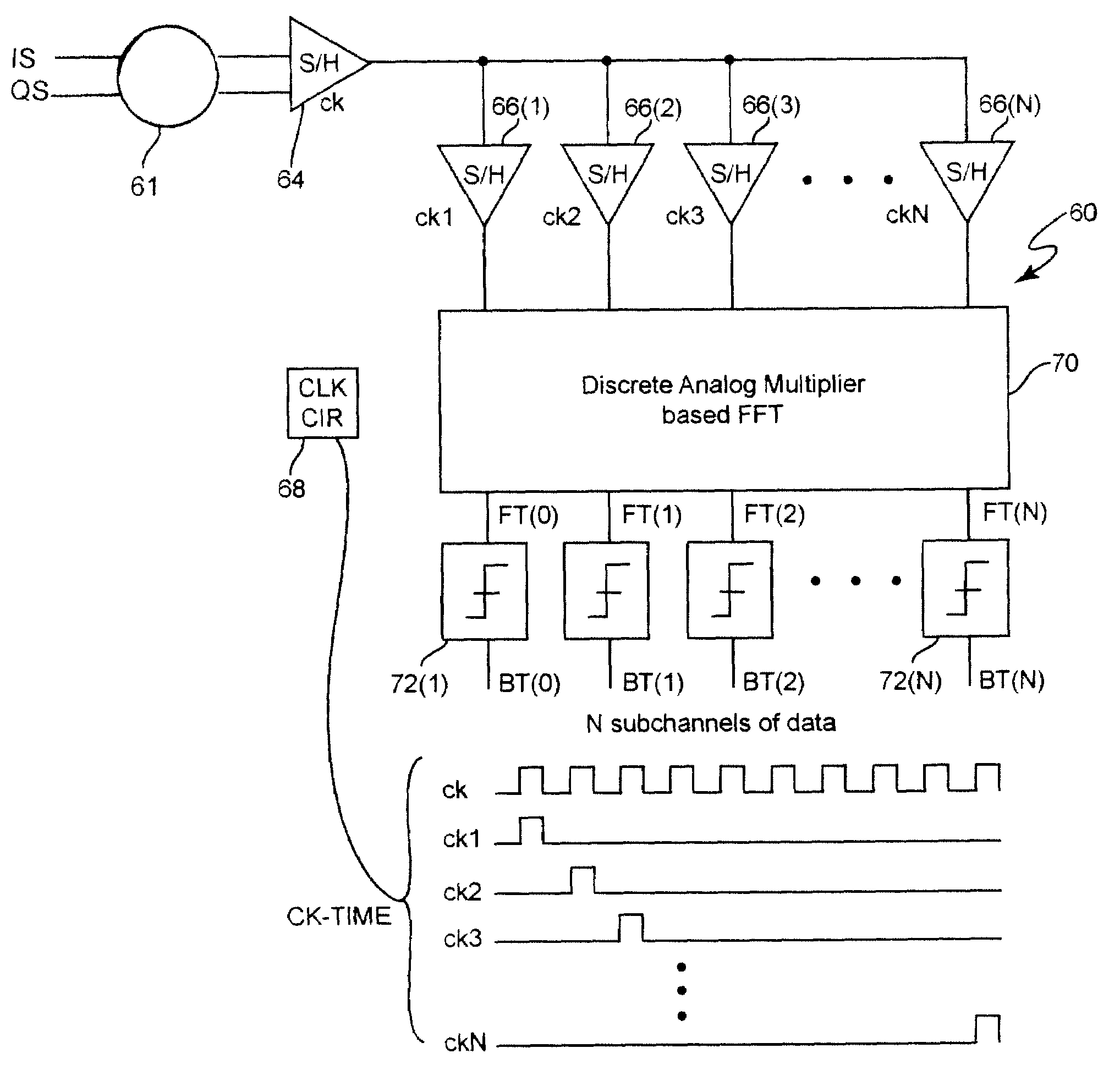

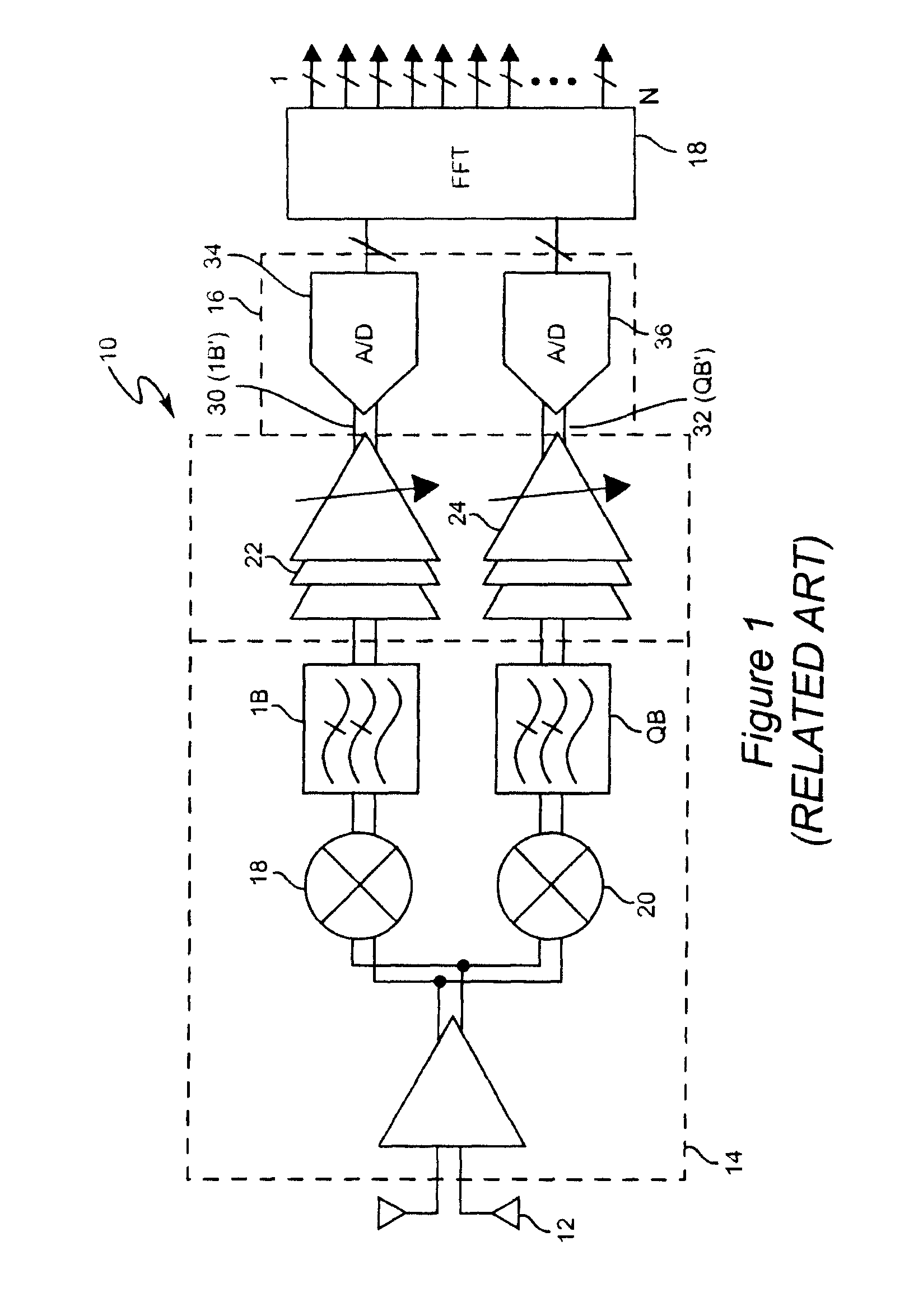

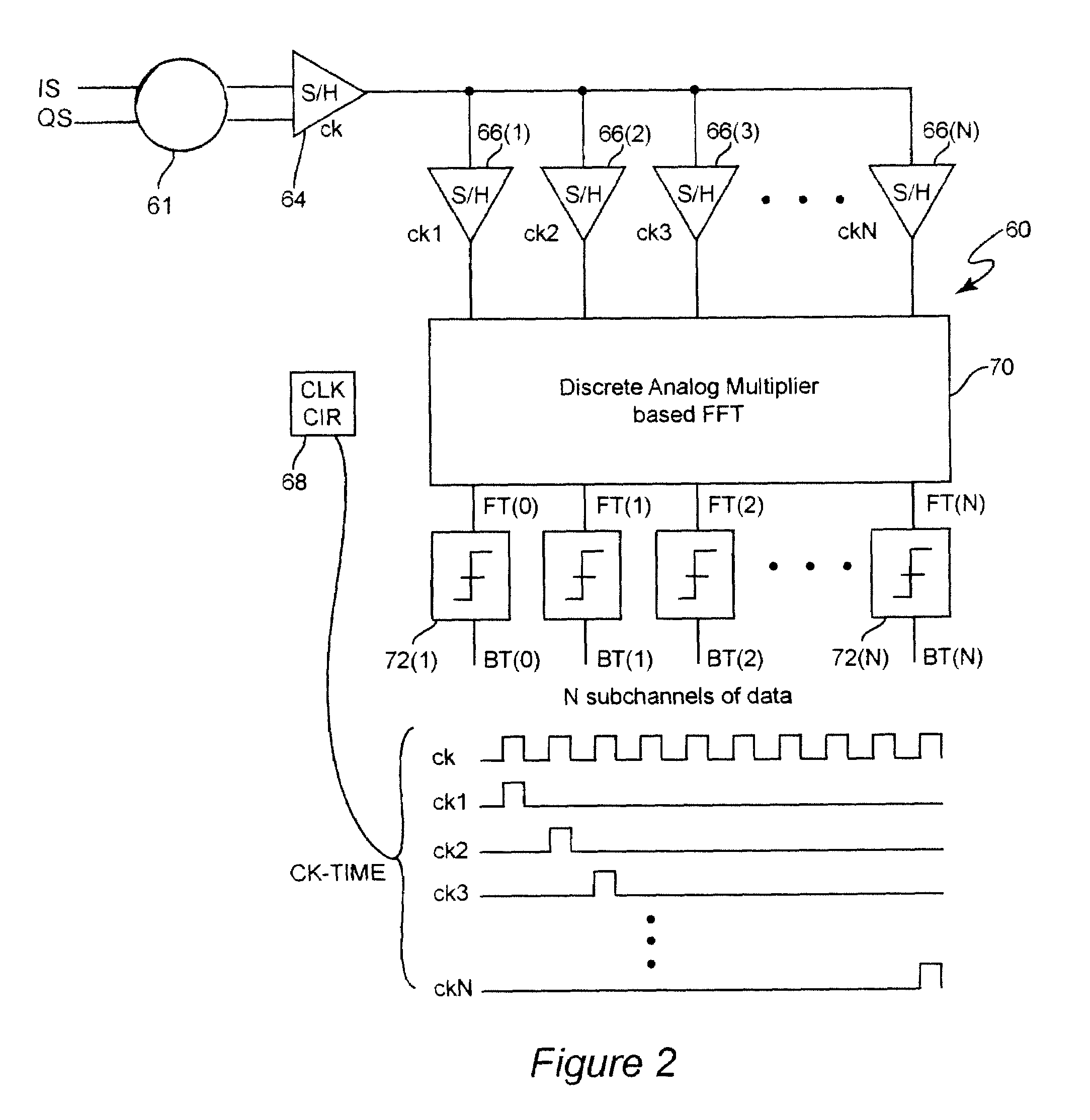

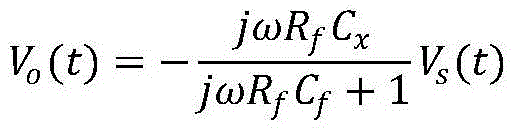

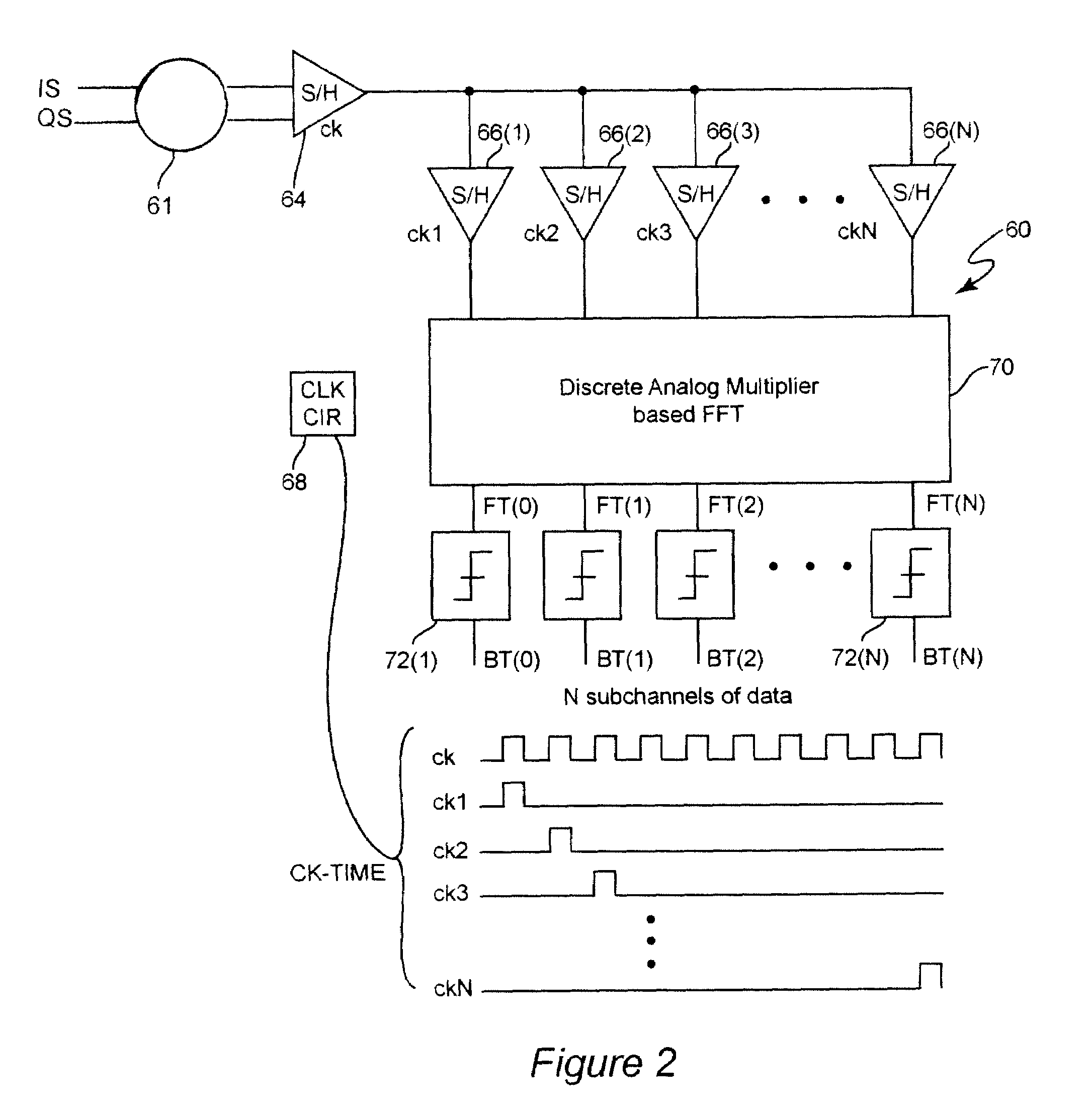

Analog Fourier Transform Channelizer and OFDM Receiver

ActiveUS20070223607A1Amplitude-modulated carrier systemsSecret communicationPhase shiftedRelative phase

An OFDM receiver having an analog multiplier based I-Q channelizing filter, samples and holds consecutive analog I-Q samples of an I-Q baseband, the I-Q basebands having OFDM sub-channels. A lattice of analog I-Q multipliers and analog I-Q summers concurrently receives the held analog I-Q samples, performs analog I-Q multiplications and analog I-Q additions to concurrently generate a plurality of analog I-Q output signals, representing an N-point discrete Fourier transform of the held analog samples, the I-Q signals having relative phase and magnitude representing bits in the OFDM sub-channels. The phase and magnitude may represent QPSK. Optionally, a phase shift decoder receives the analog transform I-Q output signals and generates a corresponding binary bit data.

Owner:VIRGINIA TECH INTPROP INC

Analog power amplifier predistortion methods and apparatus

ActiveUS20090085658A1Improve efficiencyImprove linearityAmplifier modifications to reduce non-linear distortionEnergy efficient ICTLow noiseCarrier signal

An embodiment of the invention is a predistortion approach to linearize a power amplifier by using one or more analog multiplier(s) and a DSP-based processor. For the analog embodiment, the inherent nature of the analog circuitries allows digital predistortion processing structured directly at the RF band, and enables a single power amplifier to support multi-modulation schemes, multi-carriers and multi-channels. As a result, the predistortion architecture is particularly suitable for wireless transmission systems, such as base-stations, repeaters, and indoor signal coverage systems. The wireless system performance can be improved and upgraded just by using the new PA module rather than change or rebuild new subsystem in existing base station. The analog embodiment can also mix and match its analog multipliers with other analog components such as phase splitters, phase shifters, attenuators, filters, couplers, mixers, low-noise amplifiers, buffers, envelope detectors, and etc., to provide additional features.

Owner:DALI SYST LTD

Wideband monolithic tunable high-Q notch filter for image rejection in RF application

InactiveUS20060154638A1Low costEasy to integrateMultiple-port networksContact mechanismsInductorWide band

A notch filter with a high Q factor, which is integrated with a first and a second cascoded LNA, is totally contained on an integrated chip. The notch filter, comprising two Q-enhancement circuits, is coupled to the second differential LNA. The two Q-enhancement circuits are combined to generate sufficient negative impedance to compensate for the loss in the on-chip low Q inductors. To improve the image rejection of the notch filter in a wide frequency band, the notch filter uses an automatic current tuning circuit which consists of an analog multiplier and fixed and voltage controlled current sources. Furthermore, by modifying the connection and location of the tunable varactor, another wideband tunable notch filter is implemented. The notch filter can be applied in all current wireless receiver systems.

Owner:AGENCY FOR SCI TECH & RES

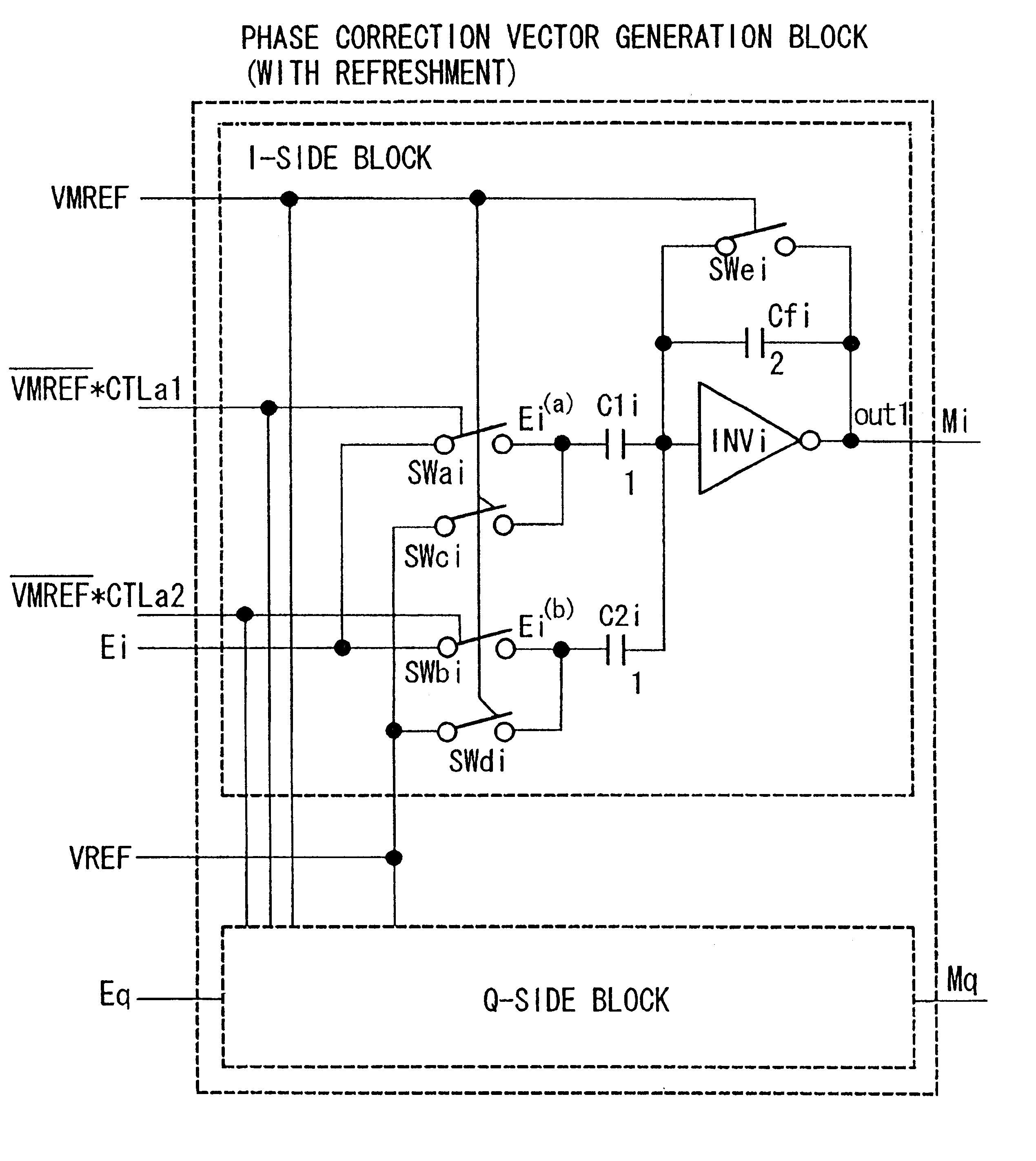

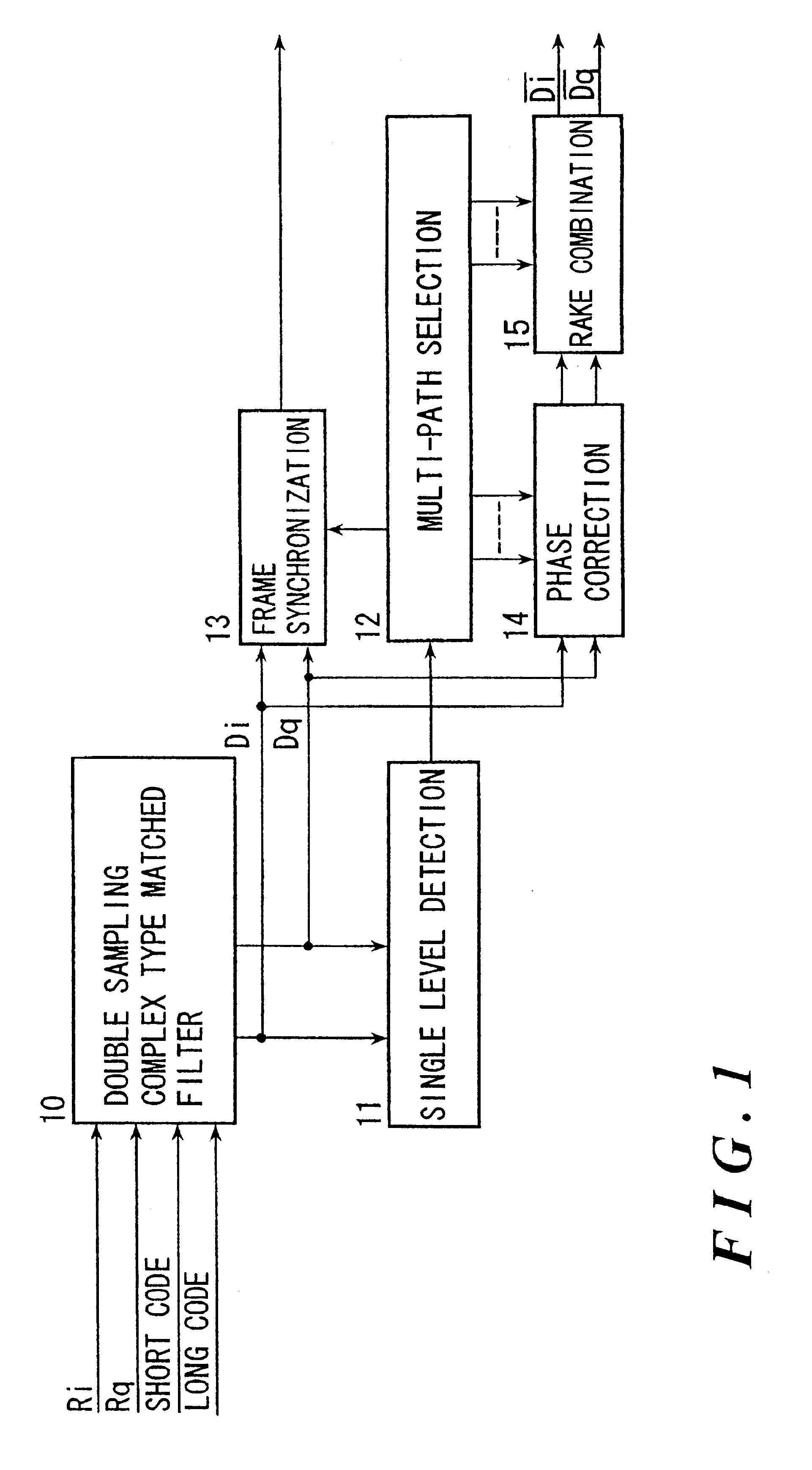

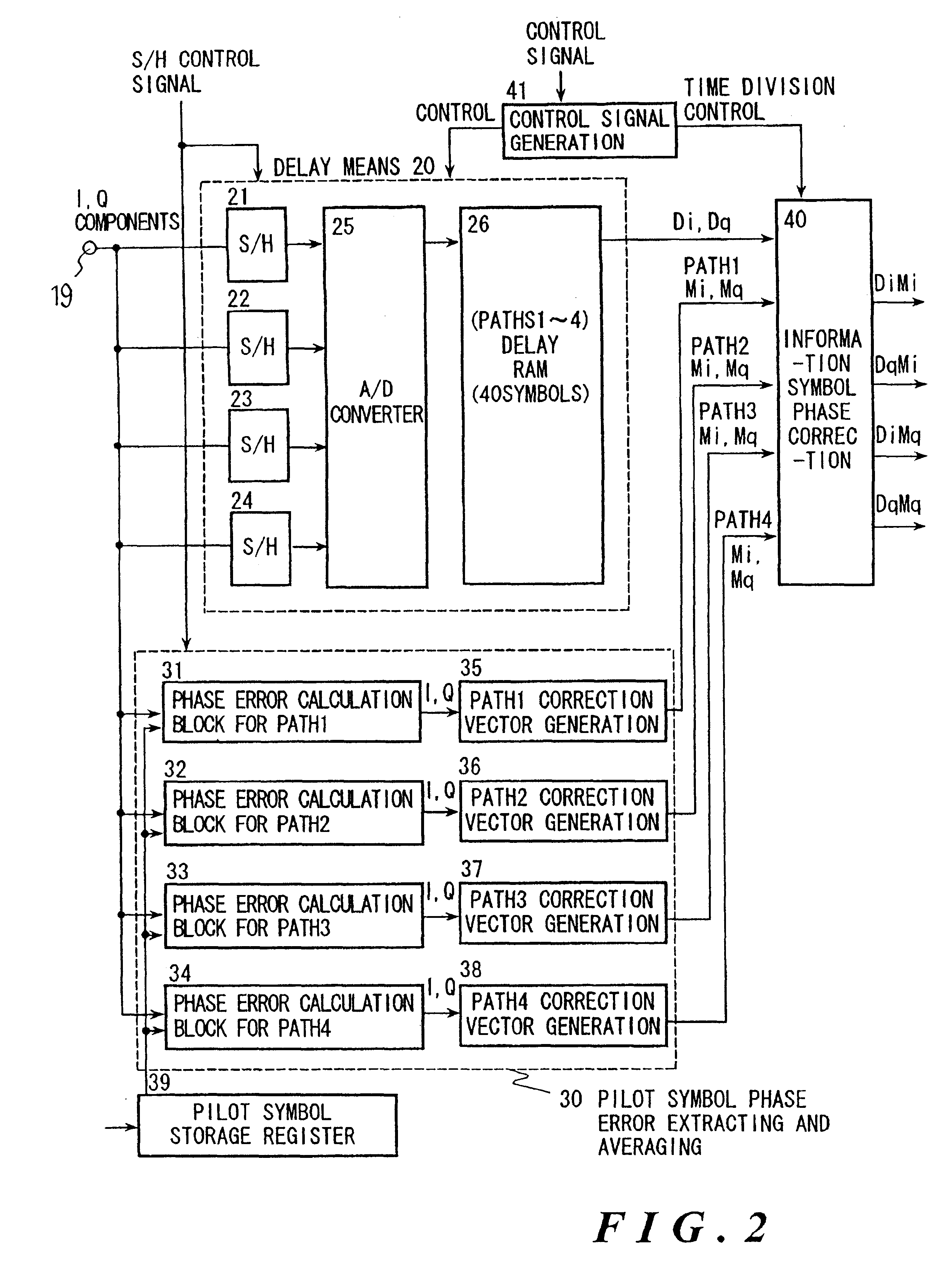

Receiver in a spread spectrum communication system having low power analog multipliers and adders

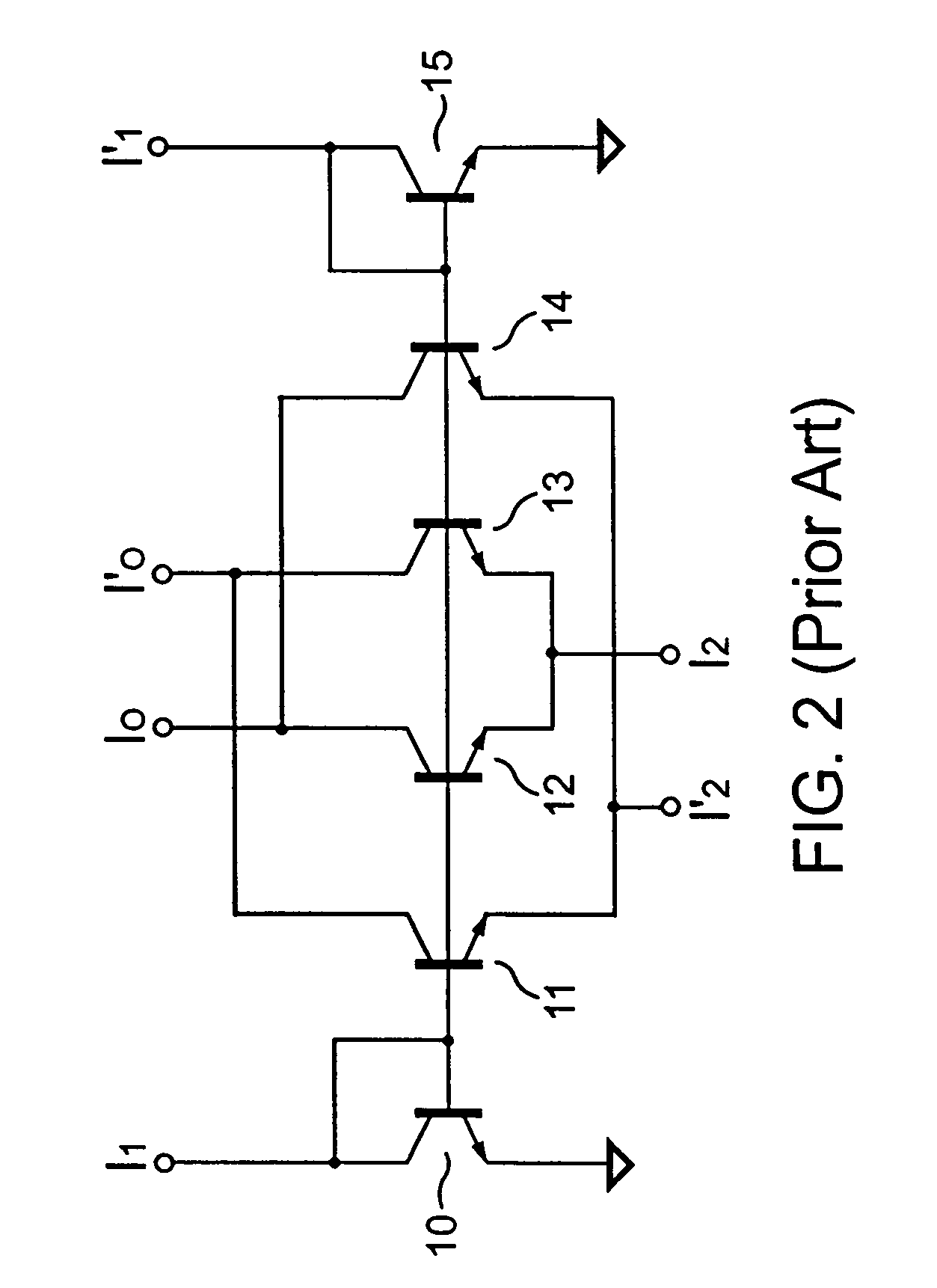

InactiveUS6278724B1Multiple input and output pulse circuitsComputations using contact-making devicesComplex typePhase correction

A signal reception apparatus in the spread spectrum communication system requires only a small amount of circuitry and consumes a small amount of electric power. A quadrature detector decomposes received signals into in-phase components and quadrature components, and supplies them to a complex-type matched filter. The complex-type matched filter de-spreads the in-phase components and the quadrature components and sends them to a multi-path selector. The multi-path selector selects, from among the received de-spread signals, multiple paths having high levels of signal electric powers and sends the received signals of the selected paths to multiple phase correction blocks. Analog operation circuits calculate phase errors of the received signals of two successive pilot symbol blocks for each path. An analog operation circuit corrects the phases of the received signals of the information symbol block that has been received between the two successive pilot symbol blocks. A rake combiner synchronously combines the phase-corrected de-spread received signals of each path.

Owner:YOZAN INC +1

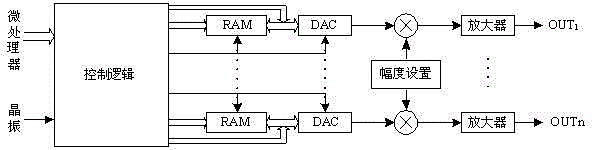

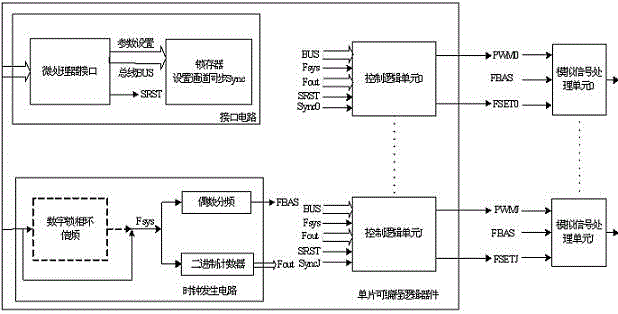

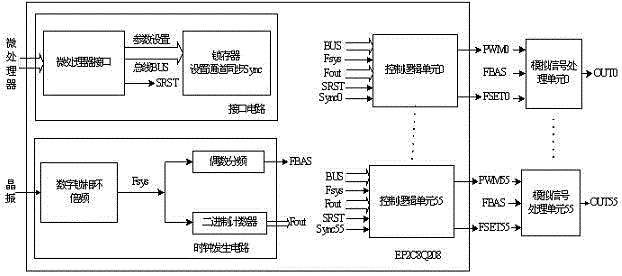

Multi-channel sinusoidal signal generator and method for generating multi-channel sinusoidal signals

InactiveCN103607174AImprove scalabilityPromote expansionElectrical apparatusControl signalPhase difference

The invention discloses a multi-channel sinusoidal signal generator and a method for generating multi-channel sinusoidal signals. By the adoption of the multi-channel sinusoidal signal generator and the method for generating the multi-channel sinusoidal signals, the sinusoidal signals of tens of or hundreds of channels can be directly generated, and the amplitude, the frequency, and the initial phase of each signal can be digitally set; synchronization of the signals of all channels or signals of a plurality of channels can be achieved, and phase difference can be set between every two same-frequency signals. A waveform generation circuit is composed of a single programmable logic device and multiple analog units. Each analog unit is controlled by an amplitude control signal, a phase frequency control signal and a public fundamental frequency square signal. At least 2N+1 control lines, for driving the N channel analog units, of the programmable logic device are arranged. According to the multi-channel sinusoidal signal generator, a storage, a DAC and an analog multiplier are not applied to the waveform generation circuit, and only one programmable logic device, N analog multi-channel switches, N four-operational-amplifiers and N dual-operation-amplifiers are adopted, so that the hardware cost is low, and an analog circuit is simple. The multi-channel sinusoidal signal generator and the method for generating the multi-channel sinusoidal signals are suitable for application occasions requiring one or more characteristics such as a large number of channels, channel synchronization, and channel isolation.

Owner:HARBIN UNIV OF SCI & TECH

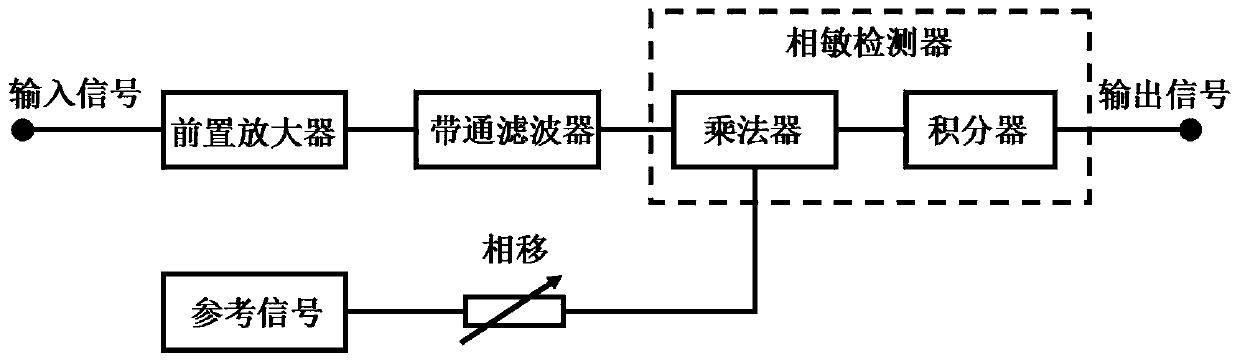

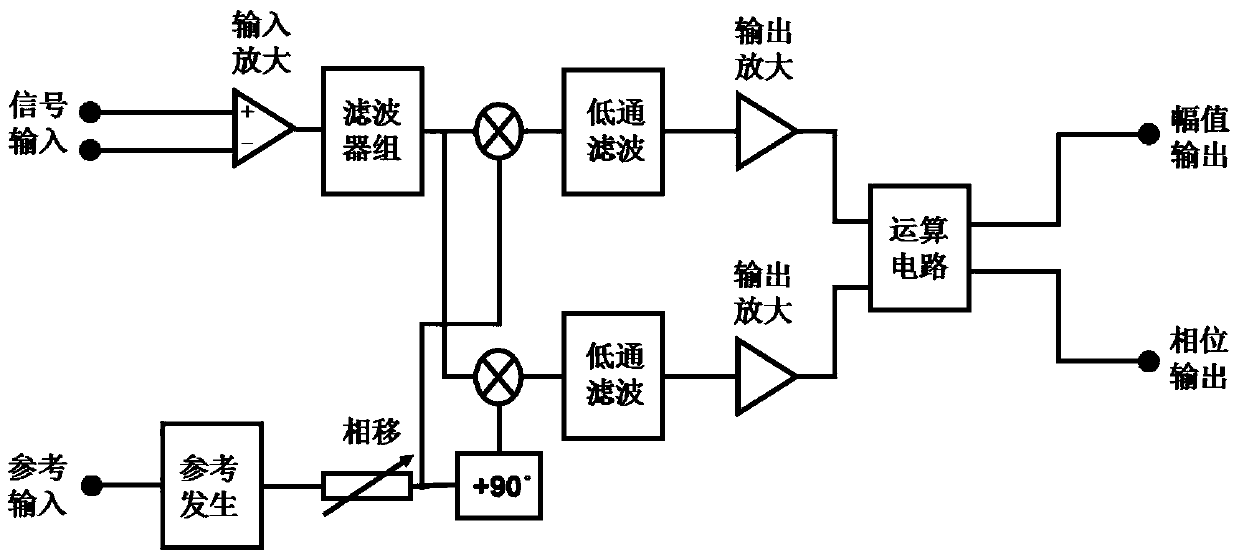

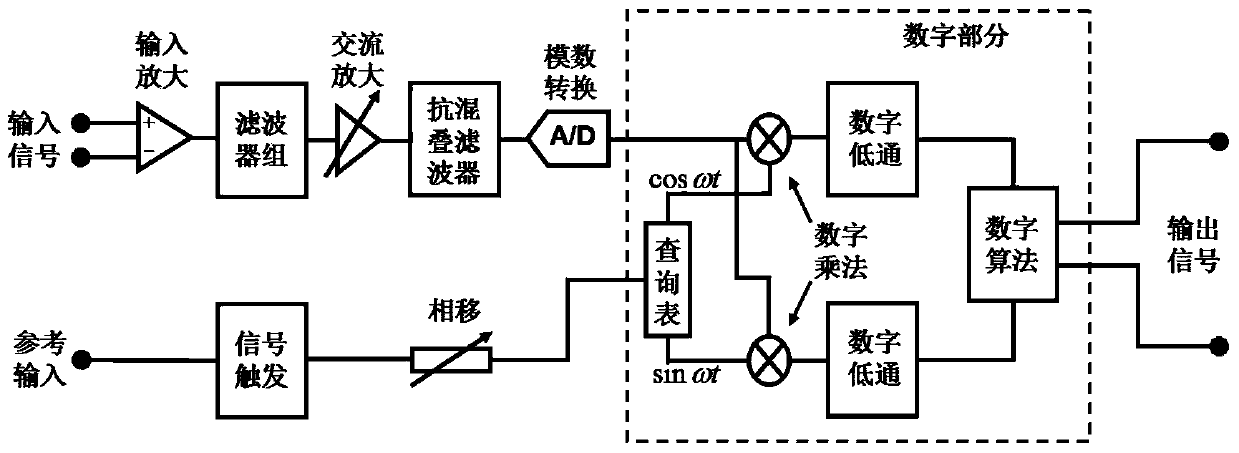

Lock-in amplifier of analog-digital mixed structure and lock-in amplification method of lock-in amplifier

ActiveCN104092442ALow hardware requirementsRealize detectionPulse automatic controlParametric amplifiersLow-pass filterEngineering

The invention discloses a lock-in amplifier of an analog-digital mixed structure and a lock-in amplification method of the lock-in amplifier. The lock-in amplifier comprises an input signal processing system, a reference signal generation system, an analog processing system, an analog-to-digital conversion system and a digital processing system, wherein the first output end and the second output end of the reference signal generation system output two paths of sine wave reference signals which are mutually orthogonal; the analog processing system comprises two analog multipliers and an analog low-pass filter; the digital processing system comprises two digital low-pass filters and a digital operational unit. According to the lock-in amplifier, an aliasing signal is allowed to exist in a signal detection process; through the combination of the analog low-pass filter and the digital low-pass filters, an interference signal in an input signal can be effectively filtered, and a high-frequency interference signal and the aliasing signal are filtered, so that various frequency signals can be detected, the signal to noise ratio is effectively improved, hardware requirements are reduced, and the production cost is lower; the lock-in amplifier can be widely applied to the field of weak signal measurement.

Owner:SYSU CMU SHUNDE INT JOINT RES INST +1

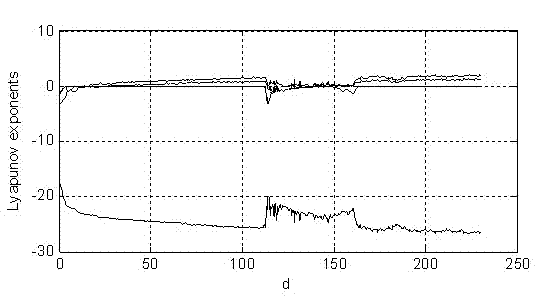

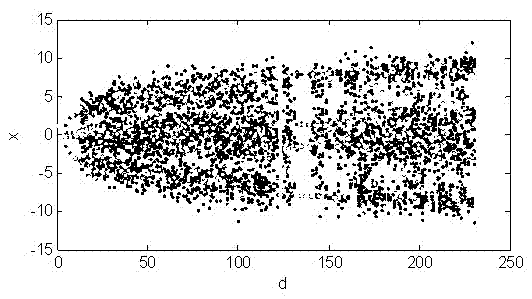

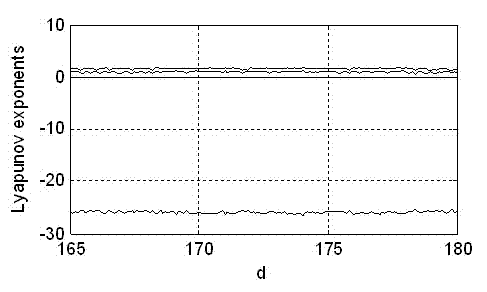

Dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system

InactiveCN103248473AEasy to implementRich Dynamic BehaviorSecuring communicationCapacitanceElectrical resistance and conductance

The invention discloses a dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system. The dual-parameter constant-Lyapunov-exponent four-dimensional autonomous super-chaos system comprises a math model and a realization circuit, and is characterized in that the realization circuit comprises a first channel circuit, a second channel circuit, a third channel circuit and a fourth channel circuit; the first channel circuit, the second channel circuit, the third channel circuit and the fourth channel circuit comprise three operational amplifiers, and auxiliary resistance and capacitor components that can realize four functions of the math model, respectively; and the realization circuit also comprises four analog multipliers used for realizing two quadratic product terms and a cubic product term of the math model. The realization circuit of the invention is simple in structure and convenient for integration, and can greatly promote the development of the chaos system in the technical fields of electronic measuring, weak signal detection, image encryption and privacy communication.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

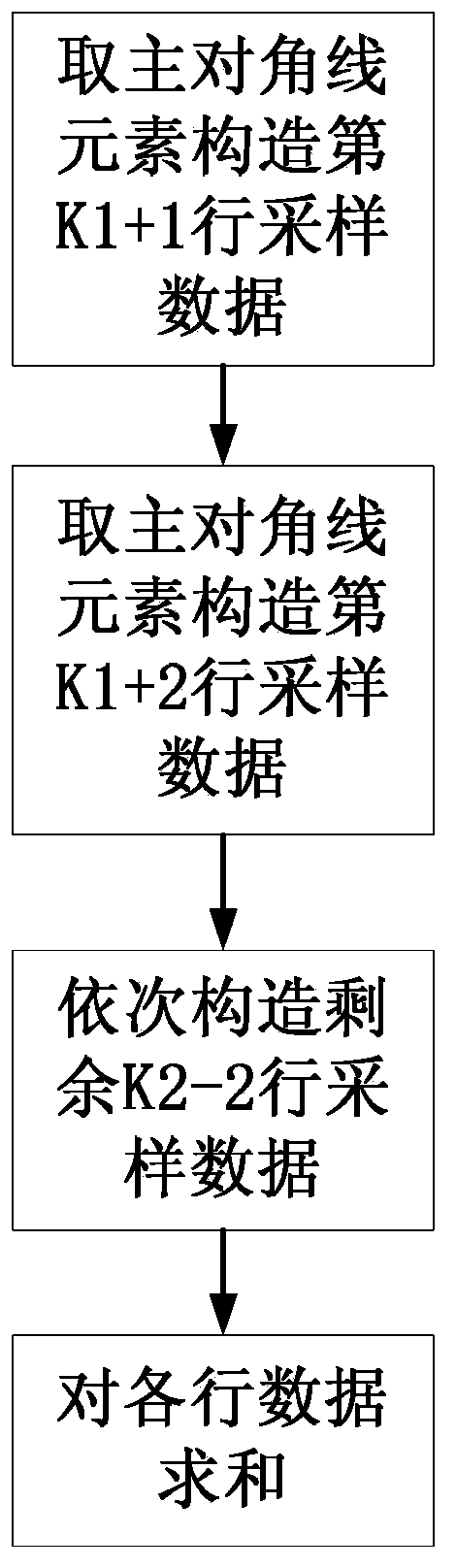

Beam forming device based on sparse signals and method of device

InactiveCN103389490AOvercoming the pitfalls of precise phase compensationEasy to implementWave based measurement systemsMulti inputMain diagonal

The invention discloses a beam forming device based on sparse signals and a method of the device. The beam forming device comprises an array element receiving antenna, a multi-input analog adder, an analog multiplier, a pseudorandom sequence generator, an integrator and an A / D convertor, wherein weight coefficients of the multi-input analog adder are submitted to random Bernoulli distribution. After sampling, data reconstruction steps are as follows: 1), main diagonal elements are taken, and sampling data of (K1+1)th row are constructed; 2), the main diagonal elements are taken, and sampling data of (K1+2)th row are constructed; 3); sampling data of left (K2-2) rows are constructed sequentially; and the data of all the rows are summed. According to the beam forming device and the method, a compressed sampling technology is adopted, so that broadband signals can be sampled at a low sampling rate; an airspace projection measurement matrix selects a random Bernoulli array, a phase shifter and a multiplier are not required; a multi-channel structure and a sampling data reconstruction manner are used during time-domain observation projection; and more sampling data comprising a large amount of information can be acquired by the aid of fewer channels.

Owner:XIDIAN UNIV