Patents

Literature

34 results about "Analog delay line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An analog delay line is a network of electrical components connected in cascade, where each individual element creates a time difference or phase change between its input signal and its output signal. It operates on analog signals whose amplitude varies continuously. An example is a bucket-brigade device.

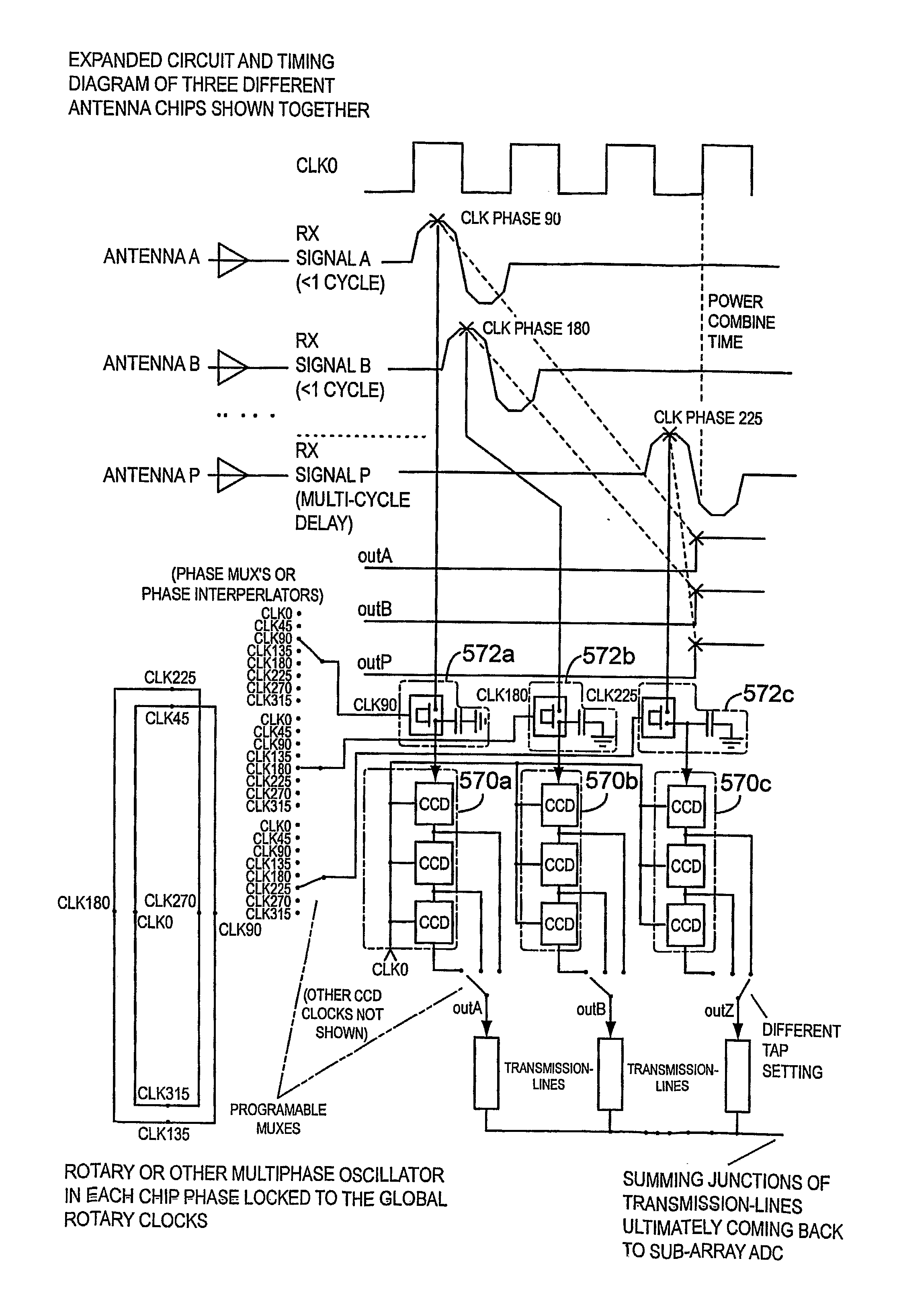

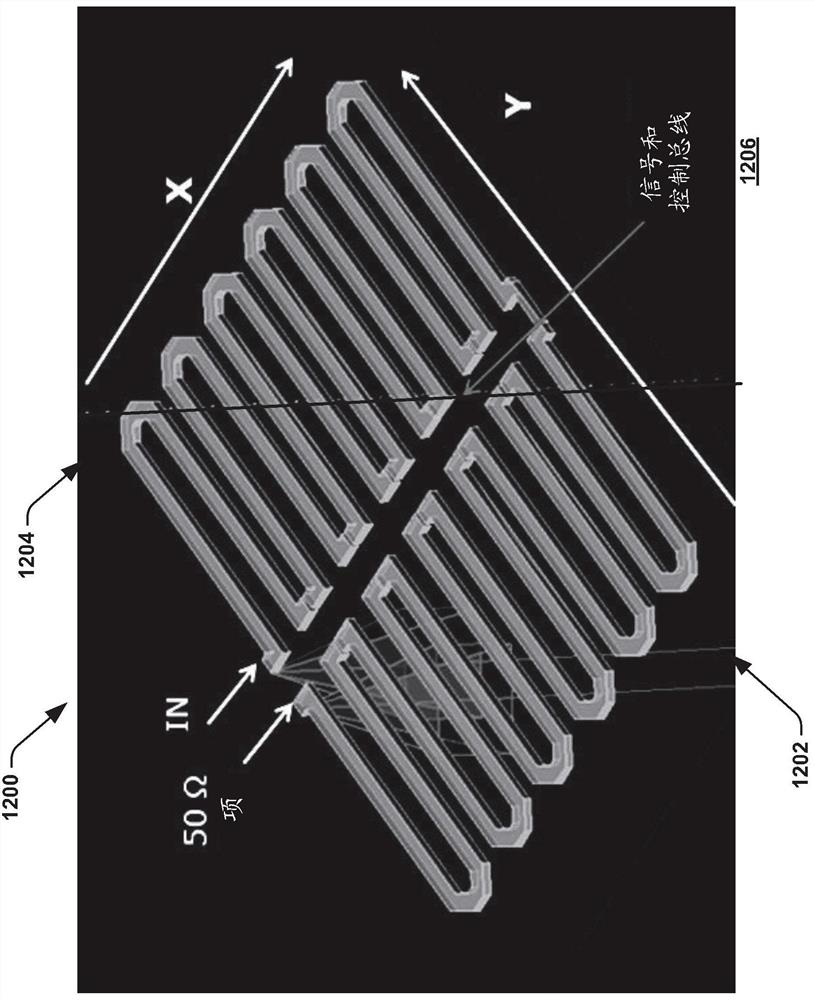

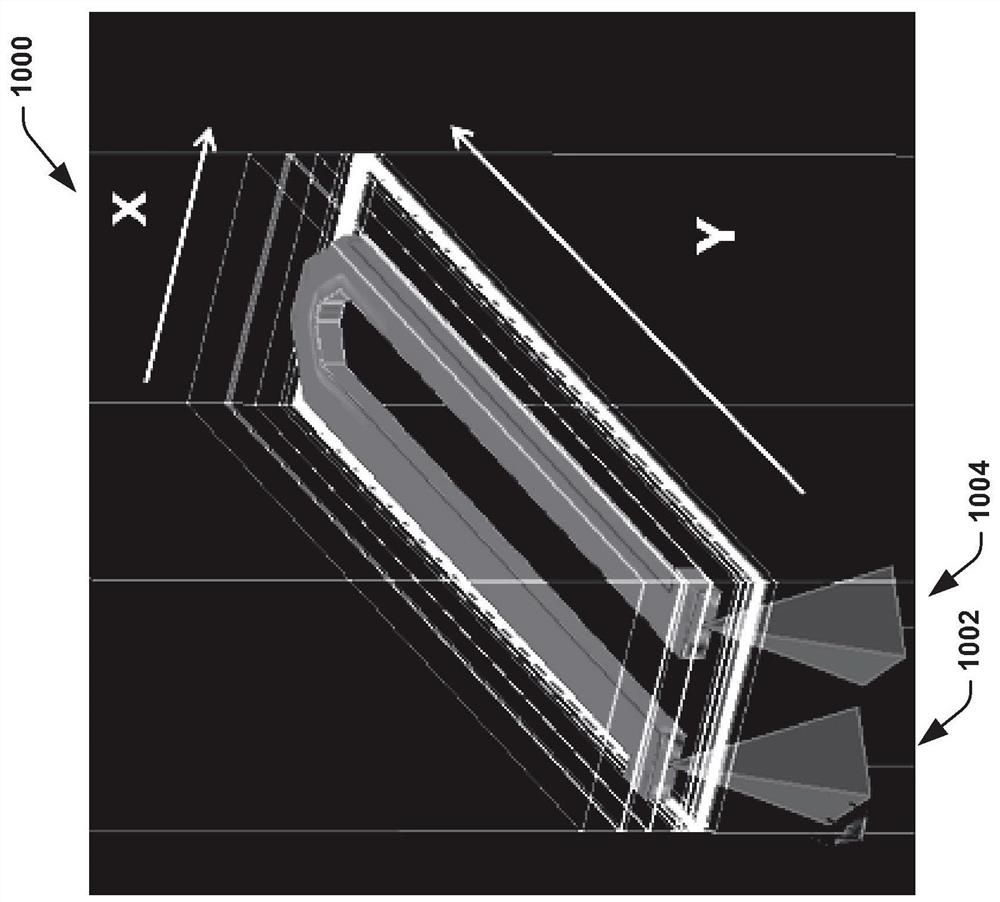

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

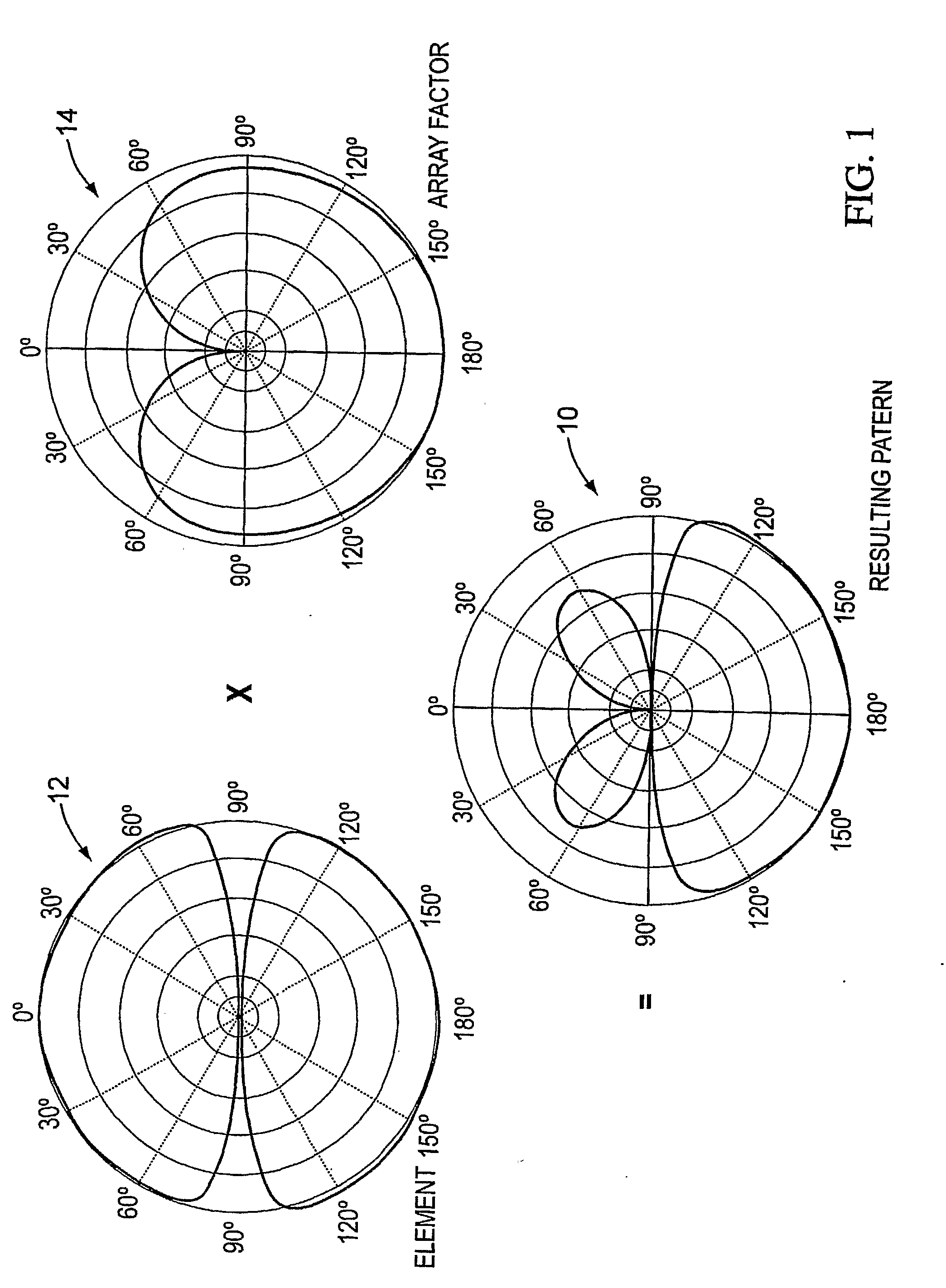

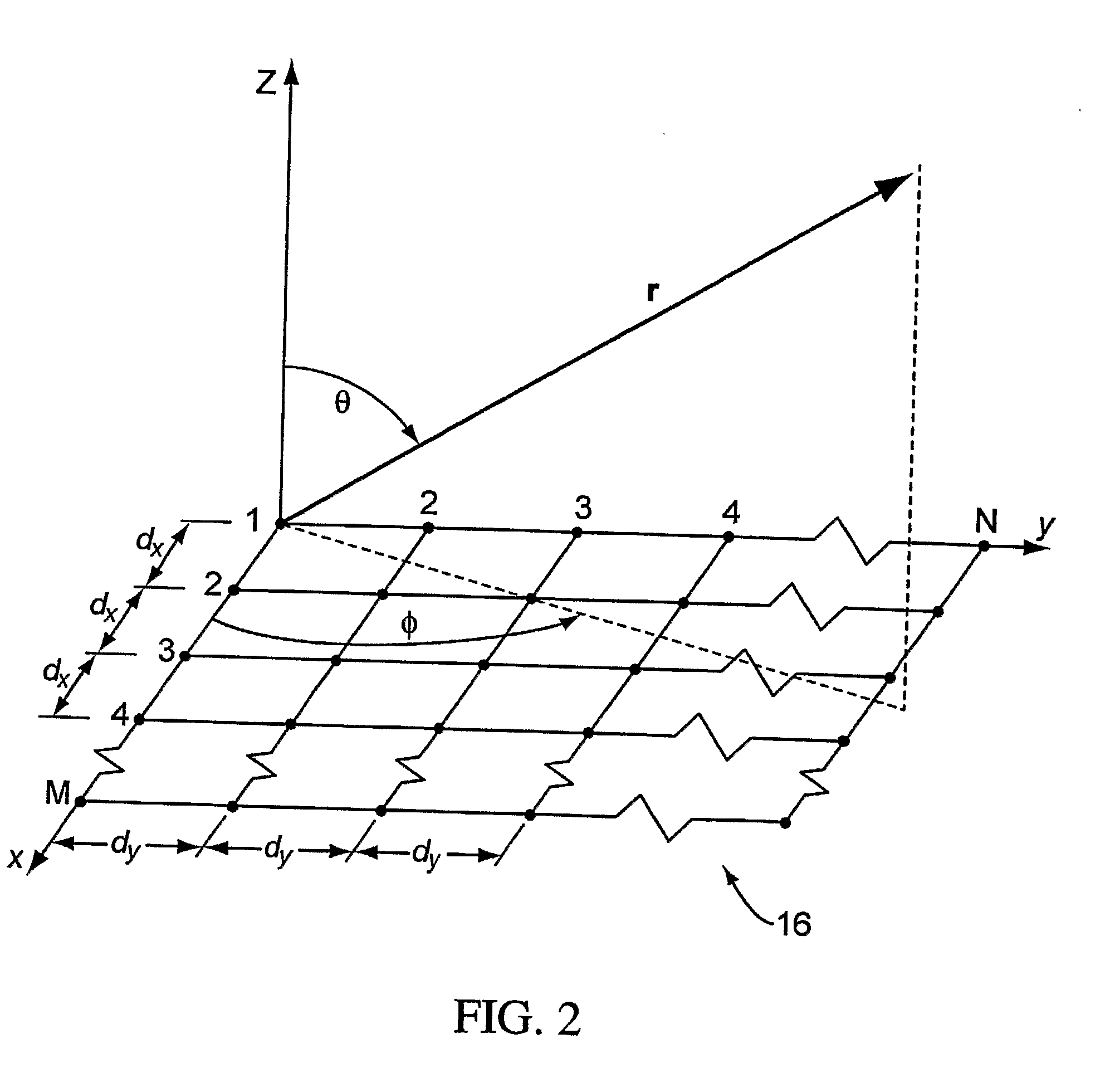

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

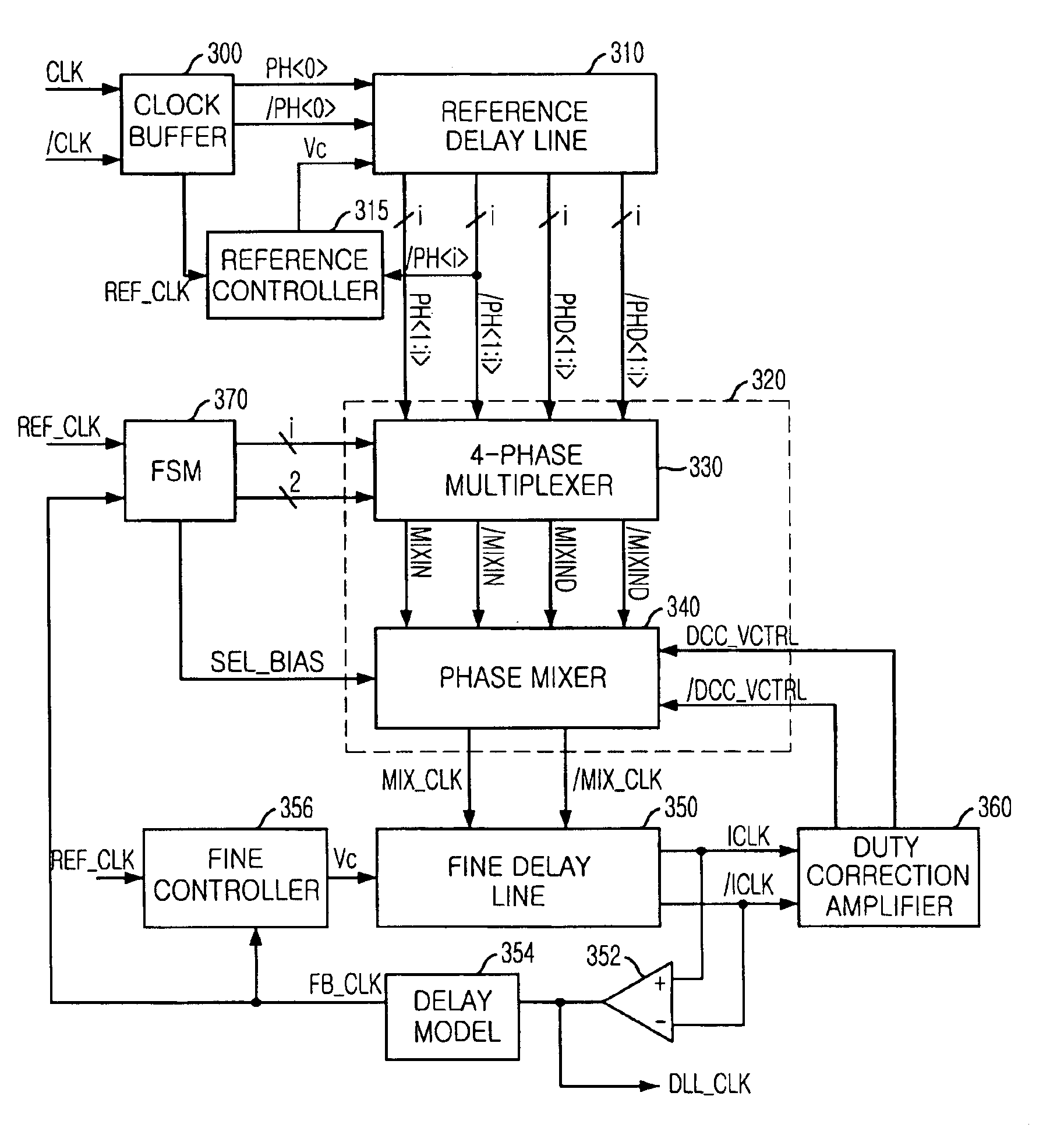

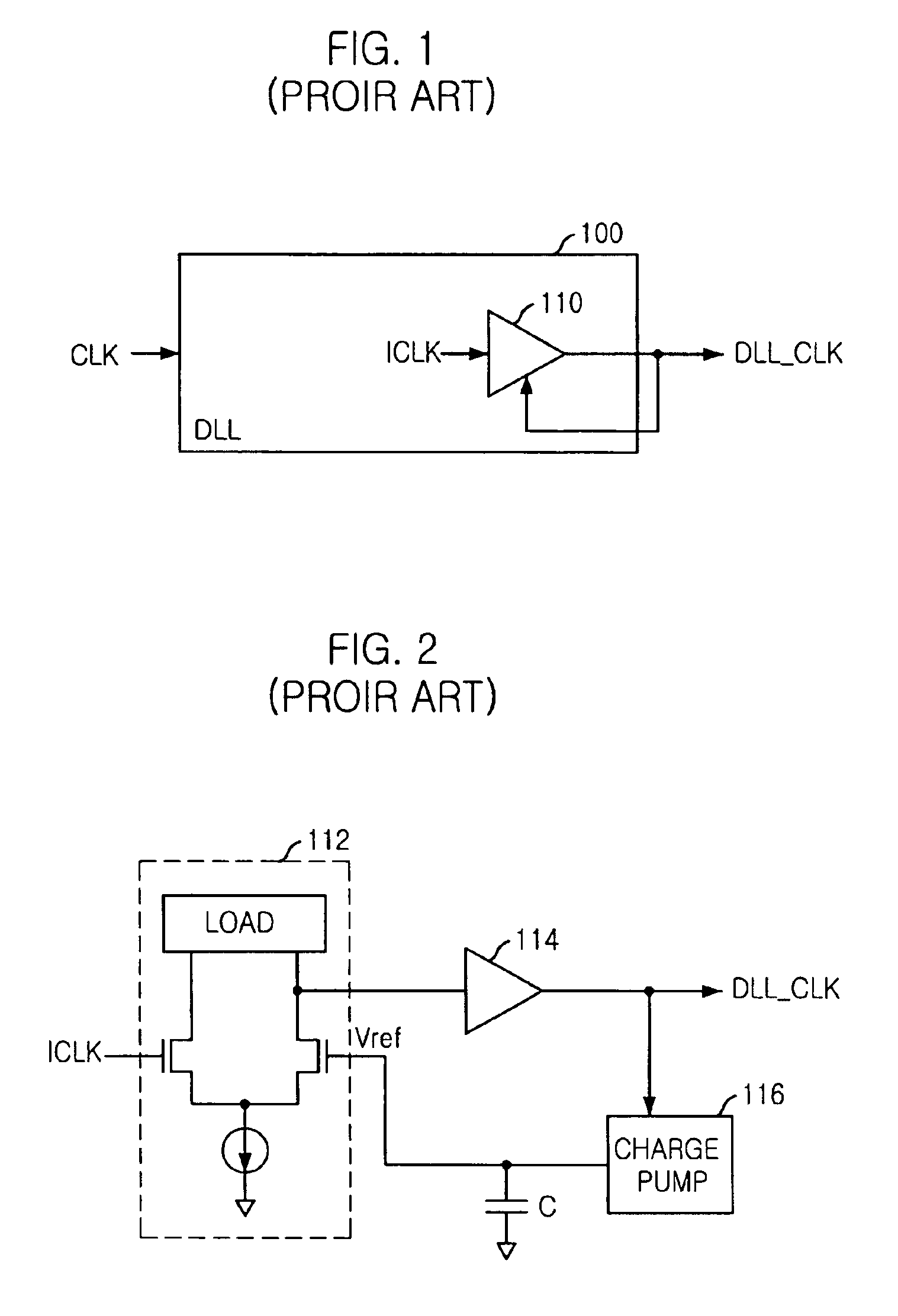

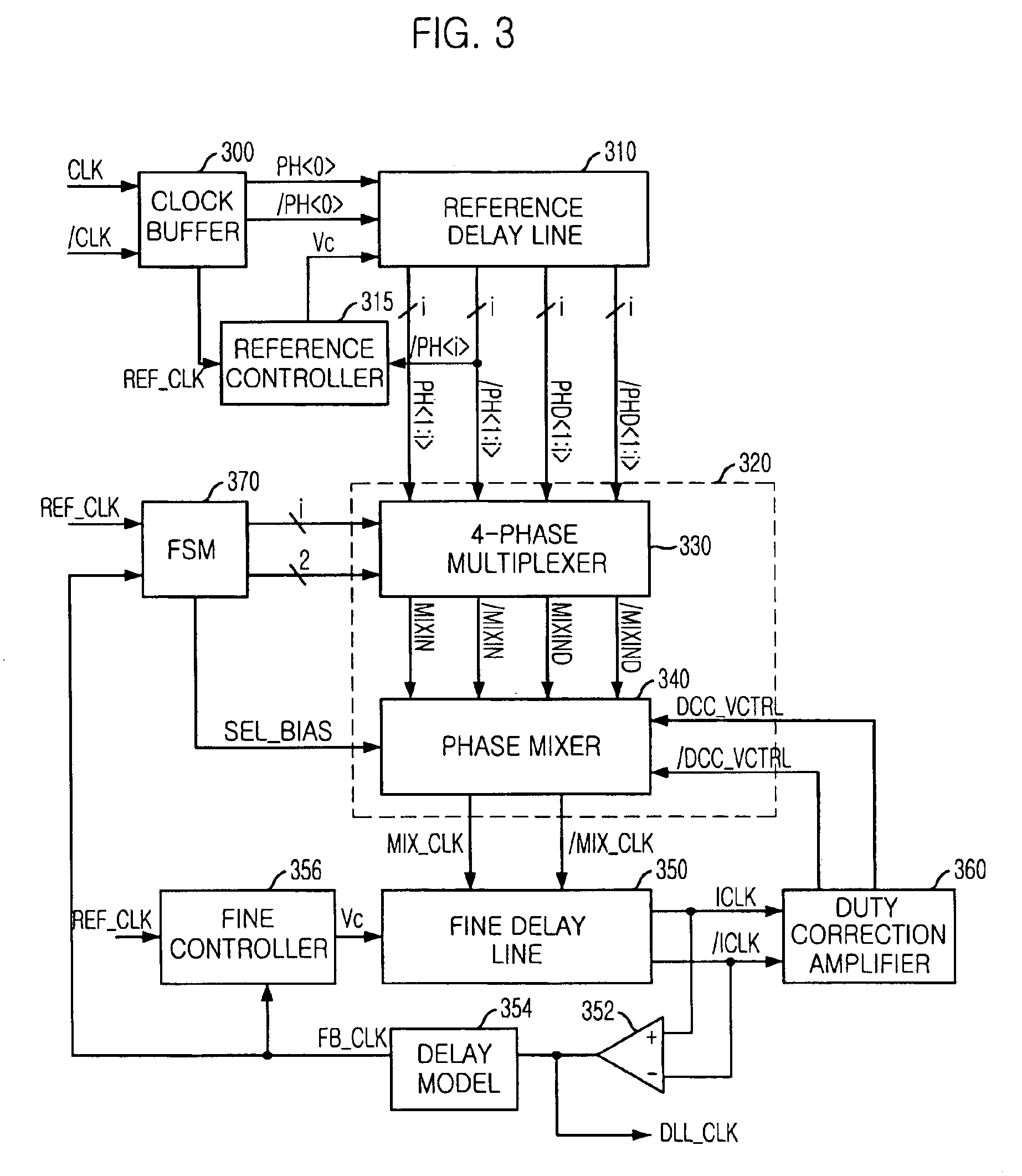

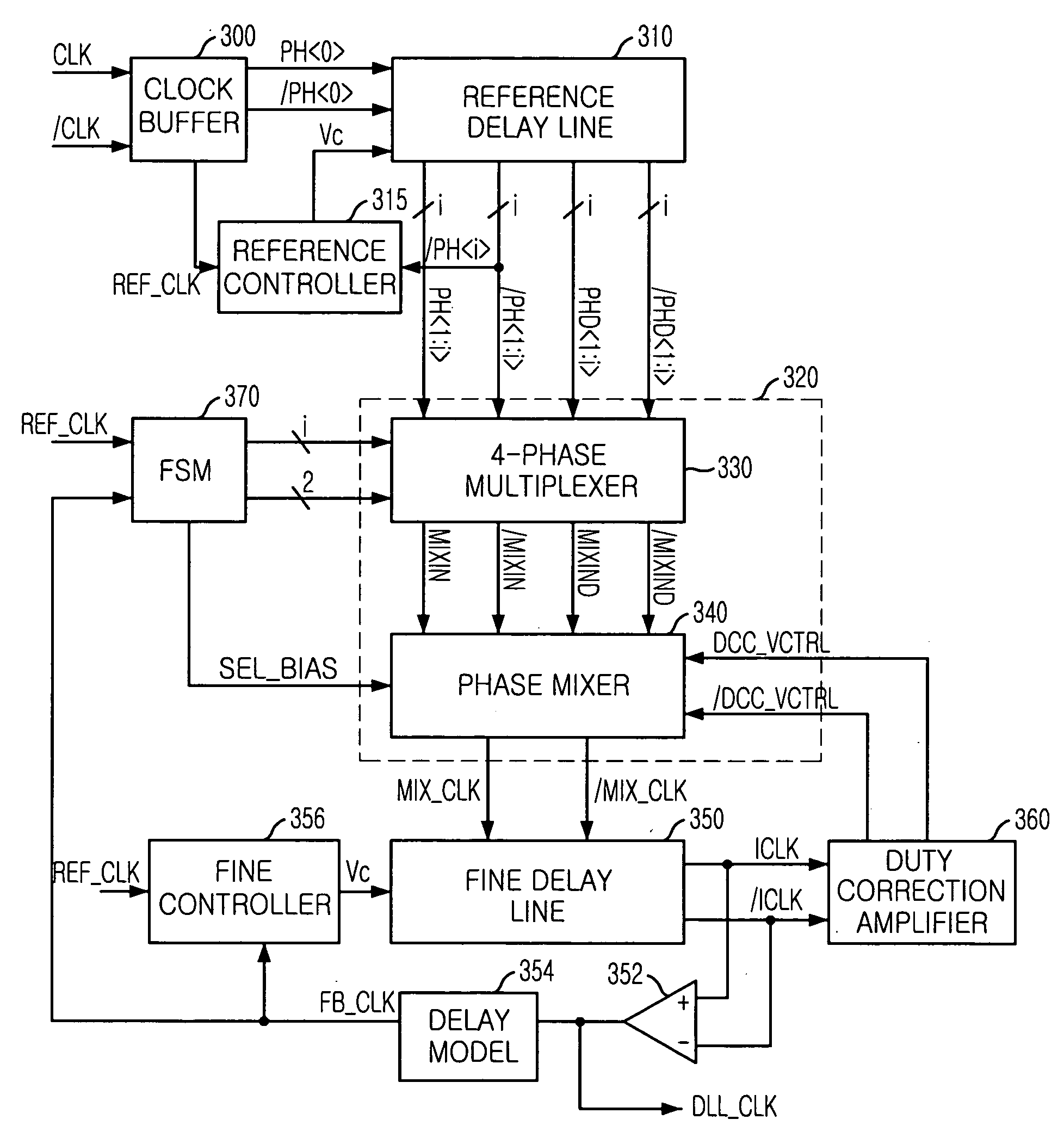

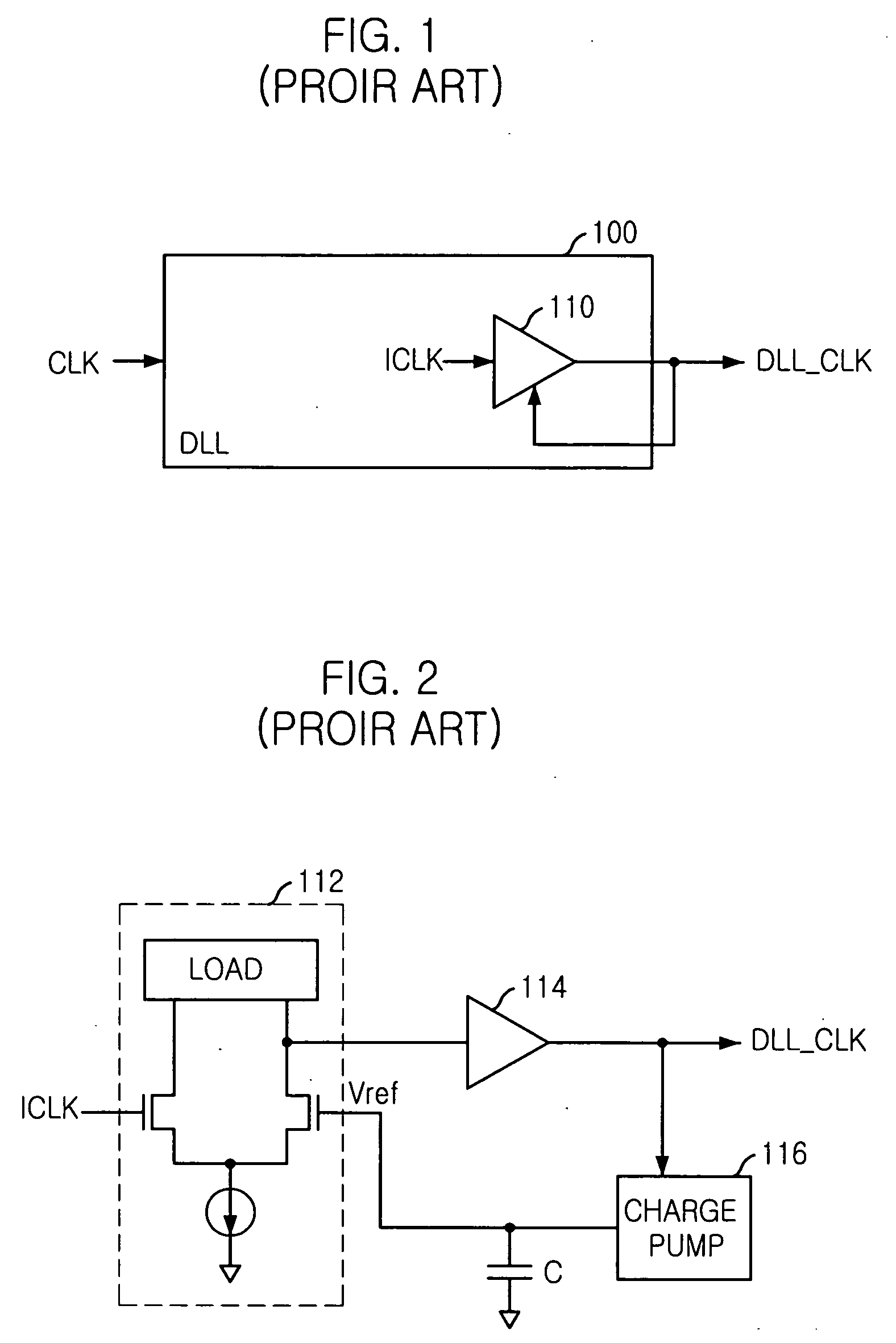

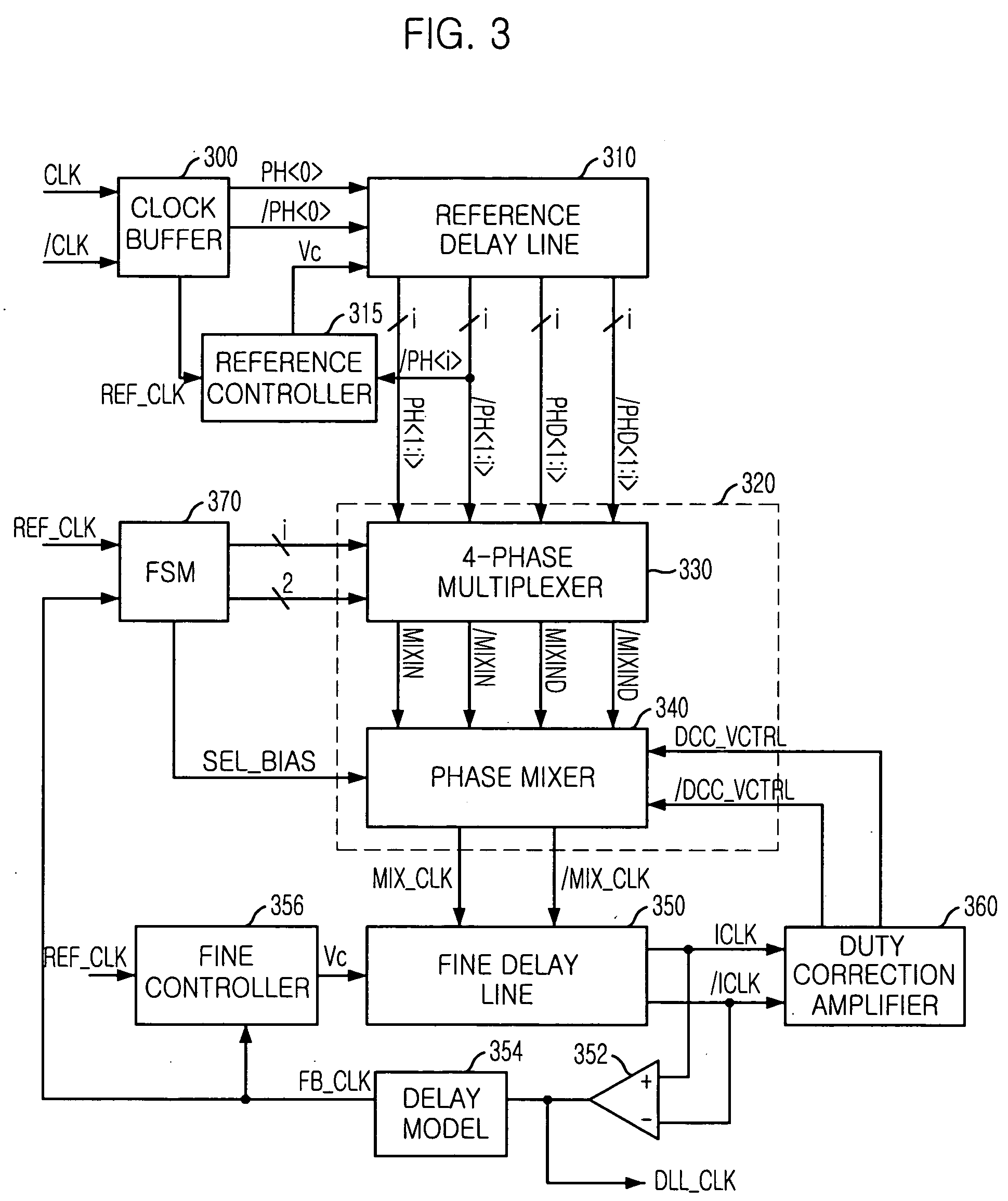

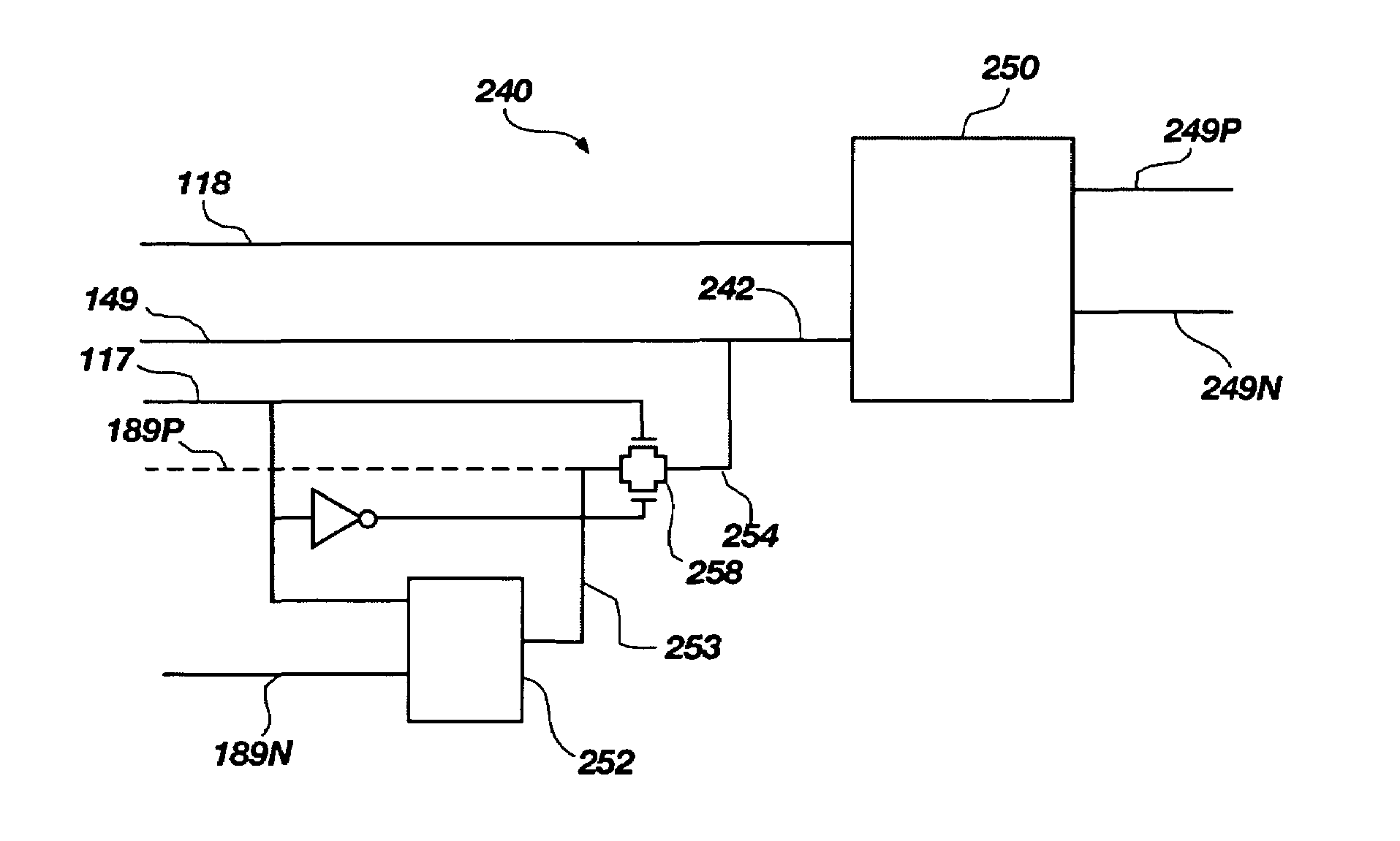

Analog delay locked loop having duty cycle correction circuit

InactiveUS7078949B2Correct wide rangeReduce initial timePulse automatic controlContinuous to patterned pulse manipulationAnalog delay lineDelay-locked loop

An analog delay locked loop device includes a first block for receiving an internal clock signal and a reference clock signal to generate normal multi phase clock signal pairs and dummy multi phase clock signal pairs; and a second block for receiving the reference clock signal to generate a delay locked internal clock signal having a corrected duty cycle based on the normal multi phase clock signal pairs and the dummy multi phase clock signal pairs.

Owner:SK HYNIX INC

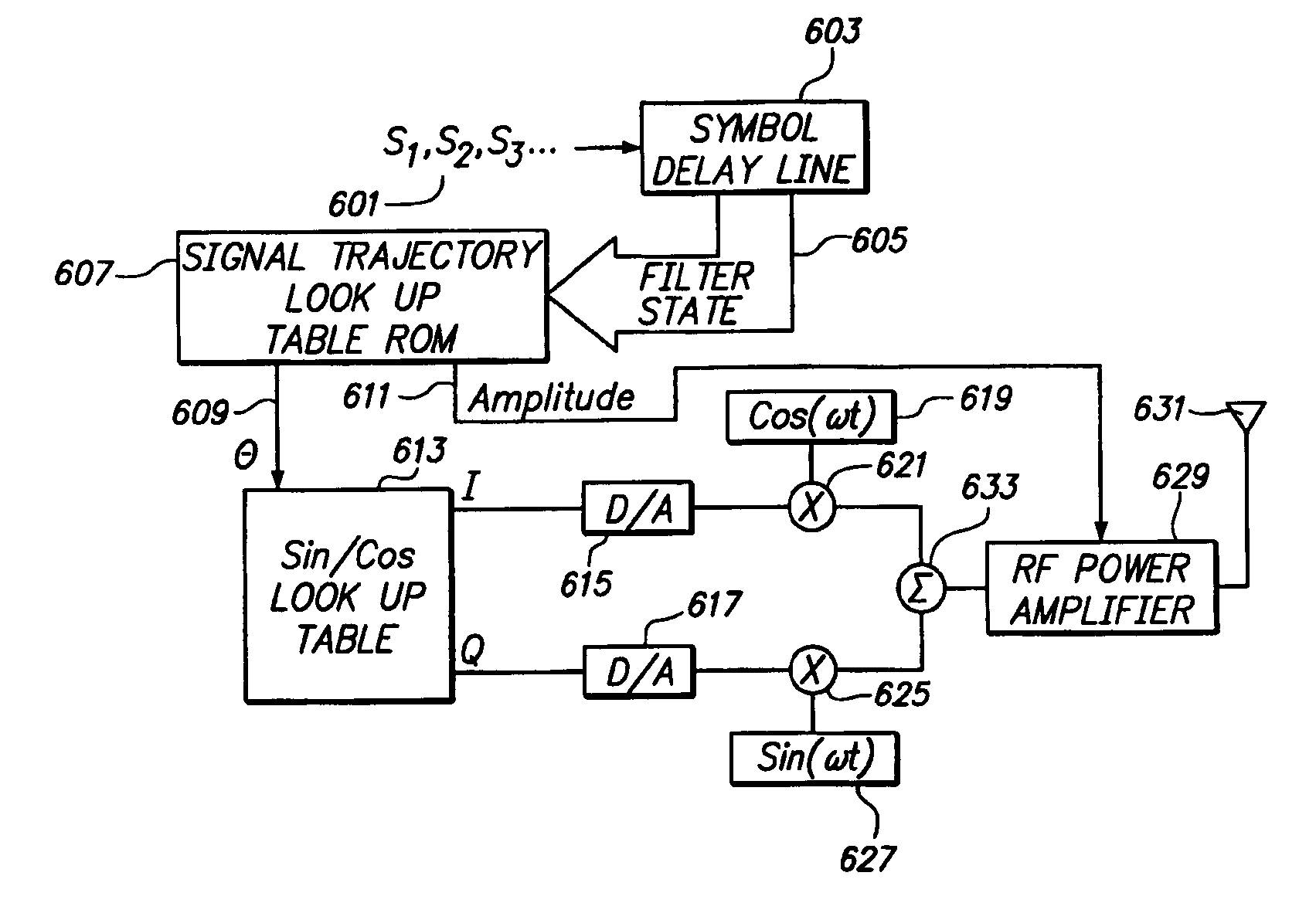

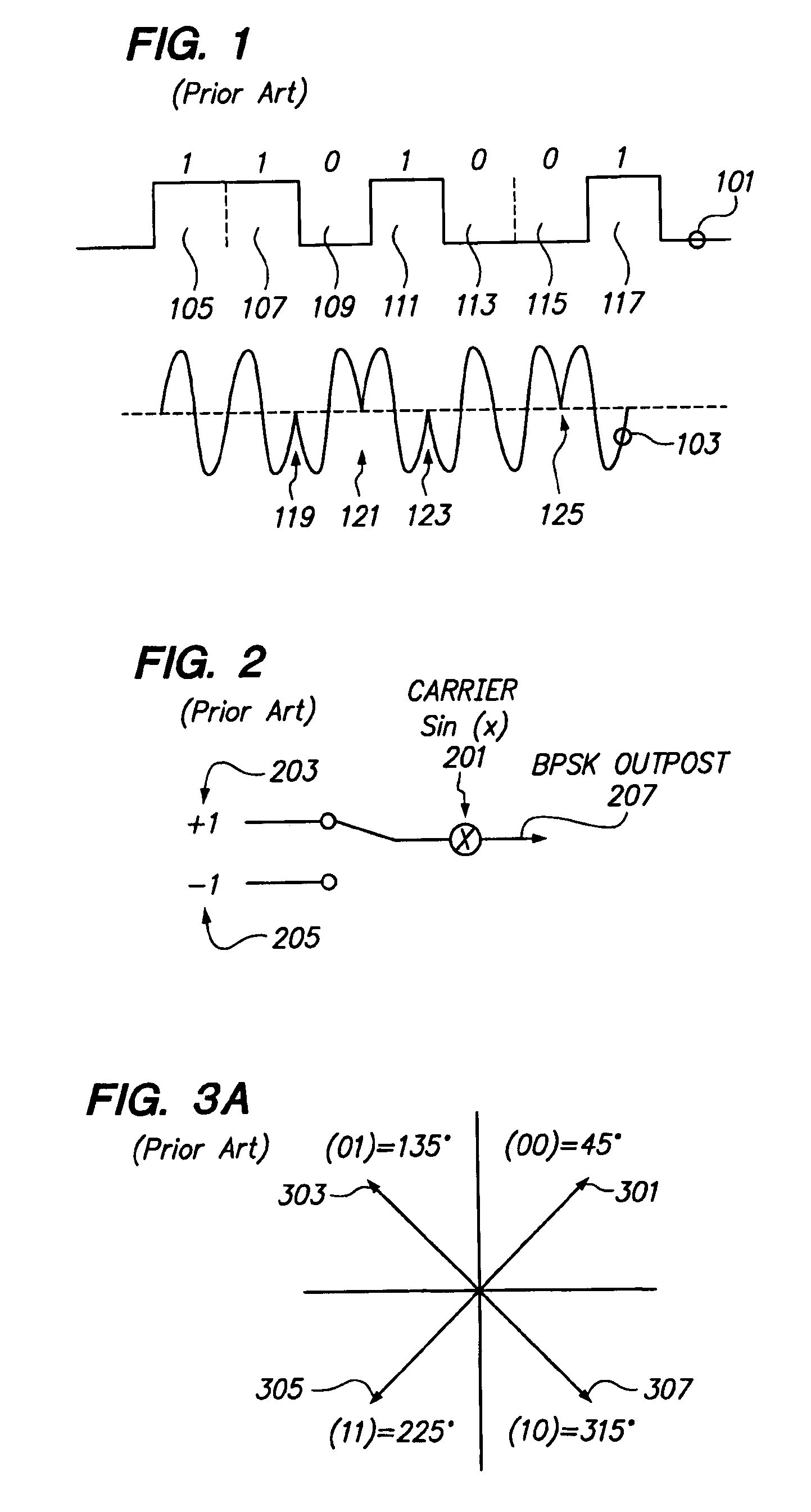

Efficient accurate controller for envelope feedforward power amplifiers

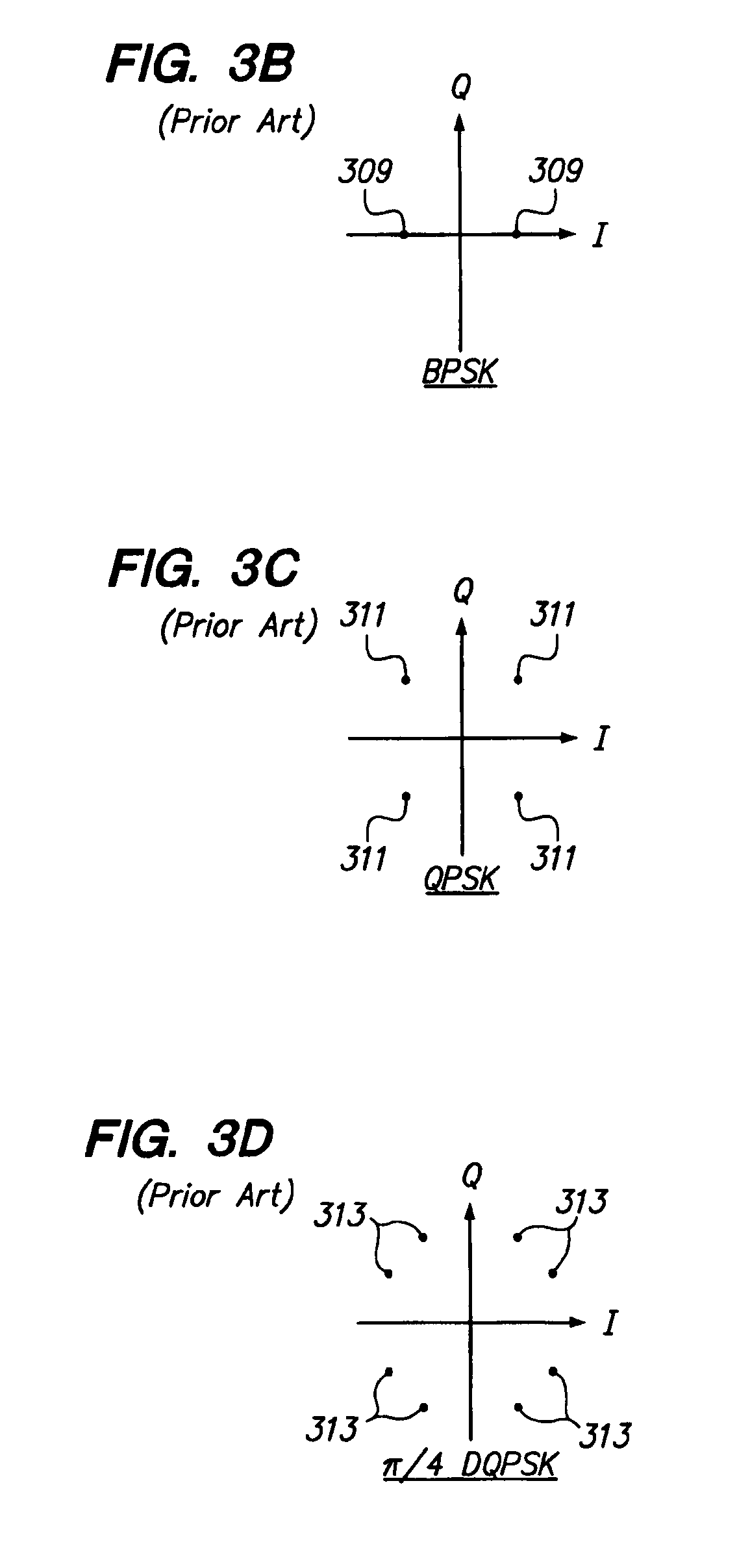

The disclosure is directed toward improved methods and apparatus for producing PSK signals. Commonly, such signals as Differential Quadrature Phase Shift Keying (DQPSK) are produced by coupling the outputs of an encoder to finite impulse response (FIR) filters. The filters shape the path that the signal takes between the transmission of one symbol and the next symbol The present disclosure discloses a method of generating a signal so that the path taken between transmitted symbols is determined by looking up the intermediate values along the path, using a look-up table. An embodiment of the disclosure receives the present symbol and the next symbol to be transmitted and then serially accesses a series of intermediate points comprising a preferred signal path between the present symbol and the next symbol to be transmitted. Commonly some PSK signals are transmitted by processing the phase and the amplitude of the signal separately. In those applications it is common to delay the amplitude portion of the signal in an analog delay line in order to ensure that the recombined signal will have the proper relationship of phase and amplitude. One preferred embodiment adds a phase offset to the phase signal instead of adding a delay to the amplitude signal. Another preferred embodiment performs phase amplitude synchronization by introducing phase offsets in the look-up table values which represent the signal path between sequentially transmitted signals. The phase offset achieves the same result as the traditional amplitude delay mechanism in synchronizing the phase and amplitude portions of the signal without the traditional delay line hardware.

Owner:SKYWORKS SOLUTIONS INC

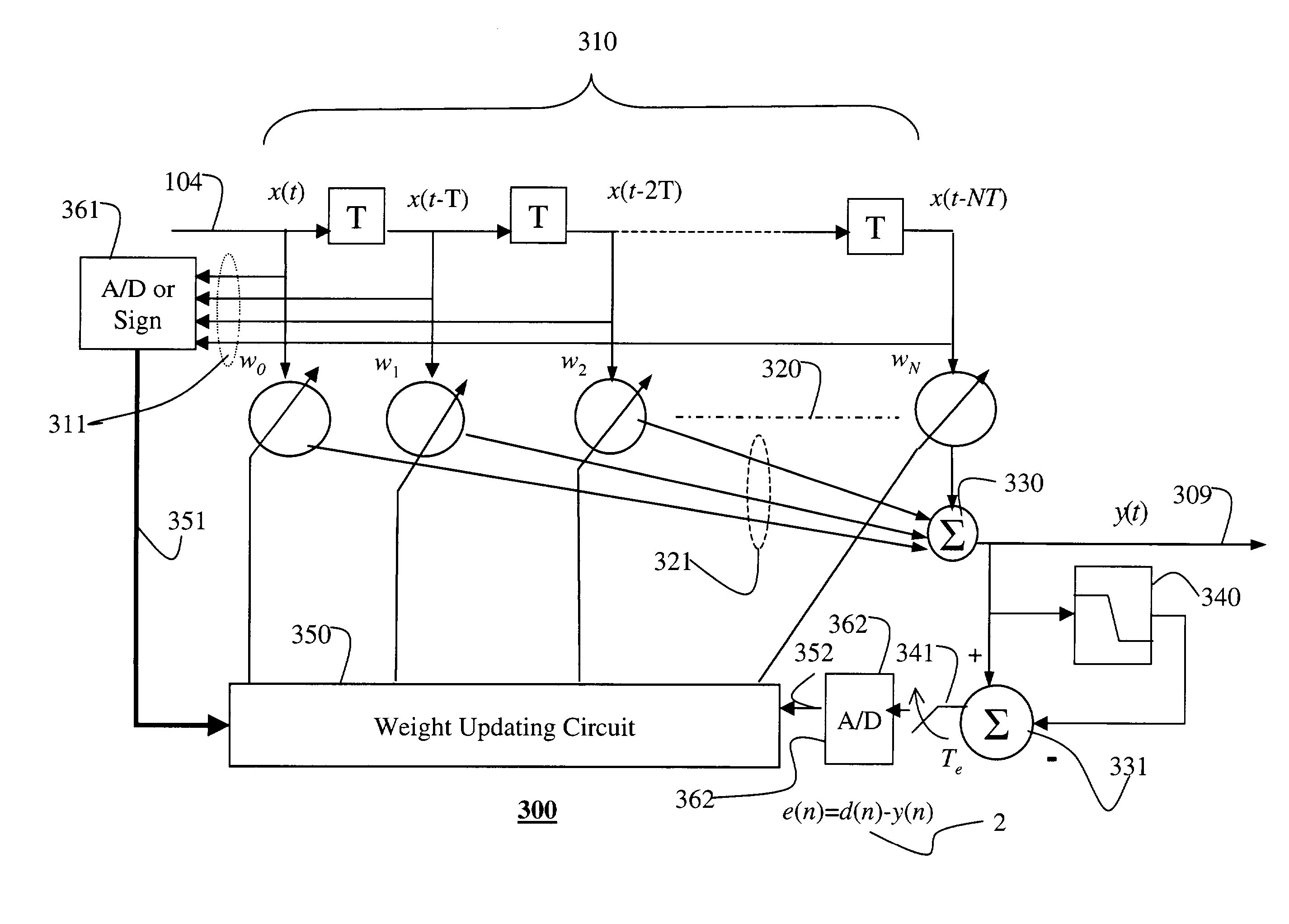

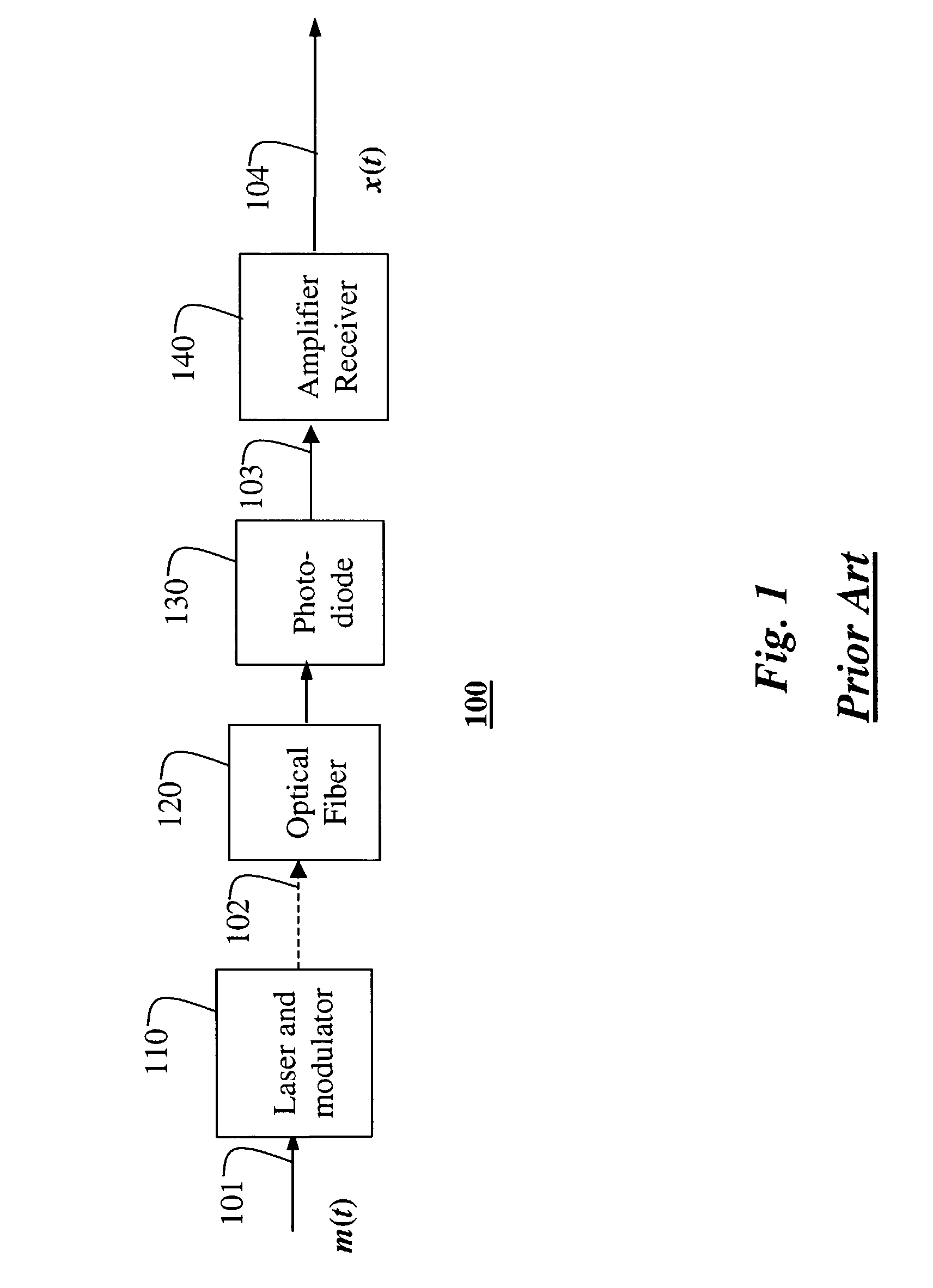

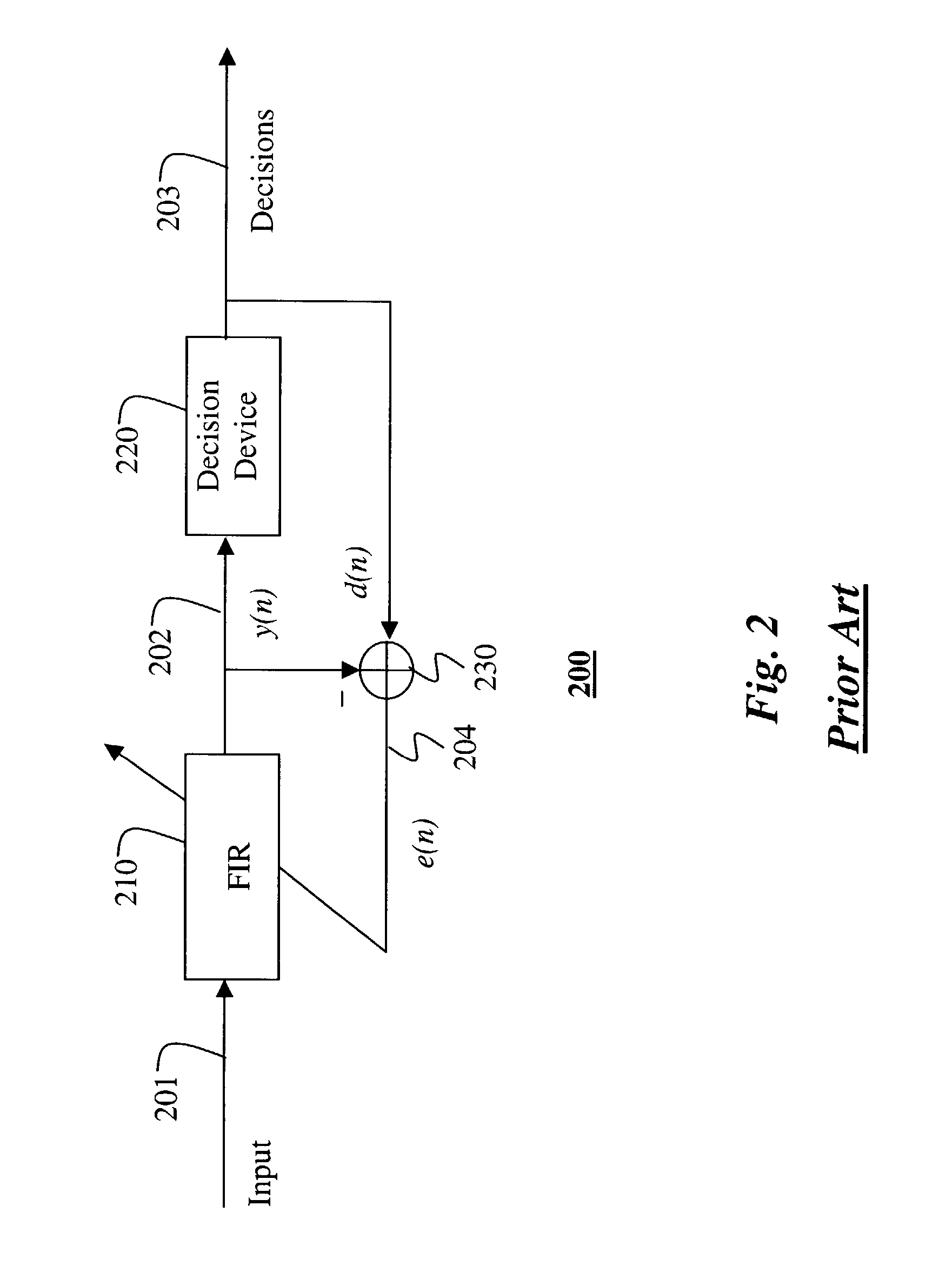

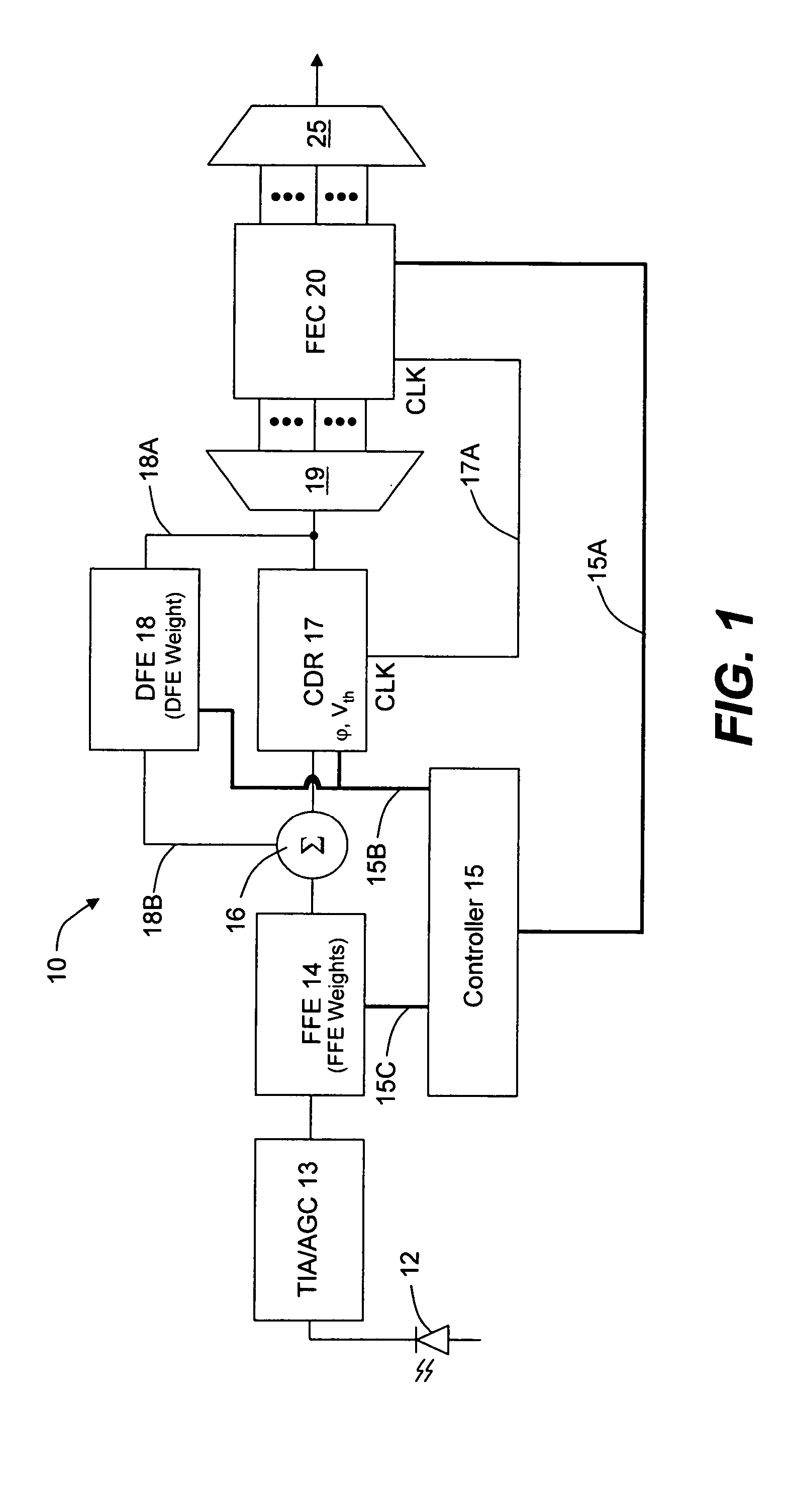

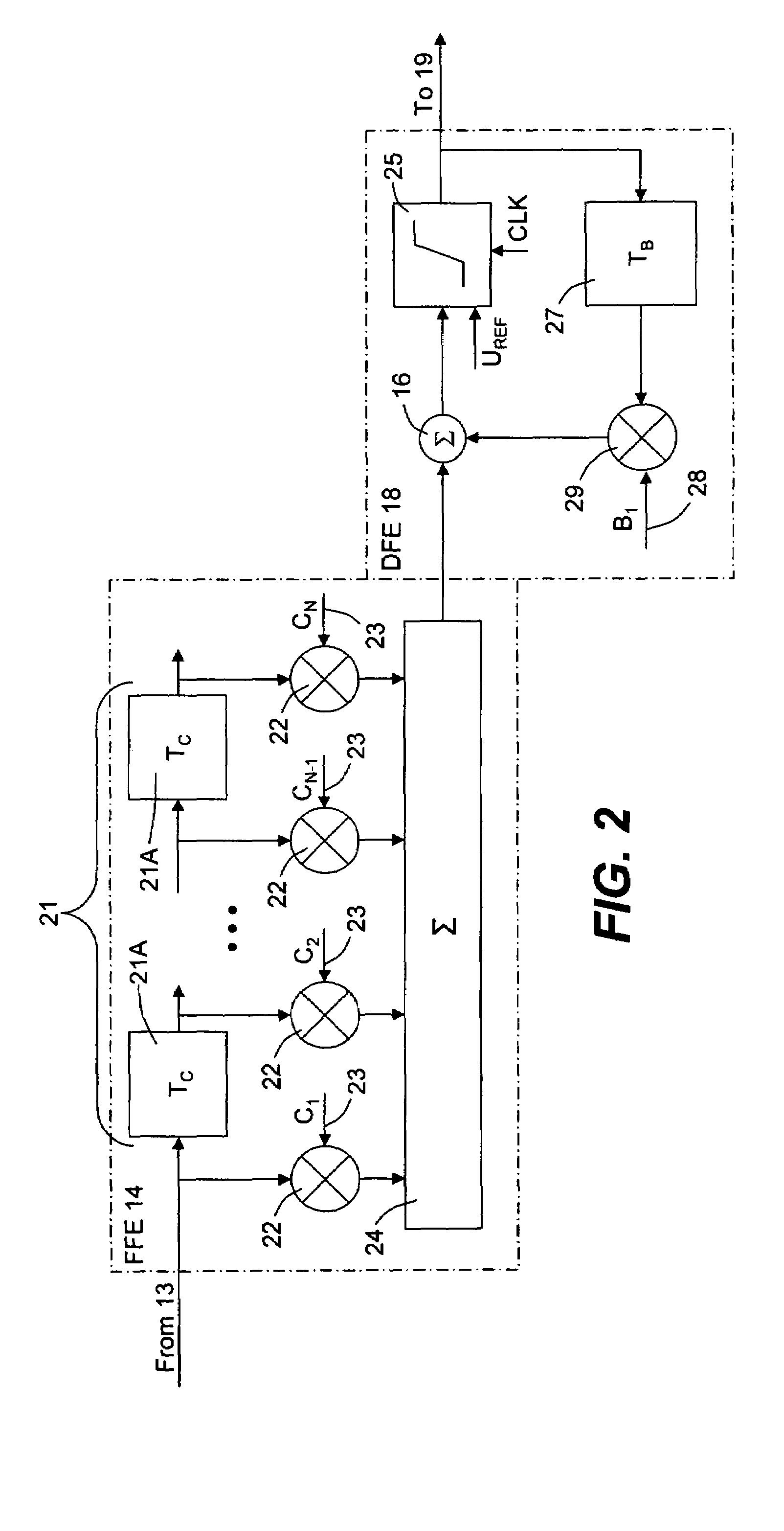

Hybrid adaptive equalizer for optical communications systems

InactiveUS7023912B2Reduce Intersymbol InterferenceEliminate needMultiple-port networksTransmission control/equlisationCommunications systemAnalog delay line

A method equalizes a received signal in an optical communications system. The received signal is passed through an analog delay line where it is tapped to generate a set of delayed copies of the received signal. In a set of analog multipliers, each delayed copy of the received signal is multiplied by a corresponding weight to generate a set of weighted signals that are then summed to produce an output signal. The output signal is thresholded and subtracted from the output signal to produce an error signal, which is periodically sampled. In a digital weight updating circuit, the weights are produced from digitized versions of the sampled error signal and samples of the delayed copies of the received signal.

Owner:MITSUBISHI ELECTRIC RES LAB INC

Analog delay locked loop having duty cycle correction circuit

InactiveUS20040155686A1Correct wide rangeReduce initial timePulse automatic controlContinuous to patterned pulse manipulationAnalog delay lineDelay-locked loop

An analog delay locked loop device includes a first block for receiving an internal clock signal and a reference clock signal to generate normal multi phase clock signal pairs and dummy multi phase clock signal pairs; and a second block for receiving the reference clock signal to generate a delay locked internal clock signal having a corrected duty cycle based on the normal multi phase clock signal pairs and the dummy multi phase clock signal pairs.

Owner:SK HYNIX INC

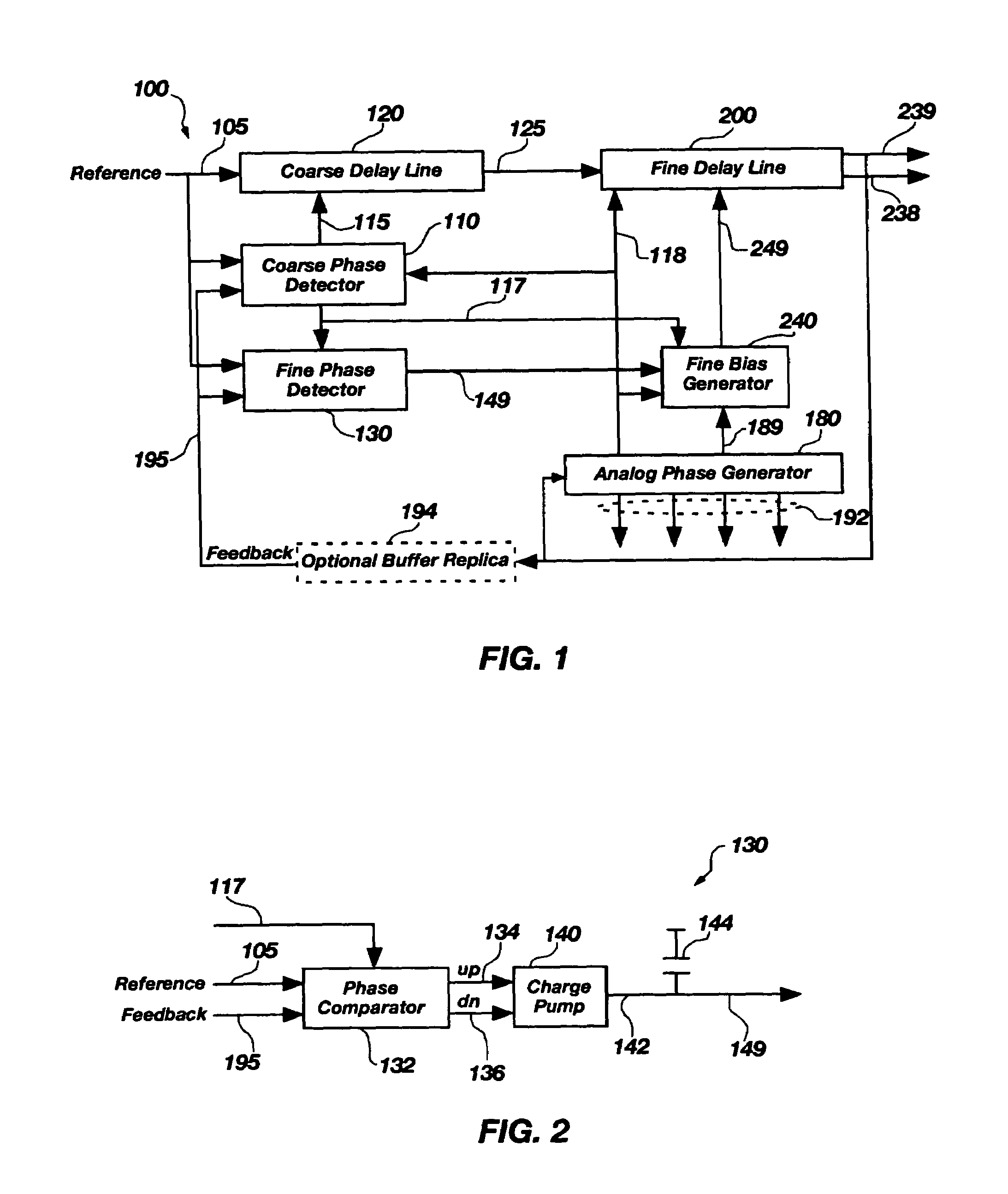

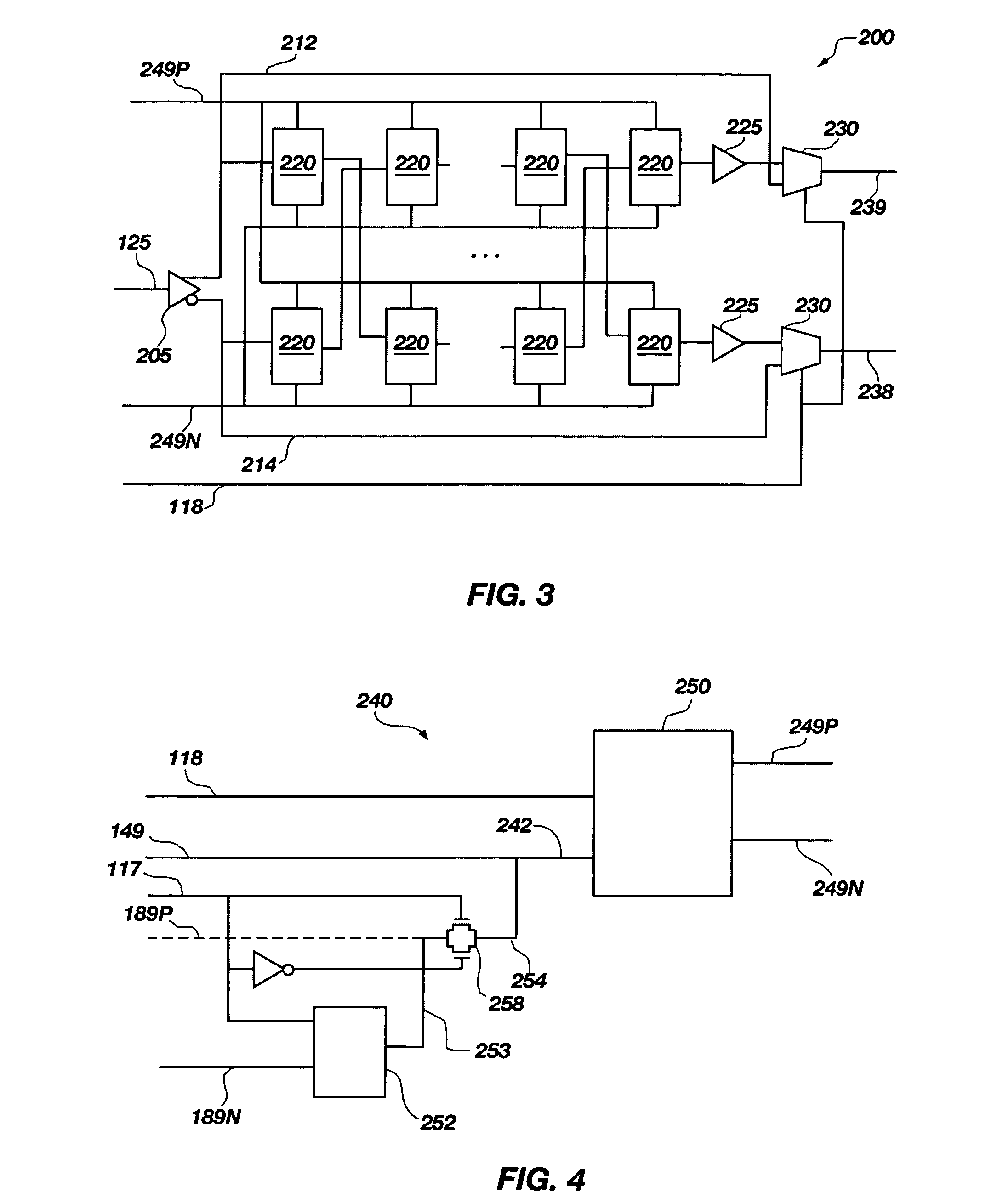

Method and apparatus to set a tuning range for an analog delay

An apparatus and method for an analog fine delay line, a hybrid delay line, and a delay locked loop (DLL) is described. In the DLL, a coarse phase detector compares a reference signal and feedback signal in controlling coarse phase adjustment signals indicating whether a delay of a coarse delay line should be increased or decreased. Similarly, a fine phase detector compares the reference signal and feedback signal to generate a locking bias signal, which may increase or decrease a delay of an analog fine delay line. The analog fine delay line and coarse delay line may be connected in series creating the hybrid delay line having a total delay comprised of the coarse delay and the fine delay. Additionally, a fine bias generator may control the fine delay in response to an initiating bias signal from an analog phase generator or the locking bias signal.

Owner:MICRON TECH INC

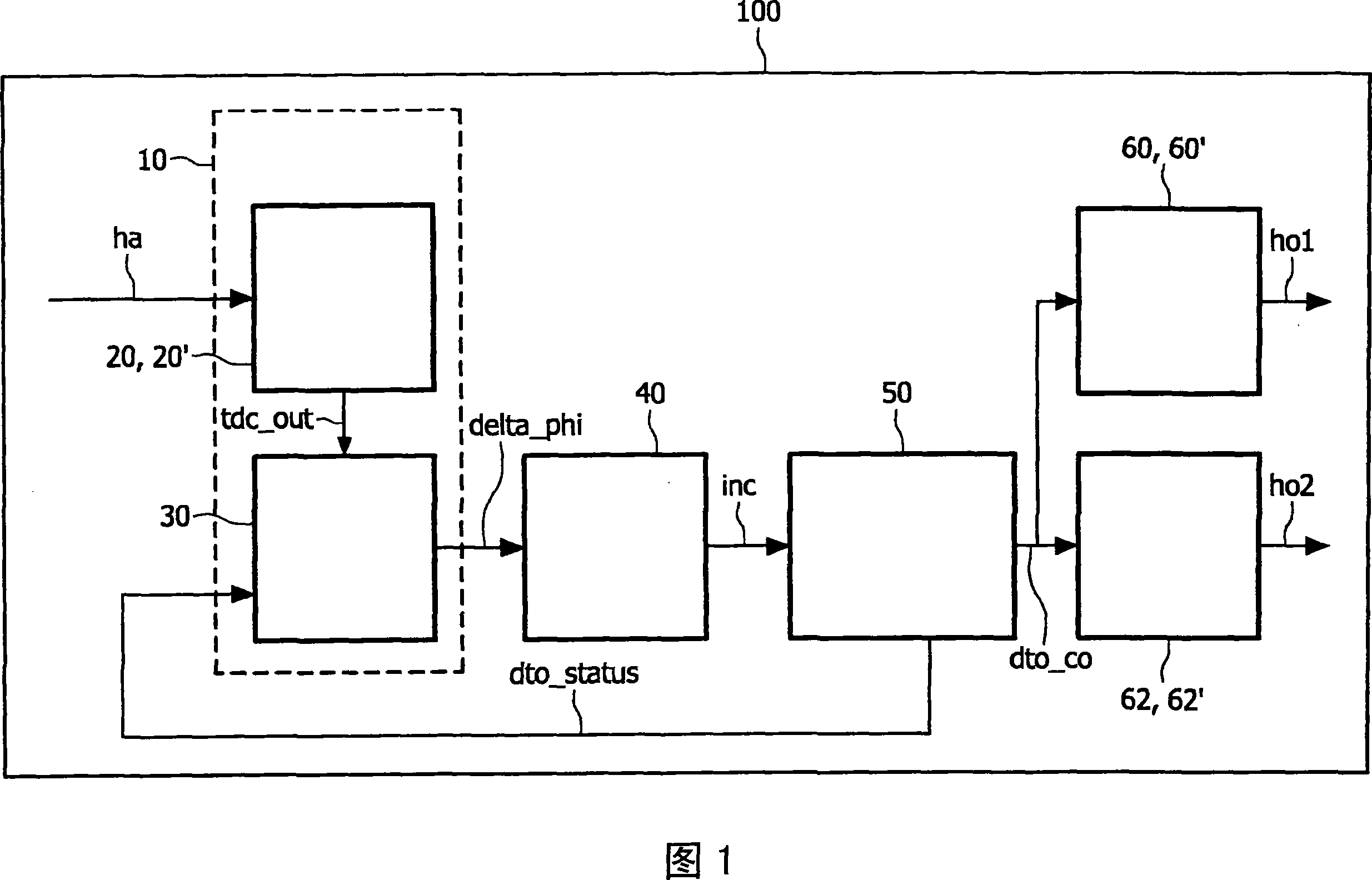

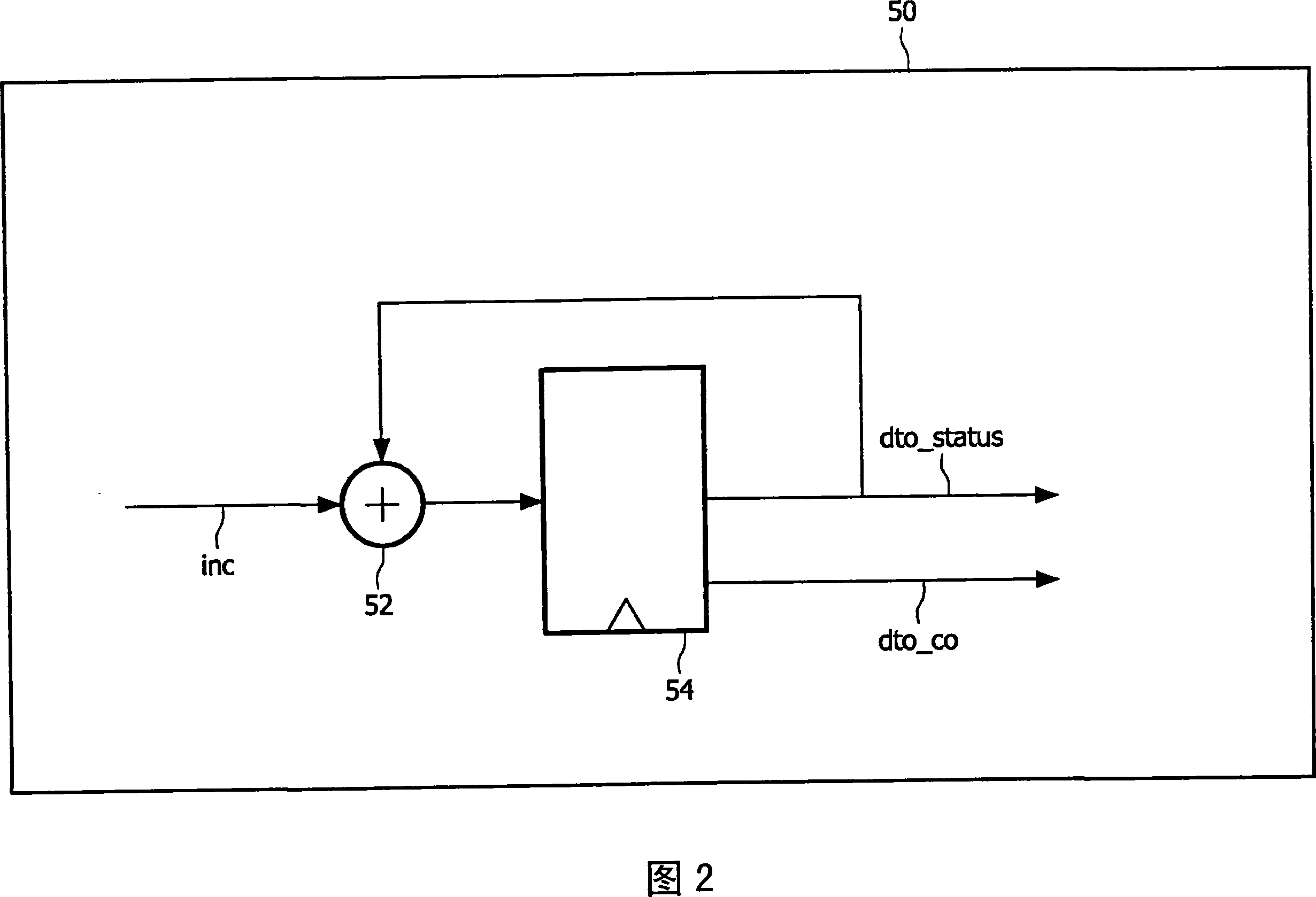

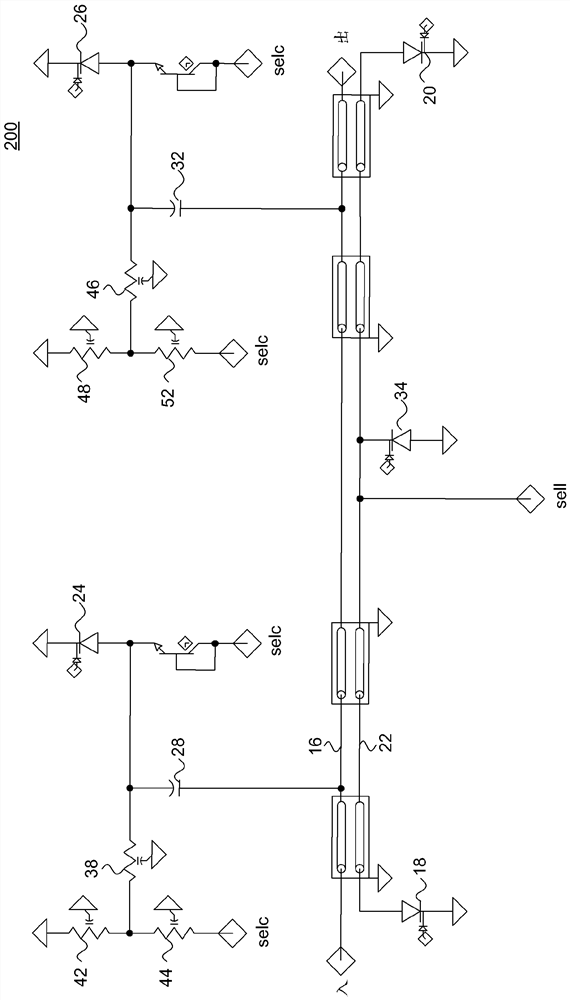

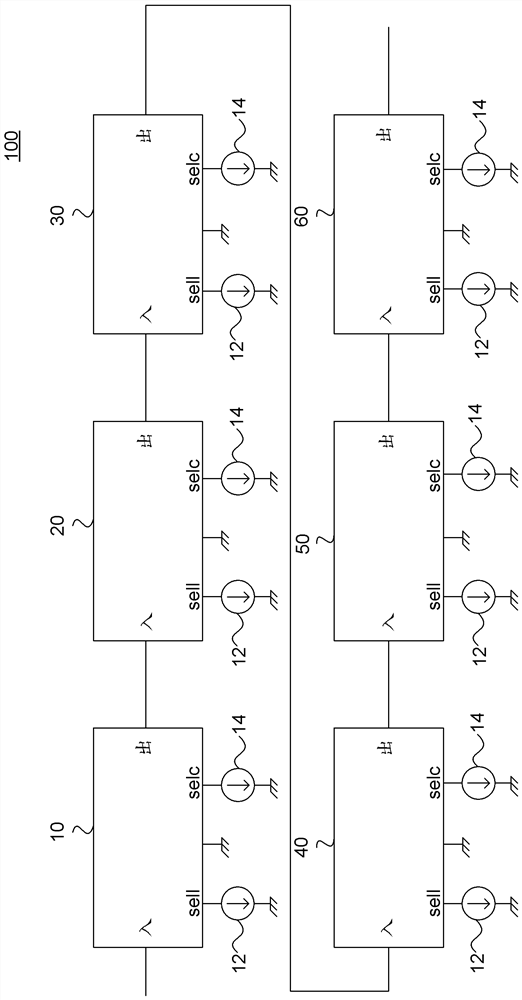

Circuit arrangement, in particular phase-locked loop, as well as corresponding method

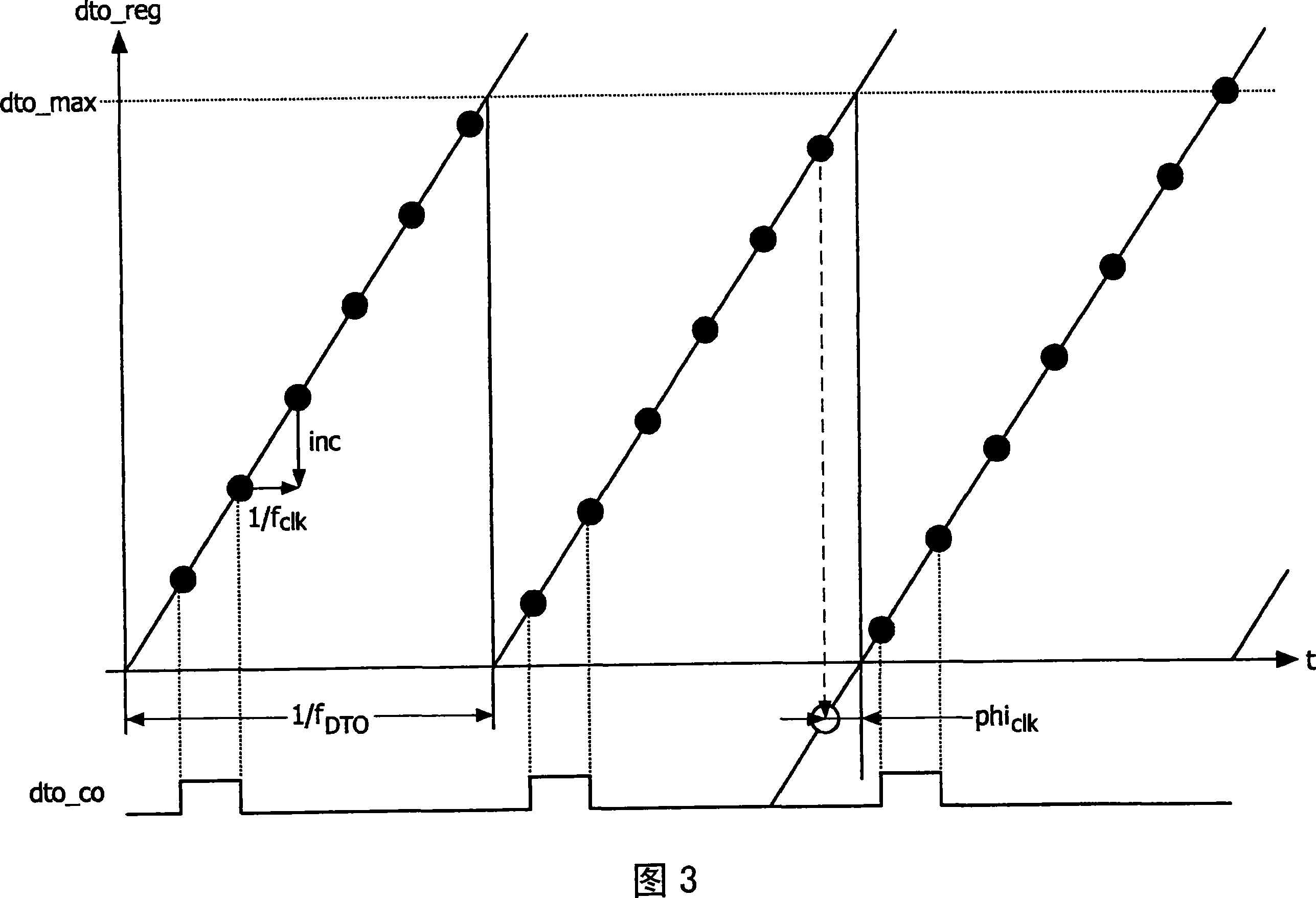

In order to further develop a circuit arrangement (100), in particular to a phase-locked loop for sub-clock or sub-pixel accurate phase-measurement and phase-generation, as well as a corresponding method in such way that no clock multiplier phase-locked loop is to be provided behind the time-to-digital converter and that neither an analog delay line nor a signal divider unit is to be provided between the digital ramp oscillator or discrete time oscillator and the digital-to-time converter, wherein less analog circuitry is susceptible for noise and for ground bounce in the digital environment, it is proposed to provide at least one phase measurement unit (10); - at least one loop filter unit (40; 40') being provided with at least one output signal (delta-phi) of at least one phase detector unit (30); at least one digital ramp oscillator unit or discrete time oscillator unit (50; 50') being provided with at least one output signal, in particular with at least one increment (inc), of the loop filter unit (40; 40'), the status signal (dto-status) of at least one register unit (54; 54') of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') being fed back as input signal to the phase detector unit (30); and at least one digital-to-time converter unit (60, 62; 60', 62') being provided with at least one output signal (dto-co) of the digital ramp oscillator unit or discrete time oscillator unit (50; 50') and generating at least one output signal (hoi, ho2).

Owner:NXP BV

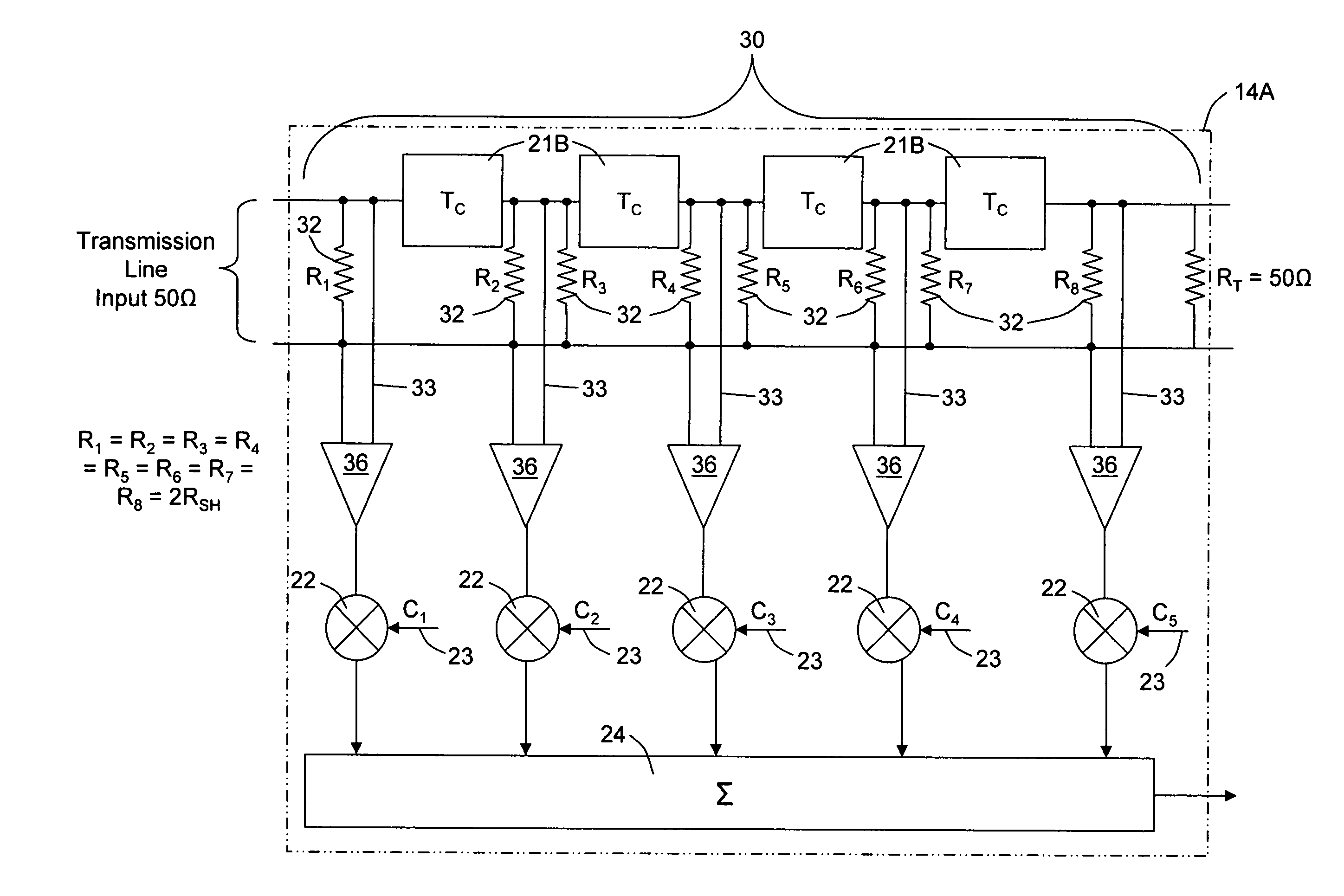

Transmission line with low dispersive properties and its application in equalization

ActiveUS7446622B2Transmission control/equlisationTransmitter/receiver shaping networksElectrical resistance and conductanceAnalog delay line

A transmission line is provided with added shunt resistance, RSH, distributed along the length of the micro transmission line permitting the extension of constant characteristic impedance to the transmission line to lower signal frequencies. The loss in gain to the signal propagating the transmission line due to the added resistance can be compensated for by amplification provided at the output of the transmission line or at output taps provided along the length of the transmission line such as in cases where the line is utilized as a circuit delay line. An exemplified application disclosed is an analog delay line formed as a metal microstrip in an IC chip circuit provided, for example, in a feed forward equalizer (FFE).

Owner:INFINERA CORP

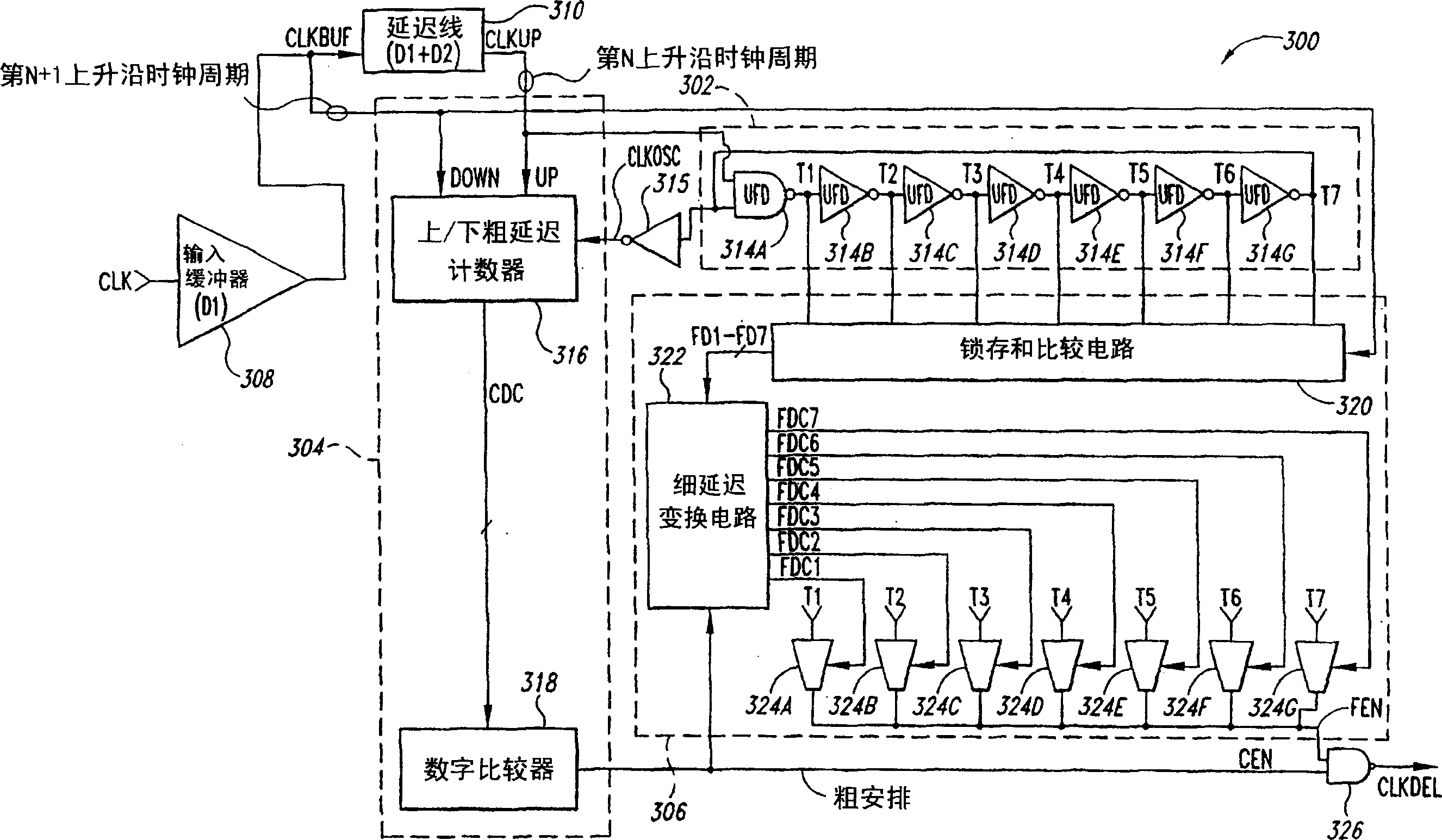

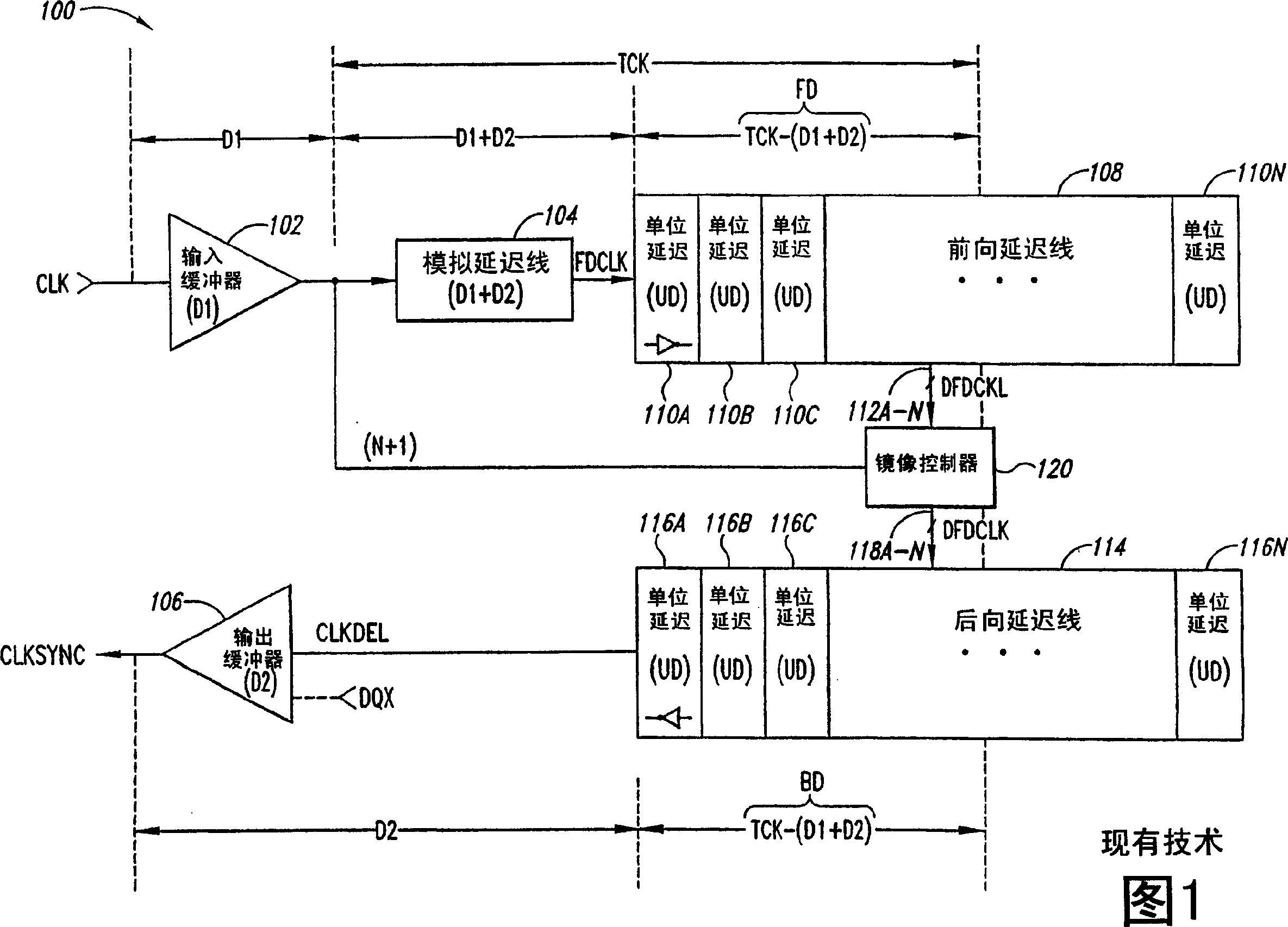

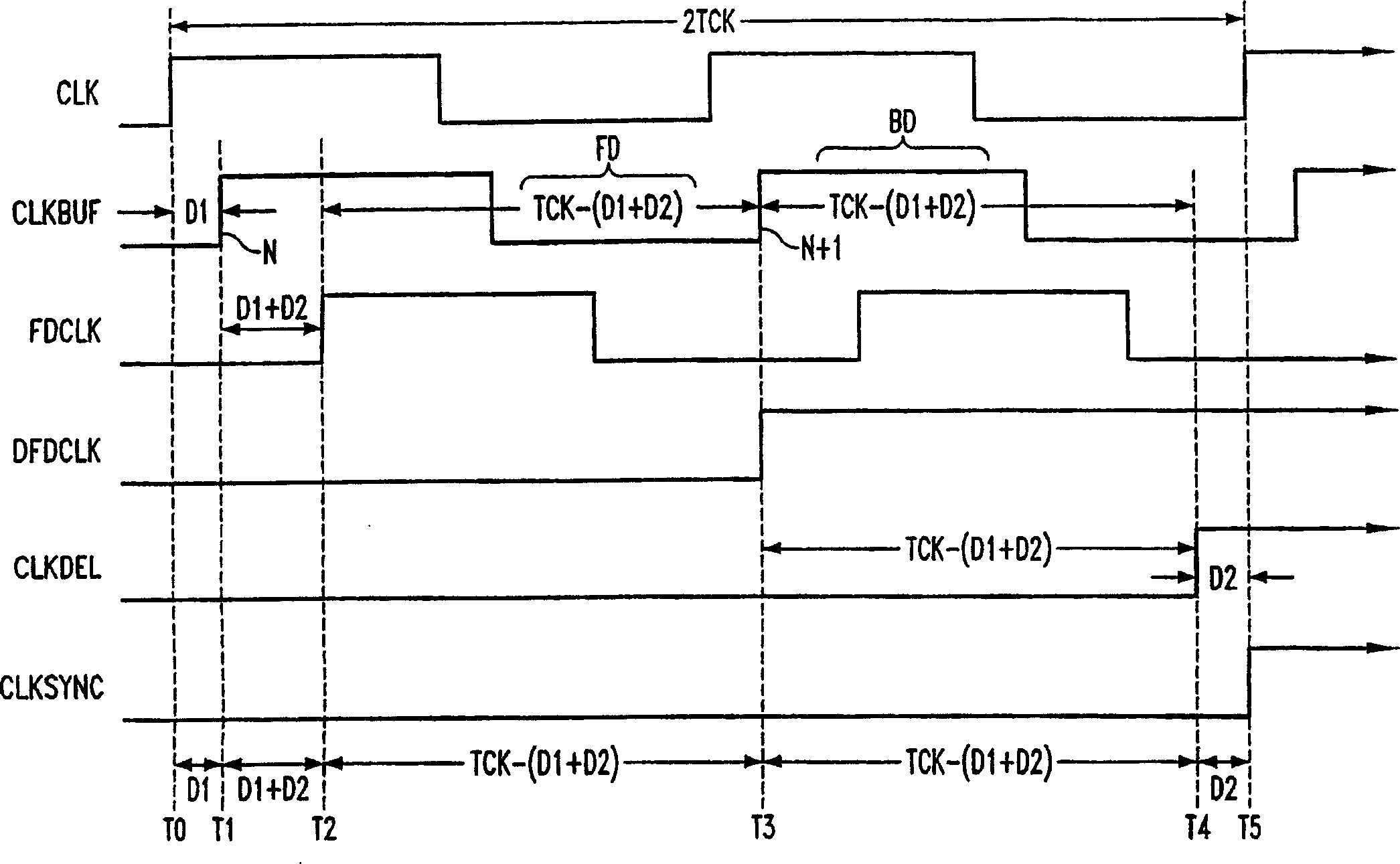

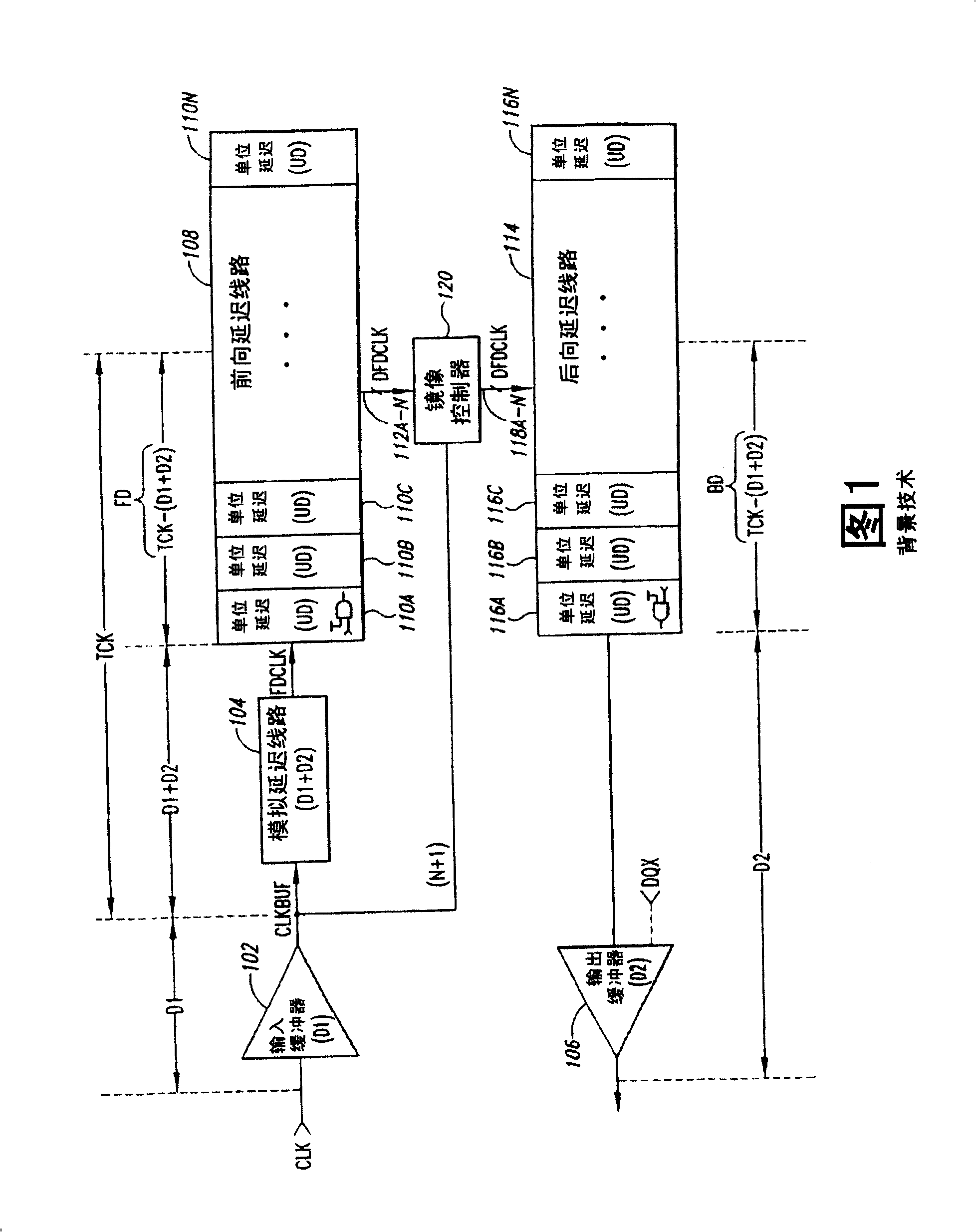

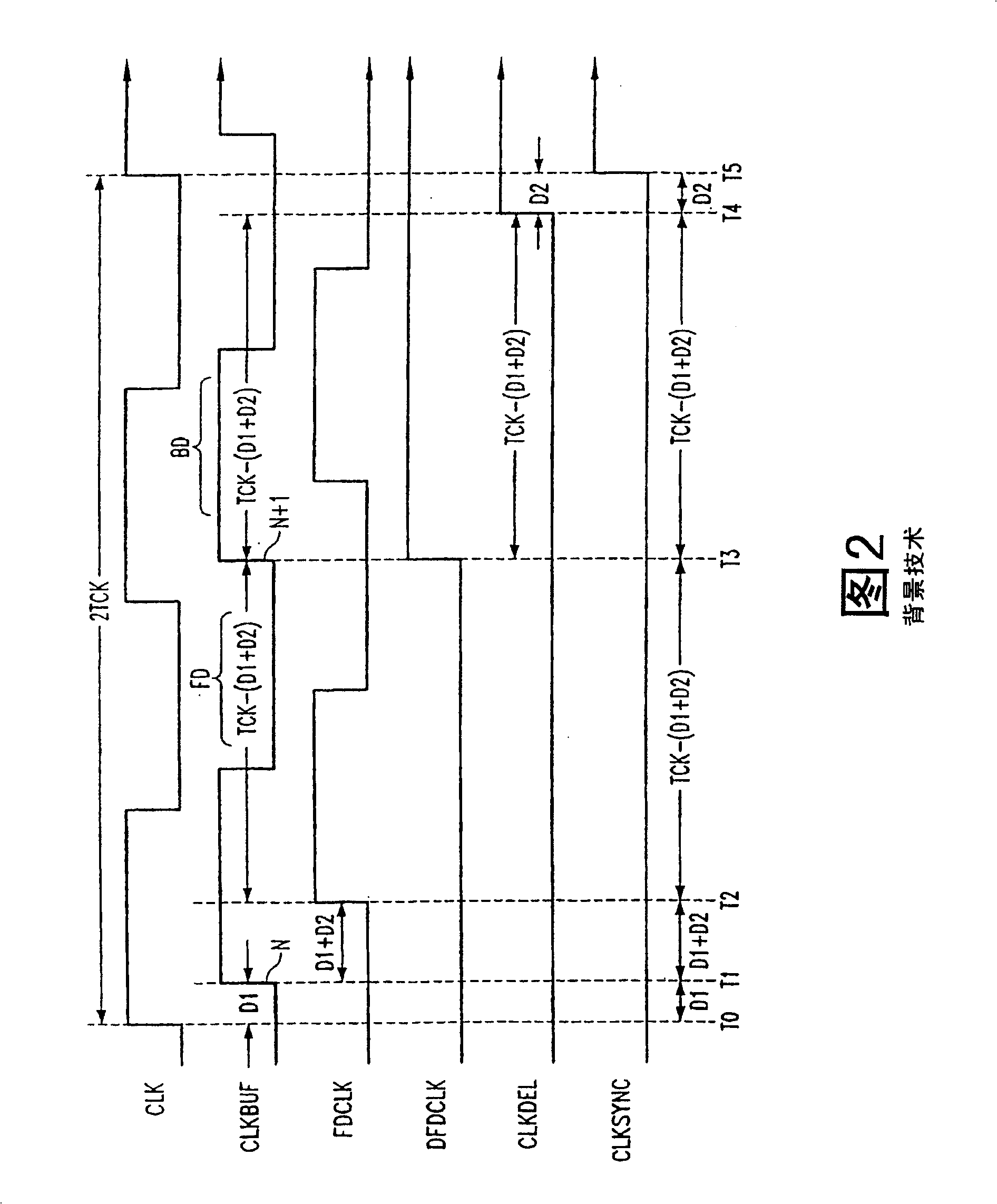

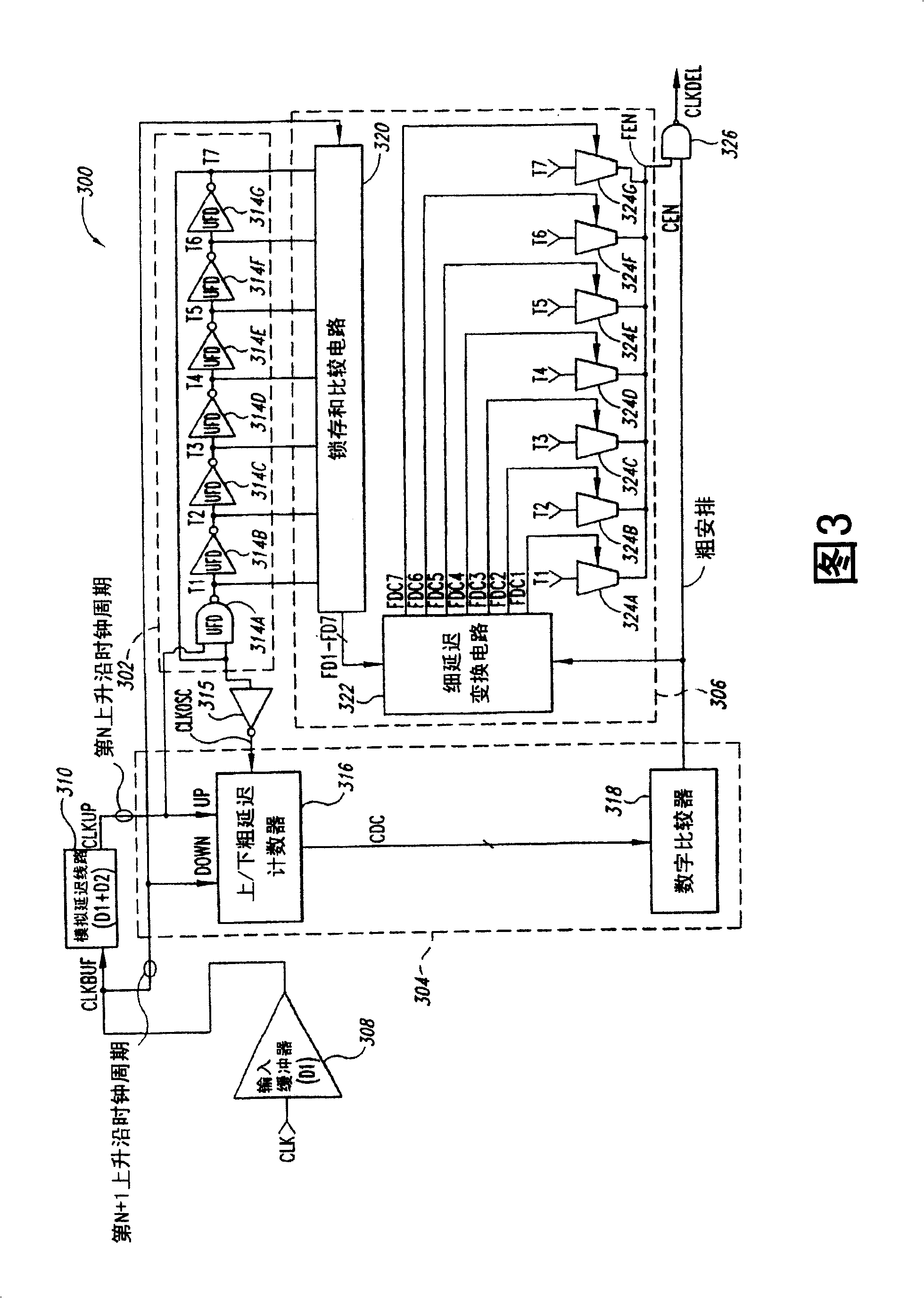

Synchronous mirror delay (SMD) circuit and method including a ring oscillator for timing coarse and fine delay intervals

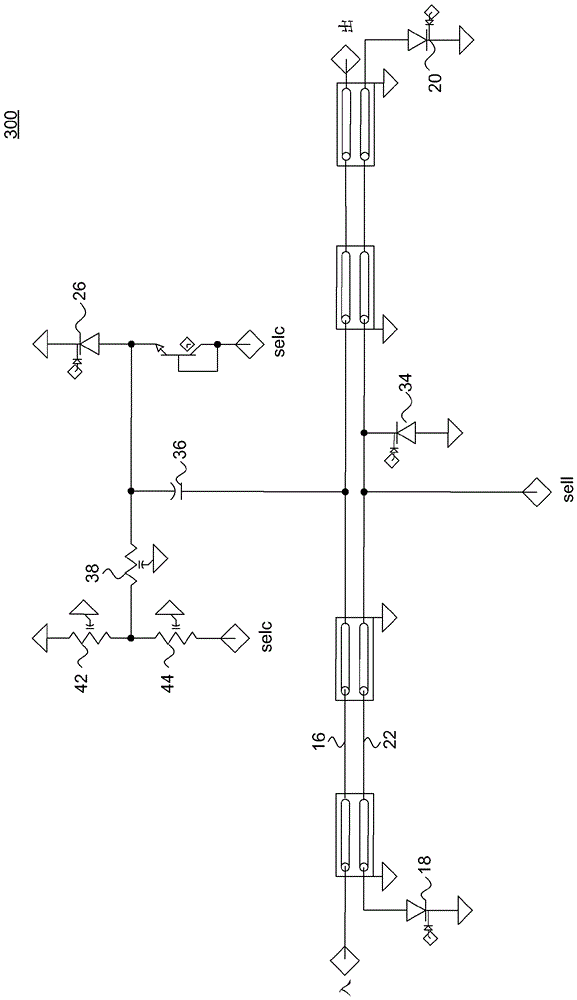

A synchronous mirror delay (300) includes a ring oscillator that generates a plurality of tap clock signals (T1-T7) with one tap clock signal being designated an oscillator clock signal. In response to an input clock signal, a model delay line generates a model delayed clock signal having a model delay relative to the input clock signal. A coarse delay circuit generates a coarse delay count (316) responsive to the oscillator, input, and model delayed clock signals, and activates a coarse delay enable signal responsive to the delay count being equal to a reference count value. A fine delay circuit latches the tap clock signals and develops a fine delay from the latched signals, and activates a fine delay enable signal having the fine delay in response to the coarse delay enable signal. An output circuit generates a delayed clock signal responsive to the coarse and fine delay enable signals going active.

Owner:MICRON TECH INC

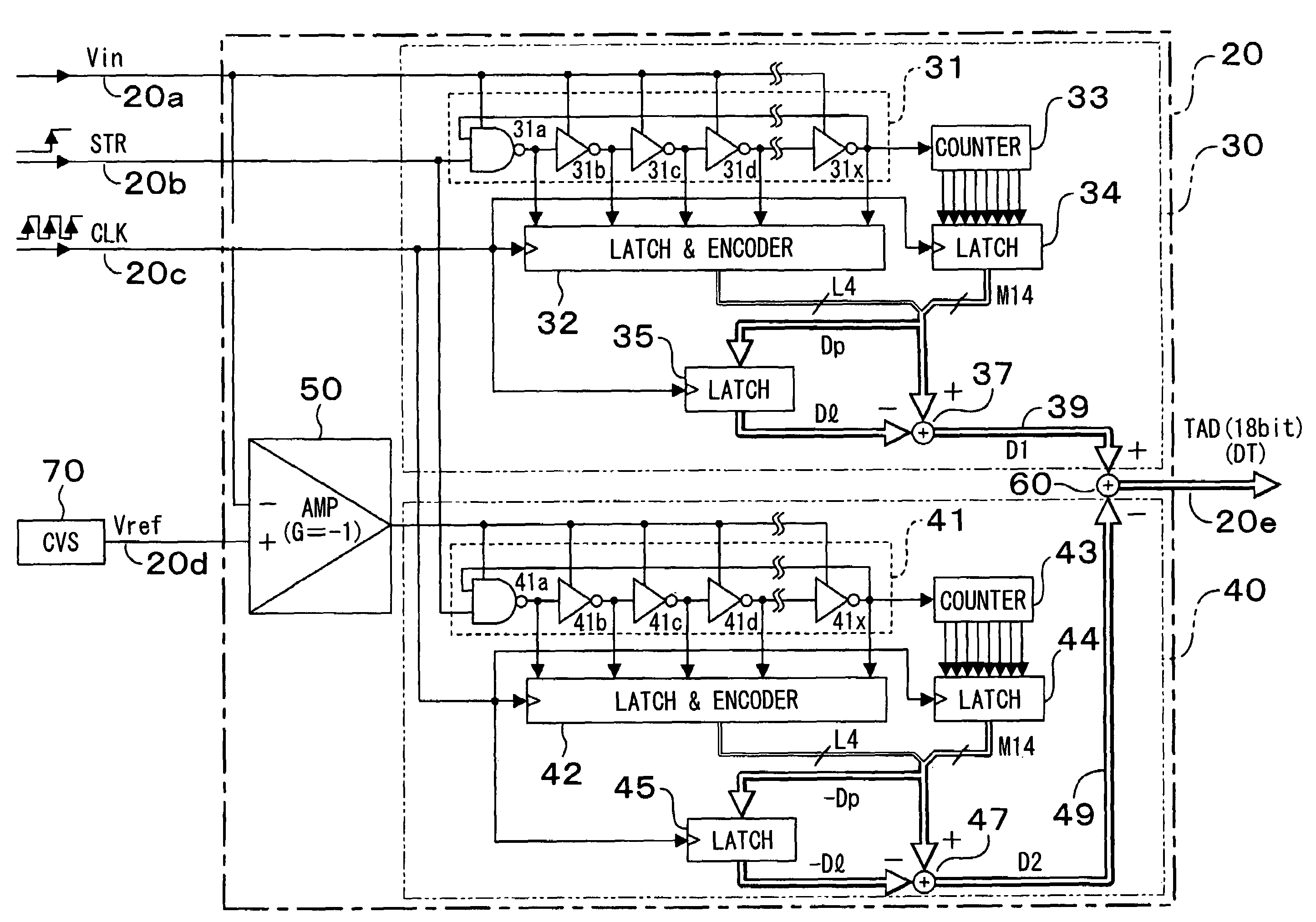

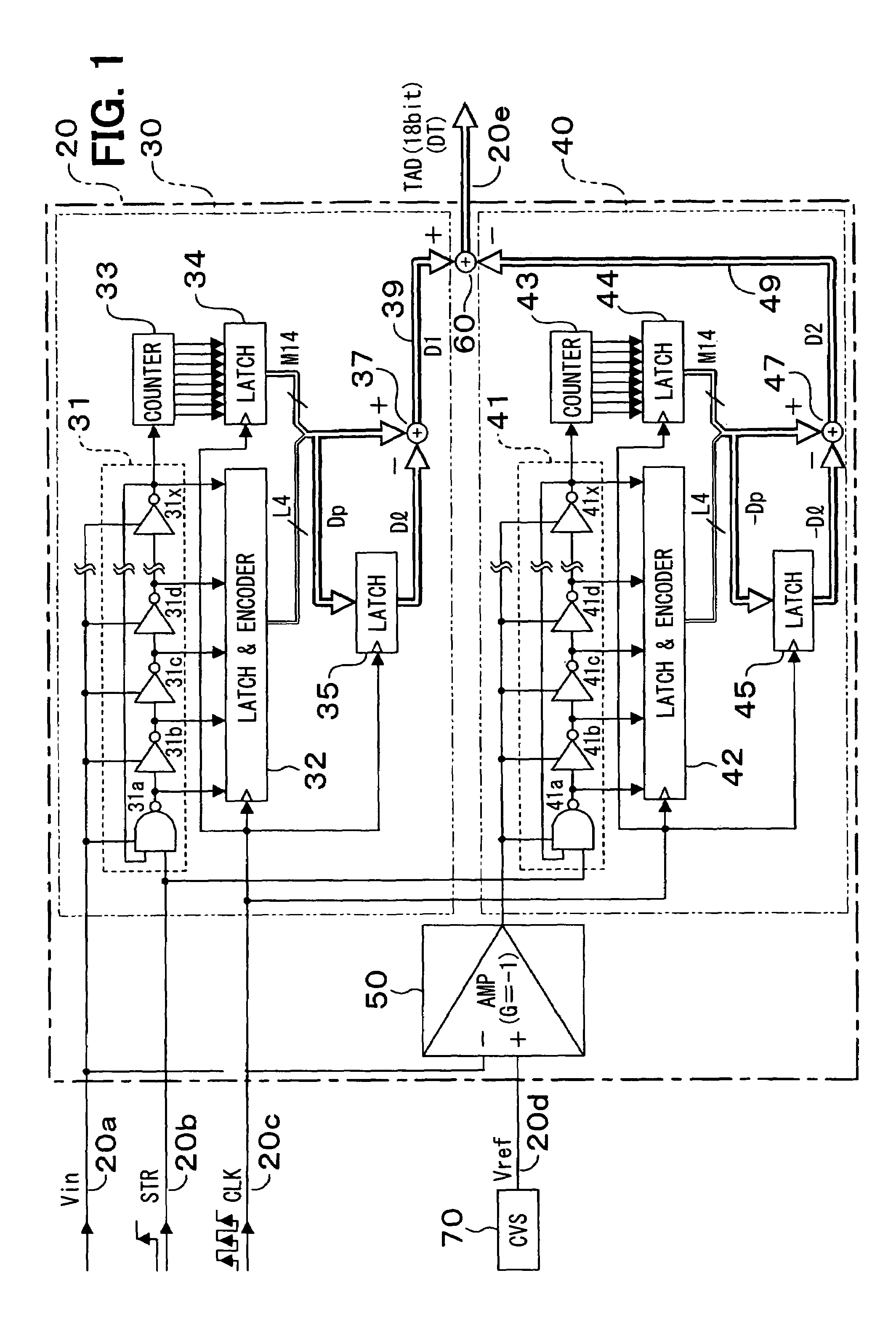

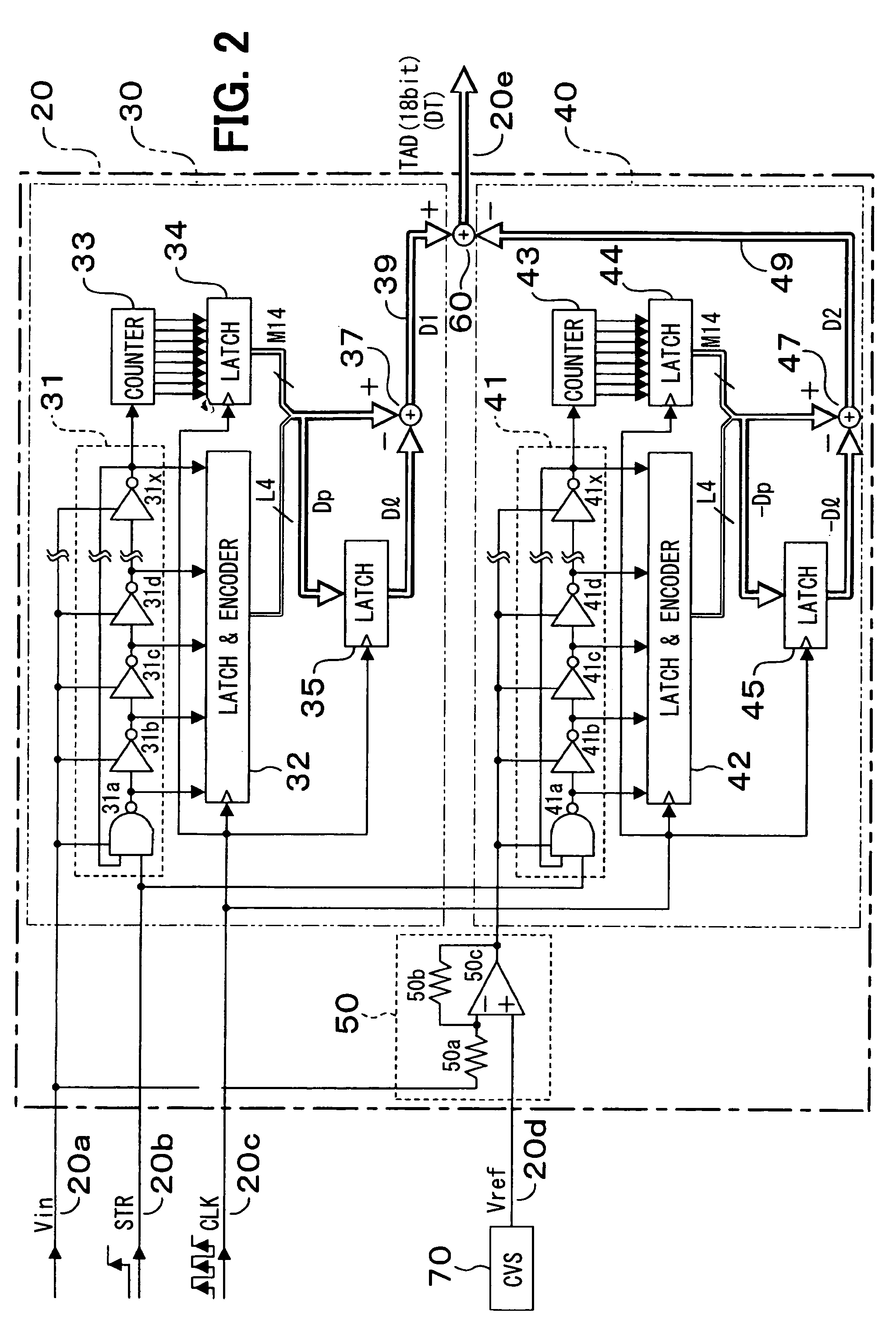

A/D converter circuit and A/D conversion method

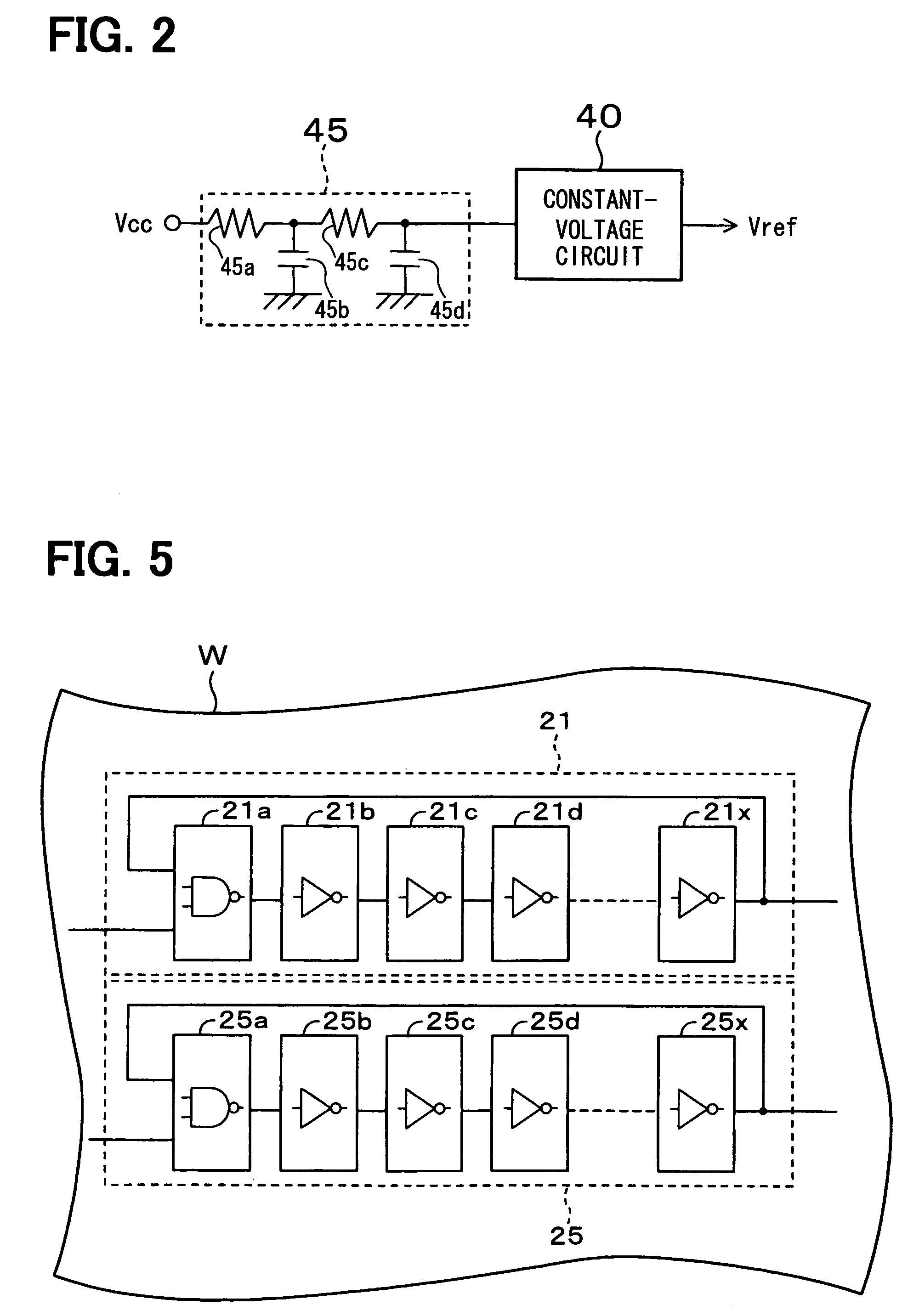

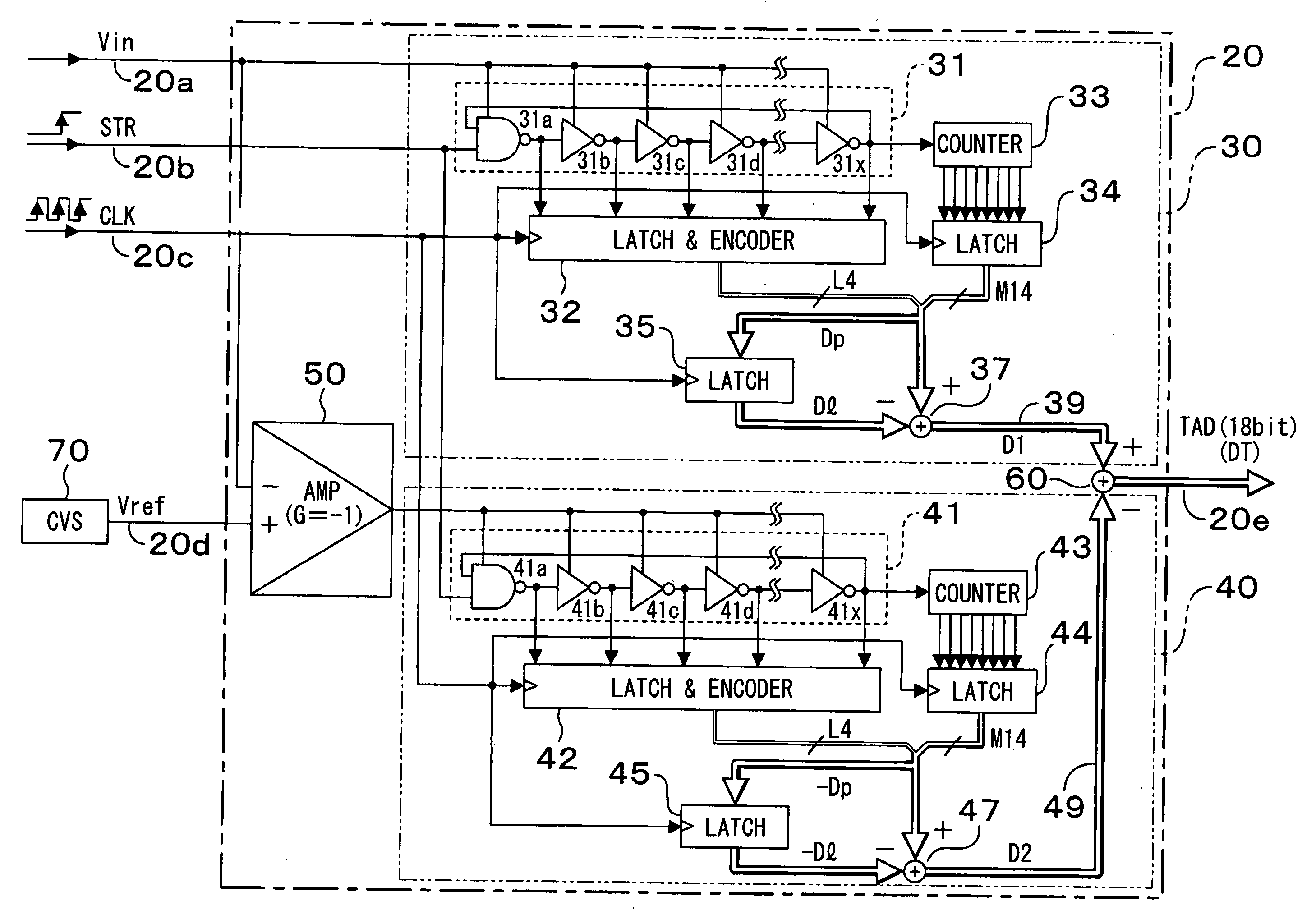

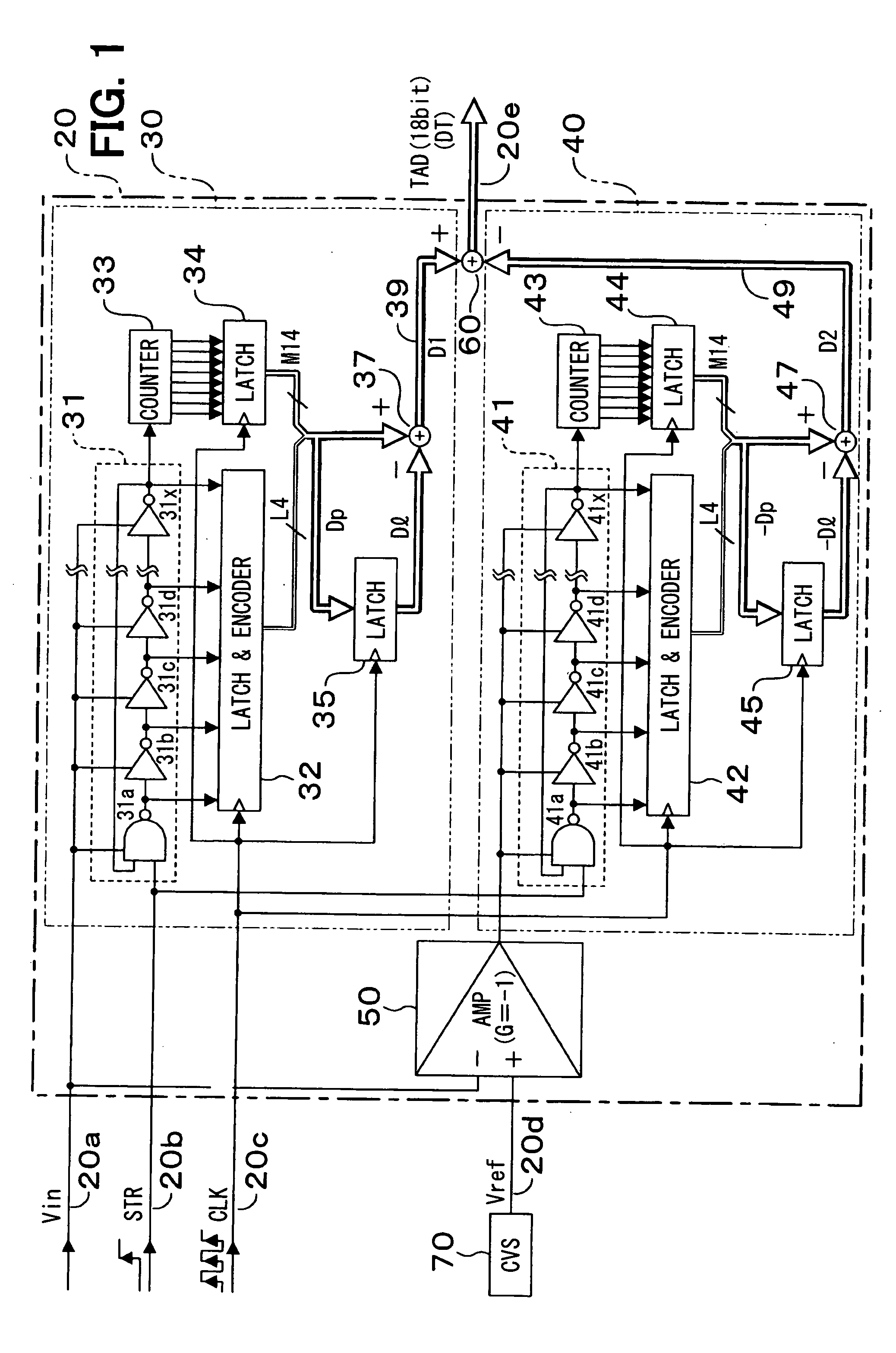

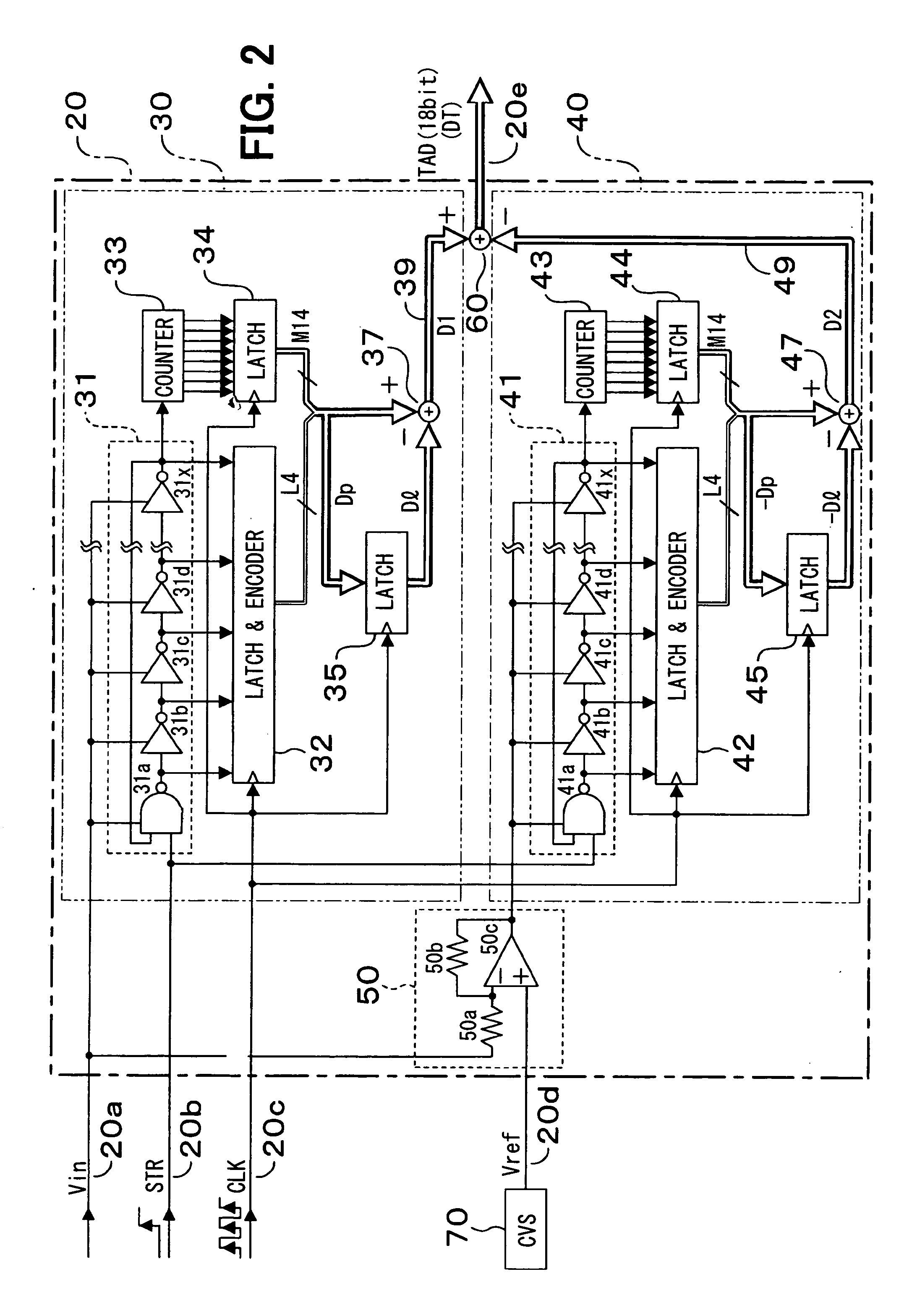

InactiveUS7612699B2Improve linearityElectric signal transmission systemsAnalogue-digital convertersDigital dataAnalog delay line

An A / D converter circuit uses first and second ring delay lines. The first and second ring delay lines are supplied with input signals, which increase / decrease oppositely from each other with respect to change directions. In each ring delay line, a first counter counts the number of times of circulation of a pulse signal circulating therein to find a digital data, and a last digital data is subtracted from a present digital data. By adding the resulting first and second digital data of the first and second ring delay lines, a digital data of the input voltage of linear characteristics is provided.

Owner:DENSO CORP

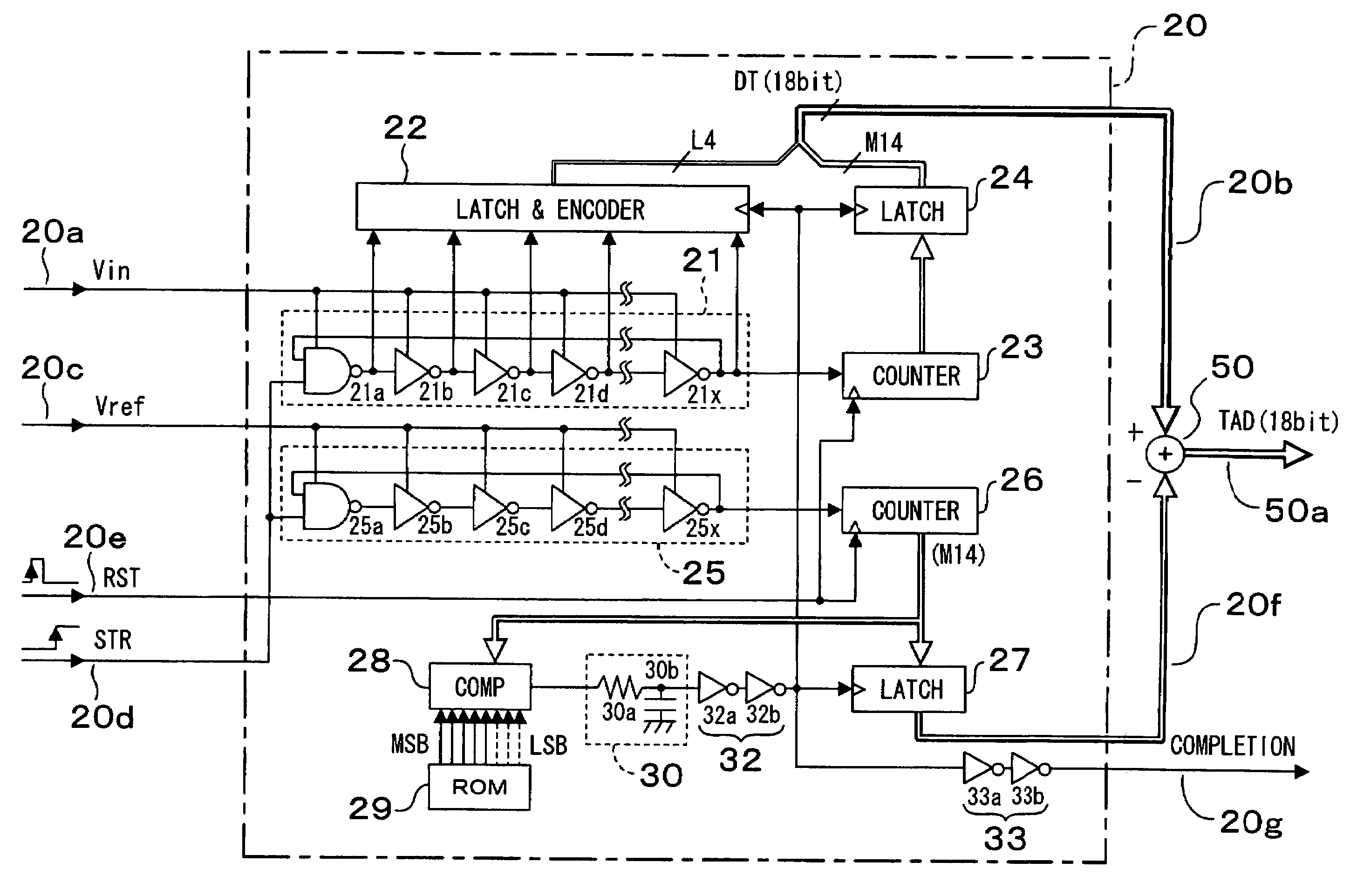

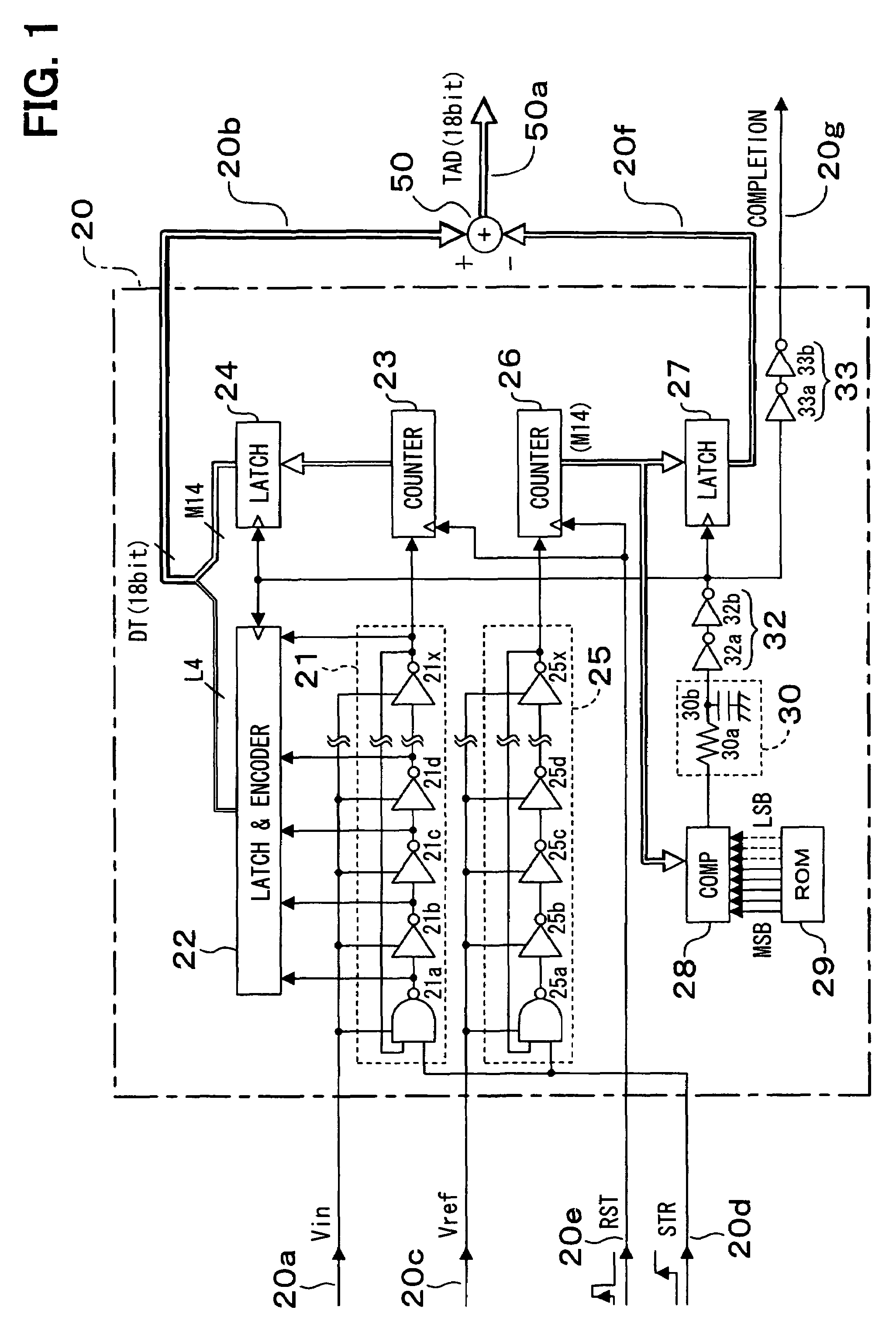

A/D converter circuit and A/D conversion method

ActiveUS7639169B2Suppress mutationElectric signal transmission systemsAnalogue-digital convertersDigital dataAnalog delay line

An A / D converter circuit has a first ring delay line and a second ring delay line configured to vary respective characteristics in the same manner relative to a change in the ambient temperature. A reference voltage, which is free from a change in temperature, is fed as a power supply voltage to the second ring delay line. Digital data produced by the first ring delay line is temperature-compensated by digital data produced by the second ring delay line.

Owner:DENSO CORP

A/D converter circuit and A/D conversion method

InactiveUS20080284633A1Improve linearityElectric signal transmission systemsAnalogue-digital convertersDigital dataAnalog delay line

An A / D converter circuit uses first and second ring delay lines. The first and second ring delay lines are supplied with input signals, which increase / decrease oppositely from each other with respect to change directions. In each ring delay line, a first counter counts the number of times of circulation of a pulse signal circulating therein to find a digital data, and a last digital data is subtracted from a present digital data. By adding the resulting first and second digital data of the first and second ring delay lines, a digital data of the input voltage of linear characteristics is provided.

Owner:DENSO CORP

Compressive sampling based ultra wideband (IR-UWB) signal detection method

The invention relates to a compressive sampling based ultra wideband (IR-UWB) signal detection method, which comprises an IR-UWB signal compressive sampling receiving system, and the IR-UWB signal compressive sampling receiving system comprises a multi-channel parallel sampling unit for carrying out sampling on a plurality of channels of the IR-UWB signals, a measuring waveform generator for respectively sending measuring waveforms to the channels of the multi-channel sampling unit, and a digital back-end processing component for receiving the measuring values of the channels sampled by the multi-channel sampling unit; and the channels carry out linear projection on the IR-UWB signals respectively according to the measuring waveforms generated by the measuring waveform generator. The method comprises the following steps: obtaining a compressive sampling sequence of pilot-symbol receiving signals, obtaining a compressive sampling sequence of data-symbol receiving signals, and obtaining a symbol decision. The compressive sampling based IR-UWB (ultra wideband) signal detection method can realize the low-sampling-rate and low-hardware-cost on the detection of the IR-UWB signals without high sampling rate, analog delay line and compressive sampling receiving mode with accurate channel estimation.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

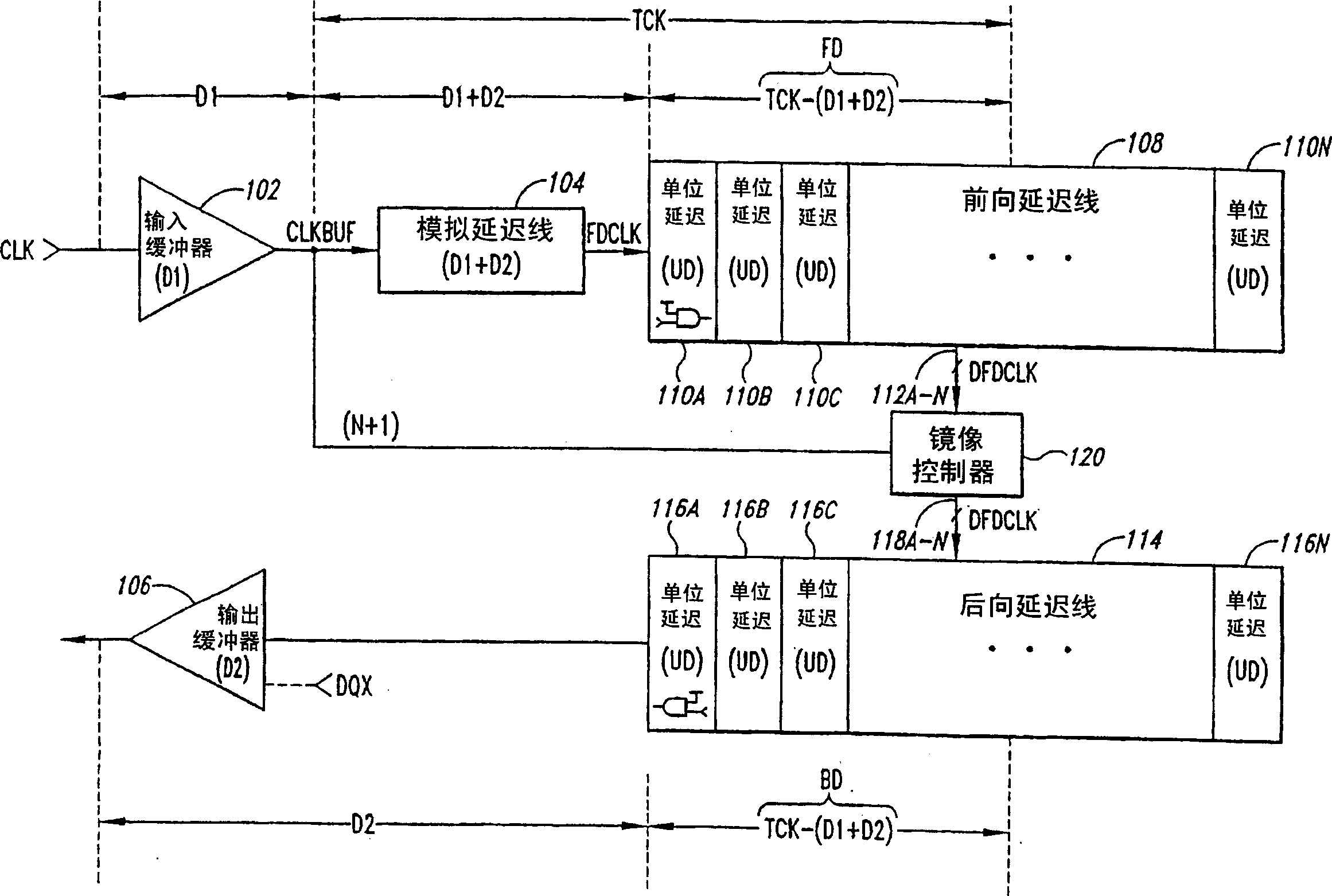

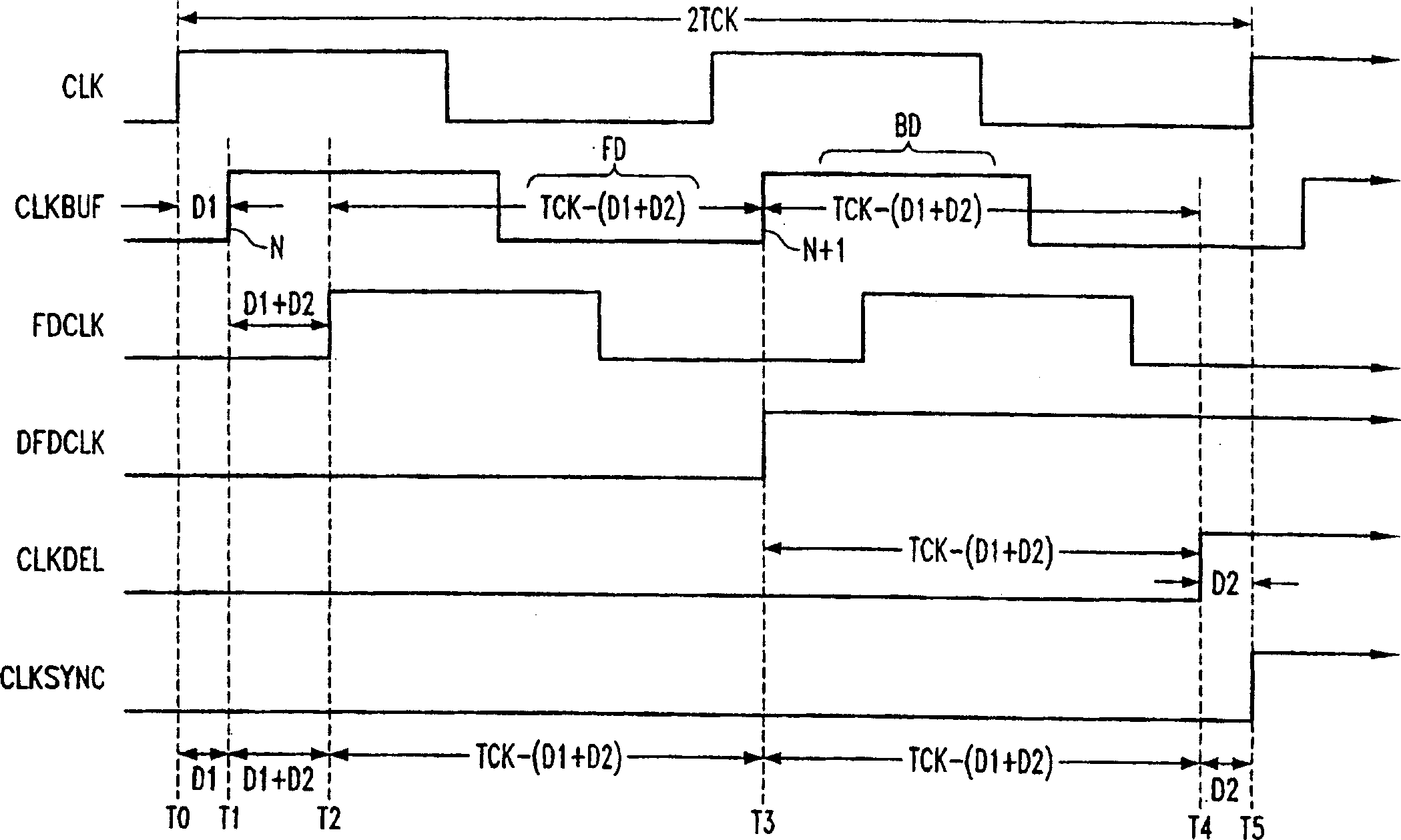

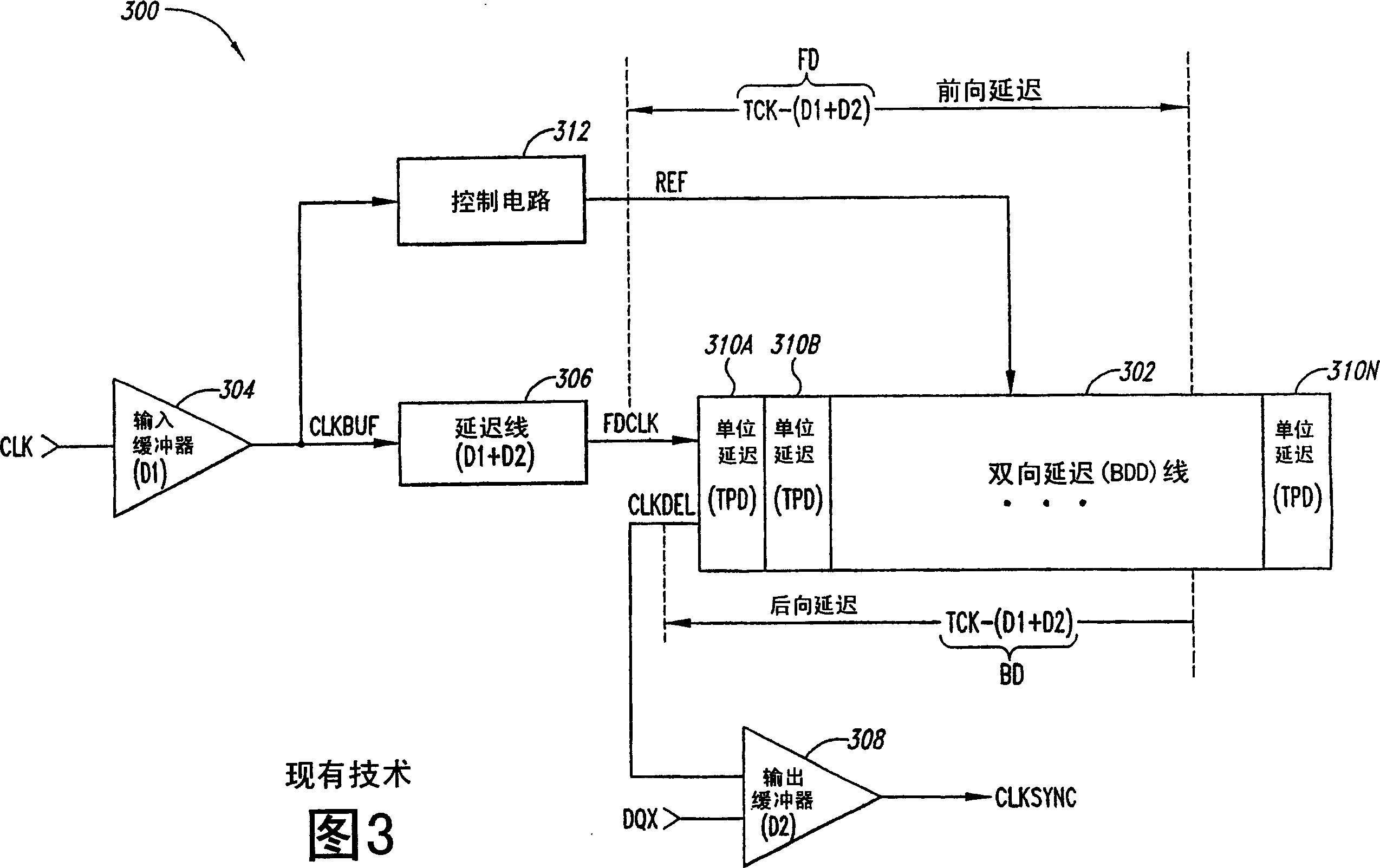

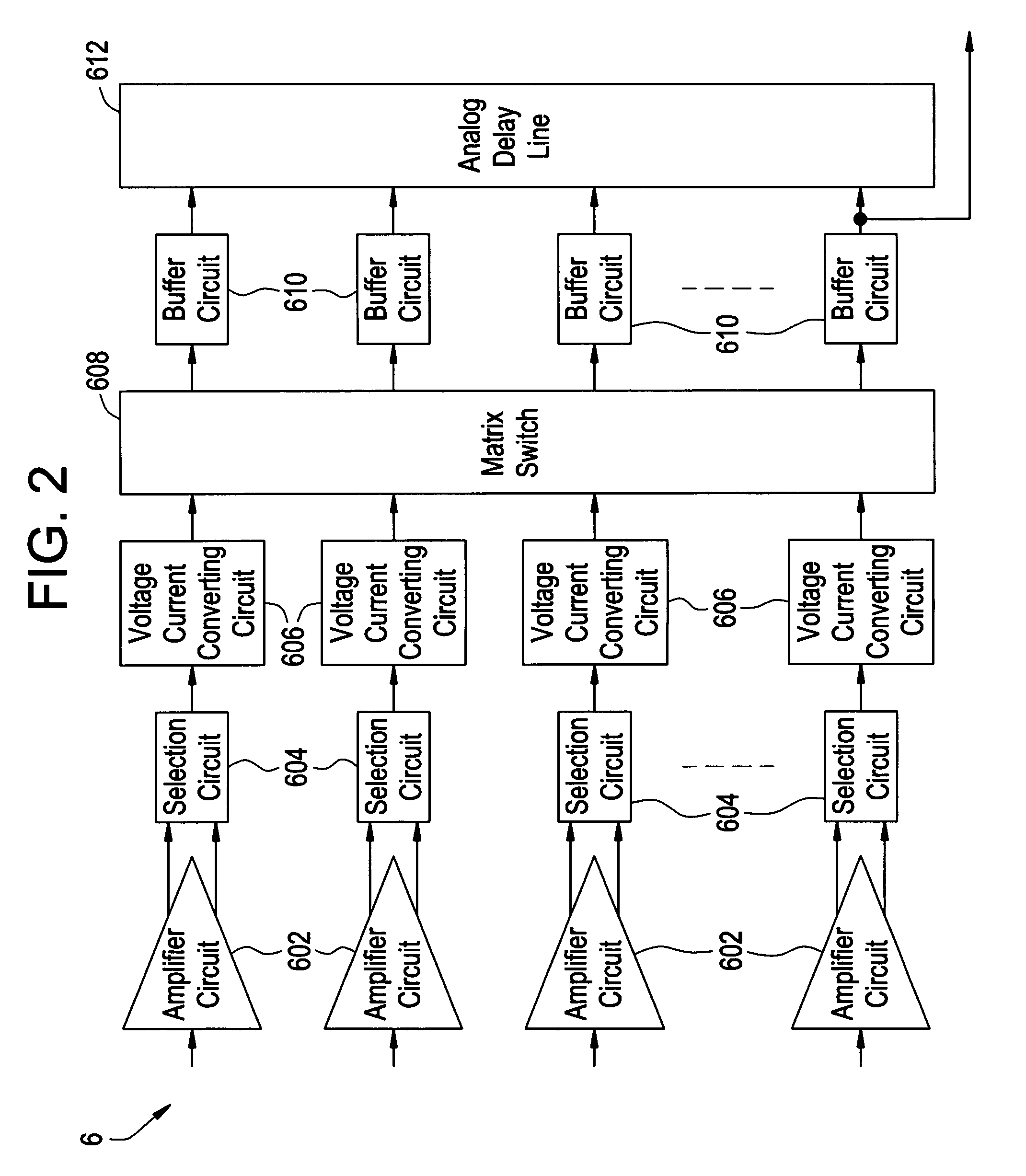

Synchronous mirror delay (SMD) circuit and method including a counter and reduced size bi-directional delay line

A synchronous mirror delay (600) includes a model delay line (610) that is coupled to a bi-directional delay line (602). In operation, an initial edge an input clock signal is applied through the model delay line to the bi-directional delay line. The (SMD) thereafter operates in a forward delay mode to alternately operate the bi-directional delay line in a forward mode and a backward mode to propagate the initial edge of the input clock signal through the bi-directional delay line and delay the initial edge of the input clock signal by a forward delay. In response to a subsequent edge of the input clock signal, the SMD mirrors the propagation of the input clock signal through the bi-directional delay line during the forward mode and further delay the initial edge of the input clock signal by a backward delay that is substantially equal to the forward delay.

Owner:MICRON TECH INC

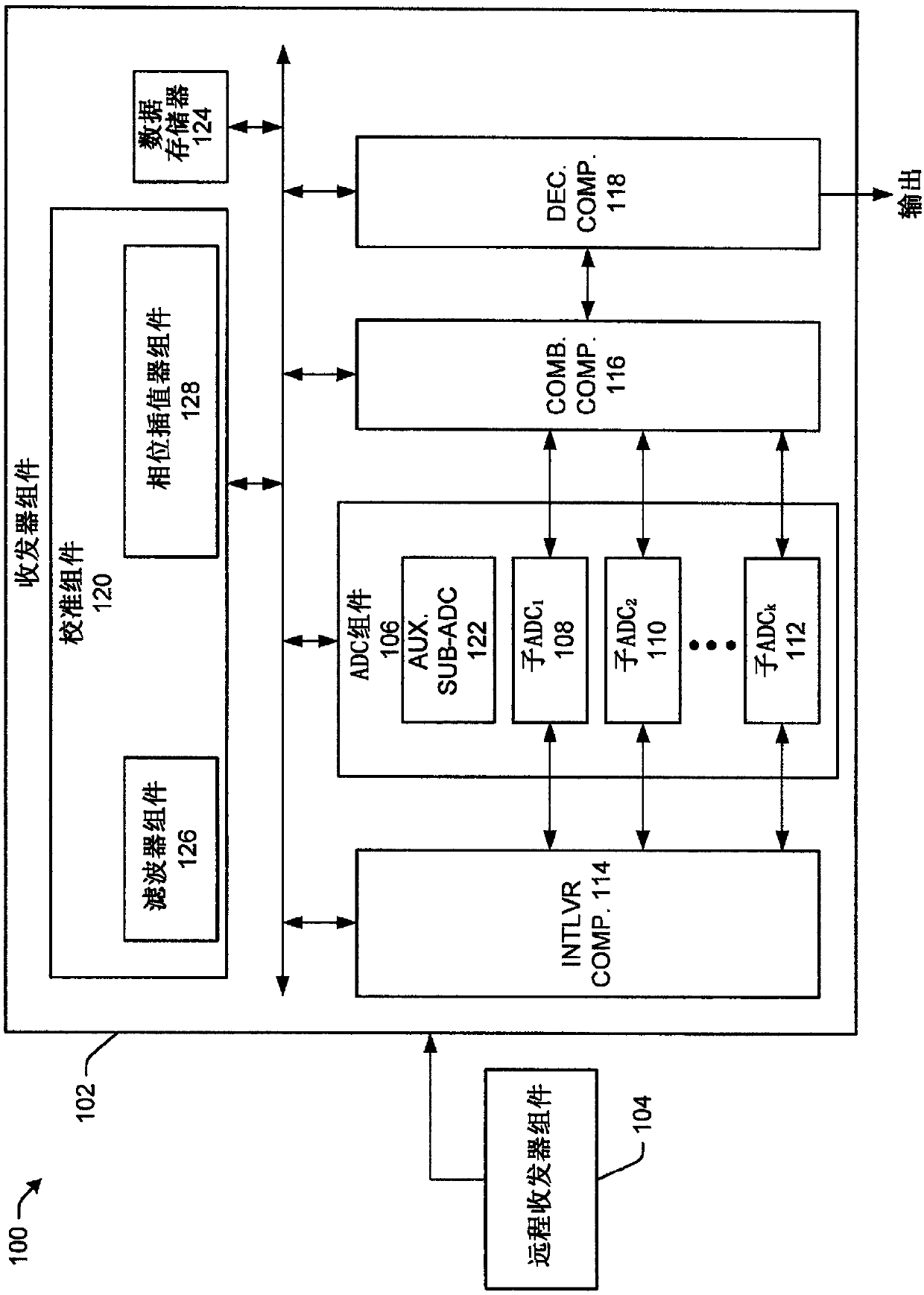

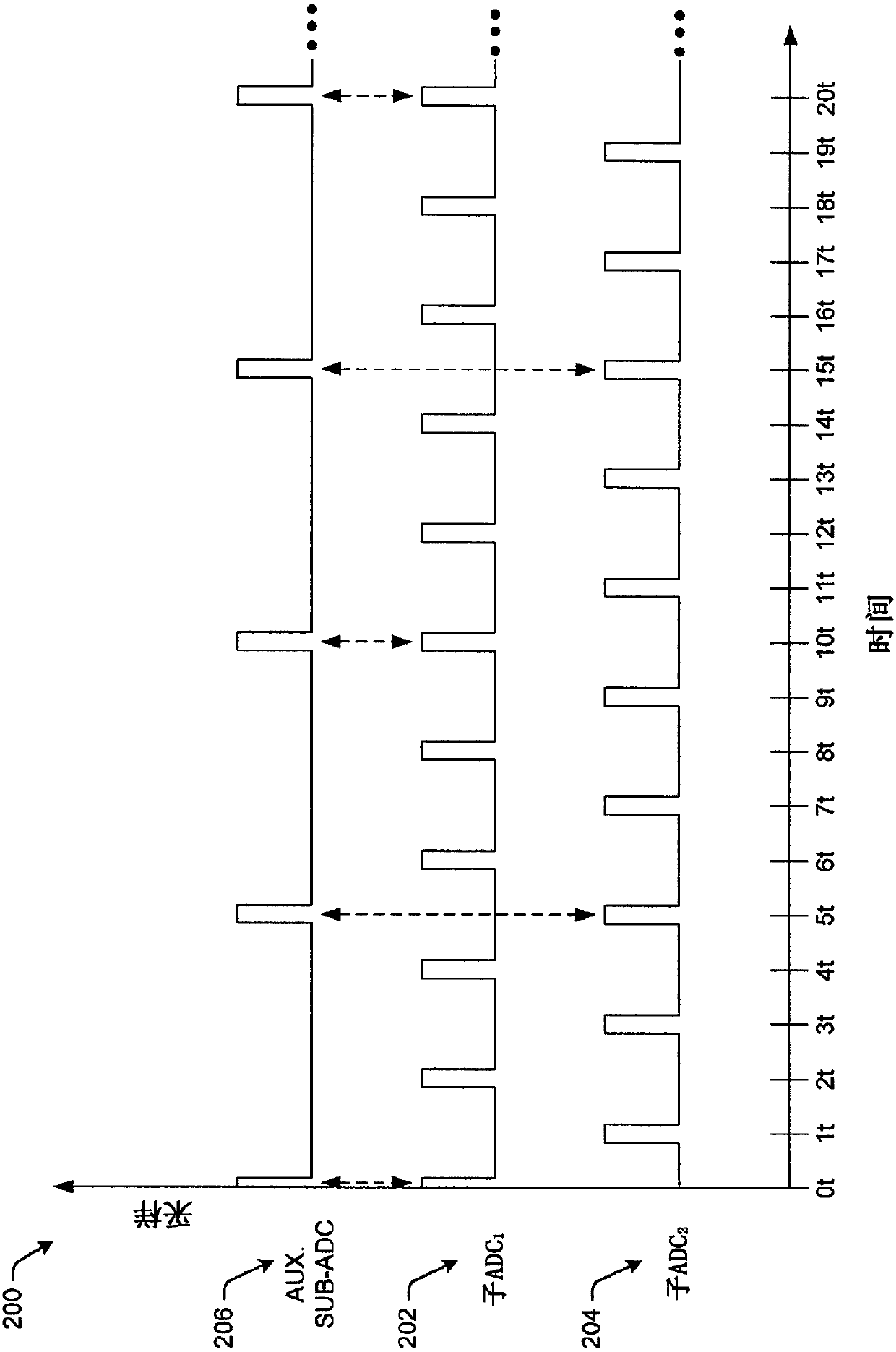

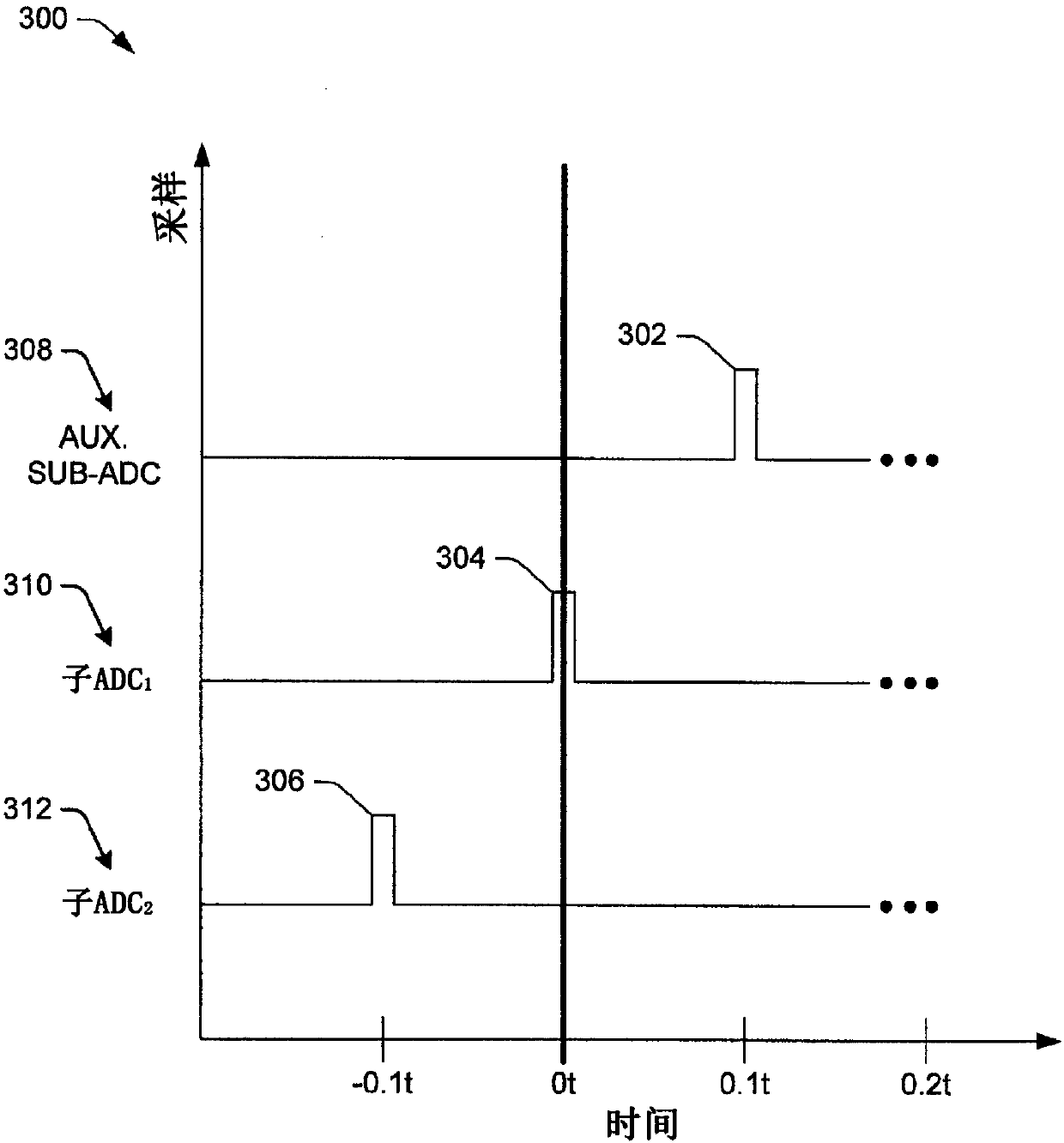

Calibration and tracking of receiver

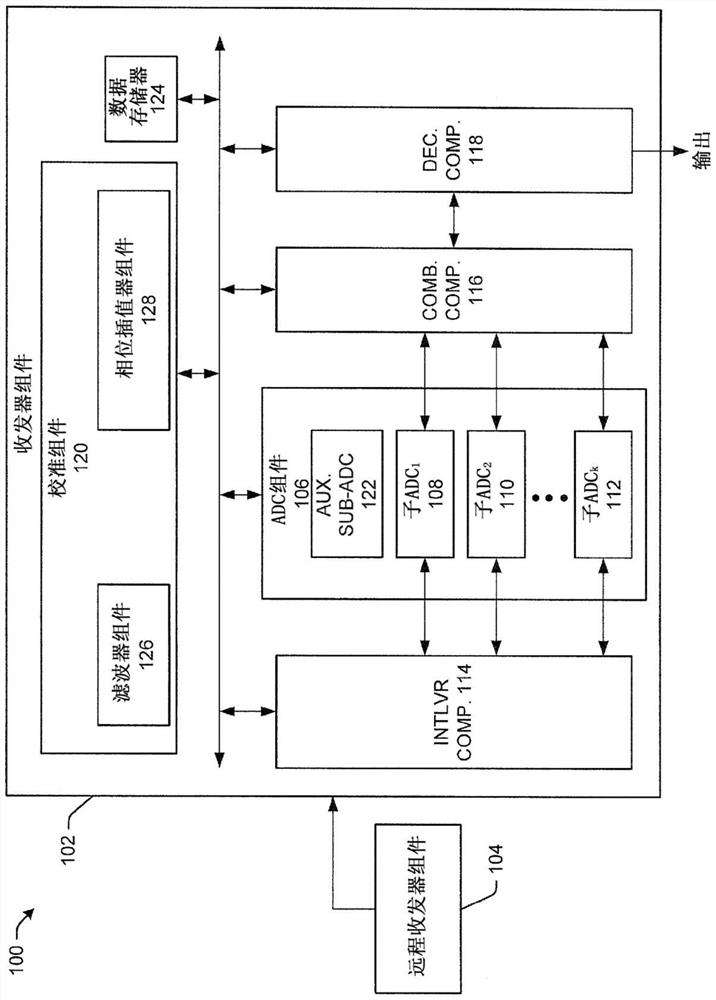

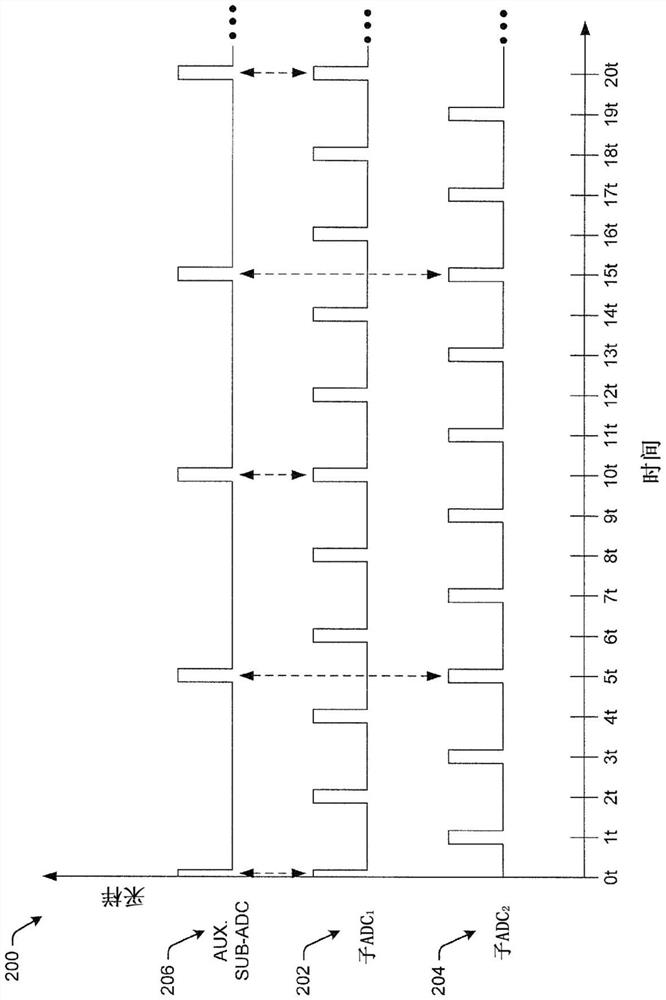

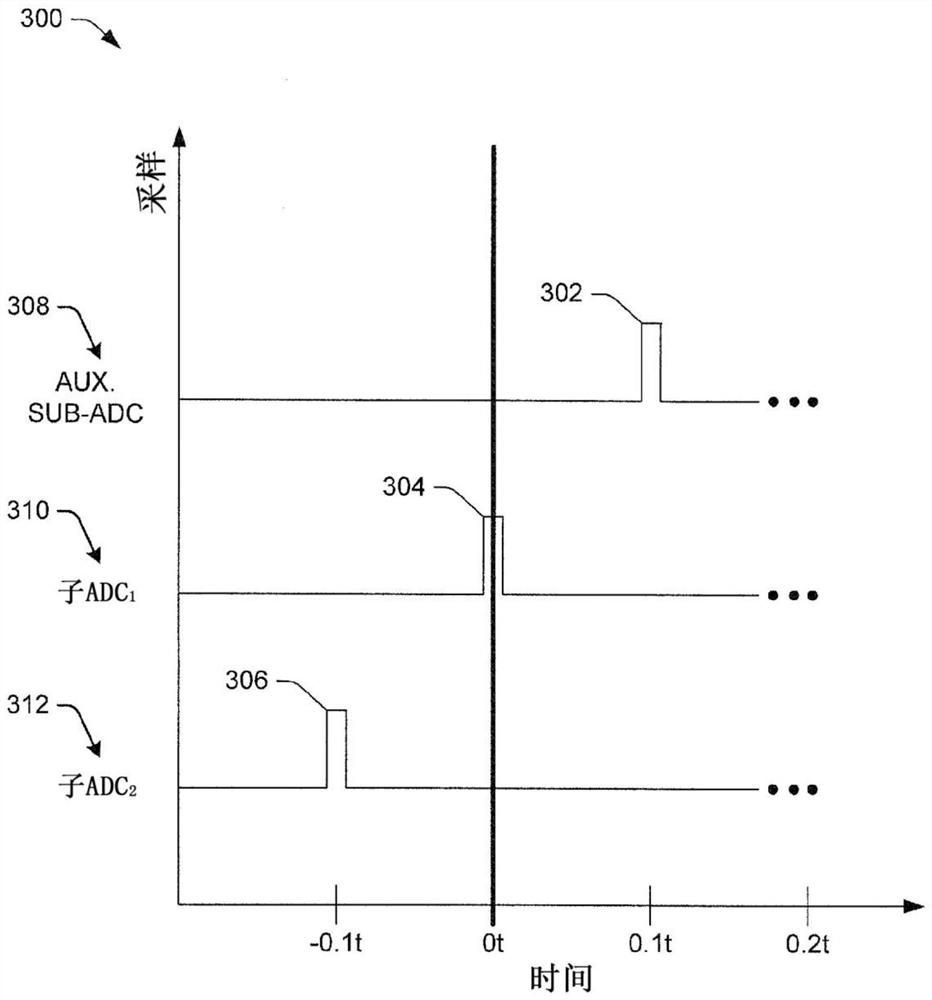

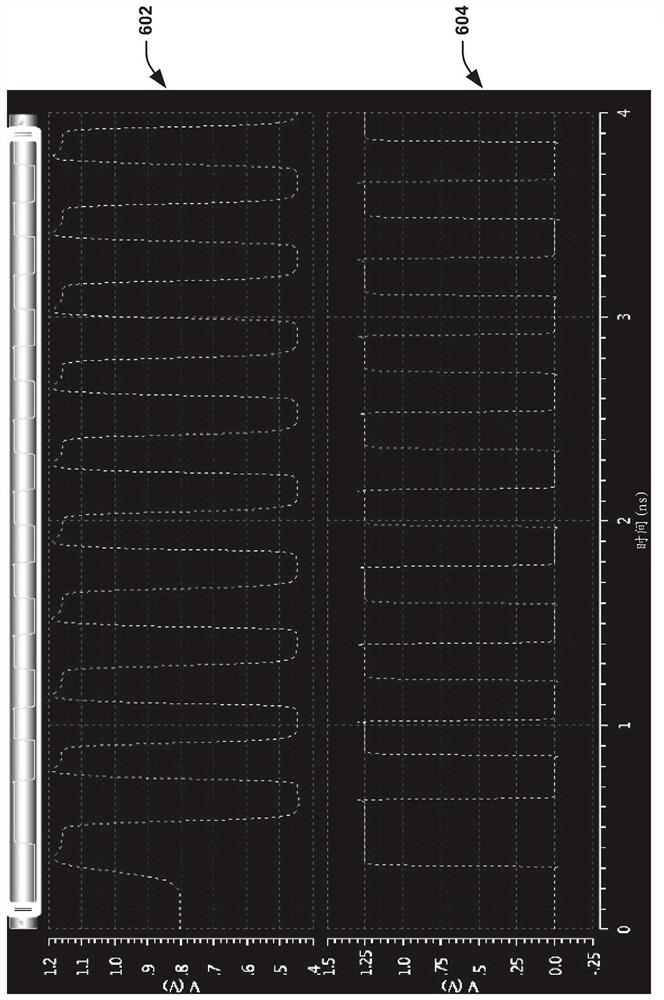

ActiveCN108028661AReduced path varianceTransmitters monitoringReceivers monitoringTransceiverSoftware engineering

Techniques for calibrating interleaved analog-to-digital converter (ADC) arrays are presented. A transceiver comprises an ADC component comprising an array of interleaved sub-ADCs, and an auxiliary path associated with an auxiliary sub-ADC used to facilitate calibrating a sampling array by comparing the auxiliary path signal to signals of the sub-ADCs in the array. A calibration component employsa phase-interpolator and analog delay lines to adjust the auxiliary sub-ADC to enable the auxiliary sub-ADC to be lined up to any one of the sampling instants of the sampling array. The calibration component compares the auxiliary signal to sub-ADC signals, determines path differences between the sub-ADC paths based on the comparison results, and calibrates the sub-ADCs and sub-ADC paths to reducethe path differences to mitigate distortion in a digital stream produced from combining the digital substreams produced by the sub-ADCs in the array.

Owner:镁可联通解决方案有限公司

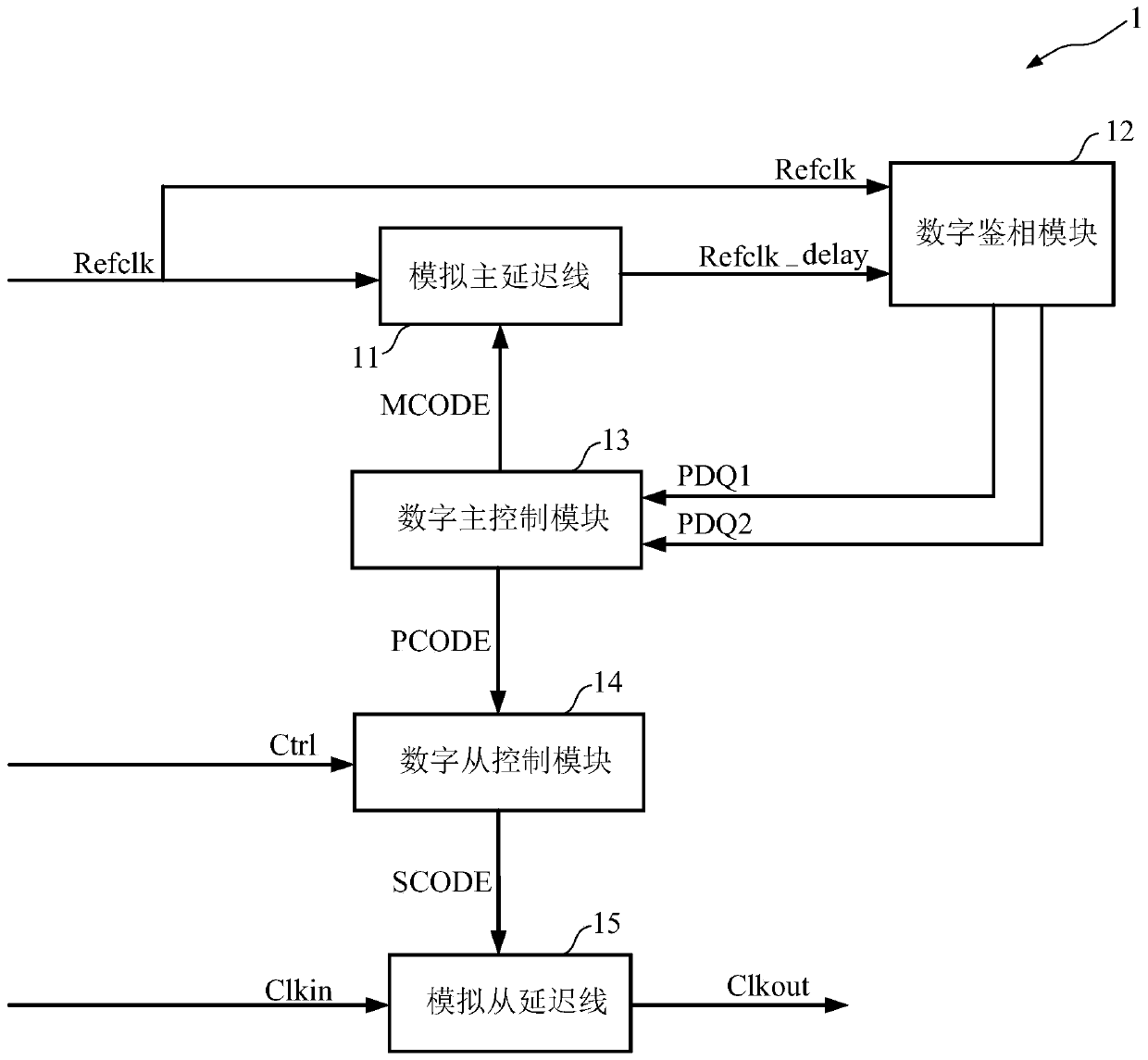

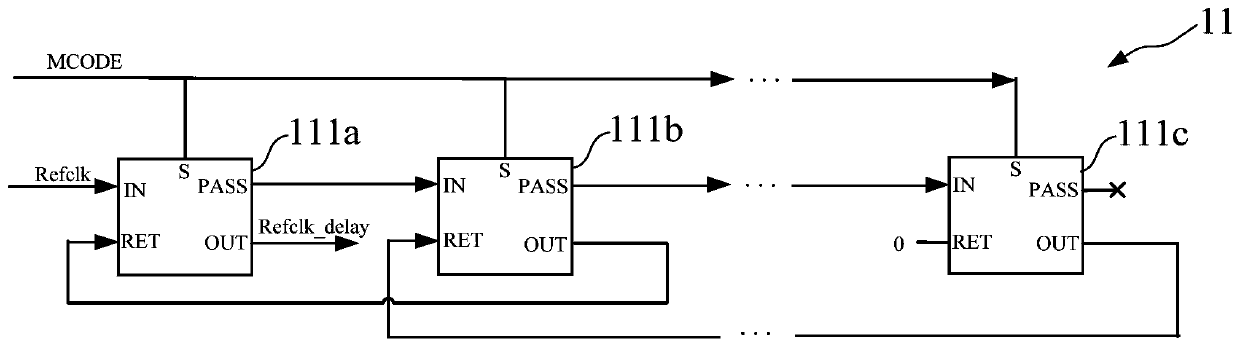

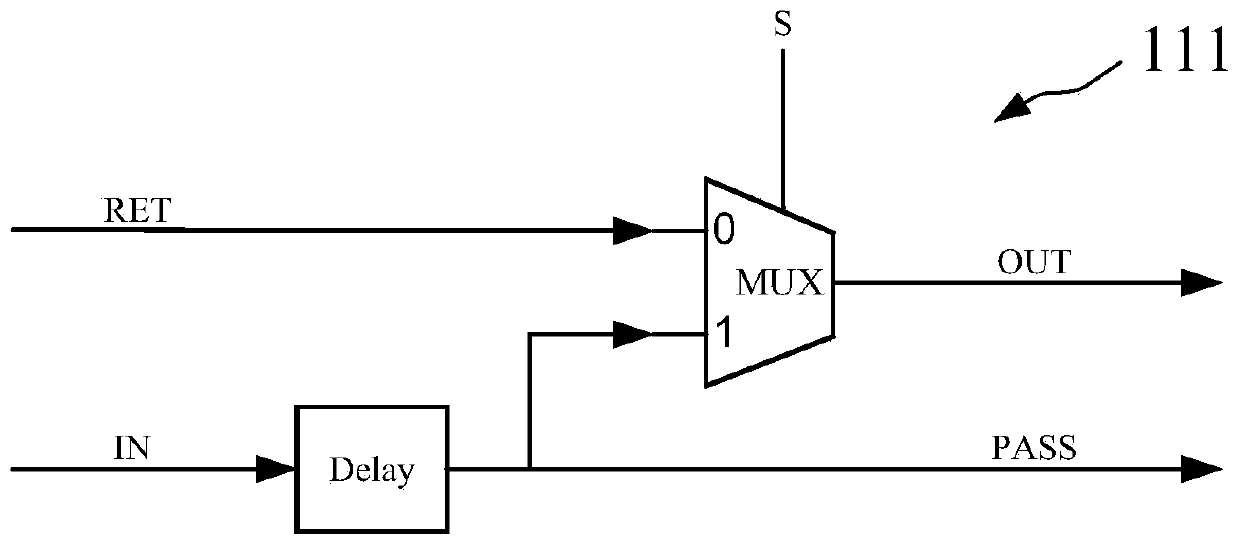

A delay locked loop and a delay locked method

ActiveCN109831206AImprove reliabilitySimplify debugging difficultyPulse automatic controlEnergy efficient computingDiscriminatorPhase difference

The invention provides a delay locking ring and a delay locking method. The delay locking ring comprises the following steps: delaying an analog main delay line of a reference clock signal based on amain delay control word; enabling the digital phase discrimination module identify the phase difference before and after the reference clock signal delay; the digital main control module is used for adjusting the main delay control word based on the phase difference and assigning the main delay control word corresponding to the delay period to the set delay control word; the digital slave controlmodule takes a set delay control word with a set proportion as a slave delay control word; an analog slave delay line that delays an input clock signal is controlled based on the slave delay control word. Controlling the reference clock signal to be delayed for a period based on the phase-locked loop; assigning the corresponding main delay control word to a set delay control word, multiplying themain delay control word by a set proportion, and adjusting the delay of the input clock signal. According to the invention, the digital phase discriminator and the digital controller are adopted, thereliability is high, and a loop is more stable; and an analog delay line is adopted, so that delay adjustability can be realized, and the circuit debugging difficulty is reduced.

Owner:VERISILICON MICROELECTRONICS SHANGHAI +1

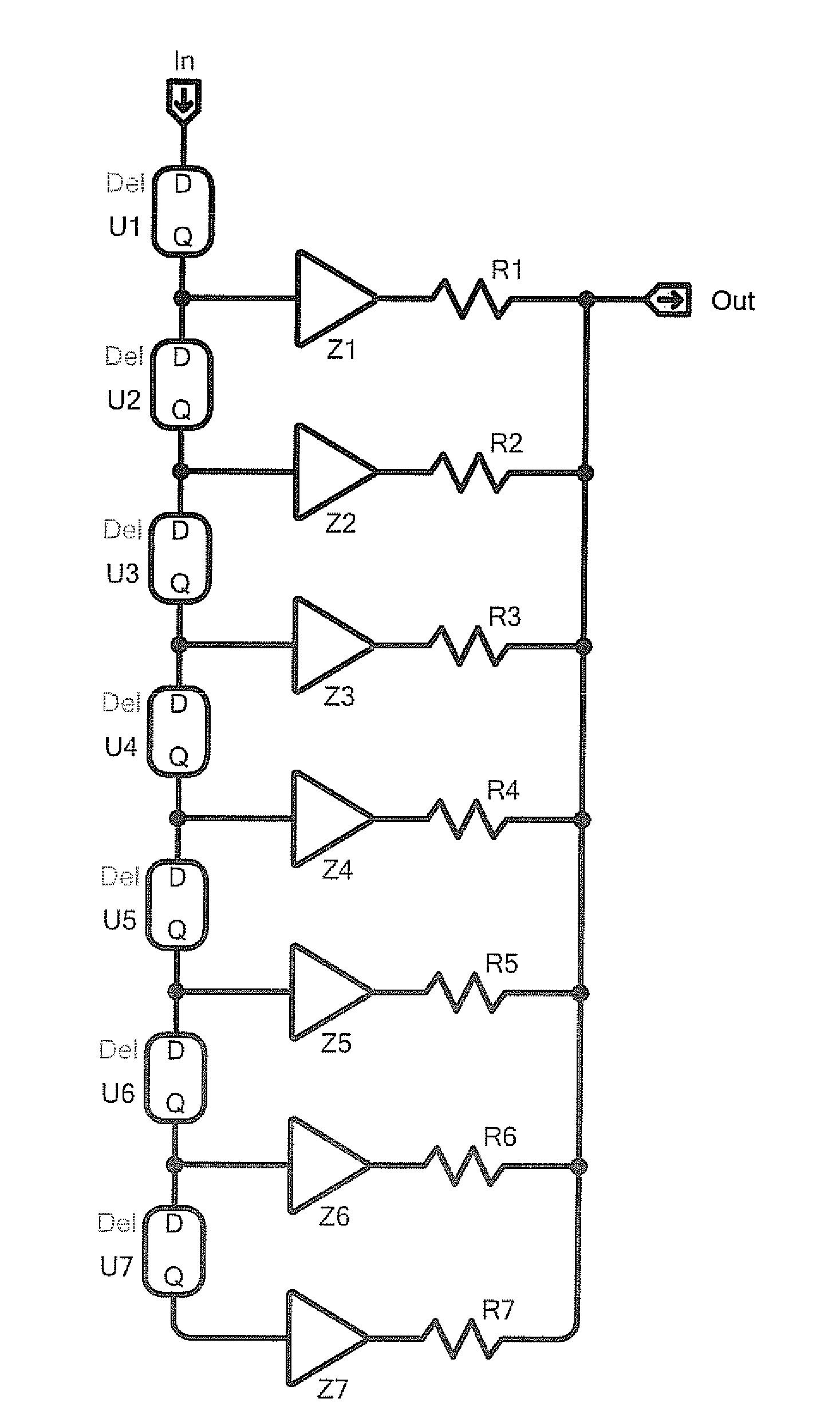

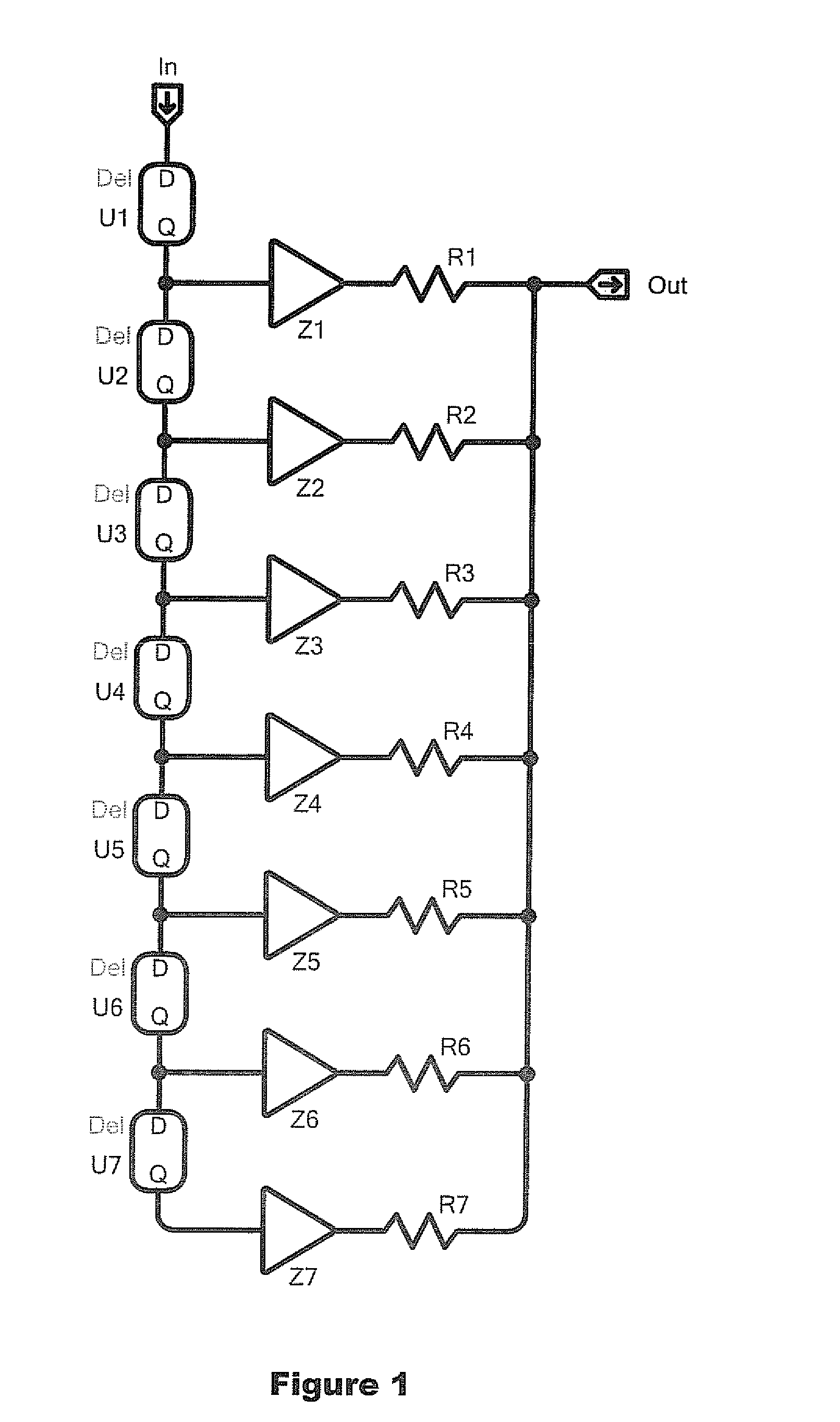

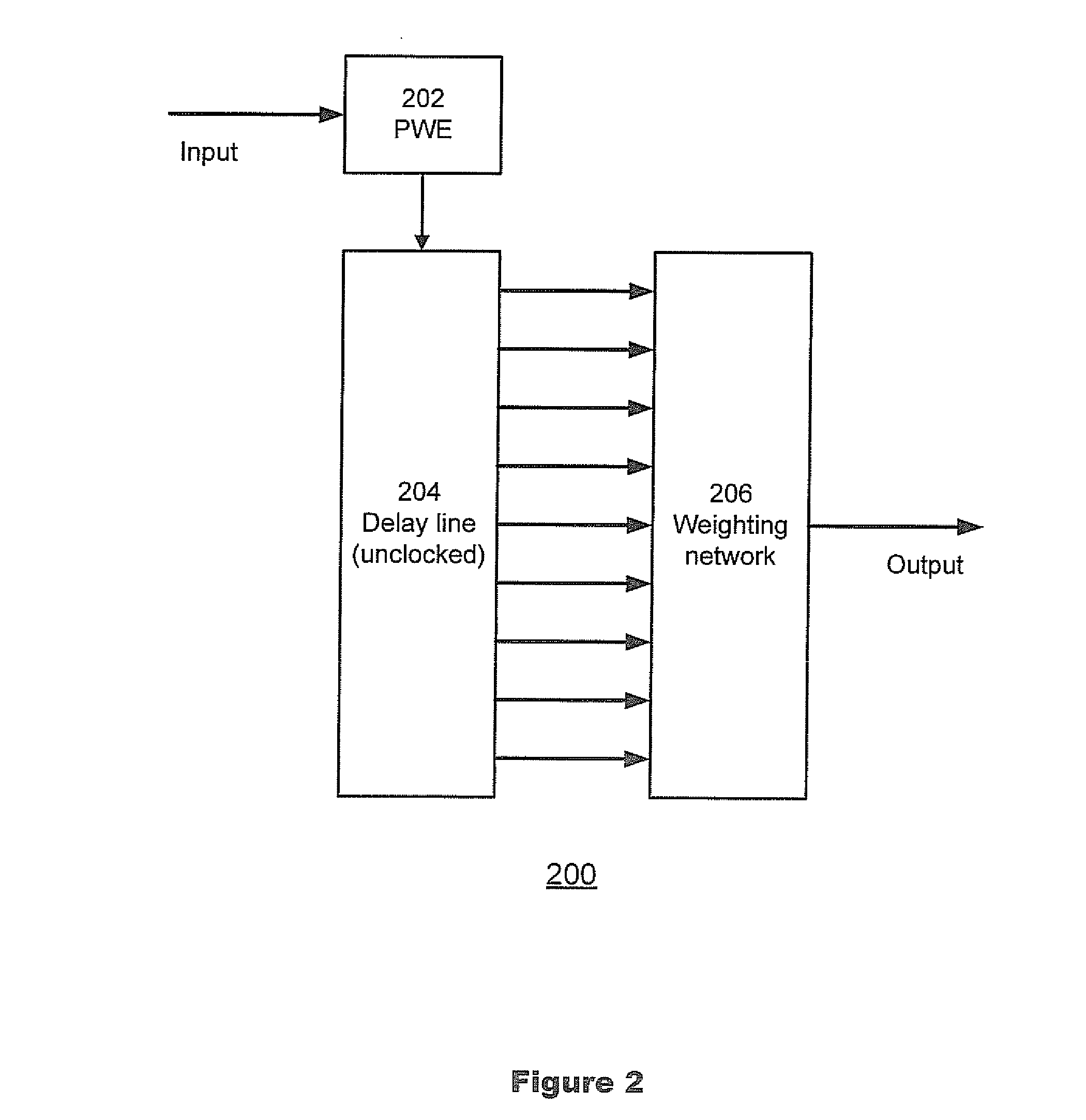

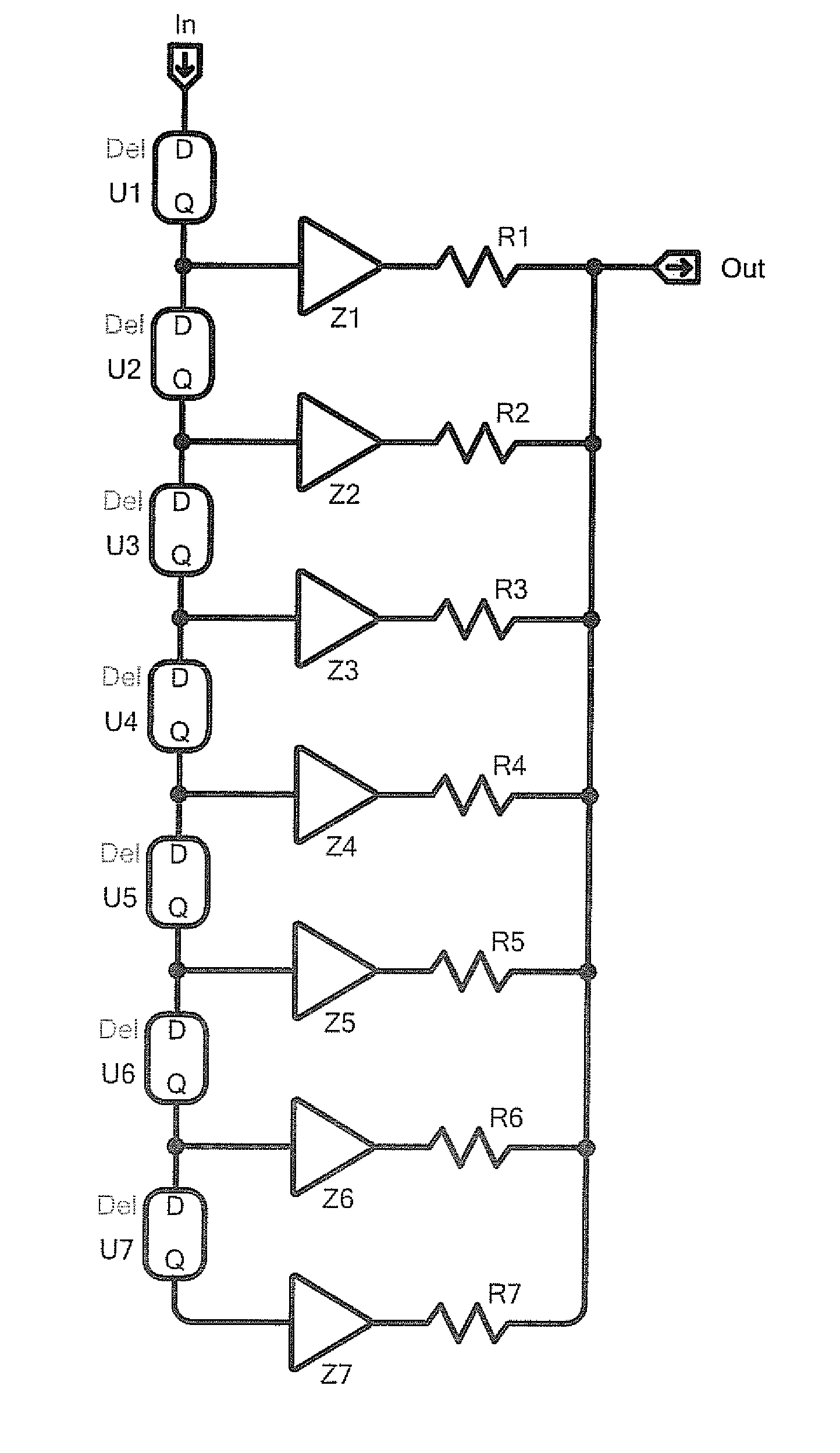

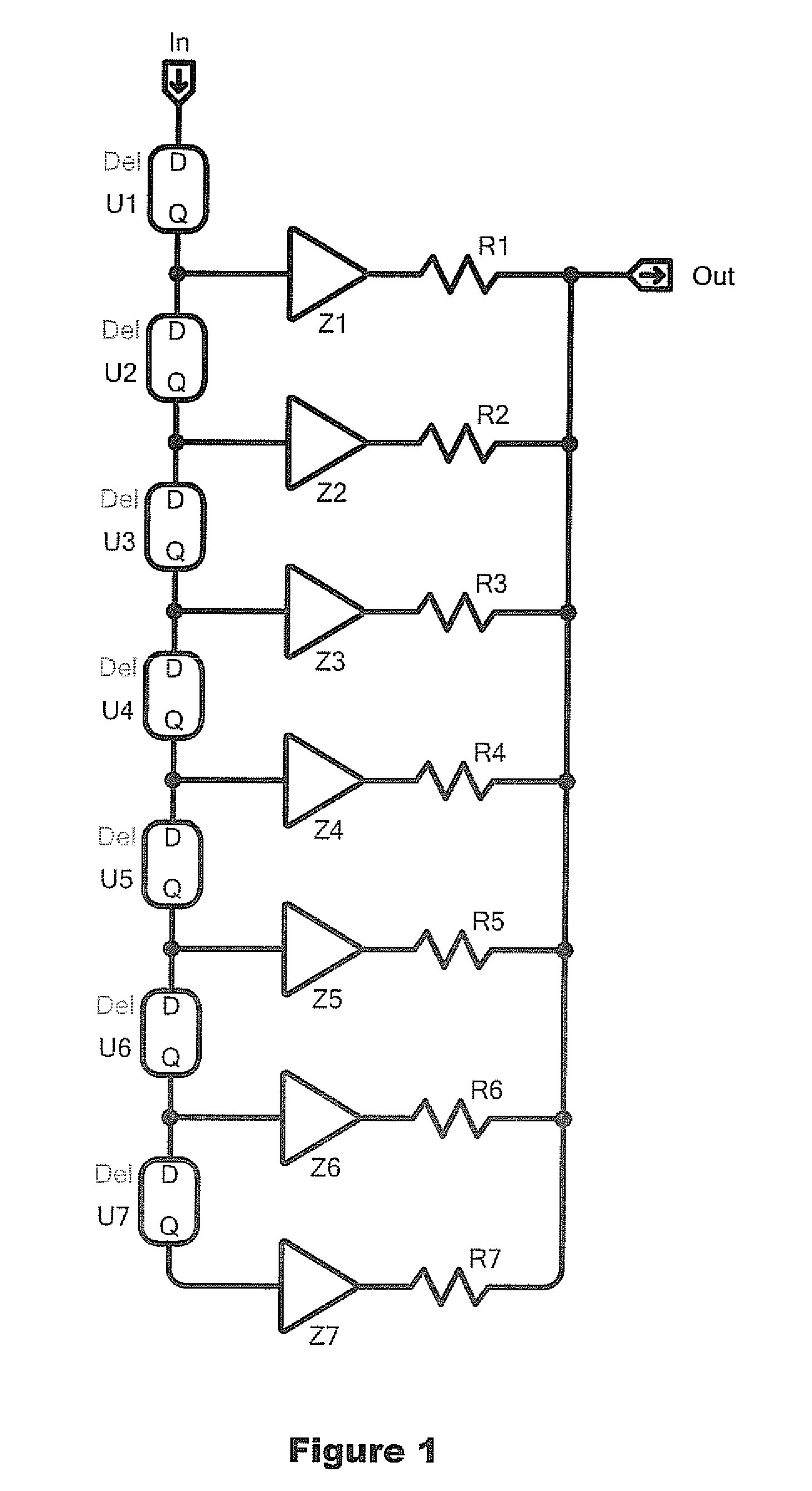

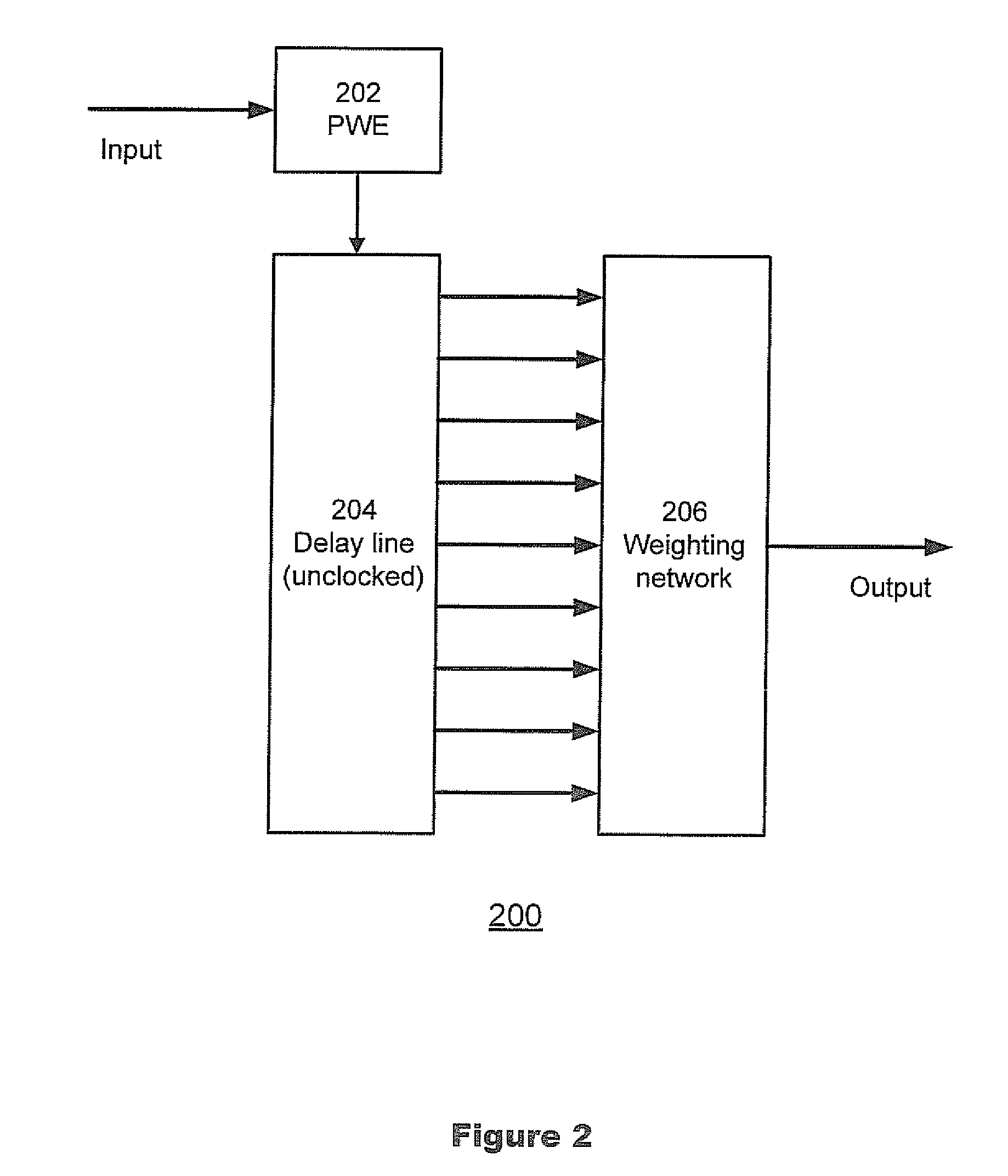

FIR Filter Using Unclocked Delay Elements

ActiveUS20140105269A1Digital technique networkDuration/width modulated pulse demodulationFinite impulse responseAnalog delay line

A system and method for filtering an analog signal with a finite impulse response (FIR) filter that does not require analog delay elements are disclosed. An analog signal is pulse-width encoded, and the pulse-width encoded signal passed to a delay line comprising unclocked delay elements, such as logic gates, rather than clocked delay elements such as are used in conventional FIR filters. The propagation of the input signal is thus due only to the delay inherent in each gate, and occurs based upon when a signal reaches the gate rather than being caused by a clock signal. As with a conventional FIR filter, weighting elements having impedance are used to weigh the output of each delay element, and the resulting outputs summed to obtain a filtered output signal. For certain signals, such a circuit and method provides a simpler way of filtering than conventional filters.

Owner:ESS TECHNOLOGY

Synchronous mirror delay (SMD) circuit and method including a ring oscillator for timing coarse and fine delay intervals

Owner:MICRON TECH INC

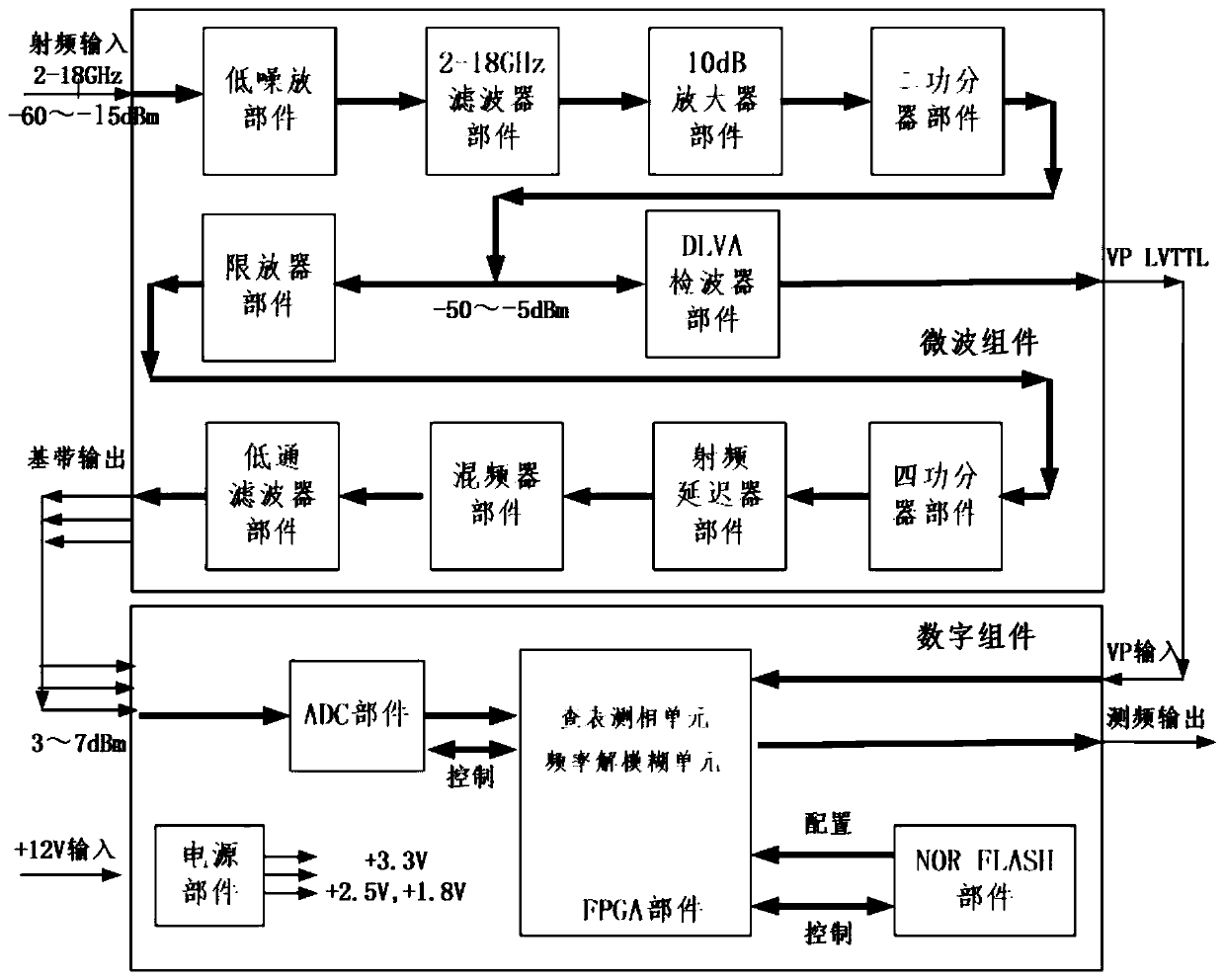

Analog delay line receiver and implementation method thereof

InactiveCN111147088ASolving the Difficulty of Noise Error DetectionHigh sensitivityTransmissionNoise (radio)Intermediate frequency

The invention discloses an analog delay line receiver and an implementation method thereof. The analog delay line receiver comprises a microwave assembly and a digital assembly, wherein the microwaveassembly comprises a low-noise amplifier component, a 2-18GHz filter component, a 10dB amplifier component, a two-power divider component, a DLVA detector component, a limiter component, a four-powerdivider component, a radio frequency delayer component, a mixer component and a low-pass filter component; the digital assembly comprises a power supply part, an NOR FLASH part, an ADC part and an FPGA part. The power supply part is divided into an analog power supply module and a digital power supply module; the NOR FLASH component is connected with the power supply component and the FPGA component; the ADC part is connected with the power supply assembly and the FPGA part; and the FPGA component is connected with the ADC component and the power supply component. According to the invention, the sensitivity of the width-preserving detection VP is further optimized, the dynamic range of the input signal is increased, better quantization precision is provided for digital channelization, andthe difficulty of digital channelization in false detection of the pulse-to-pulse noise of the saturated intermediate frequency signal is solved.

Owner:南京航天工业科技有限公司

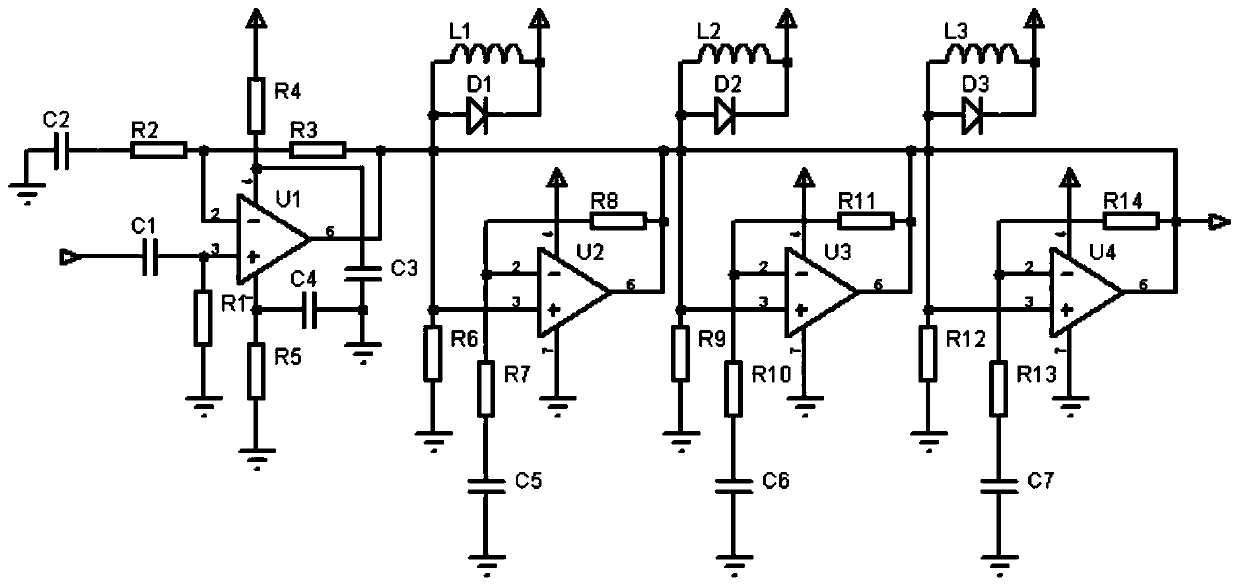

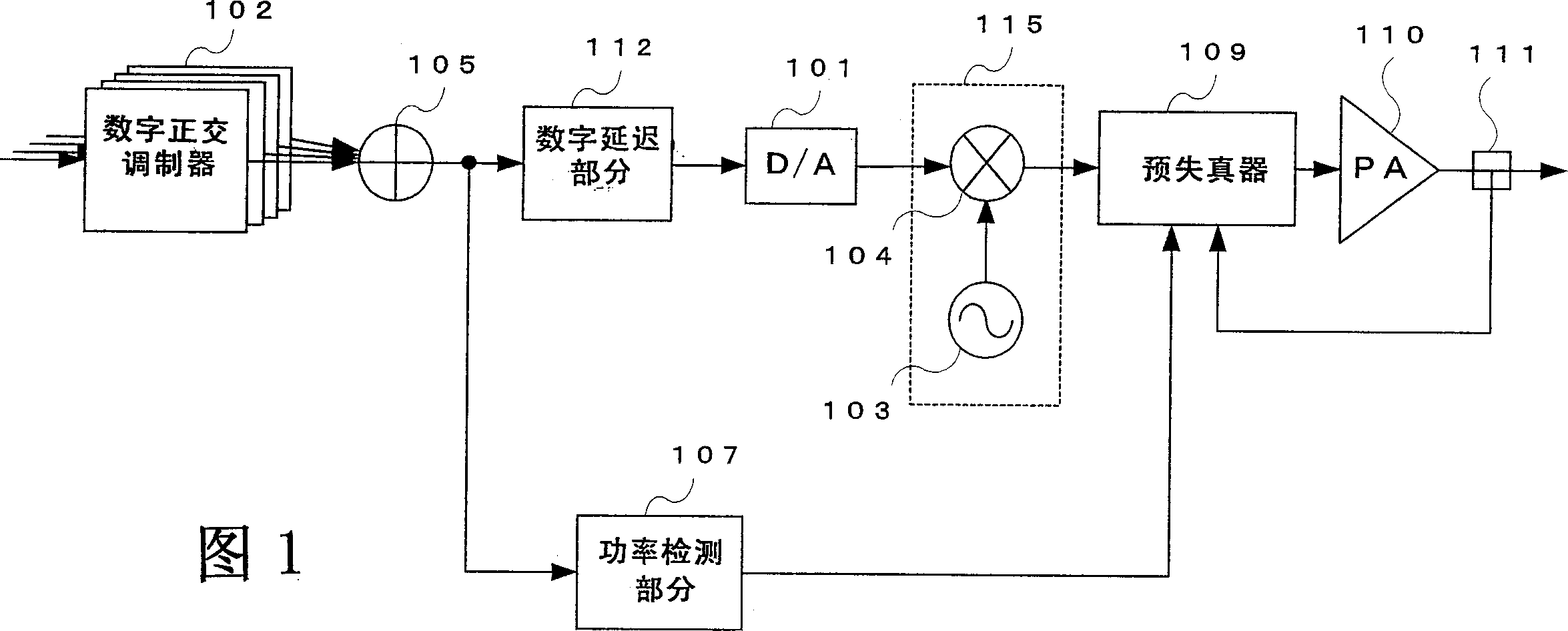

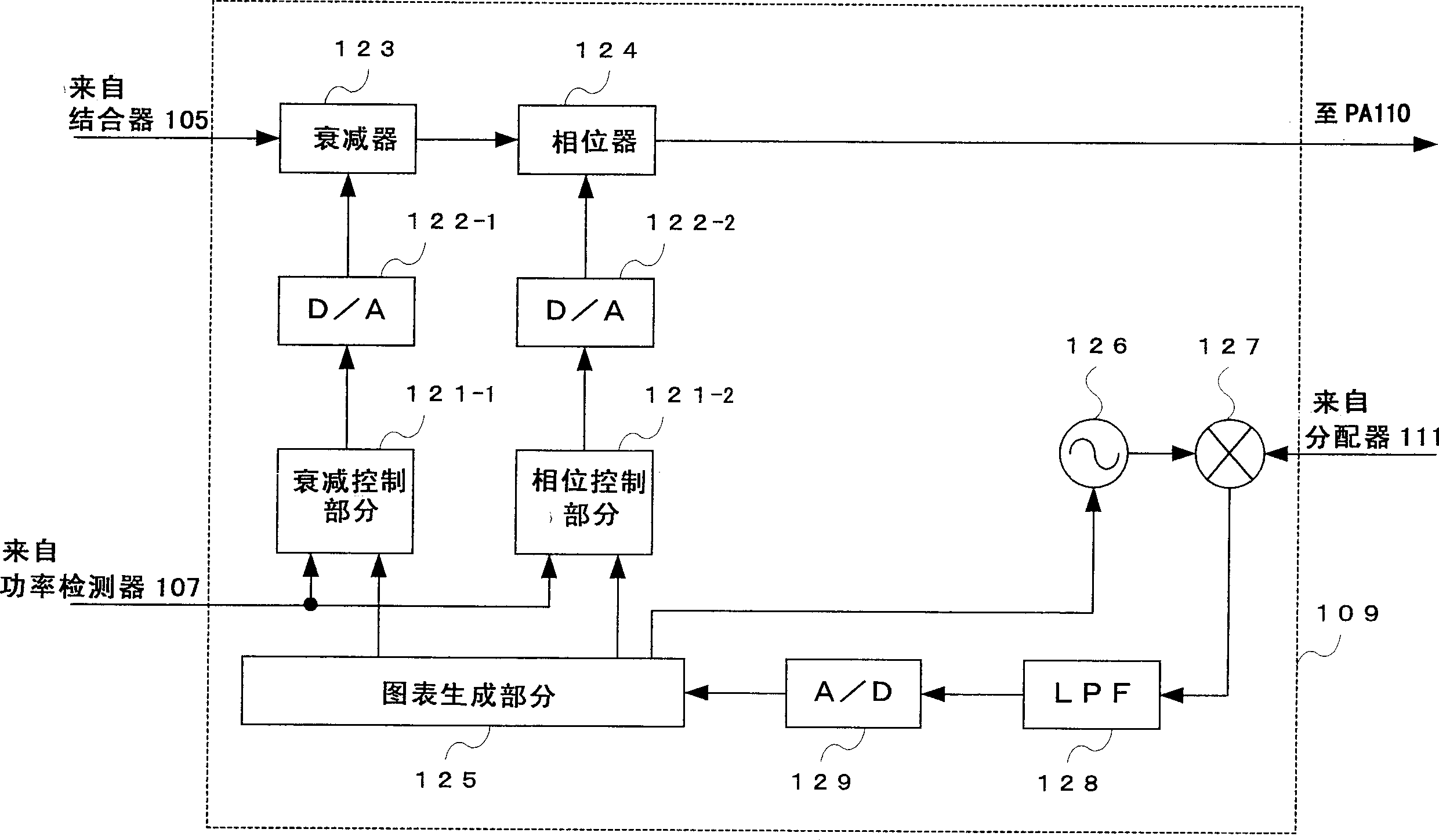

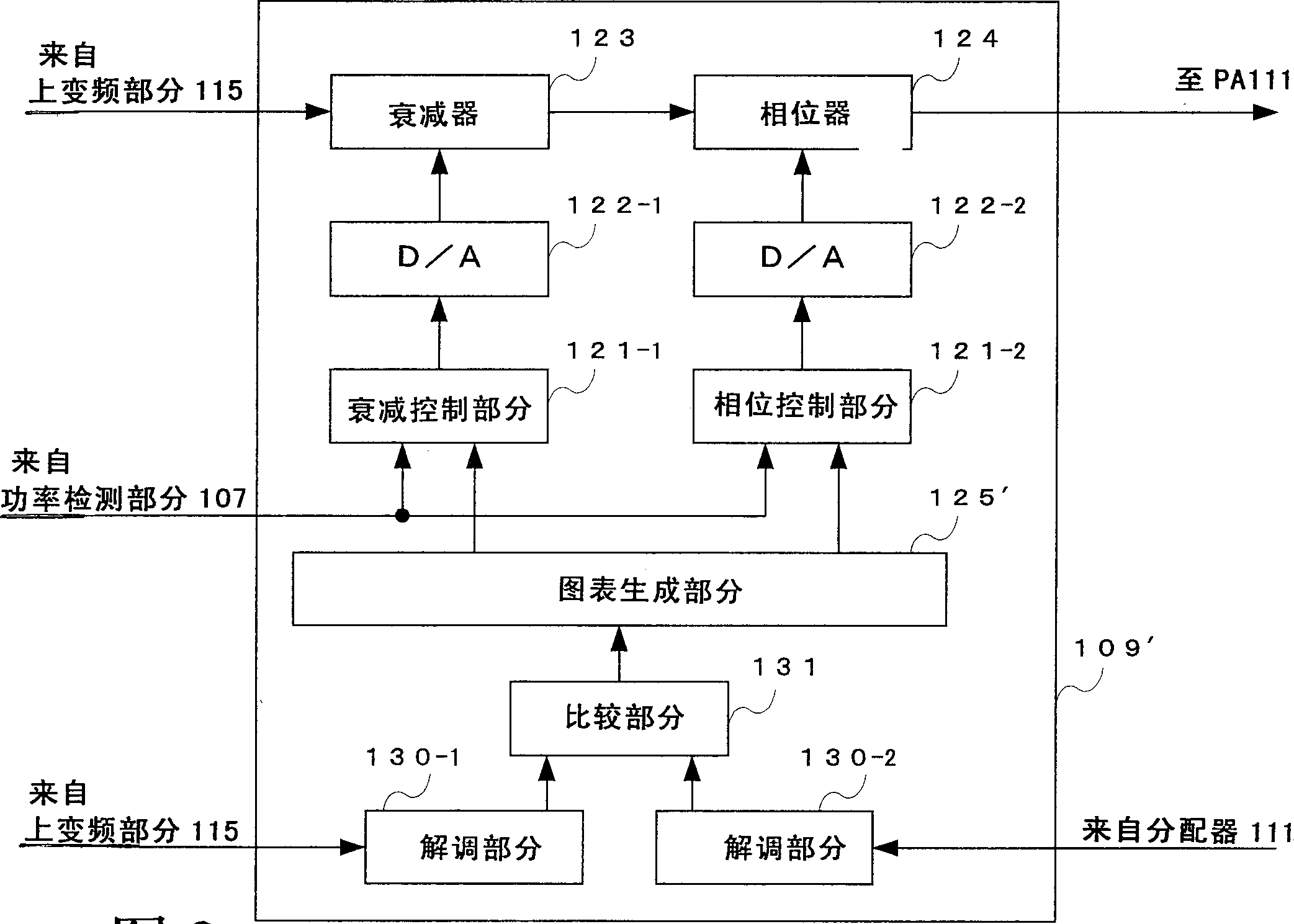

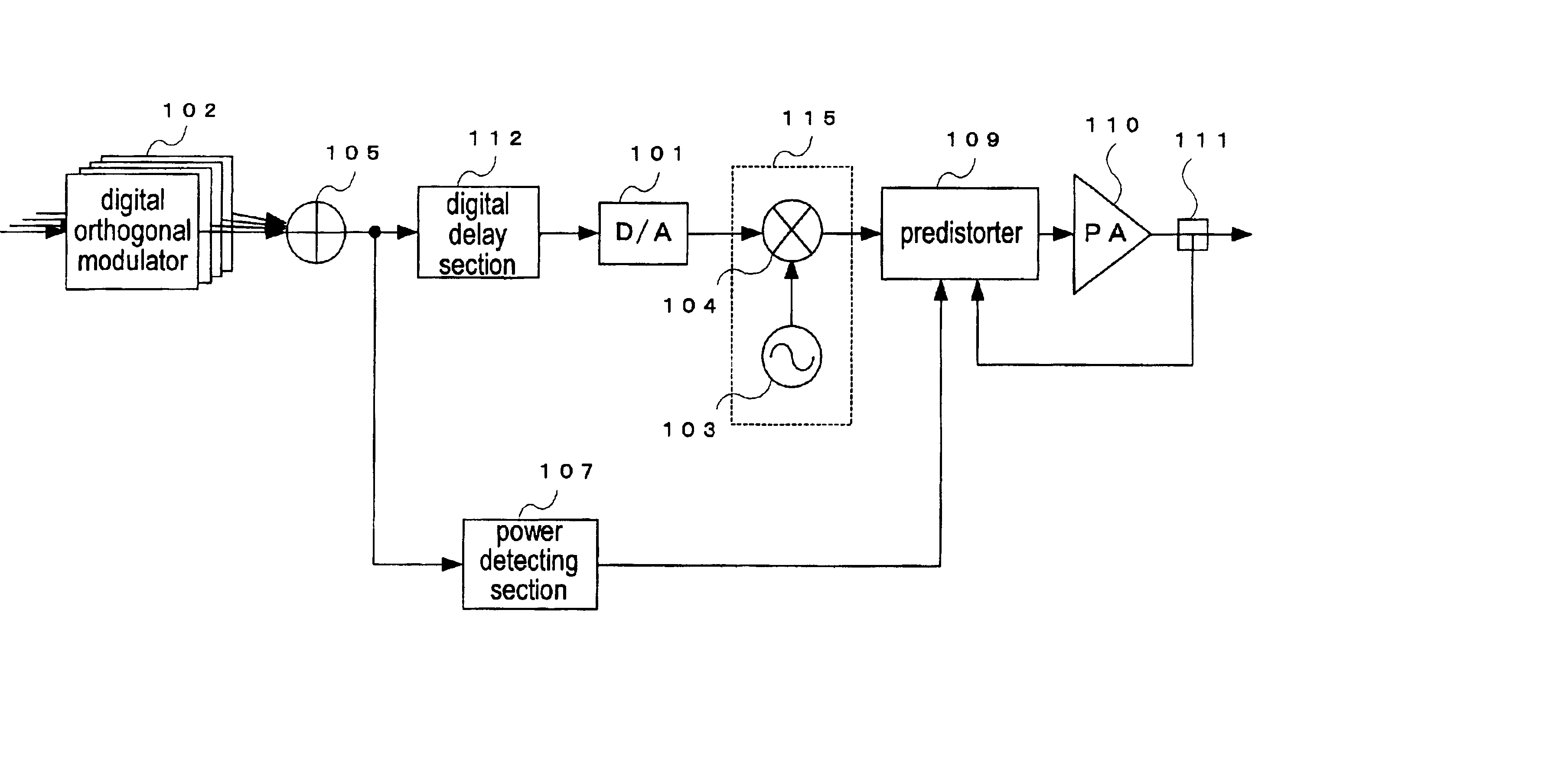

Amplifier

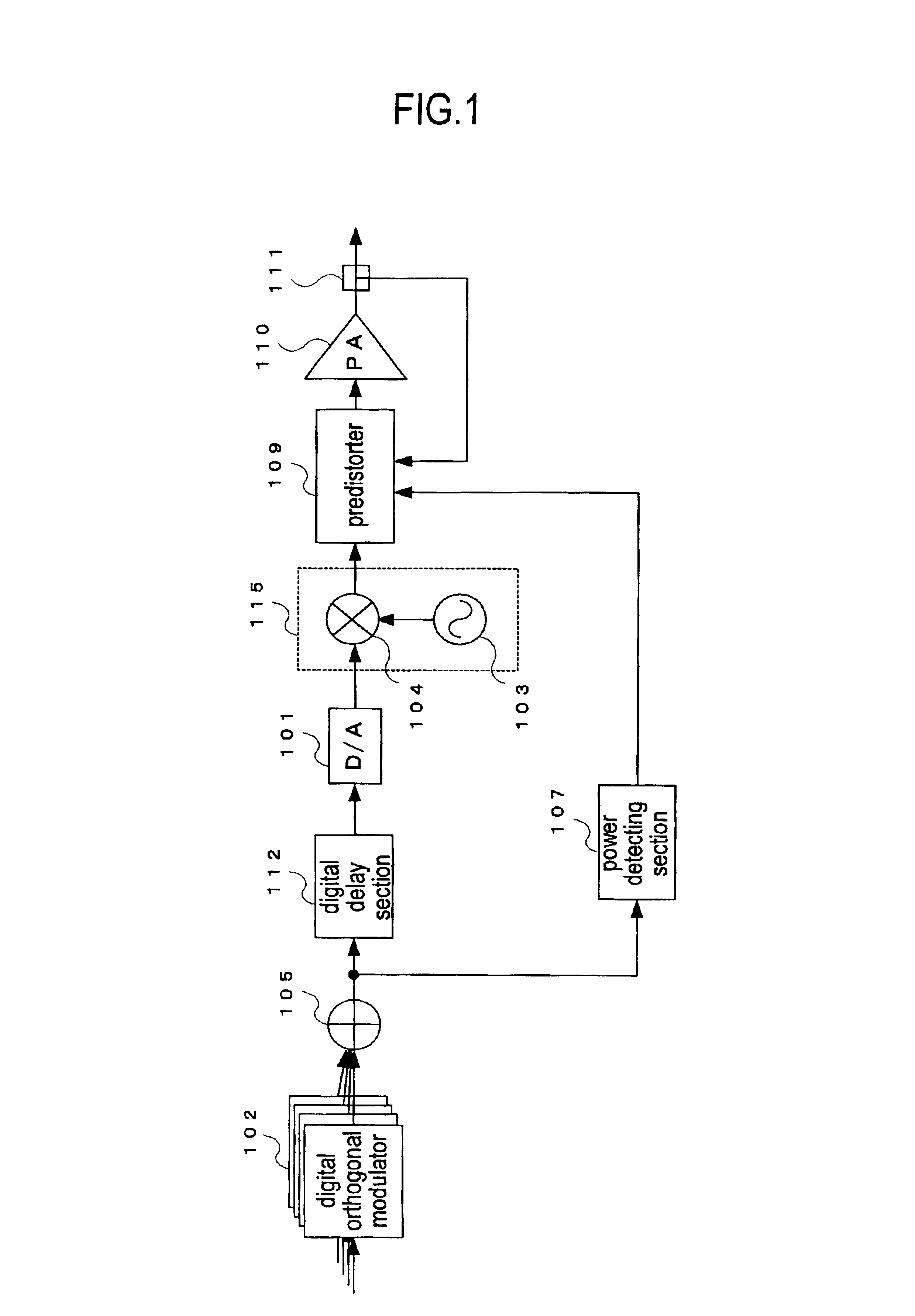

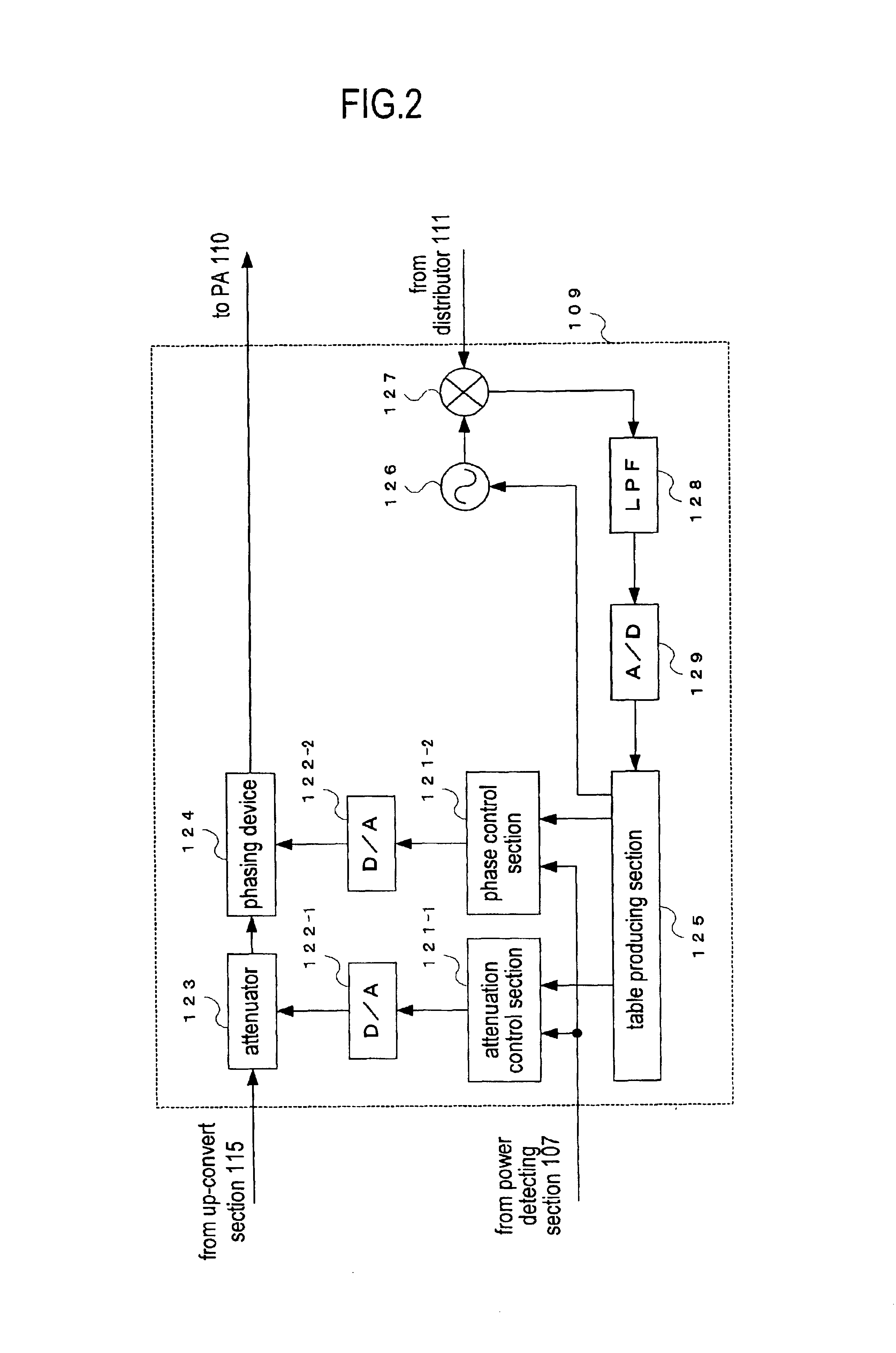

InactiveCN1404217AReduce mistakesLow costAmplifier modifications to reduce non-linear distortionAmplifier modifications to reduce temperature/voltage variationQuadrature modulatorQuadrature modulation

To provide an amplifying device which is reduced in size, weight and cost and which can improve the distortion compensation performance. In the amplifying device, input signals are each subjected to digital orthogonal modulation using an IF and further to offset rotation processing in digital orthogonal modulators, then bifurcated into a main signal system and a control system, and detection of a power value is performed at an IF band in a power detecting section of the control system. Therefore, offset rotation processing of the input signals in the power detection is not required, so that a structure for matching phases of a multi-carrier signal and a power value signal is not required, resulting in improving the distortion compensation performance without using an analog delay line.

Owner:KOKUSA ELECTRIC CO LTD

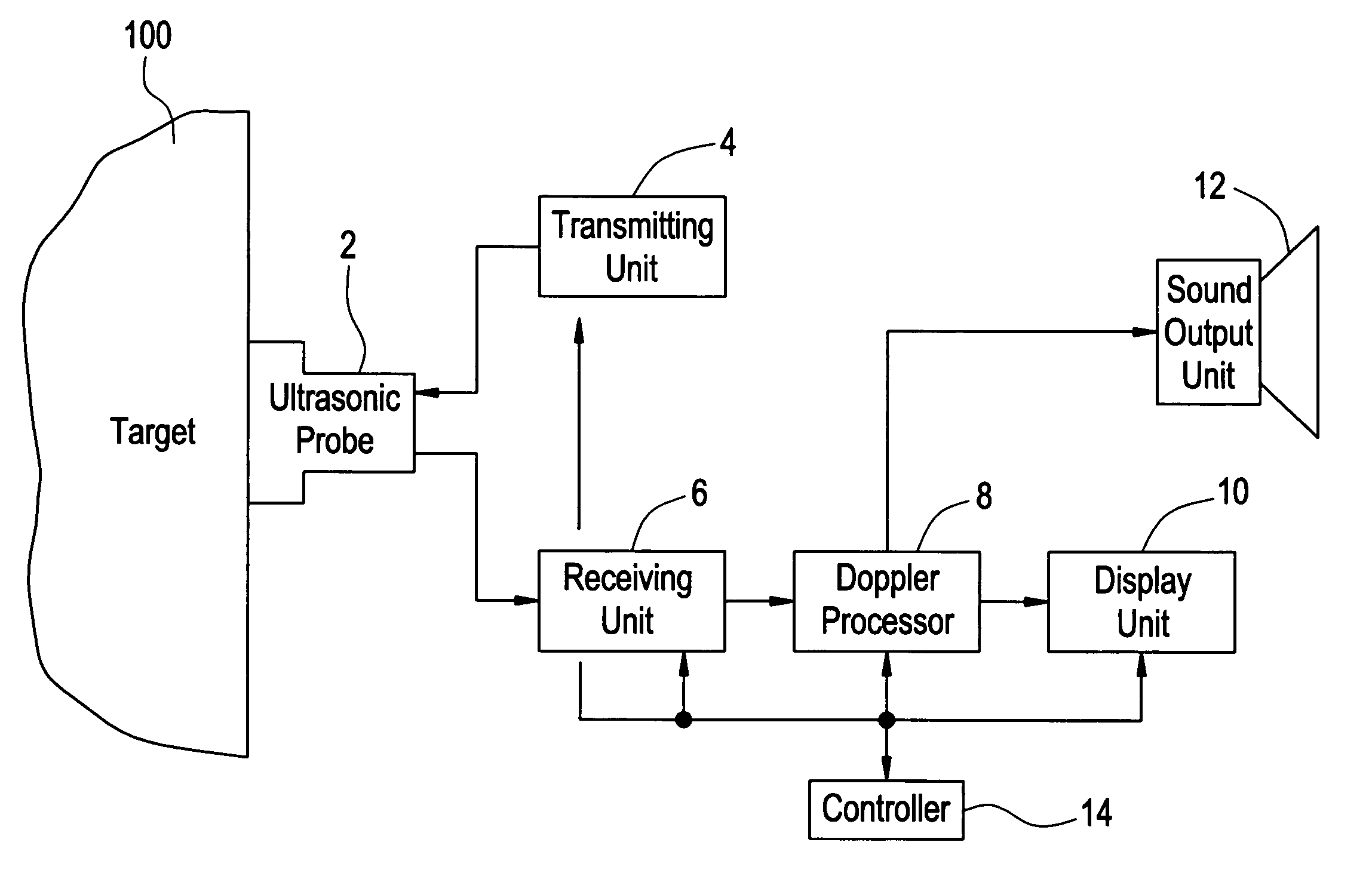

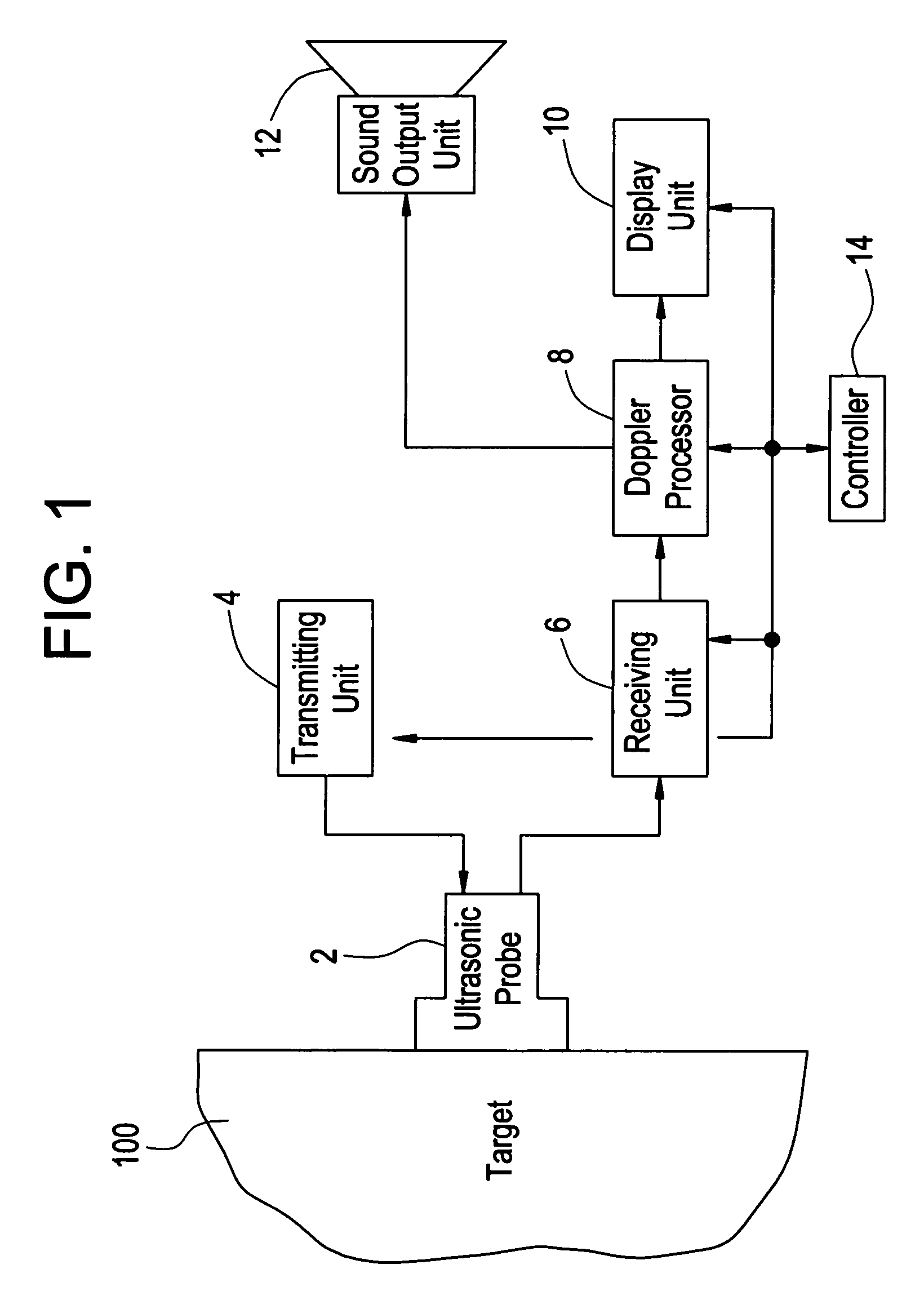

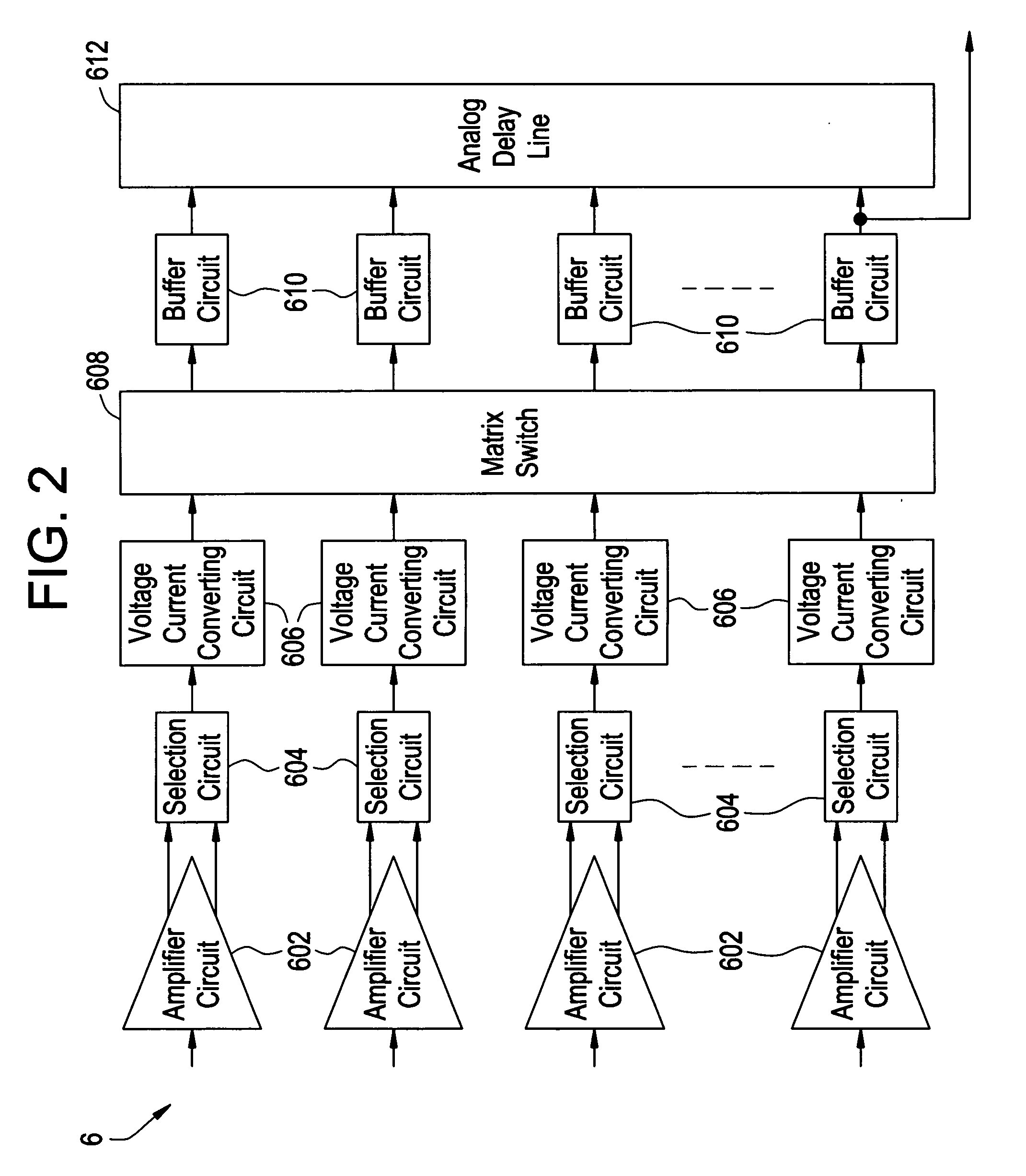

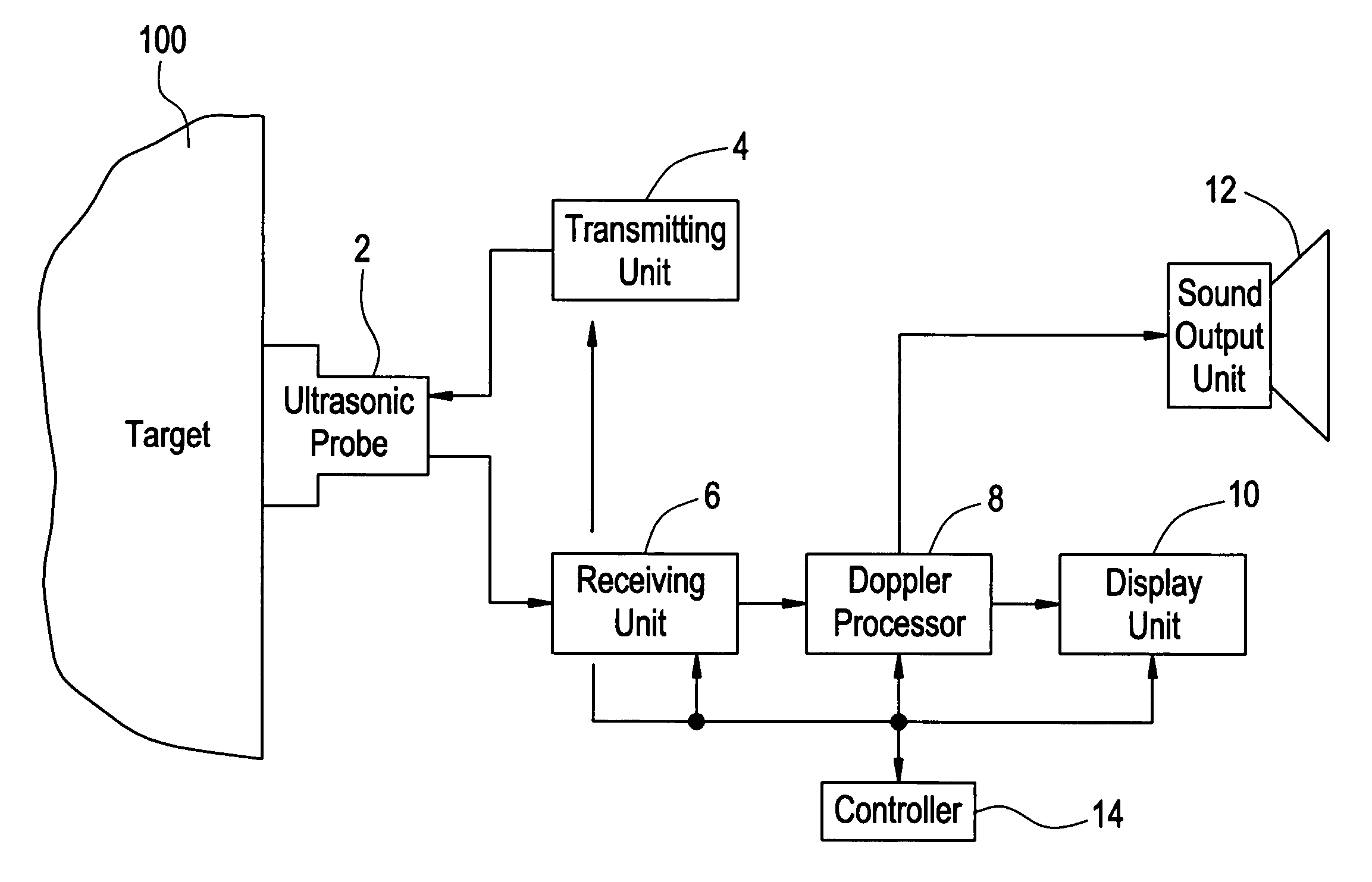

Delay adding device and ultrasonic diagnostic apparatus

InactiveUS20070038107A1Reduce the number of tapsReduce the numberMultiple-port networksFluid pressure measurementAnalog delay lineLength wave

The present invention aims to provide a delay device having an analog delay line adaptable to a plurality of frequencies with a less number of taps. The analog delay line has a maximum delay amount equivalent to a wavelength from over a ⅜ wavelength of a predetermined maximum wavelength of an input signal to under a 1 wavelength thereof. Tap intervals up to a delay point equivalent to ½ of a predetermined minimum wavelength of the input signal are different from tap intervals placed ahead of those. The maximum wavelength is a wavelength of a signal having a frequency of 2 MHz, for example, and the minimum wavelength is a wavelength of a signal having a frequency of 5 MHz, for example.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

Delay adding device and ultrasonic diagnostic apparatus

InactiveUS7678053B2Reduce the numberMultiple-port networksFluid pressure measurementAnalog delay lineLength wave

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

FIR filter using unclocked delay elements

ActiveUS8937991B2Multiple-port networksDigital technique networkFinite impulse responseAnalog delay line

A system and method for filtering an analog signal with a finite impulse response (FIR) filter that does not require analog delay elements are disclosed. An analog signal is pulse-width encoded, and the pulse-width encoded signal passed to a delay line comprising unclocked delay elements, such as logic gates, rather than clocked delay elements such as are used in conventional FIR filters. The propagation of the input signal is thus due only to the delay inherent in each gate, and occurs based upon when a signal reaches the gate rather than being caused by a clock signal. As with a conventional FIR filter, weighting elements having impedance are used to weigh the output of each delay element, and the resulting outputs summed to obtain a filtered output signal. For certain signals, such a circuit and method provides a simpler way of filtering than conventional filters.

Owner:ESS TECHNOLOGY

Receiver Calibration and Tracking

ActiveCN108028661BReduced path varianceTransmitters monitoringReceivers monitoringTransceiverSoftware engineering

Techniques for calibrating interleaved analog-to-digital converter (ADC) arrays are presented. The transceiver includes an ADC assembly including an array of interleaved sub-ADCs and an auxiliary path associated with the auxiliary sub-ADCs for facilitating calibration of the sampling array by comparing auxiliary path signals with signals of sub-ADCs in the array. The calibration component uses a phase interpolator and an analog delay line to adjust the auxiliary sub-ADC so that the auxiliary sub-ADC is queued to any sampling instant of the sampling array. The calibration component compares the auxiliary signal to the sub-ADC signal, determines the path difference between the sub-ADC paths based on the comparison, and calibrates the sub-ADC and the sub-ADC paths to reduce the path difference to reduce the number generated by combining the sub-ADCs in the array Distortion in the digital stream produced by combining substreams.

Owner:镁可联通解决方案有限公司

Integrated Analog Delay Line for Pulse Width Modulator

ActiveCN107046417BSingle output arrangementsPulse duration/width modulationSoftware engineeringAnalog delay line

The present invention relates to integrated analog delay lines for pulse width modulators. A pulse width modulation (PWM) system includes analog and digital components. The analog component introduces an offset (ie, a time delay) to the analog signal received at the input in the analog (continuous time) domain with tuning operations fine-tuned in the analog signal. The analog components include an analog delay line comprising a plurality of analog delay components configured to introduce a time delay to the analog signal based on a model of the transmission line.

Owner:INFINEON TECH AG

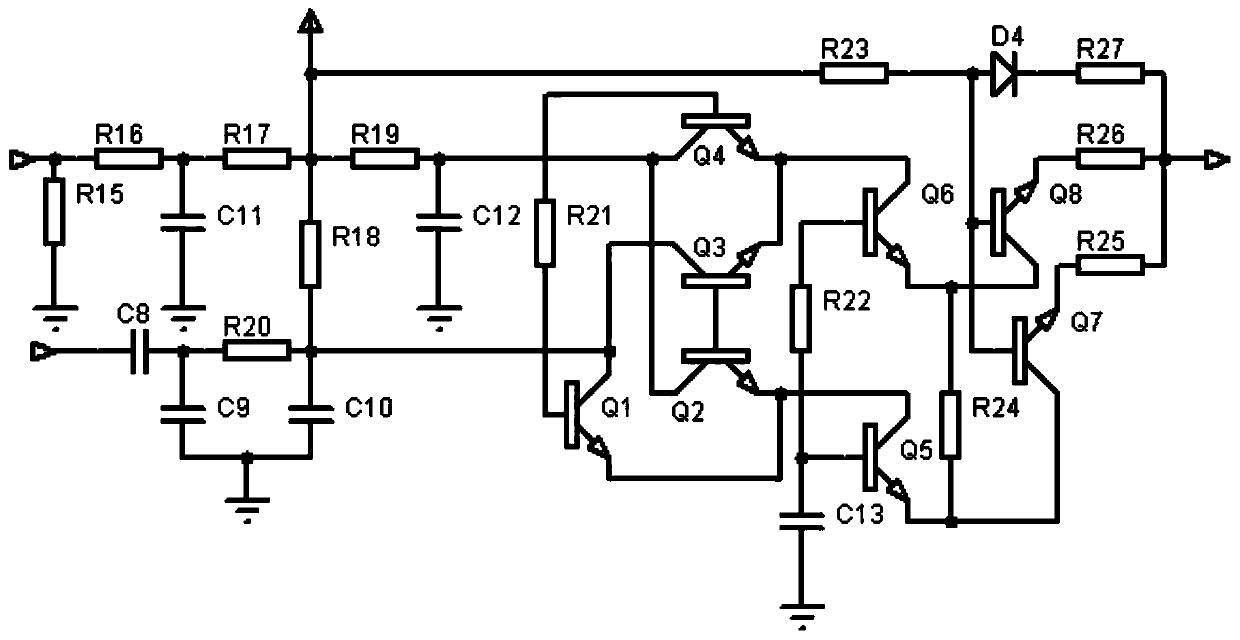

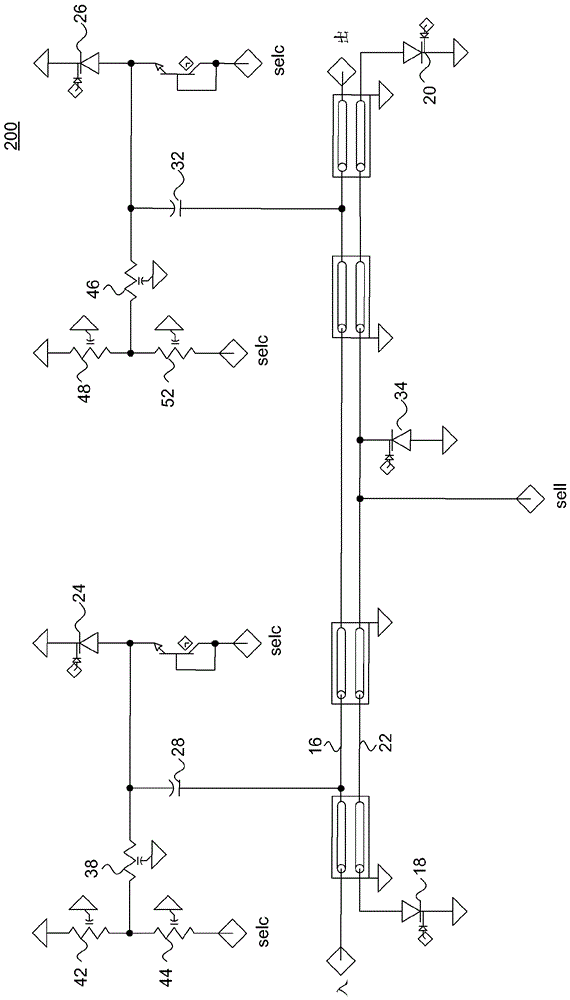

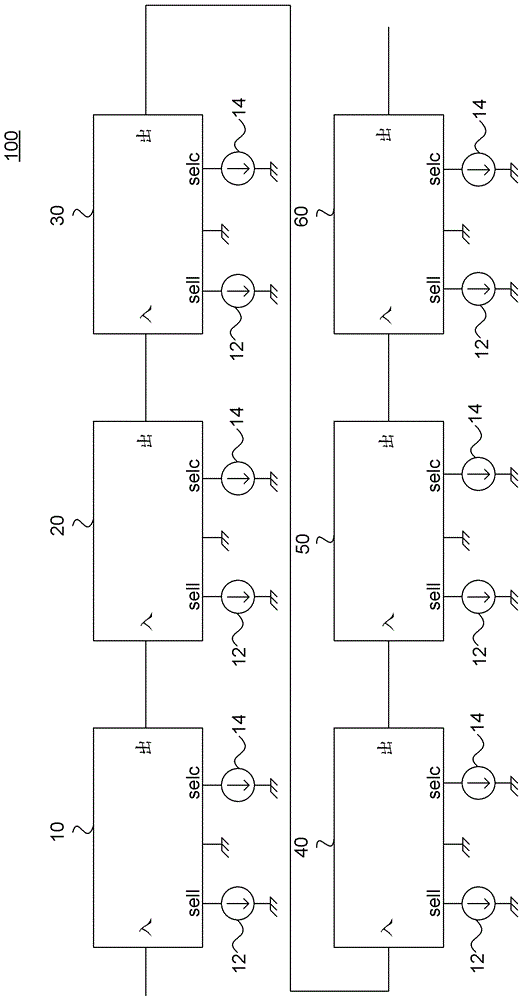

Electronically variable analog delay line

ActiveCN106257834BMultiple-port networksSingle output arrangementsTelecommunicationsAnalog delay line

An electronically variable analog delay line includes at least one section having electronically variable inductance. At least one segment includes a signal path, a ground return path, and a plurality of switches configured to vary the inductance of the segment.

Owner:TEKTRONIX INC

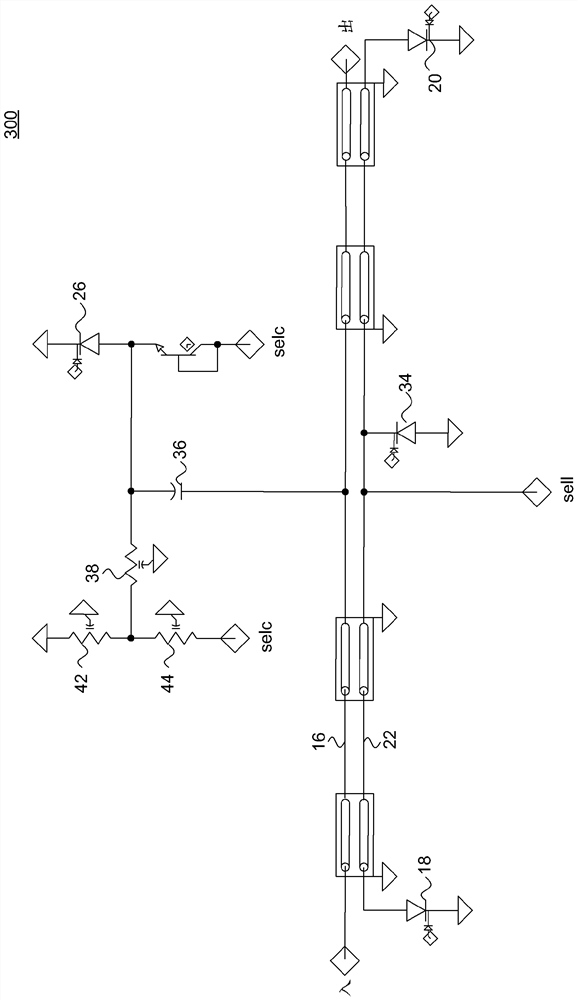

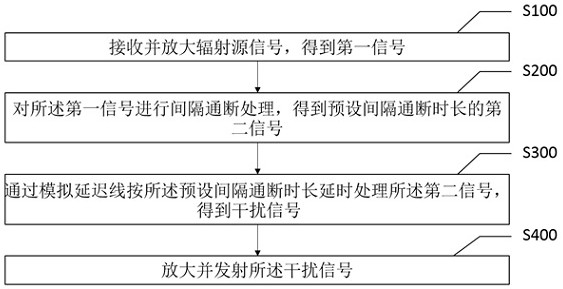

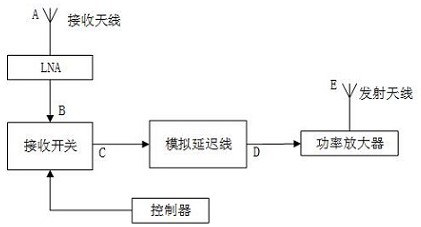

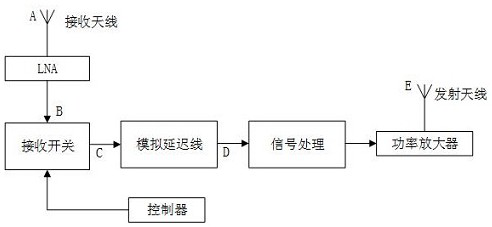

Transceiving isolation forwarding interference method and forwarding interference device based on analog delay line

PendingCN114720948ASimple designSatisfy large bandwidthWave based measurement systemsTelecommunicationsAnalog delay line

The invention discloses a transmitting-receiving isolation forwarding interference method and a forwarding interference device based on an analog delay line. The forwarding interference method comprises the following specific steps: receiving and amplifying a radiation source signal to obtain a first signal; performing interval on-off processing on the first signal to obtain a second signal with a preset interval on-off duration; performing delay processing on the second signal through an analog delay line to obtain an interference signal; and amplifying and transmitting the interference signal. According to the invention, fast time-division isolation forwarding is realized through the analog delay line, the system design difficulty and the forwarding interference cost are effectively reduced, and the bandwidth processing range is widened.

Owner:BEIJING HUNRAY TECH

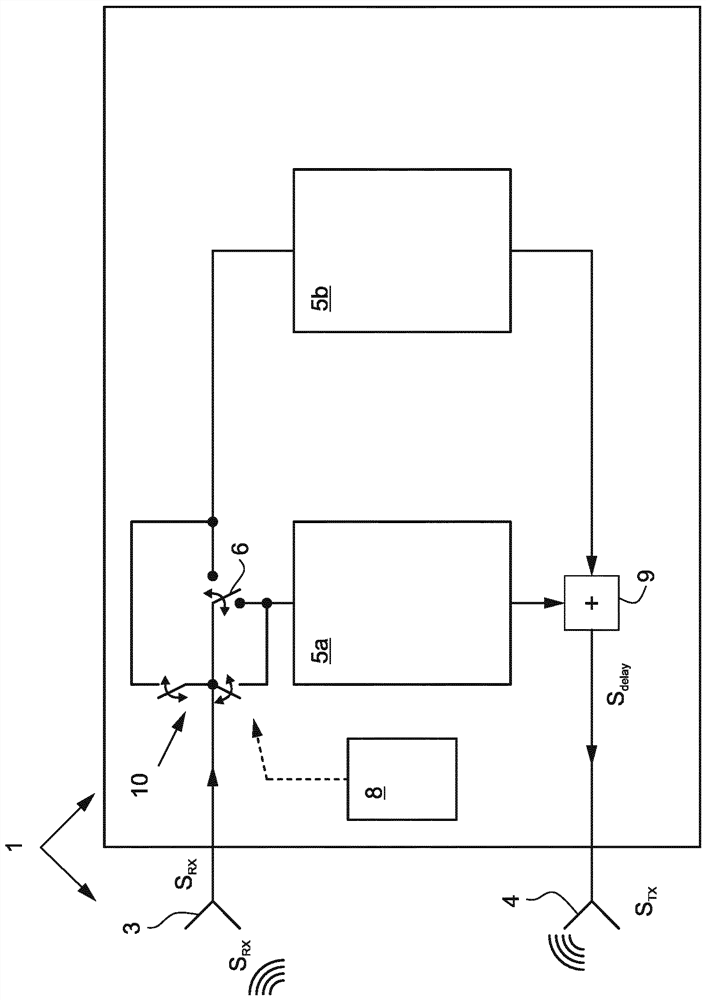

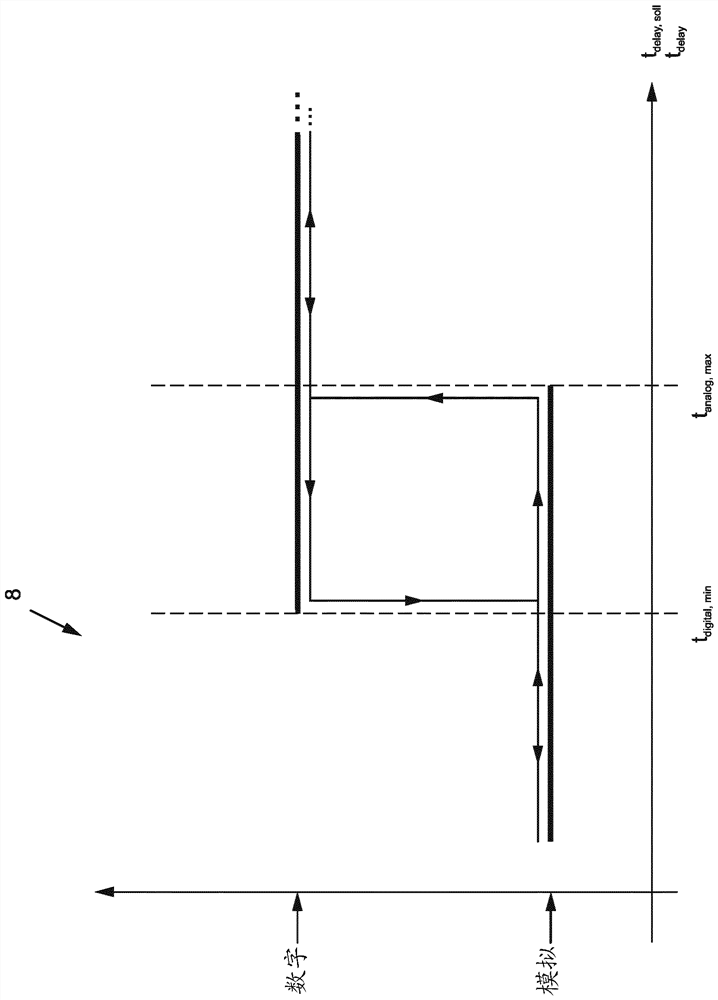

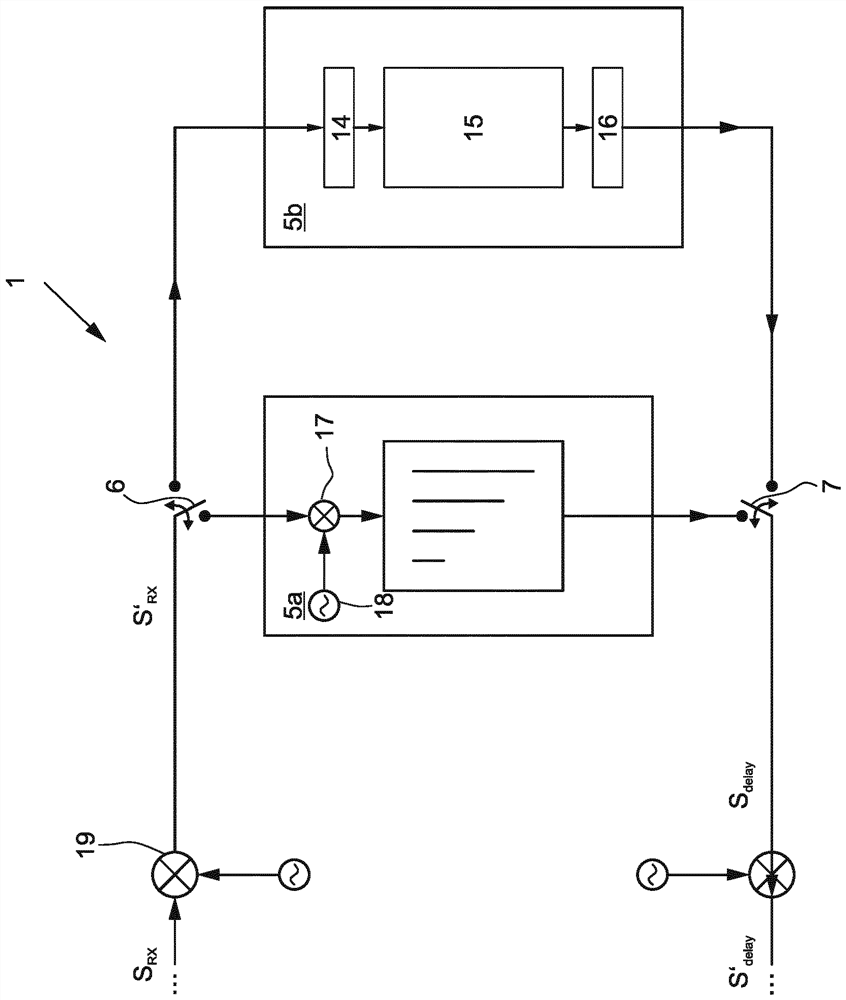

Testing device for testing a distance sensor that operates using electromagnetic waves

PendingCN113544531ASwitching frequency is minimizedElectromagnetic wave reradiationRadio wave reradiation/reflectionTime delaysDigital delay line

The invention relates to a testing device (1) for testing a distance sensor (2) that operates using electromagnetic waves, comprising a receiving element (3) for receiving an electromagnetic free-space wave as a received signal SRX and an emission element (4) for emitting a simulated electromagnetic reflection signal STX, the received signal SRX or a signal S'RX derived from the received signal SRX being fed through a time-delay circuit (5) having a specifiable time delay tdelay, soll and thus being time-delayed to form a time-delayed signal Sdelay, the time-delayed signal Sdelay or a signal S'delay derived from the time-delayed signal Sdelay being emitted as the simulated reflection signal STX by means of the emission element (4). A large range of specifiable time delays can be covered because the time-delay circuit (5) comprises an analog delay segment (5a) having a specifiable time delay tdelay, soll and a digital delay segment (5b) having a likewise specifiable time delay tdelay, soll , because the analog delay segment (5a) effects shorter time delays than the digital delay segment (5b), apart from a possible range of overlap, and because the received signal SRX or the signal S'RX derived from the received signal SRX is switched either to the input of the analog delay segment (5a) or to the input of the digital delay segment (5b) by means of an input switching apparatus (6) and the signal becomes the time-delayed signal Sdelay after passing through the switched delay segment.

Owner:디스페이스게엠베하

Amplifying device

ActiveUS6959174B2Small sizeReduce weightAmplifier modifications to reduce non-linear distortionResonant long antennasQuadrature modulatorAudio power amplifier

To provide an amplifying device which is reduced in size, weight and cost and which can improve the distortion compensation performance. In the amplifying device, input signals are each subjected to digital orthogonal modulation using an IF and further to offset rotation processing in digital orthogonal modulators, then bifurcated into a main signal system and a control system, and detection of a power value is performed at an IF band in a power detecting section of the control system. Therefore, offset rotation processing of the input signals in the power detection is not required, so that a structure for matching phases of a multi-carrier signal and a power value signal is not required, resulting in improving the distortion compensation performance without using an analog delay line.

Owner:KOKUSA ELECTRIC CO LTD

Electronically variable analog delay line

An electronically variable analog delay line including at least one segment with an electronically variable inductance. The at least one segment includes a signal path, a ground return path, and a plurality of switches configured to vary the inductance of the segment.

Owner:TEKTRONIX INC