Synchronous mirror delay (SMD) circuit and method including a counter and reduced size bi-directional delay line

A delay circuit, delay line technology, applied in digital memory information, instruments, electrical components, etc., can solve problems such as difficulty in obtaining delay resolution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

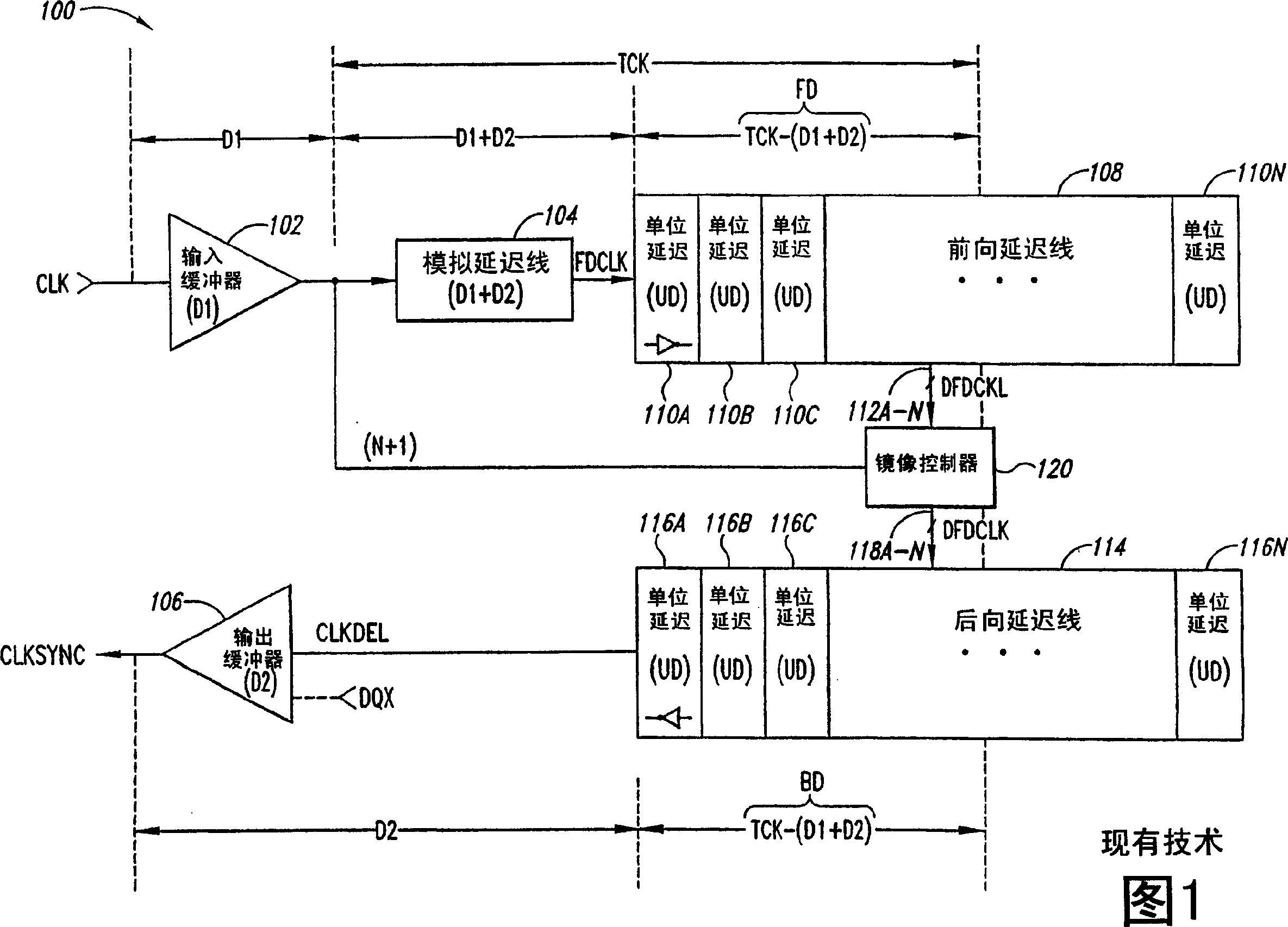

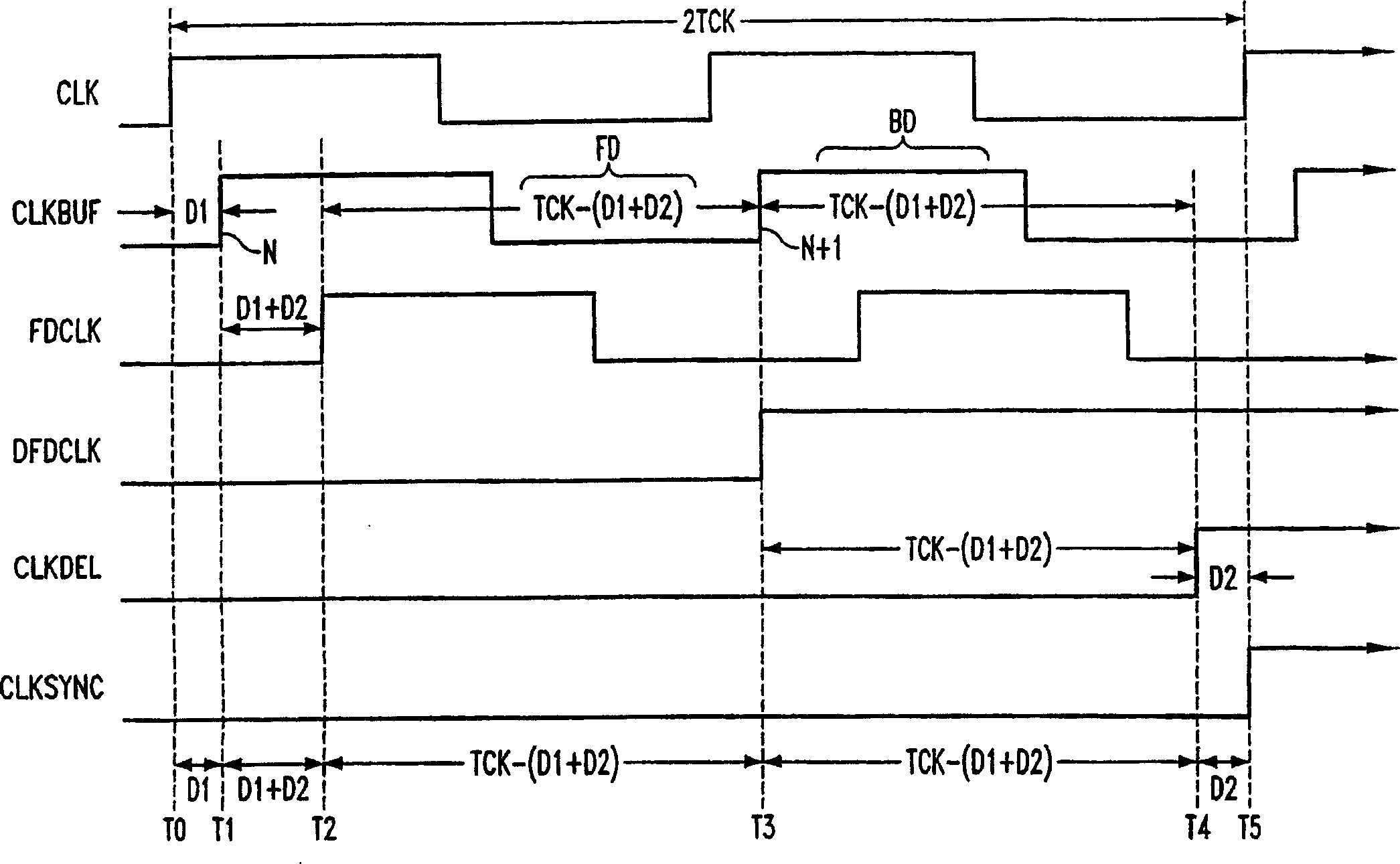

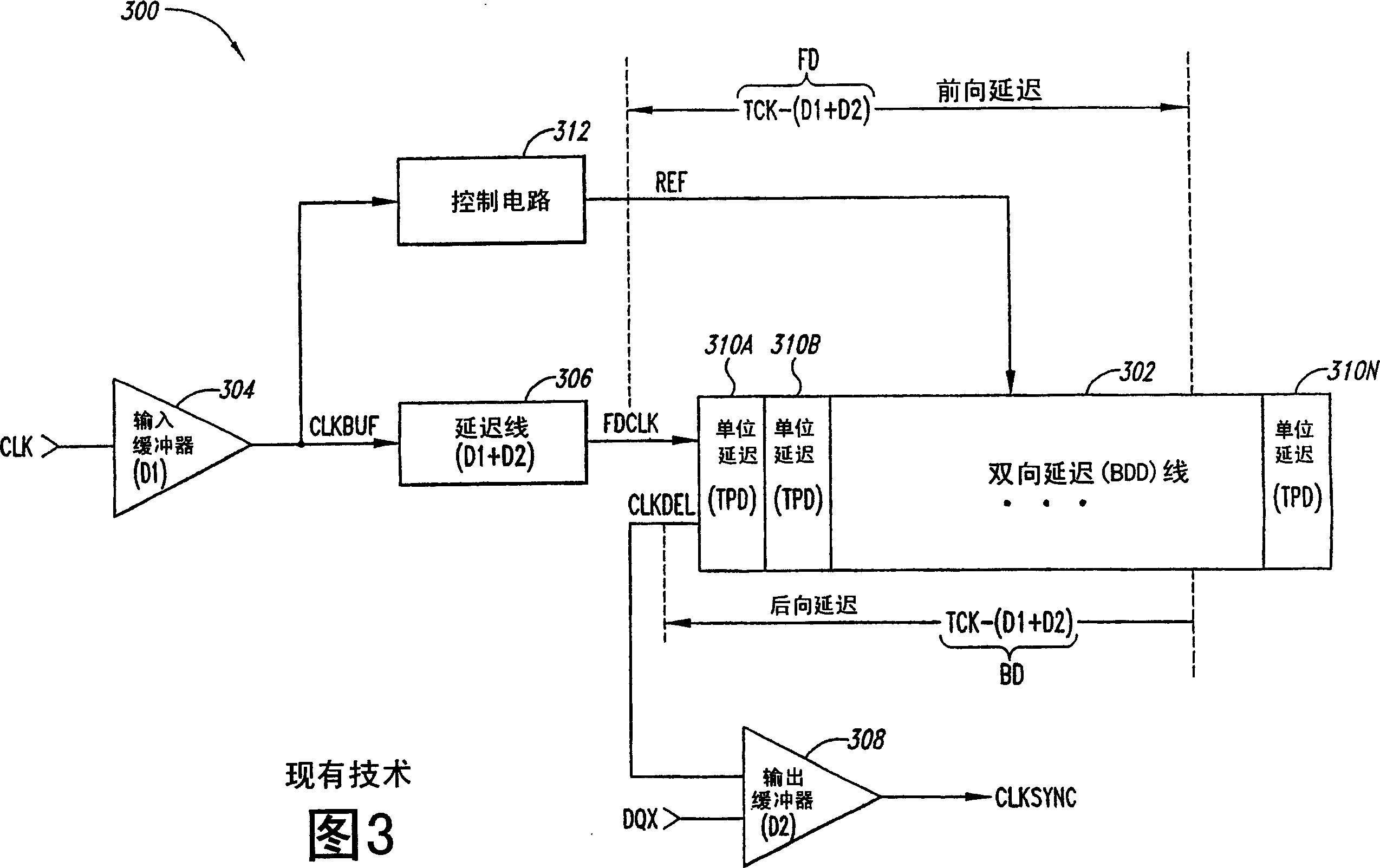

Method used

Image

Examples

Embodiment Construction

[0045] Figure 6is a functional block diagram depicting an SMD 600 containing a reflective bidirectional delay line 602 comprising a relatively small number of unit delays 604A-H and up / down counters 606 which cooperate to generate a forward delay FD and a backward delay BD are used to generate a synchronous clock signal CLKSYNC which is synchronous with the applied clock signal CLK, as will be described in more detail below. Briefly, delay line 602 operates in a forward delay mode to pass the initial rising edge of forward delayed clock signal FDCLK via unit delays 604A-H in both directions. Meanwhile, each time the signal passes through the first unit delay 604A, the counter 606 increments by one count CNT. Delay line 602 then operates in backward delay mode to reverse the direction of propagation of the rising edge of the FDCLK signal at a given point in time, and thereafter, counter 606 decrements CNT each time the signal passes through the first unit delay, Until the cou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More