Circuit arrangement, in particular phase-locked loop, as well as corresponding method

A technology of circuit layout and phase, applied in the field of phase-locked loop, can solve the problem of reducing PLL frequency, etc., and achieve the effect of easy work contraction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

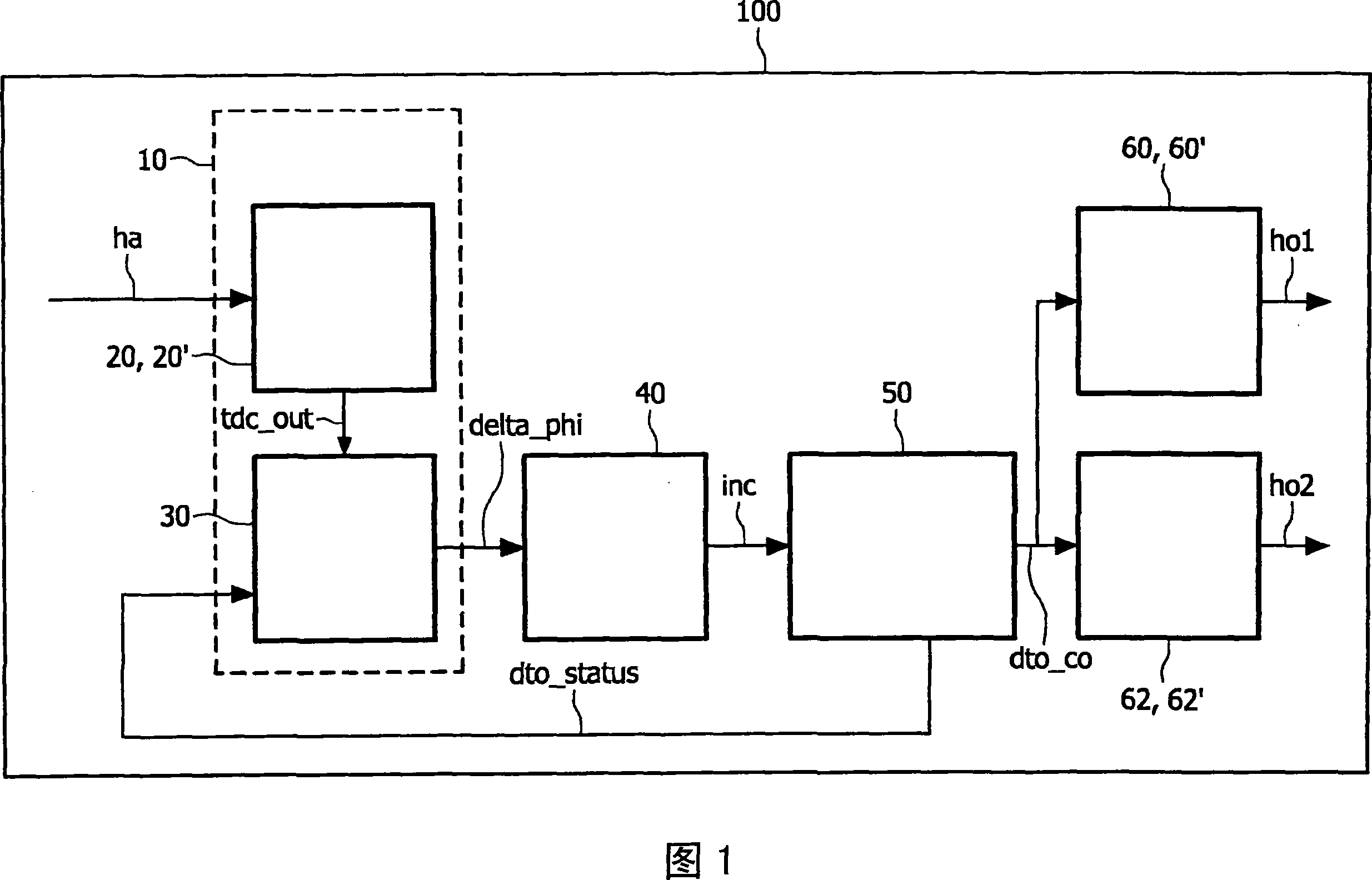

[0314] - time-to-digital converter 20 (see Figures 8, 9: first embodiment, without sample-and-hold stage) or 20' (see Figures 10, 11, 12: second embodiment, with sample-and-hold stage ss);

[0315] ---filter 40 (see Fig. 2: first embodiment, proportional (P) control is arranged) or 40 ' (see Fig. 3: second embodiment, proportional integral (PI) control is arranged);

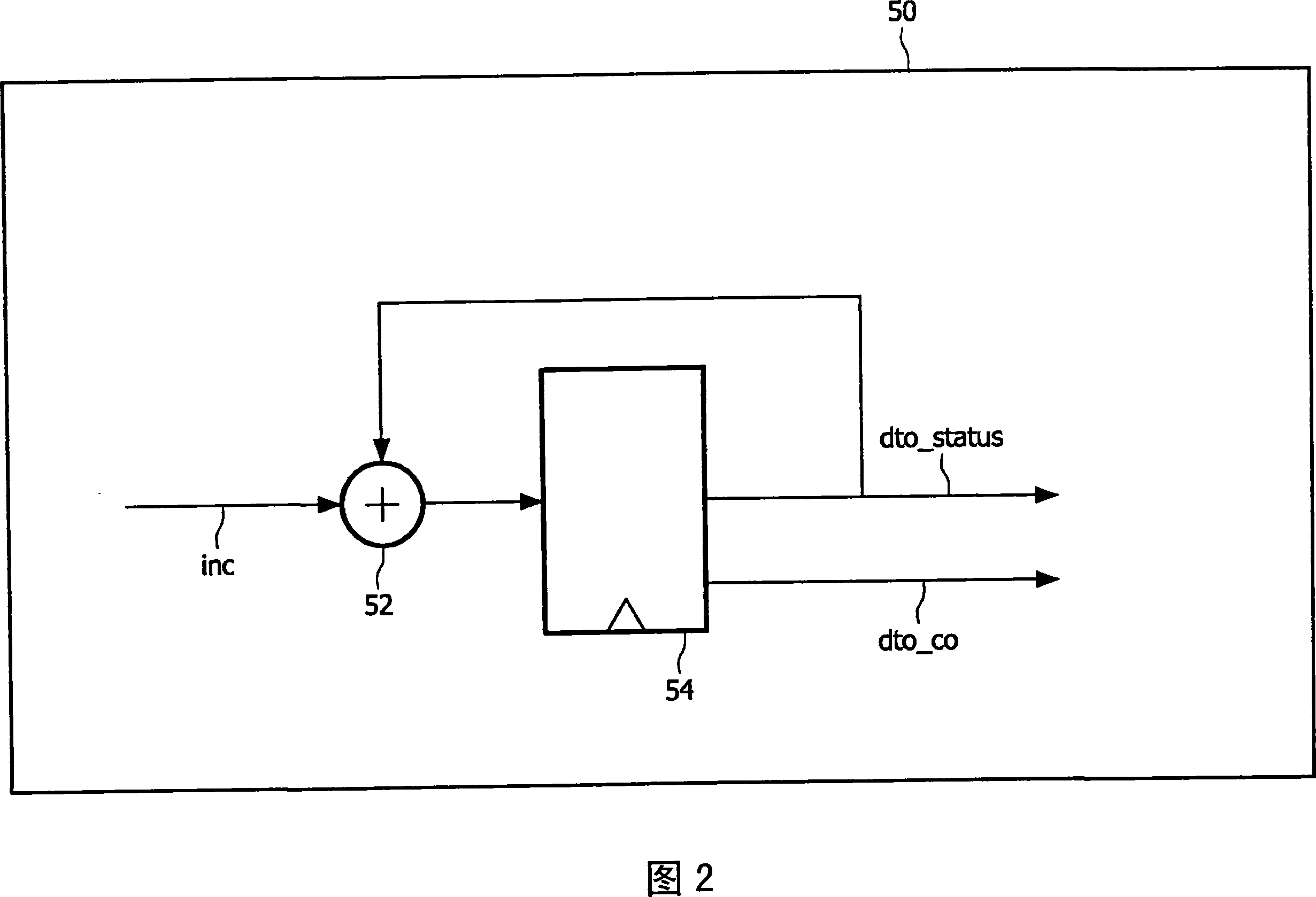

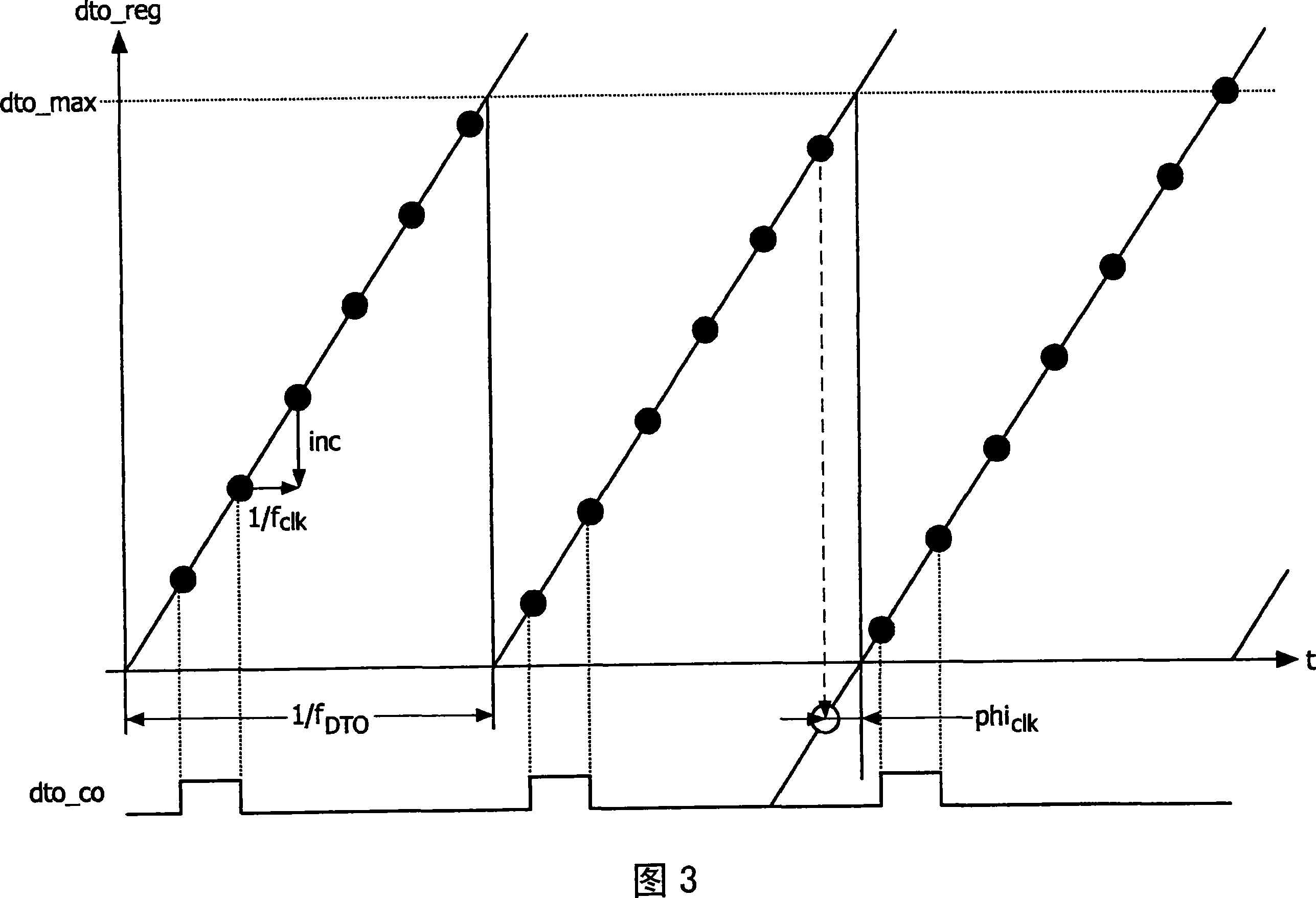

[0316] - Digital Ramp Oscillator or Discrete Time Oscillator 50 (see Figures 4, 5: first embodiment, no control of flyback value, maximum content or maximum value dto_max; see also Figure 20: no pipelining and Embodiment of adder unit split; FIG. 21 : embodiment with pipeline without adder unit split; FIG. 22 : embodiment without pipeline with split of adder units 502 and 504) or 50′ (see Figures 6, 7: Second embodiment with control of flyback value, maximum content or maximum value dto_max); and / or

[0317] --Digital-to-time converters 60, 62 (see Fig. 13, 14: first embodiment, without sample-and-hold stage) or...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More