Patents

Literature

376 results about "Digital controlled oscillator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A digitally controlled oscillator, or DCO, is an oscillator circuit that generates an analog signal, but whose frequency is controlled by a digital control input (as opposed to a voltage controlled oscillator, whose frequency is set by a control voltage ).

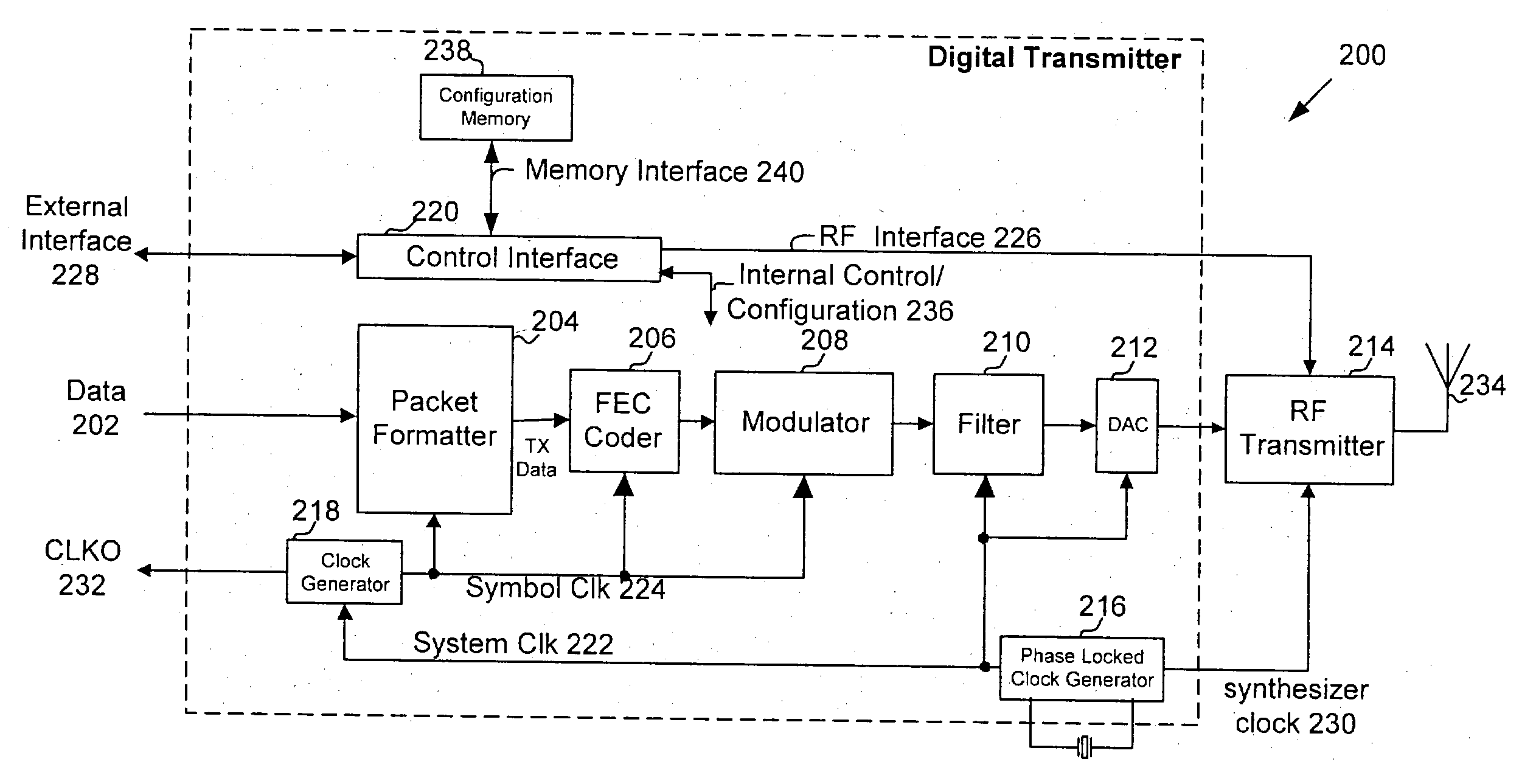

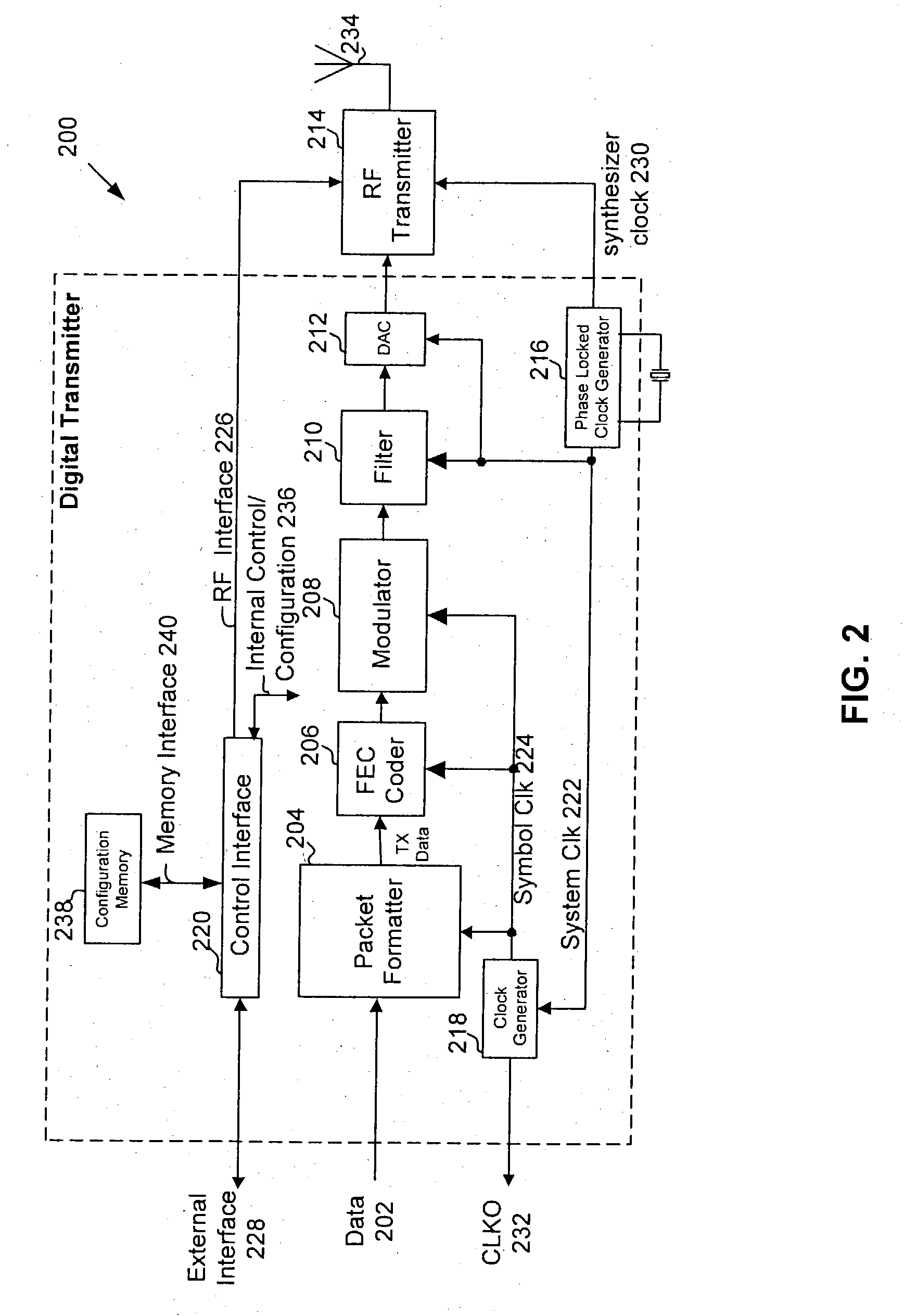

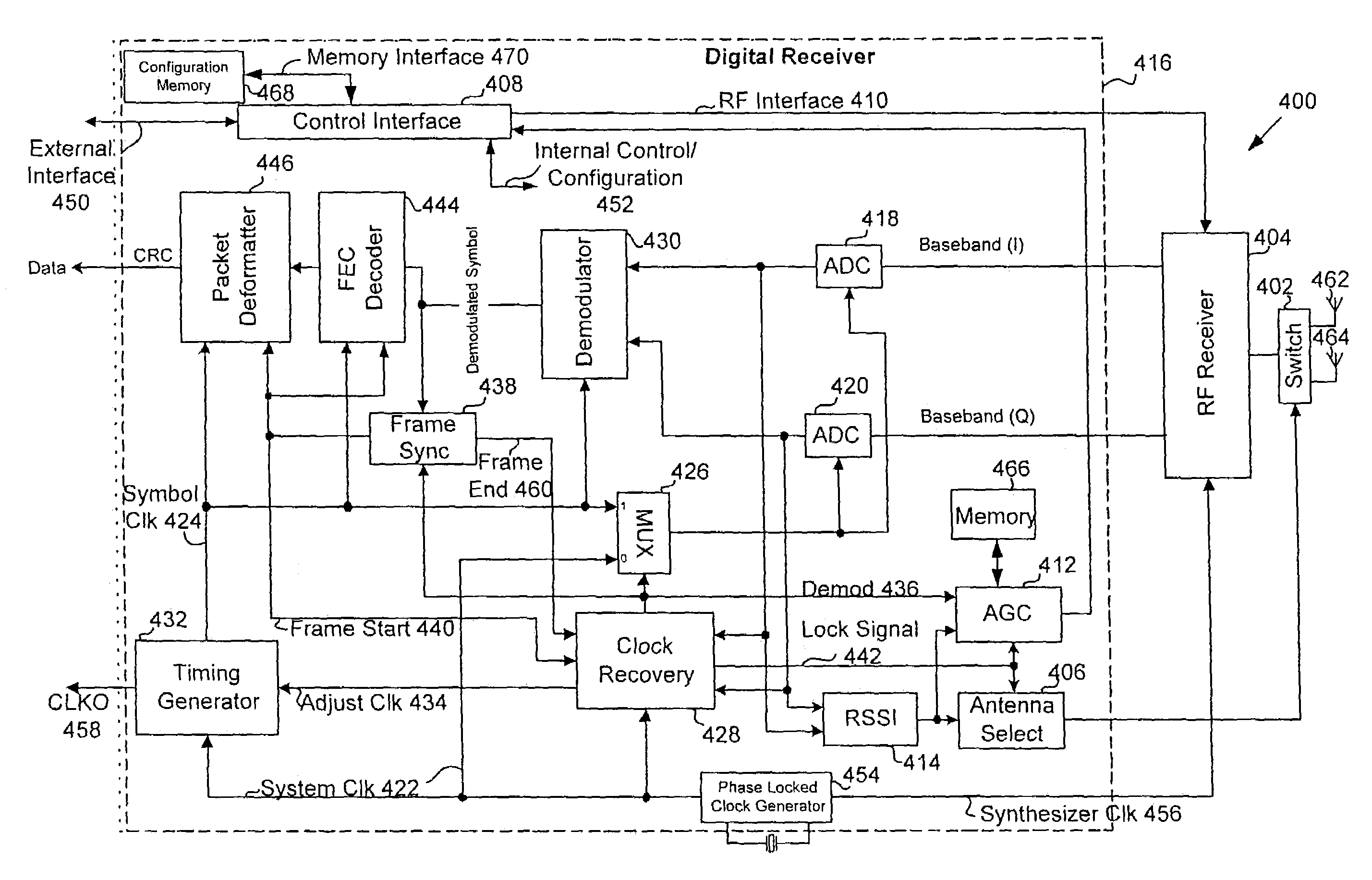

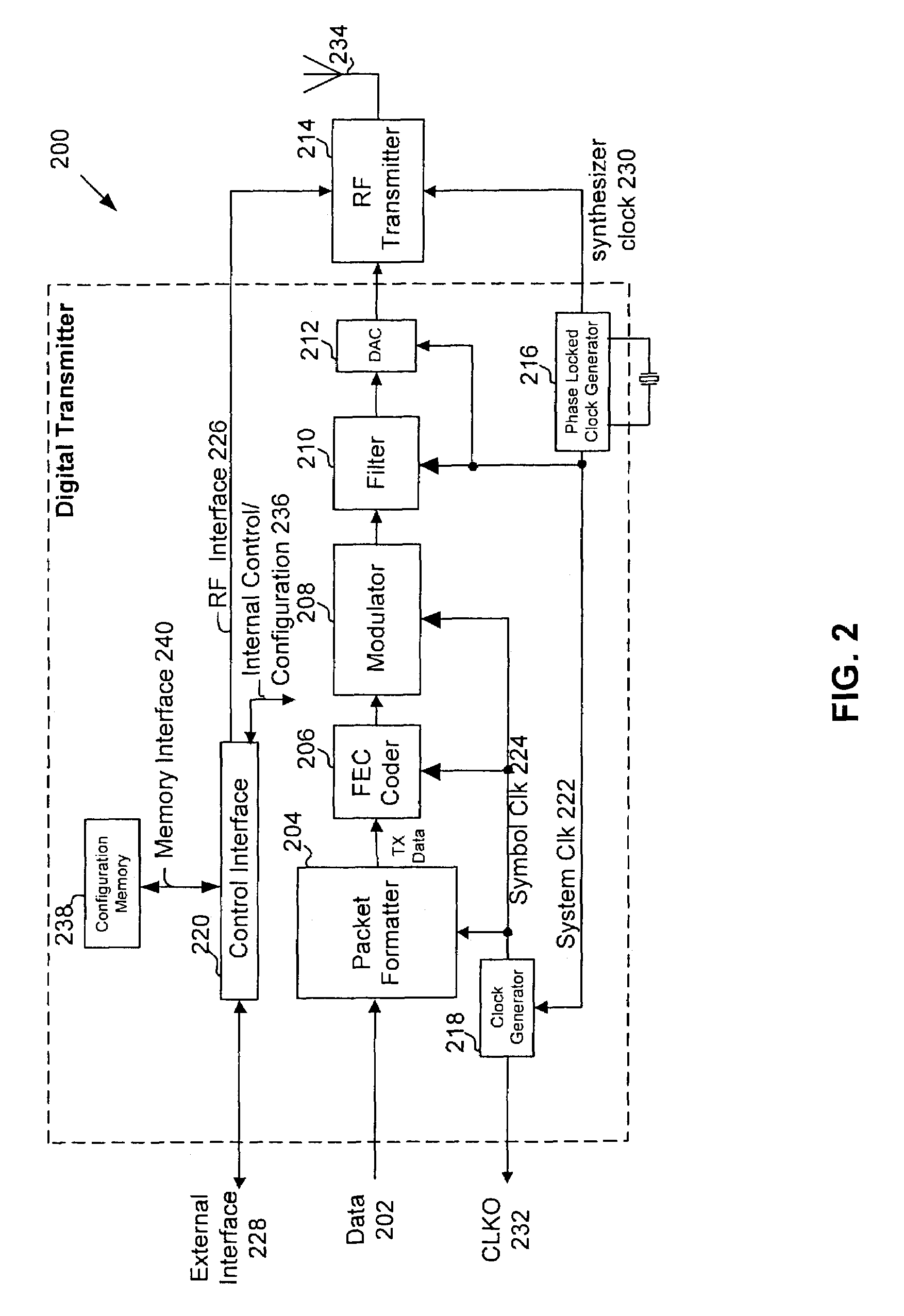

Low complexity synchronization for wireless transmission

ActiveUS20040196926A1Eliminate needInexpensive and low-complexity synchronization for communication systemsAmplitude-modulated carrier systemsSynchronisation signal speed/phase controlDigital dataCommunications system

A receiver, system and method for providing symbol timing recovery that allows for inexpensive and low-complexity synchronization for communication systems. A receiver receives a signal including digital data in the form of packets that is transmitted from a transmitter. The receiver uses information contained in each of the packets to align a phase of the receiver clock with a phase of the transmitter clock. The receiver further controls a sampling device such that the in-phase (I) and quadrature (Q) components are sampled at an optimum sample rate and at an optimum instance of time without requiring a numerically controlled oscillator or voltage controlled oscillator.

Owner:MICROCHIP TECH INC

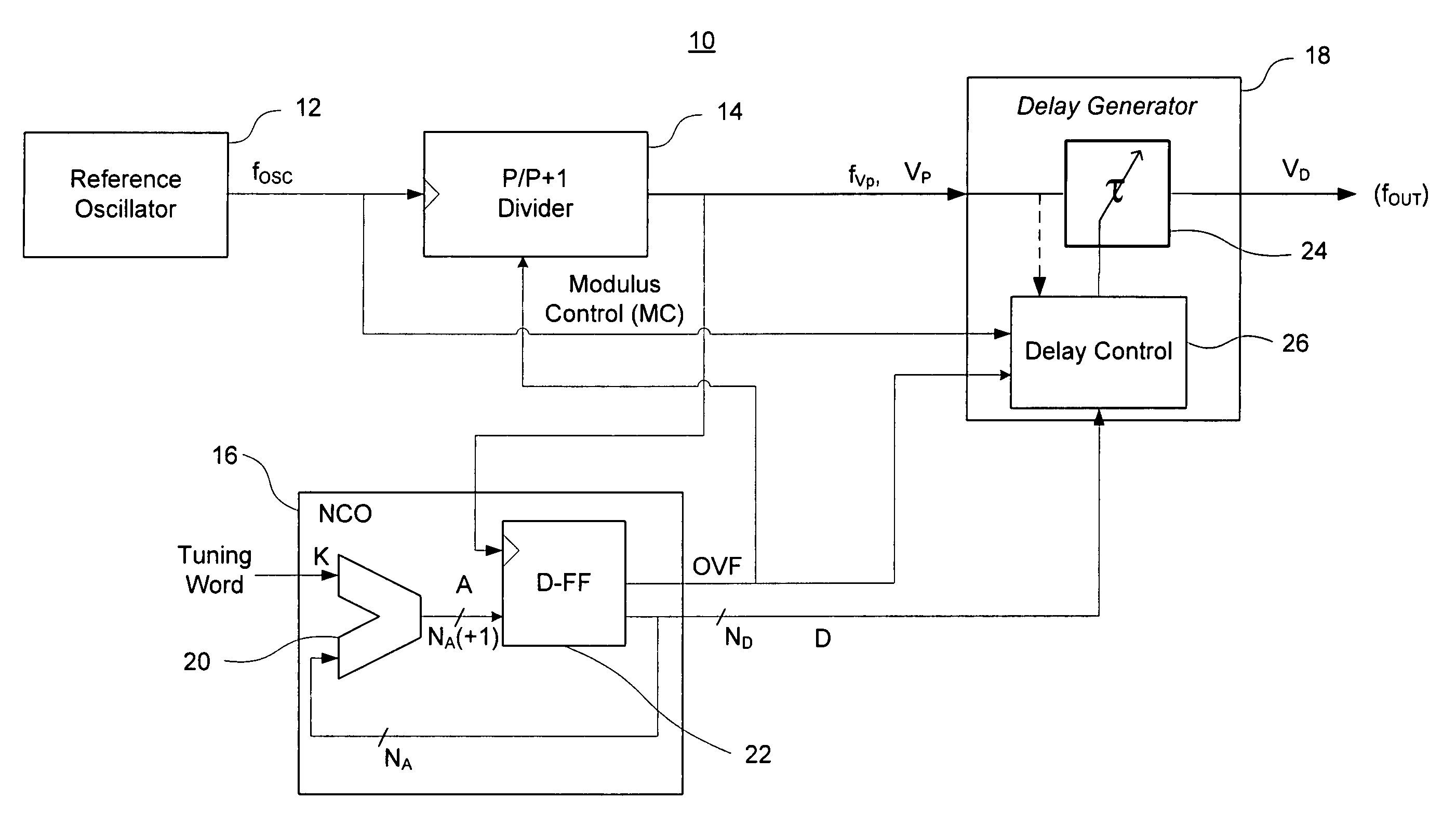

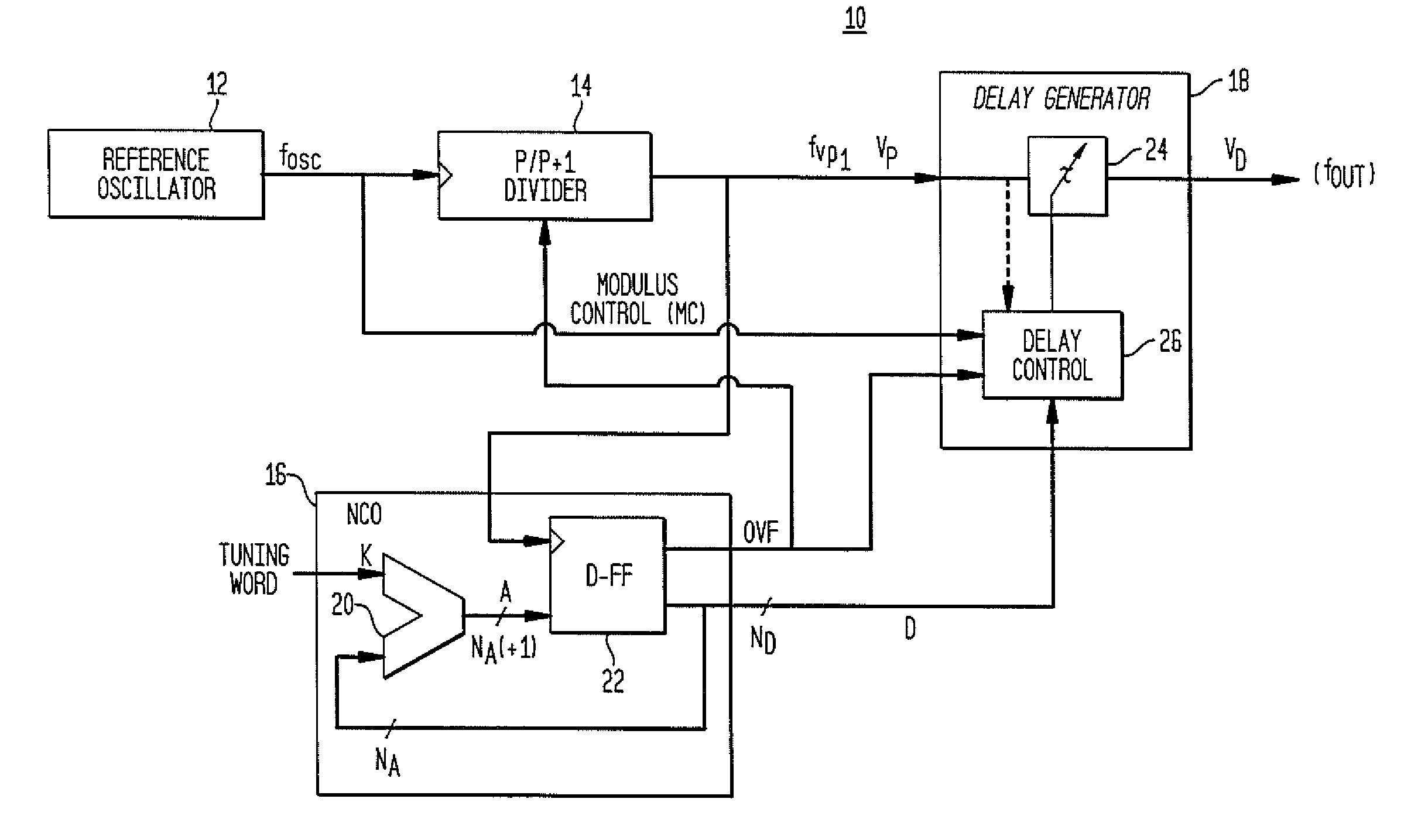

Direct digital synthesizer for reference frequency generation

InactiveUS7724097B2Improve noiseImprove performancePulse automatic controlCounting chain pulse countersFrequency generationDigital controlled oscillator

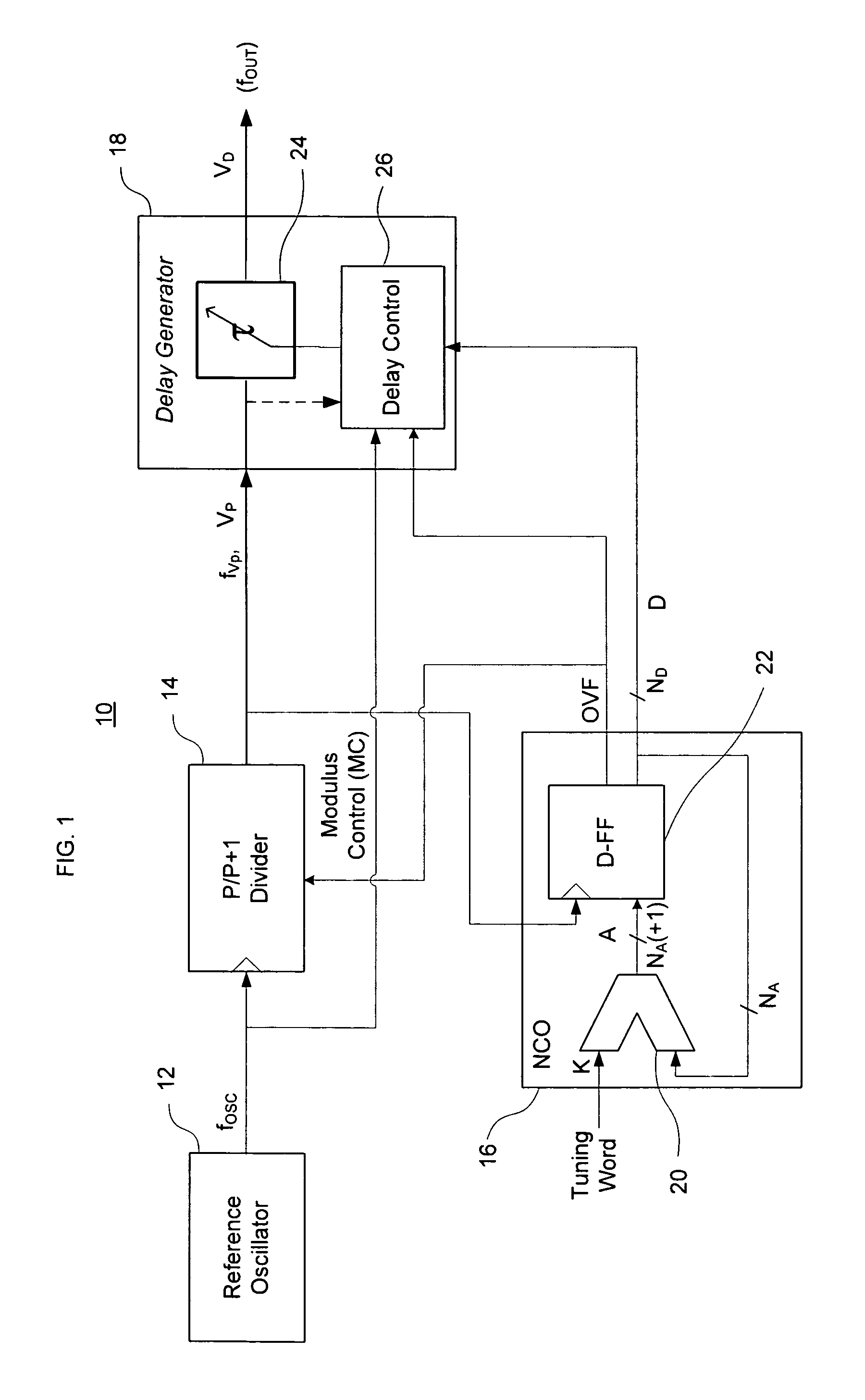

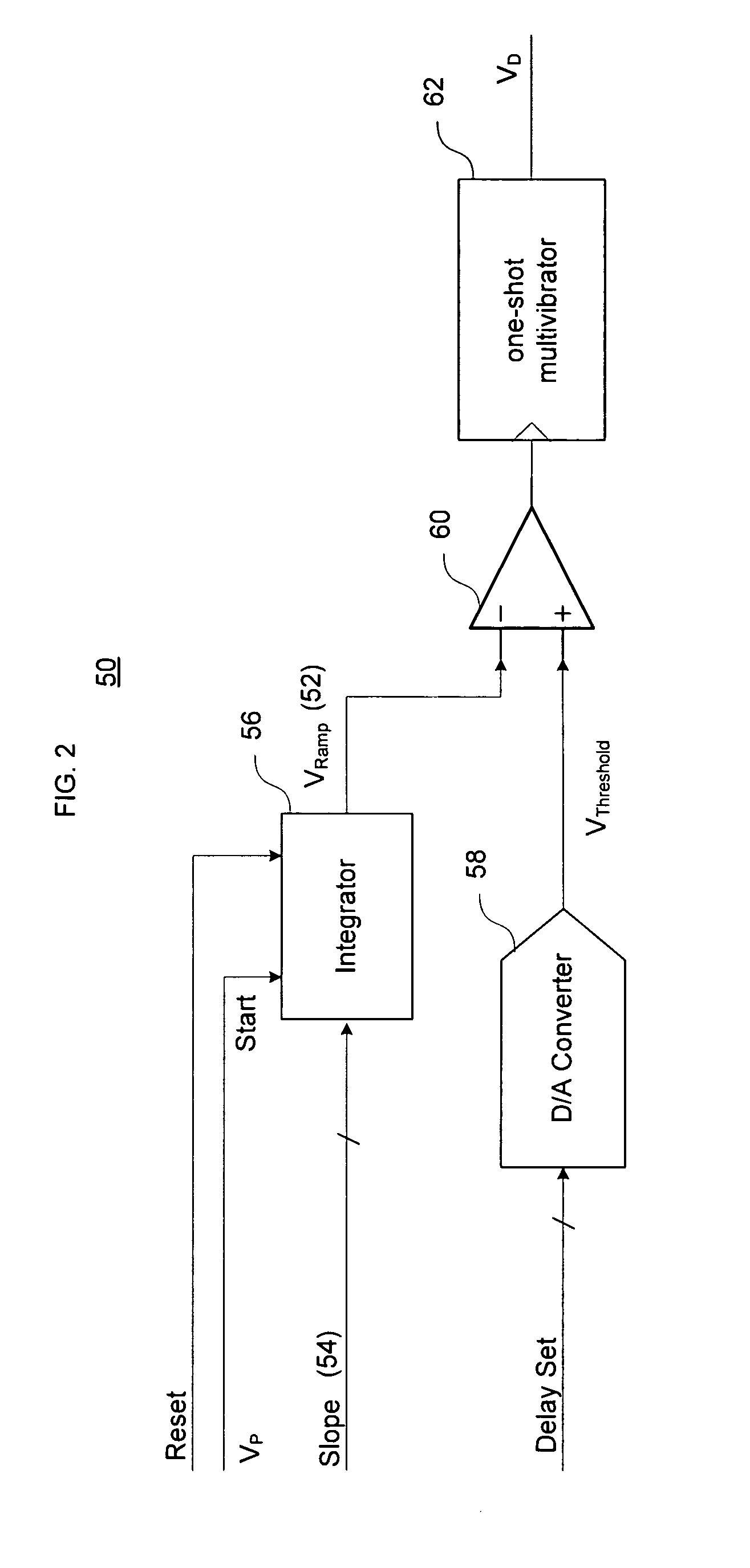

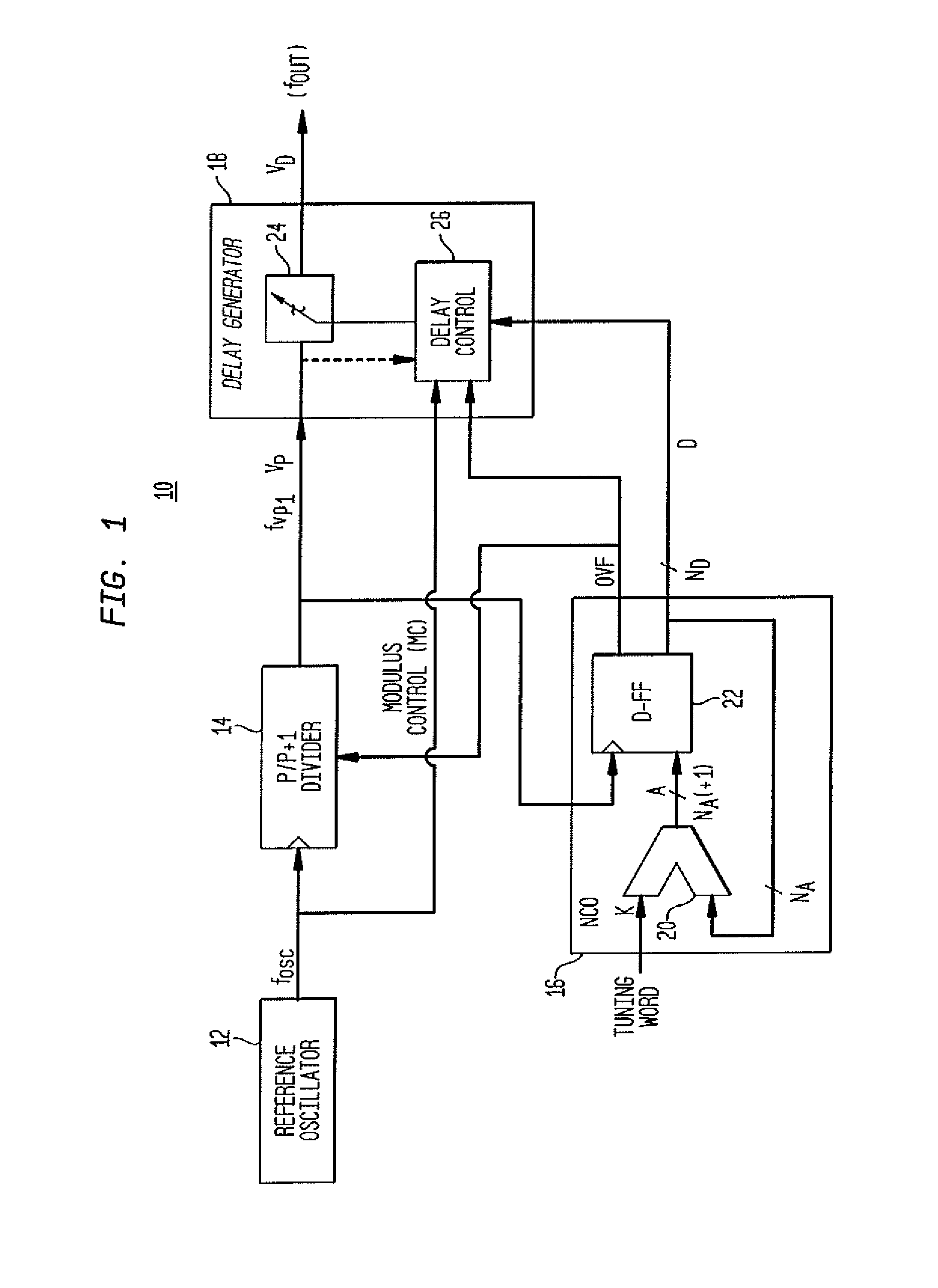

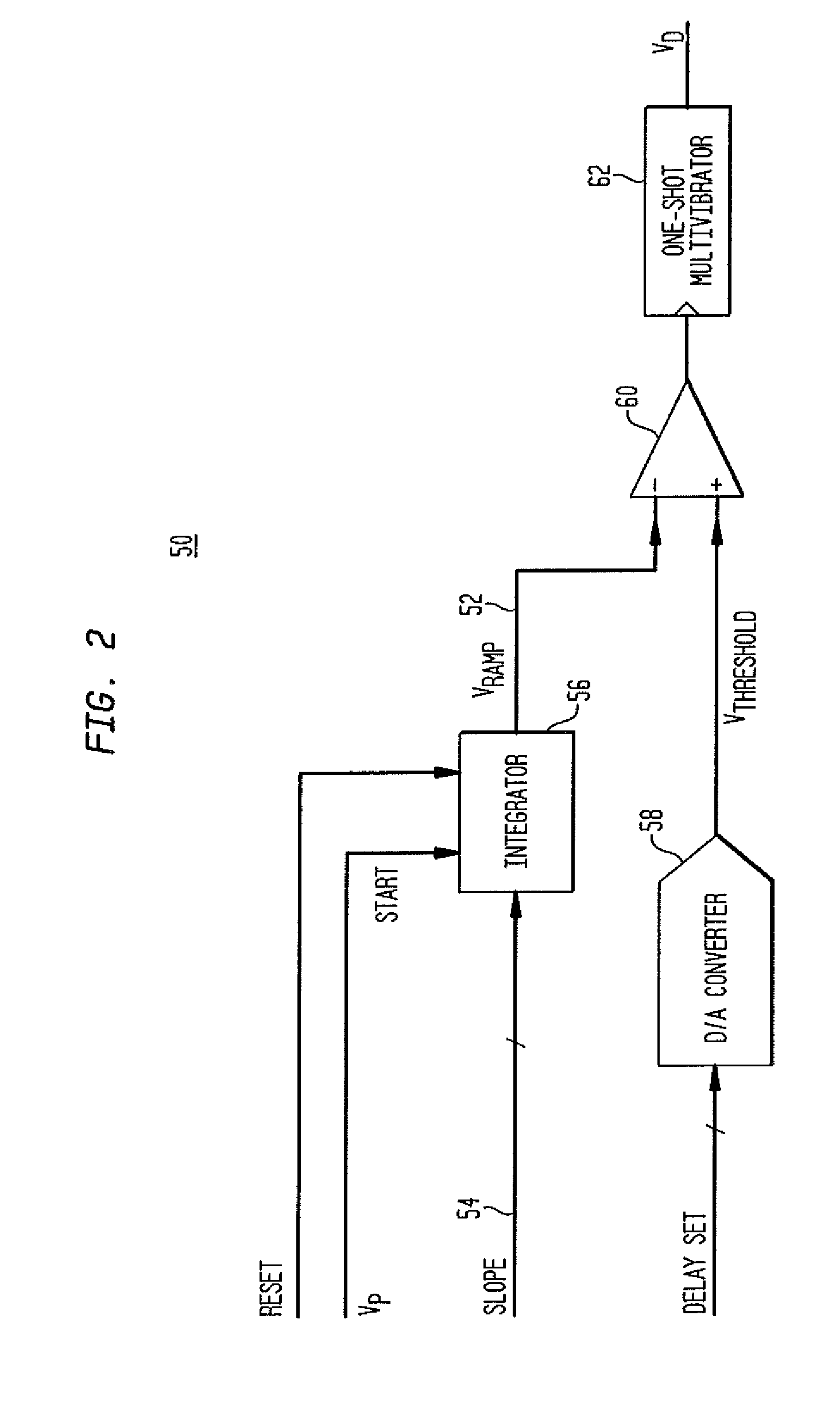

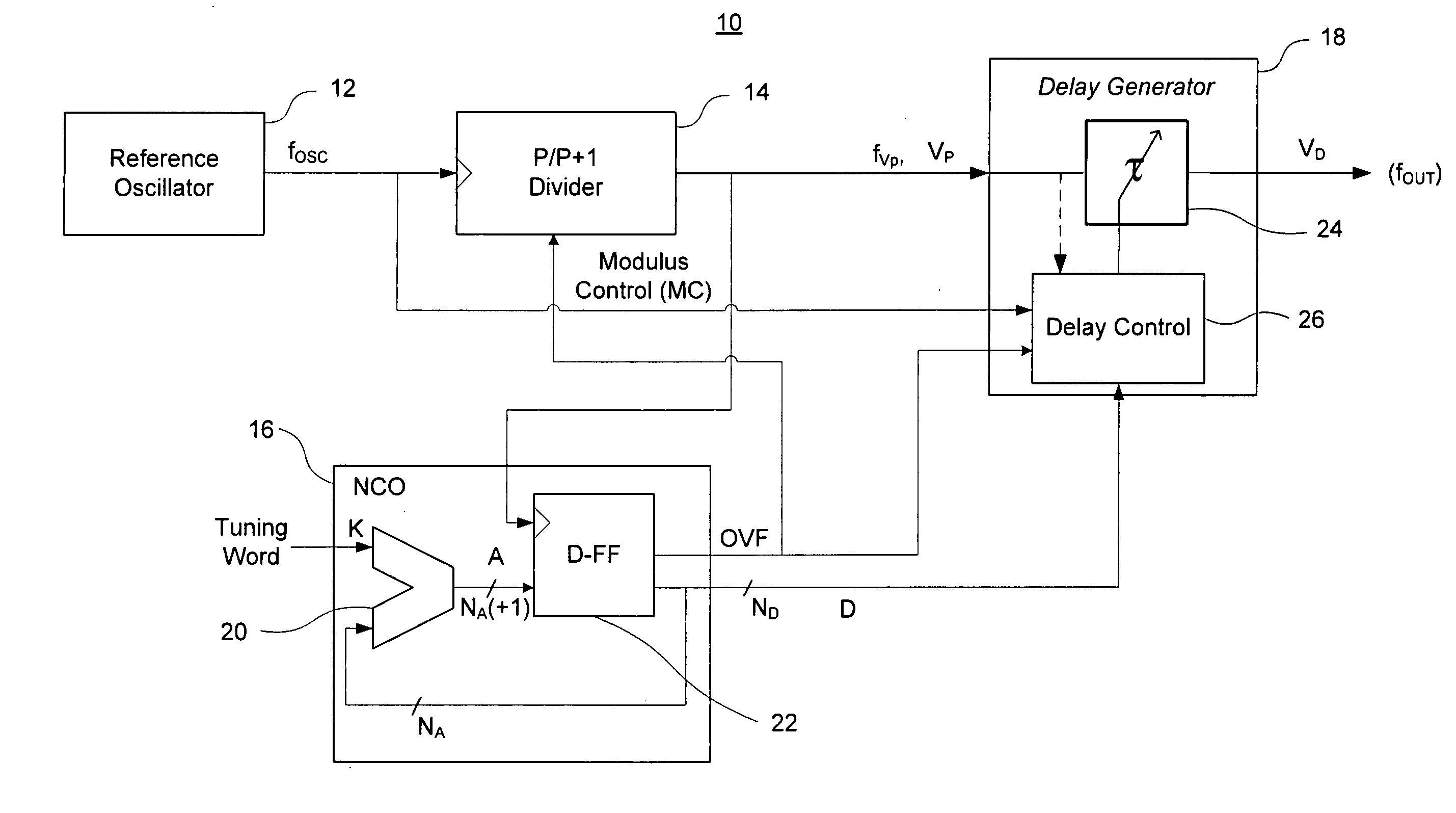

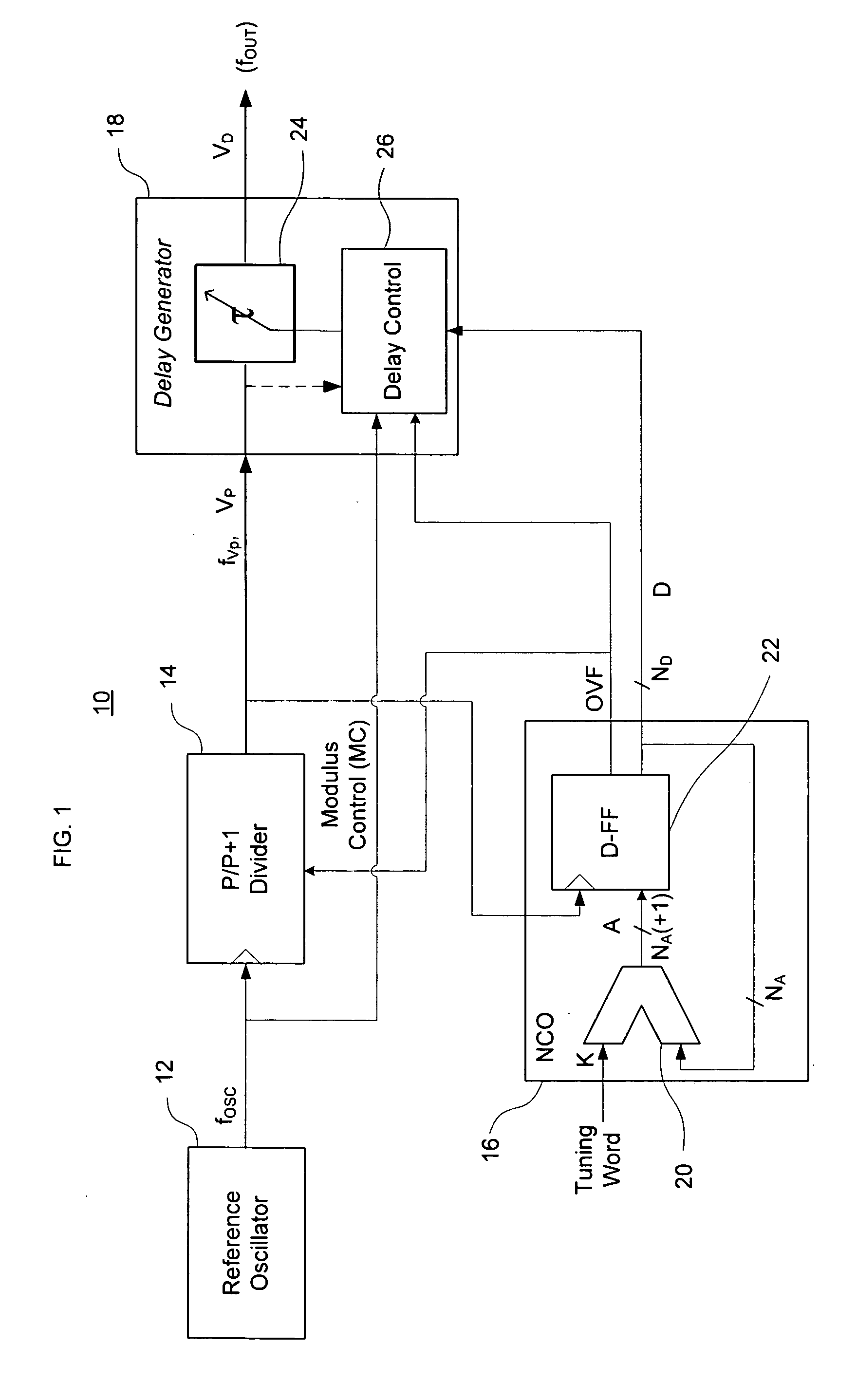

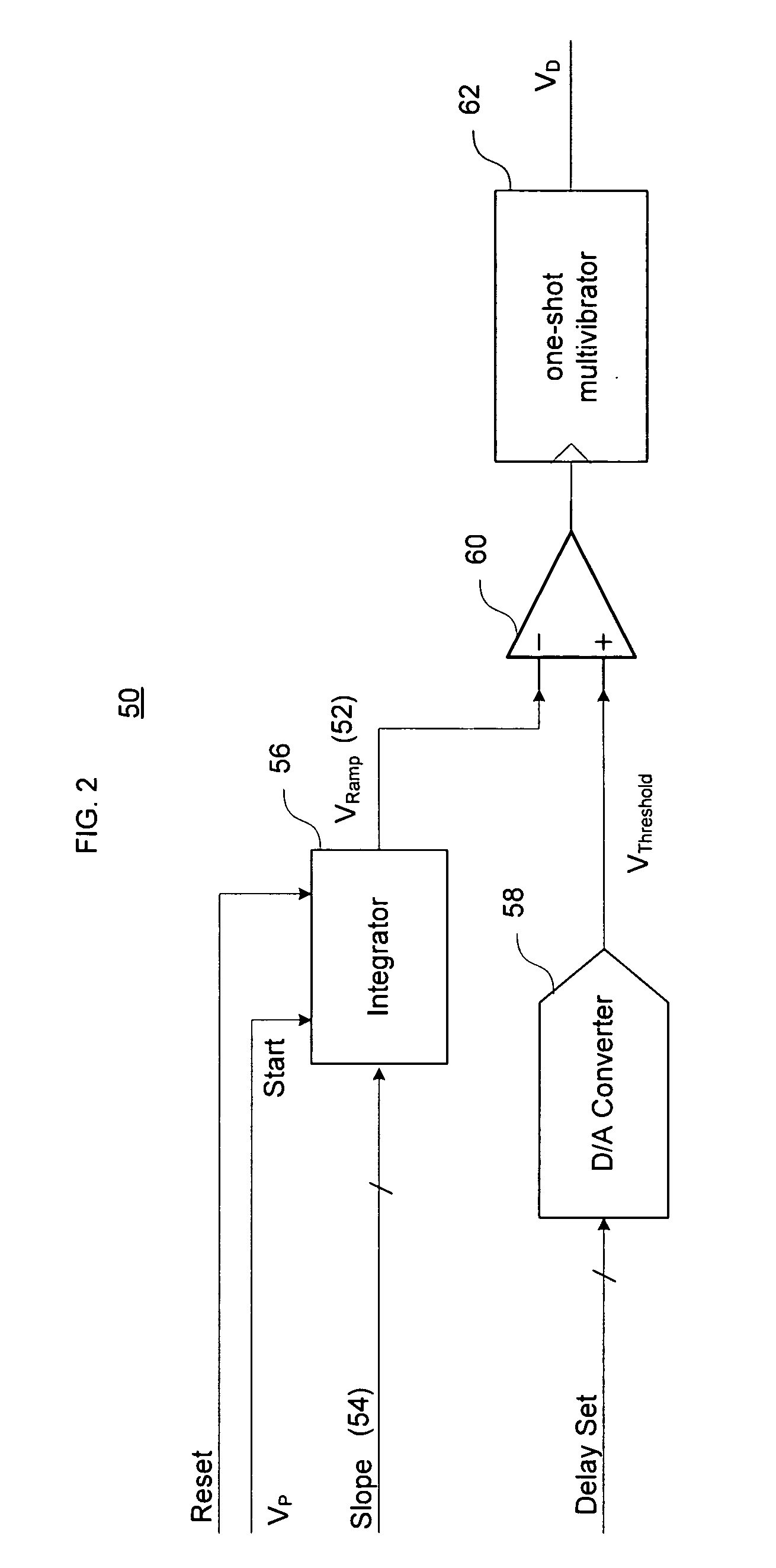

A direct digital frequency synthesizer having a multi-modulus divider, a numerically controlled oscillator and a programmable delay generator. The multi-modulus divider receives an input clock having an input pulse frequency fosc and outputs some integer fraction of those pulses at an instantaneous frequency fVp that is some integer fraction (1 / P) of the input frequency. The multi-modulus divider selects between at least two ratios of P (1 / P or 1 / P+1) in response to a signal from the numerically controlled oscillator. The numerically controlled oscillator receives a value which is the accumulator increment (i.e. the number of divided pulse edges) required before an overflow occurs that causes the multi-modulus divider to change divider ratios in response to receiving an overflow signal. The numerically controlled oscillator also outputs both the overflow signal and a delay signal to the delay generator that further controls the frequency of the multi-modulus divider output signal (Vp) to provide an output signal (VD) with an fout that has improved phase and timing jitter performance over prior art direct digital frequency synthesizer architectures.

Owner:CYMATICS LAB CORP

Multiple-loop absolute type rotary encoder based on rotating transformer

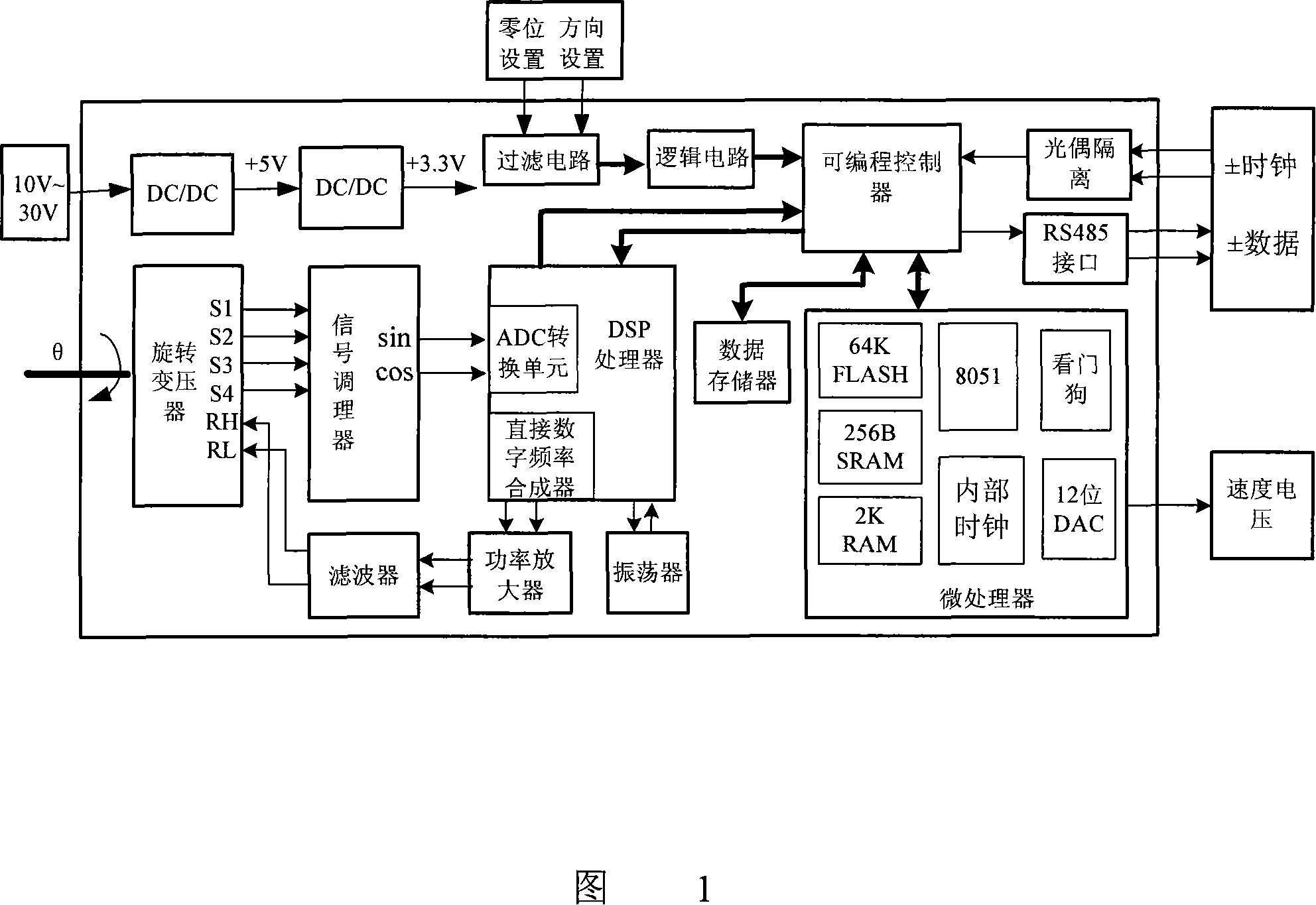

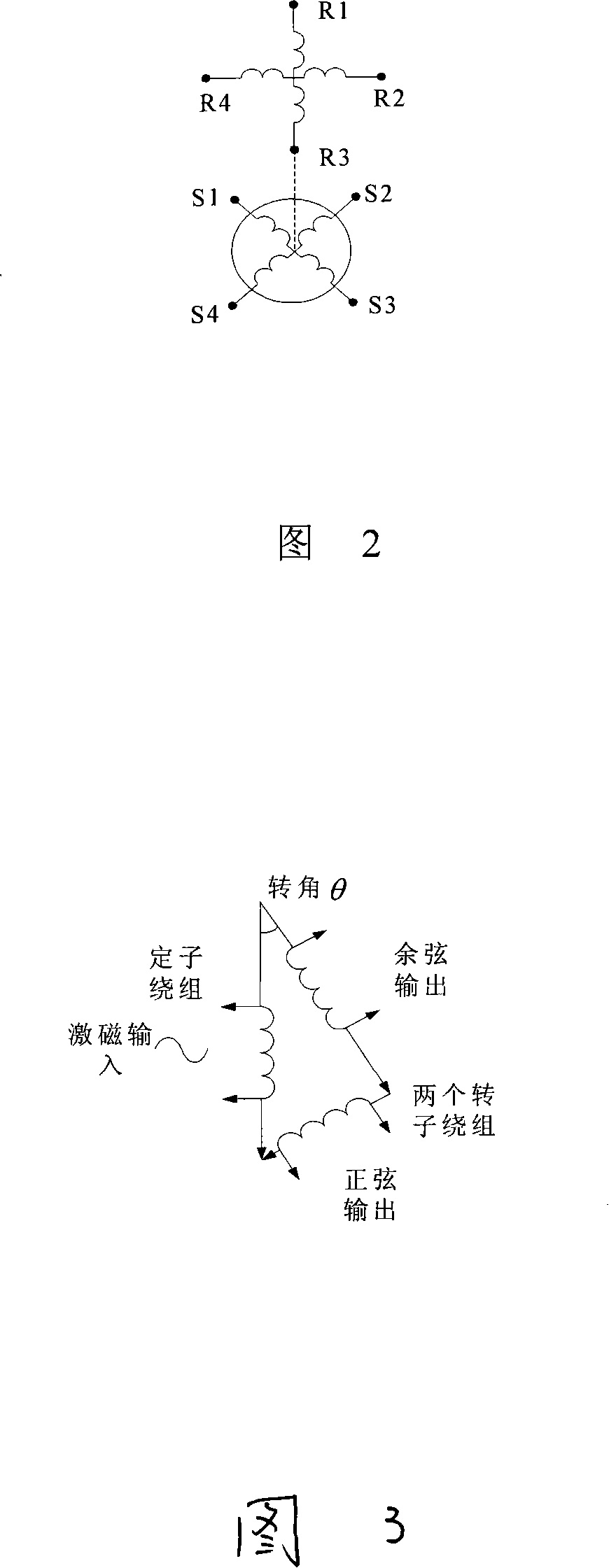

ActiveCN101226066AImprove anti-interference abilityImprove moisture resistanceConverting sensor outputDigital signal processingAxis–angle representation

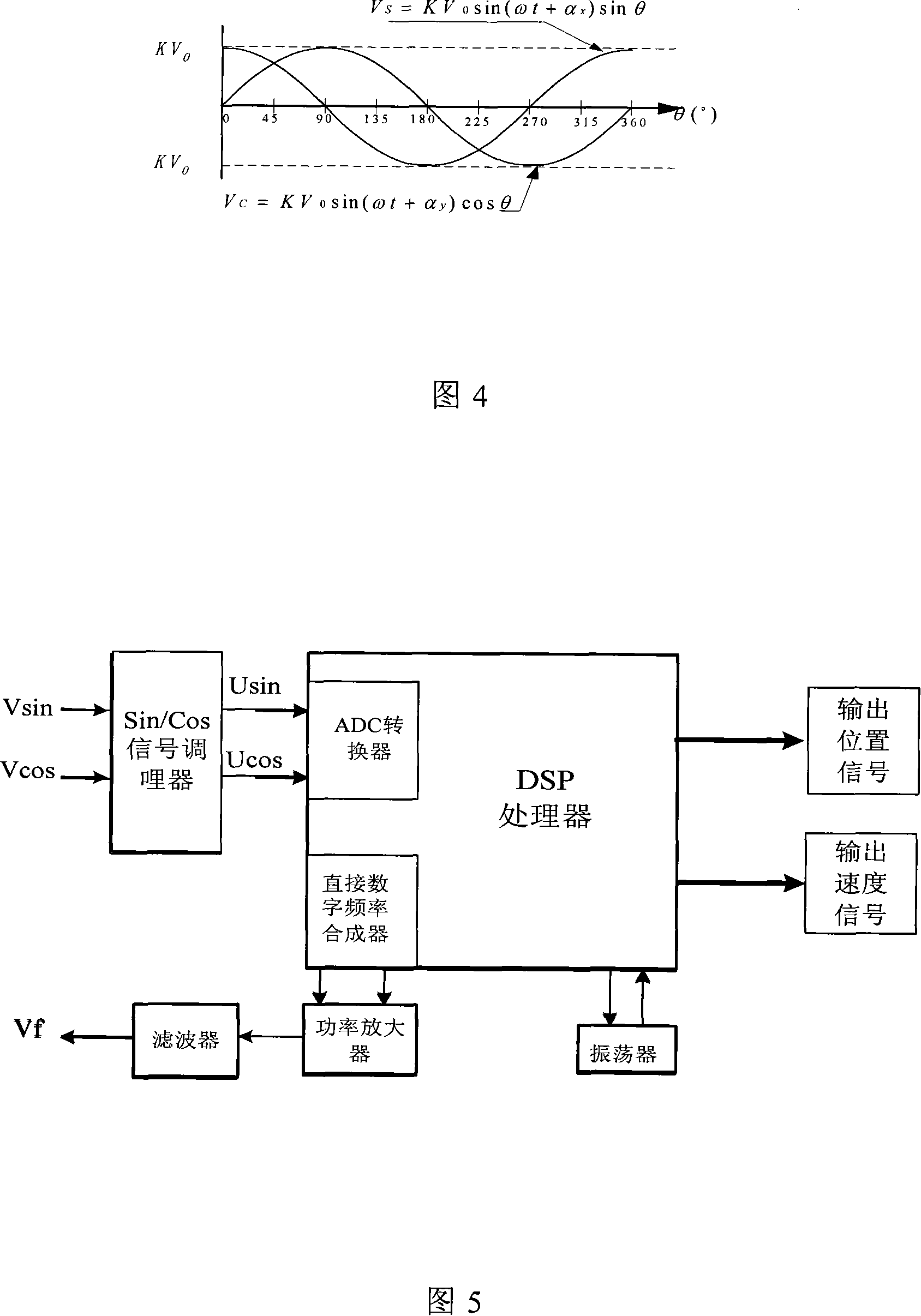

The invention relates to a multiturn absolute rotary encoder based on a rotary transformer, which is characterized in that: a sensor is displaced by taking the rotary transformer as a shaft angle; a shaft angle decoding circuit can be formed by adopting DSP as a core processor; a sine wave which can be controlled by frequency and phase in the method that the circuit is synthesized by direct digital frequency for the numerical control of an oscillator; and the sine wave is directly taken as an excitation rotary transformer signal via a power amplifier and a filter circuit; the rotary transformer signal is transferred to A / D converter after being run through a matching circuit of electronic transformer; after sampling, digital filtering and digital signal processing, the sine and cosine value for the actual angle of two channels is generated; the angle error change is tracked dynamically by the PI algorithm; the mechanical displacement of the rotating object is converted into digital shaft angle position and speed. The multiturn absolute rotary encoder based on a rotary transformer has the advantages of high tracking speed, high conversion accuracy, high reliability, simple structure, sensitive movement, low environmental condition, strong anti-interference capability, high measuring accuracy and speed voltage output.

Owner:连云港杰瑞电子有限公司

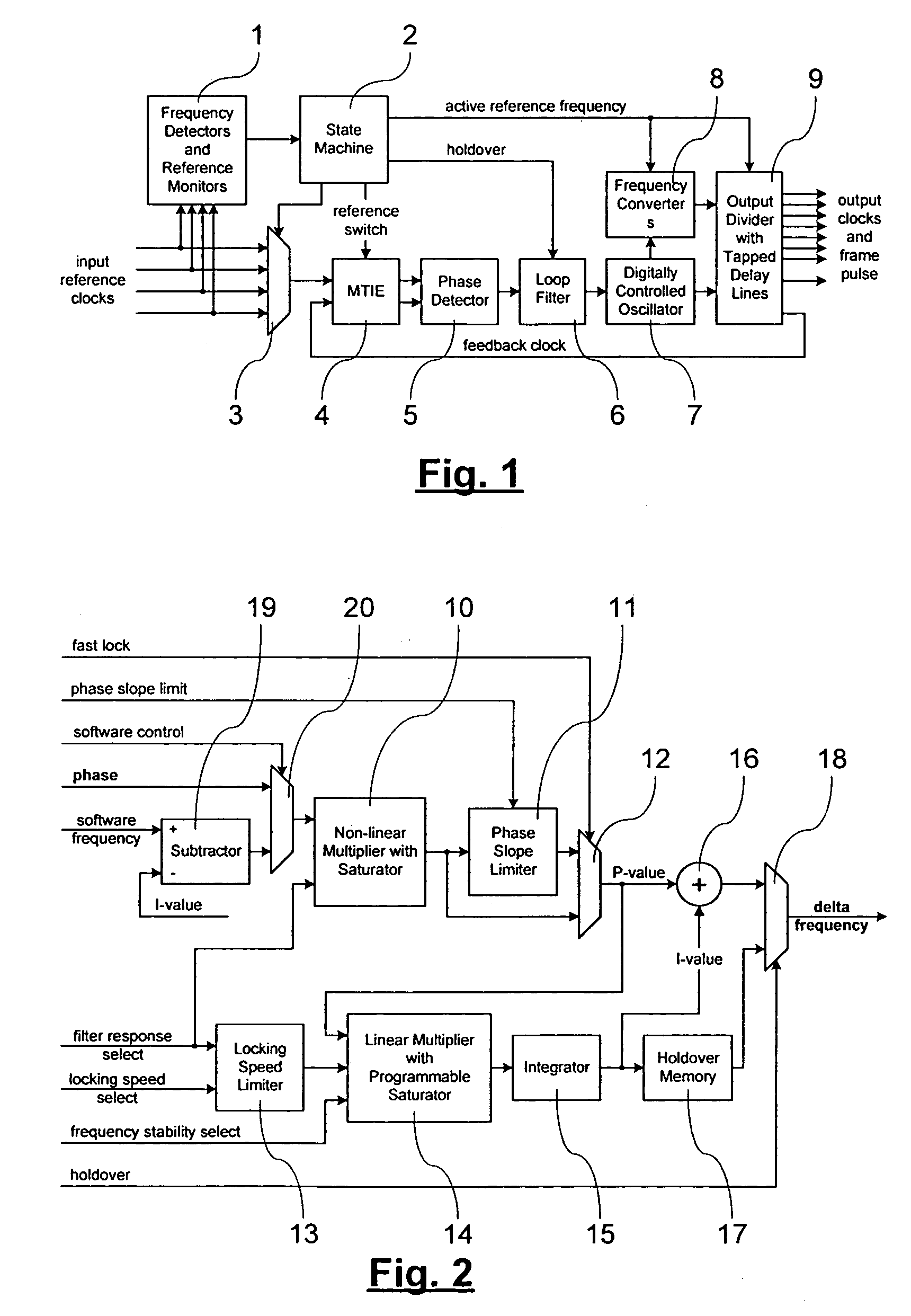

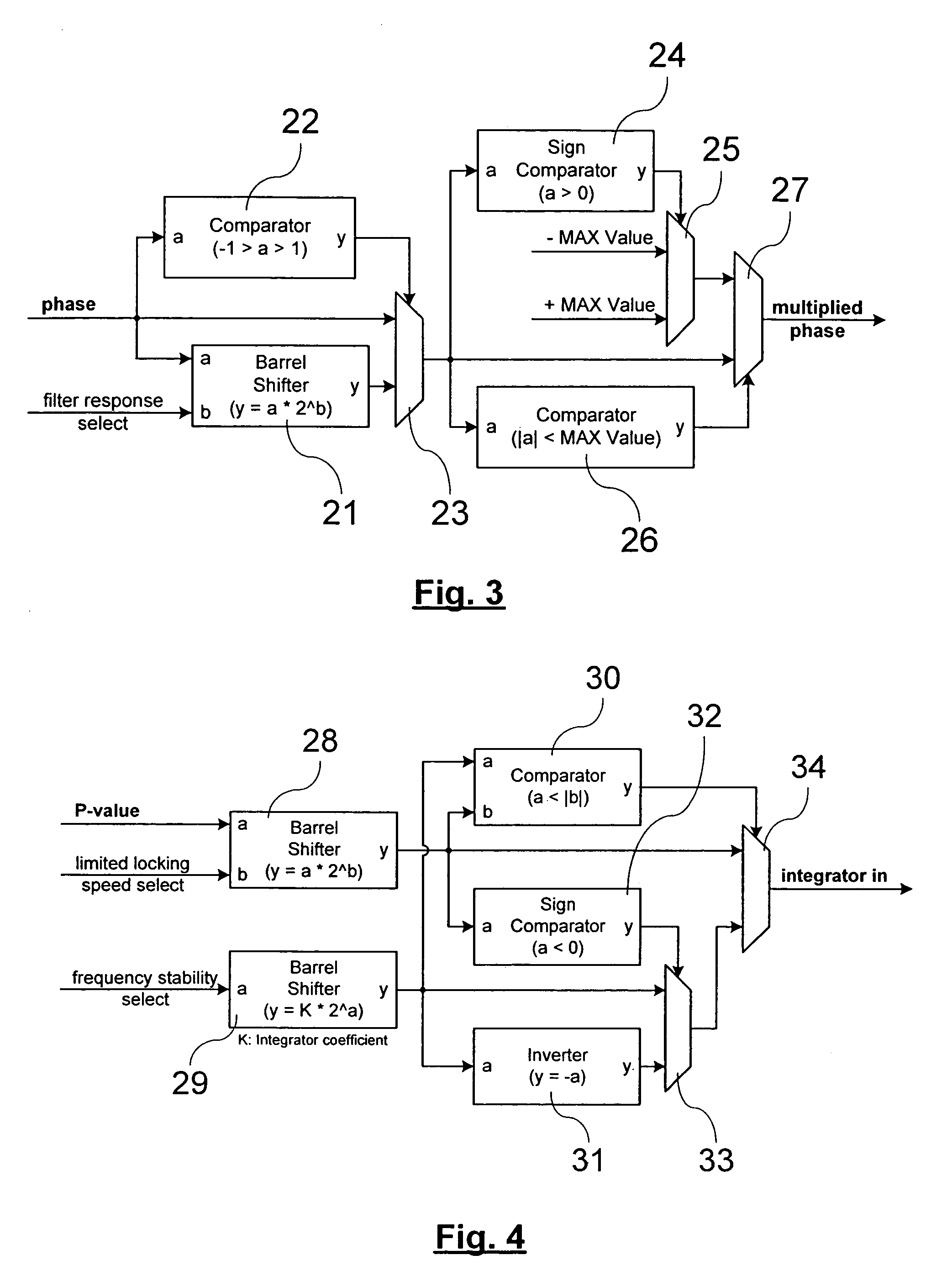

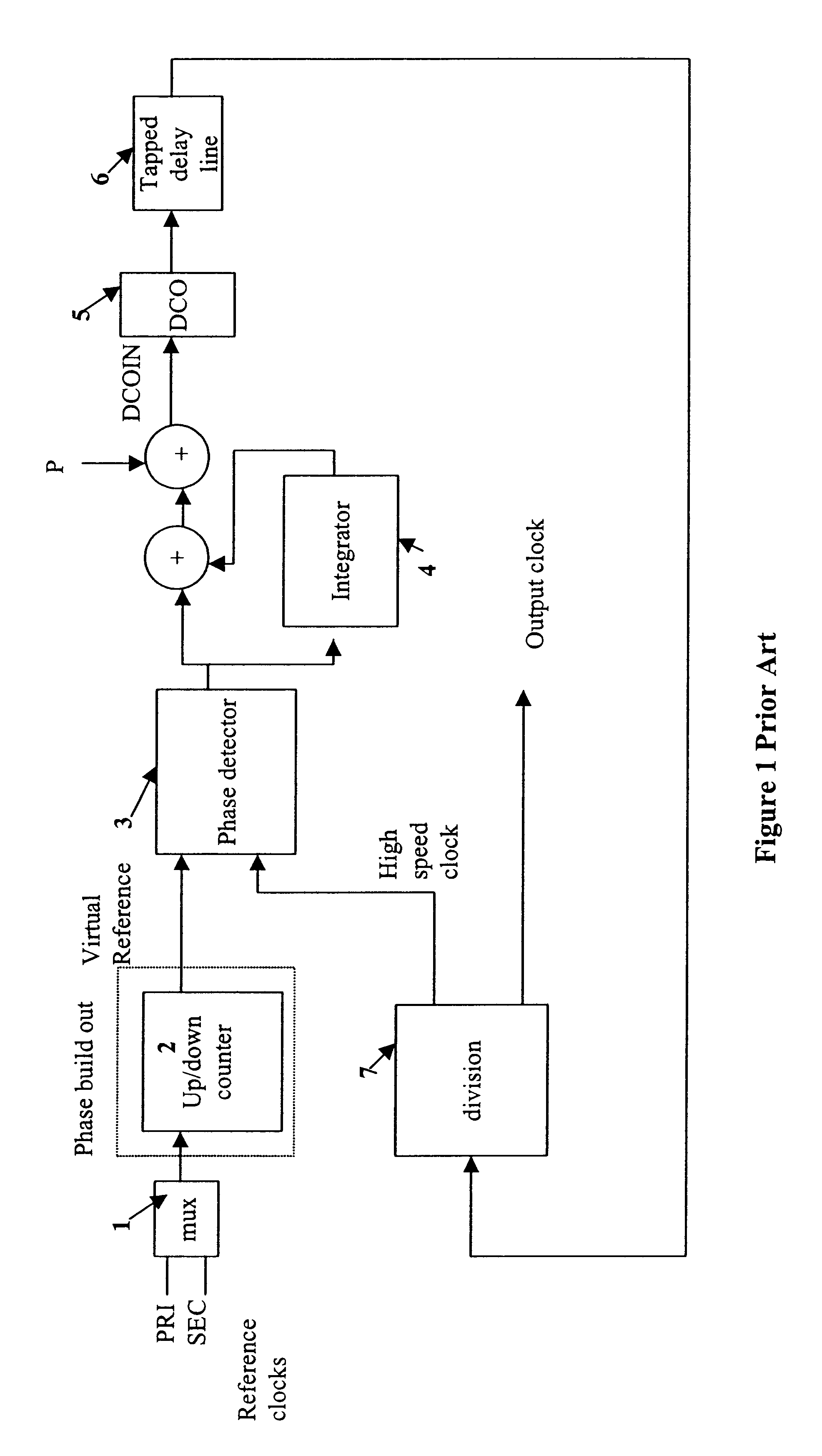

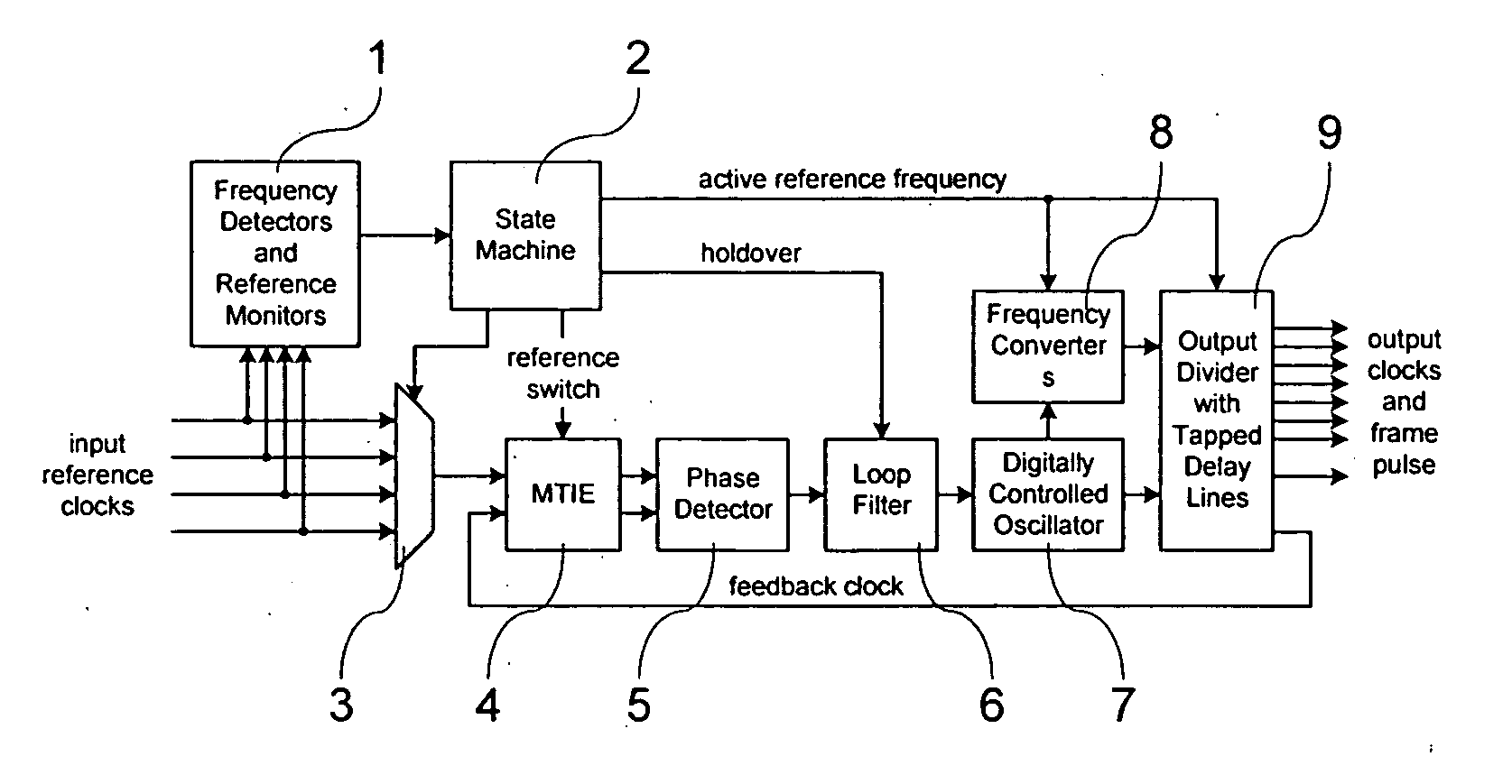

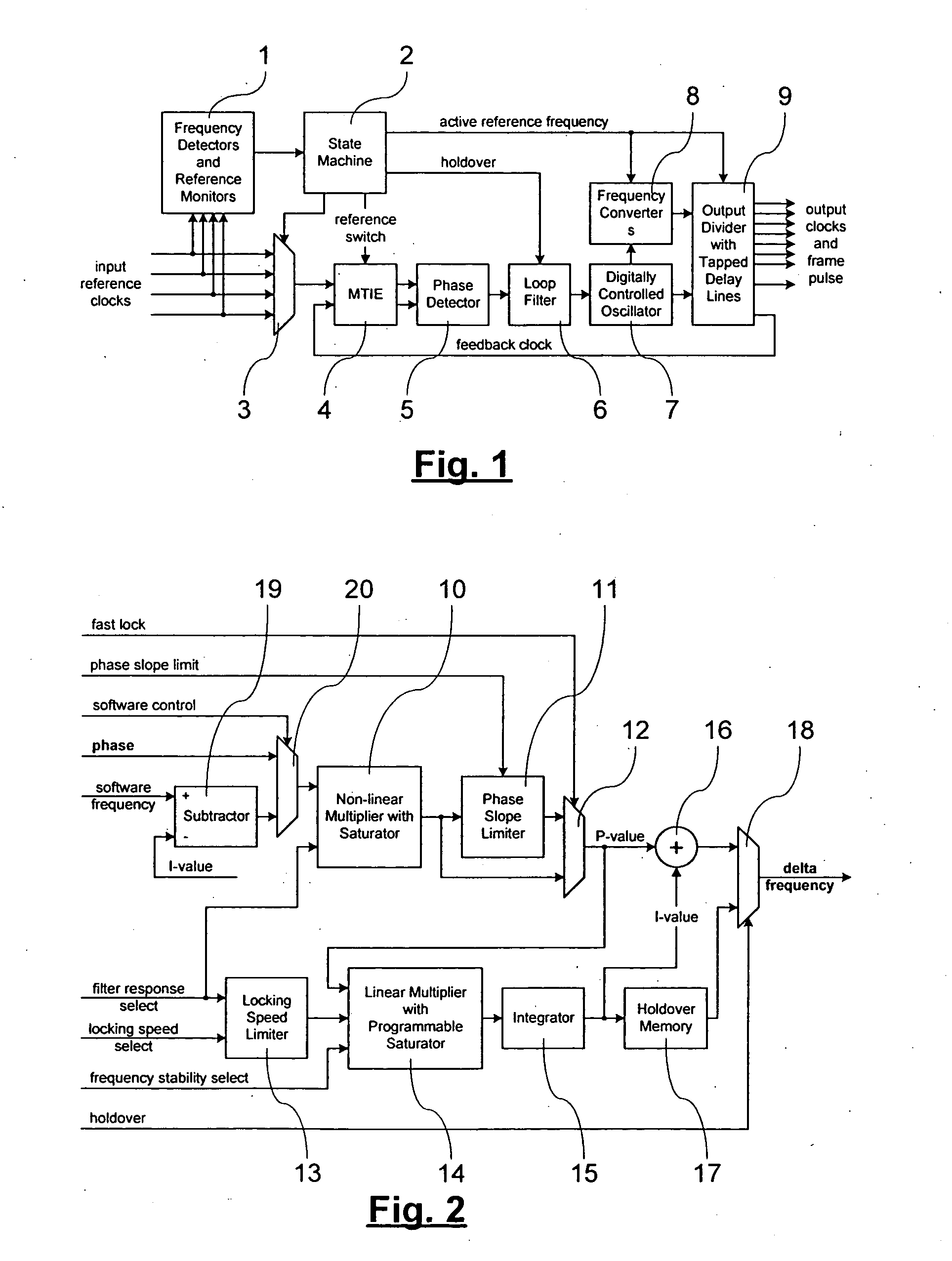

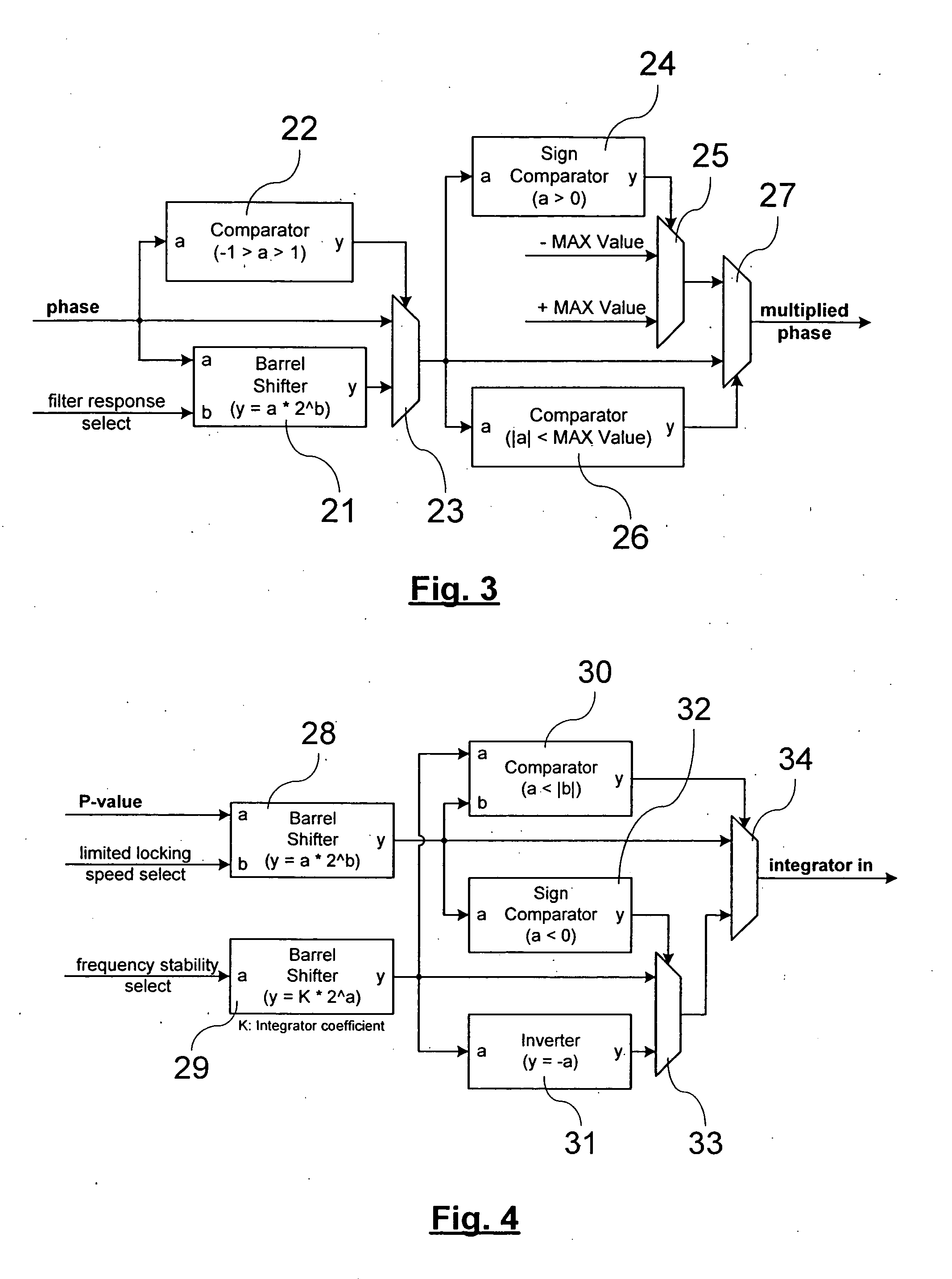

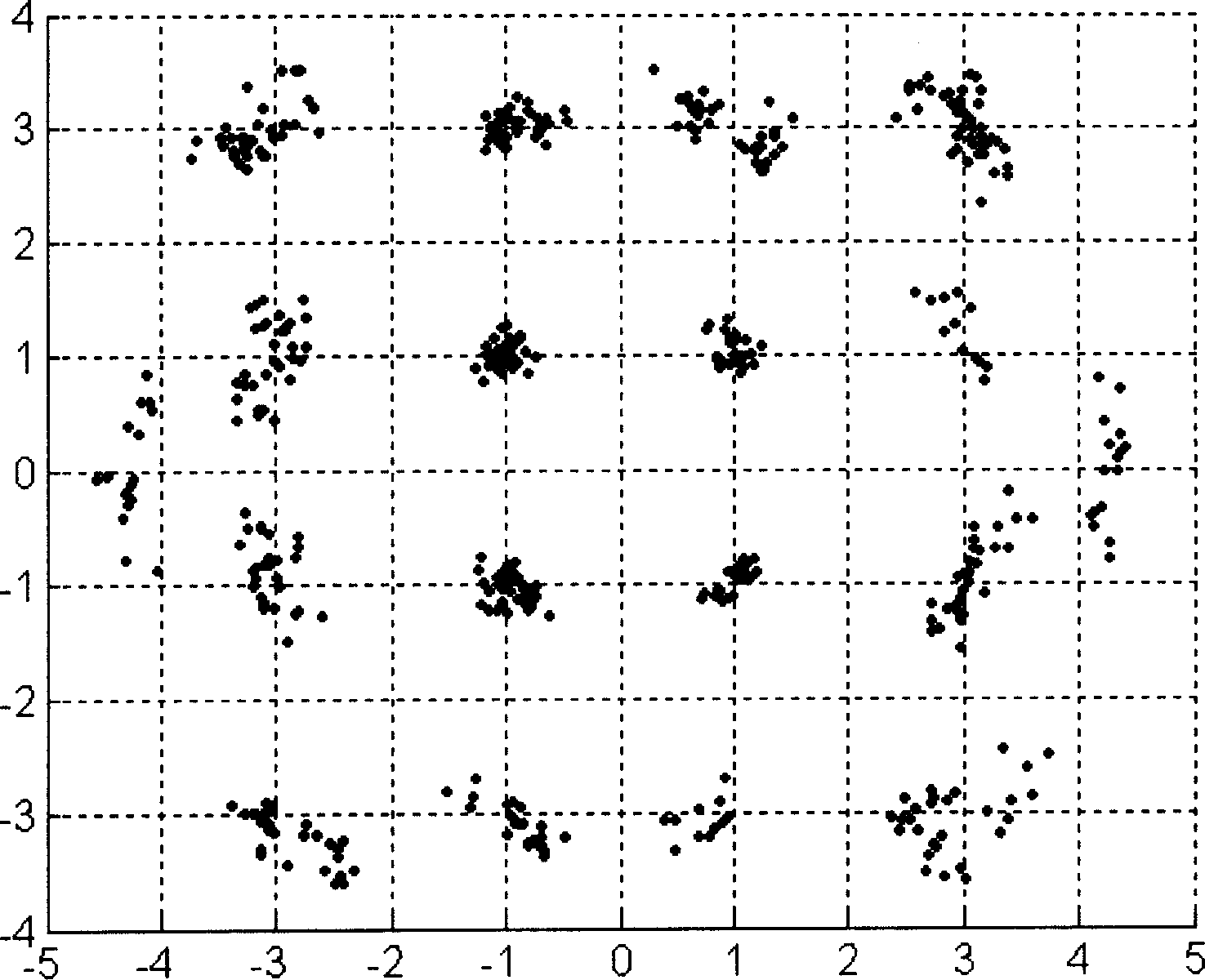

Digital phase locked loop with selectable normal or fast-locking capability

A digital phase locked loop with fast locking capability includes a digitally controlled oscillator for producing an output signal phase locked to an input reference clock, a phase detector for measuring the phase difference between said input reference clock and a feedback clock, and a loop filter for producing a control signal for the digitally controlled oscillator The loop filter includes a proportional circuit for developing a first signal proportional to said phase difference, an integrator for developing a second integrated signal from said first signal, an adder for adding said first and second signals to develop said control signal, and a weighting circuit, preferably a linear multiplier, for selectively adding extra weight to the first signal at an input to the integrator to shorten the locking time of the phase locked loop in a fast locking mode and to rapidly achieve a stable frequency in holdover mode.

Owner:ZARLINK SEMICON LTD

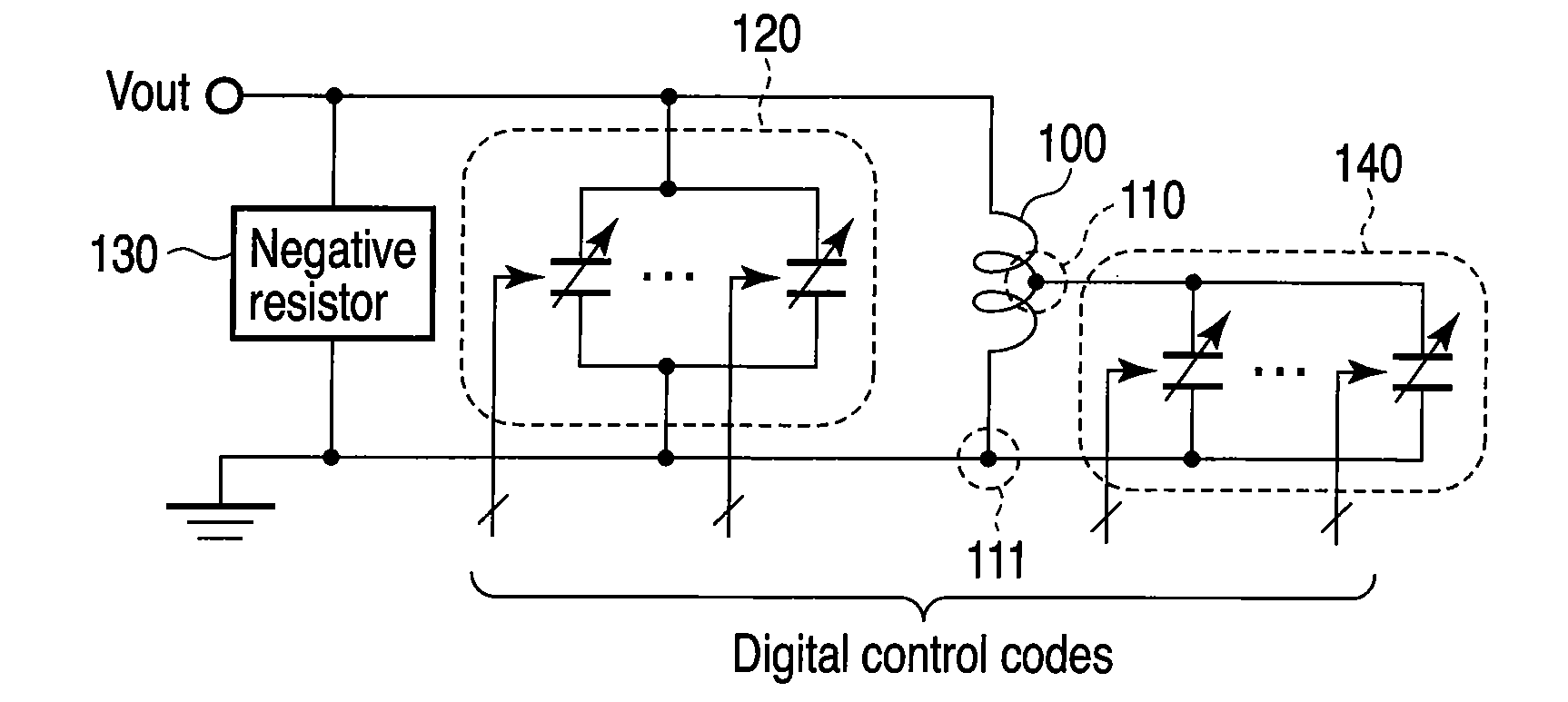

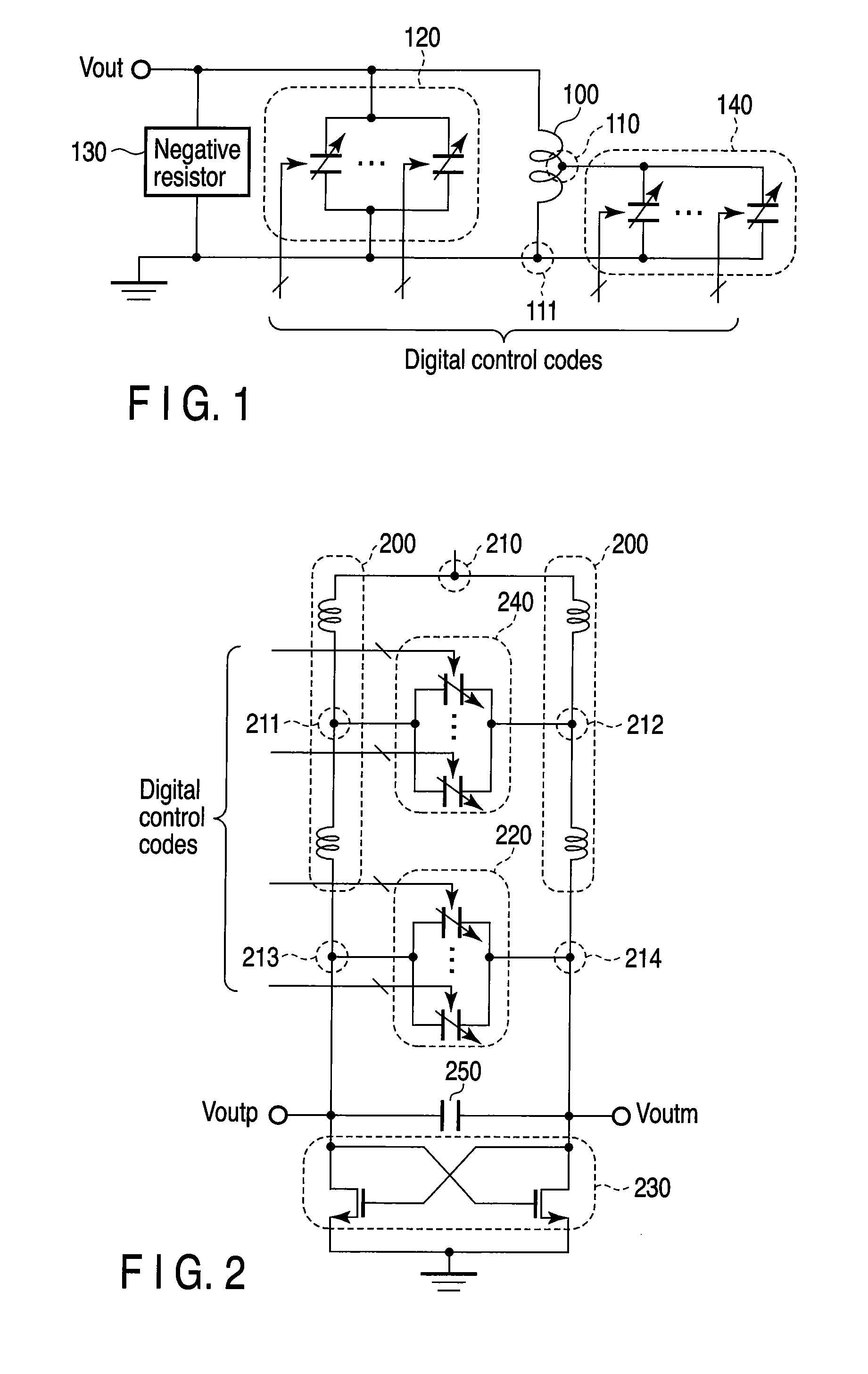

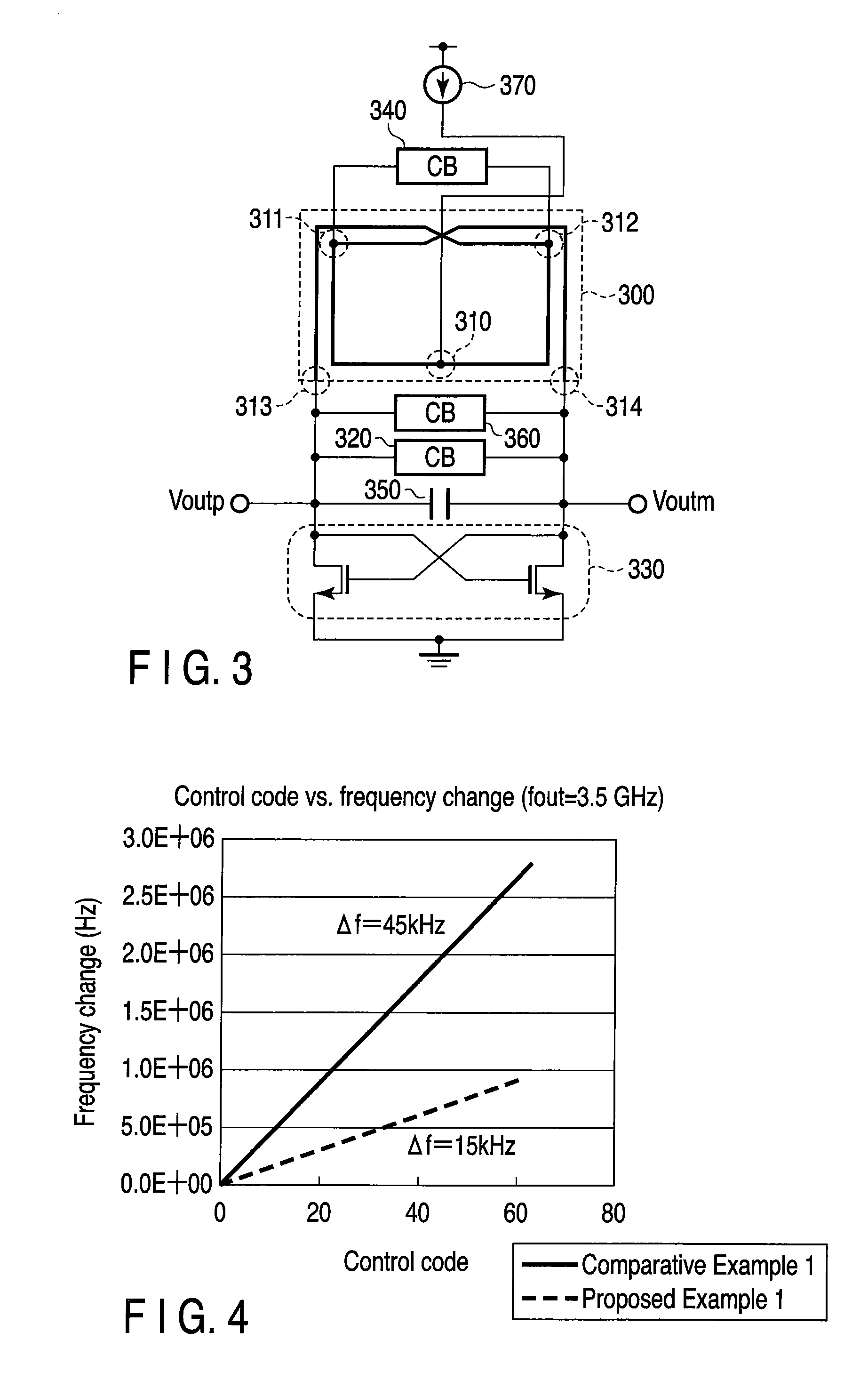

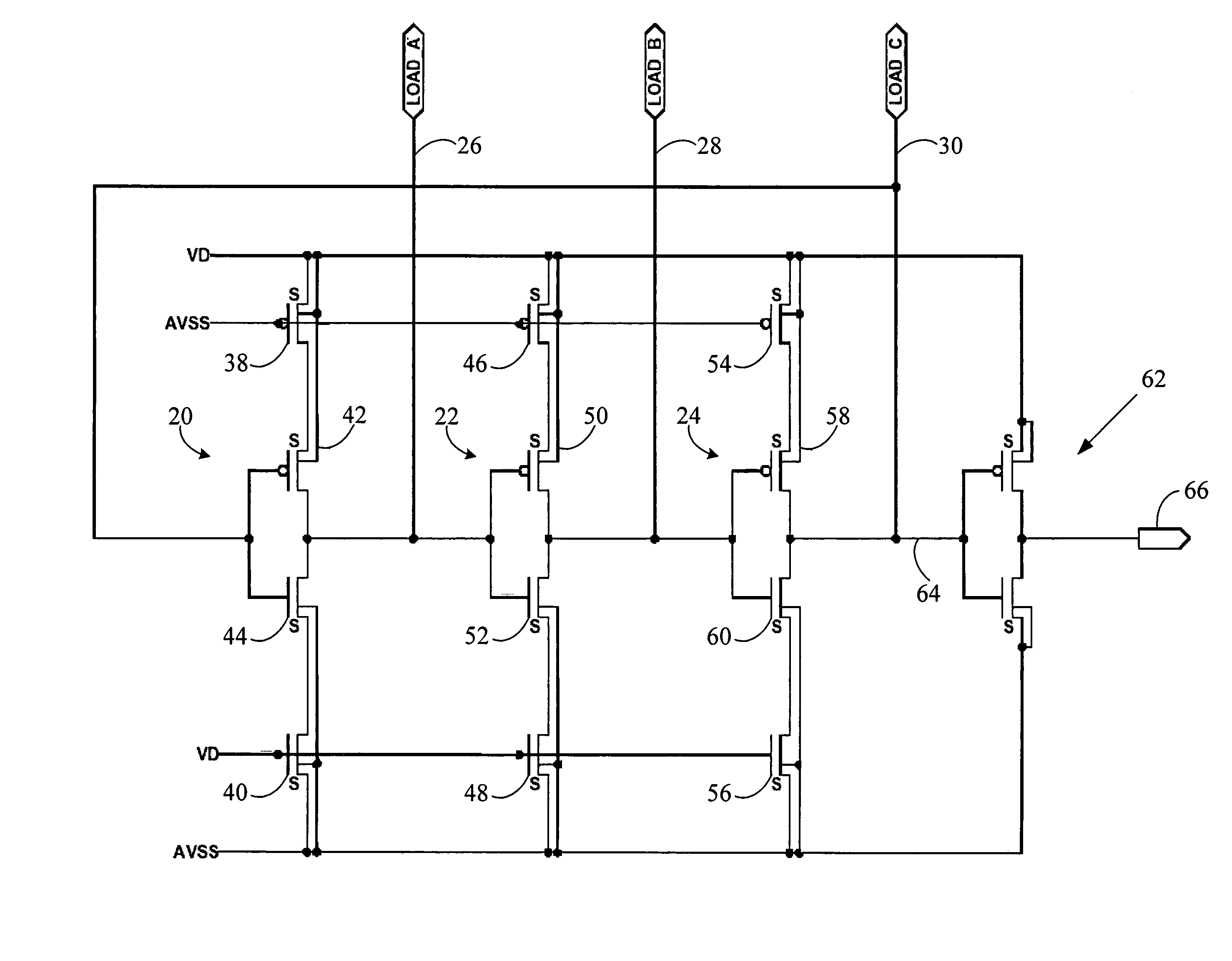

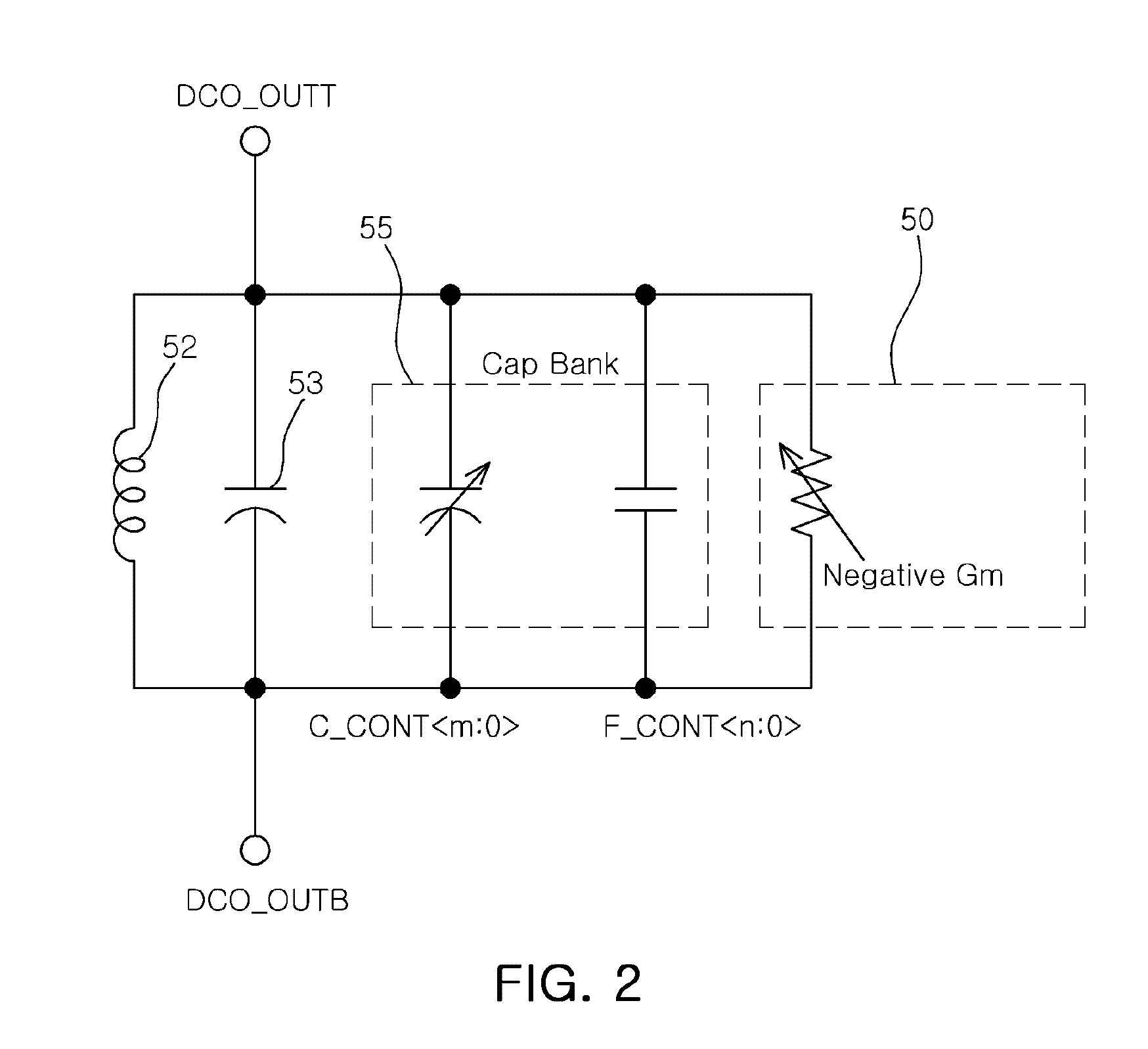

Digitally controlled oscillator and phase locked loop circuit using the digitally controlled oscillator

InactiveUS20090302958A1Pulse automatic controlOscillations generatorsDigitally controlled oscillatorDigital controlled oscillator

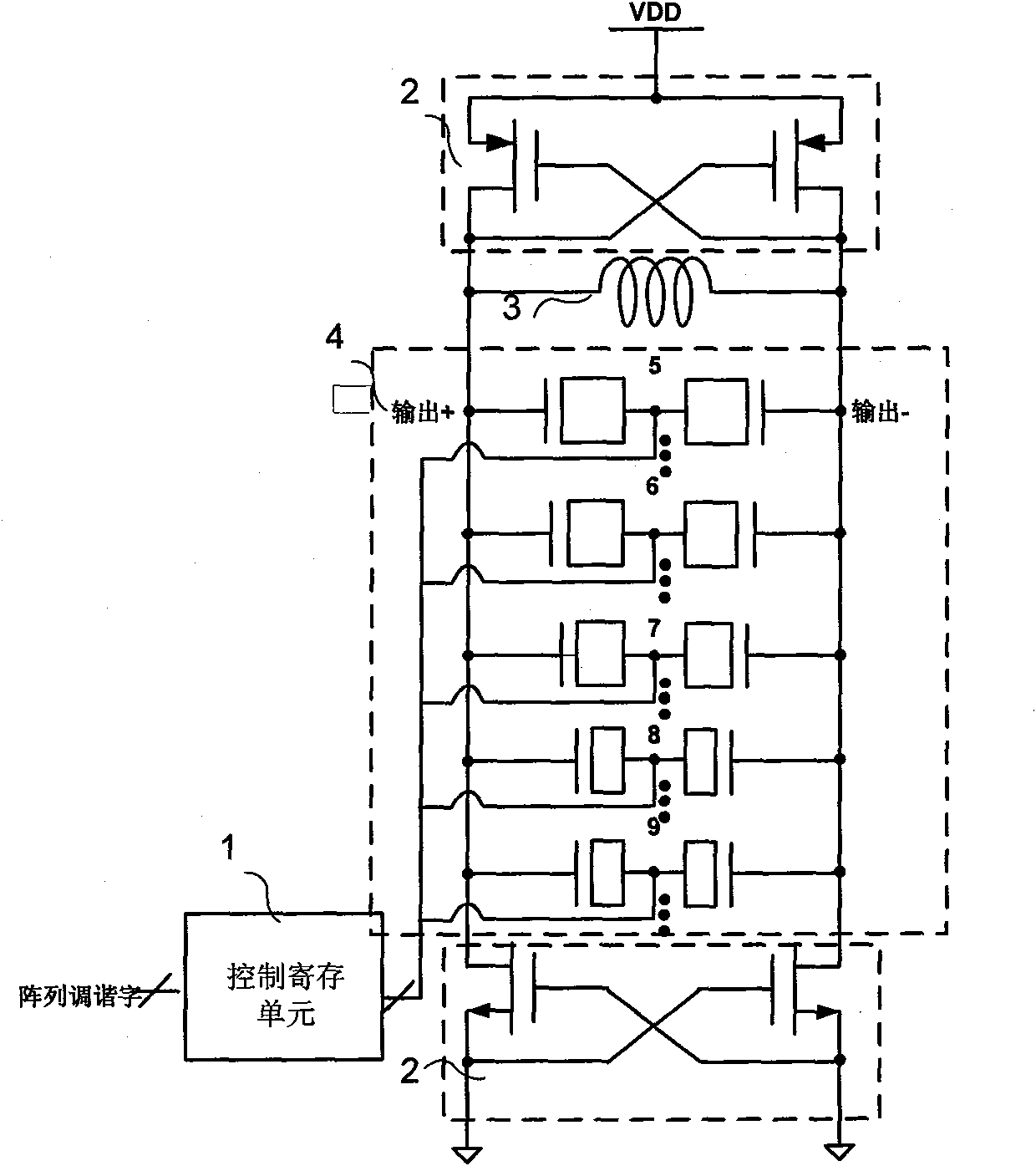

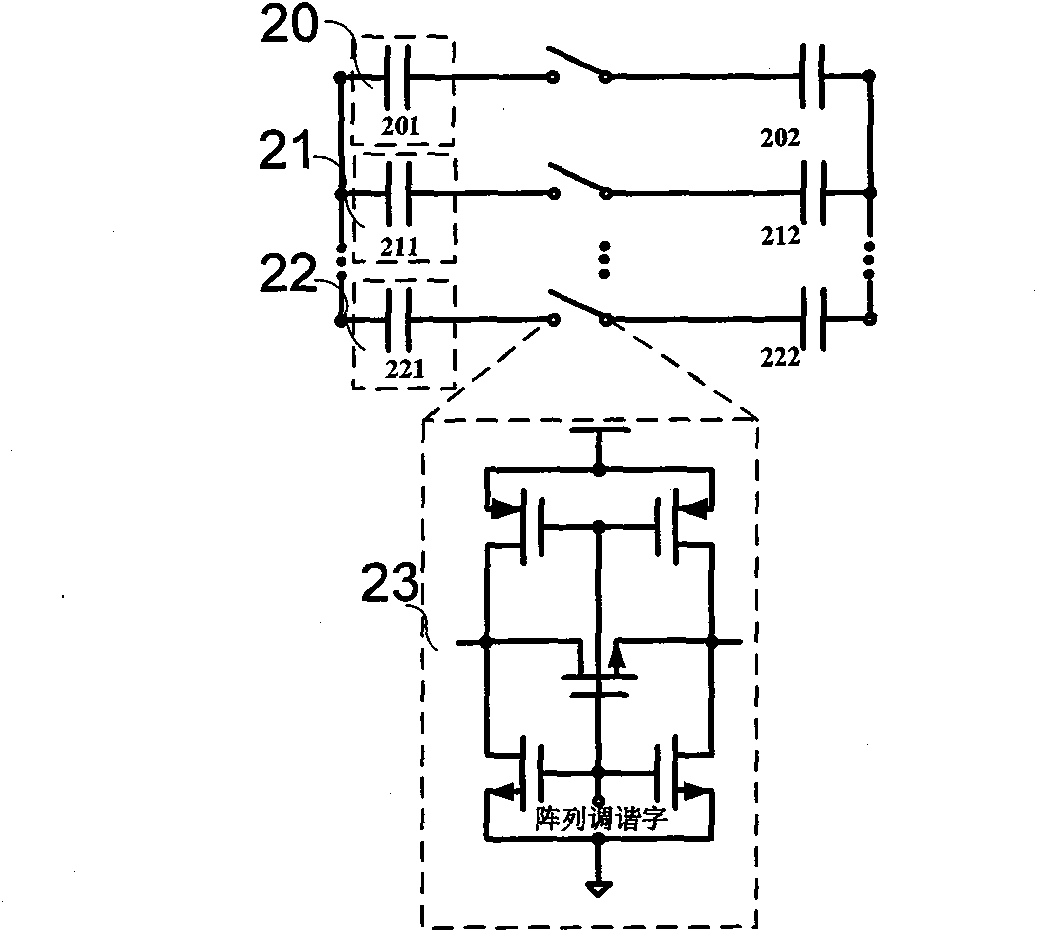

A digitally controlled oscillator includes a differential inductor including a positive terminal which outputs a positive-phase oscillation signal, a negative terminal which outputs a negative-phase oscillation signal, and a center tap, and including a first contact point in an arbitrary position between the positive terminal and the center tap, and a second contact point in a position corresponding to the first contact point between the negative terminal and the center tap, a first variable capacitor bank connected between the positive terminal and the negative terminal and including a plurality of first variable capacitors which switch capacitance between two values according to a first digital control code, and a second variable capacitor bank connected between the first contact point and the second contact point and including a plurality of second variable capacitors which switch capacitance between two values according to a second digital control code.

Owner:KK TOSHIBA

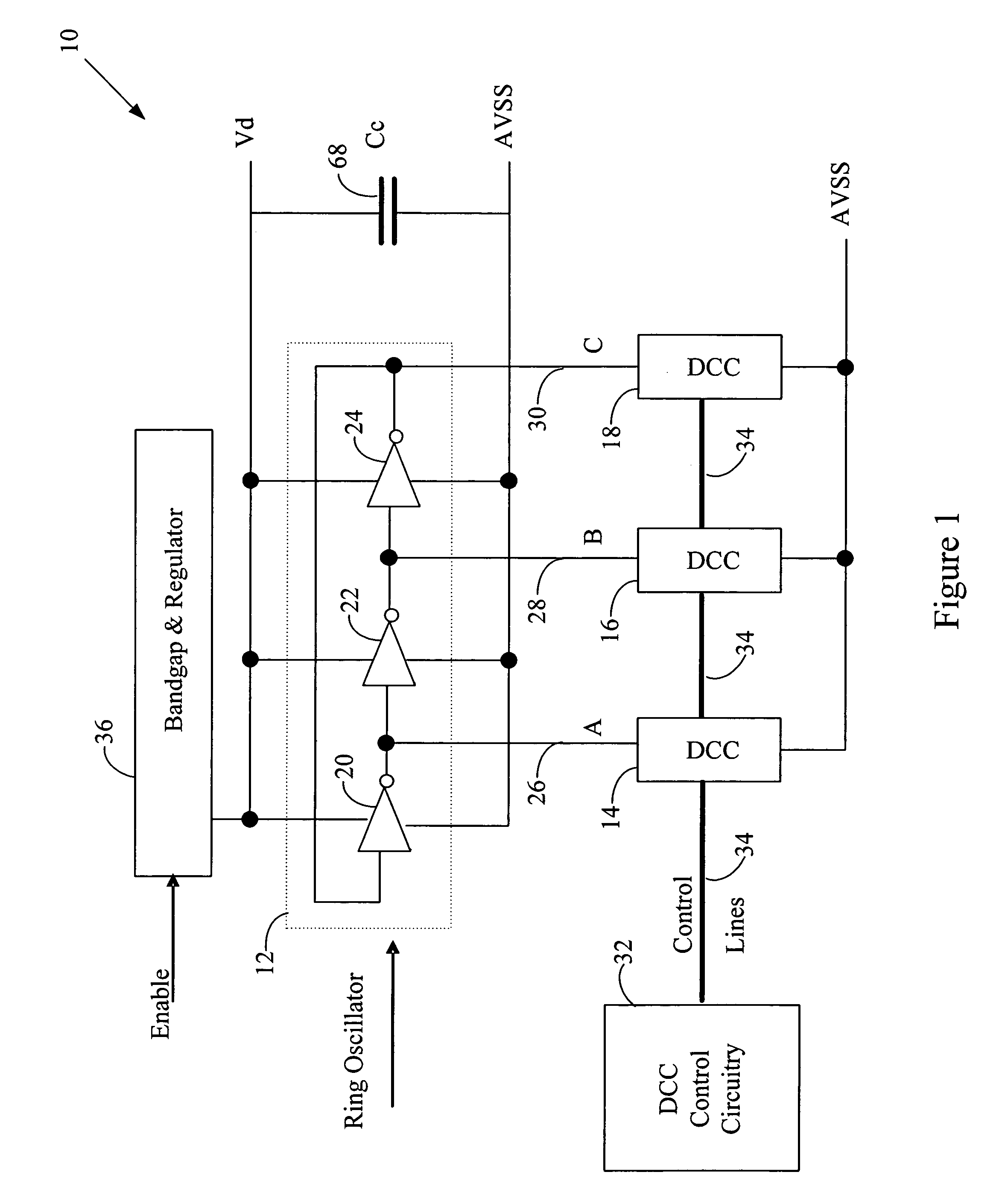

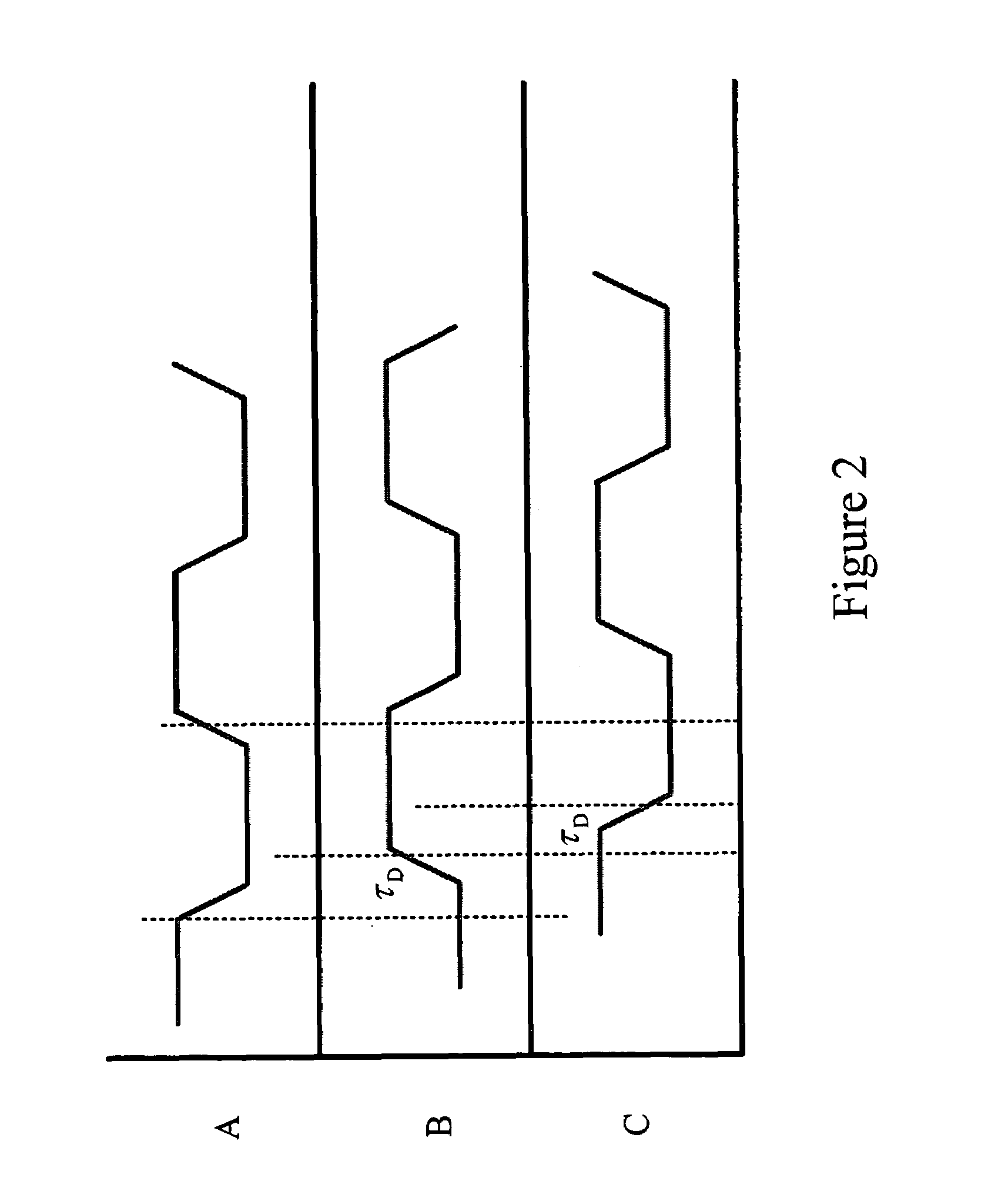

Digitally controlled oscillator and associated method

ActiveUS7330081B1Reduce riskReduce noisePulse automatic controlGenerator stabilizationCapacitanceDigital controlled oscillator

A digitally controlled oscillator circuit is provided that comprises a ring oscillator including multiple inverters; multiple digitally controlled capacitors (DCCs), each coupled to apply a digitally controllable amount of capacitance to an output of a different one of the inverters; and control circuitry operable to change an amount of capacitance applied to each inverter during operation of the ring oscillator and to cause the multiple DCCs to apply substantially the same amounts of capacitance to each of the inverter throughout operation of the ring oscillator.

Owner:MARVELL ISRAEL MISL

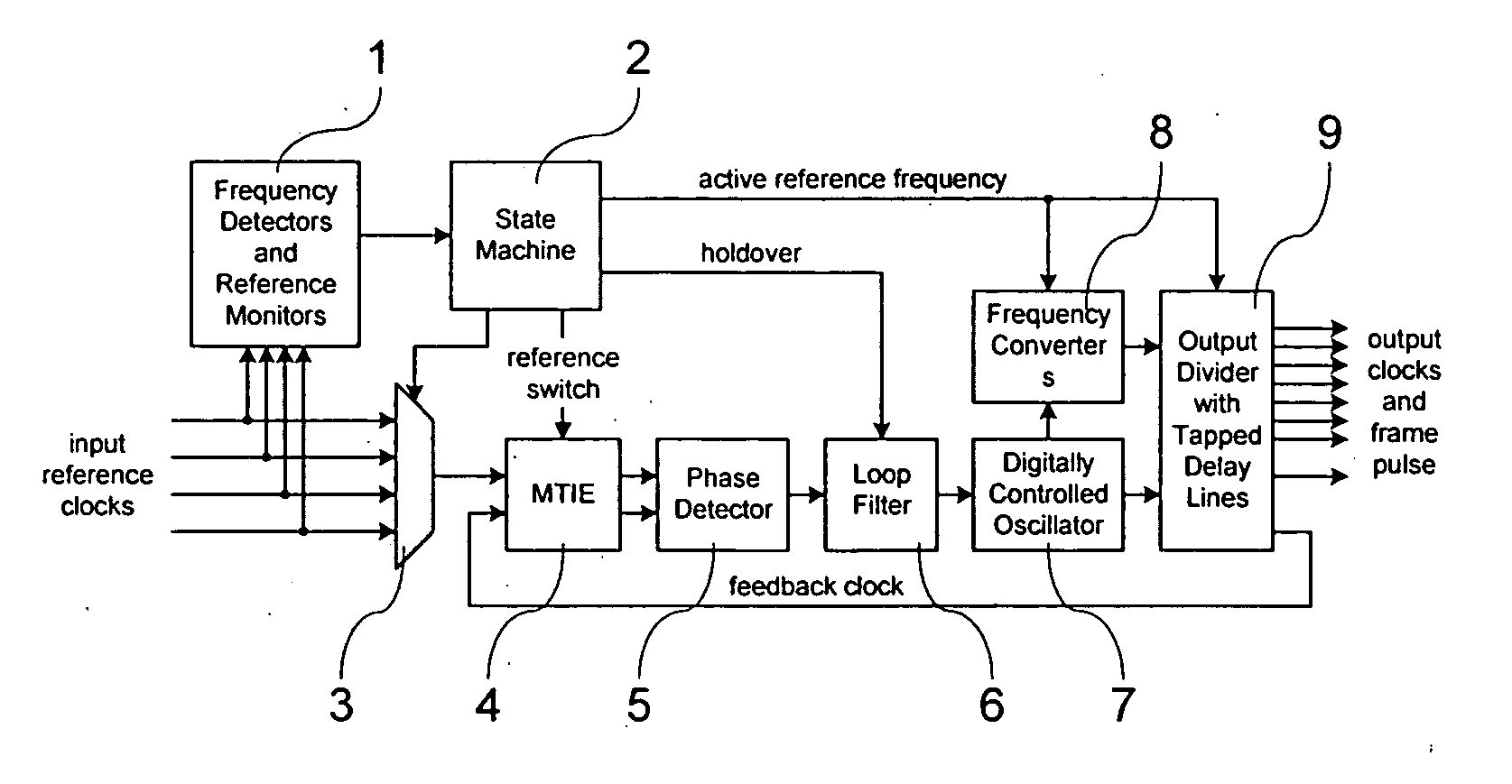

Multiple input phase lock loop with hitless reference switching

InactiveUS6570454B2Reduce jitterPulse automatic controlTime-division multiplexClock recoveryDigital controlled oscillator

Owner:ZARLINK SEMICON LTD

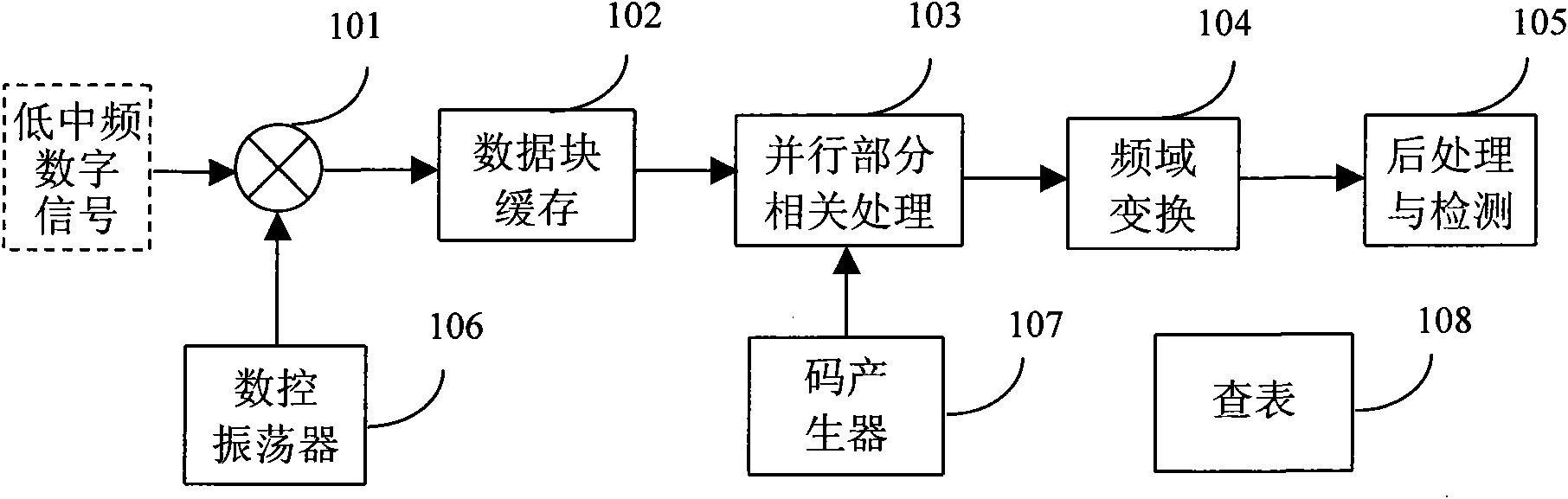

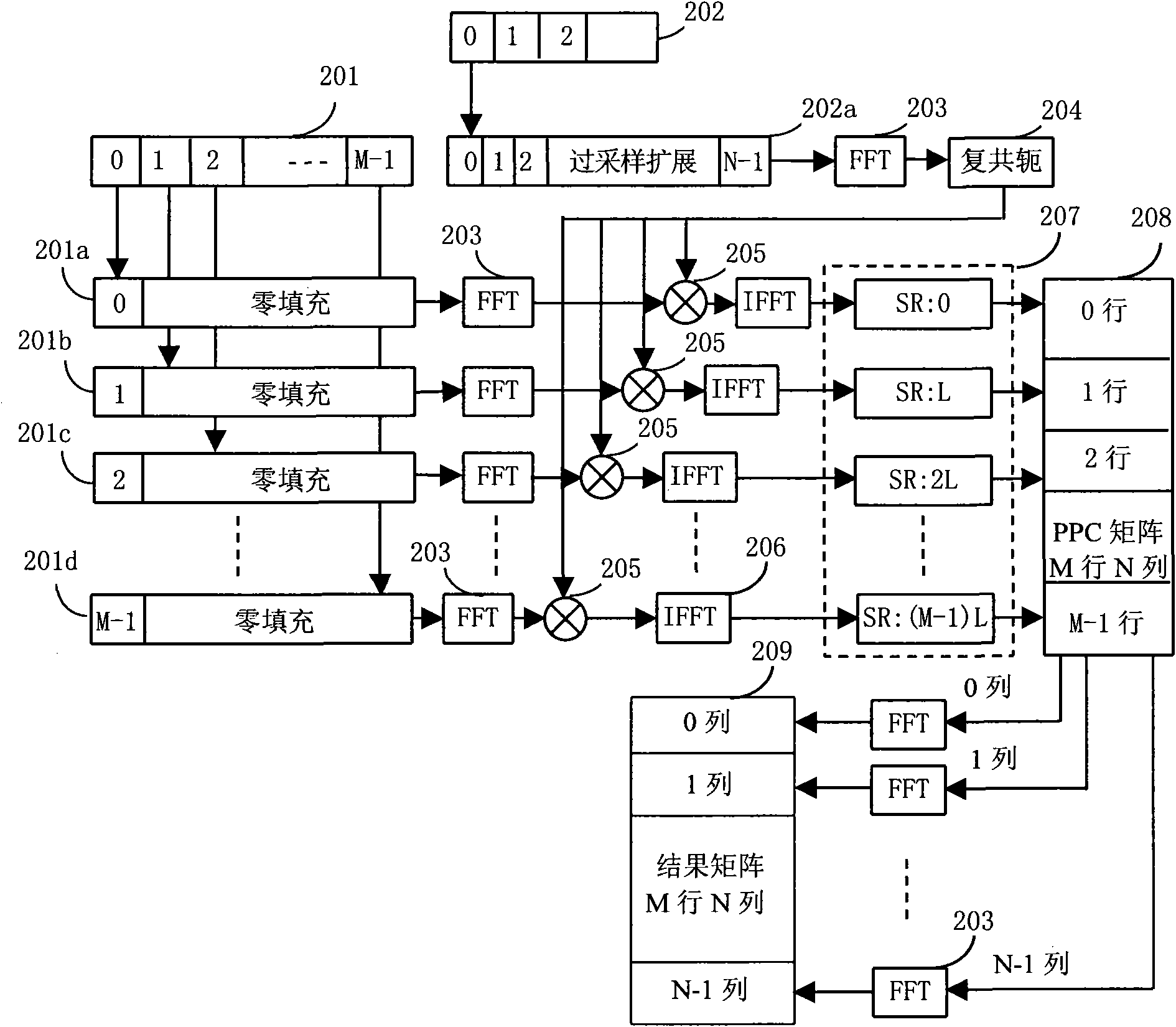

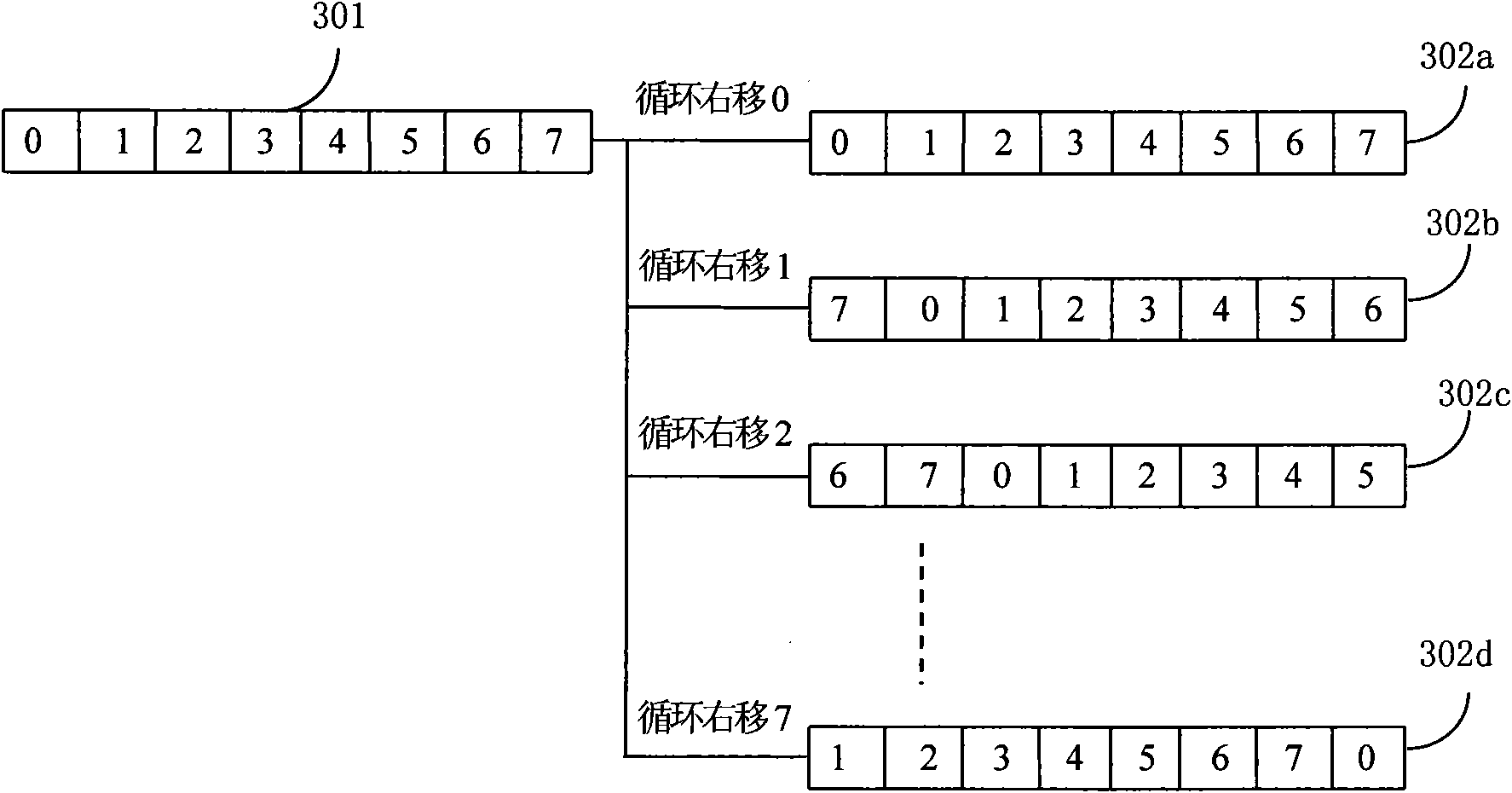

GPS signal large-scale parallel quick capturing method and module thereof

ActiveCN101625404ALow costCapture flexibleBeacon systemsTransmissionData segmentIntermediate frequency

The invention discloses a GPS signal large-scale parallel quick capturing method, which comprises the following steps: configuring a large-scale parallel quick capturing module firmware comprising submodules of multiplier, data block cache, parallel part correlative processing, frequency domain transformation, postprocessing and digital controlled oscillator, code generator and the like in a system CPU; through the calling computation, converting low-medium frequency digital signals into baseband signals in a processing procedure to combine a data block; performing zeroing extension of the length and the data block on each equational data section in the data block; then based on FFT transformation computation, performing parallel part correlative PPC processing on each extended data section and local spreading codes, and performing FFT transformation on each line of a formed PPC matrix to obtain a result matrix; and performing coherent or incoherent integration on a plurality of result matrixes formed by processing a plurality of data blocks to increase the processing gain, improve the capturing sensitivity, roughly determine the code phase and the Doppler frequency of GPS signals, and achieve two-dimensional parallel quick capturing of the GPS signals. The method has high processing efficiency and high capturing speed, and can be applied to various GPS positioning navigation aids.

Owner:杭州中科微电子有限公司

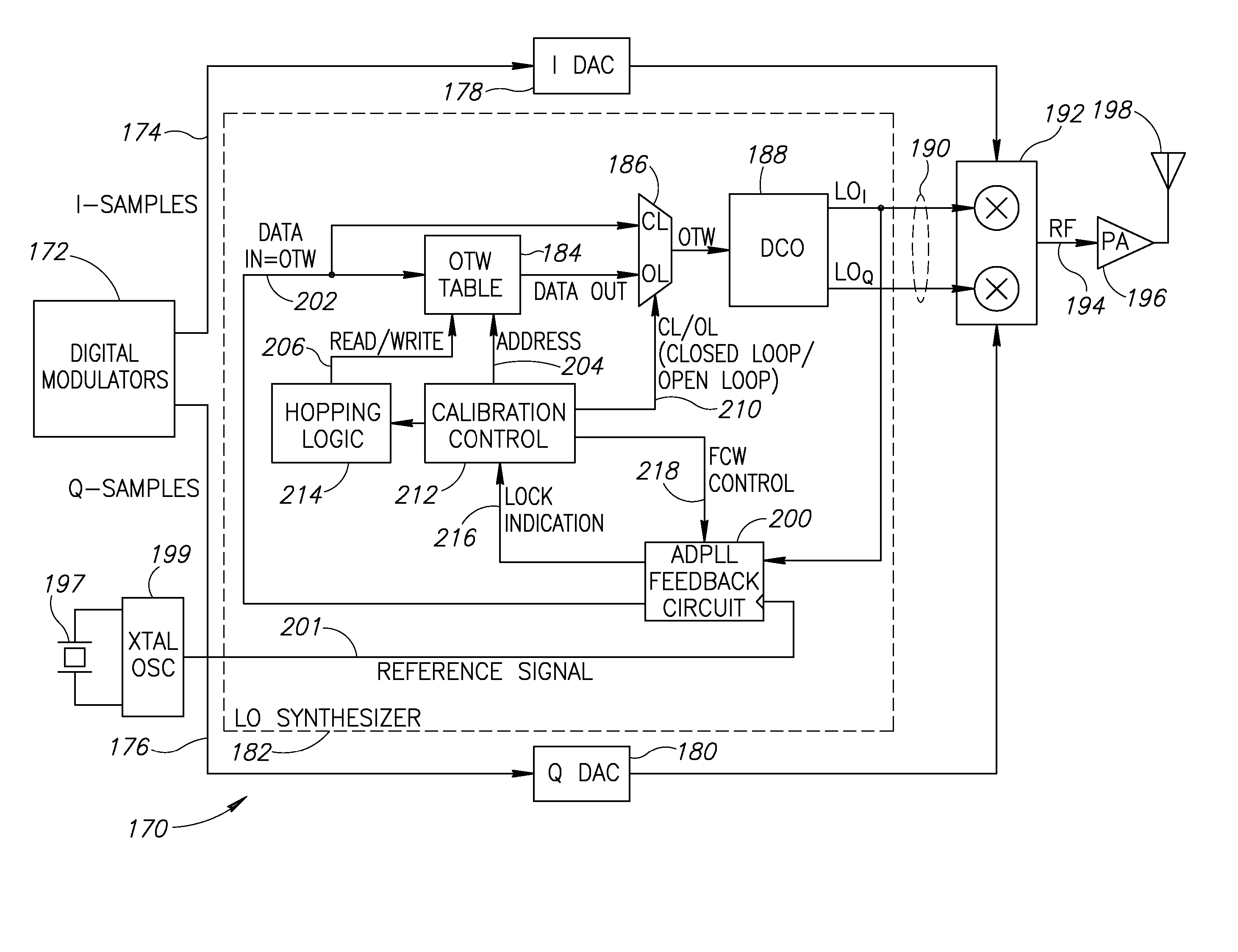

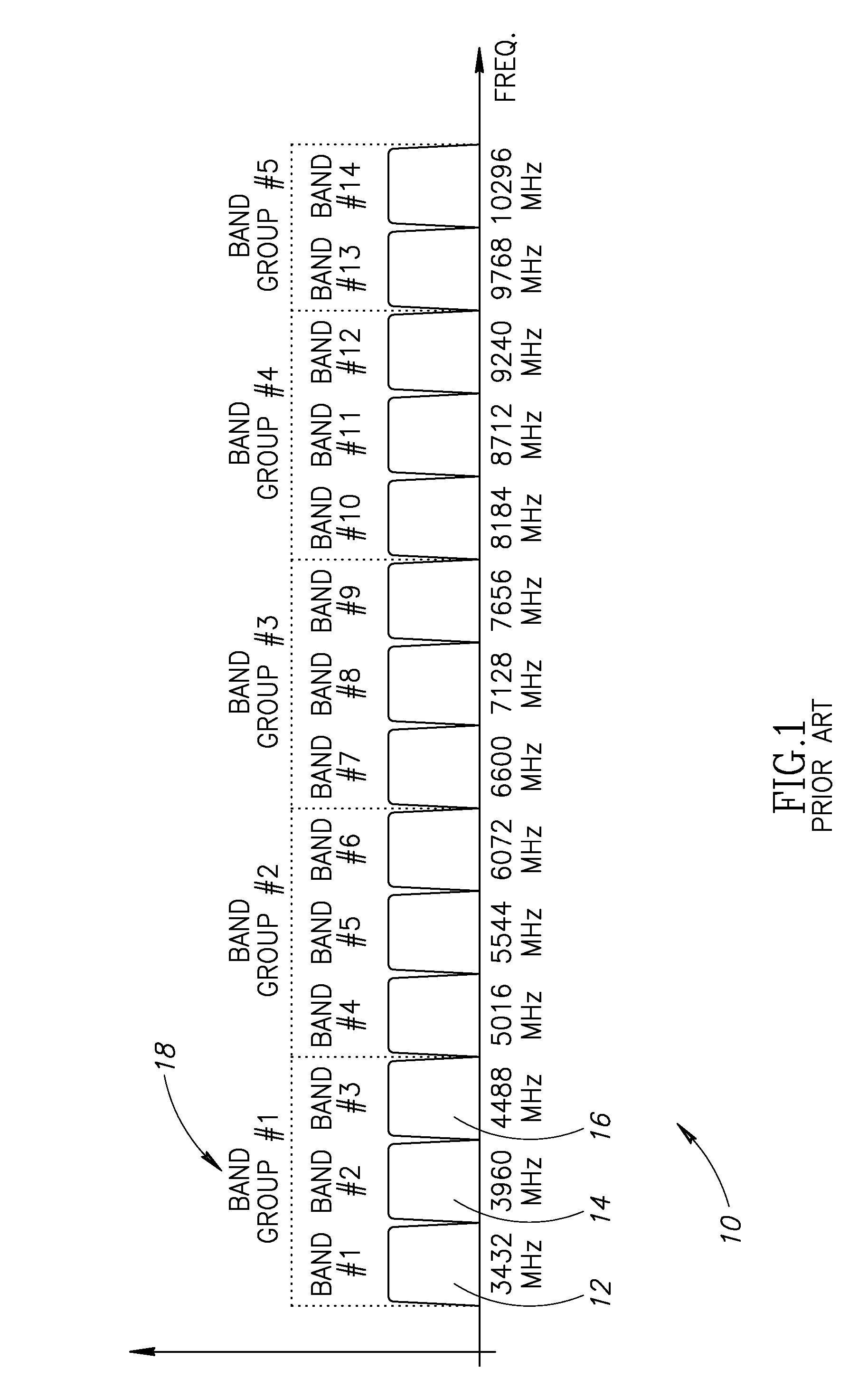

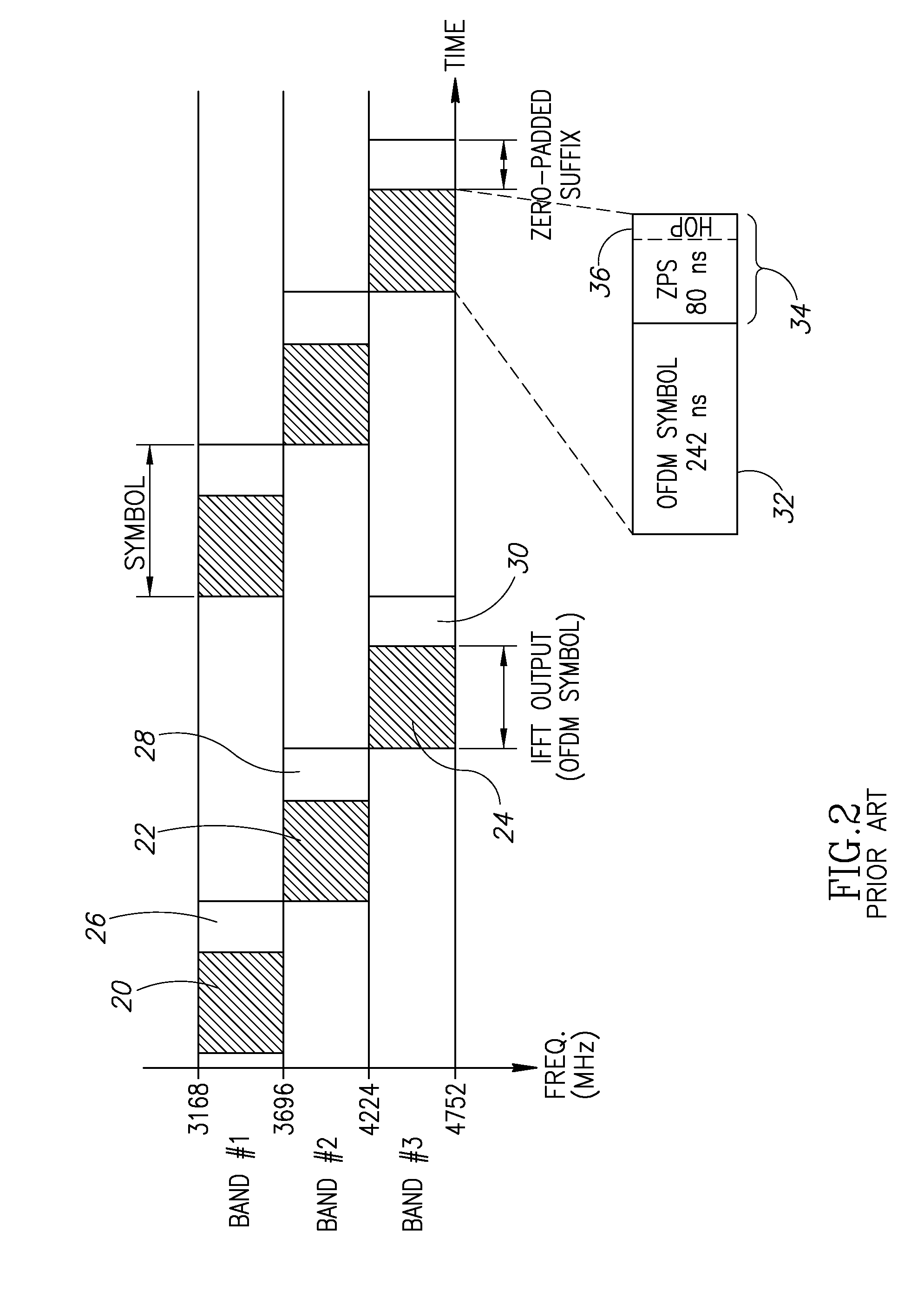

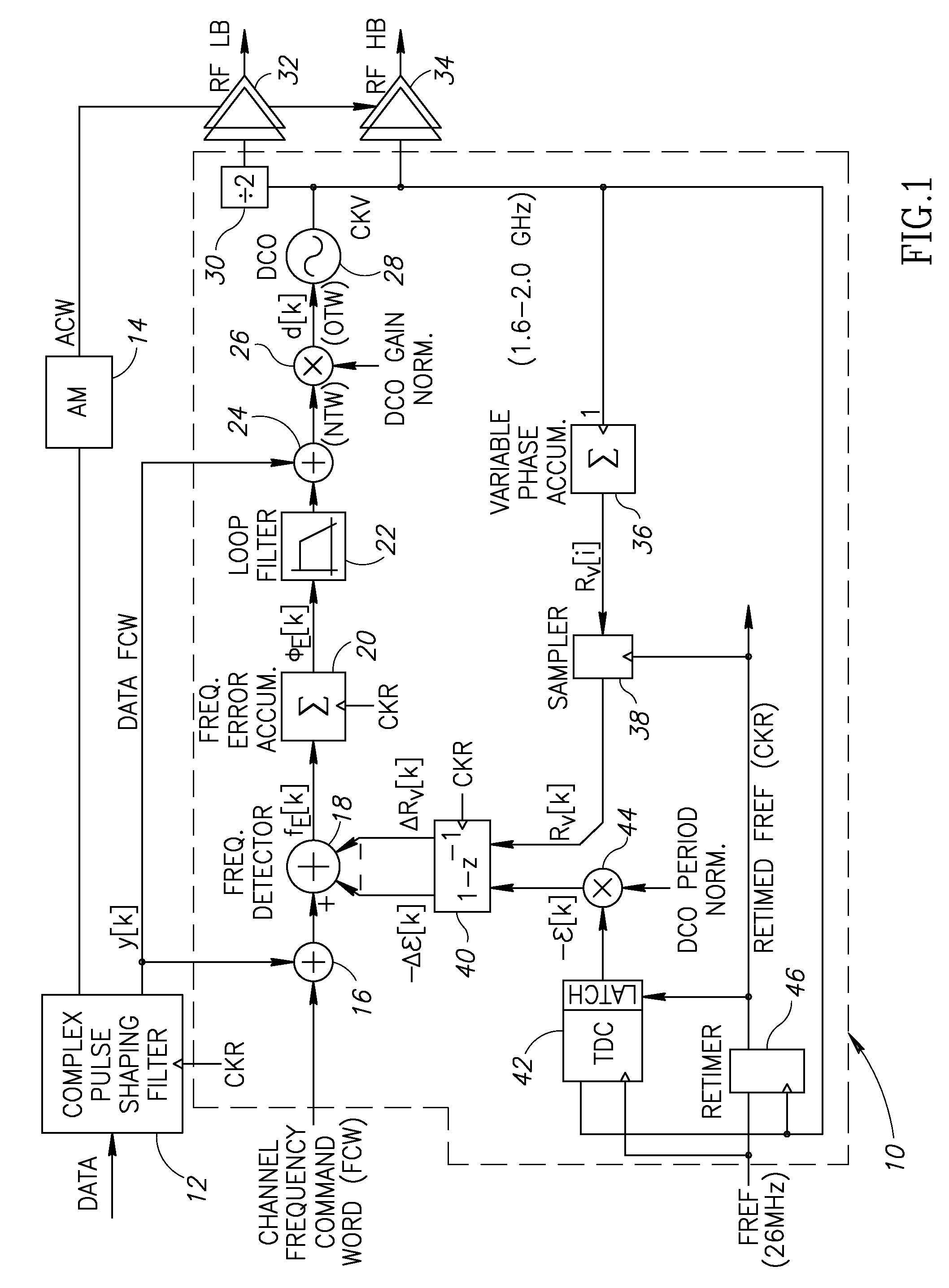

Fast hopping frequency synthesizer using an all digital phased locked loop (ADPLL)

ActiveUS20060256910A1Eliminate needReduce power consumptionPulse automatic controlTransmissionPhase shiftedFrequency mixer

A novel and useful fast hopping frequency synthesizer and transmitter associated therewith. The frequency synthesizer and transmitter incorporates a digitally controlled oscillator (DCO) adapted to operate open loop. Instantaneous frequency switching is achieved by changing an oscillator tuning word (OTW) to imitate the three oscillators of a UWB transmitter. In one embodiment, the DCO can change the frequency instantaneously within the 1 / fT of the varactor devices used to construct the DCO. An all digital phase lock loop (ADPLL) is used for offline calibration prior to the start of packet transmission or reception. Any phase shift during the switching is tracked by a digital circuit in the transmitter. In a second embodiment, additional frequency accuracy is provided by use of a numerically controlled oscillator (NCO) that functions to generate a fine resolution complex exponential waveform which effectively shifts the synthesized frequency. A mixer applies the waveform to the I and Q data samples prior to conversion to the digital domain.

Owner:TEXAS INSTR INC

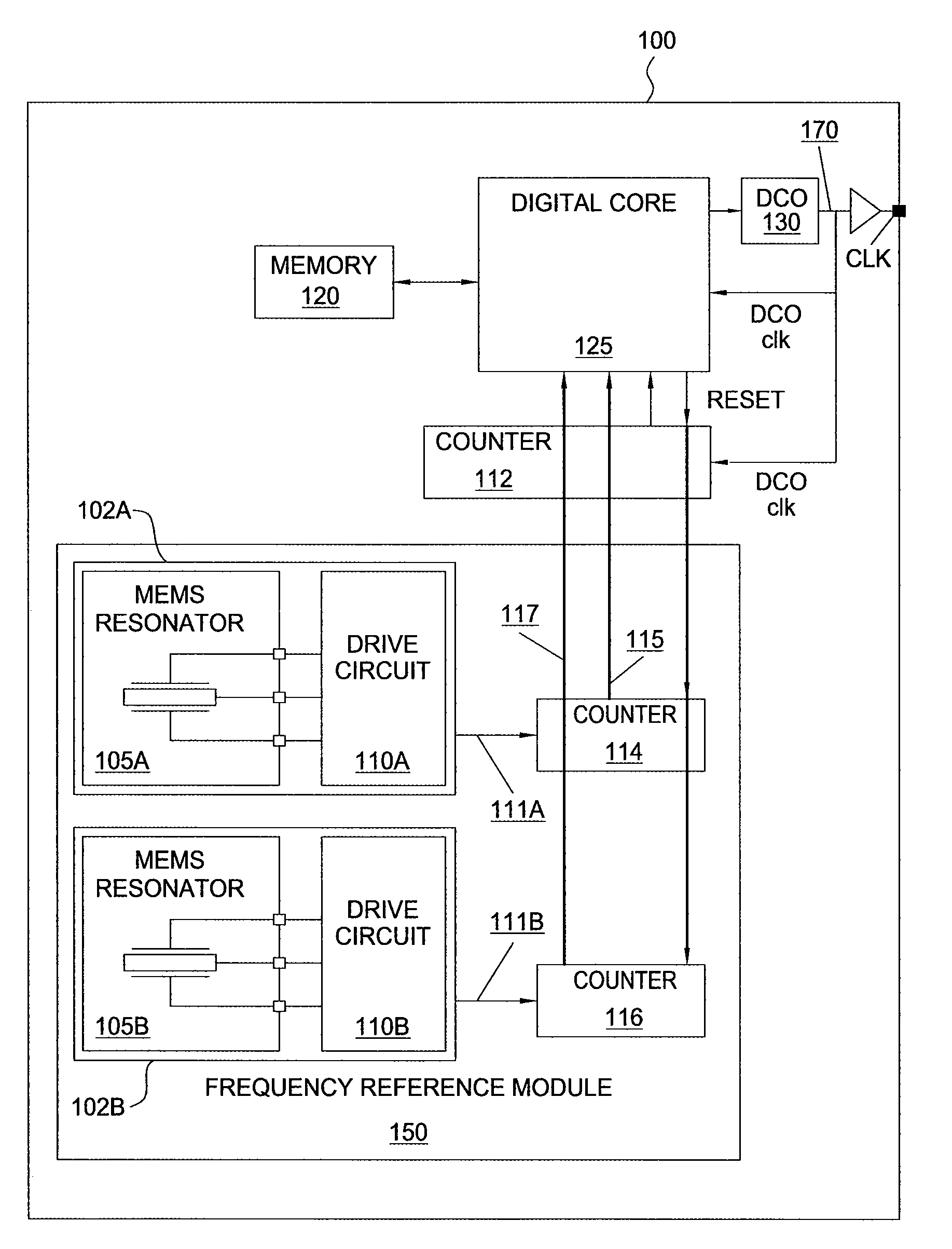

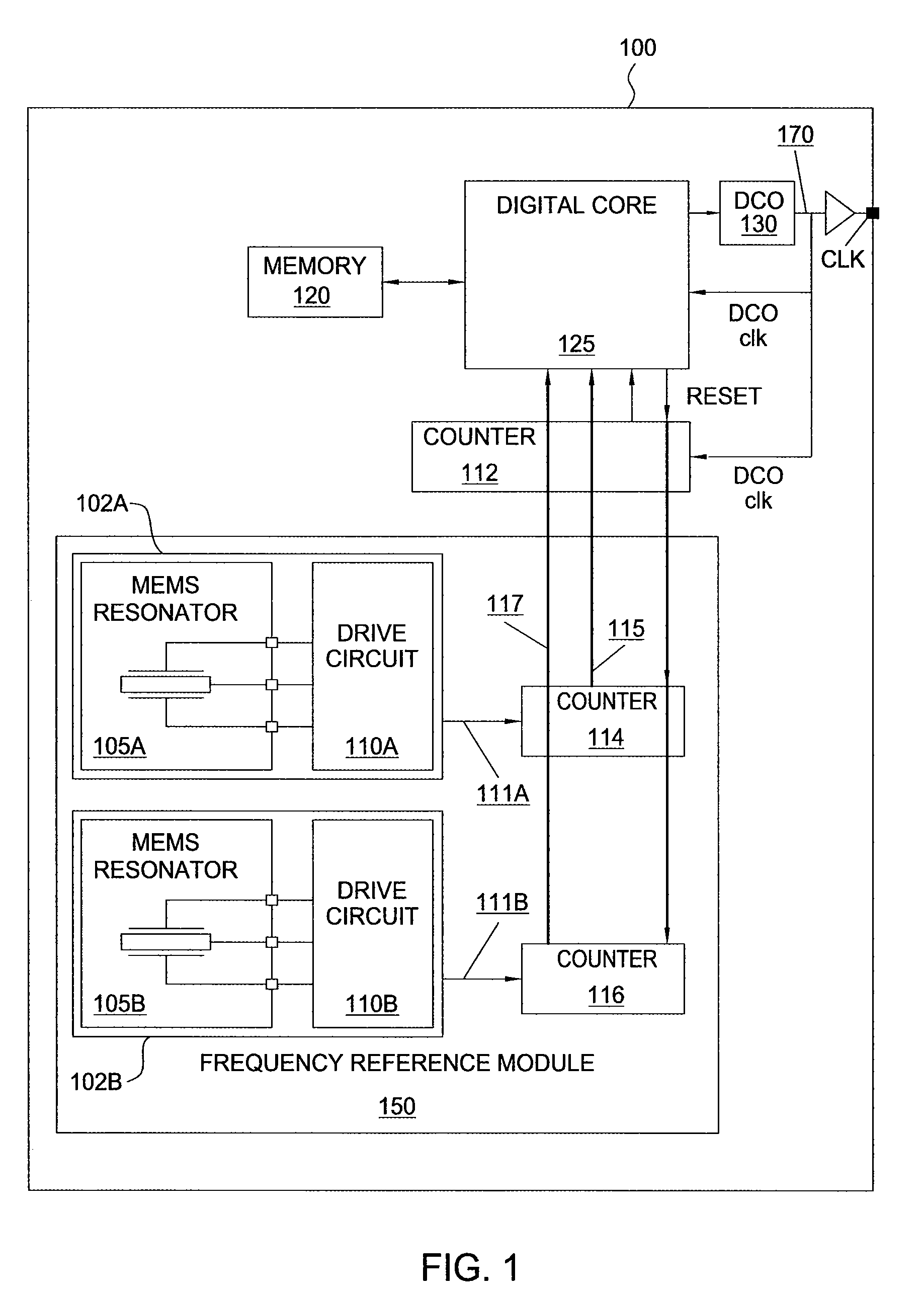

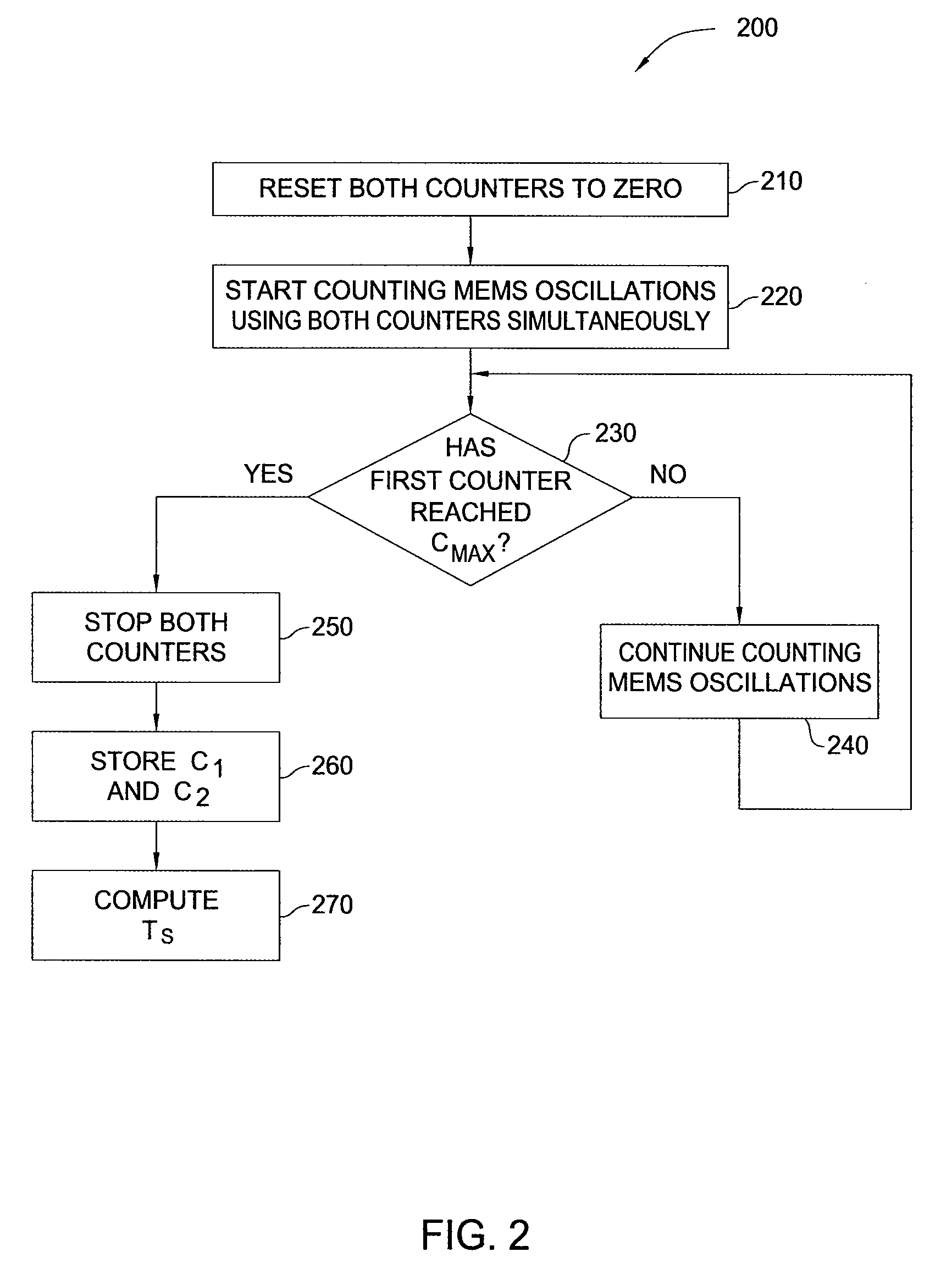

Dynamic temperature compensation for a digitally controlled oscillator using dual MEMS resonators

ActiveUS7545228B1Accurate temperature compensationThermometer detailsPiezoelectric/electrostriction/magnetostriction machinesDigital controlled oscillatorComputer science

A method for generating a temperature-compensated timing signal that includes counting, within an update interval, a first number of oscillations of a first micro-electromechanical (MEMS) resonator, a second number of oscillations of a second MEMS resonator and a third number of oscillations of a digitally controlled oscillator (DCO), computing a target DCO count based on the first number and second number of oscillations, computing a loop error signal based on the target DCO count and the third number of oscillations, and modifying an output frequency of a temperature-dependent (DCO) timing signal based on the loop error signal. The duration of the update interval may also be modified based on temperature conditions, and the update interval may also be interrupted and the output frequency immediately adjusted, if a significant temperature change is detected. Thus, dynamic and precise temperature compensation is achieved that accommodates constant, slowly changing, and rapidly changing temperature conditions.

Owner:SITIME

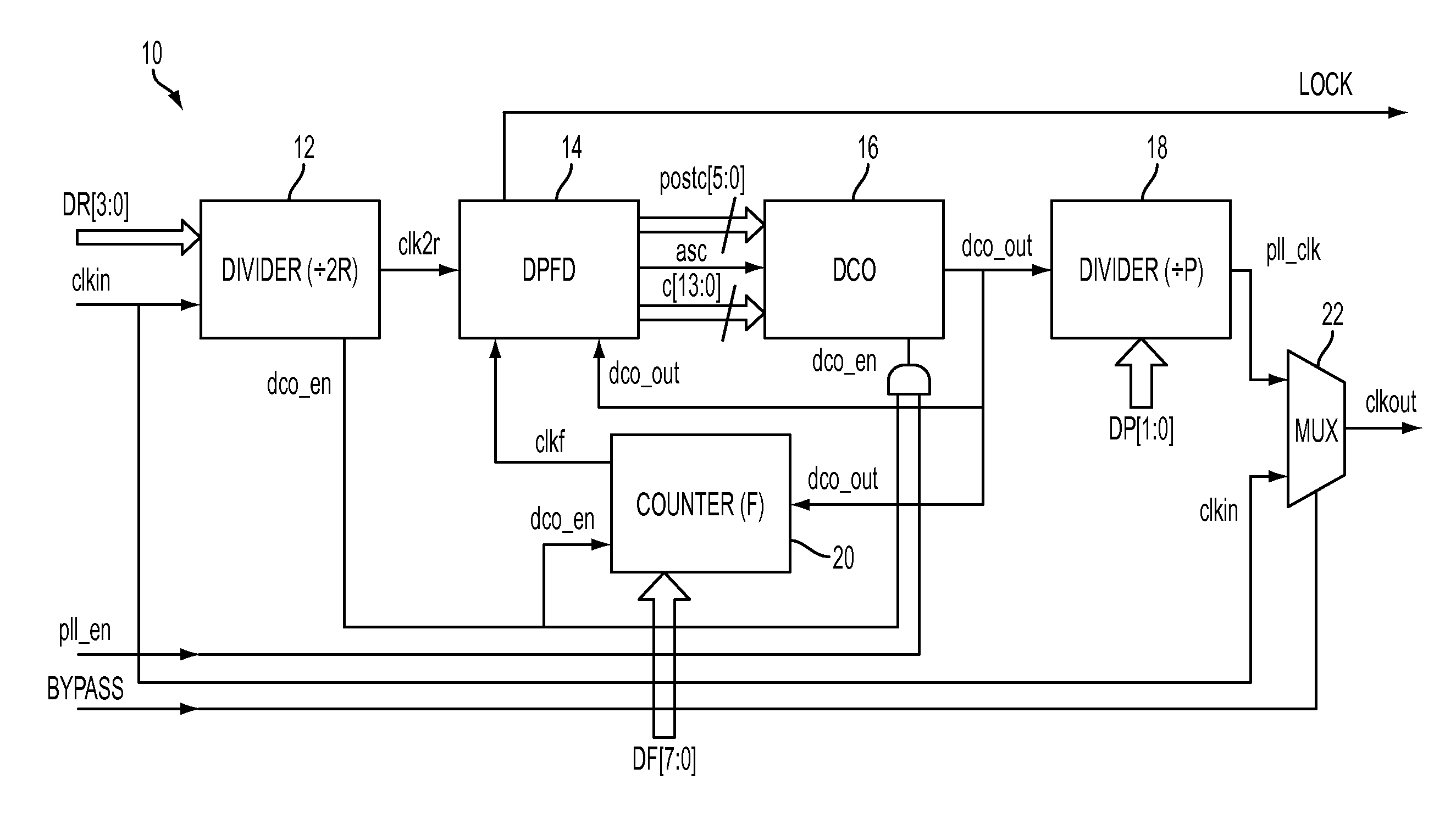

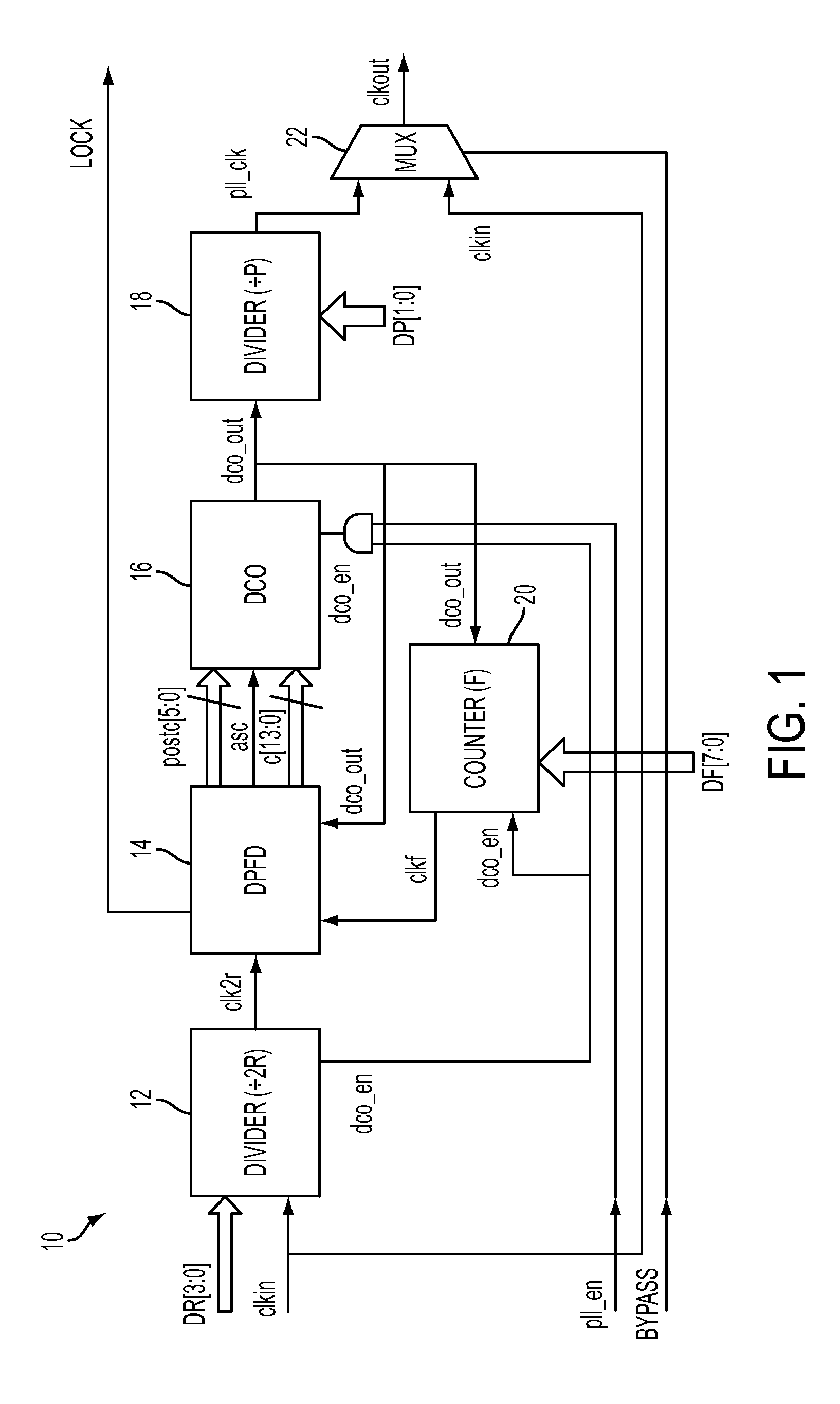

Digital phase locked loop system and method

ActiveUS20120319748A1Good precisionMitigate effect of any driftPulse automatic controlCycle controlControl system

A phase locked loop control system includes a digital controlled oscillator (DCO) that is controlled by logic cells in response to comparison of the oscillator output with a reference clock related signal. Delay cell number adjustment, delay cell load adjustment and cycle control are operative to digitally control the DCO frequency to obtain wide frequency range and limited jitter.

Owner:MEDIATEK INC

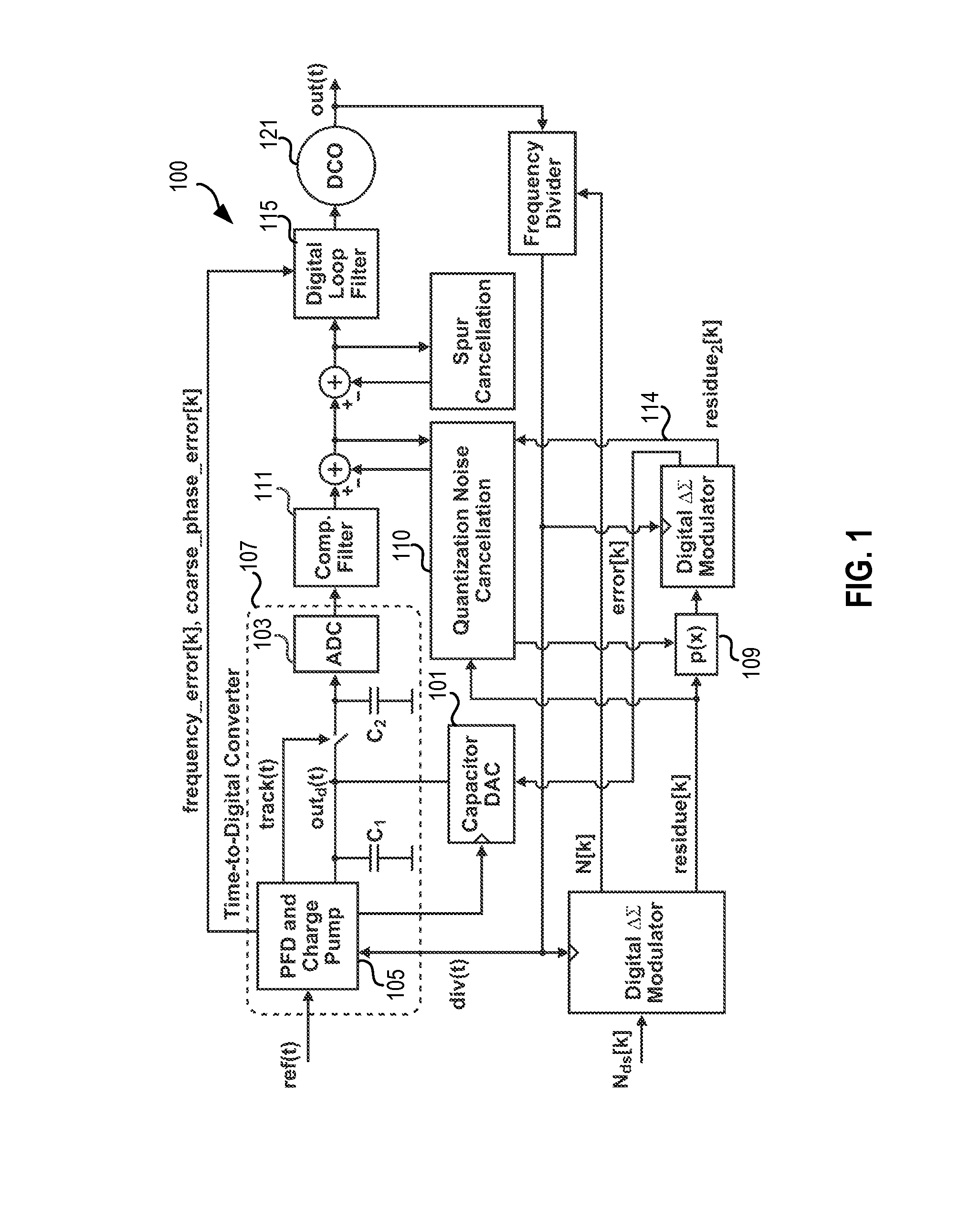

Mixed-domain circuit with differential domain-converters

ActiveUS10895850B1Analogue/digital conversionElectric signal transmission systemsConvertersHemt circuits

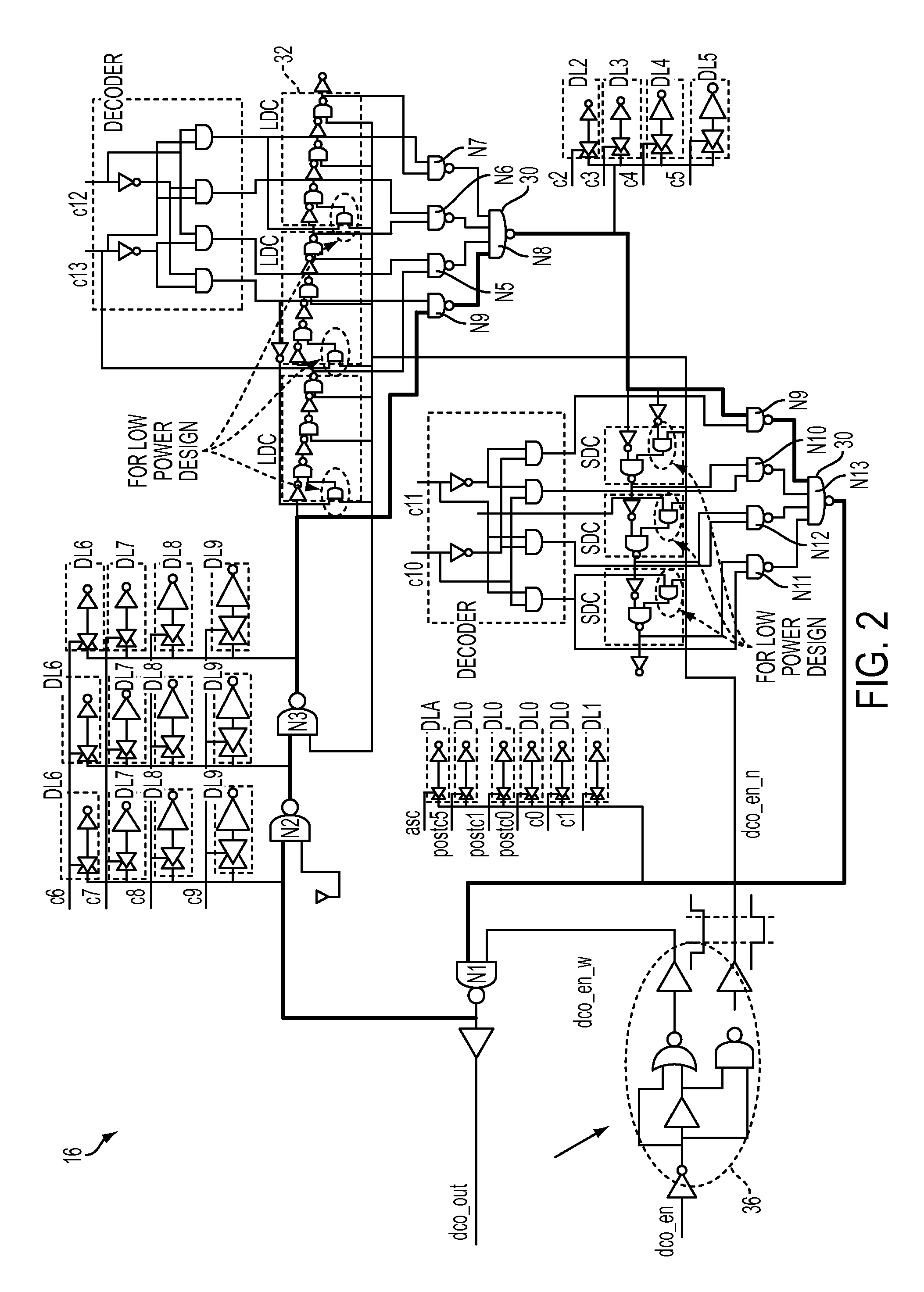

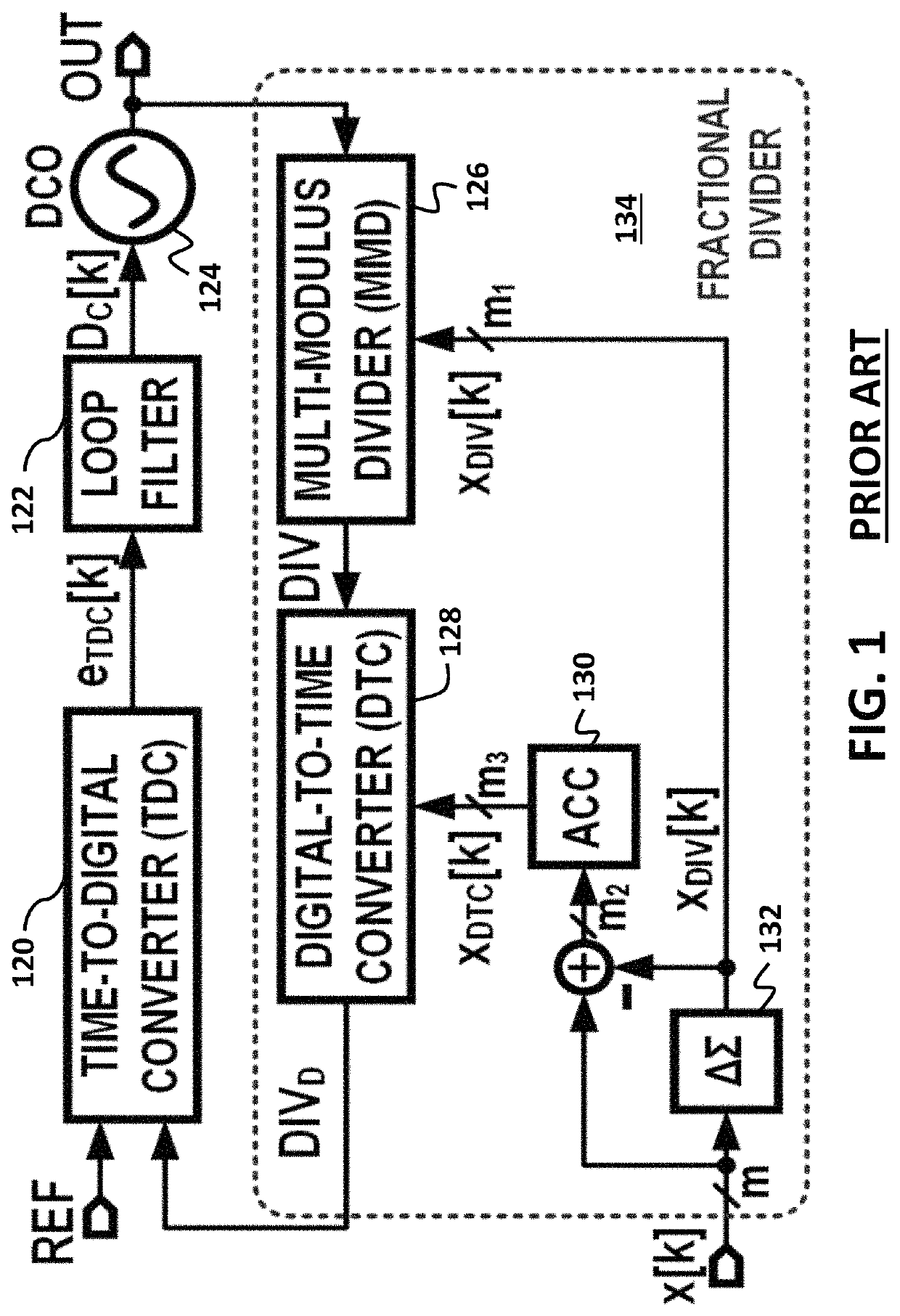

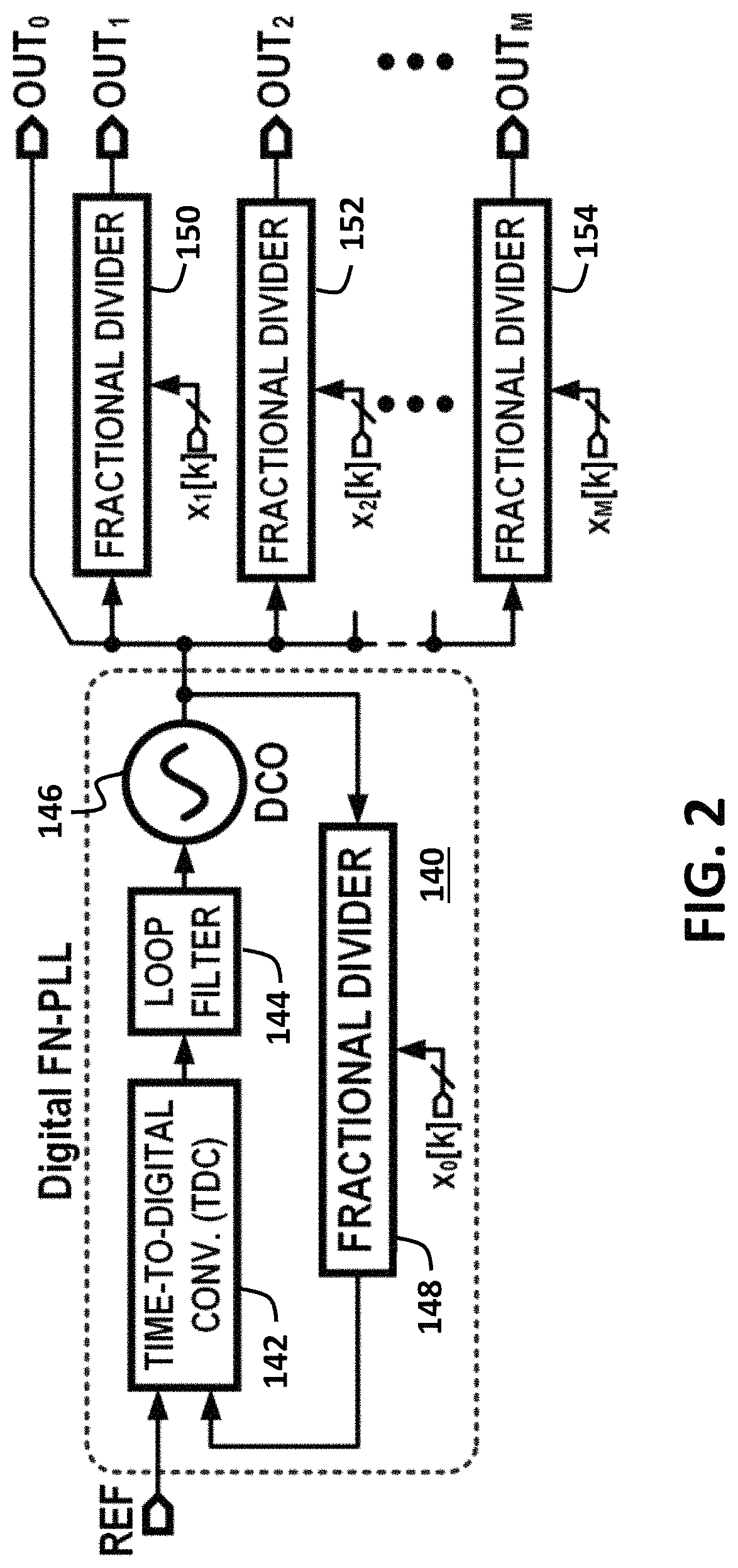

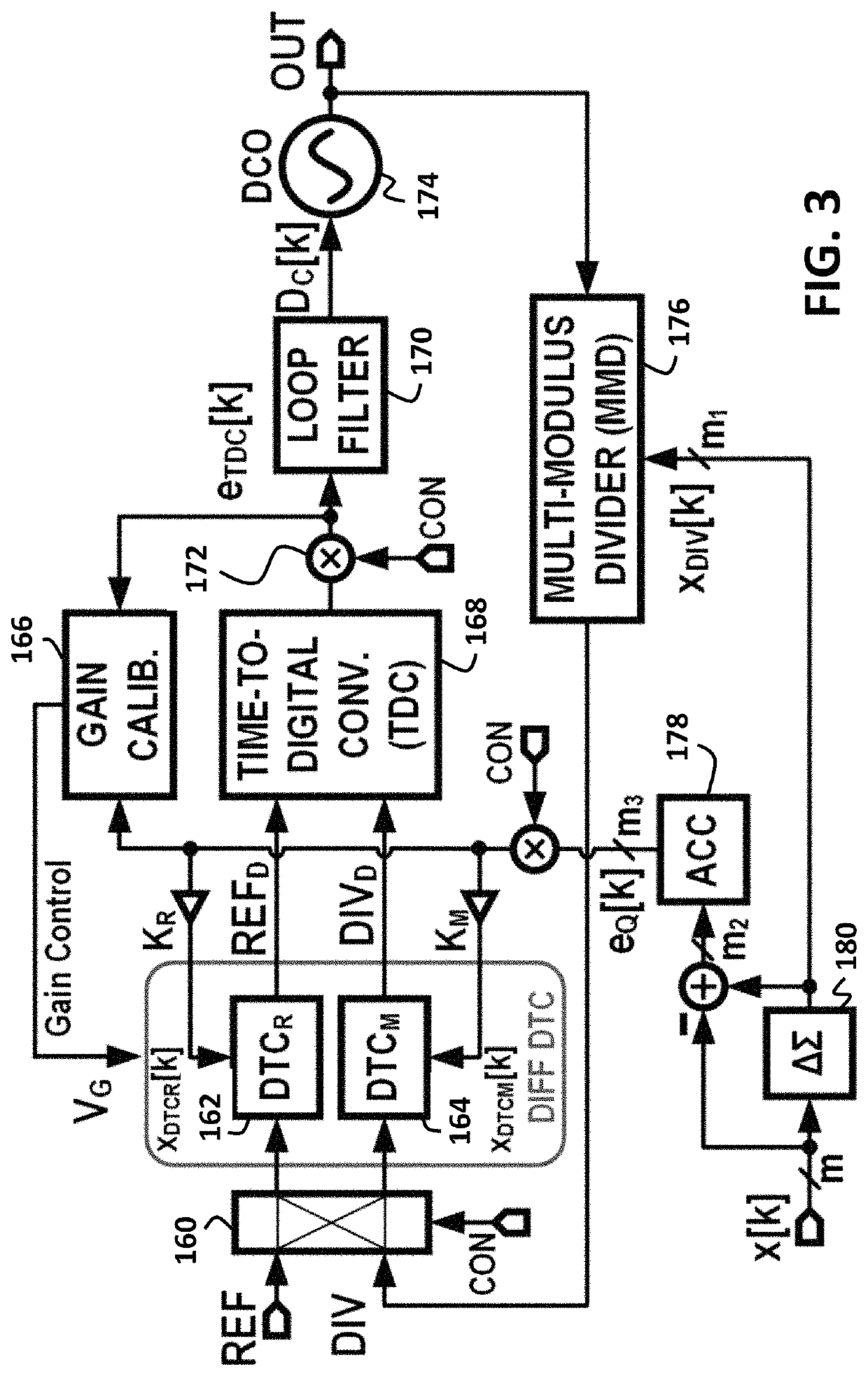

A mixed-domain circuit has a differential pair of Digital-to-Time Converters (DTCs), one receiving a reference clock and the other receiving a feedback clock. A Time-to-Digital Converter (TDC) compares outputs from the differential pair of DTCs and generates a digital error value that controls a digital loop filter that controls a Digitally-Controlled Oscillator (DCO) that generates an output clock. A Multi-Modulus Divider (MMD) generates the feedback clock. An accumulated modulation from a delta-sigma modulator is compared to the digital error value by a Least-Mean Square (LMS) correlator to adjust supply voltage or current sources in the pair of DTCs to compensate for errors. A capacitor in each DTC has a charging time adjusted by the accumulated modulation. The DTC can be reduced to a Time-to-Voltage Converter (TVC) and the analog voltages on the capacitors input to an Analog-to-Digital Converter (ADC) to generate the digital error value.

Owner:SI WARE SYST S AE

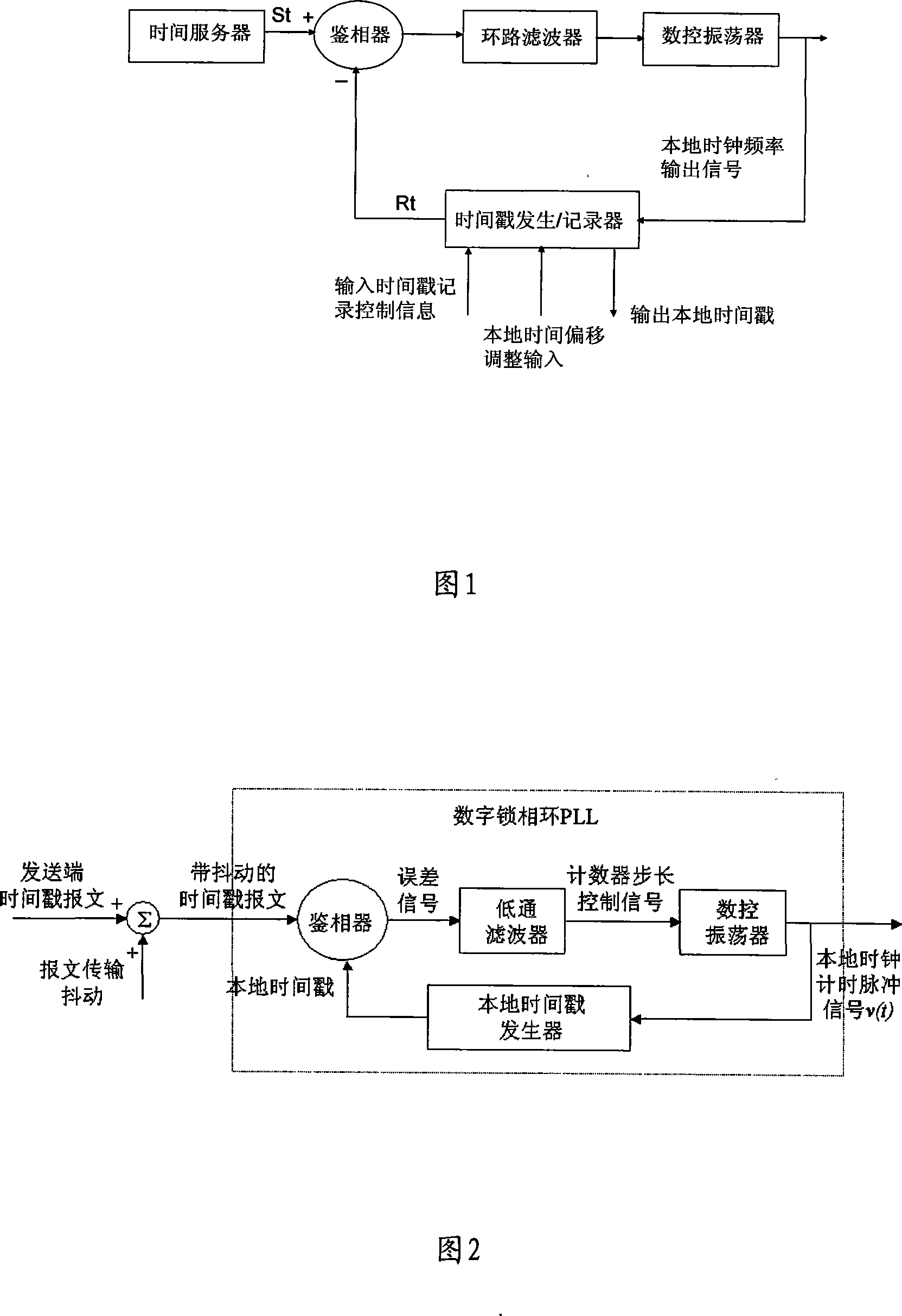

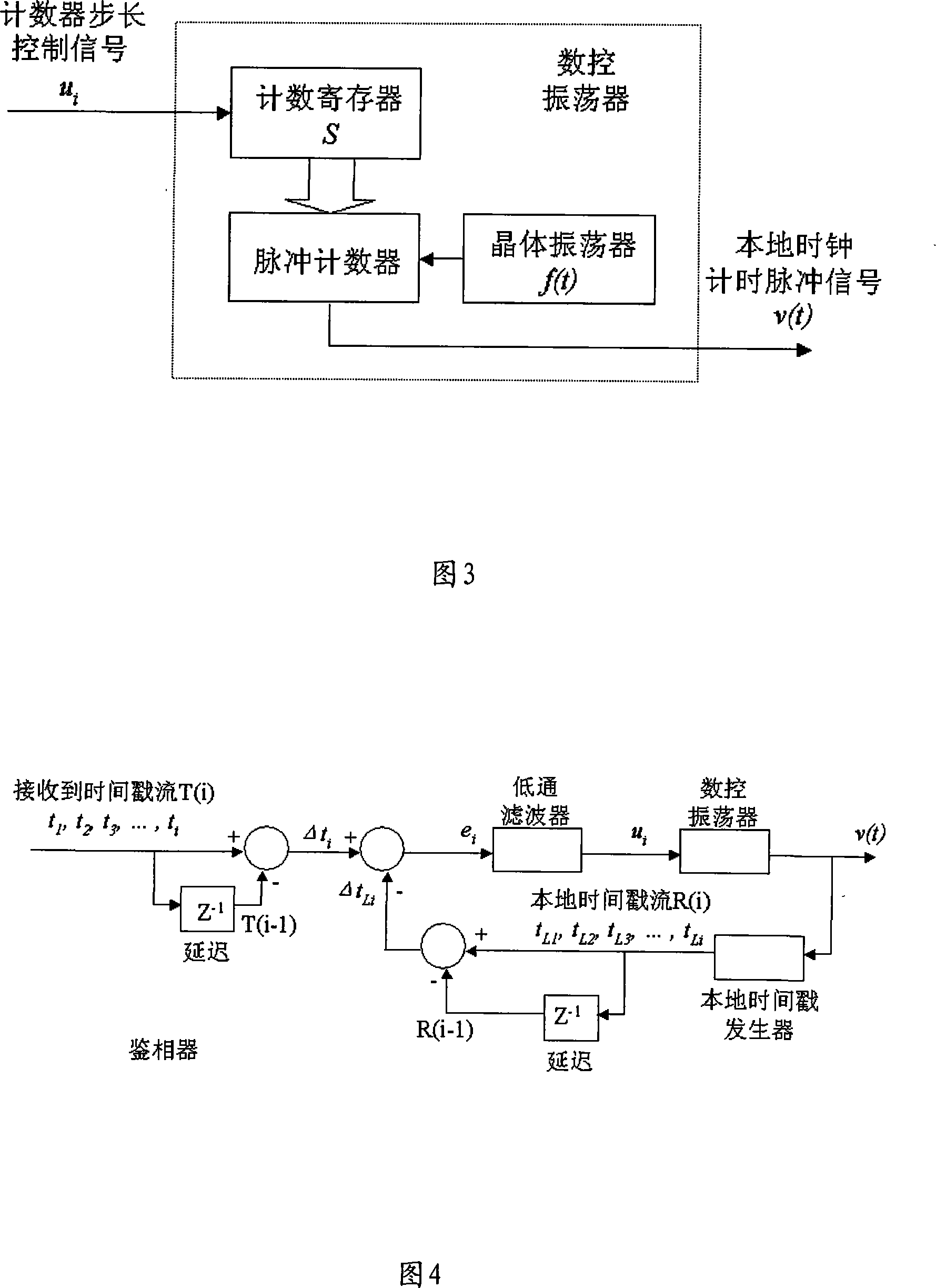

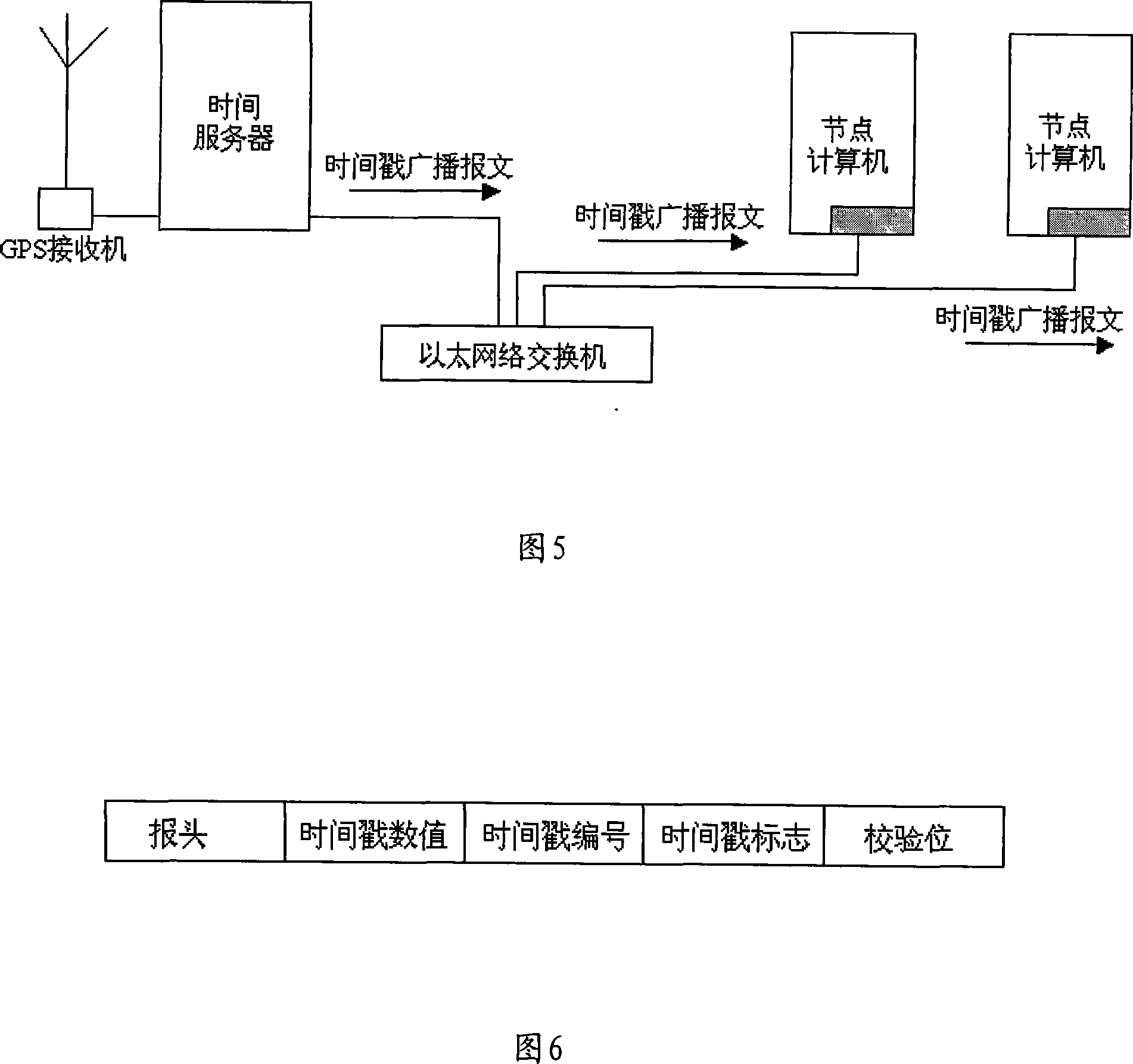

Method for realizing integrated time stamp clock synchronous phase-locked loop

InactiveCN101083523AGuaranteed validityPulse automatic controlSynchronising arrangementLoop filterRing circuit

The invention involves a method of digital phase-locked loop for timestamp clock synchronization and equipment. Firstly, the server sends a value, which includes the message S (t) to timestamp, as the input synchronized signal. Take the time on which timestamp the server sent arriving at phase-locked loop as the recording time R (t) of local time. Then take the local timestamp according to the local clock frequency as reference input signal. The numerically controlled adjusts the output frequency according to ring circuit signal by filter. Lastly, the timestamp creater / recorder output the signal as the local clock frequency according to the output signal created by DOC. Under the condition that the invention use larger drift mobility and the lower stability oscillator, the system can provide high accuracy time synchronism.

Owner:SOUTH CHINA UNIV OF TECH

Direct digital synthesizer for reference frequency generation

InactiveUS20110095830A1Reduce power consumptionLow frequency signalPulse automatic controlCounting chain pulse countersFrequency generationRandom noise

A direct digital frequency synthesizer having a multi-modulus divider, a numerically controlled oscillator and a programmable delay generator. The multi-modulus divider receives an input clock having an input pulse frequency fosc and outputs some integer fraction of those pulses at an instantaneous frequency fVp that is some integer fraction (1 / P) of the input frequency. The multi-modulus divider selects between at least two ratios of P (1 / P or 1 / P+1) in response to a signal from the numerically controlled oscillator. The numerically controlled oscillator receives a value which is the accumulator increment (i.e. the number of divided pulse edges) required before an overflow occurs that causes the multi-modulus divider to change divider ratios in response to receiving an overflow signal. The numerically controlled oscillator also outputs both the overflow signal and a delay signal to the delay generator. The delay signal contains phase-dithering noise that is induced by input into the accumulator of an increment generated from a pseudo-random noise generator. The delay signal further controls the frequency of the multi-modulus divider output signal (Vp) to provide an output signal (VD) with an fOUT that has improved phase and timing jitter performance over prior art direct digital frequency synthesizer architectures.

Owner:CYMATICS LAB CORP

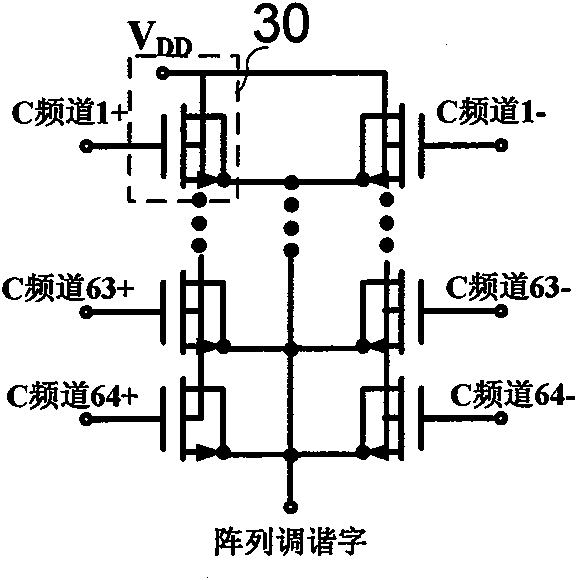

Inductance-capacitance numerical control oscillator

InactiveCN101662281ASimple designReduce power consumptionPulse automatic controlCapacitanceNumerical control

An inductance-capacitance numerical control oscillator in the communication technical field comprises a control deposit unit, a coupling MOS tube, an integrated inductance and a plurality of capacitance arrays, wherein, an input end of the control deposit unit receives an array tuning word output by a numerical control bus, an output end of the control deposit unit is connected with a plurality ofthe capacitance arrays in parallel, and the coupling MOS tube and the integrated inductance are respectively connected with the capacitance arrays in parallel. Compared with the prior art, output frequency resolution ratio is 10 times higher in the case of no capacitance shaking; and if applied in an all digital phase-locked loop, the high frequency resolution ratio of the numerical control oscillator means the integrally output low-phase noise. In addition, the numerical control oscillator of the invention can eliminate the capacitance arrays using delta-sigma modulator shaking control in abetter process (characteristic dimension is less than 65nm) or some communication standards, thus realizing simplifying circuit design further and reducing power consumption and occupied area.

Owner:SHANGHAI JIAO TONG UNIV

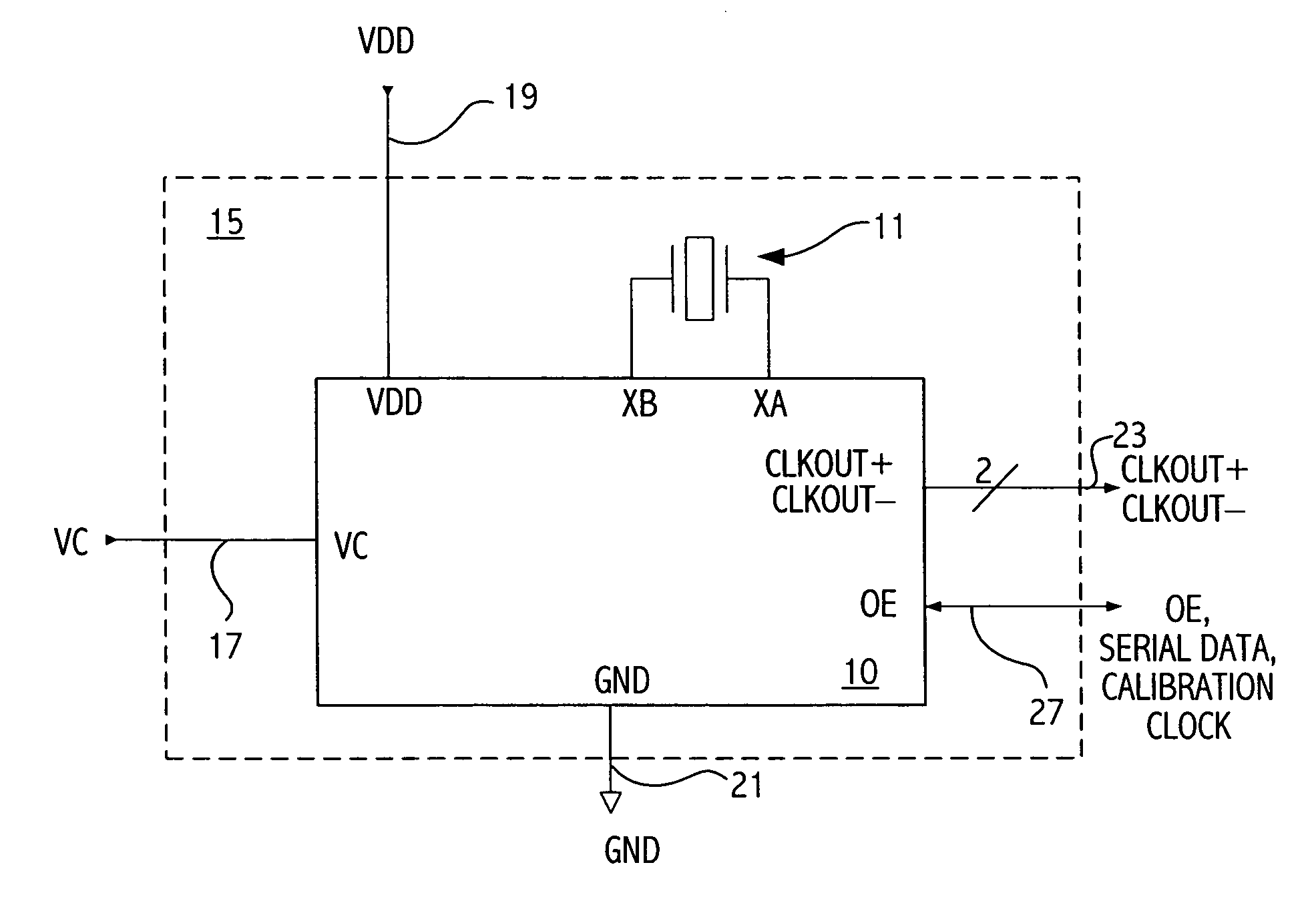

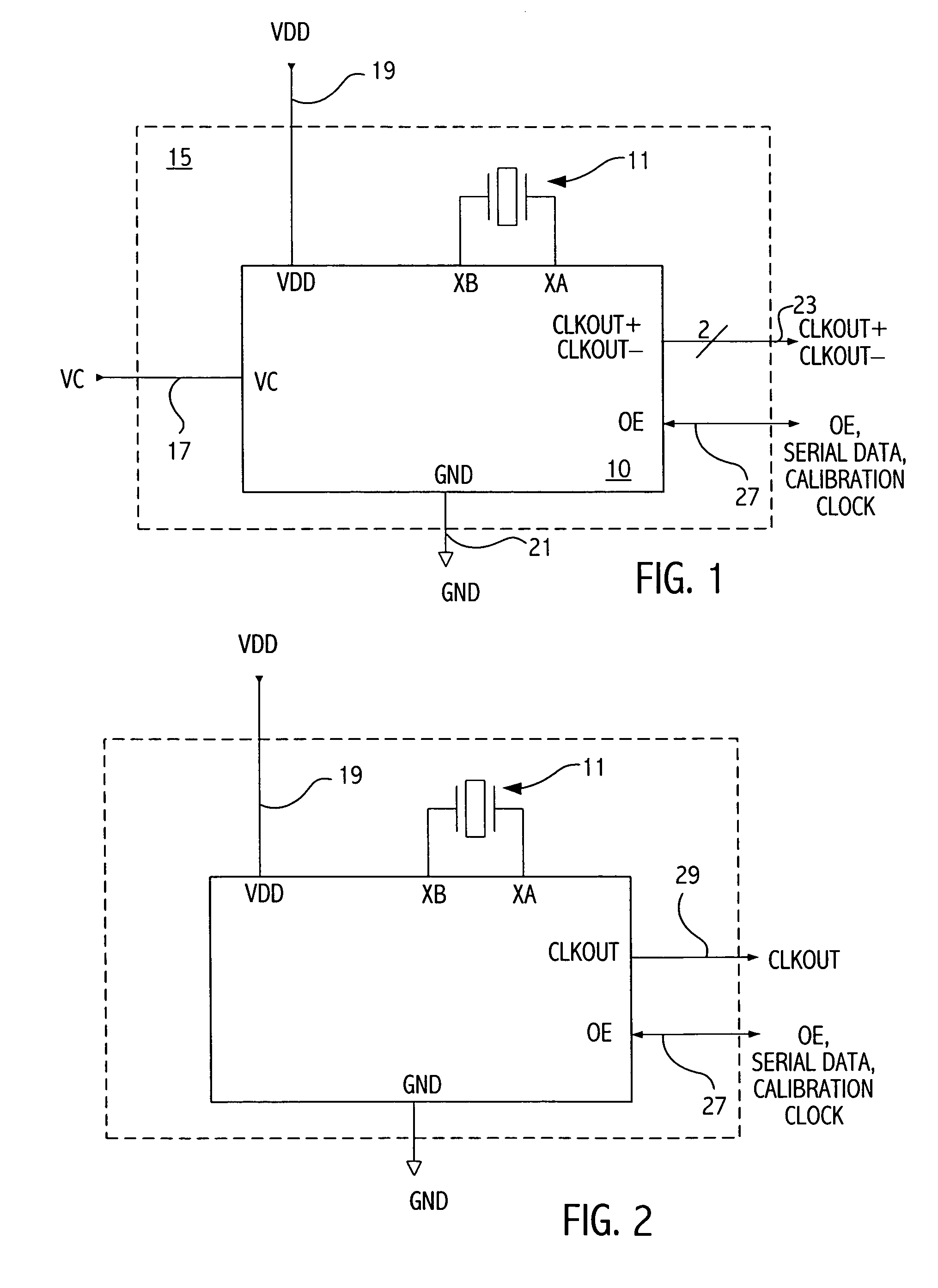

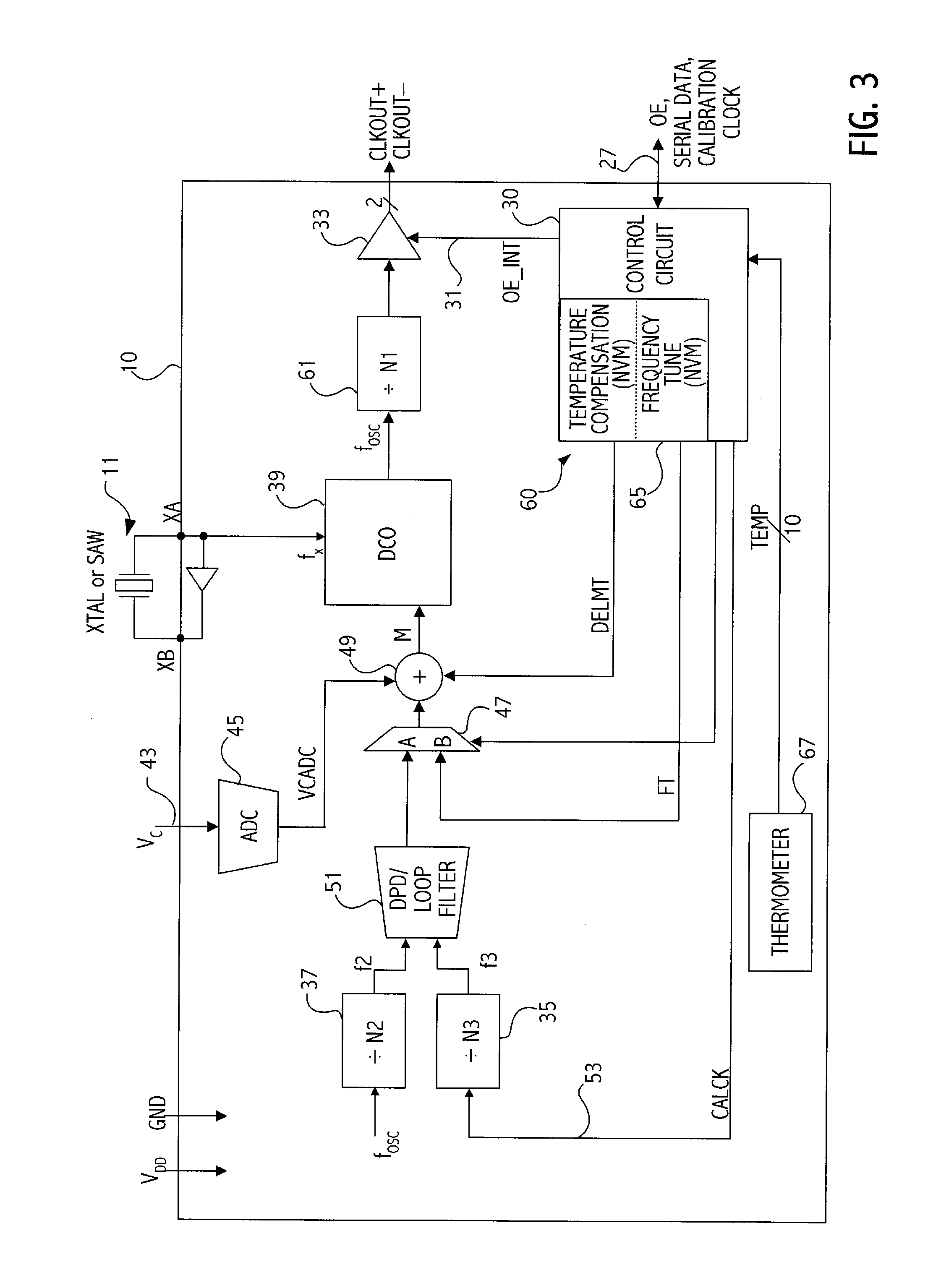

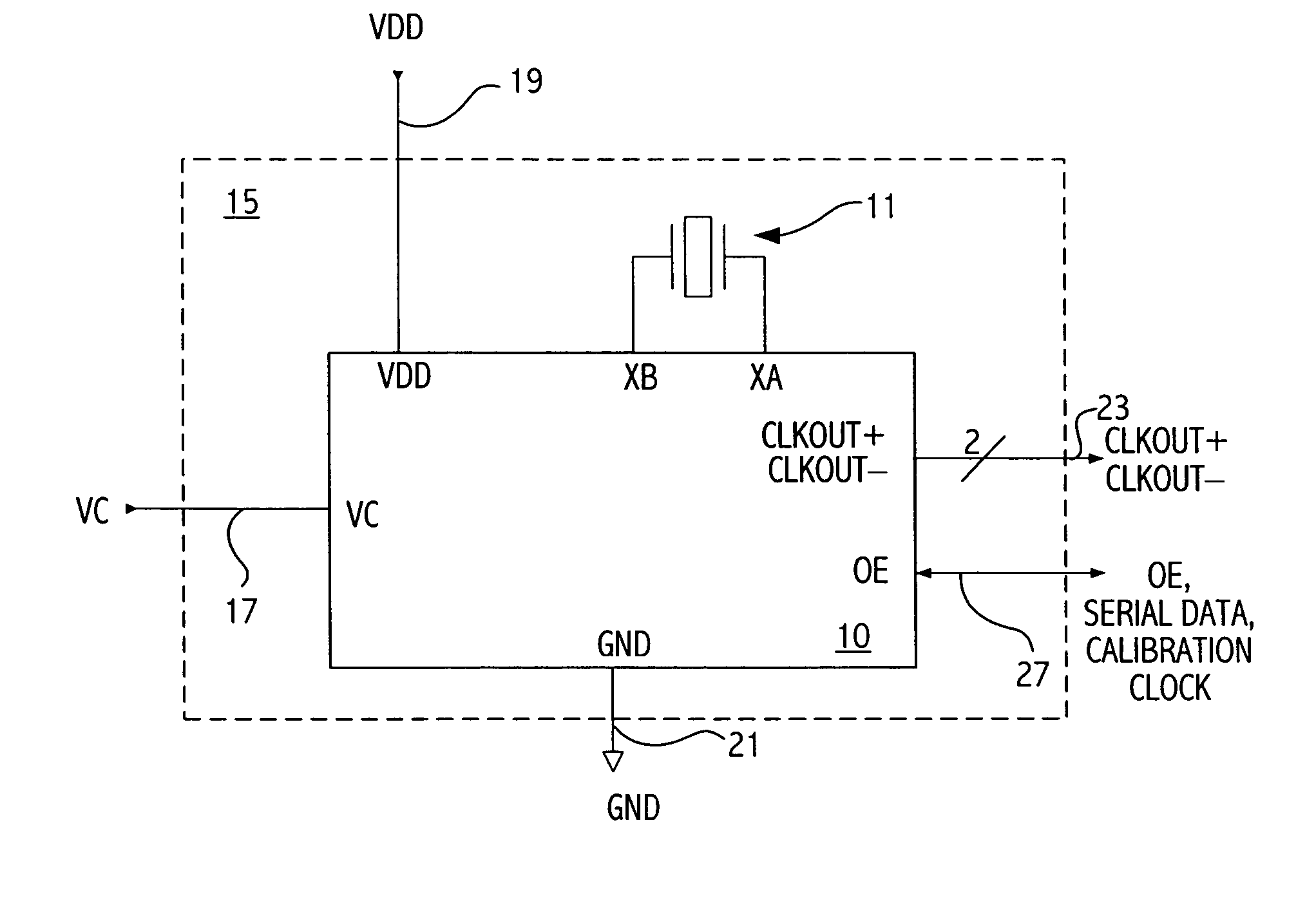

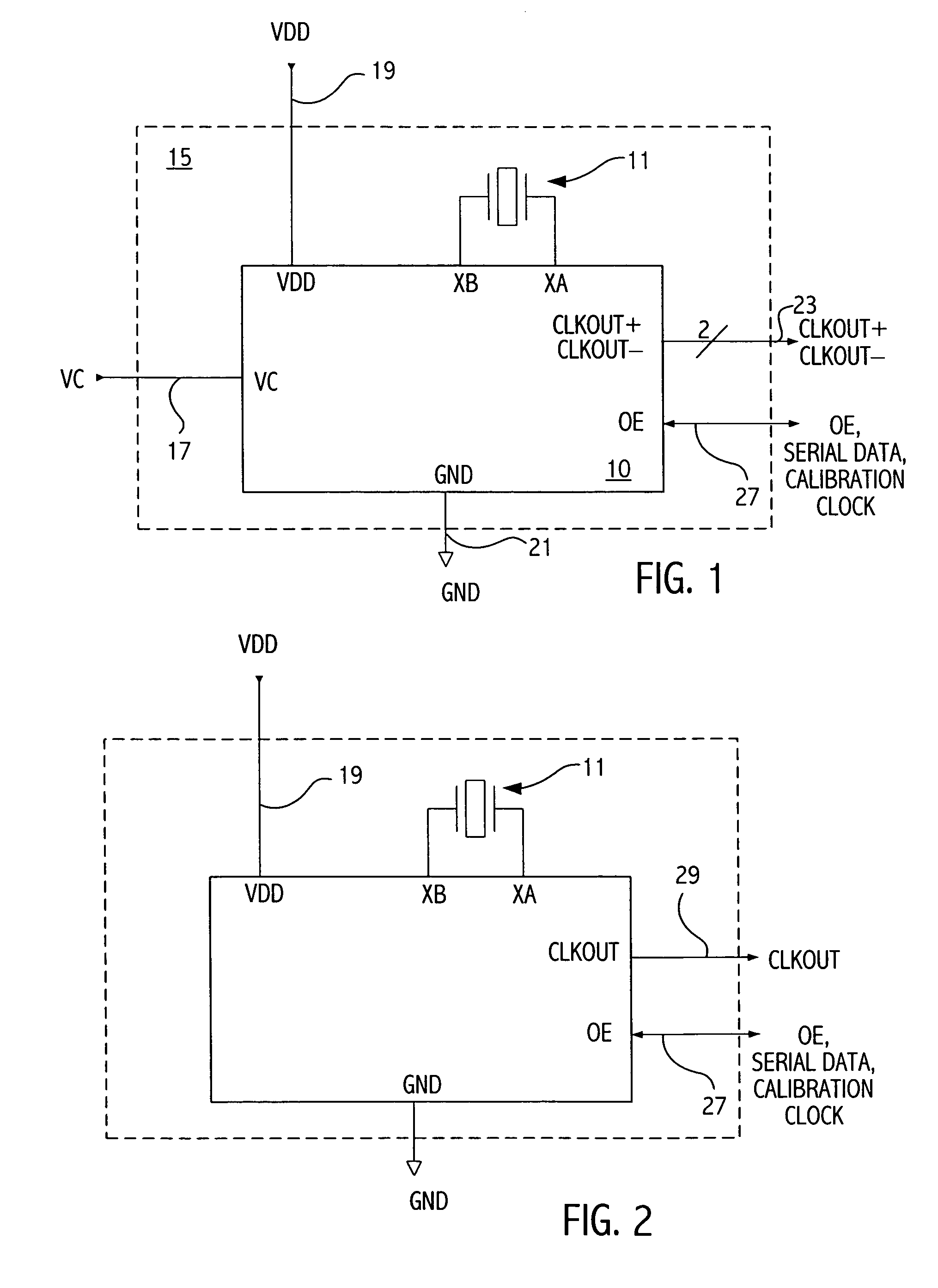

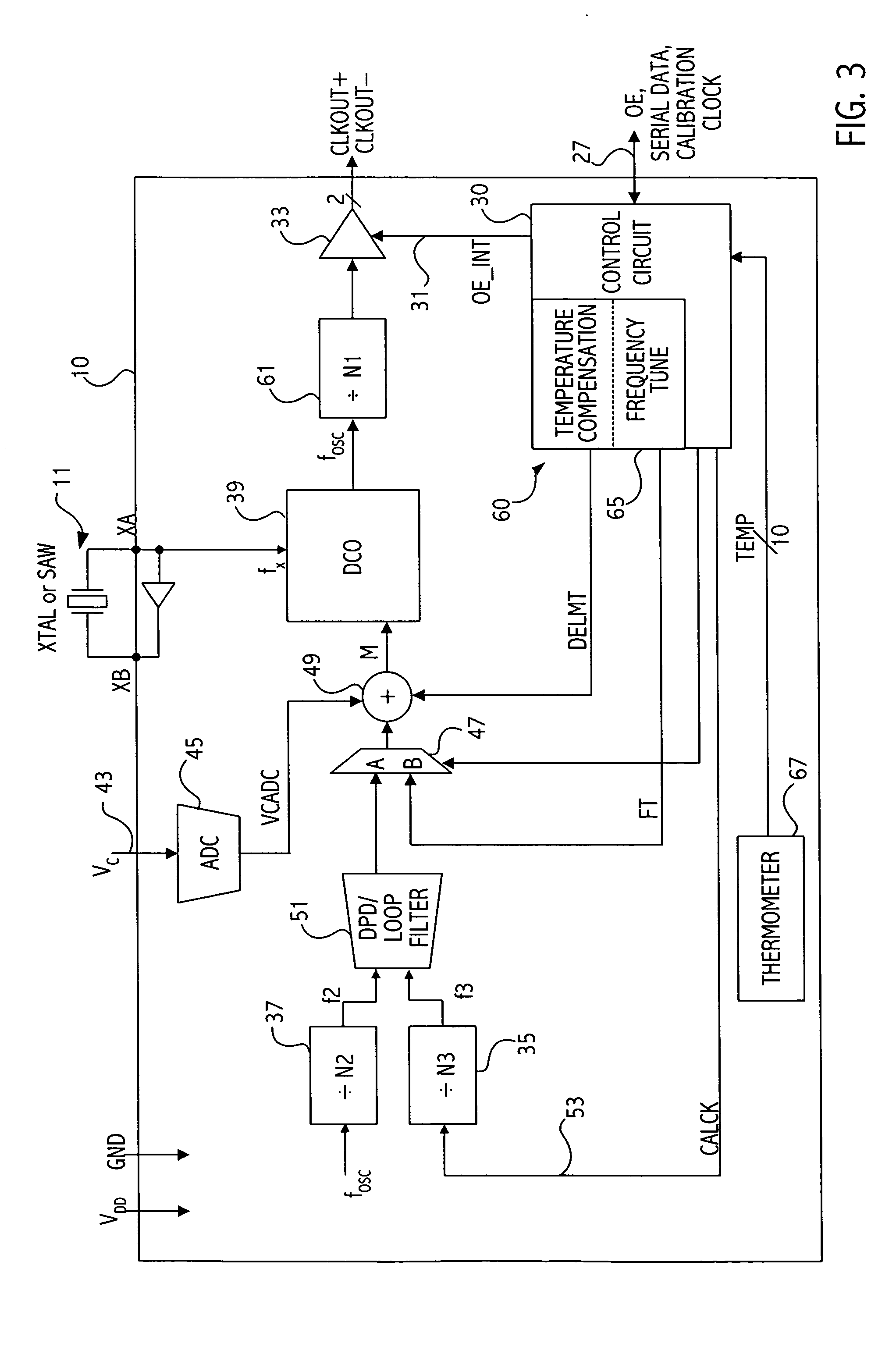

Calibration of oscillator devices

ActiveUS7187241B2Pulse automatic controlGenerator stabilizationDigital controlled oscillatorNon-volatile memory

A clock device having a resonating device such as a crystal of SAW supplying a controllable oscillator such as a digitally controlled oscillator is calibrated by supplying a calibration clock. A phase-locked loop is utilized to generate one or more correction factors causing the PLL to lock to the calibration clock. The one or more correction factors are then stored in non-volatile memory.

Owner:SKYWORKS SOLUTIONS INC

Calibration of oscillator devices

ActiveUS20040222856A1Pulse automatic controlGenerator stabilizationDigital controlled oscillatorNon-volatile memory

A clock device having a resonating device such as a crystal of SAW supplying a controllable oscillator such as a digitally controlled oscillator is calibrated by supplying a calibration clock. A phase-locked loop is utilized to generate one or more correction factors causing the PLL to lock to the calibration clock. The one or more correction factors are then stored in non-volatile memory.

Owner:SKYWORKS SOLUTIONS INC

Digital phase locked loop with selectable normal or fast-locking capability

ActiveUS20050258908A1Fast outputPulse automatic controlTime-division multiplexPhase detectorLoop filter

A digital phase locked loop with fast locking capability includes a digitally controlled oscillator for producing an output signal phase locked to an input reference clock, a phase detector for measuring the phase difference between said input reference clock and a feedback clock, and a loop filter for producing a control signal for the digitally controlled oscillator The loop filter includes a proportional circuit for developing a first signal proportional to said phase difference, an integrator for developing a second integrated signal from said first signal, an adder for adding said first and second signals to develop said control signal, and a weighting circuit, preferably a linear multiplier, for selectively adding extra weight to the first signal at an input to the integrator to shorten the locking time of the phase locked loop in a fast locking mode and to rapidly achieve a stable frequency in holdover mode.

Owner:ZARLINK SEMICON LTD

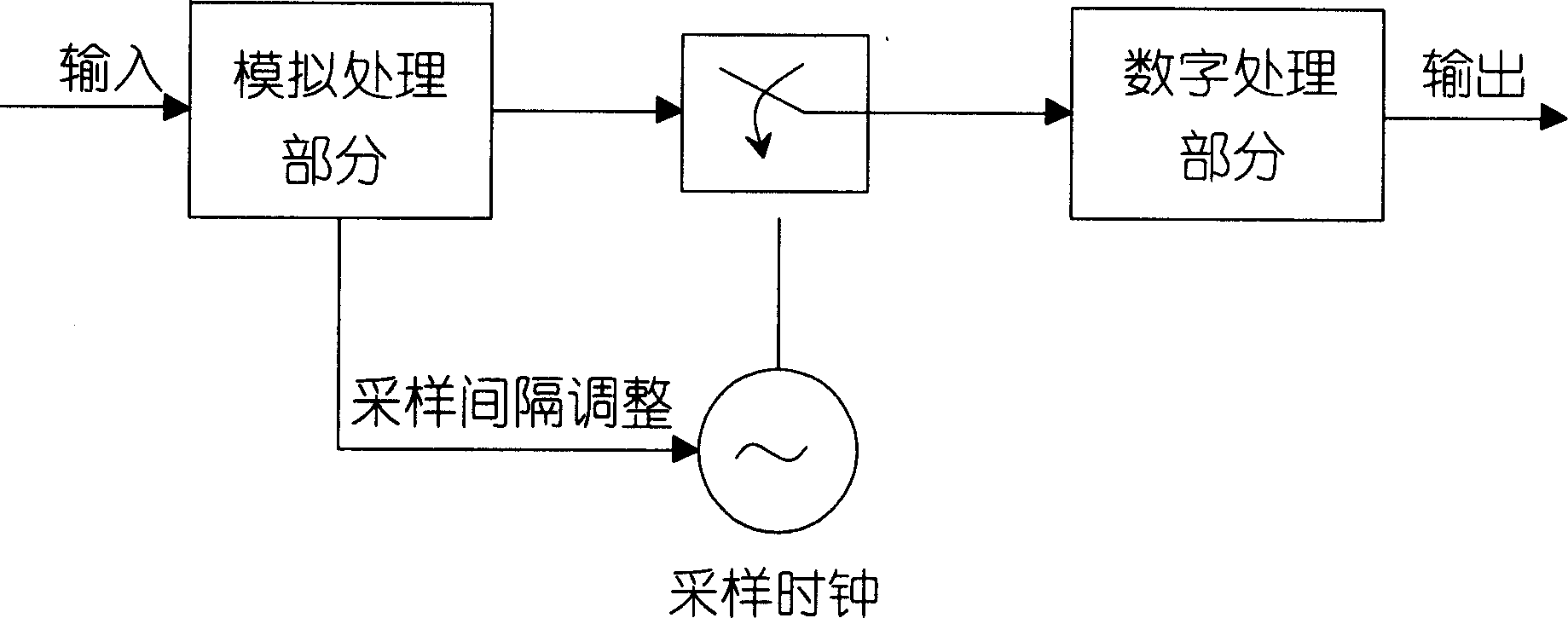

Apparatus and method for processing sampling frequency deviation tracking signal in orthogonal frequency division multiplex system

A sample frequency offset tracing signal process device of an FDM system and a method includes a digital converter, an inter potation filter, a FIR filter, a serial-parallel transformer, a rough timing test device and a latter timing error test device, among which, an interpolation control loop composed of orderly connected loop filter device, a re-sample control device and a digital control oscillator is set for computing the interpolation control offset value to regulate the interpolation positions by related offset computation between the latter timing error test device and the interpolation filter and the integer part of the timing error got by the latter timing error test device is used to regulate the Fourier transformation computation window position, the decimal fraction part is used as the error input signal of the loop to drive the loop filter and re-sample controller, the digital control oscillator and computing the deviation value by the phase deviation value to regulate the position.

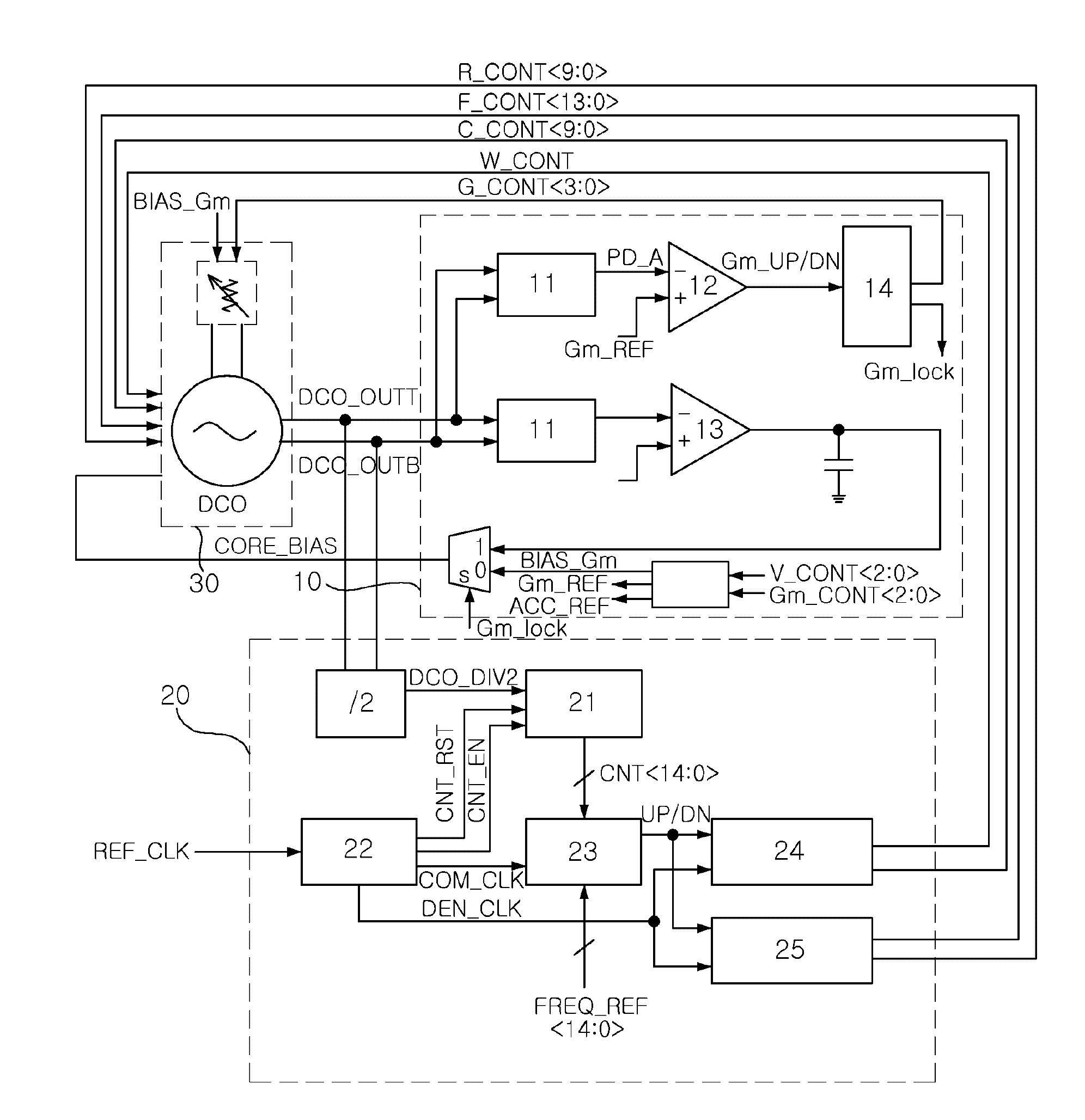

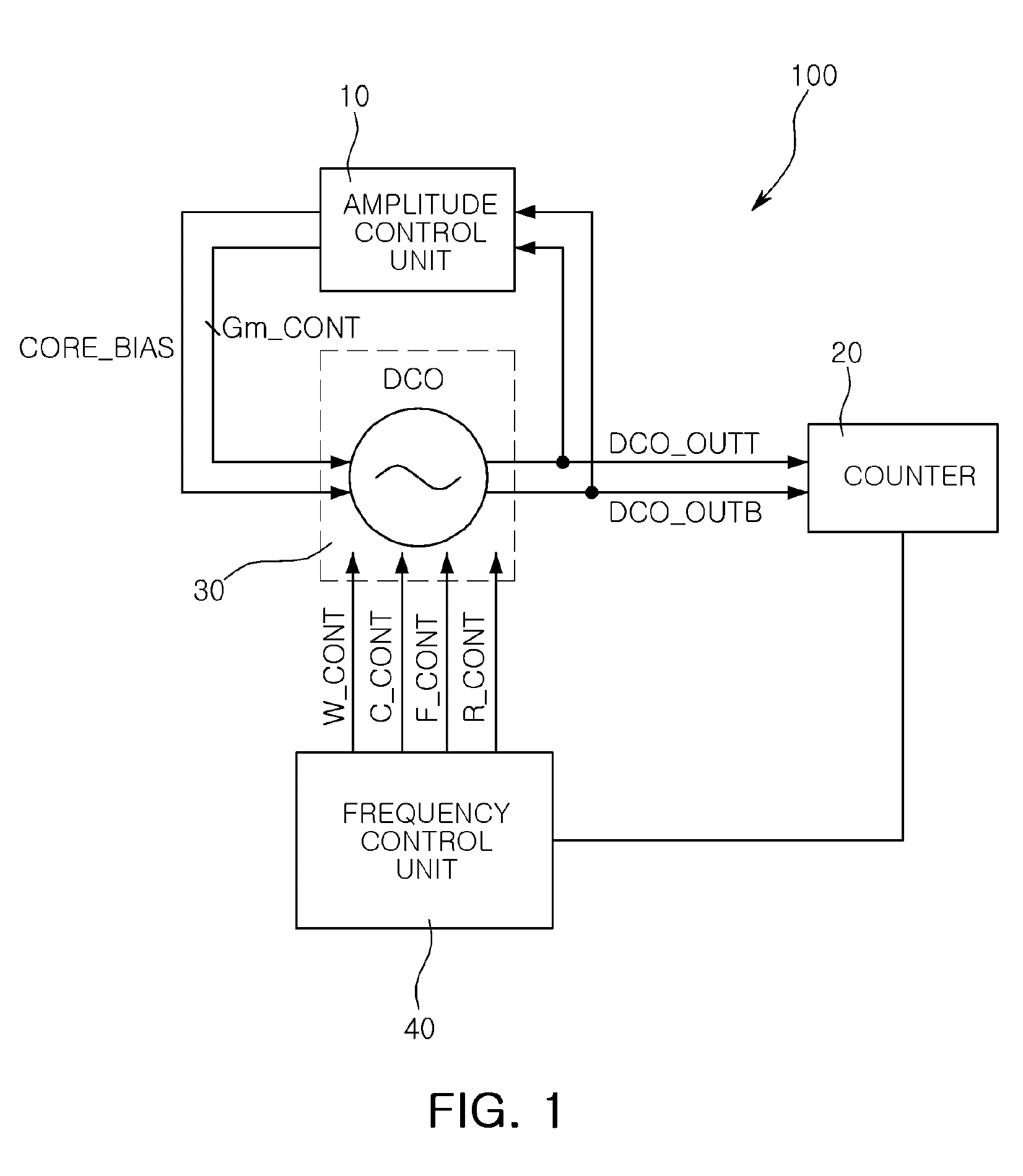

Control circuit and apparatus for digitally controlled oscillator

InactiveUS20140035684A1Compensation changesPulse automatic controlDigital controlled oscillatorPeak value

There are provided a control circuit for a digitally controlled oscillator and a control apparatus for a digitally controlled oscillator using the same. The control circuit for a digitally controlled oscillator includes: a peak detection circuit detecting amplitude of a signal output from the digitally controlled oscillator; and a transconductance control circuit comparing an output of the peak detection circuit with a predetermined reference signal to control a transconductance value of a negative transconductance circuit included in the digitally controlled oscillator.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD +1

Direct digital synthesizer for reference frequency generation

InactiveUS20100052797A1Reduce power consumptionLow frequency signalPulse automatic controlDigital data processing detailsFrequency generationEngineering

A direct digital frequency synthesizer having a multi-modulus divider, a numerically controlled oscillator and a programmable delay generator. The multi-modulus divider receives an input clock having an input pulse frequency fosc and outputs some integer fraction of those pulses at an instantaneous frequency fVp that is some integer fraction (1 / P) of the input frequency. The multi-modulus divider selects between at least two ratios of P(1 / P or 1 / P+1) in response to a signal from the numerically controlled oscillator. The numerically controlled oscillator receives a value which is the accumulator increment (i.e. the number of divided pulse edges) required before an overflow occurs that causes the multi-modulus divider to change divider ratios in response to receiving an overflow signal. The numerically controlled oscillator also outputs both the overflow signal and a delay signal to the delay generator that further controls the frequency of the multi-modulus divider output signal (Vp) to provide an output signal (VD) with an fOUT that has improved phase and timing jitter performance over prior art direct digital frequency synthesizer architectures.

Owner:CYMATICS LAB CORP

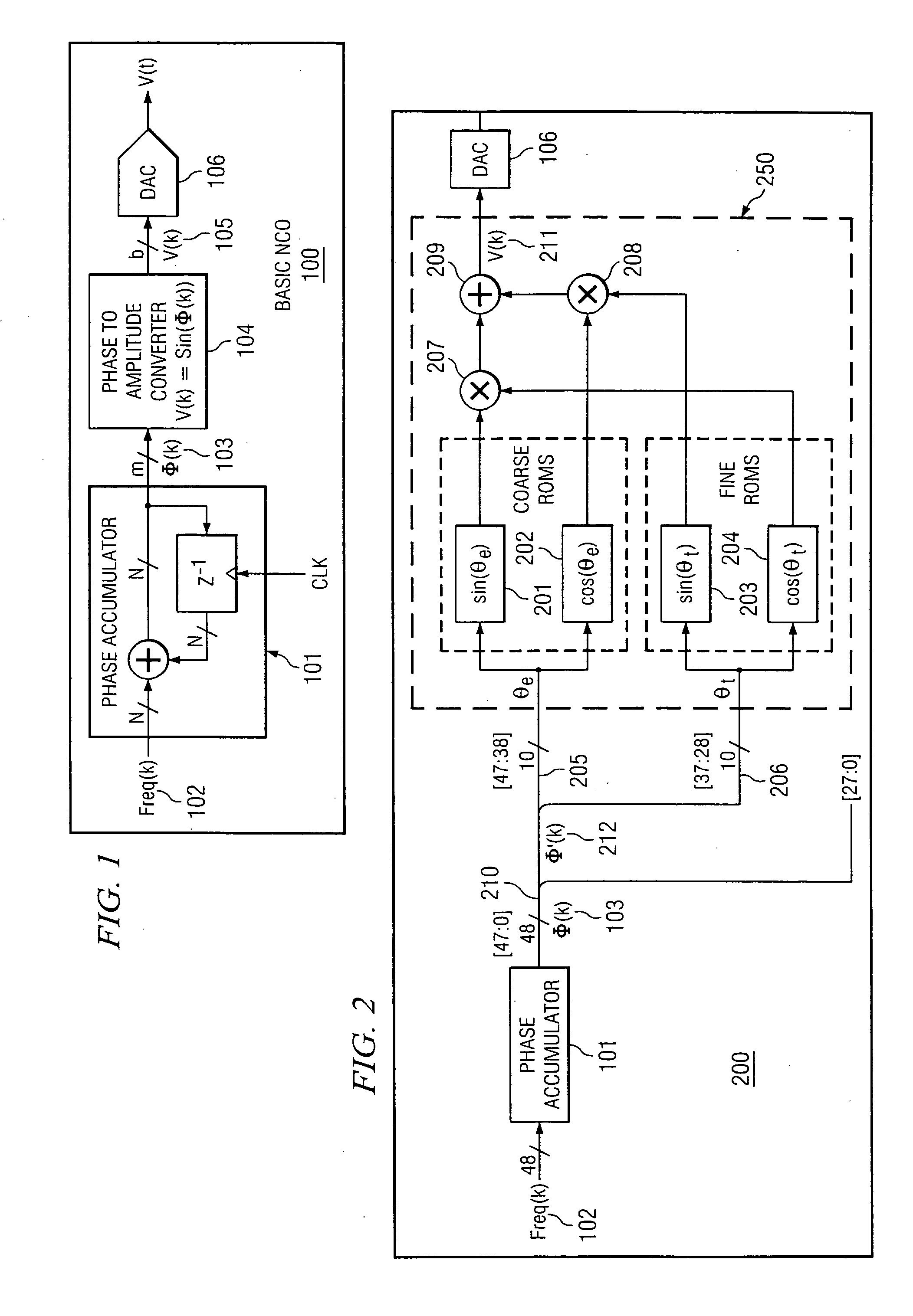

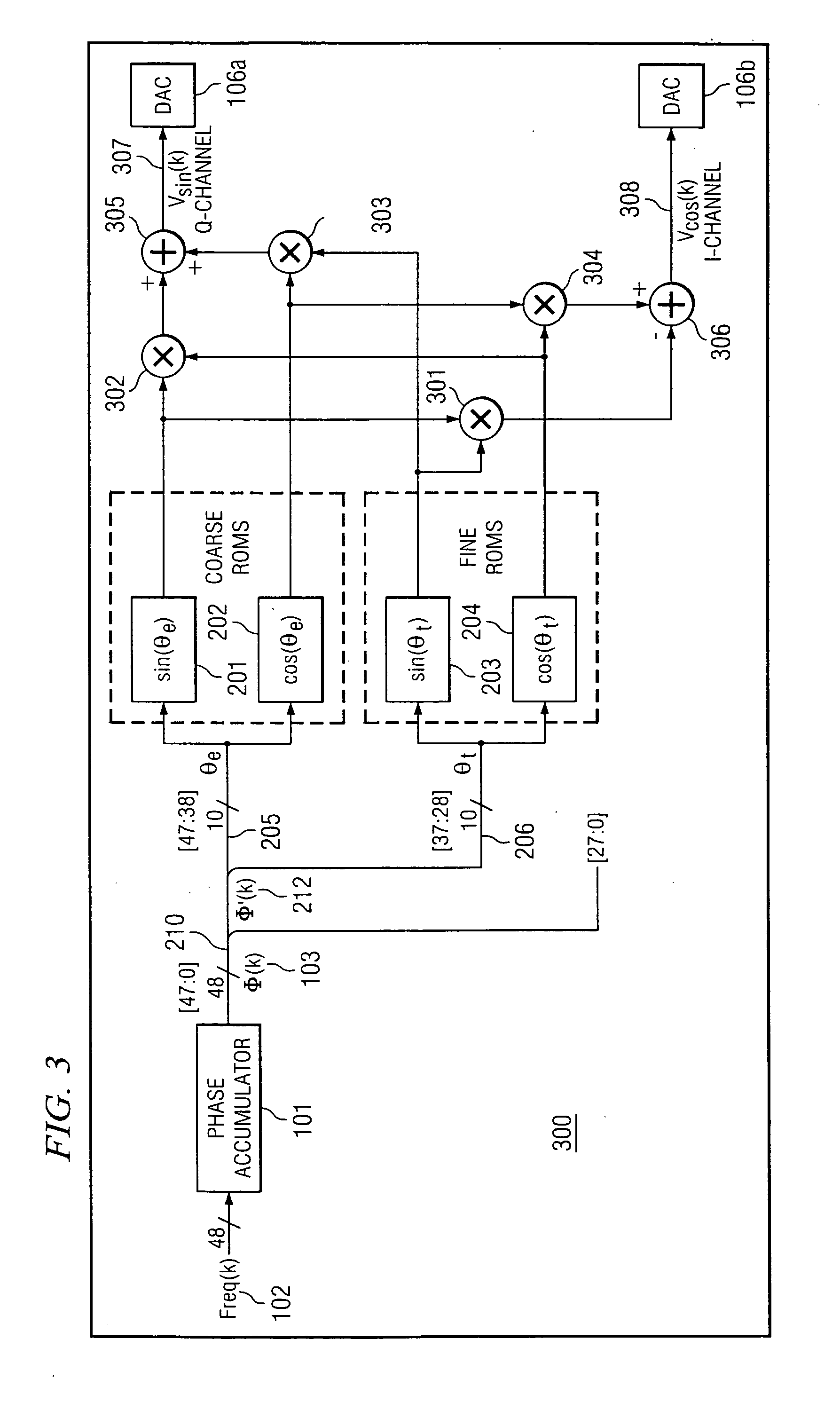

Numerically controlled oscillator and method of operation

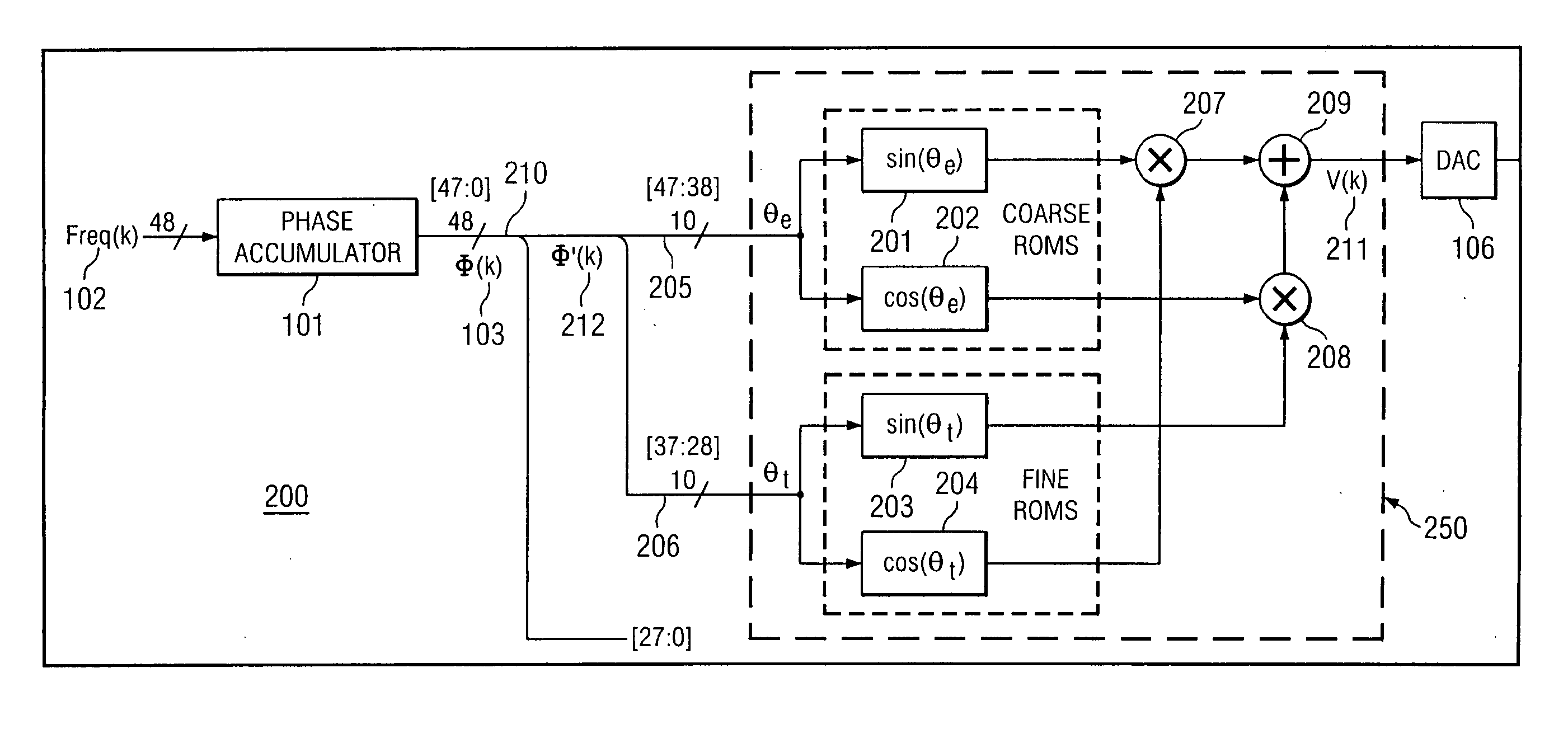

InactiveUS20050278403A1Reduce amountReduce the amount requiredDigital function generatorsDigital controlled oscillatorDigitally controlled oscillator

In one embodiment, the present invention is directed to a numerically controlled oscillator. The numerically controlled oscillator comprises: a phase accumulator for receiving an input digital word; and a phase to amplitude converter that is operatively coupled to the phase accumulator to receive a first phase signal and a second phase signal, the phase to amplitude converter calculating a sine value and a cosine value of each of the first and second phase signals, the phase to amplitude converter generating a summation of (i) a product of the sine value of the first phase signal and the cosine value of the second phase signal and (ii) a product of the sine value of the second phase signal and the cosine value of the first phase signal.

Owner:AGILENT TECH INC

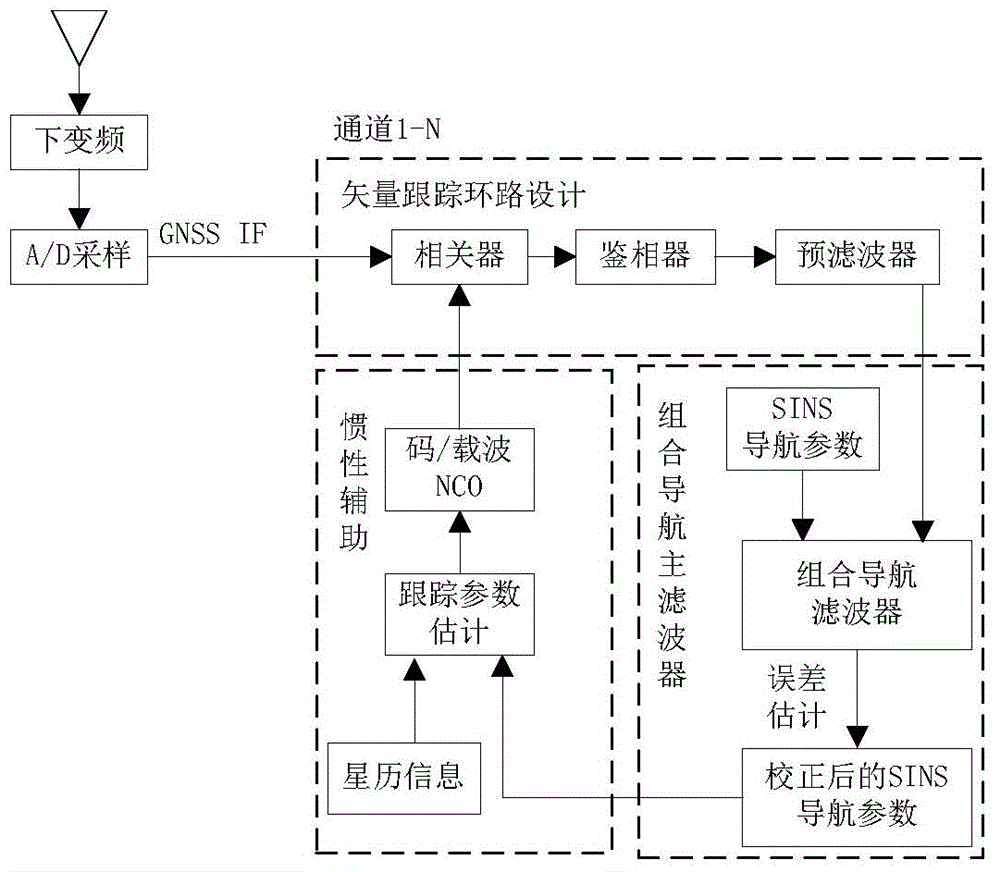

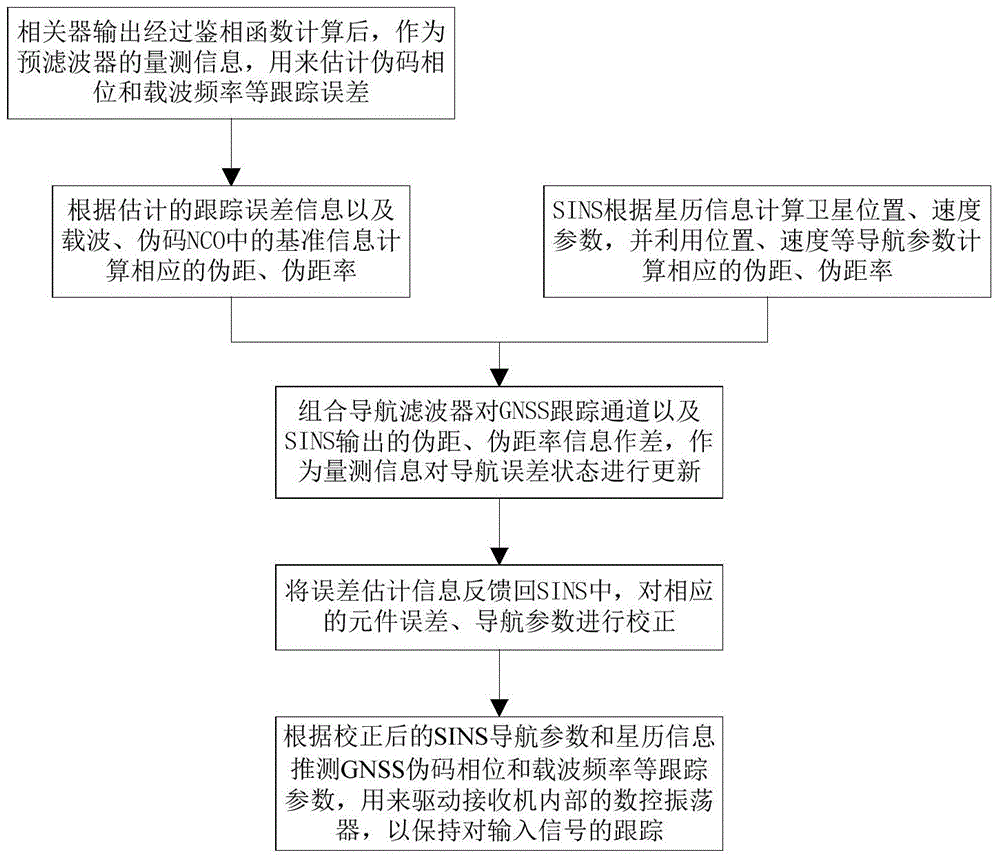

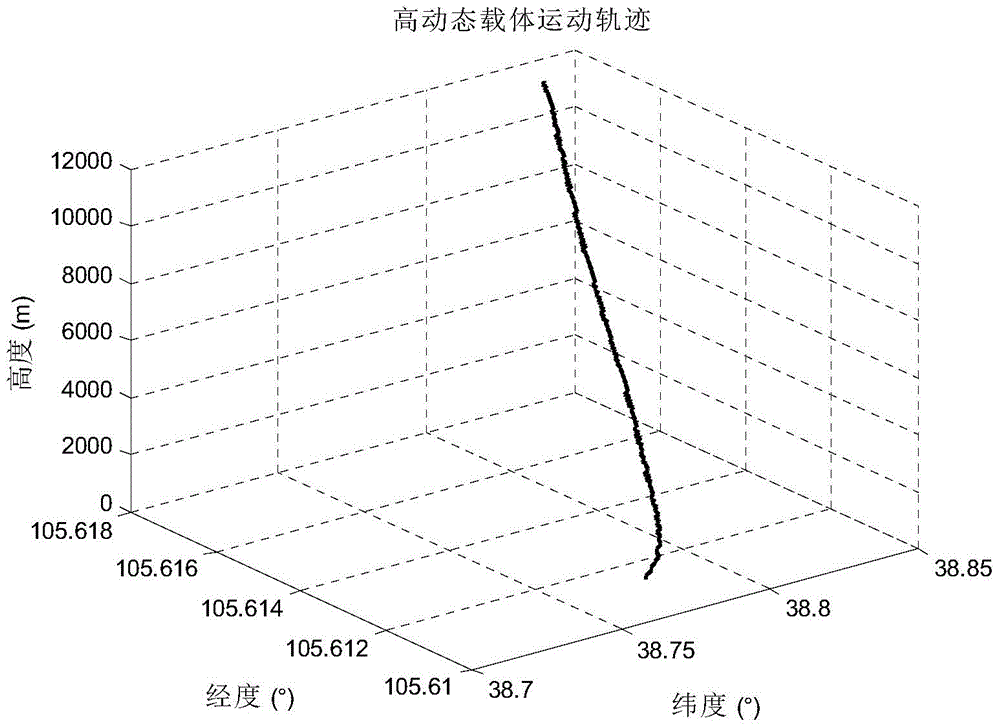

Vector tracking-based GNSS/SINS deep integrated navigation method

InactiveCN104931995ARealize assistanceImprove performanceNavigation by speed/acceleration measurementsSatellite radio beaconingAnti jammingVector tracking

The invention discloses a vector tracking-based GNSS / SINS deep integrated navigation method. The method includes the following steps that: after in-phase orthogonal signals outputted by a correlator are calculated by a phase discrimination function, an obtained phase discrimination result is adopted as measurement information of a pre-filter, so that a pre-filter model can be constructed to estimate tracking error information, and therefore, the pseudo-range and pseudo-range rate of a GNSS tracking channel can be obtained; an integrated navigation main filter performs processing according to the pseudo-ranges and pseudo-range rates outputted by the GNSS tracking channel and an SINS, so that pseudo-range deviation and range rate deviation can be obtained and are adopted as measurement variables quantity, and the measurement quantity is used for updating navigation error state variables, and updated navigation error parameters are fed back to the SINS, so that the navigation parameters of the SINS can be calibrated; and an integrated navigation system infers the signal tracking parameters of a GNSS according to the calibrated SINS navigation parameters and ephemeris information so as to control the local pseudo codes of a receiver and a carrier digital-controlled oscillator, and therefore, tracking for input signals can be maintained. The method of the invention has excellent anti-jamming performance and dynamic tracking ability, and has a bright application prospect.

Owner:NANJING UNIV OF SCI & TECH

Low complexity synchronization for wireless transmission

ActiveUS7394870B2Inexpensive and low-complexity synchronization for communication systemsEliminate needAmplitude-modulated carrier systemsSynchronisation signal speed/phase controlDigital dataCommunications system

A receiver, system and method for providing symbol timing recovery that allows for inexpensive and low-complexity synchronization for communication systems. A receiver receives a signal including digital data in the form of packets that is transmitted from a transmitter. The receiver uses information contained in each of the packets to align a phase of the receiver clock with a phase of the transmitter clock. The receiver further controls a sampling device such that the in-phase (I) and quadrature (Q) components are sampled at an optimum sample rate and at an optimum instance of time without requiring a numerically controlled oscillator or voltage controlled oscillator.

Owner:MICROCHIP TECH INC

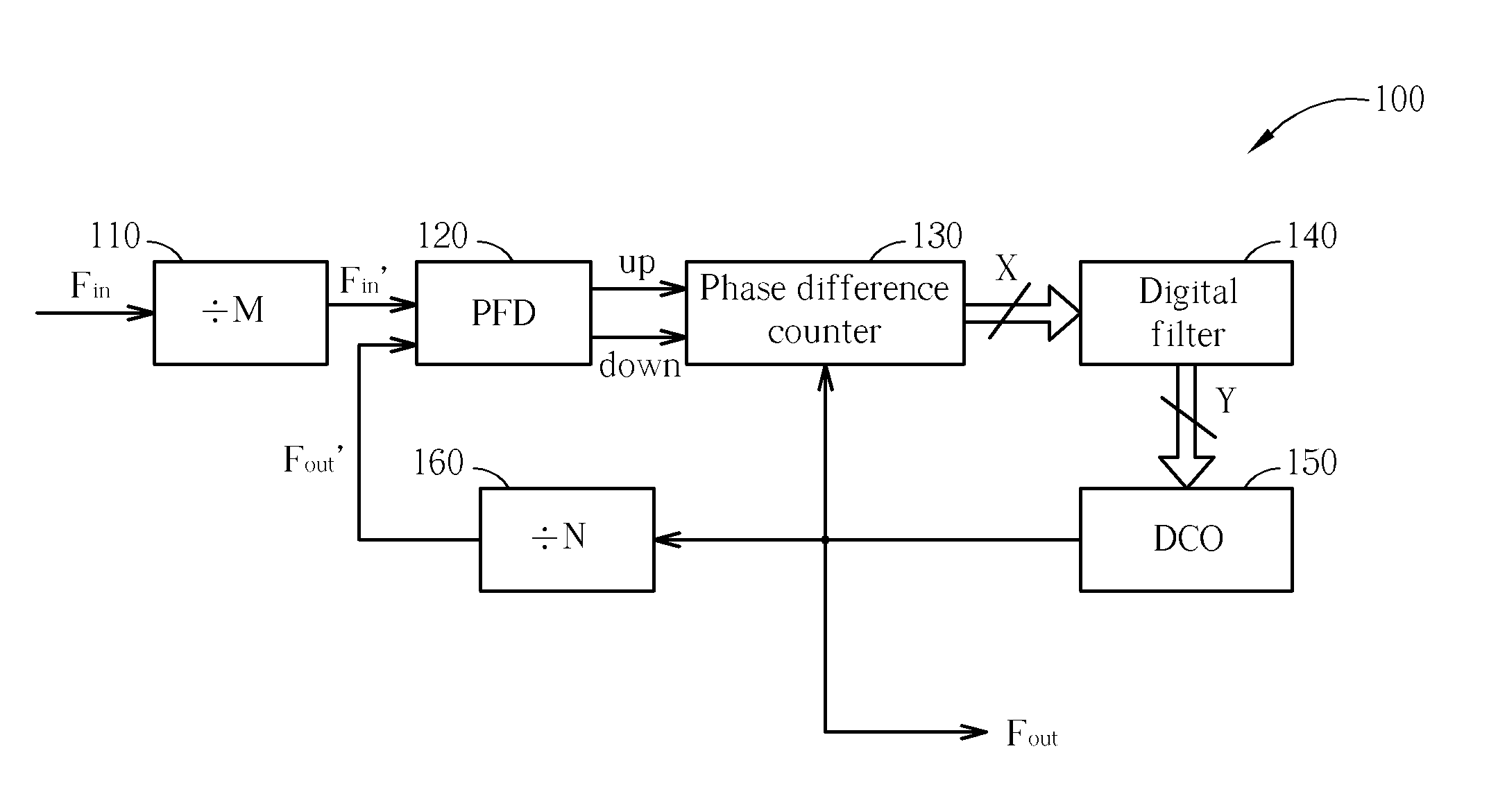

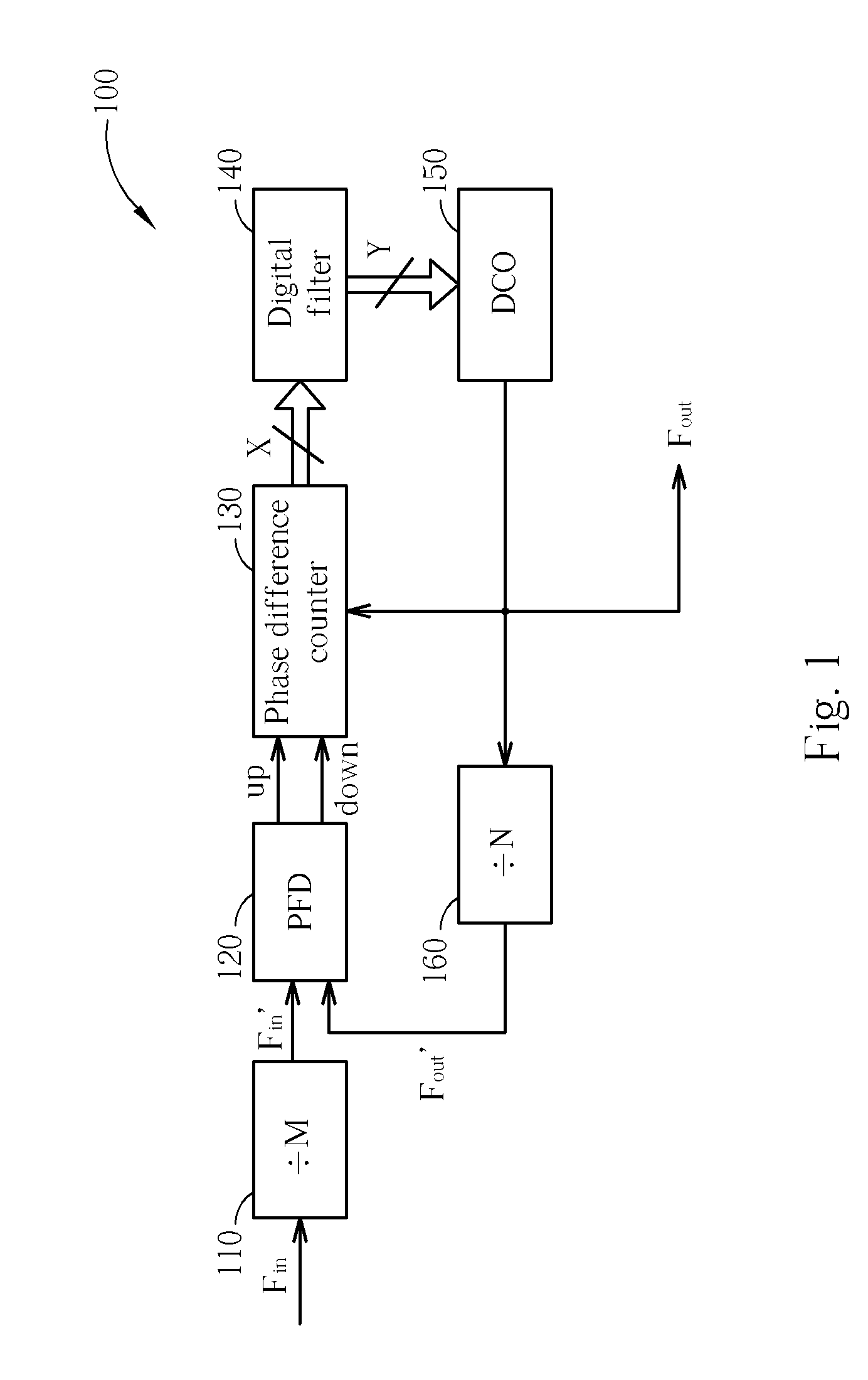

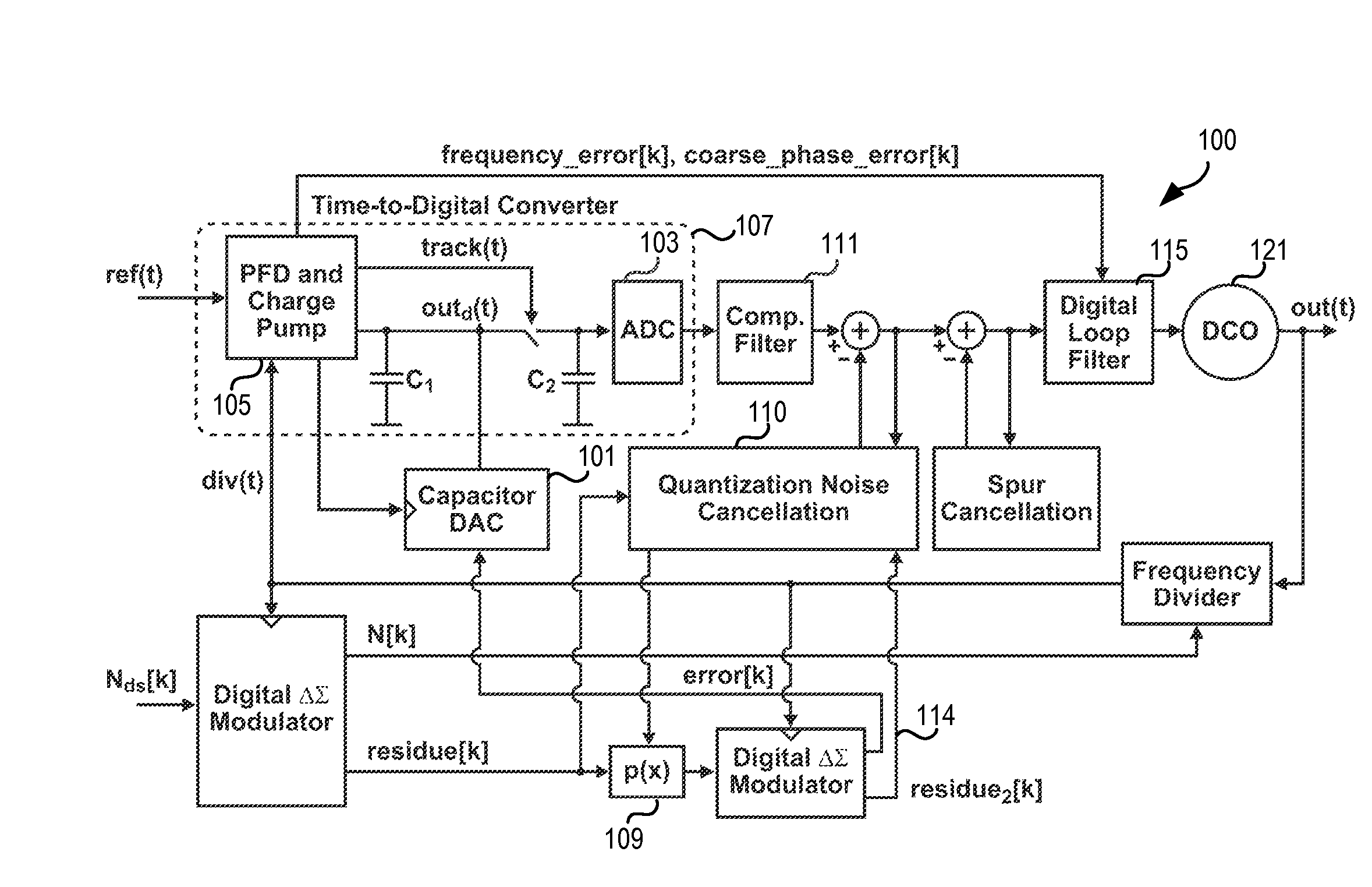

All-digital phase-locked loop

ActiveUS20050206458A1Pulse automatic controlAngle demodulation by phase difference detectionPhase differenceControl signal

An all-digital phase-locked loop (ADPLL) includes: a digital phase frequency detector (PFD) for generating a detection signal by detecting frequency difference and phase difference between a reference signal and a feedback signal; a digital phase difference counter coupled to the digital PFD for sampling the detection signal according to an oscillator signal to thereby generate a count value; a digital filter coupled to the digital phase difference counter for generating a control signal according to the count value; a digital controlled oscillator (DCO) coupled to the digital filter for generating the oscillator signal according to the control signal; and a frequency divider coupled to the DCO and the digital PFD for generating the feedback signal by dividing the oscillator signal.

Owner:REALTEK SEMICON CORP

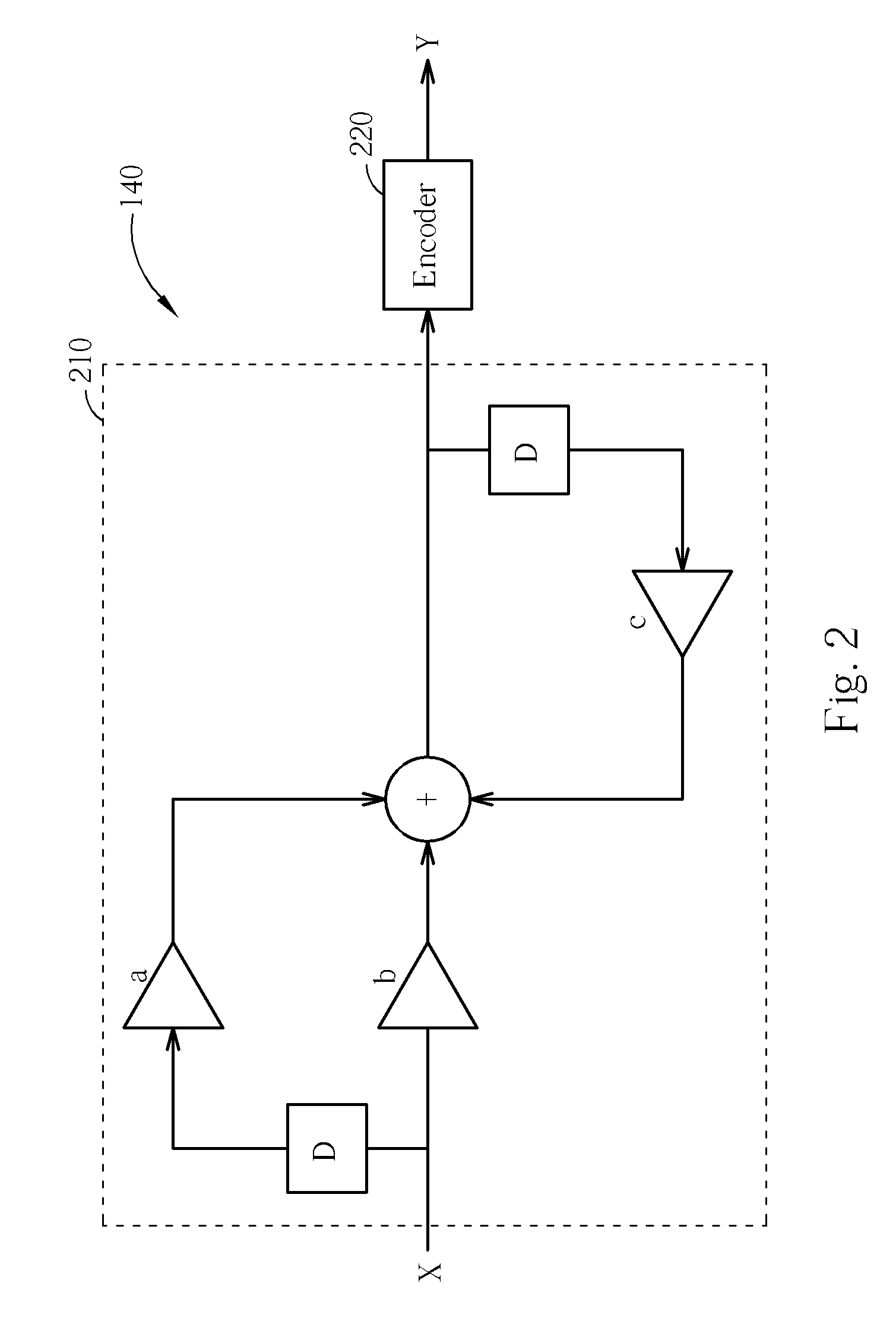

Phase lock loop and digital control oscillator thereof

InactiveUS20070291173A1Rapid responseIncrease the number of digitsPulse automatic controlEngineeringDigital controlled oscillator

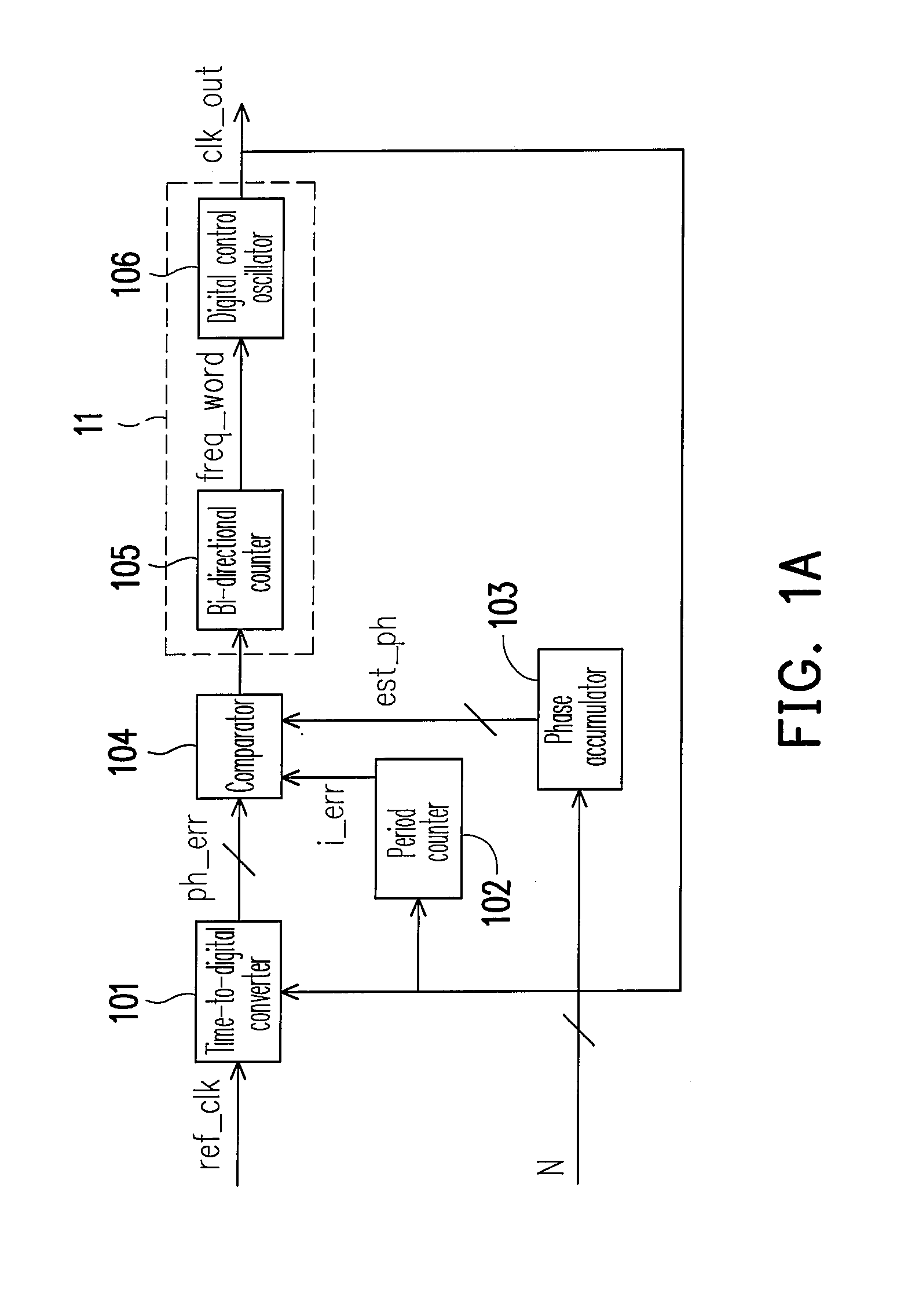

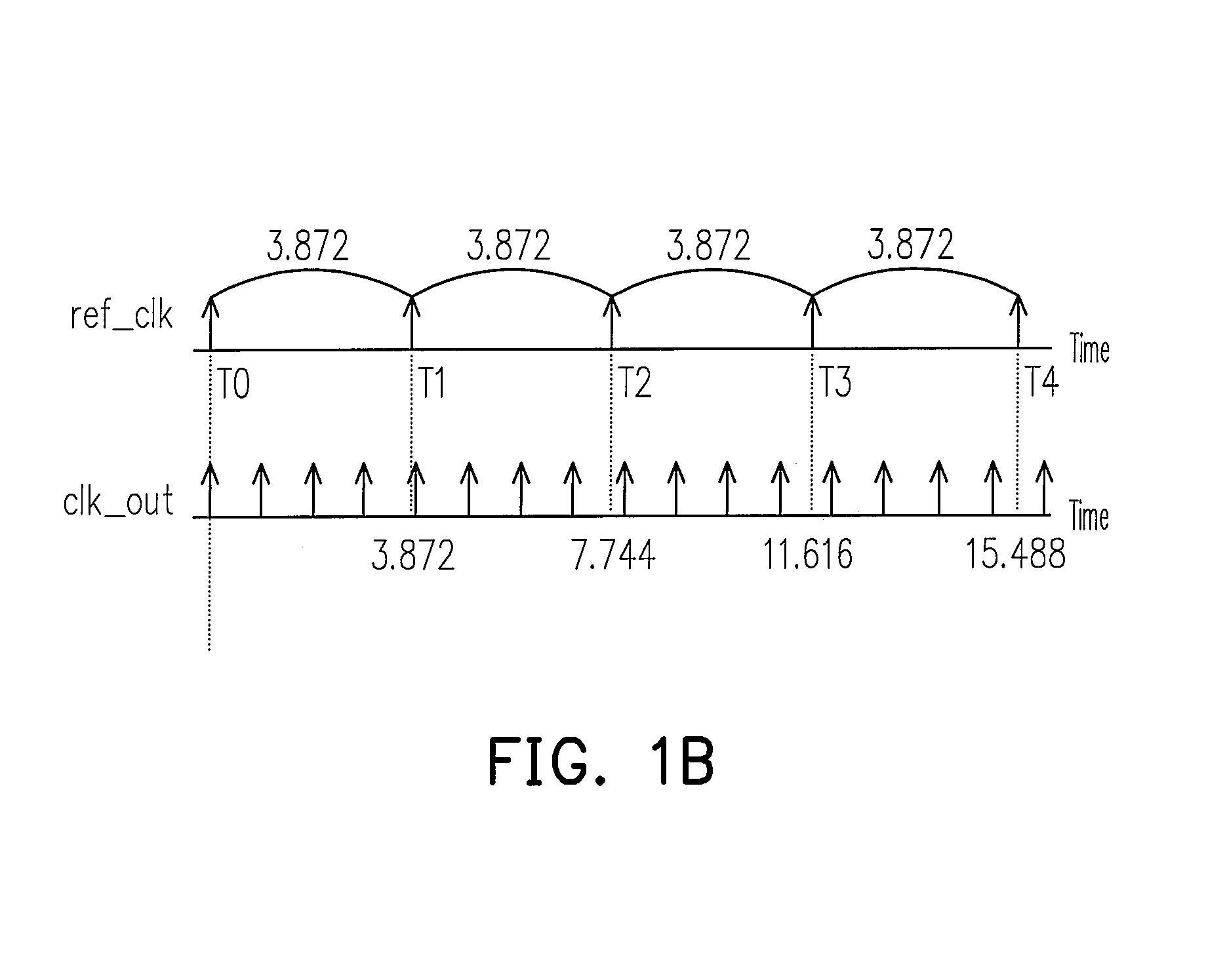

A phase lock loop including a time-to-digital converter, a period counter, a phase accumulator, a comparator, and an output unit is disclosed. The time-to-digital converter outputs a detected phase error based on the timing difference between a reference clock signal and an output clock signal. The period counter increases a first accumulative value in each period of the output clock signal. The phase accumulator increases a second accumulative value in each period of the reference clock signal and outputs the second accumulative value as an estimative phase error between the reference clock signal and the output clock signal in next period. The comparator outputs a frequency correction signal according to the detected phase error, the first accumulative value, and the estimative phase error. The output unit provides the output clock signal and adjusts its frequency according to the frequency correction signal.

Owner:NOVATEK MICROELECTRONICS CORP

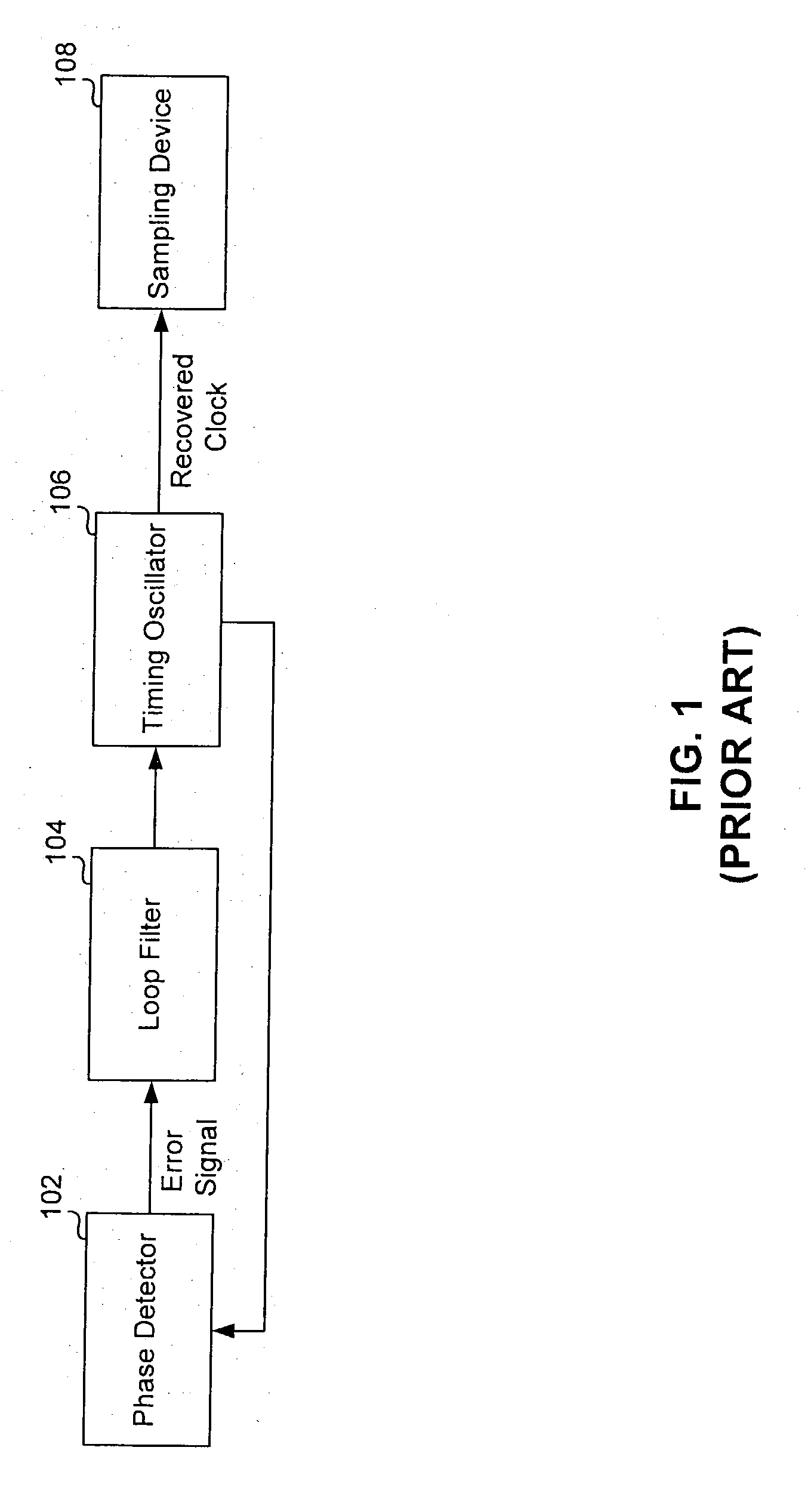

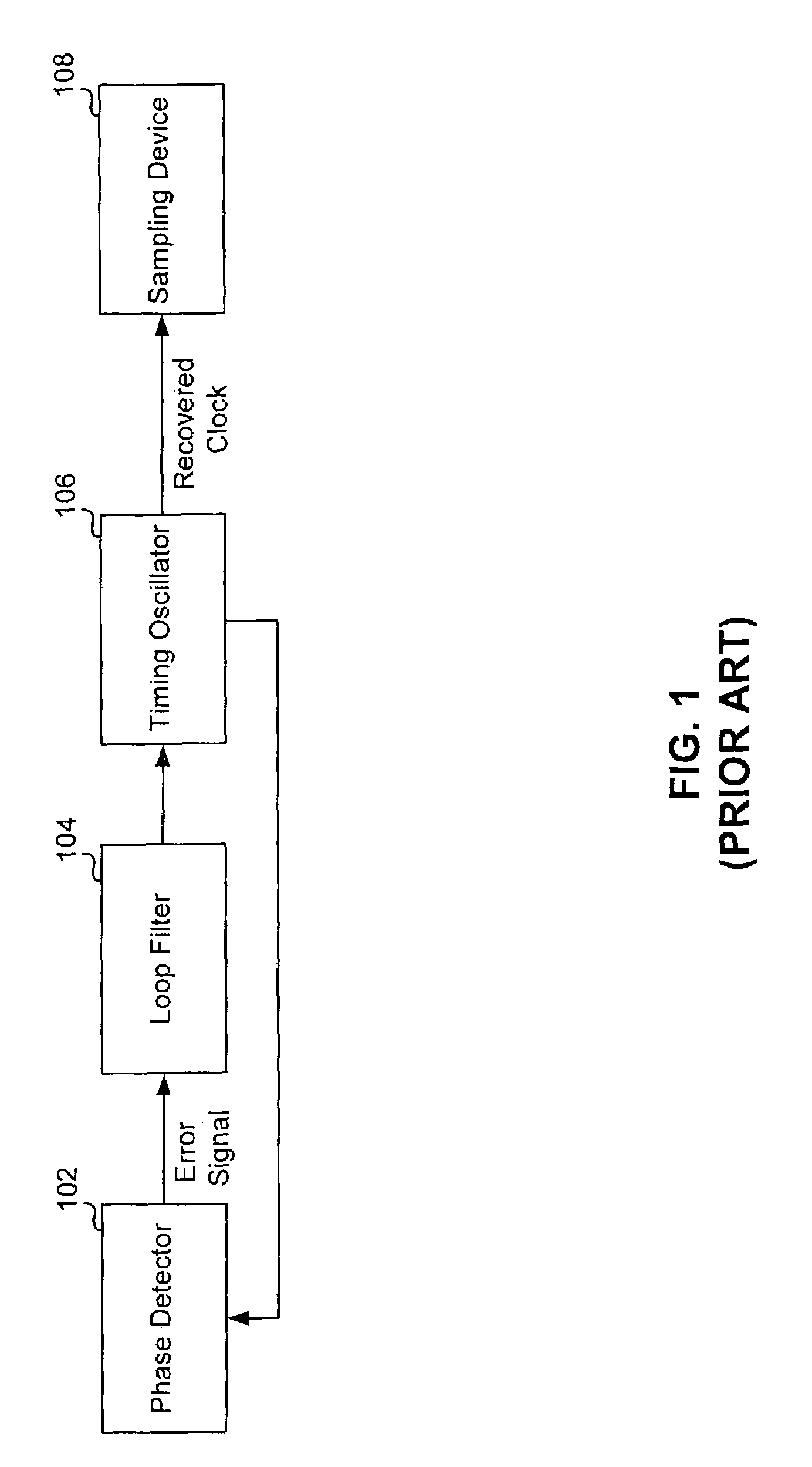

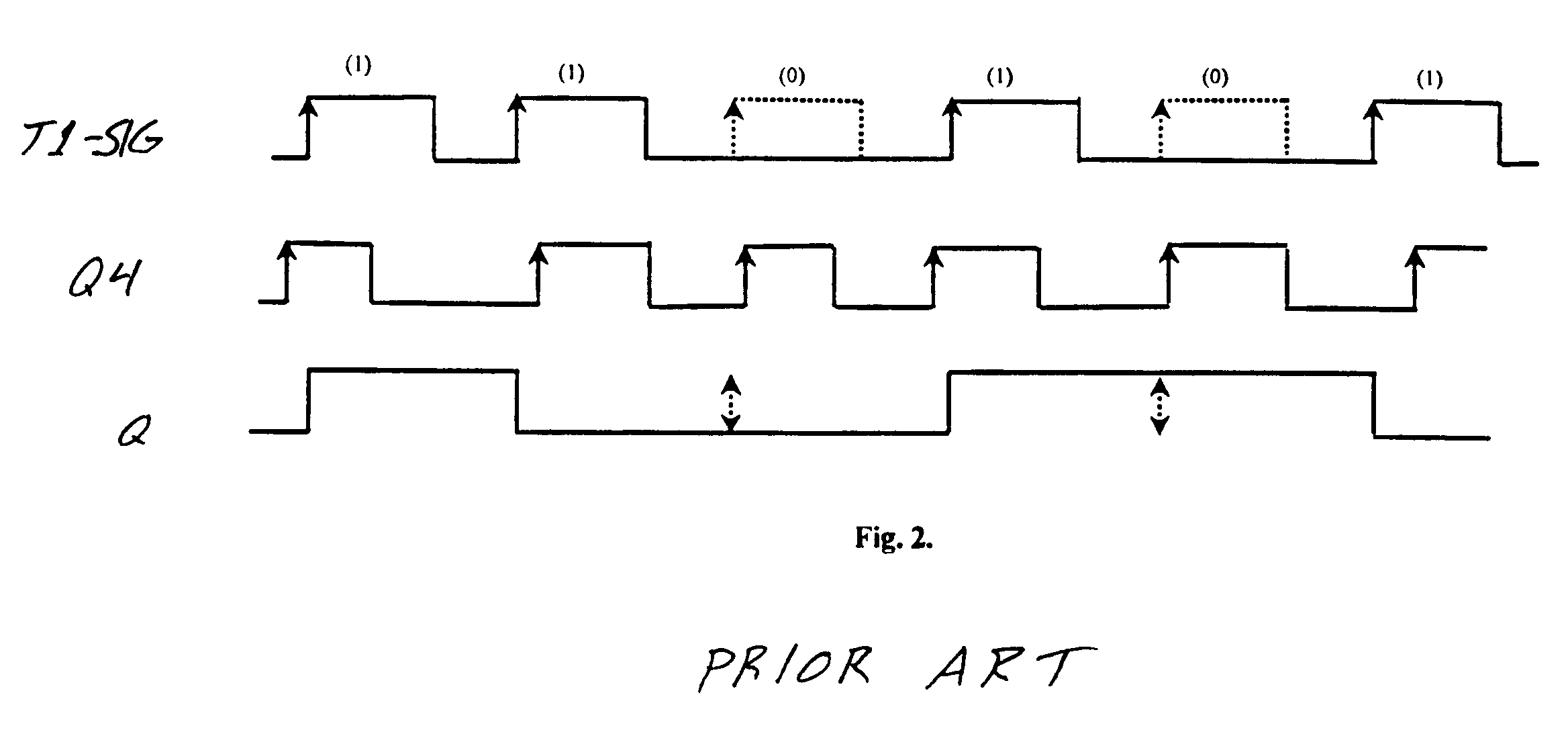

Clock recovery and detection of rapid phase transients

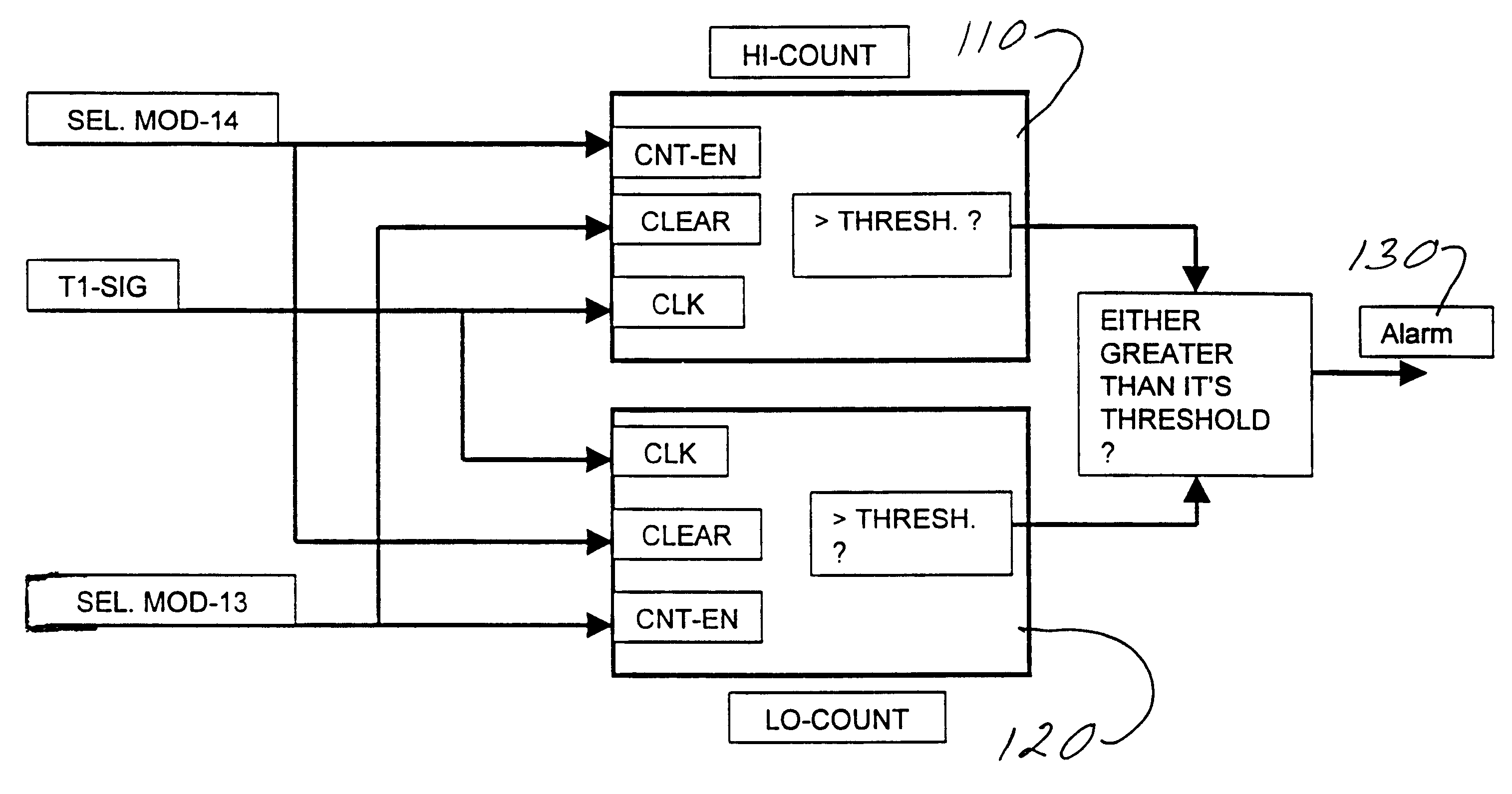

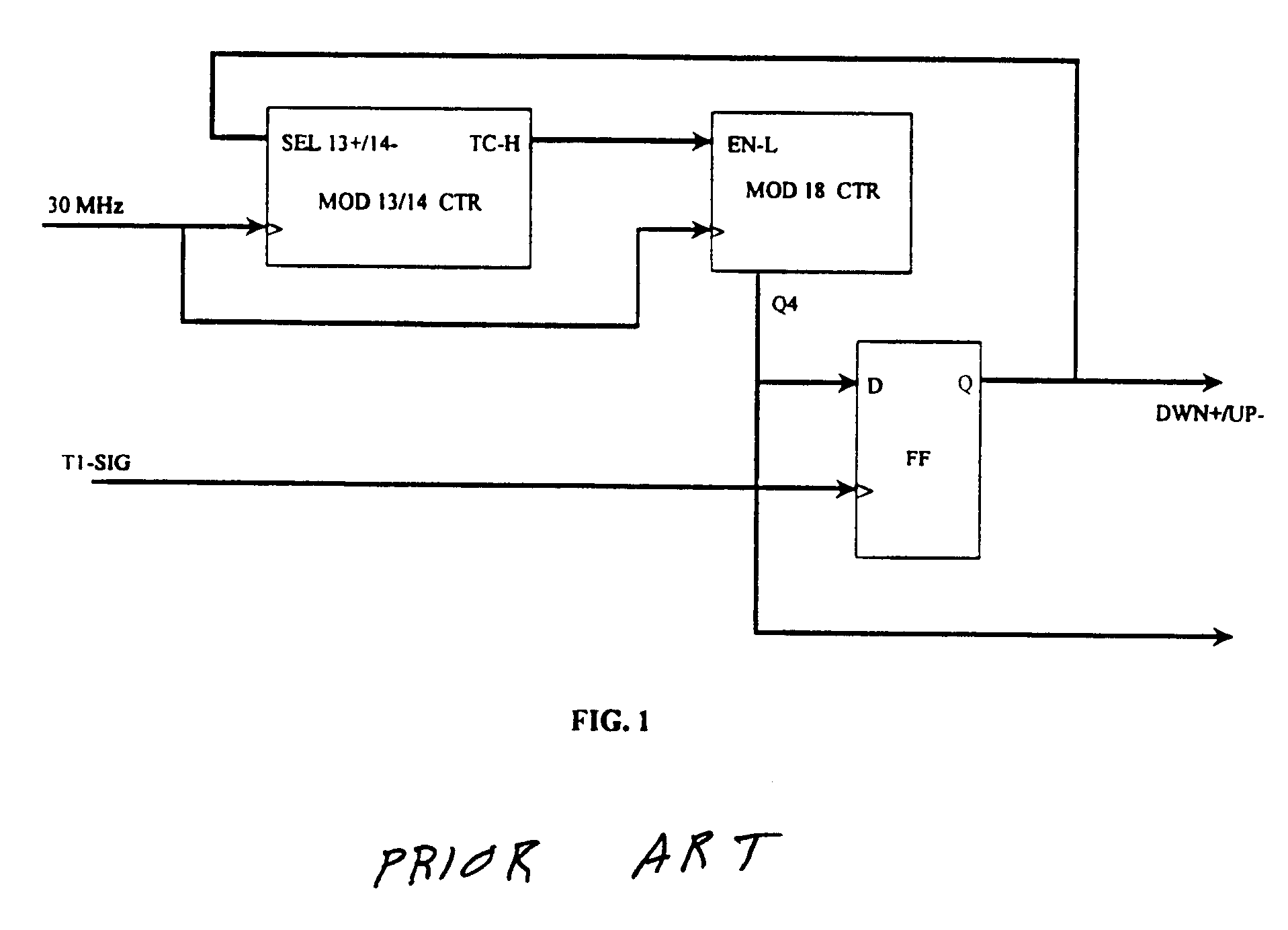

Systems and methods are described for clock recovery and detection of rapid phase transients. An apparatus includes: a numerically controlled oscillator; a phase detector coupled to the numerically controlled oscillator; and a multiplexer coupled to the phase detector and the numerically controlled oscillator, wherein a) the phase detector sets a state variable indicator to either i) a high value if an output phase of the numerically controlled oscillator lags an incoming signal phase, or ii) a low value if the output phase leads the incoming signal phase, b) the multiplexer sends either i) a high increment to the numerically controlled oscillator if the state variable indicator has been set to the high value, or ii) a low increment to the numerically controlled oscillator if the state variable indicator has been set to the low value, and c) the numerically controlled oscillator either i) advances the output phase if the high increment has been sent to the numerically controlled oscillator, or ii) retards the output phase if the low increment has been sent to the numerically controlled oscillator. A method includes incrementing a high counter once every clock cycle if a state variable indicator is high; clearing a low counter if the state variable indicator is high; incrementing the low counter once every clock cycle if the state variable indicator is low; clearing the high counter if the state variable indicator is low; and triggering an alarm signal if either i) the low counter exceeds a low count threshold or ii) the high counter exceeds a high count threshold.

Owner:MICROSEMI FREQUENCY & TIME

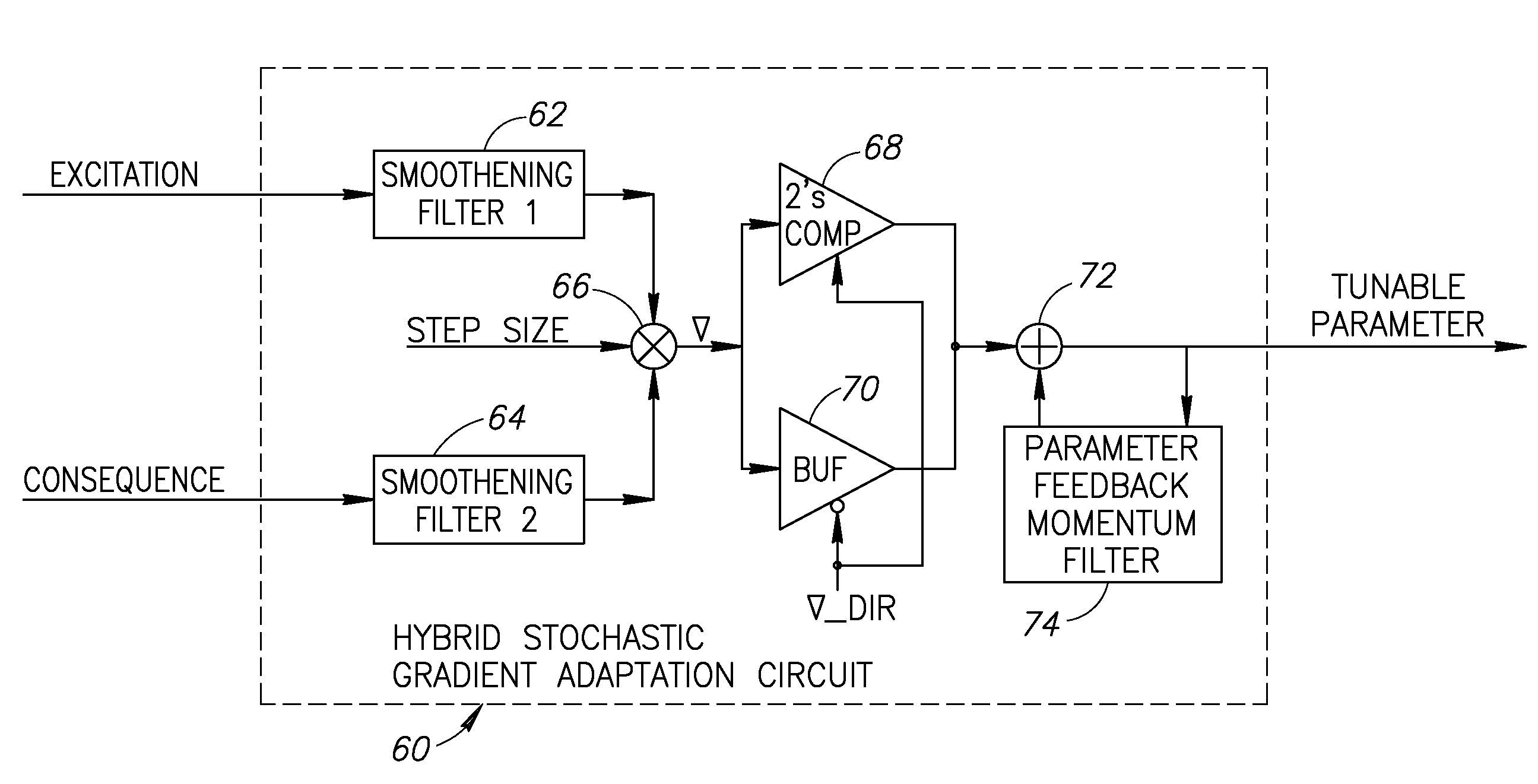

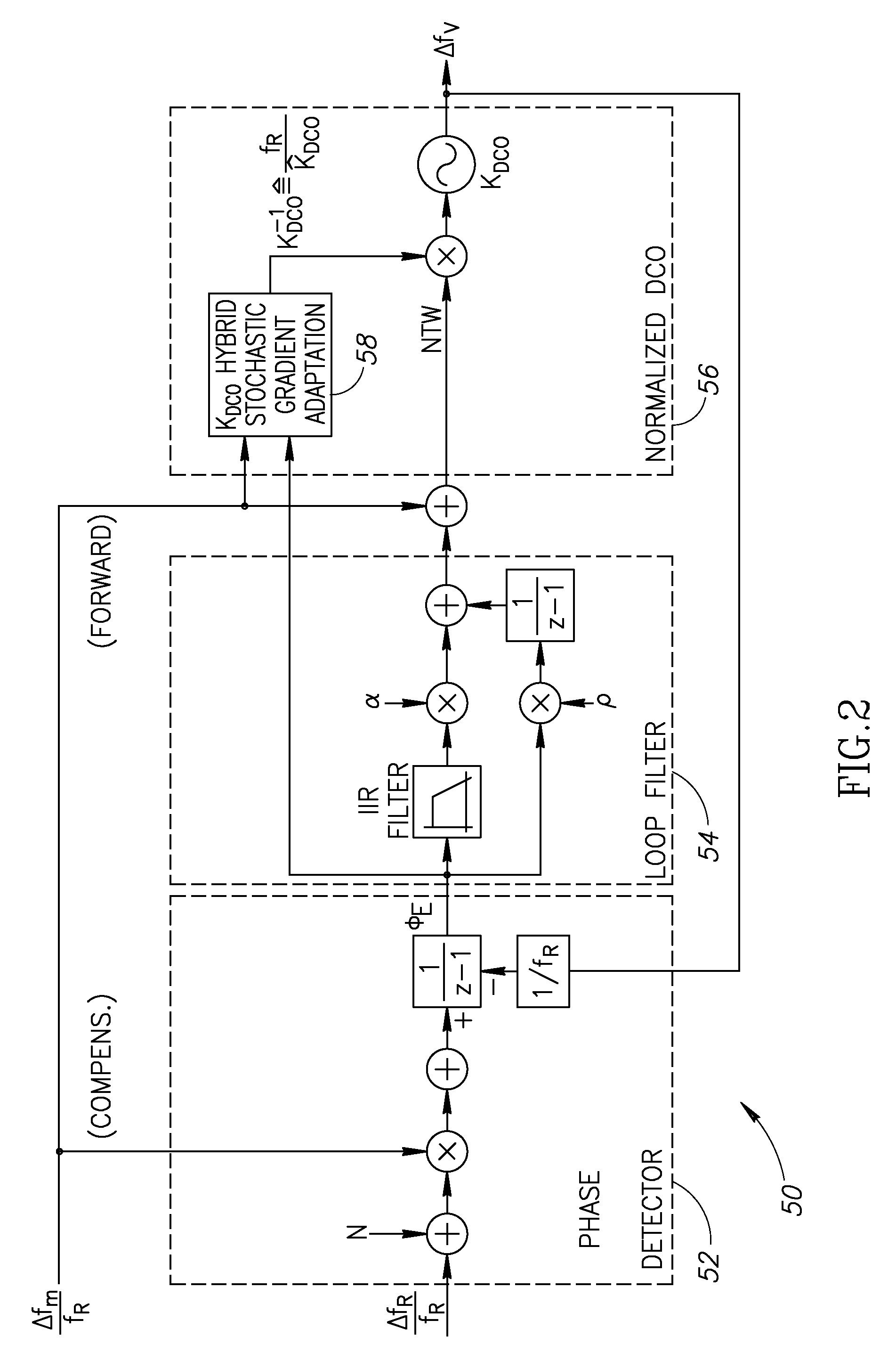

Hybrid stochastic gradient based digitally controlled oscillator gain KDCO estimation

ActiveUS7365609B2Tighter convergenceGood estimatePulse automatic controlAngle modulation detailsMomentumDigital controlled oscillator

A novel hybrid stochastic gradient adaptation apparatus and method for calibrating the gain of an RF or non-RF digitally controlled oscillator (DCO). The adaptation algorithm determines a true stochastic gradient between a forcing function and its corresponding system measure to estimate the system parameters being adapted. A momentum term is generated and injected into the adaptation algorithm in order to stabilize the algorithm by adding inertia against any large transient variations in the input data. In the case of adaptation of DCO gain KDCO, the algorithm determines the stochastic gradient between time varying calibration or actual modulation data and the raw phase error accumulated in an all digital phase locked loop (ADPLL). Two filters preprocess the observable data to limit the bandwidth of the computed stochastic gradient providing a trade-off between sensitivity and settling time.

Owner:TEXAS INSTR INC

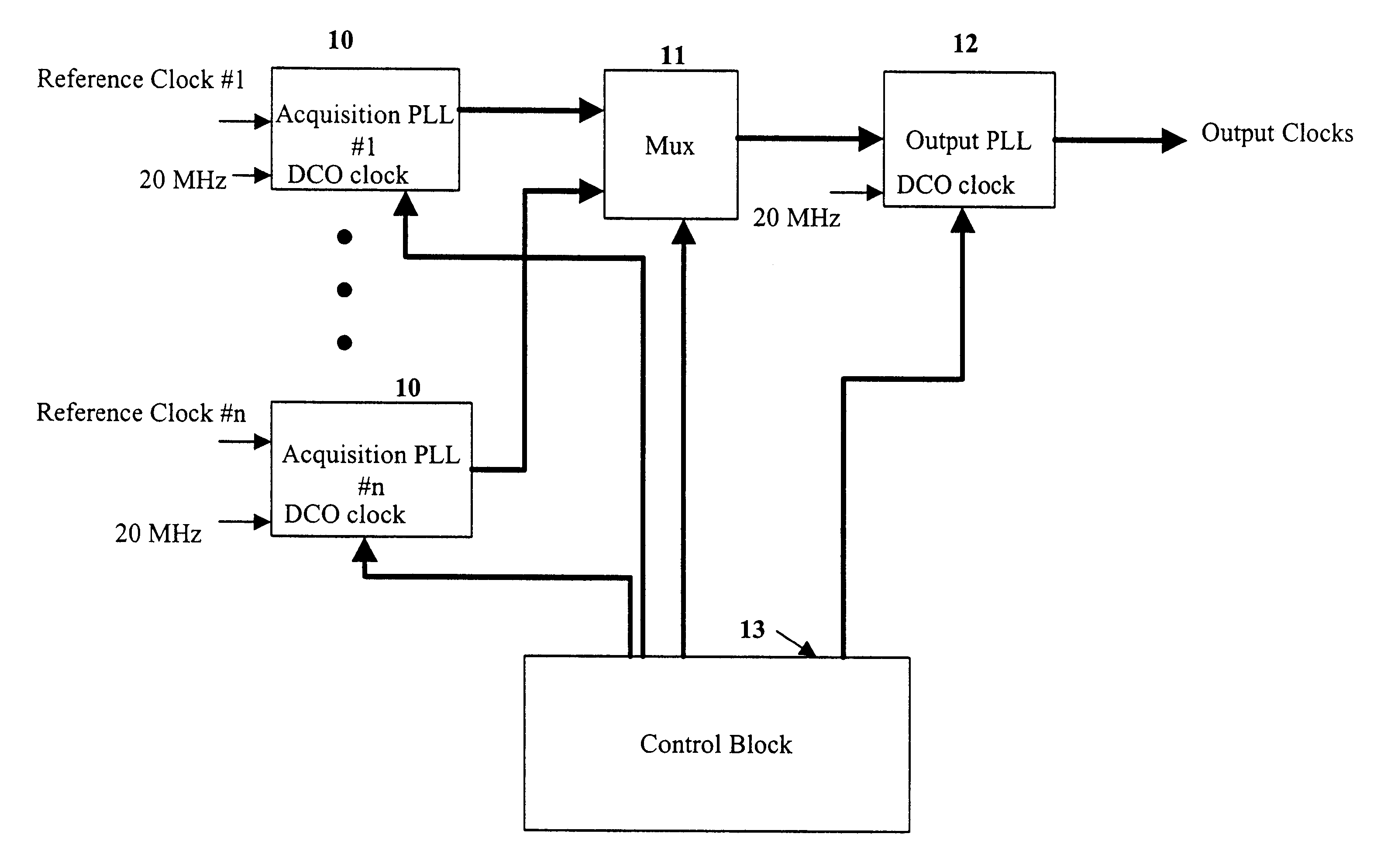

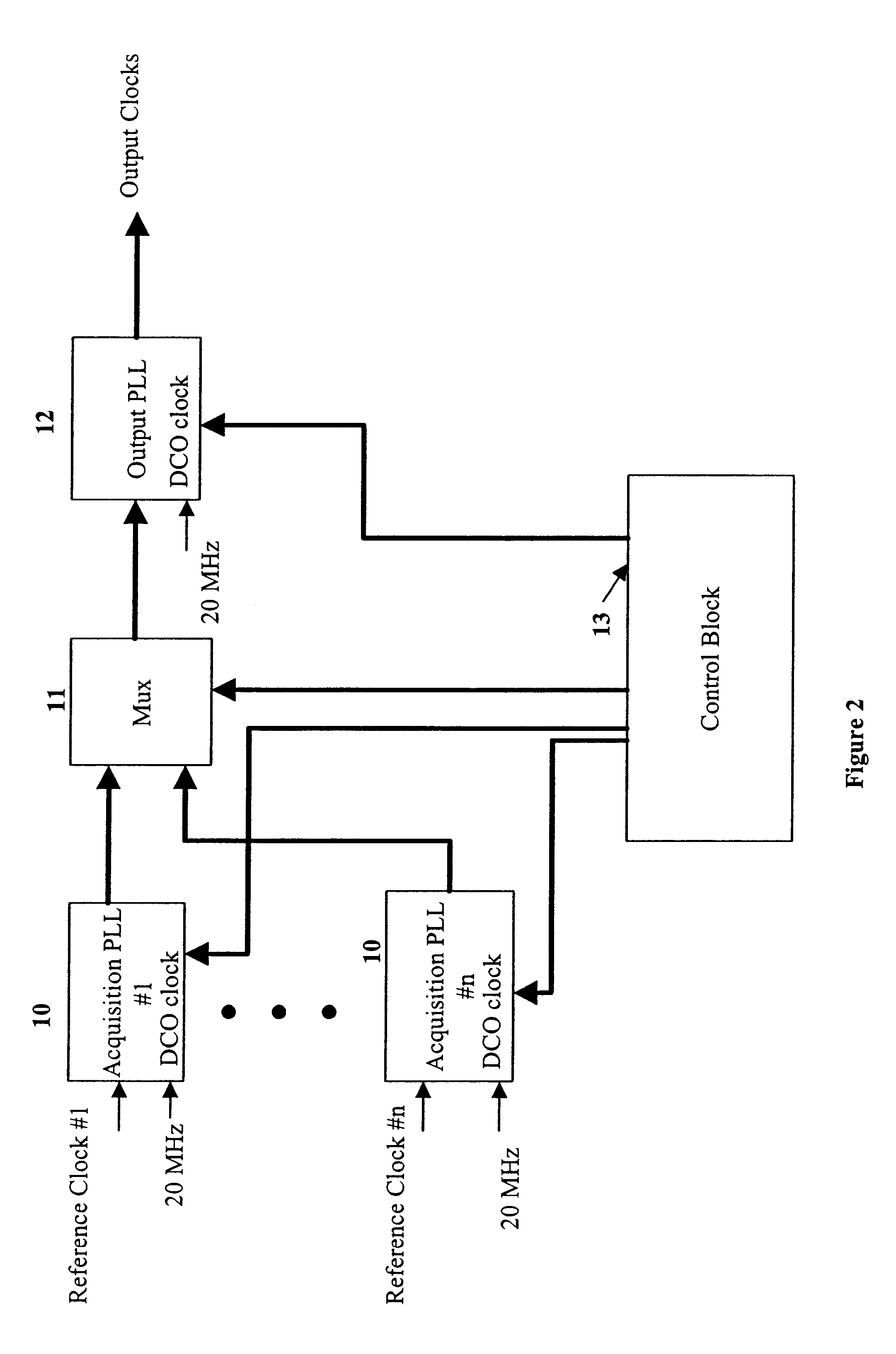

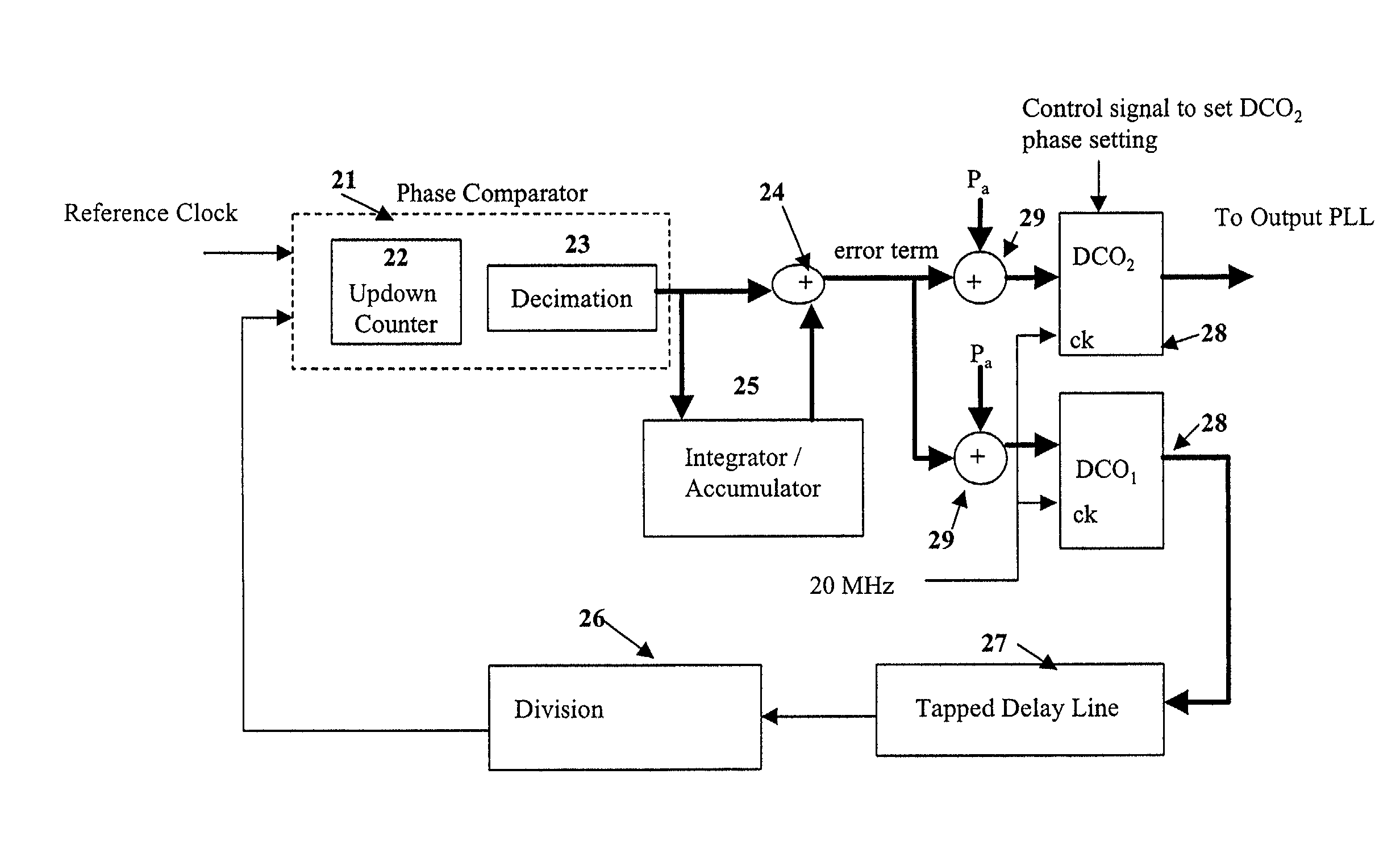

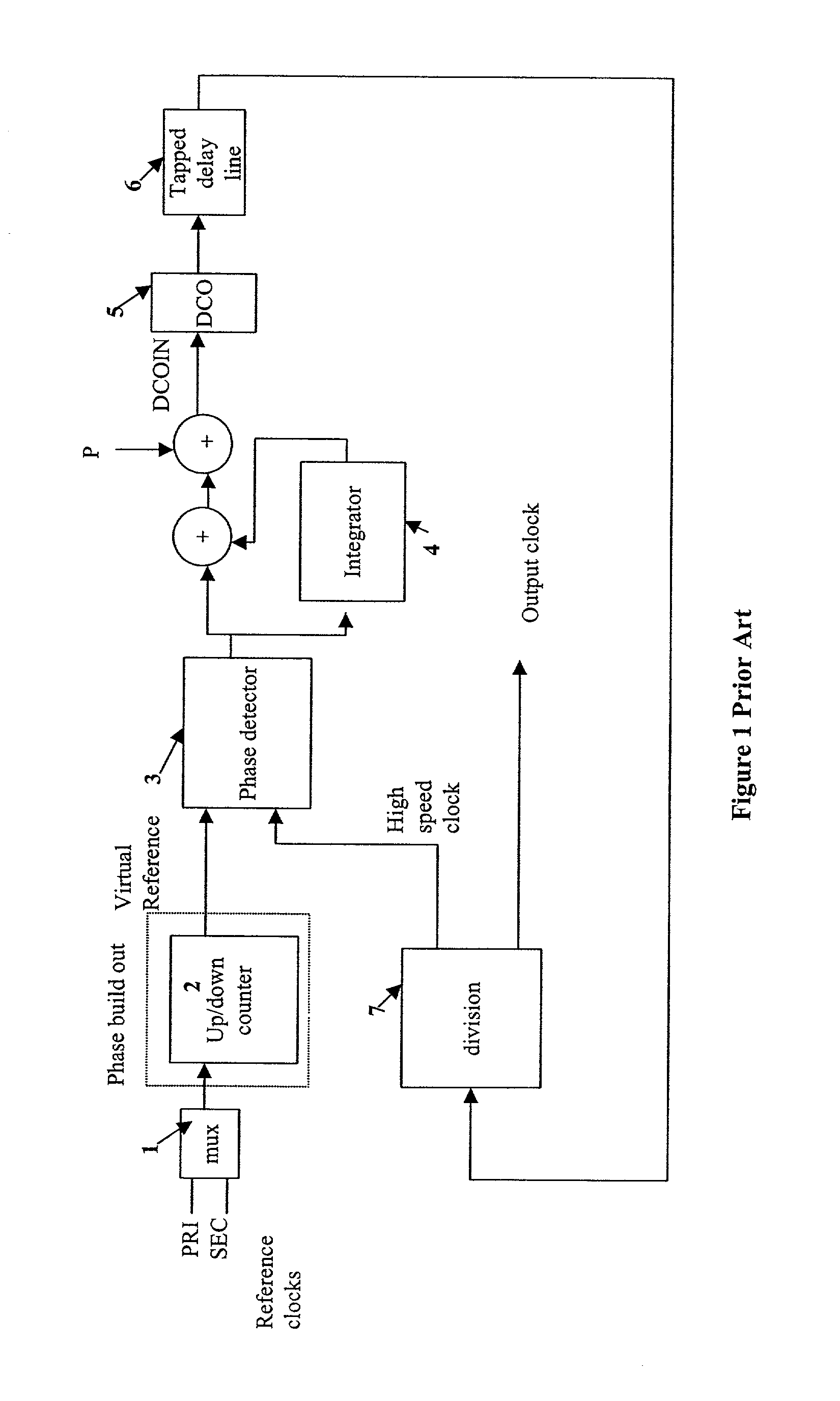

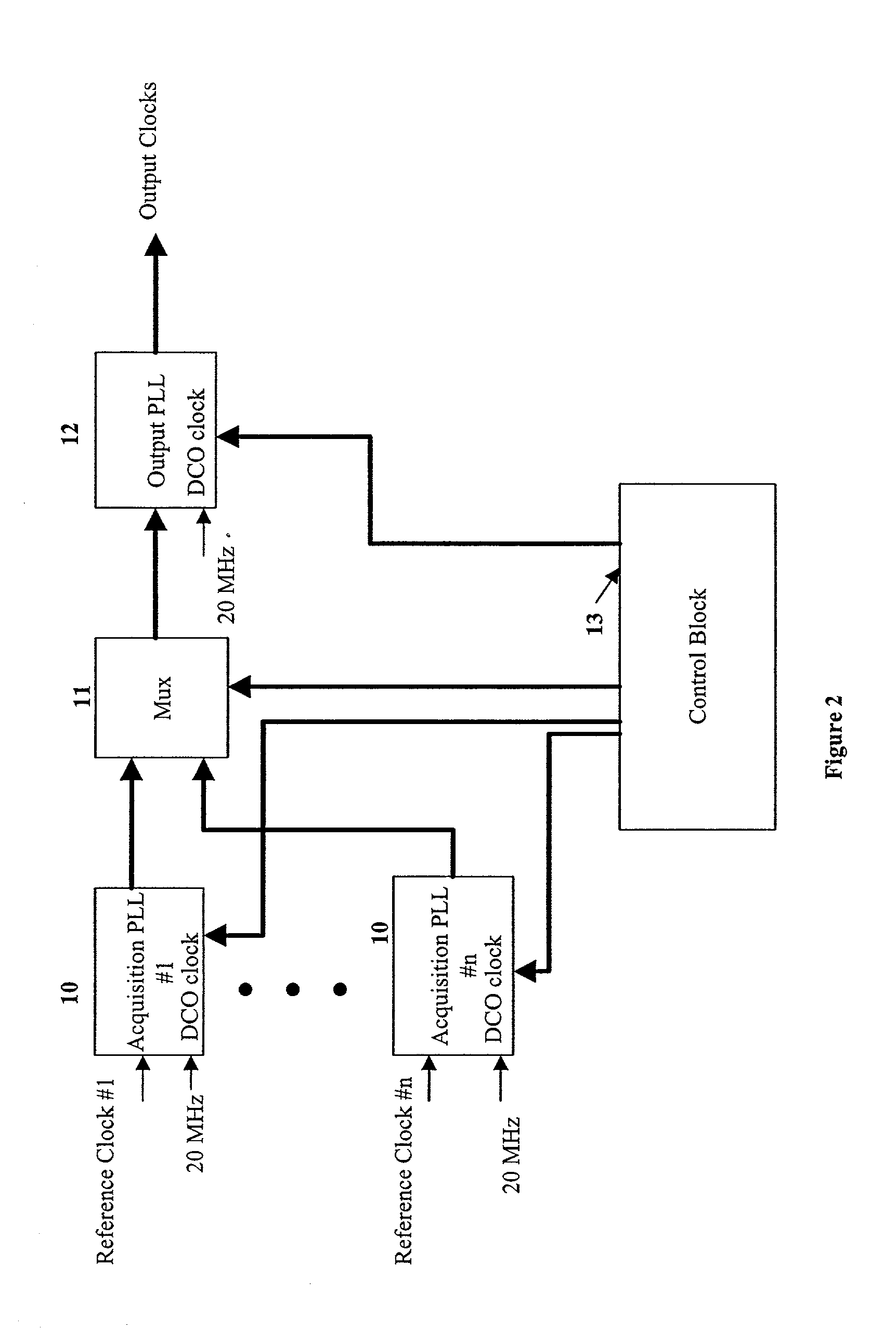

Multiple input phase lock loop with hitless reference switching

InactiveUS20020070811A1Reduce jitterPulse automatic controlTime-division multiplexClock recoveryEngineering

A clock recovery circuit for recovering clock signals from one of a plurality of input reference signals, includes an acquisition phase locked loop (PLL) for each input. The acquisition PLL having phase comparator for comparing the phase of an input signal to a feedback signal, and first and second digital controlled oscillators (DCOs) receiving an input from the phase comparator. The first DCO of the acquisition PLL is in a feedback loop to supply an input to the phase comparator and the second DCO of the acquisition PLL has a control input to introduce a phase offset therein relative to said the DCO of the acquisition PLL and provides an output for the acquisition PLL. An output PLL has a phase comparator selectively connectable to the output of each of the acquisition PLLs. The output PLL has a first DCO providing an output for the circuit and a second DCO in a feedback loop providing a feedback signal to the phase comparator of the output PLL. The second DCO of the output PLL has a control input to introduce a phase offset therein relative to the first DCO of the output PLL. A control unit for sets the phase of the second DCO of the acquisition circuit and the second DCO of the output PLL to a common value during changeover from one input to another to avoid an instantaneous phase error upon switching reference signals.

Owner:ZARLINK SEMICON LTD

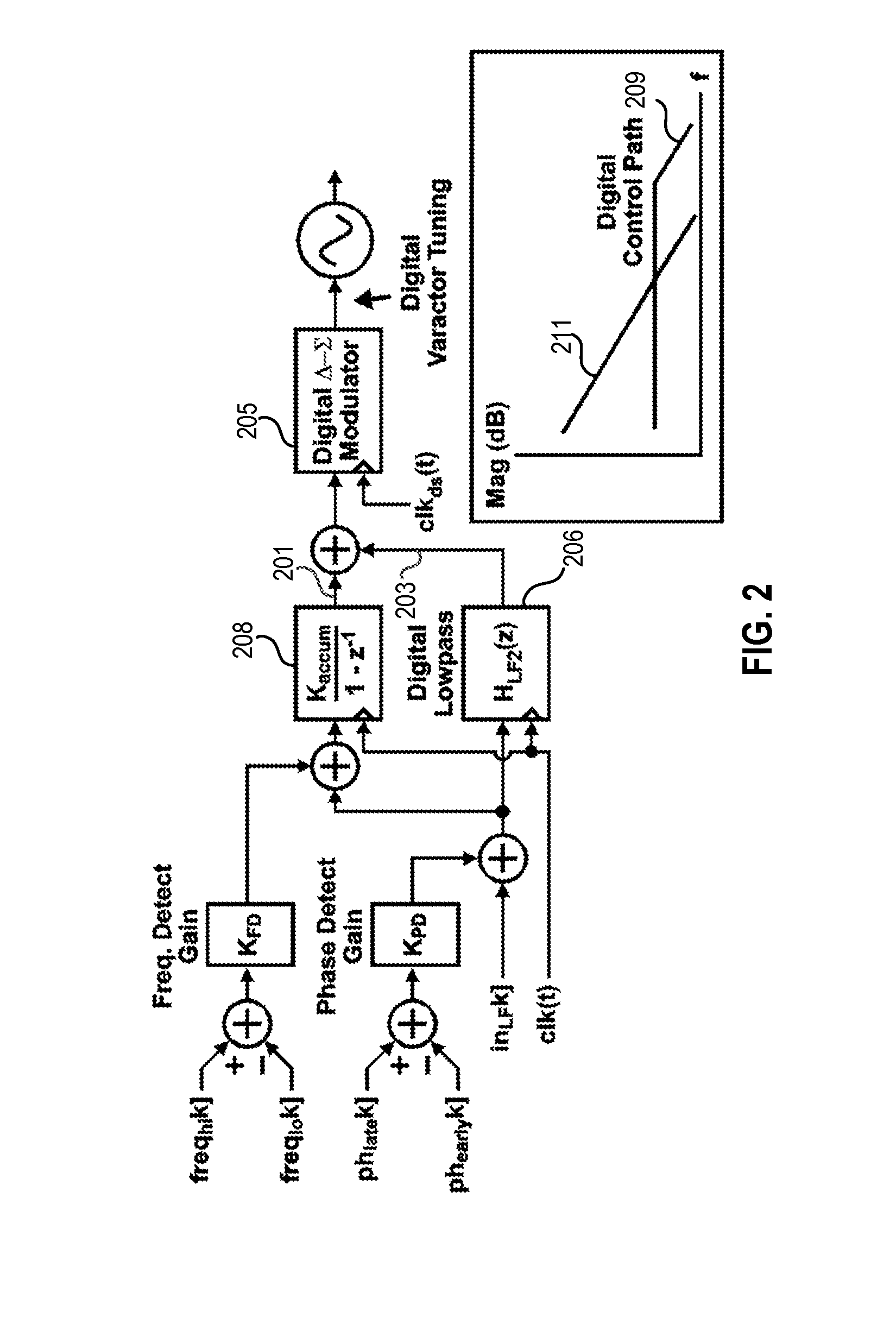

Hybrid analog and digital control of oscillator frequency

ActiveUS20150145566A1Wide rangeWide resolutionPulse automatic controlControl signalDigital controlled oscillator

A hybrid analog / digital control approach for a digitally controlled oscillator augments a digital control path with an analog control path that acts to center the digital control path control signal within its range. The digital control path controls a first group of varactors within an oscillator tank circuit using a digital filter and a delta sigma modulator, which generates a dithered control signal for at least one of the first group of varactors. The analog control path controls a second group of varactors in the tank circuit but actively tunes only one varactor at a time. The analog control path performs relatively low bandwidth centering of the digital control signal resulting in negligible impact on PLL bandwidth, stability, and noise performance. Instead, the digital control path dominates in setting the PLL dynamic and noise behavior, and has reduced range requirements due to the centering action.

Owner:SILICON LAB INC