Digital phase locked loop system and method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

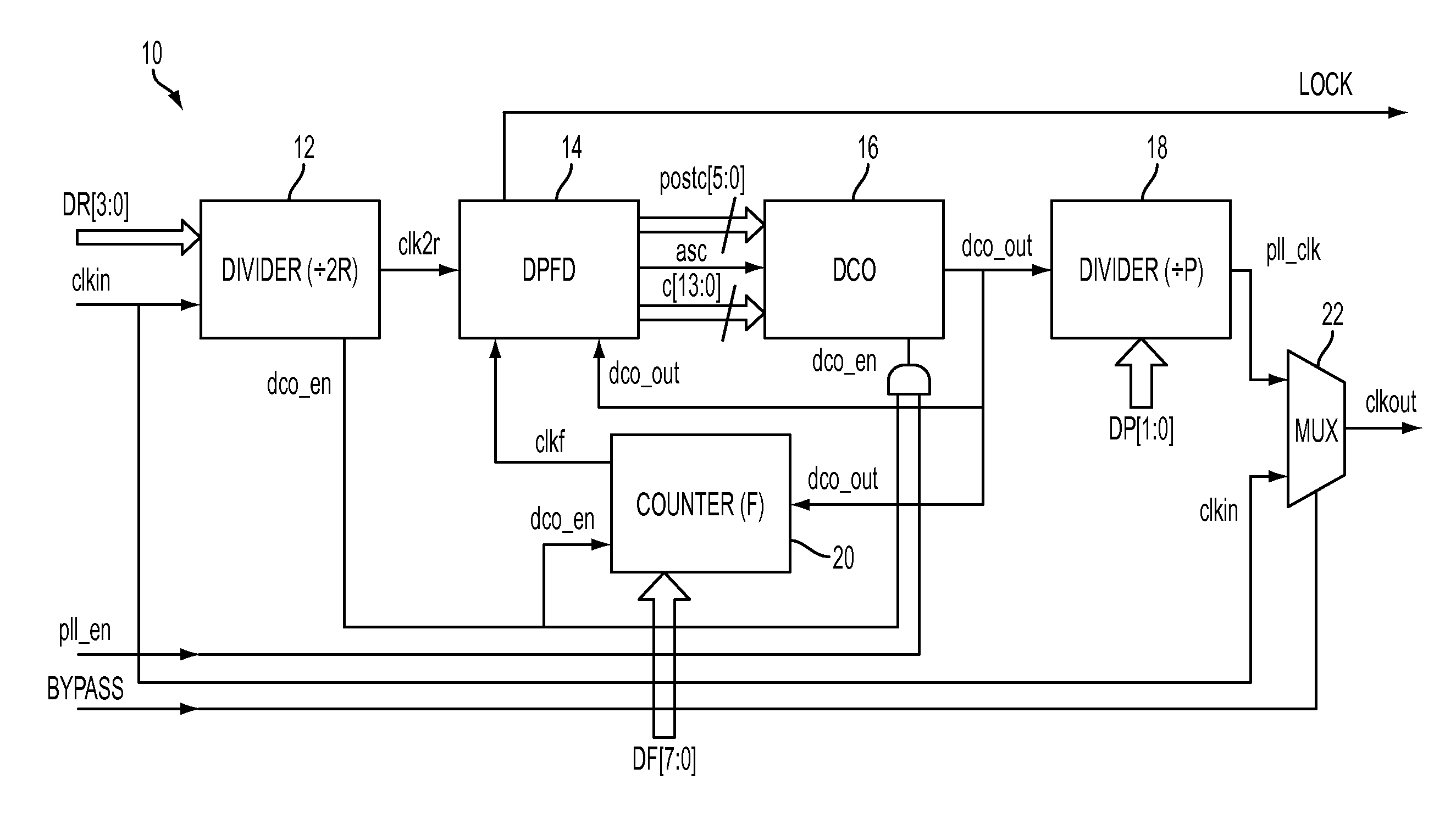

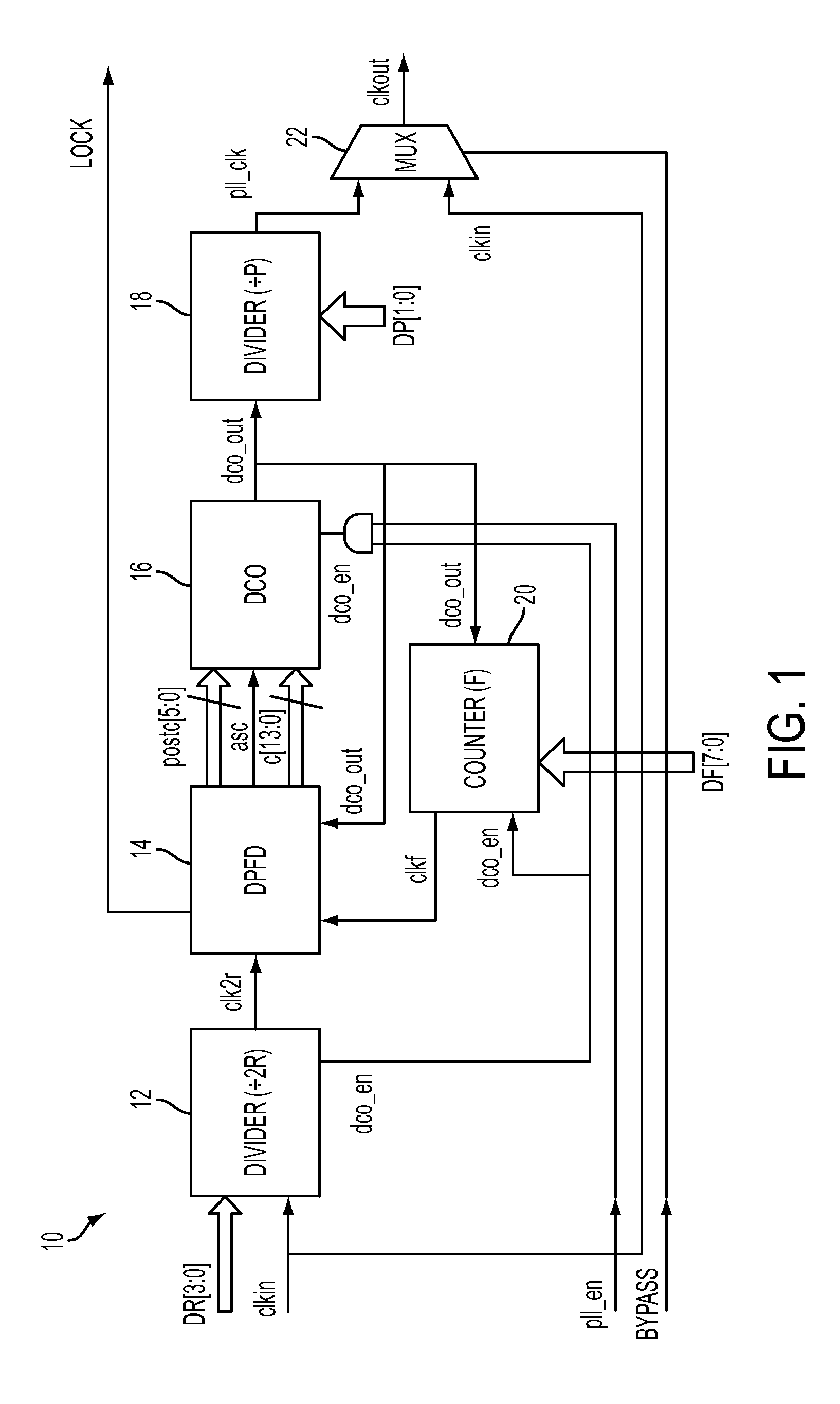

[0016]A digital controlled oscillator is controlled in response to comparison of the oscillator output with a reference clock related signal, by use of a digital phase and frequency detector. The cycling rate of the oscillator output is counted, the count is reset after a predetermined number of cycles, and the reset frequency is compared with the reference clock related signal.

[0017]An input divider can be coupled to the reference clock input for dividing the reference clock signal to one of a plurality of preset dividing rates. An output divider can be coupled to the oscillator output for dividing the oscillator output signal to one of a plurality of preset dividing rates. Each of the dividers may have a control input for selecting a respected dividing rate.

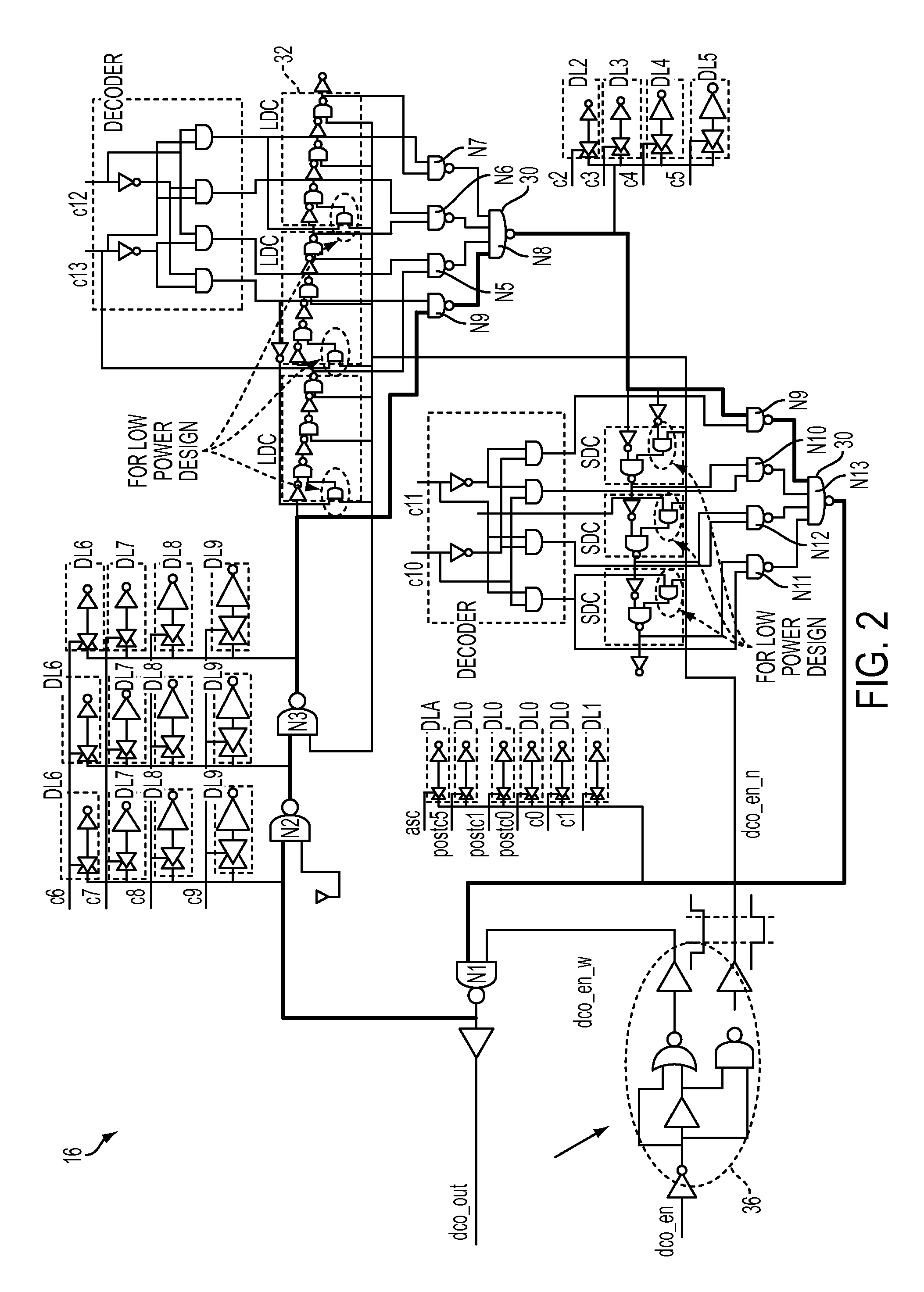

[0018]The digital controlled oscillator comprises a plurality of decoder logic cells. A first group of the decoder cells provide a relatively large signal delay; a second group of decoder cells provide a relatively smaller dela...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More