Method for realizing integrated time stamp clock synchronous phase-locked loop

A technology of time synchronization and time stamping, which is applied in the field of digital phase-locked loops, and can solve problems such as the large increase in the size of the system clock module, the increase in system construction costs, and the complexity of system implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

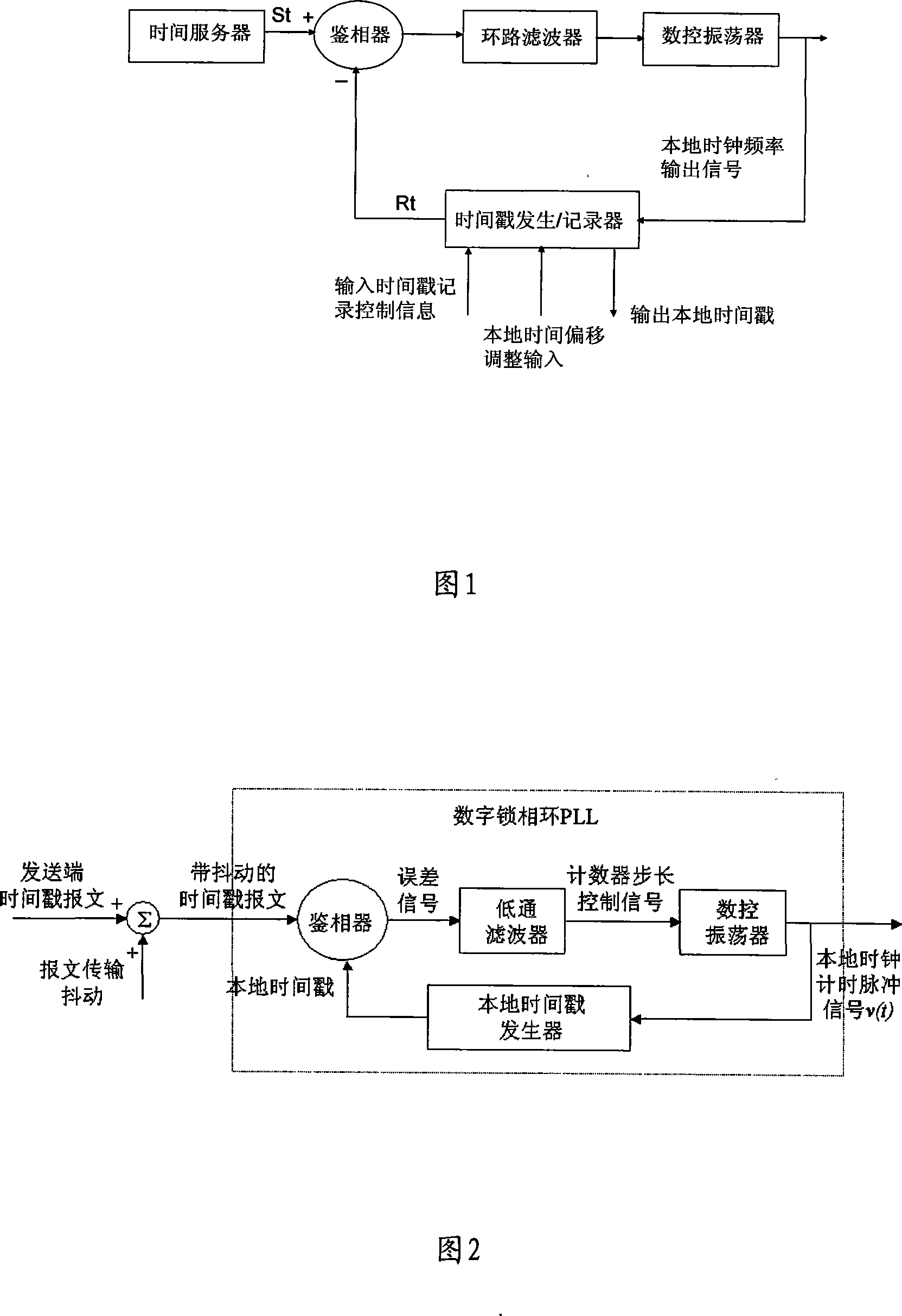

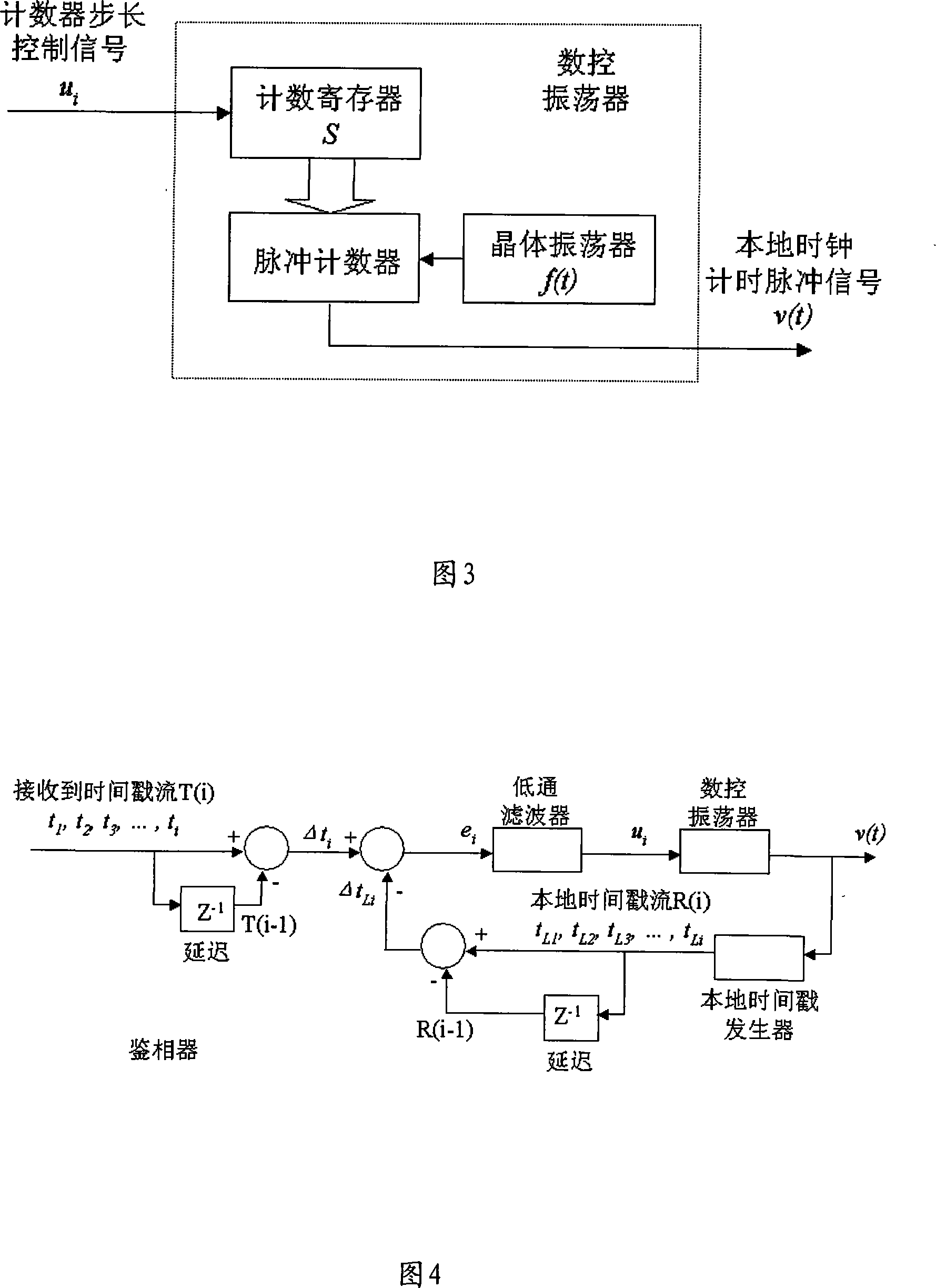

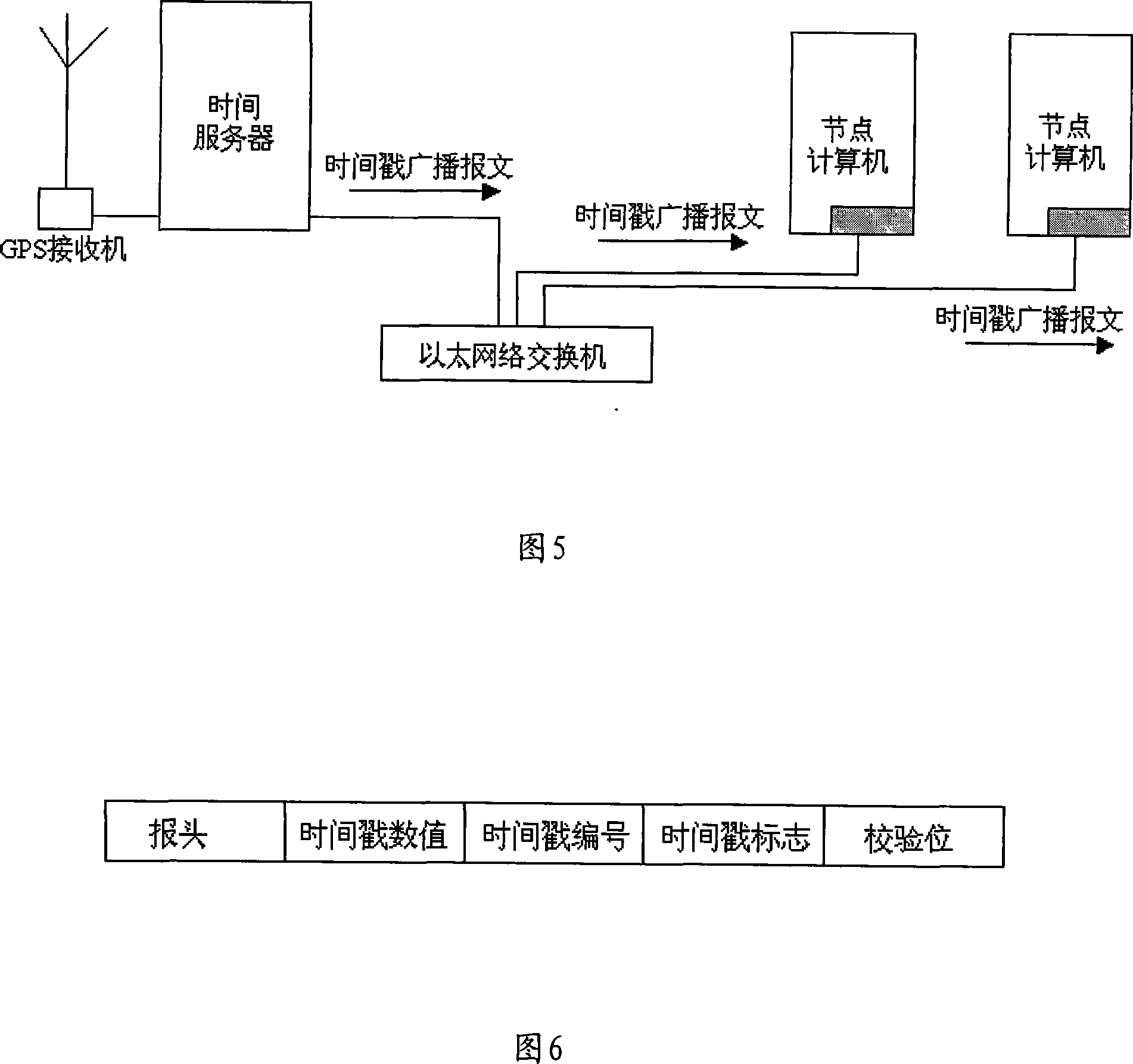

[0024] The structure of a specific embodiment of the present invention is shown in FIG. 1 . The phase-locked loop uses the time value carried in the time stamp message stream S(t) sent by the time server as the input synchronization signal of the phase detector of the digital phase-locked loop, which is used to output the phase-locked loop as the reference frequency of the local clock timing pulse The value of the local time stamp is the reference input signal of the phase detector. The acquired time of each local time stamp R(t) corresponds to the local clock time when a time stamp message sent from the time server arrives at the node where the PLL is located. The phase detector used is actually an integrated time stamp difference calculation / memory. It is mainly: calculate the difference between the timestamp values carried by the timestamp messages sent by the time server before and after arriving at the phase detector respectively; calculate the value recorded when the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More