Patents

Literature

120 results about "Loop counter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In software engineering, a loop counter is the variable that controls the iterations of a loop. It is so named because most uses of this construct result in the variable taking on a range of integer values in some orderly sequence Loop counters change with each iteration of a loop, providing a unique value for each individual iteration. The loop counter is used to decide when the loop should terminate and for program flow to continue to the next instruction after the loop. A common identifier naming convention is for the loop counter to use the variable names i, j, and k, where i would be the most outer loop, j the next inner loop, etc. The reverse order is also used by some programmers. This style is generally agreed to have originated from the early programming of FORTRAN, where these variable names beginning with these letters were implicitly declared as having an integer type, and so were obvious choices for loop counters that were only temporarily required. The practice dates back further to mathematical notation where indices for sums and multiplications are often i, j, etc.

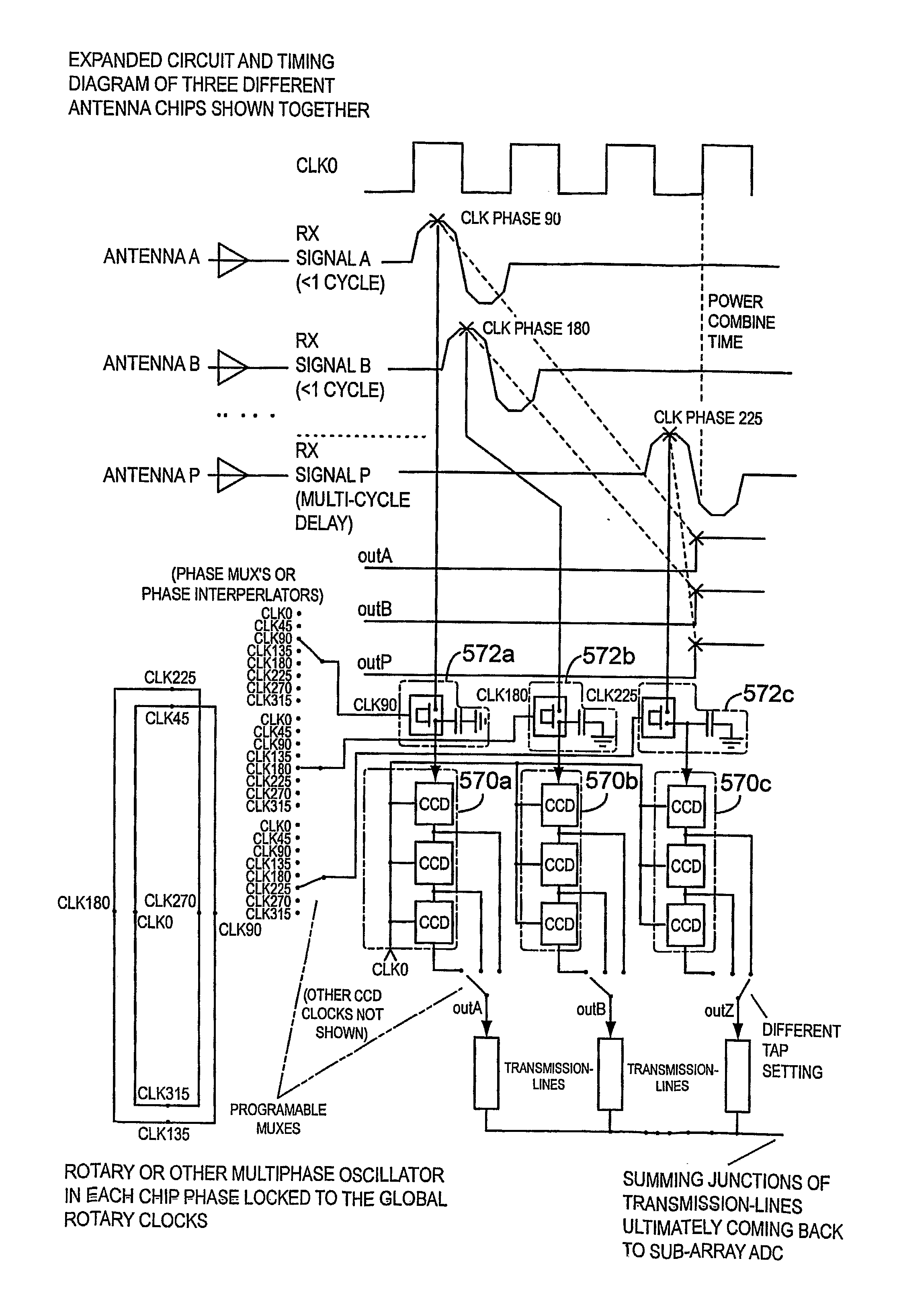

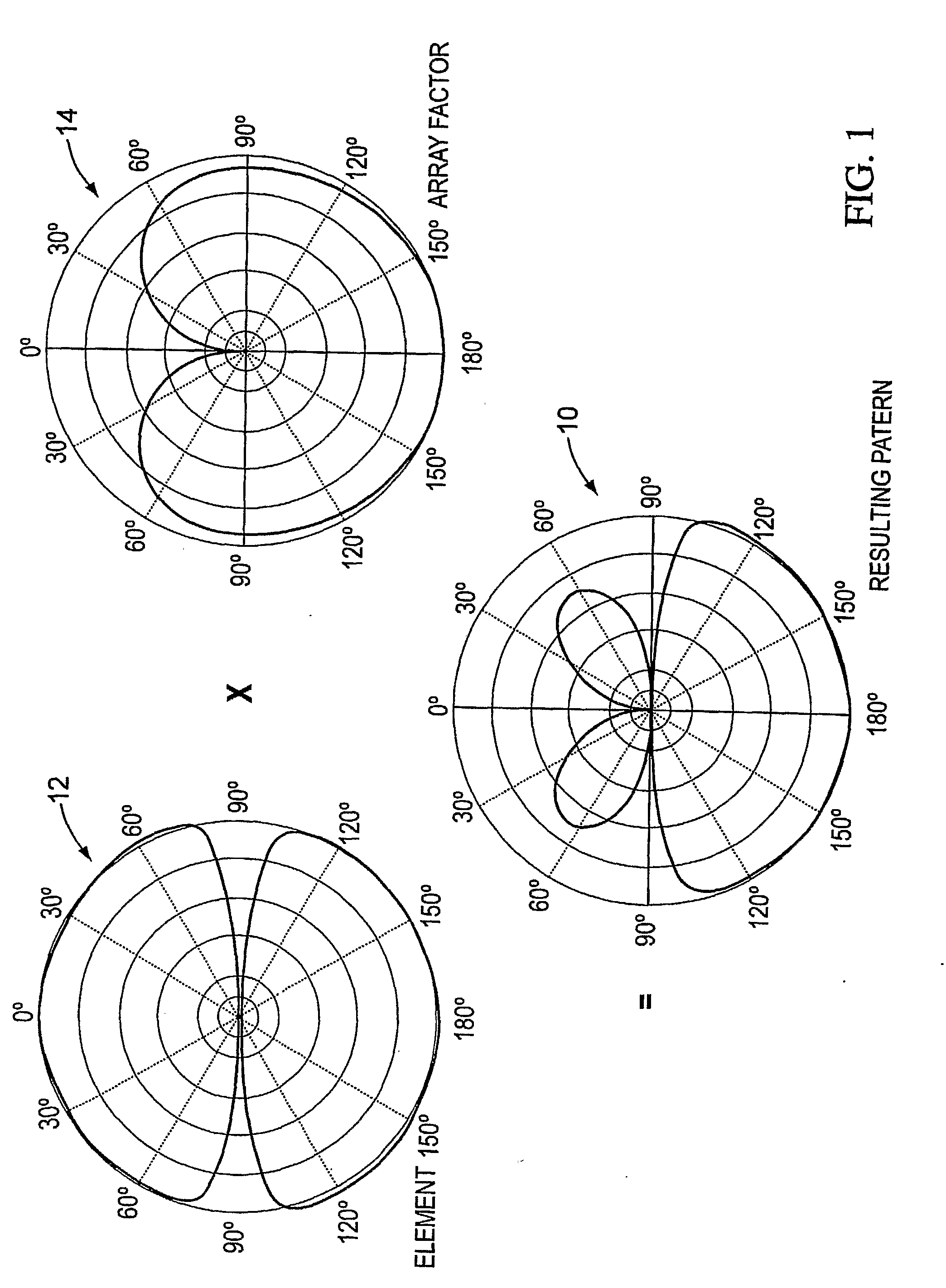

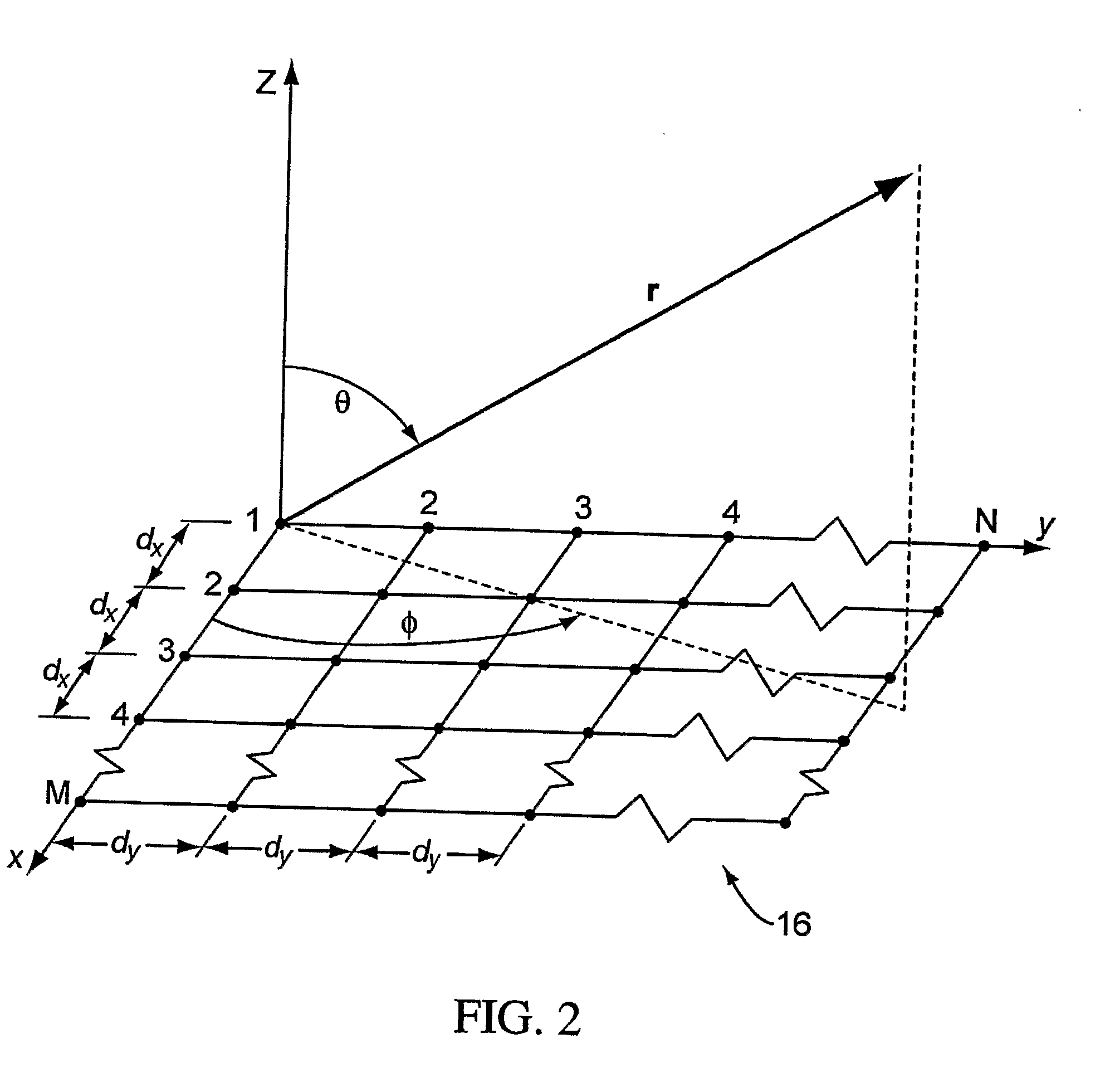

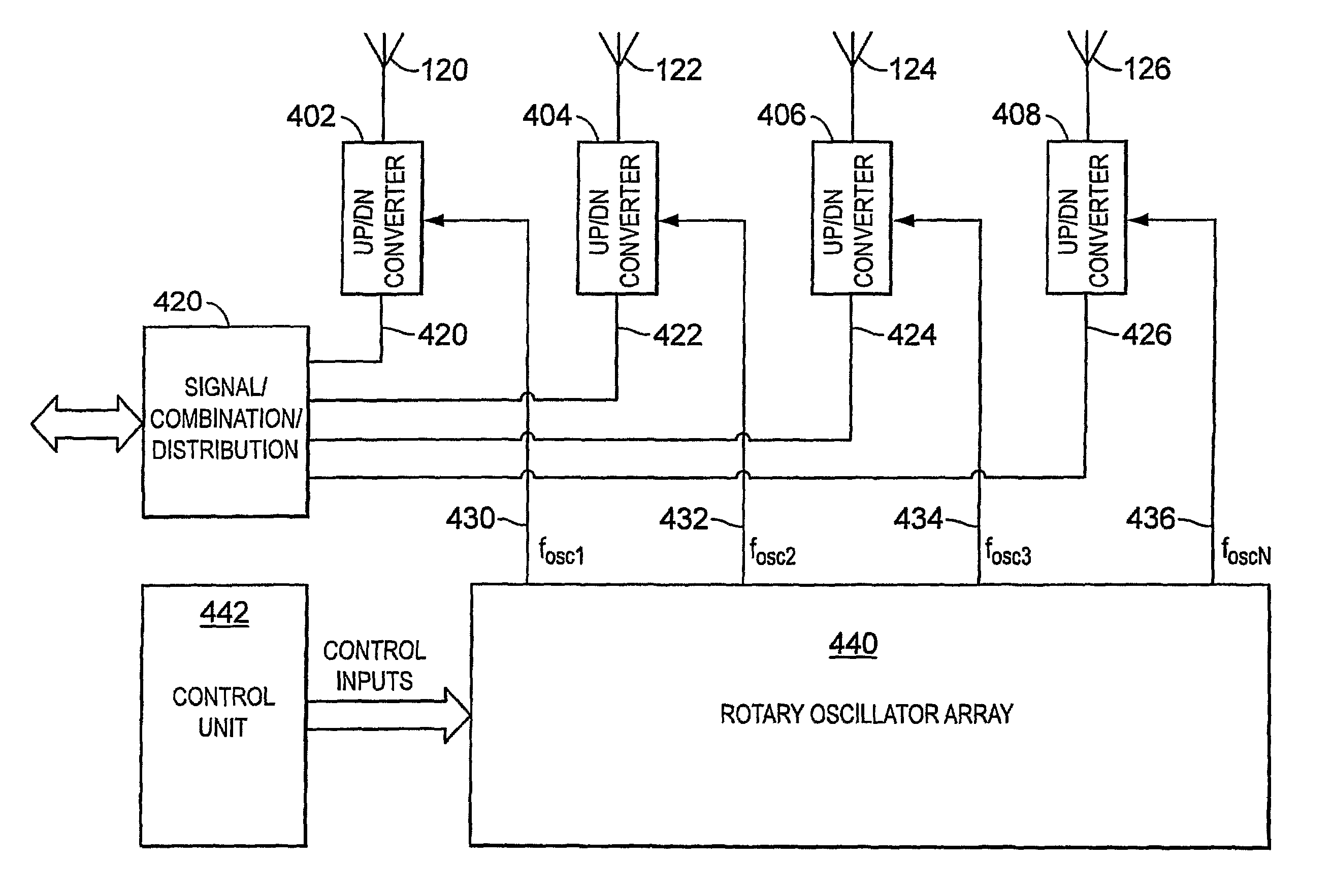

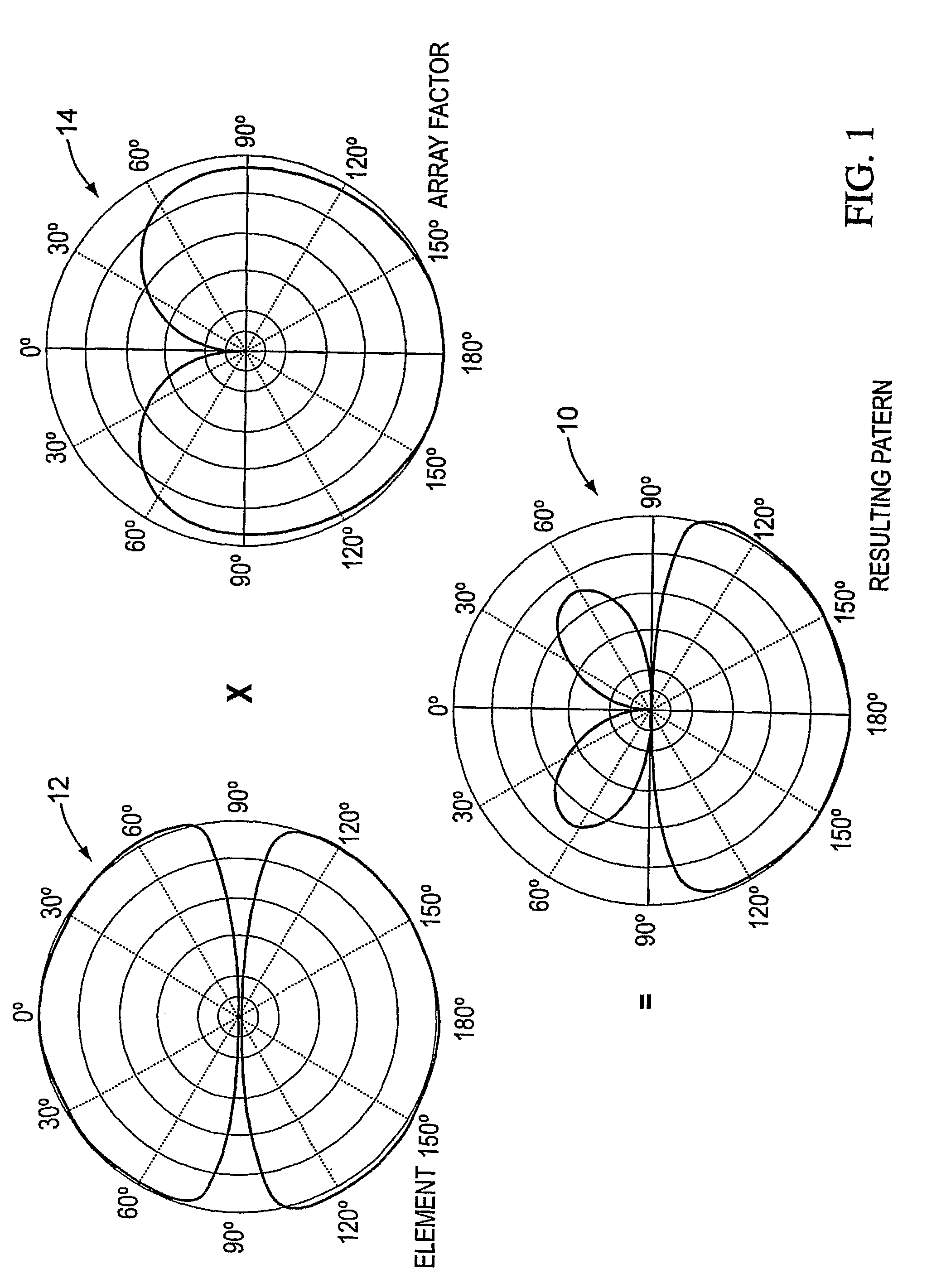

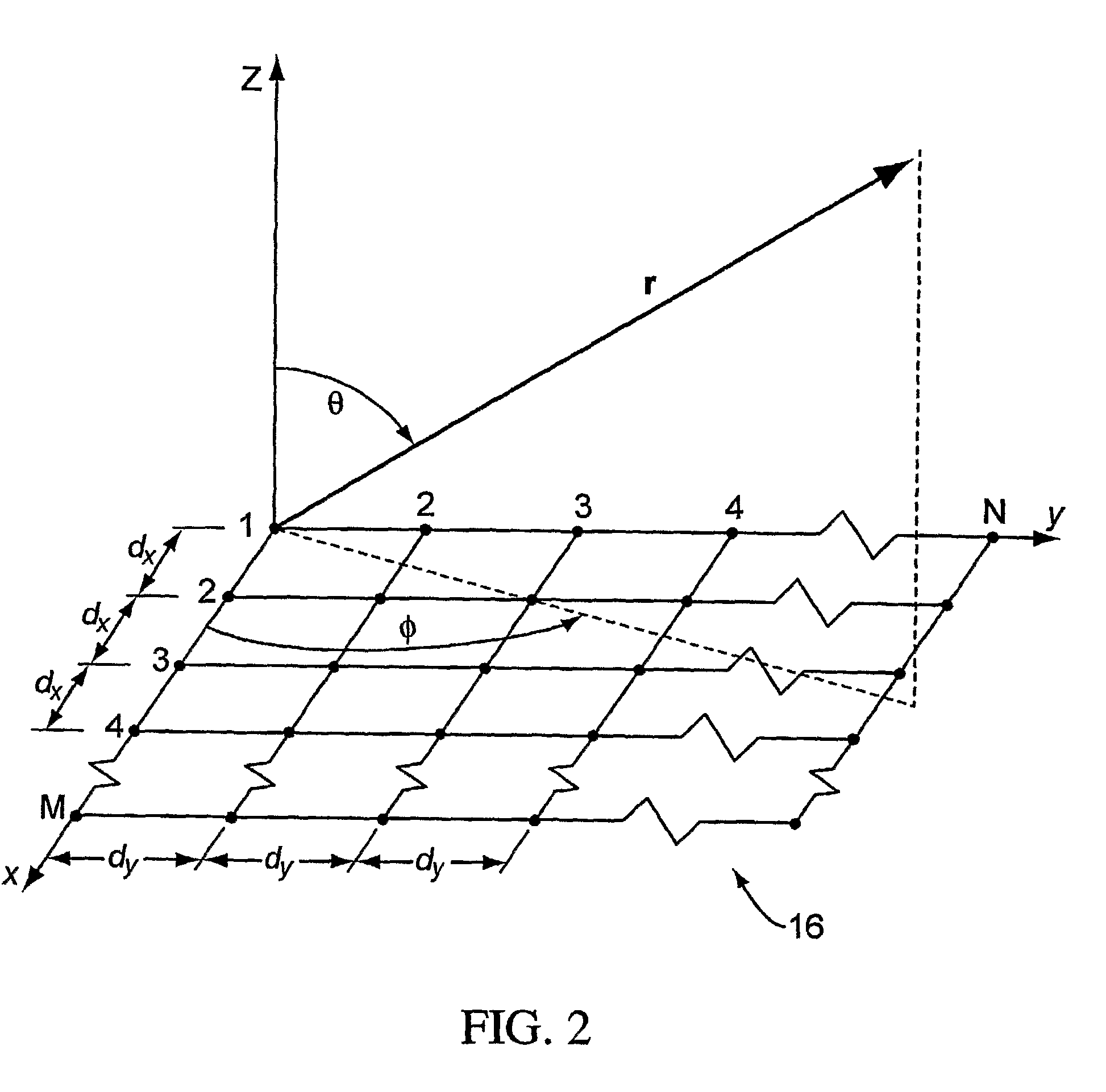

True time delay phase array radar using rotary clocks and electronic delay lines

ActiveUS20120039366A1Forming accuratelyEasy to moveAntenna arraysPulse automatic controlTime delaysAnalog delay line

Local oscillator circuitry for an antenna array is disclosed. The circuitry includes an array of rotary traveling wave oscillators which are arranged in a pattern over an area and coupled so as to make them coherent. This provides for a set of phase synchronous local oscillators distributed over a large area. The array also includes a plurality of phase shifters each of which is connected to one of the rotary oscillators to provide a phase shifted local oscillator for the array. The phase shifter optionally includes a cycle counter that is configured to count cycles of the rotary oscillator to which it is connected and control circuitry that is then operative to provide a shifted rotary oscillator output based on the count from the cycle counter. A system and method for operating a true-time delay phased array antenna system. The system includes a plurality of antenna element circuits for driving or receiving an rf signal from the elements of the array. Each element circuit has a transmit and a receive path and a local multiphase oscillator, such as a rotary traveling wave oscillator. Each path has an analog delay line for providing a true-time delay for the antenna element. Preferably, the analog delay line is a charge coupled device whose control nodes are connected to phases of the local multiphase oscillator to implement a delay that is an integer number local multiphase oscillator periods. A fractional delay is also included in the path by using a sample and hold circuit connected to a particular phase of the oscillator. By delaying each antenna element by a true time delay, broadband operation of the array is possible.

Owner:ANALOG DEVICES INC

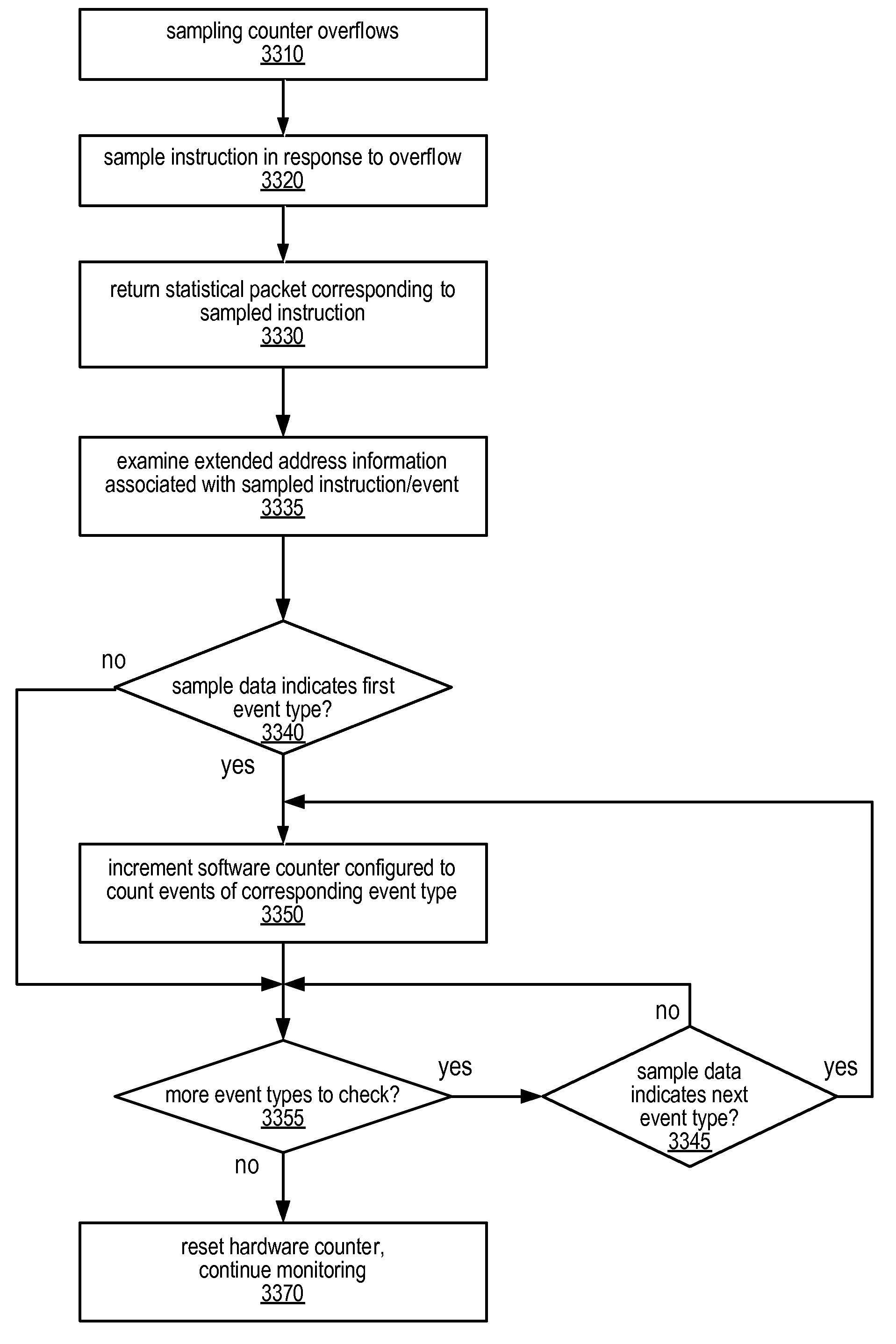

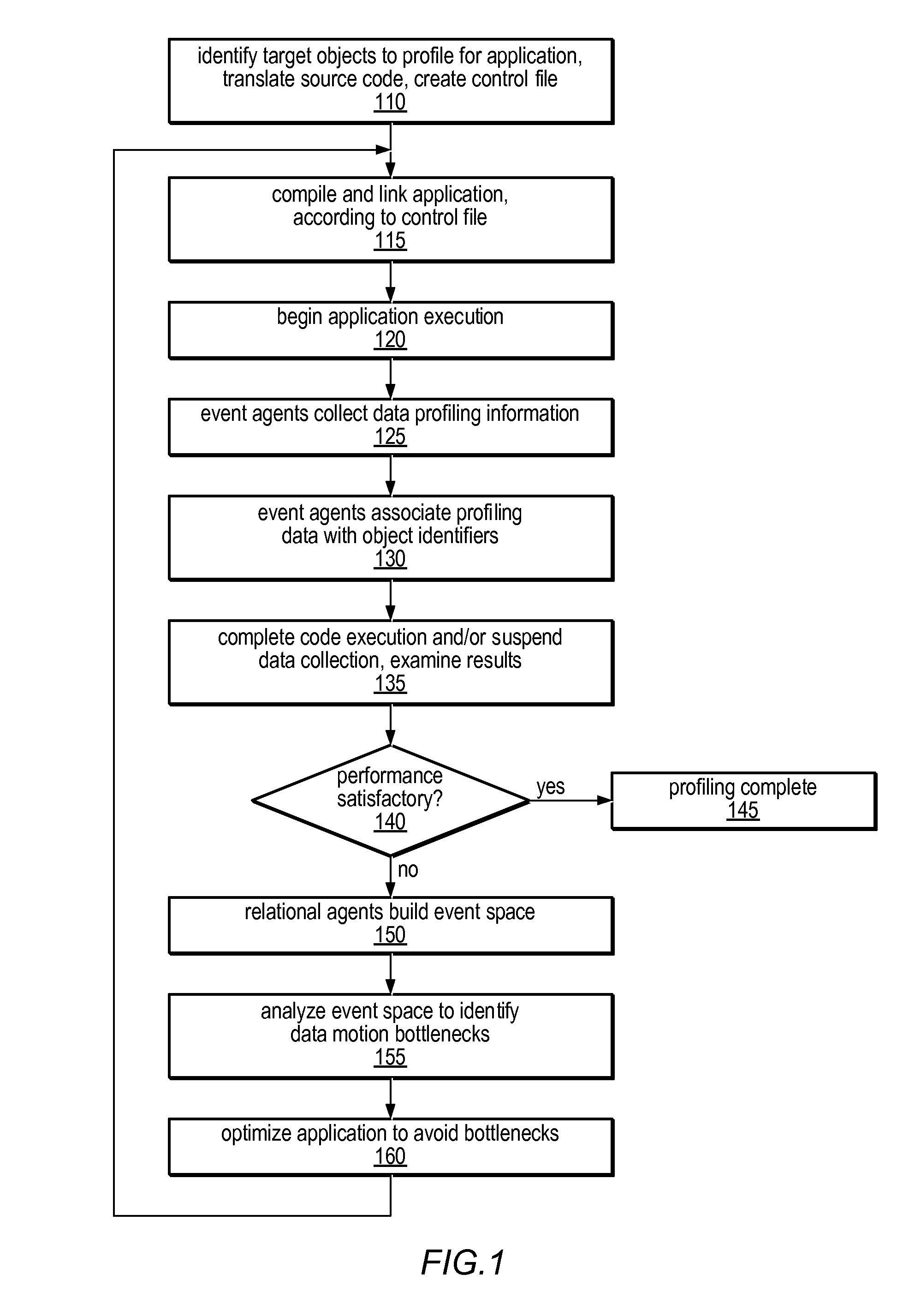

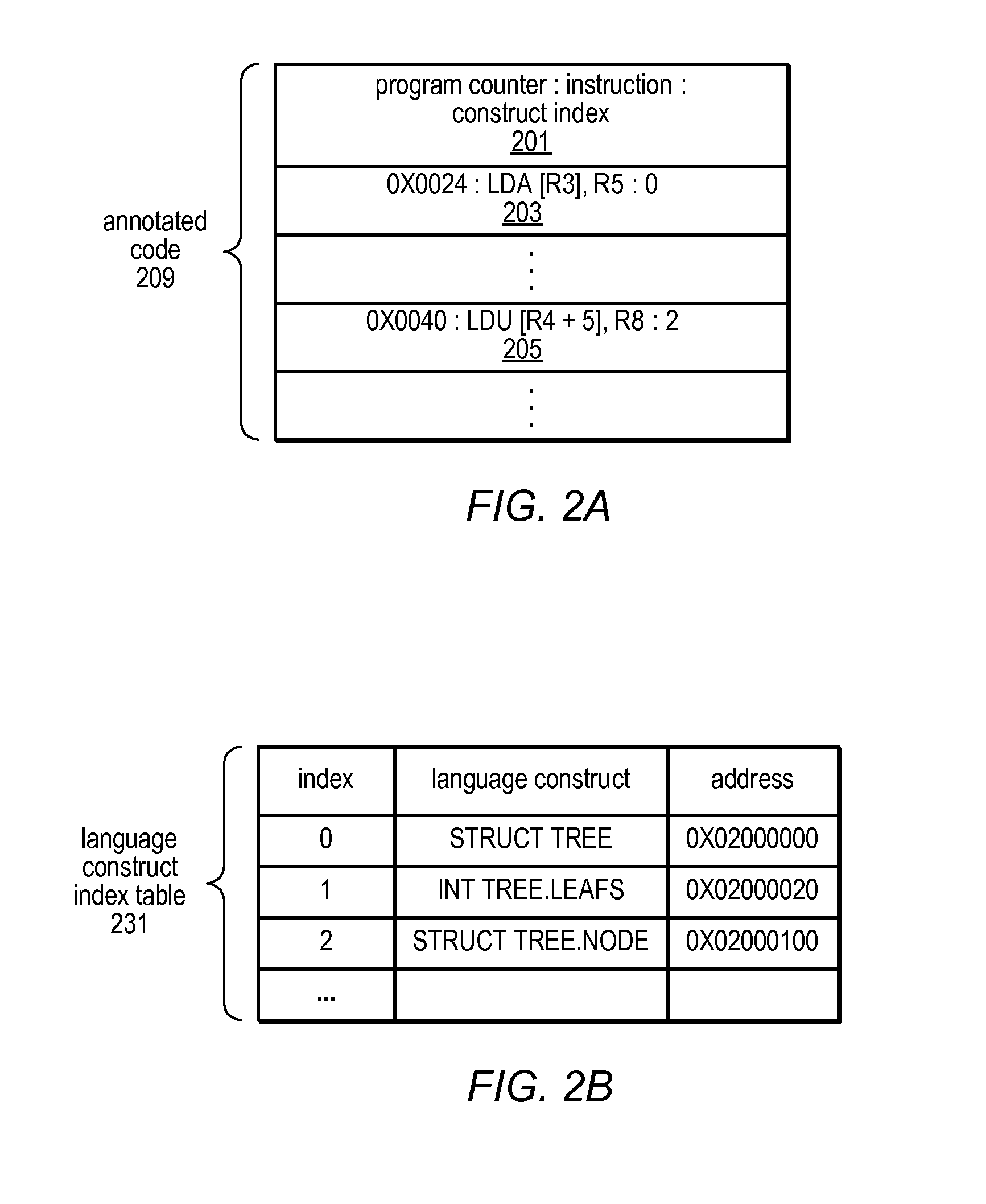

Method and apparatus for synthesizing hardware counters from performance sampling

A system and method for performance monitoring may use data collected from a hardware event agent comprising a hardware sampling mechanism and / or one or more hardware counters to increment one or more synthesized performance counters by an amount dependent on an expression involving the collected data. Each synthesized performance counter may be configured to count events of a different type and may comprise a machine addressable storage location. The event types may include various memory references or misses, branches, branch mispredictions, or any other event of interest in performance monitoring. The hardware event agent may comprise one or more instruction counters, cycle counters, timers, or other hardware performance counters. One hardware performance counter may be used in a time-multiplexed or data-multiplexed manner to monitor events of multiple event types. The hardware sampling mechanism may return a statistical packet for sampled instructions, which may be examined to determine the event type.

Owner:ORACLE INT CORP

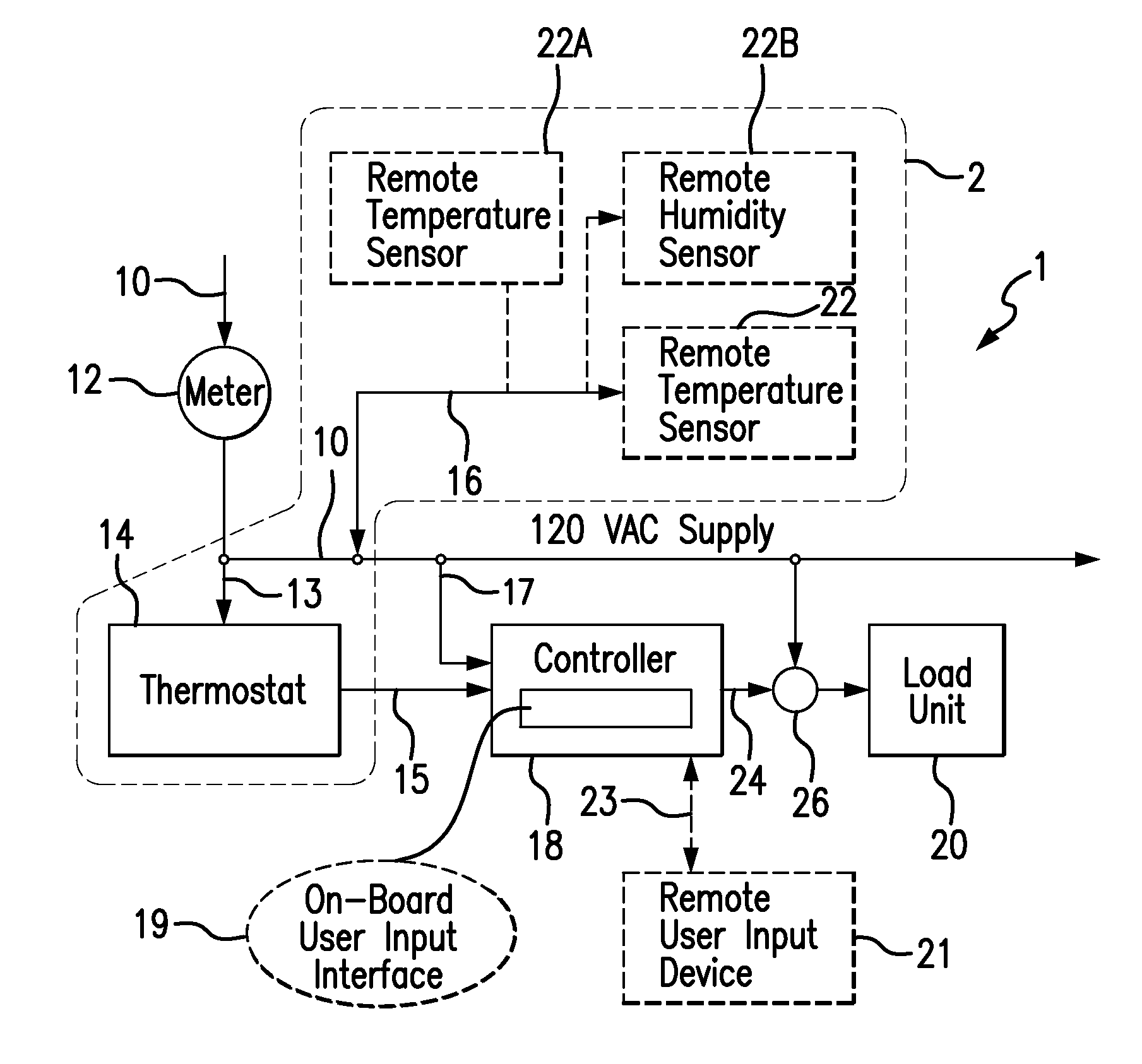

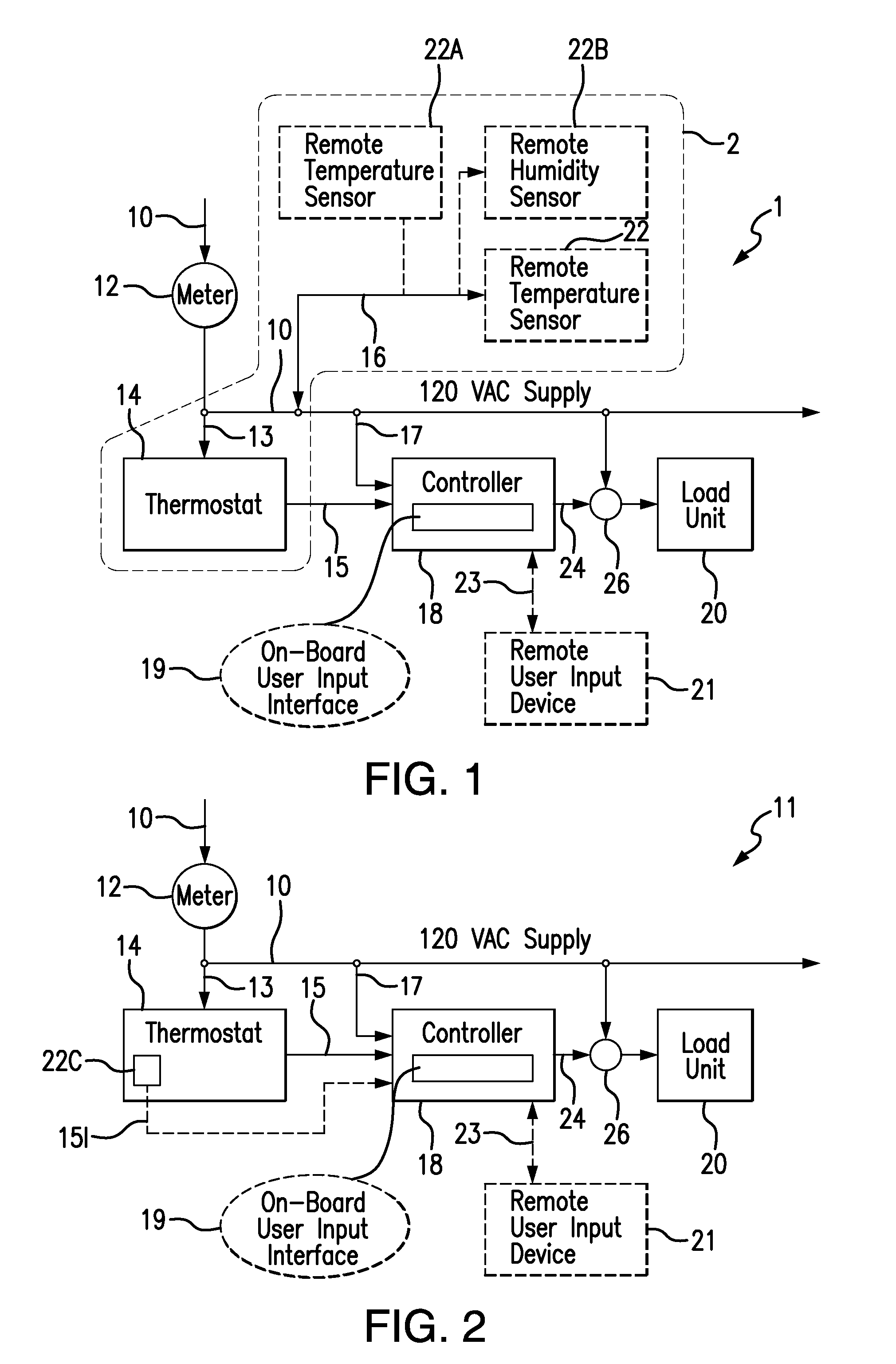

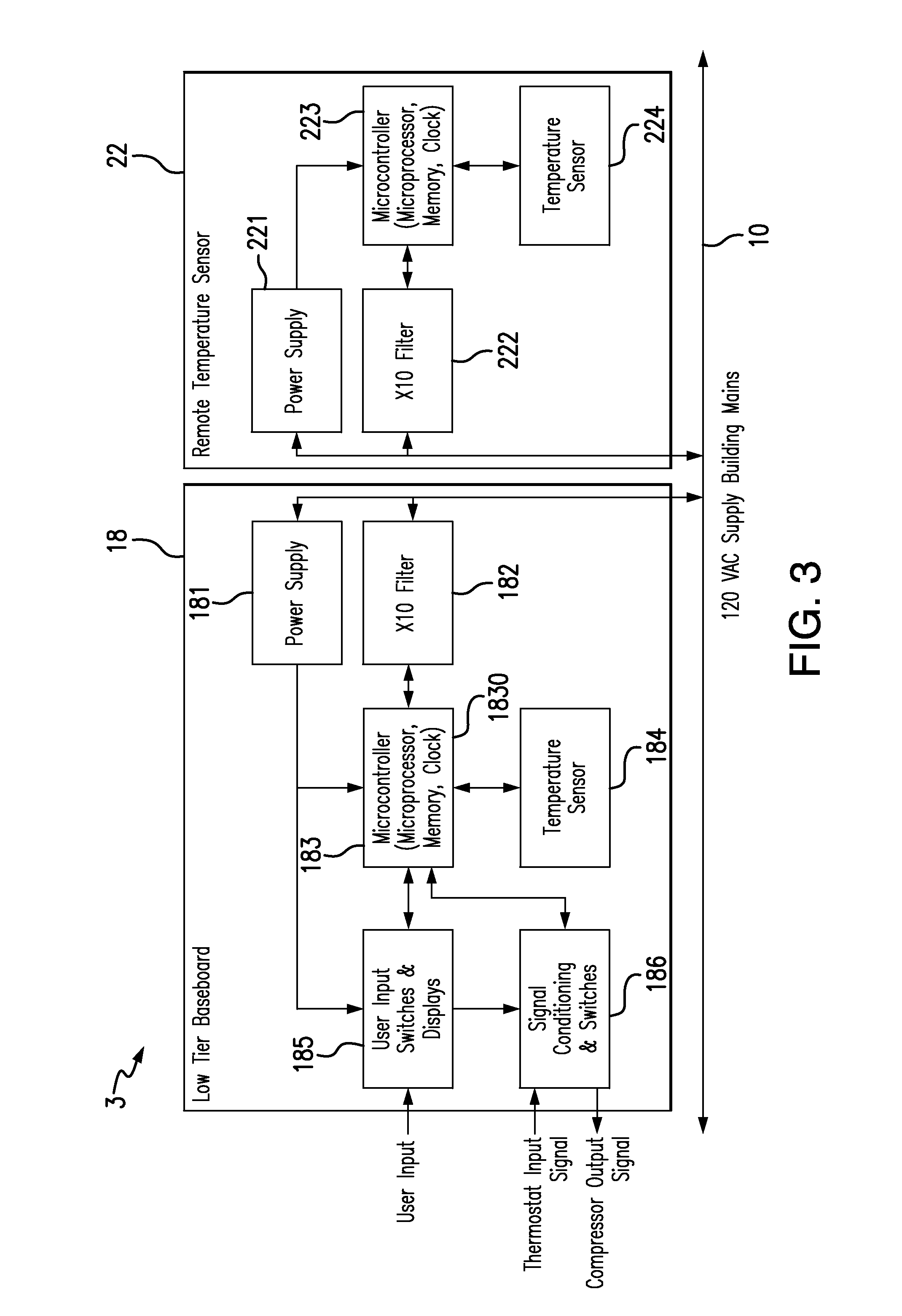

Controller For Automatic Control And Optimization Of Duty Cycled HVAC&R Equipment, And Systems And Methods Using Same

InactiveUS20120273581A1Mechanical apparatusTemperature control with auxillary non-electric powerAutomatic controlElectronic controller

An electronic controller device for automatic control of a heating, ventilating, air conditioning or refrigeration (HVAC&R) system has a digital recycle counter that is capable of intercepting a thermostat command for cooling, refrigeration, or heating and replacing the thermostat command with a modulated binary signal that operates in an “on” state or “off” state, and a computer-readable storage medium that comprises a program that includes an auto-configuration mode that is capable of determining a base line performance of the HVAC&R system through a commissioning phase and is capable of determining an adjusted performance based on energy consumption, temperature regulation, humidity regulation, or power limit or any combination thereof. The program can adjust the digital recycle counter “on” and “off” states based on the adjusted performance determination to reduce energy consumption.

Owner:PACECONTROLS

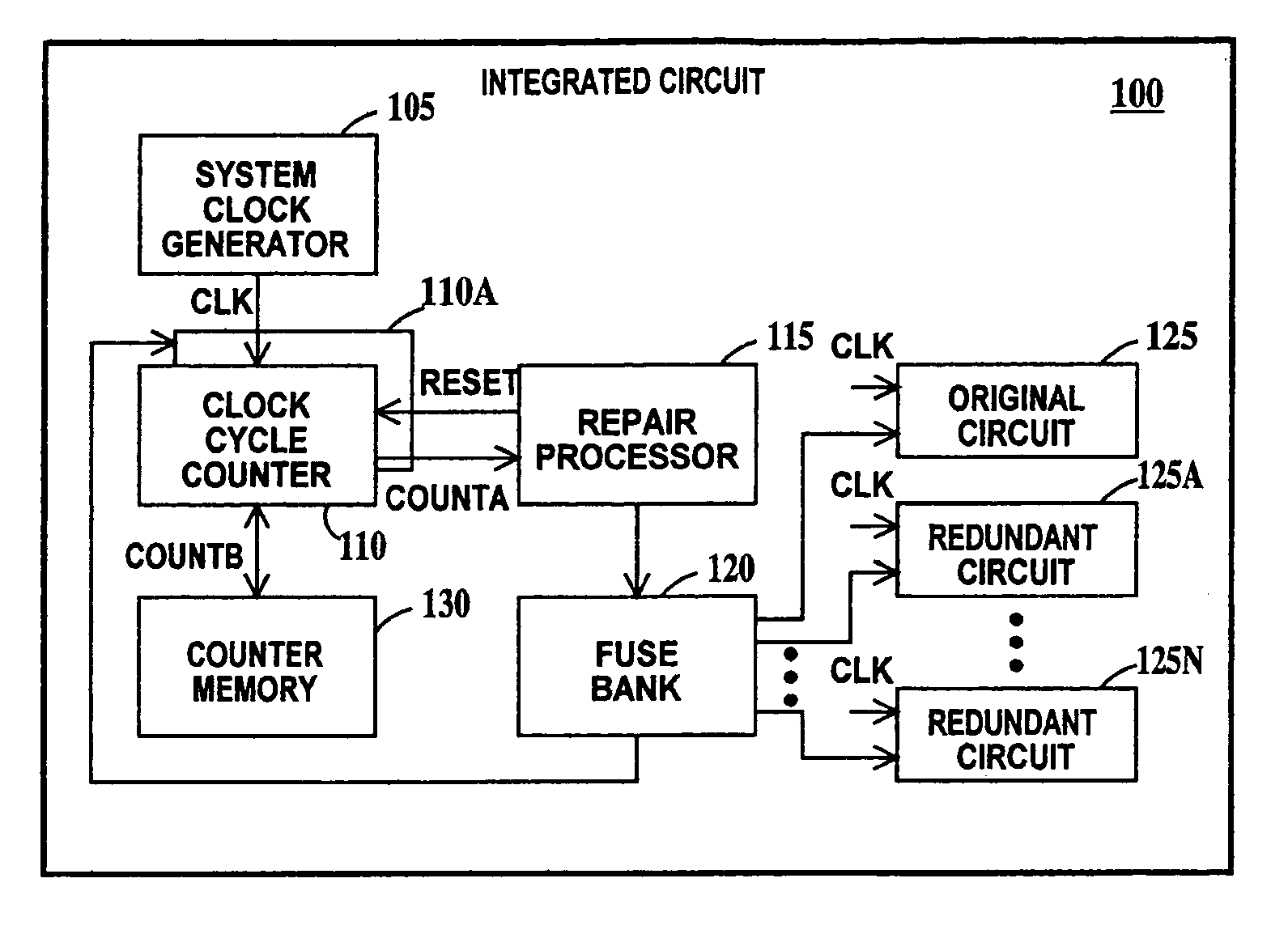

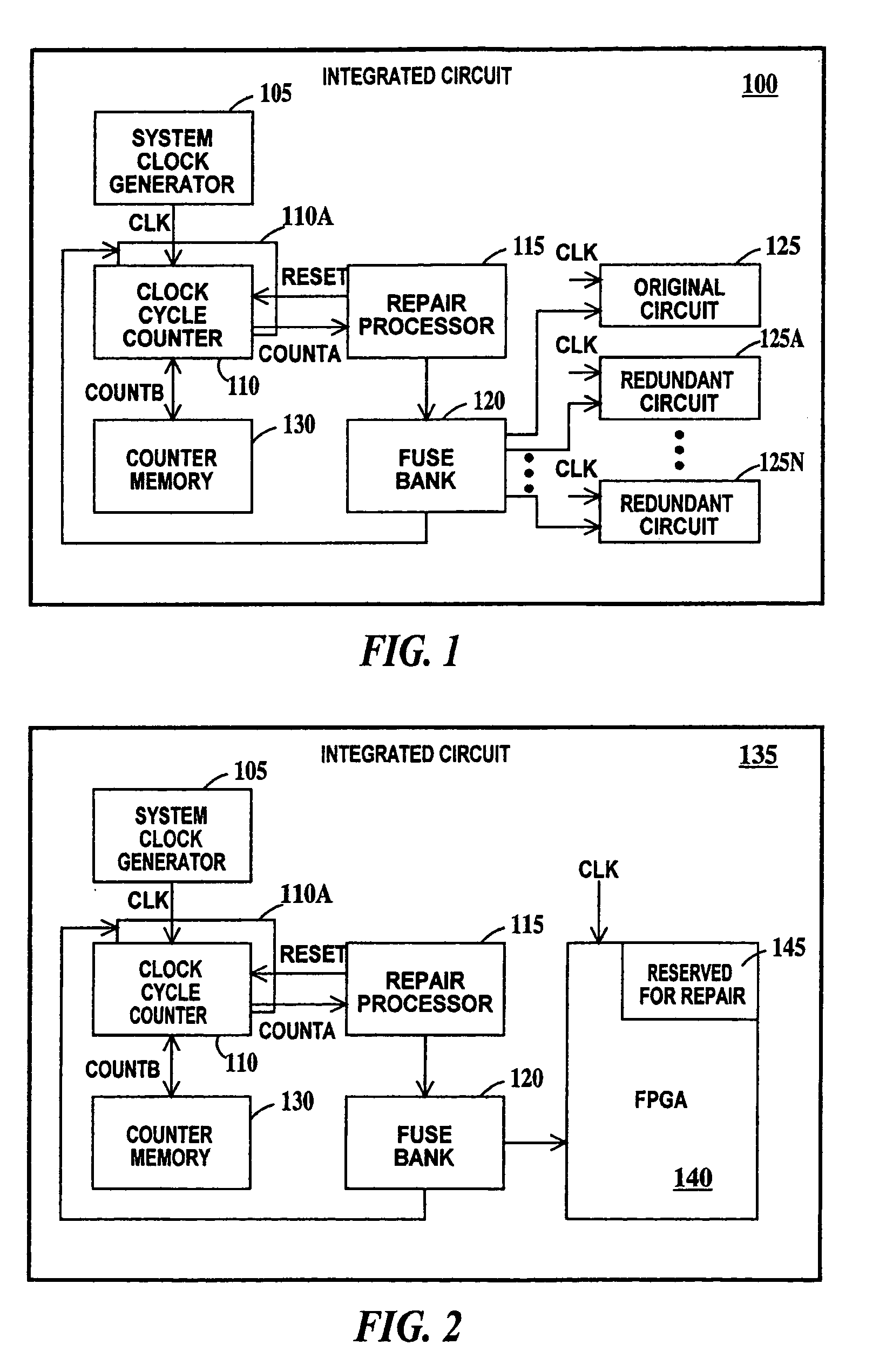

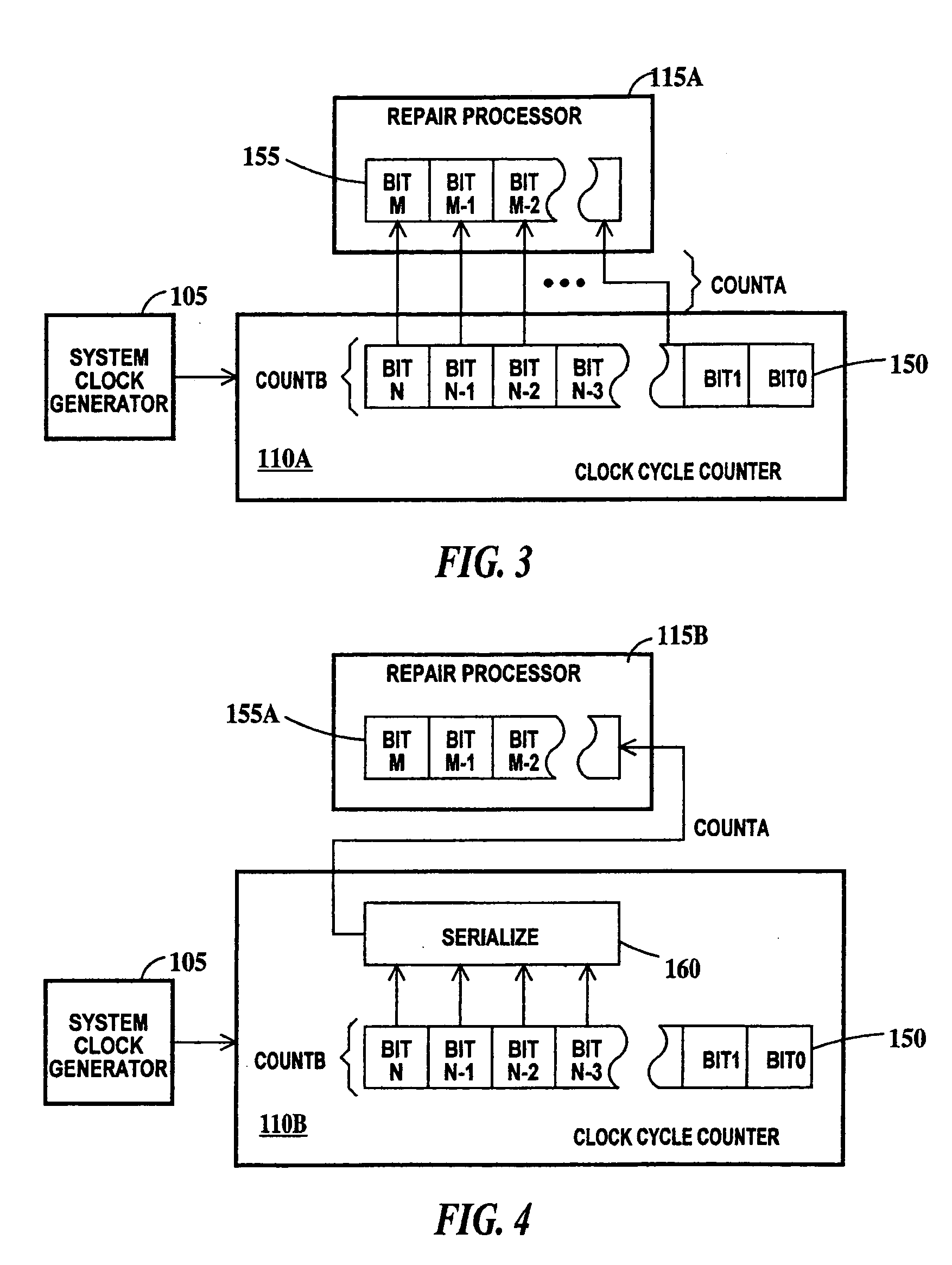

Digital reliability monitor having autonomic repair and notification capability

InactiveUS20050144524A1Avoid failureError detection/correctionGenerating/distributing signalsDependabilityIntegrated circuit

A method a circuit for preventing failure in an integrated circuit. The circuit including: an original circuit; one or more redundant circuits; and a repair processor, including a clock cycle counter adapted to count pulses of a pulsed signal, the repair processor adapted to (a) replace the original circuit with a first redundant circuit or (b) adapted to select another redundant circuit, the selection in sequence from a second redundant circuit to a last redundant circuit, and to replace a previously selected redundant circuit with the selected redundant circuit each time the cycle counter reaches a predetermined count of a set of predetermined cycle counts.

Owner:GLOBALFOUNDRIES INC

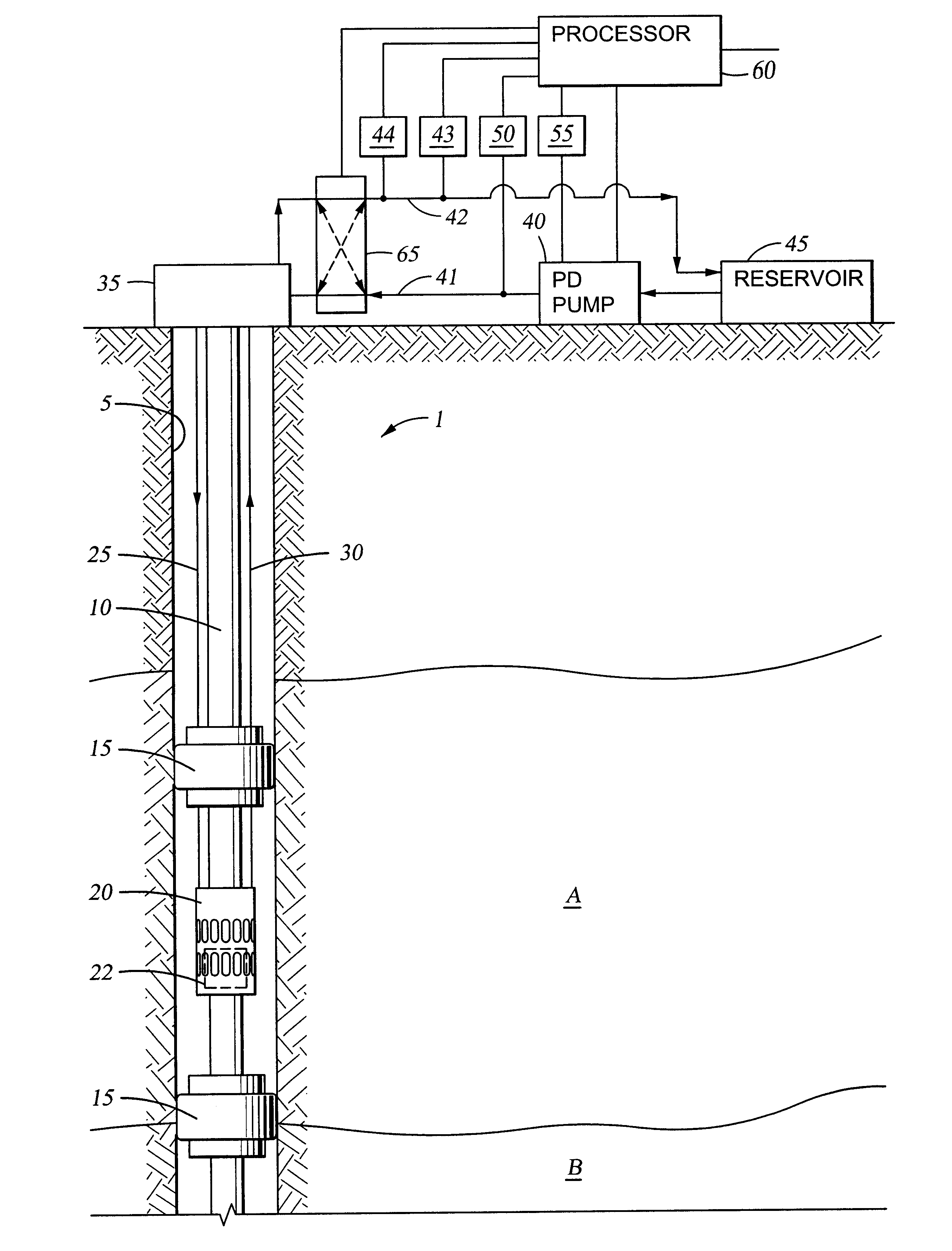

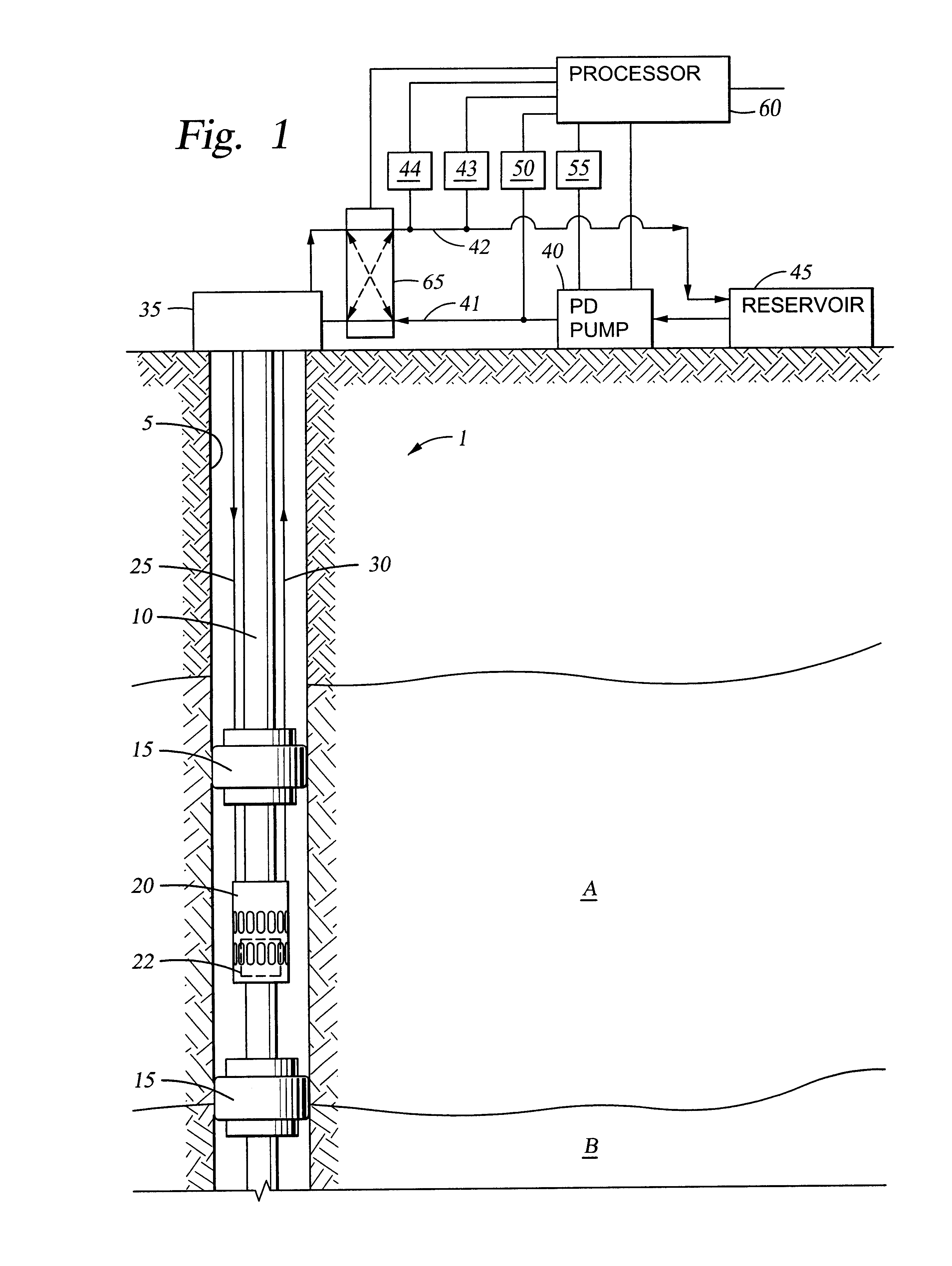

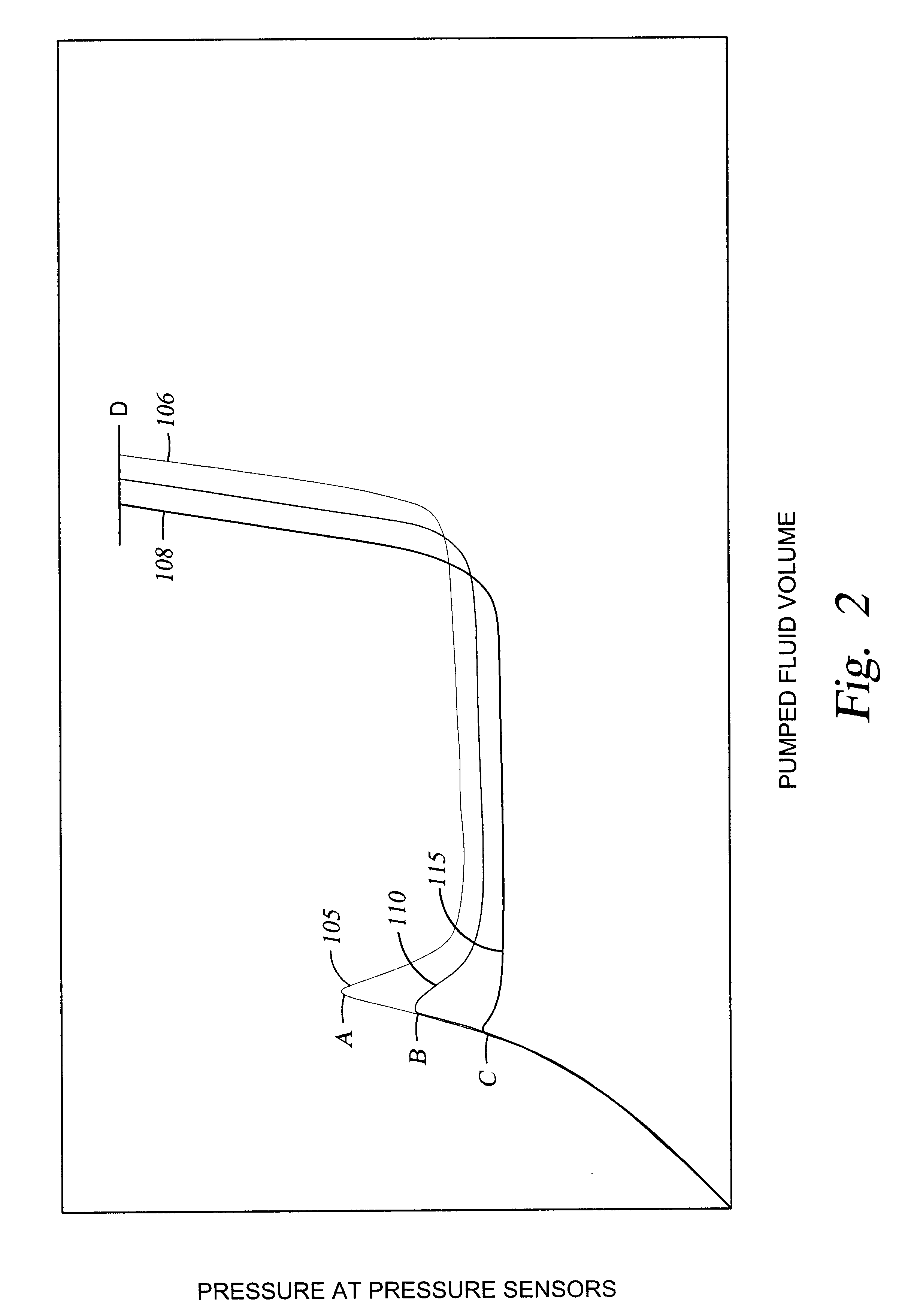

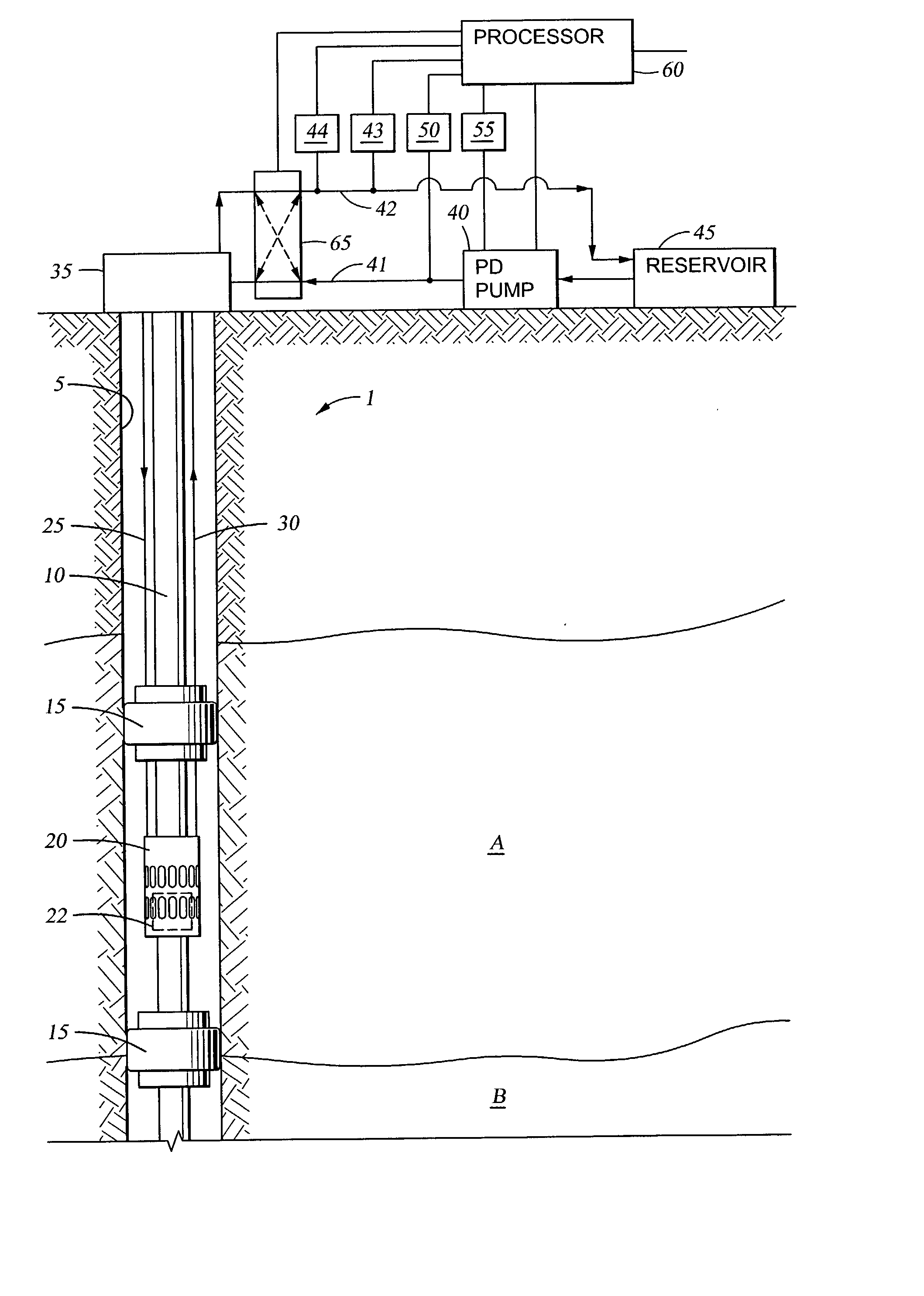

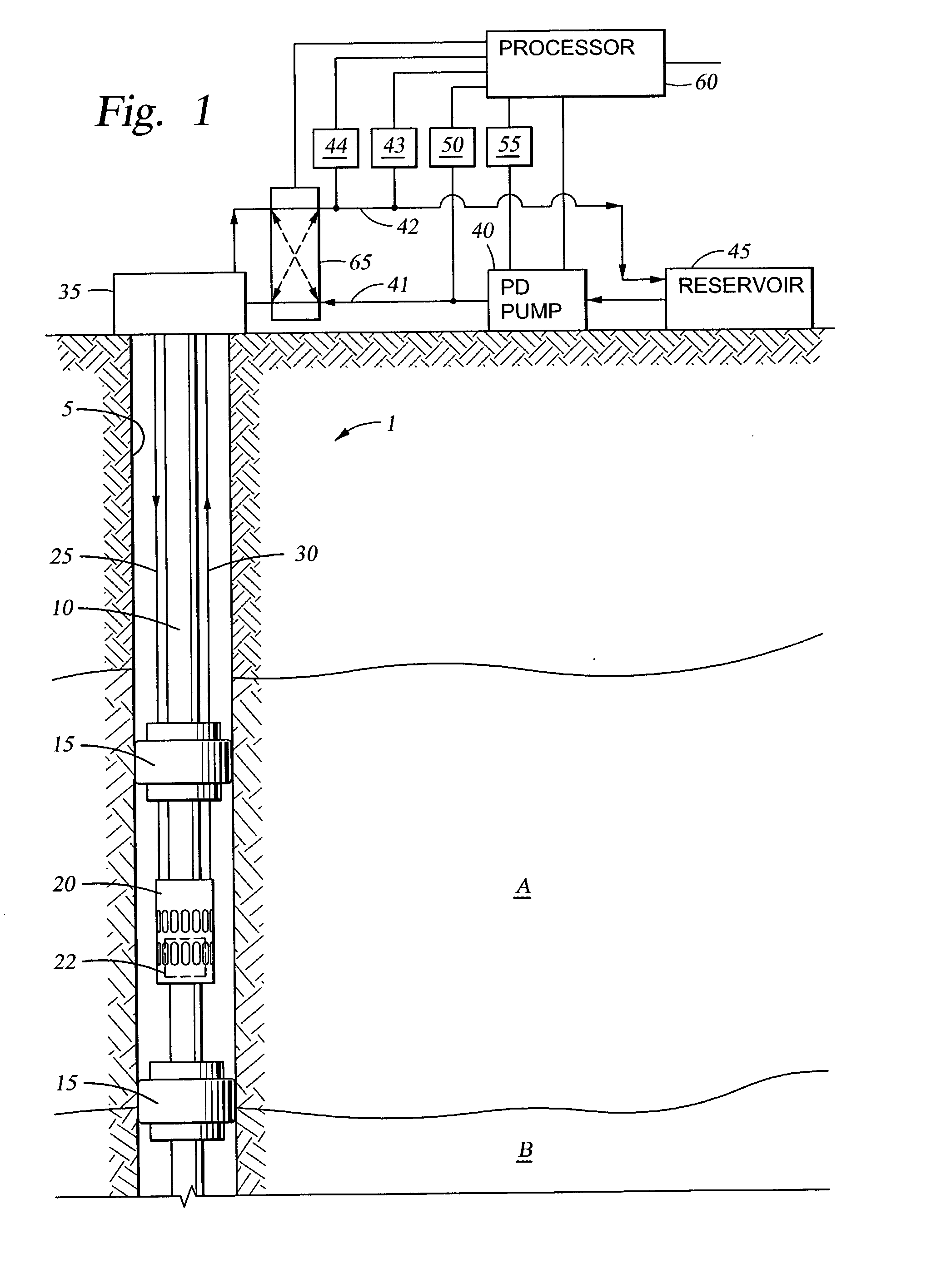

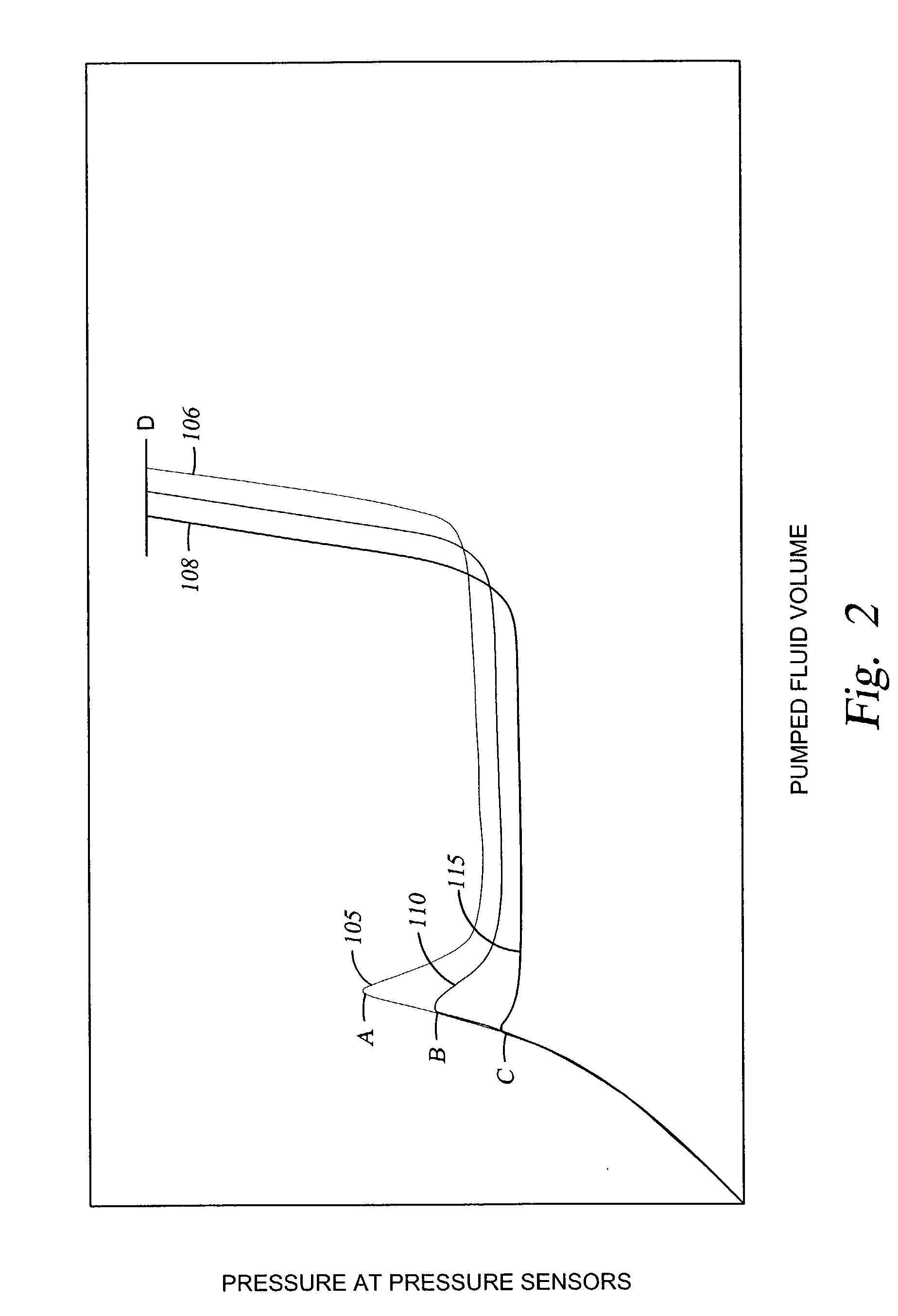

Method and system for controlling a downhole flow control device using derived feedback control

A system and methods for proportionally controlling hydraulically actuated downhole flow control devices using derived feedback control. The system comprises a downhole flow control device with a moveable element in a stationary housing. The moveable element is actuated by a balanced hydraulic piston. Hydraulic lines are fed to either side of the piston to effect actuation in either direction. A processor controlled, surface mounted hydraulic system supplies fluid to the piston. A pressure sensor measures supply pressure to the piston and a cycle counter indicates pump cycles and both sensors generate outputs to the processor. The downhole moveable element is cycled between end stops until successive moveable element breakout pressures are within a predetermined value as measured by the surface pressure sensor. A relationship is then derived between moveable element movement and pumped fluid volume and the relationship is used to move the moveable element to a predetermined position to control flow.

Owner:BAKER HUGHES HLDG LLC

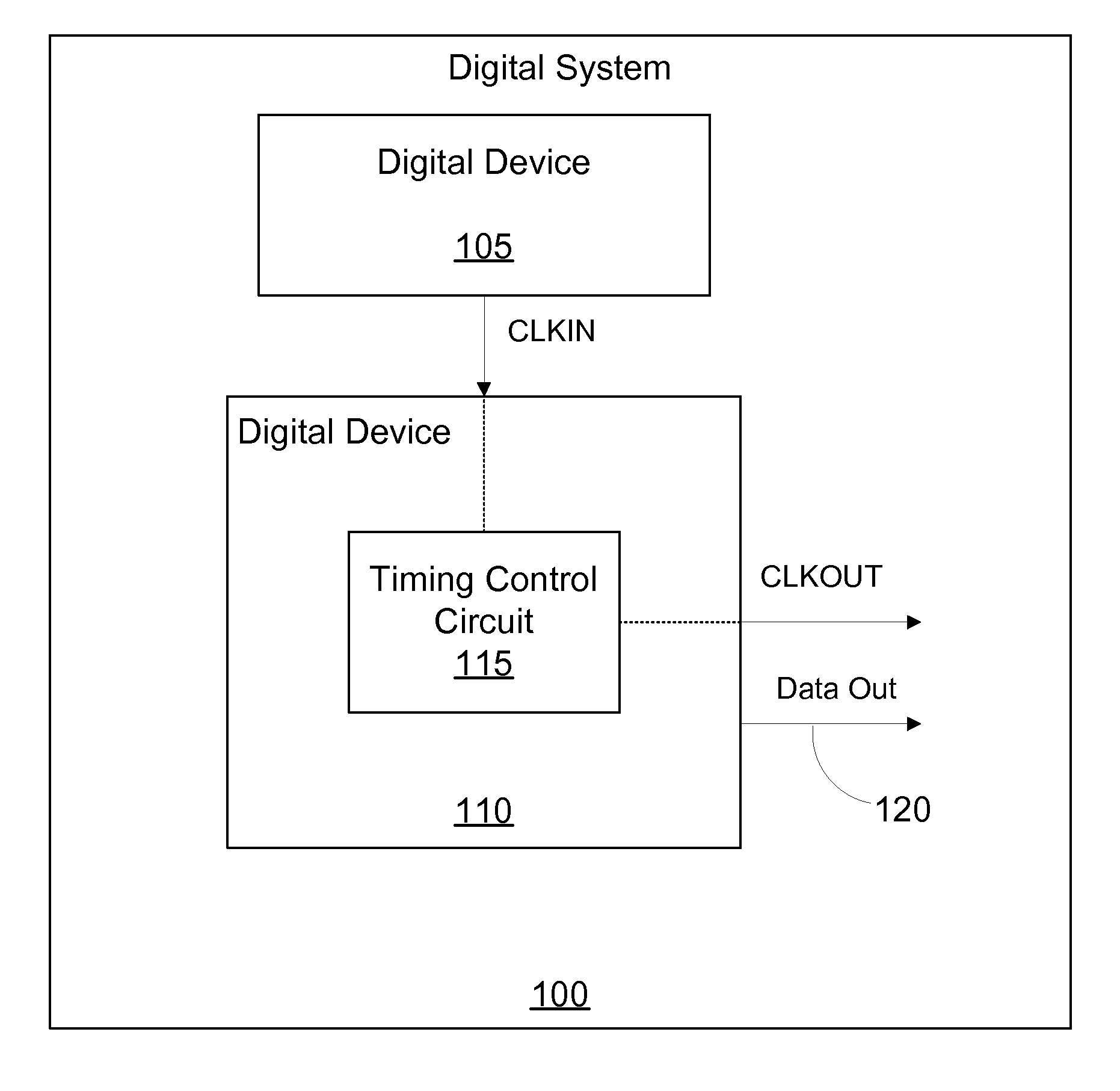

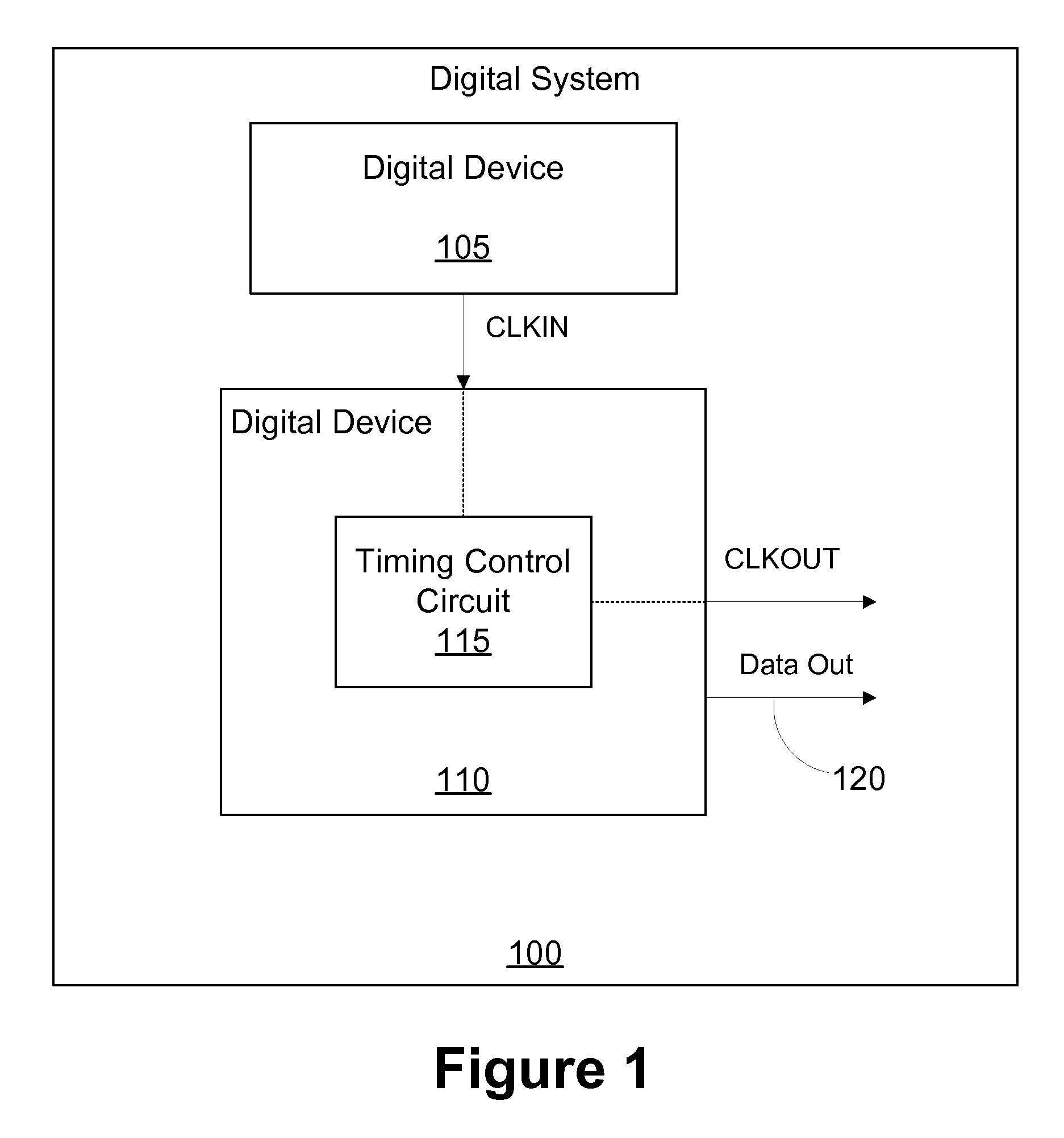

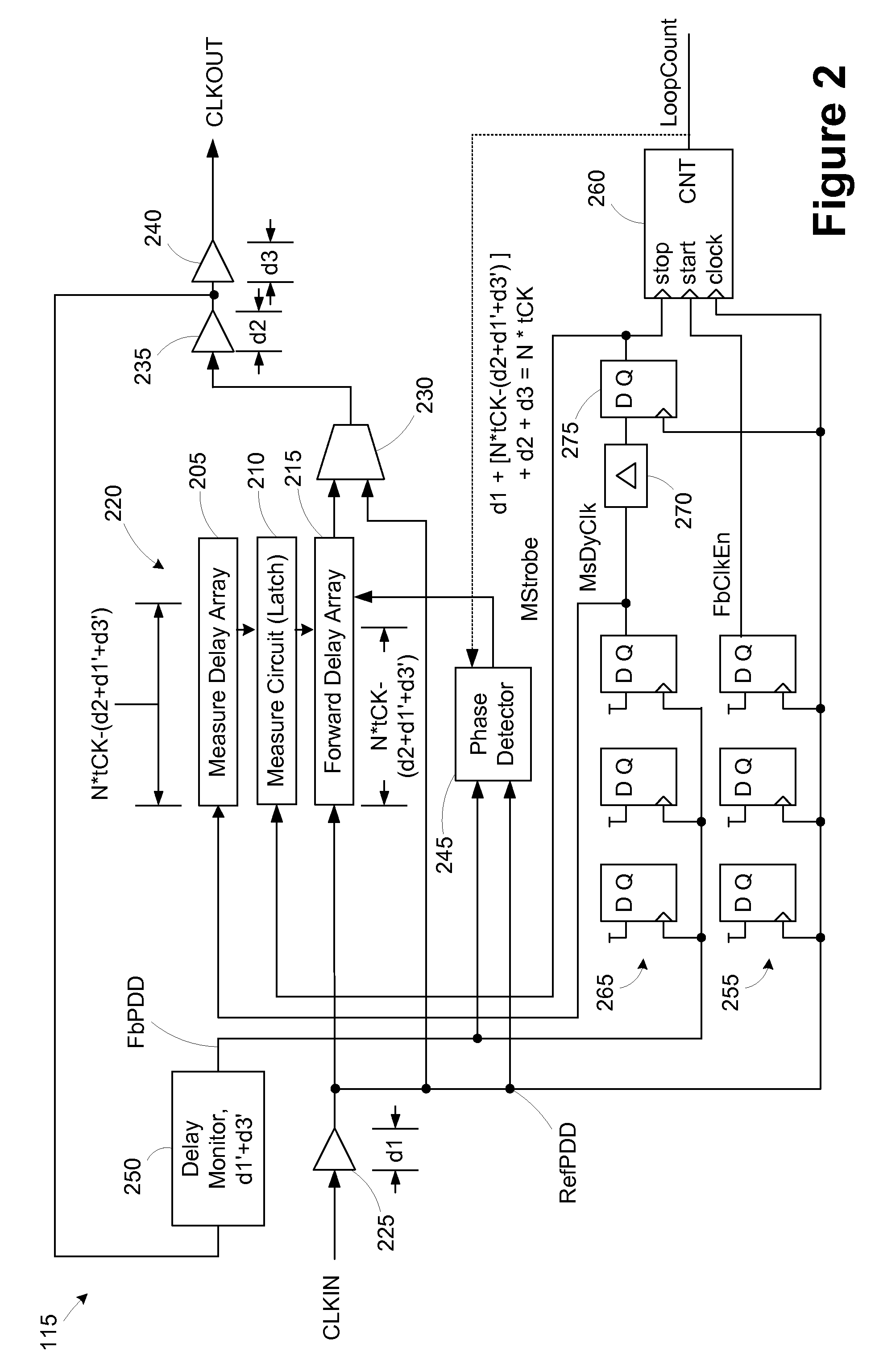

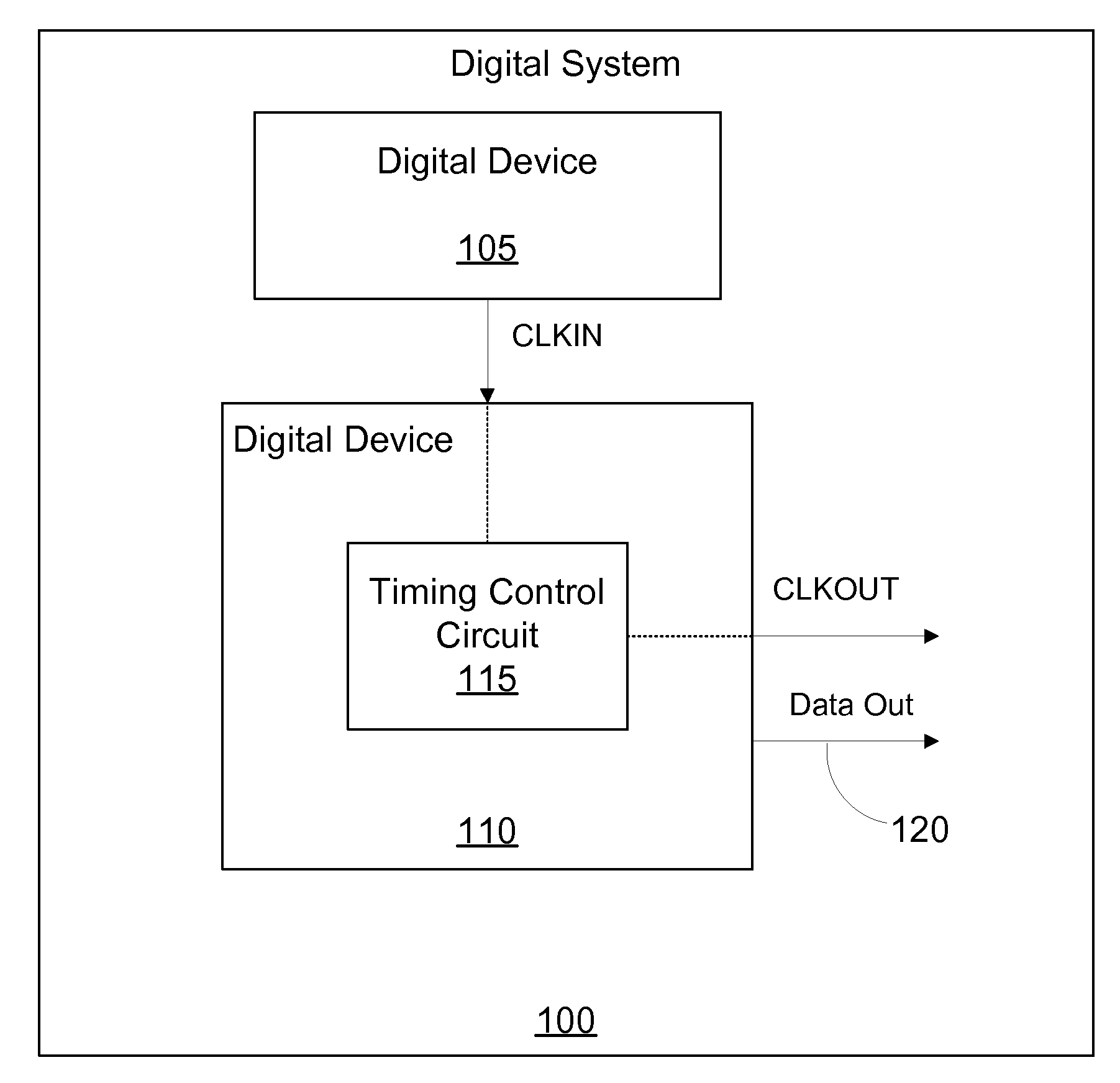

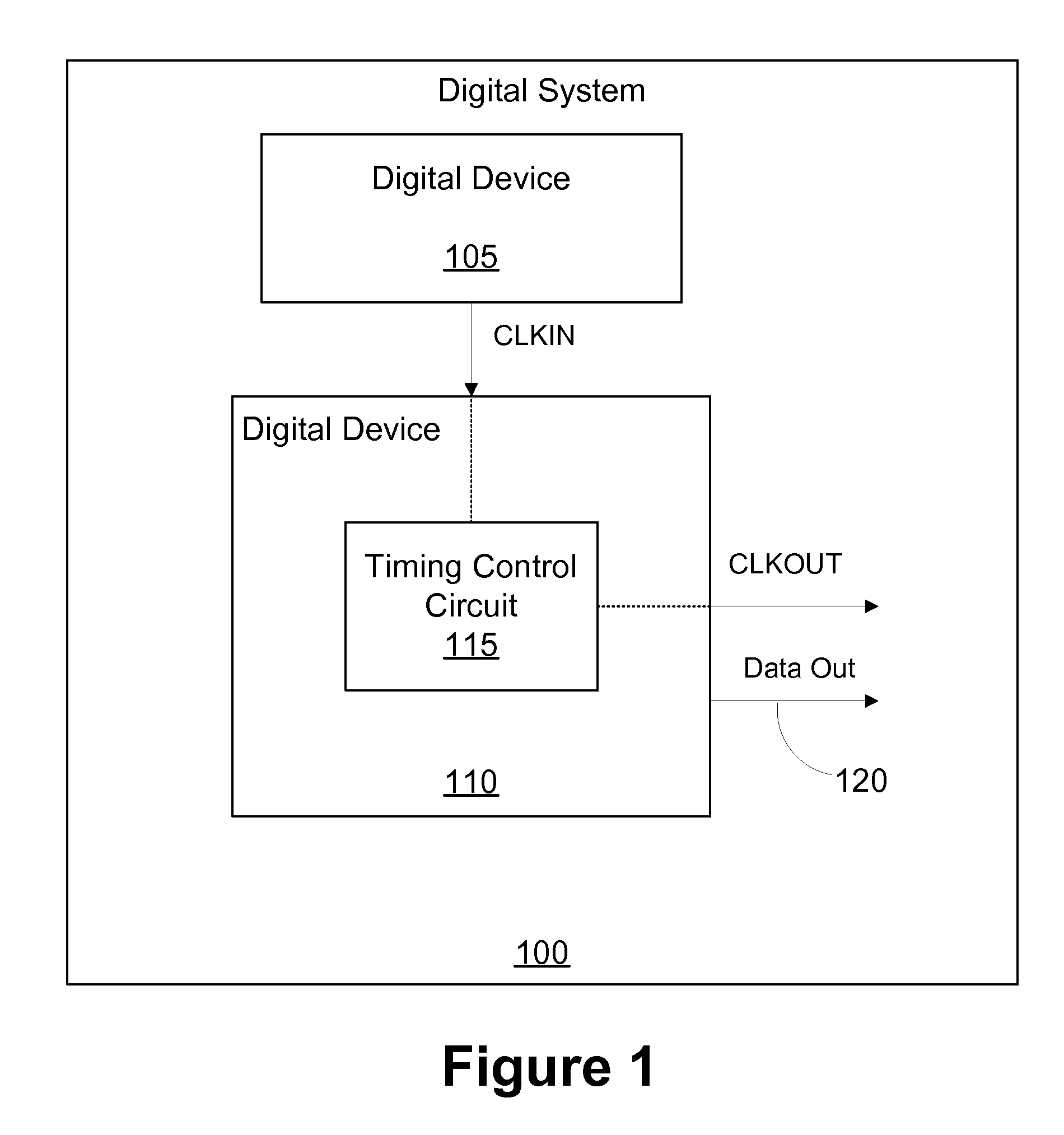

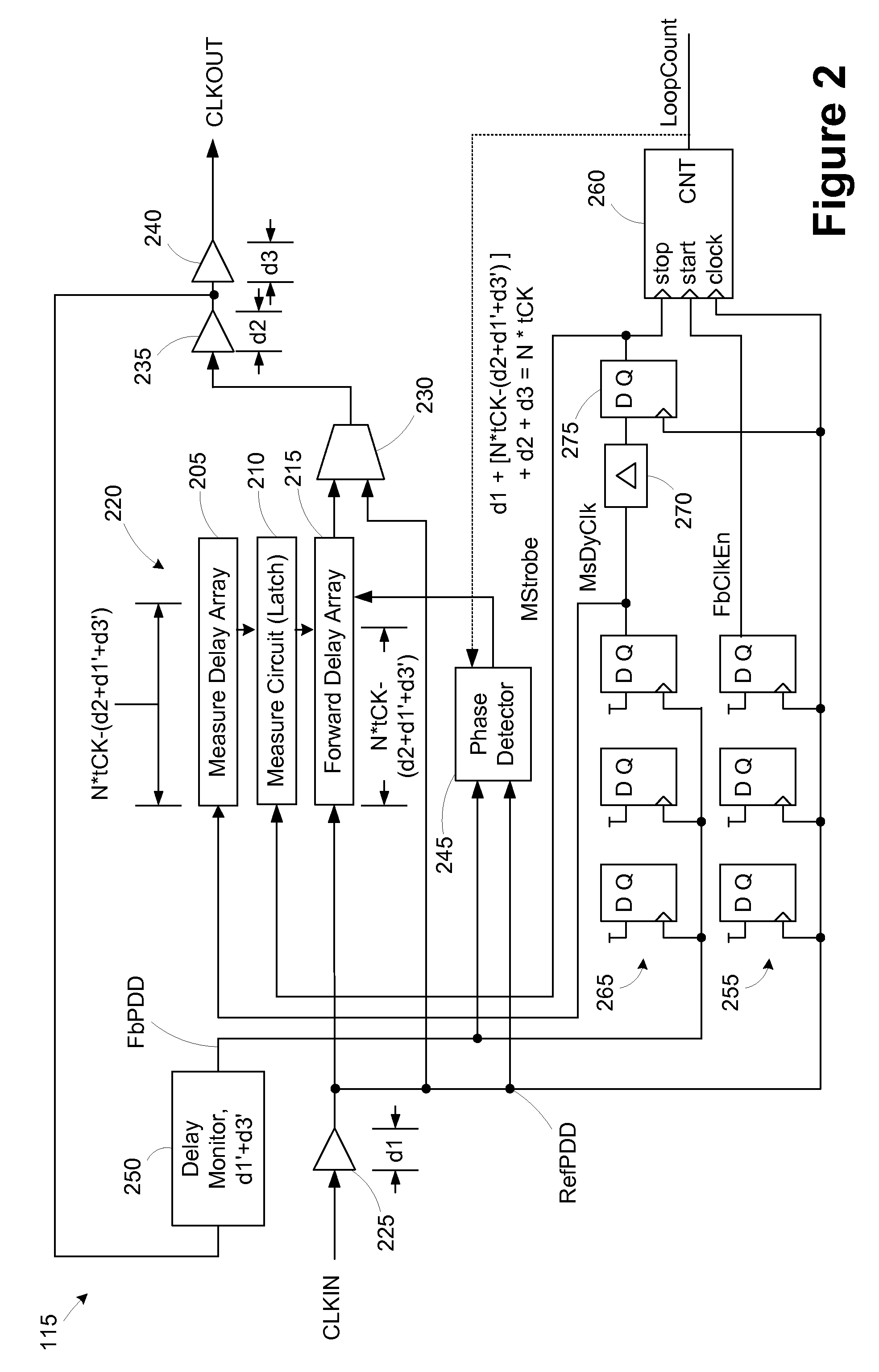

Timing synchronization circuit with loop counter

Owner:MICRON TECH INC

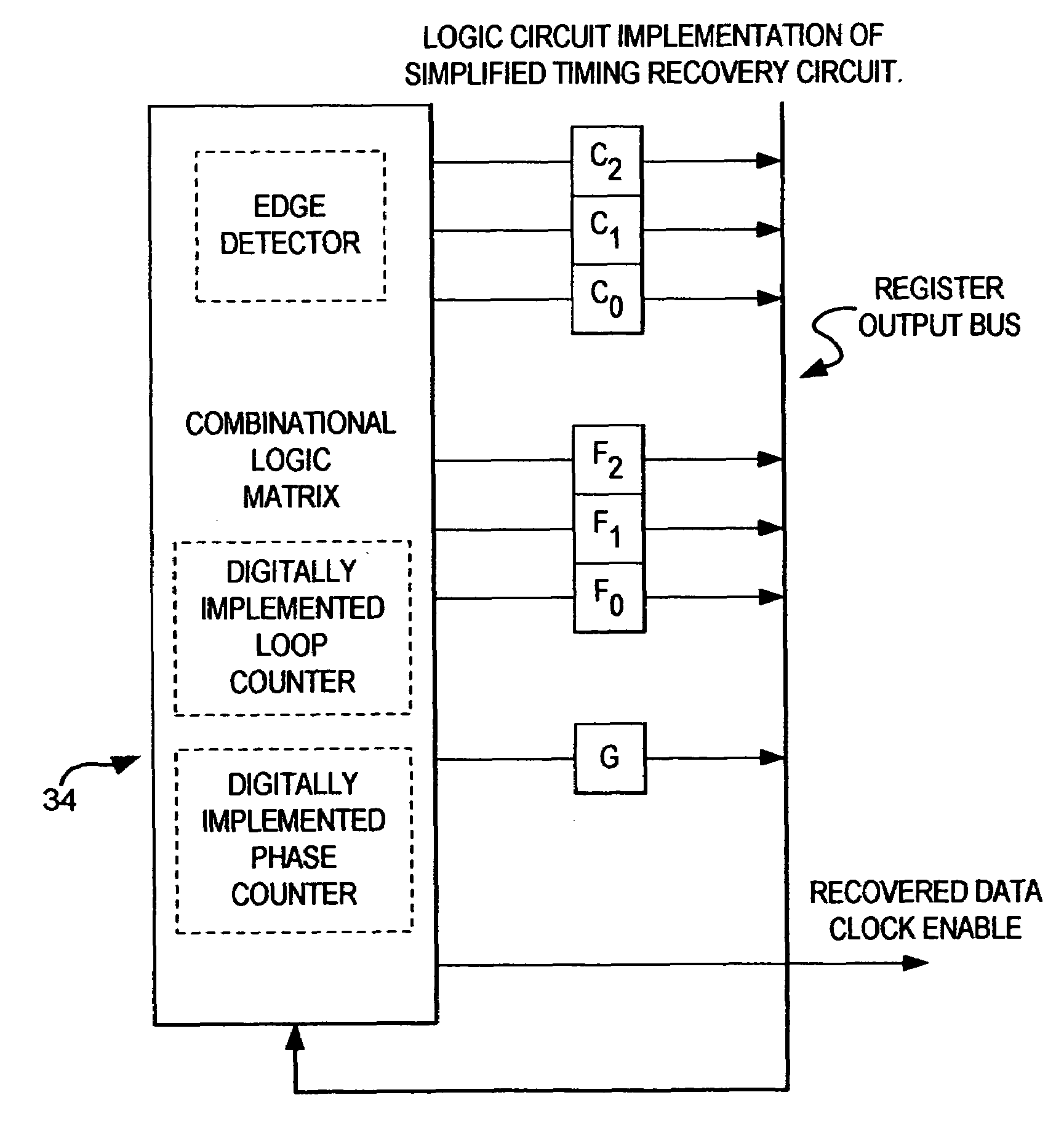

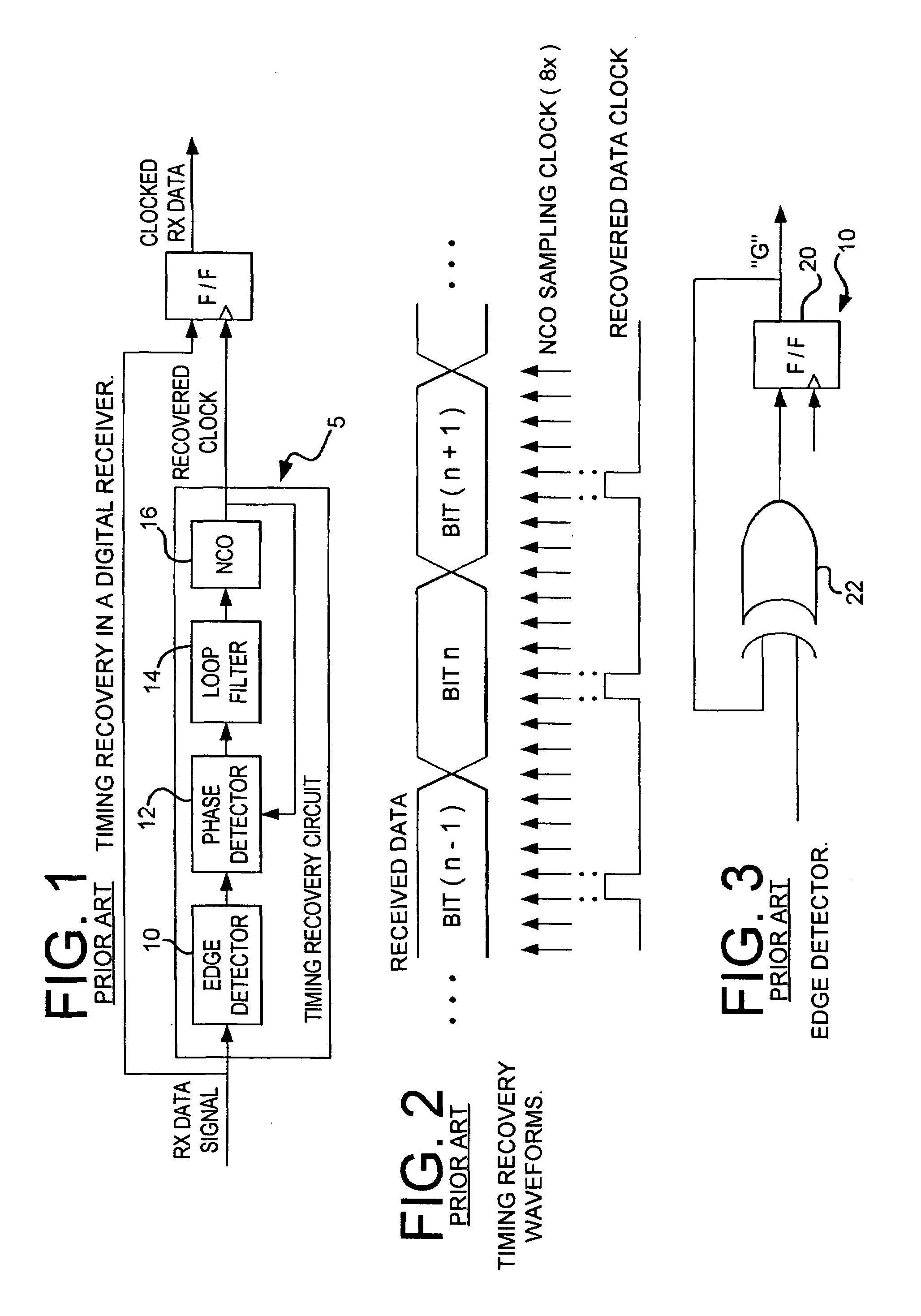

Compact digital timing recovery circuits, devices, systems and processes

InactiveUS6937683B1The process is compact and efficientMinimal requirementPulse automatic controlAngle demodulation by phase difference detectionProcessor registerComputer science

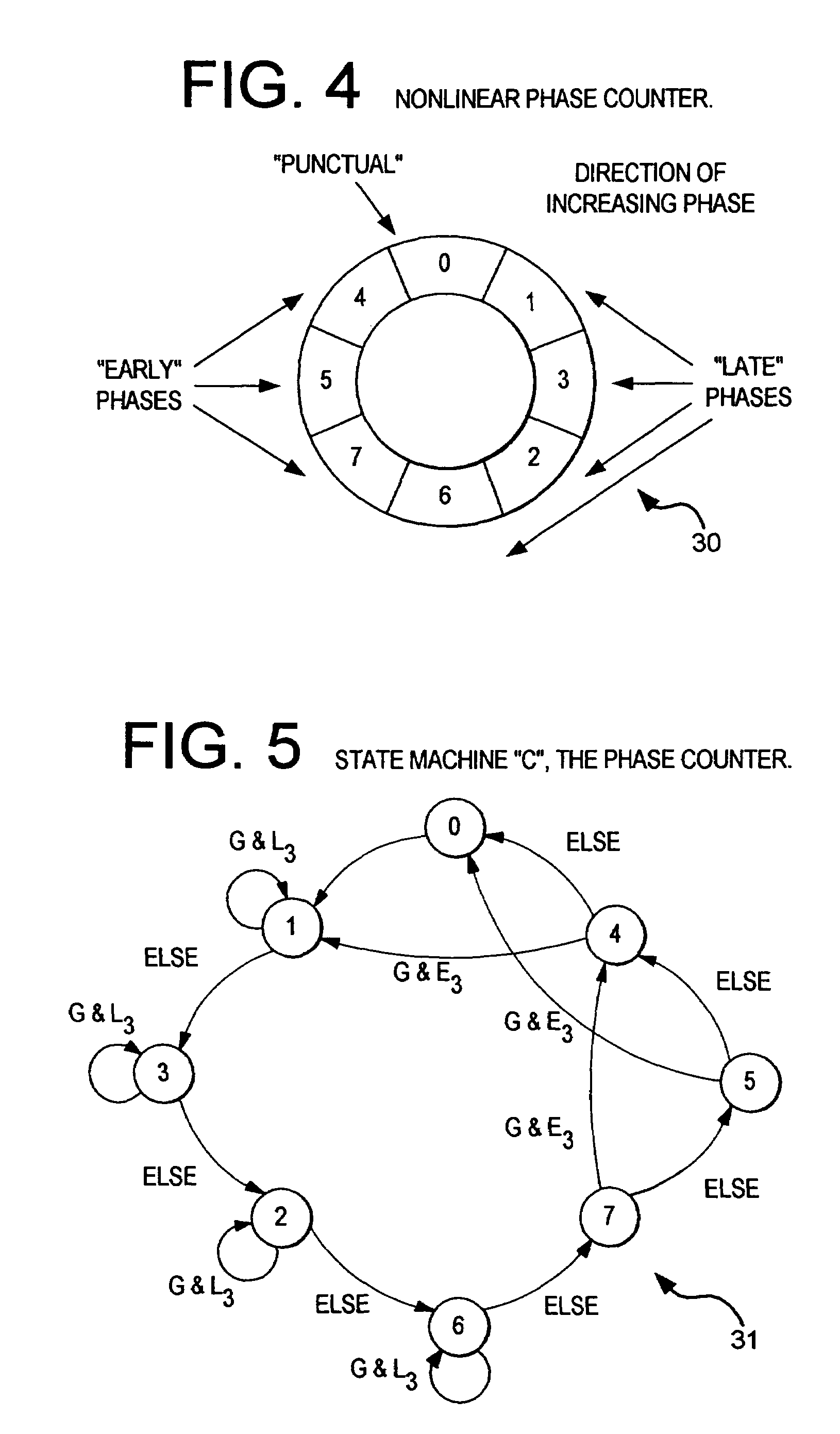

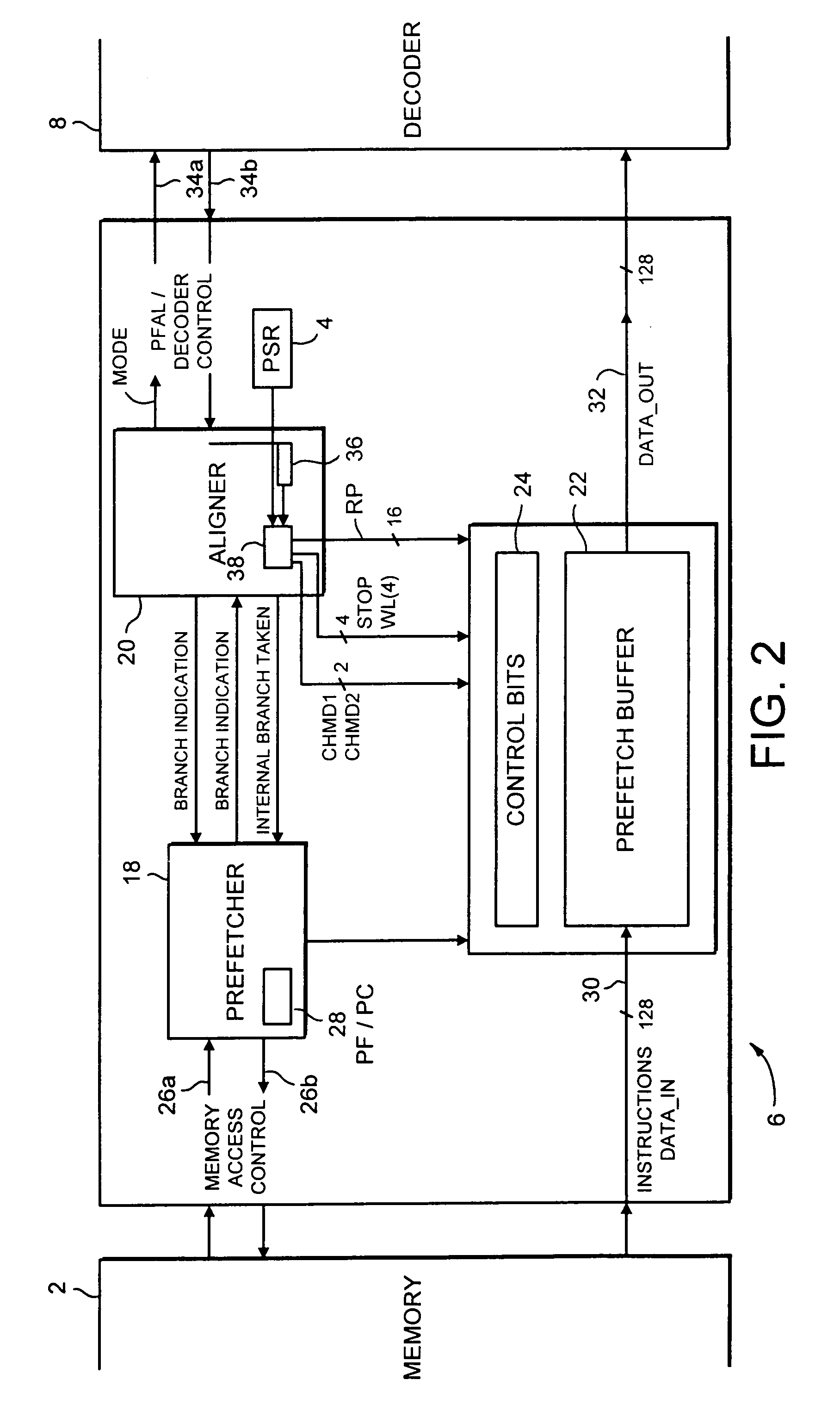

A digitally implemented timing recovery circuit for recovering a clock signal from an input bit stream. The recovery circuit comprising an edge detector for detecting a transition from “0” to “1” or “1” to “0” in the input bit stream, a phase counter having a plurality of registers indicative of the phase counter transition state, and a loop counter having a plurality of registers indicative of the loop counter transition state. When the phase counter reaches a particular transition state, a recovered clock pulse is enabled. The phase counter is preferably non-linear to optimize the circuit.

Owner:CIRRONET

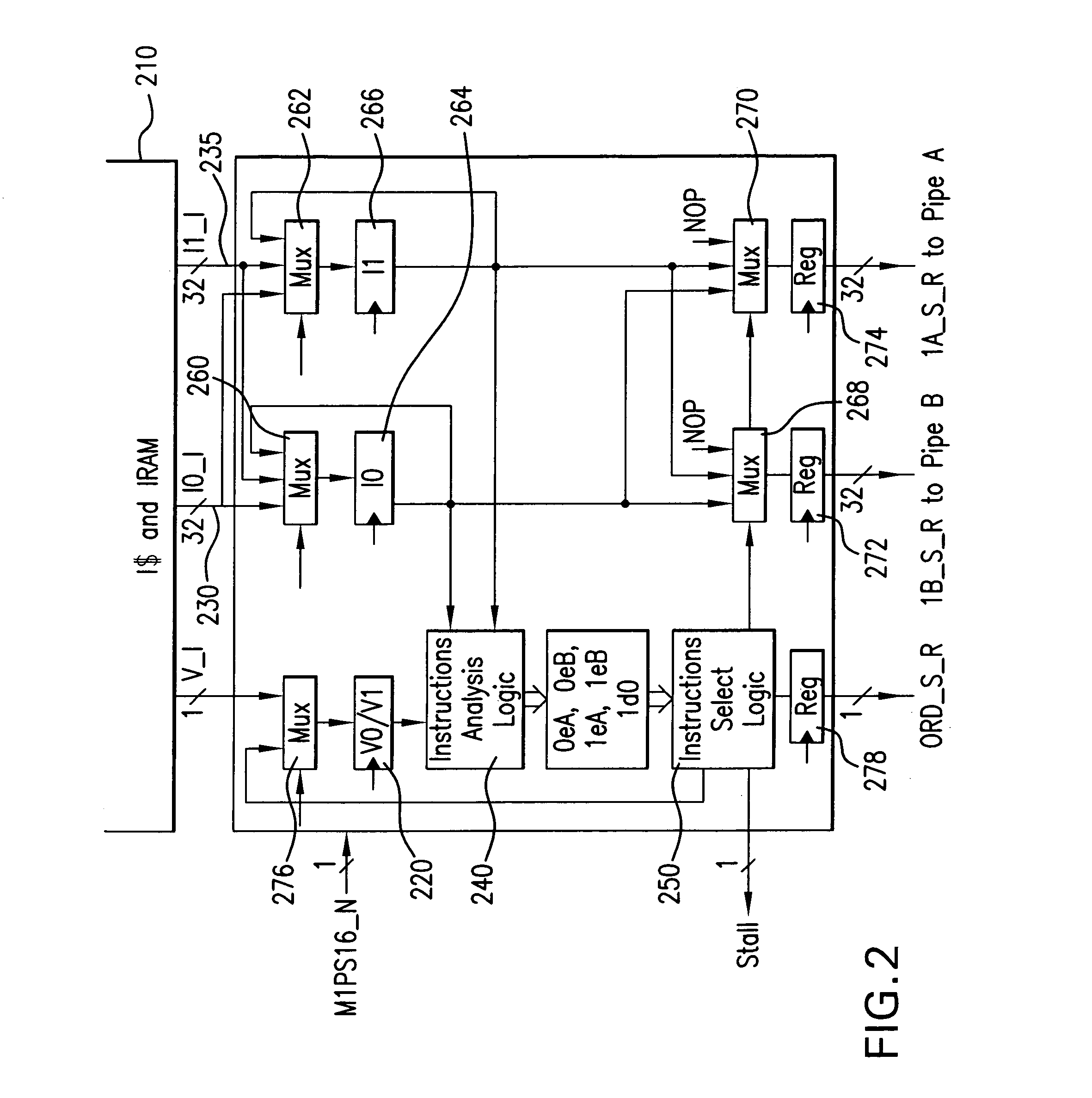

Multiple execution of instruction loops within a processor without accessing program memory

InactiveUS6959379B1Good flexibilityInstruction analysisDigital computer detailsProcessor registerComputerized system

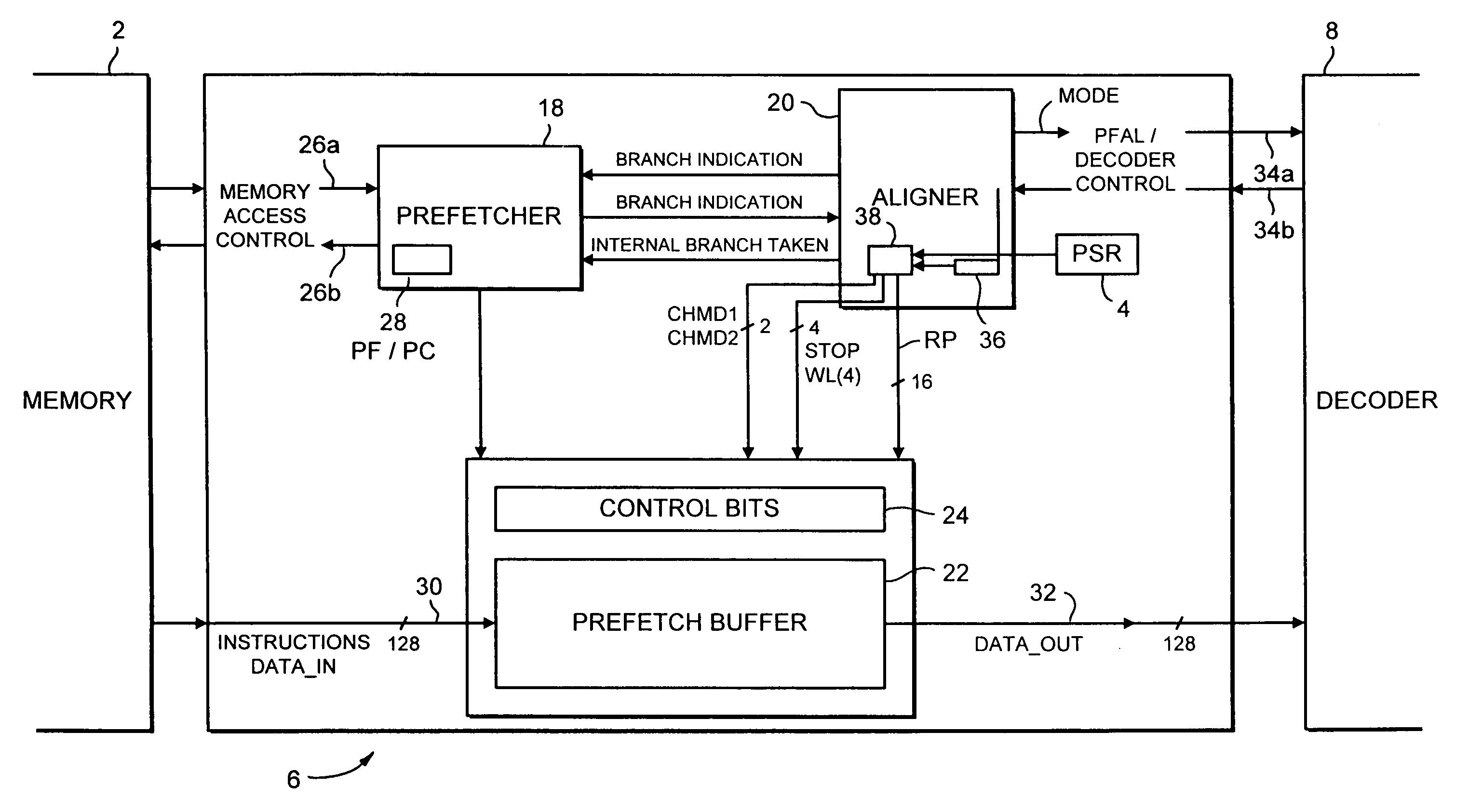

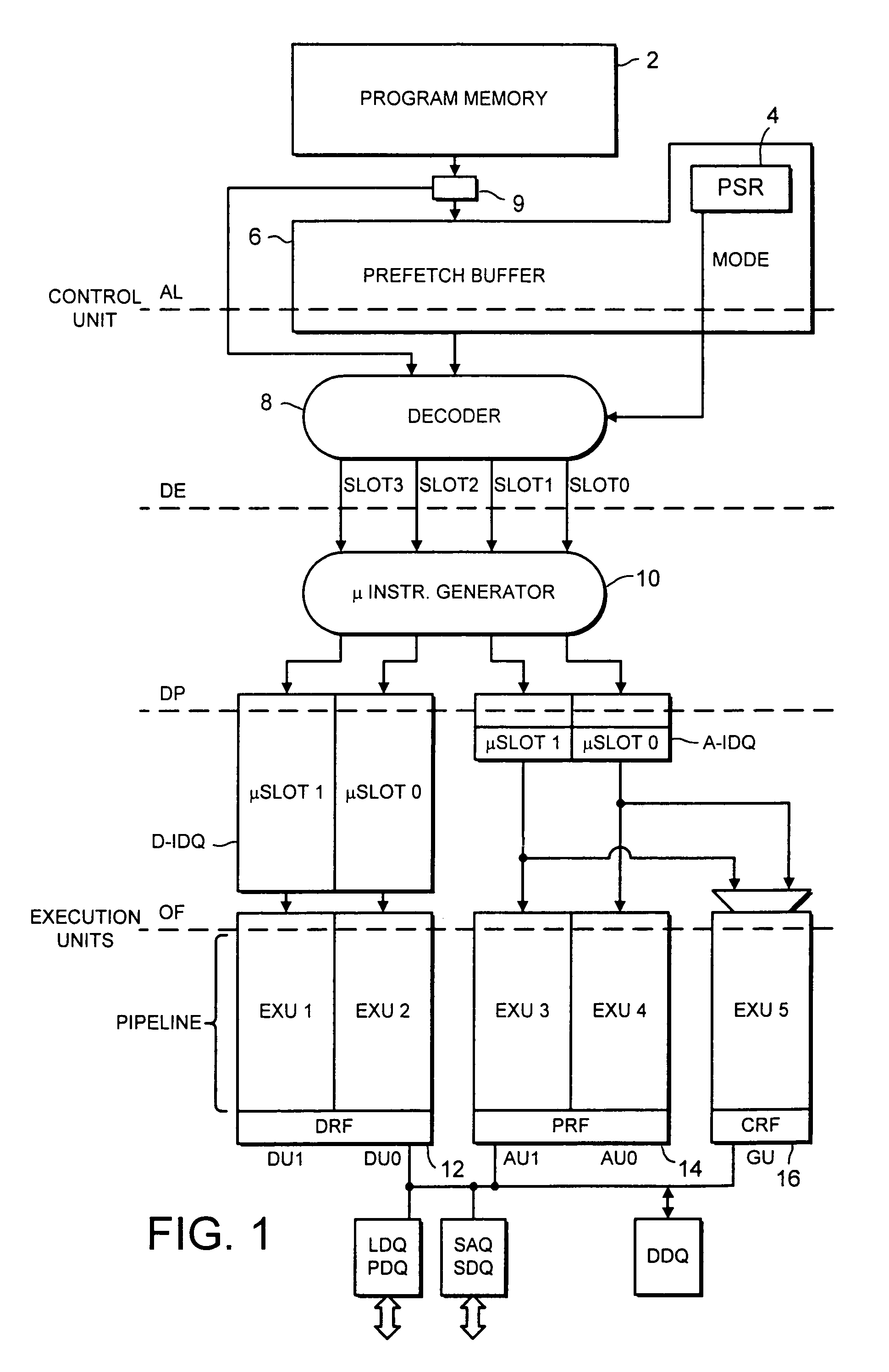

A method of executing loops in a computer system is described. The computer system has a sequence of instructions held in program memory and a prefetch buffer which holds instructions fetched from the memory ready for supply to a decoder of the computer system. If the size of the loop to be executed is such that it can by holly contained within the prefetch buffer, this is detected and a lock is put on the prefetch buffer to retain the loop within it while the loop is executed a requisite number of times. This thus allows power to be saved and reduces the overhead on the memory access buffers. According to another aspect, loops can be “skipped” by holding a value of zero in the loop counter register.

Owner:STMICROELECTRONICS SRL

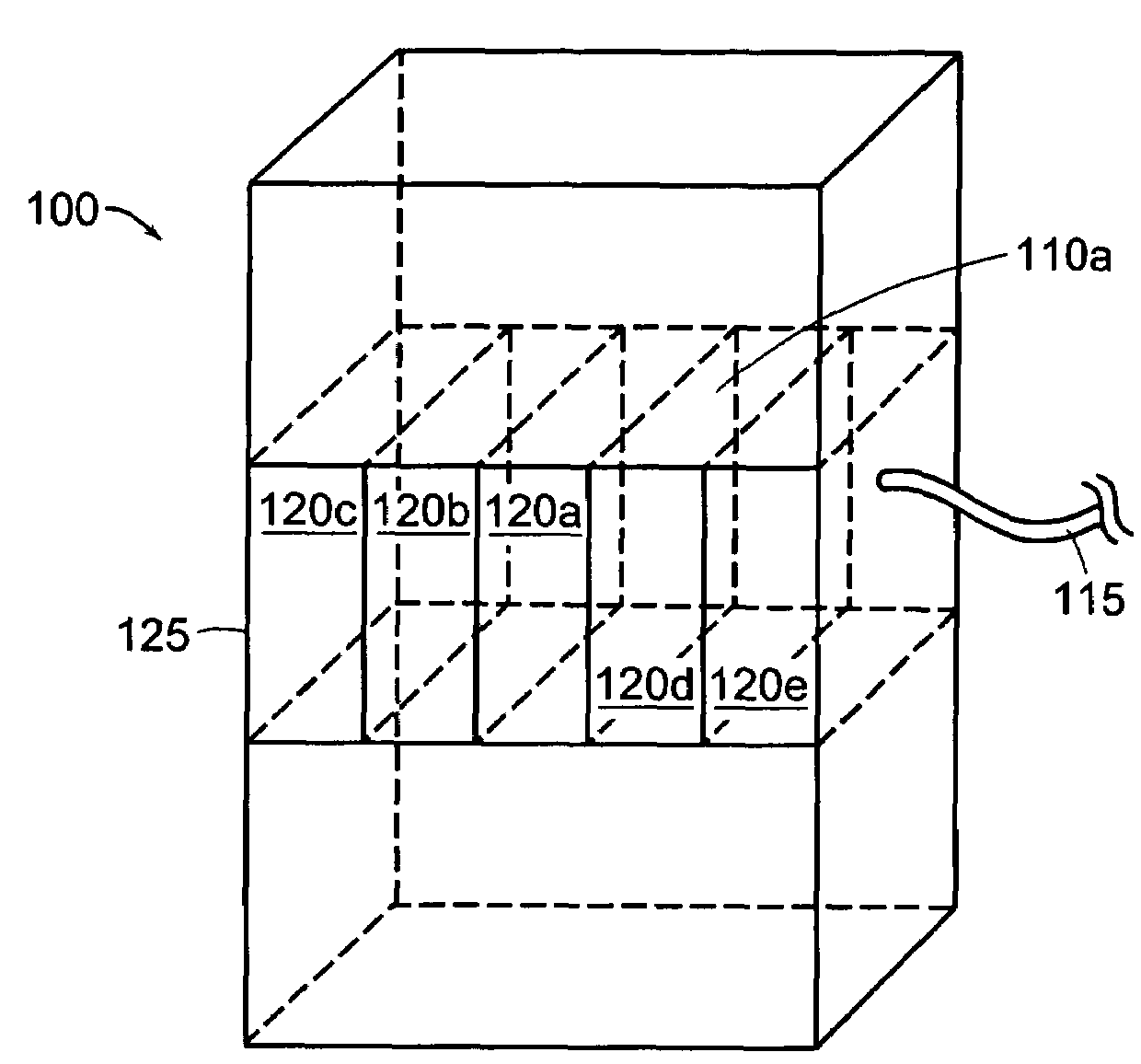

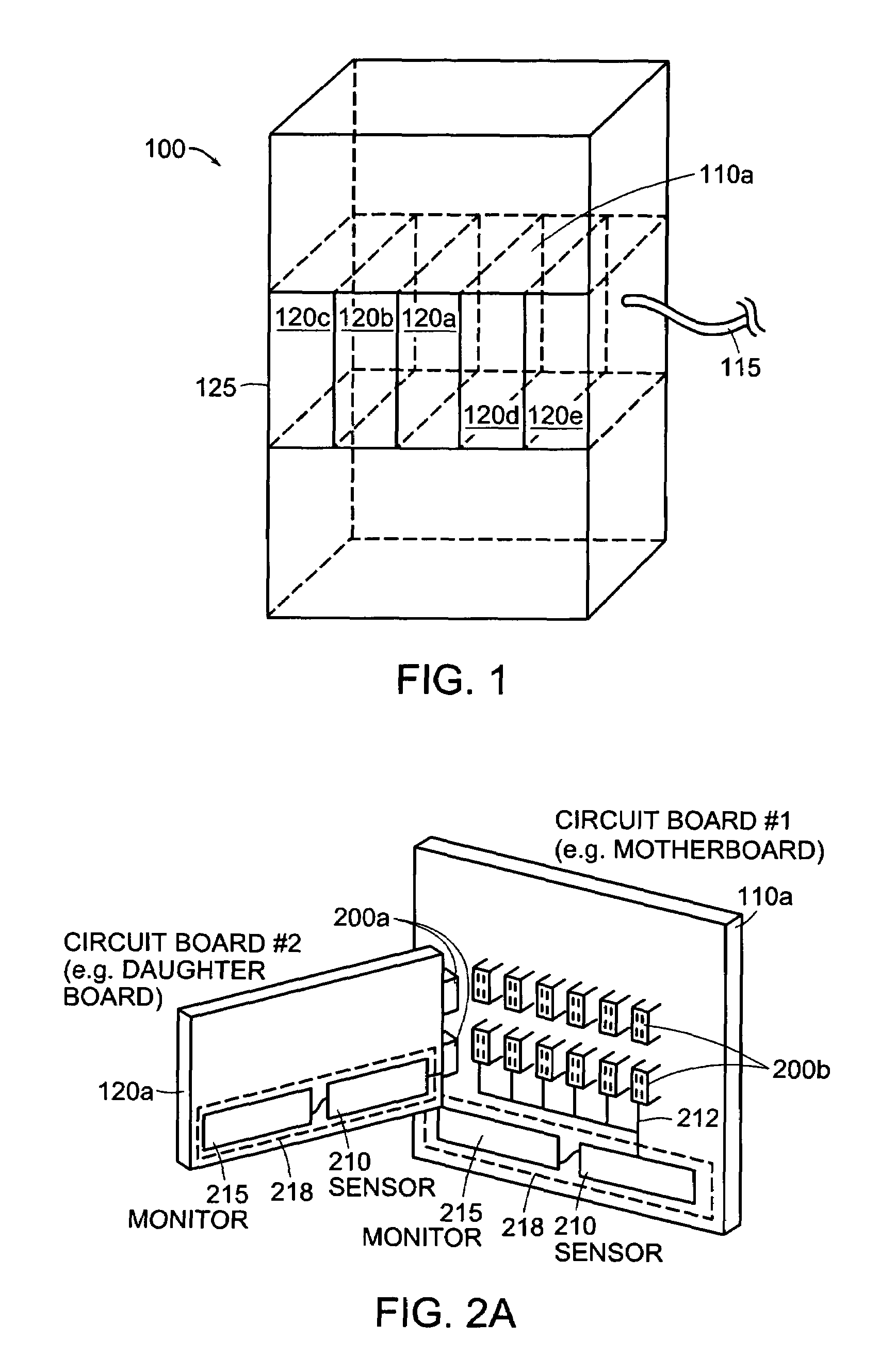

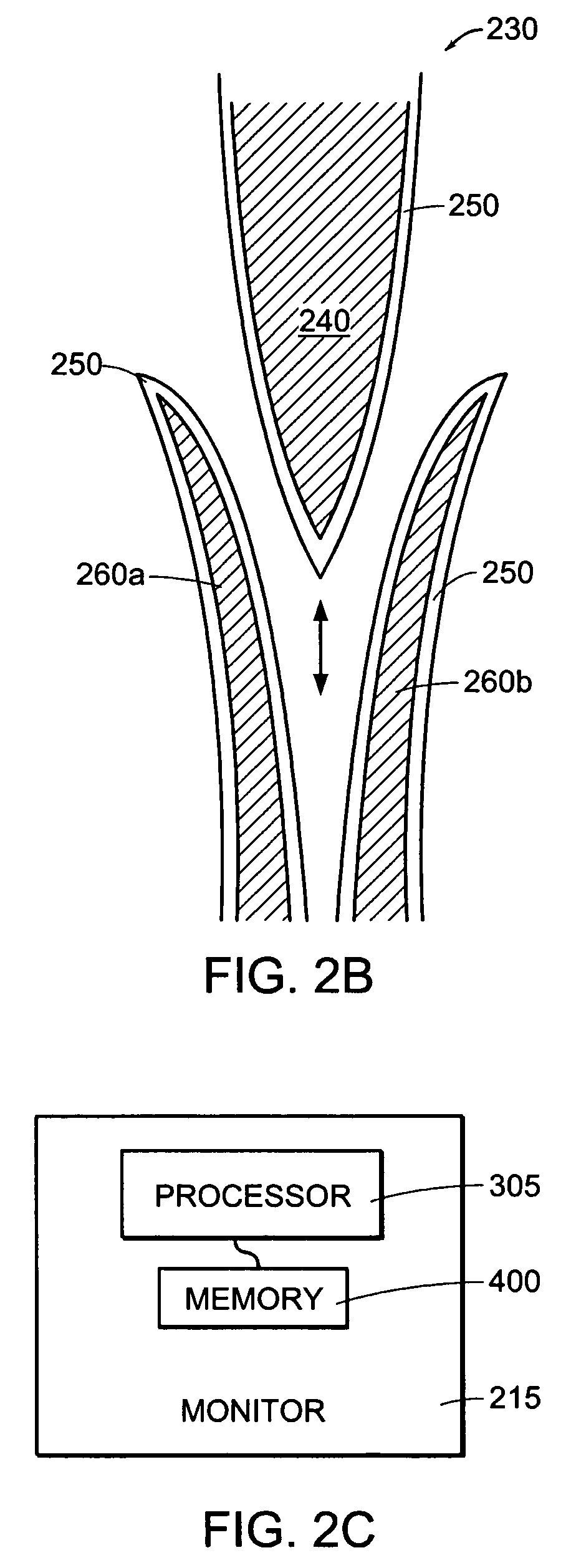

Electronic insertion/extraction cycle counter and logger device

A monitoring system monitors wear of a connector by counting insertions or extractions between circuit boards. The monitoring system includes a sensor that senses insertions or extractions through contact or non-contact sensing. The monitoring system also includes a monitor connected to the sensor to monitor insertions or extractions and, optionally, store data in memory and generate an alarm signal if a predetermined threshold has been exceeded. The monitoring system may be positioned at any location in an electronic system and may be configured such that the sensor connects to the monitor directly, indirectly, or over a network.

Owner:TELLABS OPERATIONS

Timing synchronization circuit with loop counter

An apparatus for synchronizing an output clock signal with an input clock signal includes a first timing synchronization circuit, control logic, and a counter. The first timing synchronization circuit is operable to generate a delay to synchronize a reference clock signal representative of the input clock signal with a feedback clock signal representative of the output clock signal responsive a strobe signal. The control logic is operable to generate an enable signal based on the reference clock signal and generate the strobe signal based on the feedback clock signal. The counter is operable to count cycles of the reference clock signal occurring between the enable signal and the strobe signal to generate a loop count for the first timing synchronization circuit.

Owner:MICRON TECH INC

Method and system for controlling a downhole flow control device using derived feedback control

A system and methods for proportionally controlling hydraulically actuated downhole flow control devices using derived feedback control. The system comprises a downhole flow control device with a moveable element in a stationary housing. The moveable element is actuated by a balanced hydraulic piston. Hydraulic lines are fed to either side of the piston to effect actuation in either direction. A processor controlled, surface mounted hydraulic system supplies fluid to the piston. A pressure sensor measures supply pressure to the piston and a cycle counter indicates pump cycles and both sensors generate outputs to the processor. The downhole moveable element is cycled between end stops until successive moveable element breakout pressures are within a predetermined value as measured by the surface pressure sensor. A relationship is then derived between moveable element movement and pumped fluid volume and the relationship is used to move the moveable element to a predetermined position to control flow.

Owner:BAKER HUGHES INC

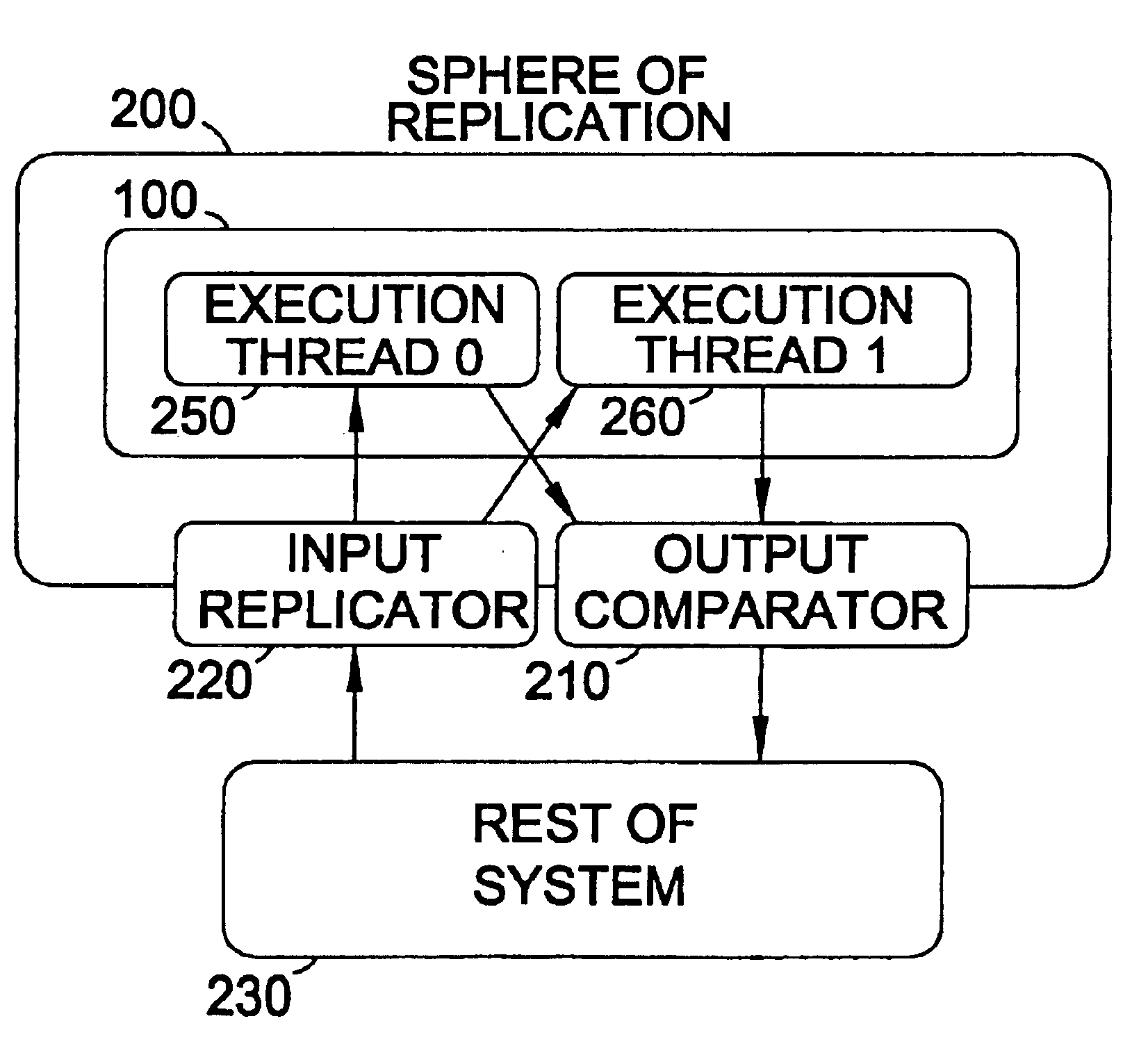

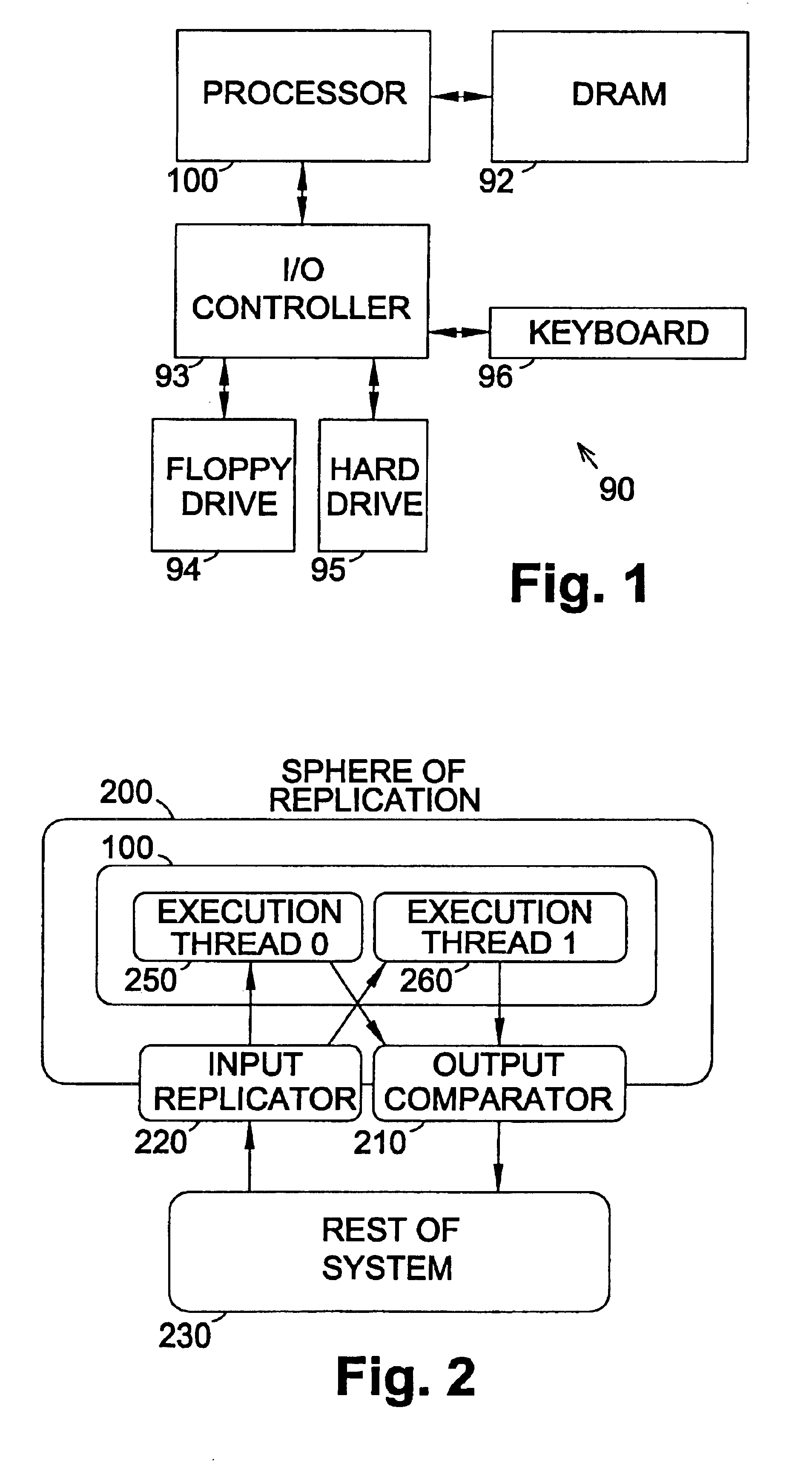

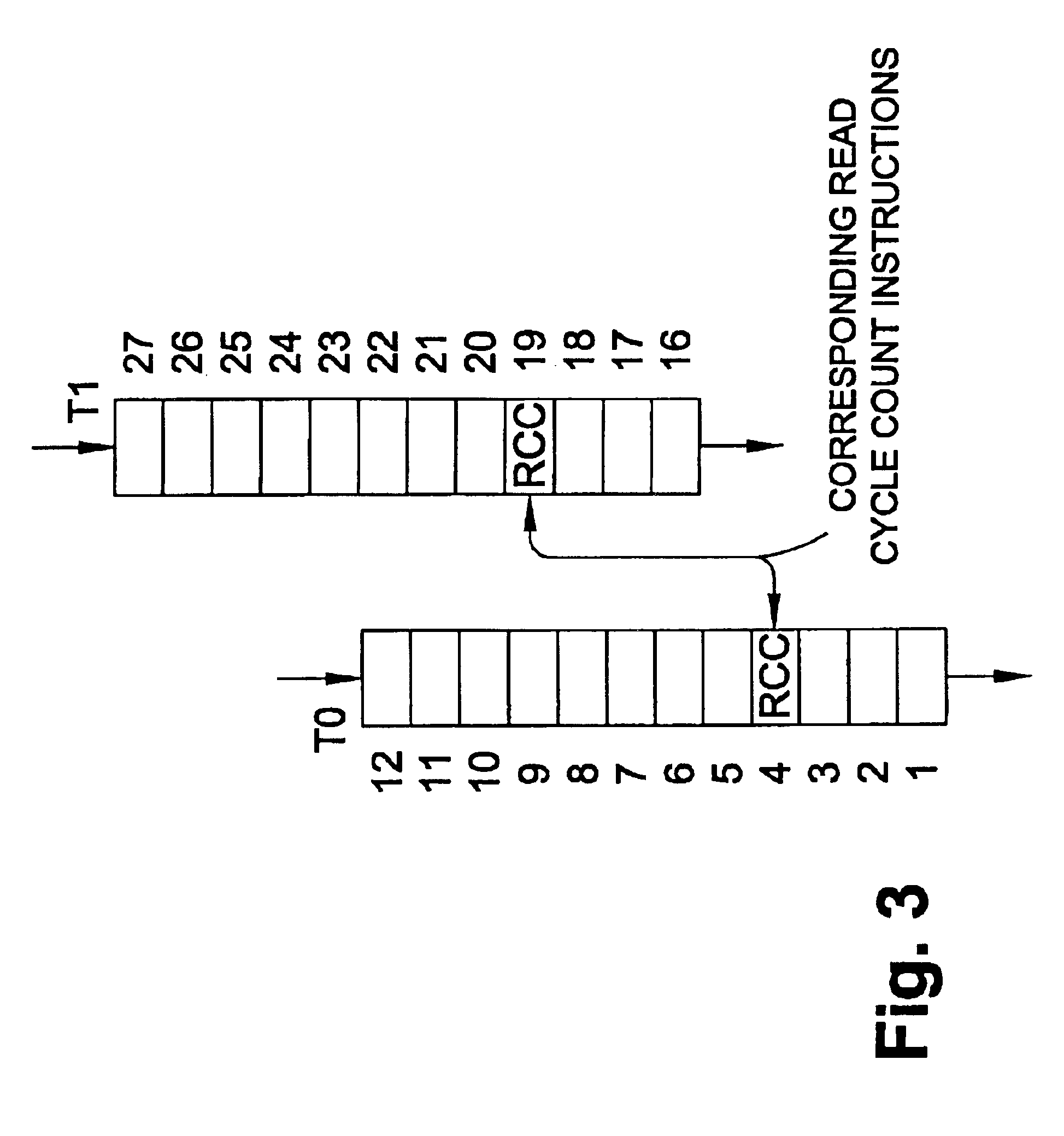

Cycle count replication in a simultaneous and redundantly threaded processor

InactiveUS6854051B2Improve performanceProviding fault toleranceInterprogram communicationDigital computer detailsProgram ThreadStorage cell

A pipelined, simultaneous and redundantly threaded (“SRT”) processor comprising, among other components, load / store units configured to perform load and store operations to or from data locations such as a data cache and data registers and a cycle counter configured to keep a running count of processor clock cycles. The processor is configured to detect transient faults during program execution by executing instructions in at least two redundant copies of a program thread and wherein false errors caused by incorrectly replicating cycle count values in the redundant program threads are avoided by implementing a cycle count queue for storing the actual values fetched by read cycle count instructions in the first program thread. The load / store units then access the cycle count queue and not the cycle counter to fetch cycle count values in response to read cycle count instructions in the second program thread.

Owner:SONRAI MEMORY LTD

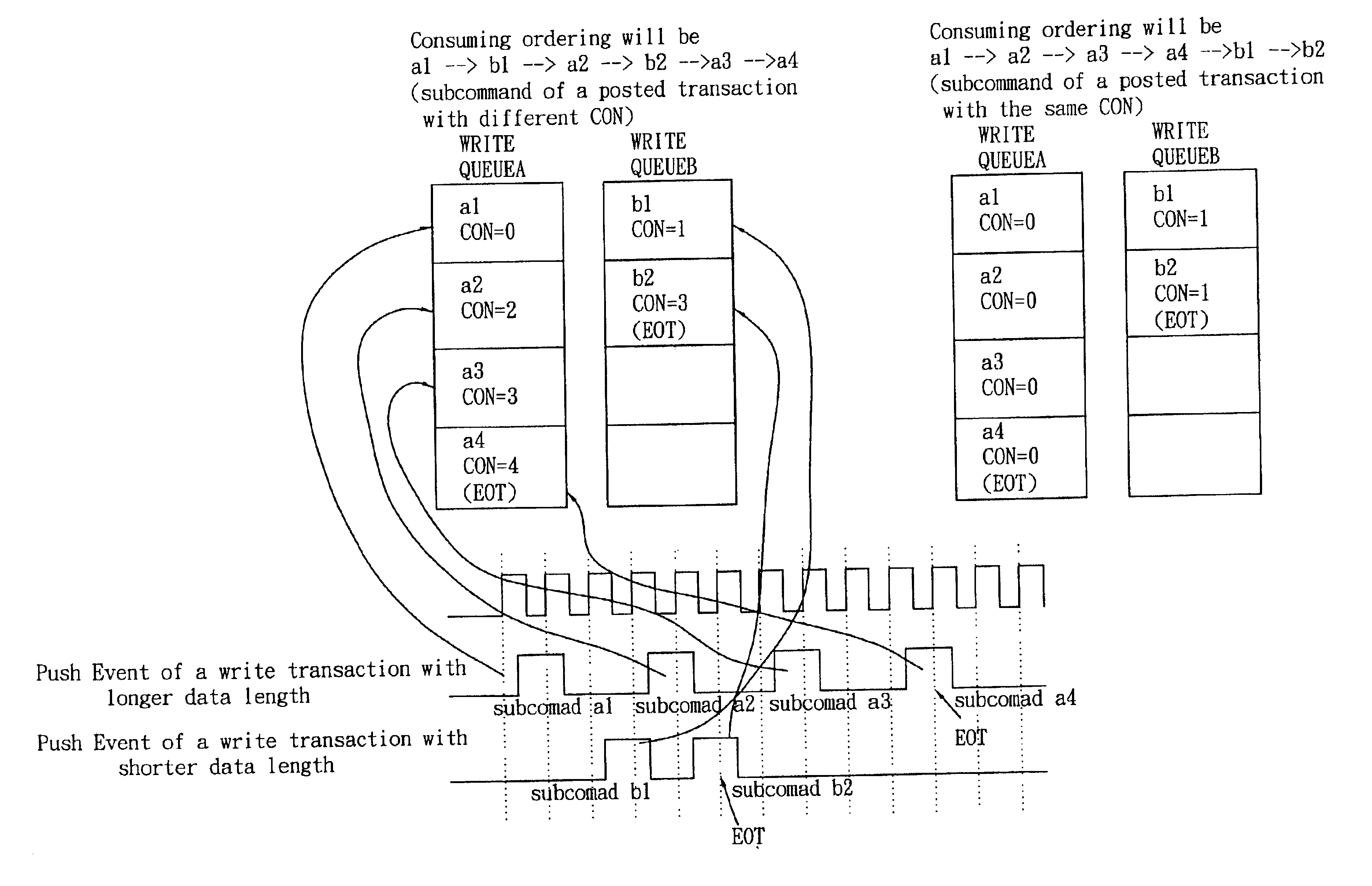

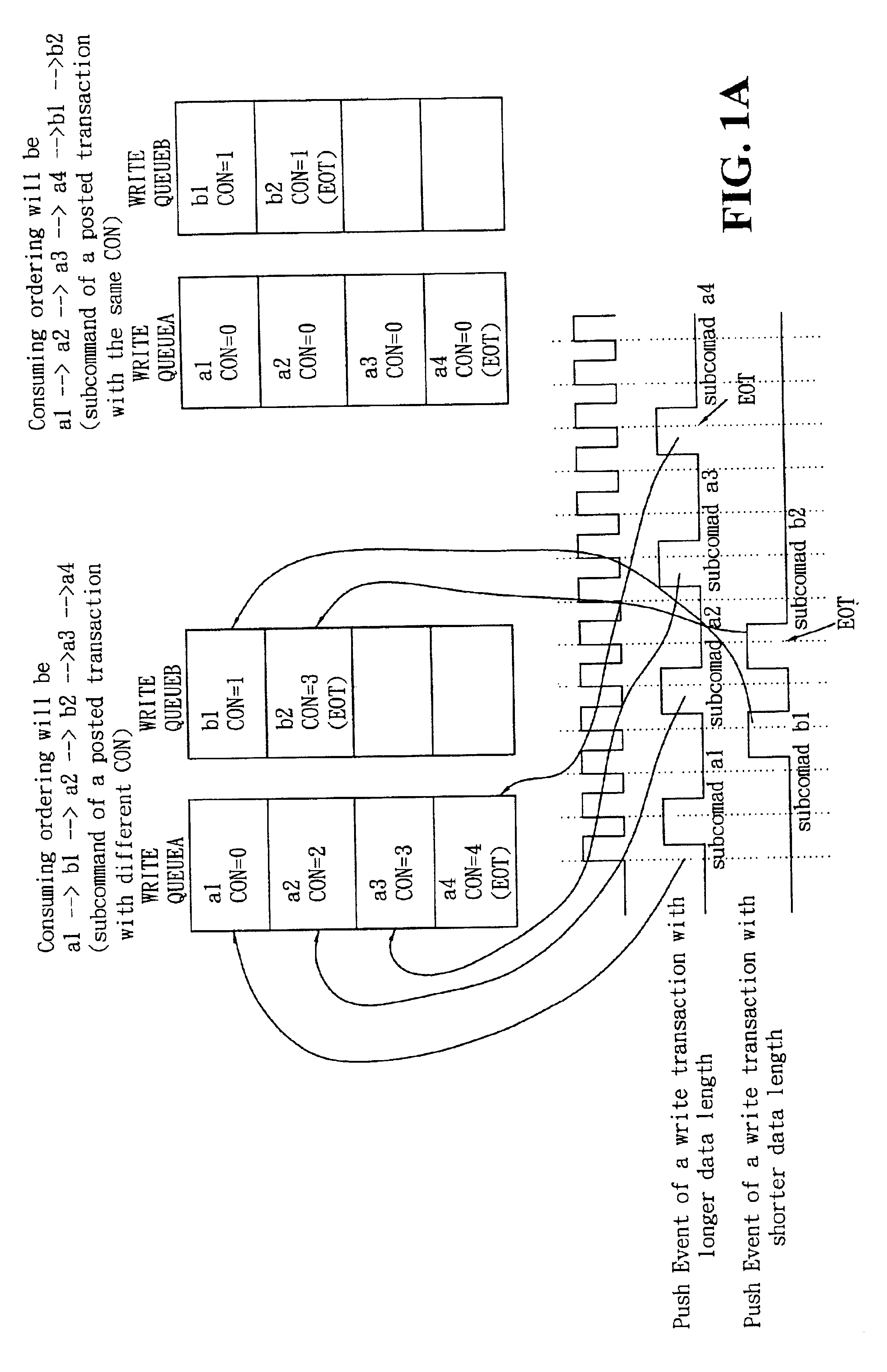

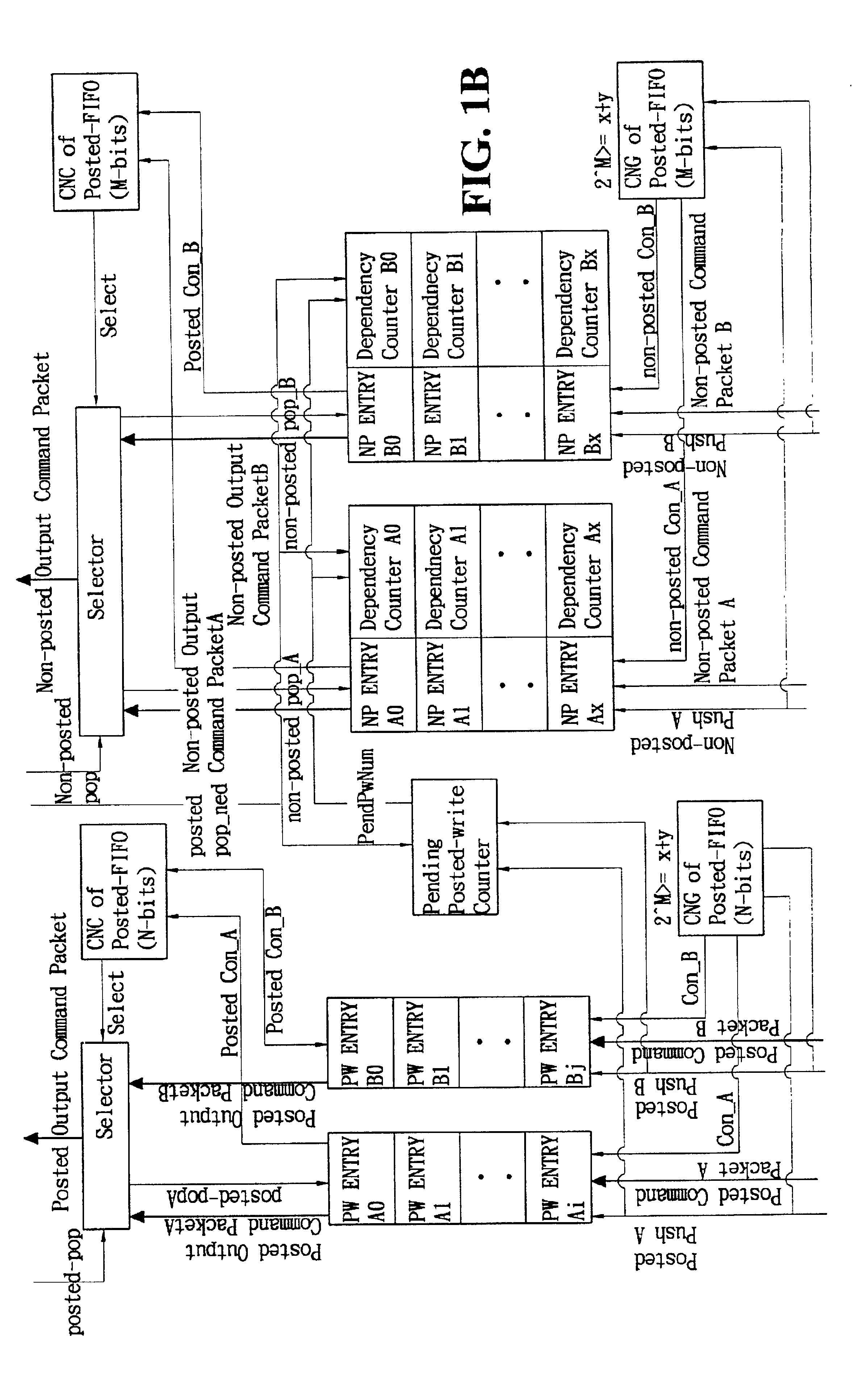

Command order maintenance scheme for multi-in/multi-out FIFO in multi-threaded I/O links

InactiveUS6862673B2Avoid lossOvercomes drawbackMemory systemsInput/output processes for data processingNumber generatorMultiple input

A mechanism for maintaining the first-in first-out order of commands in a multiple-input and multiple-output buffer structure includes a command number generator for generating and assigning a command number to each command entering the buffer structure, and a command number comparator for comparing the command number of the outgoing command at each buffer in the buffer structure to determine which command should exit. Both command number generator and command comparator have a cyclic counter that has a period greater than or equal to the total number of allowable buffer entries in the buffer structure. For maintaining order of posted and non-posted command queues, a pending posted write counter is used in the posted command queue to record the number of pending posted write command and each entry in the non-posted command queue is associated with a dependency counter.

Owner:SILICON INTEGRATED SYSTEMS

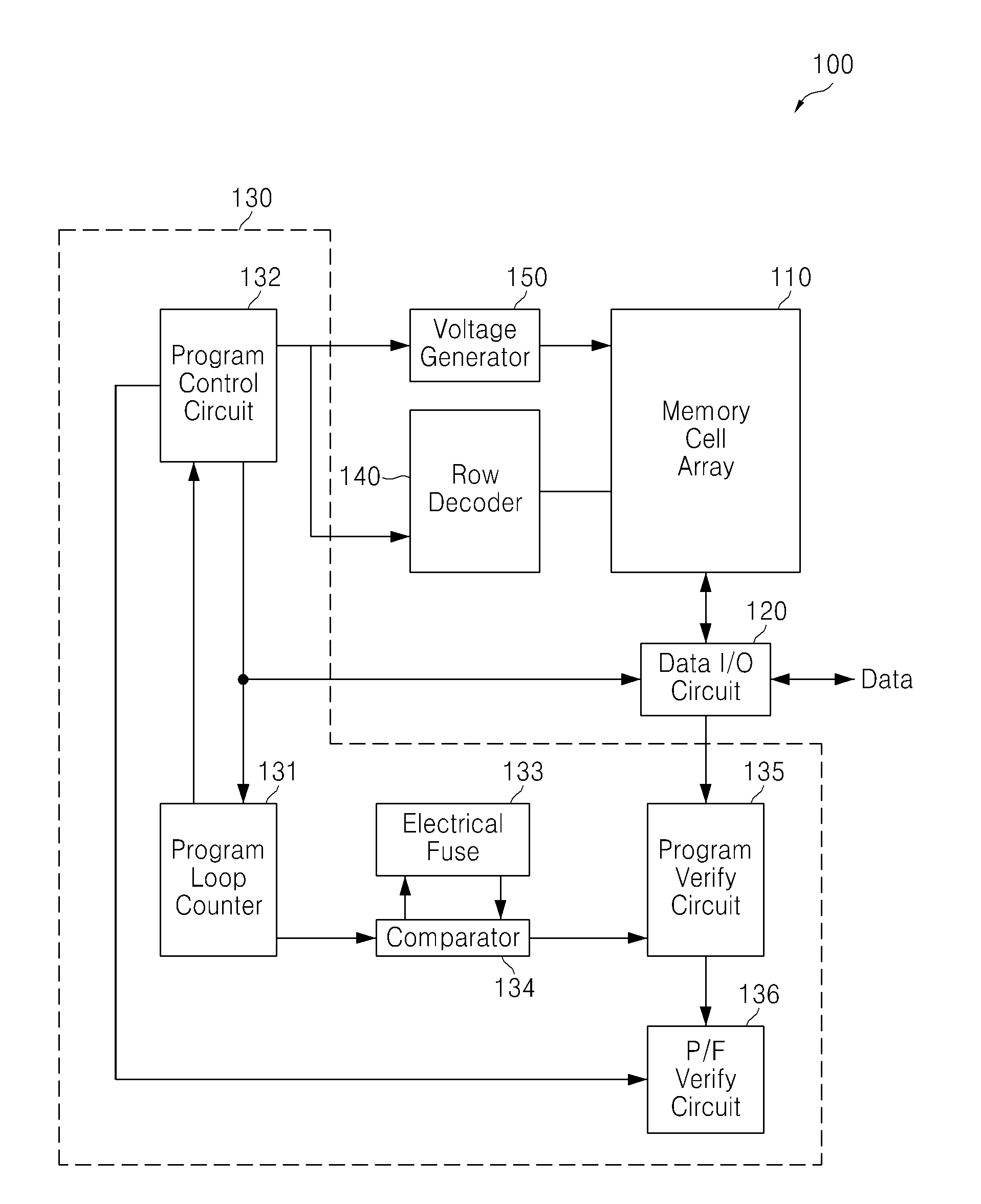

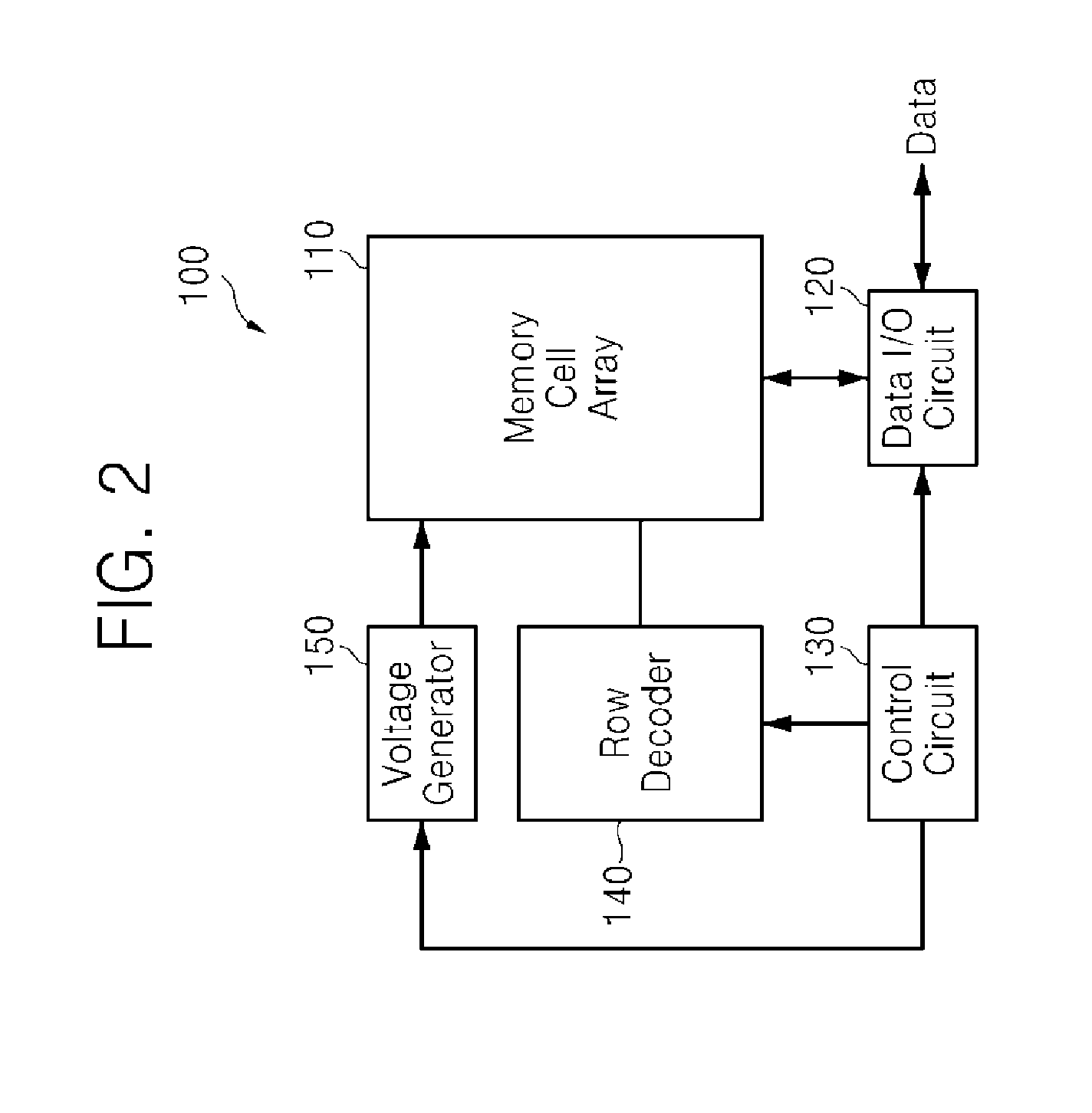

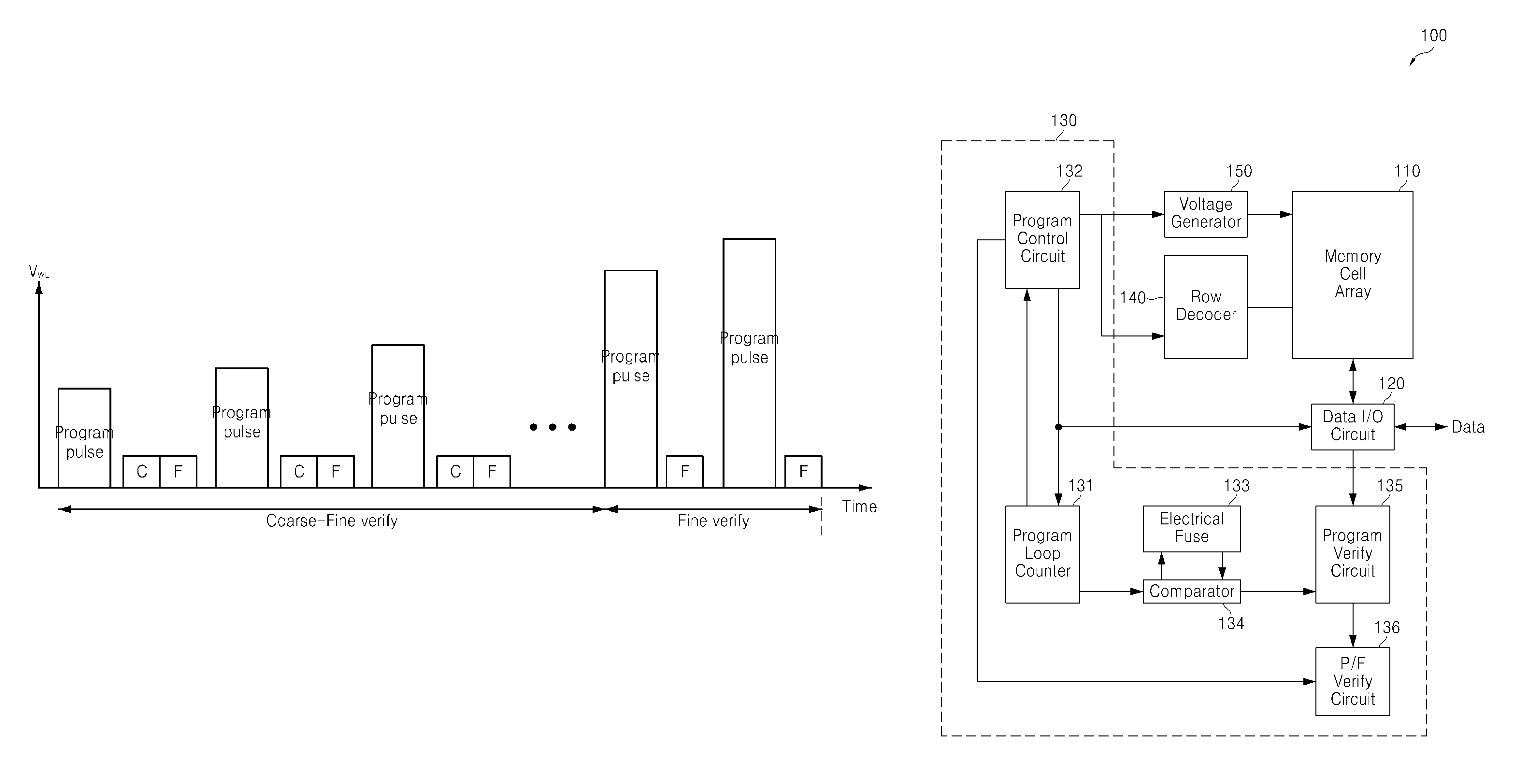

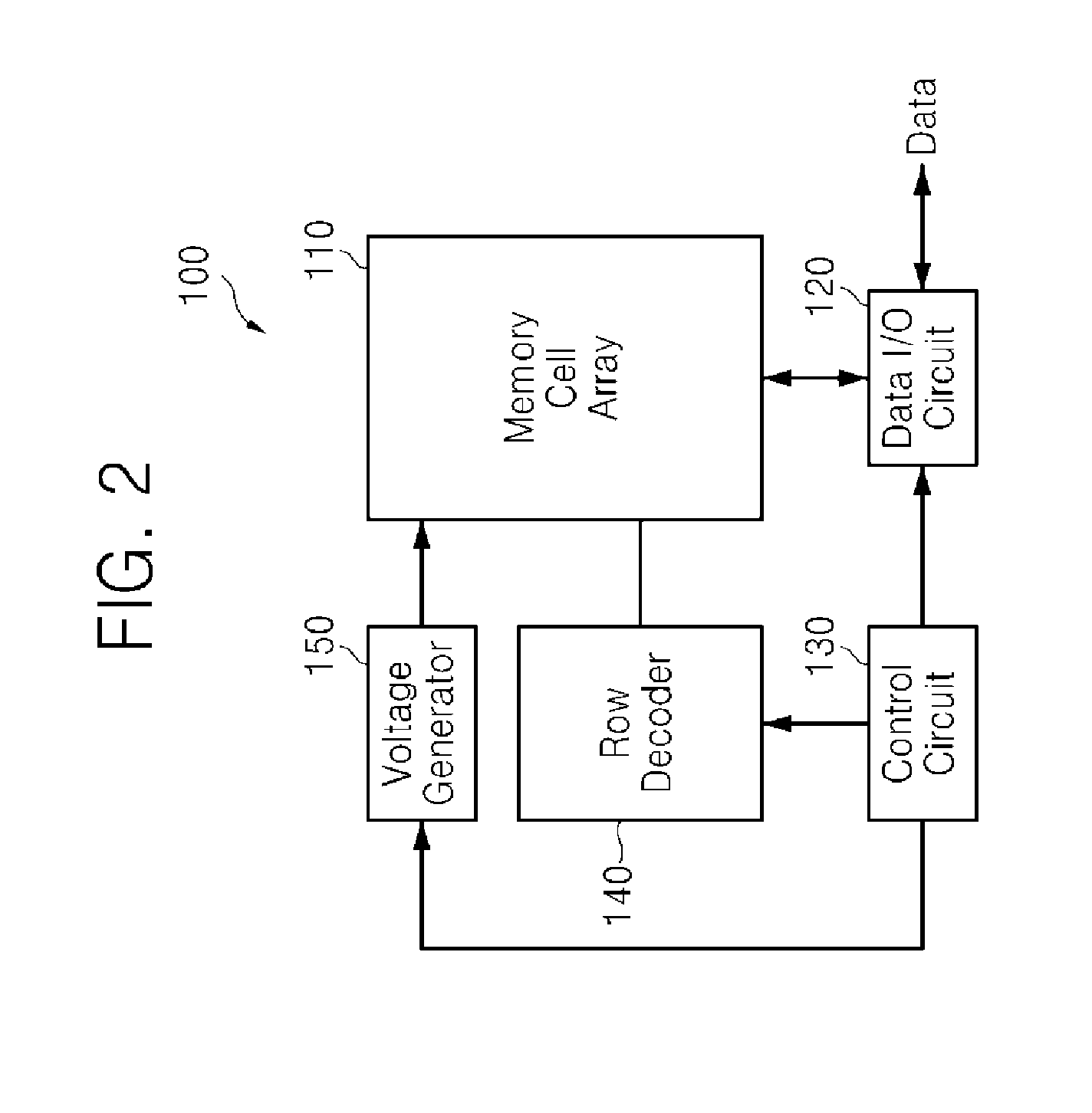

Flash memory device and related program verification method

ActiveUS20120069674A1Improve reliabilityReducing common source line noiseRead-only memoriesDigital storageNon-volatile memoryLoop counter

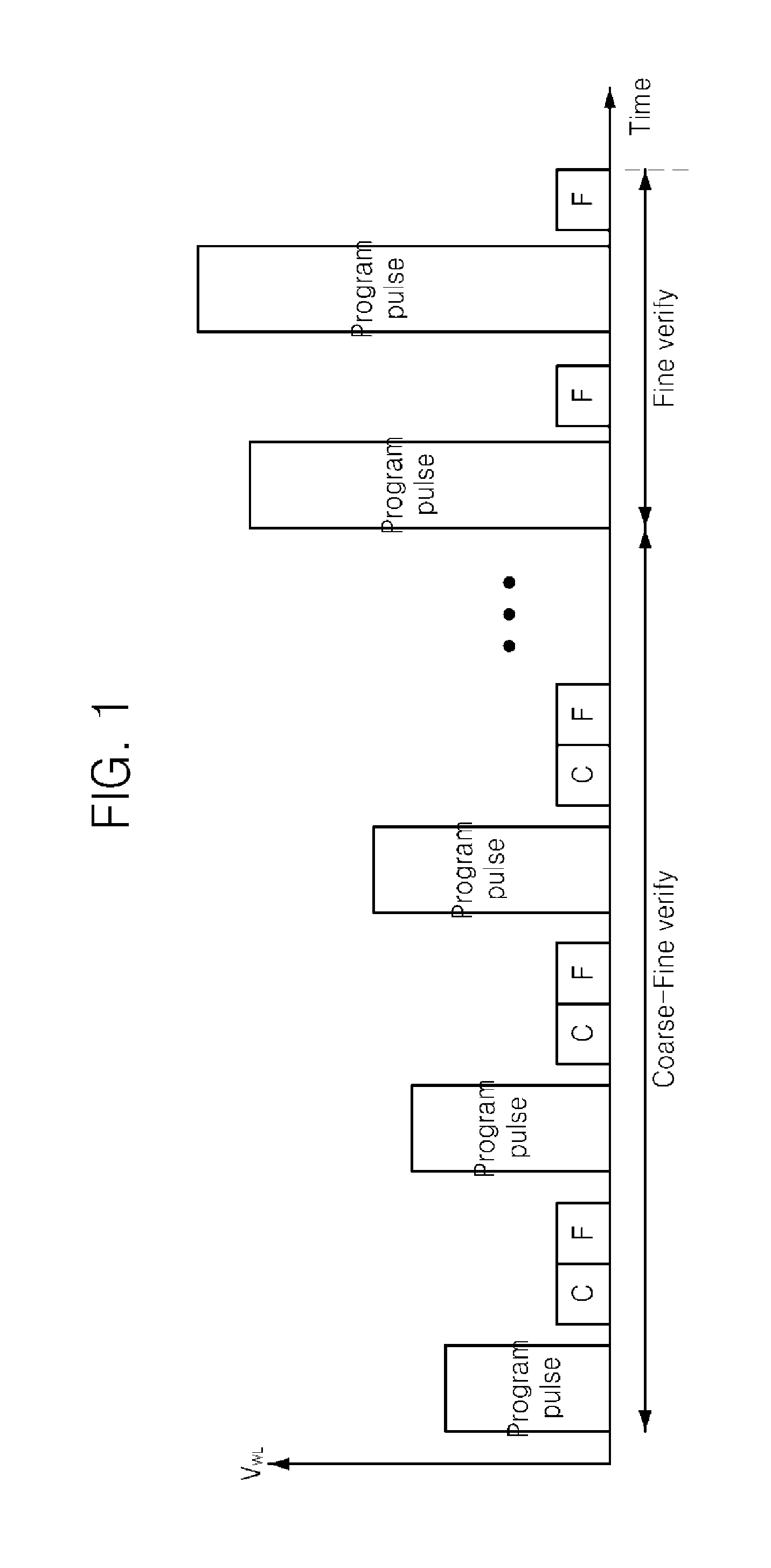

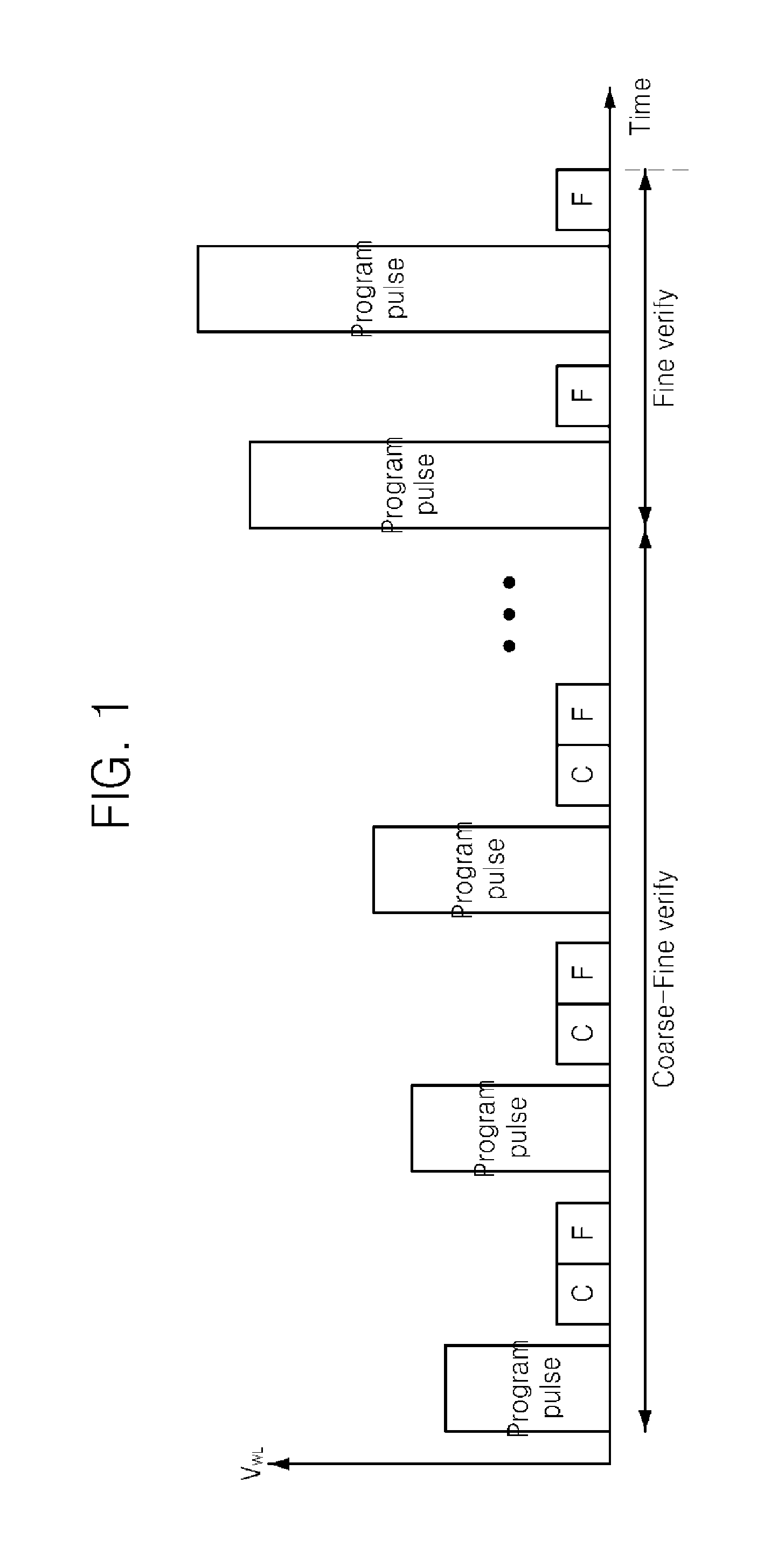

A nonvolatile memory device performs a program operation using an incremental pulse programming (ISPP) scheme in which a plurality of program loops alternate between a coarse-fine verify operation, and a fine verify operation according to a value of a program loop counter.

Owner:SAMSUNG ELECTRONICS CO LTD

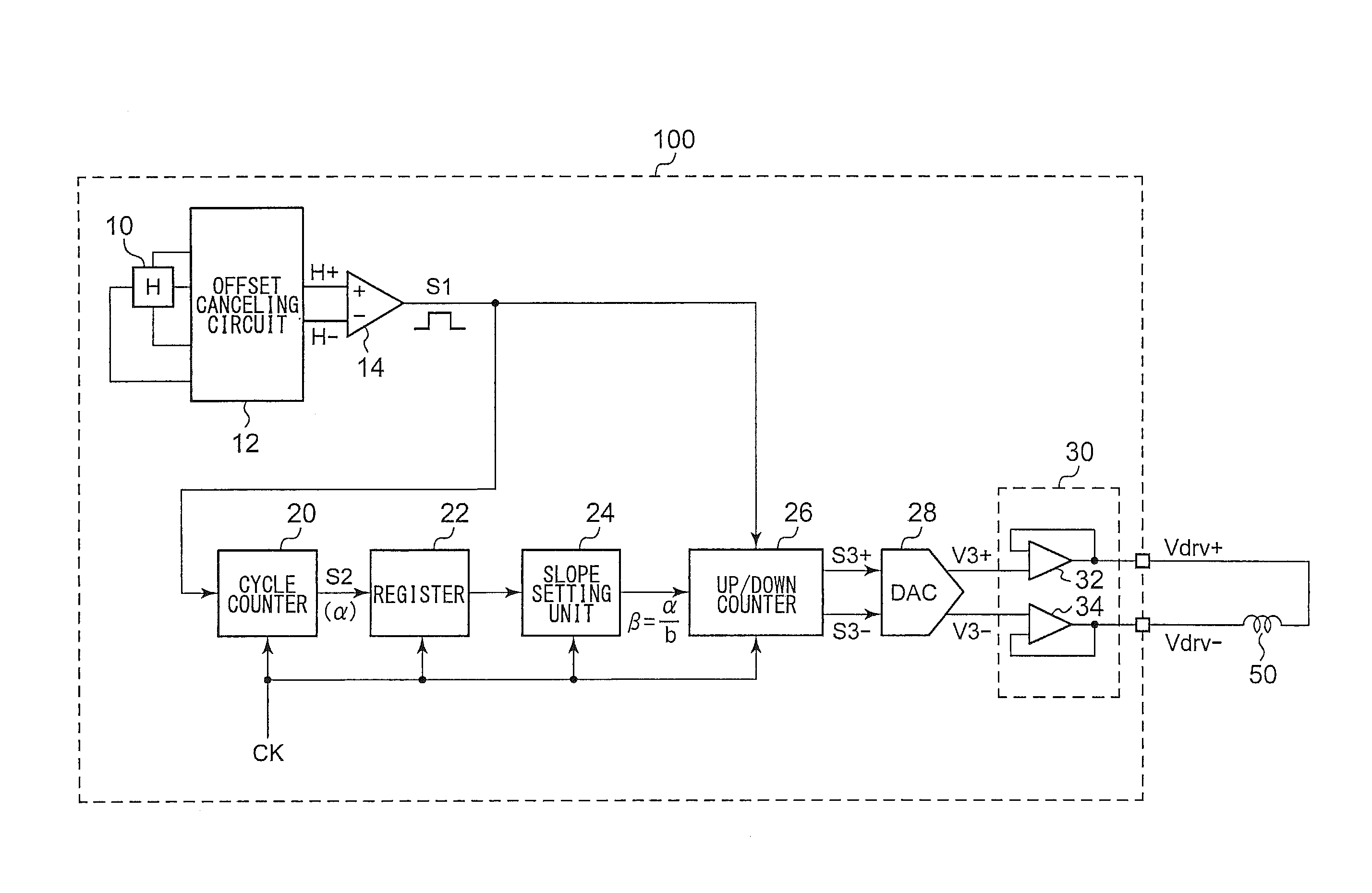

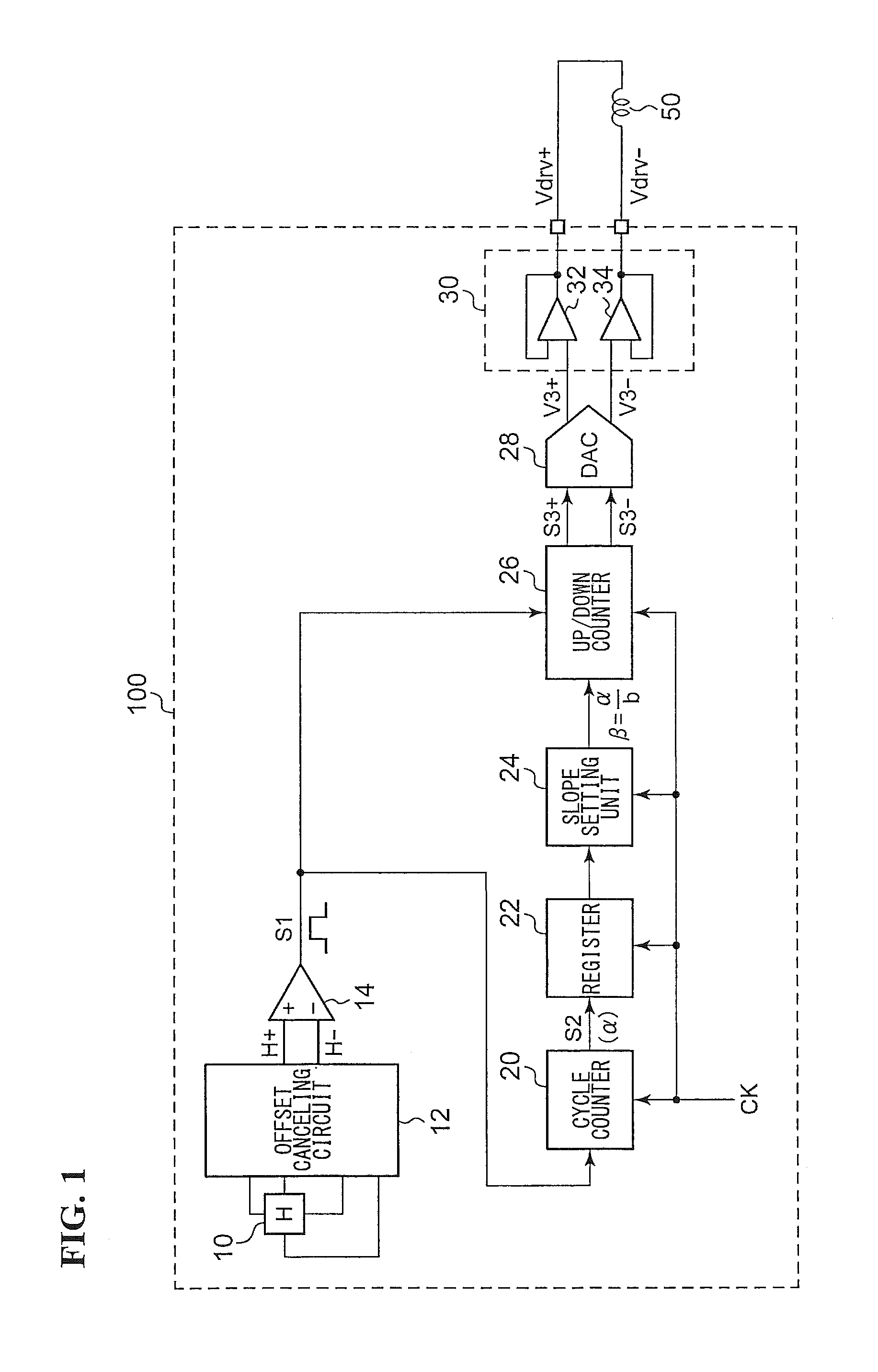

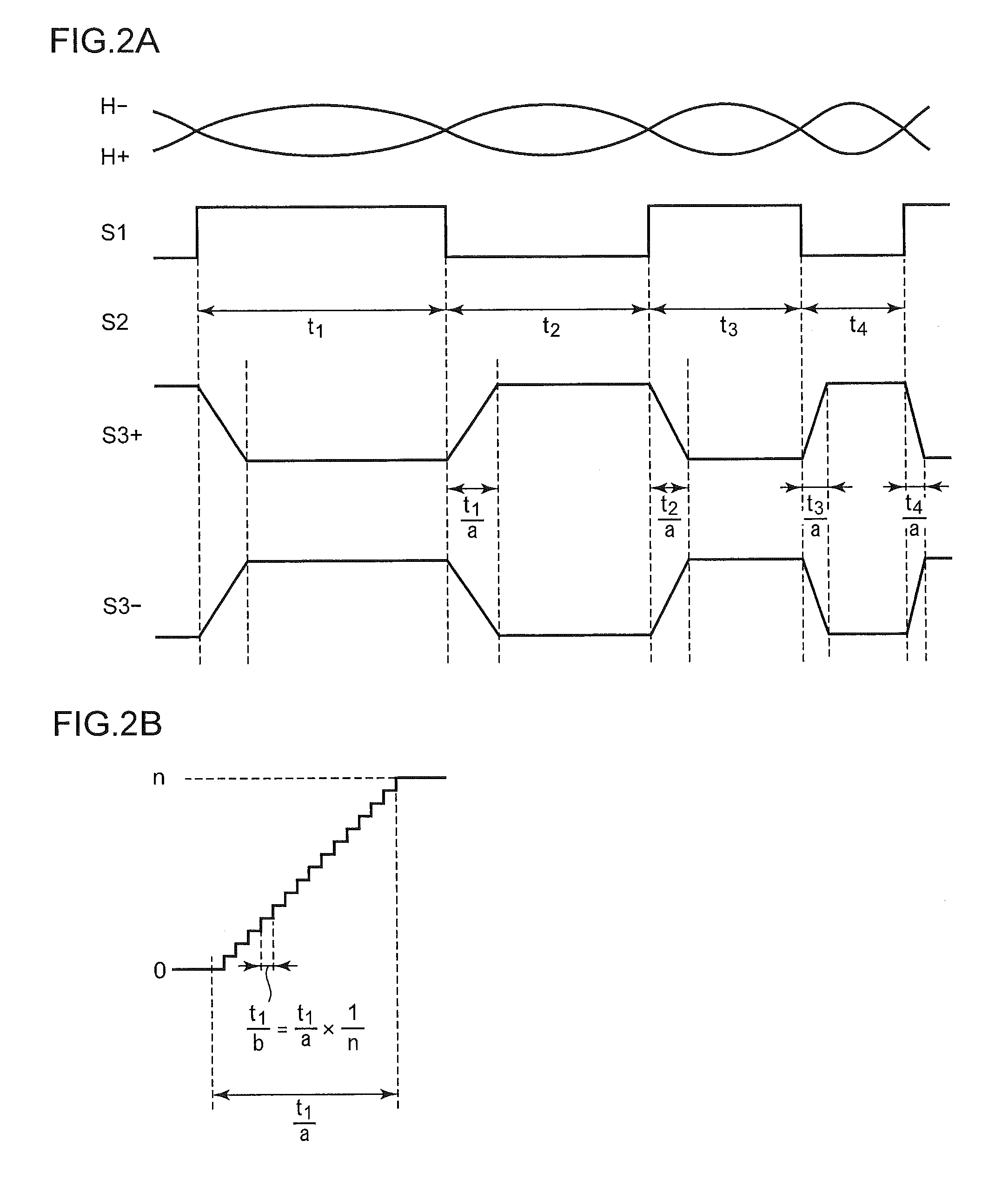

Circuit and method for driving motor

A cycle counter generates a cycle signal which indicates, in the form of a digital value, the cycle of Hall signals H+ and H− that indicate the position of a rotor of a motor to be driven. An up / down counter repeatedly alternates between counting “up” and counting “down” upon detecting phase transitions that occur in the Hall signals, and generates a digital driving waveform signal having a sloping region the slope of which is set according to the cycle signal. A D / A converter receives the driving waveform signal, and converts the driving waveform signal thus received into an analog voltage. A driving unit supplies a driving voltage to the motor according to the analog voltage thus received.

Owner:ROHM CO LTD

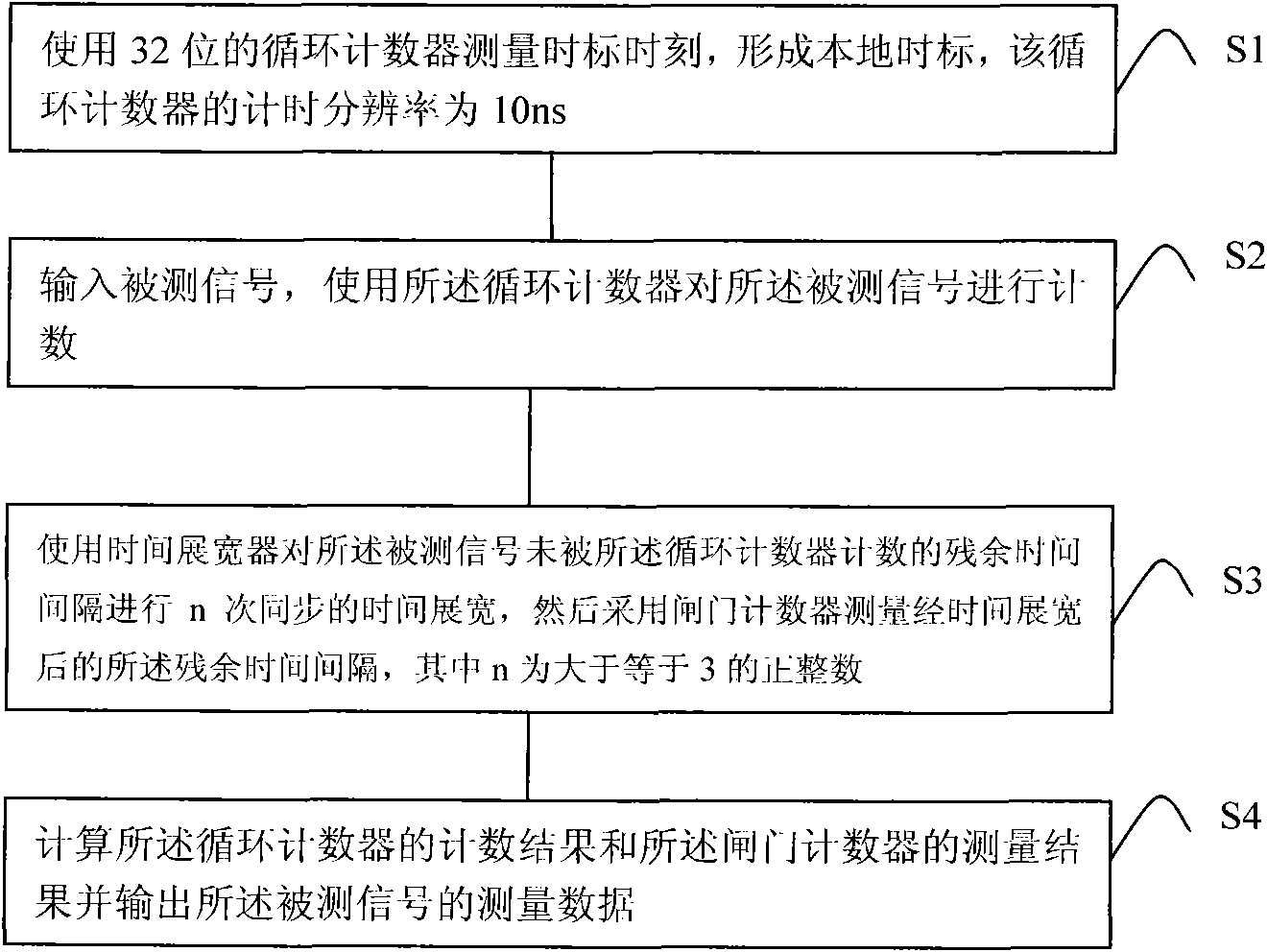

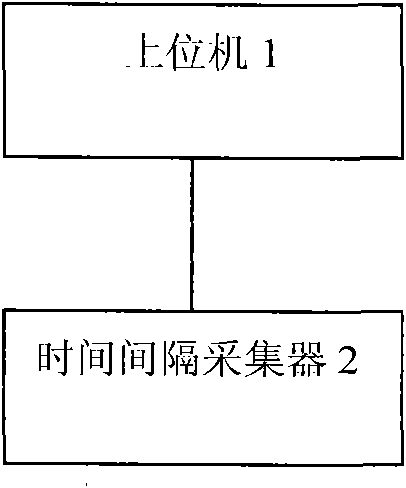

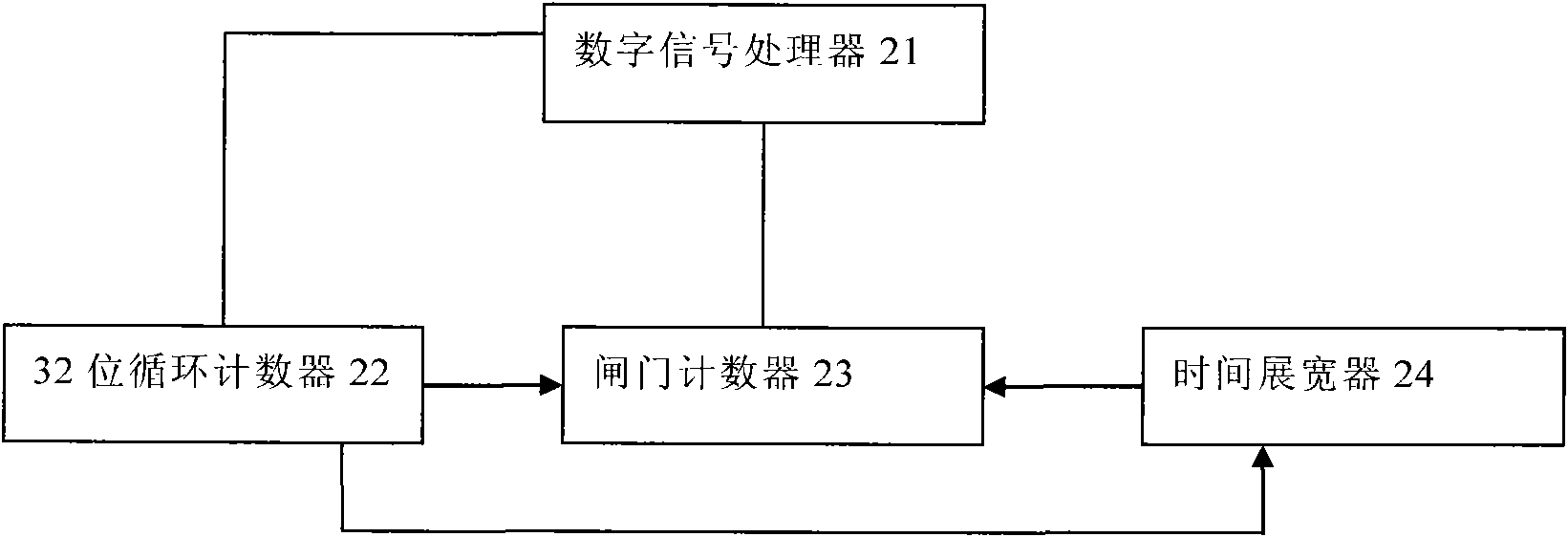

Method and device for measuring time intervals of repeated synchronous interpolation simulation

InactiveCN101976037AImprove performanceElectric unknown time interval measurementTime markComputer science

The invention provides a method and a device for measuring time intervals of repeated synchronous interpolation simulation, and the method comprises the following steps: measuring time mark moments by a 32-bit cycle counter to generate a local time mark, wherein the timing resolution of the cycle counter is 10ns; inputting a measured signal, and counting the measured signal by adopting the cycle counter; performing n numbered synchronous time spreading on residual time internals of the measured signal which is not counted by the cycle counter through a time stretcher, and adopting a gate counter to measure the residual time intervals after time spreading; and calculating the counting result of the cycle counter and the measurement result of the gate counter, and outputting the measurement data of the measured signal. The method and the device in the invention can realize the measurement accuracy within 100ps and the sampling rate of 1M / s.

Owner:北京一朴时频科技有限公司

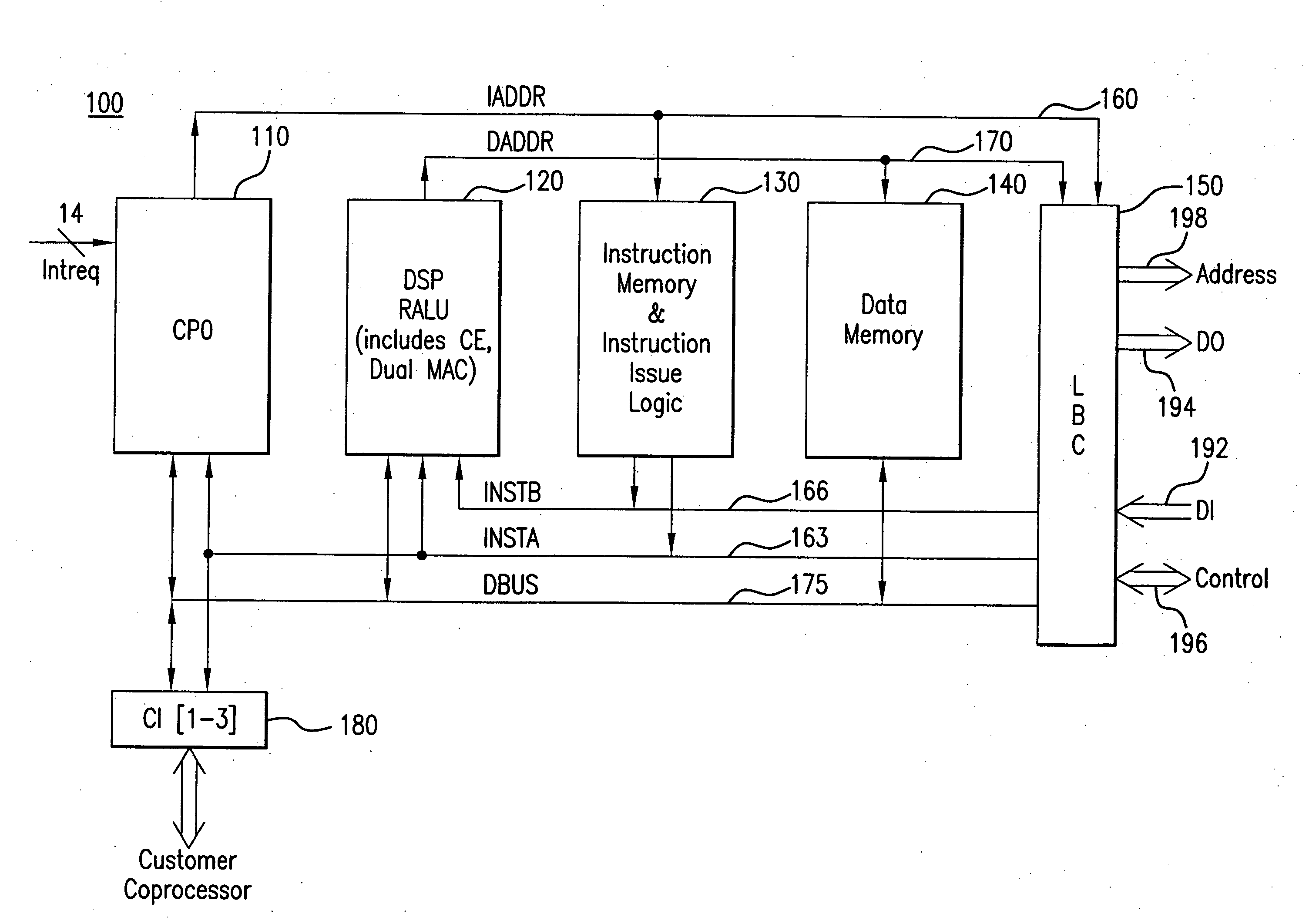

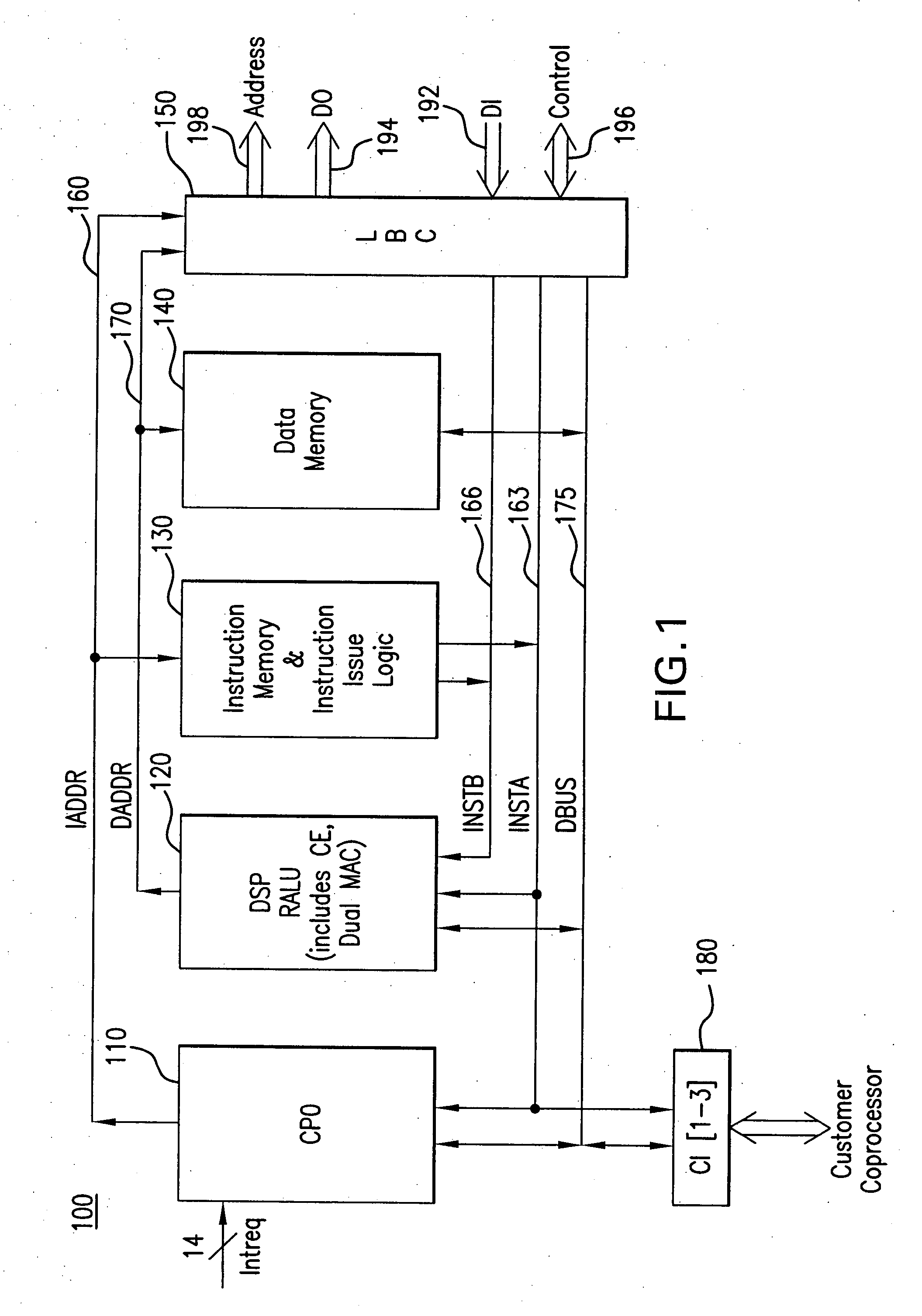

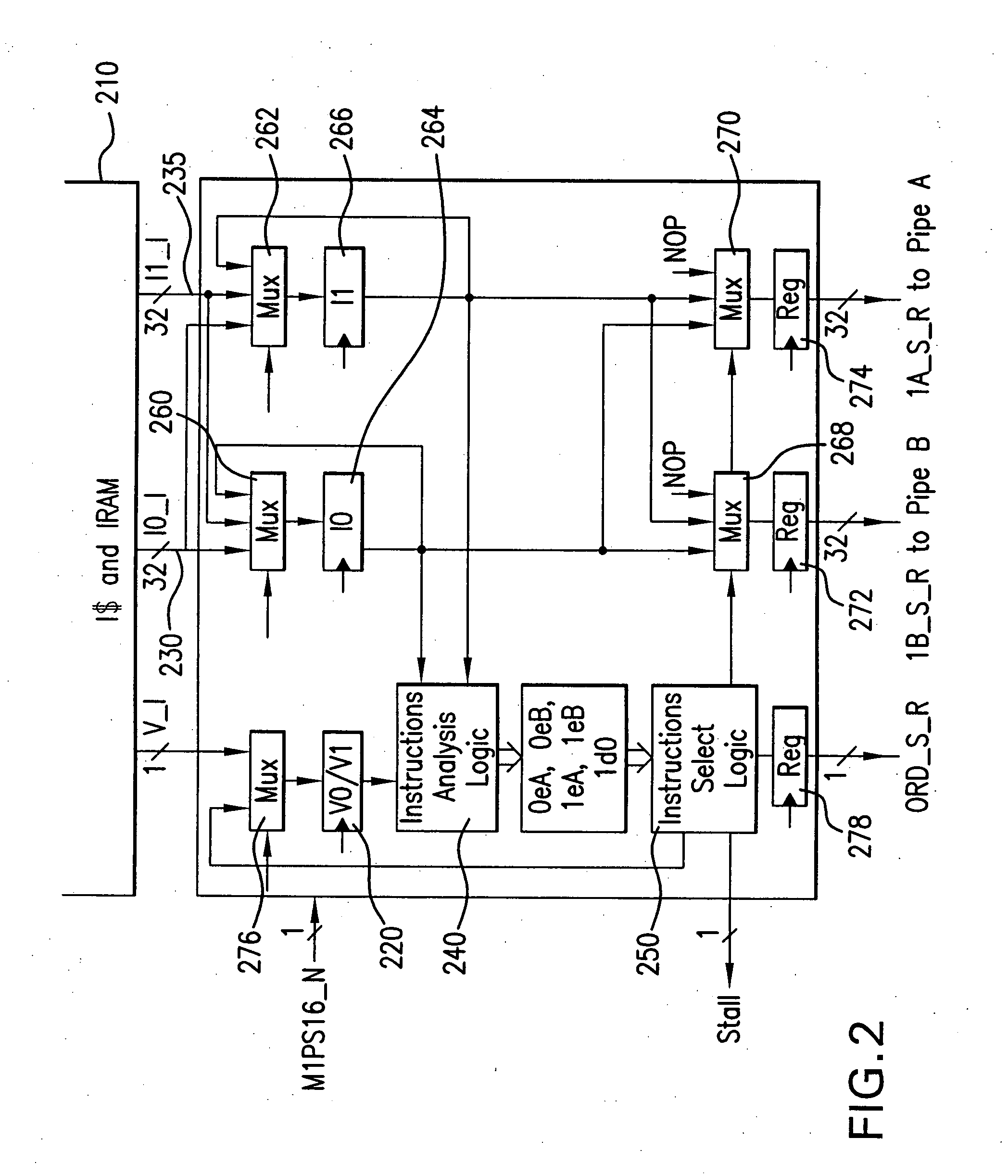

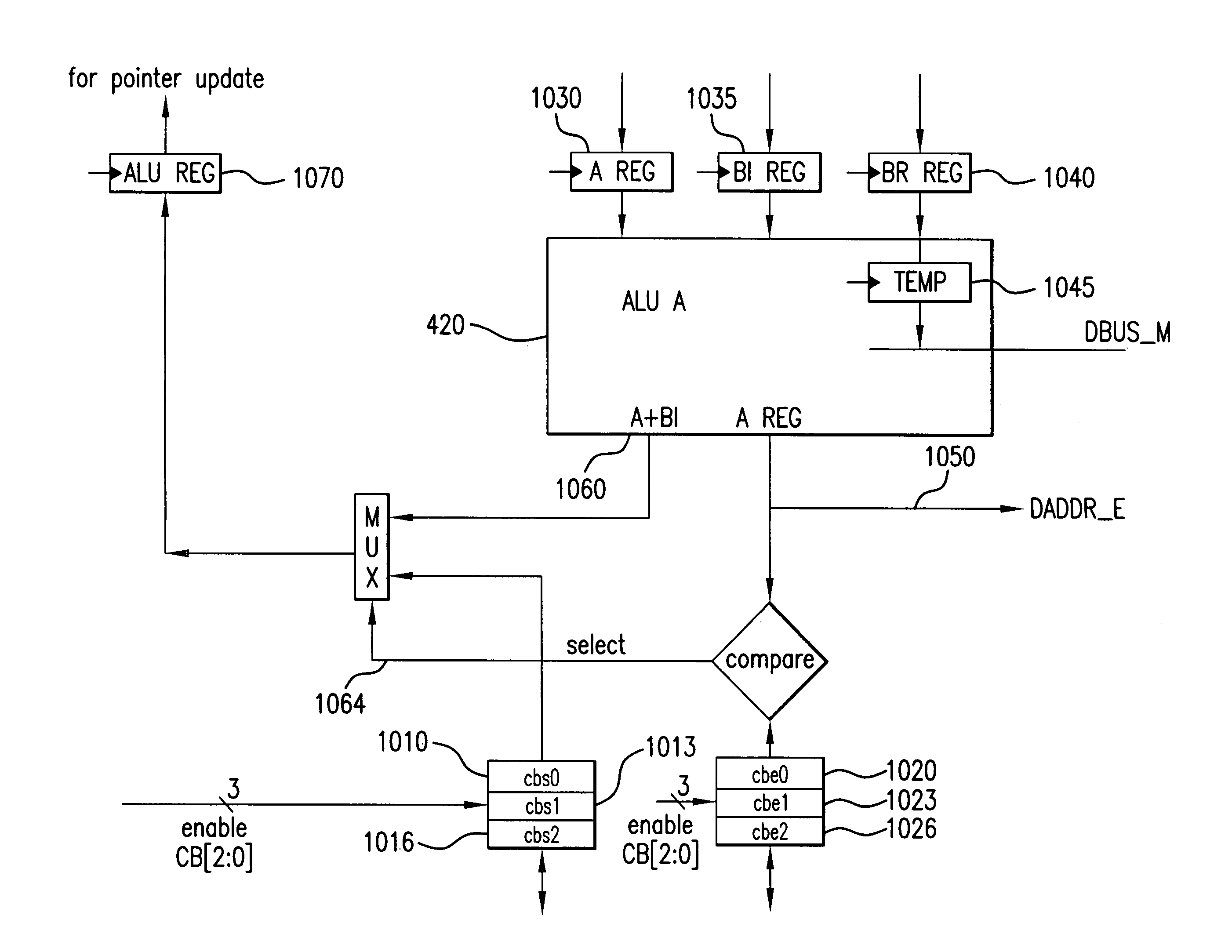

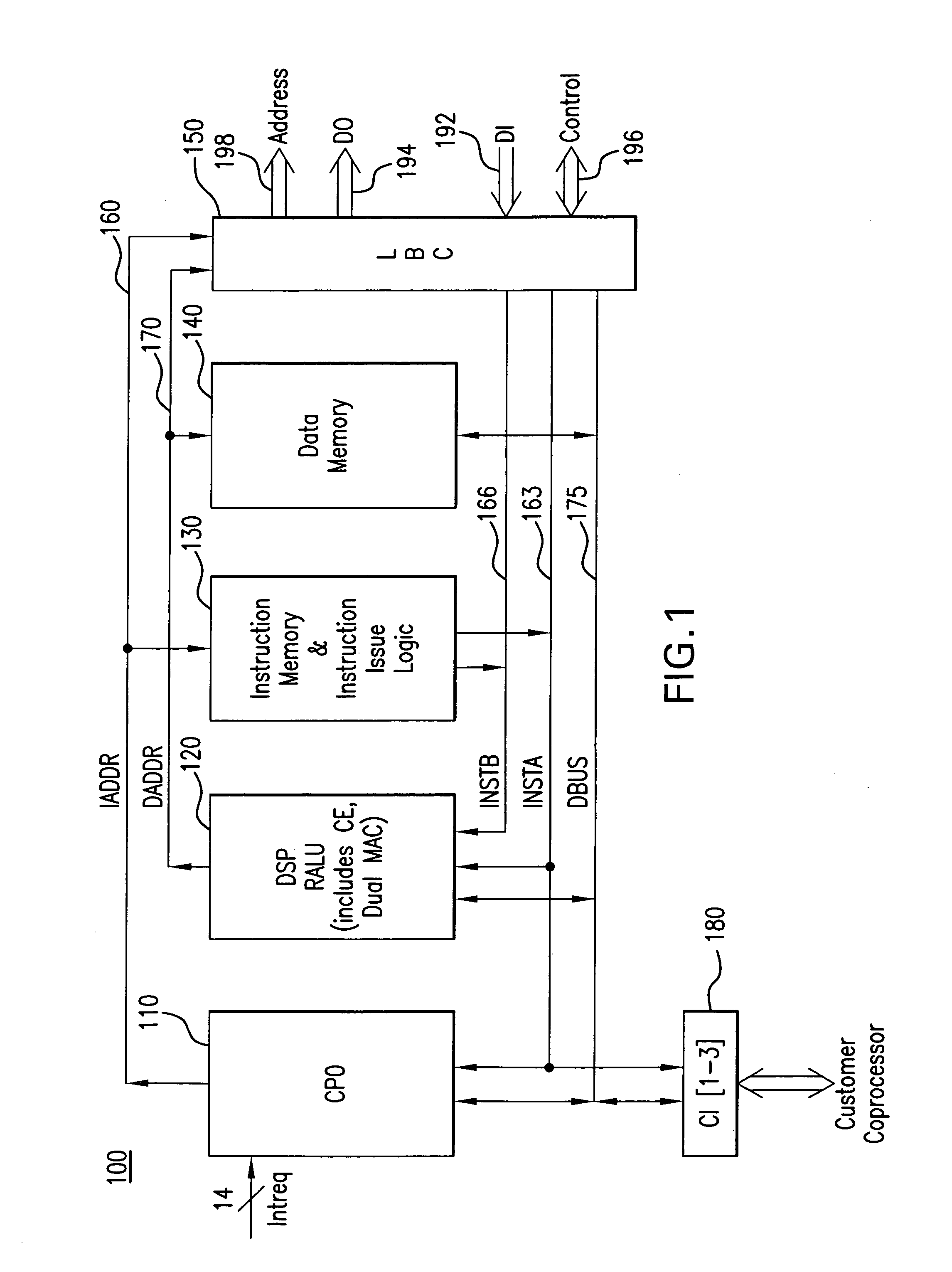

High-performance RISC-DSP

InactiveUS20070239967A1Efficient implementationDigital data processing detailsRuntime instruction translationComputer architectureCircular buffer

A DSP superscalar architecture employing dual multiply accumulate pipelines. Dual MAC pipelines allow for a seamless transition between established RISC instruction sets and extended DSP instructions sets. Relocatable opcodes are provide to allow further extensions of RISC instruction sets. The DSP superscalar architecture also provides memory pointers with hardware circular buffer support, an interruptible and nested zero-overhead loop counter, and prioritized low overhead interrupts.

Owner:ARM FINANCE OVERSEAS LTD

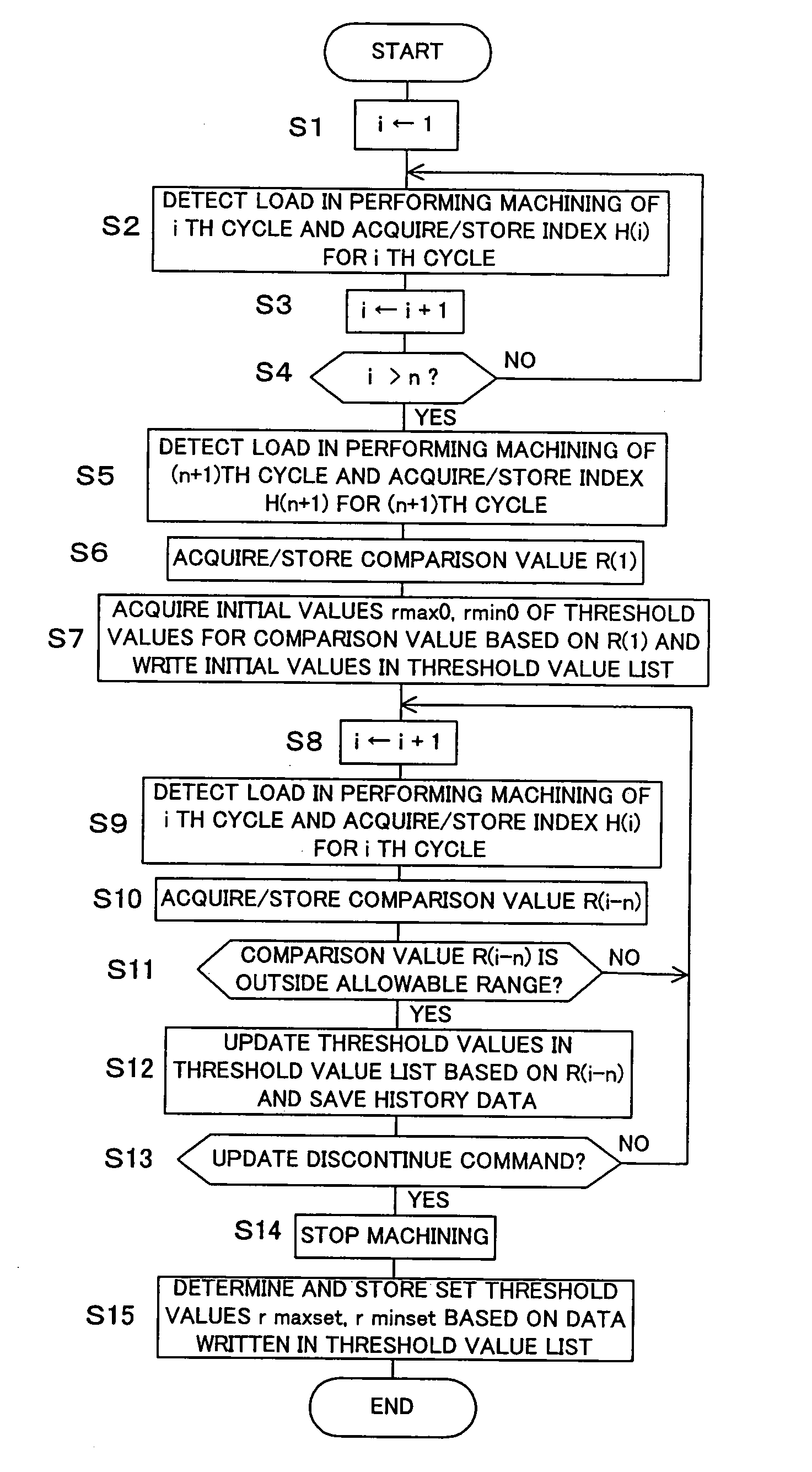

Tool damage/abnormality detecting device

InactiveUS20060142893A1Easy to set upProgramme controlDigital computer detailsValue setAnomaly detection

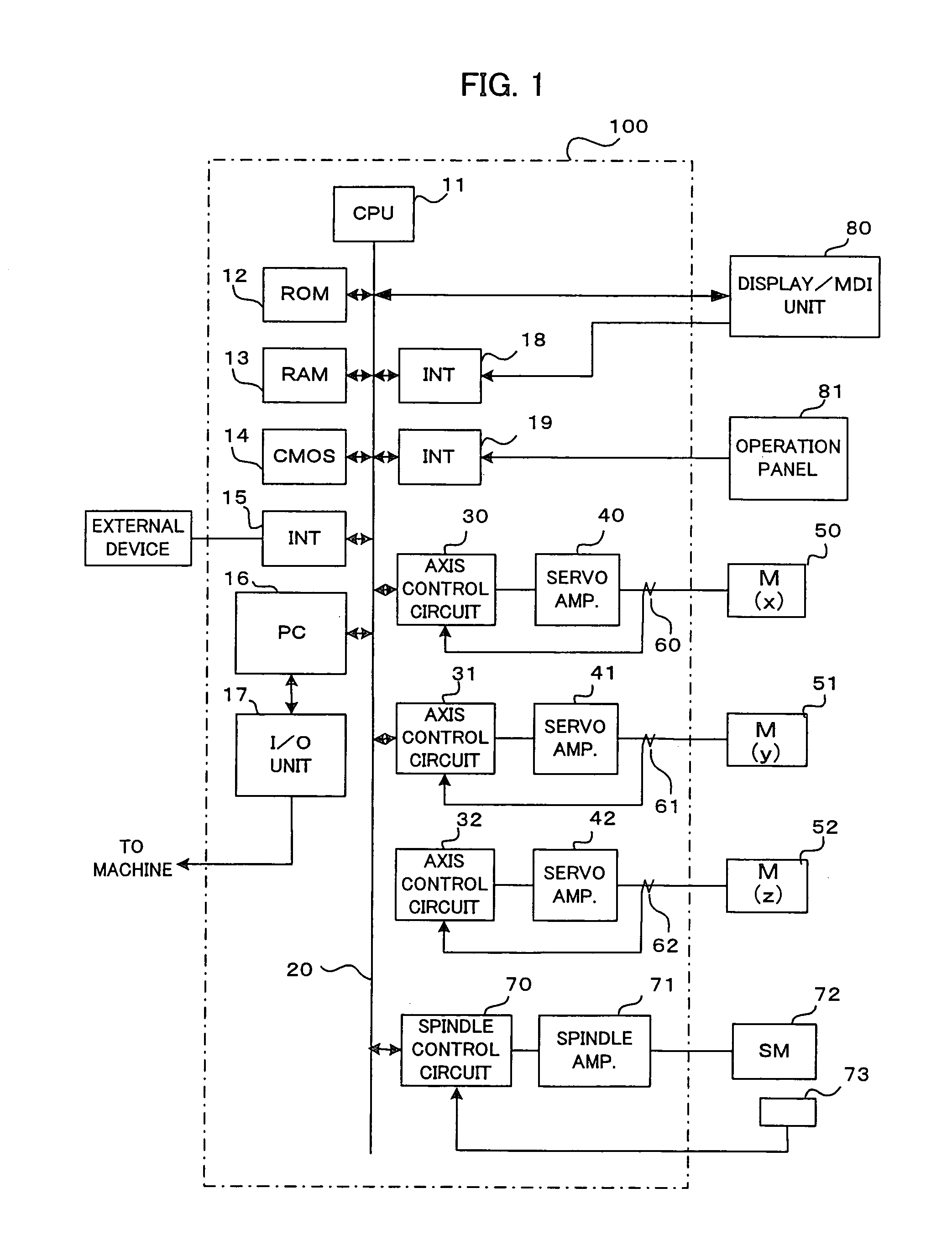

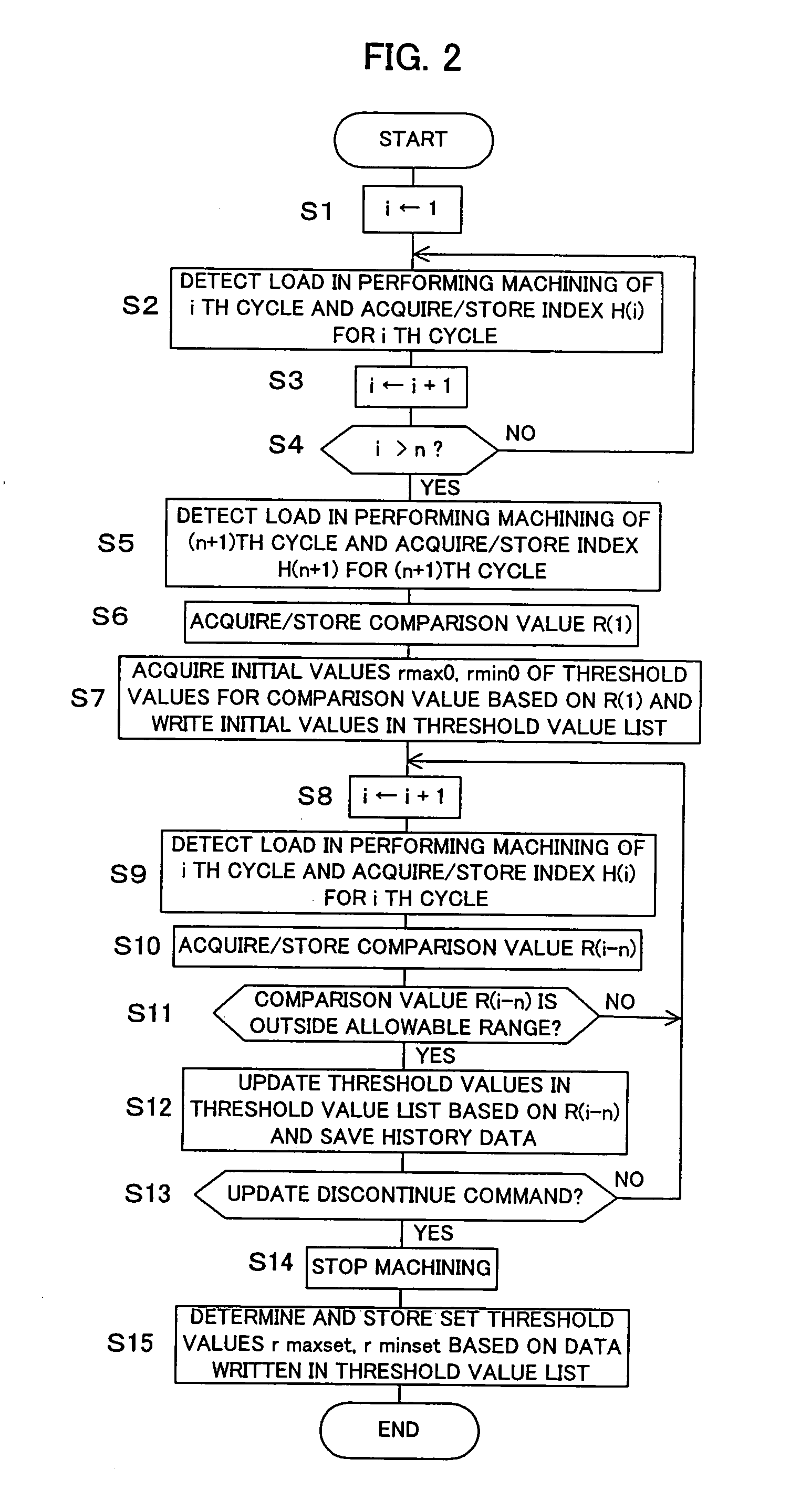

A tool damage / abnormality detecting device capable of easily appropriately setting an allowable range for a value of comparison between a present value and a near past average for indexes indicative of loads on a tool. A machining cycle counter index i is adjusted to i=0, machining is performed as the loads are detected in a given period, and indexes H(i) (area S of load values, absolute value (G−) of a maximum inclination between two points obtained during a decrease of loads, etc.) are acquired for n number of cycles. Thereafter, the indexes and values of comparison between the index value for a present cycle and the indexes for the n number of cycles are acquired. A first comparison value can be used for initial value setting for threshold values. If any of the comparison values is deviated from the allowable range, the threshold values are updated so that the allowable range extends, and an update history is saved. If damage / abnormality is observed visually or in any other manner, a threshold value update discontinue command is inputted, machining is stopped after completion of the cycle concerned, and update values for the latest threshold value are collected to be used as set threshold values.

Owner:FANUC LTD

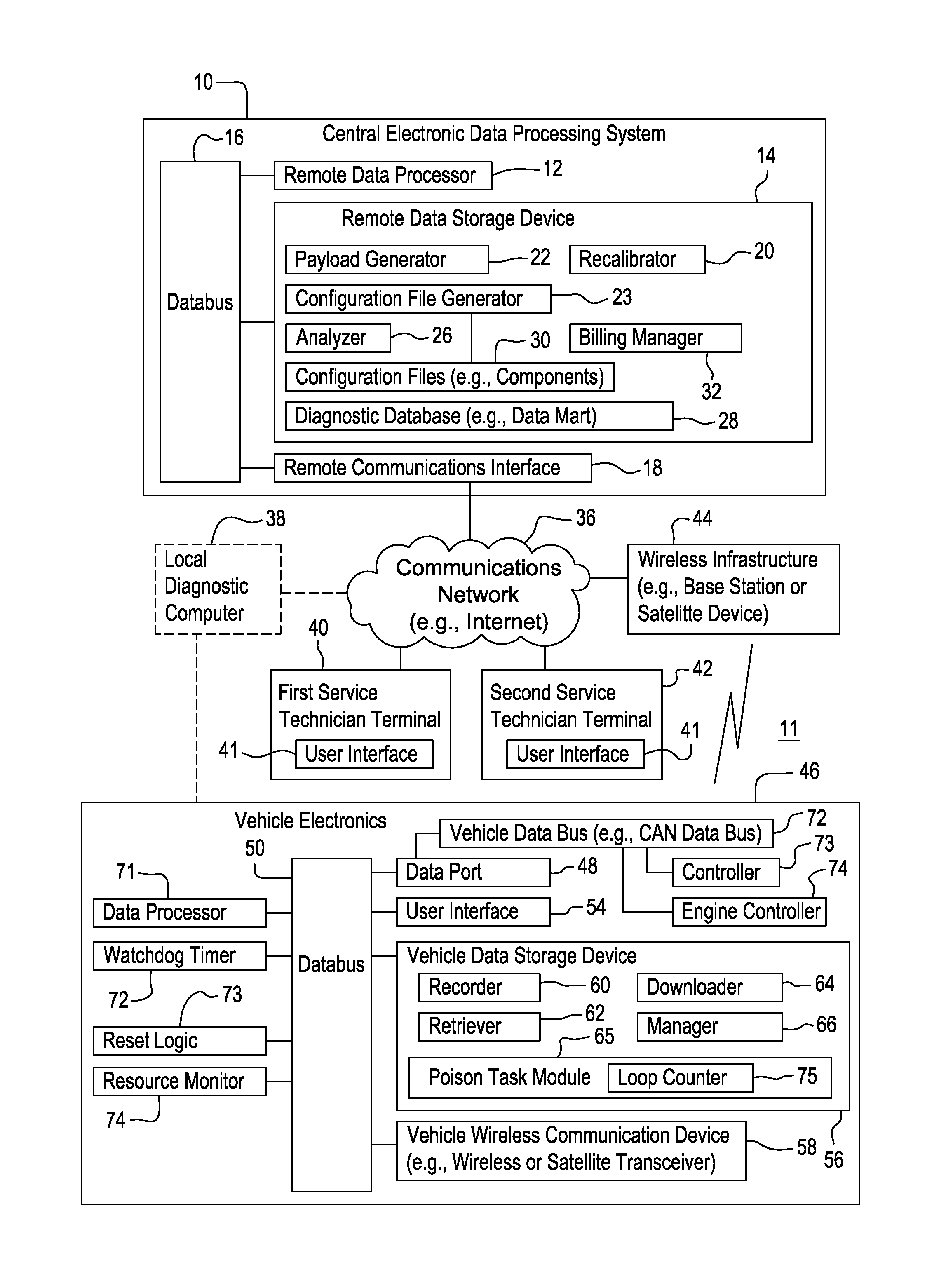

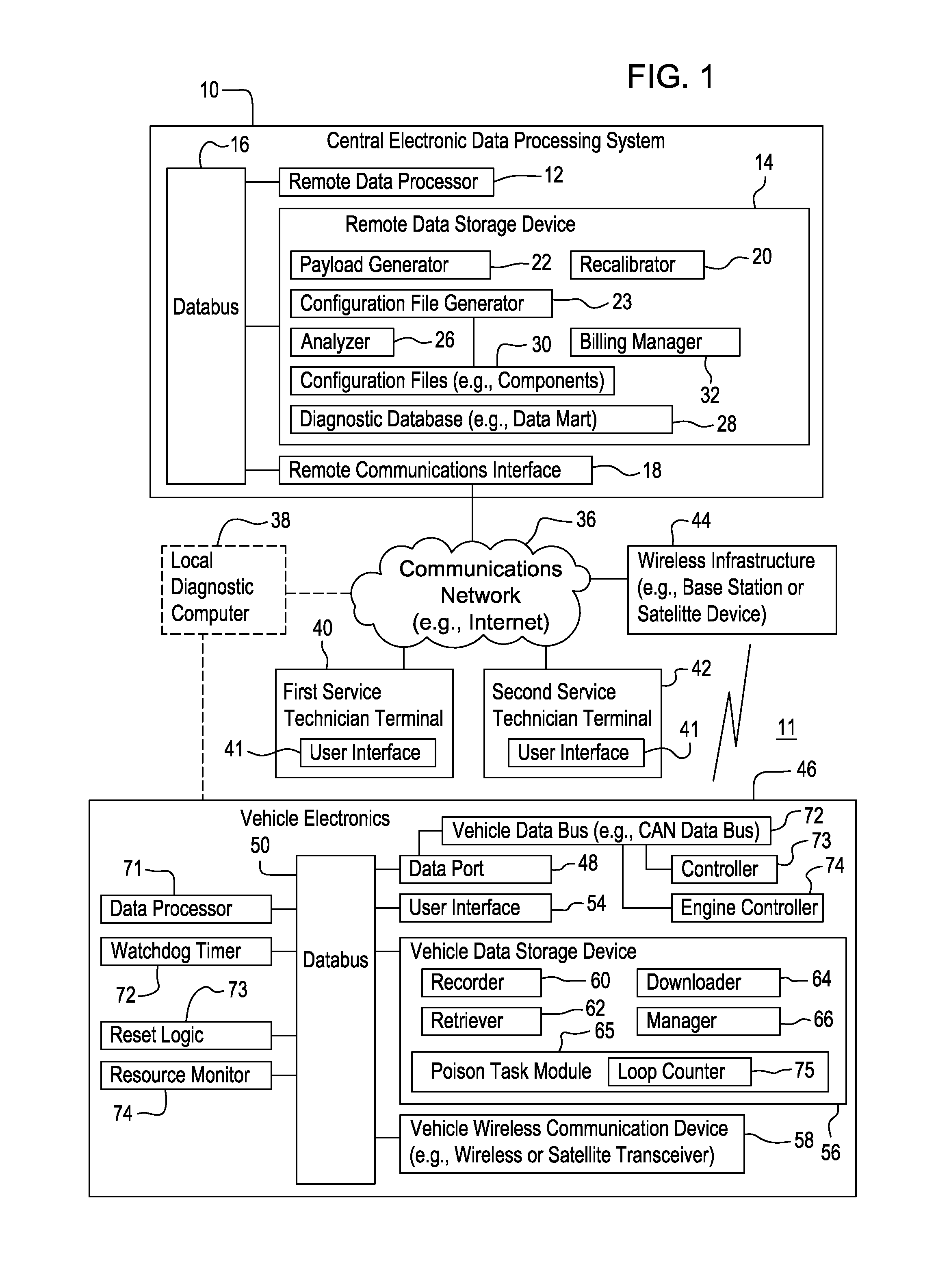

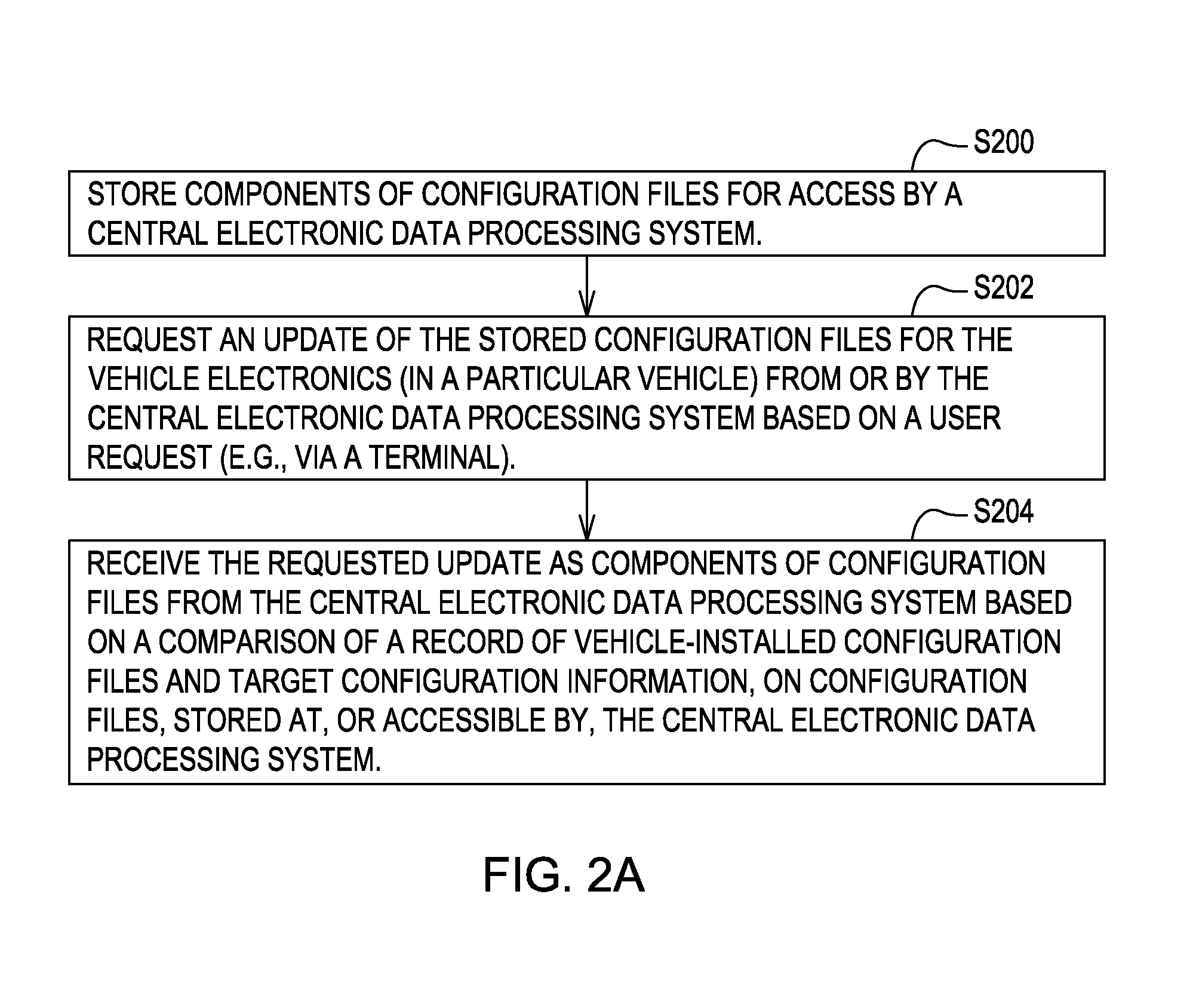

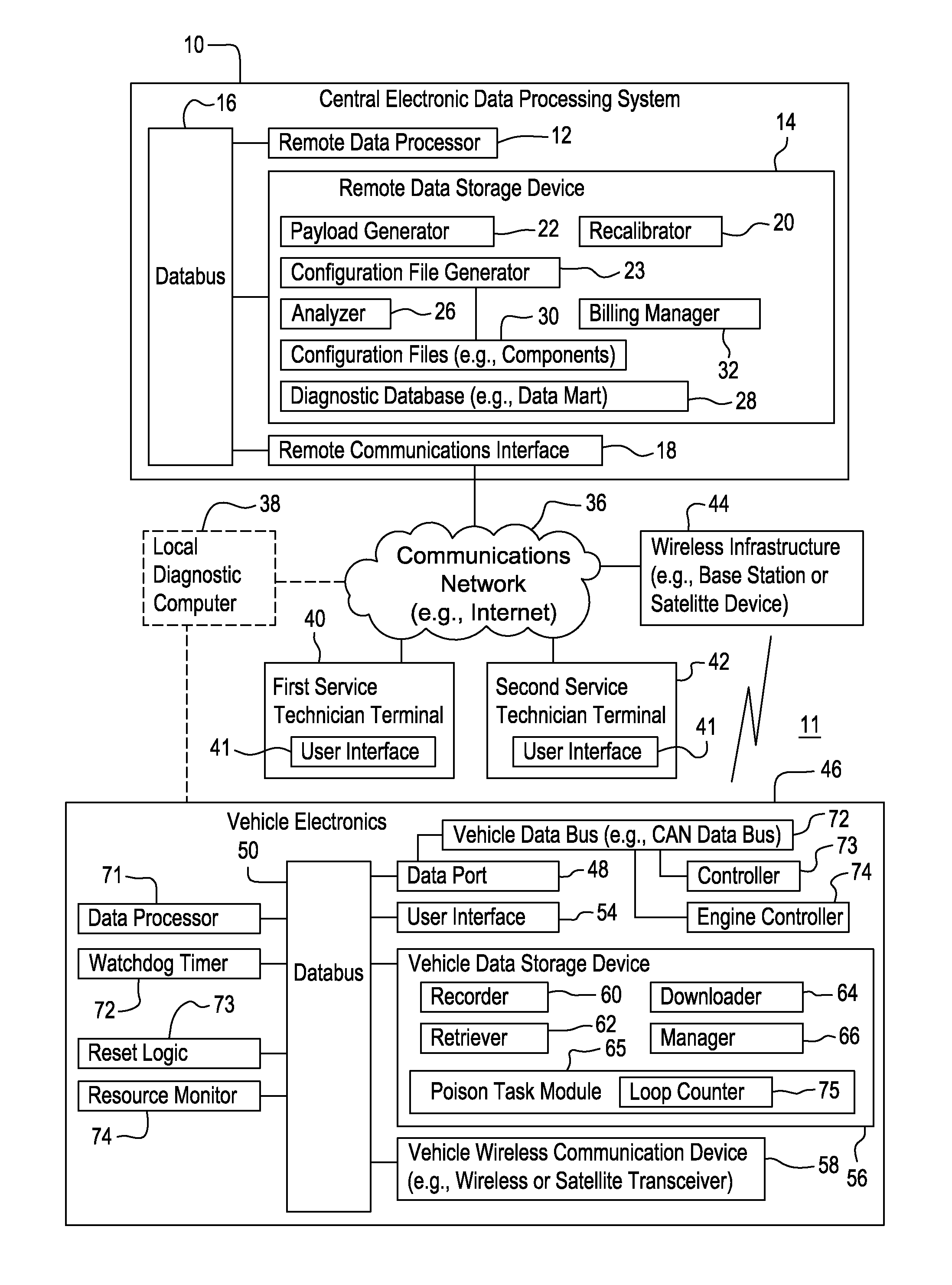

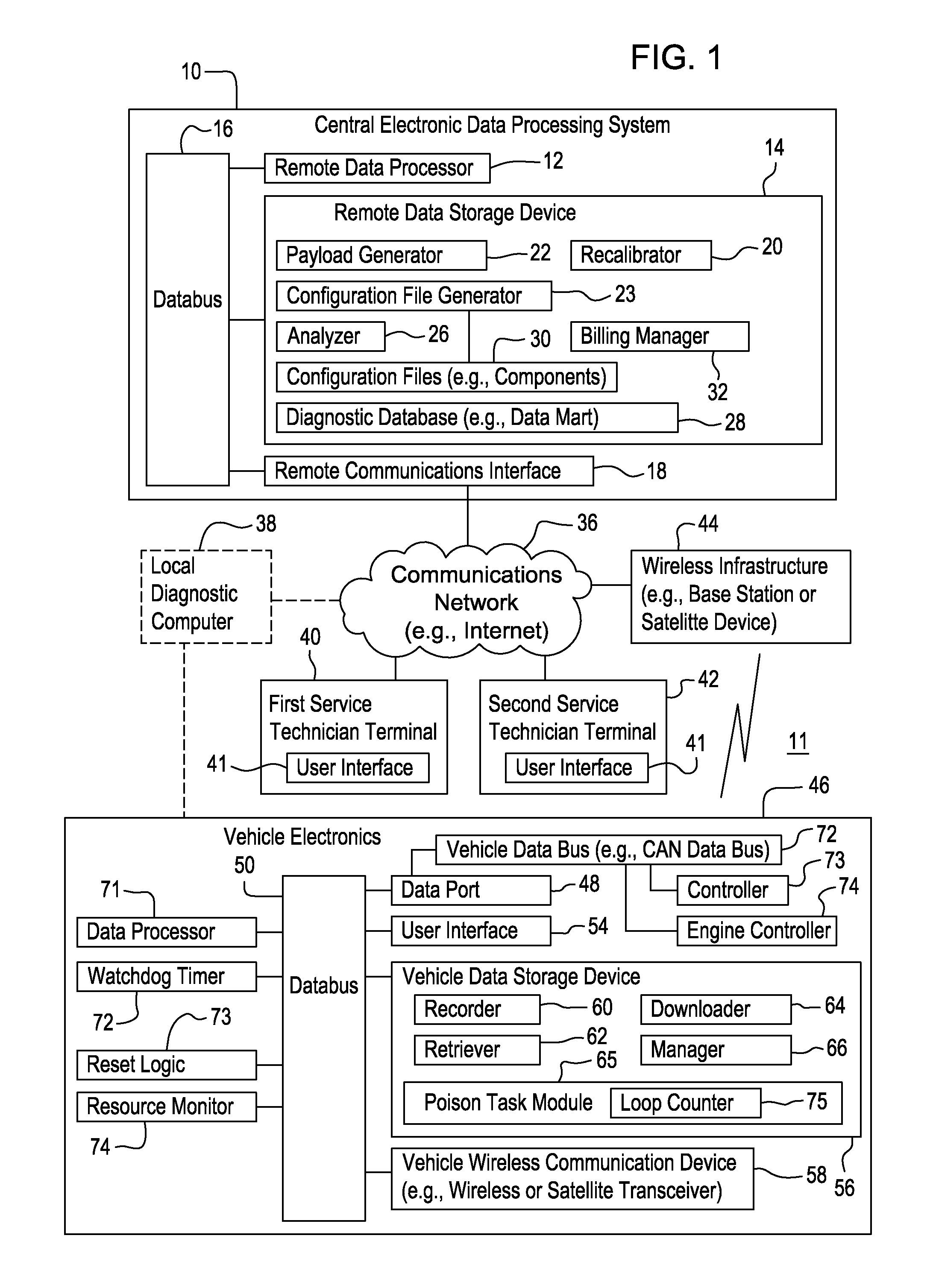

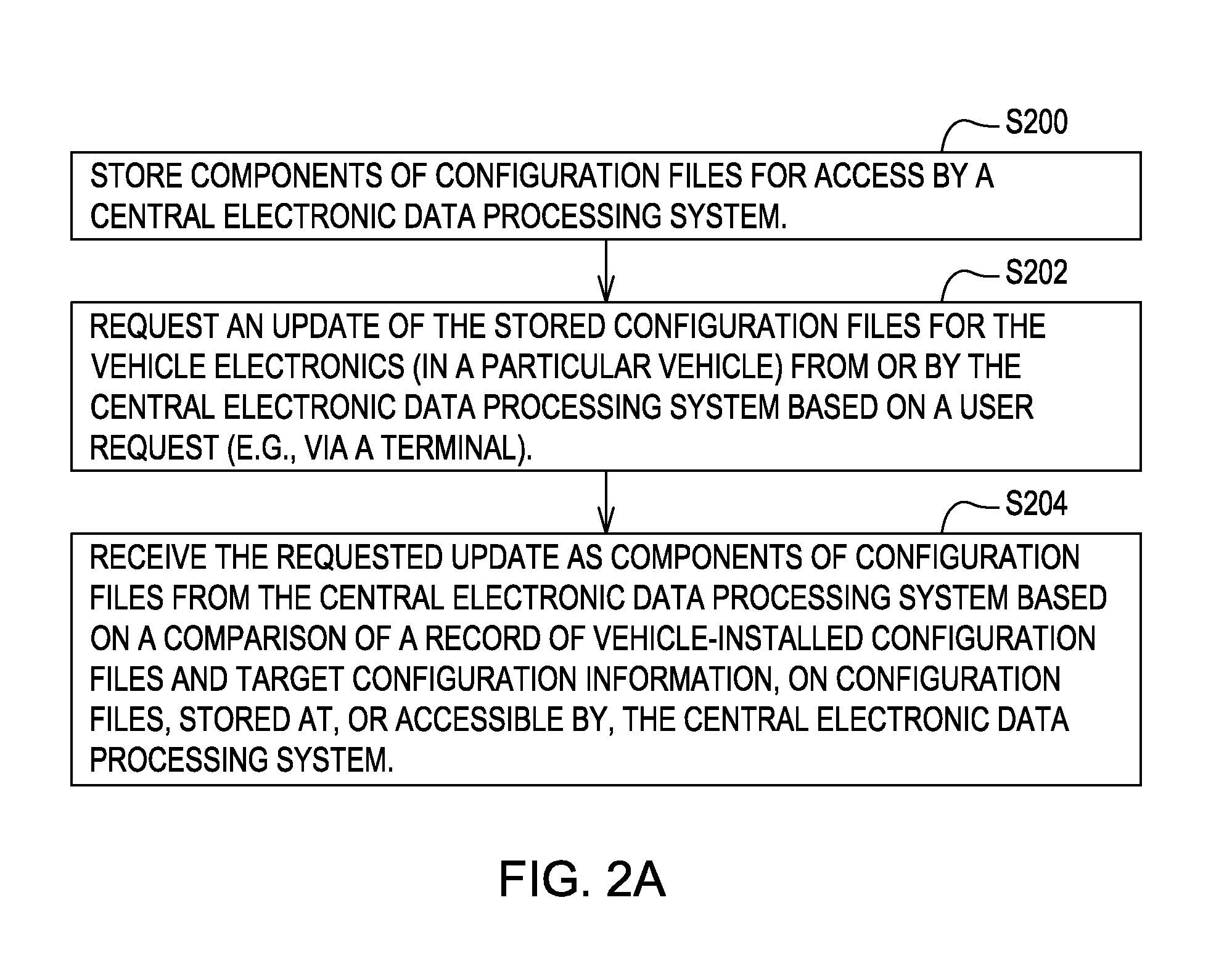

Method and system for performing diagnostics or software maintenance for a vehicle

ActiveUS20120041635A1Vehicle testingRegistering/indicating working of vehiclesResource consumptionComputer science

A method and system for performing diagnostics or software maintenance on a vehicle comprises a data processor for performing a particular task. A resource monitor is arranged for determining if resource consumption of the data processor for the respective particular task exceeds a threshold amount of resource consumption. A loop counter is arranged to increment a loop counter in a data storage device associated with the data processor if the resource consumption for the respective particular task exceeds the threshold amount. A poison task module is capable of designating the particular task as a poison message if the data processor has been rebooted a maximum number of times as indicated by the loop counter.

Owner:DEERE & CO

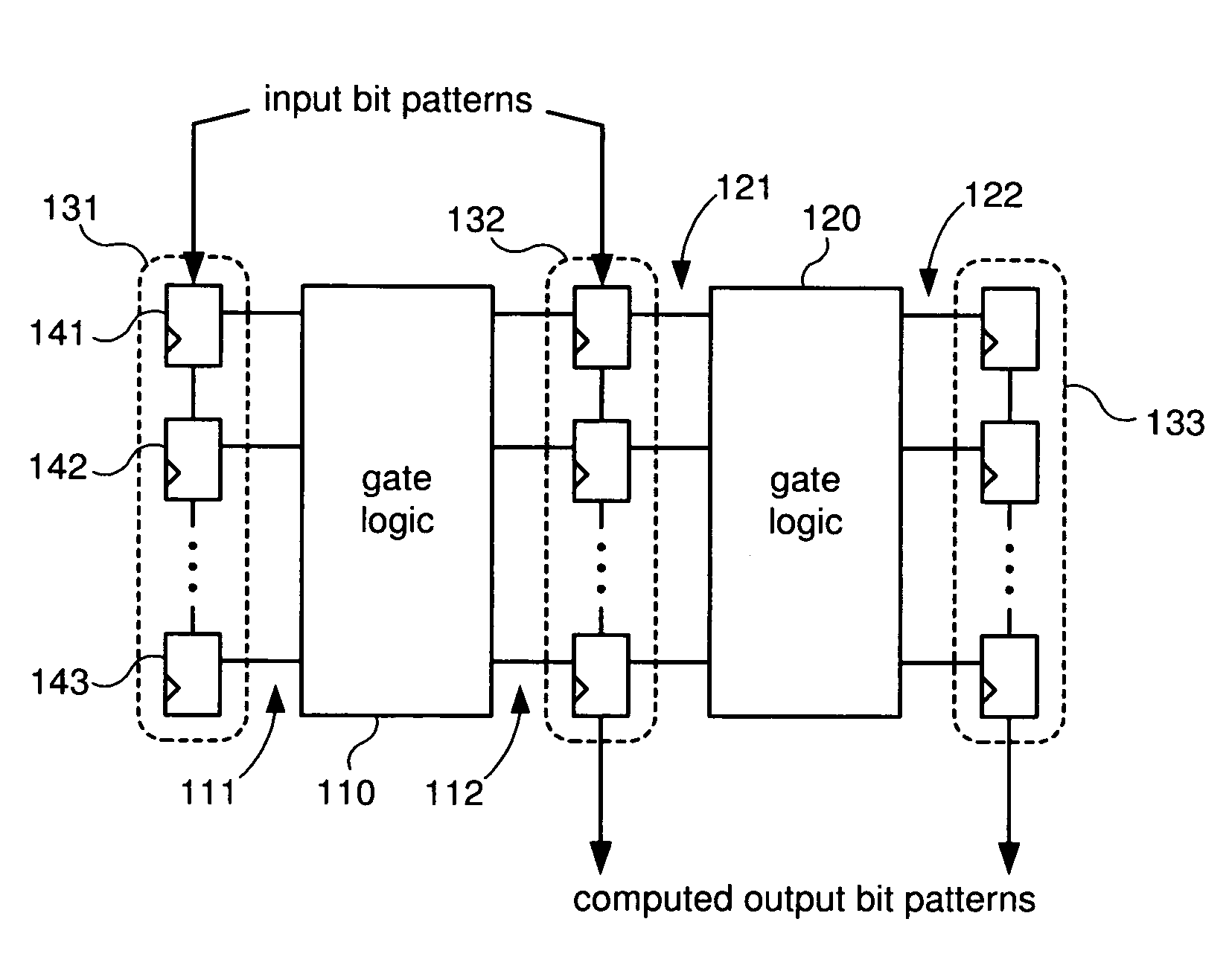

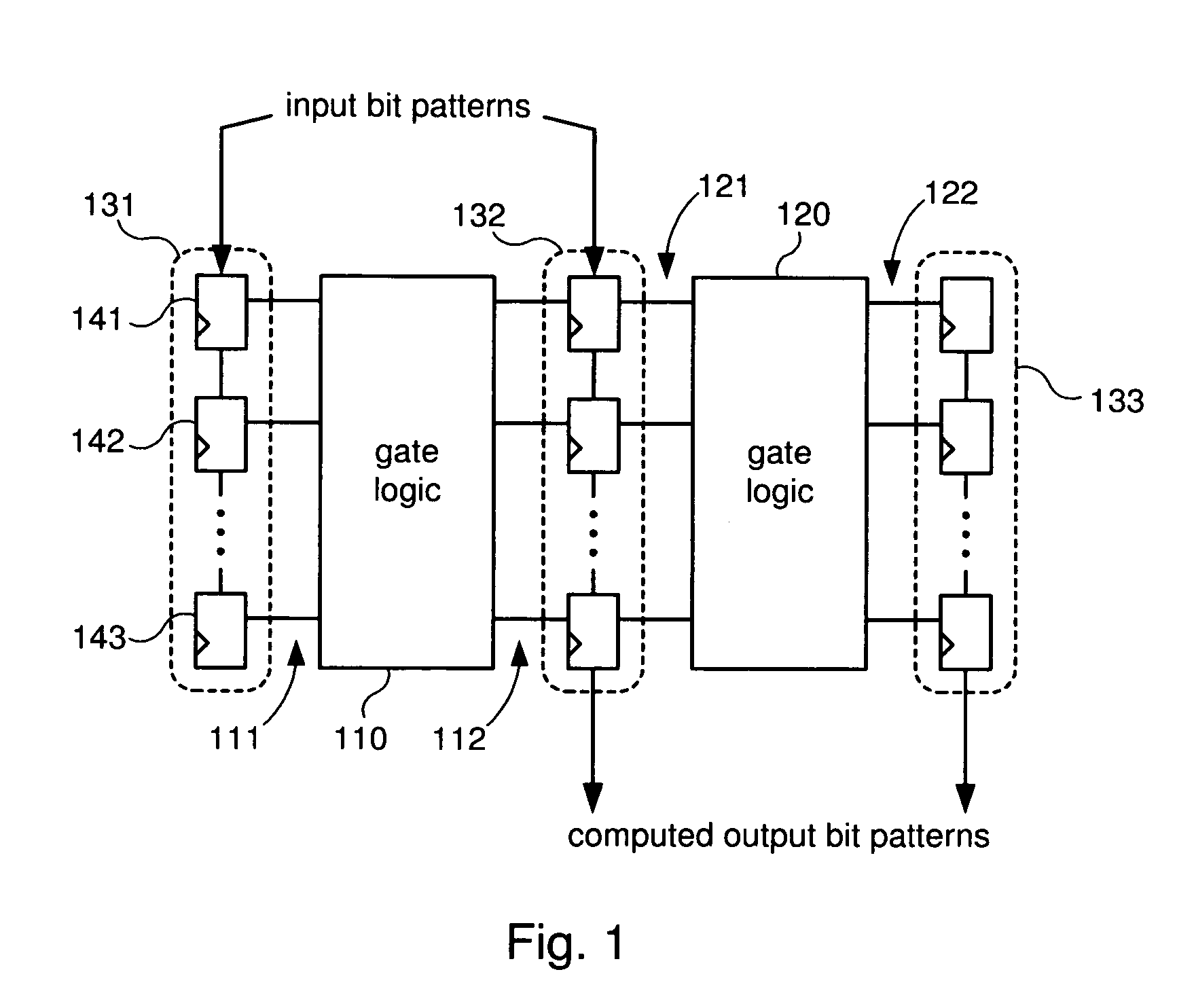

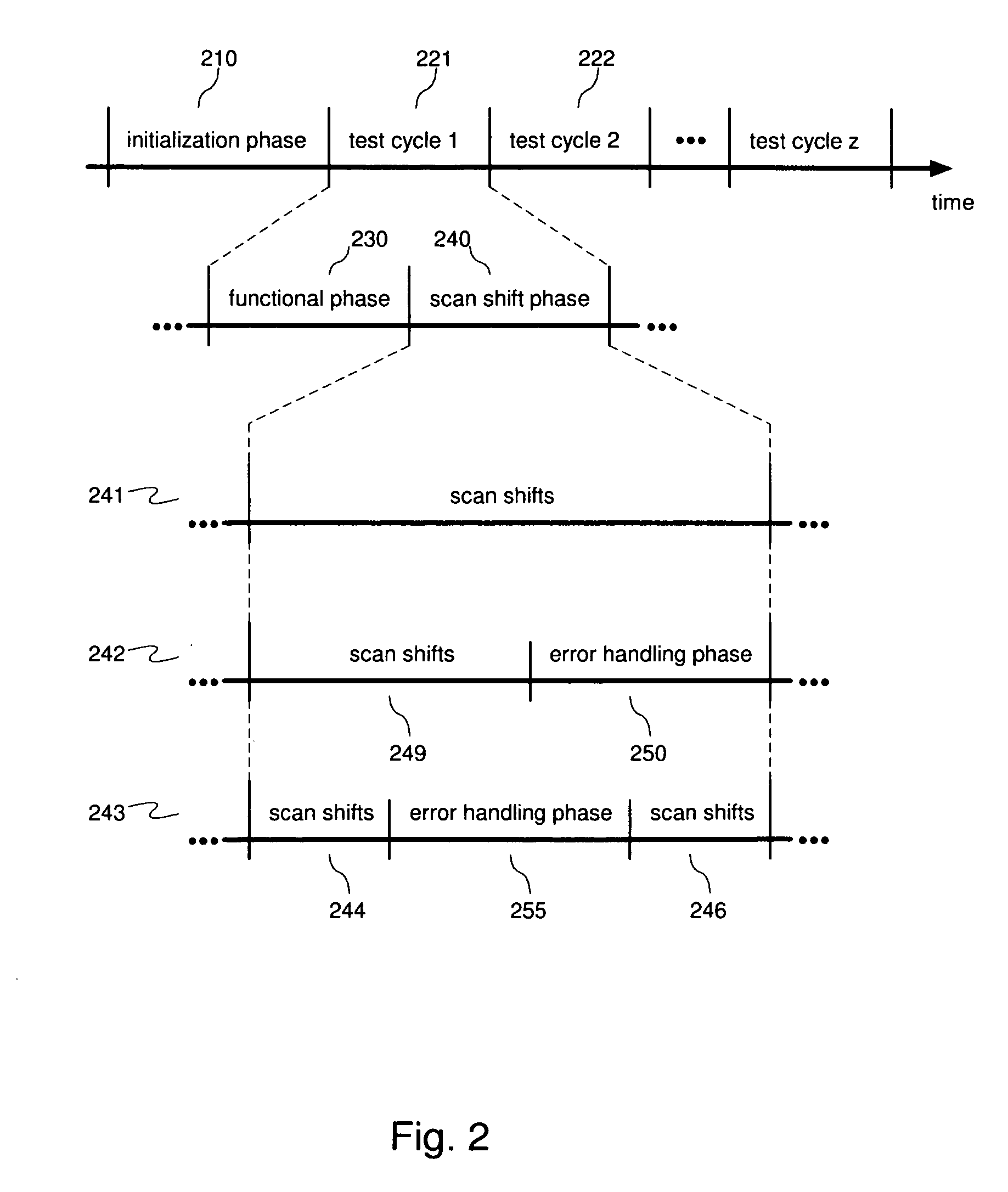

Systems and methods for self-diagnosing LBIST

Systems and methods for performing logic built-in self-tests (LBISTs) in digital circuits. In one embodiment, a system has first and second target logic, each of which has LBIST circuitry incorporated therein. The system also includes comparison circuitry which is coupled to the first and second LBIST circuitry. The comparison circuitry is configured to detect differences between data generated by the LBIST circuitry of the first target logic and data generated by the LBIST circuitry of the second target logic (e.g., MISR signature values.) The comparison circuitry is also configured to provide information localizing the sources of the differences. In one embodiment, this localizing information comprises values from a test cycle counter, a scan shift counter and a set of XOR gates that compare the bits of the MISR values.

Owner:KK TOSHIBA

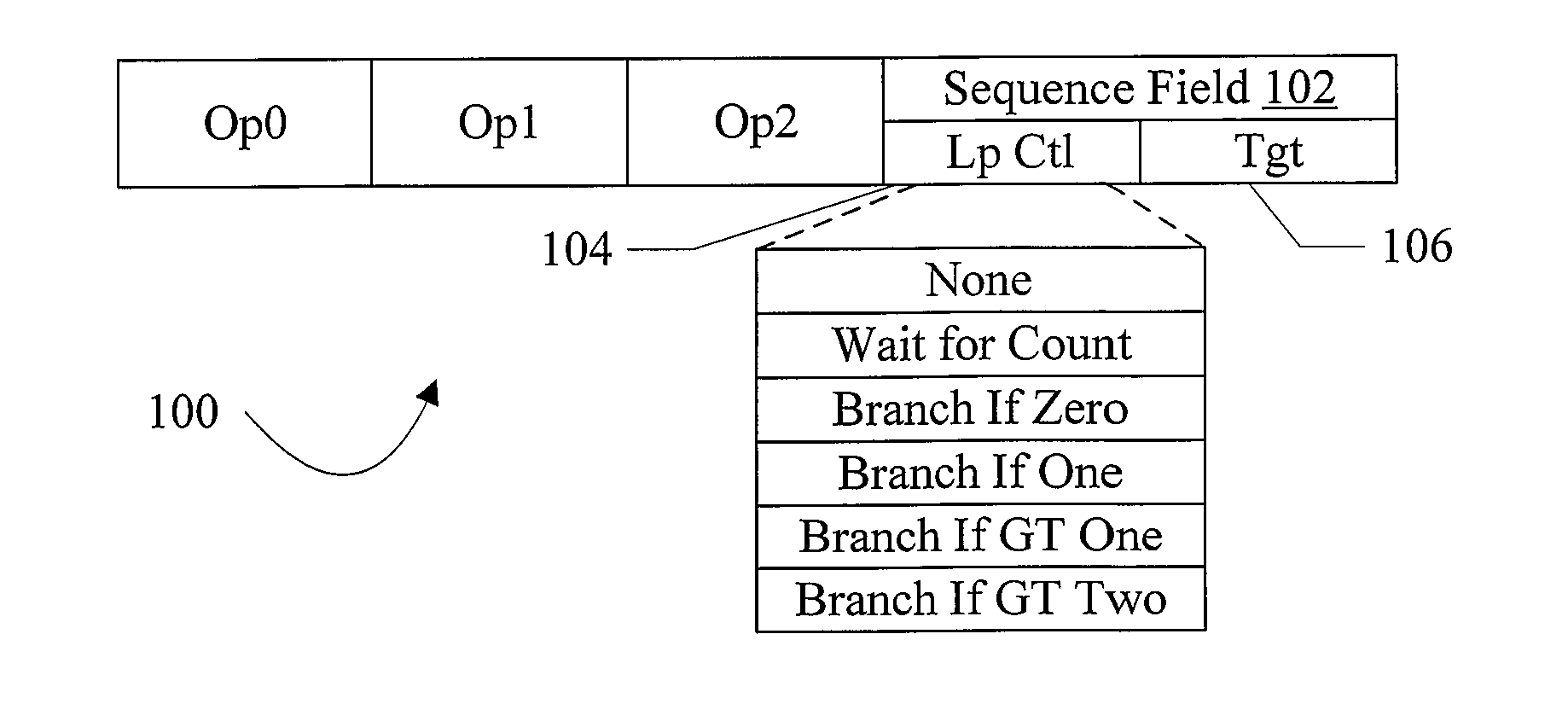

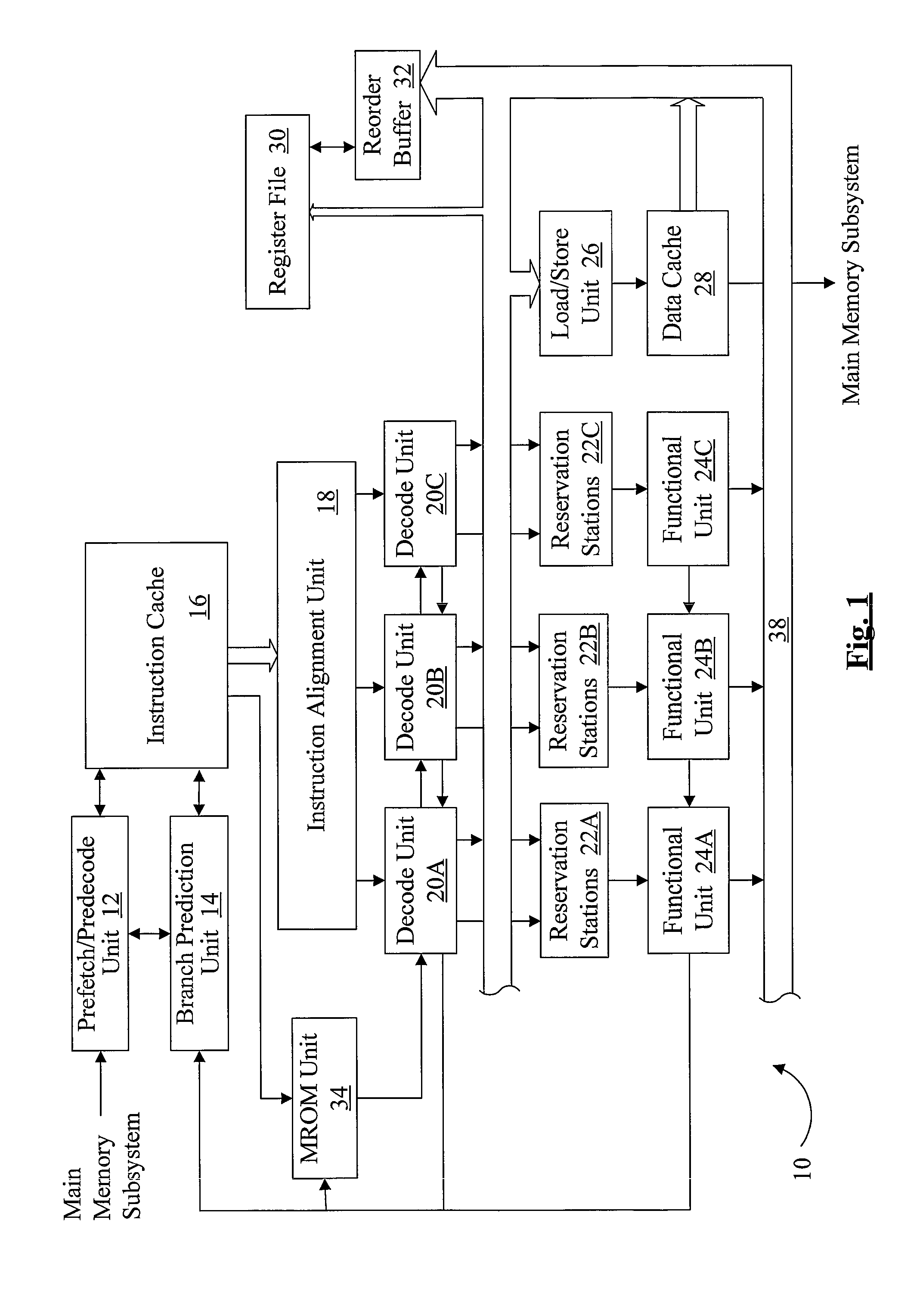

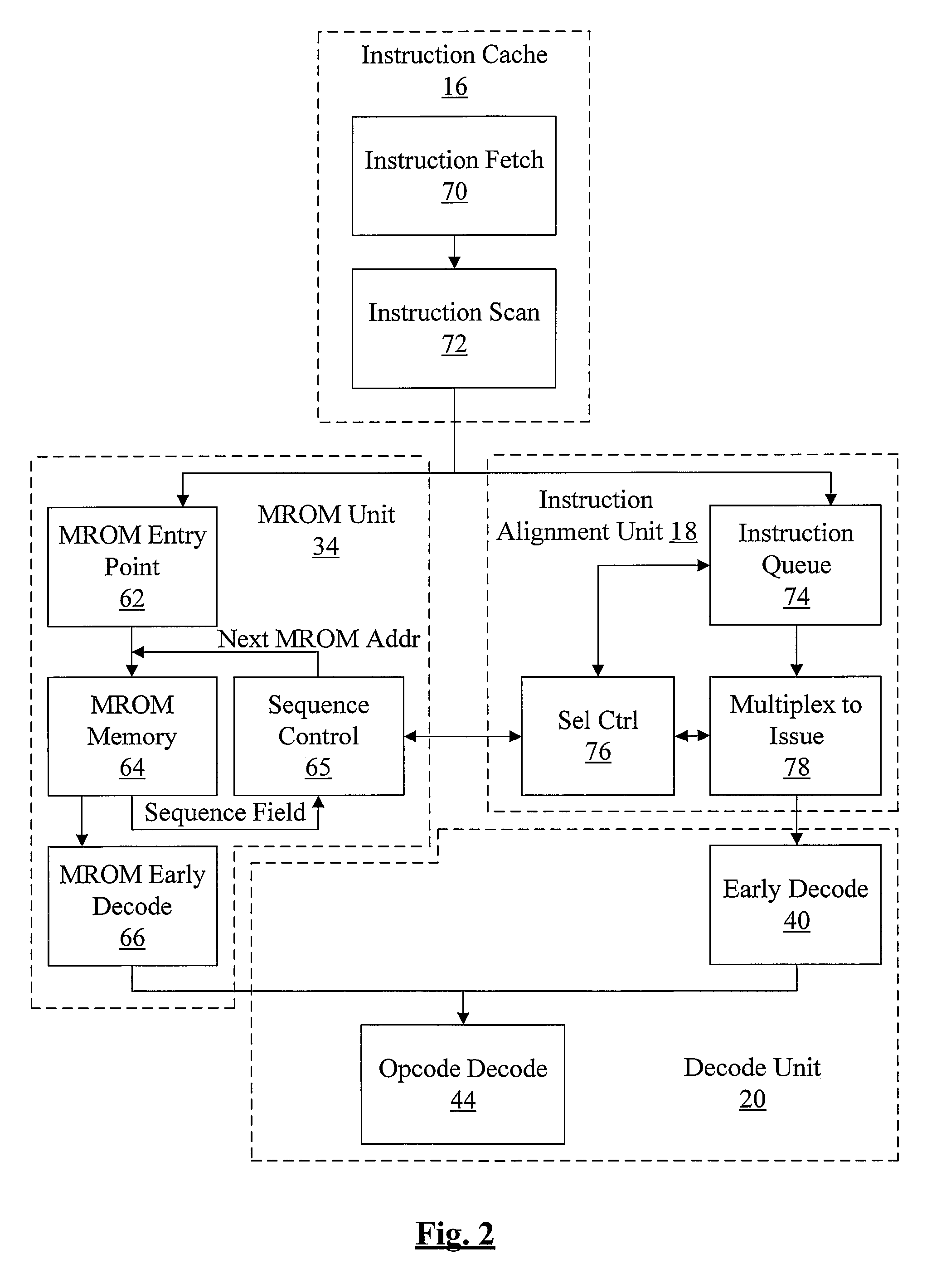

Precise counter hardware for microcode loops

In an embodiment, a microcode unit for a processor is contemplated. The microcode unit comprises a microcode memory storing a plurality of microcode routines executable by the processor, wherein each microcode routine comprises two or more microcode operations. Coupled to the microcode memory, the sequence control unit is configured to control reading microcode operations from the microcode memory to be issued for execution by the processor. The sequence control unit is configured to stall issuance of microcode operations forming a body of a loop in a first routine of the plurality of microcode routines until a loop counter value that indicates a number of iterations of the loop is received by the sequence control unit.

Owner:ADVANCED MICRO DEVICES INC

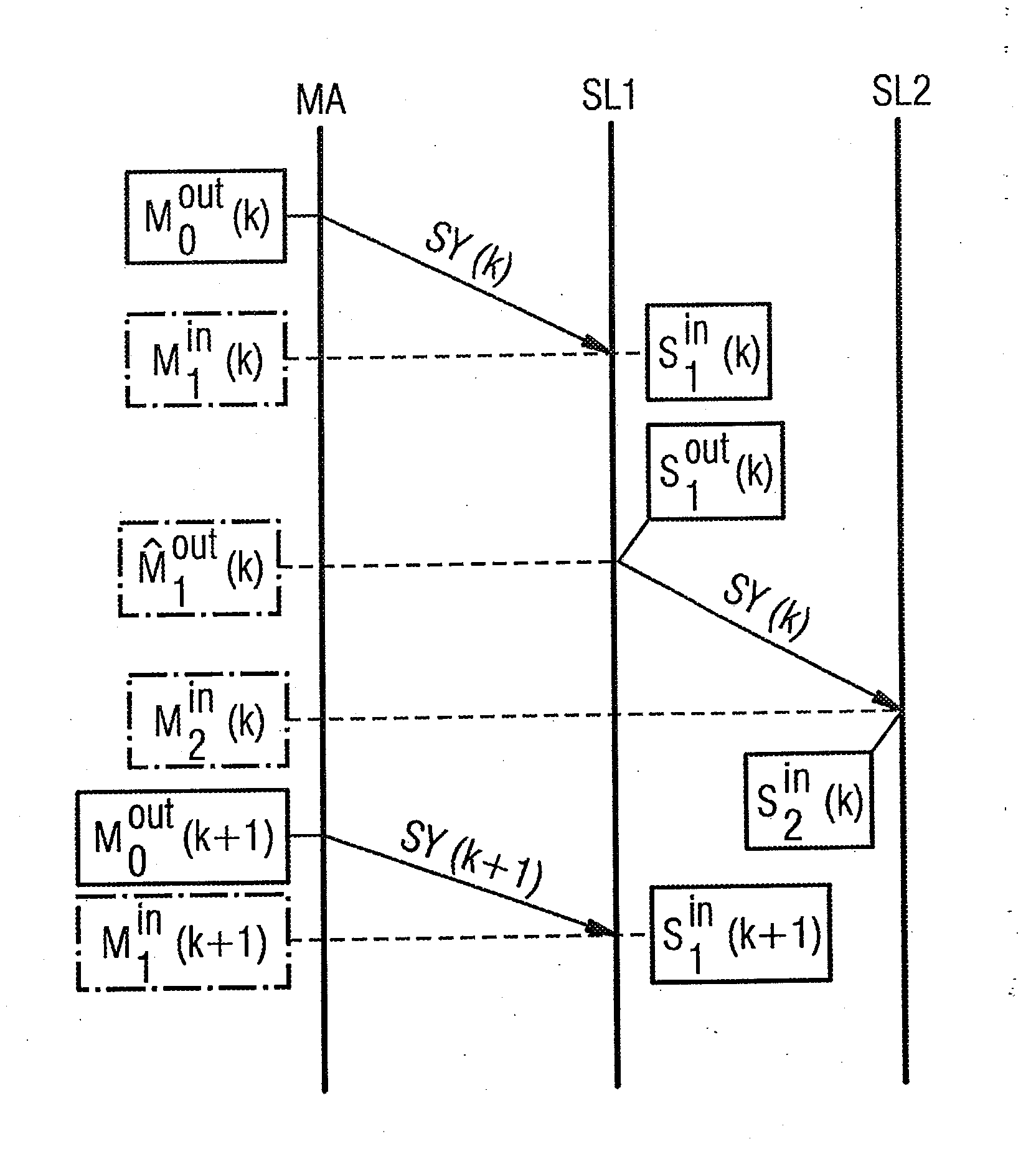

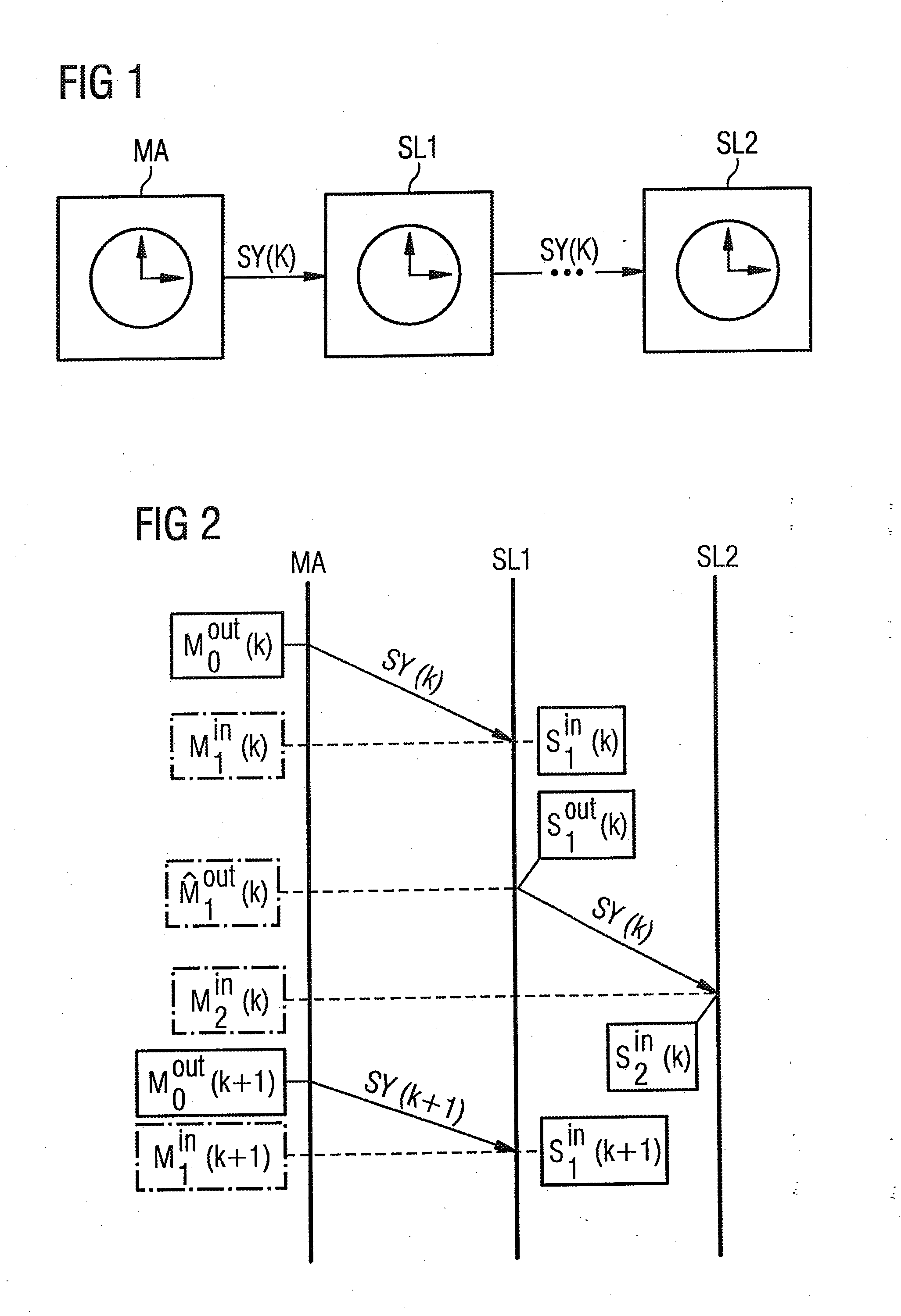

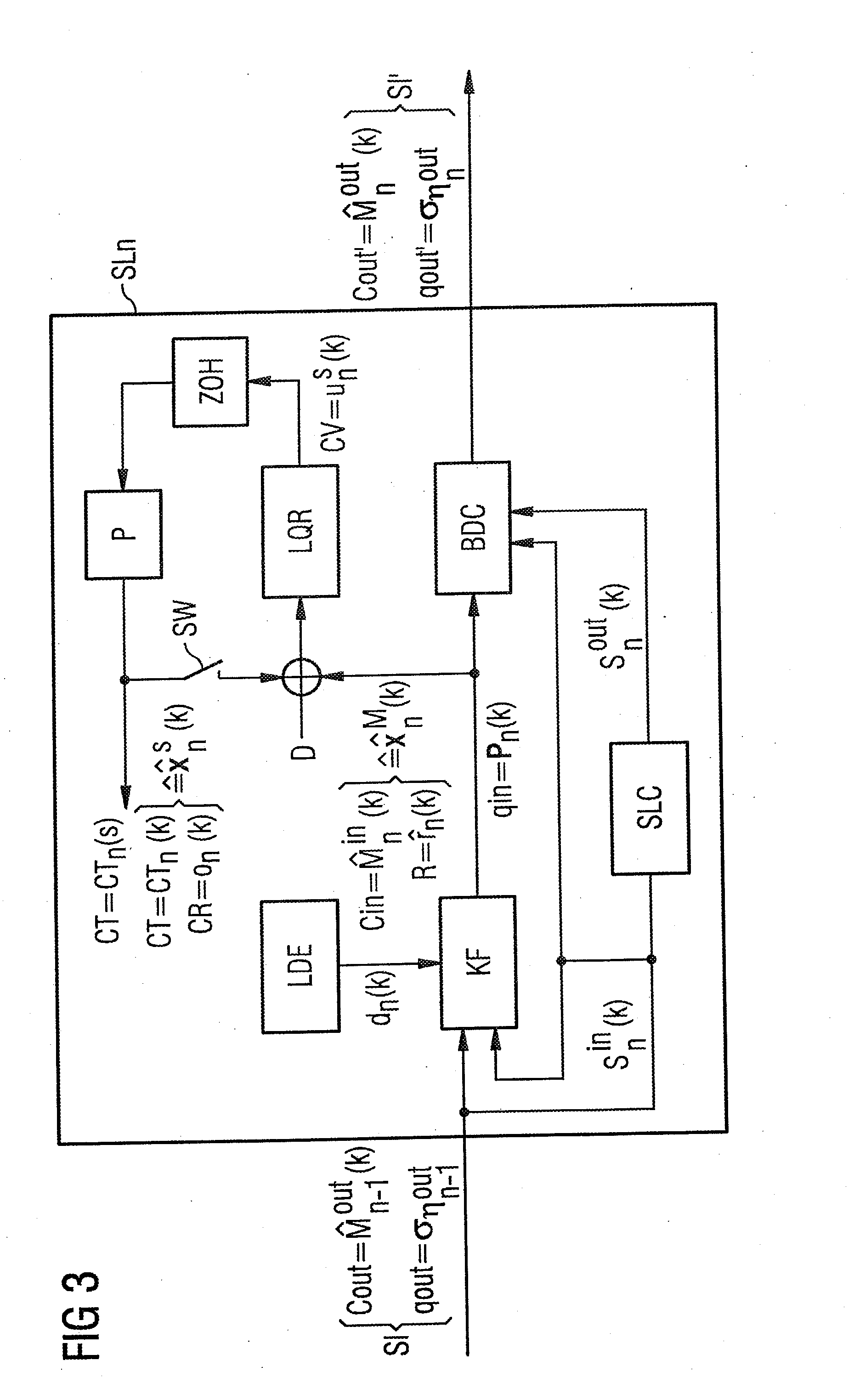

Method for Time Synchronization in a Communications Network

ActiveUS20130182806A1Highly precise and regular across timeTime synchronizationTime-division multiplexSynchronisation signal speed/phase controlClock rateDistributed computing

A method for time synchronization in a communications network having multiple nodes, wherein the nodes comprise a first node and at least one second node, where the first node generates first cycle counter states according to a reference clock frequency and the second node or nodes each generate second cycle counter states according to an internal clock frequency, where a time synchronization is carried out in sequential synchronization cycles, in which synchronization messages originating from the first node are sequentially transmitted from one node to another node, and a synchronization message transmitted by a node contains information used for time synchronization in the at least one second node receiving the synchronization message such that a time synchronization is performed in a given second node based on an estimation of a first cycle counter state and a compensation factor in combination with a linear quadratic regulator.

Owner:SIEMENS AG

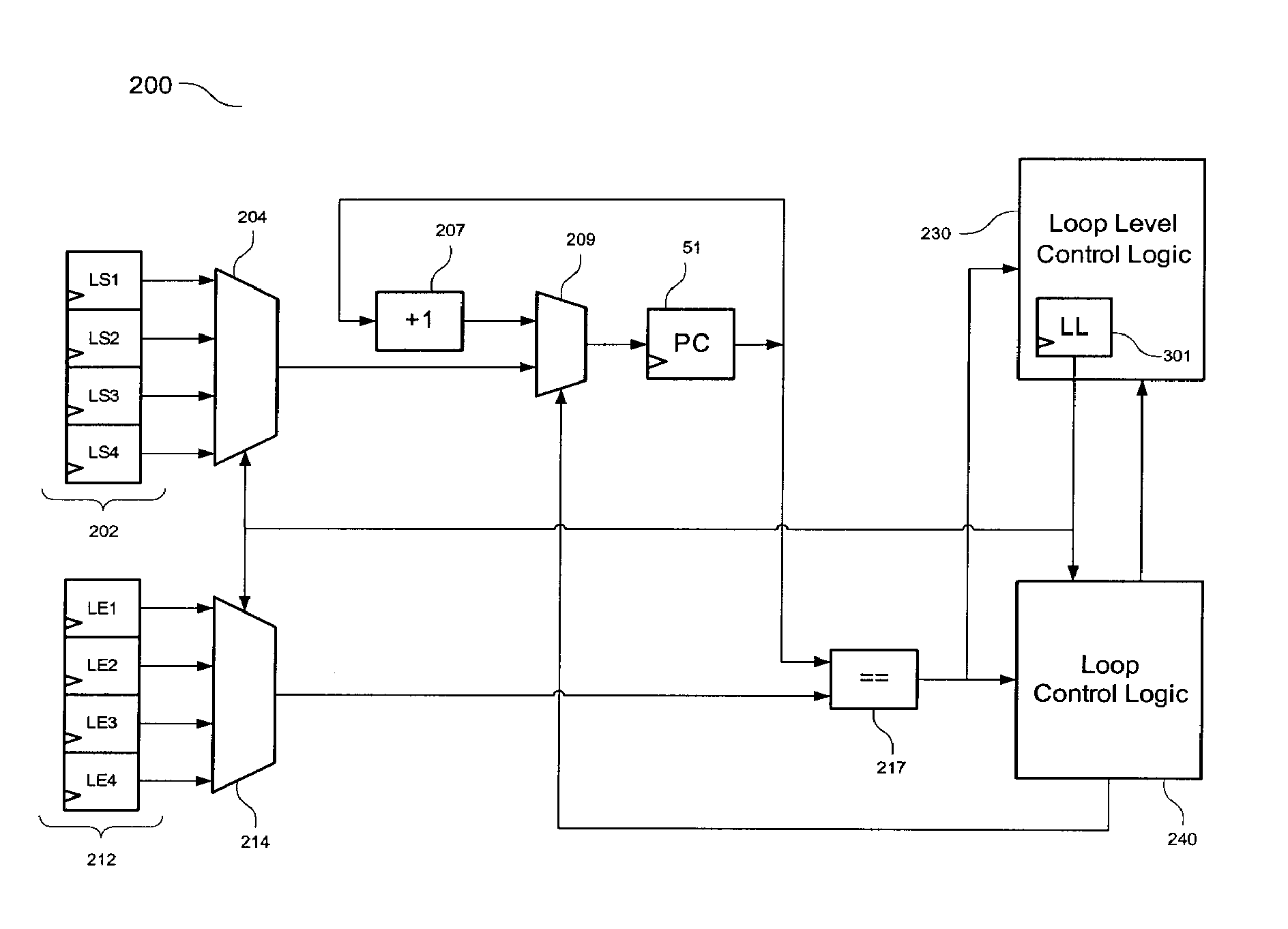

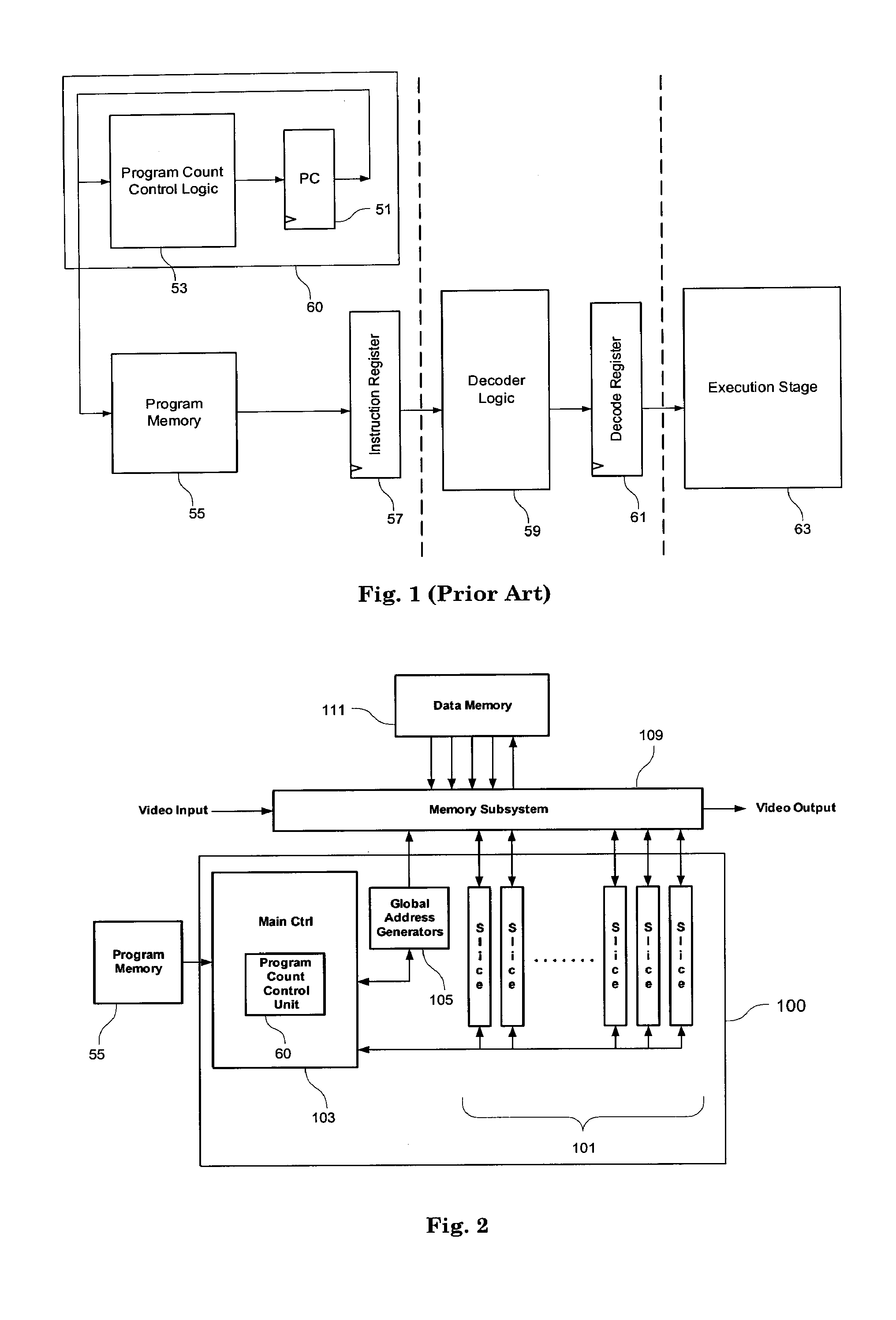

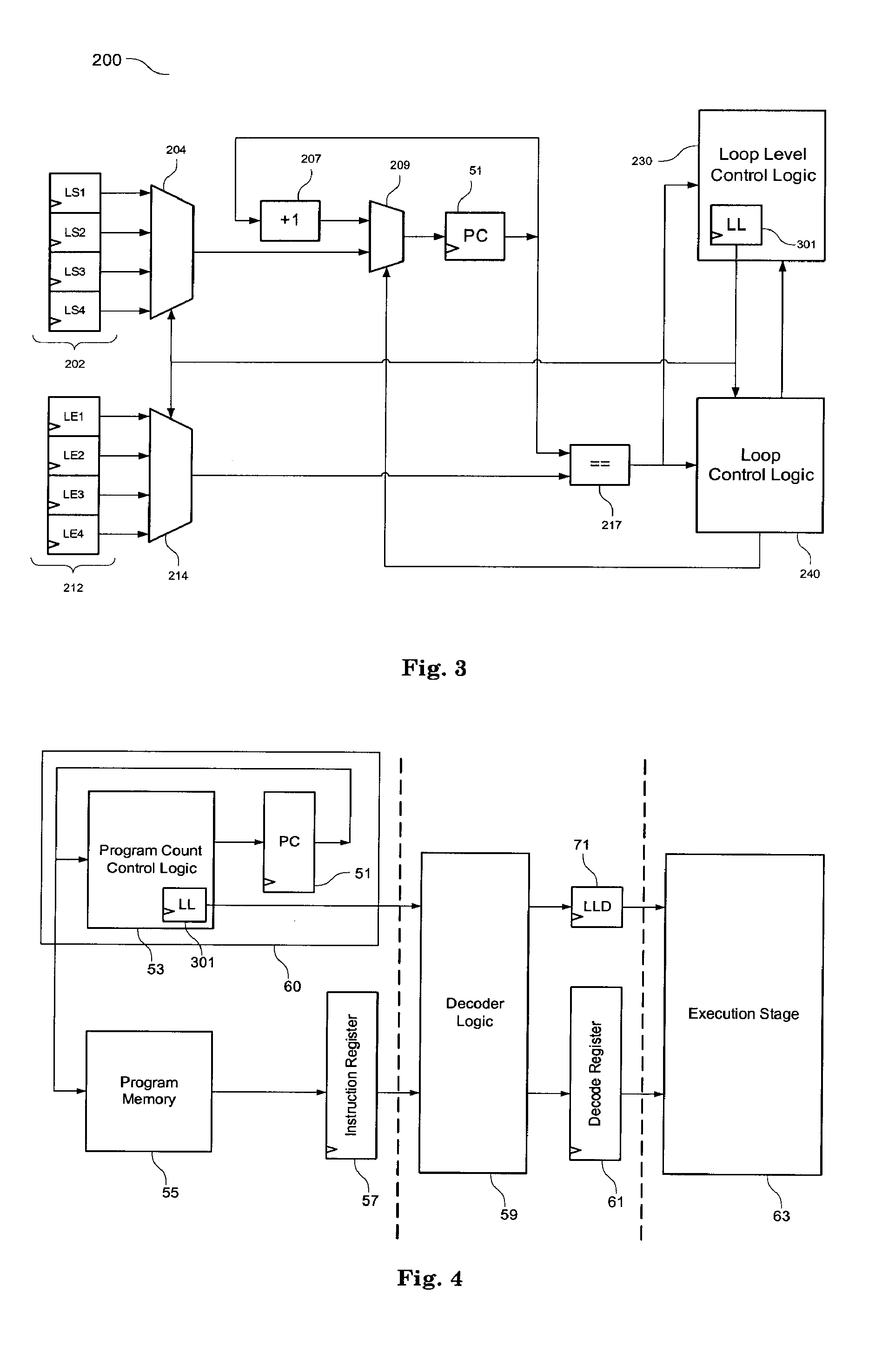

Digital processor with control means for the execution of nested loops

InactiveUS20080141013A1Without increasing complexity of circuitEasy to controlDigital computer detailsNext instruction address formationLoop controlData set

A method and apparatus to control execution of nested loops is disclosed. The method and apparatus stores the loop level of a current loop in execution and uses this loop level to manage a data set provided for each loop. The data set for each loop includes a start address, an end address, and a loop counter or a loop flag, respectively. The method and apparatus allows arbitrary nested loops to be controlled without increasing a complexity level of the circuit and allows additional loop control. The only precondition is that the loop end addresses are different.

Owner:ON DEMAND MICROELECTRONICS

High performance RISC instruction set digital signal processor having circular buffer and looping controls

InactiveUS7401205B1Efficient implementationRuntime instruction translationSpecific program execution arrangementsDigital signal processingComputer architecture

A DSP superscalar architecture employing dual multiply accumulate pipelines. Dual MAC pipelines allow for a seem less transition between established RISC instruction sets and extended DSP instructions sets. Relocatable opcodes are provide to allow further extensions of RISC instruction sets. The DSP superscalar architecture also provides memory pointers with hardware circular buffer support, an interruptible and nested zero-overhead loop counter, and prioritized low-overhead interrupts.

Owner:ARM FINANCE OVERSEAS LTD

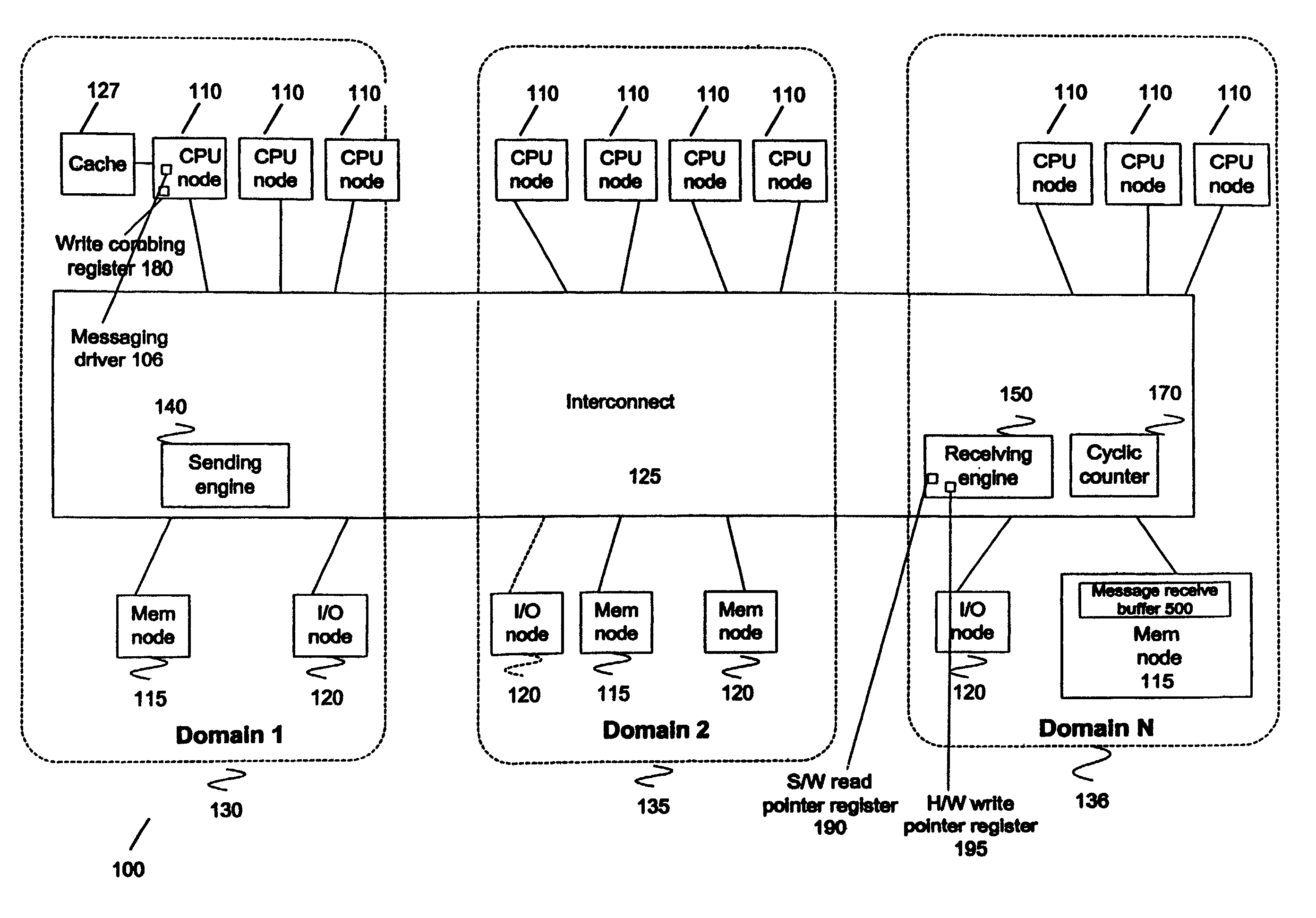

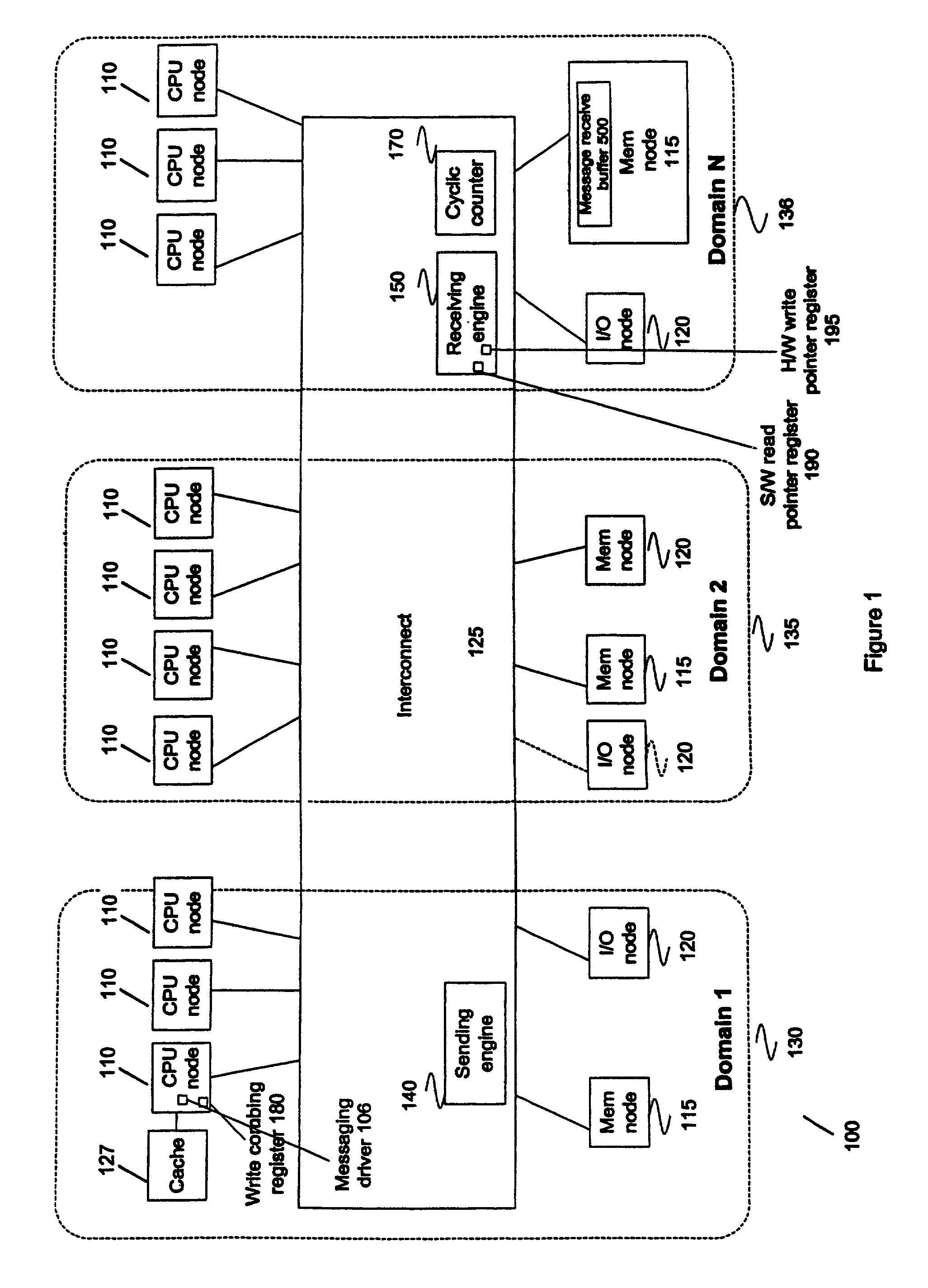

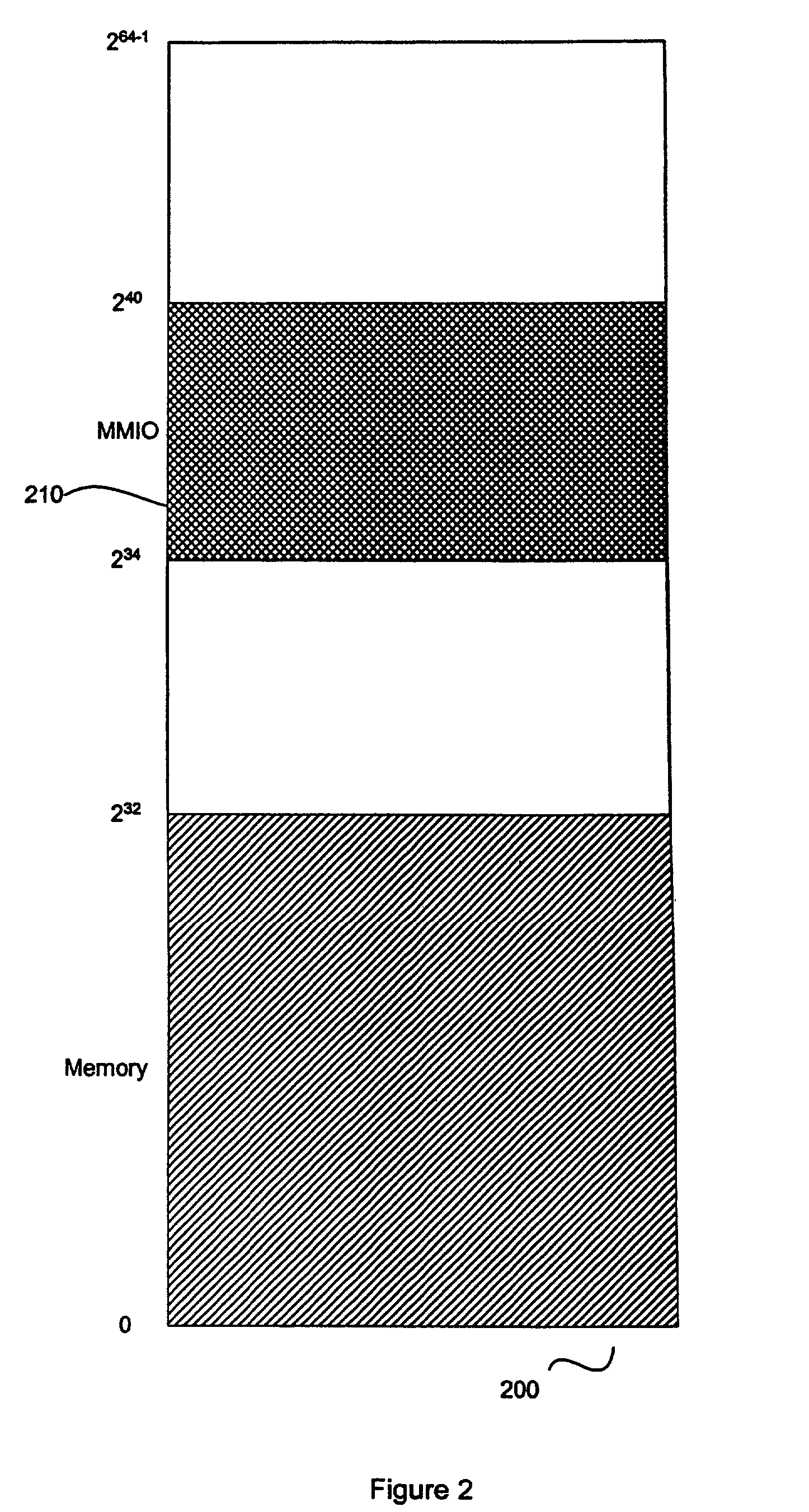

System and method for low overhead message passing between domains in a partitioned server

InactiveUS7194517B2Memory adressing/allocation/relocationDigital computer detailsMemory mapMessage passing

A system and method for passing messages between domains with low overhead in a multi-node computer system. A CPU node in a sending domain issues a request to a memory node in a receiving domain using memory-mapped input / output window. This causes the message to be transmitted to a coherent space of the receiving domain. All messages are cache-line in size. A small portion of each cache line, cyclic counter field, is overwritten before the cache line is written in the coherent address space of the receiving domain. A massaging driver polls the cyclic count field of the cache line in the processor cache to determine when the next message is written in the coherent address space of the receiving domain. This allows the CPU to detect when the last received message is written into the coherent address space of the receiving domain without generating transactions on CPU interface.

Owner:FUJITSU LTD

Flash memory device and related program verification method

ActiveUS8675416B2Improve reliabilityReduce noiseRead-only memoriesDigital storageVolatile memoryLoop counter

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for performing diagnostics or software maintenance for a vehicle

ActiveUS8412406B2Vehicle testingRegistering/indicating working of vehiclesResource consumptionData treatment

A method and system for performing diagnostics or software maintenance on a vehicle comprises a data processor for performing a particular task. A resource monitor is arranged for determining if resource consumption of the data processor for the respective particular task exceeds a threshold amount of resource consumption. A loop counter is arranged to increment a loop counter in a data storage device associated with the data processor if the resource consumption for the respective particular task exceeds the threshold amount. A poison task module is capable of designating the particular task as a poison message if the data processor has been rebooted a maximum number of times as indicated by the loop counter.

Owner:DEERE & CO

True time delay phase array radar using rotary clocks and electronic delay lines

Owner:ANALOG DEVICES INC

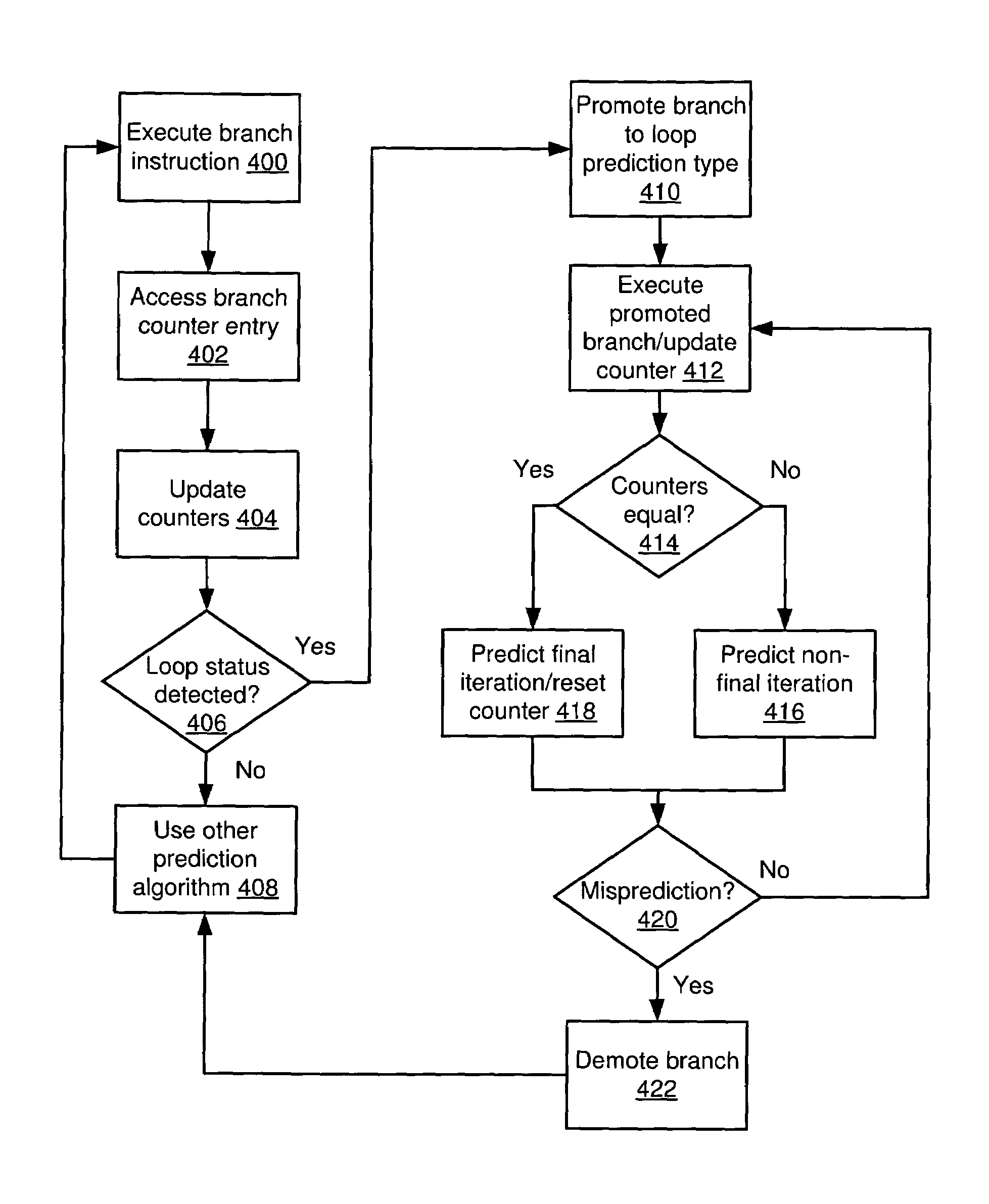

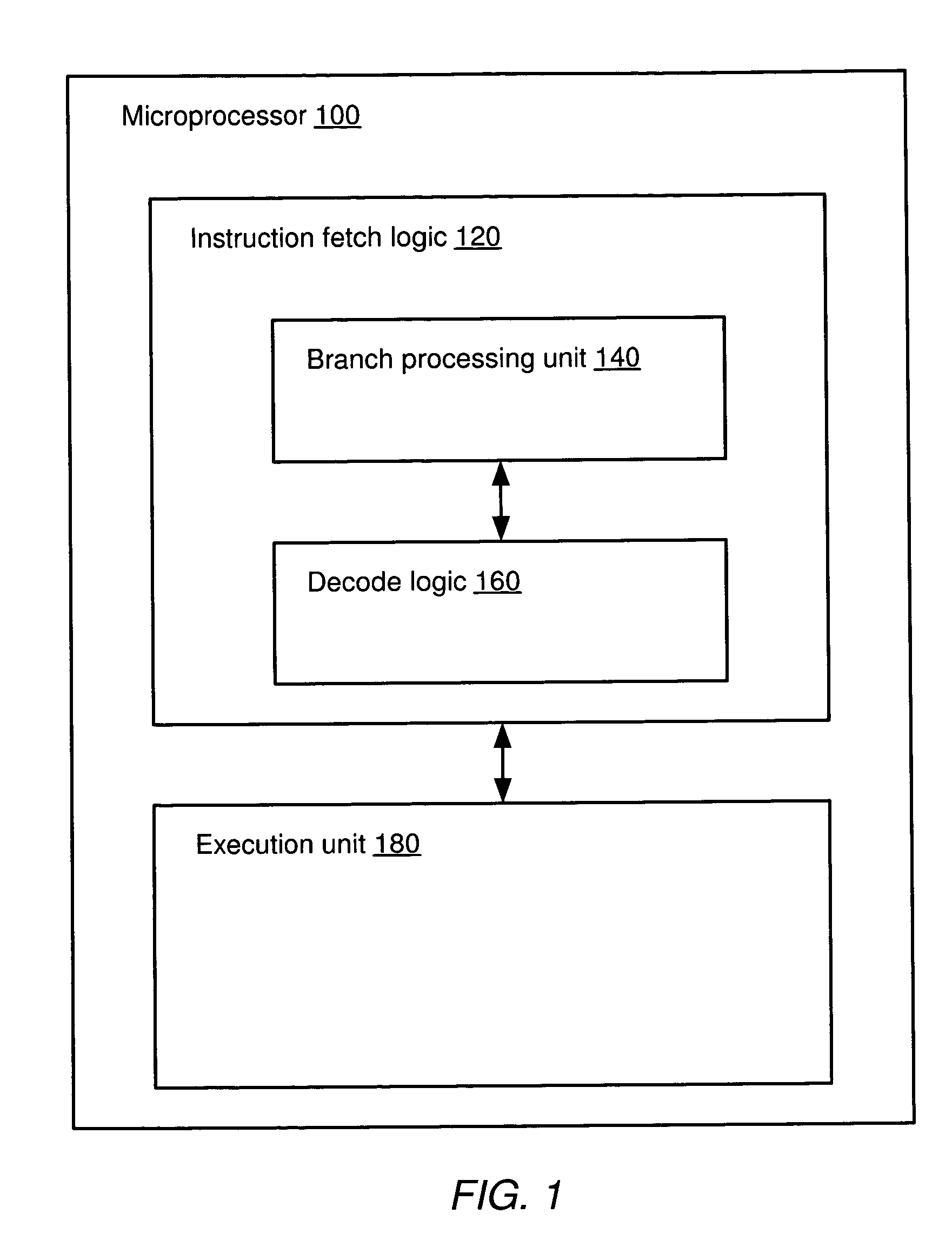

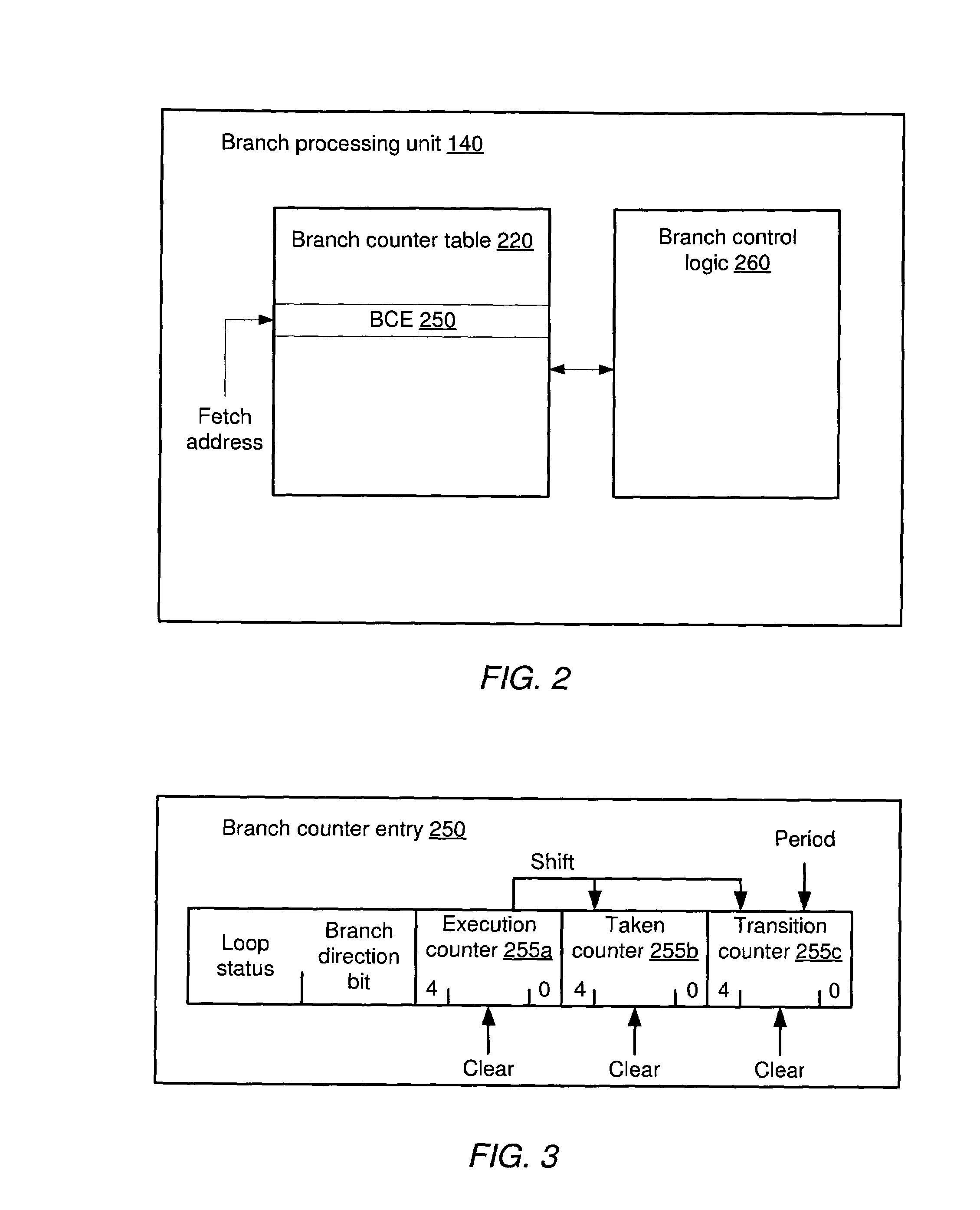

Method and apparatus for loop detection utilizing multiple loop counters and a branch promotion scheme

ActiveUS7130991B1Branch prediction accuracy can be increasedImprove forecast accuracyDigital computer detailsConcurrent instruction executionCycle detectionLoop counter

A method and apparatus for loop detection for improved branch prediction accuracy. In one embodiment, the method may comprise executing a branch instruction, updating a plurality of event counts corresponding to the branch instruction in response to its executing, determining a loop behavior status corresponding to the branch instruction in response to the event count updating, and promoting the branch instruction to a loop branch prediction type in response to the determination of loop behavior status.

Owner:ADVANCED MICRO DEVICES INC

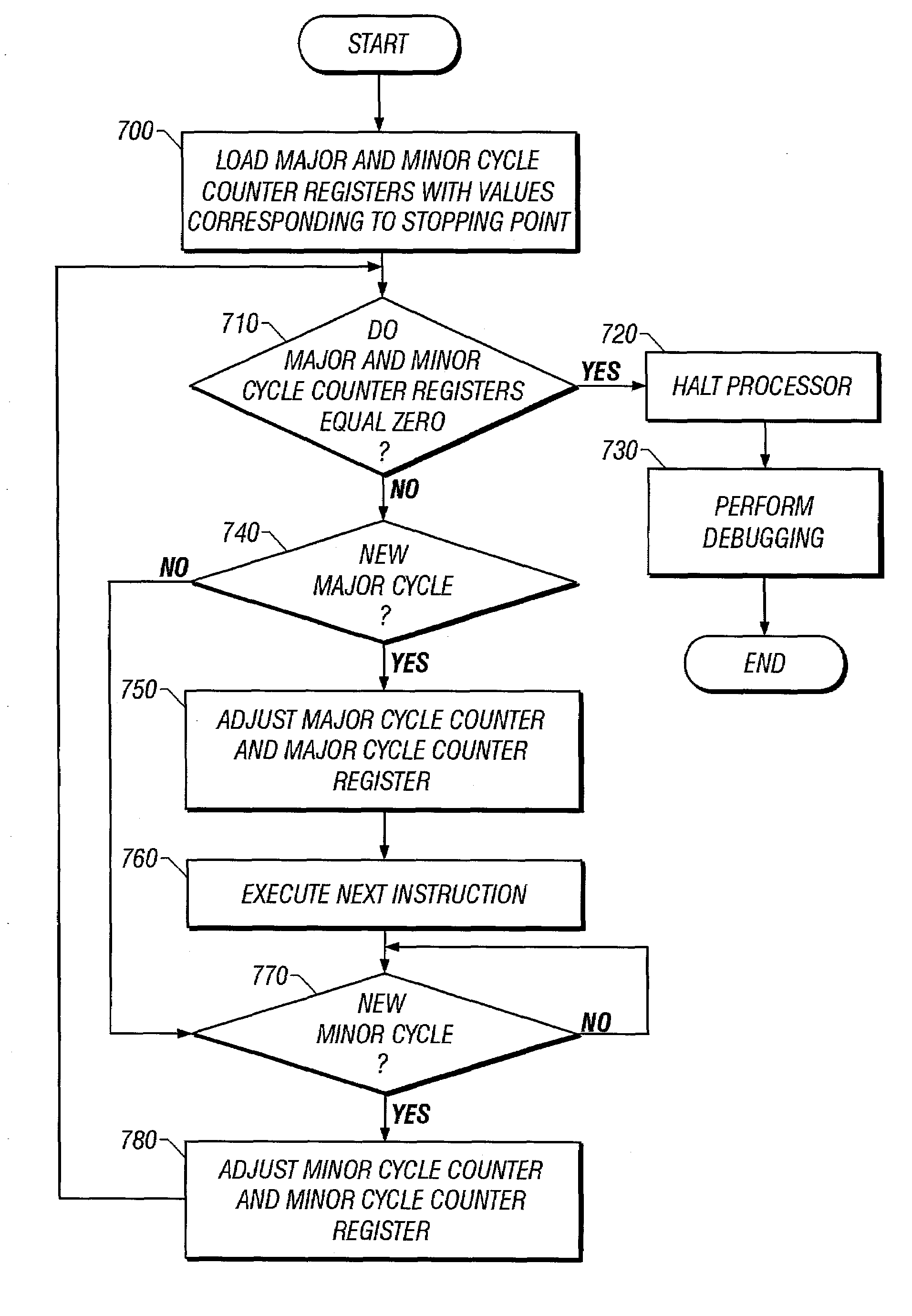

Method and apparatus for debugging in a massively parallel processing environment

A method for performing debugging of an executable source program in a massively parallel processing environment involves associating a major cycle counter and a minor cycle counter with each of a plurality of execution processors in the massively parallel processing environment, obtaining a first stopping point value associated with the major cycle counter and a second stopping point value associated with the minor cycle counter, executing instructions of the executable source program on each of the plurality of execution processors, modifying the major cycle counter and the minor cycle counter, and halting each of the plurality of execution processors and returning control to the user if the major cycle counter reaches the first stopping point value and the minor cycle counter reaches the second stopping point value.

Owner:ORACLE INT CORP