Patents

Literature

95 results about "Logic built-in self-test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logic built-in self-test (or LBIST) is a form of built-in self-test (BIST) in which hardware and/or software is built into integrated circuits allowing them to test their own operation, as opposed to reliance on external automated test equipment.

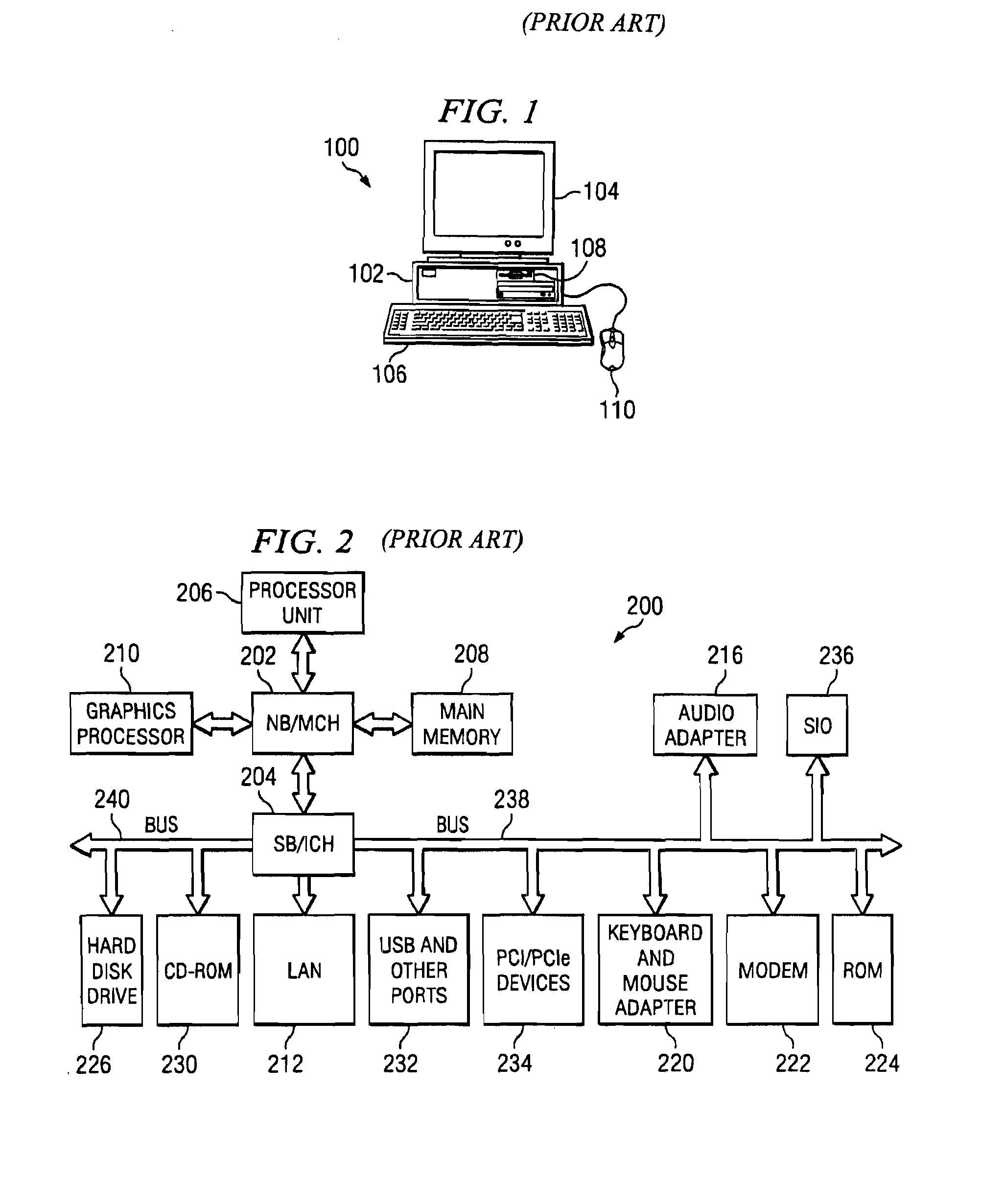

Method and apparatus for at-speed testing of digital circuits

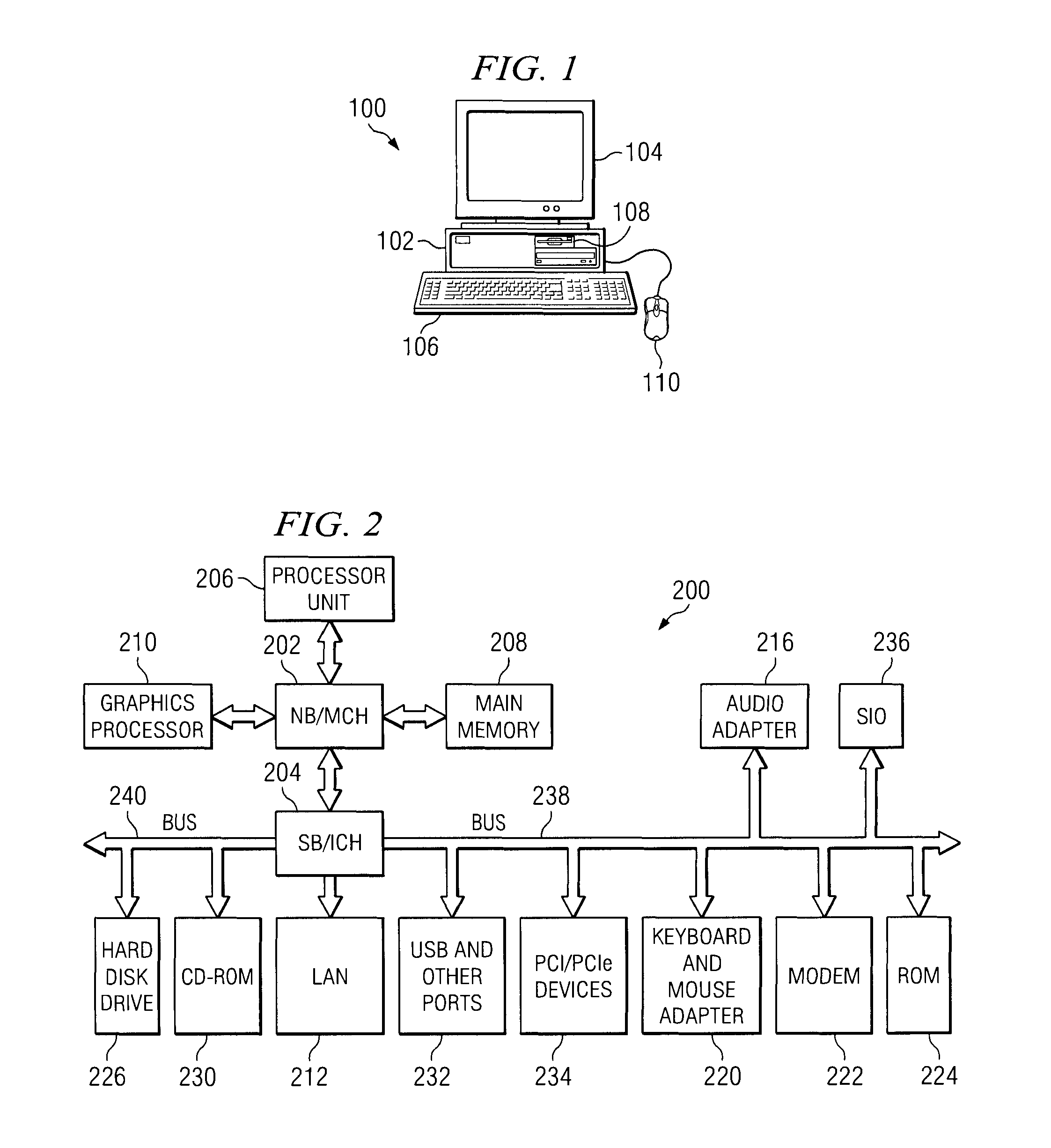

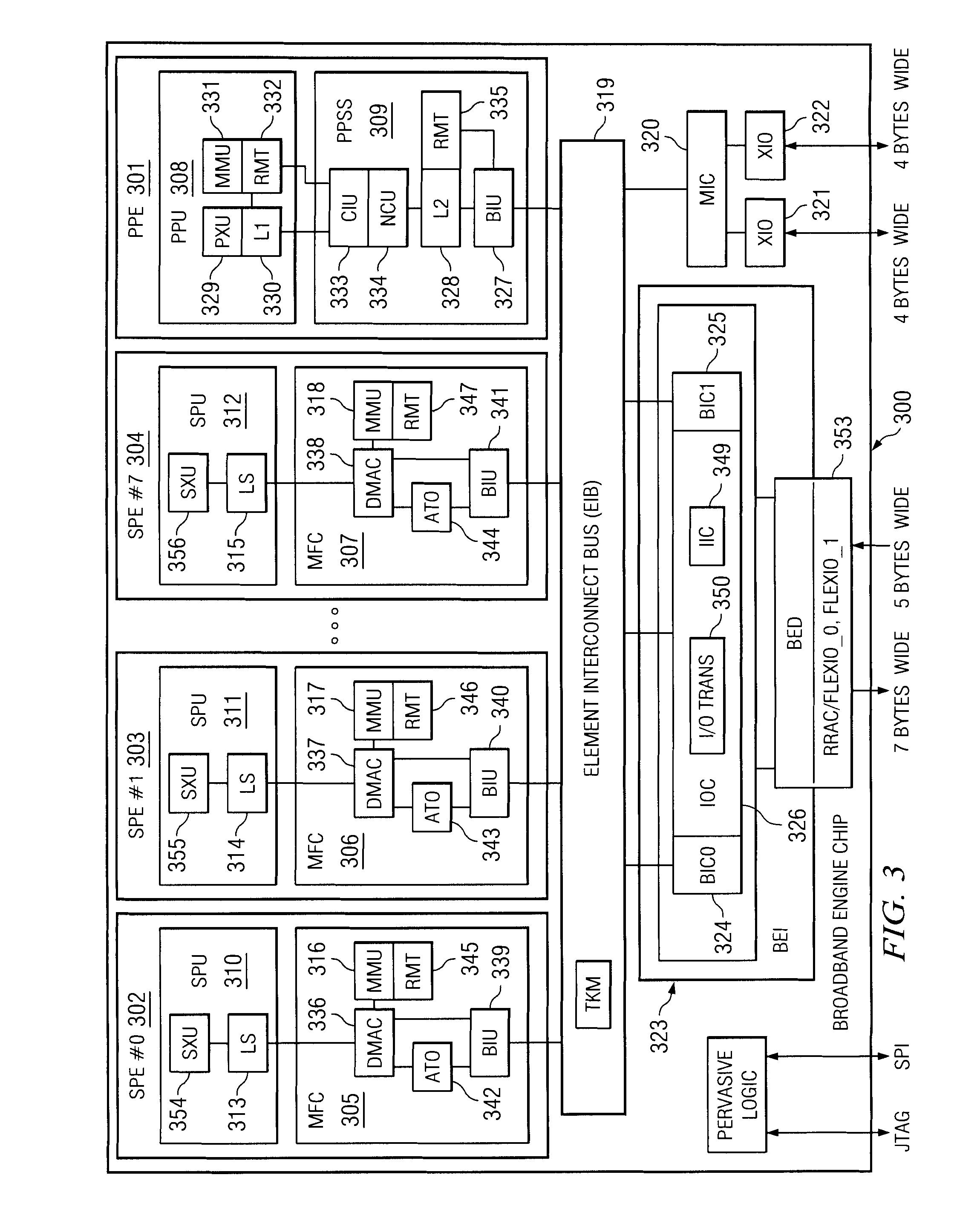

InactiveUS6966021B2Electronic circuit testingError detection/correctionMulti inputProcessor register

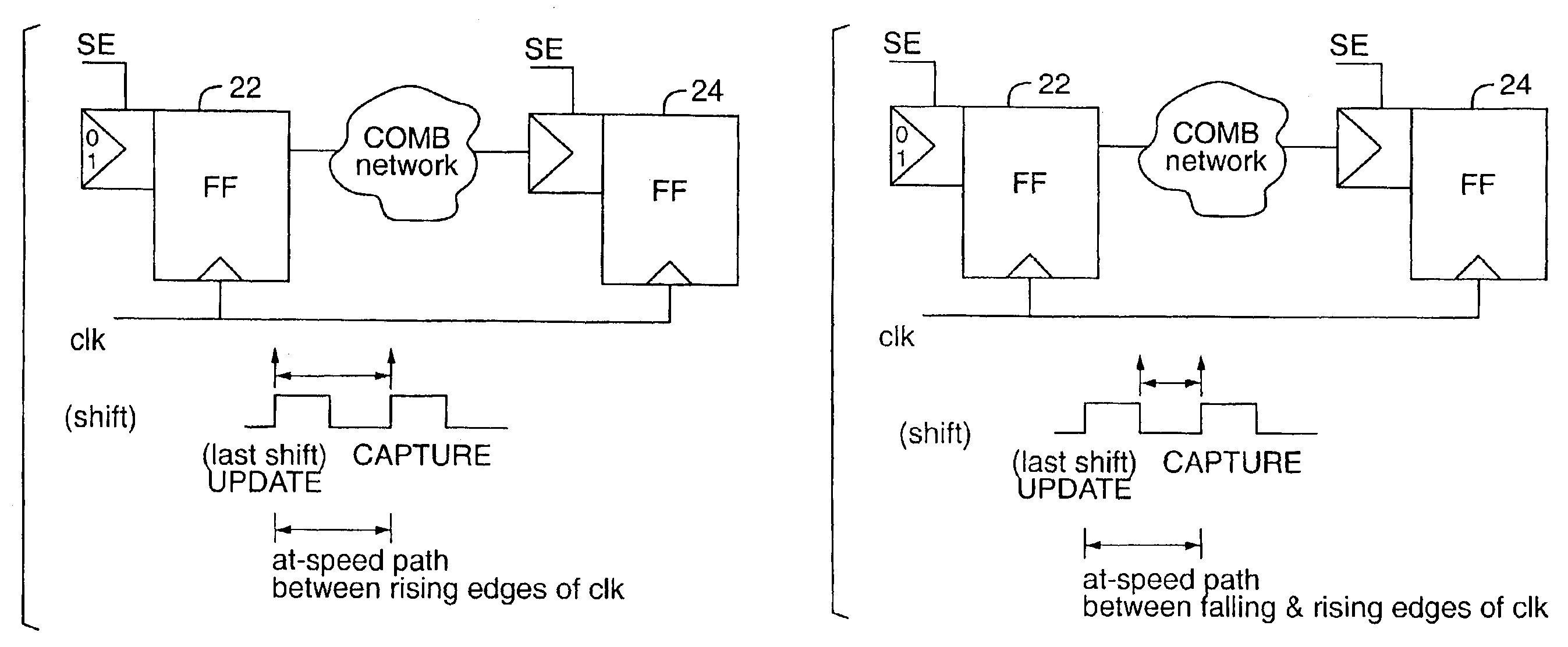

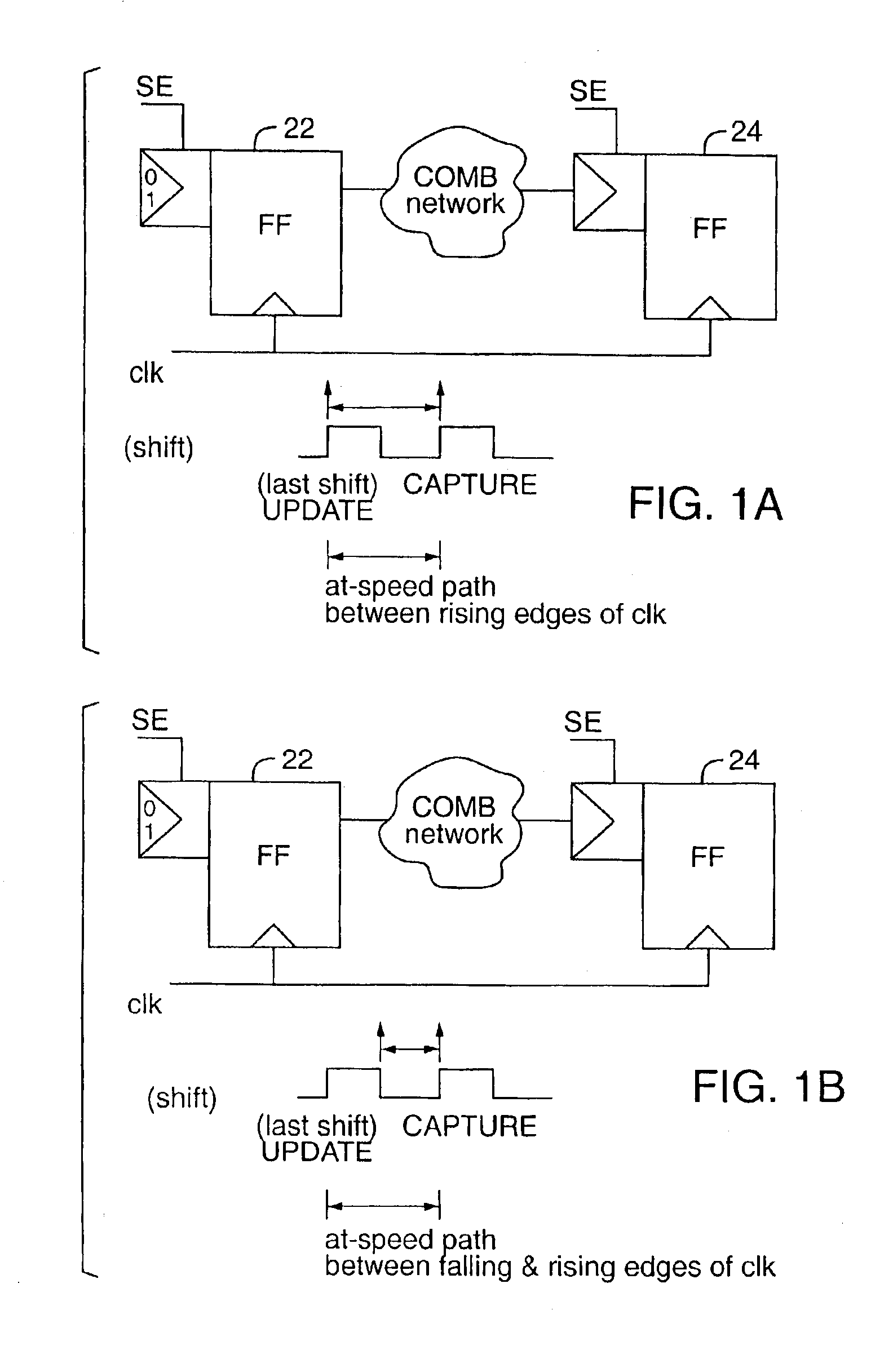

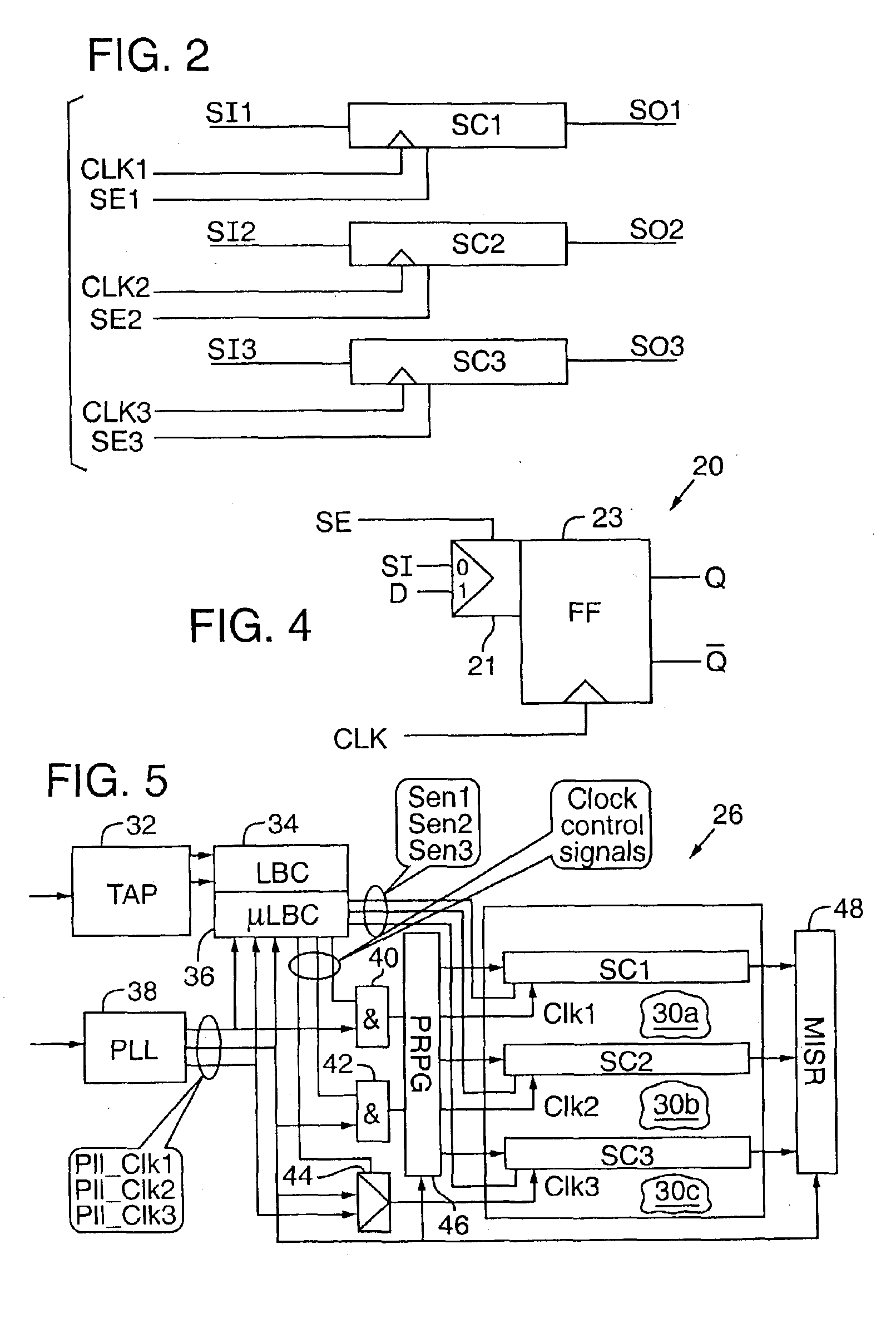

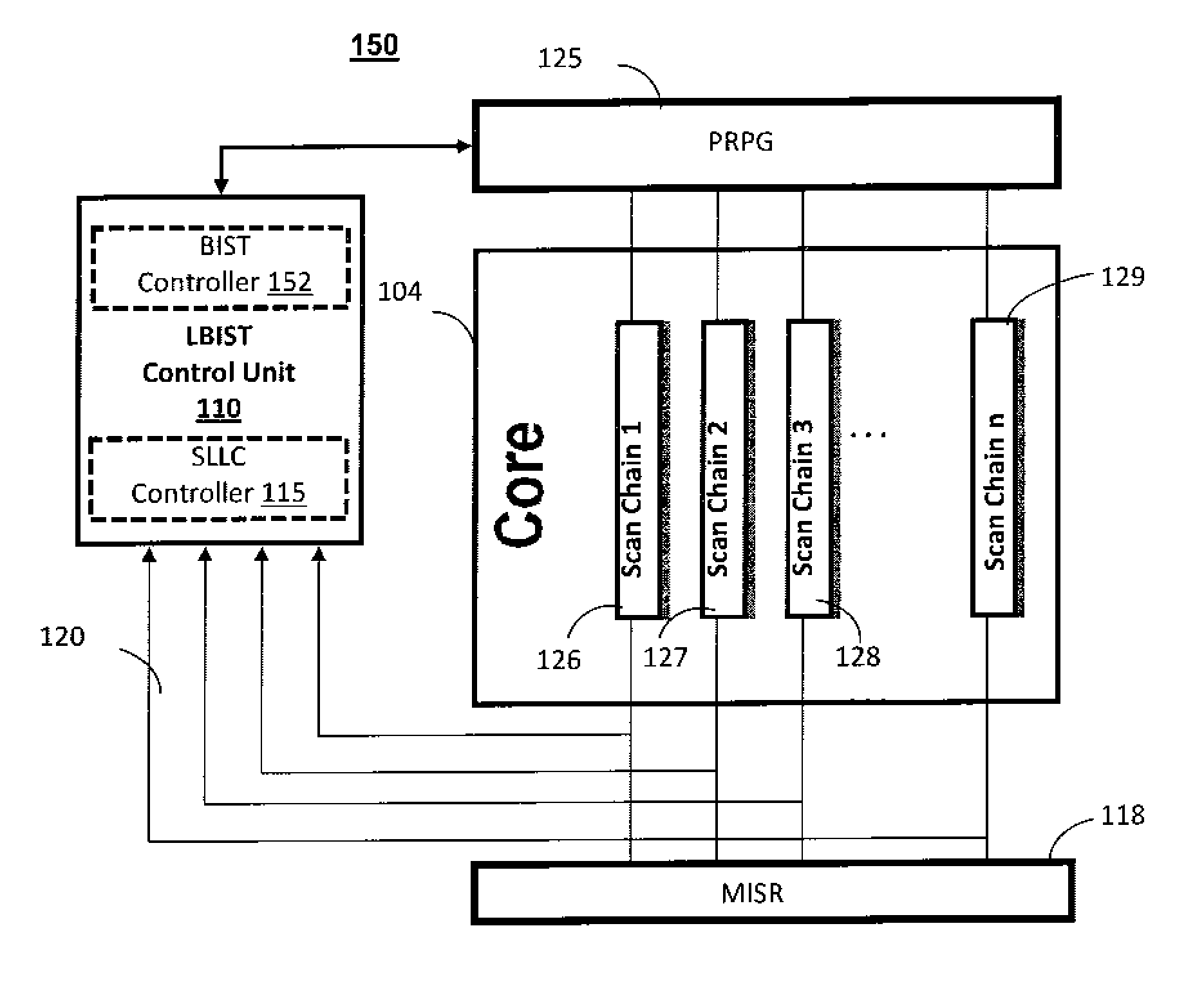

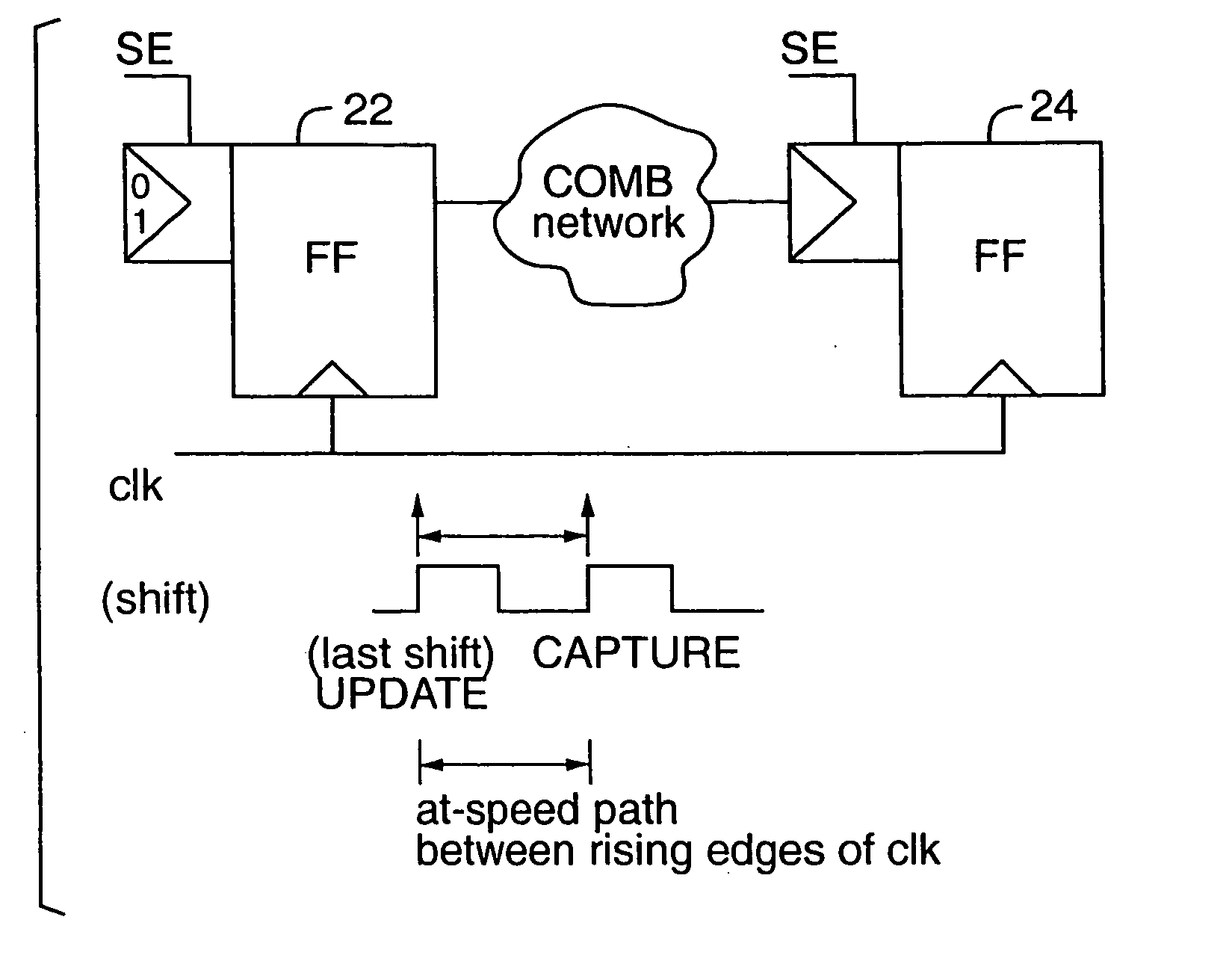

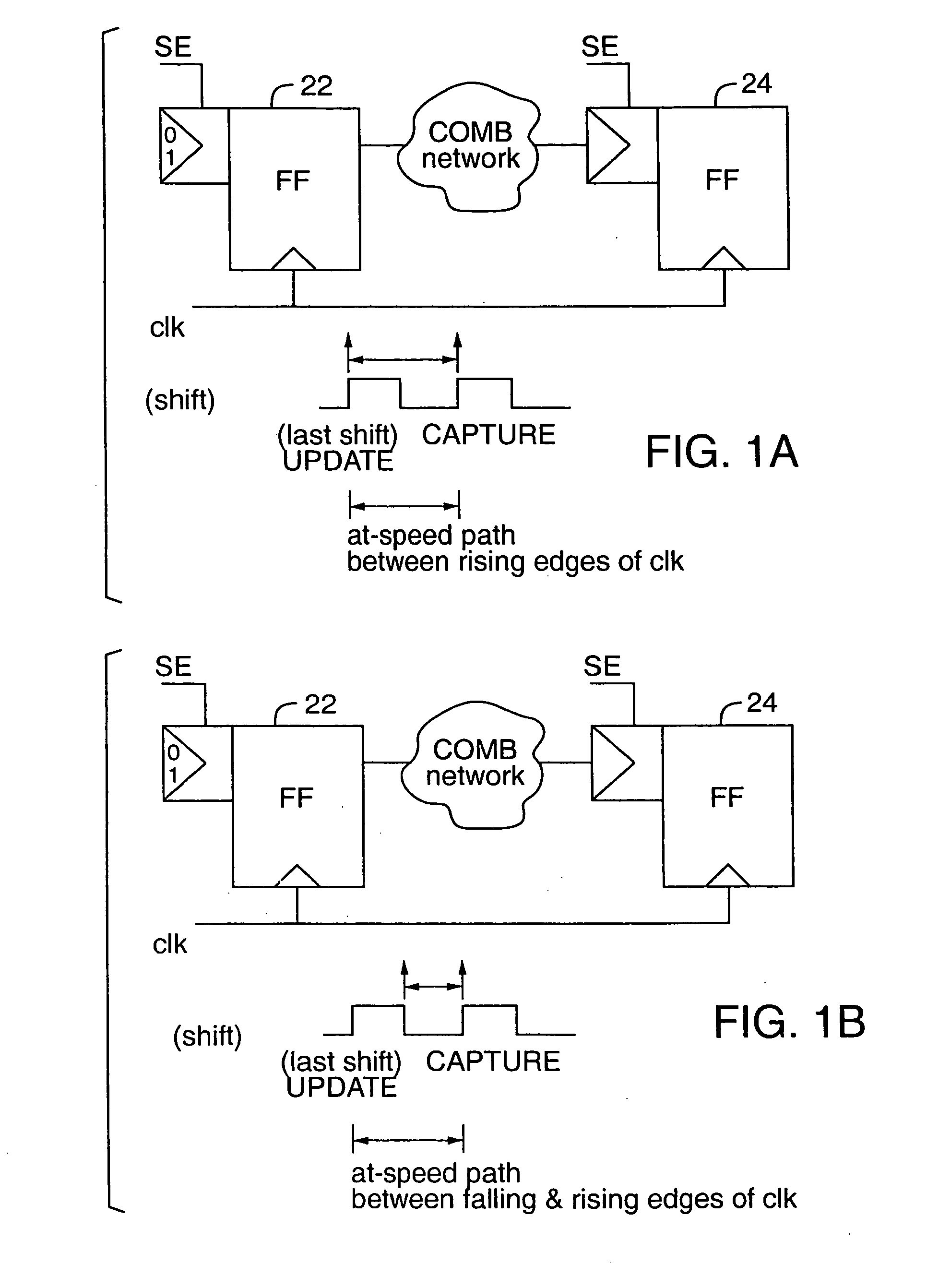

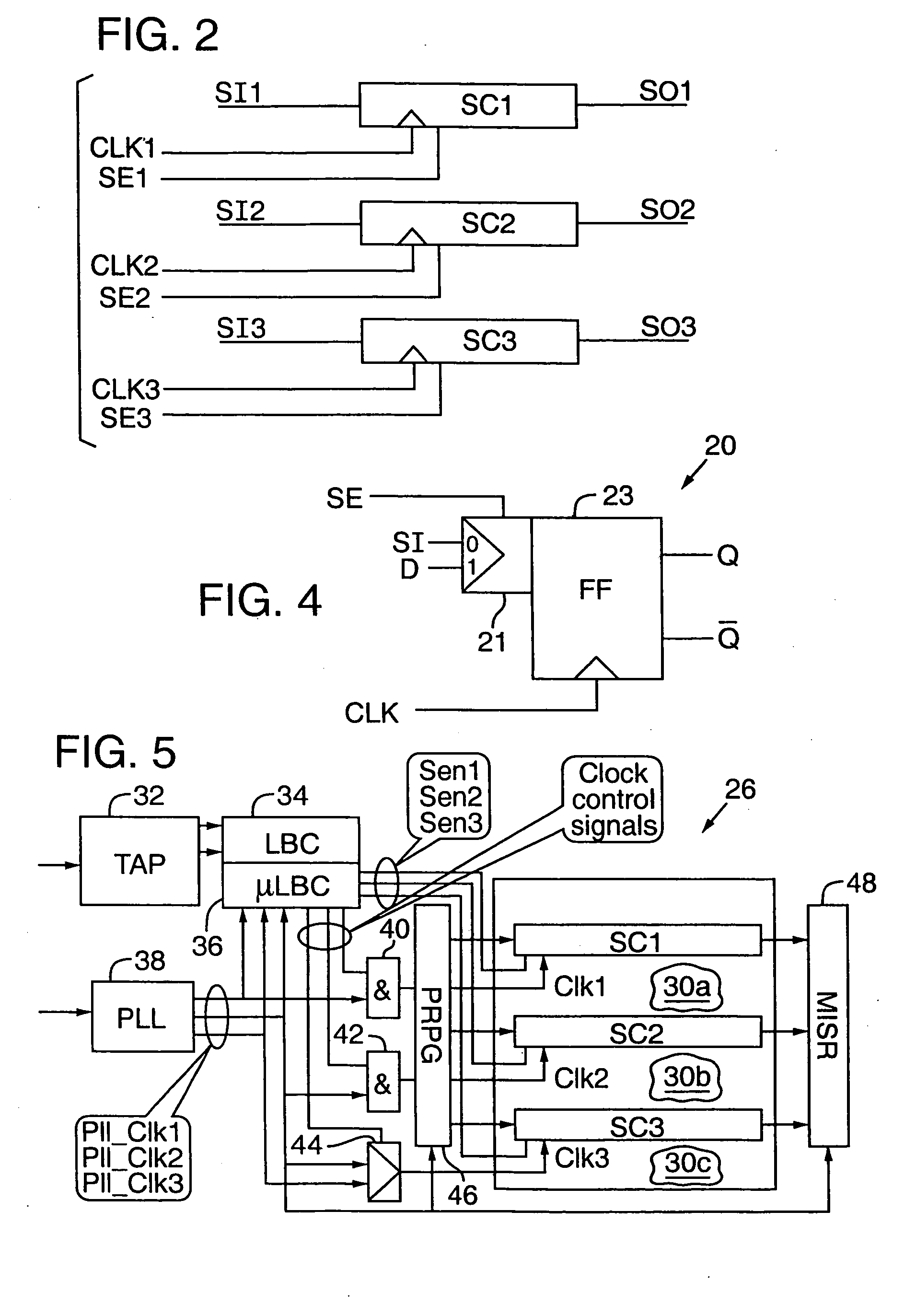

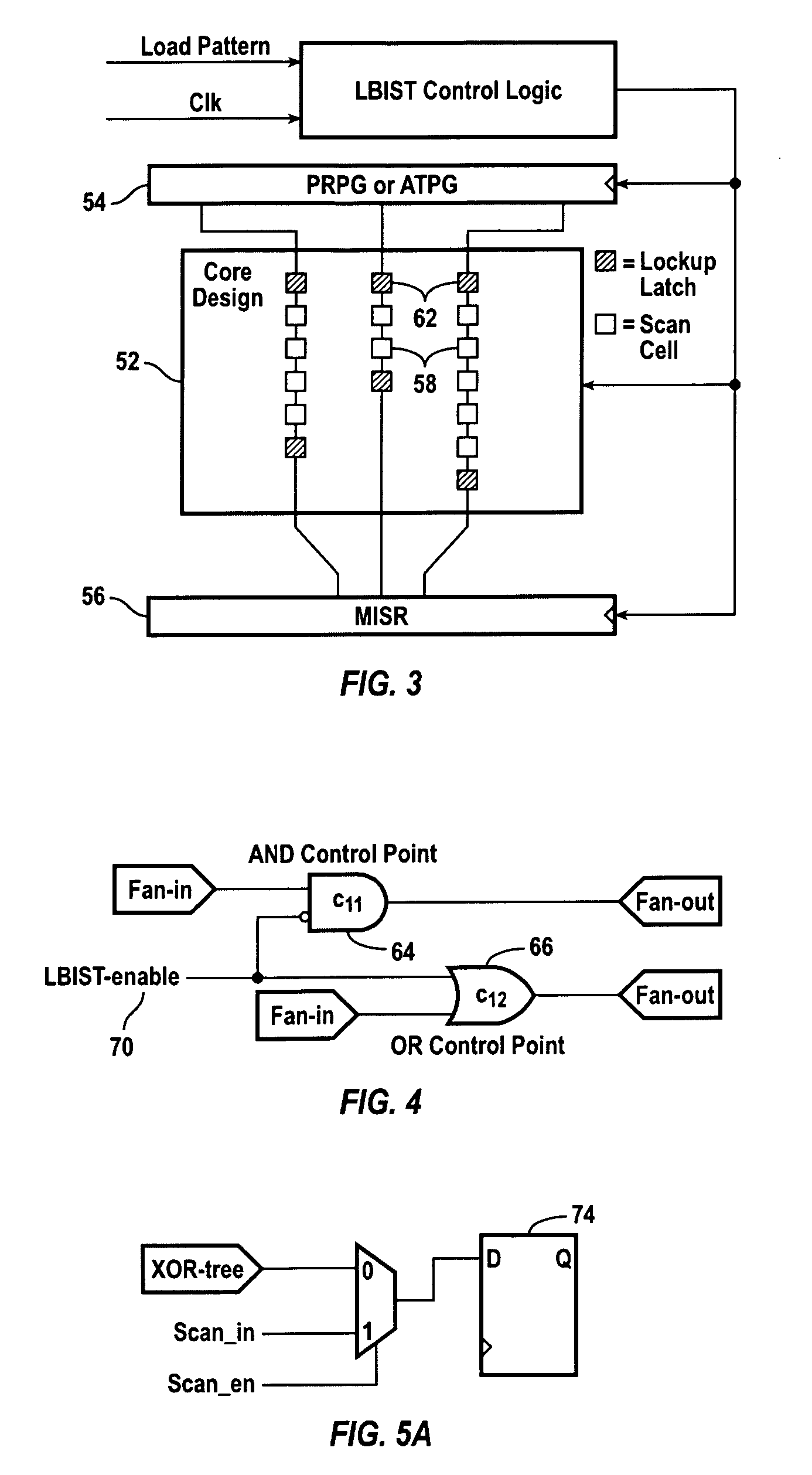

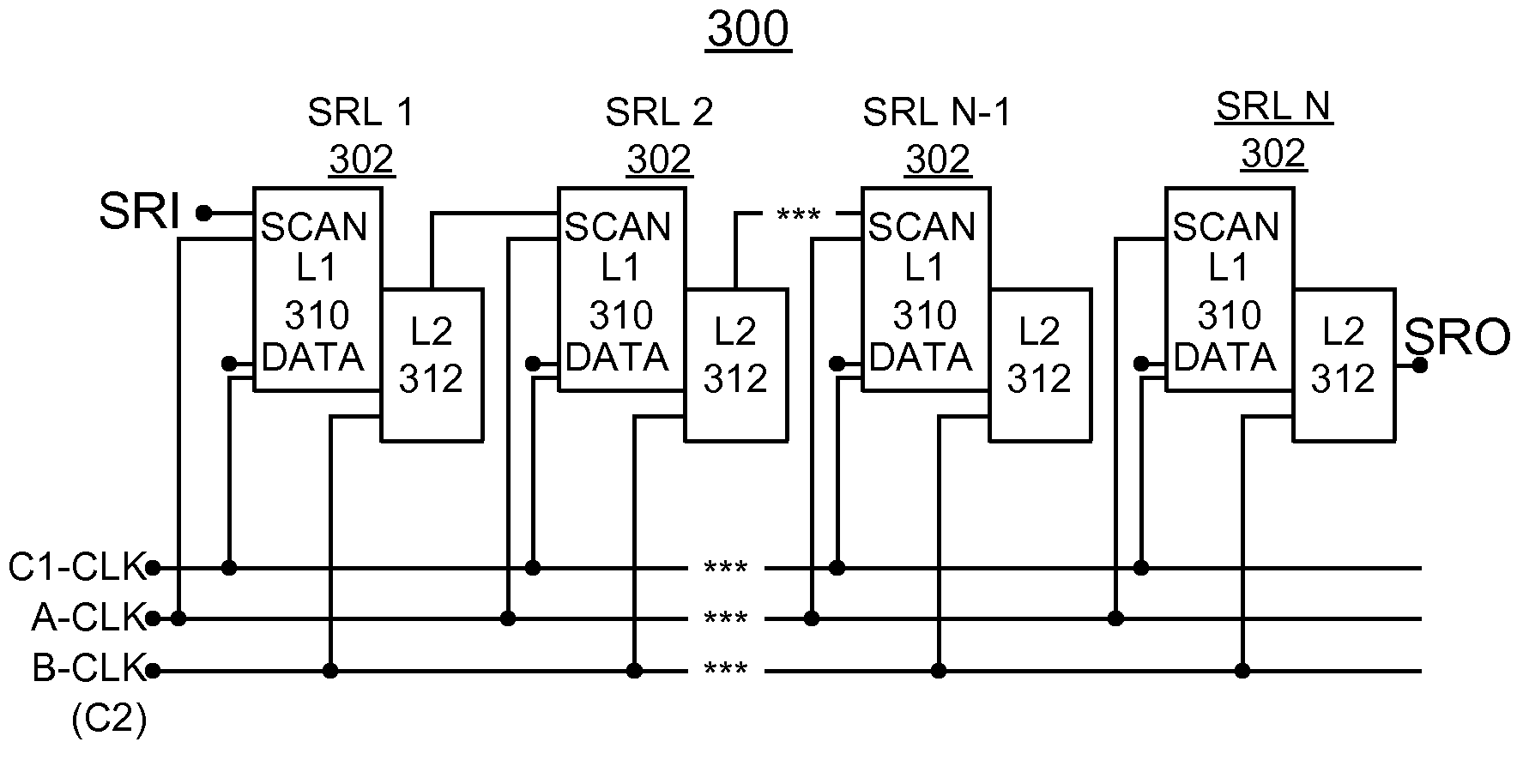

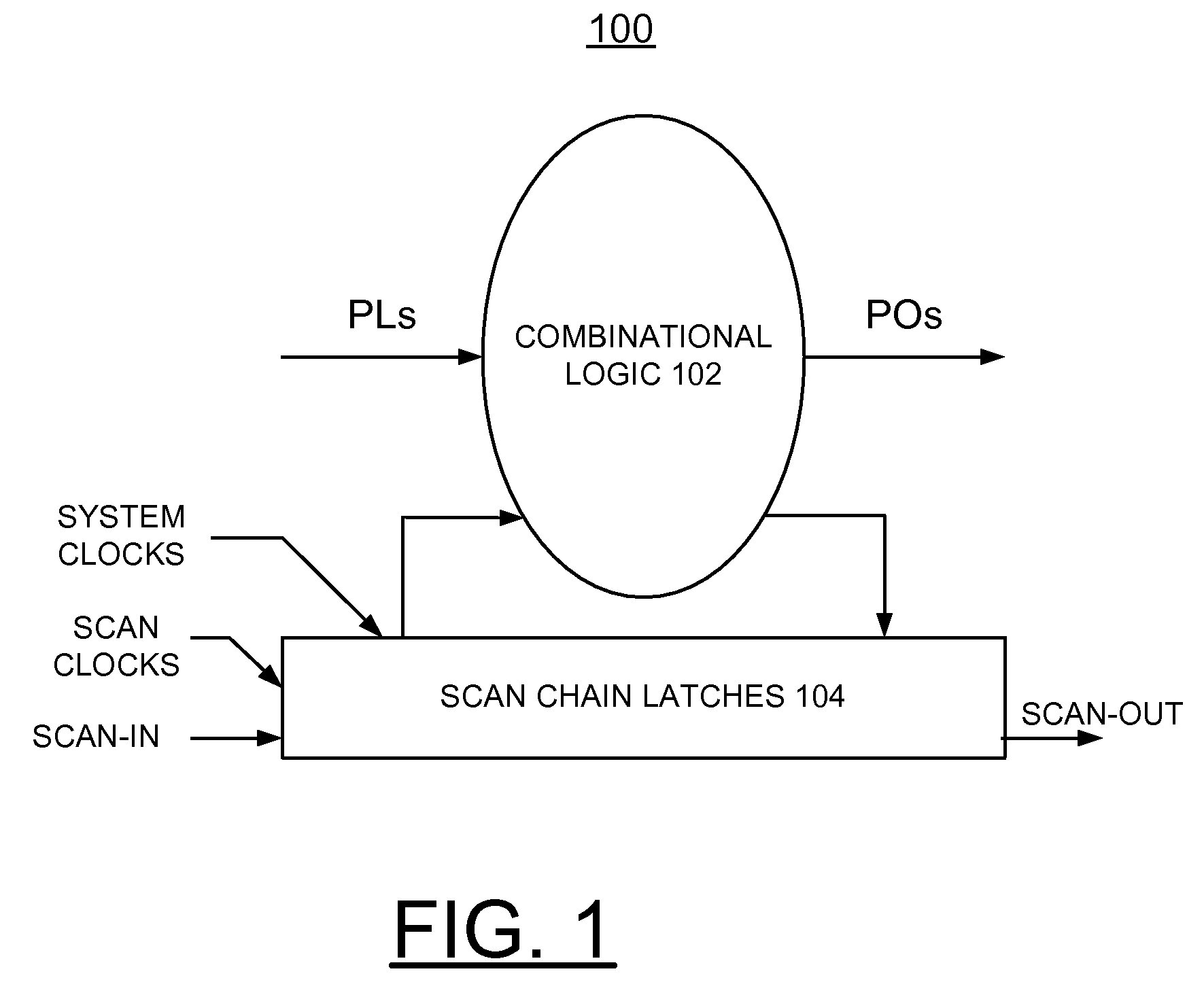

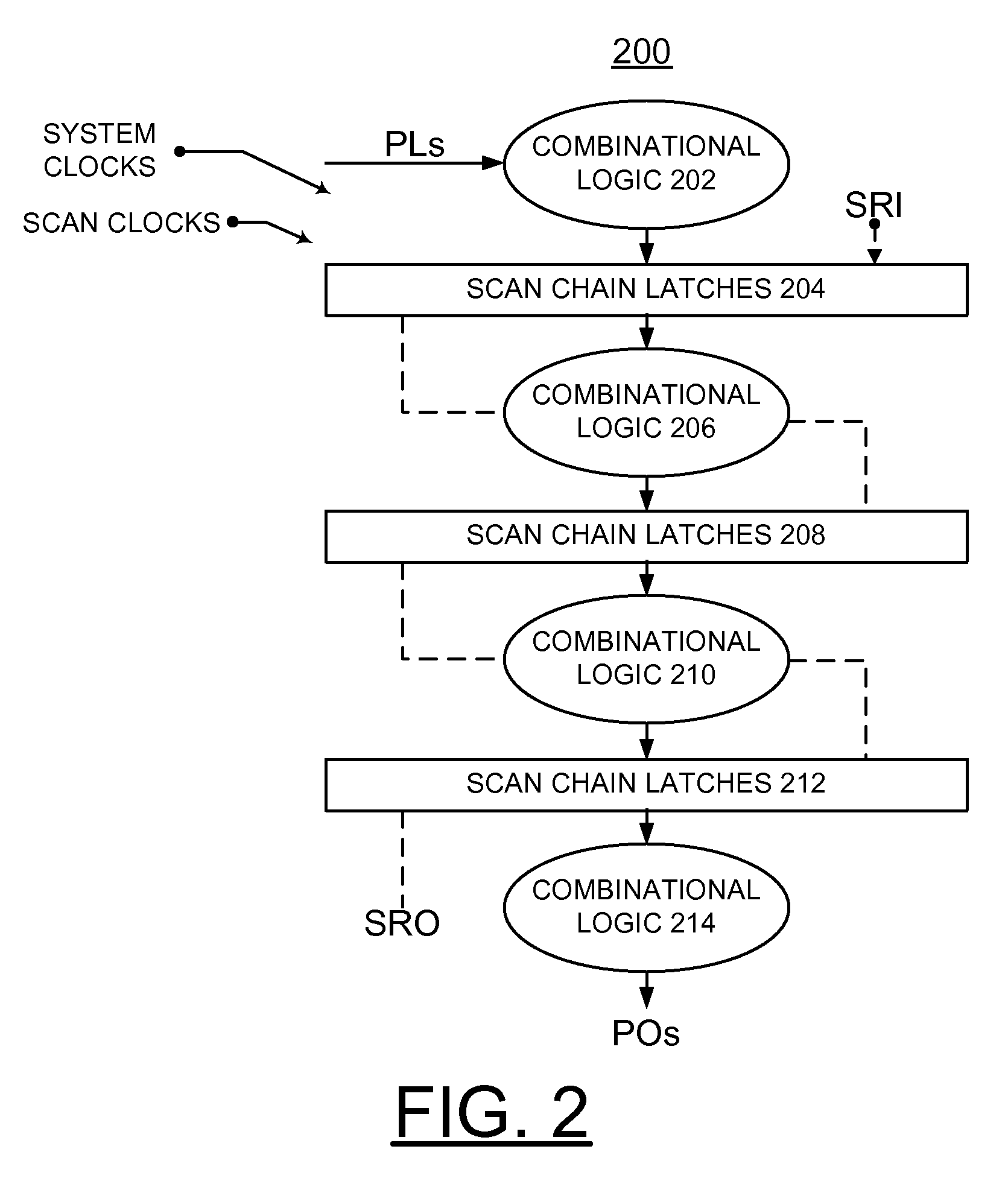

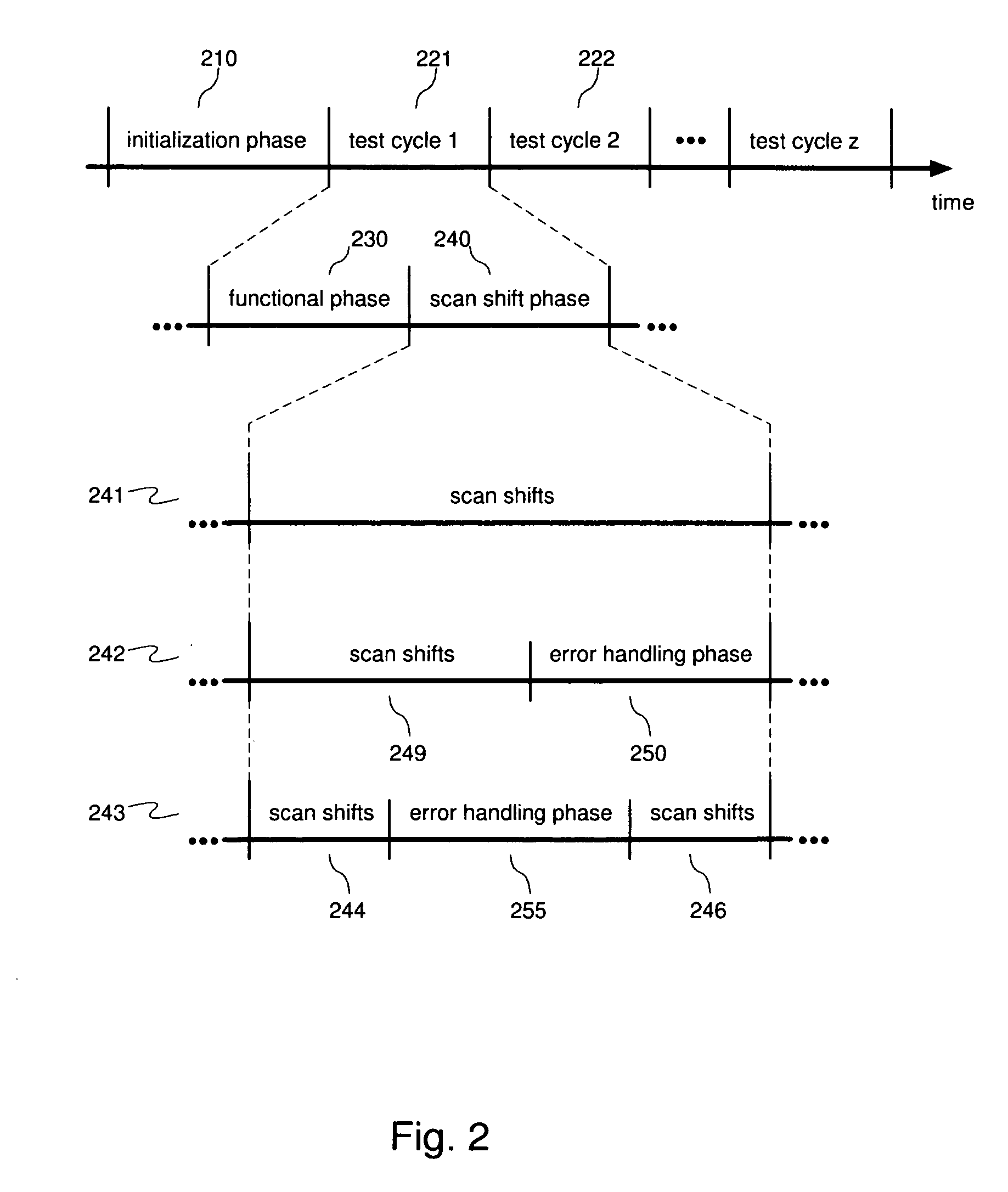

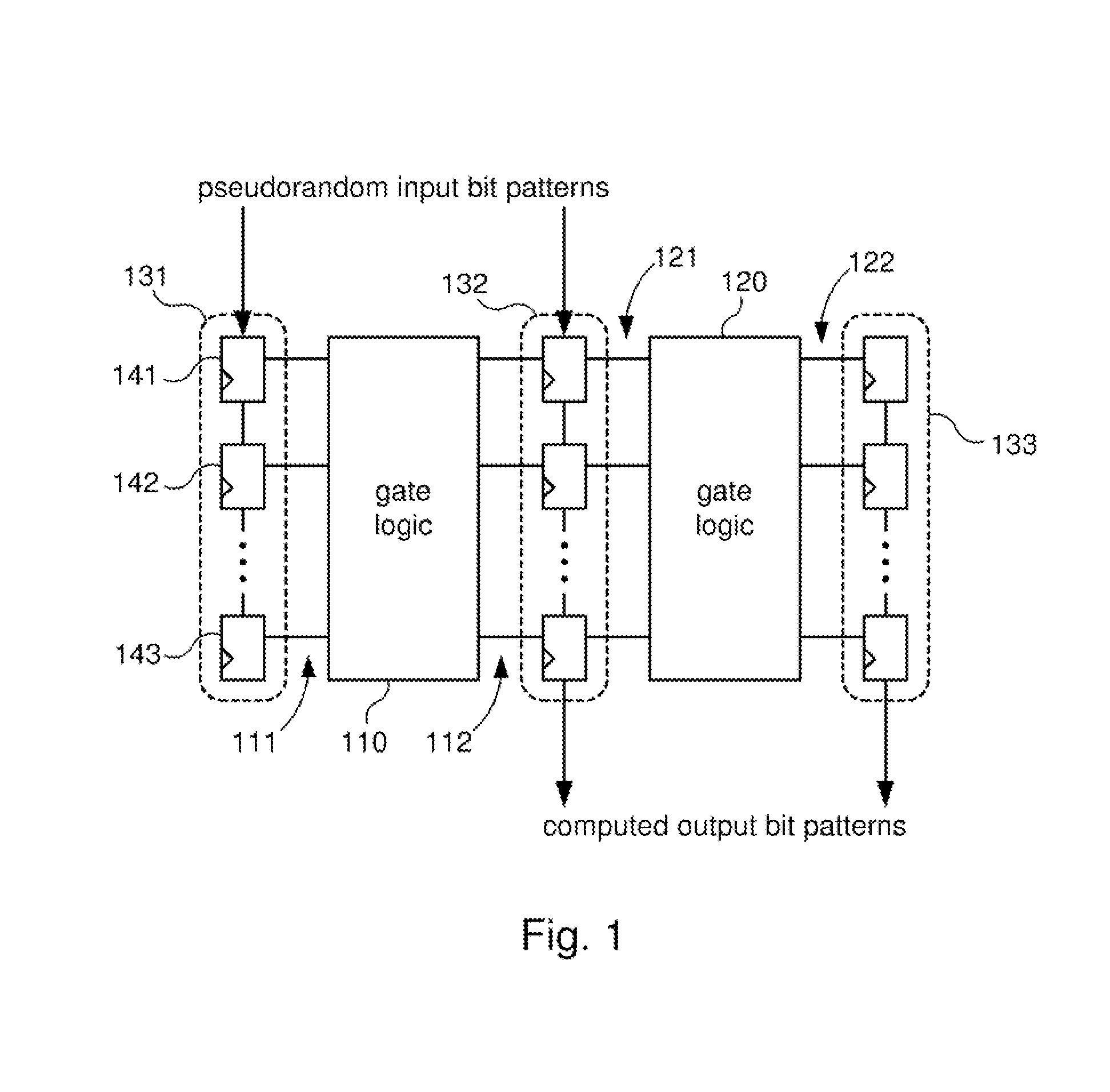

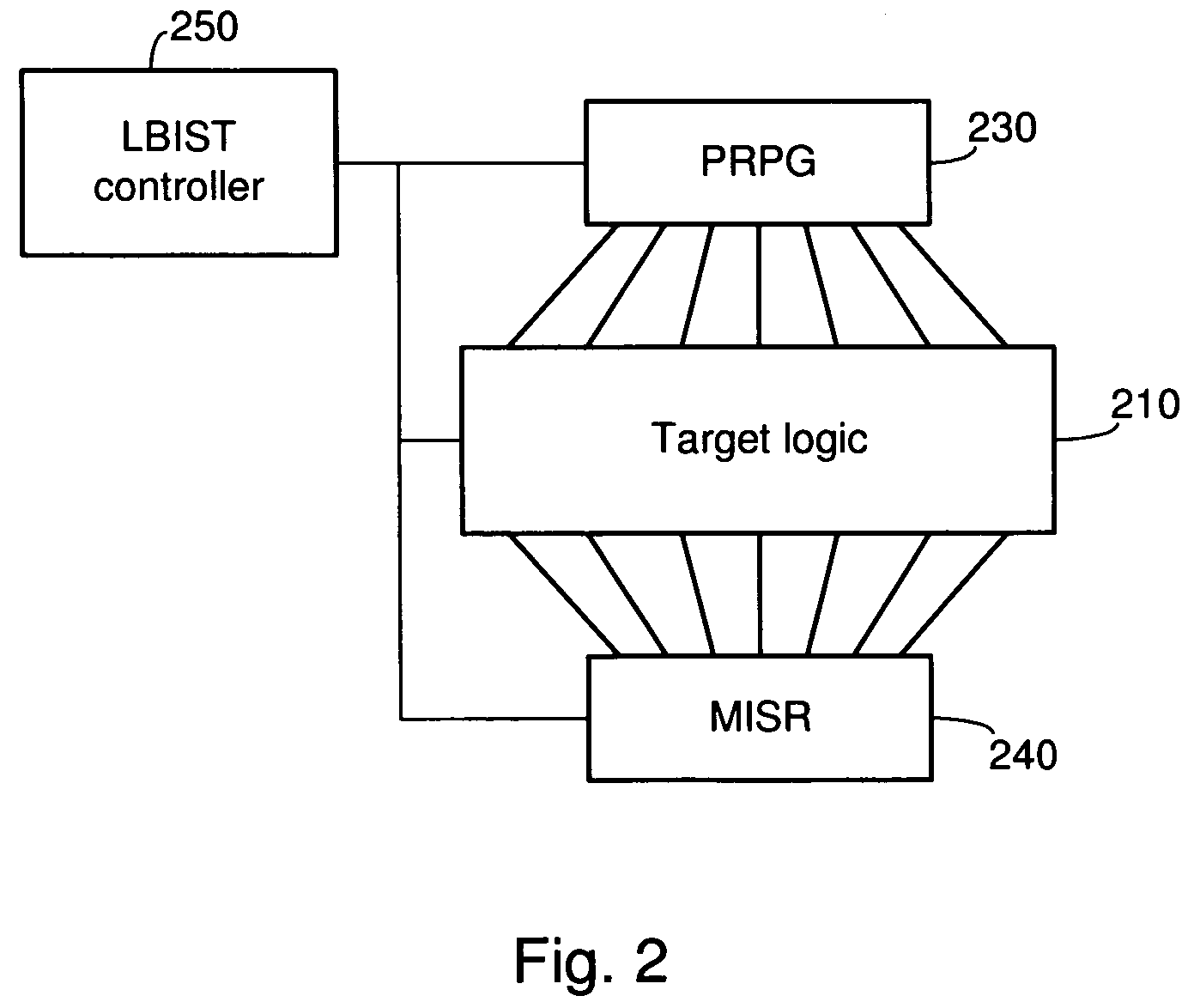

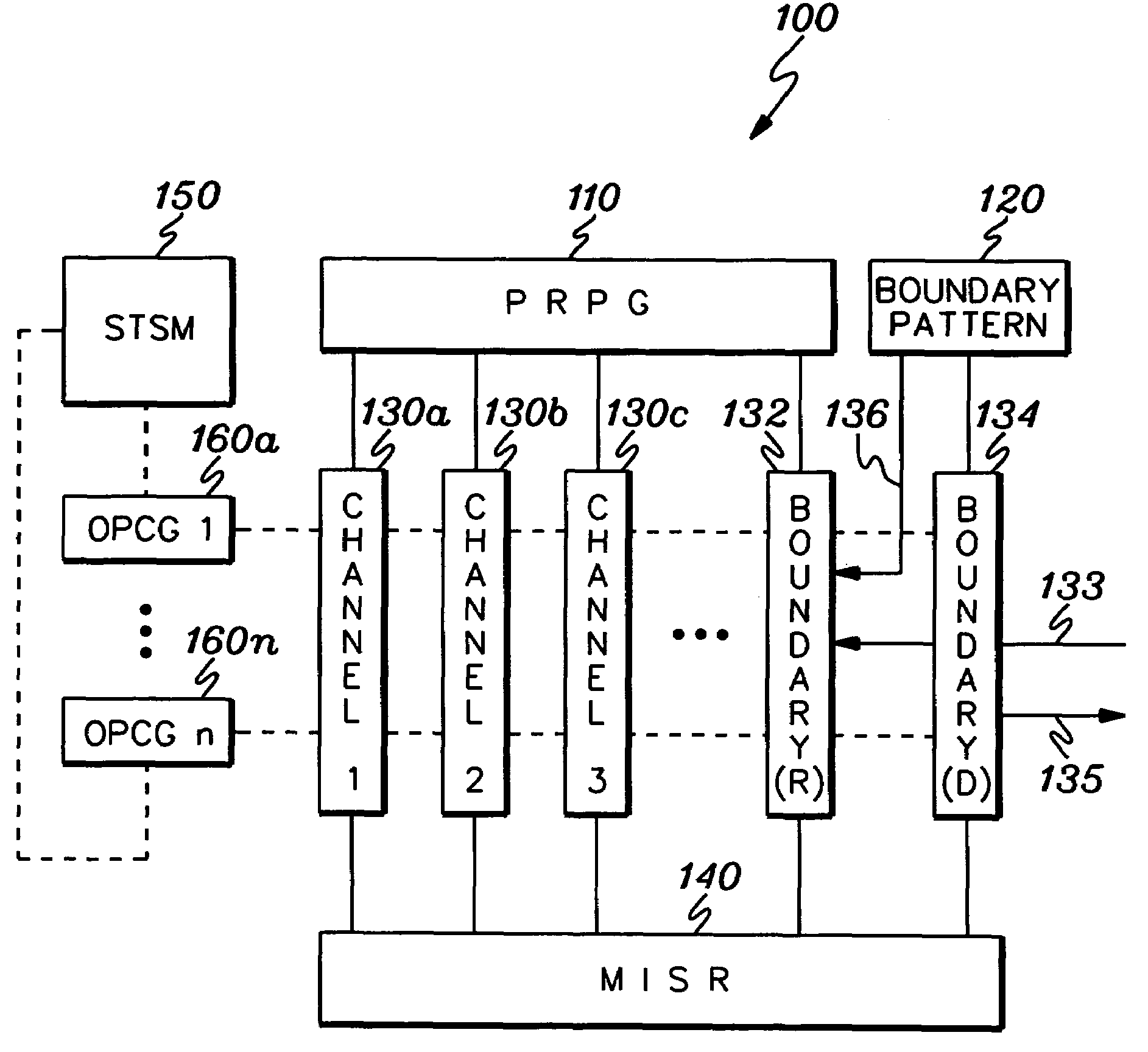

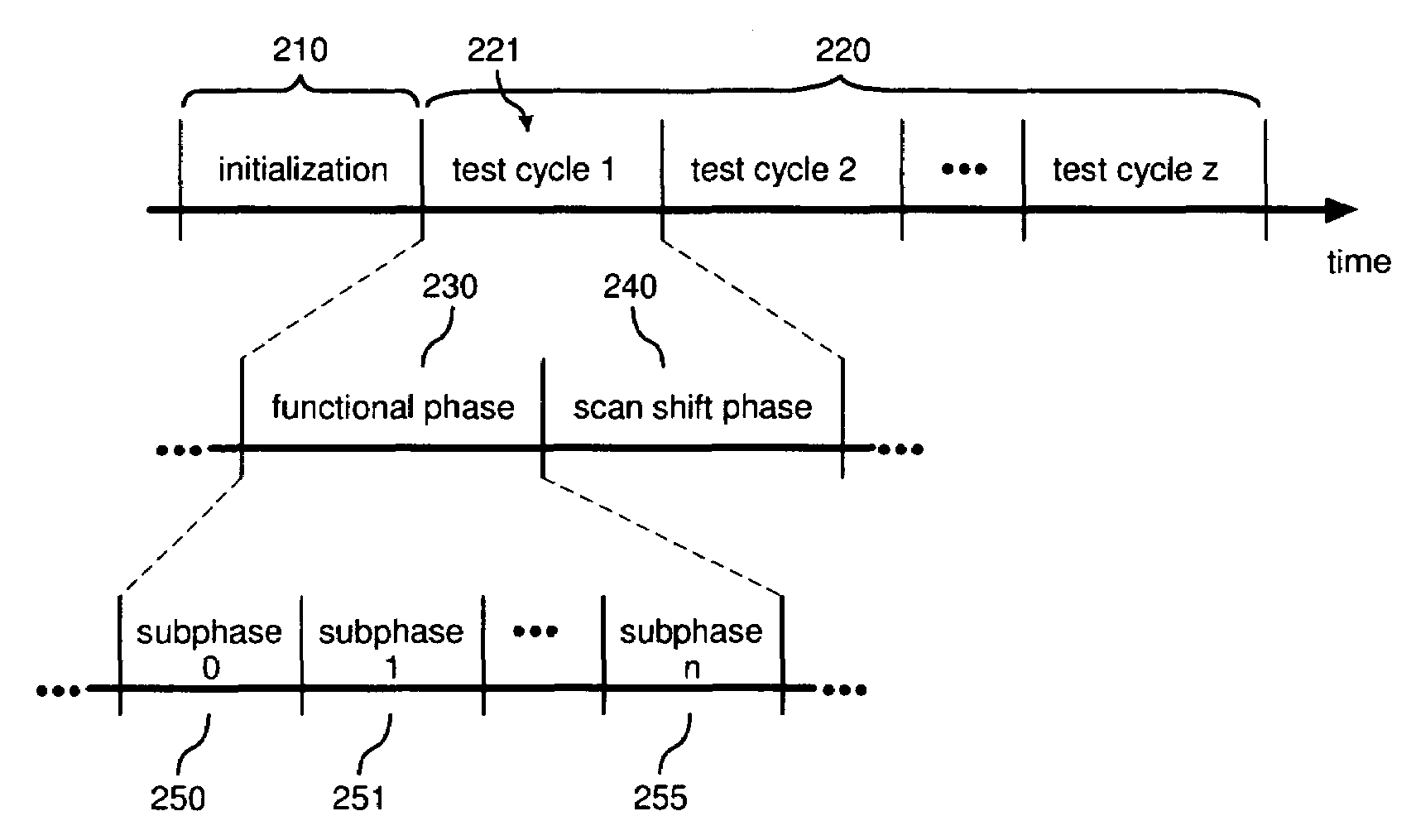

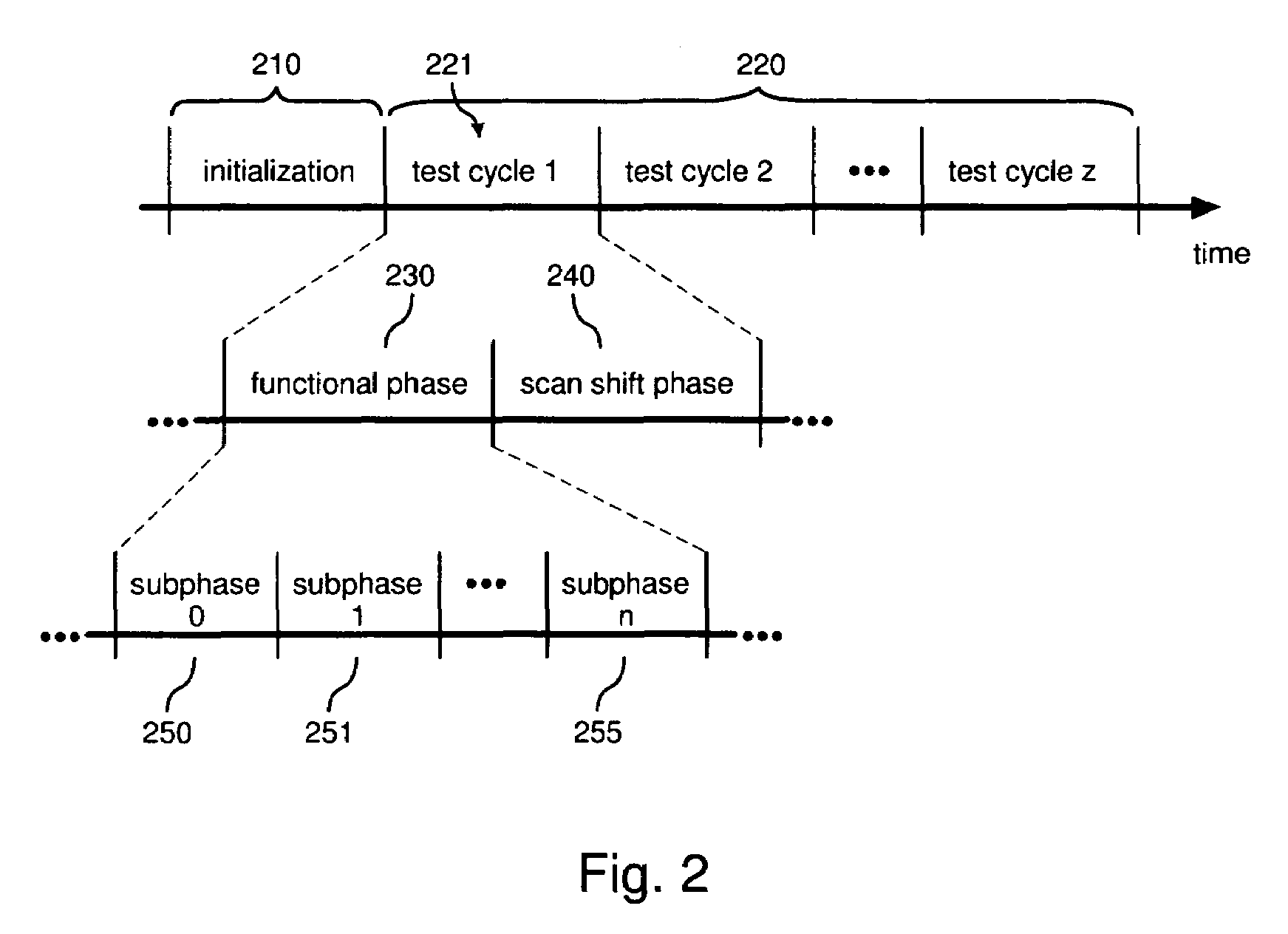

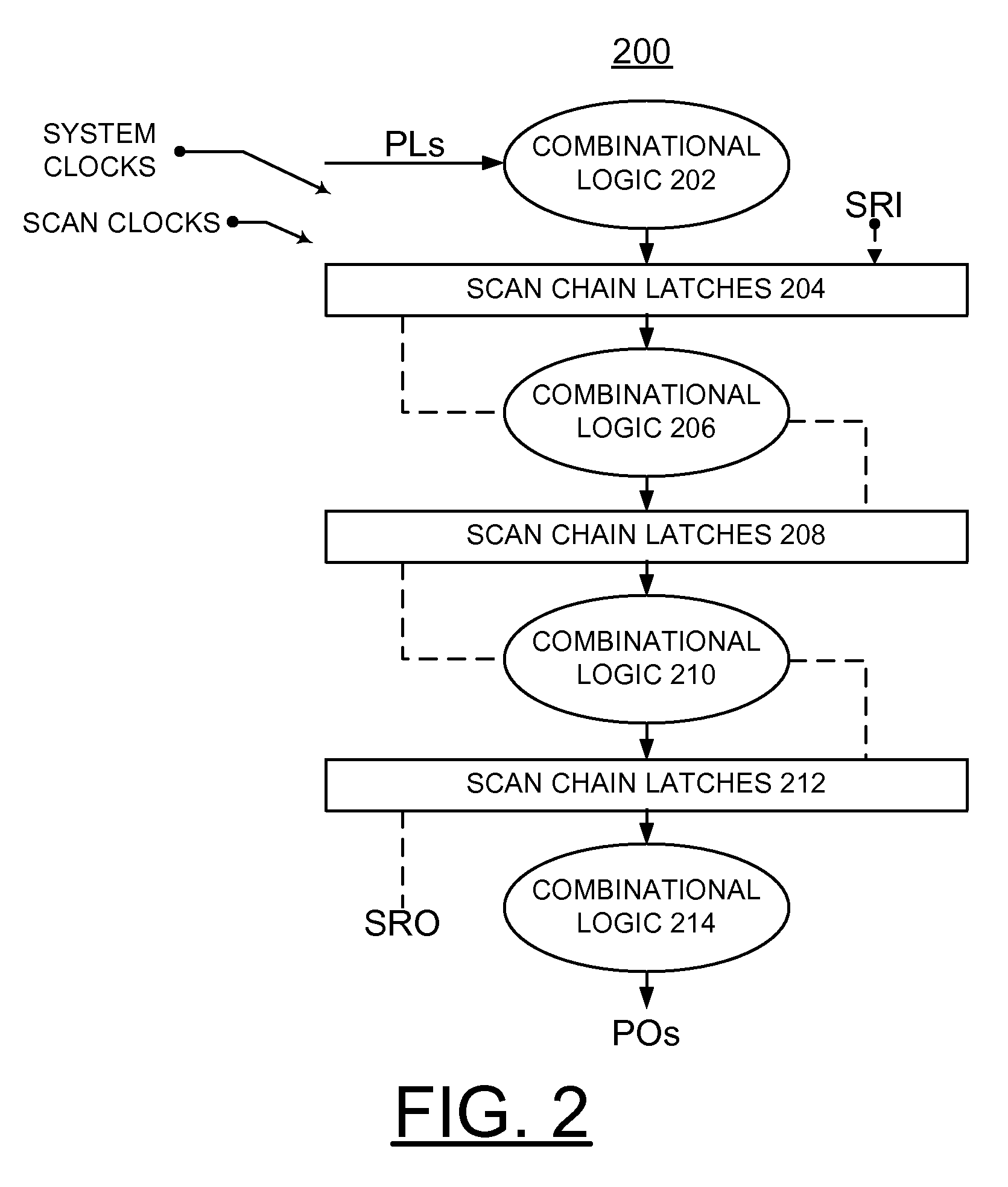

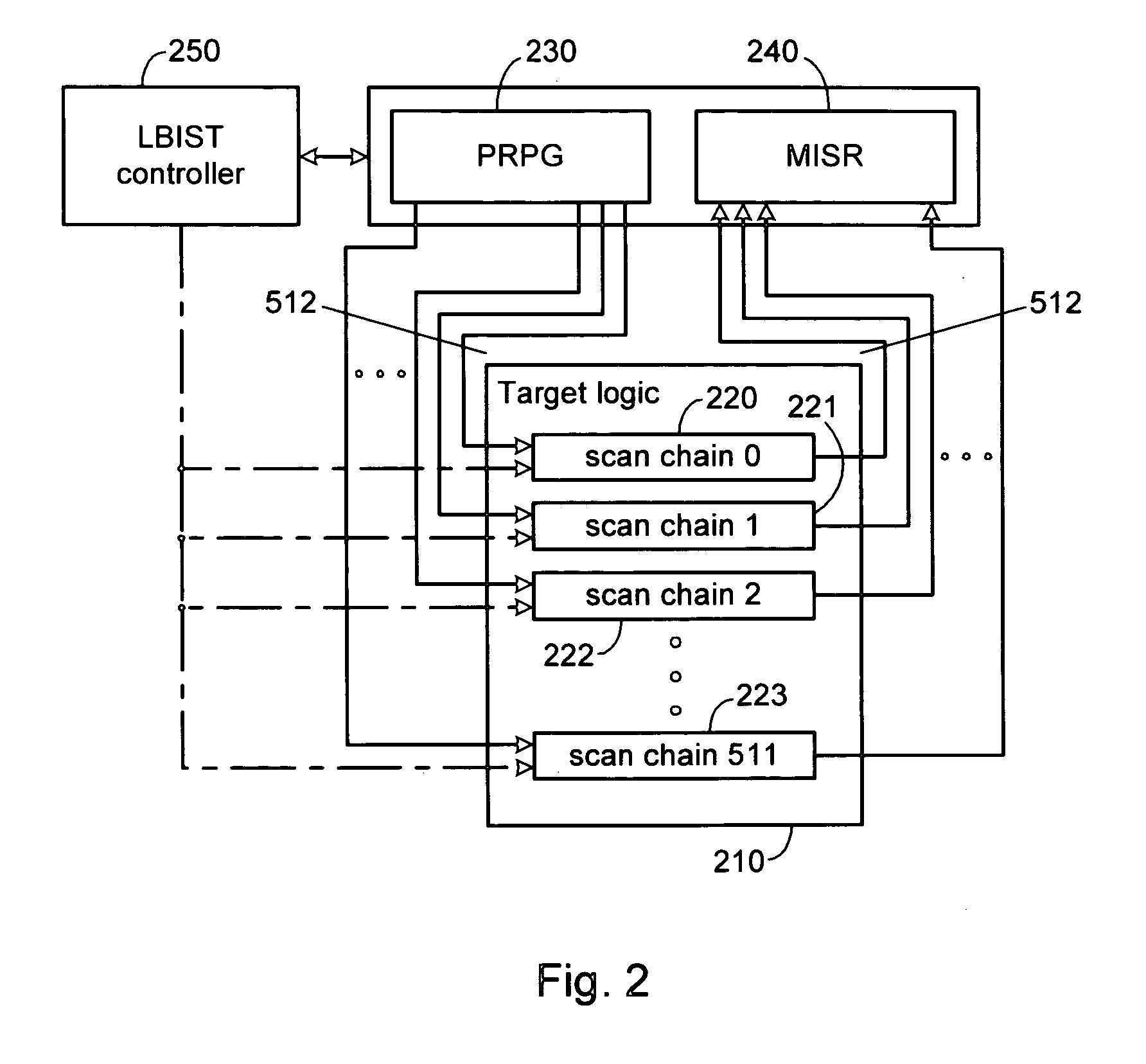

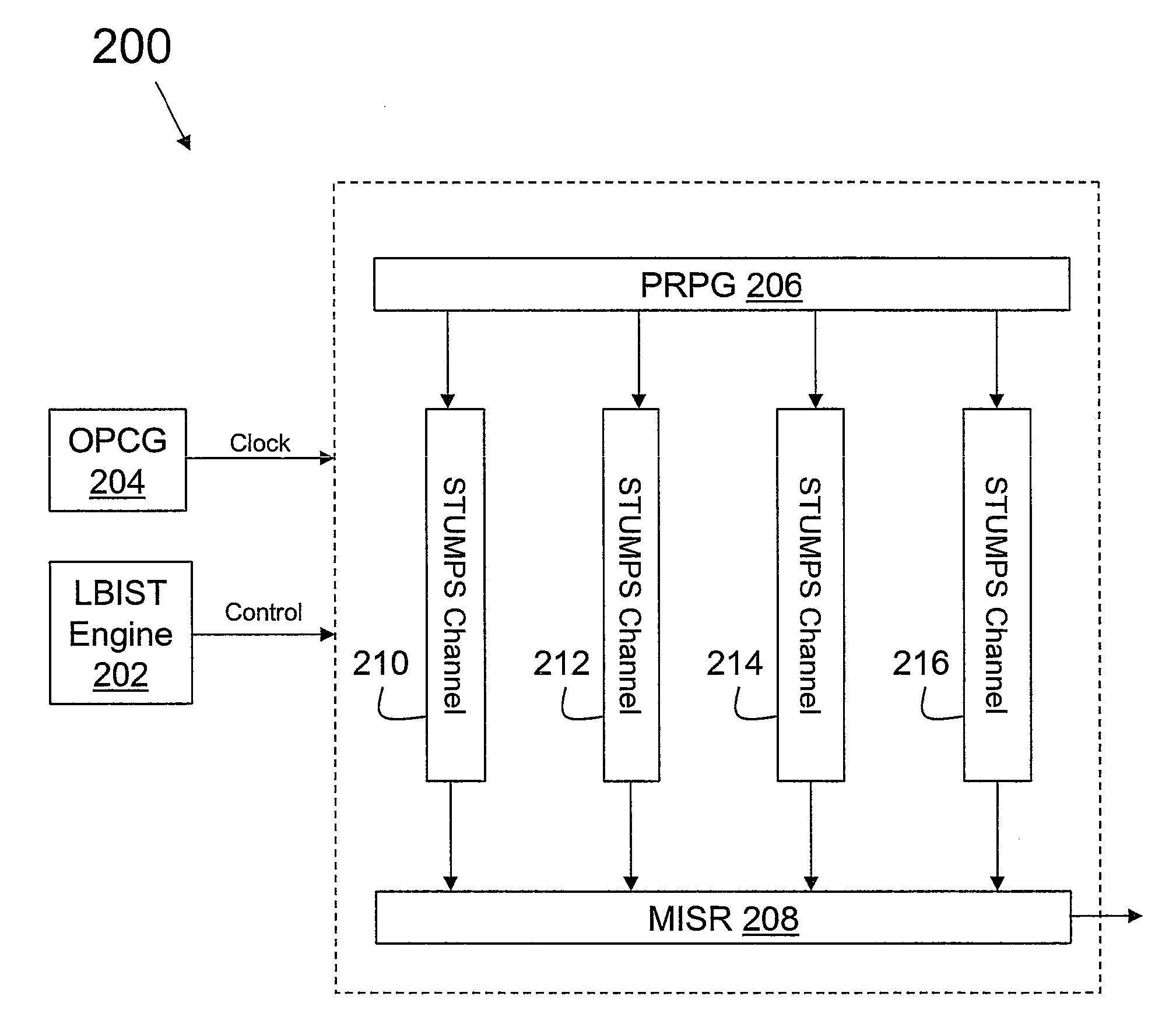

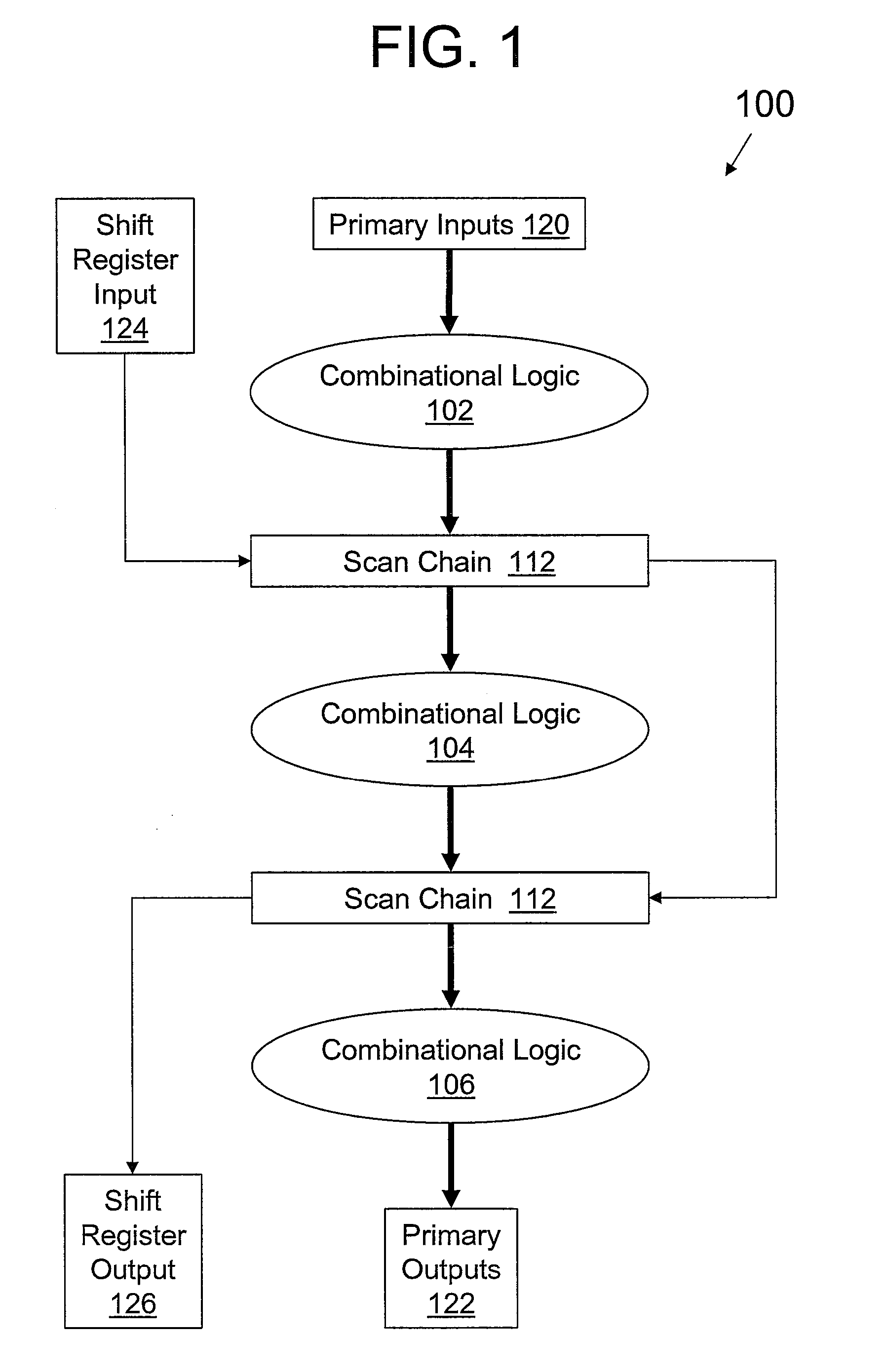

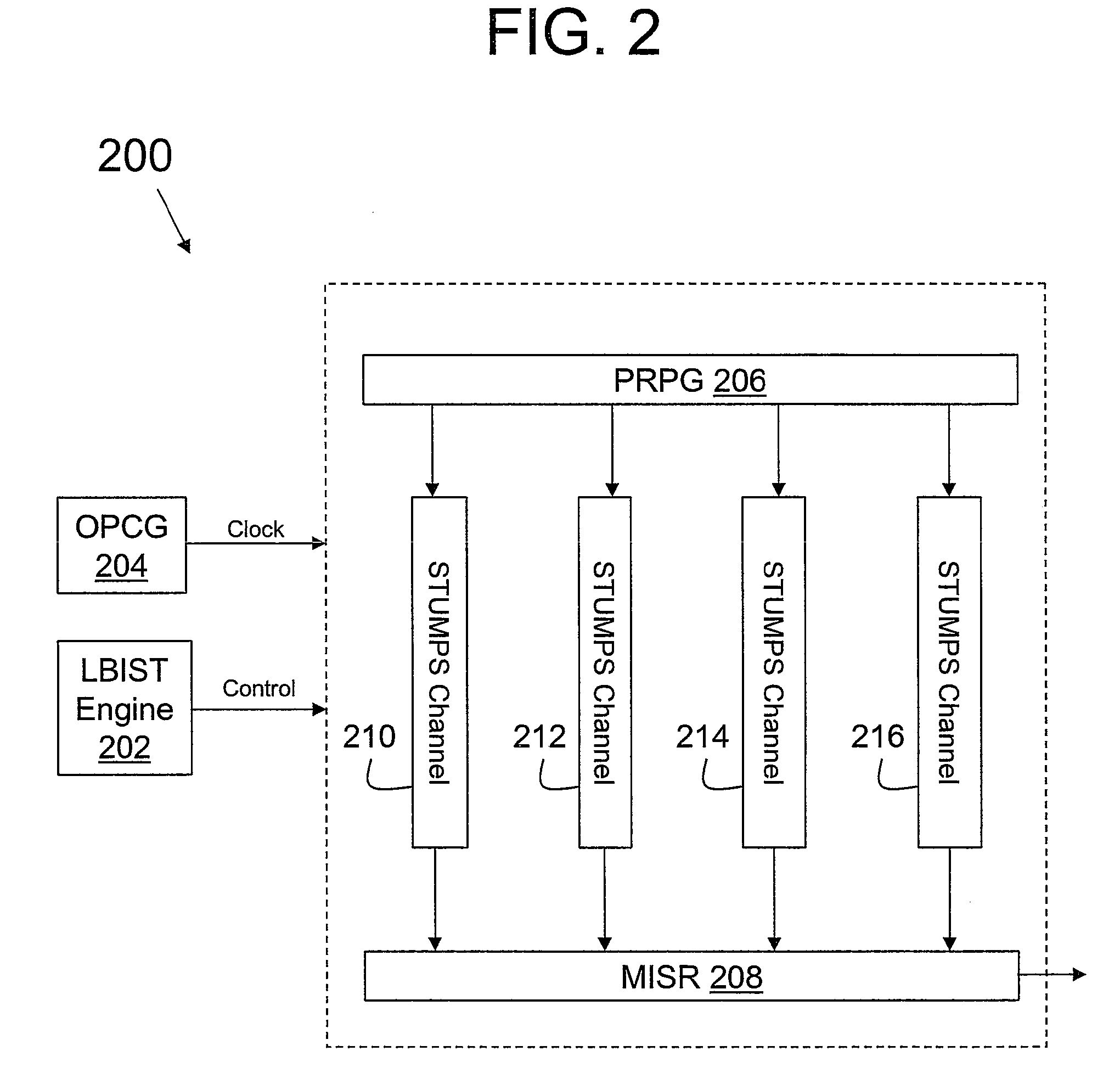

A scheme for multi-frequency at-speed logic Built-In Self Test (BIST) is provided. This scheme allows at-speed testing of very high frequency integrated circuits controlled by a clock signal generated externally or on-chip. The scheme is also applicable to testing of circuits with multiple clock domains which can be either the same frequency or different frequency. Scanable memory elements of the digital circuit are connected to define plurality of scan chains. The loading and unloading of scan chains is separated from the at-speed testing of the logic between the respective domains and may be done at a faster or slower frequency than the at-speed testing. The BIST controller, Pseudo-Random Pattern Generator (PRPG) and Multi-input Signature Register (MISR) work at slower frequency than the fastest clock domain. After loading of a new test pattern, a clock suppression circuit allows a scan enable signal to propagate for more that one clock cycle before multiple capture clock is applied. This feature relaxes the speed and skew constraints on scan enable signal design. Only the capture cycle is performed at the corresponding system timing. A programmable capture window makes it possible to test every intra- and inter-domain at-speed without the negative impact of clock skew between clock domains.

Owner:MENTOR GRAPHICS CORP

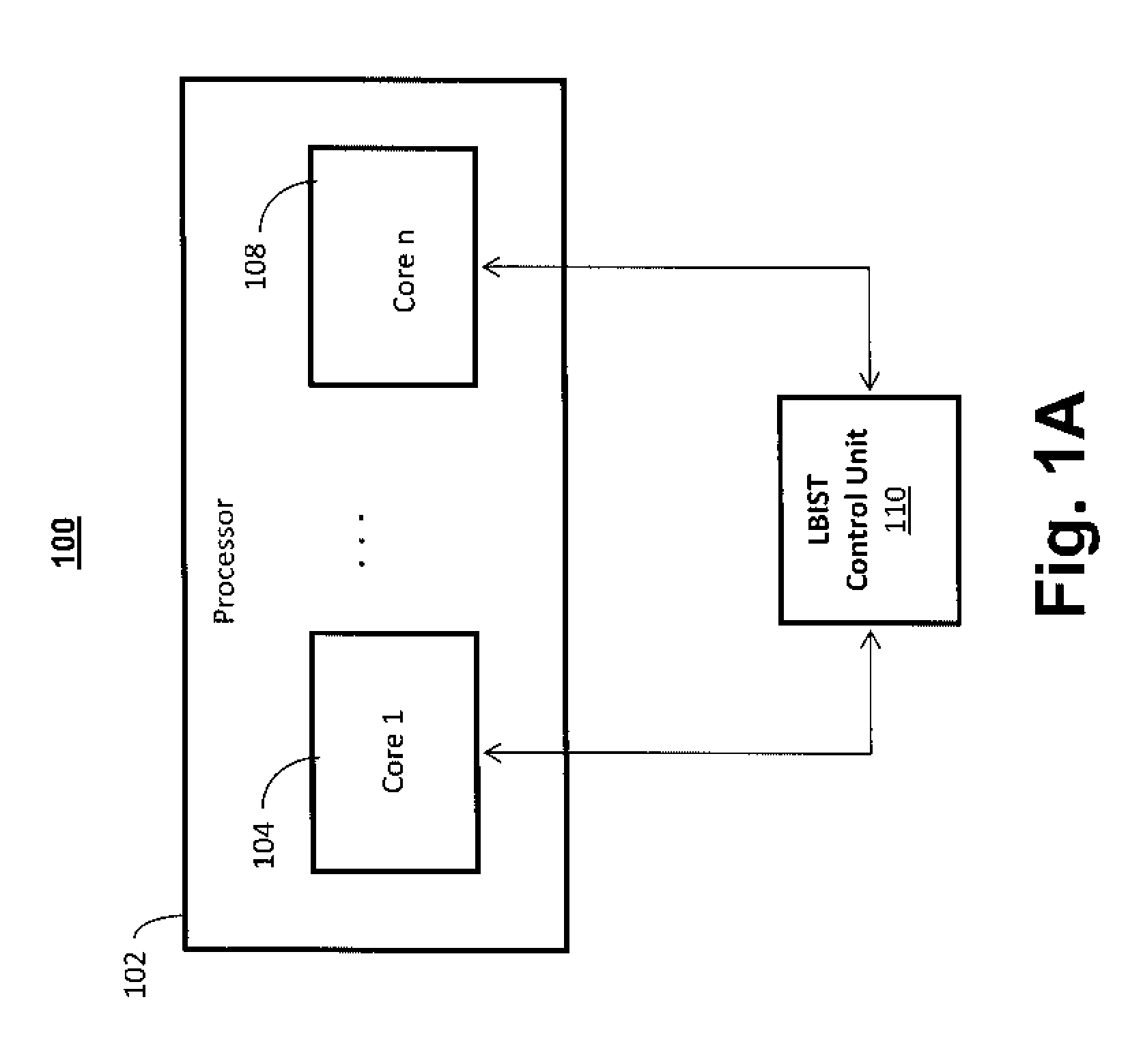

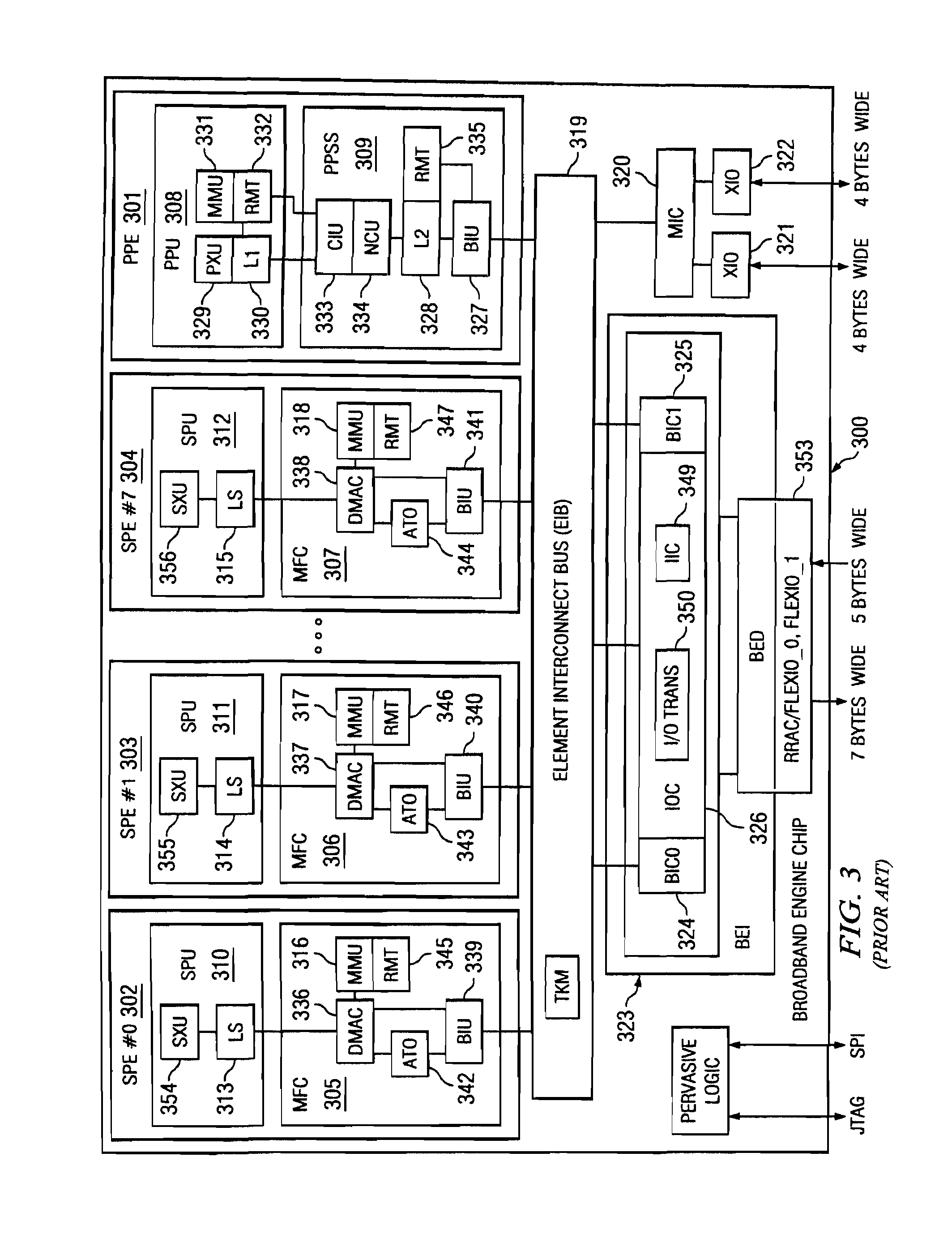

Method and apparatus for testing multi-core microprocessors

InactiveUS20070260823A1Electronic circuit testingError detection/correctionData processing systemMulti processor

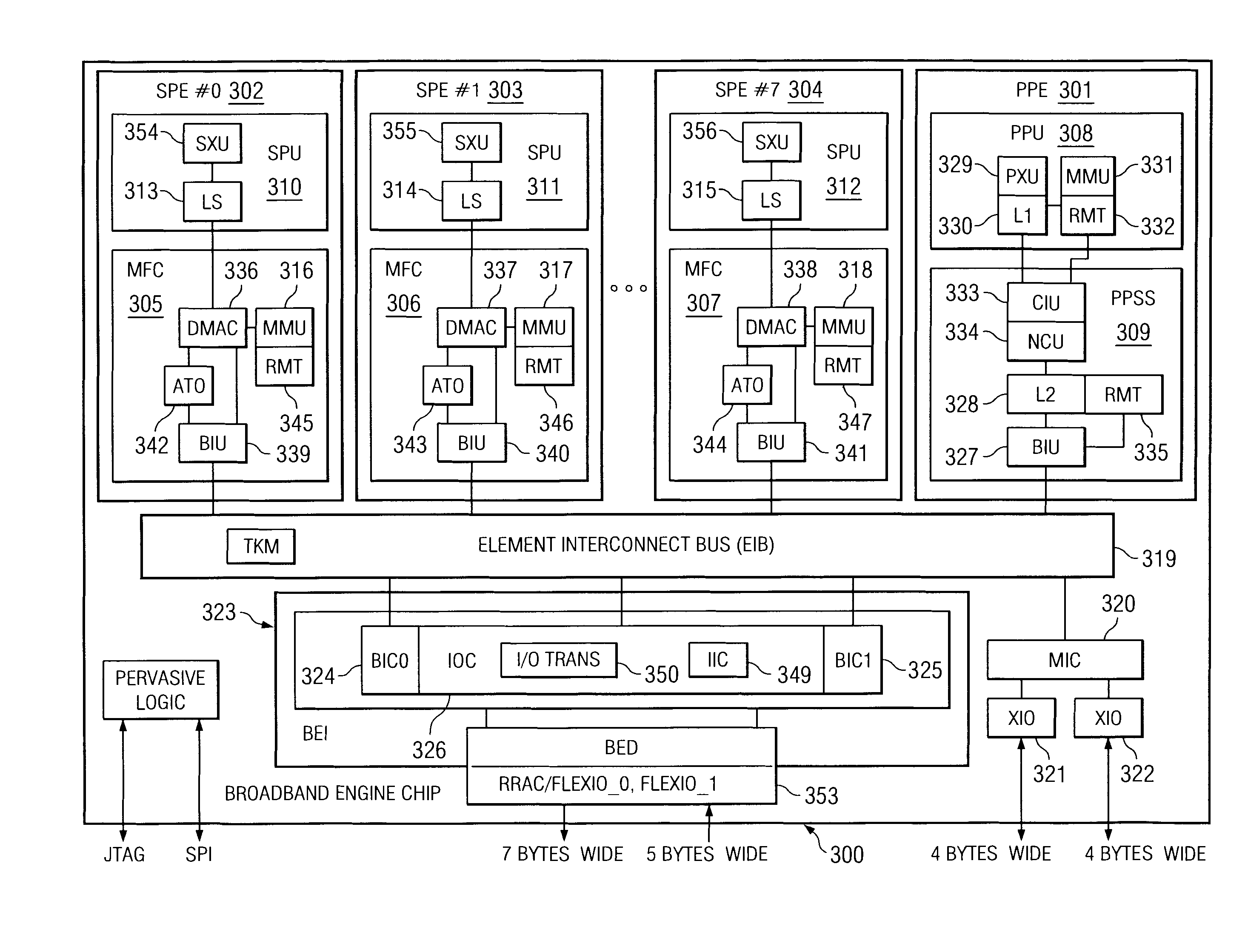

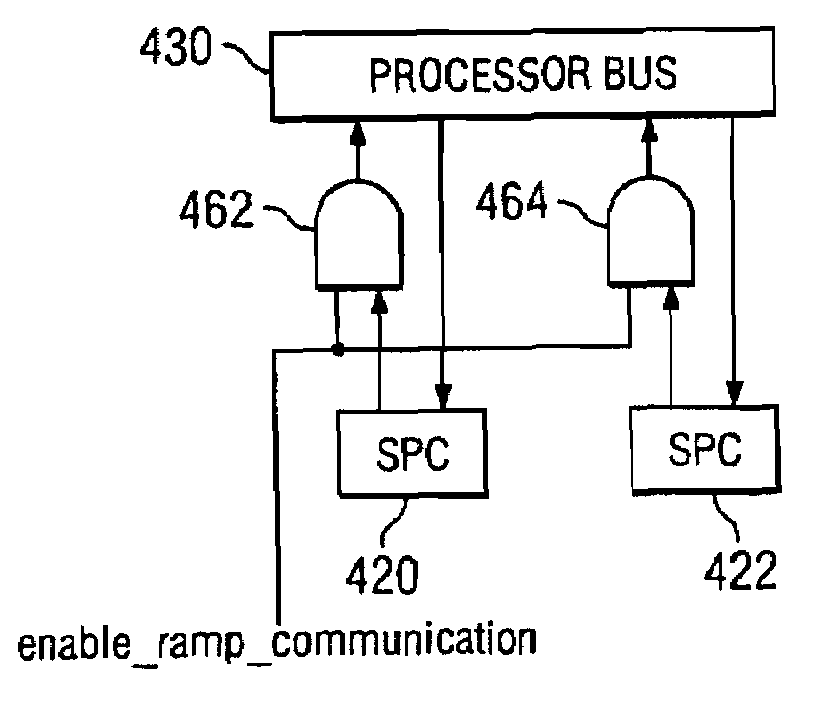

A computer implemented method, data processing system, and computer usable code are provided for testing multi-core microprocessors. A test process initiates testing on communication bus interfaces associated with a set of processor cores on the multiprocessor in which the communication bus interfaces are disabled and wherein the testing uses a set of isolation test sequences to obtain results. The process identifies a set of functional processor cores in the set of processor cores based upon the results. The process also initiates a ramp logic built-in self-test to test a ramp associated with a functional processor core in the set of functional processor cores, wherein the ramp logic built-in self-test determines if the communication bus interface associated with functional processor core in the set of functional processor cores is functional.

Owner:IBM CORP

Method and Apparatus for Logic Built In Self Test (LBIST) Fault Detection in Multi-Core Processors

InactiveUS20090089636A1Advanced technologyElectronic circuit testingLogical operation testingLogic built-in self-testMulti-core processor

Owner:IBM CORP

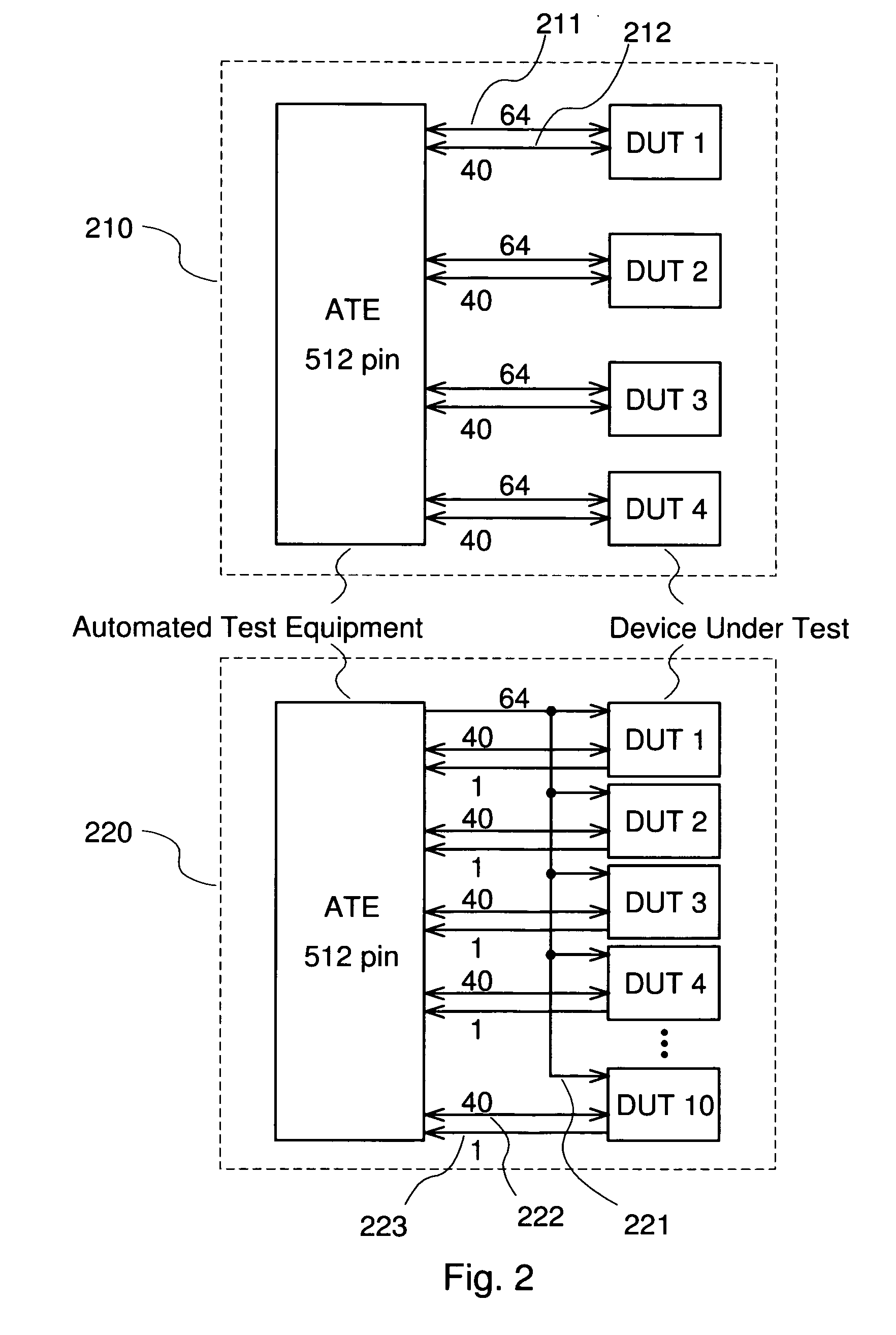

Multi-test method for using compare MISR

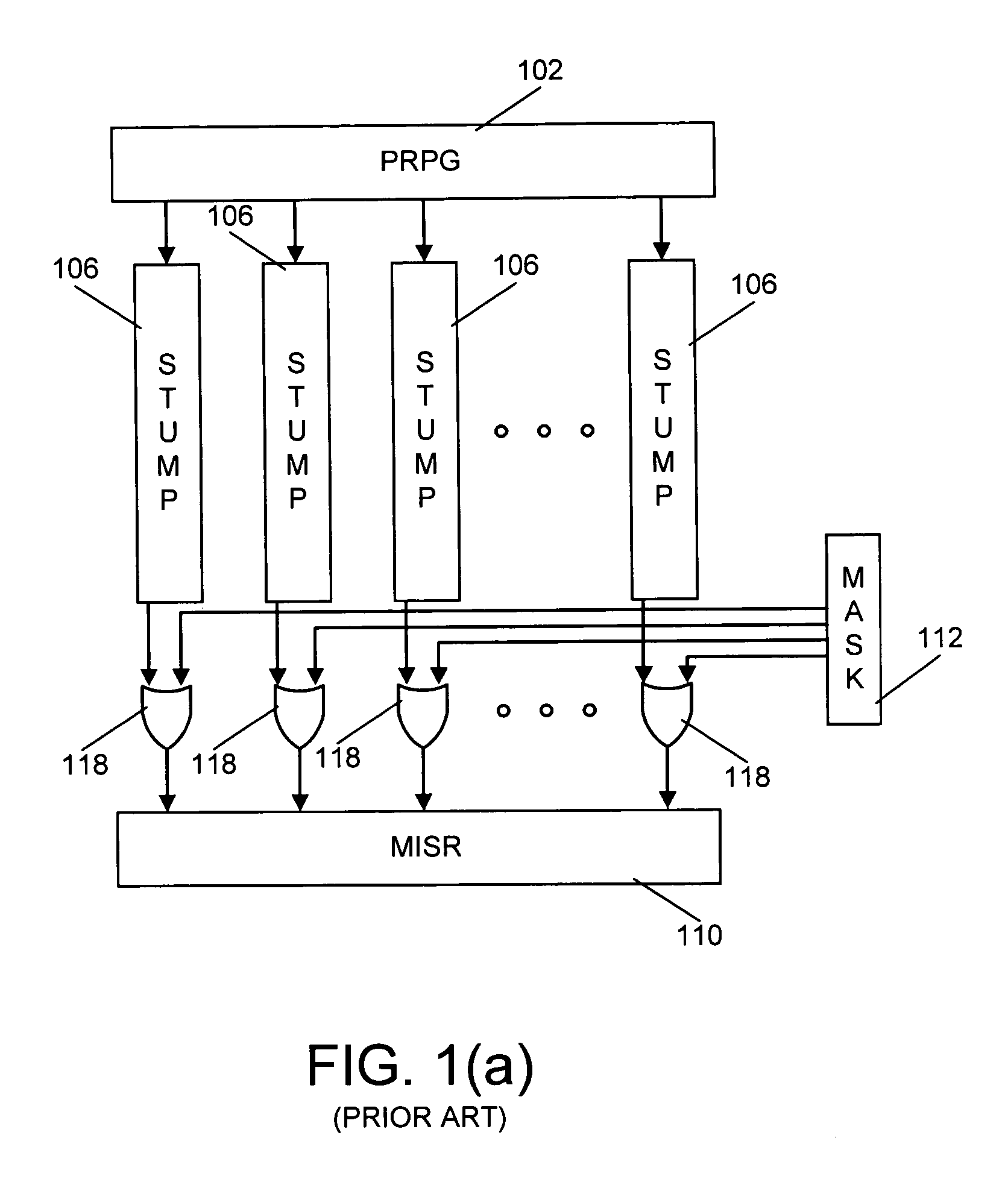

InactiveUS20060282732A1Reduce in quantityReduce the amount of processingElectronic circuit testingError detection/correctionElectricityComputer hardware

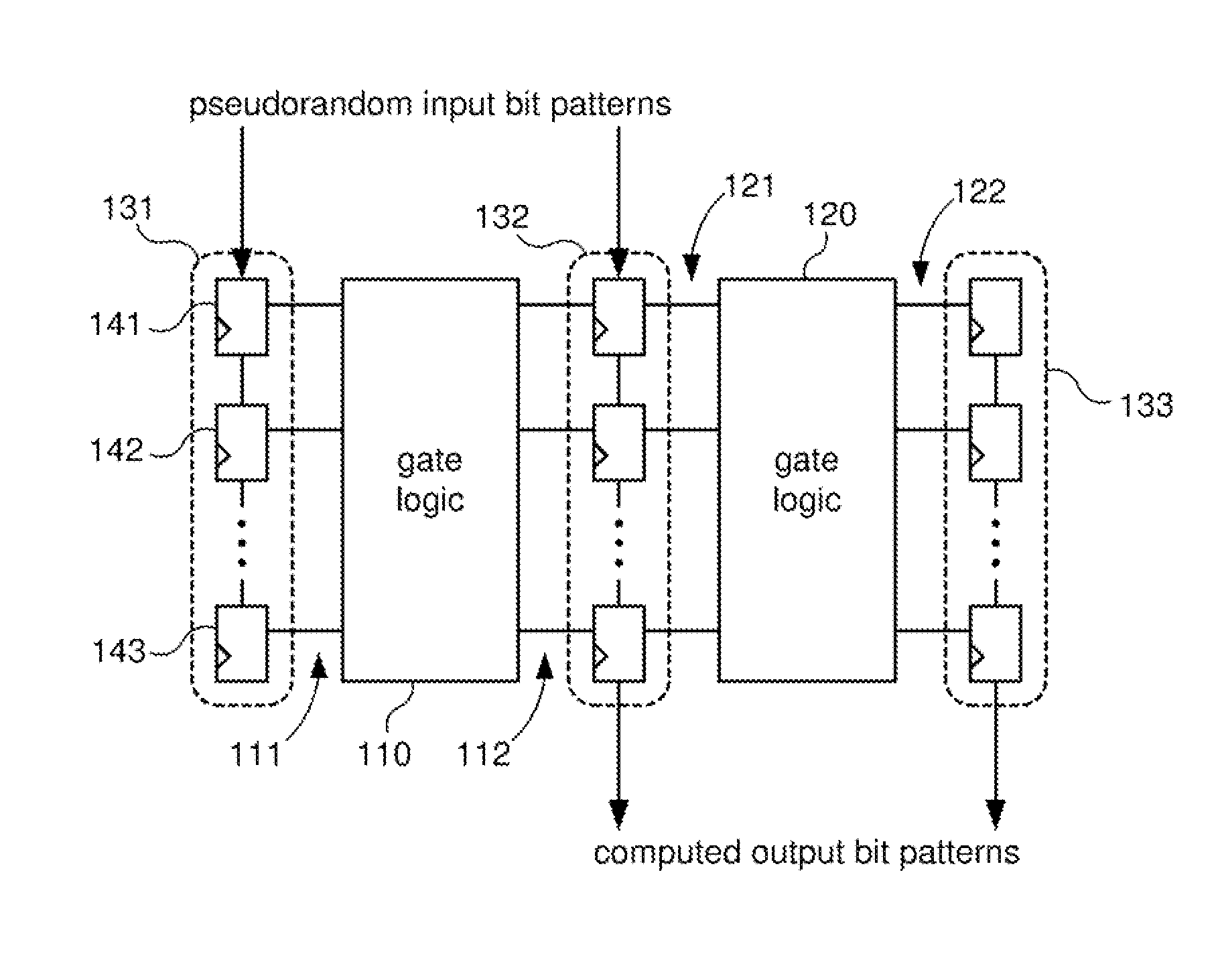

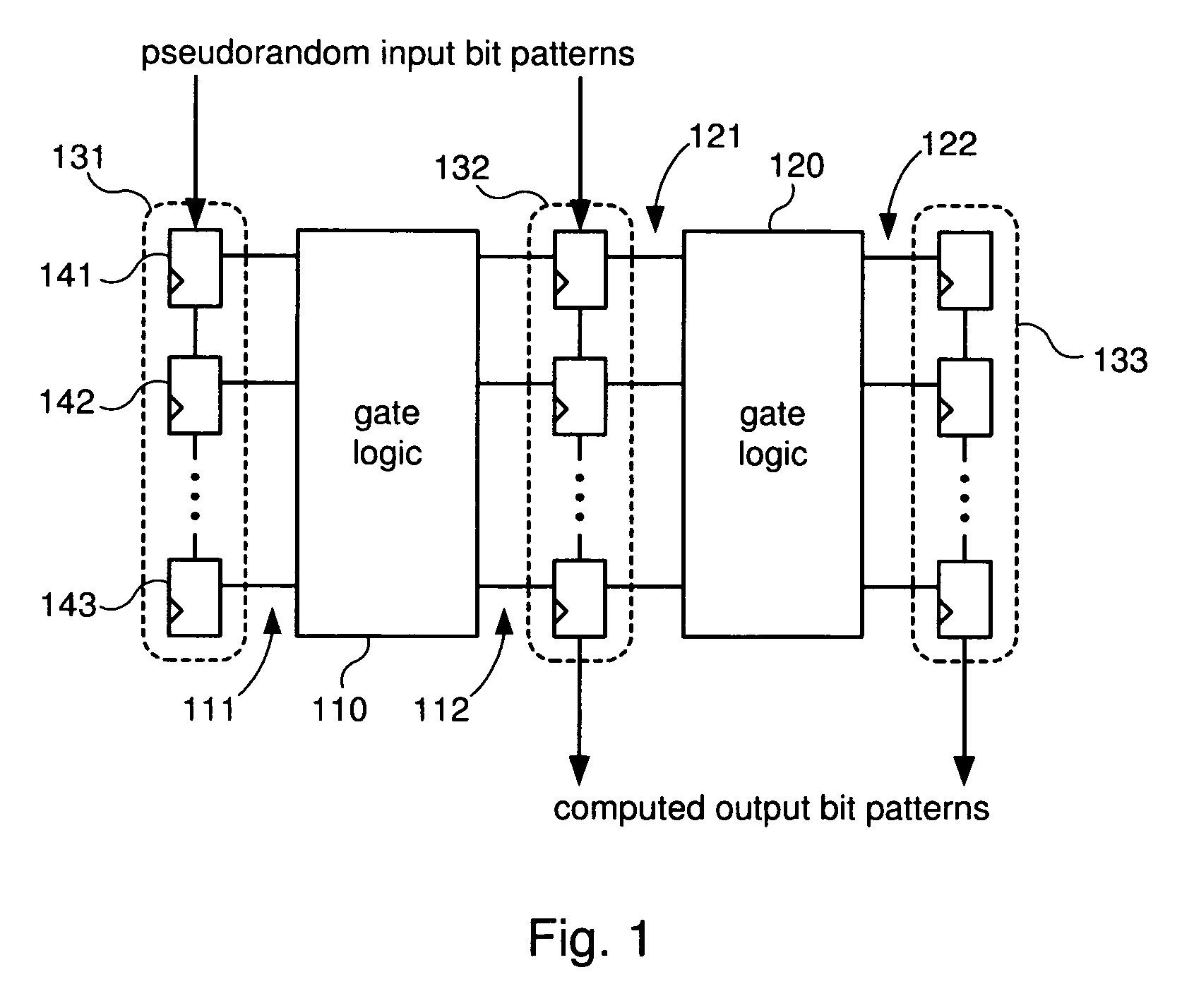

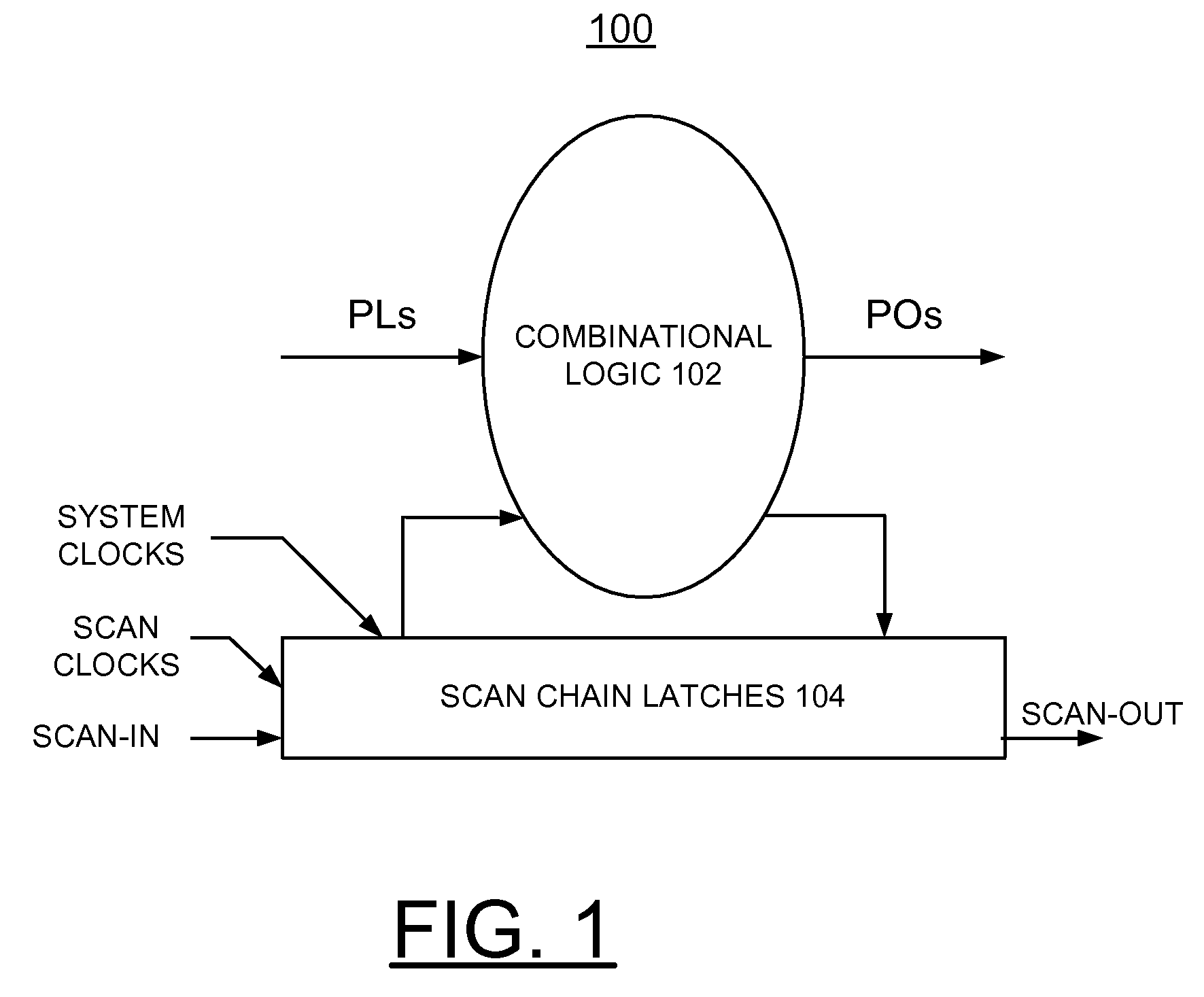

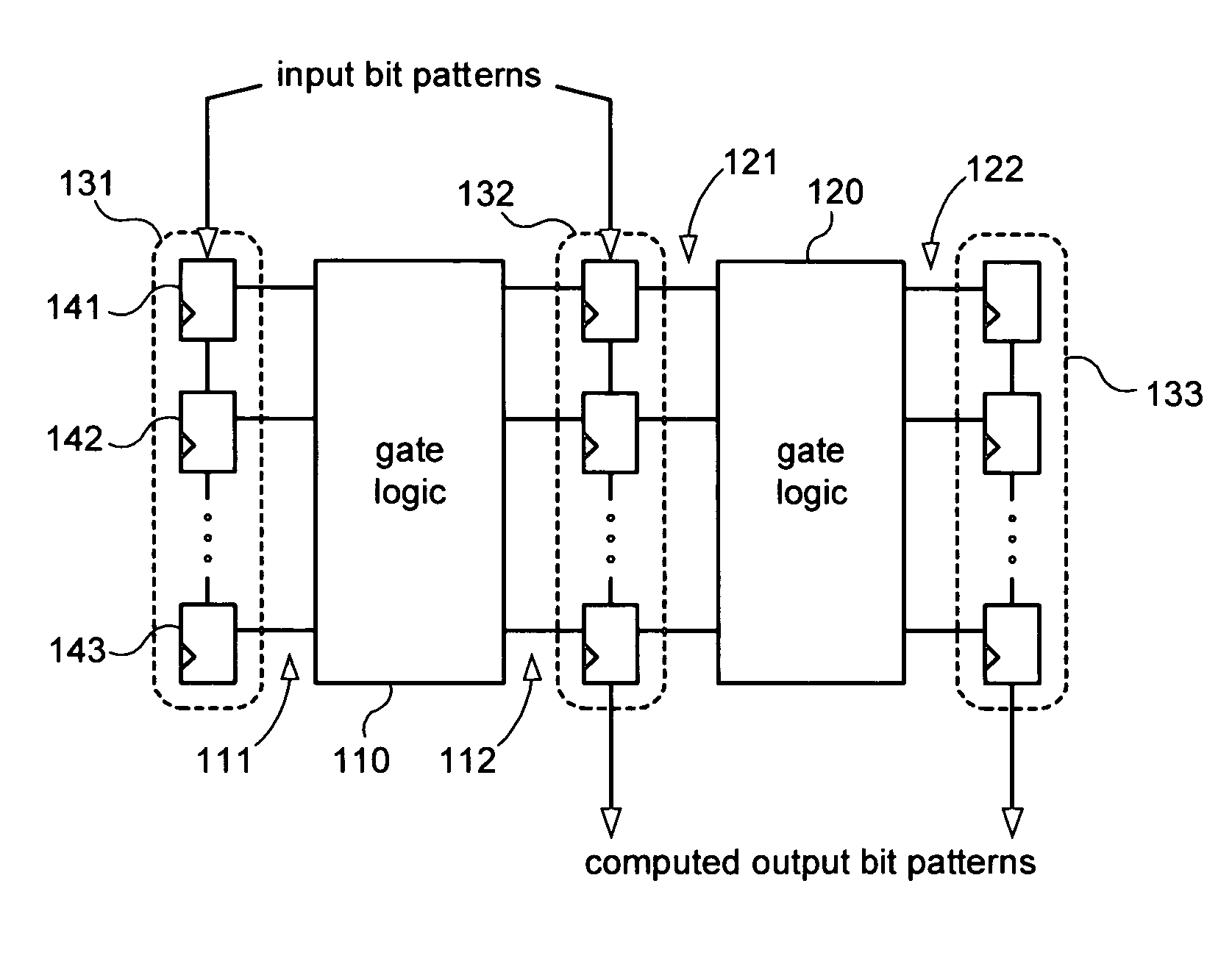

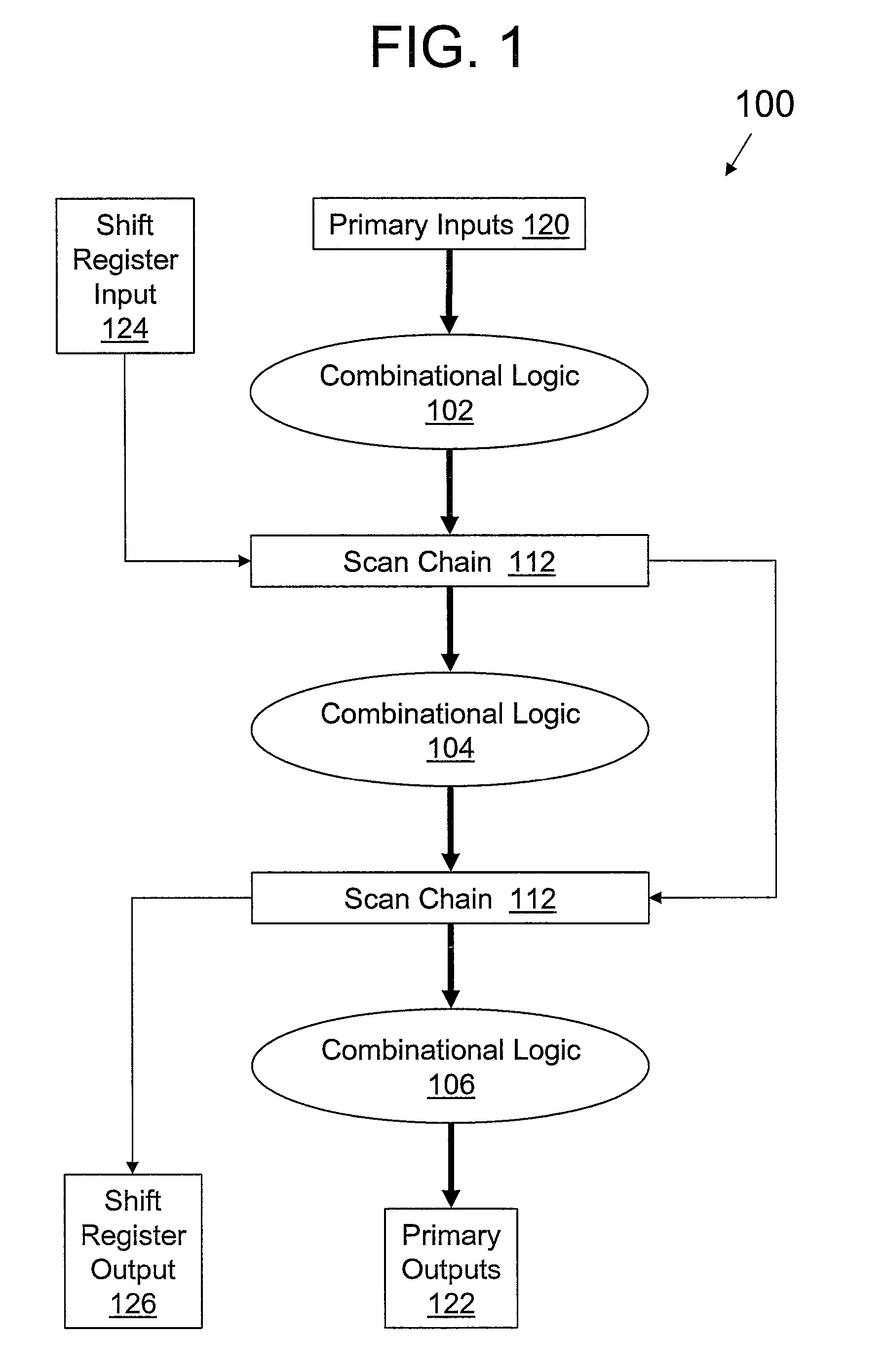

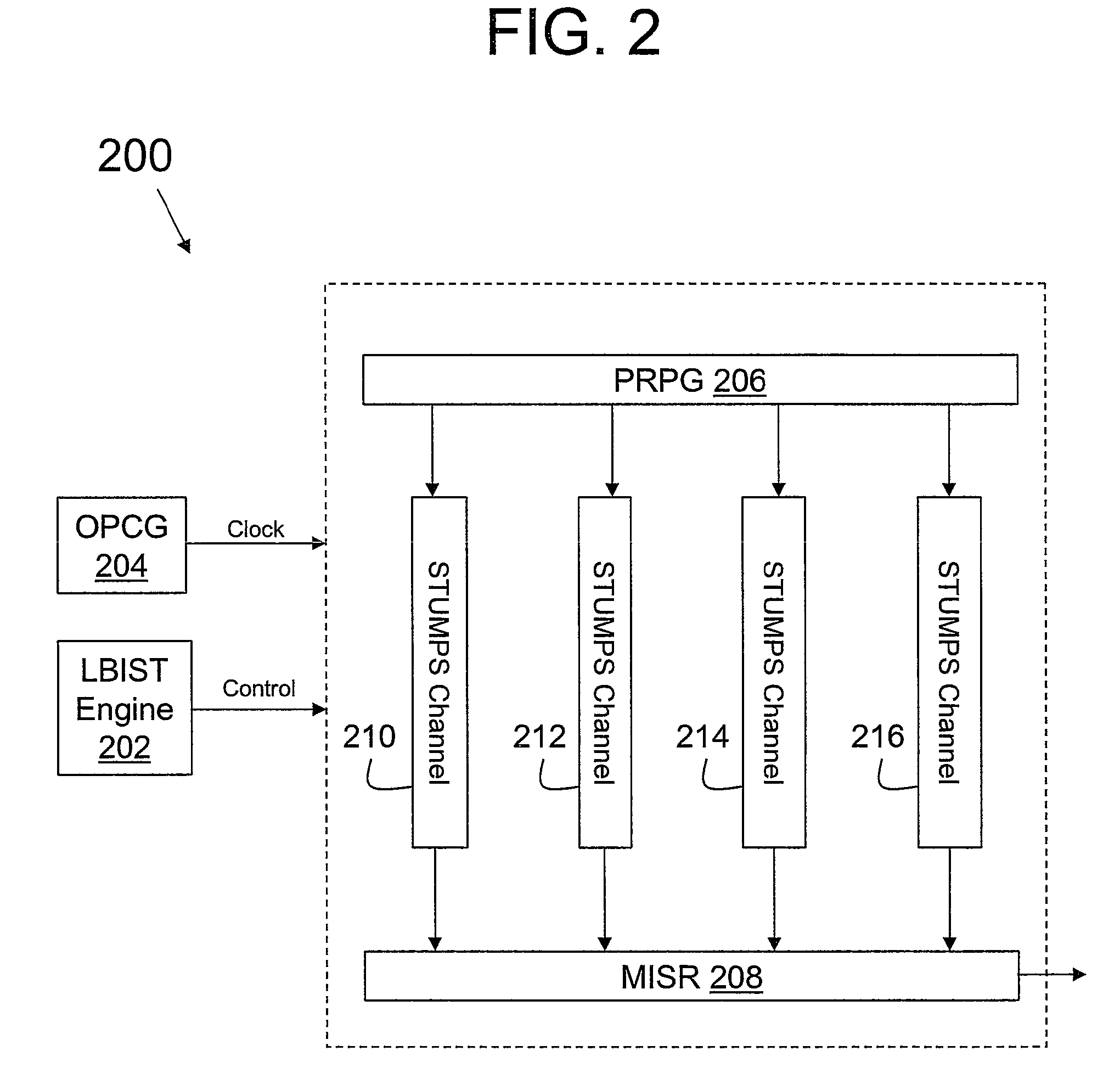

Systems and methods for performing logic built-in-self-tests (LBISTs) where data comparisons are performed in the MISR. In one embodiment, a STUMPS-type LBIST architecture includes scan chains interposed between portions of the functional logic of the logic circuit. Test bit patterns are scanned into the scan chains, propagated through the functional logic, and captured in scan chains following the functional logic. The bits are scanned out of the scan chains into a self-compare MISR that creates a signature from the computed bit patterns and then compares the signature of the computed bit patterns with an expected signature, giving a pass / fail result. This single bit result reduces the bandwidth required to communicate the result(s) of the LBIST testing to the test equipment. As a result, a larger number of devices can be tested by a given piece of test equipment.

Owner:KK TOSHIBA

Method and apparatus for at-speed testing of digital circuits

InactiveUS20060064616A1Electronic circuit testingError detection/correctionMulti inputLogic built-in self-test

Owner:MENTOR GRAPHICS CORP

Method and apparatus for testing multi-core microprocessors

InactiveUS7610537B2Electronic circuit testingError detection/correctionData processing systemMulti processor

A computer implemented method, data processing system, and computer usable code are provided for testing multi-core microprocessors. A test process initiates testing on communication bus interfaces associated with a set of processor cores on the multiprocessor in which the communication bus interfaces are disabled and wherein the testing uses a set of isolation test sequences to obtain results. The process identifies a set of functional processor cores in the set of processor cores based upon the results. The process also initiates a ramp logic built-in self-test to test a ramp associated with a functional processor core in the set of functional processor cores, wherein the ramp logic built-in self-test determines if the communication bus interface associated with functional processor core in the set of functional processor cores is functional.

Owner:IBM CORP

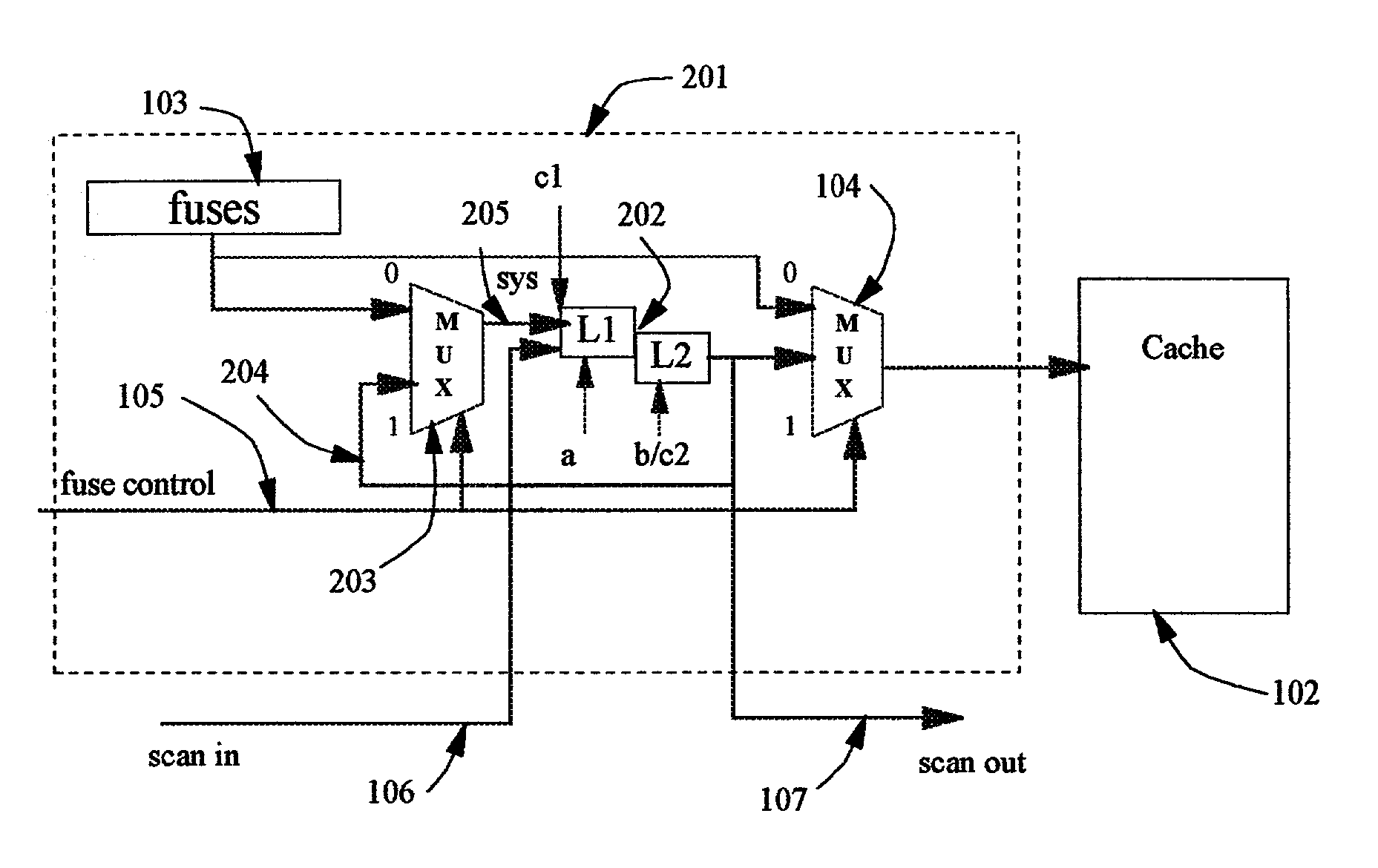

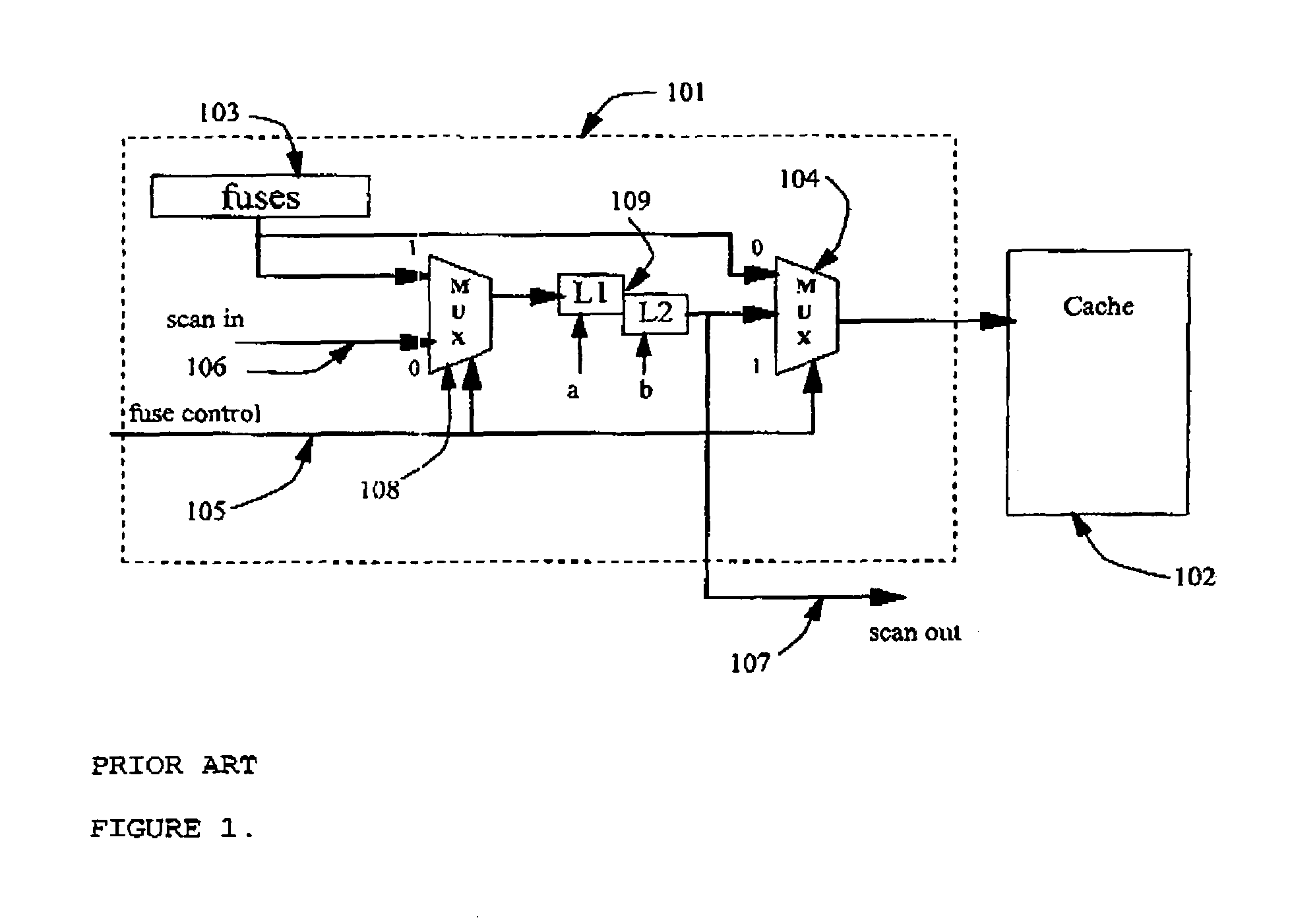

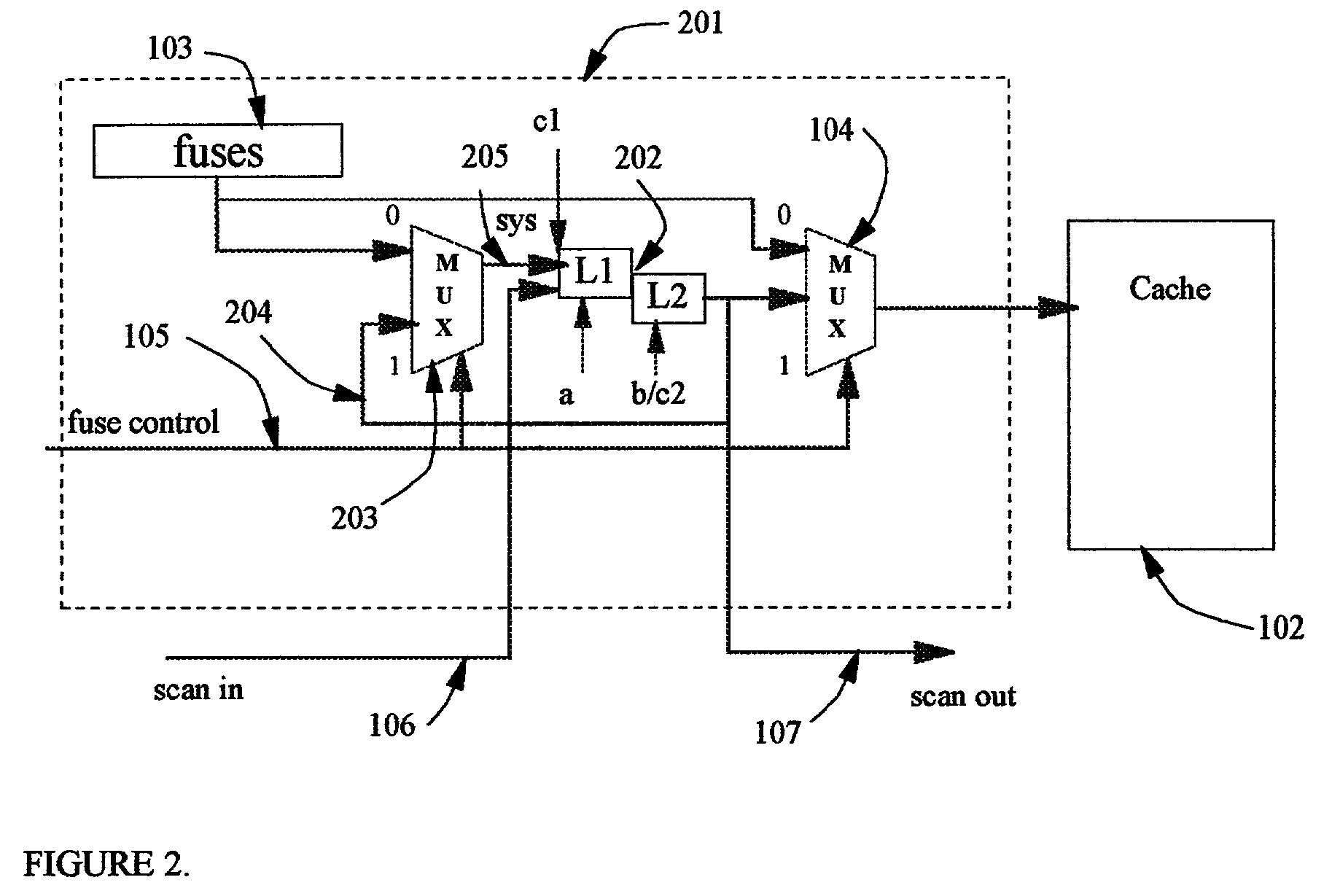

Apparatus and method for programmable fuse repair to support dynamic relocate and improved cache testing

An apparatus and method for allowing for dynamic wordline repair in a clock running system in addition to allowing for programmable fuse support of combined Array Built-In Self-Test (ABIST) and Logic Built-In Self-Test (LBIST) testing. The method makes use of programmable fuses which contain Level Sensitive Scan Design (LSSD) latches which also have a system port. The system port allows for simpler reading of the fuses as well as for the dynamic updates of the programmable fuses for wordline and other repairs.

Owner:GLOBALFOUNDRIES INC

Systems and methods for diagnosing rate dependent errors using LBIST

InactiveUS20070050693A1Electronic circuit testingError detection/correctionLogic built-in self-testComputer science

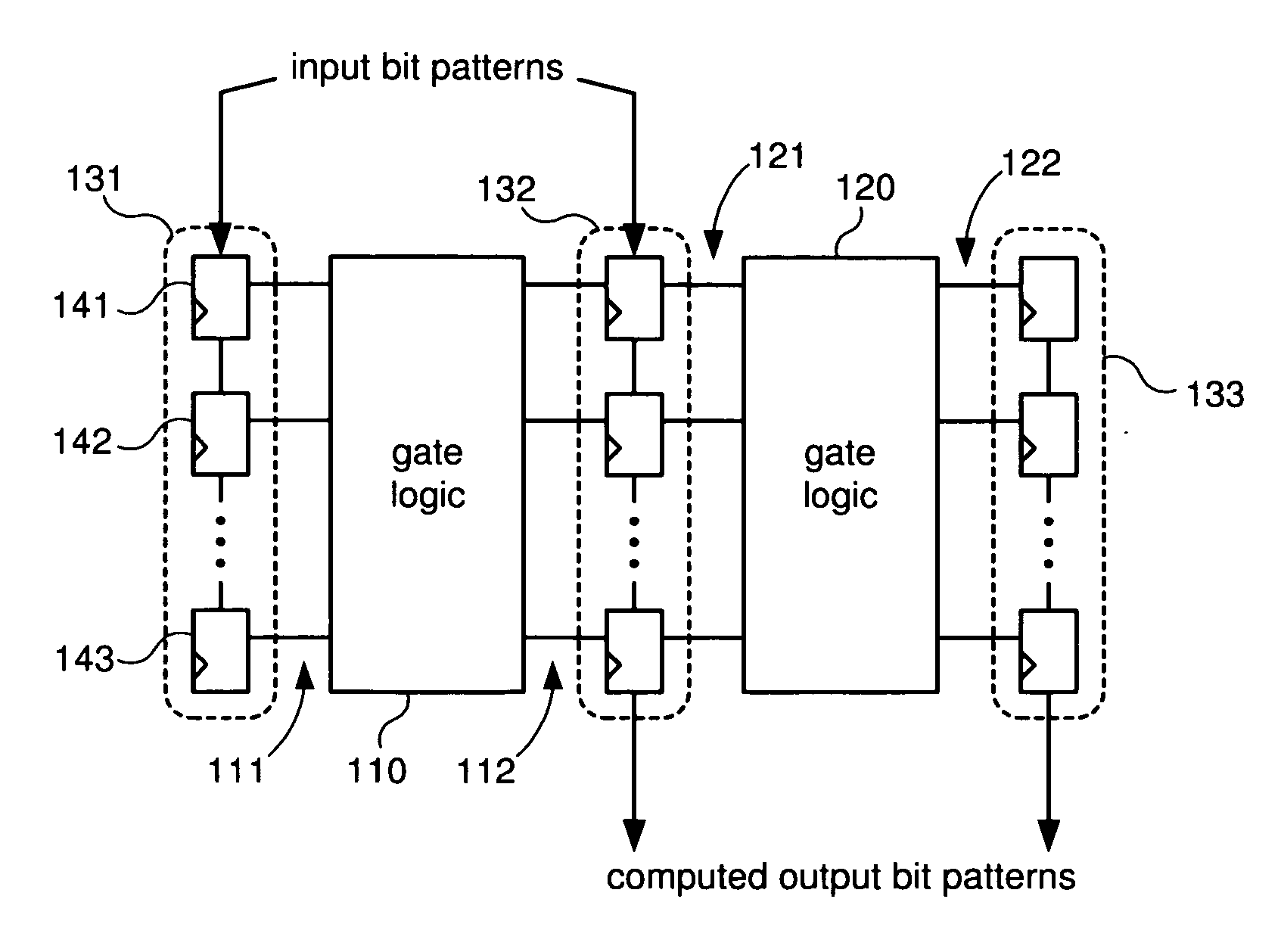

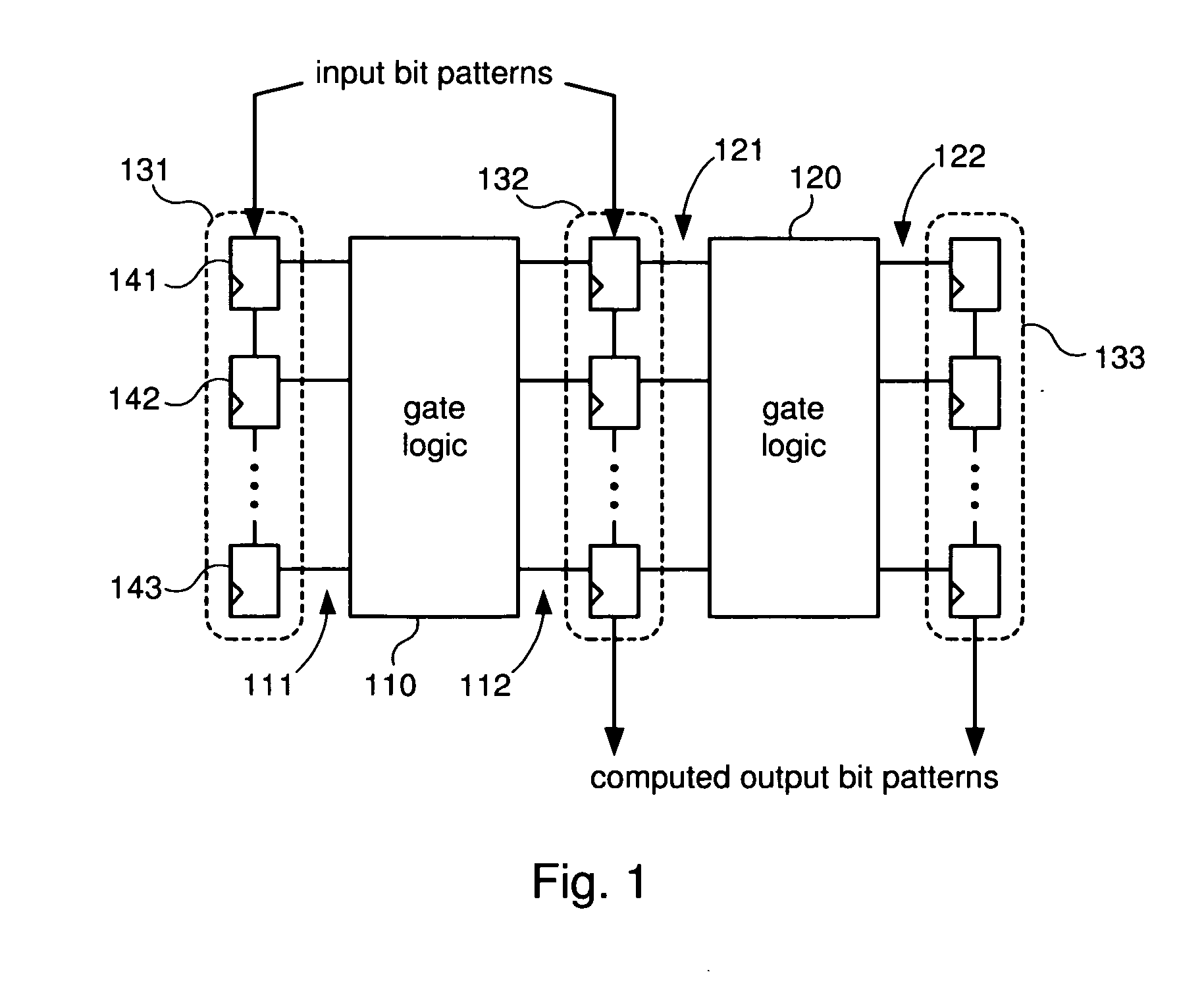

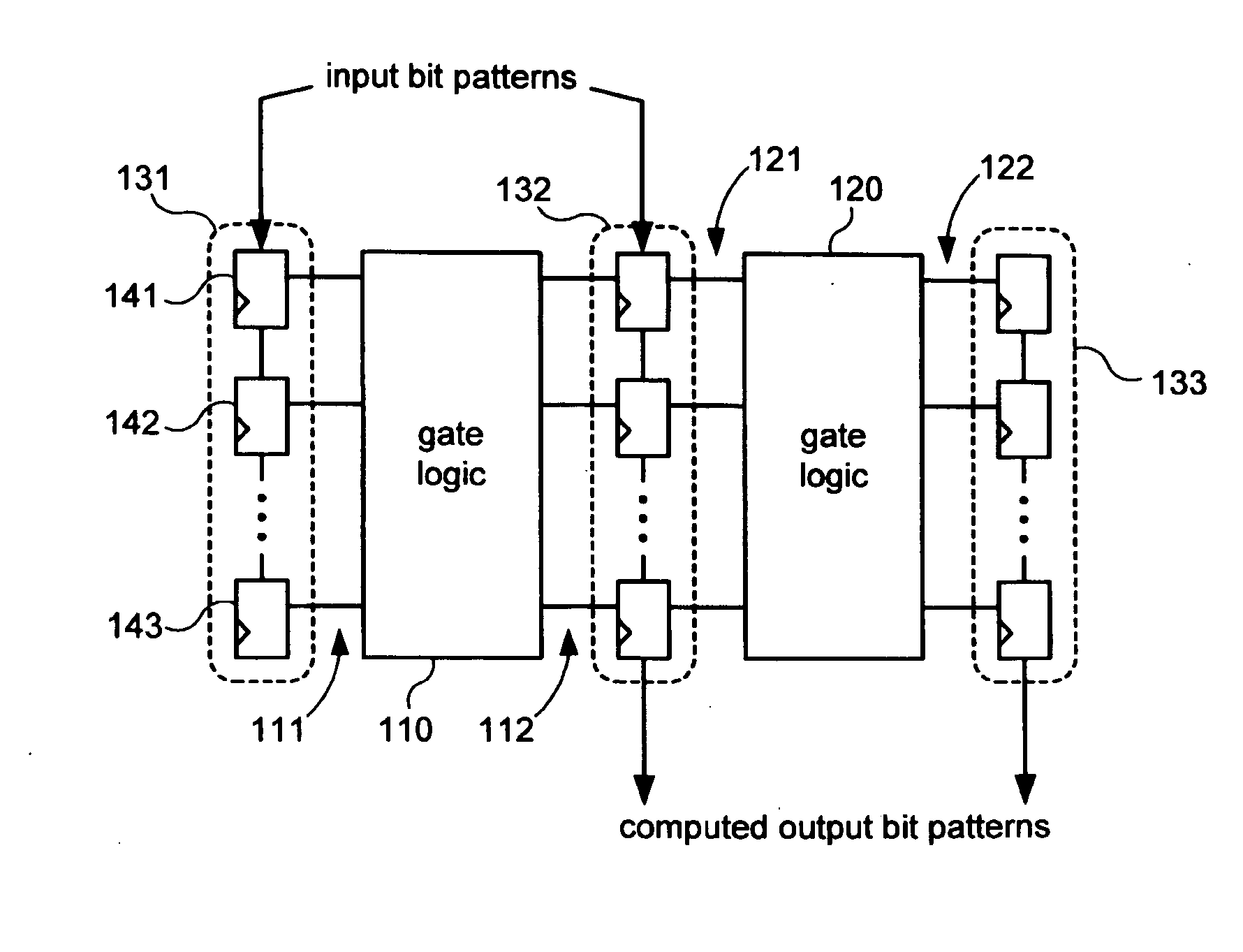

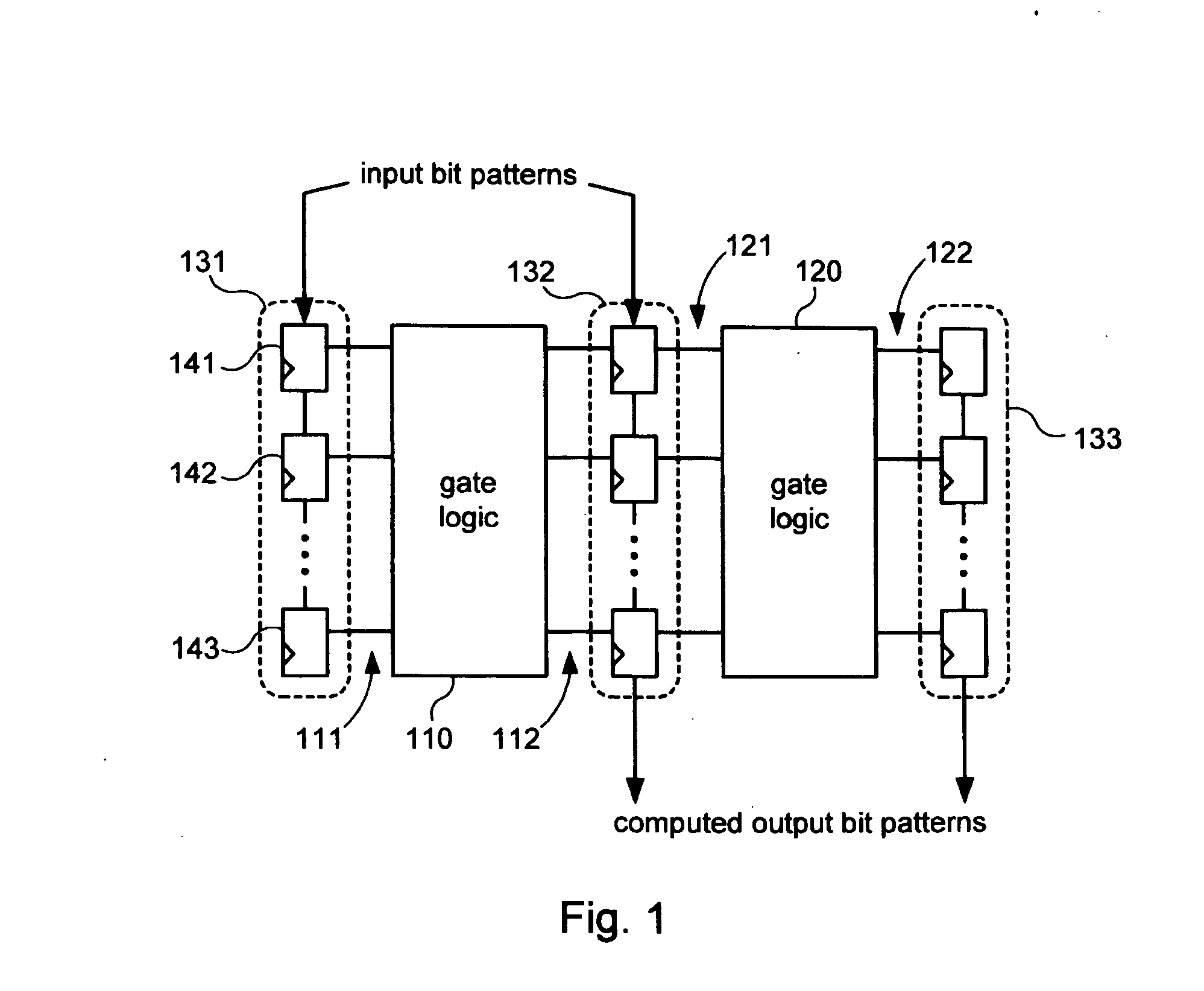

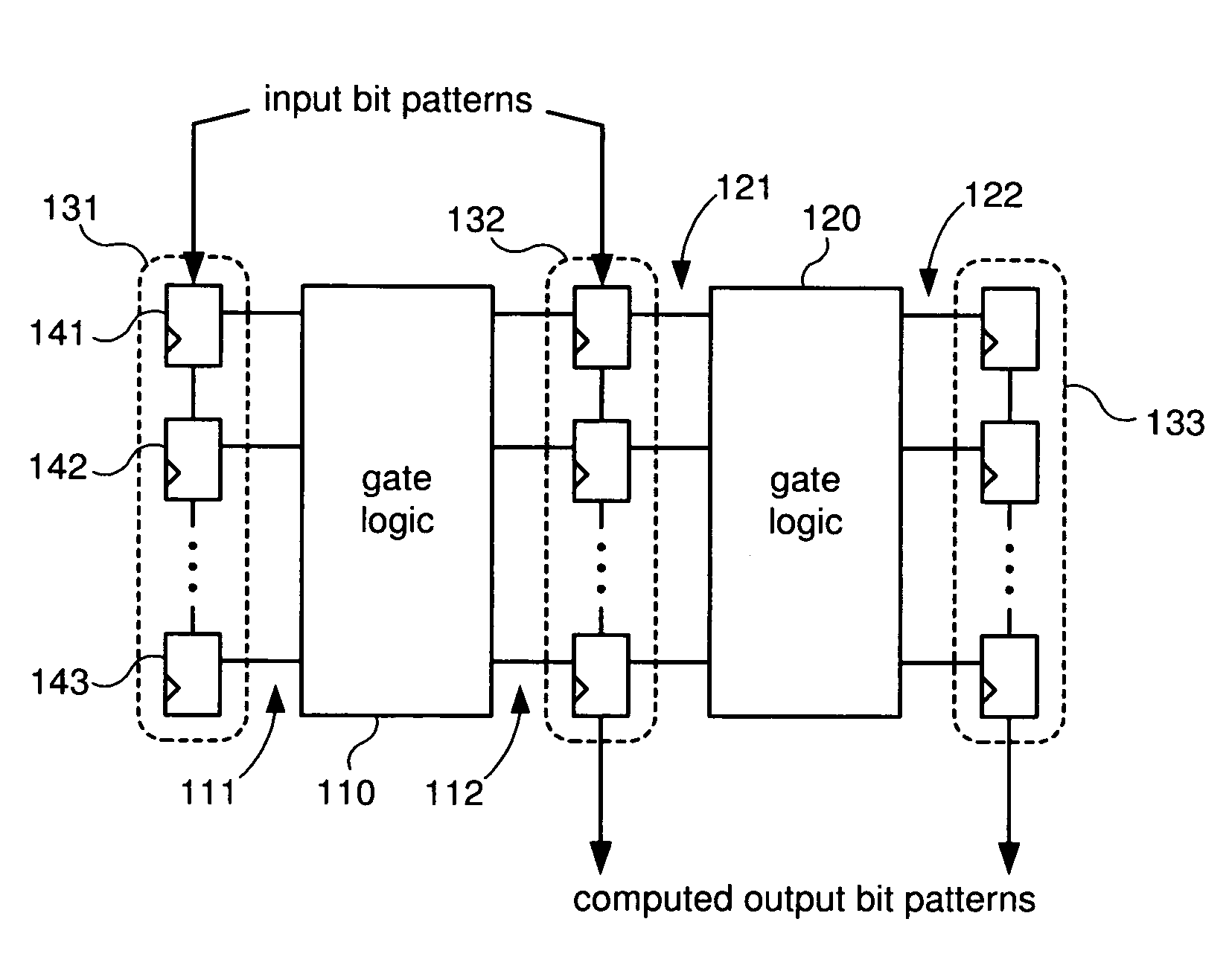

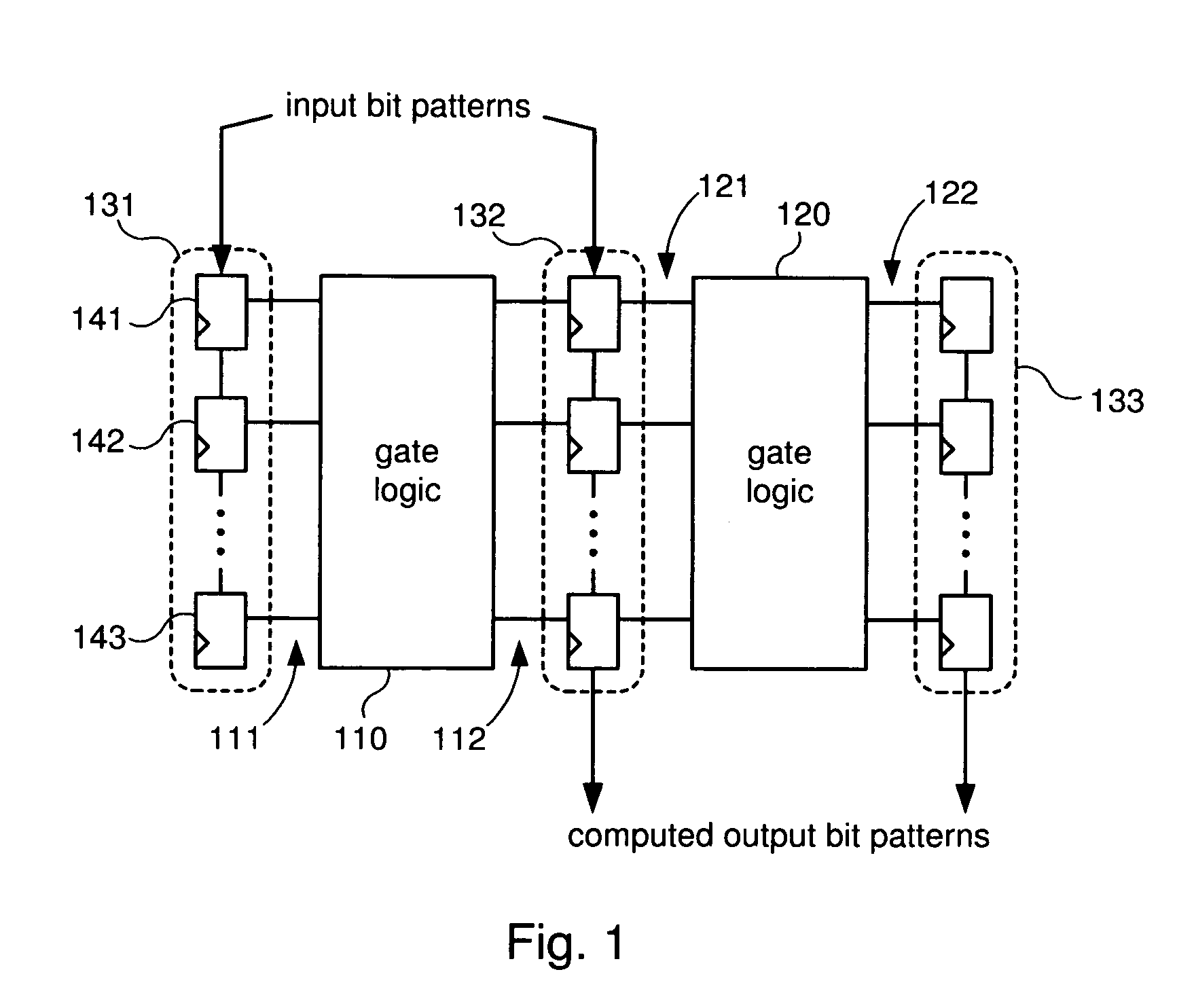

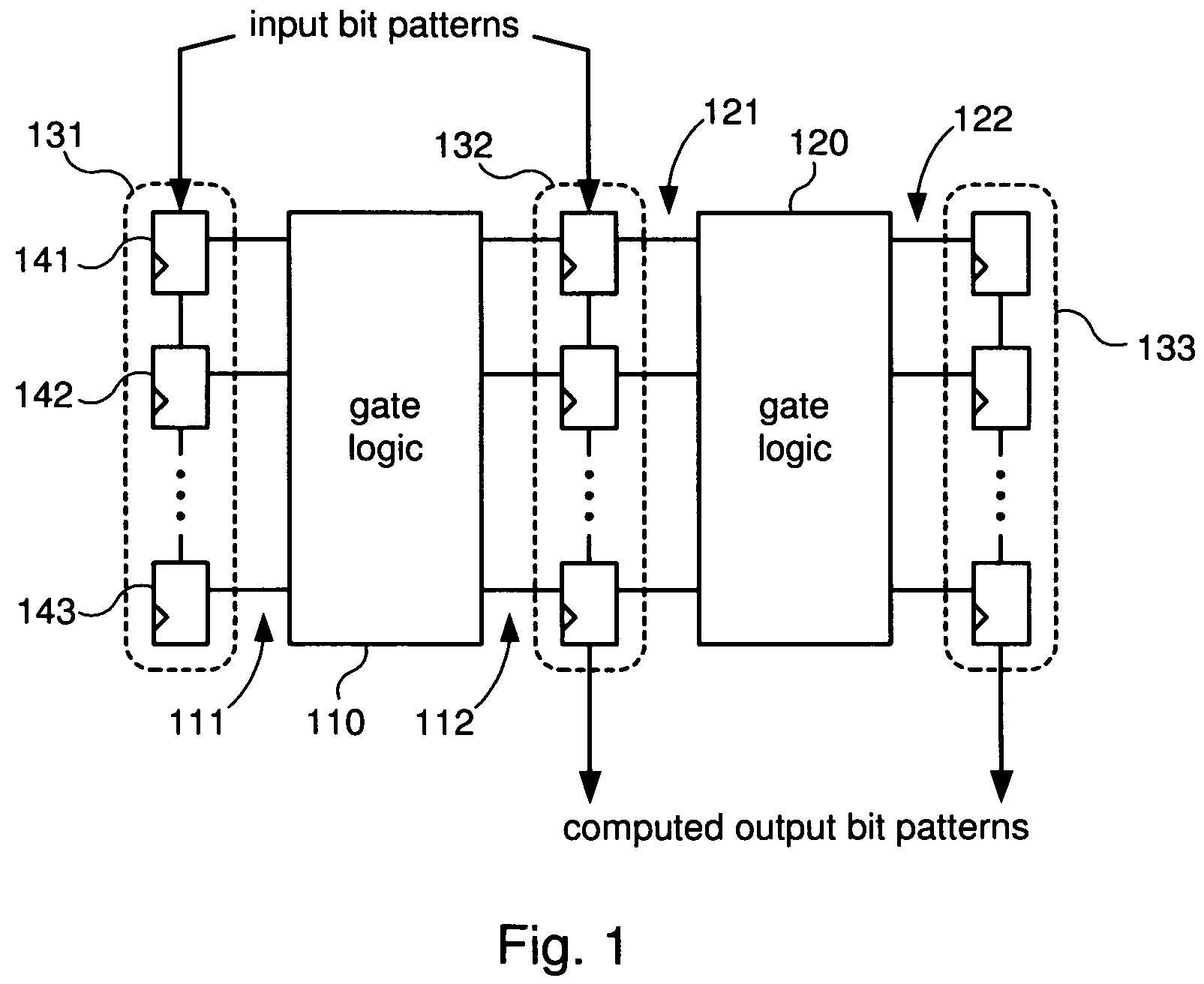

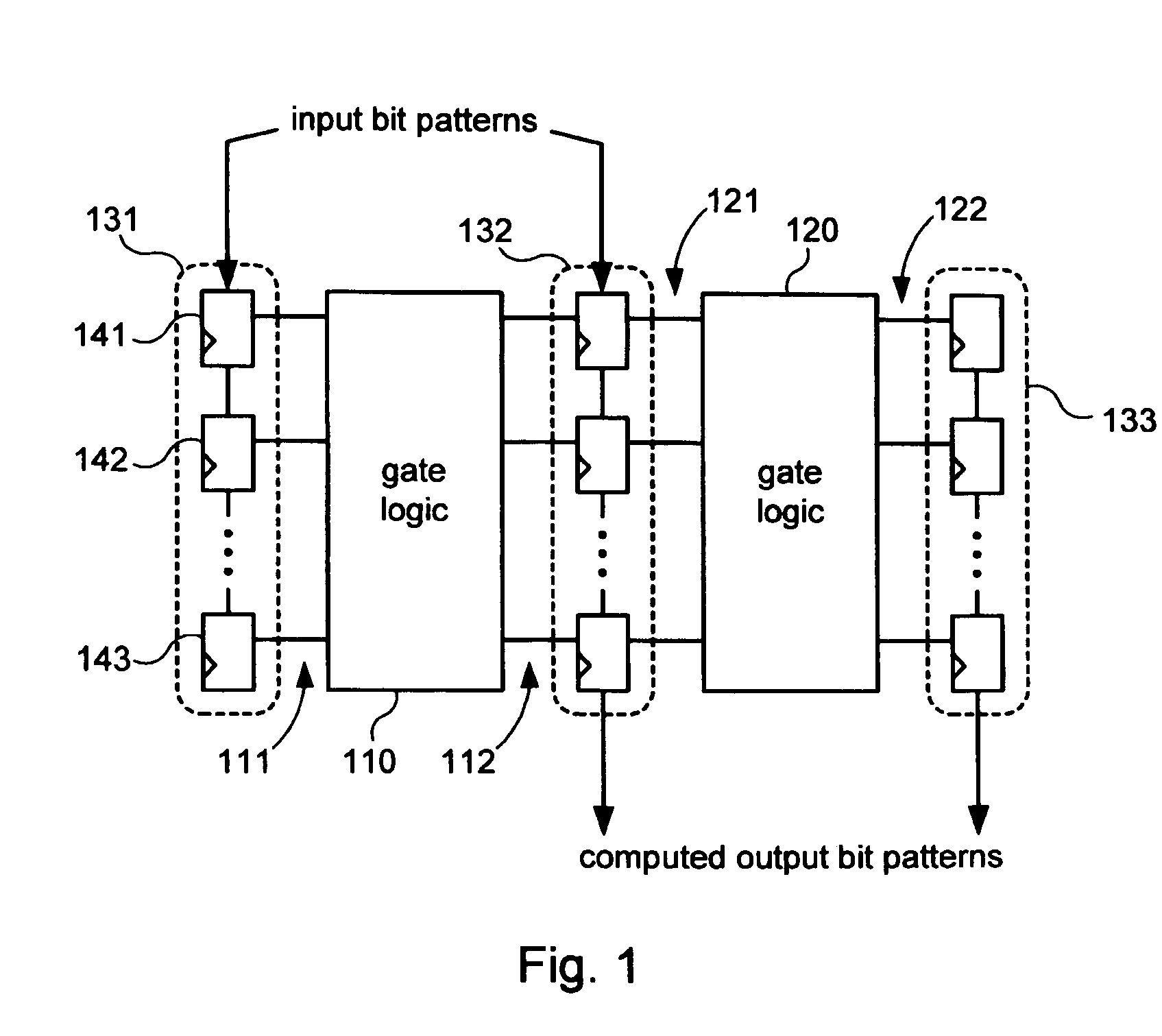

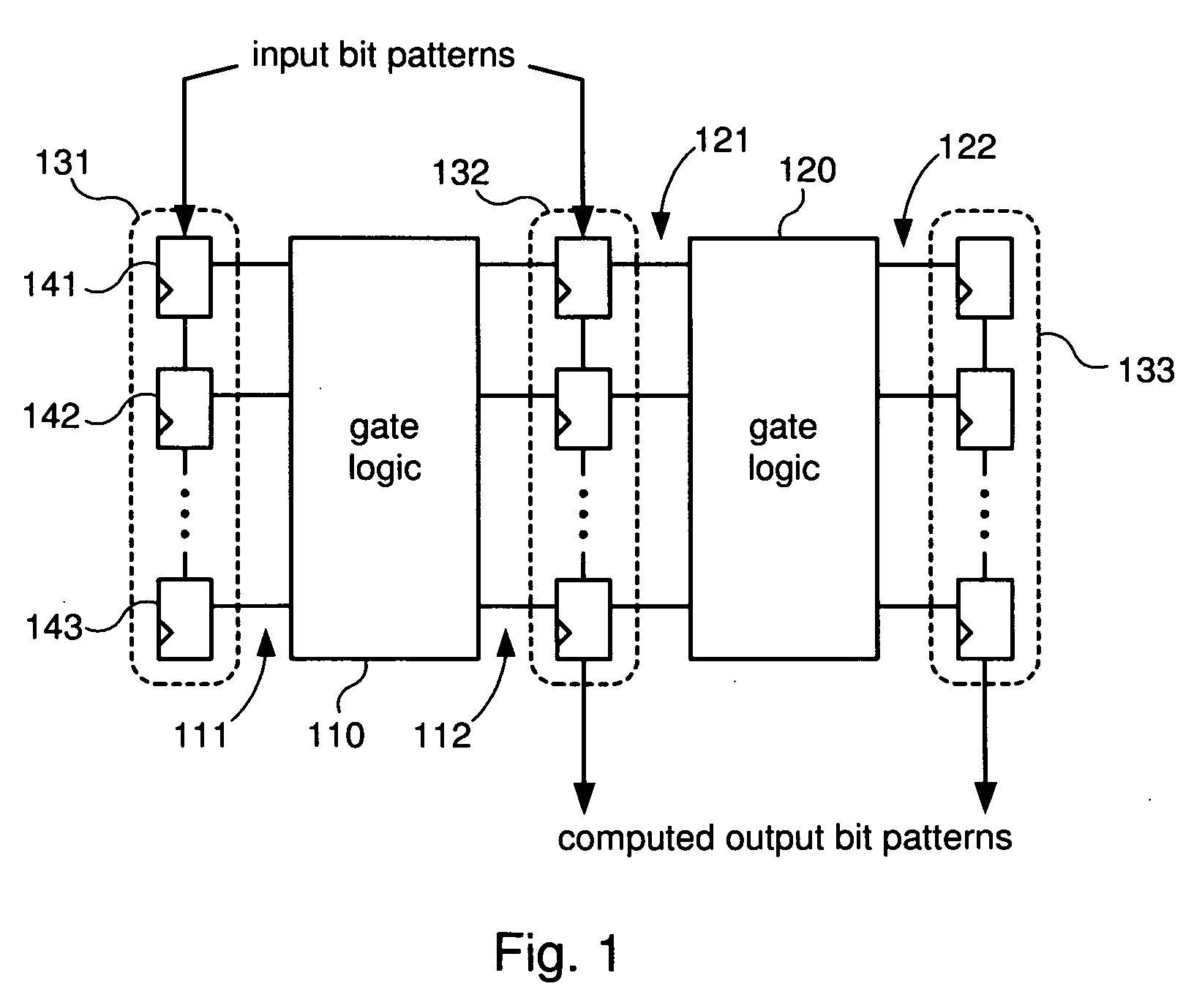

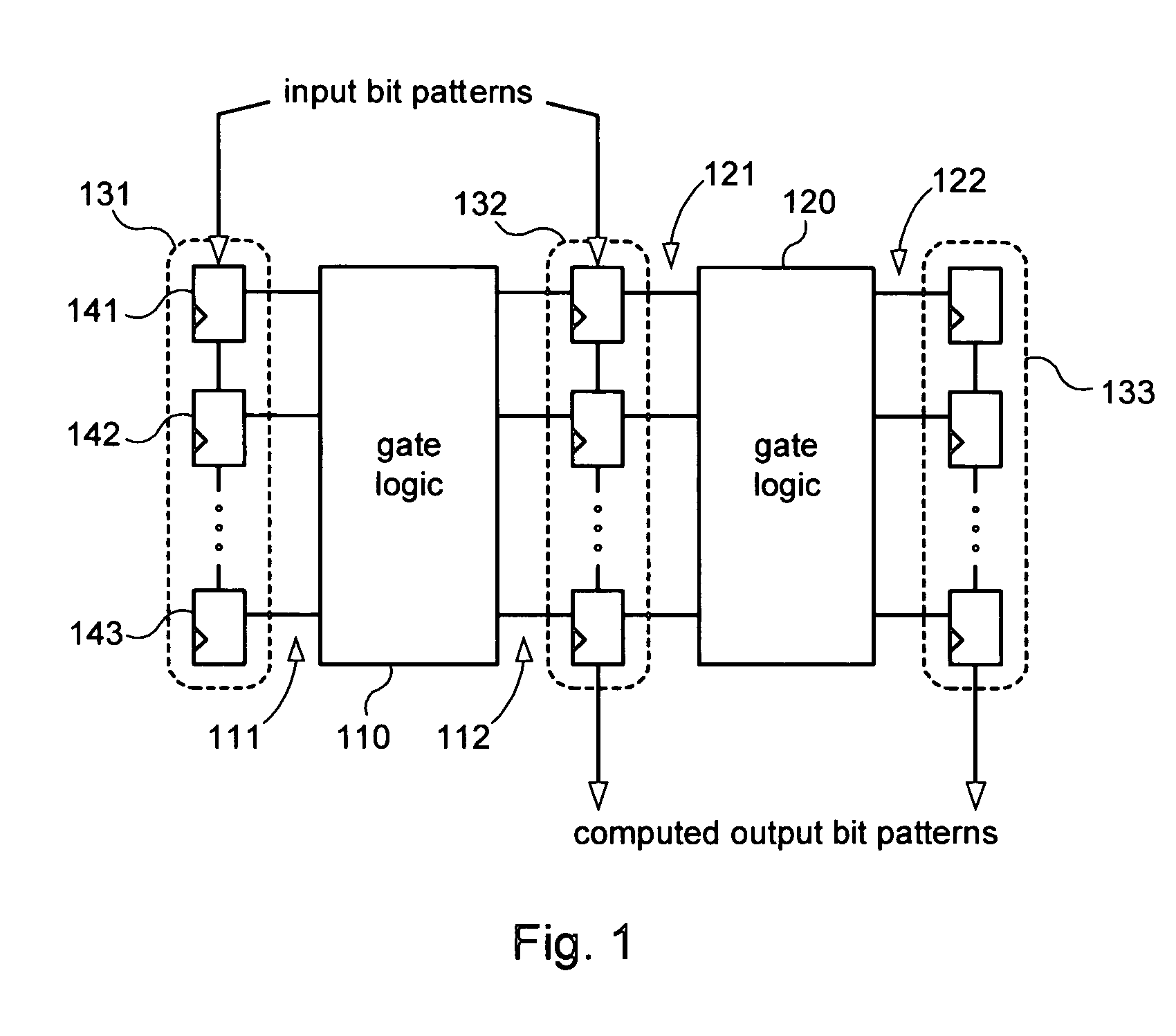

Systems and methods for performing logic built-in self-tests (LBISTs) to detect “at-speed” errors in a digital circuit. In one embodiment, an input bit pattern is propagated through target logic of the digital circuit and captured in scan chains at a normal operating speed to produce a first output bit pattern. This is repeated with the first input bit pattern at a lower test speed to produce a second output bit pattern. Differences between the first and second output bit patterns are then detected to determine whether operation of the digital circuit at the normal operating speed causes errors that are not generated at the lower test speed.

Owner:KK TOSHIBA

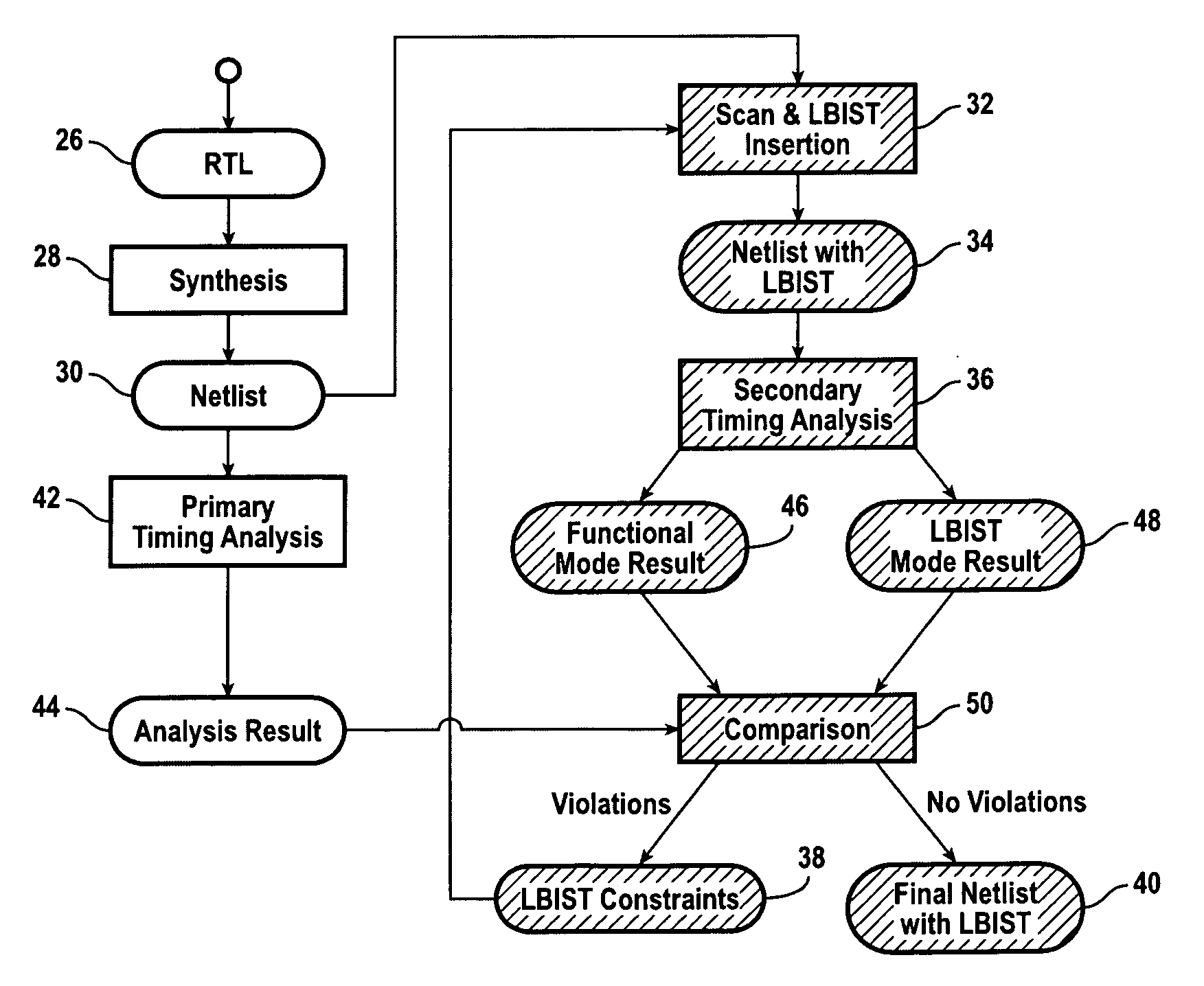

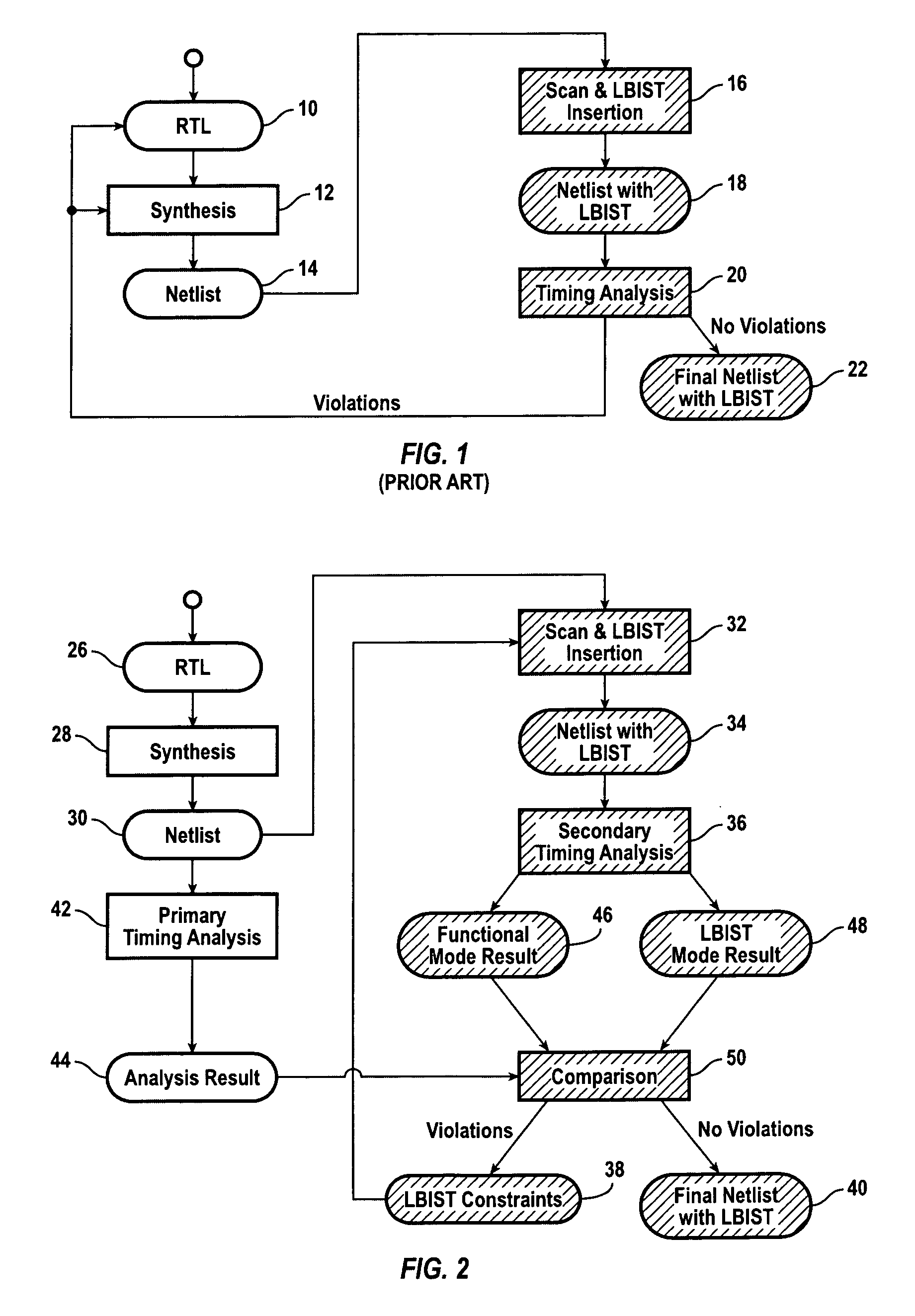

Resolving LBIST timing violations

ActiveUS6934921B1Digital circuit testingSoftware simulation/interpretation/emulationLogic built-in self-testComputer science

Resolving timing violations introduced by a logic built-in self test (LBIST) sub-circuit formed within an underlying integrated circuit includes analyzing a circuit path-list corresponding to the integrated circuit for timing violations and generating a circuit timing violations analysis output; generating a first LBIST / circuit path-list based on the circuit path-list and an LBIST path-list corresponding to the LBIST sub-circuit; analyzing the first LBIST / circuit path-list for timing violations and generating an LBIST / circuit timing violations analysis output; comparing the LBIST / circuit timing violations analysis output with the circuit timing violations analysis output; generating an LBIST / circuit constraint file based on the comparison and predetermined protocols; and generating a second LBIST / circuit path-list based on the circuit path-list, the LBIST path-list and the constraints file. In this way, timing problems are quickly and efficiently resolved.

Owner:CISCO TECH INC

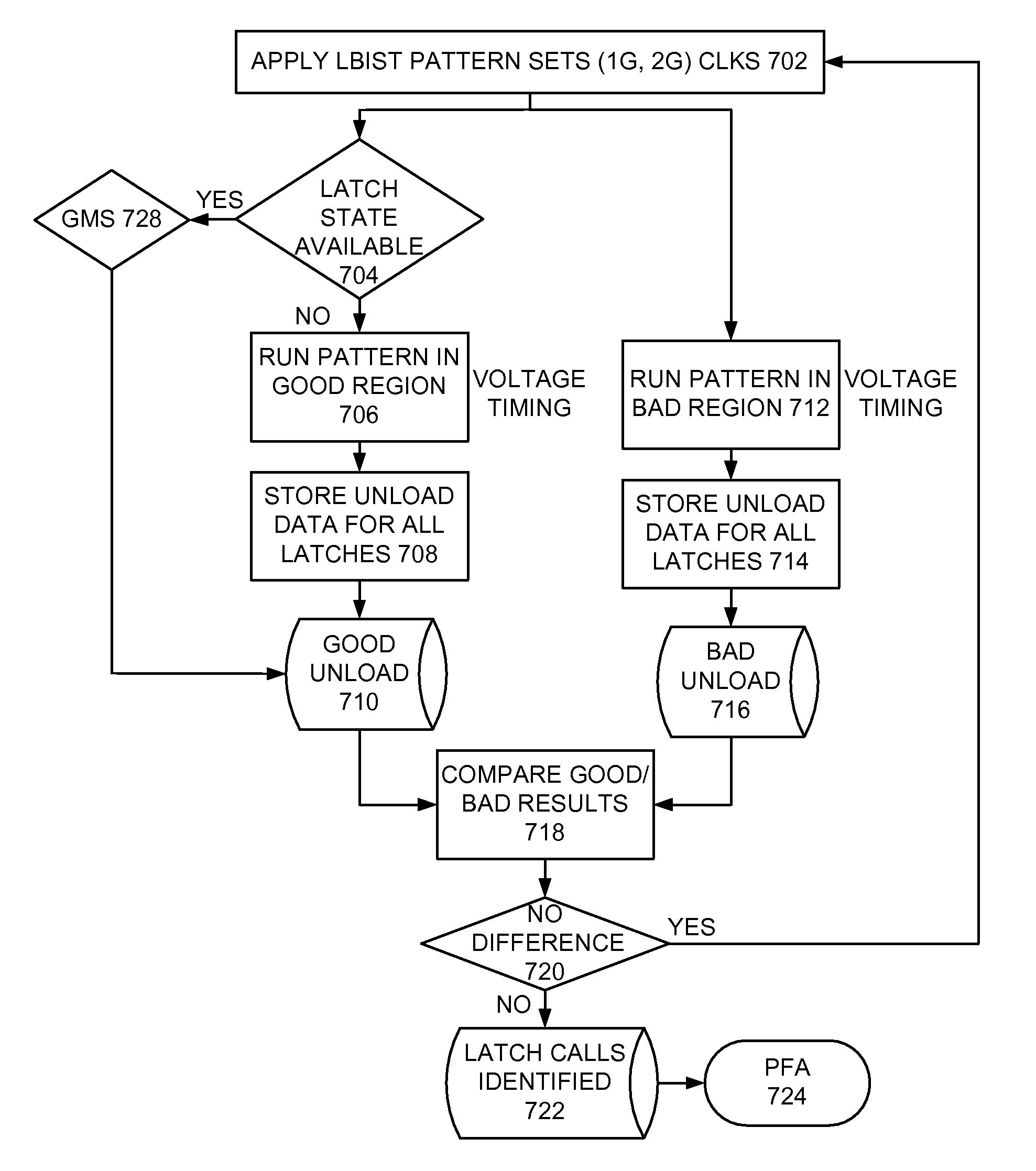

Implementing Diagnosis of Transitional Scan Chain Defects Using LBIST Test Patterns

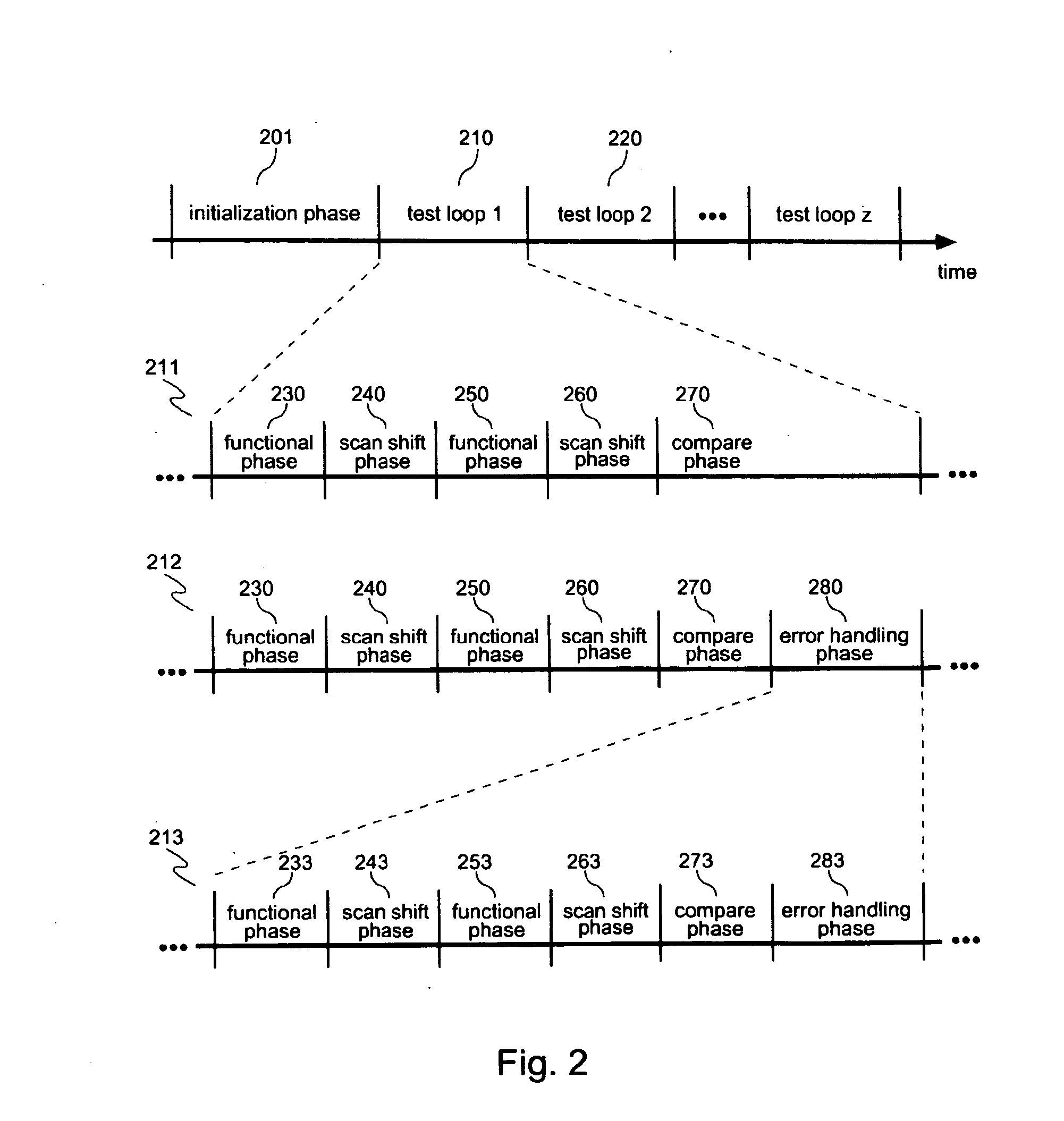

ActiveUS20100095177A1Negative effectElectronic circuit testingError detection/correctionComputer hardwareLoop control

A method, apparatus and computer program product are provided for implementing diagnostics of transitional scan chain defects using structural Logic Built In Self Test (LBIST) test patterns. A LBIST test pattern is applied to the device under test and multiple system clock sequences with variable loop control are applied in a passing operating region and scan data is unloaded. The LBIST test pattern is applied to the device under test and multiple system clock sequences with variable loop control are applied in a failing operating region for the device under test and scan data is unloaded. Then the unload data from the passing operating region and the failing operating region are compared. The identified latches having different results are identified as potential AC defective latches. The identified potential AC defective latches are sent to a Physical Failure Analysis system.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

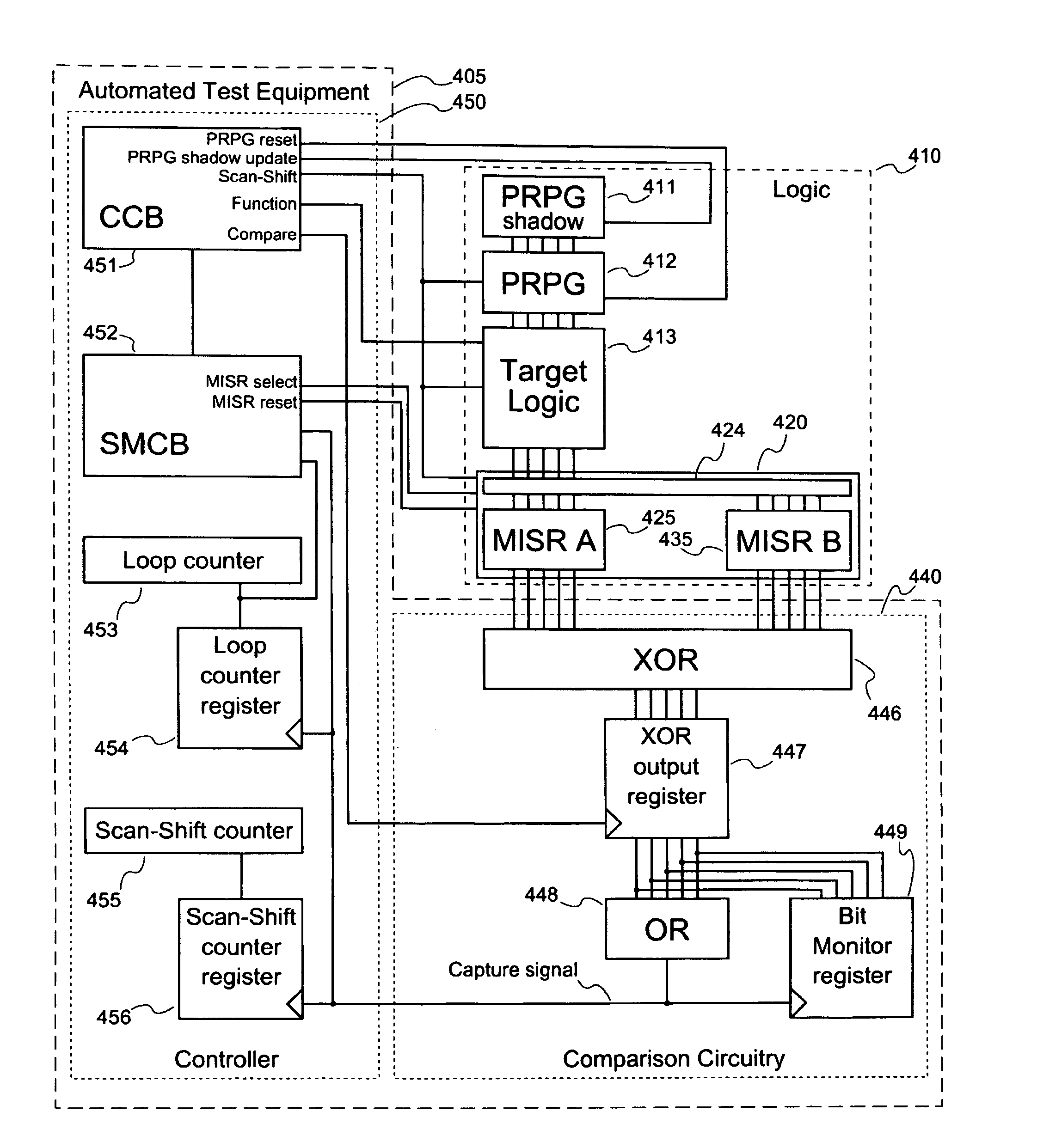

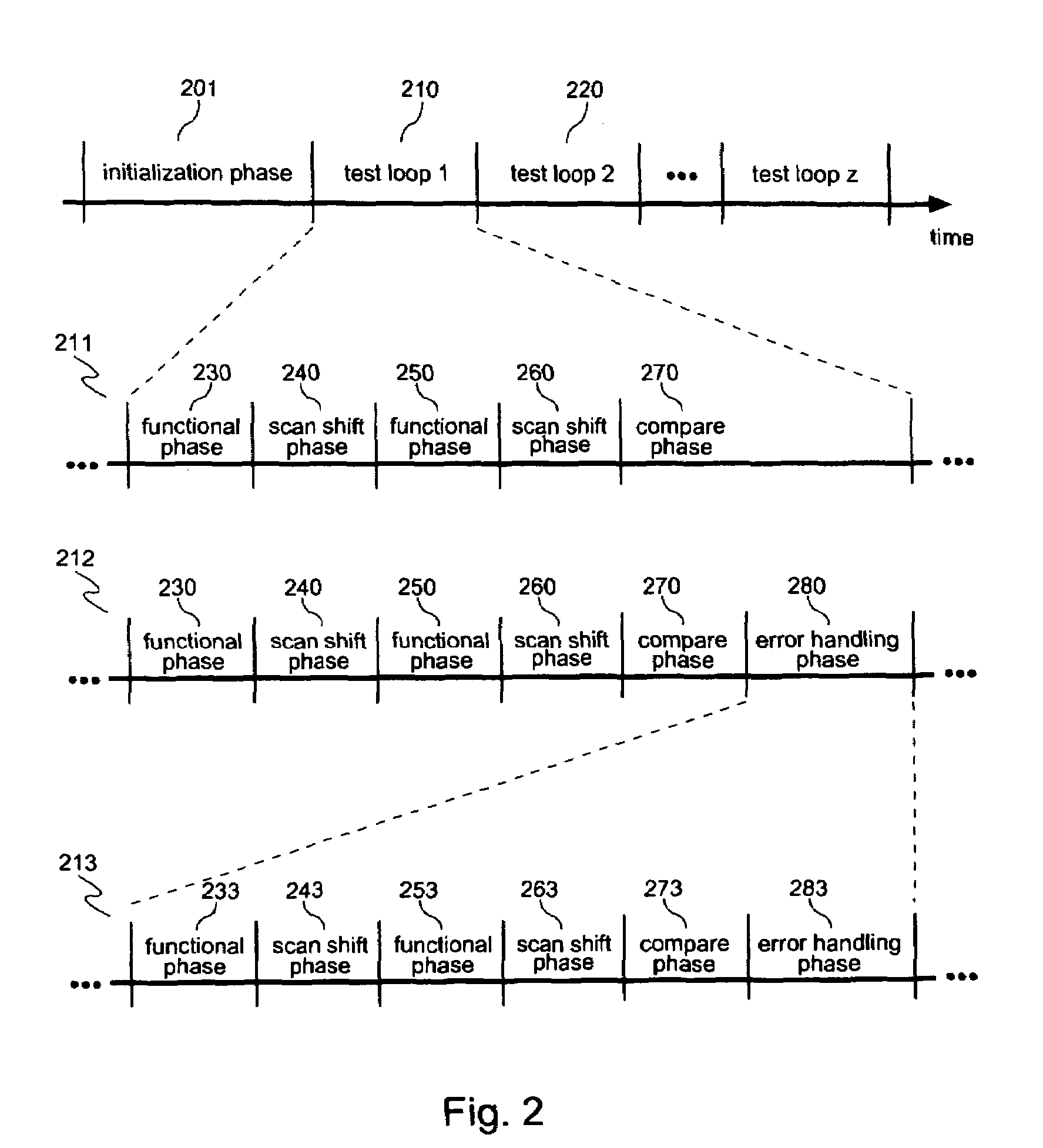

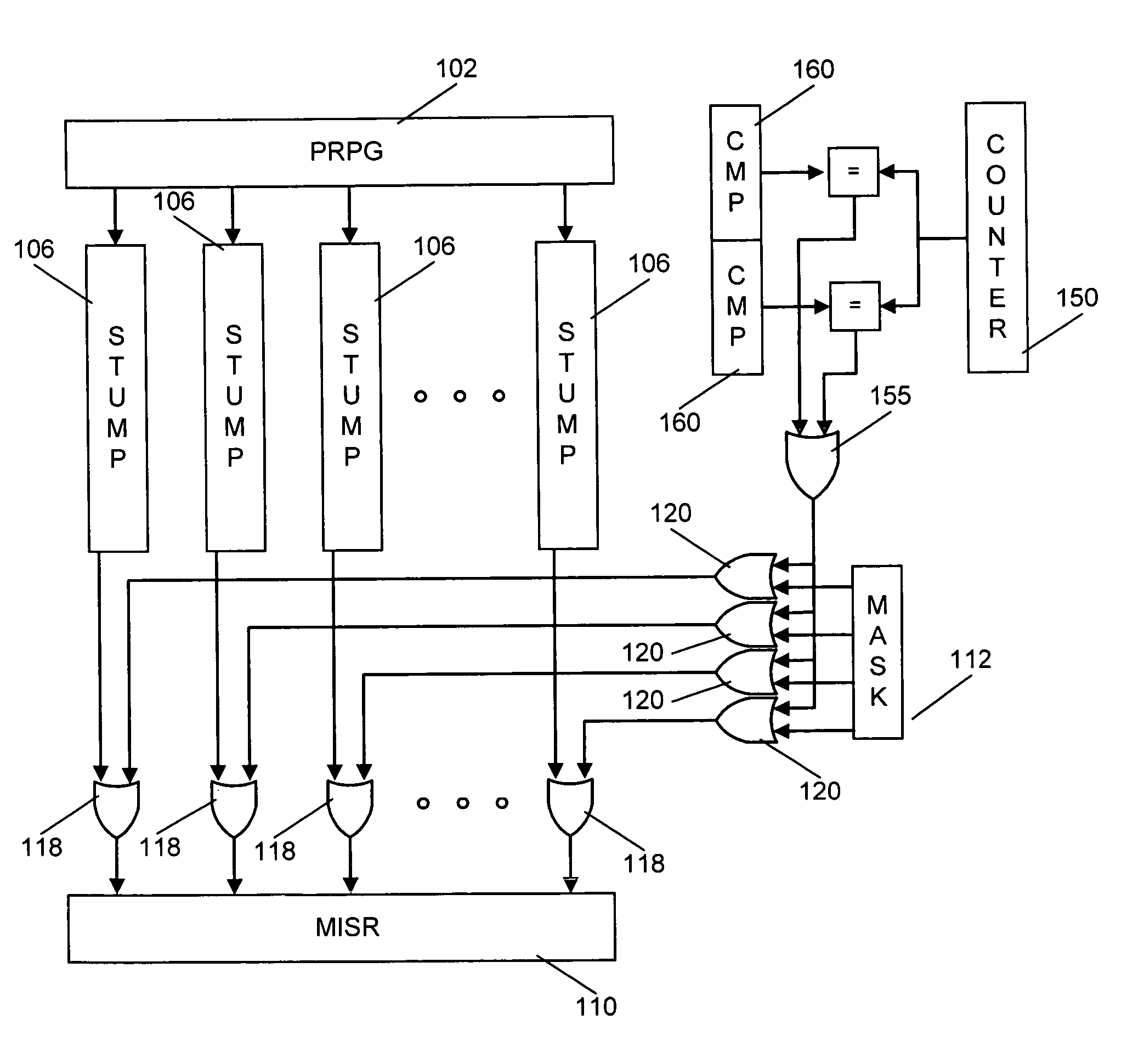

Systems and methods for self-diagnosing LBIST

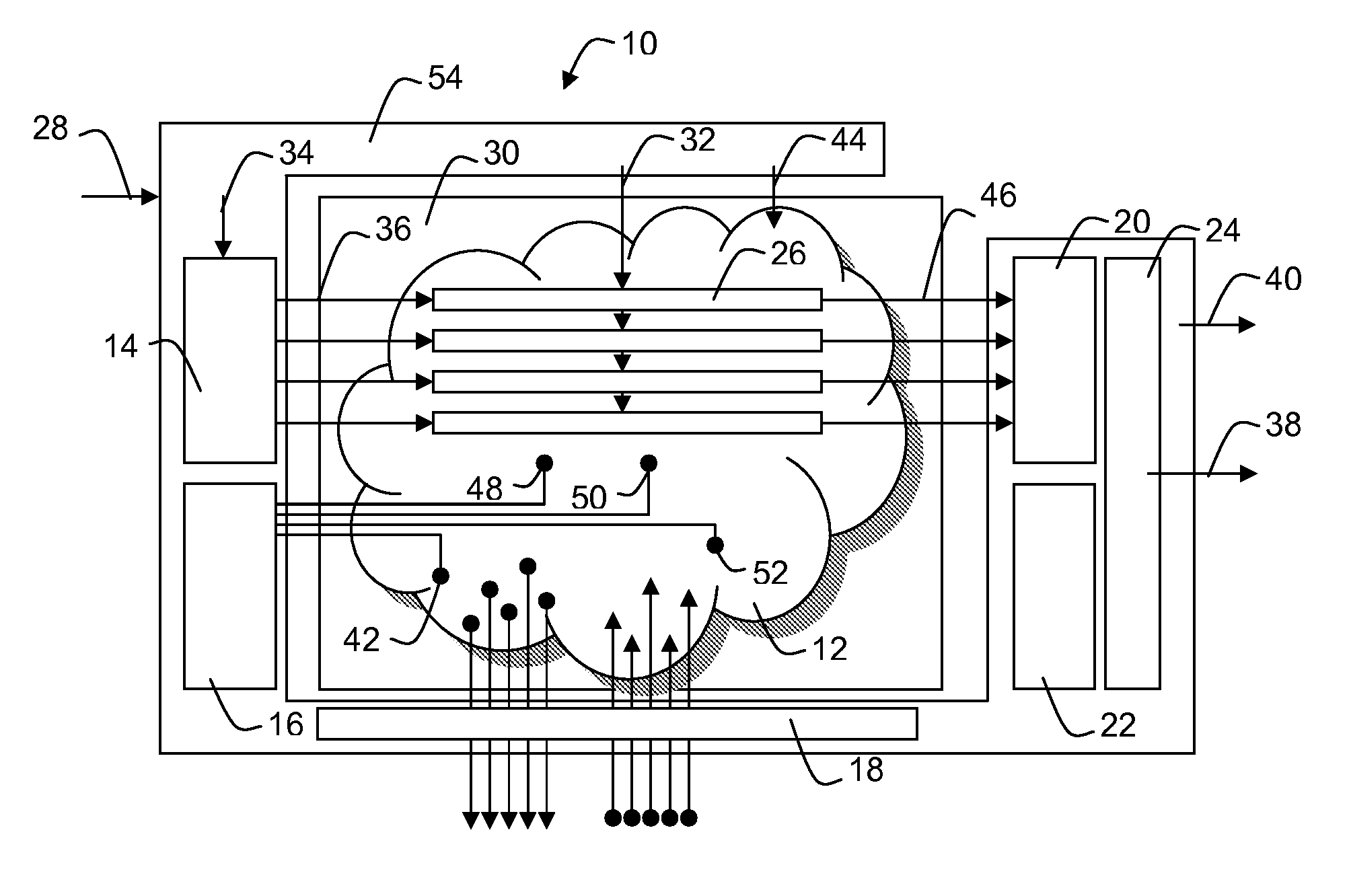

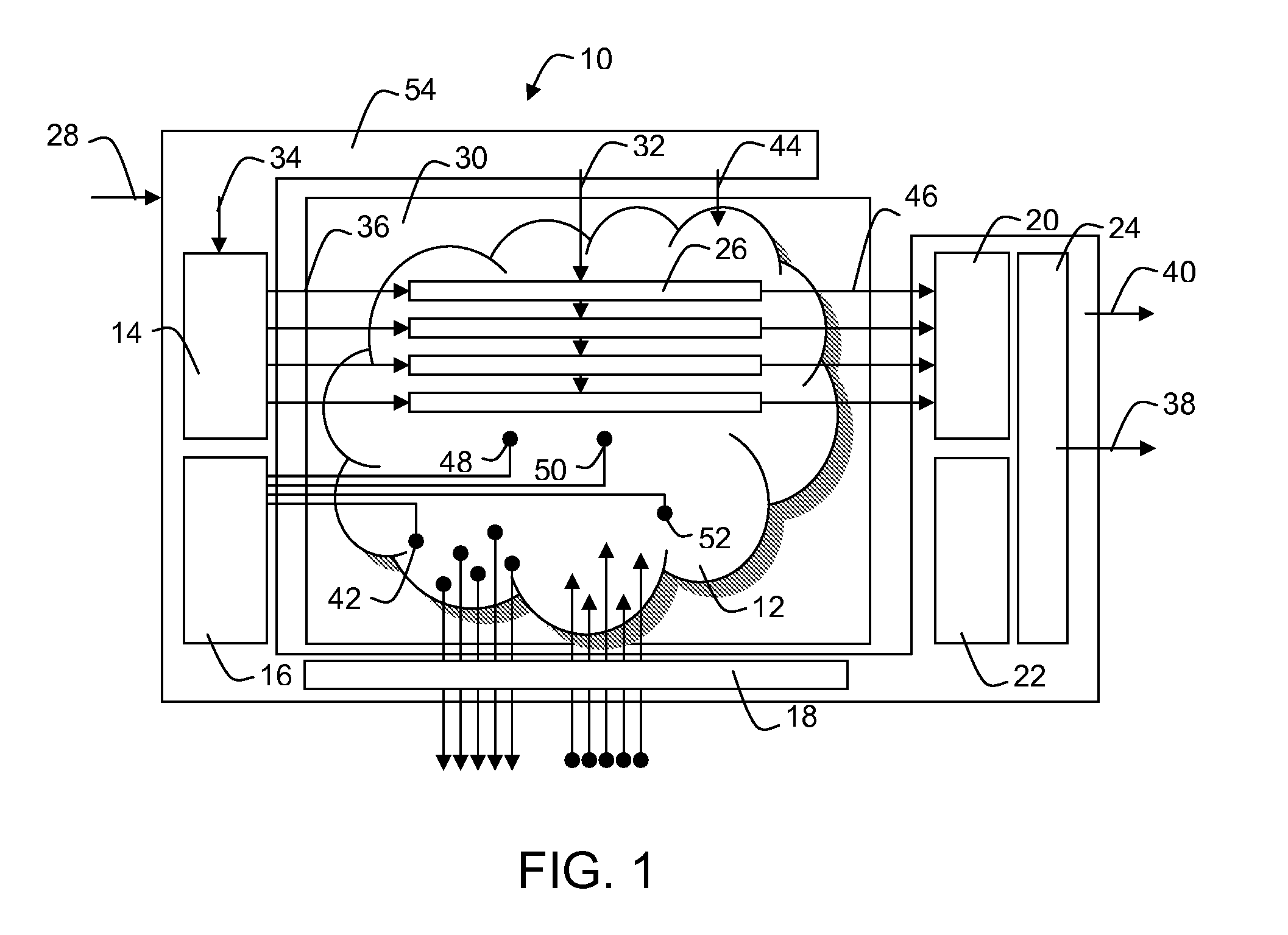

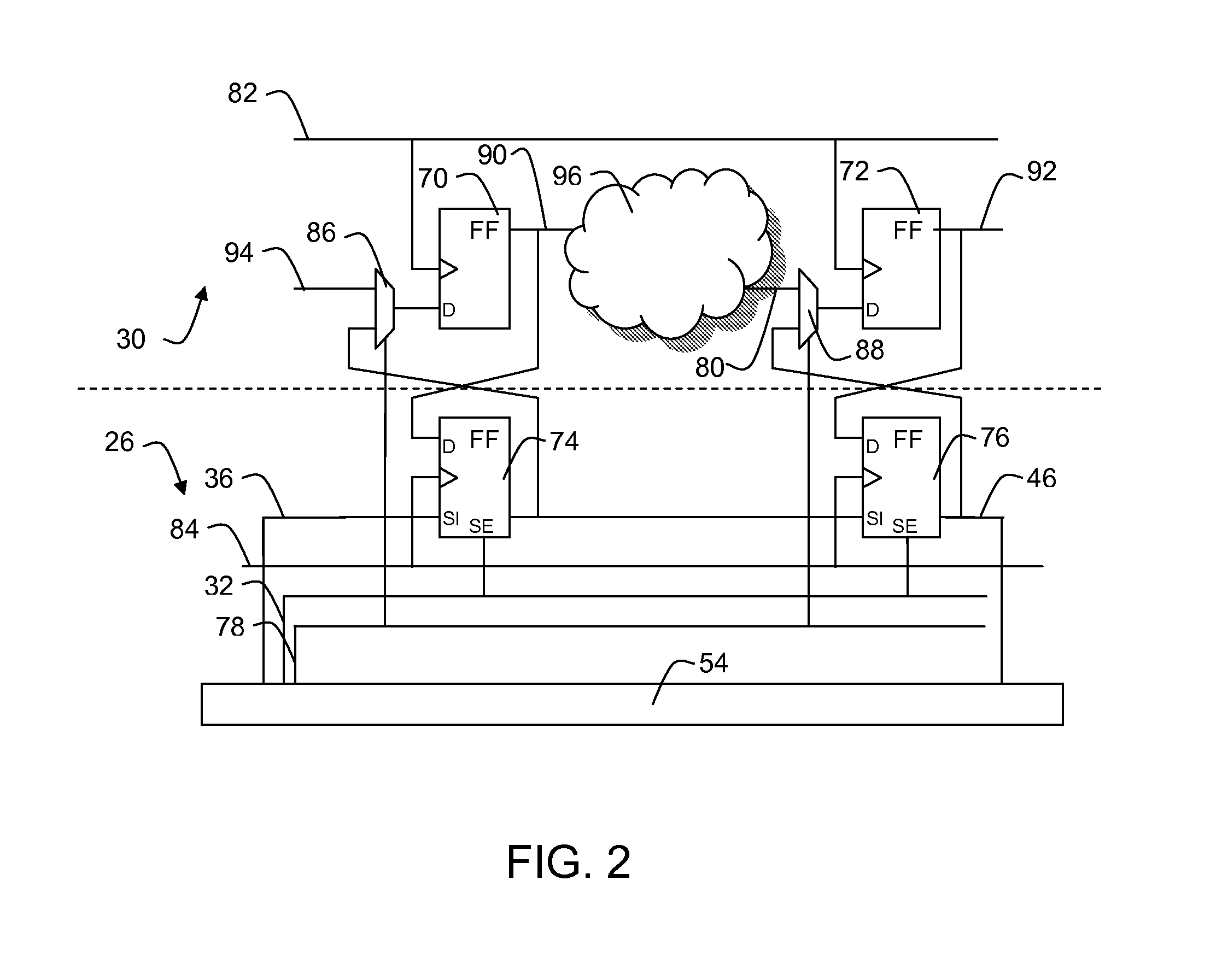

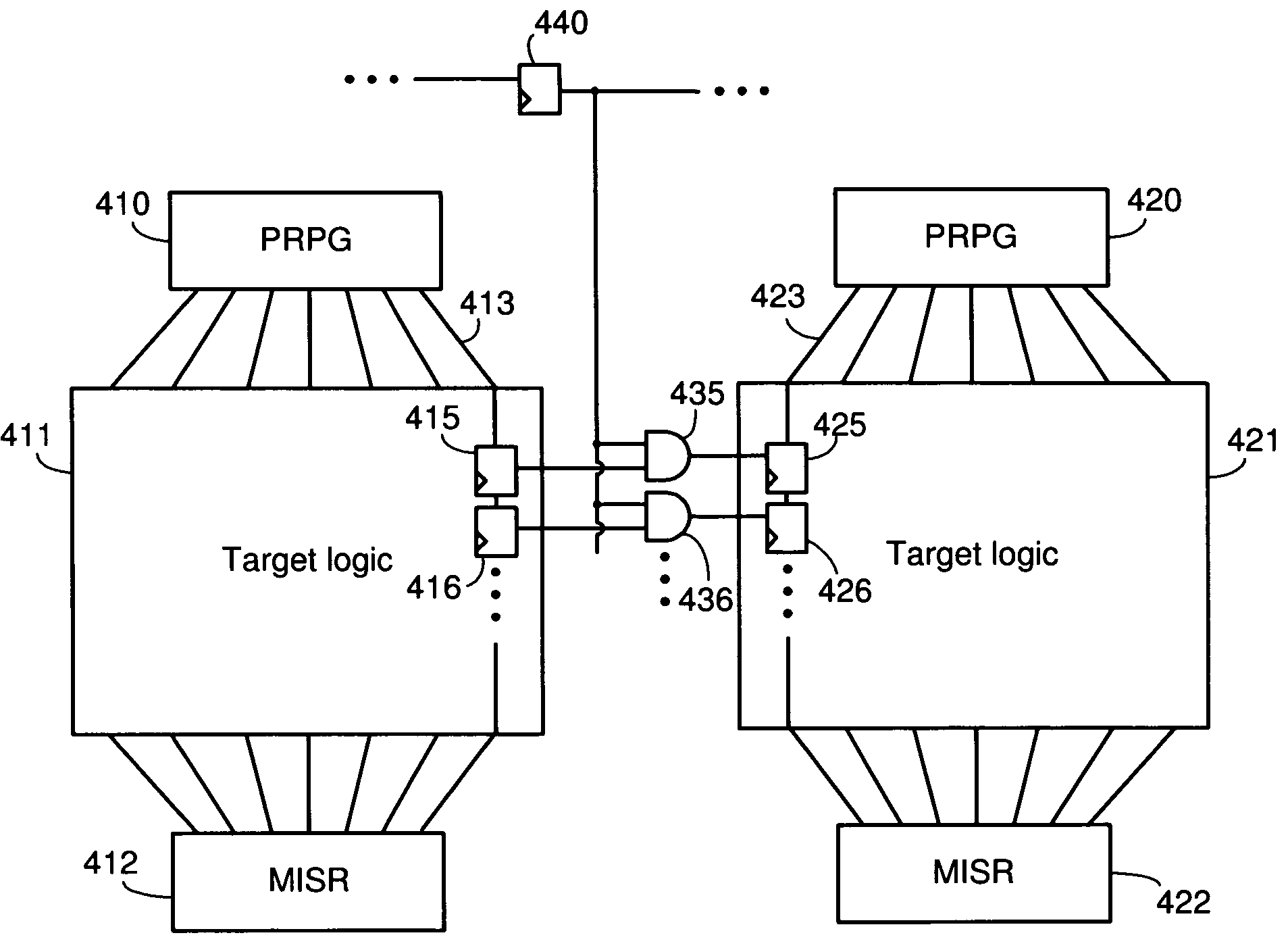

Systems and methods for performing logic built-in self-tests (LBISTs) in digital circuits. In one embodiment, a system has first and second target logic, each of which has LBIST circuitry incorporated therein. The system also includes comparison circuitry which is coupled to the first and second LBIST circuitry. The comparison circuitry is configured to detect differences between data generated by the LBIST circuitry of the first target logic and data generated by the LBIST circuitry of the second target logic (e.g., MISR signature values.) The comparison circuitry is also configured to provide information localizing the sources of the differences. In one embodiment, this localizing information comprises values from a test cycle counter, a scan shift counter and a set of XOR gates that compare the bits of the MISR values.

Owner:KK TOSHIBA

Logic built-in self-test system and method for applying a logic built-in self-test to a device under test

ActiveUS20110221469A1Electrical testingLogic circuits using elementary logic circuit componentsControl signalLogic built-in self-test

A logic built-in self test (LBIST) system comprises a device under test having a first plurality of first bistable multivibrator circuits an LBIST controller, and a second plurality of second bistable multivibrator circuits. Each second bistable multivibrator circuit is coupled to a corresponding first bistable multivibrator circuit to swap a second state value kept by the second bistable multivibrator circuit with a first state value kept by the corresponding first bistable multivibrator circuit depending on a first control signal from the LBIST controller and the second bistable multivibrator circuits are coupled to form one or more scan chains when receiving a second control signal from the LBIST controller.

Owner:NXP USA INC

System and method for burn-in test control

InactiveUS7103495B2Resistance/reactance/impedenceNuclear monitoringEquipment temperatureControl system

Owner:KK TOSHIBA

Systems and Methods for Improved Fault Coverage of LBIST Testing

InactiveUS20070273401A1Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageEngineering

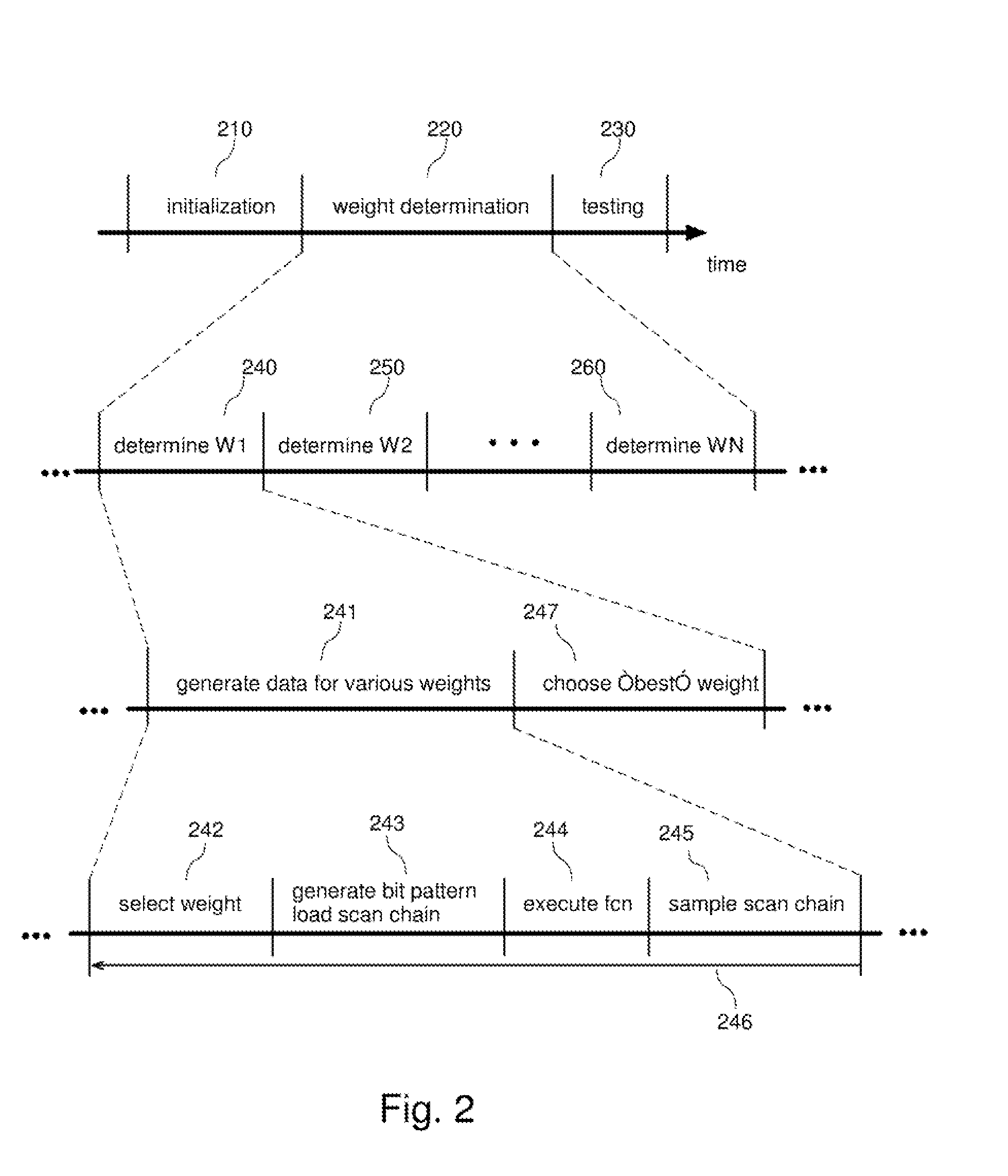

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) by determining weighting and / or seed values to be used in generating pseudorandom test bit patterns for each channel to optimize fault coverage. In one embodiment, a method includes generating a pseudorandom sequence of bits, applying a weighting value to the sequence, propagating the weighted sequence through one or more levels of logic, and capturing the resulting data. Metrics are then applied to the captured data to determine the suitability or optimality of the weighting value, and an optimal weighting value is selected. This may be performed for a plurality of trial values for each of a number of channels to obtain a set of weighting values for the different LBIST channels. The method may also include determining a seed value for the pseudorandom bit pattern generator.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

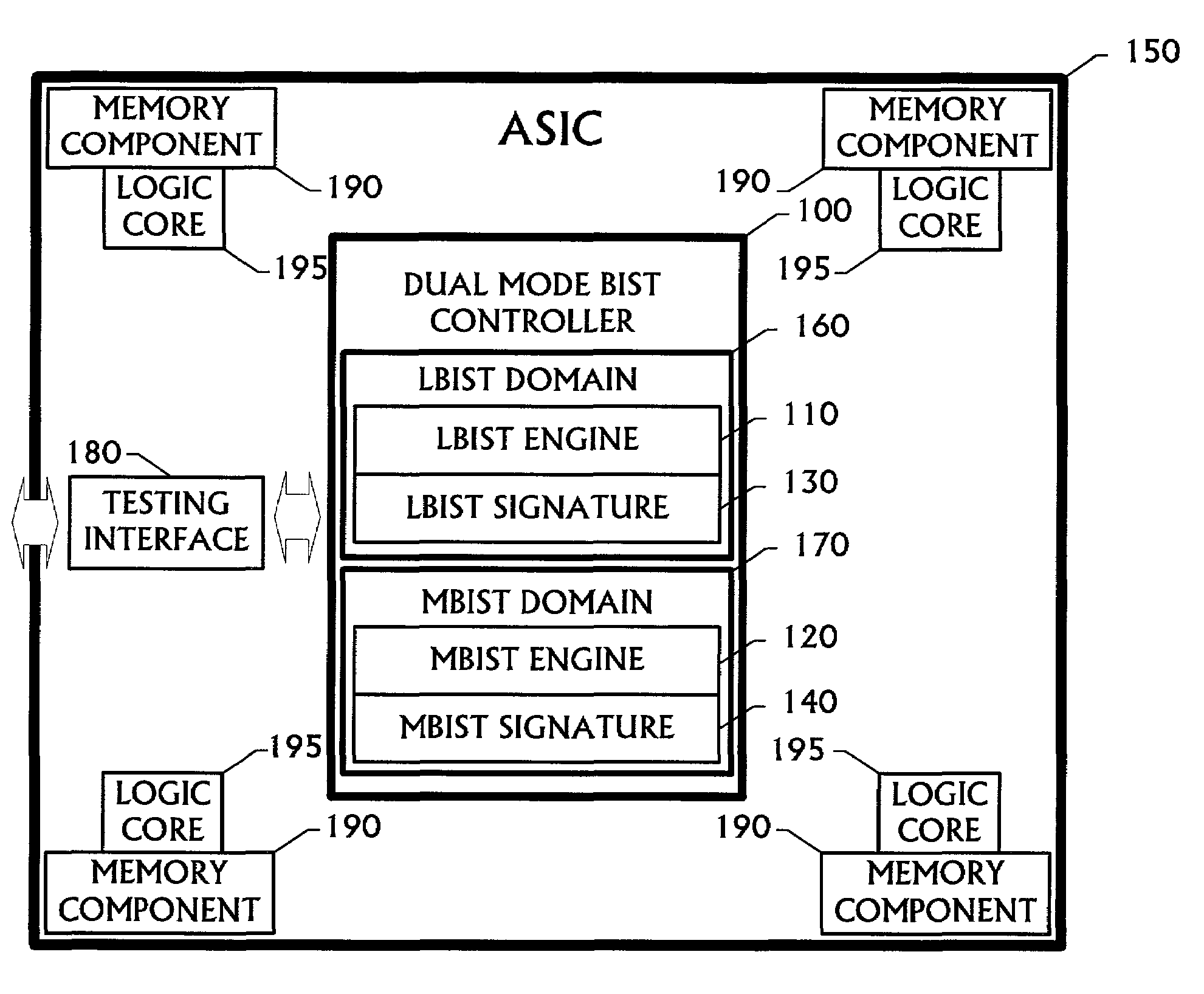

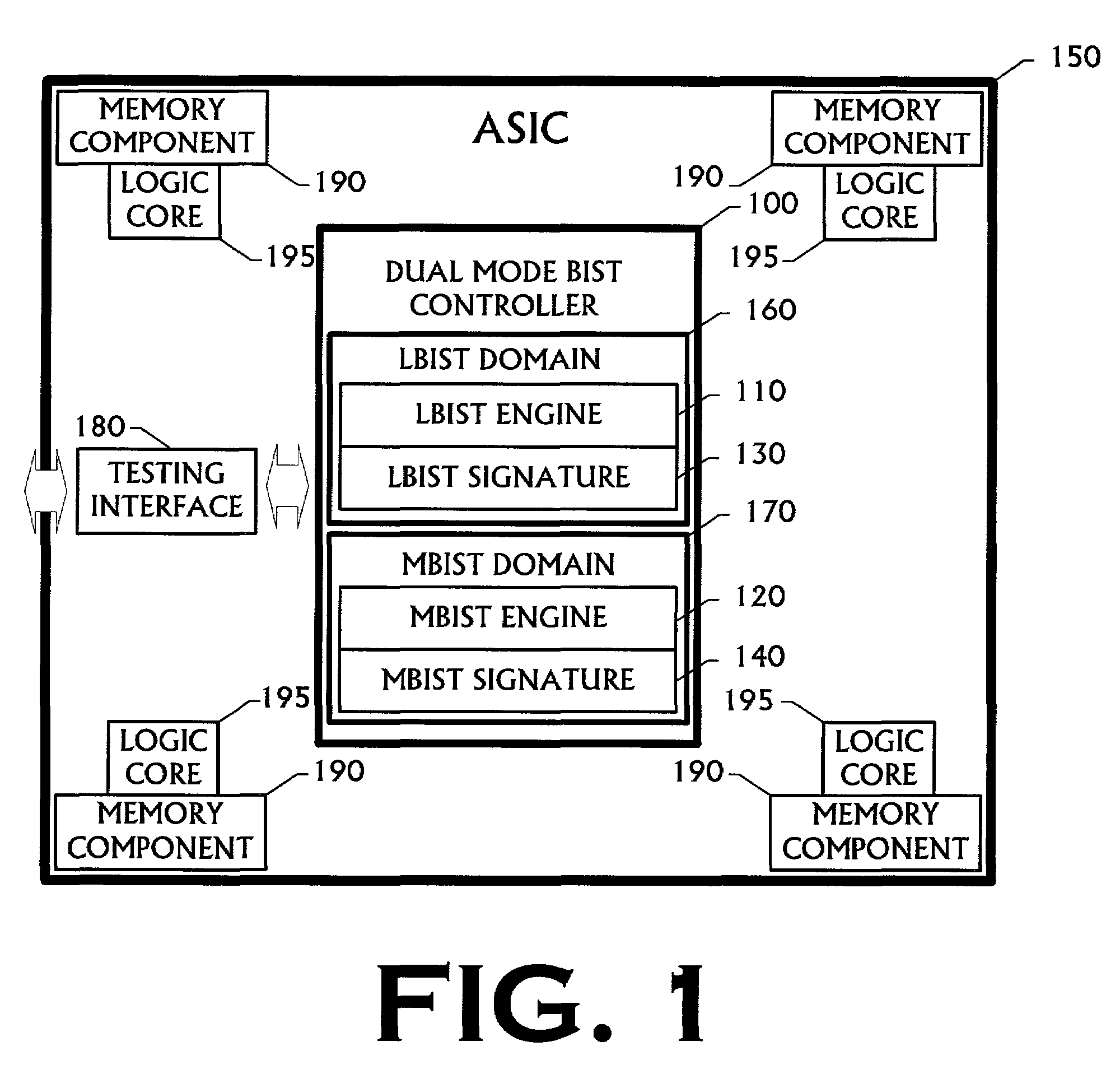

ASIC logic BIST employing registers seeded with differing primitive polynomials

InactiveUS6981191B2Electronic circuit testingError detection/correctionProcessor registerTheoretical computer science

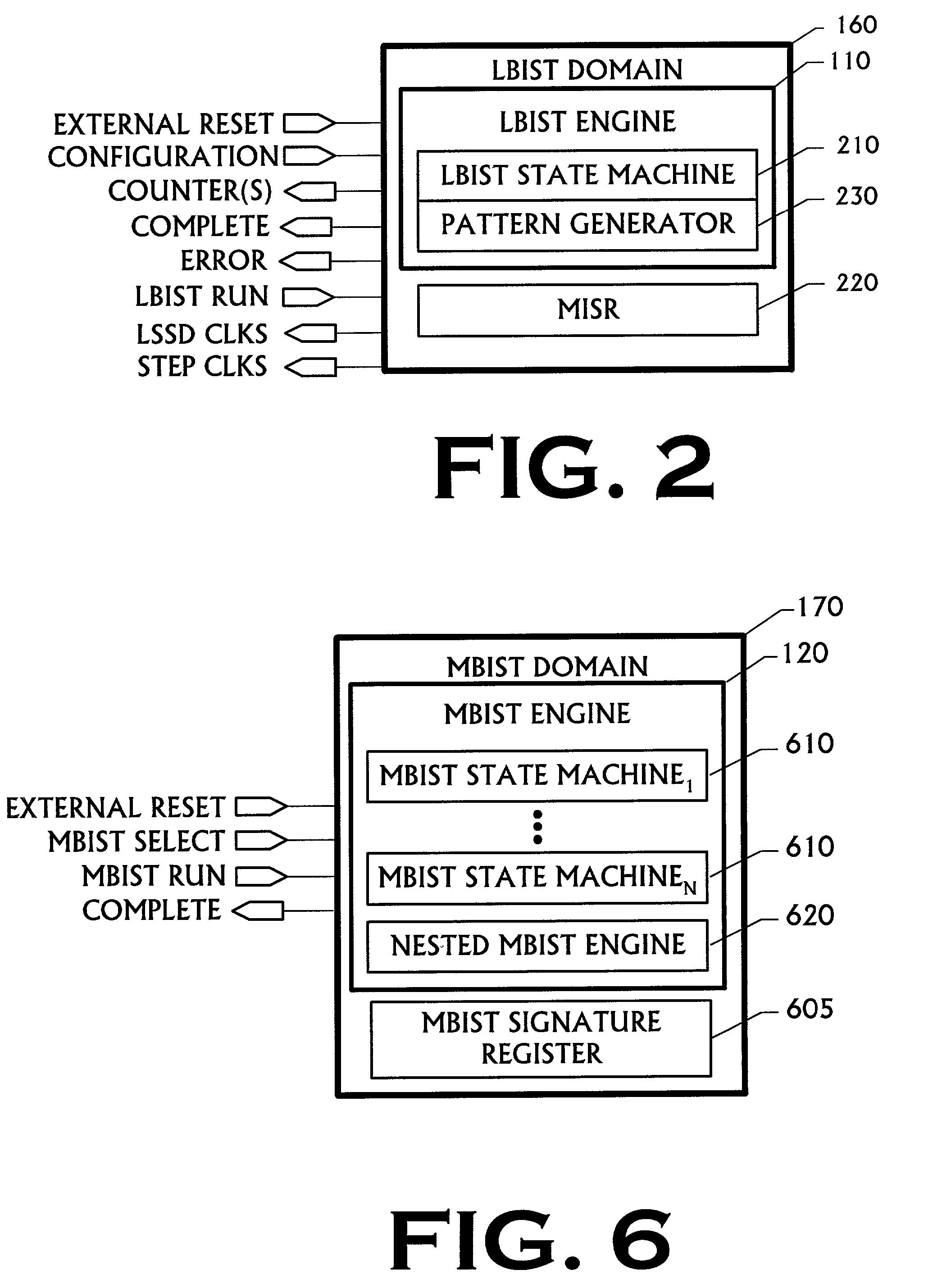

A method and apparatus for performing a built-in self-test (“BIST”) on an integrated circuit device are disclosed. A BIST controller comprises a logic built-in self-test (“LBIST”) engine capable of executing a LBIST and storing the results thereof and a multiple input signature register (“MISR”). The LBIST engine includes a LBIST state machine; and a pattern generator seeded with a first primitive polynomial. The MISR is capable of storing the results of an executed LBIST, the contents thereof being stored per a second primitive polynomial. A method for performing a LBIST comprises seeding a pattern generator in a LBIST engine with a first polynomial; executing a LBIST using the contents of the pattern generator; and storing the results of an executed LBIST in a MISR utilizing a second primitive polynomial.

Owner:ORACLE INT CORP

Systems and methods for LBIST testing using isolatable scan chains

Systems and methods for performing logic built-in self-tests (LBISTs) in digital circuits, where boundary scan chains in functional blocks of the circuits can be selectively coupled / decoupled to isolate the functional blocks during LBIST testing. In one embodiment, processor cores of a multiprocessor chip are isolated and LBIST testing is performed to determine whether any of the processor cores is malfunctioning. If none of the processor cores malfunctions, the processor cores are tested in conjunction with the supporting functional blocks of the device to determine whether the multiprocessor is fully functional. If one or more processor cores malfunctions, these processor cores are isolated and the remaining processor cores are tested in conjunction with the supporting functional blocks of the device to determine whether the multiprocessor operates properly with reduced functionality.

Owner:TOSHIBA ELECTRONICS DEVICES & STORAGE CORPORARTION +1

Systems and methods for diagnosing rate dependent errors using LBIST

InactiveUS7475311B2Electronic circuit testingError detection/correctionLogic built-in self-testComputer science

Systems and methods for performing logic built-in self-tests (LBISTs) to detect “at-speed” errors in a digital circuit. In one embodiment, an input bit pattern is propagated through target logic of the digital circuit and captured in scan chains at a normal operating speed to produce a first output bit pattern. This is repeated with the first input bit pattern at a lower test speed to produce a second output bit pattern. Differences between the first and second output bit patterns are then detected to determine whether operation of the digital circuit at the normal operating speed causes errors that are not generated at the lower test speed.

Owner:KK TOSHIBA

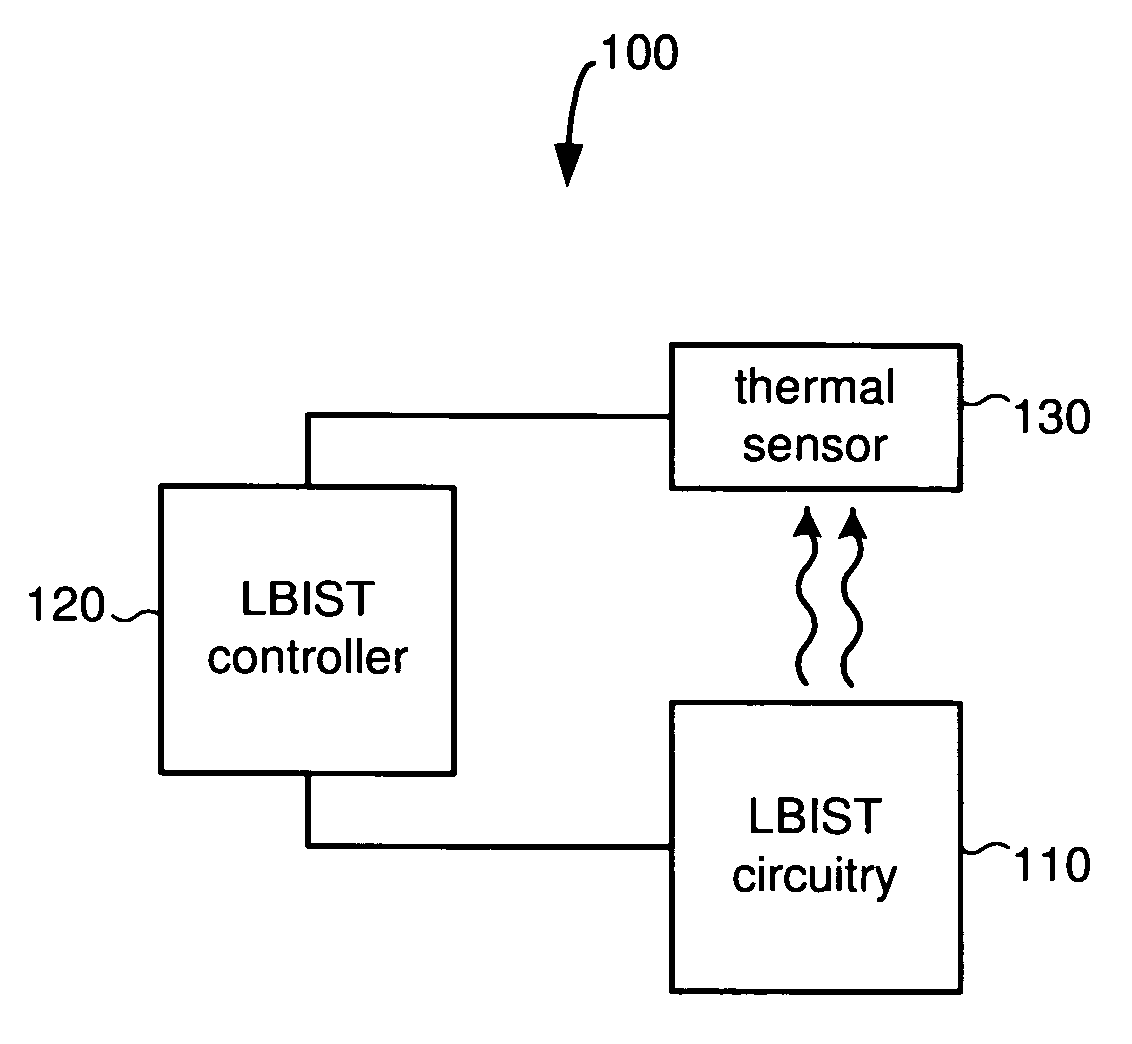

System and method for burn-in test control

InactiveUS20060064265A1Affect temperatureResistance/reactance/impedenceDigital computer detailsEquipment temperatureControl system

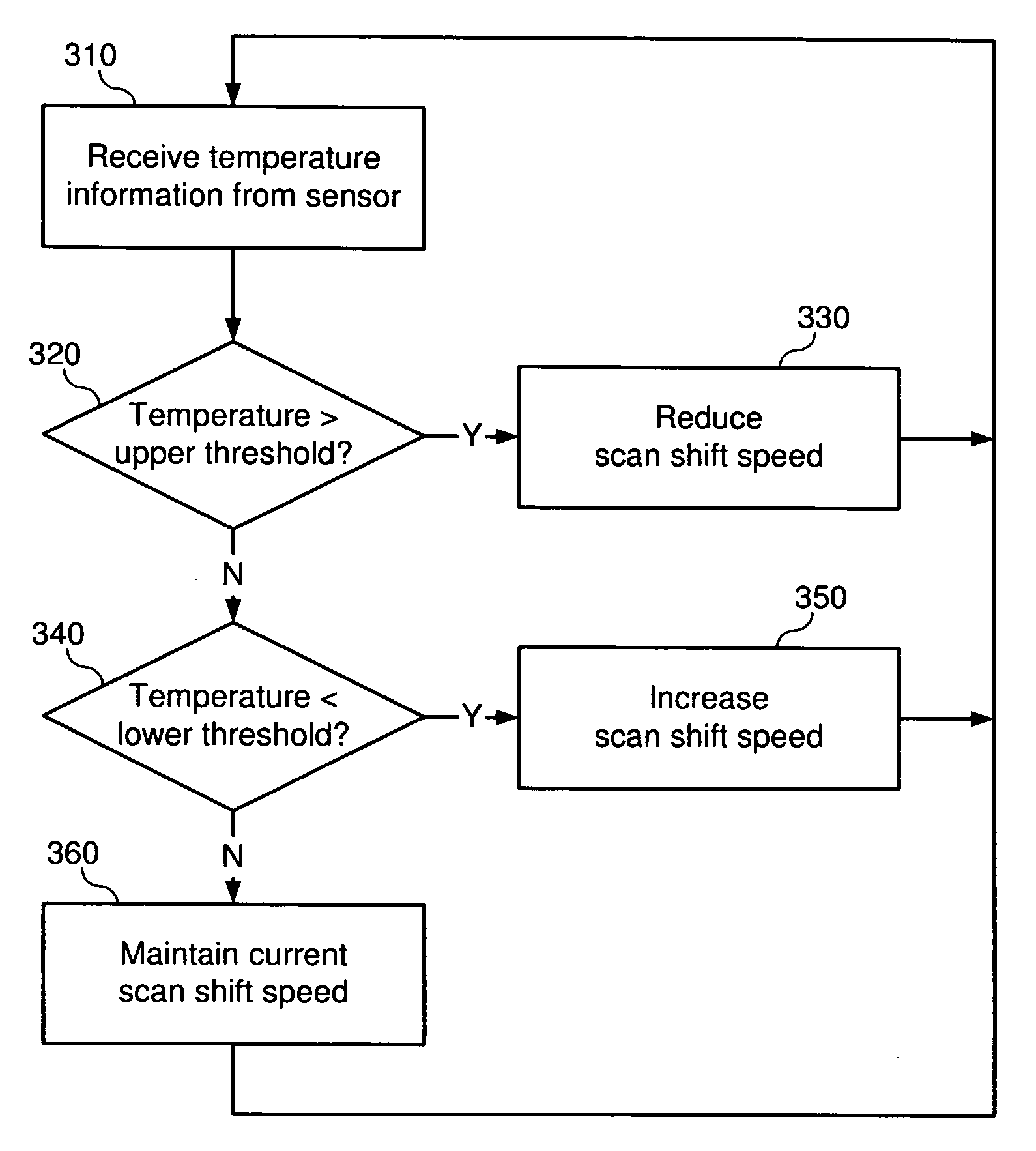

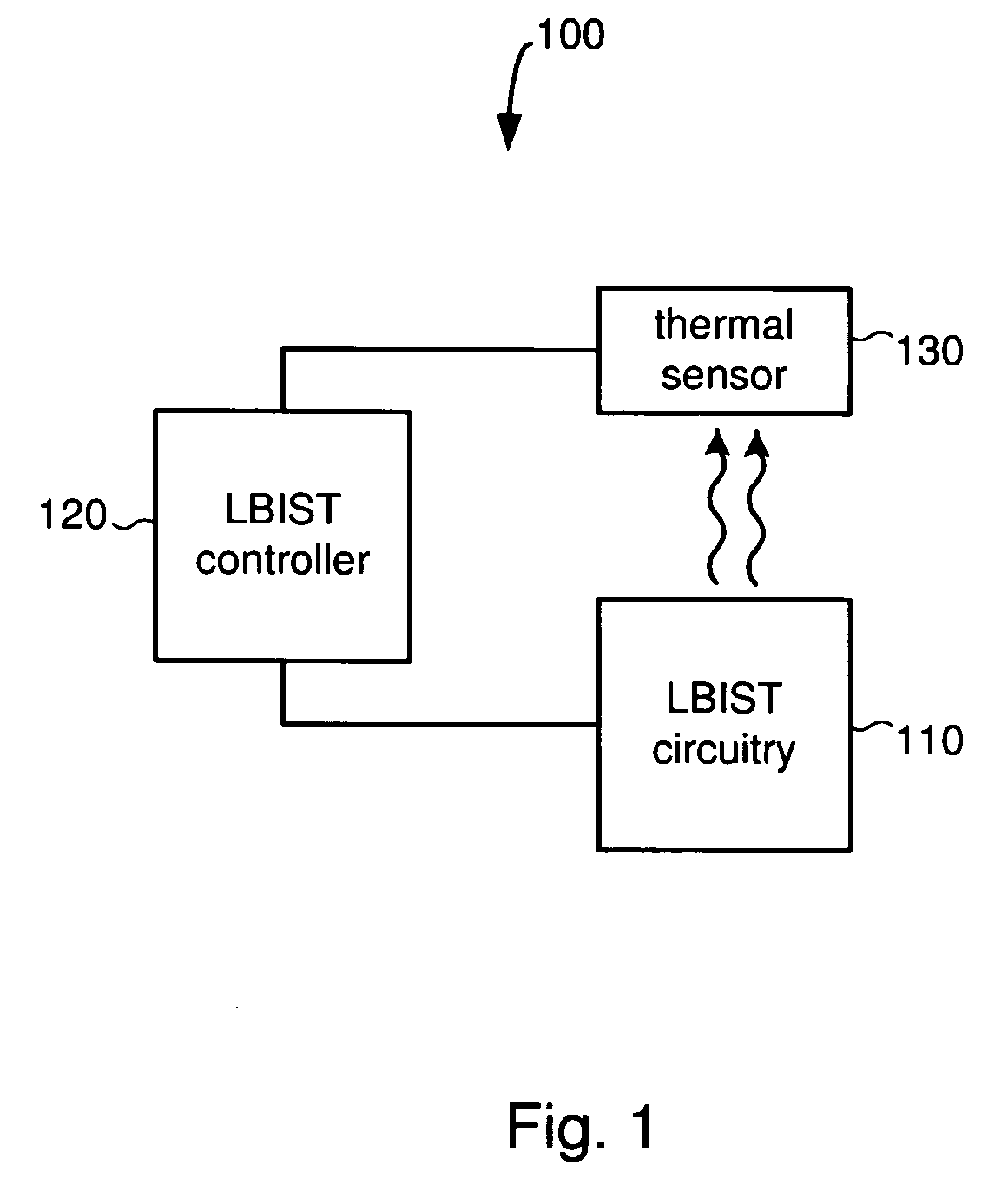

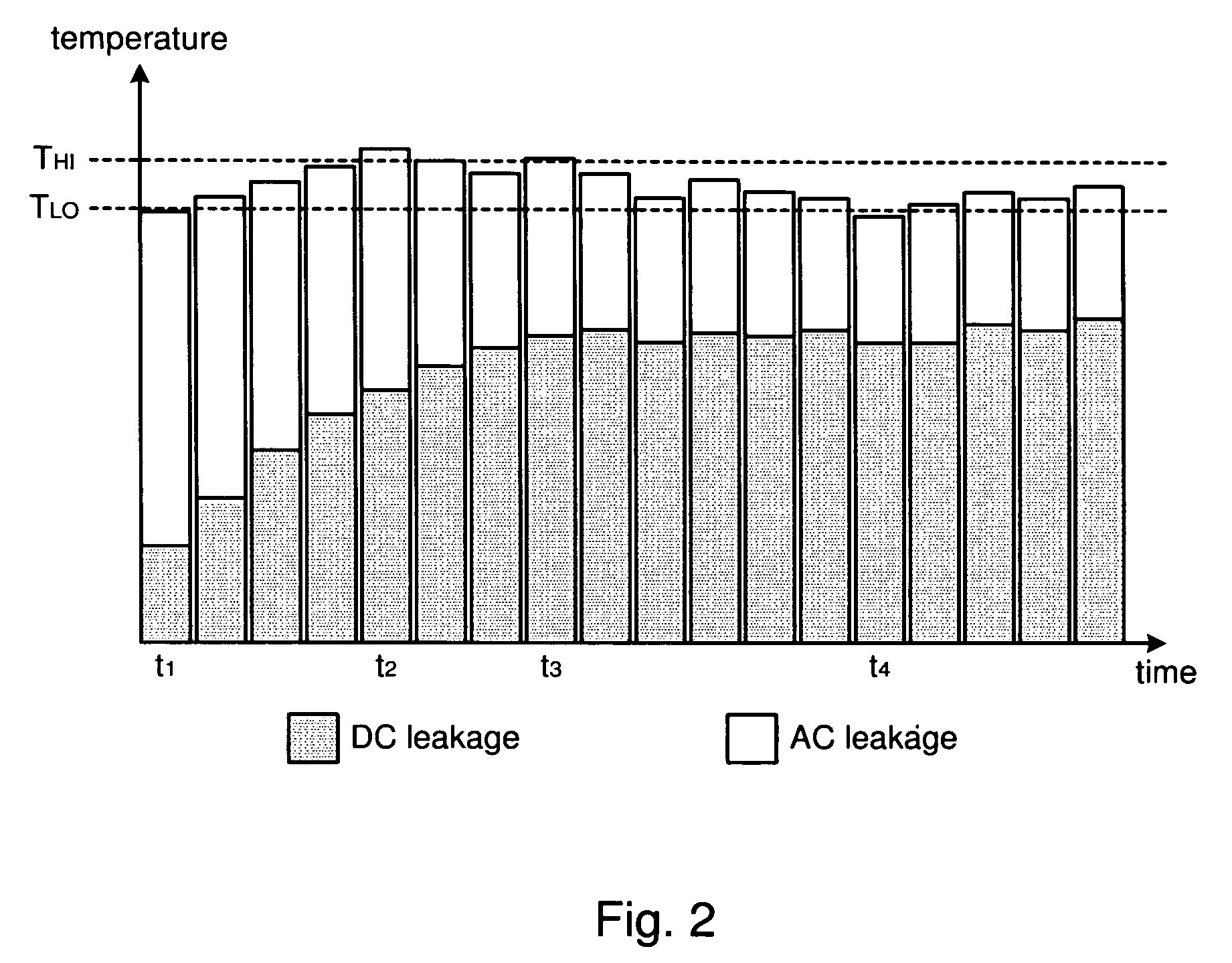

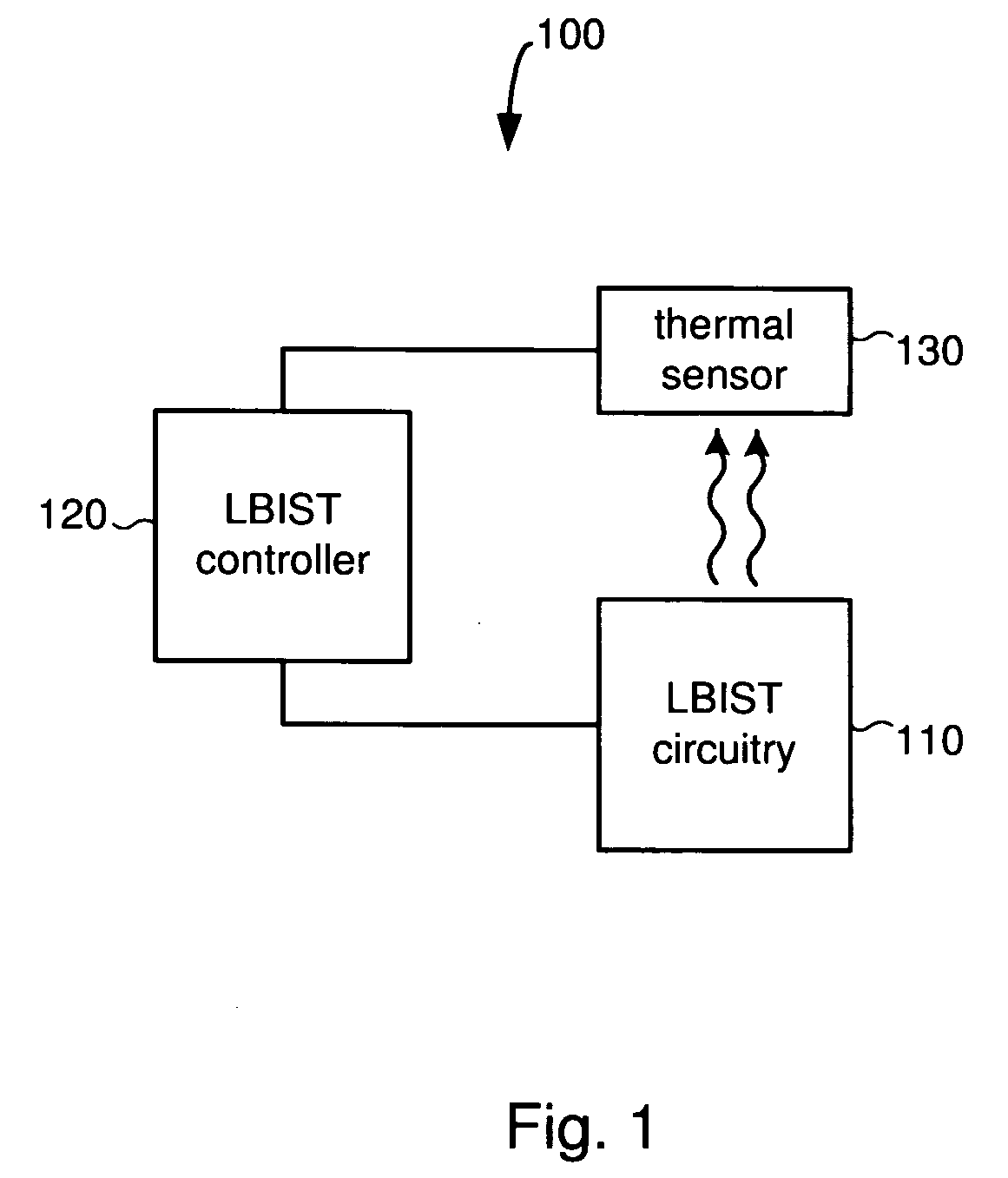

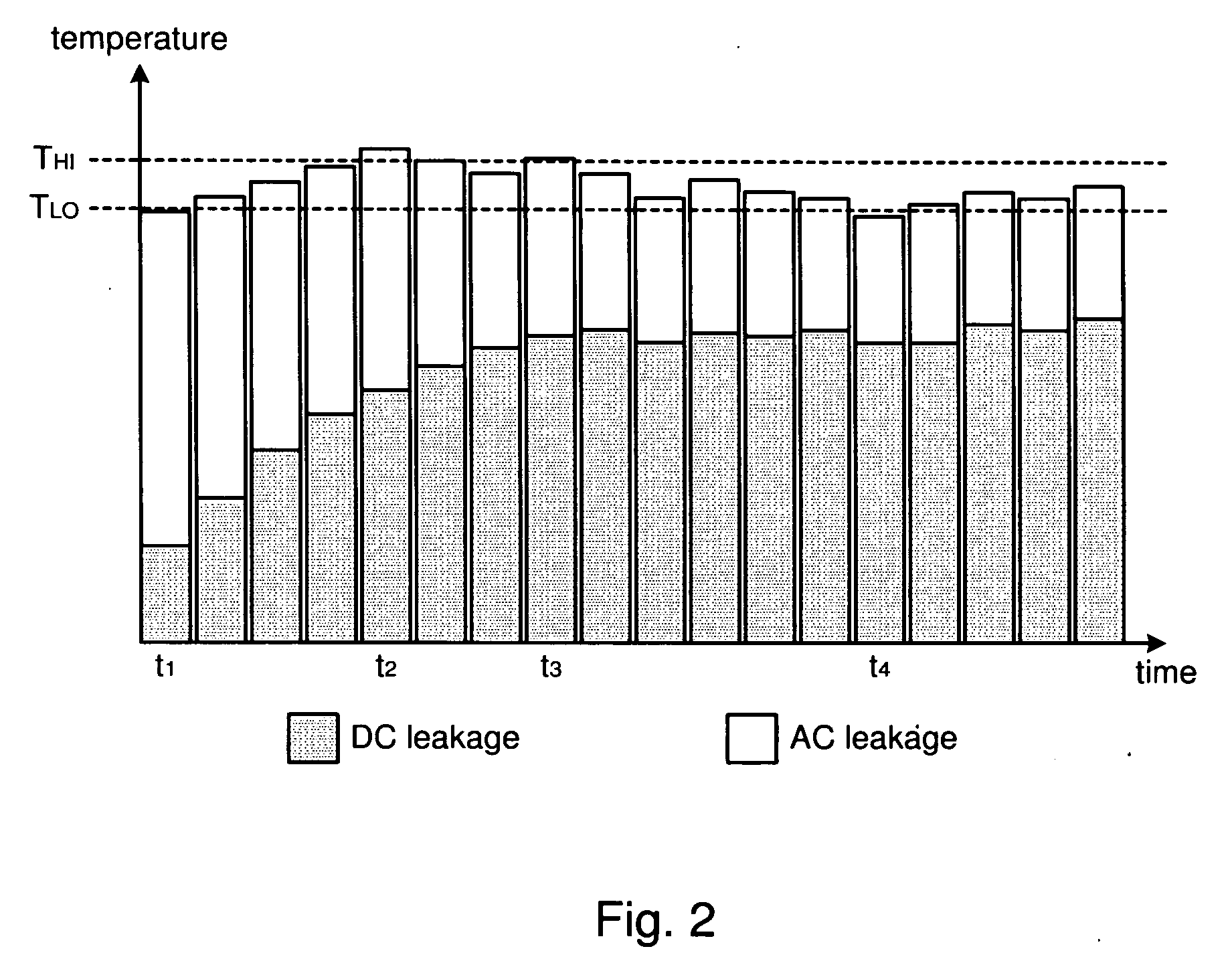

Systems and methods for controlling test conditions using logic built-in self-test (LBIST) components to affect test conditions. In one embodiment, an LBIST controller is coupled to LBIST circuitry that is incorporated into the design of a device under test, and also to a thermal sensor that is in thermal communication with the device under test. The LBIST controller is configured to receive device temperature information from the thermal sensor and to modify control signals that are provided to the LBIST circuitry in order to cause the LBIST circuitry to operate in a manner that drives the device temperature to a desired level. In one embodiment, the LBIST controller adjusts the speed with which the LBIST circuitry scans data into and out of a plurality of scan chains, thereby adjusting the amount of heat generated by this operation, which in turn affects the temperature of the device.

Owner:KK TOSHIBA

Systems and methods for LBIST testing using isolatable scan chains

Systems and methods for performing logic built-in self-tests (LBISTs) in digital circuits, where boundary scan chains in functional blocks of the circuits can be selectively coupled / decoupled to isolate the functional blocks during LBIST testing. In one embodiment, processor cores of a multiprocessor chip are isolated and LBIST testing is performed to determine whether any of the processor cores is malfunctioning. If none of the processor cores malfunctions, the processor cores are tested in conjunction with the supporting functional blocks of the device to determine whether the multiprocessor is fully functional. If one or more processor cores malfunctions, these processor cores are isolated and the remaining processor cores are tested in conjunction with the supporting functional blocks of the device to determine whether the multiprocessor operates properly with reduced functionality.

Owner:TOSHIBA ELECTRONICS DEVICES & STORAGE CORPORARTION +1

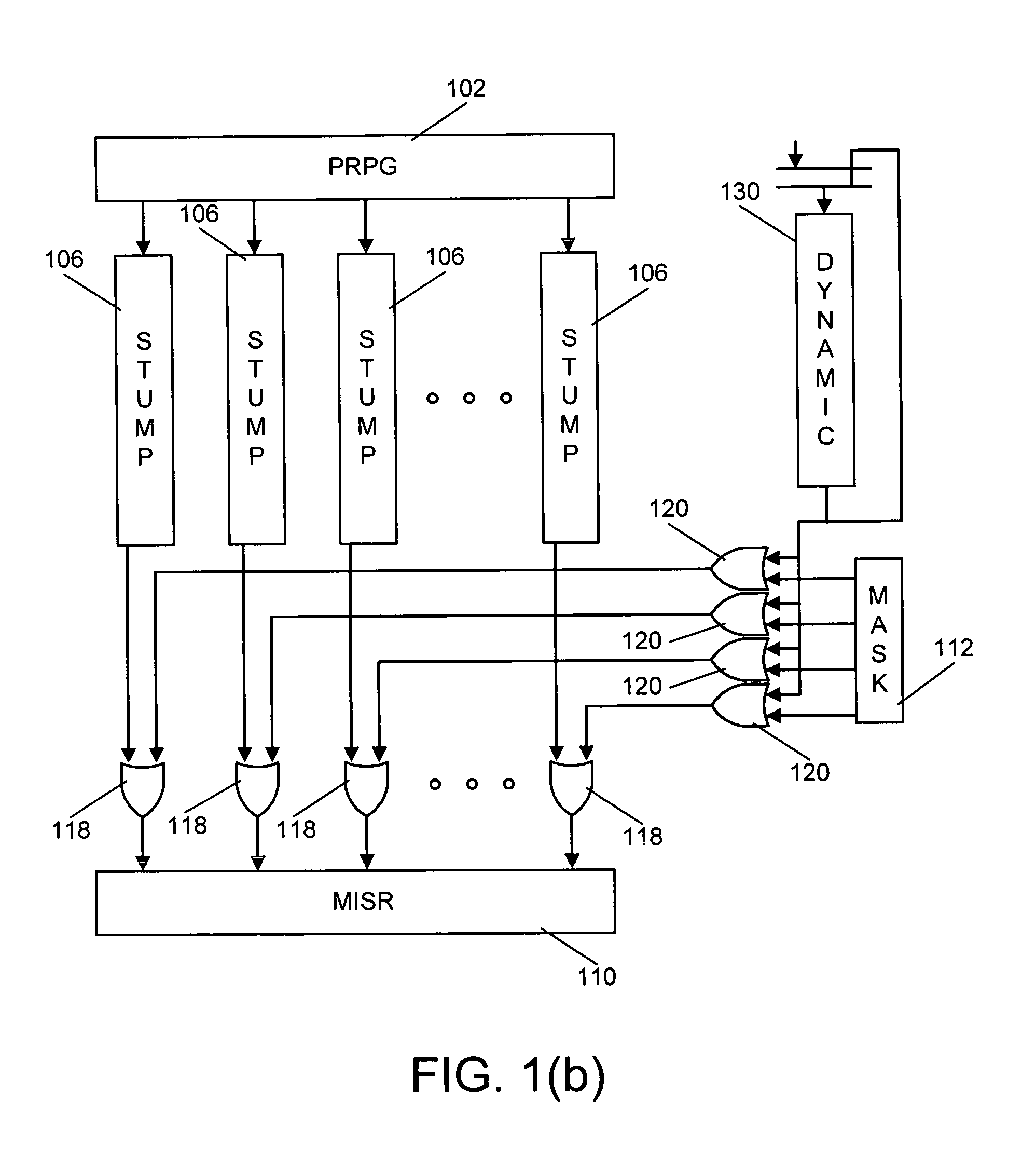

Method of improving logical built-in self test (LBIST) AC fault isolations

InactiveUS7376875B2Electronic circuit testingError detection/correctionLogic built-in self-testComputer science

A system, apparatus and method of isolating a plurality of limiting logical cones in a chip during a logical built-in self test (LBIST) are provided. An LBIST is performed on the chip in order to locate a first latch that fails the test. Particularly, latches on the chip are arranged in a plurality of scan chains wherein each latch holds data for a logical cone. The LBIST is performed on one scan chain at a time. Once the first latch is located, a first limiting cone (i.e., the cone for which the first latch is holding data) may be isolated. After isolating the first limiting cone, the data from the first latch is masked out and the LBIST is repeated on the scan chain. The data is masked out in order to facilitate the identification of any other latch that may fail the test. Again, if another latch fails the test a corresponding limiting cone may be isolated.

Owner:INT BUSINESS MASCH CORP

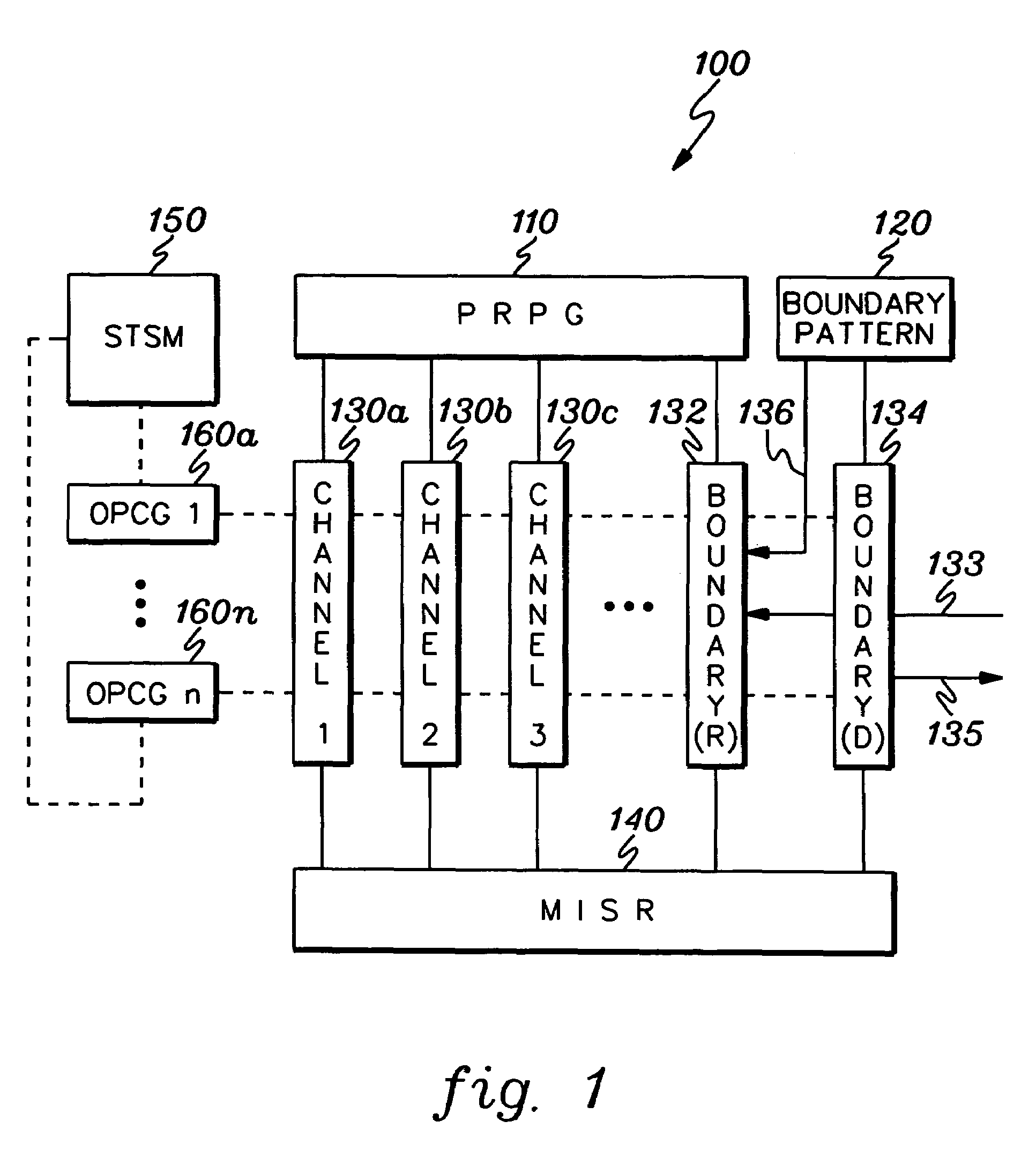

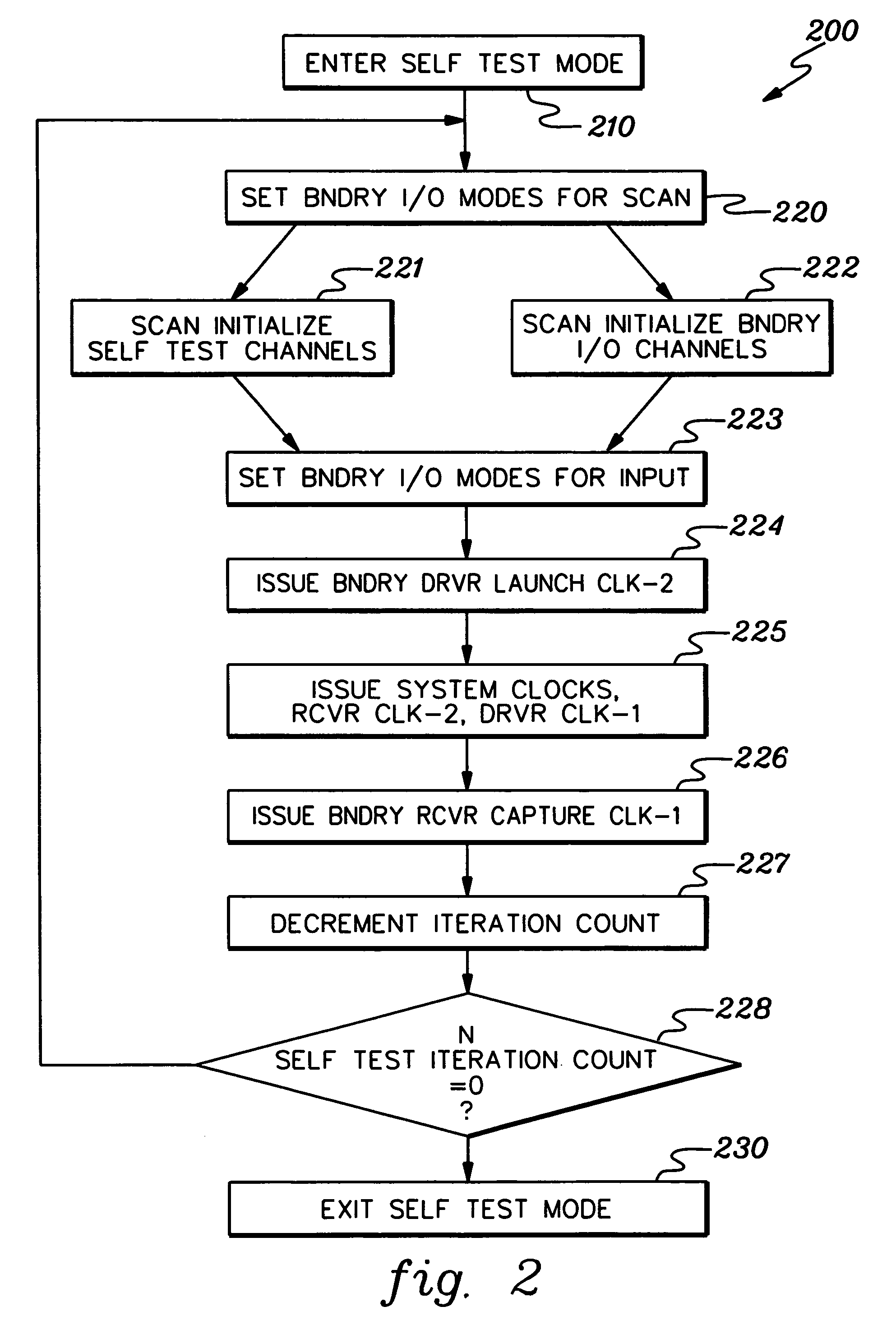

Method, system, and program product for boundary I/O testing employing a logic built-in self-test of an integrated circuit

A testing method is provided which includes verifying at least one external signal path of an electronic package environment by testing an input / output (I / O) circuit of an integrated circuit of the electronic package environment with a logic built-in self-test (LBIST) of the integrated circuit, wherein the external signal path being verified is electrically coupled to the tested I / O circuit. A result of verifying of the at least one external signal path is manifested in the integrated circuit's signature, which characterizes a response of the I / O circuit to the LBIST. In another aspect, the verifying of the at least one external signal path includes concurrently testing another I / O circuit of another integrated circuit, which is also electrically coupled to the external signal path.

Owner:INT BUSINESS MASCH CORP

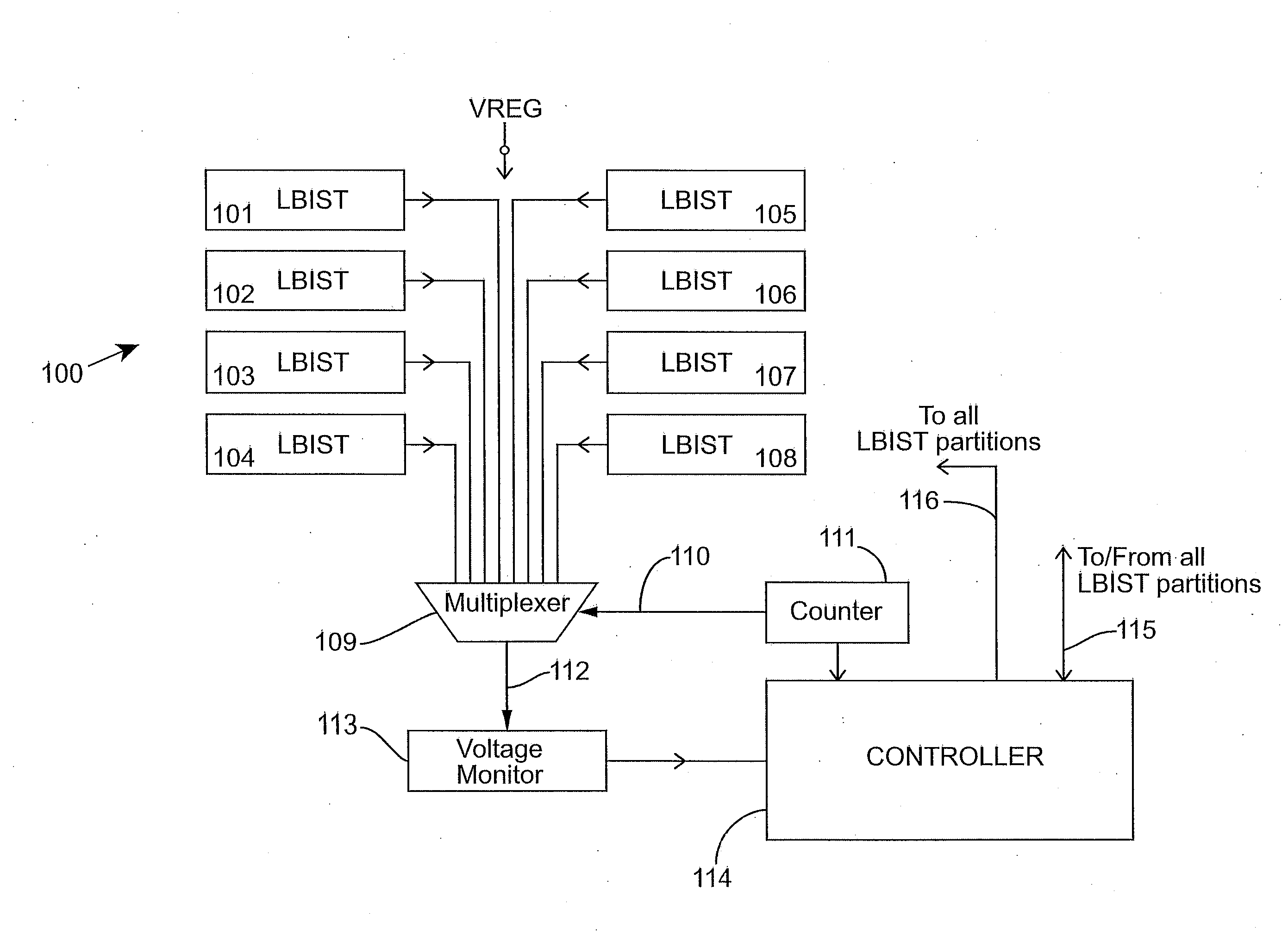

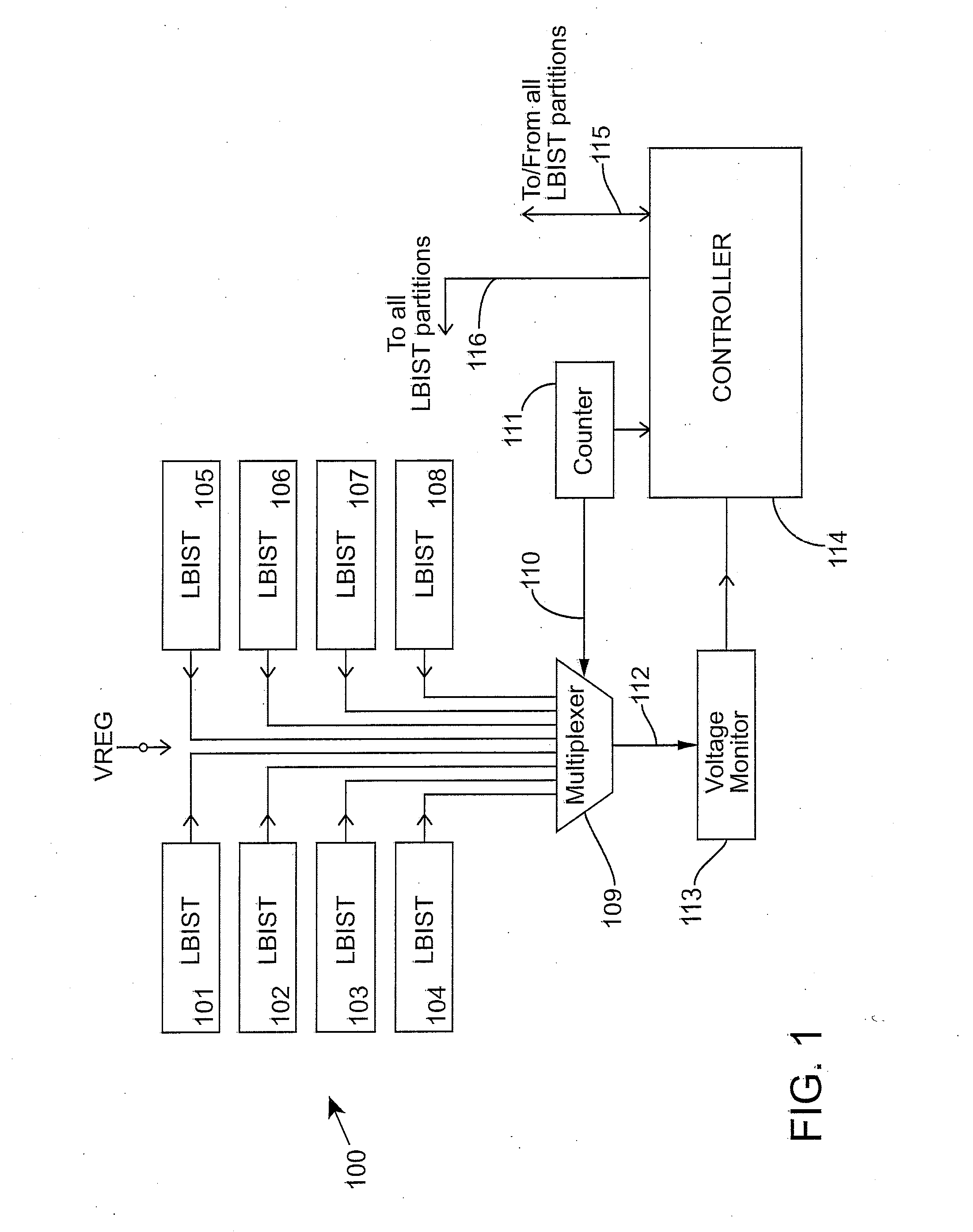

Method and system for logic built-in self-test

A controller executes a first LBIST test on a device at a first shift frequency on a plurality of partitions and detects any voltage drop at sense points in each partition during the test. If a voltage drop is detected, then the test is re-run for those partitions that failed the first test. If failures are detected during the re-execution, then a further test at a lower shift frequency is performed. The partitions can be tested sequentially or in parallel and invention has the advantage of reducing the time taken for executing LBIST when the device is booted.

Owner:NXP USA INC

Implementing diagnosis of transitional scan chain defects using logic built in self test LBIST test patterns

A method, apparatus and computer program product are provided for implementing diagnostics of transitional scan chain defects using structural Logic Built In Self Test (LBIST) test patterns. A LBIST test pattern is applied to the device under test and multiple system clock sequences with variable loop control are applied in a passing operating region and scan data is unloaded. The LBIST test pattern is applied to the device under test and multiple system clock sequences with variable loop control are applied in a failing operating region for the device under test and scan data is unloaded. Then the unload data from the passing operating region and the failing operating region are compared. The identified latches having different results are identified as potential AC defective latches. The identified potential AC defective latches are sent to a Physical Failure Analysis system.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

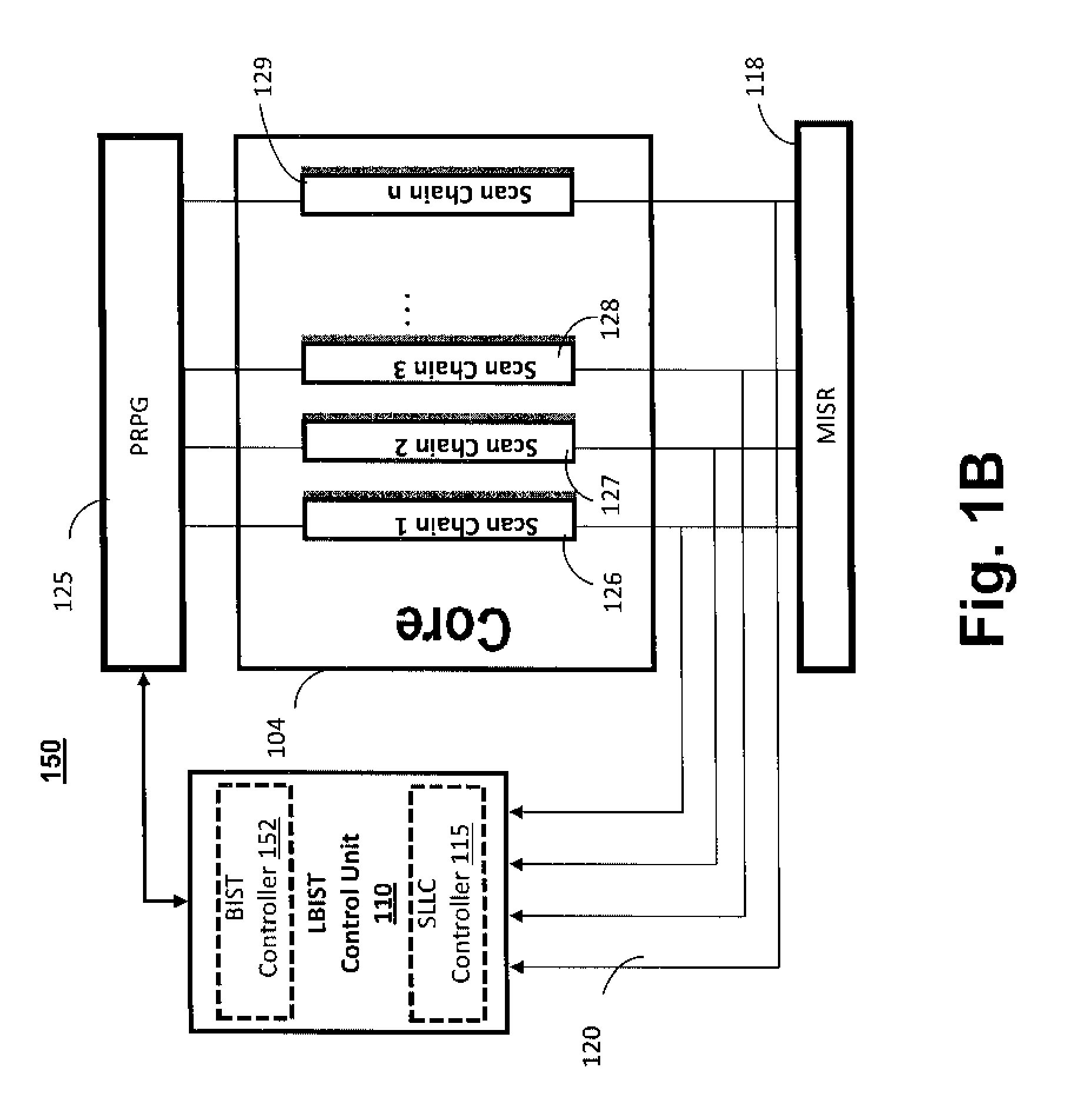

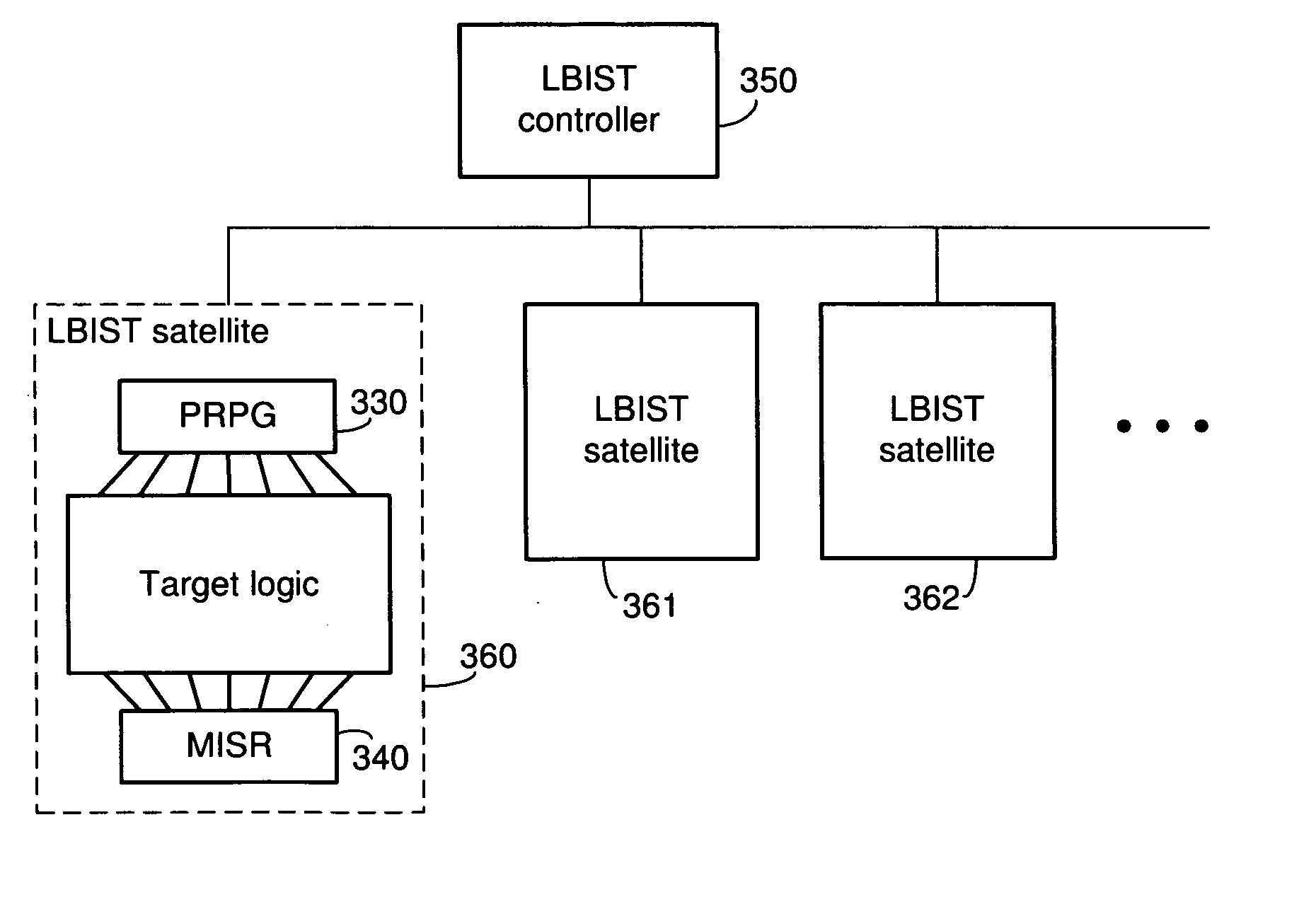

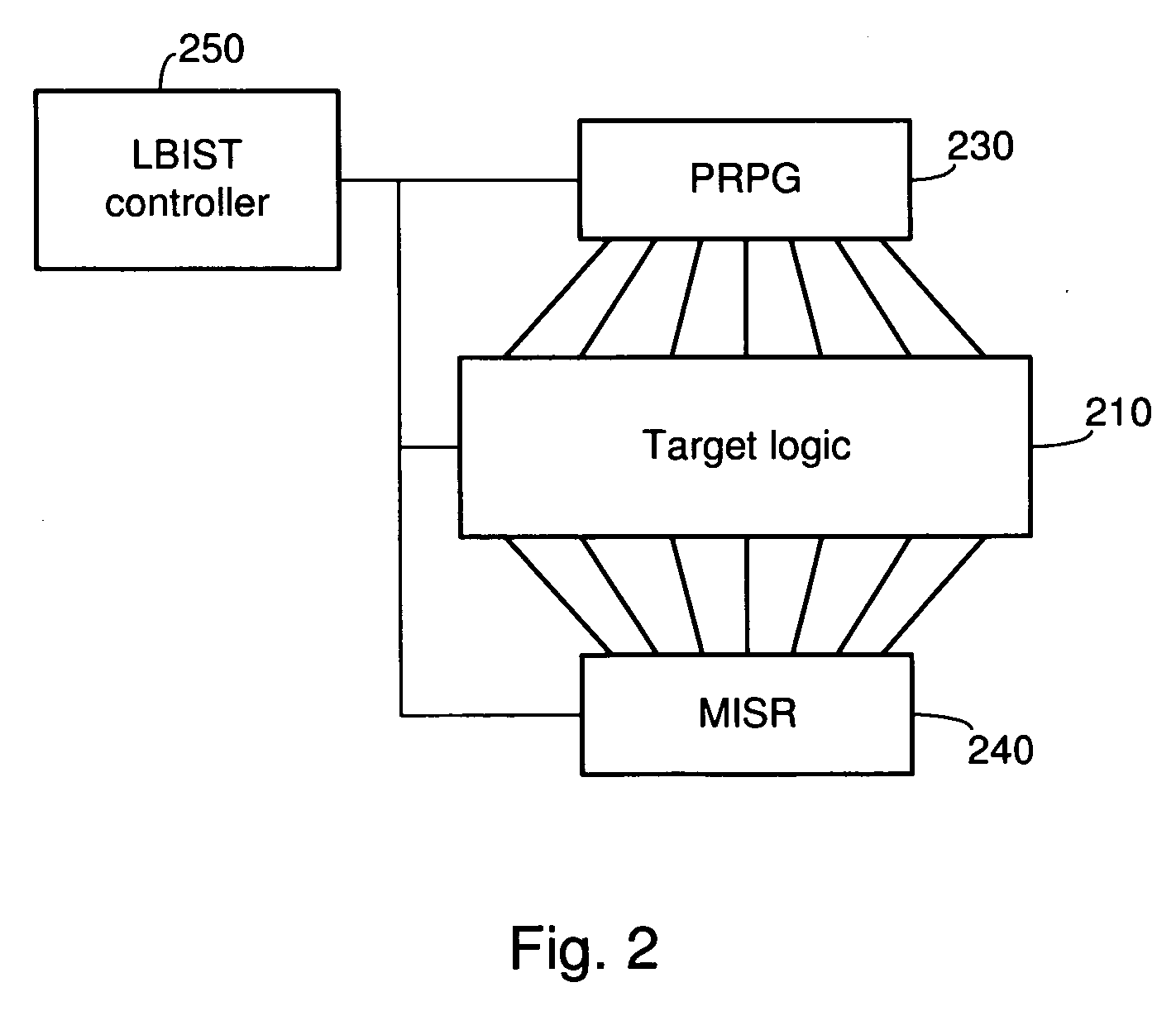

Systems and methods for LBIST testing using commonly controlled LBIST satellites

Systems and methods for performing logic built-in self-tests (LBISTs) in which an LBIST controller provides control signals to multiple LBIST satellites that are co-located with different functional blocks of the device under test, such as processor cores in a multiprocessor integrated circuit. Because the data paths for each satellite are shorter than data paths in conventional LBIST architectures, fewer latches are needed to synchronize the delivery of data to scan chains in the satellites. In one embodiment, each satellite includes a pseudorandom bit pattern generator (PRPG,) scan chains and a multiple-input signature register (MISR). In one embodiment, the LBIST circuitry also includes a control scan chain that is coupled to each of the LBIST satellites and configured to scan data into and out of the LBIST satellites.

Owner:KK TOSHIBA +1

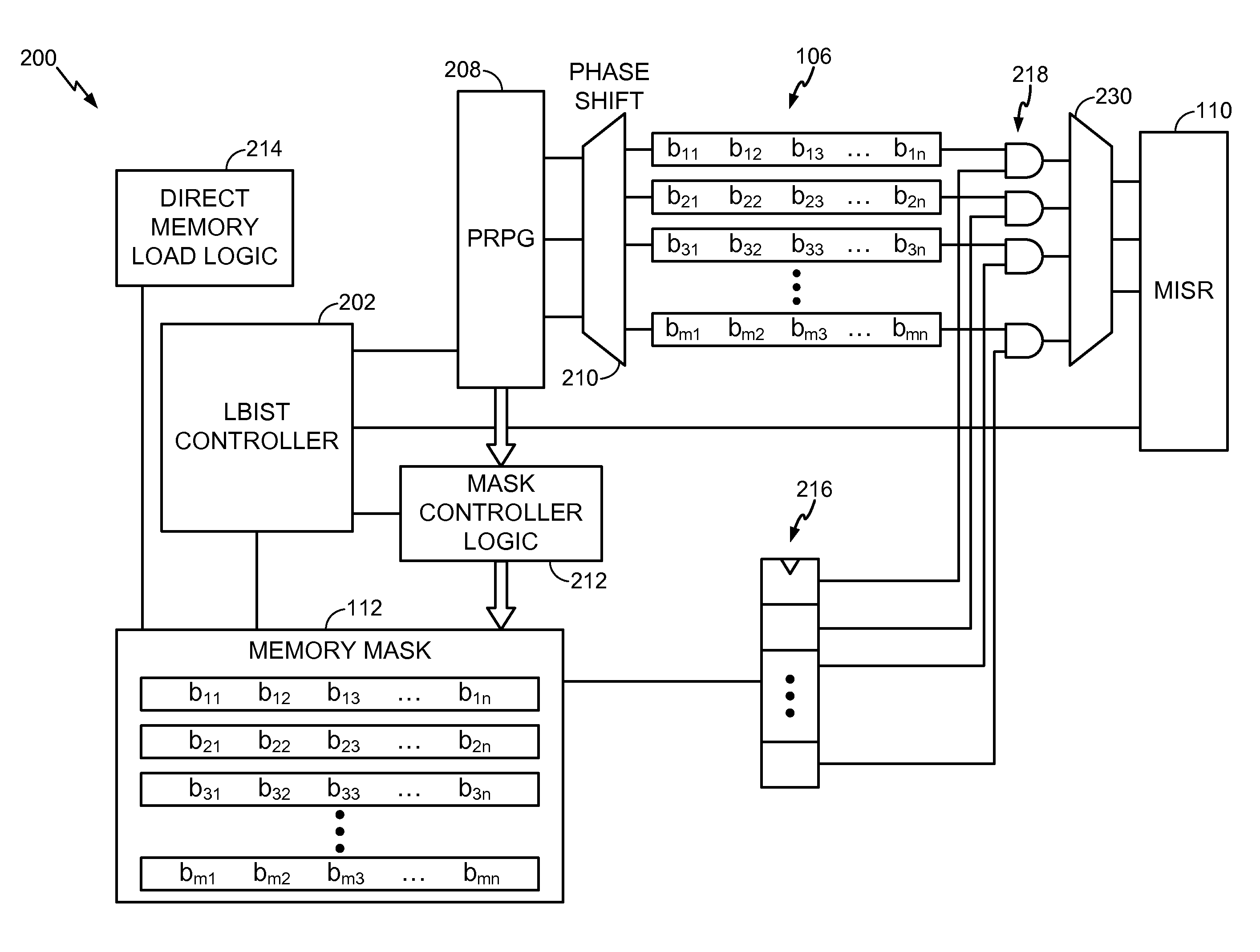

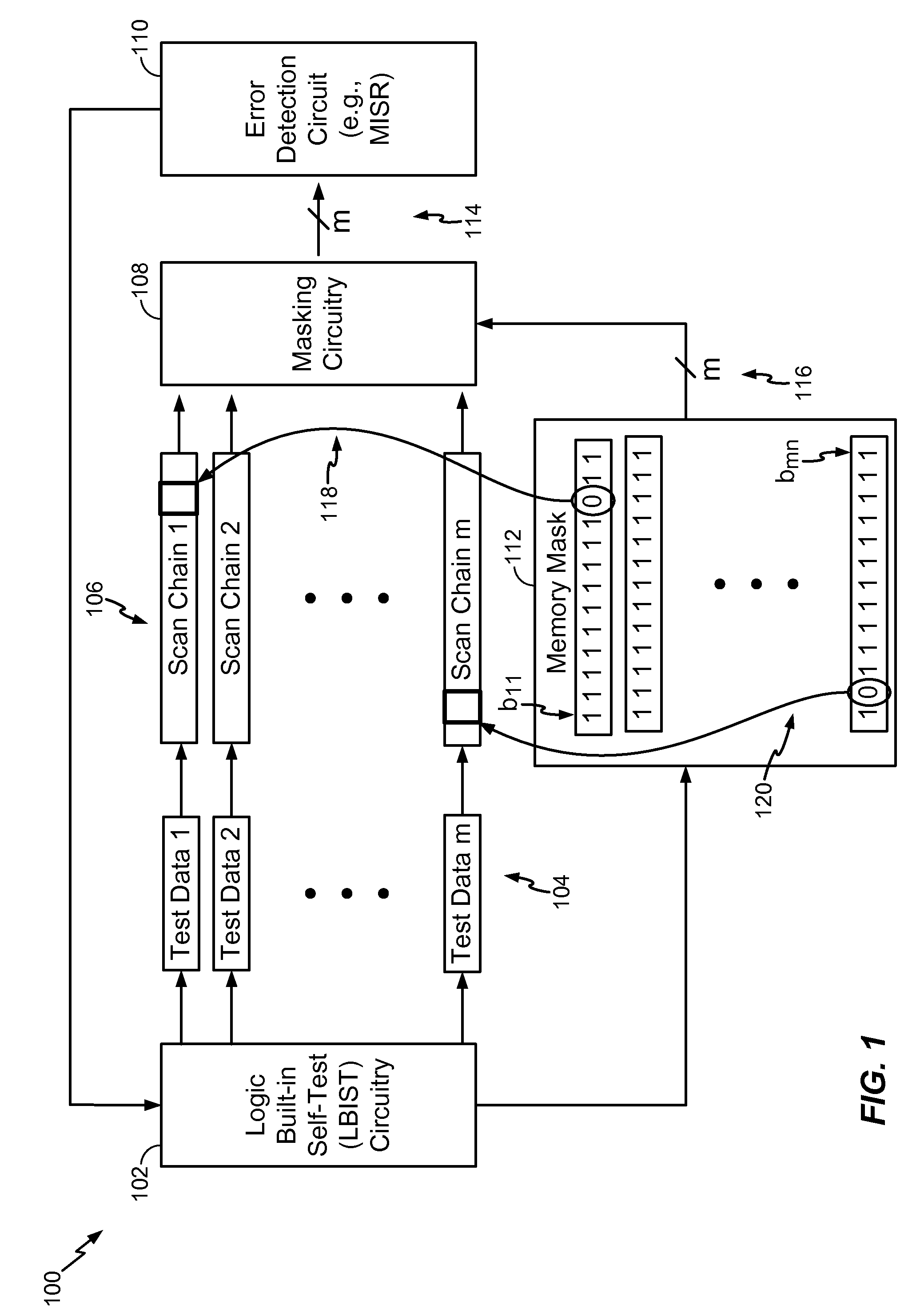

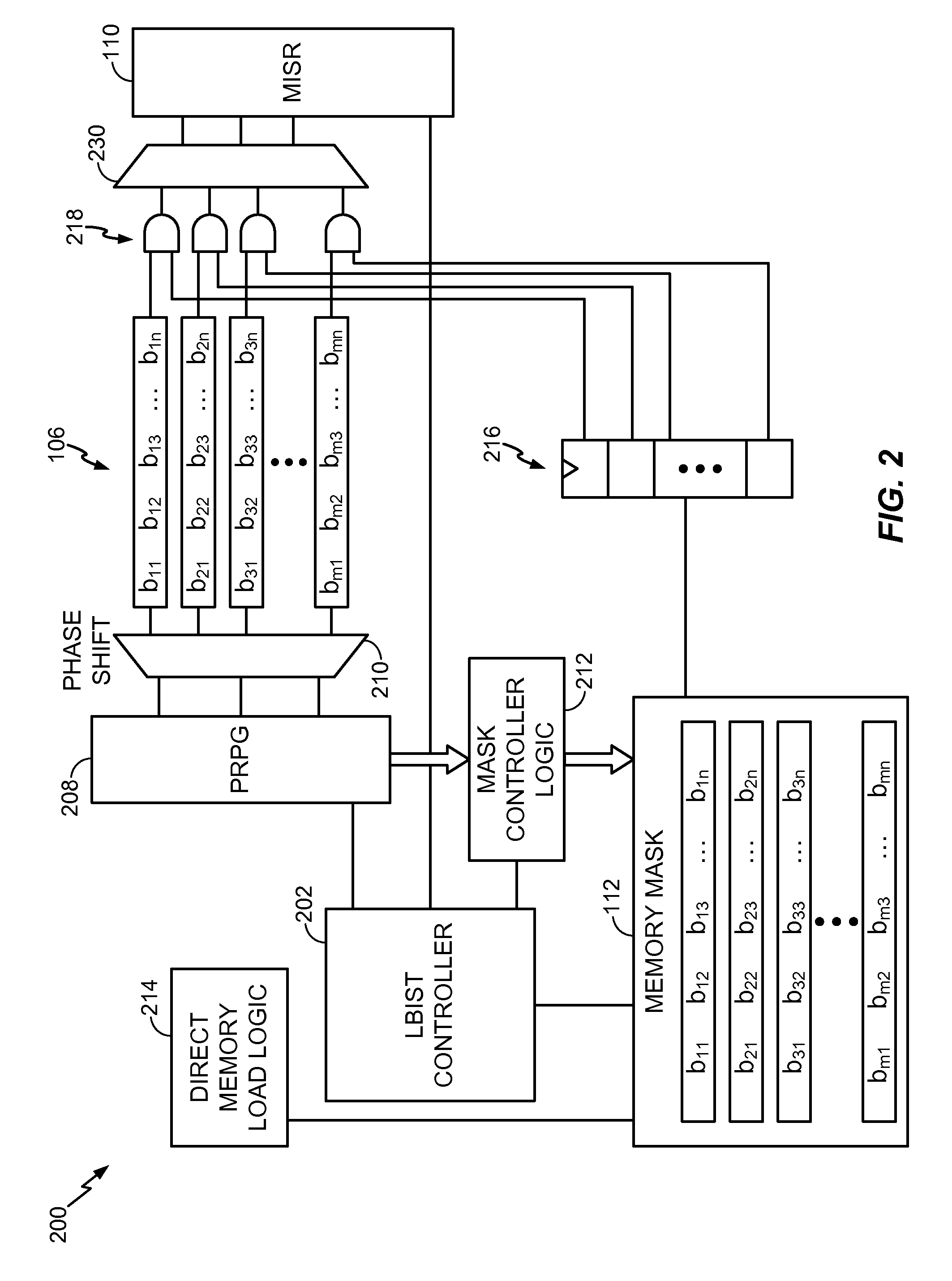

Logic built-in self-test programmable pattern bit mask

In a particular embodiment, a method is disclosed that includes mapping failing bit positions within multiple scan chains to memory locations of a memory mask. The method also includes executing logic built-in self-test (LBIST) testing on a semiconductor device using the memory mask to selectively mask certain results within the multiple scan chains. The results are associated with performance of LBIST testing on the semiconductor device.

Owner:QUALCOMM INC

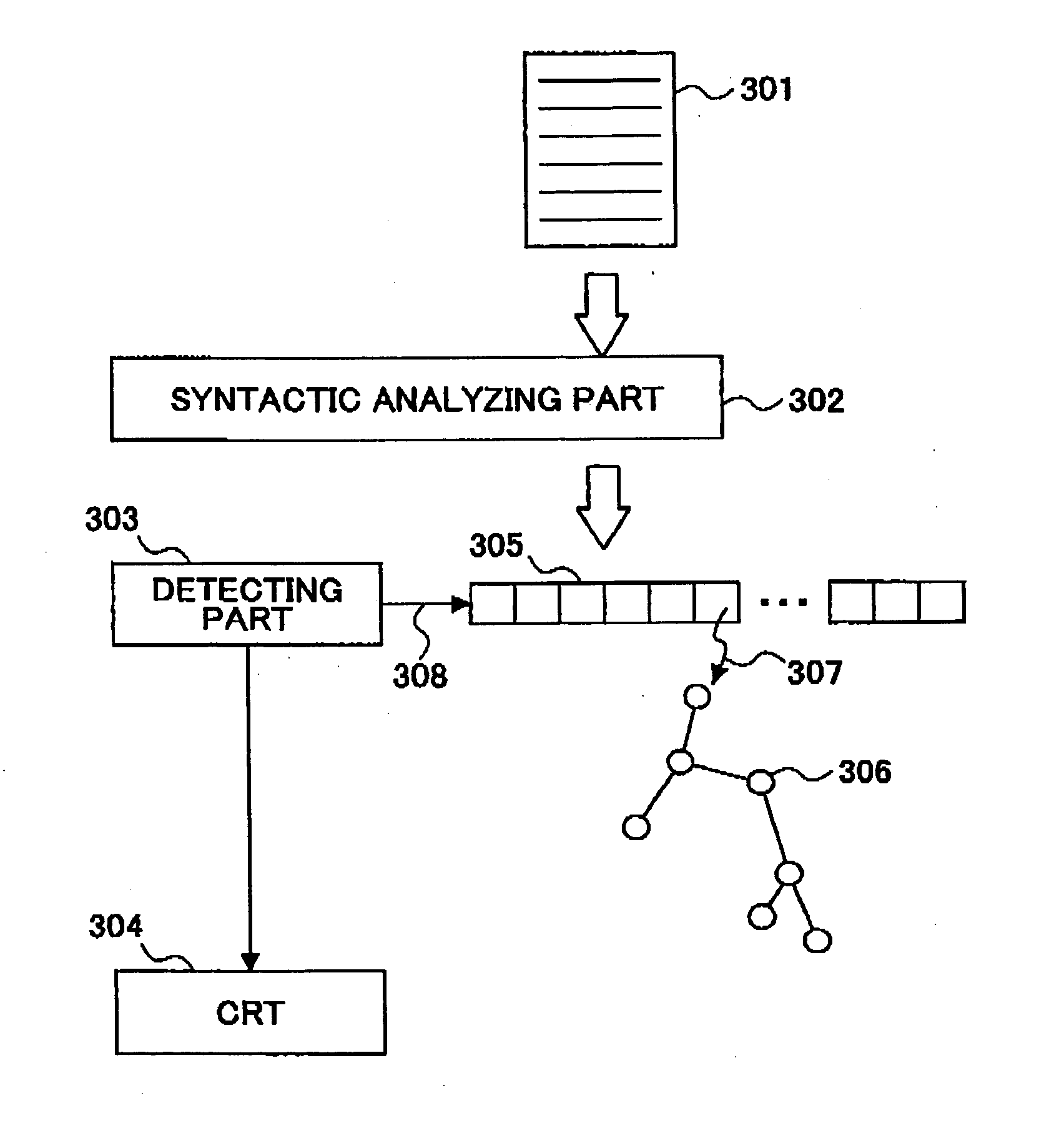

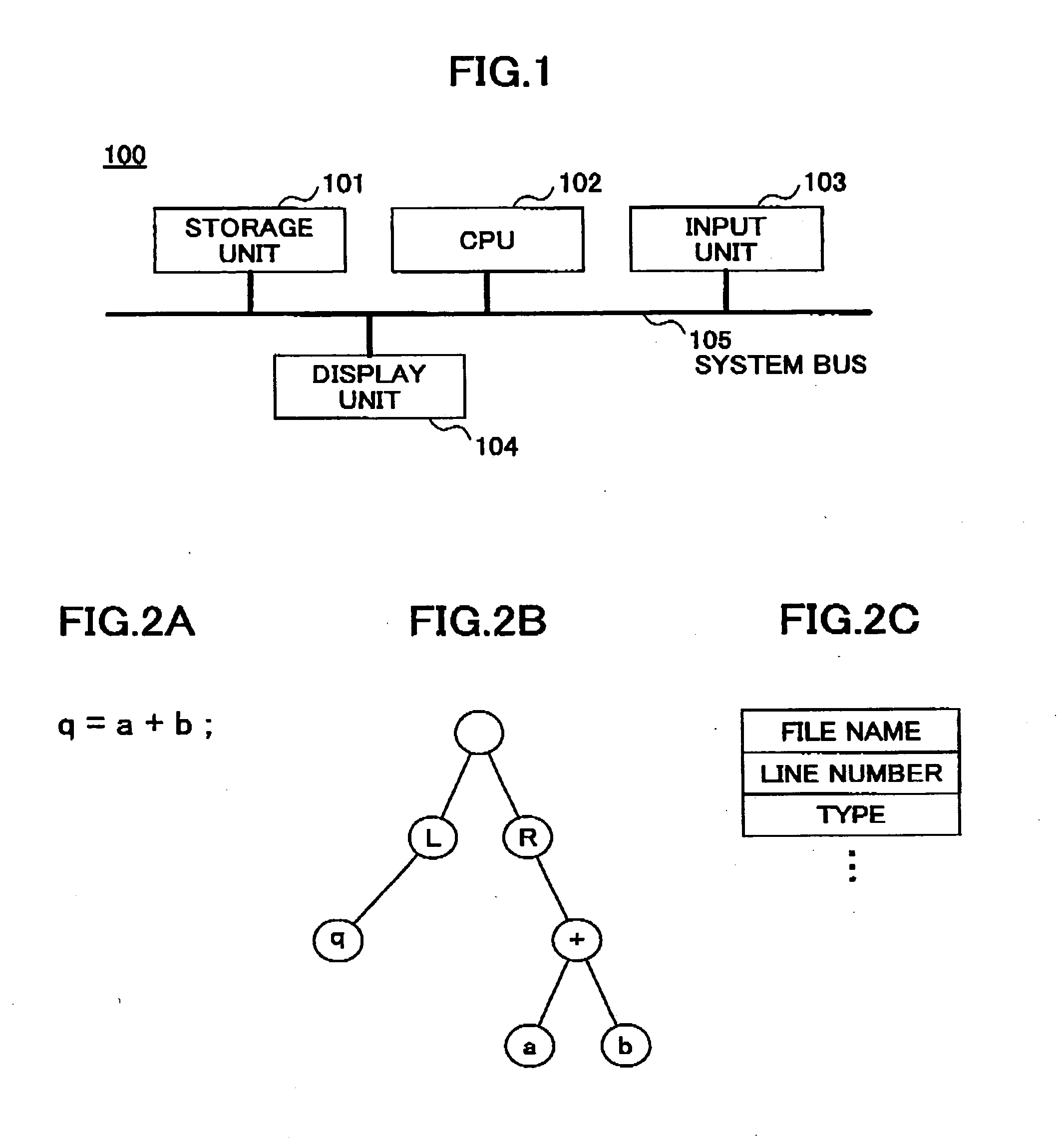

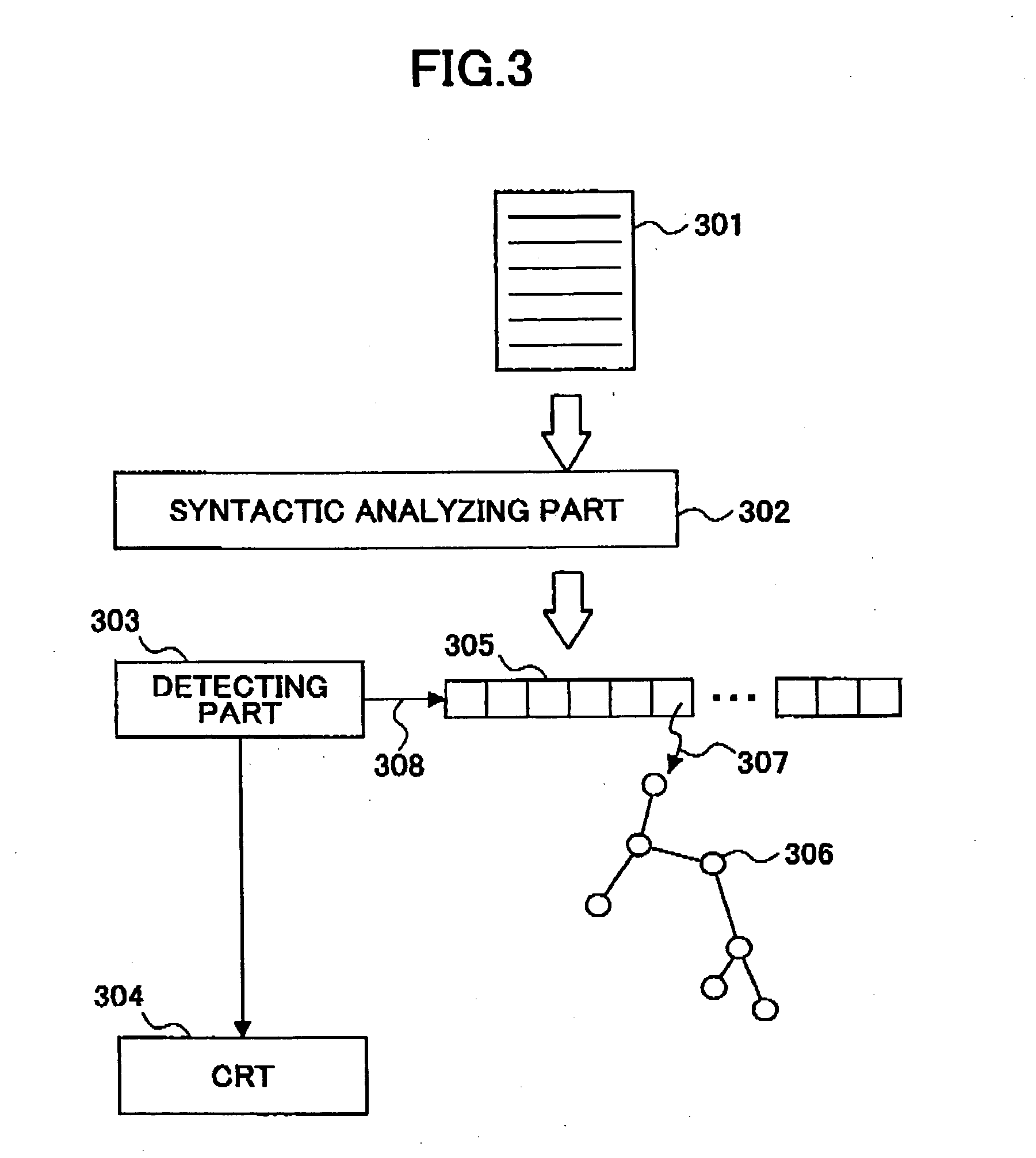

Design supporting apparatus

InactiveUS20050055612A1Improve test qualityEliminate the problemElectronic circuit testingDetecting faulty computer hardwareTheoretical computer scienceLogic built-in self-test

A design supporting apparatus is disclosed, including: an inputting part; a syntactic analyzing part; and a scanning and searching part. The inputting part inputs functional description data of a register transfer level. The syntactic analyzing part conducts a syntactic analysis for the functional description data and develops a parse tree. The scanning and searching part scans and searches for the parse tree being developed by the syntactic analyzing part and searches for a description representing a comparison operator having multiple bits, the comparison operator being difficult to detect a fault by test data formed by pseudo-random numbers, which are applied from a pseudo-random number generator of a logic built-in self-test.

Owner:RICOH KK

Method and apparatus for performing logic built-in self-testing of an integrated circuit

ActiveUS20090307548A1Electronic circuit testingError detection/correctionTest designComputer hardware

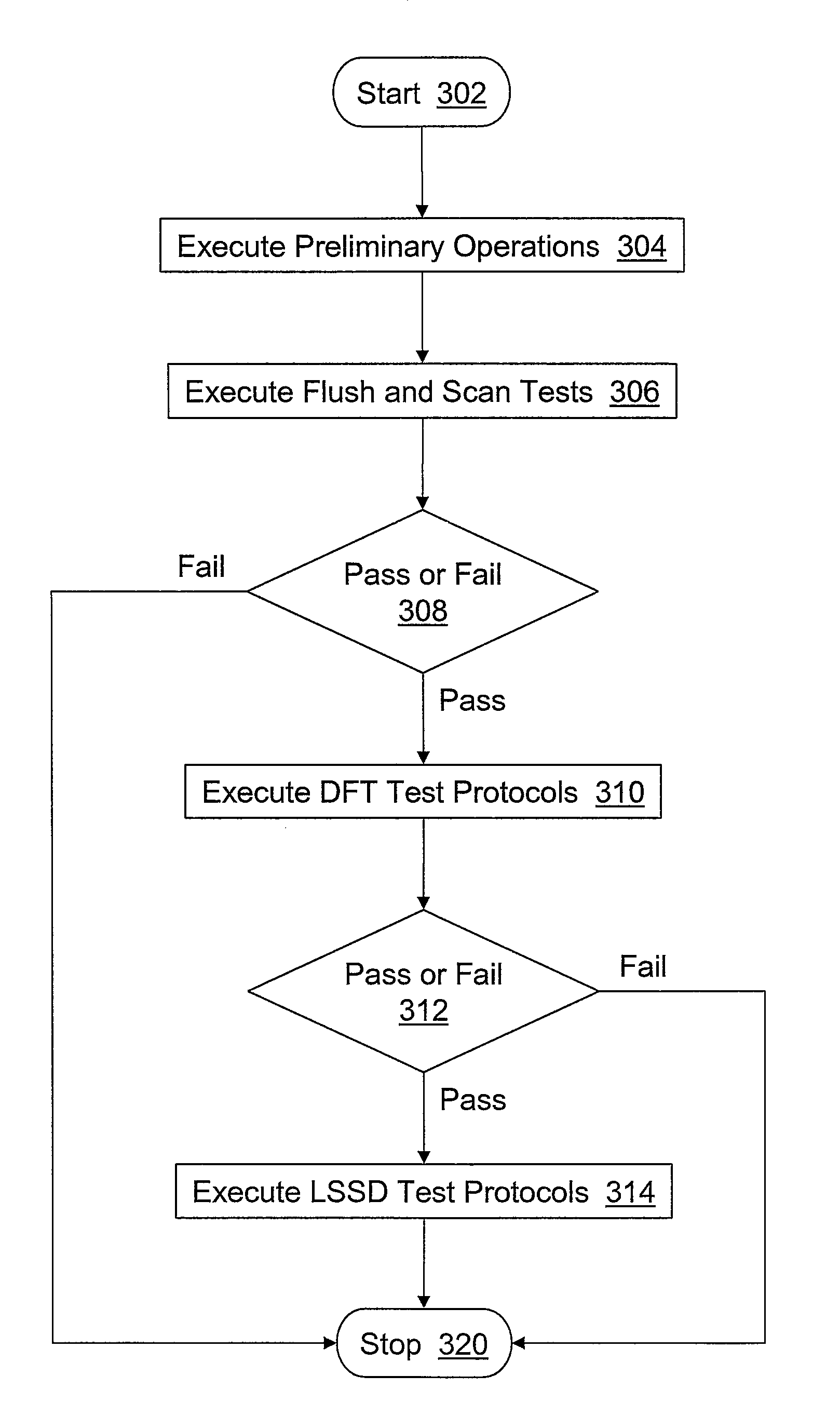

A method for performing a logical built-in self-test of an integrated circuit is disclosed. The method includes performing a flush and scan test to determine whether the scan chains function correctly. If one of the scan chains does not function correctly, the logical built-in self-test is terminated. If each of the scan chains functions correctly, a structural test of the design-for-test logic supporting LBIST is performed to determine whether the LBIST design-for-test logic functions correctly. If the LBIST design-for-test logic does not function correctly, the logical built-in self-test is terminated. If the LBIST design-for-test logic functions correctly, a level sensitive scan design test of the functional combinational logic is performed using the logic supporting LBIST design-for-test to determine if the integrated circuit functions correctly.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

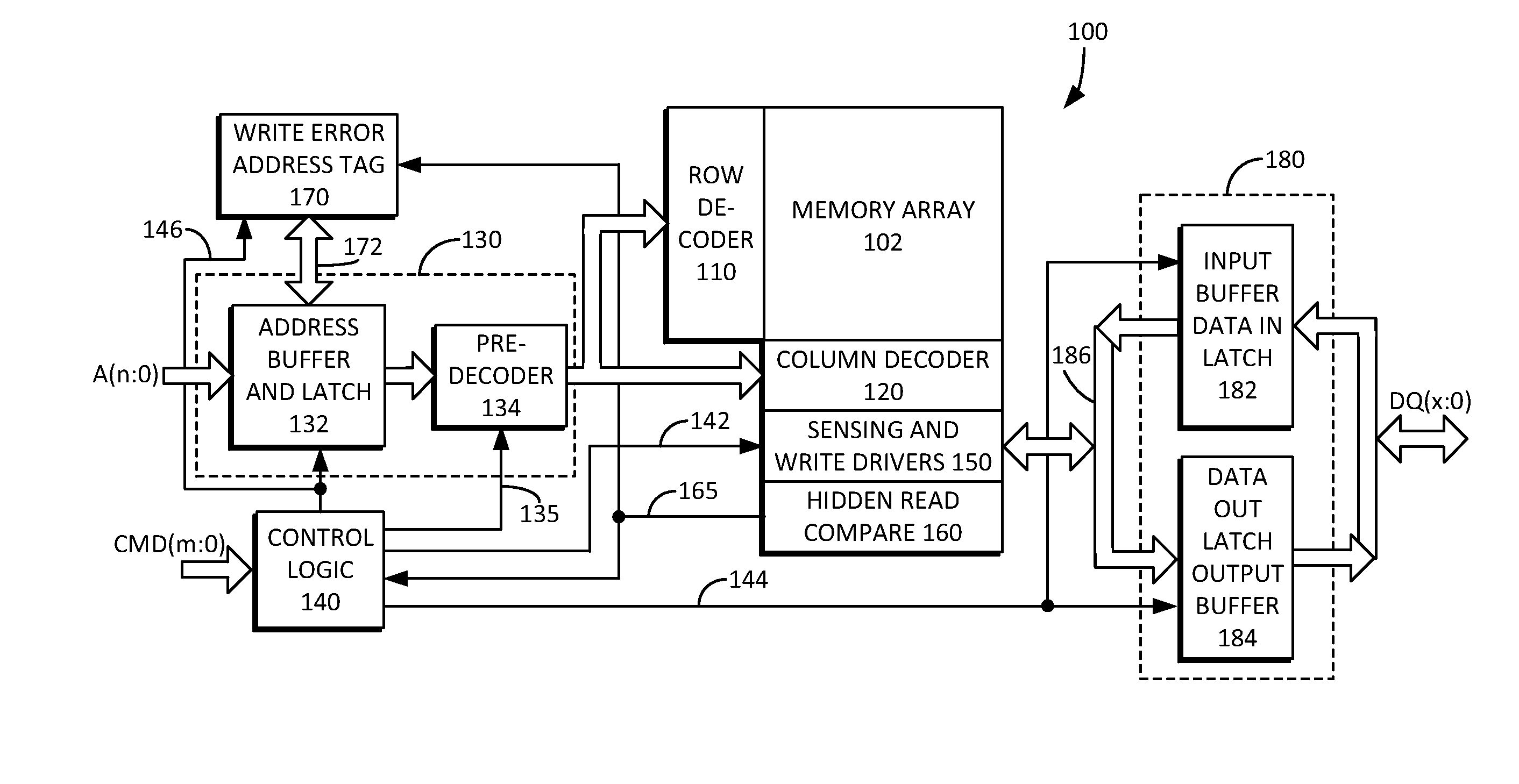

Method and system for providing a smart memory architecture

ActiveUS20160284422A9High rateHigh error rateError detection/correctionDigital computer detailsMemory chipTest error rate

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for performing logic built-in self-testing of an integrated circuit

A method for performing a logical built-in self-test of an integrated circuit is disclosed. The method includes performing a flush and scan test to determine whether the scan chains function correctly. If one of the scan chains does not function correctly, the logical built-in self-test is terminated. If each of the scan chains functions correctly, a structural test of the design-for-test logic supporting LBIST is performed to determine whether the LBIST design-for-test logic functions correctly. If the LBIST design-for-test logic does not function correctly, the logical built-in self-test is terminated. If the LBIST design-for-test logic functions correctly, a level sensitive scan design test of the functional combinational logic is performed using the logic supporting LBIST design-for-test to determine if the integrated circuit functions correctly.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC