Patents

Literature

128results about How to "Improve fault coverage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

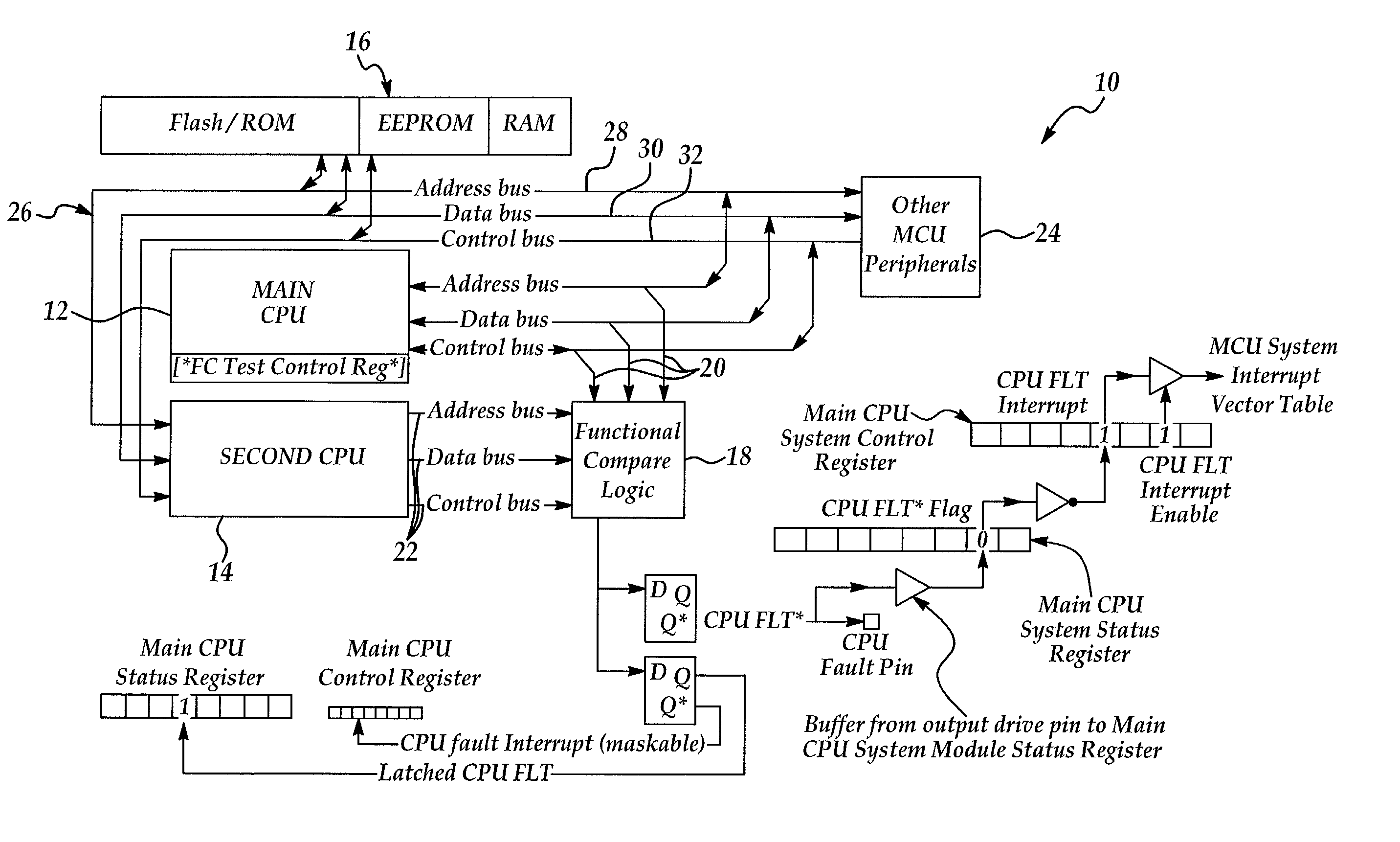

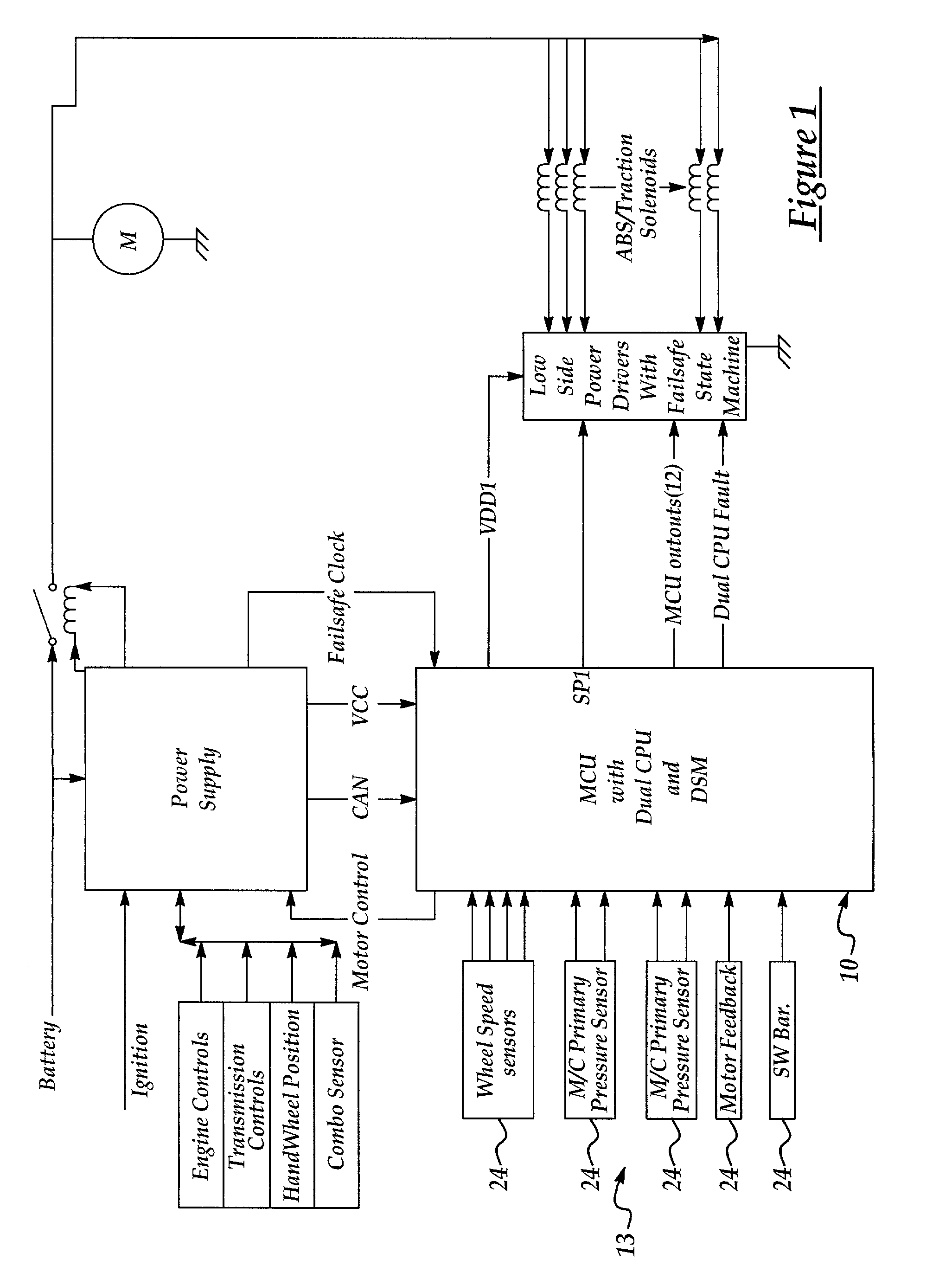

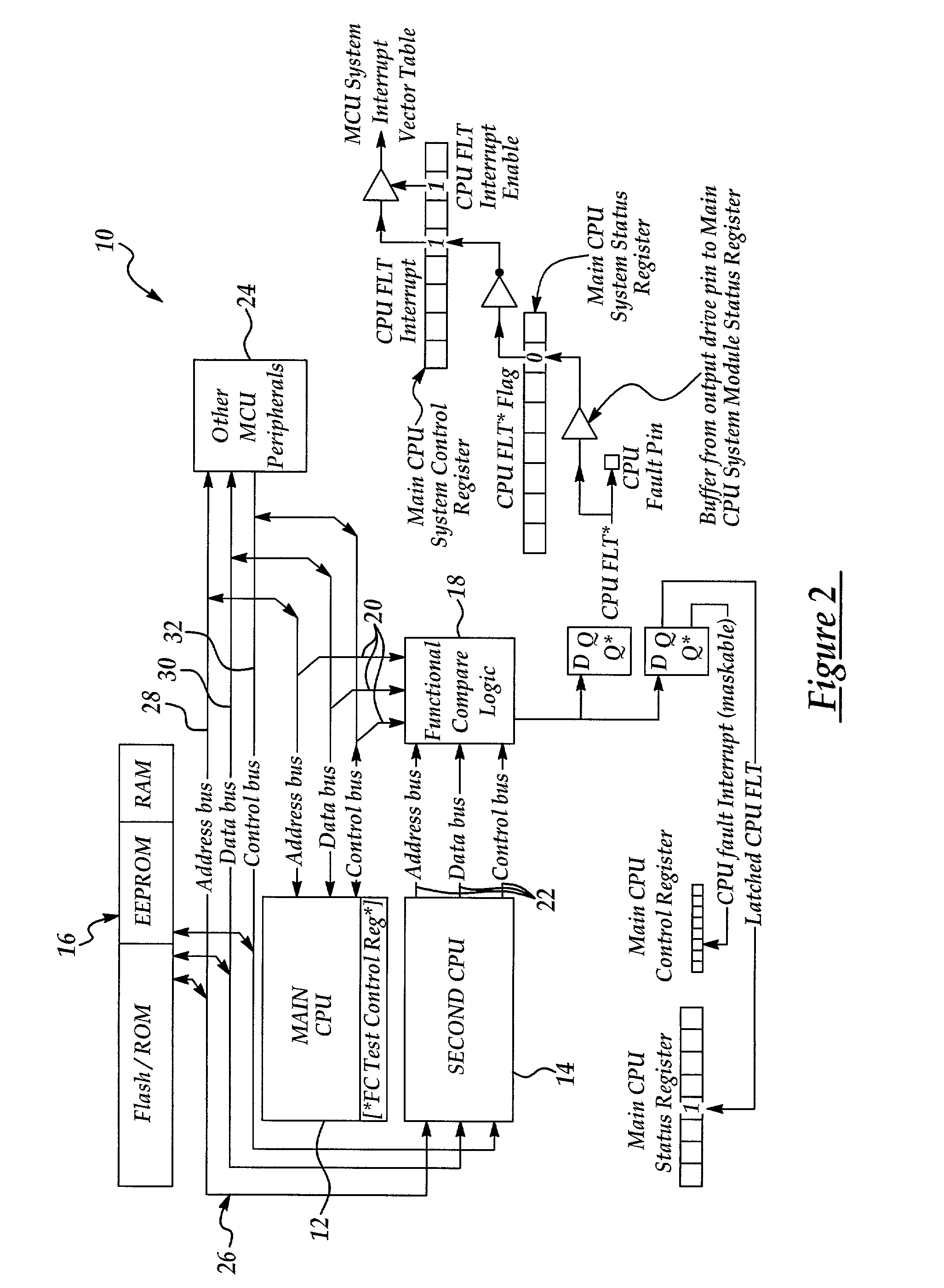

Secured microcontroller architecture

InactiveUS6981176B2Reduce sensitivityImprove system reliabilityVehicle testingRegistering/indicating working of vehiclesMicrocontrollerParallel computing

A microcontroller unit (MCU) having a primary, or main, processing unit, a secondary processing unit coupled to the primary processing unit, and a common memory coupled to the primary and secondary processing units is disclosed. A functional compare module is coupled to the primary processing unit and the secondary processing unit for comparing a primary output of the primary processing unit and a secondary output of the secondary processing units to detect a fault if the primary output and the secondary output are not the same. The invention provides a method for detecting a fault in the MCU including the steps of reading a control algorithm stored in the common memory by the primary processing unit, reading the control algorithm stored in the common memory by the secondary processing unit, comparing the primary output and the secondary output and responsively detecting a fault, if the primary output does not match the second output.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for testing on site programmable gate array

InactiveCN101413990AImprove ObservabilityImprove controllabilityElectrical testingGate arrayExclusive or

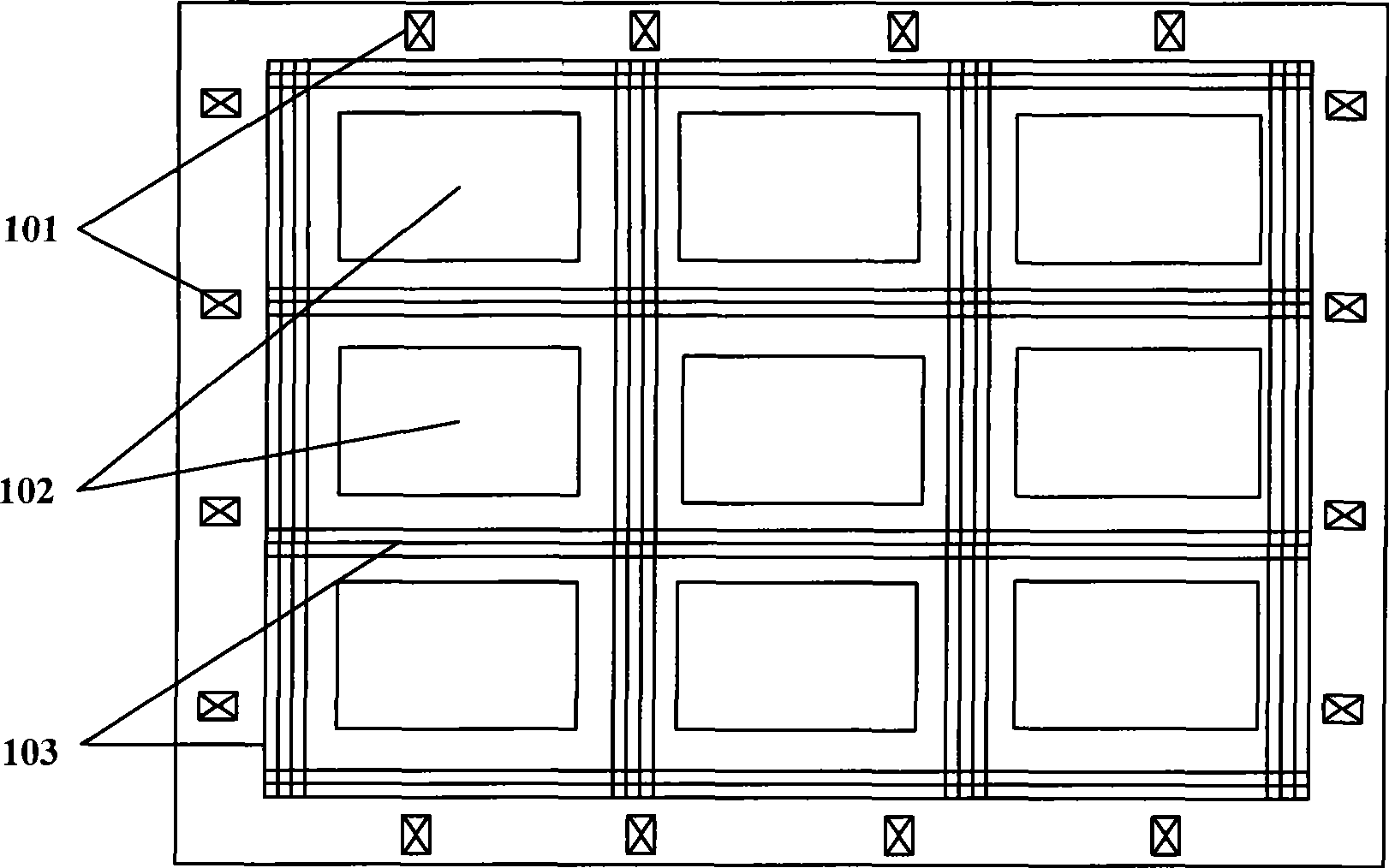

The invention relates to a testing method for a field programmable gate array (FPGA). The method comprises the following steps: obtaining an initial design netlist and an initial design configuration of the FPGA; replacing a look-up table function of the initial design netlist and the initial design configuration with an exclusive or function of a logic function to obtain an initial testing netlist and an initial testing configuration; selecting an observation node of the initial testing netlist based on a preset rule of a testability analysis method, and obtaining a testing netlist and a corresponding testing vector; configuring an output terminal of an output and input unit from the observation node to the initial testing configuration to obtain a testing configuration; connecting the testing configuration to an configuration device according to an excitation signal of the configuration device to obtain an output logic value of the testing vector; and analyzing the output logic value and a response value of the testing vector to obtain the testing result. The method can effectively detect permanent faults of interconnection lines used in the application design of FPGA chips.

Owner:无锡引速得科技有限公司

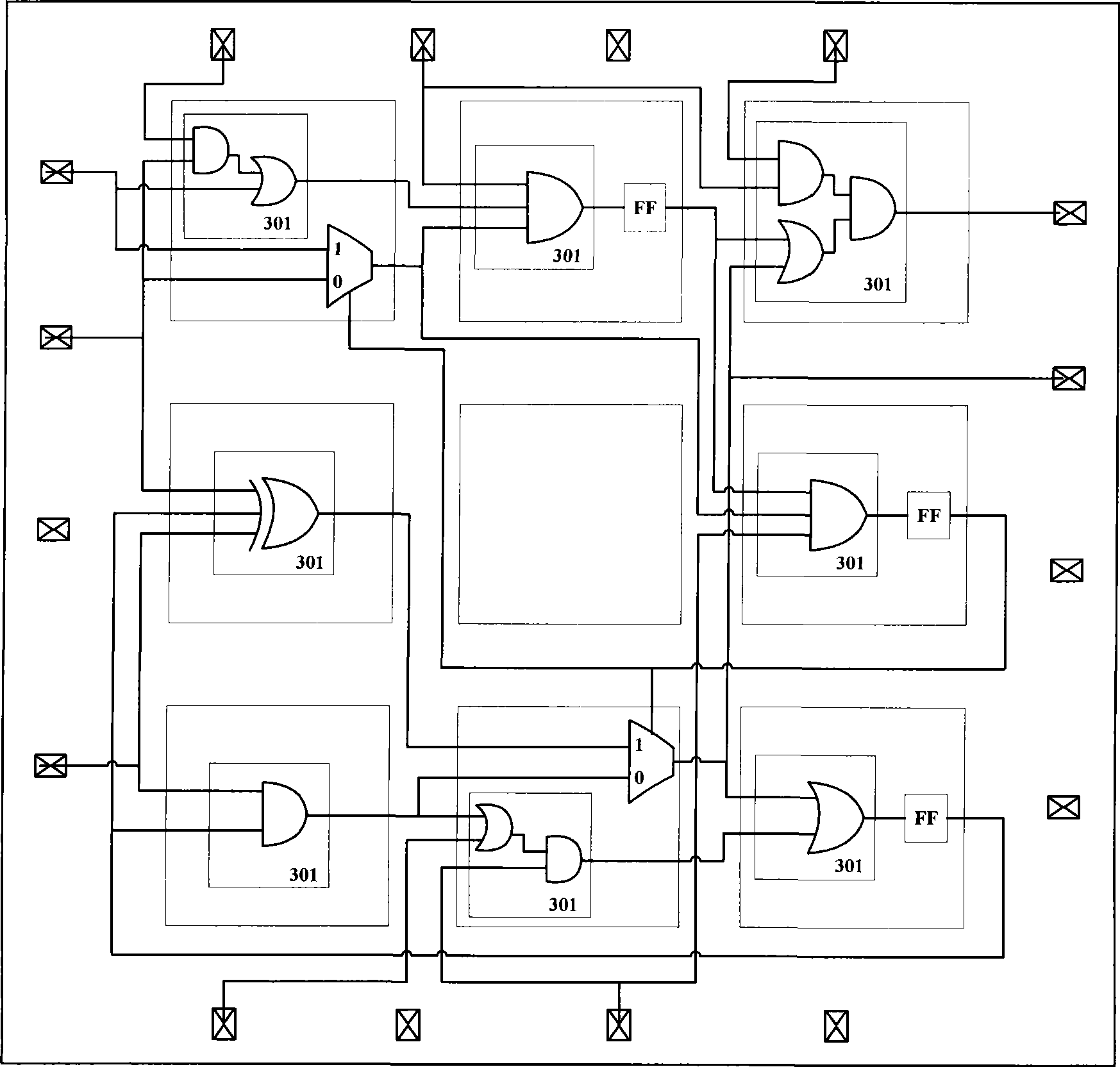

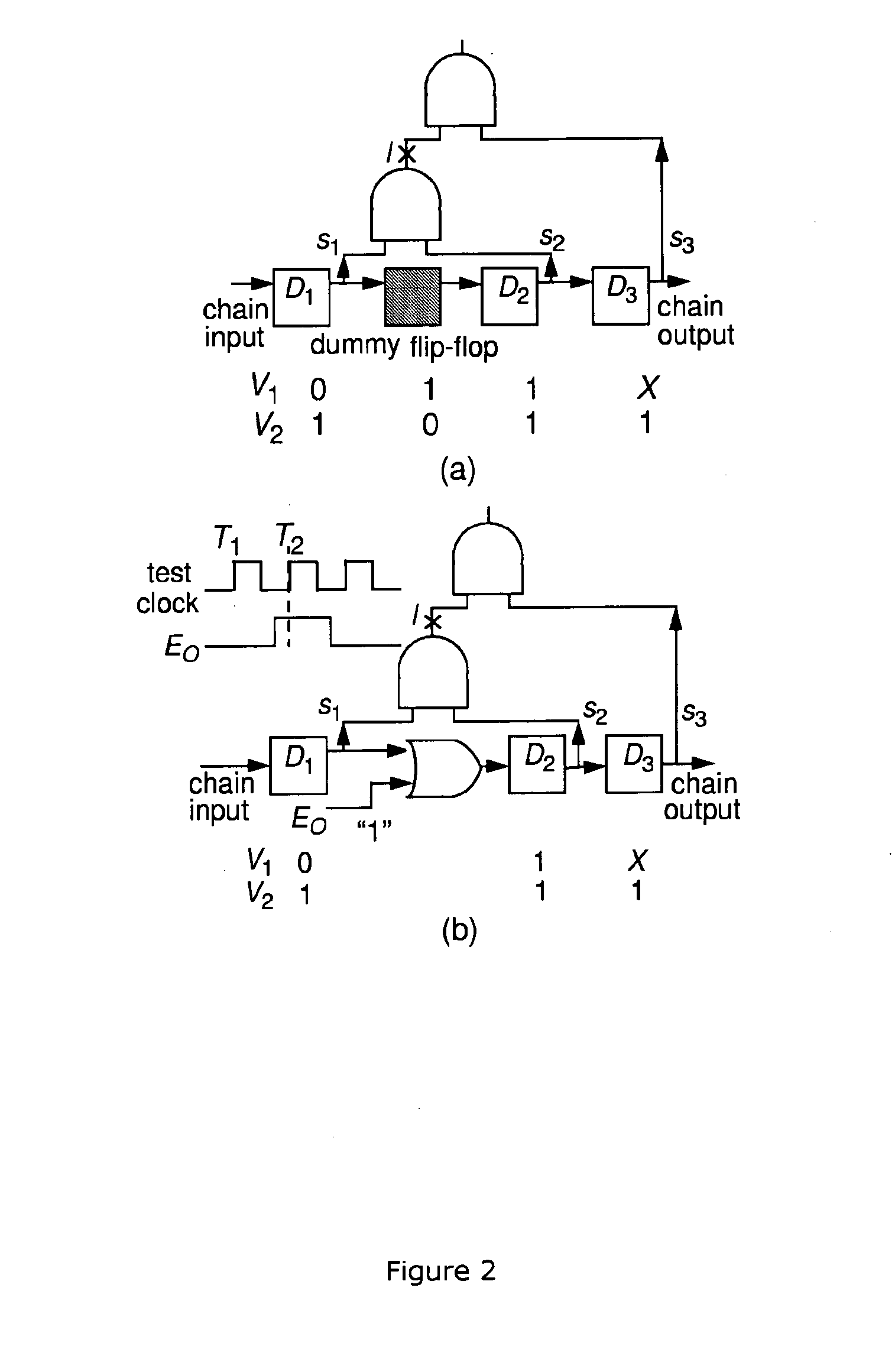

Scalable scan-path test point insertion technique

InactiveUS20040177299A1Enhance fault coverageImprove fault coverageElectronic circuit testingDetecting faulty computer hardwareEngineeringLogic circuitry

A logic circuit comprising at least one input, one output and a delay fault circuit. The delay fault circuit includes a first standard scan cell, a combinational test point positioned immediately after the first standard scan cell in a scan chain and a second standard scan cell positioned immediately after the combinational test point in the scan chain.

Owner:NEC CORP

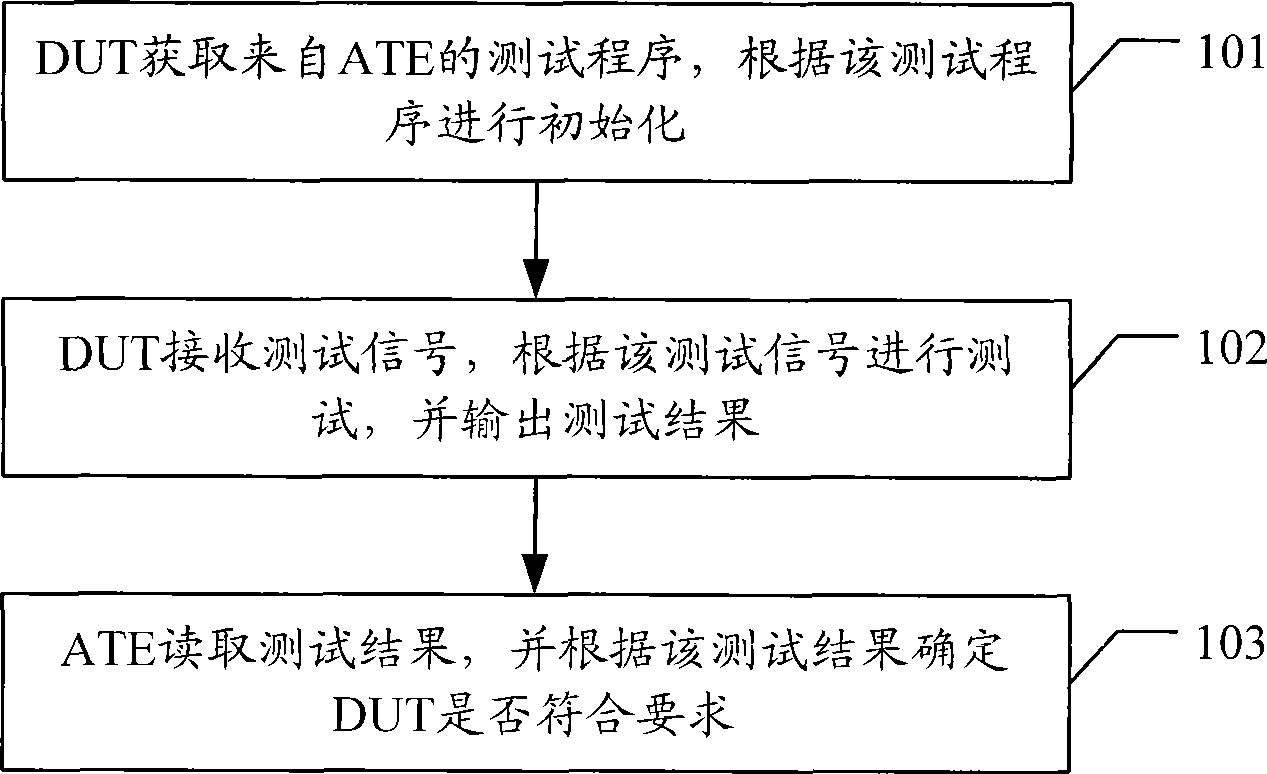

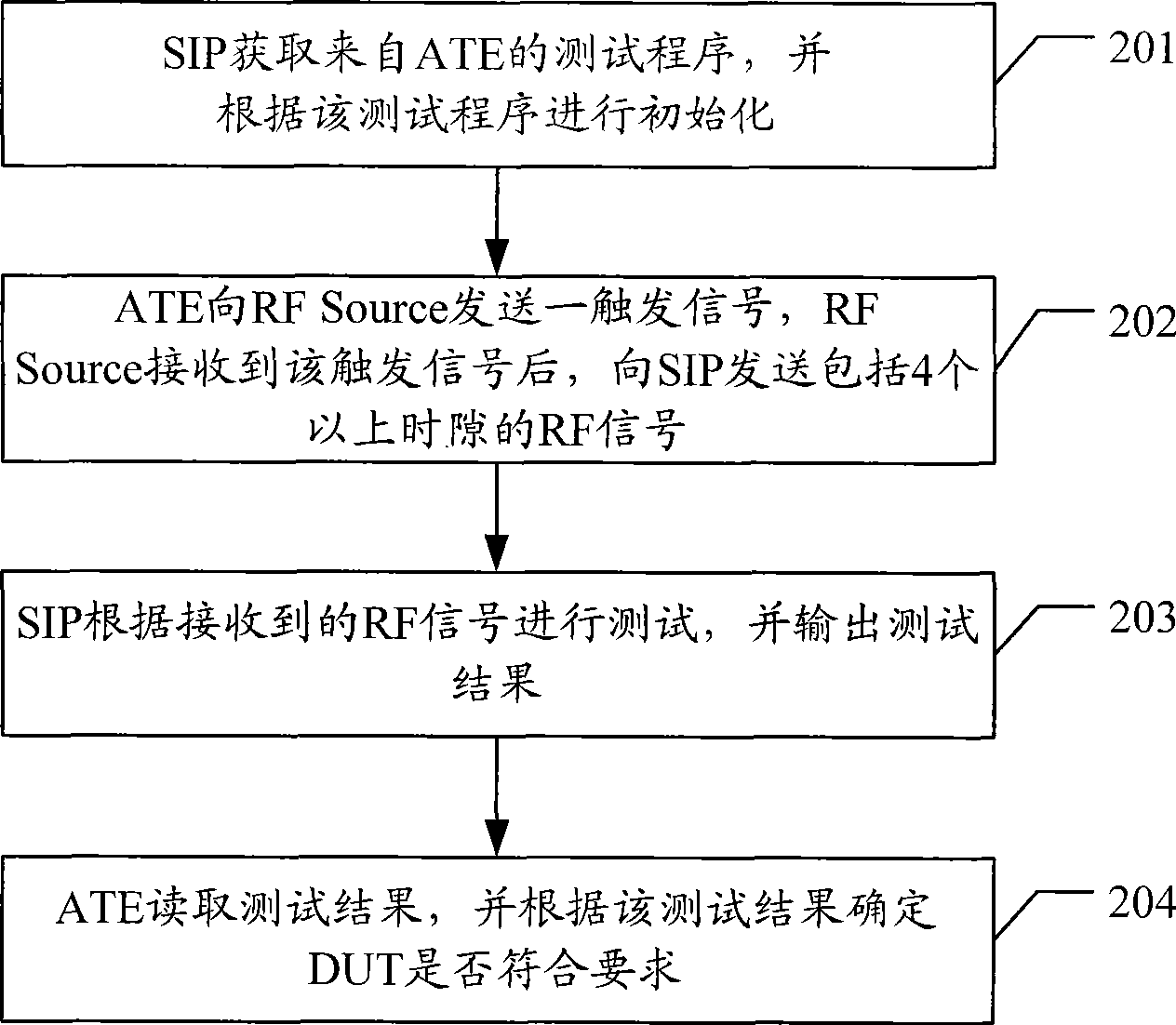

Test method and system

InactiveCN101464491AEasy to implementReduced pin countElectronic circuit testingFault coverageAutomatic test equipment

The invention discloses a testing method which comprises the following steps: acquiring the testing procedure from automatic test equipment (ATE) by using a device under test (DUT) and initializing according to the testing procedure; receiving test signals by using the DUT, and testing according the test signals, and outputting test results; and reading the test results by using the ATE and determining whether the DUT conforms to the requirements according to the test results. The invention simultaneously discloses a testing system. By applying the method and the system, the test cost can be reduced, the fault coverage can be improved, and the invention can be implemented easily.

Owner:新奇点智能科技集团有限公司

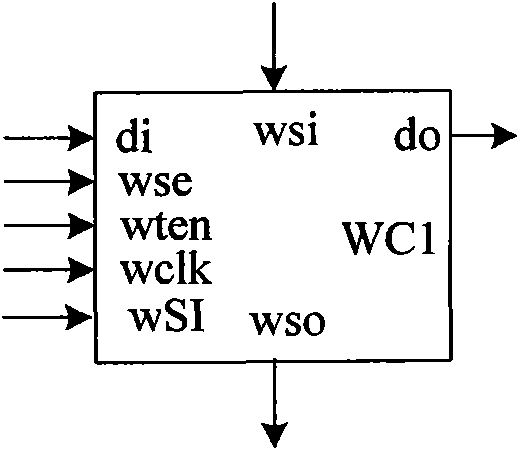

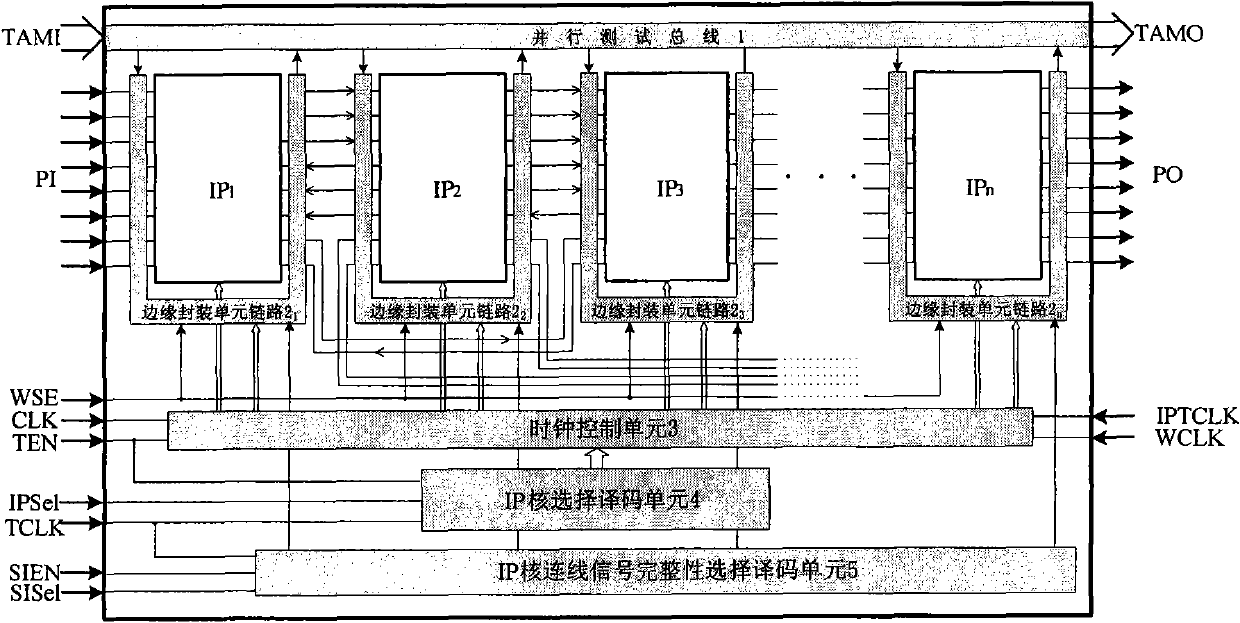

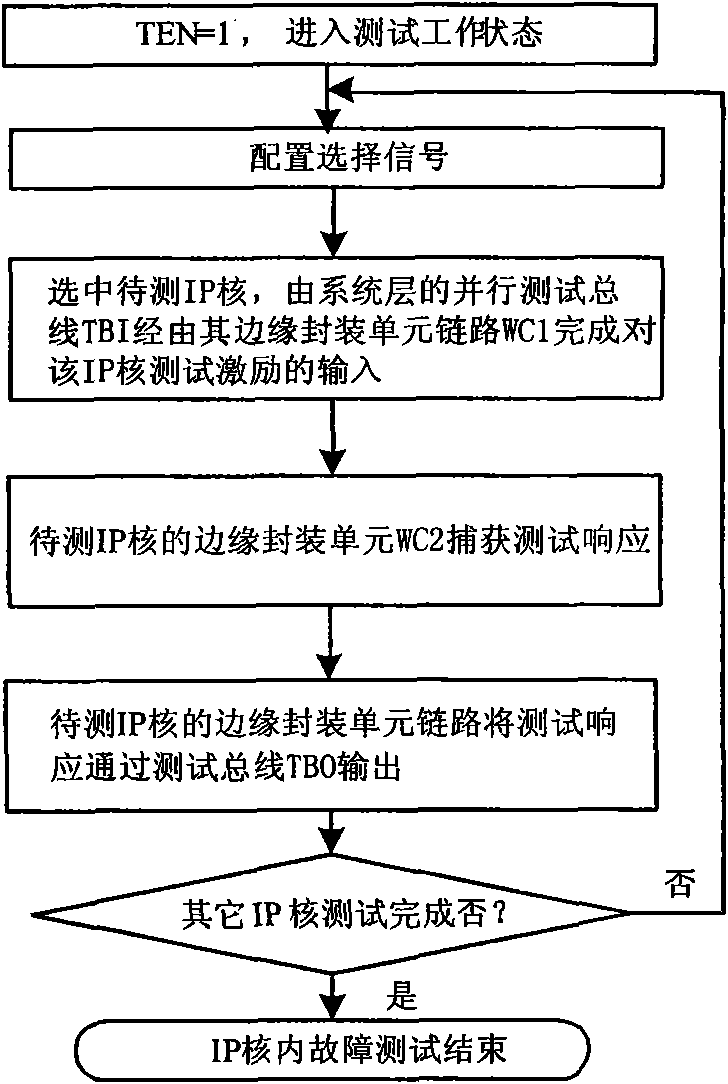

System for testing system internuclear wiring fault on integrated circuit chip and method thereof

InactiveCN101923133AShorten test timeImprove fault coverageElectrical testingFault coverageMultiplexing

The invention relates to a system for testing a system internuclear wiring fault on an integrated circuit chip and a method thereof. The system comprises a circuit structure which is added for perfecting the IP internuclear wiring fault test and the IP intranuclear fault test in a system on the integrated circuit chip and a test inquiring mechanism which runs on the basis of the circuit structure. The invention can test the IP internuclear wiring of the system on the integrated circuit chip. The fault types of the test comprises the solid-zero fault, the solid-solid fault, the open circuit fault, the short circuit fault, the delaying fault and the noise fault. By adding a hardware structure, the invention decomposes a scanning chain of edge packing units, thereby making the best of a test buss and shortening the test time; with the output type edge packing unit, the invention automatically generates a test vector; with the input type edge packing unit, the invention further shortens the test time. The structure is compatible with the intranuclear test structure, thereby realizing the higher flexibility, making the best of the test resource, and further improving the fault coverage rate of the system of the whole integrated circuit chip. The invention is simple in circuit structure, convenient in test inquiring mechanism, and suitable for the various systems on the integrated circuit chips which are designed and built with the IP multiplexing technology.

Owner:SHANGHAI UNIV

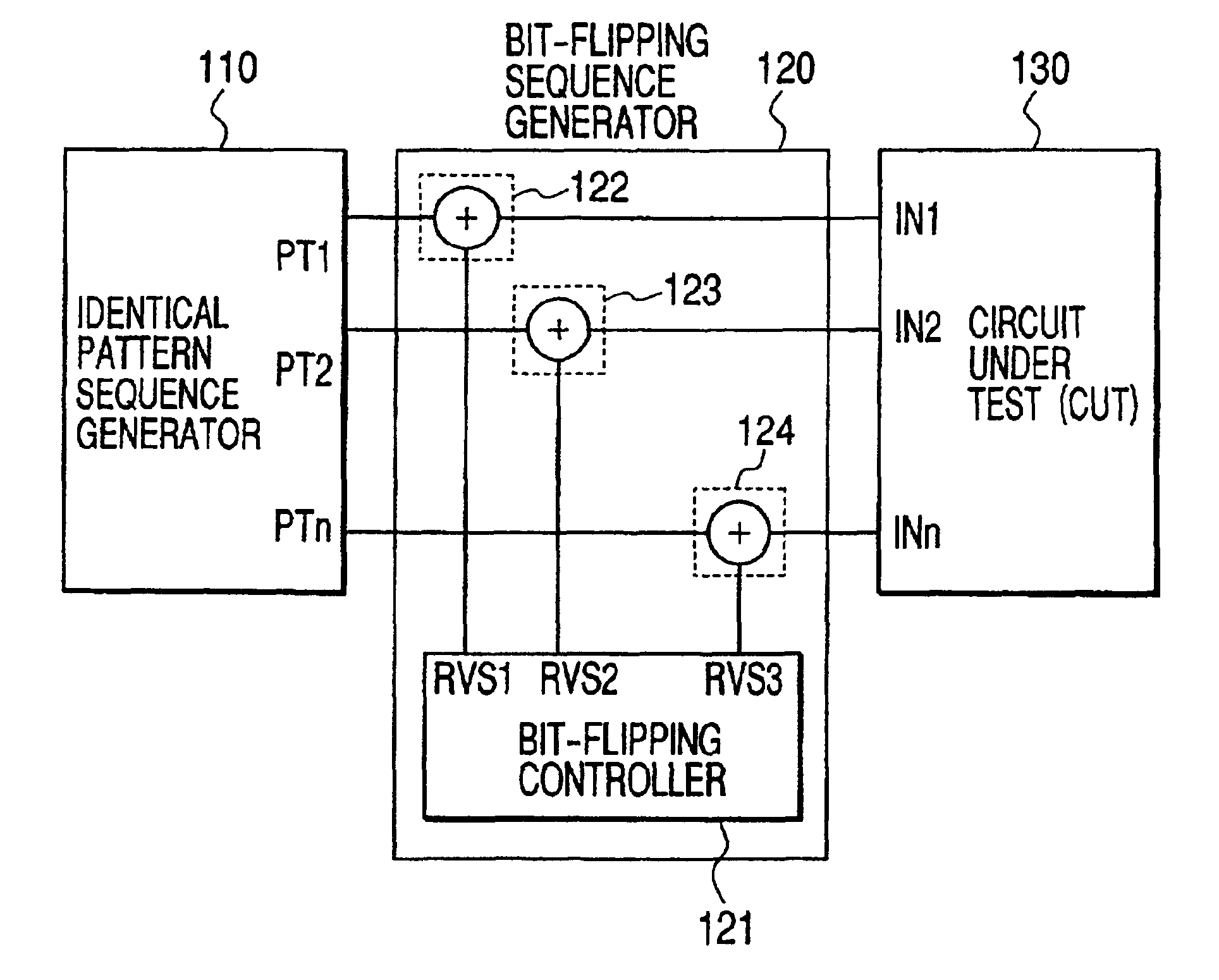

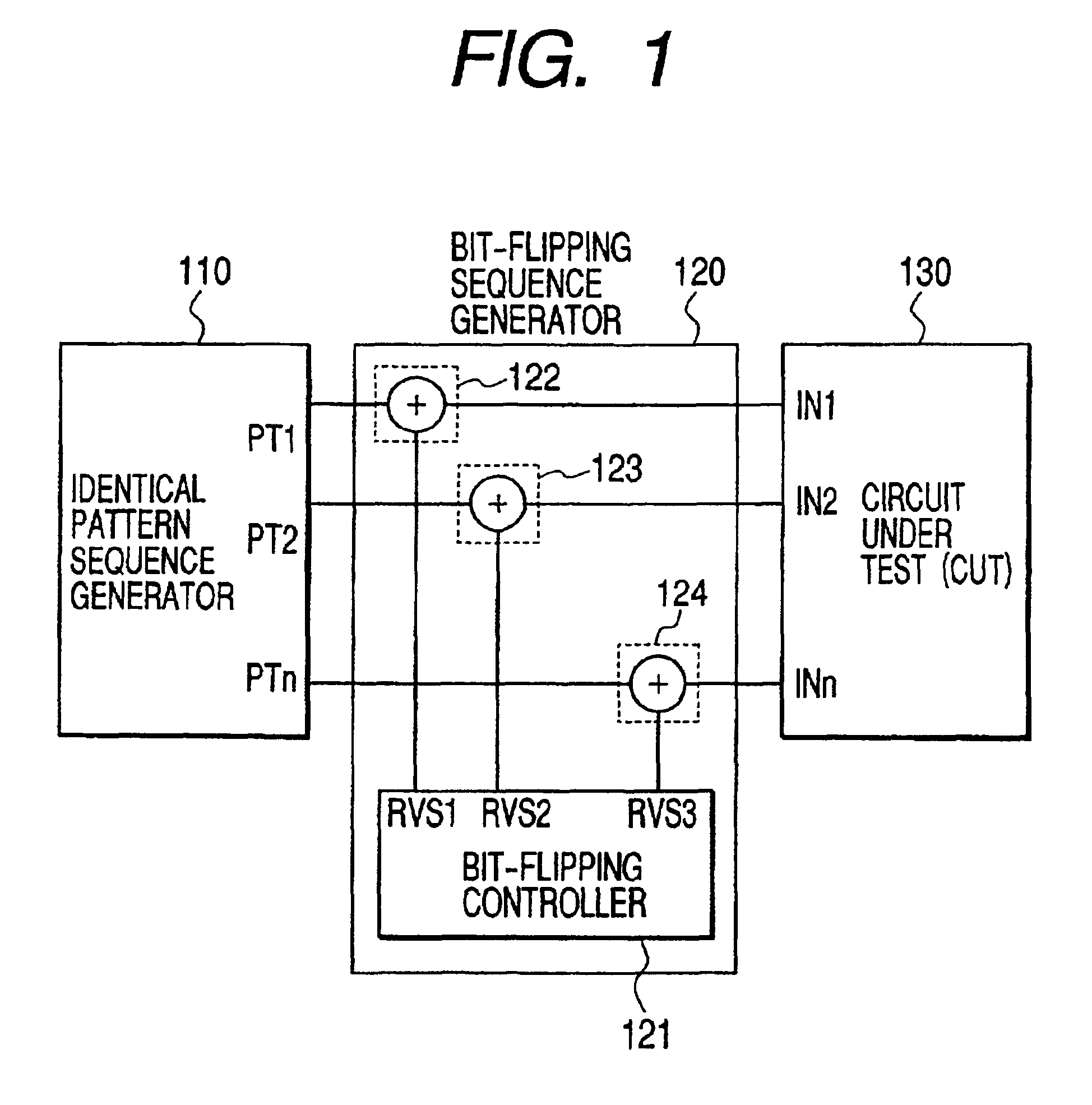

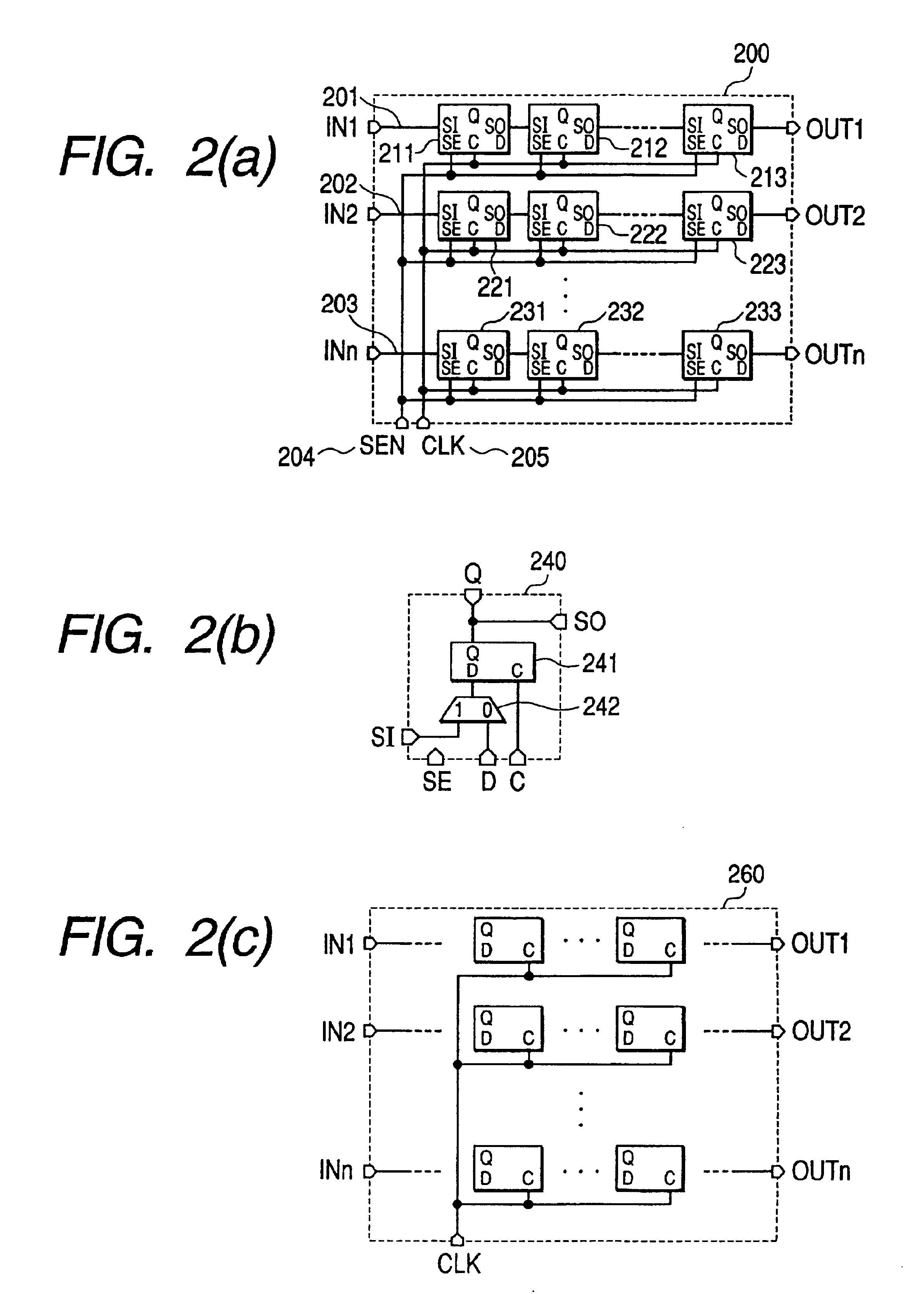

Test method of semiconductor intergrated circuit and test pattern generator

InactiveUS6922803B2Avoid problemsEliminate overheadElectronic circuit testingDetecting faulty computer hardwareFault coverageGraphics

A semiconductor integrated circuit test method which reduces the required data volume for testing and efficiently detects faults in a circuit to be tested, the method comprising means 110 to generate identical pattern sequences repeatedly and means 120 to control flipped bits in pattern sequences, in order to generate neighborhood pattern sequences and use the neighborhood patterns to test the circuit under test 130. The neighborhood patterns include, in whole or in part, such pattern sequences as ones without flipped bits, ones with all or some flipped bits in one pattern and ones with all or some flipped bits in consecutive patterns or patterns at regular intervals, the interval being equivalent to a given number of patterns. Because a test pattern generator is provided independently of the circuit to be tested, the problem of a prolonged design period can be eliminated, a loss in the operating speed of the circuit under test is minimized and a high fault coverage can be achieved with less hardware overhead and a smaller volume of test data.

Owner:HITACHI LTD

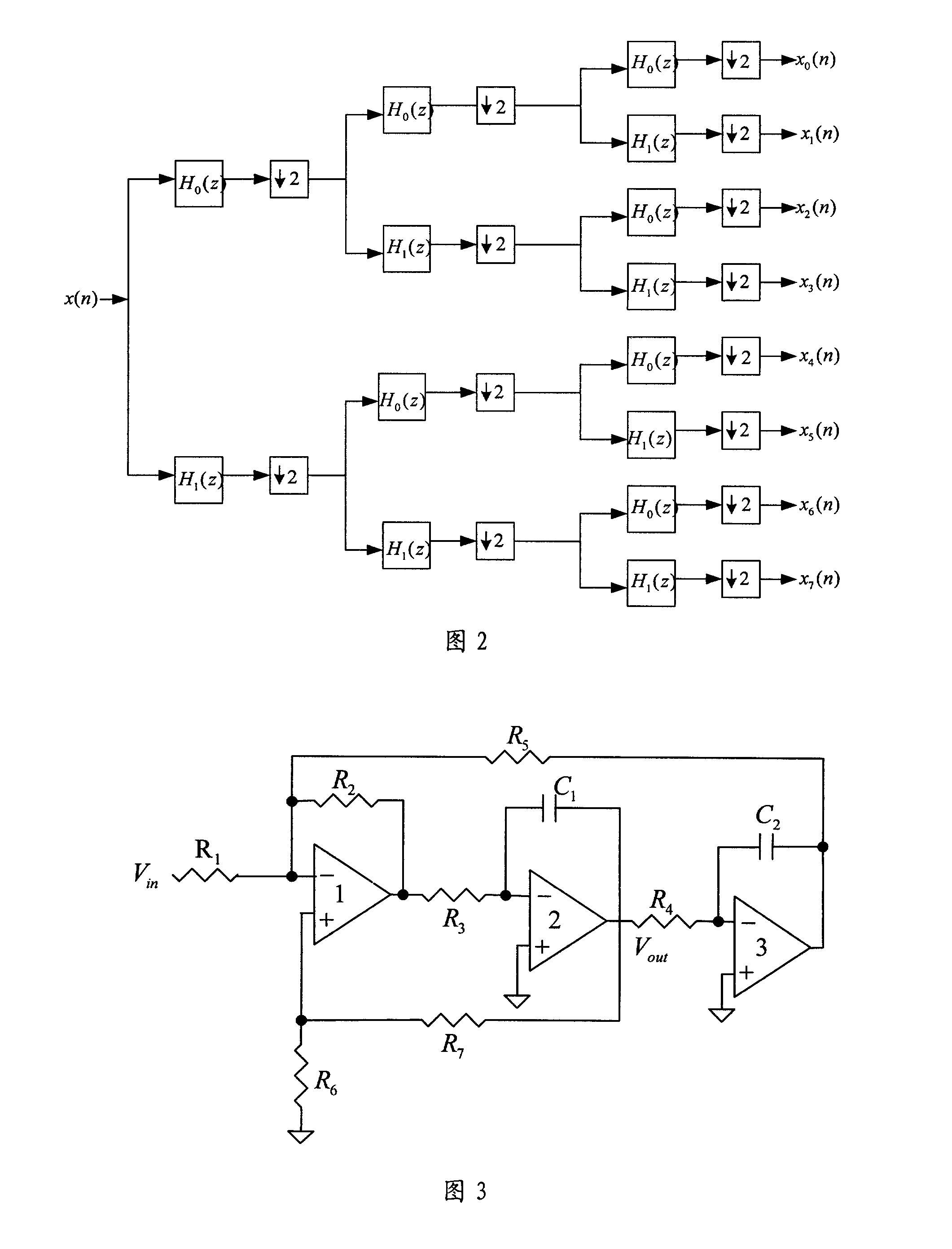

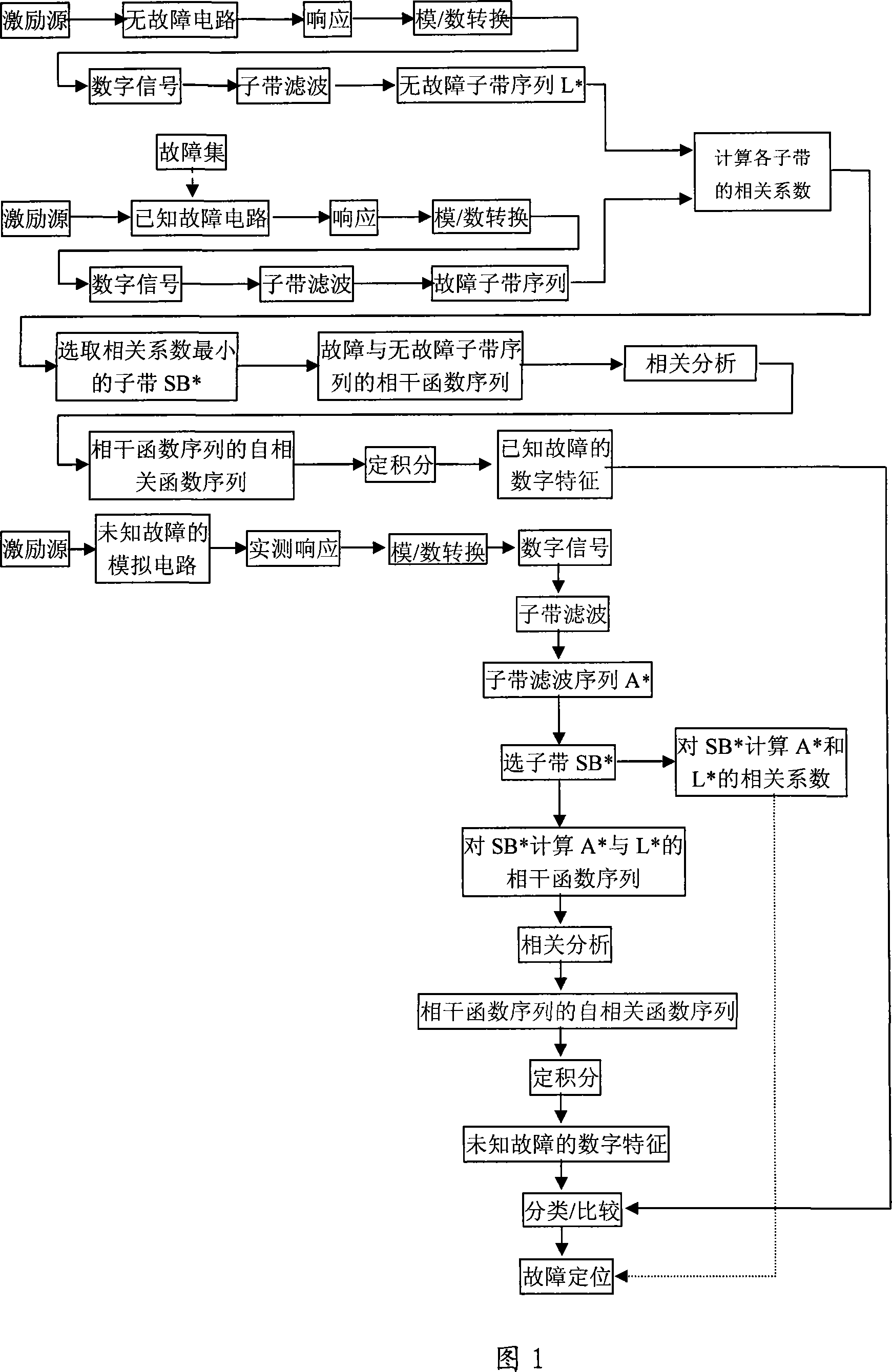

Method for locating parameter type fault of analogue integrated circuit

InactiveCN101201386AImprove the accuracy of fault diagnosisHigh fault resolutionAnalog circuit testingFault coverageImage resolution

The invention discloses a location method of the parameter type fault of the analog integrated circuit. The invention carries out the polyphase filter bank for the measured analog integrated circuit, then calculates the cohere function sequence which corresponds to the faultless sub band sequence for the fault polyphase filter bank sequence in the sub band of the highest fault resolution, and obtains the autocorrelation function sequence of the cohere function sequence, and takes the definite integral answers of the autocorrelation function sequence of the cohere function as the digital characteristic of the fault to realize the fault location. By comparing to the exist technology, the invention can realize the location of the parameter type fault of the analog integrated circuit, reach high accuracy of fault diagnosis, high fault resolution and high fault coverage, realize the multi-parameter type fault location, and easily realize the automation of the fault diagnosis by the digitized fault characteristic with the obvious difference.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

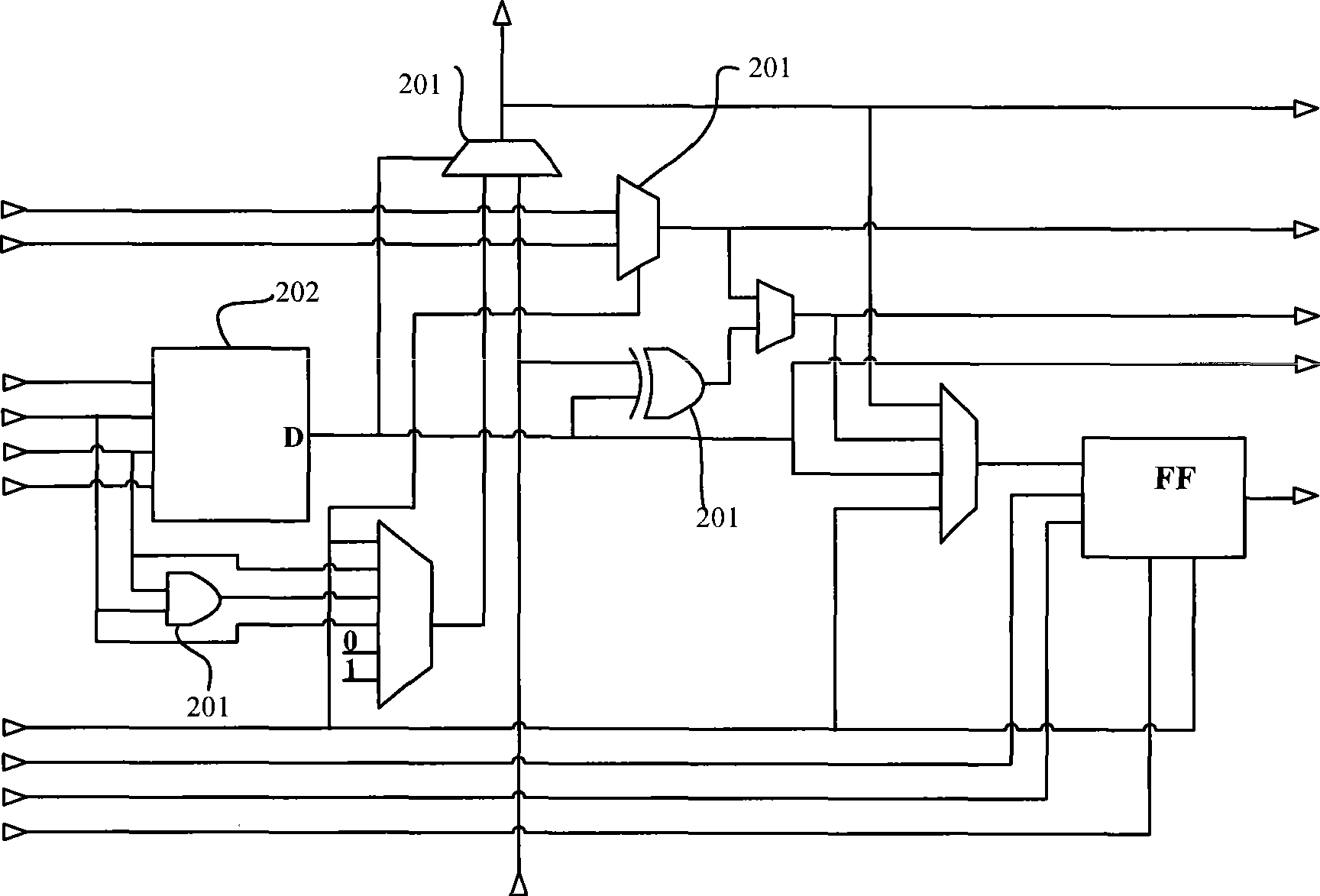

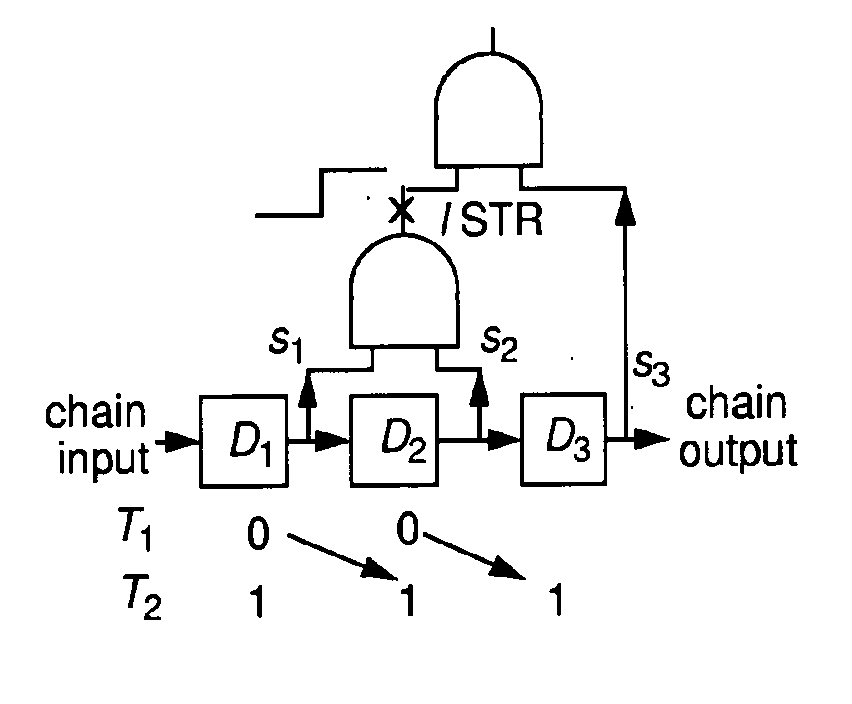

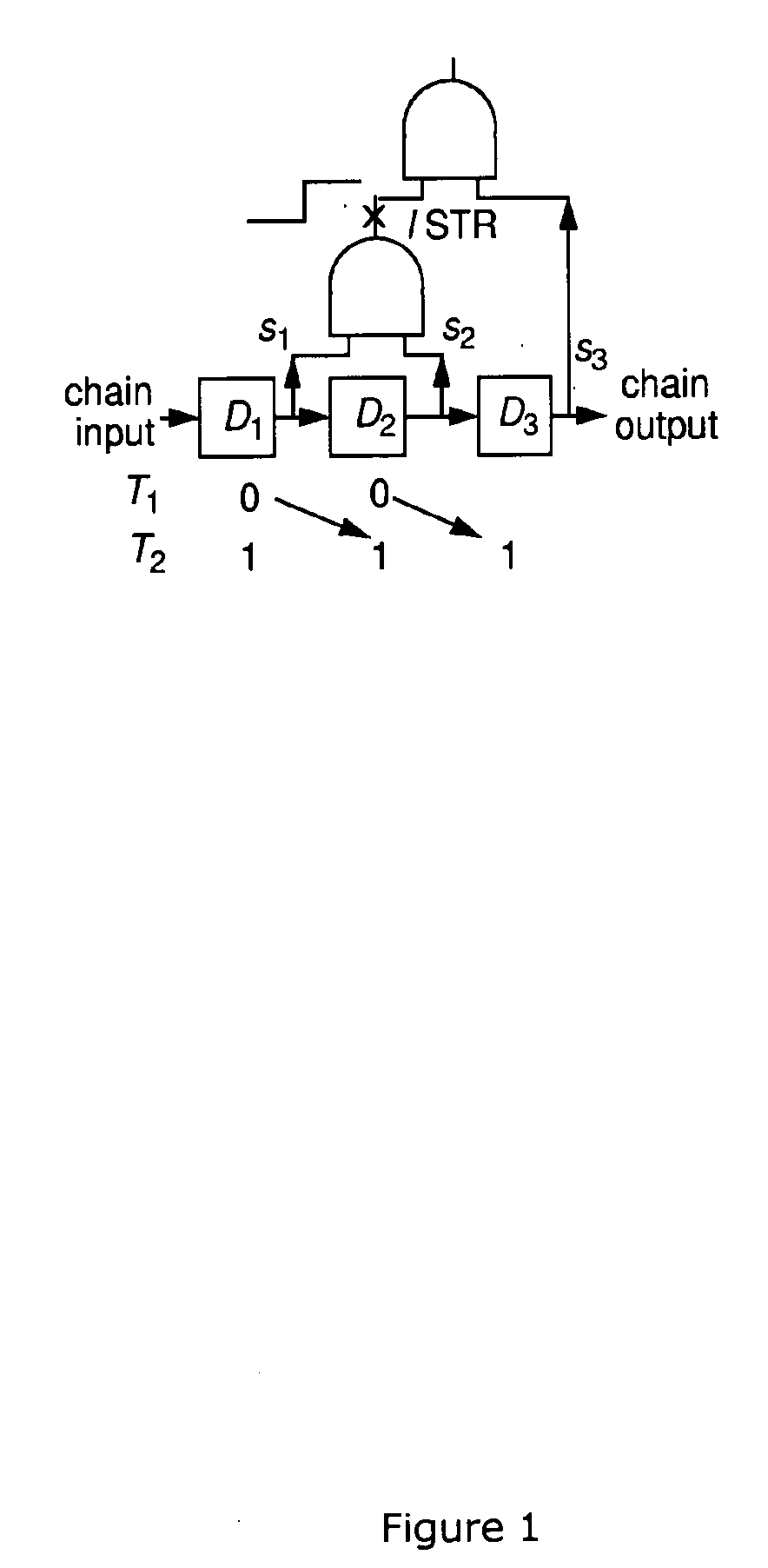

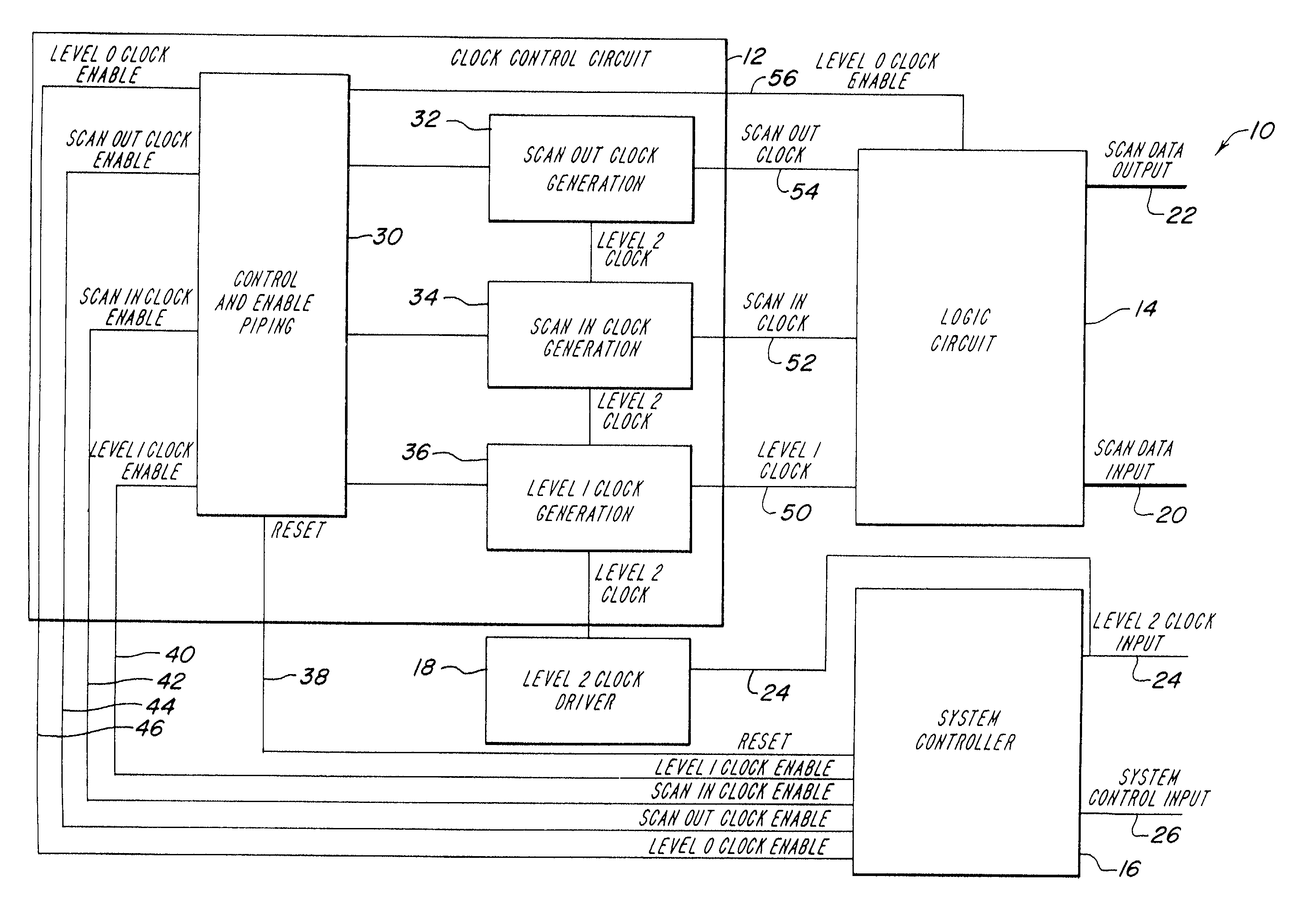

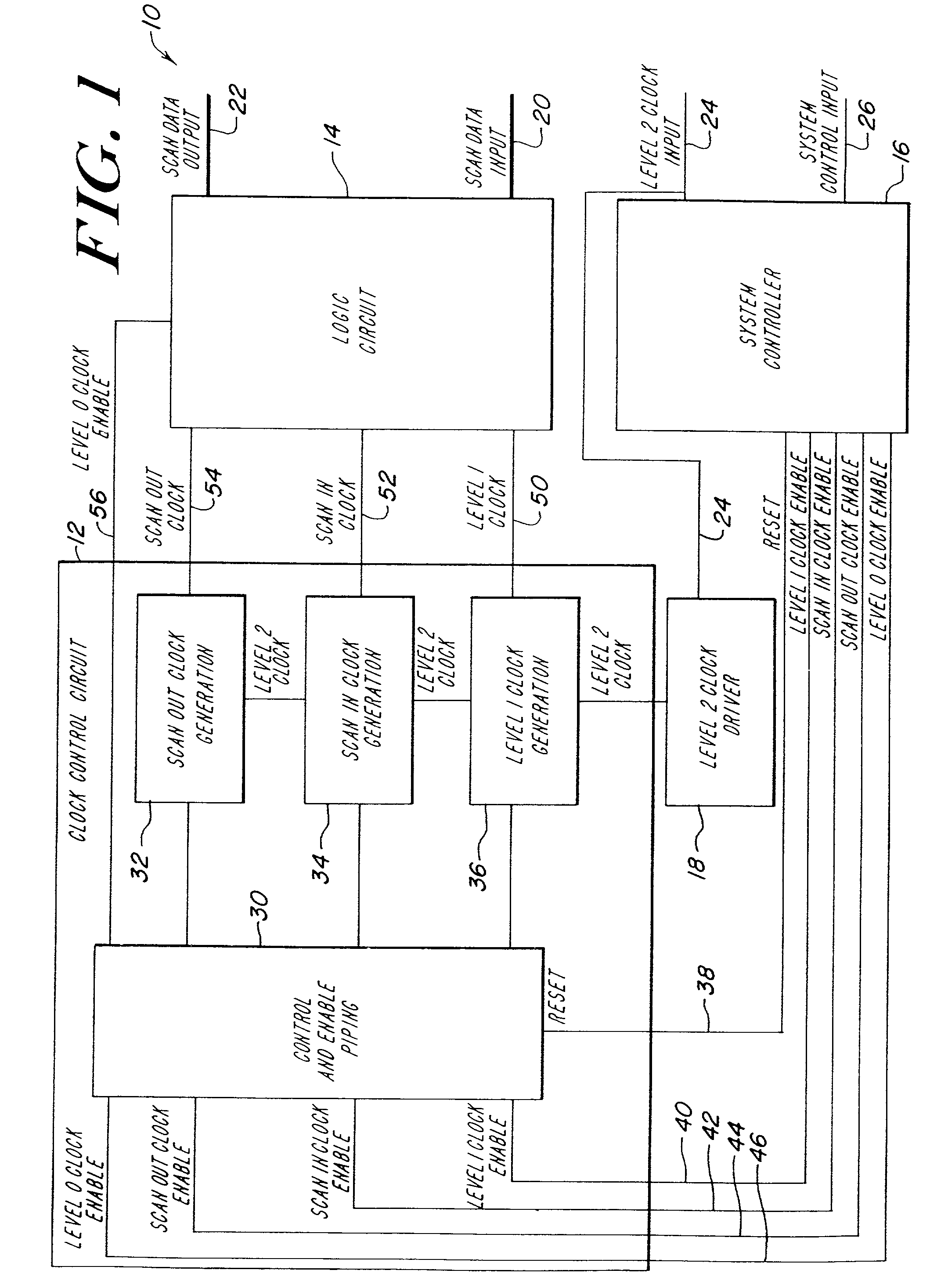

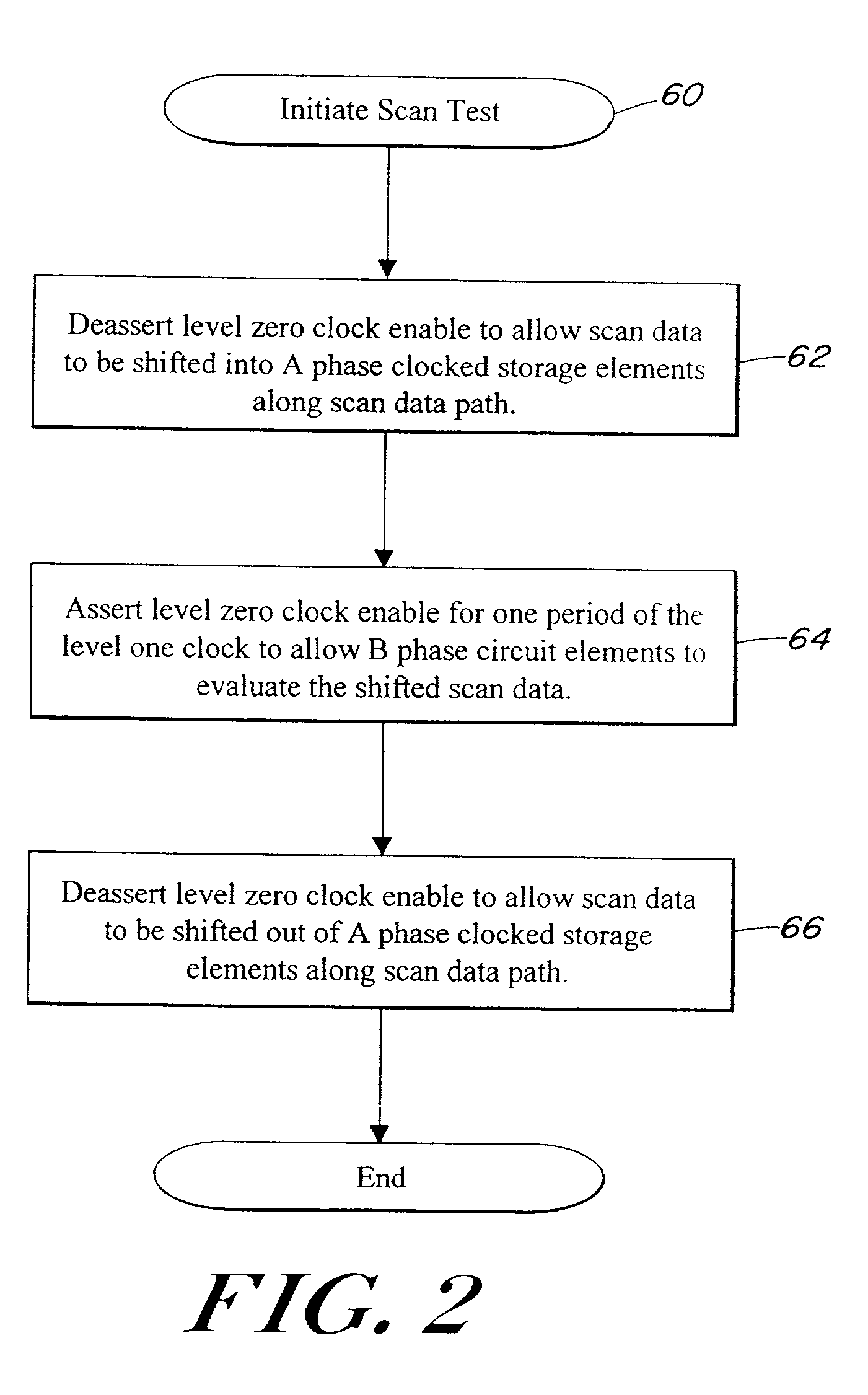

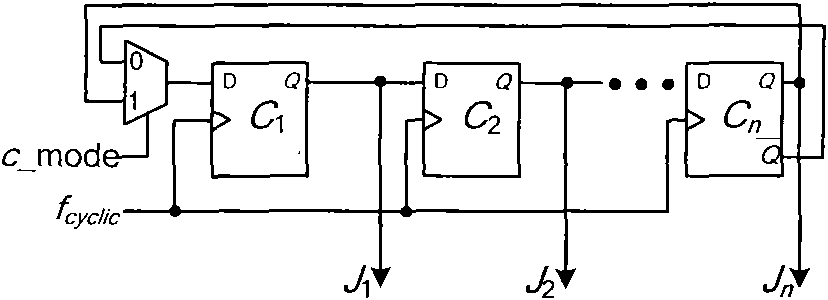

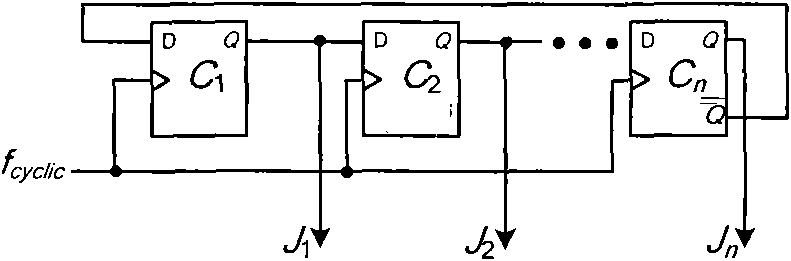

Method for scan testing and clocking dynamic domino circuits in VLSI systems using level sensitive latches and edge triggered flip flops

InactiveUS7000164B2Impacting speedImpacting efficiencyElectronic circuit testingGenerating/distributing signalsMultiplexerVlsi systems

A system and method is provided for scan control and observation of a logical circuit that does not halt the operation of the system clock. Thus, all dynamic circuits within the system continue to evaluate and precharge normally. Moreover, the traditional method of placing a multiplexer before the data input of a clocked storage element to perform scan control and observation is no longer required. Consequently, the system and method provide a more efficient manner in which to perform scan control and observation of a logical circuit.

Owner:ORACLE INT CORP

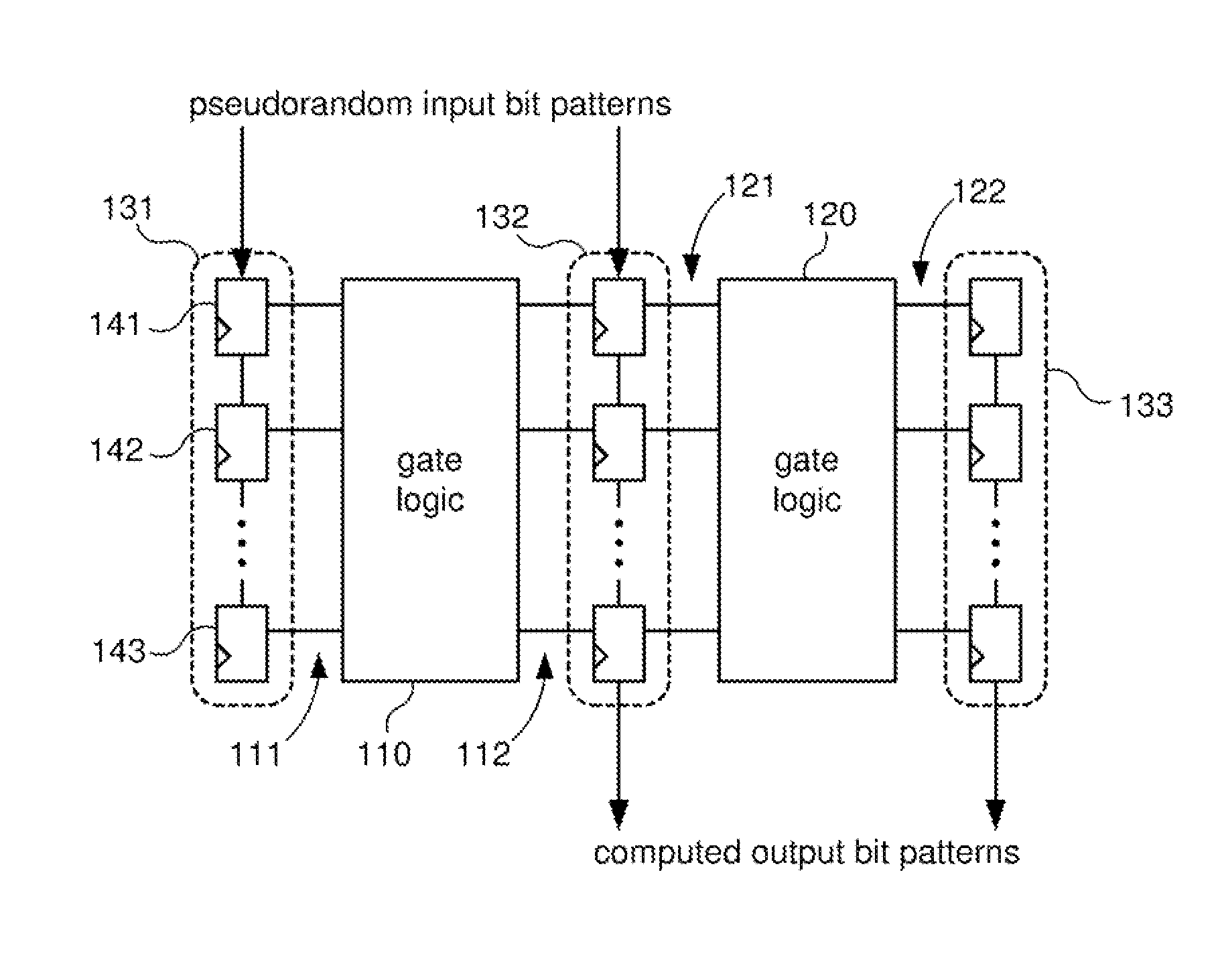

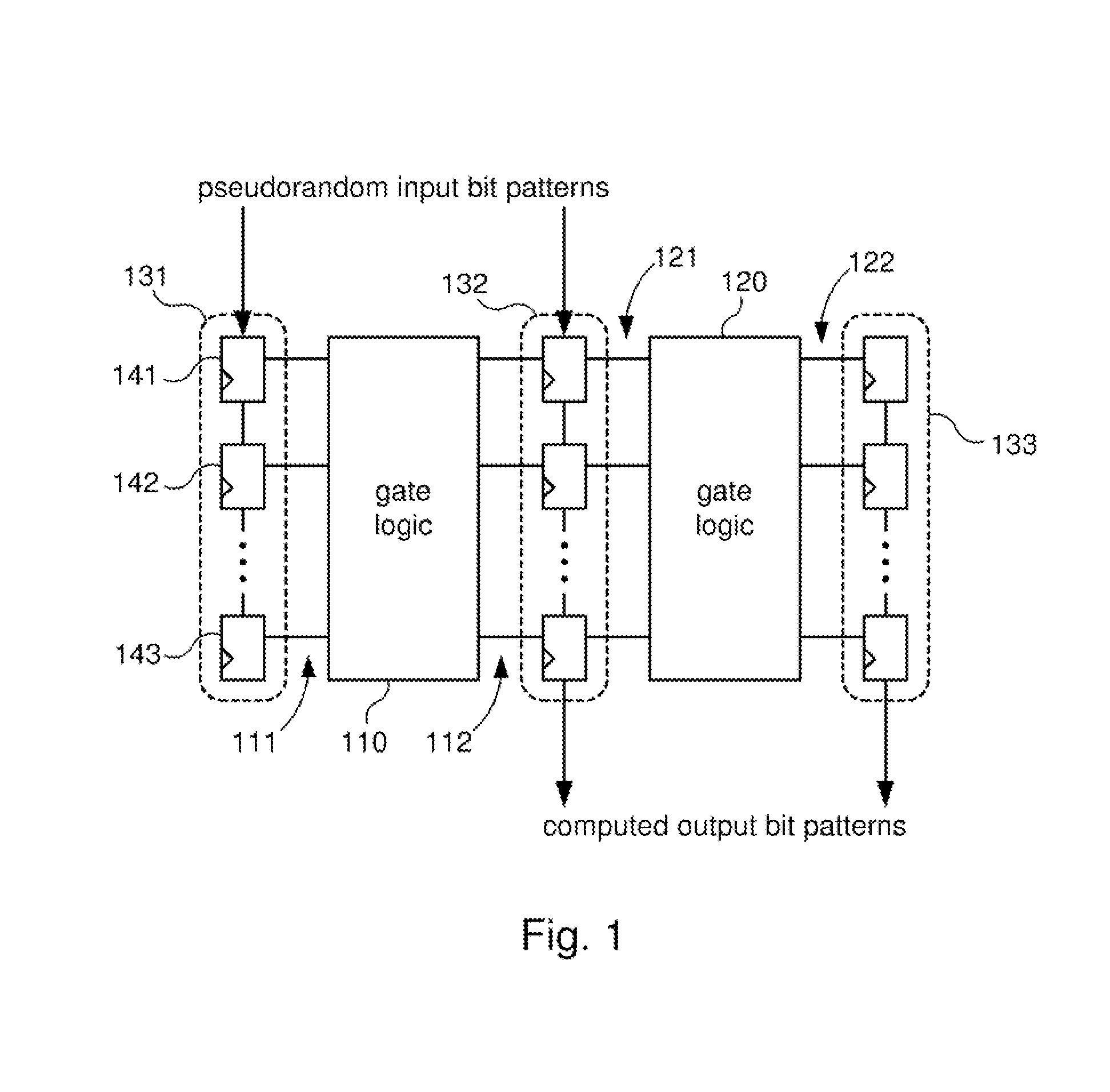

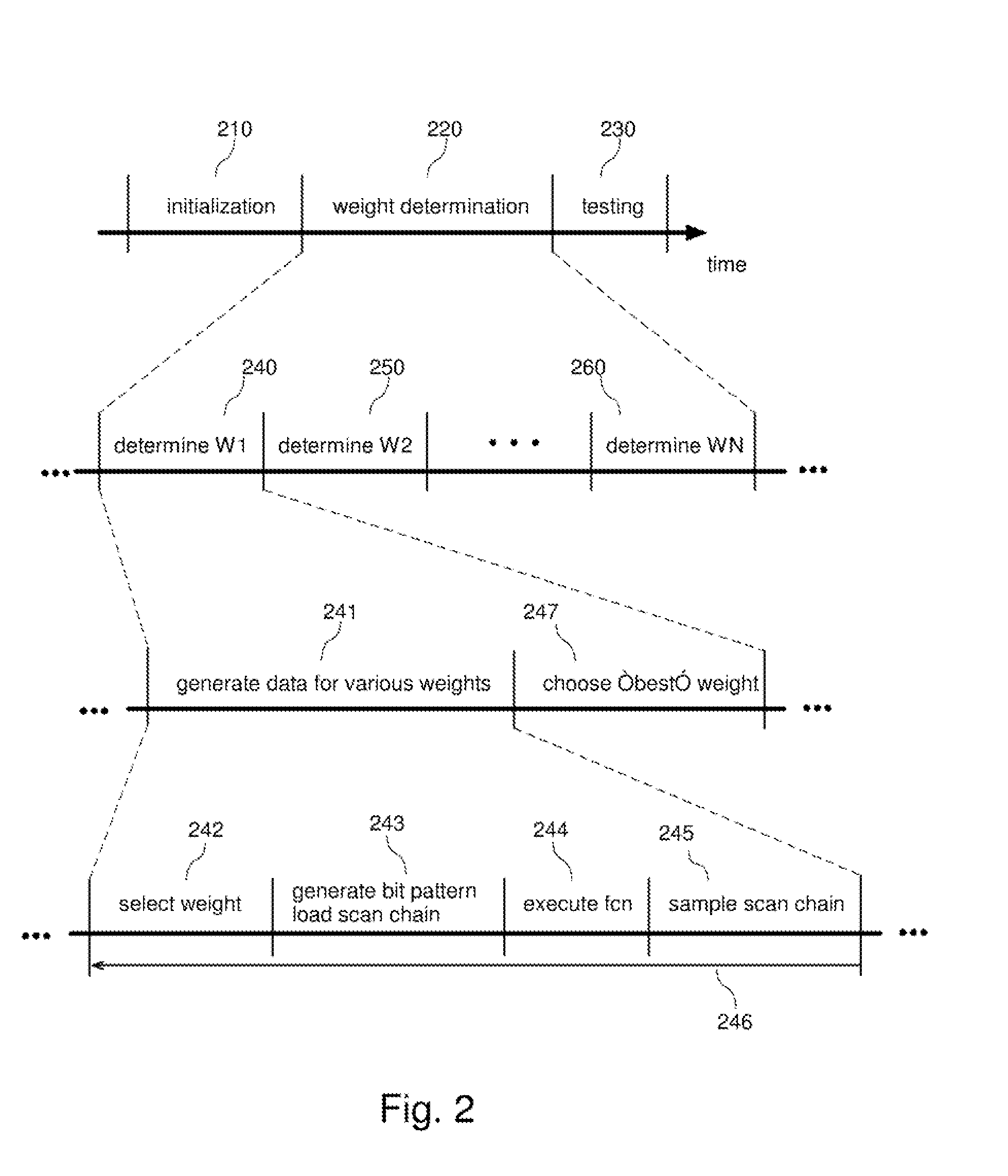

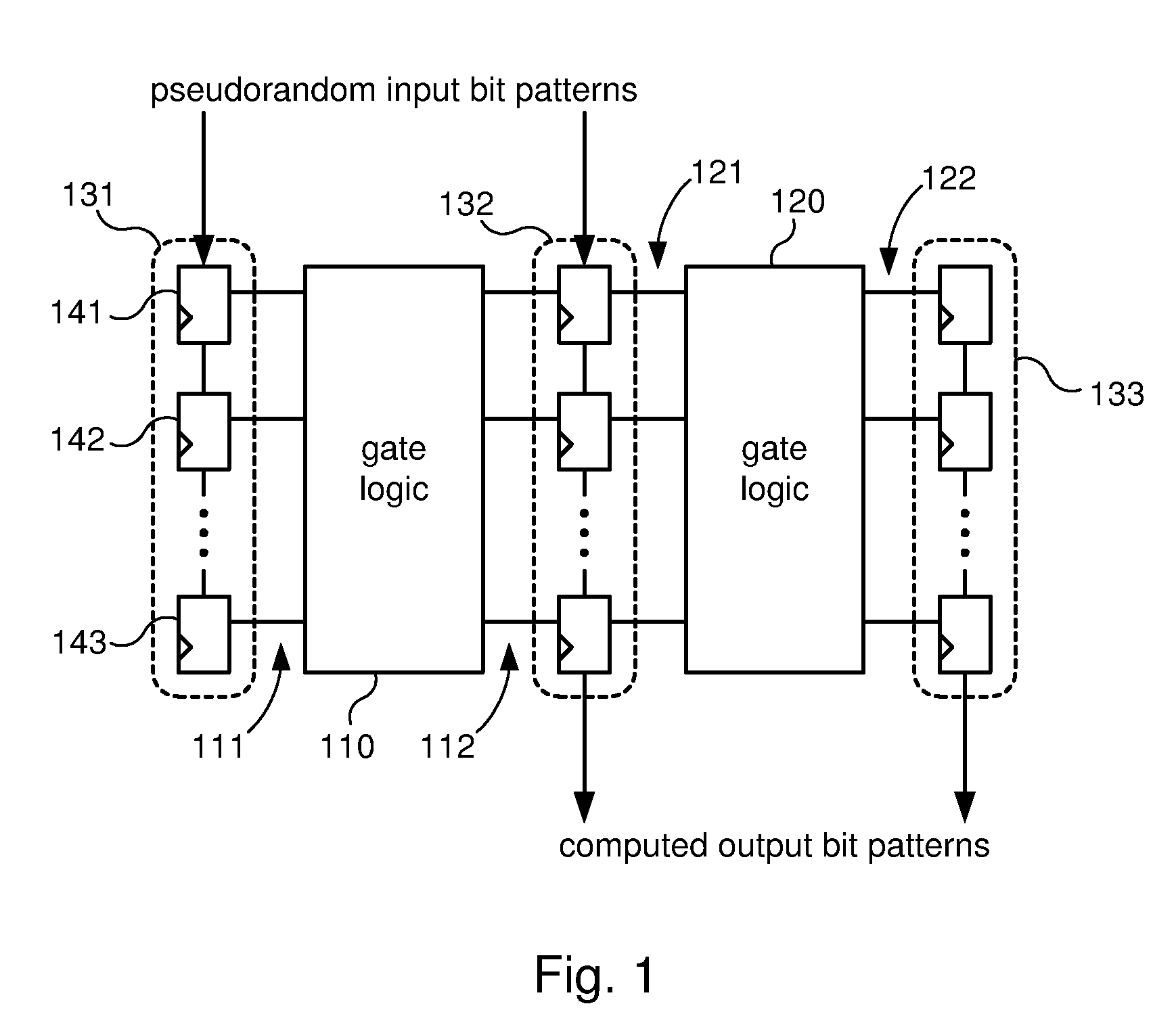

Systems and Methods for Improved Fault Coverage of LBIST Testing

InactiveUS20070273401A1Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageEngineering

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) by determining weighting and / or seed values to be used in generating pseudorandom test bit patterns for each channel to optimize fault coverage. In one embodiment, a method includes generating a pseudorandom sequence of bits, applying a weighting value to the sequence, propagating the weighted sequence through one or more levels of logic, and capturing the resulting data. Metrics are then applied to the captured data to determine the suitability or optimality of the weighting value, and an optimal weighting value is selected. This may be performed for a plurality of trial values for each of a number of channels to obtain a set of weighting values for the different LBIST channels. The method may also include determining a seed value for the pseudorandom bit pattern generator.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

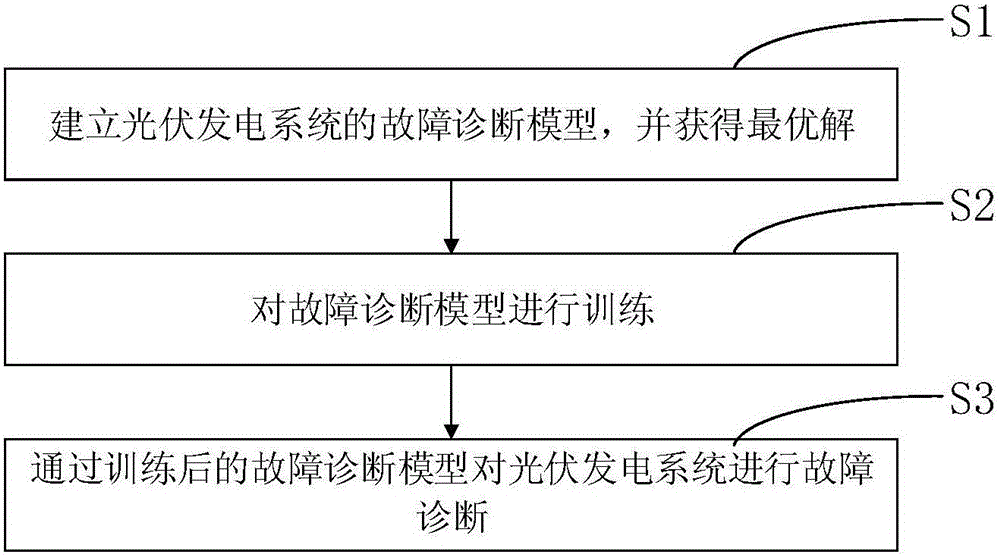

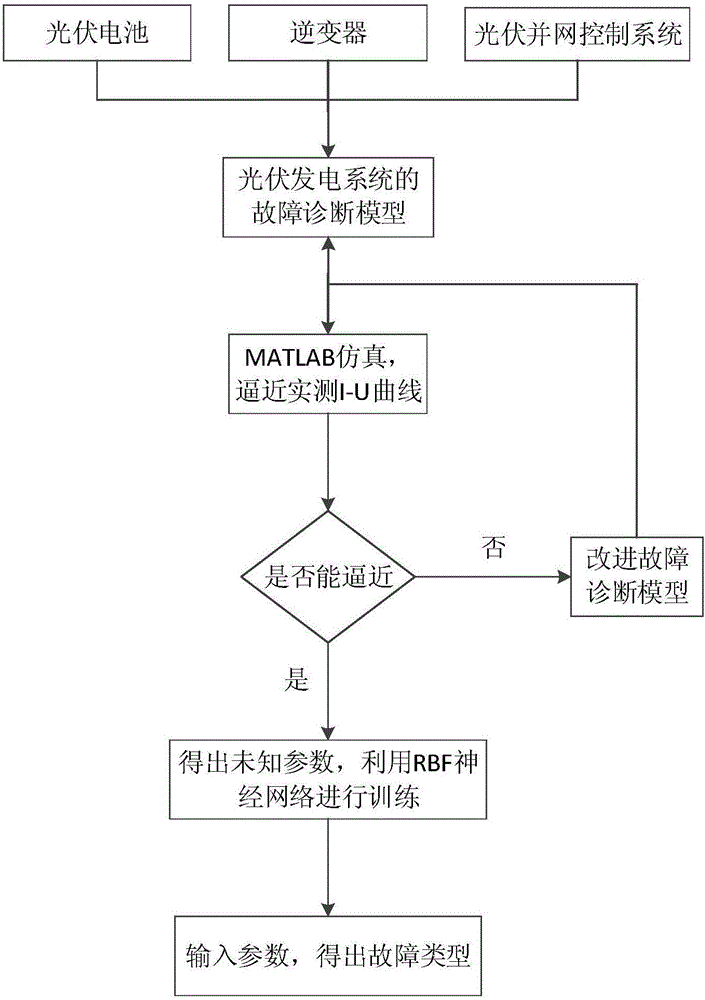

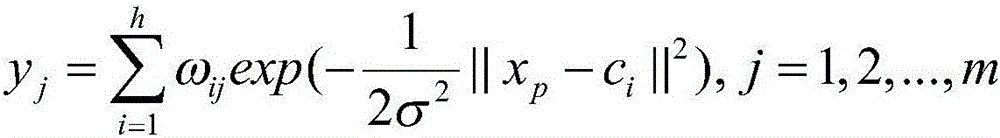

Parameter identification-based photovoltaic power generation system fault diagnosis method and system

InactiveCN106067758AExtended power generation timeImprove power generation efficiencyPhotovoltaic monitoringPhotovoltaic energy generationDiagnosis methodsControl system

The invention relates to a parameter identification-based photovoltaic power generation system fault diagnosis method and a parameter identification-based photovoltaic power generation system fault diagnosis system. The parameter identification-based photovoltaic power generation system fault diagnosis method includes the following steps that: the fault diagnosis model of a photovoltaic power generation system is built, and the optimal solutions of the fault diagnosis model are obtained; the fault diagnosis model is trained; and fault diagnosis is carried out on the photovoltaic power system based on the trained fault diagnosis model. According to the parameter identification-based photovoltaic power generation system fault diagnosis method of the invention, according to problems which easily appear in the photovoltaic power generation system, namely, open-circuiting and short-circuiting of a photovoltaic battery assembly, the overload of an inverter and the failure of a control system, the parameter identification-based photovoltaic power generation system fault diagnosis model under a mismatch condition is built; an I-U curve is obtained according to the data of a photovoltaic power plant in different working conditions; analog simulation is carried out on the actually-measured I-U curve, so that the optimal solutions of the parameters of the model are obtained; an RBF neural network is utilized to train the model, so that the trained fault diagnosis model is obtained; and test samples or real-time samples of the photovoltaic power plant are inputted to the model, so that fault diagnosis can be carried out.

Owner:HOHAI UNIV CHANGZHOU

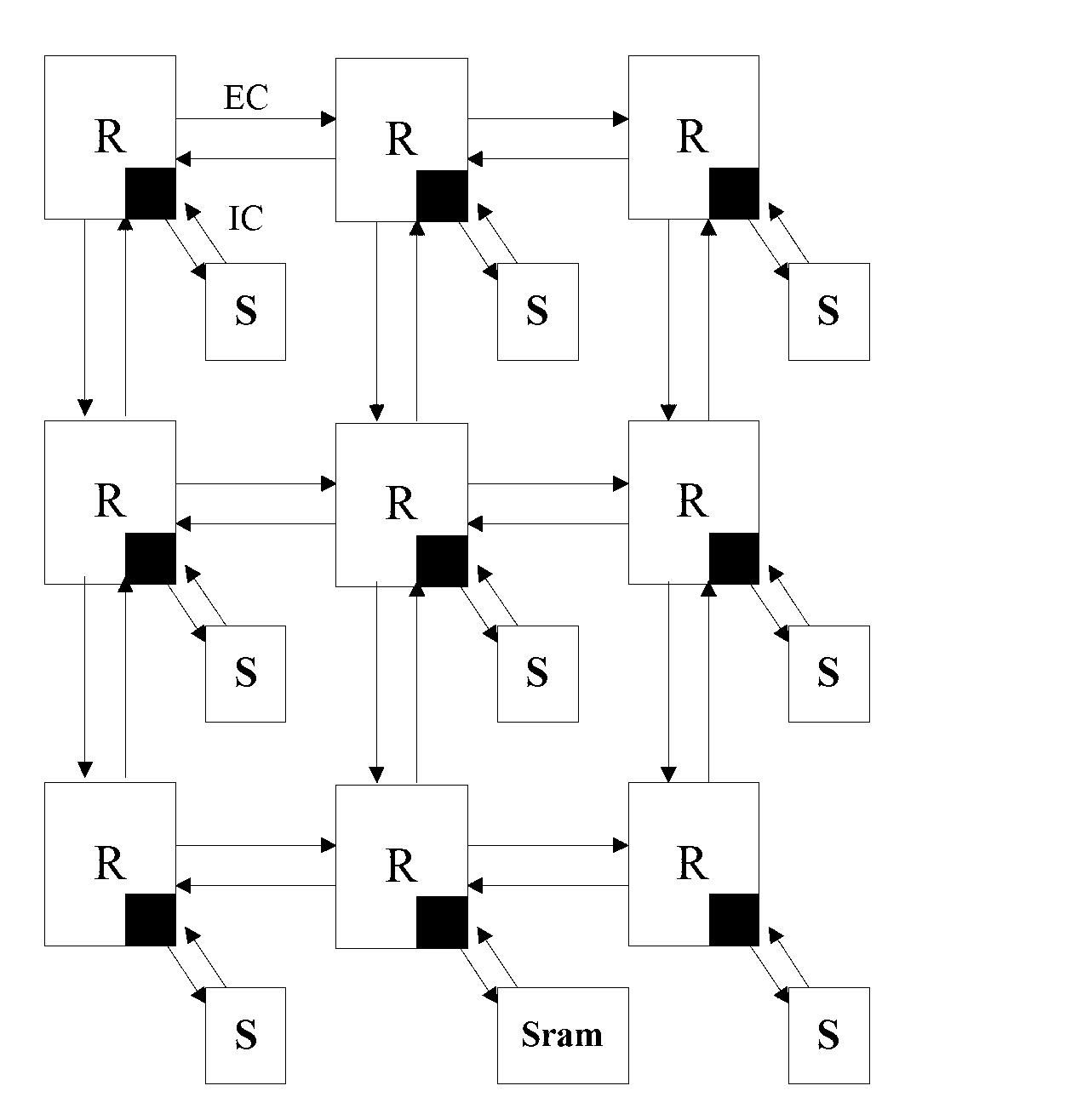

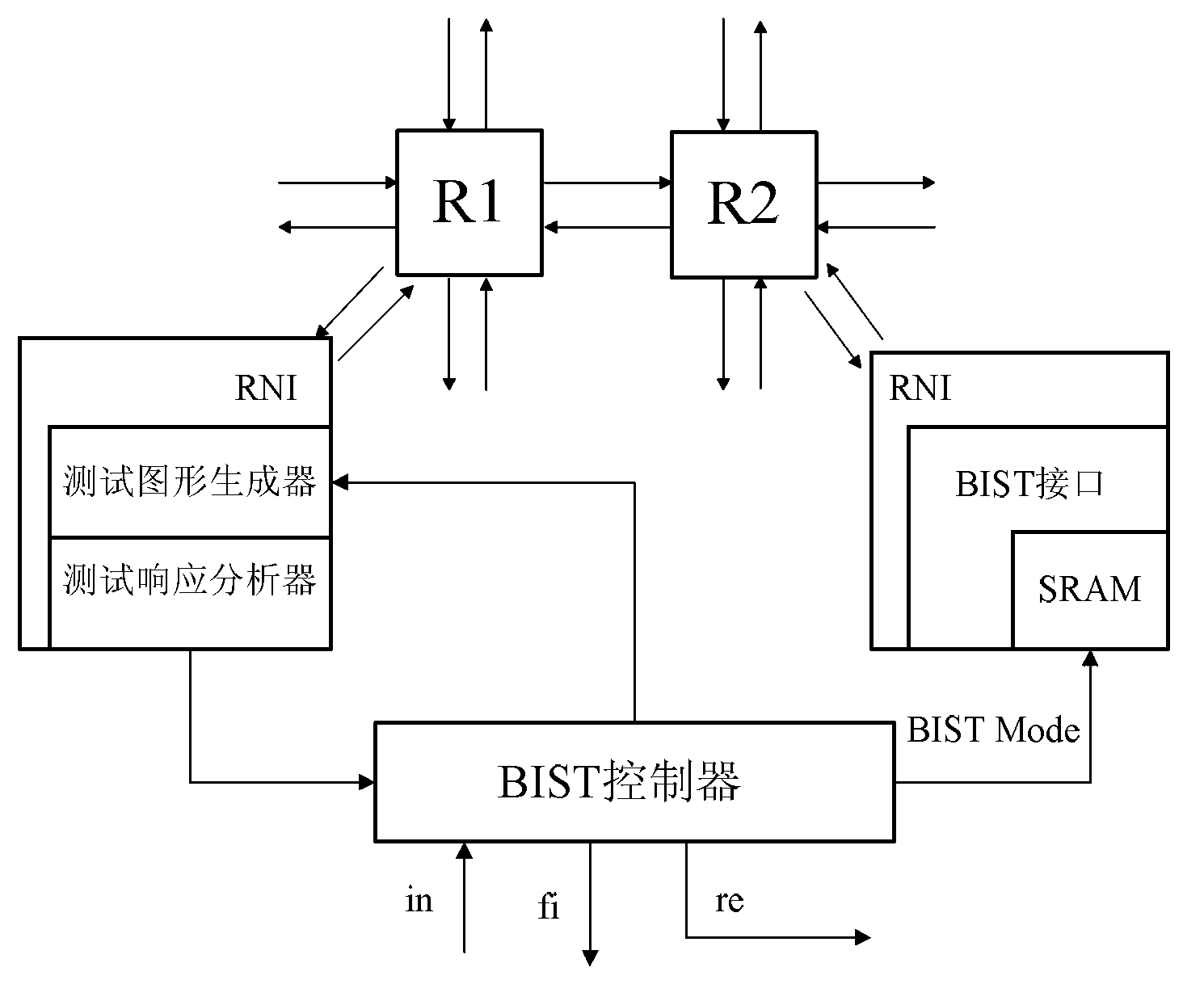

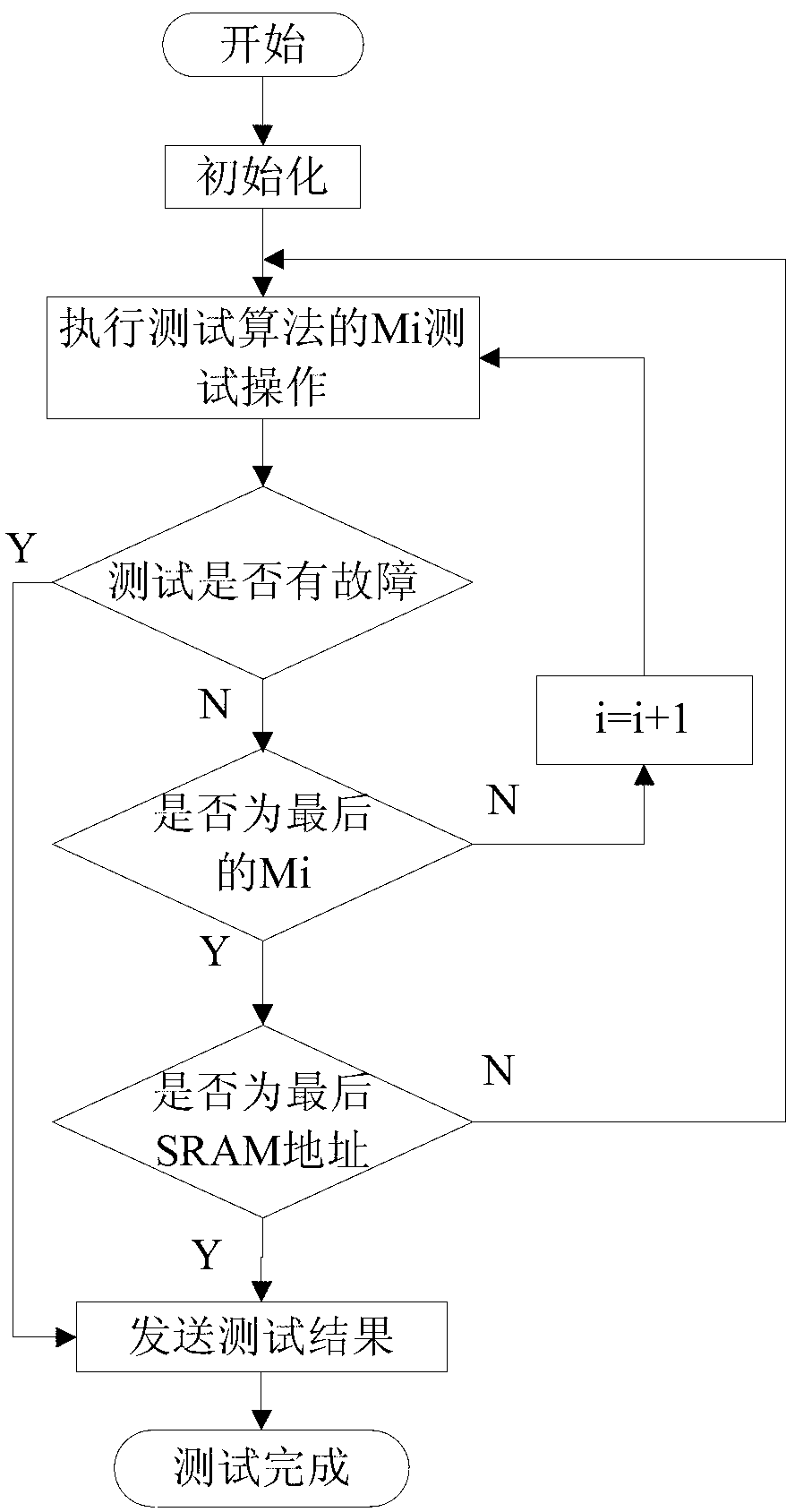

Built-in self-test structure and method for on-chip network resource node storage device

ActiveCN103310850AReduce areaSmall area overheadStatic storageStatic random-access memoryTest algorithm

The invention discloses a built-in self-test structure and method for an on-chip network resource node storage device. The built-in self-test structure comprises a built-in self-test (BIST) controller arranged on a field programmable gate array (FPGA) chip, a resource network interface and a BIST interface which are embedded into corresponding routers, a test pattern generator and a test response analyzer, wherein the BIST controller is connected with external test equipment through an external interface. The built-in self-test method comprises the following steps that: the external test equipment sends an instruction start test program to the BIST controller; the BIST controller sends an enabling signal and a state selection signal to each test module according to a March C+ test algorithm program, performs read-write operation on each address of a static random access memory (SRAM) under each test state, and stops sending the signals if failures are found out. A test result is sent to the external test equipment. According to the built-in self-test structure and method, the test time is reduced by 50 percent; a routing network of a network operation center (NoC) is reused as a test data route; data transmission is reliable and safe; a chip area is low in expense; the failure coverage rate is high.

Owner:GUILIN UNIV OF ELECTRONIC TECH

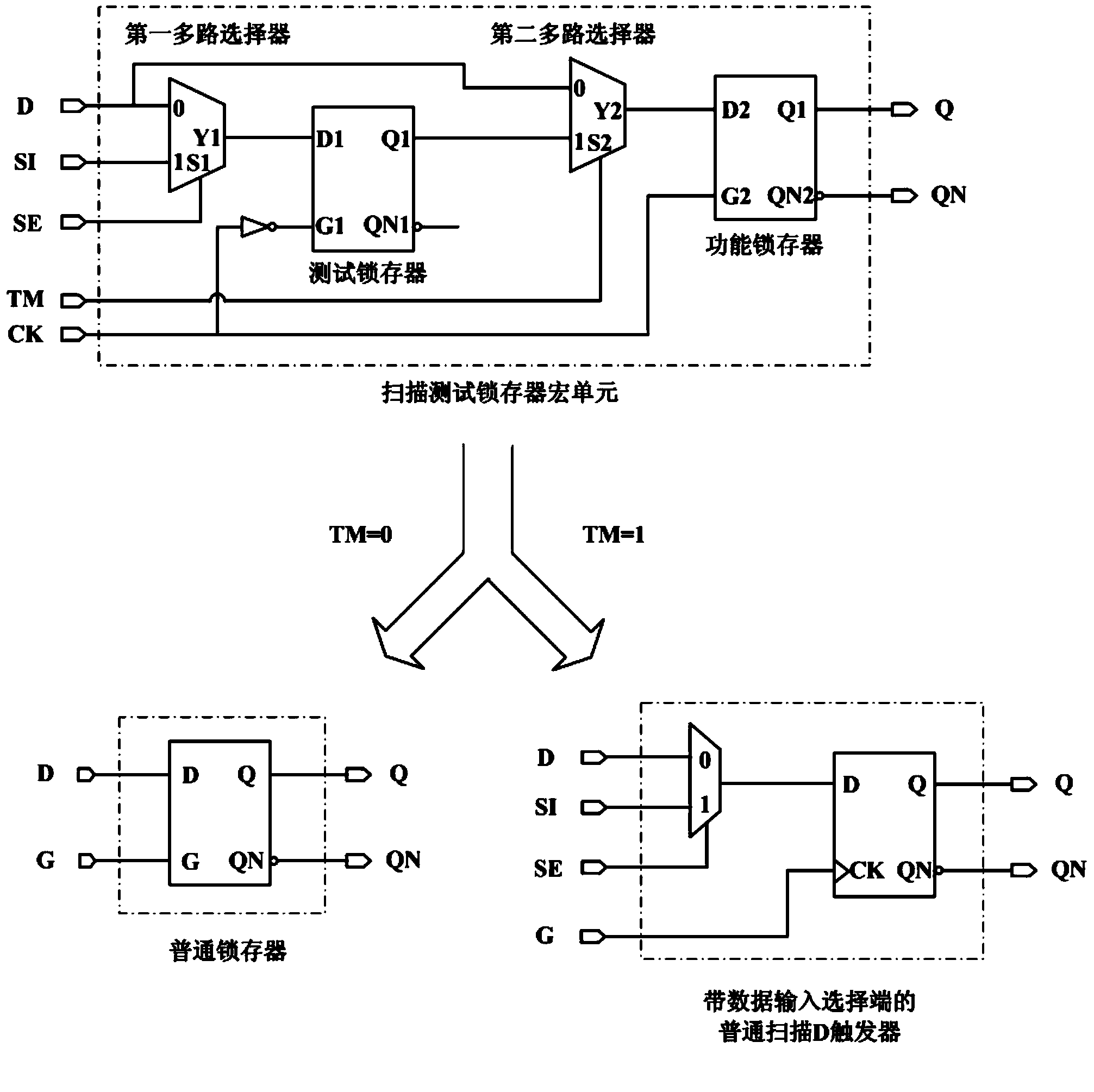

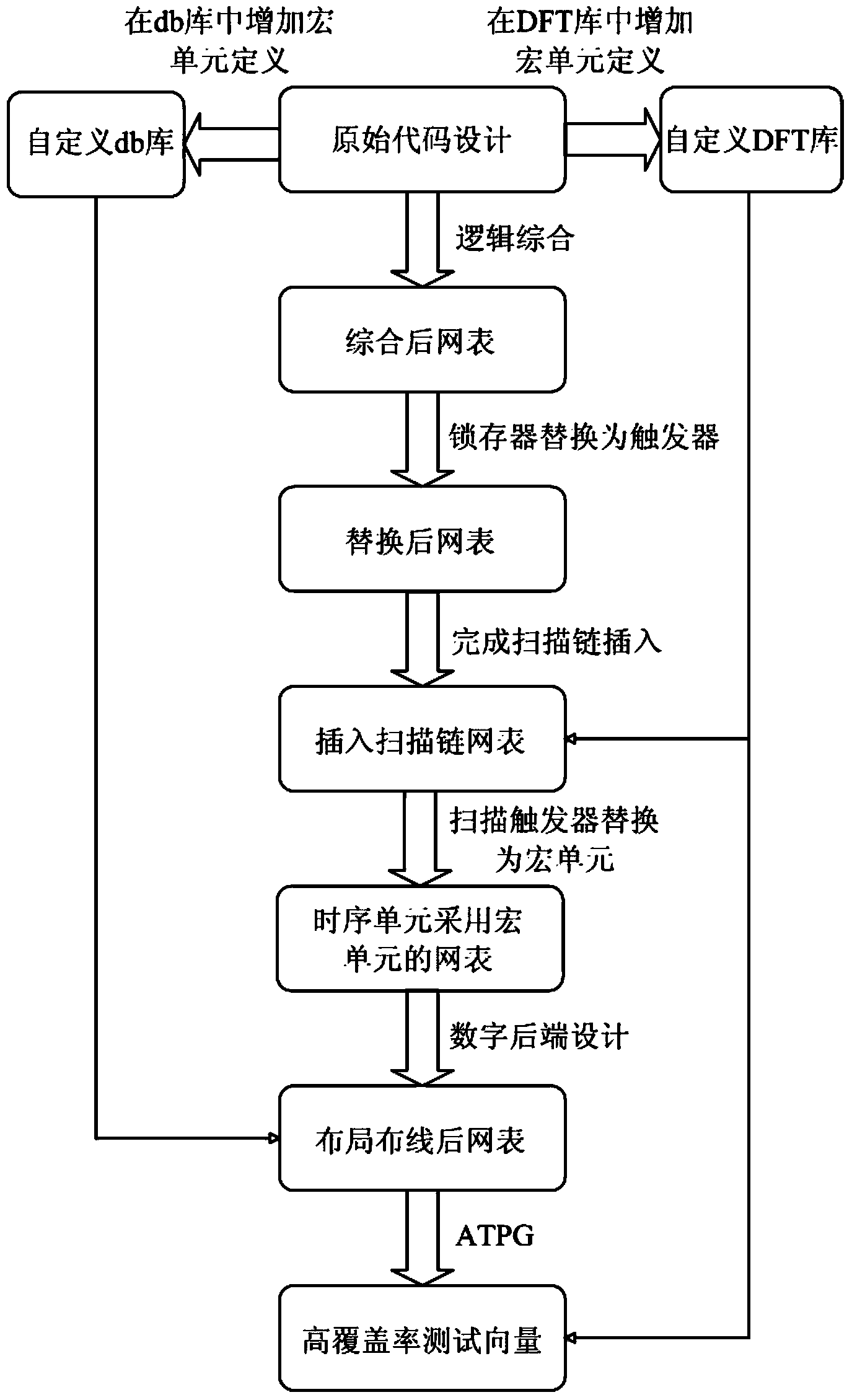

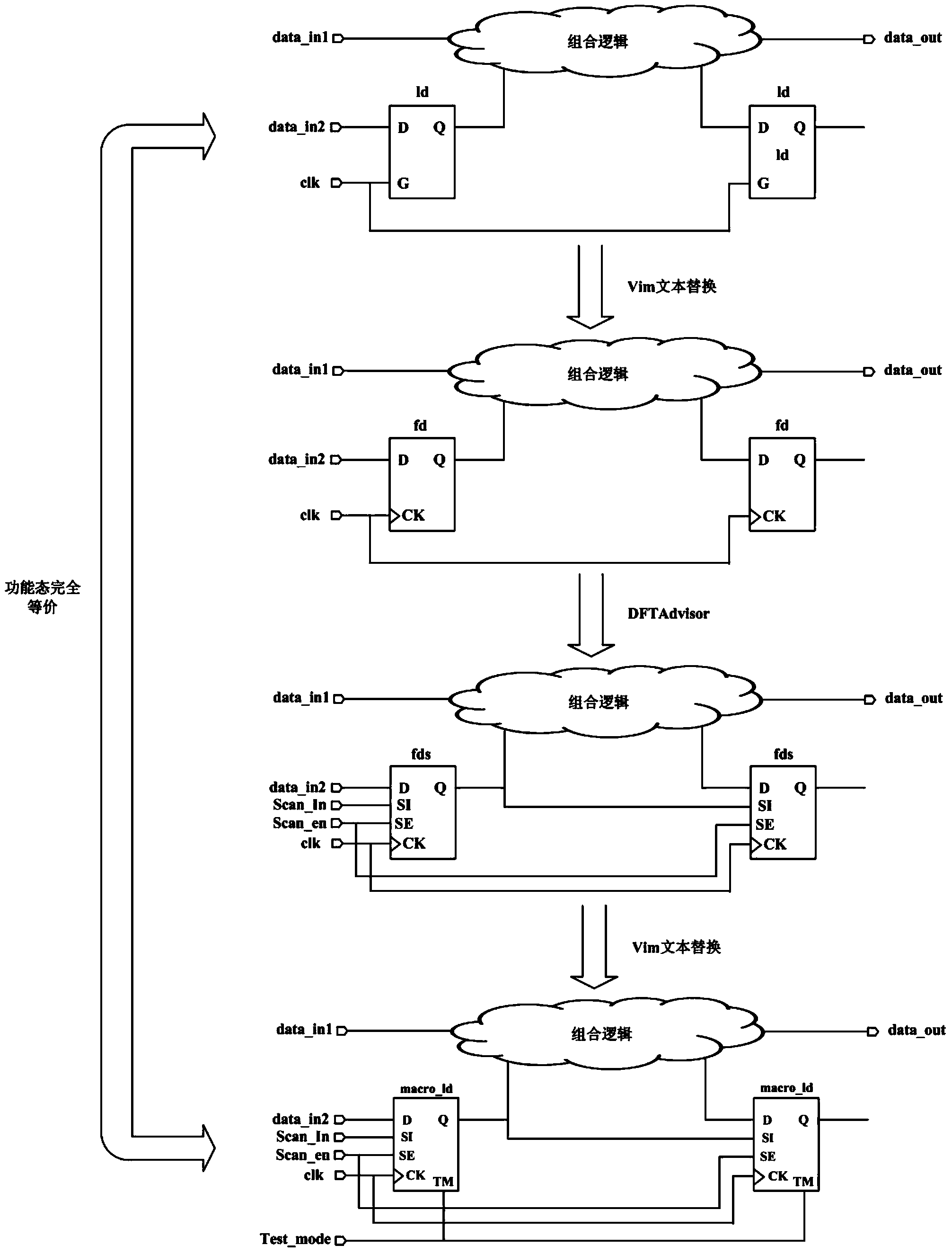

Scan test latch macrocell and scan test method

The invention provides a scan test latch macrocell and a scan test method. According to the scan test method, through a customized scan test macrocell, an ATPG test vector, based on a structure, used for a latch unit can be generated with a common scan test design method for a D trigger according to a special design process, the problems that testability design development cannot be easily performed on an existing digital special integrated circuit based on latch design, the fault coverage rate of the test vector is low, and time sequence analysis is complex are solved, the fault coverage rate of chip tests is substantially increased, the effectiveness and the completeness of the chip tests are guaranteed, and the method is mainly applied to the test vector development of the digital special integrated circuit based on latch design.

Owner:BEIJING MXTRONICS CORP +1

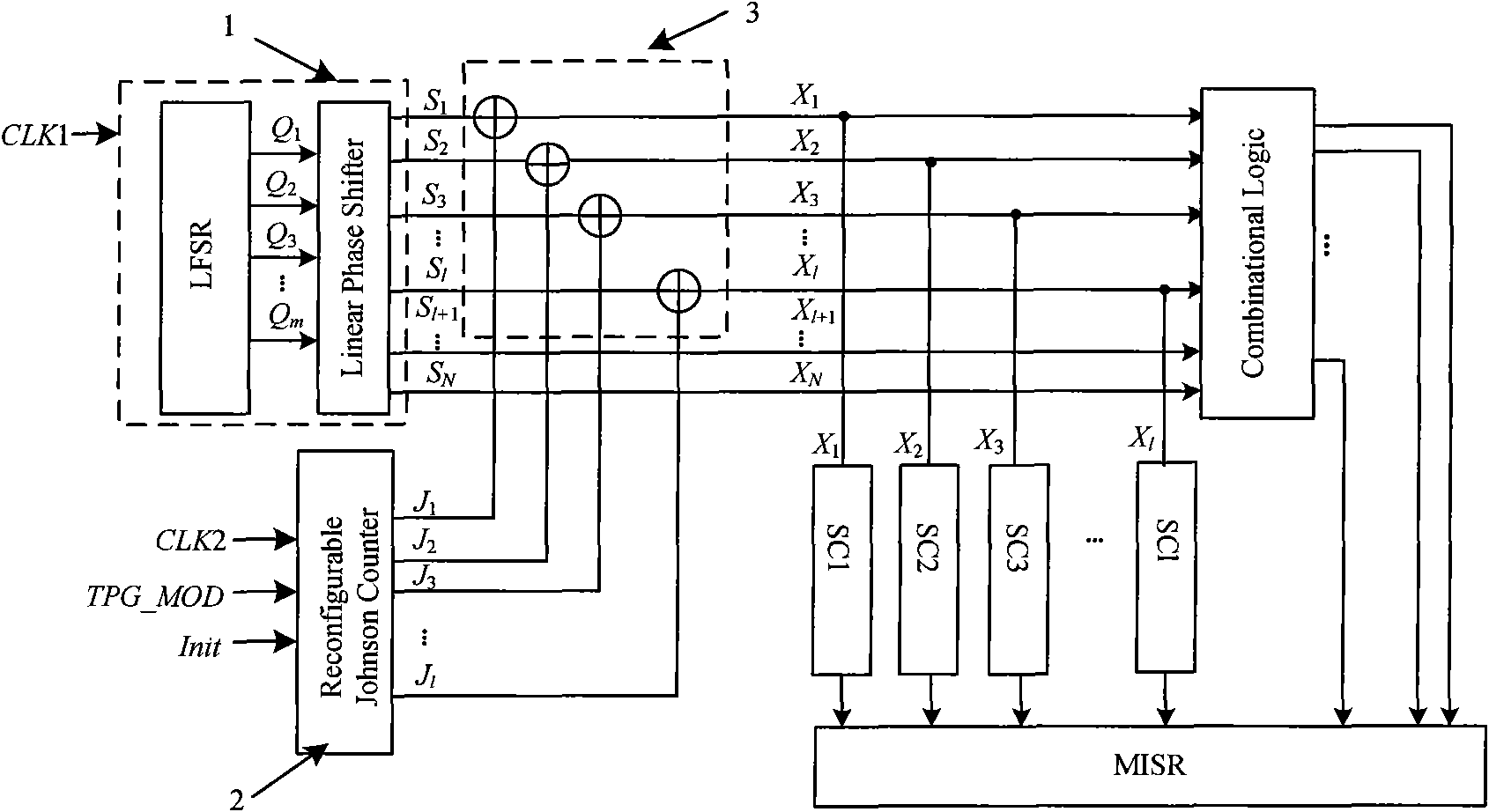

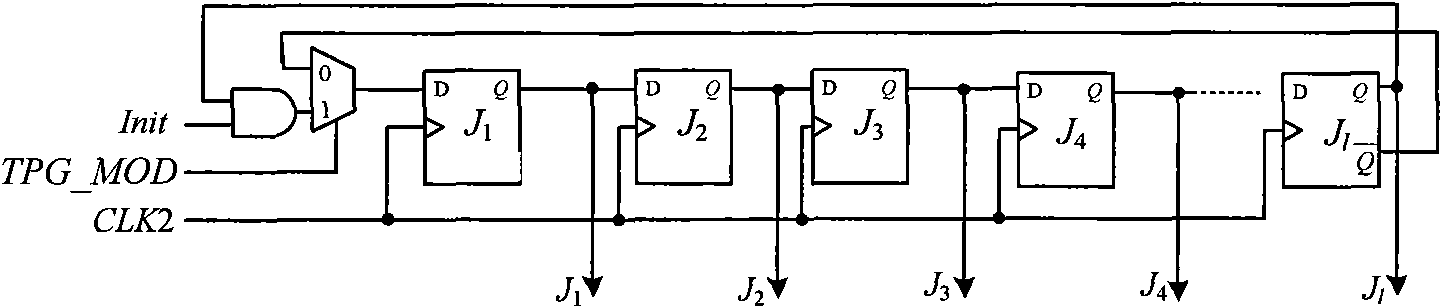

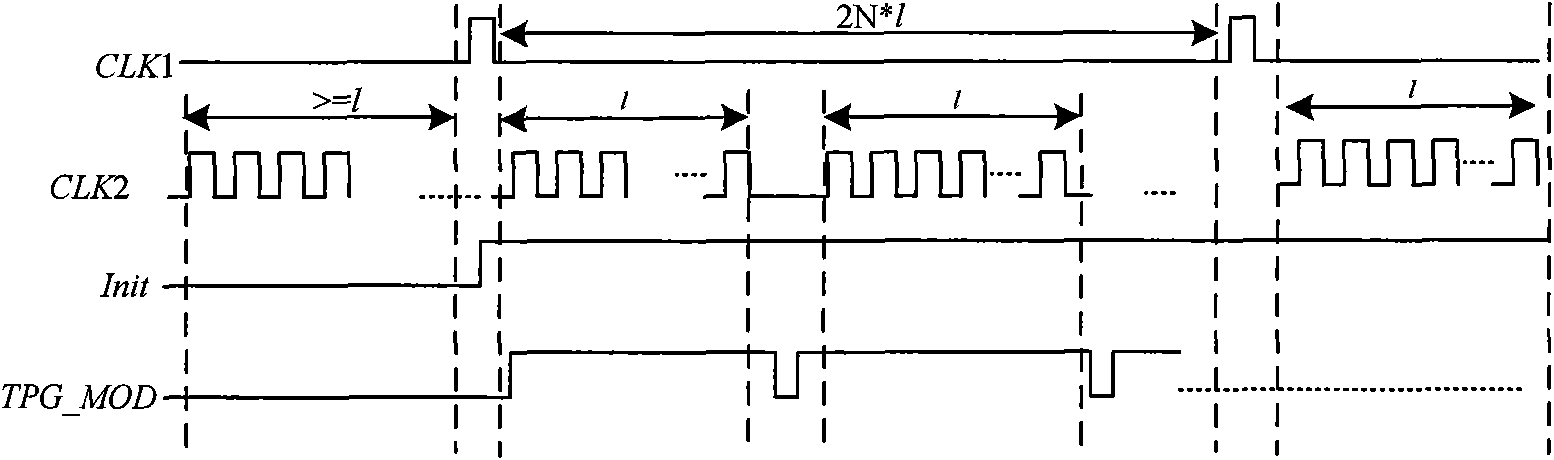

Test pattern generator of integrated circuit and test method thereof

The invention relates to the test field of integrated circuits and discloses a low power consumption test pattern generator of an integrated circuit and a test method thereof. The low power consumption test pattern generator of the integrated circuit is based on a restructurable Johnson counter; compared with a traditional test pattern generator, the low power consumption test pattern generator can ensure that a generated test sequence can simultaneously reduce the test pattern conversion times in a space domain and a time domain, has low test pattern generation frequency in the space domain and generates different single-input changed sequences to each scan chain in the time domain, thereby greatly lowering the power consumption of a combined logic circuit part of a tested integrated circuit and the scan power consumption of the scan chain.

Owner:XI AN JIAOTONG UNIV

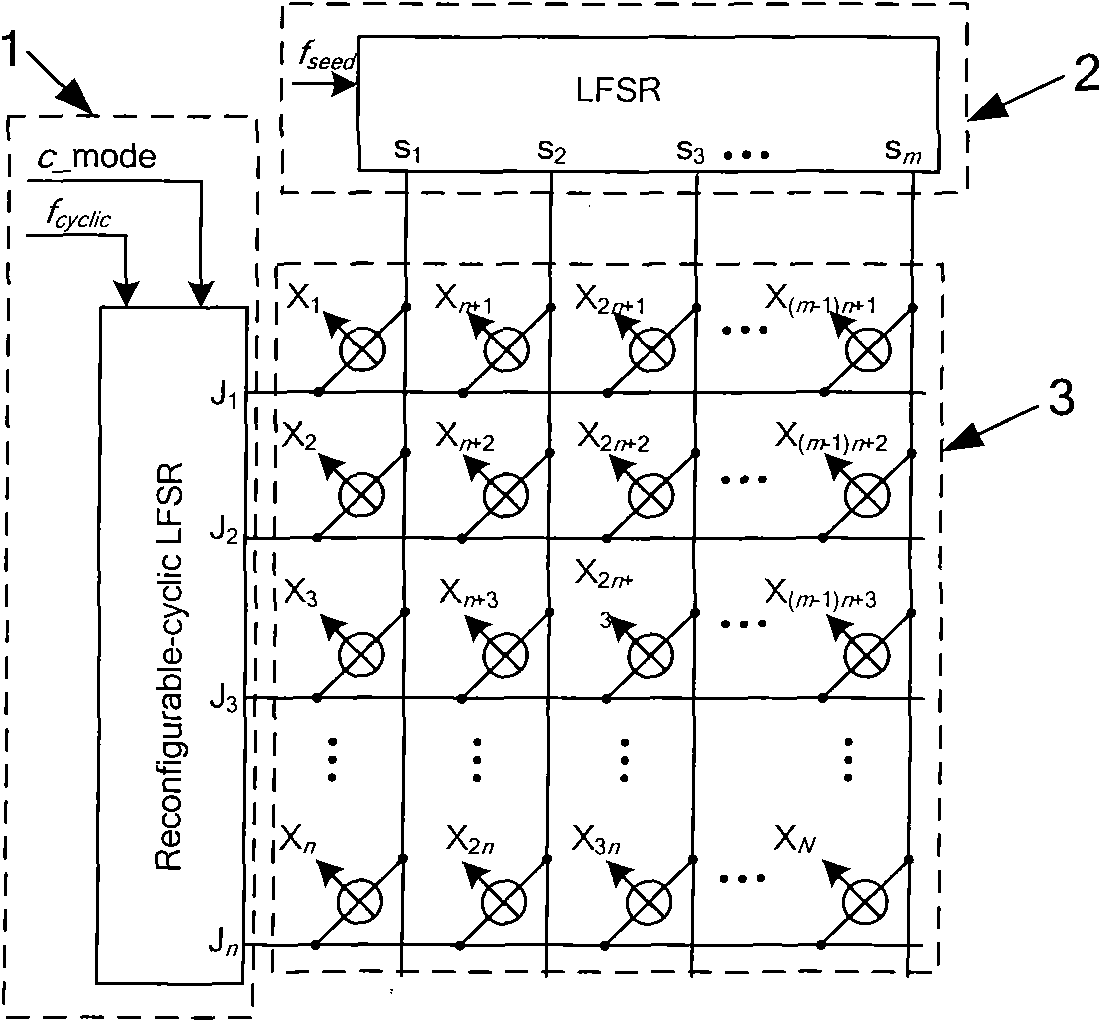

Test graphic generator of integrated circuit and test method thereof

InactiveCN101776730AReduce overheadReduce the number of test pattern transitionsElectrical testingFault coverageTest power

The invention relates to the field of an integrated circuit test, and discloses a test graphic generator of an integrated circuit and a test method thereof. The test graphic generator comprises a reconfigurable linear feedback shift register of cyclic code with single bit change, a liner feedback shift register based on a primitive polynomial and a two-dimensional exclusive or gate array; compared with the traditional test graphic generator, the test graphic generator has less hardware overhead, few quantity of repeated test graphics, short test time, uniform distribution of generated test graphics, and can obtain higher fault coverage rate; and the generated single jump test sequence reduces the conversion times of a tested circuit input end, thus greatly reducing the test power consumption of the tested integrated circuit.

Owner:XI AN JIAOTONG UNIV

Compression method for test data of irrational number storage test vector

ActiveCN104753541AReduce the number of codesReduce the number of test vectorsElectronic circuit testingCode conversionFault coverageCompression method

The invention discloses a compression method for test data of an irrational number storage test vector and relates to a fault coverage guided compression method for the test data of the irrational number storage test vector. The compression method comprises the following steps of firstly, generating a fault list according to a circuit structure of an integrated circuit to be tested; secondly, running an automatic test vector generation tool for faults to generate test vectors of corresponding faults; thirdly, counting the lengths of runs; fourthly, performing preliminary estimation on corresponding ranges of irrational numbers; fifthly, dichotomising the ranges of the irrational numbers, and successively approximating; sixthly, filling independent bits; seventhly, performing random test; eighthly, judging whether the fault list in the seventh step is empty or not, if the fault list is empty, turning to the ninth step, and otherwise, turning to the second step; ninthly, ending, and returning all records such as integers m and l corresponding to all the irrational numbers. According to the compression method disclosed by the invention, the coding of the irrational numbers and the generation of the automatic test vectors are combined, so that on one hand, coding numbers, corresponding to the test vectors, of easily-detected fault points are reduced, and on the other hand, the fault coverage is improved.

Owner:池州华宇电子科技股份有限公司

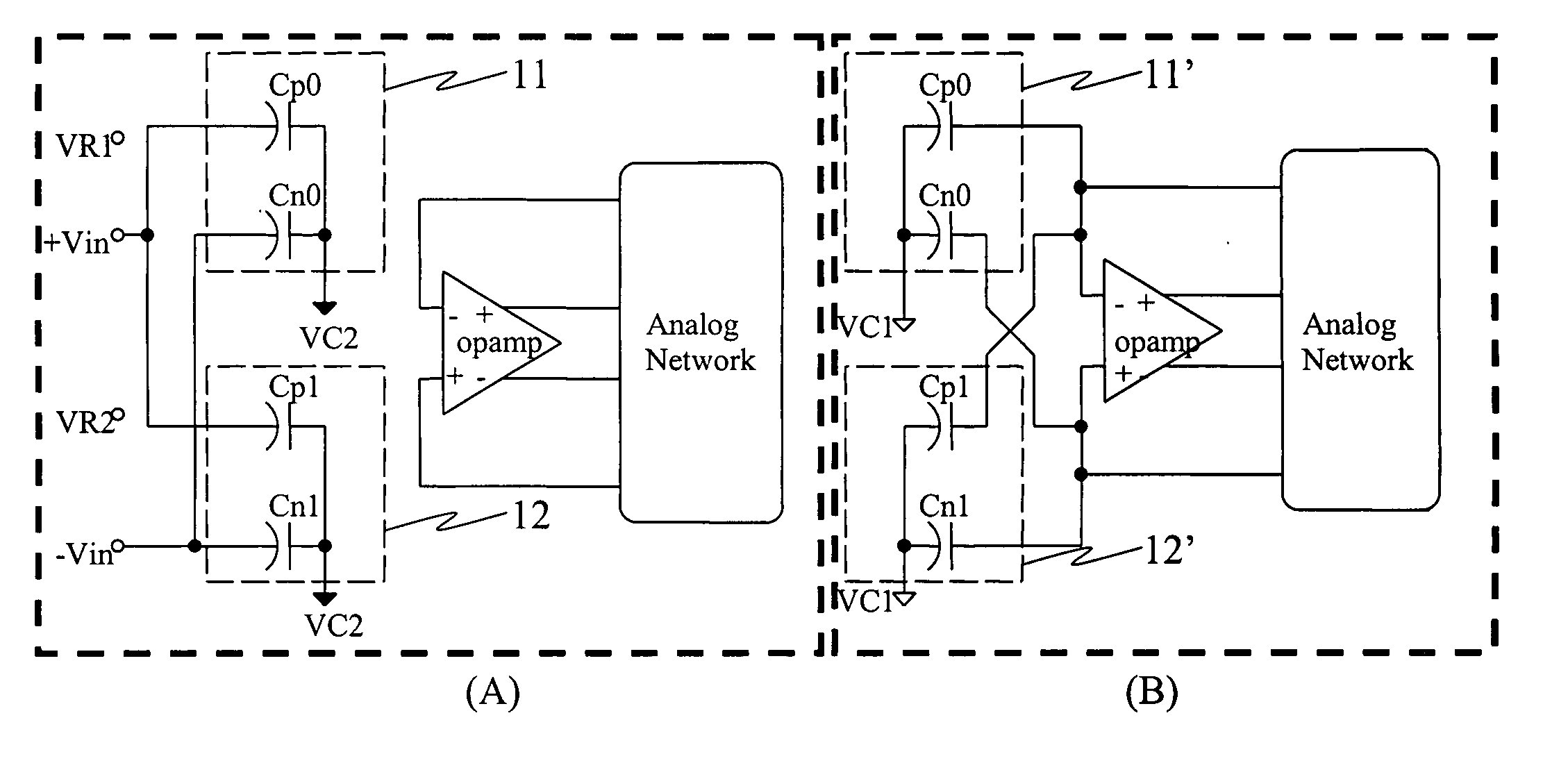

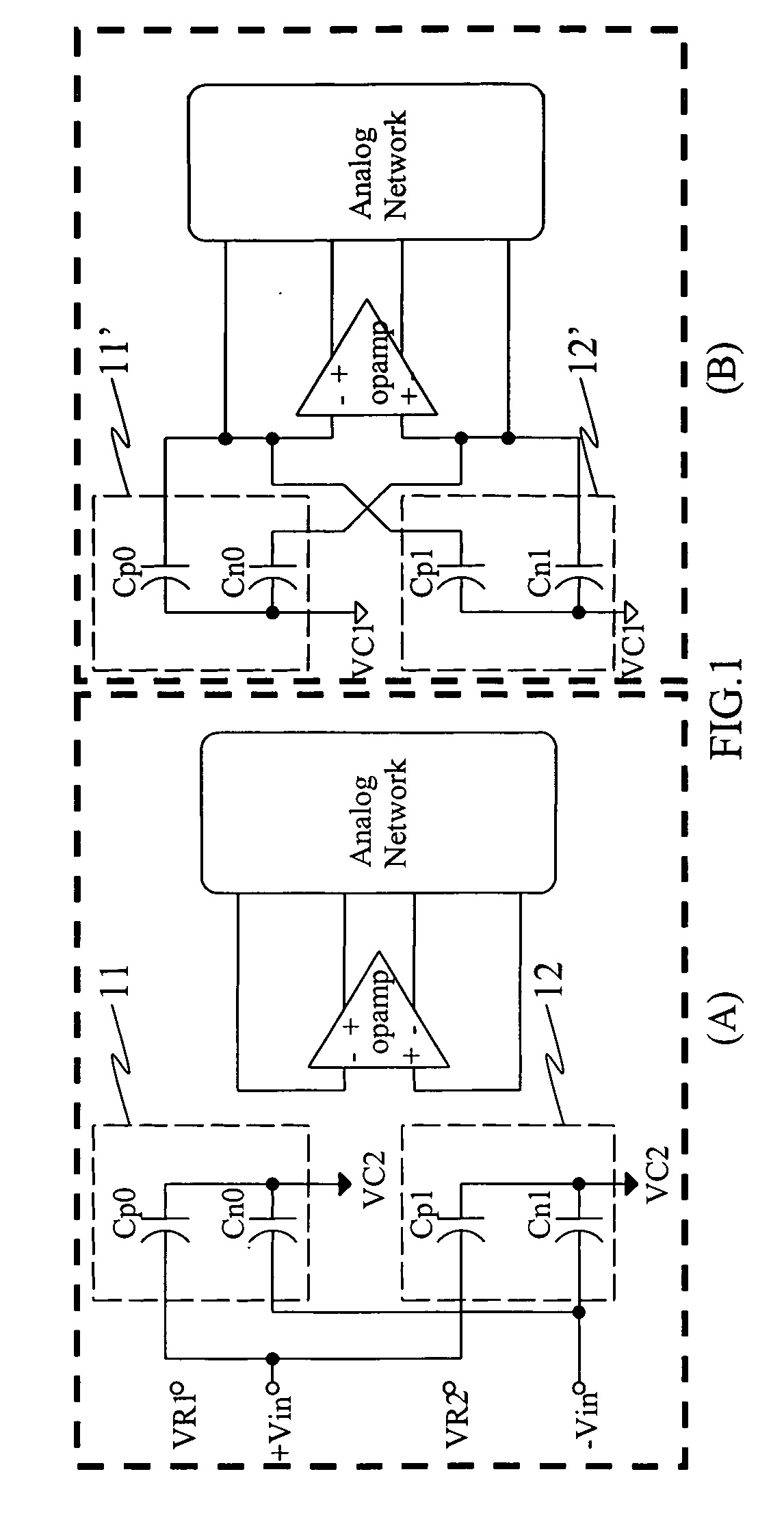

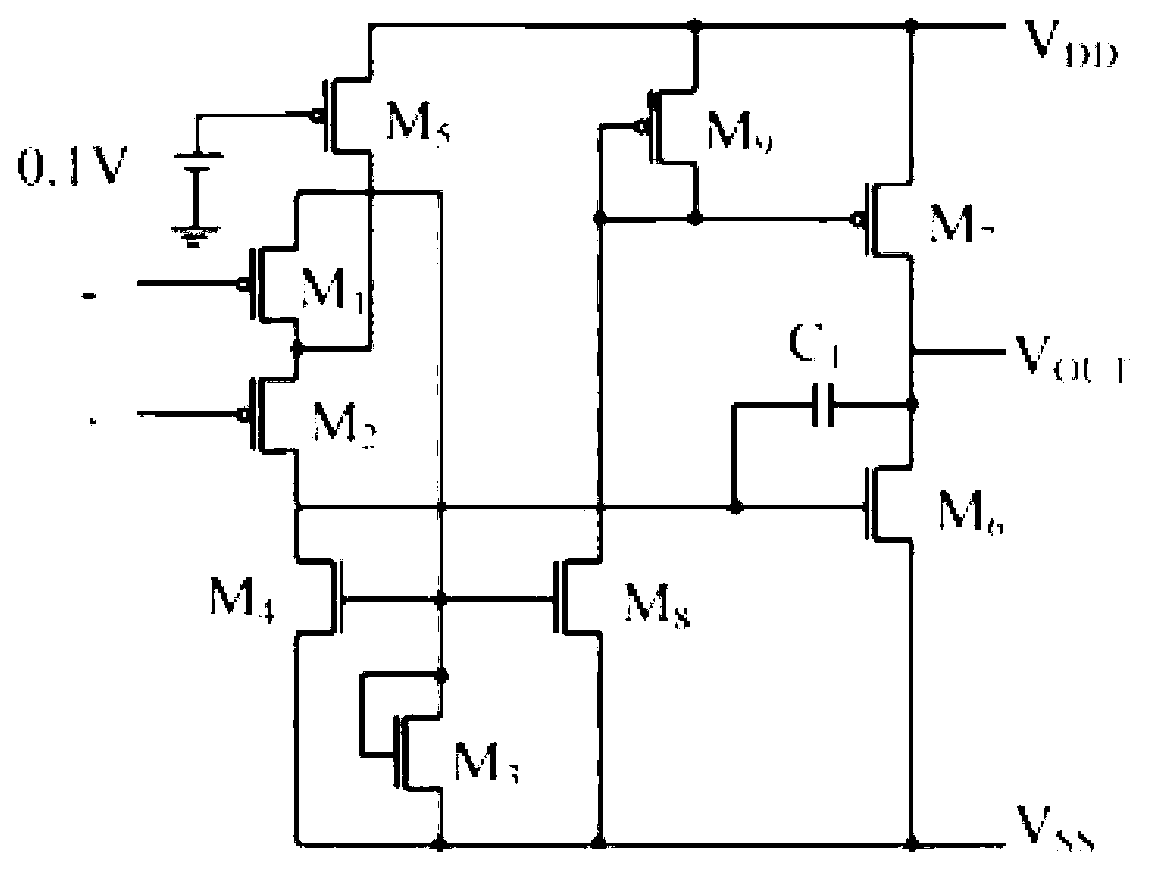

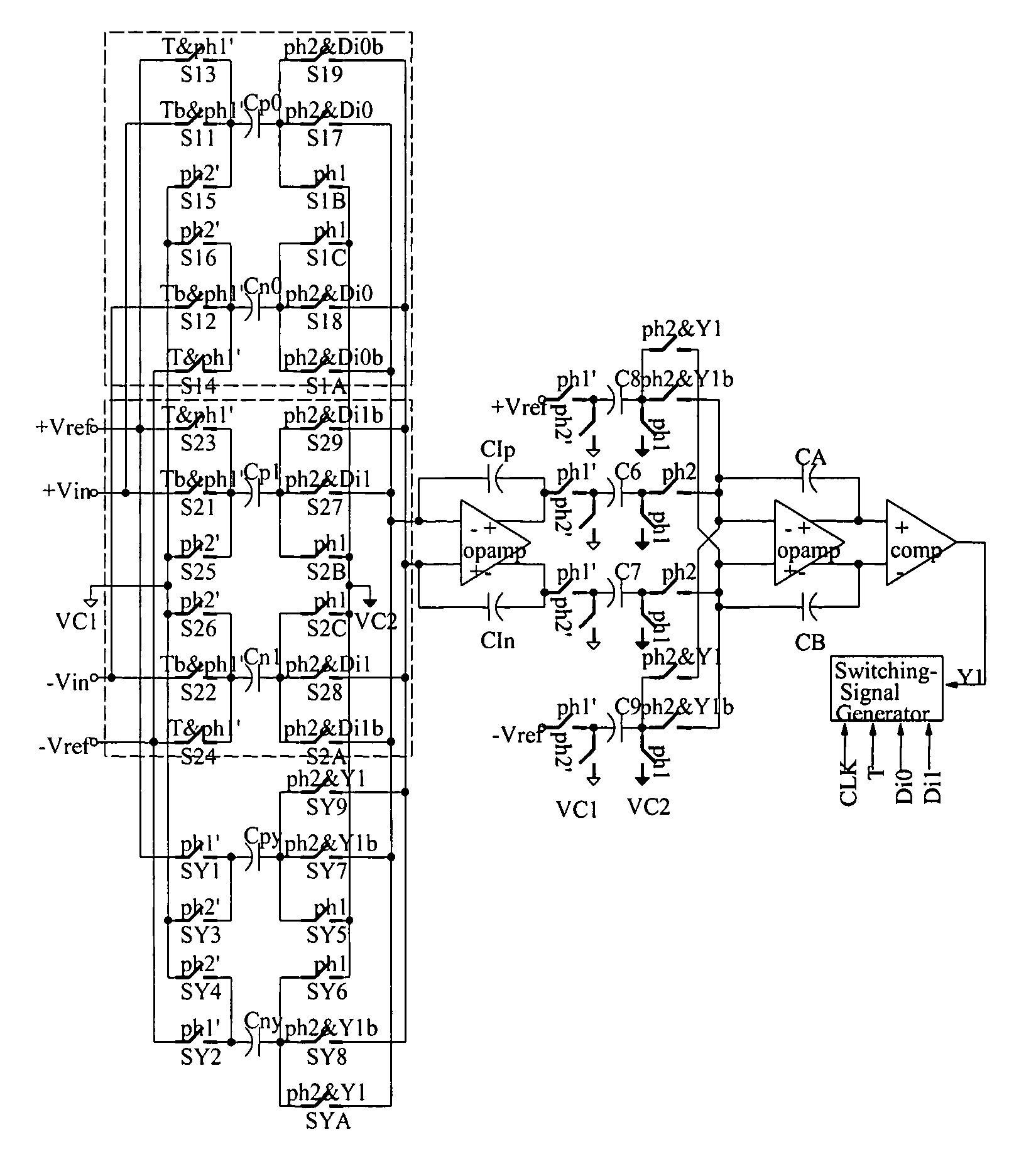

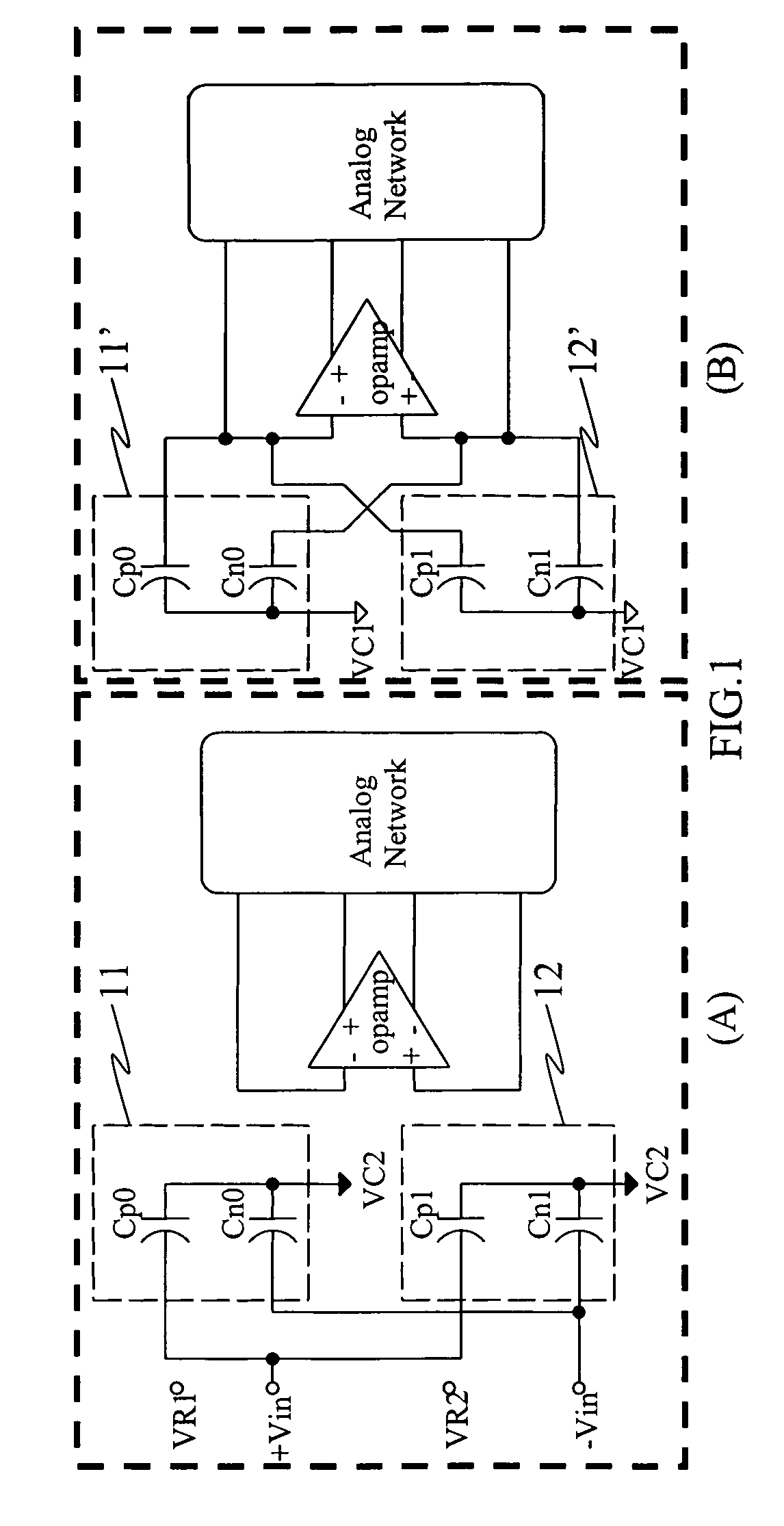

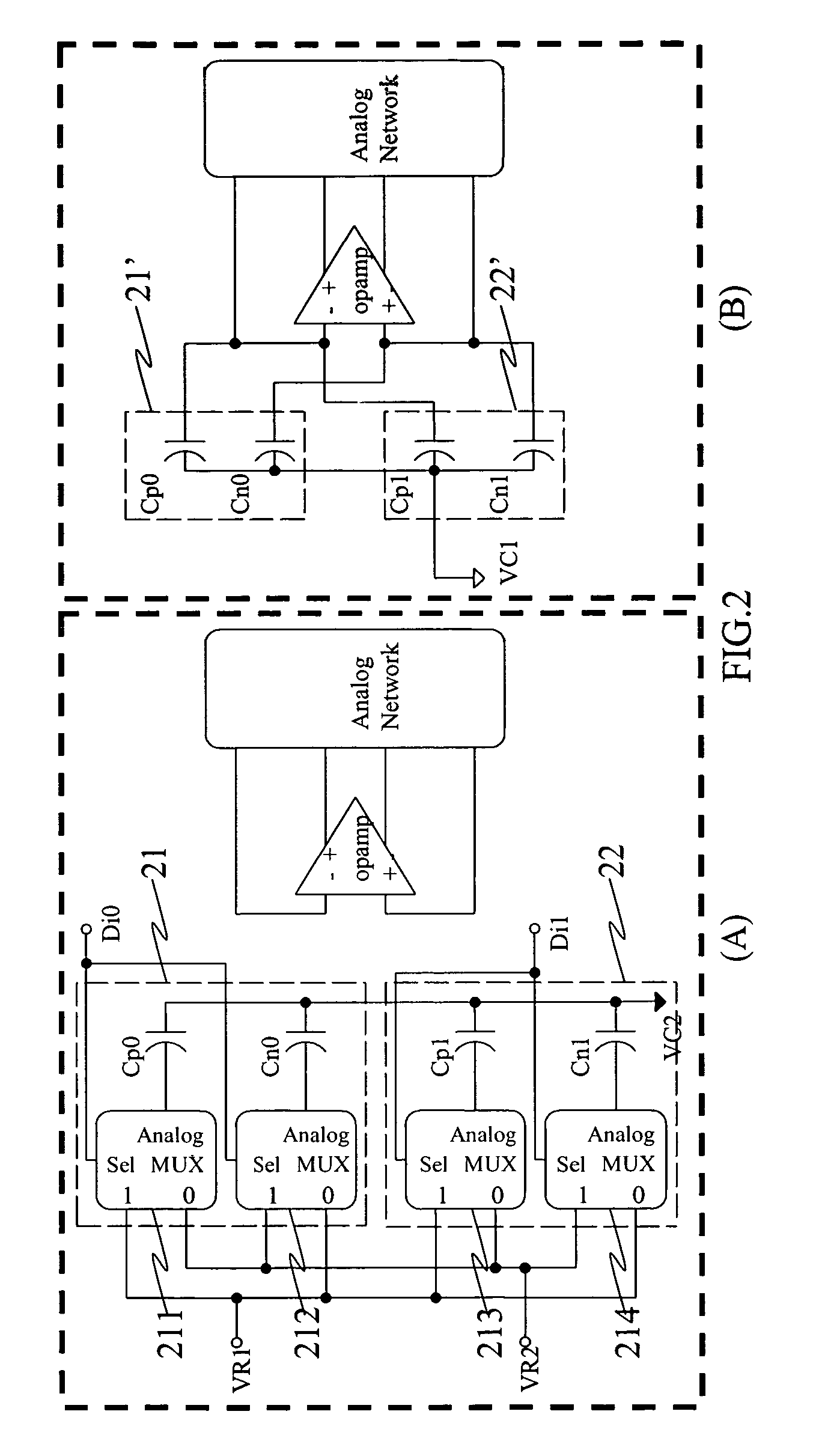

Reconfigurable switched- capacitor input circuit with digital-stimulus acceptability for analog tests

InactiveUS20070063885A1Reduce testing costsImprove test accuracyElectric signal transmission systemsAnalogue conversionAnalogue switchCapacitance

A reconfigurable switched-capacitor input circuit with digital-stimulus acceptability for analog tests disclosed in the present invention provides the digital input interfaces, which are comprised of capacitors, analog switches and digital circuits, for the usage of testing the mixed-signal circuits. The present invention provides a low-priced testing platform to accomplish the testing of circuits and to solve the problems of high-cost mixed mode tester and of utmost restrictions against the surrounding condition. Therefore, the present invention improves the testability, reduces the test cost, shorten the processes of designation and efficiently seize on the time-to-market.

Owner:NAT CHIAO TUNG UNIV

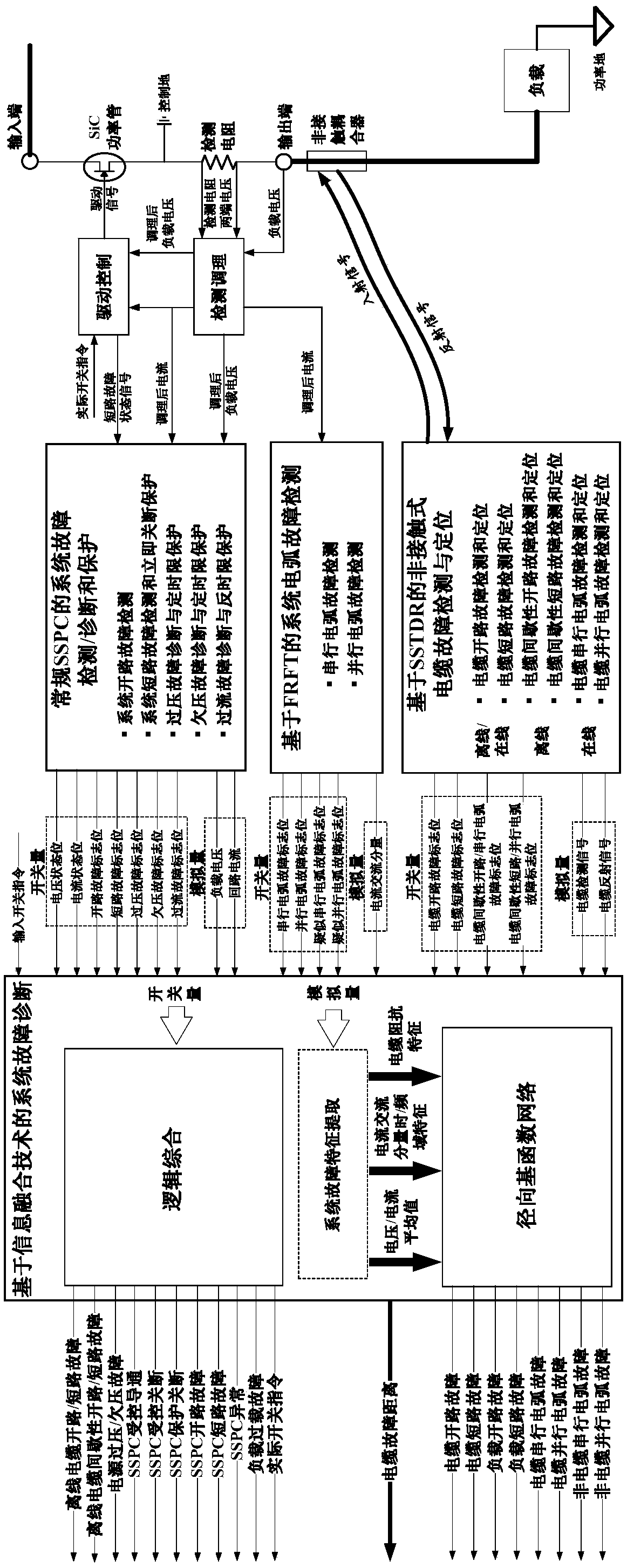

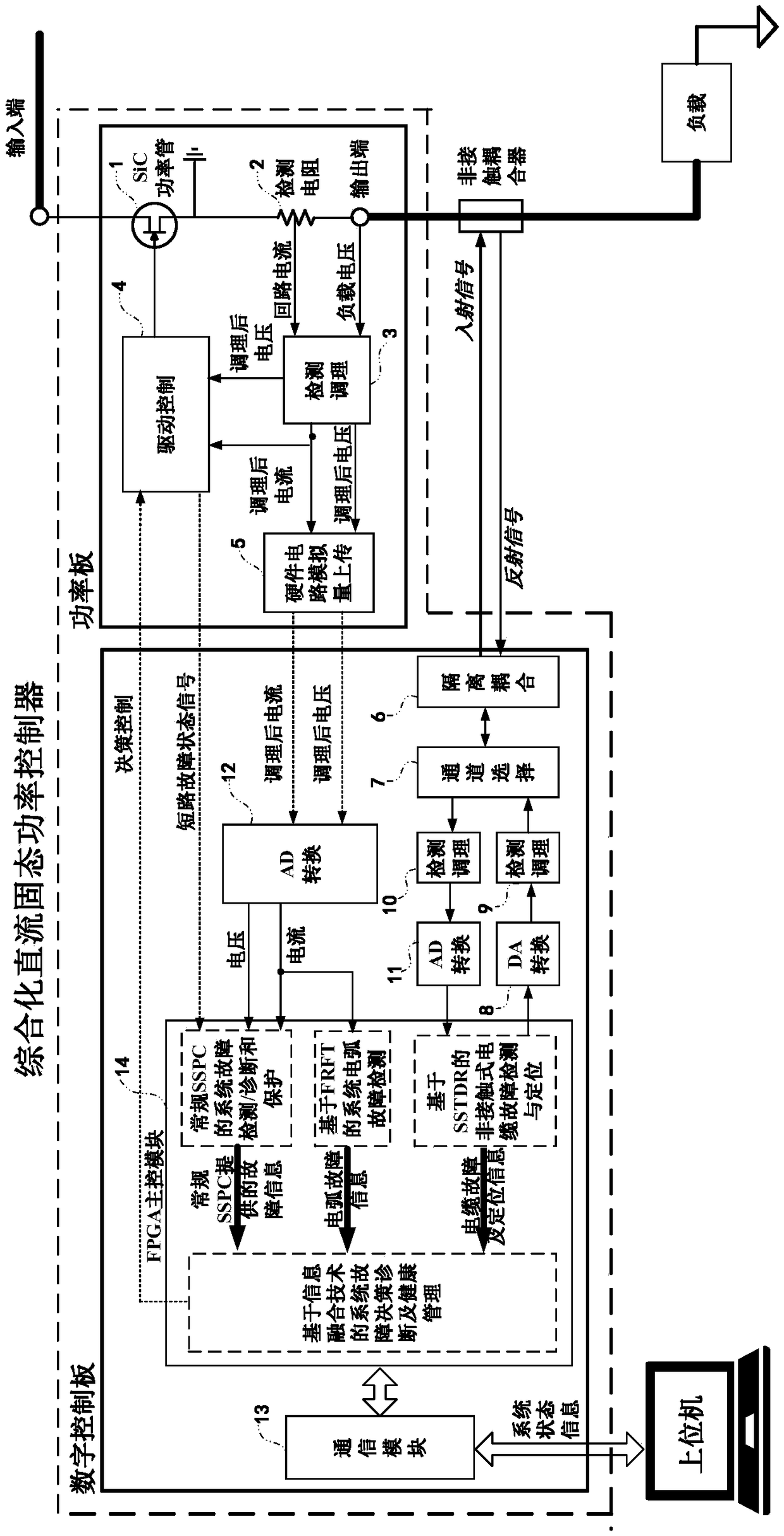

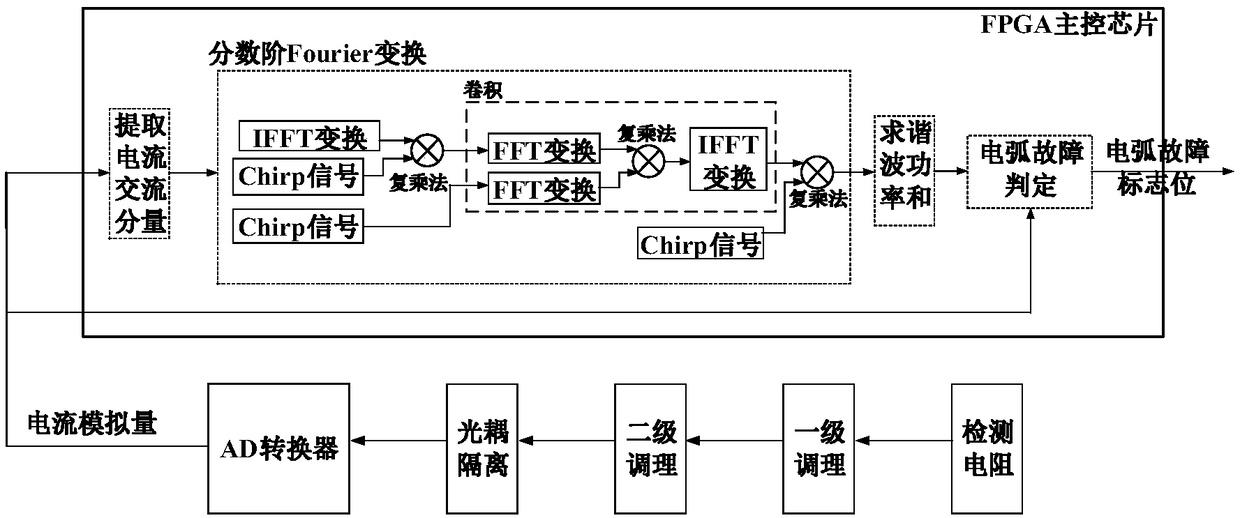

Integrated DC solid state power controller and fault decision-making diagnosis method

ActiveCN108803560AImprove detection rateSolve the problem of fault decision diagnosisElectric testing/monitoringOvervoltageTime lag

The invention discloses an integrated DC solid state power controller and a fault decision-making diagnosis method. The controller comprises a power board and a digital control board, wherein the power board is mainly responsible for system state detecting, conditioning, signal uploading and SSPC (Solid State Power Controller) driving and protection control; and the digital control board integrates related circuits for arc fault detection and cable fault detection and location, detects a conditioned system state signal based on multiple sensors, completes local fault diagnosis for the conventional SSPC such as fixed-time-lag power supply overvoltage-undervoltage fault protection, BIT self-checking of the SSPC, inverse-time-lag overload protection and additional local fault diagnosis such as system arc fault detection and cable fault detection and location in a concurrent manner in an FPGA main control module, and finally realizes decision-making diagnosis and health management for thesystem state based on a multi-source technology integration technology. The integrated DC solid state power controller can realize the enhanced system fault detection and health management ability, and improves the system safety, reliability, testability and maintenance.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

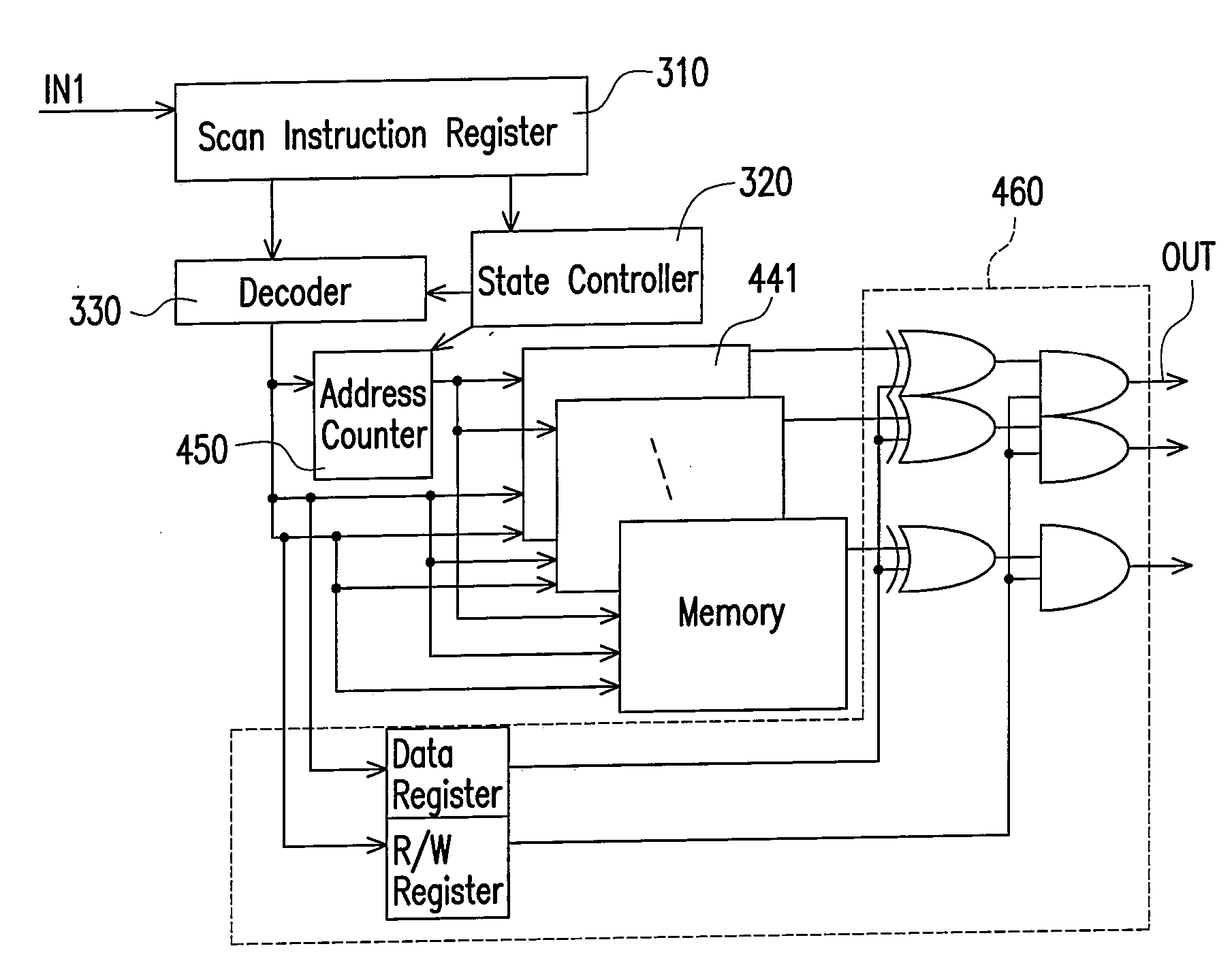

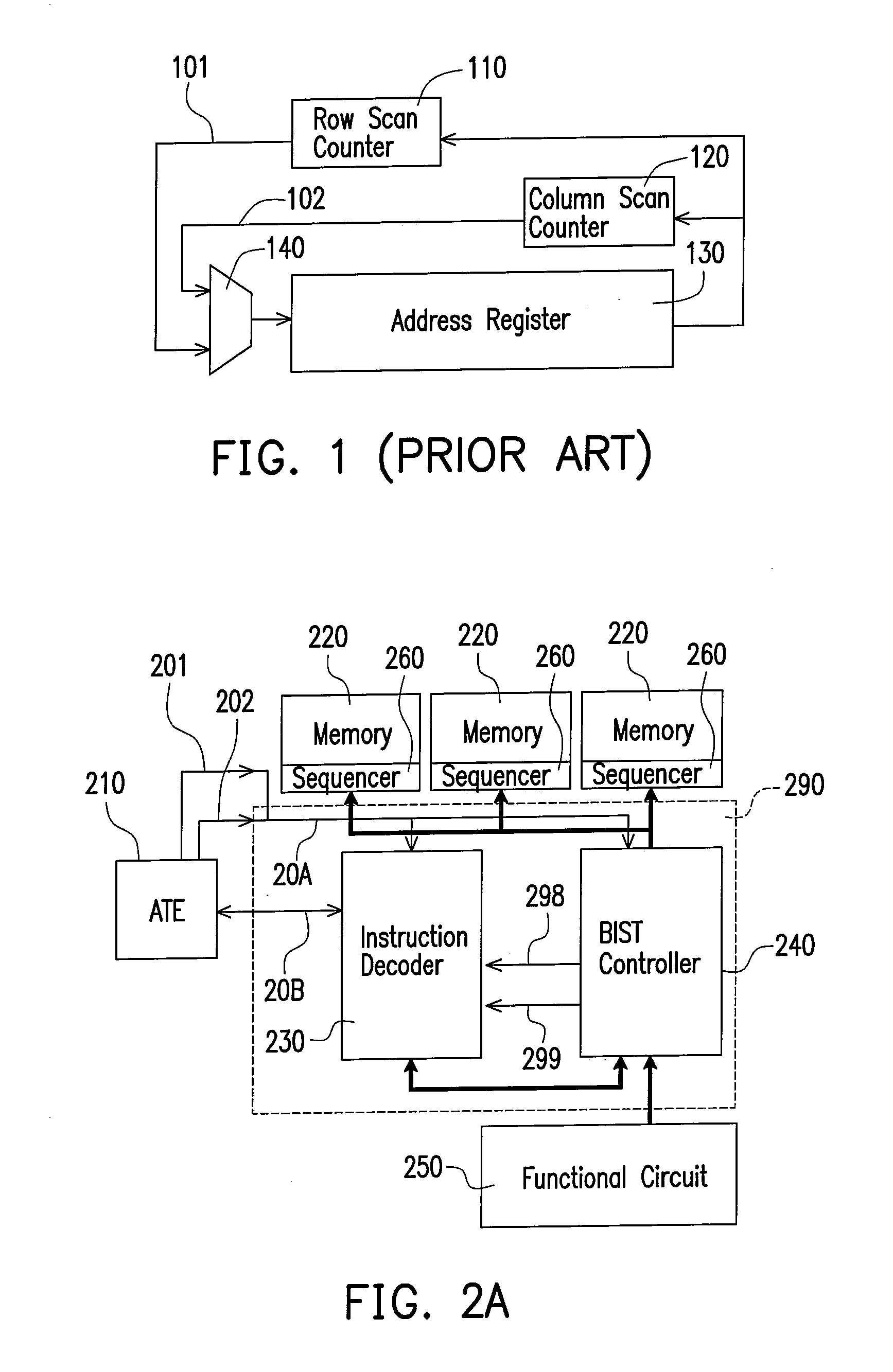

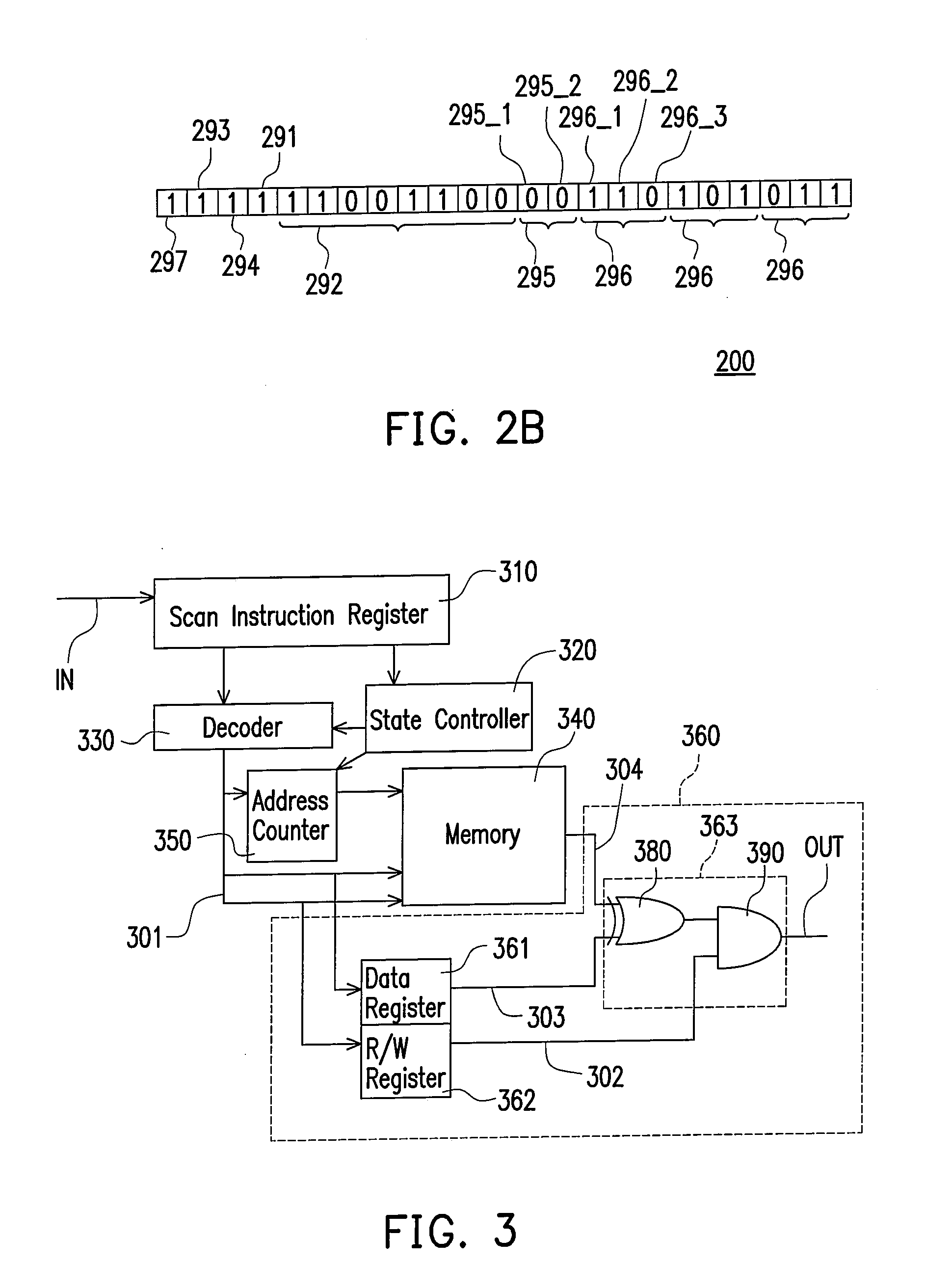

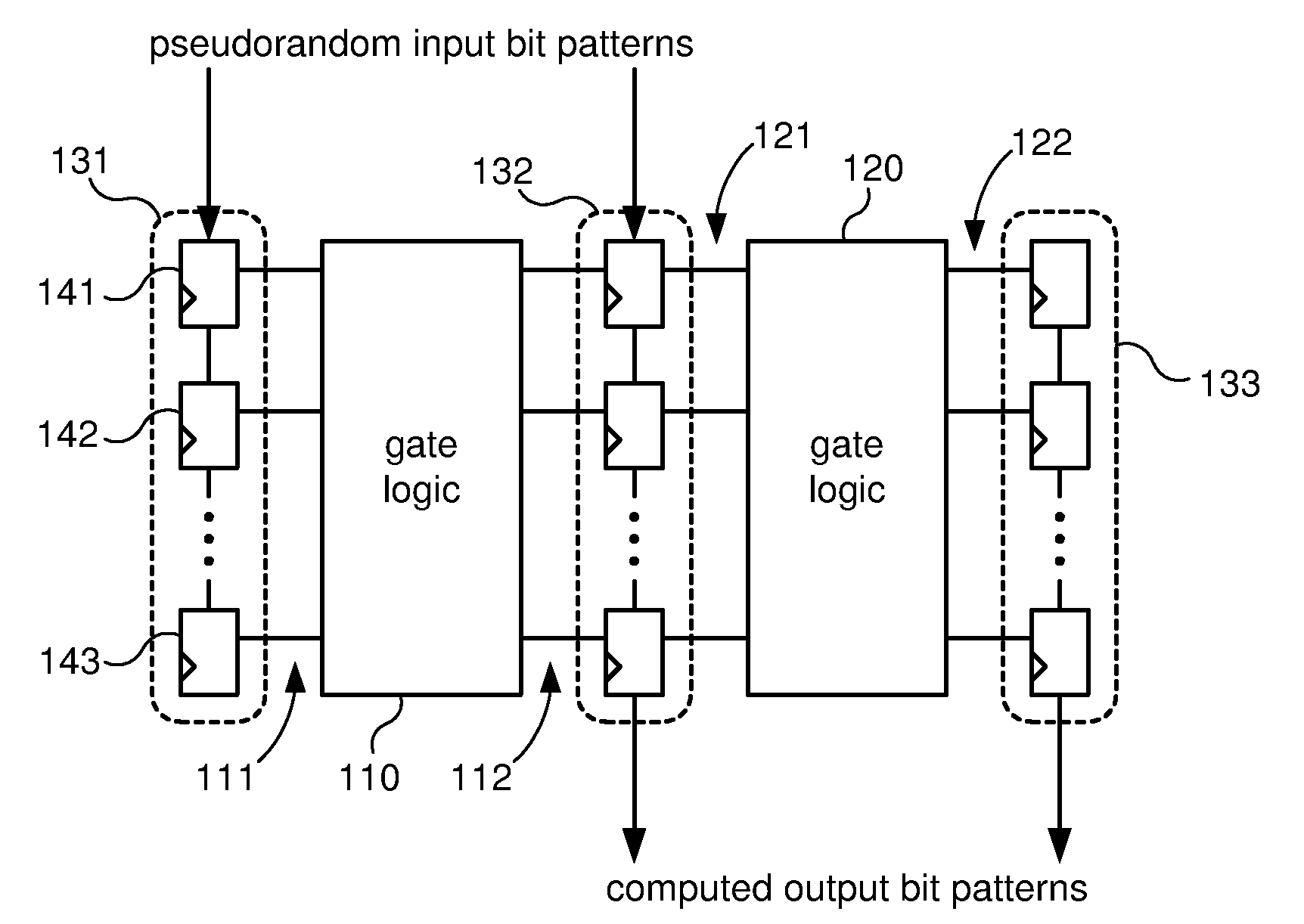

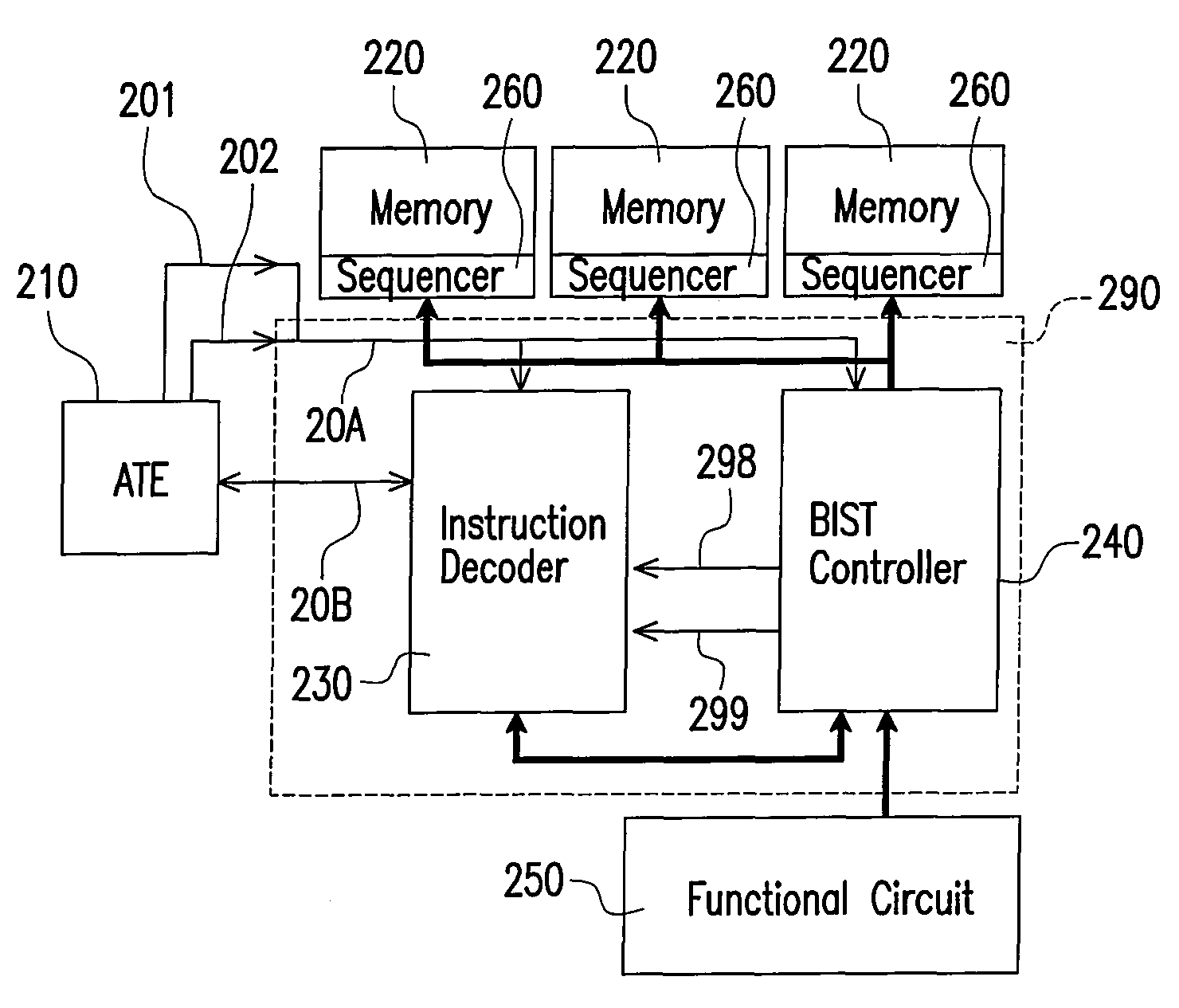

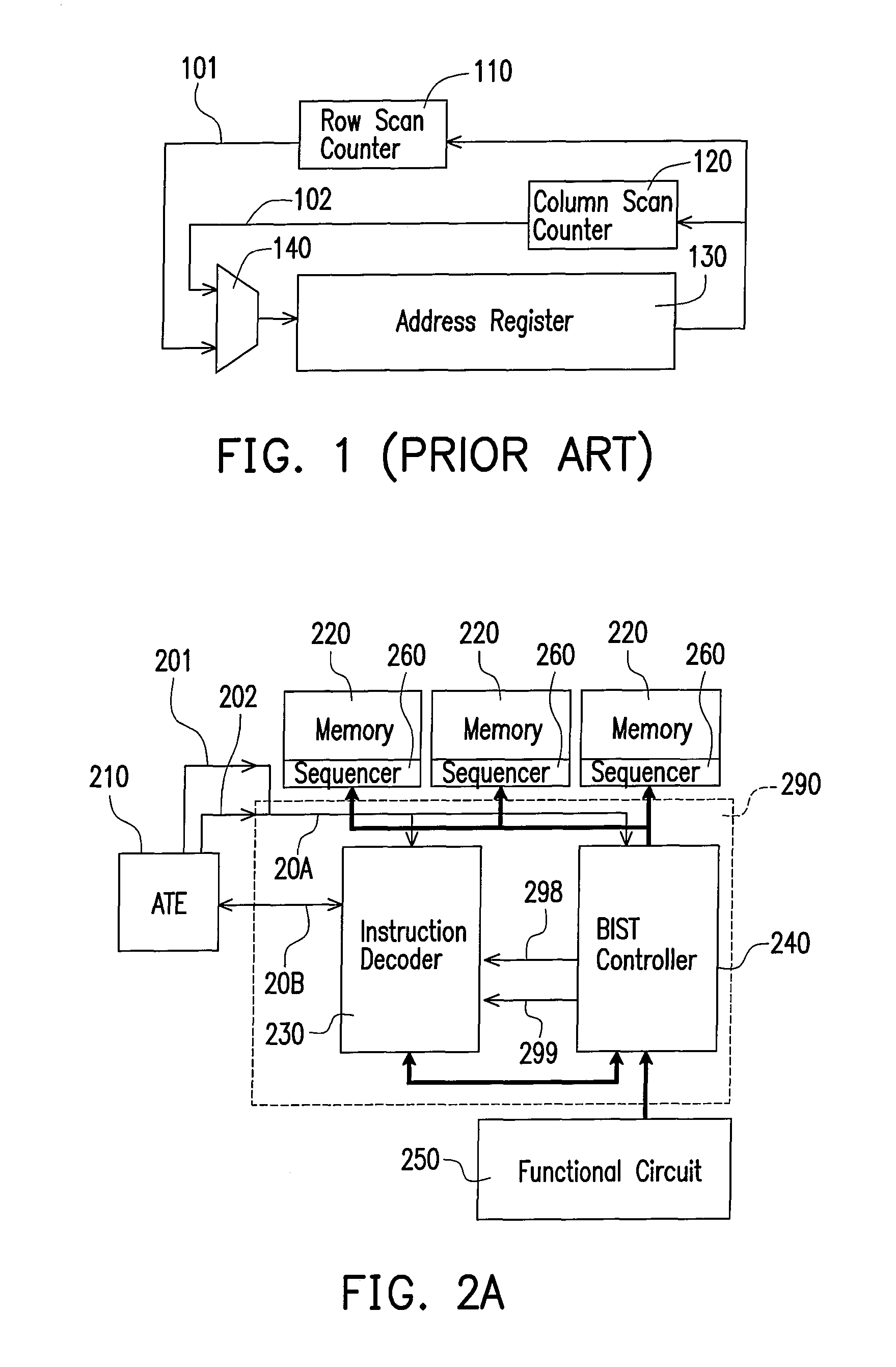

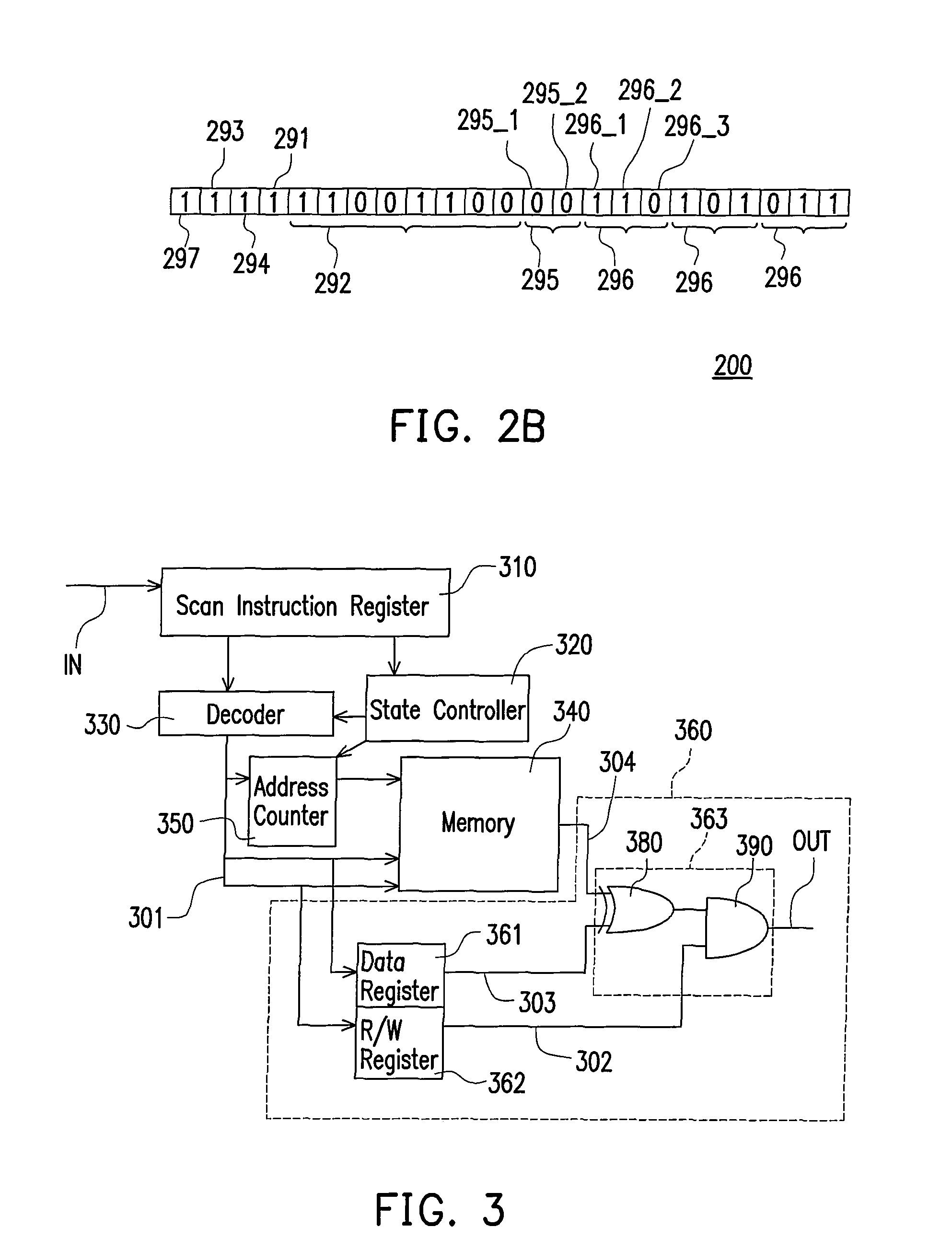

Programmable memory built-in self-test circuit and clock switching circuit thereof

InactiveUS20090125763A1Smooth switchingEasy to optimizeElectronic circuit testingFunctional testingFault coverageControl circuit

A programmable memory built-in self-test circuit and a clock switching circuit thereof are provided. The memory built-in self-test circuit is able to provide more self-test functions preset by a user, simplify the redundant circuit in the prior art and reduce chip area and lower the cost by means of an instruction decoder and a built-in self-test controller. The present invention also provides some peripheral control circuits of a memory. The control circuits occupies less area and enables the memory to be tested more flexibly. The present invention further provides a clock switching circuit enabling a chip to be correctly tested under different clock speeds, which benefits to advance the testability and the analyzability of the memory embedded in a chip and thereby increase fault coverage.

Owner:FARADAY TECH CORP

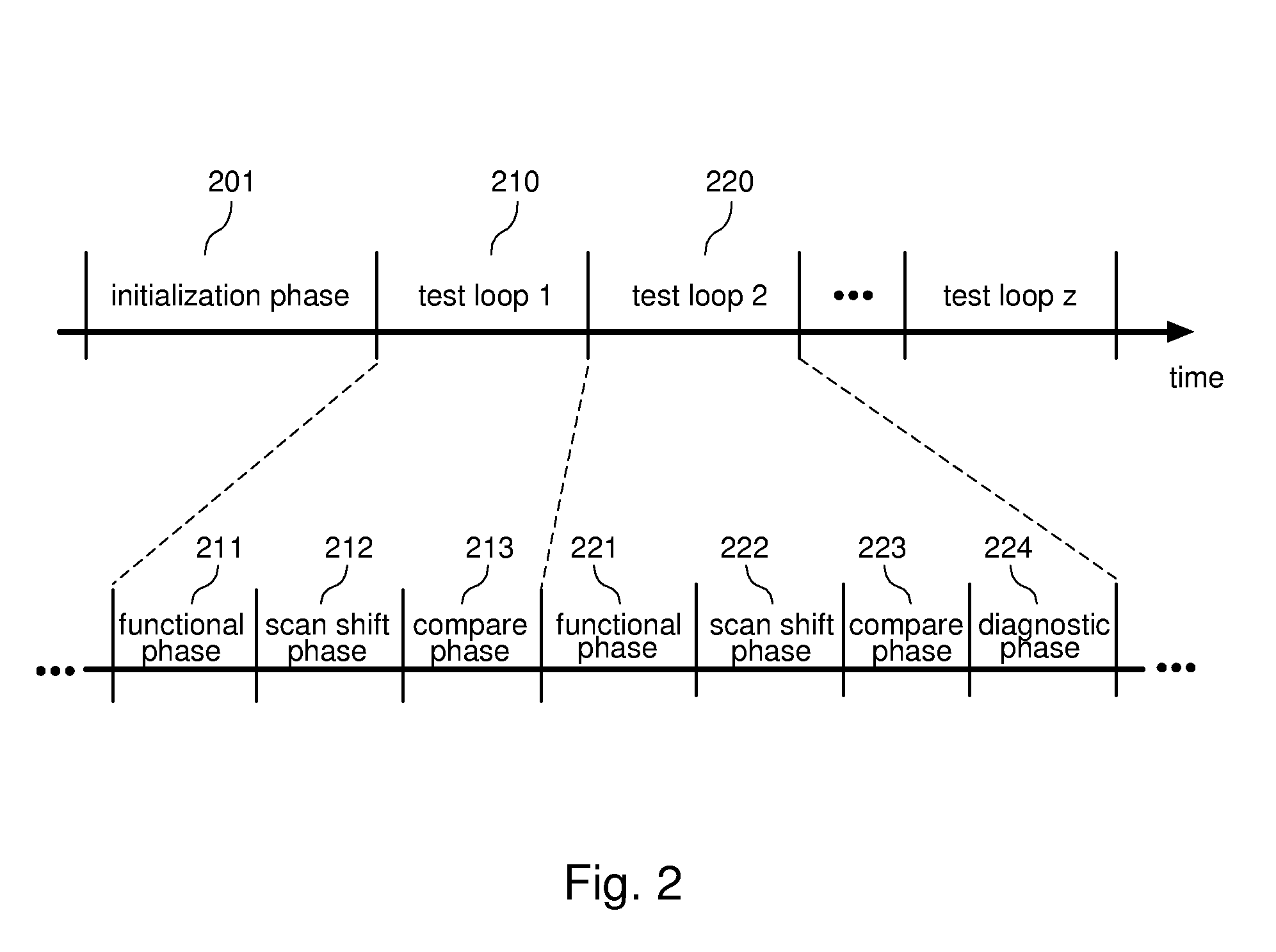

Systems and Methods for Improved Scan Testing Fault Coverage

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) which ensure testing of specific logic by forcing specific values into scan latches that contain otherwise pseudorandom test bit patterns. In one embodiment, an LBIST system comprises a plurality of scan latches and forcing logic coupled to a first set of the scan latches which provide inputs to selected target logic. The forcing logic is configured to overwrite values stored in the first set of scan latches with desired values. In one embodiment, the forcing logic includes a bypass path that enables shifting of unaltered bit patterns around the first set of scan latches. Bits in the bypass path may be inverted when the bypass path is not being used in order to help detect errors in the operation of the bypass path.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

Programmable memory built-in self-test circuit and clock switching circuit thereof

InactiveUS7716542B2Reduce chip areaMeet the test requirementsElectronic circuit testingError detection/correctionFault coverageControl circuit

A programmable memory built-in self-test circuit and a clock switching circuit thereof are provided. The memory built-in self-test circuit is able to provide more self-test functions preset by a user, simplify the redundant circuit in the prior art and reduce chip area and lower the cost by means of an instruction decoder and a built-in self-test controller. The present invention also provides some peripheral control circuits of a memory. The control circuits occupies less area and enables the memory to be tested more flexibly. The present invention further provides a clock switching circuit enabling a chip to be correctly tested under different clock speeds, which benefits to advance the testability and the analyzability of the memory embedded in a chip and thereby increase fault coverage.

Owner:FARADAY TECH CORP

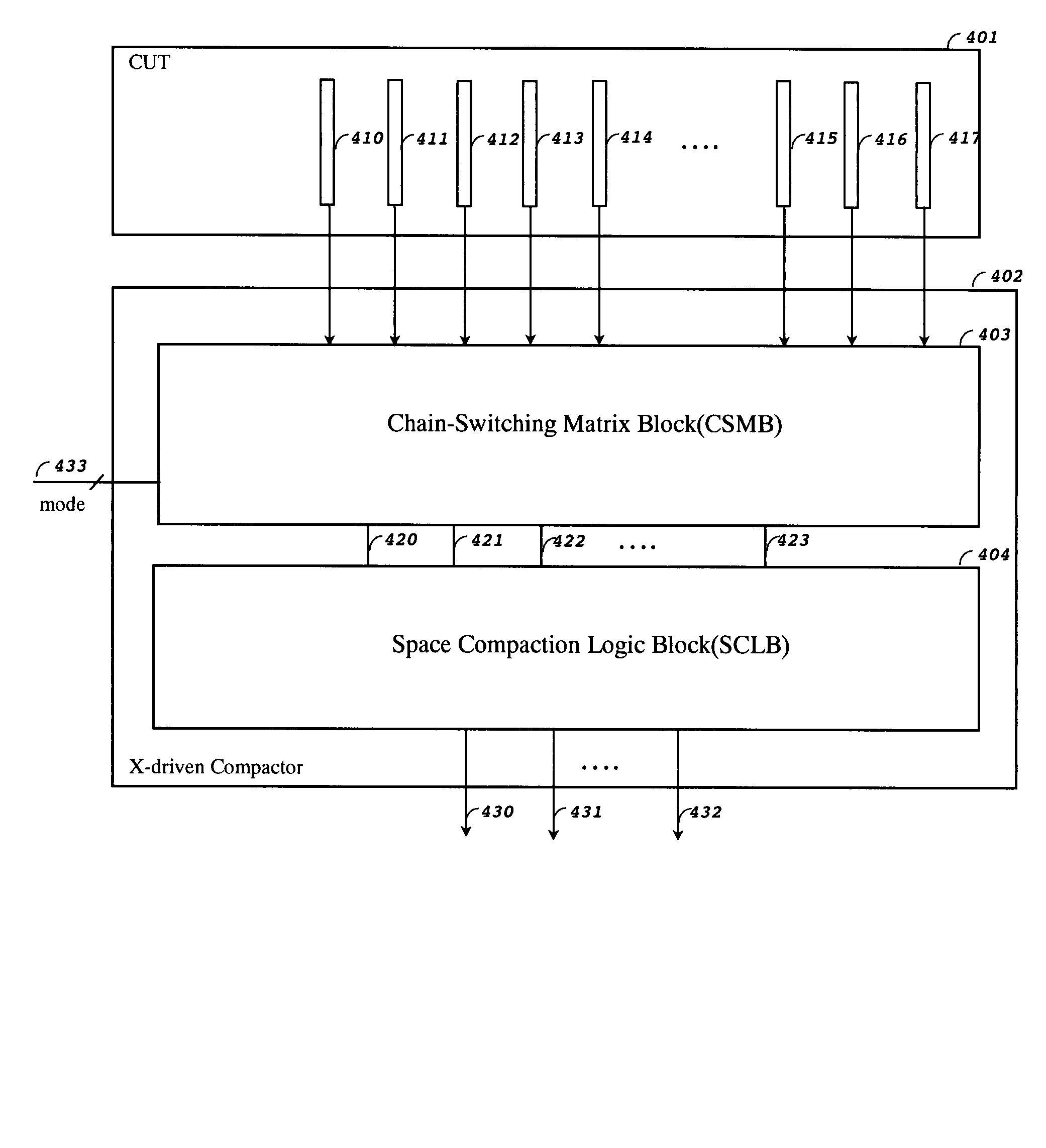

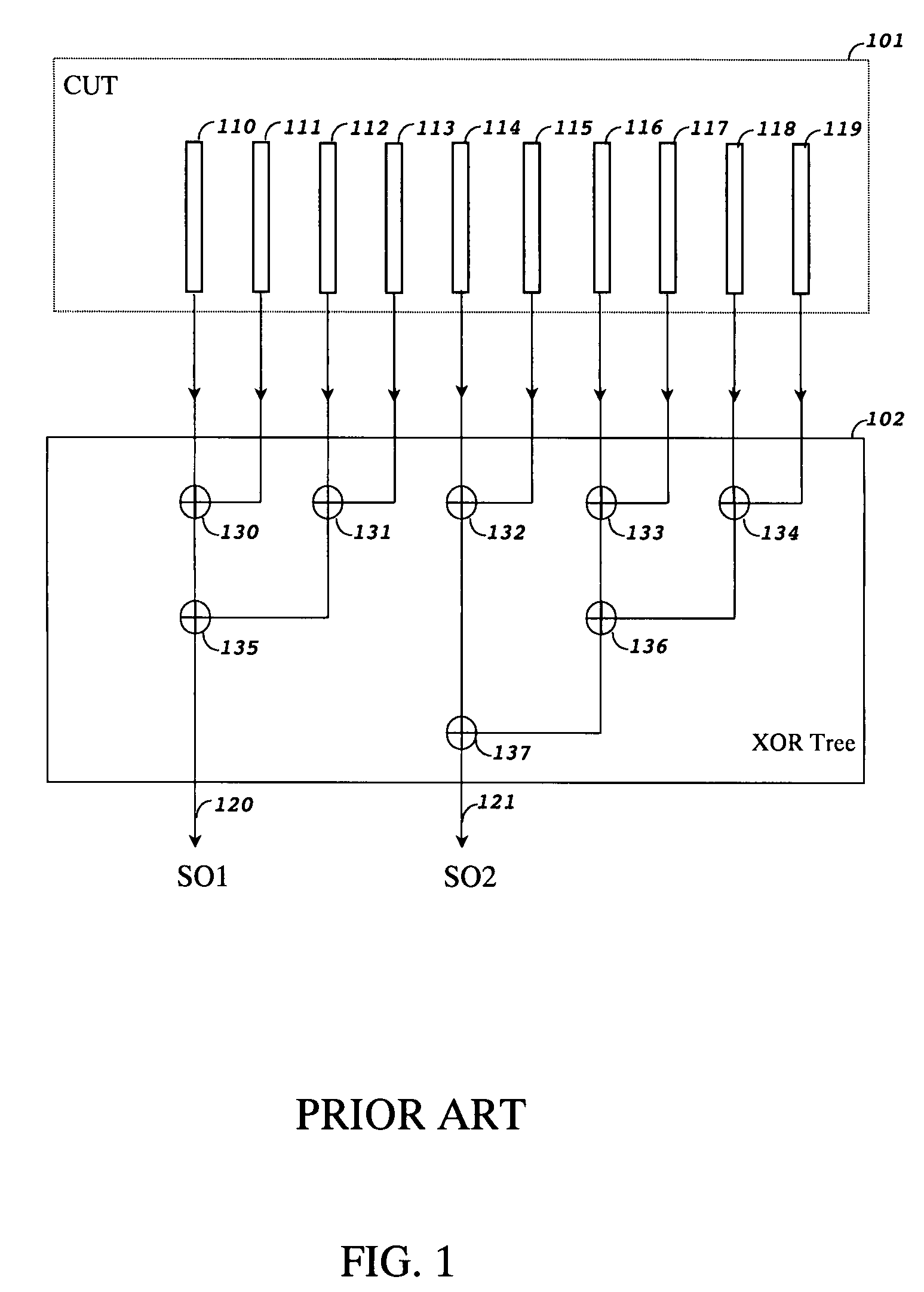

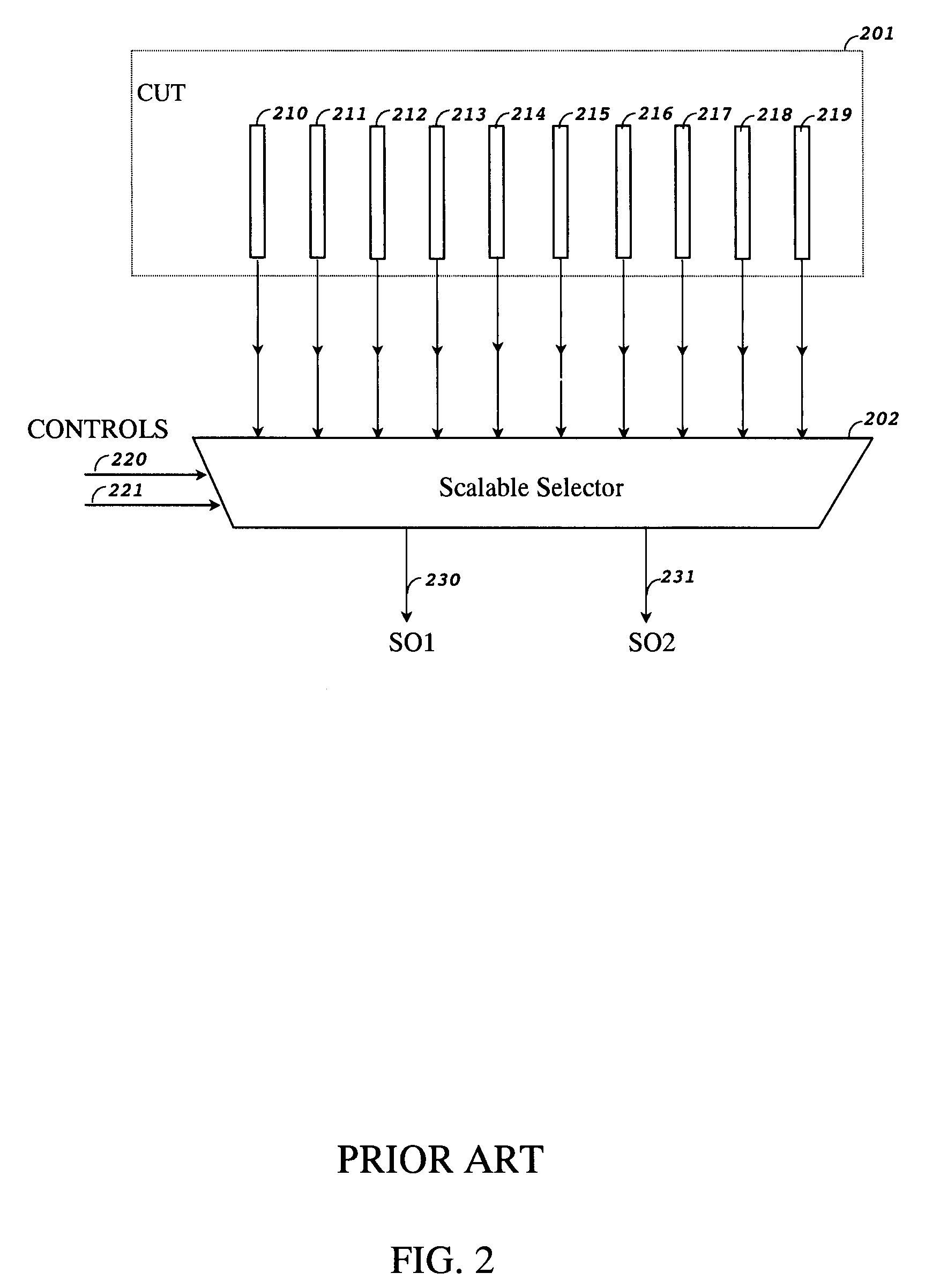

Compacting test responses using X-driven compactor

InactiveUS7779322B1Minimizes masking errorImprove fault coverageElectronic circuit testingCompression testTest response

A method and apparatus for compacting test responses containing unknown values in a scan-based integrated circuit. The proposed X-driven compactor comprises a chain-switching matrix block and a space compaction logic block. The chain-switching matrix block switches the internal scan chain outputs before feeding them to the space compaction logic block for compaction so as to minimize X-induced masking and error masking. The X-driven compactor further selectively includes a finite-memory compaction logic block to further compact the outputs of the space compaction logic block.

Owner:SYNTEST TECH

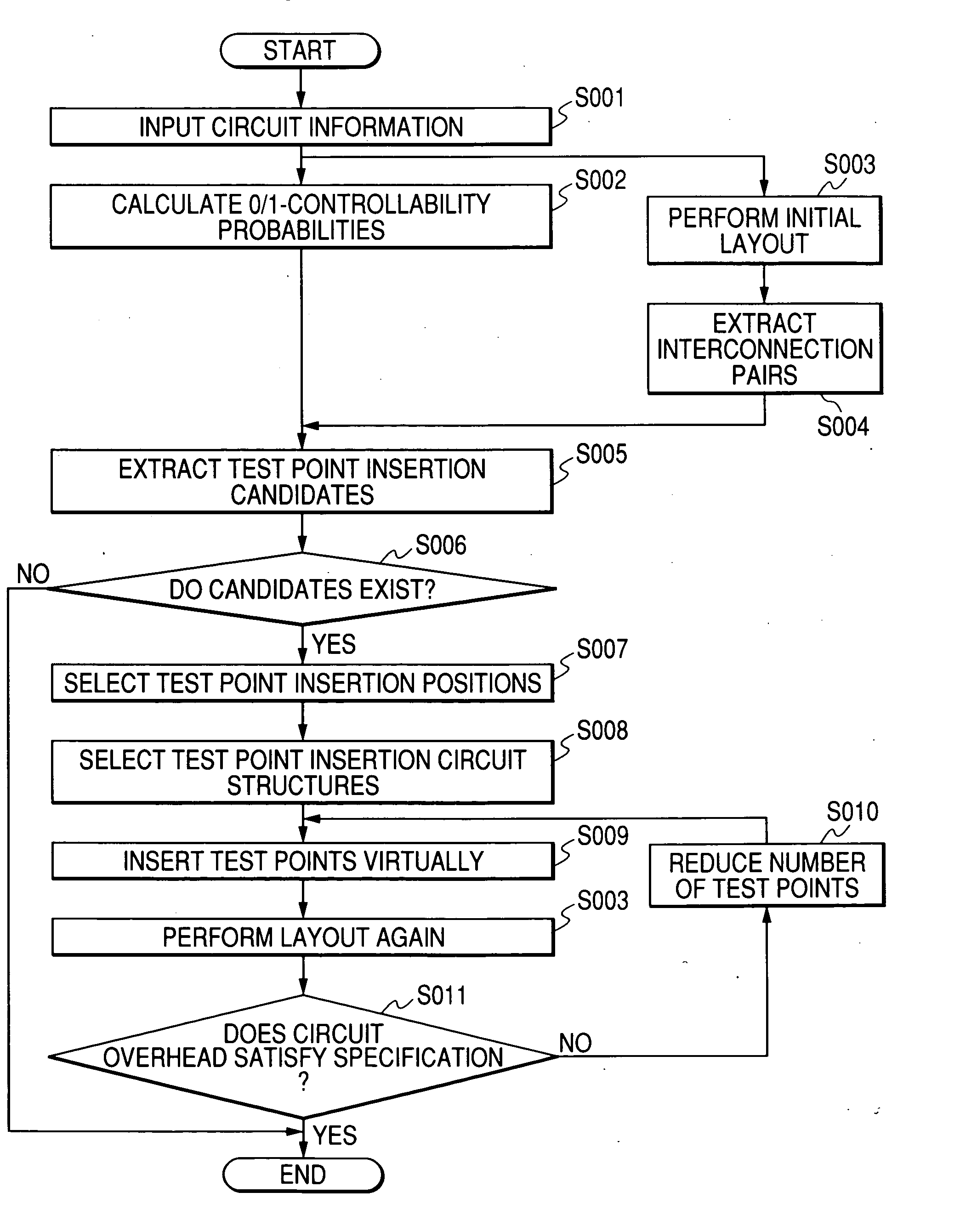

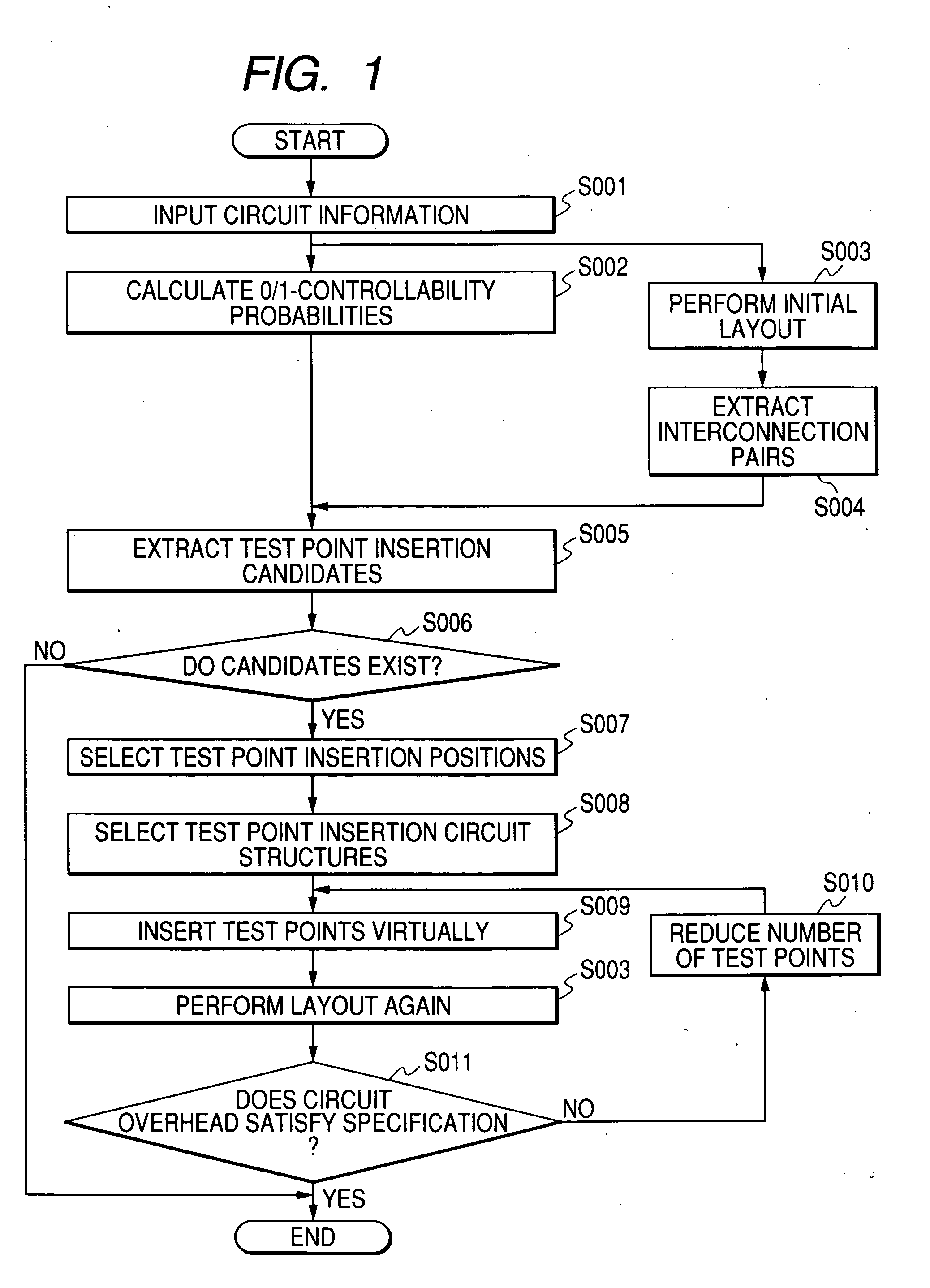

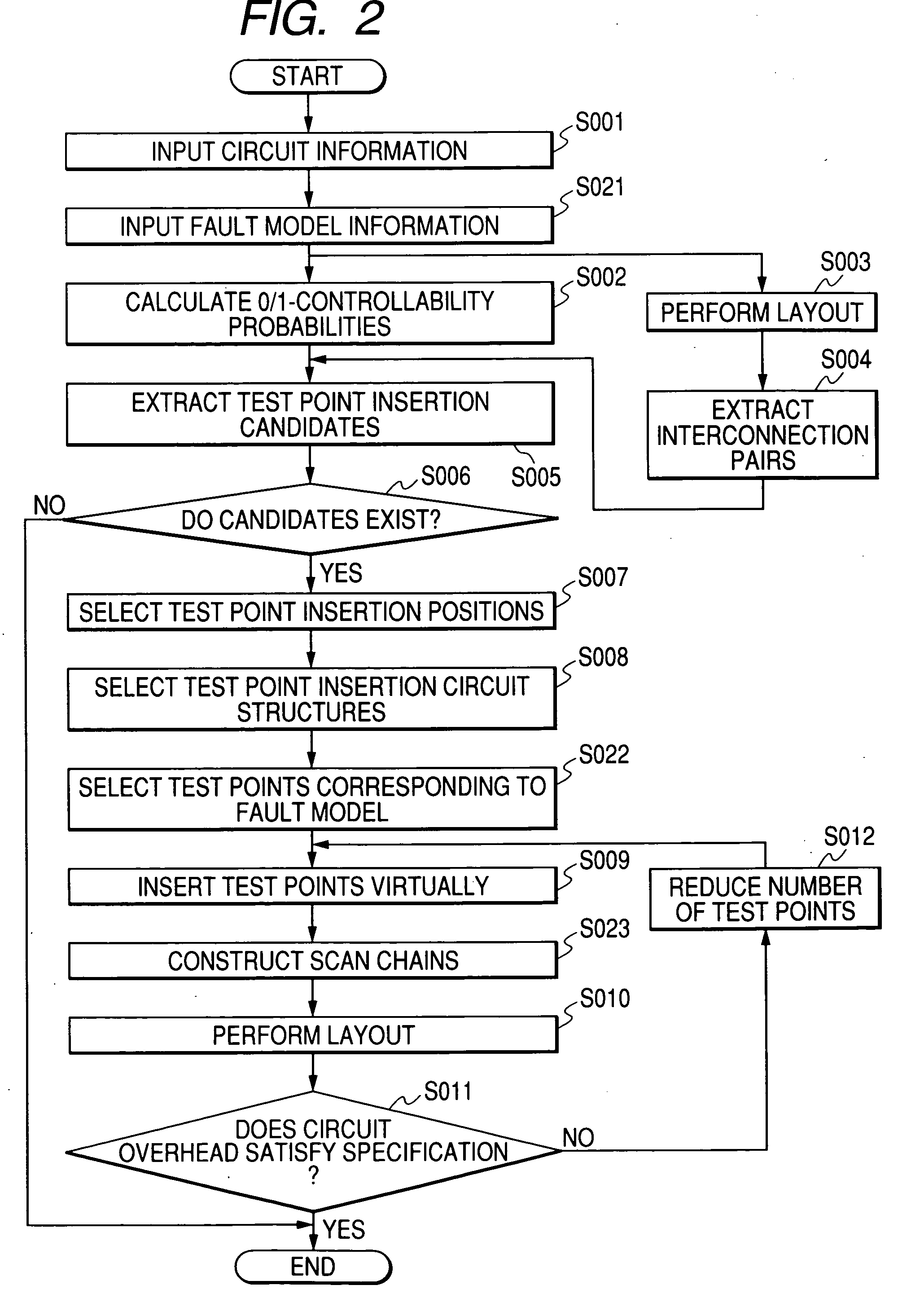

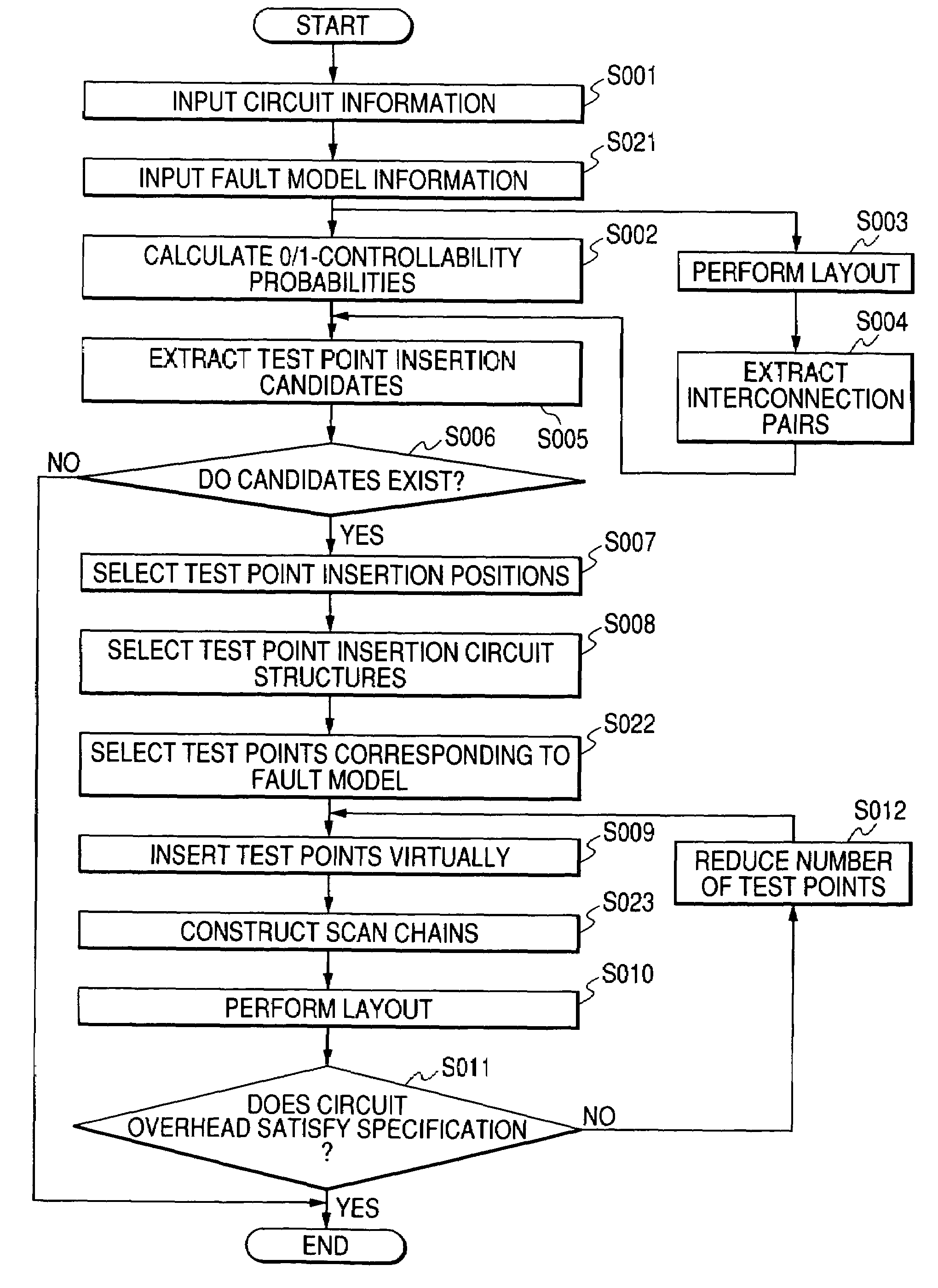

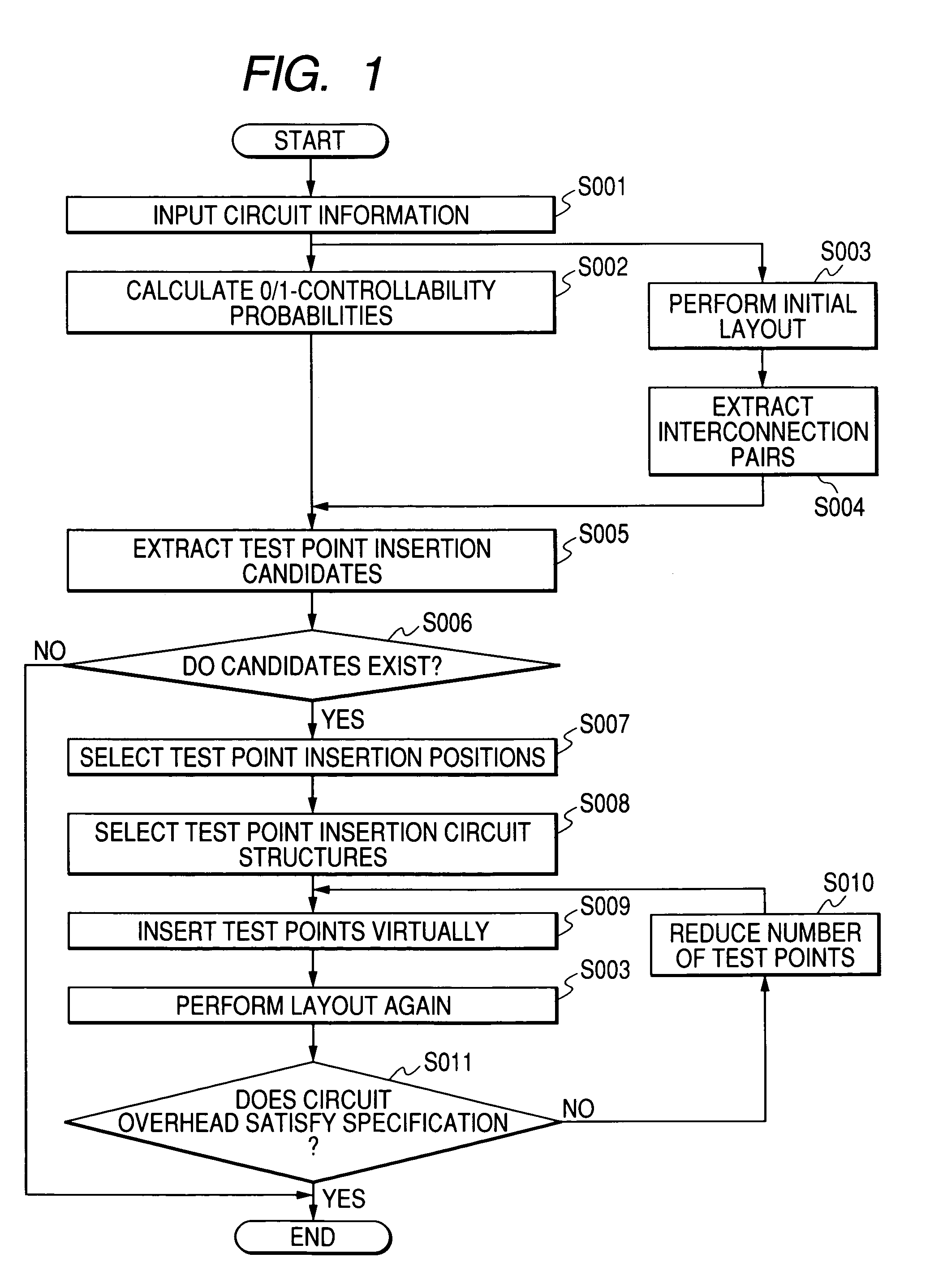

Test circuit inserting method and apparatus for a semiconductor integrated circuit

InactiveUS20050132254A1Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageChip size

To reduce the load of layout design and attain a high fault coverage while preventing increase in chip size in test point insertion for a semiconductor integrated circuit. Controllability probabilities are calculated on the basis of information of a subject circuit (S002). Initial layout is performed on the basis of the circuit information (S003). Interconnection pairs are extracted from a layout result (S004). Test point insertion candidates are extracted on the basis of the controllability probabilities and the interconnection pairs (S005). Whether the test point insertion candidates exist is judged (S006). If test point insertion candidates exist, test point insertion positions are selected (S007). Circuit structures of test points to be inserted there are selected (S008). Test points having those circuit structures are inserted virtually (S009). Layout is performed again on the test-points-inserted circuit (S010). Whether the circuit overhead of a layout result is within a prescribed range is judged (S011). If the circuit overhead exceeds the prescribed range, the number of test points is reduced (S012).

Owner:SOCIONEXT INC

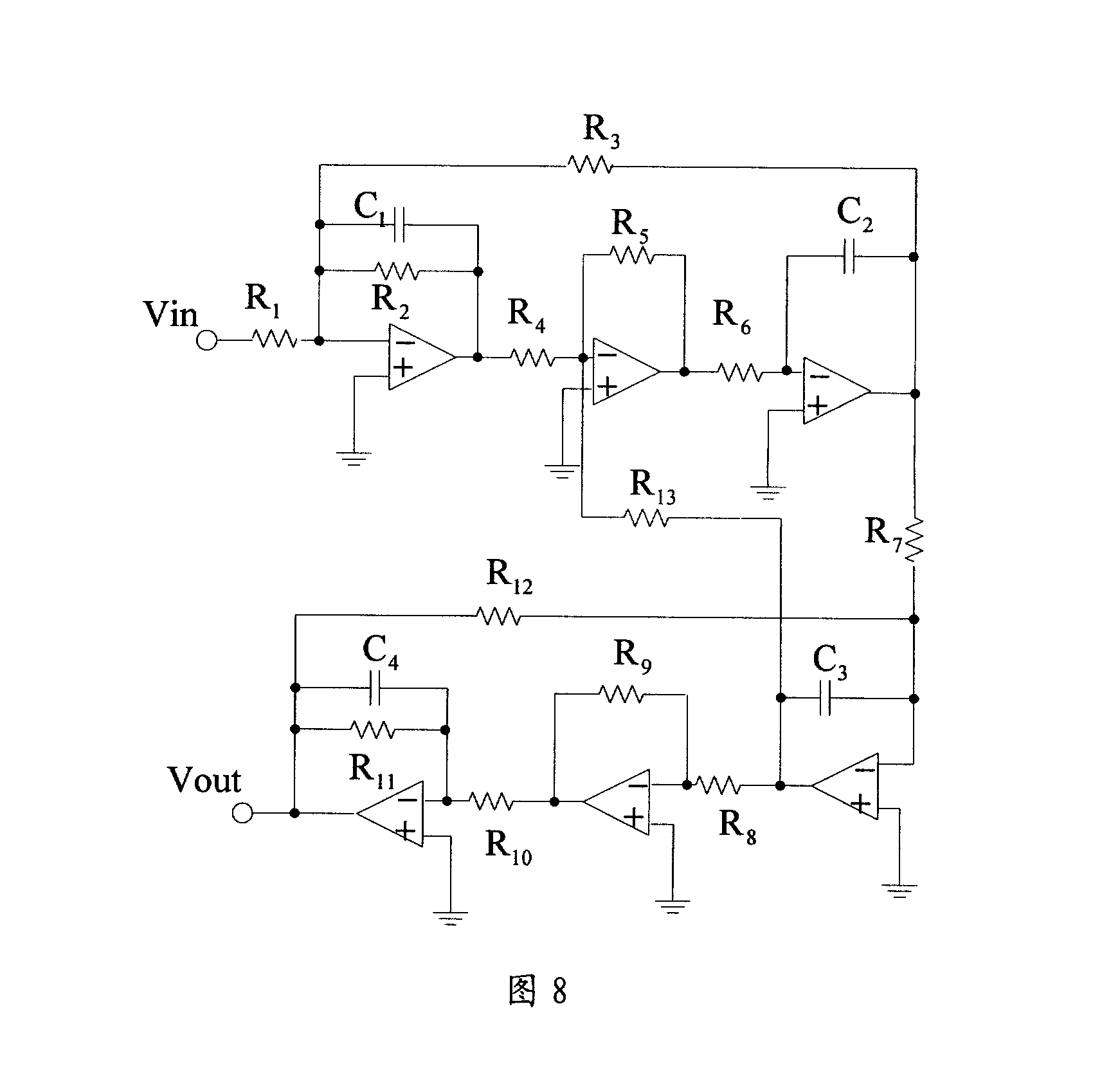

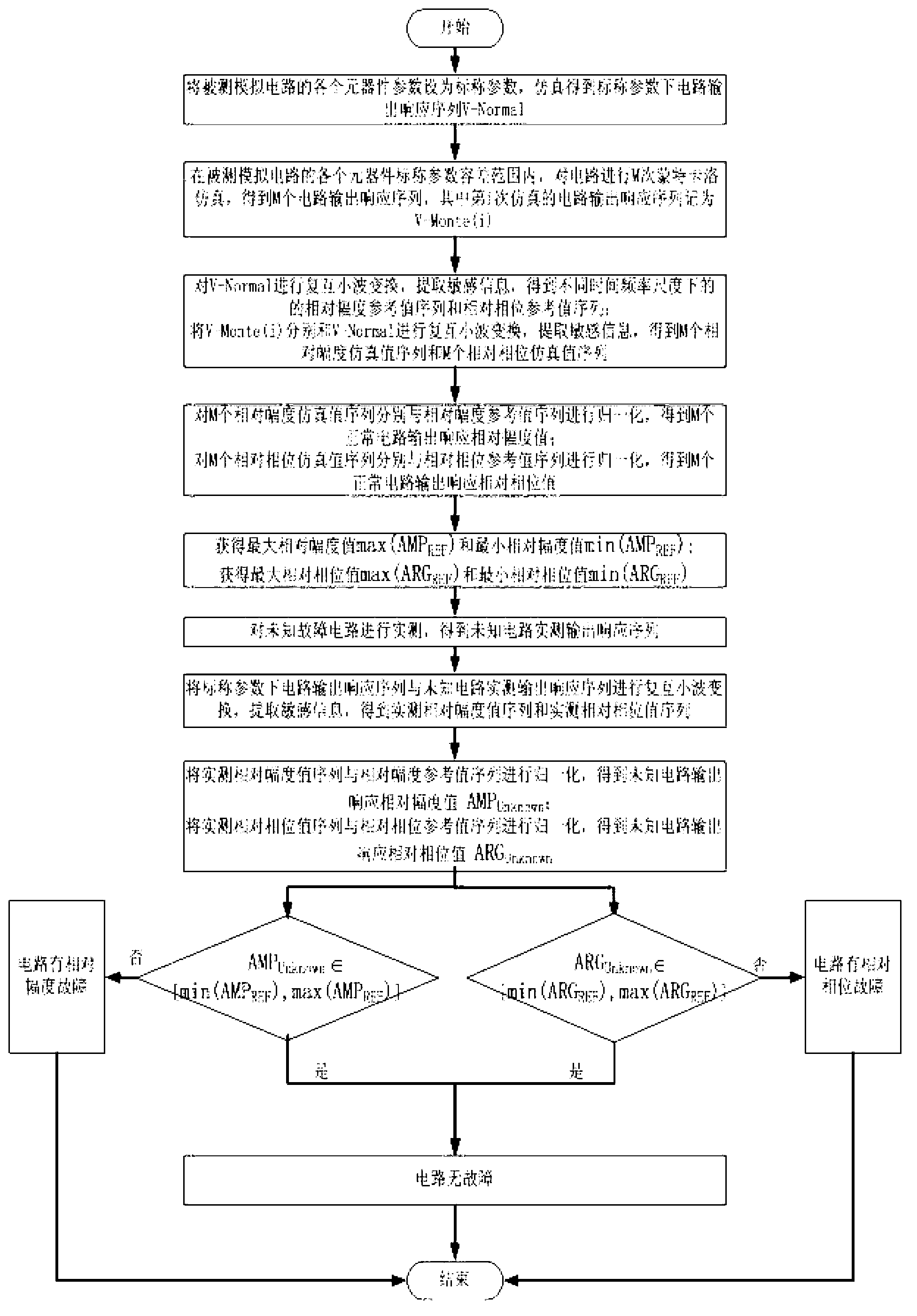

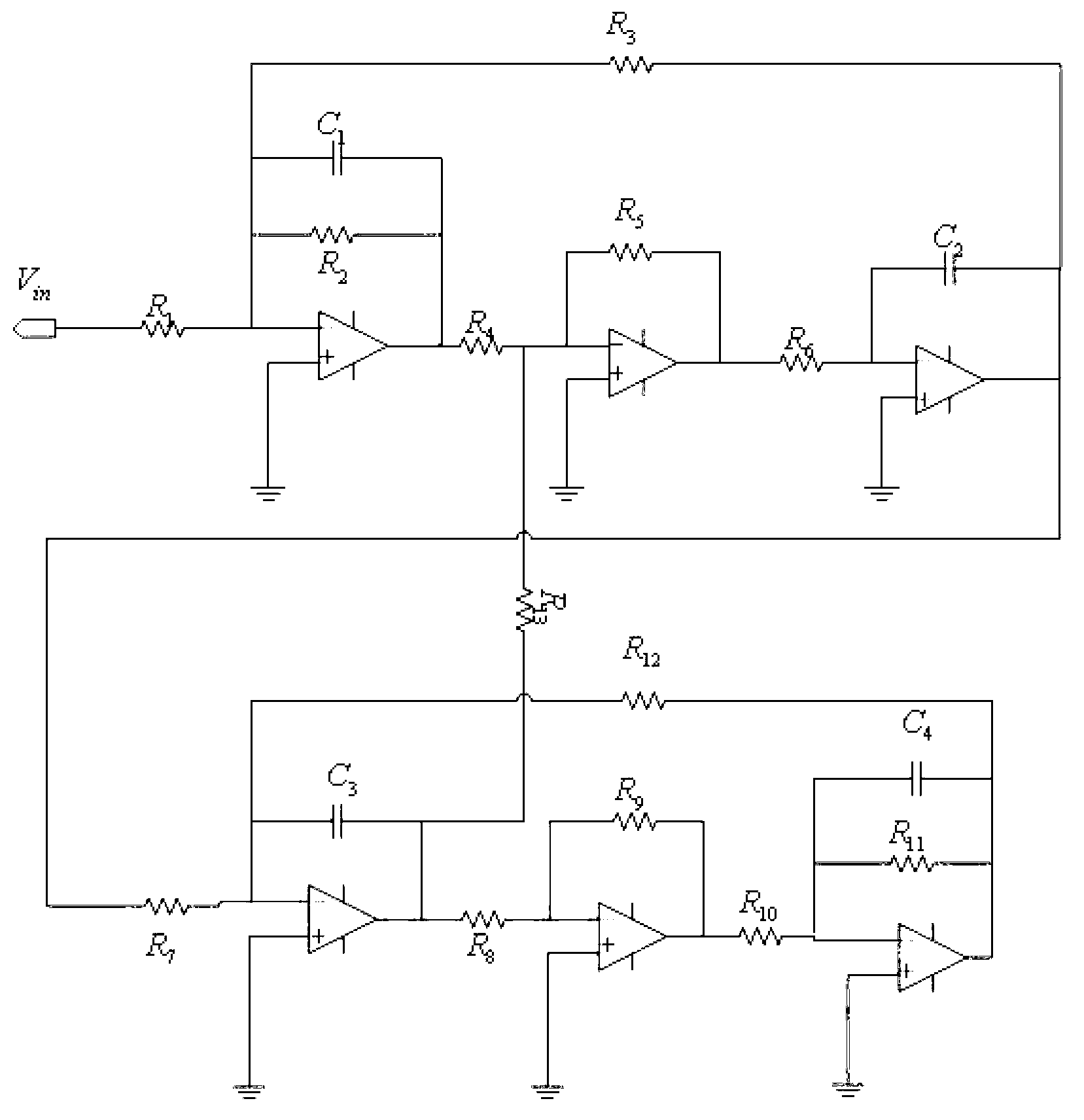

Fault detection method of analog circuit

InactiveCN103267942AImprove detection accuracyImprove fault coverageAnalog circuit testingFault coverageCircuit under test

The invention discloses a fault detection method of an analog circuit. The method includes a first step of carrying out complex cross wavelet transform on circuit output response sequences (Sn) under nominal parameters, extracting sensitive information (recorded as I), and obtaining relative amplitude / phase reference value sequences (Sr), a second step of obtaining normal circuit output response sequences through Monte-Carlo simulation, carrying out the complex cross wavelet transform with the Sn sequences respectively, extracting the sensitive information I, and obtaining relative amplitude / phase simulation value sequences (Ss), a third step of enabling the Ss sequences to be normalized with the Sr sequences respectively, and obtaining the scope (Ra-p) of the relative amplitude / phase values of normal circuit output response, a fourth step of carrying out the complex cross wavelet transform on unknown circuit actual measurement output response sequences and the Sn sequences, extracting the sensitive information I, and then obtaining actual measurement relative amplitude / phase value sequences (St), a fifth step of carrying out normalization on the Sr sequences and the St sequences, and obtaining unknown circuit output response relative amplitude / phase values (Va-p), and a sixth step of comparing the Va-p and the Ra-p, and determining whether the detected circuits have faults. Compared with the prior art, the fault detection method is high in detection precision, and high in fault coverage rate.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Reconfigurable switched-capacitor input circuit with digital-stimulus acceptability for analog tests

InactiveUS7236116B2Reduce testing costsImprove test accuracyElectric signal transmission systemsAnalogue conversionCapacitanceTime to market

A reconfigurable switched-capacitor input circuit with digital-stimulus acceptability for analog tests disclosed in the present invention provides the digital input interfaces, which are comprised of capacitors, analog switches and digital circuits, for the usage of testing the mixed-signal circuits. The present invention provides a low-priced testing platform to accomplish the testing of circuits and to solve the problems of high-cost mixed mode tester and of utmost restrictions against the surrounding condition. Therefore, the present invention improves the testability, reduces the test cost, shorten the processes of designation and efficiently seize on the time-to-market.

Owner:NAT CHIAO TUNG UNIV

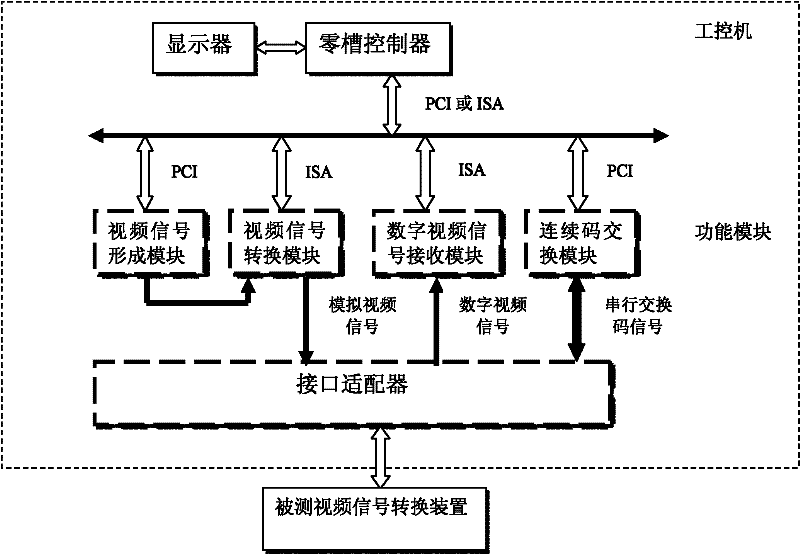

Intelligent detection method and system for video signal conversion device

InactiveCN102271276ARealize the detection functionImprove intelligenceTelevision systemsDigital videoGraphic card

The present invention relates to an intelligent detection method and system for a video signal conversion device, comprising the following steps: 1] generating multiple video signal sources, the video signal source including video signals and synchronization signals; Signal and synchronous signal are integrated and output to provide incentives for the video signal conversion device under test; 3] Collect 6 digital differential video signals of the video signal conversion device under test, convert them into a format acceptable to the graphics card and output them to the display; 4 】The system judges the test result and gives the test conclusion. The invention solves the technical problems existing in the existing video detection system. The invention has multiple video signal types, high system intelligence and high integration.

Owner:AVIC NO 631 RES INST

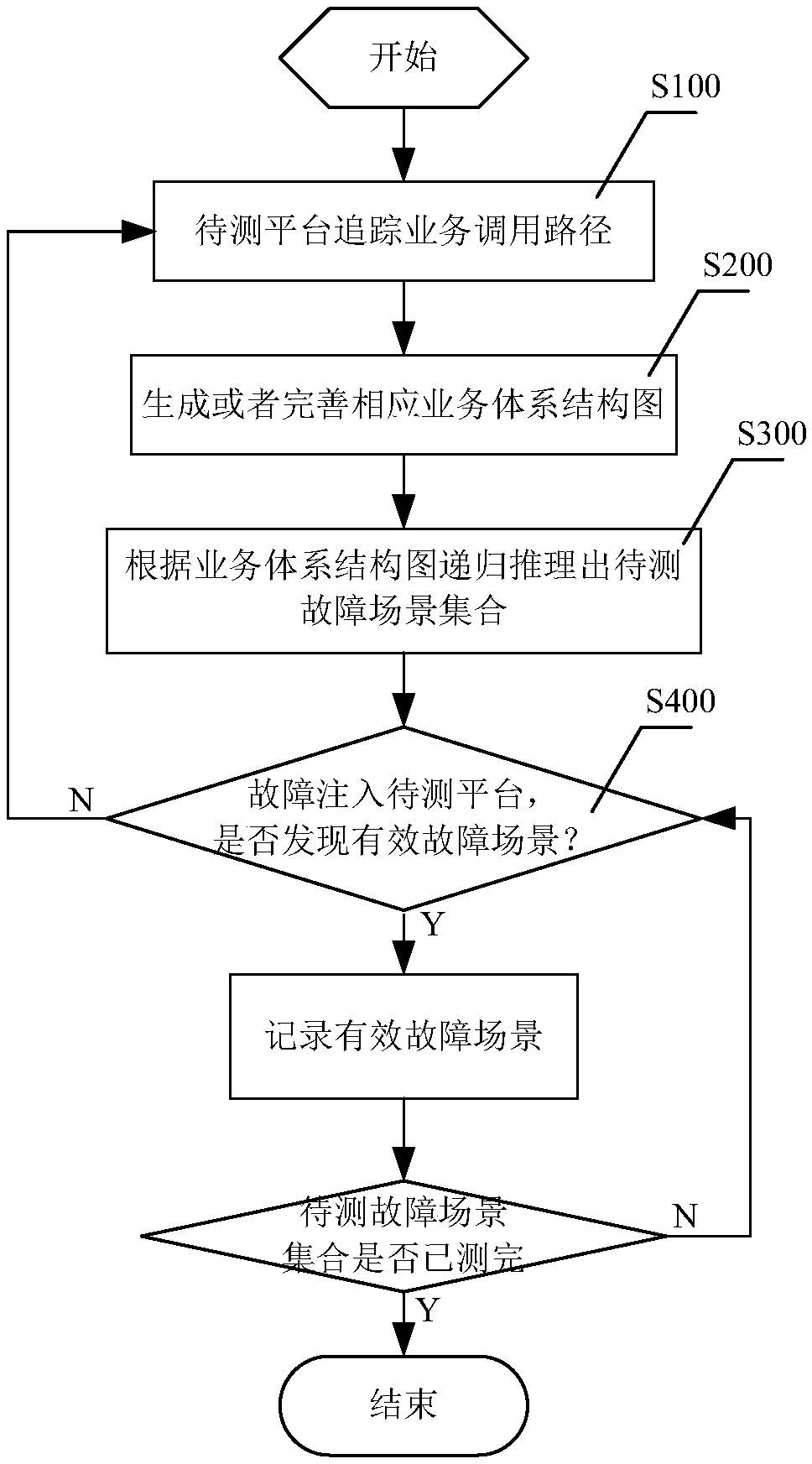

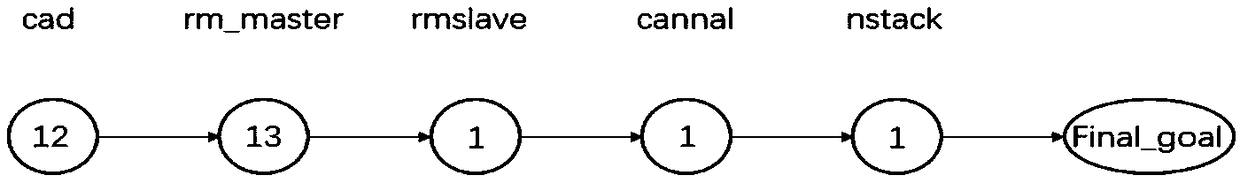

Black-box fault injection method, systems, medium and equipment

InactiveCN108874663AEfficient Fault Injection TestingImprove fault coverageSoftware testing/debuggingFault toleranceBusiness architecture

The invention discloses a black-box fault injection method, systems, a medium and equipment. The injection method includes the following steps: tracking service call paths of software under testing (SUT); generating or perfecting a corresponding service system structure graph according to the service call paths; obtaining a fault scene set, which is to be used for testing, by recursive reasoning according to the service system structure graph; and carrying out fault injection according to the fault scene set, if the software under testing can be destroyed, determining that an effective fault scene is found, and otherwise, returning to continuous tracking of all the call paths once it is found that a certain fault scene cannot destroy the software under testing. According to the method, fault tolerance evaluation can be highly efficiently carried out on a large-scale computer platform, and a set of all effective fault scenes can be found without missing.

Owner:NANJING UNIV

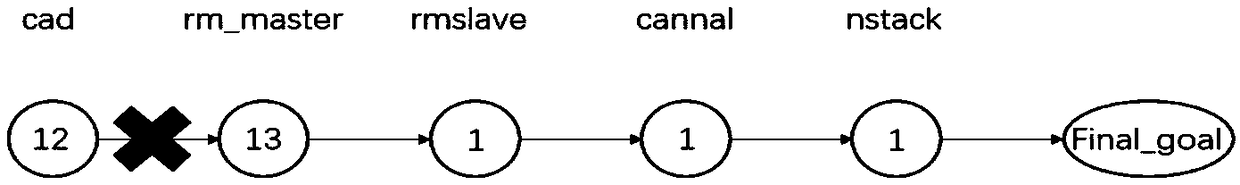

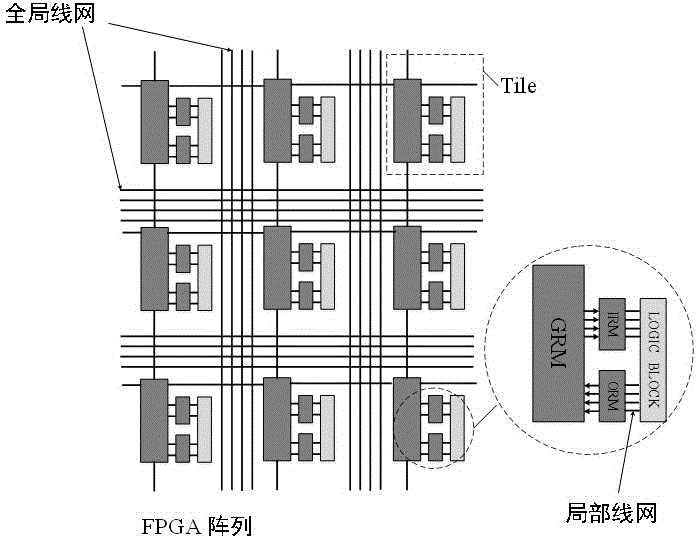

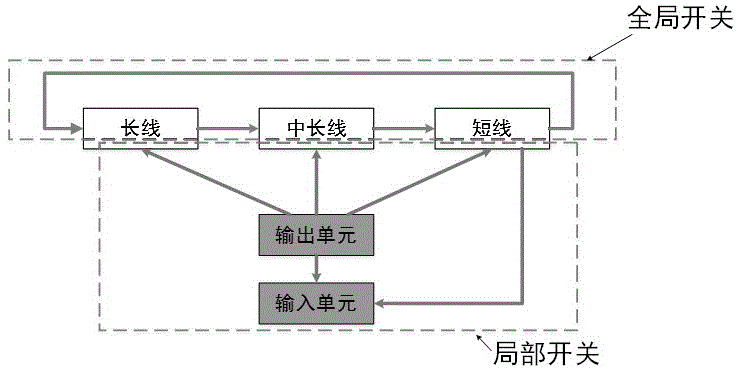

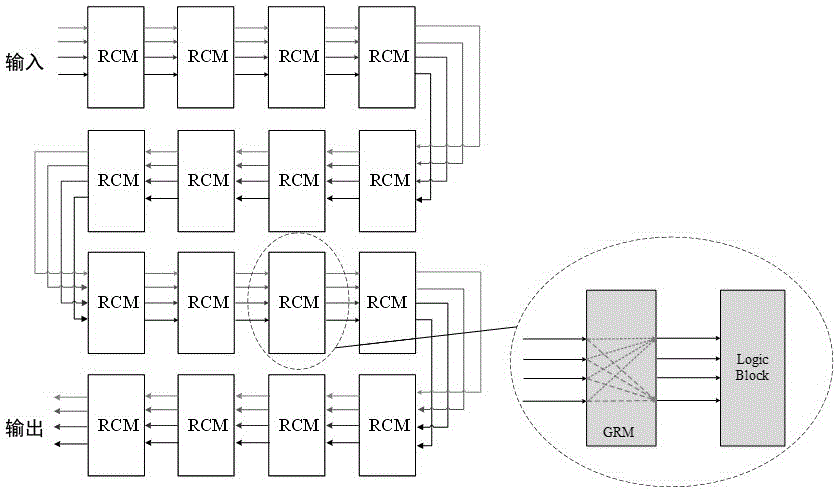

Automatic testing method for FPGA local interconnection resources on basis of repeatable configuration units

ActiveCN105677525AReduce occupancyReduce the difficulty of configuration generationDetecting faulty computer hardwareInterconnectionFpga chip

The invention belongs to the technical field of integrated circuits, and particularly relates to an automatic testing method for FPGA local interconnection resources on the basis of repeatable configuration units. The method comprises the step of testing on all local interconnection line segments and all local programmable interconnection switches in an FPGA chip. According to the method, the regularity of an FPGA is fully utilized,the FPGA is subjected to local interconnection and configured to repeatable configuration unit templates with adjacent logic circuit resources, and then the unit templates are sequentially connected end to end and repeatedly traversed to the whole FPGA. Faults capable of being tested through the method comprise open circuits of the interconnection line segments, the short-circuit fault and the normally-opened and normally-closed faults of the interconnection switches. The method can complete testing on all the local interconnection resources in the FPGA chip and has higher applicability on FPGAs with different structures and scales. The configuration number, the configuration difficulty and the testing time needed by testing are all greatly optimized.

Owner:FUDAN UNIV

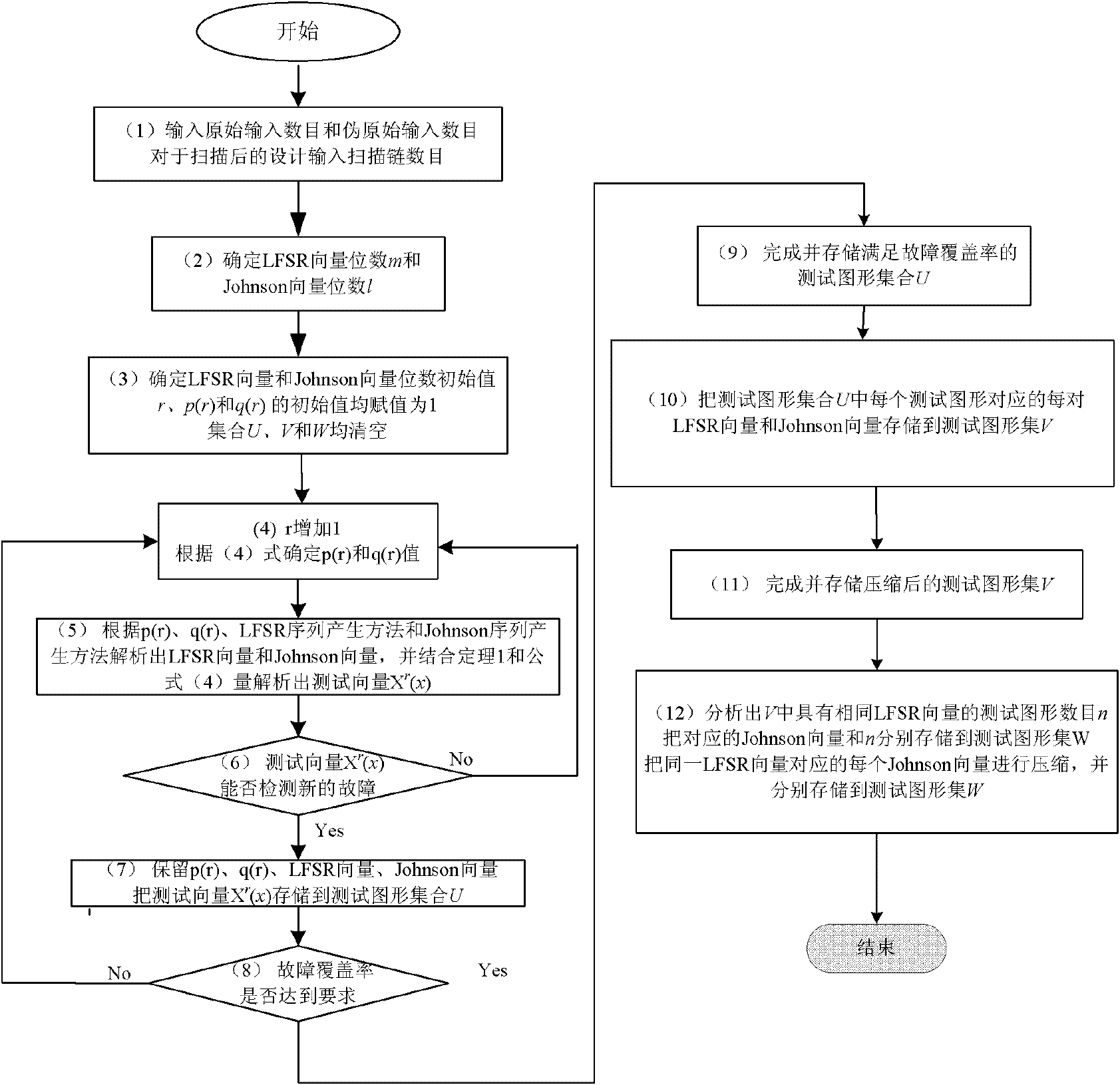

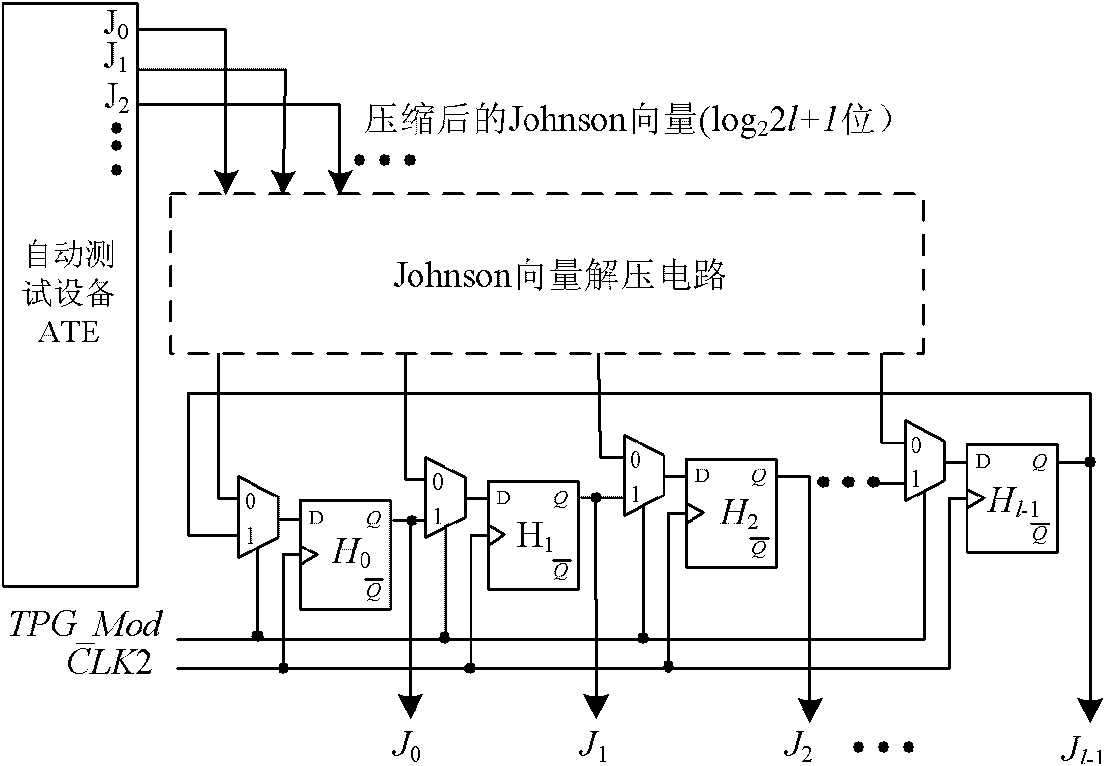

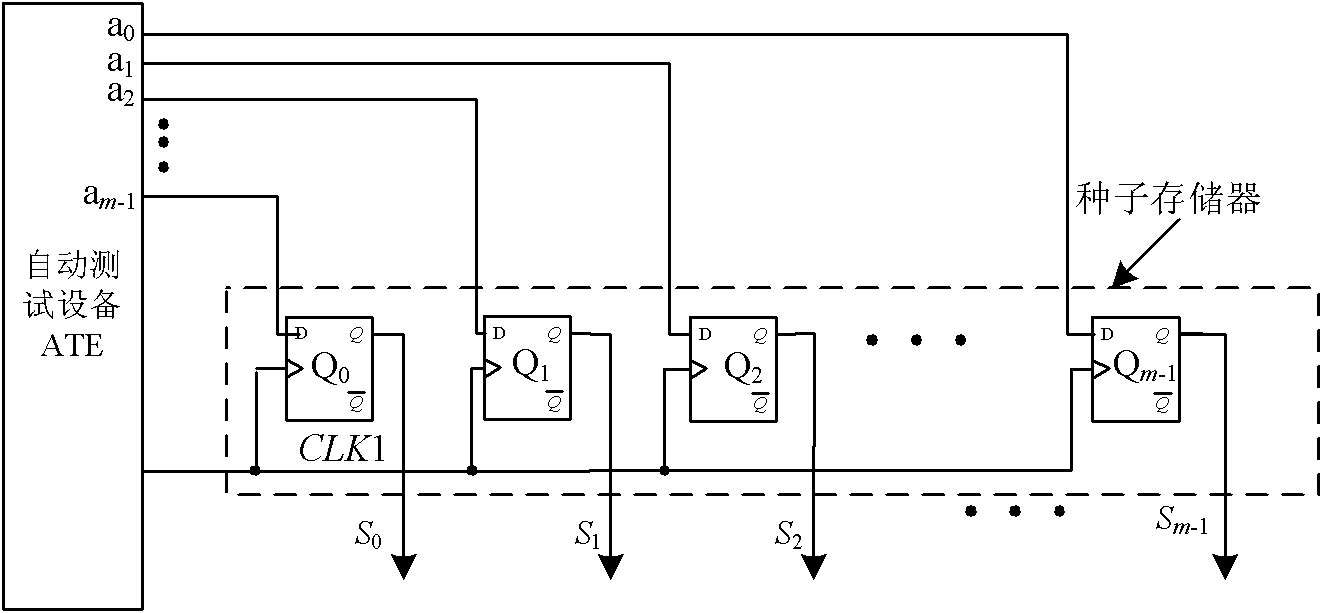

Compression generation method for testing data of digital integrated circuit

InactiveCN101937056AImprove fault coverageReduce power consumptionElectrical testingCode conversionCircuit under testLinearity

The invention discloses a compression generation method for testing data of a digital integrated circuit. Differing from a traditional testing method, the method comprises the following steps of: firstly analyzing a kind of a single input change testing sequence with linear relation; confirming a testing pattern set with a new trouble detecting capacity by a fault simulation method; considering values of a small part bit of the testing pattern set compressed by the linear relation is a compressed testing pattern set; and storing the compressed testing pattern set in automatic testing equipment (ATE). During testing application, the compressed testing pattern set is decompressed by a hardware circuit according to linear relation which is defined in advance so that an actual testing pattern set is restored. Besides, the actual testing pattern set is applied to a tested circuit. The data volume stored in the ATE is less than the data volume of the actual testing pattern set. The testing method has the characteristics of high compression ratio, easy realization, low power consumption and high coverage rate.

Owner:XI AN JIAOTONG UNIV

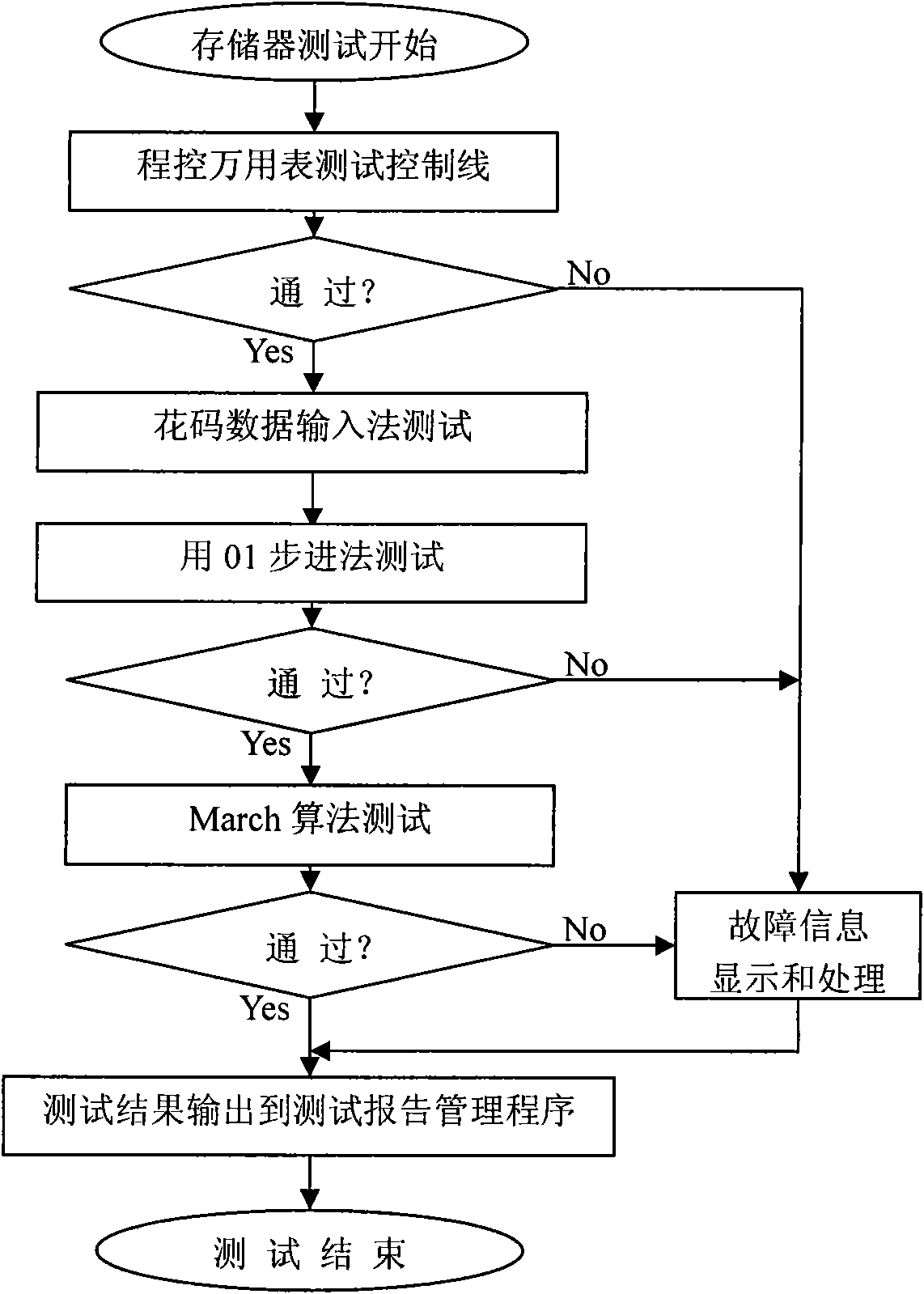

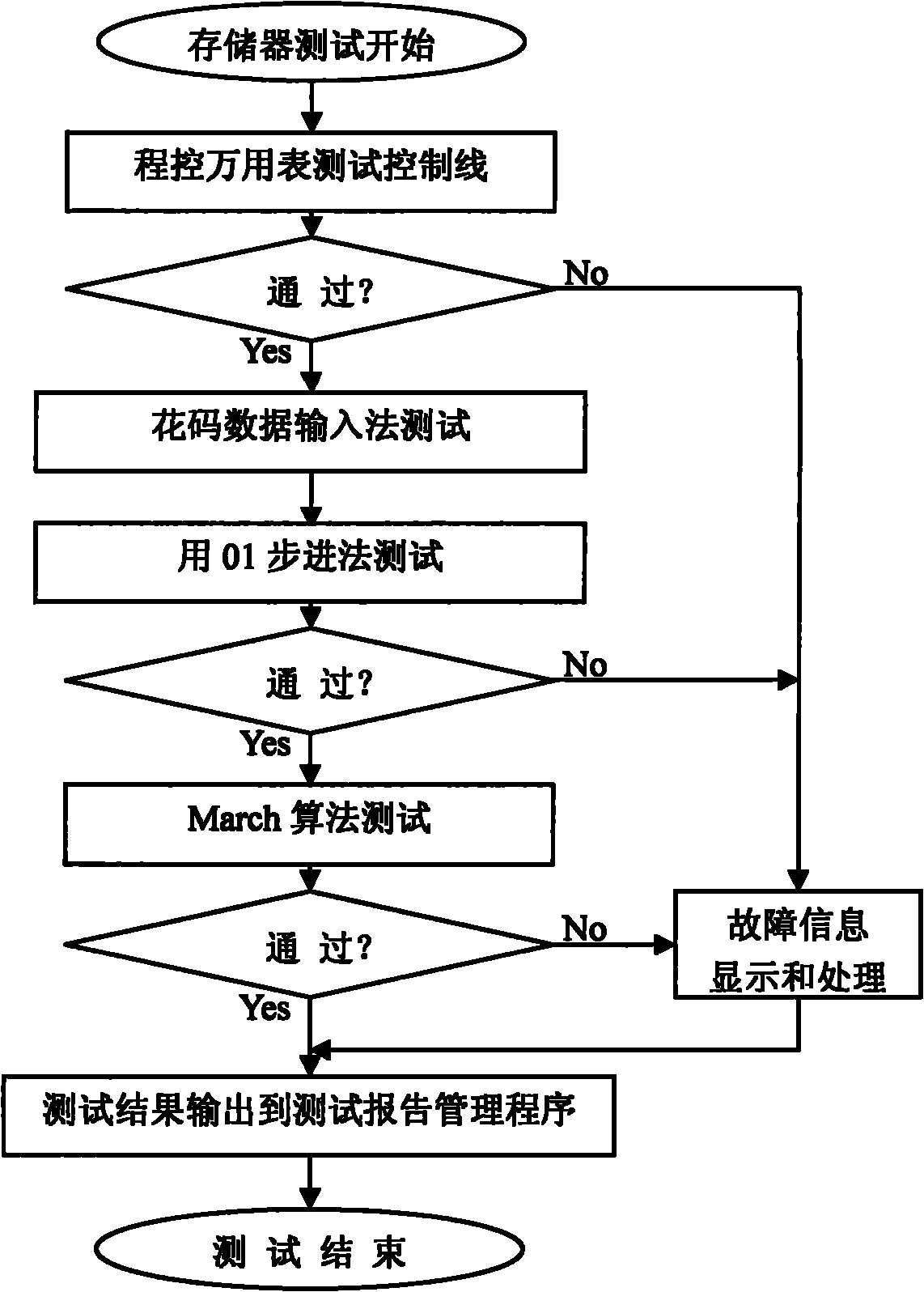

On-board test method for memory

The invention relates to a test method for a memory, comprising the following tests in sequence: control line test, Chinese numerals data input method test, 01 stepping technique test and March algorithm test. The method of the invention is supposed to have high timeliness at first; then the method is supposed to have high fault-coverage rate on line fault; in addition, the method is supposed to take into account detection of self fault of a memory chip; moreover the method of the invention covers self fault of the memory chip and circuit board line fault, strikes a good balance between test requirements and test consumption, thus enjoying good fault-coverage rate and timeliness and being applicable to on-board test of various memories.

Owner:中国航空工业第一集团公司第六三一研究所

Test circuit inserting method and apparatus for a semiconductor integrated circuit

InactiveUS7207019B2Increase in sizeImprove fault coverageElectronic circuit testingError detection/correctionFault coverageChip size

A method to reduce the load of layout design and attain a high fault coverage while preventing increase in chip size in test point insertion for a semiconductor integrated circuit. Initial layout is performed on the basis of the circuit information. Interconnection pairs are extracted from a layout result. Test point insertion candidates are extracted on the basis of the controllability probabilities and the interconnection pairs. If test point insertion candidates exist, test point insertion positions are selected. Circuit structures of test points to be inserted there are selected. Test points having those circuit structures are inserted virtually. Whether the circuit overhead of a layout result is within a prescribed range is judged. If the circuit overhead exceeds the prescribed range, the number of test points is reduced.

Owner:SOCIONEXT INC