Method and system for testing on site programmable gate array

A gate array and test vector technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of consuming FPGA chip test cost, reducing test configuration, and limited application scope, so as to improve fault coverage and improve reliability. Observational, improved measurability effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

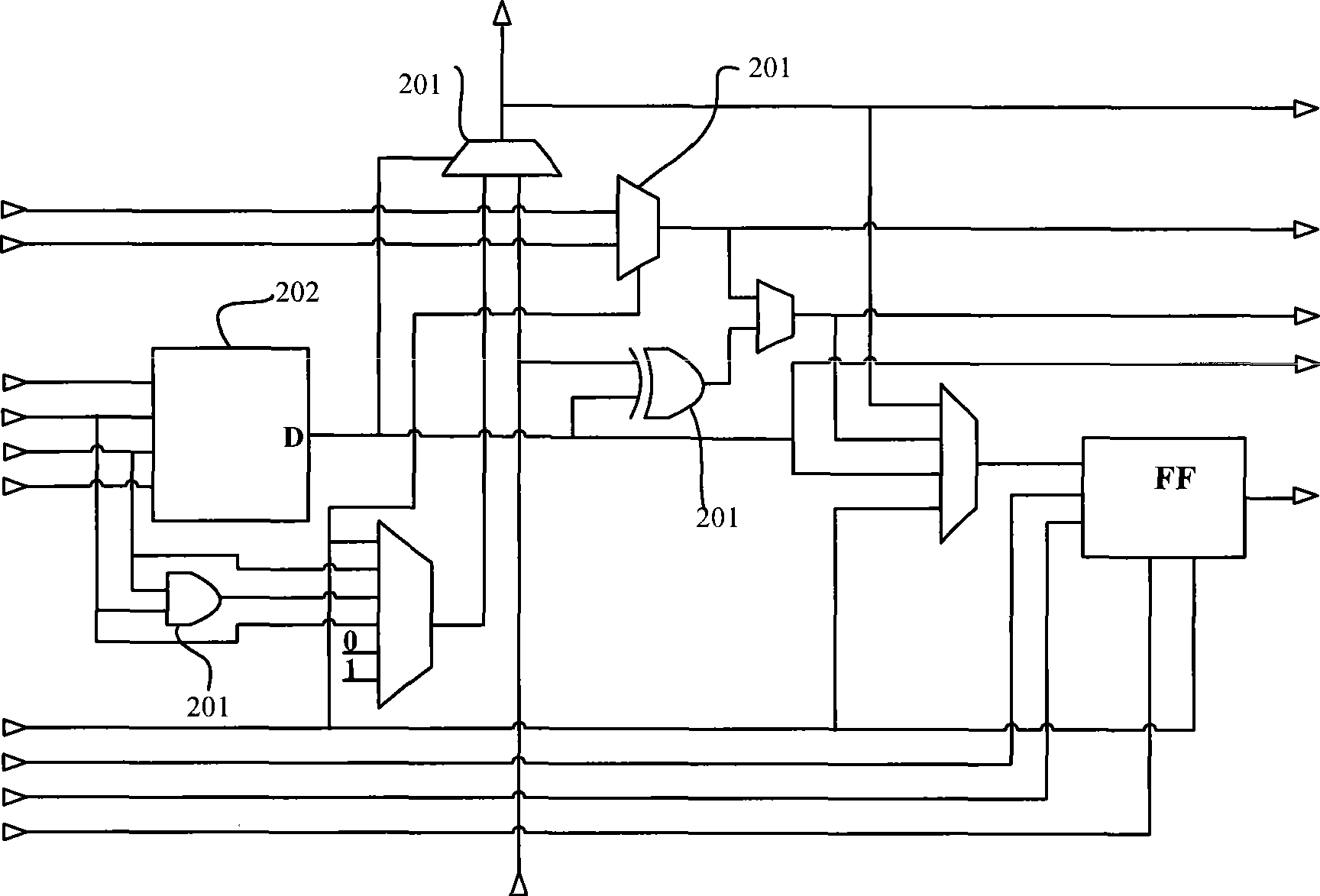

[0075] Such as Figure 4 The flow chart of an FPGA testing method of the present invention is shown; the steps of the FPGA testing method mainly include:

[0076] Step 401: Obtain the initial design netlist and initial design configuration of the field programmable gate array;

[0077] Step 402: Use the exclusive OR function of the logic function to replace the functions of the initial design netlist and the lookup table unit of the initial design configuration to obtain the initial test netlist and the initial test configuration;

[0078] Of course, the exclusive OR function of the logic function mentioned in this step replaces the function of the look-up table unit, that is, as long as any unit configured here has the function of the look-up table unit, the exclusive OR function of the logic function can be used to perform Replacement and replacement are universal, and can be a look-up table unit or a non-look-up table unit. As long as the LUT function is set in the FPGA chip, t...

Embodiment 2

[0114] Another application-oriented FPGA testing method of the present invention has the following steps:

[0115] Step A1: Get the FPGA initial design netlist N containing the LUT configuration D , And initial design configuration, where the FPGA initial design netlist refers to the FPGA initial design netlist obtained after wiring during FPGA design and development;

[0116] Step A2: The FPGA initial design netlist N D The LUT configuration functions in are all modified to XOR logic functions to get the initial test netlist For a LUT, when the input controllability is determined, configuring the LUT as an XOR gate can improve the output controllability;

[0117] Those skilled in the art should know that the controllability and observability of any node involved in the embodiments of the present invention are between 0 and 1. The closer the controllability value of a node is to 1, the higher the controllability of the node, and vice versa. Because the input port is directly cont...

Embodiment 3

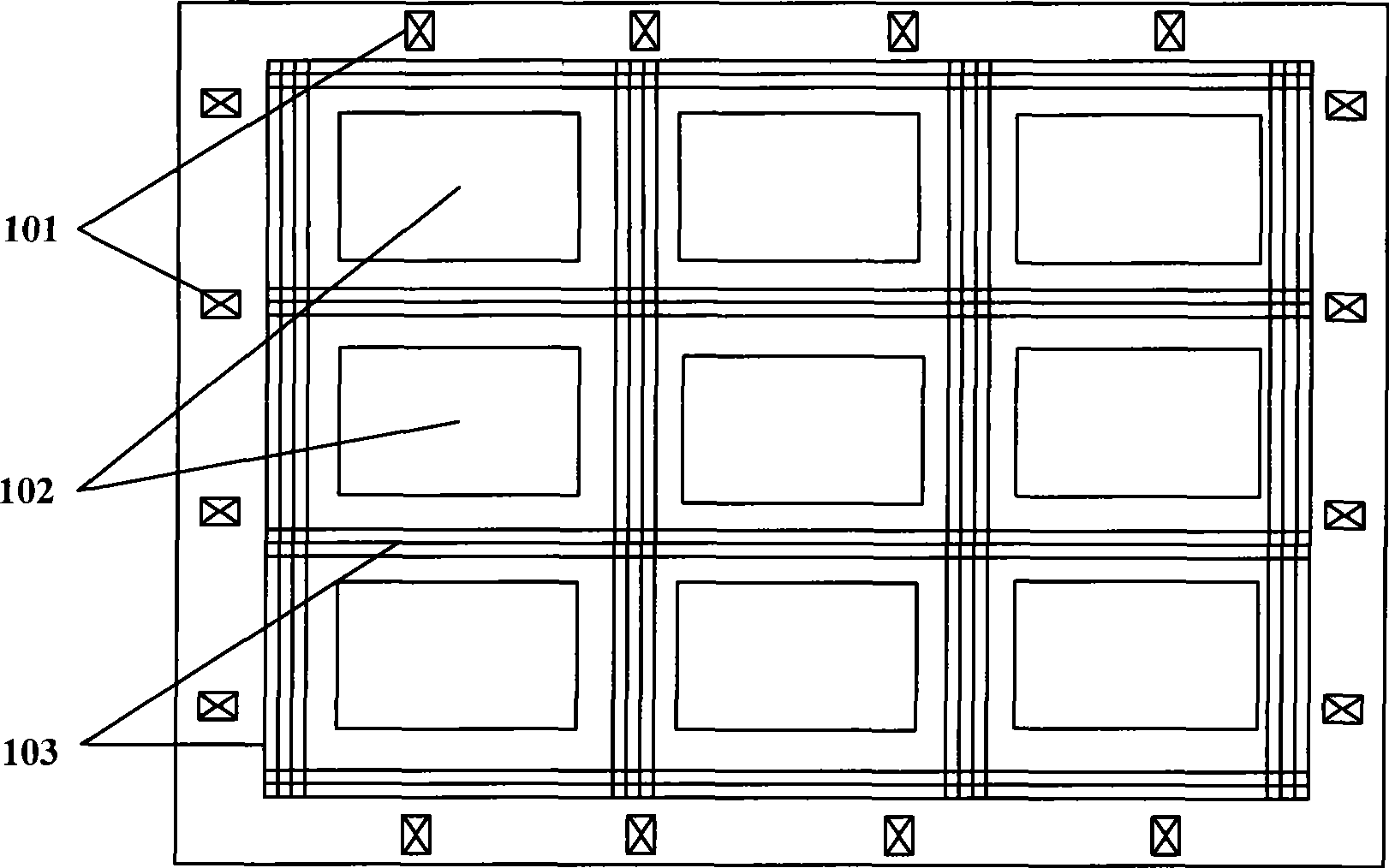

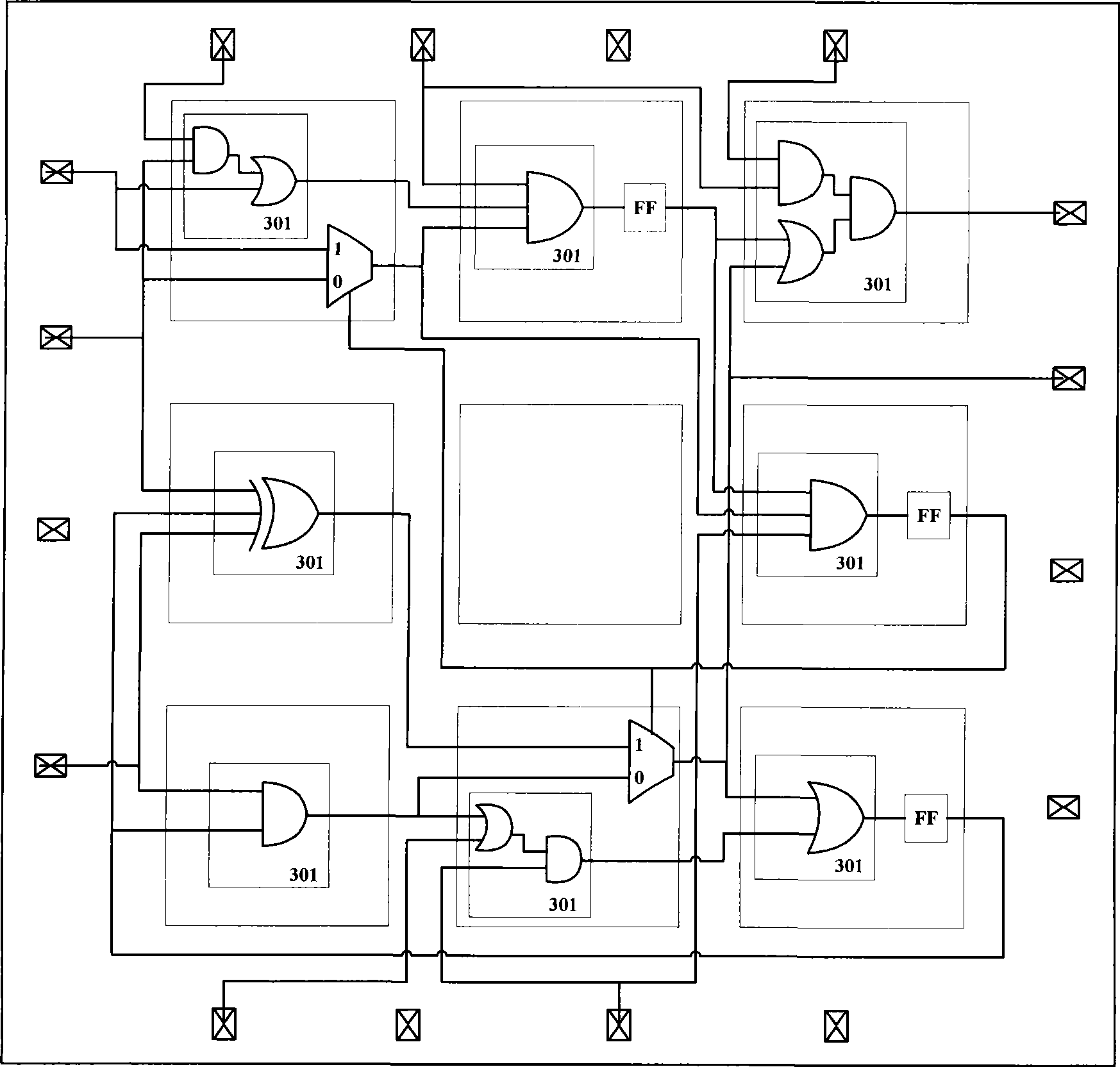

[0138] An application-oriented FPGA test usually uses part of the FPGA resources. The present invention can utilize the reconfigurable characteristics of the FPGA chip to perform application-oriented test analysis, such as image 3 Shown. Can put image 3 The FPGA design configuration example shown is abstracted into Figure 5 The FPGA initial design network example shown. Since there is no scan chain in the FPGA initial design netlist, the testability of its internal nodes is very low, resulting in a low coverage rate of the test vector generated by the automatic test vector generation tool for the netlist.

[0139] In order to improve the testability of the netlist without inserting a scan chain, an FPGA chip that needs to be tested for application is obtained. An example of the test process is as follows:

[0140] Step W1: firstly modify all the configuration logic functions 501 of the LUTs into exclusive OR logic functions to improve the controllability of its internal nodes. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More