On-board test method for memory

A test method and memory technology, applied in static memory, instruments, etc., can solve problems such as high time consumption, and achieve the effects of high timeliness, good fault coverage, good fault coverage and timeliness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

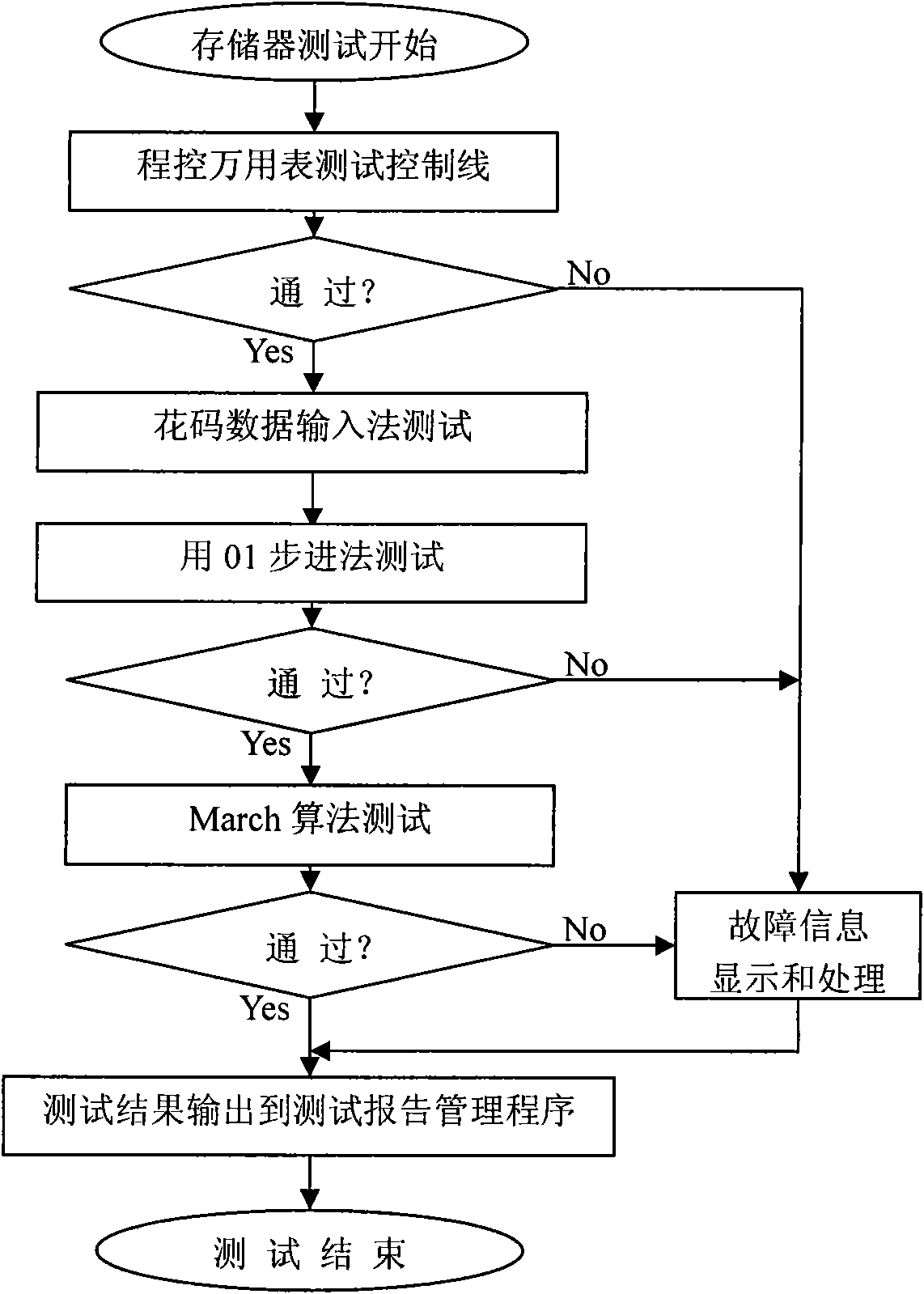

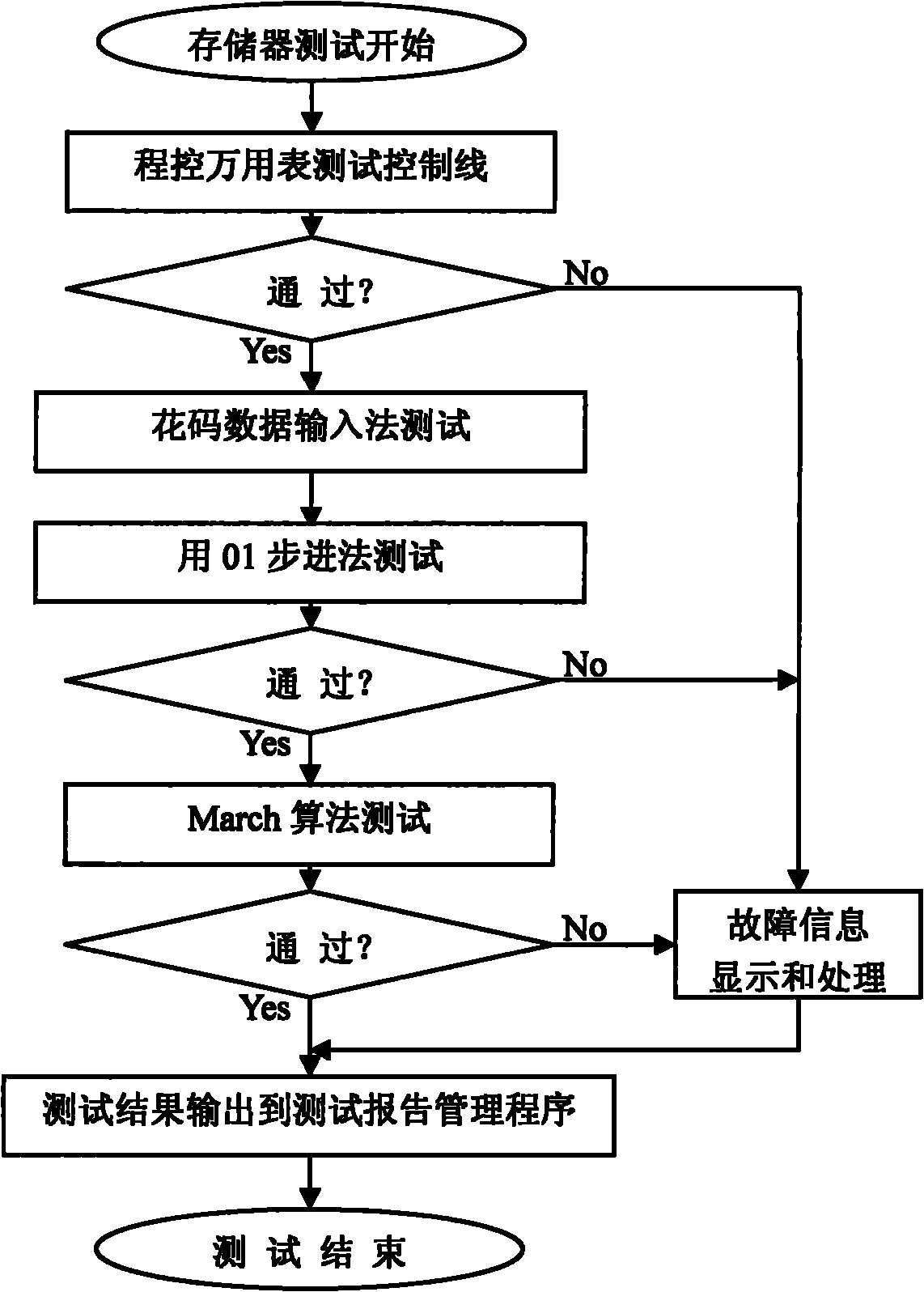

[0025] see figure 1 , the test method of the present invention is mainly divided into three-step tests in order: the first step is a code input method test, the second step 01 step method is used to test data lines and address lines, and the third step is March algorithm test. The first step is basically to test the data line and address line. If it is not a memory fault, the fault pattern can provide help in locating the faulty chip; the second step is to locate the specific data / address line, and you can also test part of the memory. unit; the third step memory test.

[0026] 1. Test with fancy code data input method

[0027] For the test input data, according to the distance effect (the Hamming distance of the two test vectors - the greater the number of corresponding bits of the two test vectors, the more different faults they can detect), select the flower with the largest difference between the two groups The code data is used as data input, and the data bus is set to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More