Patents

Literature

269 results about "Memory testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

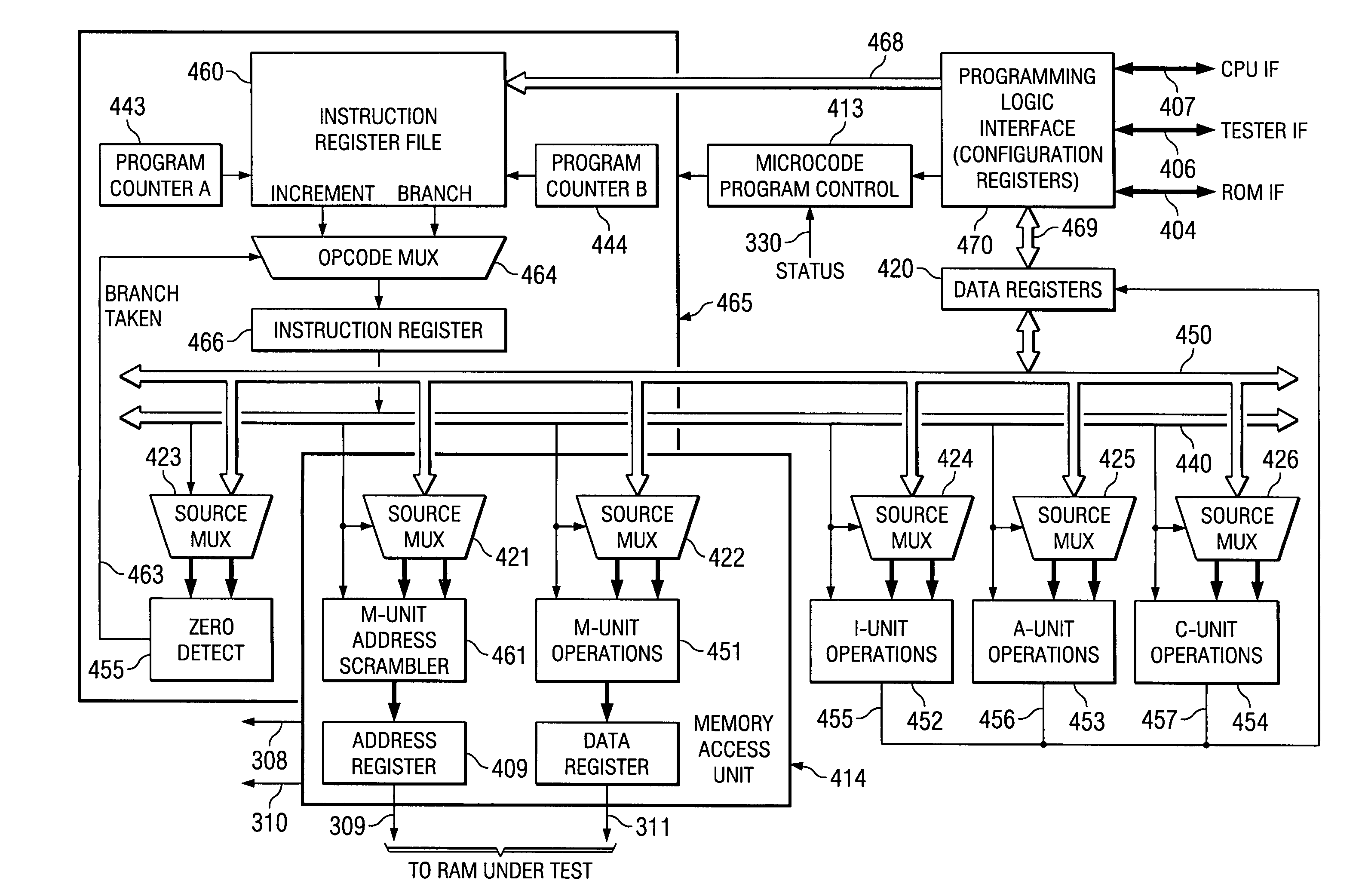

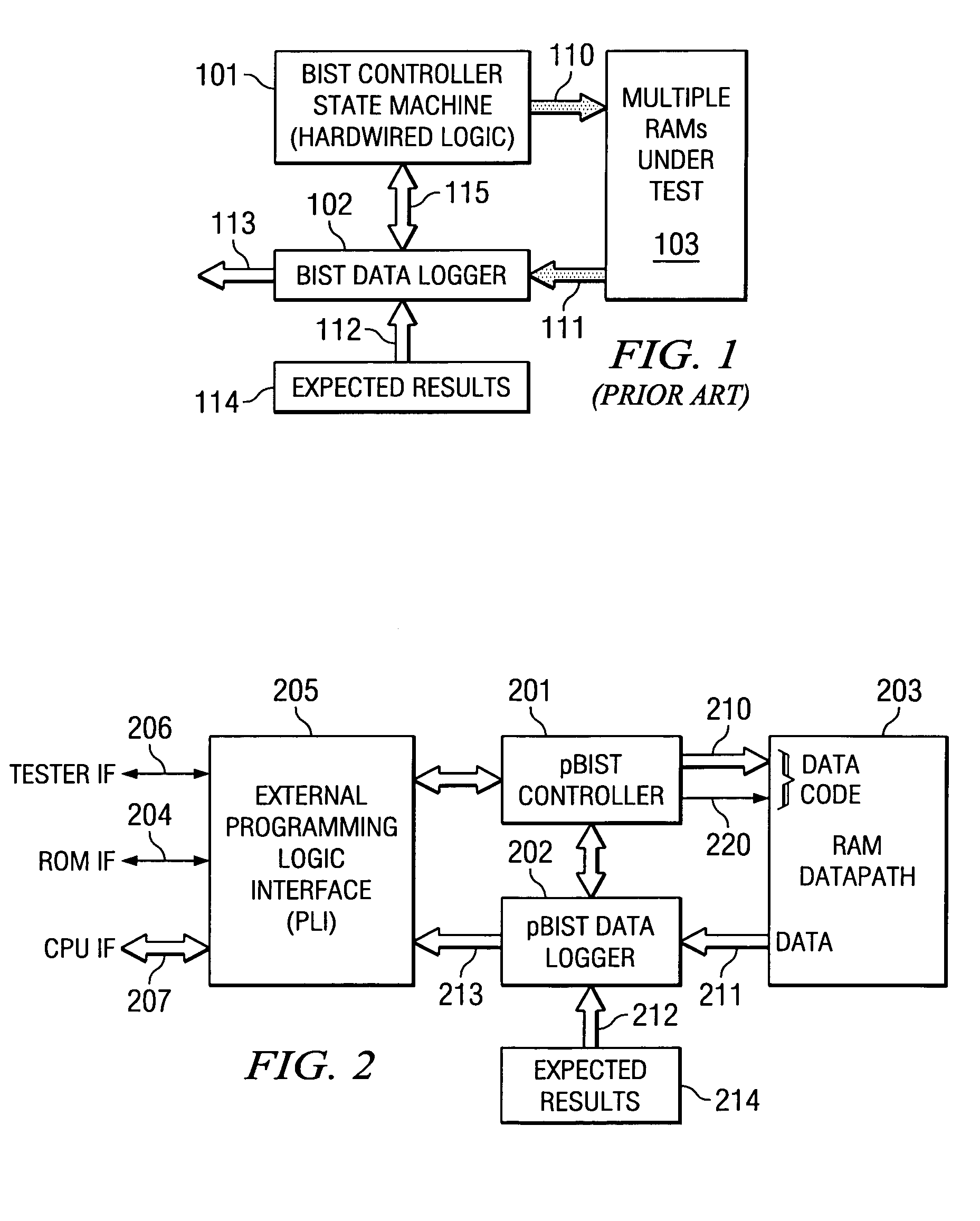

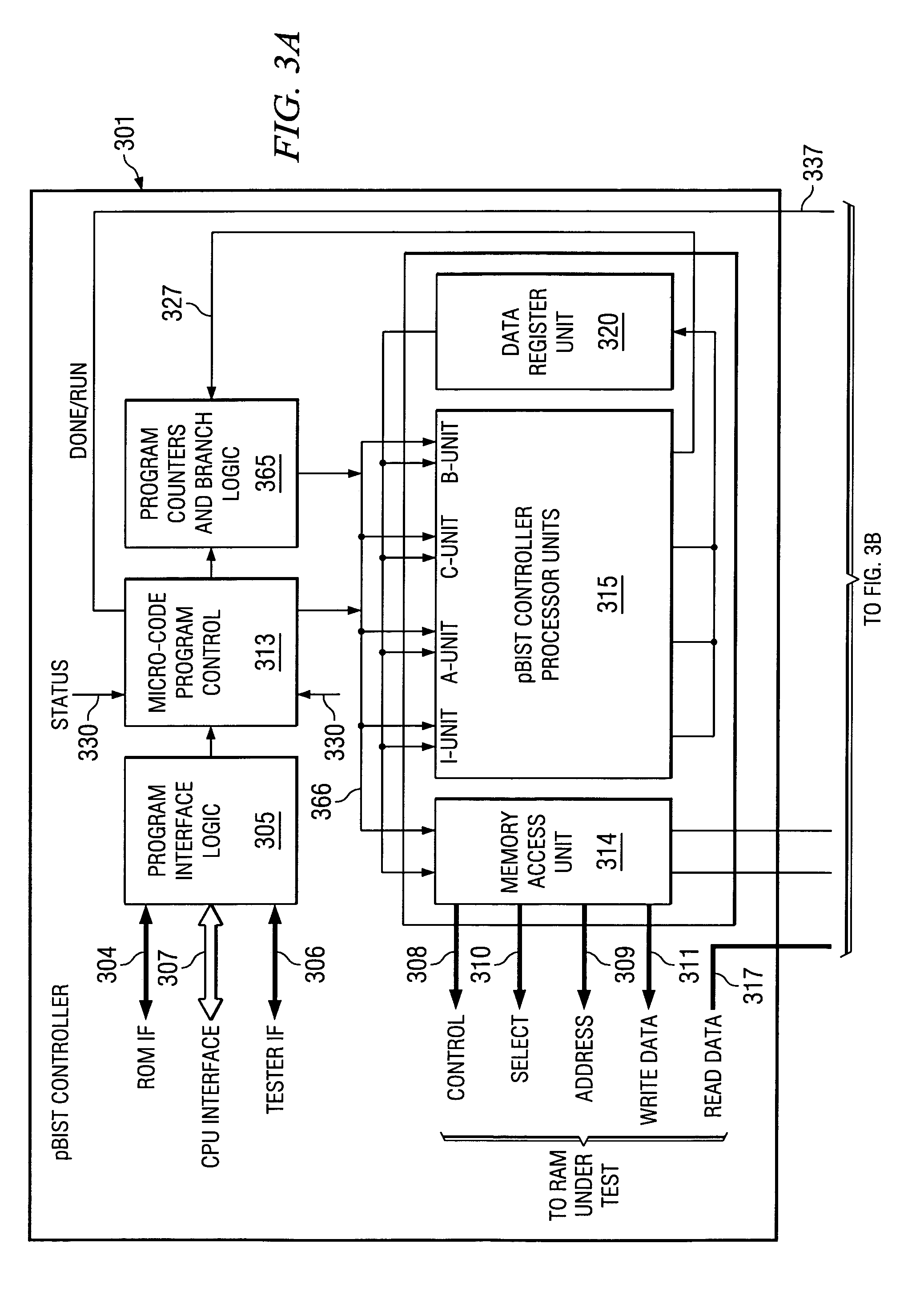

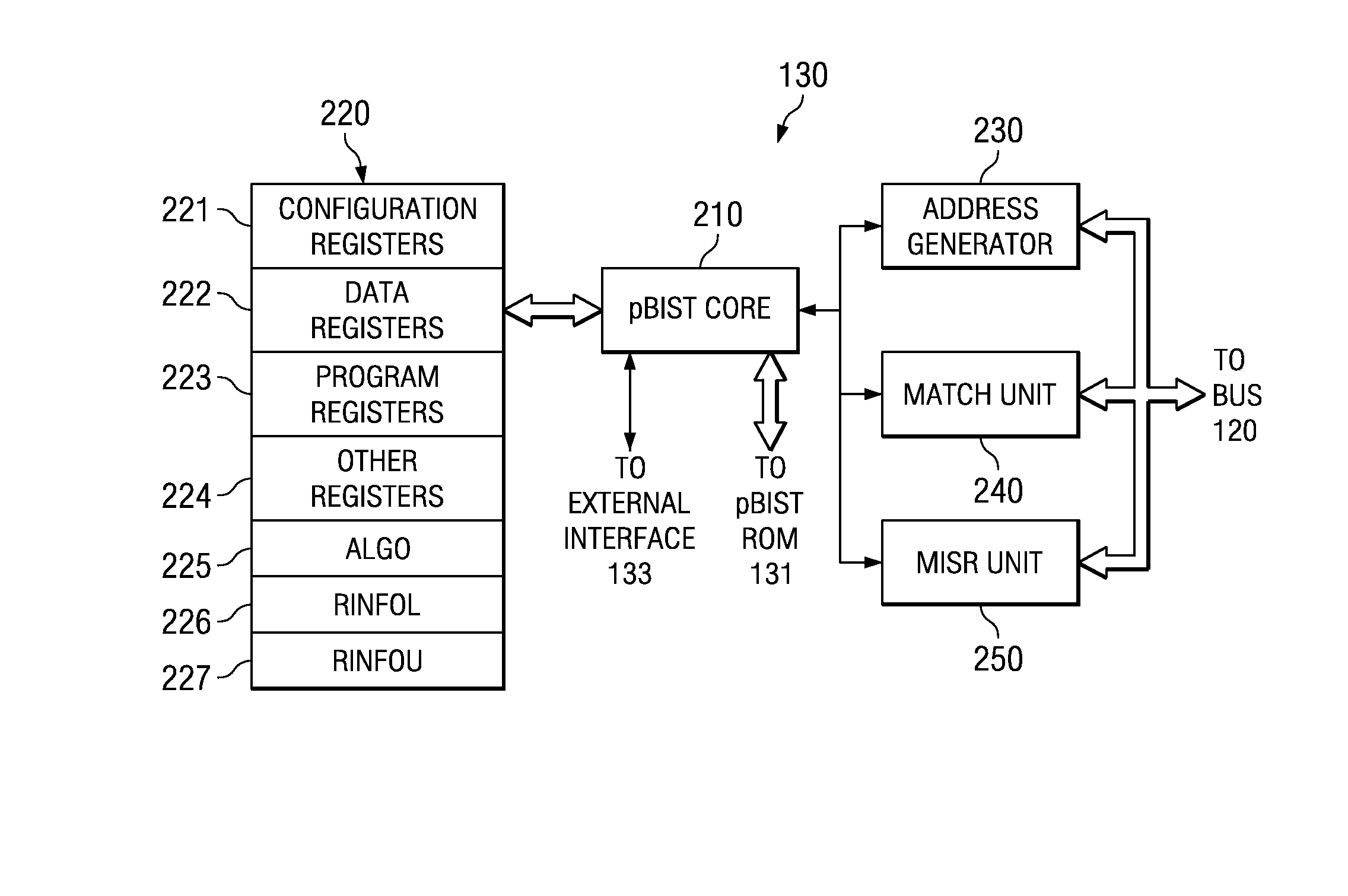

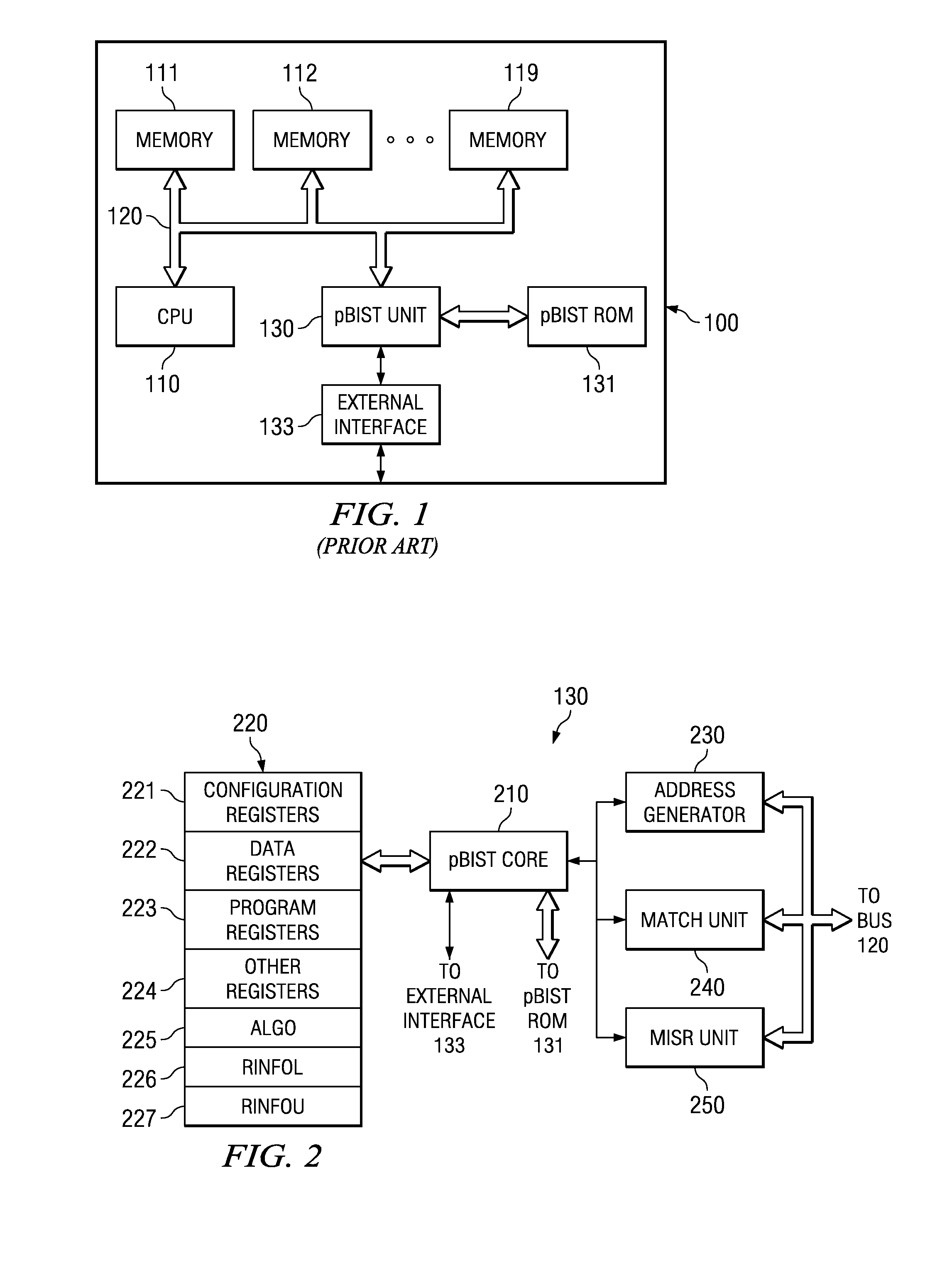

Programmable built in self test of memory

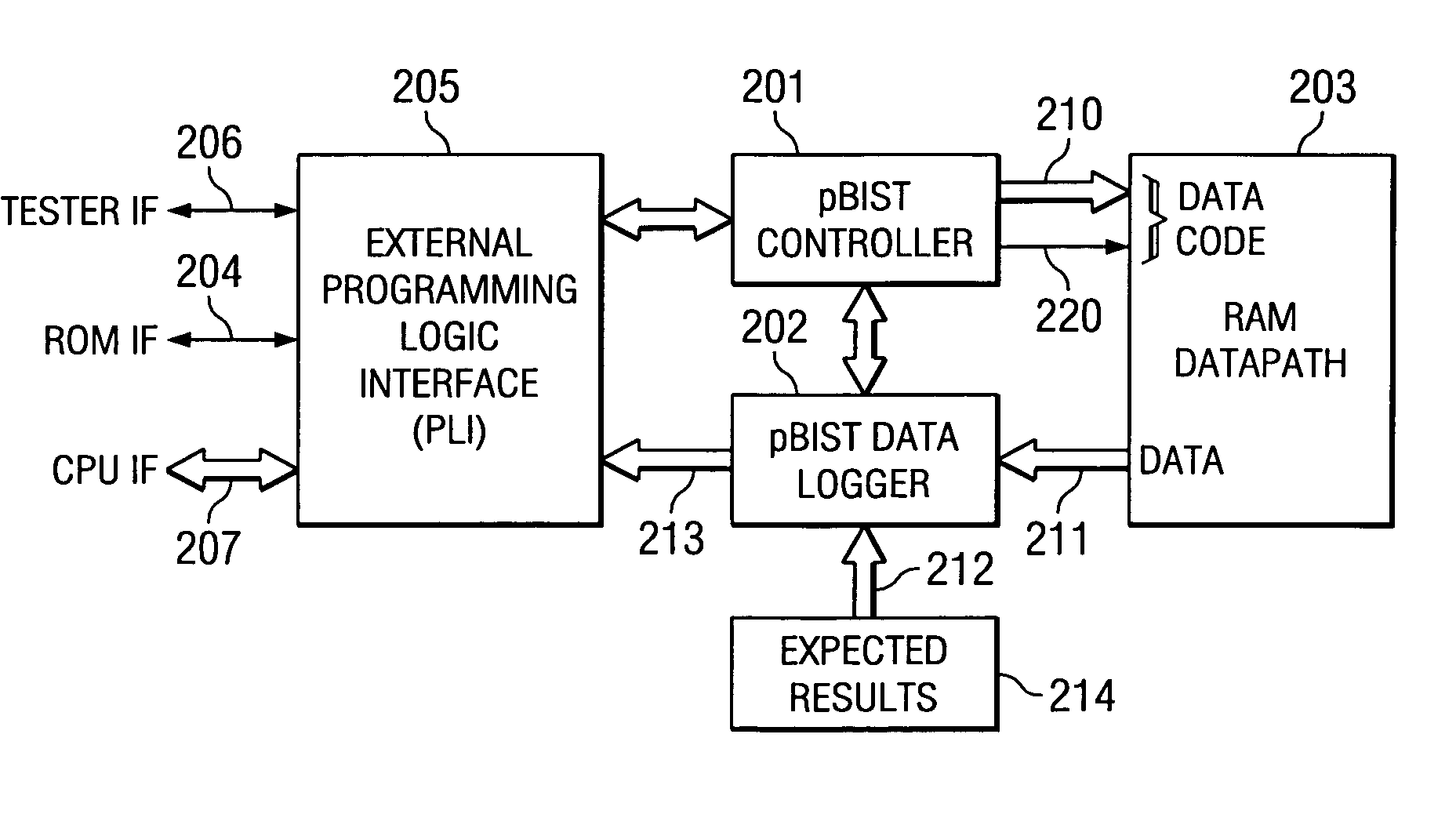

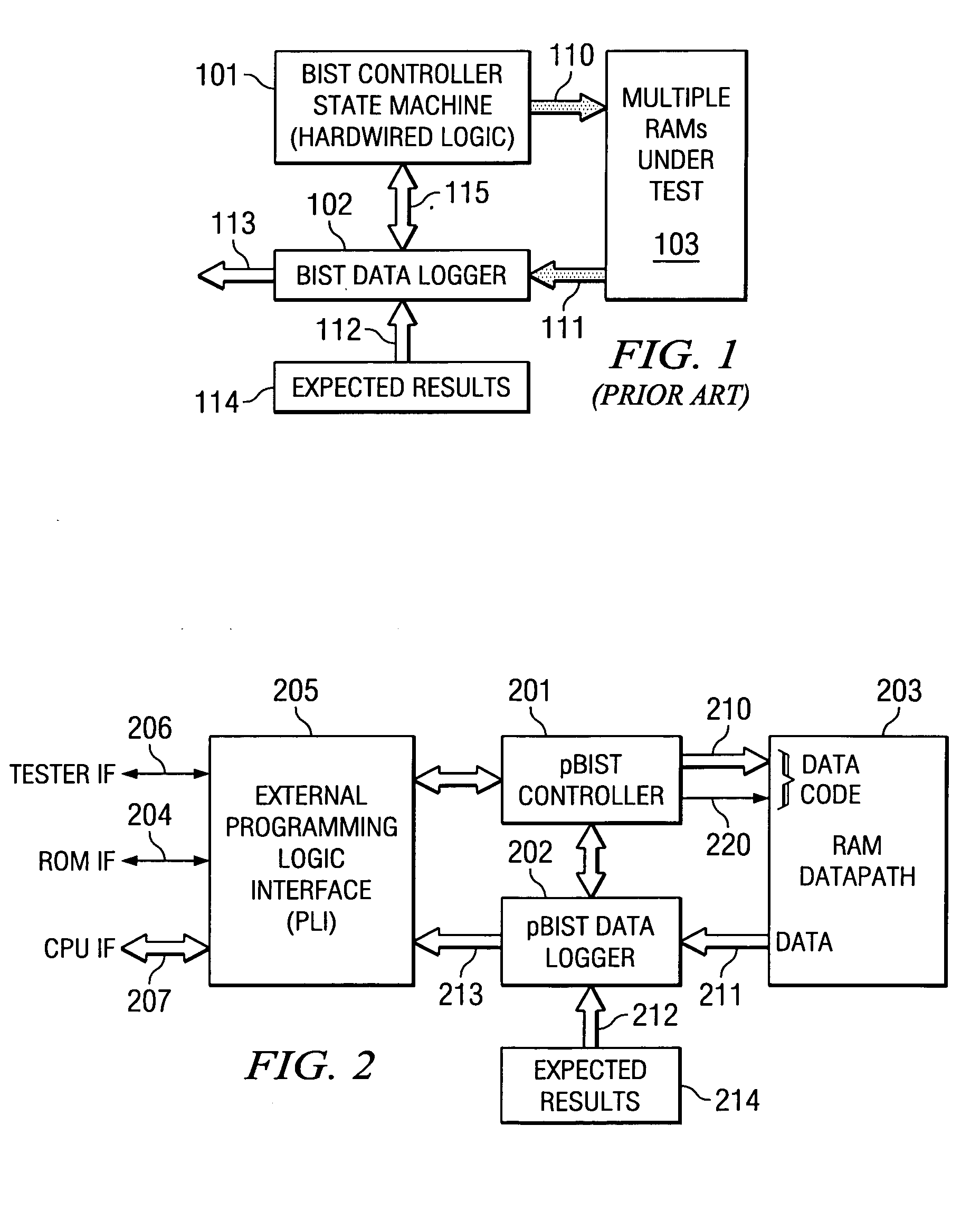

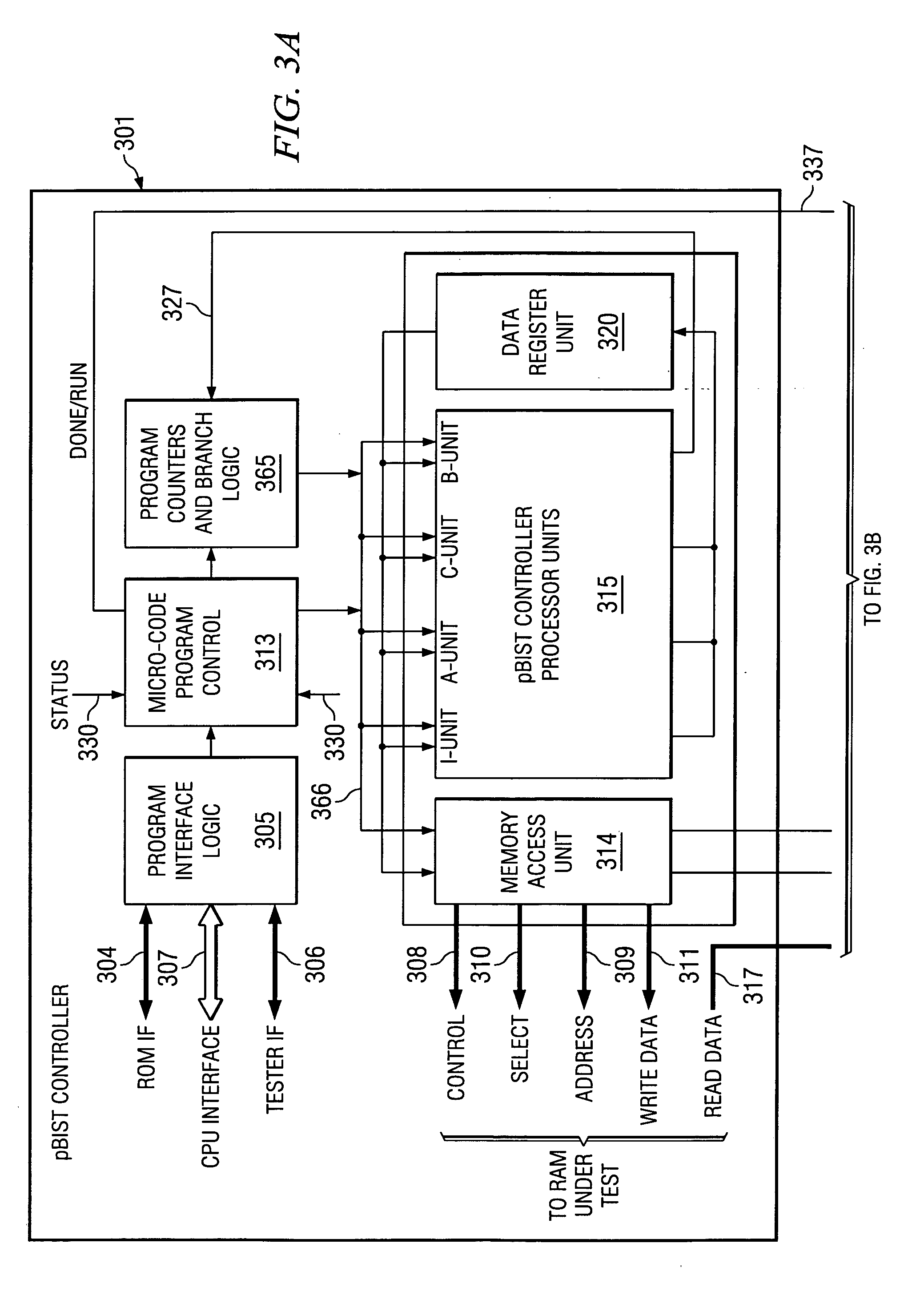

The pBIST solution to memory testing is a balanced hardware-software oriented solution. pBIST hardware provides access to all memories and other such logic (e.g. register files) in pipelined logic allowing back-to-back accesses. The approach then gives the user access to this logic through CPU-like logic in which the programmer can code any algorithm to target any memory testing technique required. Because hardware inside the chip is used at-speed, the full device speed capabilities are available. CPU-like hardware can be programmed and algorithms can be developed and executed after tape-out and while testing on devices in chip form is in process.

Owner:TEXAS INSTR INC

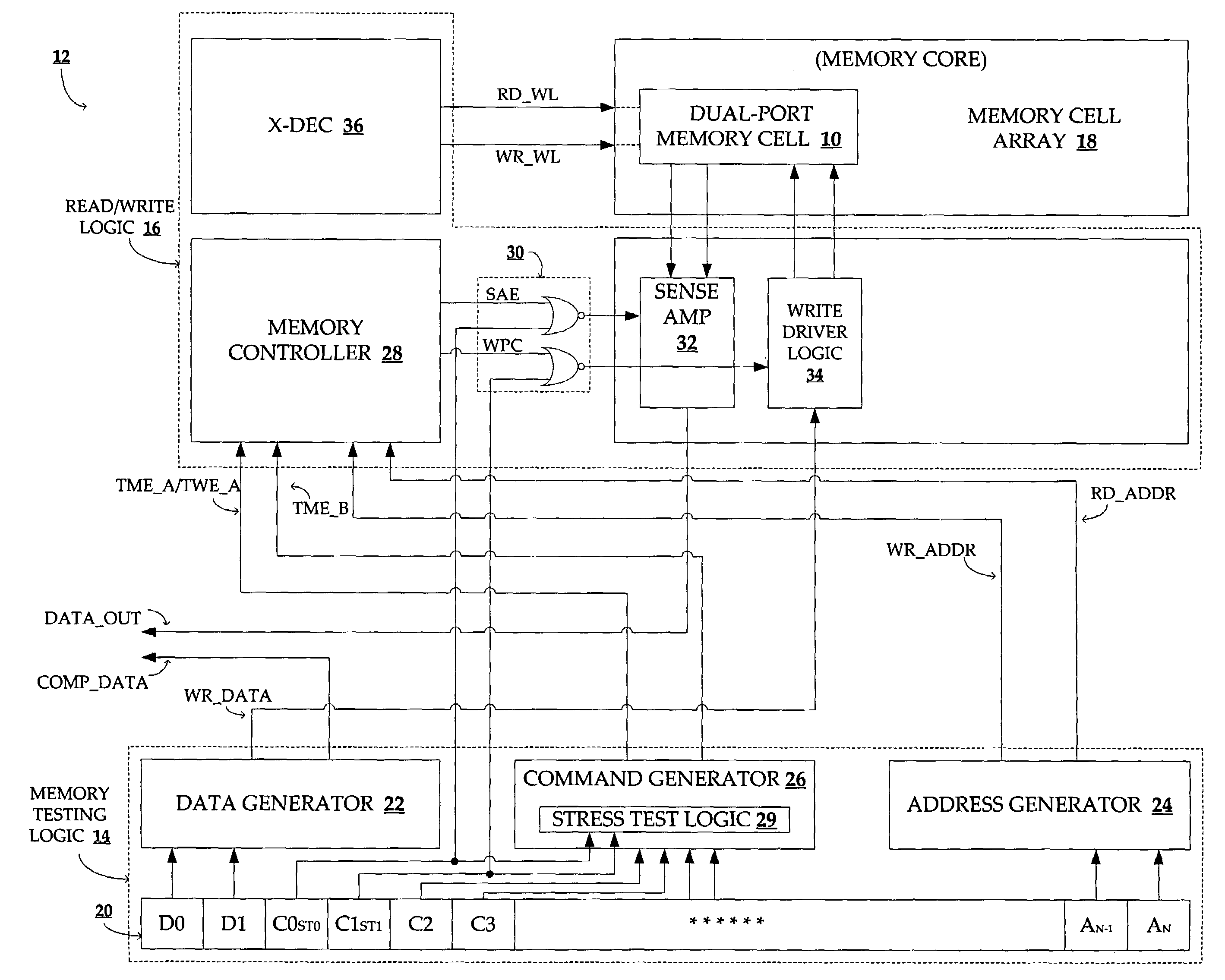

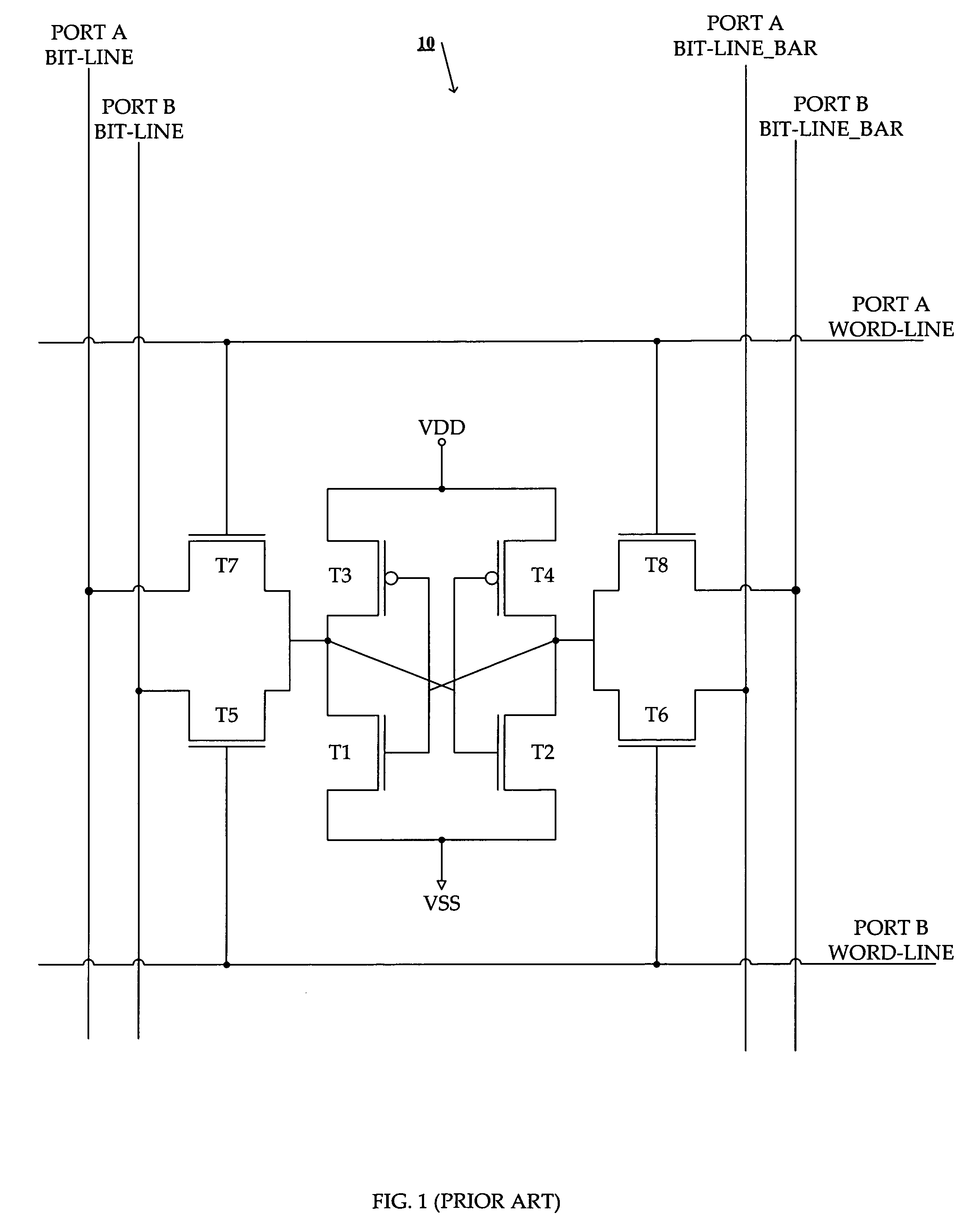

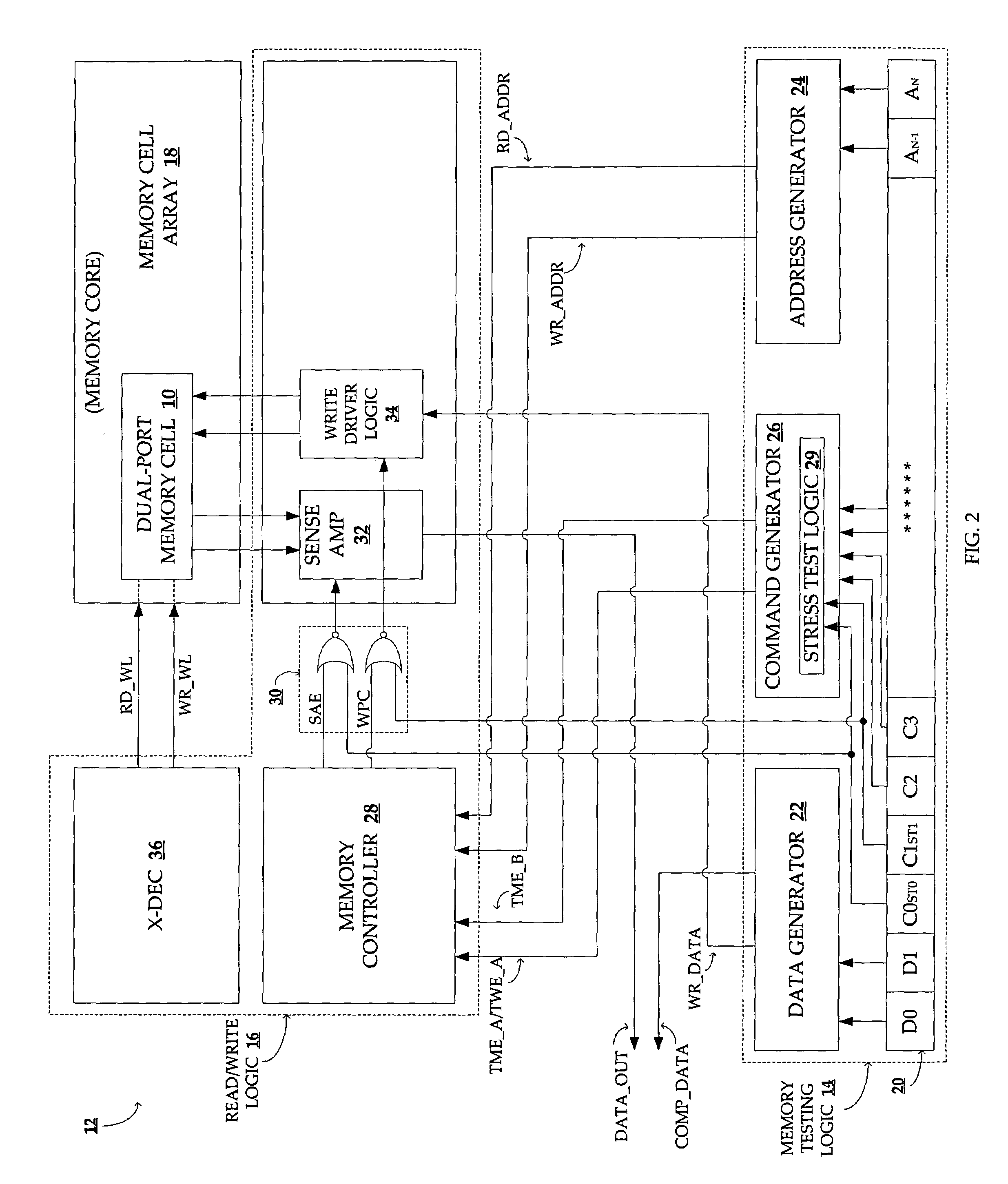

Method and system for testing a dual-port memory at speed in a stressed environment

A method and system for testing a multi-port memory cell are described. According to one embodiment of the invention, a multi-port memory device comprises an array of multi-port memory cells. Accordingly, each multi-port memory cell is connected to one word-line and two bit-lines per read / write port. The memory device includes memory testing logic to perform a first memory access operation (e.g., read / write) at a first port of the multi-port memory cell while the memory cell is in a stressed condition. For example, the first memory access operation occurs while a second memory access operation is emulated on a second port. Moreover, the memory access operations occur at a frequency that is substantially equivalent to a maximum operating frequency of the dual-port memory device.

Owner:SYNOPSYS INC

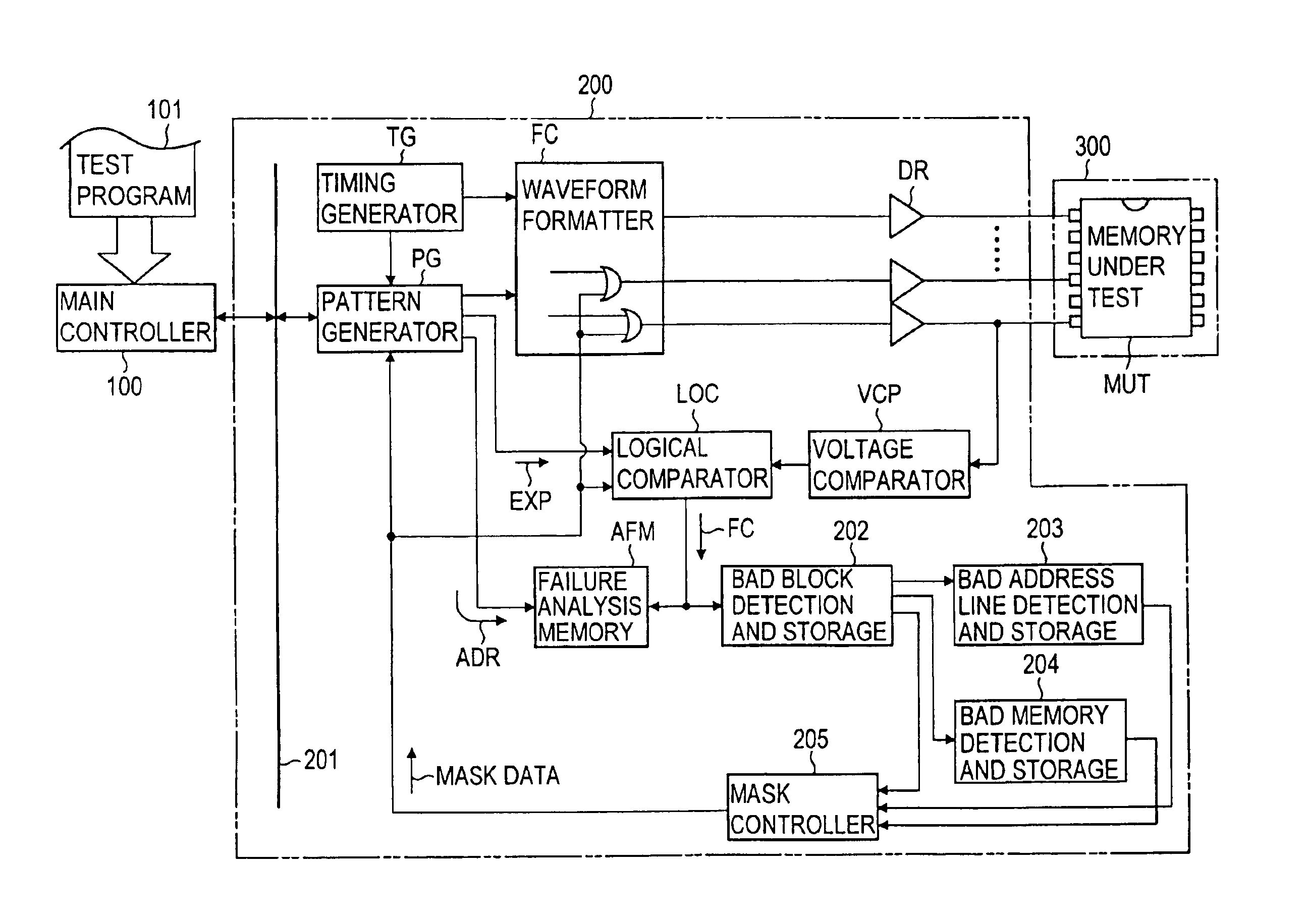

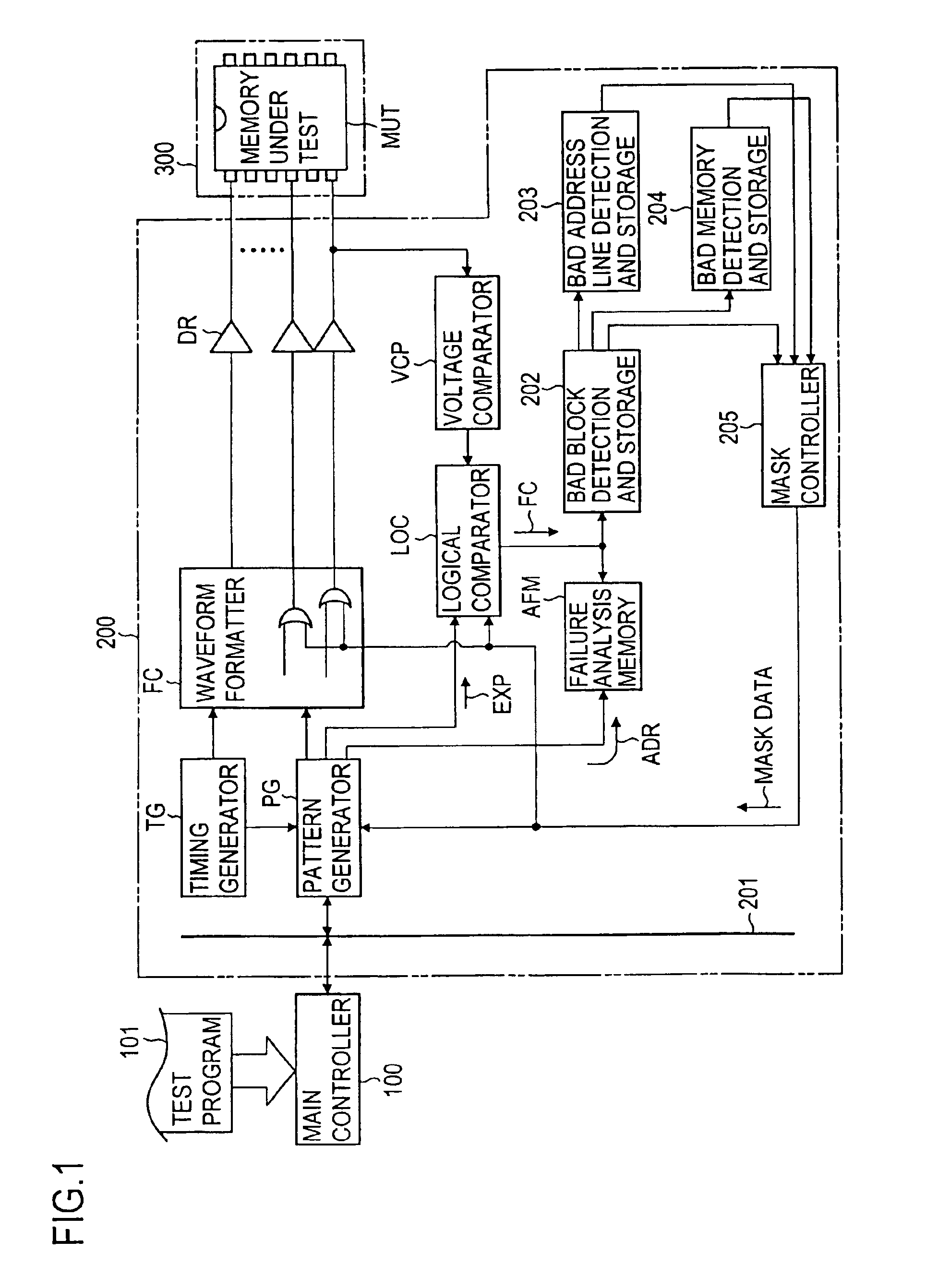

Memory testing method and memory testing apparatus

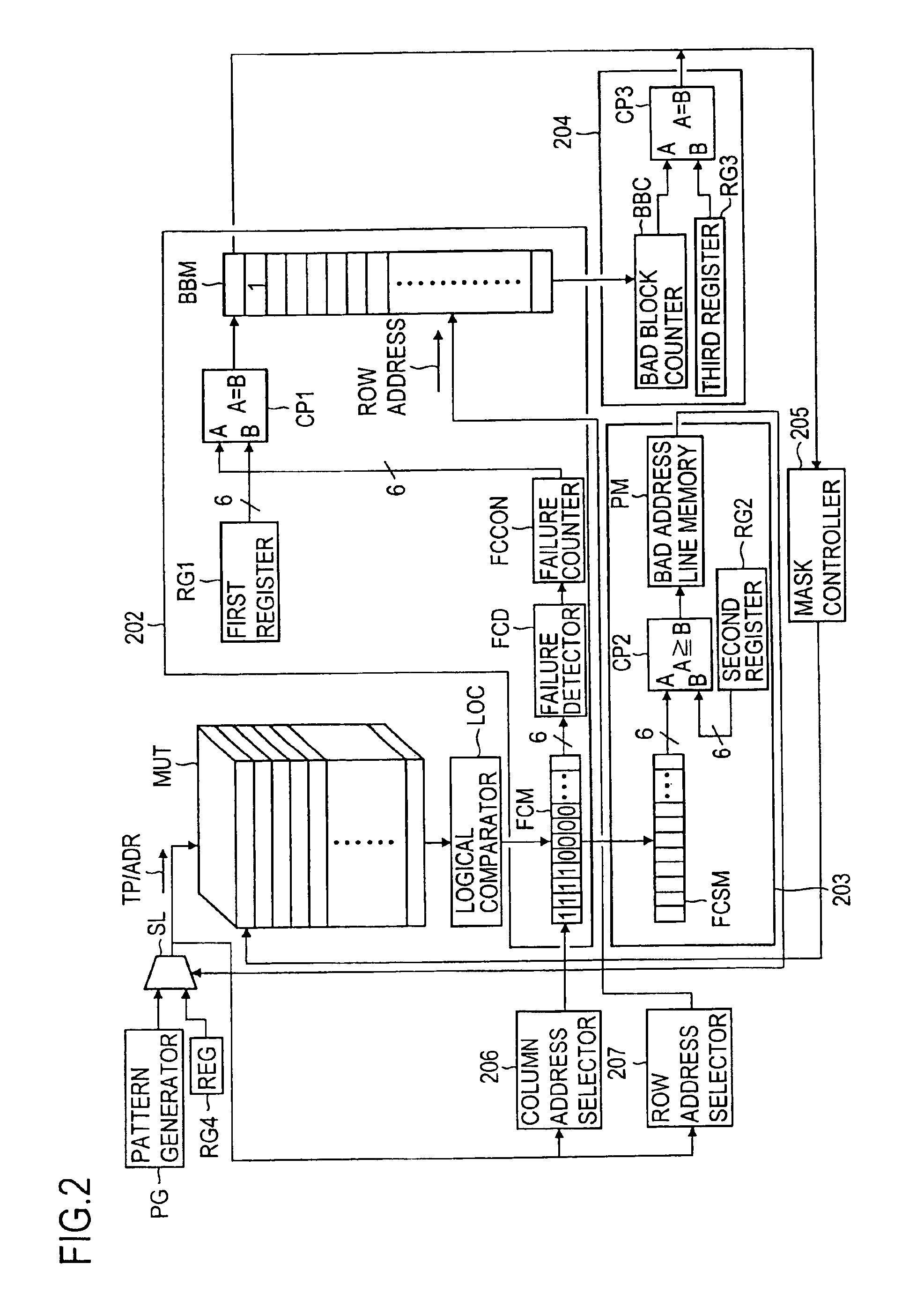

InactiveUS6877118B2Shorten the durationUnnecessary testMemory loss protectionElectronic circuit testingMemory testingStorage cell

A memory testing method and apparatus are provided, which can test in short time a flash memory. In case of testing a flash memory having block function, in a memory testing method and apparatus in which a predetermined logical value is written in memory cells constituting each of blocks of the memory, the written logical value is read out from the memory cells to compare it with an expected value, and a decision that, when the read-out logical value and the expected value do not coincide with each other, such memory cell is a failure memory cell, a decision is rendered that, when the number of failure memory cells in each block reaches a predetermined number, such block is a bad block, and the test of such block is stopped. In addition, a decision is rendered that, when the number of failure memory cells on the same address line reaches a predetermined number, such address line is a bad address line, and after such decision has rendered, the test of memory cells on the bad address line is substantially not effected.

Owner:ADVANTEST CORP

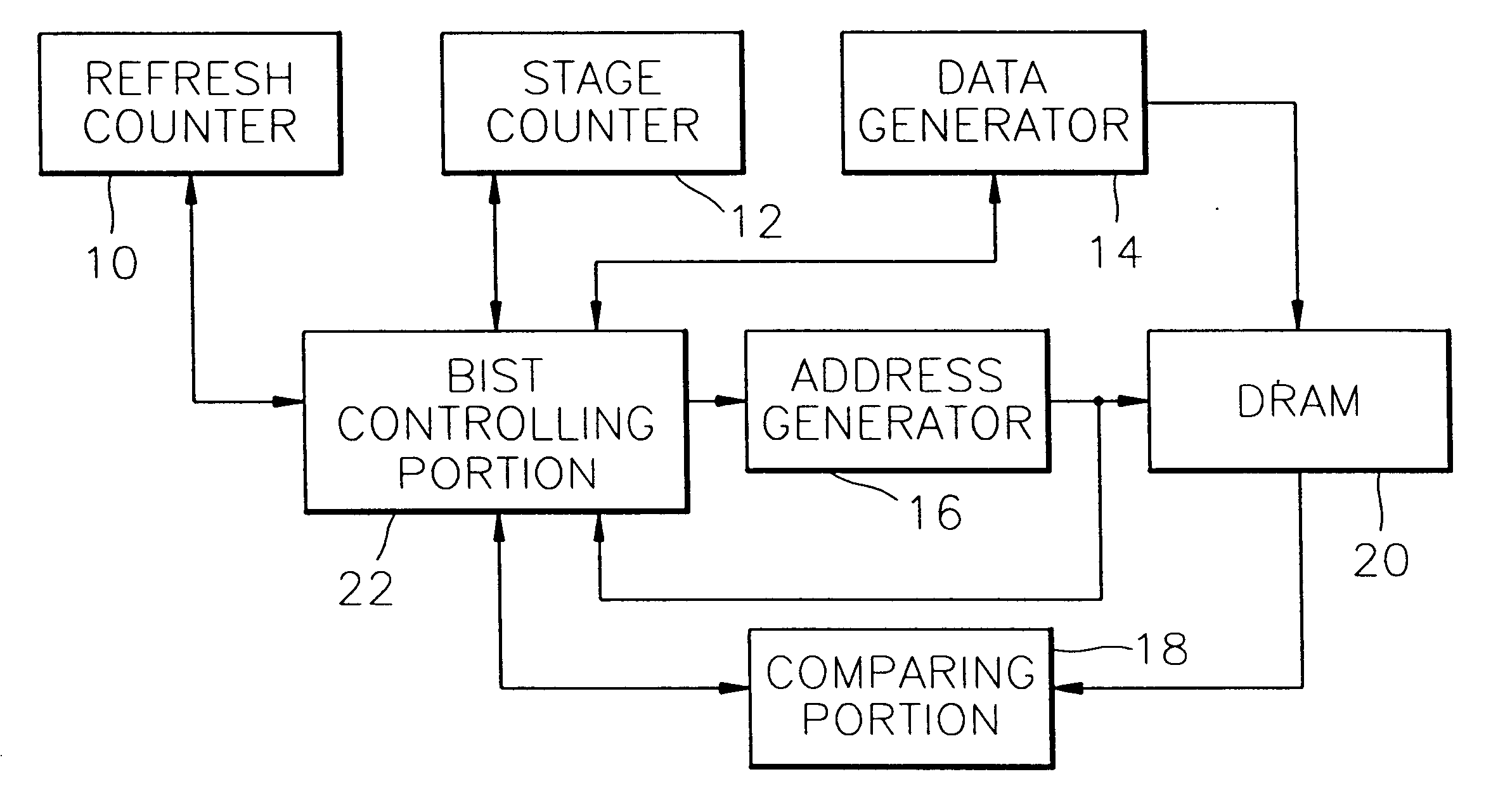

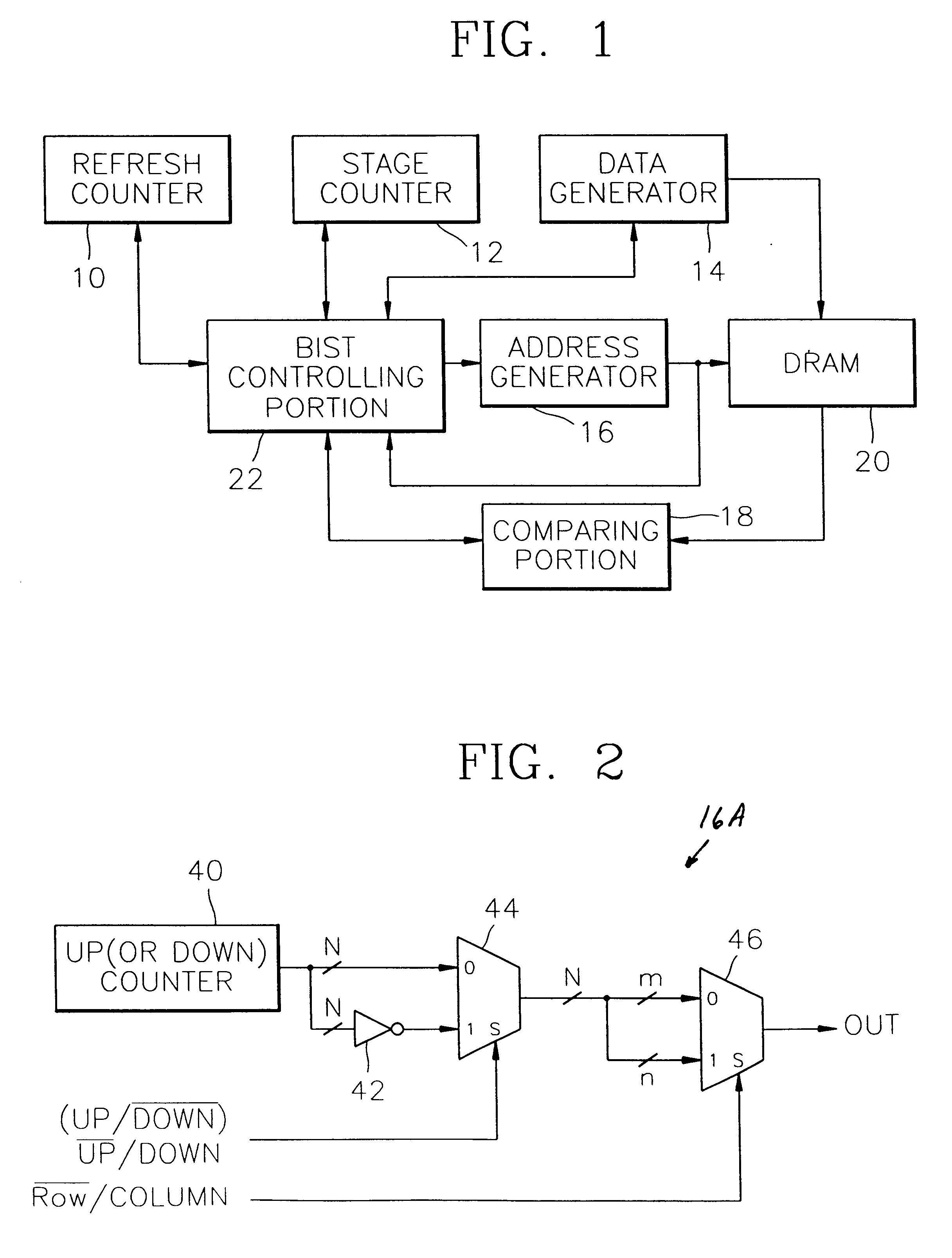

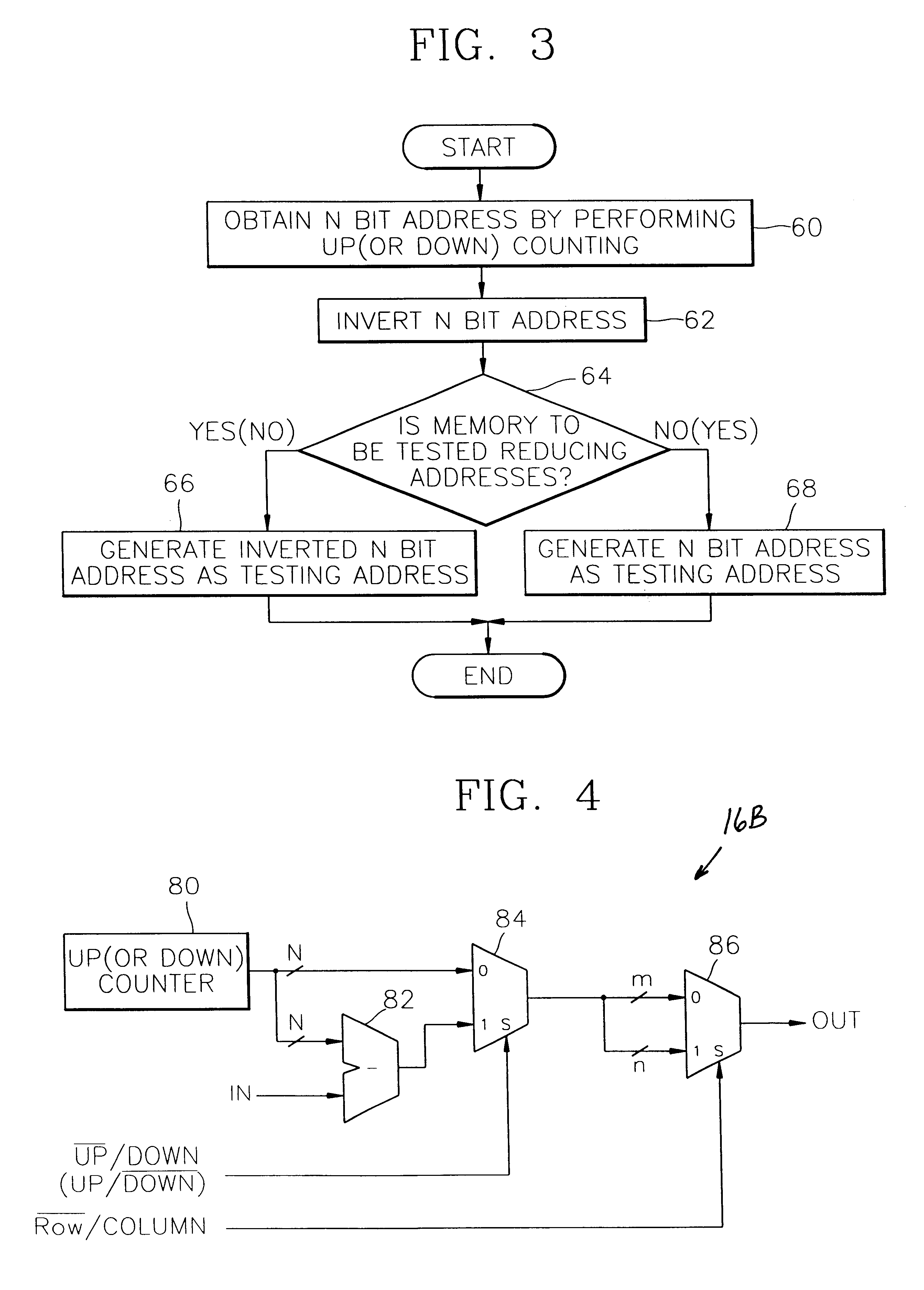

Apparatus and method for generating addresses in a built-in self memory testing circuit

InactiveUS6338154B2Saving in complexitySaving in sizeElectronic circuit testingDigital data processing detailsMemory addressAddress generator

A memory address generating apparatus and method of a dynamic memory testing circuit for generating addresses for testing a dynamic memory which uses all the available addresses of the dynamic memory, which does not use the most significant addresses, and which does not use middle addresses among all the available addresses are provided. The address generator can obtain an up-counted address by up counting the addresses used by the dynamic memory. It can obtain a down-counted address by inverting the N-bit up-counted value, or by subtracting the N-bit up-counted value from the maximum address, or by combining the inverted MSB portion of the N-bit up-counted value with the LSB portion of the N-bit up-counted value subtracted from the LSB portion of the maximum address used in the dynamic memory. The down and up counted addresses are used as addresses for selectively testing the dynamic memory according to a selected testing method.

Owner:SAMSUNG ELECTRONICS CO LTD

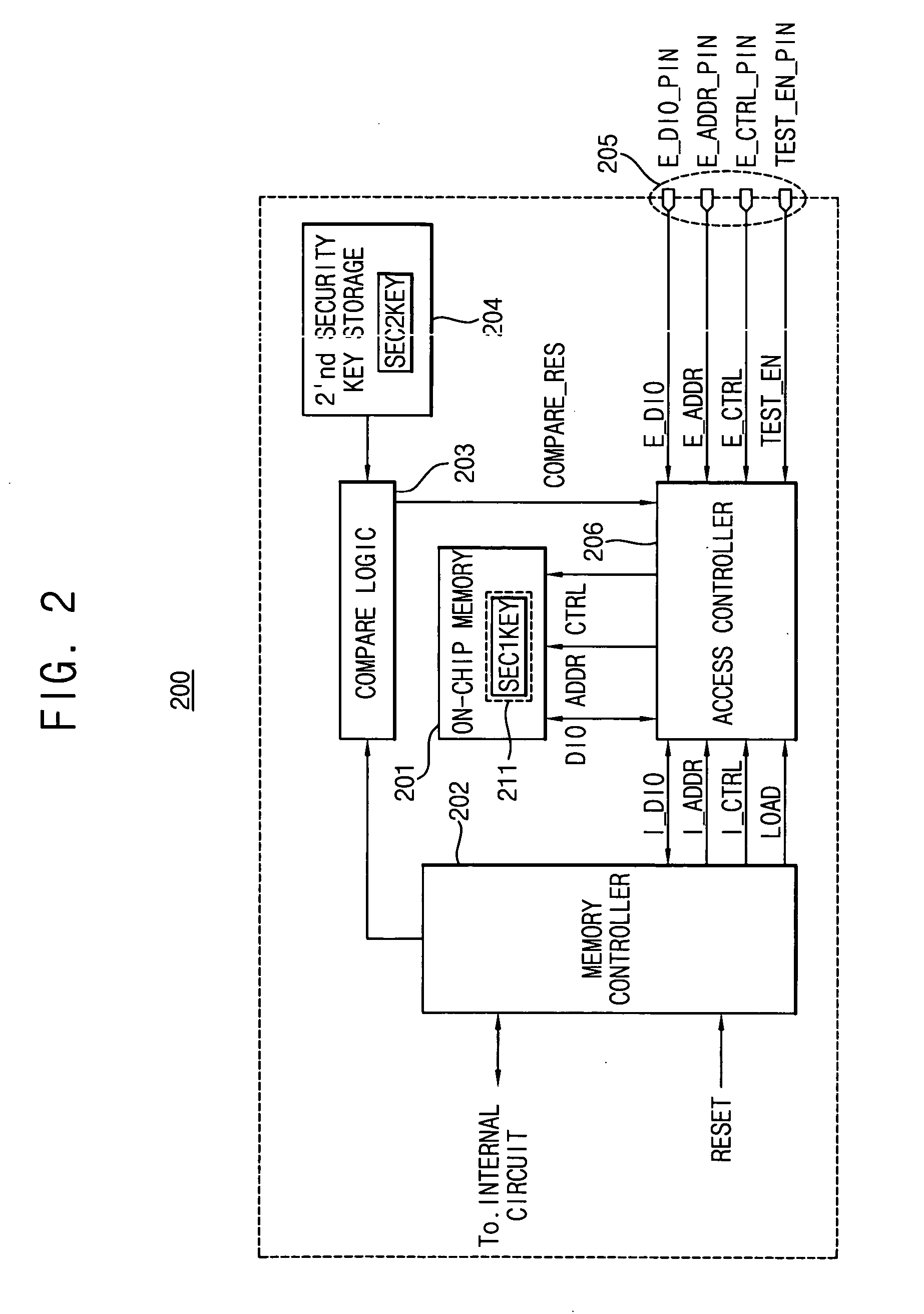

Security circuit and method to secure information in a device

InactiveUS20060184799A1Avoid destructionInternal/peripheral component protectionPackaging under special atmospheric conditionsExternal storageOutput compare

A circuit and method for securing information (e.g., a product serial number or certification key) stored in non-volatile on-chip memory from unauthorized read-out or destruction. External access is prevented by writing a first n-bit security key-word into the memory. A compare circuit compares the first security key-word with a second n-bit security key-word and outputs a comparison signal that either grants or denies external access to the memory based on a predetermined compare condition. The values of each of the first and second key-word and the comparison algorithm (predetermined compare condition) may be selected to avoid any interference with external memory-testing. The predetermined compare condition may be a pre-selected one of a match and a mismatch between the first security key word and the second security key word. At least one bit of the first or second security key word may be a fuse programmable bit.

Owner:SAMSUNG ELECTRONICS CO LTD

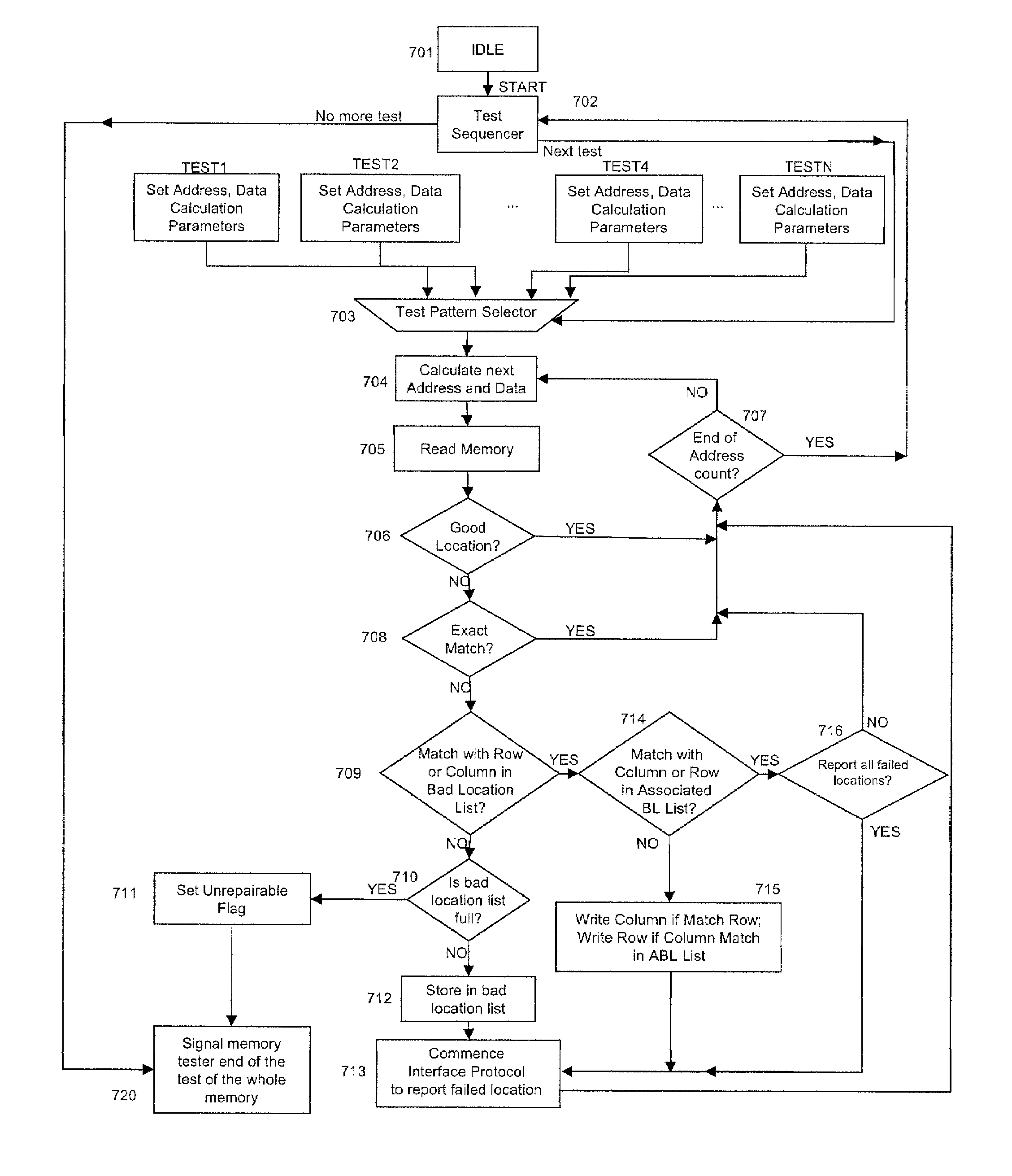

Method and system for memory testing and test data reporting during memory testing

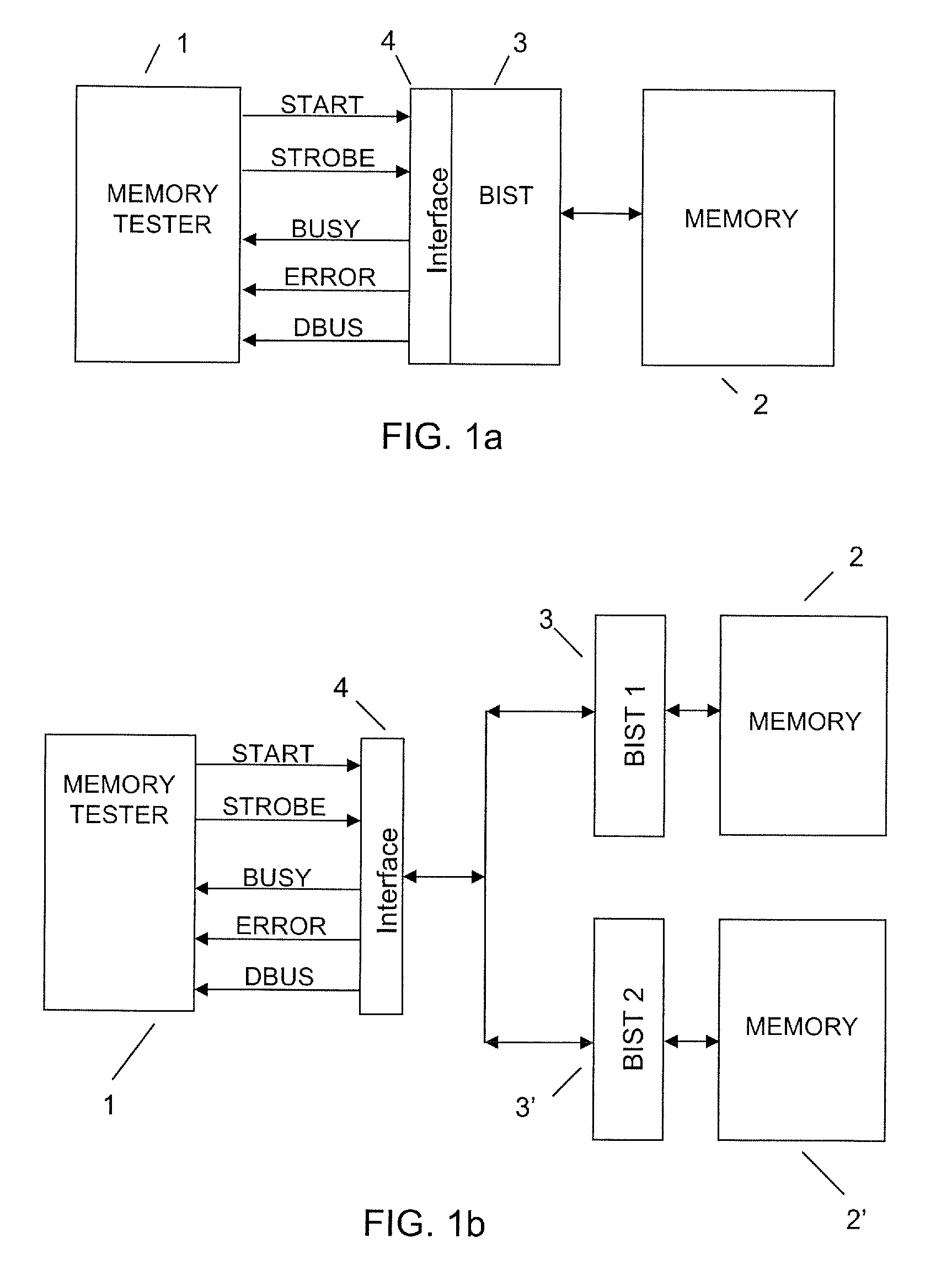

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

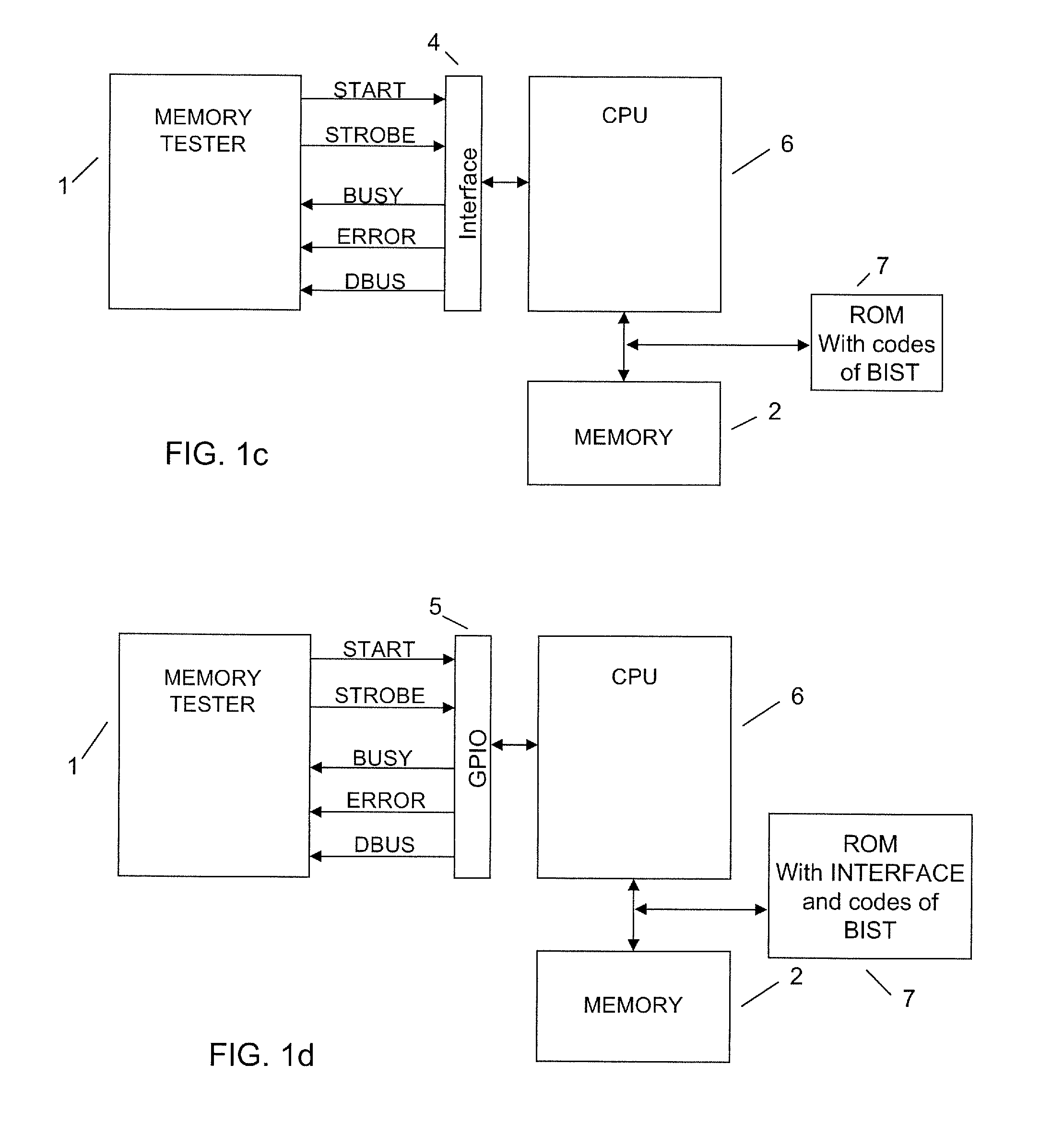

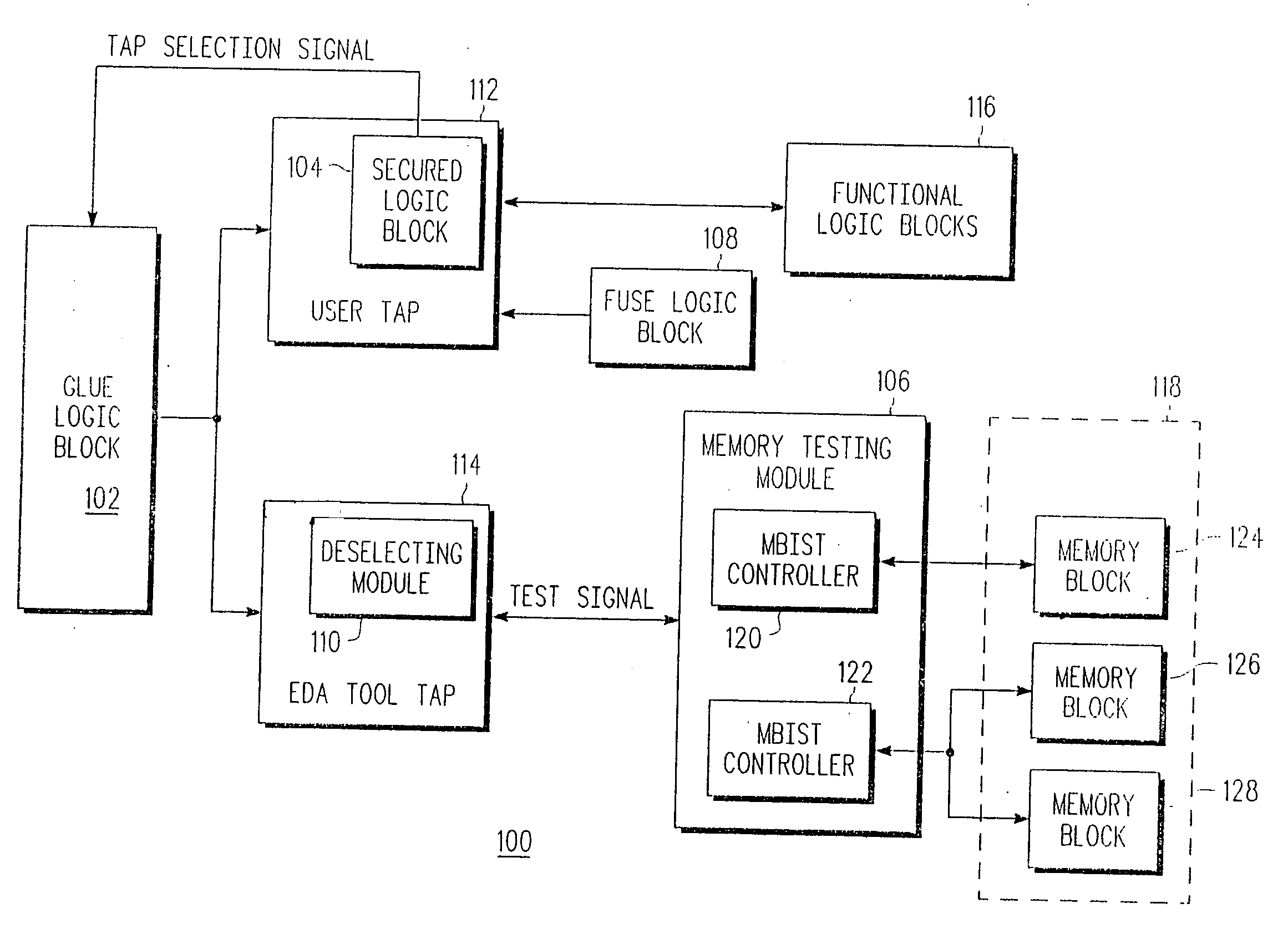

System and method for testing memory blocks in an soc design

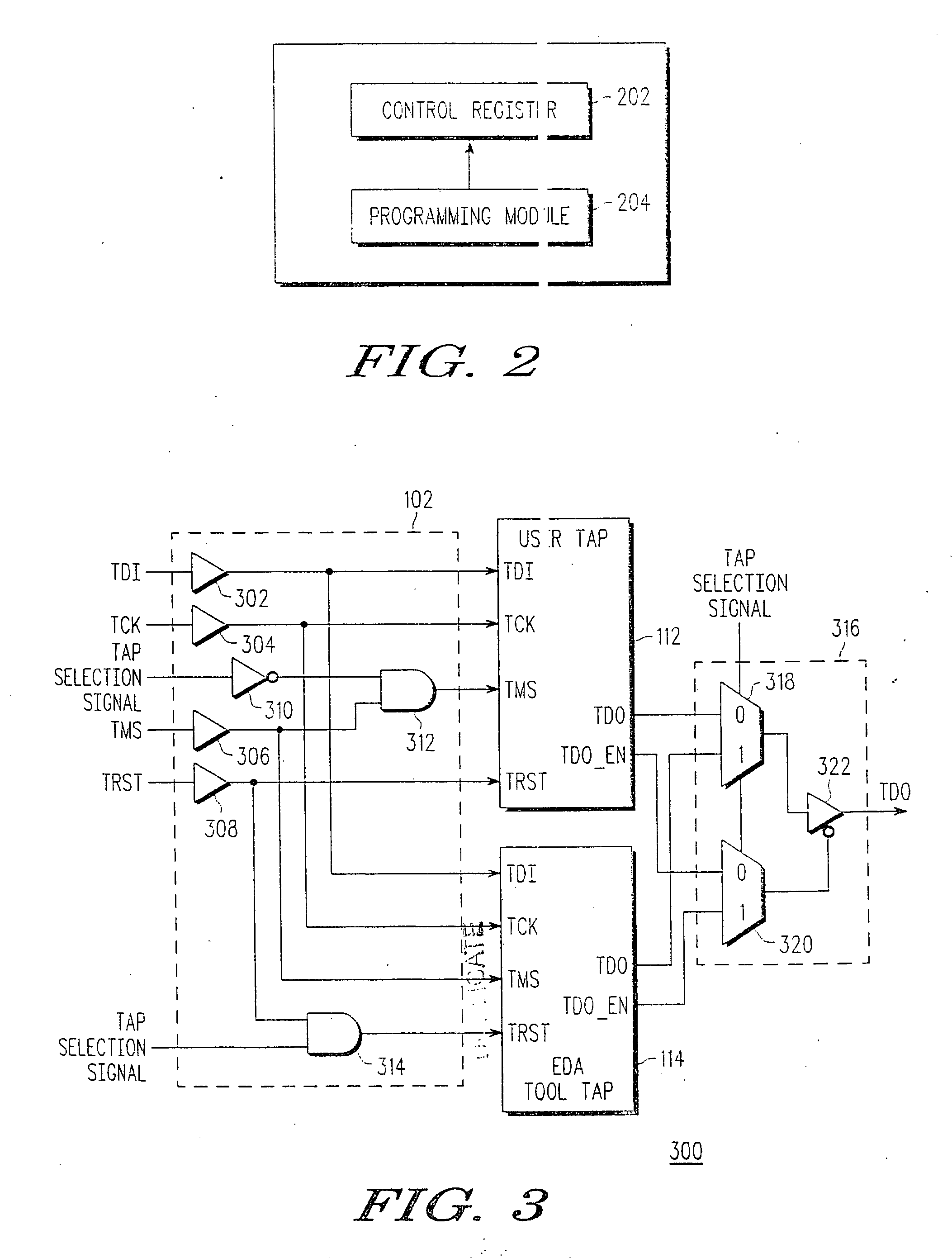

A system and method for testing a plurality of memory blocks in a System on Chip (SOC) design uses two Test Access Ports (TAPs), a user TAP and an EDA tool TAP, to provide instructions and test data to the SOC. The system includes a glue logic block, a secured logic block and a memory testing module. The glue logic block selects the user TAP at the outset of the testing phase. The secured logic block is coupled with the user TAP and generates a TAP selection signal, which controls the selection of the EDA tool TAP. The memory testing module is used to carry out the process of testing the memory blocks when the EDA tool TAP is selected.

Owner:NXP USA INC

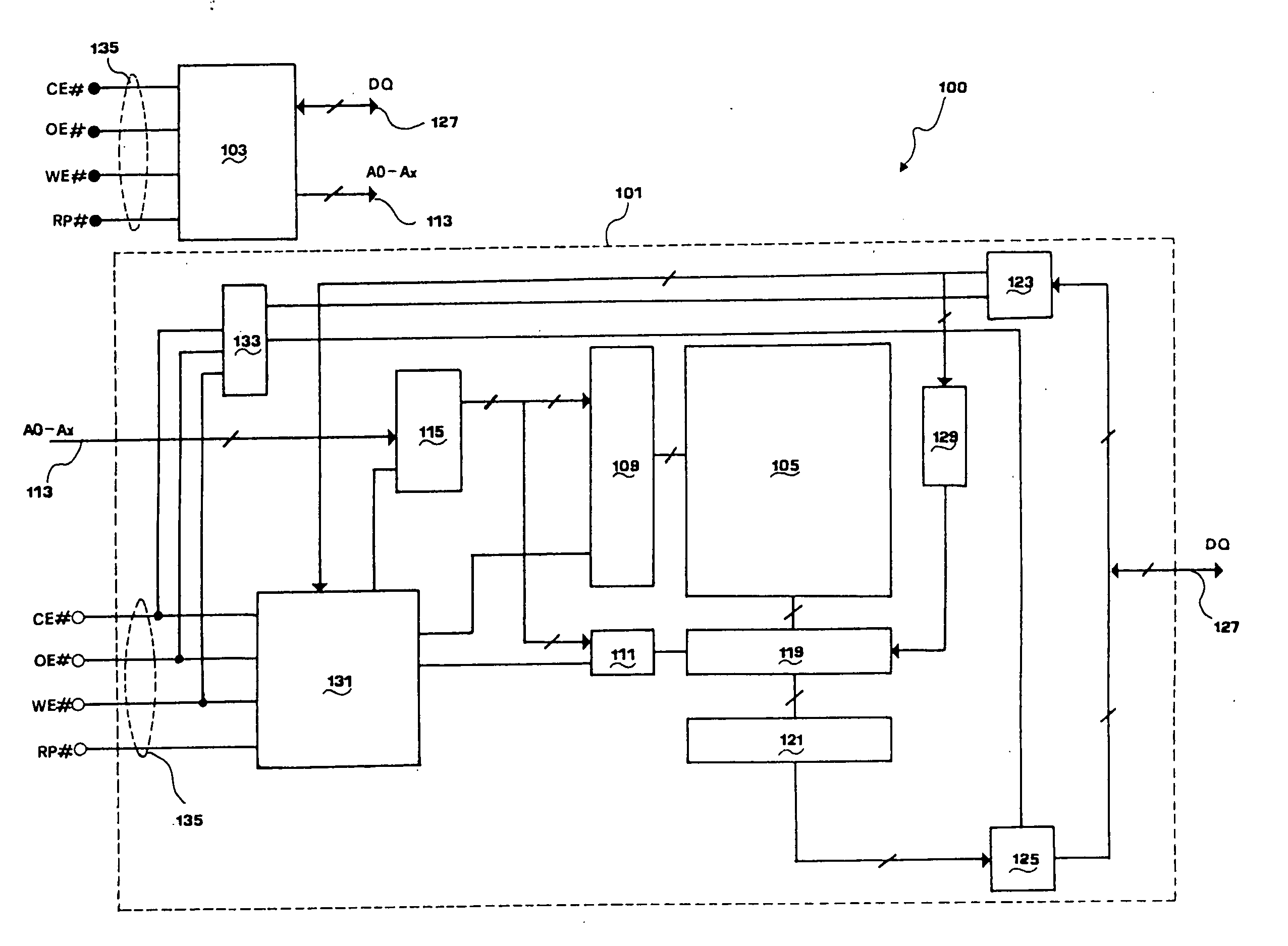

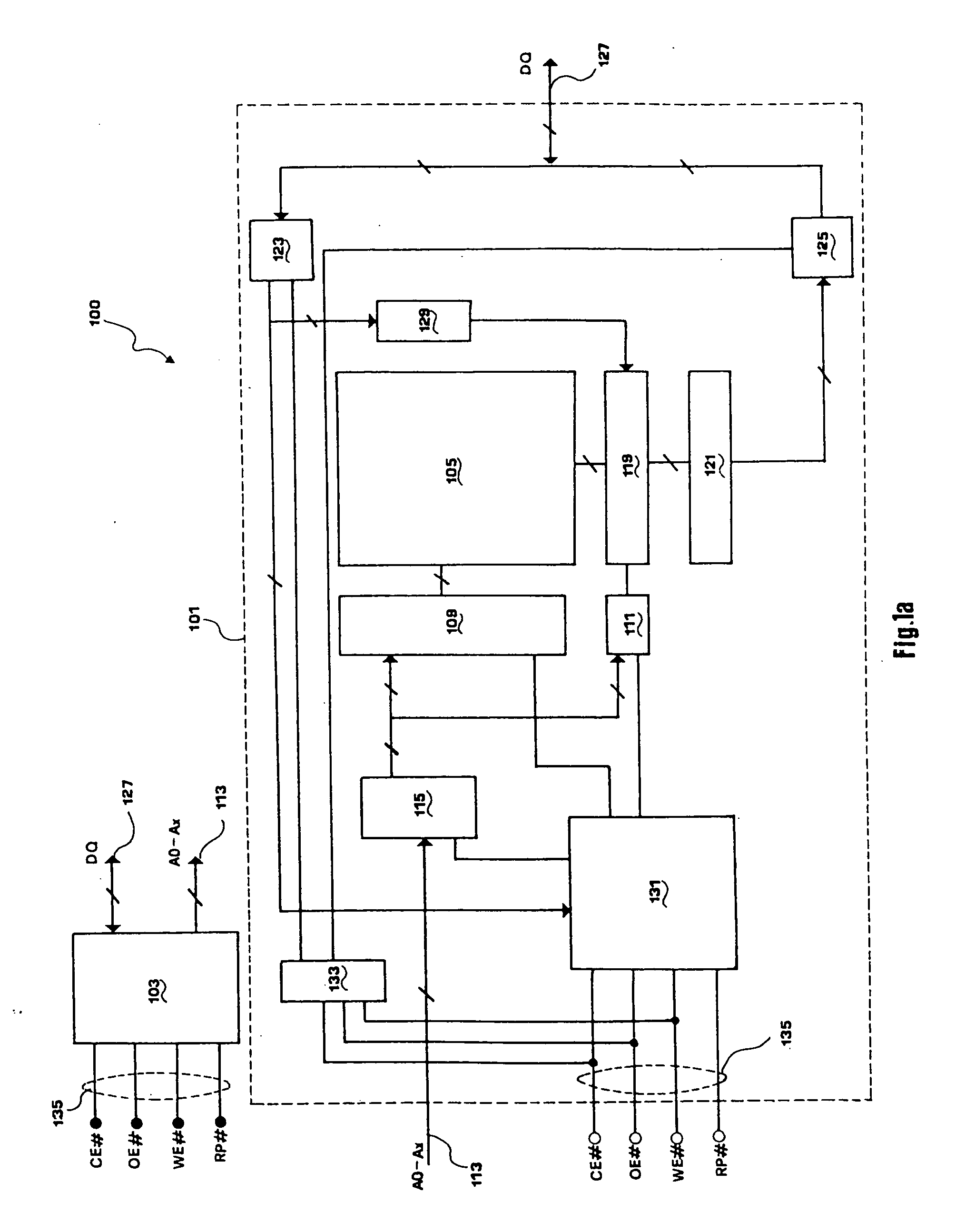

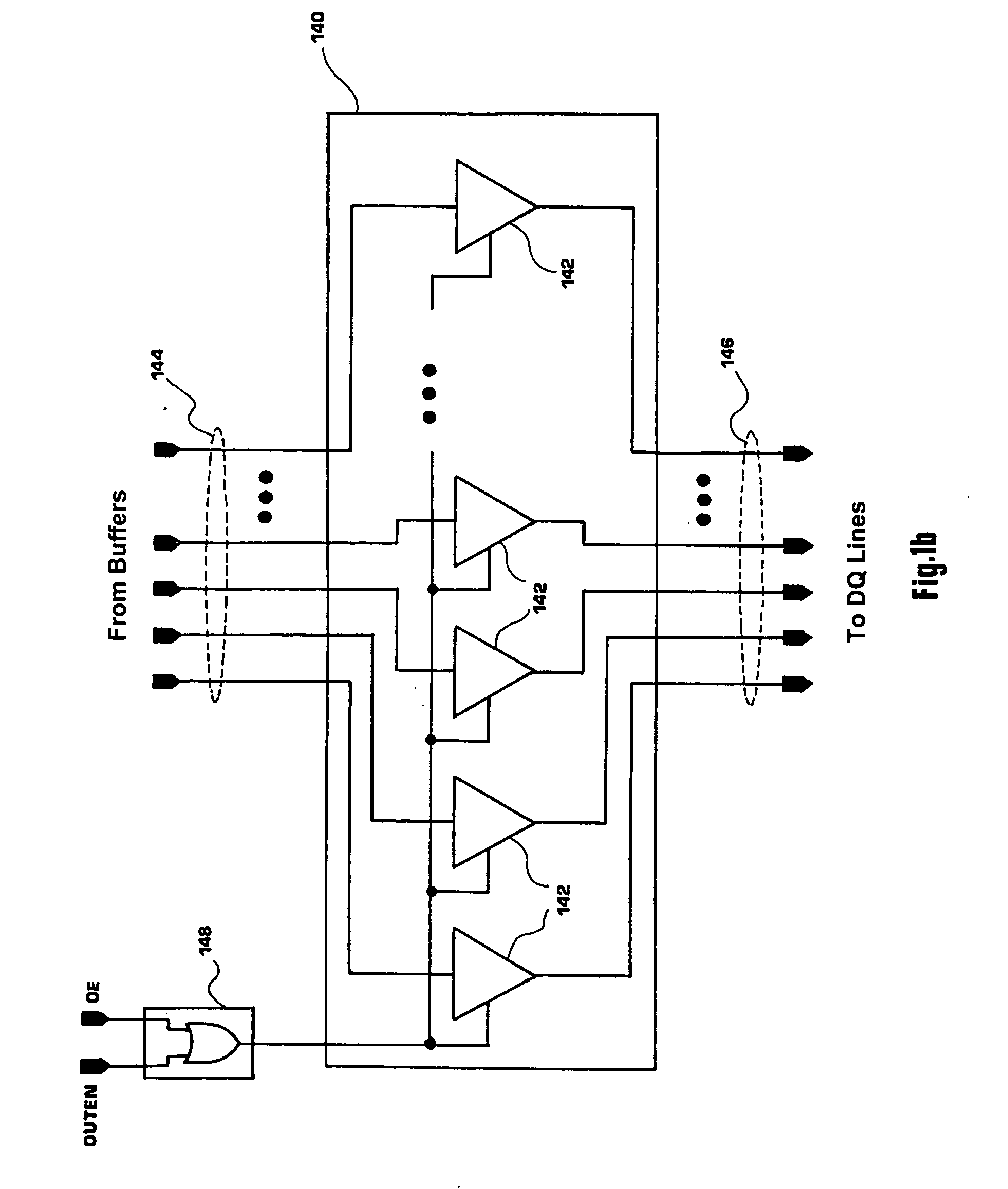

Circuit and method for test and repair

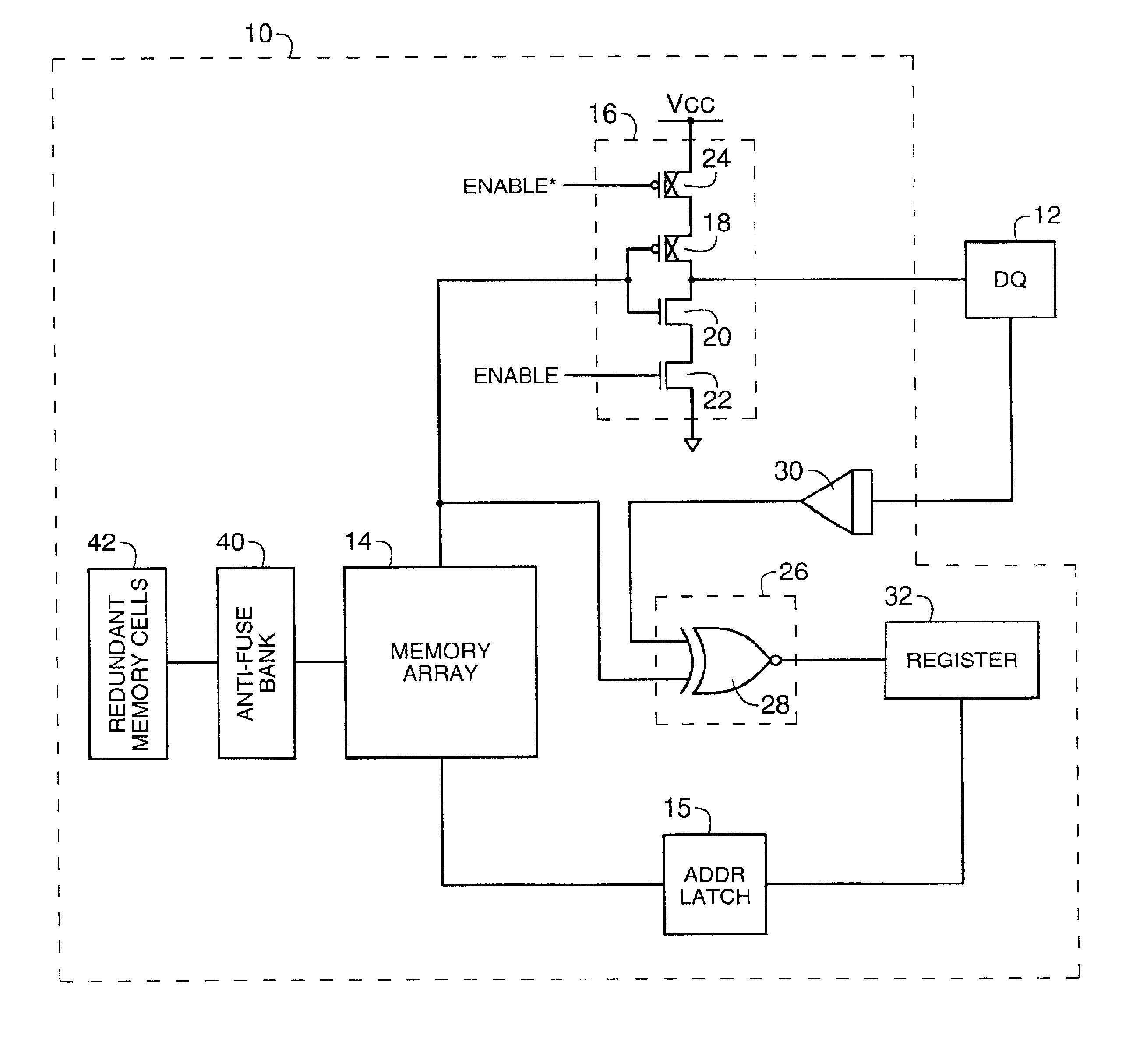

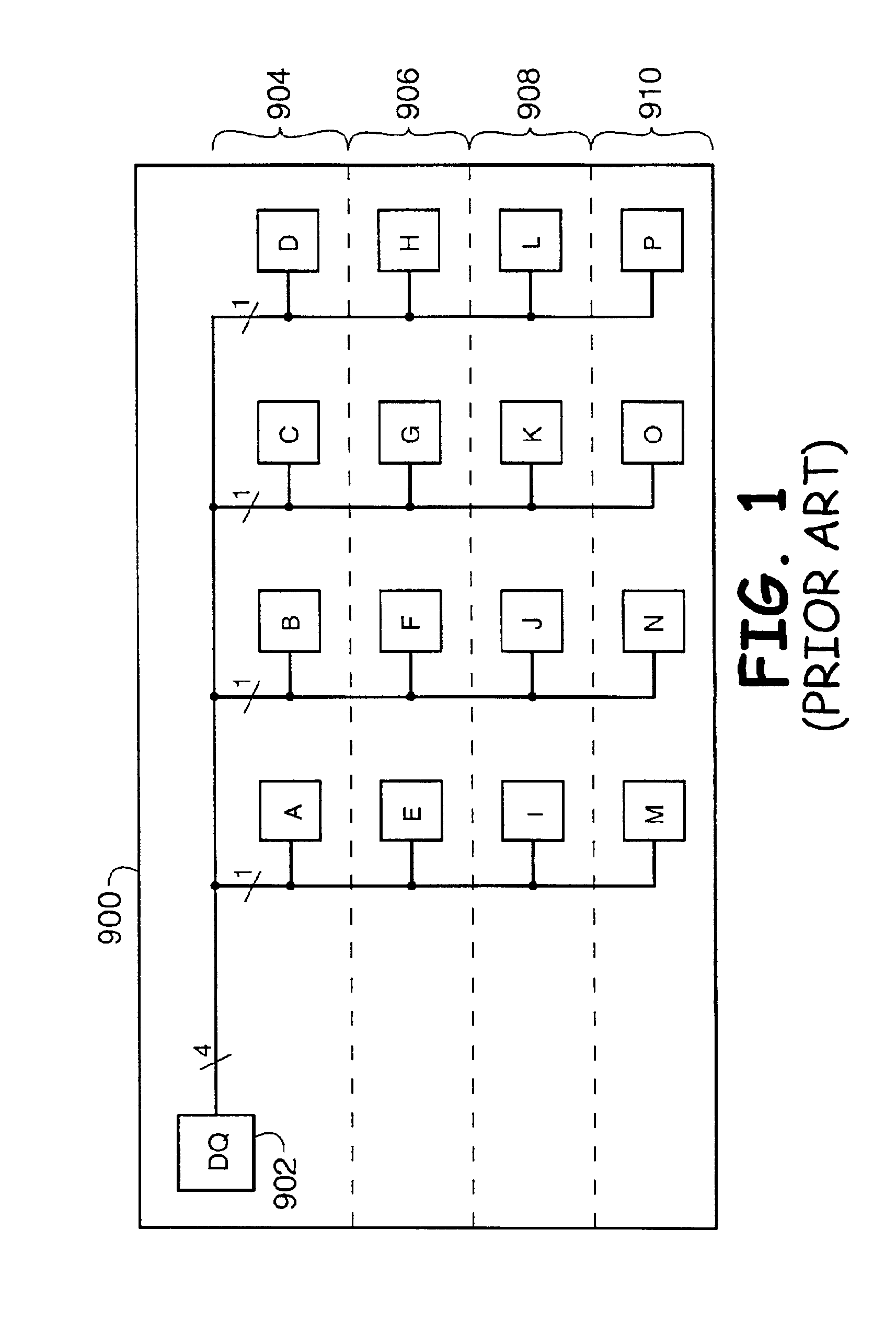

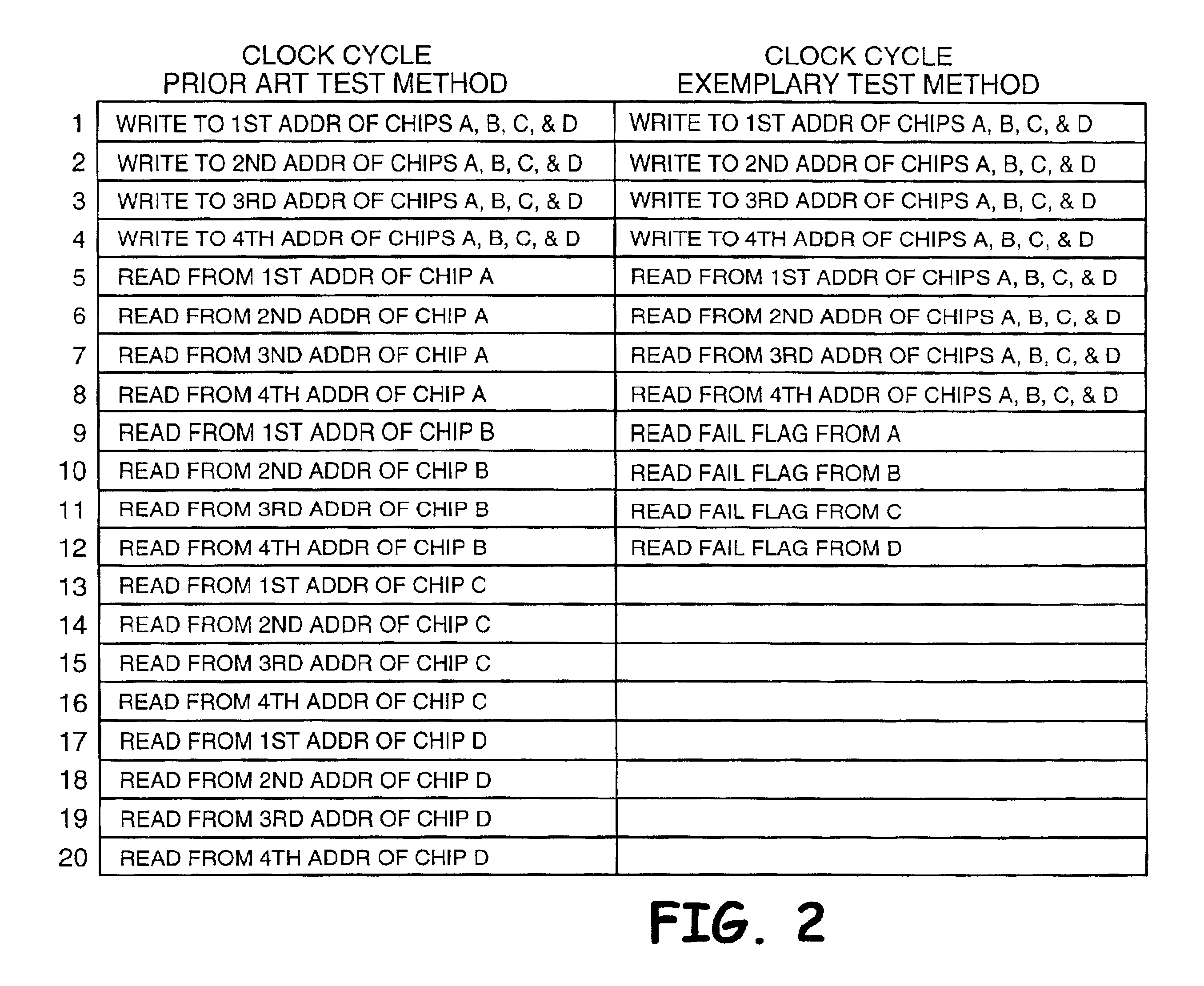

A preferred exemplary embodiment of the current invention concerns a memory testing process, wherein circuitry is provided on a chip to allow on-chip comparison of stored data and expected data. The on-chip comparison allows the tester to transmit in a parallel manner the expected data to a plurality of chips. In a preferred embodiment, at most one address—and only the column address—corresponding to a failed memory cell is stored in an on-chip register at one time, with each earlier failed addresses being cleared from the register in favor of a subsequent failed address. Another bit—the “fail flag” bit—is stored in the register to indicate that a failure has occurred. If the fail flag is present in a chip, that chip is repaired by electrically associating the column address with redundant memory cells rather than the original memory cells. Subsequently, the chip's register may be cleared and testing may continue. It is preferred that the register and related logic circuitry be configured to avoid storing an address that is already associated with a redundant cell, even though that redundant cell has failed.

Owner:MICRON TECH INC

Programmable built in self test of memory

The pBIST solution to memory testing is a balanced hardware-software oriented solution. pBIST hardware provides access to all memories and other such logic (e.g. register files) in pipelined logic allowing back-to-back accesses. The approach then gives the user access to this logic through CPU-like logic in which the programmer can code any algorithm to target any memory testing technique required. Because hardware inside the chip is used at-speed, the full device speed capabilities are available. CPU-like hardware can be programmed and algorithms can be developed and executed after tape-out and while testing on devices in chip form is in process.

Owner:TEXAS INSTR INC

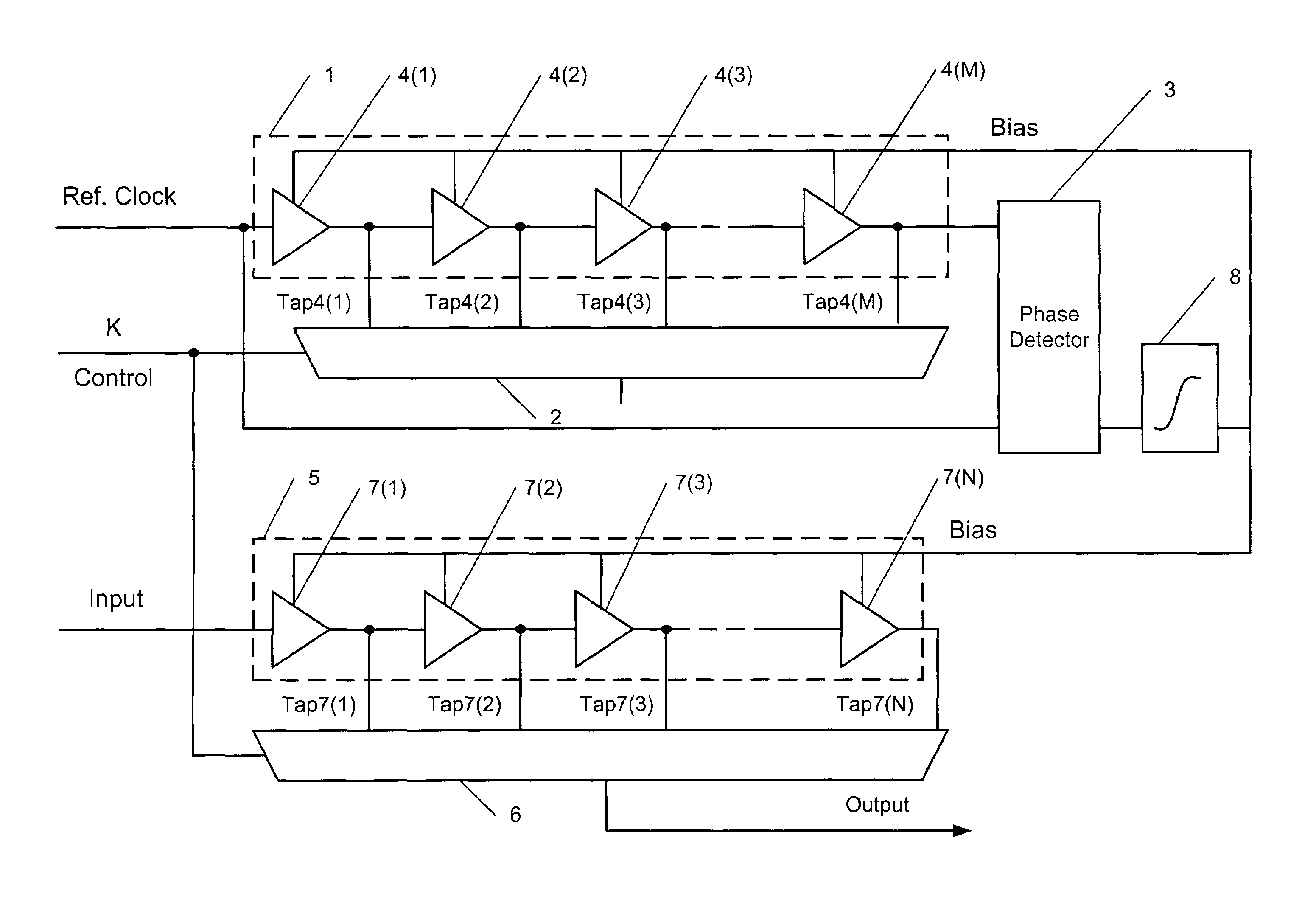

Programmable self-calibrating vernier and method

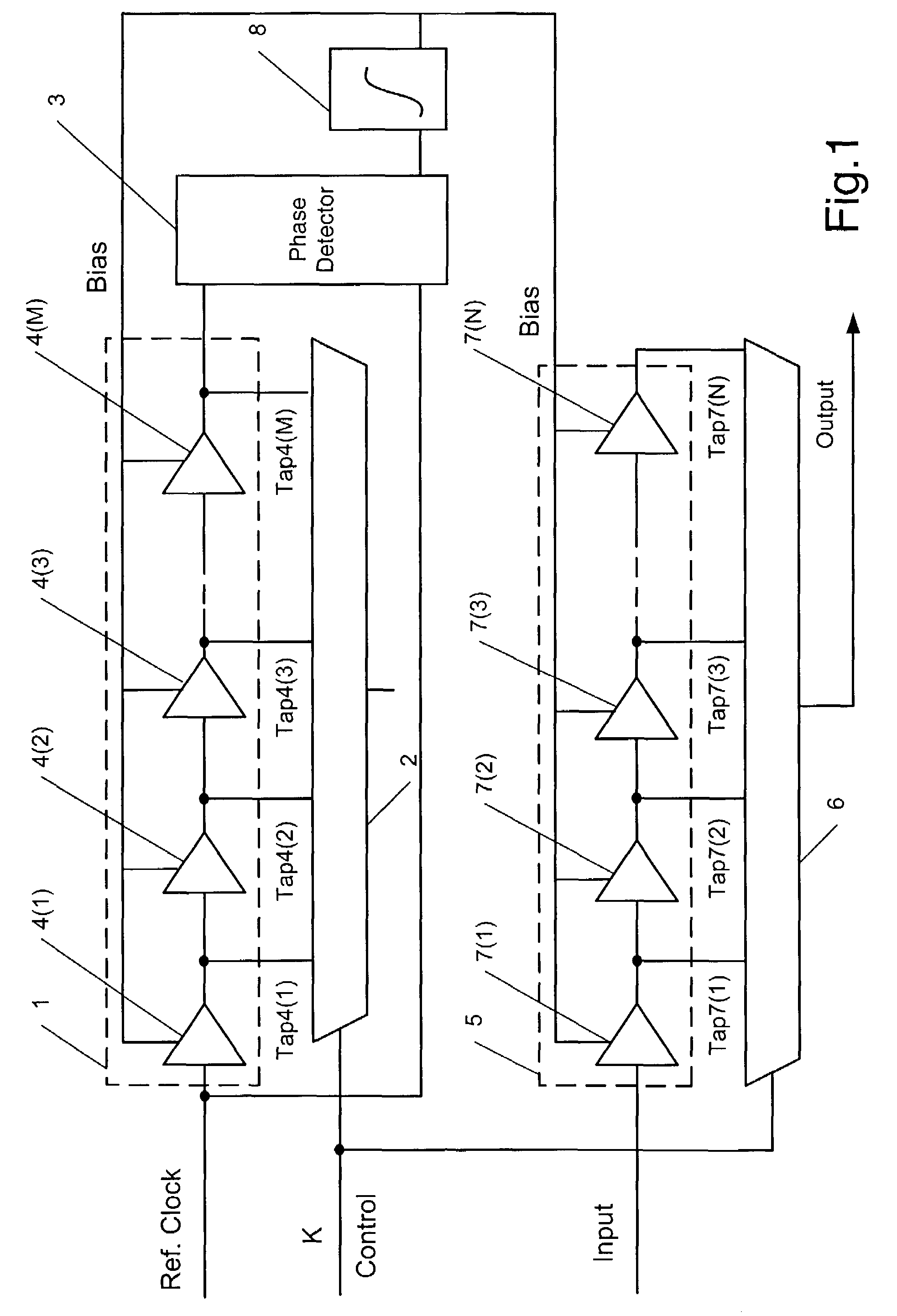

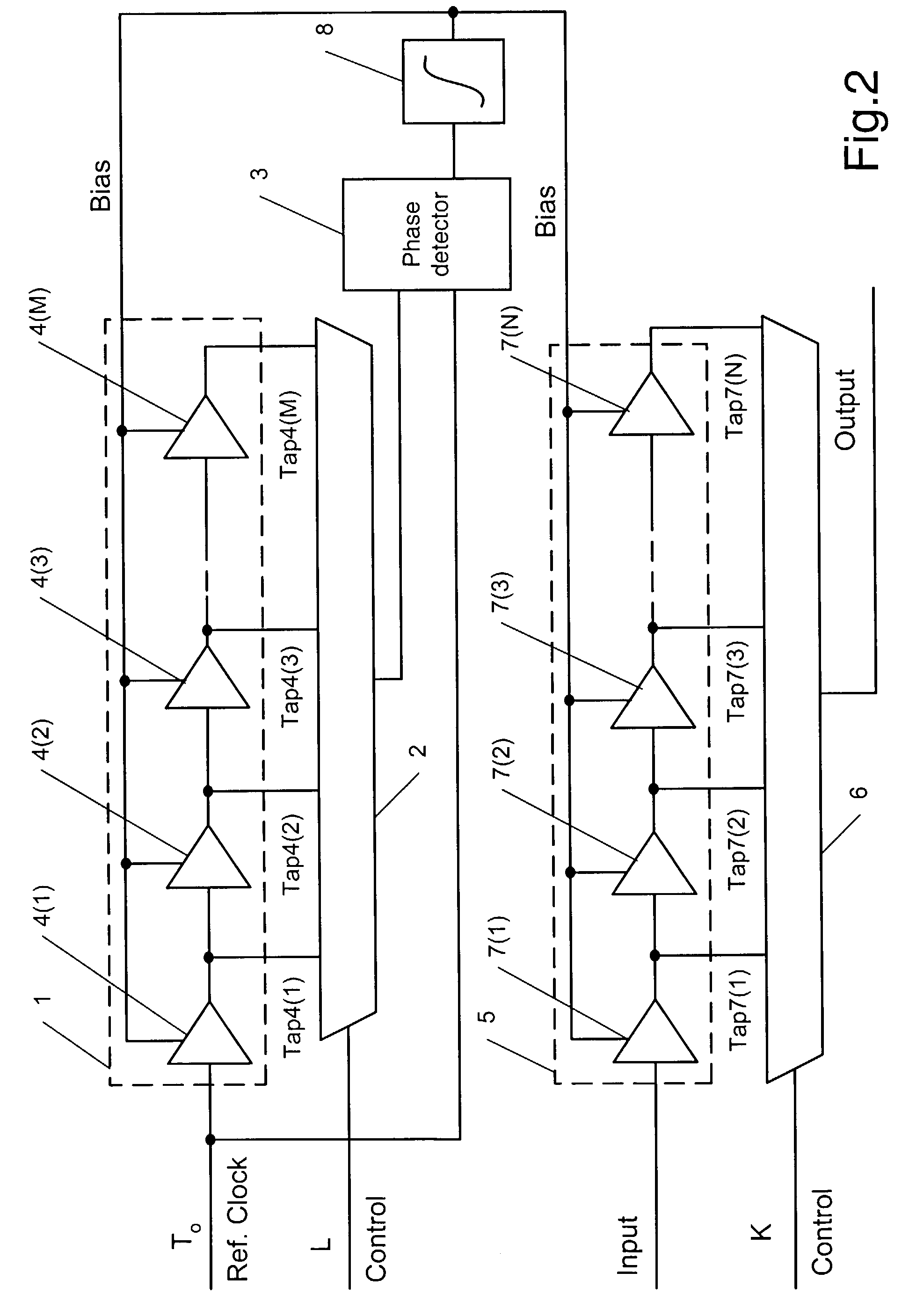

The present invention relates in general to the field of generation of precise electrical signals, in particular, to a technique for providing accurate delays of signals using a controllable delay line, and is applicable to the areas of high speed communication and memory testing equipment. According to the present invention, an auxiliary reference channel having a delay line which is identical to the main delay line is incorporated into vernier silicon die to allow automatic adjustment of the delay in the main delay line using a reference periodical signal applied to the auxiliary delay line.

Owner:TOP BOX ASSETS L L C

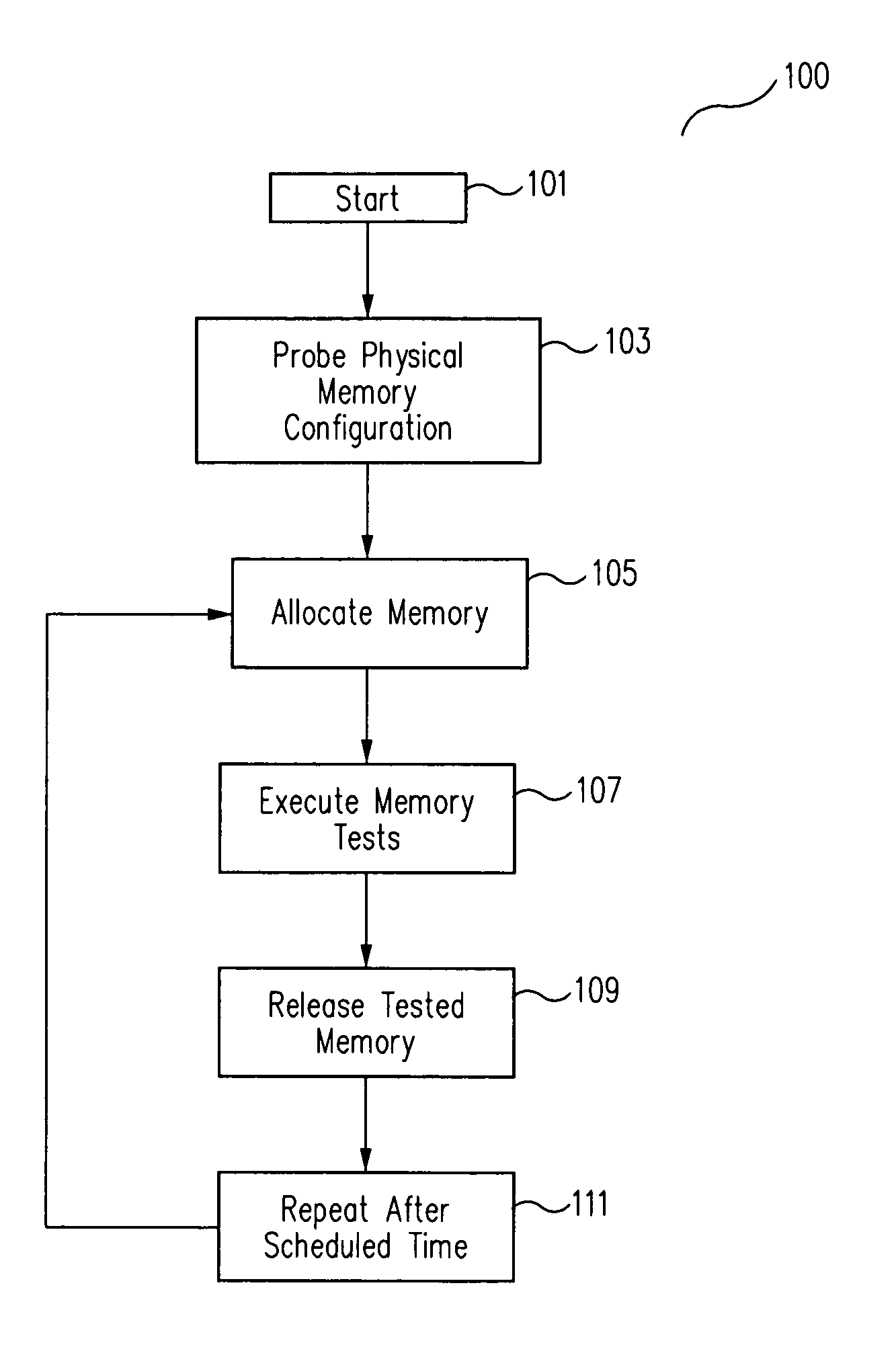

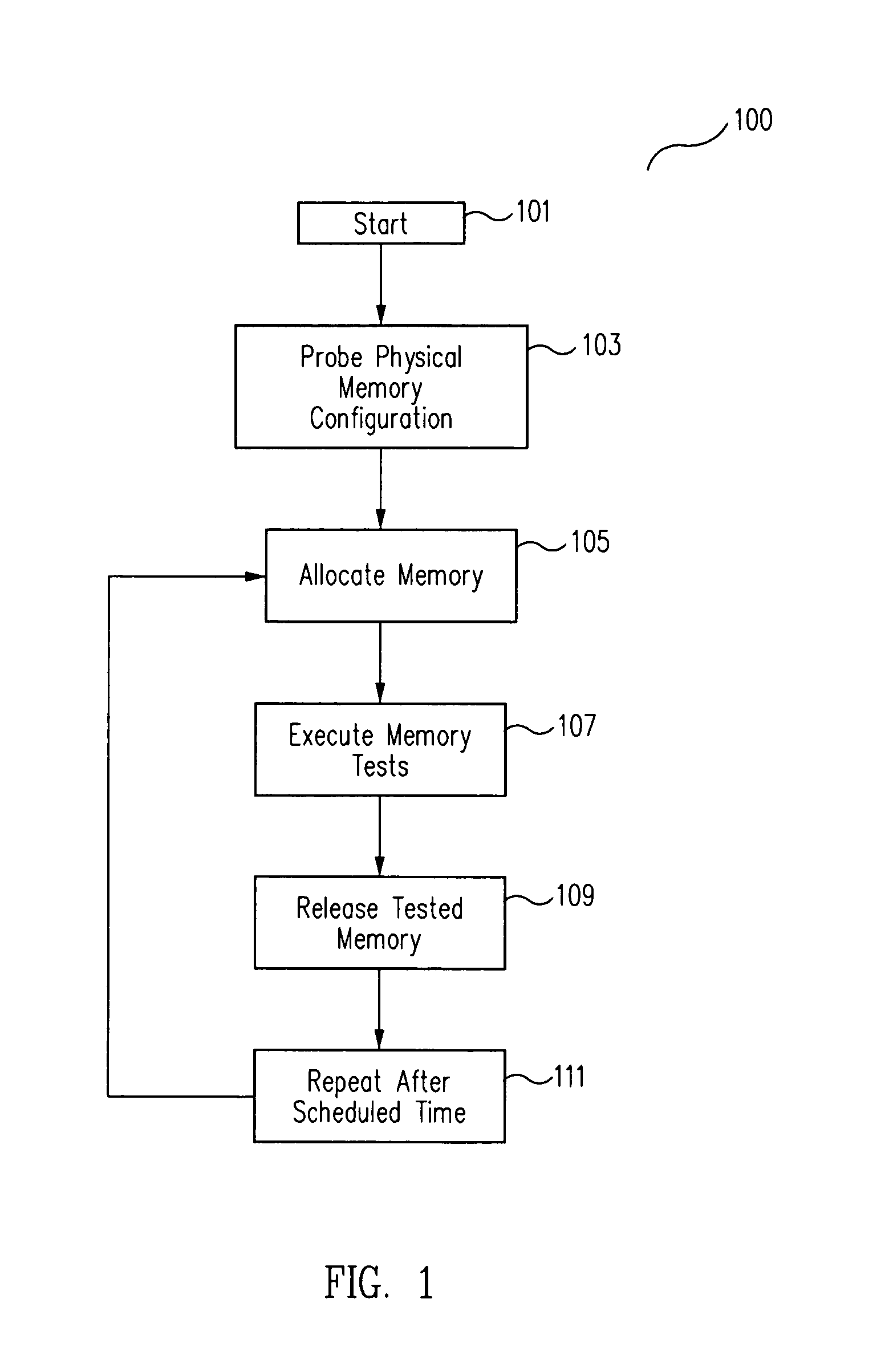

Method and template for physical-memory allocation for implementing an in-system memory test

An in-system memory testing method includes transparently selecting and “stealing” a portion of memory from the memory system for running memory tests, then running one or more of the numerous known memory system tests on the selected portion of memory, and then inserting the selected, and now tested, portion of memory back into the system for normal application use. The disclosed in-system memory testing method is capable of testing system memory in both offline and online environments, without imposing any additional hardware requirements or significantly affecting system performance. The disclosed in-system memory testing method is compatible with any conventional prior art functional test algorithm for in-system memory testing and can be performed under real life system environmental conditions. Therefore, the disclosed in-system memory testing method complements other test techniques like BIST / POST that are conventionally used only at the time of system boot up.

Owner:ORACLE INT CORP

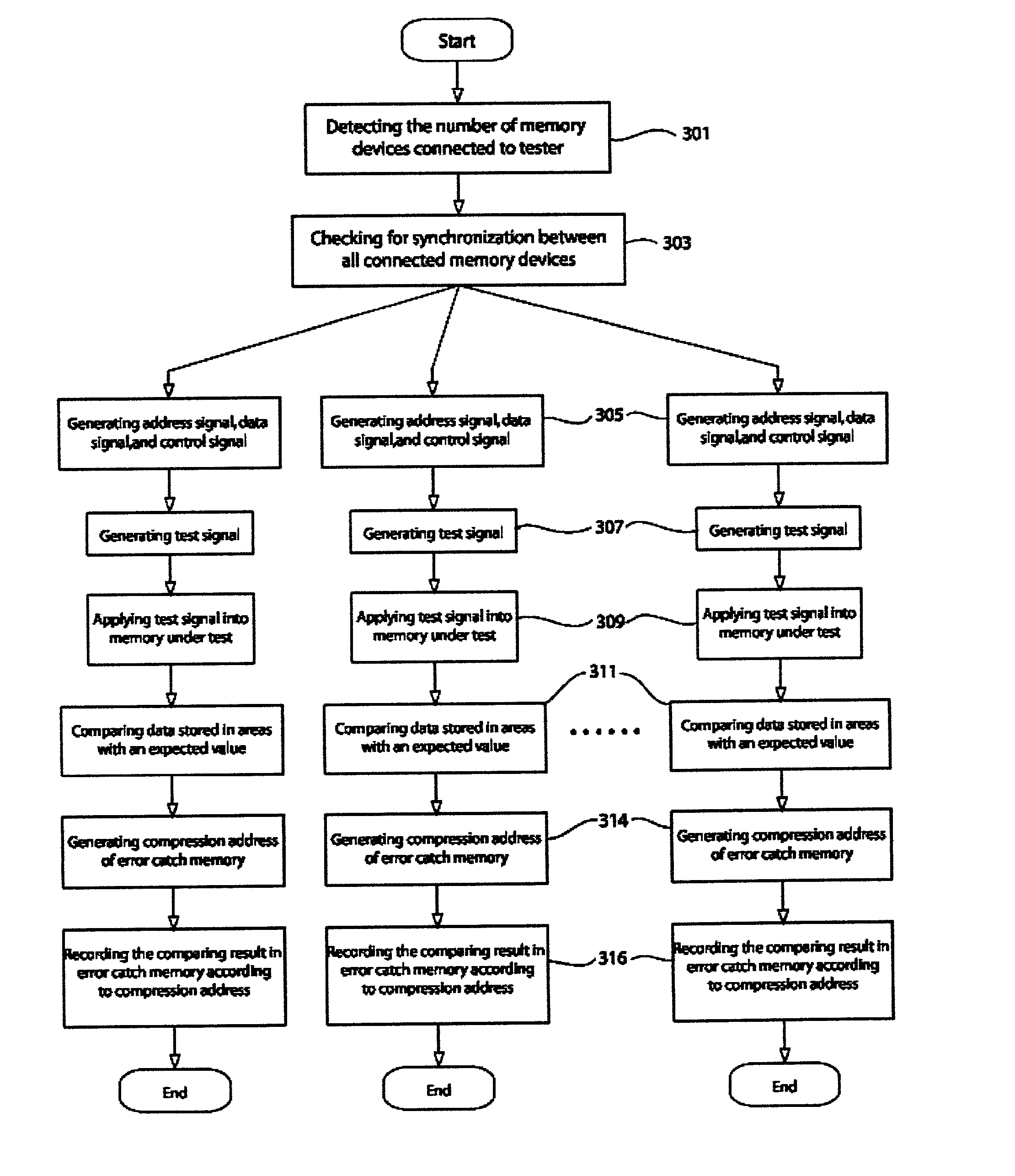

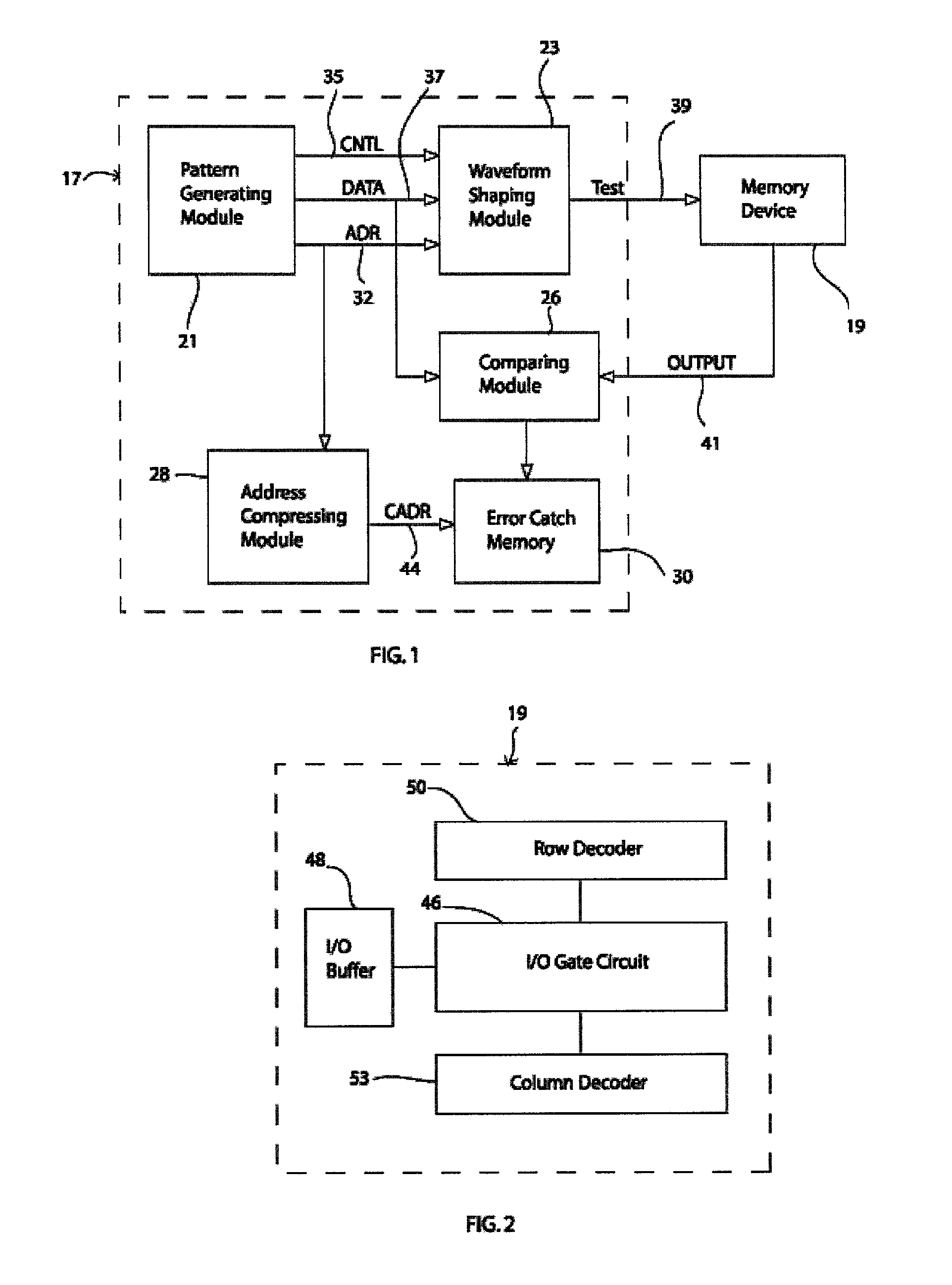

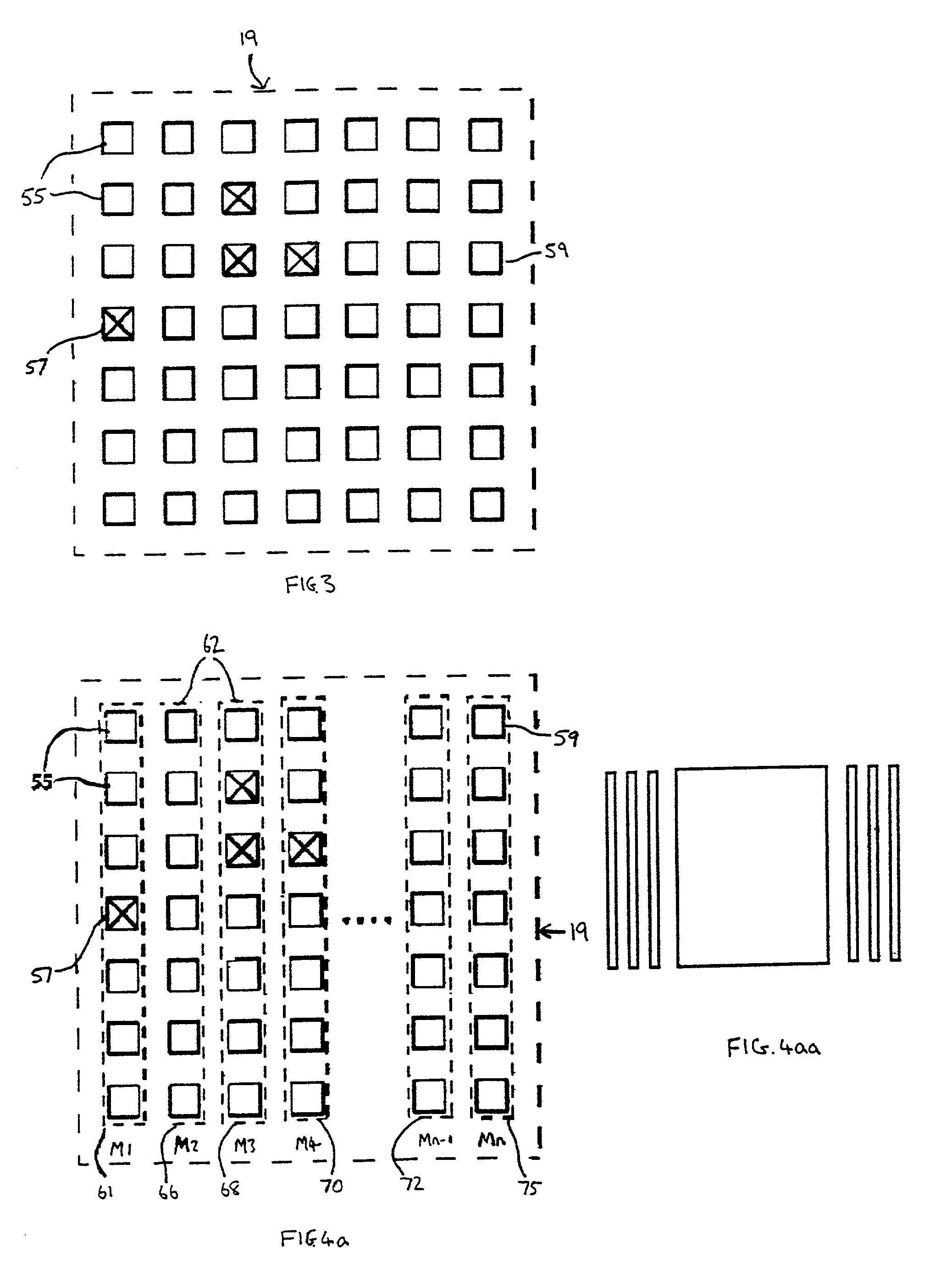

Memory testing device and method

InactiveUS20030204797A1Electronic circuit testingError detection/correctionComputer moduleMemory testing

A memory testing apparatus rapidly tests memory devices with a relatively small error catch memory. The memory testing apparatus provides an address compressing module that minimizes an amount of error catch memory necessary to test one or more memory devices. The memory testing apparatus further divides each of the memory devices into a plurality of areas, and tests each area sequentially until a bit failure is detected in the area thereby attenuating testing time.

Owner:MACRONIX INT CO LTD

Data compression read mode for memory testing

InactiveUS6930936B2Improve end-use reliabilityAccurate timingDigital storageData compressionNormal mode

Memory devices having a normal mode of operation and a test mode of operation are useful in quality programs. The test mode of operation includes a data compression test mode. In the data compression test mode, reading one word of an output page provides an indication of the data values of the remaining words of the output page. The time necessary to read and verify a repeating test pattern can be reduced as only one word of each output page need be read to determine the ability of the memory device to accurately write and store data values. The memory devices include data compression circuits to compare data values for each bit location of each word of the output page. Output is selectively disabled if a bit location for one word of the output page has a data value differing from any remaining word of the output page.

Owner:MICRON TECH INC

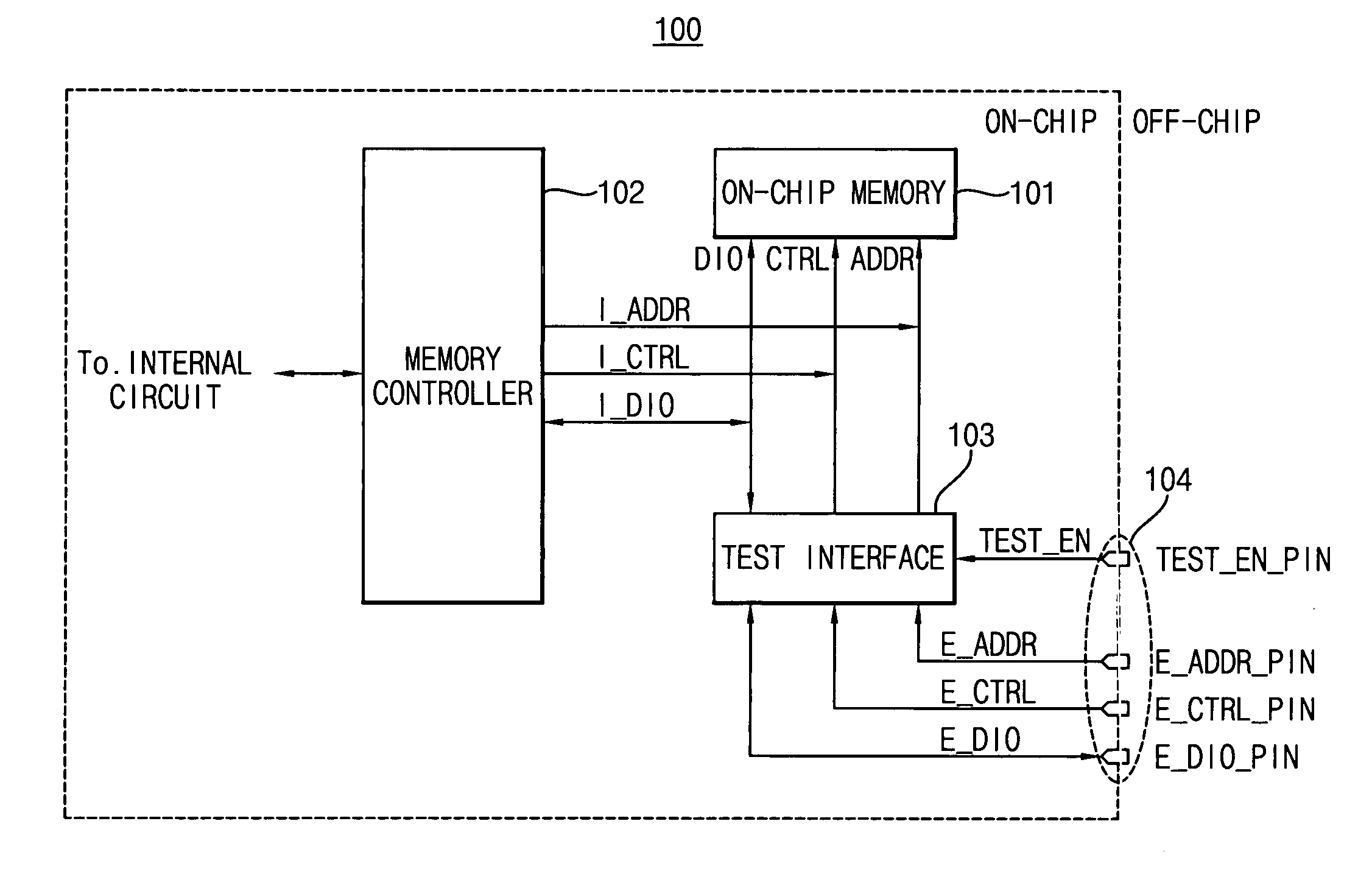

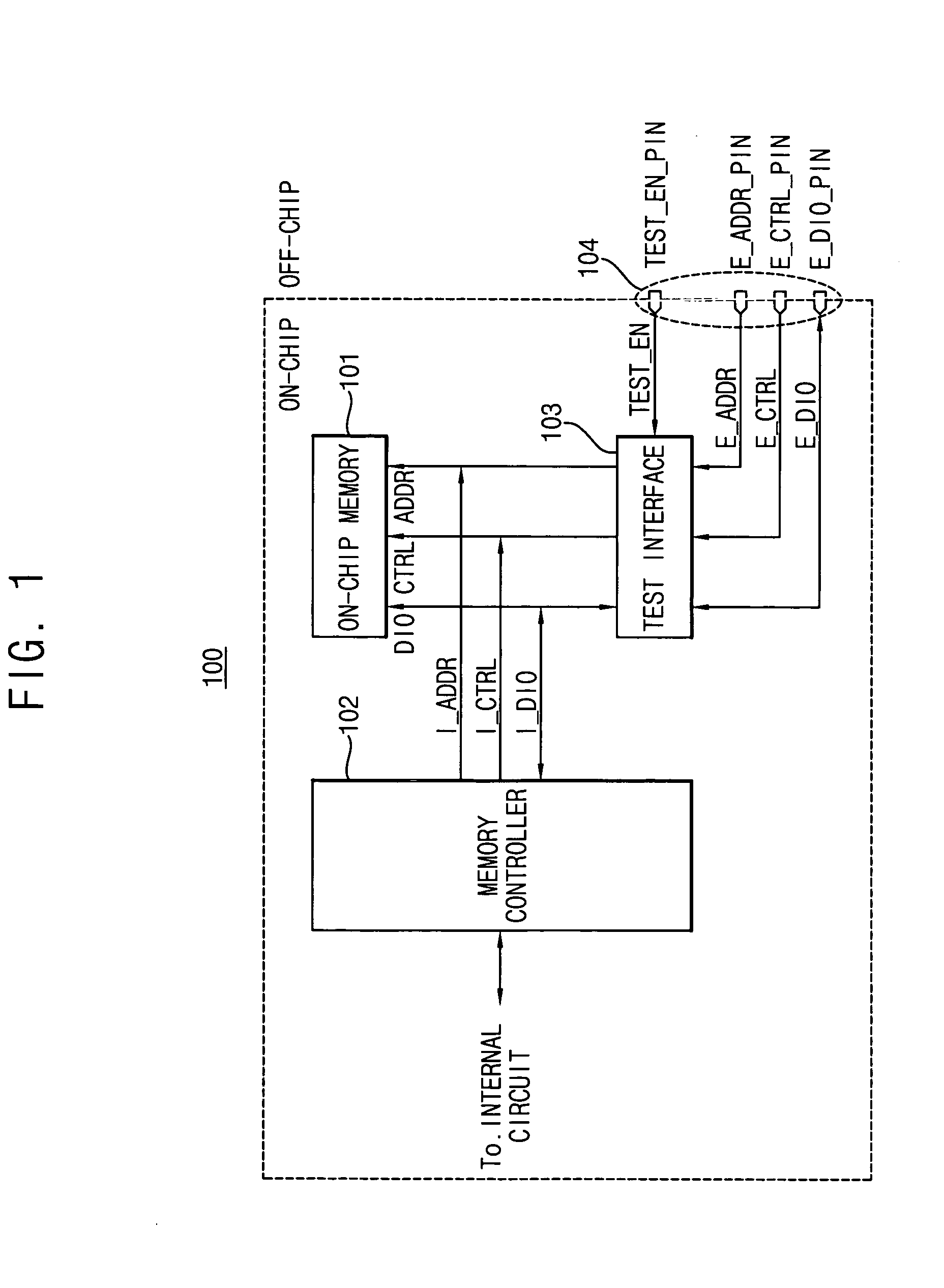

On-Chip Memory Testing

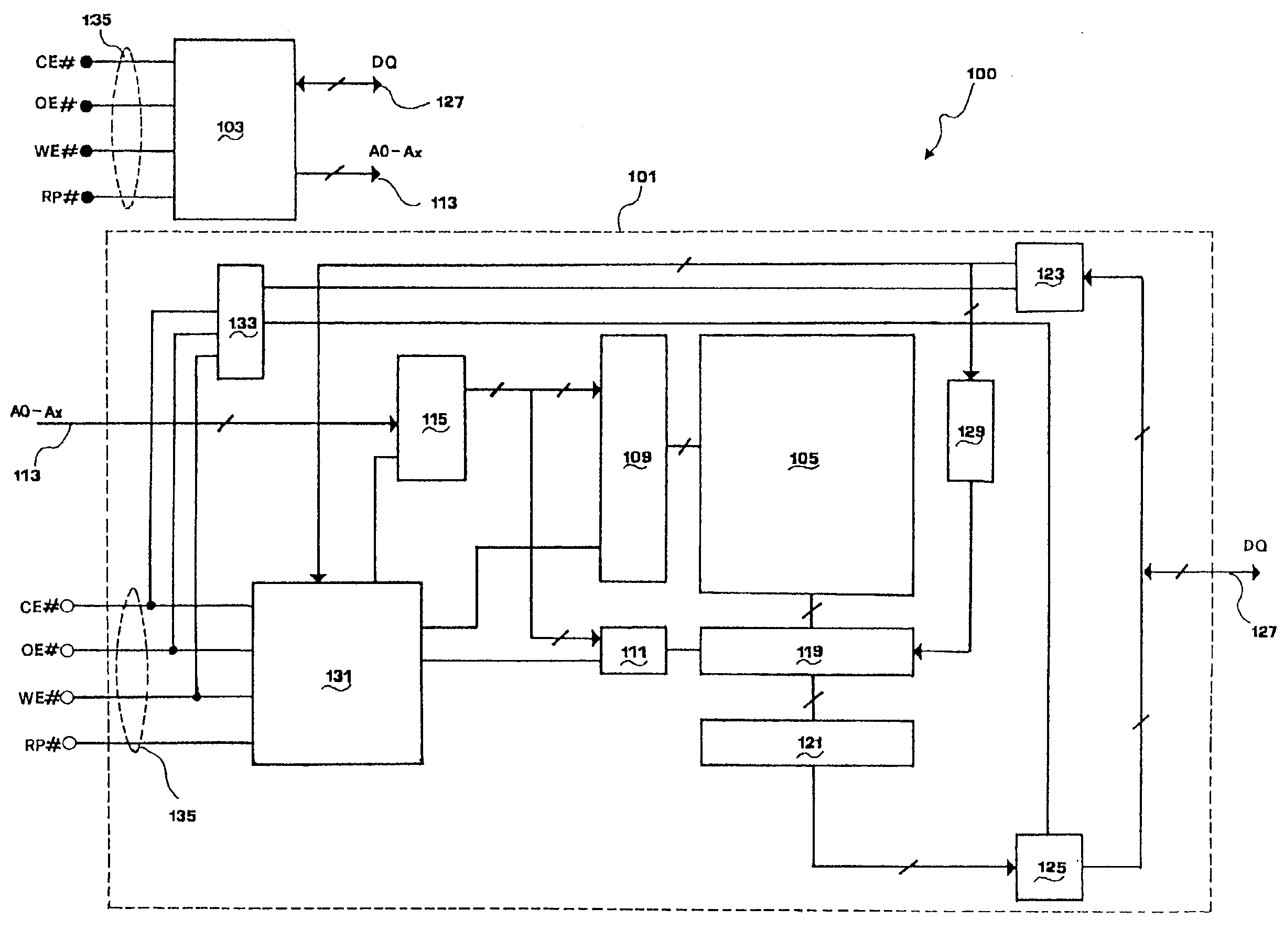

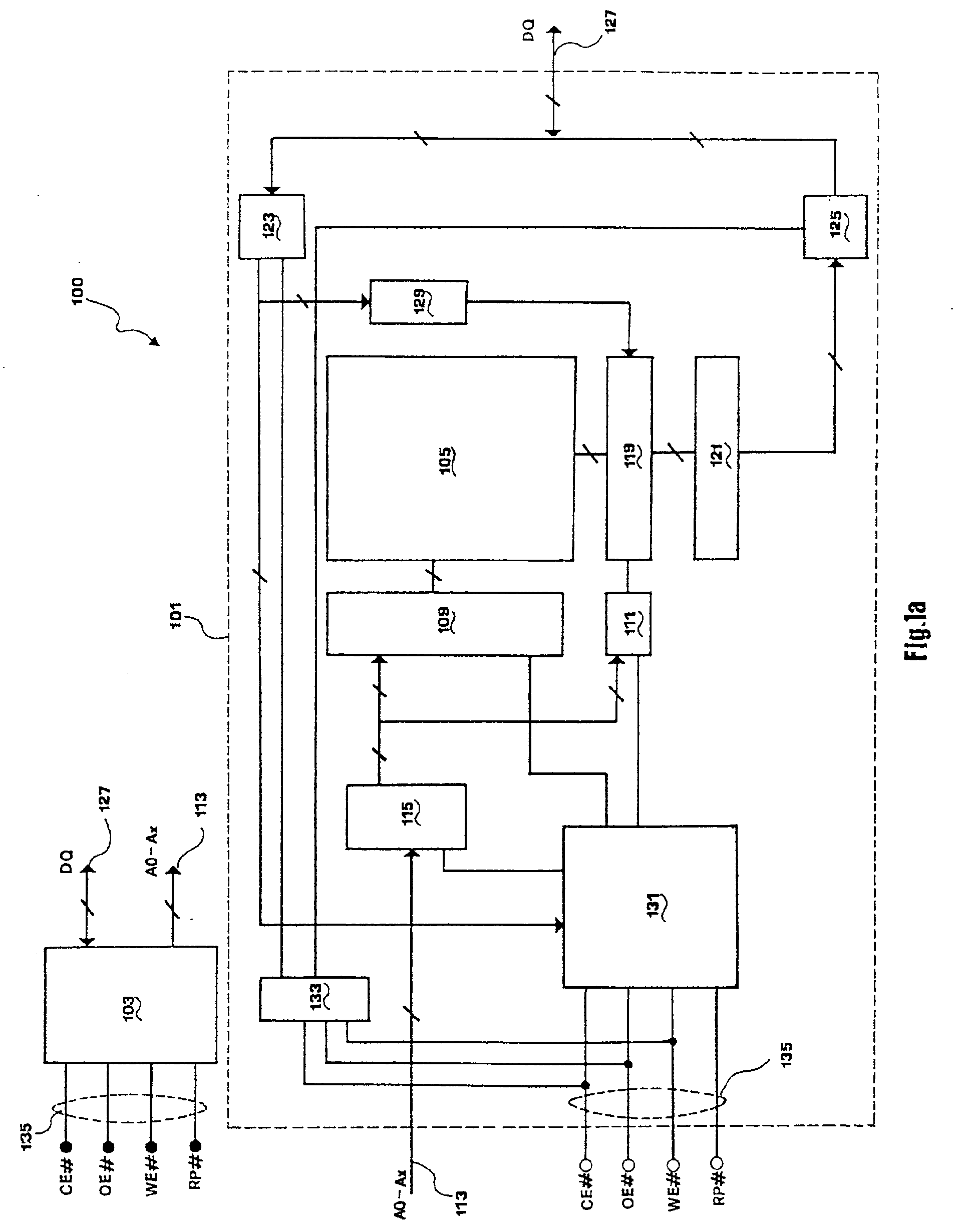

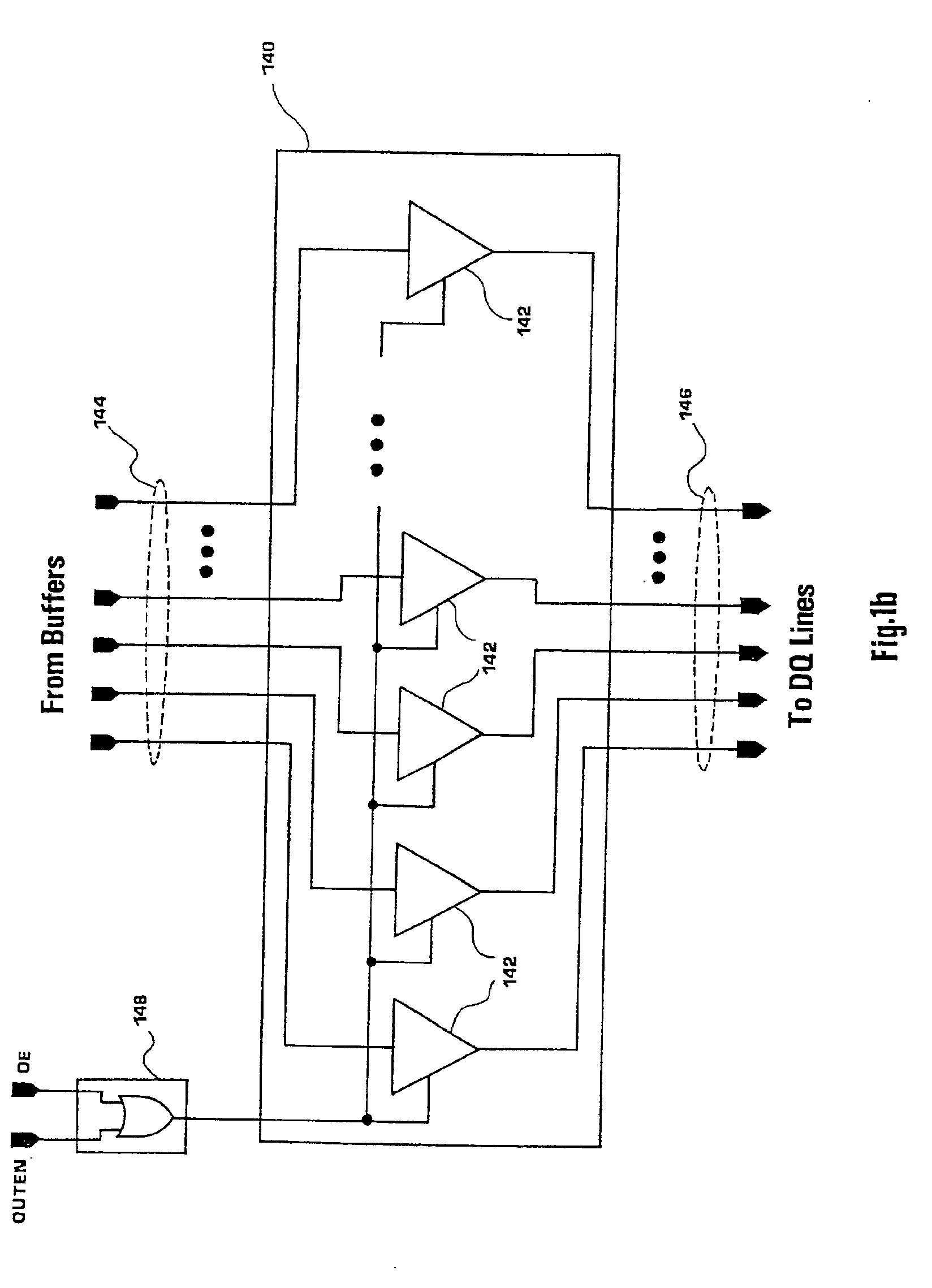

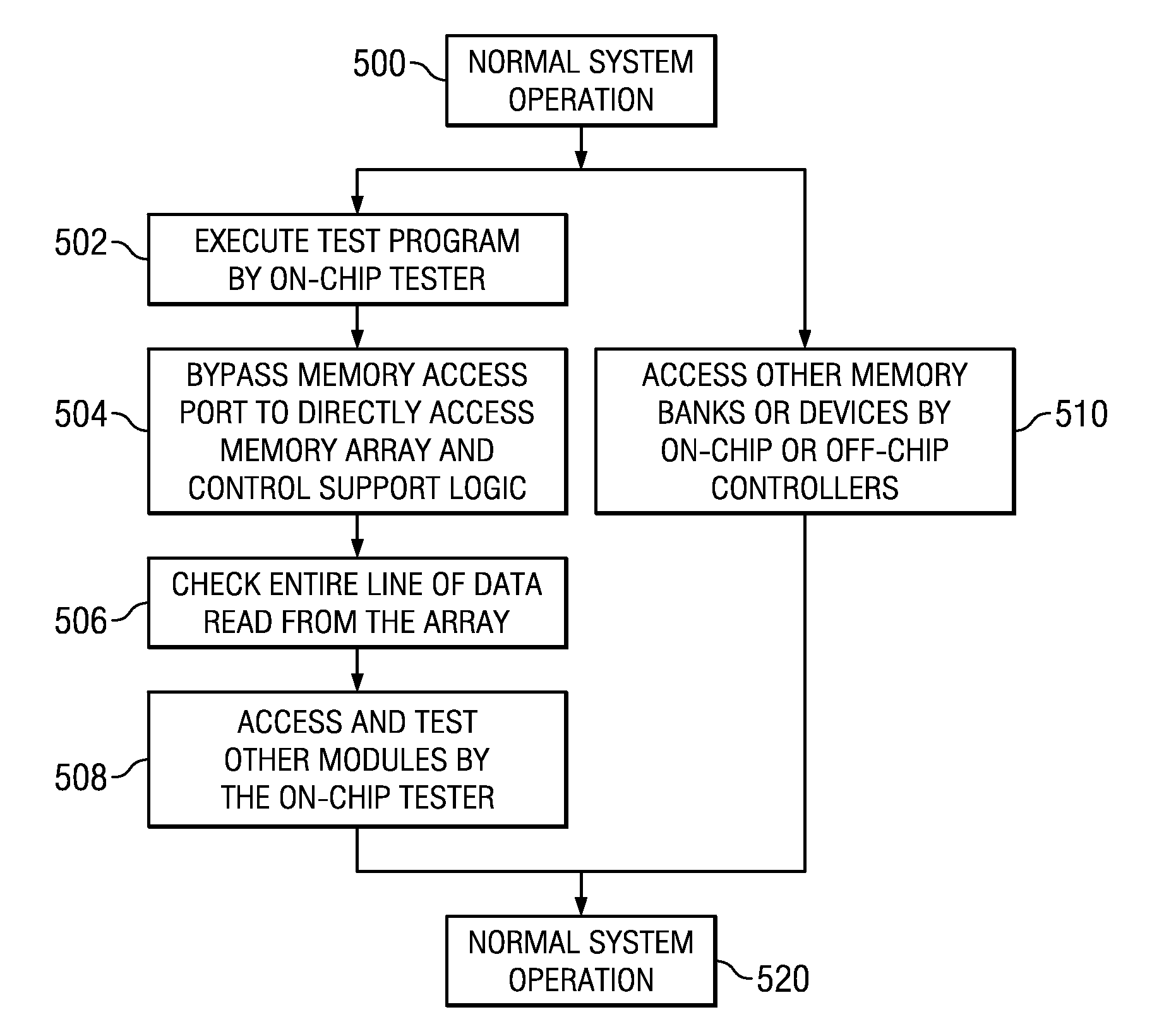

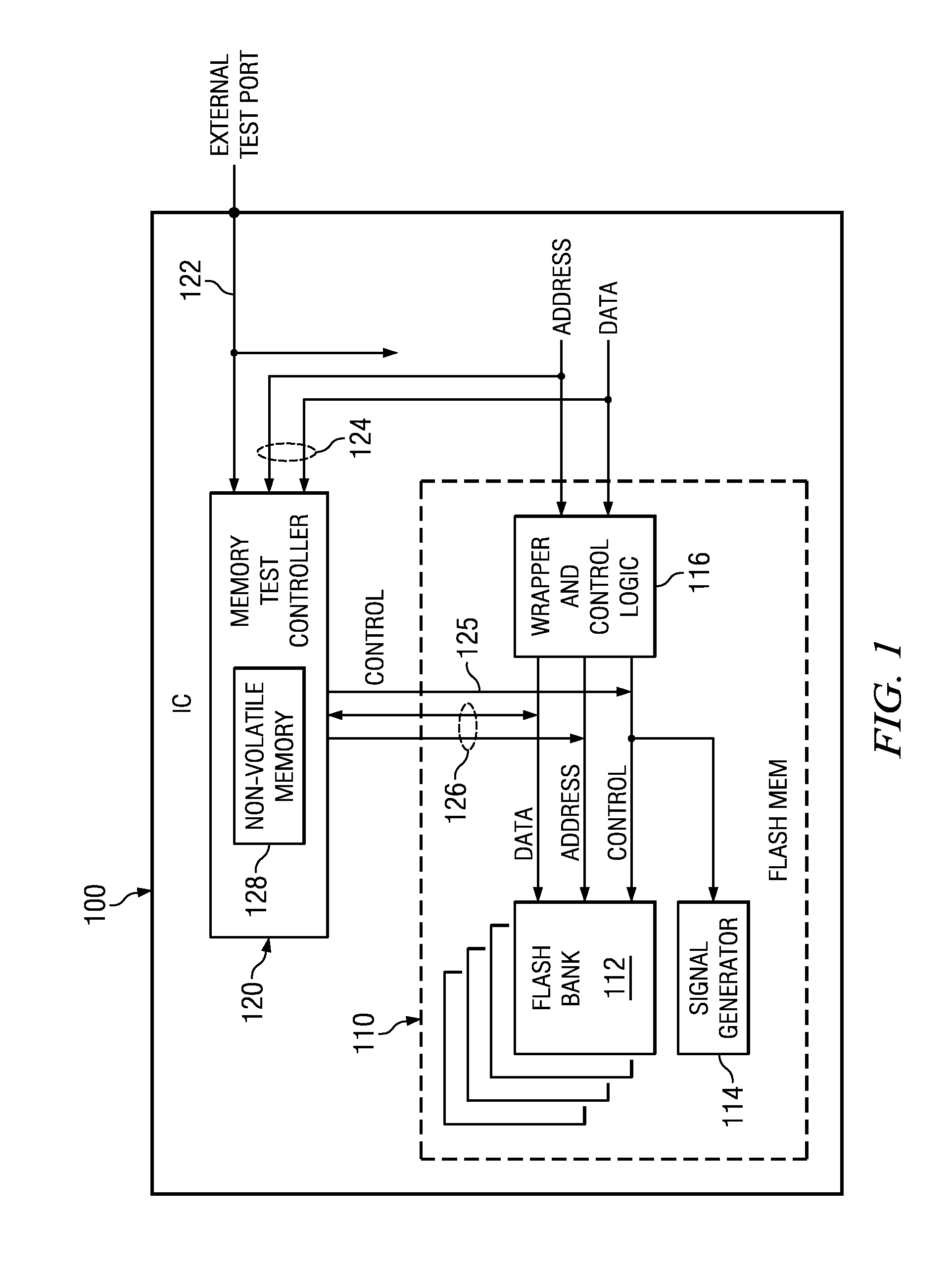

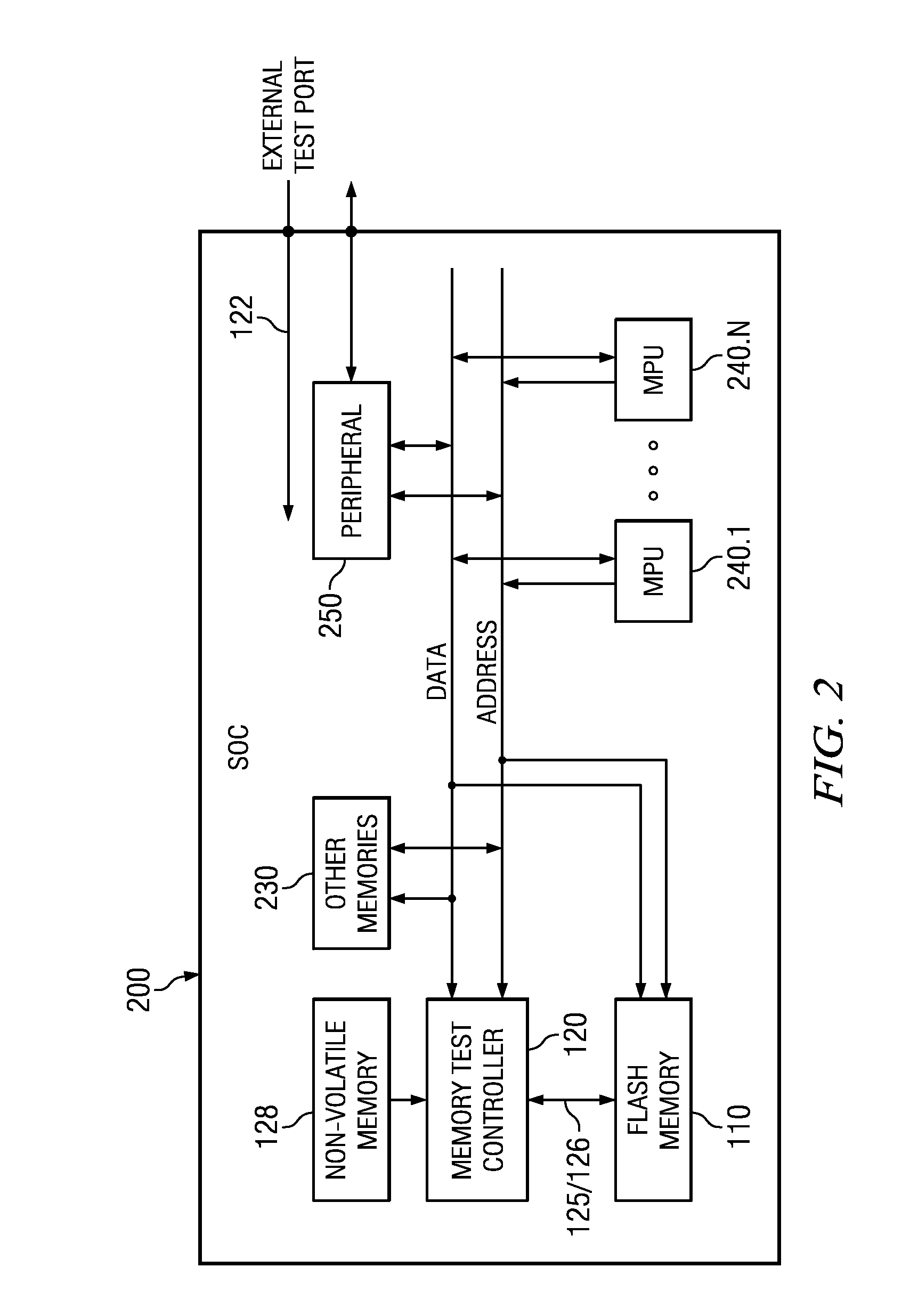

ActiveUS20120072790A1Electronic circuit testingDetecting faulty computer hardwareControl signalControl line

An integrated circuit is described that has a substrate with a memory array with dedicated support hardware formed on the substrate. An access wrapper circuit is coupled to address and data lines of the memory array and to control lines of the dedicated support hardware. The wrapper circuit is configured to provide an access port to the memory array. A test controller is formed on the substrate and coupled in parallel with the access wrapper circuit to the address and data lines of the memory array and to the control lines of the dedicated support hardware, wherein the test controller is operable to perform a test of the memory array by manipulating control signals to the support hardware in addition to those required to write data patterns into the memory array and to read the contents of the memory array.

Owner:TEXAS INSTR INC

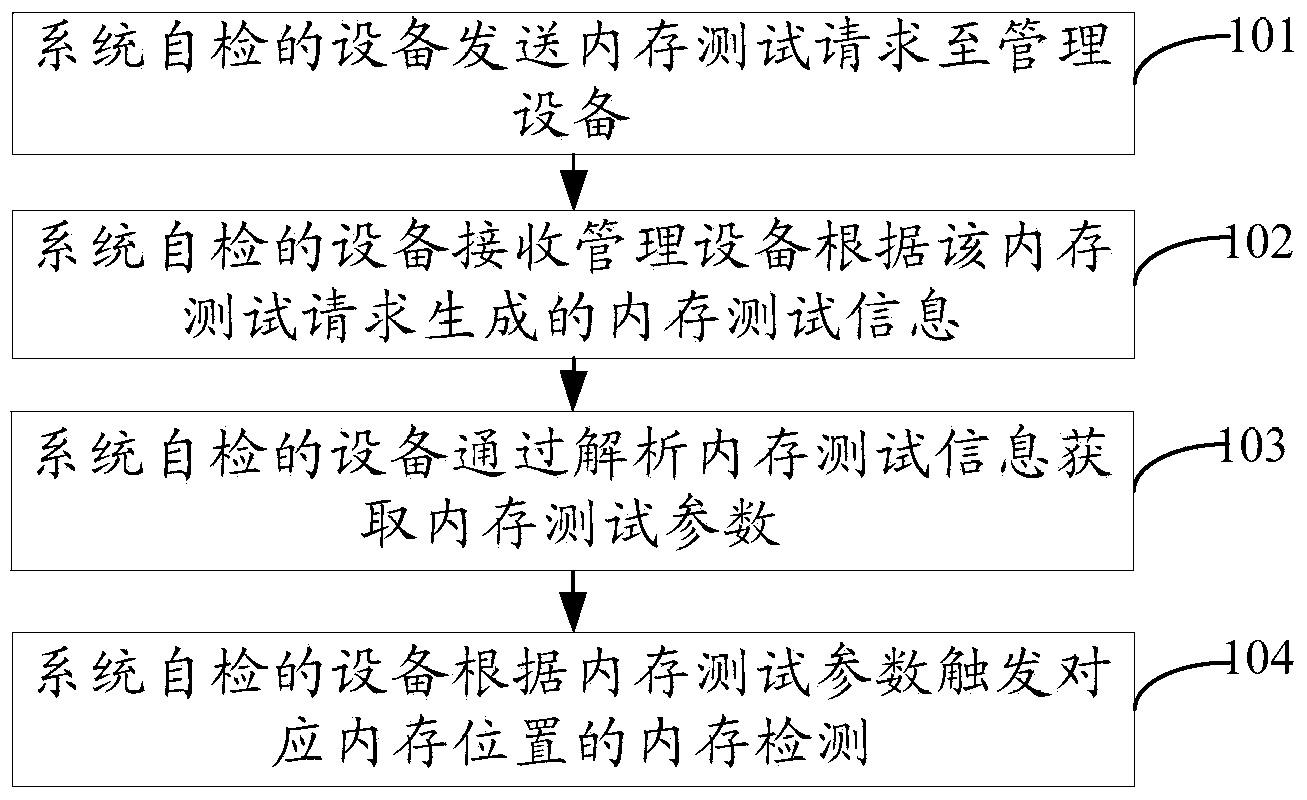

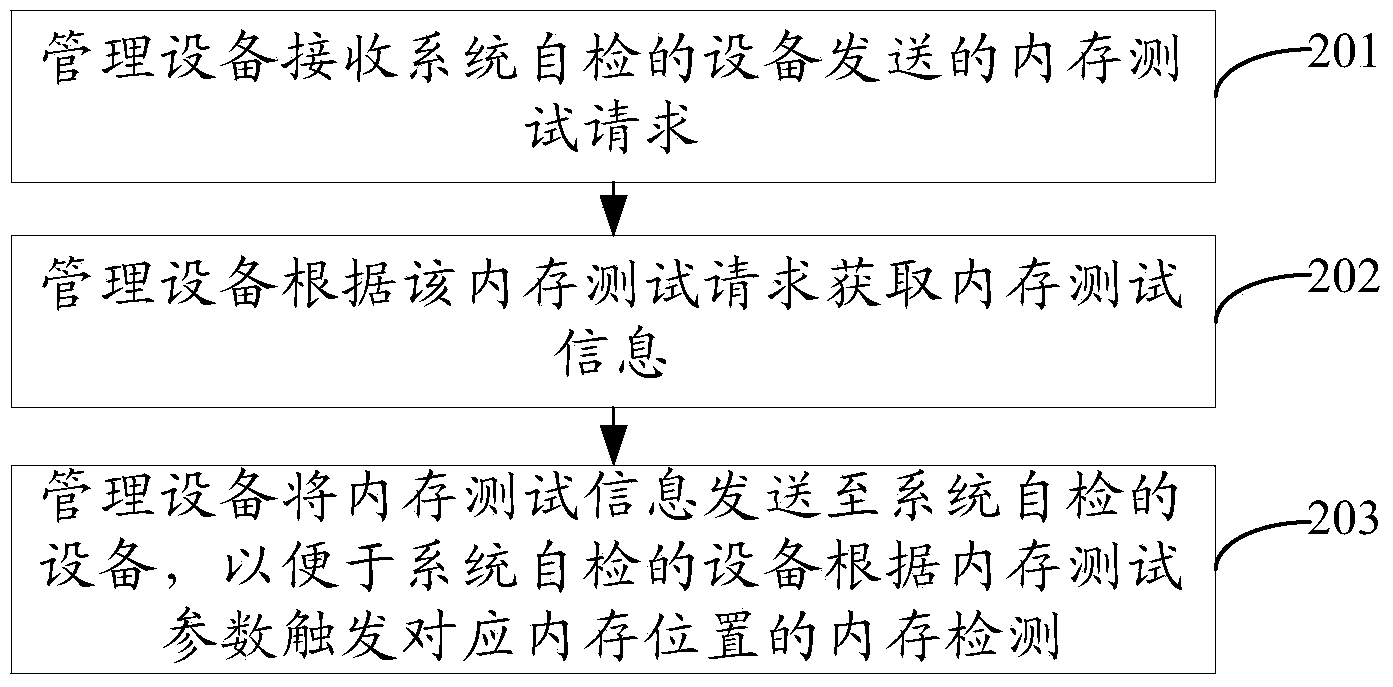

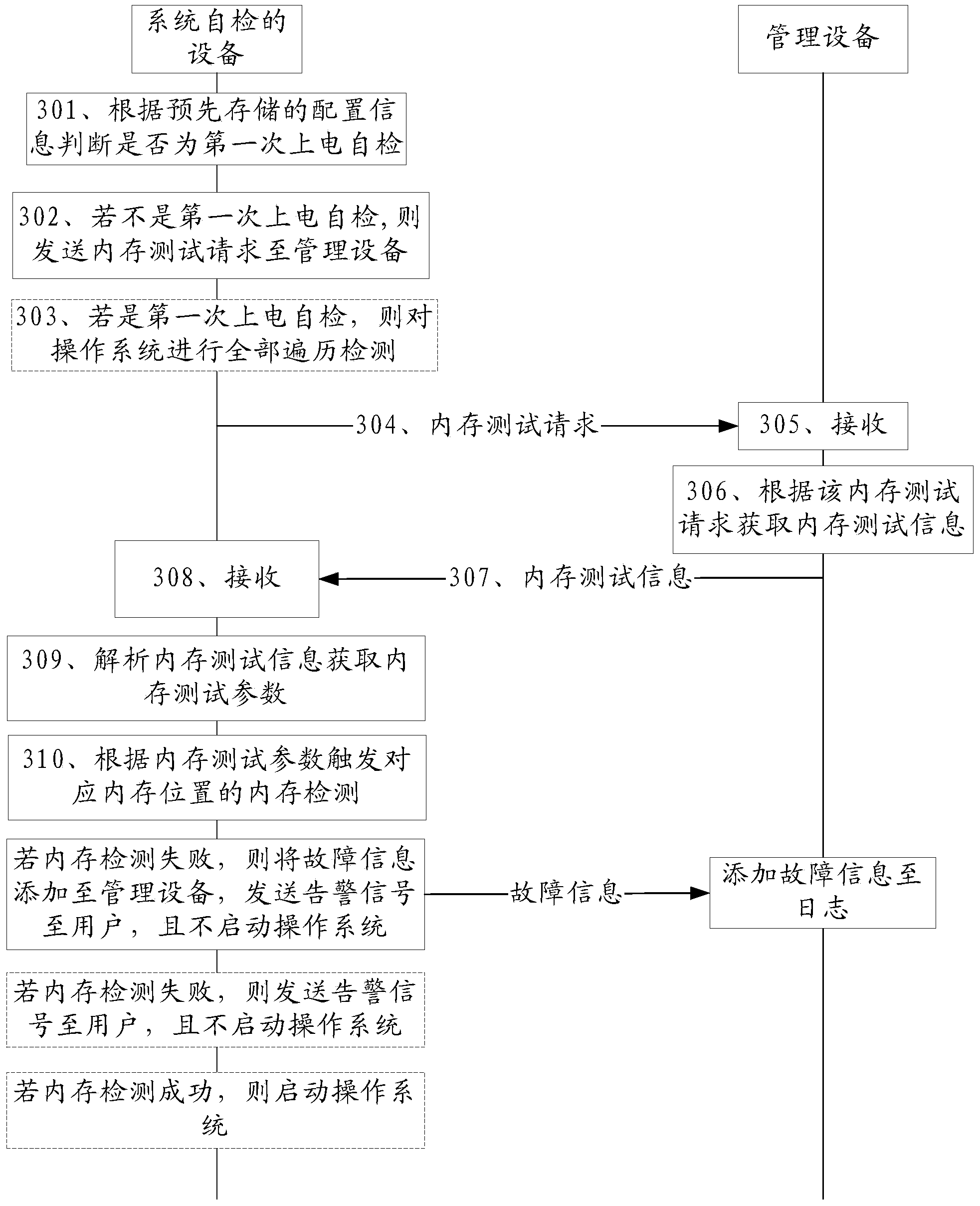

System self-test method, equipment and system

The embodiment of the invention discloses a system self-test method, equipment and system, which relate to communication application technology and are used for solving the problems of long startup response time when a memory self-test function is started and shut off in power-on self-test and low reliability in a system self-test process. The method comprises the following steps: transmitting a memory test request to management equipment through system self-test equipment; receiving memory testing information generated by the management equipment according to the memory test request; acquiring a memory test parameter by resolving the memory test information, wherein the memory test parameter comprises a memory test target and / or memory test strategy information; and triggering memory detection of a corresponding memory position according to the memory test parameter. The embodiment of the invention is applied to power-on self-test of a server.

Owner:HANGZHOU HUAWEI DIGITAL TECH

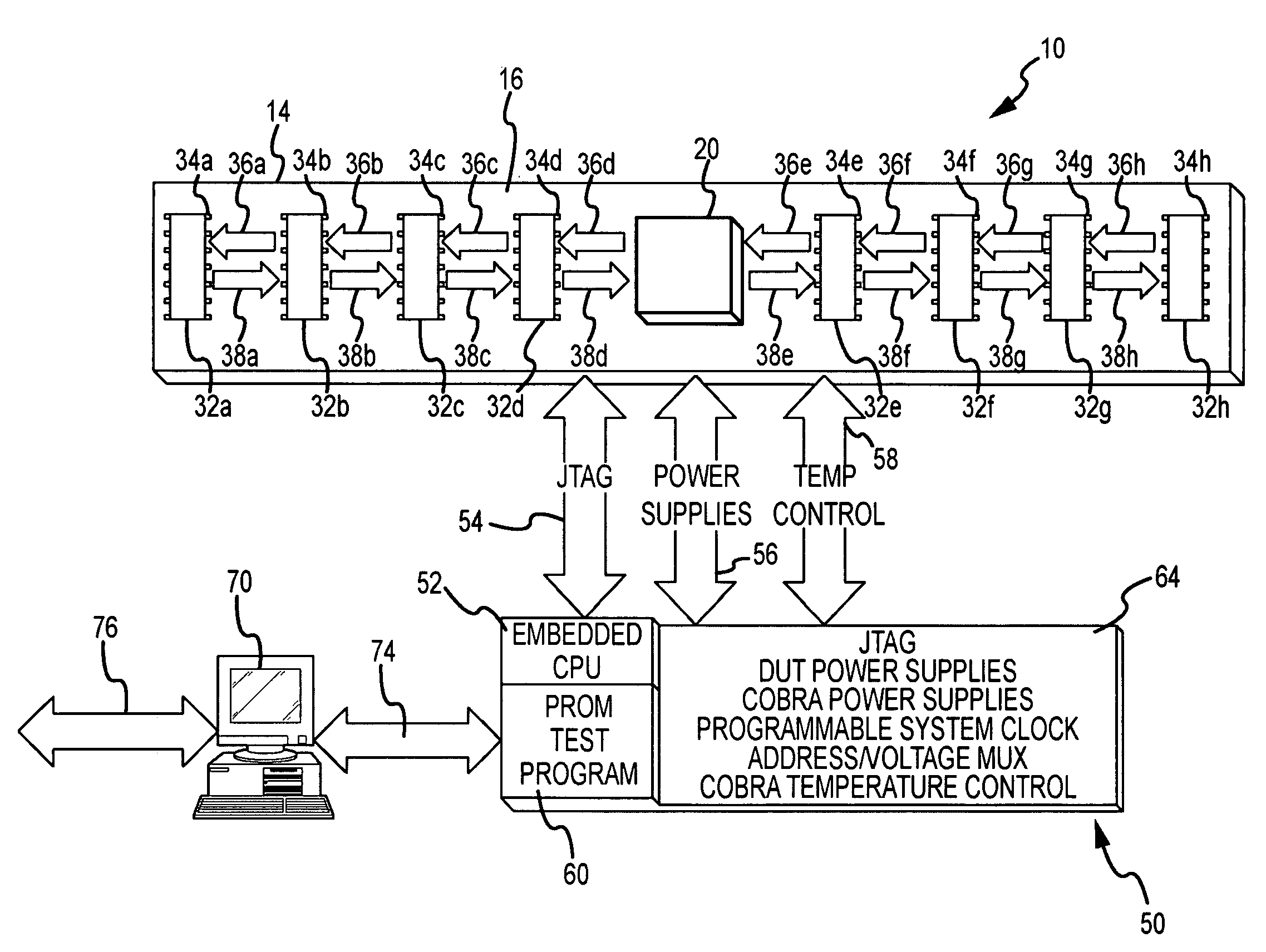

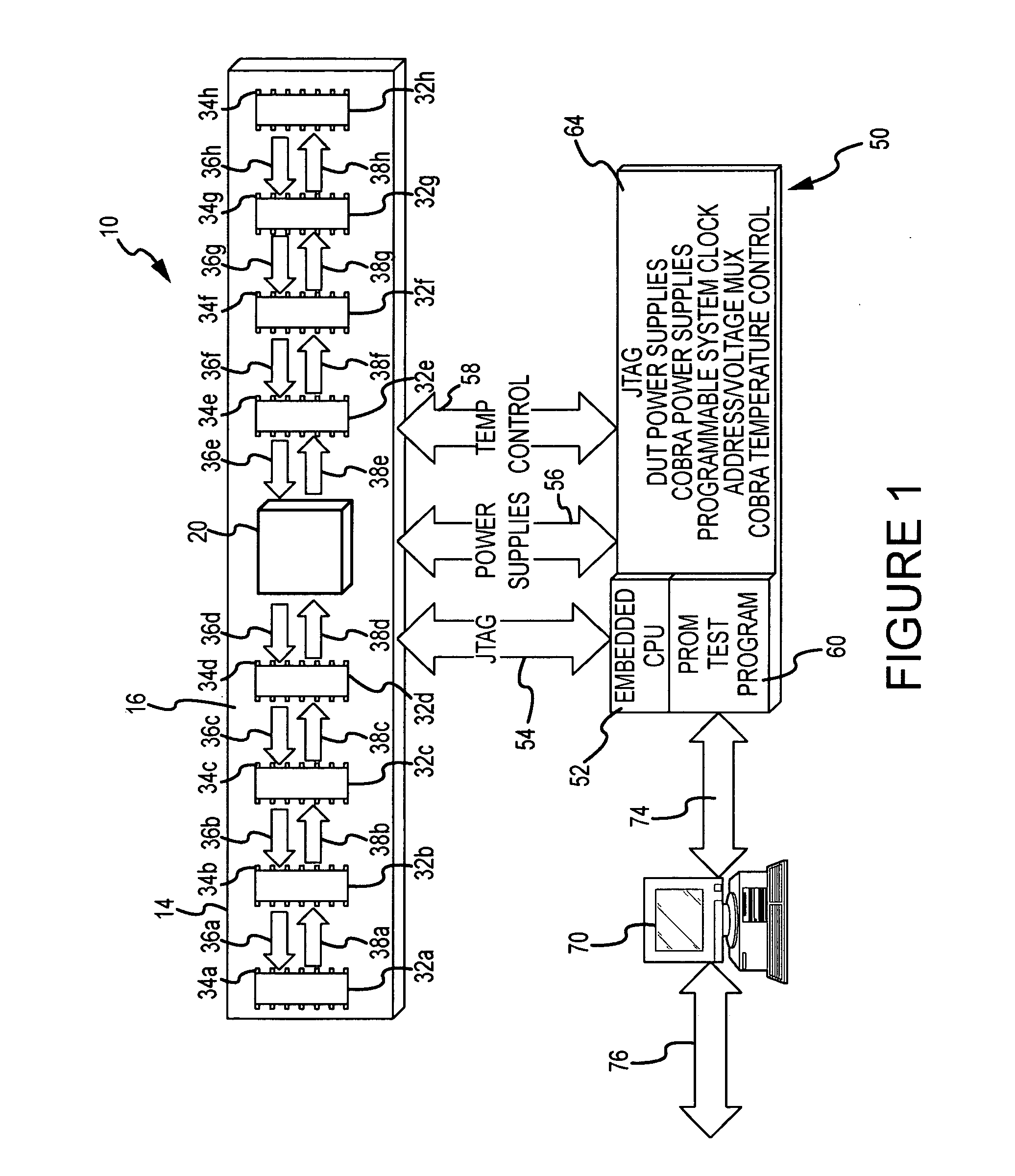

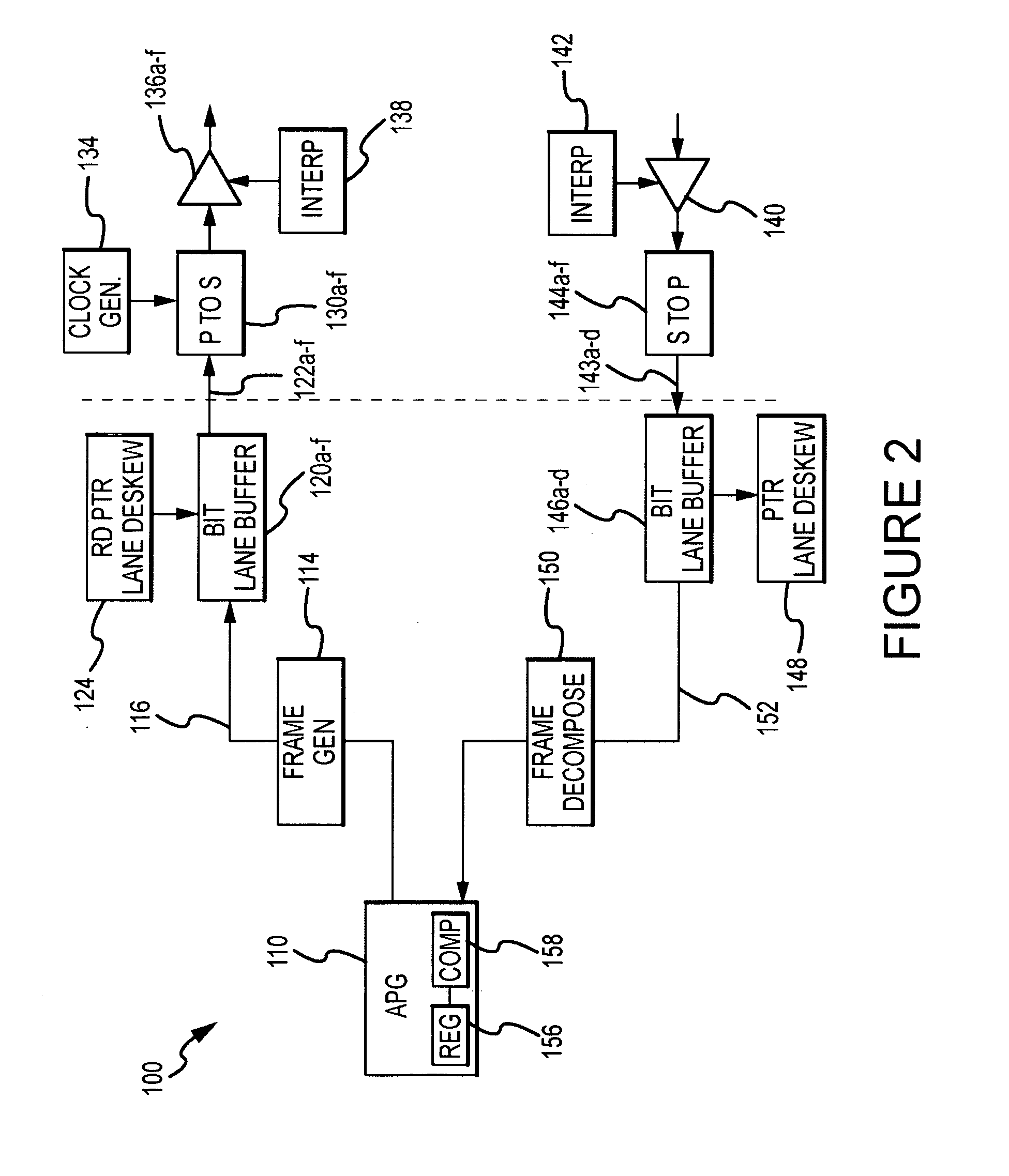

System and method for testing a packetized memory device

InactiveUS20090172480A1Electronic circuit testingError detection/correctionNetwork packetMemory testing

Integrated circuits, load boards and methods are disclosed, such as those associated with a memory testing system that includes an algorithmic pattern generator generating a pattern of command, address or write data digits according to an algorithm. In one such embodiment, the pattern of digits are applied to a frame generator that arranges the pattern of digits into a packet. The packet is then applied to a plurality of parallel-to-serial converters that convert the packet into a plurality of serial digits of a command / address packet or a write data packet, which are output through a plurality of bit lanes. The system might also include a plurality of serial-to-parallel converters receiving respective sets of digits of a read data packet through respective bit lanes. The read data packet is applied to a frame decomposer that extracts a pattern of read data digits from the packet. An error detecting circuit then determines if any of the received read data digits are erroneous.

Owner:MICRON TECH INC

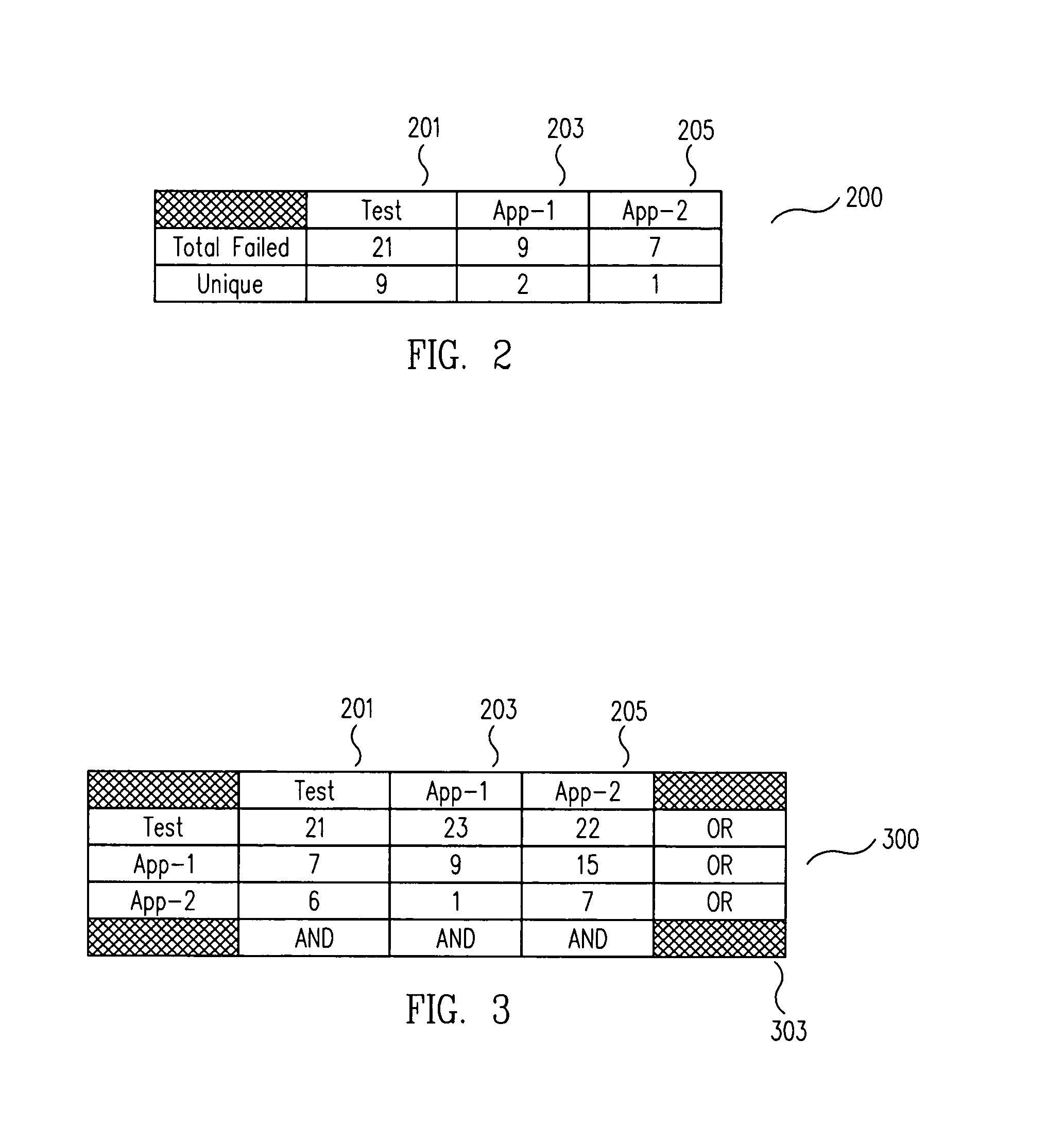

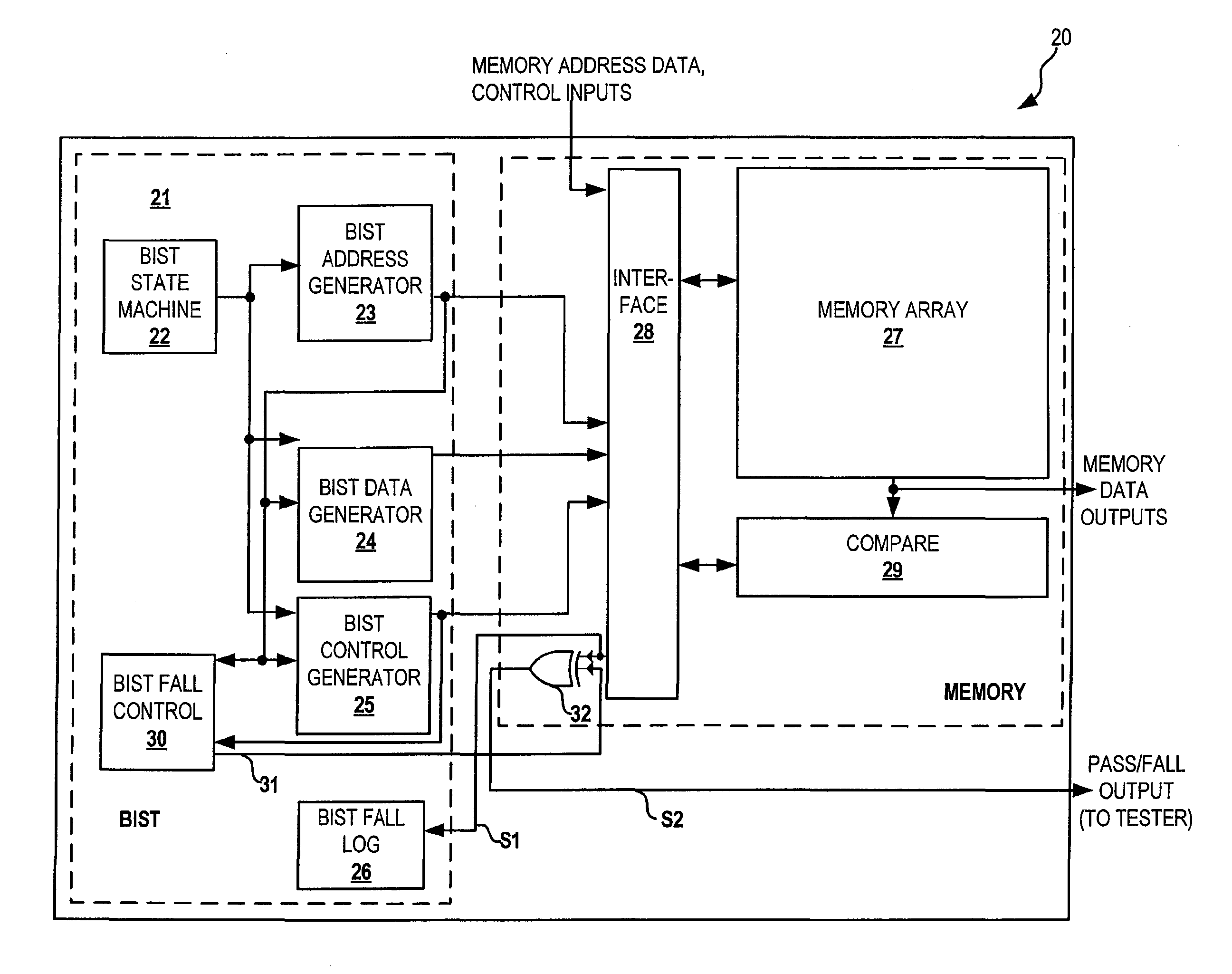

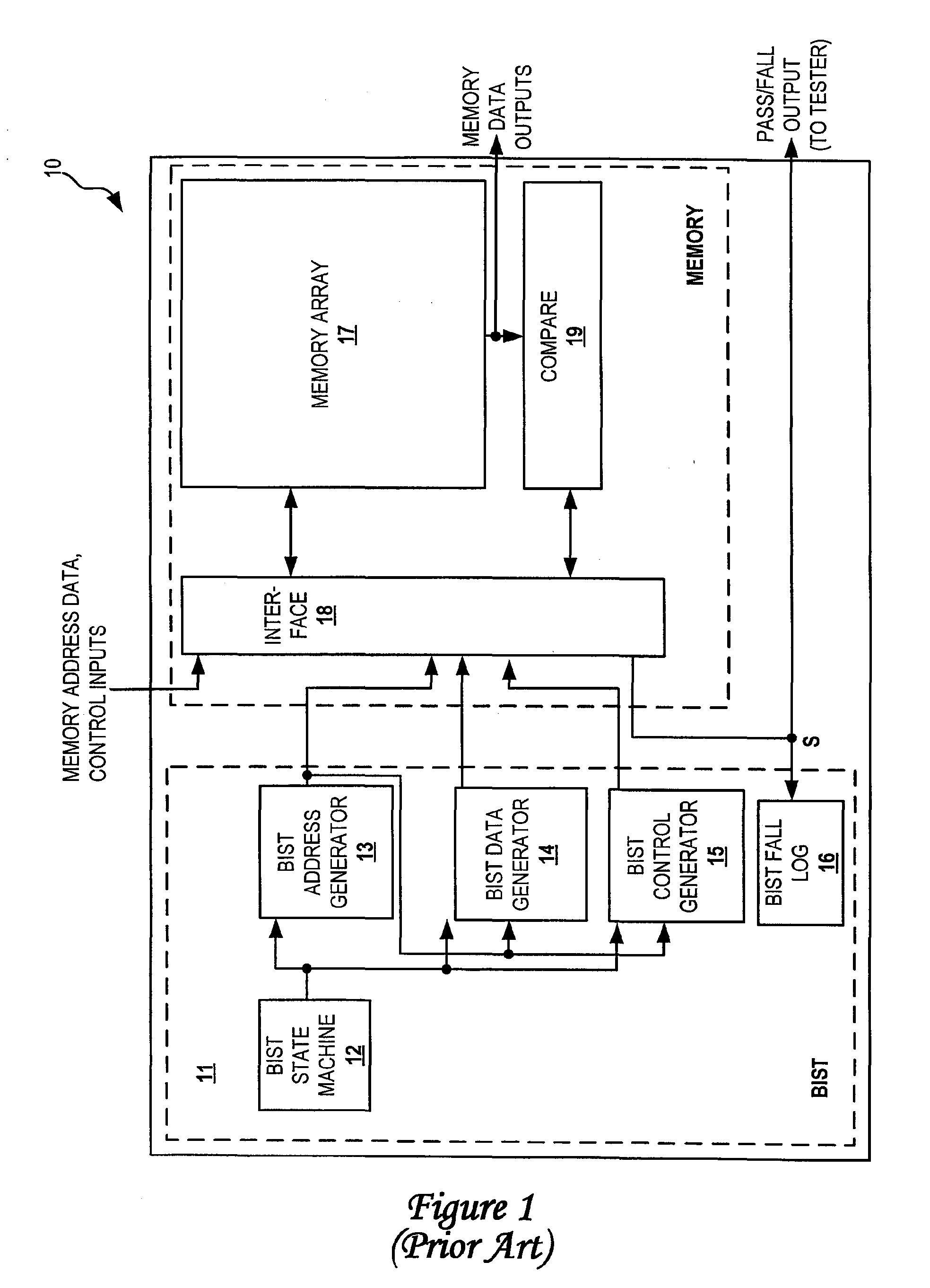

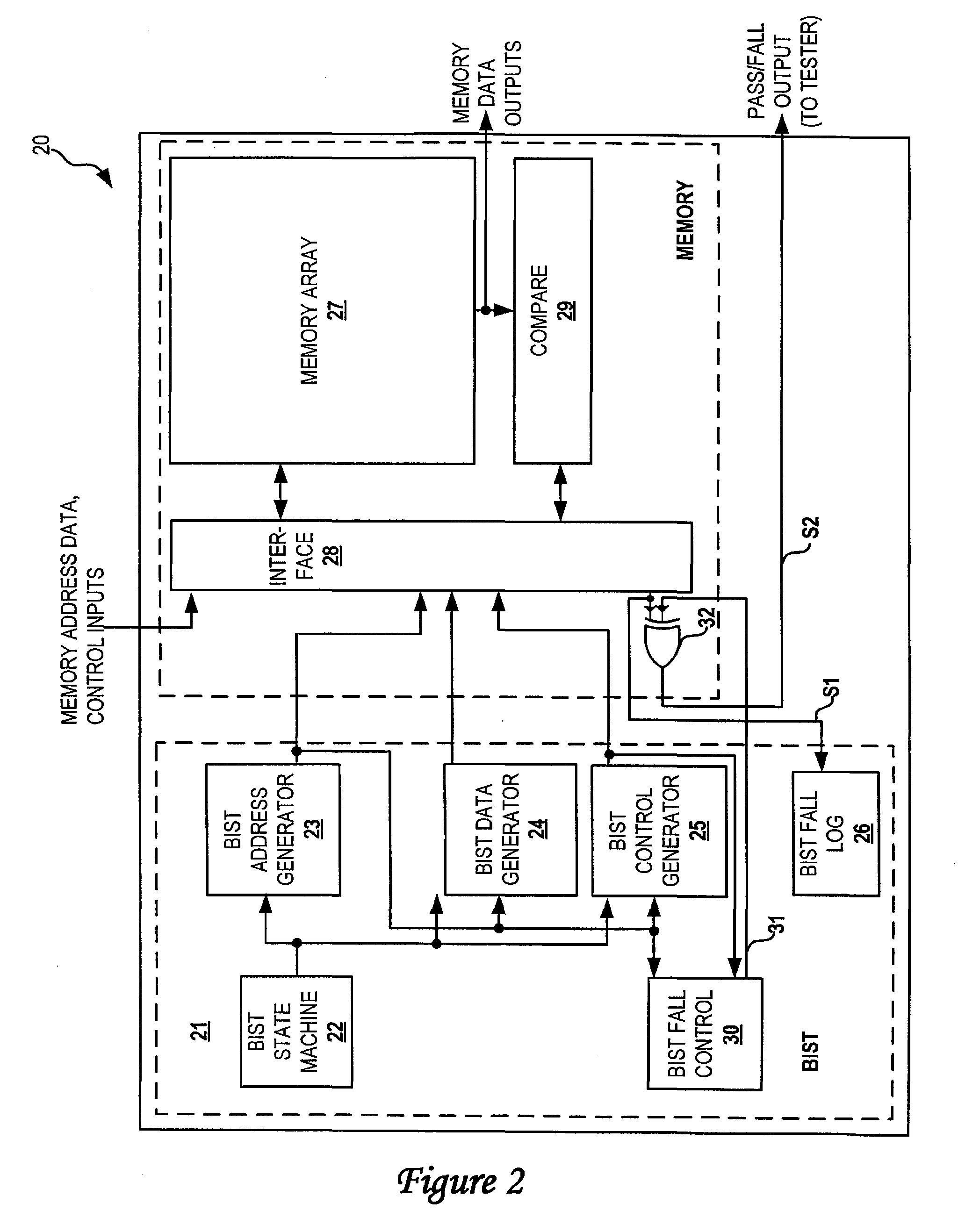

Method and apparatus for verifying memory testing software

ActiveUS20060190788A1Verify accuracyElectronic circuit testingError detection/correctionMemory faultsParallel computing

A method for verifying the accuracy of memory testing software is disclosed. A built-in self test (BIST) fail control function is utilized to generate multiple simulated memory fails at various predetermined locations within a memory array of a memory device. The memory array is then tested by a memory tester. Afterwards, a bit fail map is generated by the logical-to-physical mapping software based on all the memory fails indicated by the memory tester. The bit fail map provides all the fail memory locations derived by the logical-to-physical mapping software. The fail memory locations derived by the logical-to-physical mapping software are then compared to the predetermined memory locations to verify the accuracy of the logical-to-physical mapping software.

Owner:MARVELL ASIA PTE LTD

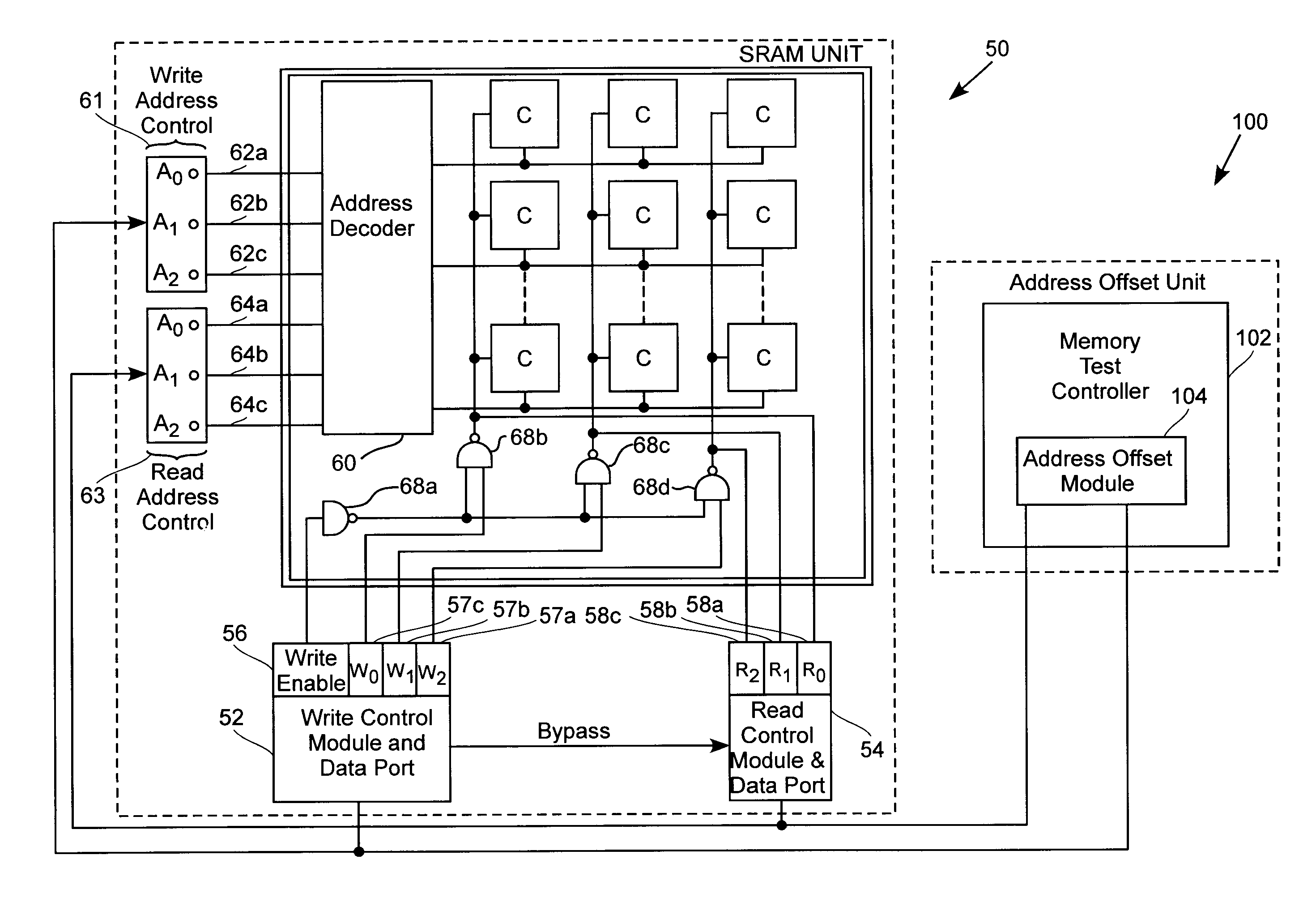

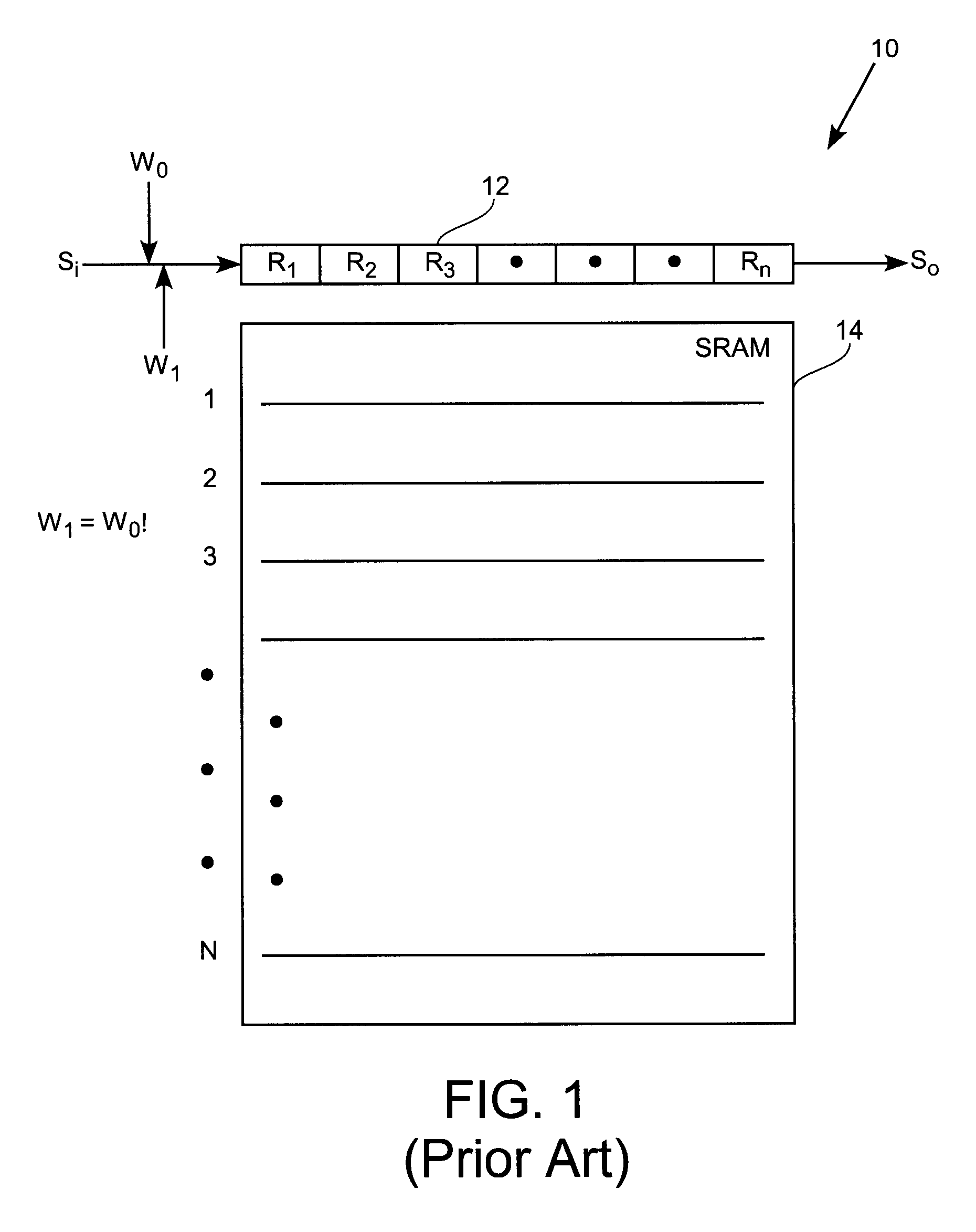

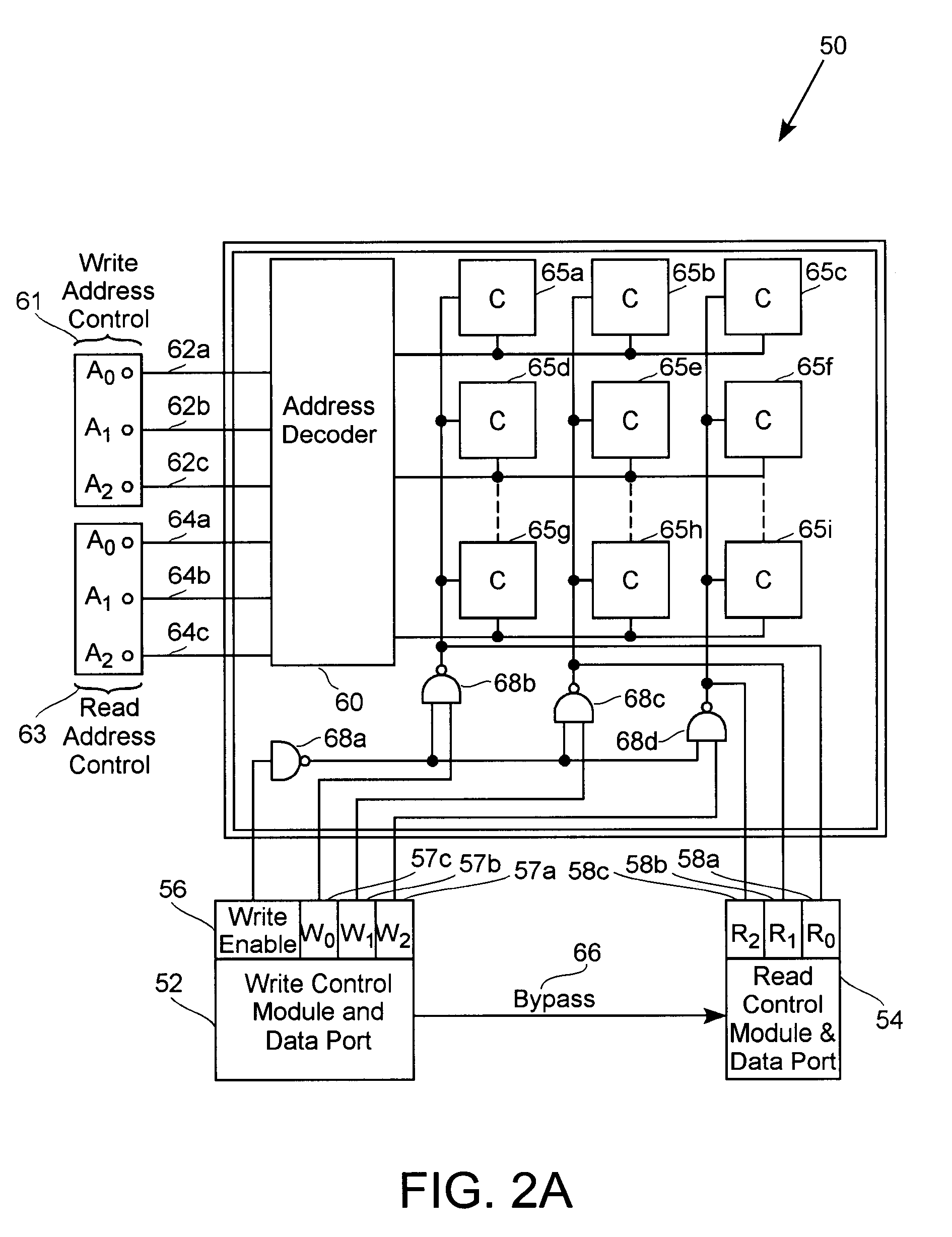

System and method for implementing memory testing in a SRAM unit

The present invention provides a system and method for performing a memory test algorithm with a static random access memory (SRAM) unit having a read control module with no read enable control and write control module with write enable control. The system and method conduct read and write operations to the SRAM unit by avoiding simultaneously reading and writing to the same memory address. Simultaneously reading and writing to the same memory address is avoided by offsetting the read and write signals provided to the SRAM unit.

Owner:ORACLE INT CORP

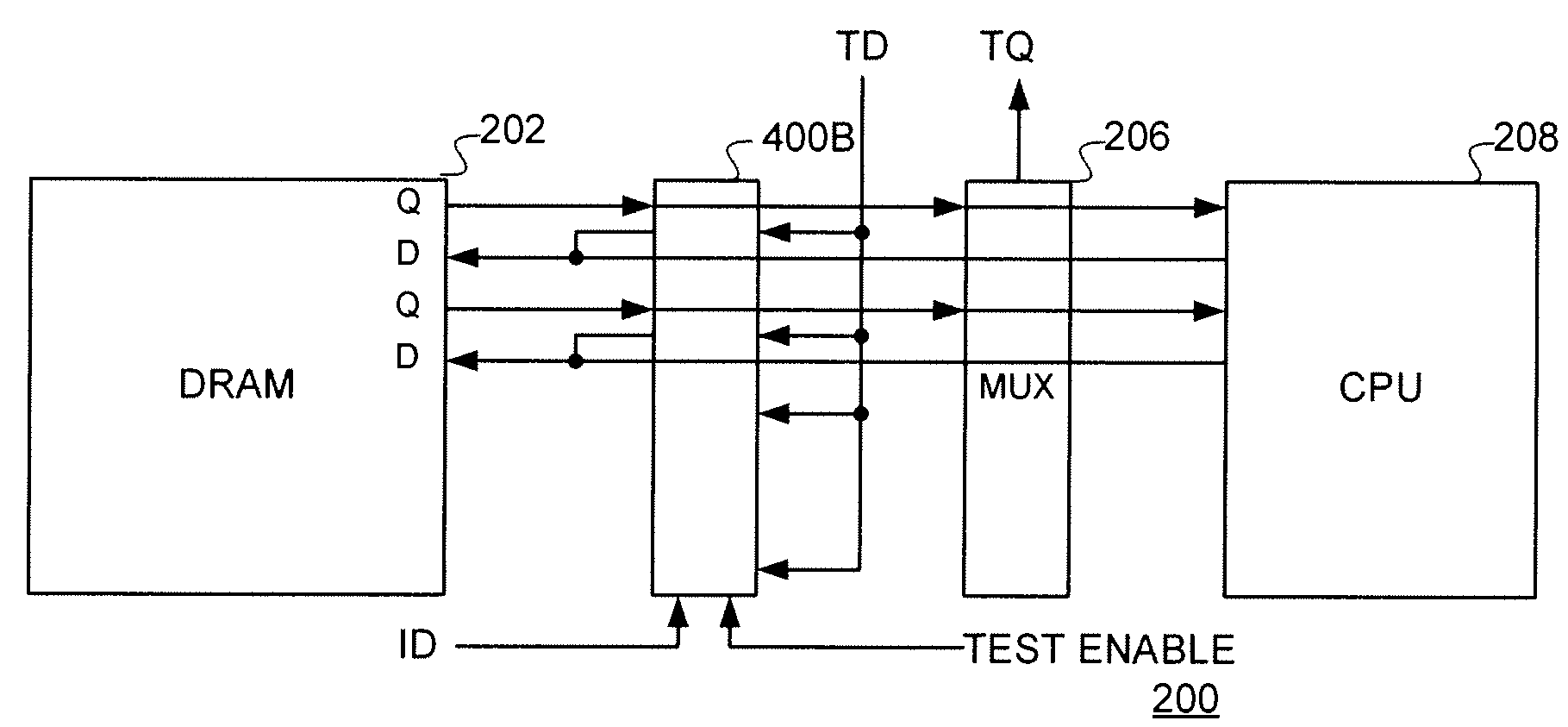

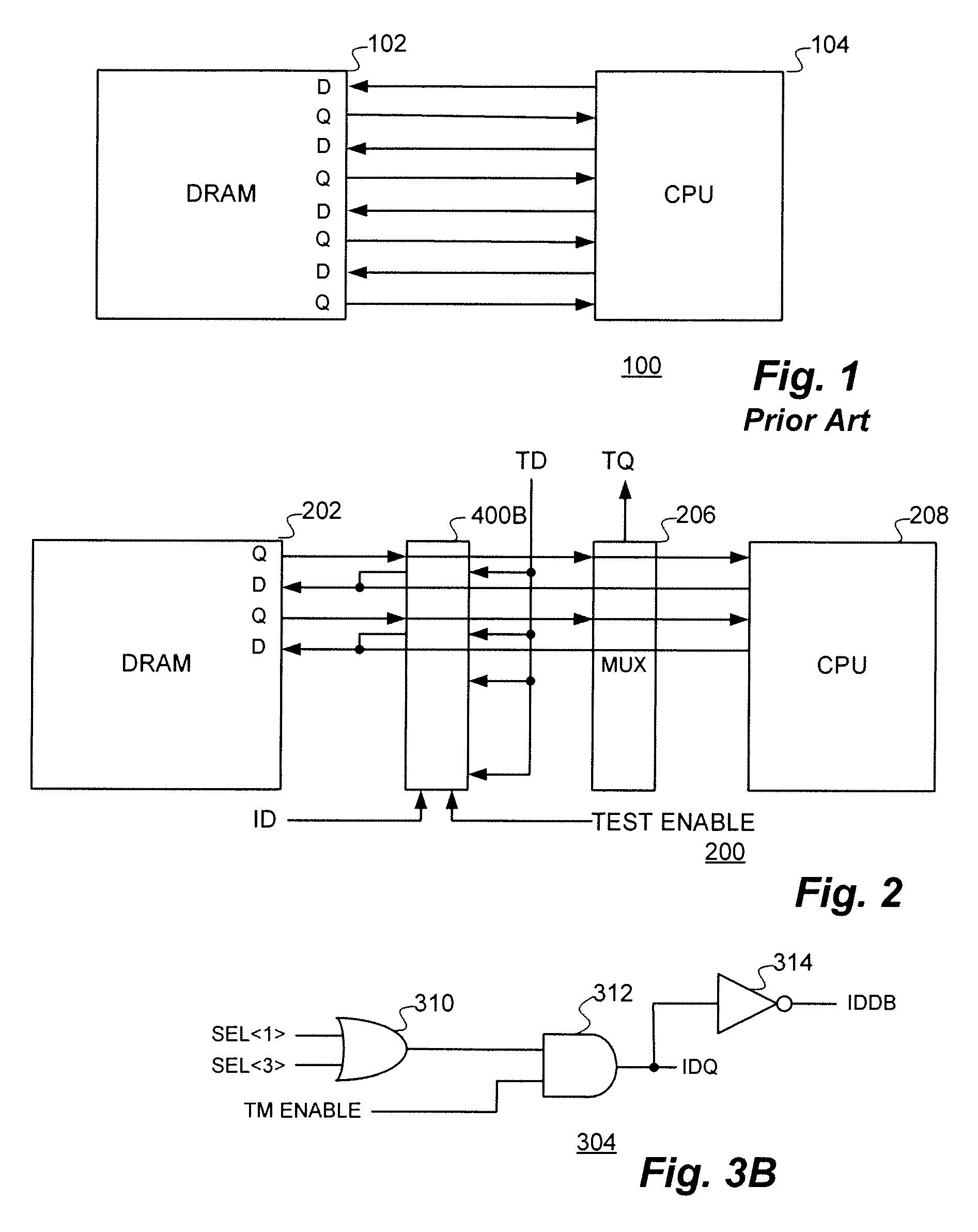

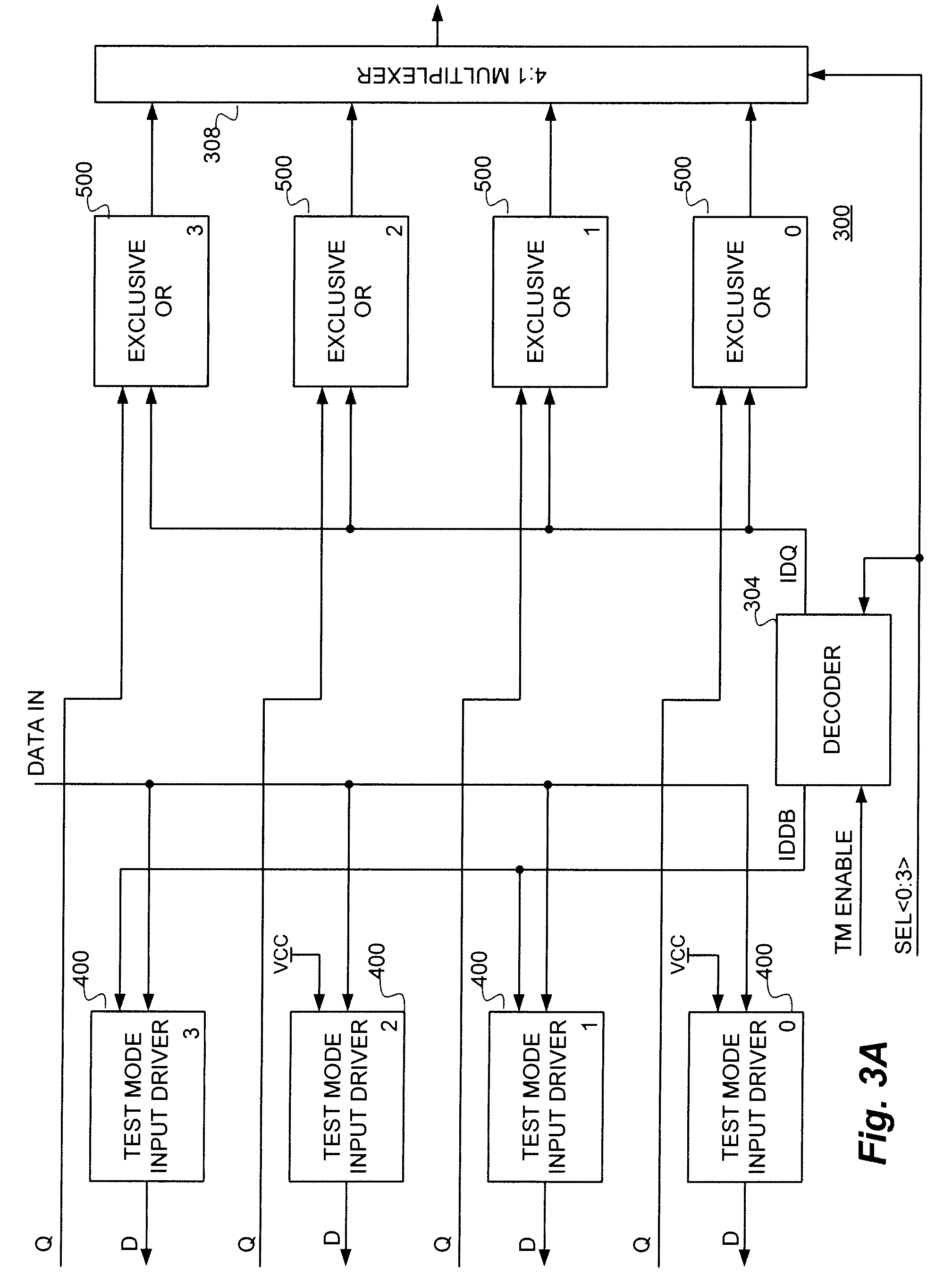

Data inversion register technique for integrated circuit memory testing

ActiveUS7631233B2Maximize probabilityReduce in quantityError preventionElectronic circuit testingMemory testerProcessor register

A data inversion register technique for integrated circuit memory testing in which data input signals are selectively inverted in a predetermined pattern to maximize the probability of identifying failures during testing. In accordance with the technique of the present invention, on predetermined input / outputs (I / Os,) data inputs may be inverted to create a desired test pattern (such as data stripes) which are “worst case” for I / O circuitry or column stripes which are “worst case” for memory arrays. A circuit in accordance with the technique of the present invention then matches the pattern for the data out path, inverting the appropriate data outputs to obtain the expected tester data. In this way, the test mode is transparent to any memory tester.

Owner:INVENSAS CORP

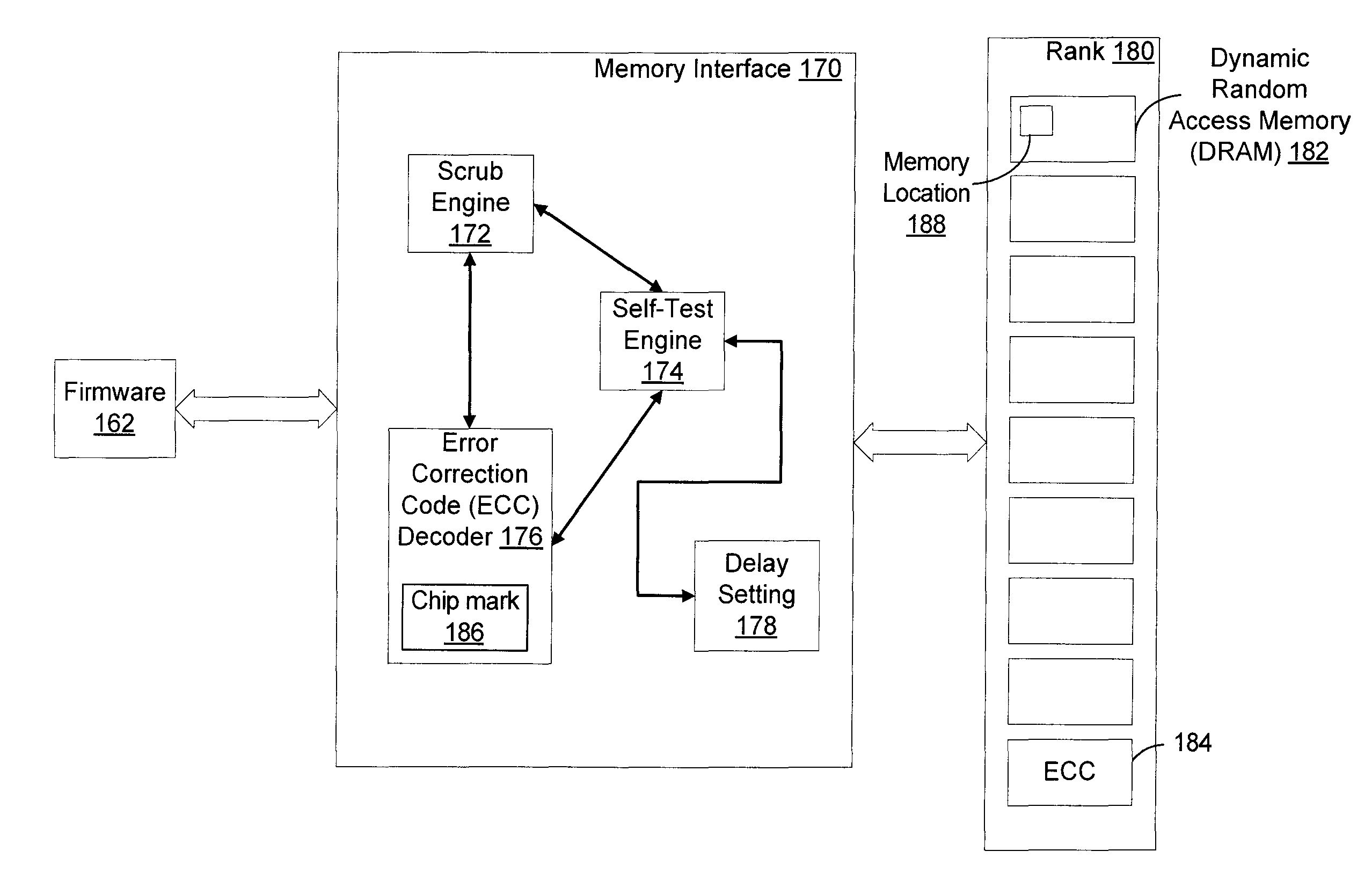

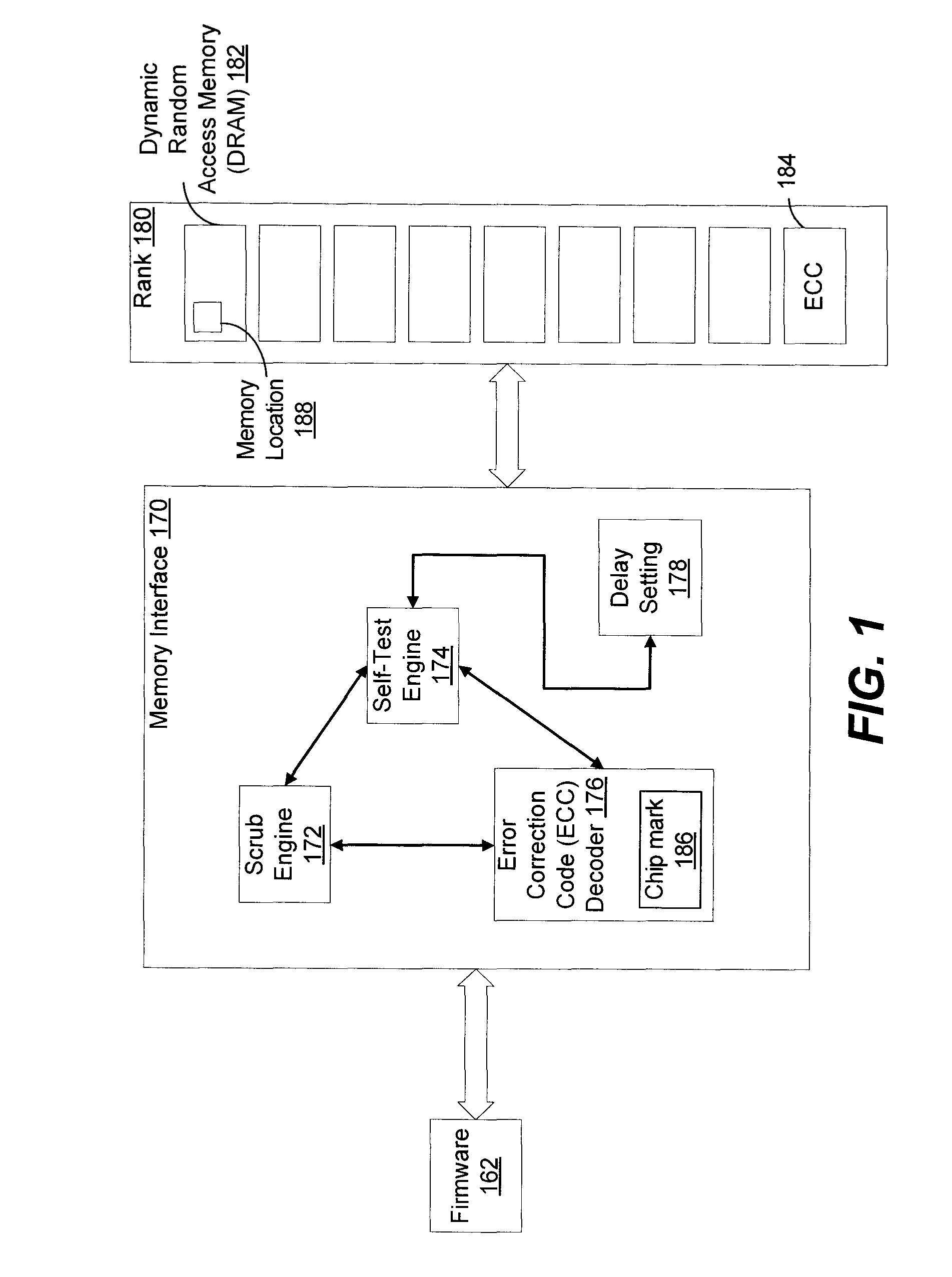

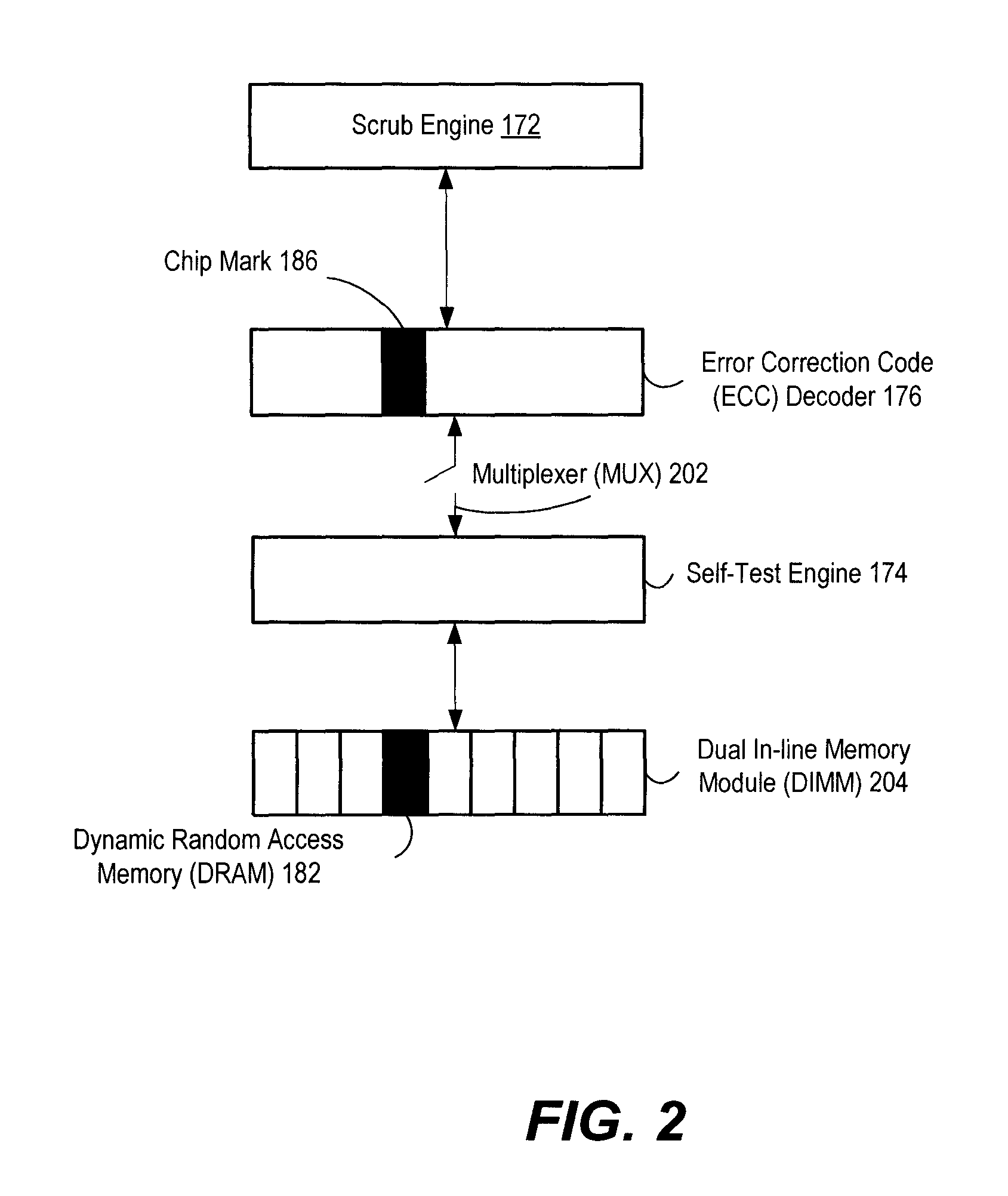

Memory testing with selective use of an error correction code decoder

InactiveUS20140195867A1Error detection/correctionStatic storageBiological activationComputer science

A method includes directing an access of a memory location of a memory device to an error correction code (ECC) decoder in response to receiving a test activation request indicating the memory location. The method also includes writing a test pattern to the memory location and reading a value from the memory location. The method further includes determining whether a fault is detected at the memory location based on a comparison of the test pattern and the value.

Owner:IBM CORP

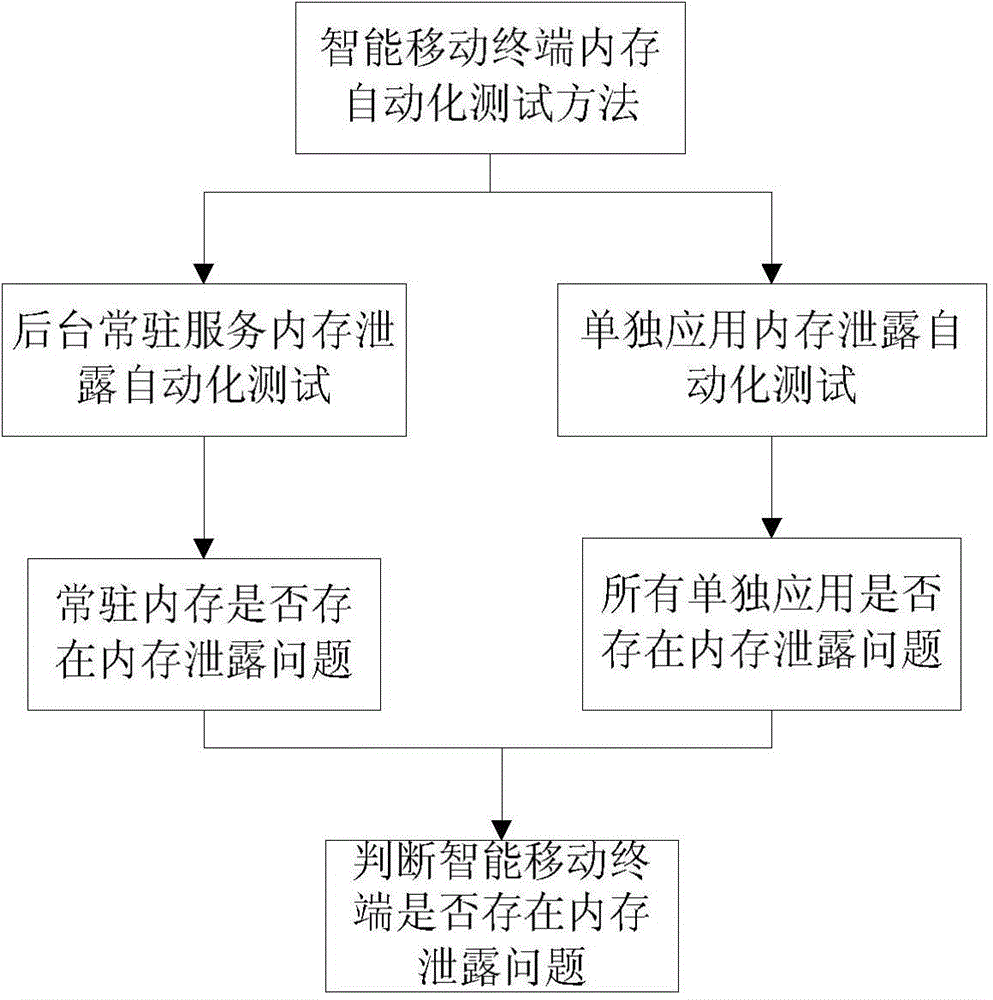

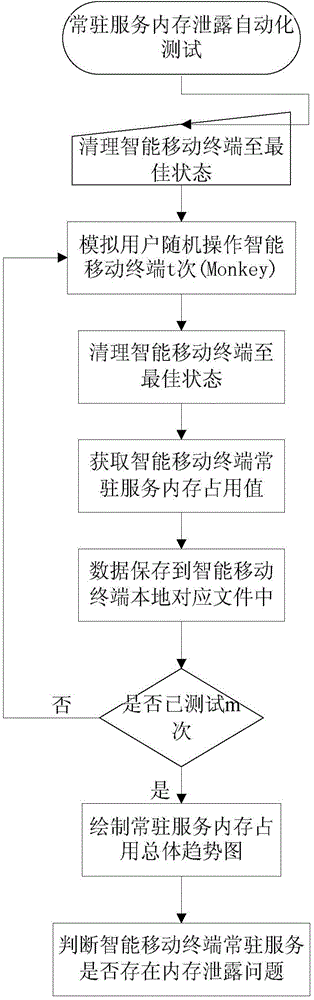

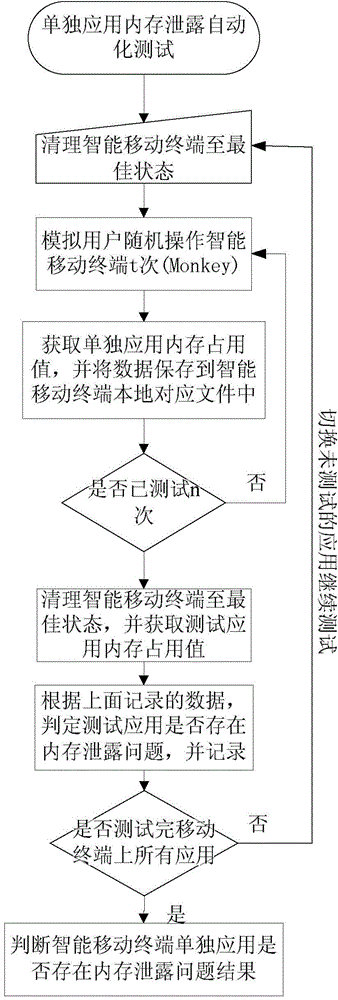

Method and device for automatic testing of memory of intelligent mobile terminal

ActiveCN104317702AEnsure comprehensivenessQuality assuranceSoftware testing/debuggingComputer terminalUltimate tensile strength

The invention discloses a method for automatic testing of a memory of an intelligent mobile terminal, which is applied to the intelligent mobile terminal using an Android operation system. The method comprises two parts, namely automatic testing and judgment of memory leakage problems of resident services of the intelligent mobile terminal, and automatic testing and judgment of memory leakage problems of a single application, so the completeness of the memory leakage testing is guaranteed, the testing frequency each time and the recording frequency of memory values can be set, the stronger memory testing can be performed, and the relevant quality of the memory of the intelligent mobile terminal using the Android operation system is furthest guaranteed. The method has the advantages that the whole testing process is the full-automatic process, so the participation of persons is not needed in the testing process; a testing result report is automatically generated after the testing is finished, so the testing efficiency of the memory is greatly improved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

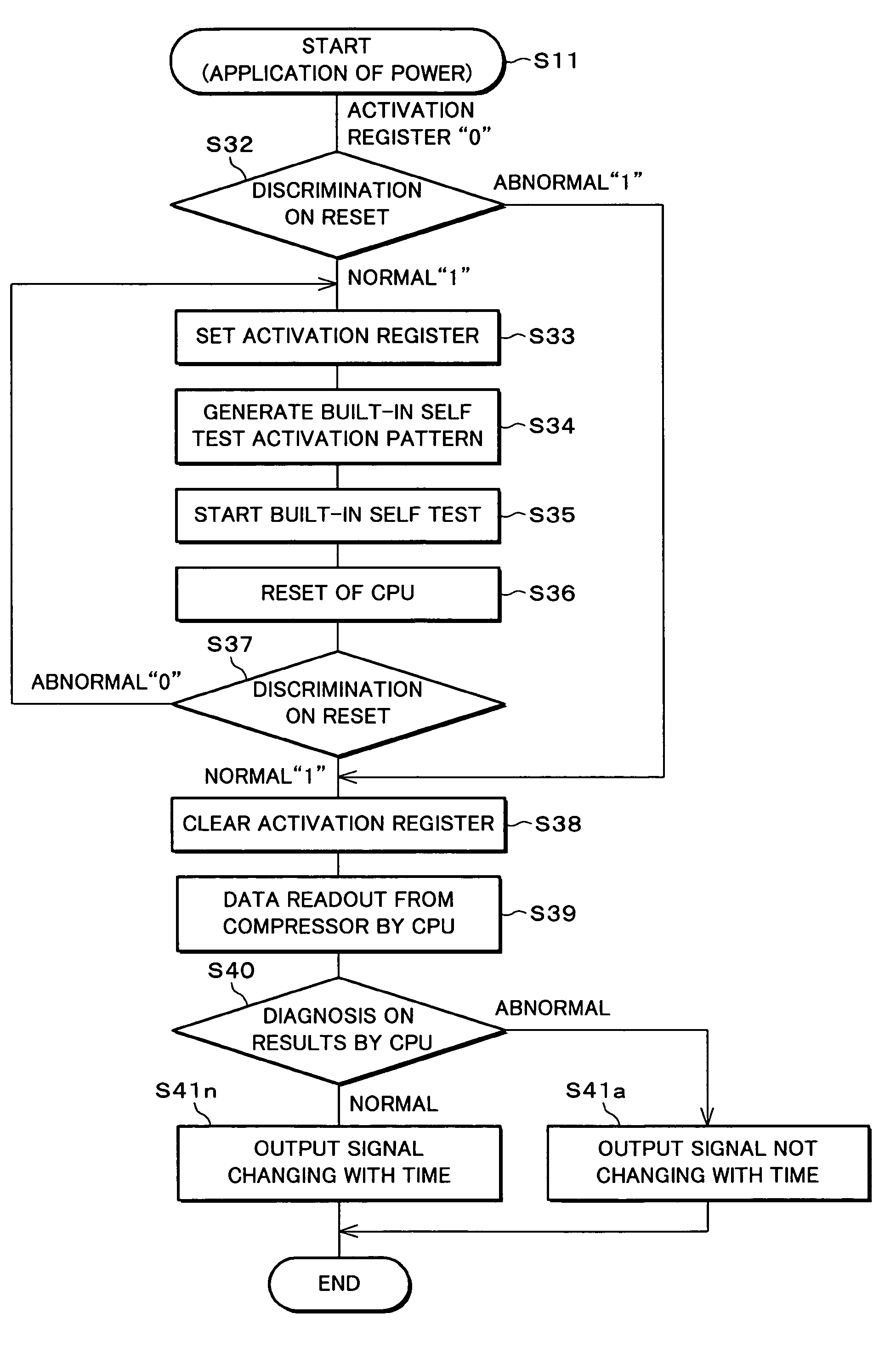

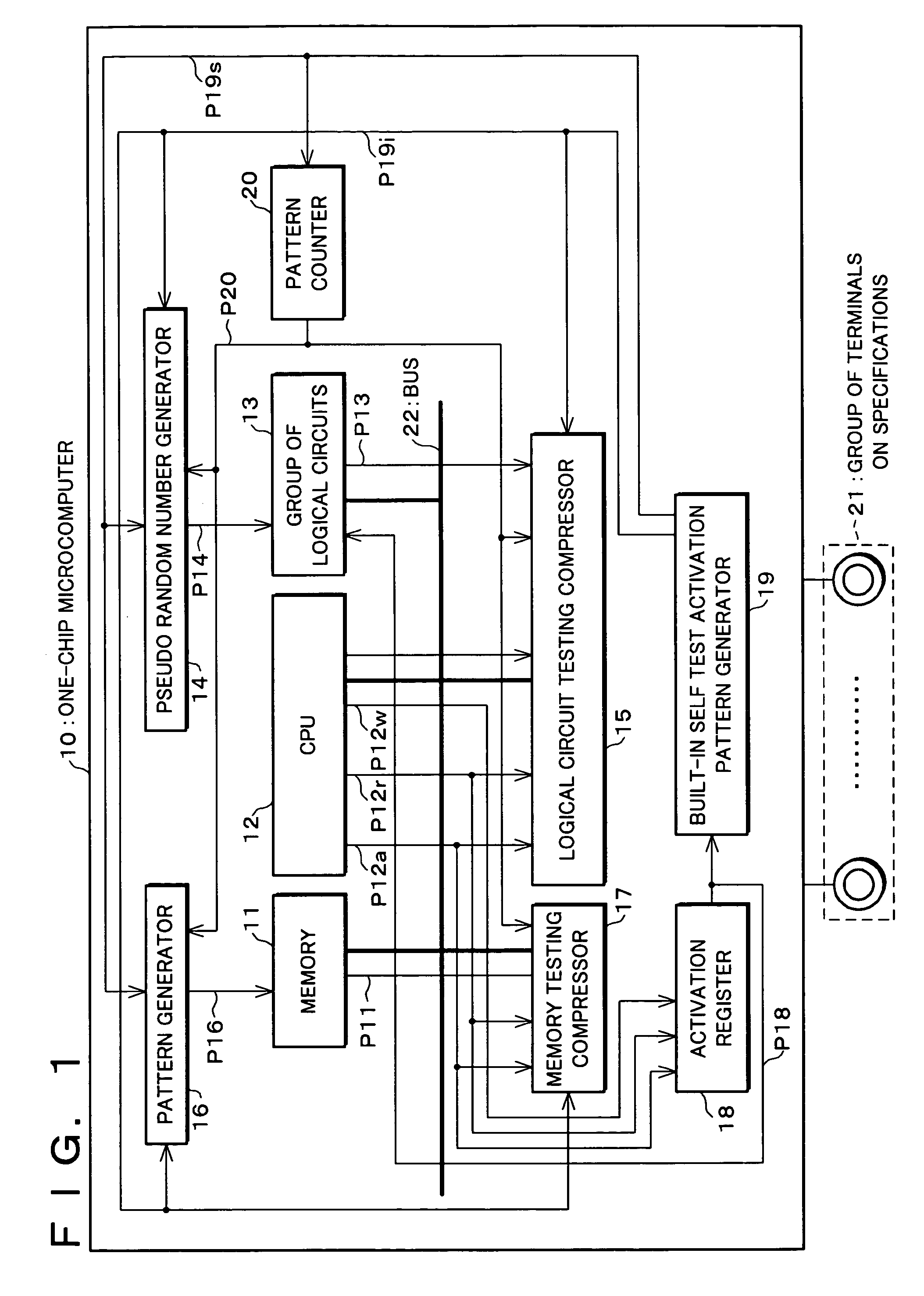

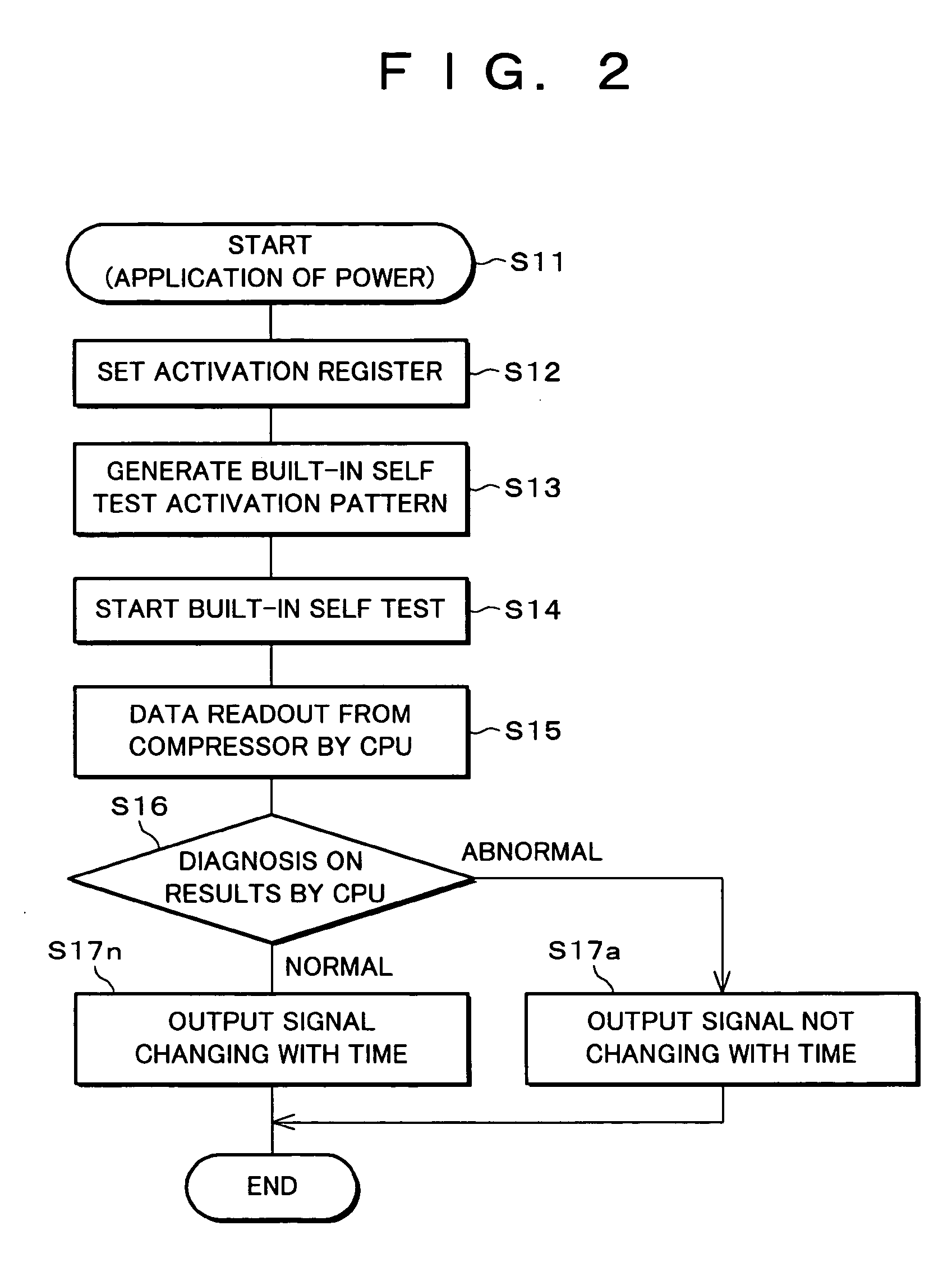

One-chip microcomputer and control method thereof as well as an IC card having such a one-chip microcomputer

InactiveUS6934884B1Increase the number ofDevelopment periodElectronic circuit testingFunctional testingMicrocontrollerBiological activation

In order to provide a built-in self testing function, a one-chip microcomputer is equipped with an activation register for activating the test operation and a built-in self test activation pattern generator for setting initial values at test control circuits (pseudo random number generator, logical circuit testing compressor, pattern generator, and memory testing compressor). In accordance with an instruction from the CPU, a built-in self test is activated so that the results of tests of the memory and the group of logical circuits are read from the memory testing compressor and the logical circuit testing compressor, and respectively compared with expected values preliminarily stored in the memory in the one-chip microcomputer; thus, the results are diagnosed. Thus, it is possible to carry out a built-in self test without using a plurality of exclusively-used test terminals.

Owner:SHARP KK +1

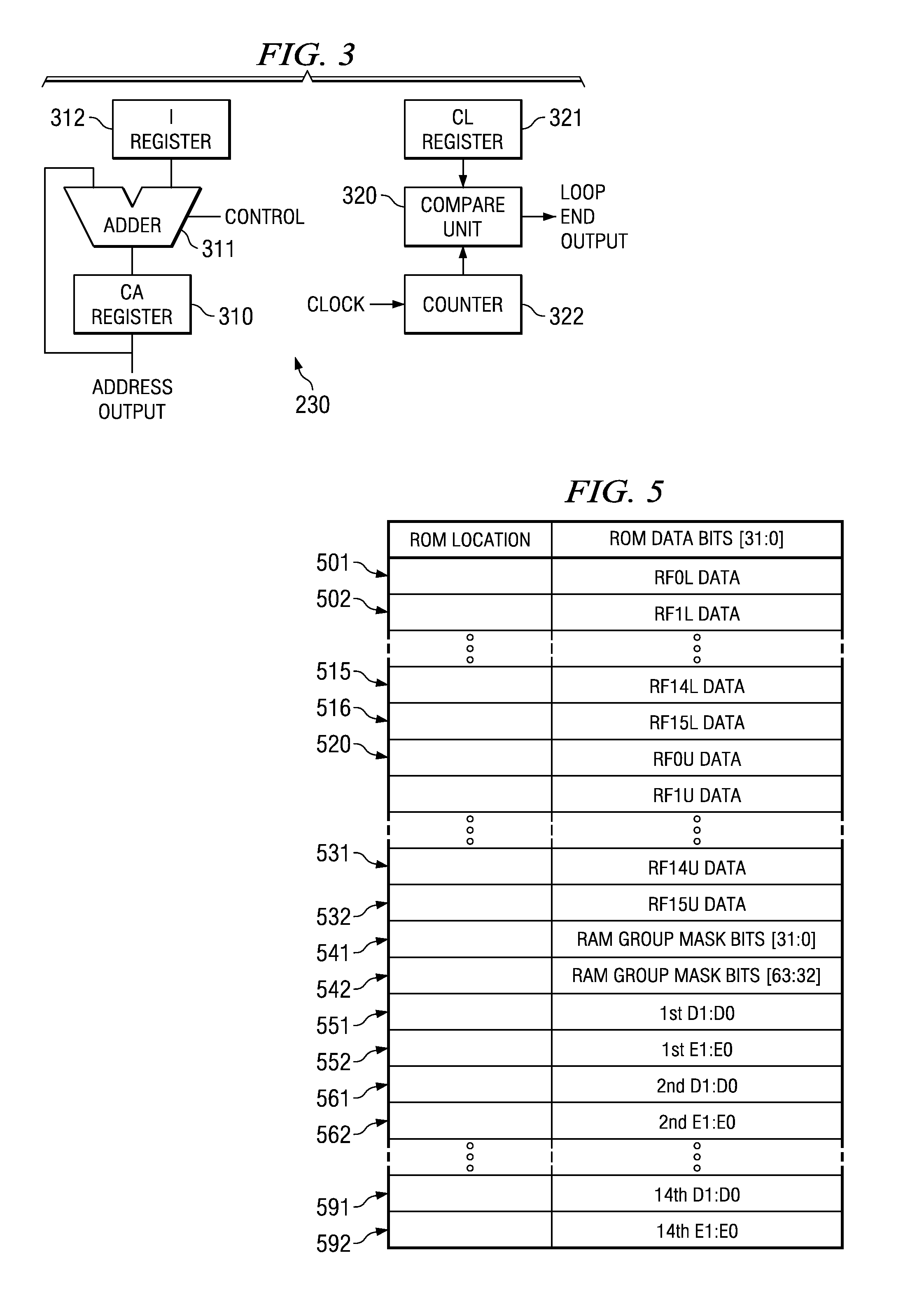

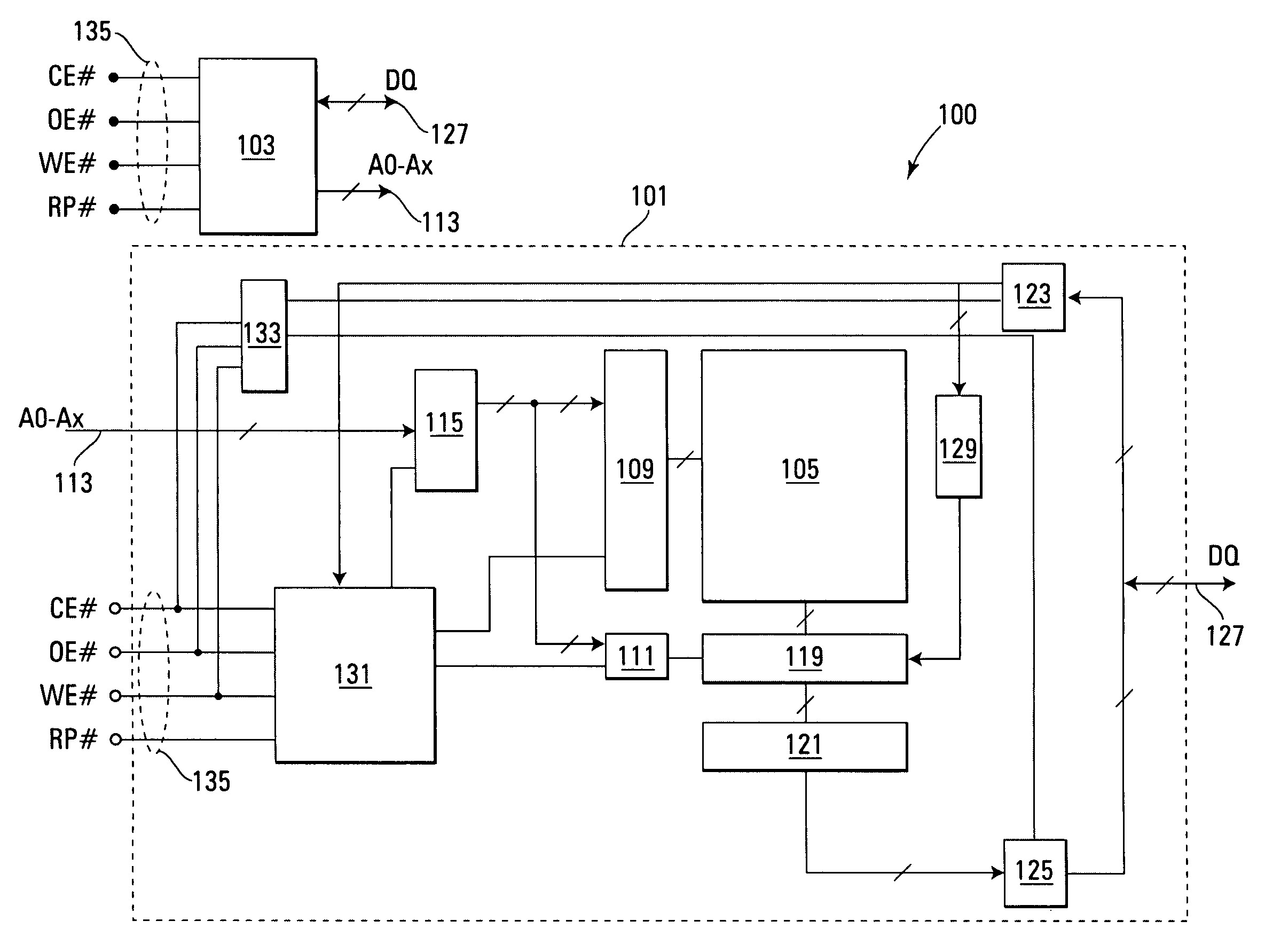

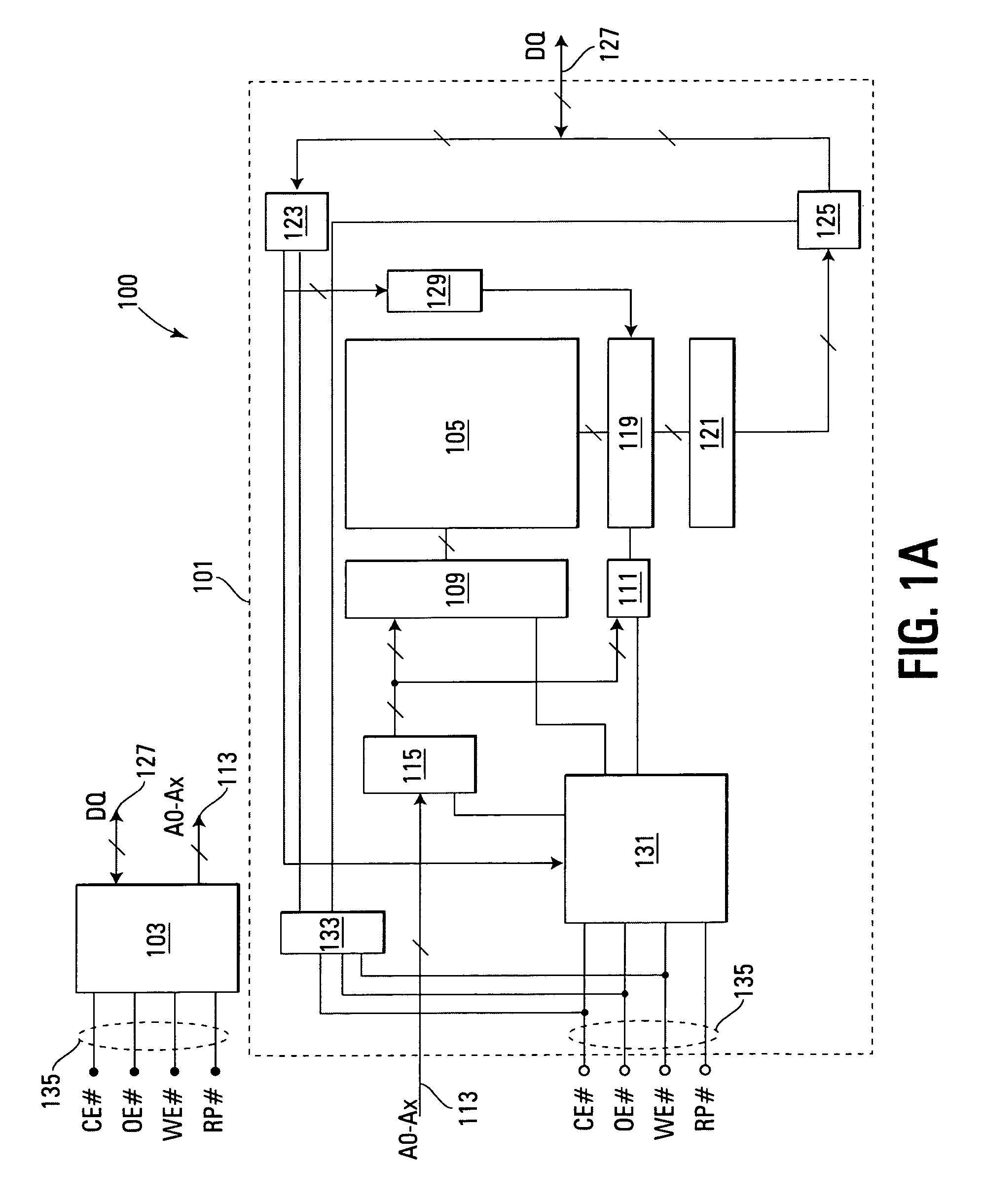

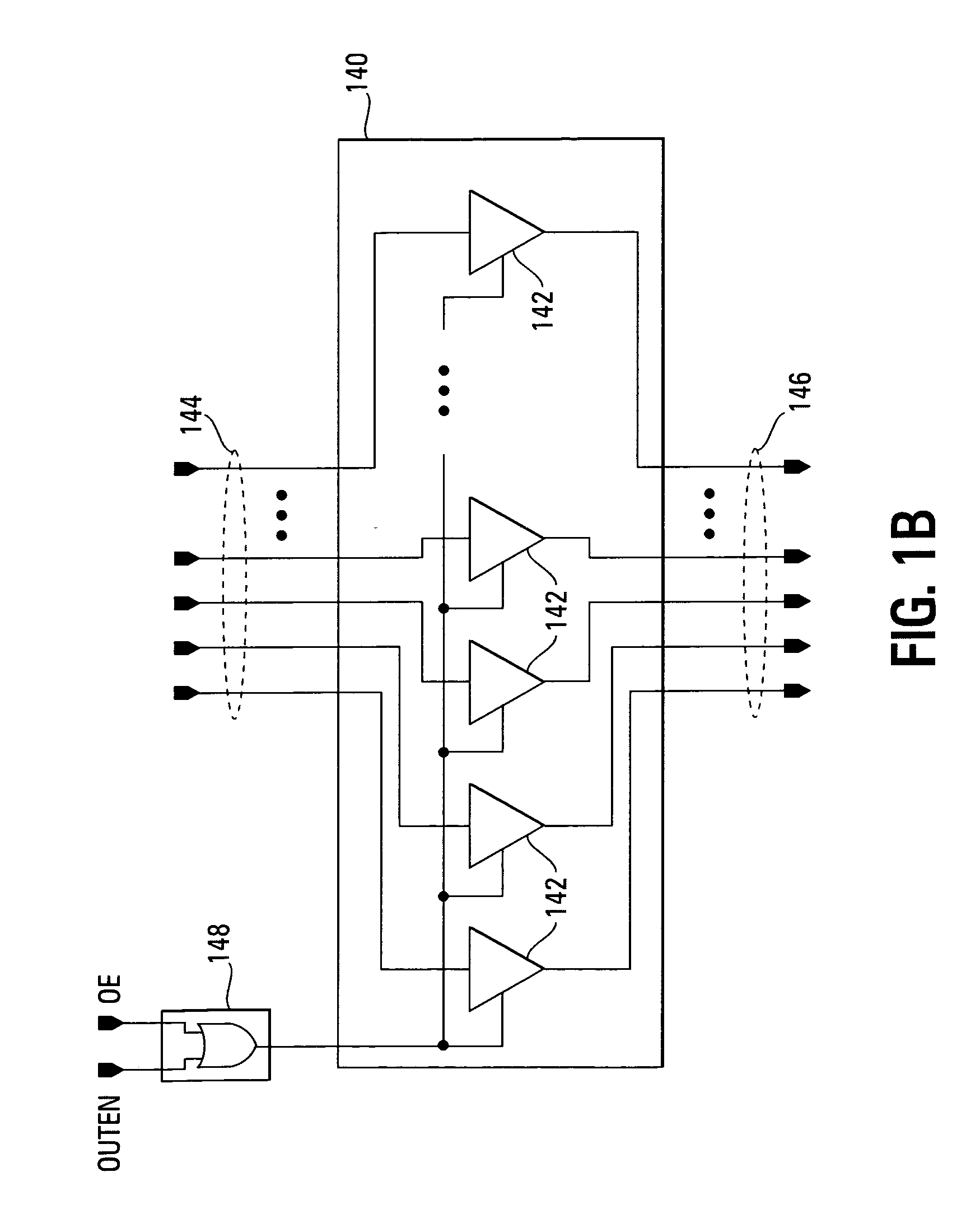

ROM-based memory testing

ActiveUS7324392B2Sufficient flexibilityElectronic circuit testingError detection/correctionData informationProcessor register

Owner:TEXAS INSTR INC

Data compression read mode for memory testing

InactiveUS20050213397A1Improve reliabilityAccurate timingError preventionElectronic circuit testingData compressionNormal mode

Memory devices having a normal mode of operation and a test mode of operation are useful in quality programs. The test mode of operation includes a data compression test mode. In the data compression test mode, reading one word of an output page provides an indication of the data values of the remaining words of the output page. The time necessary to read and verify a repeating test pattern can be reduced as only one word of each output page need be read to determine the ability of the memory device to accurately write and store data values. The memory devices include data compression circuits to compare data values for each bit location of each word of the output page. Output is selectively disabled if a bit location for one word of the output page has a data value differing from any remaining word of the output page.

Owner:MICRON TECH INC

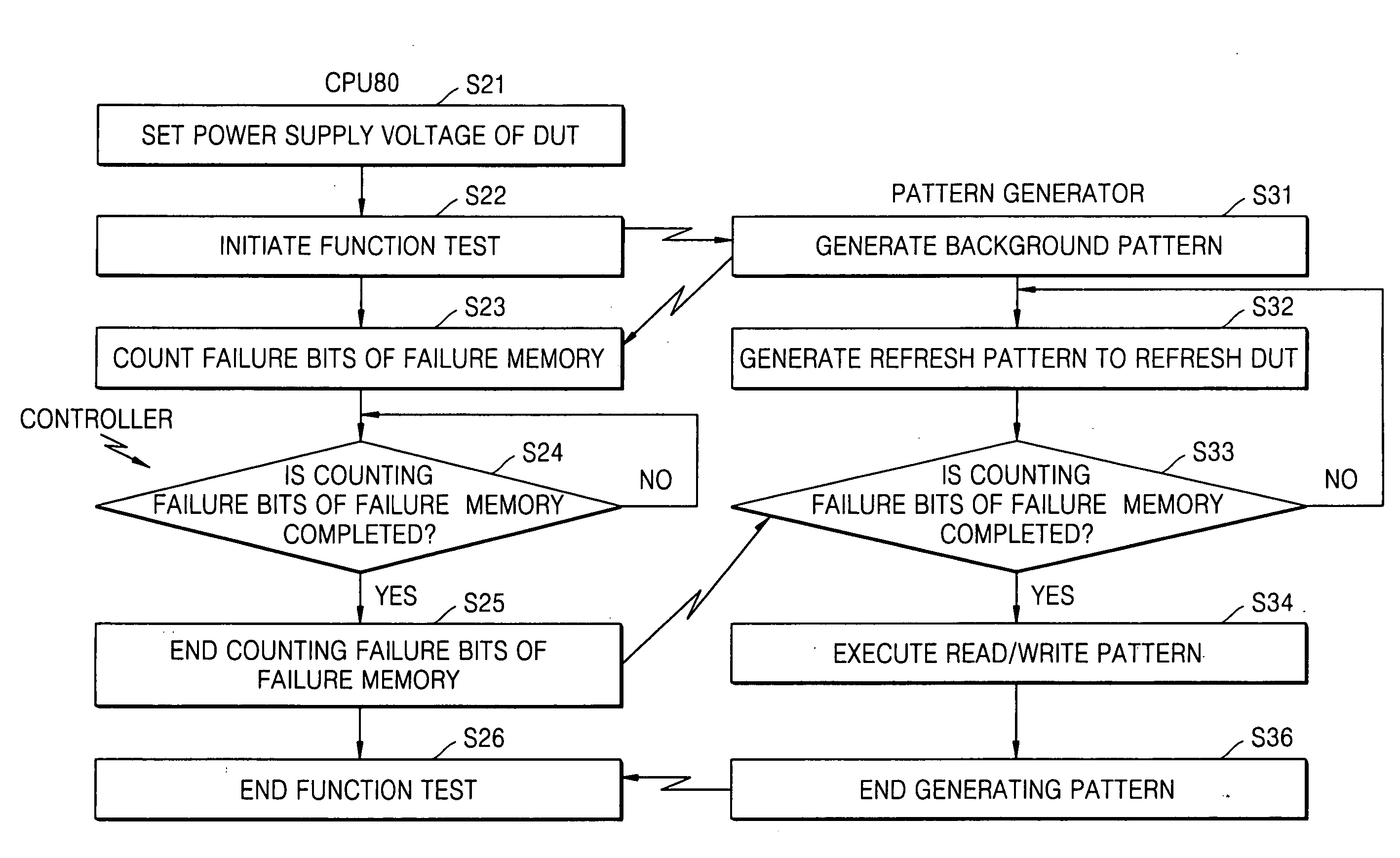

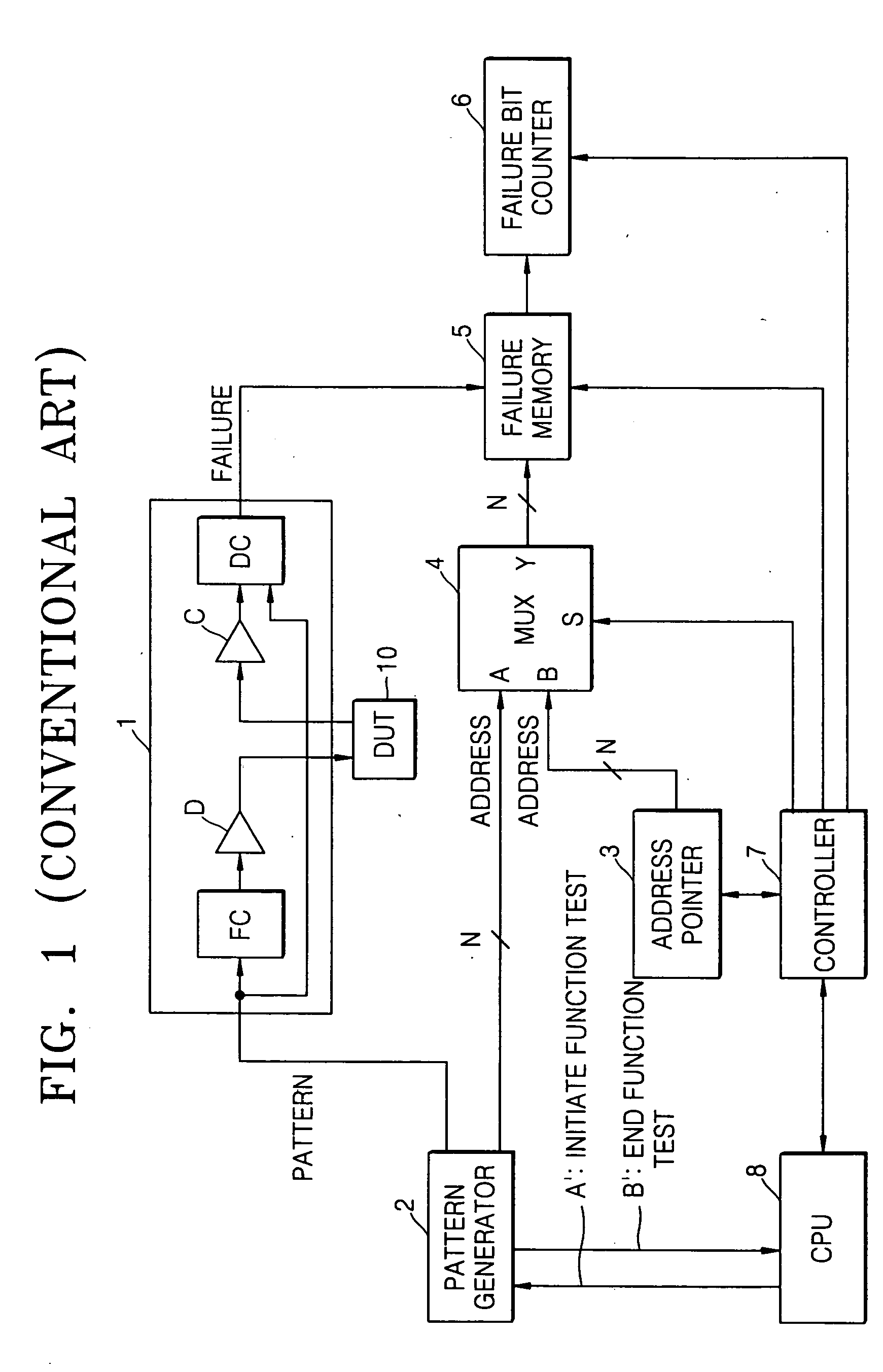

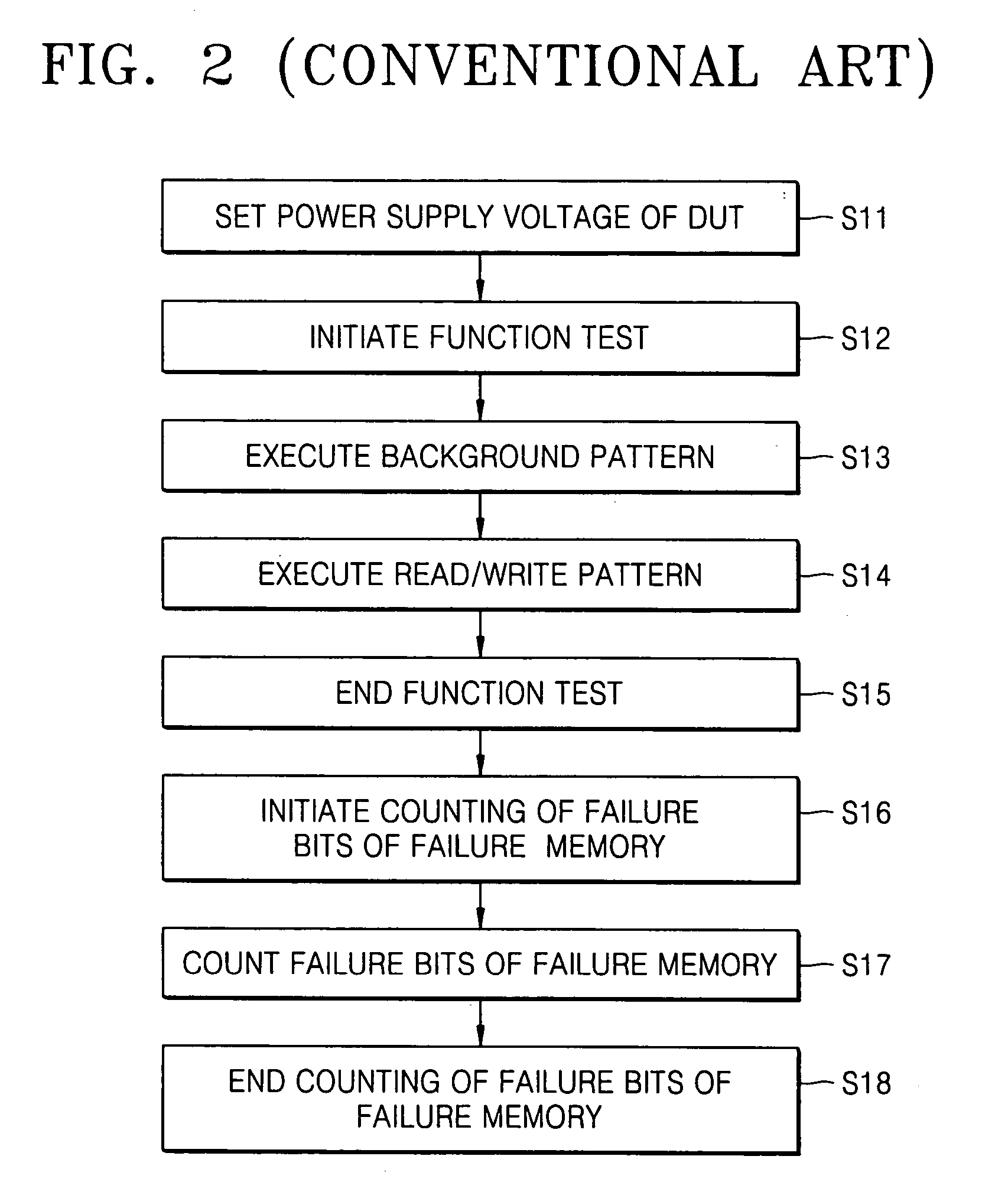

Memory testing apparatus and method

ActiveUS20050043912A1Shorten the timeSemiconductor/solid-state device testing/measurementElectronic circuit testingFunctional testingTerm memory

Provided are a memory device testing apparatus and method of operating such an apparatus that can reduce the time required to test a memory device such as a DRAM. The memory testing apparatus includes a pattern generator, a test head, an address pointer, a selector, a failure memory, a failure bit counter and a controller for coordinating the operation of the various elements. Depending on the signals received from the controller, the pattern generator will generate background pattern(s) or test patterns and address information that are, in turn, output to the memory device under test and the selector. During funtional testing of the memory device, failure data is accumulated in a failure memory and subsequently output to a failure bit counter using address information from the address pointer while the background or test pattern is being written to the memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

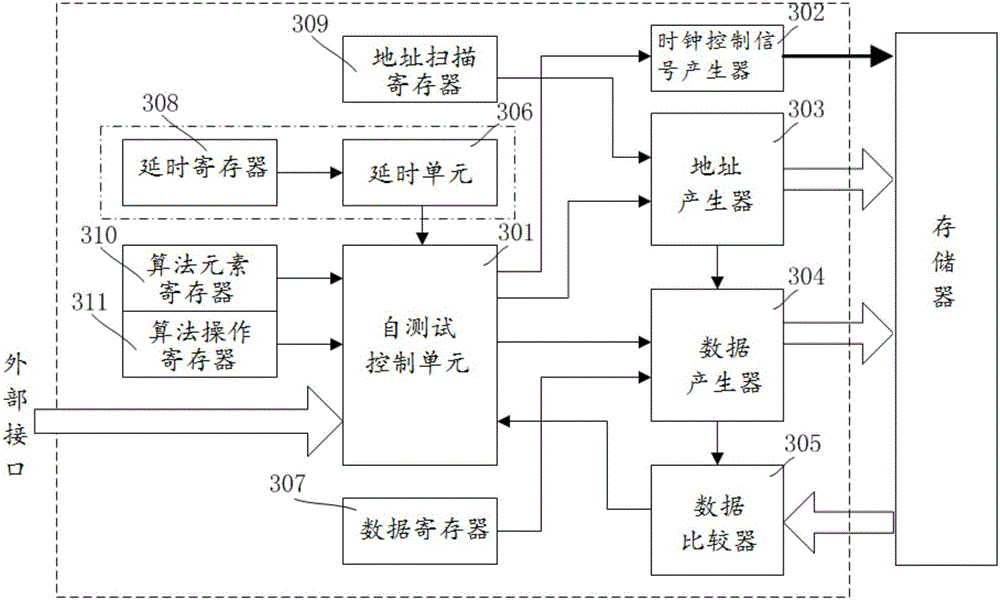

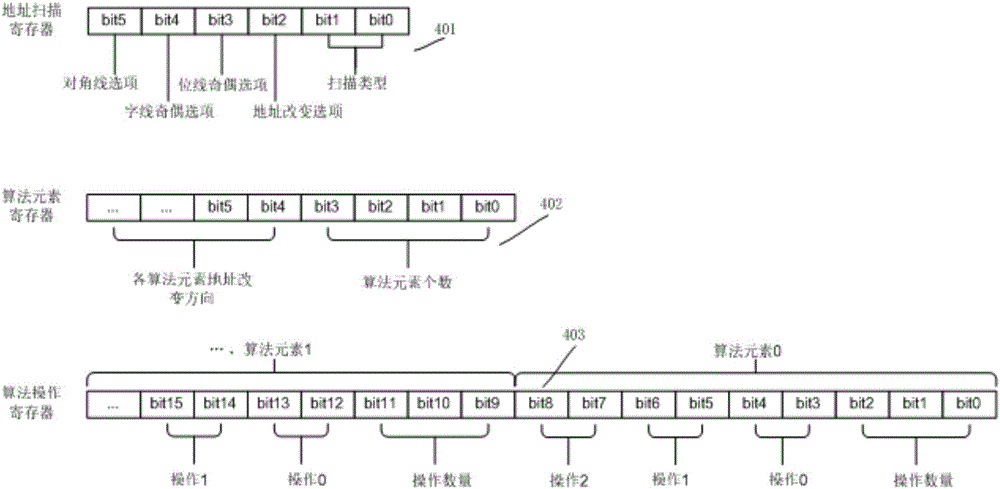

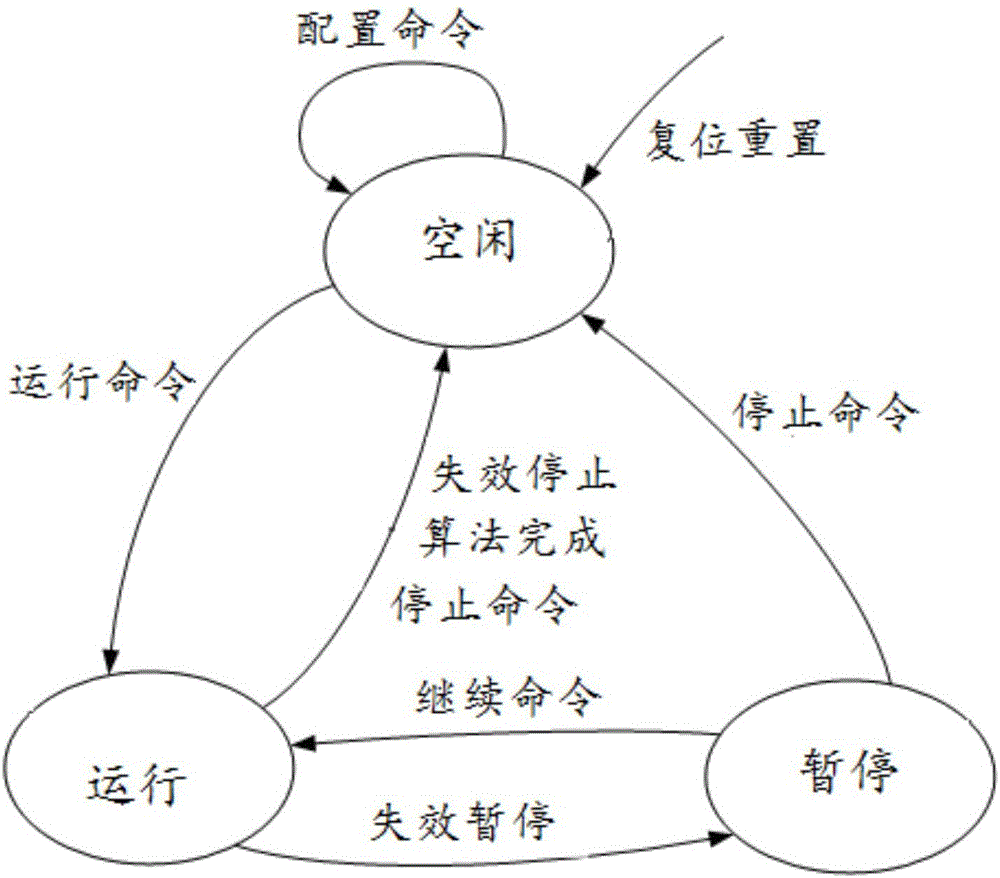

Built-in self-testing circuit of memory suitable for various periodic testing algorithms

ActiveCN106409343AReduce design difficultyImprove testing flexibilityStatic storageAddress generatorTest algorithm

The invention provides a built-in self-testing circuit of a memory suitable for various periodic testing algorithms. A composition module comprises a built-in self-testing control unit, a clock control signal generator, an address generator, a data generator, a data comparator, an optional delay unit and a plurality of control registers, wherein each control register comprises an address scanning register, an algorithm element register, an algorithm operation register, a data register and a delay register; the built-in self-testing control unit controls other modules to cooperatively work; the clock control signal generator, the address generator and the data generator generate a clock control signal, an address signal and a data signal required by the memory for operation respectively; and the data comparator judges the data reading correctness of the memory and feeds the result back to the built-in self-testing control unit. Various common periodic memory testing algorithms can be achieved by arranging the control registers; and testing and problem analysis work of the memory can be conveniently completed by a corresponding command and an operating state machine design.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

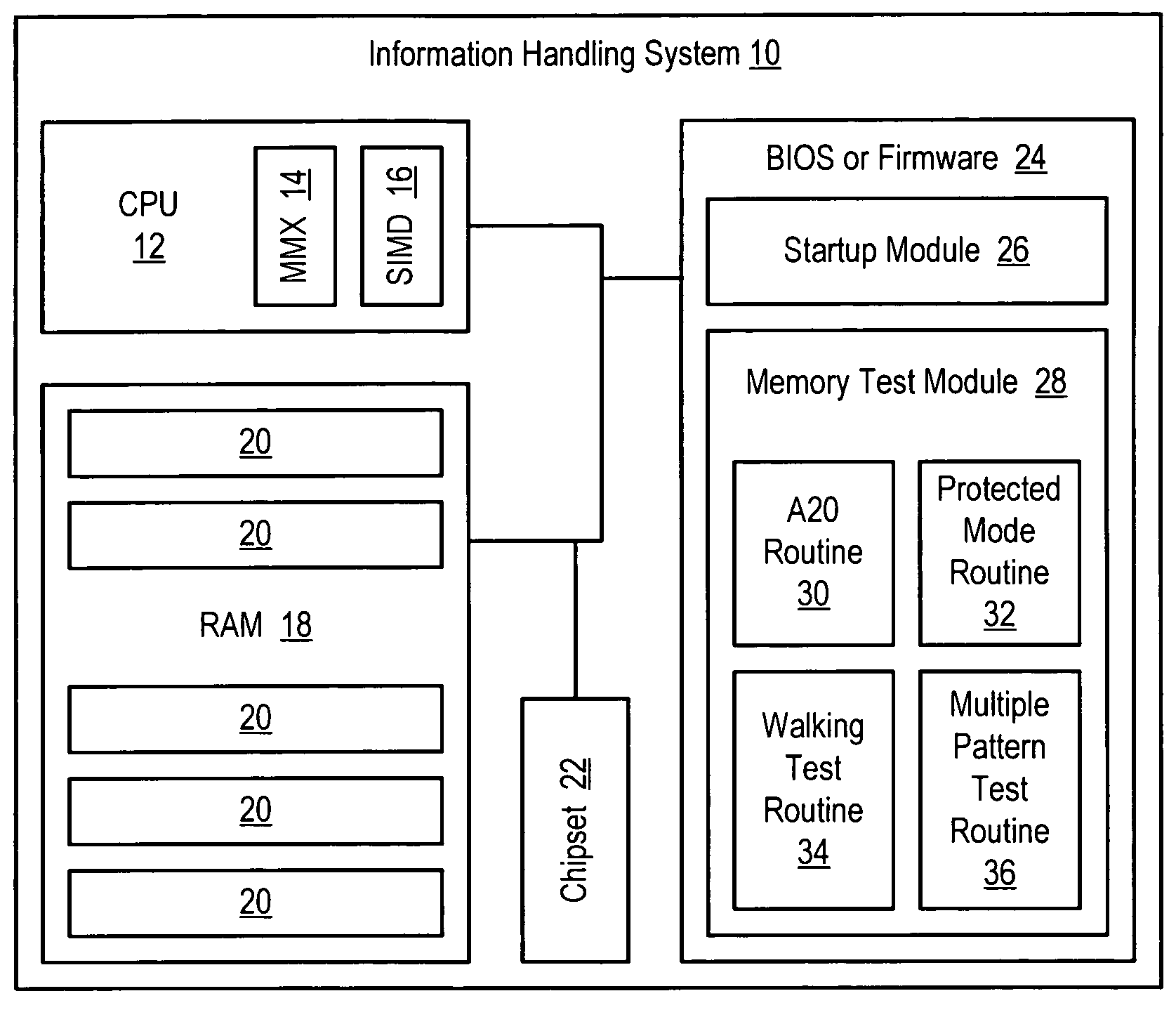

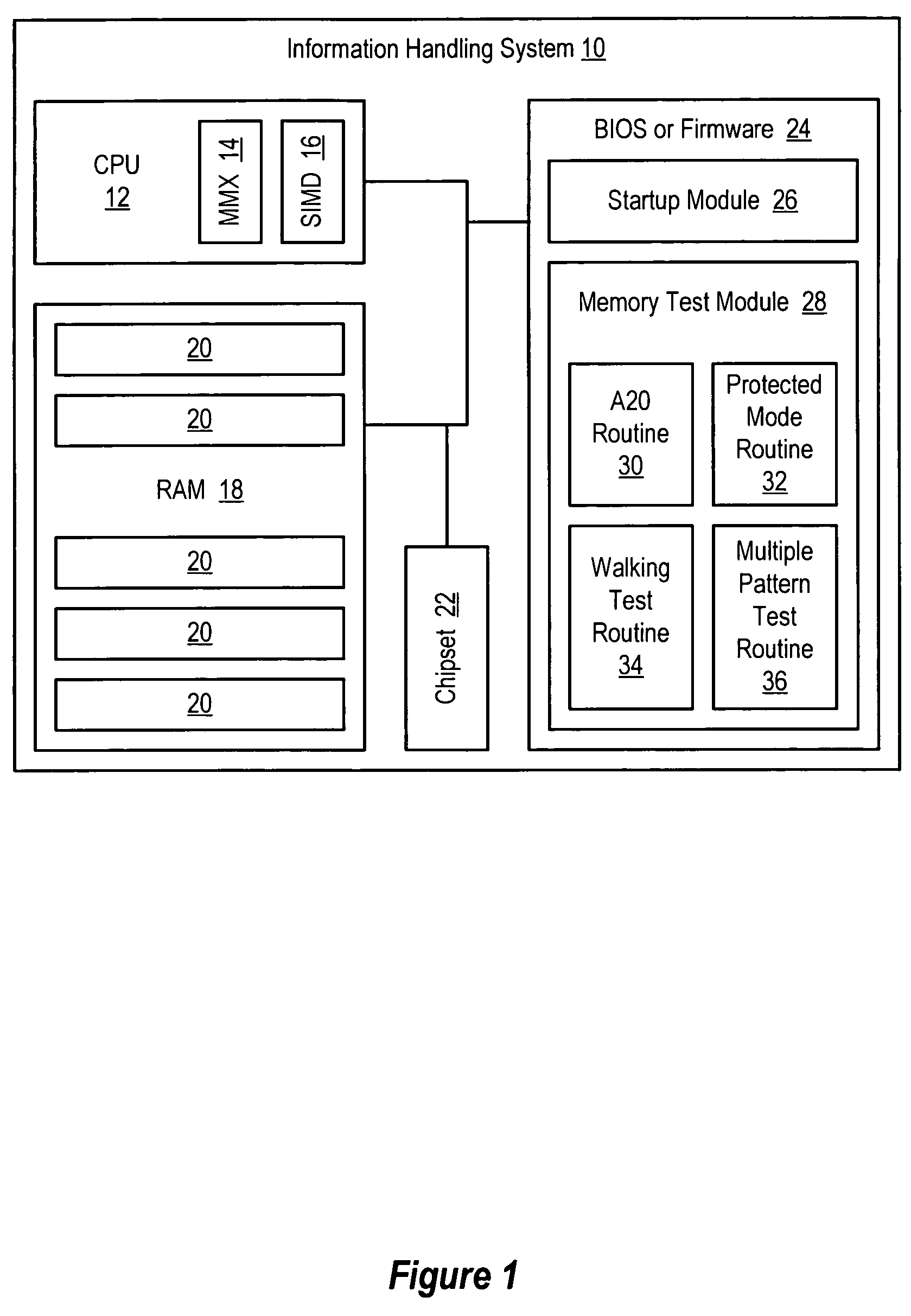

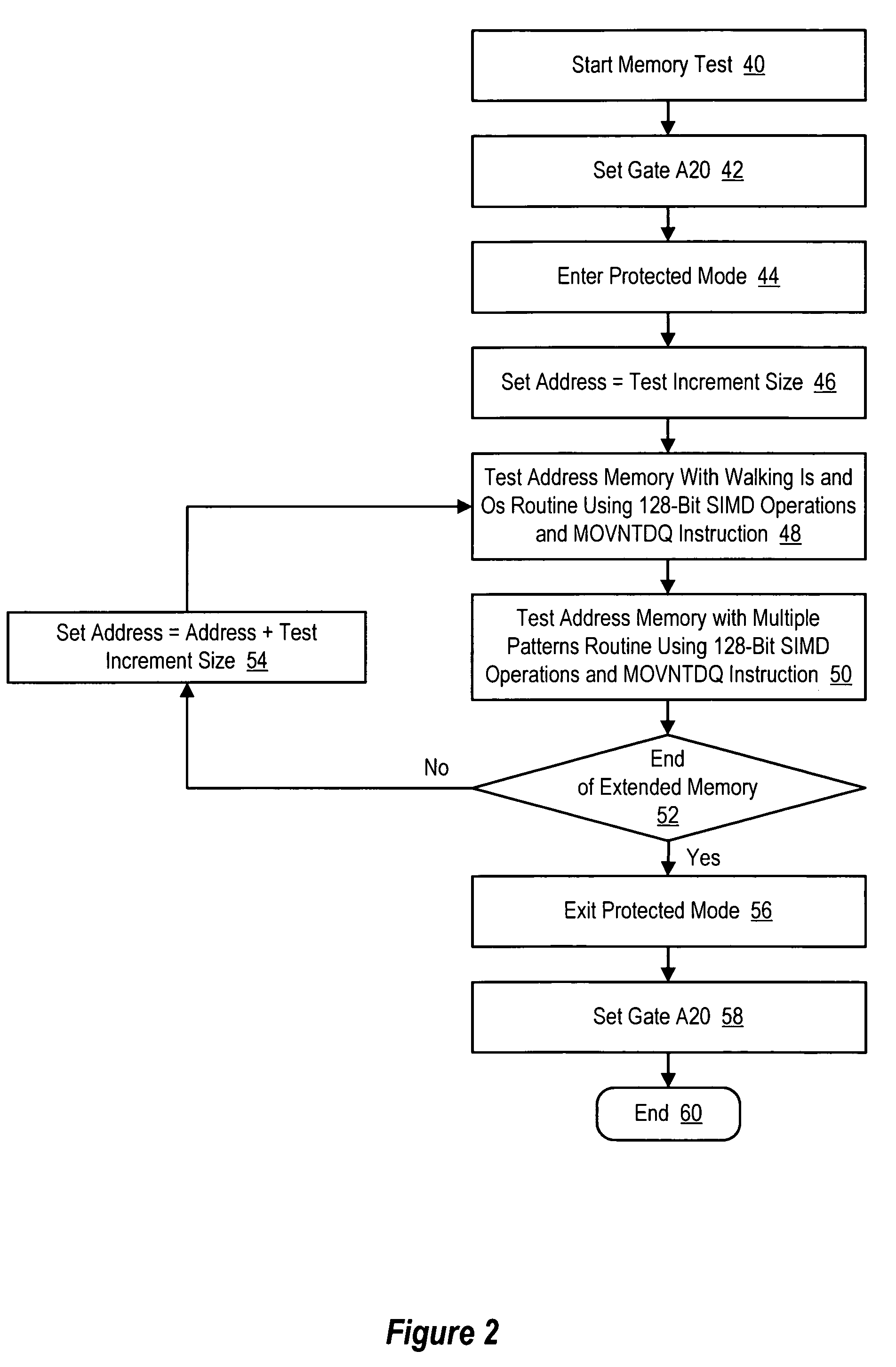

System and method for accelerated information handling system memory testing

ActiveUS7325176B2Easy to testReduce disadvantagesError detection/correctionDigital storageCpu architectureProtected mode

Owner:DELL PROD LP

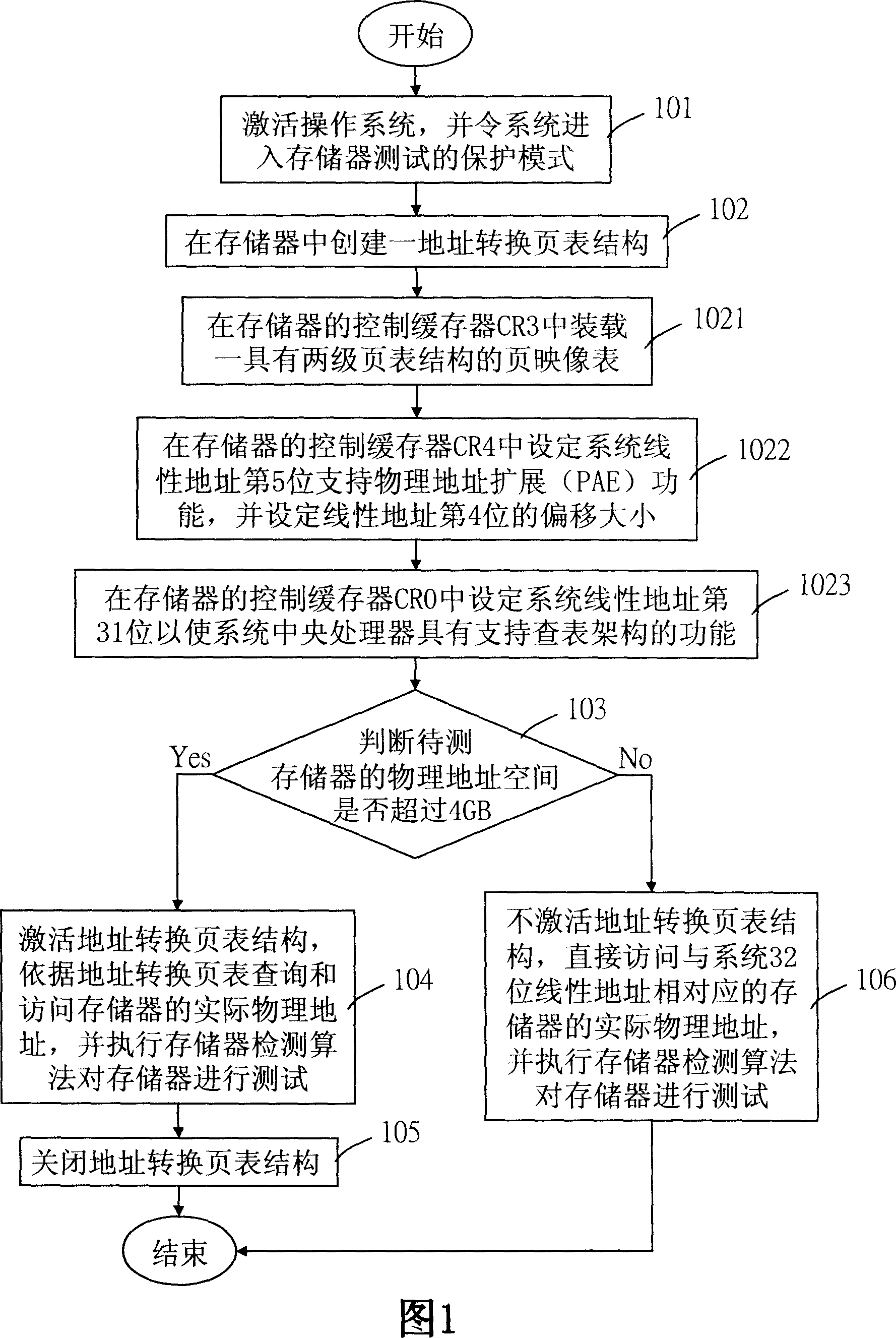

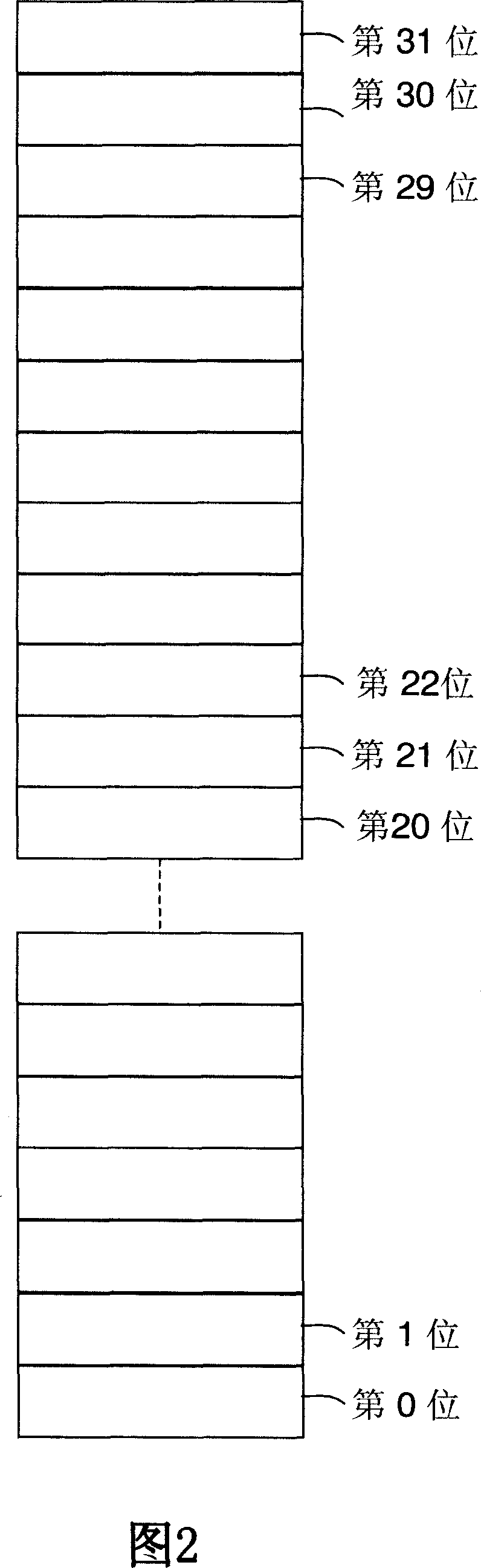

Method of testing memory

InactiveCN1920783AExpand the scope of testingReduce testing costsError detection/correctionMemory adressing/allocation/relocationMemory addressOperational system

The invention relates to a memory testing method, wherein it comprises: activating operation system, to make the system enter into protective mode of memory test; building one address transfer page list in memory; judging if the physical address space of memory is over 4GB; if it is, activating address transfer page list, to transform appointed 32-bit linear address to relate with real physical address of memory; controlled by system central processor, based on the address transfer page list, inquiring and accessing the real physical address of memory, and executing the memory test algorism to test memory; if it is not, controlled by system central processor, directly accessing the real physical address of memory relative to the 32-bit linear address of system, and executing memory test algorism to test the memory. The invention can access and test the accidence and failure of memory address space more than 4GB, to improve the memory test range and save test cost.

Owner:XUZHOU LIFANG MECHANICAL & ELECTRICAL EQUIP MFG CO LTD

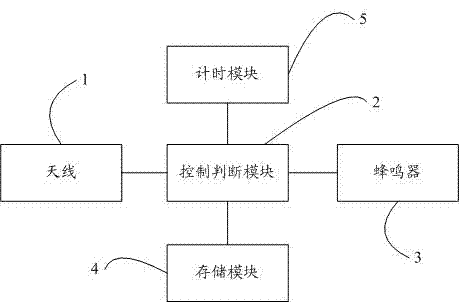

Testing method for remote control buttons and testing device

InactiveCN103033713AEasy to testAvoid mistakesCircuit interrupters testingRemote controlComputer module

The invention provides a testing device used for a testing method for remote control buttons. The testing device comprises a signal receiving module, a control judging module and a prompt device which are connected in sequence. The testing device further comprises a memory module and a timing module which are respectively connected with the control judging module. The invention further provides the testing method for the remote control buttons. According to the testing method and the testing device, mistakes caused by relying of manual visual and memory testing are avoided, efficiency is improved, probability of missing detection can be reduced to the greatest extent, products in a large scale are convenient to test, producing and testing efficiency is improved, and product quality is guaranteed.

Owner:SHENZHEN C&D ELECTRONICS

Multiple-level data compression read more for memory testing

ActiveUS20060044880A1Improve end-use reliabilityImprove test efficiencyElectronic circuit testingCode conversionData compressionNormal mode

Memory devices having a normal mode of operation and a test mode of operation are useful in quality programs. The test mode of operation includes a data compression test mode having more than one level of compression. The time necessary to read and verify a repeating test pattern can be reduced as only a fraction of the words of the memory device need be read to determine the ability of the memory device to accurately write and store data values. Output is selectively disabled if a bit location for one word of a group of words has a data value differing from any remaining word of its group of words for a number of groups of words.

Owner:MICRON TECH INC