System and method for accelerated information handling system memory testing

a technology of information handling system and memory testing, applied in the field of information handling system memory testing, can solve the problems of excessive startup time, reduced memory cost of all types, and increased system startup time, so as to accelerate memory testing of information handling system, reduce disadvantages and problems, and efficiently and quickly execute the test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

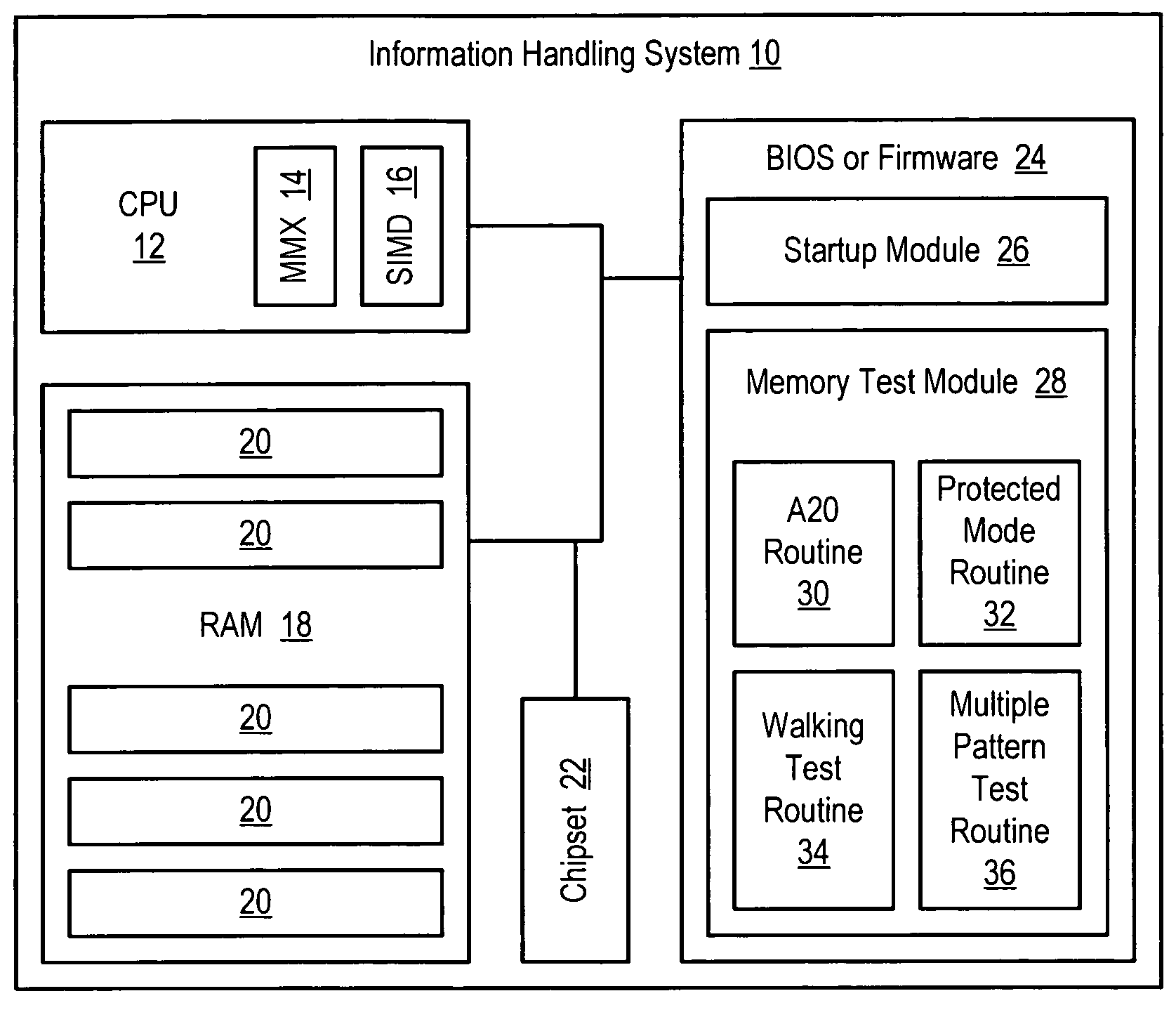

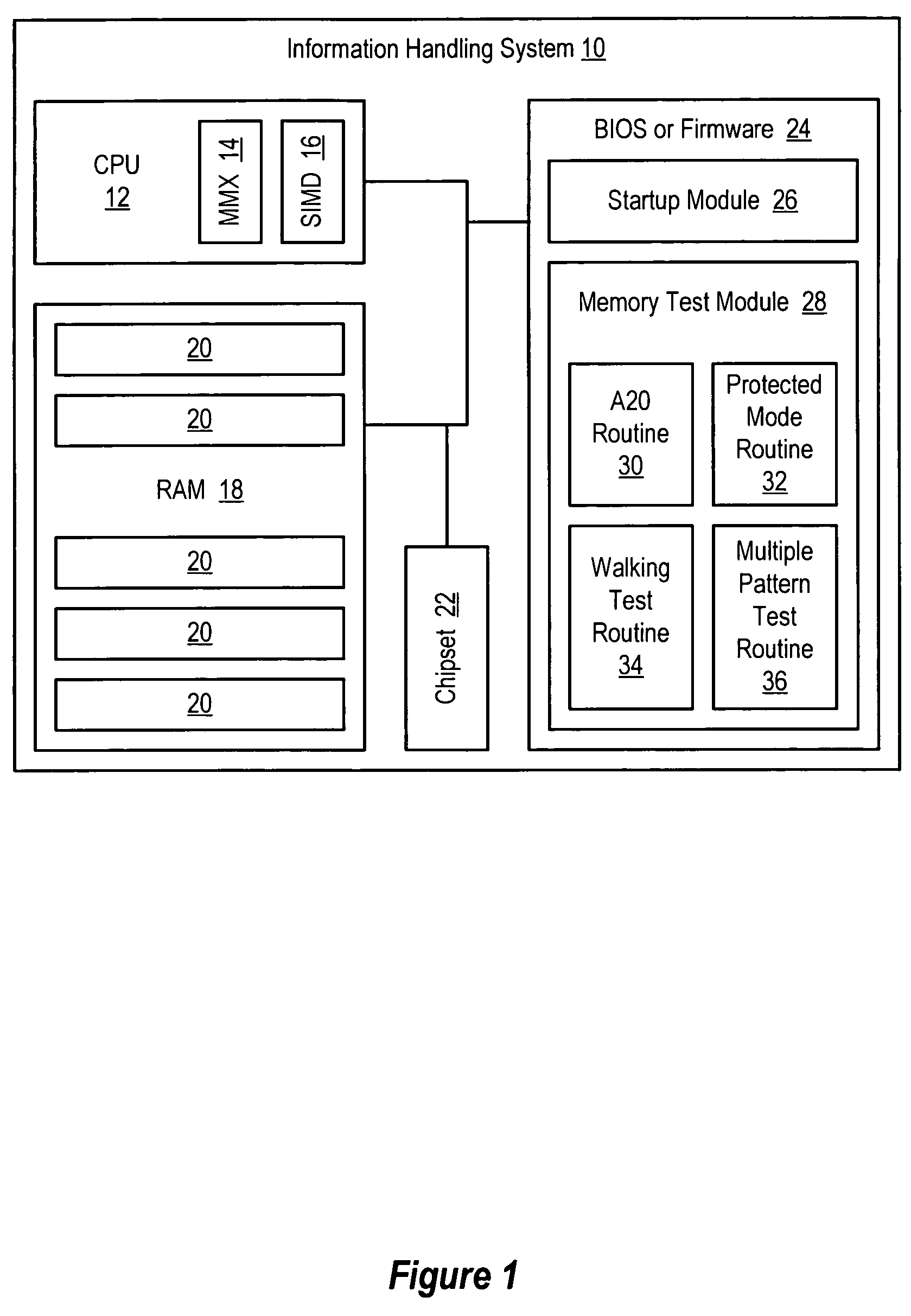

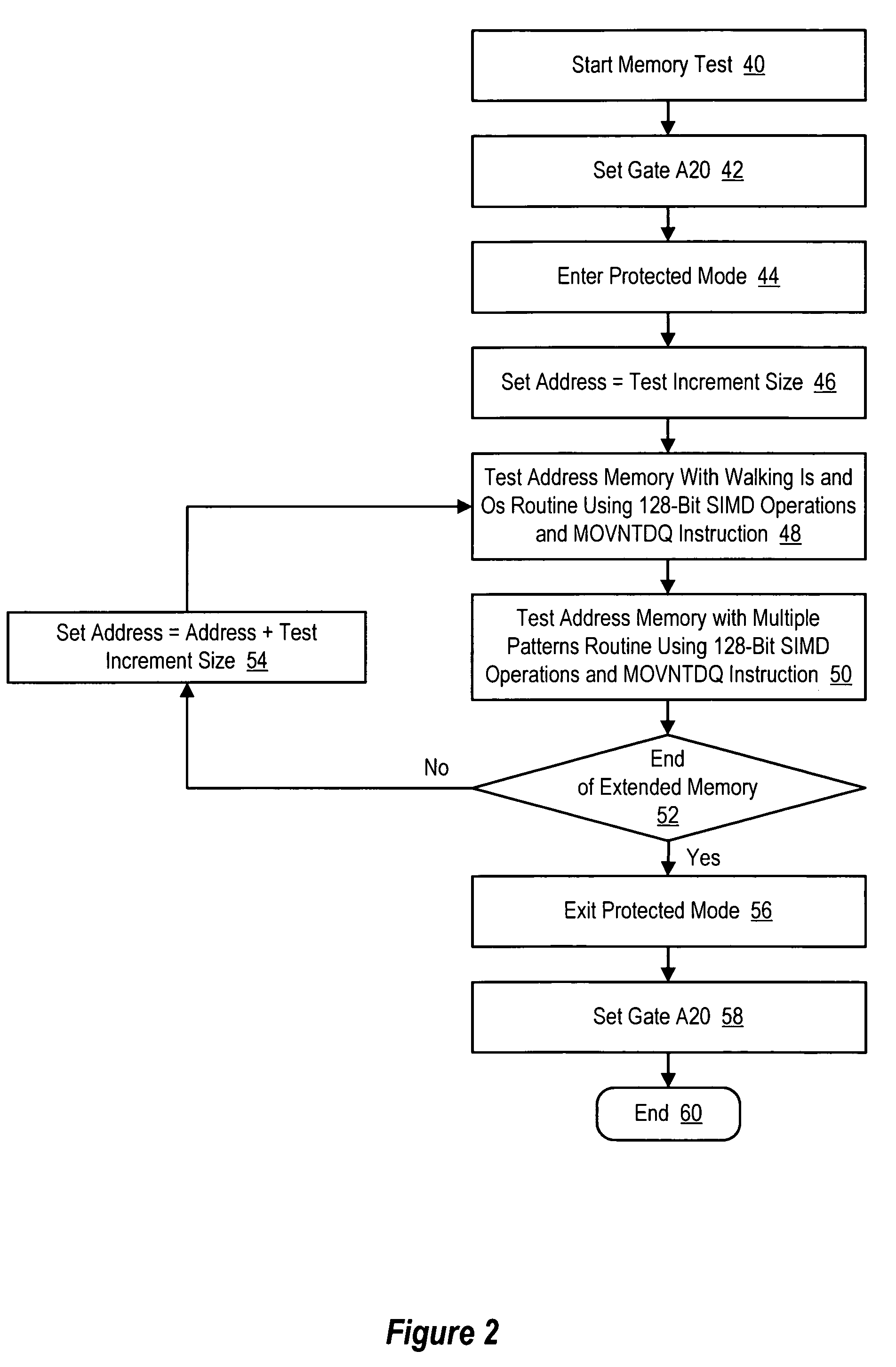

[0015]Acceleration of an information handling system memory test provides more rapid system startup without compromising the integrity of the testing performed. For purposes of this disclosure, an information handling system may include any instrumentality or aggregate of instrumentalities operable to compute, classify, process, transmit, receive, retrieve, originate, switch, store, display, manifest, detect, record, reproduce, handle, or utilize any form of information, intelligence, or data for business, scientific, control, or other purposes. For example, an information handling system may be a personal computer, a network storage device, or any other suitable device and may vary in size, shape, performance, functionality, and price. The information handling system may include random access memory (RAM), one or more processing resources such as a central processing unit (CPU) or hardware or software control logic, ROM, and / or other types of nonvolatile memory. Additional componen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More