Method of testing memory

A memory test and memory technology, applied in static memory, memory systems, instruments, etc., can solve the problems of inability to perform memory test, inability to access and execute data reading and writing or data, so as to improve the memory test range and save test cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings.

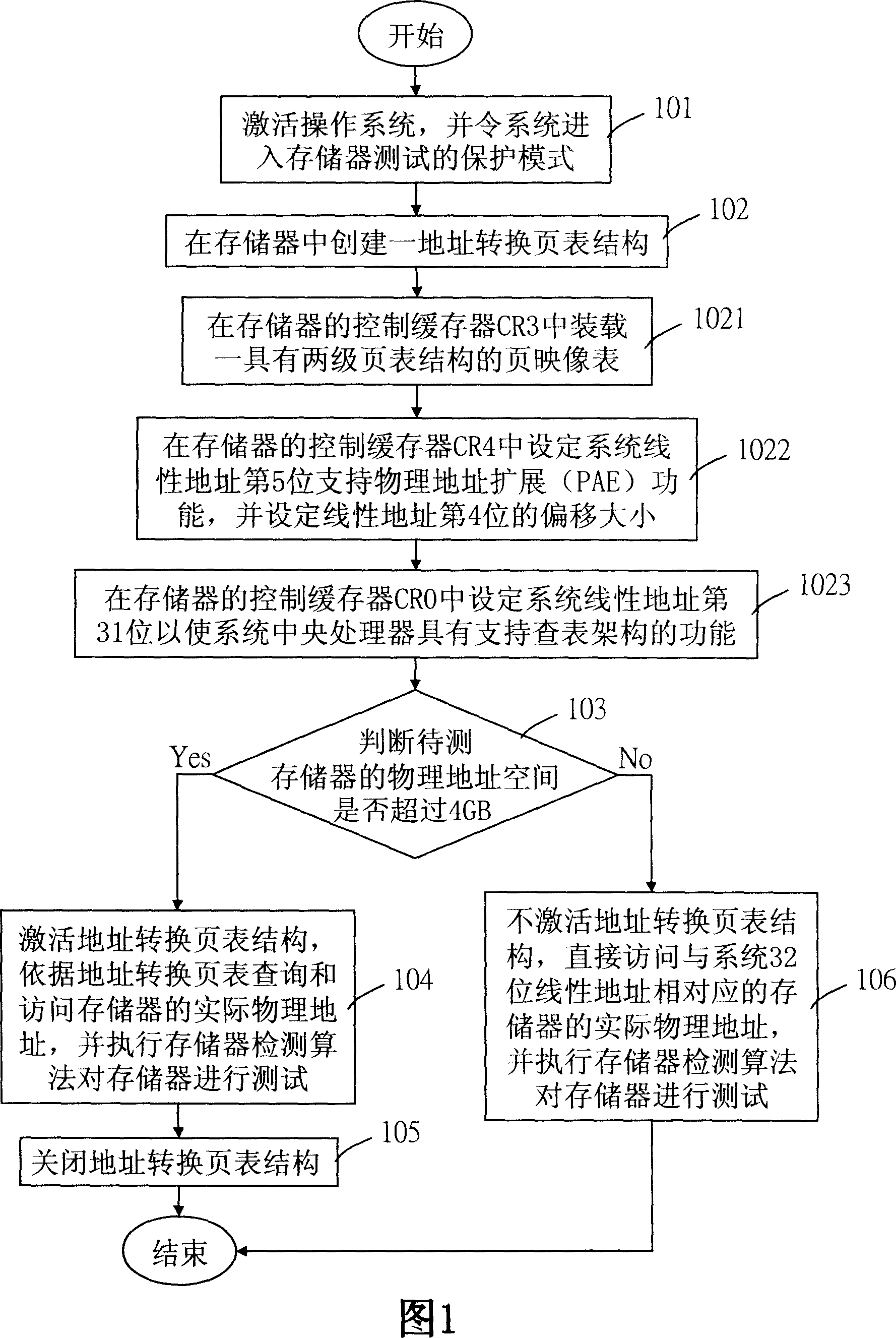

[0022] As shown in FIG. 1 , this figure is a flow chart of the overall steps of a memory testing method of the present invention. As shown in the figure, a kind of memory test method of the present invention is applied to the memory detection process in the computer server system or the personal microcomputer system using the Intel central processing unit, and the method includes the following steps:

[0023] Activate the operating system and make the system enter the protection mode of the memory test (step 101). The operating system in this step is preferably a DOS operating system.

[0024] Create an address conversion page table structure (step 102) in the memory, in order to convert the 32-bit linear address given by the system into the physical address of the memory with more than 4GB of physical address space in the subsequent ste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More