Patents

Literature

1006 results about "32-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 32-bit integers, memory addresses, or other data units are those that are 32 bits (4 octets) wide. Also, 32-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size. 32-bit microcomputers are computers in which 32-bit microprocessors are the norm.

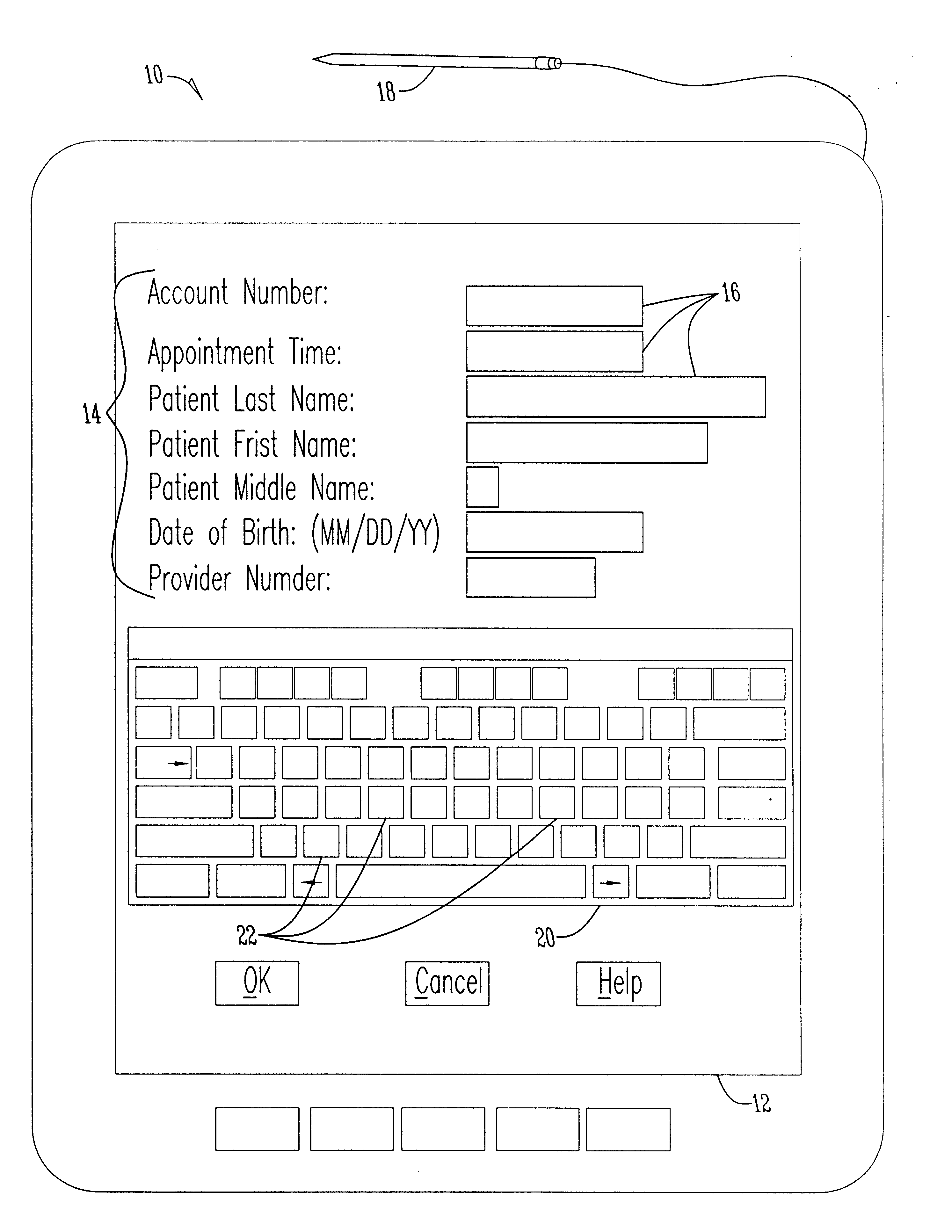

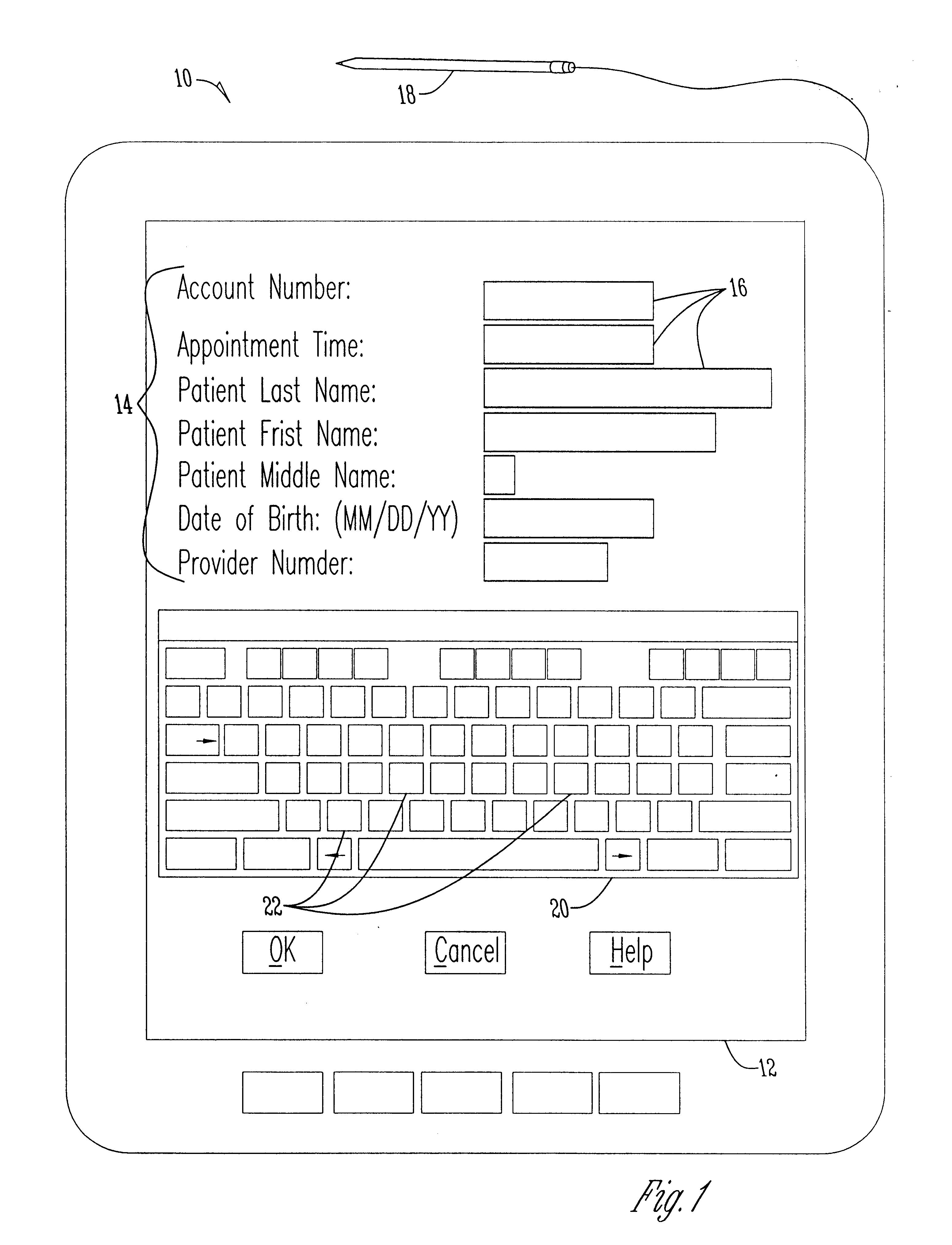

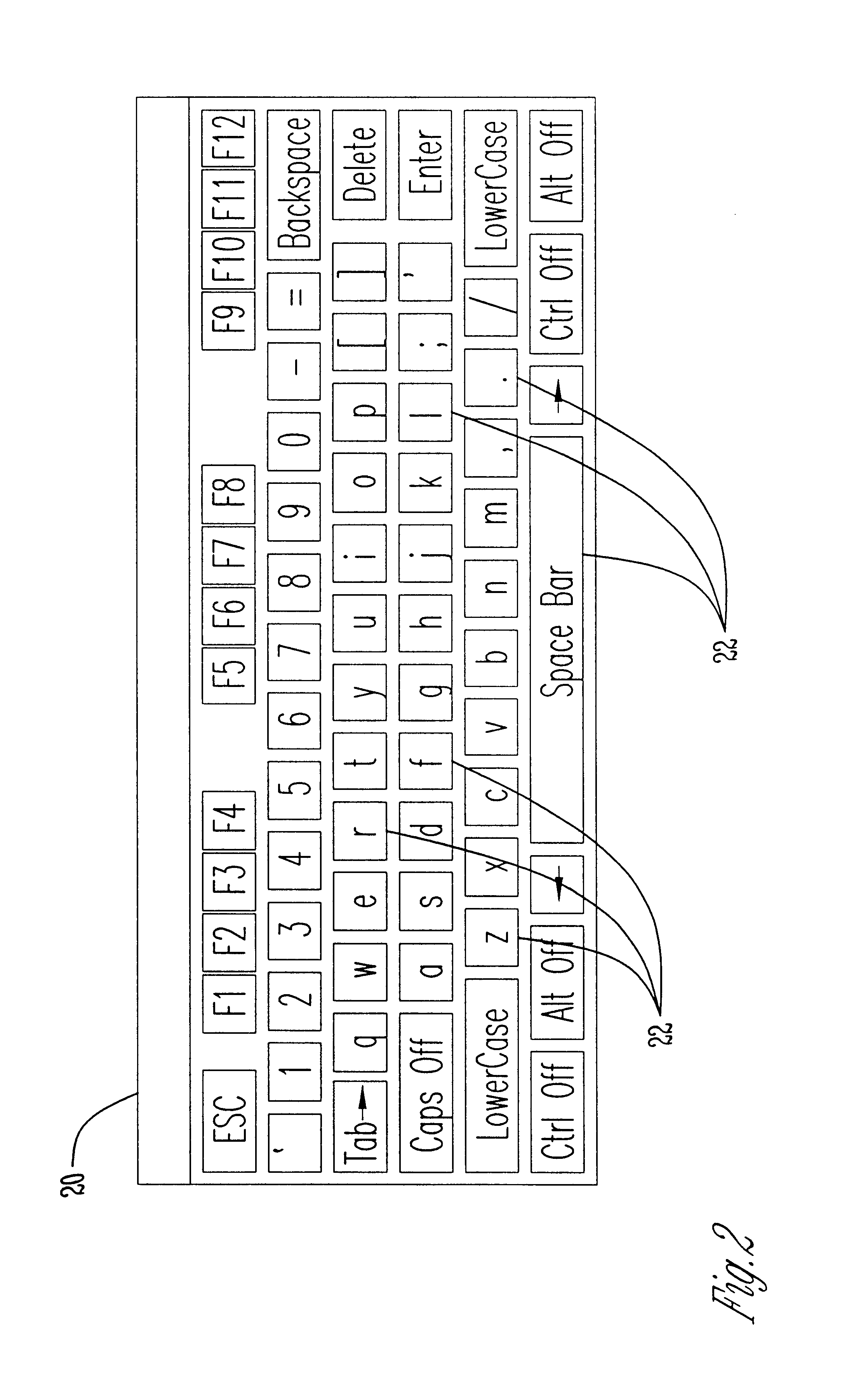

Method and medium for computer readable keyboard display incapable of user termination

InactiveUS6784873B1Easy to useReliable methodInput/output for user-computer interactionCathode-ray tube indicatorsDisplay deviceTouchscreen

A method and medium for a computer readable input area. The input area is created by a computer program on a display capable of receiving touch-screen input. The computer on which the input area in used is at least a 32-bit system. The input area may contain a keyboard which is an image map. External programming may selectively access the input area through a dynamic link library. The input area has no task bar and may not be minimized, maximized, or deleted. Therefore, the input area becomes an integral component and provides the user with a constant and reliable method of inputting information into the computer program.

Owner:BOESEN PETER V

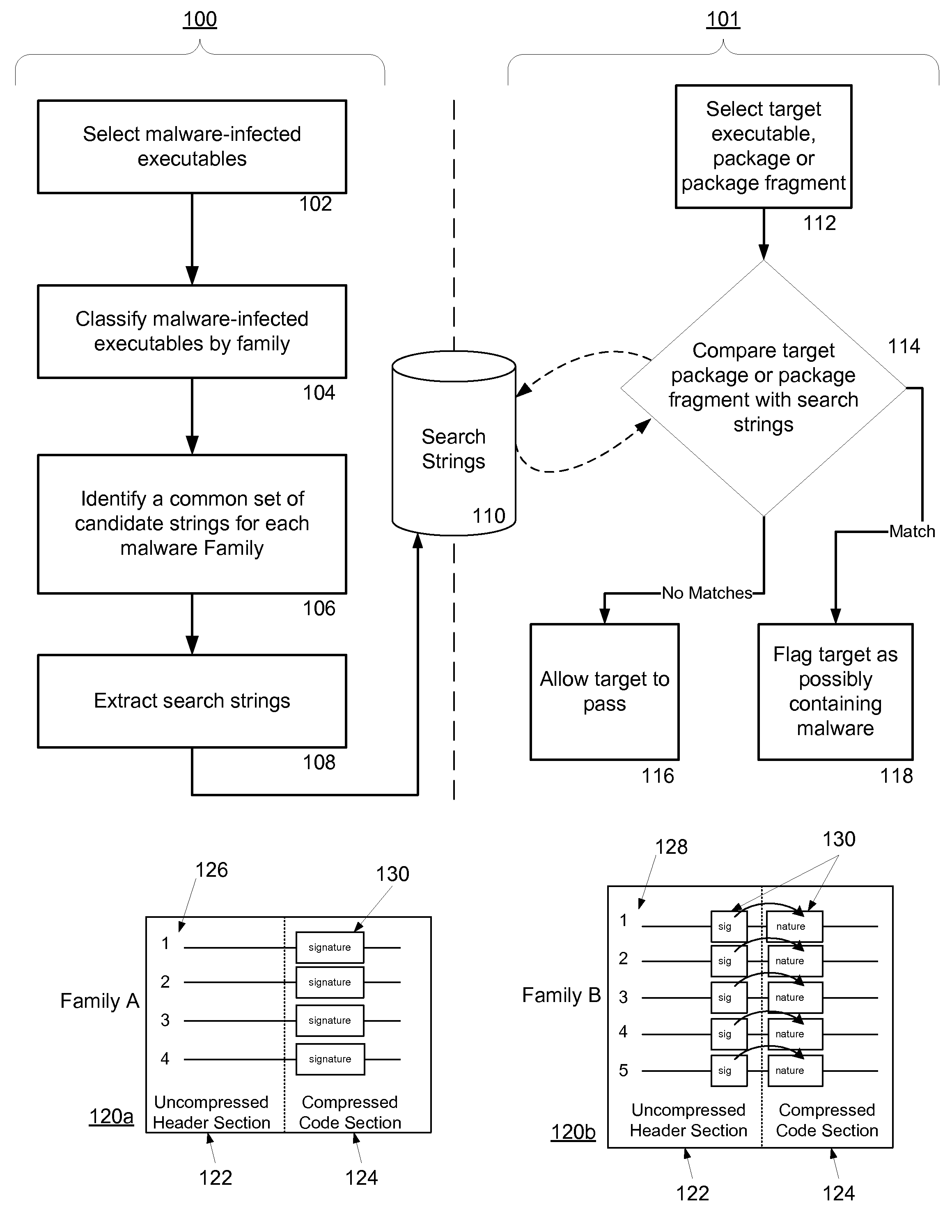

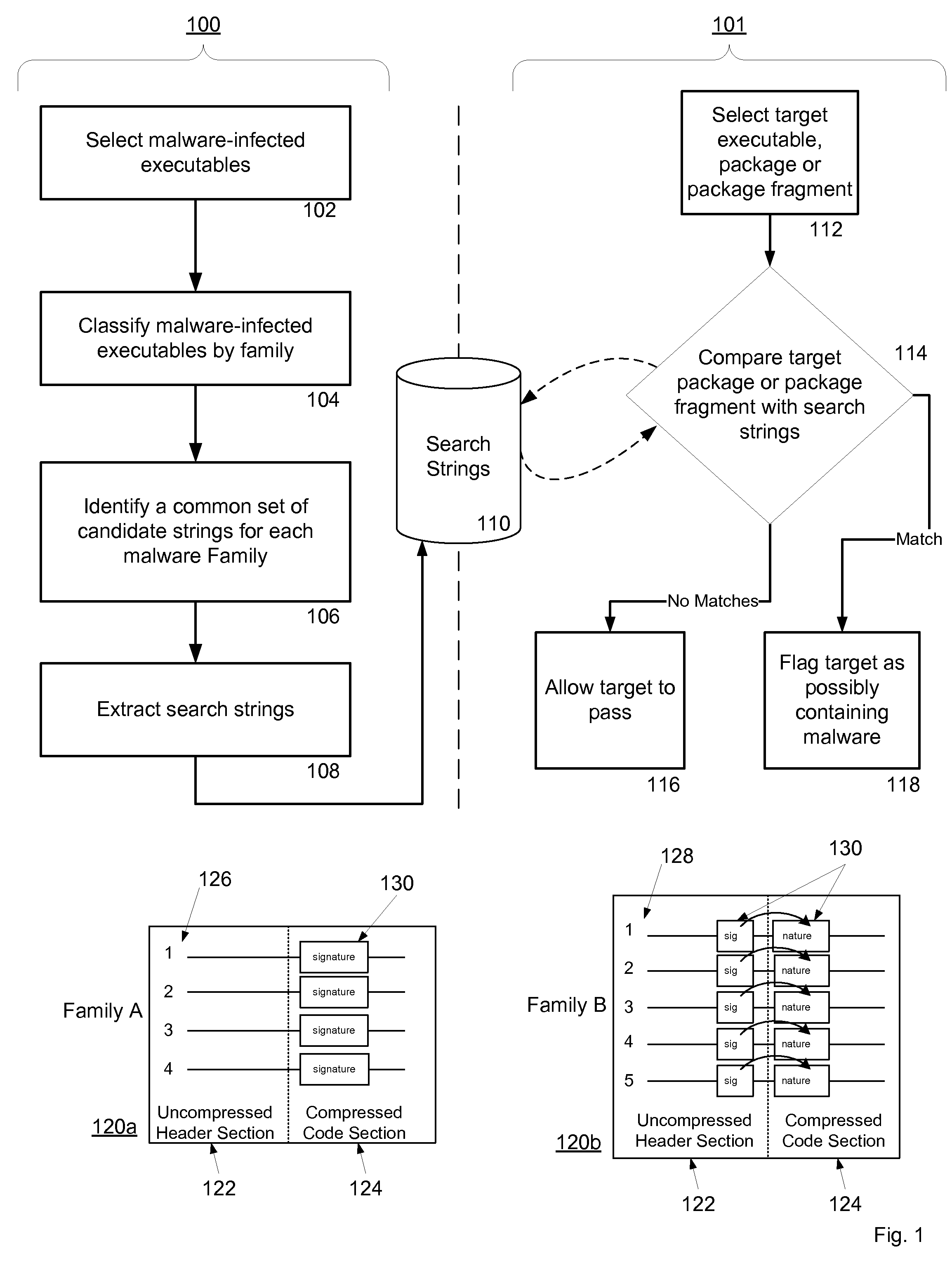

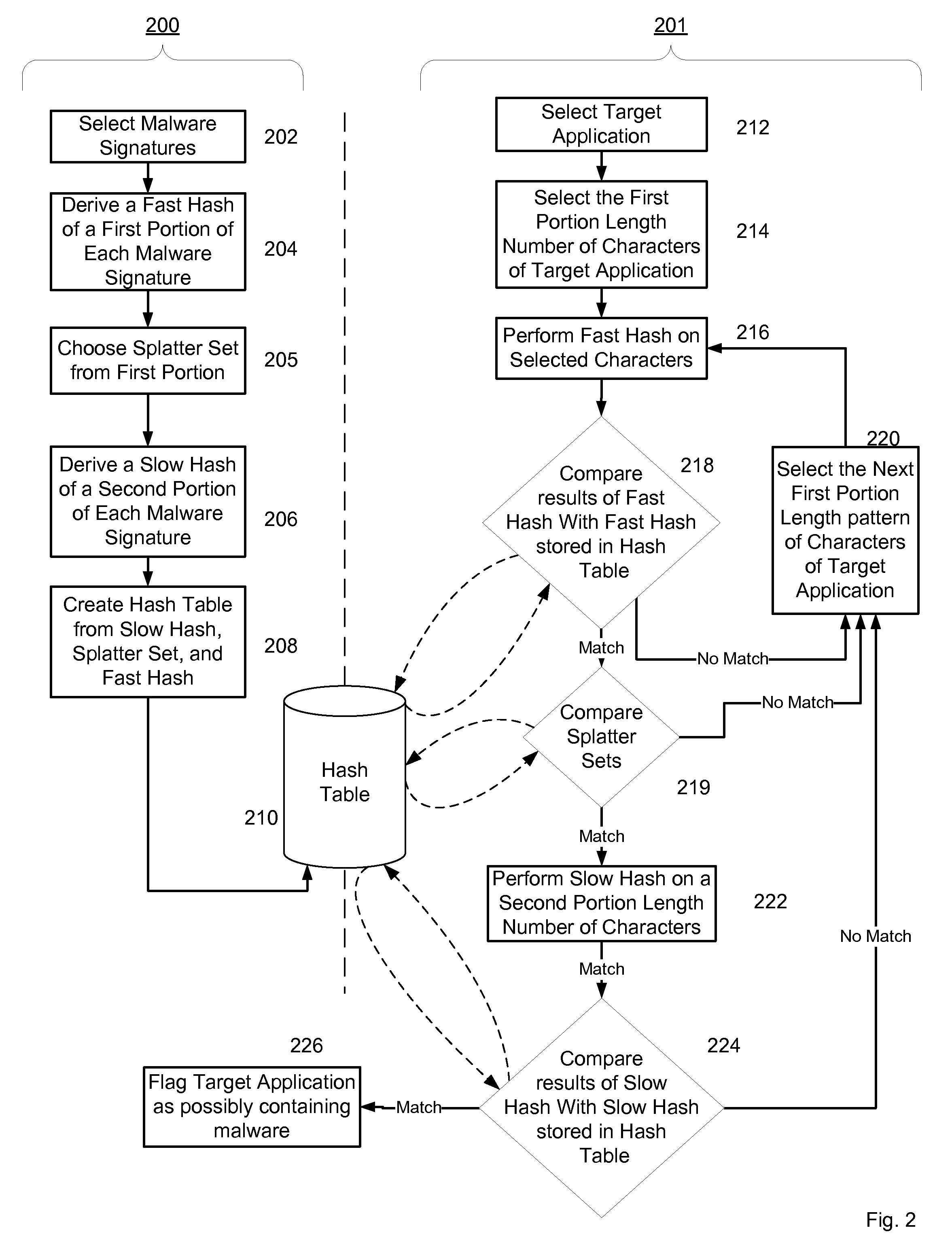

Non-Signature Malware Detection System and Method for Mobile Platforms

ActiveUS20070240221A1Suitable for useReliable detectionMemory loss protectionError detection/correctionEntry pointChecksum

A system and method for detecting malware on a mobile platform in a mobile network. The system and method verifies that an executable is malware-free by computing the checksum of the executable and comparing that checksum with a checksum obtained from a malware-free copy of the executable. The checksum is a sum of all 32-bit values in a code section and an import section of said executable, a byte sequence at an entry point in said executable, a size descriptor of an import table, a size descriptor of said import section, a cyclic redundancy check of said executable, or a combination thereof.

Owner:PULSE SECURE

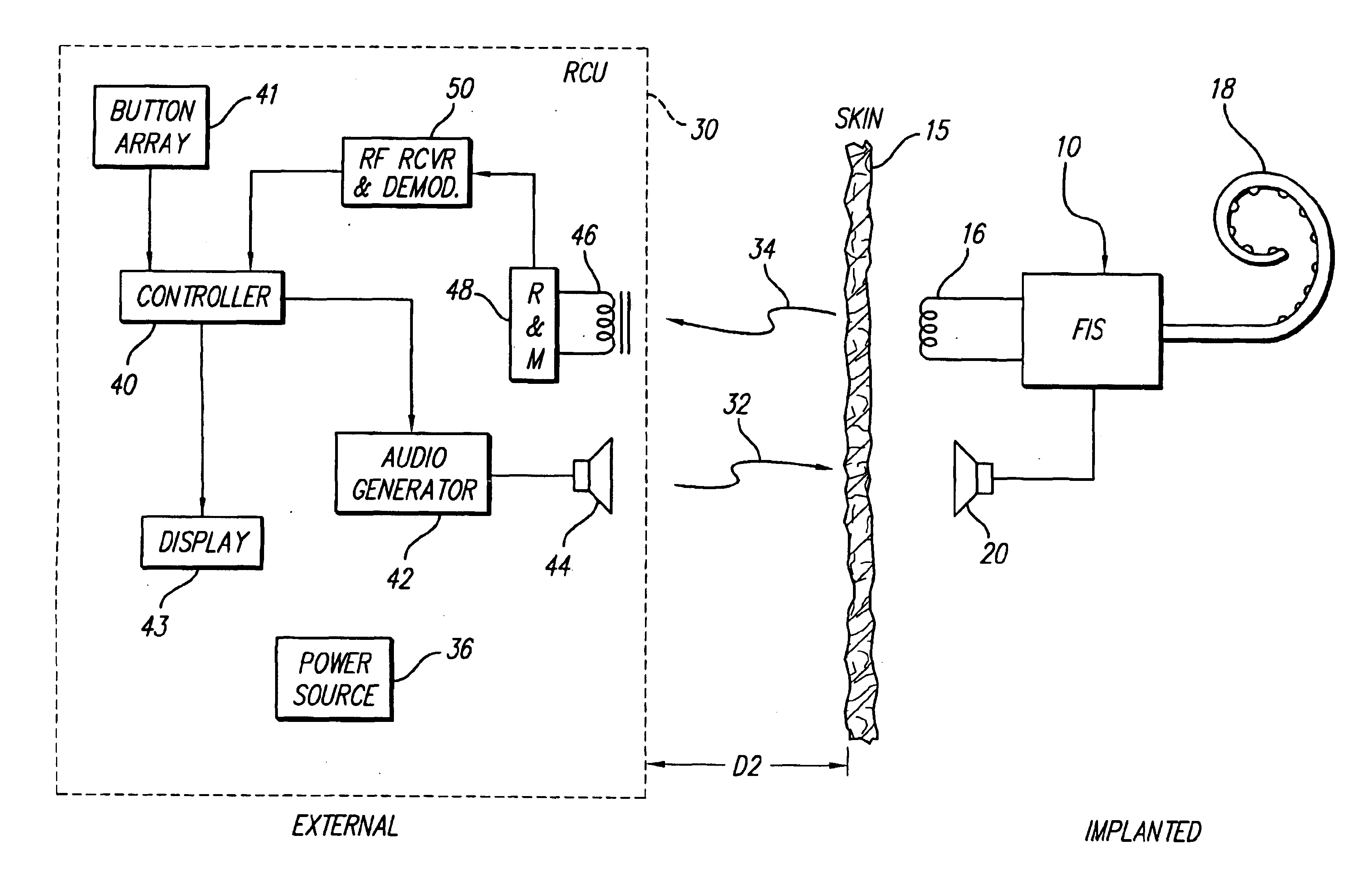

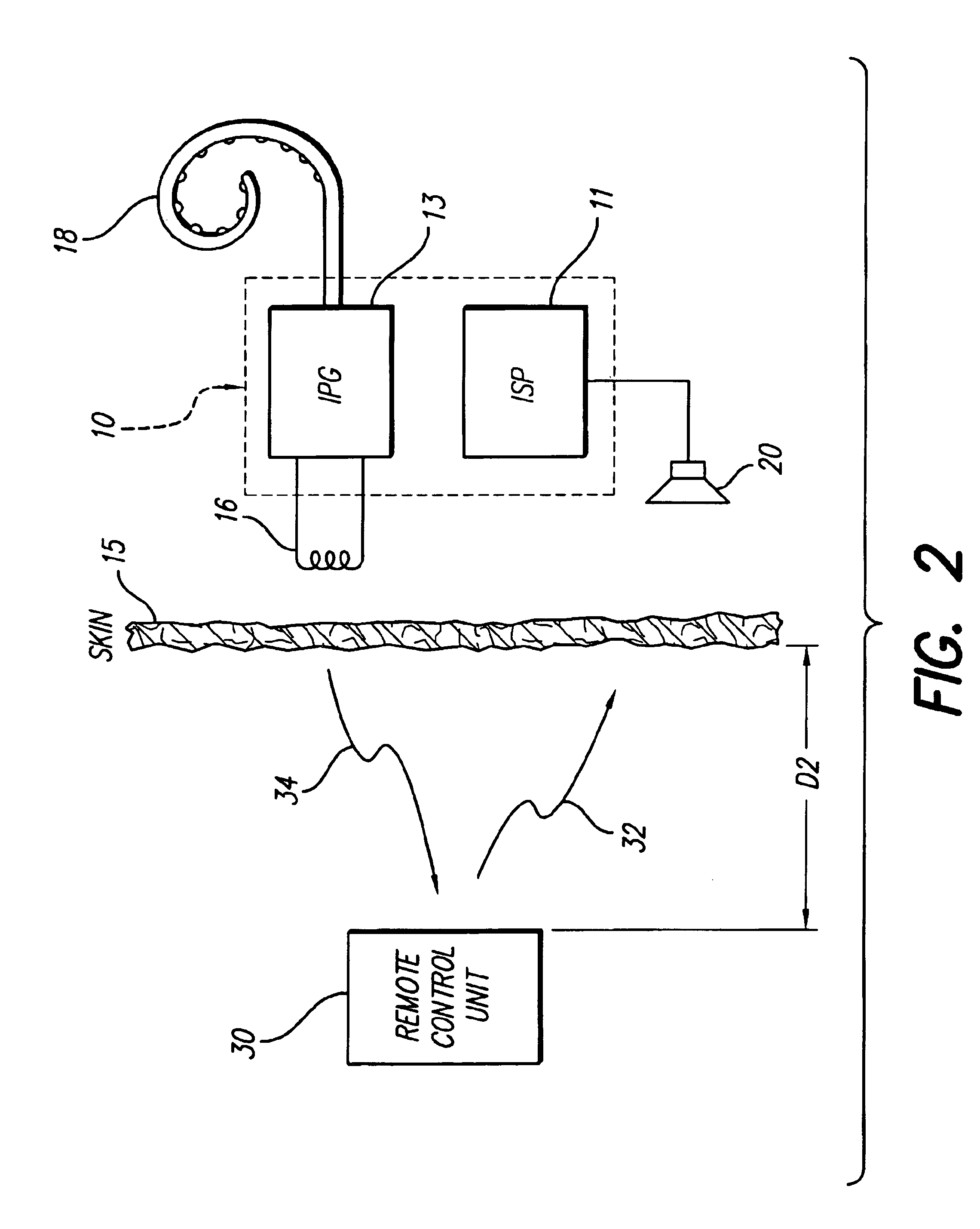

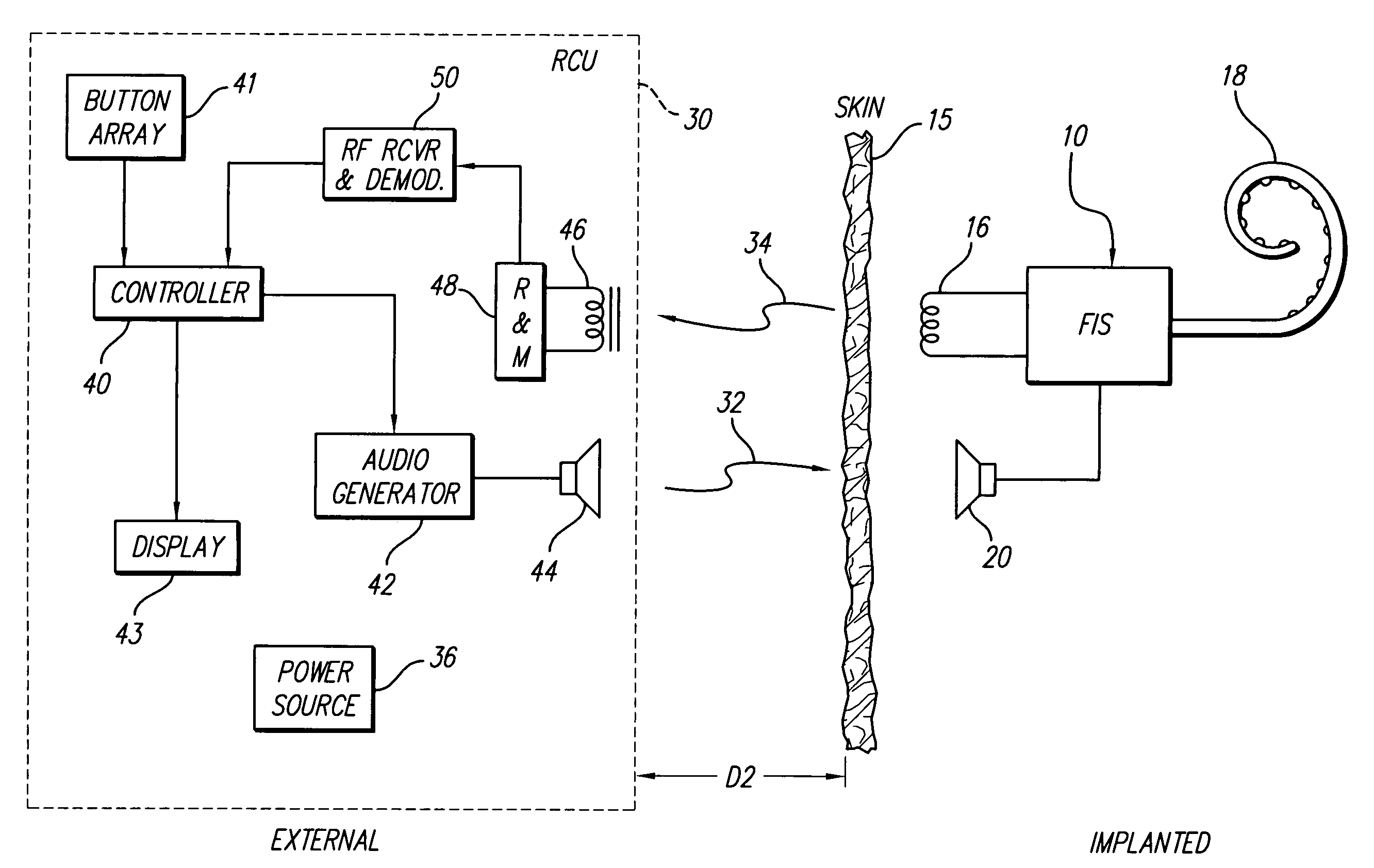

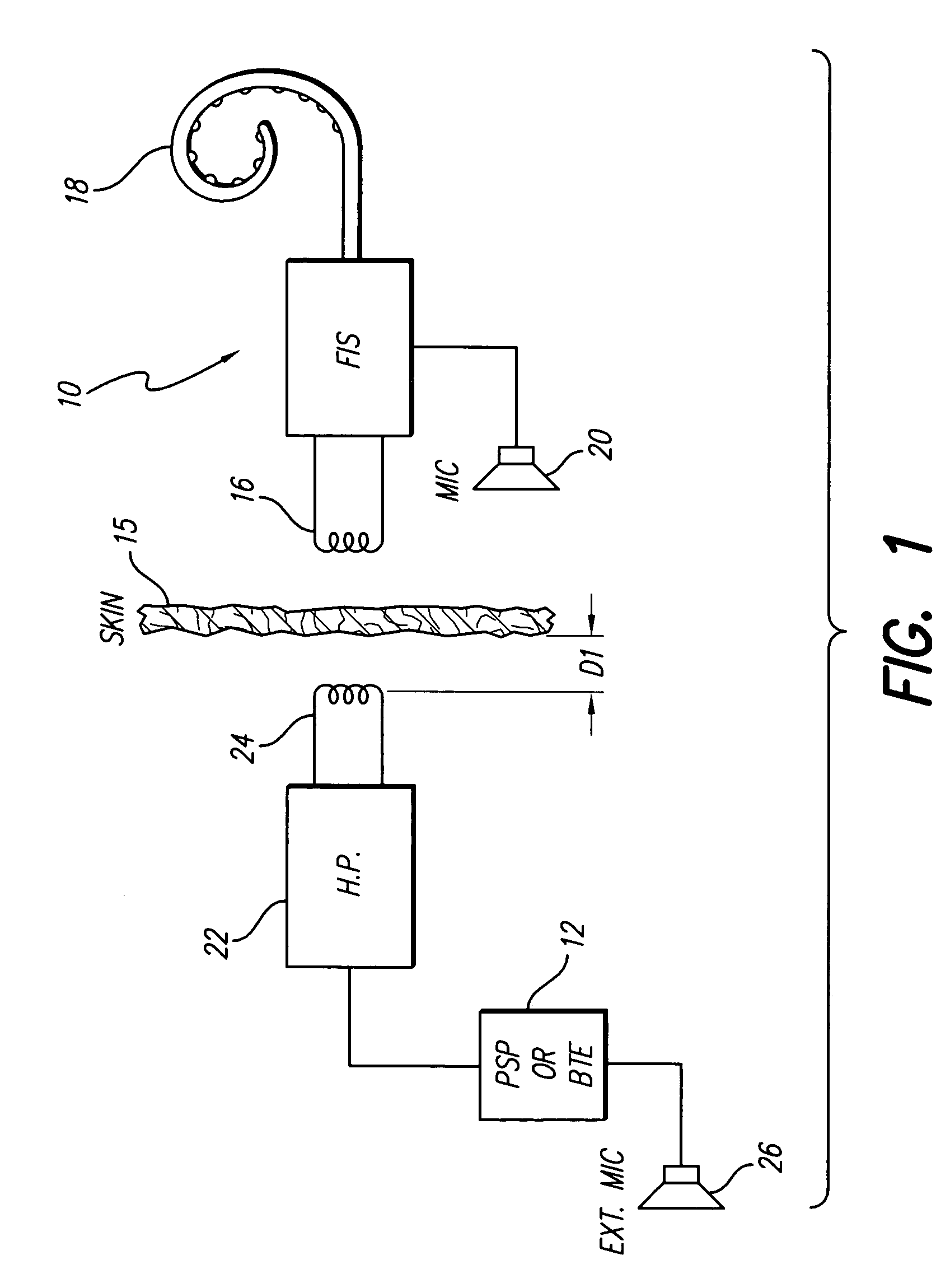

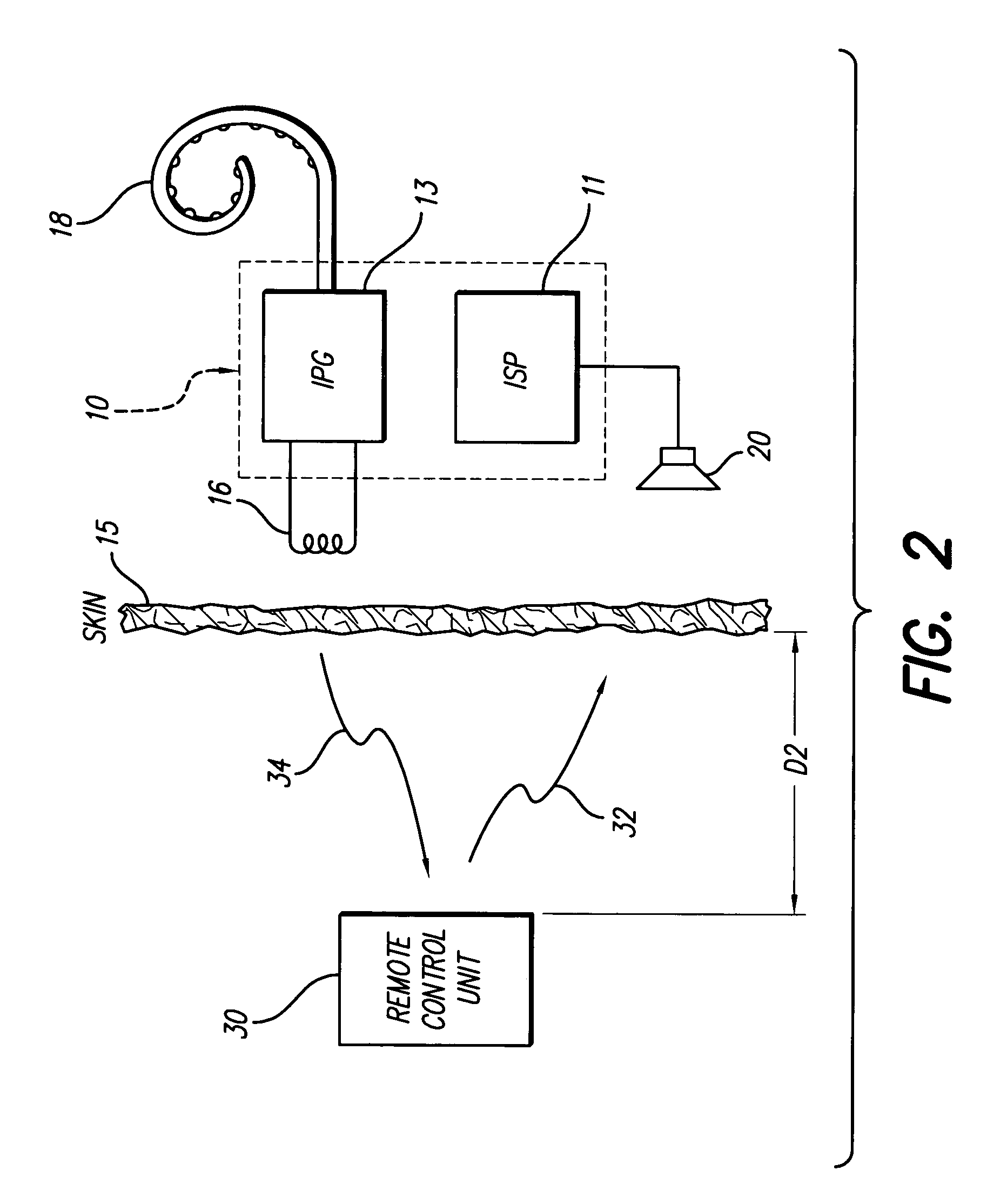

Implantable neural stimulator system including remote control unit for use therewith

InactiveUS6842647B1Reliable transmissionElectrotherapyImplantable hearing aidsControl signalRemote control

An implantable neural stimulation system, such as an auditory Fully Implantable System (FIS), includes: (1) an implanted device capable of providing desired tissue or nerve stimulation; and (2) a remote control unit that provides a mechanism for readily controlling the implant device, i.e., for selectively adjusting certain stimulation parameters associated with the tissue stimulation of the implanted device. The remote control unit uses a first signal path to send signals to the implant device, and a second signal path to receive signals from the implant device. The combination of these two signal paths provides a full-duplex channel between the remote control unit and the implant device through which air appropriate control and status signals may be sent and received. In one embodiment, the first signal path comprises an audio signal path through which audio control signals, e.g., a tone sequence or a 32-bit word FSK modulated between 300 and 1200 Hz, are sent; and the second signal path comprises a RF signal path through which a BPSK, QPSK or FM modulated RF signal is received. The full-duplex channel allows operation of the remote control unit, i.e., allows signals to be successfully sent to and received from the implant device, from as far away as 45-60 cm from the implant device.

Owner:ADVNACED BIONICS LLC

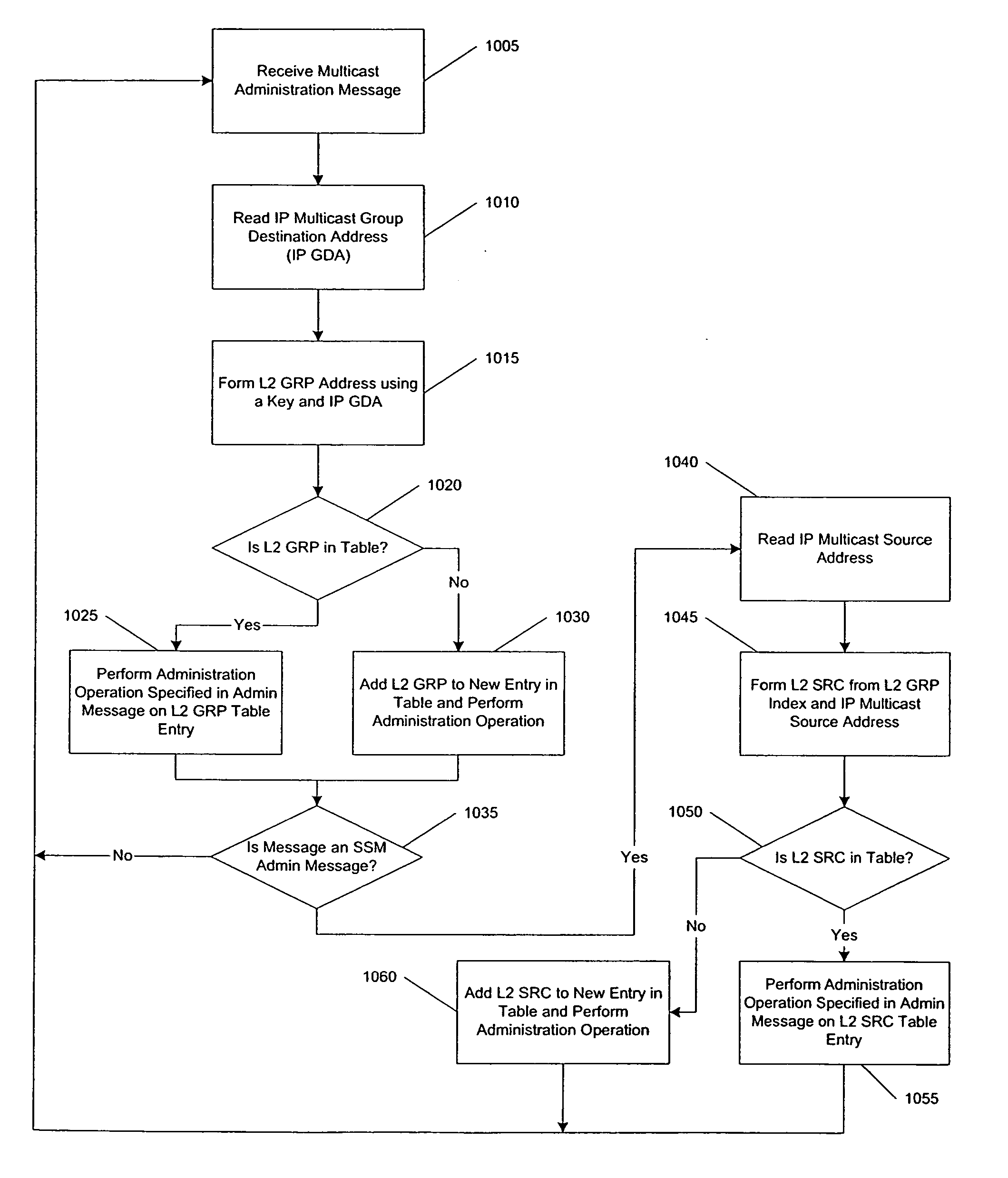

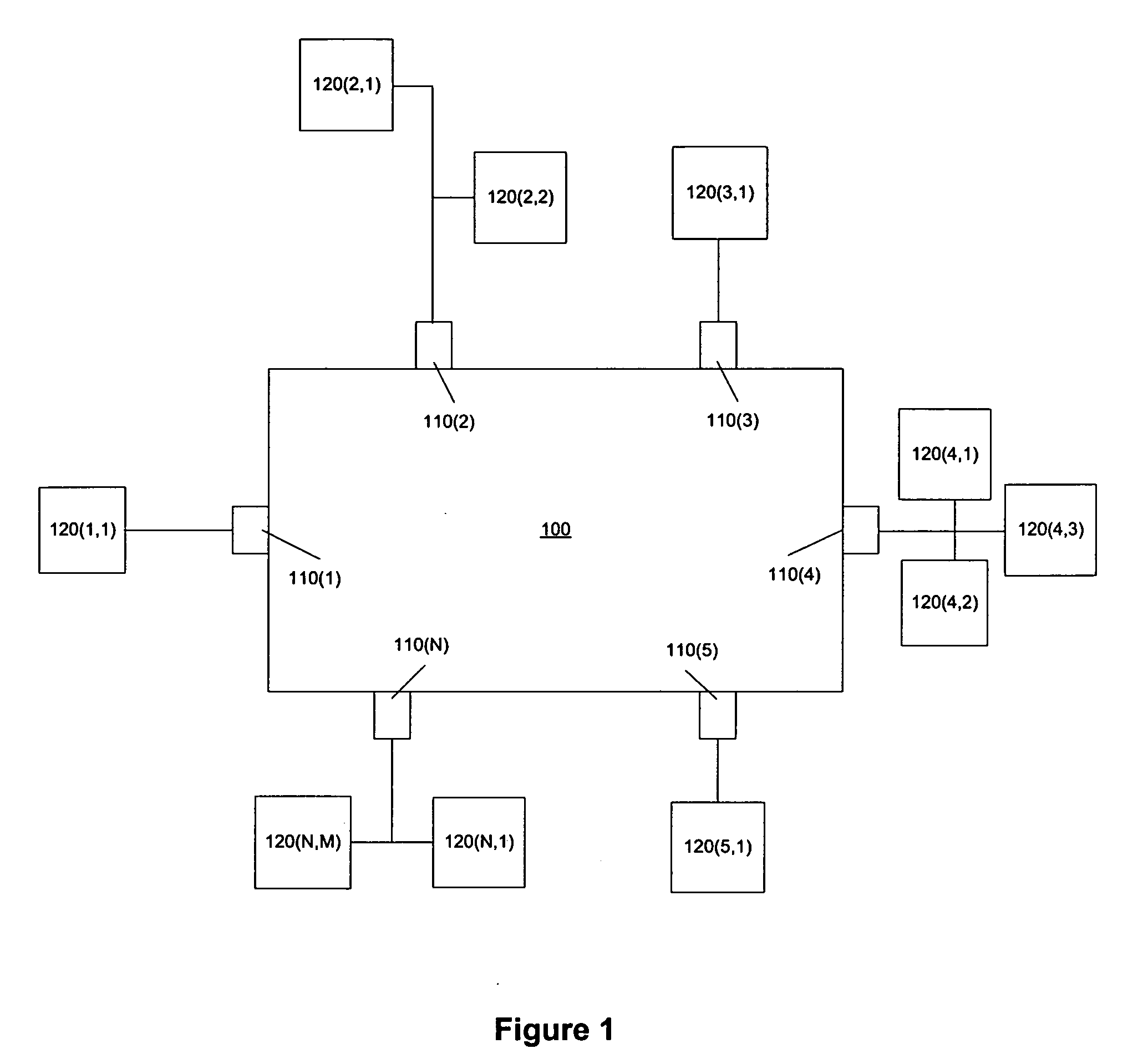

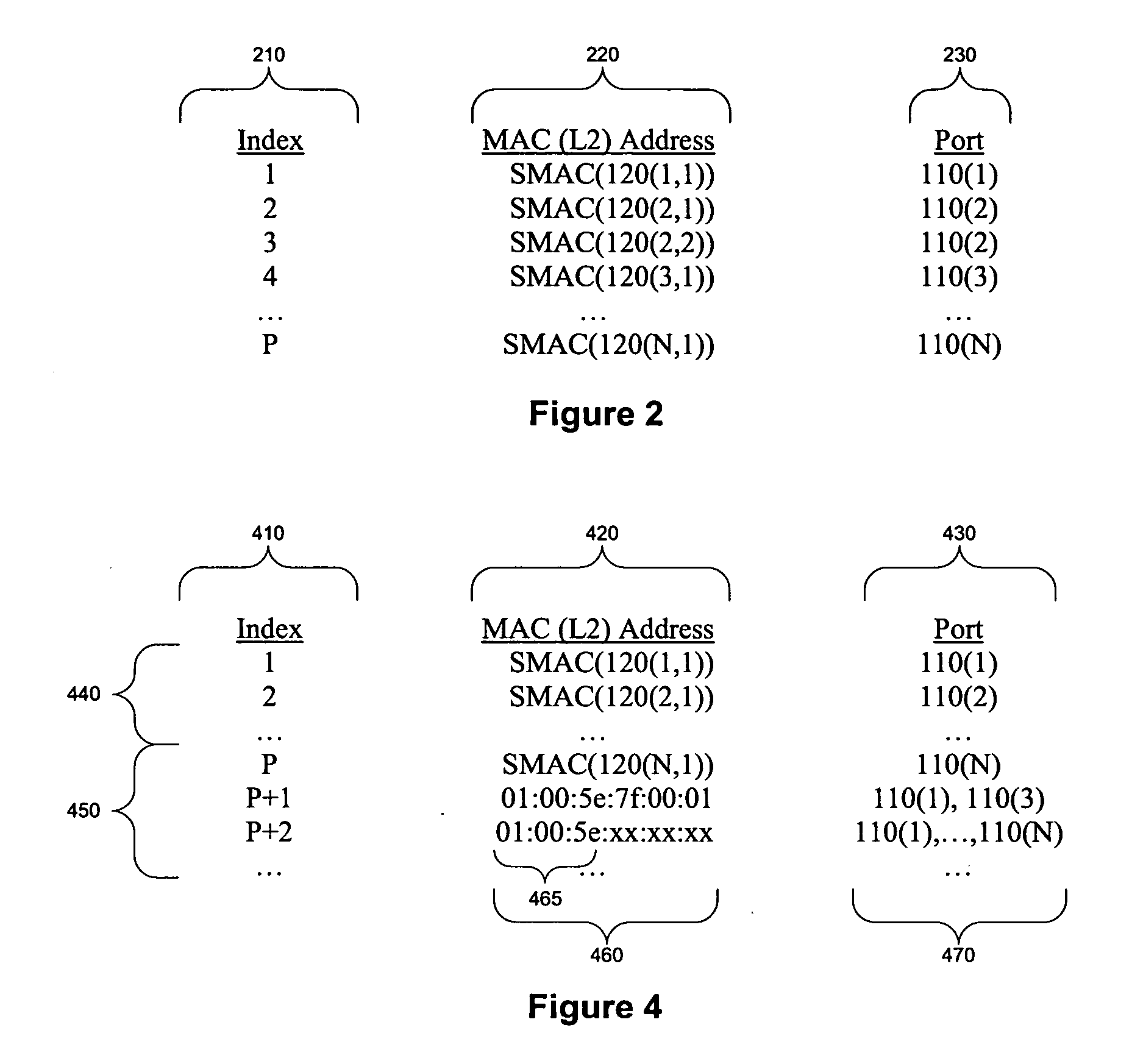

Performing extended lookups on mac-based tables

ActiveUS20060221960A1Special service provision for substationTime-division multiplexInternet trafficIp address

A method, system, and computer program product are presented to optimize OSI Level 2 switch forwarding of frames comprising IP addresses, 802.1 QinQ VLAN identifiers, multi-protocol label switching labels, and any other usable information meaningful to derive an L2 forwarding result on frames. In one embodiment, a 16-bit key is included as a prefix to a 48-bit OSI Level 2 address entry, thereby allowing the inclusion of a 32-bit OSI Level 3 address in the lookup table (e.g., a complete IP version 4 address). Implementations of such a solution are presented to resolve address aliasing issues experienced with multicast group destination addresses, including single source multicast. Solutions to optimizing forwarding of frames in an IEEE 802.1 QinQ environment are also presented. A result of these implementations can be reduction of the amount of unnecessary network traffic generated by a network switch incorporating such an OSI Level 2 address lookup table.

Owner:CISCO TECH INC

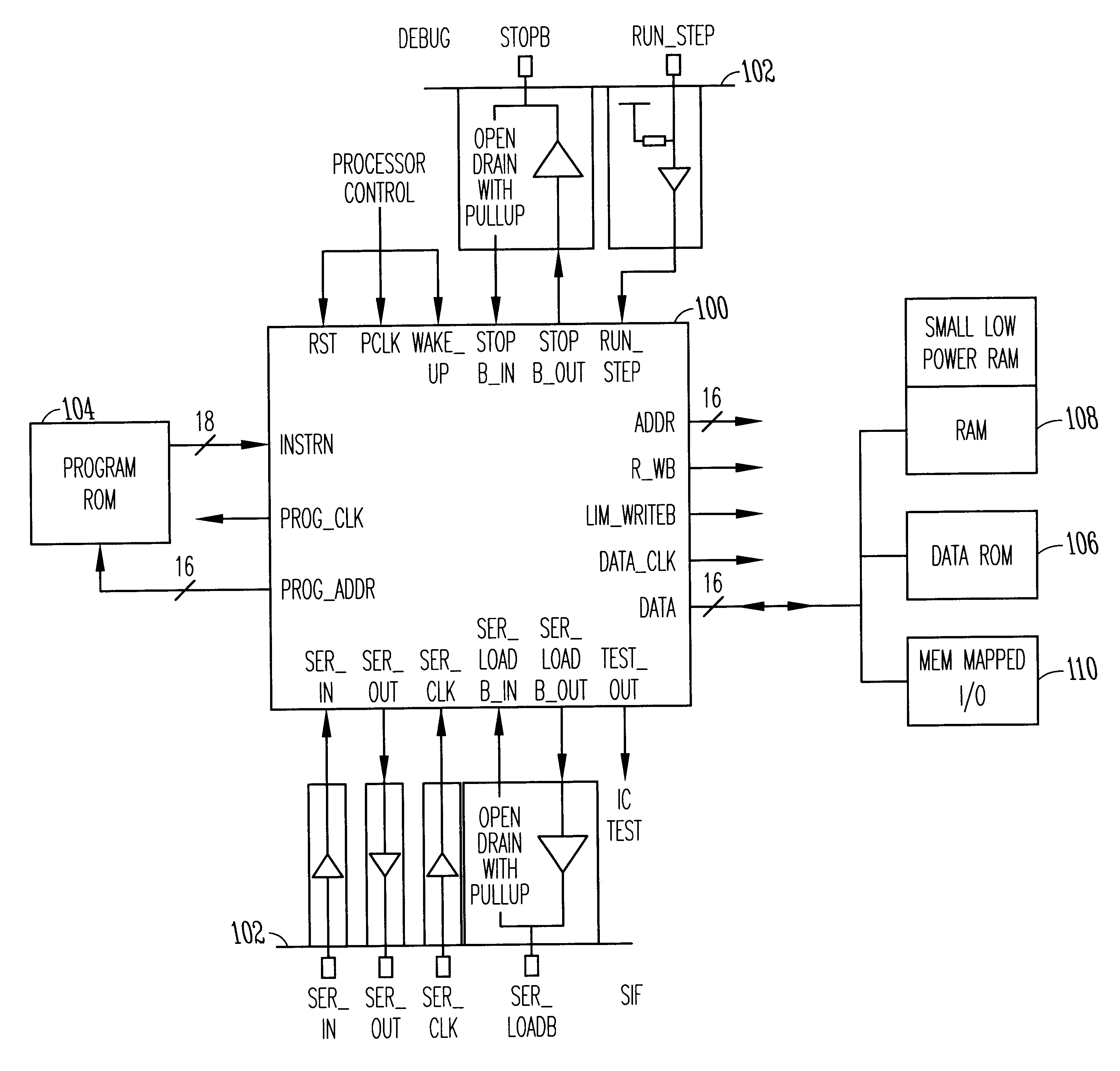

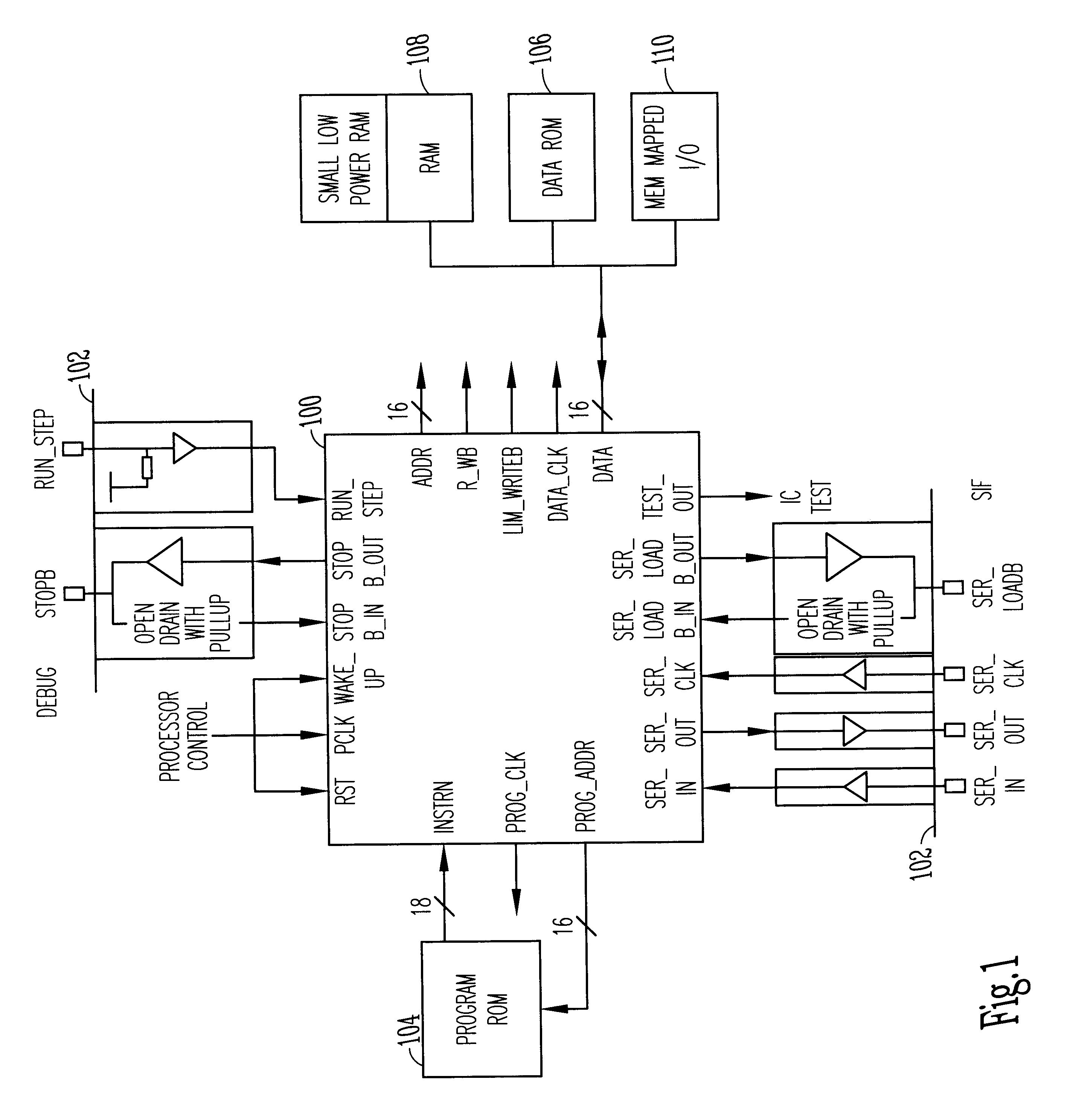

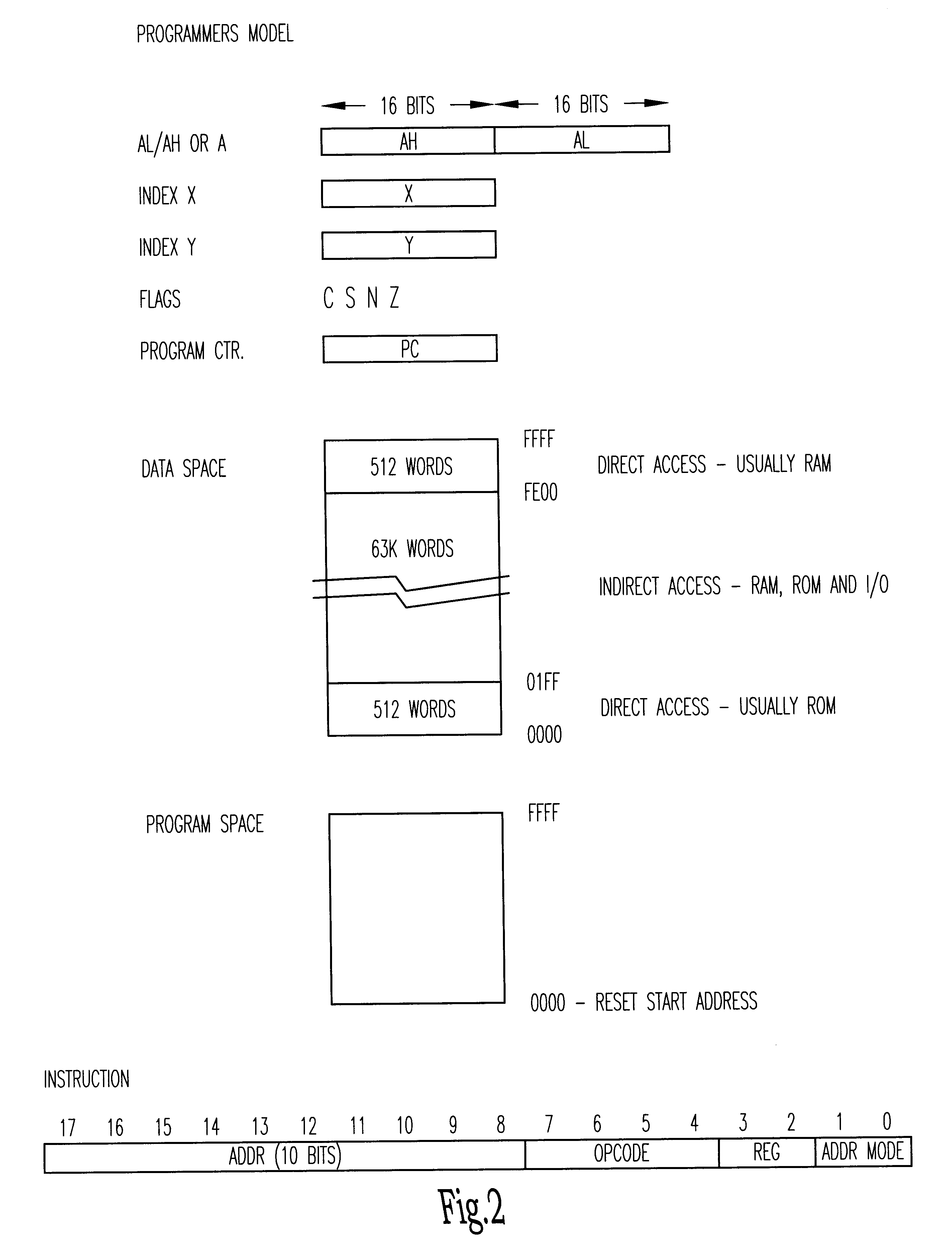

Data processing circuits and interfaces

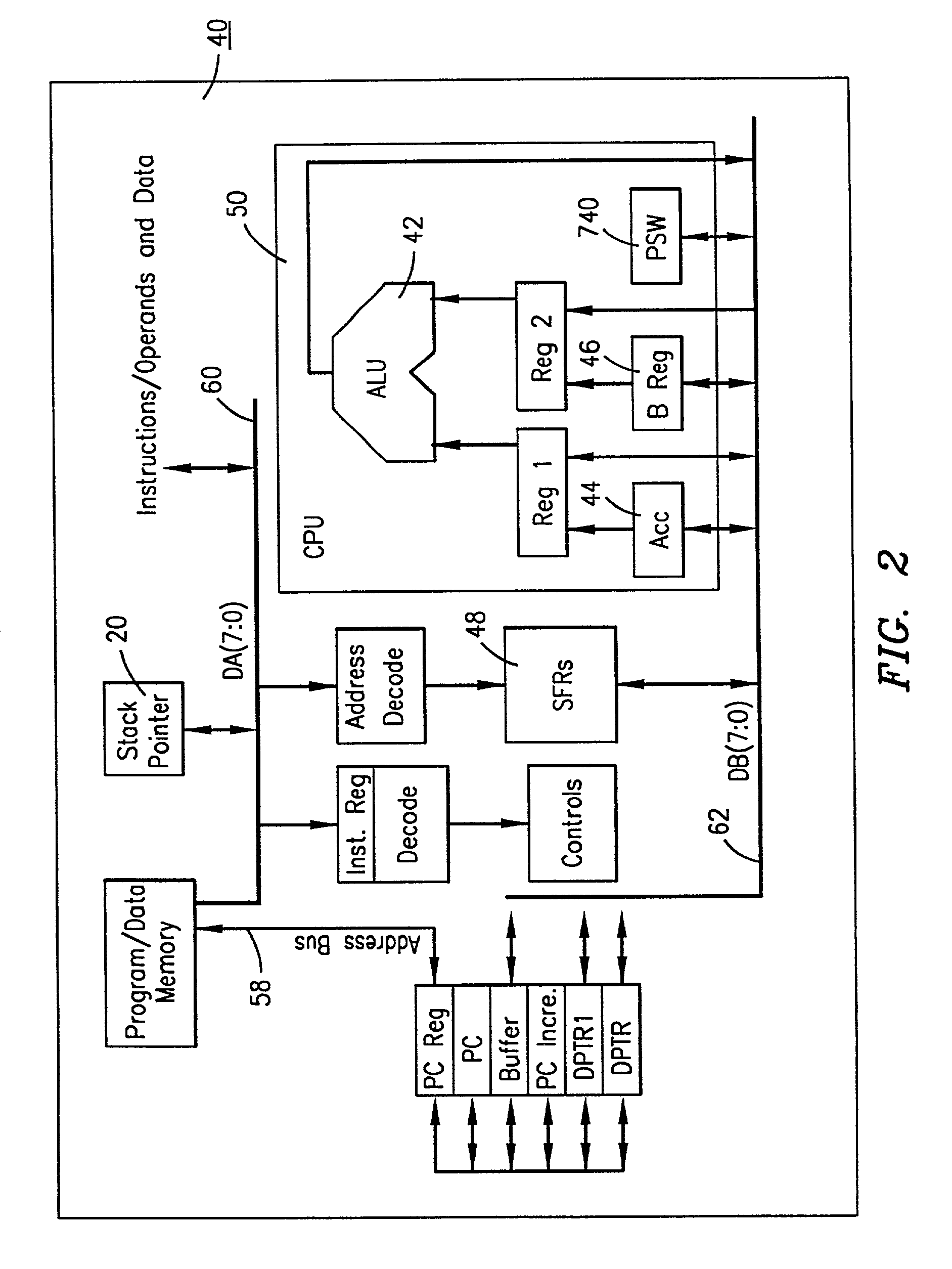

An integrated circuit contains a microprocessor core, program memory and separate data storage, together with analogue and digital signal processing circuitry. The ALU is 16 bits wide, but a 32-bit shift unit is provided, using a pair of 16-bit registers. The processor has a fixed length instruction format, with an instruction set including multiply and divide operations which use the shift unit over several cycles. No interrupts are provided. External pins of the integrated circuit allow for single stepping and other debug operations, and a serial interface (SIF) which allows external communication of test data or working data as necessary. The serial interface has four wires (SERIN, SEROUT, SER-CLK, SERLOADB), allowing handshaking with a master apparatus, and allowing direct access to the memory space of the processor core, without specific program control. Within each processor cycle, the processor circuitry is divided into plural stages, and latches are interposed between the stages to minimize power consumption.

Owner:CAMBRIDGE CONSULTANTS LTD

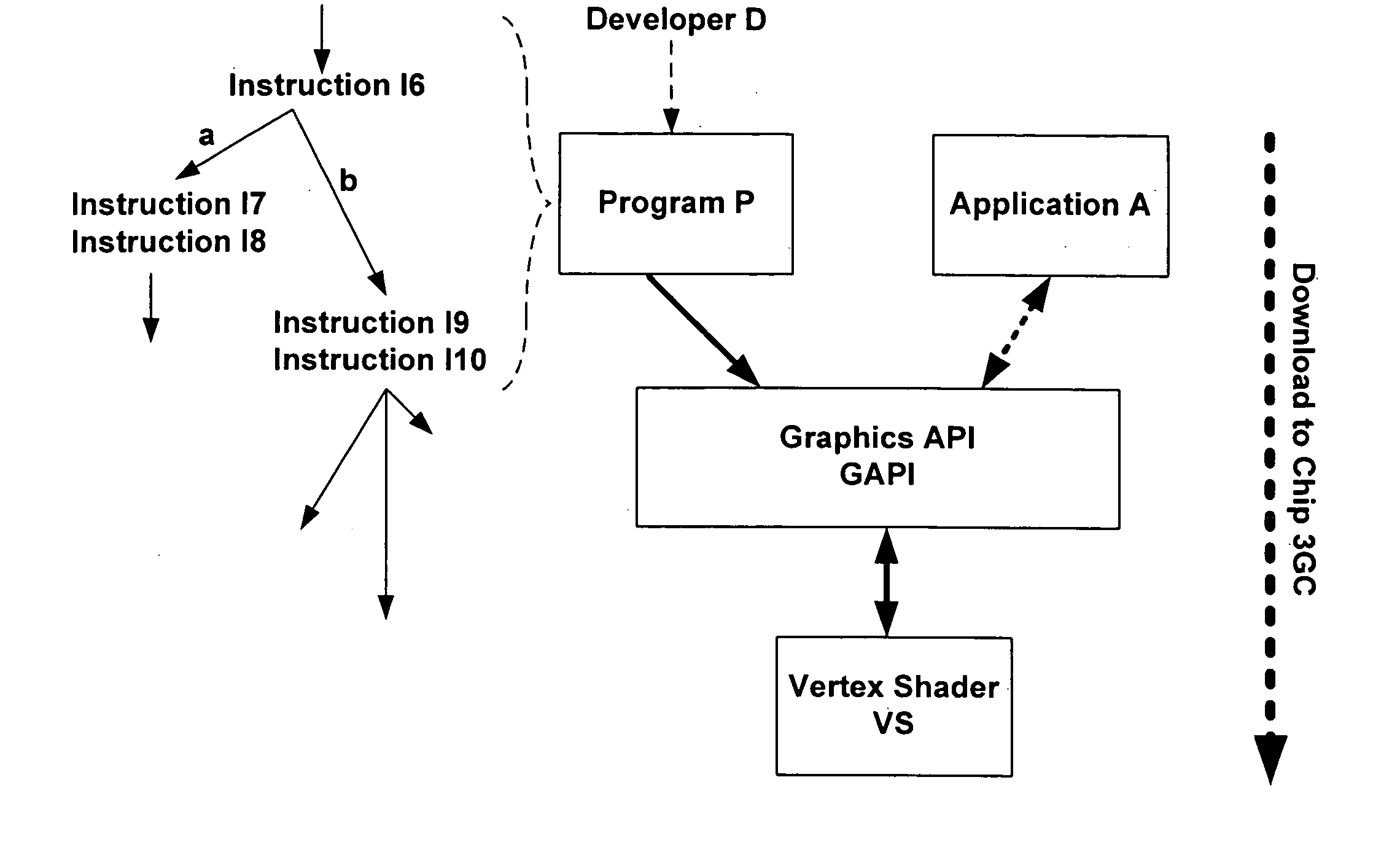

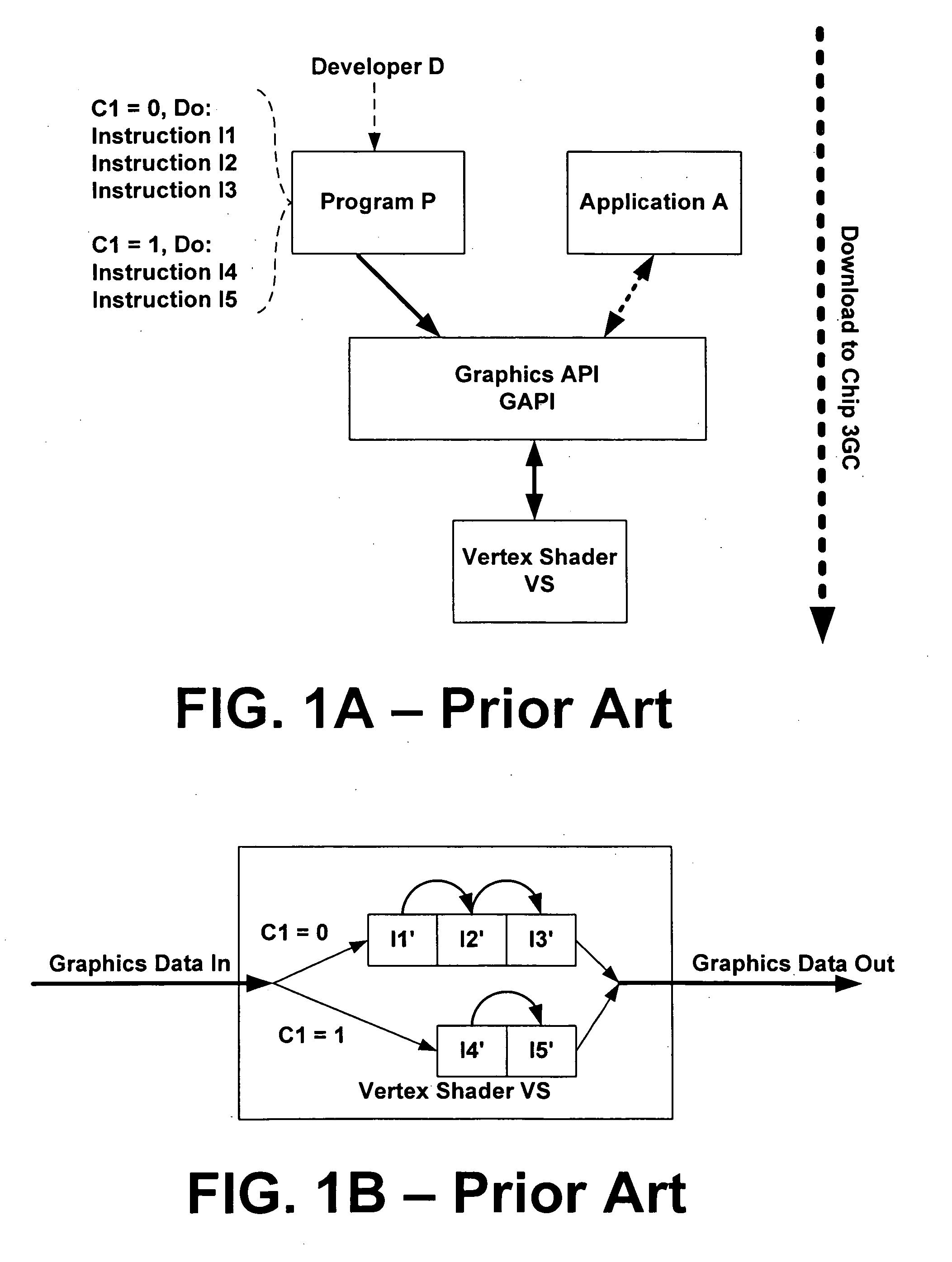

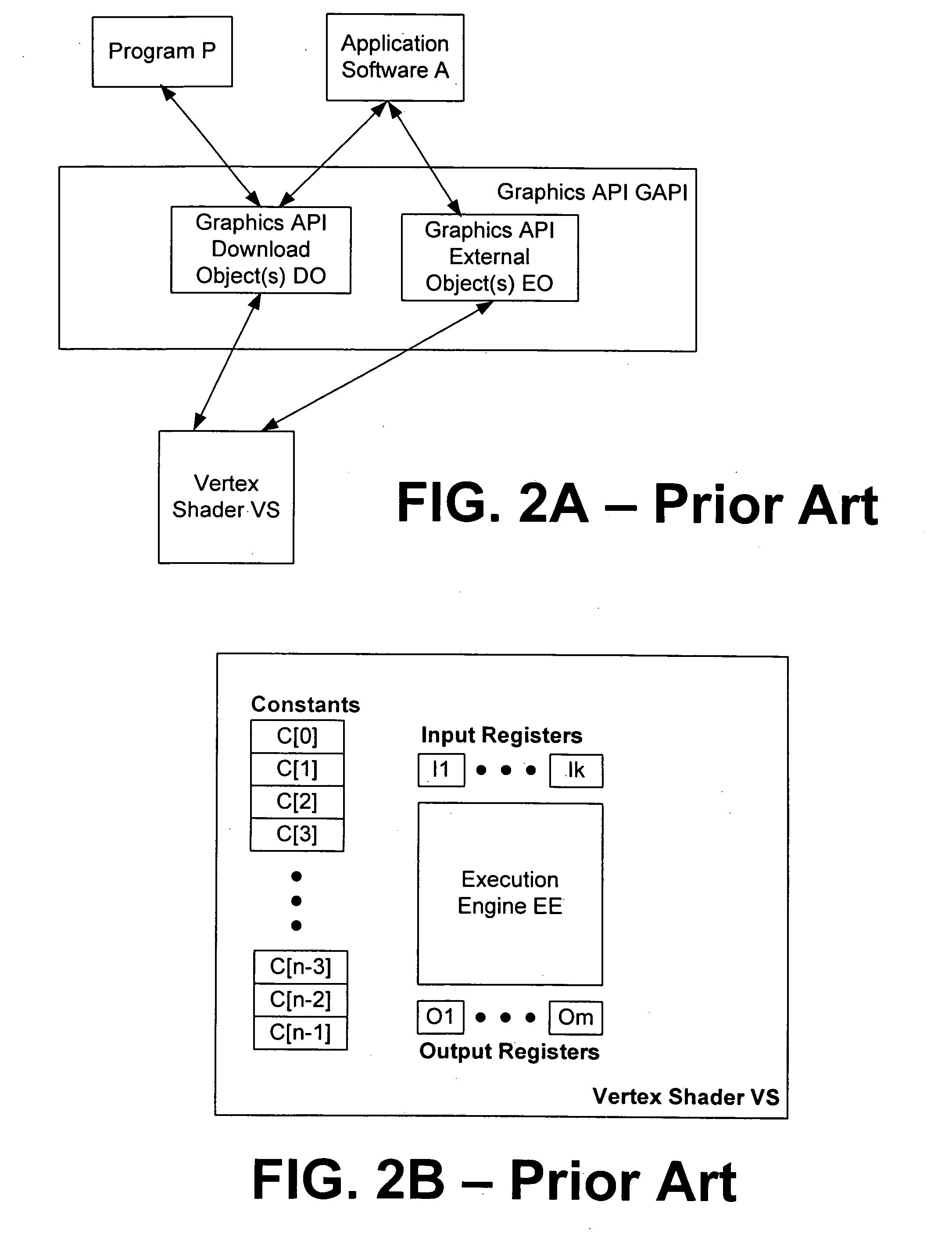

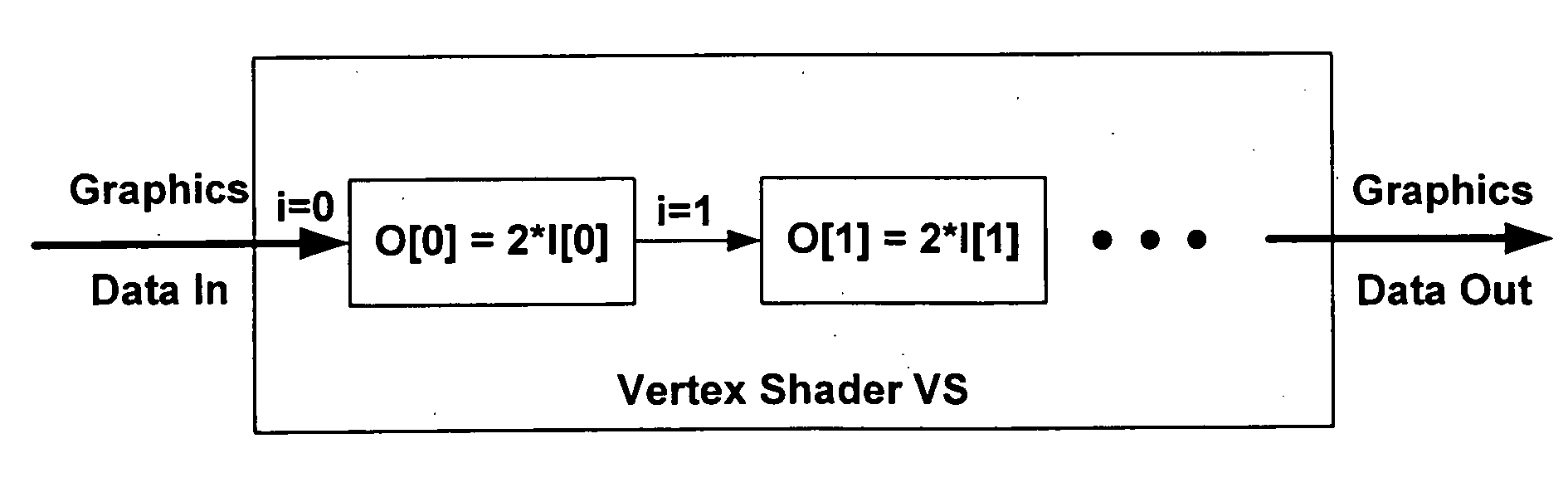

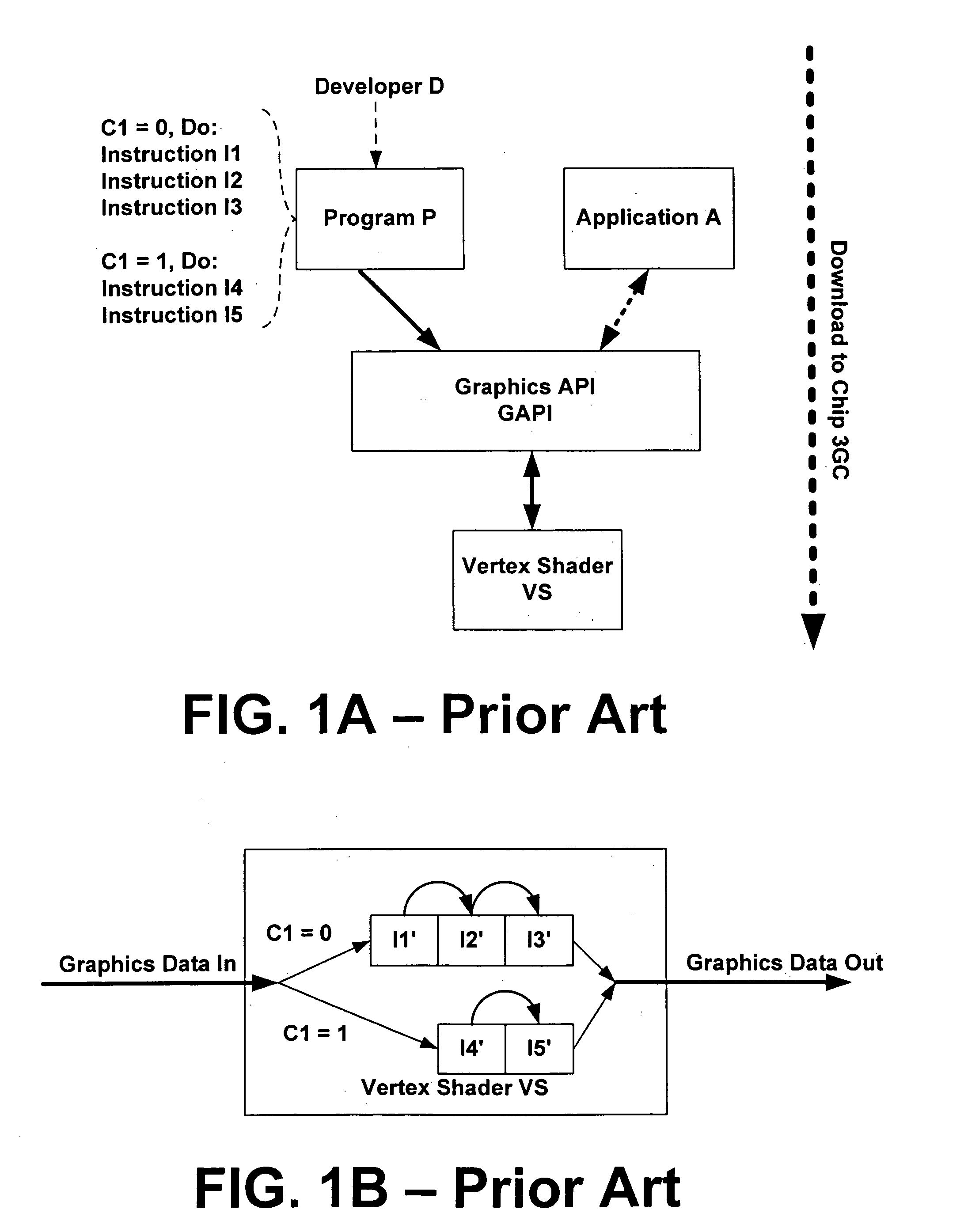

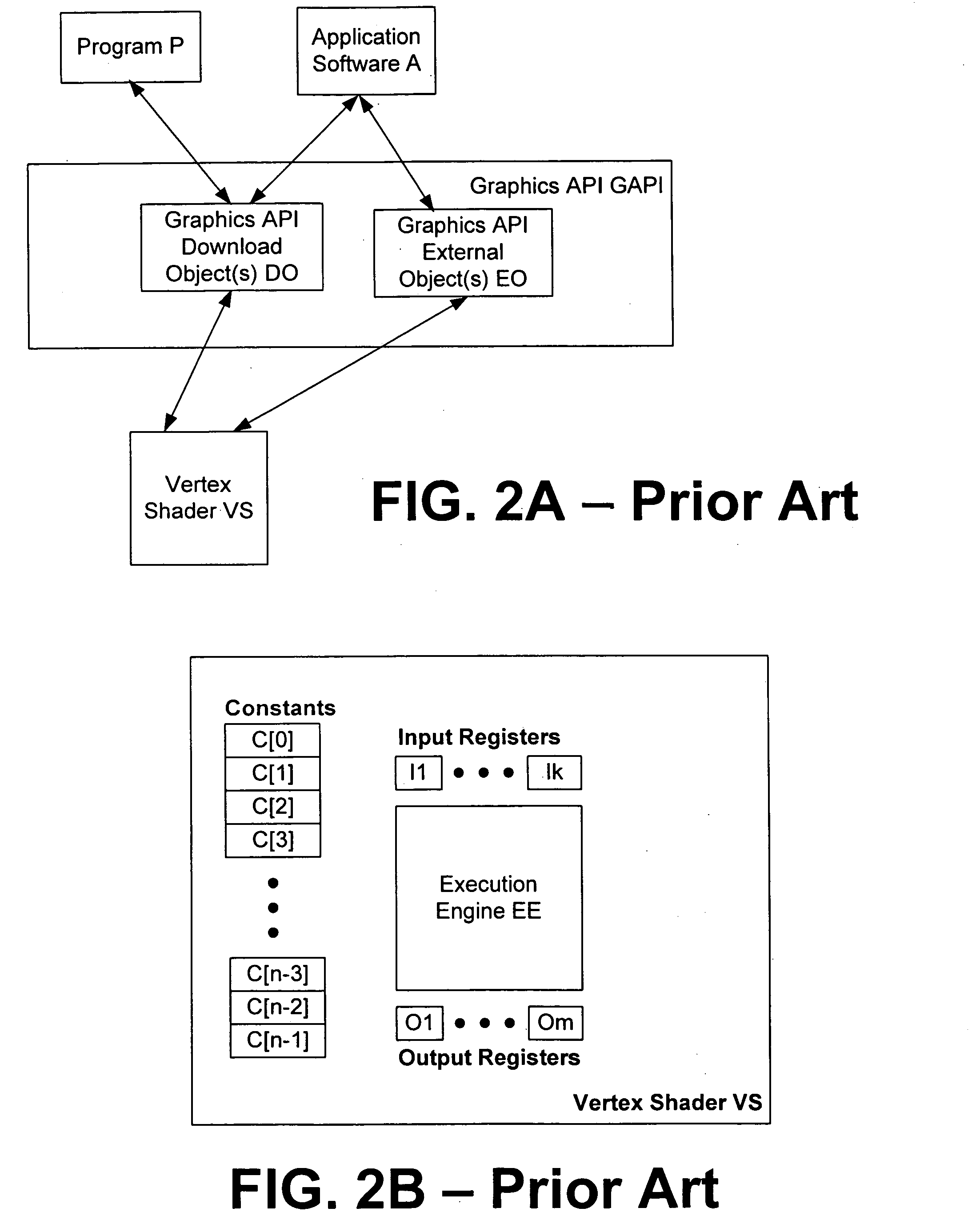

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122330A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

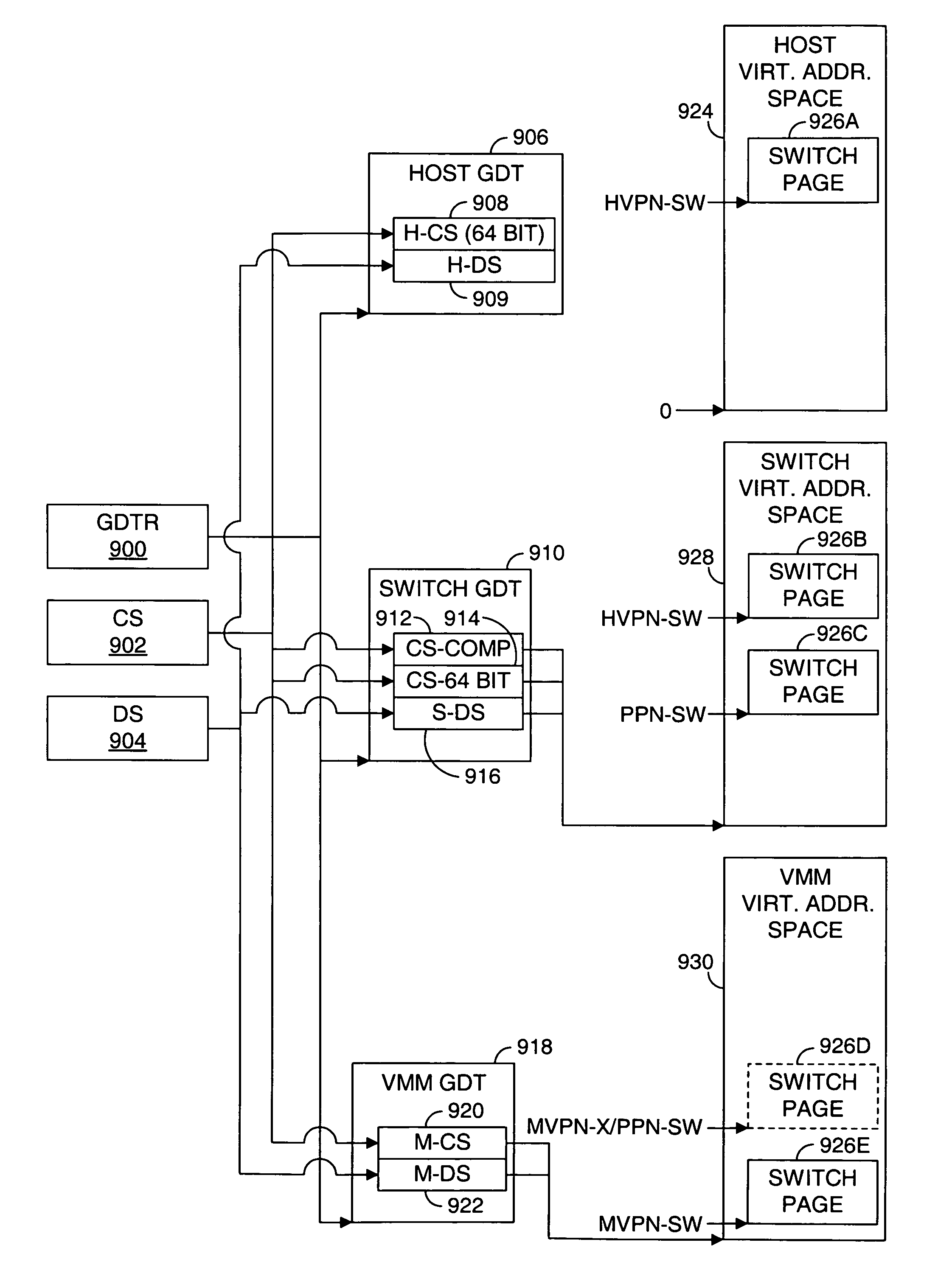

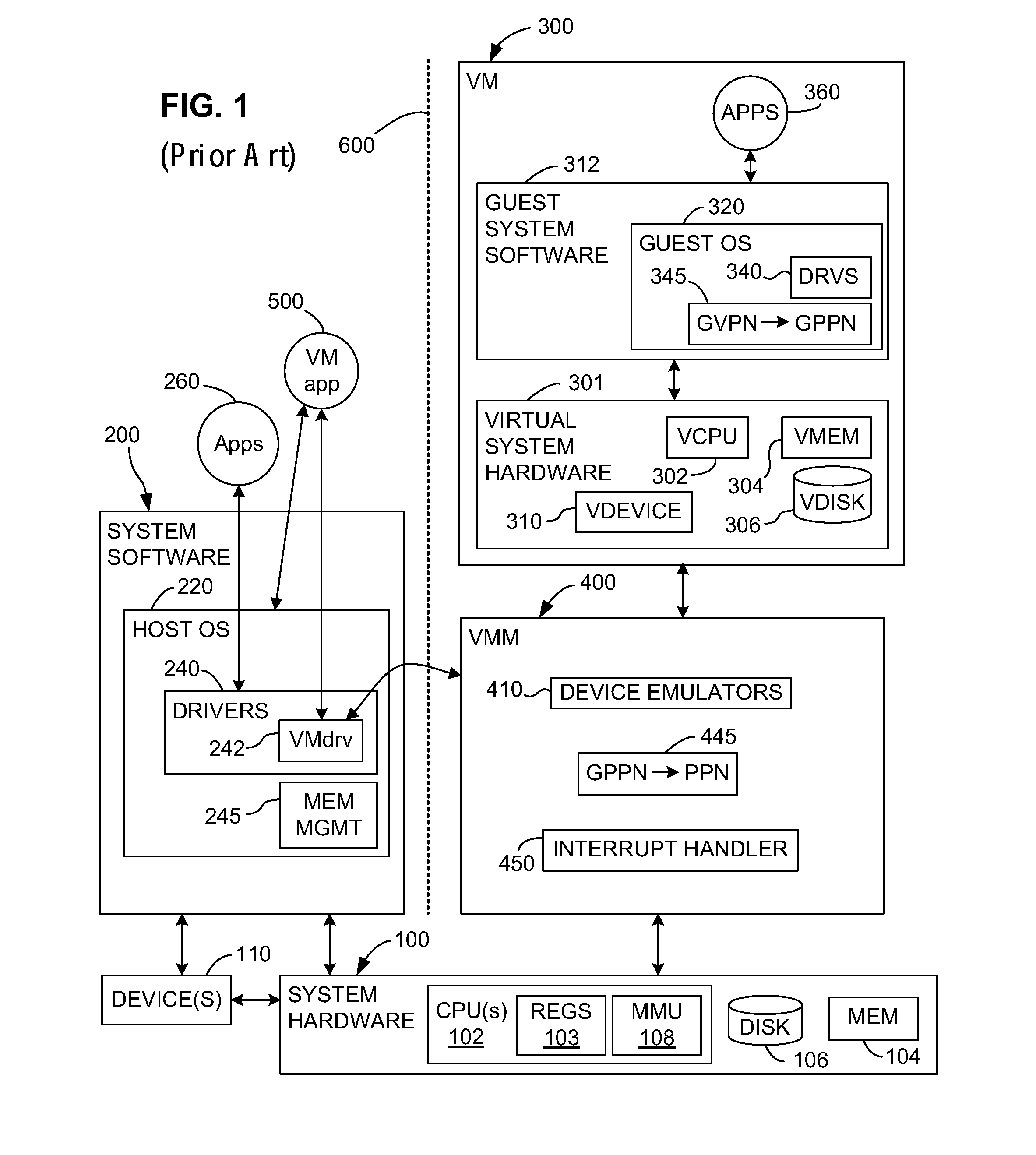

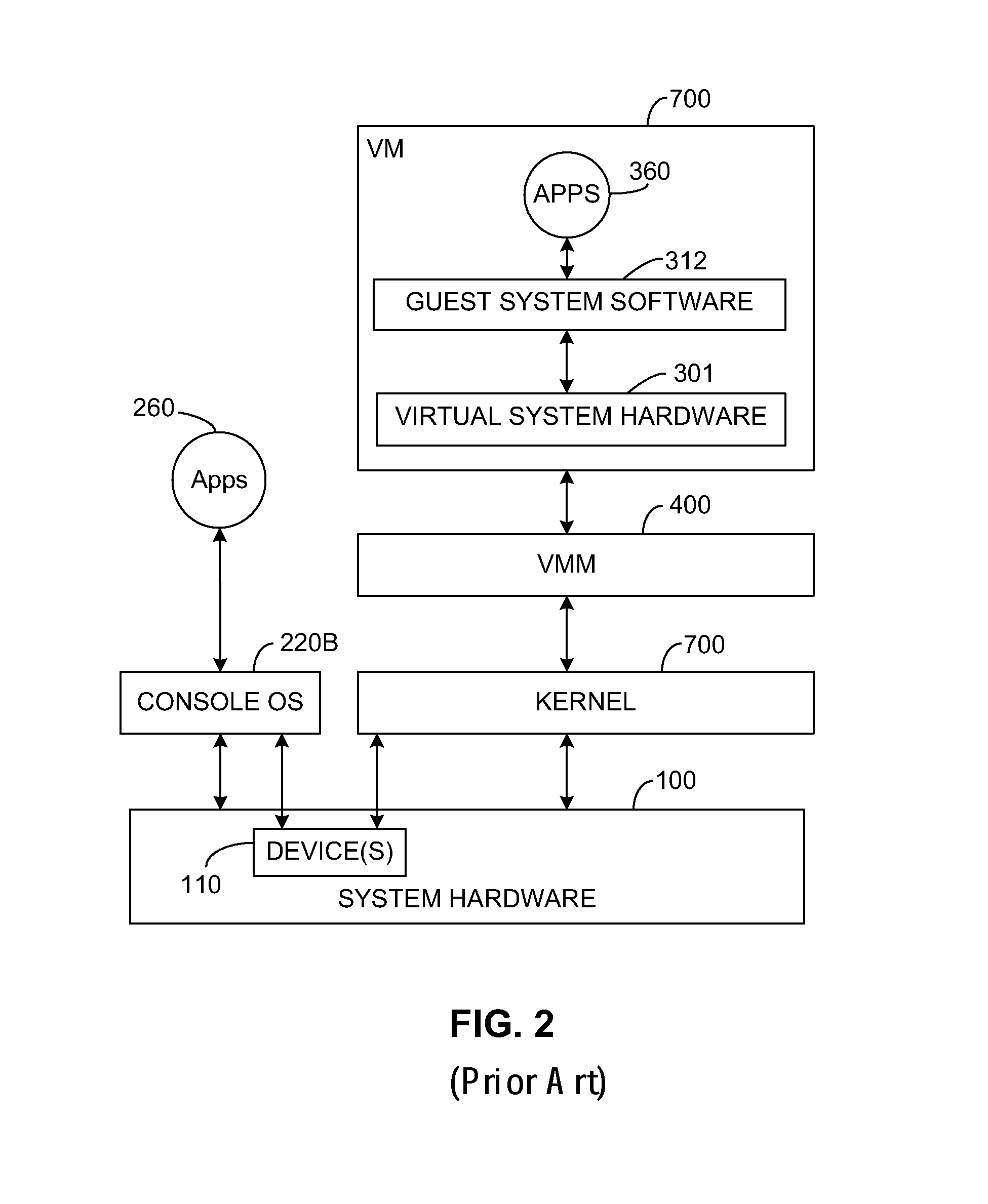

Switching between multiple software entities using different operating modes of a processor in a computer system

ActiveUS7478388B1Restoring contextSoftware simulation/interpretation/emulationMemory systemsLong modeOperational system

A processor has multiple operating modes, such as the long / compatibility mode, the long / 64-bit mode and the legacy modes of the x86-64 microprocessor. Different software entities execute in different ones of these operating modes. A switching routine is implemented to switch from one operating mode to another and to transfer control from one software entity to another. The software entities may be, for example, a host operating system and a virtual machine monitor. Thus, for example, a virtual computer system may comprise a 64-bit host operating system and a 32-bit virtual machine monitor, executing on an x86-64 microprocessor in long mode and legacy mode, respectively, with the virtual machine monitor supporting an x86 virtual machine. The switching routine may be implemented partially or completely in an identity-mapped memory page. Execution of the switching routine may be initiated by a driver that is installed in the host operating system of a virtual computer system.

Owner:VMWARE INC

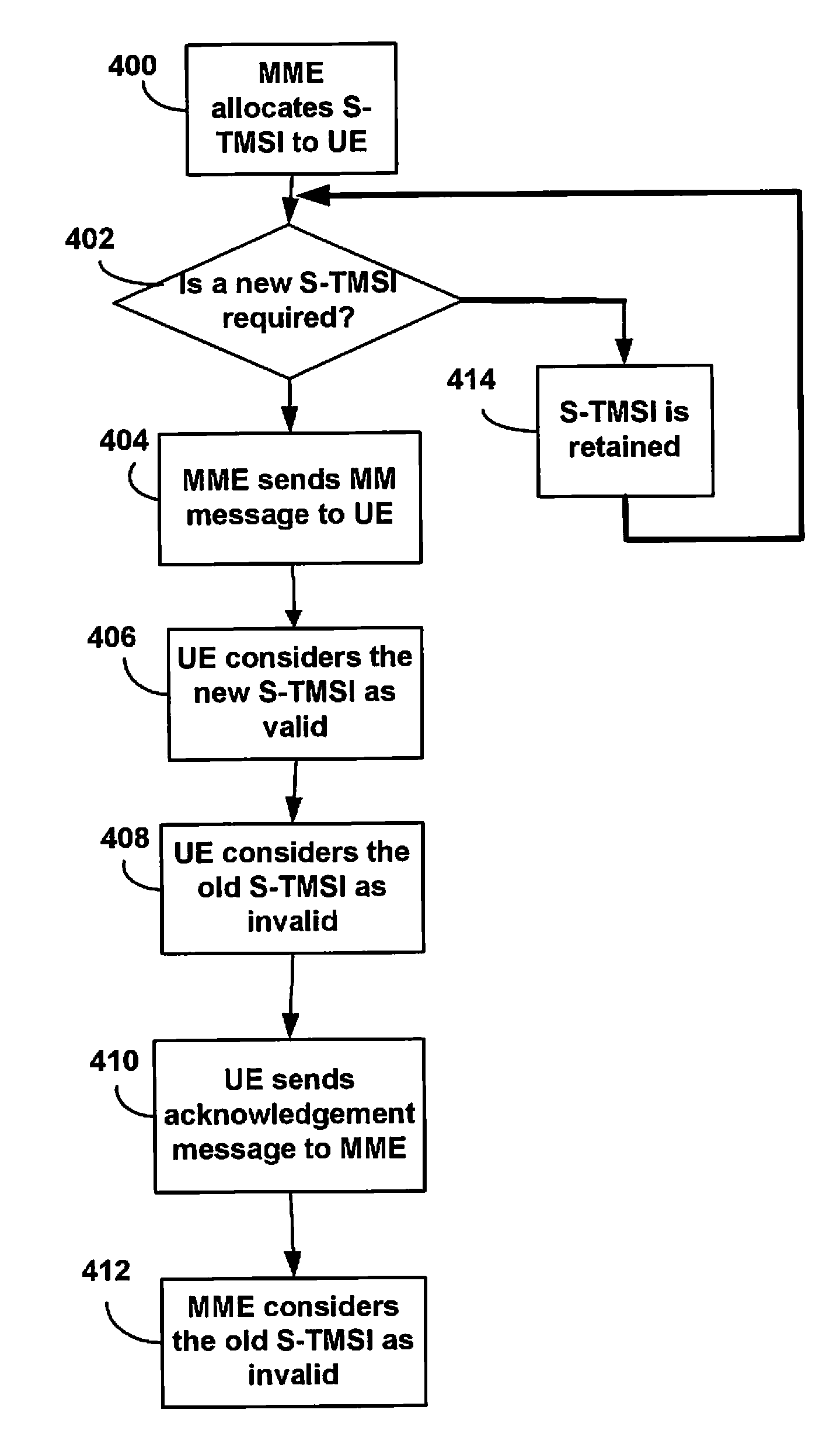

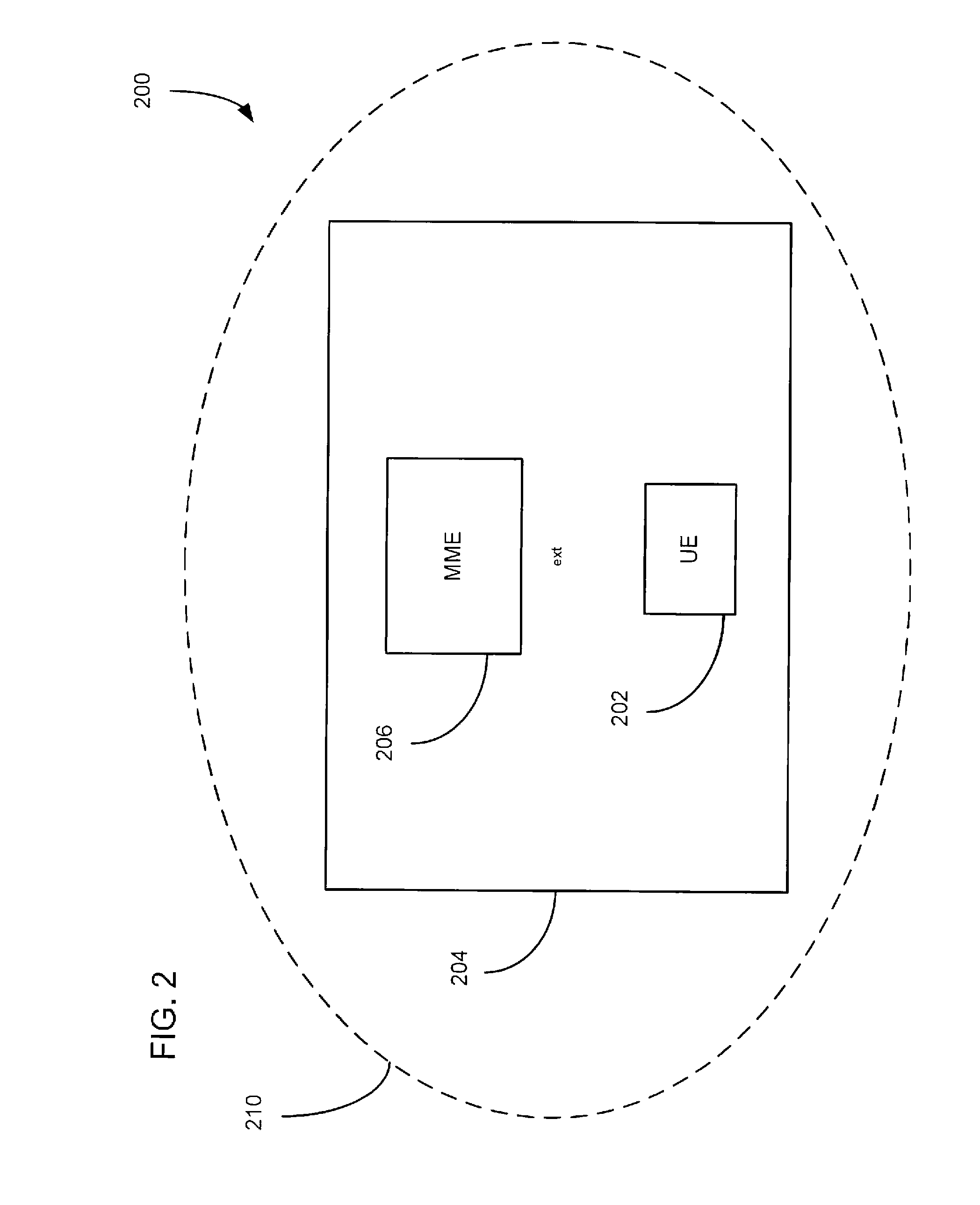

System and method for utilizing a temporary user identity in a telecommunications system

InactiveUS20080268842A1Substation equipmentRadio/inductive link selection arrangementsDiscriminatorPublic land mobile network

A system and method for allocating an S-TMSI in a telecommunication system. The System includes a UE operating within a tracking area of a Public Land Mobile Network. A Mobility Management Entity controls allocation of the S-TMSI to the UE. The S-TMSI has a 32-bit structure with a discriminator for discriminating Circuit Switched, CS, services and Packet Switched, PS, services utilized by the UE. The discriminator utilizes the two significant bits to indicate the CS or PS services.

Owner:TELEFON AB LM ERICSSON (PUBL)

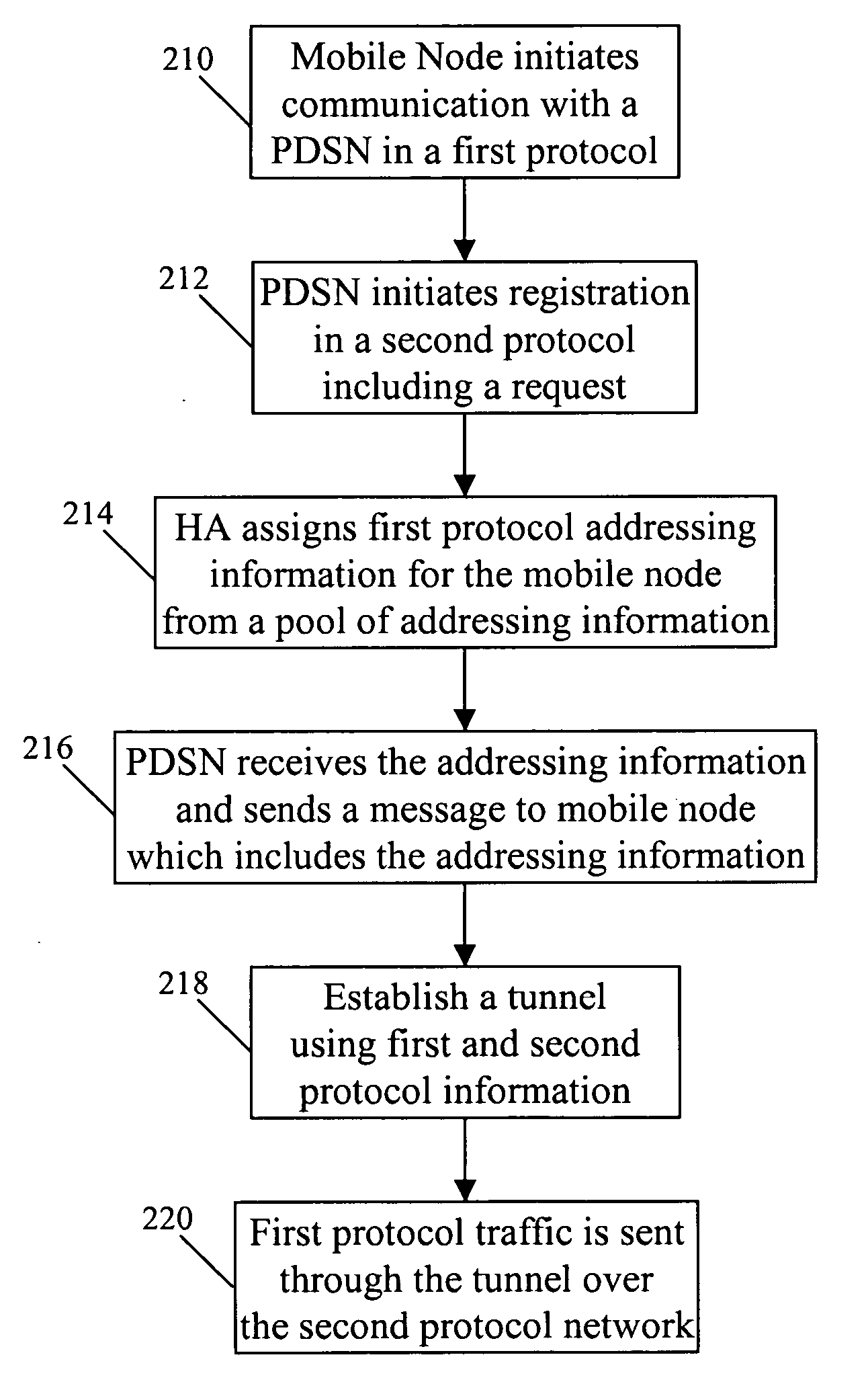

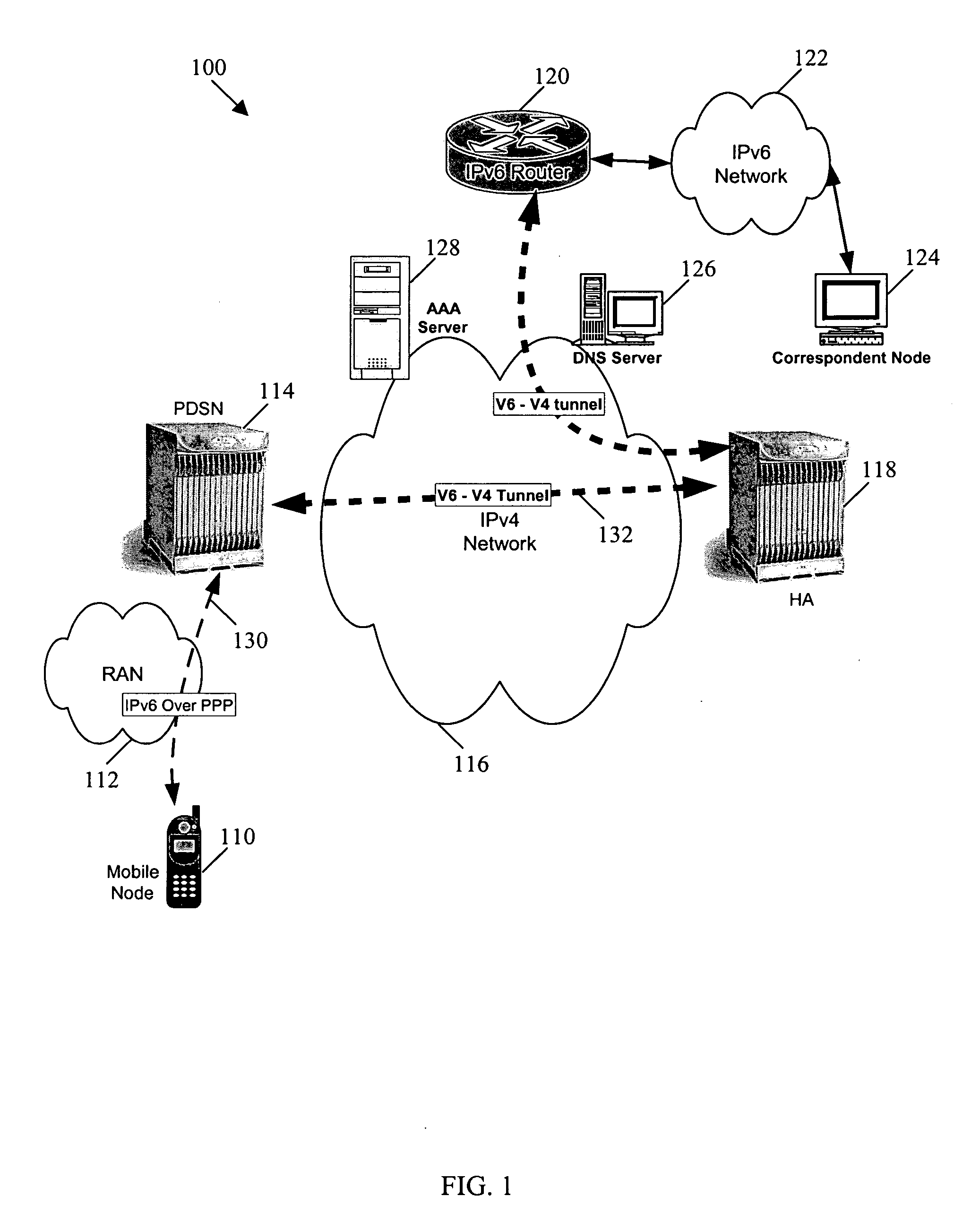

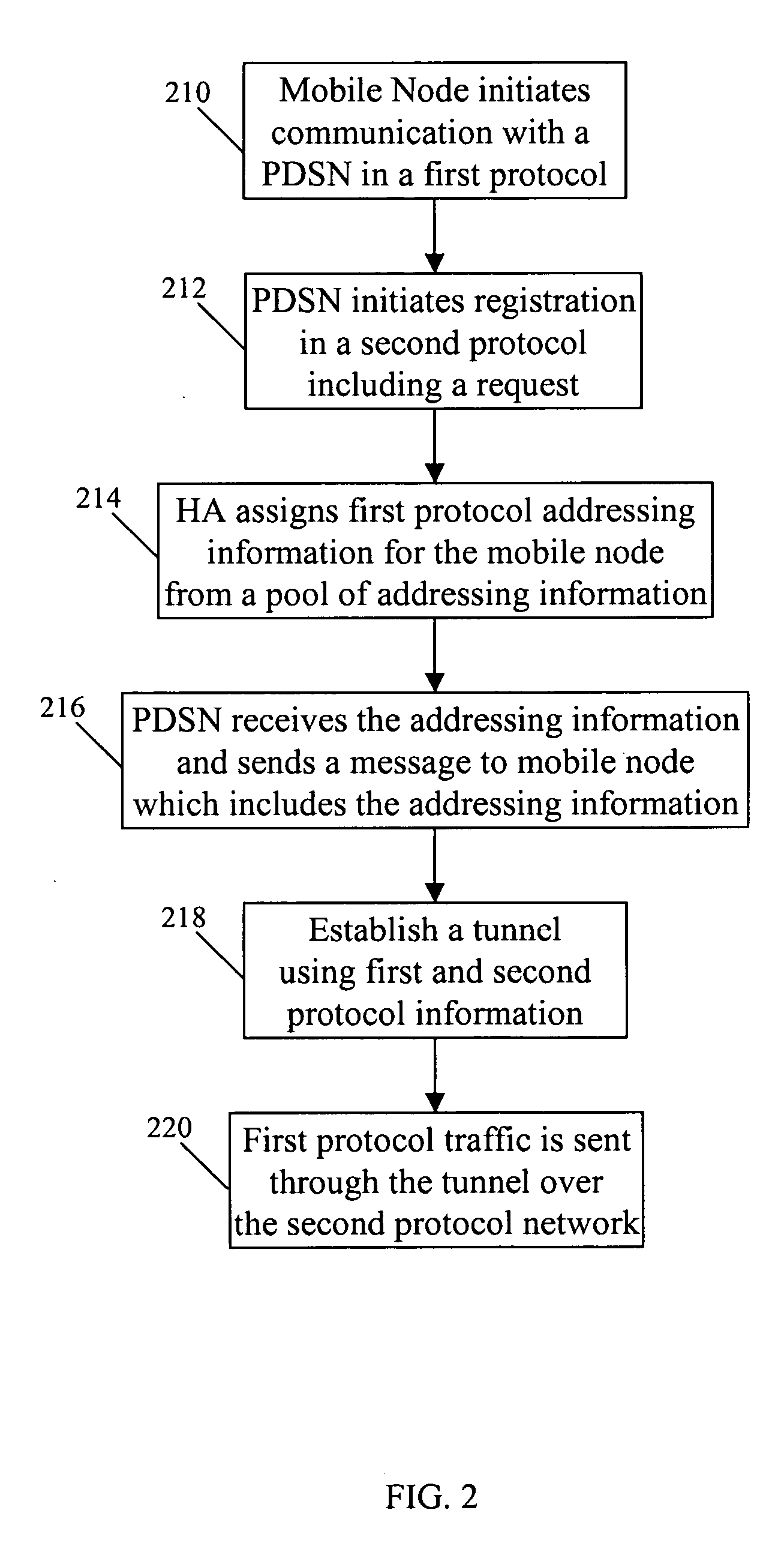

Internet protocol tunneling on a mobile network

InactiveUS20070189219A1Wireless network protocolsRadio/inductive link selection arrangementsIp addressIPv6 packet

Systems and methods are provided for sending information in a first protocol over a network that supports a second protocol. A tunnel is used to provide a roaming mobile node with IPv6 packet data over an IPv4 core network. When the mobile node is handed off while roaming, the same IP address is provided to the mobile node and the IPv6 packet data is again tunneled over the IPv4 core network. Certain embodiments allow an IPv4 core network to support a mobile node that uses Simple IPv6 or MIPv6 addressing. This system and method can be applicable to situations where the mobile node uses addressing greater than 32 bits, while the core network supports 32 bit addressing.

Owner:CISCO TECH INC

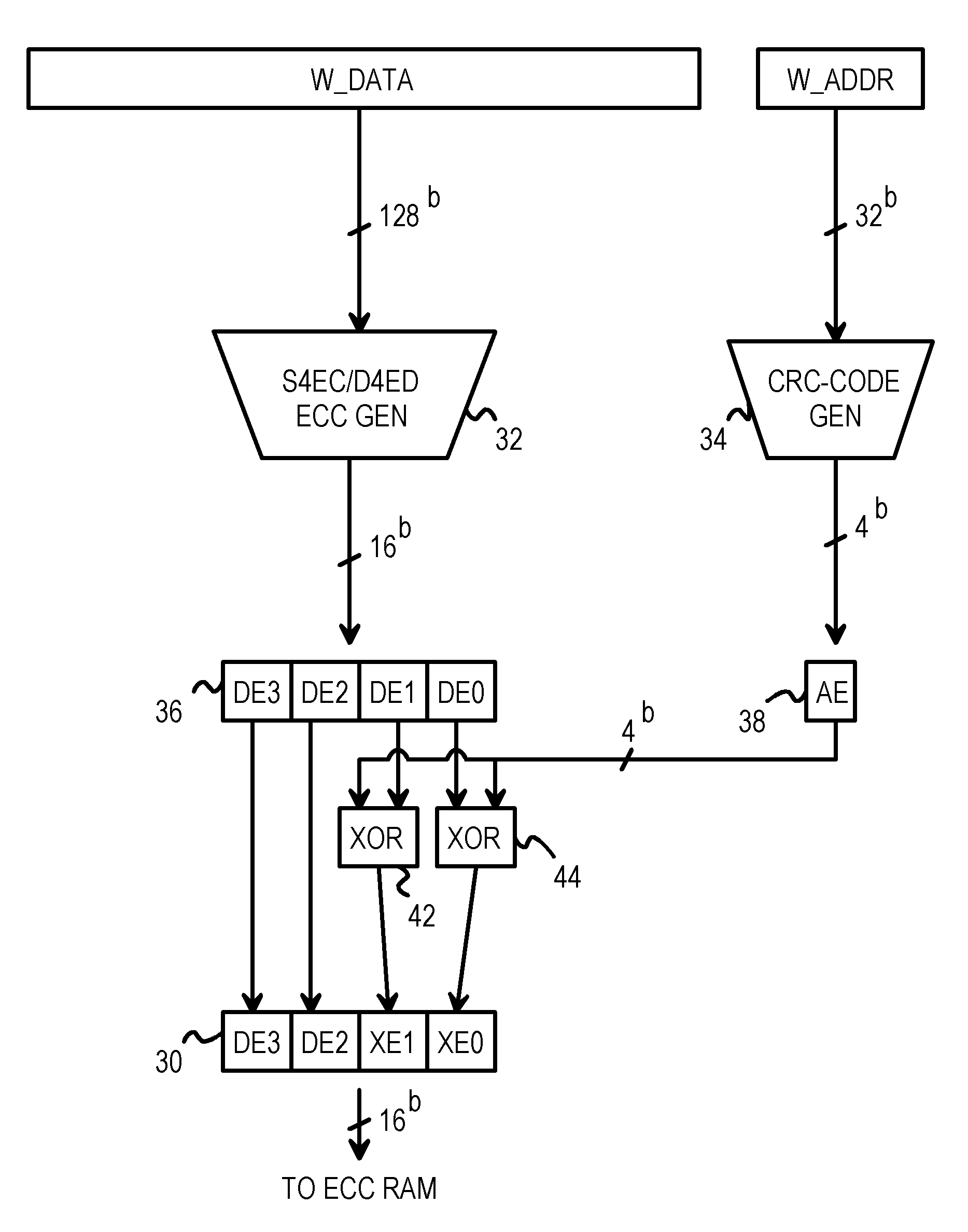

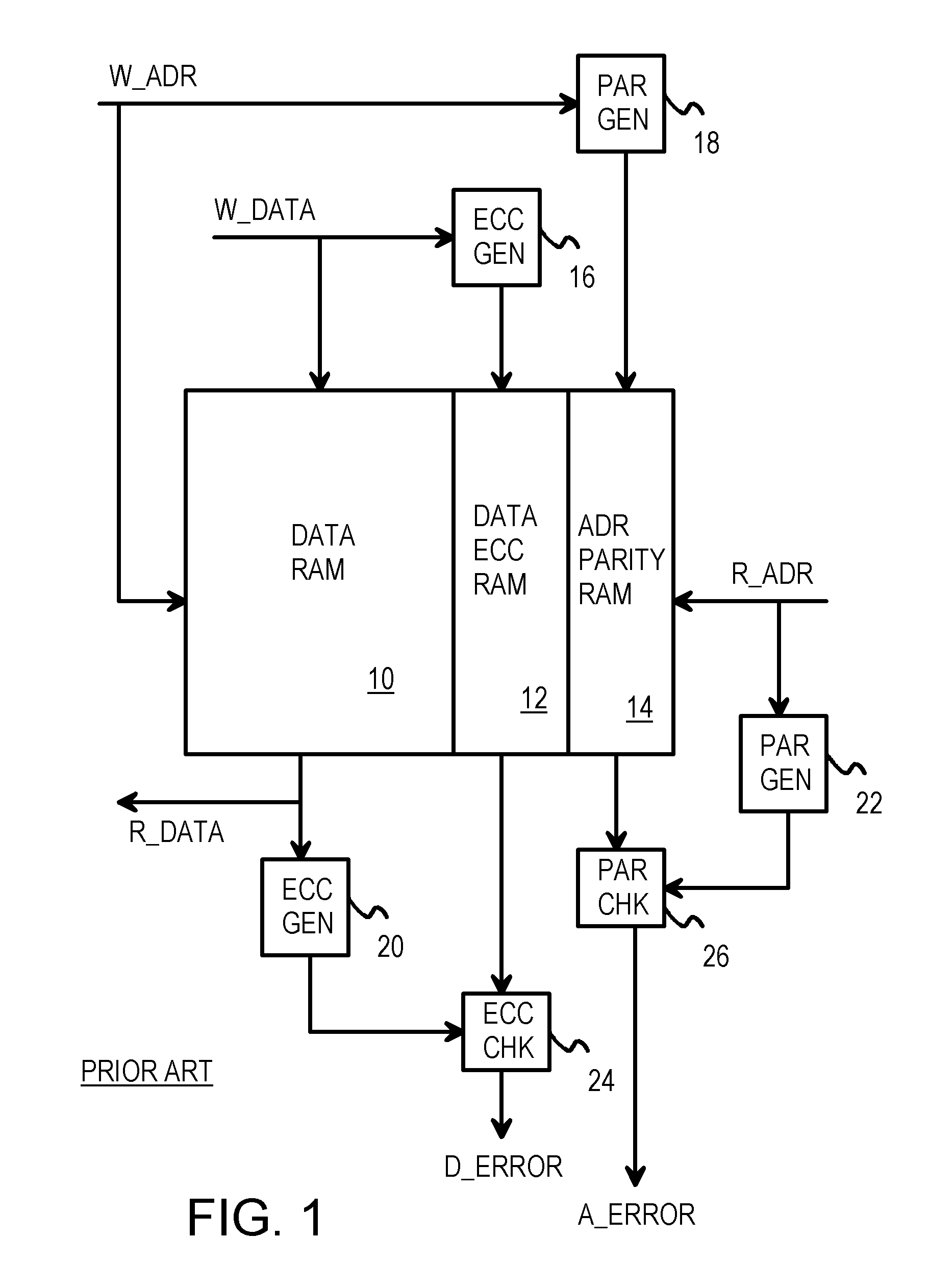

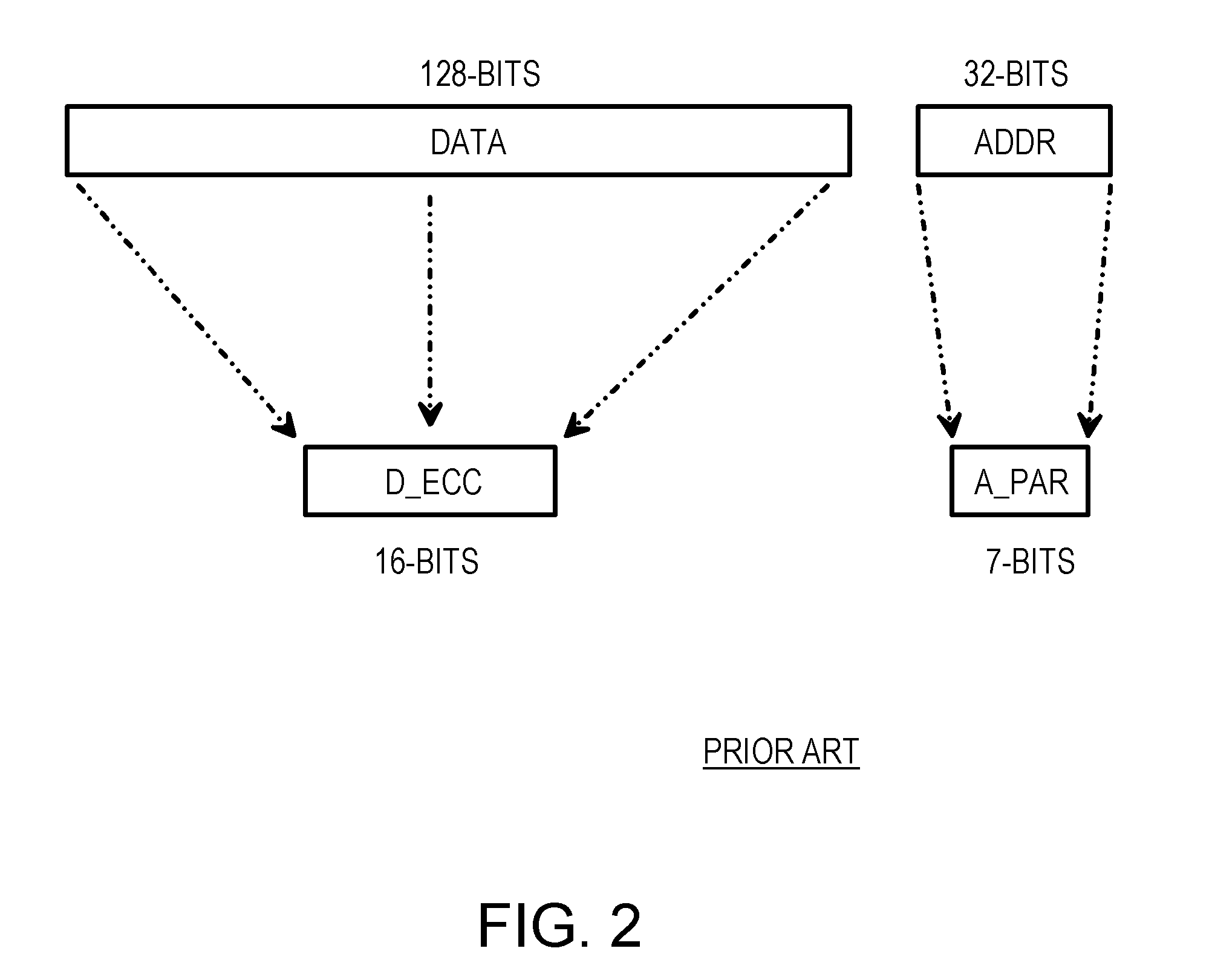

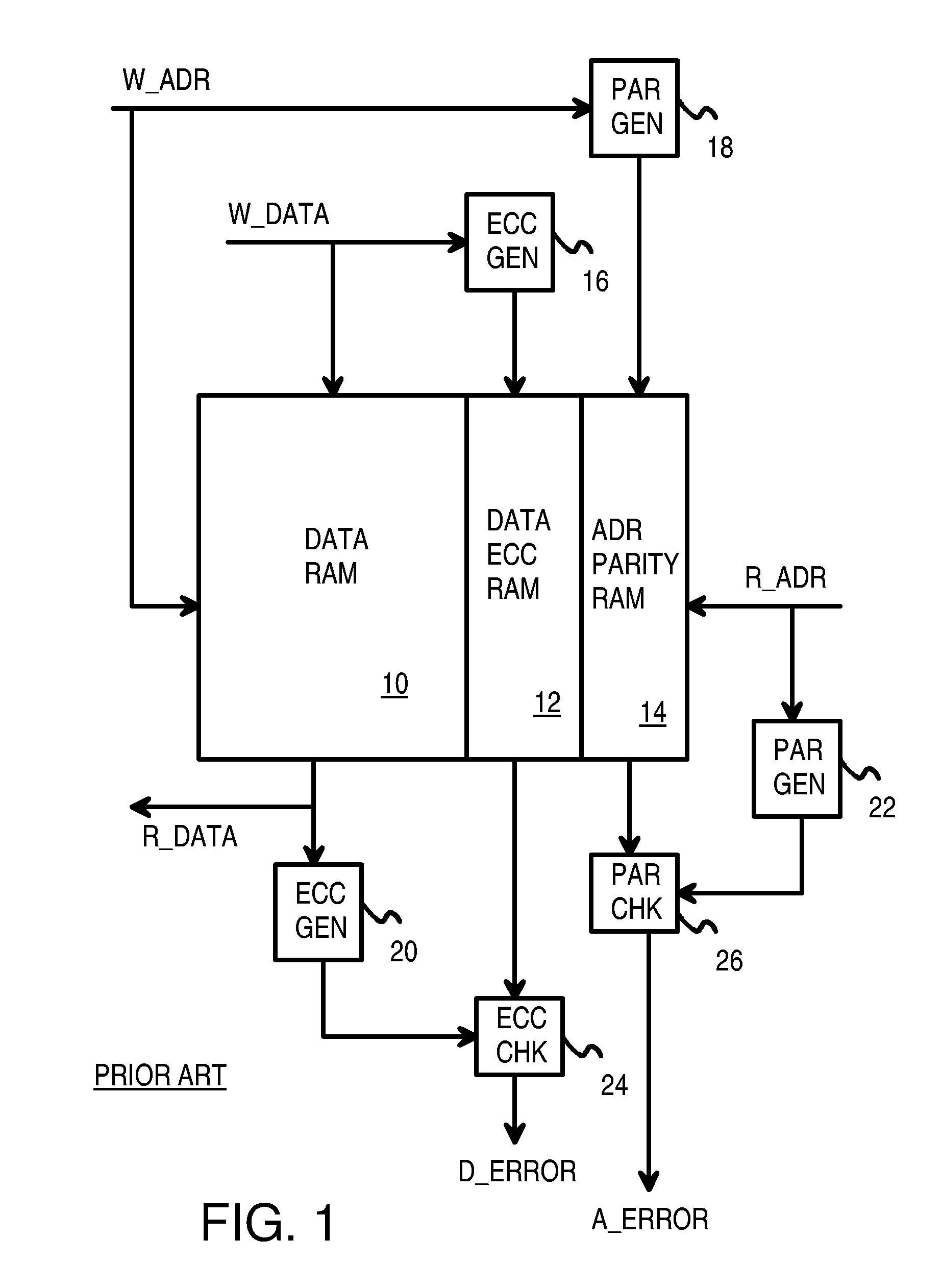

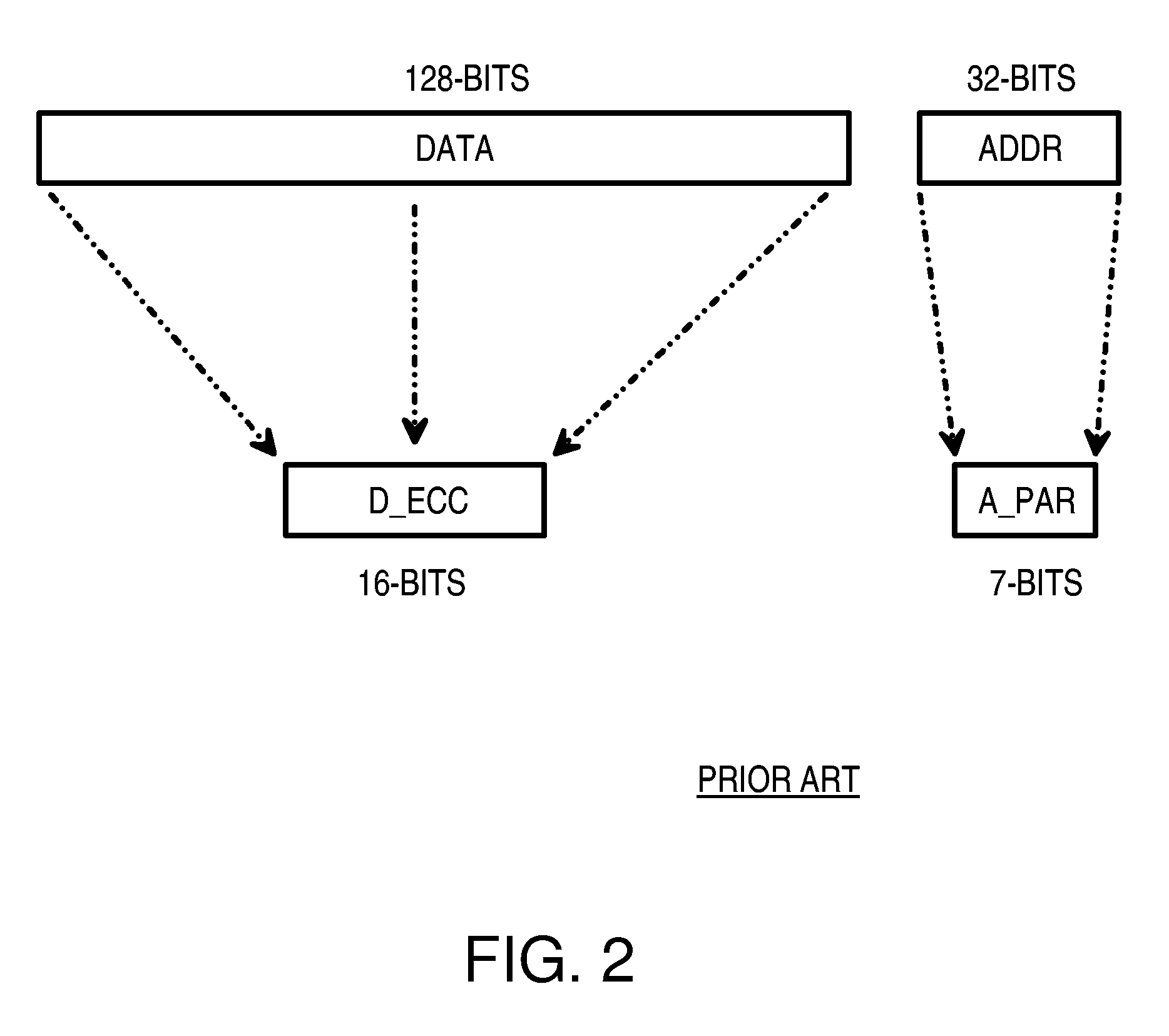

Address error detection by merging a polynomial-based CRC code of address bits with two nibbles of data or data ECC bits

A memory system provides data error detection and correction and address error detection. A Single-byte Error-Correcting / Double-byte Error-Detecting (SbEC / DbED) code with the byte being a 4-bit nibble is used to detect up to 8-bit errors and correct data errors of 4 bits or less. Rather than generating address parity, which is poor at detecting even numbers of errors, a cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to just 4 address check bits using the CRC code. The 4 address check bits are merged (XOR'ed) with two 4-bit nibbles of the data SbEC / DbED code to generate a merged ECC codeword that is stored in memory. An address error causes a 2-nibble mis-match due to the redundant merging of the 4 address check bits with 2 nibbles of data correction code. The CRC code is ideal for detecting even numbers of errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

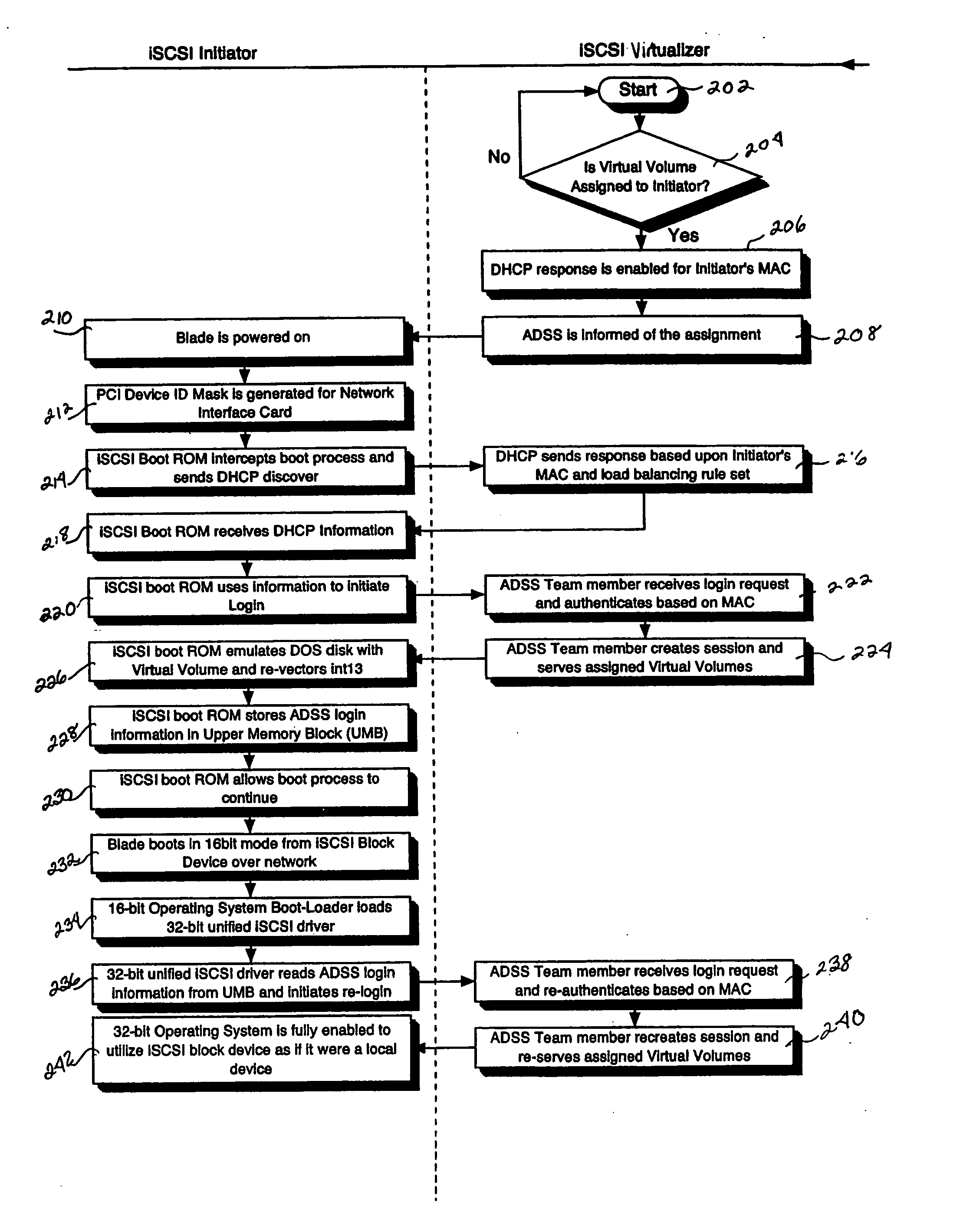

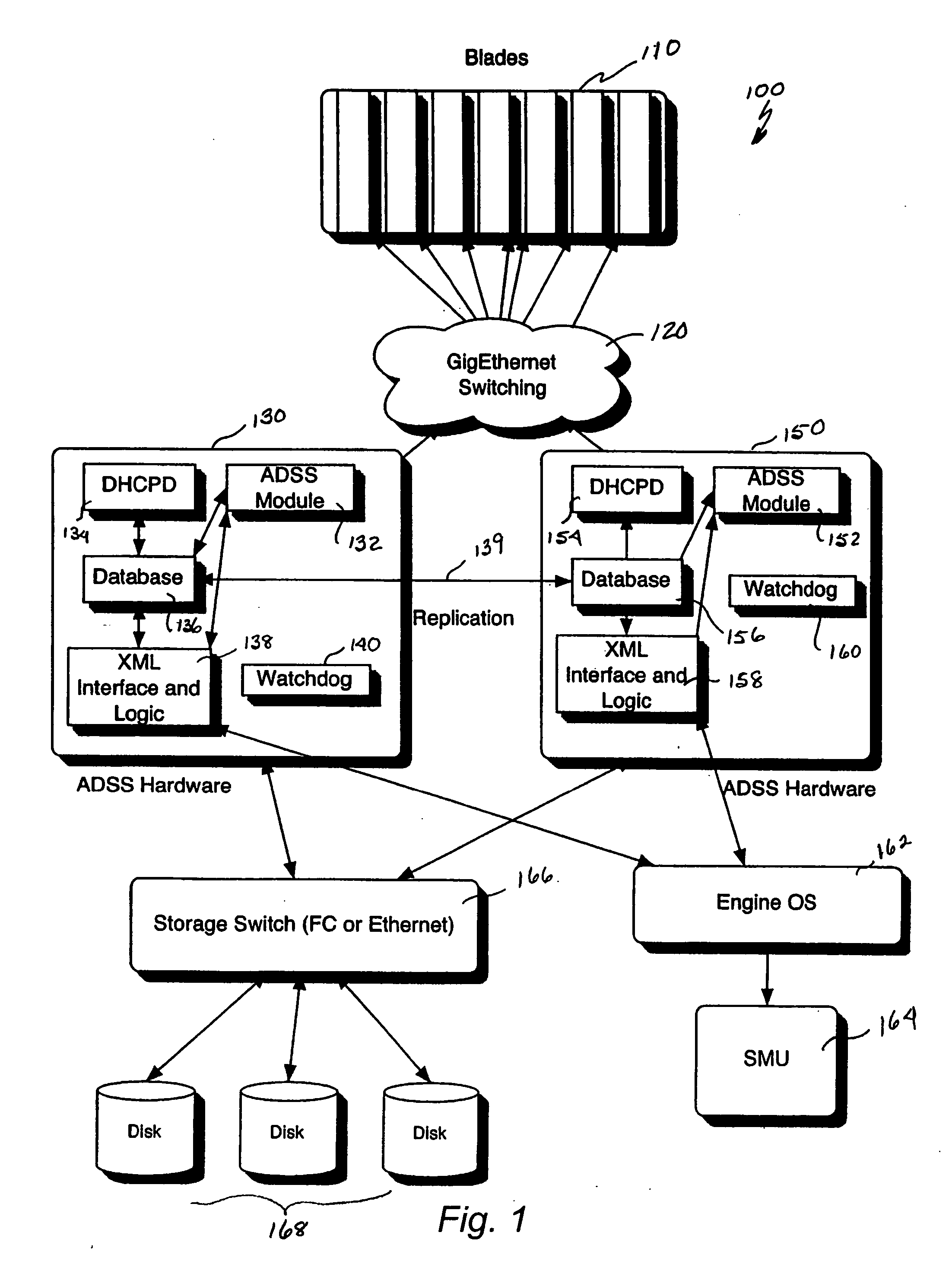

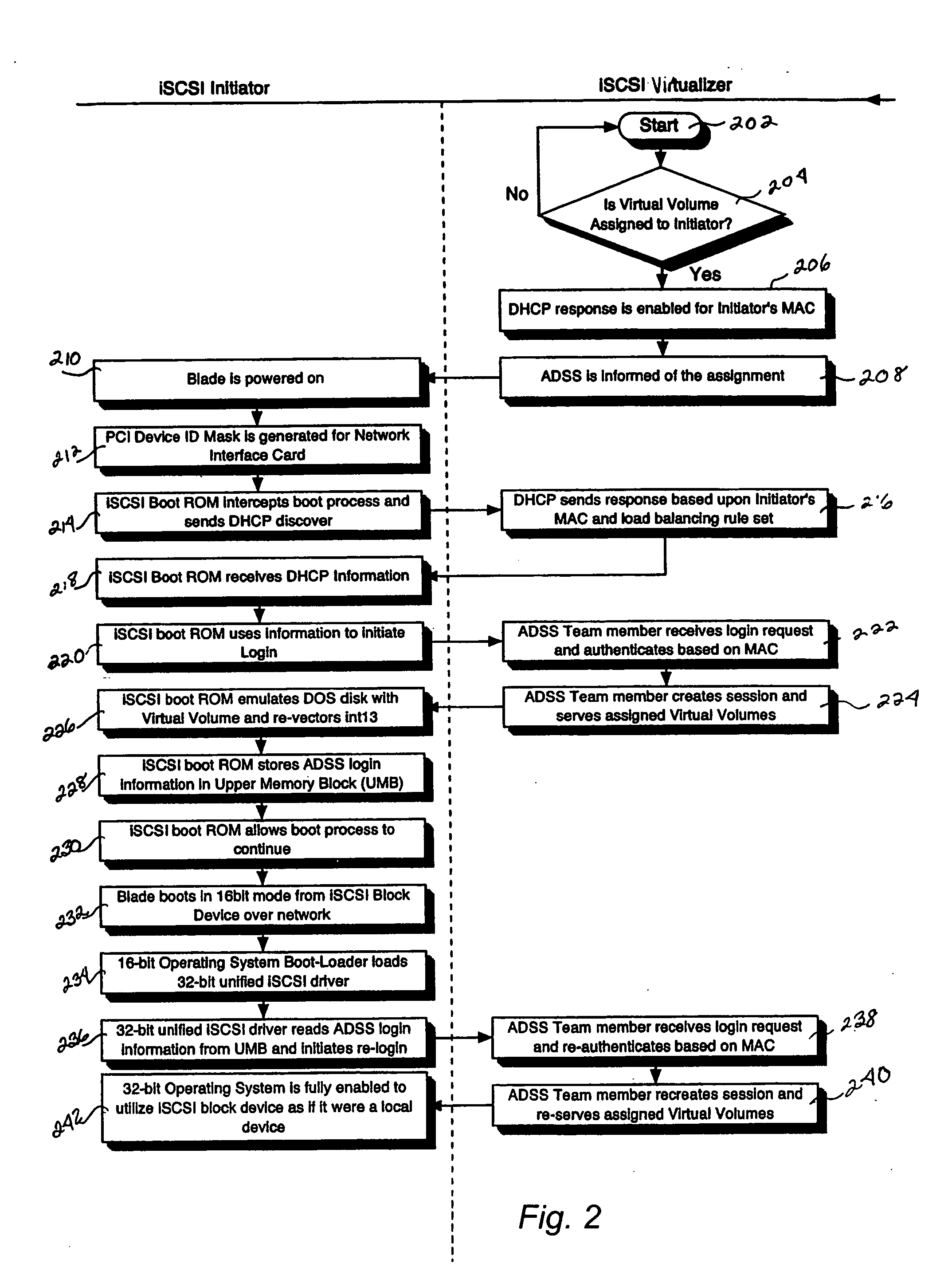

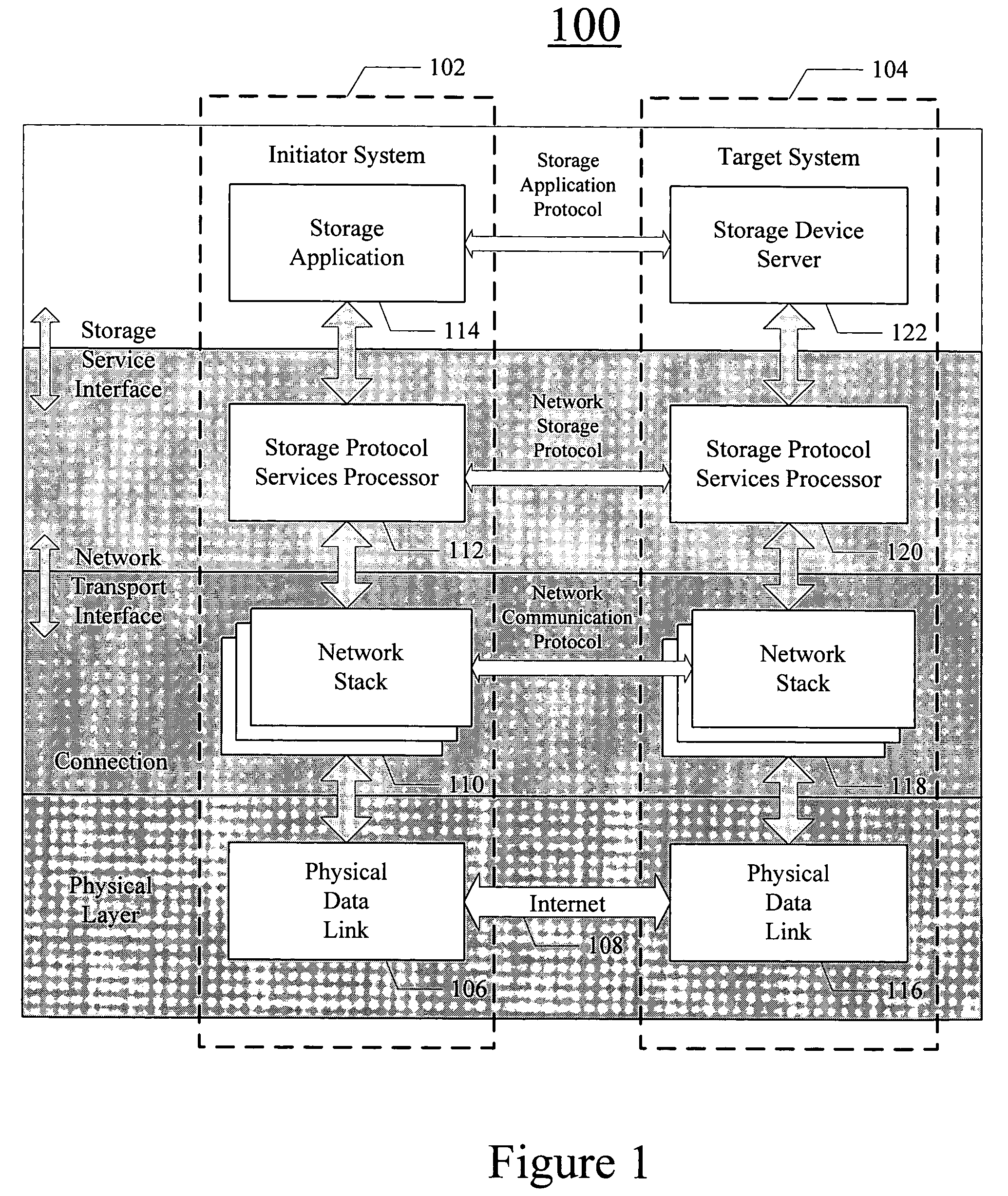

iSCSI boot drive system and method for a scalable internet engine

InactiveUS20050138346A1Digital computer detailsProgram loading/initiatingOperational systemThe Internet

A system for remote booting of a server generally includes a client initiator, an iSCSI virtualizer, and an iSCSI initiator. The client initiator requests access to the server and the iSCSI virtualizer receives the access request. Then, the iSCSI initiator acts upon the request received by the iSCSI virtualizer to initiate login to the server through use of an iSCSI Boot ROM on the server and to emulate a disk operating system through use of the iSCSI Boot ROM, which enables the server to boot. The server boots in both an 8-bit and a subsequent 32-bit mode. The iSCSI Boot ROM appears as a local device upon the completion of the server boot. The iSCSI virtualizer authenticates the login at least twice. The iSCSI virtualizer includes a pair of replicated active directory service servers (ADSS).

Owner:RPX CORP

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122334A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

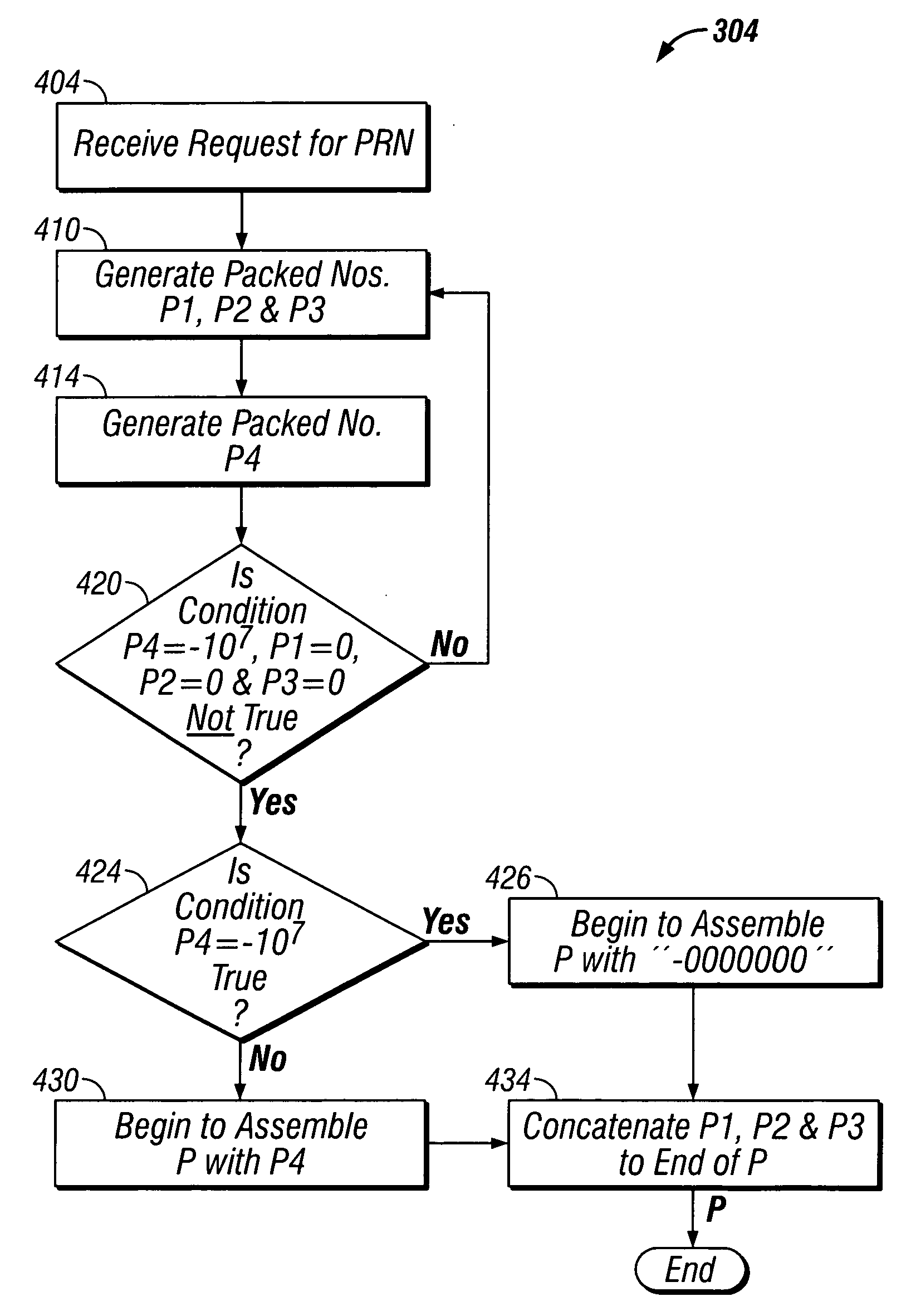

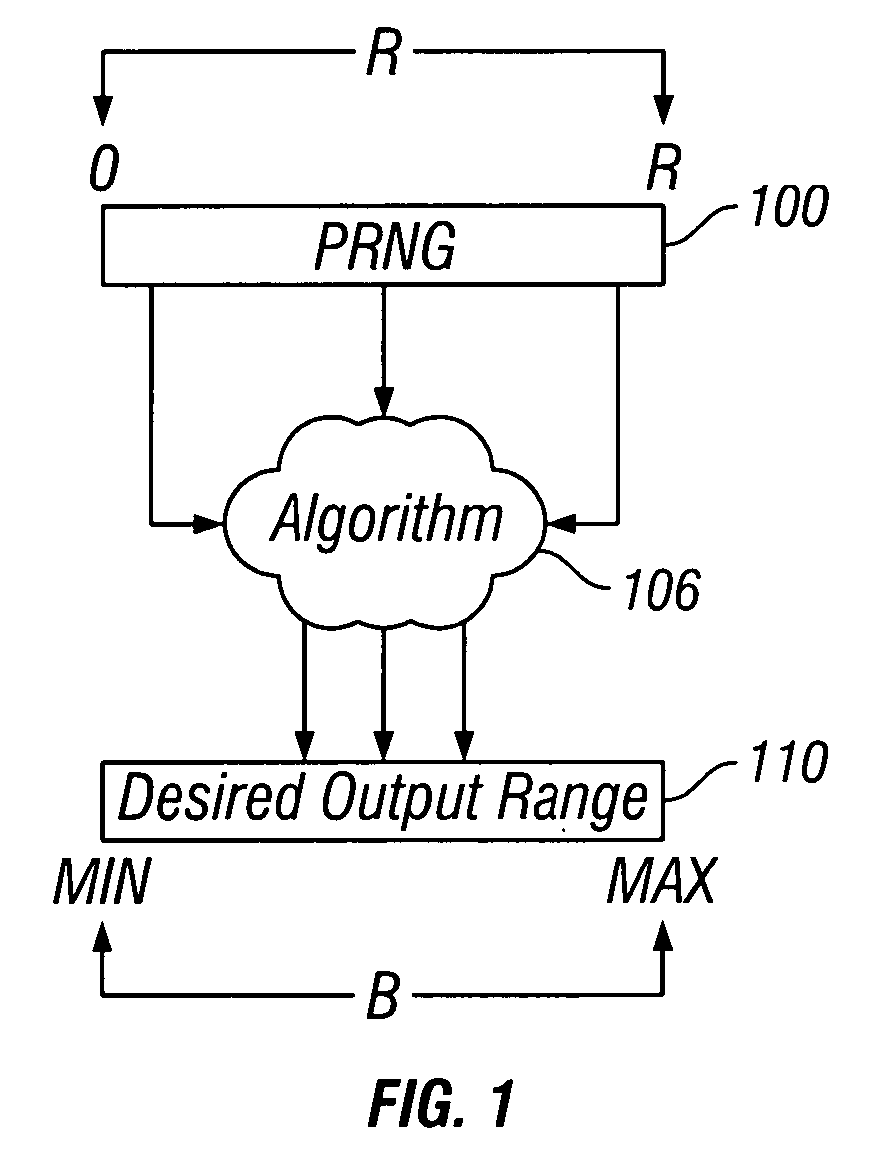

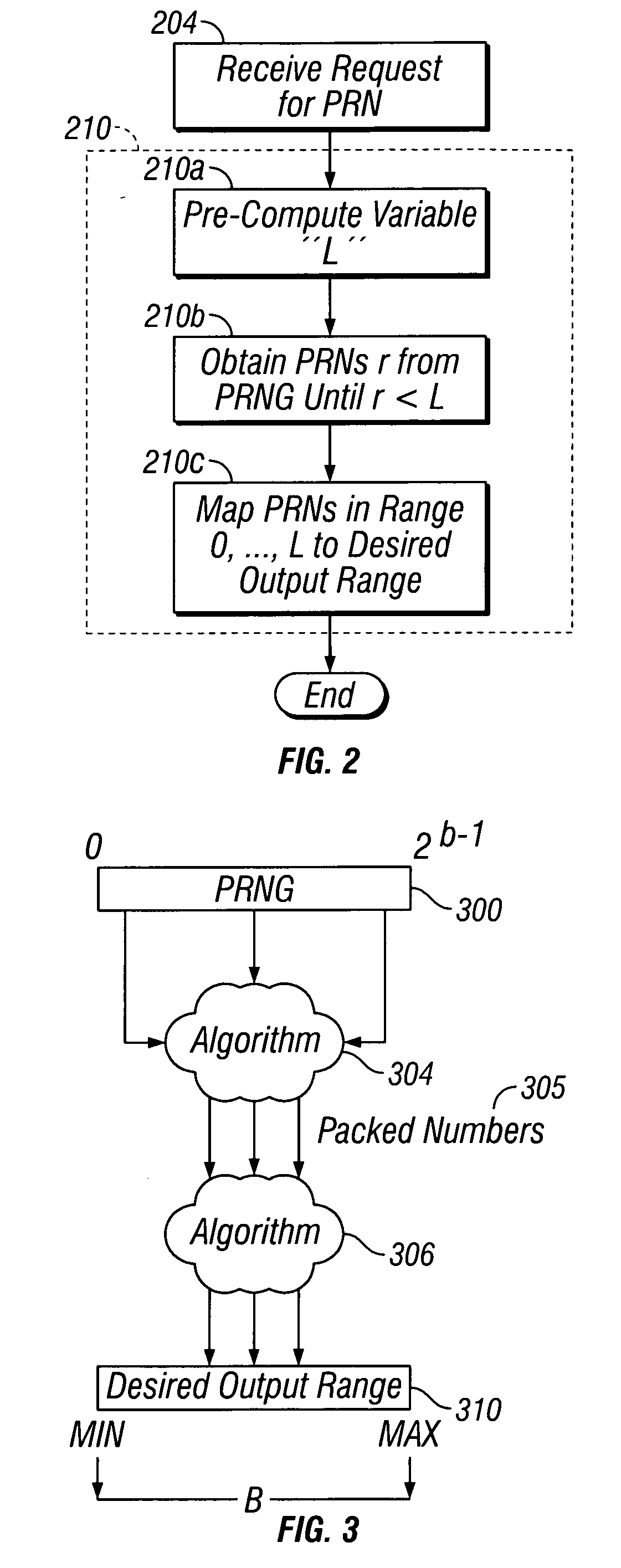

Mapping pseudo-random numbers to predefined number ranges

ActiveUS20050050121A1Low costDiminish pseudo randomnessRandom number generatorsDigital function generatorsSmall targetComputer science

Pseudo-random numbers (PRNs) generated by a PRN generator are mapped to predefined number ranges or target ranges. The target range may be smaller or larger than the range of the PRN generator. Mapping to a smaller target range may include generating PRNs (e.g., integers) from a particular bit-input stream (e.g., 32-bit) having a uniform distribution across the range of numbers; selecting an optimal subset of the generated PRNs to map; and mapping the selected PRNs to a corresponding number in a target range such that the mapped numbers are uniformly distributed across the target range. Mapping to a larger target range may include generating uniformly distributed PRNs; applying a generation function to the PRNs to generate uniformly distributed packed numbers; and applying a mapping function to map selected packed numbers to the target range such that the mapped numbers are uniformly distributed.

Owner:SAP AG

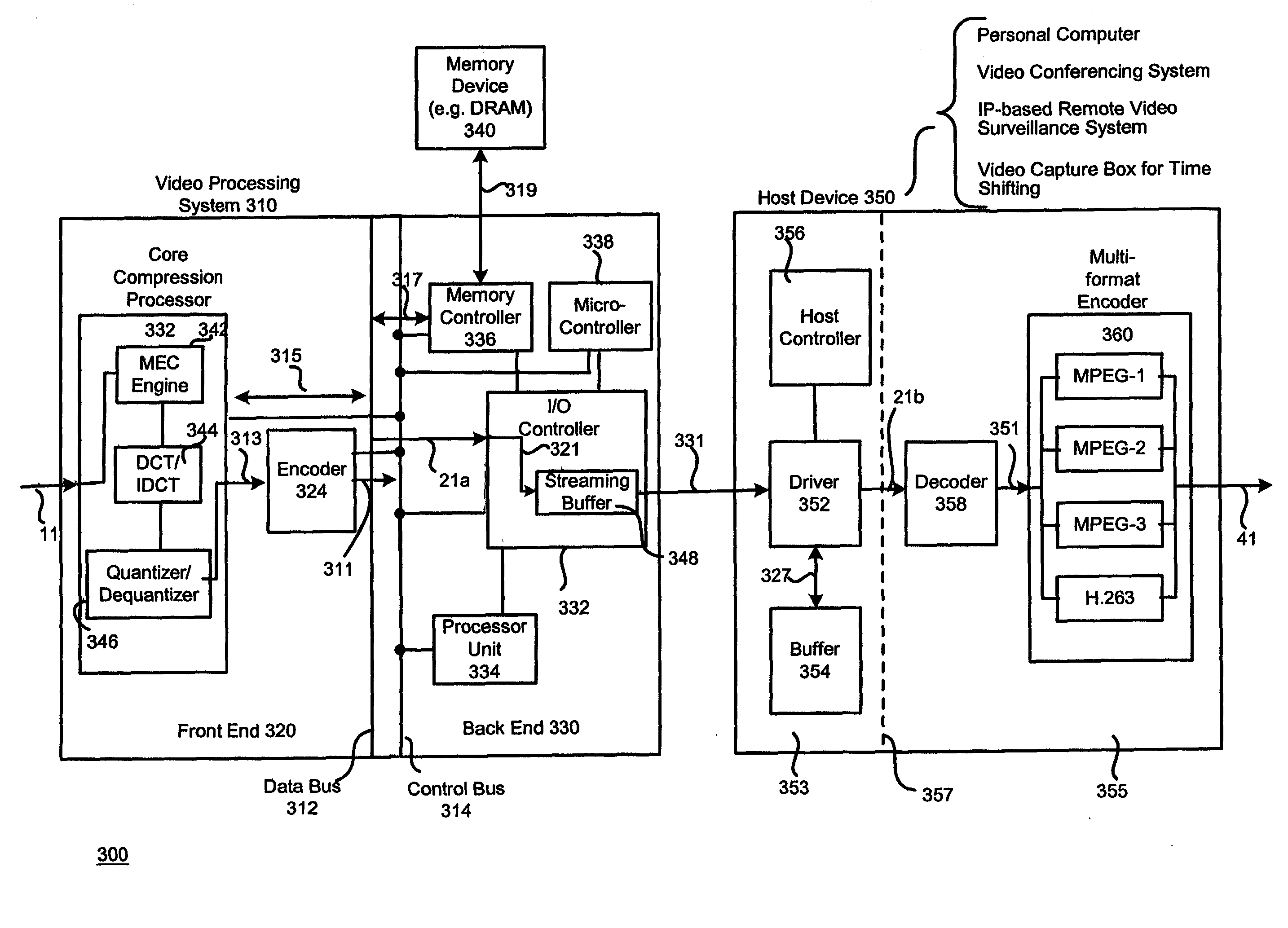

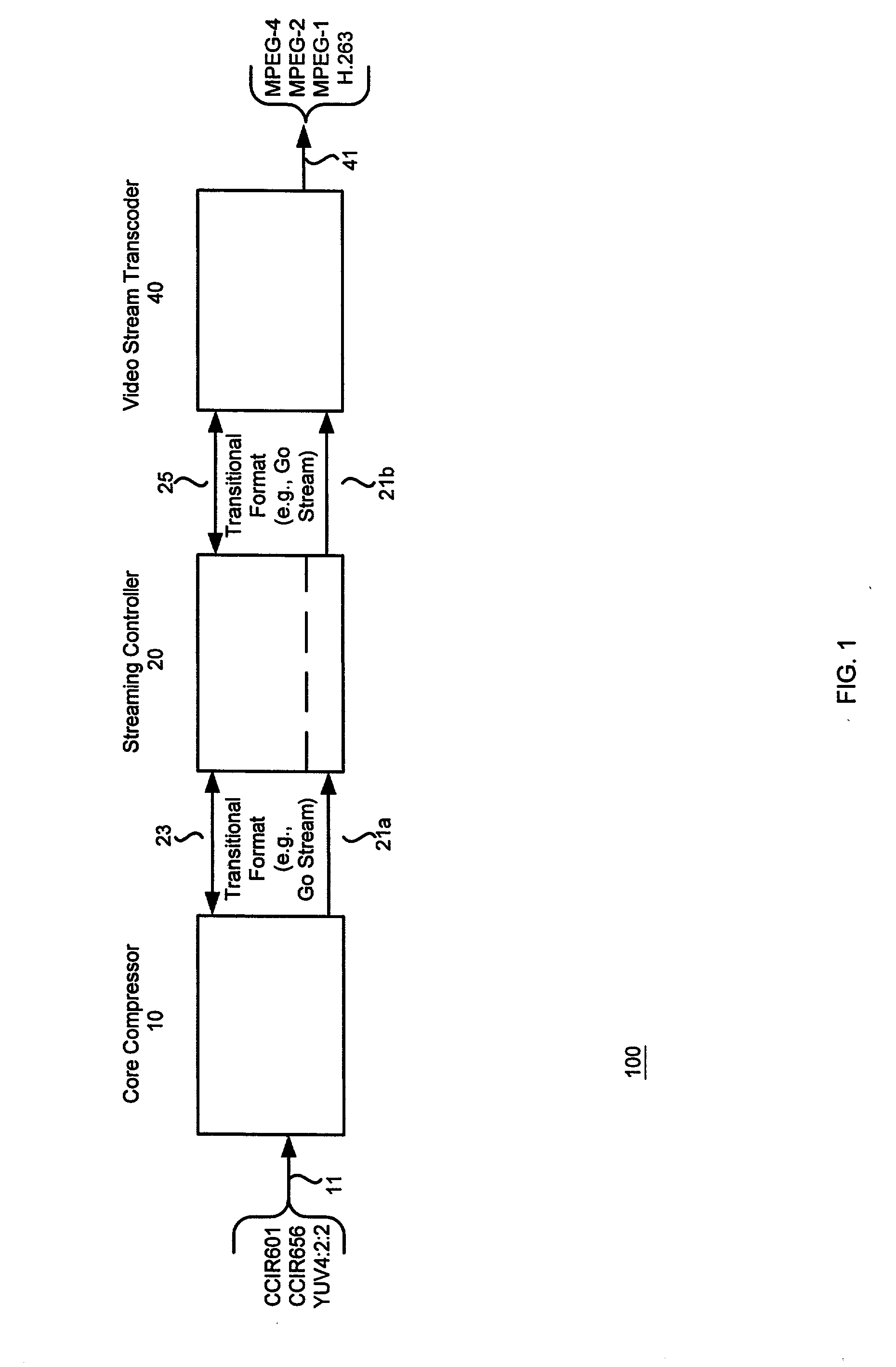

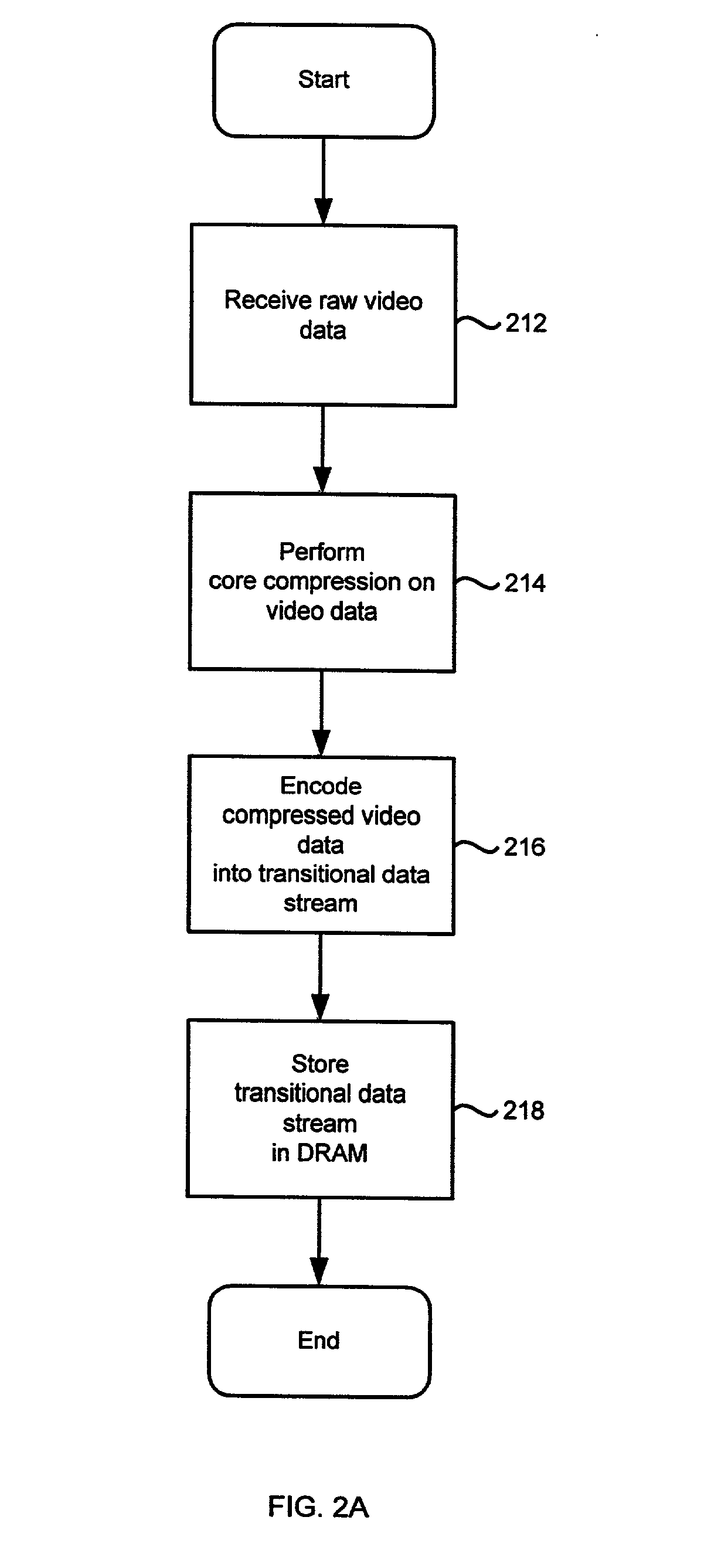

Multiple format video compression

InactiveUS20050226324A1Promote divisionEasy to usePicture reproducers using cathode ray tubesCode conversionMPEG-1Dirac (video compression format)

A video compression scheme enables the user to select one of many video compression formats, including the widely-used standard video formats such as MPEG-1, MPEG-2, MPEG-4 and H.263. In one embodiment, the scheme is implemented as a hardware-software combination, with the hardware portion, preferably implemented as an ASIC chip, performing the core compression and the software portion dealing with the detailed formatting. In another embodiment, a 32-bit aligned transitional data format is used.

Owner:MICRONAS

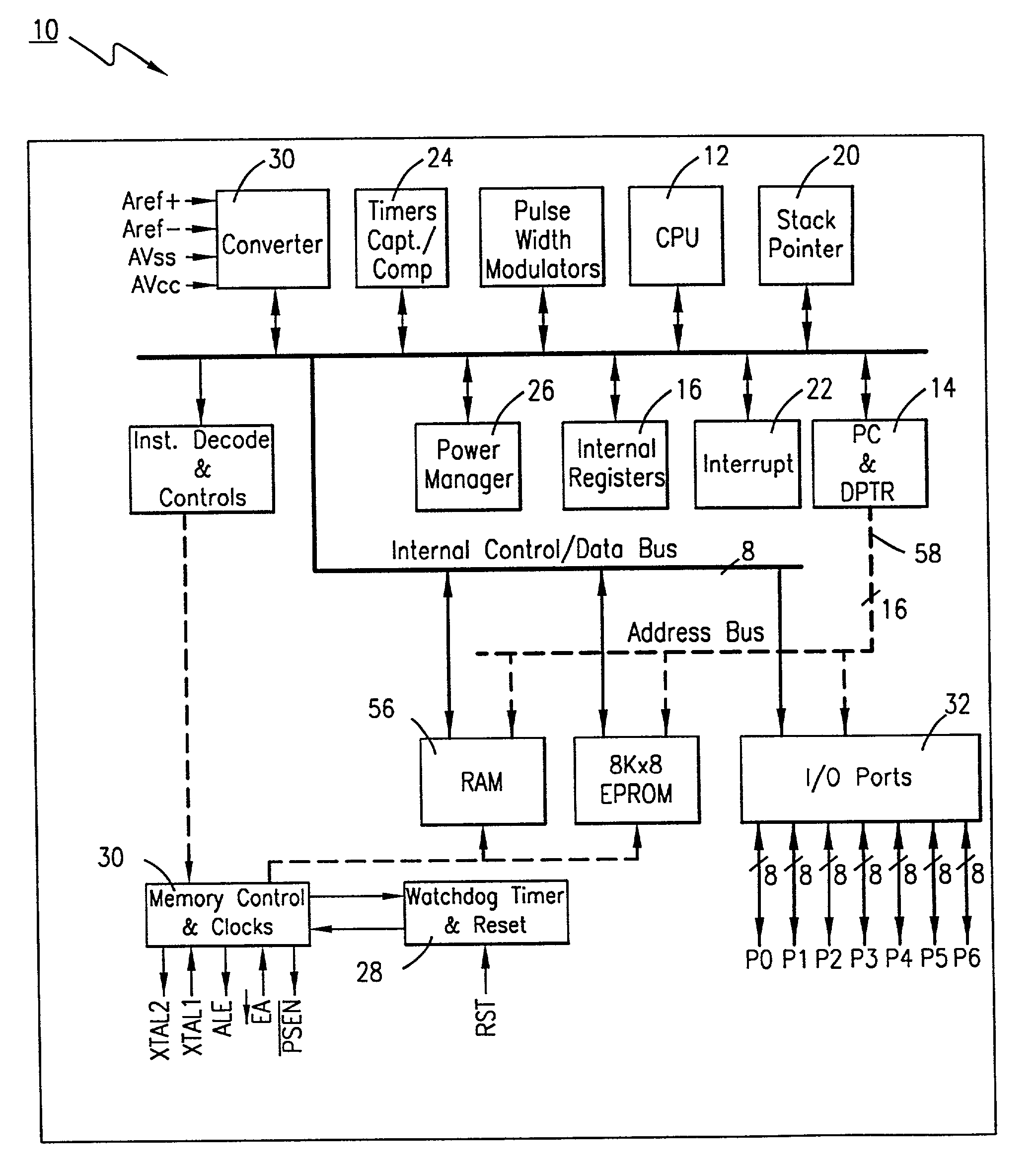

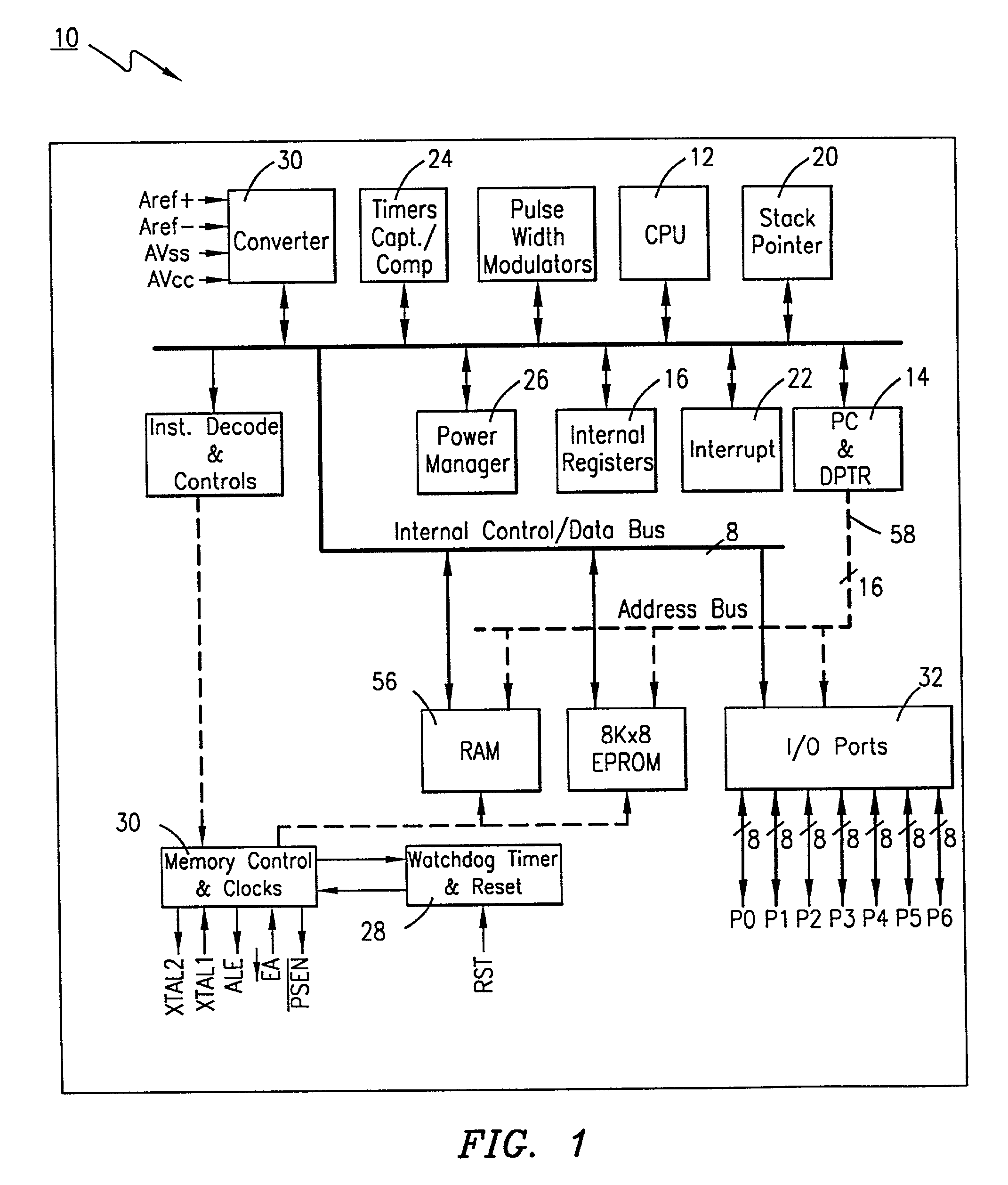

Microcontroller with a user configurable pulse width modulator

A microcontroller integrated circuit incorporating a user configurable pulse width modulator. The pulse width modulator circuitry is configurable to be a single, for example 32-bit pulse width modulator, or a plurality of pulse width modulators each having a bit width that is divisible by the single 32-bit pulse width modulator (e.g., 2, 4, 8 or 16-bit pulse width modulators).

Owner:MA EDWARD TANG KWAI +2

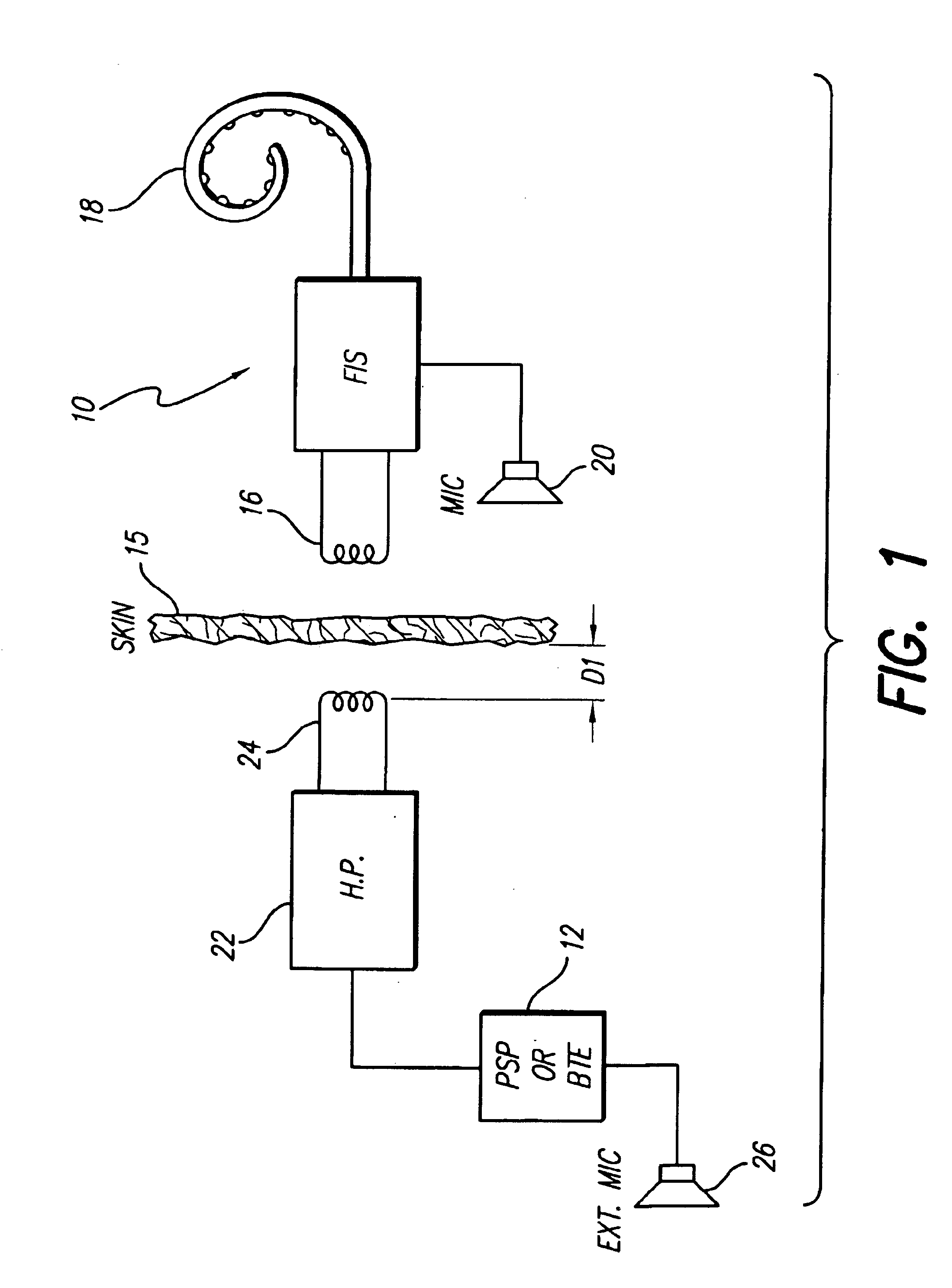

Remote control unit for use with an implantable neural stimulator system

InactiveUS7092763B1Reliable transmissionElectrotherapyImplantable hearing aidsControl signalRemote control

An implantable neural stimulation system, such as an auditory Fully Implantable System (FIS), includes: (1) an implanted device capable of providing desired tissue or nerve stimulation; and (2) a remote control unit that provides a mechanism for readily controlling the implant device. The remote control unit uses a first signal path to send signals to the implant device, and a second signal path to receive signals from the implant device. The combination of these two signal paths provides a full-duplex channel between the remote control unit and the implant device through which appropriate control and status signals may be sent and received. In one embodiment, the first signal path comprises an audio signal path through which audio control signals, e.g., a tone sequence or a 32-bit word FSK modulated between 300 and 1200 Hz, are sent; and the second signal path comprises a RF signal path through which a BPSK, QPSK or FM modulated RF signal is received. The full-duplex channel allows operation of the remote control unit, i.e., allows signals to be successfully sent to and received from the implant device, from as far away as 45–60 cm from the implant device.

Owner:ADVNACED BIONICS LLC

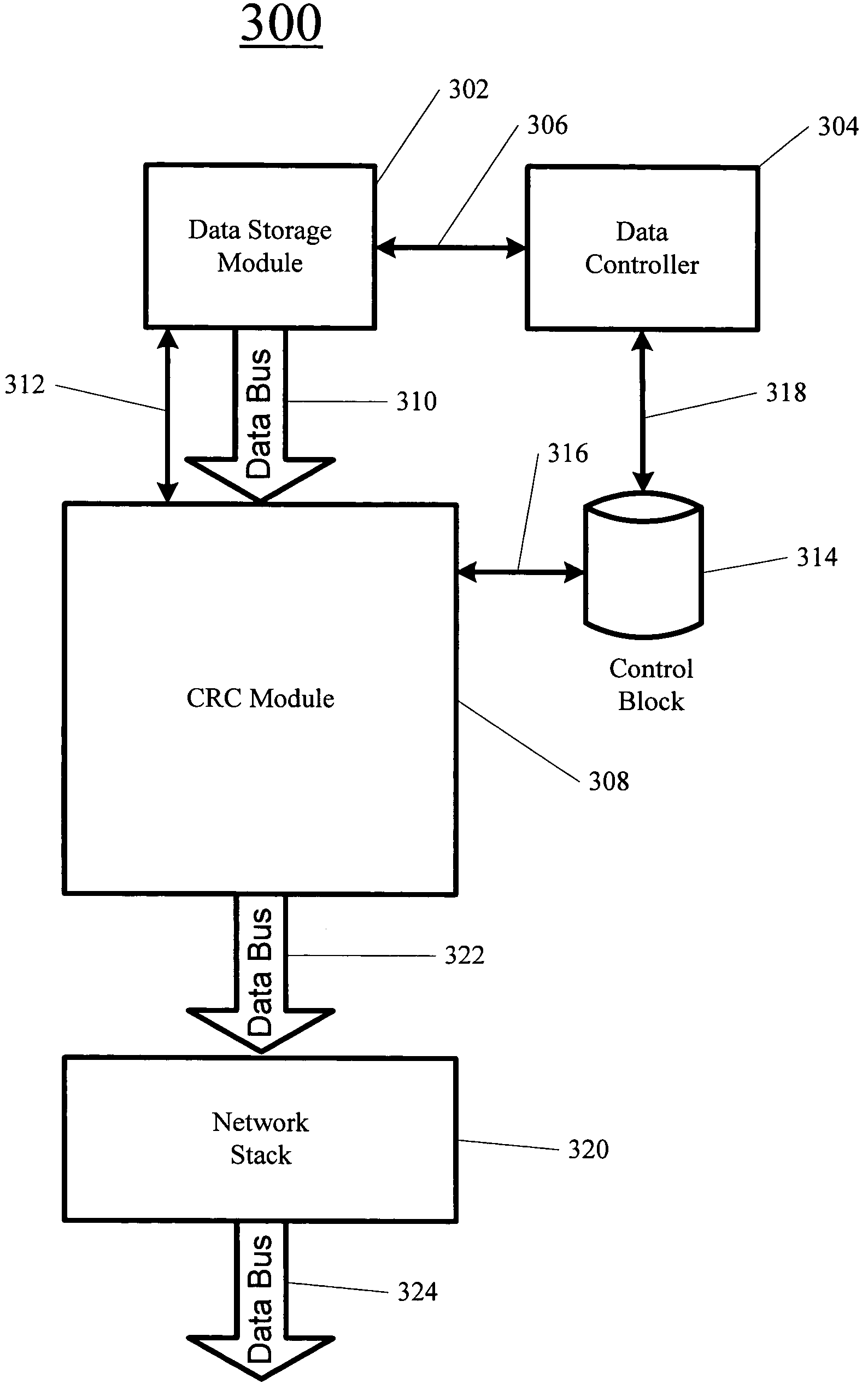

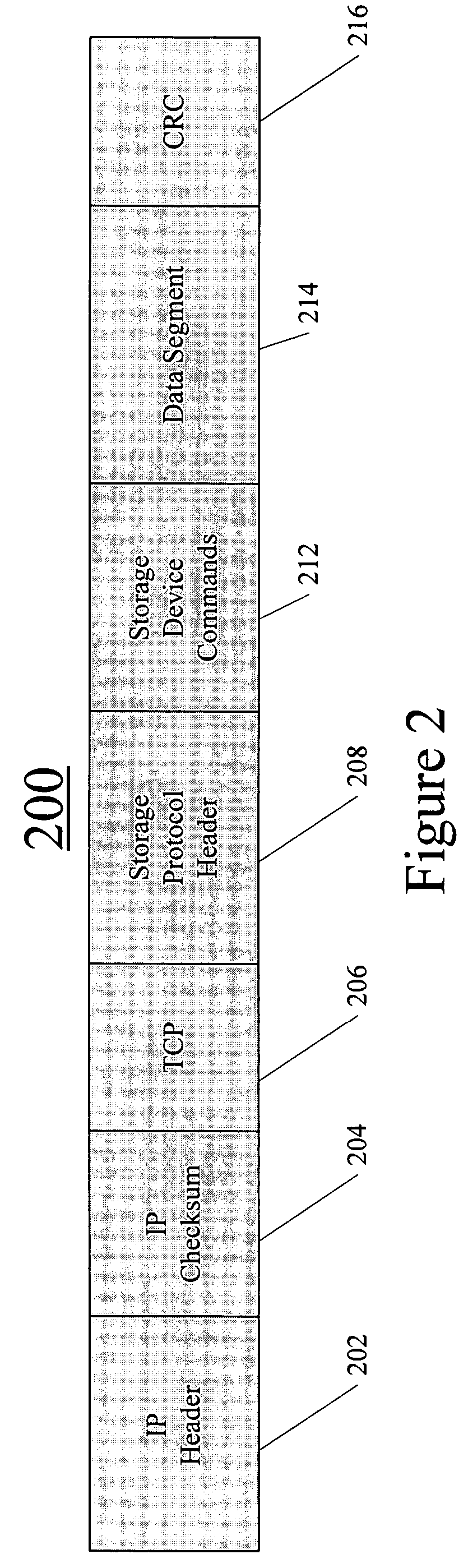

System and method for generating 128-bit cyclic redundancy check values with 32-bit granularity

A System and Method for generating Cyclic Redundancy Check (CRC) values in a system adapted simultaneously handling a plurality of blocks in parallel is described. Included is a memory or other storage device for storing data blocks, wherein the memory or storage device is adapted to output a plurality of data blocks in parallel. A data bus provides a data path wide enough to accommodate the parallel data blocks and is further coupled to a plurality of CRC cores coupled to the data bus, wherein CRC values are calculated for every combination of data blocks on the data bus. A multiplexer coupled to the CRC cores selects the output of one of the CRC cores based on the number of valid data blocks on the data bus. Once the correct CRC value has been calculated, it is appended to a data segment, comprised of a group of data blocks, for transmission to another device.

Owner:NVIDIA CORP

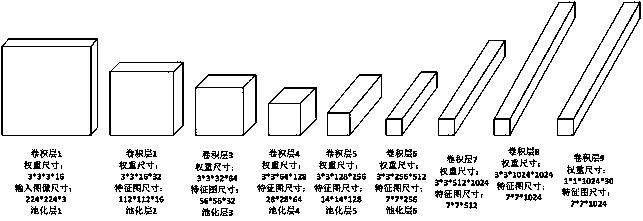

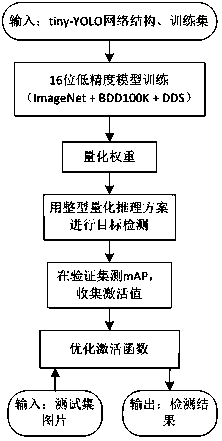

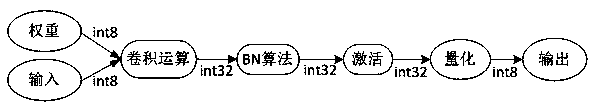

A CNN-based low-precision training and 8-bit integer quantitative reasoning method

InactiveCN109902745AReduce computing timeImprove computing efficiencyCharacter and pattern recognitionNeural architecturesAlgorithmFloating point

The invention provides a CNN-based low-precision training and 8-bit integer quantization reasoning method. The method mainly comprises the steps of carryin gout low-precision model training; Performing model training by using a 16-bit floating point type low-precision fixed point algorithm to obtain a model for target detection; Quantifying the weight; Proposing an 8-bit integer quantization scheme, and quantizing the weight parameters of the convolutional neural network from 16-bit floating point type to 8-bit integer according to layers; carrying out 8-bit integer quantitative reasoning; quantizing the activation value into 8-bit integer data, i.e., each layer of the CNN accepts an int8 type quantization input and generates an int8 quantization output. According to the invention, a 16-bit floating point type low-precision fixed point algorithm is used to train a model to obtain a weight; Compared with a 32-bit floating point type algorithm, the method has the advantages that the 8-bit integer quantization reasoning is directly carried out on the weight obtained by training the model, the reasoning process of the convolutional layer is optimized, and the precision loss caused by the low-bit fixed point quantization reasoning is effectively reduced.

Owner:成都康乔电子有限责任公司 +1

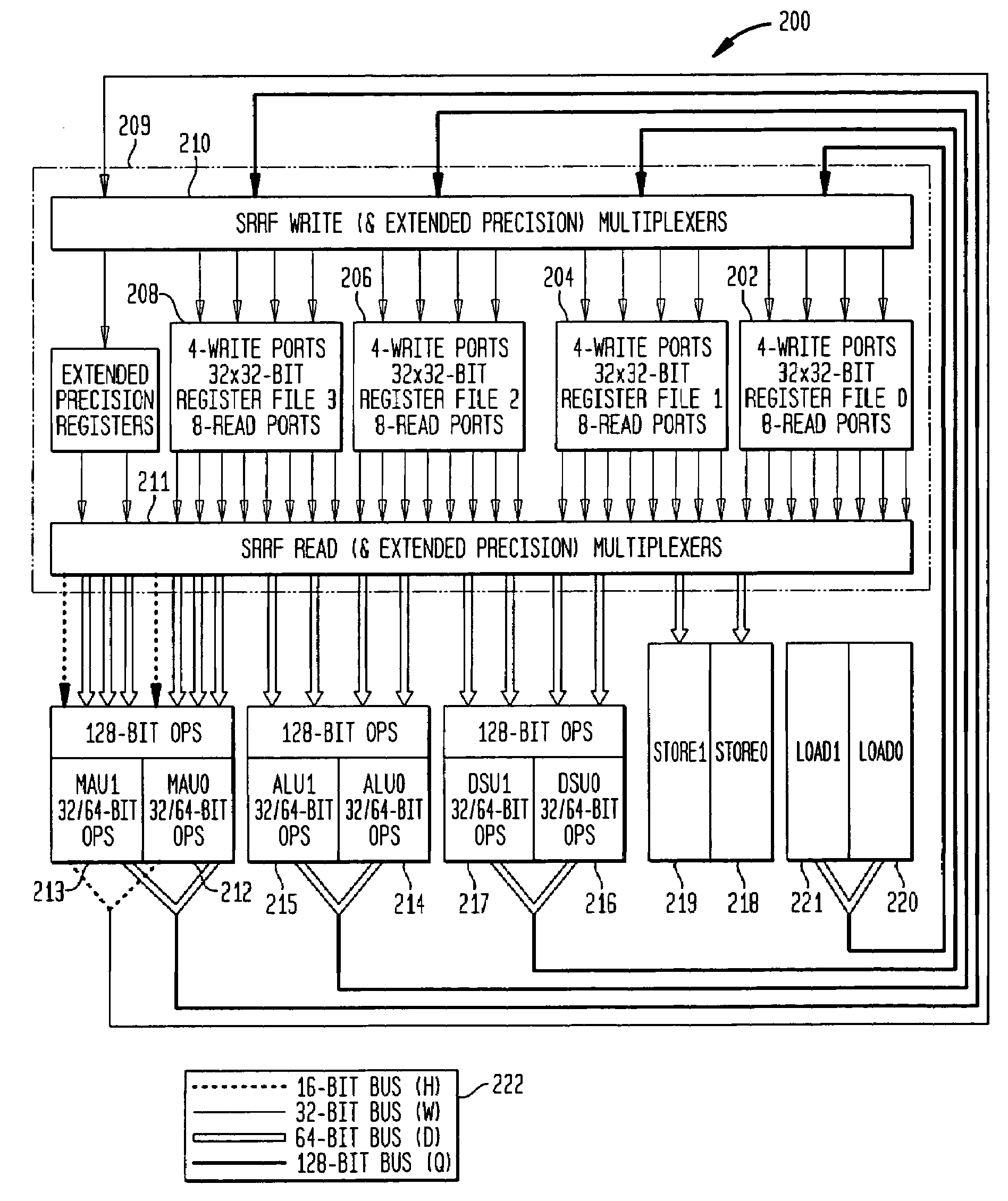

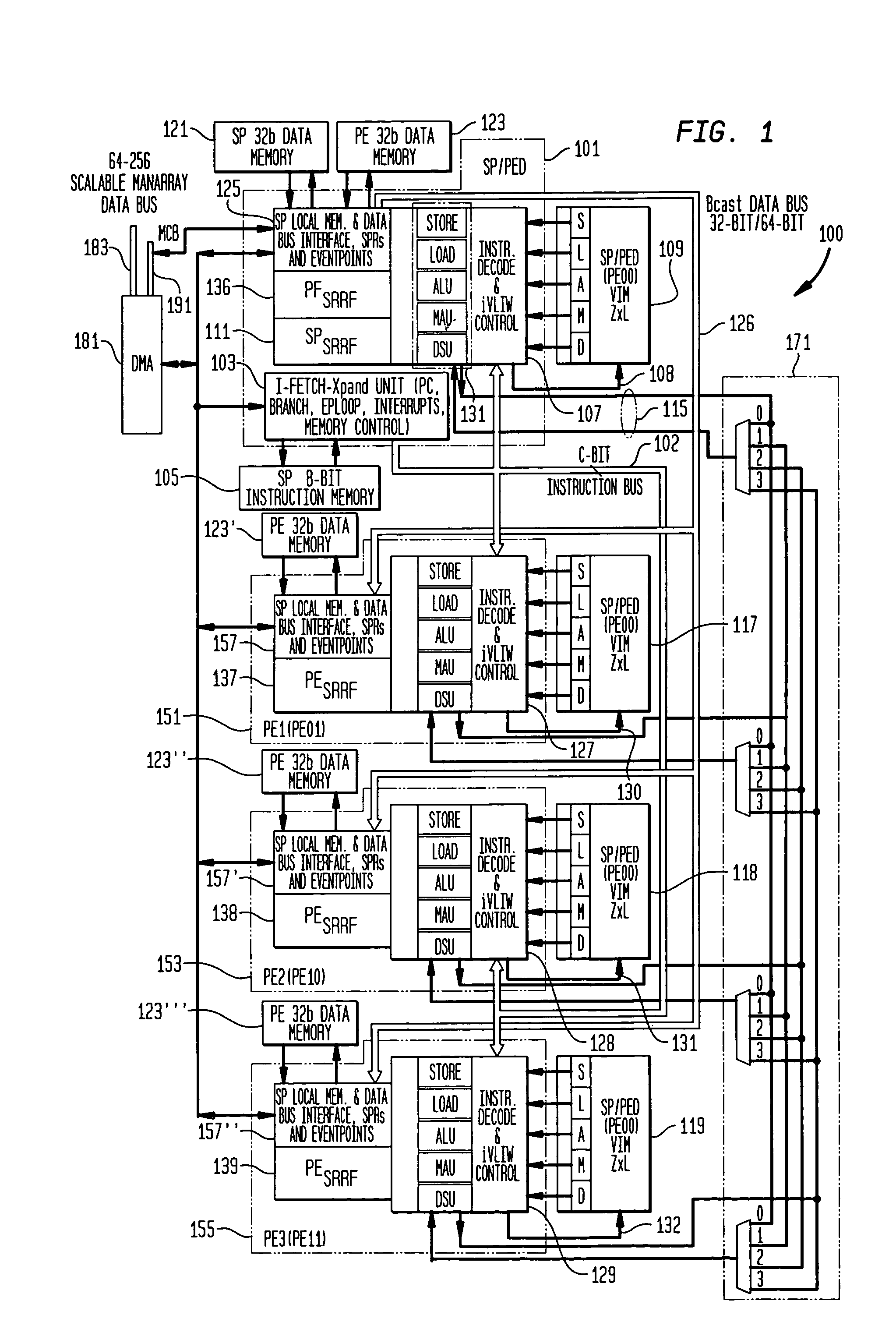

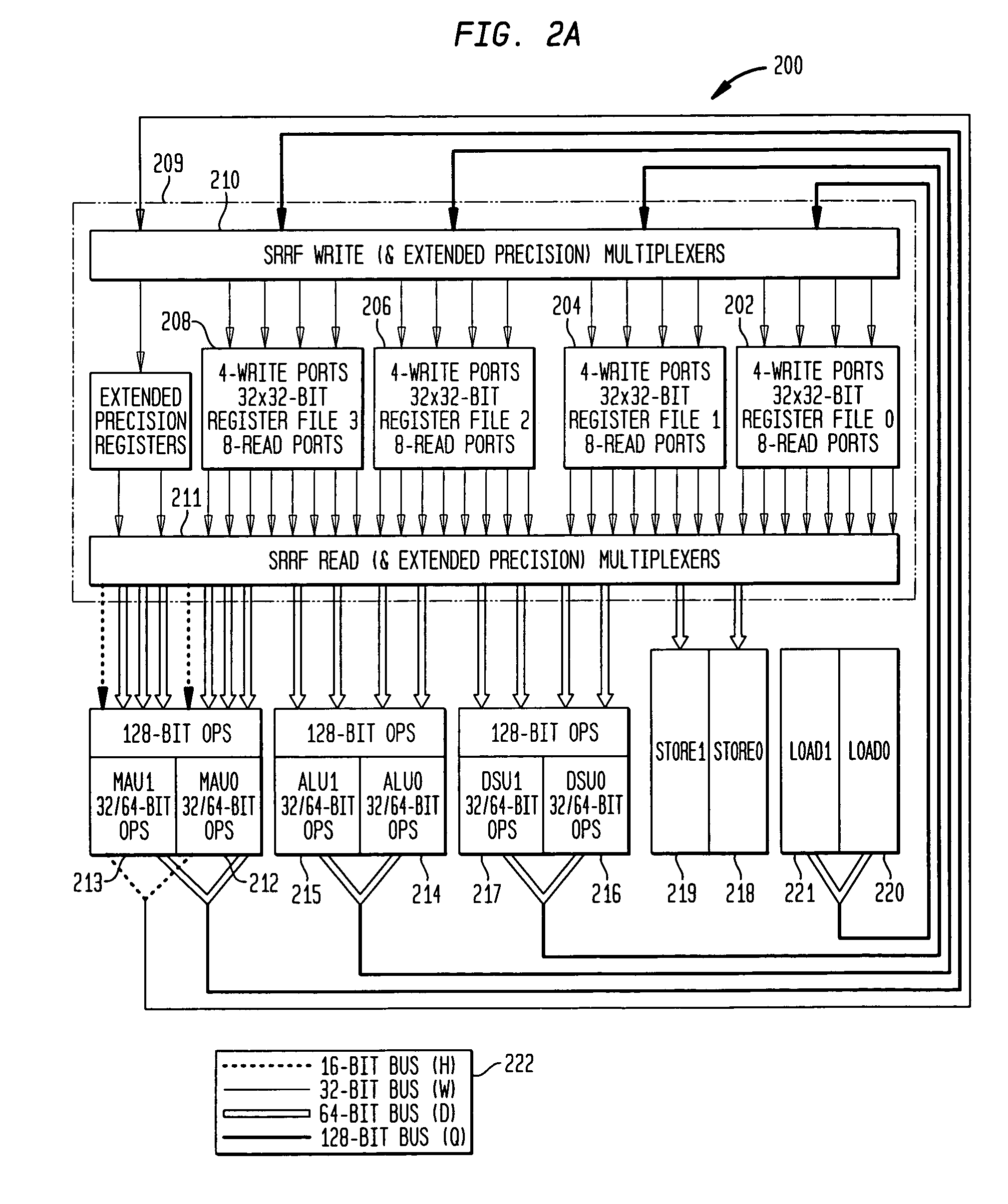

Methods and apparatus for dynamic instruction controlled reconfigurable register file

InactiveUS7398347B1Instruction analysisMemory adressing/allocation/relocationProcessor registerMultiplexer

A scalable reconfigurable register file (SRRF) containing multiple register files, read and write multiplexer complexes, and a control unit operating in response to instructions is described. Multiple address configurations of the register files are supported by each instruction and different configurations are operable simultaneously during a single instruction execution. For example, with separate files of the size 32×32 supported configurations of 128×32 bit s, 64×64 bit s and 32×128 bit s can be in operation each cycle. Single width, double width, quad width operands are optimally supported without increasing the register file size and without increasing the number of register file read or write ports.

Owner:ALTERA CORP

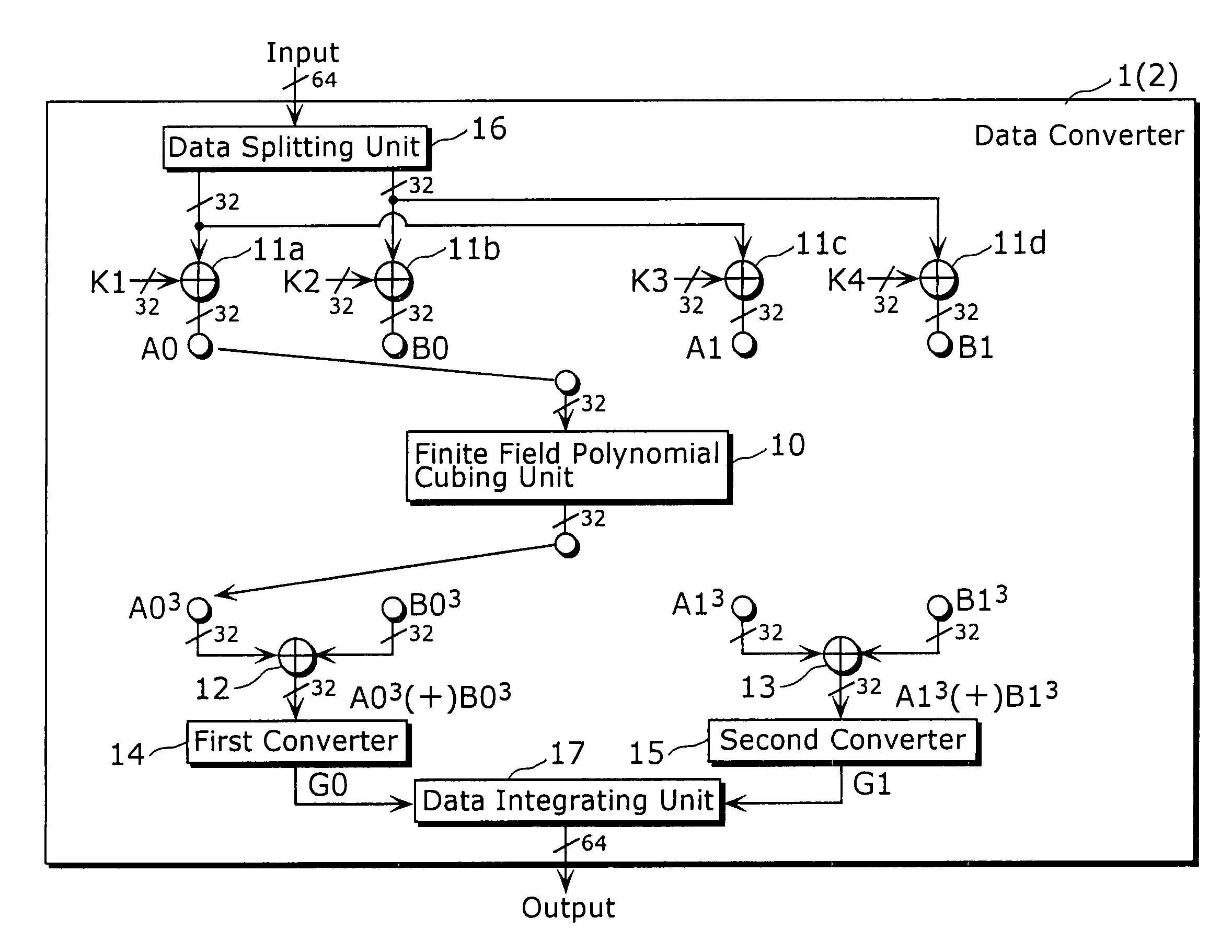

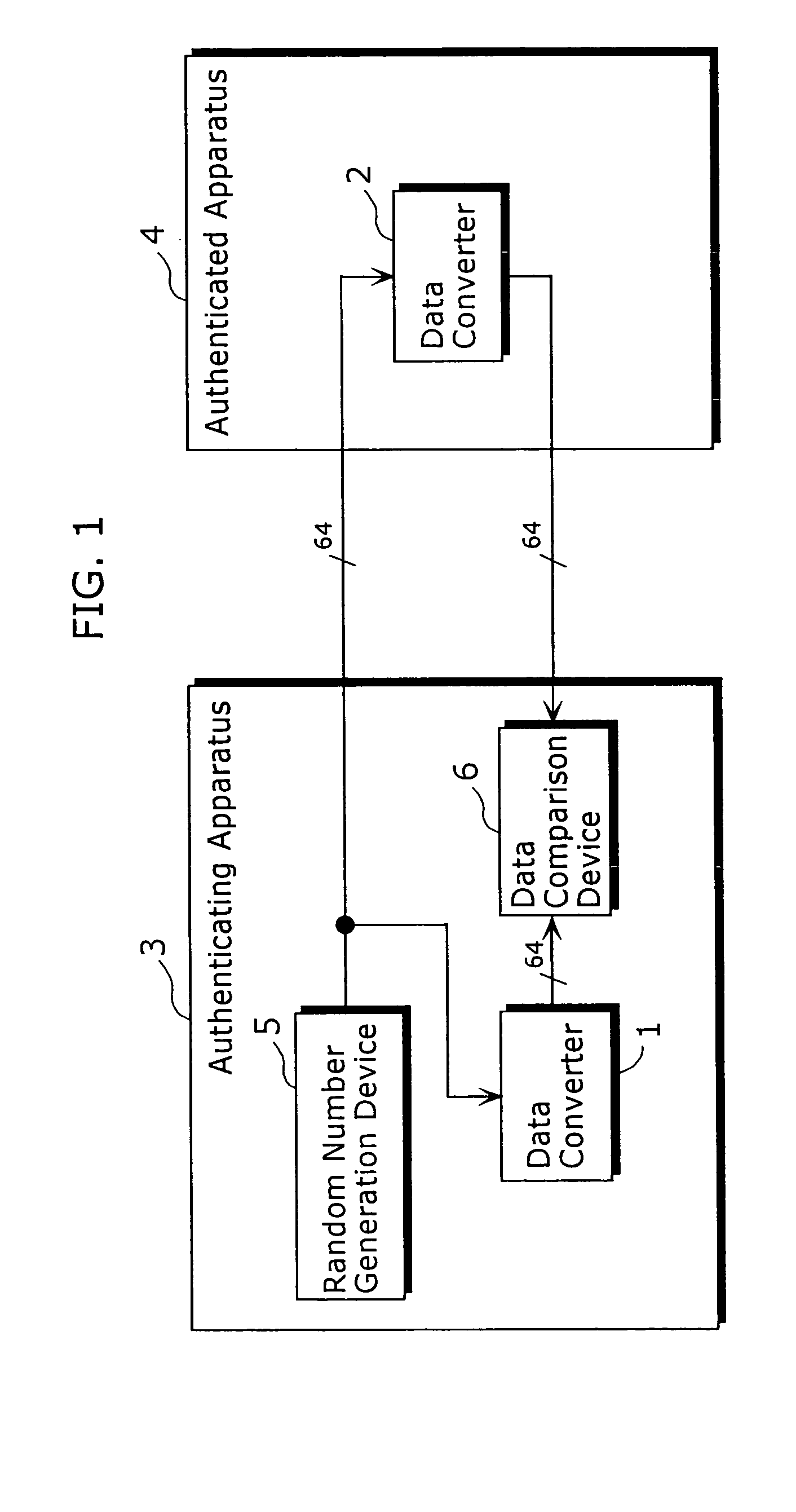

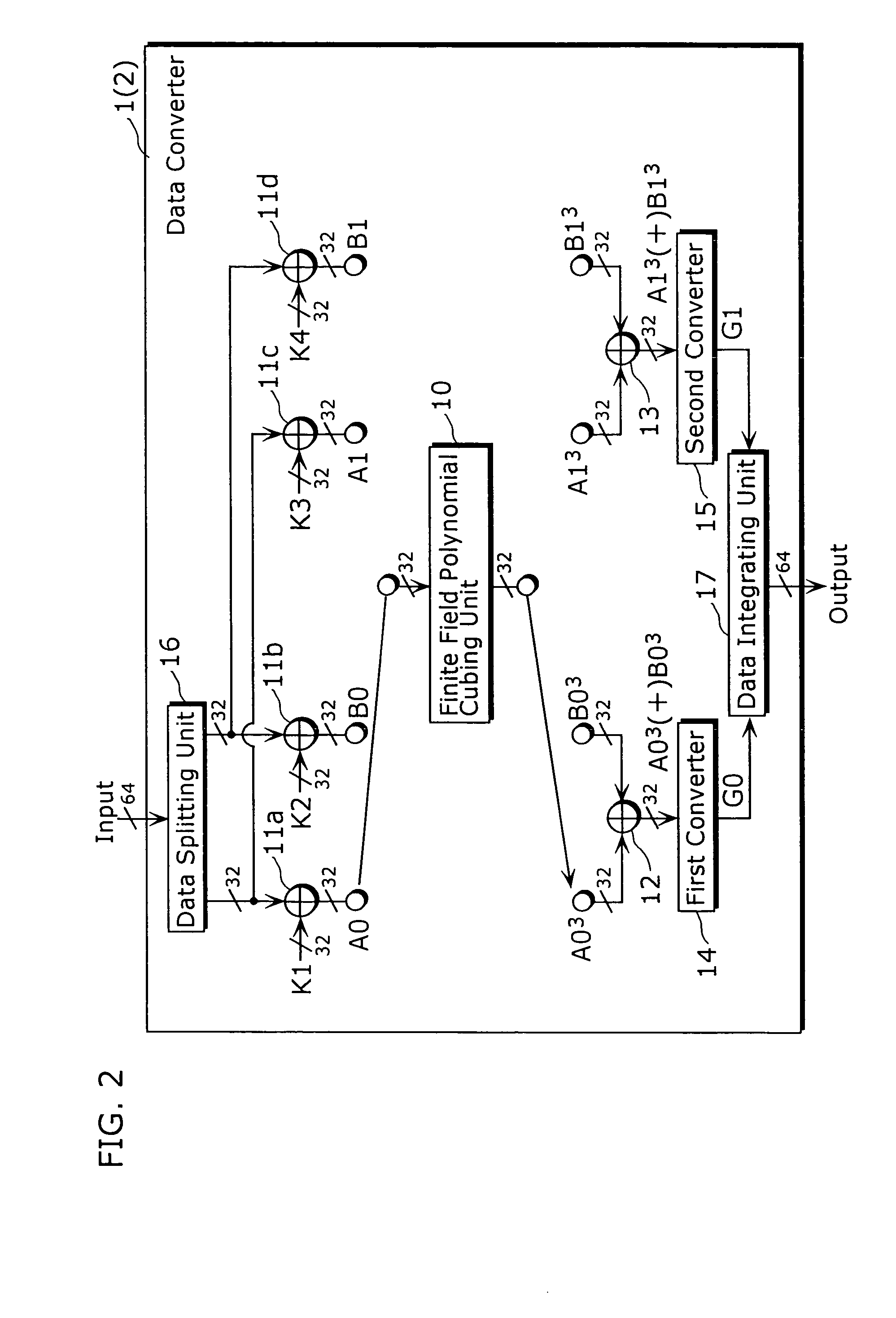

Data converter and method thereof

ActiveUS6995692B2Good data confusion performanceData augmentationError prevention/detection by using return channelUser identity/authority verificationData translationData splitting

A data converter (1) capable of reducing a size of the total implementation in a device is a processing apparatus that performs secret converting processing predetermined to input data with 64 bits, the data converter including a finite field polynomial cubing unit (10), data integrating units (11a) to (11d), (12) and (13), a first converter (14), a second converter (15), a data splitting unit (16), and a data integrating unit (17). The finite field polynomial cubing unit (10) performs cubing, on the 32 bits data, in the polynomial residue class ring with a value in the finite field GF (28) as a coefficient and respectively outputs data with 32 bits.

Owner:PANASONIC CORP

Processor having a compare extension of an instruction set architecture

InactiveUS7242414B1Increase speedReduce in quantityConditional code generationRegister arrangementsOperandFloating point

A processor having a compare extension of an instruction set architecture which incorporates a set of high performance floating point operations. The instruction set architecture incorporates a variety of data formats including single precision and double precision data formats, as well as the paired-single data format that allows two simultaneous operations on a pair of operands. The extension includes instructions directed to a magnitude compare of floating point numbers and conversions between a pair of 32-bit fixed point integers and paired-single floating point format.

Owner:ARM FINANCE OVERSEAS LTD

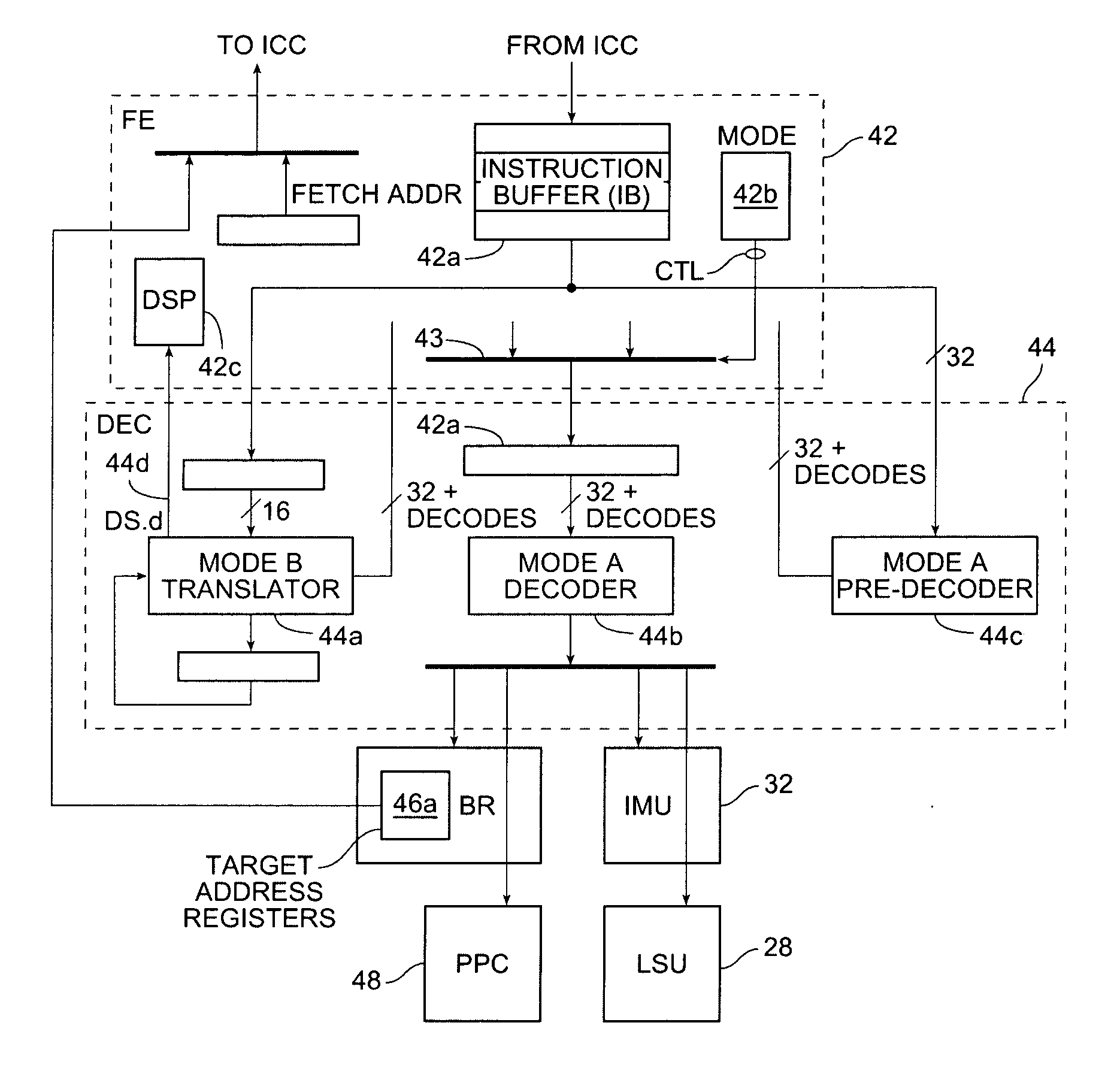

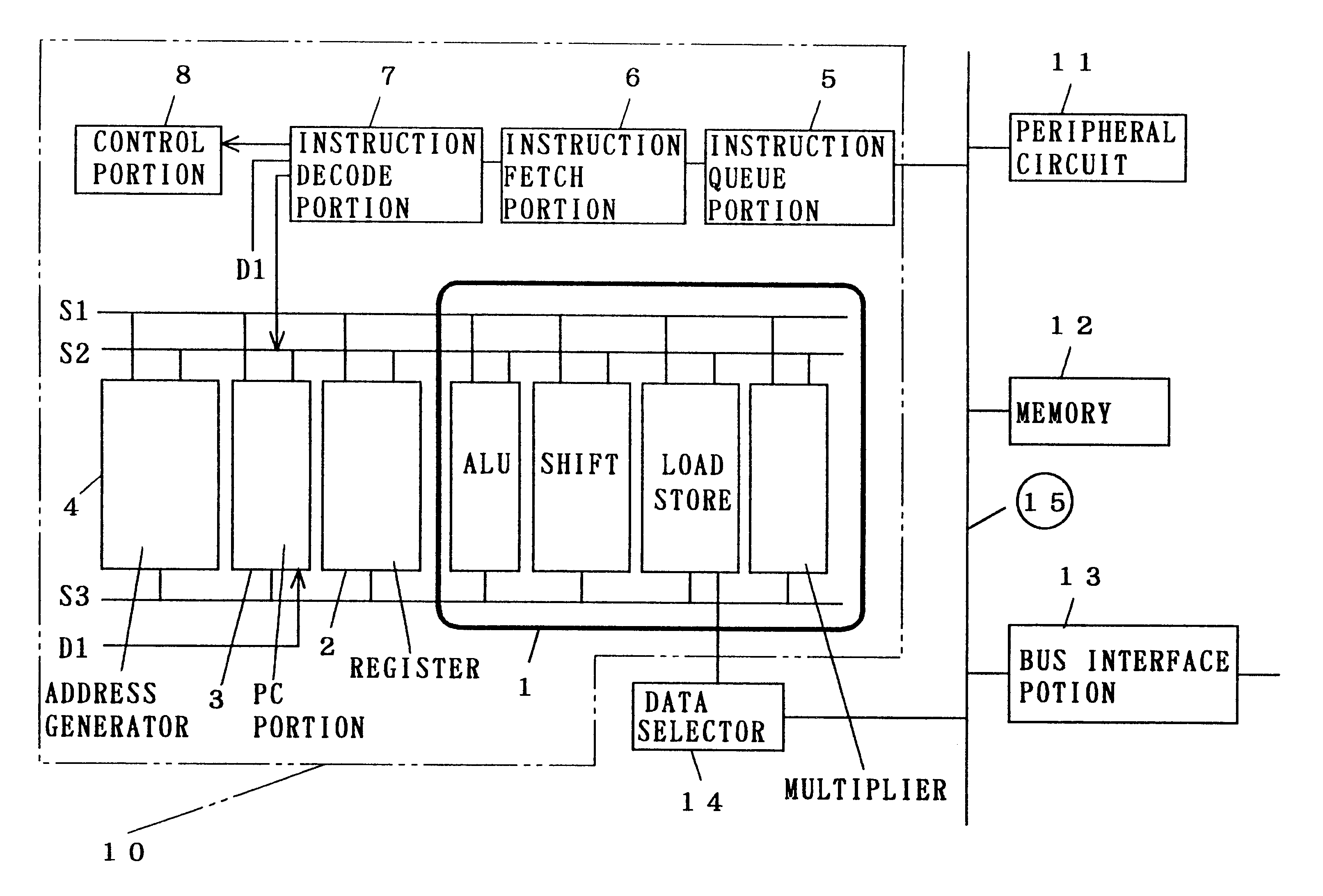

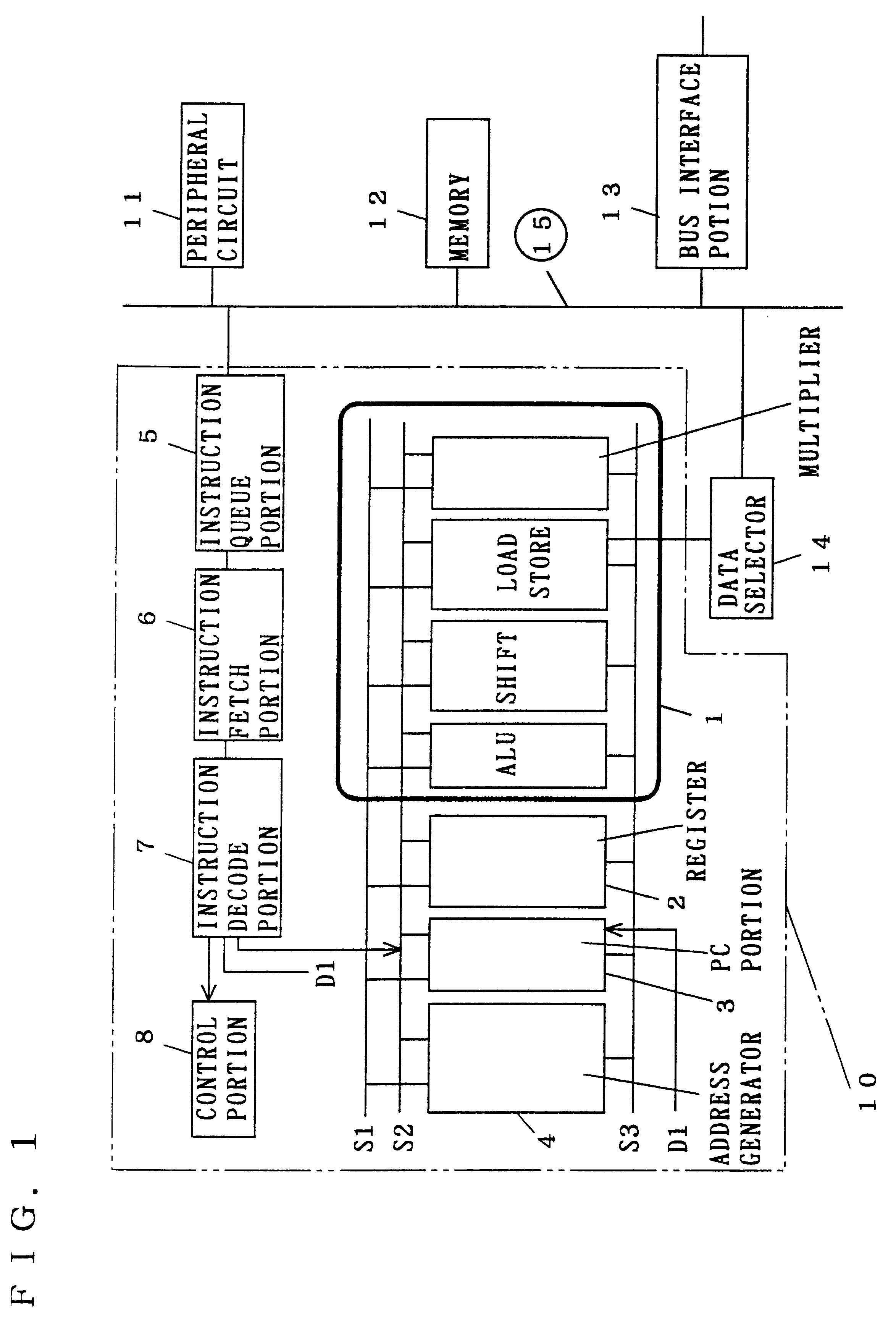

Processor architecture for executing two different fixed-length instruction sets

InactiveUS20050262329A1High simulationSave memory spaceDigital computer detailsNext instruction address formationProcessor elementLeast significant bit

A processor element, structured to execute a 32-bit fixed length instruction set architecture, is backward compatible with a 16-bit fixed length instruction set architecture by translating each of the 16-bit instructions into a sequence of one or more 32-bit instructions. Switching between 16-bit instruction execution and 32-bit instruction execution is accomplished by branch instructions that employ a least significant bit position of the address of the target of the branch to identify whether the target instruction is a 16-bit instruction or a 32-bit instruction.

Owner:HITACHI LTD

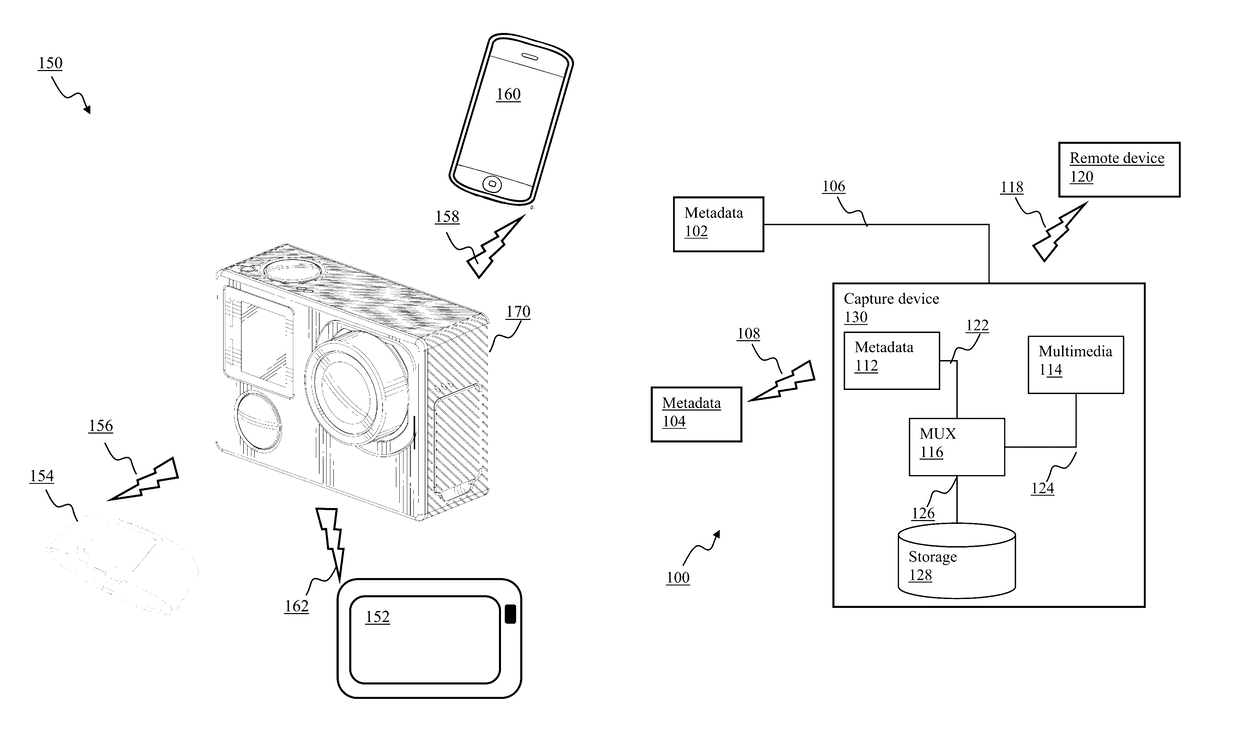

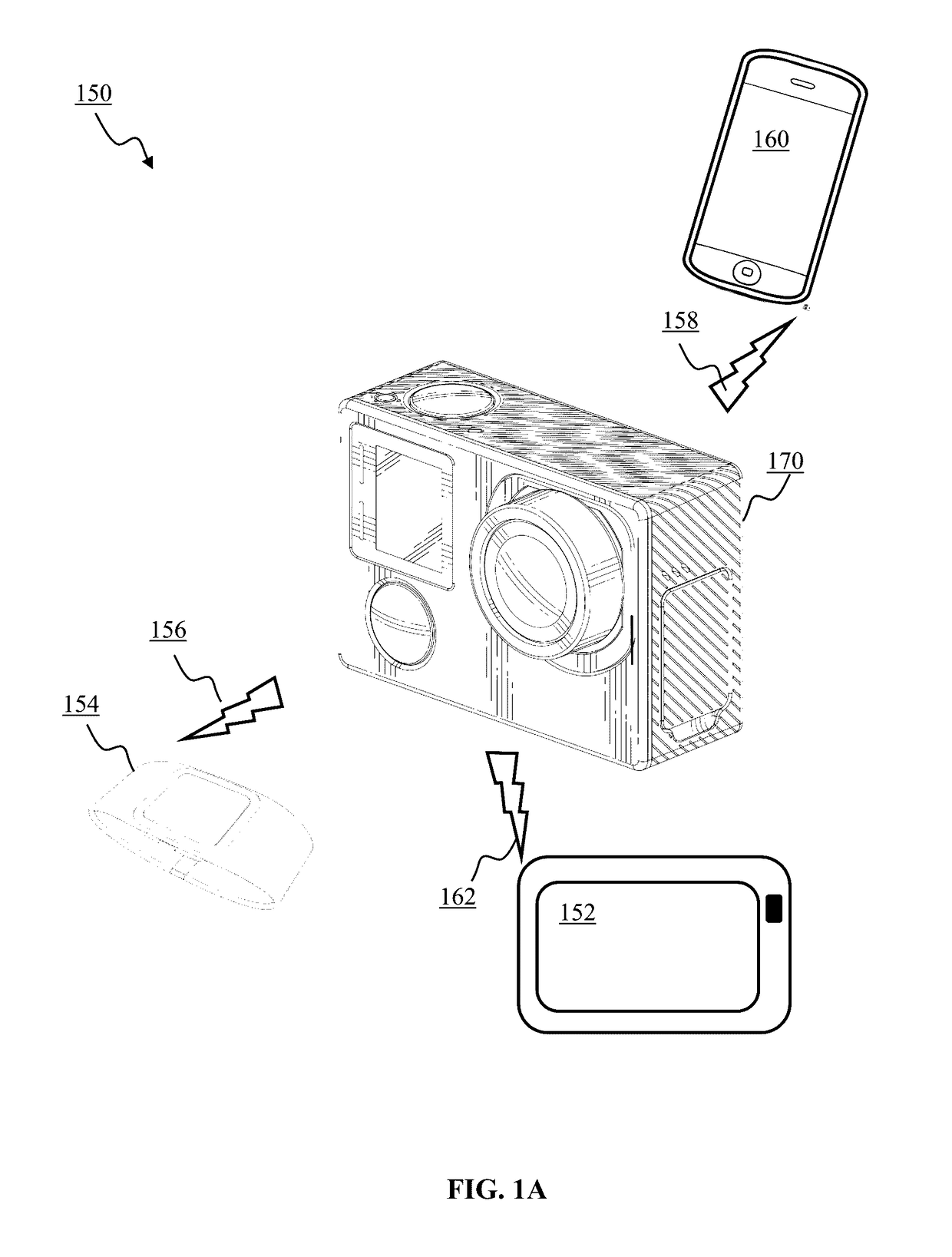

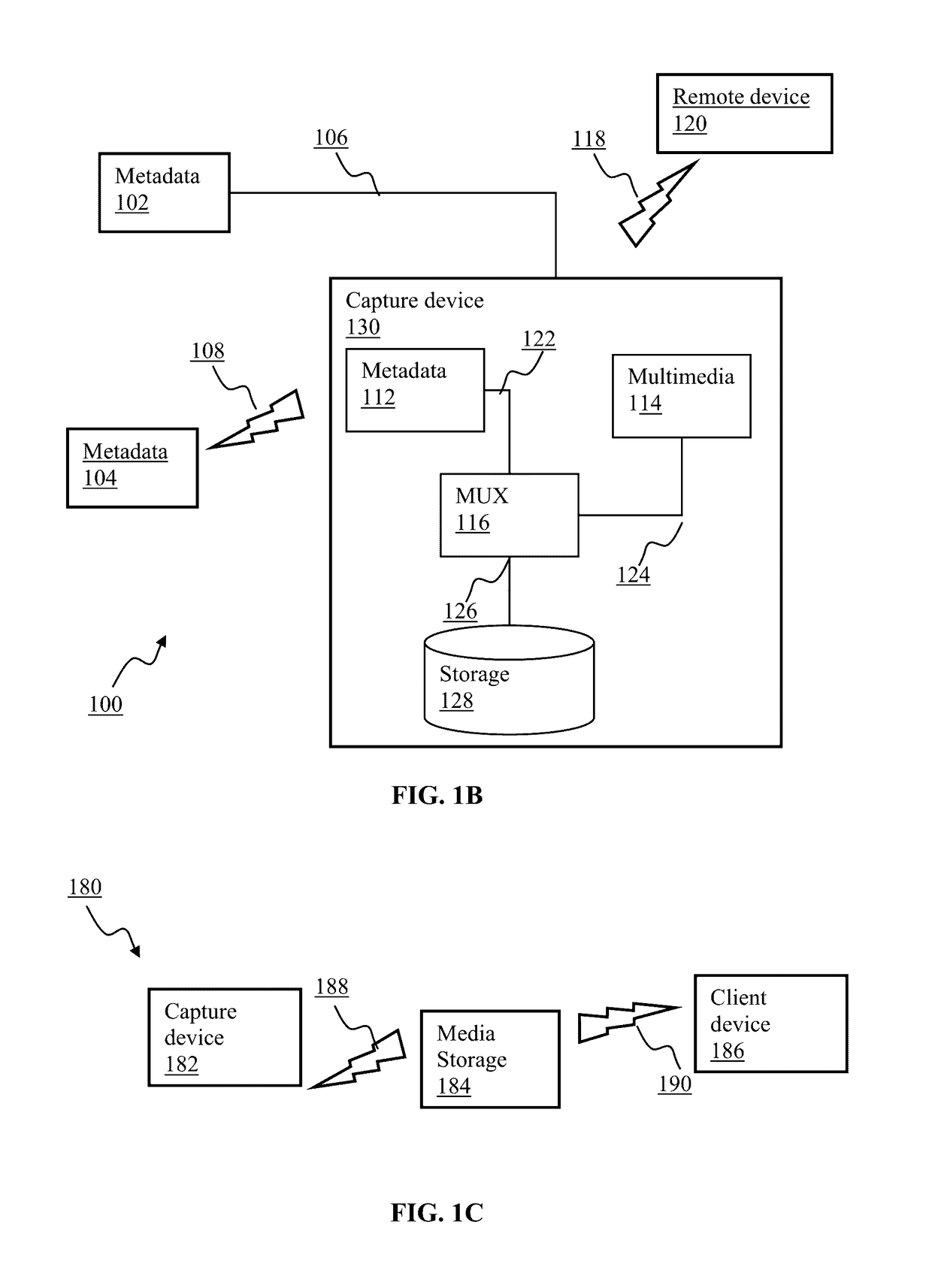

Apparatus and methods for embedding metadata into video stream

ActiveUS9681111B1Satisfies needTelevision system detailsElectronic editing digitised analogue information signalsComputer graphics (images)Application software

Apparatus and methods for combining metadata with video into a video stream using a 32-bit aligned payload, that is computer storage efficient and human discernable. The metadata is stored in a track in a self-describing structure. Metadata track may be decoded using an identifier reference table that is substantially smaller than typical fourCC identifier tables. The combined metadata / video stream is compatible with a standard video stream convention and may be played using conventional media player applications that reads media files compliant with MP4 / MOV container format. The proposed format may enable decoding of metadata during streaming, partitioning of combined video stream without loss of metadata. The proposed format and / or metadata protocol provides for temporal synchronization of metadata with video frames.

Owner:GOPRO

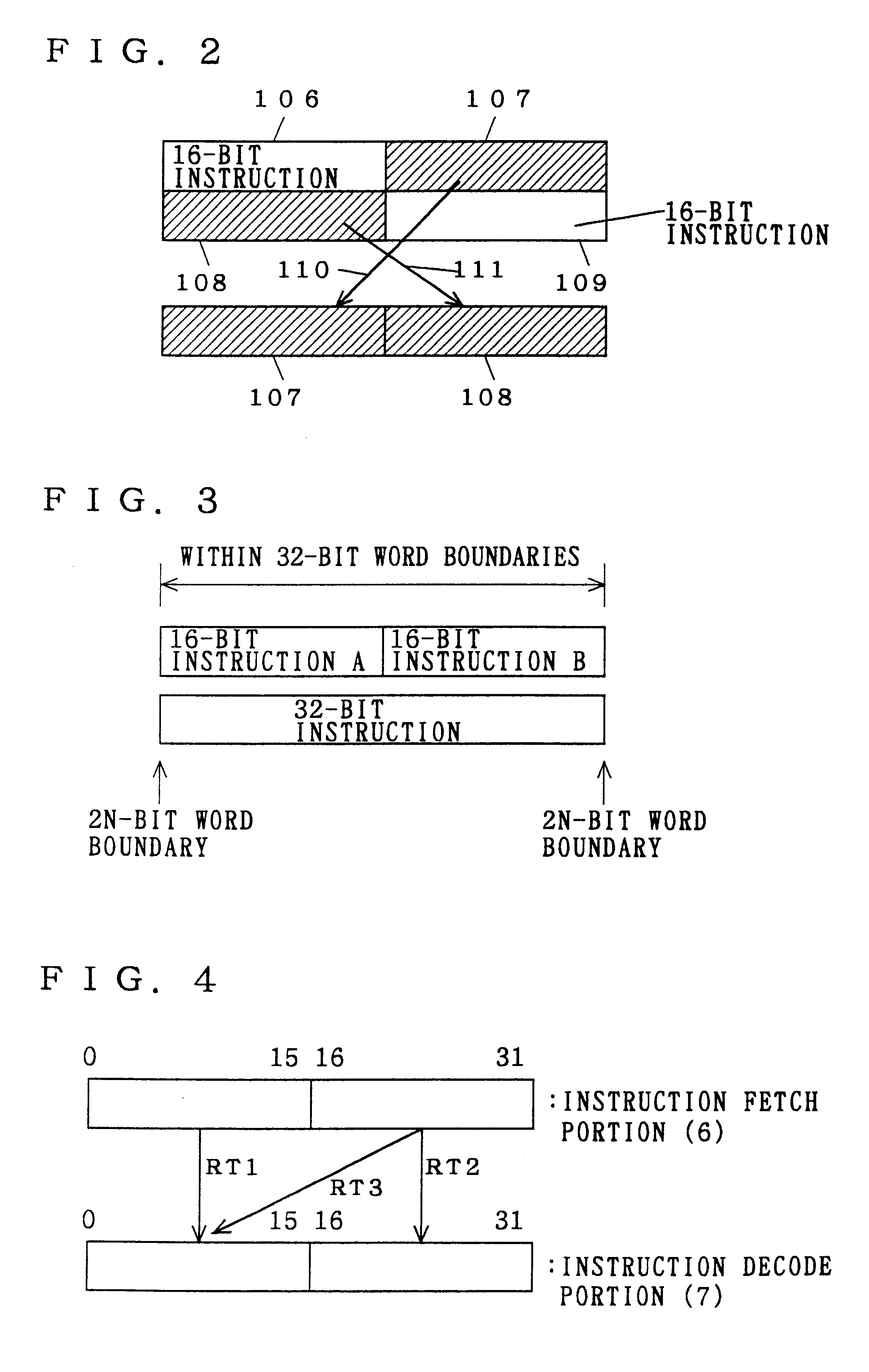

Processor for executing instruction codes of two different lengths and device for inputting the instruction codes

InactiveUS6209079B1Small sizeSmall amountInstruction analysisDigital computer details16-bitParallel computing

For a processor having instruction codes of two instruction lengths (16 bits and 32 bits), methods of locating the instruction codes are limited to two types: (1) two 16-bit instruction codes are stored within 32-bit word boundaries, and (2) a single 32-bit instruction code is stored intactly within the 32-bit word boundaries. A branch destination address is specified only on the 32-bit word boundary. The MSB of each instruction code serves as a 1-bit instruction length identifier for controlling the execution sequence of the instruction codes. This provides two transfer paths from an instruction fetch portion to an instruction decode portion within the processor, achieving reduction in code side and in the amount of hardware and, accordingly, the increase in operating speed.

Owner:RENESAS ELECTRONICS CORP

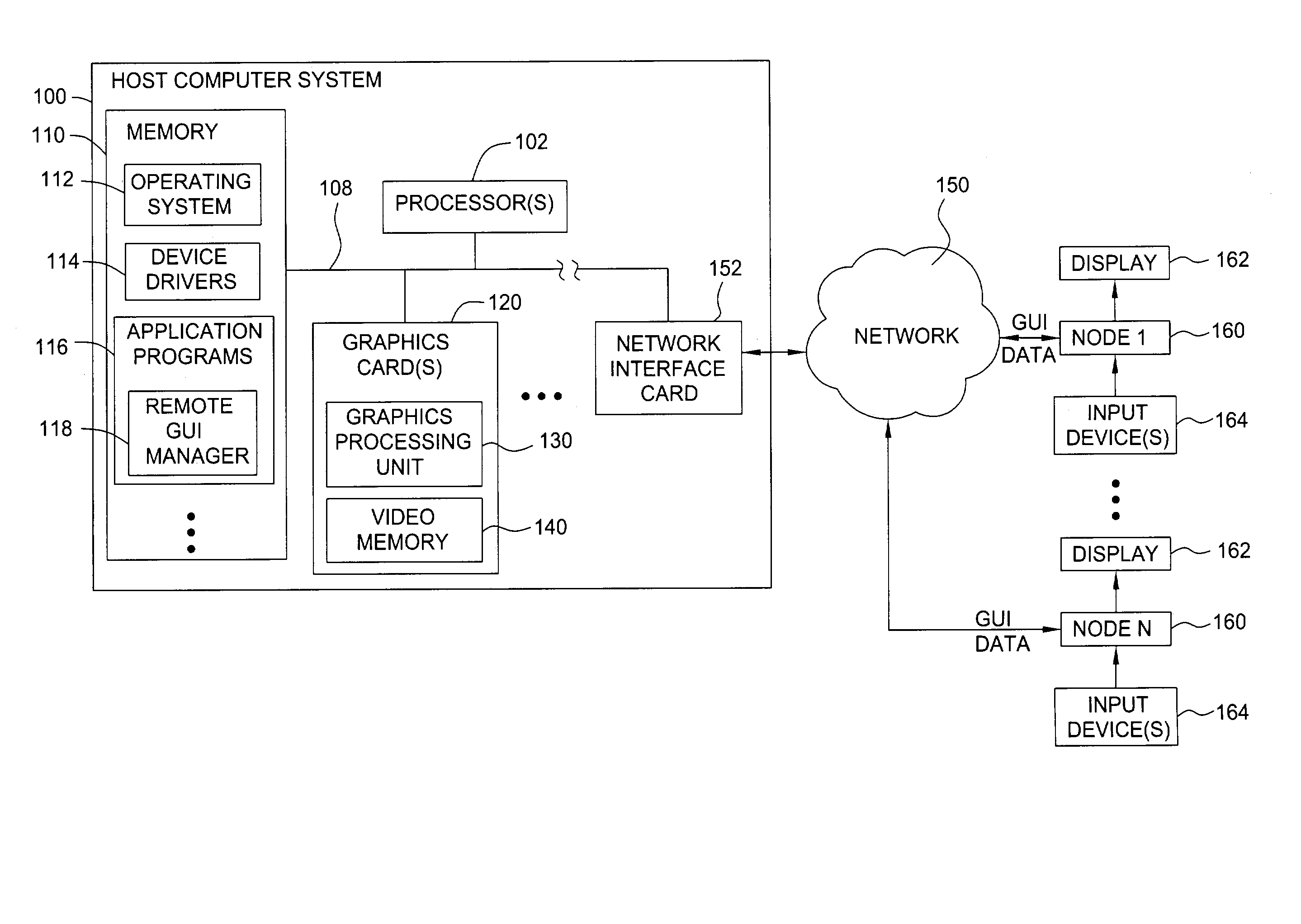

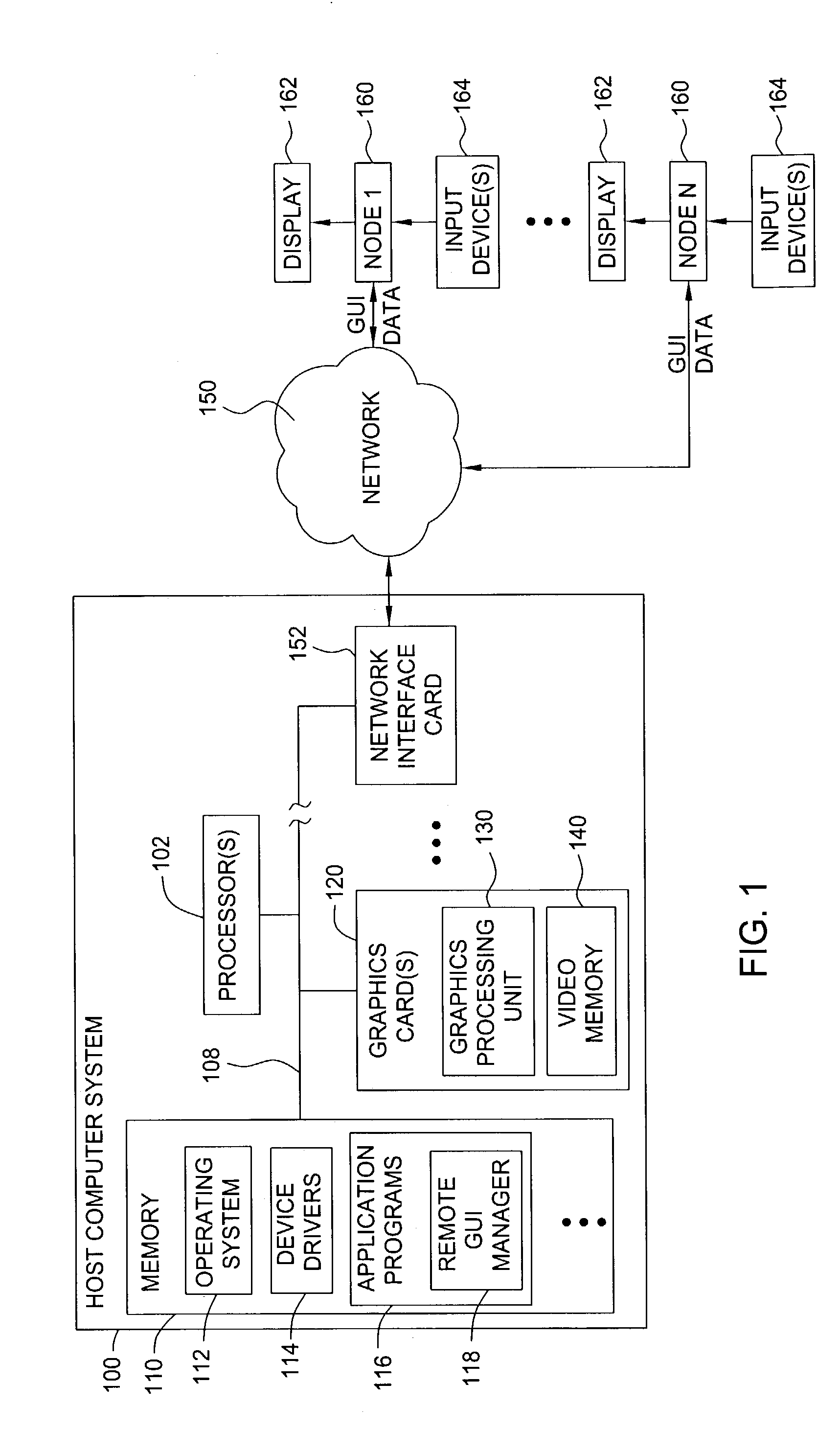

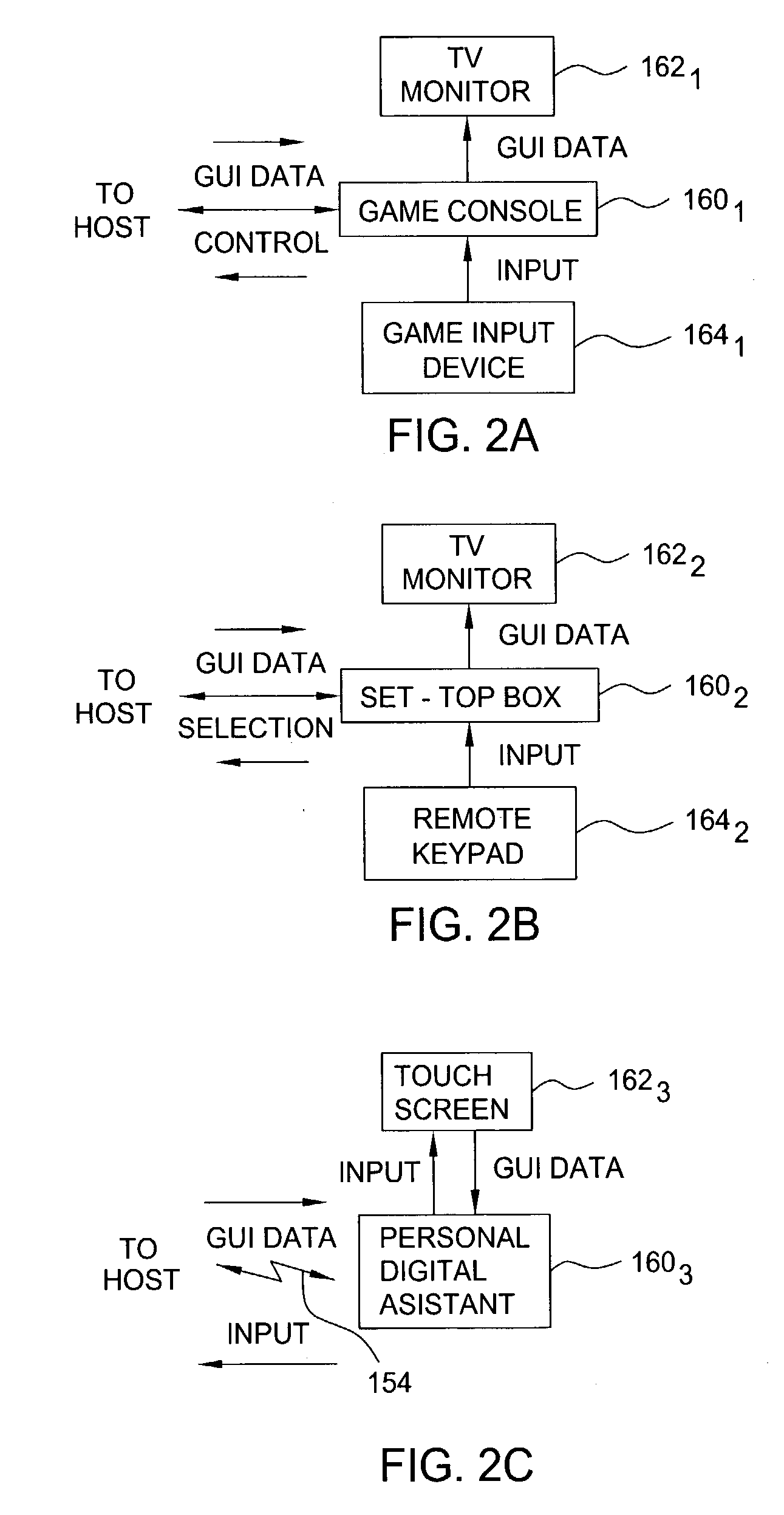

Remote graphical user interface support using a graphics processing unit

ActiveUS7173635B2Few data bitCathode-ray tube indicatorsMultiple digital computer combinationsGraphics24-bit

Methods, apparatus and systems for the display, on a remote node, of a three-dimensional (3D) image rendered on a host system in a first image format are described. In general, the 3D image is transformed into a second image format that is compressed (i.e., uses fewer data bits per pixel) relative to the first image format, (optionally) scaled to a screen size of remote node, and subsequently transferred to remote node for display. In instances, the transformation of the image from the first image format to the second image format and the optional scaling of the image to the screen size of remote node may be done in a graphics processing unit (GPU) on the host system. As an example, the first image format may be an RGB-based format, such as RGBA (32-bits per pixel) or standard RGB (24-bits per pixel) and the second image format may be a YUV-based format, such as YV12 (12-bits per pixel).

Owner:NVIDIA CORP

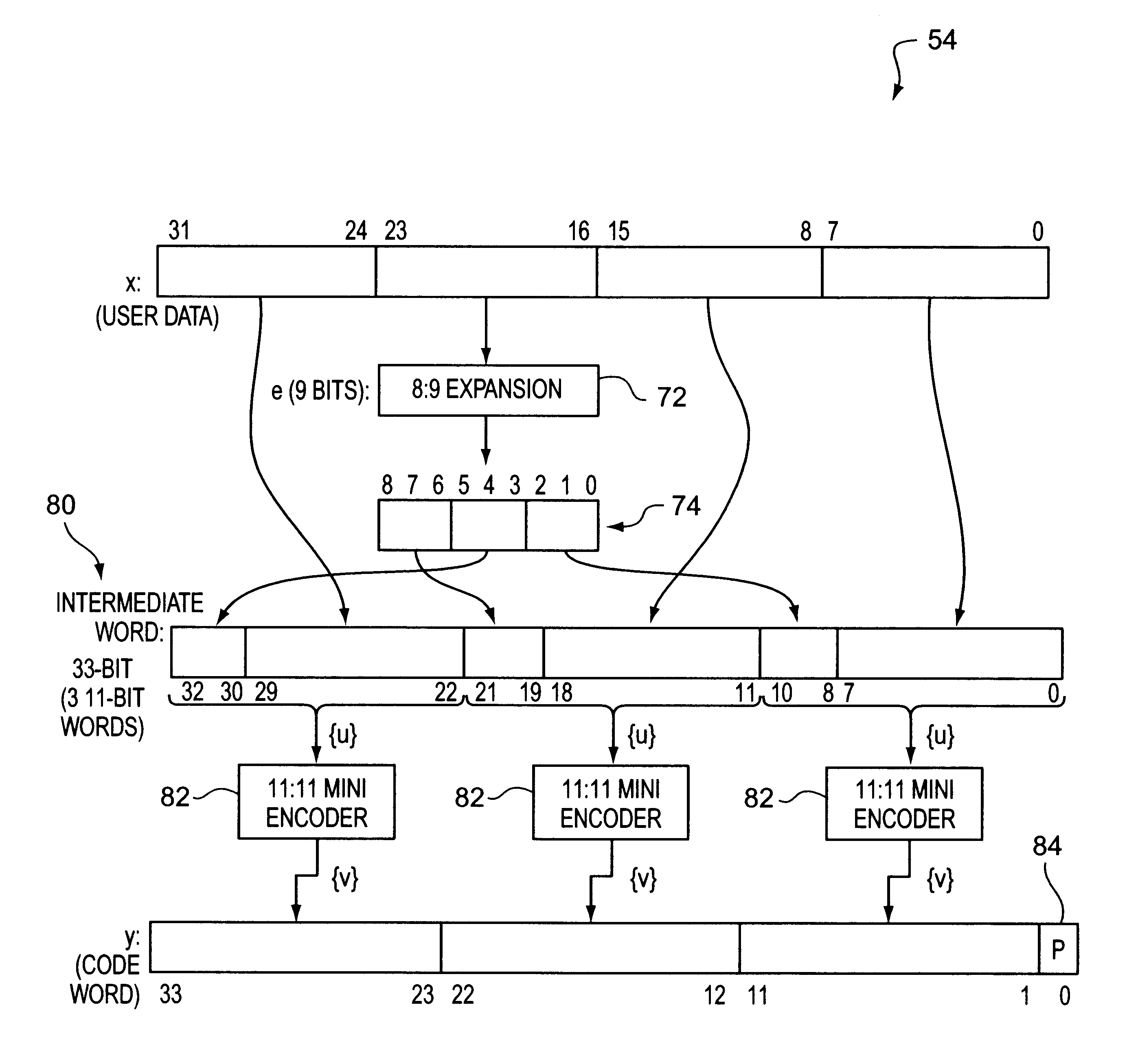

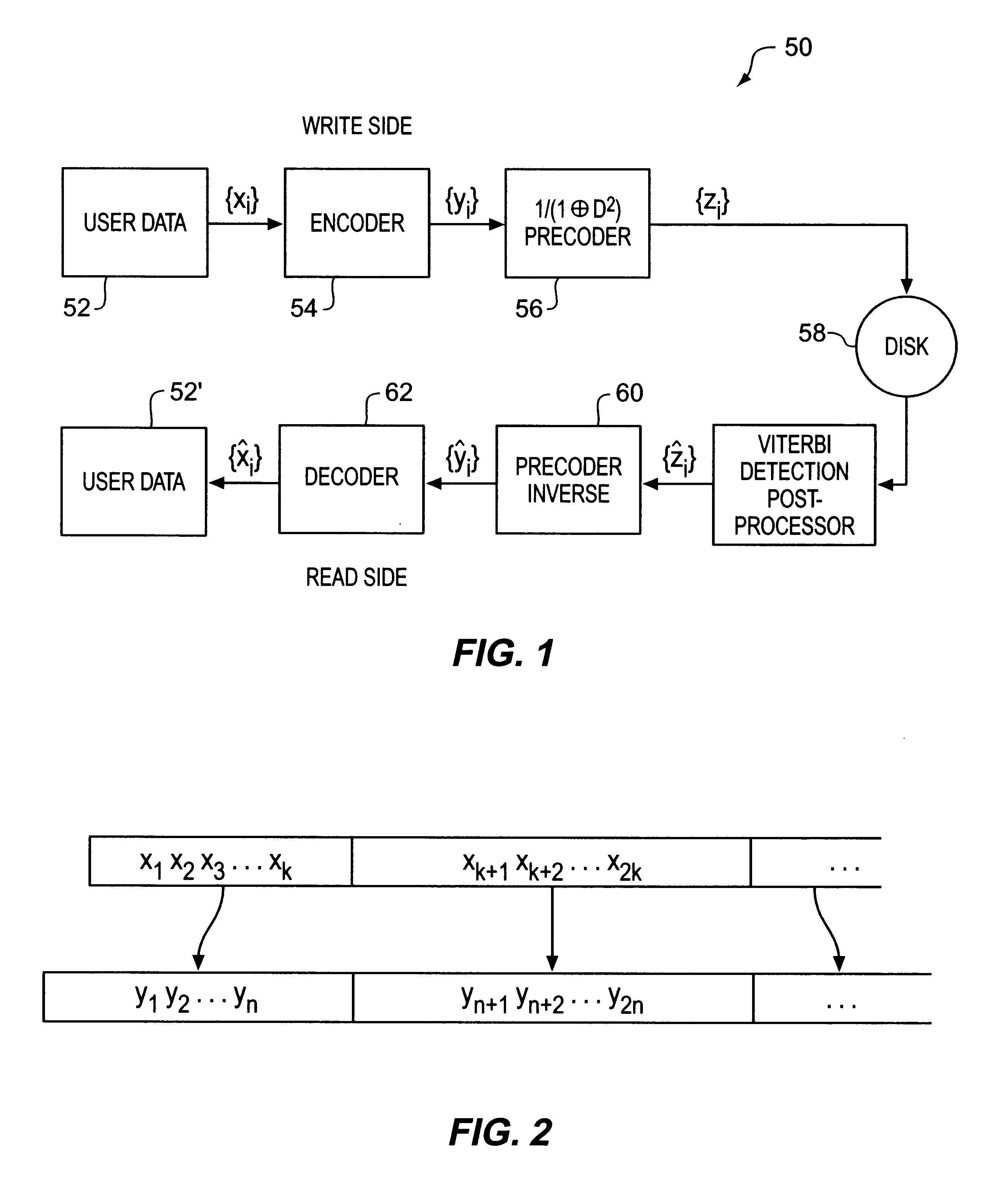

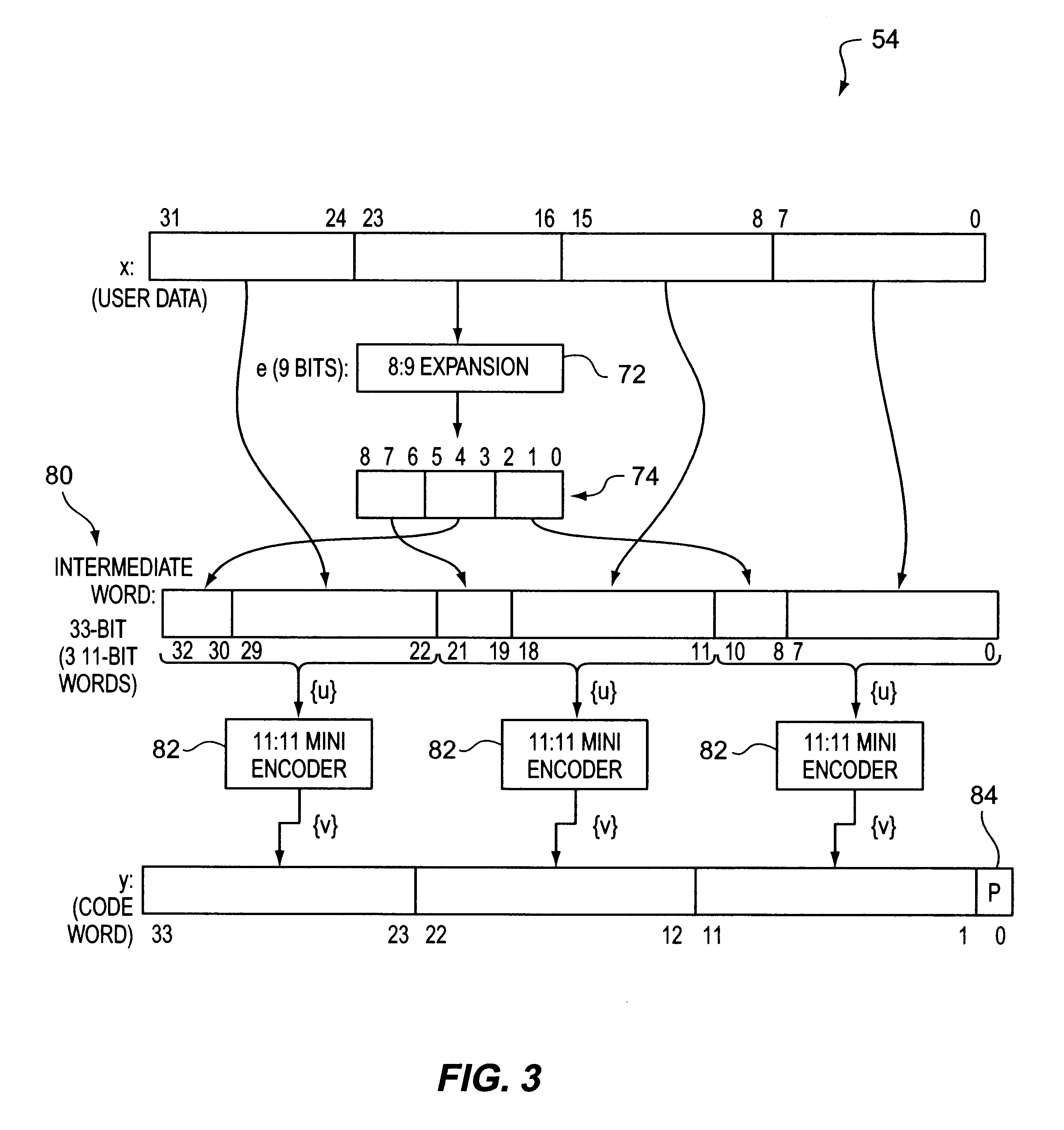

Rate 32/34 (D=0, G=9/I=9) modulation code with parity for a recording channel

A system and method for encoding a sequence of 32 bit digital data words into a sequence of 33 or more bit codewords having constraints of (d=0, G=9 / I=9) for recording upon a magnetic medium within a magnetic recording channel are disclosed. The method includes dividing each 32 bit digital data word into three 8-bit bytes and another 8-bit byte, expanding the another 8-bit byte into a 9-bit word, dividing the 9-bit word into three 3-bit subparts, forming three 11-bit intermediate blocks, each comprising one of the three 3-bit subparts and one of the three 8-bit bytes, encoding each of the three 11-bit intermediate blocks to generate three 11-bit encoded words, and forming each codeword from a set of the three 11 -bit encoded words. The set of the three 11-bit encoded words satisfies a predetermined minimum zero run length (d) constraint, a predetermined maximum zero run length (G) constraint, and a predetermined maximum interleave zero run length (I) coding constraint.

Owner:AVAGO TECH INT SALES PTE LTD

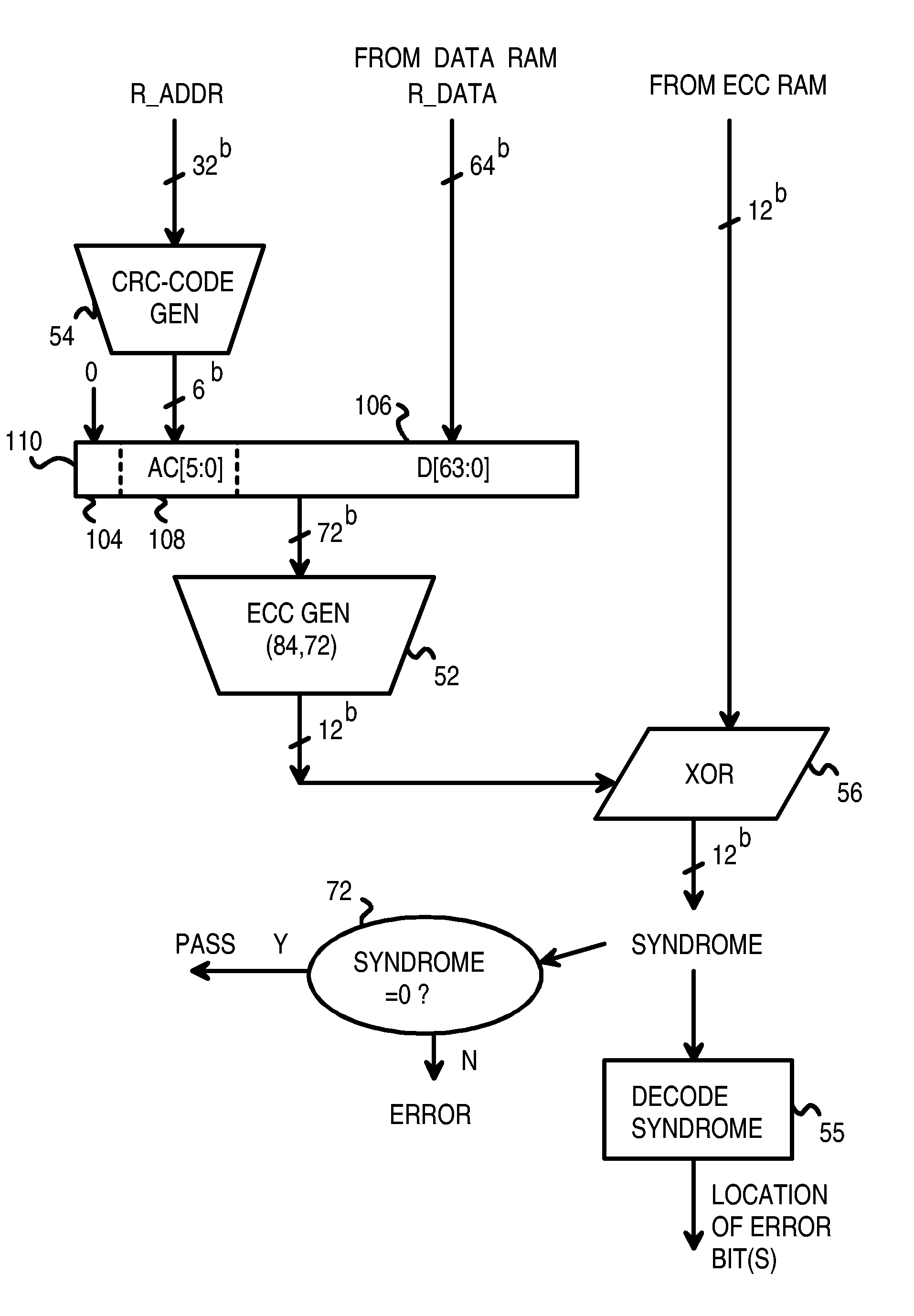

Encoding 64-bit data nibble error correct and cyclic-redundancy code (CRC) address error detect for use on a 76-bit memory module

A memory system provides data error detection and correction and address error detection. A cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to 6 address check bits using the CRC code. The 6 address check bits are concatenated with 64 data bits and 2 flag bits to generate a 72-bit check word. The 72-bit check word is input to an error-correction code (ECC) generator that generates 12 check bits that are stored in memory with the 64 data bits. A 76-bit memory module can store the 64 data and 12 check bits. Nibble errors can be corrected, and all nibble+1 bit errors can be detected. Also, a 6-bit error in a sequence of bits can be detected. This allows all errors in the 6-bit CRC of the address to be detected. The CRC code and ECC are ideal for detecting double-bit errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

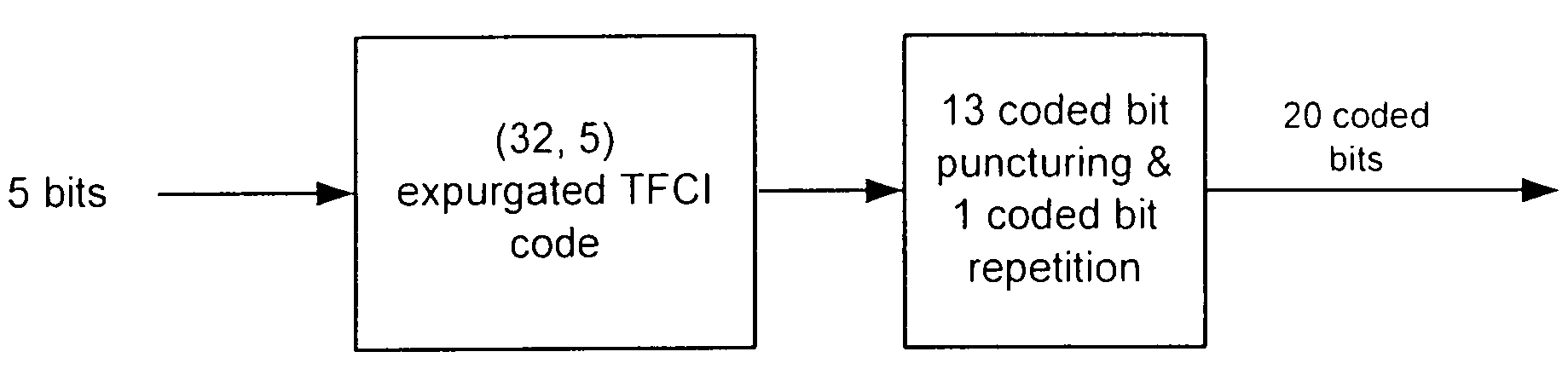

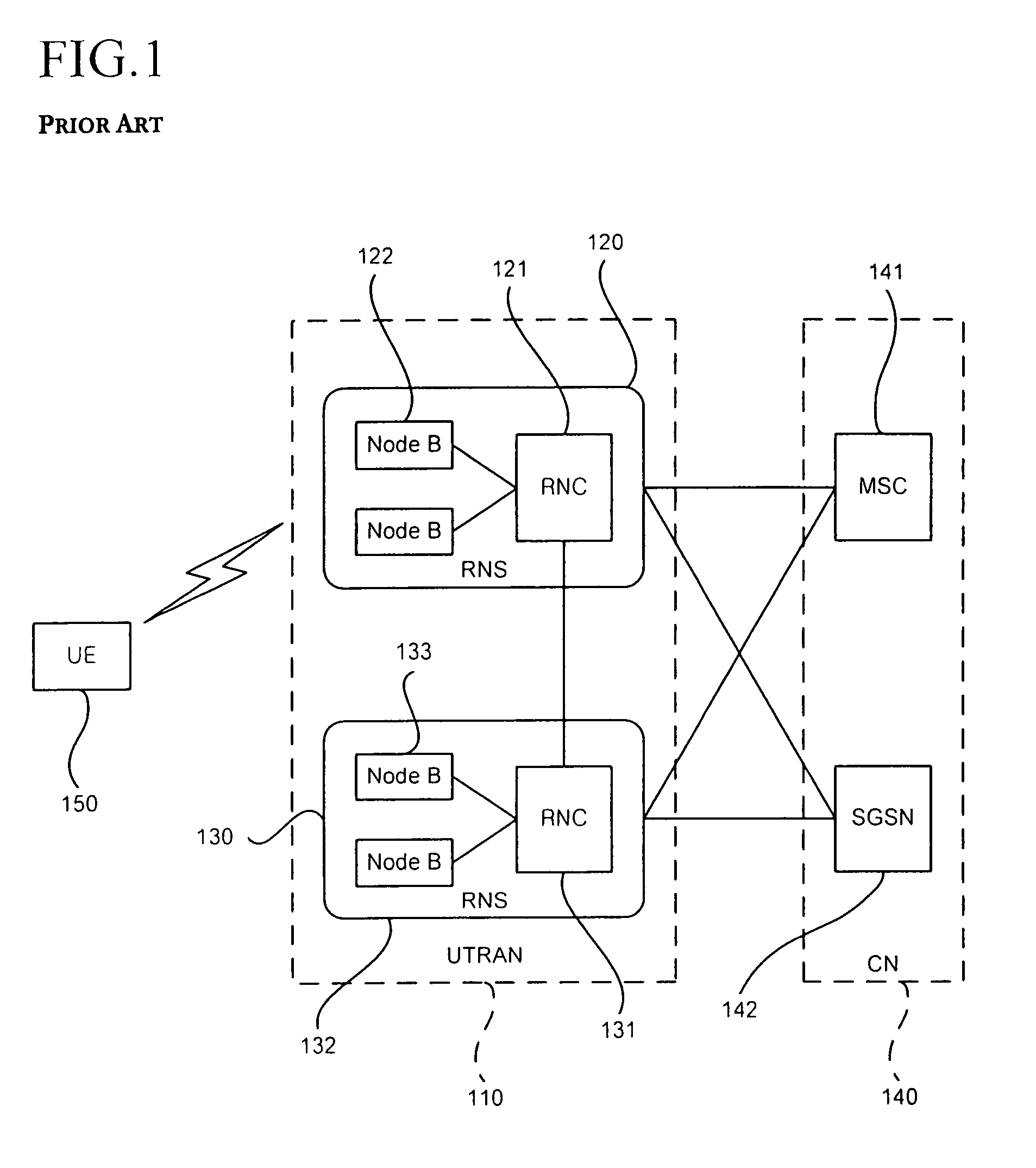

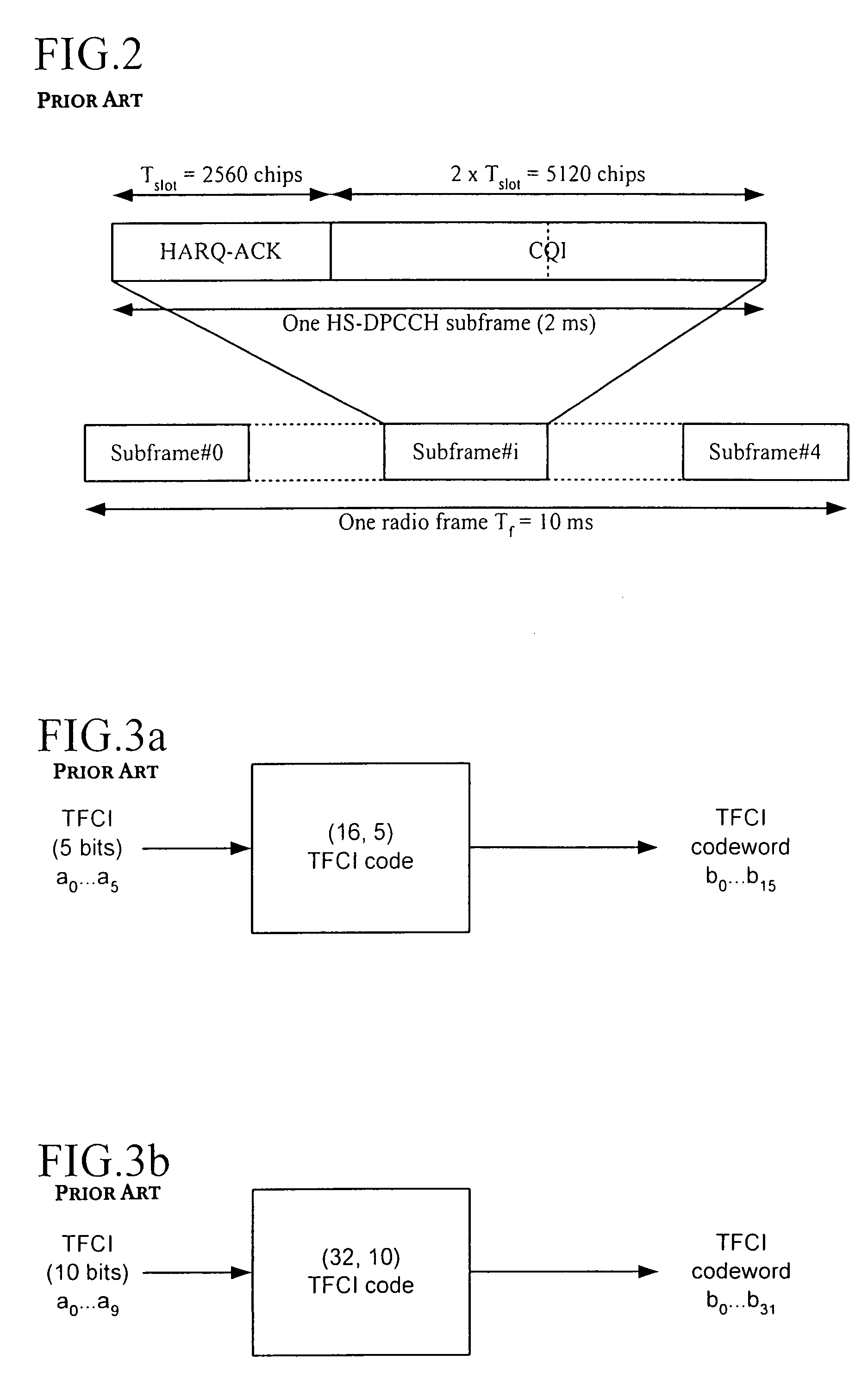

CQI coding method for HS-DPCCH

ActiveUS7319718B2System throughput is maximizedMaximize throughputError detection/prevention using signal quality detectorFrequency-division multiplex detailsComputer architectureDPCCH

In the channel quality information (CQI) coding method of the present invention, first basis sequences for generating sub-codes of 32 bits are created, and second basis sequences for generating codewords of 20 bits are created using the first basis sequences, the second basis sequence maximizing system throughput such that five information bits are coded into CQI code using the second basis sequences. Also, since HSDPA system has been designed in order to increase the system throughput, the CQI coding method of the present invention, which shows the best system throughput in the simulation, can be the optimum CQI coding scheme for HS-DPCCH.

Owner:3G LICENSING SA

Micro-strapdown altitude heading reference system and working method thereof

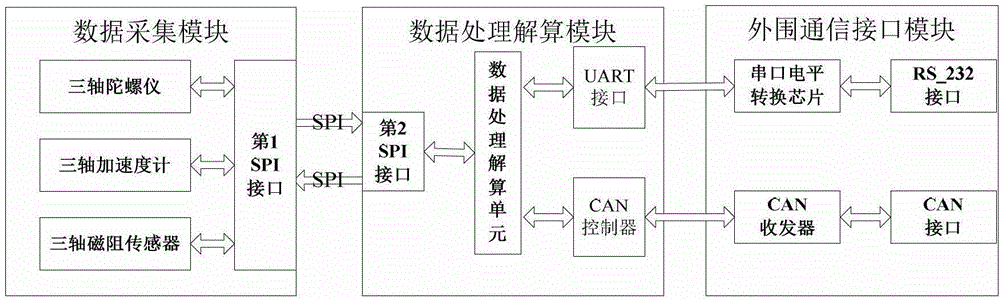

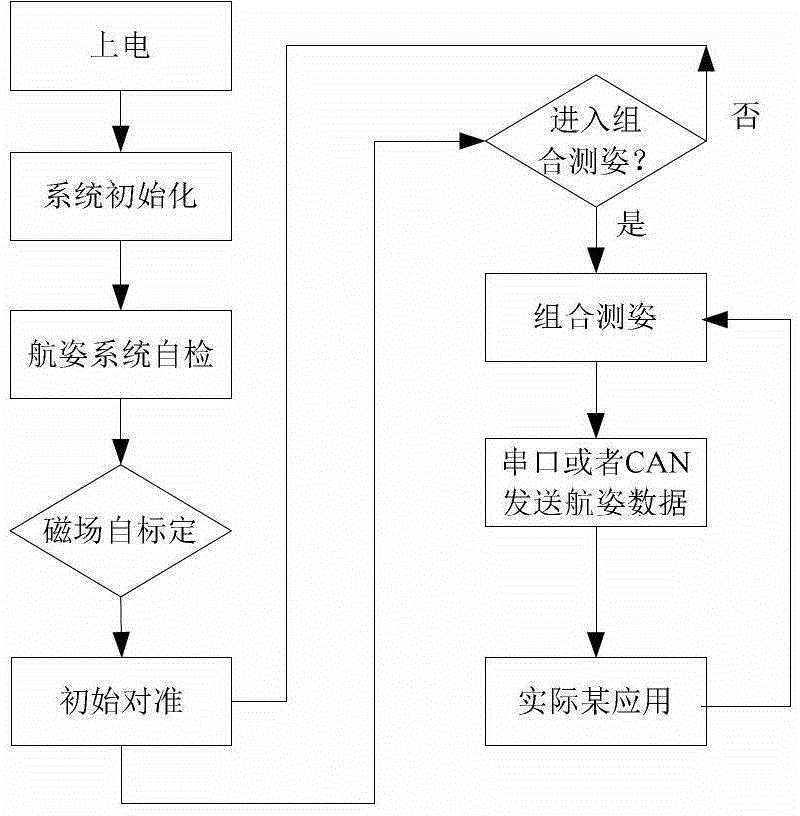

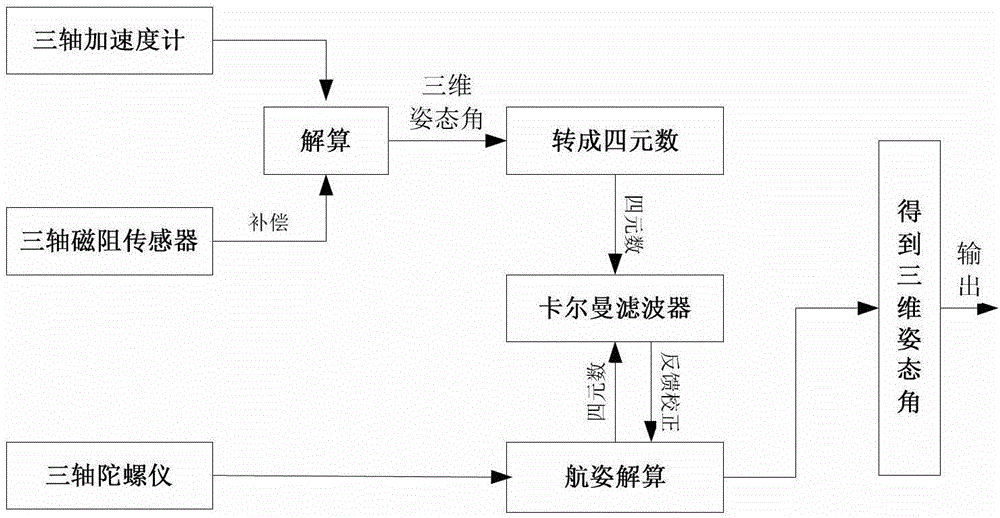

InactiveCN102980577ALow costHighly integratedNavigation by speed/acceleration measurementsMicrocontrollerArea network

The invention relates to a micro-strapdown altitude heading reference system and a working method of the micro-strapdown altitude heading reference system. The system comprises a data acquisition module, a data processing resolving module and a peripheral communication interface module, wherein the data acquisition module integrates a three-axis gyroscope, a three-axis accelerometer, a three-axis magnetic resistance sensor and an SPI (Serial Peripheral Interface) into an integrated micro-electronic mechanical system sensor; the data processing resolving module adopts a 32-bit ARM (Advanced RISC Machine) microcontroller; and the peripheral communication interface module consists of a serial port level switching chip, an RS-232 interface, a CAN (Controller Area Network) transceiver and a CAN interface. The working method of the system comprises the working steps as follows: the system is electrified and initialized; the system is self-tested; a magnetic field is self-calibrated; initial alignment is conducted; measured attitudes are combined: resolving the information of attitude headings according to initial three-dimensional altitude and altitude resolving algorithm of the strapdown altitude heading reference system, and resolving the three-dimensional magnetic altitude angle according to the compensated magnetic field information and acceleration information, conducting the information merging algorithm and finally obtaining the stable altitude heading reference information; and the altitude heading reference information is sent to application equipment.

Owner:NANJING UNIV OF SCI & TECH

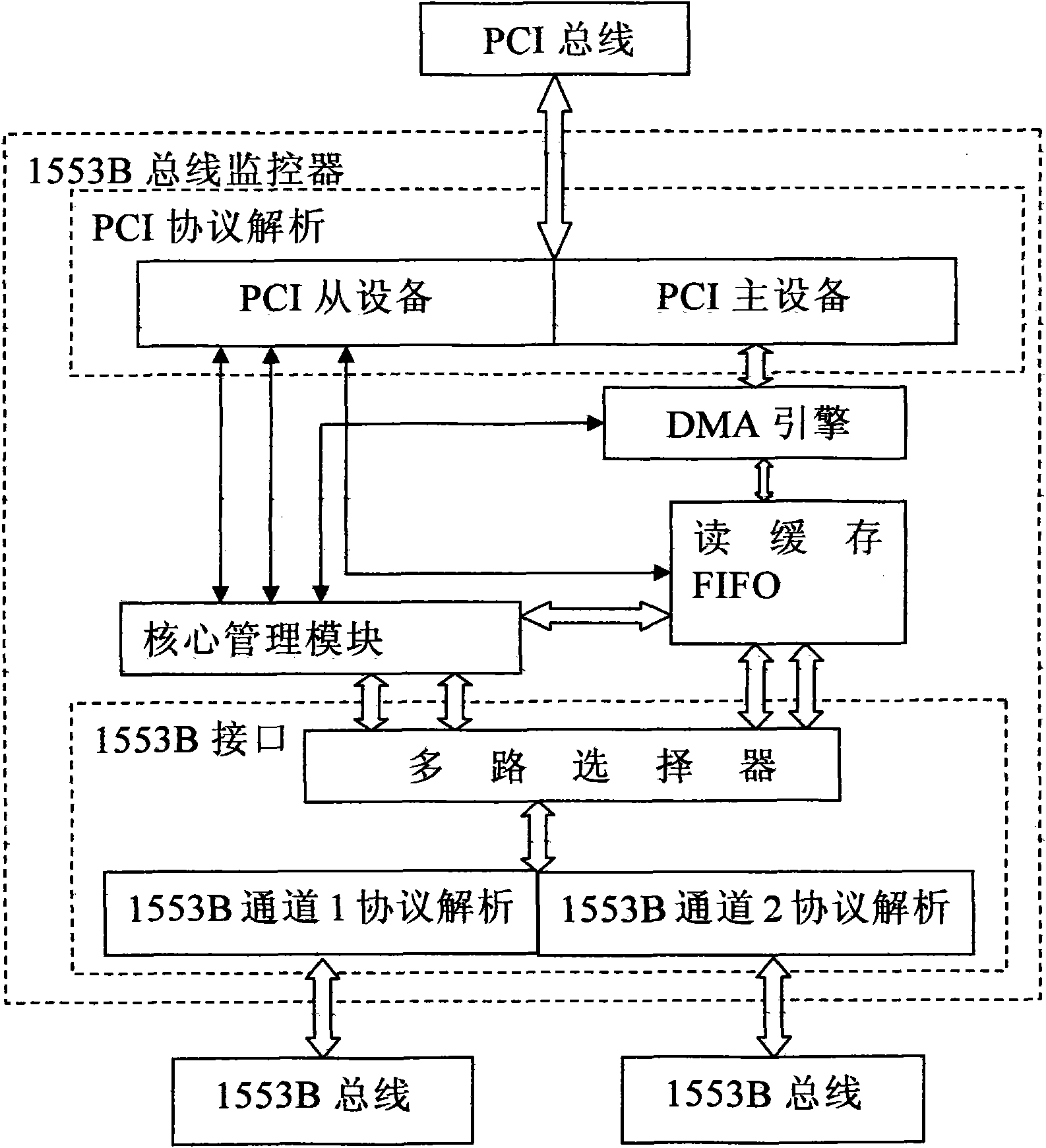

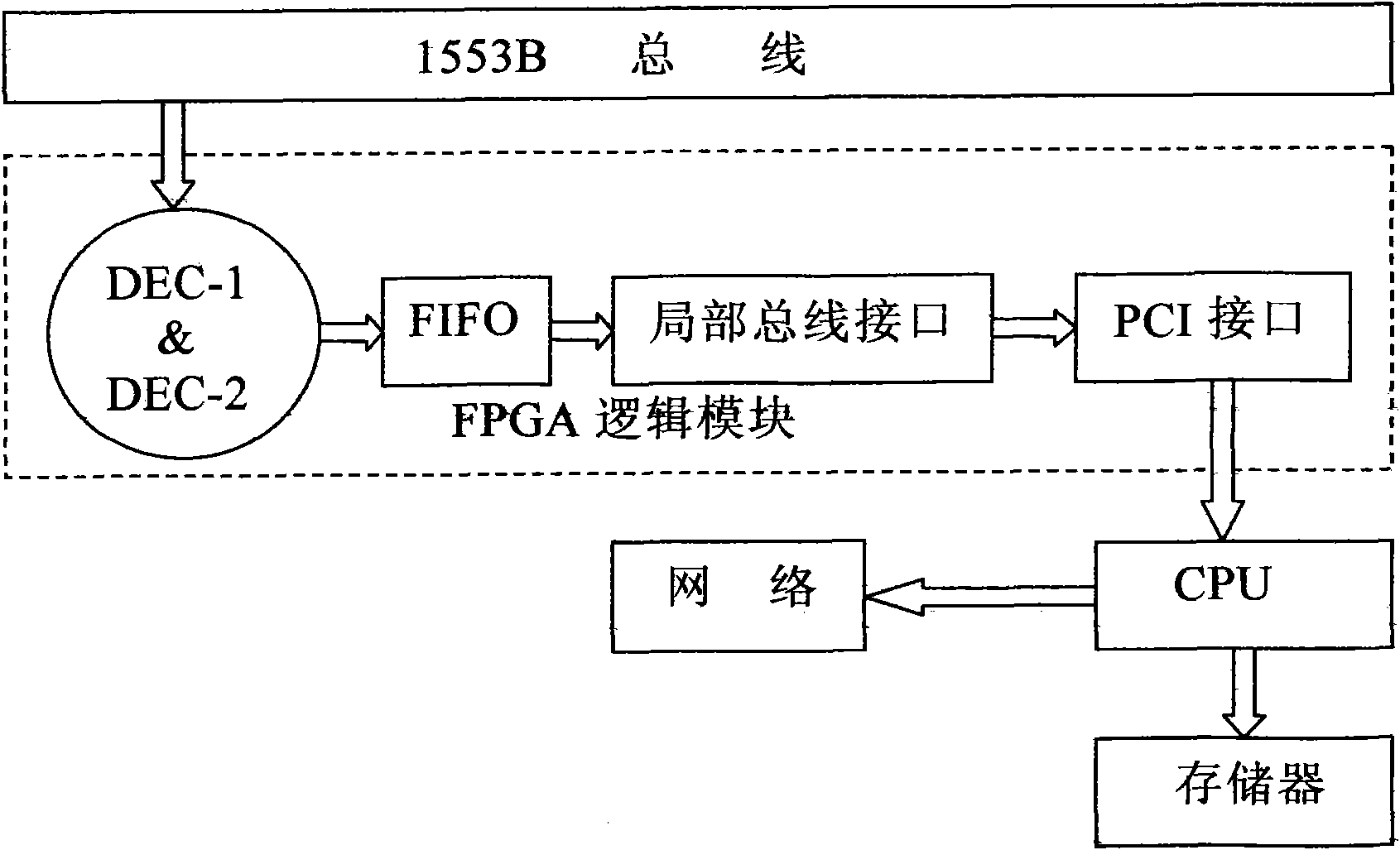

1553B bus monitor and bus system with same

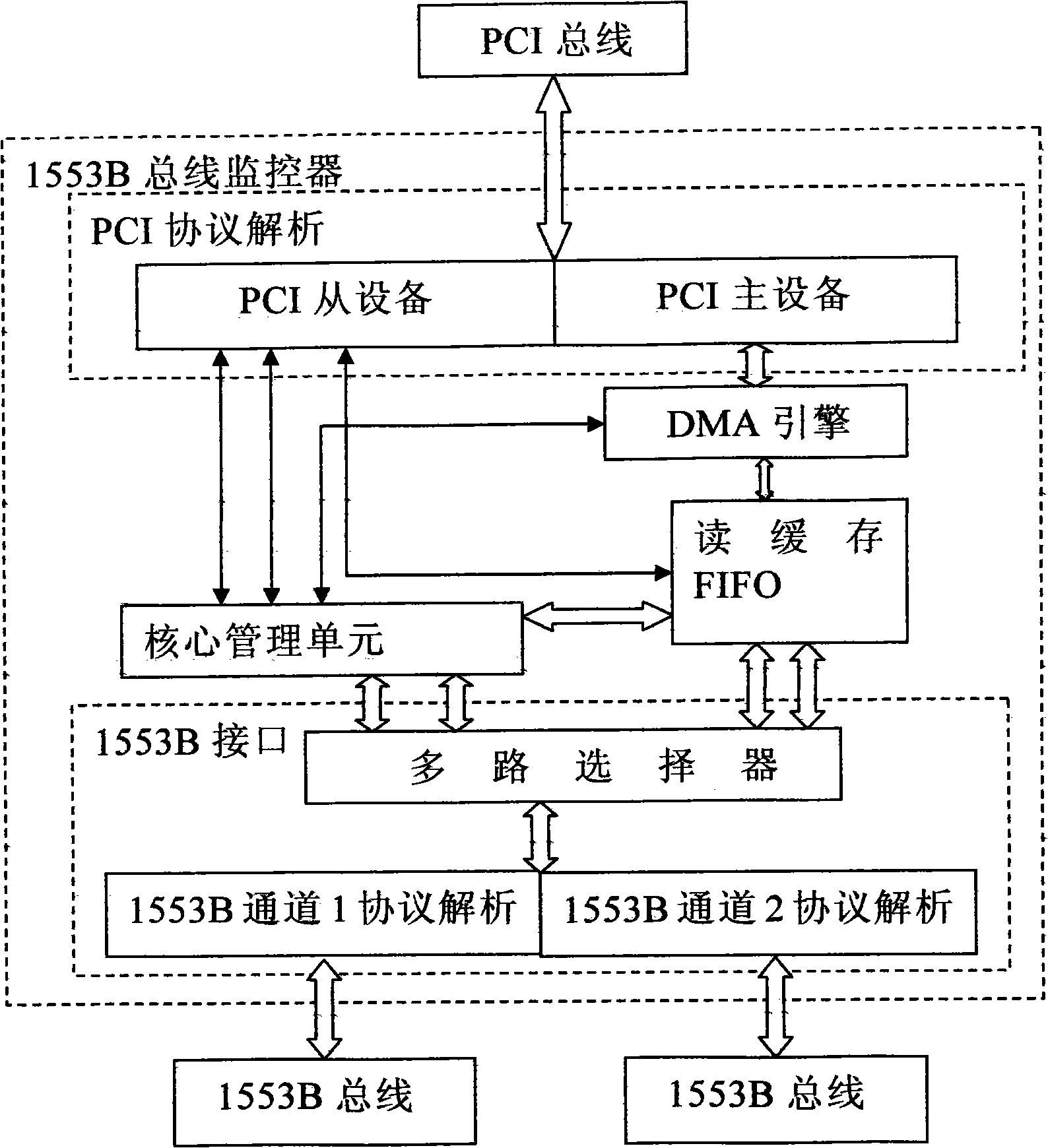

ActiveCN101799795AEasy to mountImprove data transfer efficiencyElectric digital data processingBurst transmissionPci interface

The invention discloses a 1553B bus monitor. A local bus module of the 1553B bus monitor connected with a PCI bus comprises a PCI master equipment unit and a PCI slave equipment unit, wherein the PCI master equipment unit and the PCI slave equipment unit provide a 32-bit PCI interface together; the PCI slave equipment unit supports passive access; and the PCI master equipment unit realizes direct memory transmission and actively transmits data to memory space pre-allocated by a central processing unit (CPU). This invention also discloses a 1553B bus system with the 1553B bus monitor. The 32-bit 1553B bus monitor adopting PCI interface design can be conveniently hung to the PCI bus outside a microprocessor, has processing bandwidth of 32 bits, integrates DMA modules, can automatically initiate data transmission after CPU configuration, supports a BURST transmission mode, and greatly improves the efficiency of data transmission.

Owner:LOONGSON TECH CORP