Patents

Literature

397 results about "Pci interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

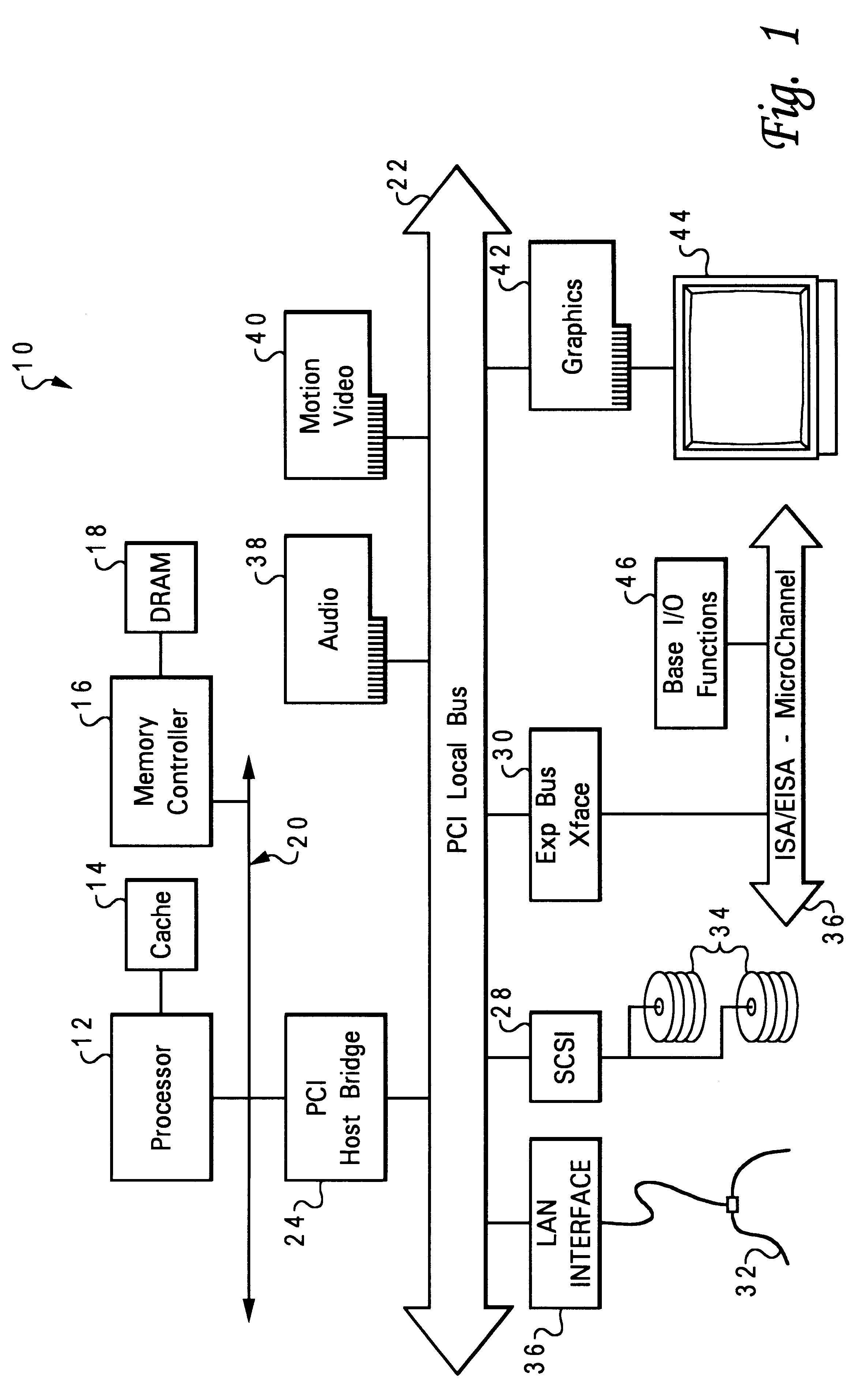

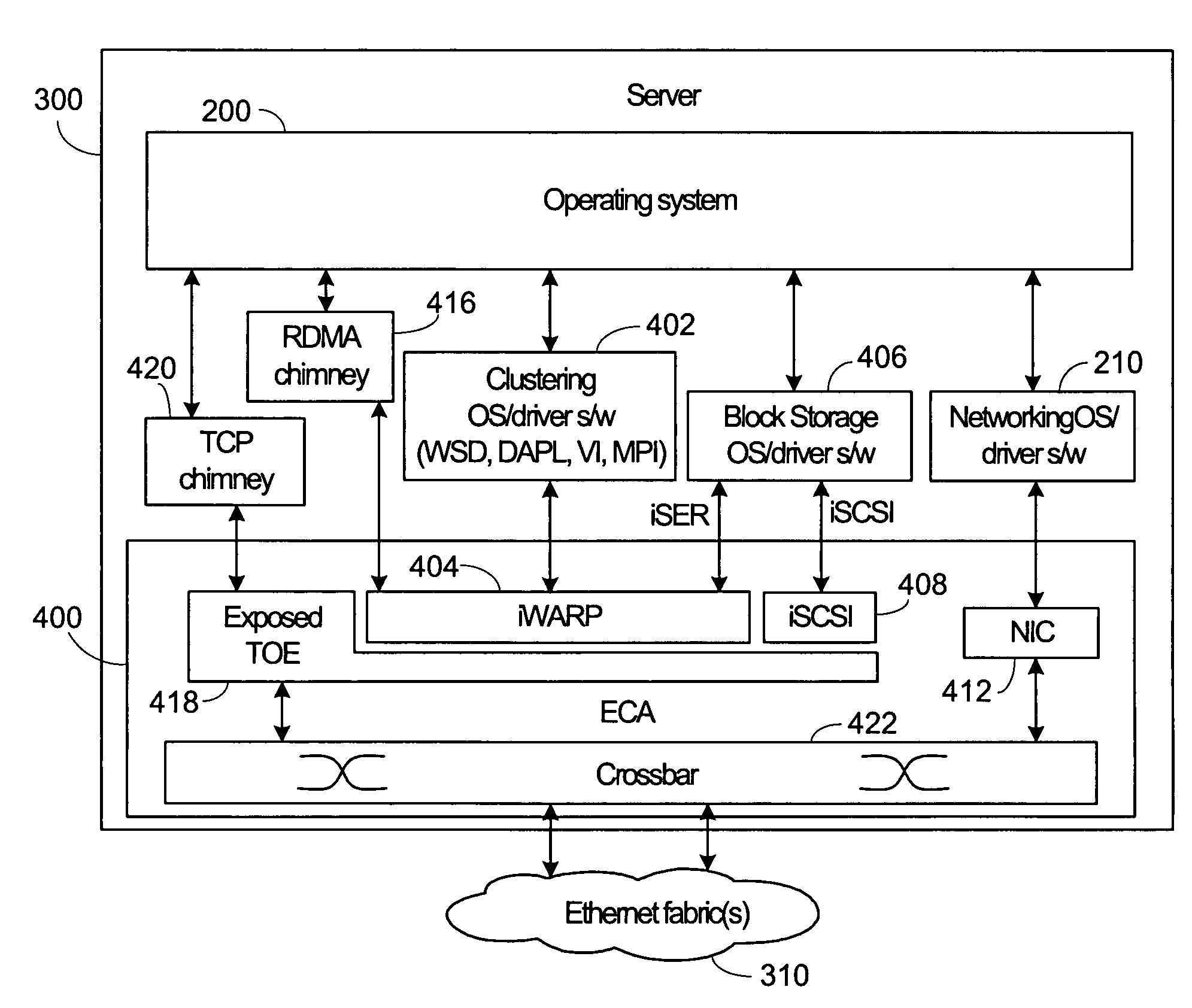

The PCI Express interface allows high bandwidth communication between the device and the motherboard, as well as other hardware. While not very common, an external version of PCI Express exists as well, unsurprisingly called External PCI Express but often shortened to ePCIe.

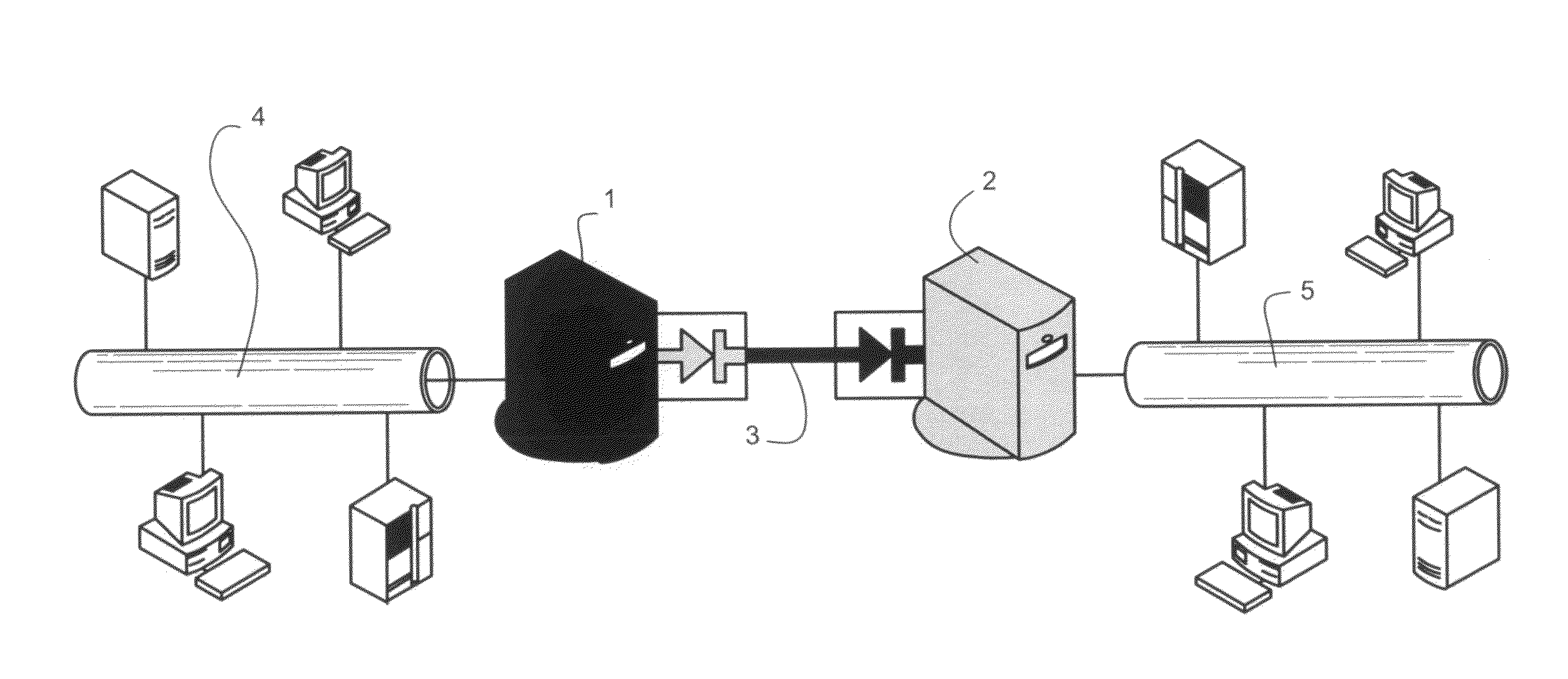

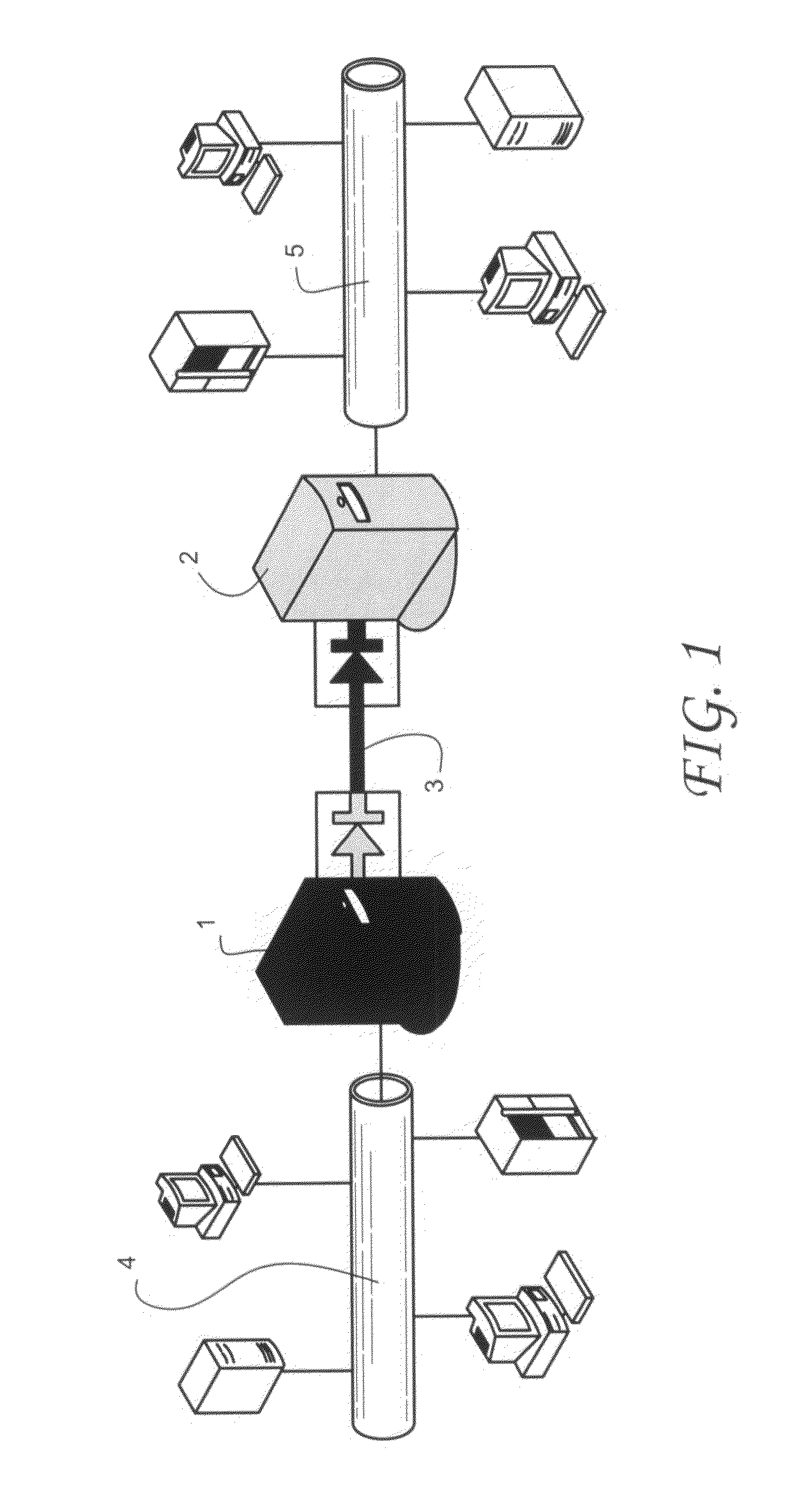

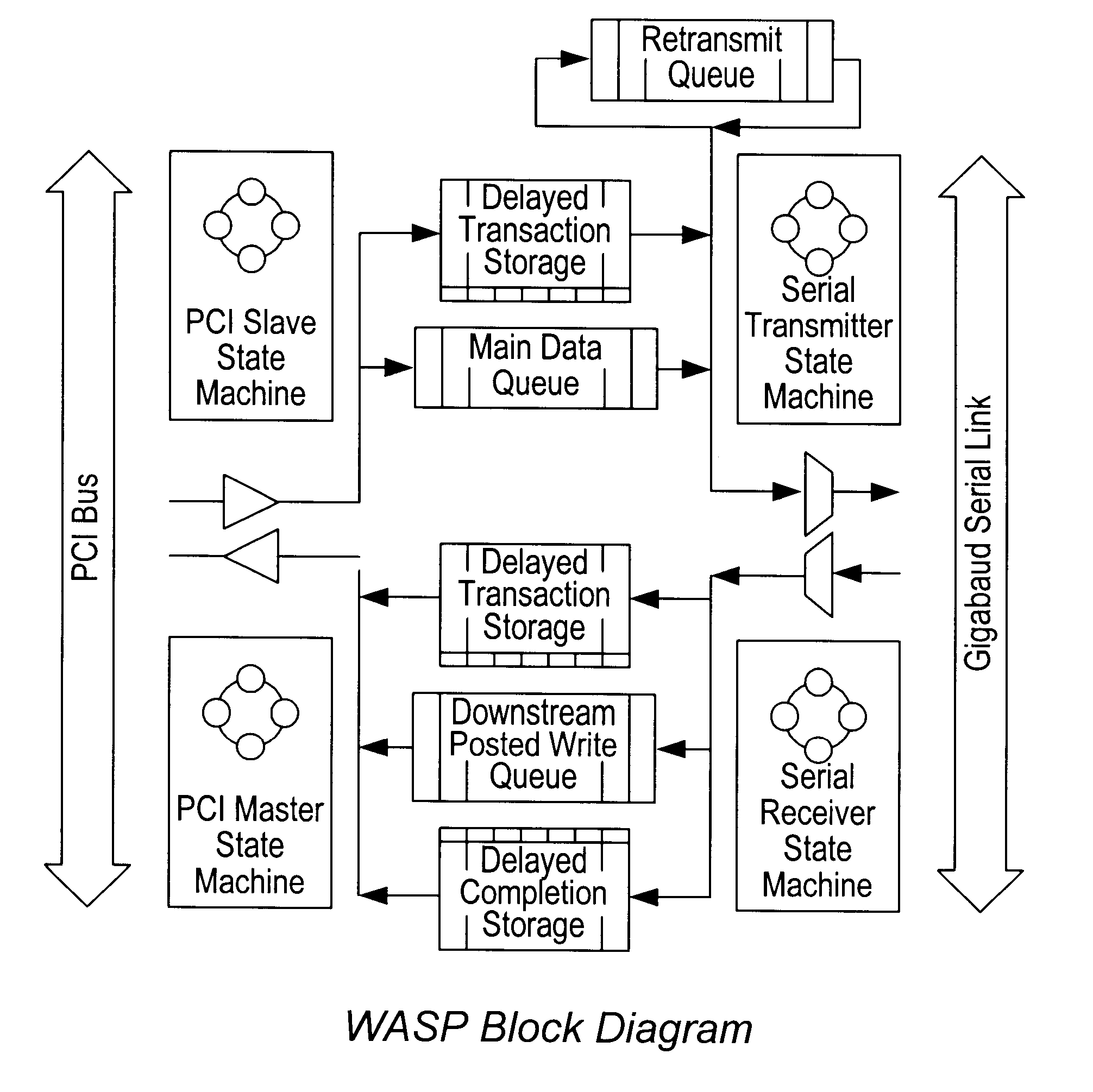

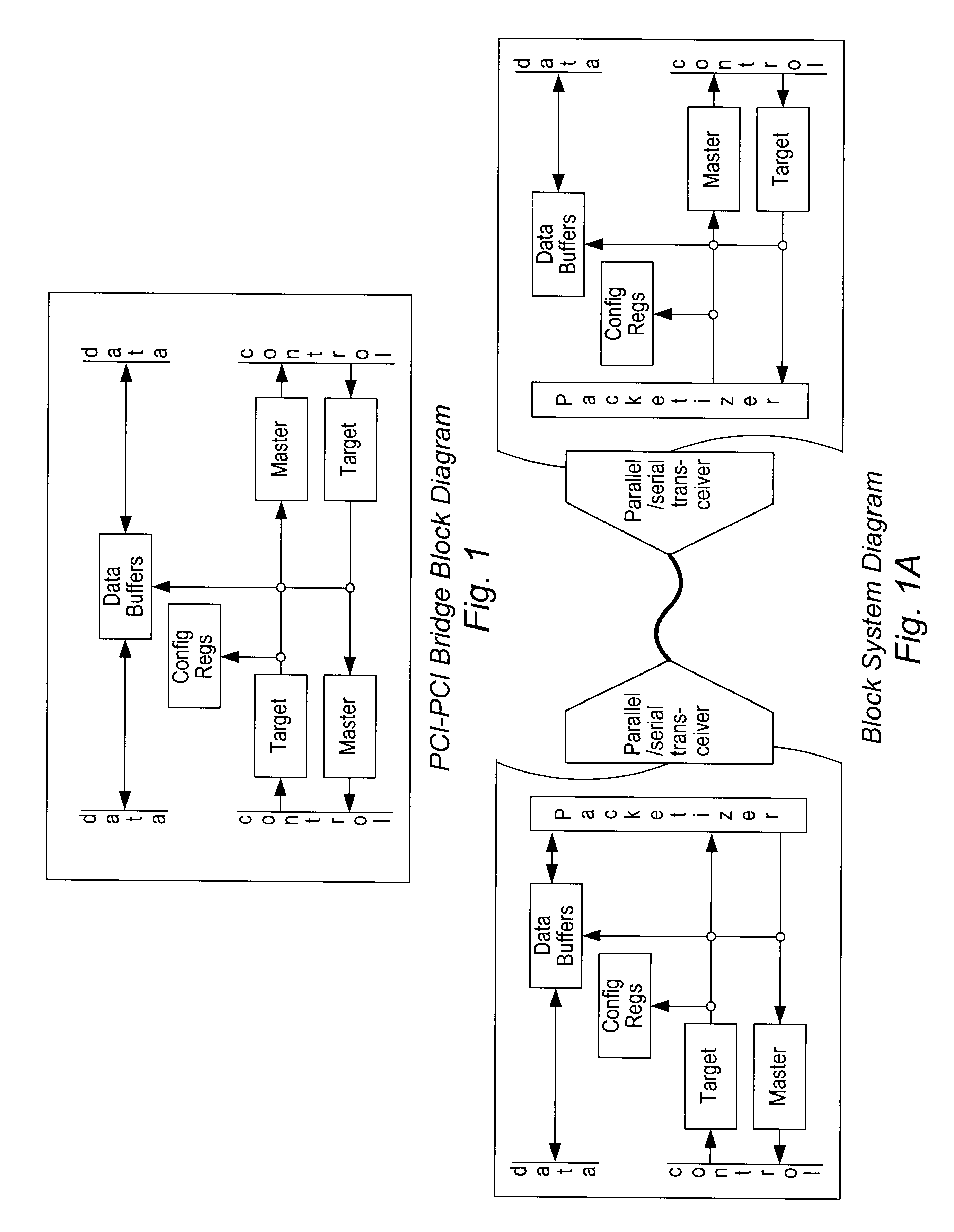

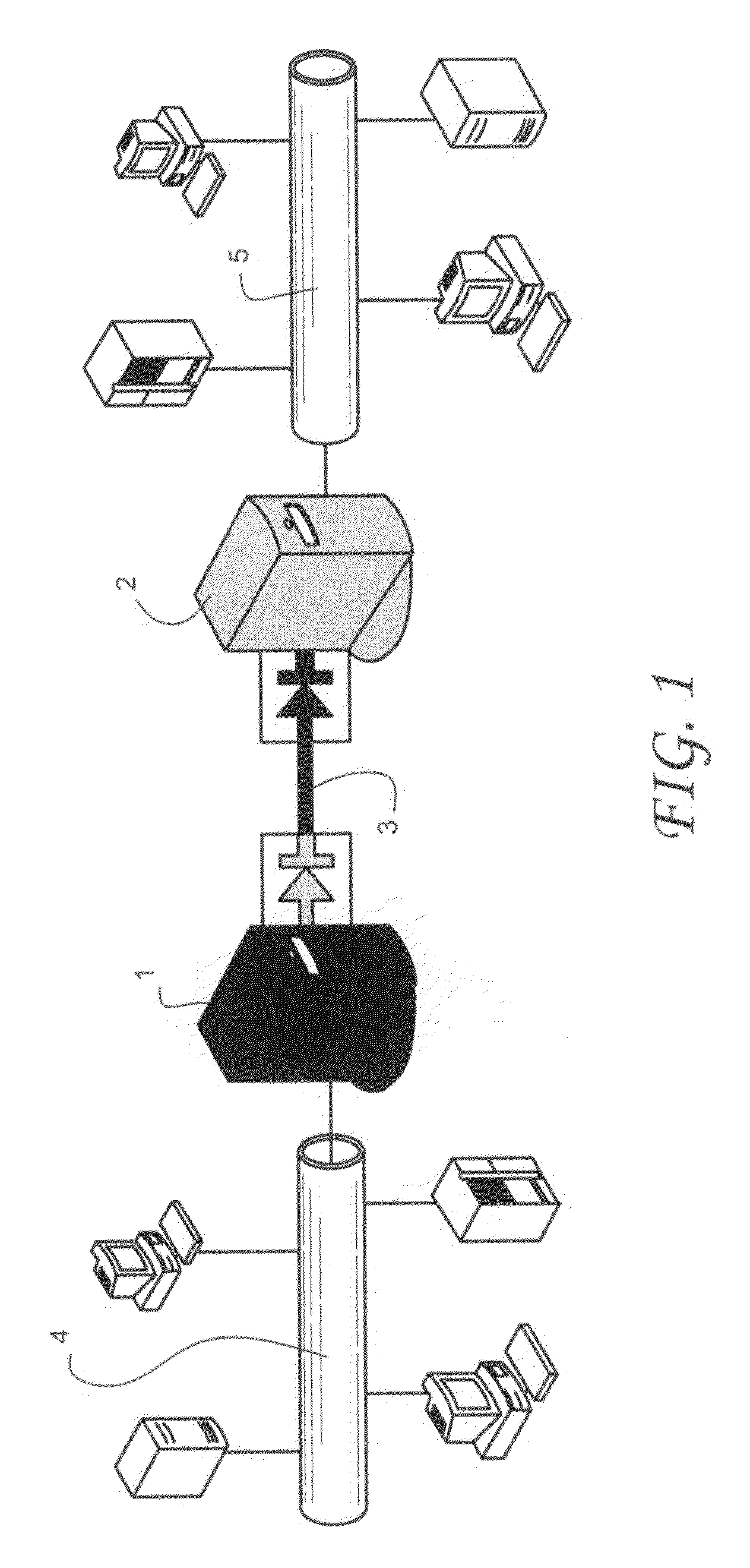

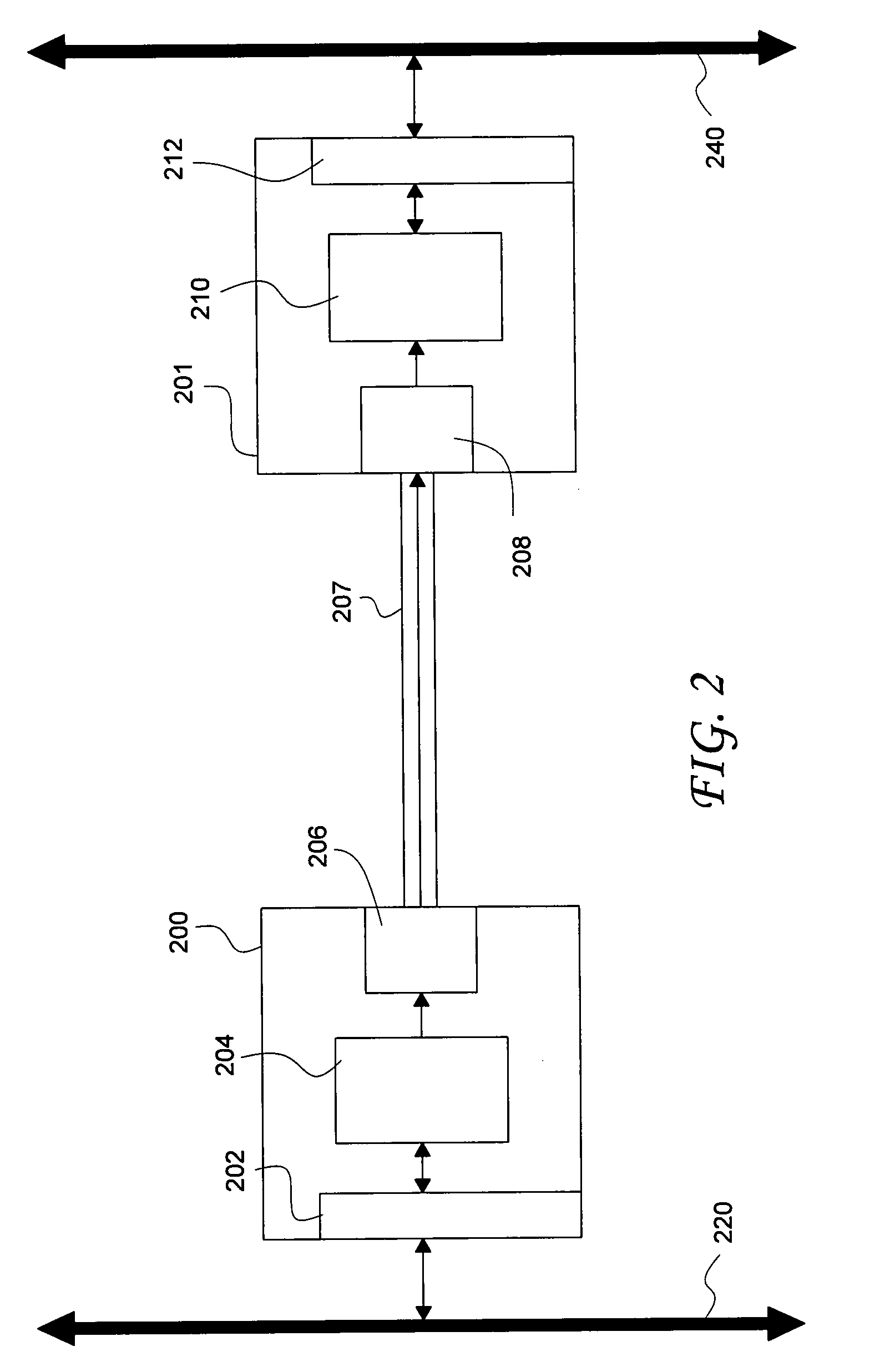

System and method for connecting peripheral buses through a serial bus

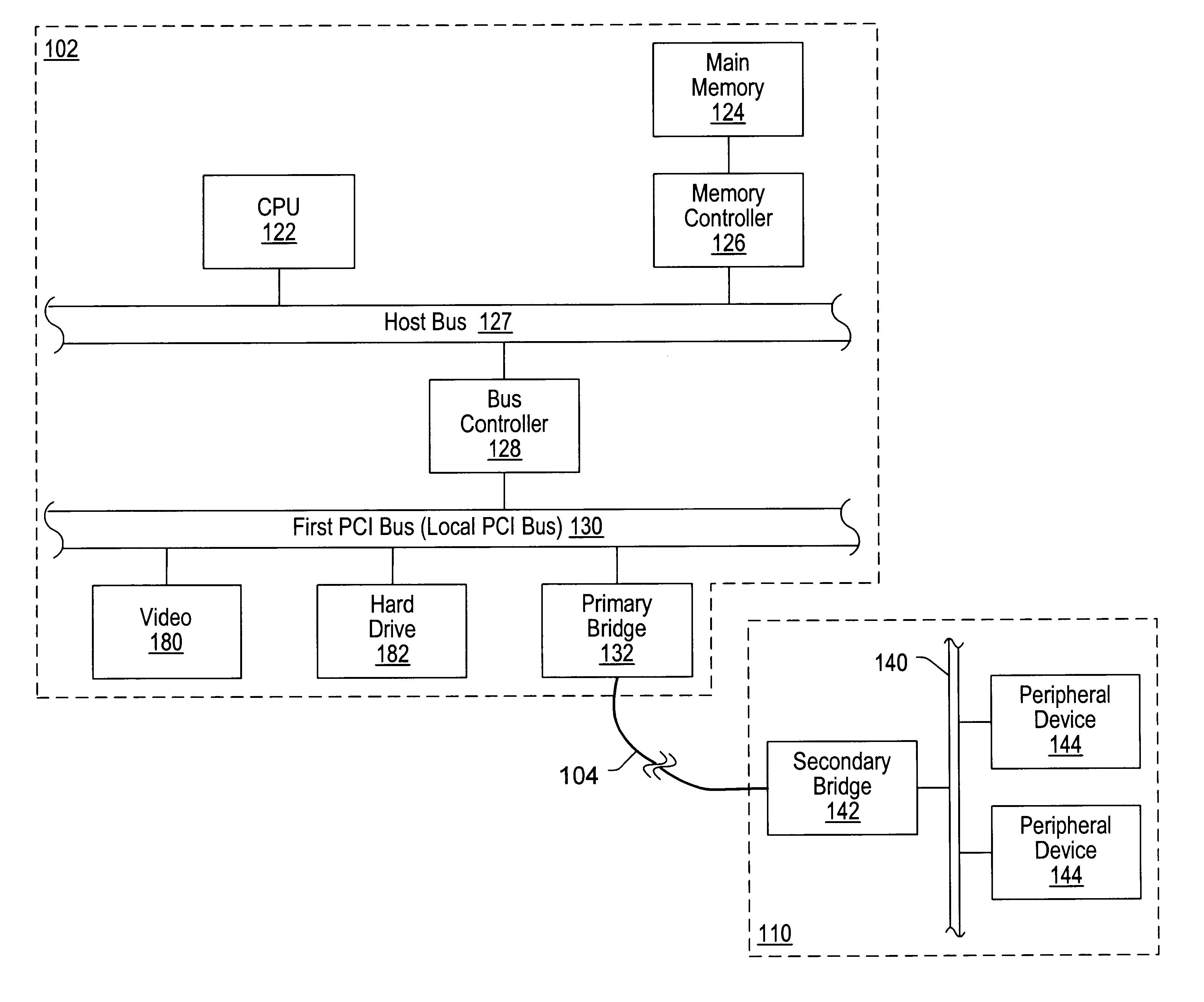

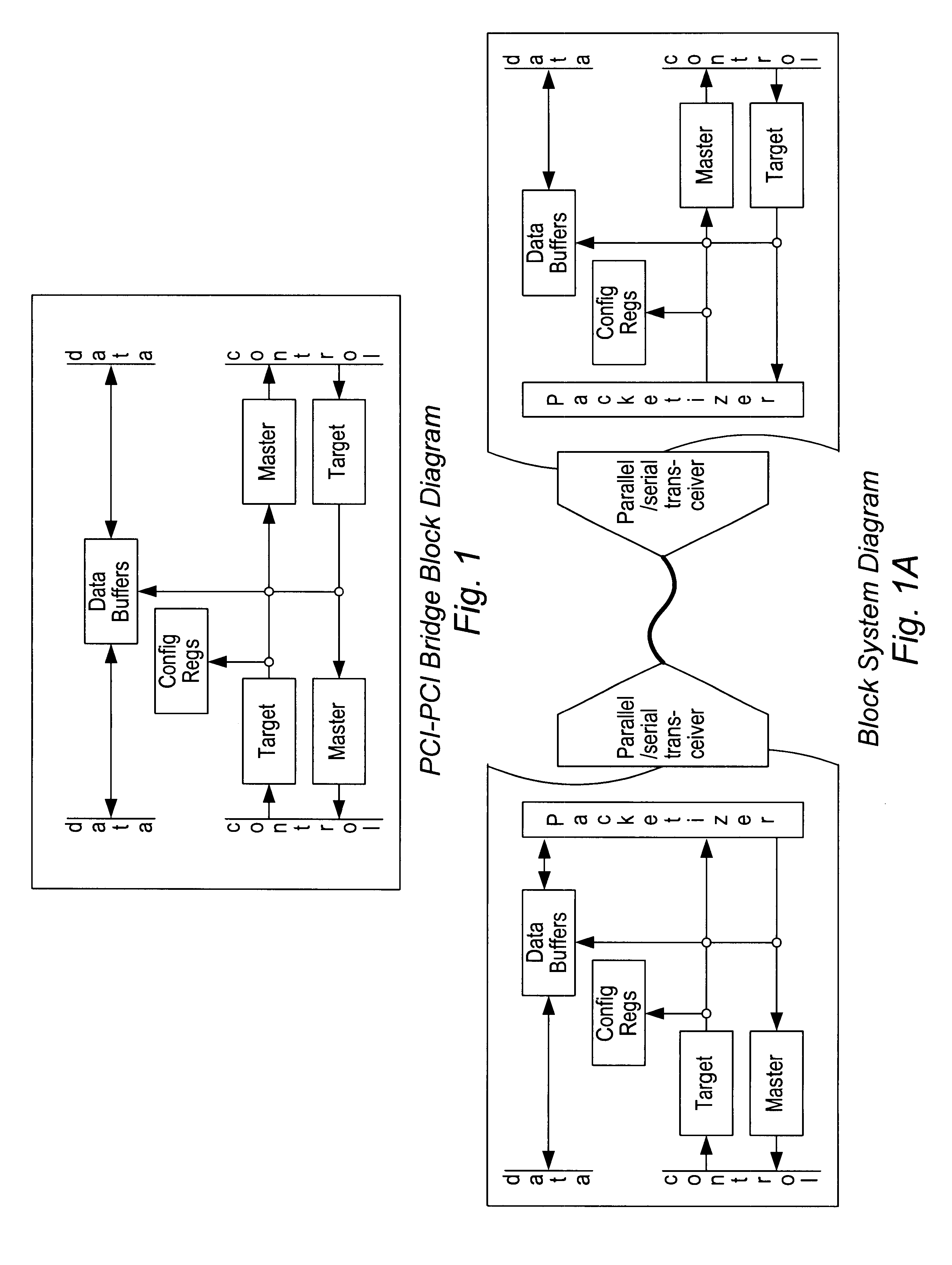

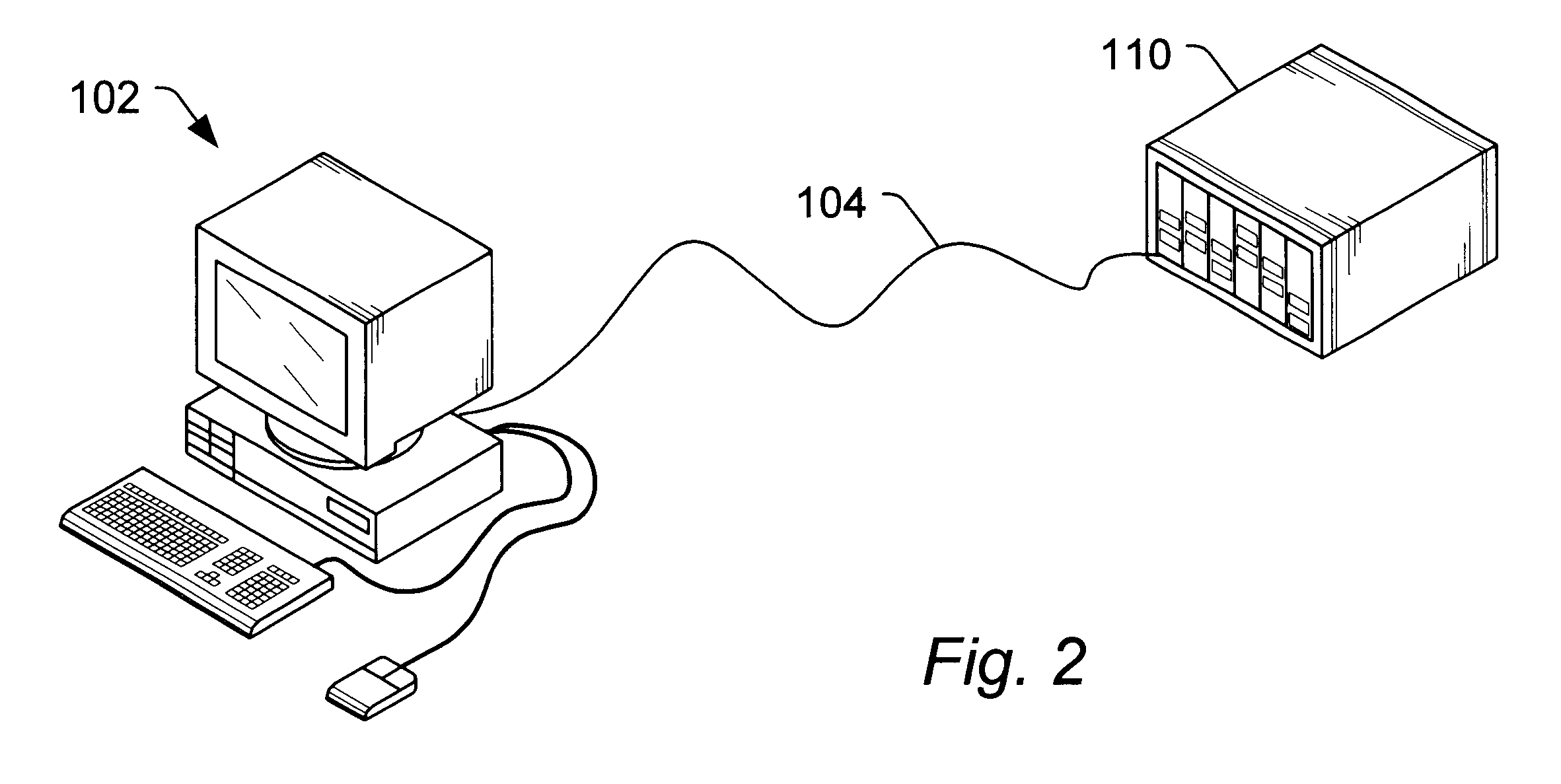

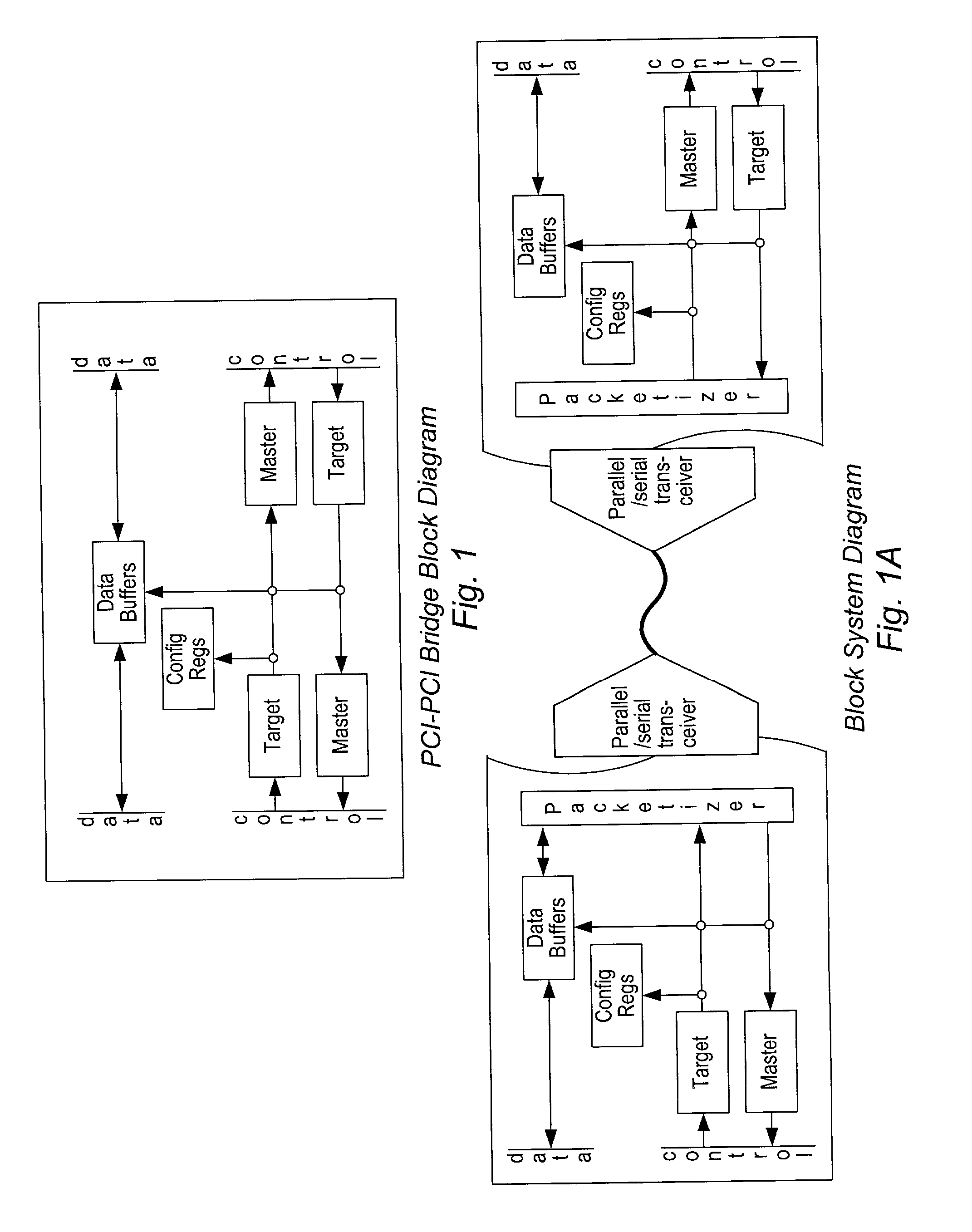

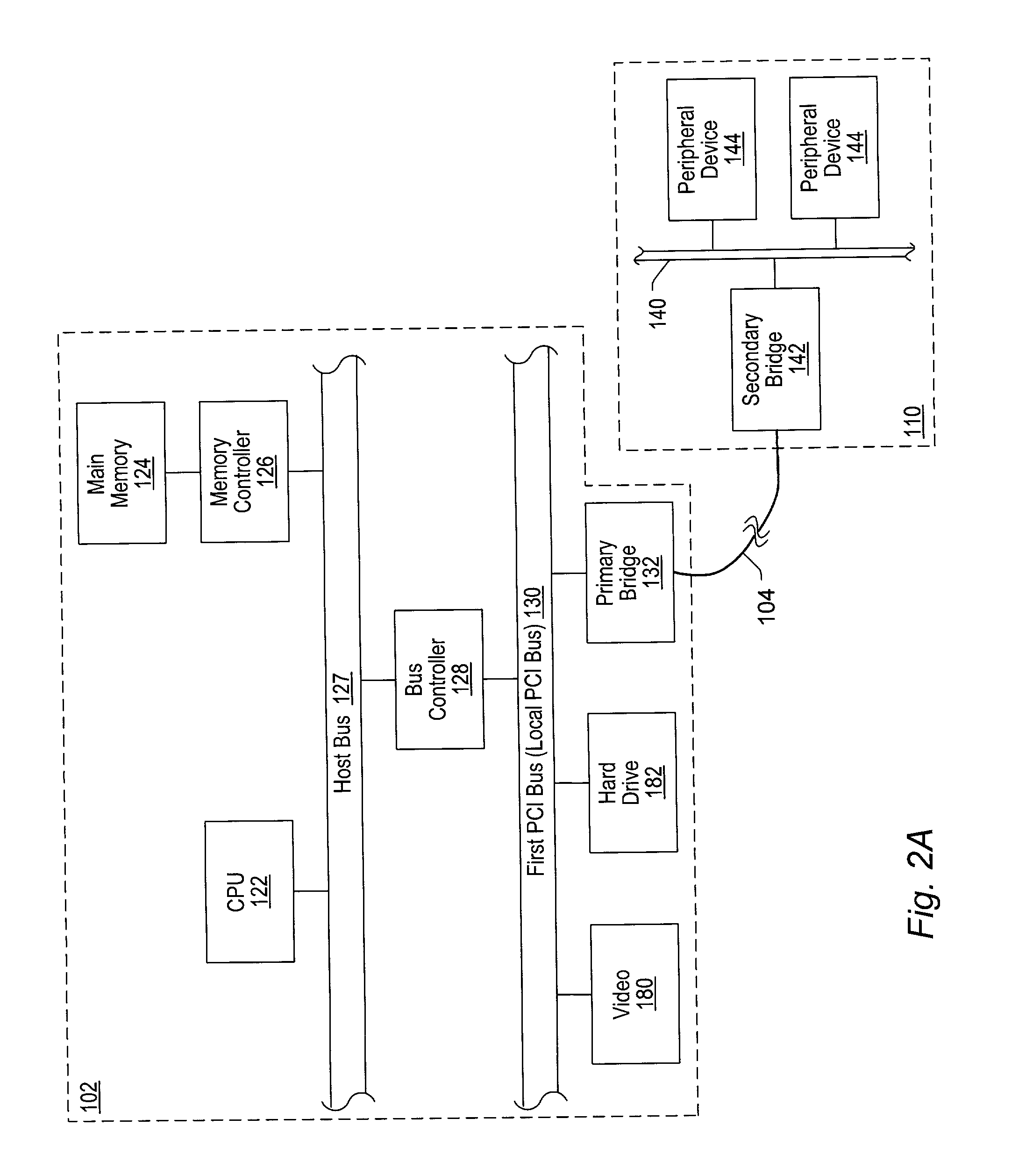

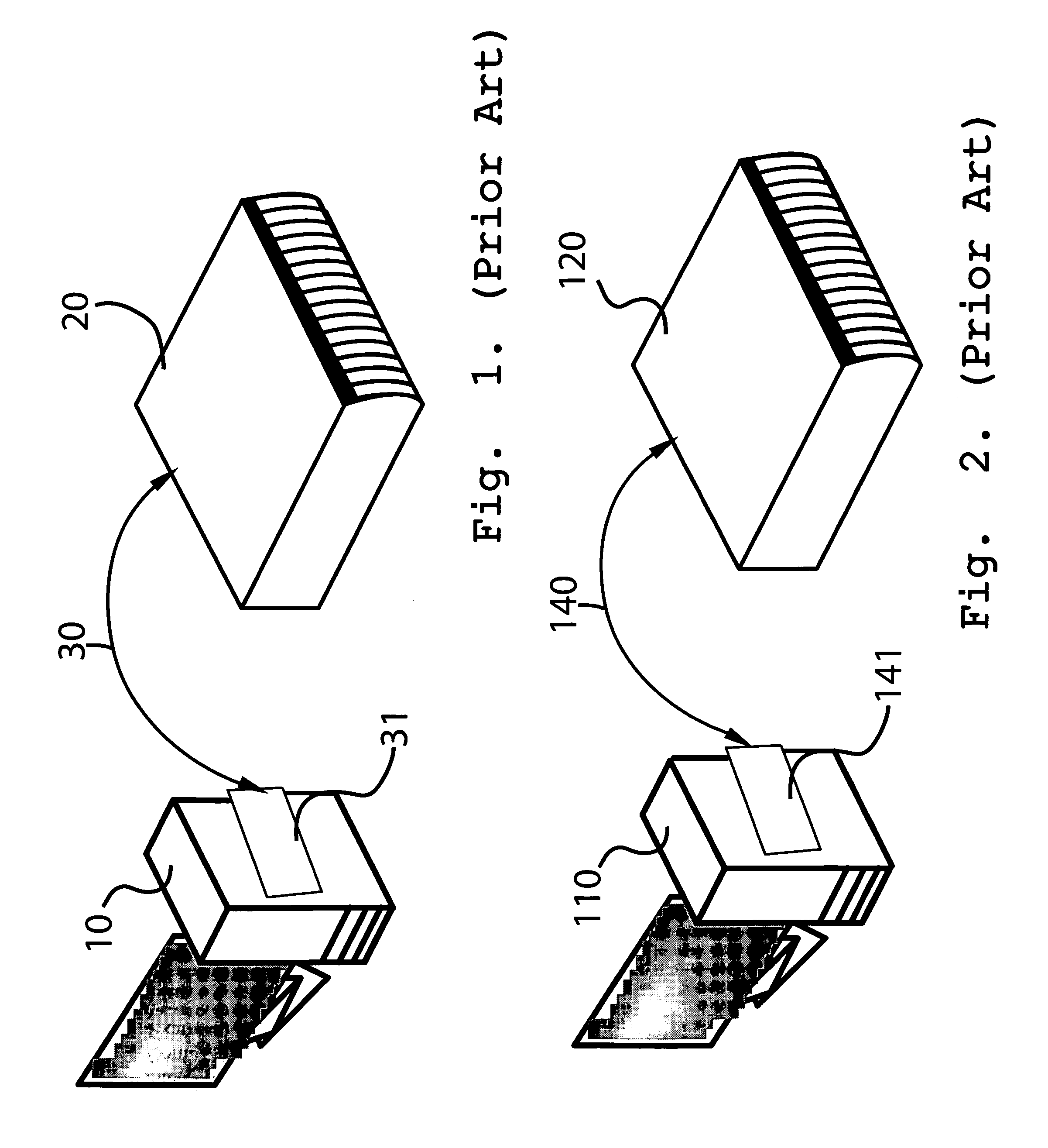

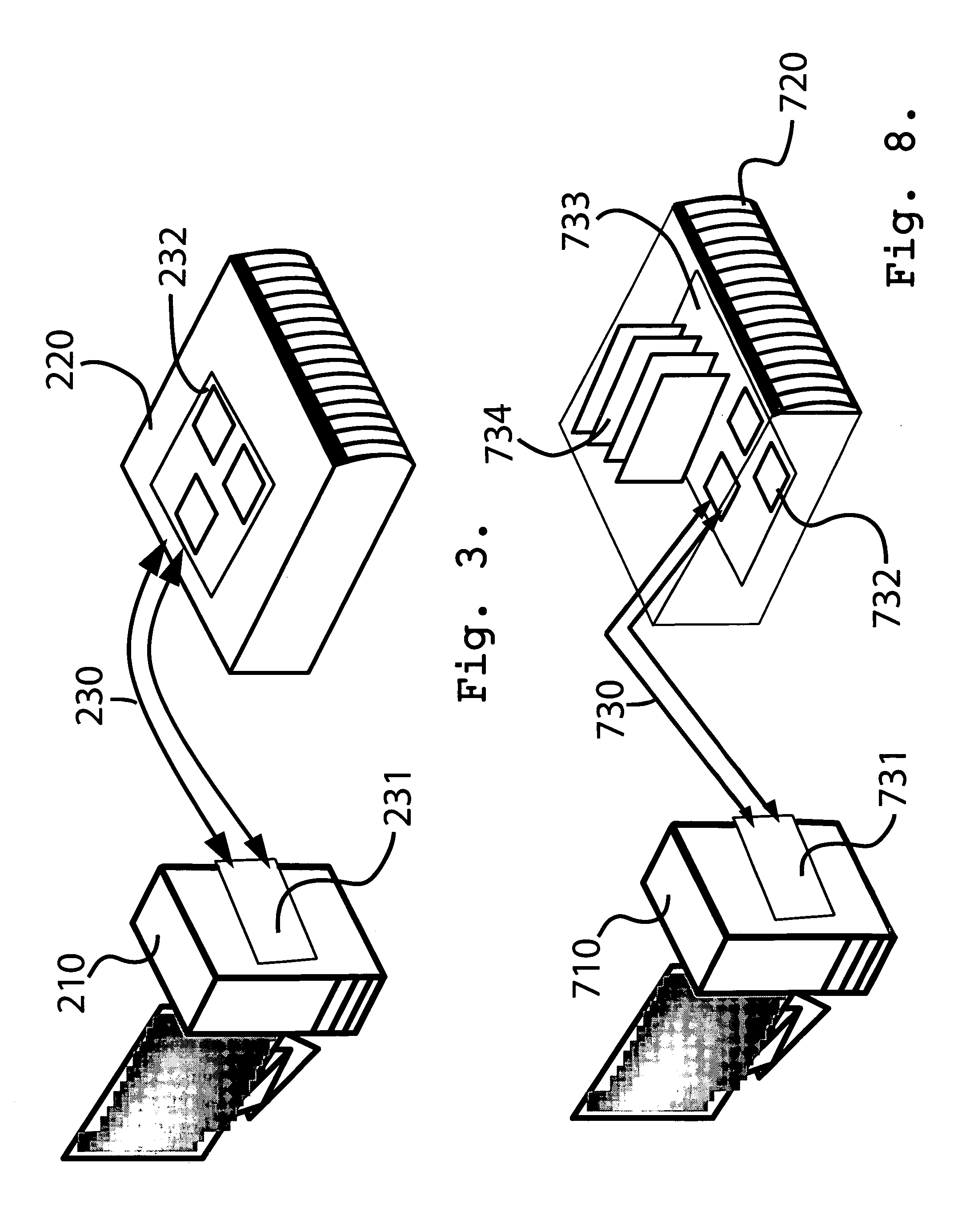

A Wide Area Serial PCI system for connecting peripheral devices to a computer. The WASP system includes a host computer system connected through a serial bus to a remote device. The serial bus can range from several meters to several kilometers or more. The host computer system includes a CPU and memory, and also includes a first Peripheral Component Interconnect (PCI) bus, also referred to as the local PCI bus. A primary bridge according to the present invention is coupled to the first PCI bus. The primary bridge includes PCI interface circuitry for interfacing to the first PCI bus. The remote device is located remotely from the computer system and comprises a second or remote PCI bus and one or more peripheral devices coupled to the second PCI bus. The remote device also includes a secondary bridge coupled to the second PCI bus. The secondary bridge includes PCI interface circuitry for interfacing to the second PCI bus. The serial bus is coupled between the primary bridge and the secondary bridge. Each of the primary bridge and secondary bridge include parallel / serial transceivers for converting parallel data generated on the first PCI bus and second PCI bus, respectively, to serial data for transmission on the serial bus and for converting serial data received from the serial bus to parallel data for generation on the first PCI bus and second PCI bus, respectively. The primary bridge and the secondary bridge collectively implement a PCI-PCI bridge register set.

Owner:NATIONAL INSTRUMENTS

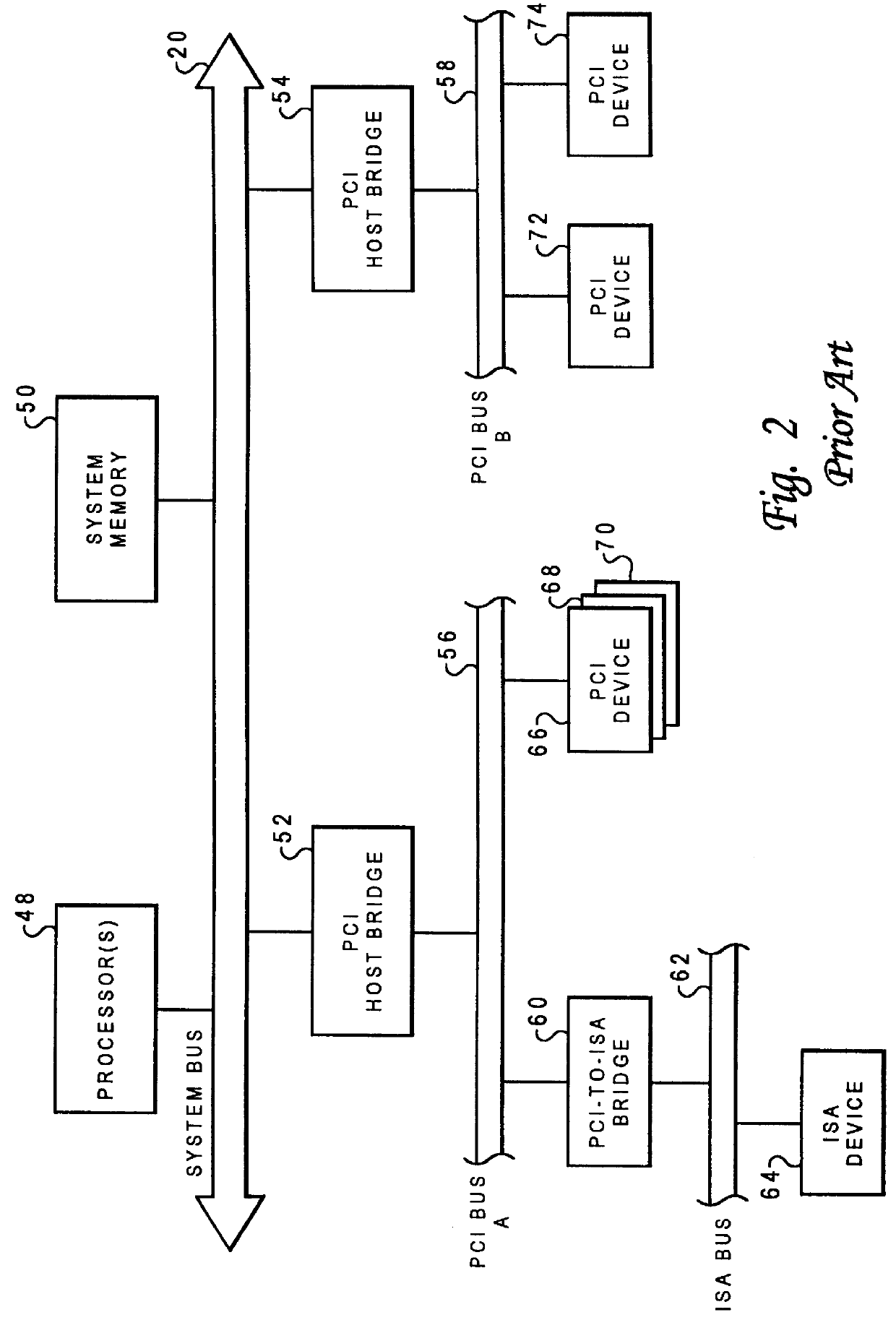

Method and system for supporting peripheral component interconnect (PCI) peer-to-peer access across a PCI host bridge supporting multiple PCI buses

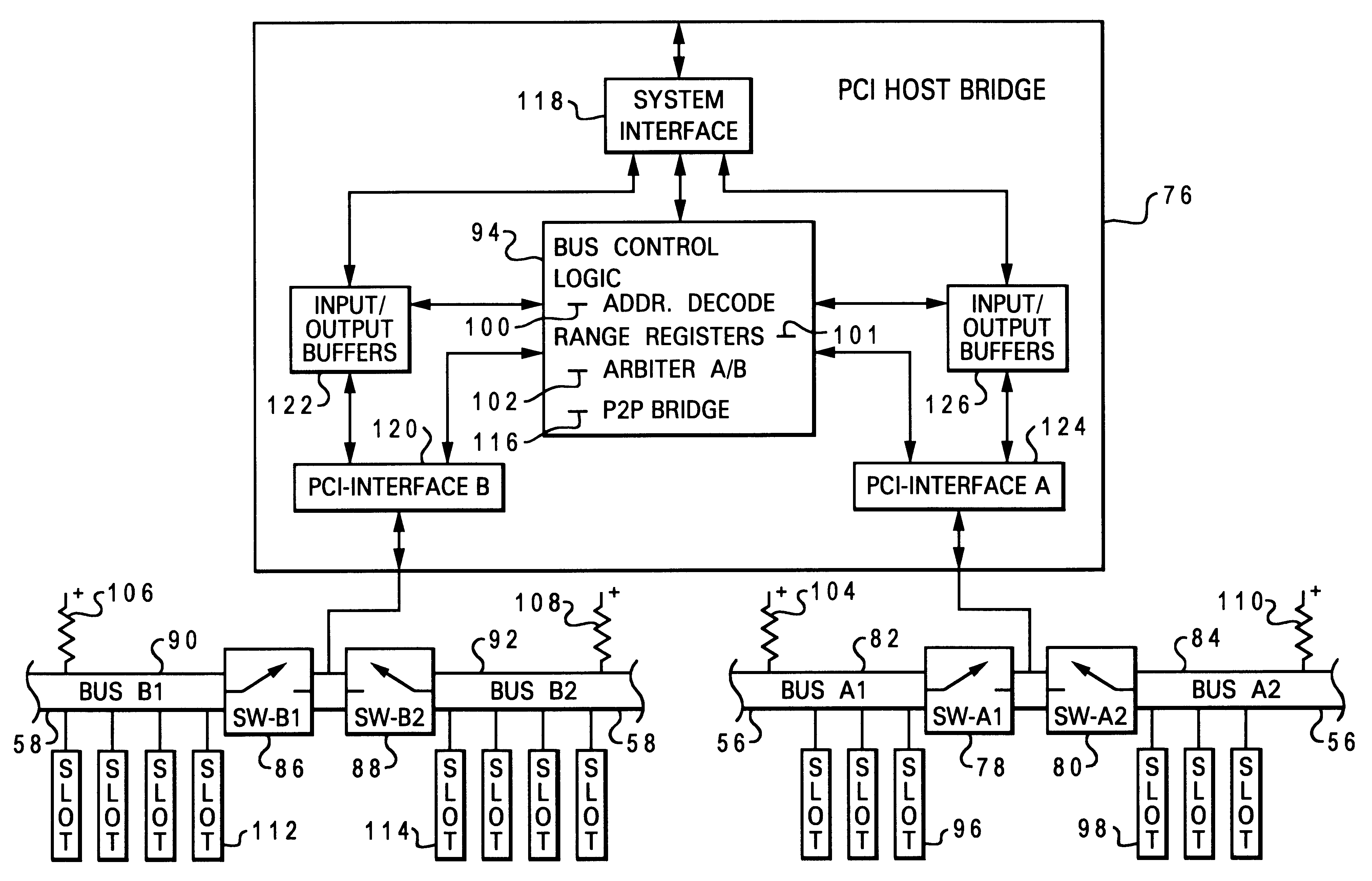

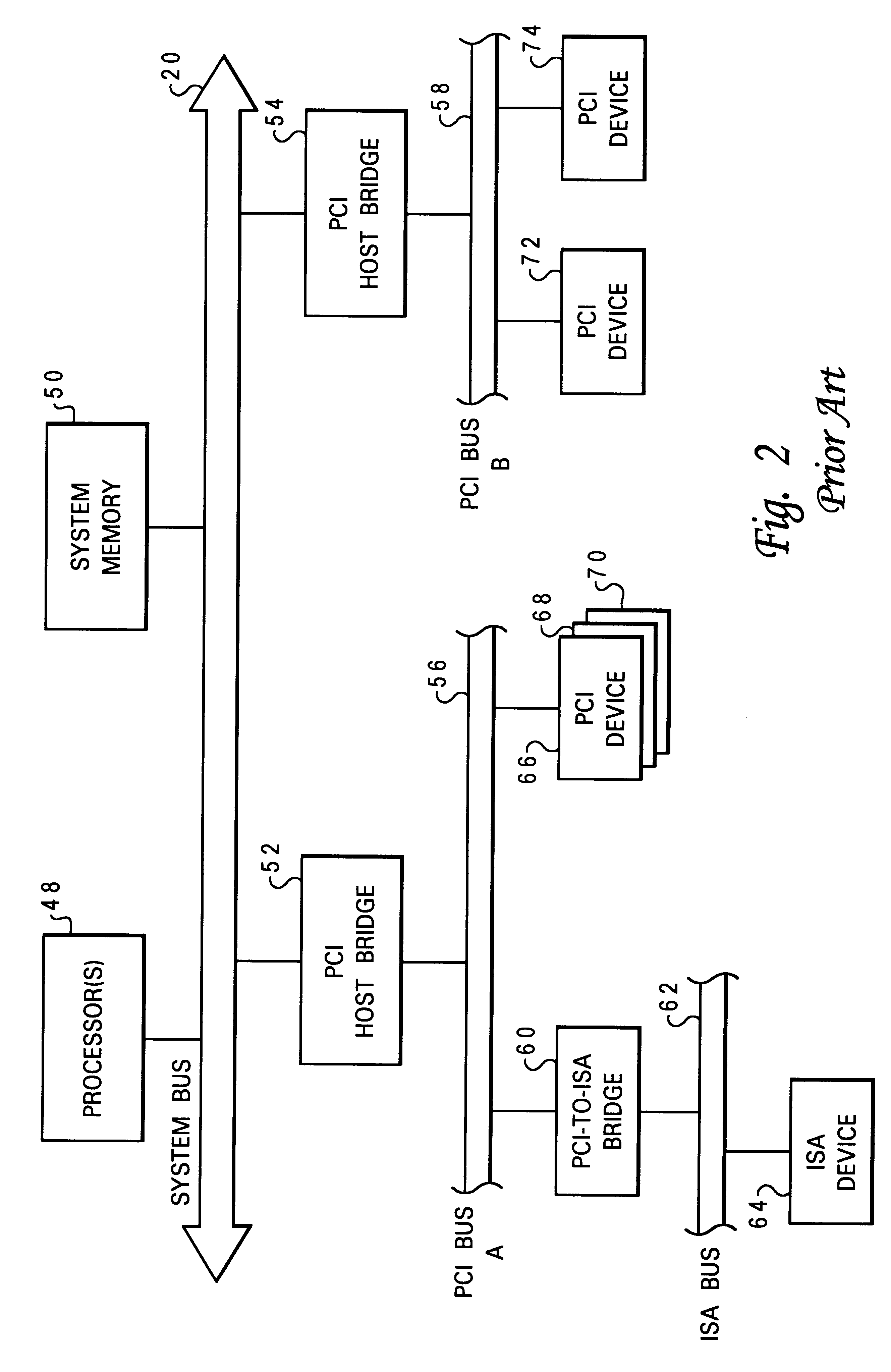

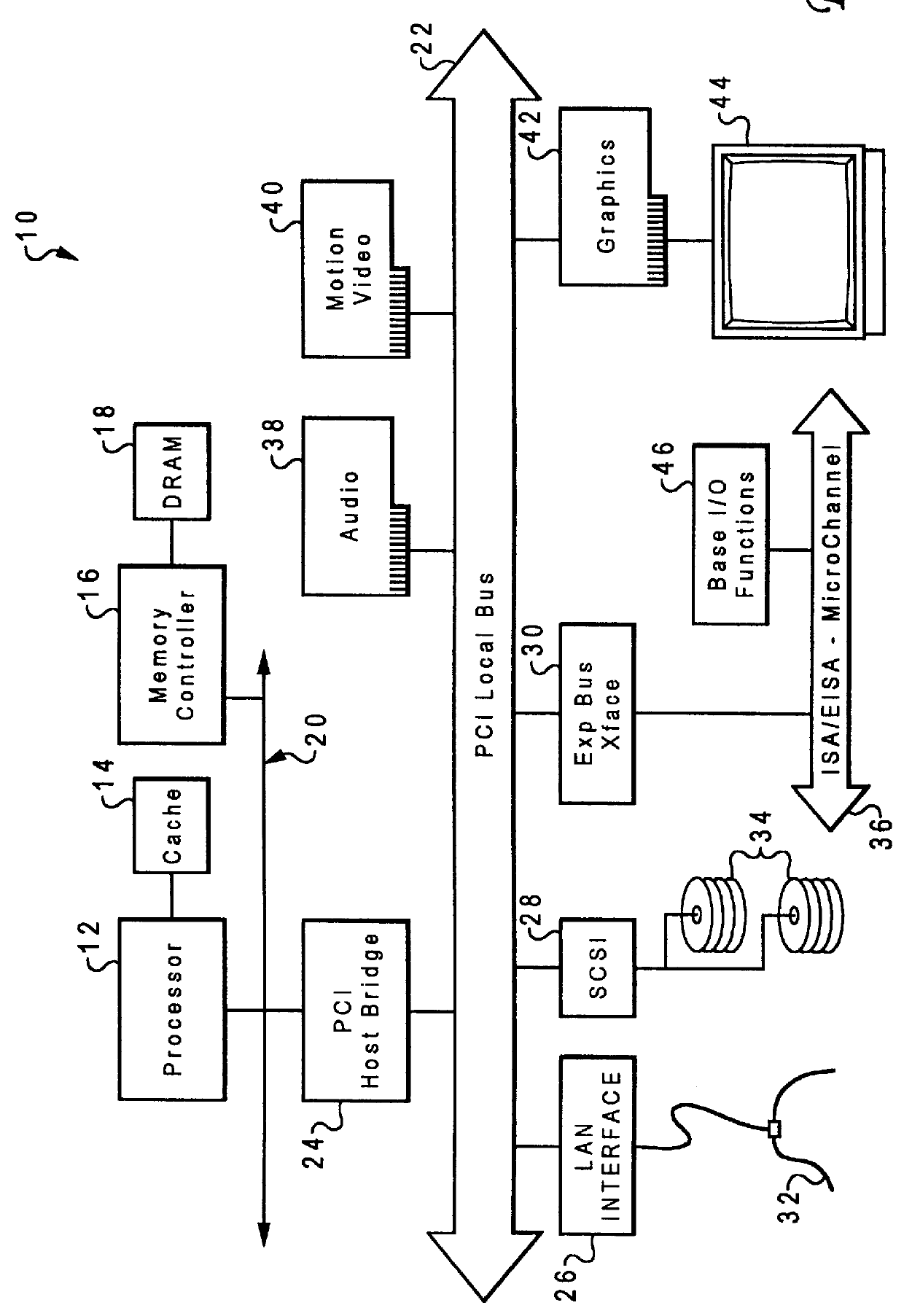

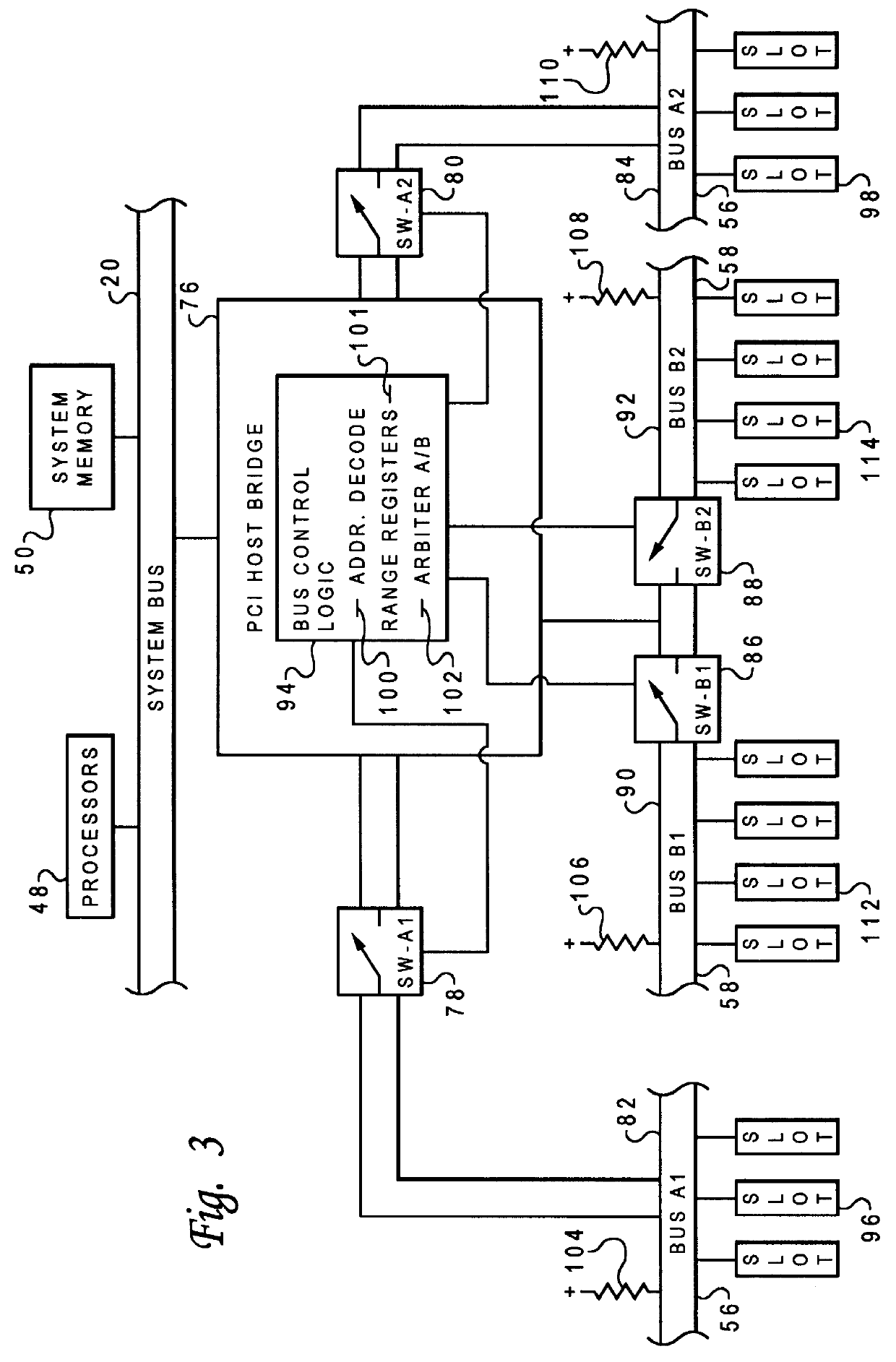

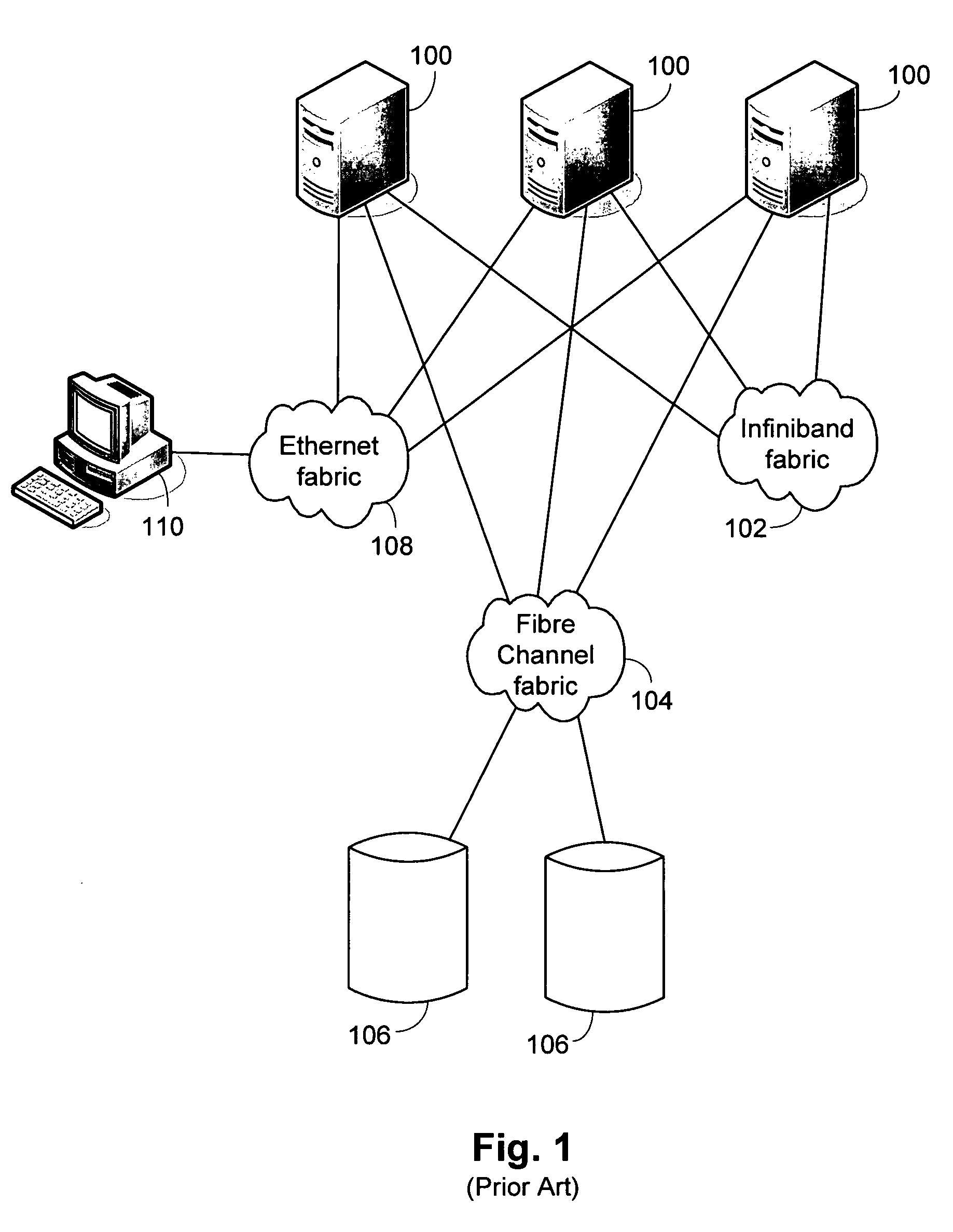

A method and system for supporting multiple Peripheral Component Interconnect (PCI) local buses through a single PCI host bridge having multiple PCI interfaces within a data-processing system are disclosed. In accordance with the method and system of the present invention, a processor and a system memory are connected to a system bus. First and second PCI local buses are connected to the system bus through a PCI host bridge. The first and second PCI local buses have sets of in-line electronic switches, dividing the PCI local buses into PCI local bus segments supporting a plurality of PCI peripheral component slots for connecting PCI devices. The sets of in-line electronic switches are open and closed in accordance with bus control logic within the PCI host bridge allowing up to fourteen or more PCI peripheral component slots for connecting up to fourteen PCI devices to have access through a single PCI host bridge to the system bus. An internal PCI-to-PCI bridge is provided to allow a PCI device to share data with another PCI device as peer-to-peer devices across the first and second PCI local bus segments.

Owner:IBM CORP

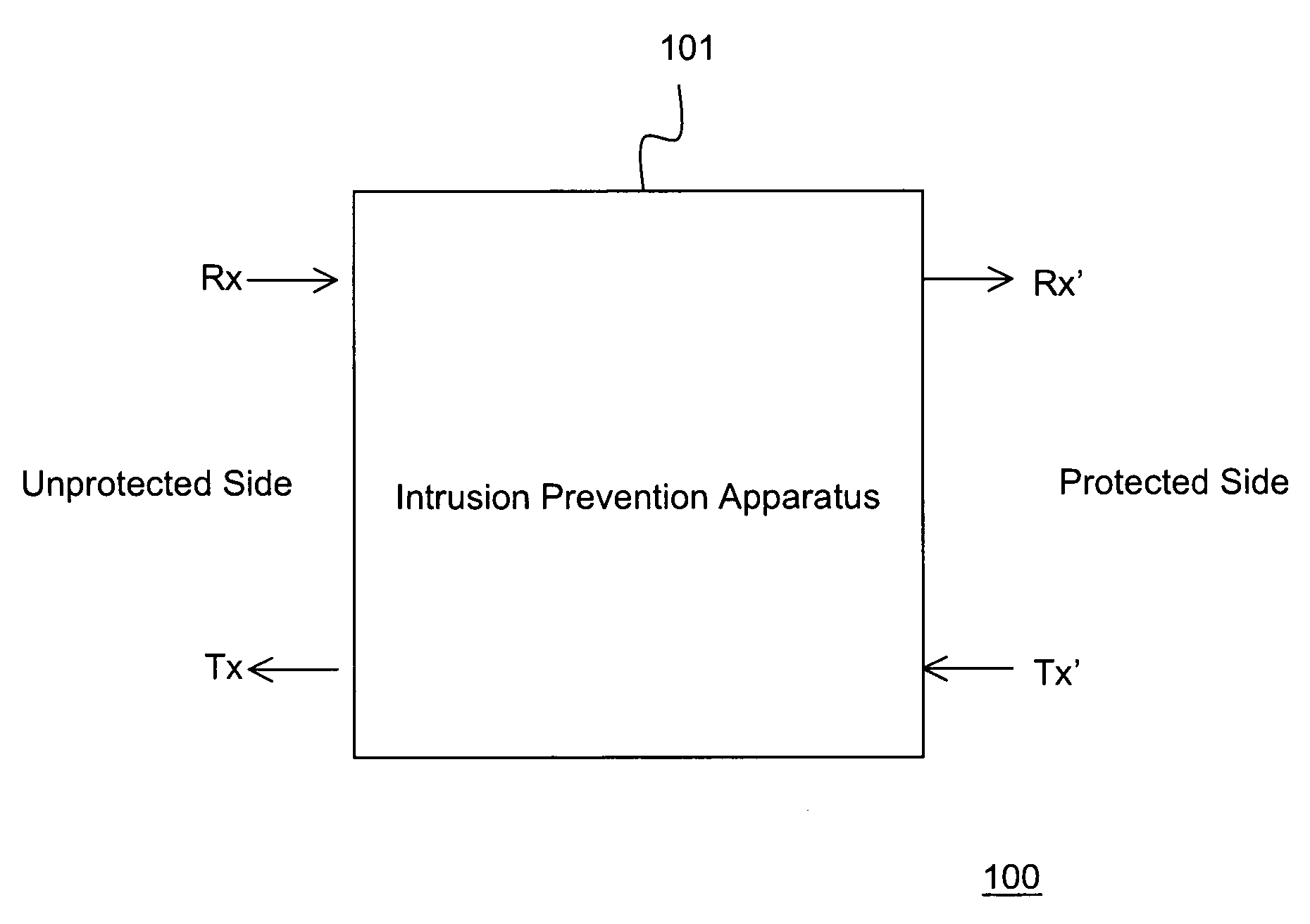

Method and apparatus for rate based denial of service attack detection and prevention

ActiveUS7426634B2Easy to detectIncrease blockingMemory loss protectionError detection/correctionMultiplexingPci interface

The present invention provides a method and apparatus for detecting and preventing a plurality of denial of service (DOS) and distributed denial of service (DDOS) attacks. The apparatus includes classifiers for parsing packets; meters storing statistics for the classified packets and detecting flood thresholds; an Ager for maintaining timeouts; a decision multiplexer for multiplexing inputs from various meters and determines whether to allow or deny the packet; and a threshold estimation means for estimating thresholds based on past data from meters, baselines, trends and seasonality. The apparatus includes a PCI interface through which a host can interact, learn continuously and set thresholds in a continuous and adaptive manner so as to prevent rate based DOS and DDOS attacks. The apparatus includes a mechanism to track culprit sources at layer 2 and layer 3 through a multiplicative increment method.

Owner:FORTINET

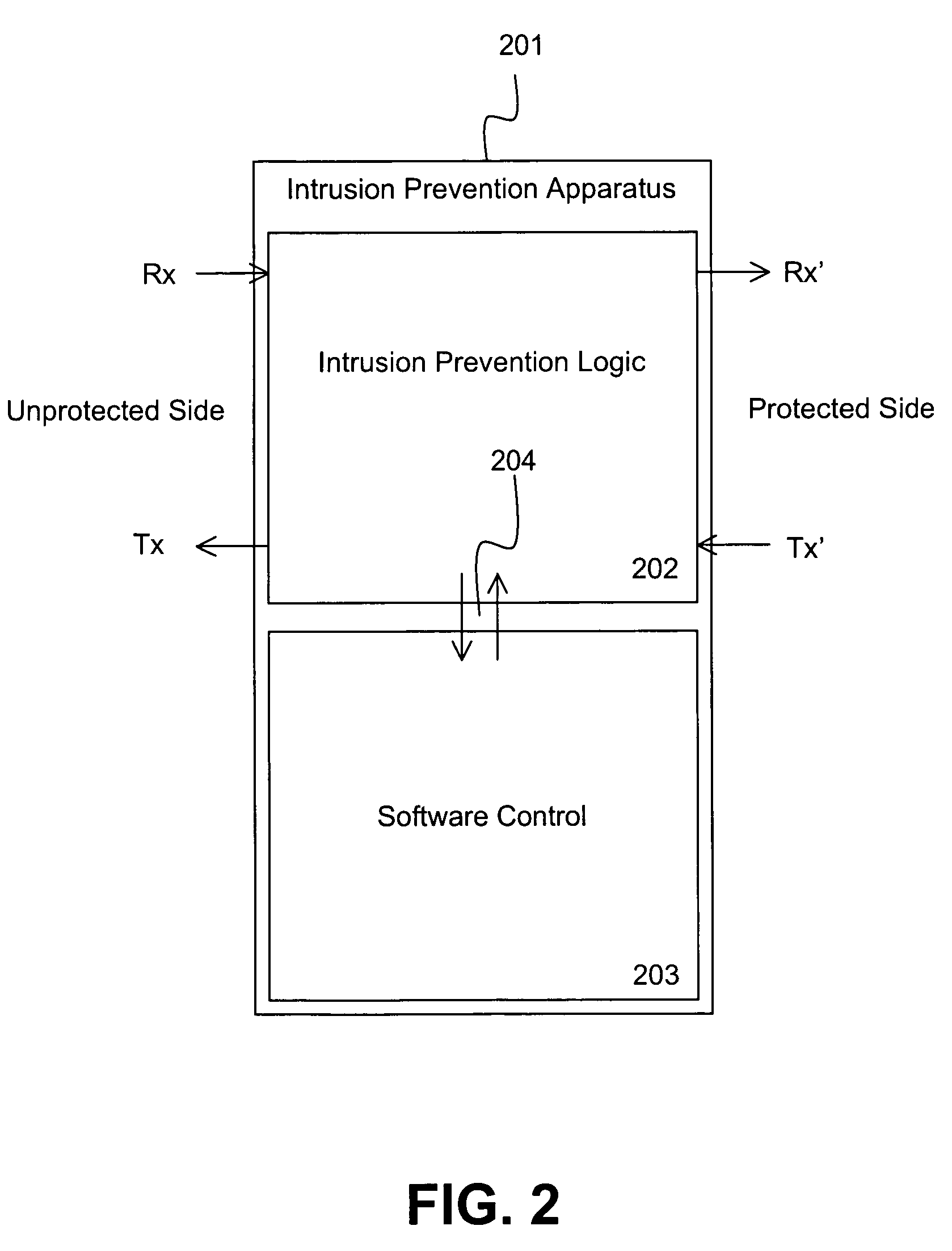

Secure one-way data transfer using communication interface circuitry

ActiveUS8068415B2Error preventionFrequency-division multiplex detailsCommunication interfacePci interface

Owner:OWL CYBER DEFENSE SOLUTIONS LLC

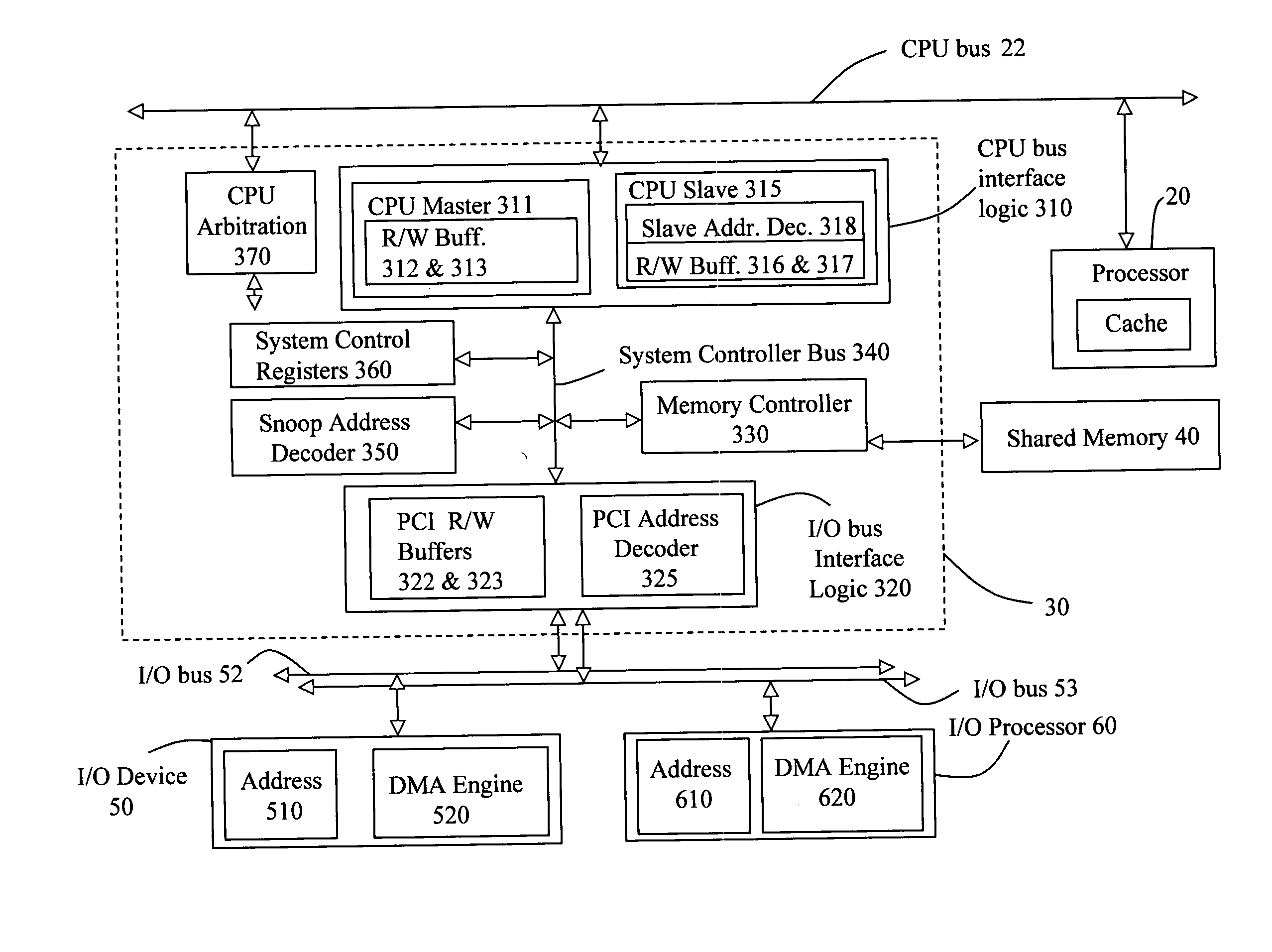

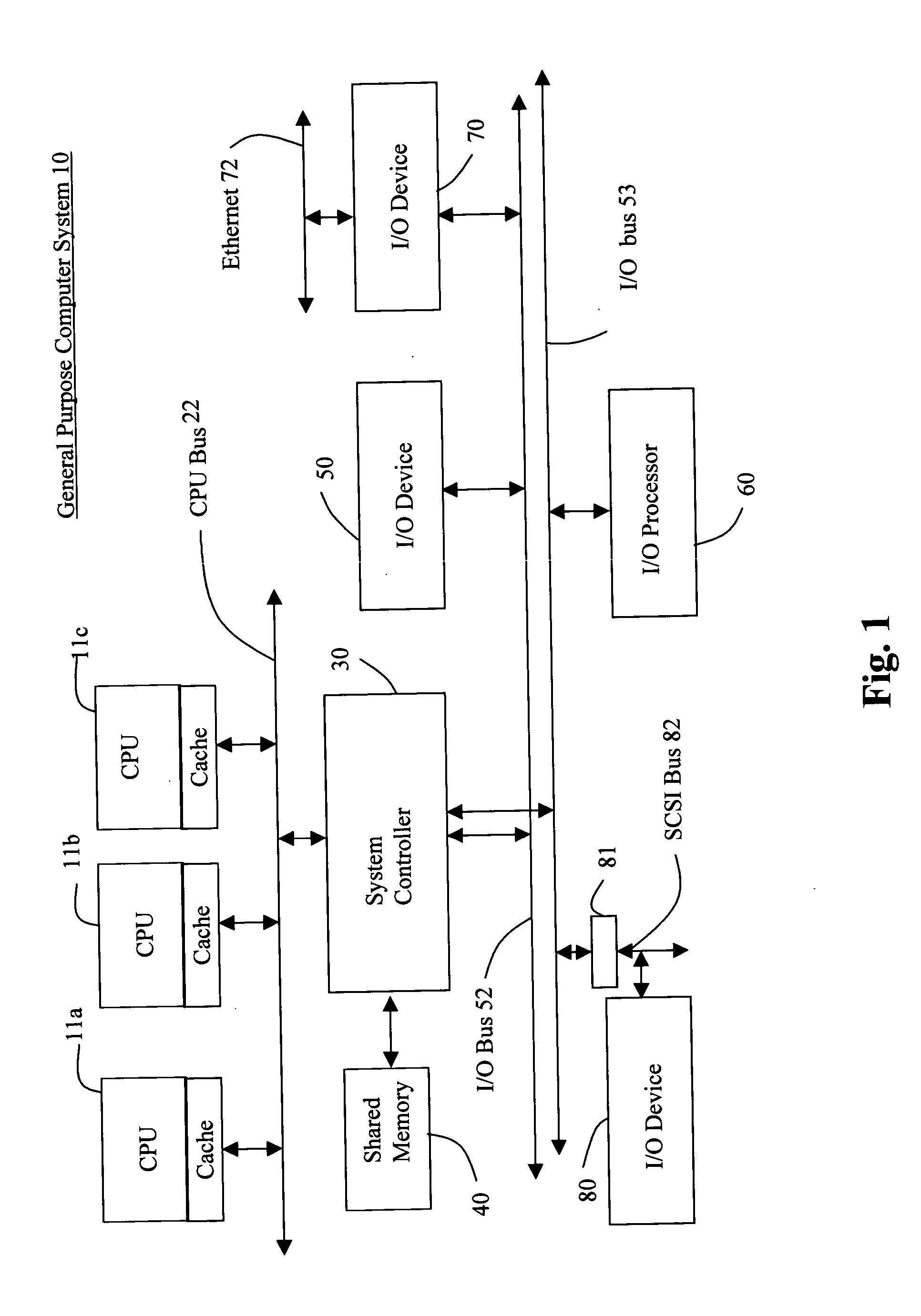

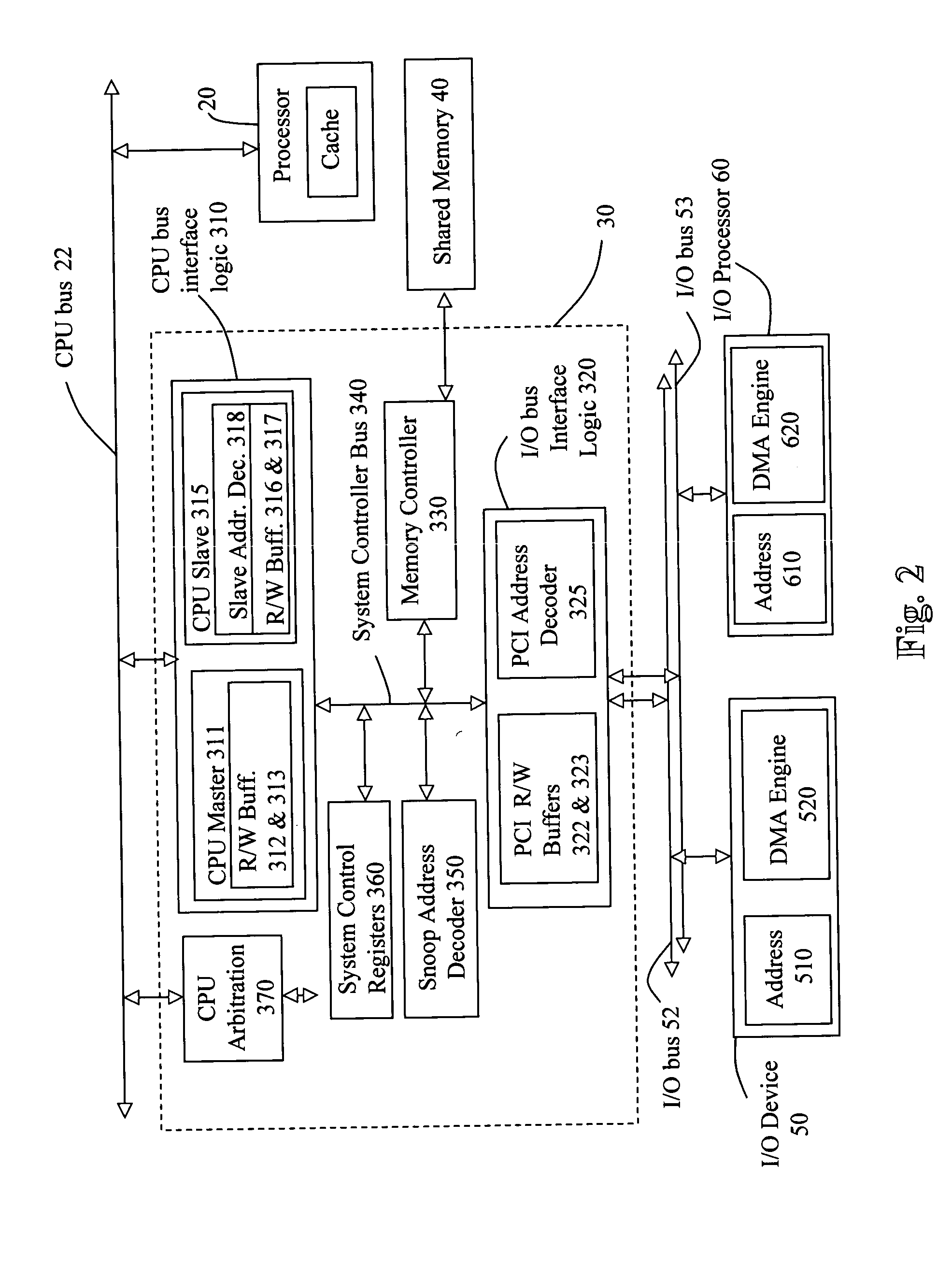

Method for efficiently processing DMA transactions

InactiveUS20050114559A1High data rateEfficient use ofMemory adressing/allocation/relocationMemory addressProcessing type

The data rate at which DMA transactions are processed by a General Purpose Computer System can be significantly improved by directing housekeeping type transactions directly to the CPU bus and by directing data type transactions directly to Shared Memory. By assigning memory address ranges to particular I / O devices and by programming PCI Interface Logic on a System Controller to detect these ranges and to direct DMA requests directly to either the CPU bus or to the Memory Controller depending upon the address range detected, the speed with which DMA transactions can be processed is enhanced.

Owner:MILLER GEORGE B

Method and system for supporting multiple peripheral component interconnect PCI buses by a single PCI host bridge within a computer system

A method and system for supporting multiple Peripheral Component Interconnect (PCI) local buses through a single PCI host bridge having multiple PCI interfaces within a data-processing system are disclosed. In accordance with the method and system of the present invention, a processor and a system memory are connected to a system bus. First and second PCI local buses are connected to the system bus through a PCI host bridge. The first and second PCI local buses have sets of in-line electronic switches, dividing the PCI local buses into PCI local bus segments supporting a plurality of PCI peripheral component slots. The sets of in-line electronic switches are open and closed in accordance with bus control logic within the PCI host bridge allowing up to fourteen PCI peripheral component slots to have access through a single PCI host bridge to the system bus.

Owner:GOOGLE LLC

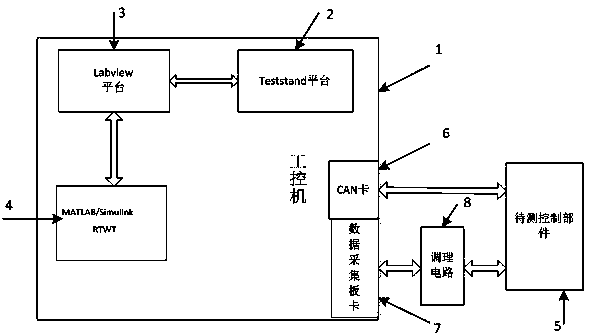

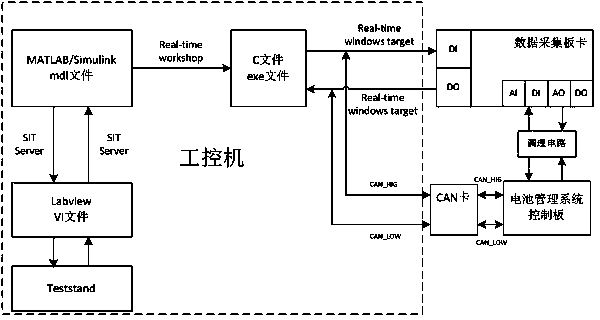

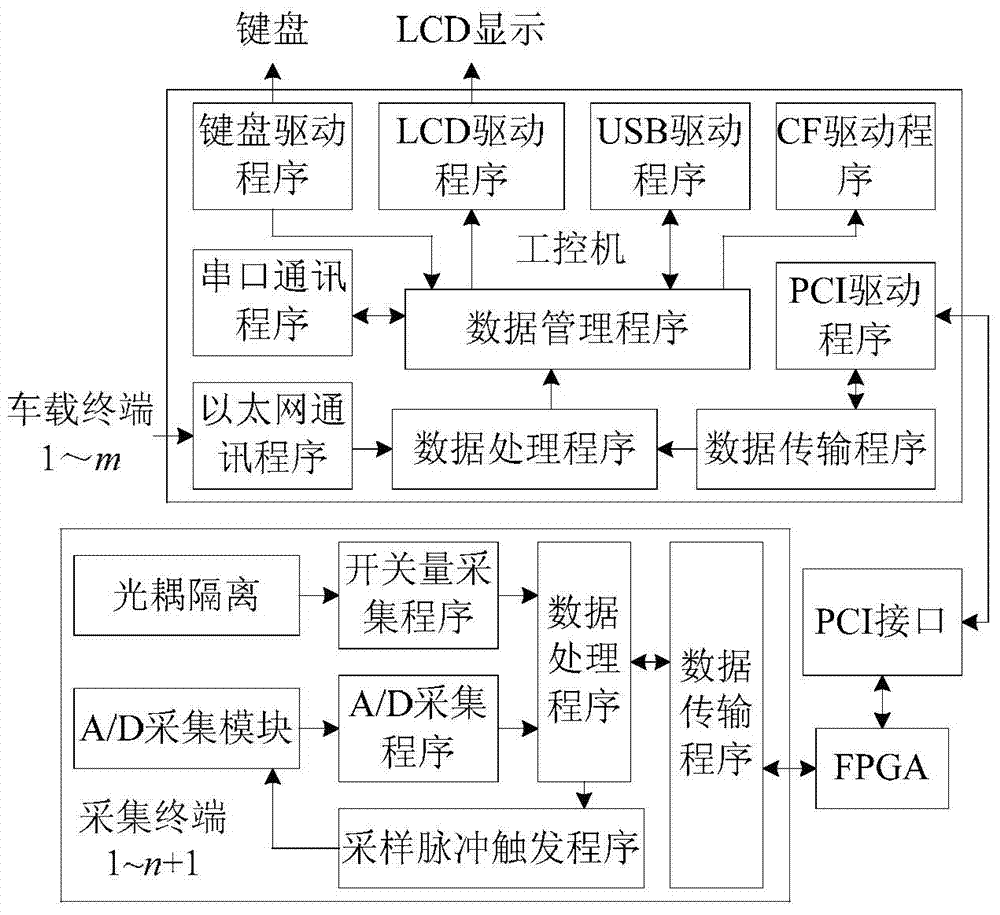

Hardware-in-loop simulation testing system and testing method for automobile

ActiveCN104062969ATake up less resourcesLow costElectric testing/monitoringComputer hardwareLabview software

The invention discloses a hardware-in-loop simulation testing system for an automobile, and the system comprises an industrial control computer, a to-be-tested controller part, a data collection card of a PCI bus type, a CAN card of a PCI interface, and a signal conditioning circuit. The industrial control computer is provided with a MATLAB / Simulink software platform and a Labview software and Teststand software platform. The industrial control computer communicates with the to-be-tested controller part through the data collection card and the CAN card. The testing system occupies fewer resources, is low in cost, is simple in configuration, and is convenient and practical. One industrial control computer not only can achieve a function of real-time simulation of a target machine, but also can achieve a function of controlling and checking of a monitoring interface of an upper computer. The testing system achieves on-line adjusting of parameters and data recording. A testing method is high in speed of operation and is wide in range of application, and a driver with various types of data collection cards can be supplied to a user.

Owner:清华大学苏州汽车研究院(吴江)

System and method for coupling peripheral buses through a serial bus using a split bridge implementation

A Wide Area Serial PCI system for connecting peripheral devices to a computer. The WASP system includes a host computer system connected through a serial bus to a remote device. The serial bus can range from several meters to several kilometers or more. The host computer system includes a CPU and memory, and also includes a first Peripheral Component Interconnect (PCI) bus, also referred to as the local PCI bus. A primary bridge according to the present invention is coupled to the first PCI bus. The primary bridge includes PCI interface circuitry for interfacing to the first PCI bus. The remote device is located remotely from the computer system and comprises a second or remote PCI bus and one or more peripheral devices coupled to the second PCI bus. The remote device also includes a secondary bridge coupled to the second PCI bus. The secondary bridge includes PCI interface circuitry for interfacing to the second PCI bus. The serial bus is coupled between the primary bridge and the secondary bridge. Each of the primary bridge and secondary bridge include parallel / serial transceivers for converting parallel data generated on the first PCI bus and second PCI bus, respectively, to serial data for transmission on the serial bus and for converting serial data received from the serial bus to parallel data for generation on the first PCI bus and second PCI bus, respectively. The primary bridge and the secondary bridge collectively implement a PCI-PCI bridge register set.

Owner:NATIONAL INSTRUMENTS

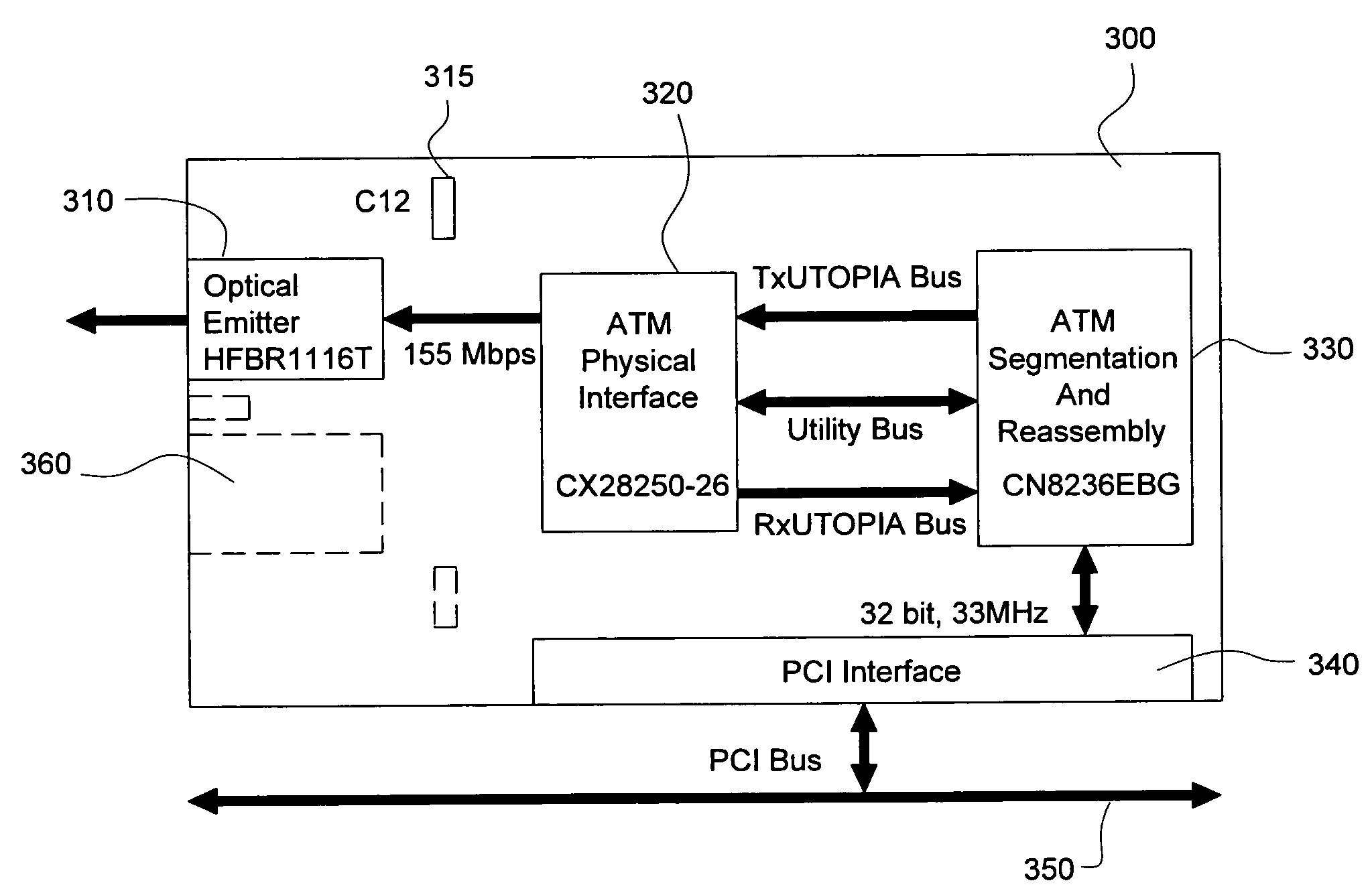

Secure one-way data transfer system using network interface circuitry

Network interface circuitry for a secure one-way data transfer from a sender's computer (“Send Node”) to a receiver's computer (“Receive Node”) over a data link, such as an optical fiber or shielded twisted pair copper wire communication cable, comprising send-only network interface circuitry for transmitting data from the Send Node to the data link, and receive-only network interface circuitry for receiving the data from the data link and transmitting the received data to the Receive Node, wherein the send-only network interface circuitry is configured not to receive any data from the data link, and the receive-only network interface circuitry is configured not to send any data to the data link. The network interface circuitry may use various interface means such as PCI interface, USB connection, FireWire connection, or serial port connection for coupling to the Send Node and the Receive Node.

Owner:OWL CYBER DEFENSE SOLUTIONS LLC

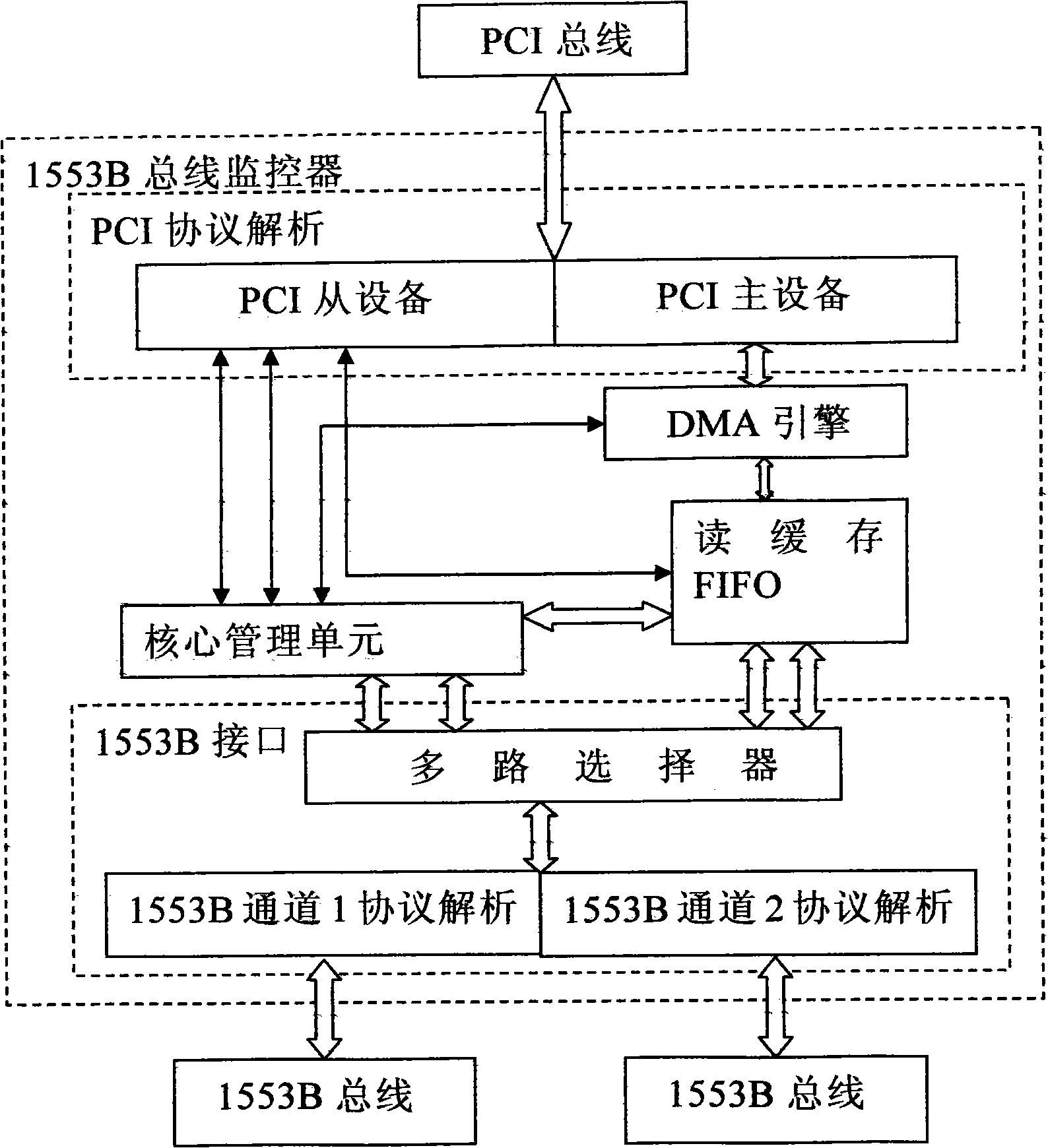

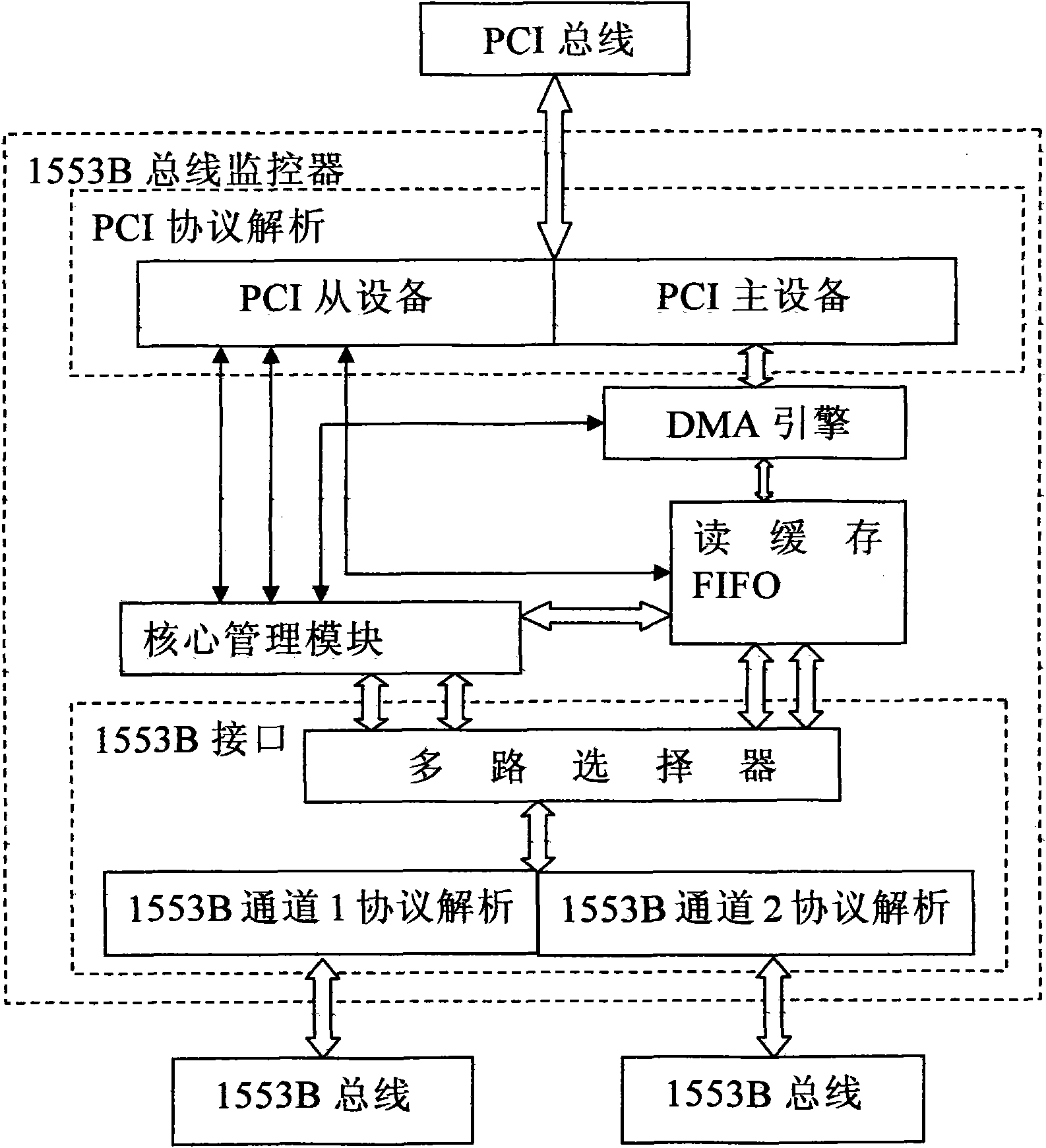

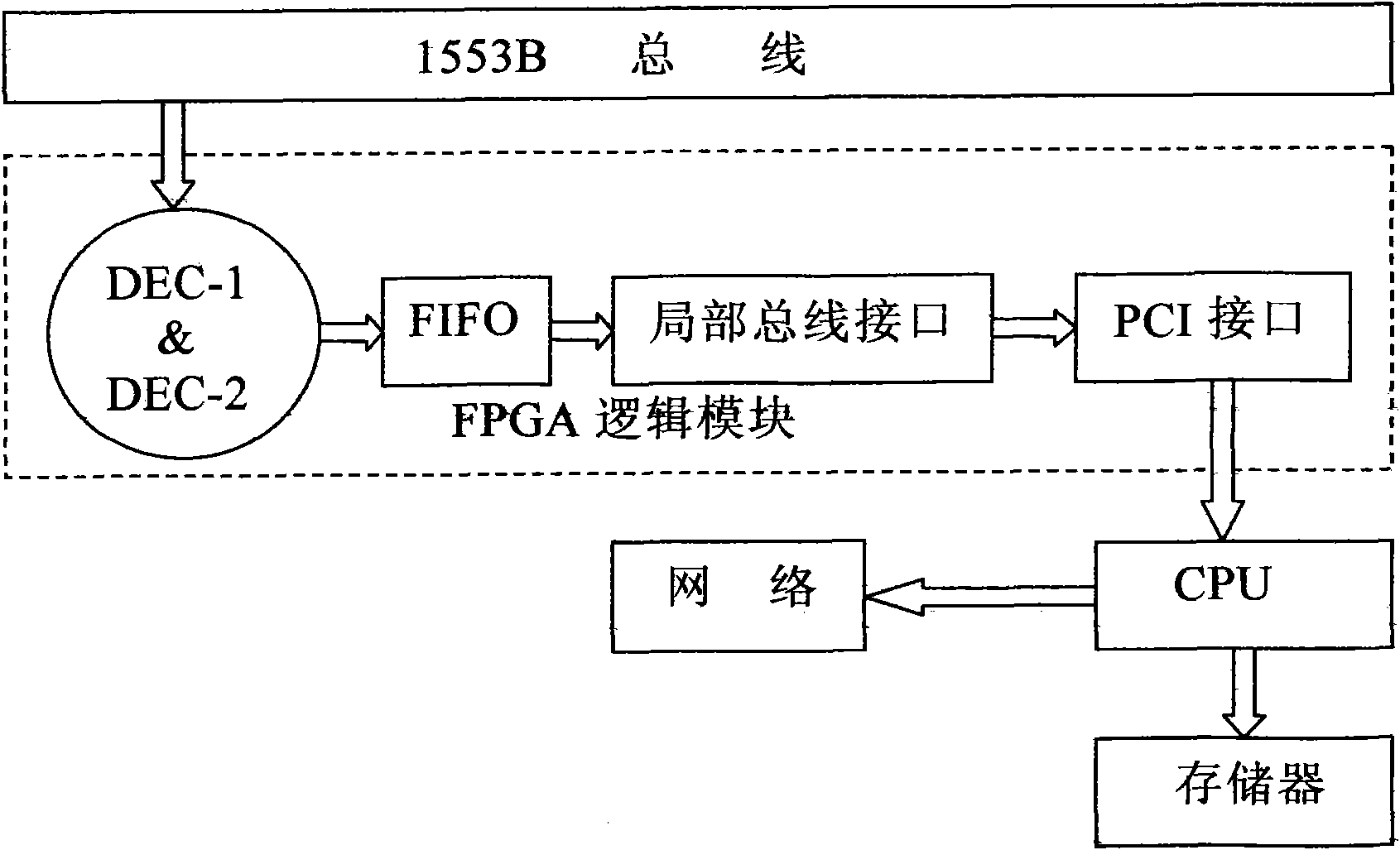

1553B bus monitor and bus system with same

ActiveCN101799795AEasy to mountImprove data transfer efficiencyElectric digital data processingBurst transmissionPci interface

The invention discloses a 1553B bus monitor. A local bus module of the 1553B bus monitor connected with a PCI bus comprises a PCI master equipment unit and a PCI slave equipment unit, wherein the PCI master equipment unit and the PCI slave equipment unit provide a 32-bit PCI interface together; the PCI slave equipment unit supports passive access; and the PCI master equipment unit realizes direct memory transmission and actively transmits data to memory space pre-allocated by a central processing unit (CPU). This invention also discloses a 1553B bus system with the 1553B bus monitor. The 32-bit 1553B bus monitor adopting PCI interface design can be conveniently hung to the PCI bus outside a microprocessor, has processing bandwidth of 32 bits, integrates DMA modules, can automatically initiate data transmission after CPU configuration, supports a BURST transmission mode, and greatly improves the efficiency of data transmission.

Owner:LOONGSON TECH CORP

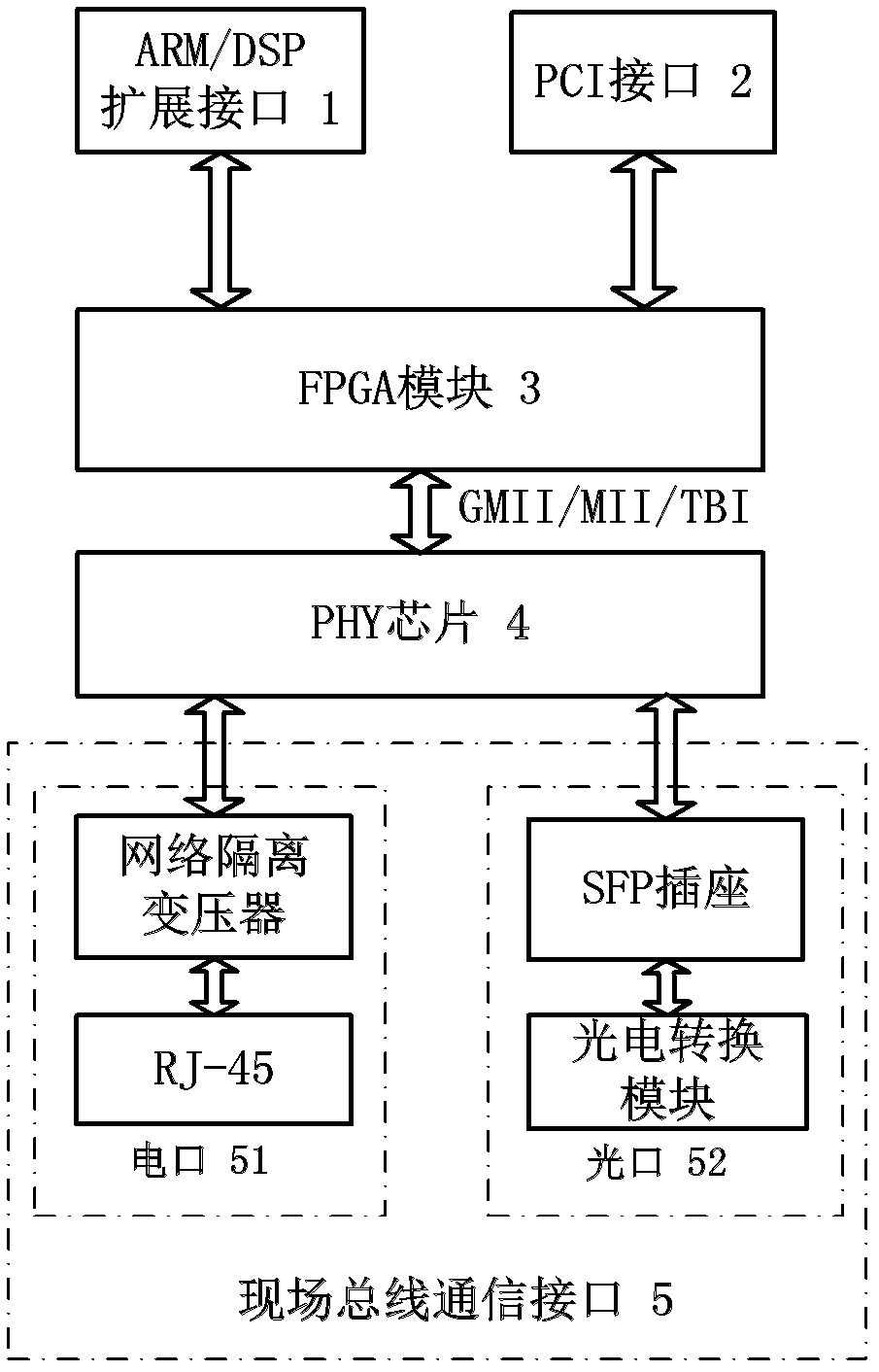

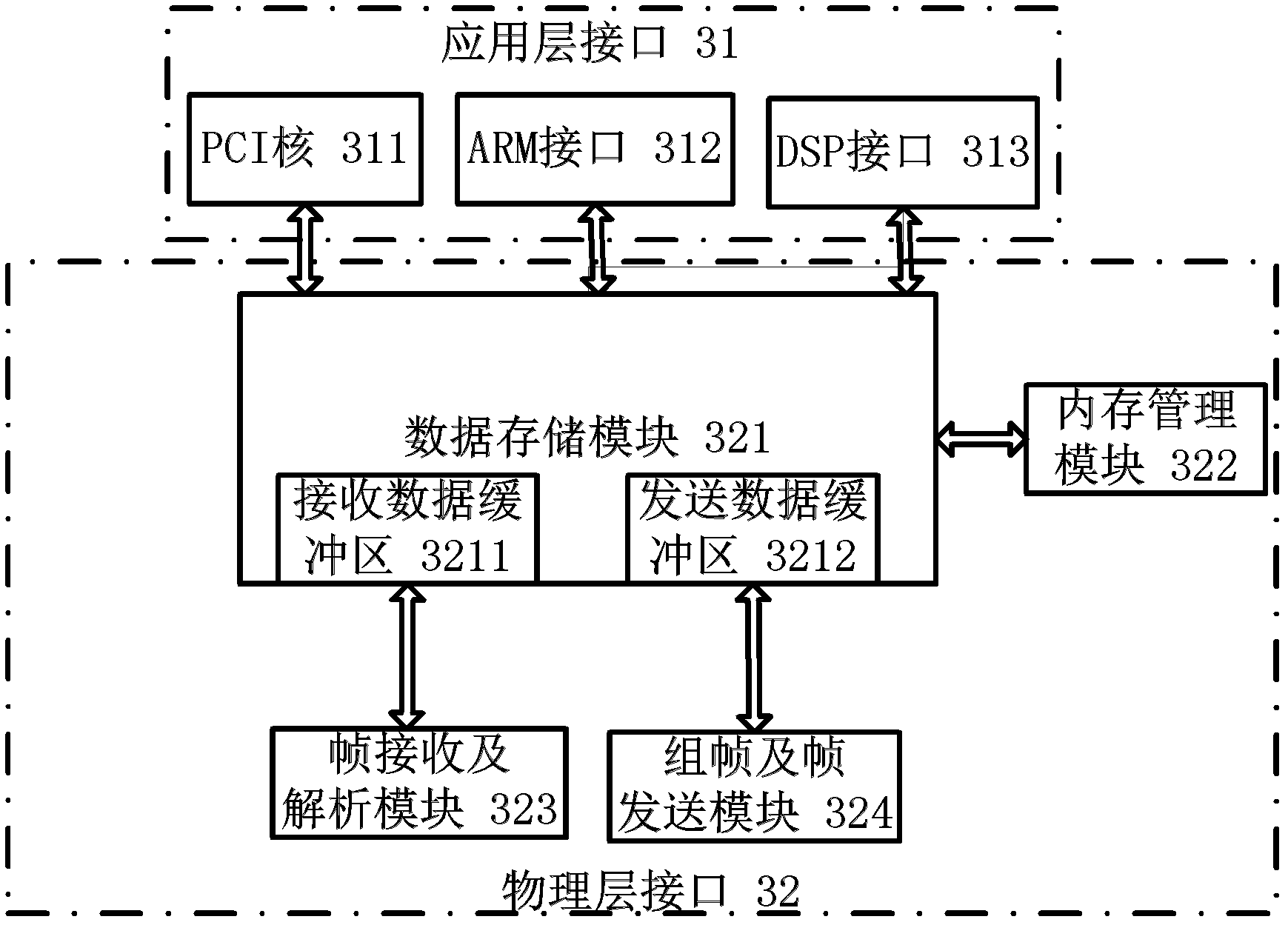

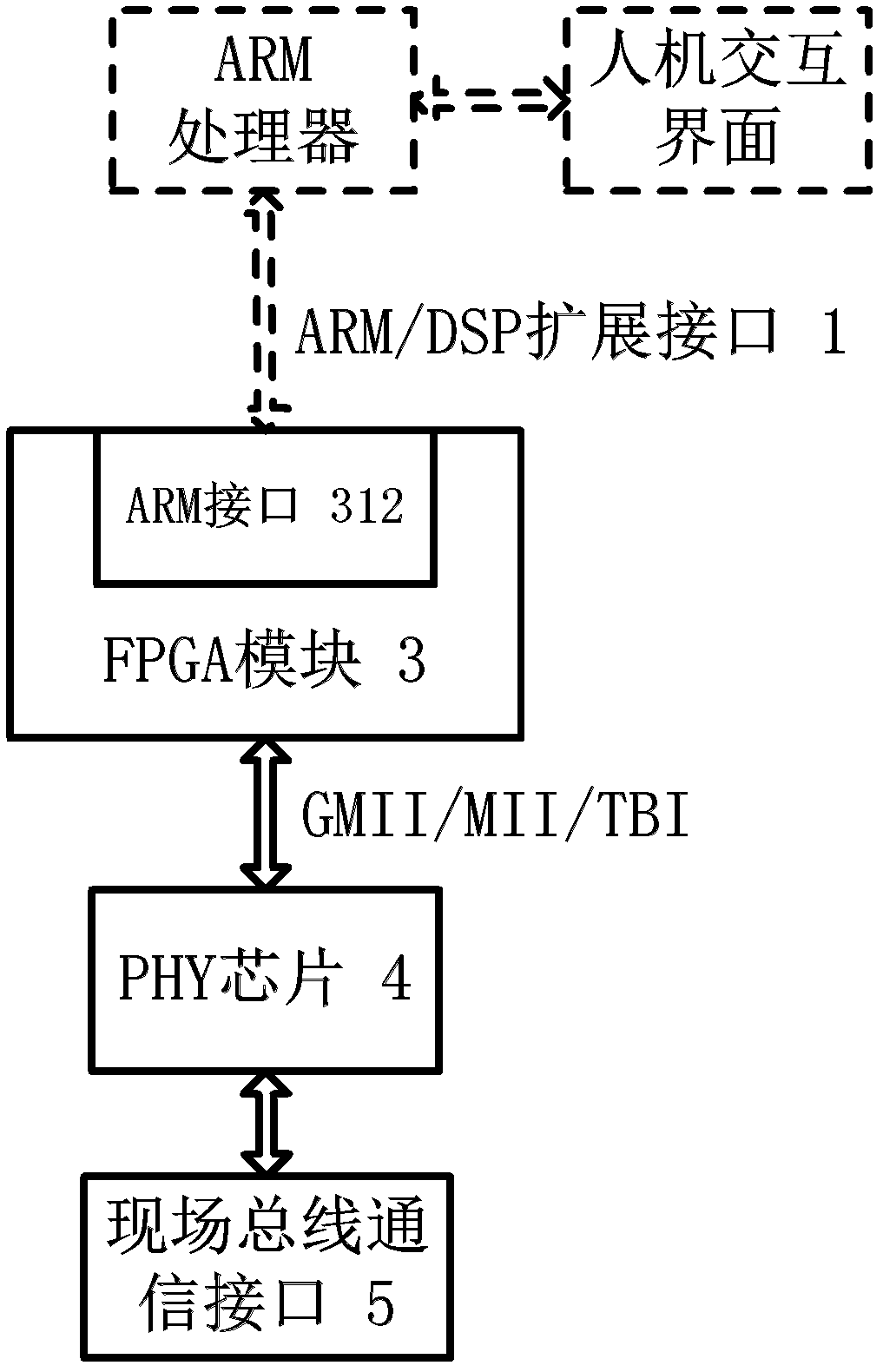

Gigabit Ethernet field bus communication device based on FPGA

InactiveCN102594627AReal time monitoringReal-time communicationBus networksCommunication interfaceSignal on

The invention discloses a gigabit Ethernet field bus communication device based on an FPGA (Field Programmable Gate Array). The device comprises an ARM (Asynchronous Response Mode) / DSP (Digital Signal Processor) expansion interface, an FPGA module, a PHY (Physical Layer) chip and a field bus communication interface and is characterized in that an electrical signal or an optical signal on a field bus is converted into a differential signal through a field bus interface; data is downloaded into the FPGA module through the gigabit PHY chip; and the FPGA module is used for receiving and analyzing the downloaded data and then transmitting the analyzed data to an ARM or a DSP connected with the ARM / DSP expansion interface through the ARM / DSP expansion interface for processing; the data processed by the ARM / DSP is packaged into a data frame by the FPGA module and is then converted into the differential signal through the gigabit PHY chip; and the differential signal is converted into the electrical signal or the optical signal through the field bus communication interface to be transmitted onto a the field bus. The gigabit Ethernet field bus communication device has the beneficial effects that the data transmission rate of 1000 Mbps can be realized, the communication with external equipment with the PCI (Peripheral Component Interconnect) interface can be realized, and different controllers can be externally connected according to the actual needs, the flexibility is high, and the gigabit Ethernet field bus communication device can be flexibly applied to real-time monitoring and communication of an industrial control field.

Owner:HUAZHONG UNIV OF SCI & TECH

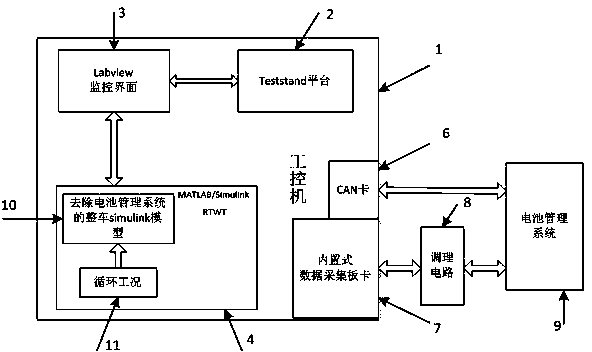

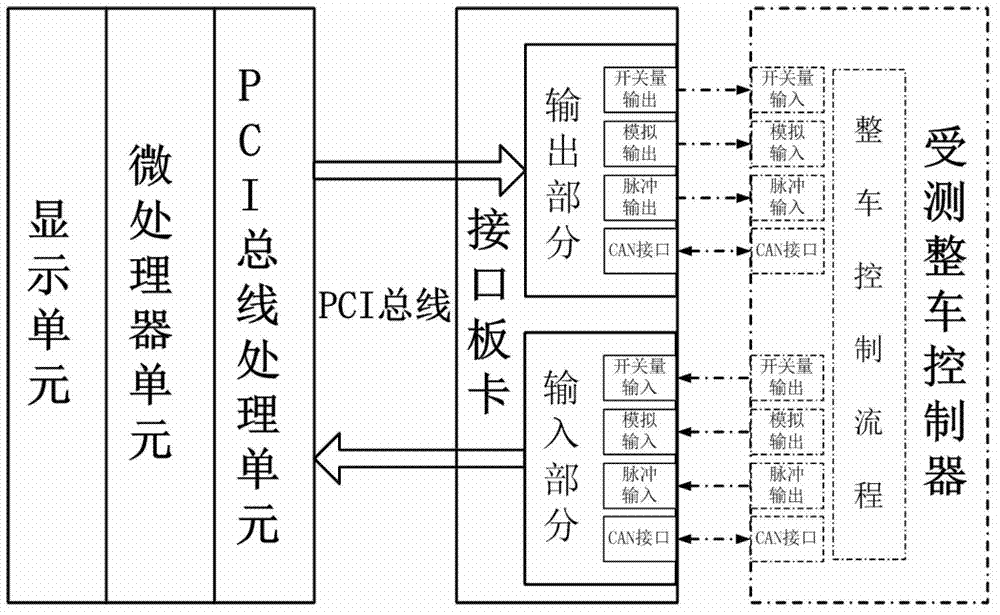

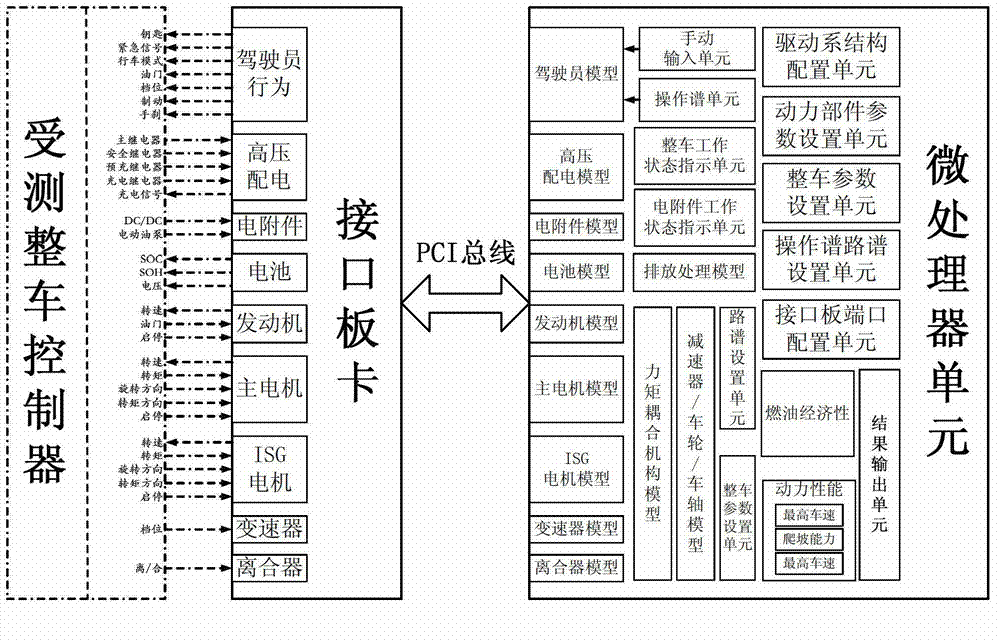

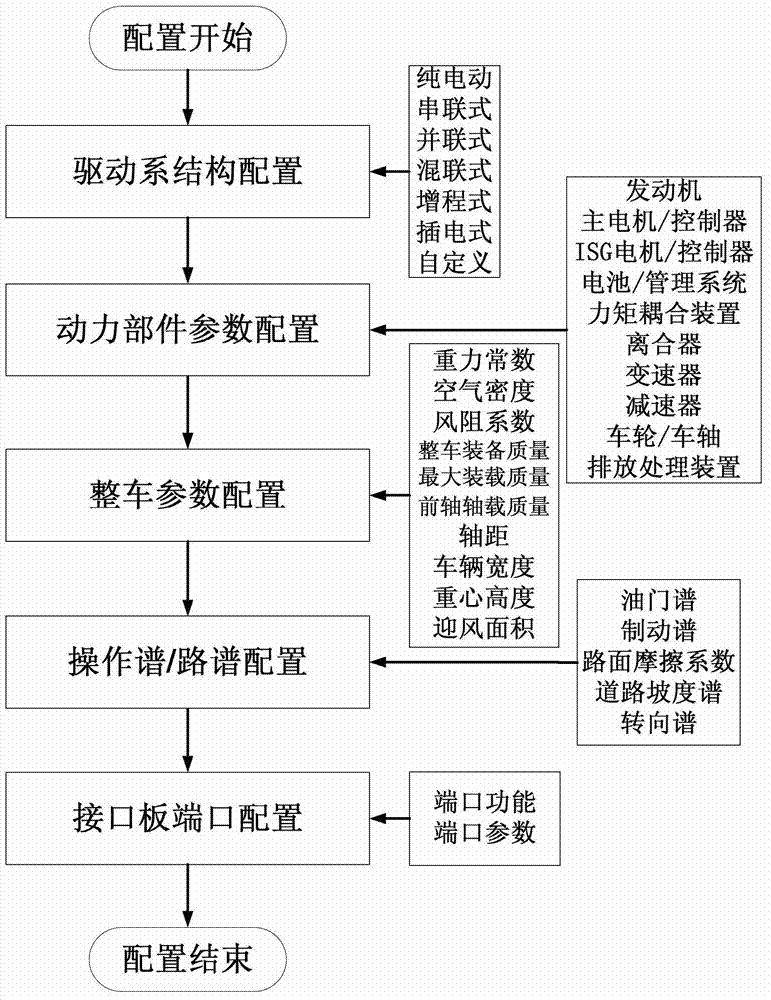

Device and method of simulation and testing of finished car controller of hybrid power car

ActiveCN103197667AImprove stabilityImprove reliabilityElectric testing/monitoringPci interfaceTest fixture

The invention discloses a device and a method of simulation and testing of a finished car controller of a hybrid power car. Due to the fact that a PCI interface and a micro processor are used for communication, the device of simulation and testing of the finished car controller of the hybrid power car has the advantages of being good in reliability, high in transmission rate of data, and good in extendibility. Due to the fact that a mathematical model of a power unit is used for simulating a working state of an actual power unit, cost of a system is greatly reduced. The device of simulation and testing of the finished car controller of the hybrid power car comprises a micro processor unit, a PCI bus processing unit, a display unit and an interface board card. The display unit and the PCI bus processing unit are respectively connected with the micro processor unit. The interface board card is connected with the PCI bus processing unit through a PCI bus. The interface board card is connected with the finished car controller to be detected. Therefore, configuration can be conveniently carried out on the structure of a finished car, relevant power unit parameters, an operation spectrum / a road spectrum, and port attributes of an interface board, and the system is good in generality. When the device and the method of simulation and testing of the finished car controller of the hybrid power car are used for testing a hybrid power finished car controller, a test period is shortened, test cost is reduced, and test results are good in stability and high in accuracy.

Owner:HUNAN UNIV

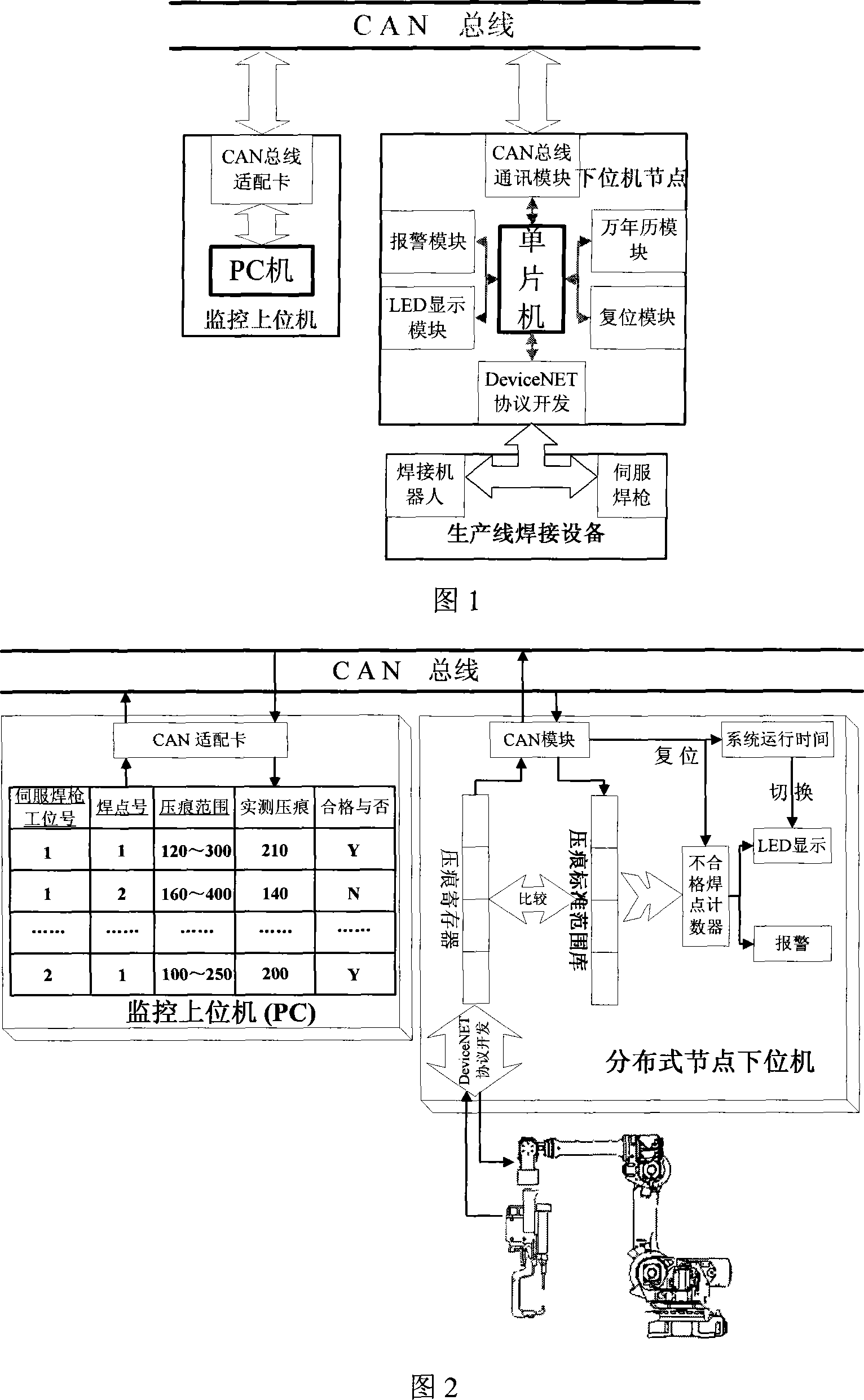

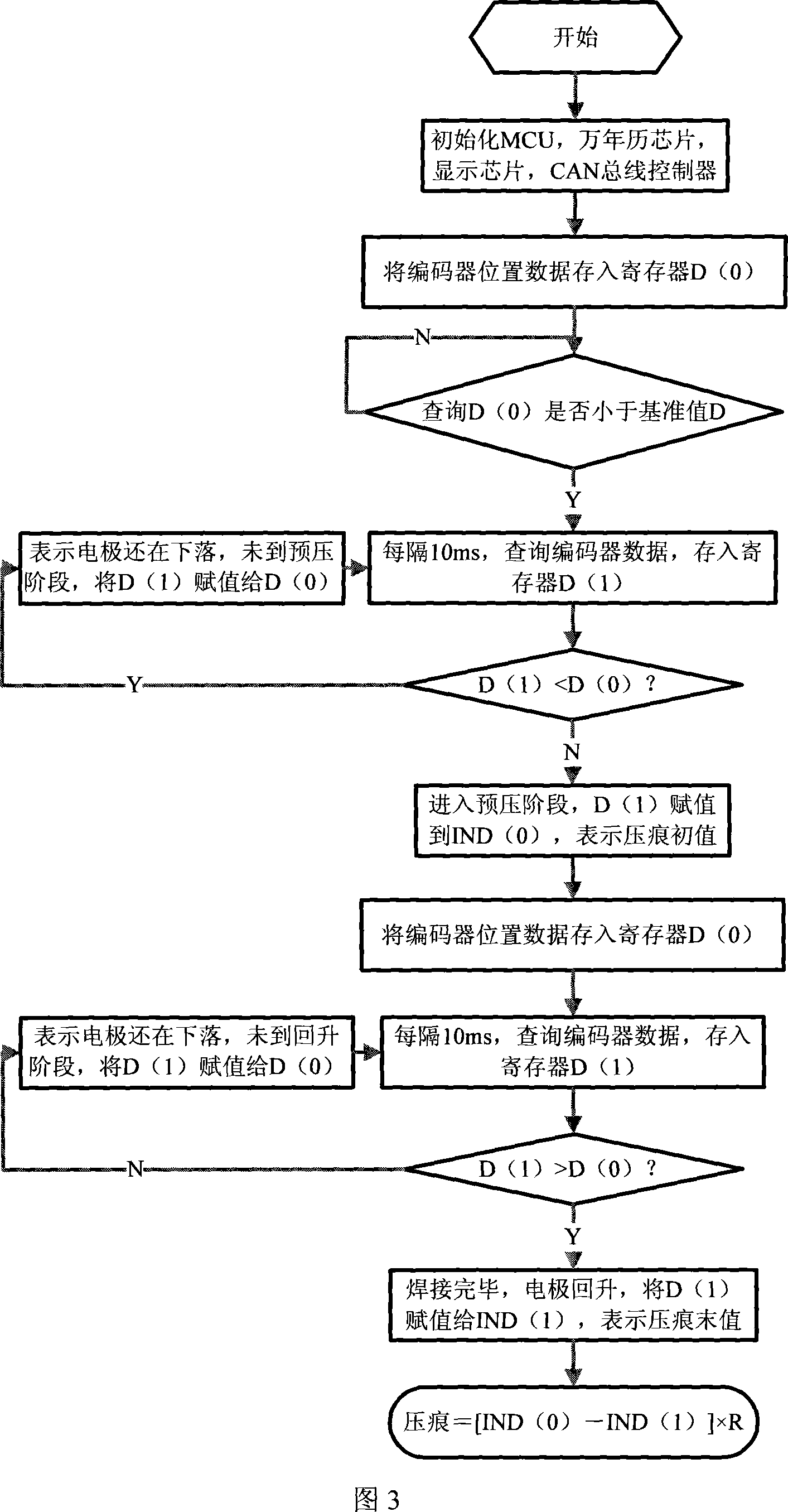

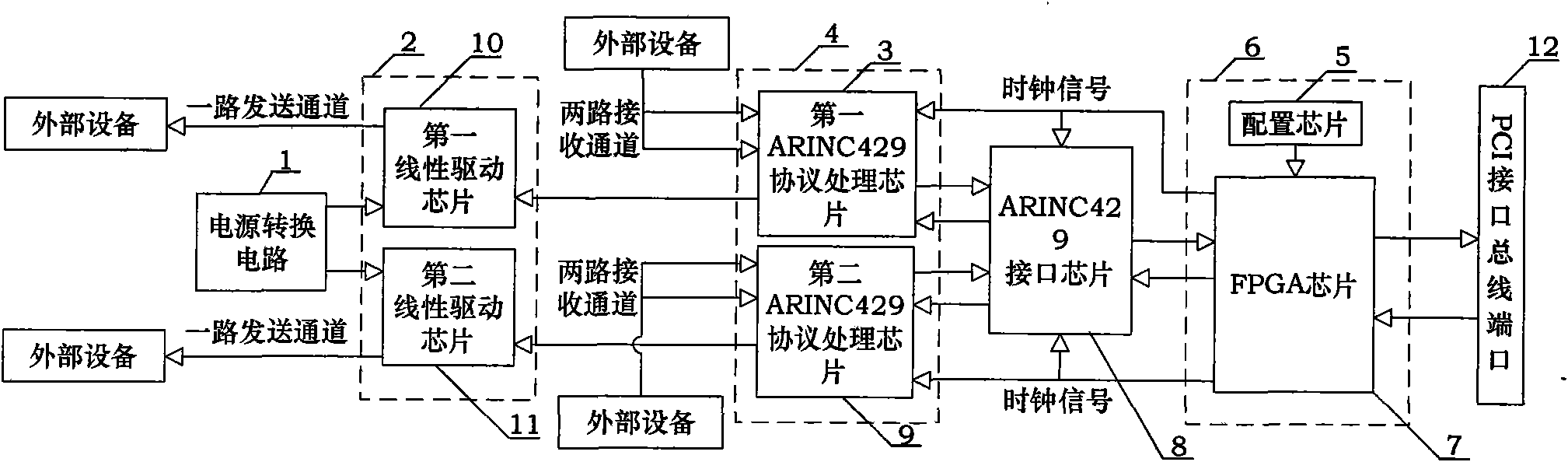

Distributed soldering point quality monitoring system and method

InactiveCN101226398AImprove reliabilityMeet transfer requirementsComputer controlSimulator controlPci interfaceSimulation

The invention relates to a distribution welding point quality detection system and a relative method, belonging to welding technical field. The system comprises a detection host computer, a controller local network bus and a distribution node lower computer, wherein the detection host computer comprises a PC and a controller local network bus communication adaptive card which are connected via a PCI interface, the controller local network bus communication adaptive card is connected with each distribution node lower computer via a controller local network bus. The inventive method comprises that each lower computer online real-time extracts the impression of welding point to be sent to the controller local network bus, the PC sends the welding point match change information caused by the change of servo welding gun position to a lower computer of relative ID number, real-time refreshes the standard base of the distribution node lower computer that judges the welding point, and returns the off-grade welding point counter. The inventive system and method have high reliability, strong bus correct function, better real-time property, remote transmission distance and better expansibility.

Owner:SHANGHAI JIAO TONG UNIV

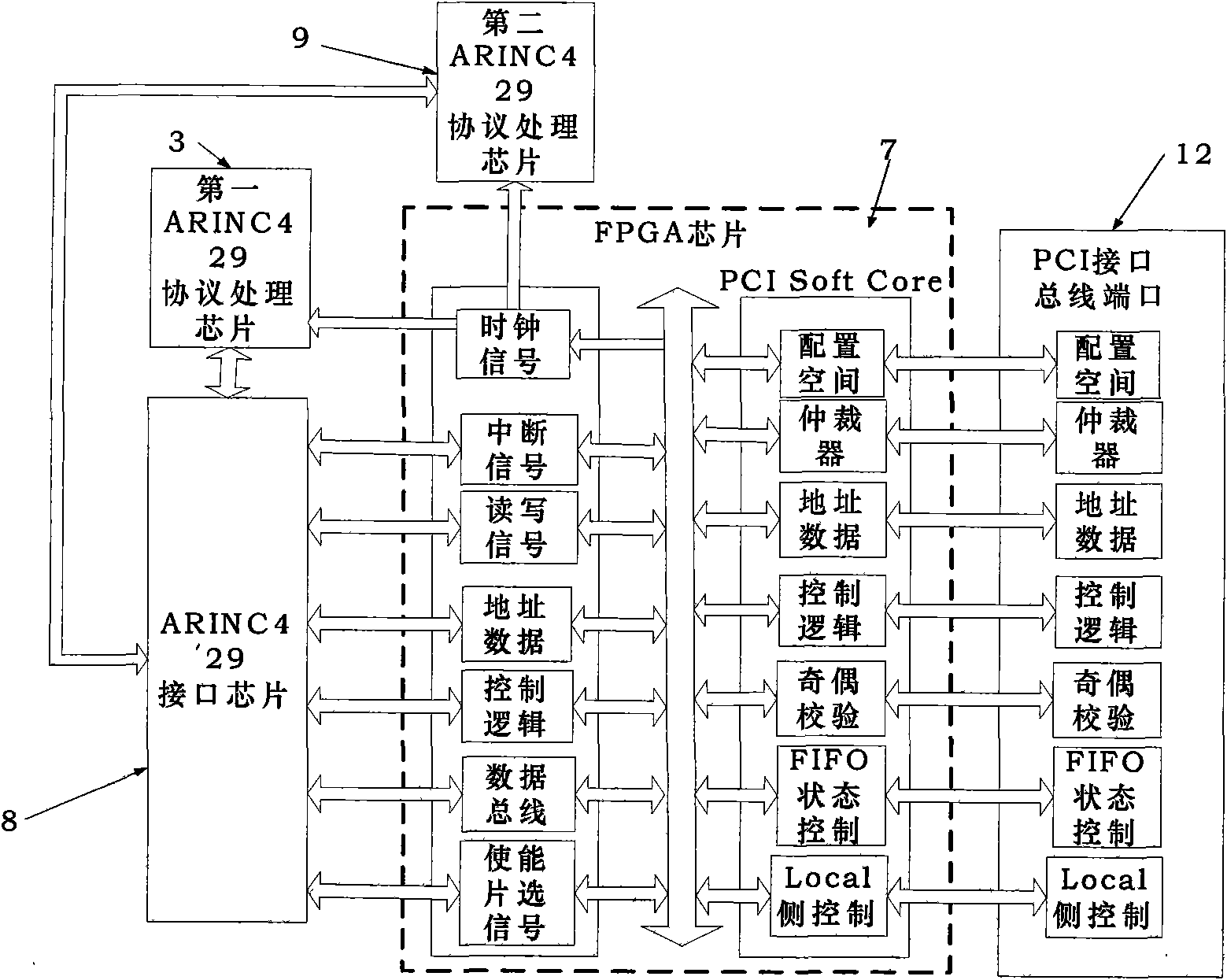

PCI integrated circuit board device used for ARINC429 communication

InactiveCN101571842ASimple structureIncrease flexibilityElectric digital data processingProtocol processingPci interface

The invention discloses a PCI integrated circuit board device used for ARINC429, mainly comprising an FPGA module, an ARINC429 interface chip, two ARINC429 protocol processing chips, two ARINC429 signal output linear drive chips and a power switching circuit. The FPGA chip is used for realizing PCI interface protocol and completing information interaction and control of a host computer and the board; the FPGA chip executes instruction of the host computer, initializes the ARINC429 interface chip and realizes control and caching of sending and receiving data to realize independent four receiving and two sending function and data sending rate adjustable function. The invention is flexible in configuration, the sending rate is adjustable and is wide in adjustable range, circuit construction is simple, processing cost of the circuit board is low, and different requirements of ARINC429 communication can be completed only by modifying FPGA software without changing hardware, thus the invention has strong commonality and flexibility.

Owner:BEIHANG UNIV

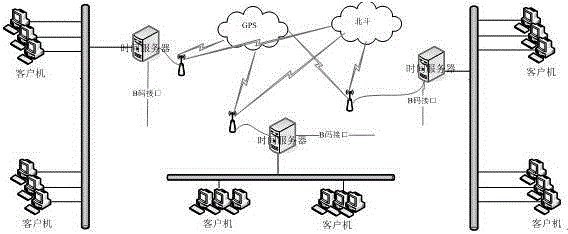

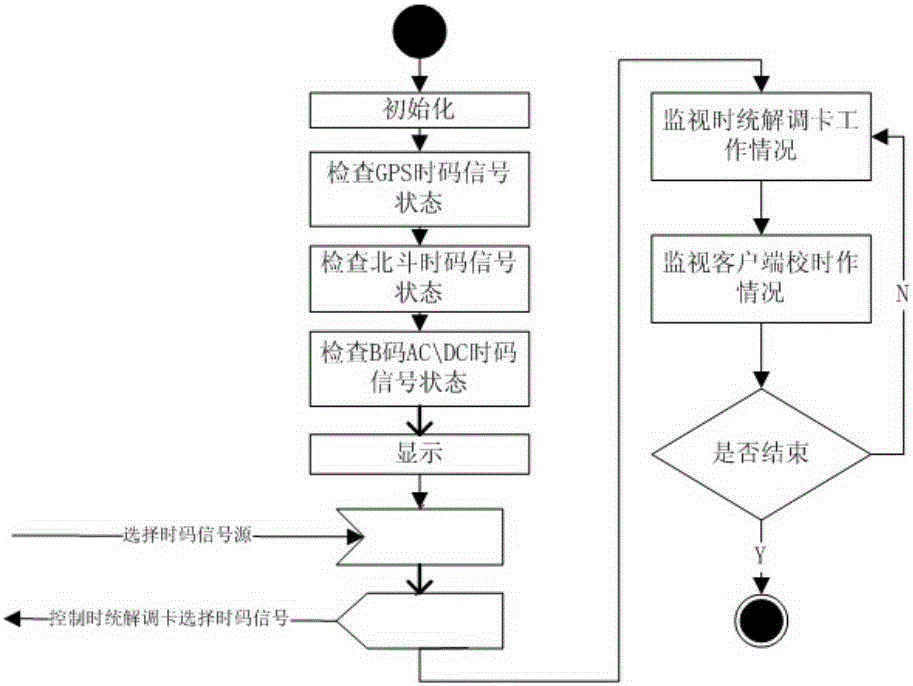

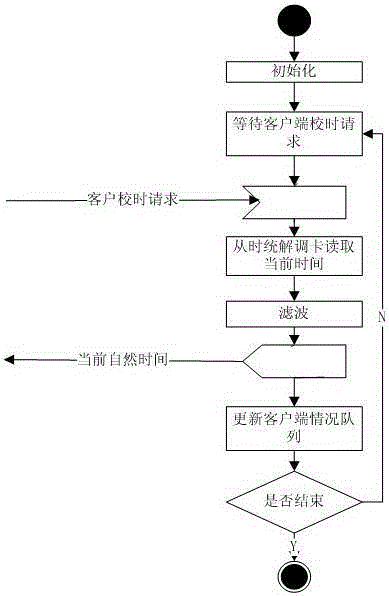

High-precision network time unifying device and method

The invention relates to the technical field of space-time consistency of all simulation real objects in a network, and discloses a high-precision network time unifying device and method. The device employed by the method comprises a time server and a client. The time server is connected with the client through the network, and the time server is formed by the connection of a PCI interface and a PCI time unifying demodulation card. A radio frequency input end of the PCI time unifying demodulation card is connected with a GPS / BD dual-mode antenna through a signal line. A data input end of the PCI time unifying demodulation card is connected with an IRIG-B time code signal source through a signal line. The high-precision network time setting and network frequency modulation enables the time bias of each network client to be less than or equal to 1ms. The device can provide in-network overall consistent natural time or simulation time for a plurality of application progresses or users, and can achieve the accelerating or slowing of the in-network overall simulation time. The device is low in cost, and is small in network bandwidth occupation and computer resource occupation.

Owner:UNIT 63892 OF PLA

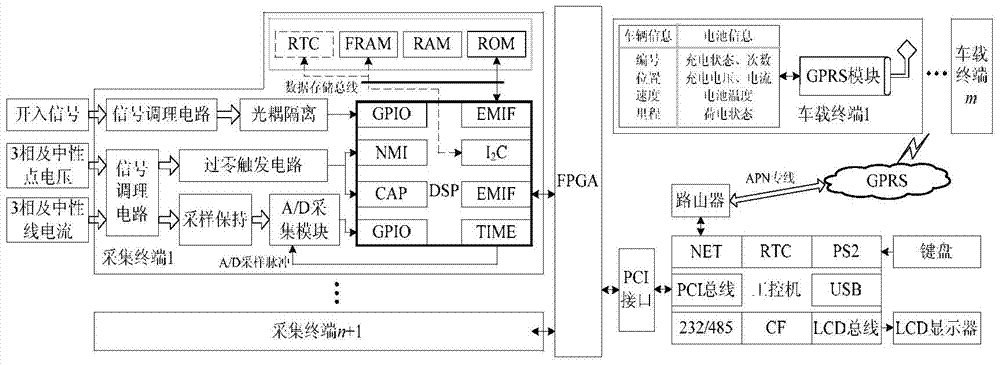

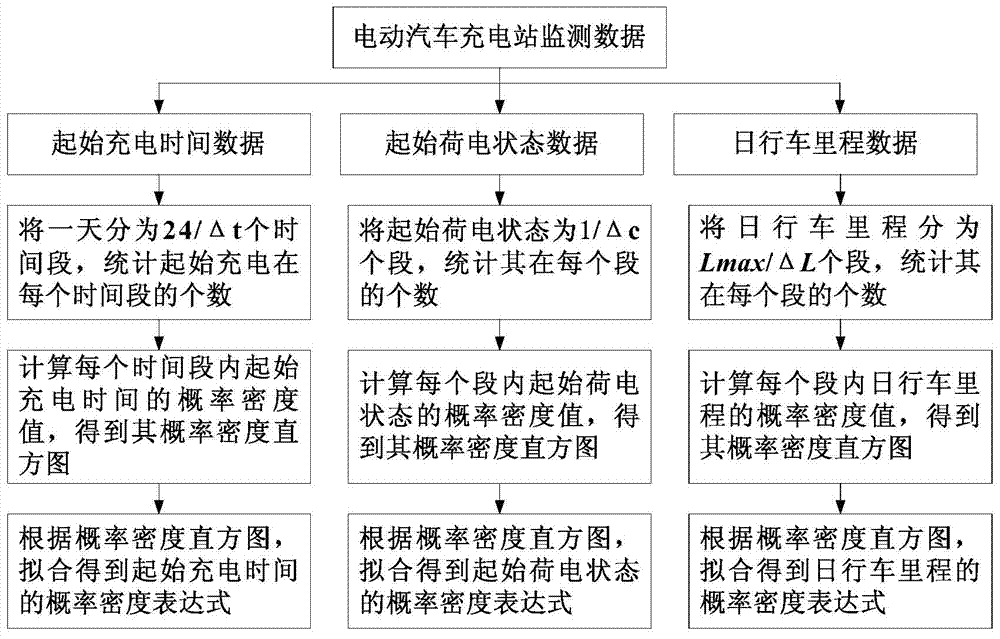

Online monitoring, analysis and evaluation system of electric vehicle charging station

ActiveCN103529340ARealize data transmissionHigh speed data transmissionElectrical testingTerminal unitCharging station

The invention discloses an online monitoring, analysis and evaluation system of an electric vehicle charging station. The system comprises collecting terminal units, a vehicle-mounted terminal unit, an FPGA (field programmable gate array) and PCI (peripheral component interconnect) interface unit and an embedded industrial personal computer; a plurality of the collecting terminal units and the embedded industrial personal computer constitute an electric vehicle charging station online monitoring platform which is used for collecting a point of common connection of the charging station as well as voltage and current of each charger; the FPGA and PCI interface unit is used for realizing data exchange of the plurality of the collecting terminal units and the industrial personal computer; the vehicle-mounted terminal unit transmits information about changing and the operation state of an electric vehicle to the embedded industrial personal computer; and comprehensive evaluation on states of the electric vehicle is performed with a radar map method, and probability distribution of the initial charging time, the initial charge state and a daily travelled distance is counted and analyzed. The system is stable and reliable, can realize long-term monitoring of the charging station, and provides a large quantity of reliable monitoring data for operation and planning of the charging station.

Owner:CHONGQING UNIV

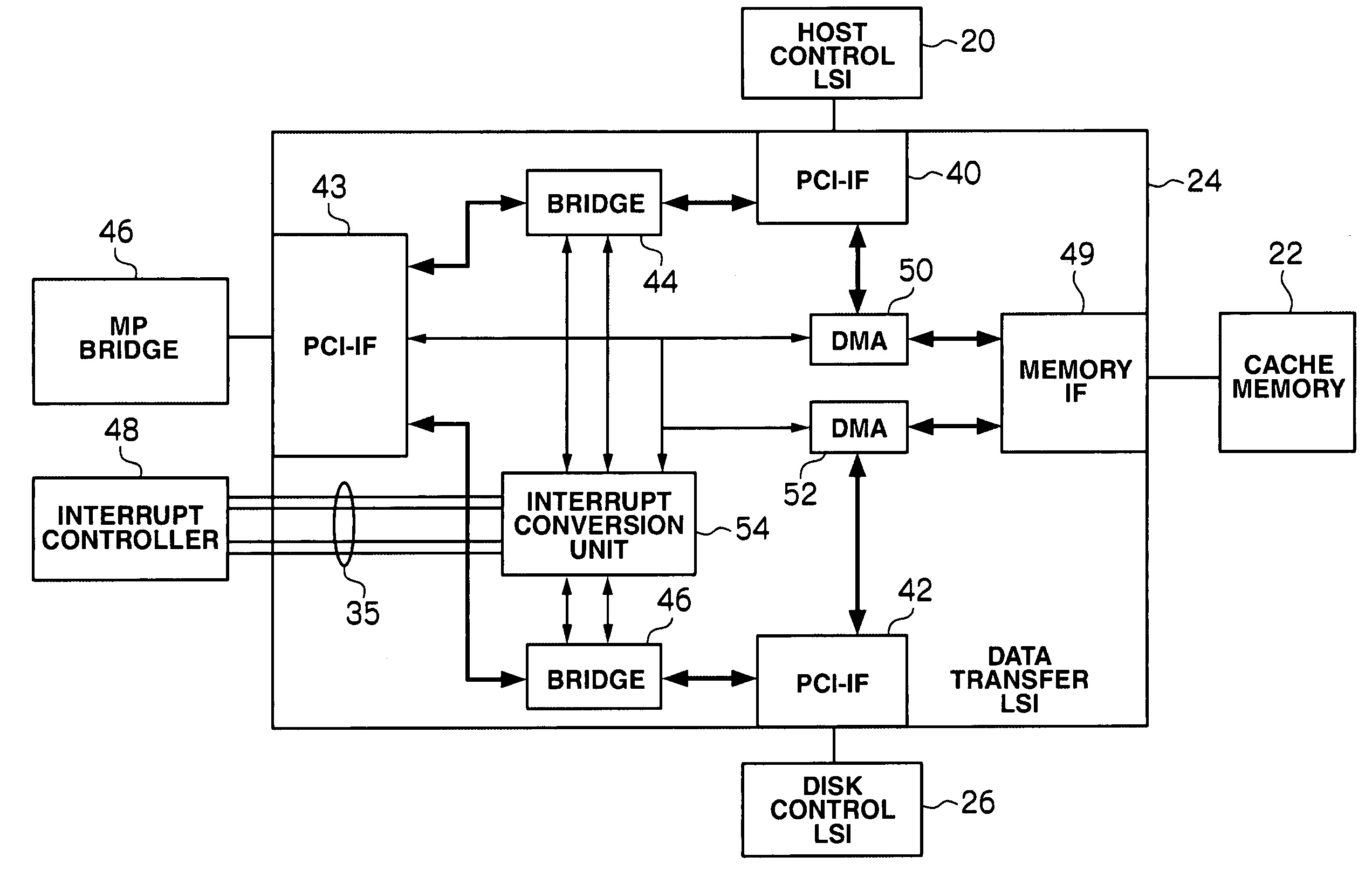

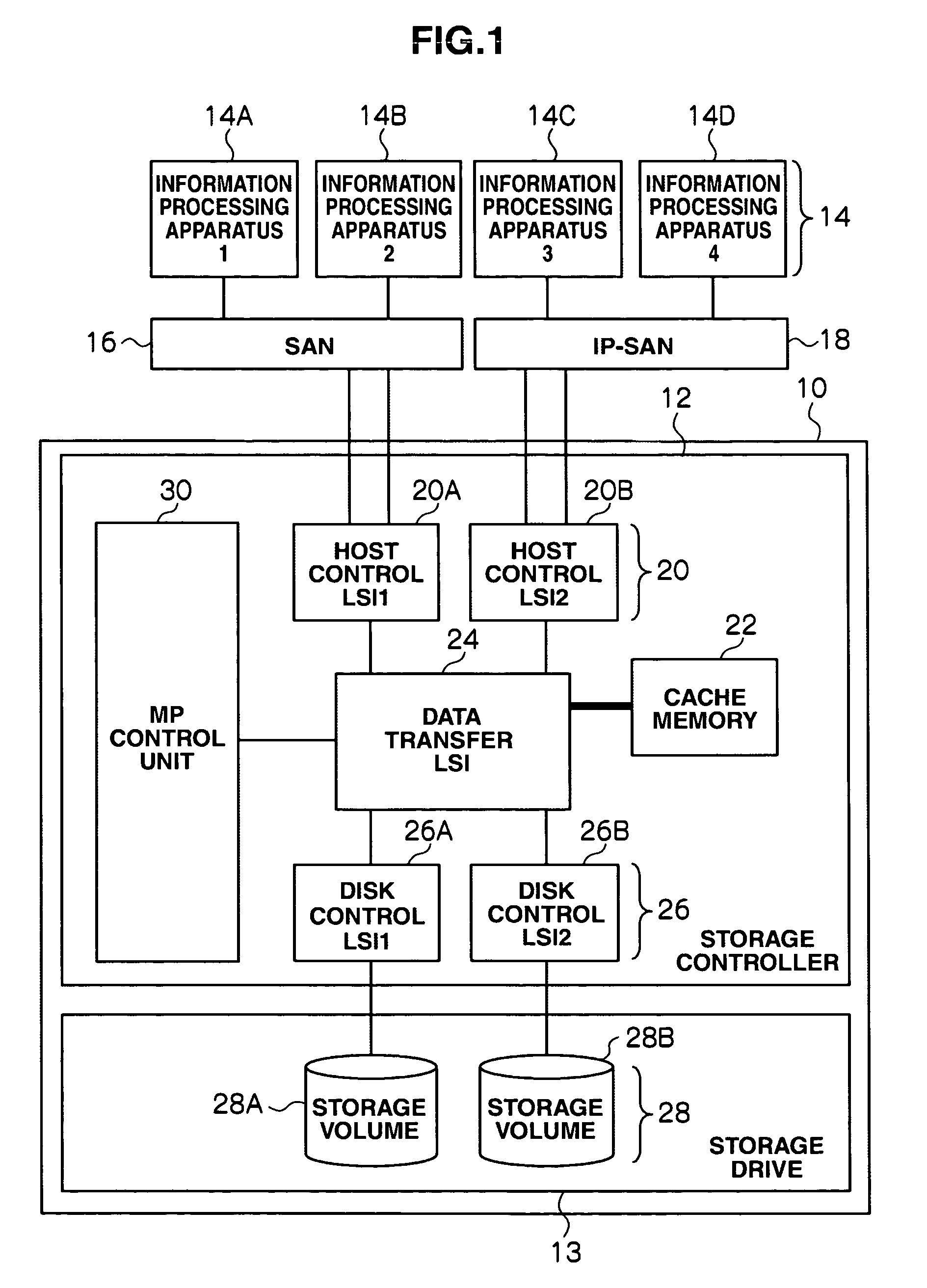

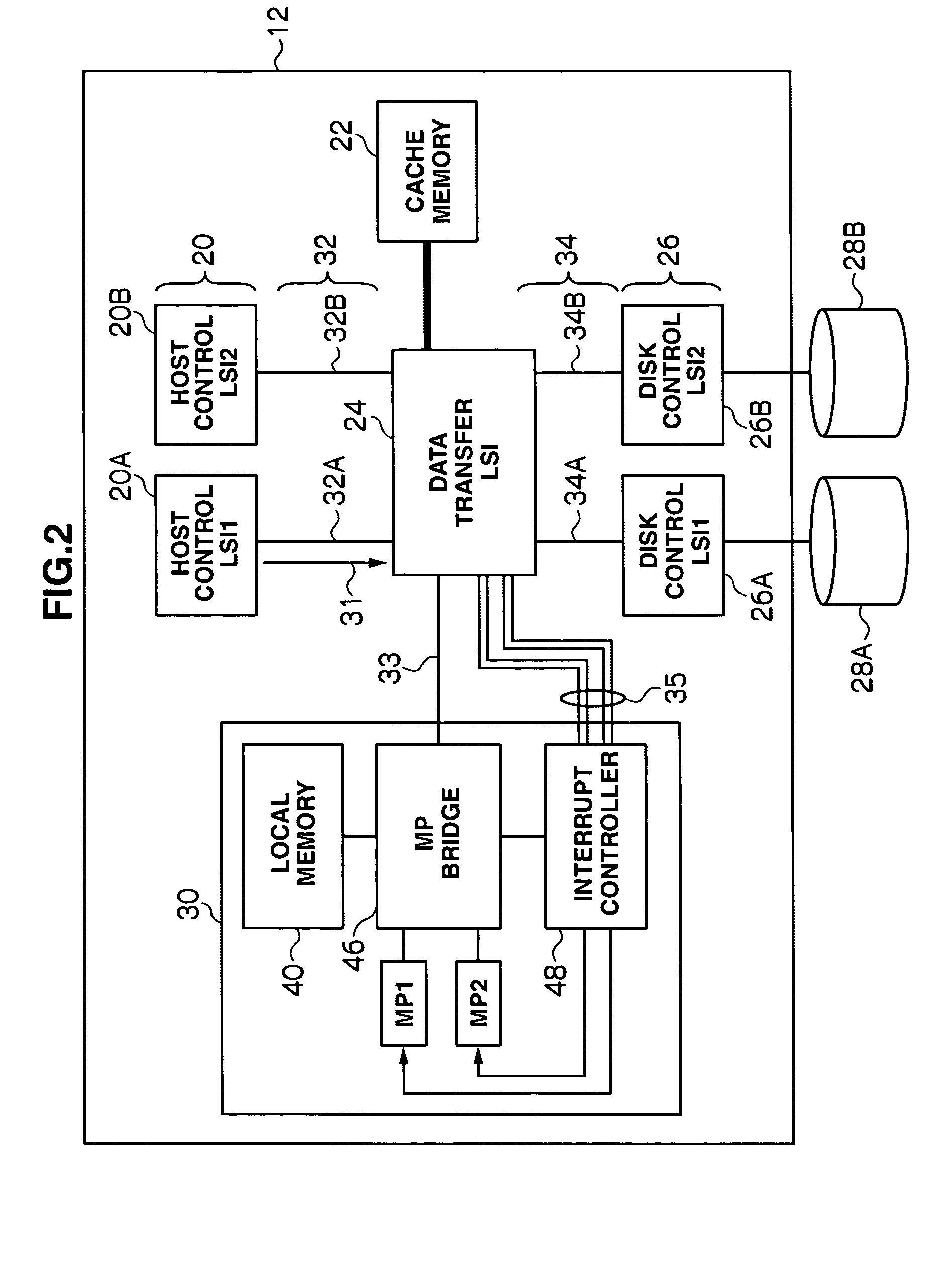

Interrupt control system and storage control system using the same

ActiveUS7526592B2Effective installationImprove efficiencyElectric digital data processingControl breakPci interface

An interrupt control system is provided where a signal-line-based interrupt system can be incorporated into interrupt control using MSIs (Message Signal Interrupts). The interrupt control system includes a first PCI interface, a second PCI interface, a PCI bridge serving as a bridge between the first PCI interface and the second PCI interface, and a control circuit for controlling an interrupt signal. The PCI bridge recognizes a message signal interrupt issued from the first PCI interface to the second PCI interface and transfers the message signal interrupt to the control circuit, and the control circuit is provided with an interrupt conversion unit for converting the message signal interrupt into an interrupt signal and outputting it via a signal line.

Owner:GOOGLE LLC

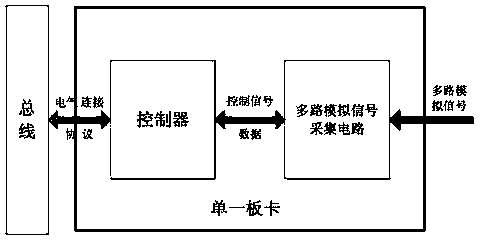

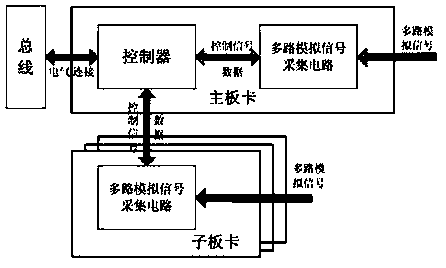

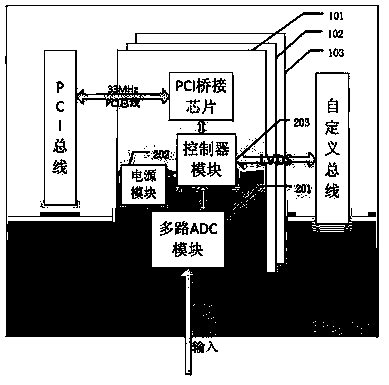

PCI interface protocol based array expandable data collection system realized by adopting FPGA (field programmable gate array)

InactiveCN103353725AIncrease flexibilityImprove confidentialityProgramme controlComputer controlData streamPci interface

The invention discloses a PCI interface protocol based array expandable data collection system realized by adopting an FPGA (field programmable gate array). The system comprises a plurality of identical analog signal collection boards. Each of the boards comprises a controller module, a multipath ADC module, a power supply module and a PCI bridging chip, wherein the controller module is composed of an FPGA chip and an SRAM chip, and used for controlling the sampling process, generating between-board bus signals and controlling caching and transmission of data; the multipath ADC module is composed of 64 paths of single-path ADC modules with the same structure, and used for converting analog signals into digital signals and transmitting the data to the controller module; the power supply module is composed of two identical power supply sub-modules, and used for providing stable and low-noise power for the chips; and the PCI bridging chip is used for realizing communication between the analog signal collection boards and an upper computer through a PCI bus. The PCI interface protocol based array expandable data collection system realizes sampling control of a multipath ADC and control of data flows by using the FPGA, and greatly increases the flexibility and the reliability of the design.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

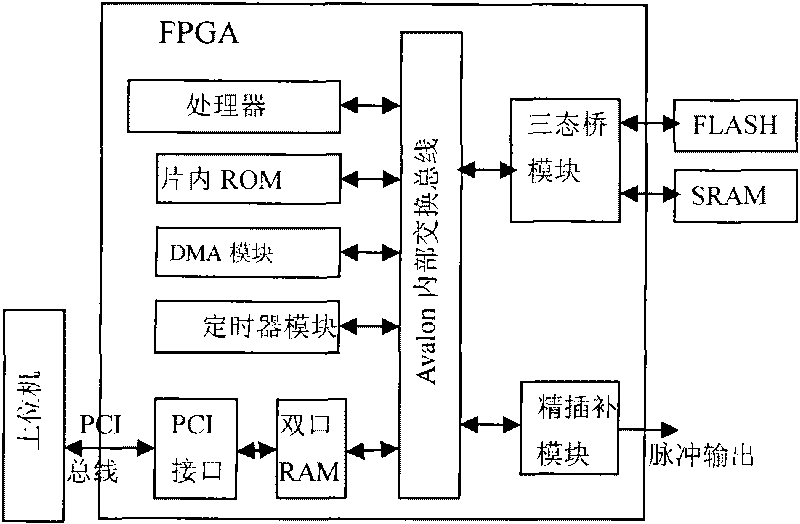

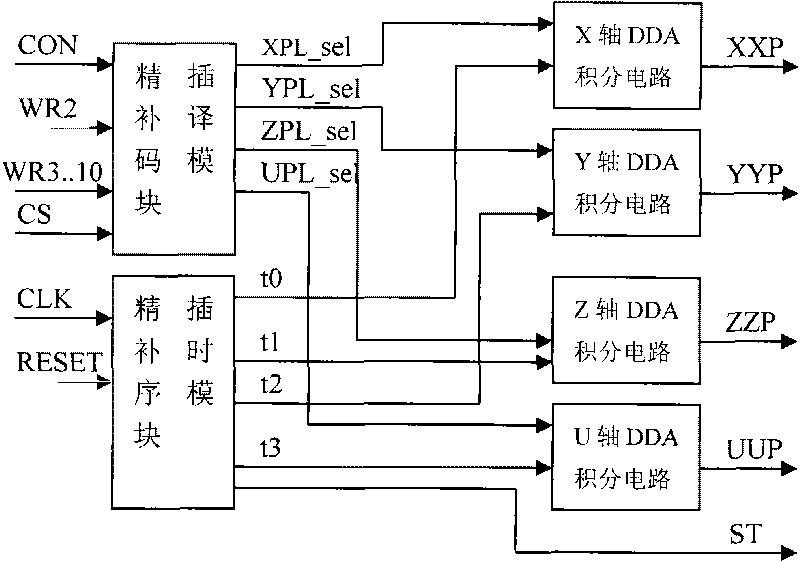

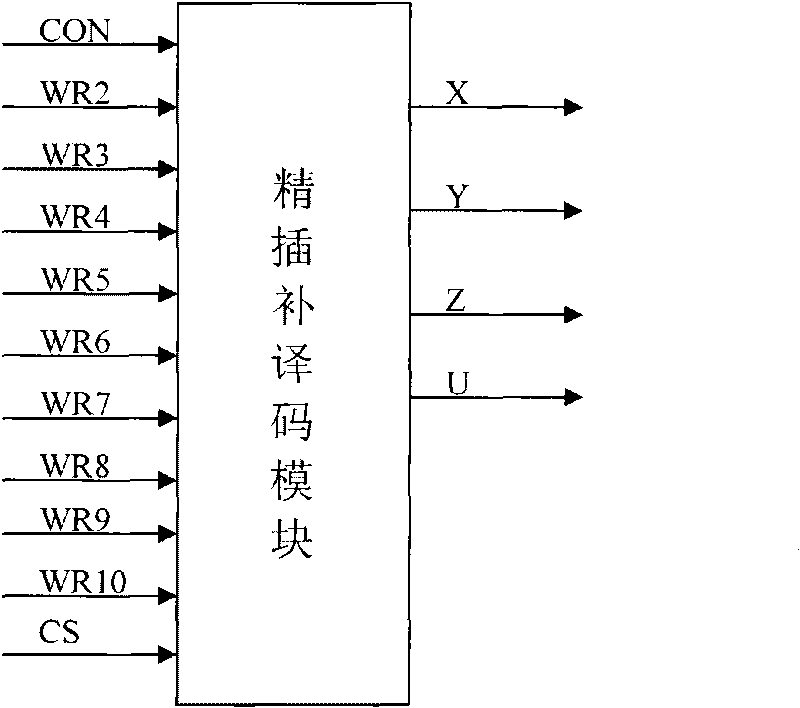

NC system fine interpolator and control method thereof based on SOPC

ActiveCN101751009AImprove confidentialityEasy to integrateProgramme controlComputer controlInternal memorySystems design

The invention relates to a NC system fine interpolator and a control method thereof based on SOPC; the fine interpolator is based on the FPGA structure, a processor is connected with a fine interpolation module, a tri-state bridge, a dual-port RAM, a DMA module, a timer module and a chip-interior ROM; wherein, the fine interpolation module is used for receiving the control signal of the processor and is controlled by the processor to output a fine interpolation pulse signal according to the thick interpolation command transmitted by the dual-port RAM; the processor is connected with a FLASH and SRAM on the exterior of the FPGA through the tri-state bridge; the dual-port RAM is connected with the microprocessor of an upper computer through a PCI interface module; the timer module outputs base frequency to the fine interpolation module for generating pulse signals; the DMA module copies the fine interpolation control program stored in the FLASH to the internal memory of the processor' and the internal switching bus module provides internal connection bus for each module. The invention adopts the FPGA-based on-chip system design to improve the confidentiality and integration of the fine interpolator, the processing stability and speed of the fine interpolator, and reduce the data throughput of the upper computer.

Owner:中国科学院沈阳计算技术研究所有限公司

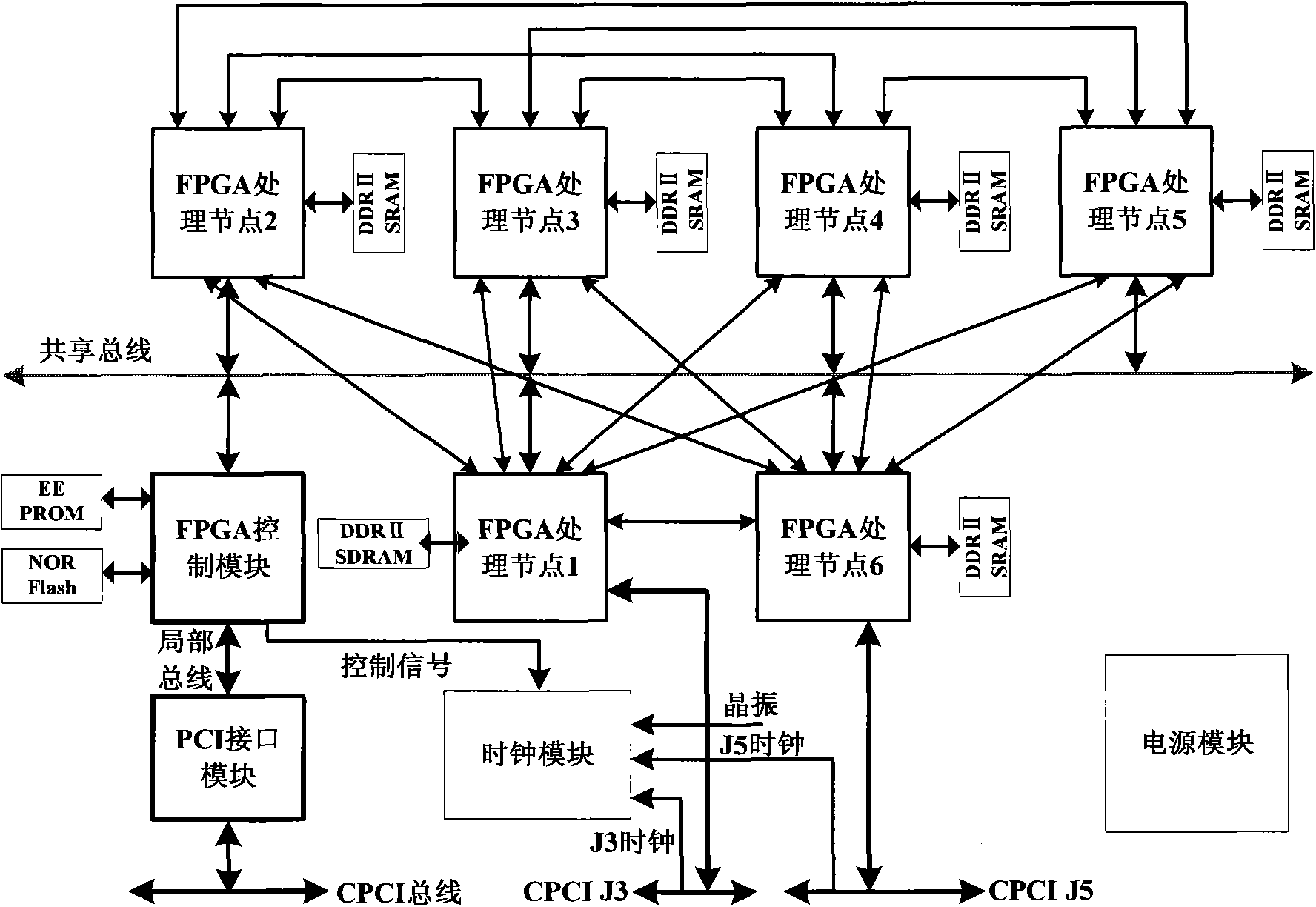

Signal-processing board

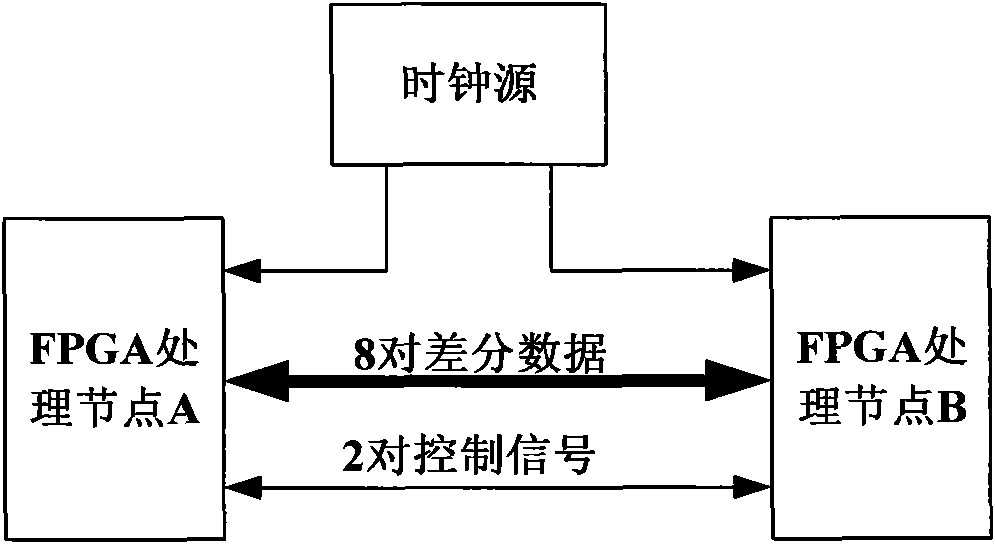

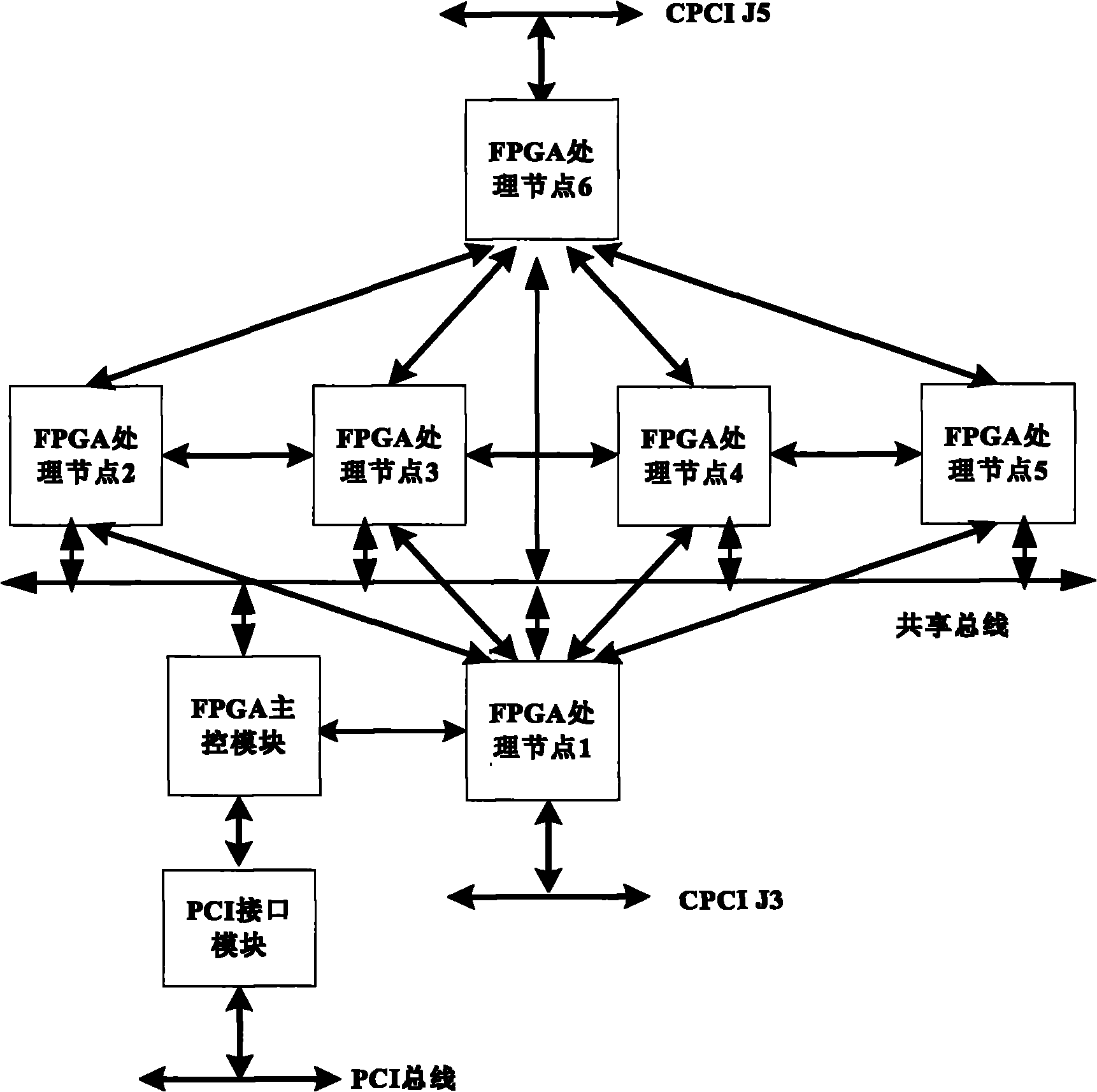

ActiveCN101819556AEfficient use ofIncrease flexibilityElectric digital data processingPci interfaceControl signal

The invention provides a signal-processing board, which comprises a plurality of FPGA processing nodes, an FPGA main control module, a PCI interface module, a clock module and a power supply module, wherein the plurality of FPGA processing nodes are interconnected by an interconnection bus in a totally communicated topological structure and the interconnection bus is used for transmitting a high-speed data signal; the FPGA main control module is interconnected with the plurality of FPGA processing nodes through a shared bus which is used for transmitting a control signal; the PCI interface module is connected with the FPGA main control module through a local bus; the clock module is connected with the FPGA main control module, controlled by the main control module and used for supplying aworking clock to the signal-processing board; and the power supply module is used for supplying a voltage required by the signal-processing board. The topological structure of the plurality of FPGA processing nodes of the signal-processing board is flexible and the reconfiguration of the interconnection structure can be implemented according to specific application.

Owner:BEIJING RUNKE GENERAL TECH

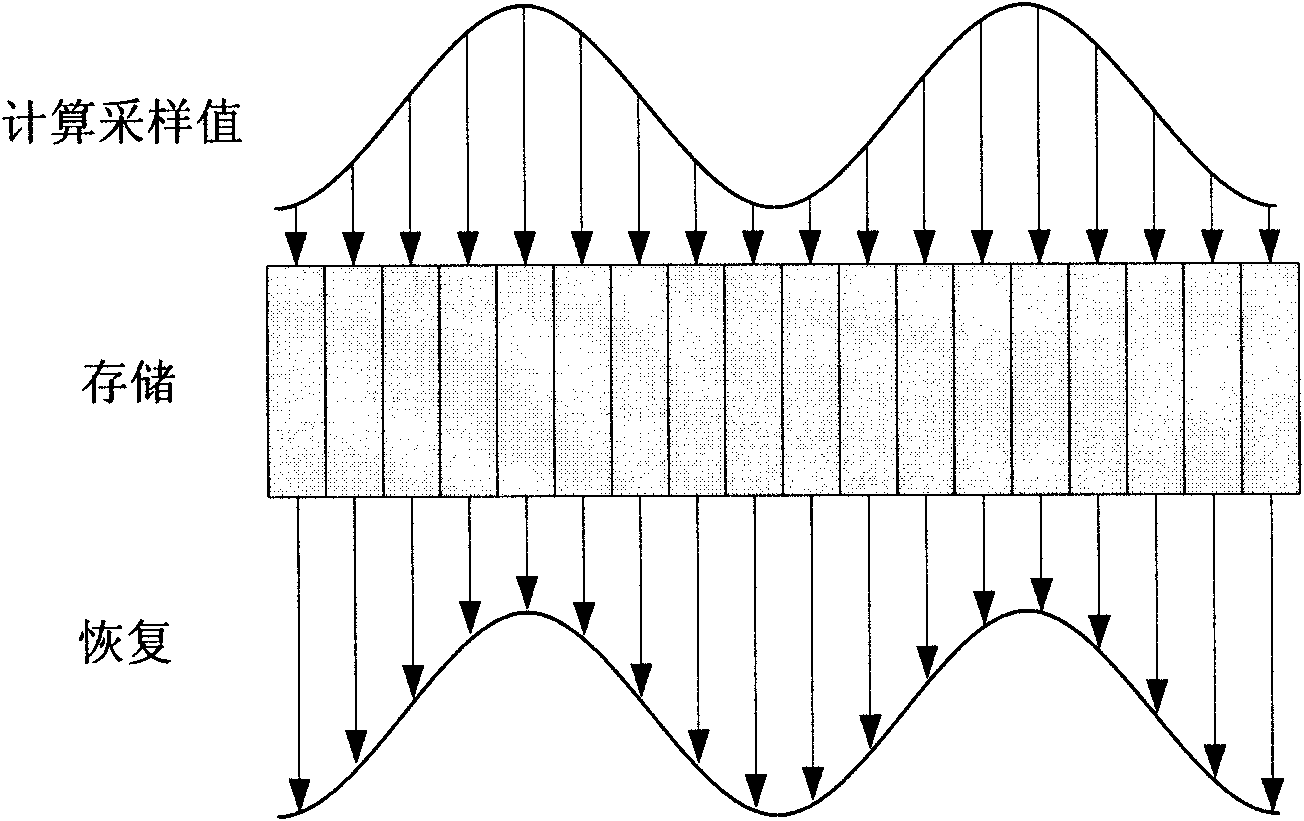

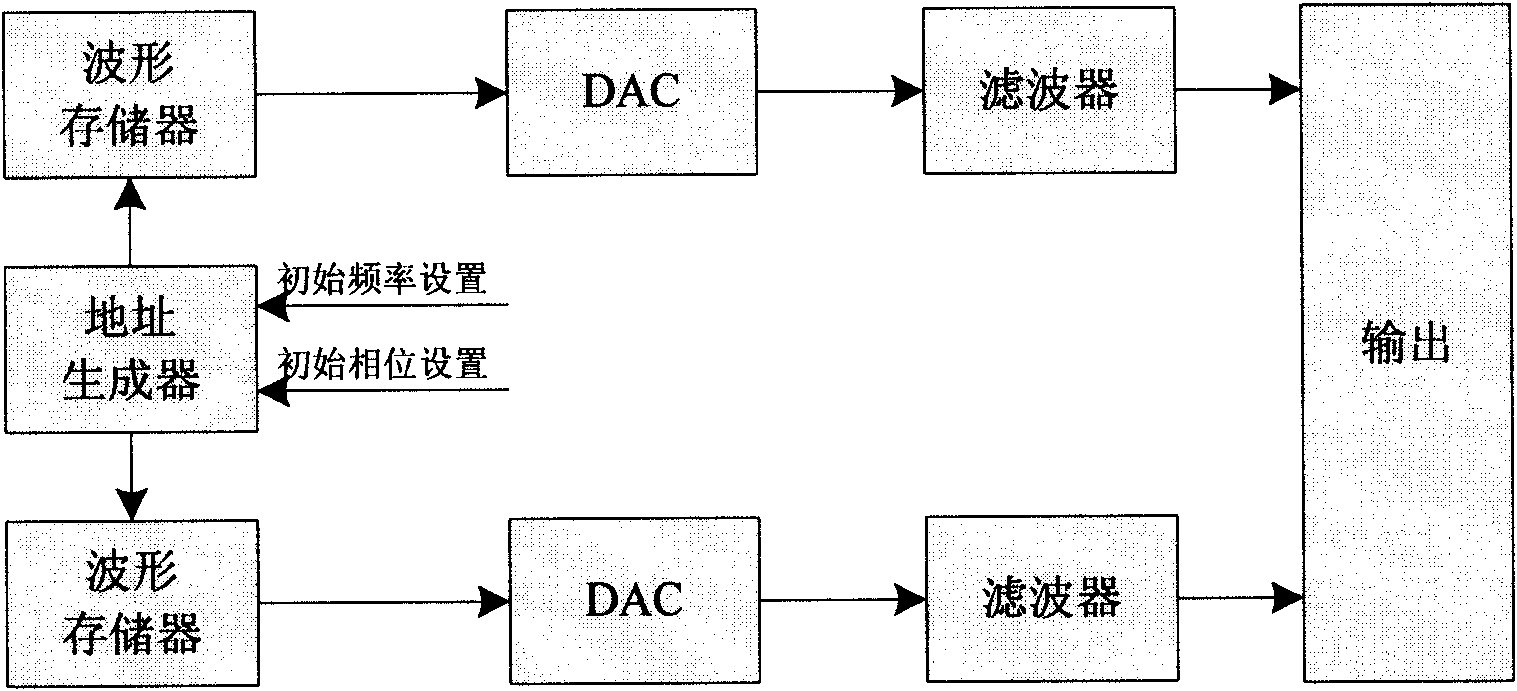

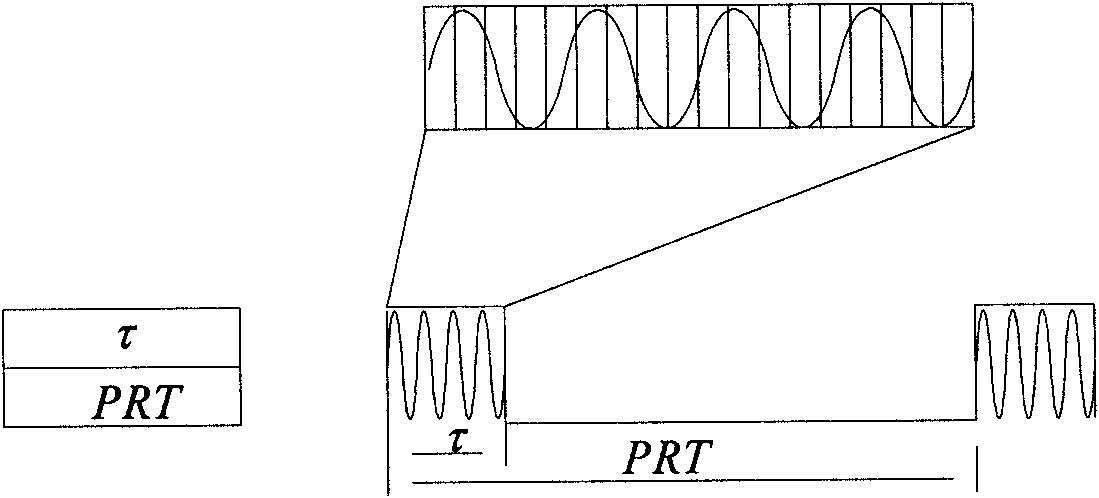

UWB radar signal simulator based on FPGA and UWB radar signal generation method

InactiveCN101576619ASimplify writingGuaranteed flexibilityWave based measurement systemsRadar waveformsPci interface

Owner:BEIHANG UNIV

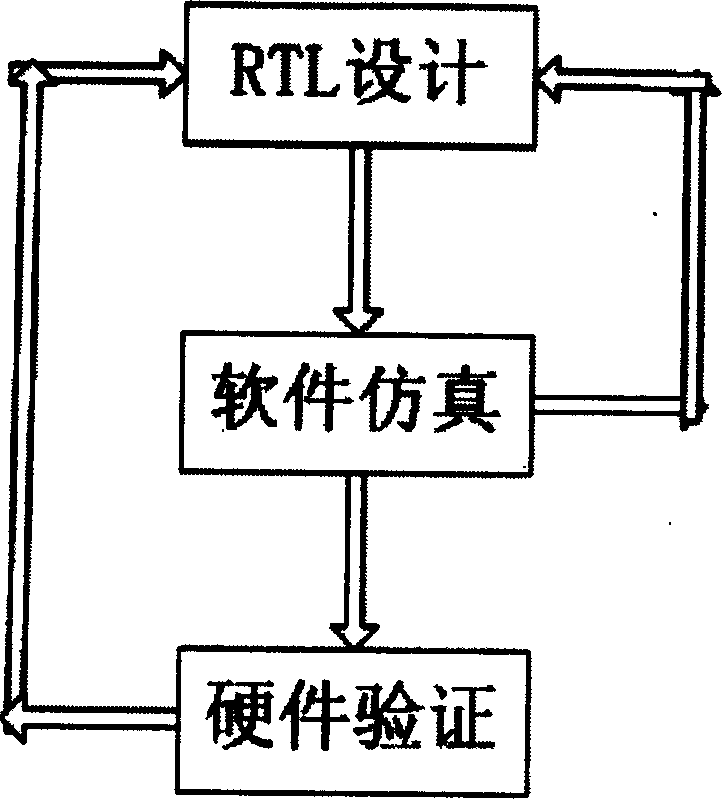

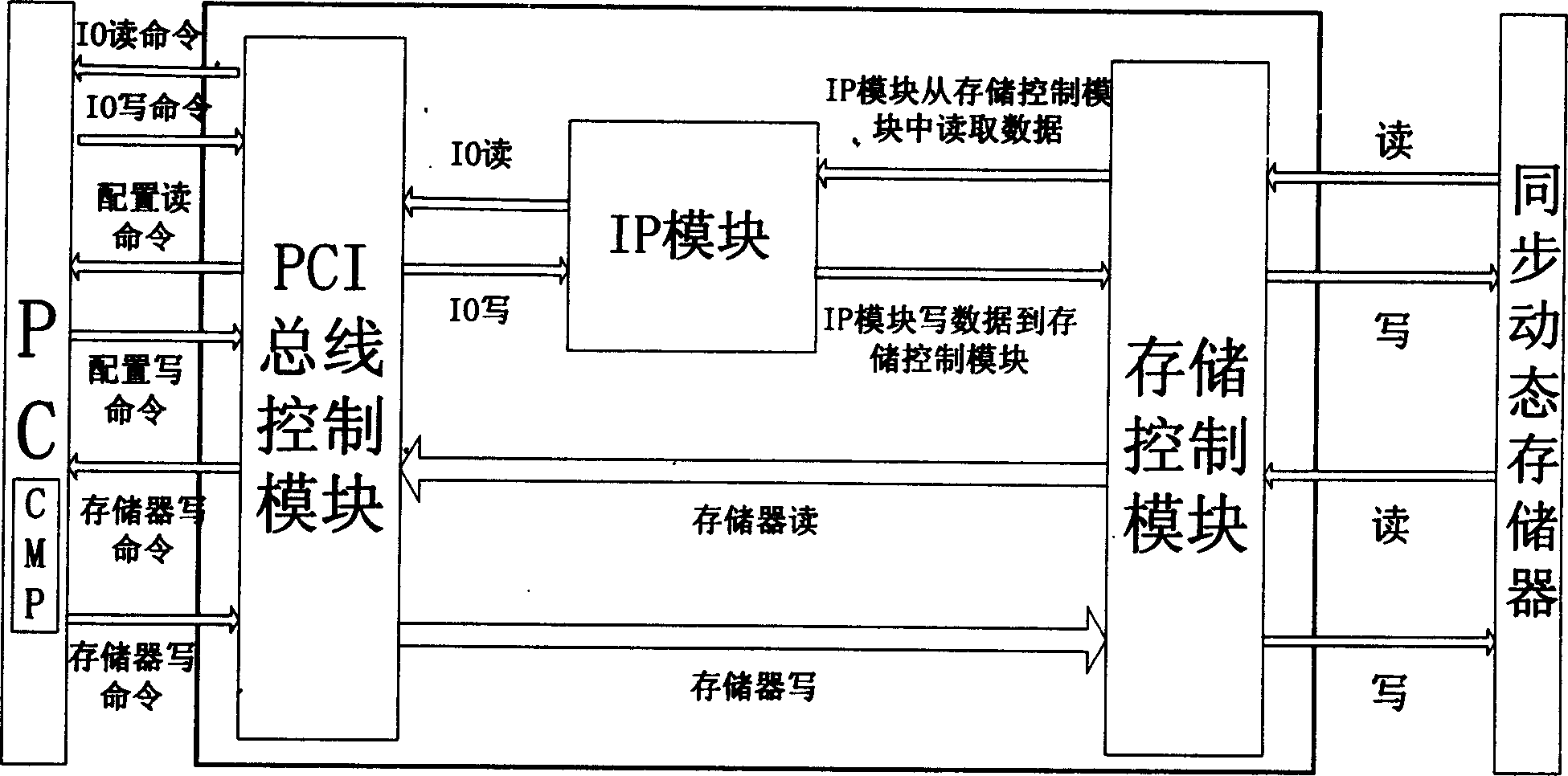

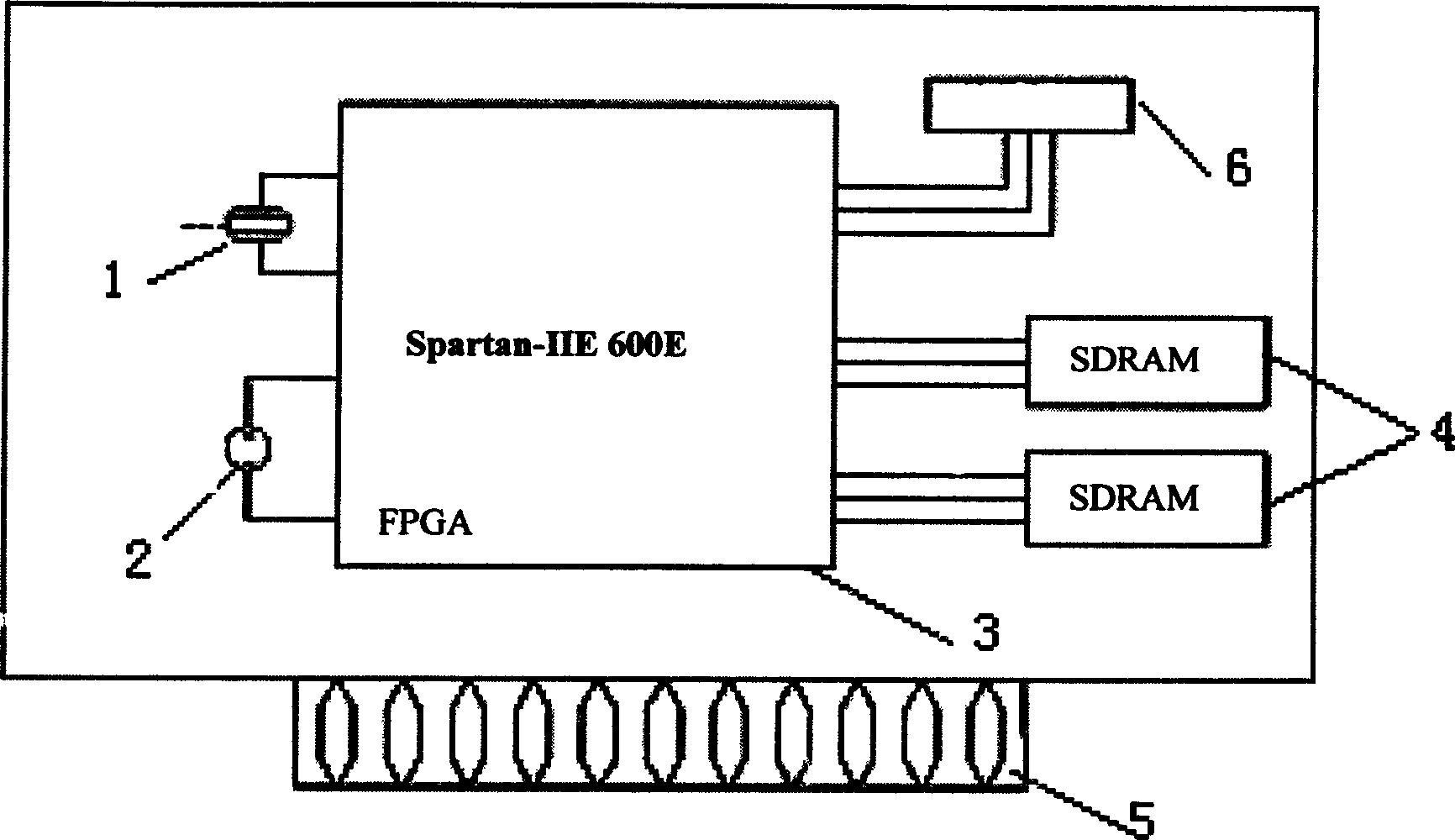

IP nuclear simulation confirmation platform based on PCI bus and proving method thereof

InactiveCN1609862ASimple structureReasonable designError detection/correctionSpecial data processing applicationsComputer hardwareValidation methods

The IP kernel simulating verification platform based on PCI bus includes crystal vibrator, DC voltage regulator, FPGA, programming interface, SDRAM and PCI interface. The verification process includes describing IP kernel system in Verilog HDL language, interconnecting the top layer simulating modules with PCI bus, interconnecting hardware modules with internal bus the same as that in SoC inside the chip, embedding verified IP kernel into the verification platform, and controlling the platform to test IP kernel in PC. The present invention has verification platform with simple structure and convenient use, and verification process capable of simulating effectively SoC environment of IP, utilizing FPGA and PC in the hardware verification of IP, real-time creating test data for IP kernel to test and real-time accessing the register and memory inside IP kernel to obtain the verification finishing data.

Owner:SOUTH CHINA UNIV OF TECH

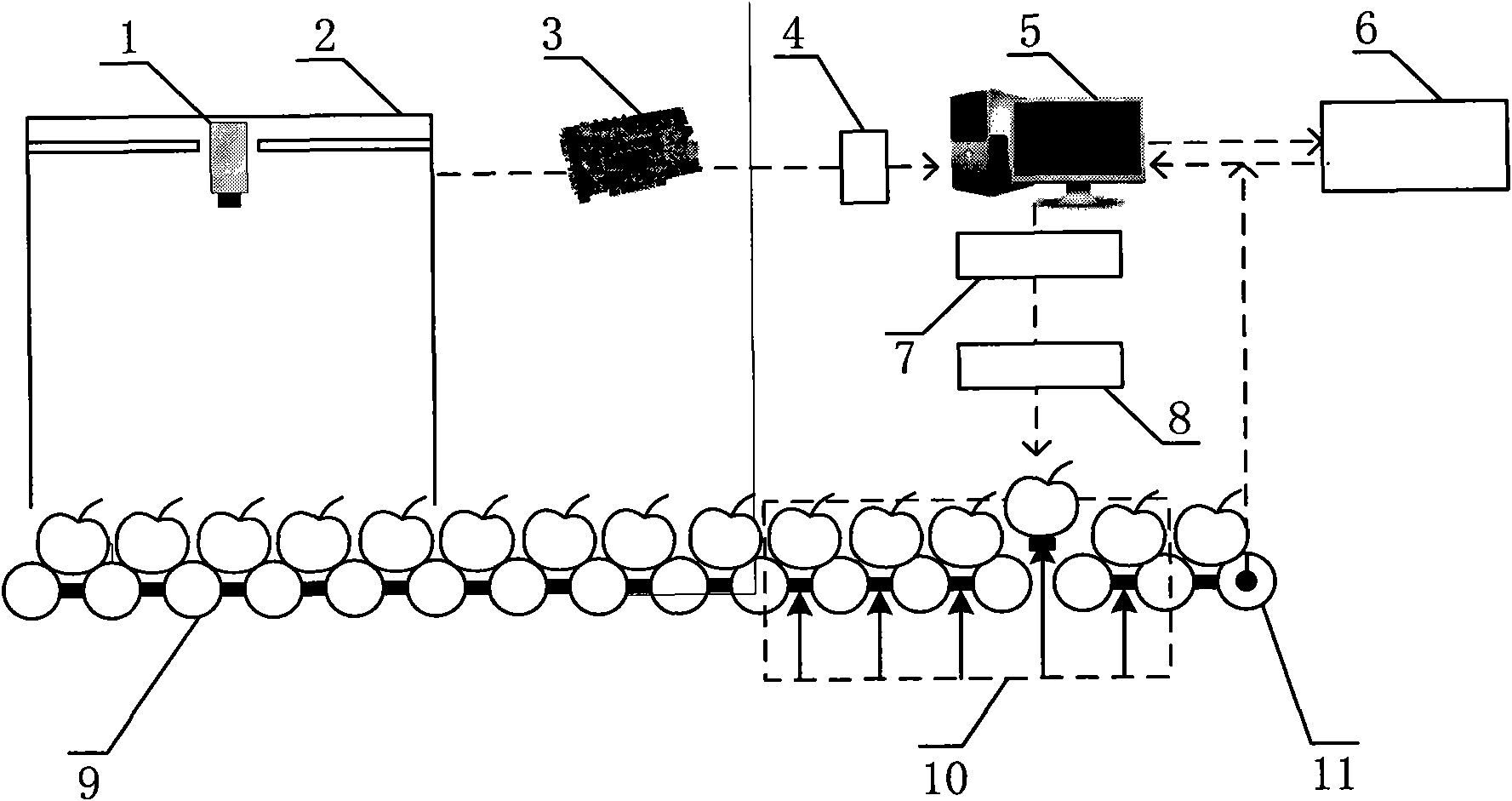

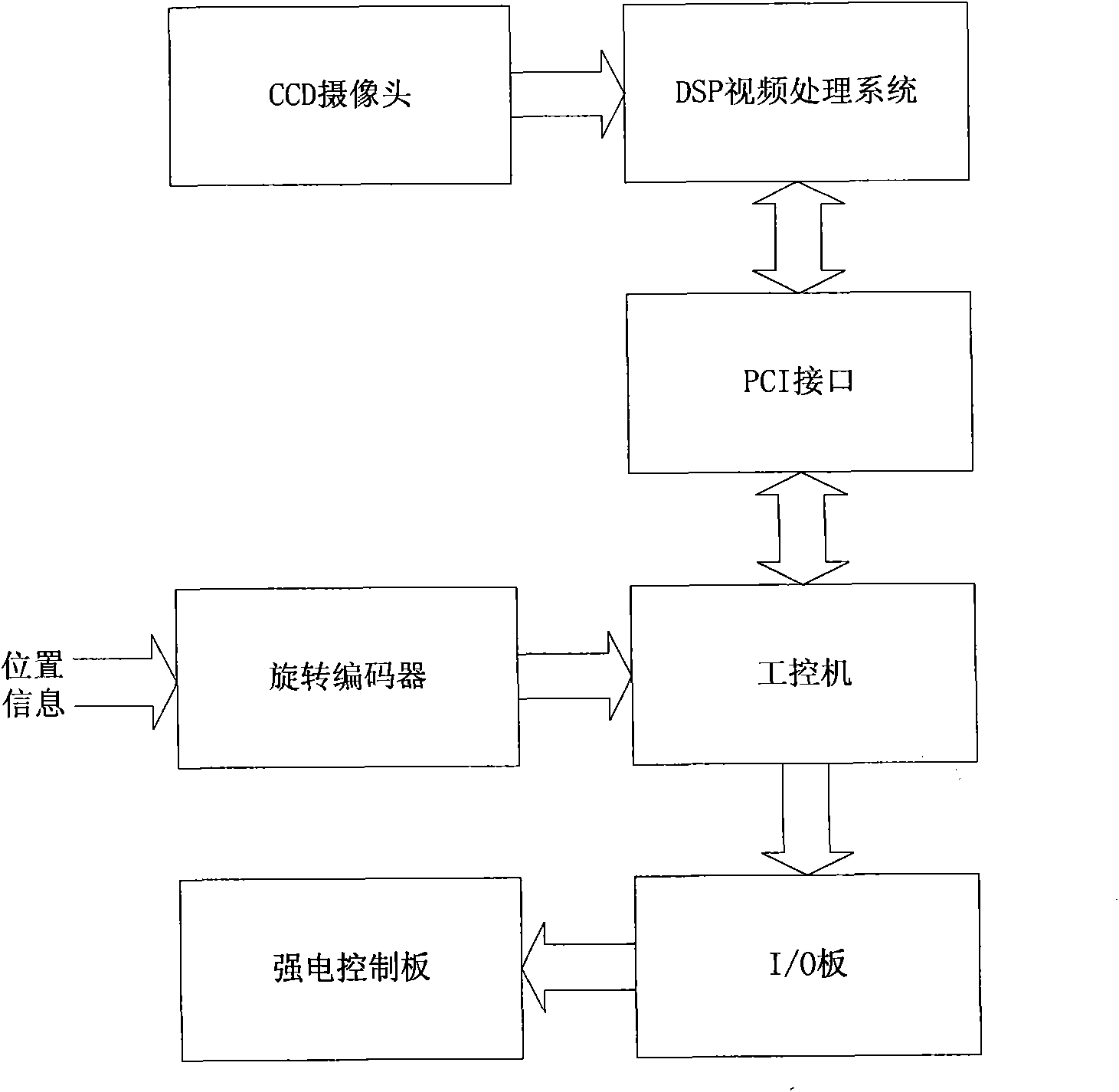

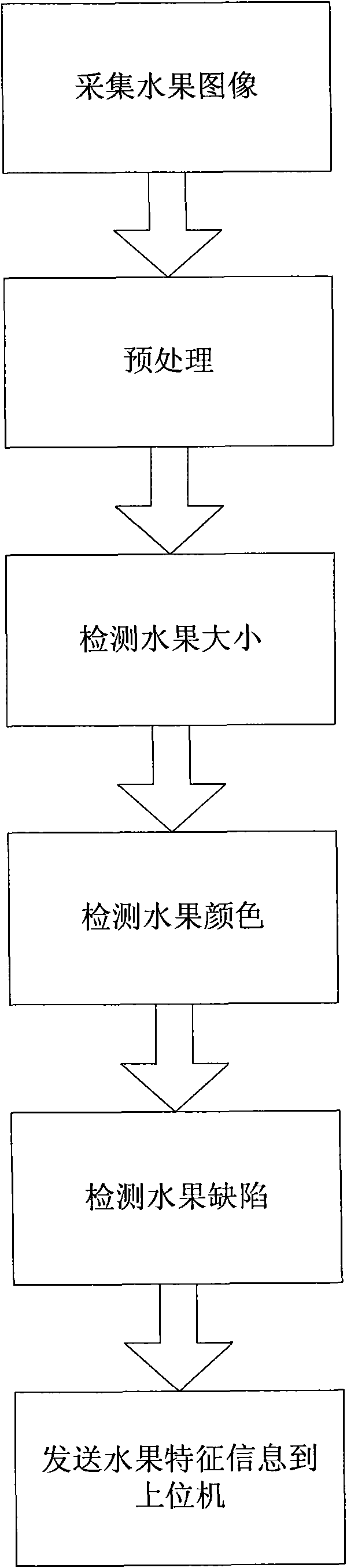

Fruit grading system and method based on DSP machine vision

ActiveCN101912847AImprove real-time performanceImprove classification accuracySortingImaging processingPci interface

The invention discloses a fruit grading system and a method based on DSP machine vision. The system comprises a DSP machine vision system, a man-machine interactive system, a conveying module, a grading trigger module and the like. The method comprises the following steps: a camera acquires fruit images to a DSP video processing system, and the DSP video processing system identifies the external feature information of the fruit; the fruit information is supplied to grading software installed in an industrial personal computer through a PCI interface; and the grading software distinguishes the grade of the current fruit according to the fruit information and the fruit grade information preset by the user through a man-machine interactive module, and finally transmits a triggering signal to an actuating mechanism to carry out grading. The image acquisition and image processing tasks are executed by the special DSP high-speed image processing system, the DSP system adopts the fruit grading method of the invention, and the DSP system and the industrial personal computer transmit data by using the high-speed PCI interfaces, so the fruit grading speed and grading accuracy are greatly enhanced.

Owner:金湖县农副产品营销协会

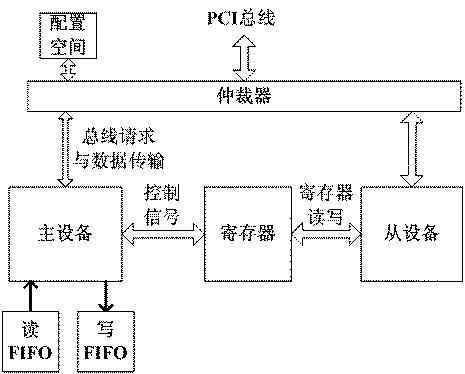

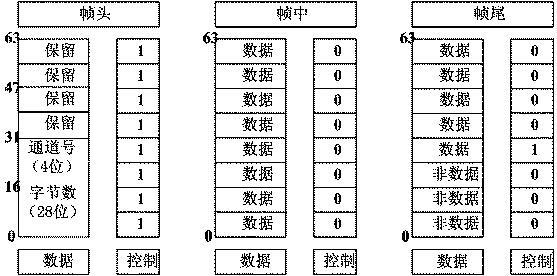

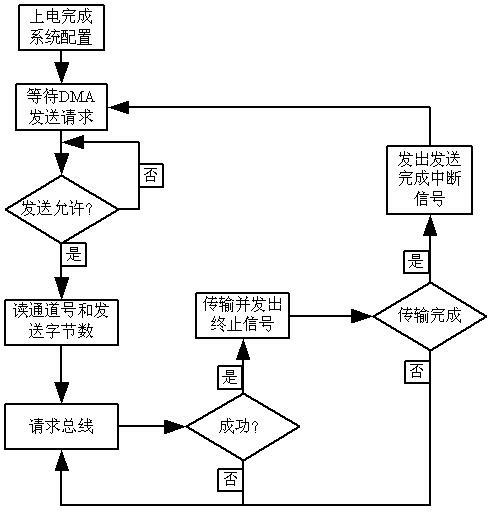

PCI (Peripheral Component Interconnect) interface and data transmission method thereof under FPGA (Filed-Programmable Gate Array) environment

The invention discloses a multipurpose PCI interface and the data transmission method thereof under an FPGA environment. A method for implementing the PCI interface with the DMA (Direct Memory Access) function is adopted, and the interface is independently implemented through a PCI master device module, a PCI slave device module and a PCI register module. A simple FIFO (First Input First Output) interface easy to implement is adopted and used for a PCI user-side interface, DMA control details are concealed from a user, and the design complexity of the user interface is reduced. In high-capacity data transmission, data are encapsulated according to a data format required by the interface and can be realized in a DMA way by being simply written into FIFO, the control logic complexity is simplified, and the efficiency of development of the user interface is improved.

Owner:UNIV OF JINAN

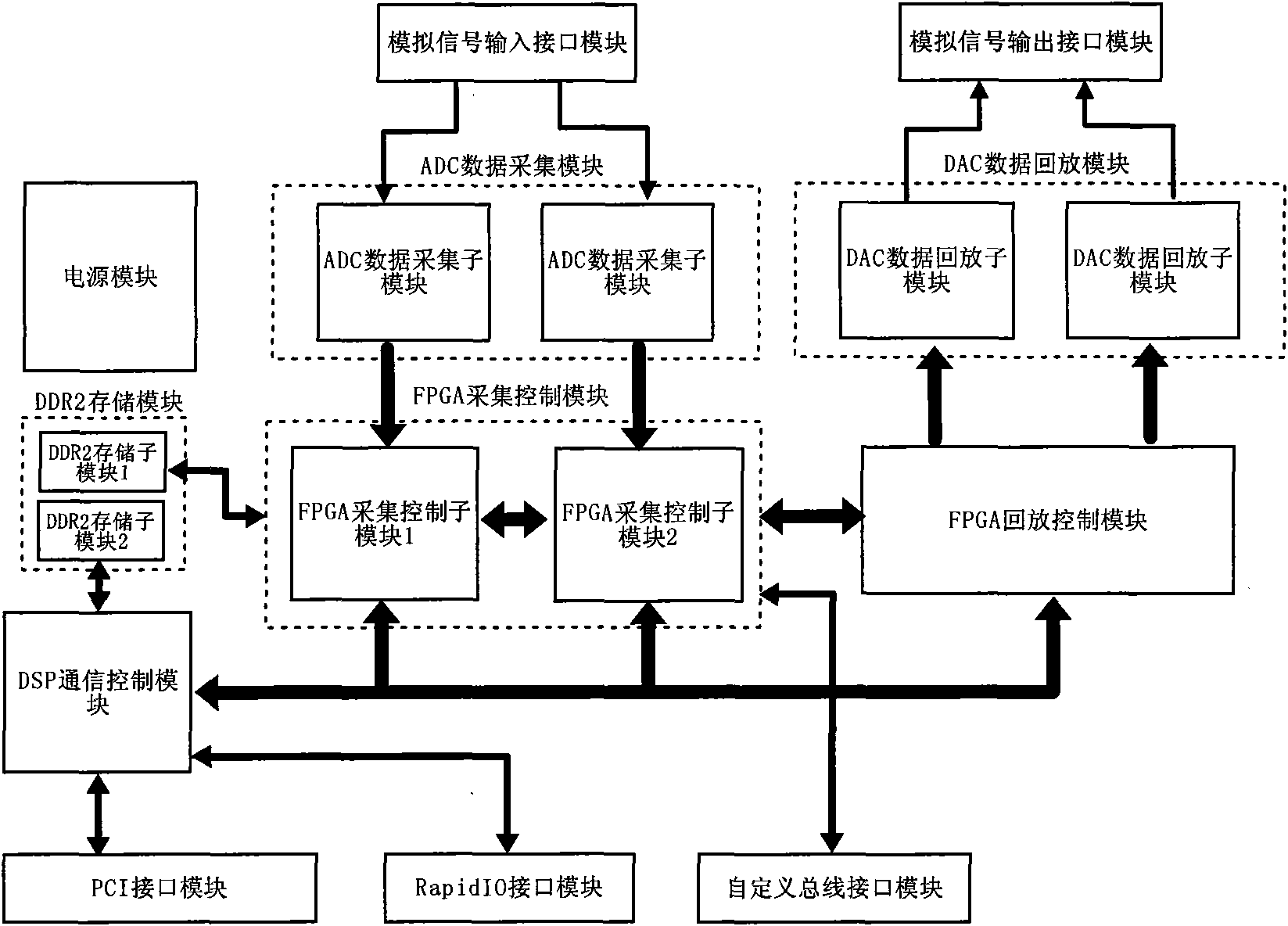

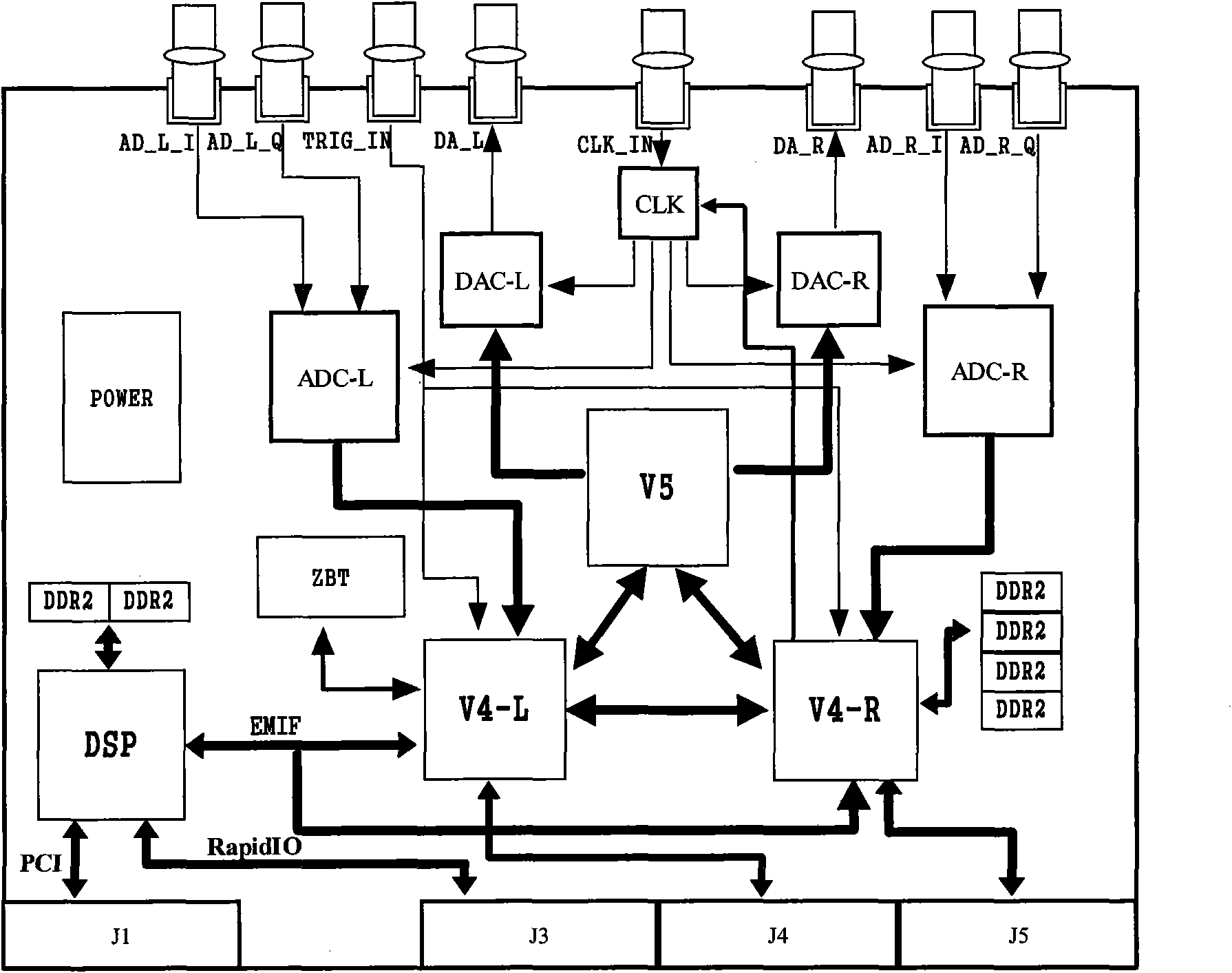

Two-channel digital radio-frequency memory board

InactiveCN101604541AHigh frequencyEasy to storeData switching by path configurationDigital recording/reproducingData acquisitionData memory

The invention relates to a two-channel digital radio-frequency memory board, and belongs to the technical field of data memory. The two-channel digital radio-frequency memory board comprises a power module, an ADC data acquisition module, a DAC data playback module, a DDR2 memory module, an FPGA acquisition control module, an FPGA playback control module, a DSP communication control module, an analog signal input interface module, an analog signal output interface module, a PCI interface module, a Rapid IO interface module and a customized bus interface module. The two-channel digital radio-frequency memory board is provided with two signal acquisition processing playback circuit branches, and each circuit branch has the sampling rate of 1.2GSPS and the playback rate of 1.2GSPS; and the two-channel digital radio-frequency memory board has various signal acquisition processing playback modes and data transmission mode, can realize functions of memorizing and forwarding signals with high frequency, and is suitable to be applied to the field of radar and electronic warfare confrontation.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

System and method for coupling peripheral buses through a serial bus using a split bridge implementation

A Wide Area Serial PCI system for connecting peripheral devices to a computer. The WASP system includes a host computer system connected through a serial bus to a remote device. The serial bus can range from several meters to several kilometers or more. The host computer system includes a CPU and memory, and also includes a first Peripheral Component Interconnect (PCI) bus, also referred to as the local PCI bus. A primary bridge according to the present invention is coupled to the first PCI bus. The primary bridge includes PCI interface circuitry for interfacing to the first PCI bus. The remote device is located remotely from the computer system and comprises a second or remote PCI bus and one or more peripheral devices coupled to the second PCI bus. The remote device also includes a secondary bridge coupled to the second PCI bus. The secondary bridge includes PCI interface circuitry for interfacing to the second PCI bus. The serial bus is coupled between the primary bridge and the secondary bridge. Each of the primary bridge and secondary bridge include parallel / serial transceivers for converting parallel data generated on the first PCI bus and second PCI bus, respectively, to serial data for transmission on the serial bus and for converting serial data received from the serial bus to parallel data for generation on the first PCI bus and second PCI bus, respectively. The primary bridge and the secondary bridge collectively implement a PCI-PCI bridge register set.

Owner:NATIONAL INSTRUMENTS

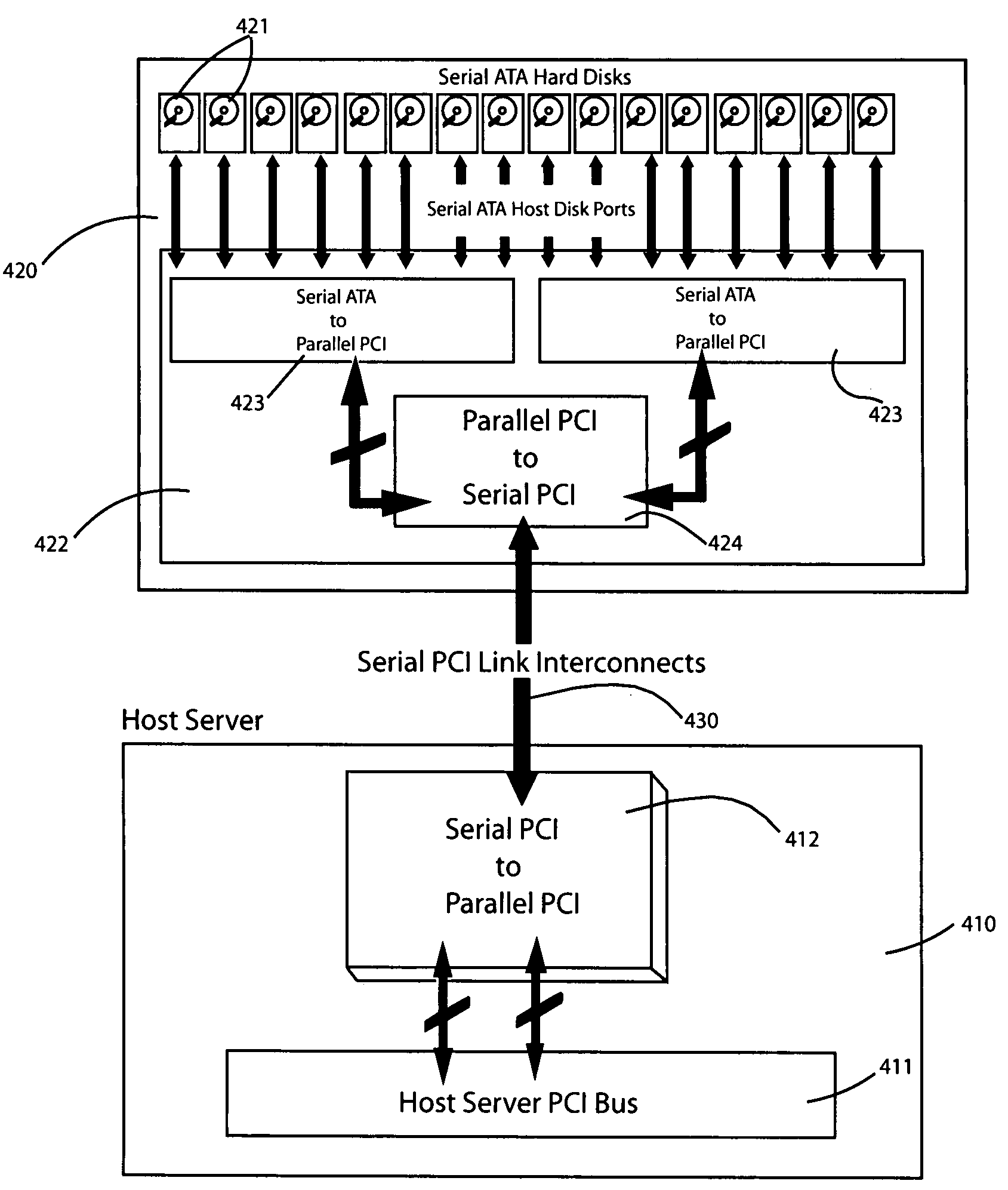

Large array of mass data storage devices connected to a computer by a serial link

A peripheral data storage subsystem is for use with a computer system. The computer system has a host PCI bus and a serial PCI host bus adapter coupled to the host PCI bus. The peripheral data storage subsystem includes a plurality of data storage devices and a data storage device to parallel PCI interface that is coupled to each of the data storage devices, a parallel PCI to serial PCI interface coupled to the data storage device to parallel PCI interface and a serial PCI link interconnect. The serial PCI link-interconnect couples the parallel PCI to serial PCI interface of the peripheral data storage subsystem to the serial PCI host bus adapter of the computer system.

Owner:RABINOVITZ JOSEF +1

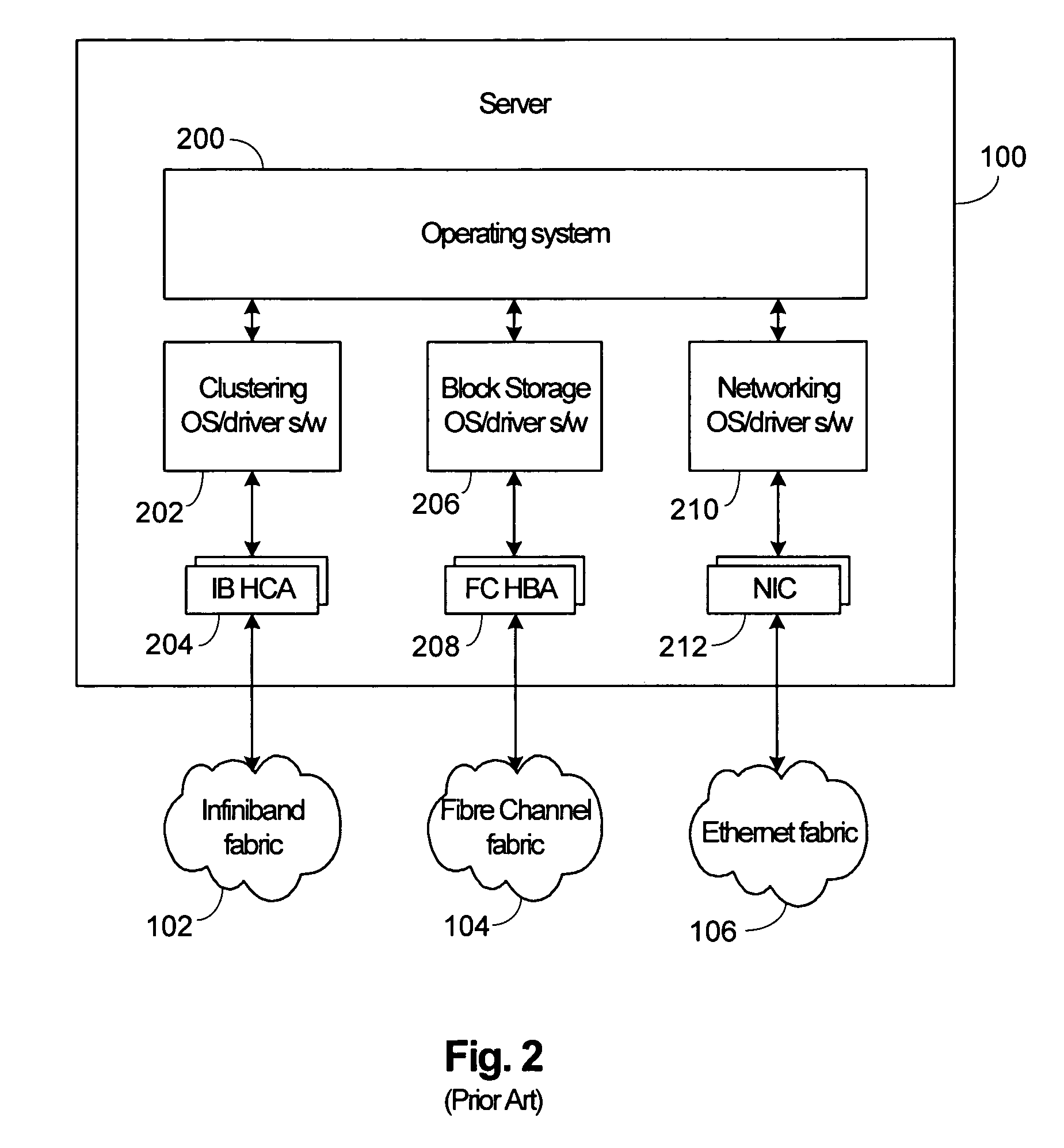

Method and apparatus for using a single multi-function adapter with different operating systems

ActiveUS7849232B2Precise processingDigital computer detailsMultiprogramming arrangementsOperational systemPci interface

Owner:TAHOE RES LTD

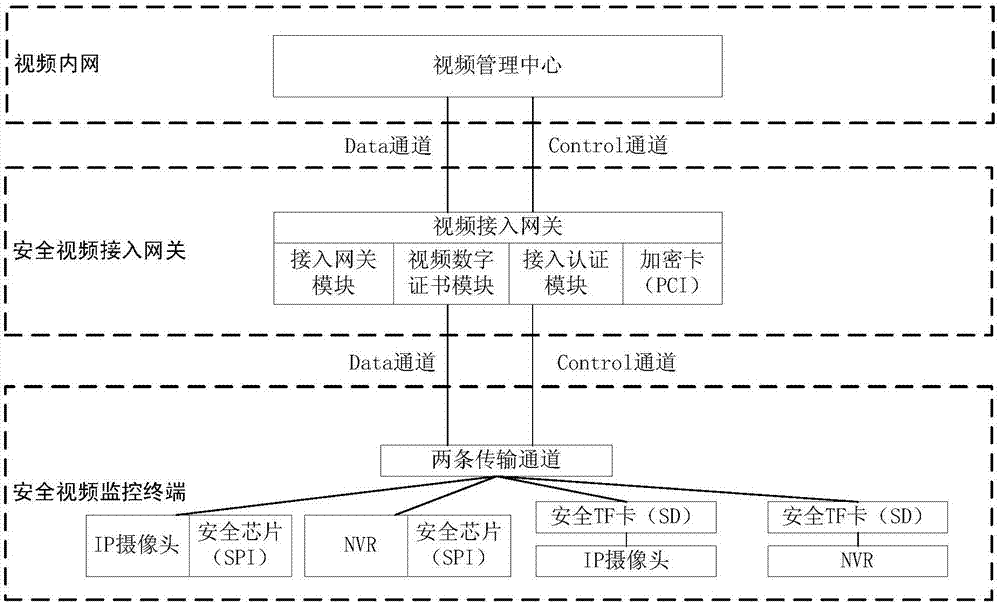

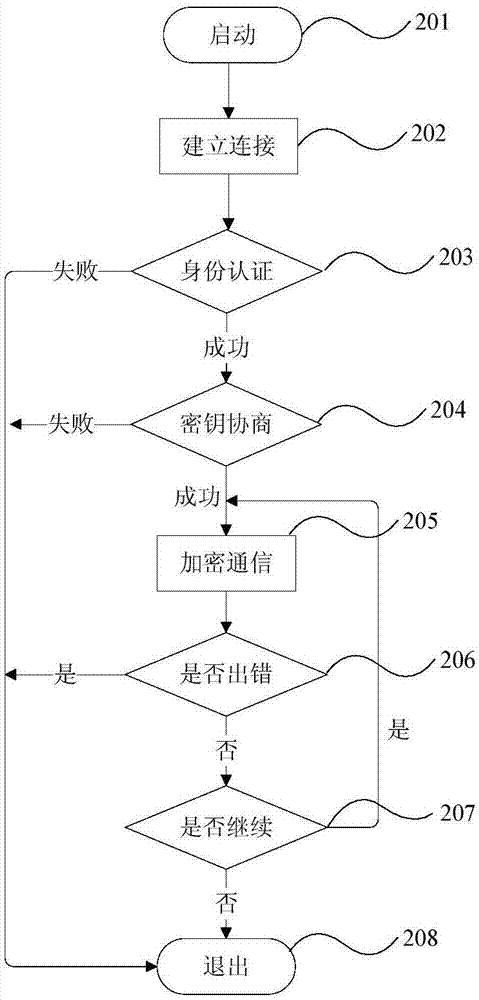

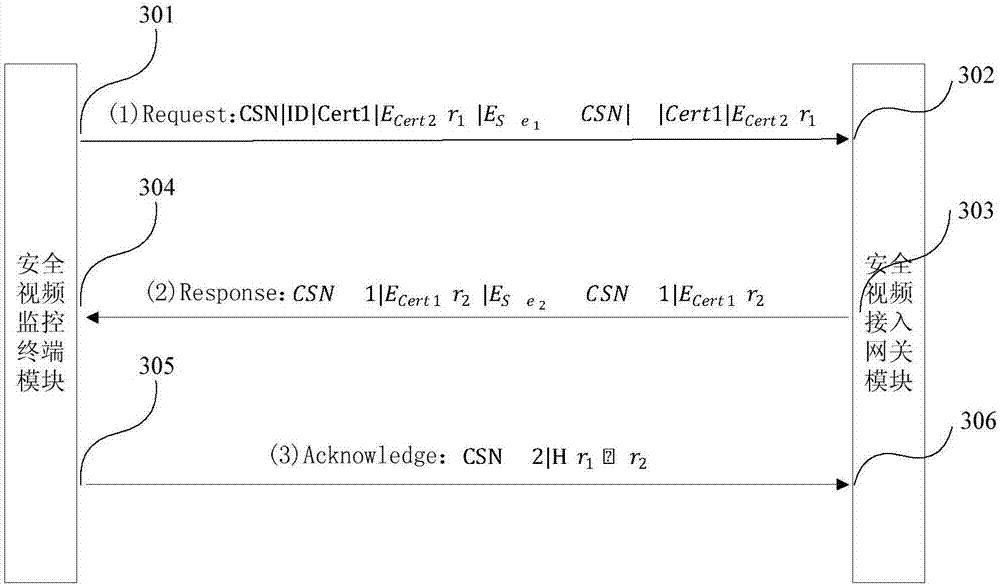

Video information encryption and video terminal security certification system, certification method, and application

ActiveCN107343179ARealize secure transmissionAvoid safety hazardsClosed circuit television systemsInformation repositoryVideo monitoring

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

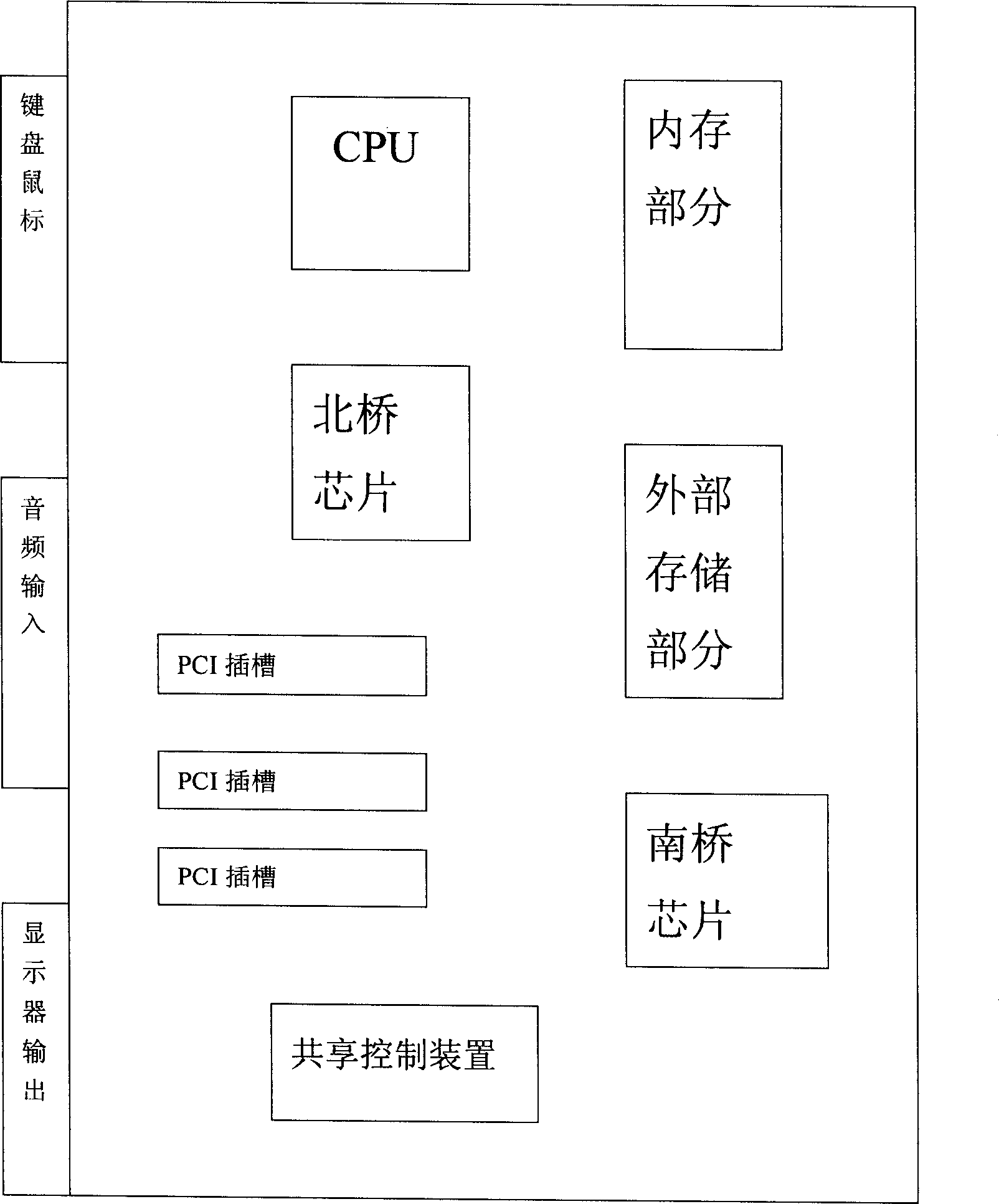

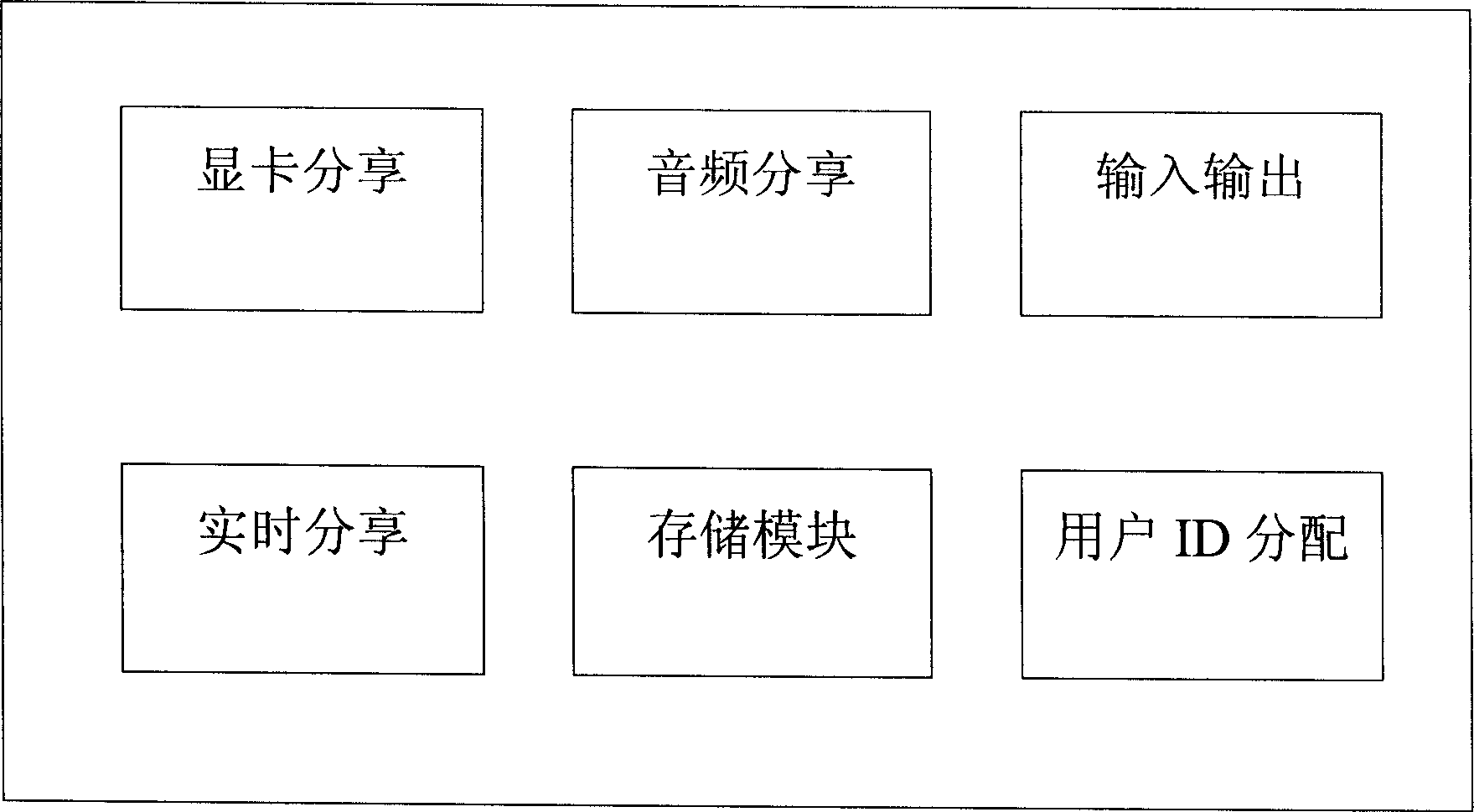

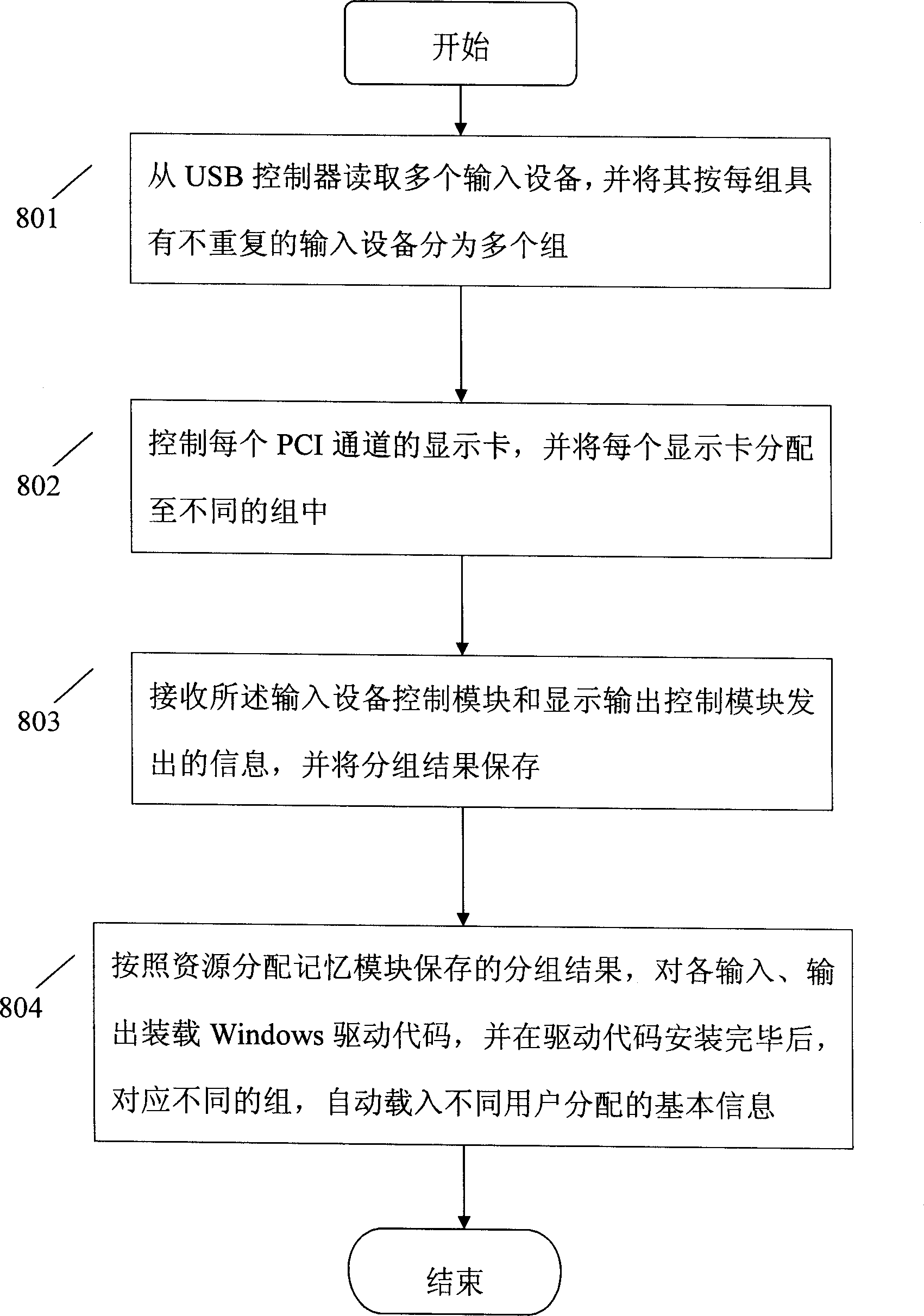

System for multi-user sharing internal and external storage of computer

An internal and external system of computer shared by multiuser consists of a multiuser operation system, host board, central processor, internal memory and external storage. It is featured as forming said host board by multiple USB interface, USB controller, multiple PCI interface, PCI controller and a shared control unit including an input unit control device, a display output control unit, a resource distribution memory unit and multiuser bottom layer analog core. The method of utilizing said system is also disclosed.

Owner:广州市立本电器有限公司