Patents

Literature

269results about How to "High speed data transmission" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

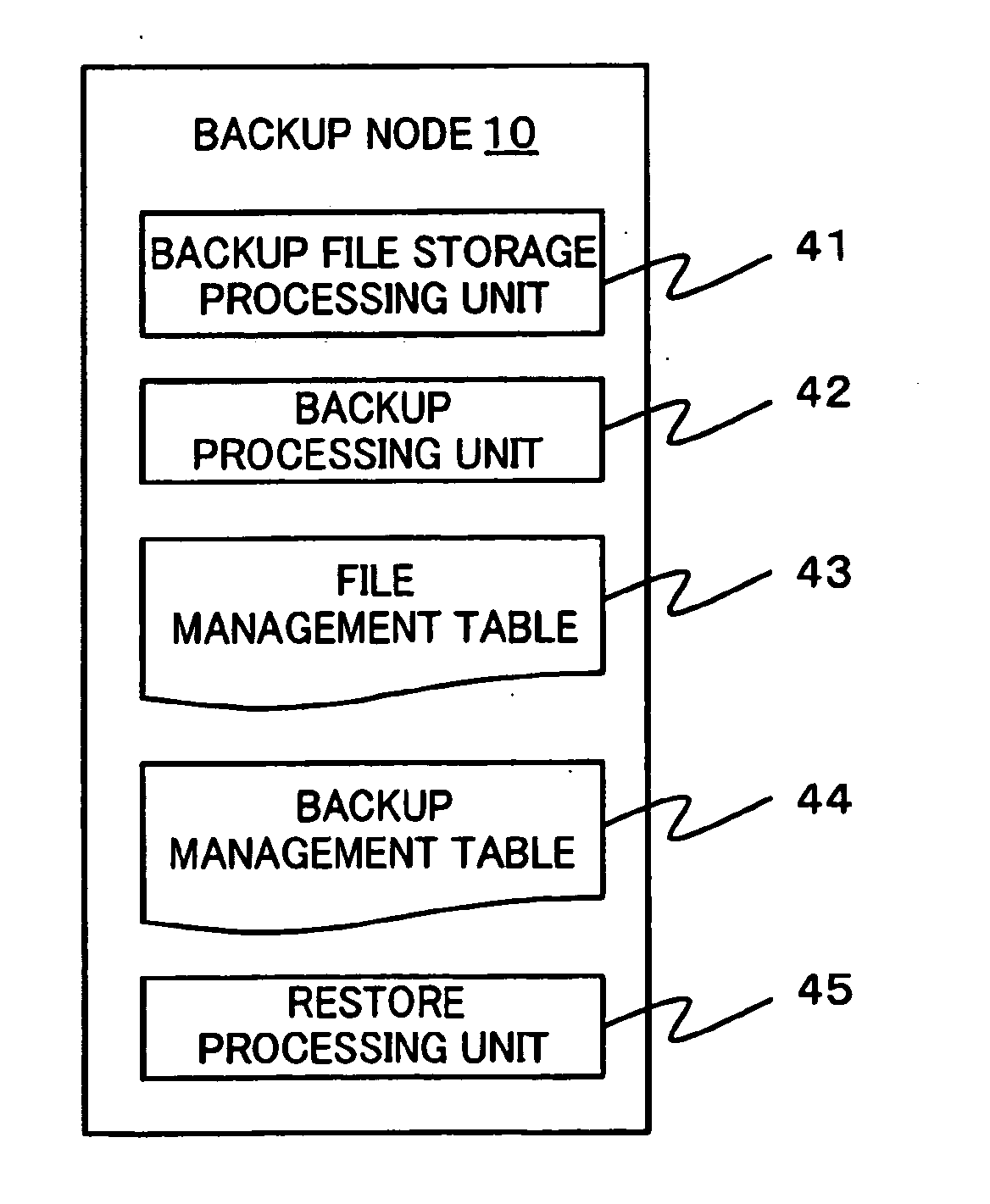

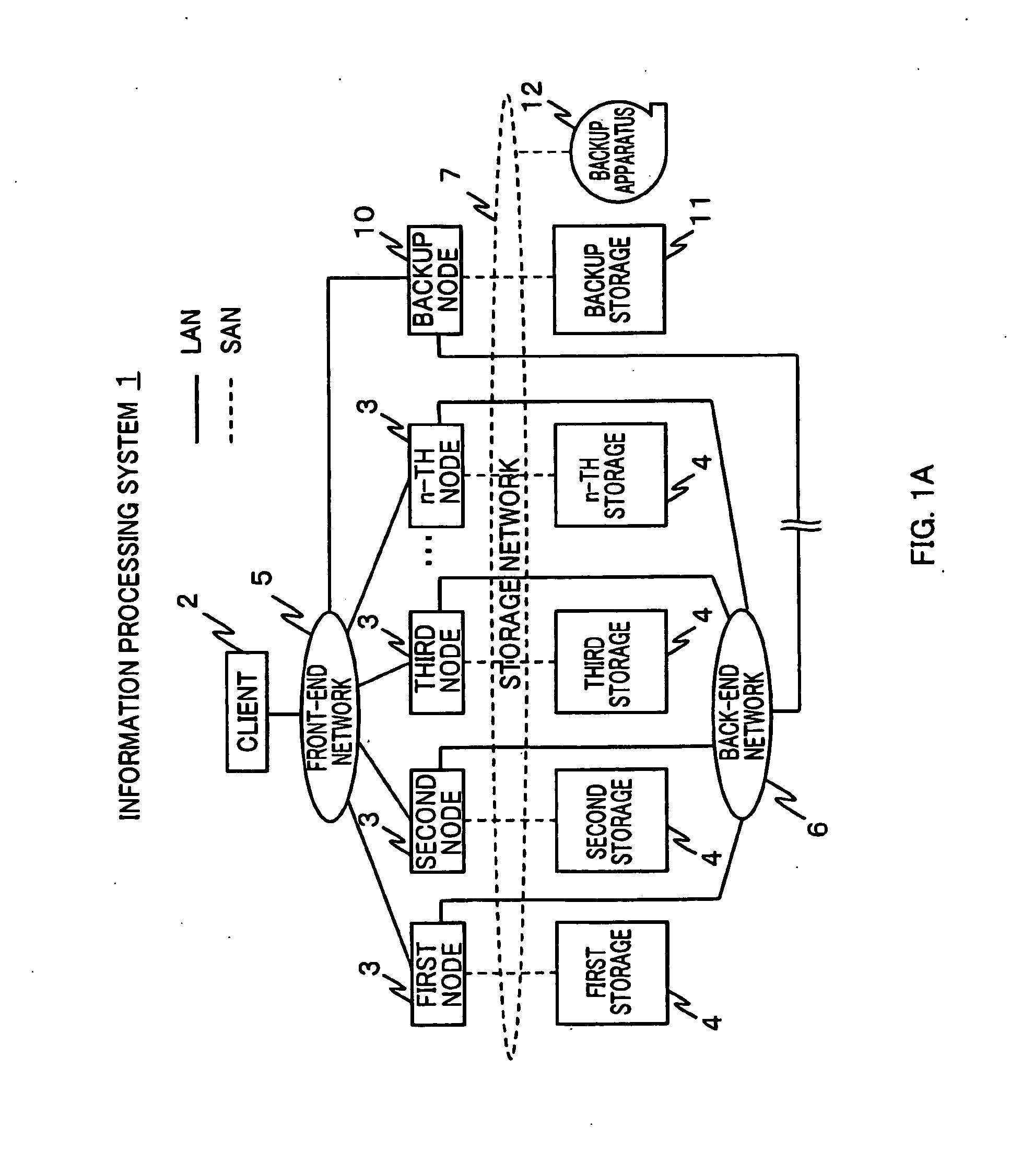

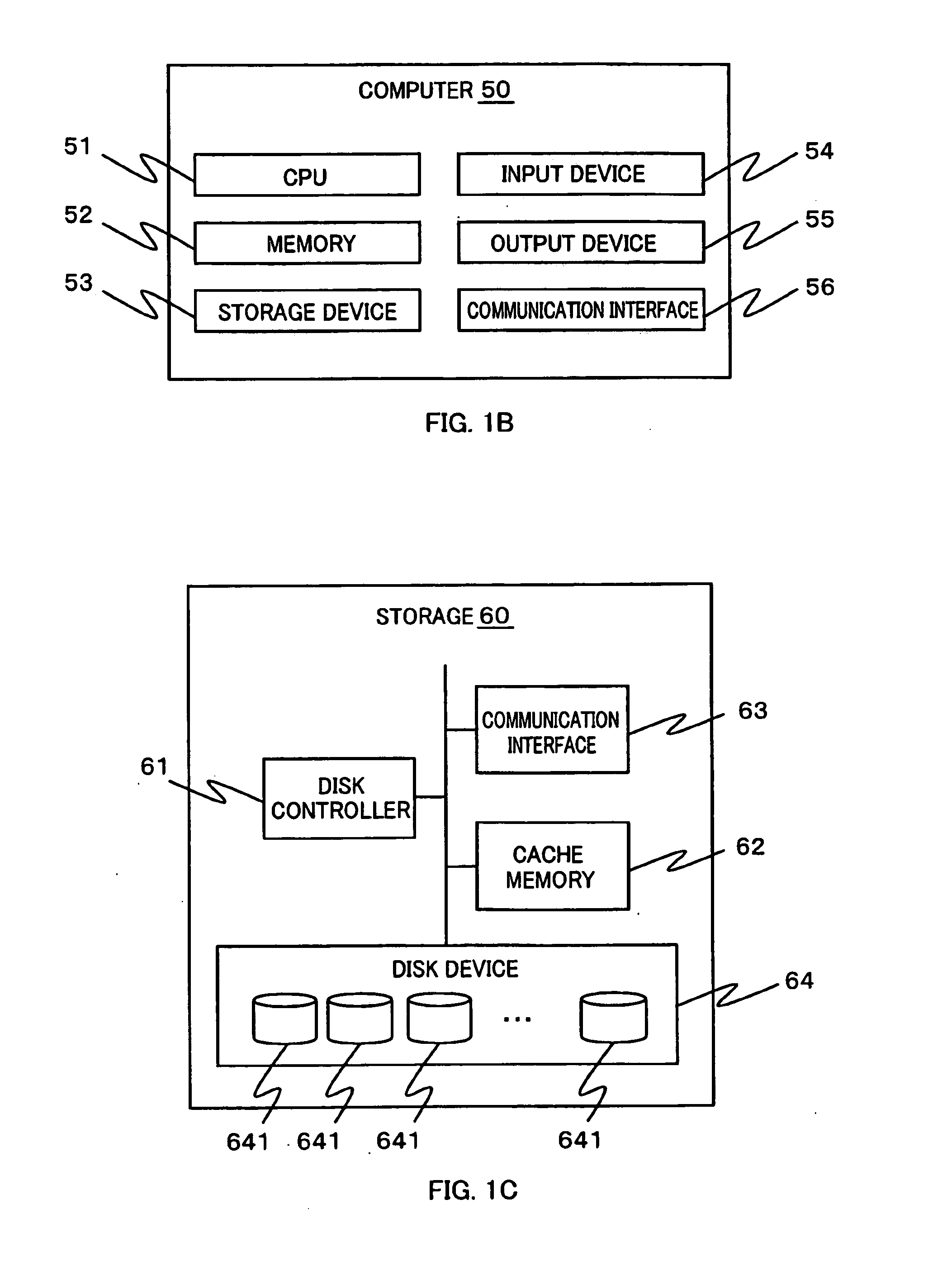

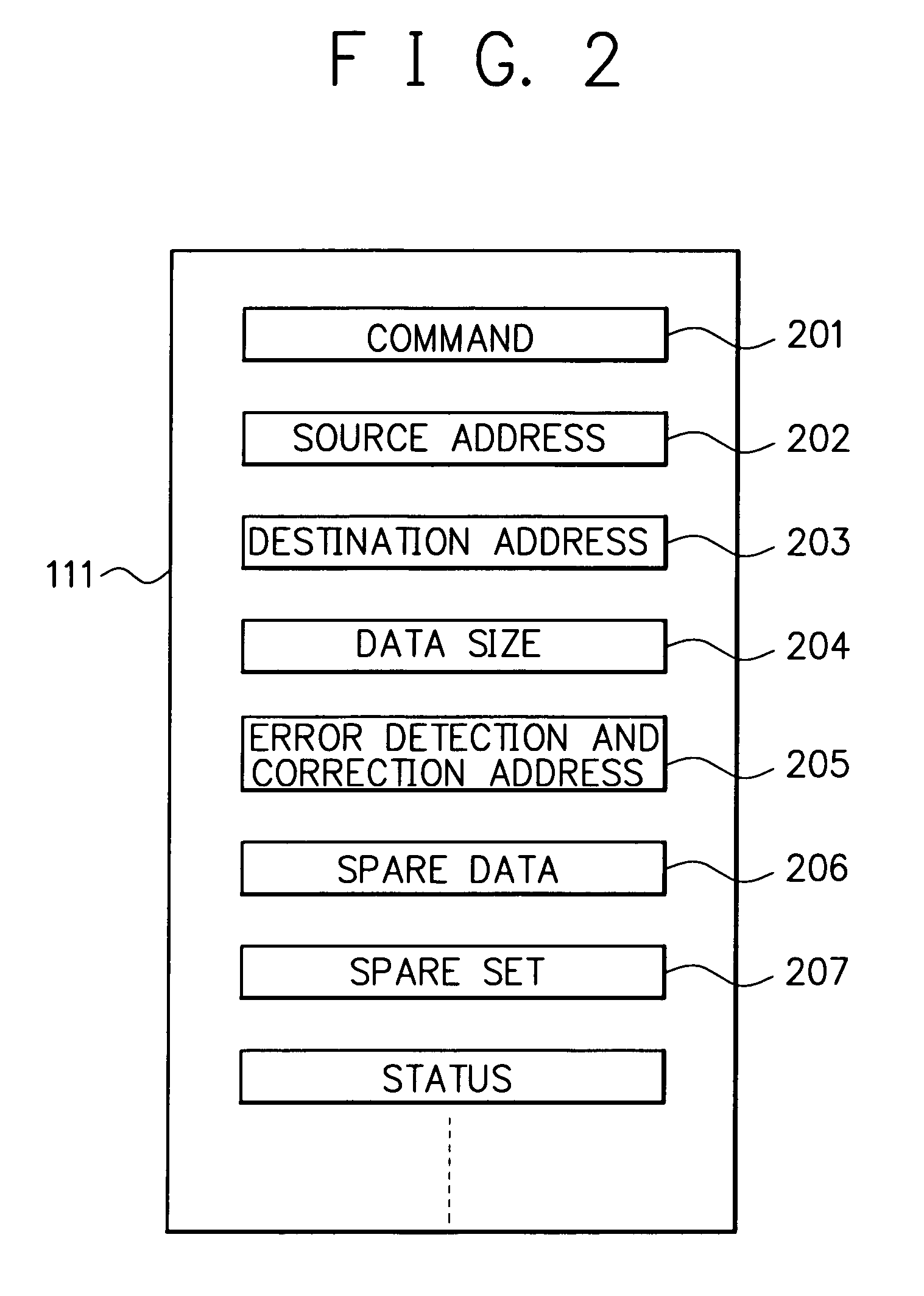

Information processing system and method of acquiring backup in an information processing system

InactiveUS20110238625A1Backup fileCreate efficientlyError detection/correctionDigital data processing detailsInformation processingVirtual file system

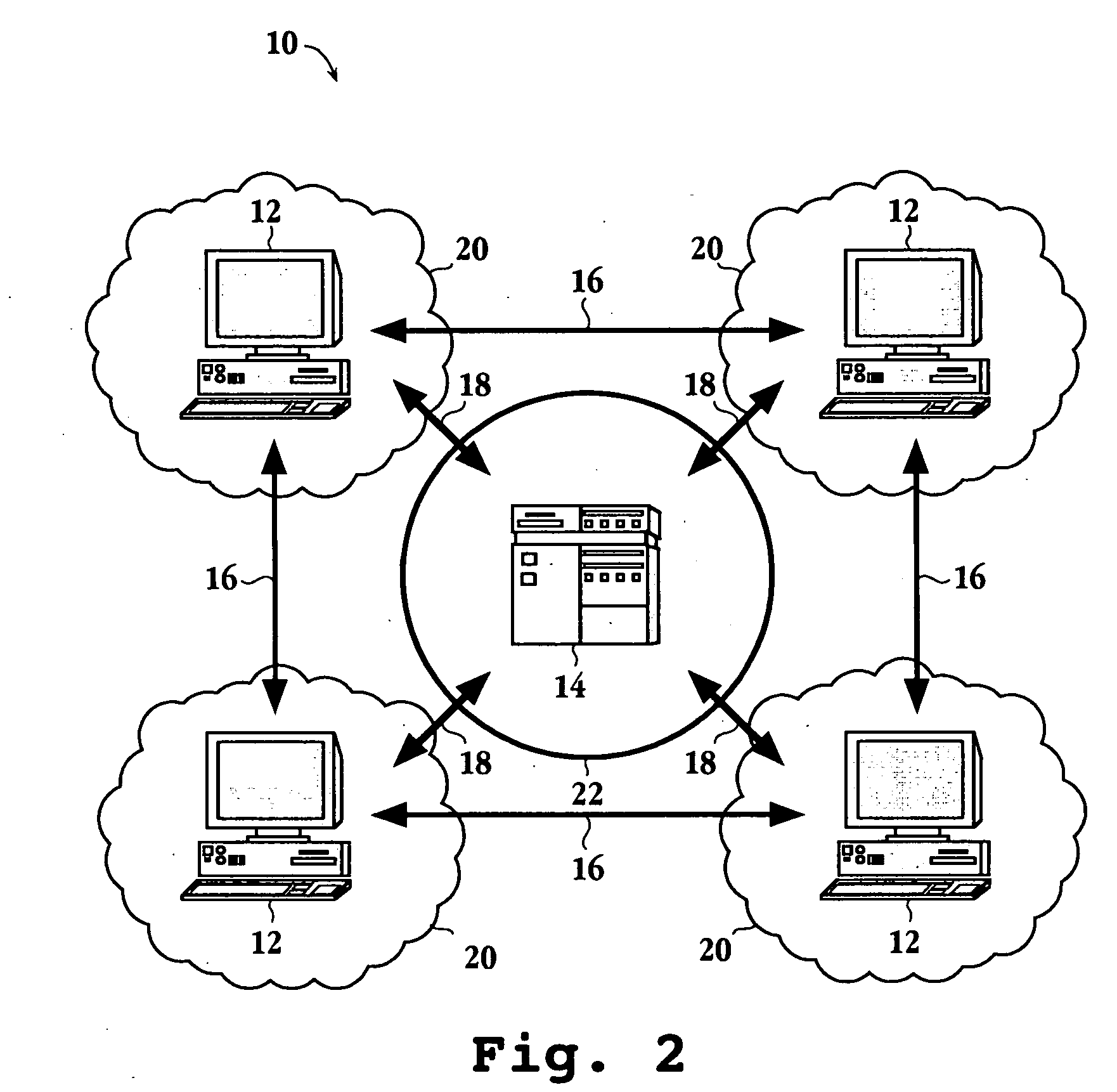

Provided is an information processing system including a plurality of nodes 3 and a plurality of storages 4 coupled subordinately to each of the nodes 3, each of the nodes 3 functioning as a virtual file system that provides a client 2 with storage regions of each of the storages 4 as a single namespace. This information processing system is further provided with a backup node 10 and a backup storage 11 coupled subordinately to the backup node 10. The backup node 10 synchronizes and holds location information (file management table 33) held by each of the nodes 3. Then, the backup node 10 creates a backup file, and stores the backup file in the backup storage 11 by accessing a location identified by the location information (file management table 43) synchronized and held by the backup node 10 itself to acquire a file.

Owner:HITACHI LTD

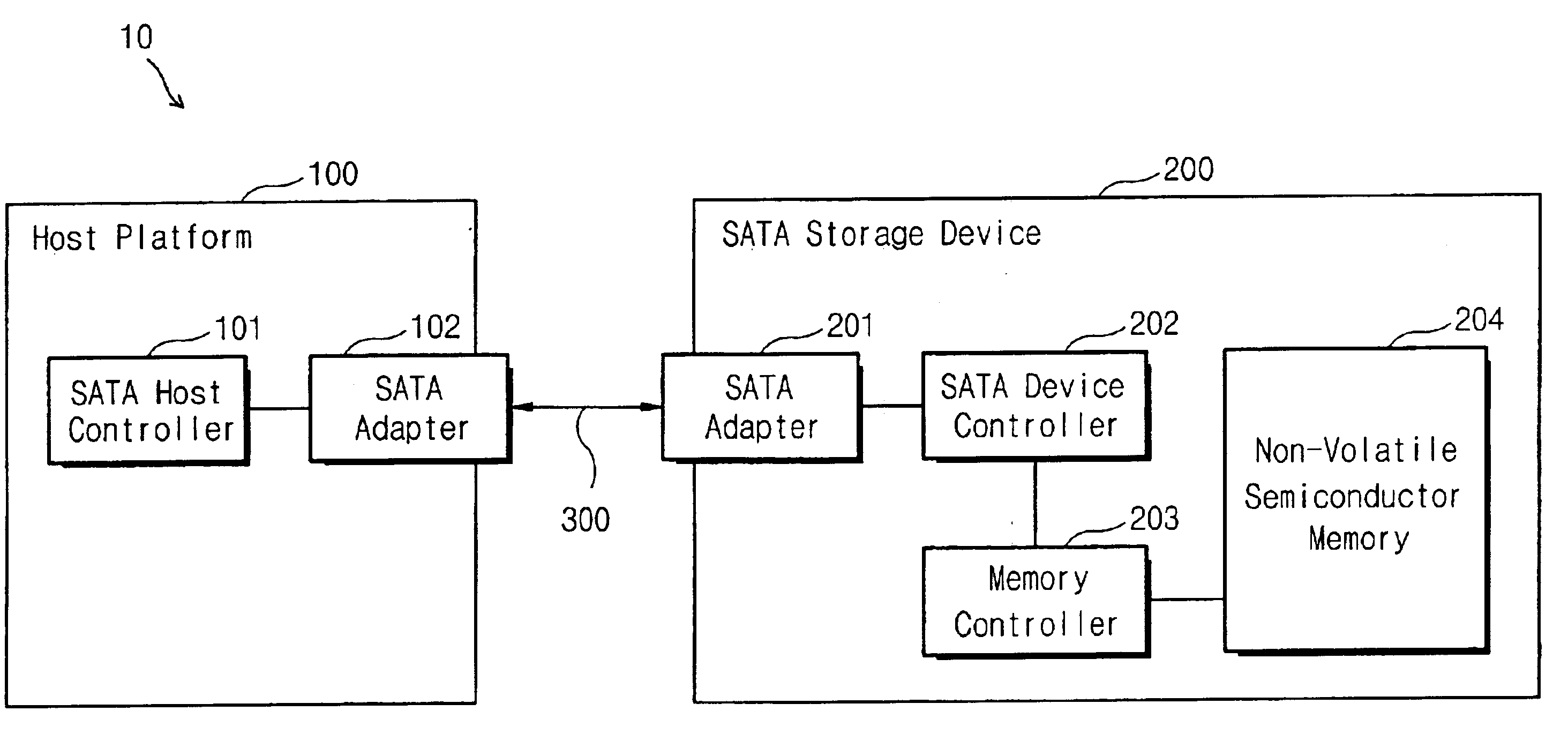

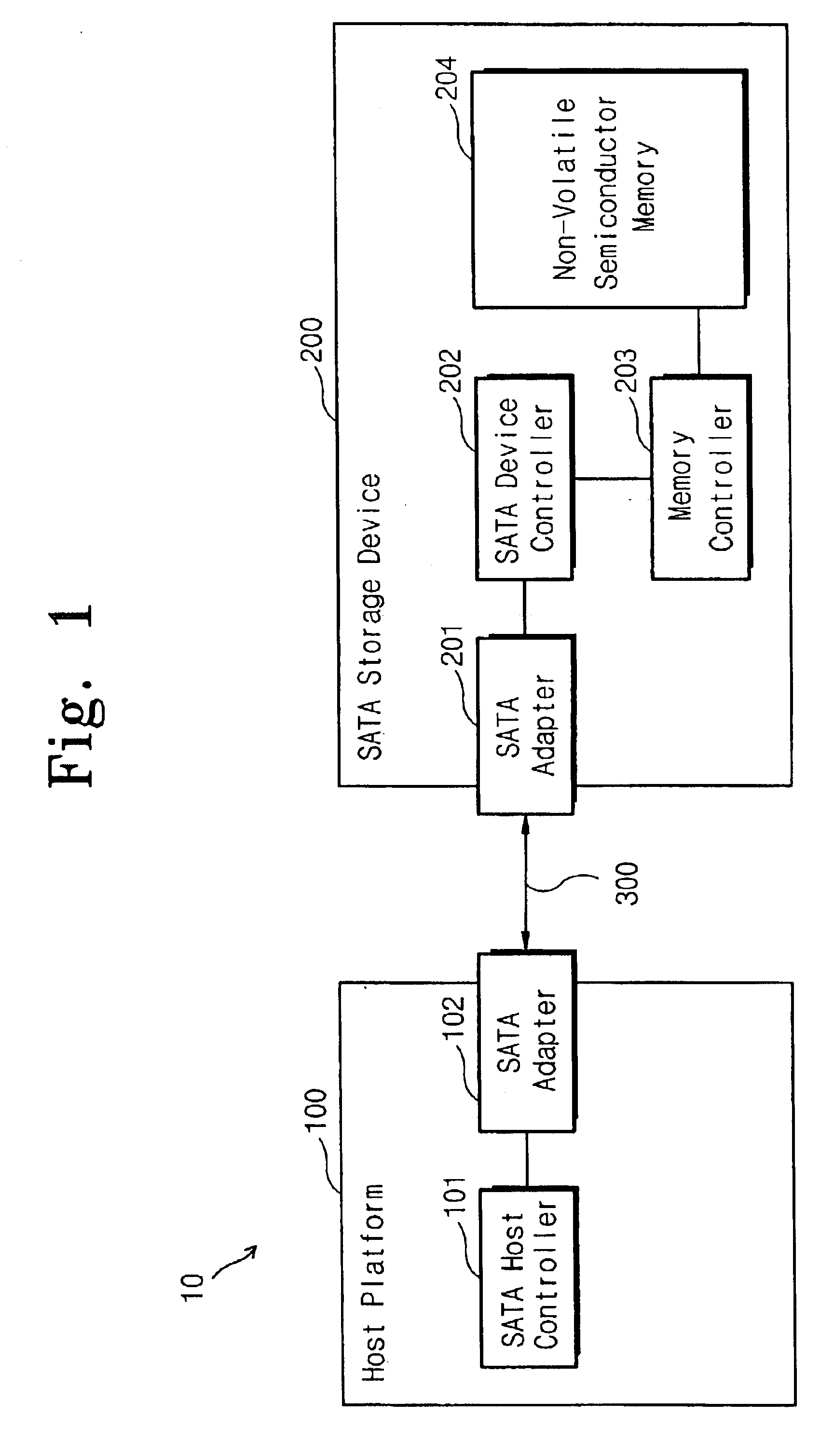

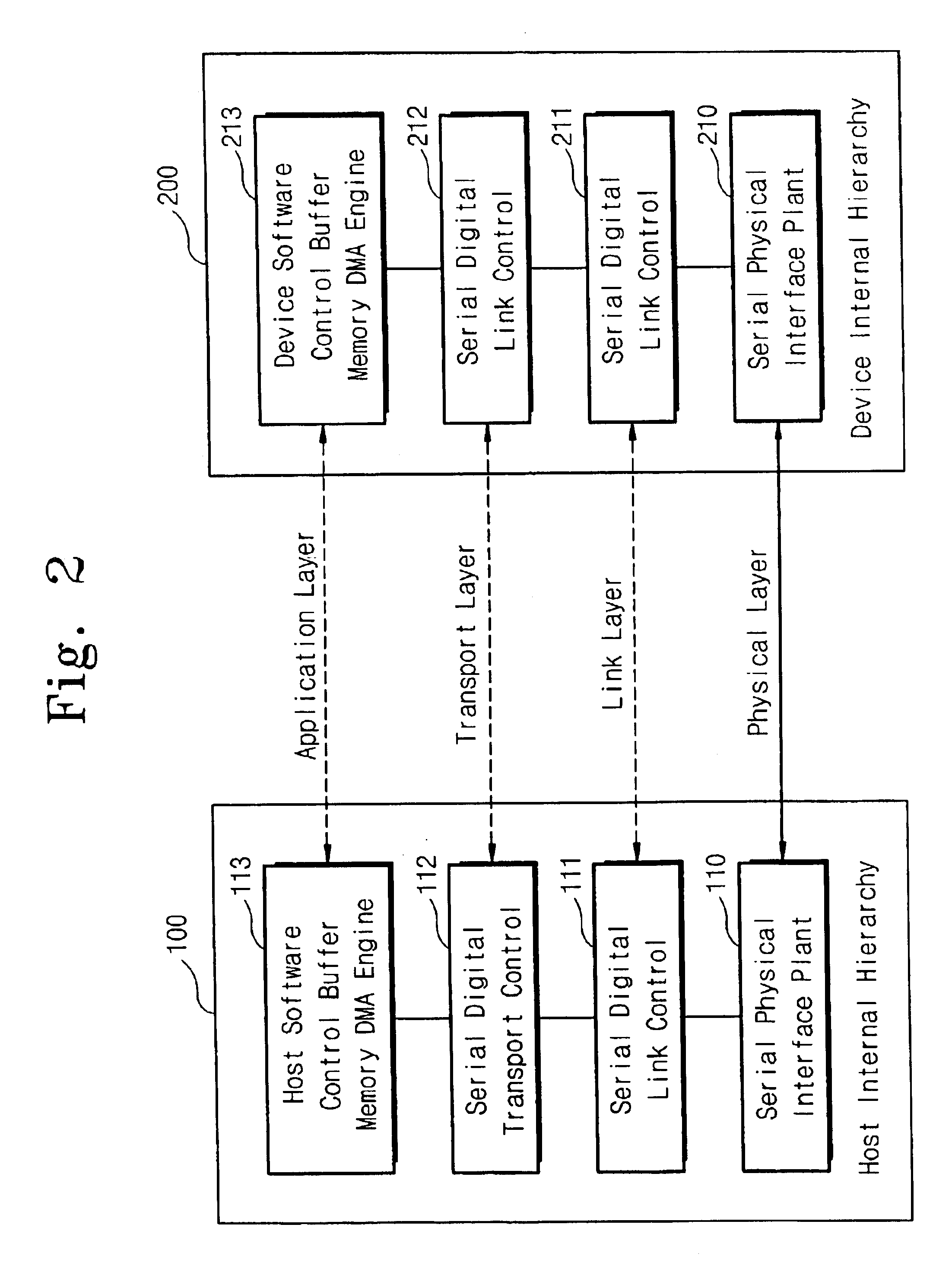

Non-volatile semiconductor memory device for connecting to serial advanced technology attachment cable

ActiveUS6853573B2High speed data transmissionInput/output to record carriersRead-only memoriesMemory controllerData transmission

A serial advanced technology attachment (SATA) storage device supports an SATA protocol that provides for high data transfer speed. The storage device is for connecting to an SATA cable, and includes at least one non-volatile semiconductor memory device for storing data therein; an SATA adapter, connected to the SATA cable, for transferring / receiving data signals to / from the SATA cable; a memory controller for controlling the non-volatile semiconductor memory device in response to data signals transferred from the SATA adapter; and an SATA device controller, connected between the SATA adapter and the memory controller, for interfacing transmitted / received data signals between the SATA adapter and the memory controller.

Owner:SAMSUNG ELECTRONICS CO LTD

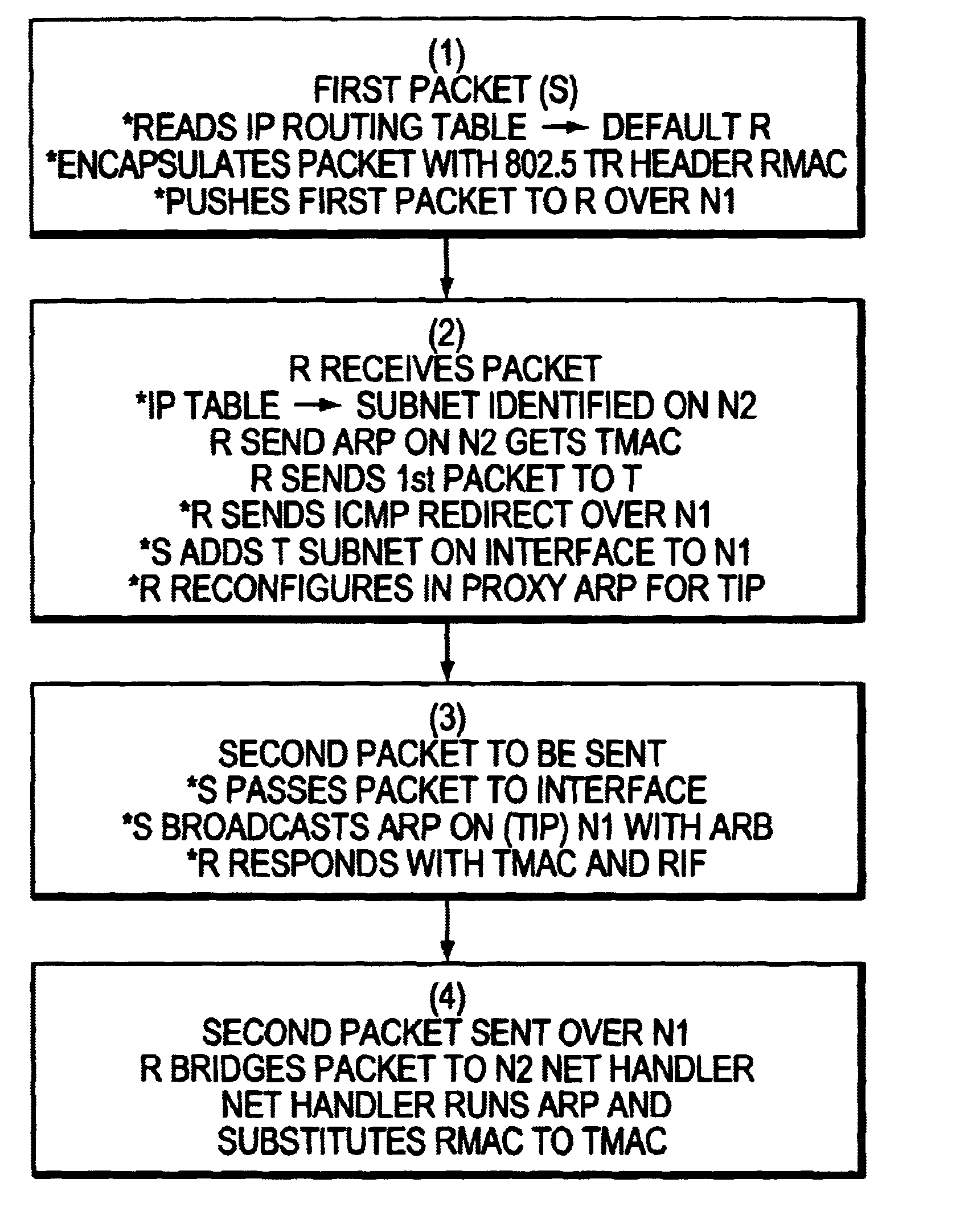

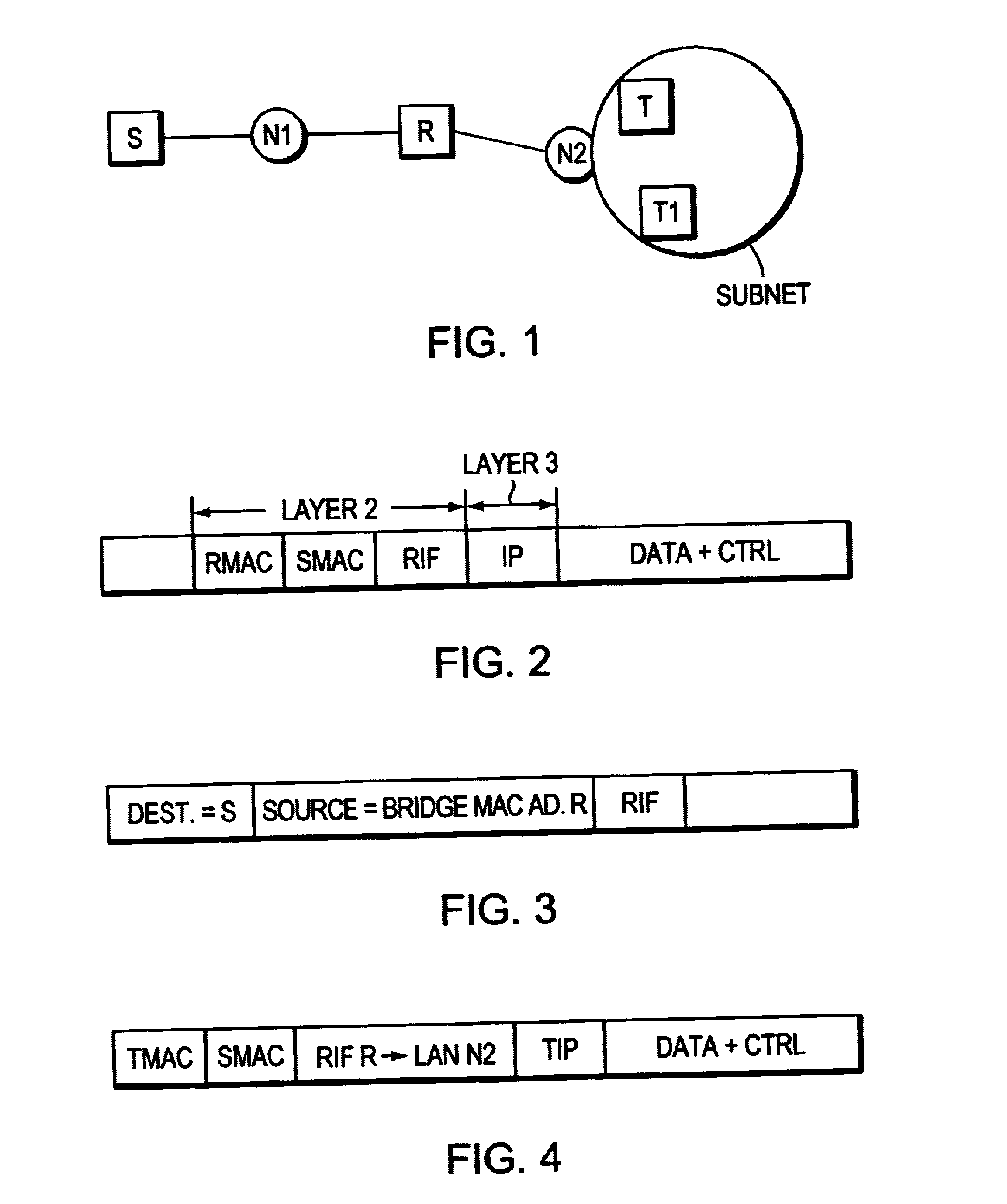

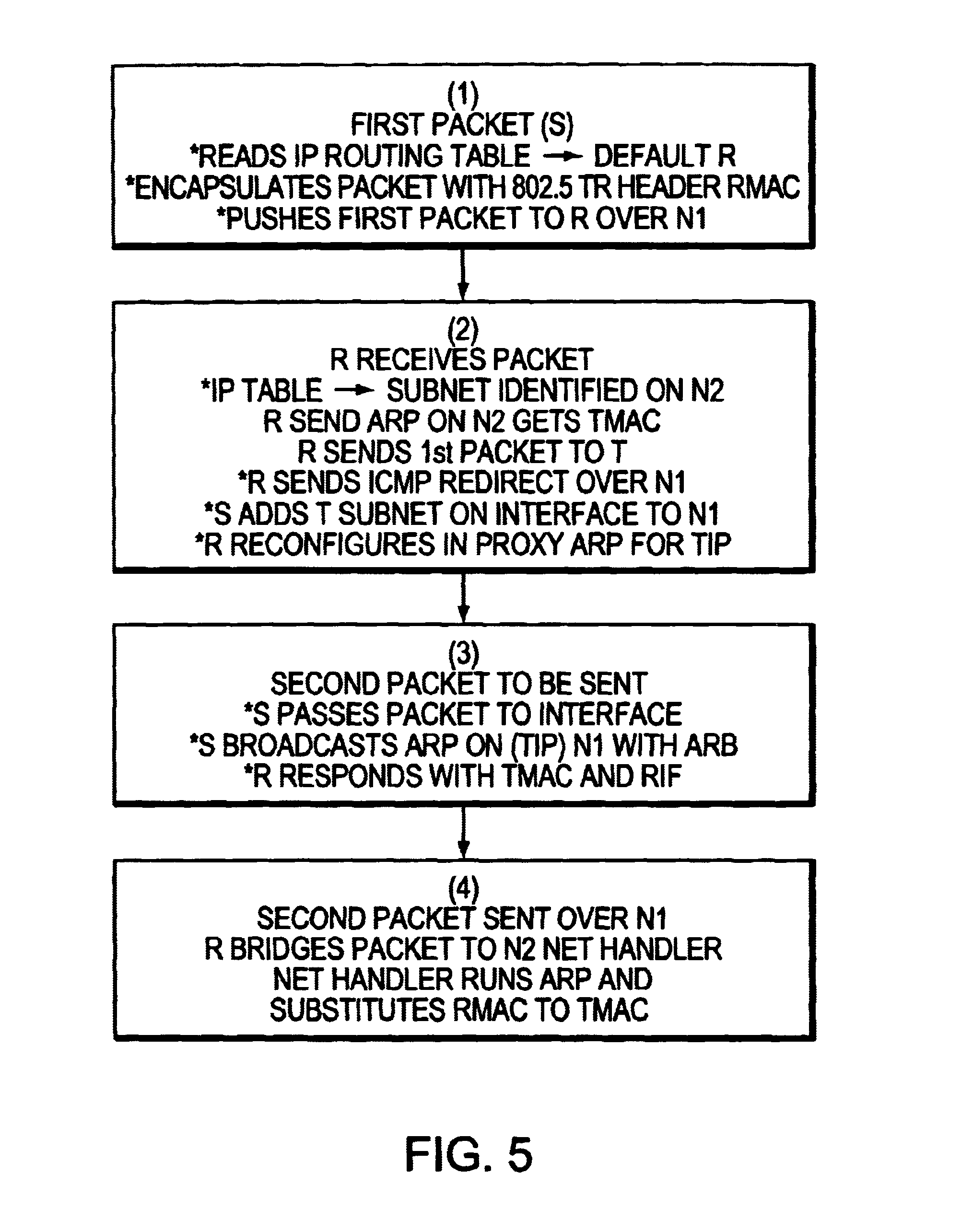

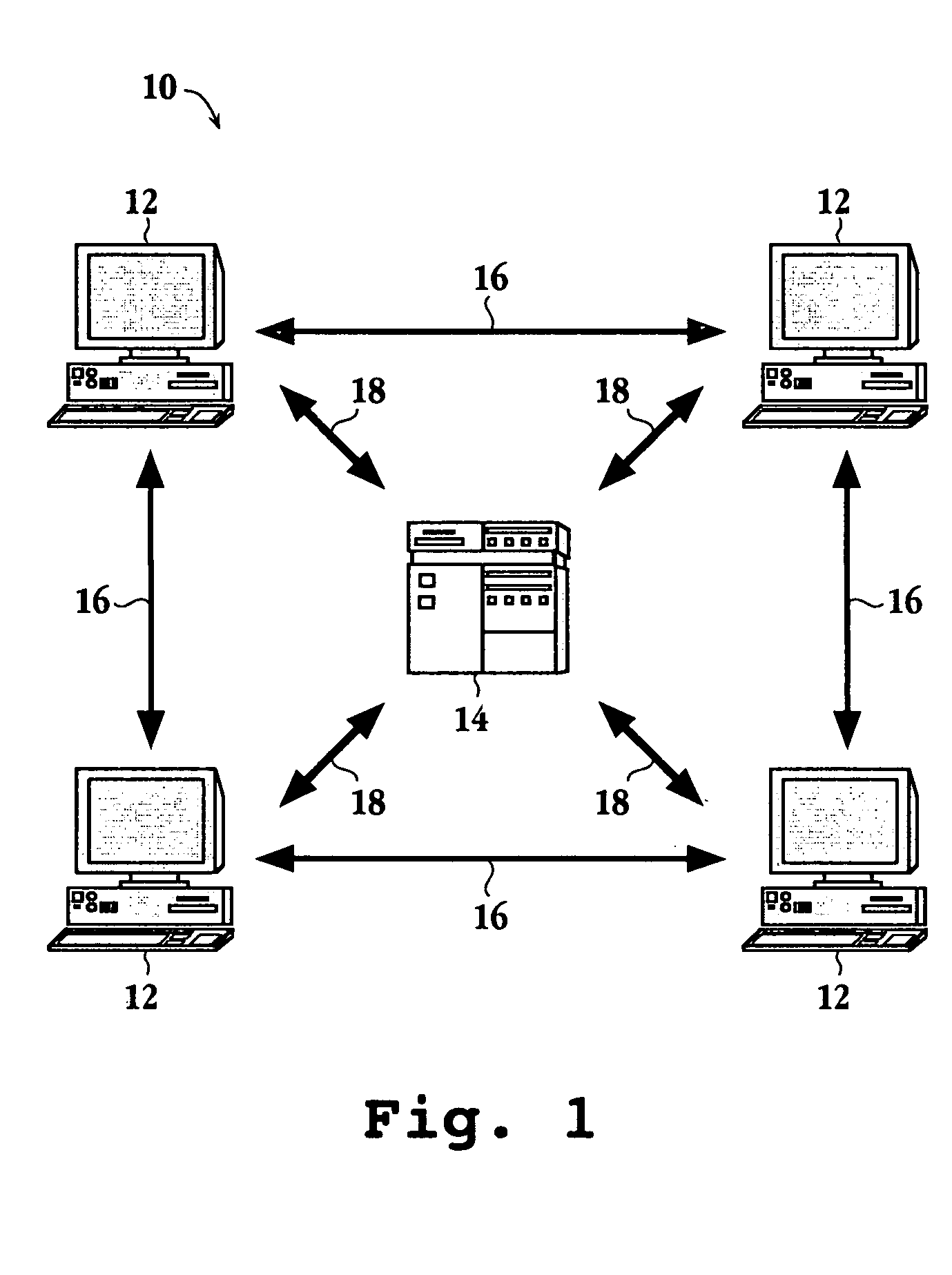

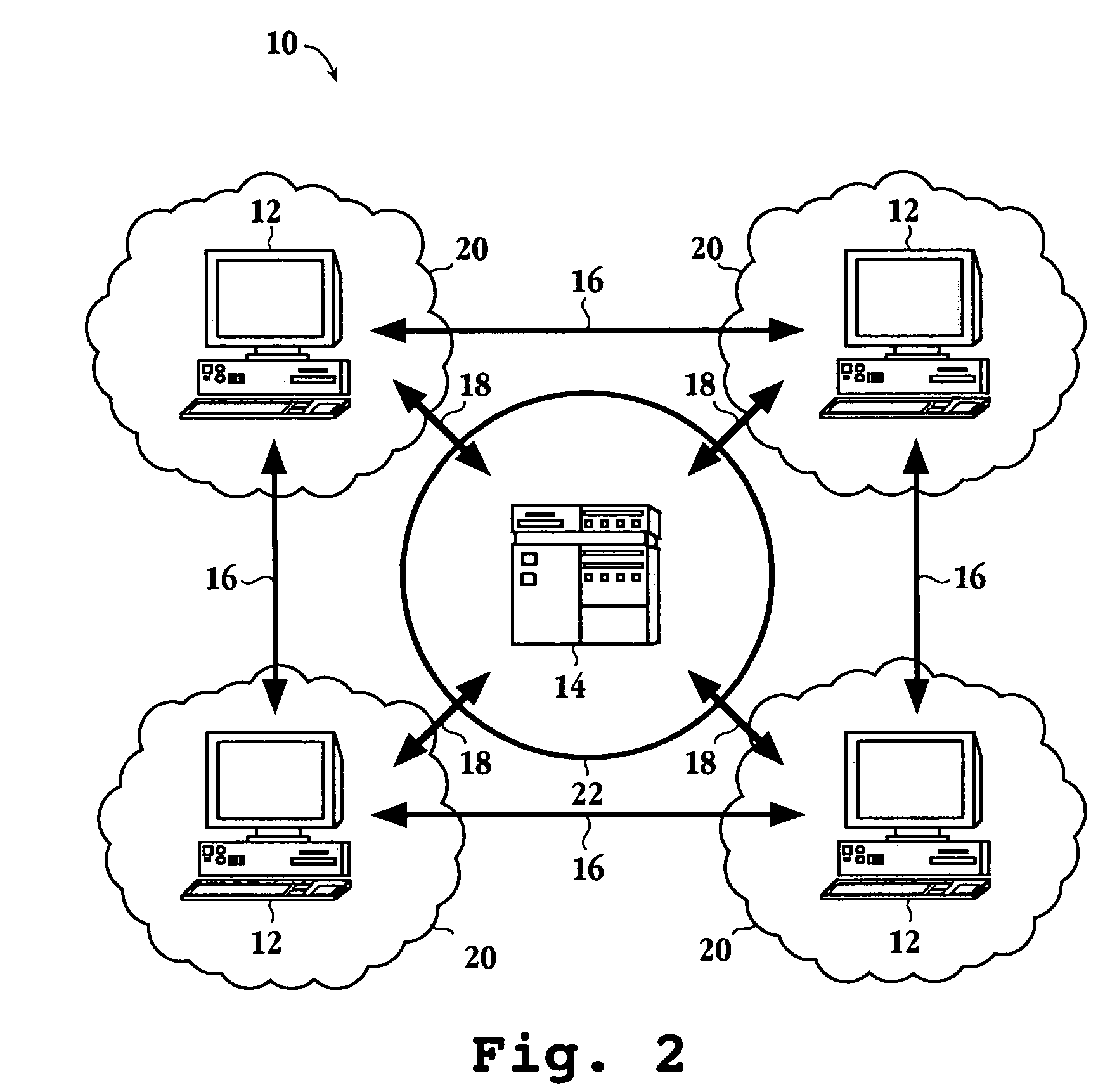

Method and system for improving high speed internetwork data transfers

InactiveUS6631137B1Improving high speed traffic operationHigh speed data transmissionNetworks interconnectionSecuring communicationVirtual LANIp address

A method for creating a single virtual LAN including a source (S) attached to a first Token ring LAN (N1), a target (T) within a subnet attached to a different Token ring LAN (N2), and an interconnecting router (R). The source (S) encapsulates the first packet with a Token ring header including the router MAC address (RMAC), SMAC as source MAC address as layer 2 information, and IP address of T (TIP) as layer 3 data and sends this packet over N1 toward the router. When receiving the first packet, R reads its IP table for best match with TIP address to identify the subnet including T. The net handler runs an ARP protocol to identify TMAC address, substitutes the MAC header with said TMAC address into said first packet destination MAC address field and forwards said first packet over N2. R then sends a conventional ICMP message over N1 limited broadcast and reconfigures itself in proxy ARP for the defined subnet. For the second packet, S runs an ARP and R answers with RMAC address and the RIF data to be used for next packets.

Owner:CISCO TECH INC

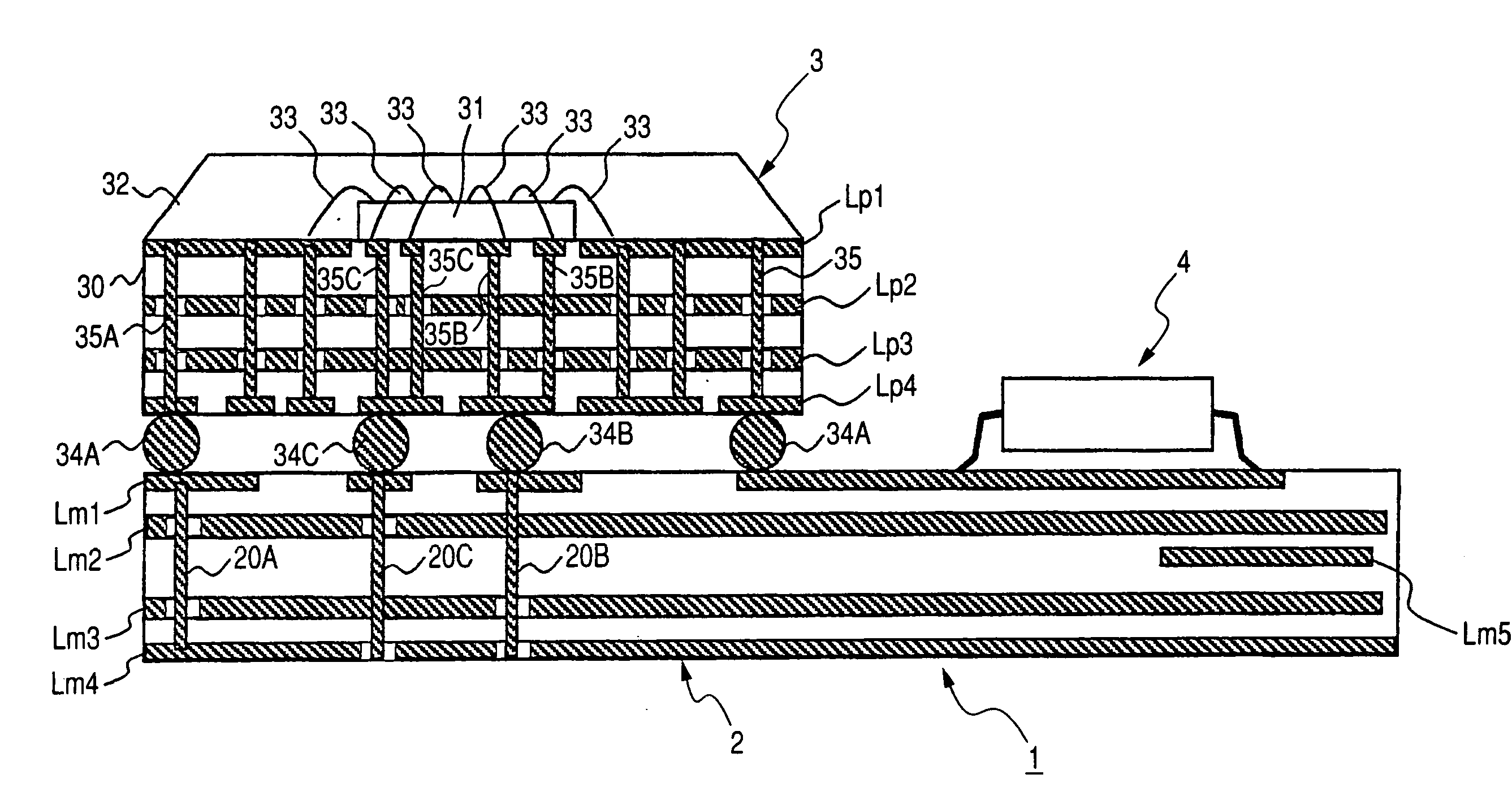

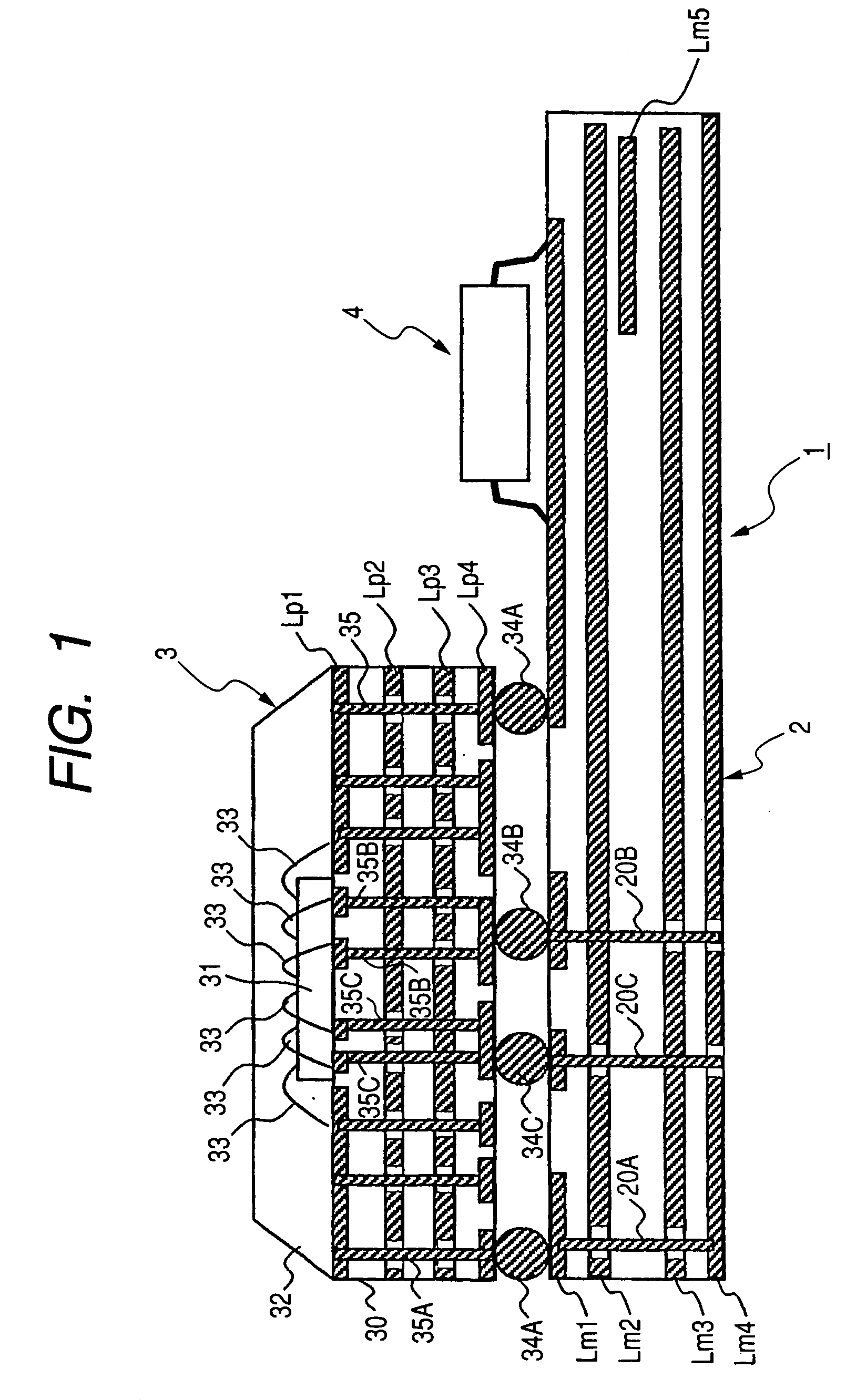

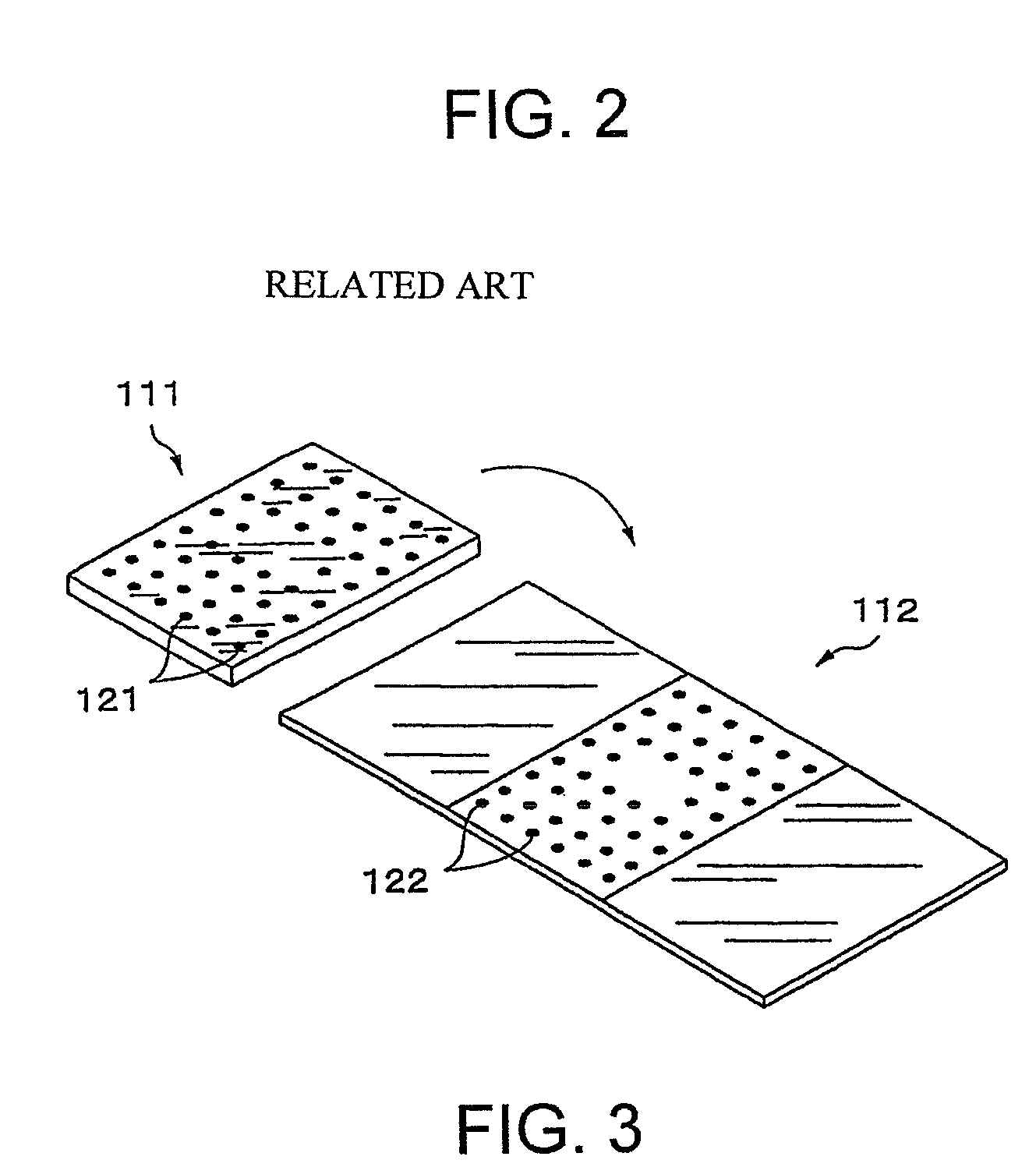

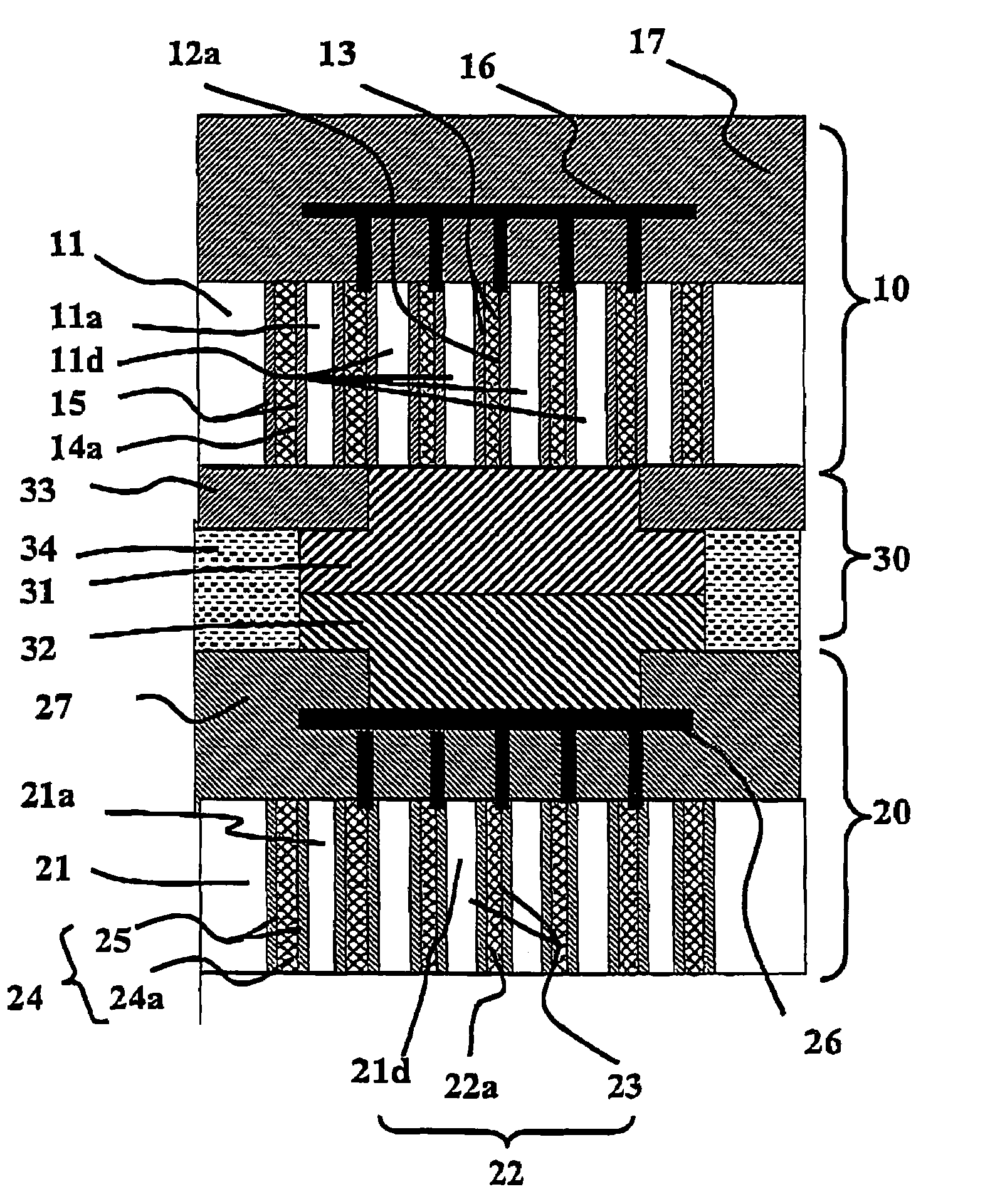

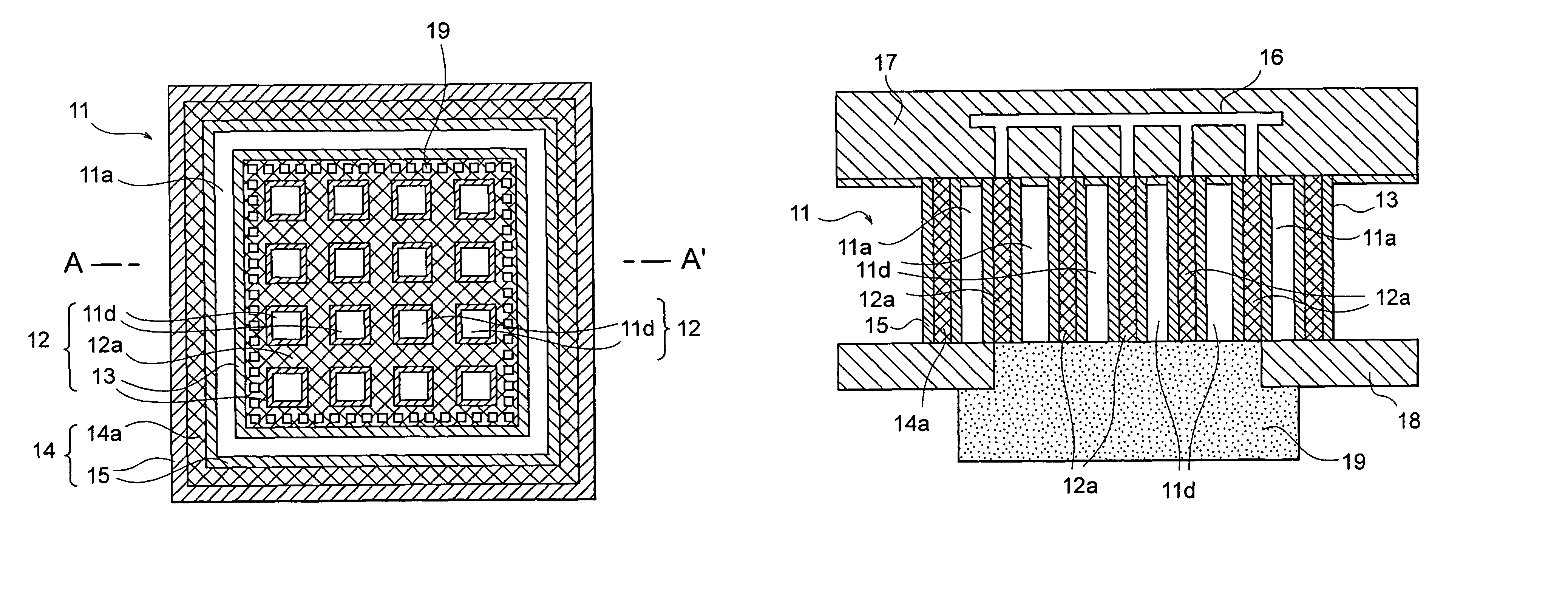

Electronic circuit, a semiconductor device and a mounting substrate

InactiveUS20070194433A1Improve conversion accuracyPrevent switching noiseFinal product manufactureCross-talk/noise/interference reductionDevice materialSemiconductor chip

An electronic circuit includes a first semiconductor device (4) and a second semiconductor device (3) on a mounting substrate. The mounting substrate includes a plurality of mounting substrate lines (201 to 204) which are connected in common with external terminals of a plurality of bits of the first semiconductor device and external terminals of a plurality of bits of the second semiconductor device for every bit. The mounting substrate lines have lengths thereof from the external terminals of the first semiconductor device to the external terminals of the second semiconductor device made unequal for respective bits. Assembling lines (361 to 364) which reach connecting electrodes of a semiconductor chip from the external terminals of the second semiconductor device have made lengths thereof unequal for respective bits. Here, the unequal lengths of the mounting substrate lines have a relationship which offsets the unequal lengths of the assembling lines. According to such a constitution, it is unnecessary to set lengths between the external terminals of the second semiconductor device and the connecting electrodes of the semiconductor chip equal.

Owner:RENESAS ELECTRONICS CORP

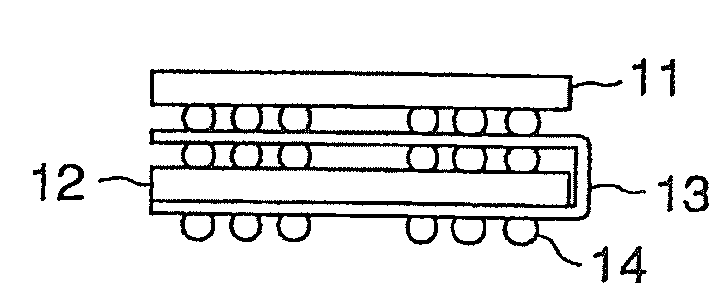

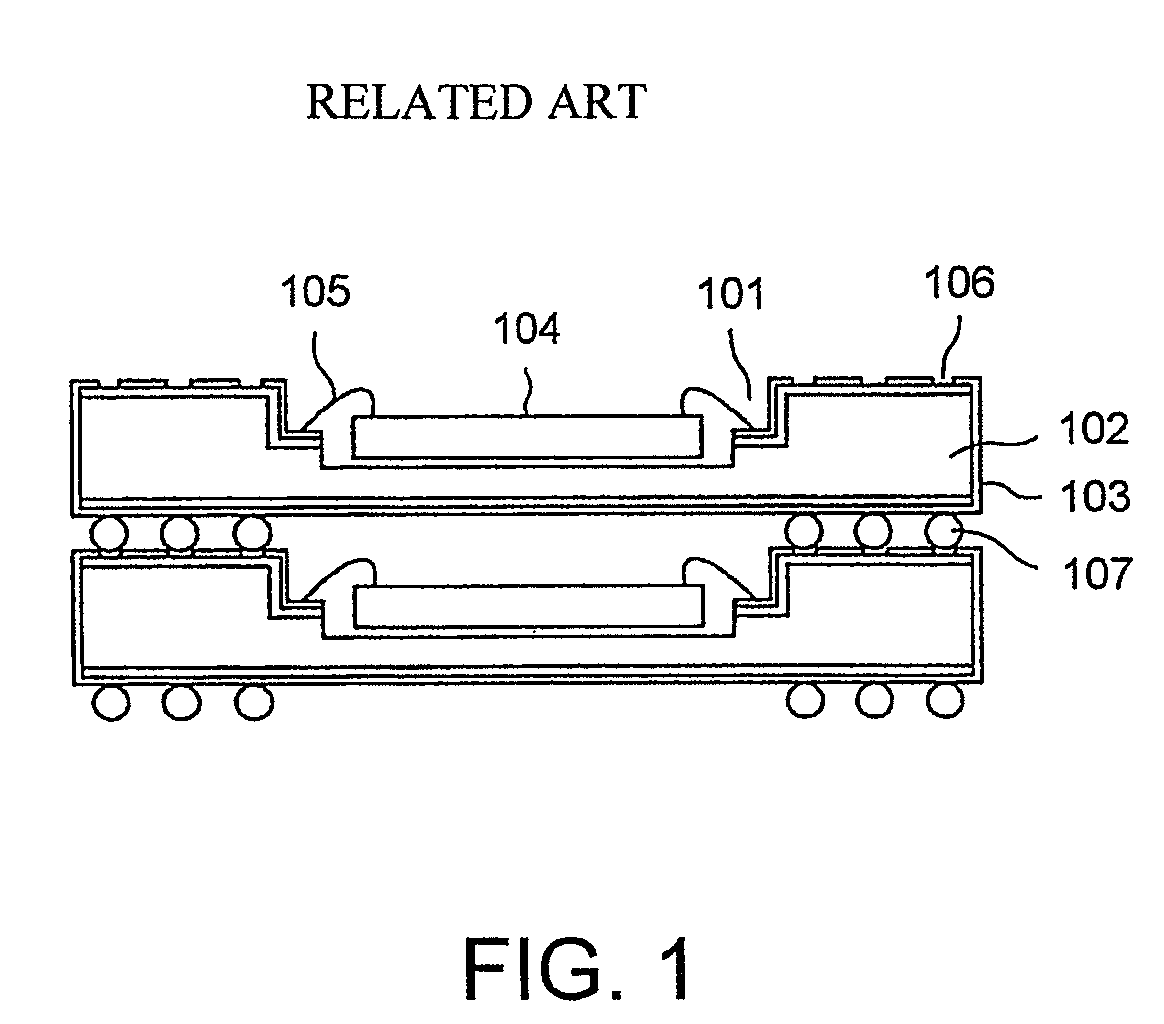

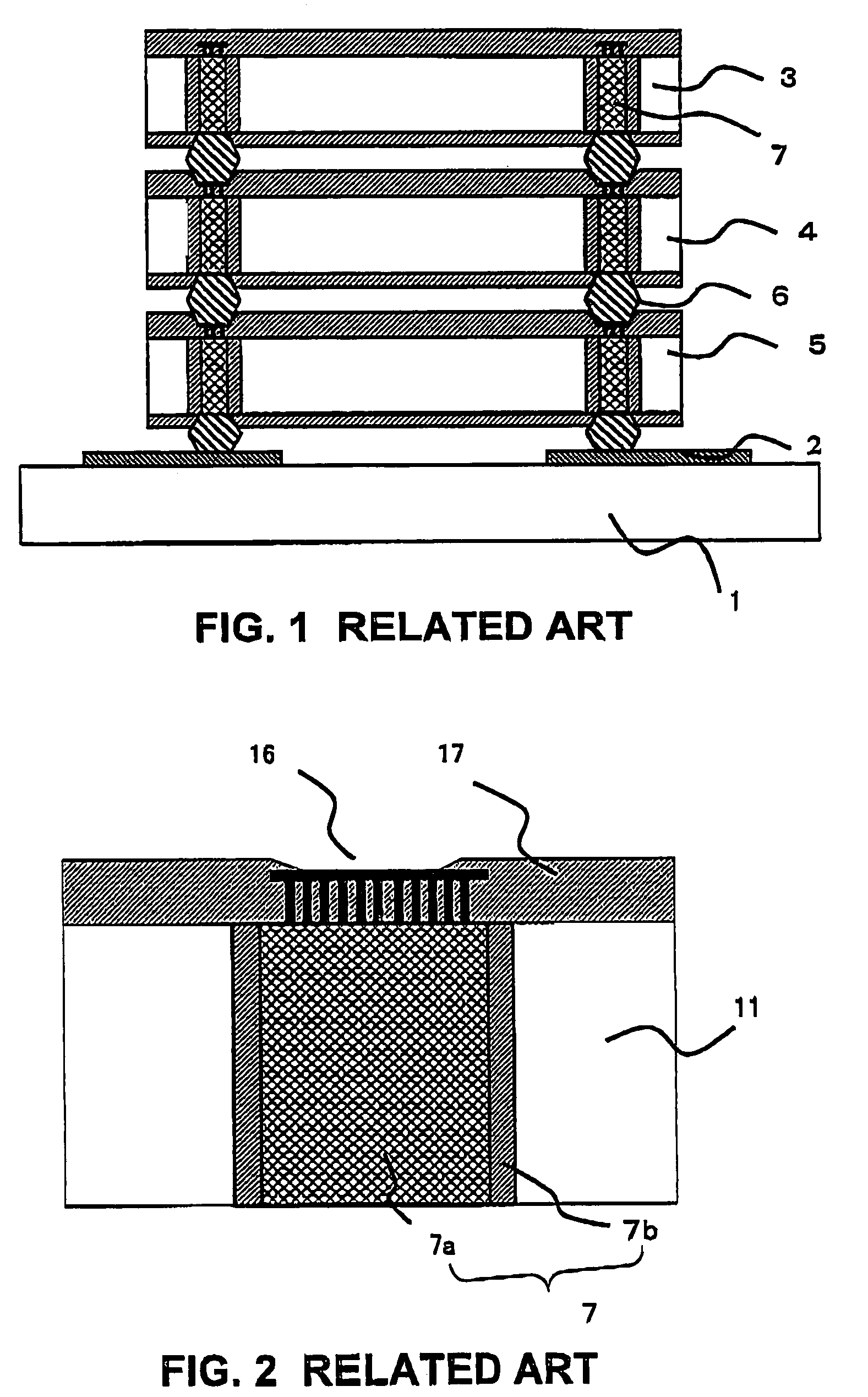

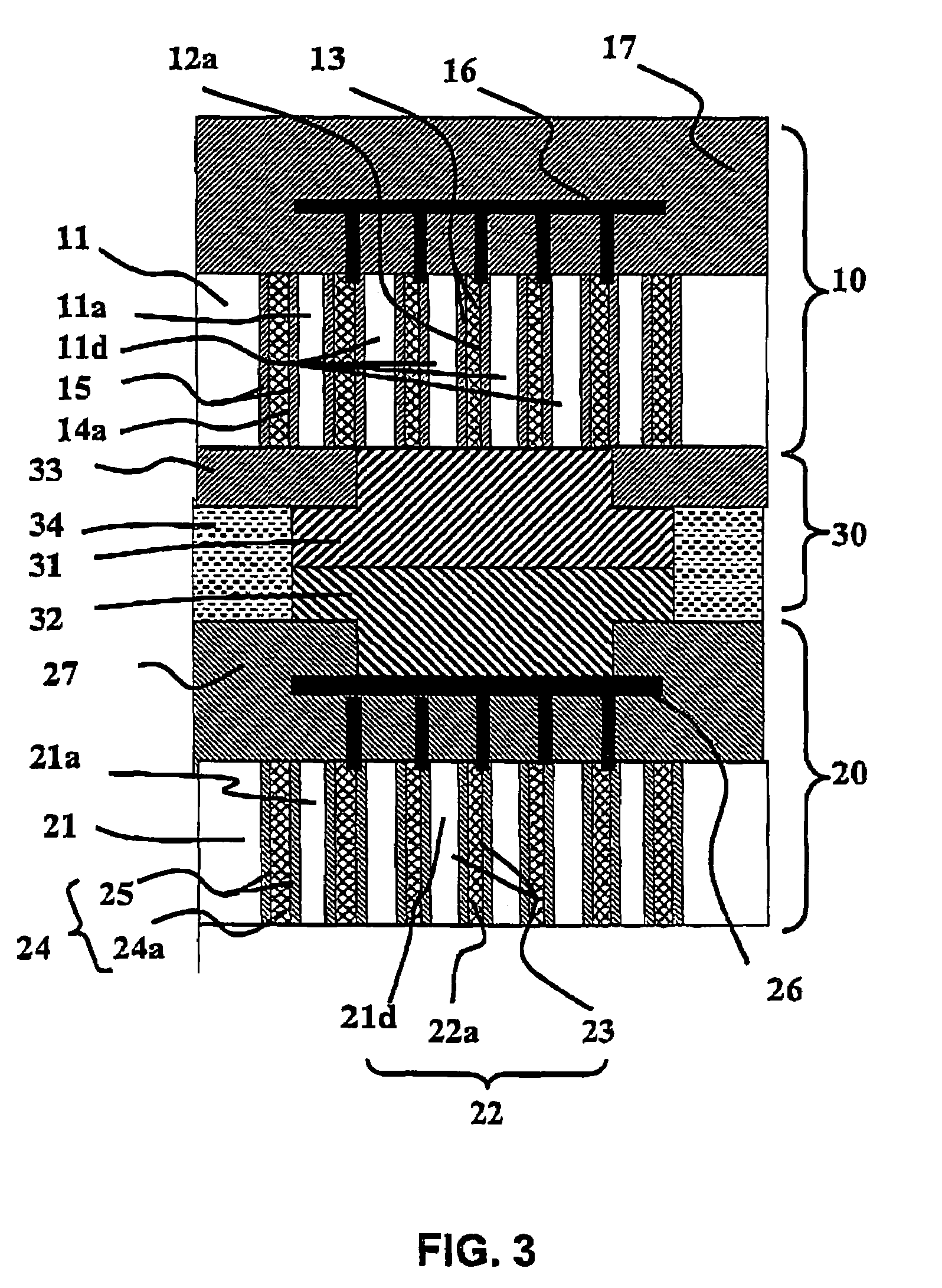

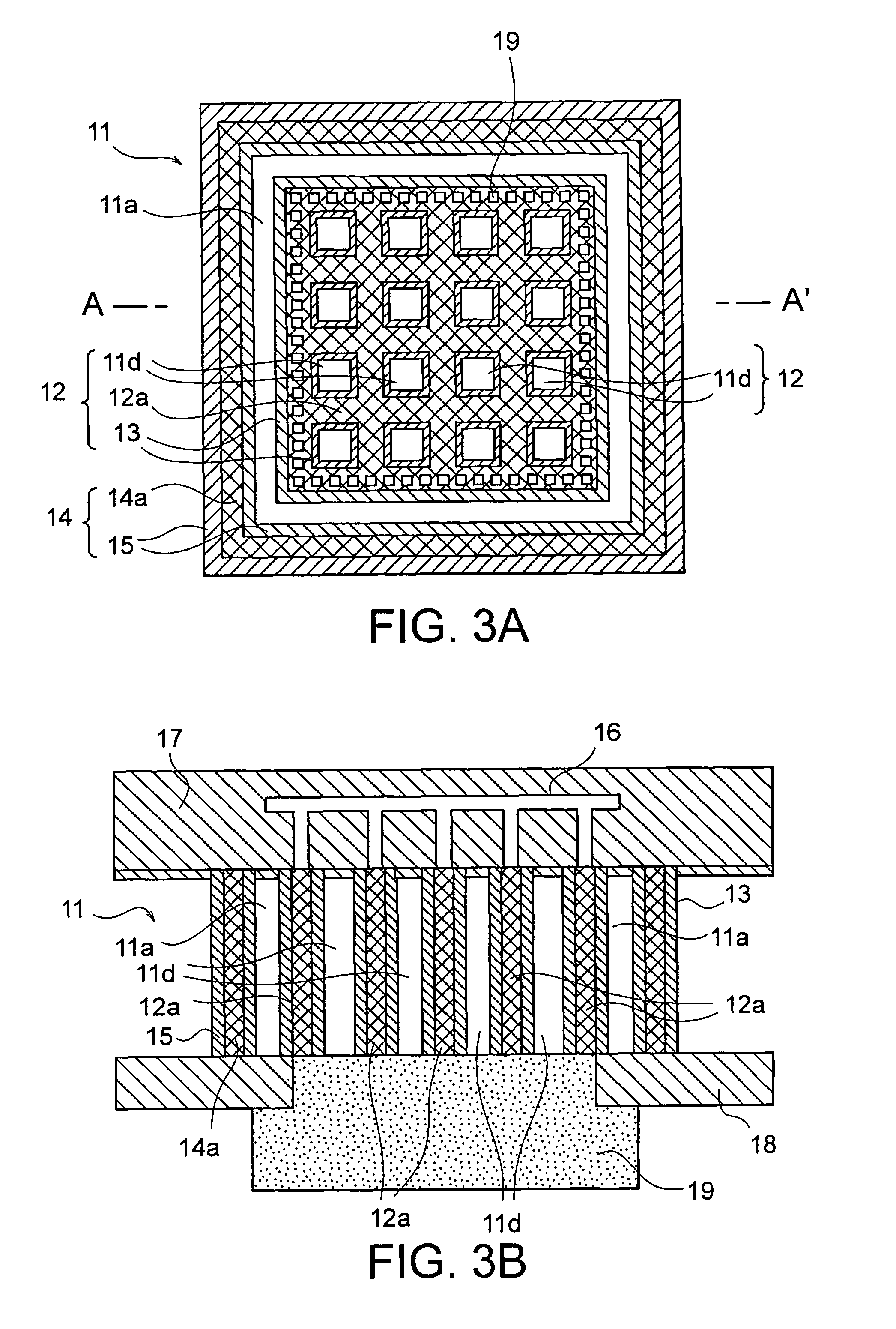

Stacked semiconductor package

InactiveUS7642635B2High speed data transmissionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A stacked semiconductor package comprises two semiconductor chips (11, 12) each of which has a mounting surface provided with a plurality of chip pins arranged in a predetermined pattern. The semiconductor chips are mounted on opposite surfaces of a substrate (13) so that the mounting surfaces are faced to each other through the substrate. The substrate is provided with a plurality of package pins formed in an area other than a chip mounting area and arranged in a pattern identical to the predetermined pattern. A pair of the corresponding chip pins of the semiconductor chips are connected to a via formed at an intermediate position therebetween by the use of branch wires equal in length to each other. The via is connected by a common wire to the package pin corresponding to the chip pins connected to the via.

Owner:LONGITUDE SEMICON S A R L

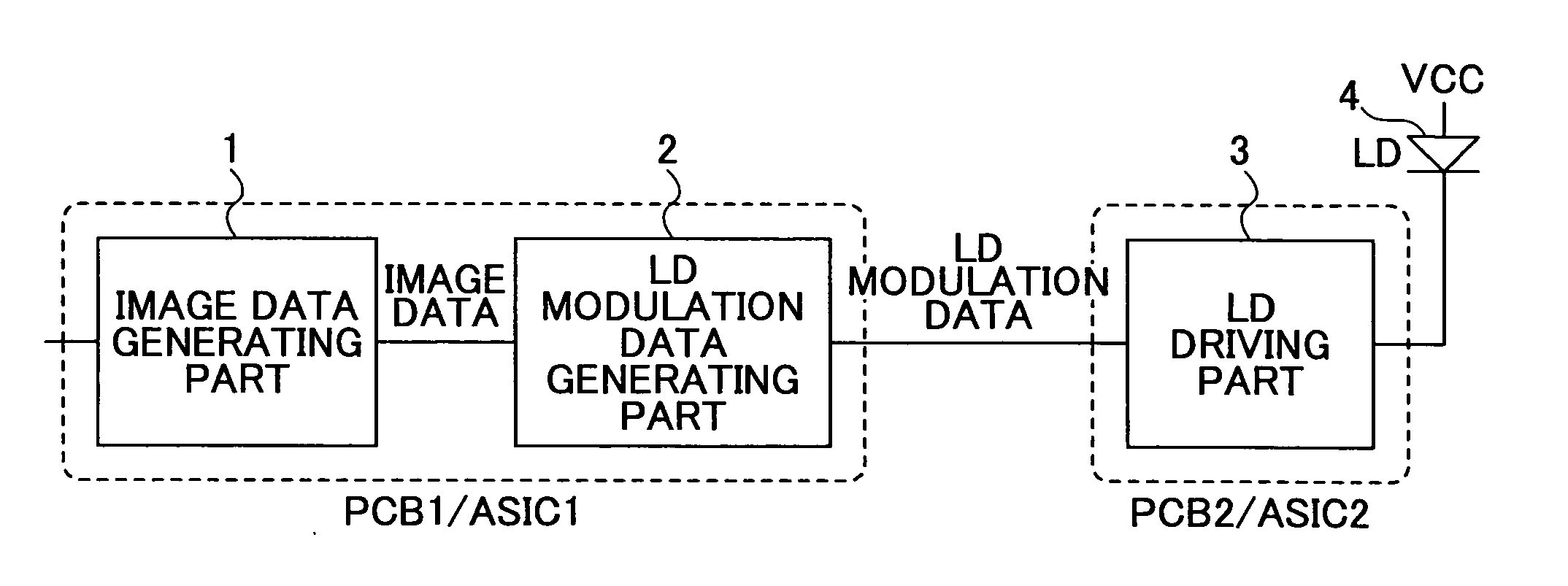

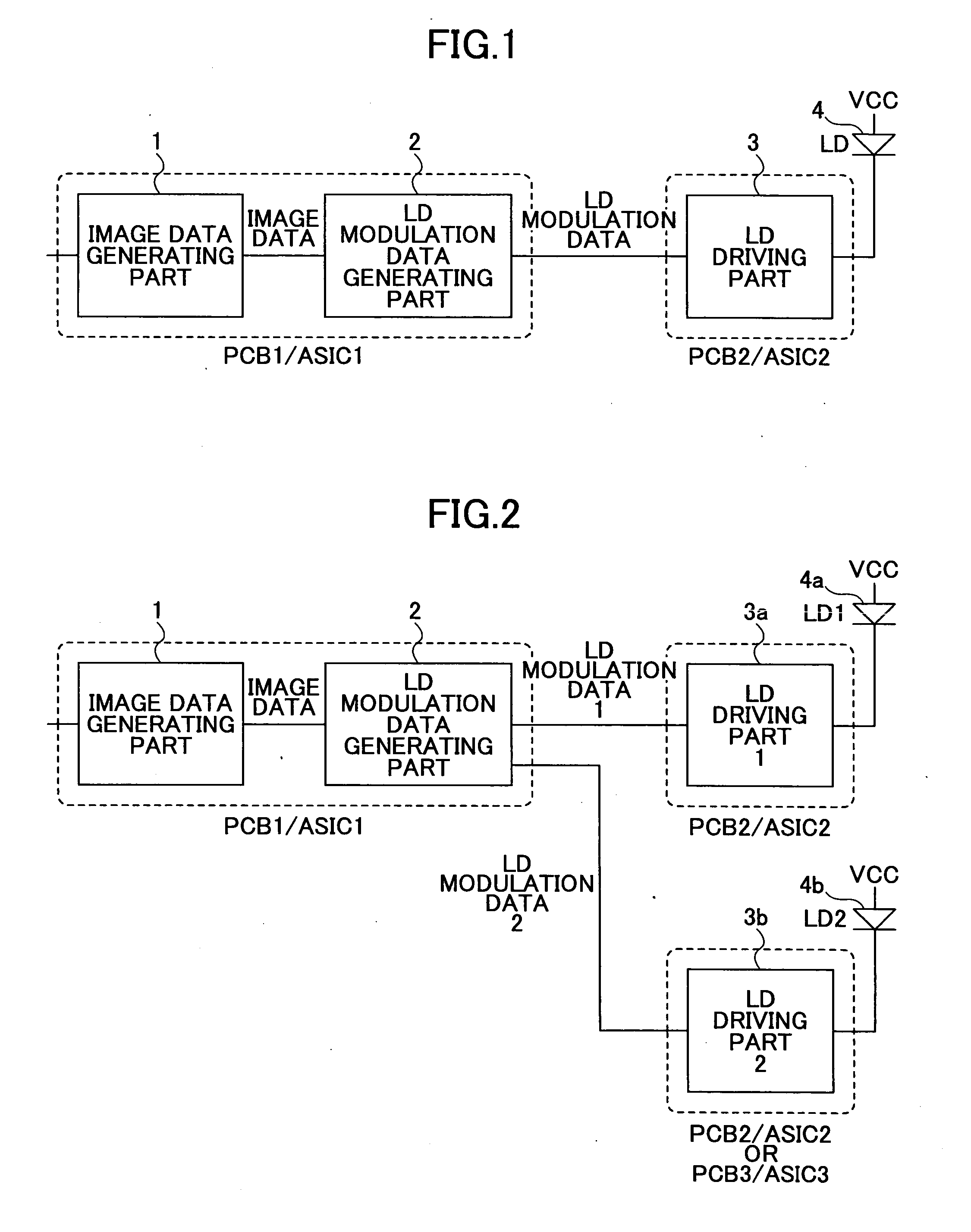

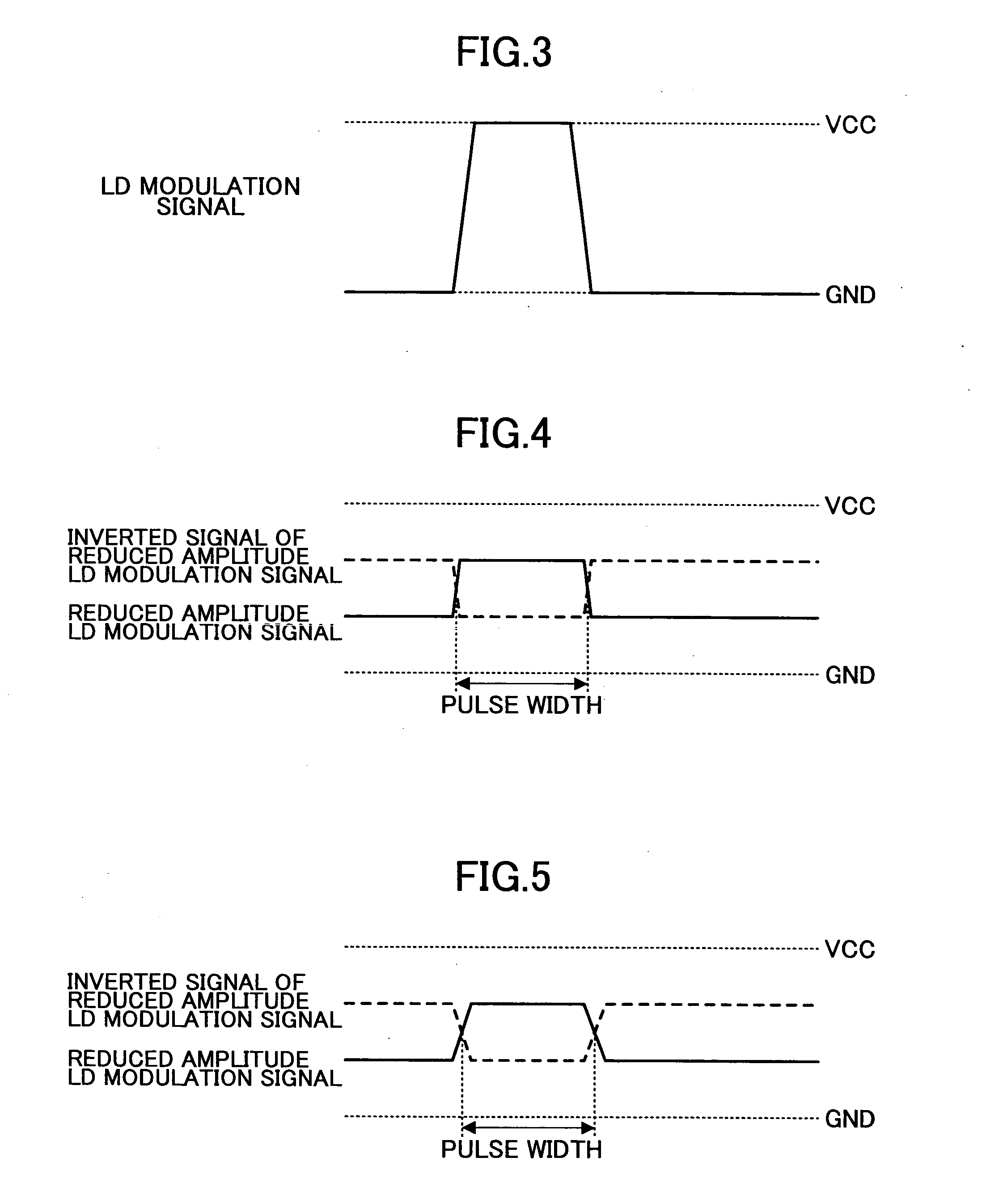

Image forming apparatus and semiconductor laser modulation driving apparatus

InactiveUS20050089069A1Guaranteed high-speed signal transmissionReduce swing of signalLaser detailsVisual representatino by photographic printingColor imageLatent image

A color image forming apparatus produces a latent image on a photosensitive body based on a signal output from a scanning light detecting part in response to detection of scanning light; a semiconductor laser modulation signal generating part includes a clock generating part and a clock modulation part; a semiconductor laser and a semiconductor laser driving part are provided for each color of yellow, magenta, cyan and black; and further, a plurality of the semiconductor lasers are provided for at least one color of yellow, magenta, cyan and black.

Owner:RICOH KK

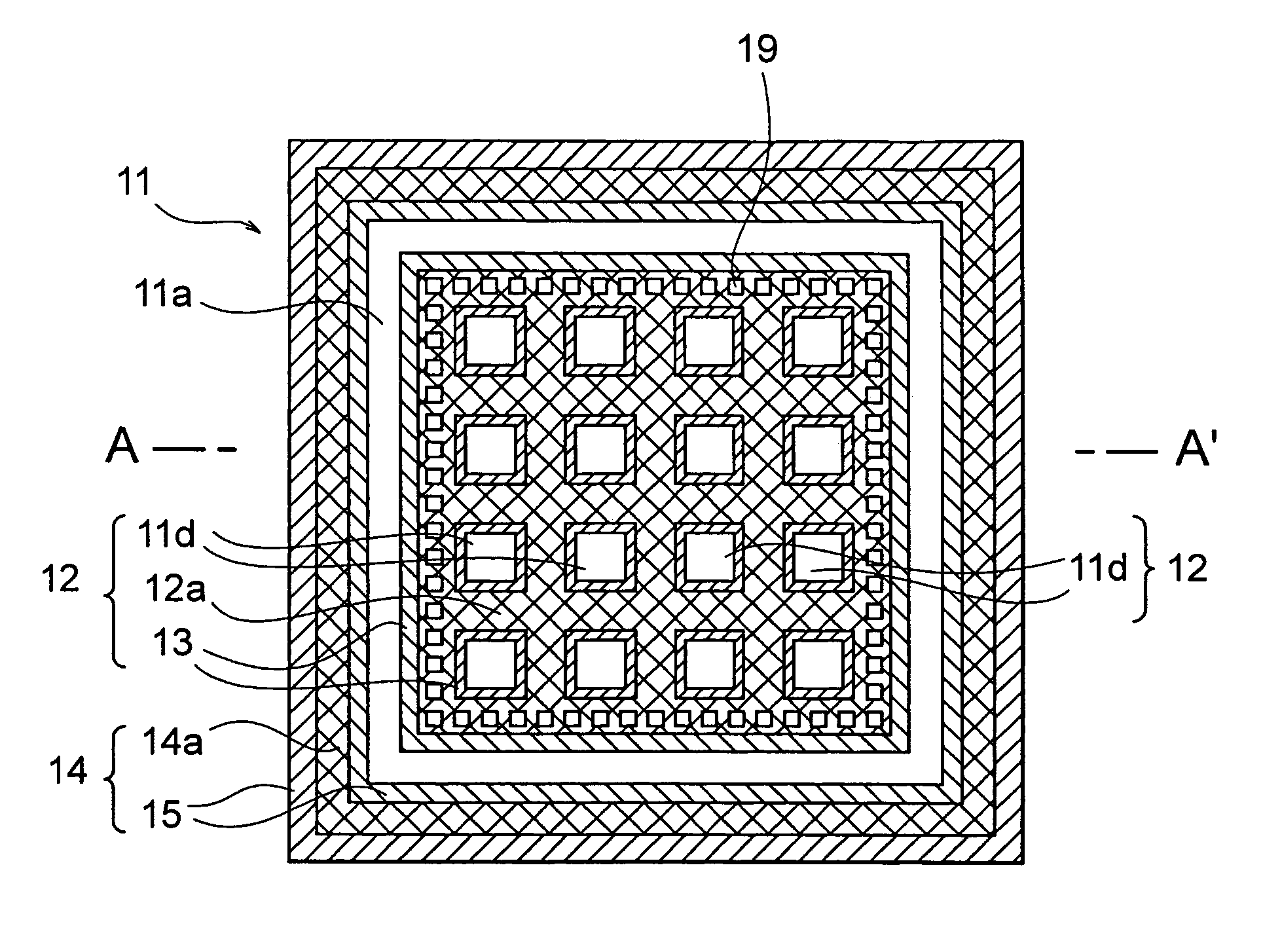

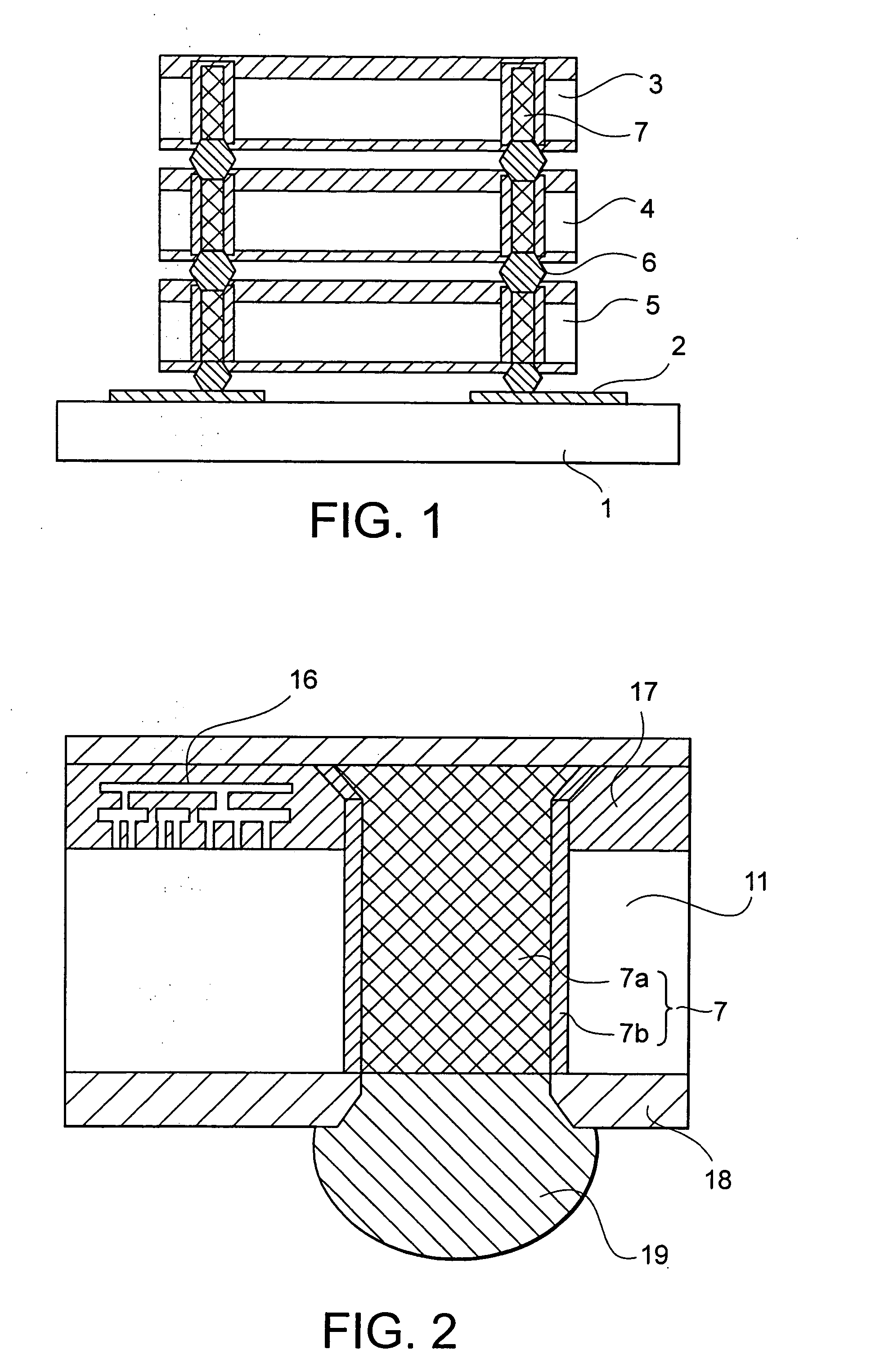

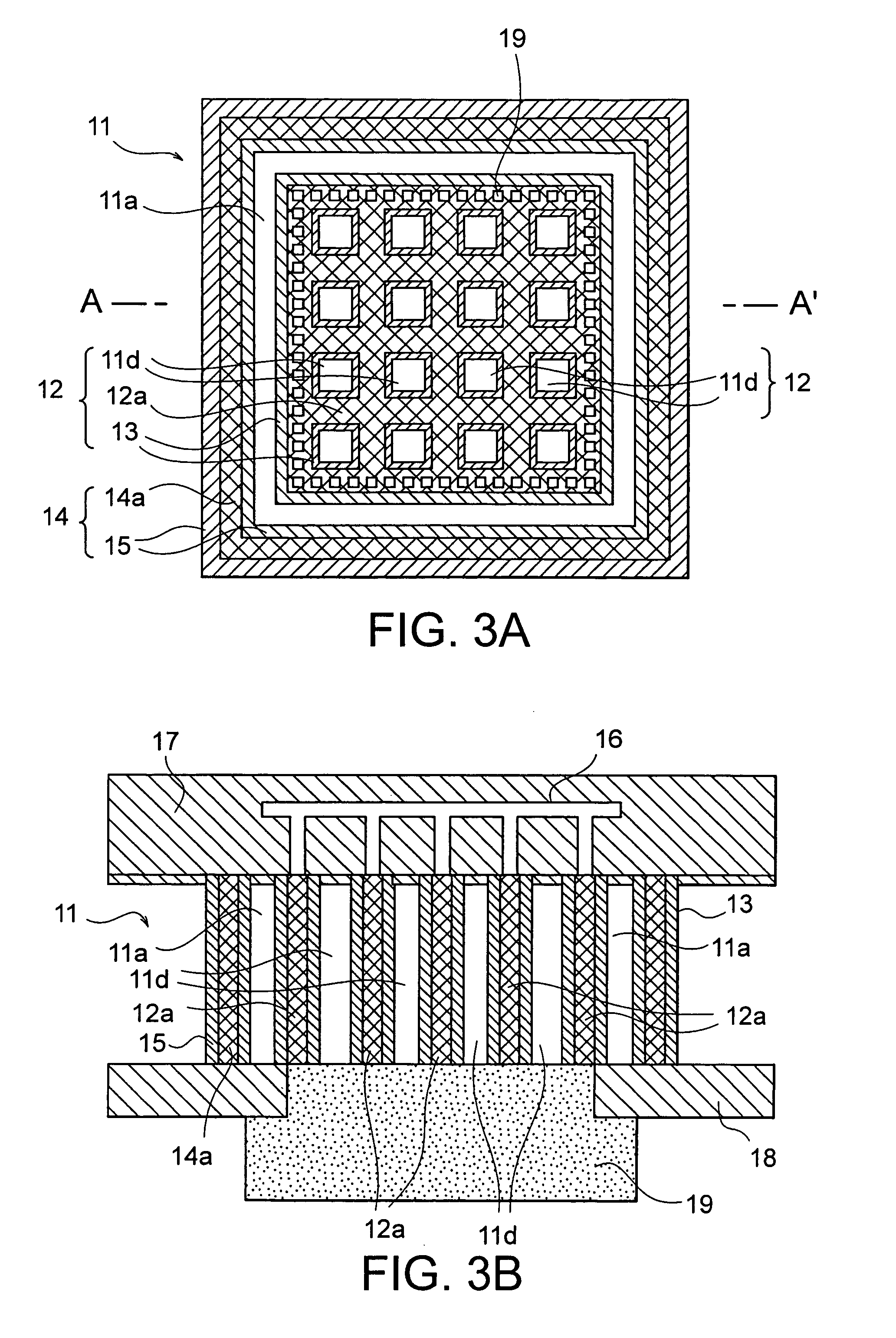

Semiconductor device and method of manufacturing the same

ActiveUS20070134819A1Lower resistanceShorten the time periodSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A method of manufacturing a through electrode. While using at least a first conductive film for a gate electrode as a mask, an inner trench and a peripheral trench is formed. The Inner trench is provided for an inner through electrode having a columnar semiconductor. The peripheral trench is provided for a peripheral through electrode around an annular semiconductor surrounding the inner trench. The inner trench and the peripheral trench are filled with a through electrode insulation film and a through electrode conductive film, respectively, to form an inner through electrode and a peripheral through electrode.

Owner:MICRON TECH INC

Semiconductor device

ActiveUS7323785B2Solve large capacityUniform qualitySemiconductor/solid-state device detailsSolid-state devicesSemiconductorSemiconductor device

A through-electrode that penetrates a semiconductor substrate and that is insulatively separated from the semiconductor substrate includes an inner through-electrode, a quadrangular ring-shaped semiconductor, and an outer peripheral through-electrode. The quadrangular ring-shaped semiconductor is formed around the inner through-electrode, and the outer peripheral through-electrode is formed around the quadrangular ring-shaped semiconductor.

Owner:MICRON TECH INC

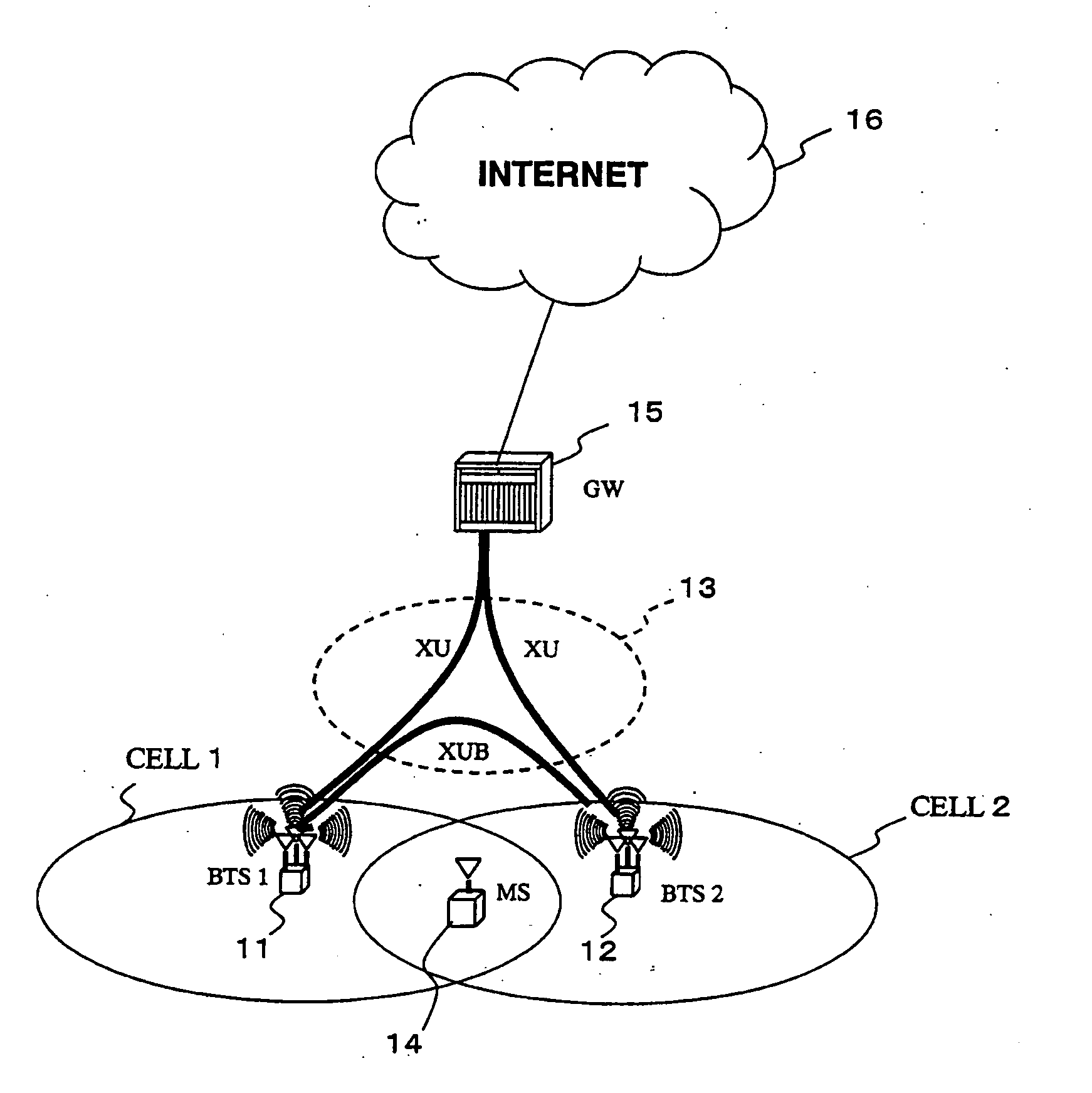

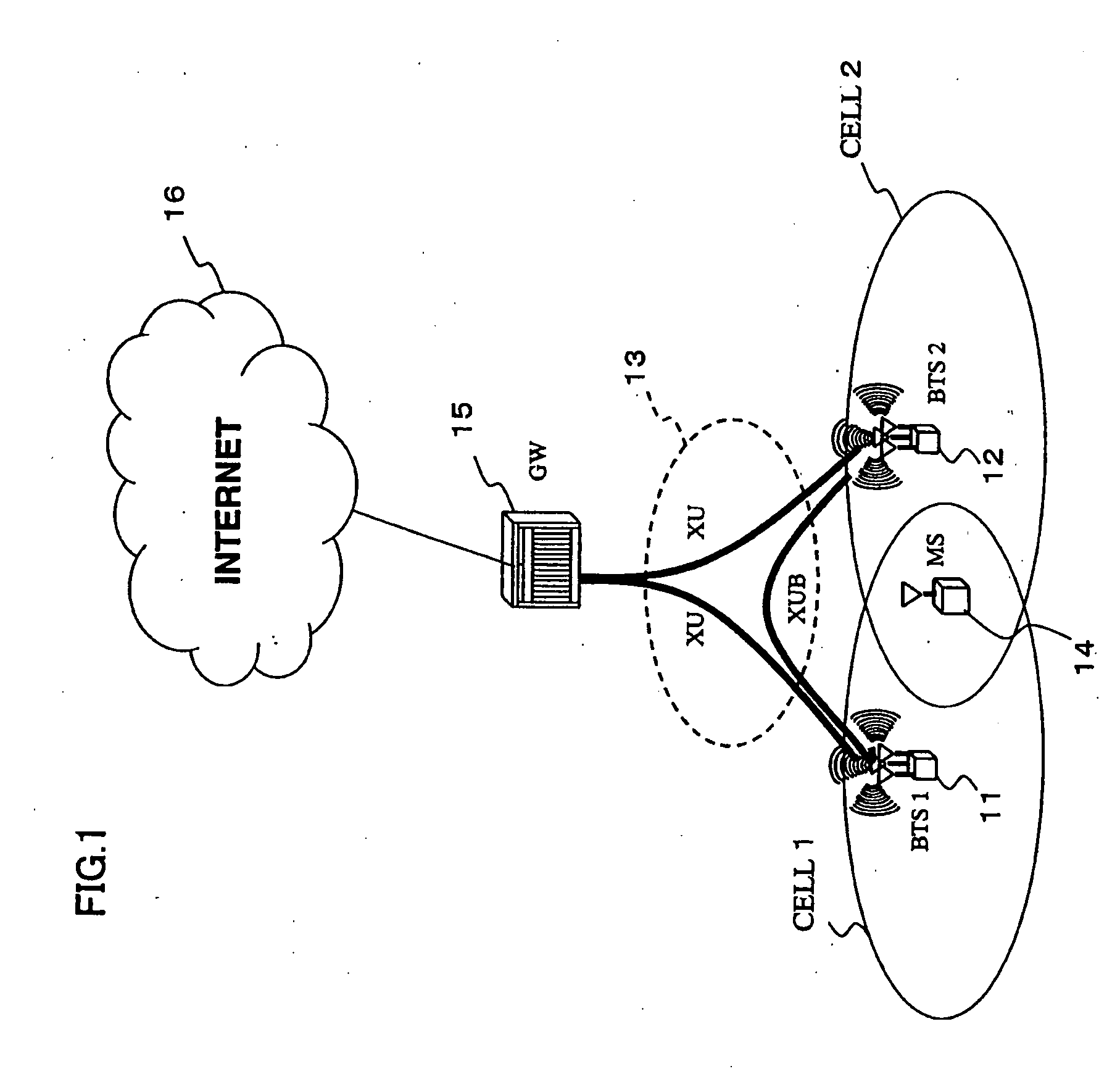

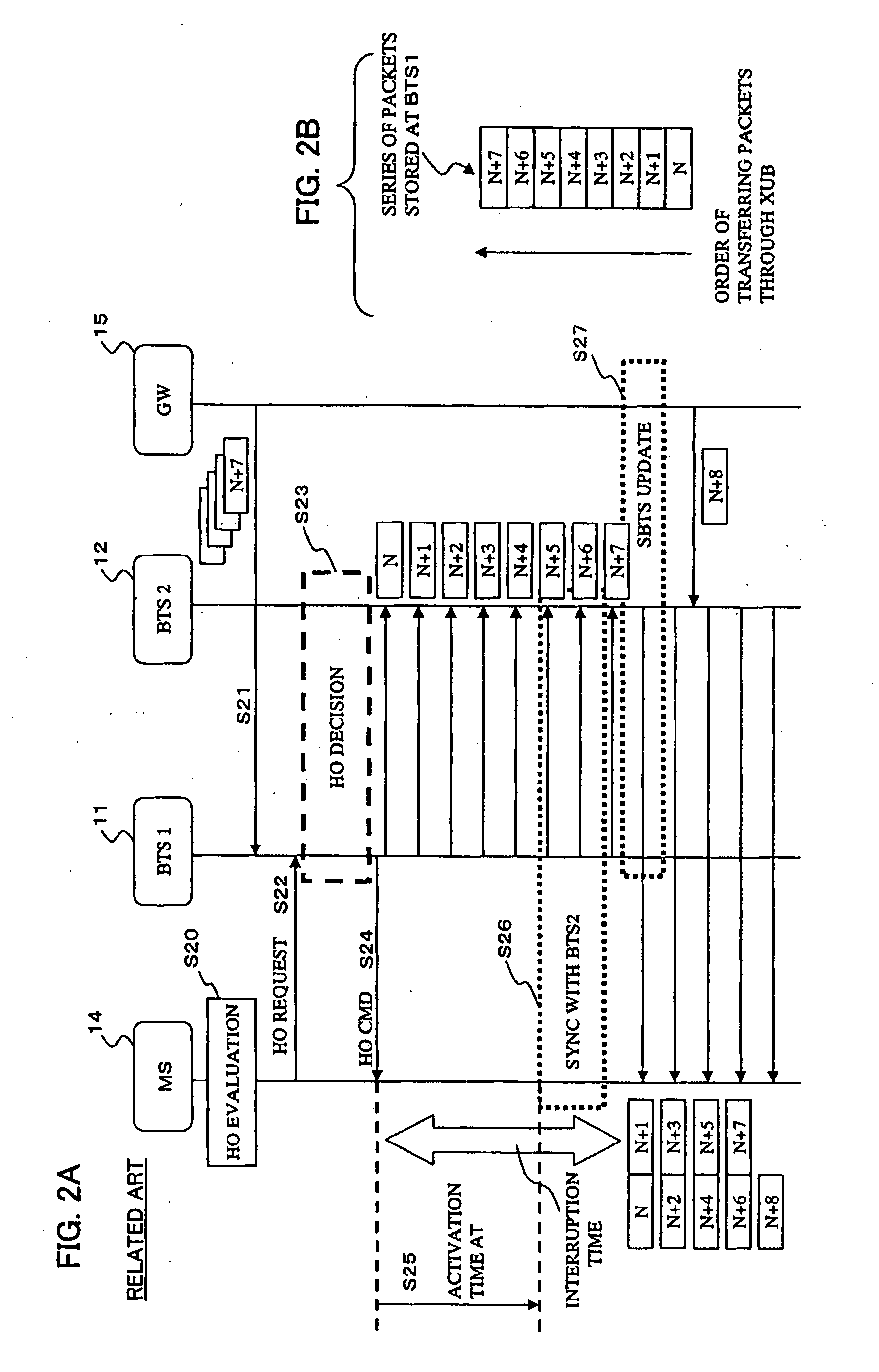

Method and system for transmitting data in mobile communications system

ActiveUS20070286125A1Reduce amountShortened communication interruption durationAssess restrictionNetwork topologiesCommunications systemMobile communication systems

A new data transmission method and system that can enhance the speed of data transfer between base stations are provided. Unsent data stored at a base station is transmitted through a plurality of routes. The base station stores unsent packets destined for a mobile station or a gateway. The base station transmits some of the unsent packets to the mobile station or the gateway and transfers the other remaining packets to a handover-target base station. The handover-target base station transmits the received other packets to the mobile station or the gateway.

Owner:NEC CORP

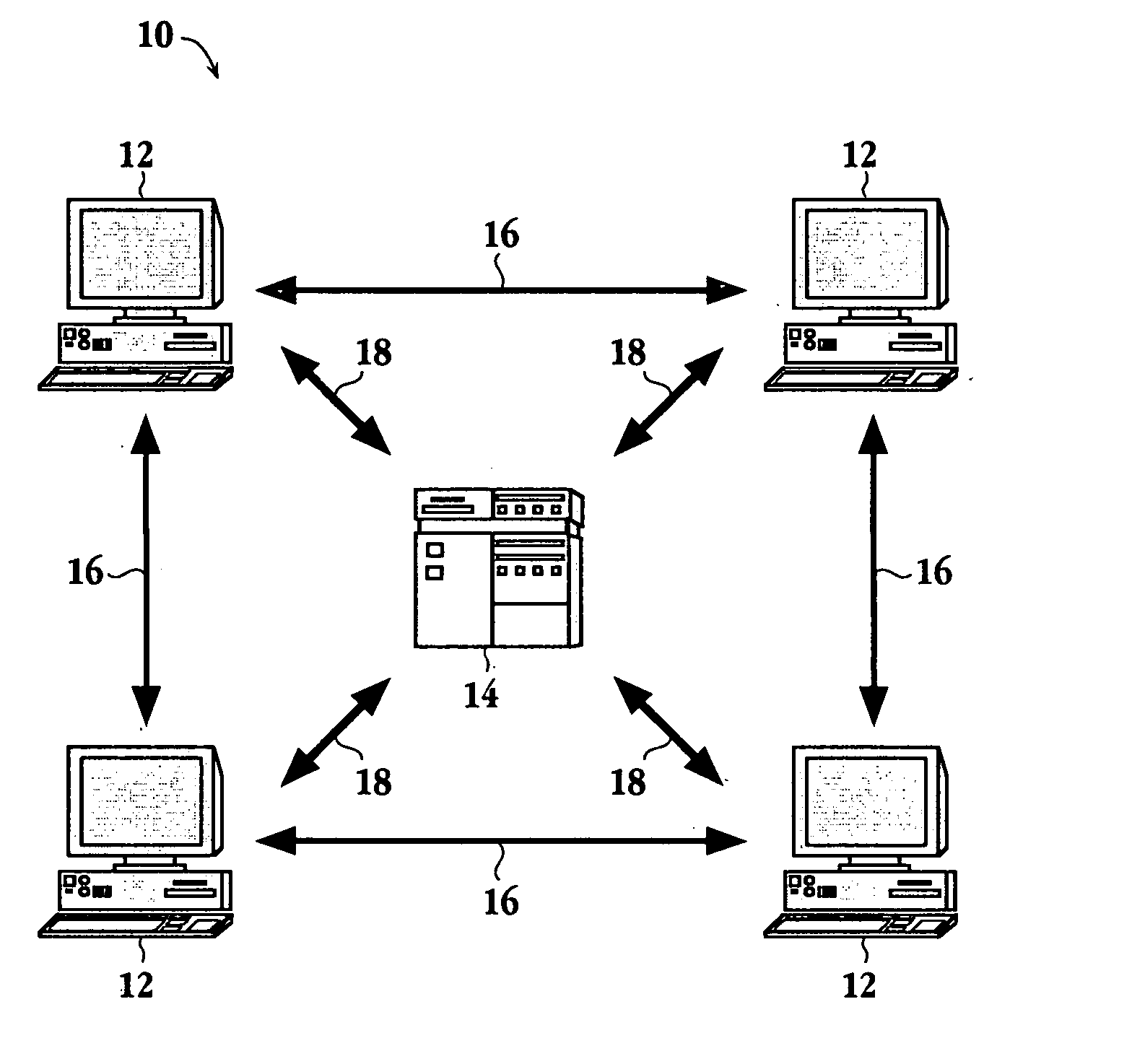

Connectionless TCP/IP data exchange

InactiveUS20050078604A1High speed data transmissionMultiplex system selection arrangementsSpecial service provision for substationChecksumComputer science

A communication protocol, and a method and system of communication exchange between systems over a communication network includes establishing a connection between a first system and a second system. Data is formatted by the first system into an IP datagram with an IP header and one of a TCP and a UDP header. A connectionless TCP / IP header is constructed to add to the formatted data. The connectionless TCP / IP header includes a pre-defined identifying value in a designated field, and a checksum to validate that a connectionless TCP / IP header has been identified. The formatted data having the connectionless TCP / IP header is transmitted from the first system to the second system, and the pre-defined identifying value in the designated field is verified to identify the connectionless TCP / IP header. The connectionless TCP / IP header is then removed from the IP datagram, and the IP datagram is processed.

Owner:SEIKO EPSON CORP

Method of storing both large and small files in a data storage device and data storage device thereof

InactiveUS20070239957A1Efficient space utilizationHigh speed data transmissionMemory systemsInput/output processes for data processingFile sizeData store

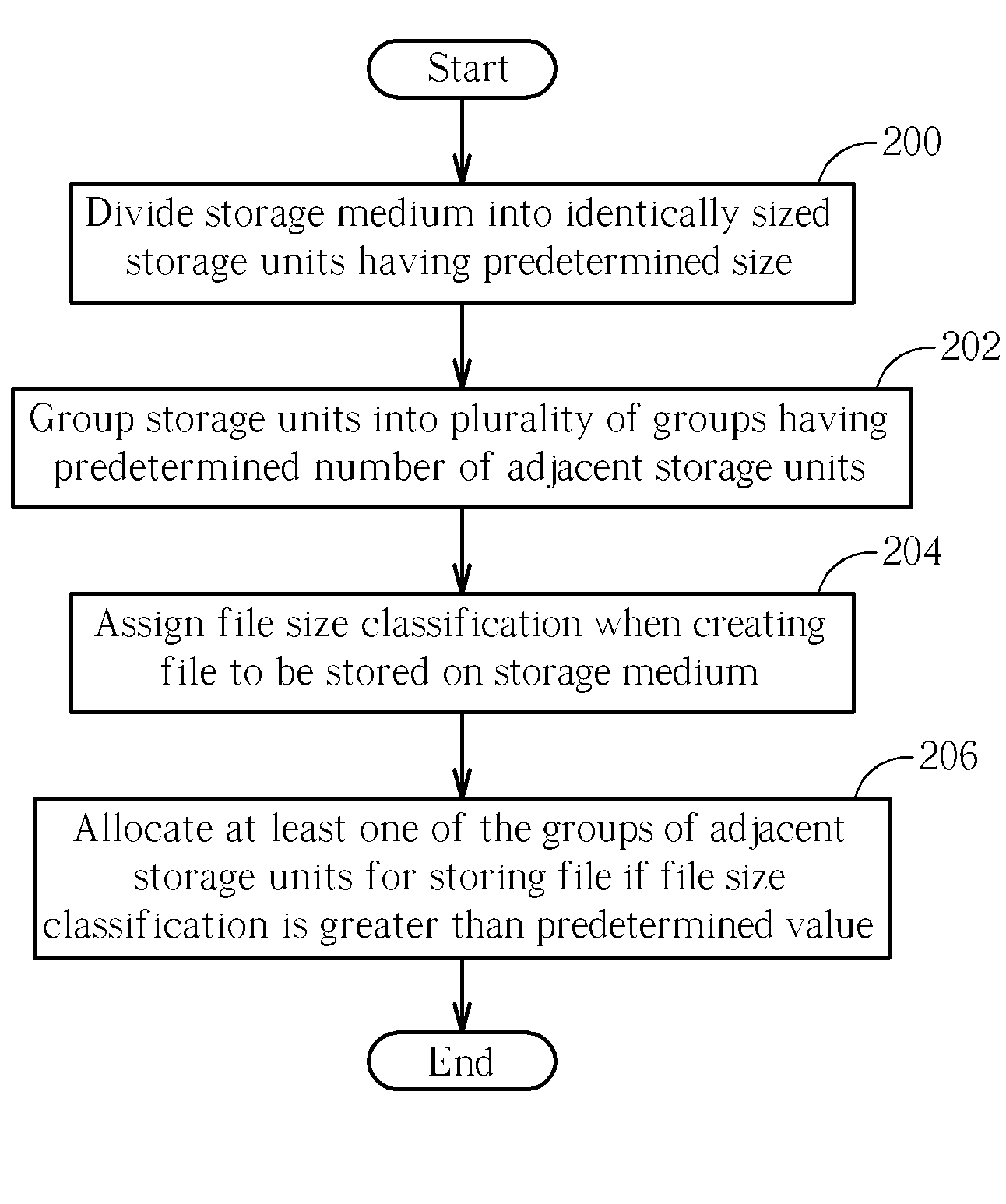

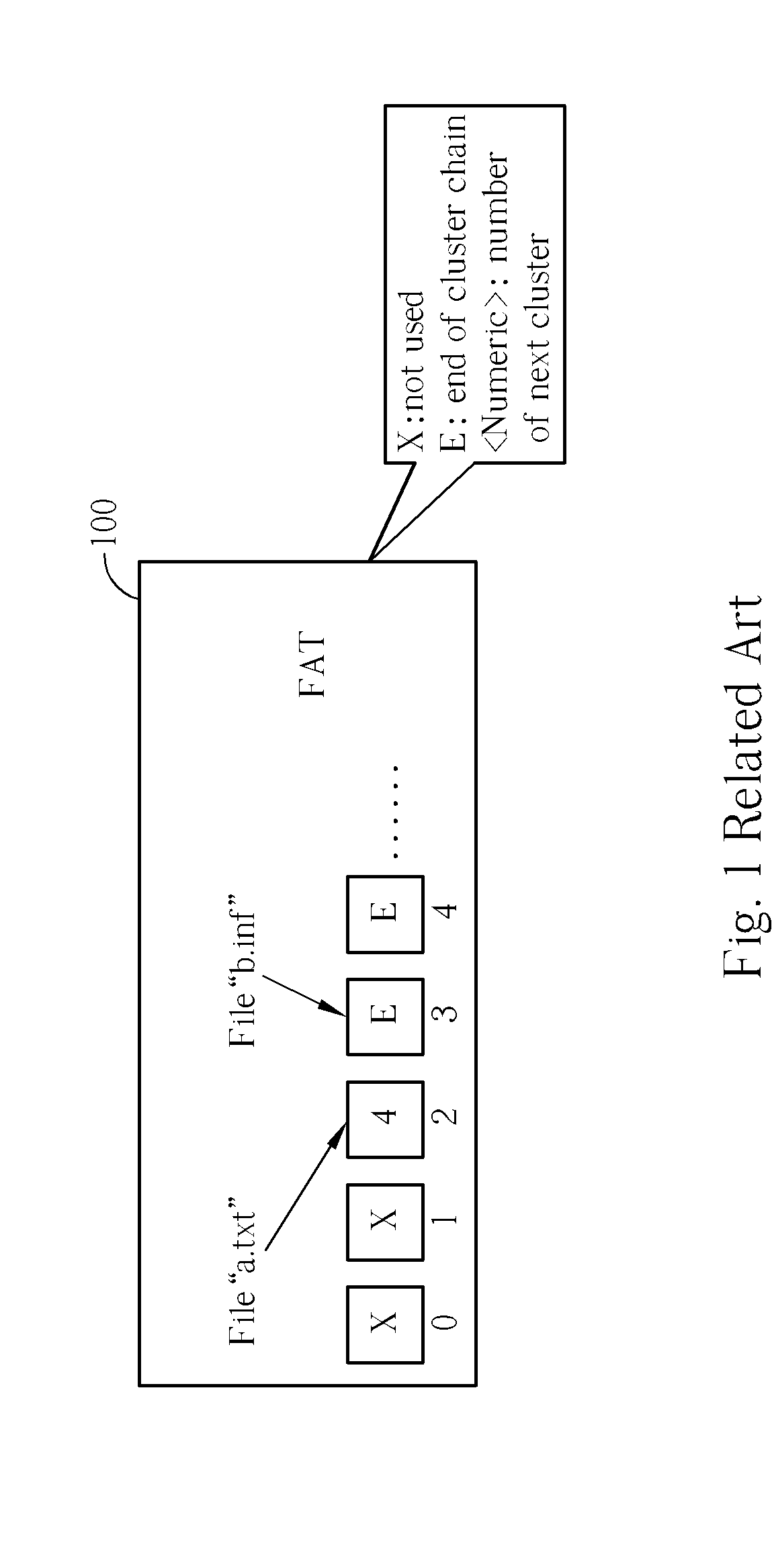

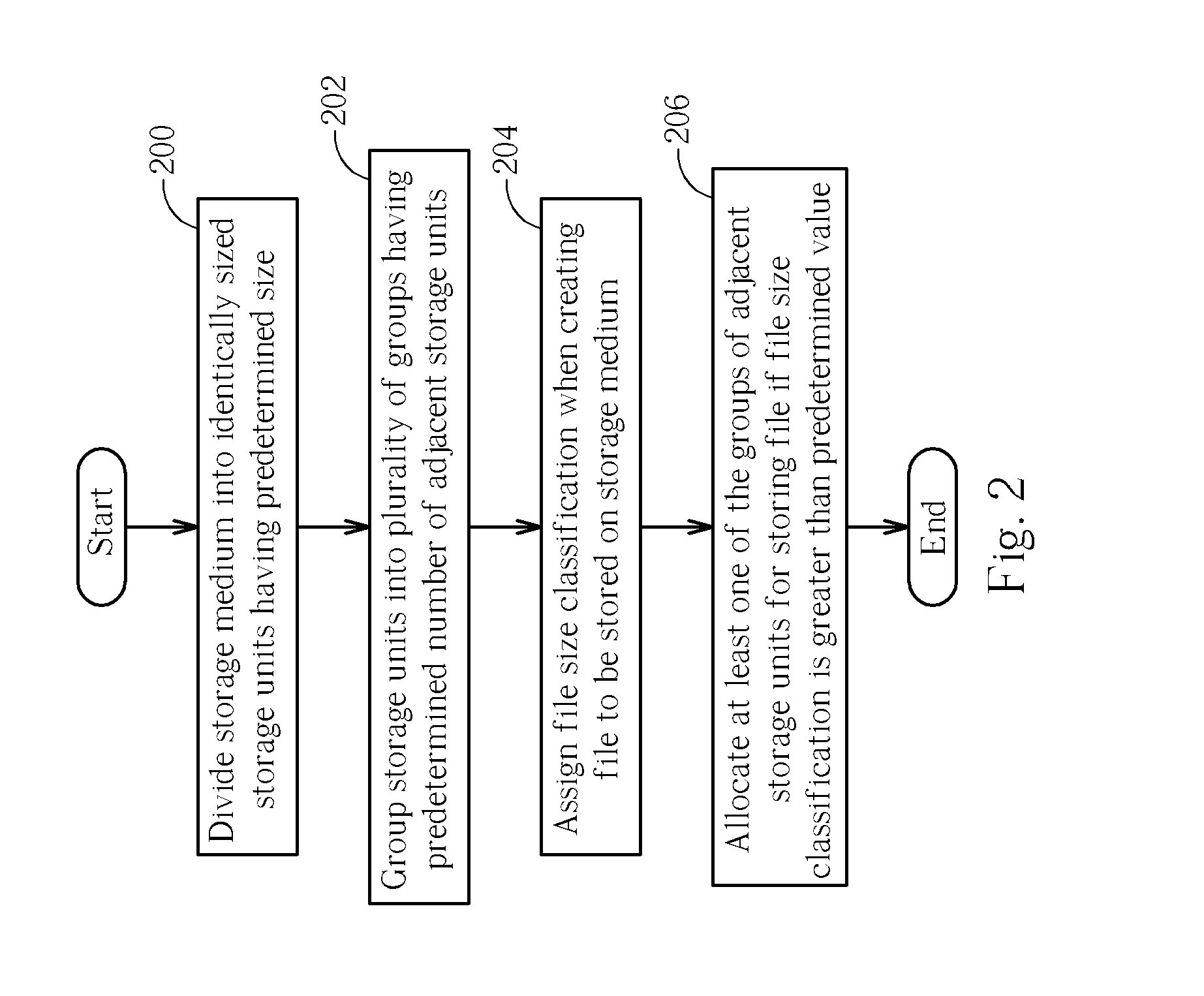

A method of storing files in a data storage device includes dividing a storage medium of the data storage device into identically sized storage units having a predetermined size, and indicating a status of each storage unit and relating chains of storage units storing a same file in a file allocation table on the storage medium; grouping the storage units into a plurality of groups having a predetermined number of adjacent storage units; assigning a file size classification when creating a file to be stored on the storage medium, the file size classification corresponding to an estimated amount of data in the file to be stored on the storage medium; and allocating at least one of the groups of adjacent storage units for storing the file if the file size classification is greater than a predetermined value.

Owner:MEDIATEK INC

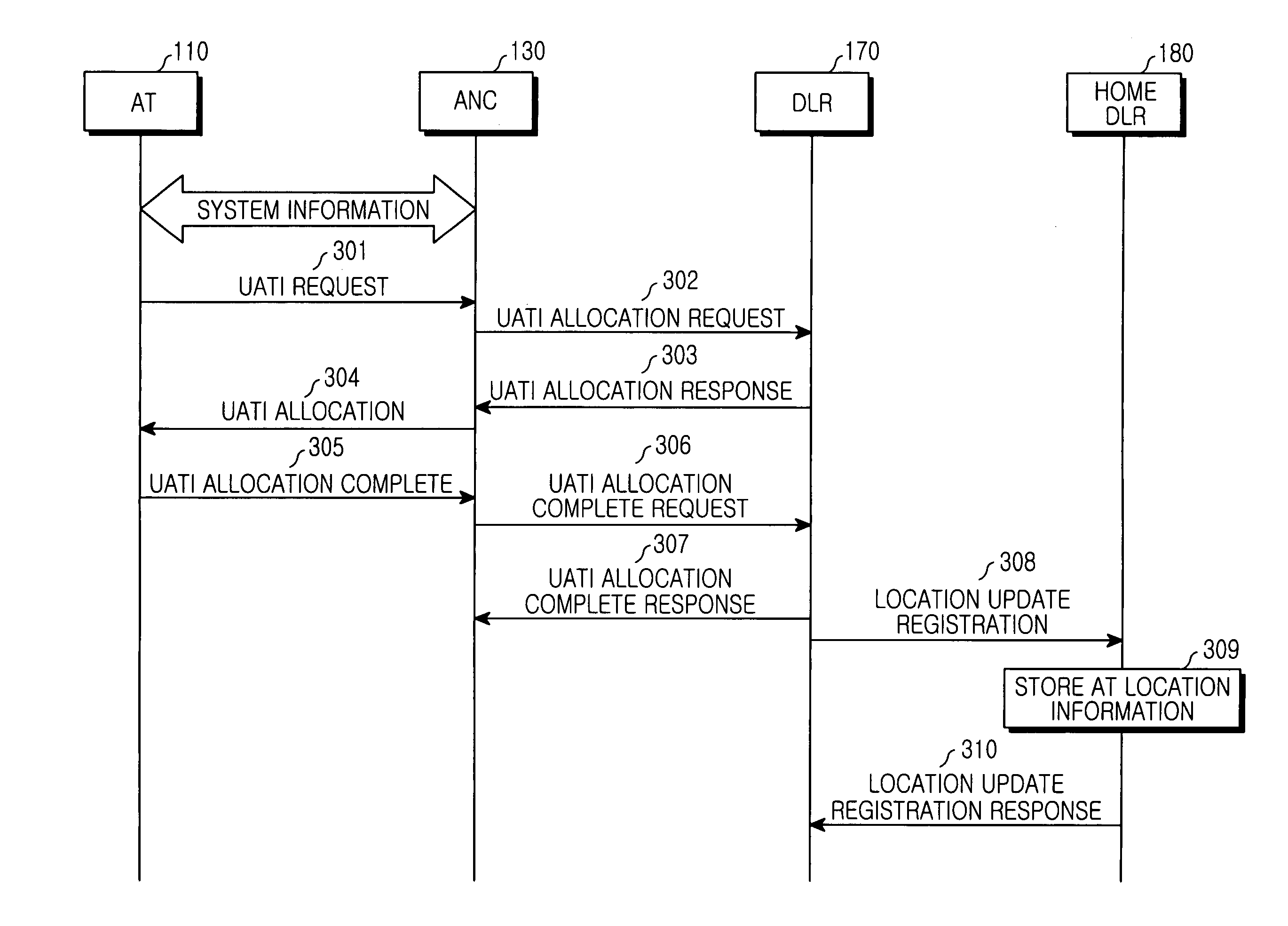

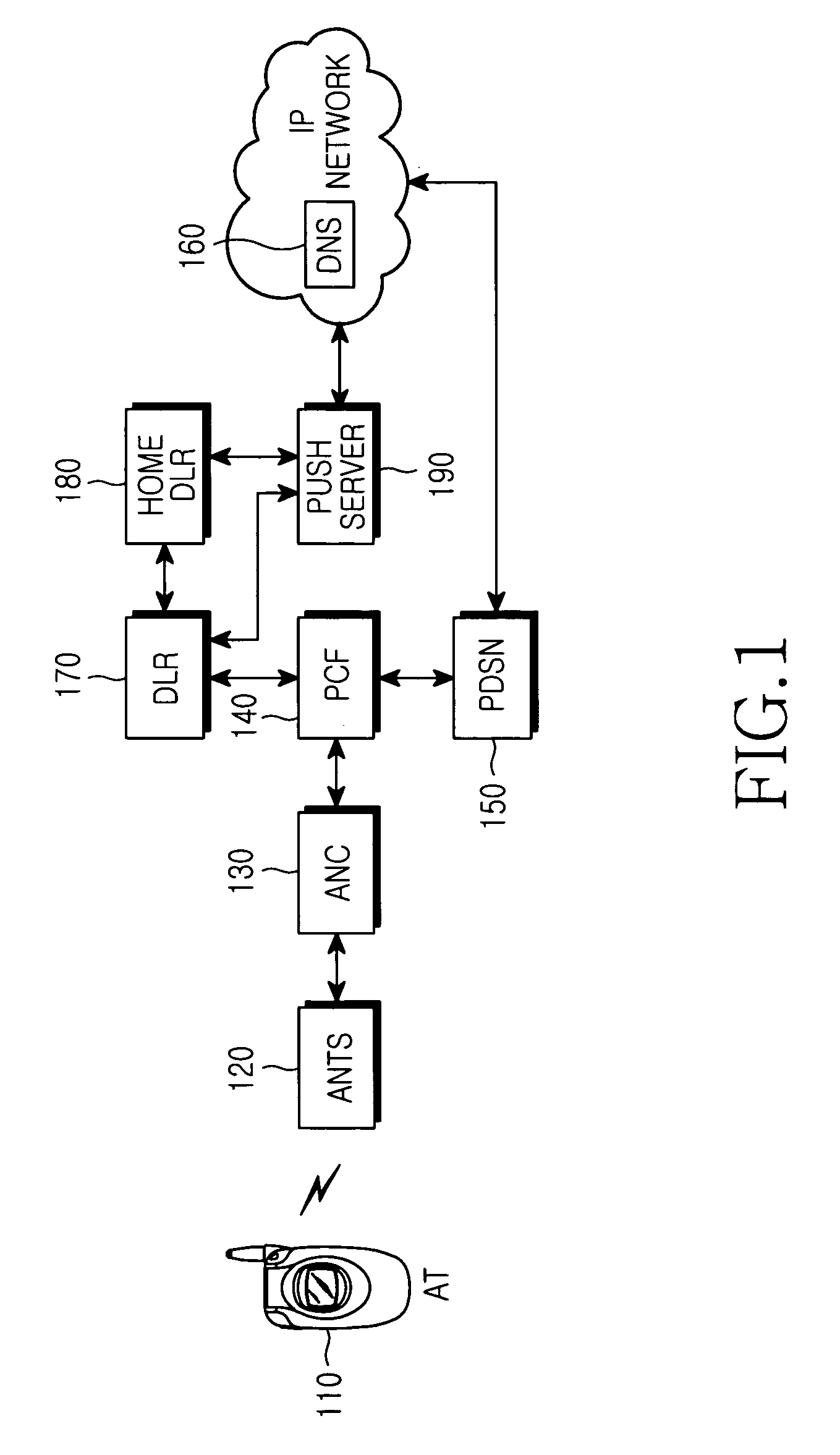

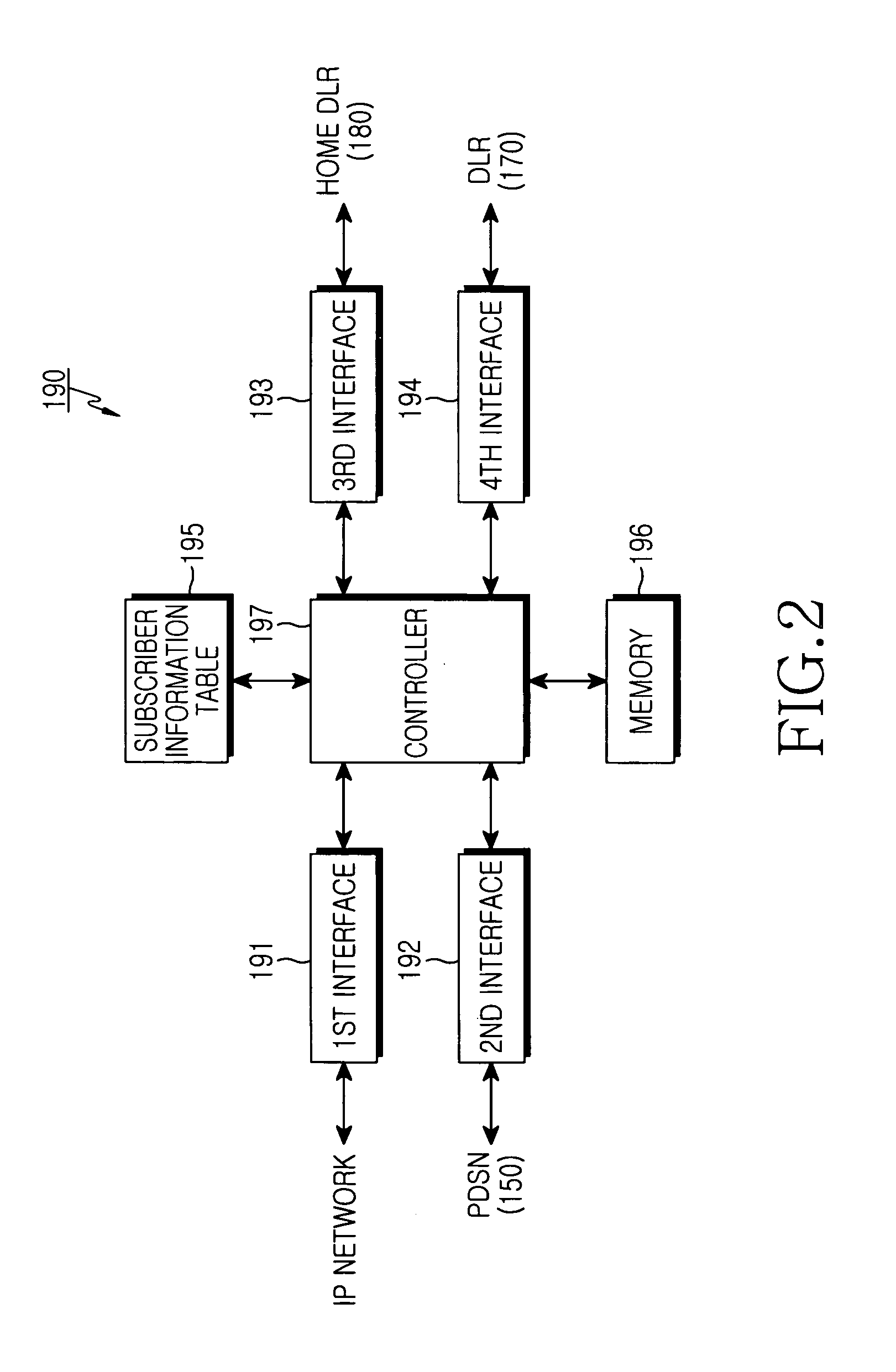

Method of providing push service to mobile terminal in a mobile communication system for high-speed data transmission and push server apparatus using the same

InactiveUS20050172026A1High speed data transmissionMultiple digital computer combinationsWireless network protocolsPagingMobile communication systems

A method of providing a push service to an AT and a push server apparatus using the same to facilitate a data receiving service comprising reception of paging messages at the AT in a mobile communication system for high-speed data transmission are provided. The mobile communication system comprises at least one DLR for allocating a UATI to the AT when a communication is connected to the AT, a home DLR for storing the ID of the AT with respect to the identification information of the DLR, a PDSN for establishing a PPP session with the AT, a DNS, and a push server for buffering push data for the AT received from a CN and requesting paging of the AT for push data transmission to the AT from which the PPP session has been terminated.

Owner:SAMSUNG ELECTRONICS CO LTD

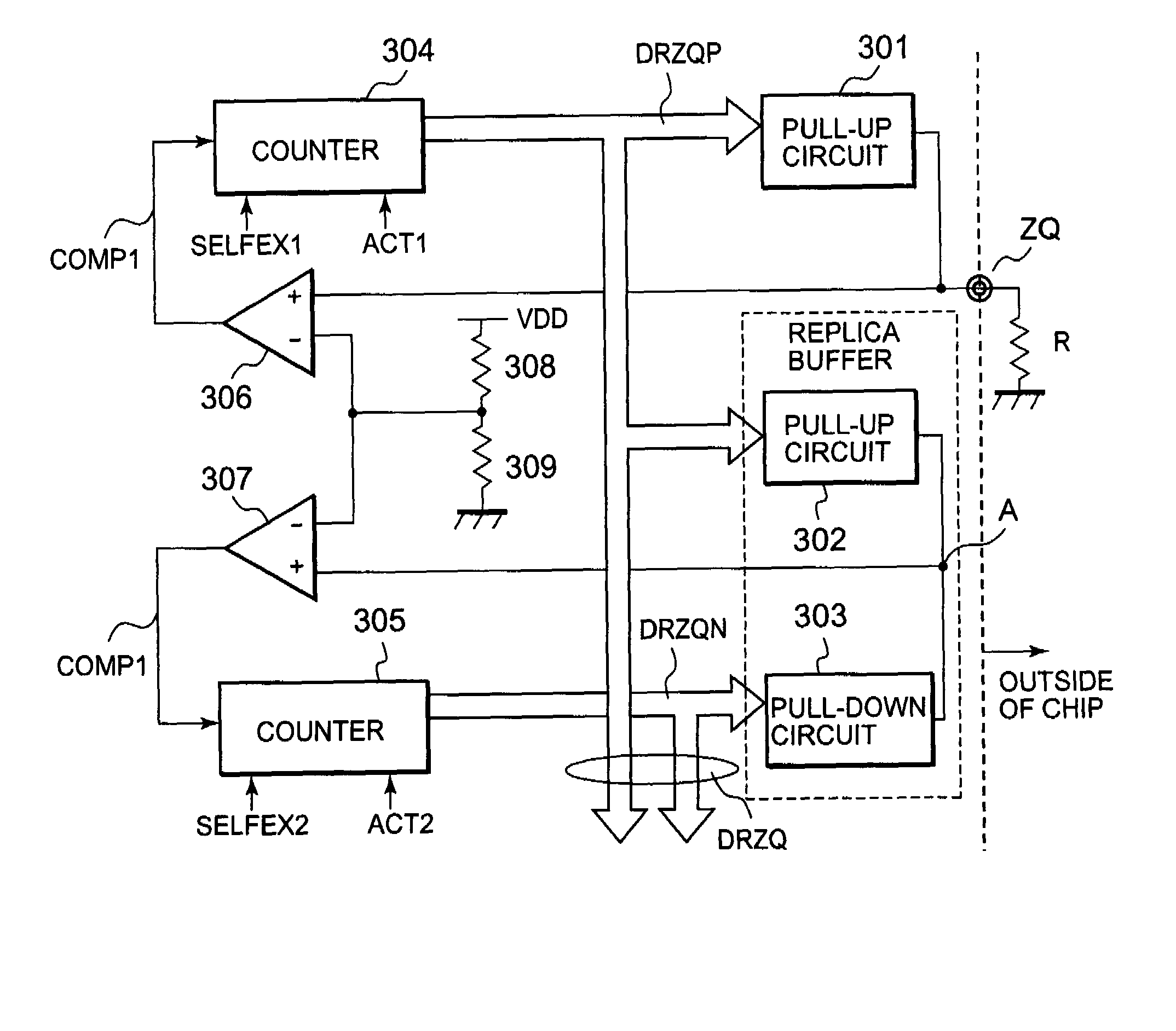

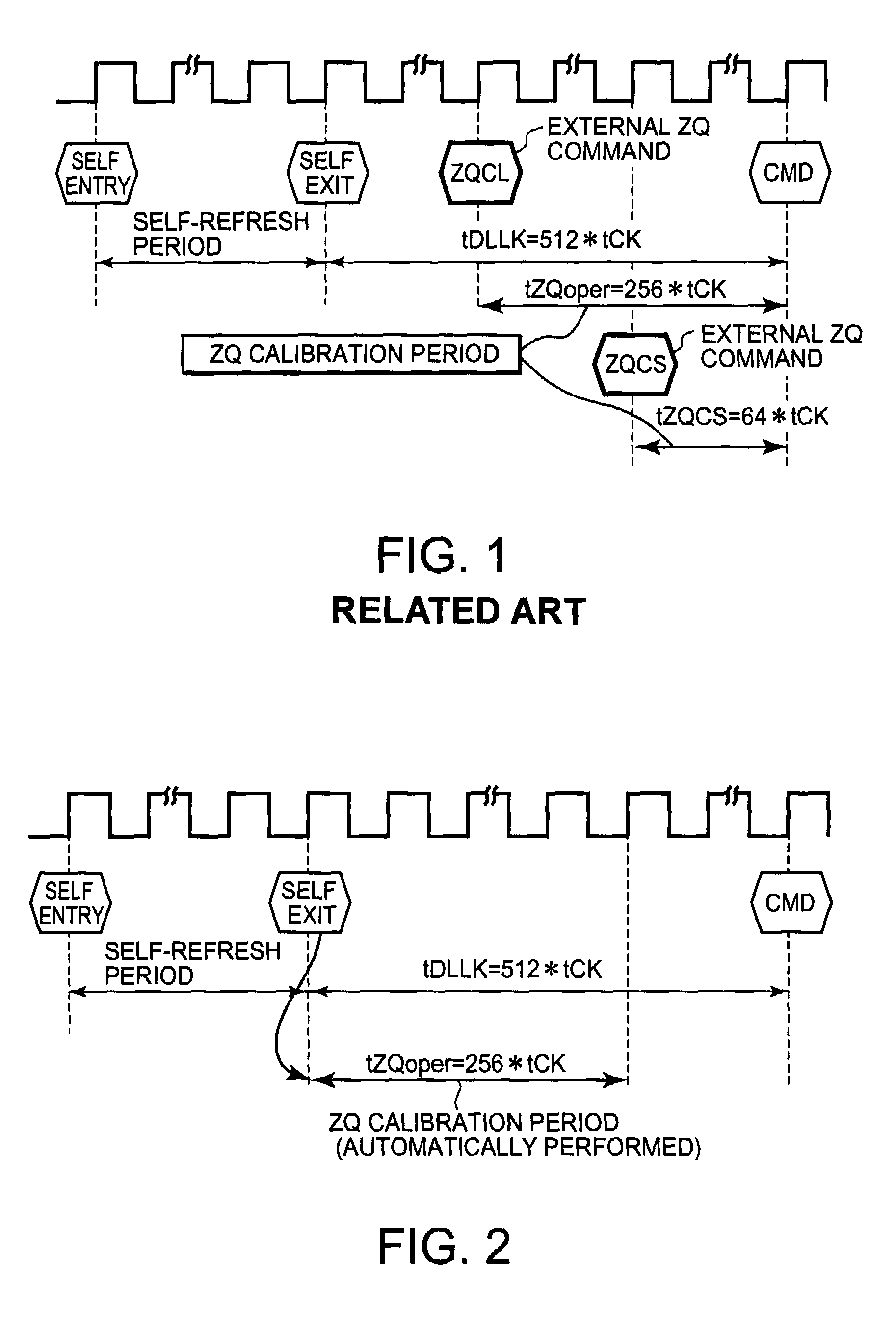

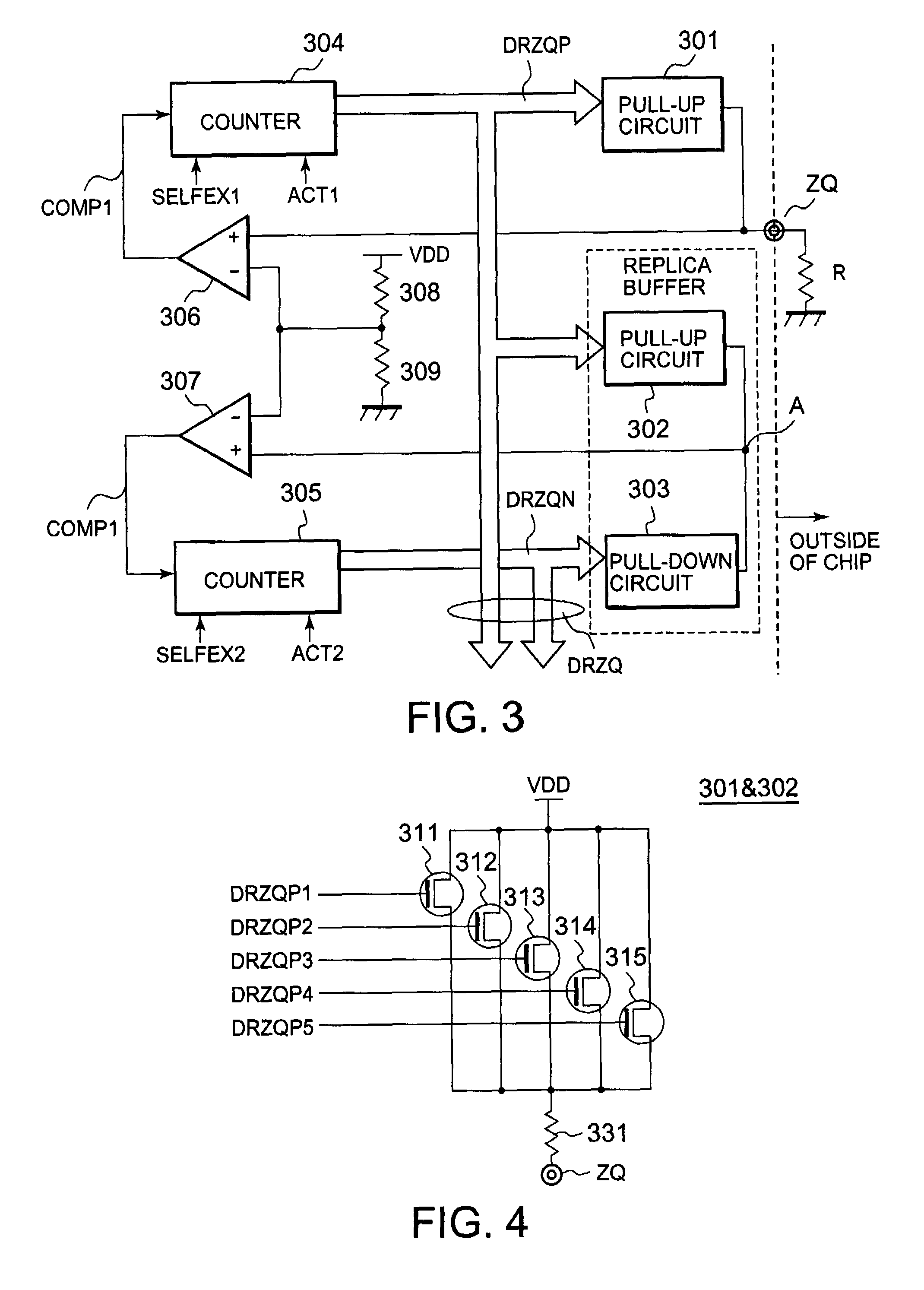

ZQ calibration circuit and a semiconductor device including a ZQ calibration circuit

ActiveUS7839159B2Increase the number ofHigh speed data transmissionSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsComputer hardwareSemiconductor

Owner:LONGITUDE LICENSING LTD

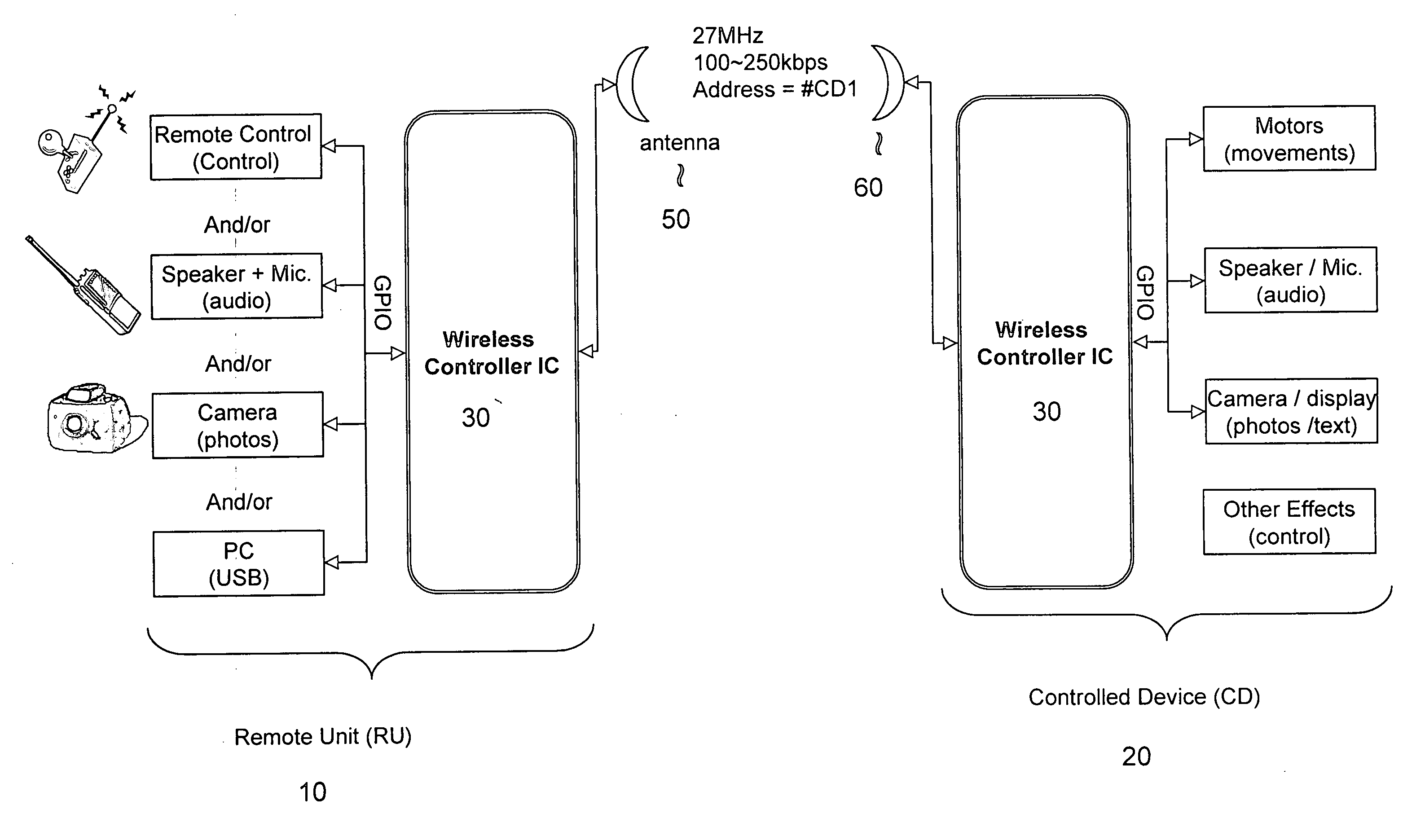

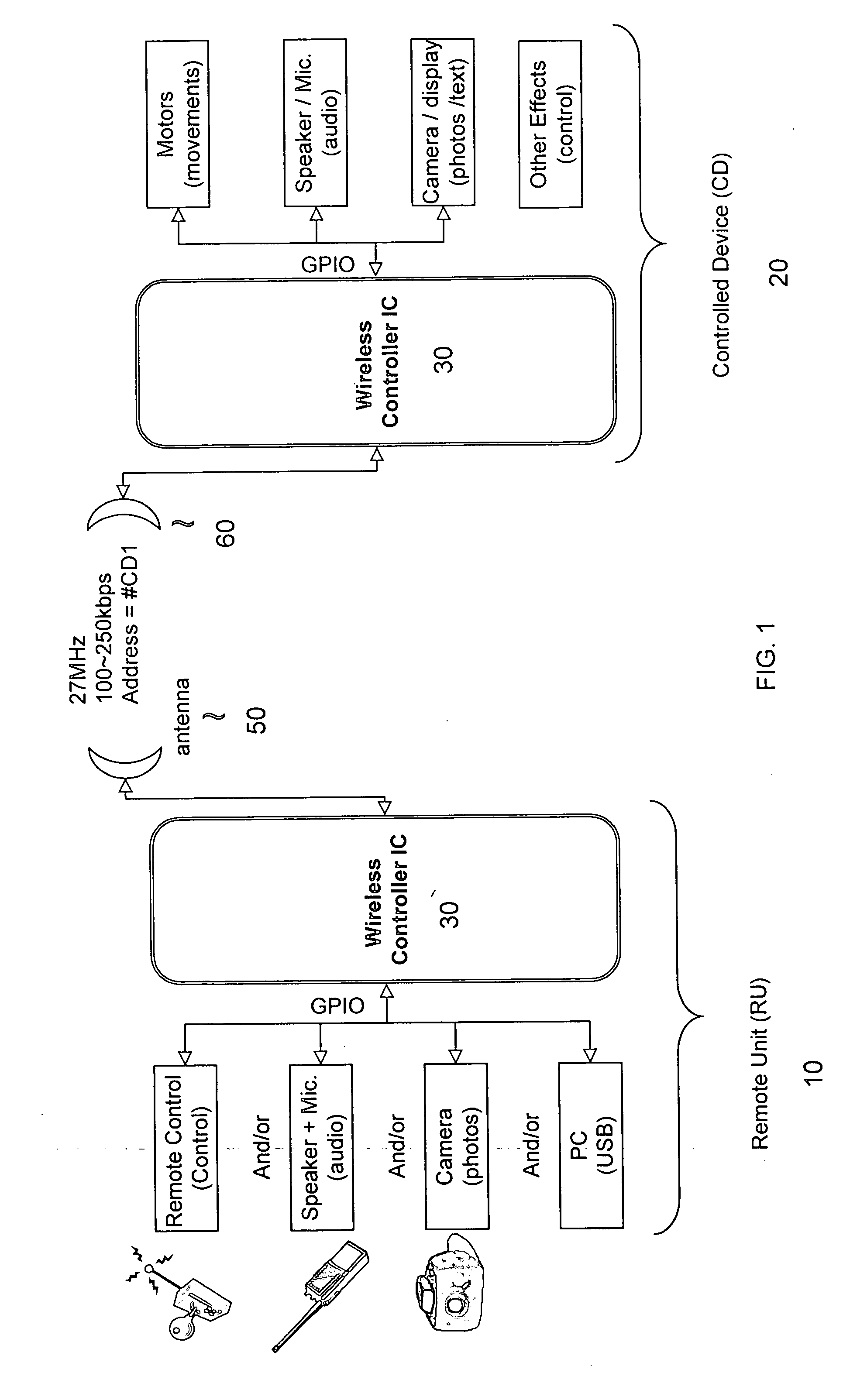

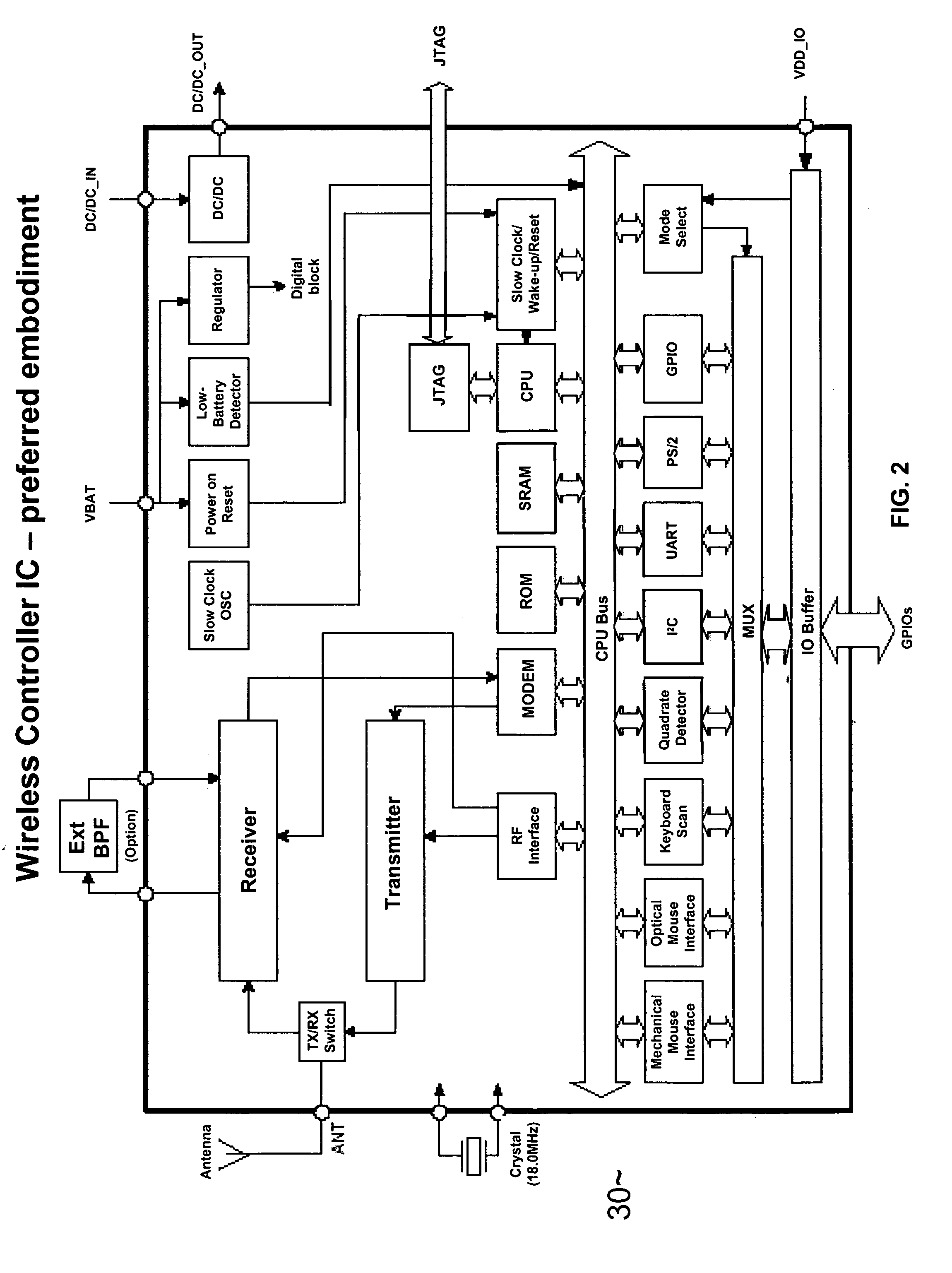

Wireless remote control and data transfer system

InactiveUS20050157668A1High speed data transmissionEasy to implementElectric signal transmission systemsBroadcast transmission systemsRemote controlTransfer system

Owner:SIVAN MICHAEL

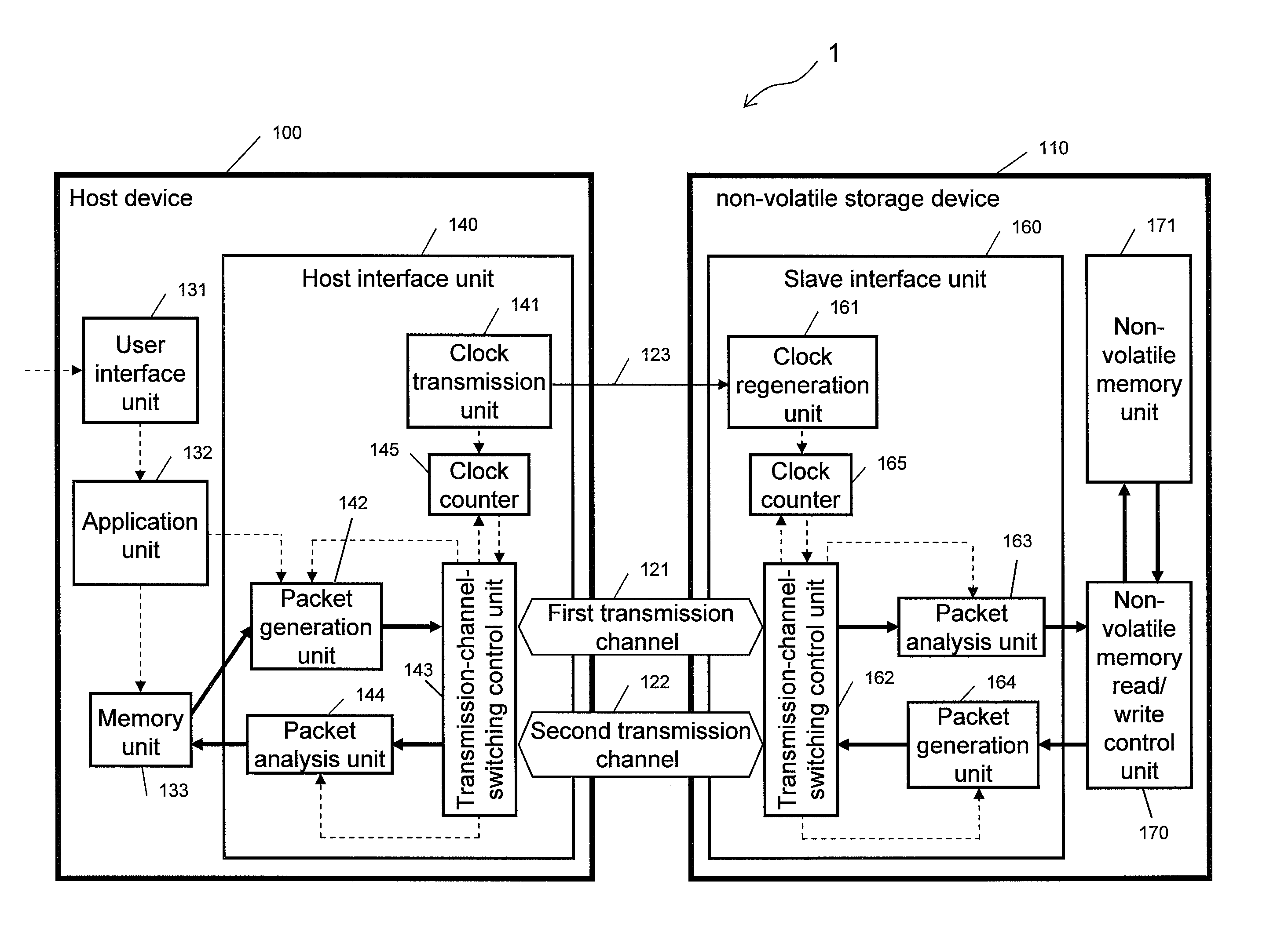

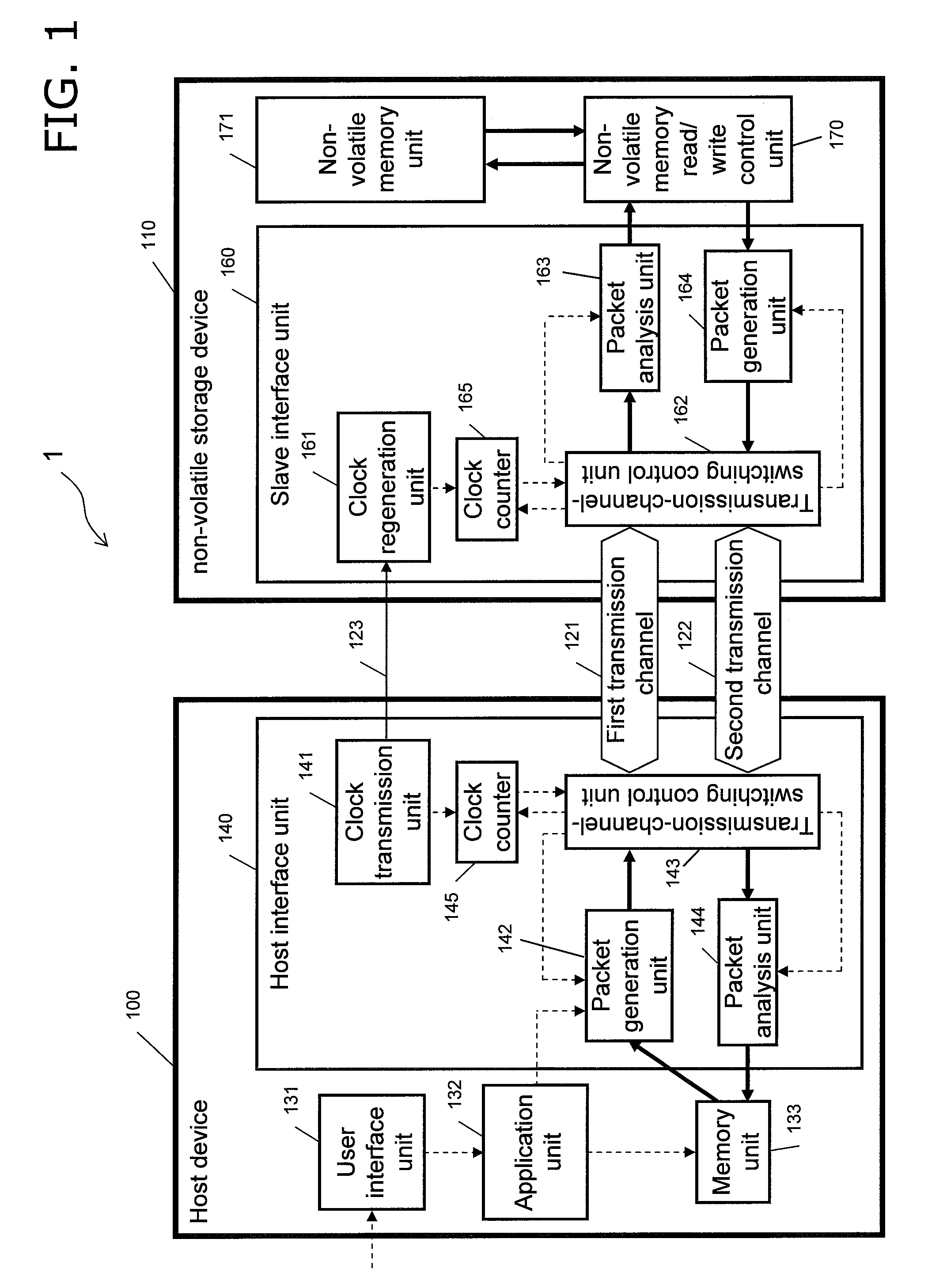

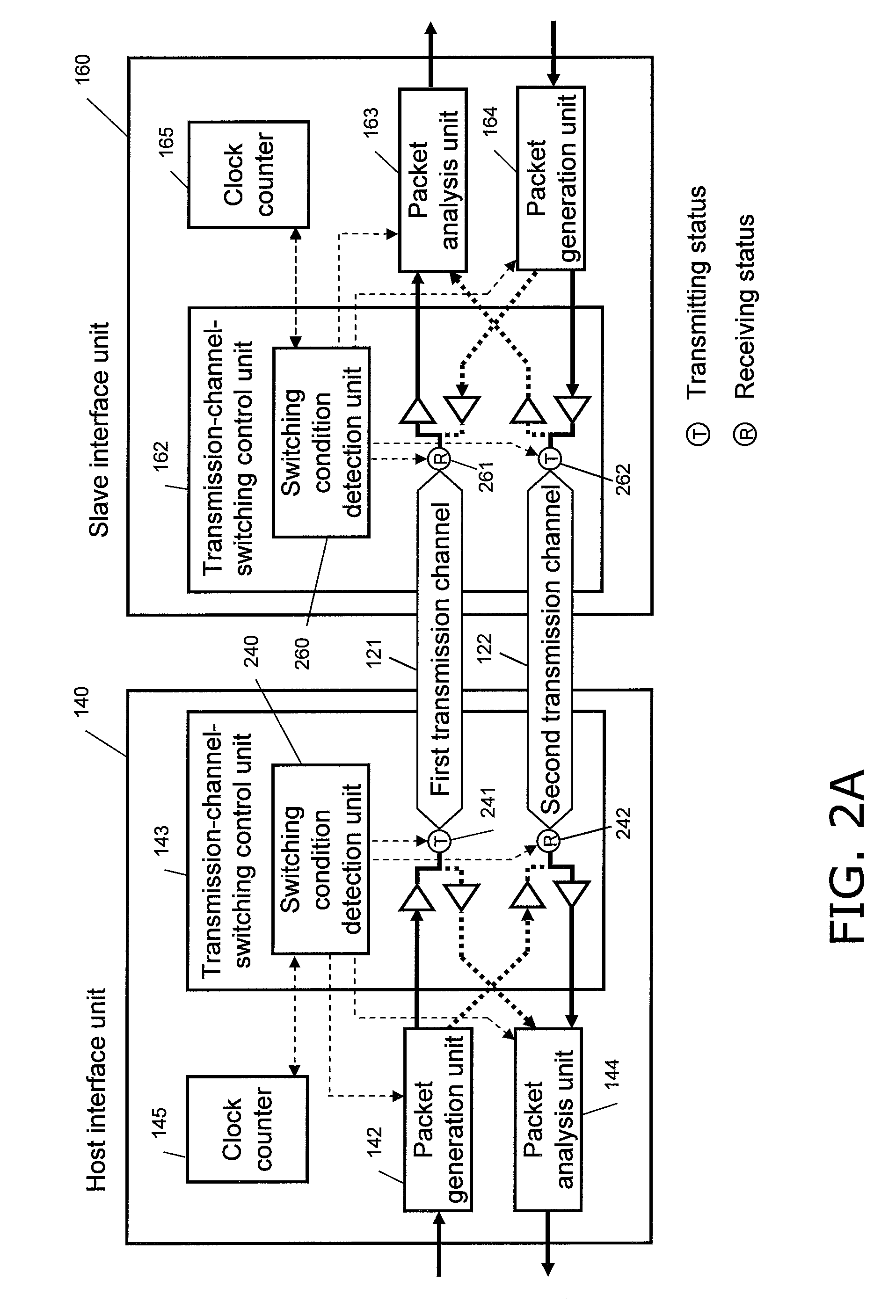

Interface device, communications system, non-volatile storage device, communication mode switching method and integrated circuit

ActiveUS20110182216A1High speed data transmissionEasy to processChannel dividing arrangementsDuplex signal operationState dependentIntegrated circuit

An interrupt request cannot be transmitted while a data read command or a data write command transmitted from a host device to a slave device is being processed in a half-duplex mode. Disclosed are a host device and a slave device that are set to a full-duplex mode by temporarily switching the communication direction of a first transmission channel or a second transmission channel after completing transmission and reception of a predetermined number of data packets in the half-duplex mode. The host device or the slave device can thus transmit an interrupt request, such as a request associated with a wait status or a busy status, to its communication target using the temporary full-duplex mode. This enables the host device or the slave device to process such an interrupt request during high-speed data transfer performed in the half-duplex mode.

Owner:PANASONIC CORP

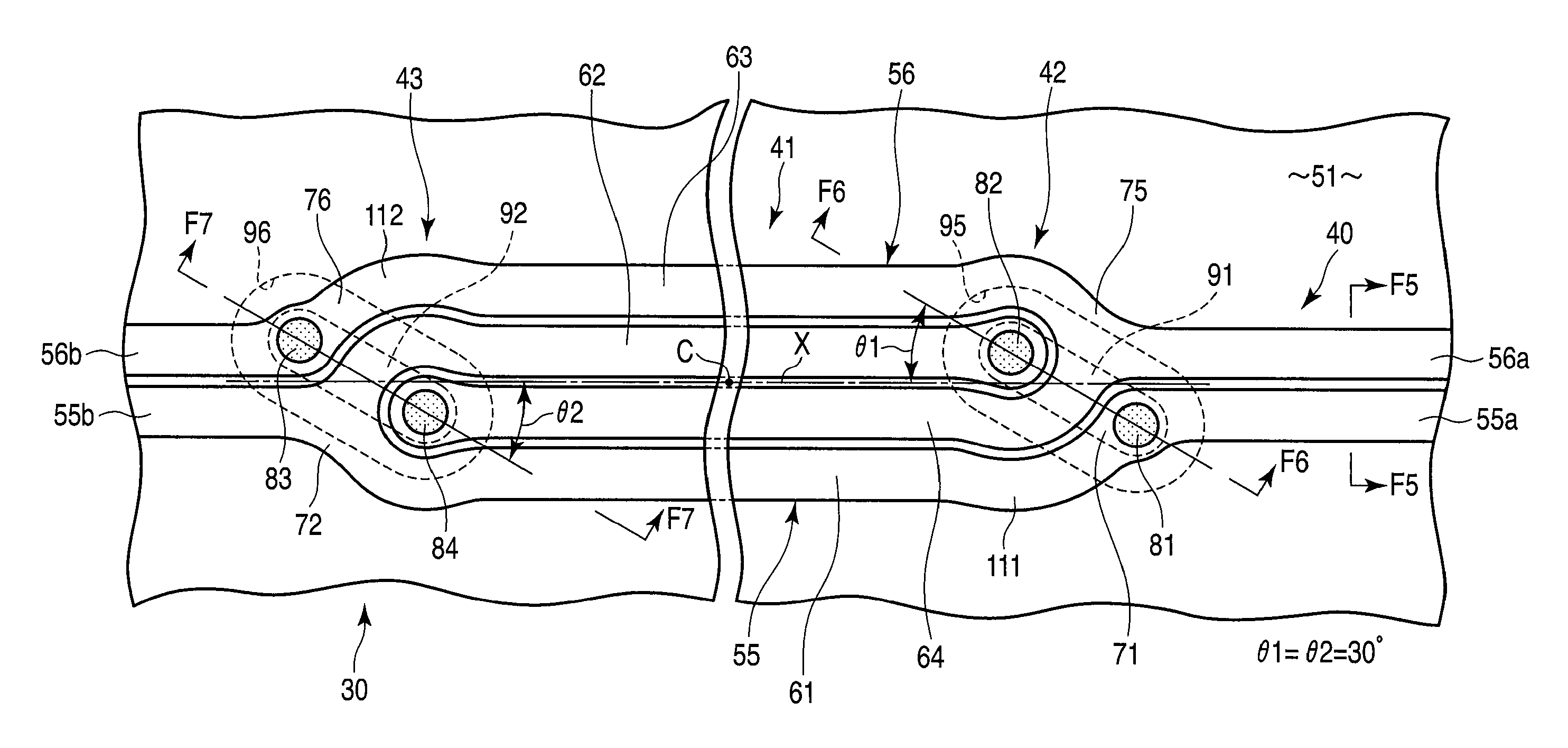

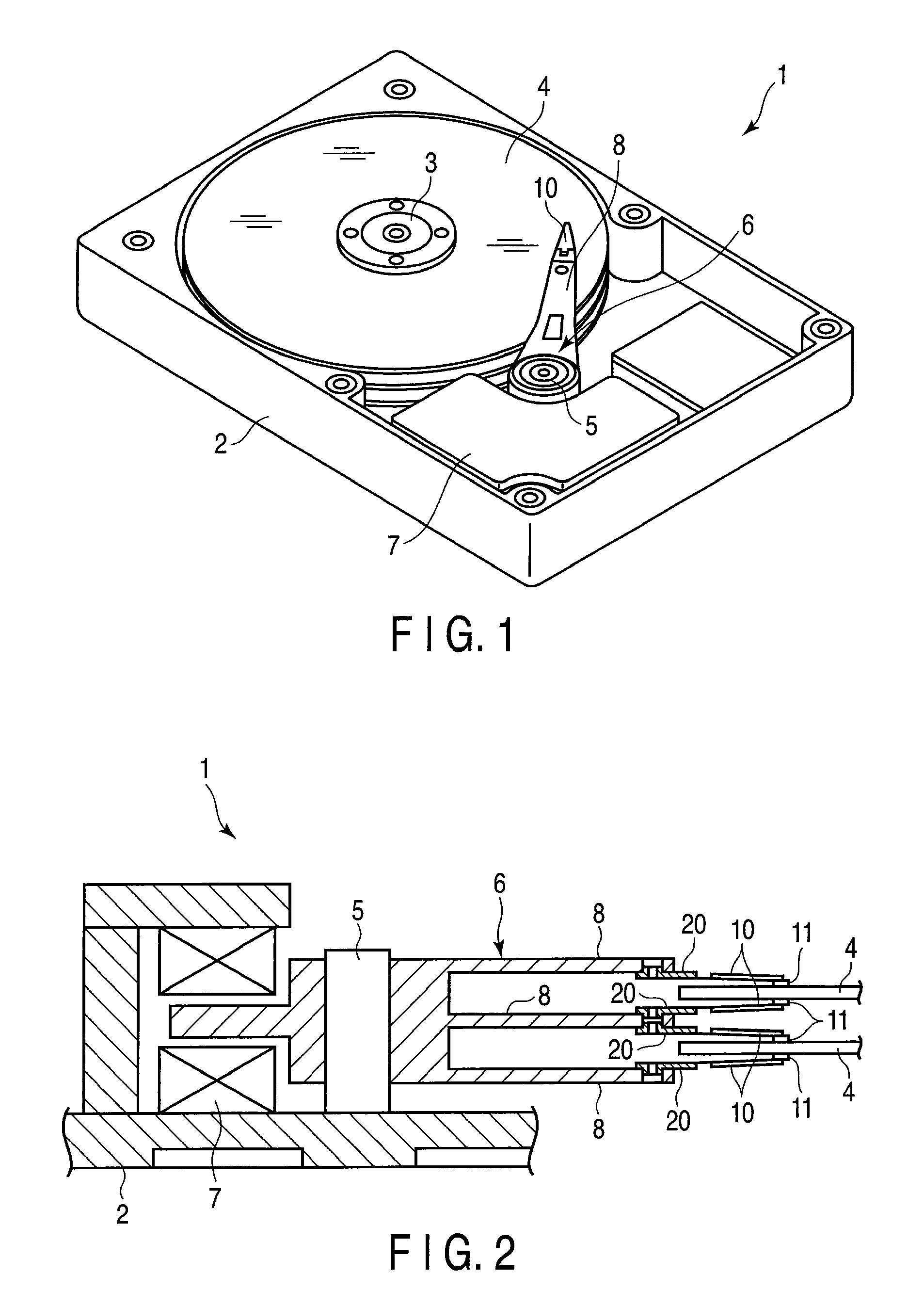

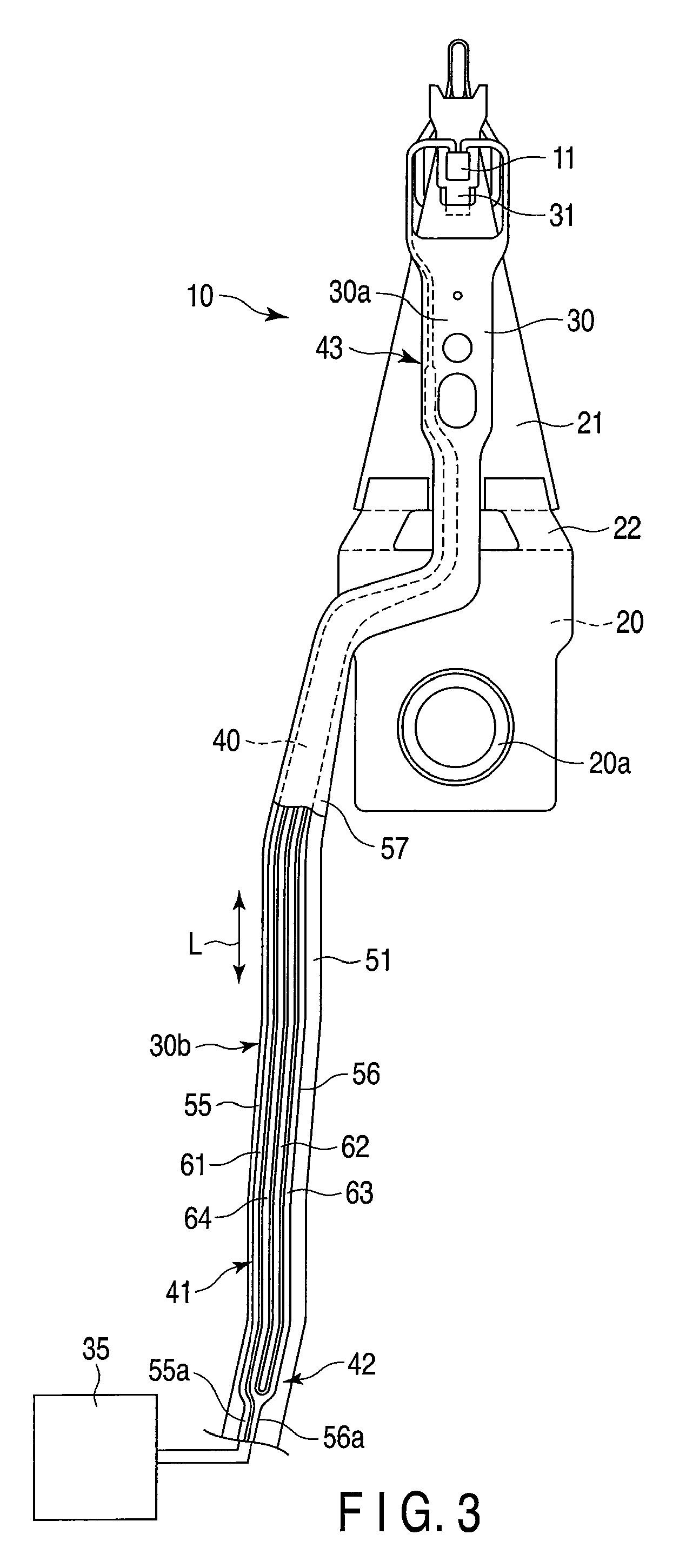

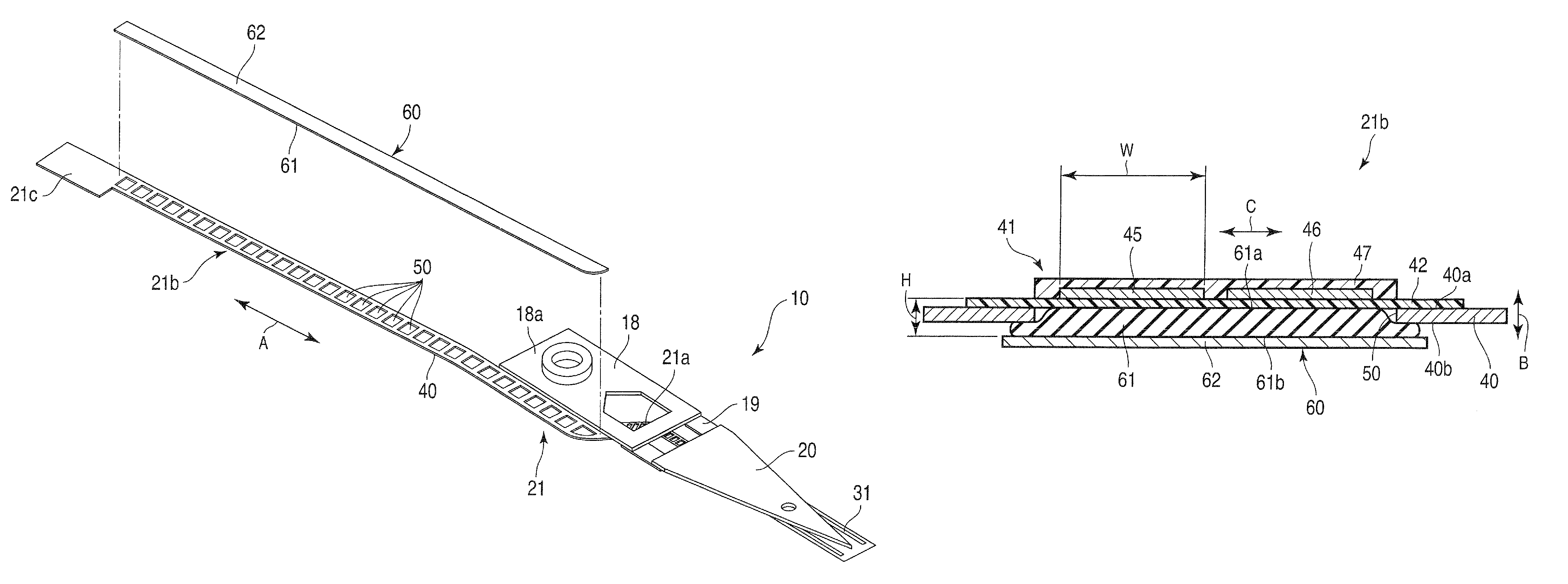

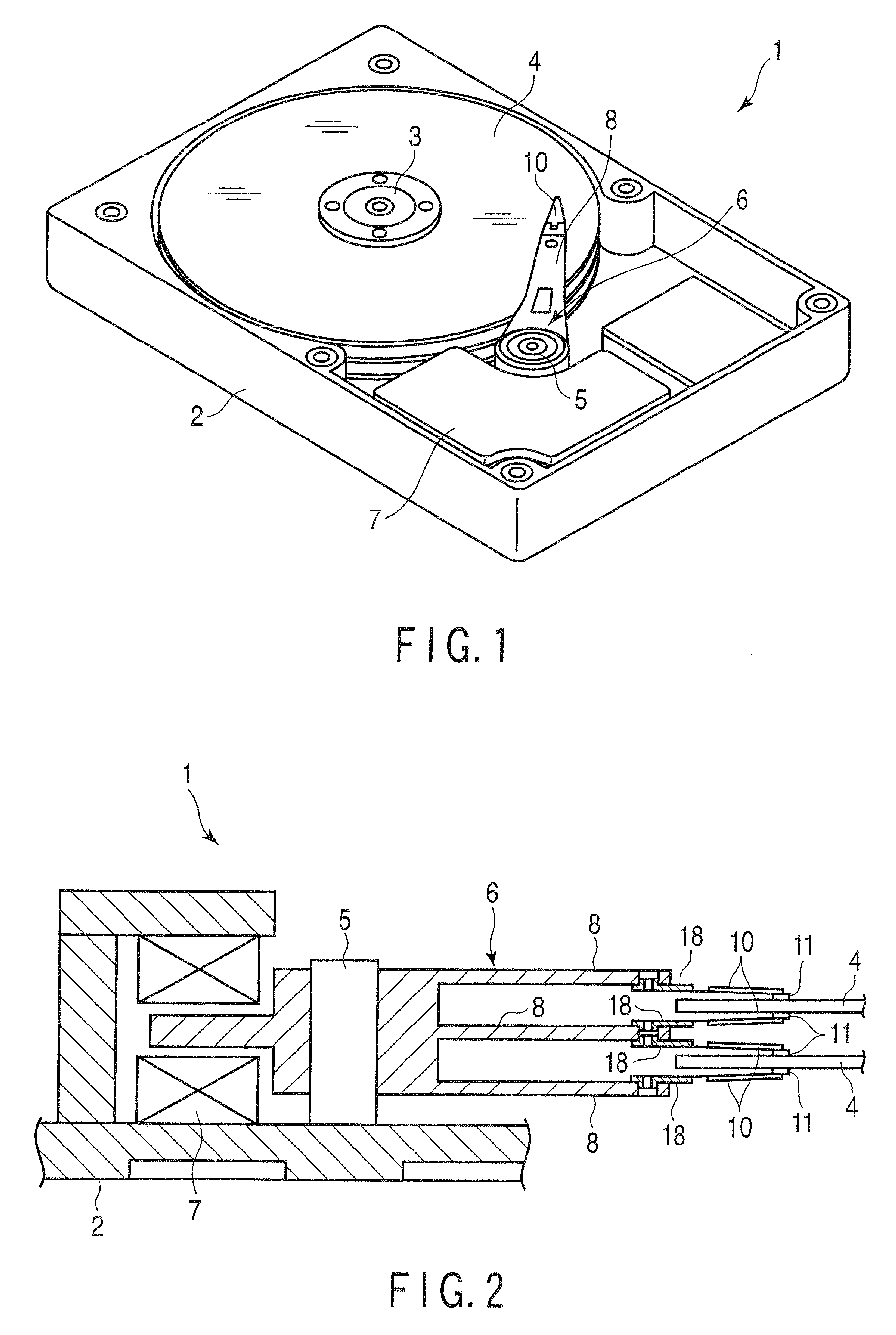

Disk drive flexure

ActiveUS8111483B2Improve electrical performanceAvoid thickerRecord information storageStructure of arm assemblyElectrical conductorAudio power amplifier

A first conductor member includes an amplifier-side first conductor, a head-side first conductor, and first and second interleaved conductors. A second conductor member includes an amplifier-side second conductor, a head-side second conductor, and third and fourth interleave conductors. The second interleaved conductor is connected to the amplifier-side first conductor through a first jumper conductor. The fourth interleave conductor is connected to the head-side second conductor through a second jumper conductor. The jumper conductors are formed by partially etching a metal base. The jumper conductors are individually inclined at angles of 45° or less to an axis which extends in a wiring direction of each of the interleaved conductors.

Owner:NHK SPRING CO LTD

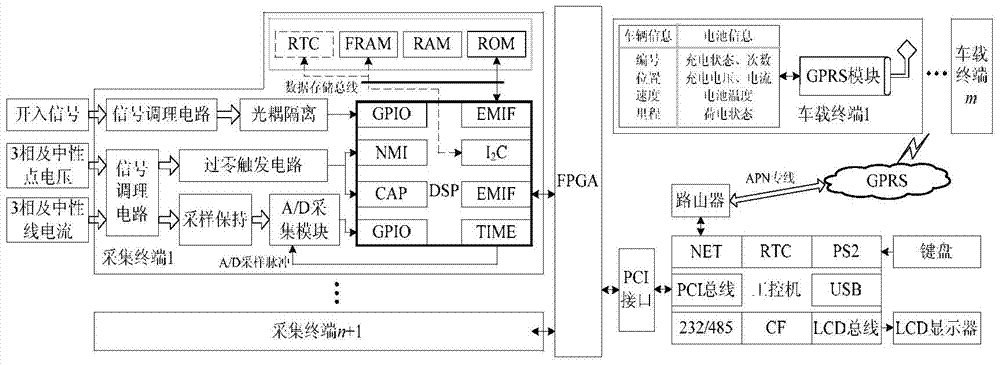

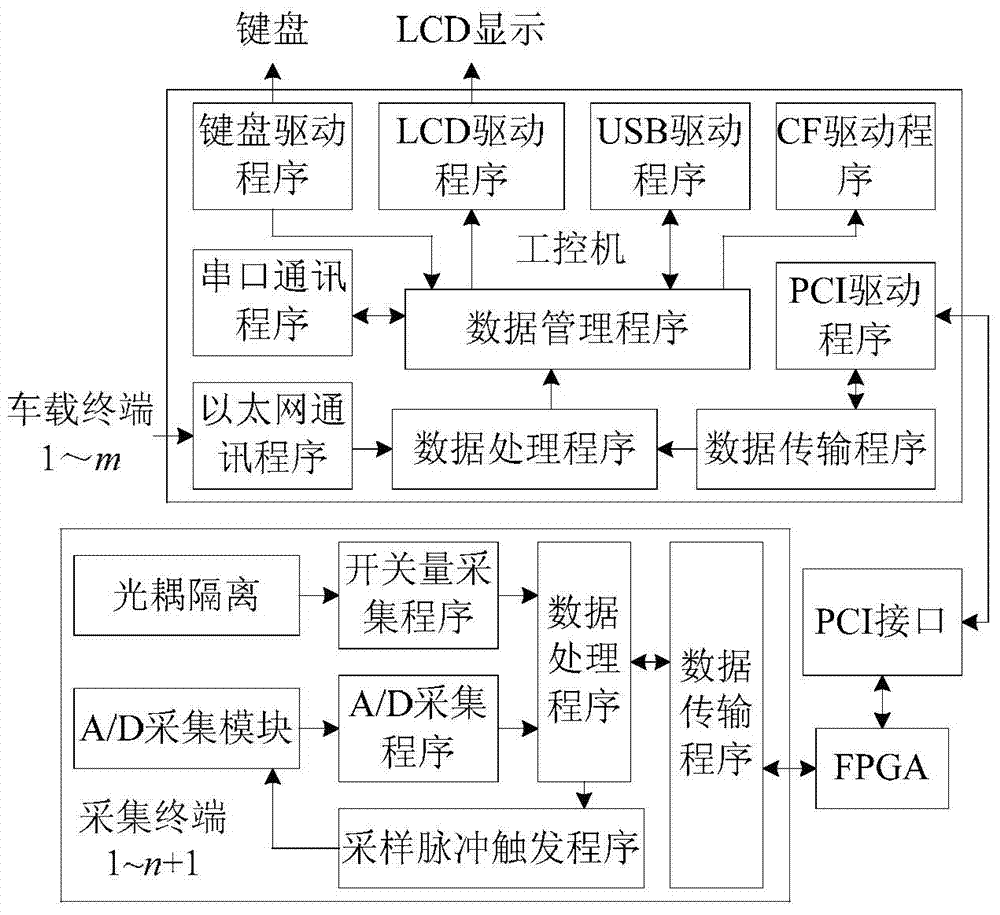

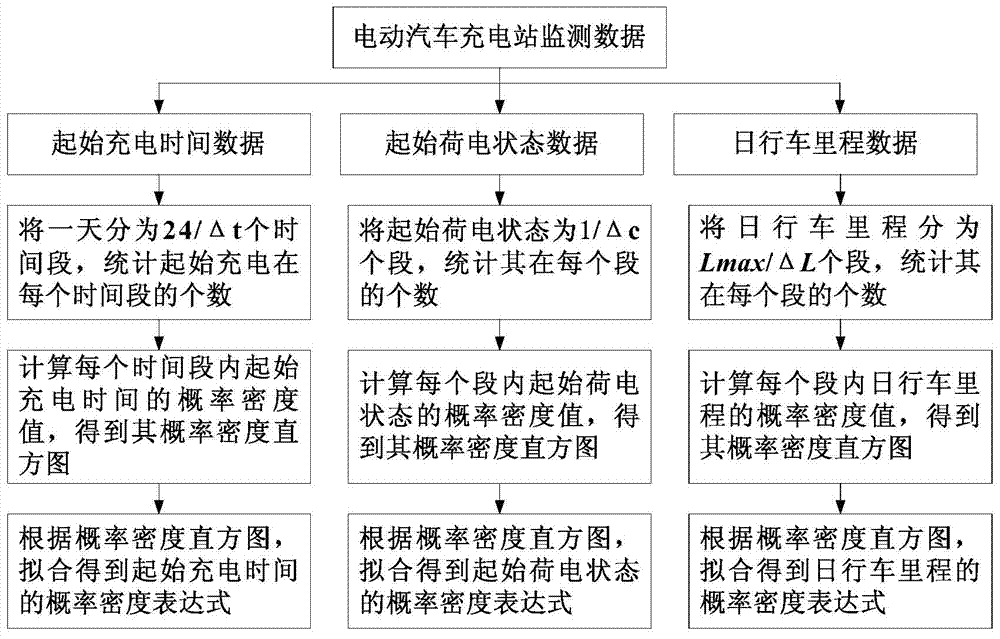

Online monitoring, analysis and evaluation system of electric vehicle charging station

ActiveCN103529340ARealize data transmissionHigh speed data transmissionElectrical testingTerminal unitCharging station

The invention discloses an online monitoring, analysis and evaluation system of an electric vehicle charging station. The system comprises collecting terminal units, a vehicle-mounted terminal unit, an FPGA (field programmable gate array) and PCI (peripheral component interconnect) interface unit and an embedded industrial personal computer; a plurality of the collecting terminal units and the embedded industrial personal computer constitute an electric vehicle charging station online monitoring platform which is used for collecting a point of common connection of the charging station as well as voltage and current of each charger; the FPGA and PCI interface unit is used for realizing data exchange of the plurality of the collecting terminal units and the industrial personal computer; the vehicle-mounted terminal unit transmits information about changing and the operation state of an electric vehicle to the embedded industrial personal computer; and comprehensive evaluation on states of the electric vehicle is performed with a radar map method, and probability distribution of the initial charging time, the initial charge state and a daily travelled distance is counted and analyzed. The system is stable and reliable, can realize long-term monitoring of the charging station, and provides a large quantity of reliable monitoring data for operation and planning of the charging station.

Owner:CHONGQING UNIV

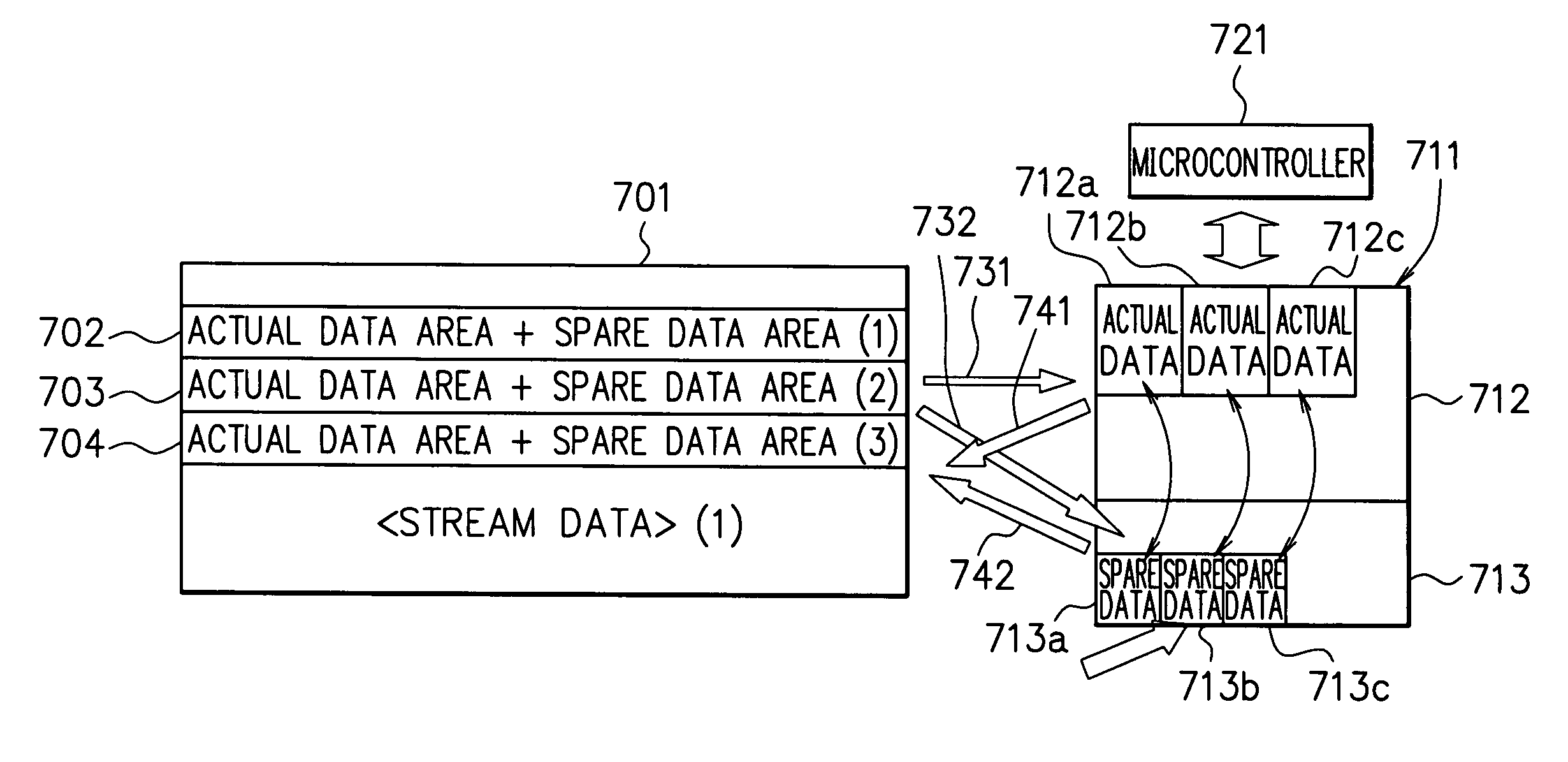

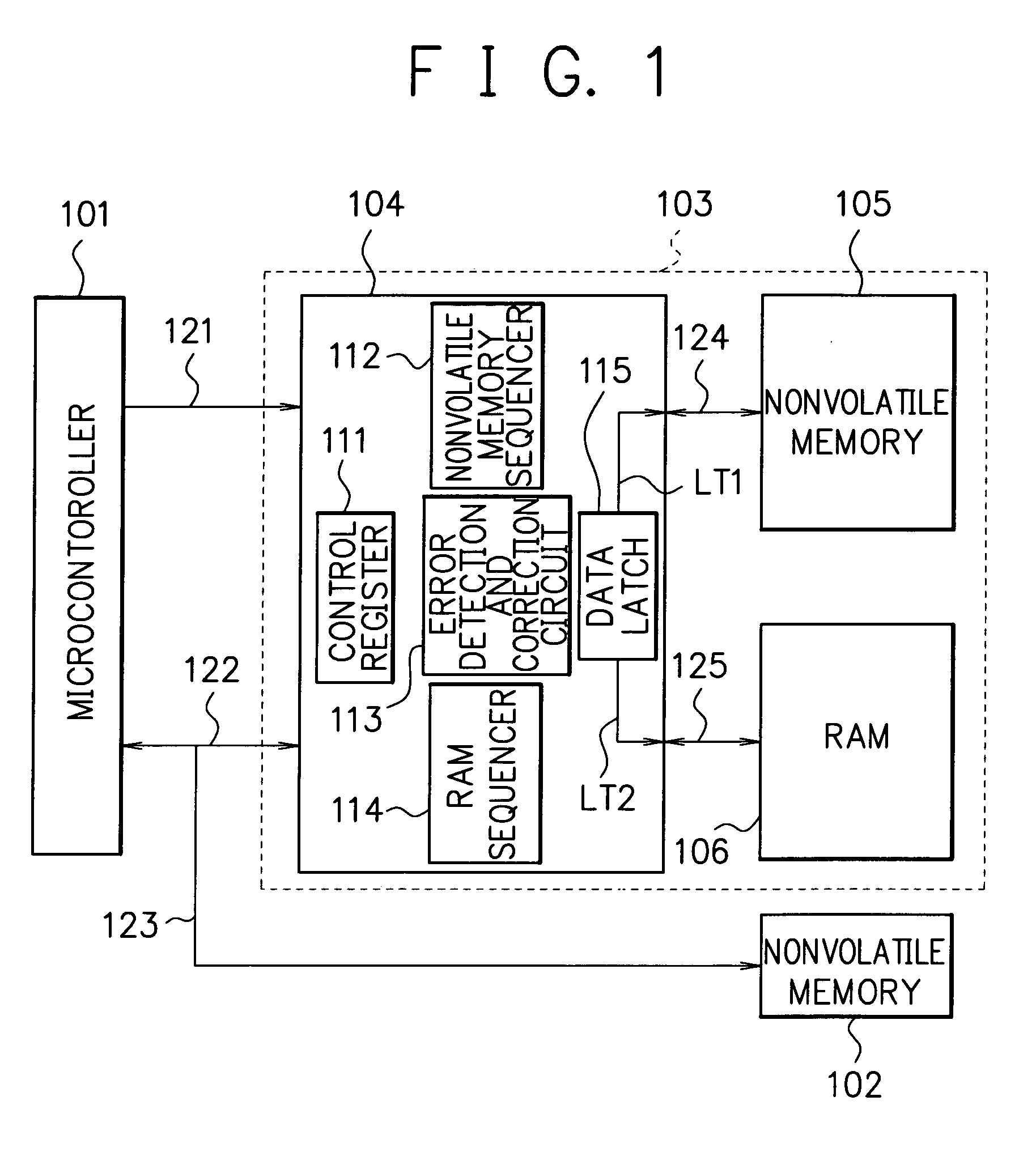

Memory device for controlling nonvolatile and volatile memories

InactiveUS7266664B2Increase speedHigh speed data transmissionMemory loss protectionMemory adressing/allocation/relocationData transmissionVolatile memory

A memory device includes a nonvolatile memory capable of storing data, a volatile memory capable of being random-accessed, and a controller for transferring data between the nonvolatile memory and the volatile memory and enabling a pseudo access as if the volatile memory were externally directly accessed in accordance with an instruction through an external bus when the data transfer is not performed.

Owner:VALLEY DEVICE MANAGEMENT

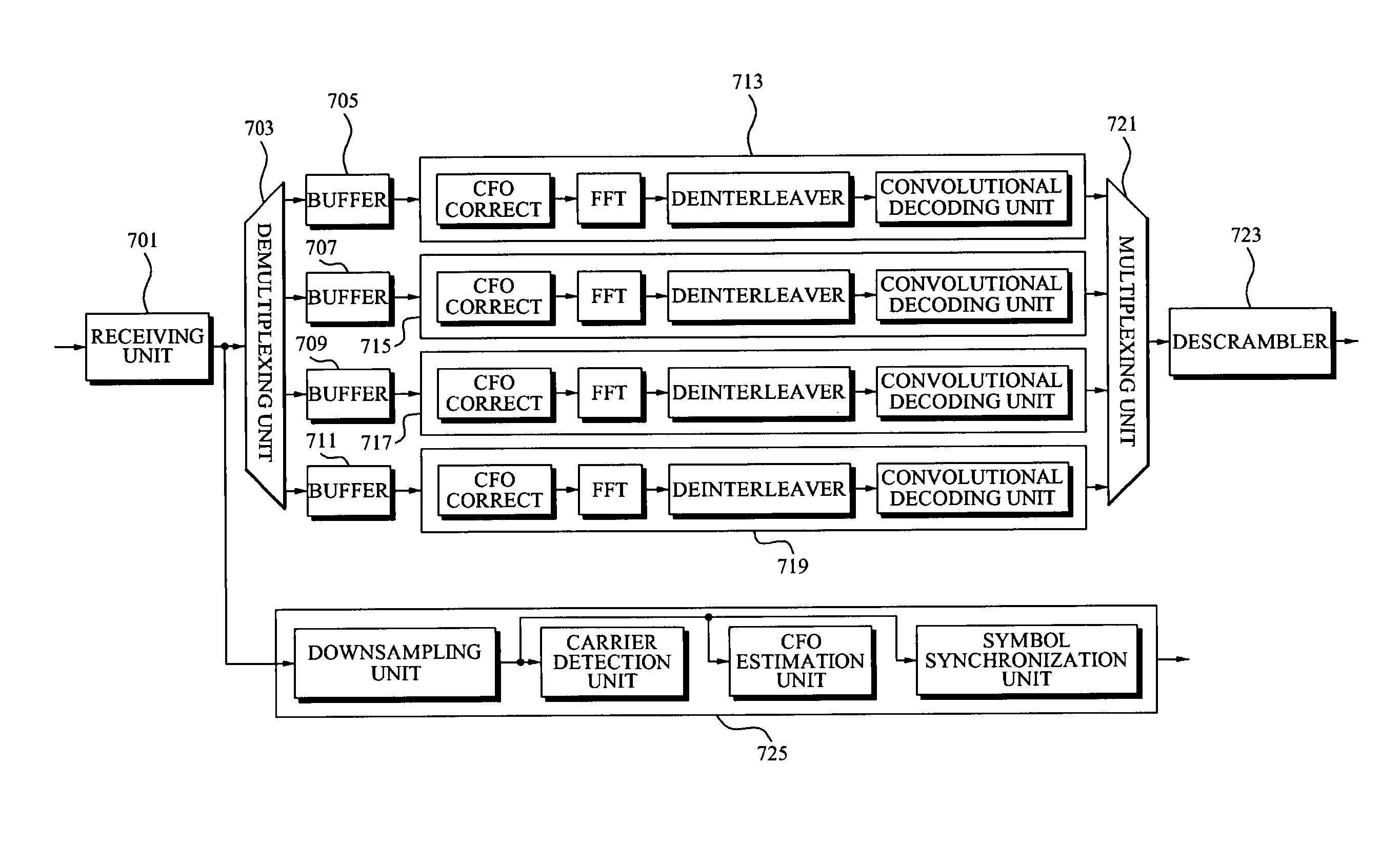

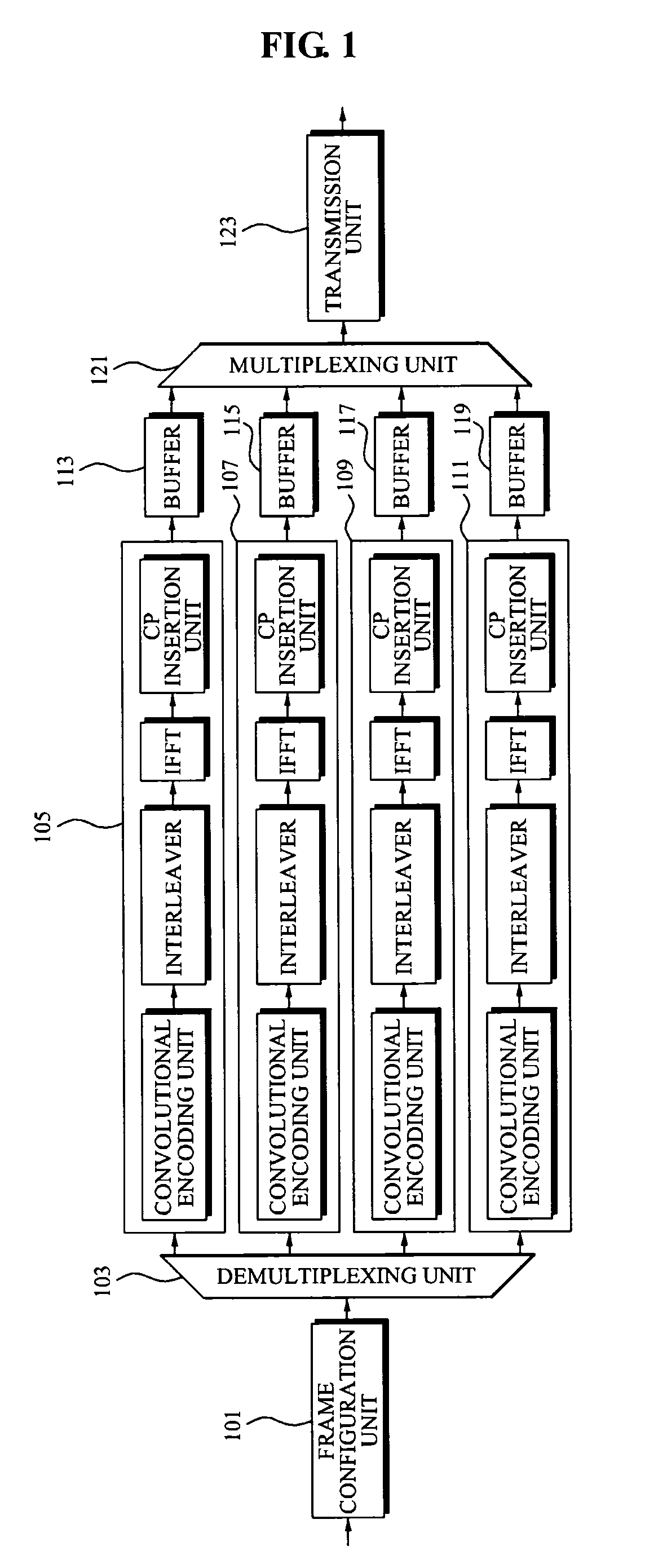

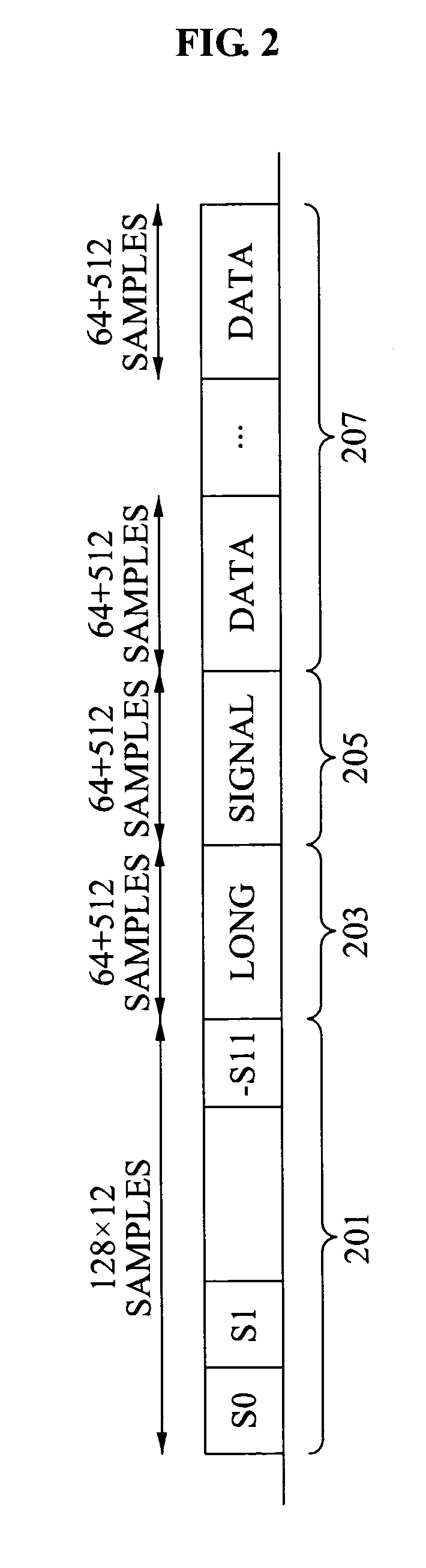

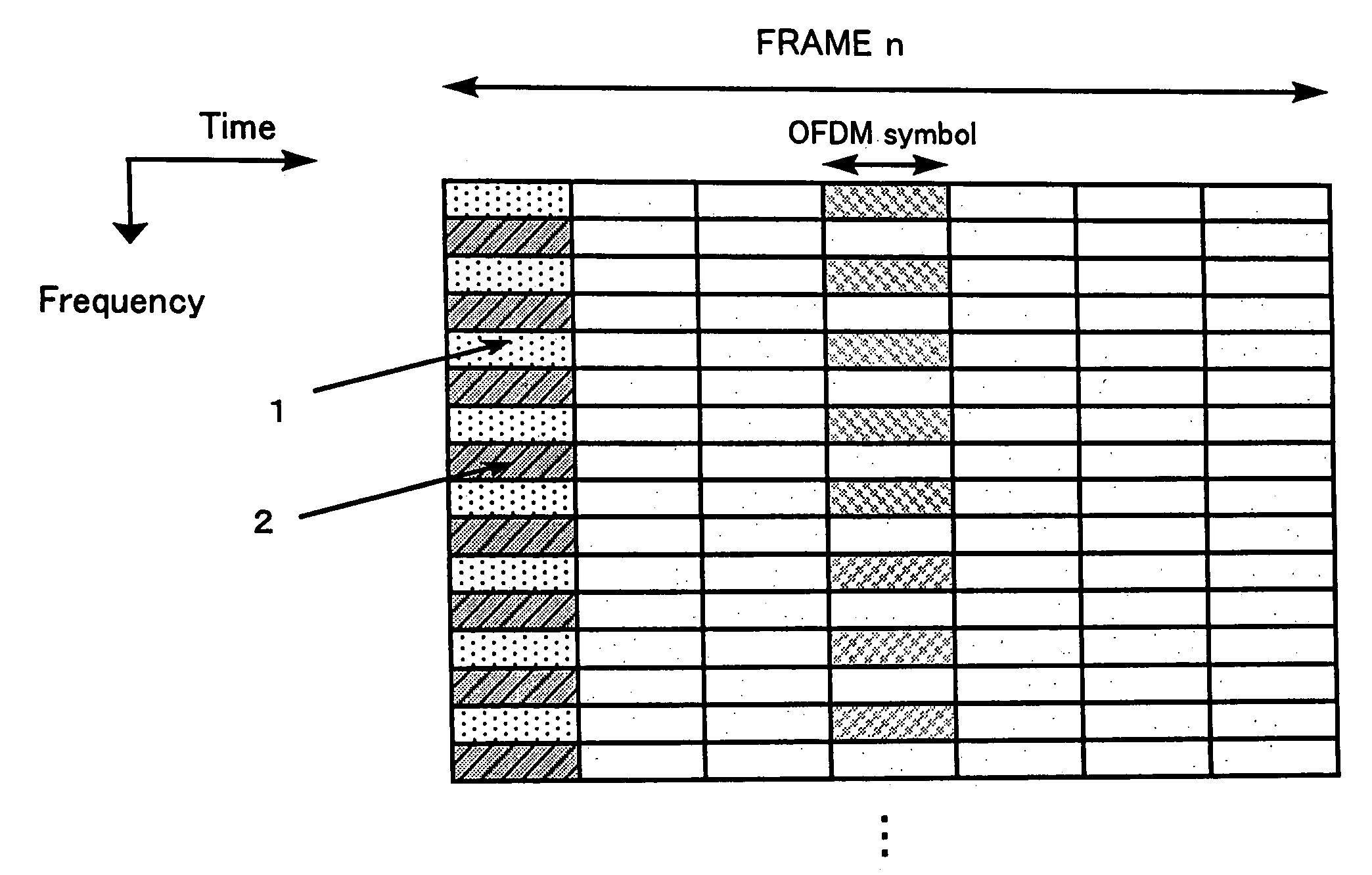

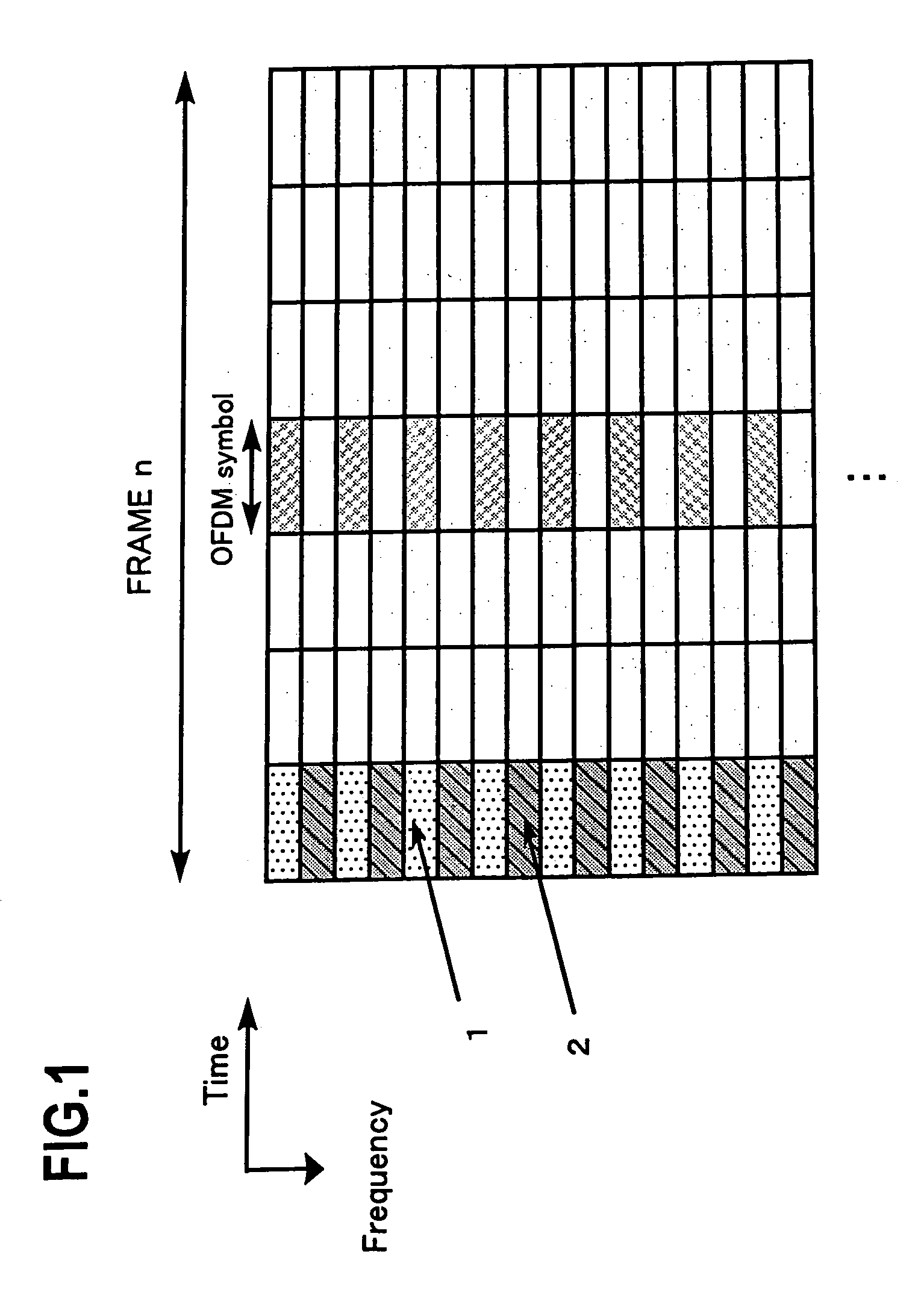

Frame structure for fast wireless communication system and apparatus for fast wireless communication using the frame

InactiveUS20100208832A1Quantity of data can not be reducedImprove system speedSecret communicationRadio transmissionMultiplexingCommunications system

A method of configuring a frame for fast wireless communication and an apparatus for fast wireless communication are provided. The apparatus for fast wireless communication includes: a frame configuration unit configuring a frame including transmission data; a demultiplexing unit demultiplexing the transmission data included in the frame into N number of parallel streams (N: positive number greater than 2); N number of coding and modulation units connected in parallel to perform error correction coding and orthogonal frequency division multiplexing (OFDM) with respect to each of the N number of parallel streams; and a multiplexing unit multiplexing outputs of the N number of coding and modulation units into serial streams.

Owner:ELECTRONICS & TELECOMM RES INST

Semiconductor device having a through electrode with a low resistance and method of manufacturing the same

ActiveUS7732926B2Shorten the timeLower resistanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A method of manufacturing a through electrode. While using at least a first conductive film for a gate electrode as a mask, an inner trench and a peripheral trench is formed. The Inner trench is provided for an inner through electrode having a columnar semiconductor. The peripheral trench is provided for a peripheral through electrode around an annular semiconductor surrounding the inner trench. The inner trench and the peripheral trench are filled with a through electrode insulation film and a through electrode conductive film, respectively, to form an inner through electrode and a peripheral through electrode.

Owner:MICRON TECH INC

Connectionless TCP/IP data exchange

InactiveUS7263071B2High speed data transmissionMultiplex system selection arrangementsSpecial service provision for substationNetwork Communication ProtocolsChecksum

A communication protocol, and a method and system of communication exchange between systems over a communication network includes establishing a connection between a first system and a second system. Data is formatted by the first system into an IP datagram with an IP header and one of a TCP and a UDP header. A connectionless TCP / IP header is constructed to add to the formatted data. The connectionless TCP / IP header includes a pre-defined identifying value in a designated field, and a checksum to validate that a connectionless TCP / IP header has been identified. The formatted data having the connectionless TCP / IP header is transmitted from the first system to the second system, and the pre-defined identifying value in the designated field is verified to identify the connectionless TCP / IP header. The connectionless TCP / IP header is then removed from the IP datagram, and the IP datagram is processed.

Owner:SEIKO EPSON CORP

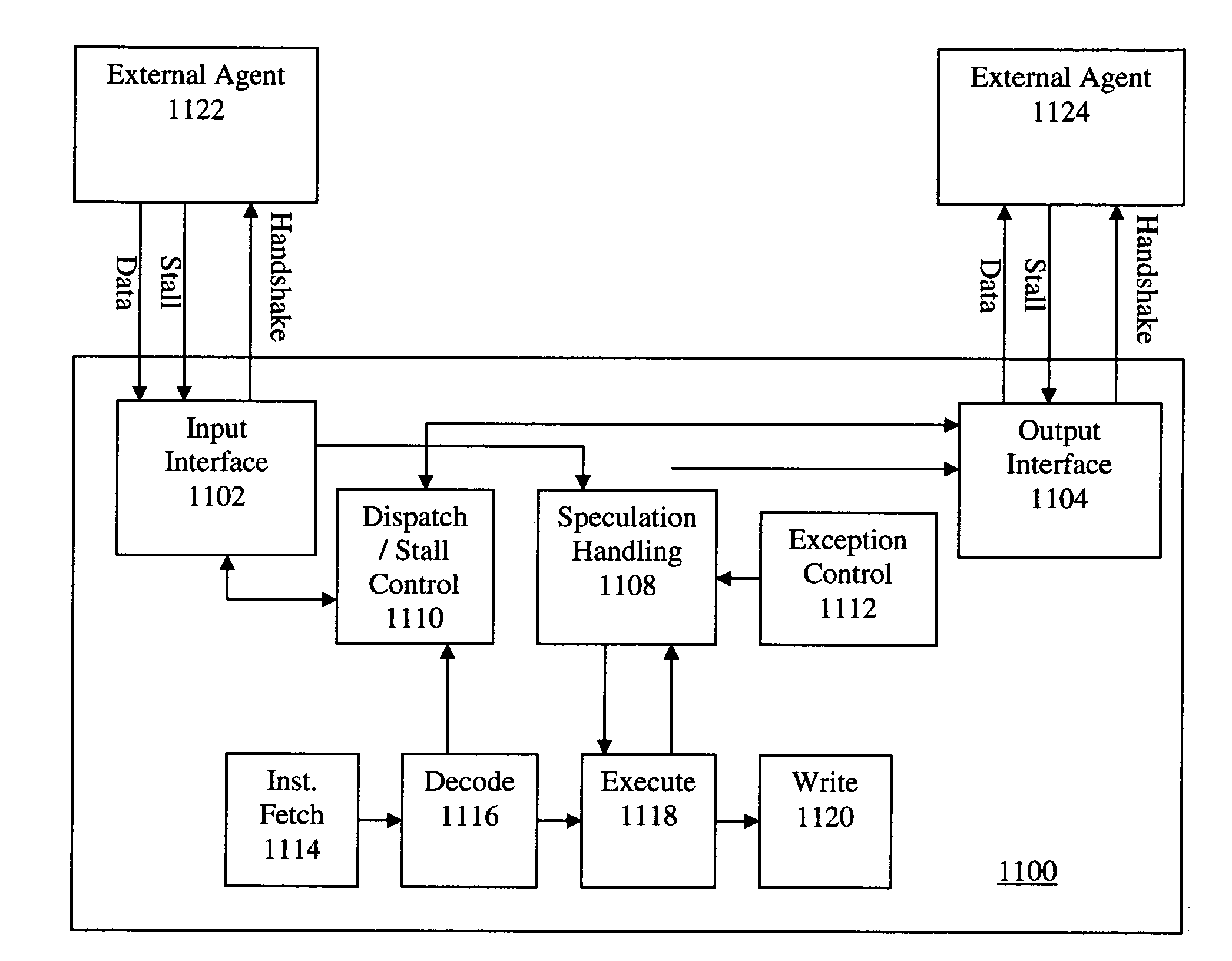

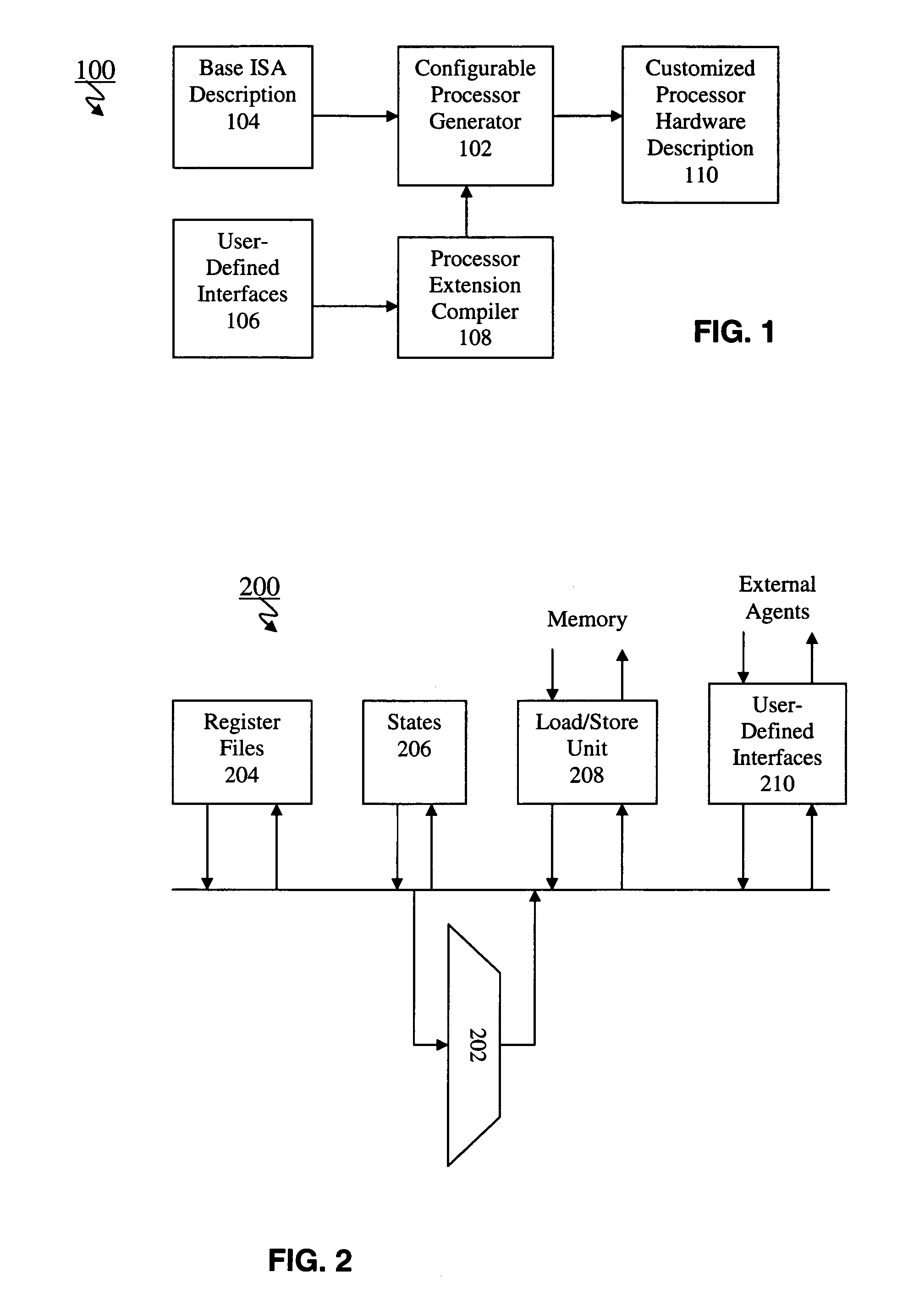

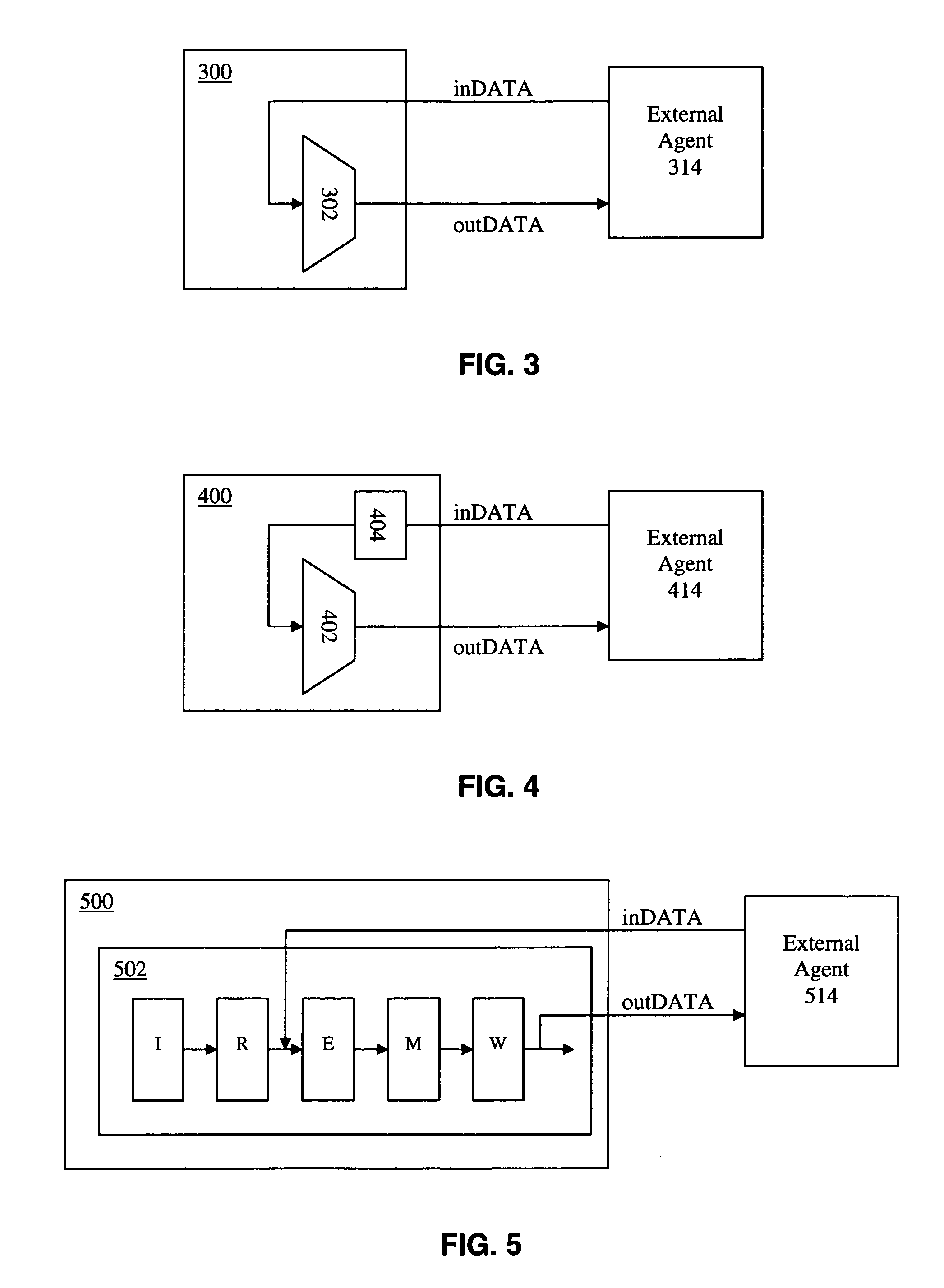

Method and apparatus for providing user-defined interfaces for a configurable processor

ActiveUS7664928B1High bandwidthImprove performanceGeneral purpose stored program computerProgram controlTime to marketComputer architecture

A technique that improves both processor performance and associated data bandwidth through user-defined interfaces that can be added to a configurable and extensible microprocessor core. These interfaces can be used to communicate status or control information and to achieve synchronization between the processor and any external device including other processors. These interfaces can also be used to achieve data transfer at the rate of one data element per interface in every clock cycle. This technique makes it possible to design multiprocessor SOC systems with high-speed data transfer between processors without using the memory subsystem. Such a system and design methodology offers a complete shift from the standard bus-based architecture and allows designers to treat processors more like true computational units, so that designers can more effectively utilize programmable solutions rather than design dedicated hardware. This can have dramatic effects not only in the performance and bandwidth achieved by designs, but also in the time to market and reuse of such designs.

Owner:TENSILICA

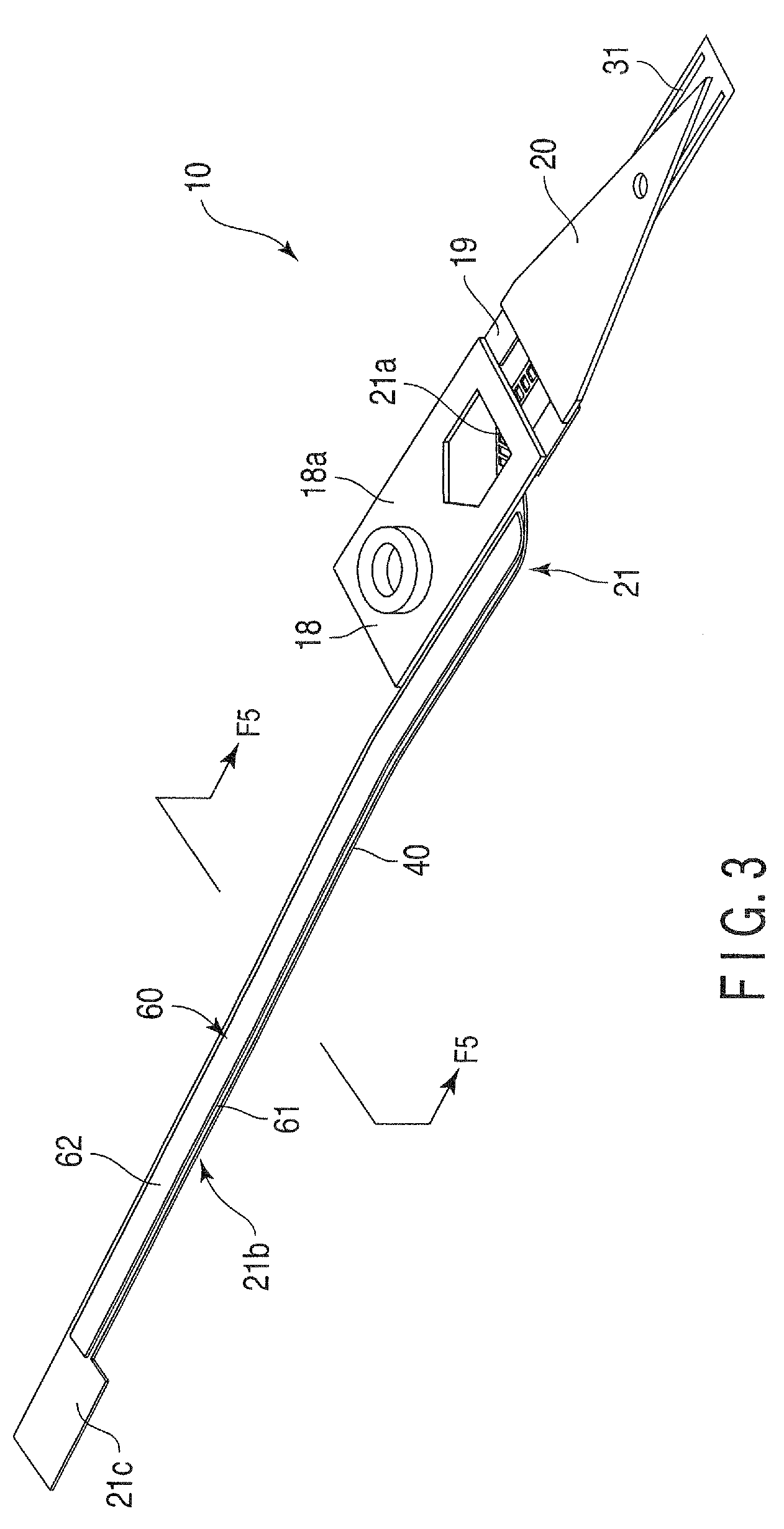

Flexure to be secured to a load beam of a disk drive suspension

ActiveUS8503133B2Avoid swingingHigh speed data transmissionRecord information storageStructure of arm assemblyElectrical conductorEngineering

A flexure with conductors is provided with a flexure tail portion. The flexure tail portion includes a metal base, an electrically insulating layer, and a conductive member. The metal base is formed with a plurality of apertures. A damper is attached to the flexure tail portion. The damper includes a viscoelastic member and a metallic constrained plate. The viscoelastic member has first and second surfaces. The first surface of the viscoelastic member is secured to the flexure tail portion. The constrained plate is secured to the second surface of the viscoelastic member. The constrained plate extends longitudinally relative to the metal base along the conductive member. The conductive member and the constrained plate face each other with the viscoelastic member therebetween.

Owner:NHK SPRING CO LTD

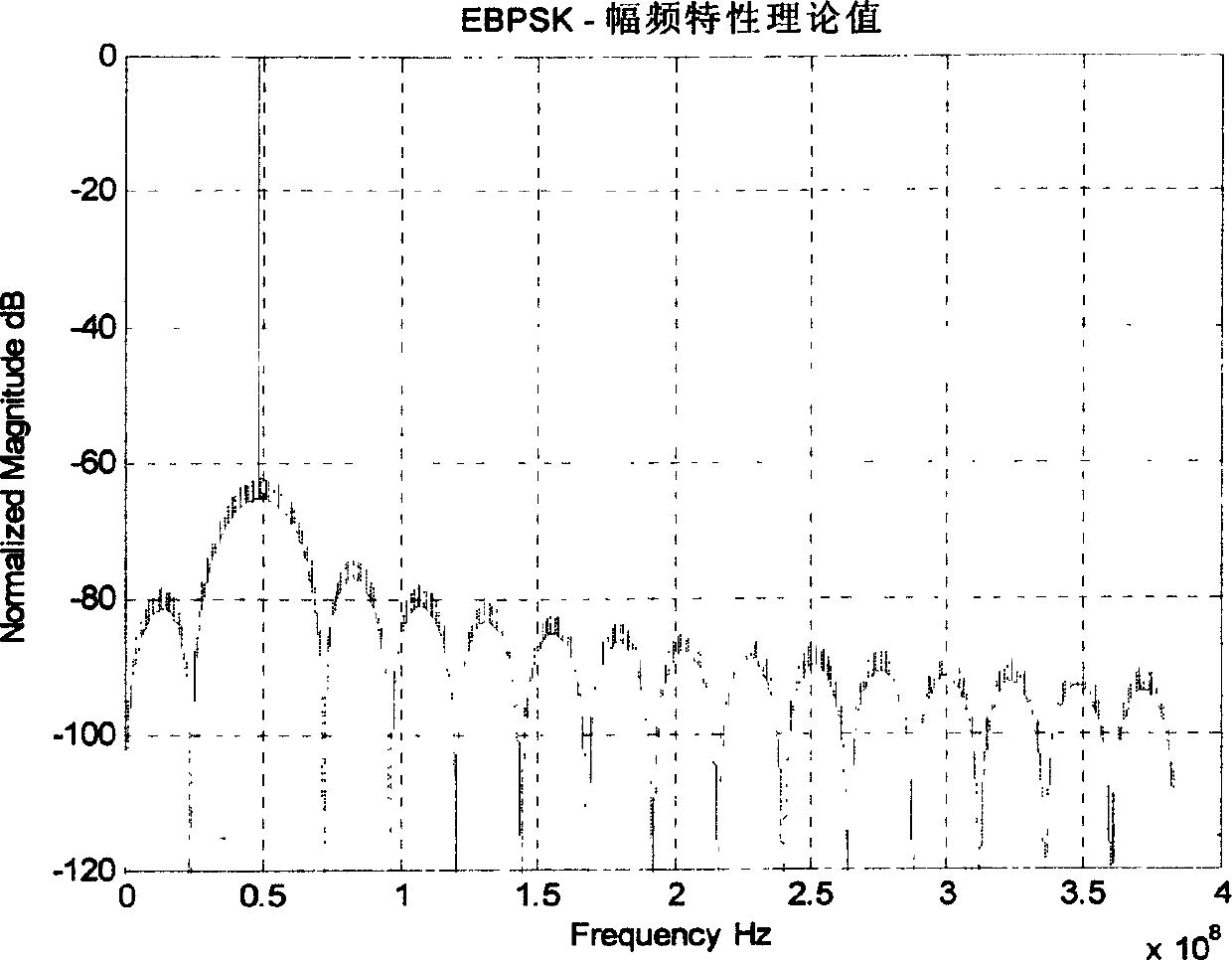

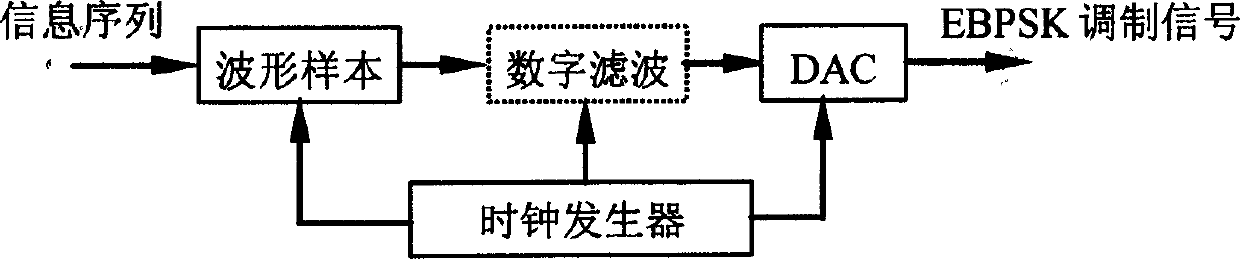

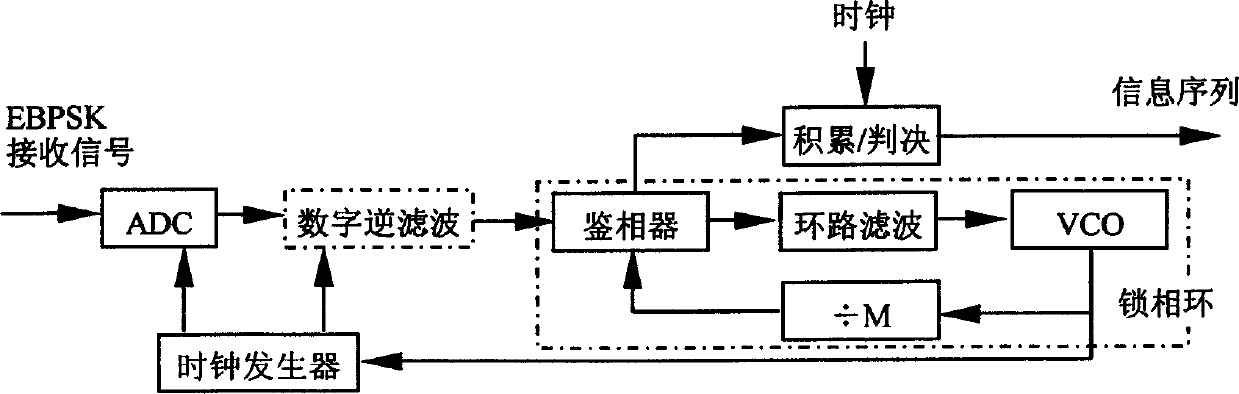

Unified binary phase modulating and demodulating method

InactiveCN1889550ARealize high-speed data transmissionHigh speed data transmissionSynchronous/start-stop systemsBinary informationCarrier signal

A information modulating and demodulating method used on digital communication includes realizing modulation by utilizing binary information code element to directly vary abrupt phase of sine carrier wave, utilizing lock phase ring to realize demodulation, making modulated signal g0(t) corresponding to number zero be sine wave of N carrier wave period and making g1(t) corresponding to number one be in sine wave of N carrier wave period with frequency of fc, applying phase jump off angle theta and parameter tau as modulation index for varying signal bandwidth and transmission code rate as well as demodulation property.

Owner:SOUTHEAST UNIV

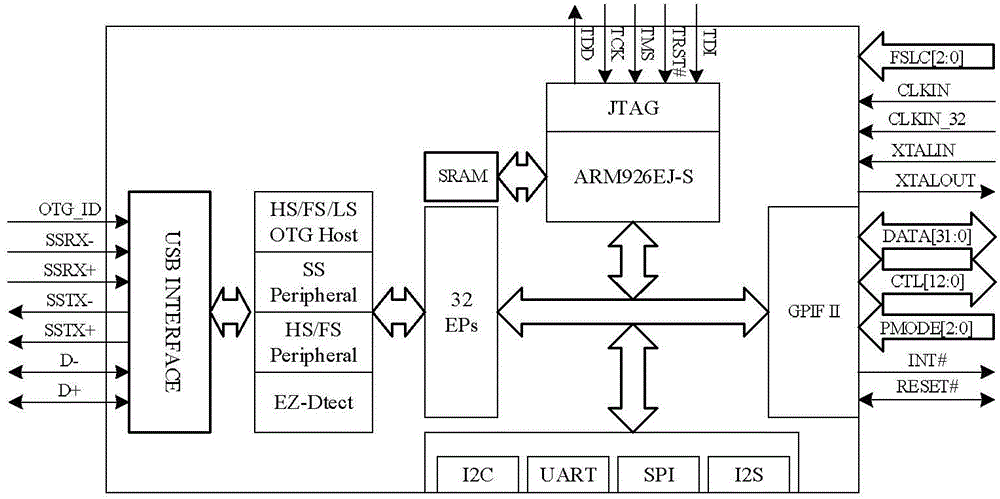

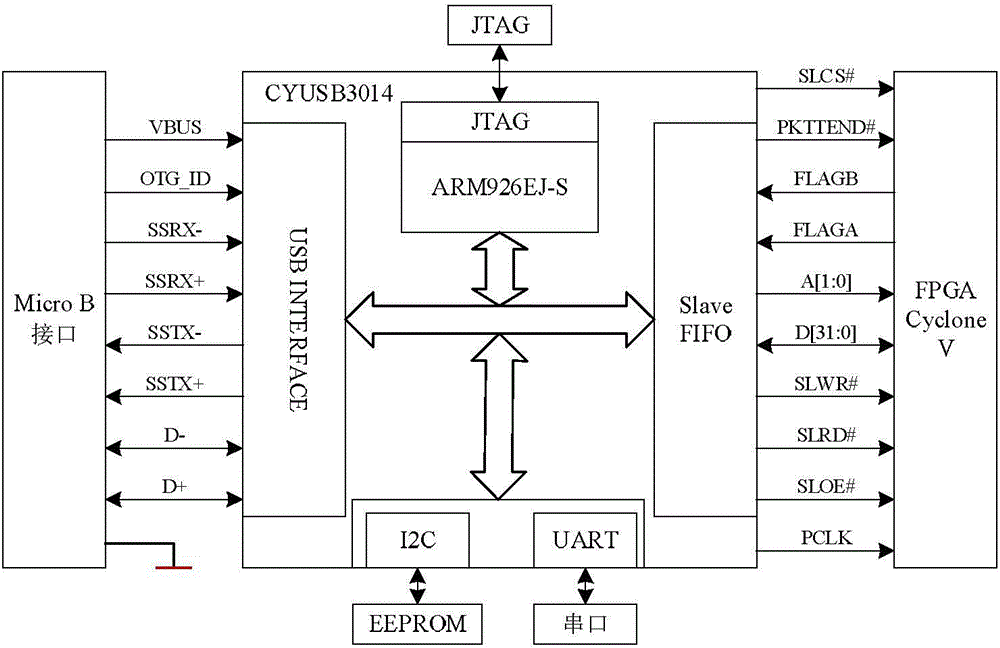

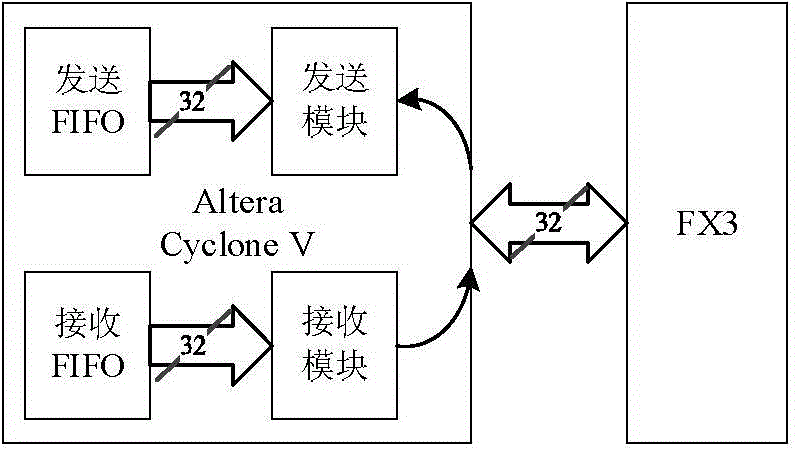

FPGA (field programmable gate array) based USB3.0 interface module

InactiveCN104881388AVersatilityHigh speed data transmissionElectric digital data processingFpga implementationsData transmission

The invention discloses an FPGA (field programmable gate array) based USB3.0 interface module, and relates to a USB3.0 interface module in order to realize compatibility with a USB2.0 high-speed interface as well as high-speed data transmission between a computer and an FPGA. According to the interface module, the FPGA is adopted to realize logic control, and the high-speed data transmission is realized through data read-write operation of synchronous slave equipment FIFO (first input first output) in a chip FX3; the interface module control logic comprises a USB3.0 transmitting module, a USB3.0 receiving module, an FIFO transmitting module for clock domain crossing operation and an FIFO receiving module for the clock domain crossing operation. The FPGA based USB3.0 ultrahigh-speed interface is compatible with the USB2.0 high-speed interface, and the high-speed data transmission between the computer and the FPGA is realized.

Owner:HARBIN INST OF TECH

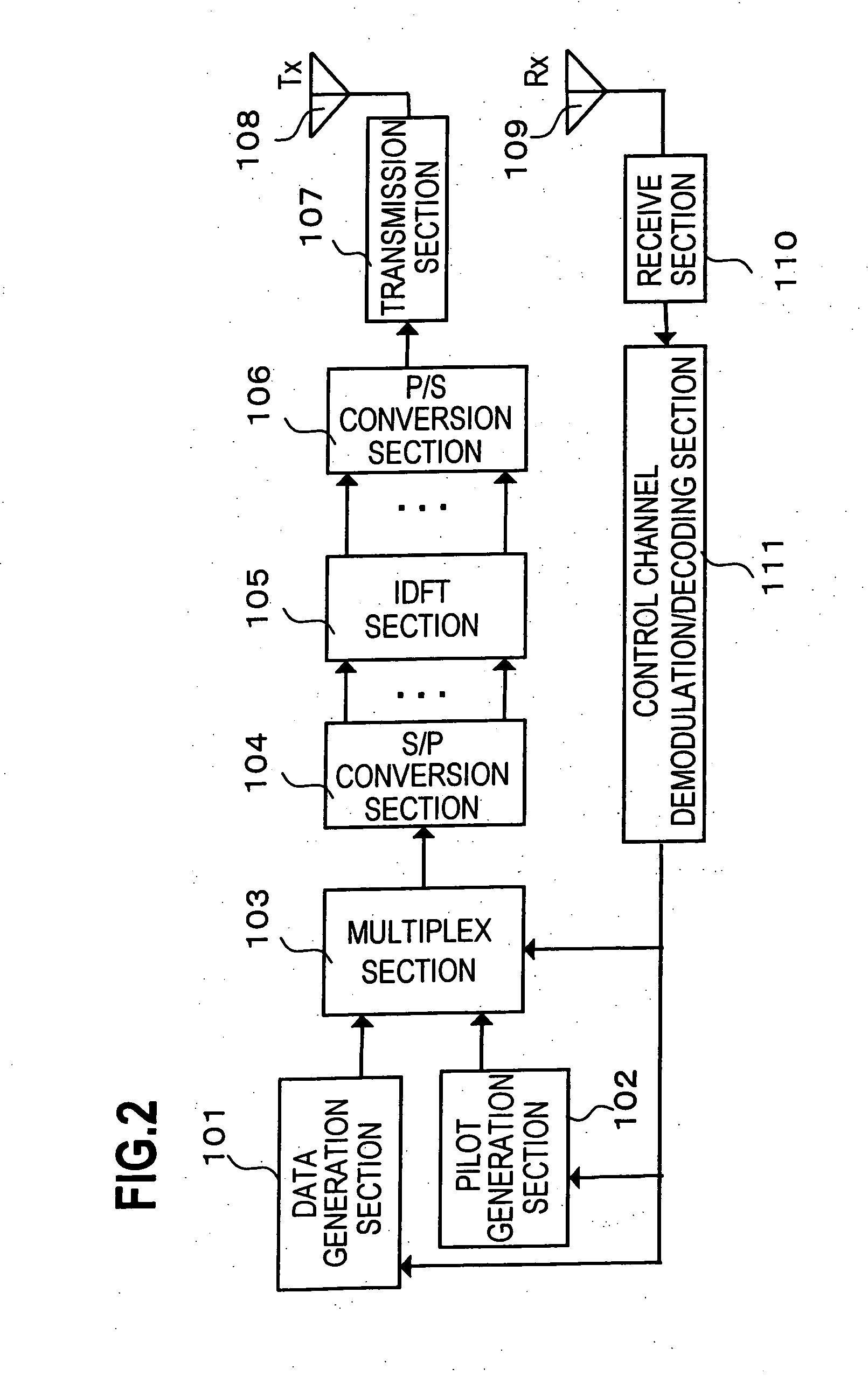

Optimum radio communication method with radio frame variable control and radio communication system using the same

InactiveUS20080123762A1Flexible high-speed data transmissionReduce controlError preventionFrequency-division multiplex detailsCommunications systemControl channel

Not only pilot channel symbols but also control channel symbols can be flexibly decreased in a radio communication system, which includes a transmission side apparatus transmitting a data frame where a plurality of continuous or discontinuous frequency areas are assigned to one transfer time block and a frame is formed of a predetermined number of transfer time blocks; and a reception side apparatus receiving a data frame from the transmission side apparatus, The transmission side apparatus transmits to the reception side apparatus a data frame which has a common pilot channel and a control channel in the beginning of the frame, the reception side apparatus measures a received quality of the data frame, decides a frame type based on the measured received quality and notifies the decided frame type to the transmission side apparatus. The transmission side apparatus sends subsequent frame data to the reception side apparatus in use of a frame format corresponding to the notified frame type.

Owner:FUJITSU LTD

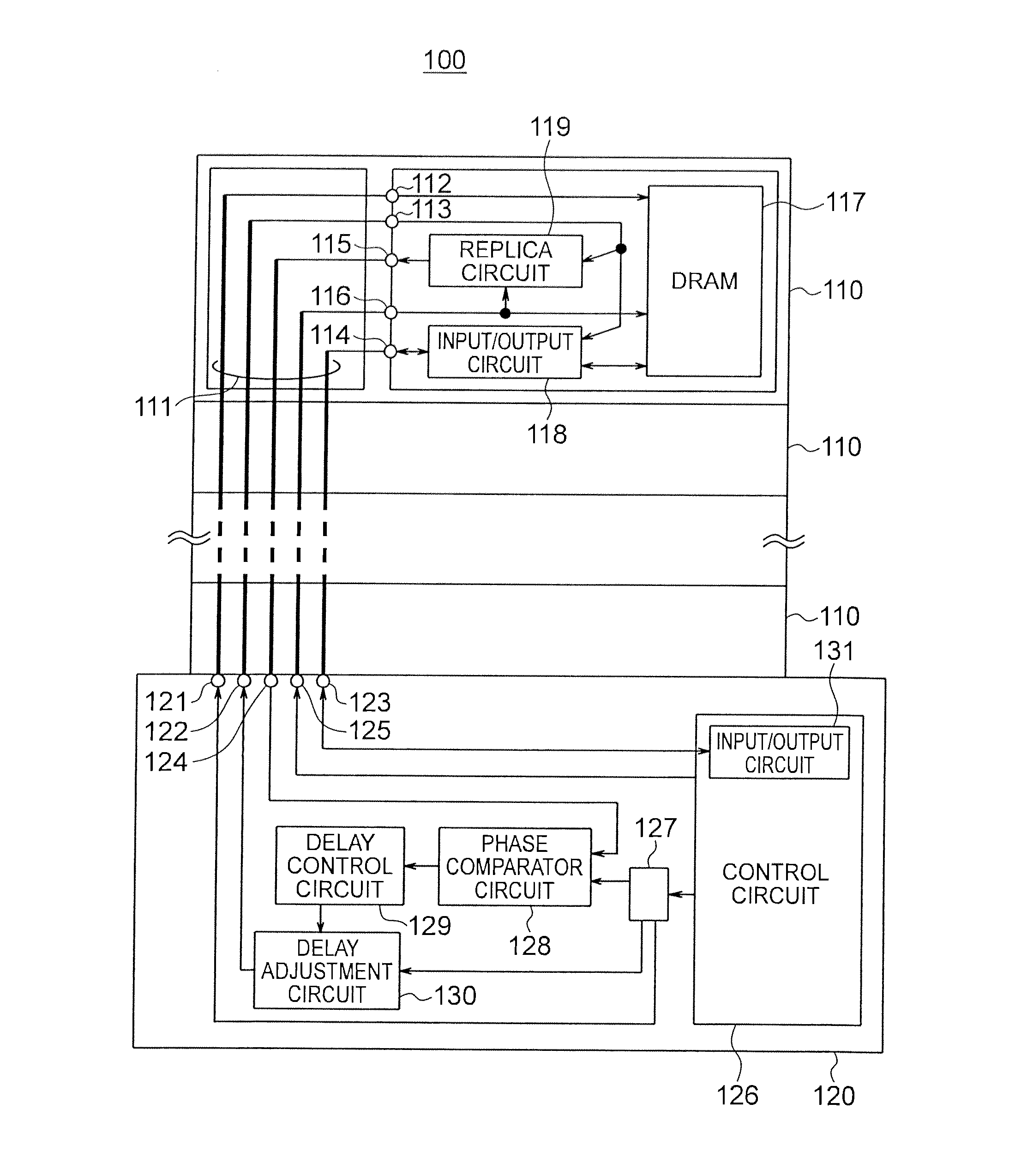

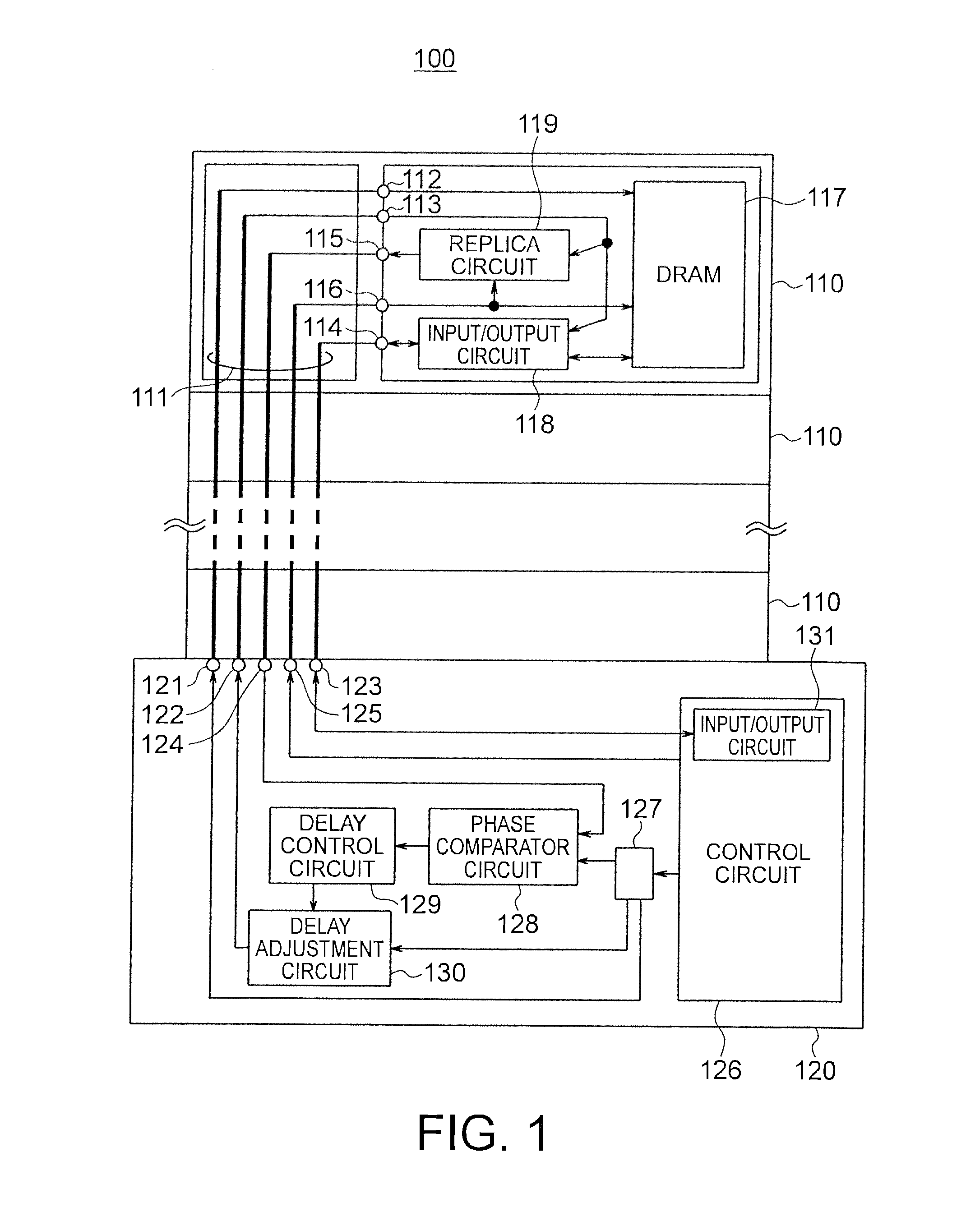

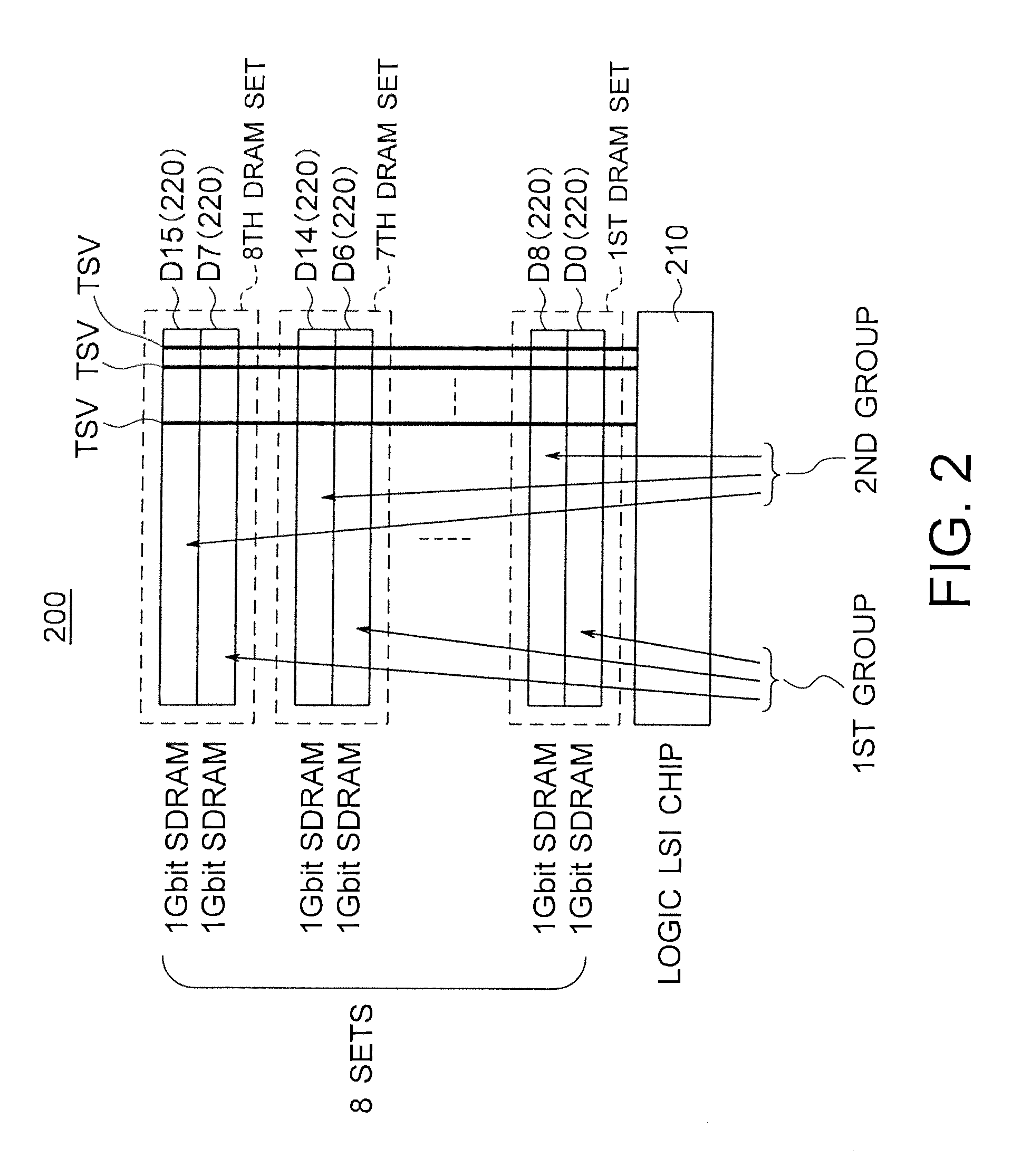

Device

ActiveUS20130094272A1Eliminates need of processingHigh speed data transmissionPulse automatic controlSolid-state devicesData terminalData signal

A semiconductor device includes a first controlled chip and a control chip stacked therewith. The first controlled chip includes a first circuit outputting a data signal in response to a synchronization signal, an input / output circuit outputting the data signal to a data terminal in synchronization with a delayed synchronization signal, and a replica circuit replicating an output circuit and outputting a replica signal to a first replica terminal in synchronization with the delayed synchronization signal. The control chip includes a first control circuit outputting a synchronization signal and receiving a data signal, a delay adjustment circuit delaying the synchronization signal and outputting the same as a delayed synchronization signal, a phase comparator circuit comparing the phases of the replica signal and the synchronization signal, and a delay control circuit controlling the delay amount of the delay adjustment circuit based on a comparison result of the phase comparator circuit.

Owner:LONGITUDE LICENSING LTD

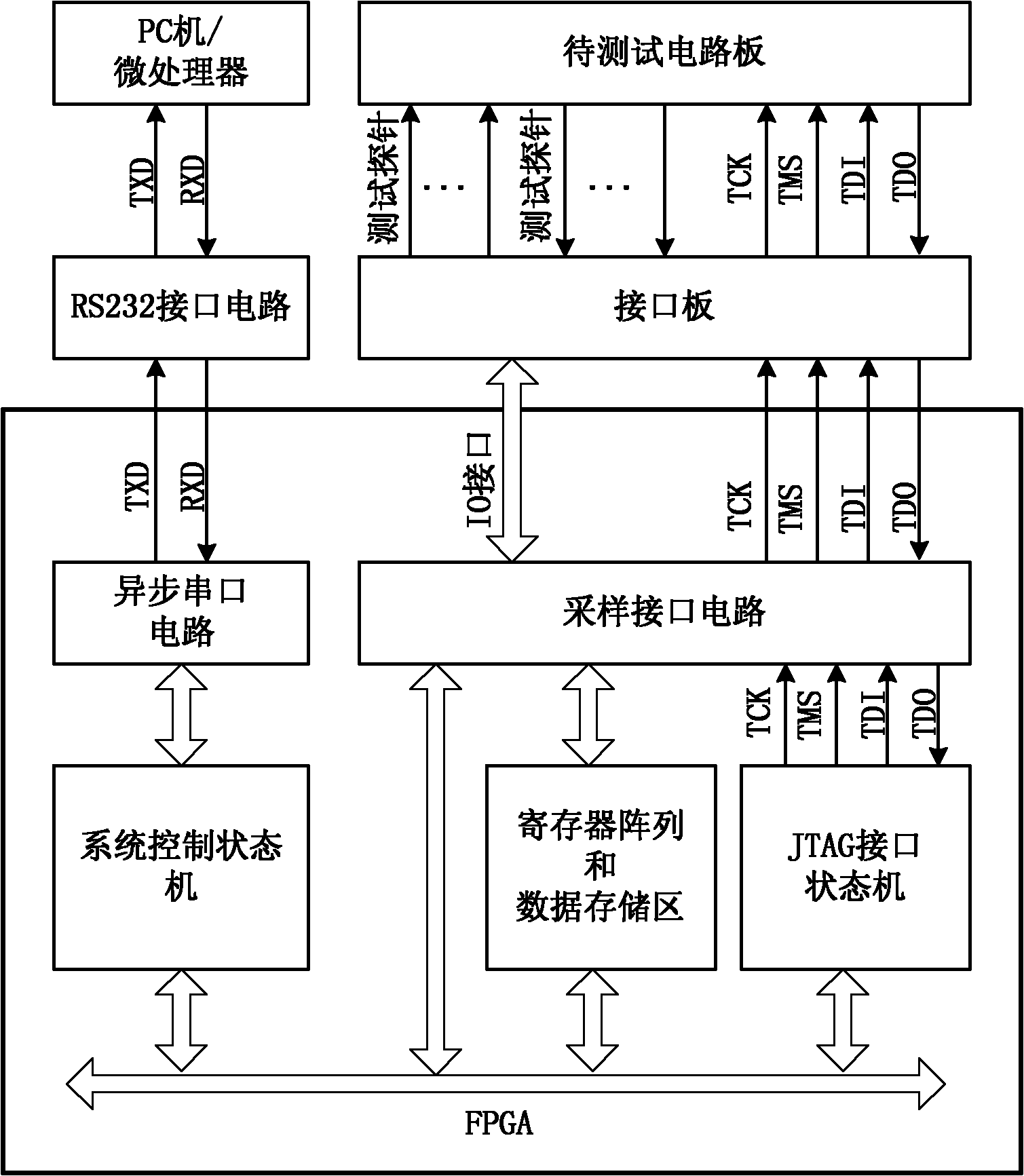

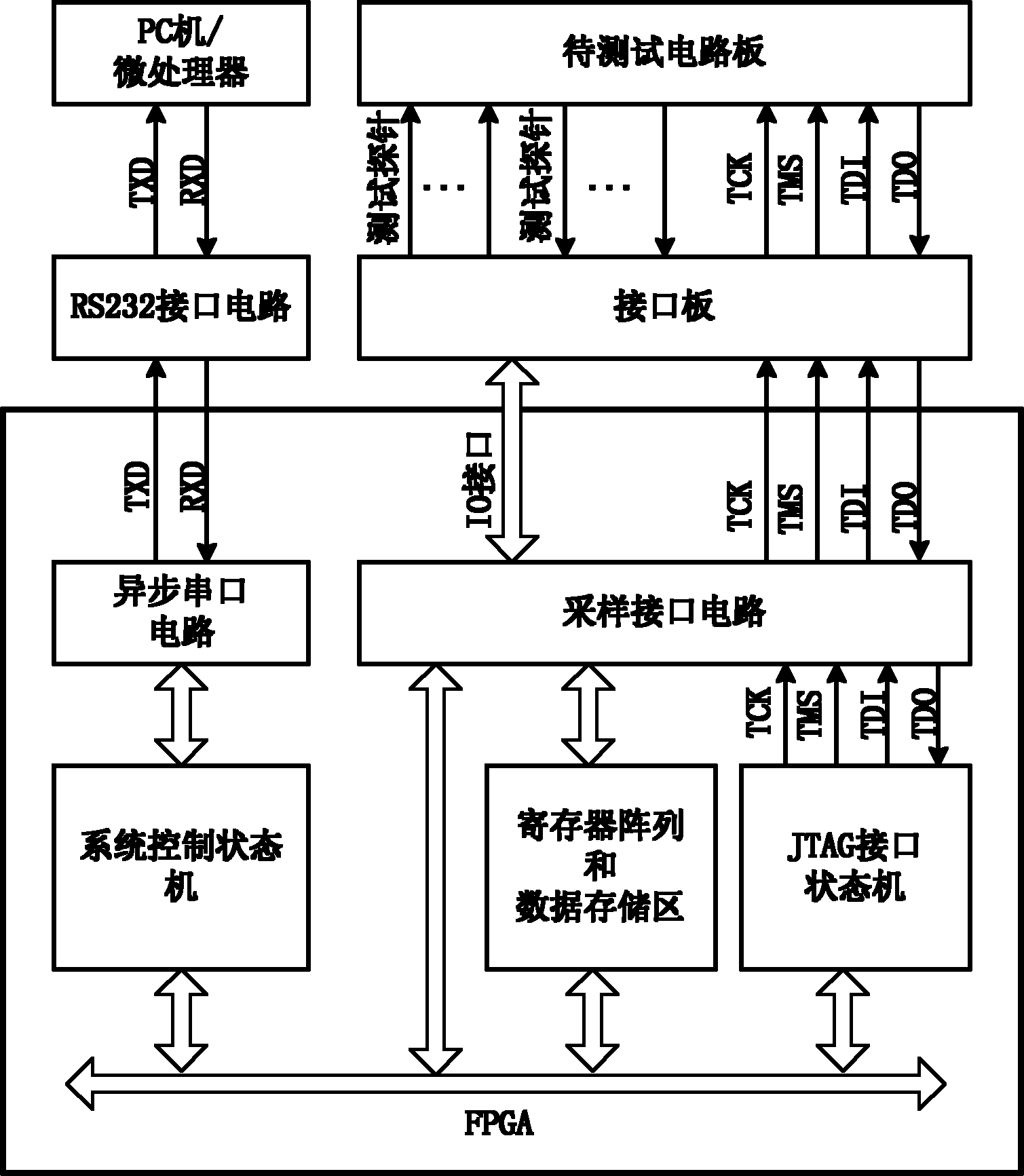

FPGA-based JTAG test method

InactiveCN101980036AGood flexibilityGood accuracyElectrical testingProgramme control in sequence/logic controllersWelding defectPersonal computer

The invention relates to a field programmable gate array (FPGA)-based joint test action group (JTAG) test method. In the method, an FPGA is connected with a circuit board to be tested by a JTAG interface and a probe; when a test is performed through the JTAG interface, the probe led out of the FPGA is connected with a monitoring point of the circuit board to be tested so as to read the data change of each point during the test; and finally, the FPGA sends the data change to a personal computer (PC) or a microprocessor for data analysis and judgment through an asynchronous series-port circuit. By the FPGA-based JTAG test method, a welding defect of a ball grid array (BGA) chip and the welding condition of the circuit around the chip can be precisely judged.

Owner:FUJIAN XINO COMM TECH

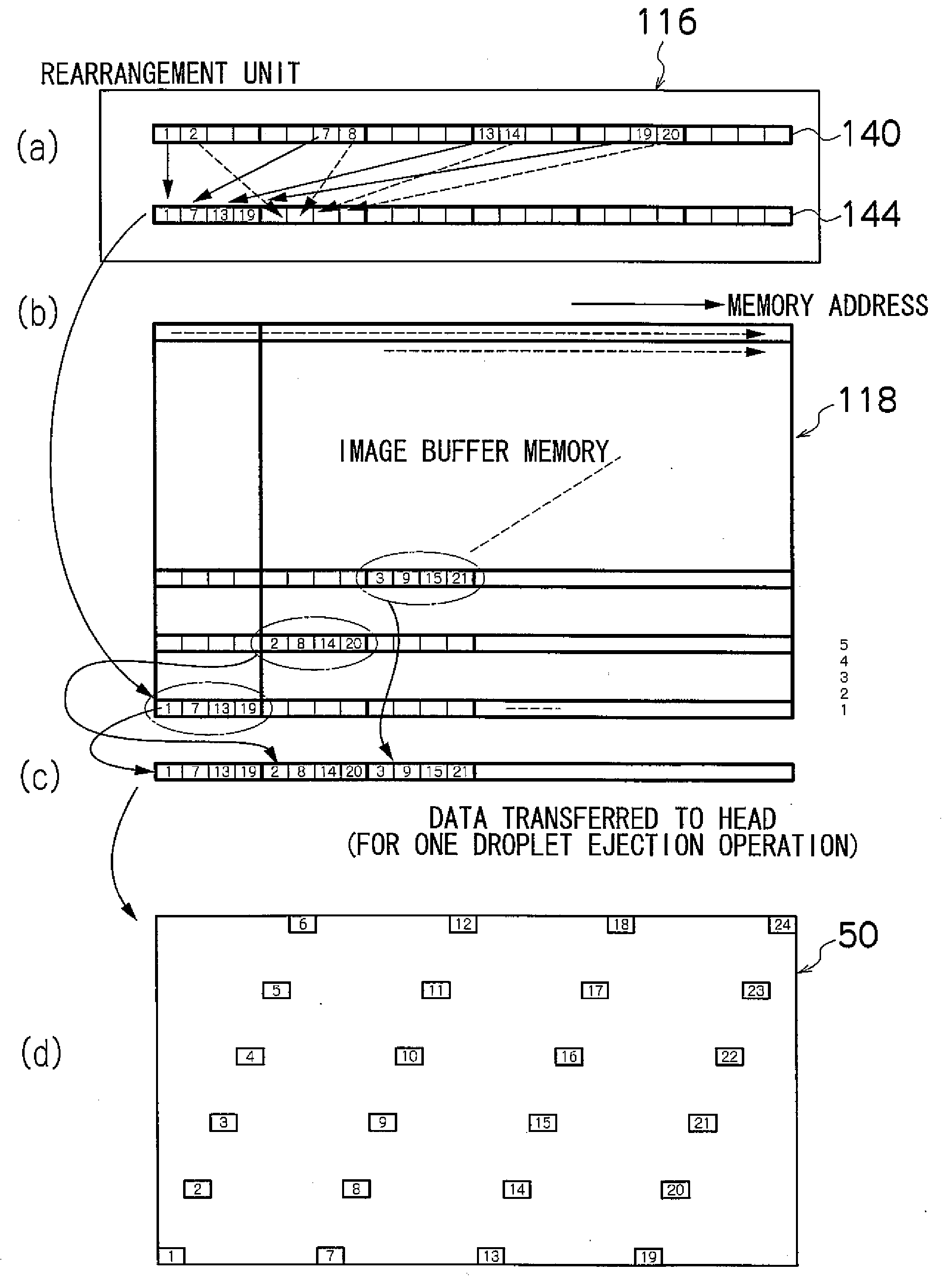

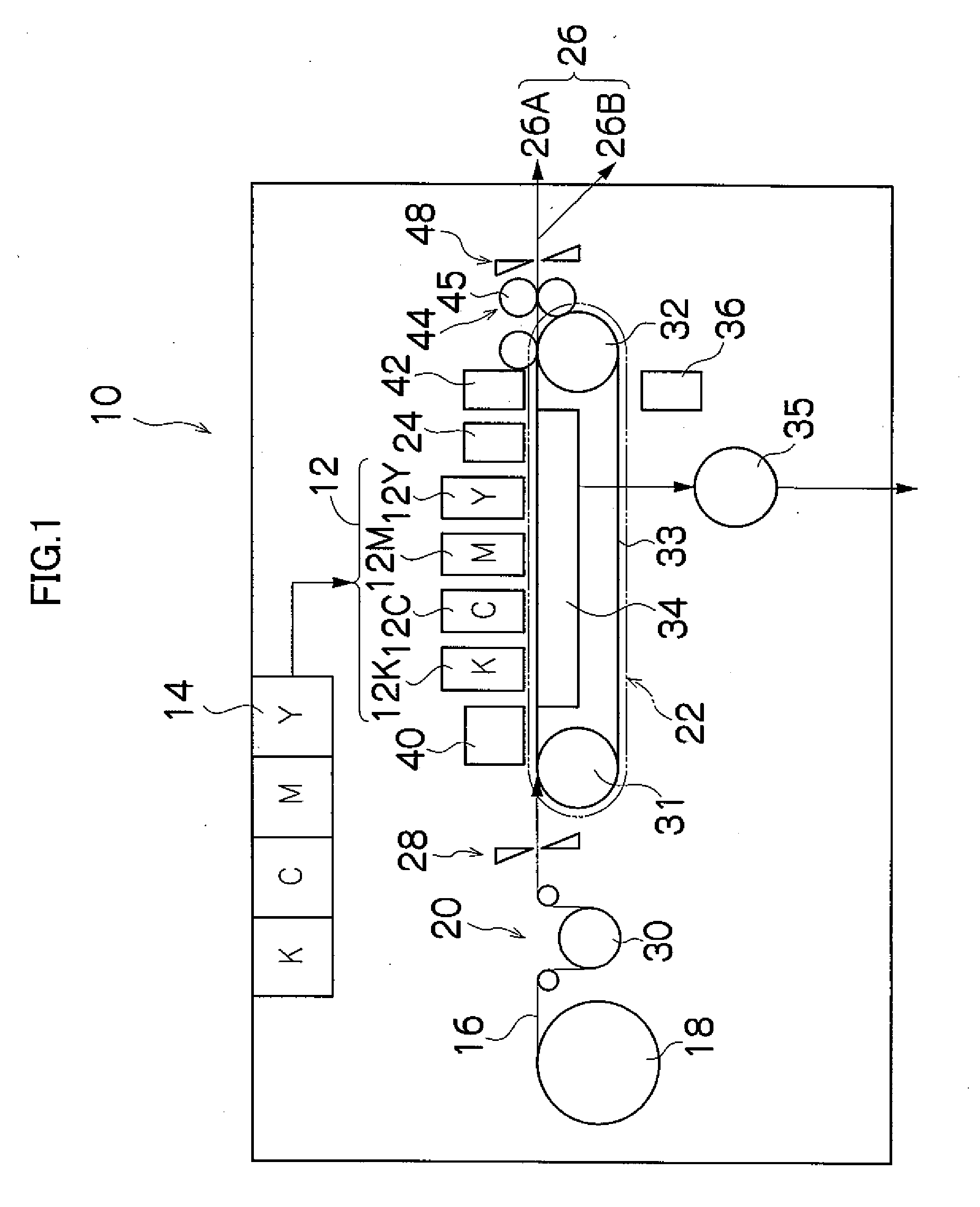

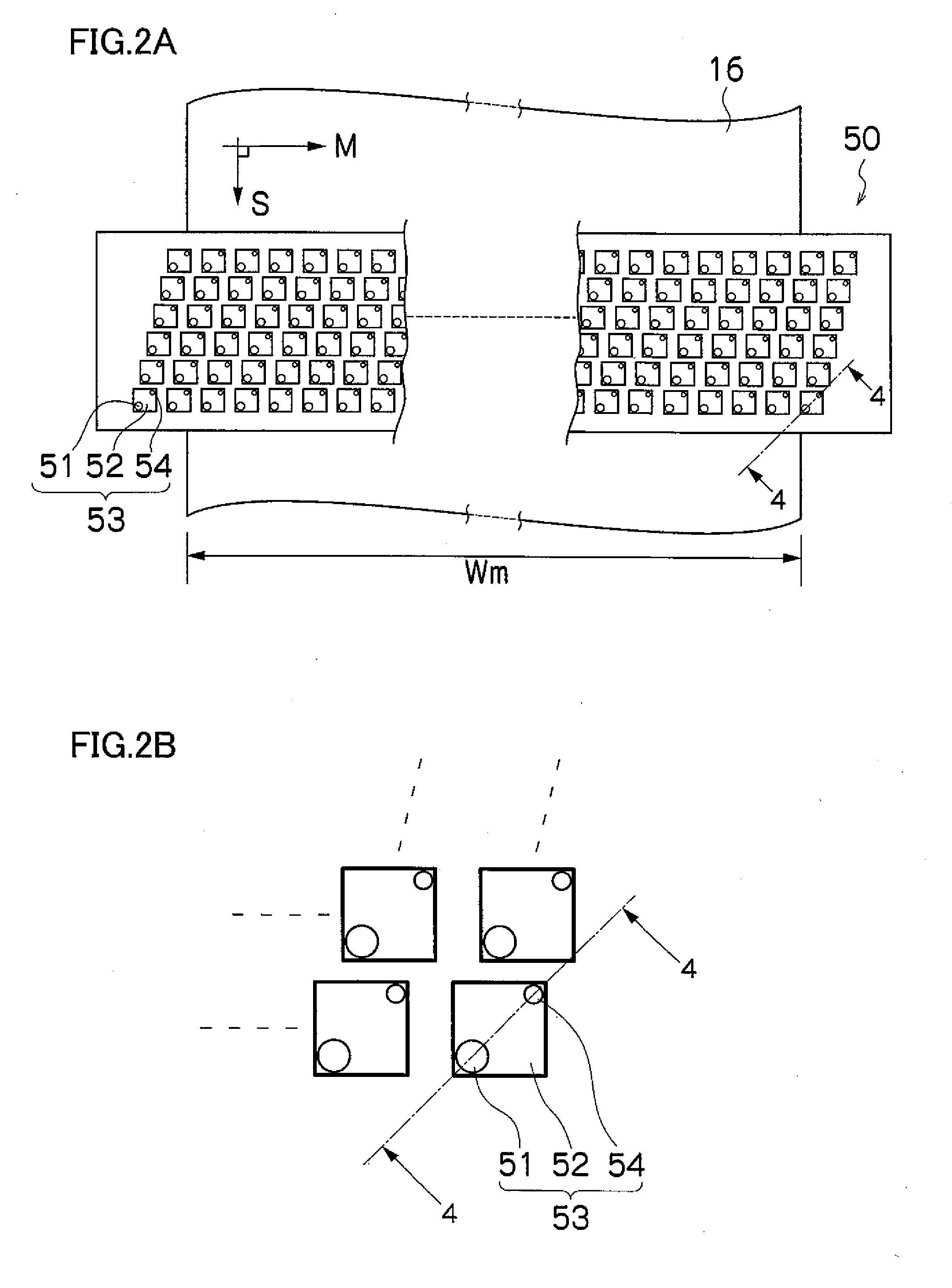

Image forming apparatus and method of transferring print data

InactiveUS20080180470A1Low costHigh speed transmissionVisual presentation using printersOther printing apparatusImage formationRecord element

An image forming apparatus includes: a rearrangement device having a configuration whereby the print data is rearranged in such a manner that data of pixels corresponding to mutually adjacent recording elements which are aligned on a straight line in the second direction in the recording head is located within a same word or within adjacent words; and an image buffer memory having at the least a storage capacity of storing the print data rearranged by the rearrangement device for an image region corresponding to a surface area occupied by a plurality of recording elements arranged in a two-dimensional matrix configuration in a recording head.

Owner:FUJIFILM CORP

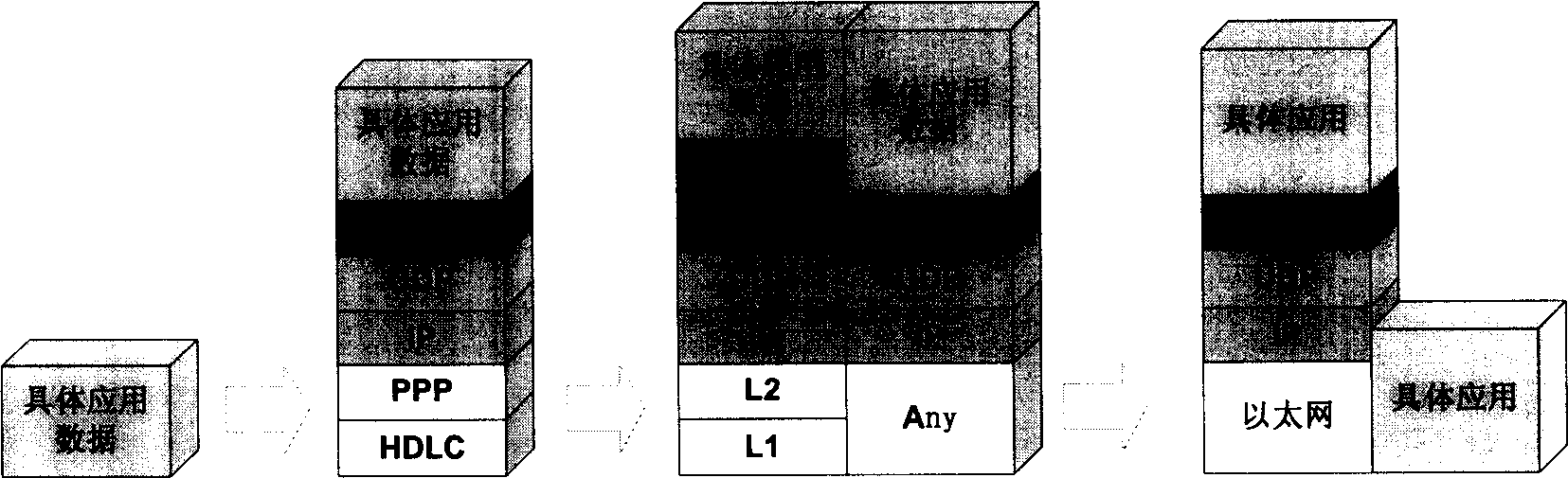

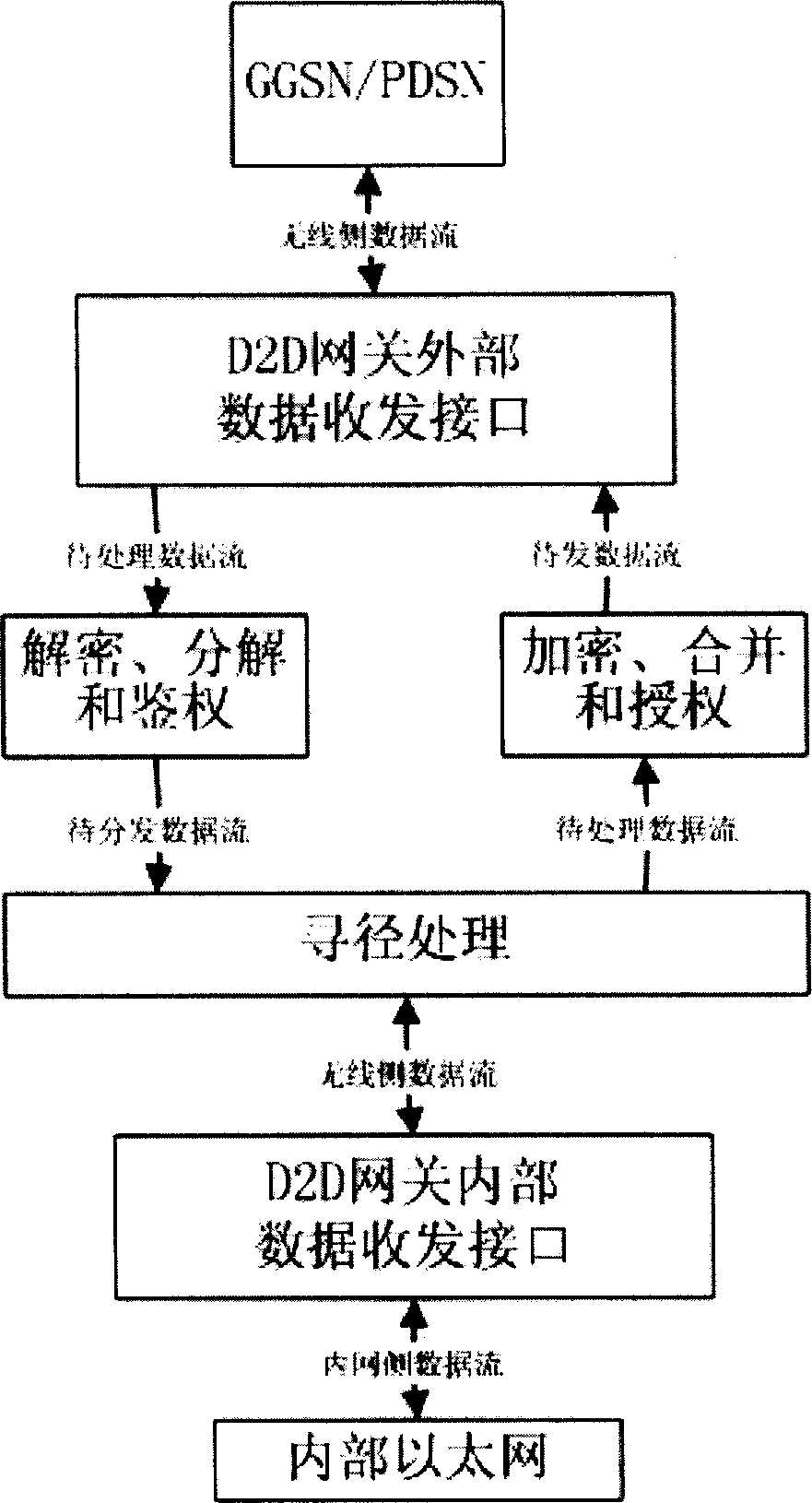

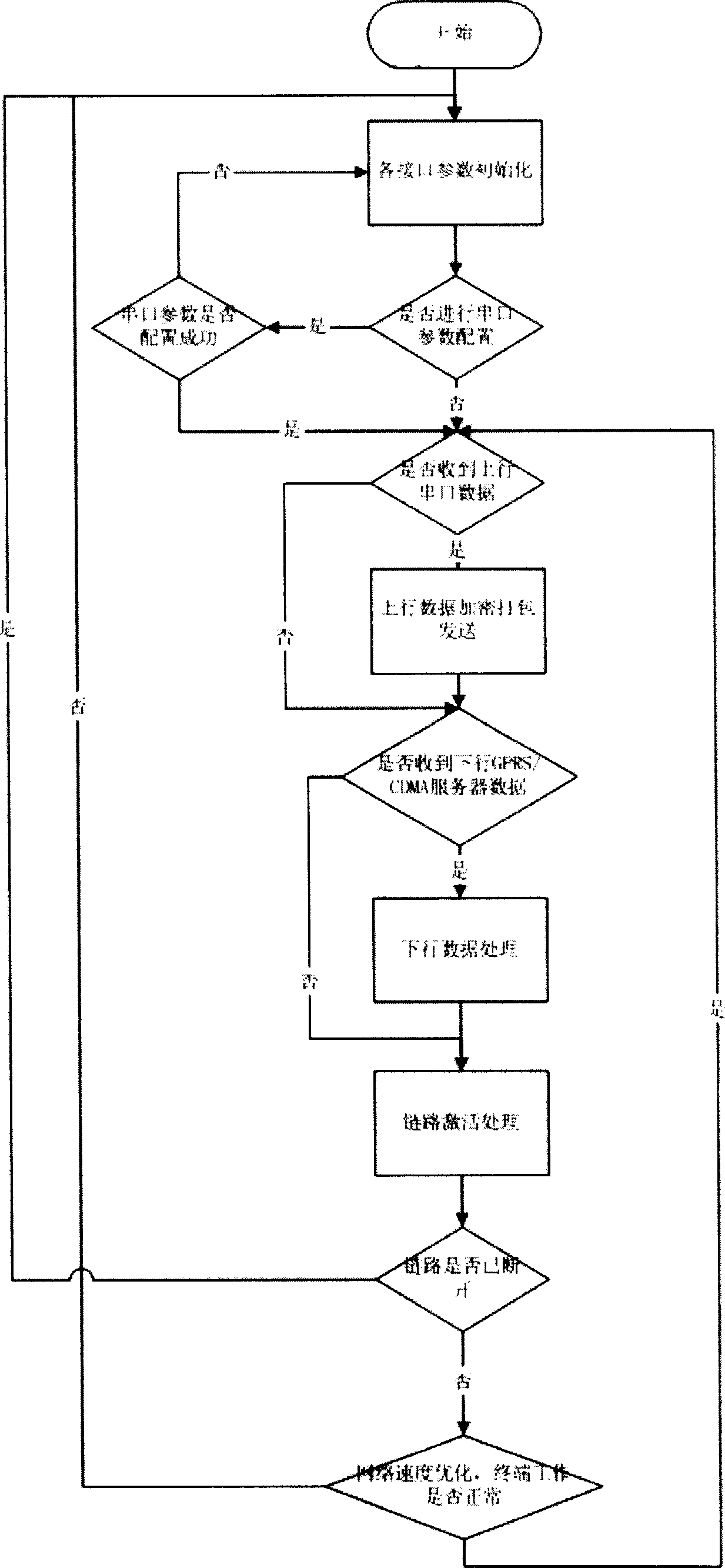

CHINAMDN based wireless transparent D2D system transmission method

InactiveCN1703023AImprove data securityImprove integrityRadio/inductive link selection arrangementsNetwork connections

This invention relates to wireless transparent D2D system transmission method based on the public mobile data communication net and the current operator provided 2.5 G mobile data communication package transmission exchange platform of GPRS / CDMA2000 1X. The invention comprises wireless D2D terminals and gates working at the common wireless network and central Ethernet linkage layer to realize the remote transparent wireless data transmission and exchanging function.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD