FPGA (field programmable gate array) based USB3.0 interface module

An interface module and interface technology, applied in the field of USB 3.0 interface modules, can solve the problems of large Ethernet transmission delay, PCI bus does not support hot plugging, and low USB2.0 transmission rate, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

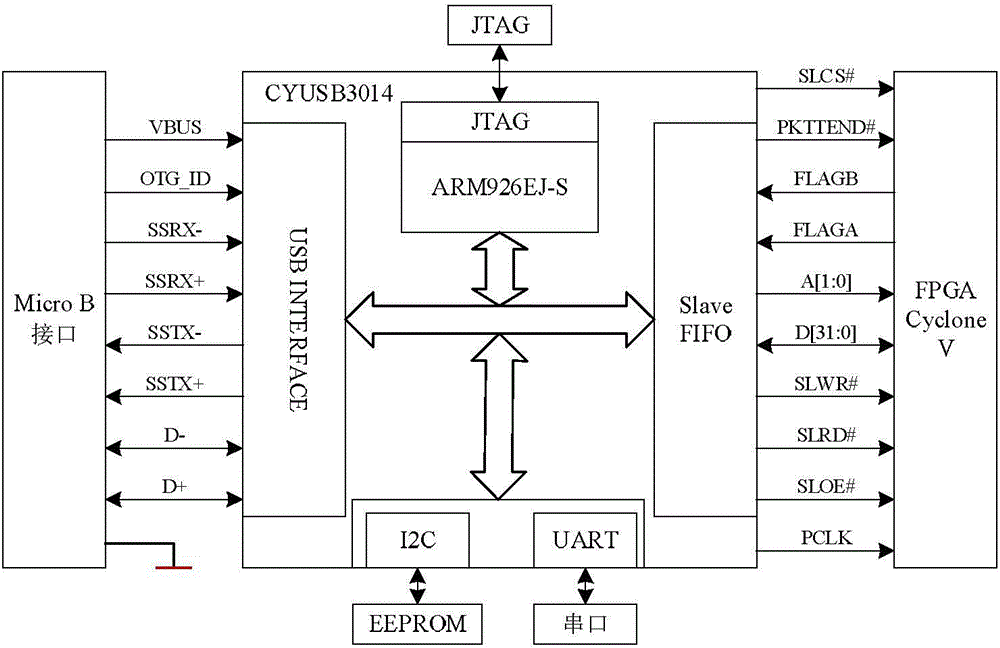

[0059] Specific implementation mode 1. Combination Figure 1 to Figure 10 Illustrate this specific implementation mode, the USB 3.0 interface module based on FPGA,

[0060] The present invention is based on the USB 3.0 peripheral controller FX3 series chip CYUSB3014 of CYPRESS Company, uses Altera Company's FPGA as the main control chip to control the read and write timing of the FX3 chip, and aims to realize the USB 3.0 high-speed interface, and designs a maximum up to 2.5 Data transfer interface with Gbps transfer rate.

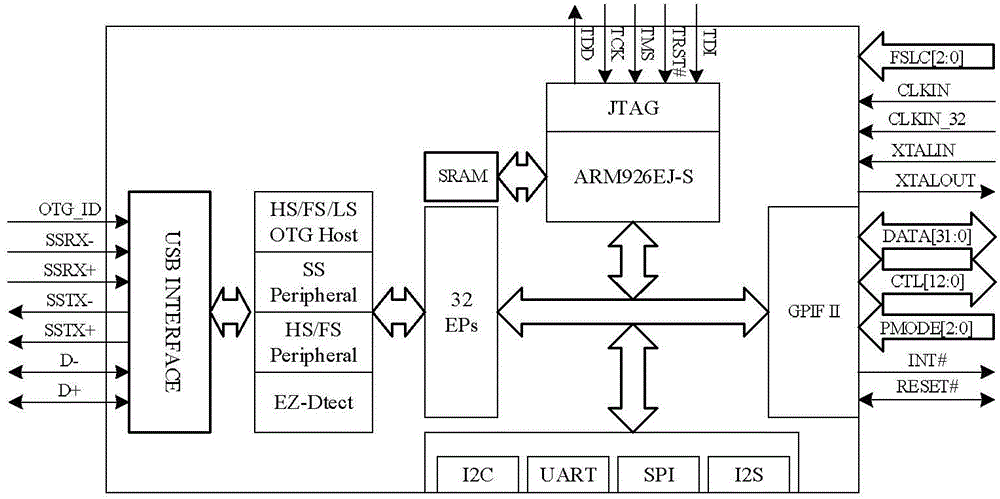

[0061] 1. Hardware circuit

[0062] The FX3 series CYUSB3014 chip of CYPRESS has become the mainstream choice of USB 3.0 peripheral controllers because of its highly integrated and flexible features. FX3 integrates a 32-bit ARM926EJ-S microprocessor with a working frequency of 200MHz and powerful data processing capabilities. The chip integrates USB 3.0 and USB 2.0 physical layers, and provides SPI, I2C, UART and I2S interfaces to communicate with extern...

specific Embodiment

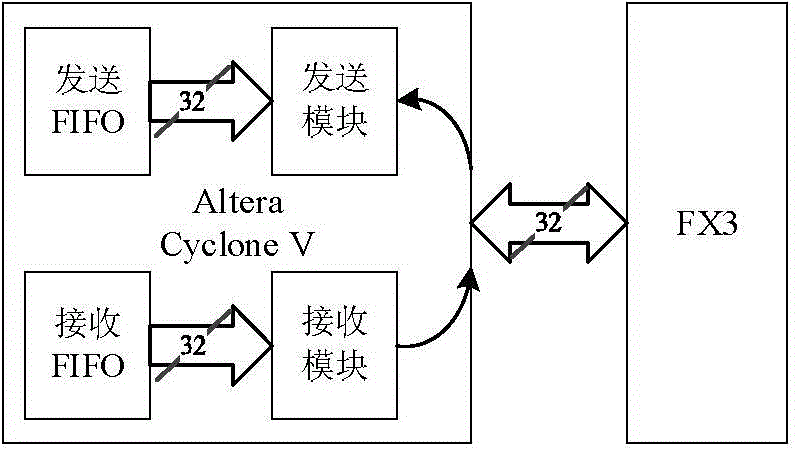

[0111] 1. Sending channel:

[0112] 1), the host software provided by CYPRESS company sends data;

[0113] 2), the FX3 chip firmware program receives the data sent by the host software and writes it into the slave device FIFO;

[0114] 3), the USB 3.0 firmware program outputs the sending status to the USB 3.0 interface logic;

[0115] 4), the USB 3.0 interface logic sending module enters the state transition, and detects the FX3 firmware state;

[0116] 5), the USB 3.0 interface logic sending module reads data from the device FIFO from the FX3 chip;

[0117] 2. Receive channel:

[0118] 1), the host software provided by CYPRESS company sends and receives the request;

[0119] 2), the USB 3.0 firmware program outputs the receiving status to the USB 3.0 interface logic;

[0120] 3), the USB 3.0 interface logic receiving module enters the state transition and receives data;

[0121] 4), the USB 3.0 interface logic receiving module writes the received data into the FX3 chip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More