Patents

Literature

403 results about "Serial advanced technology attachment" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

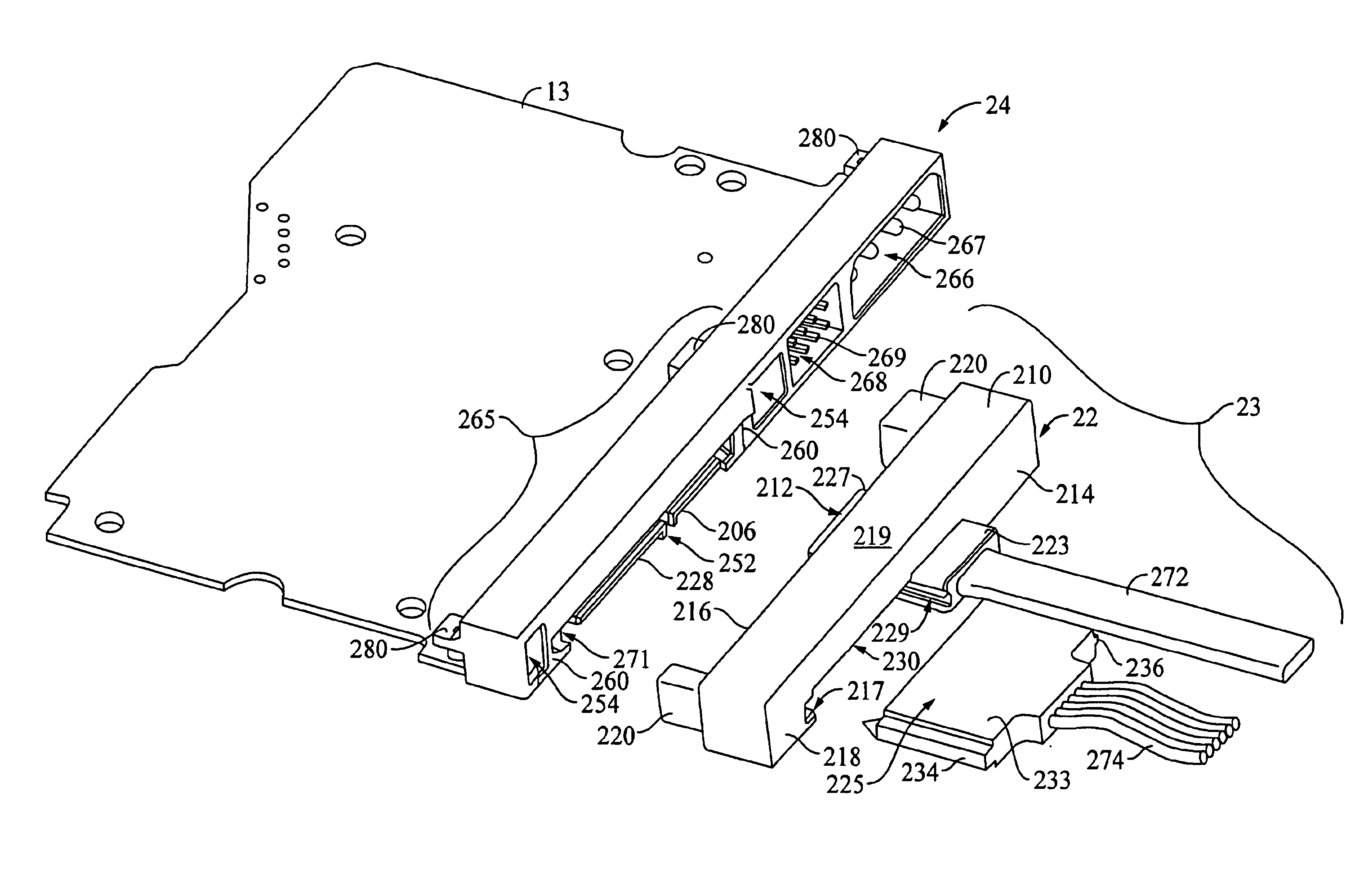

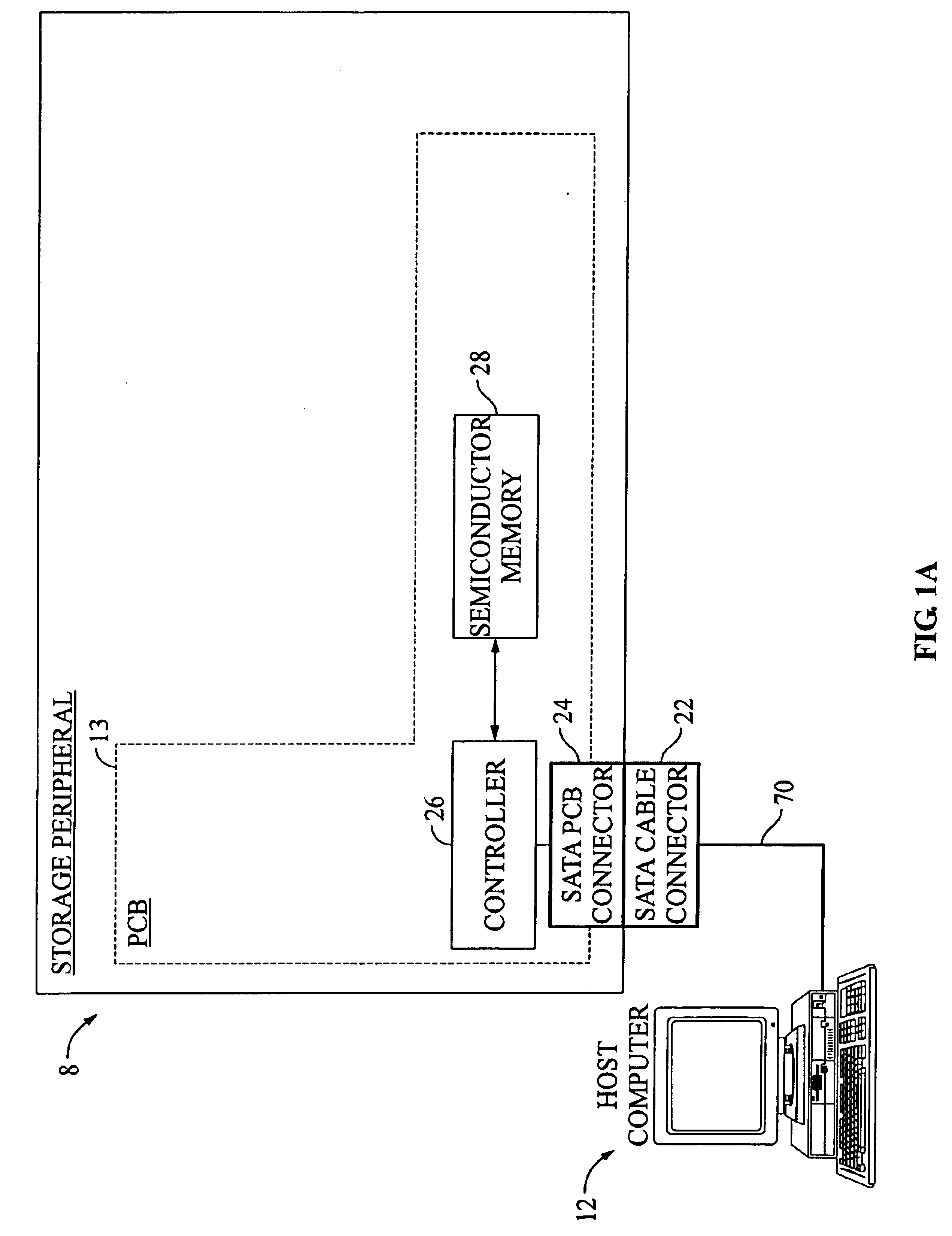

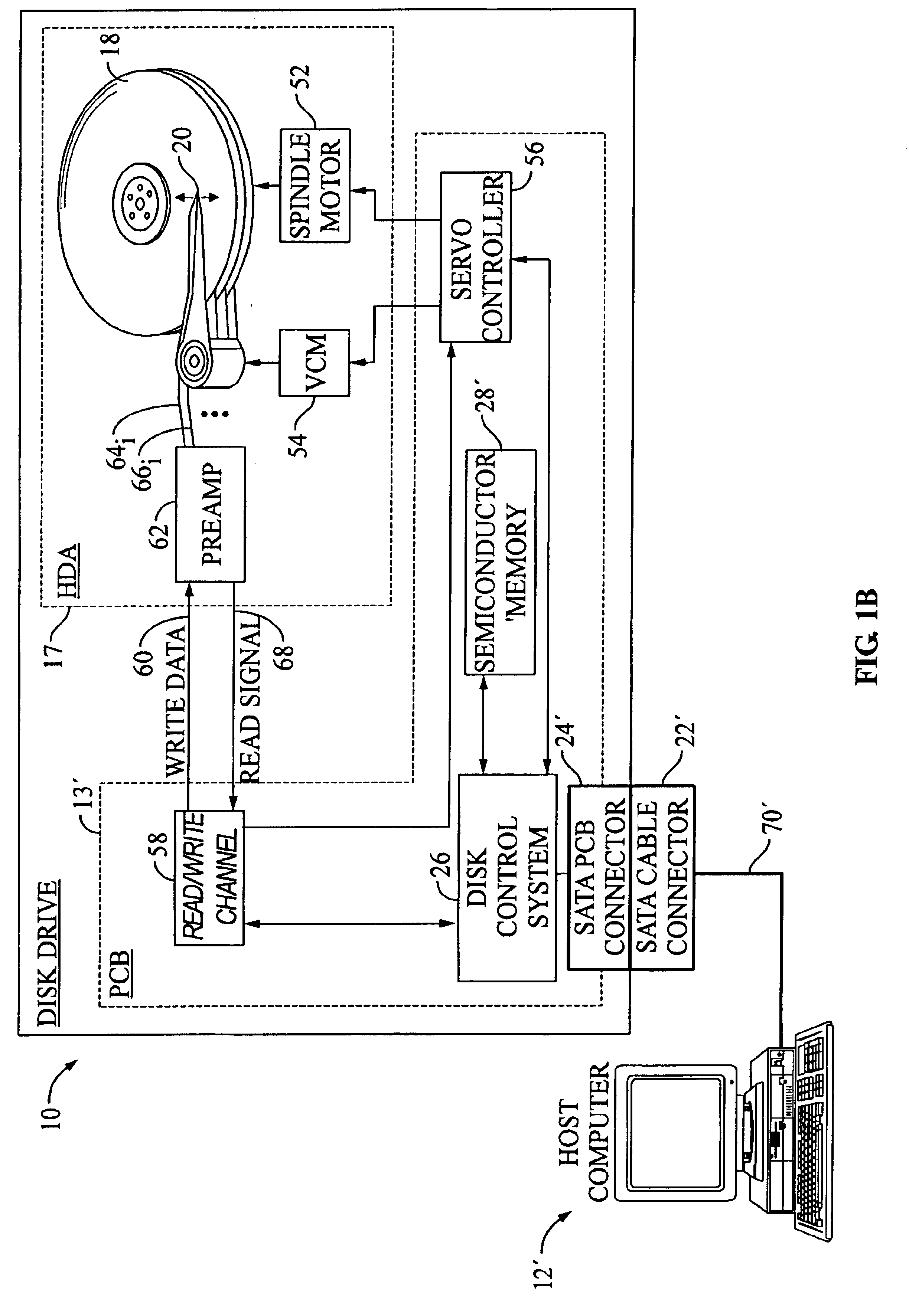

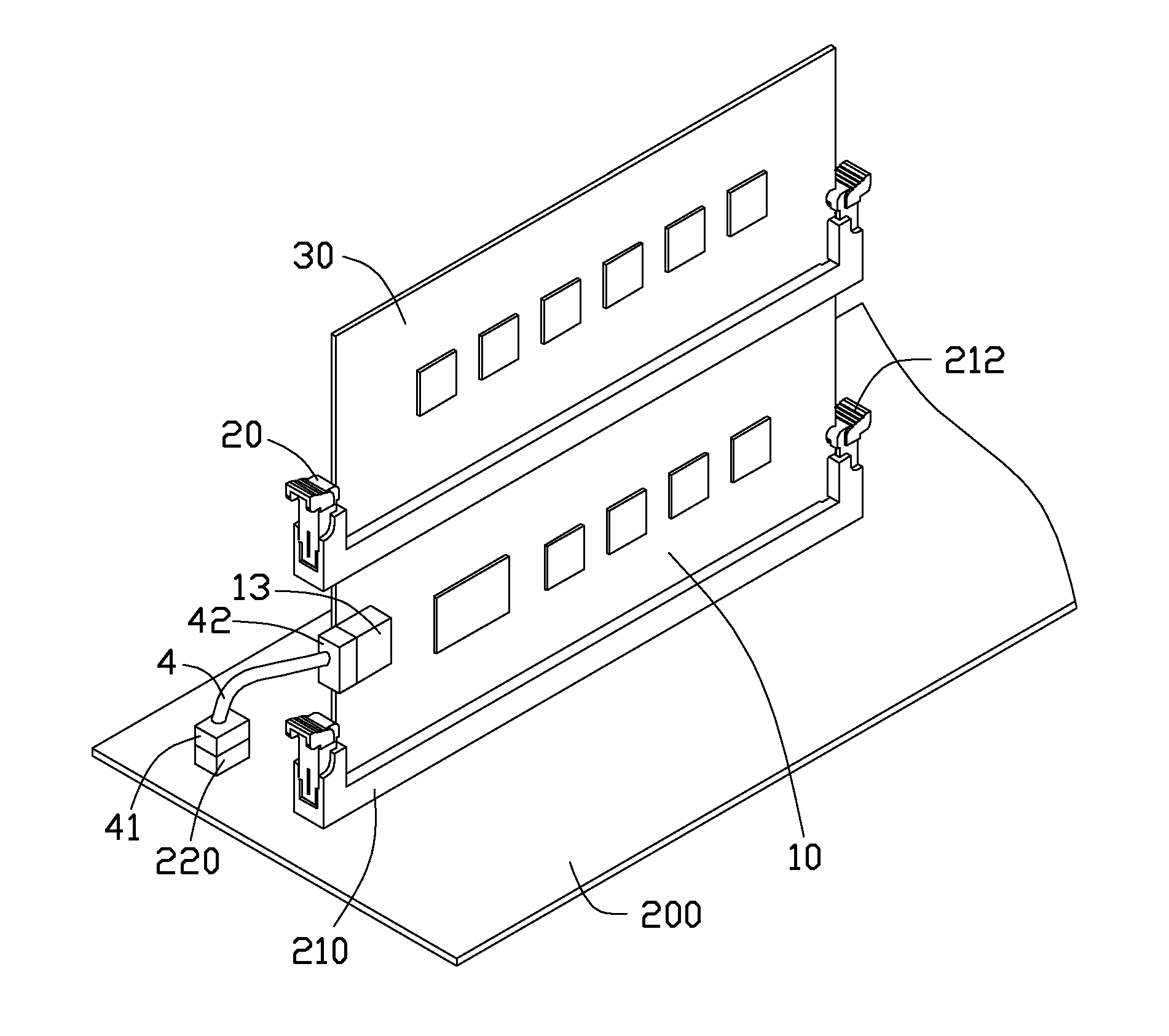

Storage peripheral having a robust serial advanced technology attachment (SATA) PCB connector

InactiveUS6908330B2Carrier constructional parts dispositionIncorrect coupling preventionDisk controllerSerial advanced technology attachment

A storage peripheral, such as disk drive, having a robust PCB connector configured in accordance with a SATA standard. The disk drive has a disk, a disk controller system, and a PCB for mounting the disk controller system, and a housing attached to the PCB. A first electrical contact arrangement in accordance with a SATA standard is connected to the PCB and is supported by a first blade connector. Both the first blade connector and the first electrical contact arrangement are enclosed by the housing. The housing further defines a cable connector receiving area around the first blade connector for the receipt of a cable connector. A pair of laterally-opposed guide arm receiving cavities are integrally formed with the housing and are disposed outside of the cable connector receiving area. The guide arm receiving cavities are adapted for the receipt of guide arms from a mating cable connector.

Owner:WESTERN DIGITAL TECH INC

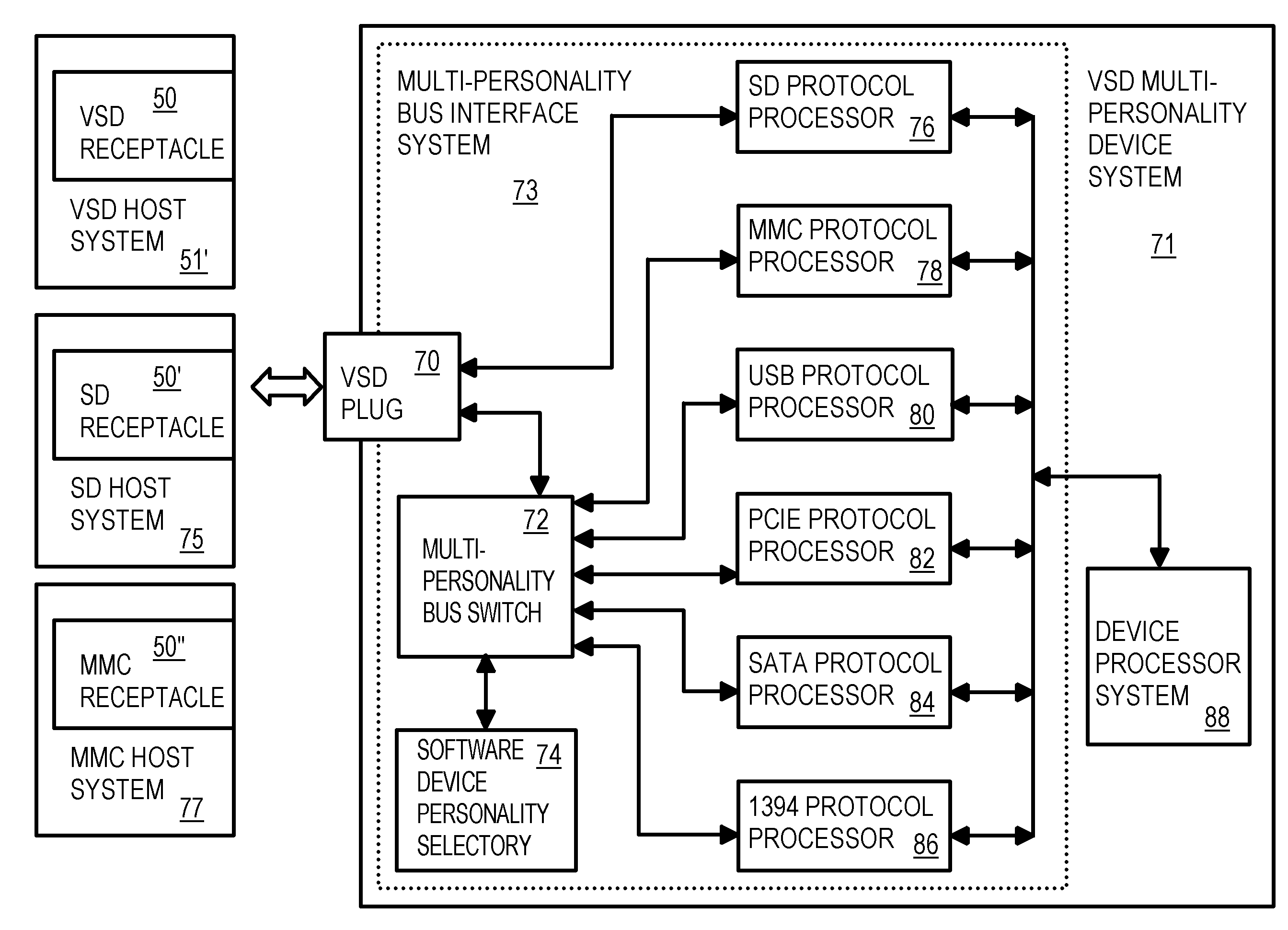

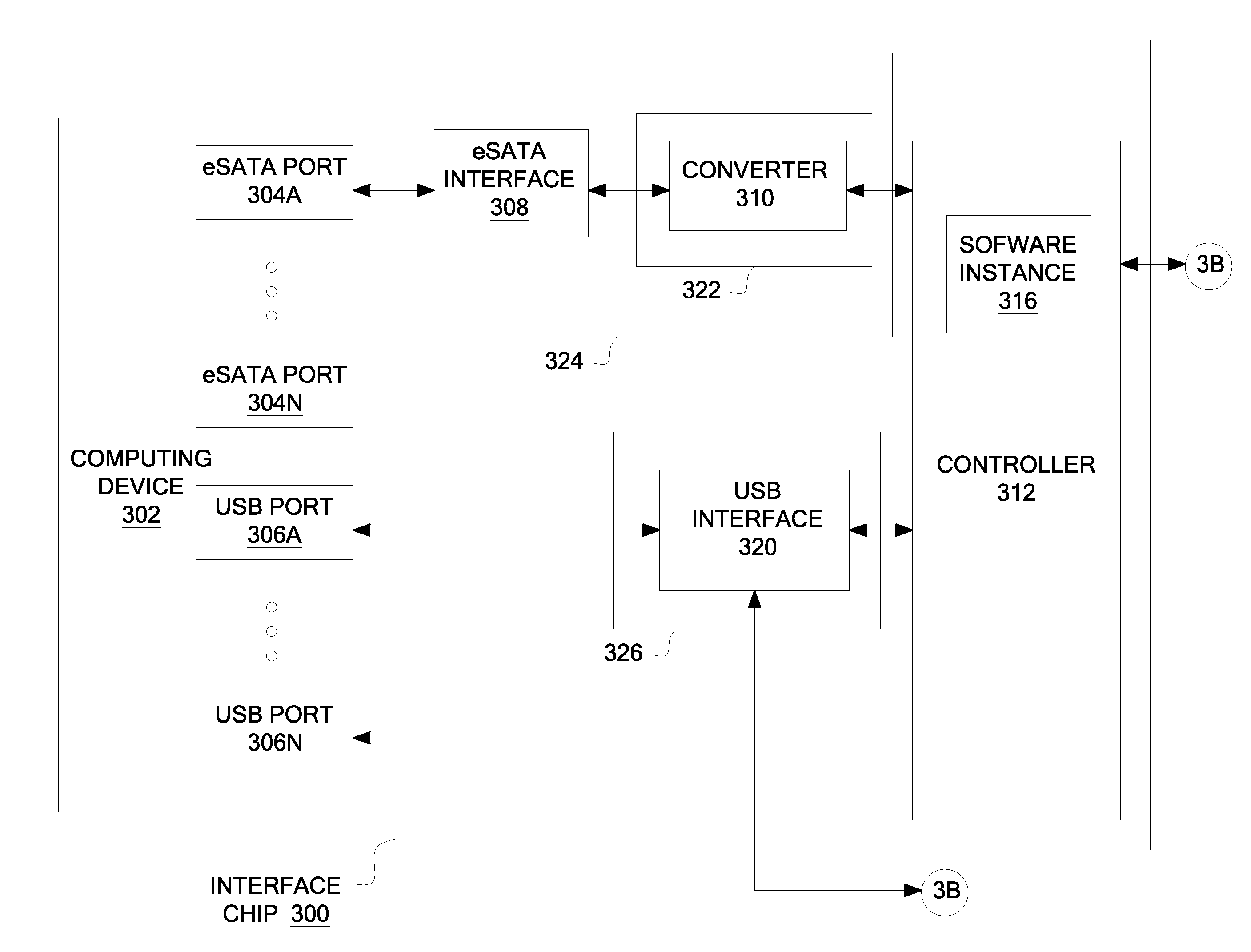

Extended-Secure-Digital interface using a second protocol for faster transfers

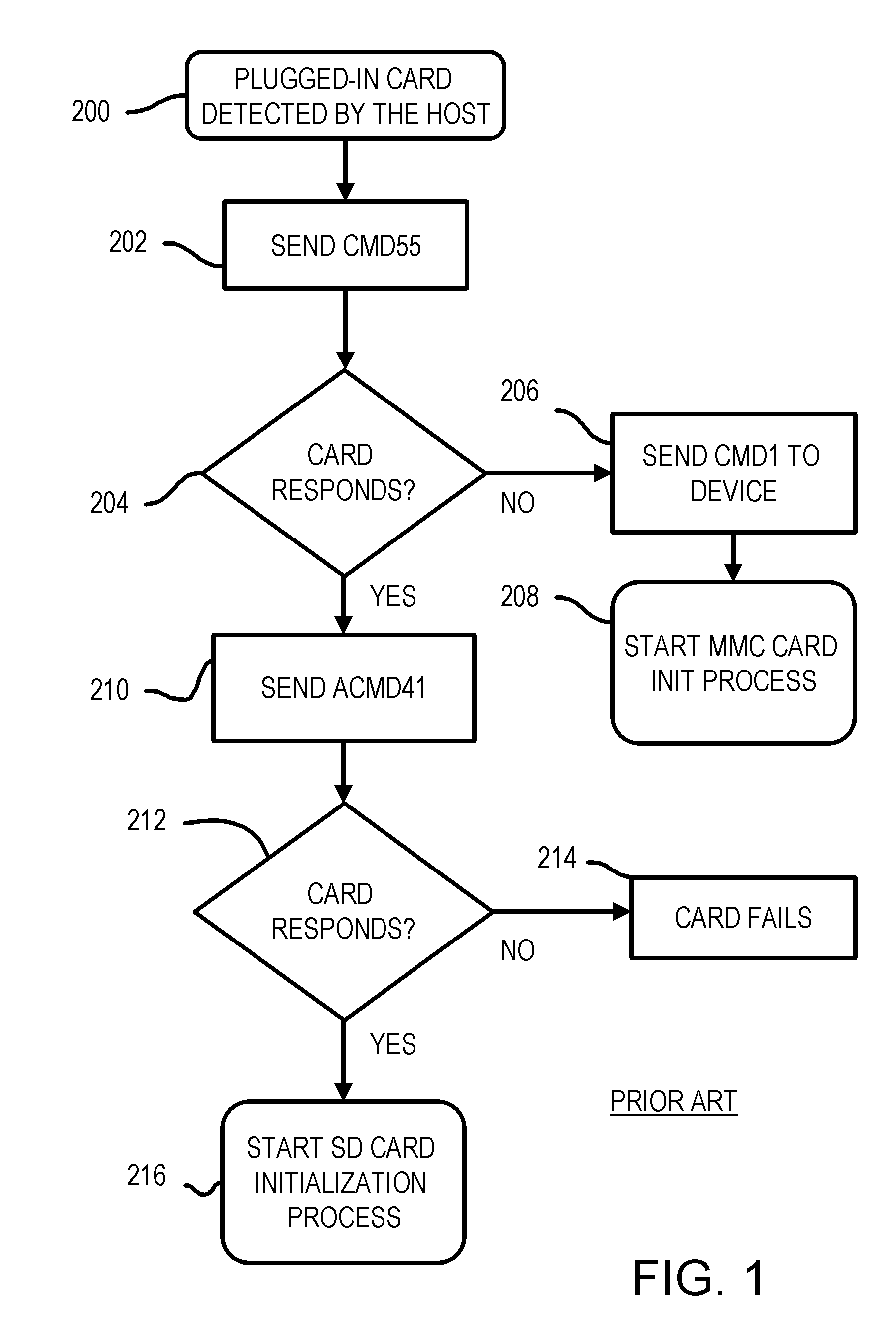

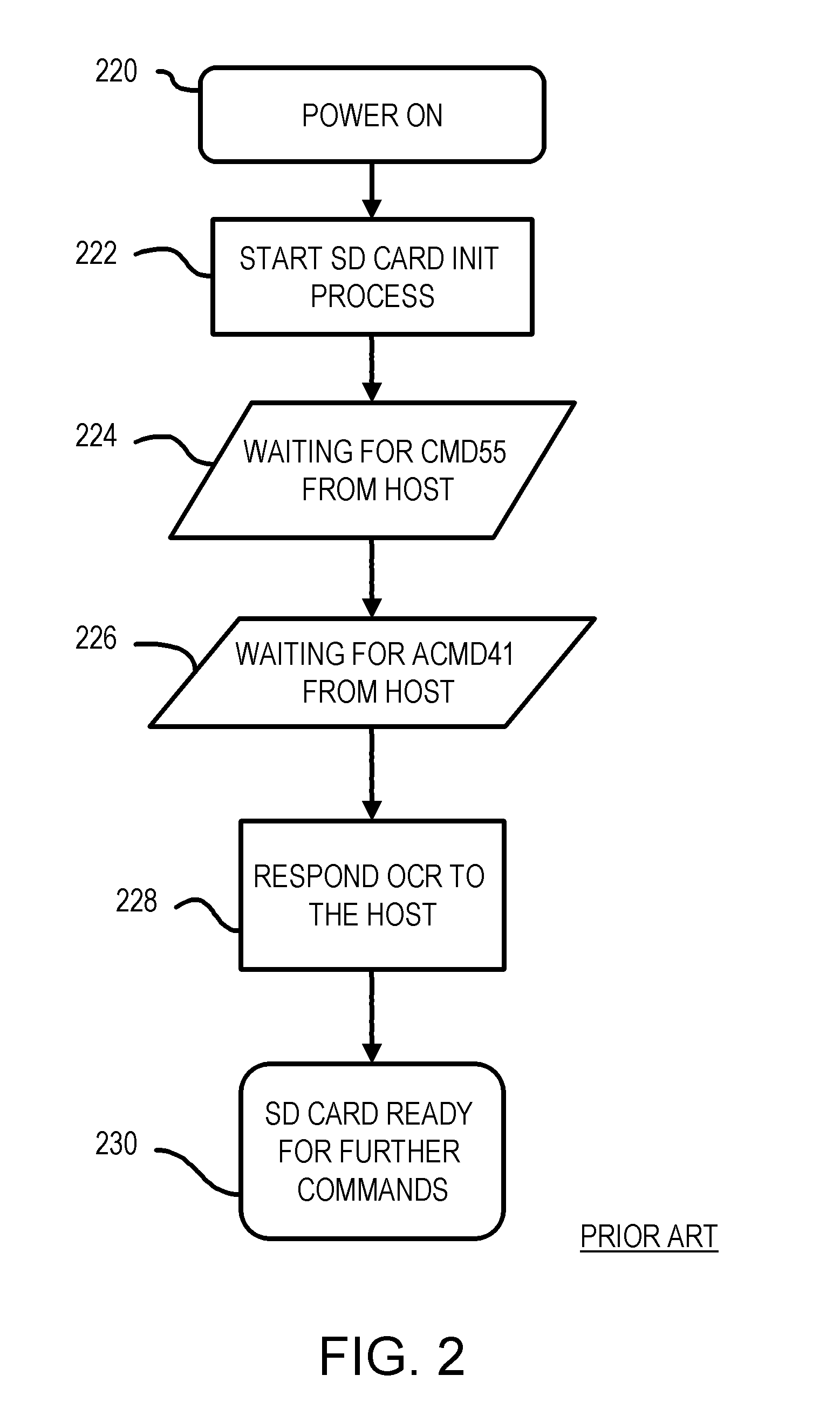

An extended Secure-Digital (SD) card has a second interface that uses some of the SD-interface lines. The SD card's mechanical and electrical card-interface is used, but 2 or 4 signals in the SD interface are multiplexed for use by the second interface. The second interface can have a single differential pair of serial-data lines to perform Universal-Serial-Bus (USB) transfers, or two pairs of differential data lines for Serial-Advanced-Technology-Attachment (SATA), Peripheral Component Interconnect Express (PCIE), or IEEE 1394 transfers. A card-detection routine on a host can initially use the SD interface to detect extended capabilities and command the card to switch to using the second interface. The extended SD card can communicate with legacy SD hosts using just the SD interface, and extended SD hosts can read legacy SD cards using just the SD interface, or extended SD cards using the second interface. MultiMediaCard and Memory Stick are alternatives.

Owner:SUPER TALENT ELECTRONICS

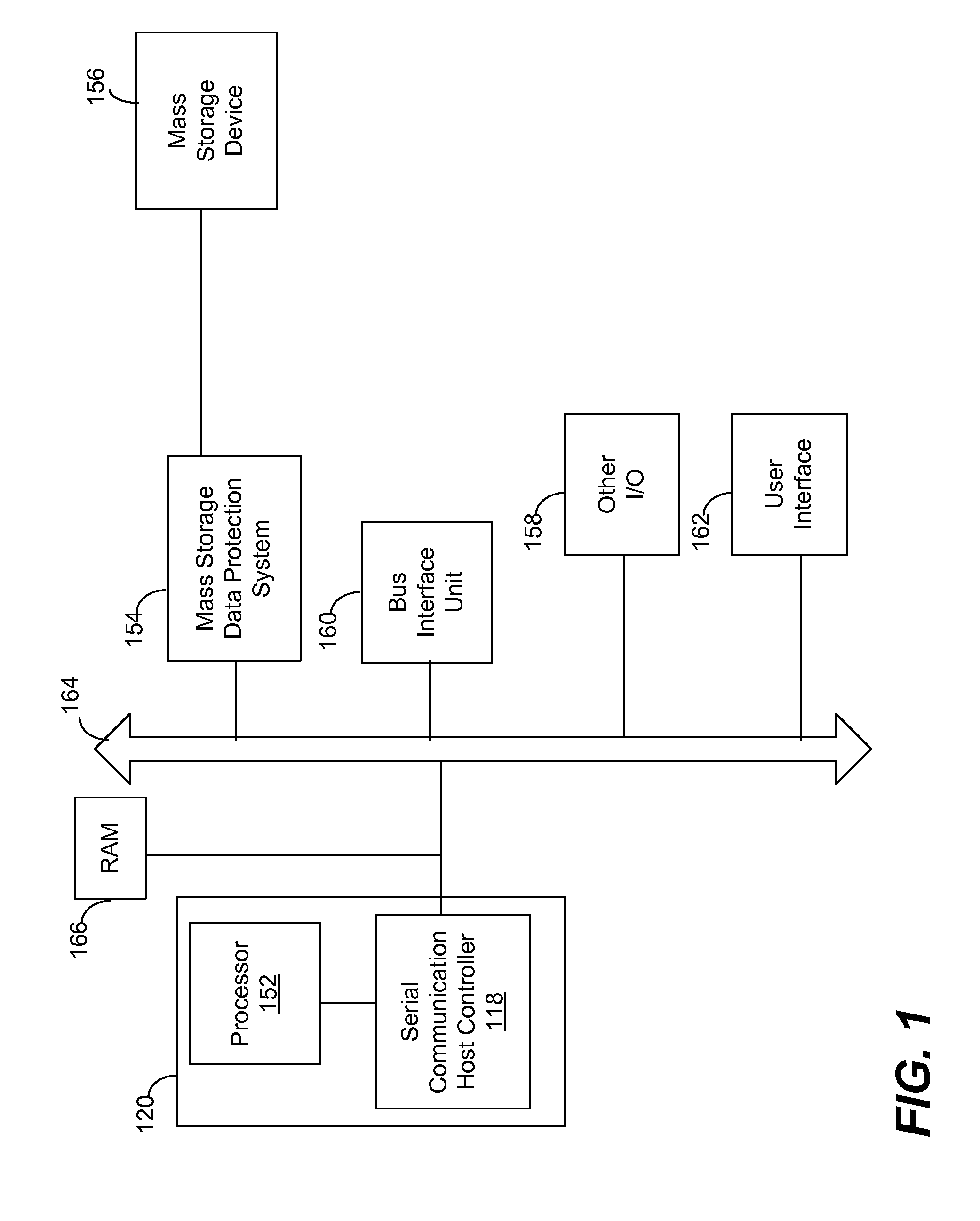

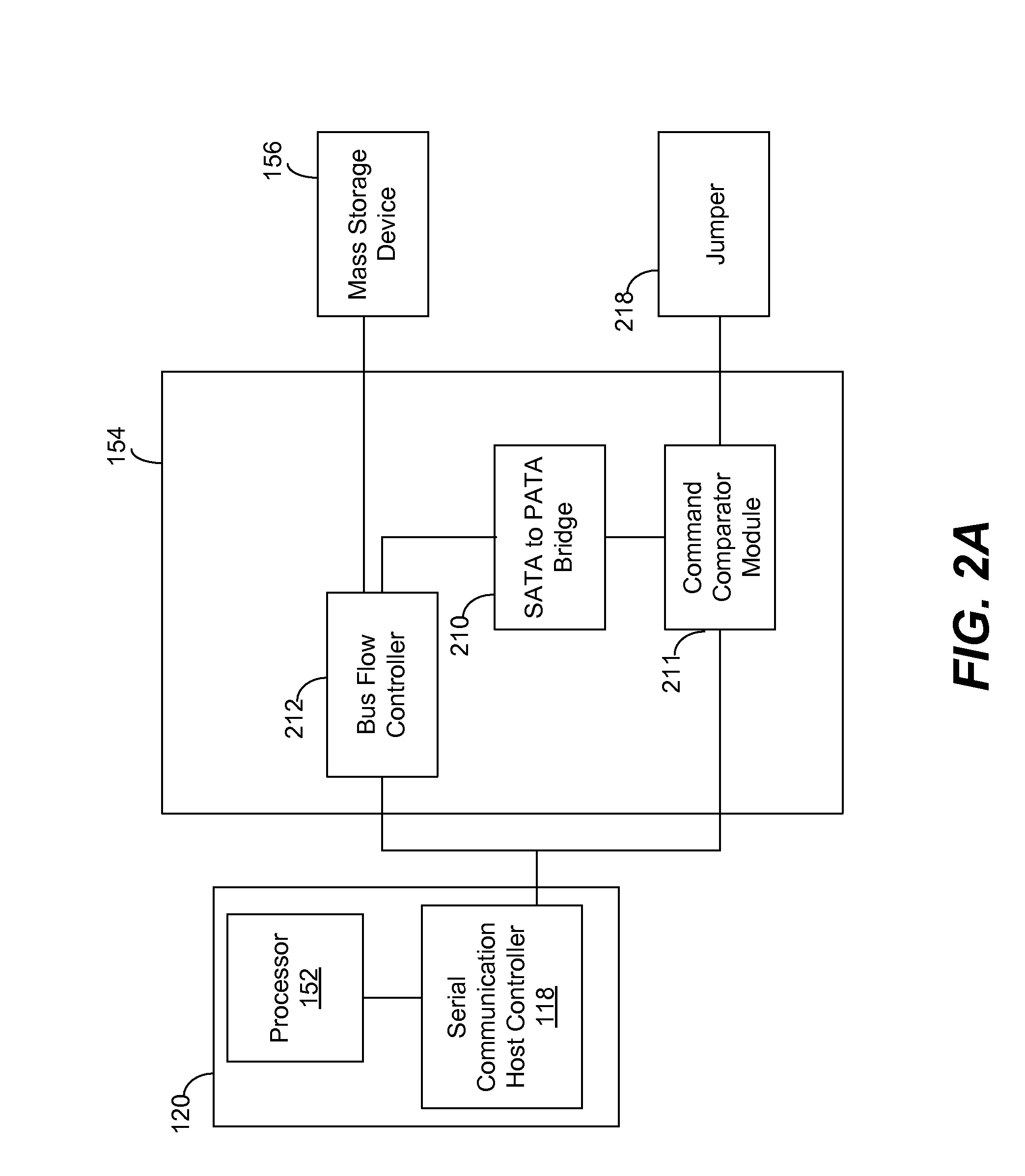

Serial advanced technology attachment write protection: mass storage data protection device

A mass storage device protection system may have a mass storage device, a processor configured to generate at least one serial write command signal to the mass storage device via a serial communication link, and a storage protector configured for communication with the processor and mass storage device, the storage protector configured to do the following: intercept the at least one serial write command signal, and determine whether the at least one serial write command signal comprises an authorized command signal or an unauthorized command signal.

Owner:IGT

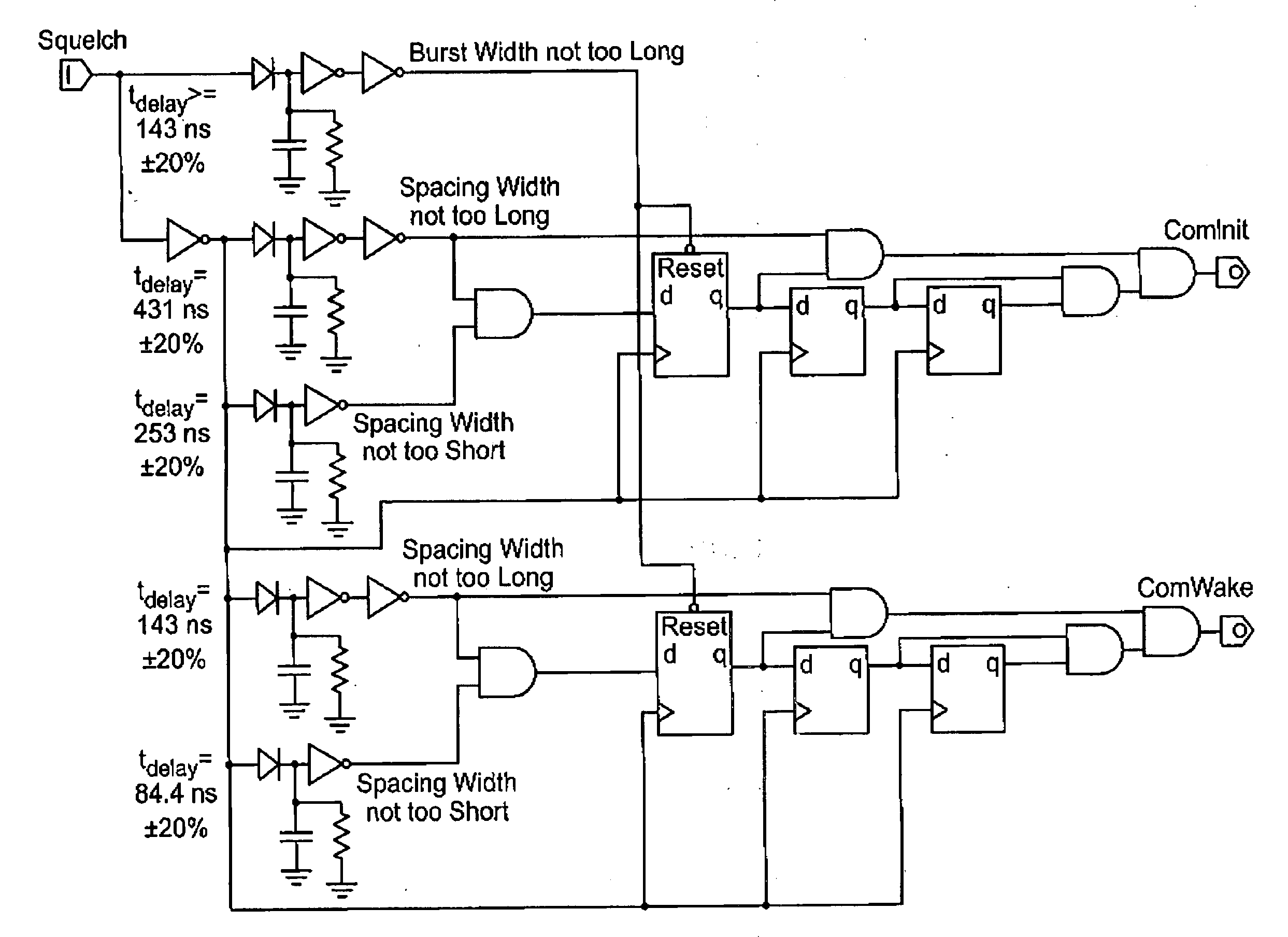

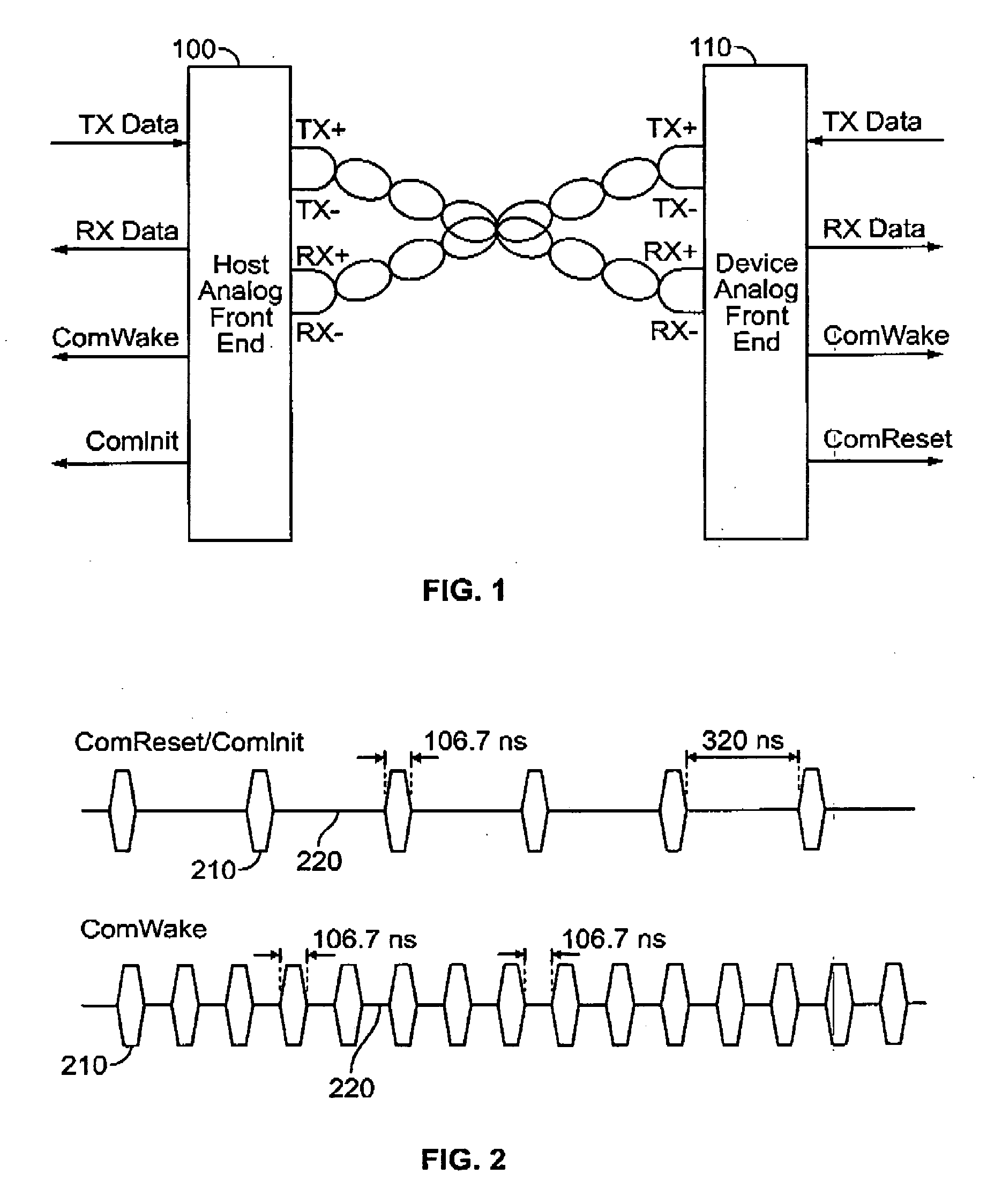

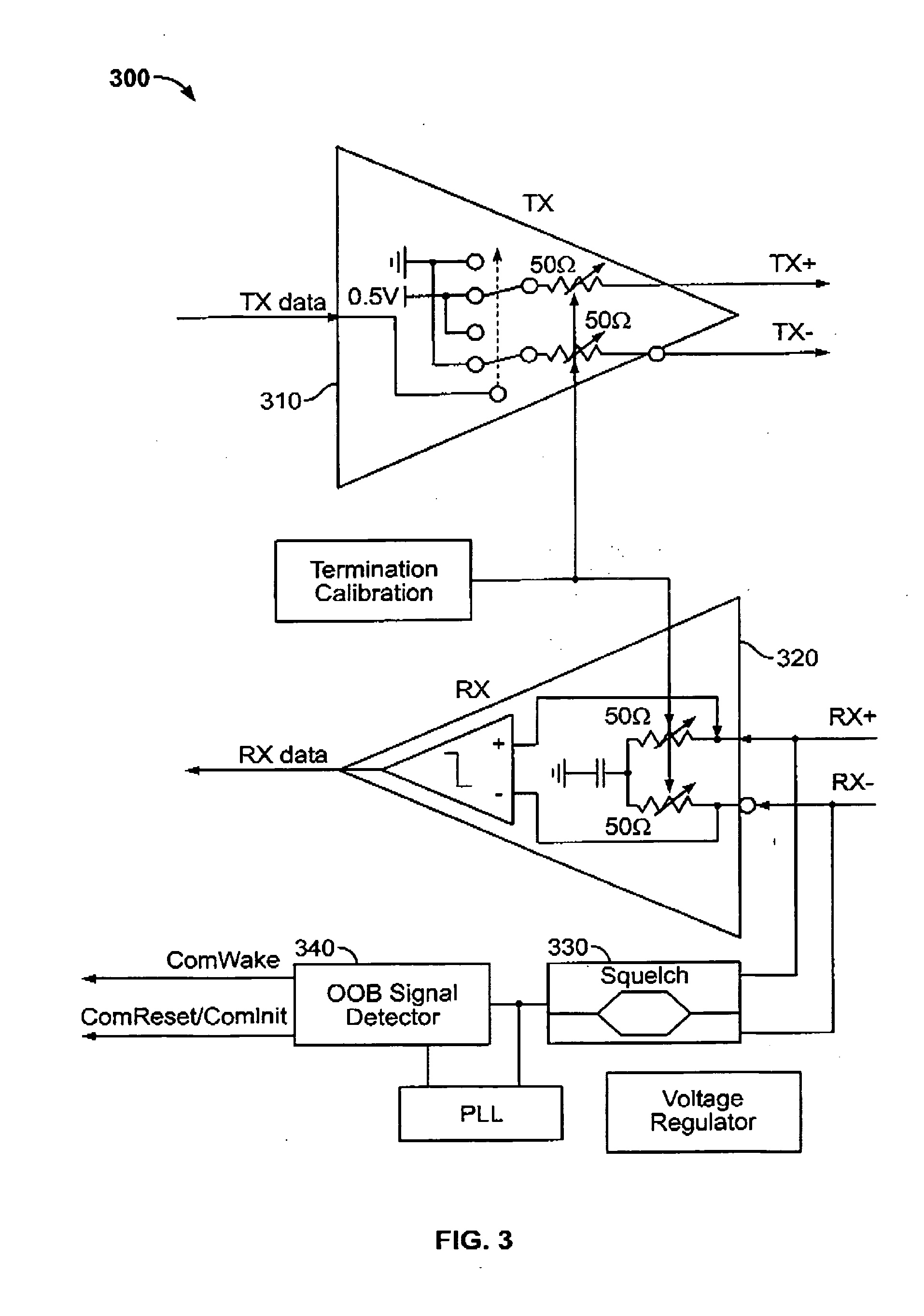

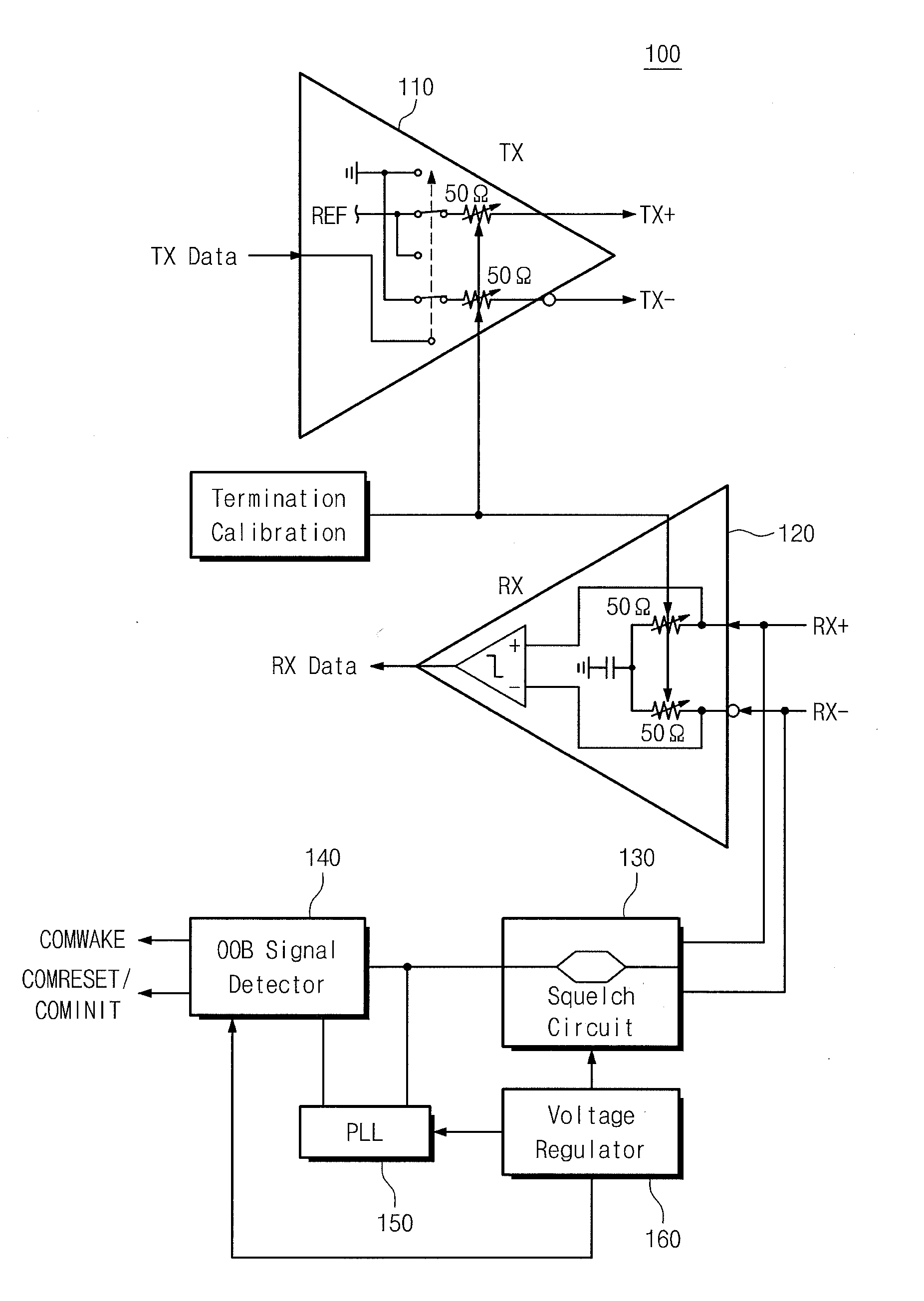

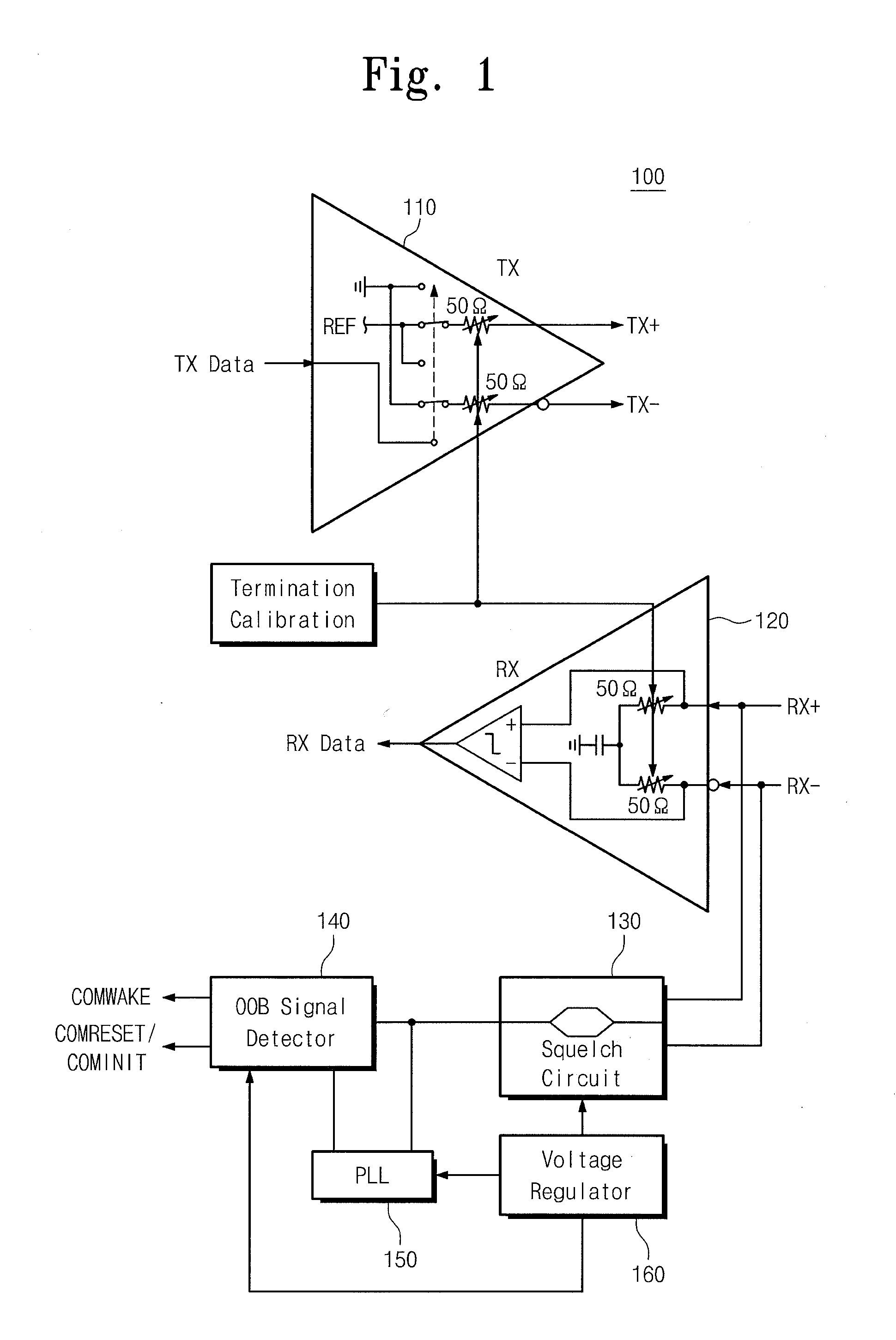

Apparatus and method for selectively enabling and disabling a squelch circuit across AHCI and SATA power states

An apparatus and a method are provided for selectively enabling and disabling a squelch circuit in a Serial Advanced Technology Attachment (SATA) host or SATA device while maintaining proper operation of the host and device. An apparatus and method are provided which allow the squelch circuit to be selectively enabled and disabled across SATA power states (PHY Ready, Partial, and Slumber) and in Advanced Host Controller Interface (AHCI) Listen mode.

Owner:INTEL CORP

Architectures for external SATA-based flash memory devices

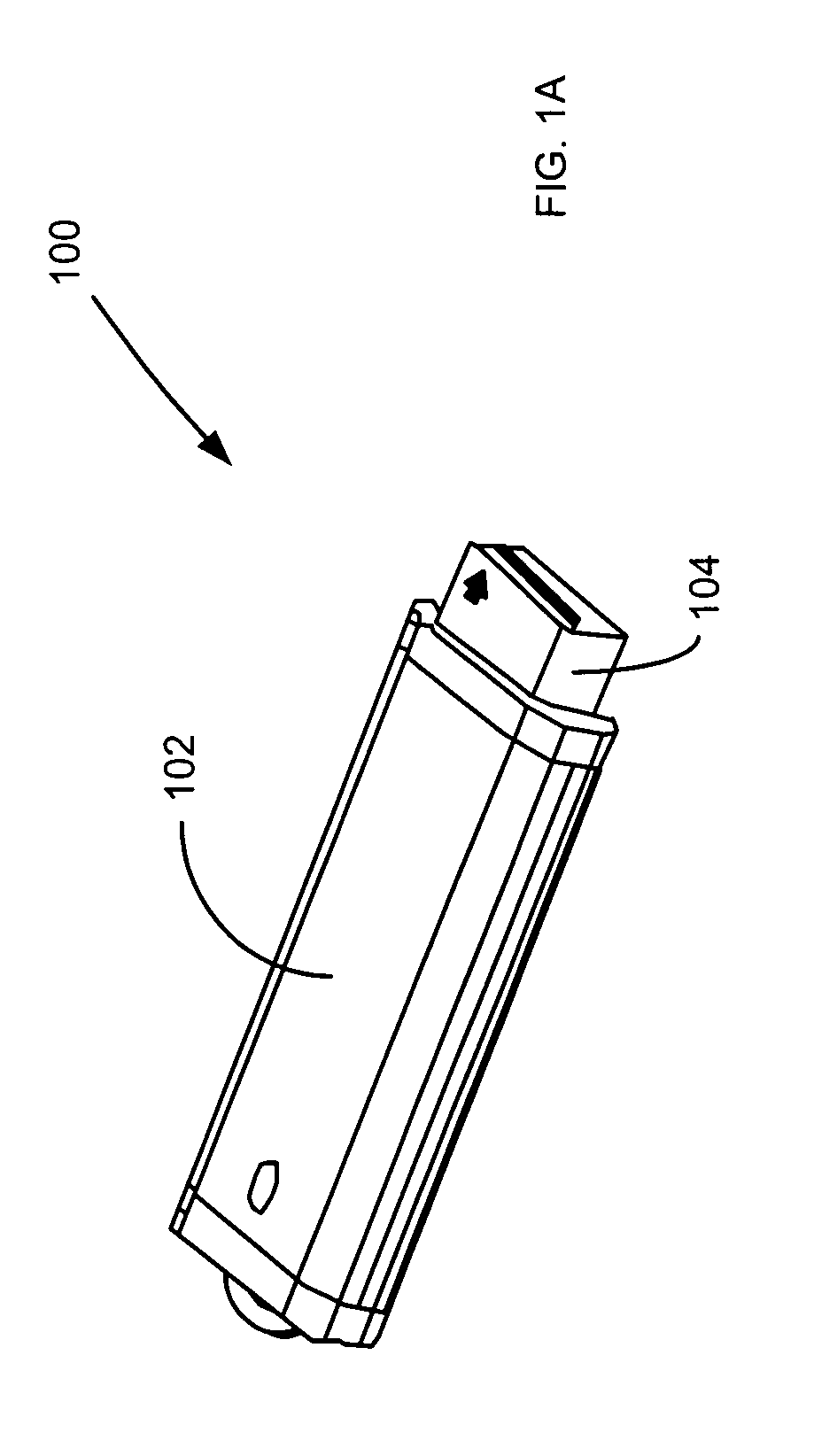

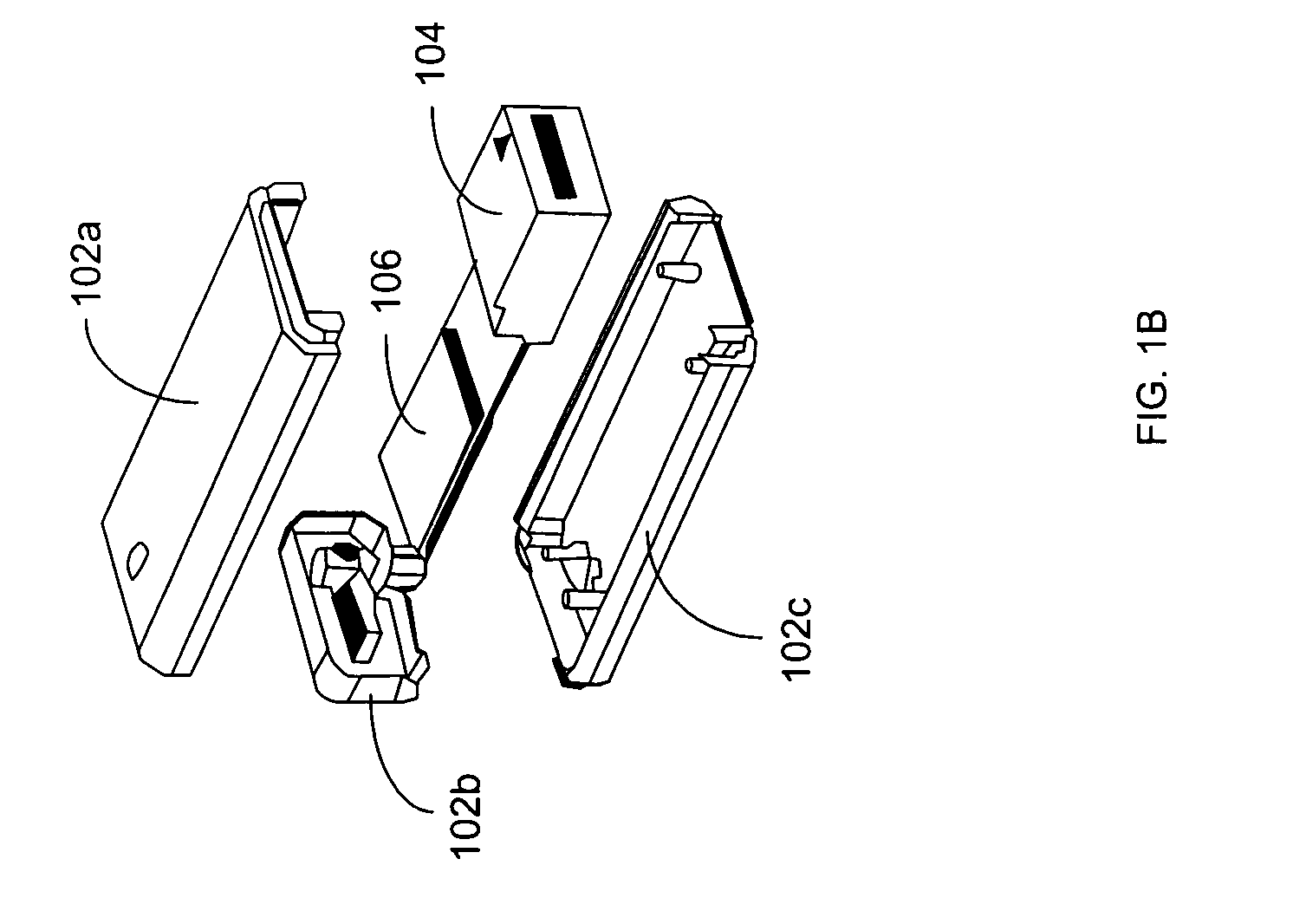

InactiveUS7393247B1Easy to store dataCoupling device connectionsElectric discharge tubesEngineeringSerial advanced technology attachment

A Serial Advanced Technology Attachment-based (SATA-based) flash memory device configured for coupling with a host machine. The device includes semiconductor memory configured for storing data and a plug having therein a plug cavity, the plug cavity having a generally L shape cavity for housing a set of SATA industry-standard signal pins in respective industry-standard positions with respect to the plug cavity. The plug additionally has a set of power pins that includes at least a first power pin. The SATA-based flash memory device employs a SATA protocol for exchanging the data with the host machine using the set of SATA industry-standard signal pins, the SATA-based flash memory device obtaining power via the set of power pins.

Owner:SUPER TALENT TECH CORP

Method and Apparatus of Providing Security to an External Attachment Device

InactiveUS20080288782A1Program control using stored programsInternal/peripheral component protectionDisk controllerSerial advanced technology attachment

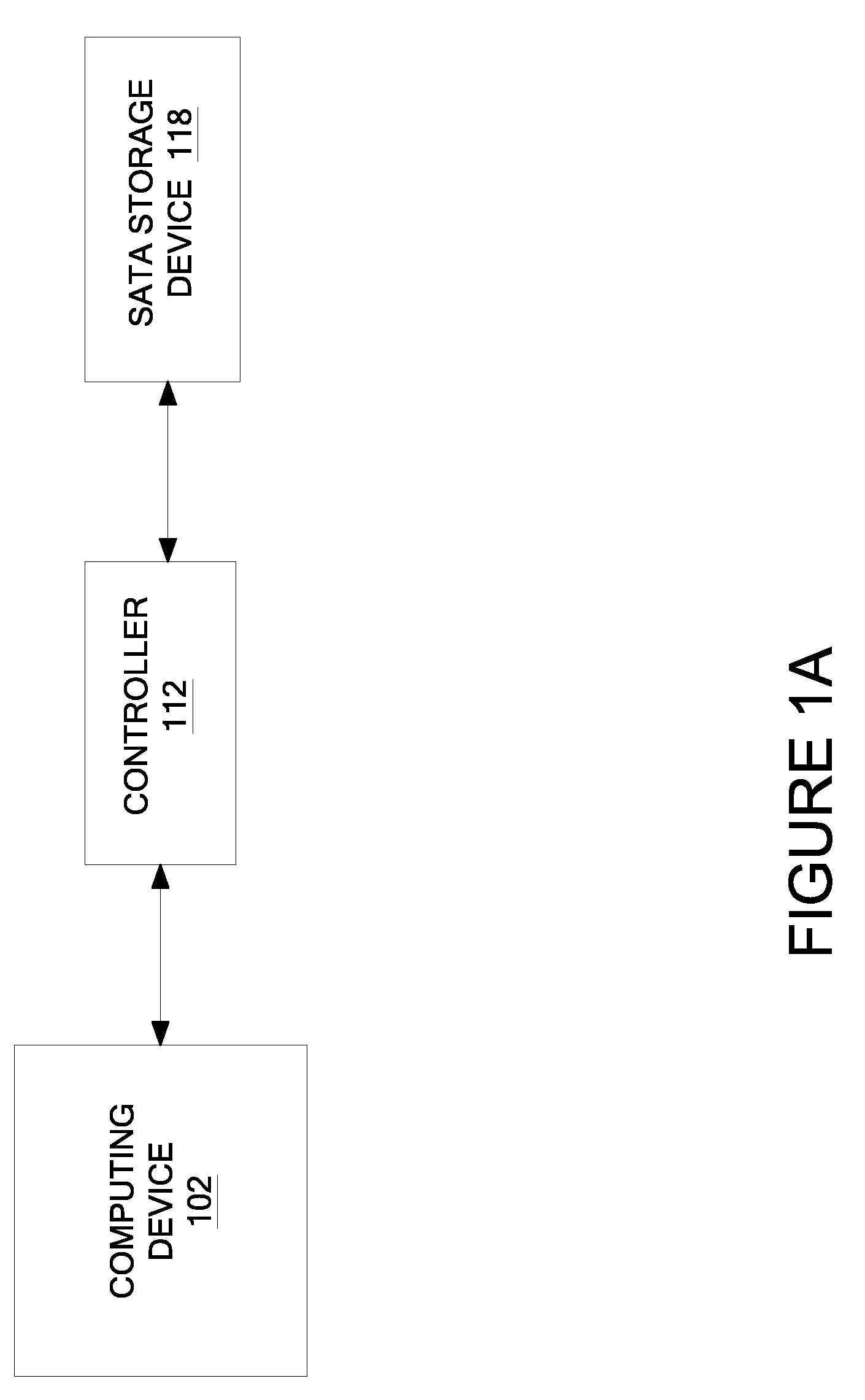

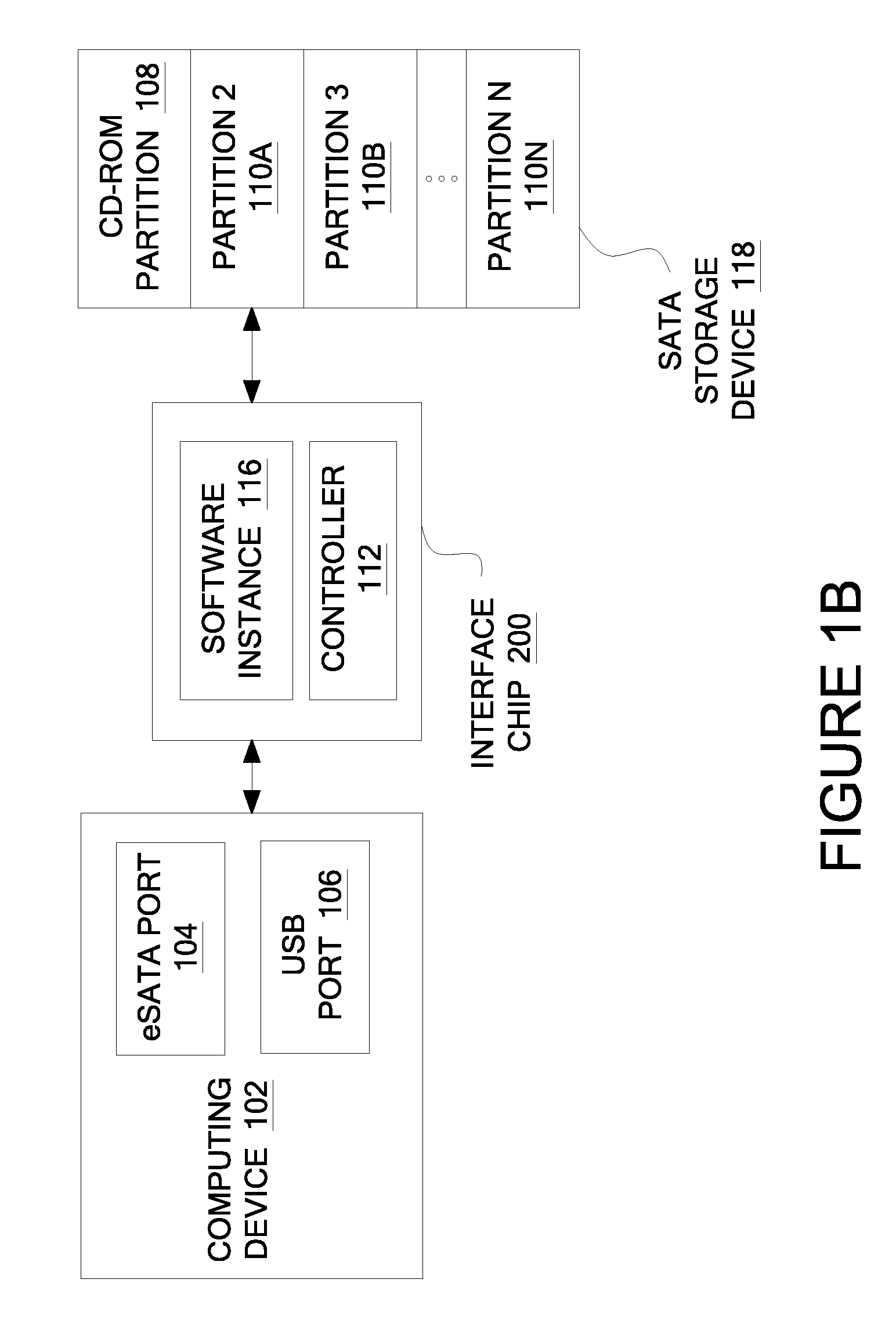

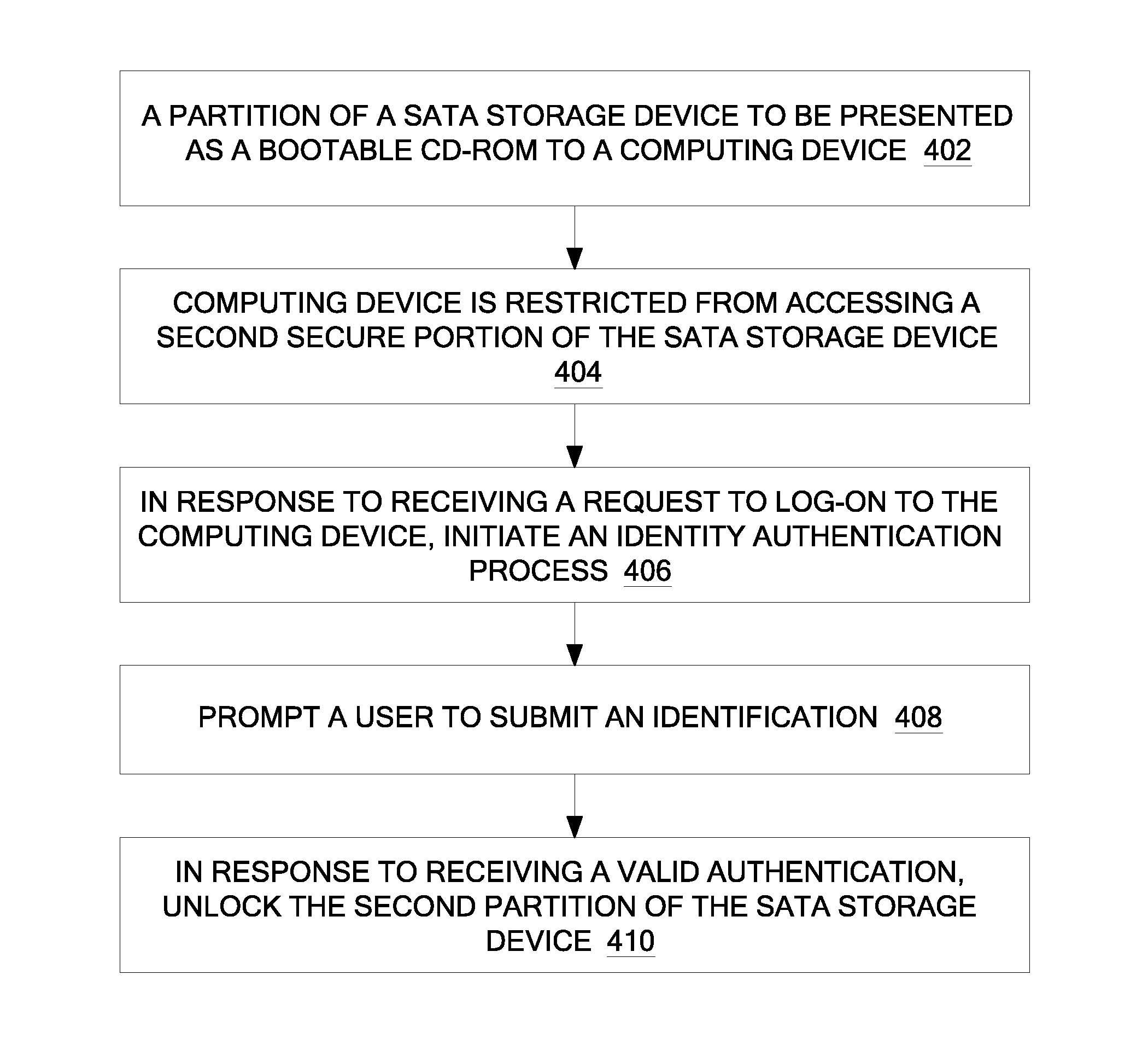

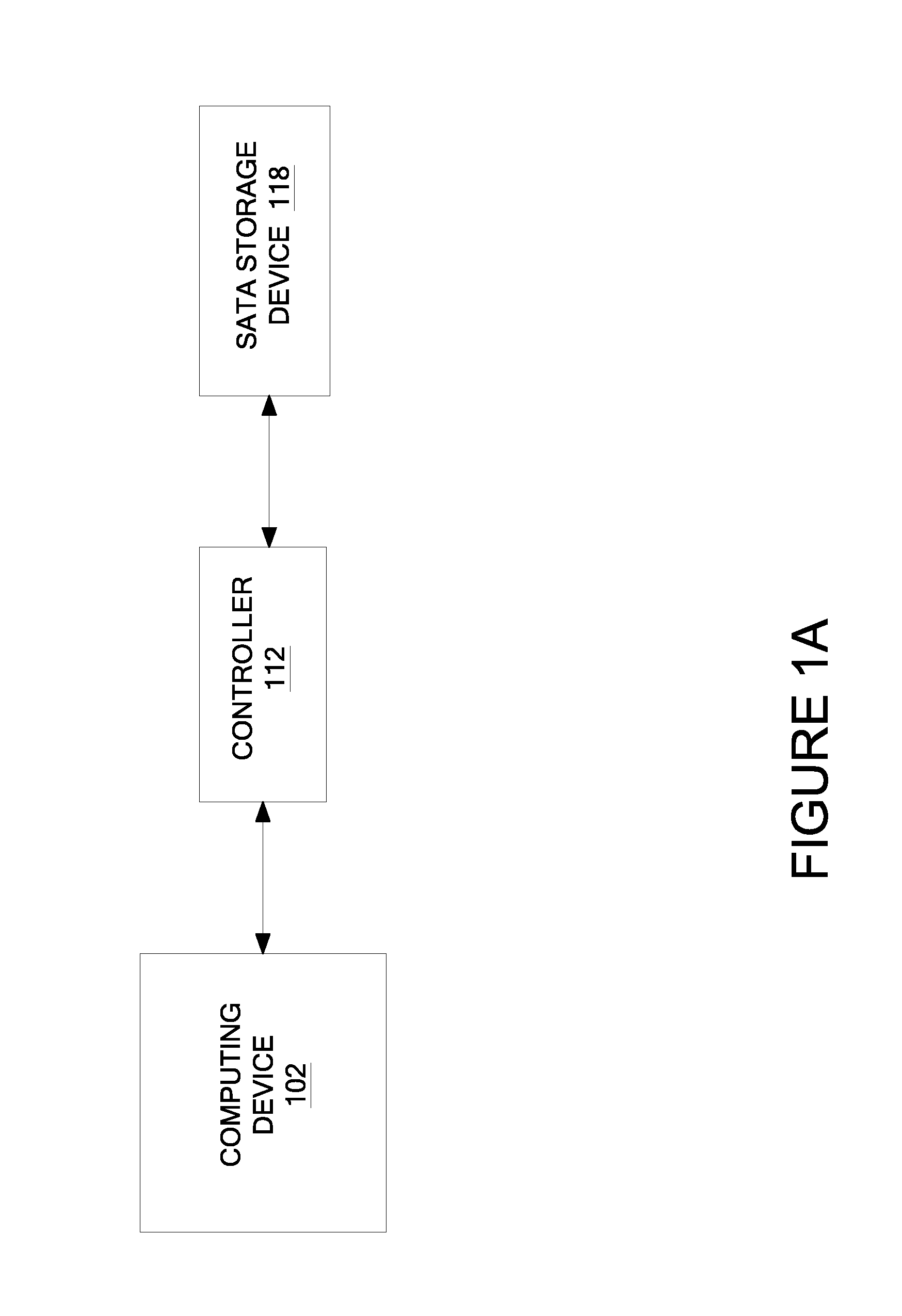

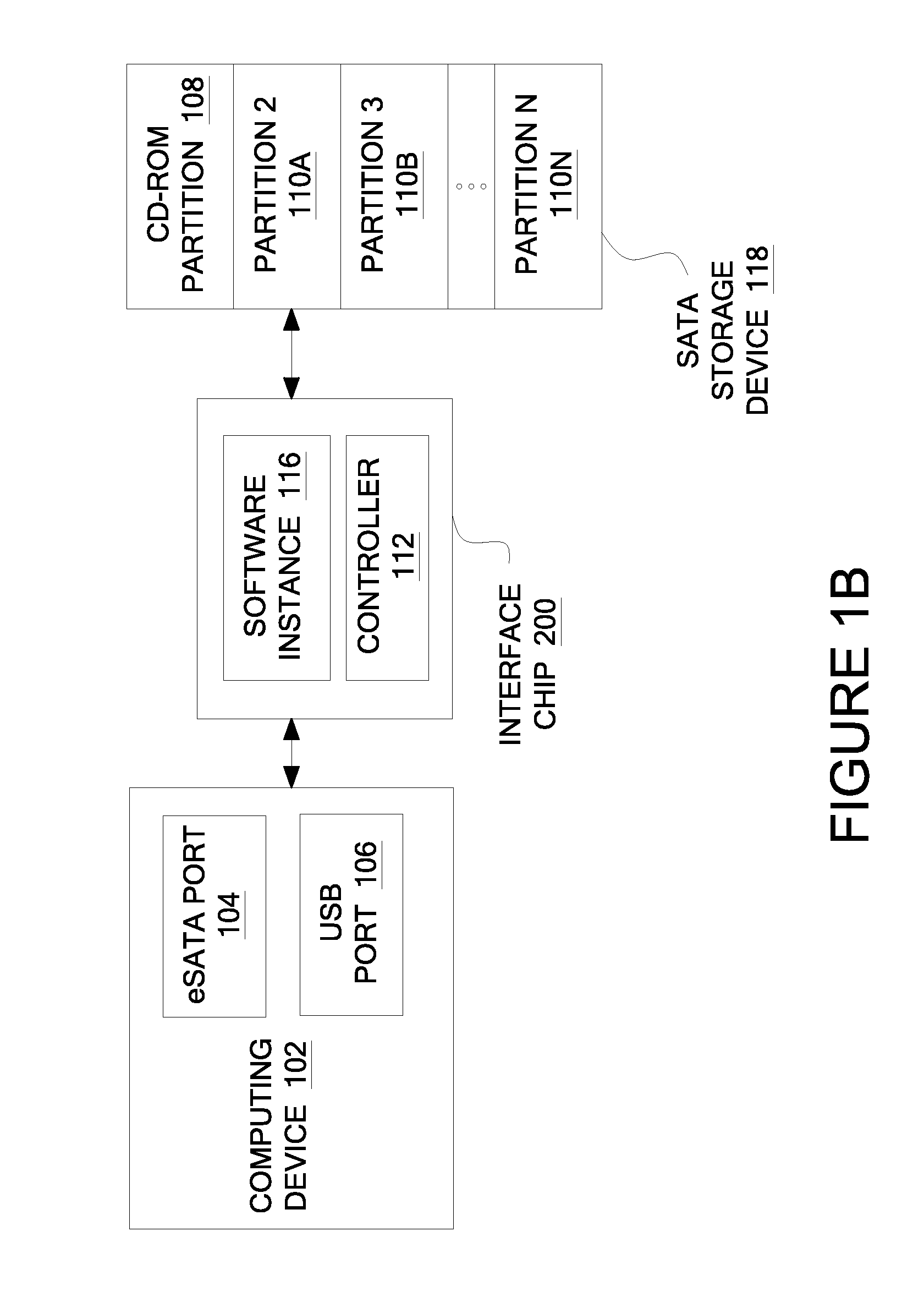

Systems and methods of providing security to an external Serial Advanced Technology Attachment (SATA) device are described herein. One embodiment includes presenting to a computing device, a first partition of an external Serial Advanced Technology Attachment storage device, as a Read Only Memory; restricting the computing device from accessing a secured second partition of the external Serial Advanced Technology Attachment storage device; and in response to receiving a valid identity authentication, unrestricting access to the second partition of the external Serial Advanced Technology Attachment storage device. In one embodiment, in response to receiving a logon request from the computing device, an identity authentication process is initiated, wherein the process is stored on the first partition. Furthermore, in one embodiment, a process stored on a disk controller receives an encryption key from the process stored on the first partition of the Serial Advanced Technology Attachment storage device, and the process stored on the disk controller uses the encryption key to decrypt the second partition of the Serial Advanced Technology Attachment storage device.

Owner:MCM PORTFOLIO LLC

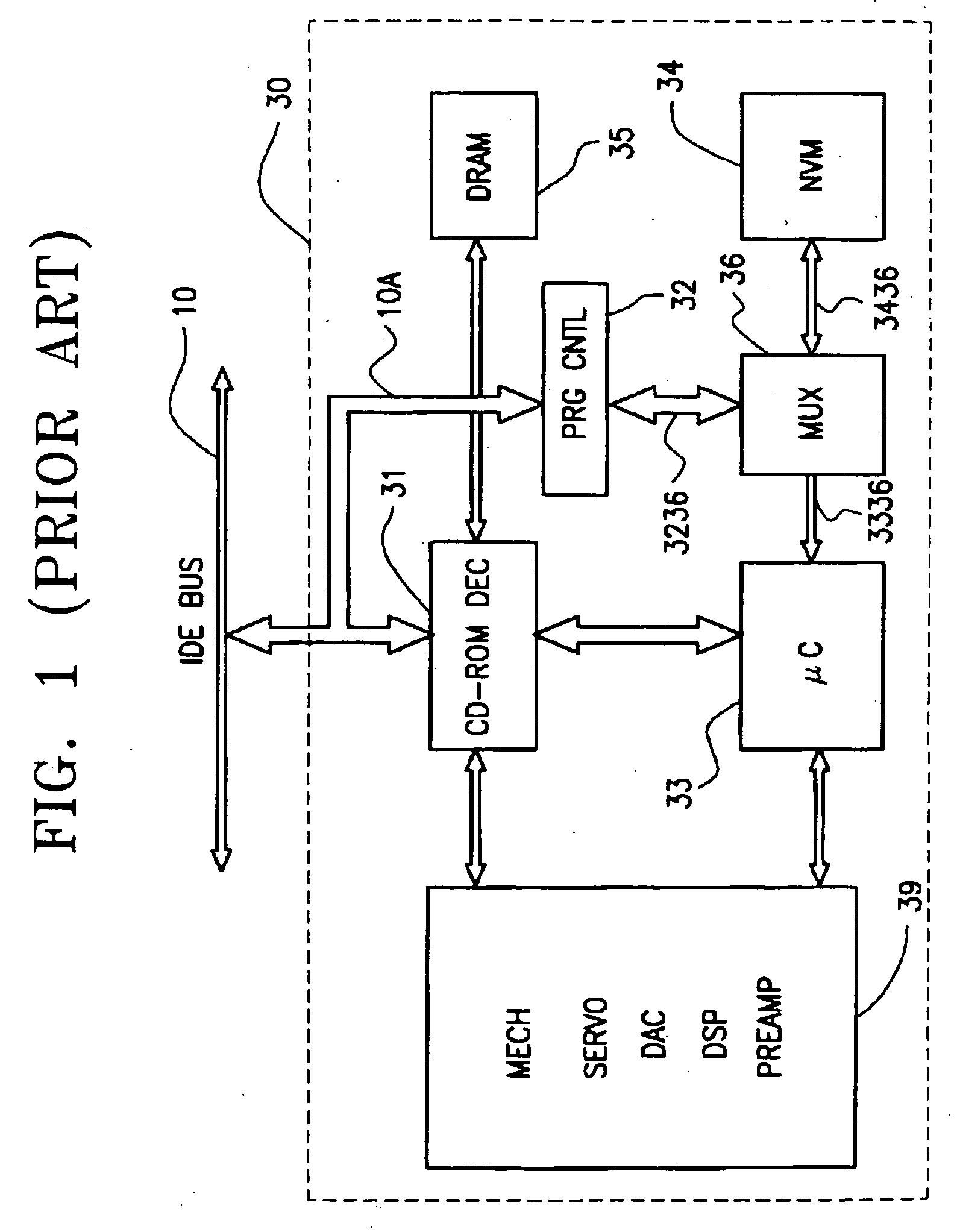

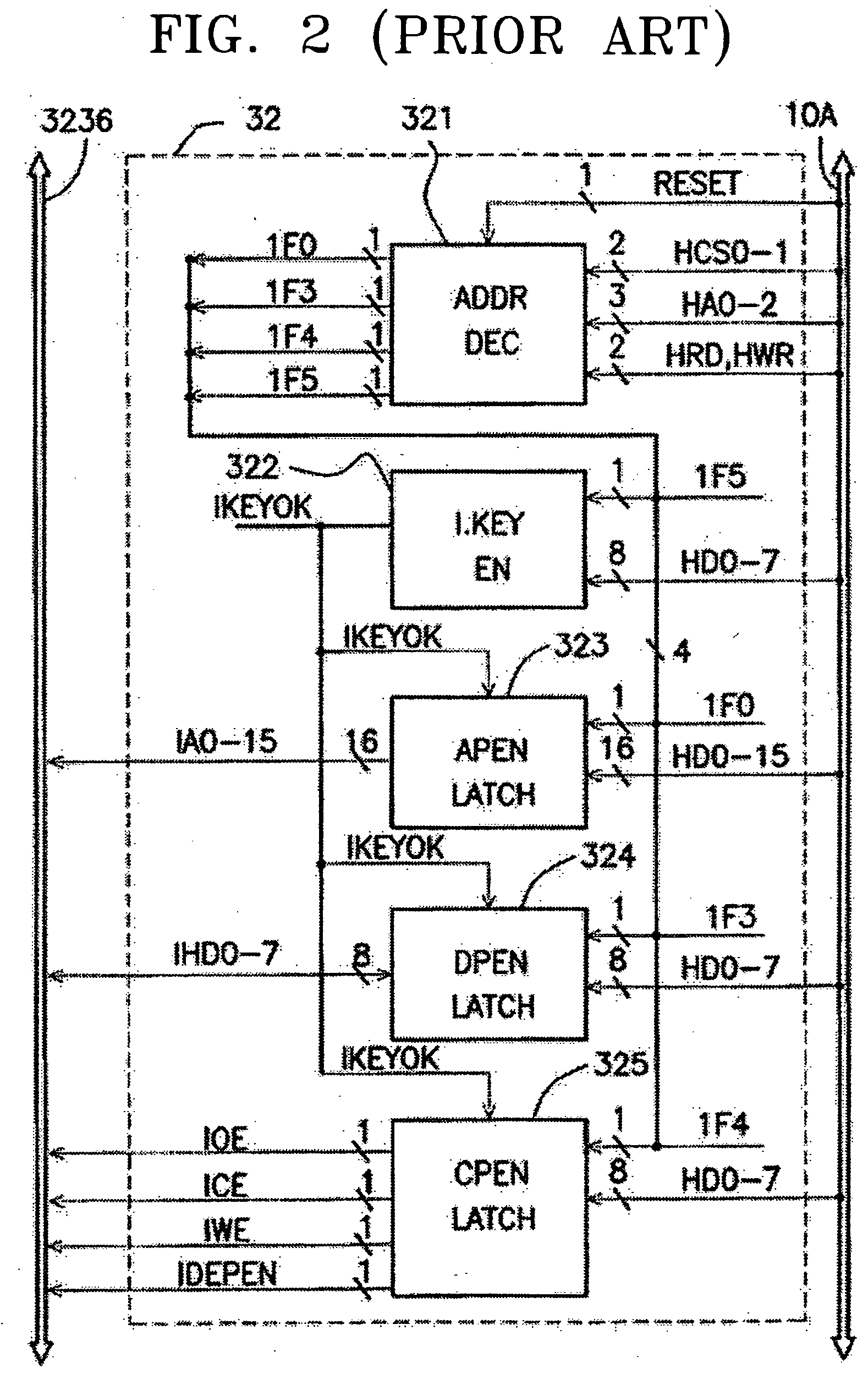

Dual port serial advanced technology attachment (SATA) disk drive

InactiveUS20050186832A1Error preventionFrequency-division multiplex detailsHard disc driveSerial advanced technology attachment

An embodiment of the present invention is disclosed to include a hard disk drive allowing for access by two hosts to a device. Further disclosed are embodiments for reducing the delay and complexity of the SATA disk drive.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

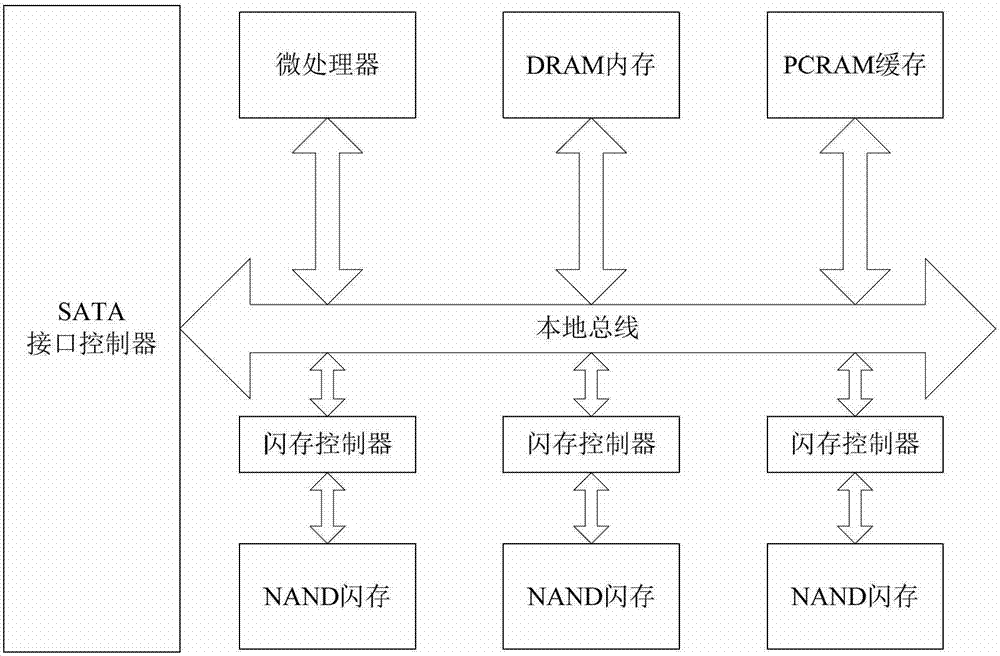

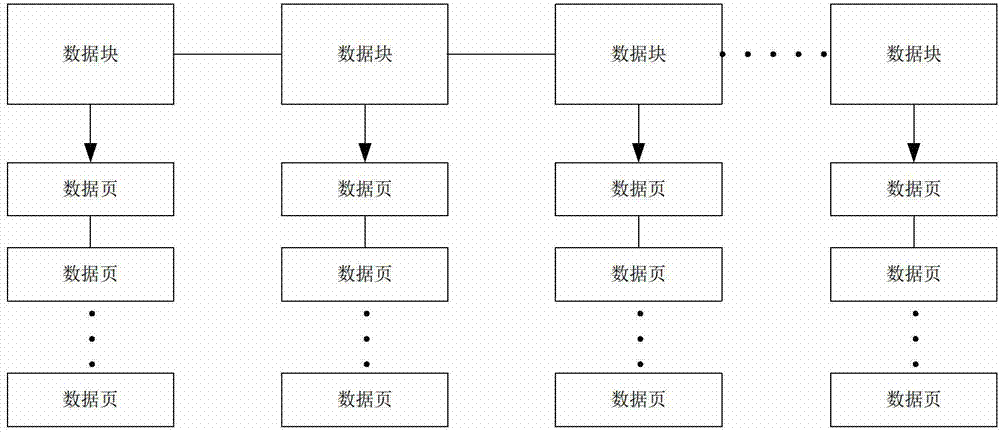

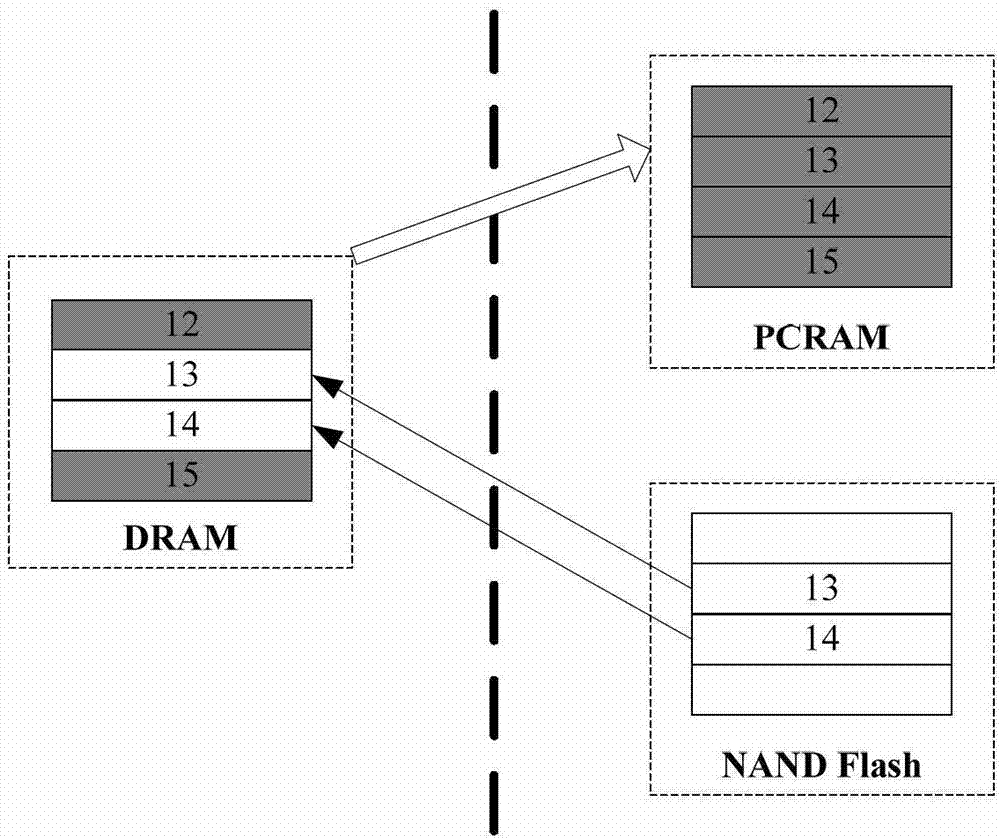

Method and system for internal cache management of solid state disk based on novel memory

ActiveCN103049397AOvercome read and write imbalanceEasy to operateMemory architecture accessing/allocationMemory adressing/allocation/relocationFlash memory controllerCache management

The invention provides a method and a system for internal cache management of a solid state disk based on a novel memory. The system for internal cache management of the solid state disk comprises an SATA (serial advanced technology attachment) interface controller, a microprocessor, a DRAM (dynamic random access memory), a local bus, a flash controller, an NAND flash and a PCRAM (phase change random access memory) cache. The PCRAM cache comprises a data block displacement area and a mapping table storage area, wherein the data block replacement area is used for storing data blocks displaced to the PCRAM cache from the DRAM, and the mapping table storage area is used for storing mapping tables among logic addresses and physical addresses of data pages. By the method for internal cache management of the SSD (solid state disk) based on the PCRAM, write cache for the solid state disk is realized to overcome read-write imbalance of the solid state disk, write performances are effectively improved, random write operation and wiping operation of the solid state disk are decreased, accordingly, the service life of the solid state disk is prolonged, and the integral I / O (input / output) performance of the solid state disk is improved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

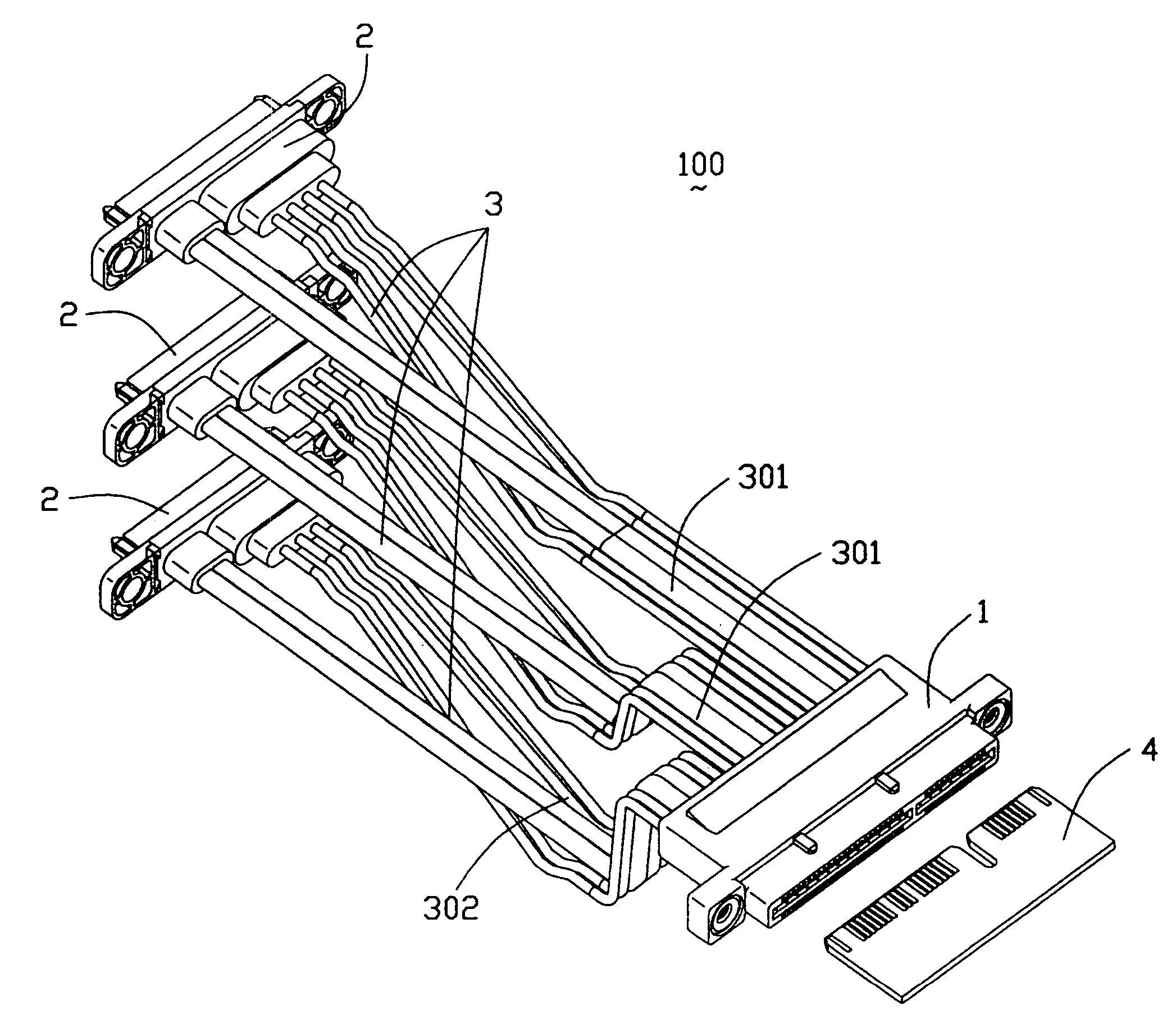

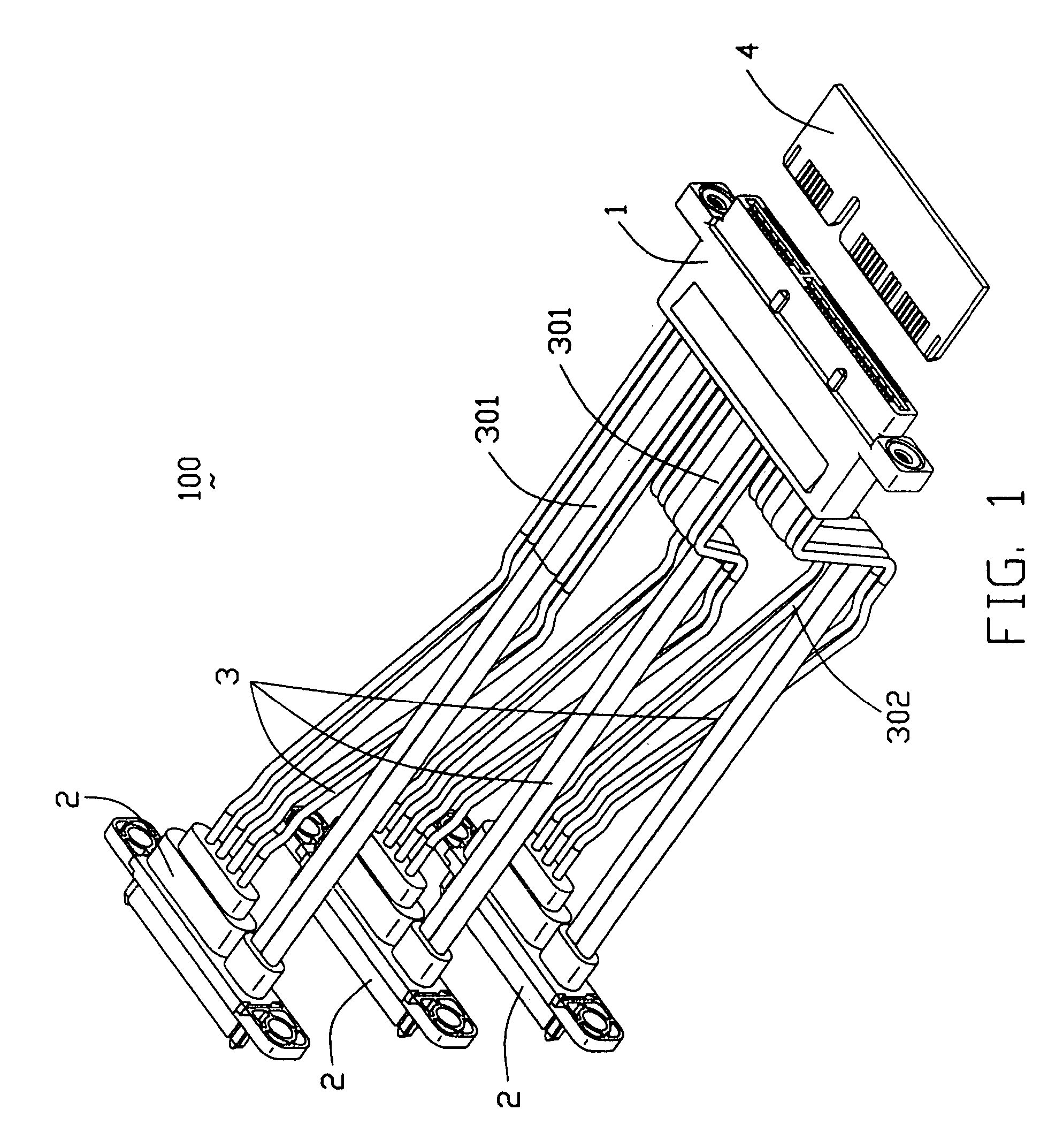

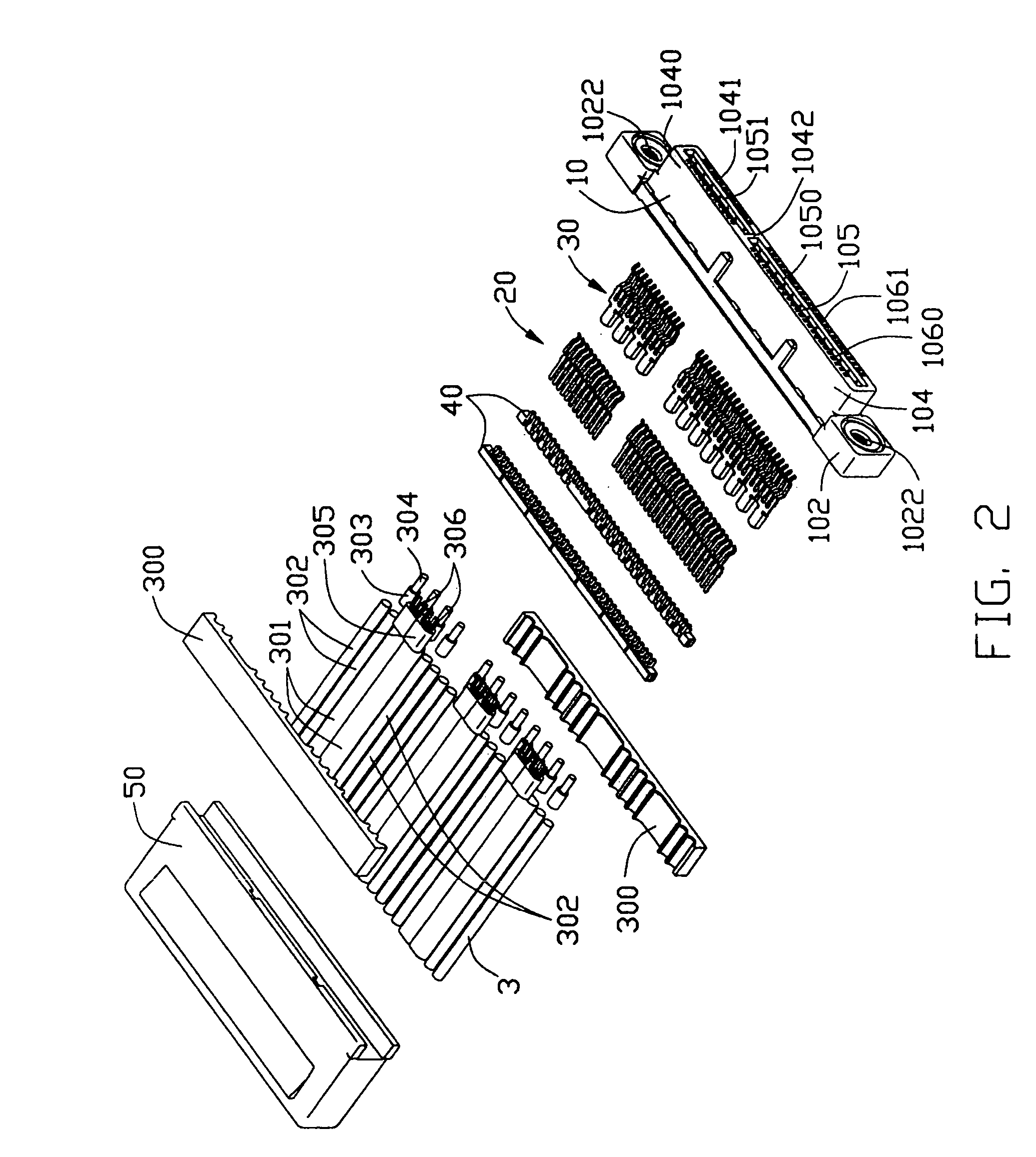

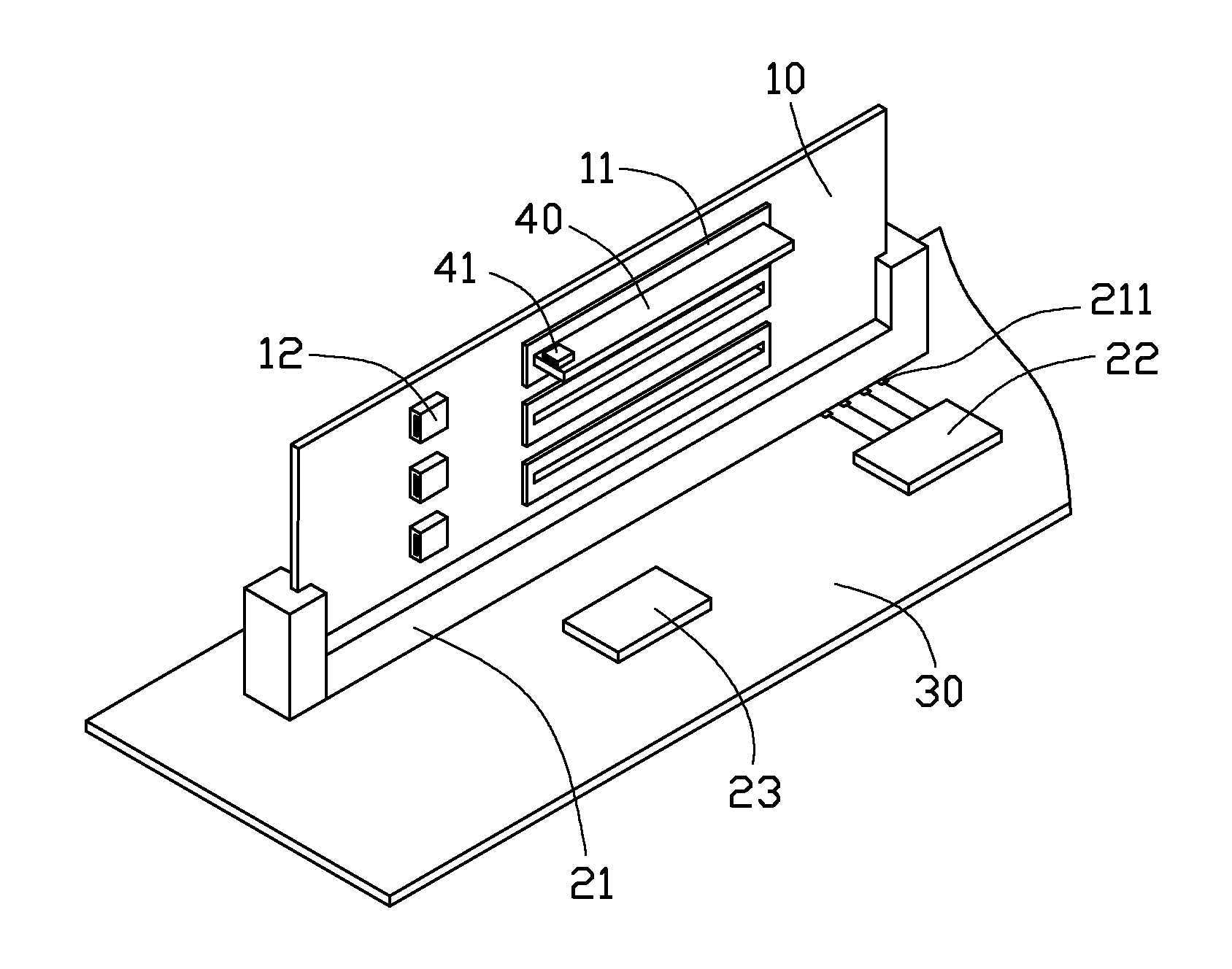

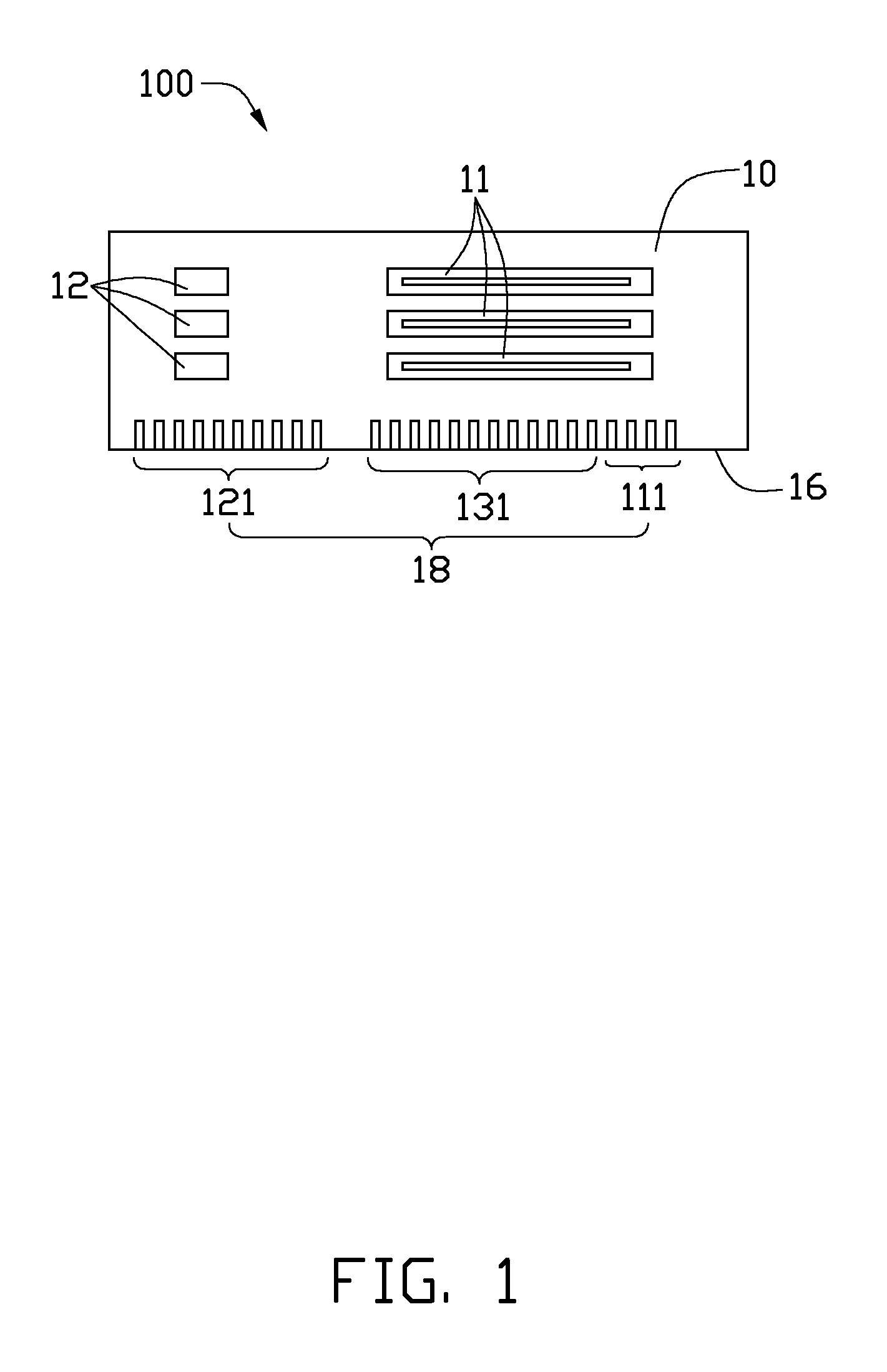

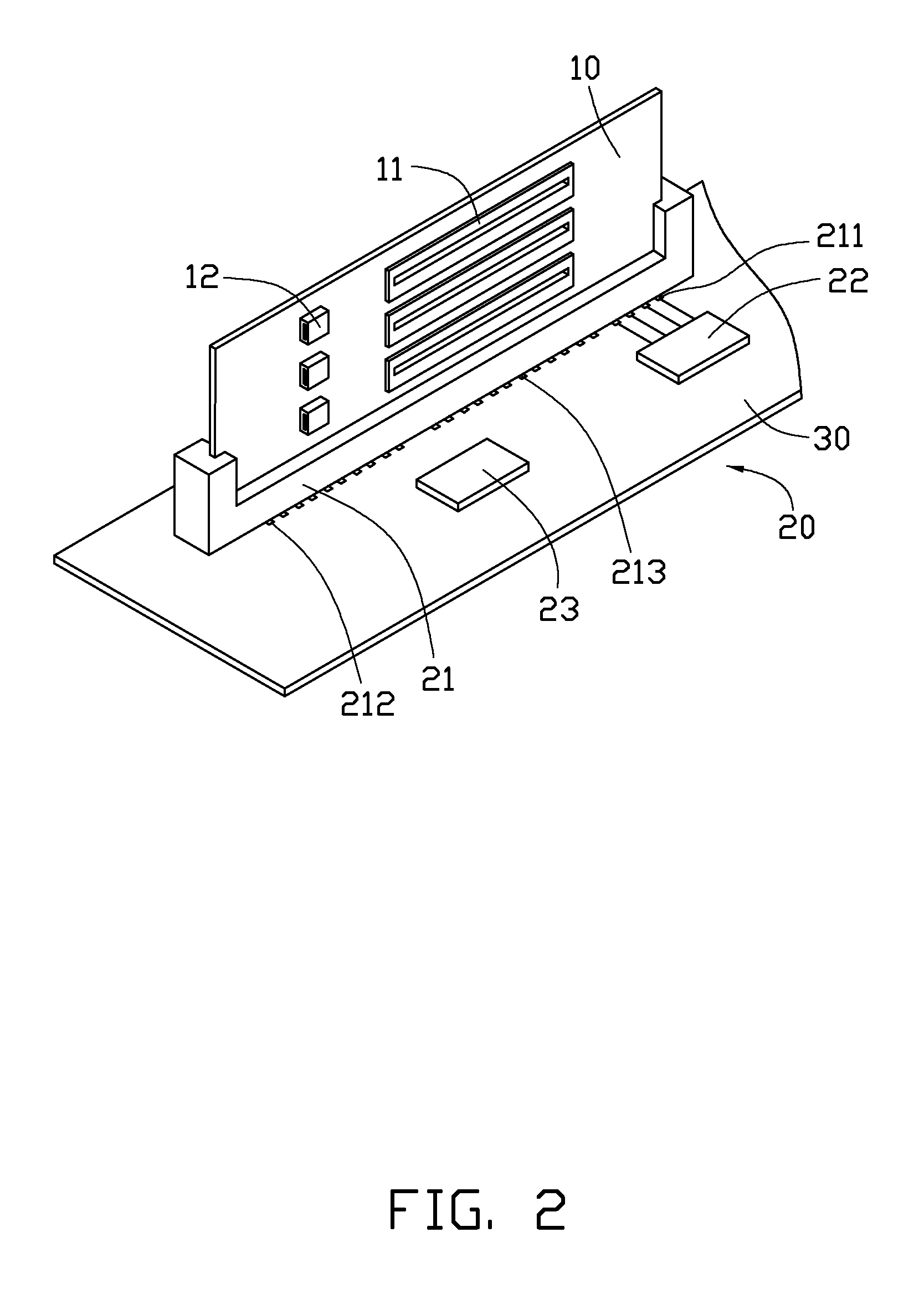

Single-port to multi-port cable assembly

InactiveUS7134908B2Electric discharge tubesTwo-part coupling devicesEngineeringSerial advanced technology attachment

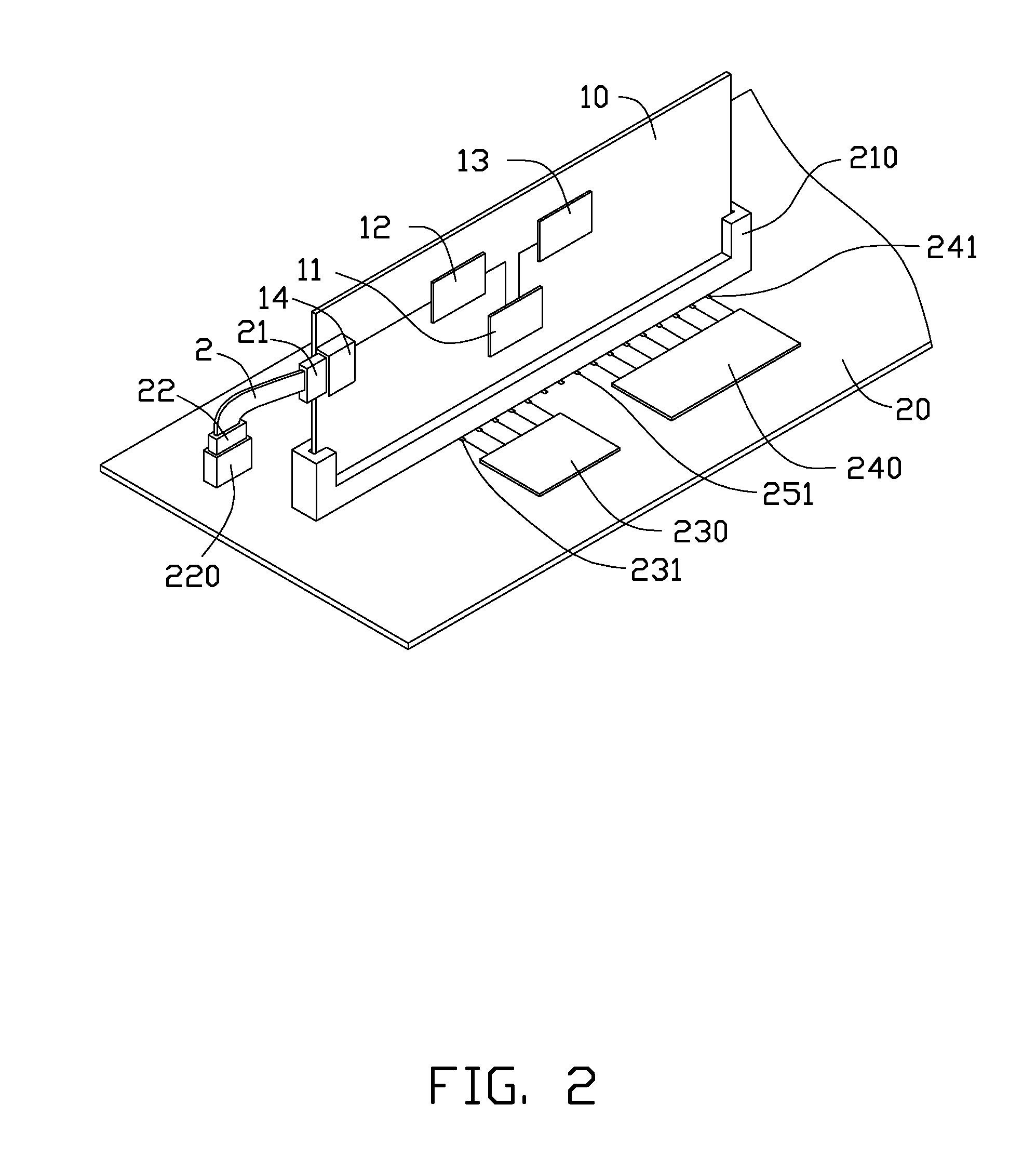

A cable assembly (100) includes a first connector (1), a number of second connectors (2) each having a serial advanced technology attachment interface, and cable means (3) connecting the first and the second connectors. The first connector includes a unitary first longitudinal insulative housing (10) having an upper and a lower elongated side walls (1040, 1041) opposite to each other in a lateral direction and respectively defining a plurality of first and second passageways therein, a number of signal contacts disposed in corresponding first passageways, and a number of power contacts disposed in corresponding second passageways. The cable means includes a plurality of sets of wires, each set electrically connecting with the first connector and a corresponding second connector.

Owner:HON HAI PRECISION IND CO LTD

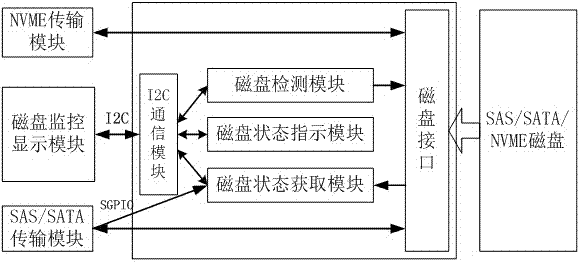

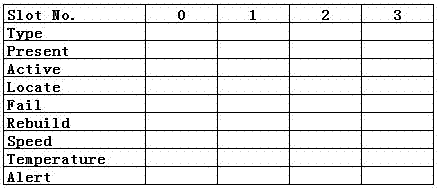

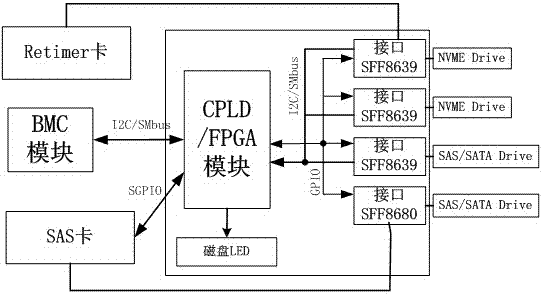

Disk monitoring system and method

InactiveCN106970866ARealize real-time monitoringRealize intelligent judgmentHardware monitoringElectricityStatistical analysis

The invention discloses a disk monitoring system and method. The system comprises a disk monitoring display module, a CPLD (Complex Programmable Logic Device) or FPGA (Field Programmable Gate Array) module, a disk interface module, an SAS (Statistical Analysis System) / SATA (Serial Advanced Technology Attachment) transmission module and an NVME transmission module. After the method and the system are started and electrified, a disk detection module carries out detection distinguishing on the type and the amount of connected disks. The system has the advantages that different types of disk states are monitored, monitoring functions are comprehensive and uniform, an implementation way is simple and reliable and clients can conveniently check.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

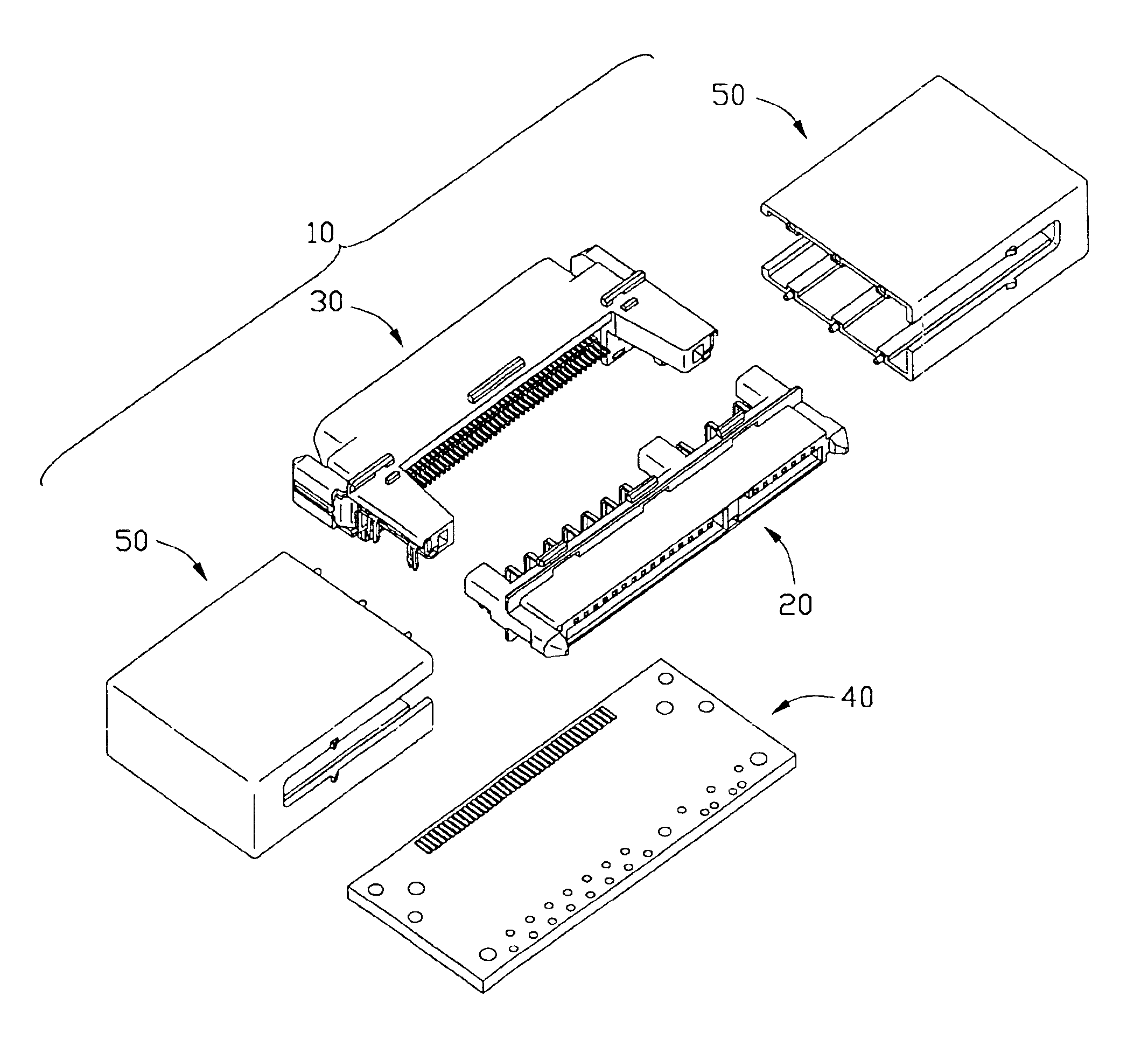

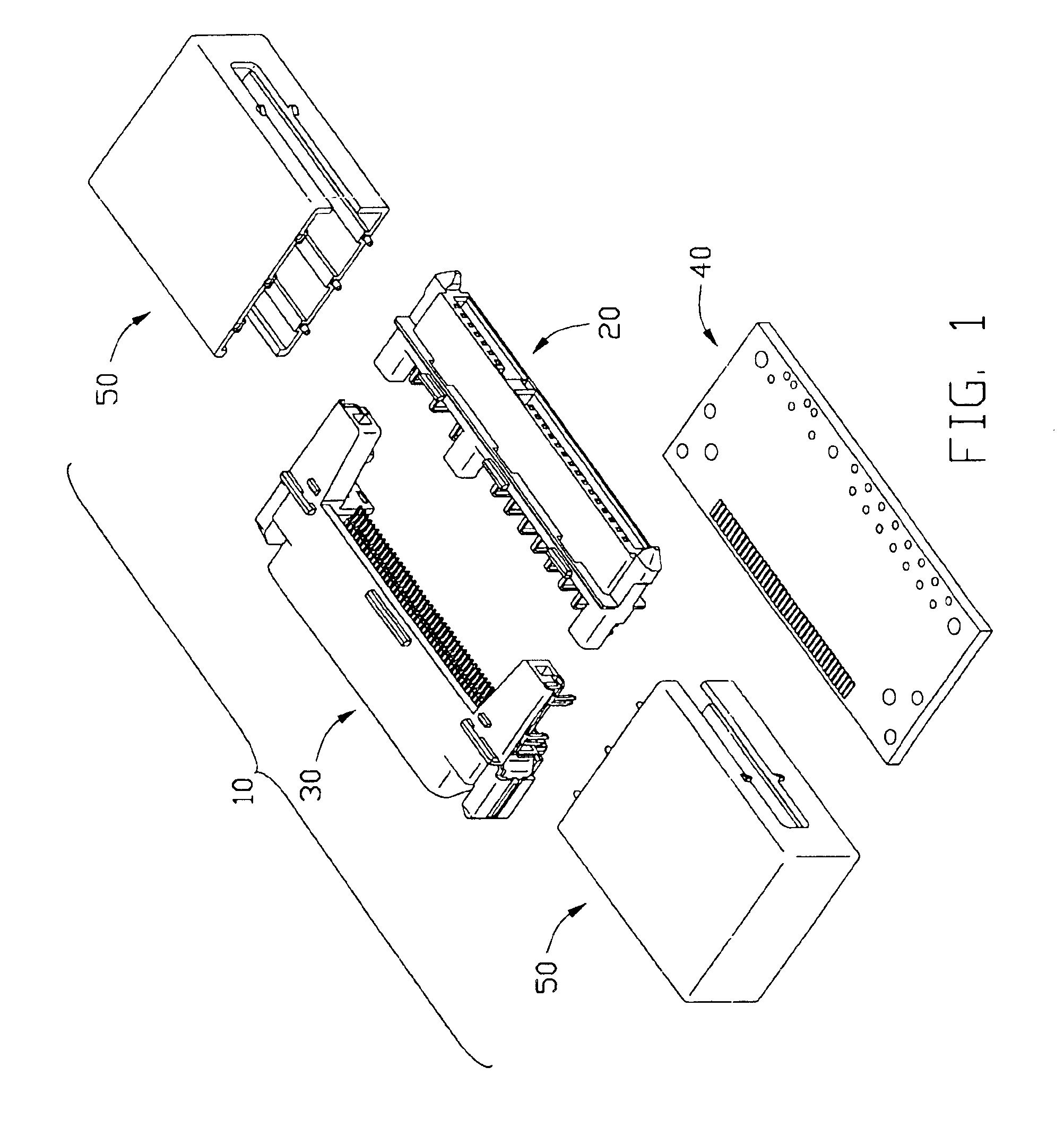

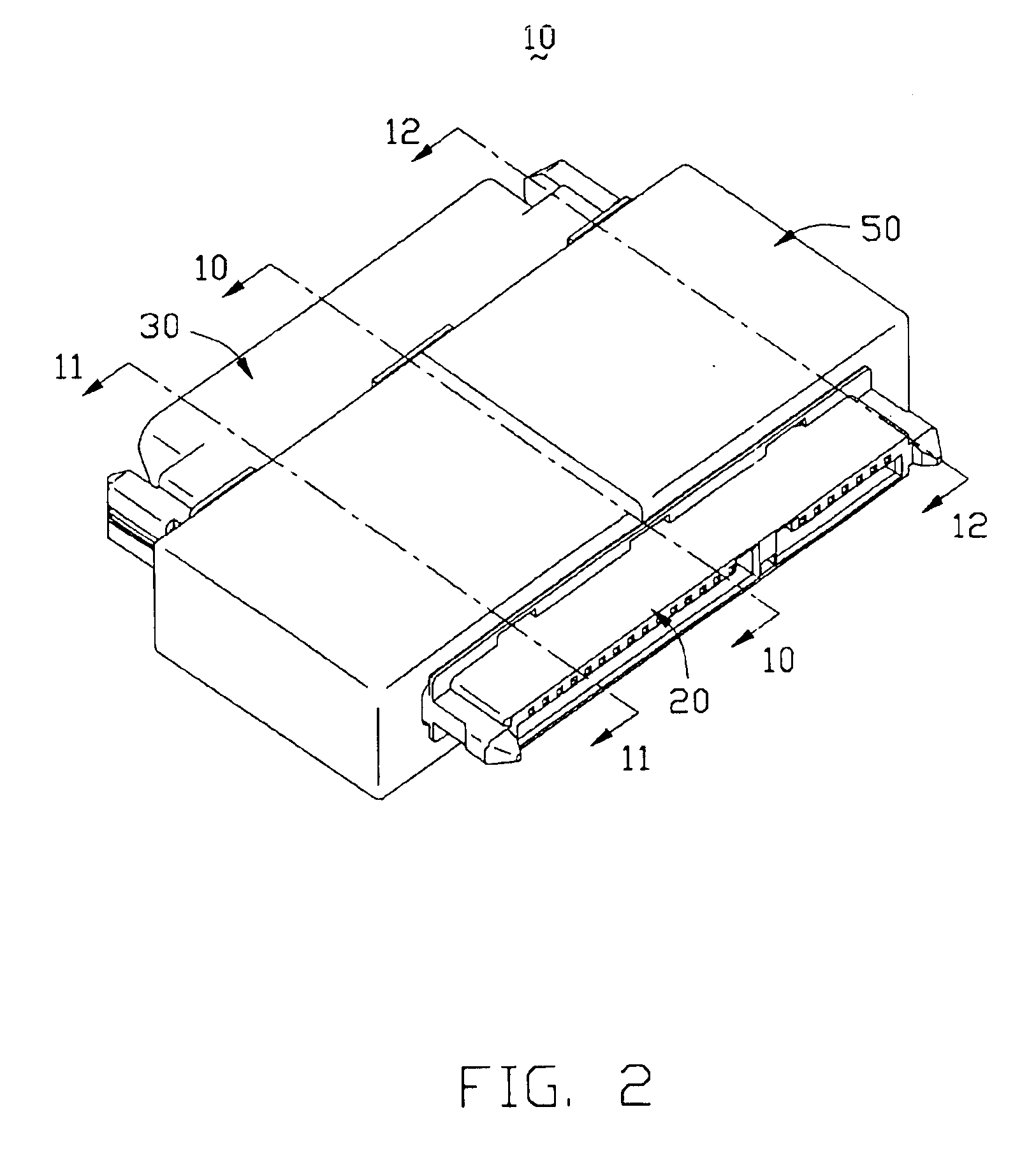

Electrical adapter

InactiveUS6887108B2Electric discharge tubesCoupling device detailsEngineeringSingle Connector Attachment

An electrical adapter (10) includes a serial advanced technology attachment (serial ATA) receptacle connector (20), a single connector attachment 2 (SCA2) plug connector (30), a printed circuit board (40) and a pair of covers (50). The serial ATA receptacle connector and the SCA2 plug connector are respectively electrically and mechanically connected to the printed circuit board. The printed circuit board performs the functions of signal transmission and conversion between the serial ATA receptacle connector and the SCA2 plug connector. The pair of covers are assembled to the subassembly of the serial ATA receptacle connector, the SCA2 plug connector and the printed circuit board, and finally combined with each other to fasten the electrical adapter. The electrical adapter interconnects the SCA2 interface with the serial ATA interface.

Owner:HON HAI PRECISION IND CO LTD

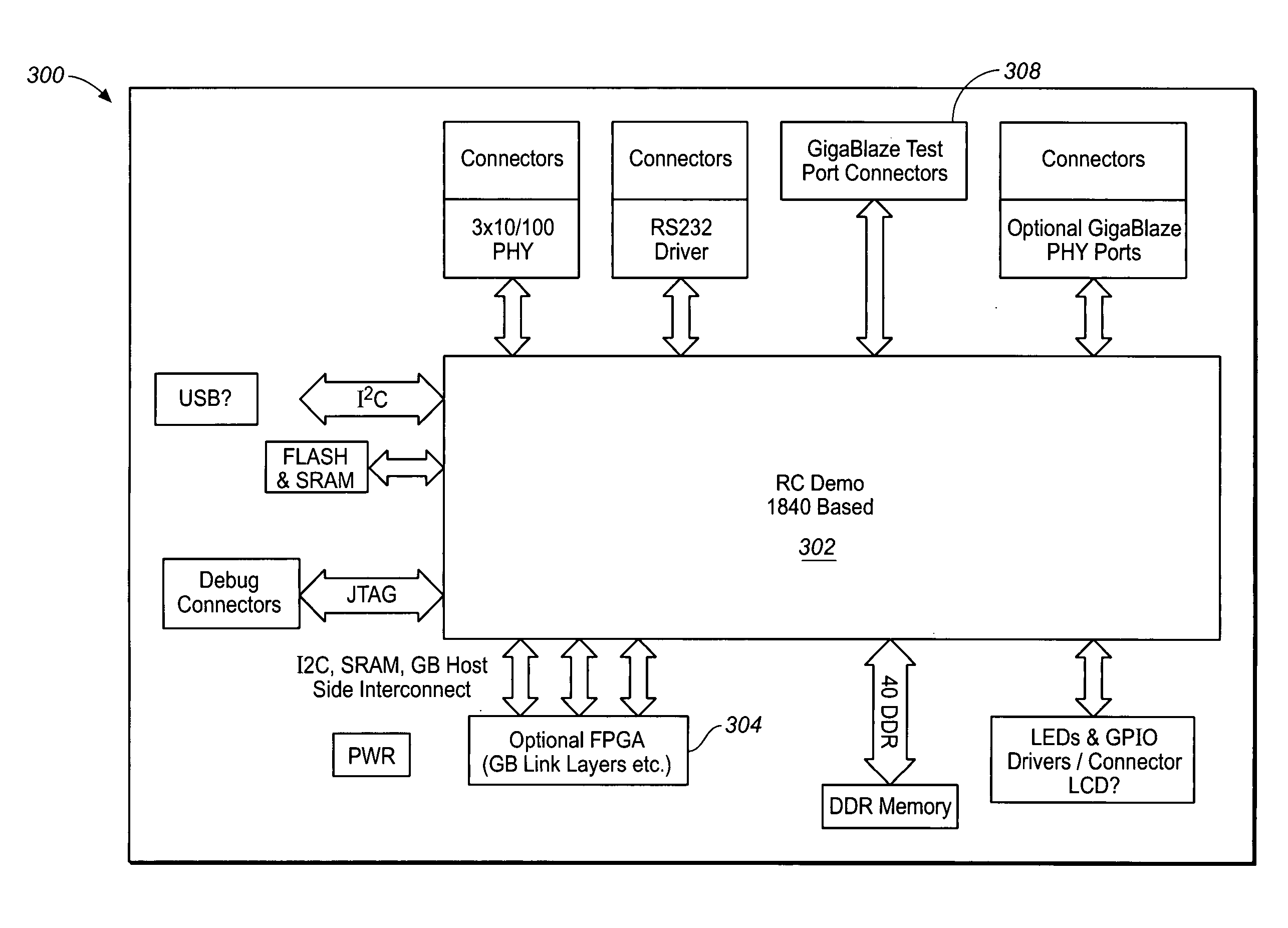

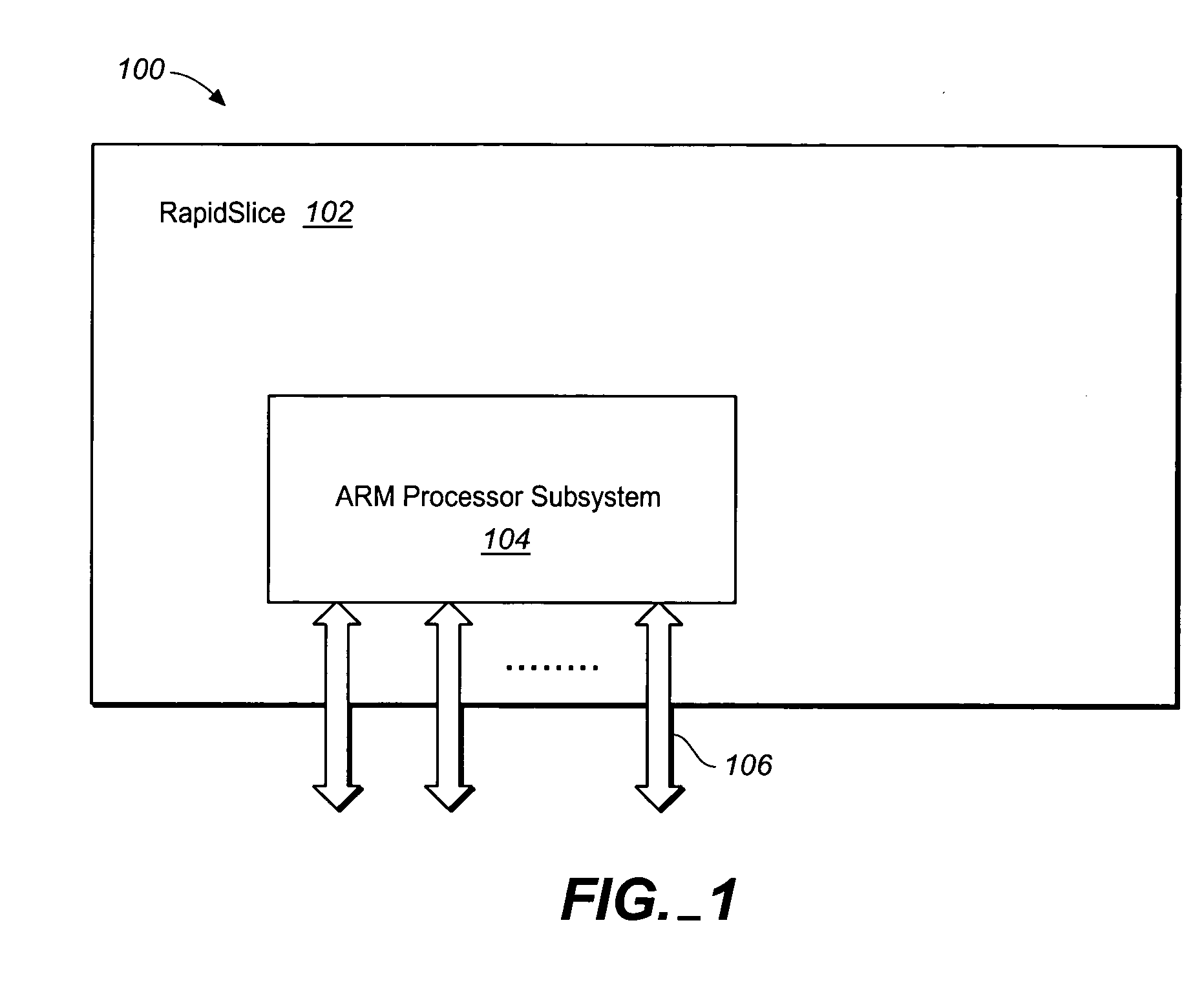

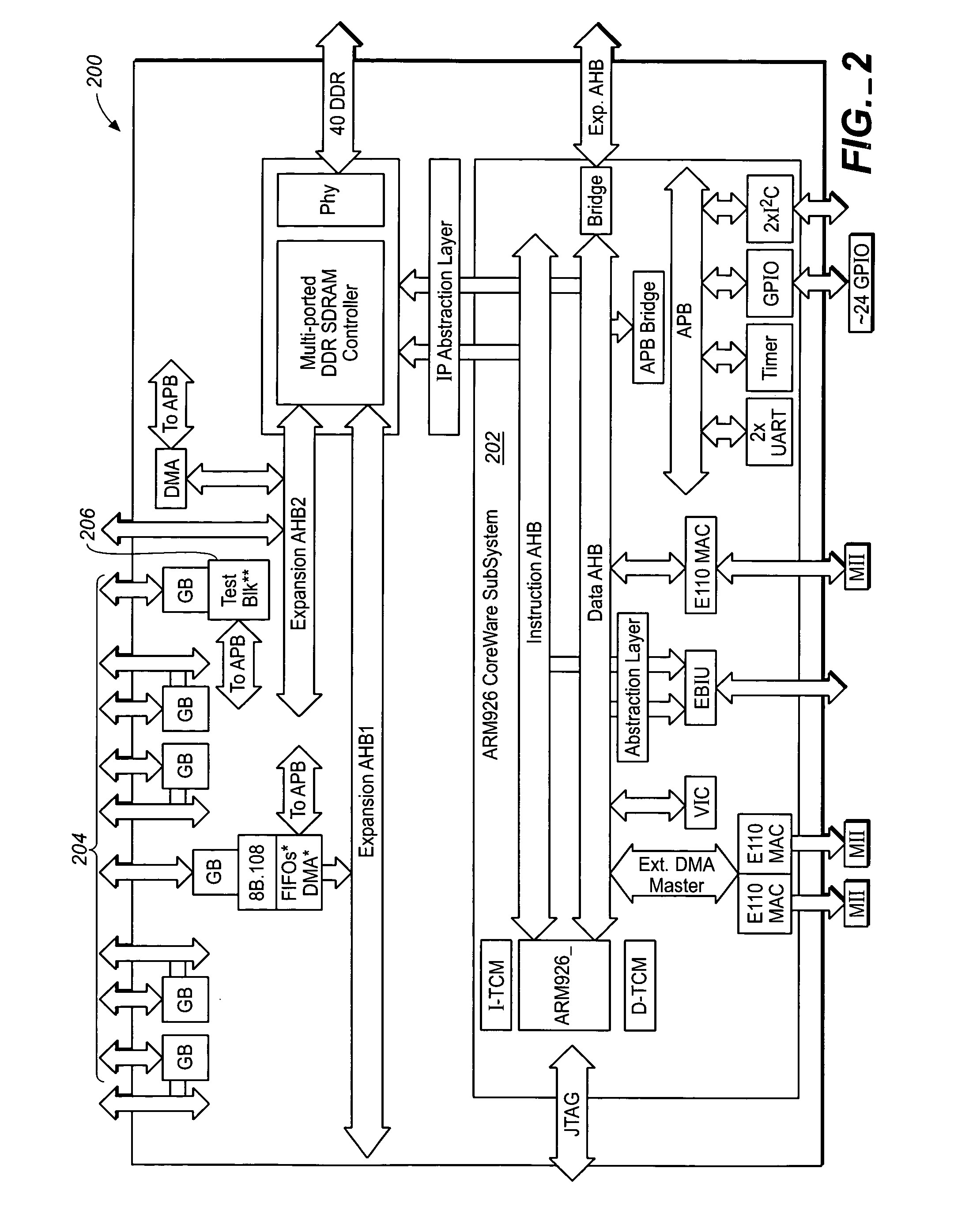

Customizable development and demonstration platform for structured ASICs

ActiveUS20050183042A1Less expenseCAD circuit designSpecial data processing applicationsXAUIFibre Channel

The present invention is directed to a customizable development and demonstration platform for structured ASICs. In an exemplary aspect of the present invention, the present platform may include a structured ASIC which is built on a slice and which may be flexible enough for a number of possible application developments. This flexibility may be achieved by incorporating a programmable processor in the structured ASIC and by defining interfaces and the use of an external FPGA in the present platform. The structured ASIC may include a complete ARM processor subsystem and a plurality of high speed SERDES ports. The processor subsystem may include a bus interface to the external FPGA, allowing custom gate development and test in the FPGA, prior to incorporating it into the customer product. Through the SERDES ports, the test block may be used to show the electrical characteristics of the SERDES IP. In addition, some SERDES ports may be driven from a link layer realized in the FPGA. This may allow the same chip and board to implement SATA (serial advanced technology attachment), GigE, XAUI, XGXS, Fibre Channel, and the like by changing the programming of the FPGA on the board.

Owner:BELL SEMICON LLC

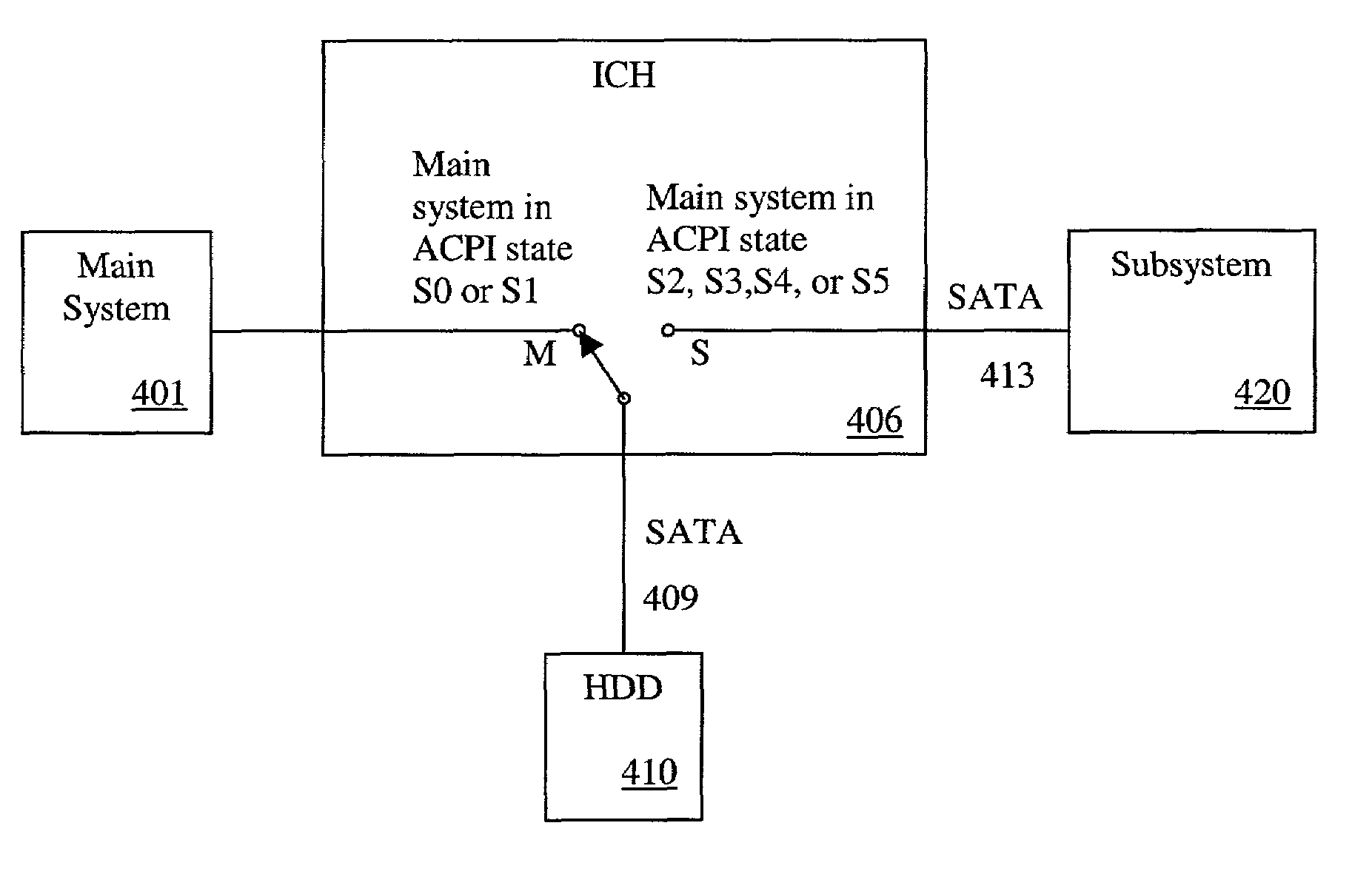

Method and apparatus facilitating direct access to a serial ATA device by an autonomous subsystem

InactiveUS7069456B2Energy efficient ICTInput/output to record carriersOperational systemSerial advanced technology attachment

A method and apparatus for facilitating direct access to a serial Advanced Technology Attachment (ATA) device by an autonomous subsystem in the absence of the main operating system (OS).

Owner:INTEL CORP

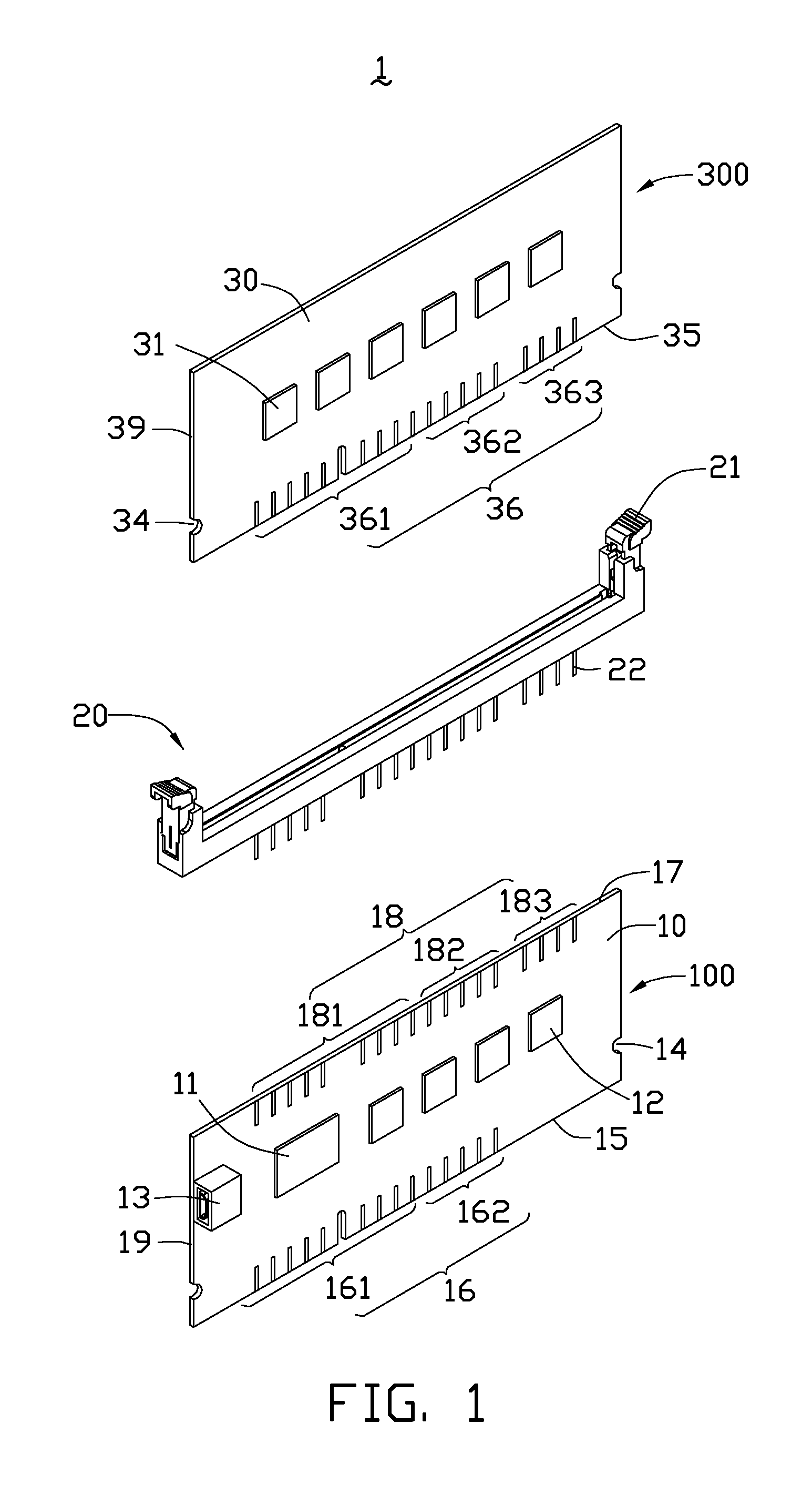

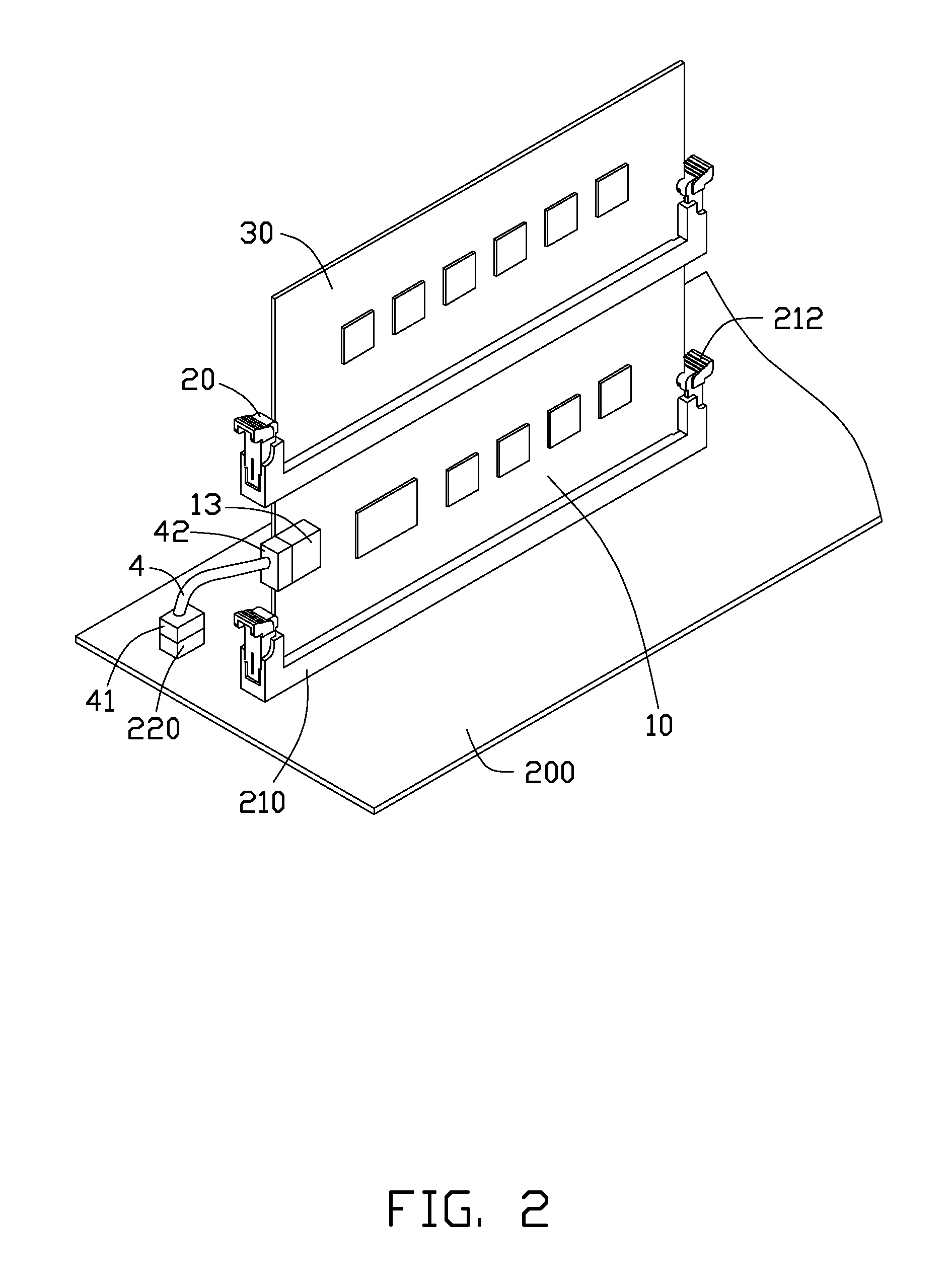

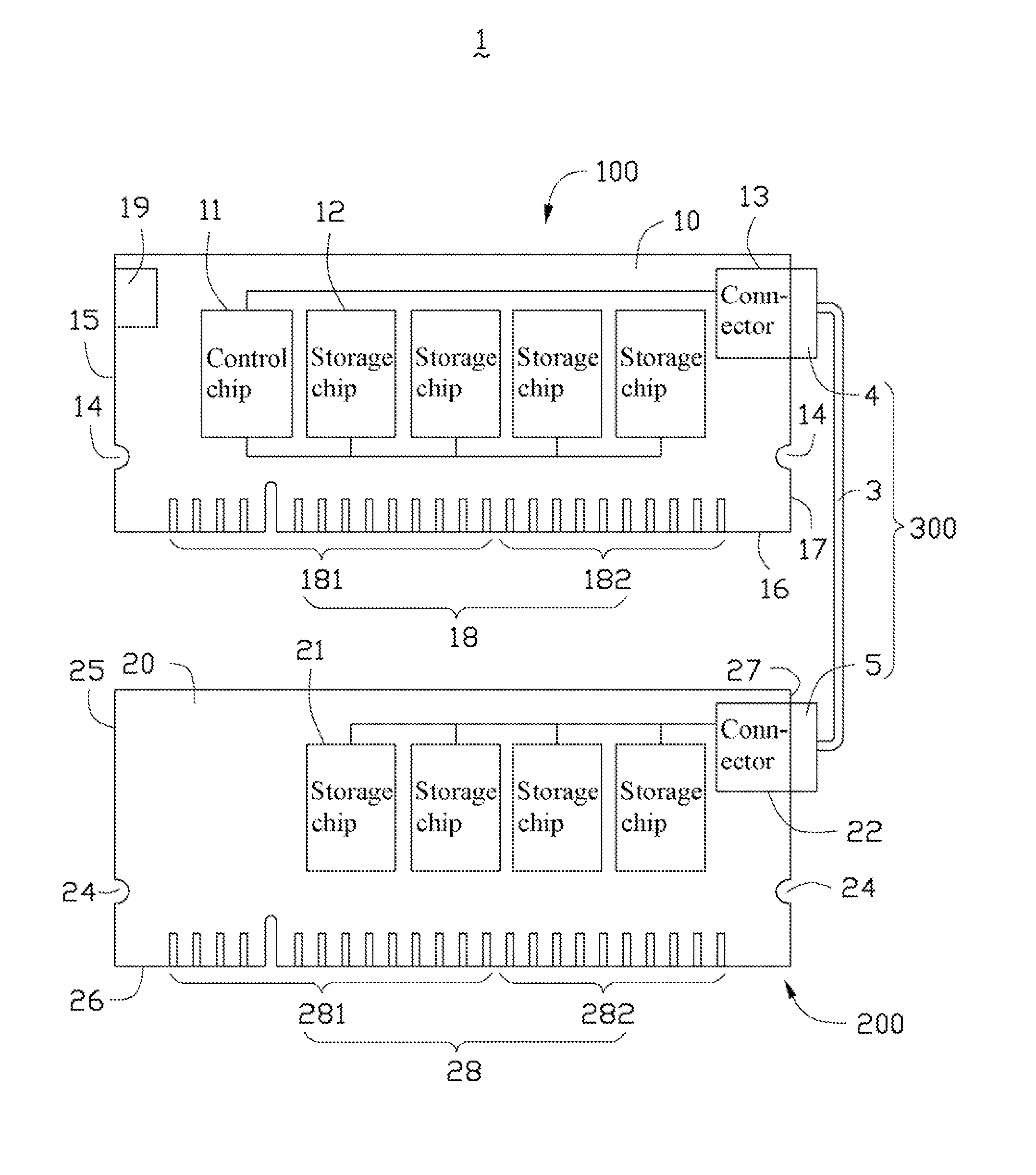

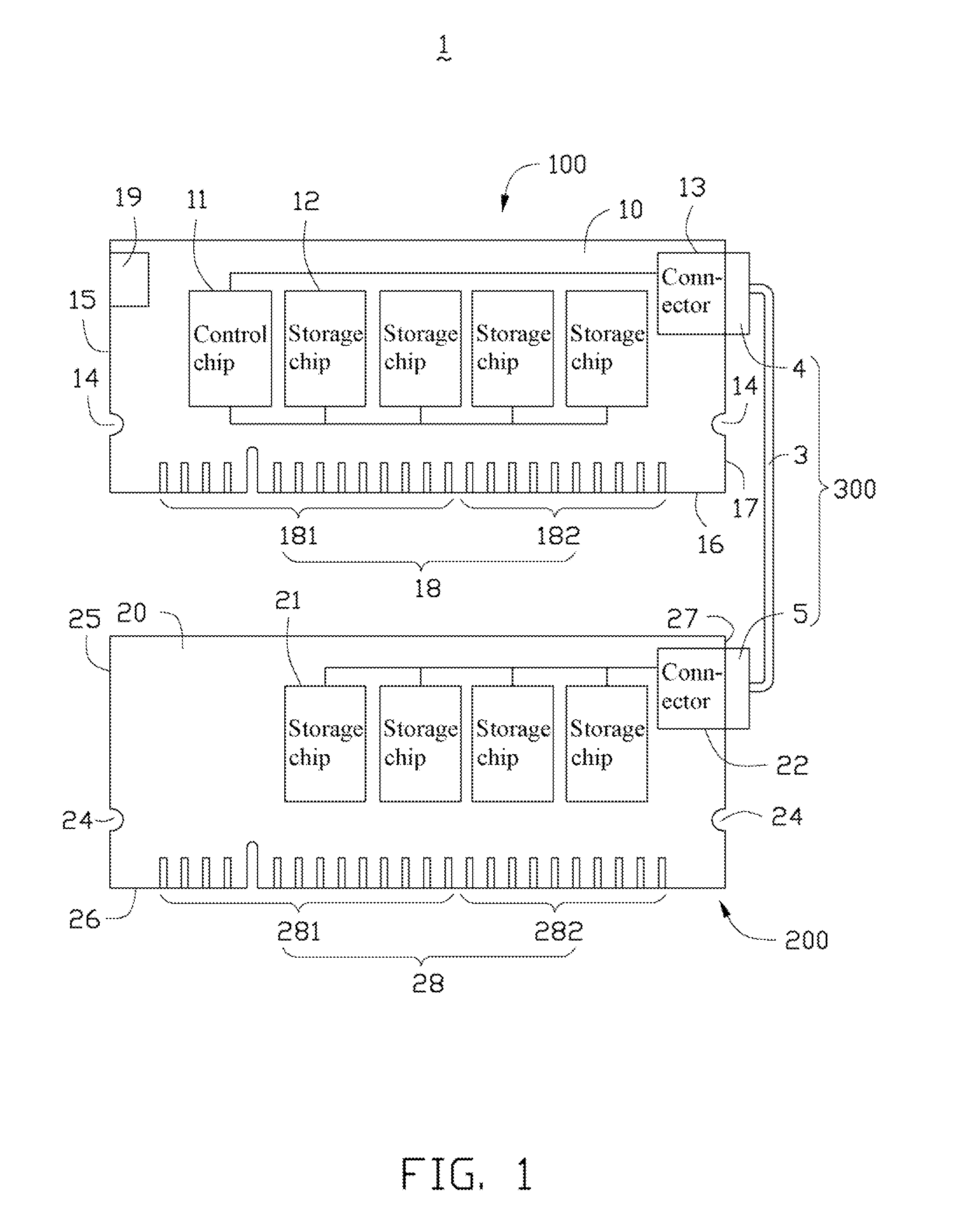

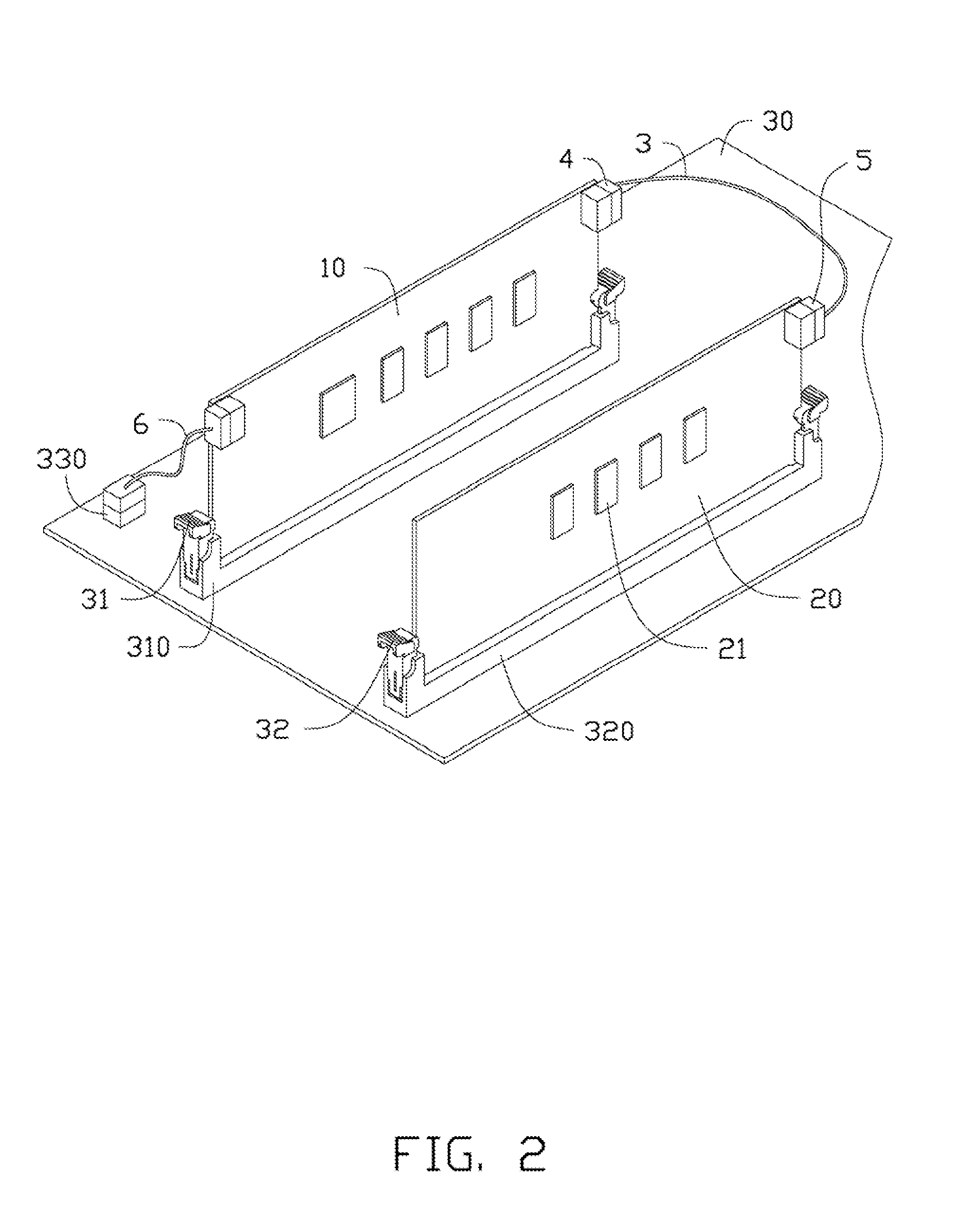

Serial advanced technology attachment dual in-line memory module assembly

A serial advanced technology attachment dual-in-line memory module (SATA DIMM) assembly includes a SATA DIMM module with a first circuit board, an expansion slot, and an expansion card with a second circuit board. A first edge connector is arranged on a bottom edge of the first circuit board and includes first power pins connected to a control chip and first storage chips, and first ground pins. A second edge connector connected to the expansion slot is arranged on a top edge of the first circuit board and includes second power pins connected to the first power pins, second ground pins, and four first signal pins connected to the control chip. A third edge connector engaged in the expansion slot is arranged on a bottom edge of the second circuit board and includes third power pins and four second signal pins connected to the second storage chips, and third ground pins.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Expansion card and motherboard for supporting the expansion card

A motherboard assembly includes a motherboard and an expansion card. The motherboard includes an expansion slot, a storage device interface, a power connector, and a central processing unit (CPU). The expansion slot includes a protrusion, first signal pins connected to the CPU, first power pins connected to the power connector. The expansion card includes a circuit board. A storage unit, a display unit, a power circuit, and a serial advanced technology attachment (SATA) connector connected to the storage unit and the storage device interface of the motherboard are all arranged on the circuit board. A notch is defined in a bottom edge of the circuit board, to receive the protrusion. An edge connector is arranged on a bottom edge of the circuit board and includes second power pins connected to the power circuit, and second signal pins connected to the display unit.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

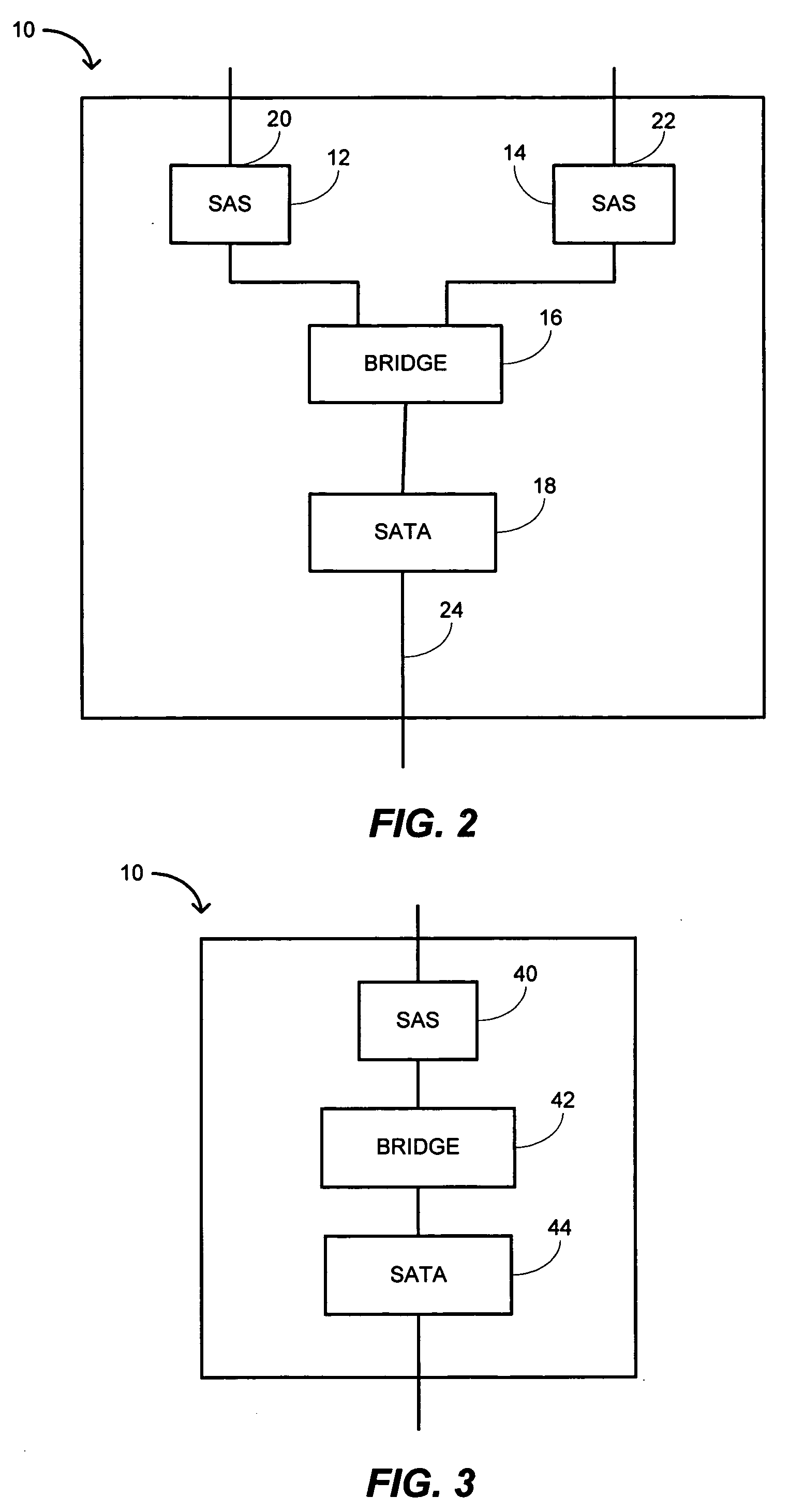

Serial attached small computer system interface (SAS) connection emulation for direct attached serial advanced technology attachemnt (SATA)

InactiveUS20060095630A1Software simulation/interpretation/emulationMemory systemsPublic interfaceSCSI

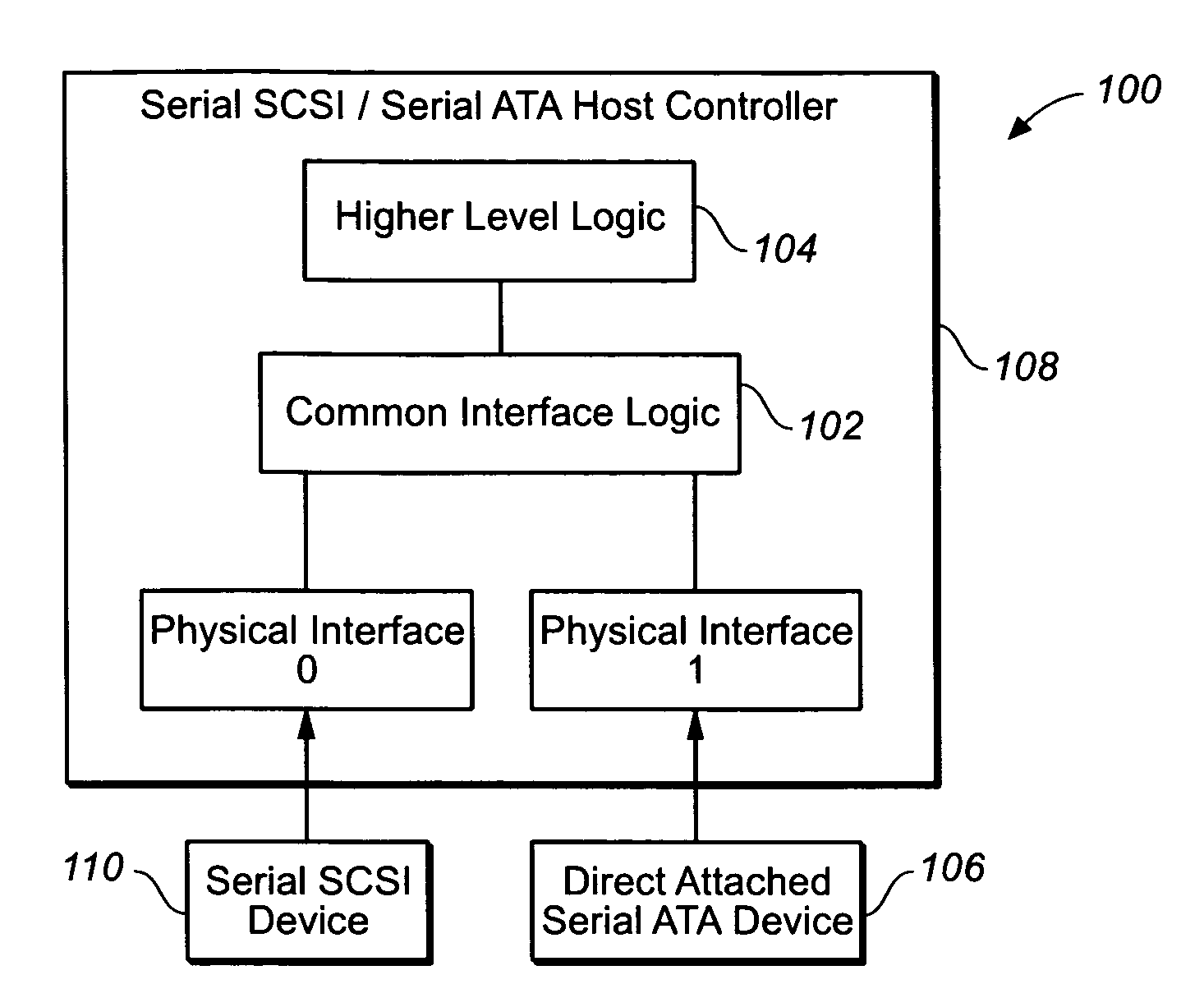

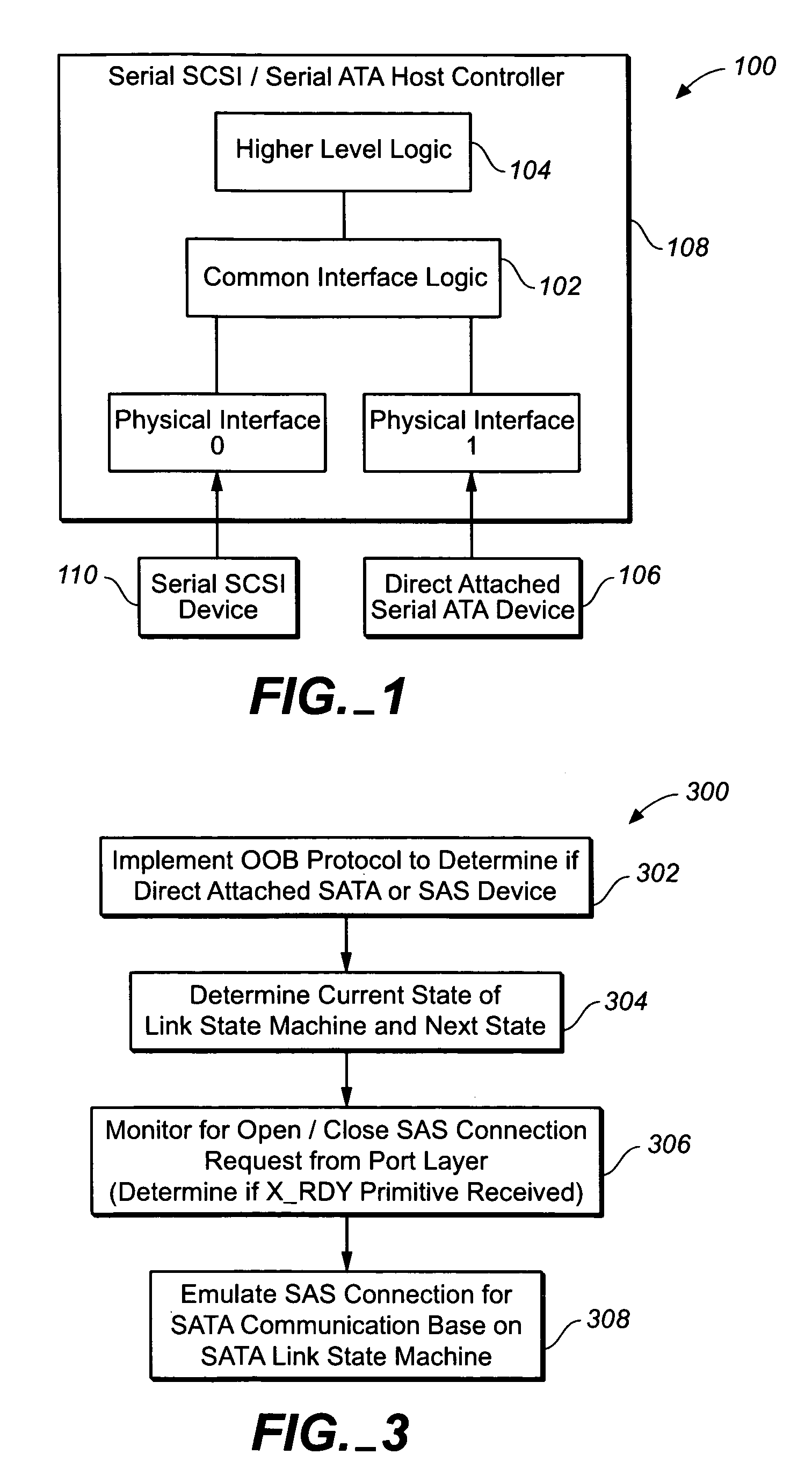

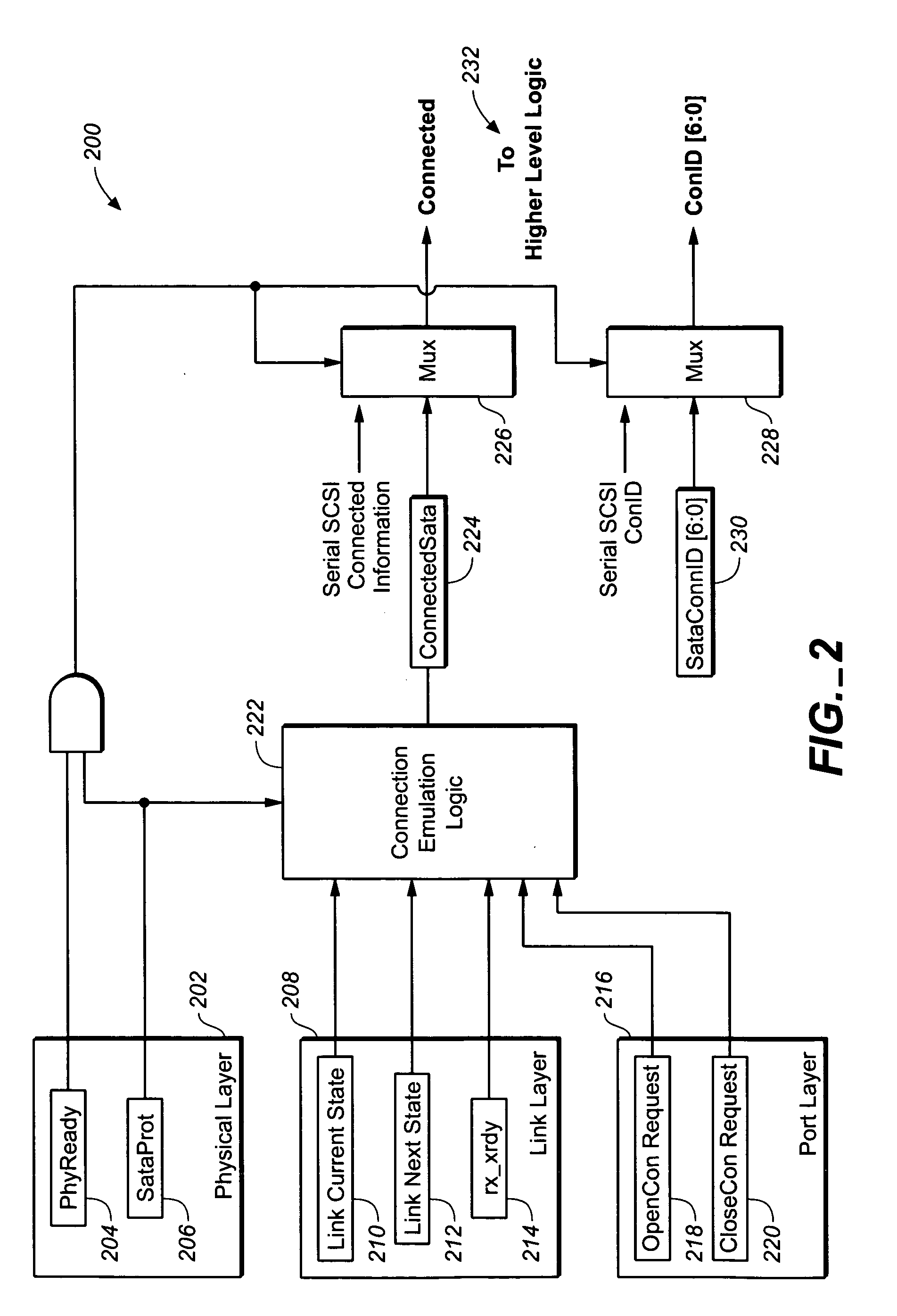

The present invention is directed to a system and method for emulating a serial small computer system interface (SAS) connection for direct attached serial advanced technology attachment (SATA) communication are disclosed. A system in accordance with the present invention includes a host controller. The host controller includes a physical interface for accepting at least one of a SAS connection or a direct attached SATA device. A common interface logic configured to receive SAS communications and SATA communications having a SAS emulated connection is included in the host controller. An emulation logic is communicatively coupled to the common interface logic. The emulation logic being configured to determine a value of a ConnectedSata signal based on the state of a SATA link state machine.

Owner:AVAGO TECH INT SALES PTE LTD

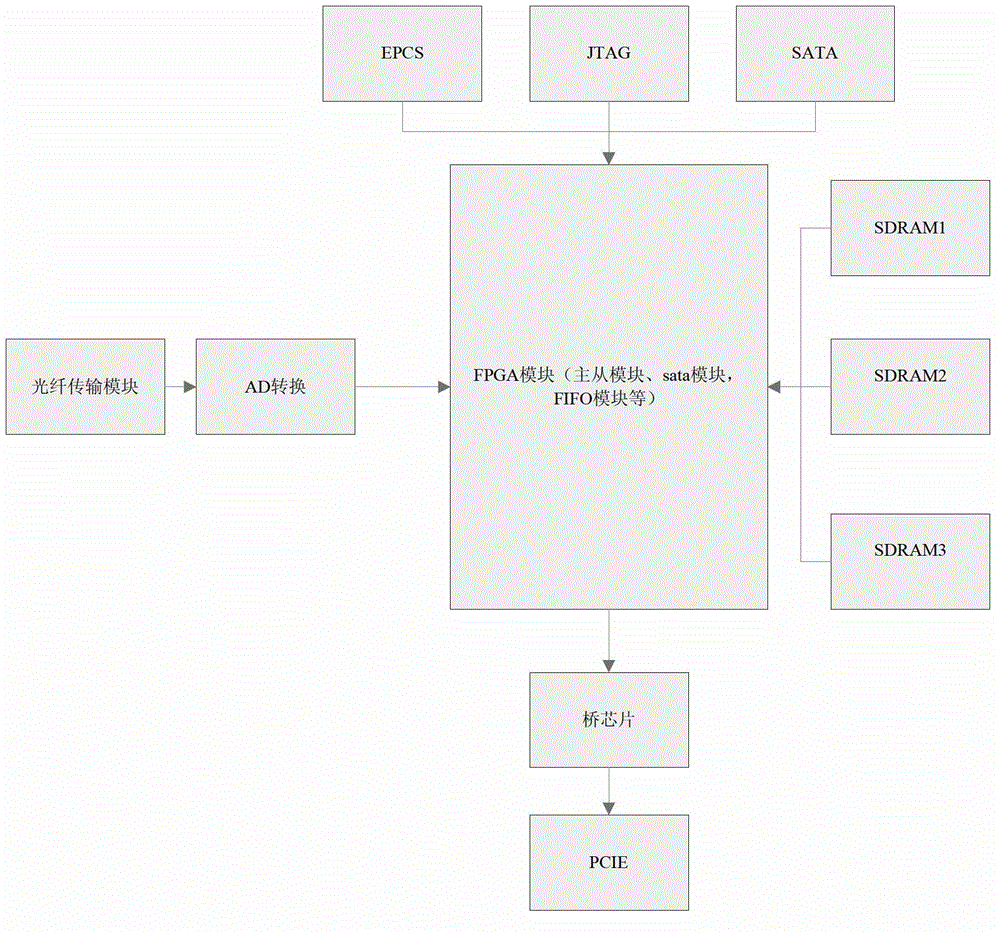

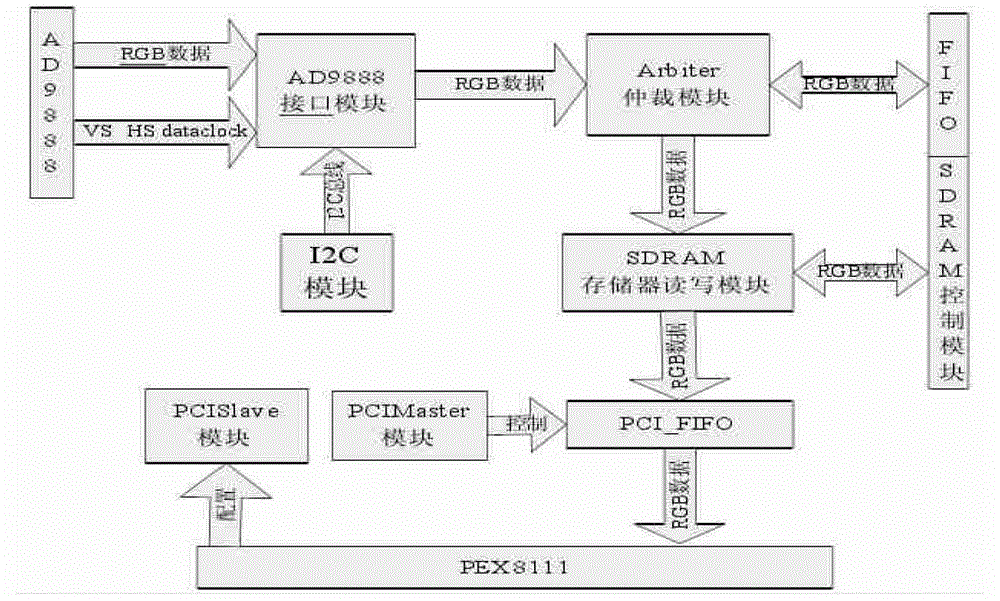

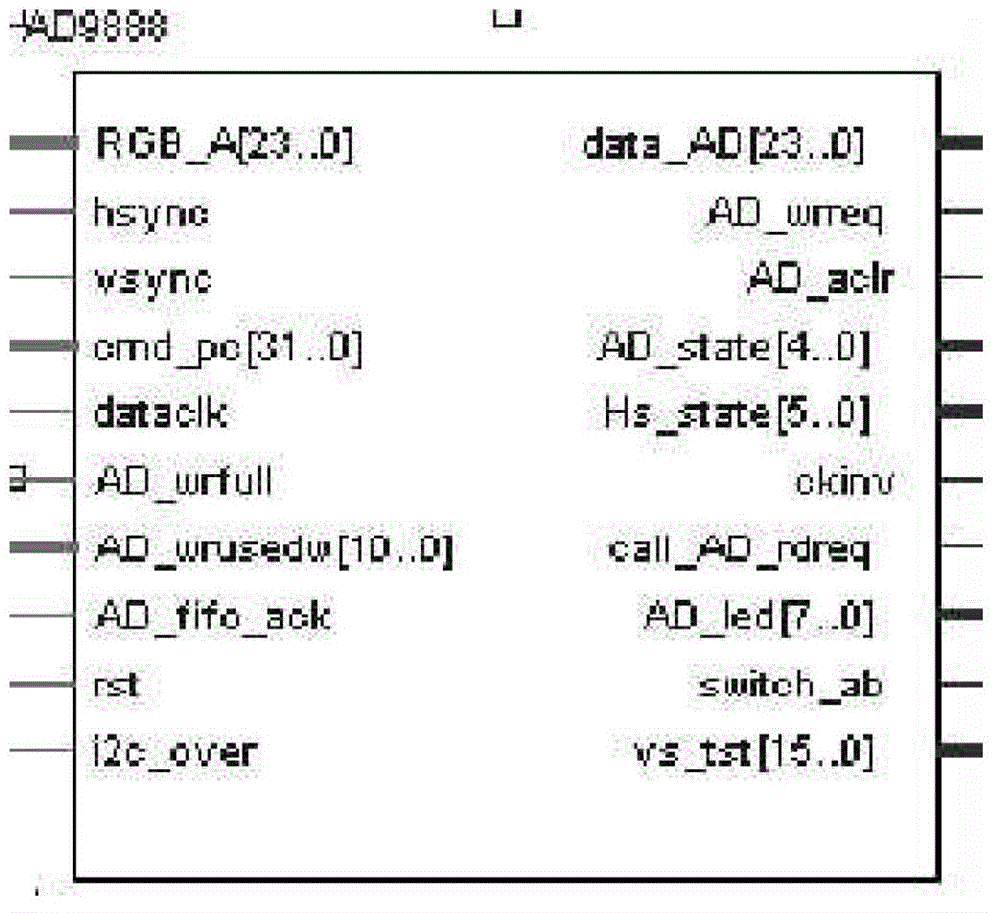

High-speed image acquisition memory card based on PCI-E (Peripheral Component Interconnect-Express)

InactiveCN102945291AMeet different needsReduced pin countData acquisition and loggingControl systemSynchronous dynamic random-access memory

The invention discloses a high-speed image acquisition memory card based on PCI-E (Peripheral Component Interconnect-Express), which comprises an optical fiber transmission module, an A / D conversion module, an FPGA (Field-Programmable Gate Array) logic module, an EPCS (Electronic Propulsion Control System) logic program memory module, a JTAG (Joint Test Action Group) program download interface, an SATA (Serial Advanced Technology Attachment) hard disk data memory module, an SDRAM (Synchronous Dynamic Random Access Memory) module, a bridge chip and a PCI-E interface, wherein the optical fiber transmission module is connected with the A / D conversion module; the PCI-E interface is connected with the bridge chip; the A / D conversion module, the EPCS logic program memory module, the JTAG program download interface, the SATA hard disk data memory module, the SDRAM module and the bridge chip are connected with the FPGA logic module respectively. Therefore, high-speed image acquisition can be realized fast.

Owner:NANJING UNIV OF SCI & TECH

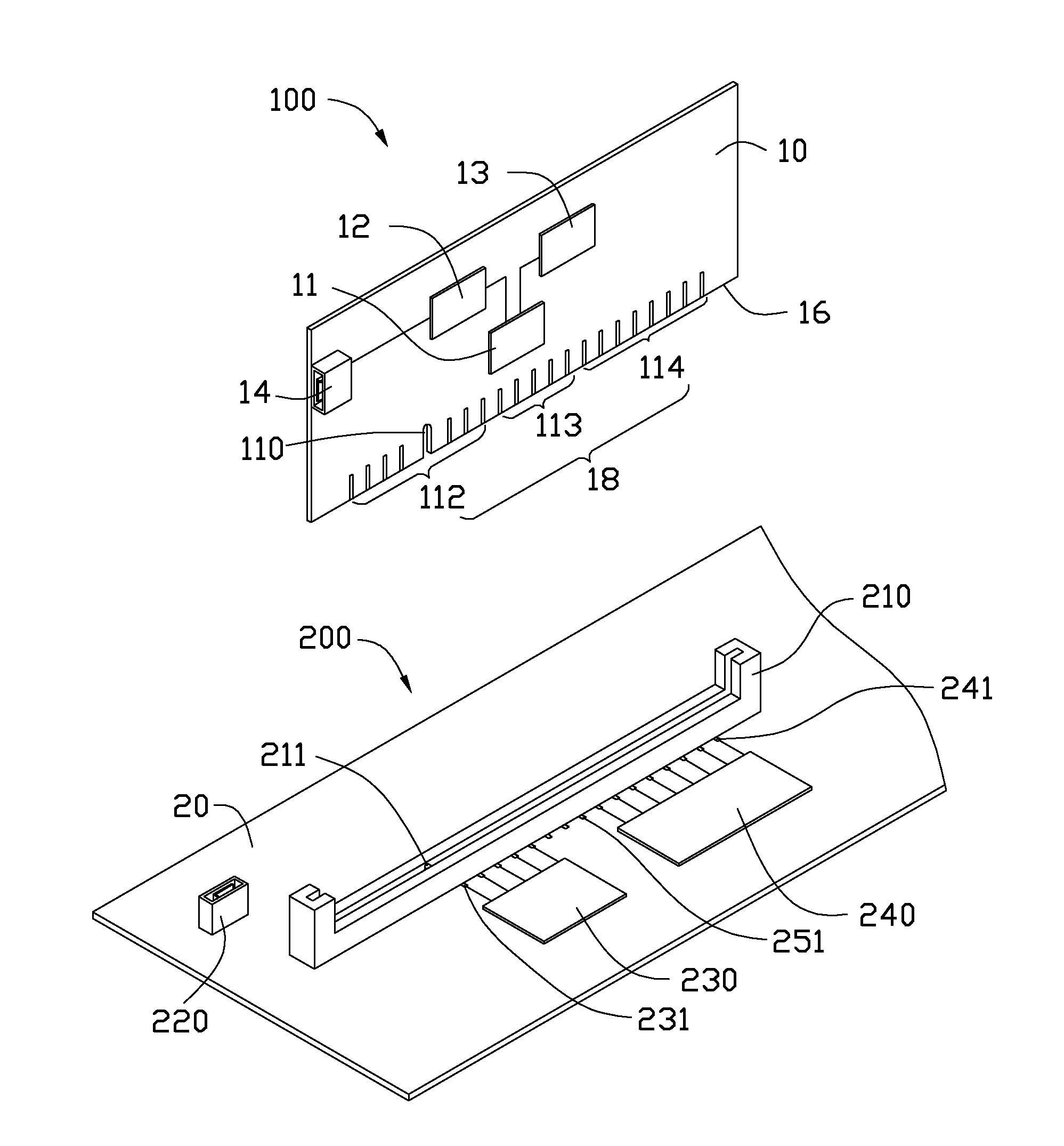

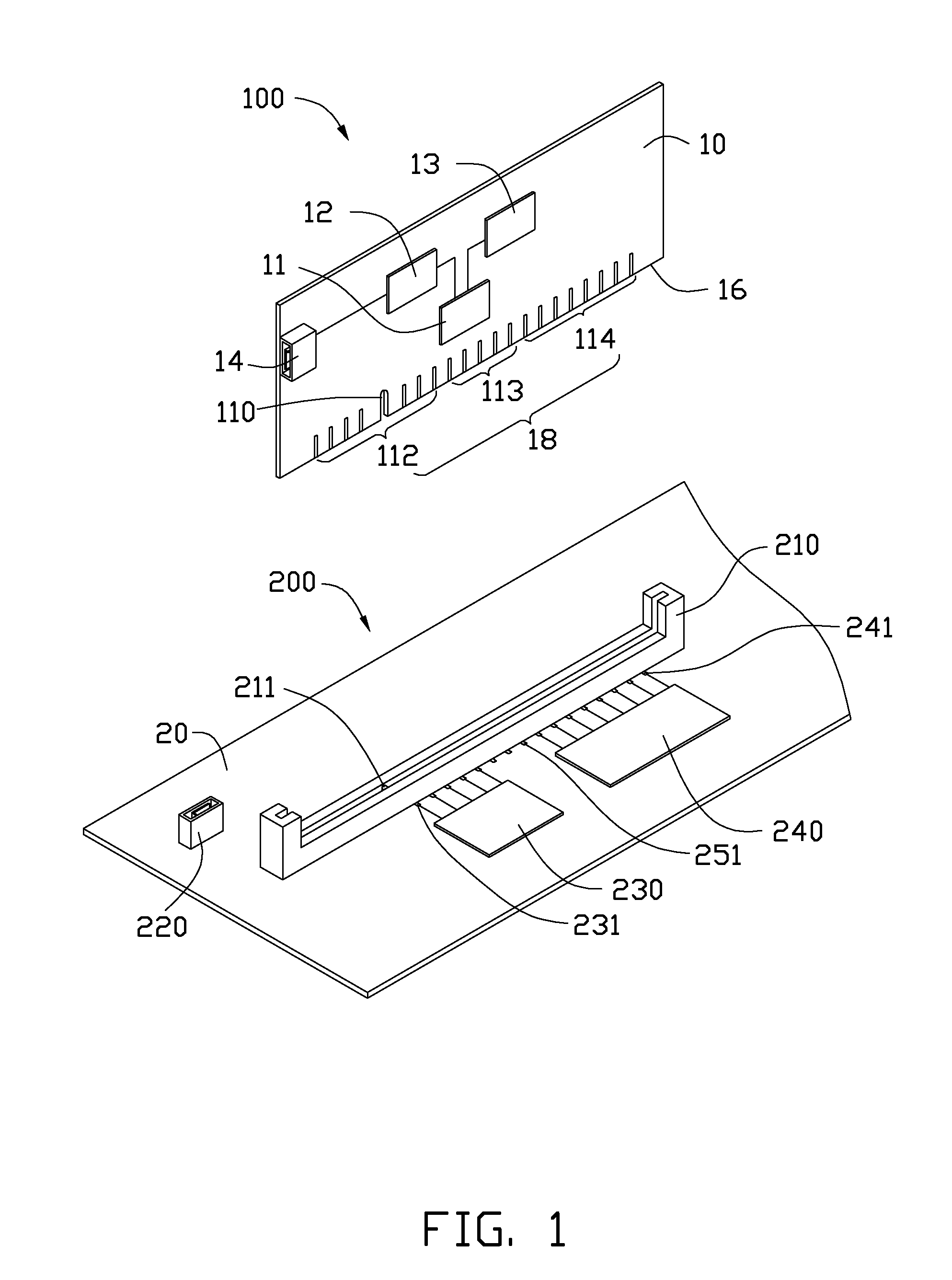

Expansion apparatus with serial advanced technology attachment dual in-line memory module

InactiveUS20130070412A1Digital data processing detailsElectrical connection printed elementsExpansion cardEngineering

An expansion apparatus includes a serial advanced technology attachment dual-in-line memory module (SATA DIMM) with a first circuit board, an expansion card with a second circuit board, and a cable member. A first edge connector is set on a bottom edge of the first circuit board and includes a number of first power pins connected to a control chip, a number of first storage chips, and a first connector, and a number of first ground pins. A second edge connector is set on a bottom edge of the second circuit board and includes a number of second power pins connected to a number of second storage chips and a second connector, and a number of second ground pins. The cable member includes a cable, a third connector connected to the first connector, and a fourth connector connected to the second connector.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

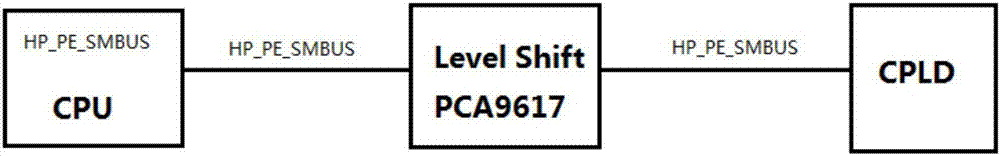

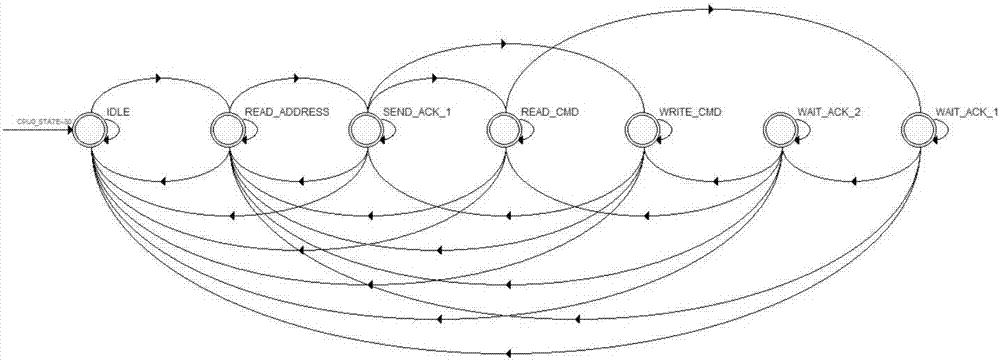

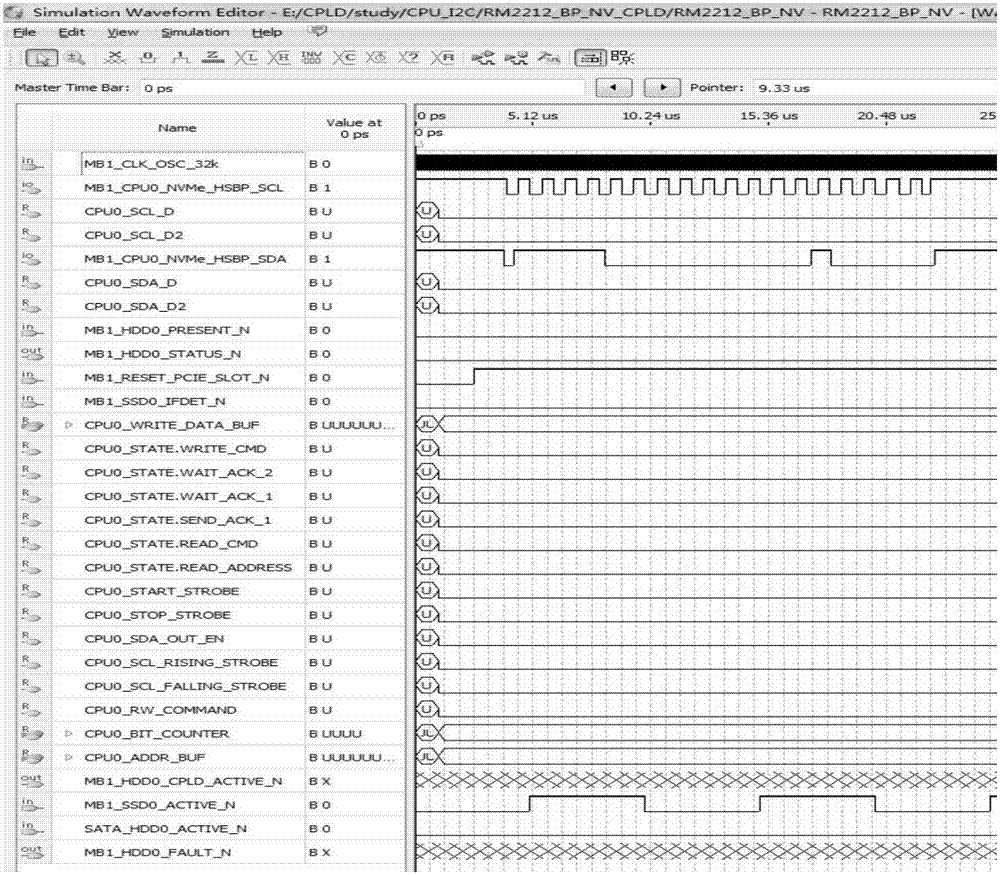

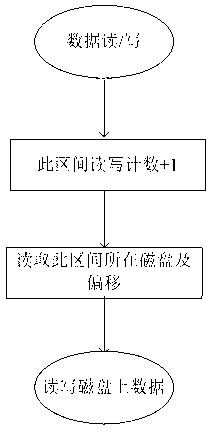

I2C (Inter-Integrated Circuit) interface-based method for realizing NVME SSD (Non-Volatile Memory Express Solid State Disk) lighting through CPLD (Complex Programmable Logic Device)

InactiveCN107145430AEasy maintenanceLow costHardware monitoringSpecific costComplex programmable logic device

The invention belongs to the field of server design and particularly discloses an I2C (Inter-Integrated Circuit) interface-based method for realizing the NVME SSD (Non-Volatile Memory Express Solid State Disk) lighting through a CPLD (Complex Programmable Logic Device). According to the I2C interface-based method for realizing the NVME SSD lighting through the CPLD, an I2C of a CPU (Central Processing Unit) is connected to the CPLD to decode the information sent by the CPU and carry out an indicator lamp function on the working condition of NVME SSD; the working condition of the NVME SSD can be effectively and intuitively seen like an ordinary SATA (Serial Advanced Technology Attachment) or SAS (Serial Attached SCSI (Small Computer System Interface)) hard disk, the working condition of the NVME SSD can be intuitively judged by seeing a condition indicating lamp on a user interface through naked eyes, which is very intuitive, convenient and fast; moreover, by adopting the scheme of the CPLD, the follow-up maintenance is easier, and if an additional function needs to be increased, only CPLD FW(Firm Ware) needs to be changed; and the method has the advantages of being low in specific cost, strong in practicality, convenient to maintain and flexible to debug.

Owner:SHENZHEN TONGTAIYI INFORMATION TECH CO LTD

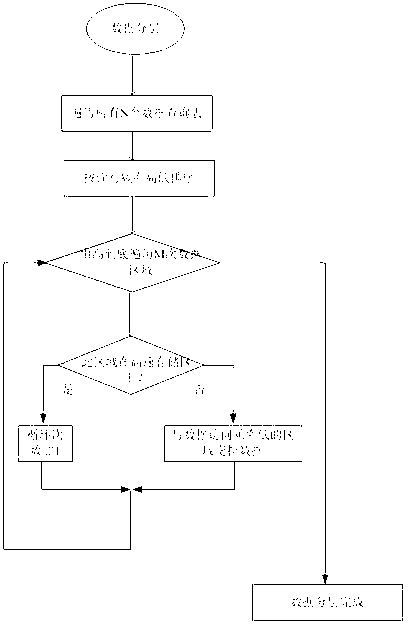

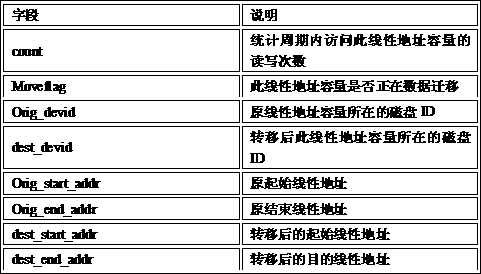

Method for achieving layered storage and copy of data of storage system

InactiveCN103106050AAchieve free movementReduce consumptionInput/output to record carriersResource consumptionData access

The invention provides a method for achieving layered storage and copy of data of a storage system. The method achieves that the storage system can automatically copy the data from a high-speed high-cost storage to a low-speed low-cost storage; or when required, the data are automatically copied from the low-speed low-cost storage to the high-speed high-cost storage. According to the method, the data are layered according to access frequency degree, data which are accessed frequently are stored in a high-speed high-cost storage medium containing a solid state disk, and data which dot not be accessed frequently are stored in a high-speed high-cost storage medium containing a high-capacity serial advanced technology attachment (SATA) state disk, so that use rate and disk array performance of a high-speed storage device are effectively improved, and total ownership cost of the disk is reduced. The method for achieving the layered storage and copy of the data of the storage system is effective and simple in design, and capable of achieving the fact that the data flow freely on different storage mediums according to data access frequency under the circumstance that system resource consumption is reduced.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

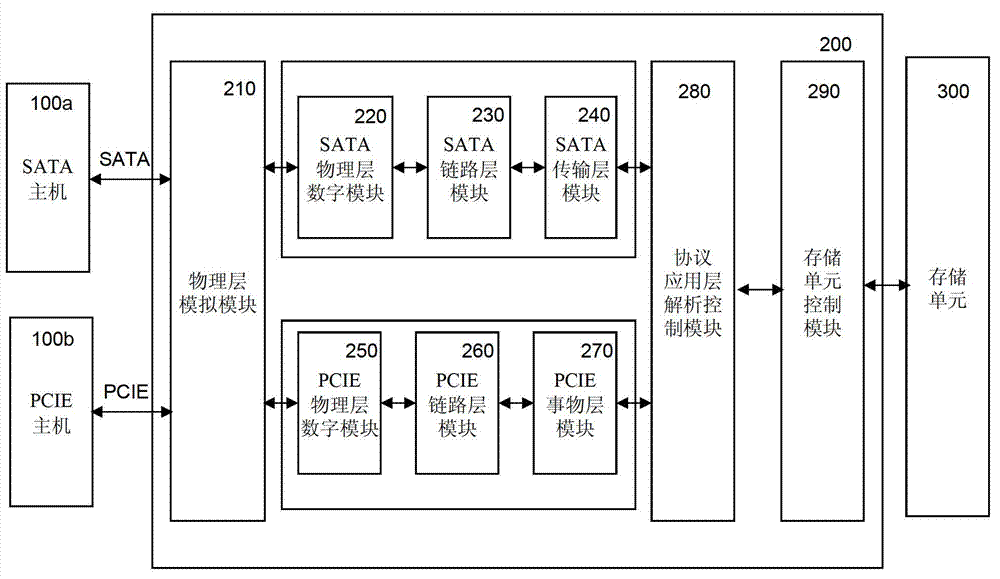

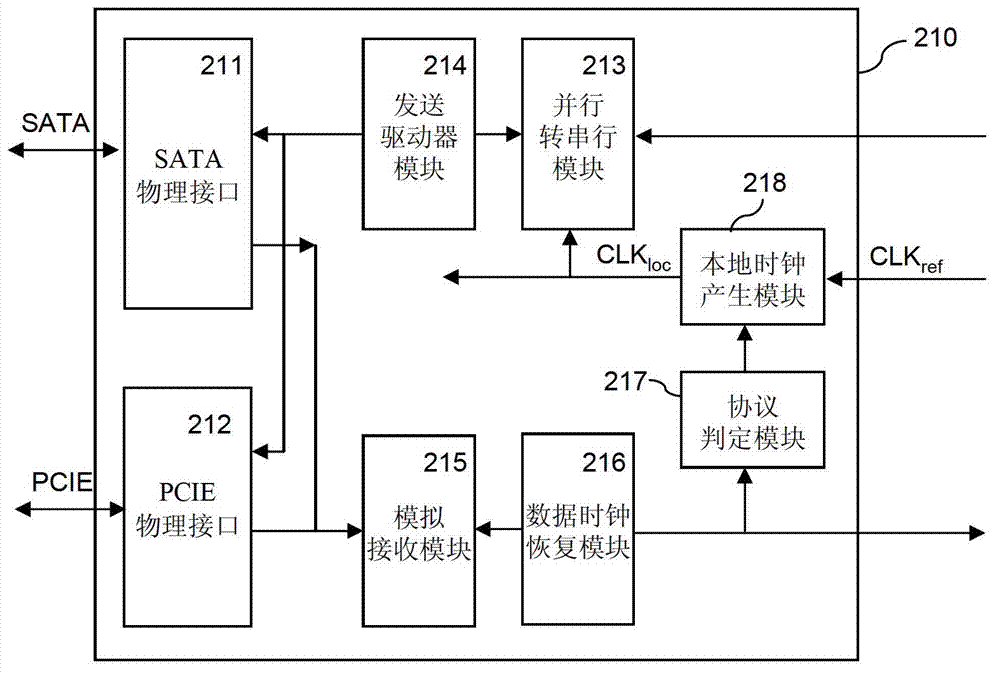

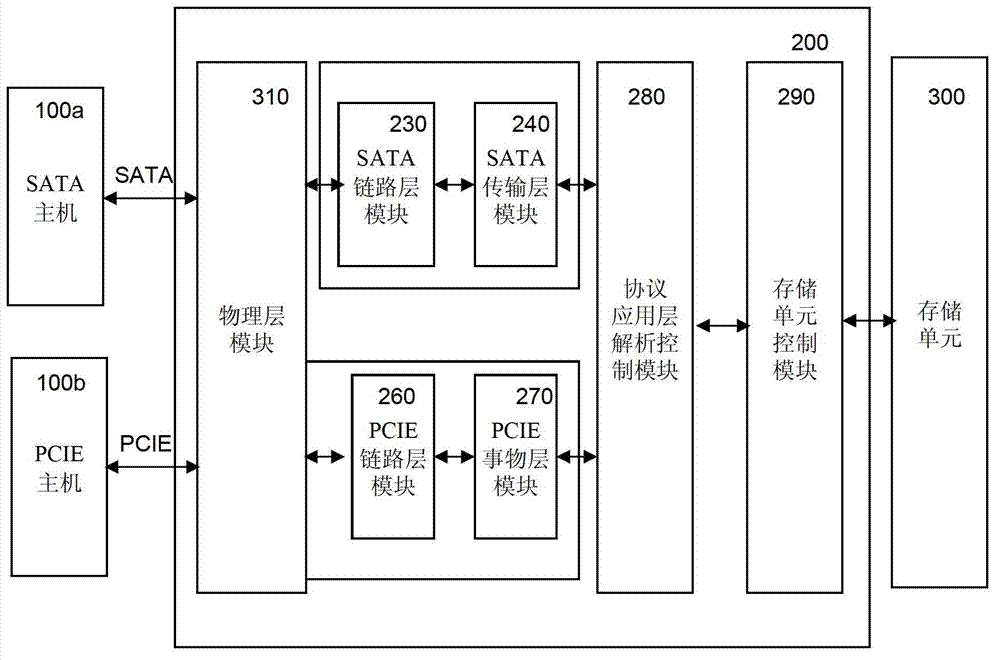

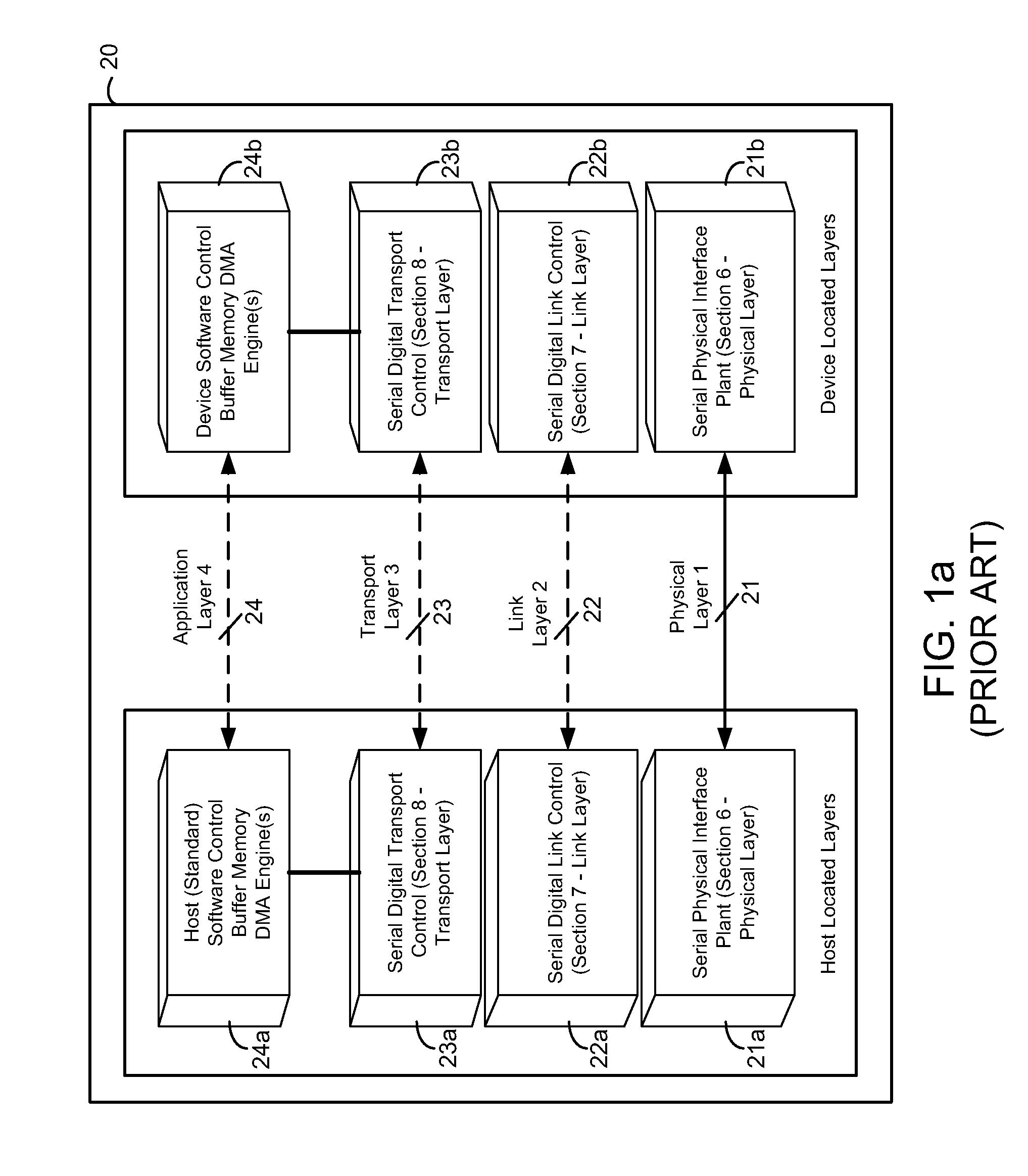

Dual-interface memory controller and system thereof

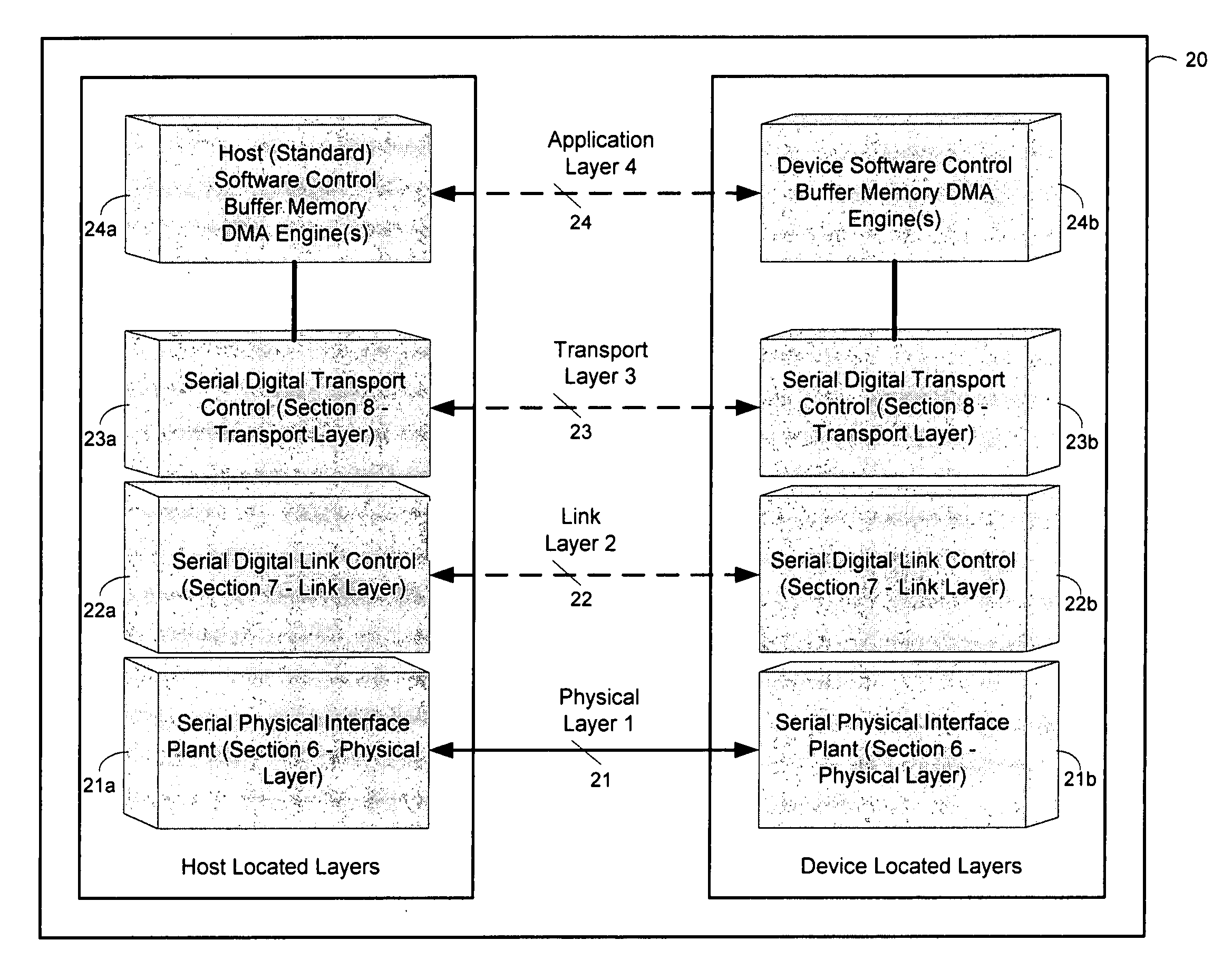

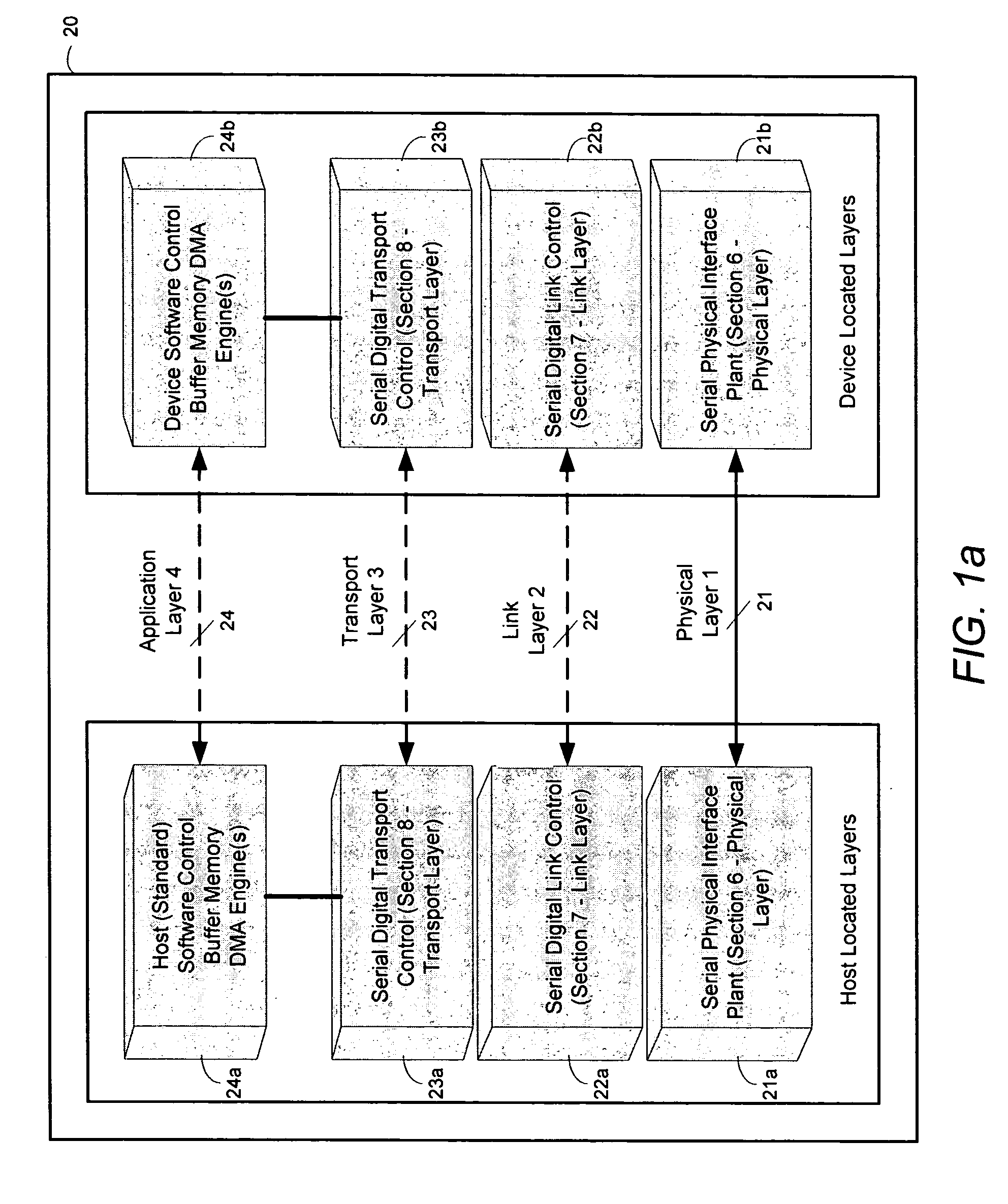

The invention discloses a dual-interface memory controller and a system thereof. The dual-interface memory controller comprises a physical layer analog module, a serial advanced technology attachment (SATA) physical layer digital module, an SATA link layer module, an SATA transport layer module, a peripheral component interface express (PCIE) physical layer digital module, a PCIE link layer module, a PCIE business layer module and a protocol layer analysis control module. The physical layer analog module comprises an SATA physical interface butting with an SATA host and a PCIE physical interface butting with a PCIE host, the protocol application layer analysis control module interacts with the SATA transport layer module or the PCIE business layer module according to an SATA protocol or a PCIE protocol, therefore the memory controller can support two interfaces, and can not only support a host of any interface, but also enable structures of two interfaces to be optimized.

Owner:SAGE MICROELECTRONICS CORP

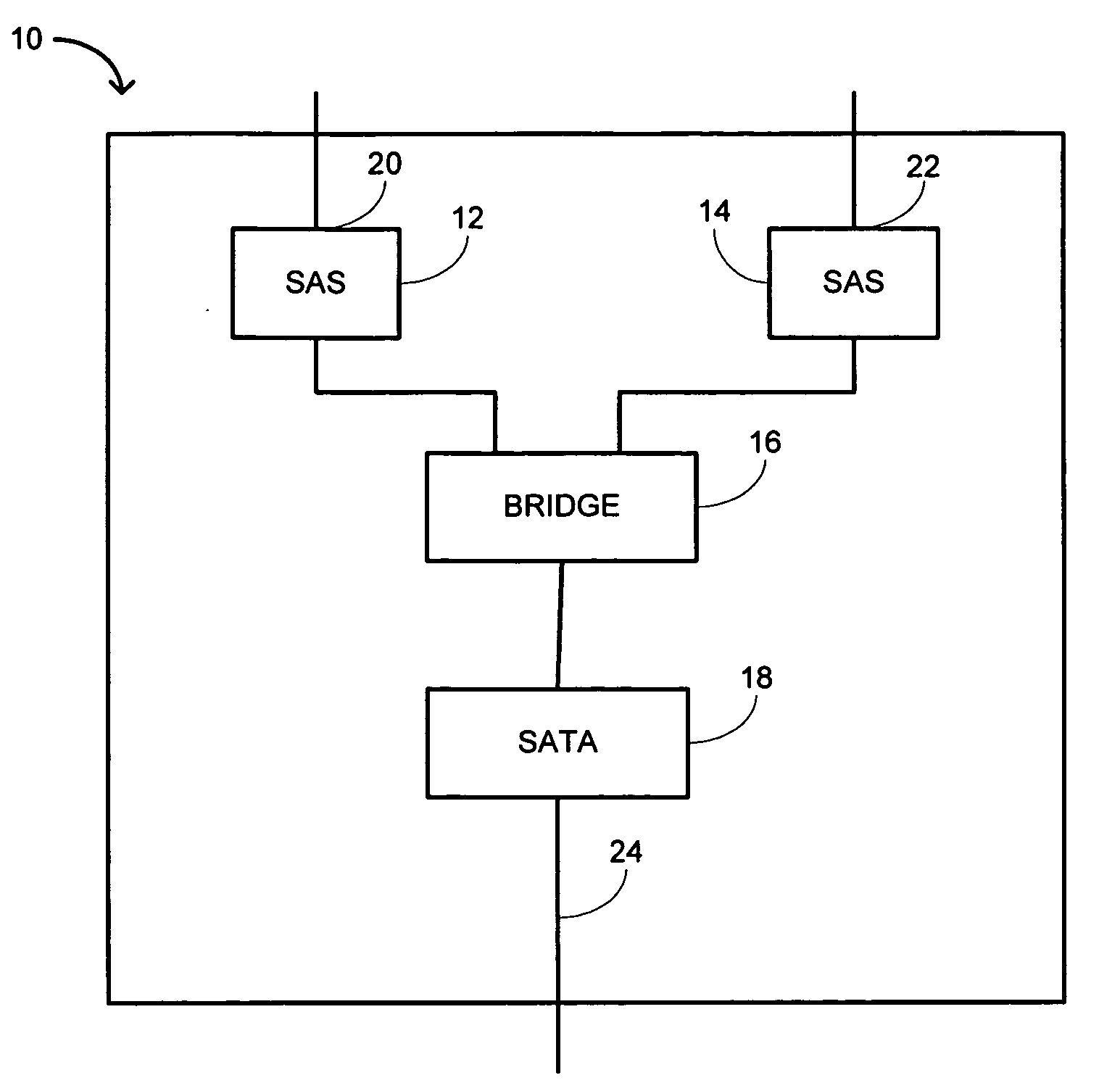

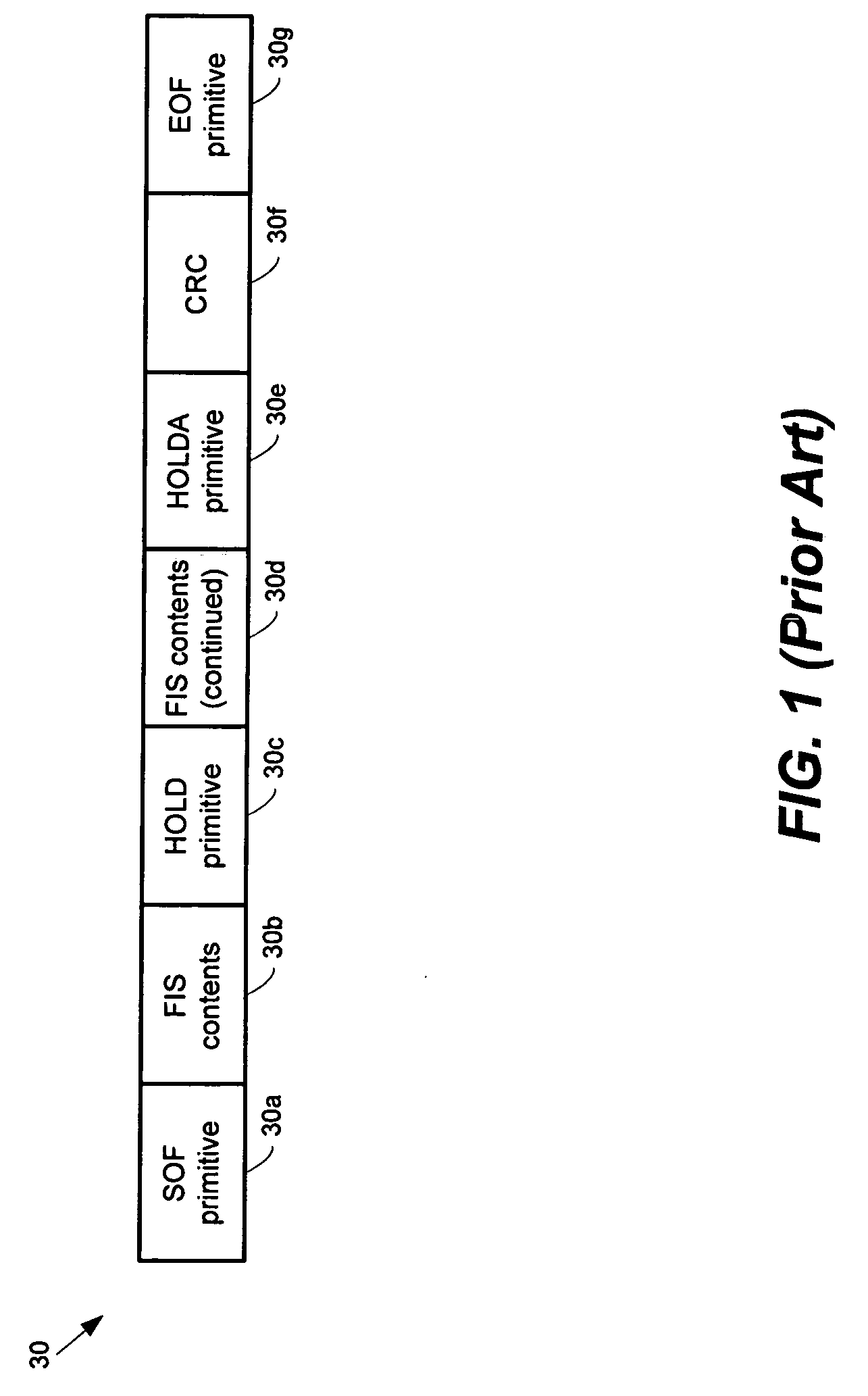

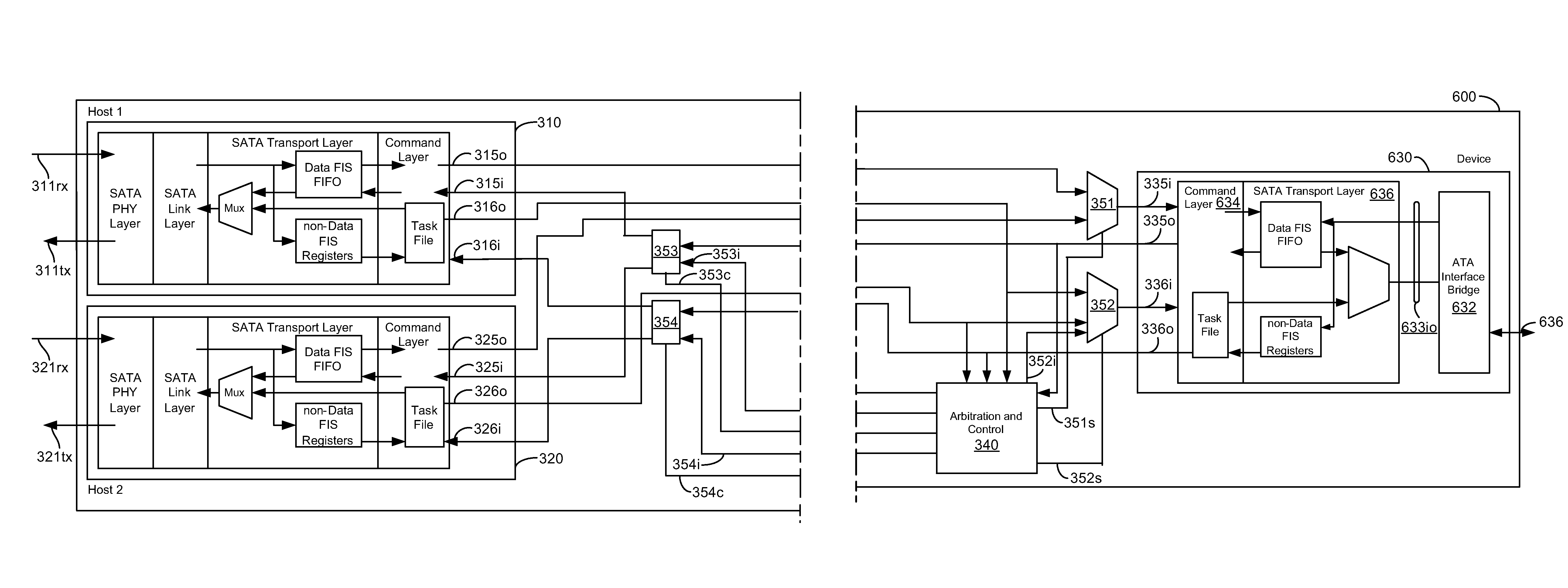

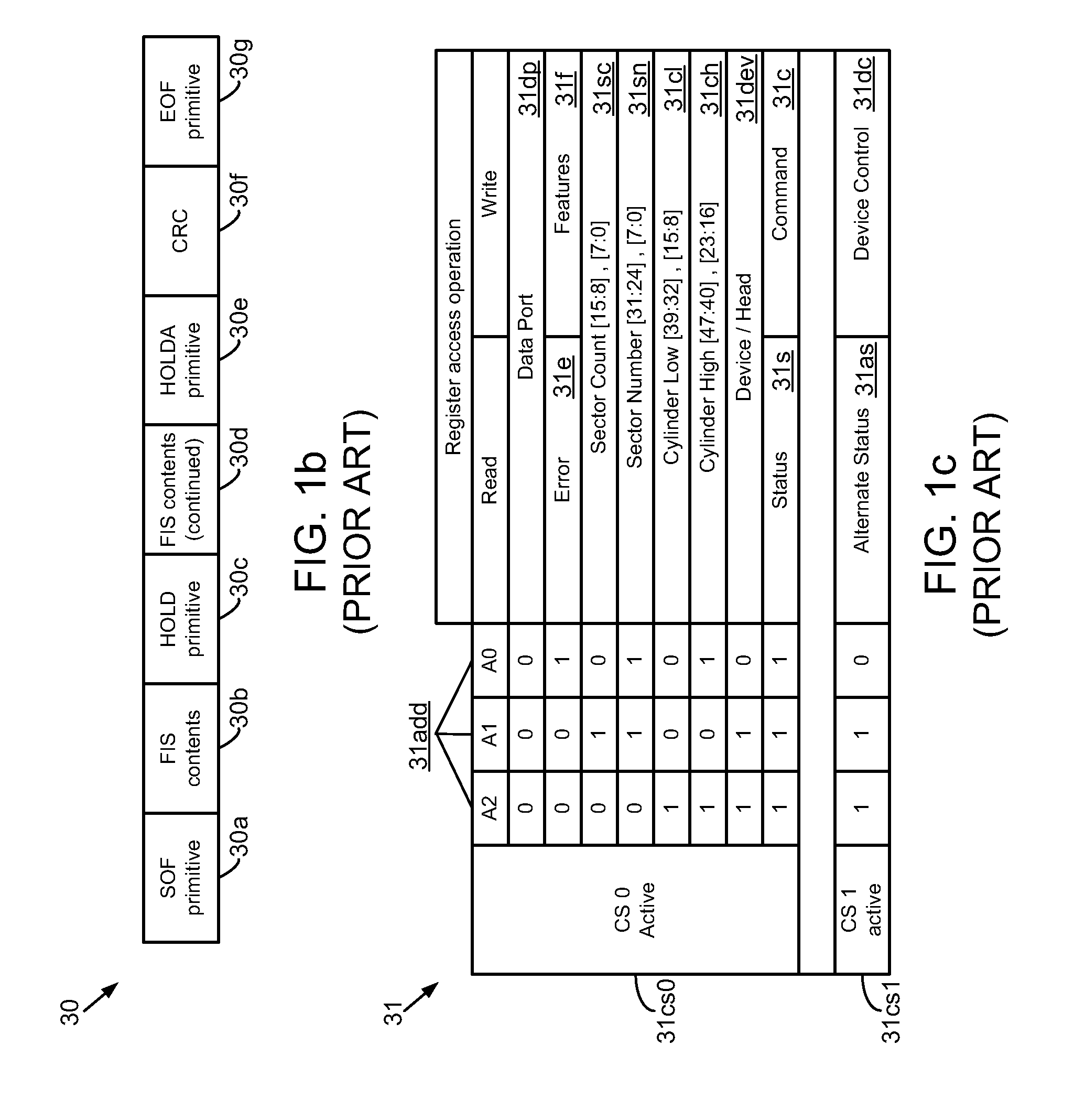

Serial advanced technology attachment (SATA) and serial attached small computer system interface (SCSI) (SAS) bridging

An embodiment of the present invention is disclosed to include a communication system configured to conform to SATA standard and causing communication between one or more hosts and a SATA device. The communication system, in accordance with one embodiment of the invention includes a multi-port bridge device having a command status manager (CSM) responsive to commands and status from one or more hosts and a data manager (DM) responsive to data from one or more hosts for buffering data substantially separately from that of commands and status.

Owner:AVAGO TECH INT SALES PTE LTD

Expansion apparatus for serial advanced technology attachment dual in-line memory module and motherboard for supporting the expansion apparatus

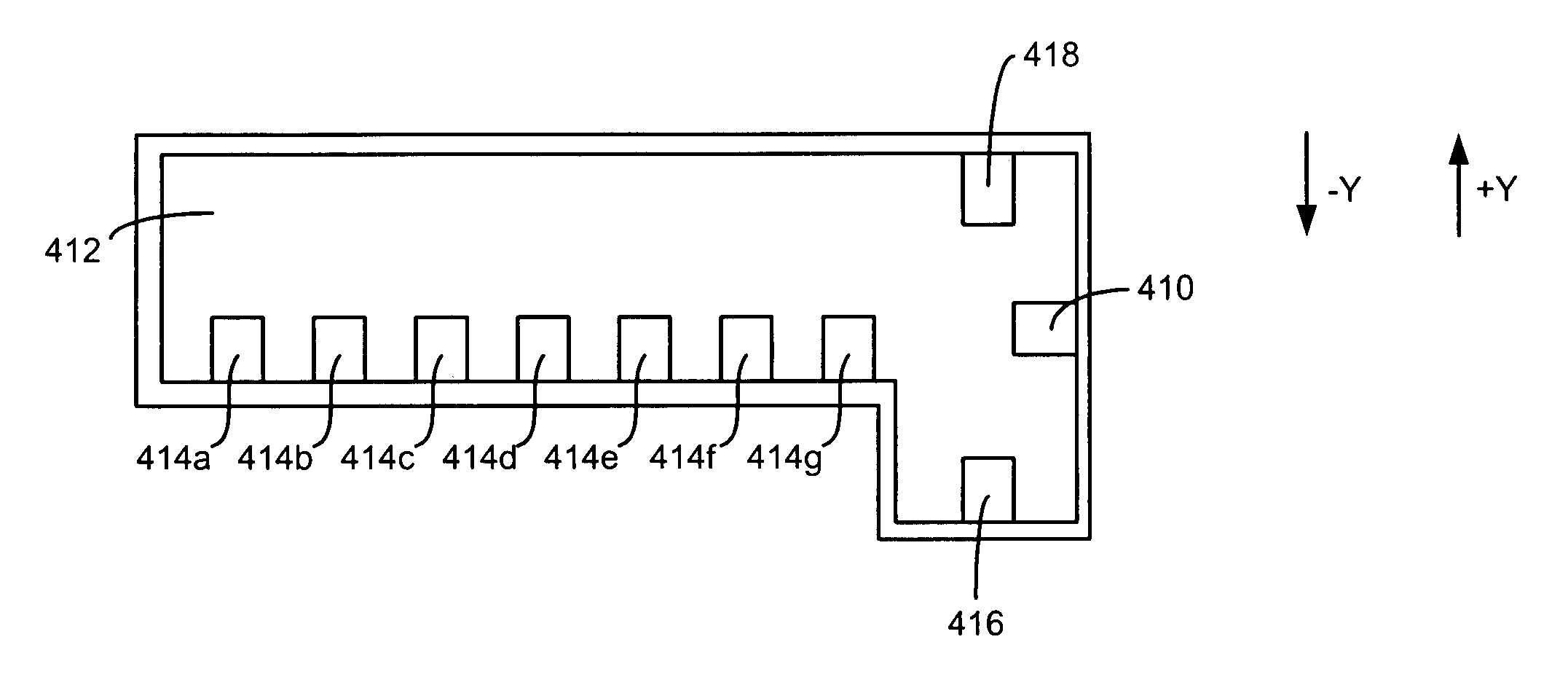

InactiveUS20130038999A1Increase storage capacityControl quantityCoupling device connectionsDigital data processing detailsSerial advanced technology attachmentMemory module

A motherboard assembly includes a motherboard and an expansion apparatus. The motherboard includes a first expansion slot. An edge connector is set on a bottom side of the expansion apparatus to be detachably engaged in the first expansion slot. A number of SATA interfaces and a number of second expansion slots are arranged on the expansion apparatus, and are connected to signal pins and power pins of the edge connector.

Owner:WARECONN TECH SERVICE (TIANJIN) CO LTD

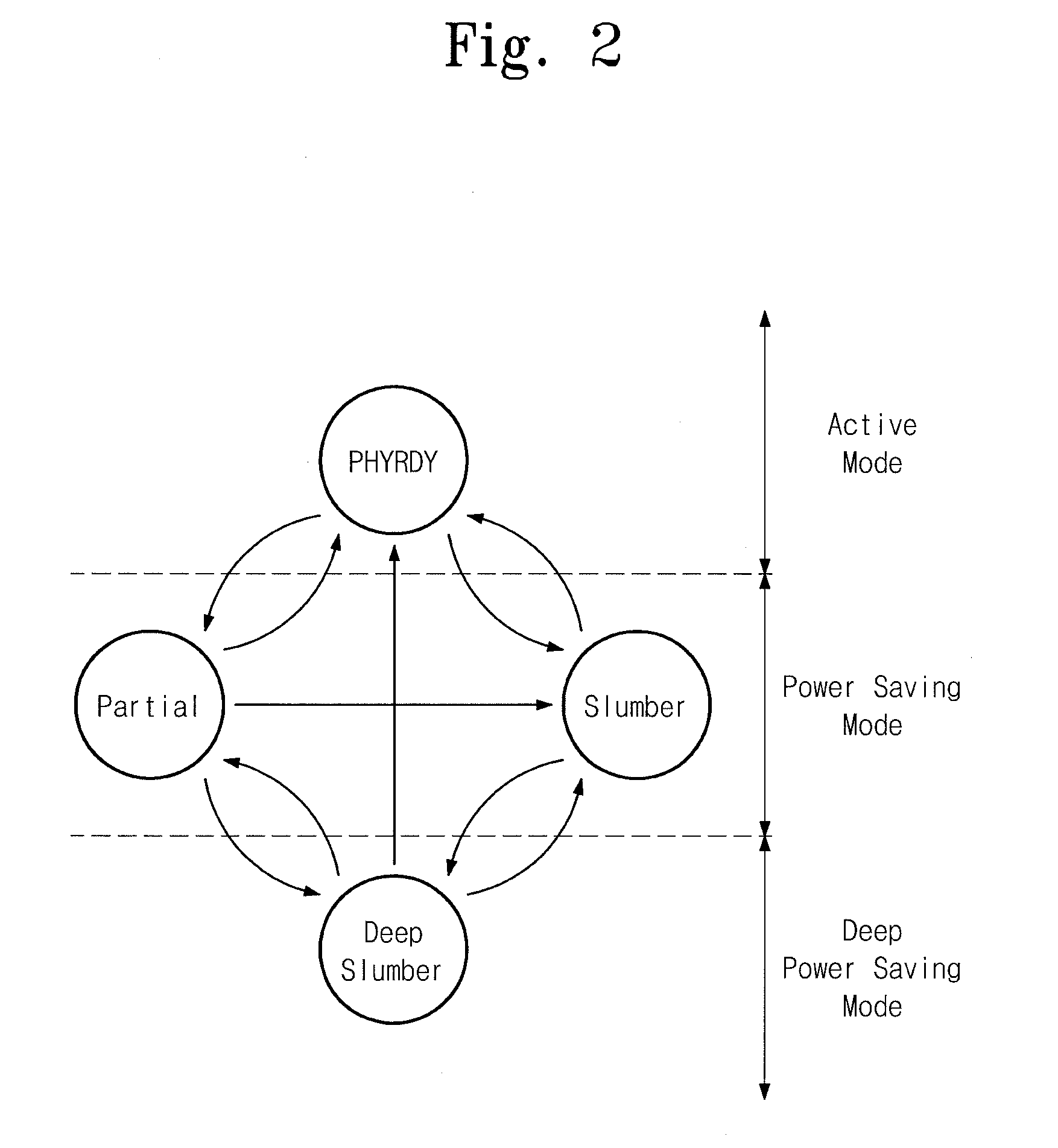

Serial Advanced Technology Attachment Interfaces And Methods For Power Management Thereof

ActiveUS20120191996A1Energy efficient ICTVolume/mass flow measurementComputer hardwareSerial advanced technology attachment

At least one example embodiment discloses a method of managing a power between a host serial advanced technology attachment (SATA) interface and a device SATA interface. The method includes first requesting to enter one of power saving states, defined by a SATA protocol, and second requesting to enter a deep power saving state if one of the host SATA interface and the device SATA interface operates at the first requested power saving state. The first requesting to enter one of power saving states and the second requesting to enter a deep power saving state are performed by one of the host SATA interface and the device SATA interface.

Owner:SAMSUNG ELECTRONICS CO LTD

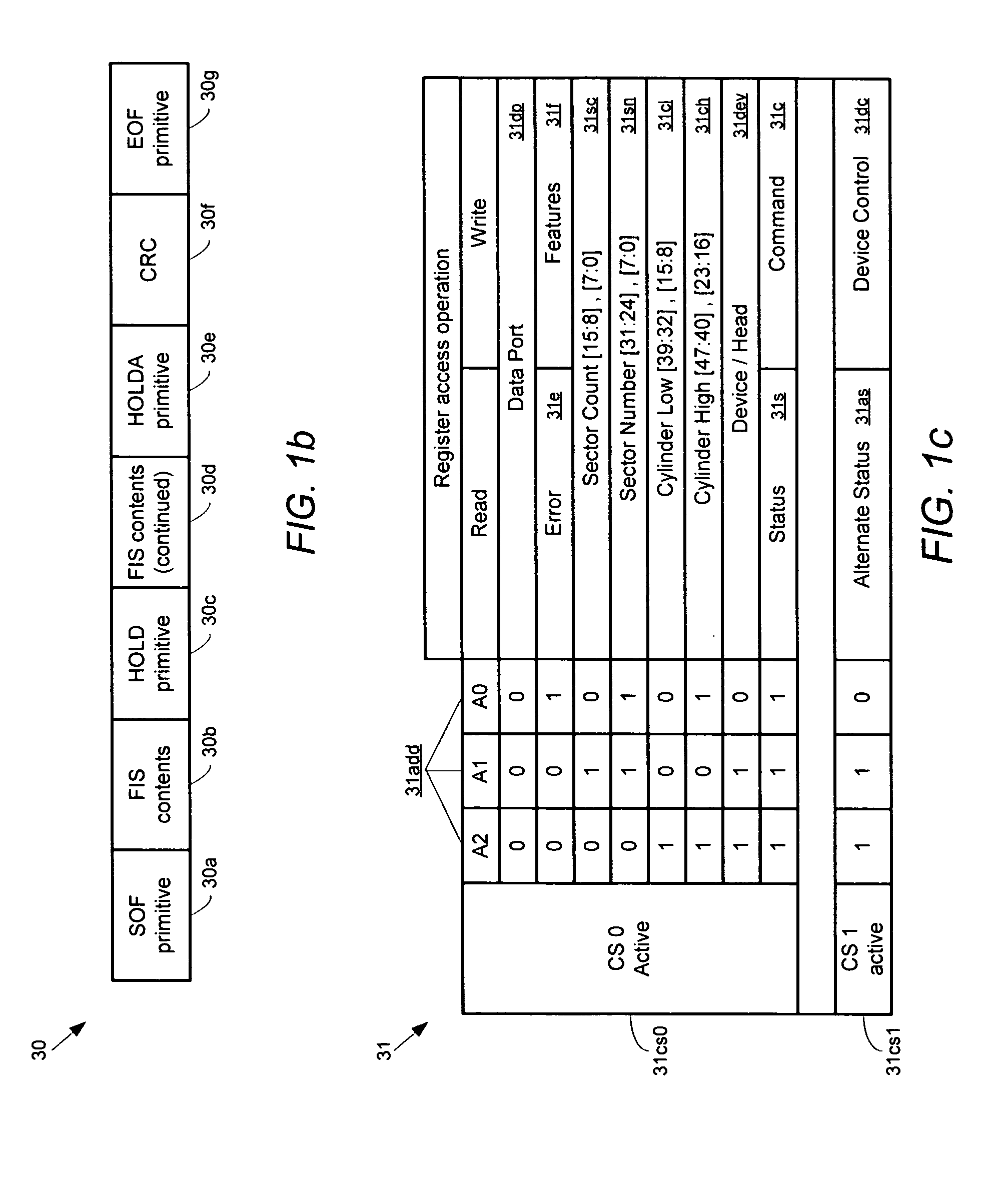

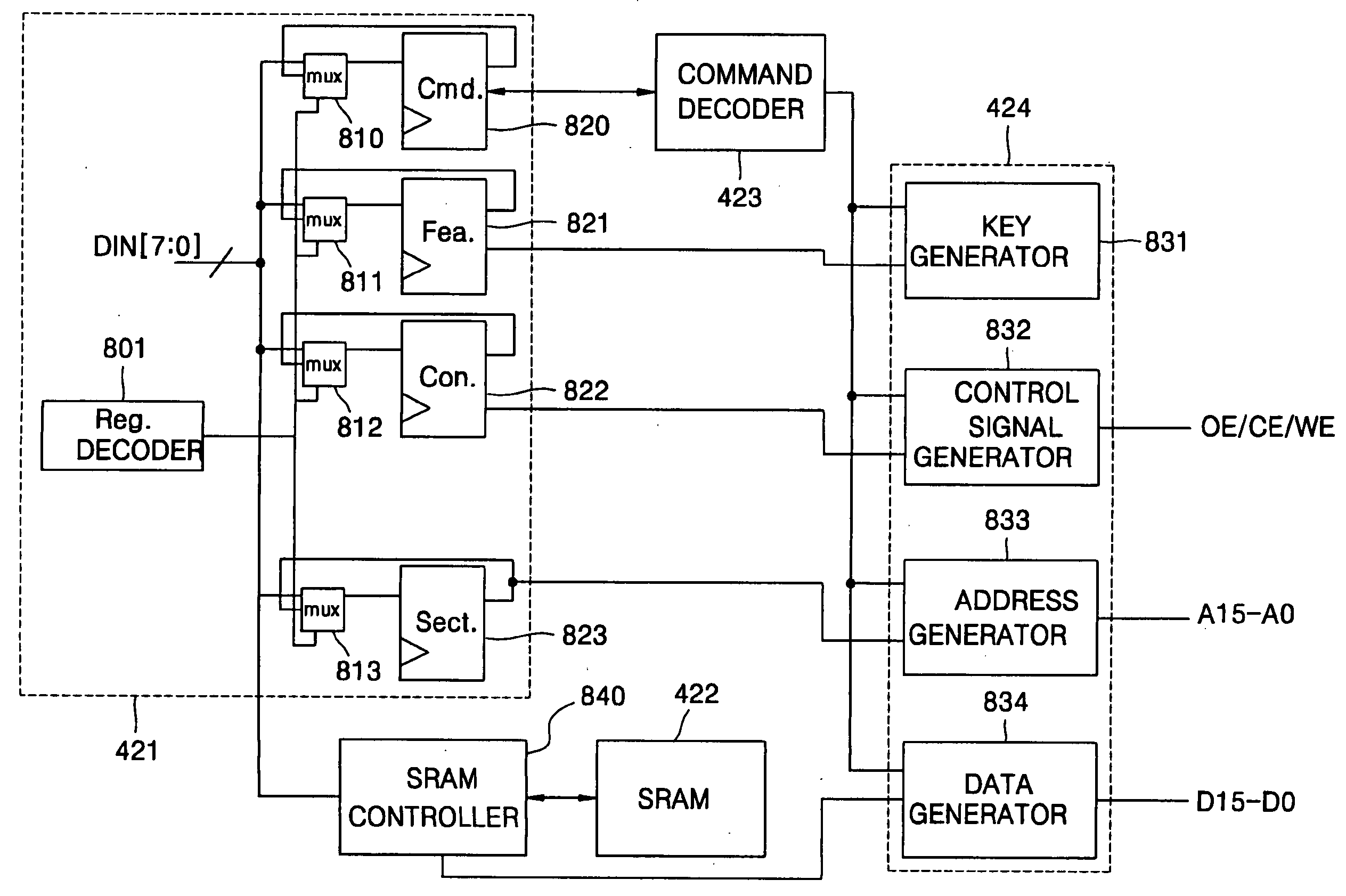

Devices and methods for updating program code via a serial ata interface

InactiveUS20060136900A1Link editingSpecific program execution arrangementsSerial advanced technology attachmentSerial ATA

An apparatus and method update a program code of an electronic device, such as an optical disk drive, using a Serial Advanced Technology Attachment (SATA) interface. The apparatus receives SATA signals from the SATA interface and generates flash memory driving signals based on a register host-to-device FIS received from a host computer system. Furthermore, the apparatus receives program data from a data host-to-device FIS received from the host computer system and updates the program code of a flash memory in the electronic device.

Owner:SAMSUNG ELECTRONICS CO LTD

Switching serial advanced technology attachment (SATA) to a parallel interface

ActiveUS7523236B1Error preventionTransmission systemsParallel ATASerial advanced technology attachment

A switch is coupled between a plurality of host units and a device, for communicating therebetween. A first serial advanced technology attachment (SATA) port includes a first host task file, and is coupled to a first host unit. A second SATA port includes a second host task file, and is coupled to a second host unit. The task files are responsive to commands sent by the respective host units, and cause access to the device by the host respective host units. A third parallel ATA port includes a device task file, and is coupled to a device, for access to the device by the first or second host units. An arbitration and control circuit is coupled to the task files, for selecting one of the first or second host units to concurrently access the device through the switch at any given time, including when the device is not idle.

Owner:NETWORK APPLIANCE INC

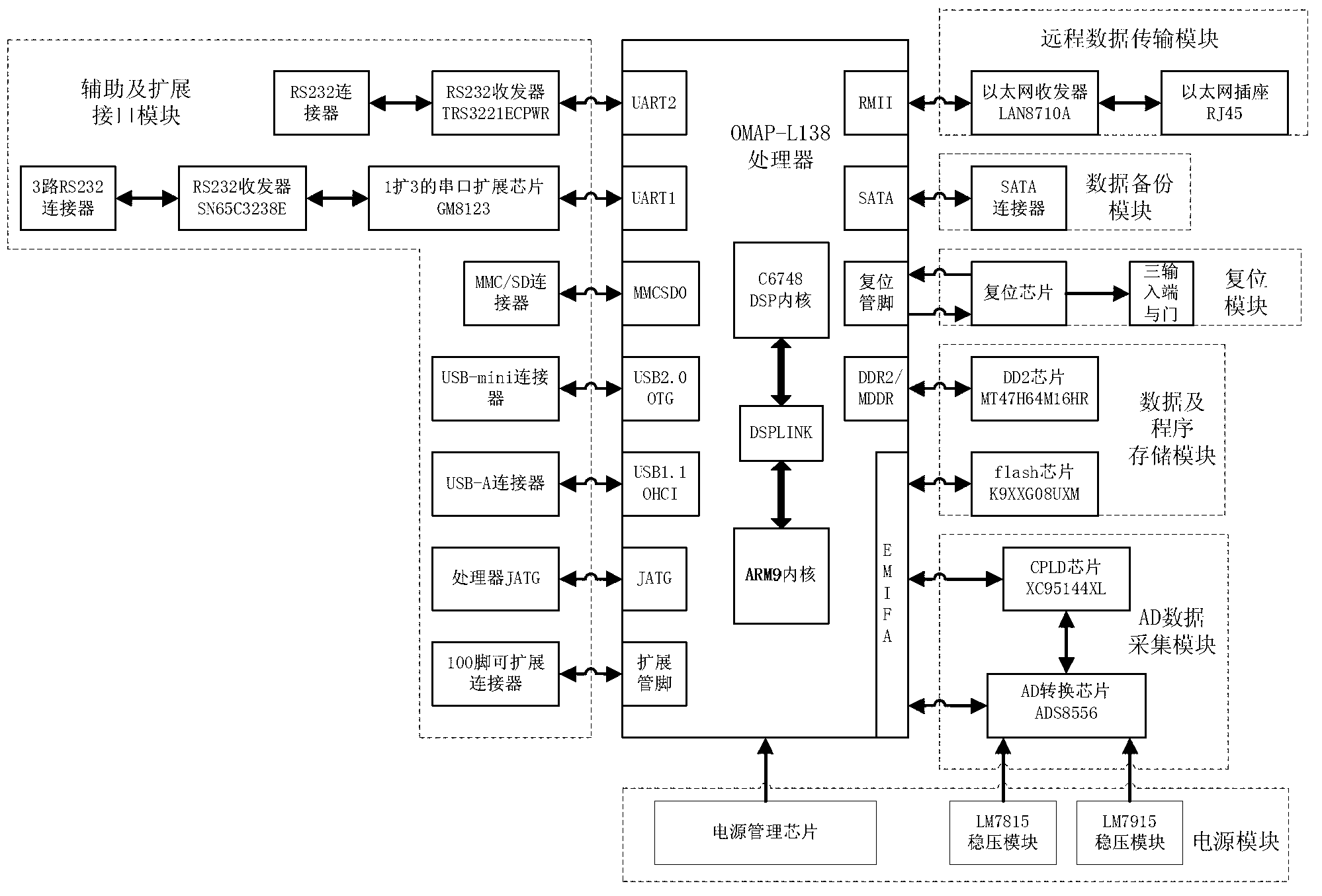

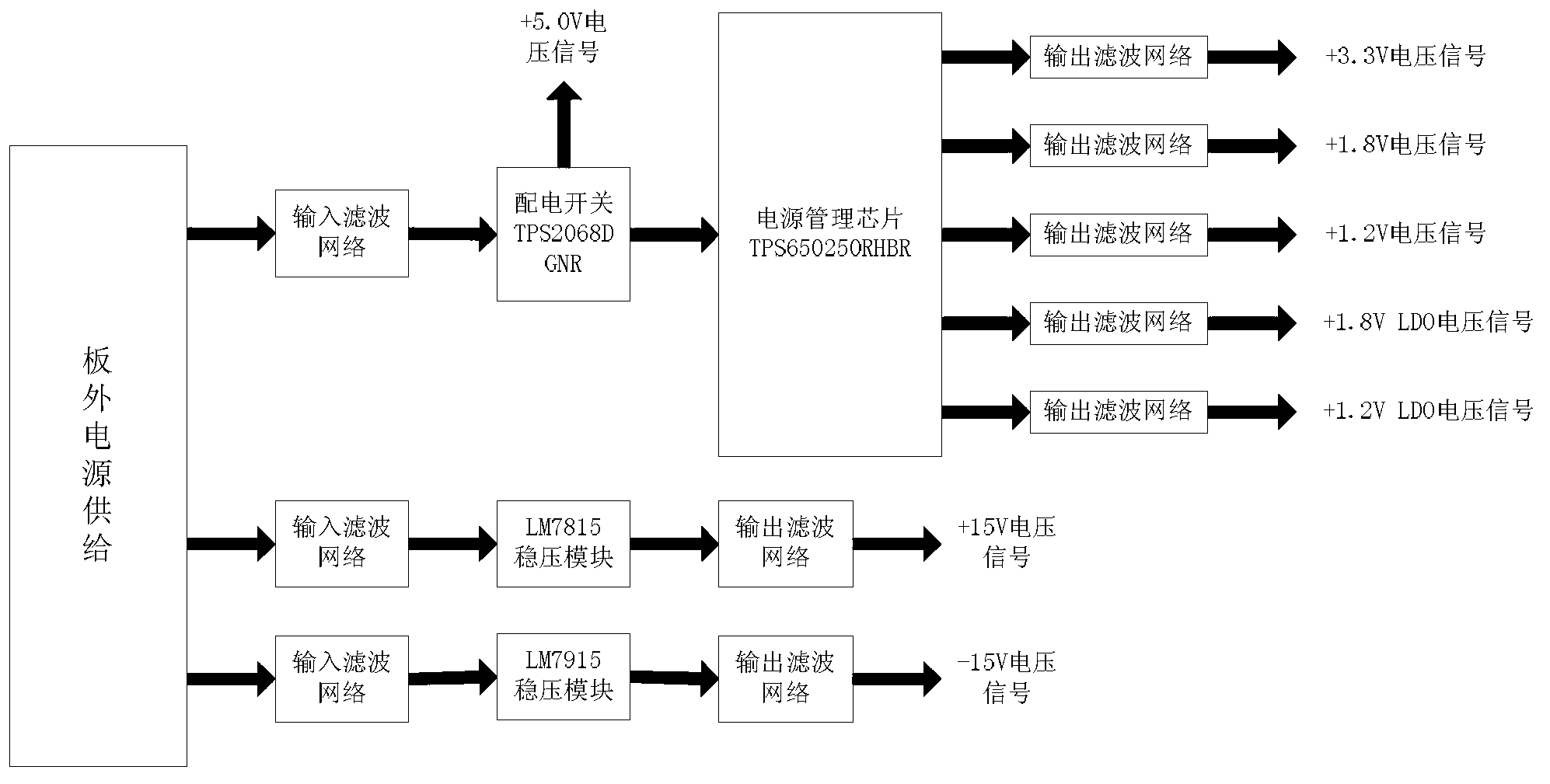

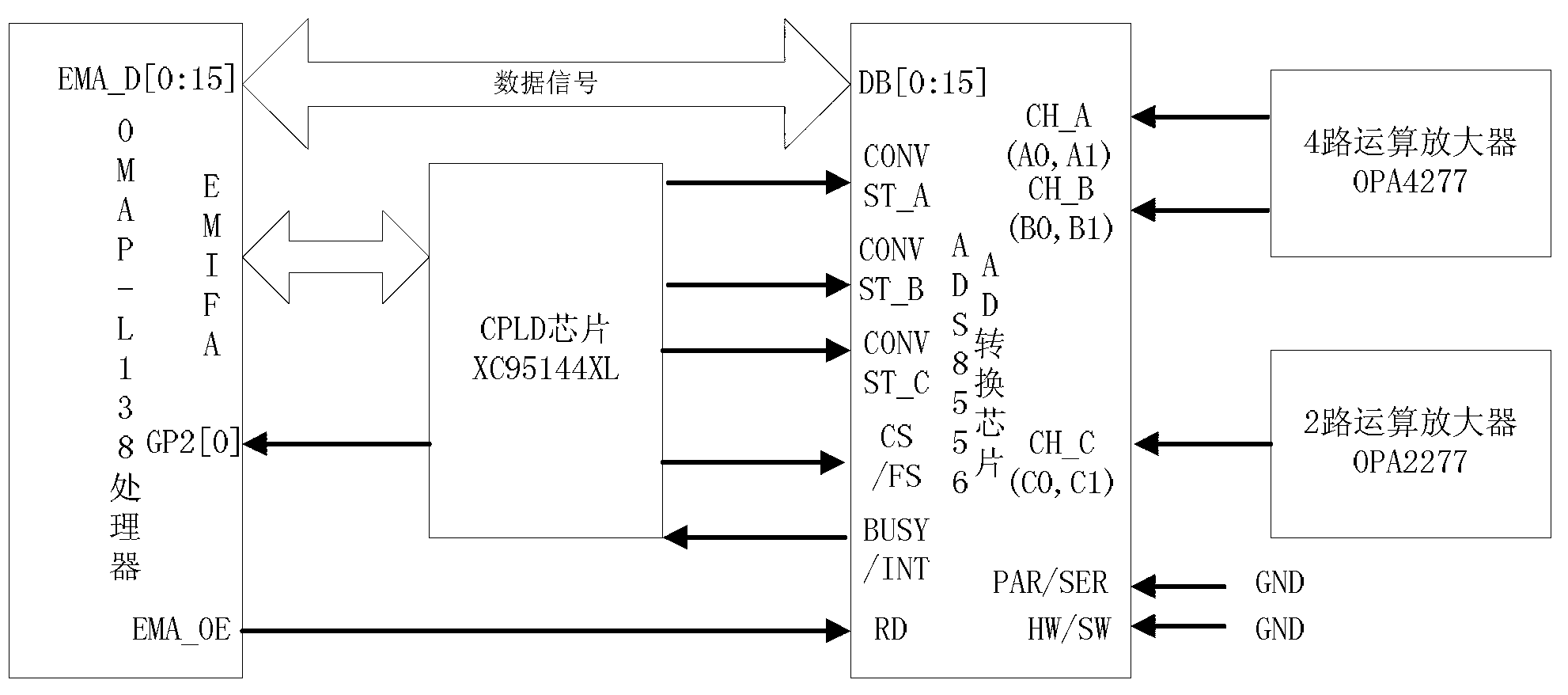

Acquisition and processing system of global system for mobile communications for railway (GSM-R) network interference signals

ActiveCN103023590AImprove work efficiencySmall output voltage rippleTransmission monitoringTransceiverDouble data rate

The invention relates to the field of wireless communication, in particular to an acquisition and processing system of embedded global system for mobile communications for railway (GSM-R) network interference signals based on multiprocessors. The system comprises a processor, a power module, an analog to digital (AD) data acquisition module, a data and program storage module, a remote data transmission module and a data backup module, the AD data acquisition module coverts collected intermediate frequency analog signals of uplink frequency ranges and downlink frequency ranges of a GSM-R into digital signals to be sent to a digital signal processor (DSP) core in the processor, the DSP core operates and processes to store the digital signals in double data rate 2 (DDR2) chip in the data and program storage module, simultaneously the serial advanced technology attachment (SATA) connector stores the digital signals in a high-capacity rigid disk, the AD data acquisition module starts the intermediate frequency analog signals in an abnormal signal-collected frequency range when data acquisition is abnormal, and the AD data acquisition module is communicated with an upper computer through an Ethernet transceiver.

Owner:北京腾华科技有限公司

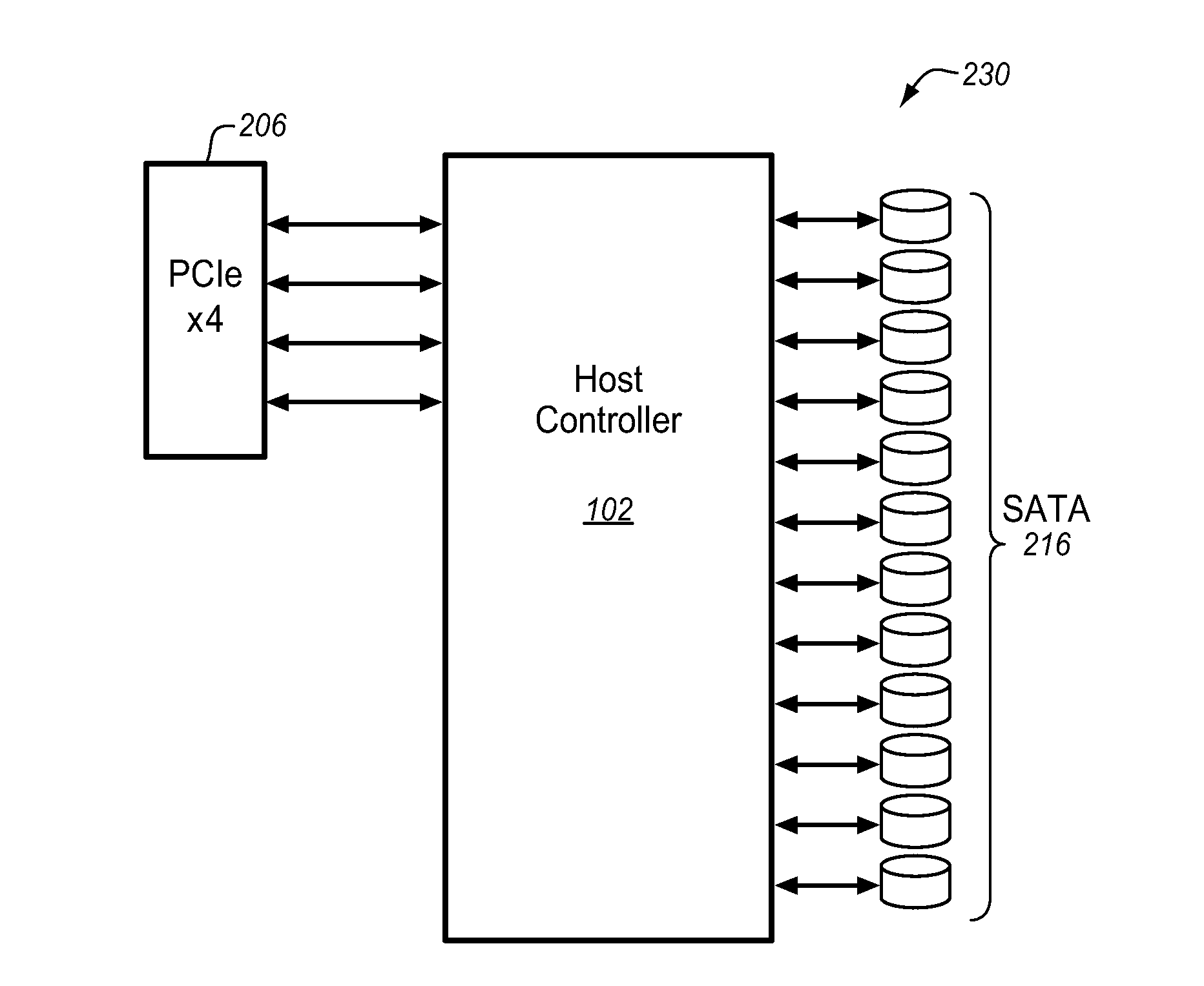

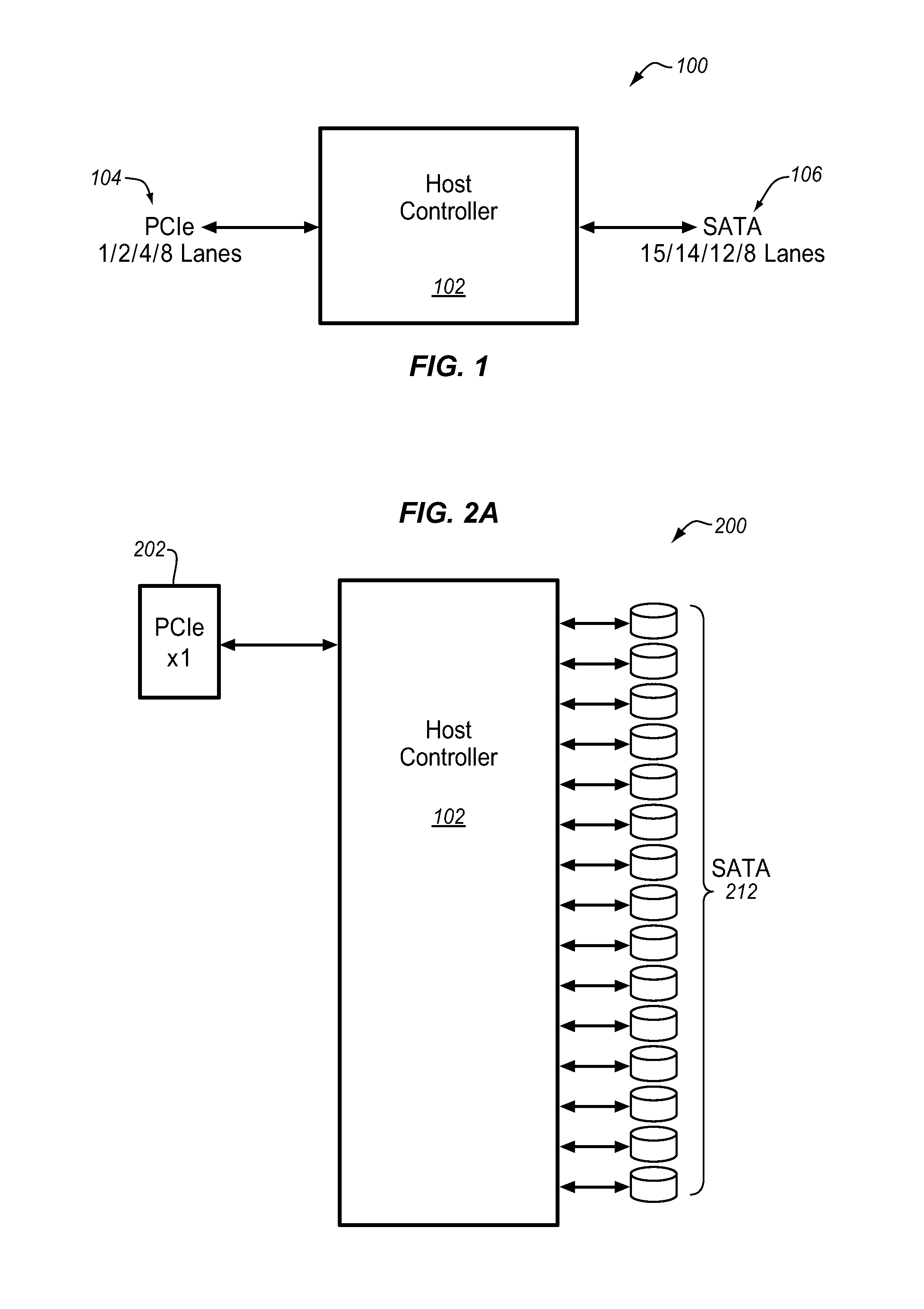

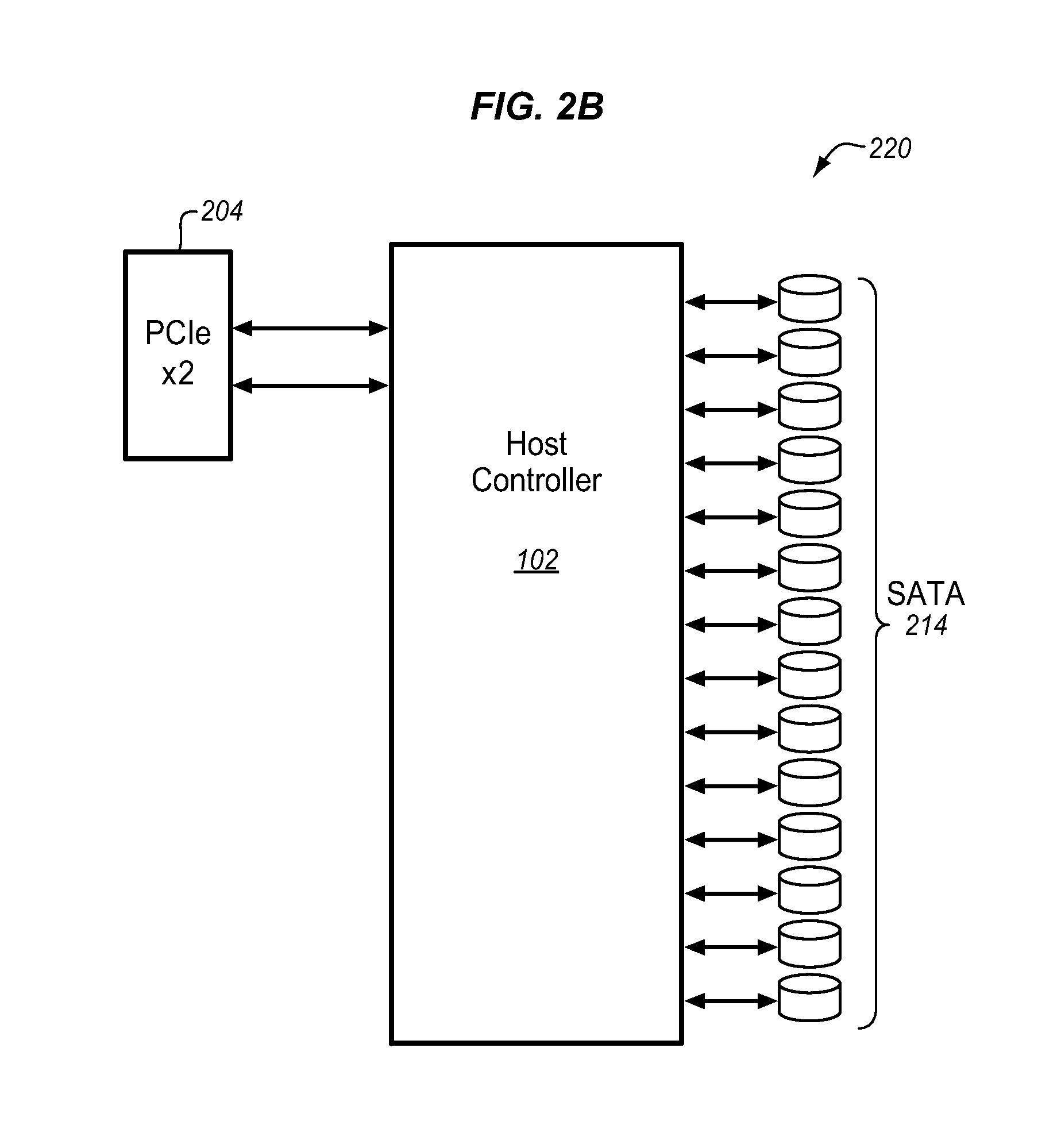

Mechanism for facilitating a configurable port-type peripheral component interconnect express/serial advanced technology attachment host controller architecture

ActiveUS20120166701A1Energy efficient computingElectric digital data processingController architectureSerial advanced technology attachment

A mechanism for facilitating configuration of port-type Peripheral Component Interconnect Express / Serial Advanced Technology Attachment host controller architecture is described. In one embodiment, an apparatus includes a plurality of PHYs to be used as Peripheral Component Interconnect Express (PCIe) ports and Serial Advanced Technology Attachment (SATA) ports, and logic to facilitate swapping of one or more of the plurality of PHYs between being the PCIe ports and the SATA ports.

Owner:LATTICE SEMICON CORP

System and Method of Providing Security to an External Attachment Device

InactiveUS20110087889A1Program control using stored programsDigital data processing detailsCD-ROMSerial advanced technology attachment

Owner:TECH PROPERTIES

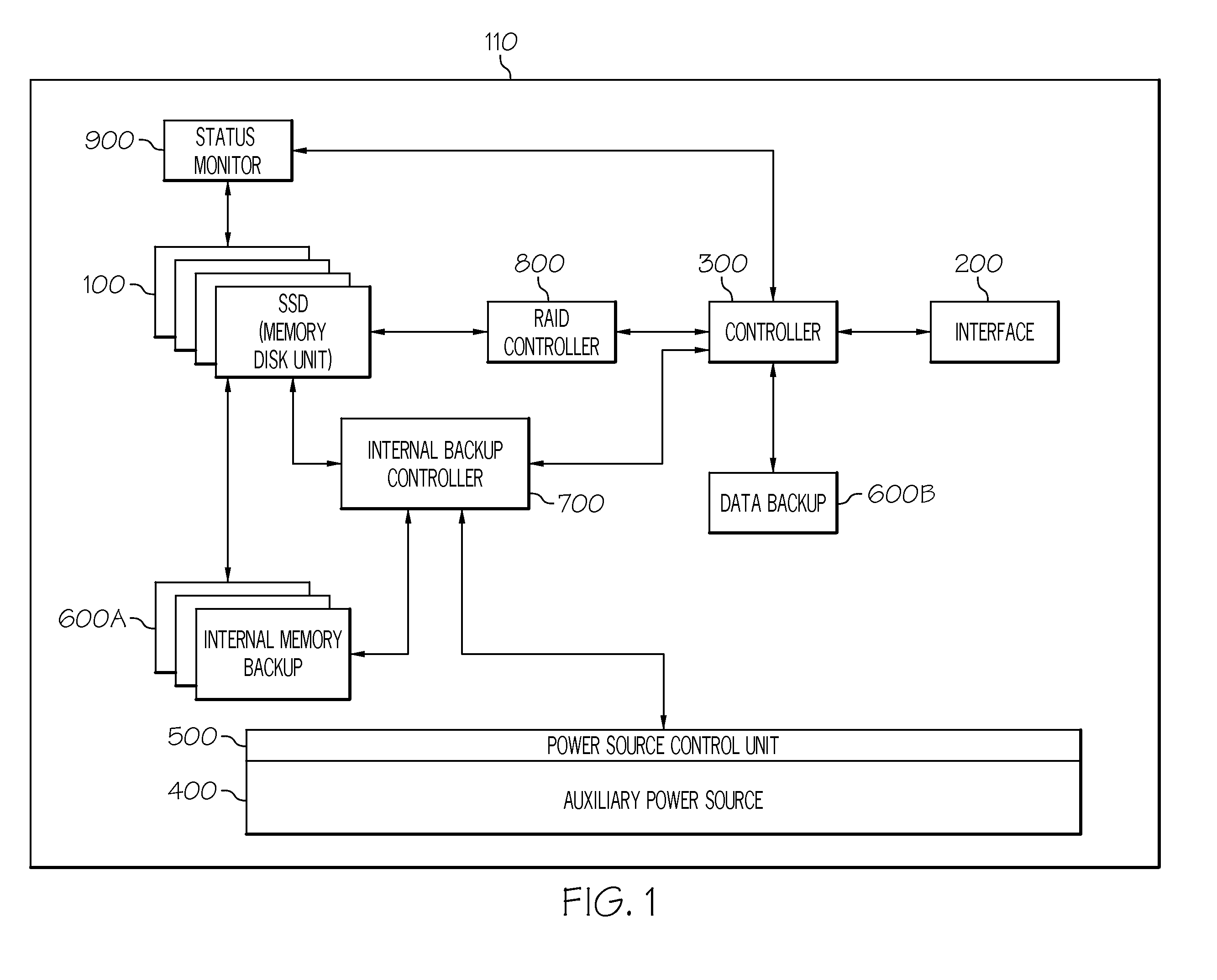

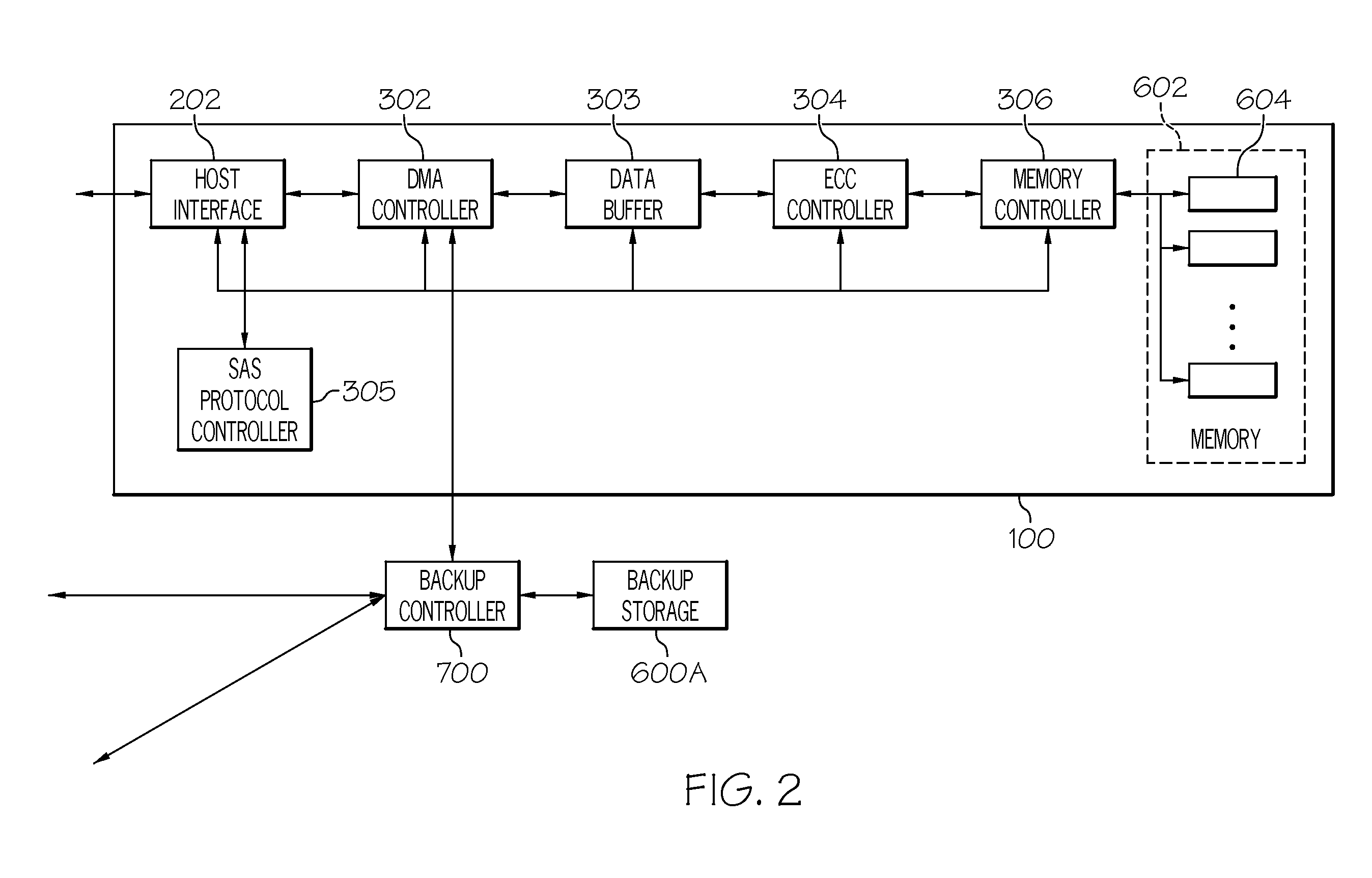

Sas-based semiconductor storage device memory disk unit

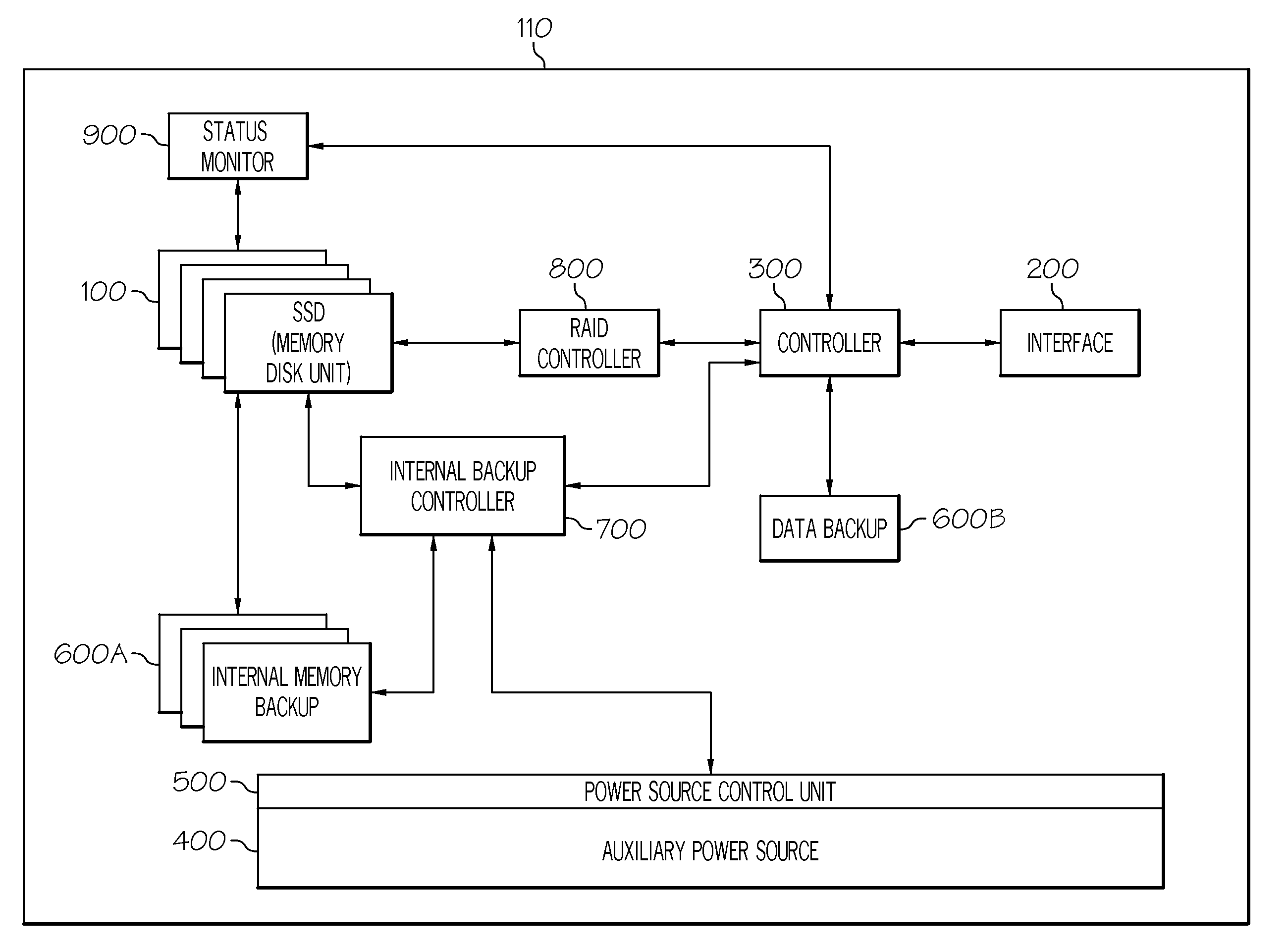

ActiveUS20120192038A1Low-speed data processing speedMemory adressing/allocation/relocationStatic storageSCSILow speed

Embodiments of the present invention provide a storage device of a serial-attached small computer system interface / serial advanced technology attachment (PCI-Express) type that supports a low-speed data processing speed for a host. Specifically, the present invention provides a SSD memory system comprising (among other components) a set (at least one) of SSD memory disk units. Each SSD memory disk unit generally comprises (among other components), a host interface unit; a serial-attached small computer system interface (SAS) protocol controller for controlling a SAS protocol of the SSD memory disk unit coupled to the host interface unit; a direct memory access (DMA) controller for controlling access to the SSD memory disk unit coupled to the host interface unit; and a data buffer for buffering data stored in the SSD memory disk unit coupled to the DMA controller.

Owner:TAJIN INFO TECH CO LTD