Patents

Literature

164 results about "Serial ATA" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

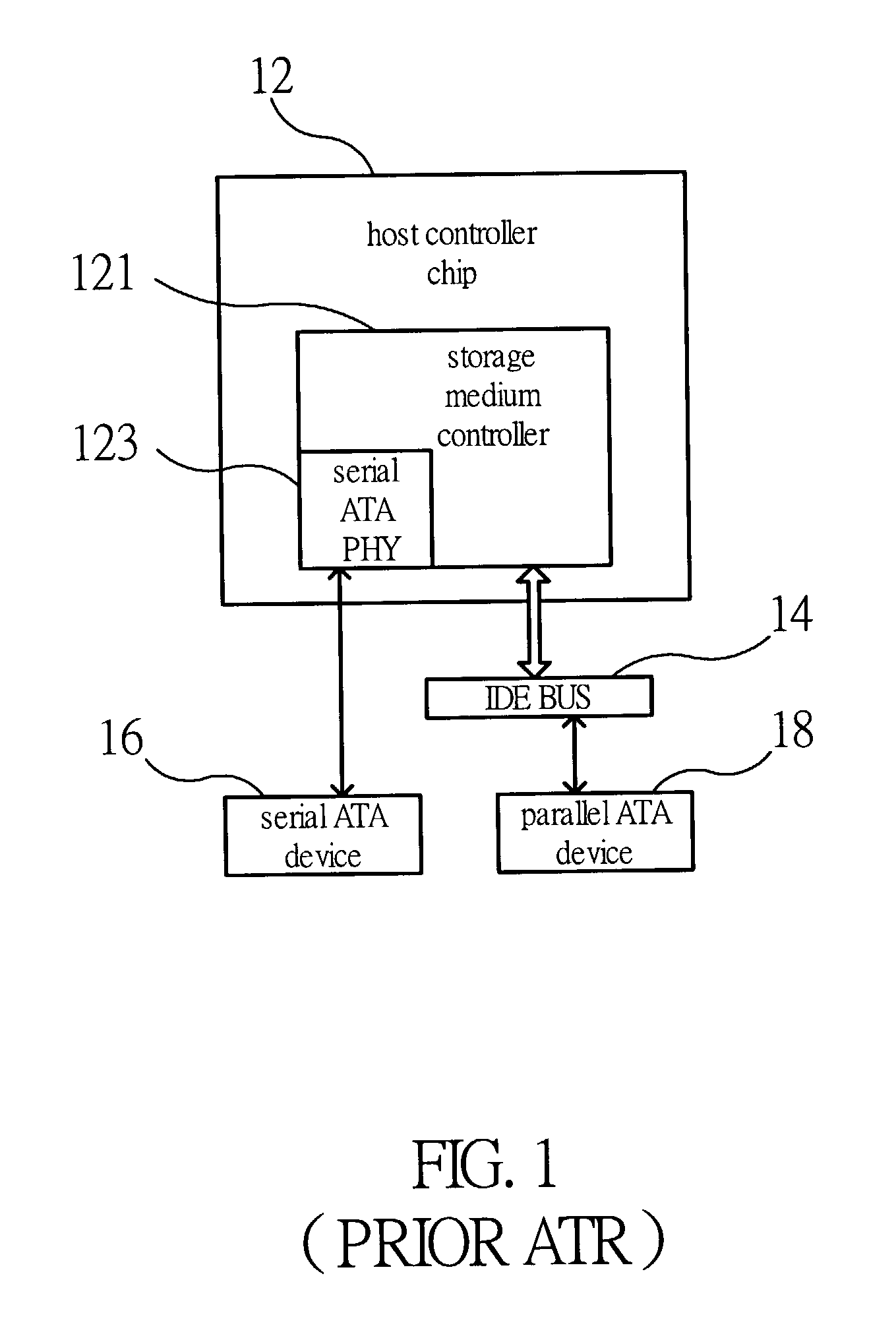

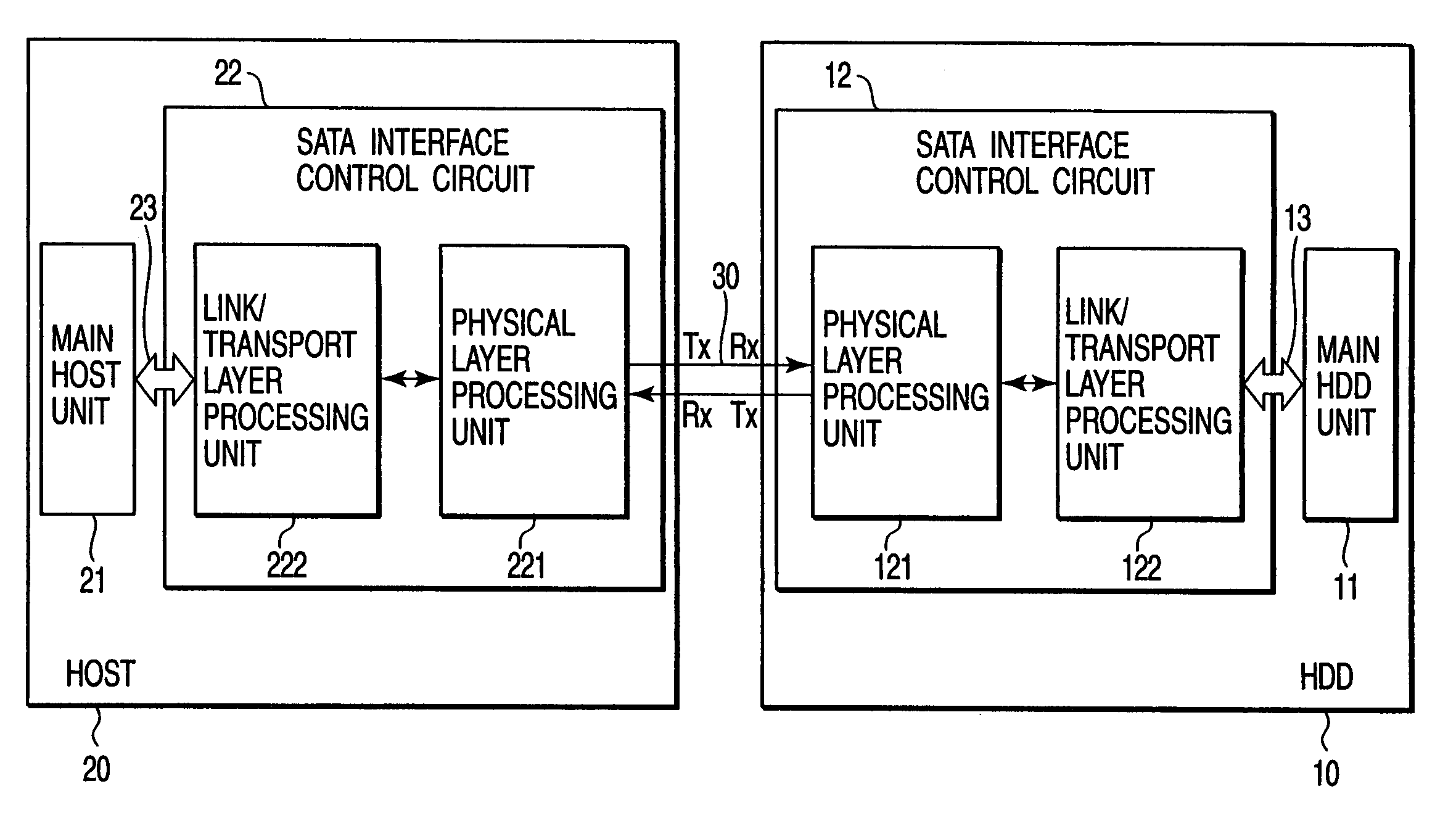

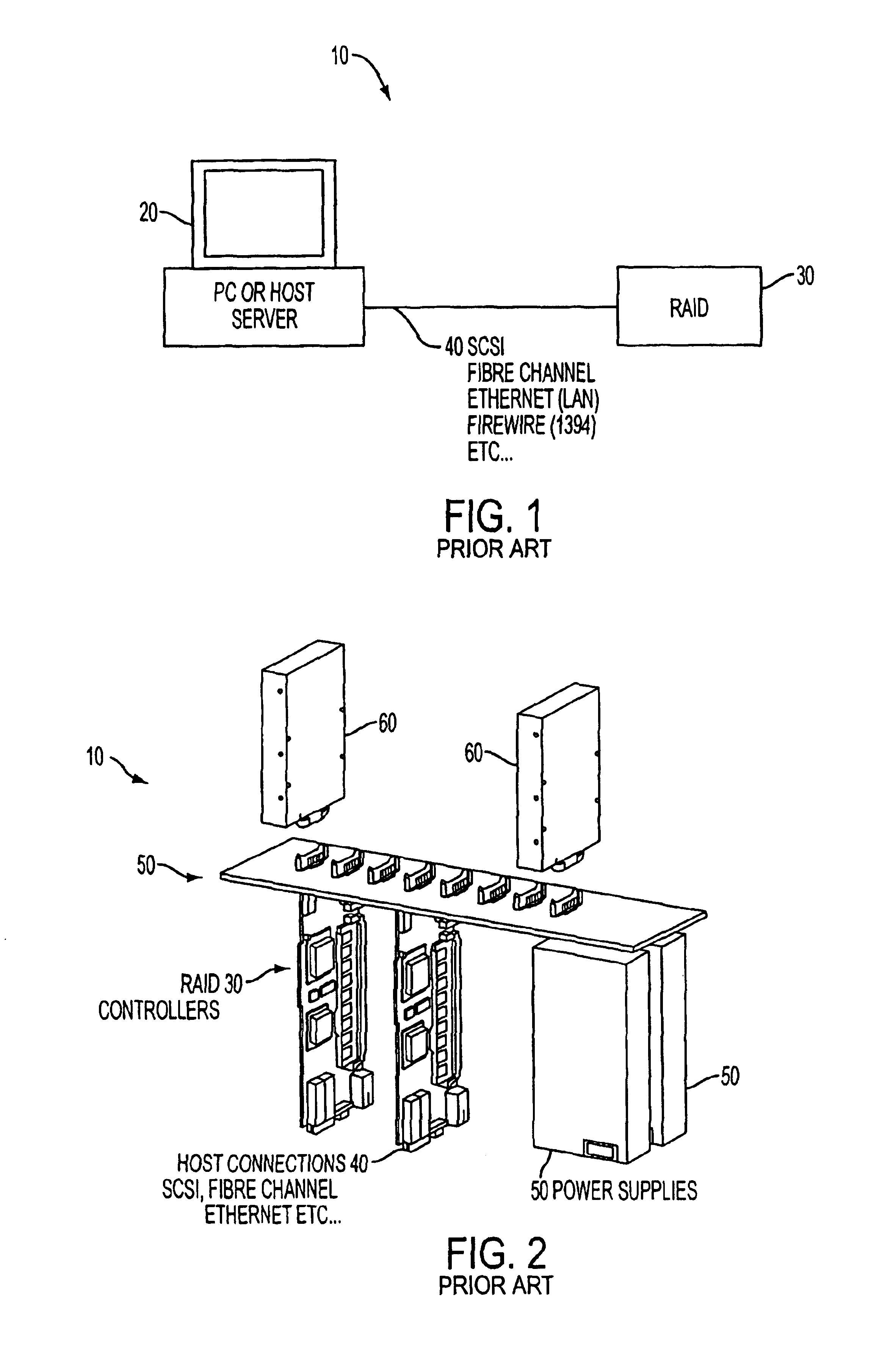

Serial ATA (SATA, abbreviated from Serial AT Attachment) is a computer bus interface that connects host bus adapters to mass storage devices such as hard disk drives, optical drives, and solid-state drives. Serial ATA succeeded the earlier Parallel ATA (PATA) standard to become the predominant interface for storage devices.

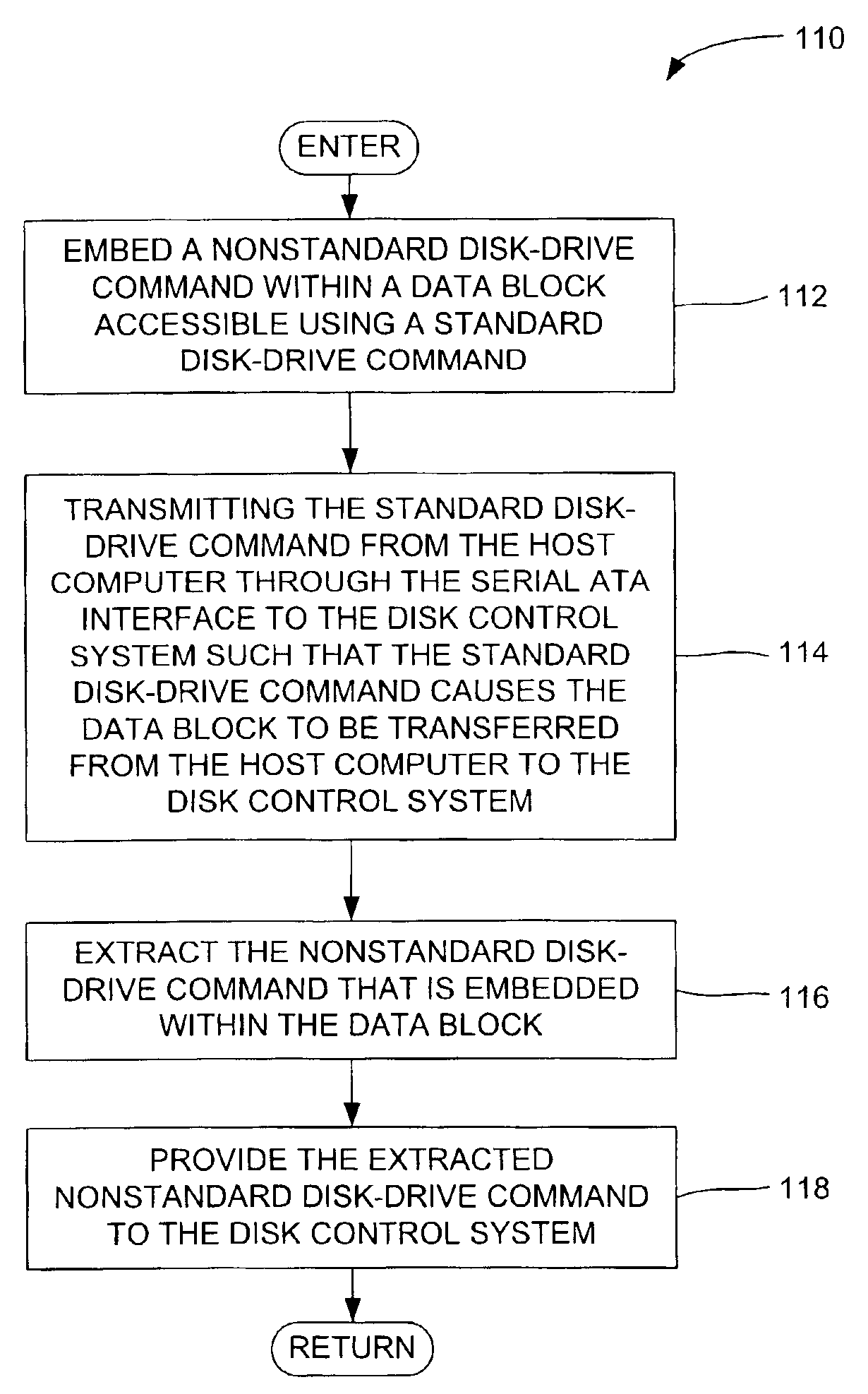

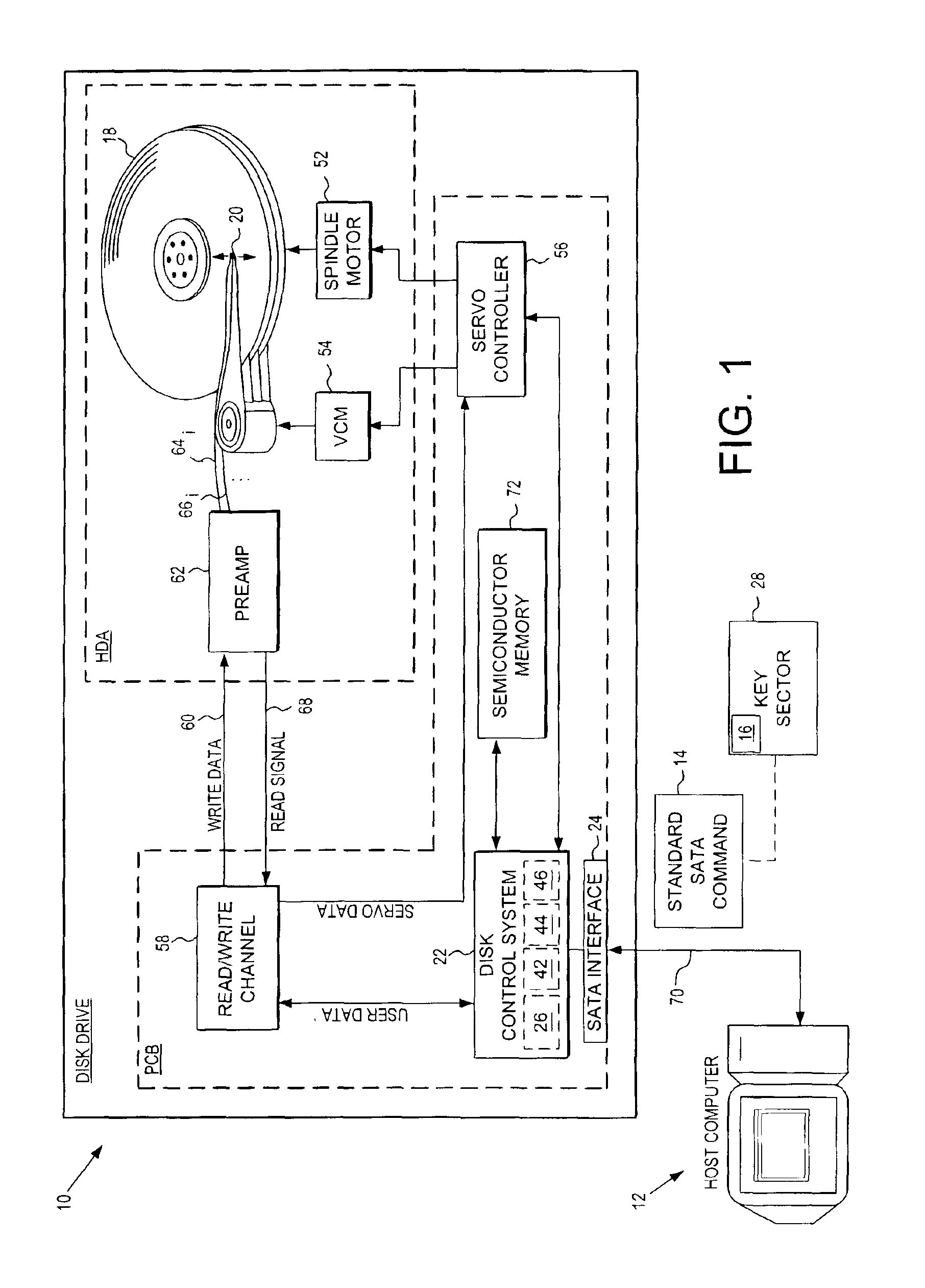

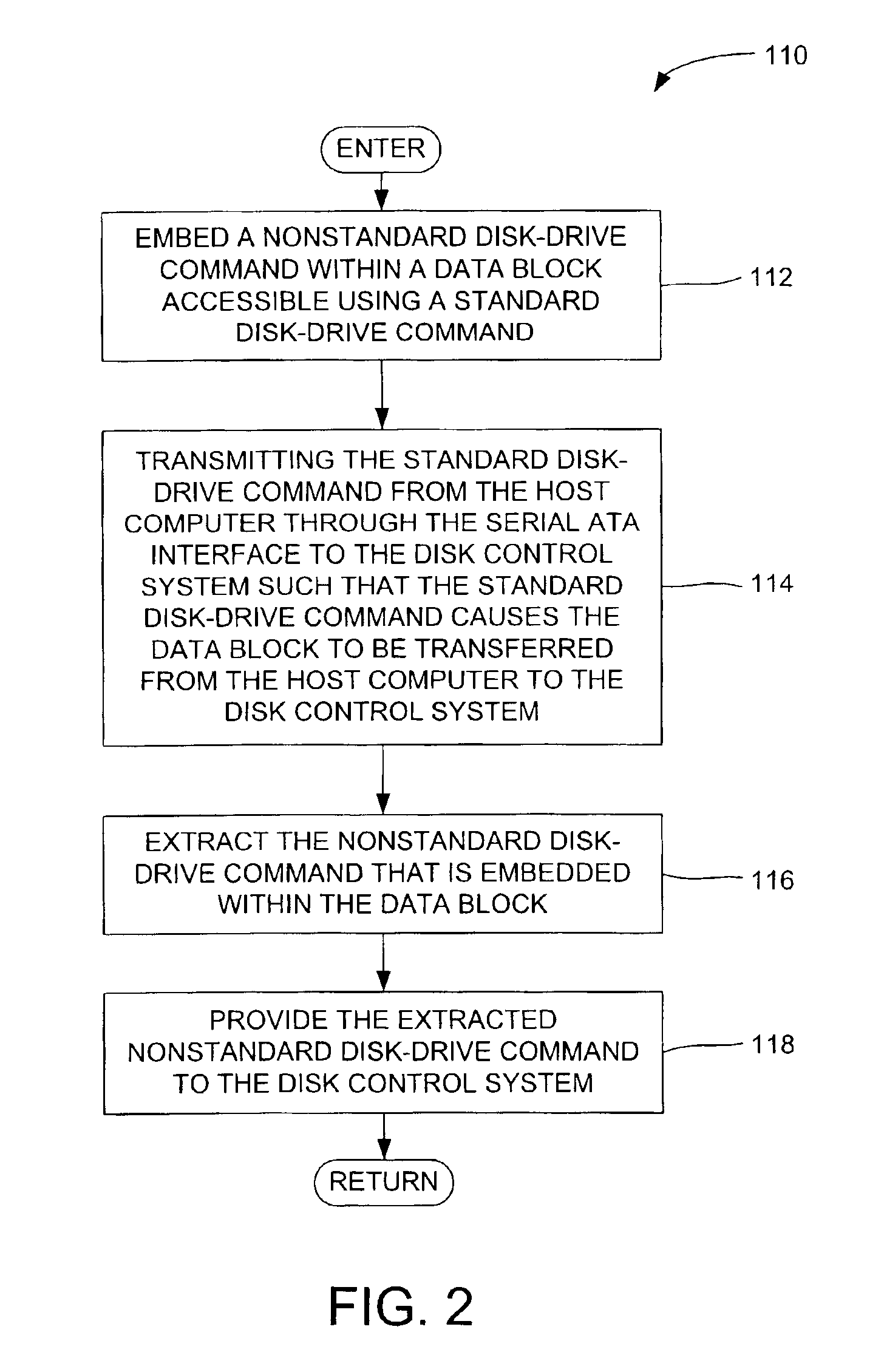

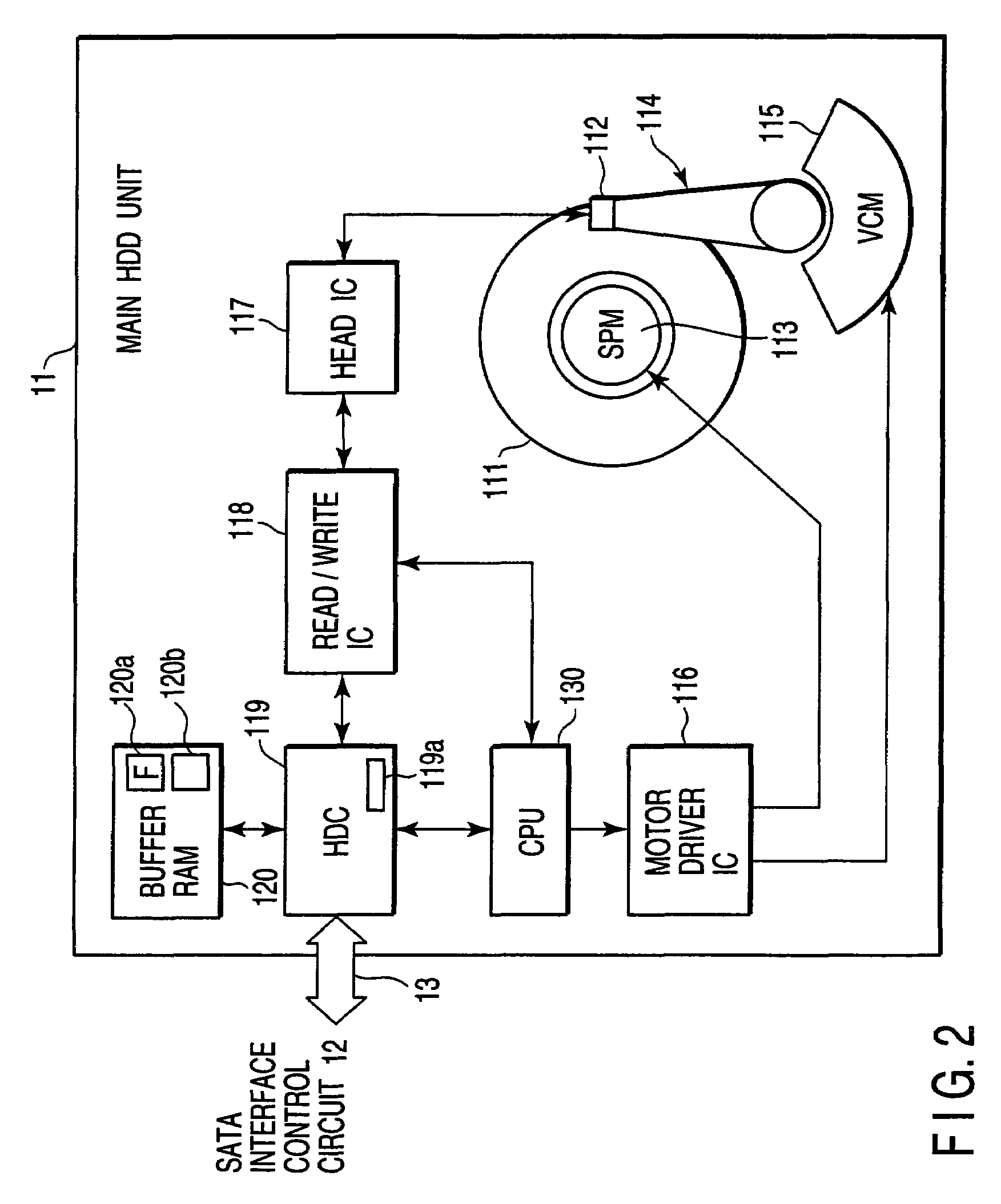

Disk drive and method for implementing nonstandard disk-drive commands on a serial ATA interface that only supports standard ATA disk-drive commands

A disk drive is disclosed that is responsive to standard disk-drive commands associated with disk-drive operations and to nonstandard disk-drive commands required for disk drive manufacture and quality testing. The disk drive includes a disk, a head actuated radially over the disk, and a disk control system. The disk control system responds to disk-drive commands and accesses data storage locations on the disk through the head. A serial ATA interface couples the disk control system to a host computer. The serial ATA interface is configured to transfer standard disk-drive commands from the host computer to the disk control system and is configured to not transfer nonstandard disk-drive commands from the host computer to the disk control system. The extracting means extracts a nonstandard disk-drive command that is embedded within a data block accessed using a standard disk-drive command and provides the extracted nonstandard disk-drive command to the disk control system.

Owner:WESTERN DIGITAL TECH INC

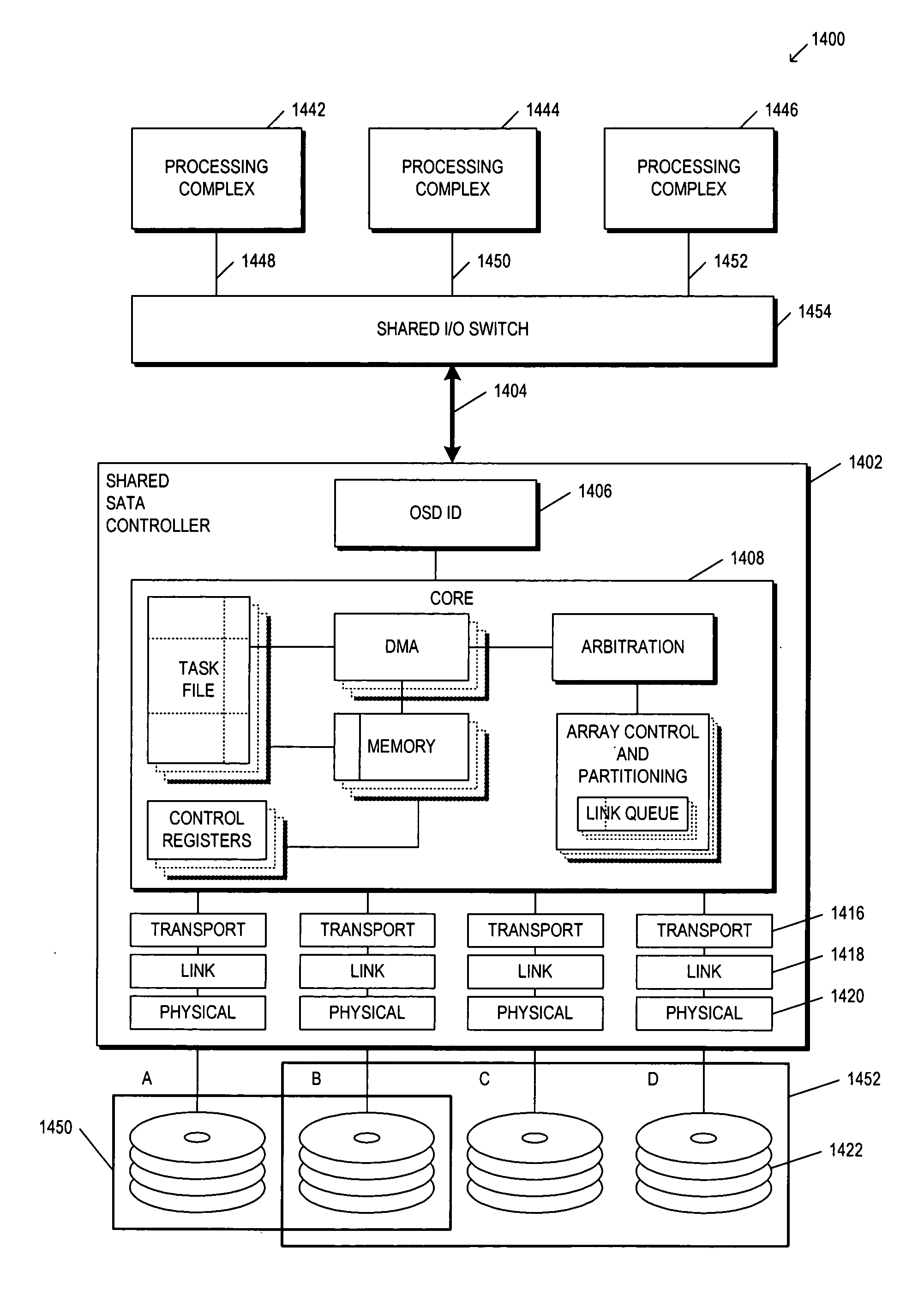

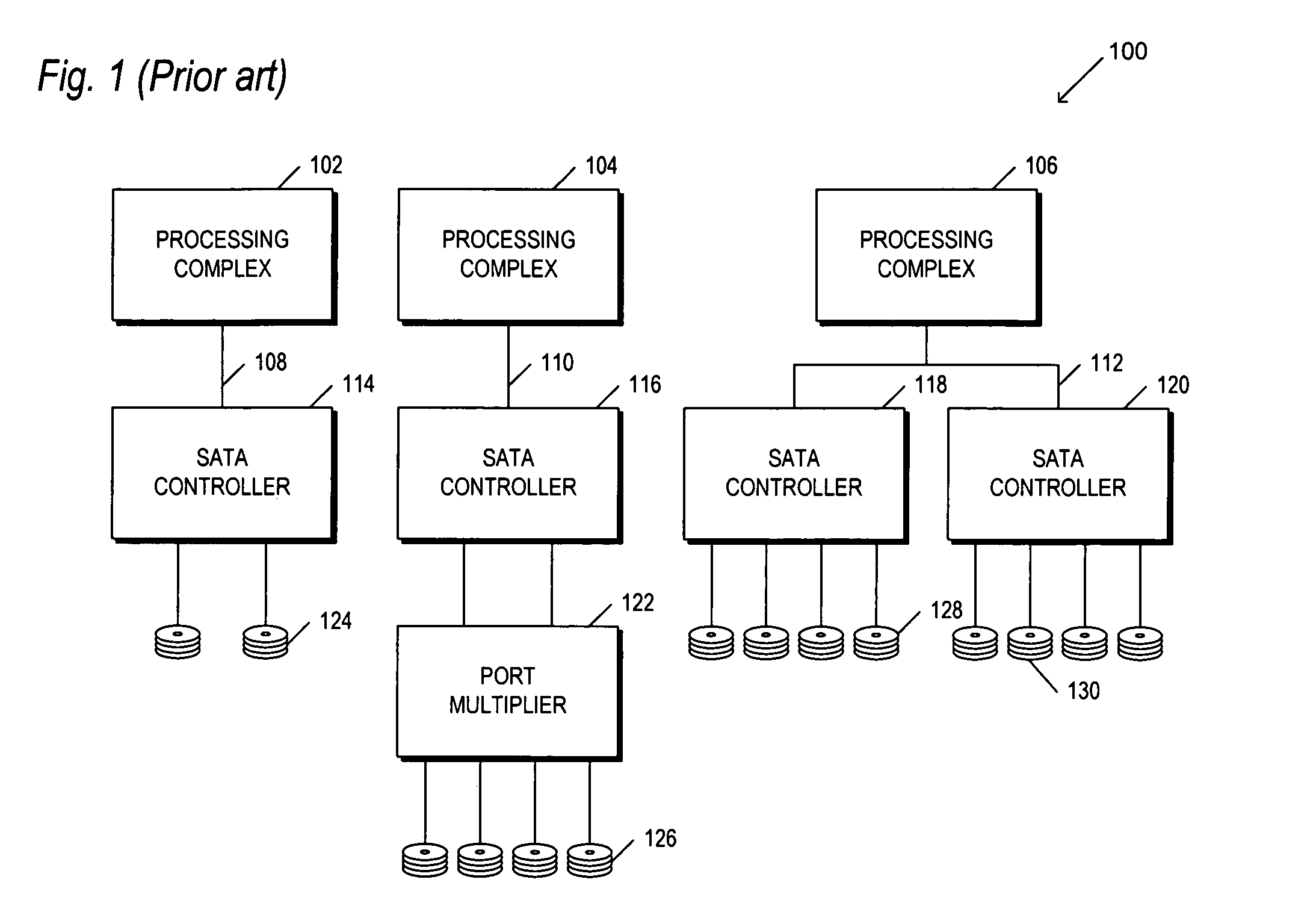

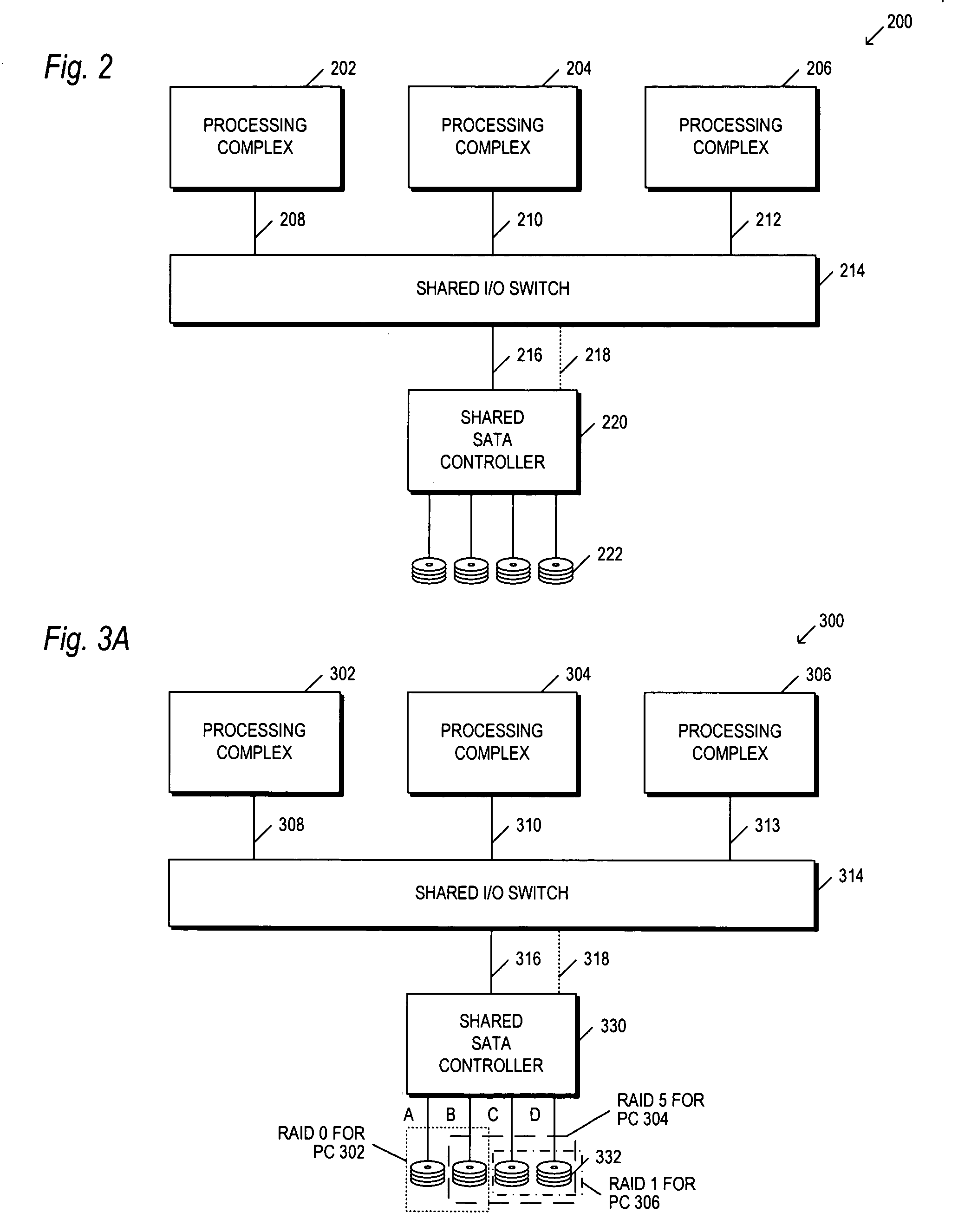

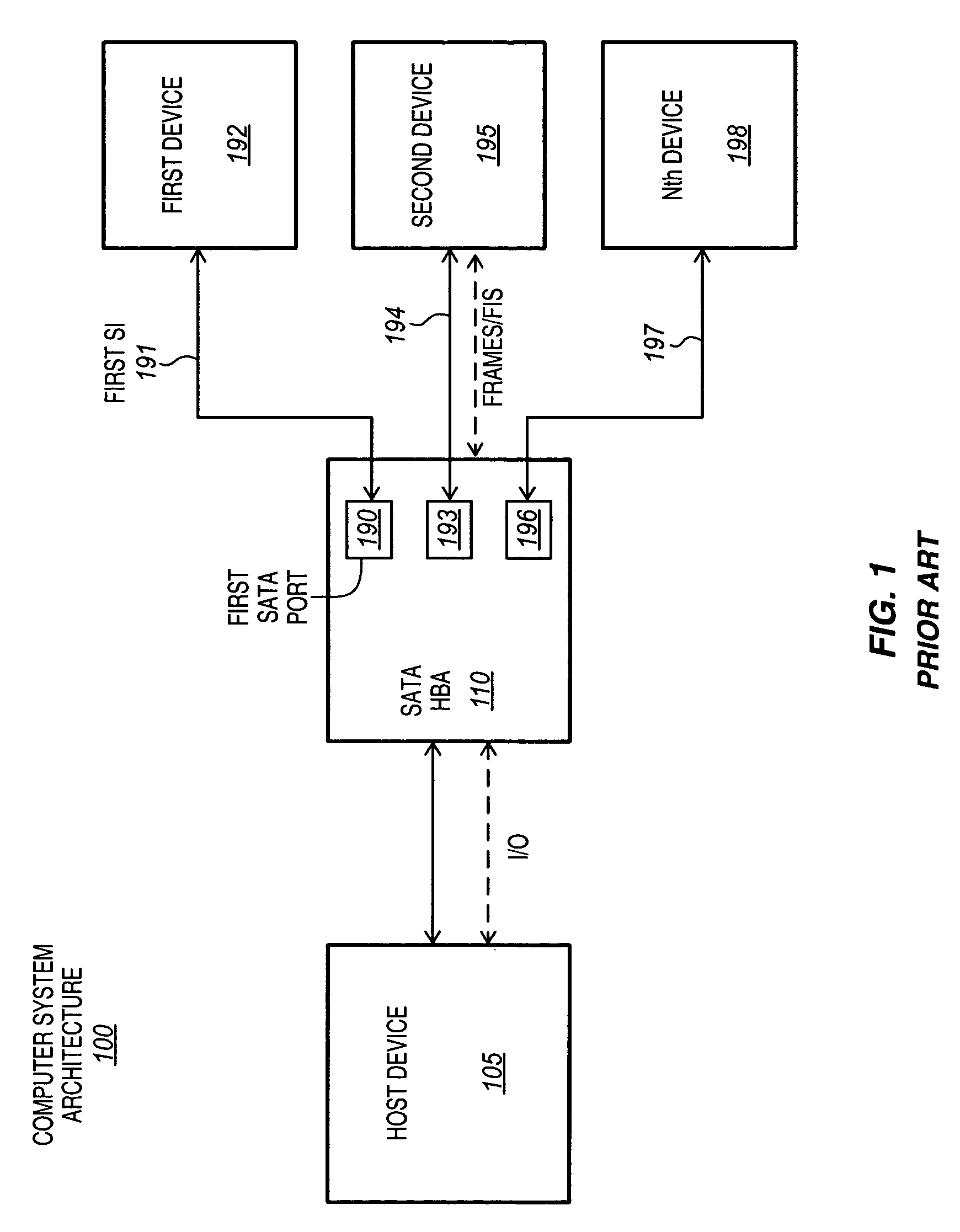

Method and apparatus for a shared I/O serial ATA controller

An apparatus and method is provided for allowing one or more processing complexes to share a disk controller, particularly a serial ATA (SATA) controller. Each processing complex utilizes its own load-store domain to couple to the shared SATA controller, either directly, or indirectly through a shared I / O switch. Ultimately, requests from the processing complexes are presented to the switch with operating system domain header (OSD header) information so that the shared SATA controller can determine which request came from which processing complex, and allocate resources accordingly. Upstream responses from the shared SATA controller include the OSD header so that the shared I / O switch can accurately route the responses to their respective processing complexes. The shared SATA controller includes OSD ID logic to determine the source / result of packets, one or more task files to support multiple processing complexes, and one or more DMA engines to improve performance for requests from multiple processing complexes.

Owner:MELLANOX TECHNOLOGIES LTD

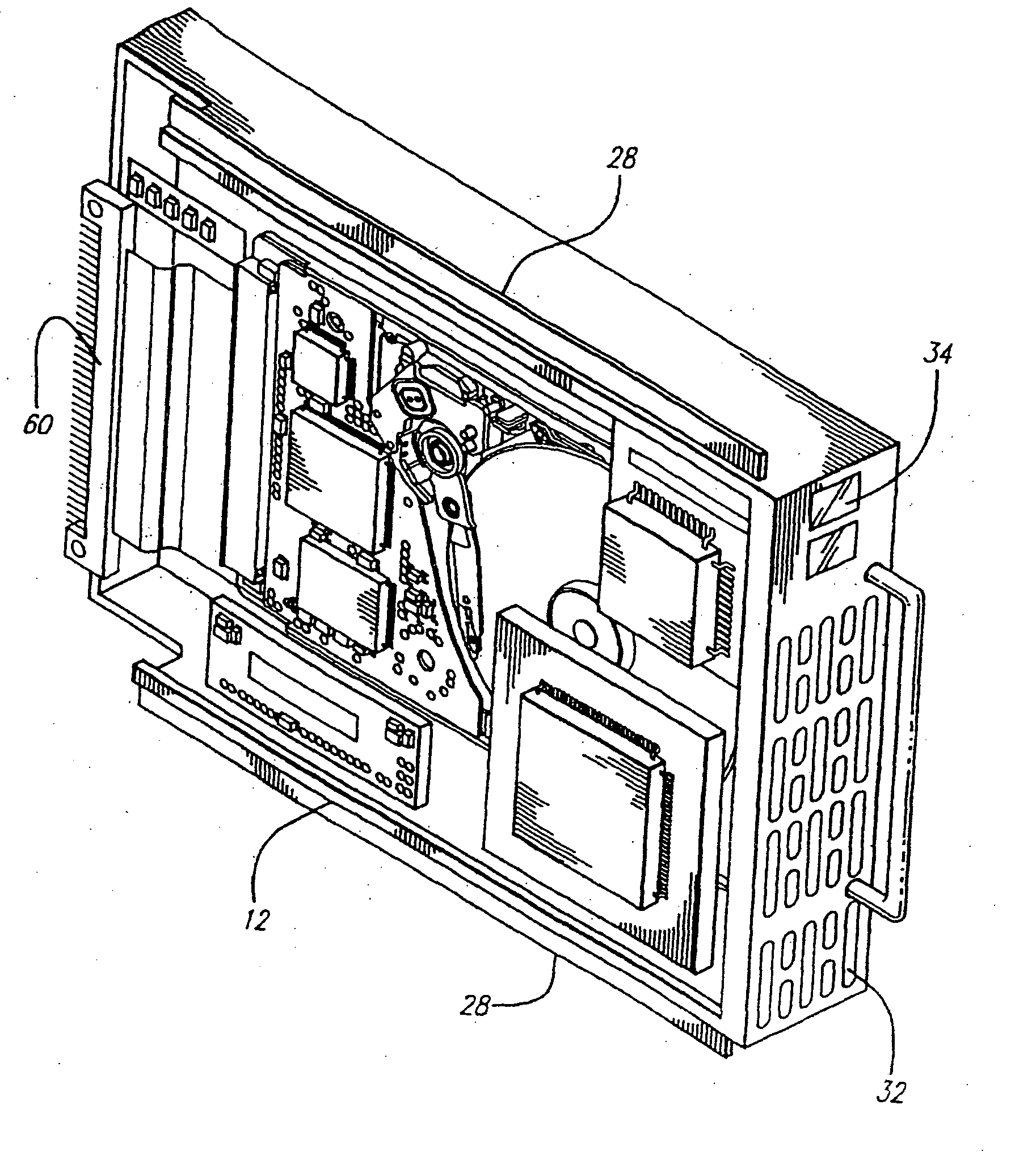

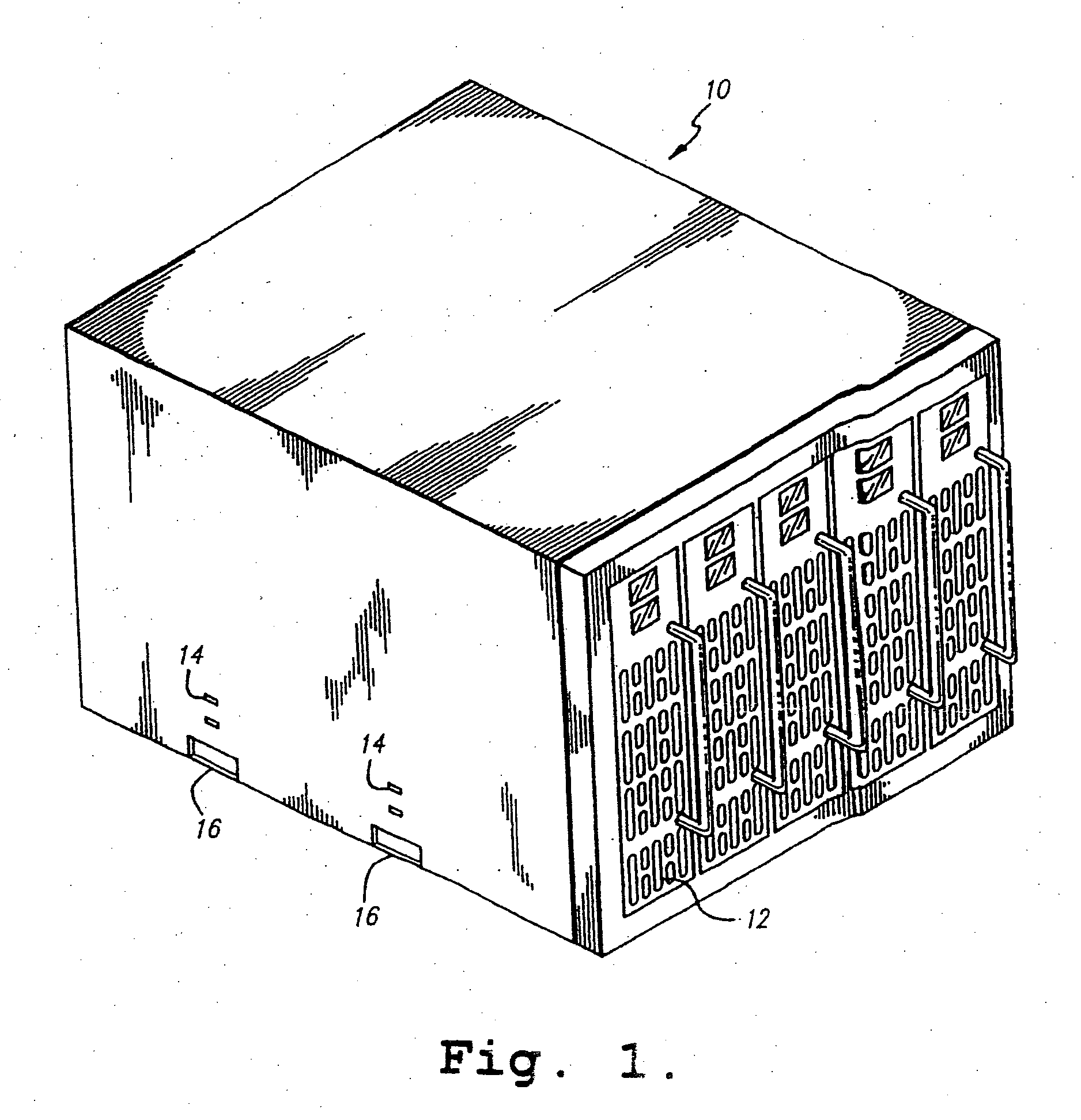

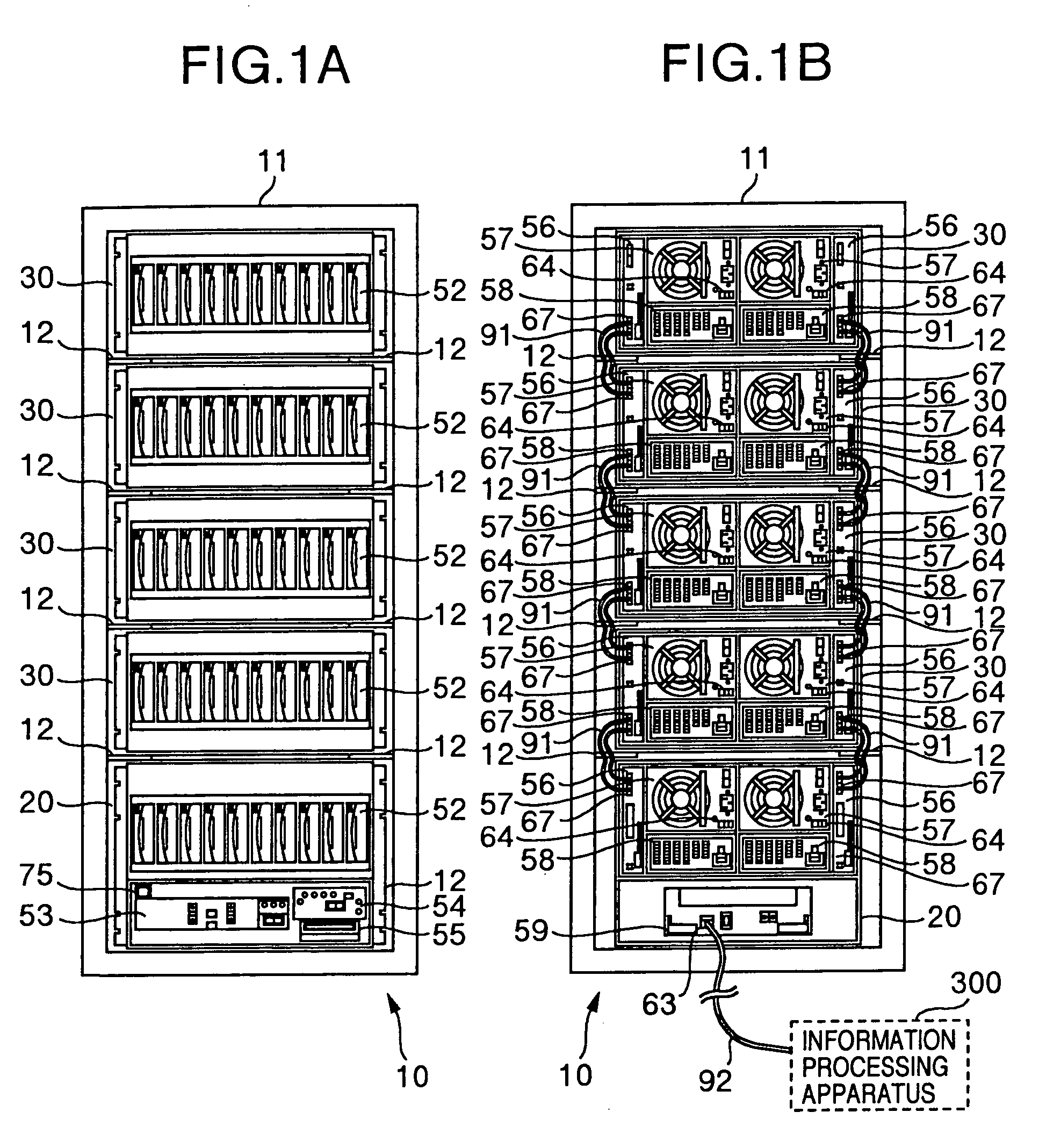

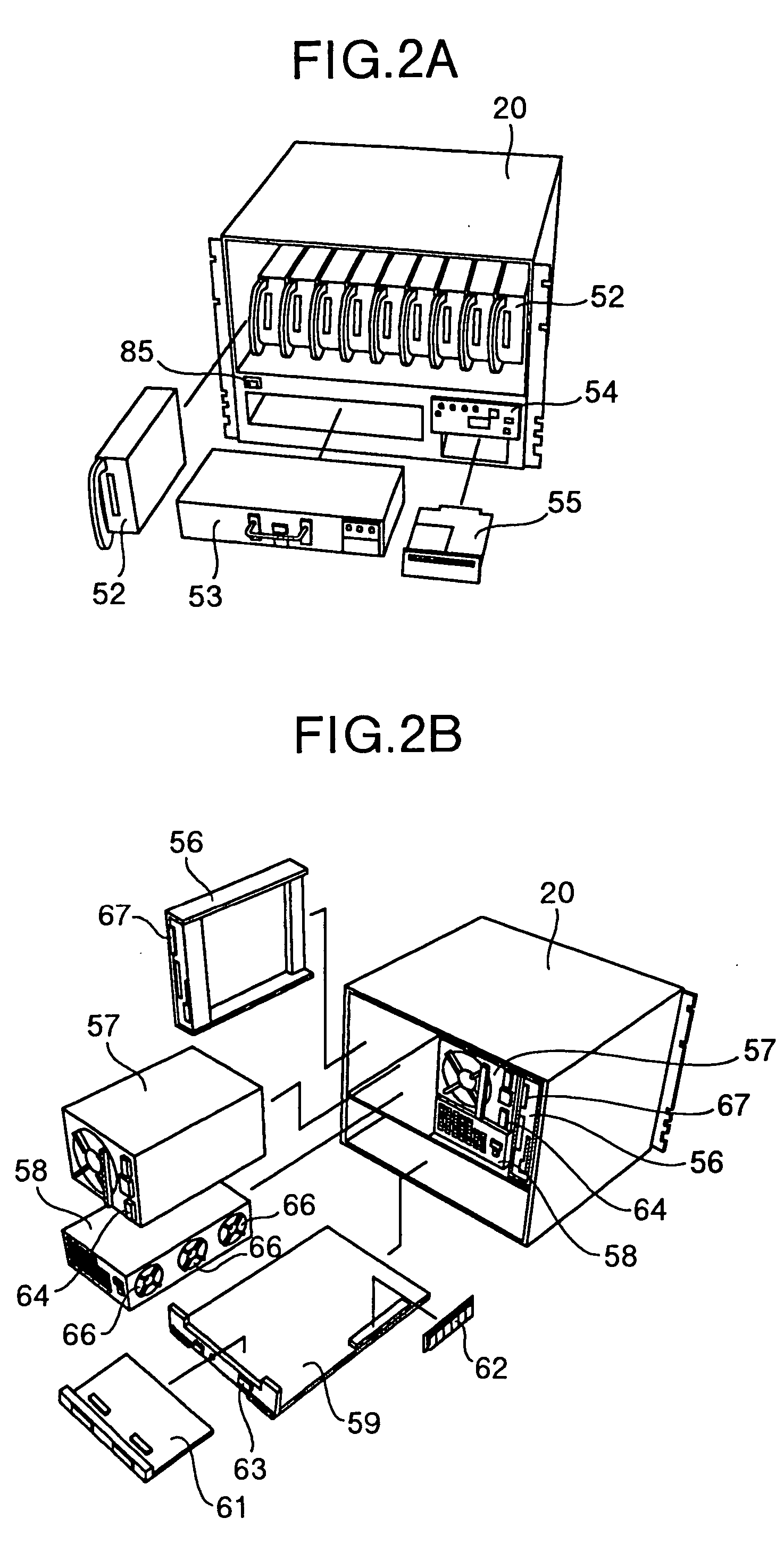

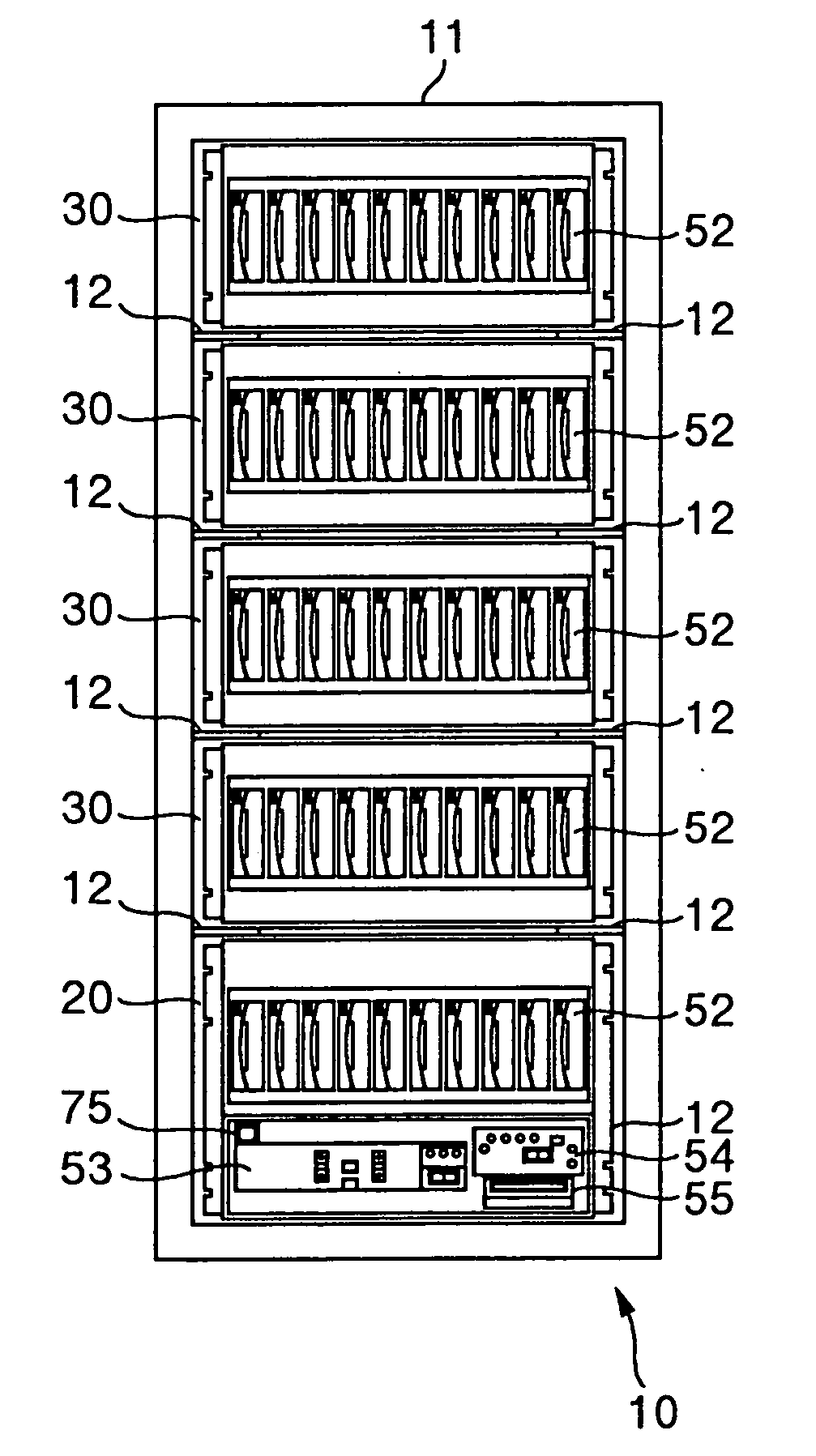

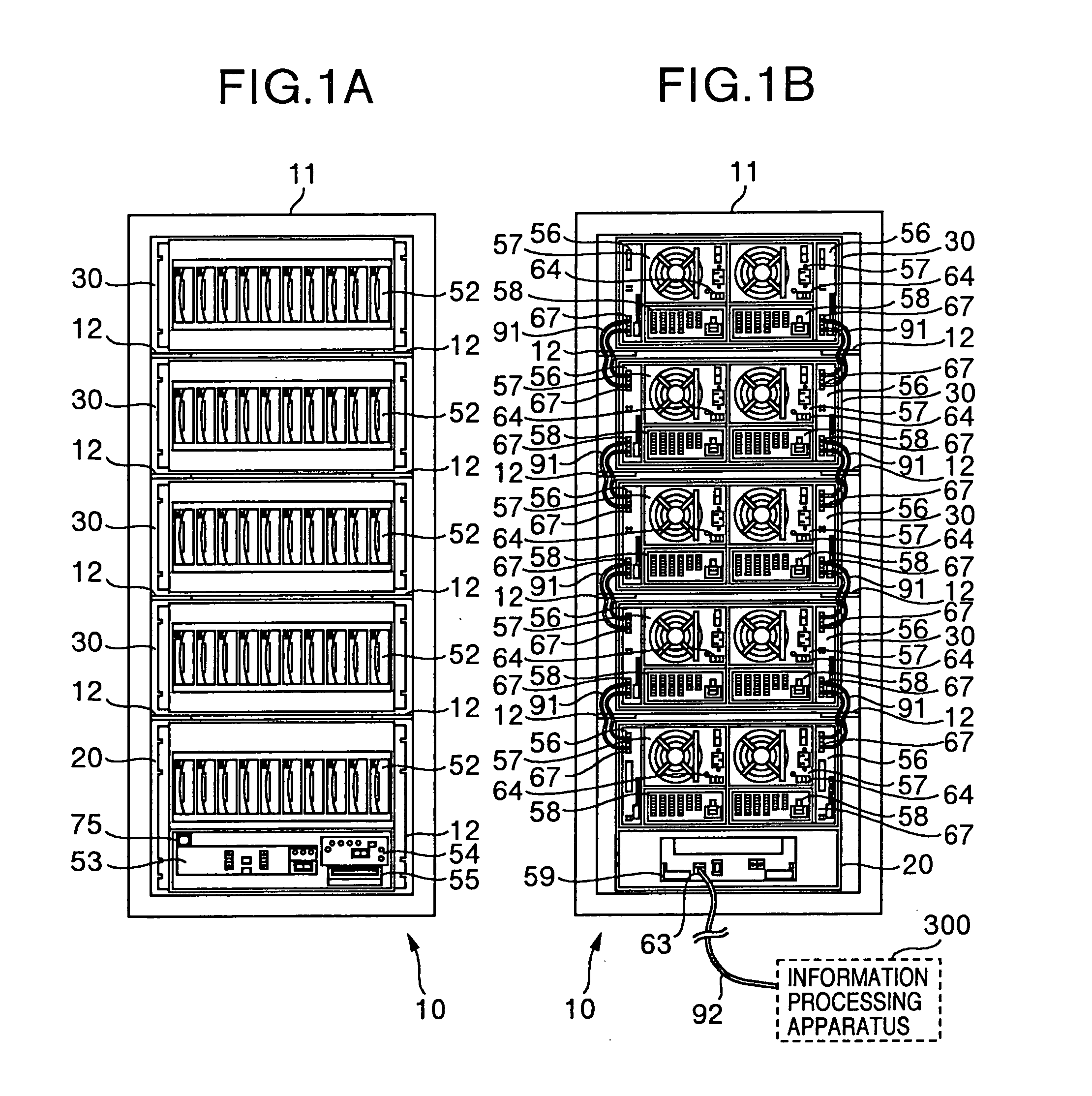

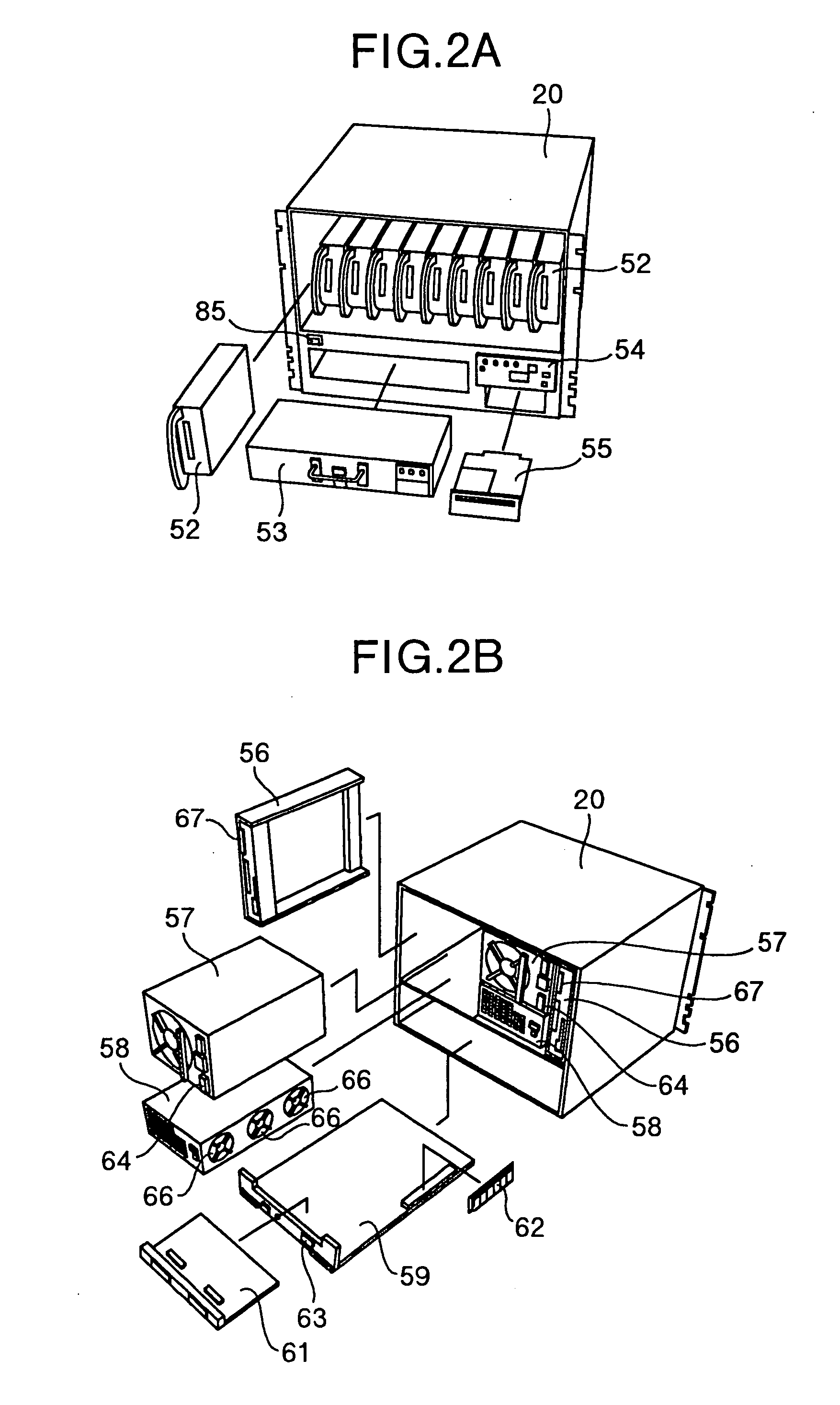

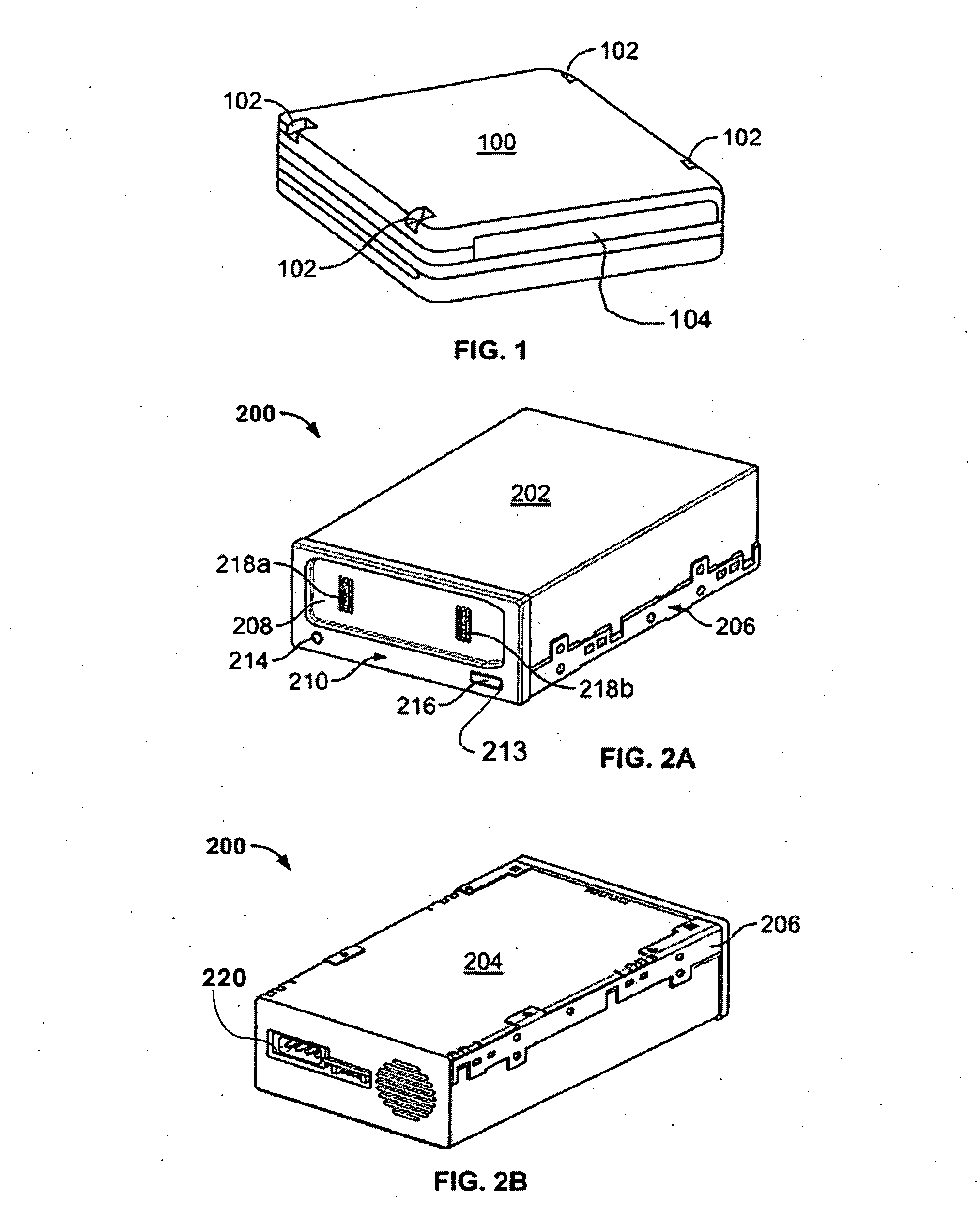

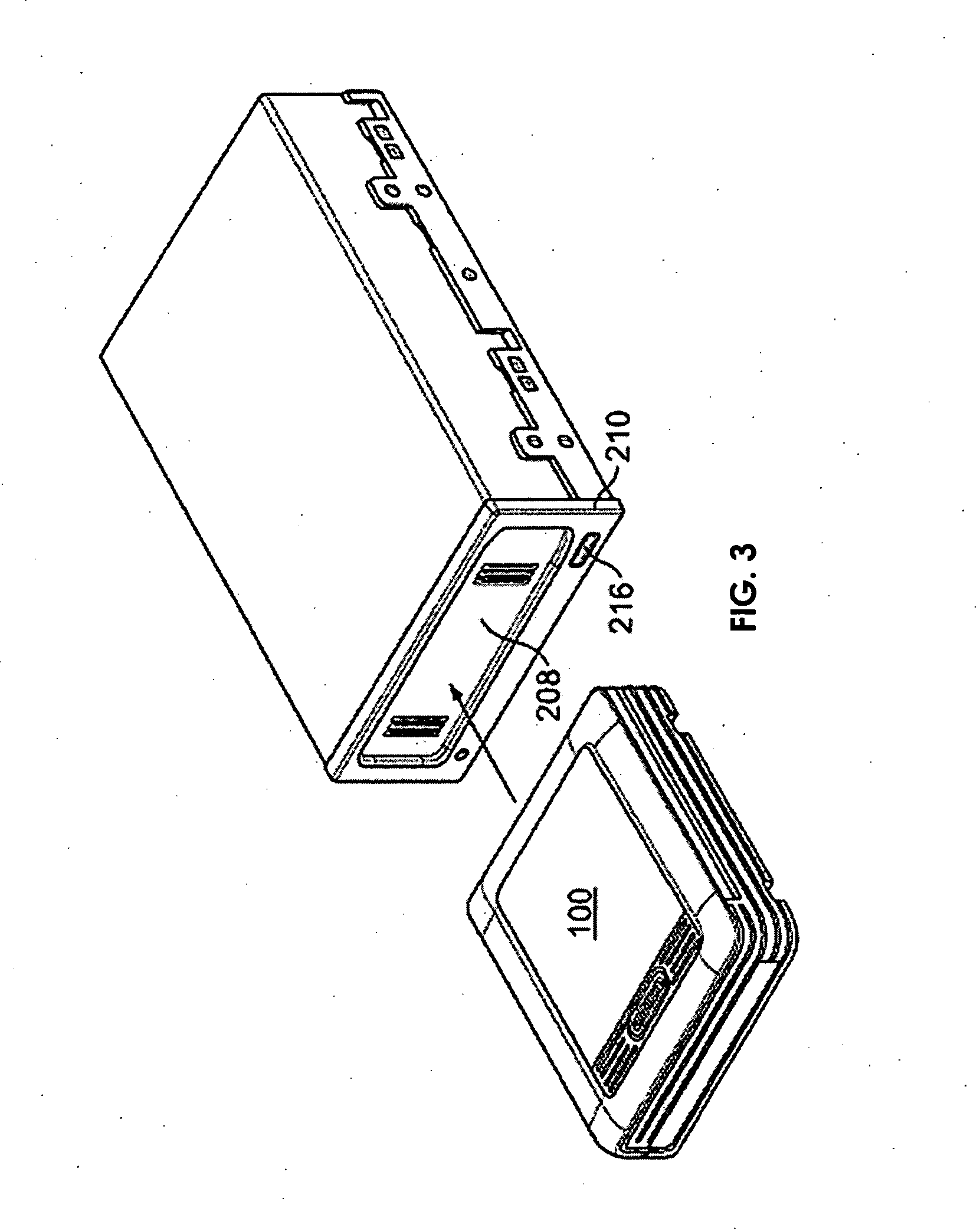

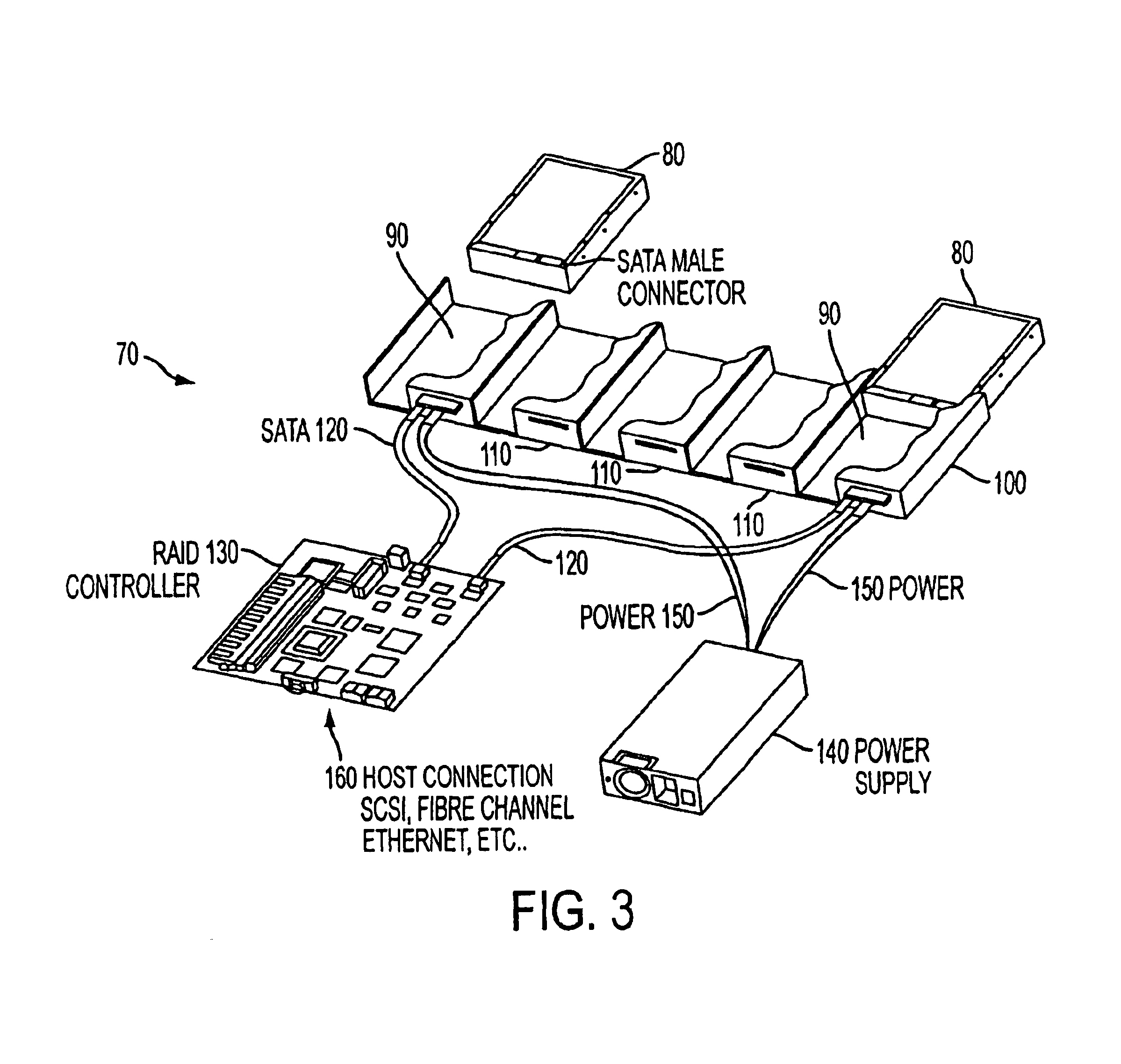

Modular sata data storage device assembly

InactiveUS20110090633A1Improve cooling effectDigital data processing detailsRecord information storageElectricityDrive bay

A modular data device assembly includes a chassis that has an open front and a back. The chassis also has exterior dimensions that correspond to the dimensions of an industry standard drive bay. The chassis further has a plurality of slots that are disposed inside the chassis. The modular data device also includes a plurality of Serial ATA disk data storage devices, a backplane, and a connector. Each Serial ATA disk data storage device is disposed in one of the plurality of slots. The backplane is disposed in the back of the chassis. The backplane has a plurality of connectors which are mechanically coupled thereto and each of which is connected to one of the Serial ATA disk data storage devices. The power source connector is mechanically and electrically coupled to the backplane.

Owner:RABINOVITZ JOSEF

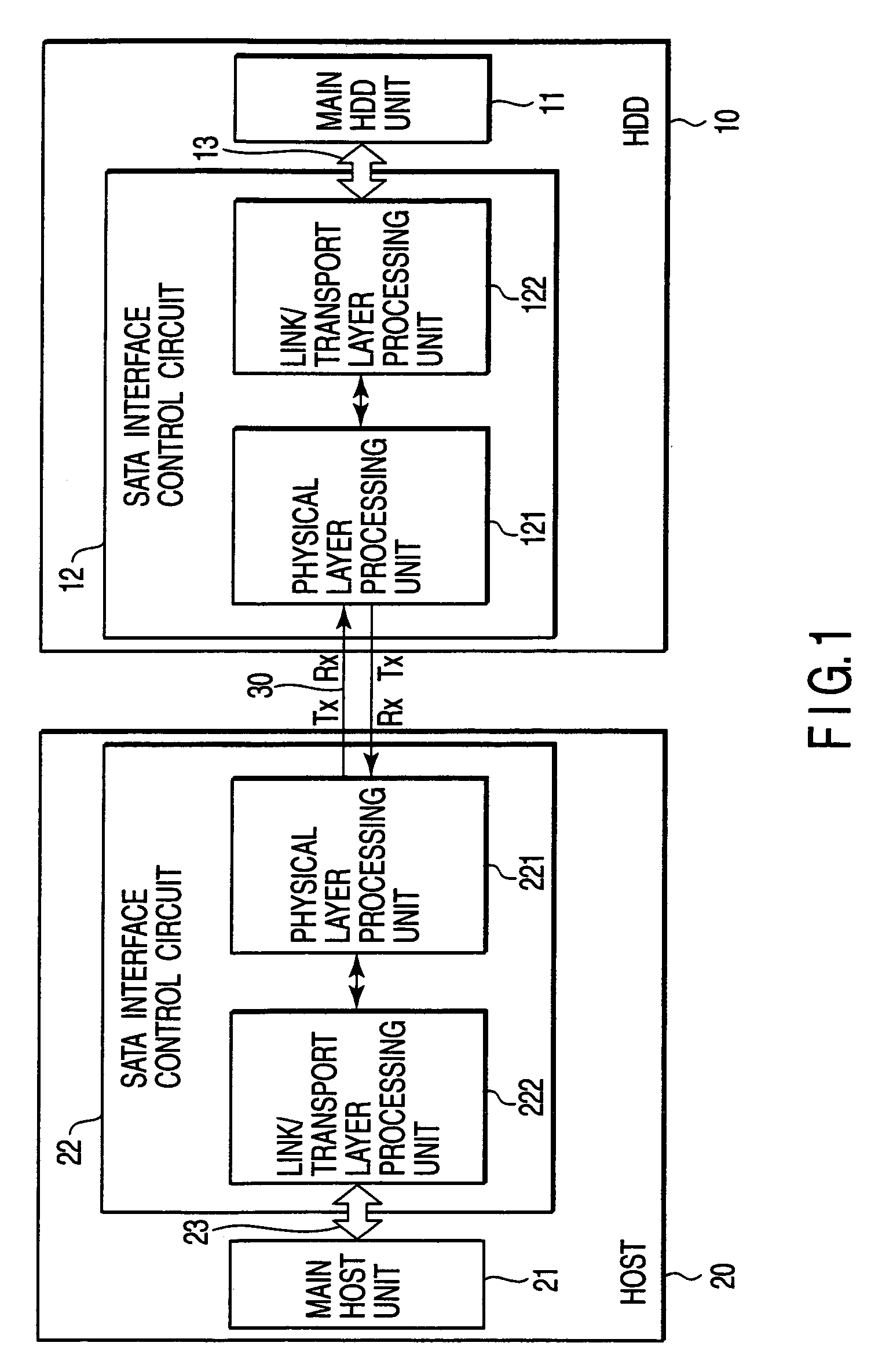

Electronic device with serial ATA interface and power saving method for serial ATA buses

ActiveUS20050235171A1Reduce power consumptionUtilizing power saving modeEnergy efficient ICTInput/output to record carriersSerial ATAElectronic equipment

In an electronic device with a serial ATA interface, upon detection of the issue or reception of a preset command, a confirmation device, such as a CPU, confirms the completion of execution of the command. Upon confirming the completion of execution of the command, a controller, which may also be the CPU, controls shifting of the serial ATA interface to a power saving mode.

Owner:KK TOSHIBA

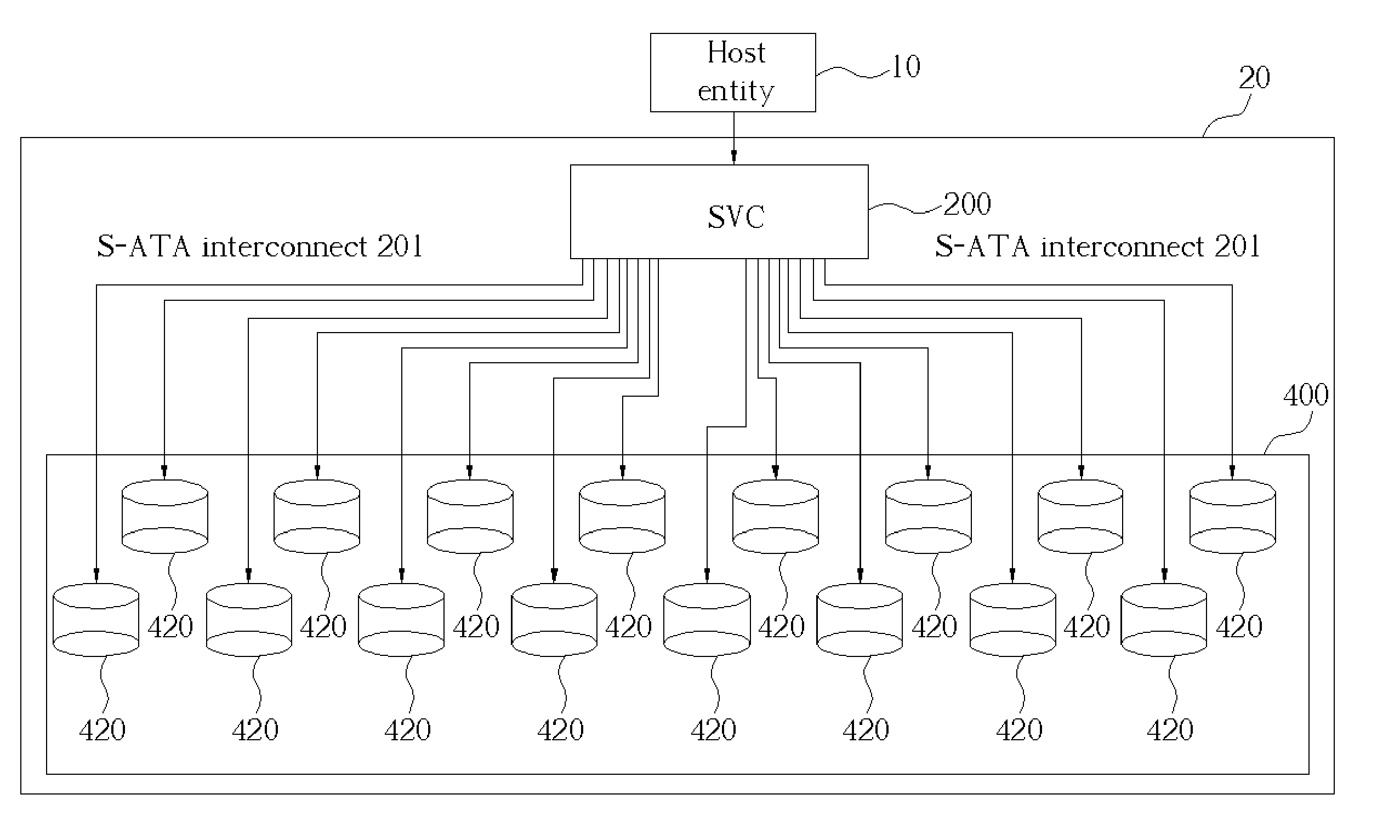

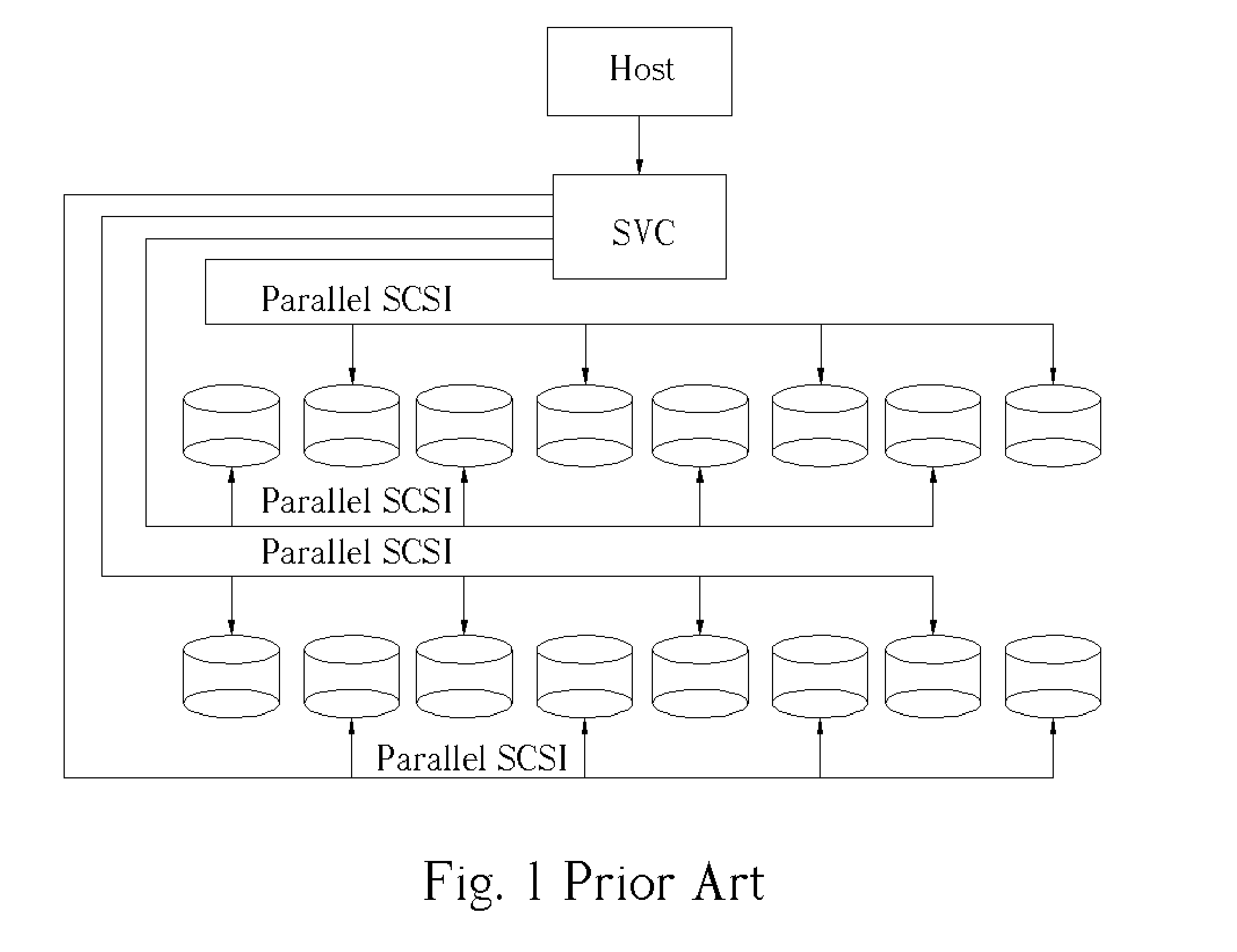

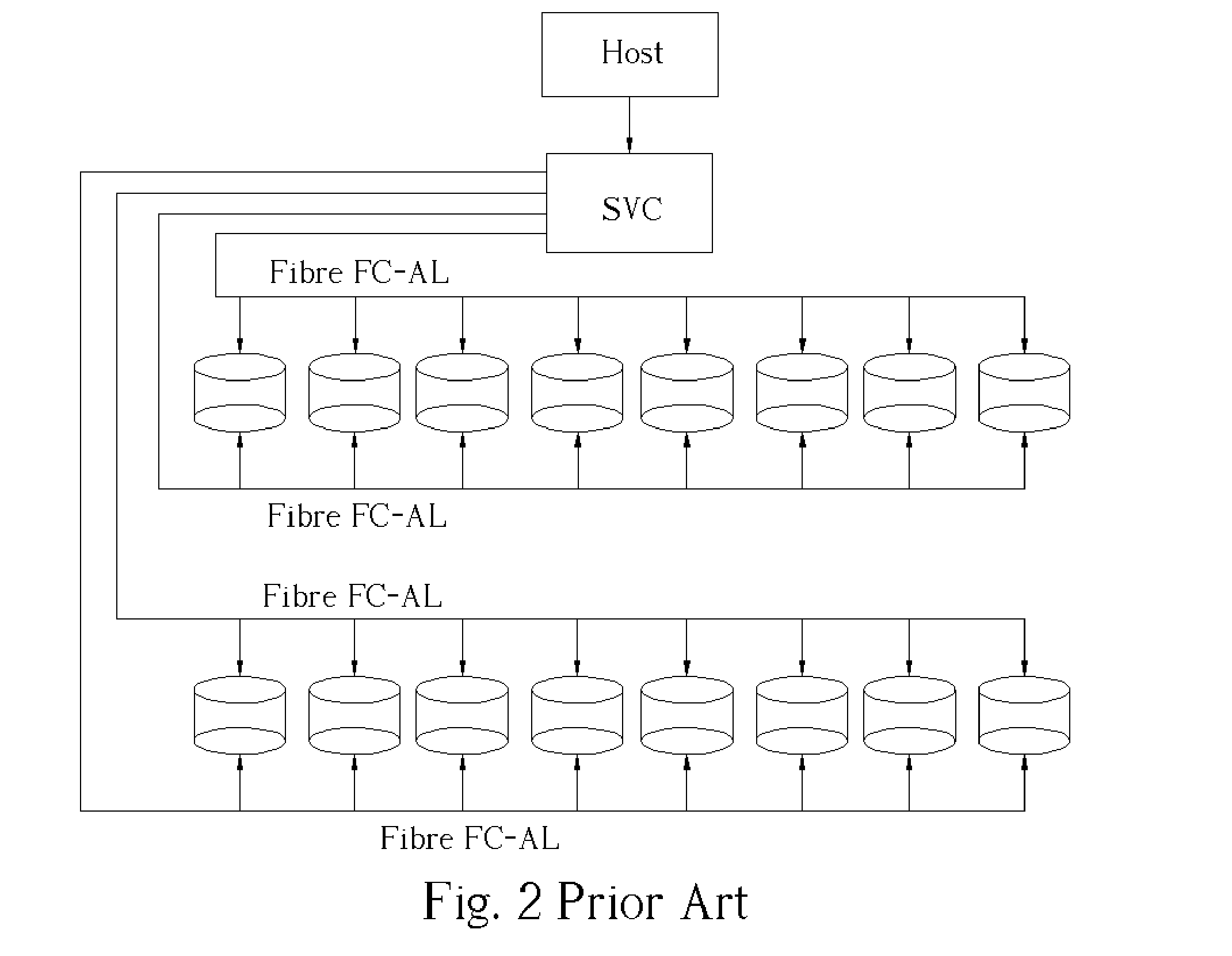

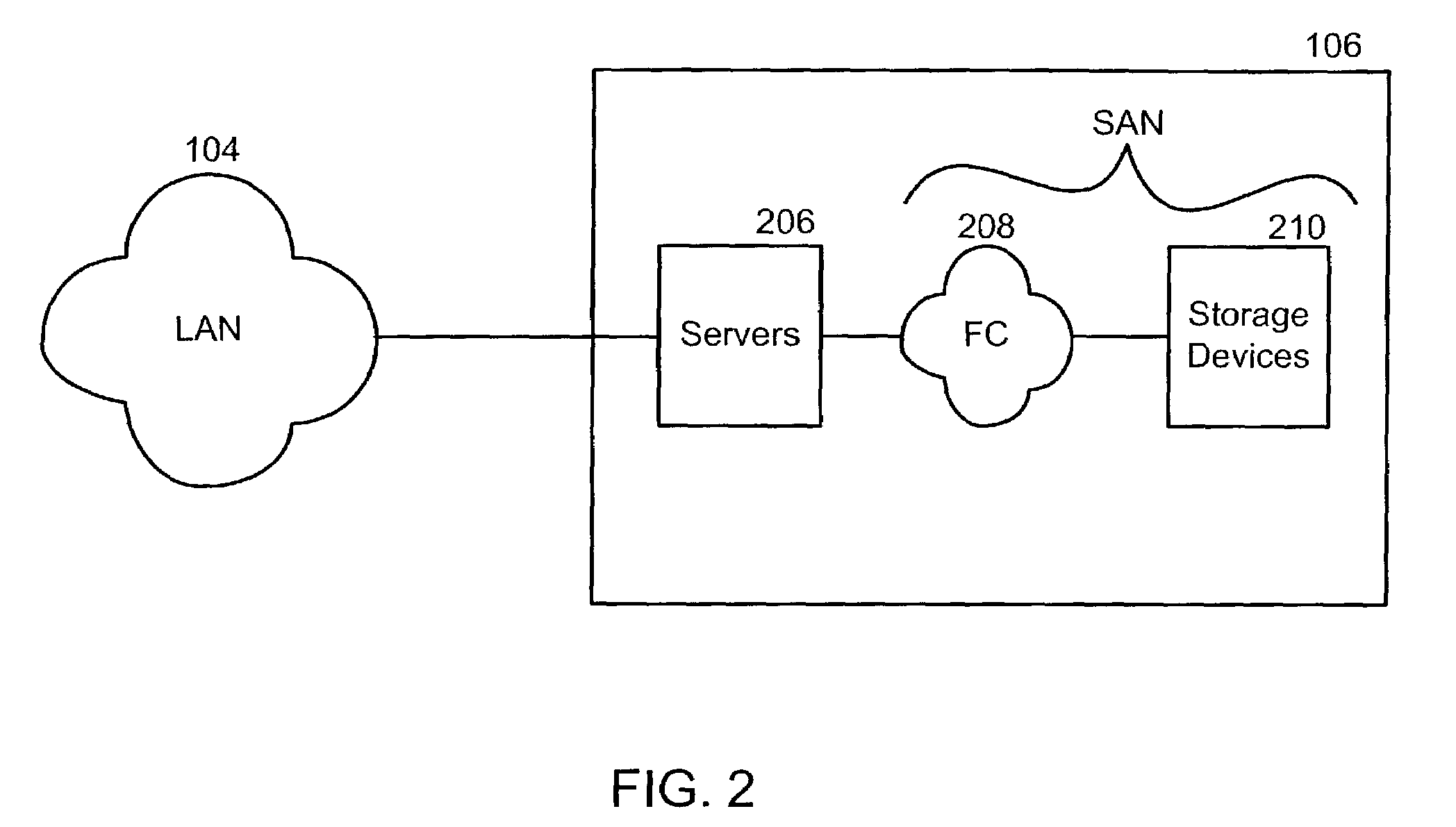

Storage virtualization computer system and external controller therefor

ActiveUS20050005044A1Input/output to record carriersMemory adressing/allocation/relocationSerial ATAHost machine

Owner:INFORTREND TECH INC

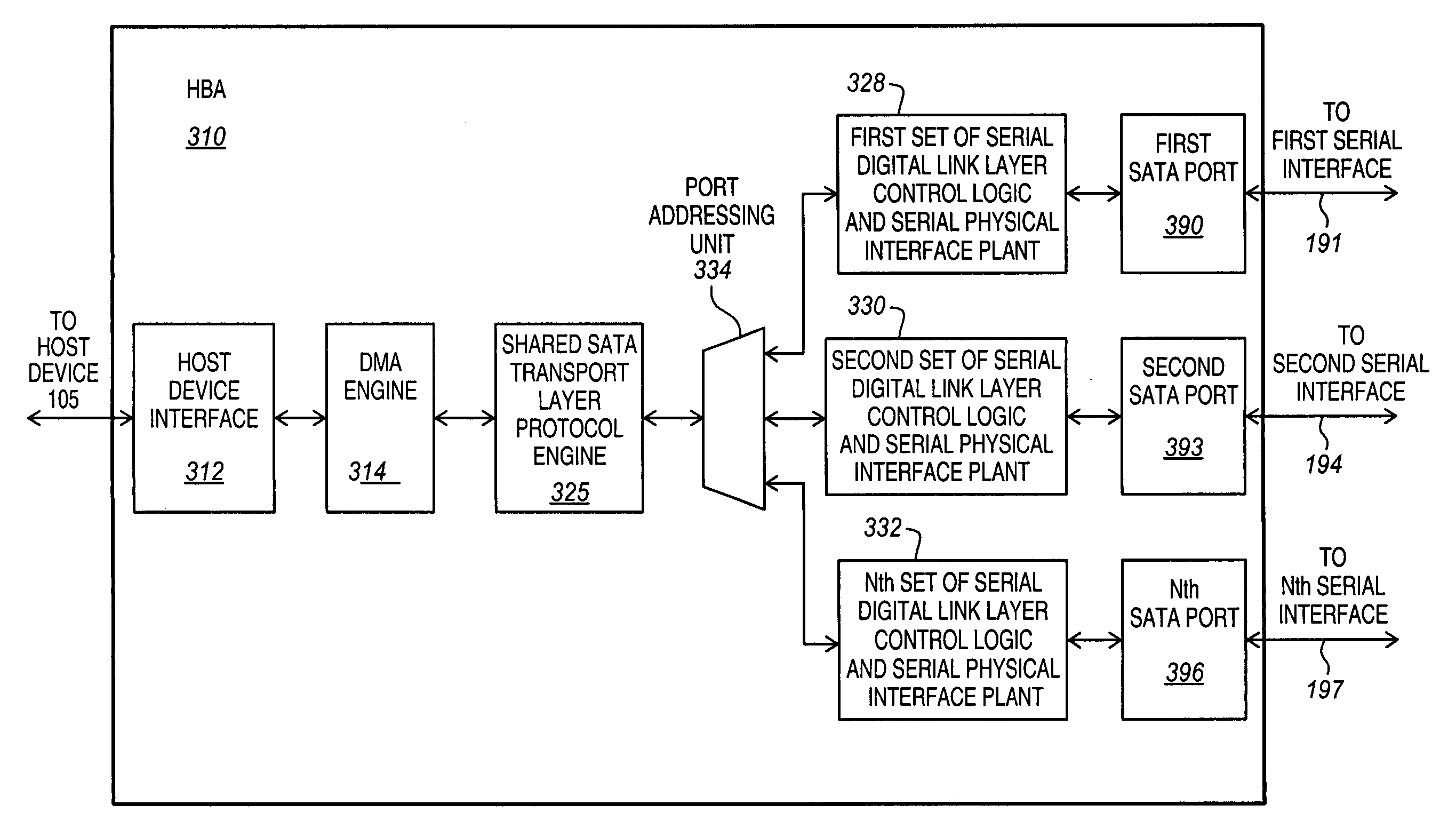

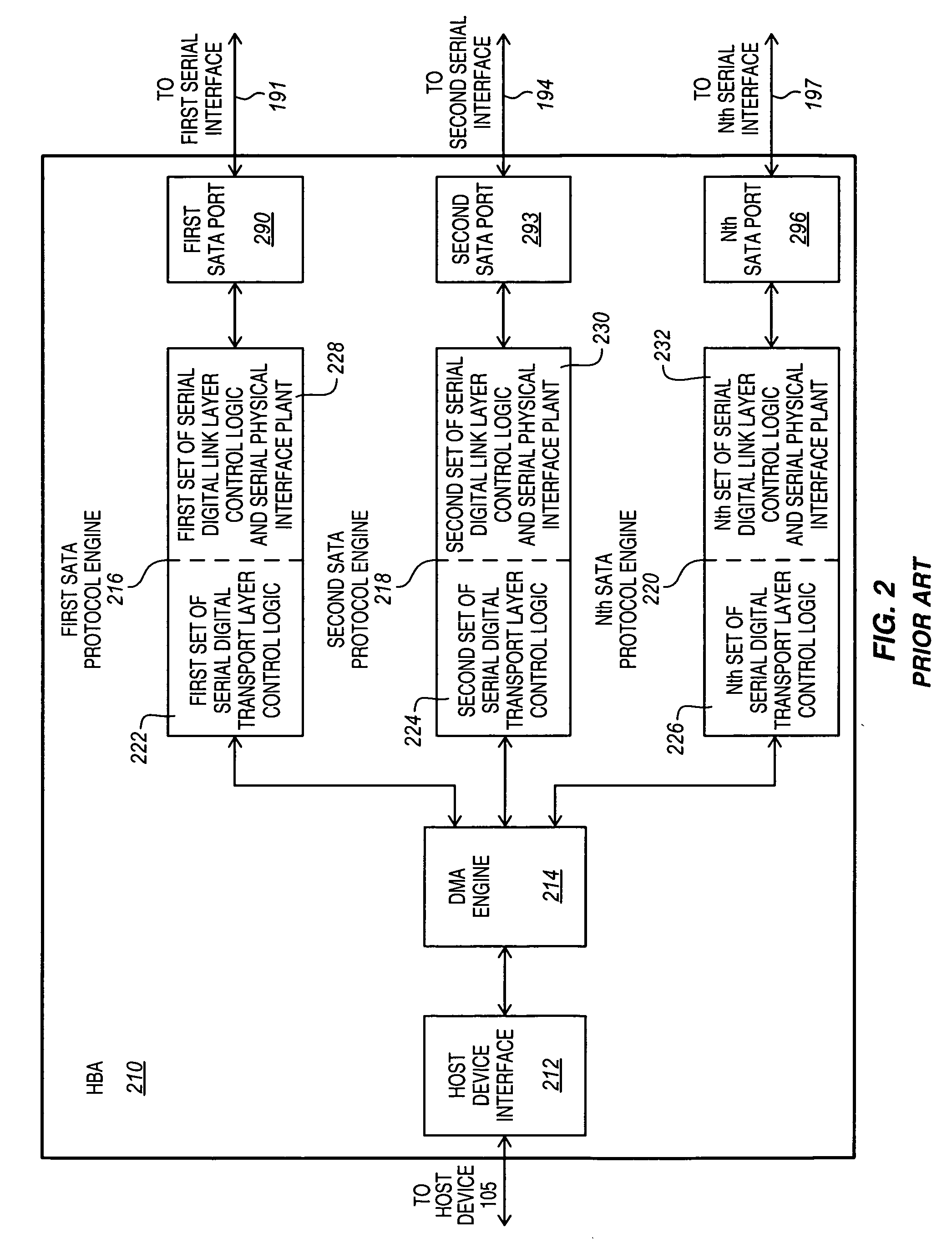

Serial ATA port addressing

ActiveUS20070005838A1Data switching networksInput/output processes for data processingTransport layerSerial ATA

In one aspect, a shared transport layer frame information structure (FIS) generation logic may generate FISes for each of a plurality of SATA ports. In a further aspect, a port addressing logic, in communication with the shared transport layer FIS generation logic, may select one of the SATA ports for each of the FISes.

Owner:INTEL CORP

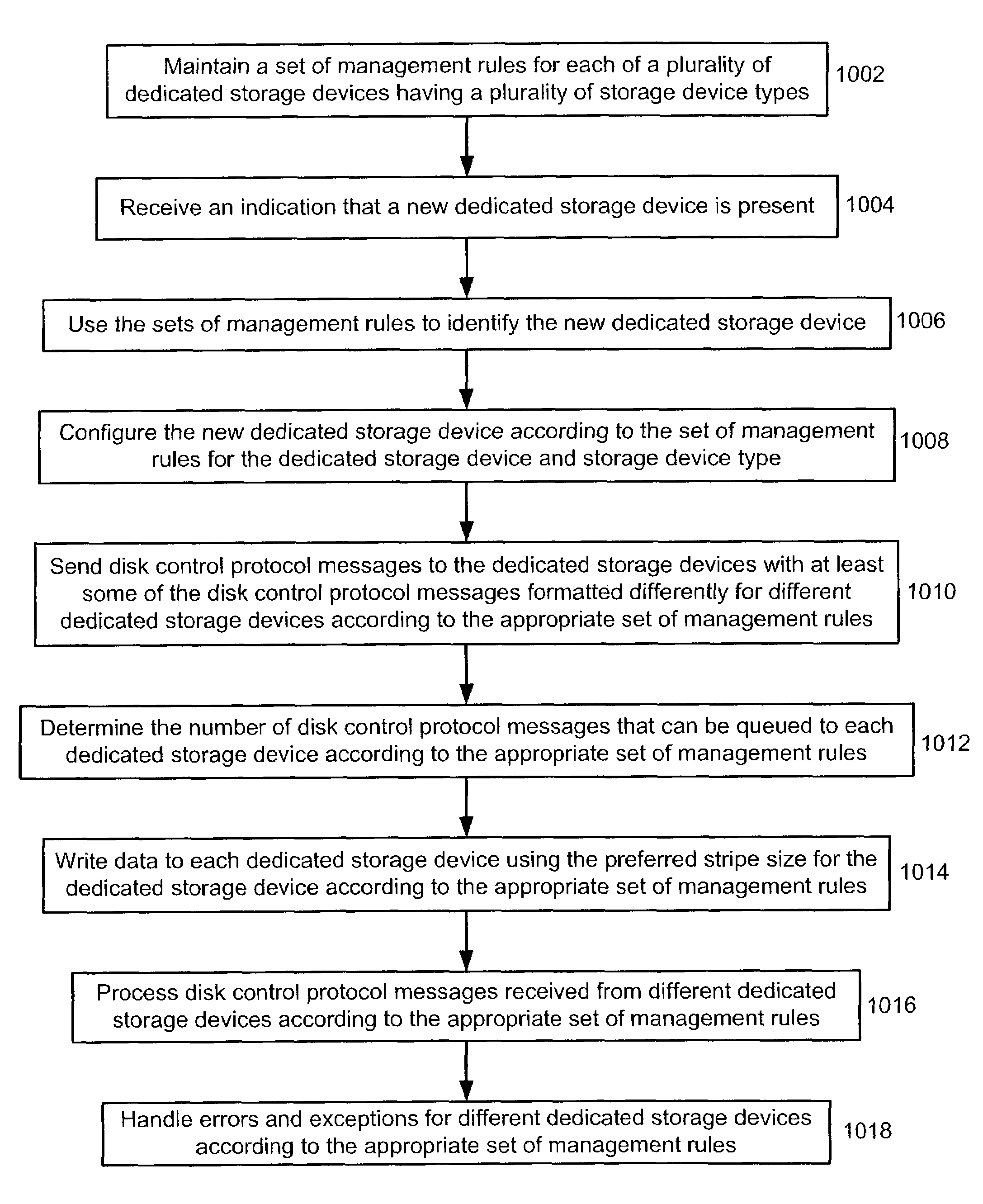

Network-attached storage system, device, and method supporting multiple storage device types

ActiveUS7237021B2Input/output to record carriersDigital computer detailsSolid-state storageDevice type

A network-attached system, device, and method supports storage devices having a plurality of storage device types, such as Fibre Channel storage devices, ATA storage devices, serial attached SCSI storage devices, serial ATA storage devices, and solid stage storage devices. Each storage device having a different storage device type is associated with a set of management rules. The management rules may includes rules for such things as identifying the dedicated storage device, configuring the dedicated storage device, sending disk protocol messages to the dedicated storage device, handling disk protocol message received from the dedicated storage device, and handling error and exception conditions.

Owner:HITACHI VANTARA LLC

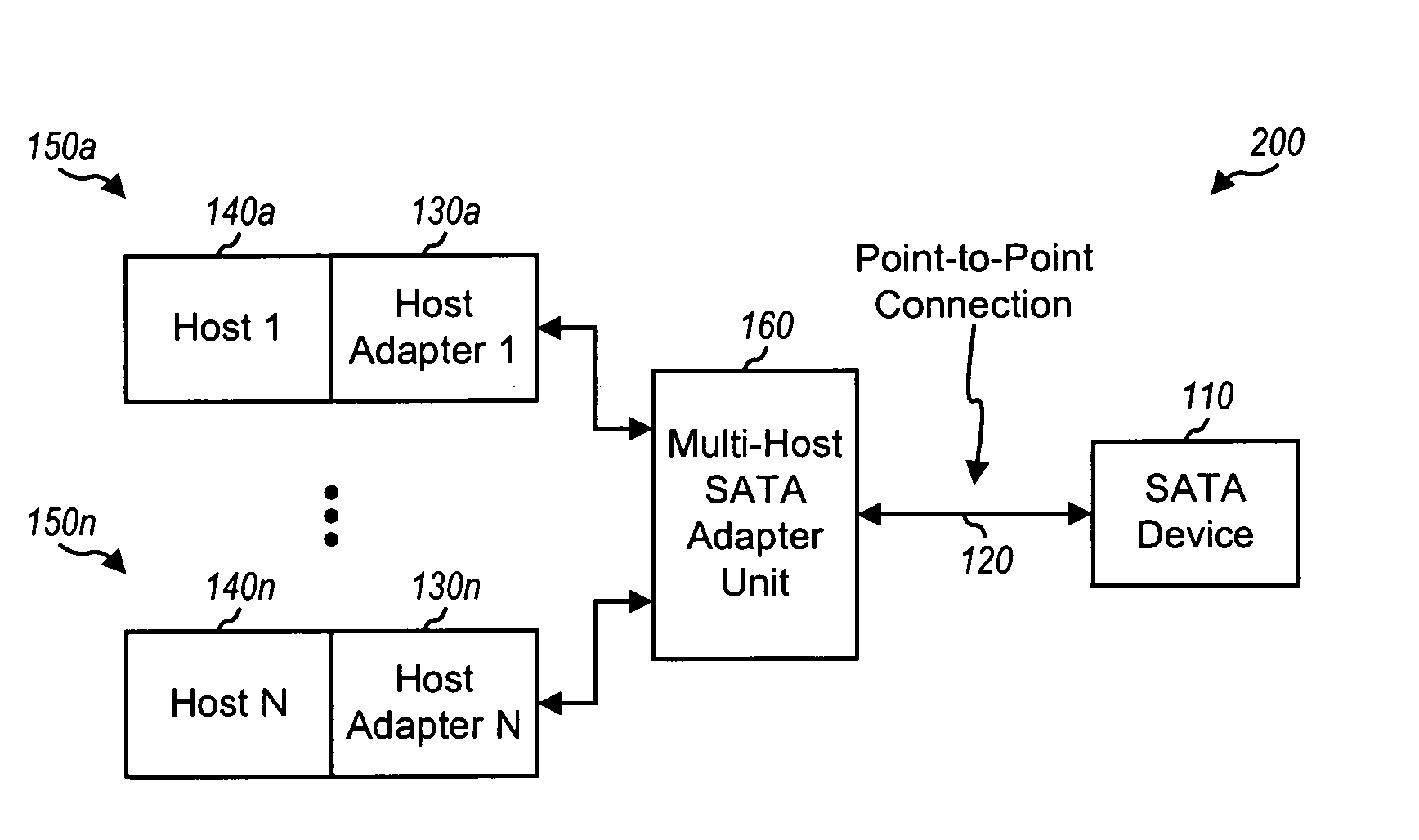

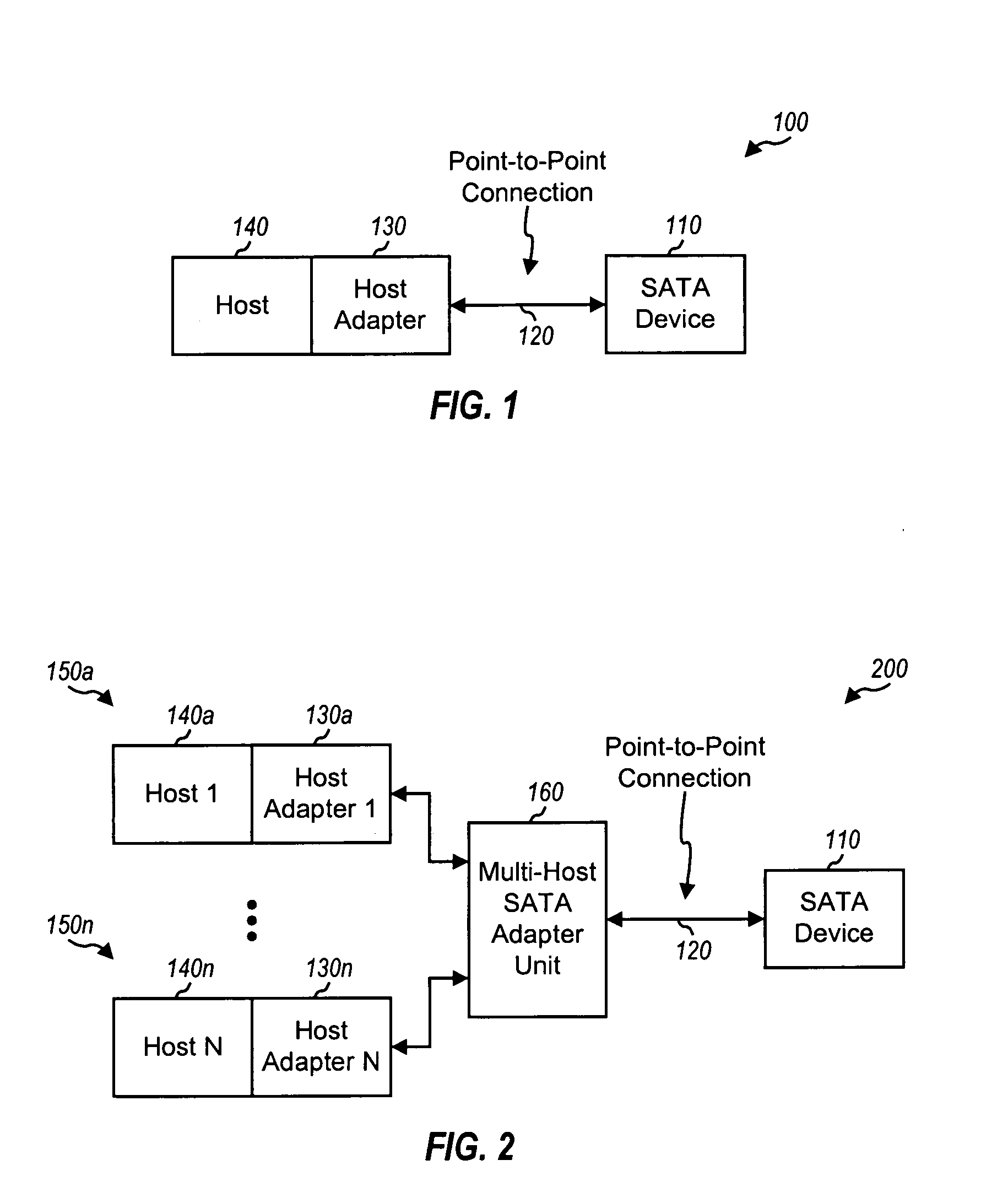

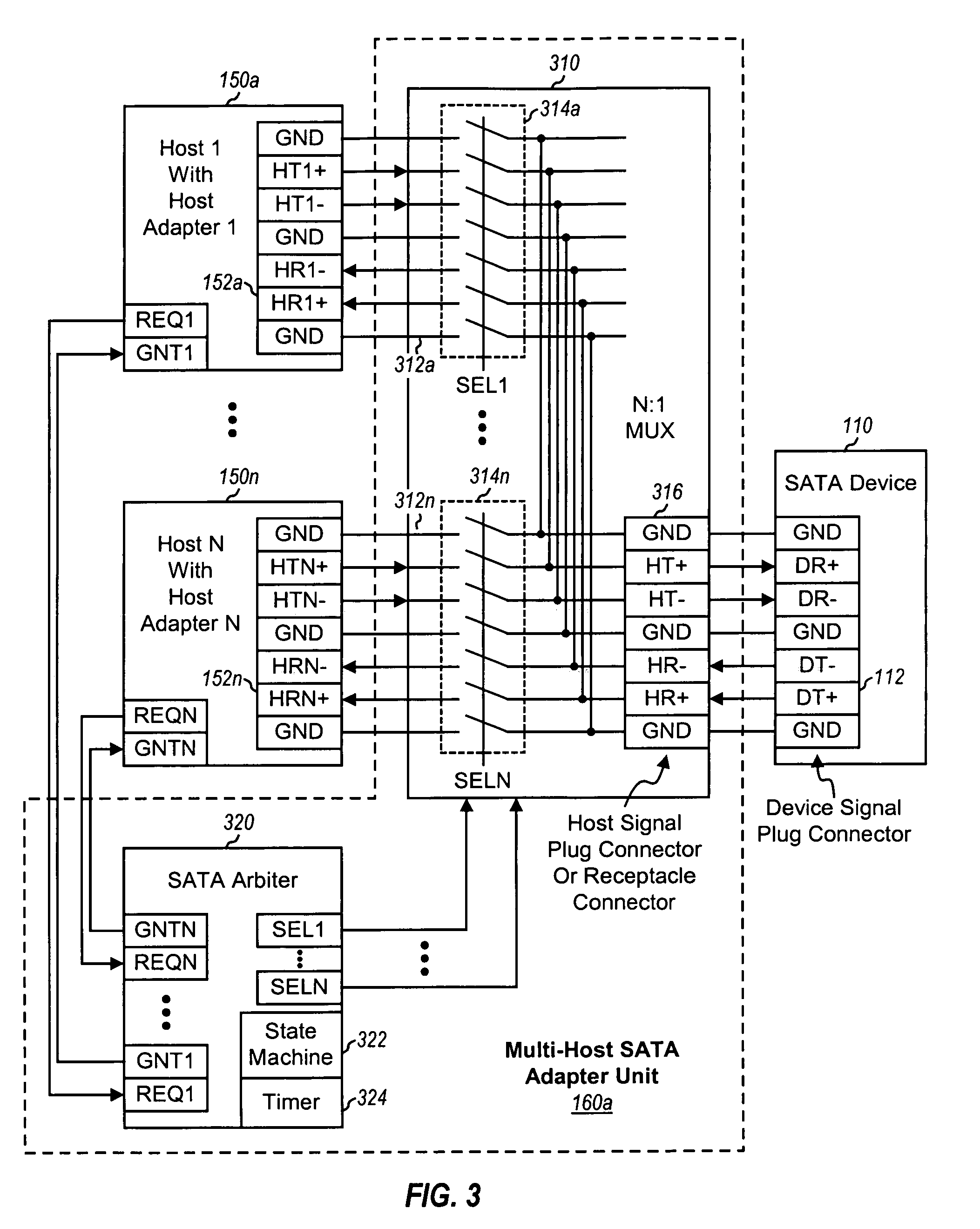

Method and apparatus for supporting access of a serial ATA storage device by multiple hosts with separate host adapters

An adapter unit operative to support access of an SATA storage device by a plurality of hosts associated with separate host adapters. The adapter unit includes a multiplexer coupled to an arbiter. The multiplexer receives a plurality of sets of communication signals, one signal set for each host adapter. The multiplexer then selects one of the signal sets based on a control signal and couples the selected signal set to its output. The arbiter receives requests from the hosts to access the SATA storage device, selects a particular requesting host, and provides the control signal indicative of the specific host granted access. The host adapter for the granted host and the SATA storage device are placed in a PHY READY power management state, prior to a read or write access, and are placed in a PARTIAL power management state after the read or write access.

Owner:RESILIENT

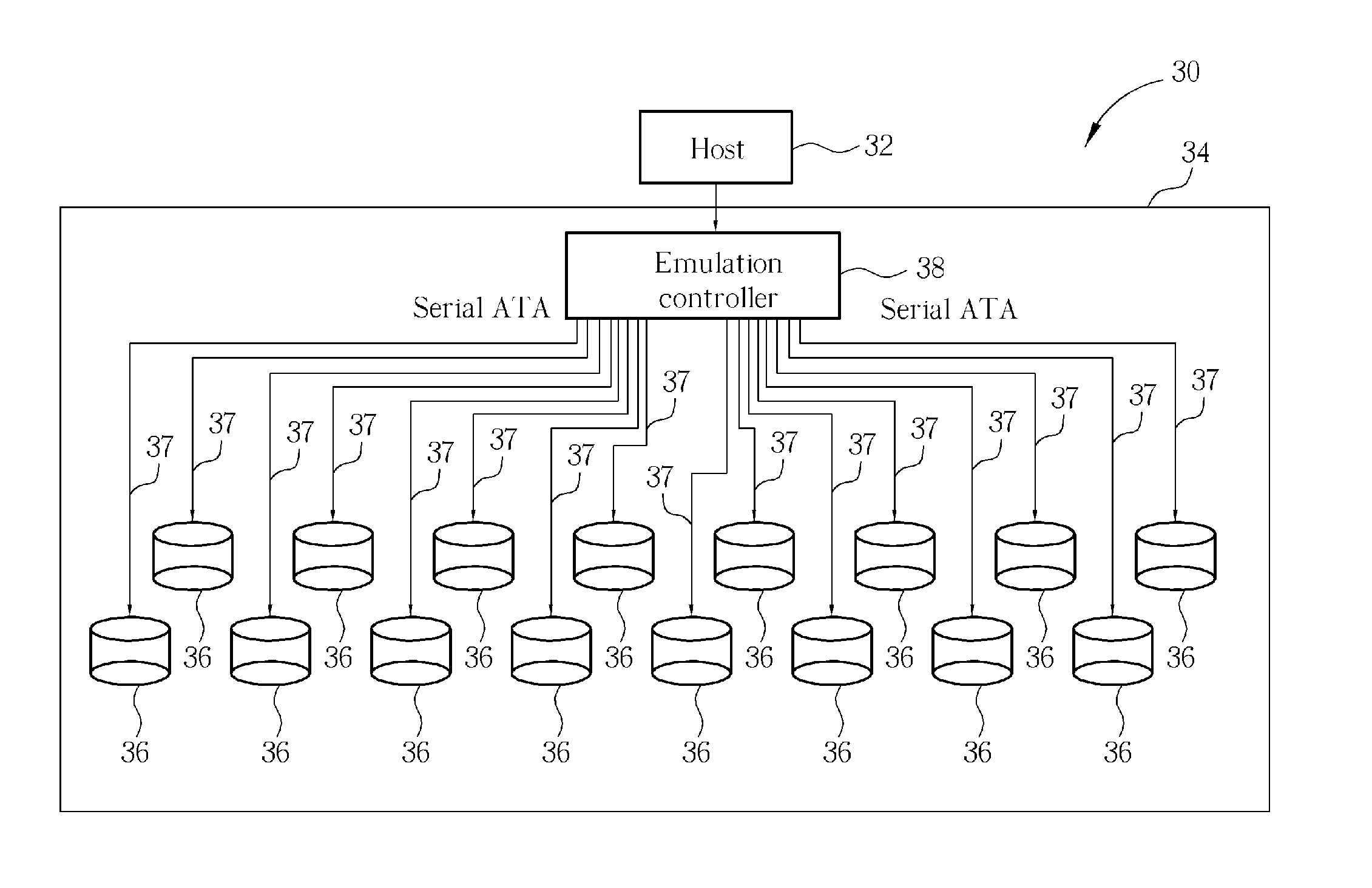

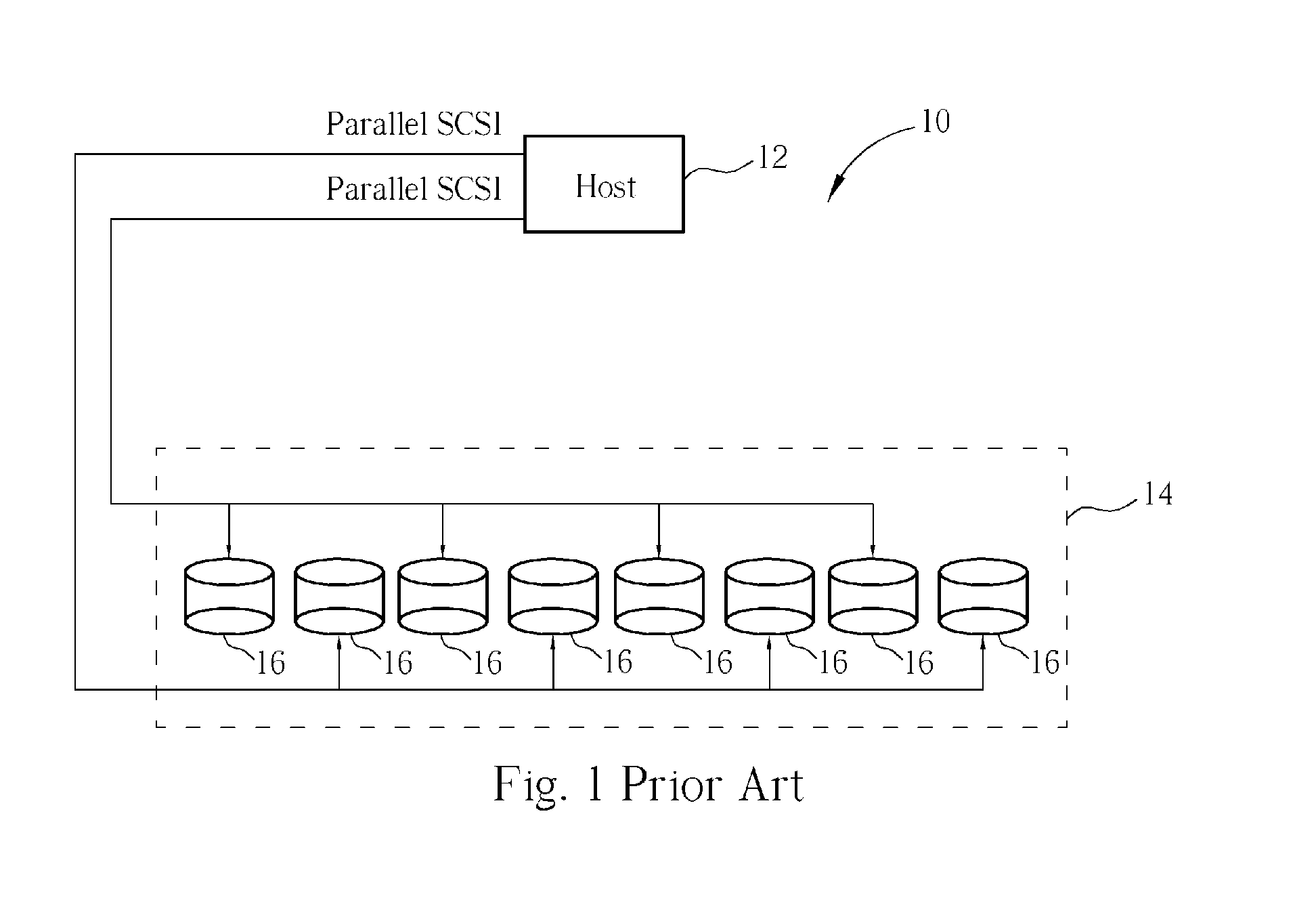

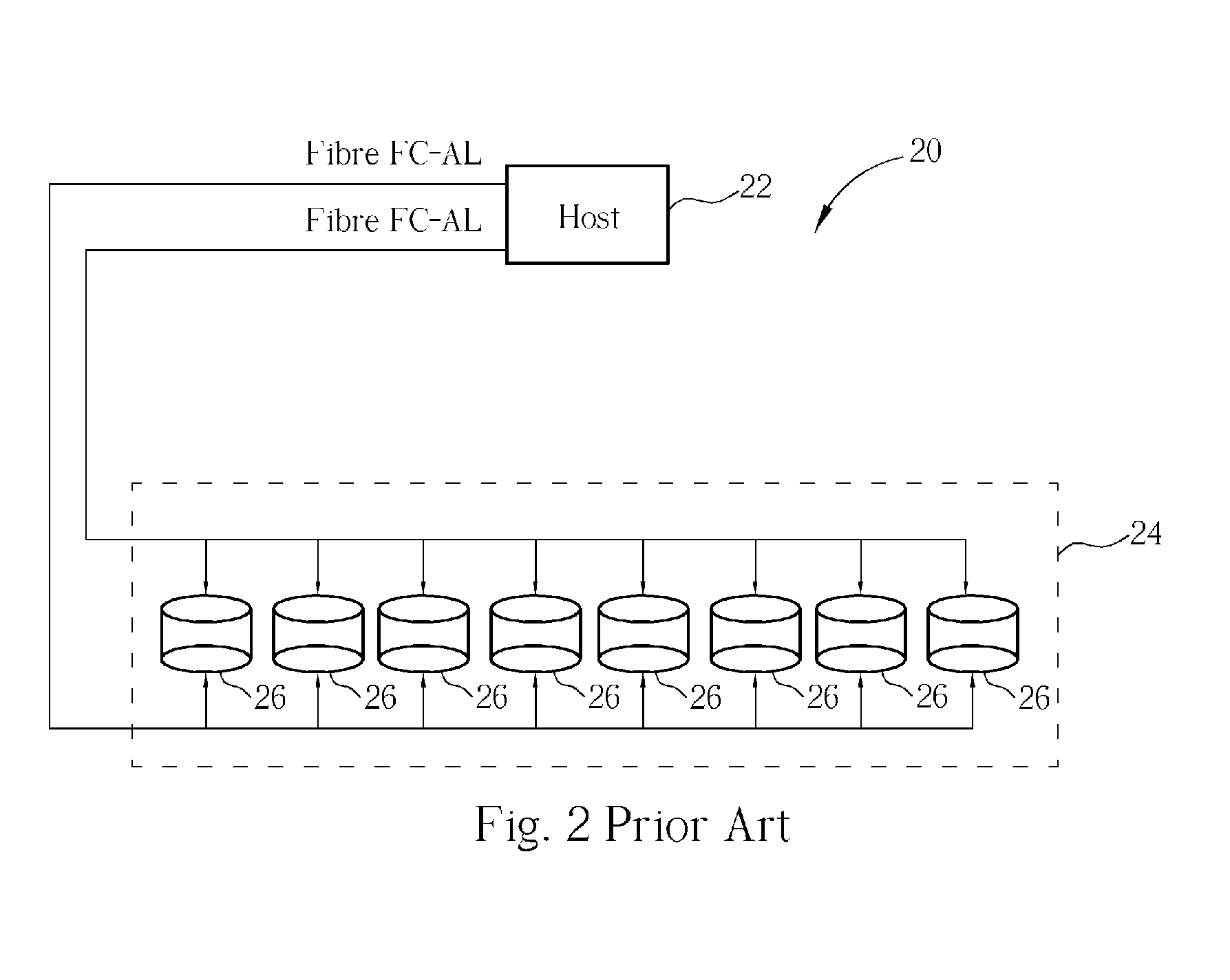

JBOD subsystem and external emulation controller thereof

ActiveUS20050005063A1Input/output to record carriersMemory adressing/allocation/relocationNon-RAID drive architecturesSerial ATA

A JBOD subsystem for providing storage to a host entity. The JBOD subsystem contains at least one external JBOD emulation controller coupled to the host entity for emulating IO operations in response to the IO requests and a set of at least one physical storage device coupled to the JBOD emulation controller for providing storage to the host entity through the JBOD emulation controller. The JBOD emulation controller defines at least one logical media unit (LMU) consisting of sections of the set of physical storage device (PSD) and communicates with the PSD through a point-to-point serial-signal interconnect. As an example, the point-to-point serial-signal interconnect can be a Serial ATA IO device interconnect.

Owner:INFORTREND TECH INC

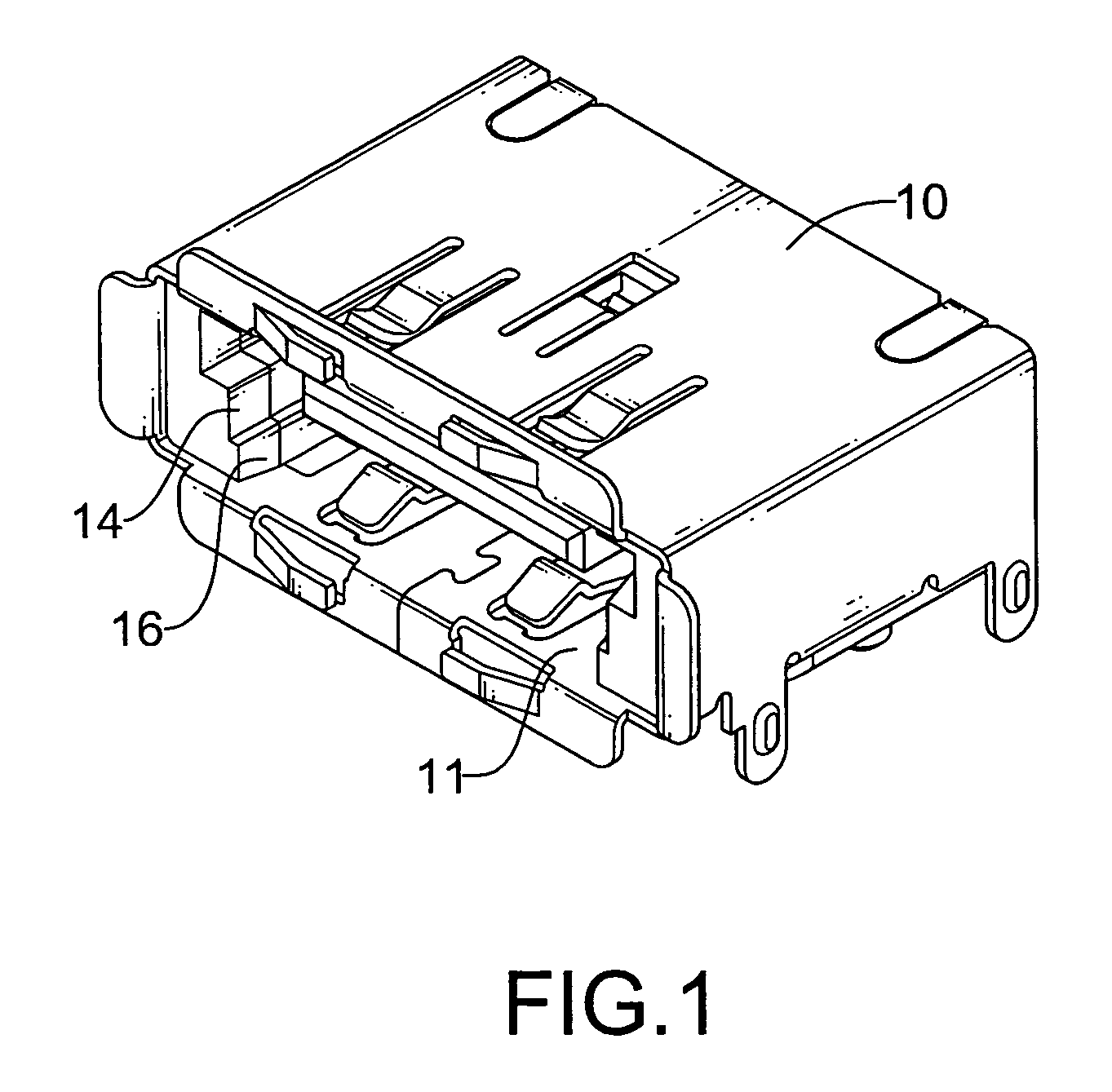

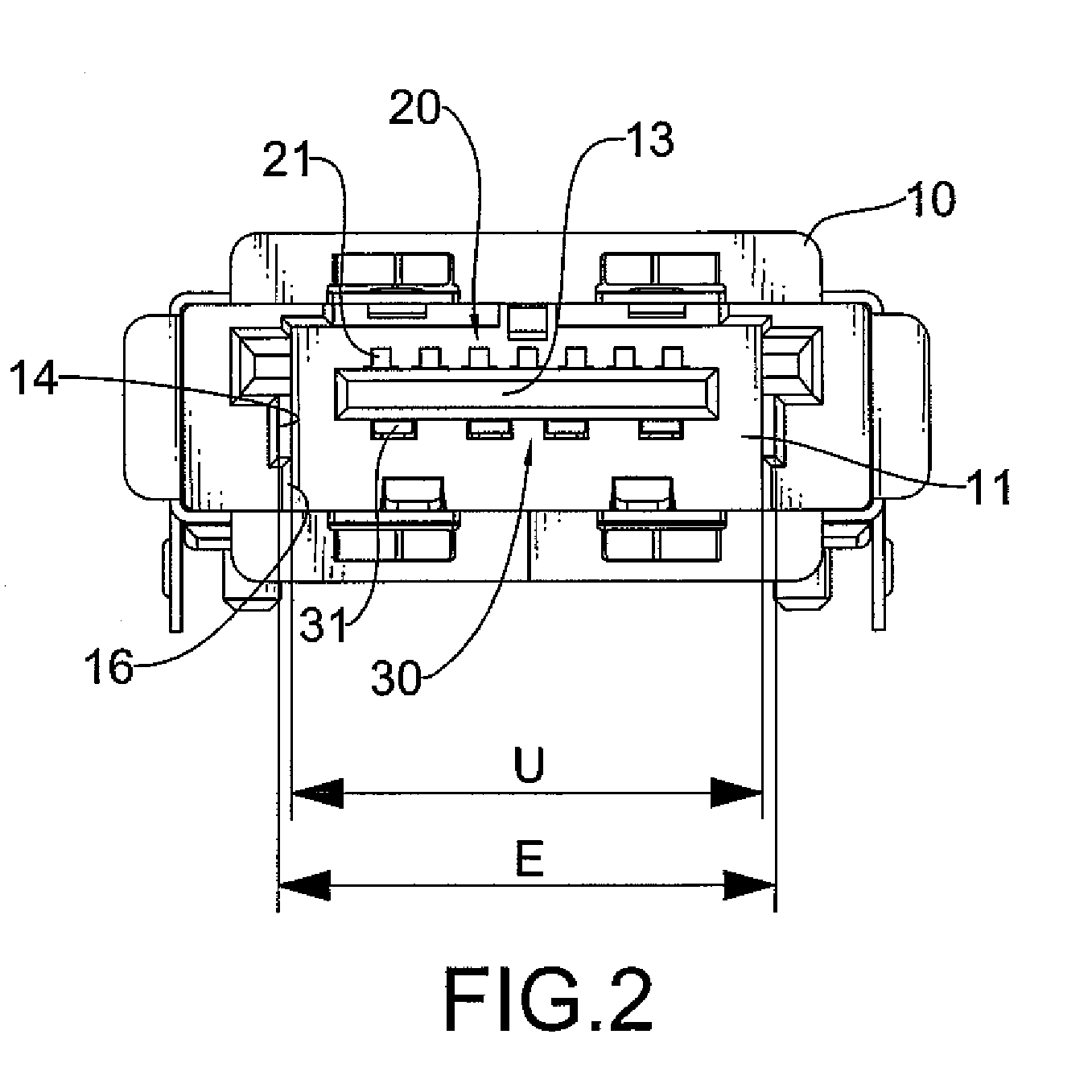

Connector socket for eSATA and USB plugs

ActiveUS7371116B2Two-part coupling devicesCoupling protective earth/shielding arrangementsEngineeringUSB

Owner:TAIWAN ELECTRONICS

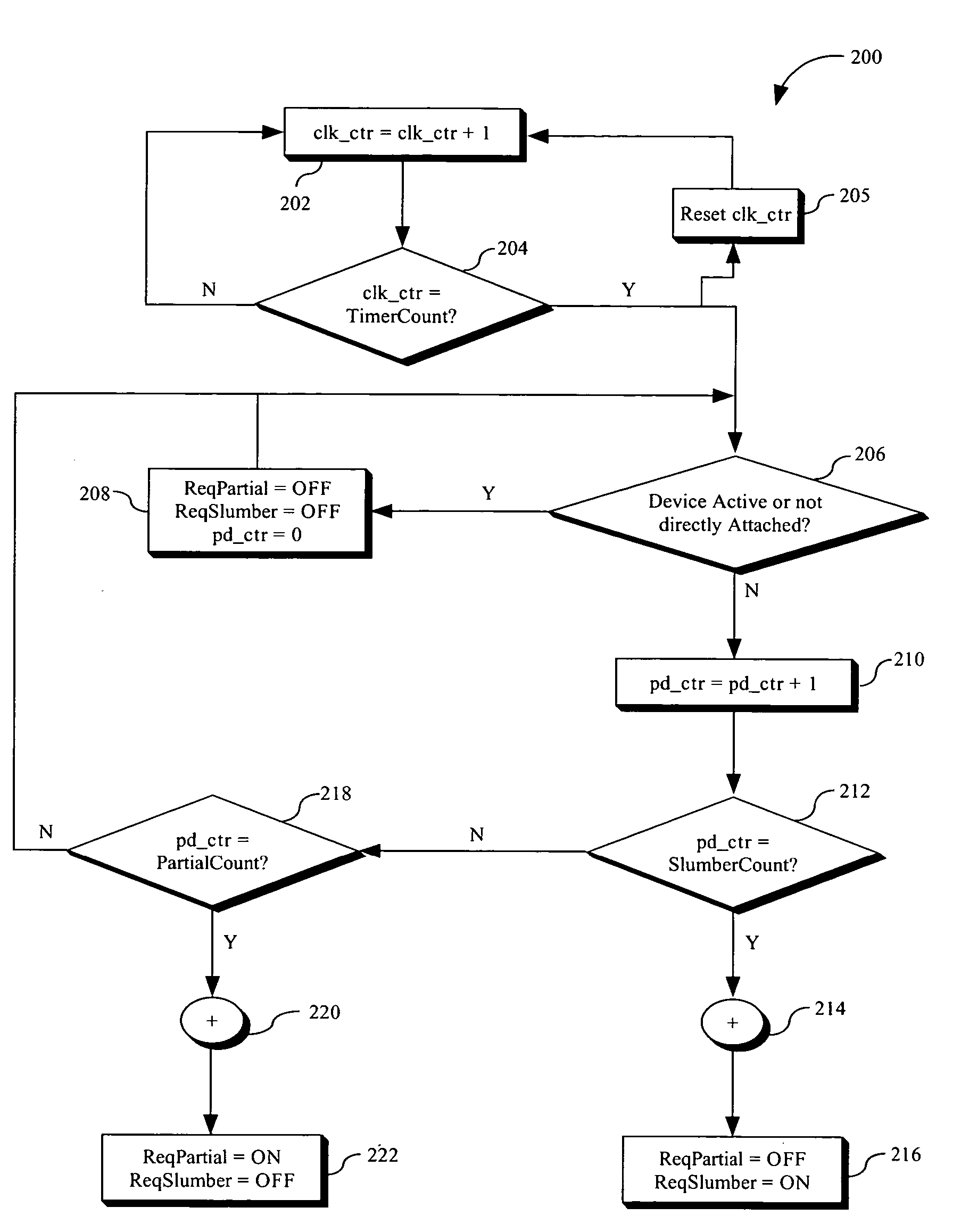

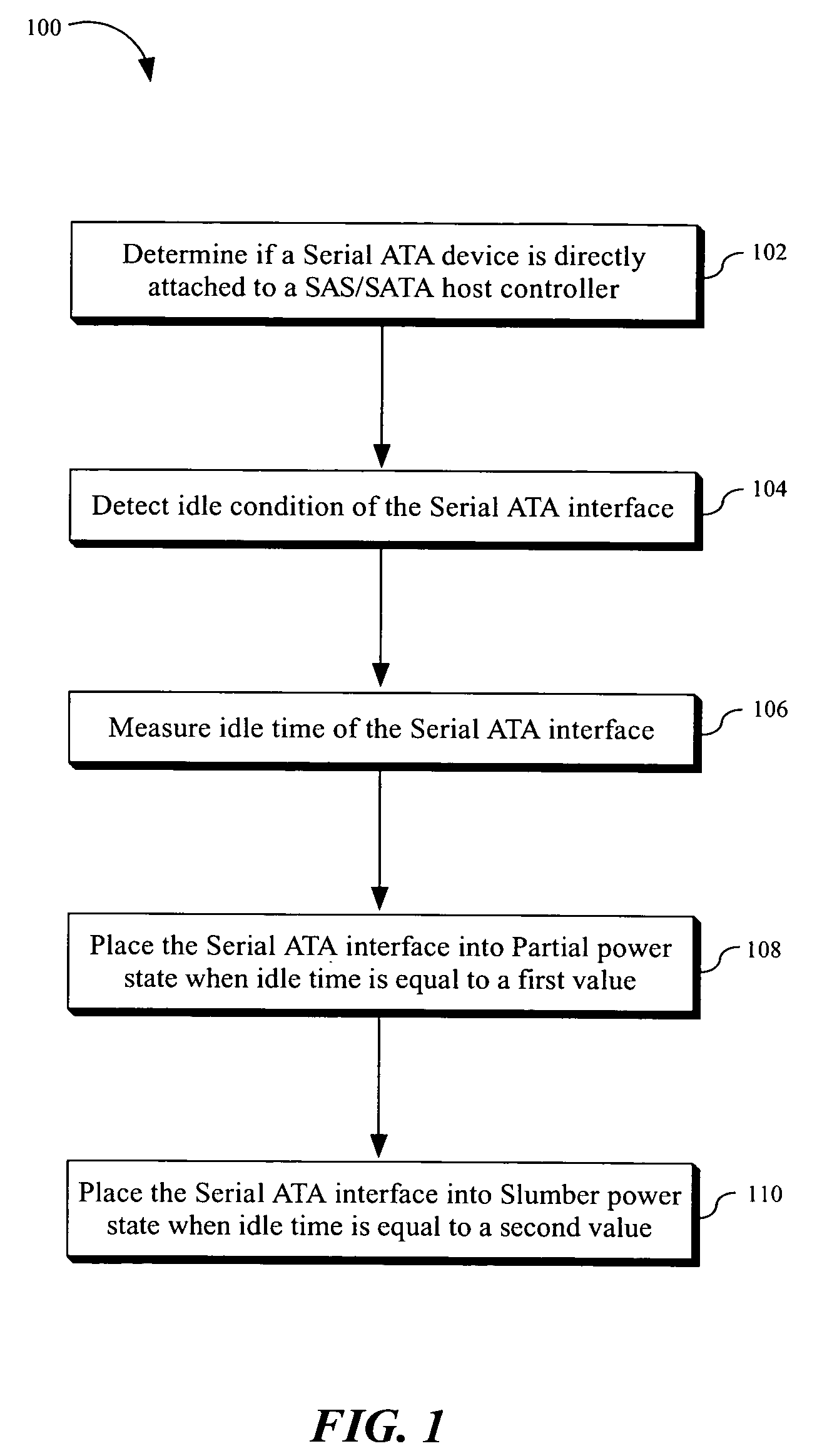

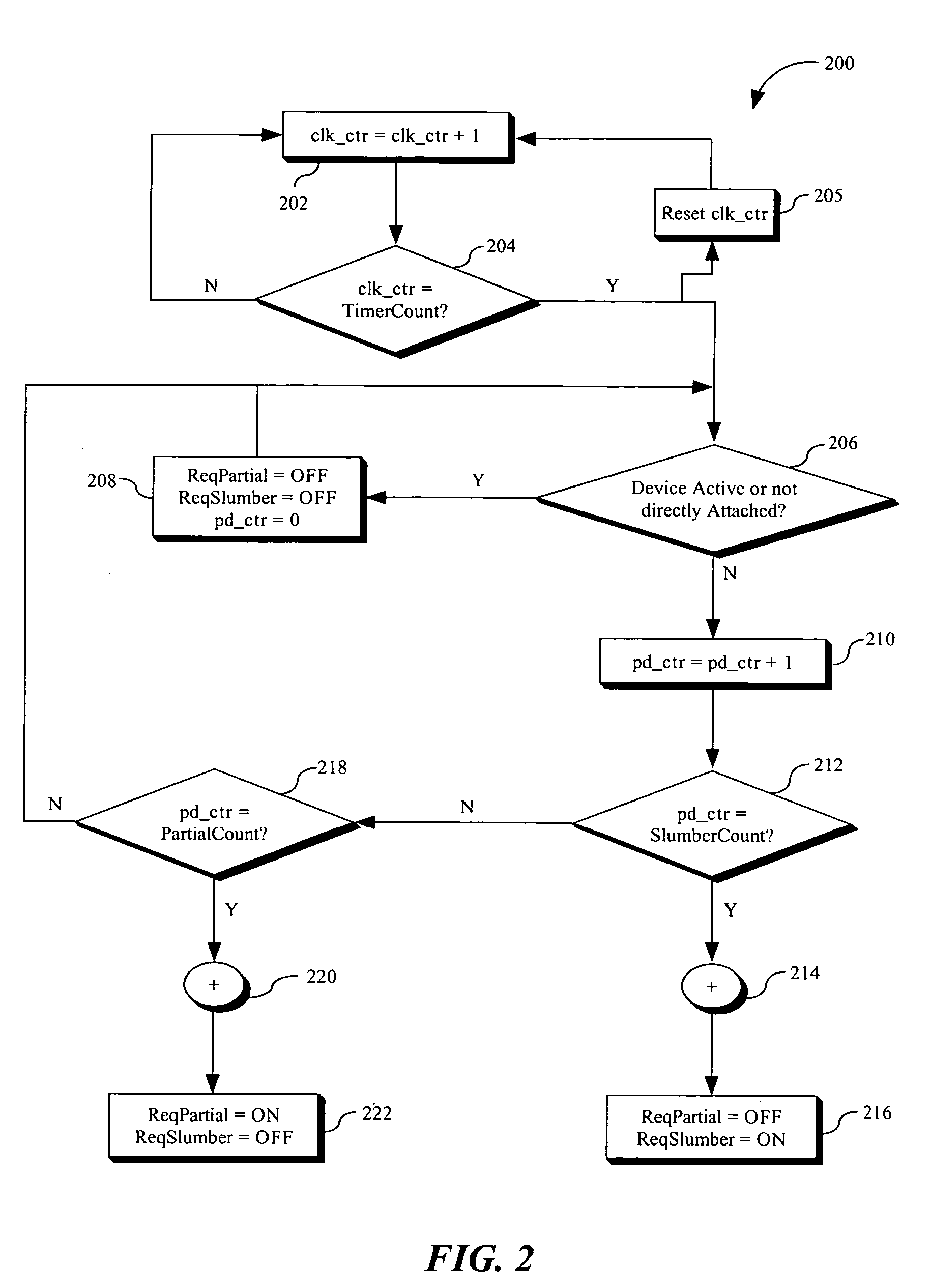

Method and apparatus of automatic power management control for serial ATA device directly attached to SAS/SATA host controller

InactiveUS7254732B2Save powerSimple interfaceEnergy efficient ICTVolume/mass flow measurementElectricitySerial ATA

The present invention is directed to a method and apparatus of automatic power management control for a Serial ATA device directly attached to a SAS / SATA host controller. In an exemplary aspect of the present invention, it is determined whether a Serial ATA device is directly attached to a SAS / SATA host controller without using a SAS expander. When it is determined that the Serial ATA device is directly attached to the SAS / SATA host controller, an idle or active condition of a Serial ATA interface including the Serial ATA device and the SAS / SATA host controller is automatically detected. When the Serial ATA interface is in an idle condition, idle time of the Serial ATA interface is measured using a power down counter whose frequency is determined by a programmable register based on an input clock. When a power down counter value is equal to a first value, a request for a Partial power state is asserted, and Serial ATA interface is put into a Partial power state. When a power down counter value is equal to a second value, a request for a Slumber power state is asserted, and Serial ATA interface is put into a Slumber power state.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

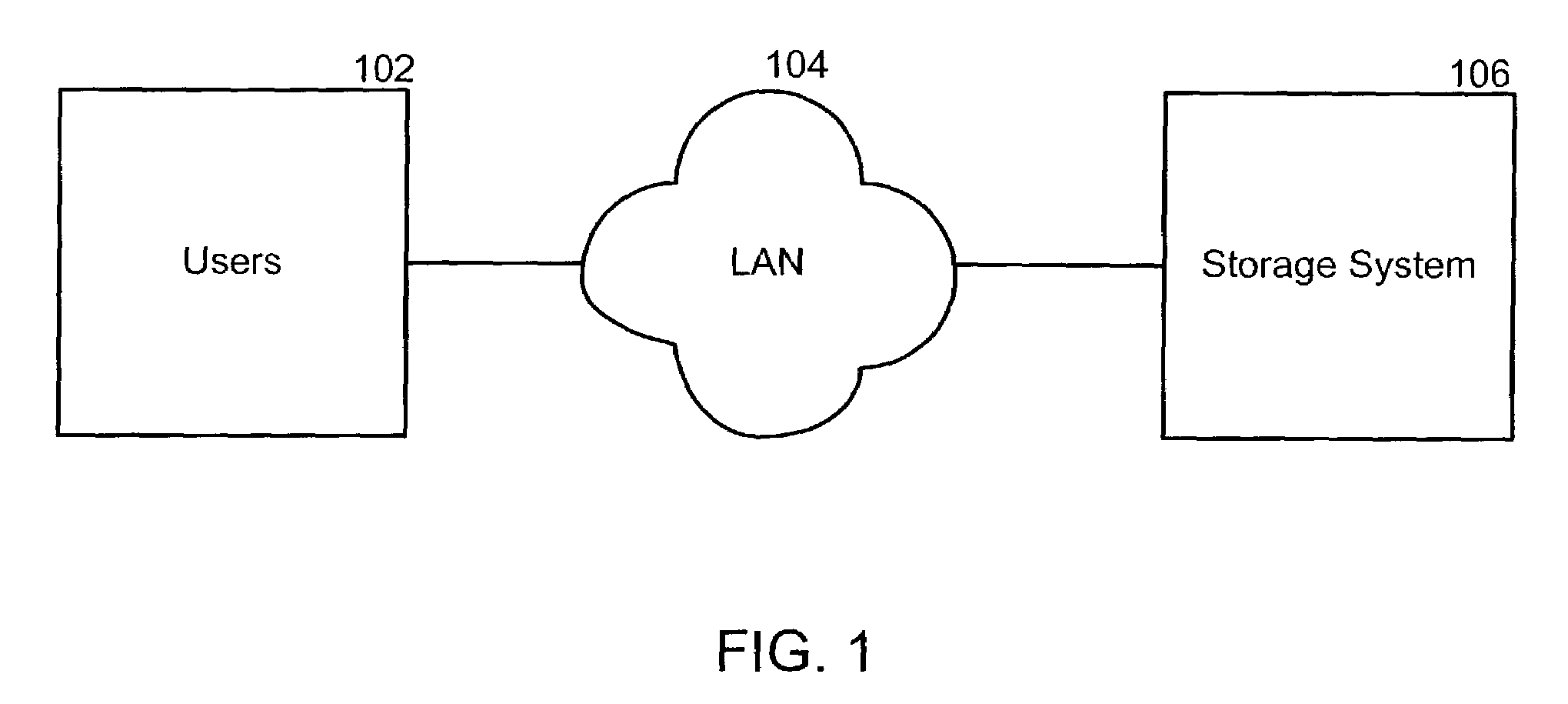

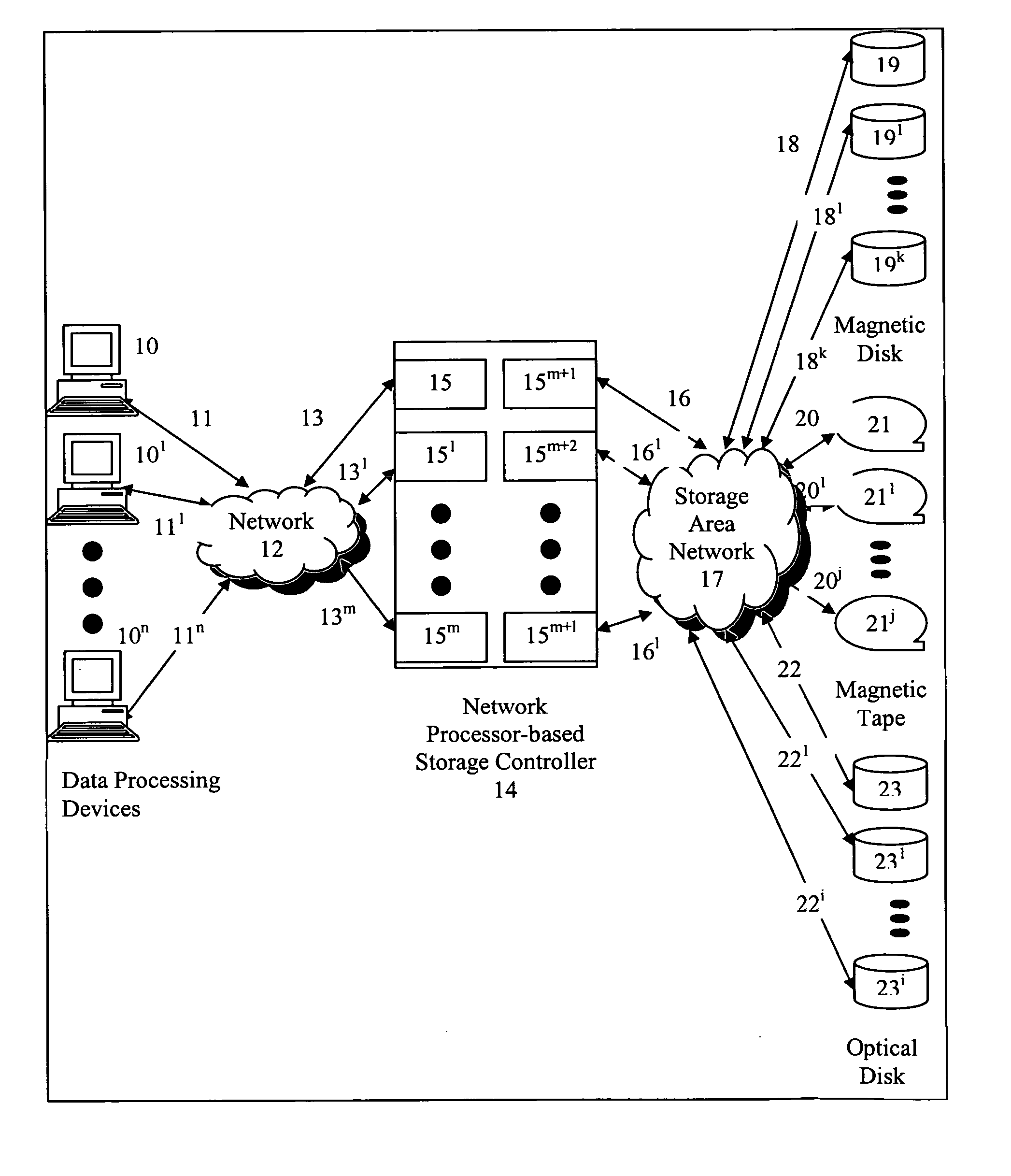

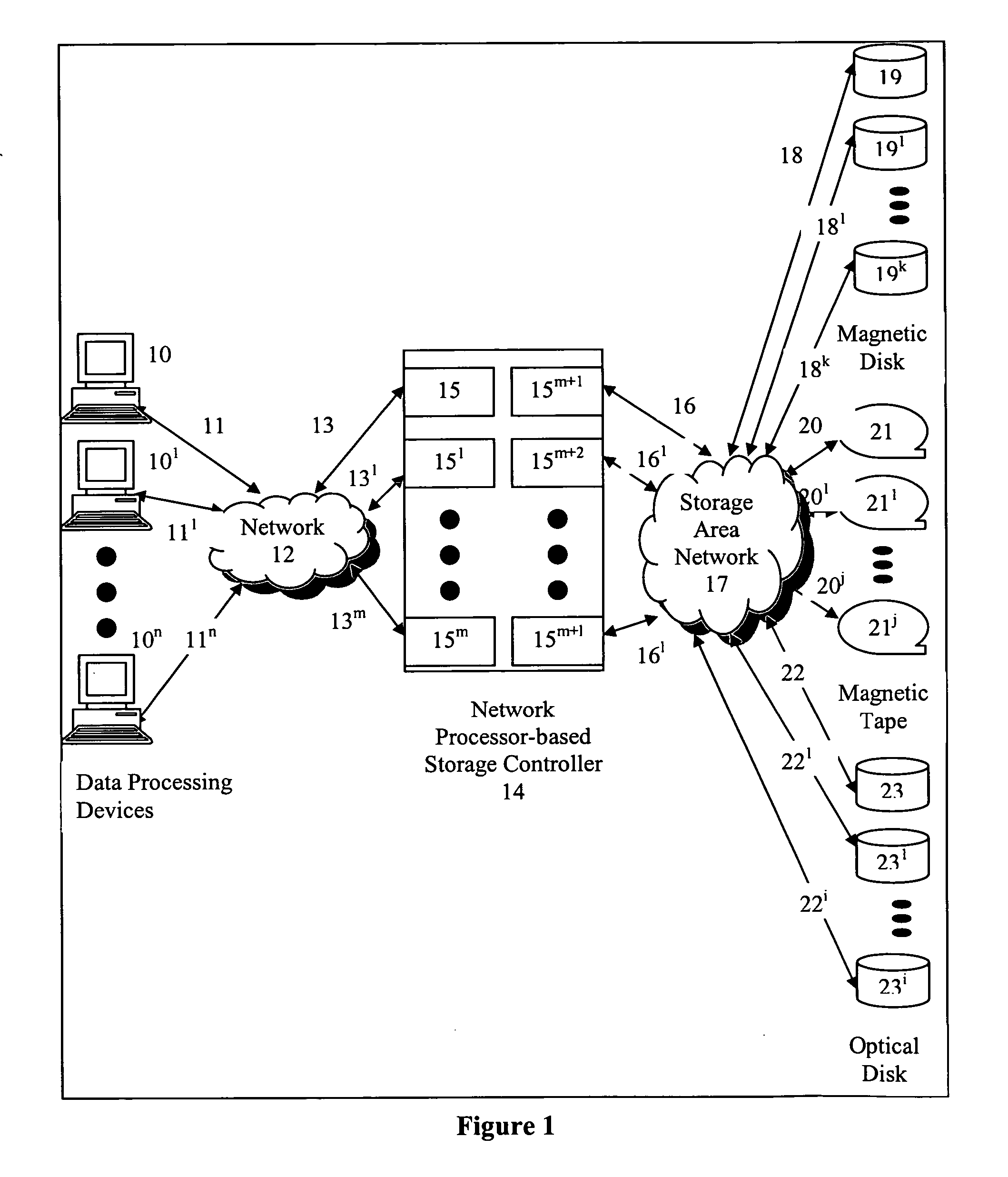

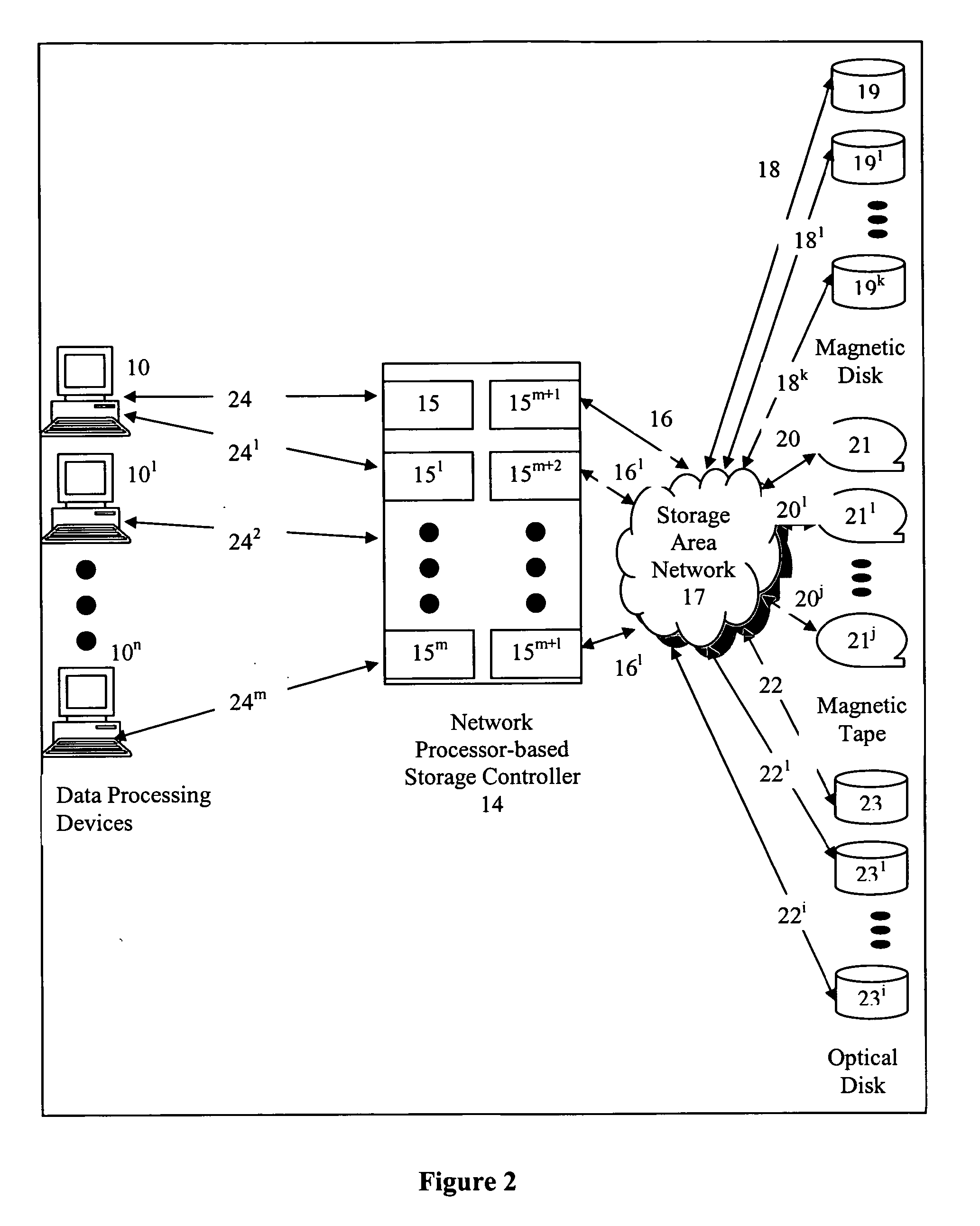

Network processor-based storage controller, compute element and method of using same

A data storage controller providing network attached storage and storage area network functionality comprising a network processor (37) and providing for volume management (preferably one or more of mirroring, RAID5, and copy on write backup), caching of data stored, protocol acceleration of low level protocols (preferably one or more of ATM, Ethernet, Fibre Channel, Infiniband, Serial SCSI, Serial ATA, and any other serializable protocol), and protocol acceleration of higher level protocols (preferably one or more of IP, ICMP, TCP, UDP, RDMA, RPC, security protocols, preferably one or both of IPSEC and SSL, SCSI, and file system services, preferably one or both of NFS and CIFS).

Owner:CORBIN JOHN R

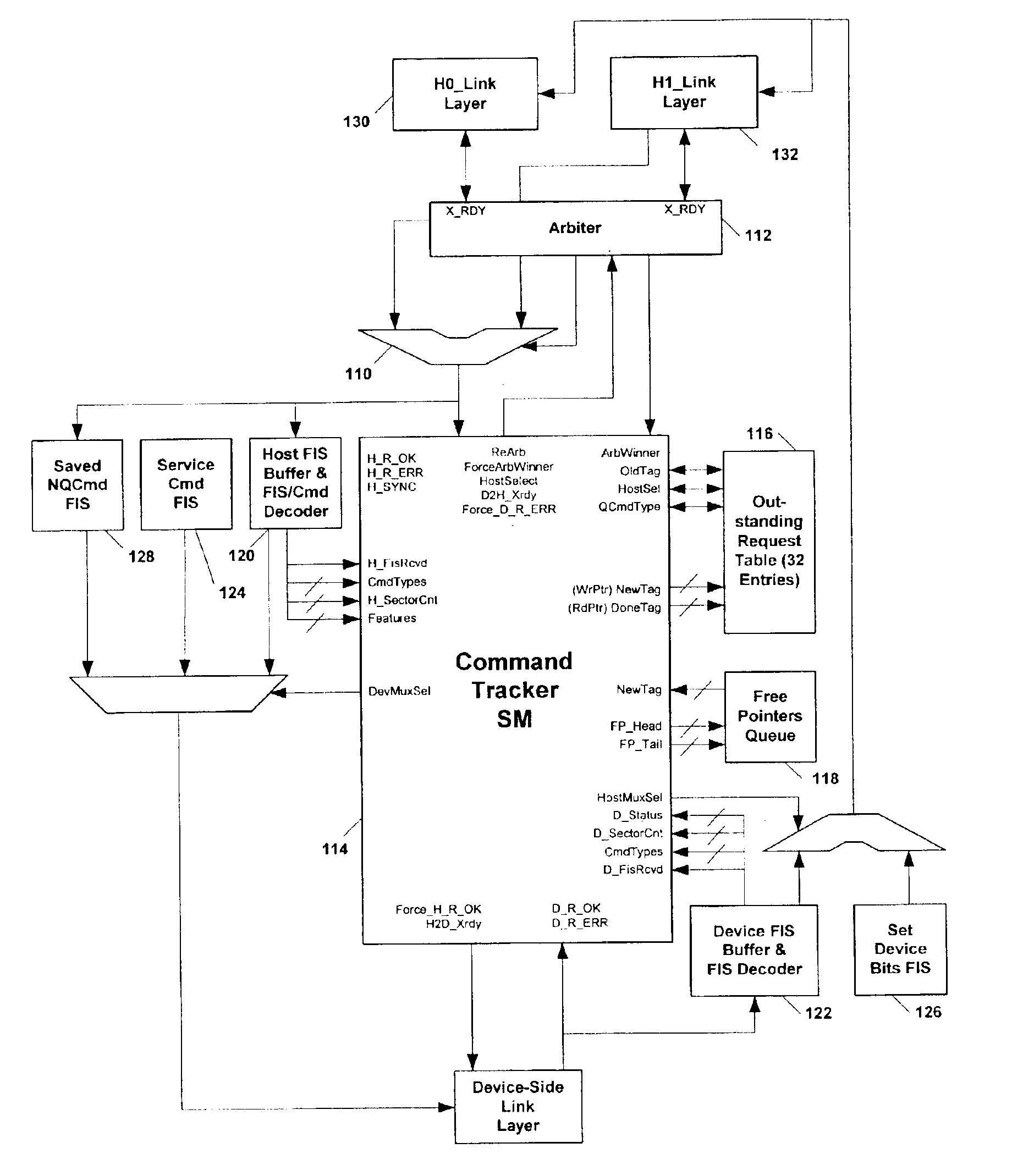

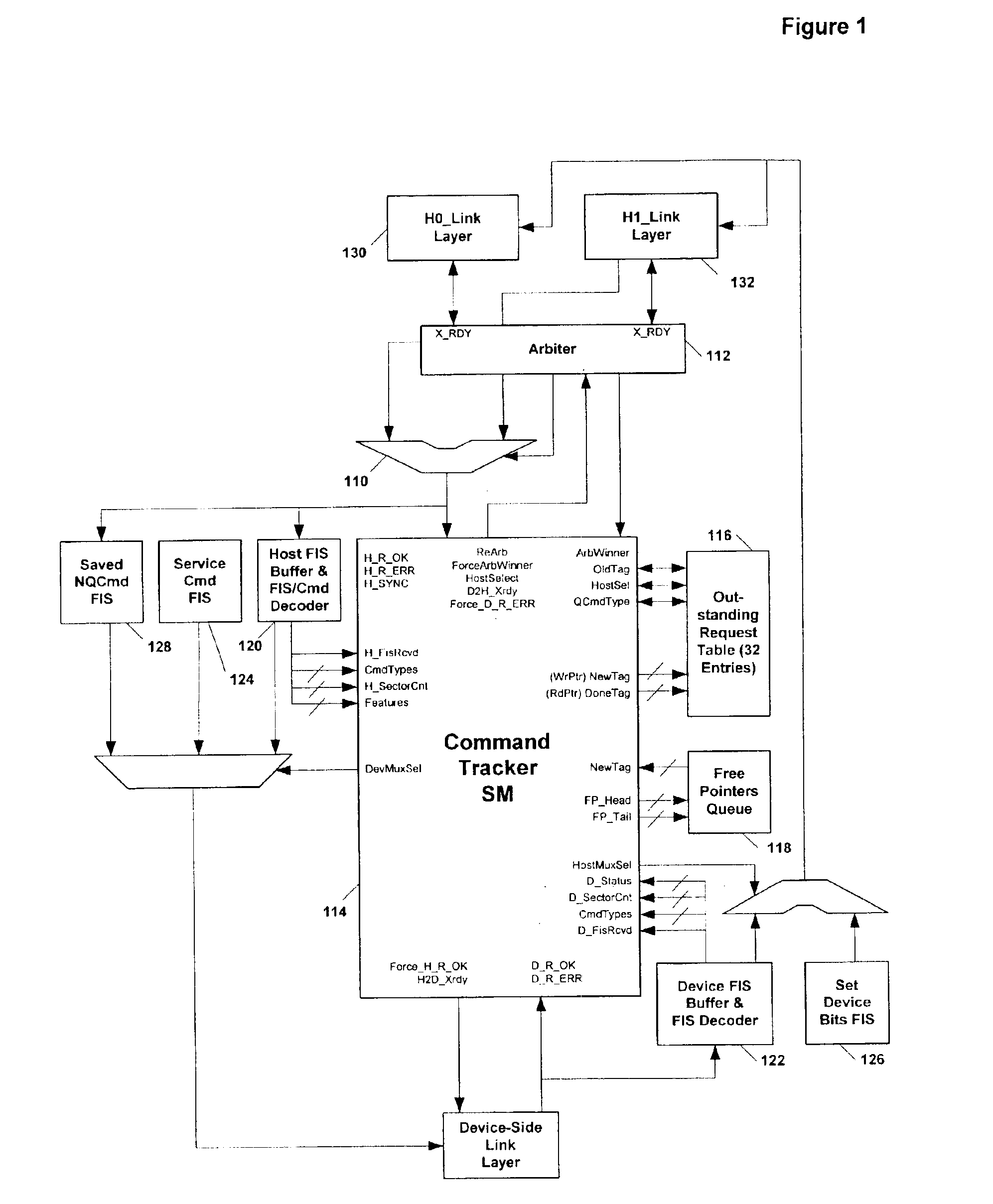

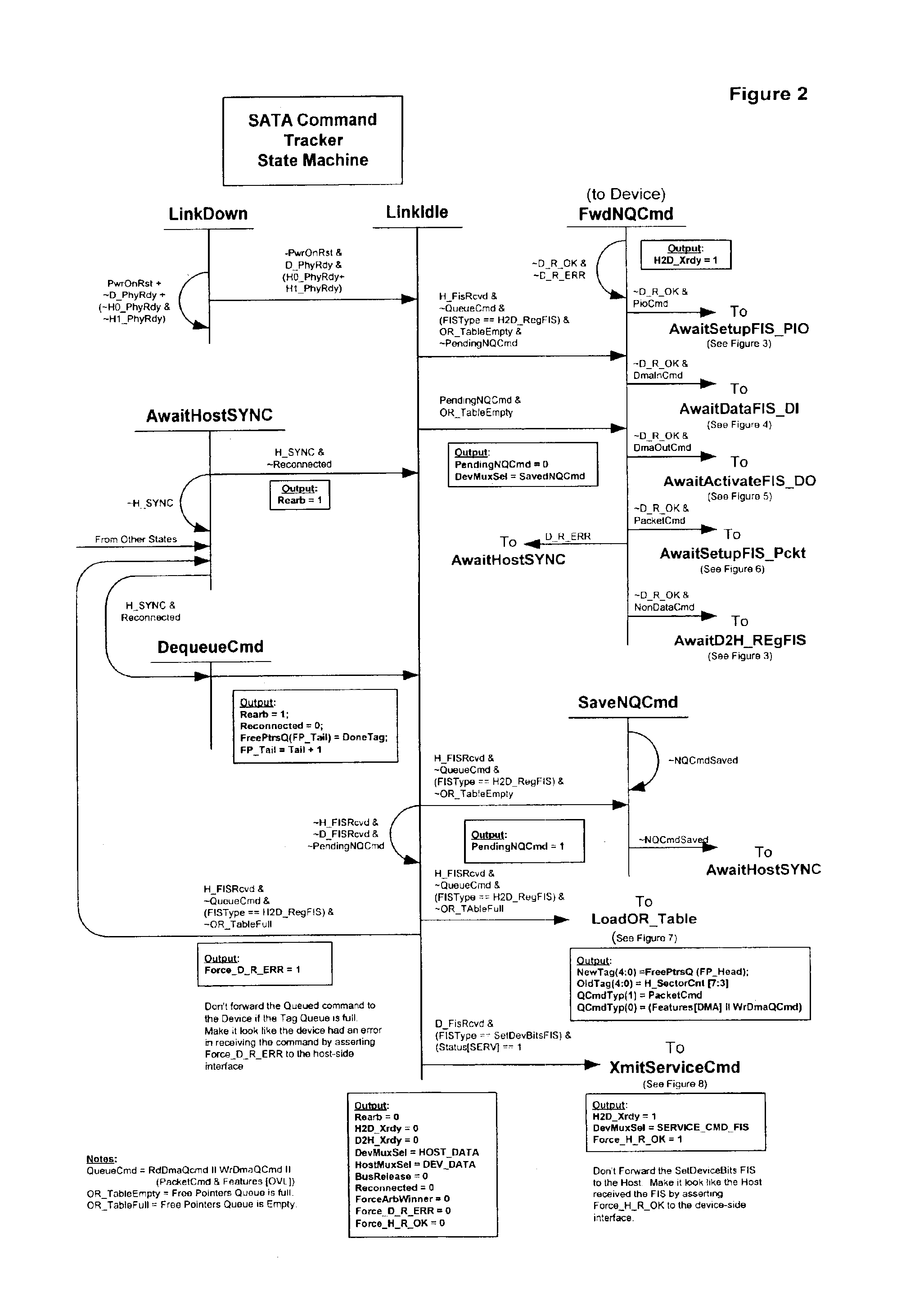

System and method for providing multi-initiator capability to an ATA drive

InactiveUS6961813B2Reduce necessityInput/output to record carriersError detection/correctionMulti portSerial ATA

A multi-port adapter and method of operation suitable for use with serial ATA devices is disclosed. An adapter includes a switch that receives input from multiple host devices and an arbiter module for assigning a priority scheme to received commands. An outstanding request table is implemented as a memory module for storing identifying information associated with commands received from multiple host devices, and a free pointers queue is maintained to track slots available in the outstanding request table. A command tracker state machine decodes incoming requests from hosts, monitors the execution by these commands by the ATA device, and updates the memory module to reflect completion of commands. Also disclosed is a storage system including an adapter of the present invention and ATA storage devices.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

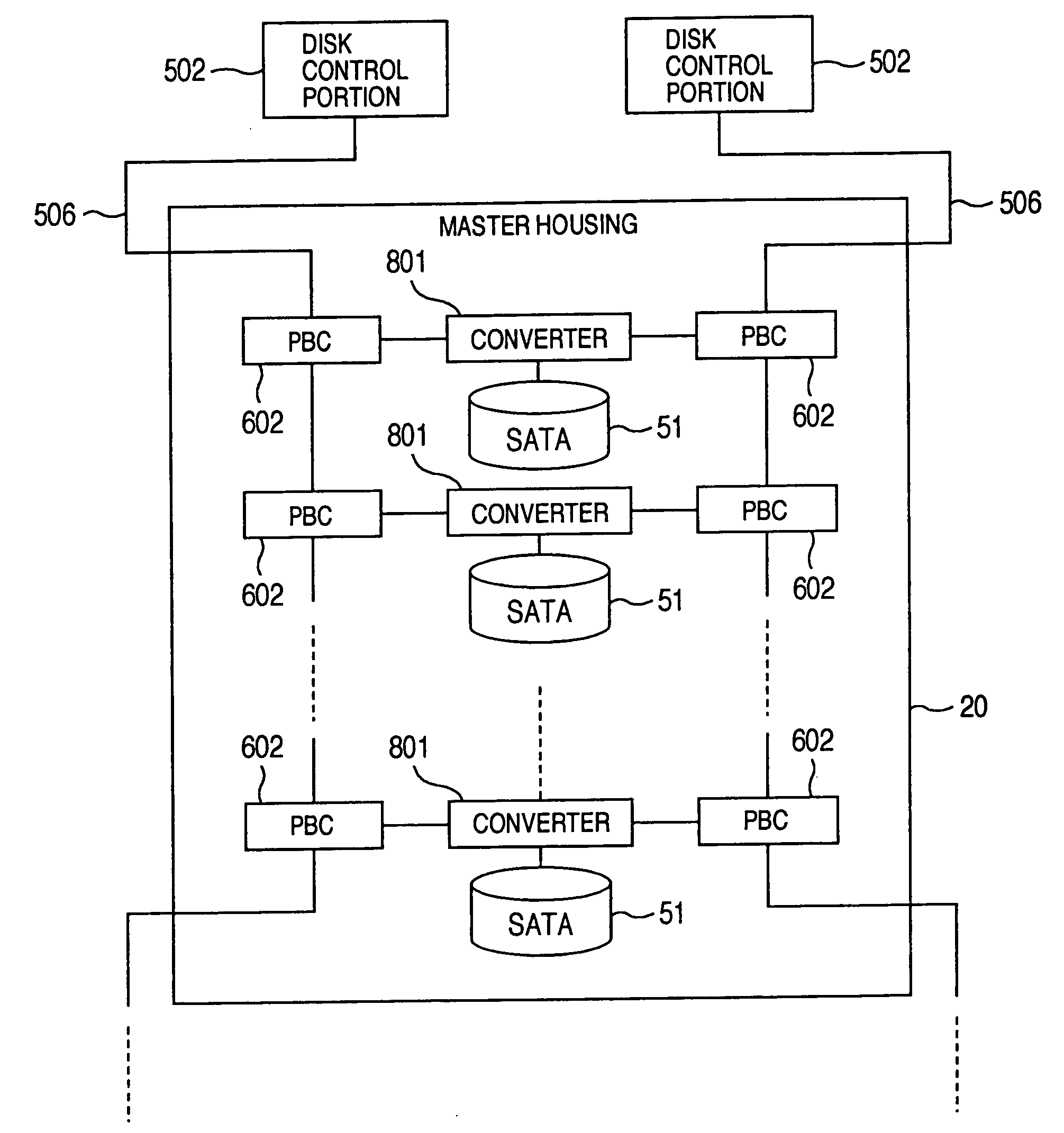

Disk array system and method for controlling disk array system

A disk array system having first and second housings and a controller for controlling the first and second housings. Fiber channel hard disk drives are received in the first housing, and serial ATA hard disk drives are received in the second housing. When reading data stored in a serial ATA hard disk drive in the second housing, the controller reads a plurality of pieces of data including the data to be read and parity data for the plurality of pieces of data from all the hard disk drives of an RAID group to which the hard disk drive storing the data to be read belongs. Thus, the controller examines whether the plurality of pieces of data including the data to be read are written in the hard disk drives with erroneous contents or not.

Owner:HITACHI LTD

Disk array system and method for controlling disk array system

A disk array system having first and second housings and a controller for controlling the first and second housings. Fiber channel hard disk drives are received in the first housing, and serial ATA hard disk drives are received in the second housing. When reading data stored in a serial ATA hard disk drive in the second housing, the controller reads a plurality of pieces of data including the data to be read and parity data for the plurality of pieces of data from all the hard disk drives of an RAID group to which the hard disk drive storing the data to be read belongs. Thus, the controller examines whether the plurality of pieces of data including the data to be read are written in the hard disk drives with erroneous contents or not.

Owner:HITACHI LTD

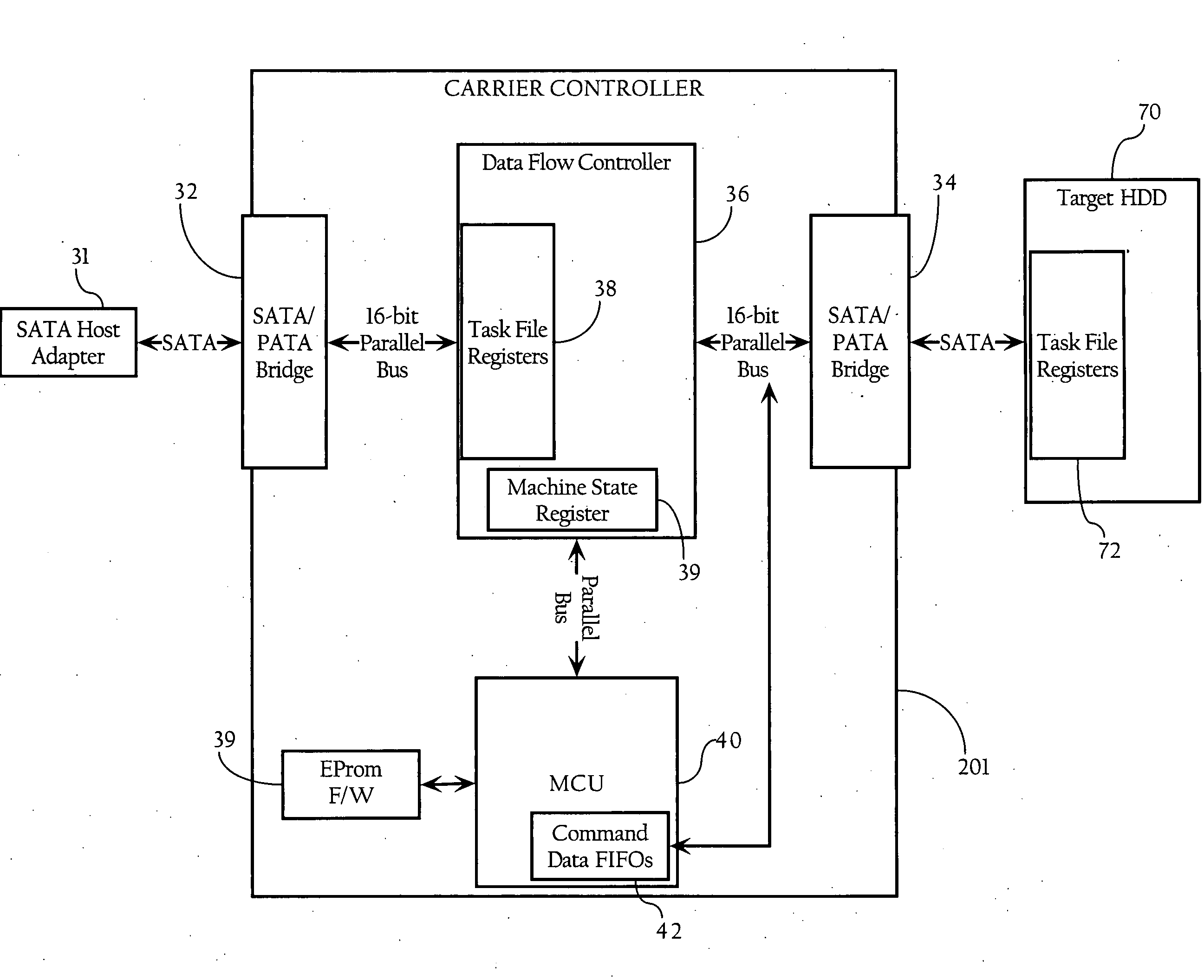

Data flow control and bridging architecture enhancing performance of removable data storage systems

InactiveUS20070016702A1Improve performanceInput/output processes for data processingData conversionData streamRemovable media

A data flow control and bridging architecture that enhances the performance of removable data storage systems. In one implementation, the present invention provides a bypass bus implementation where the data transfer phase associated with select commands occurs directly between the host computing system and the target removable data storage unit. In one implementation, the present invention further provides a data flow and bridging architecture that emulates a removable media interface, such as the ATAPI interface, to the host computing system, and translates these commands for a target removable storage unit that implements a fixed media interface, such as the ATA interface. In yet another implementation, the present invention provides a data flow and bridging architecture that supports the serial ATA interface.

Owner:QUANTUM CORP

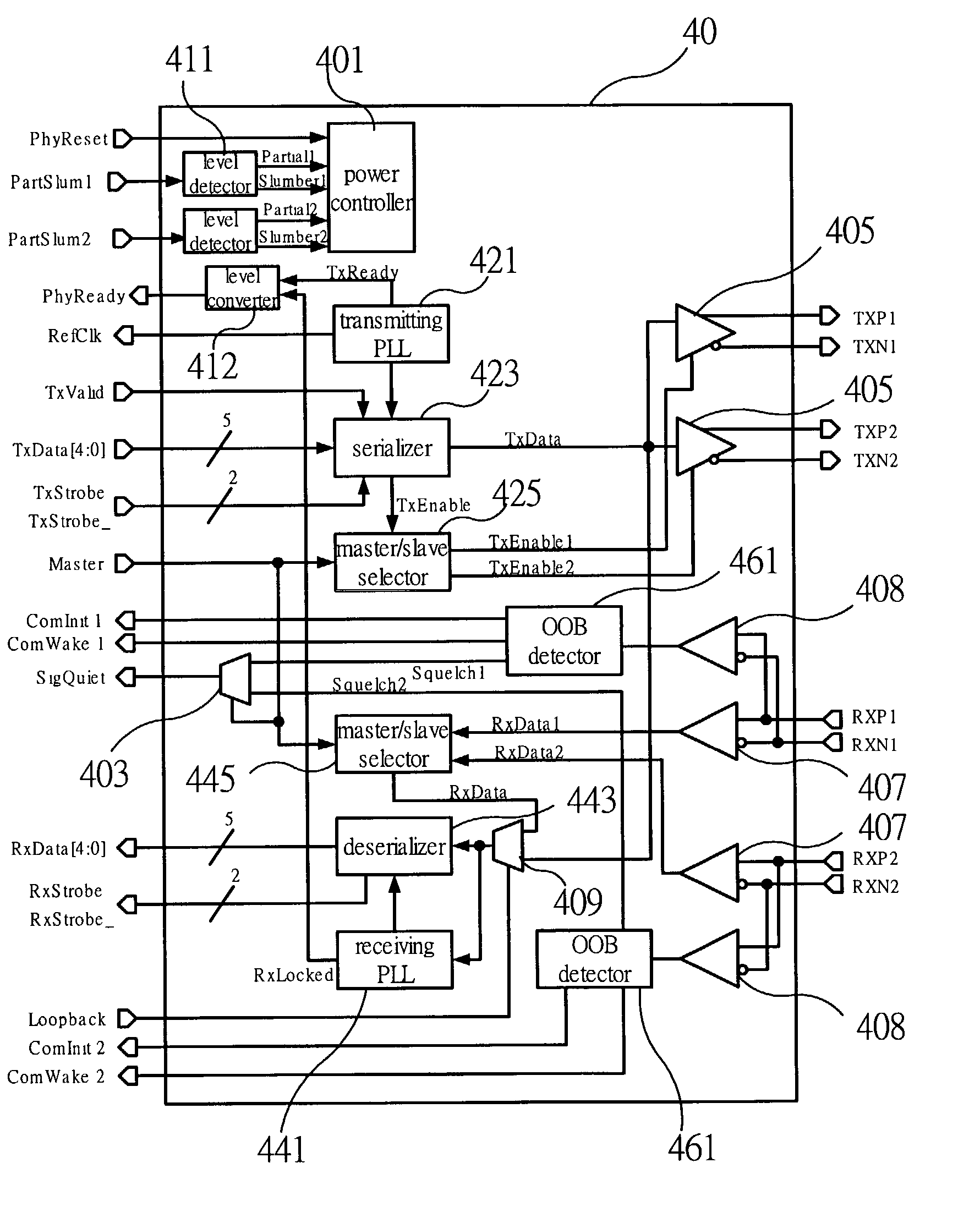

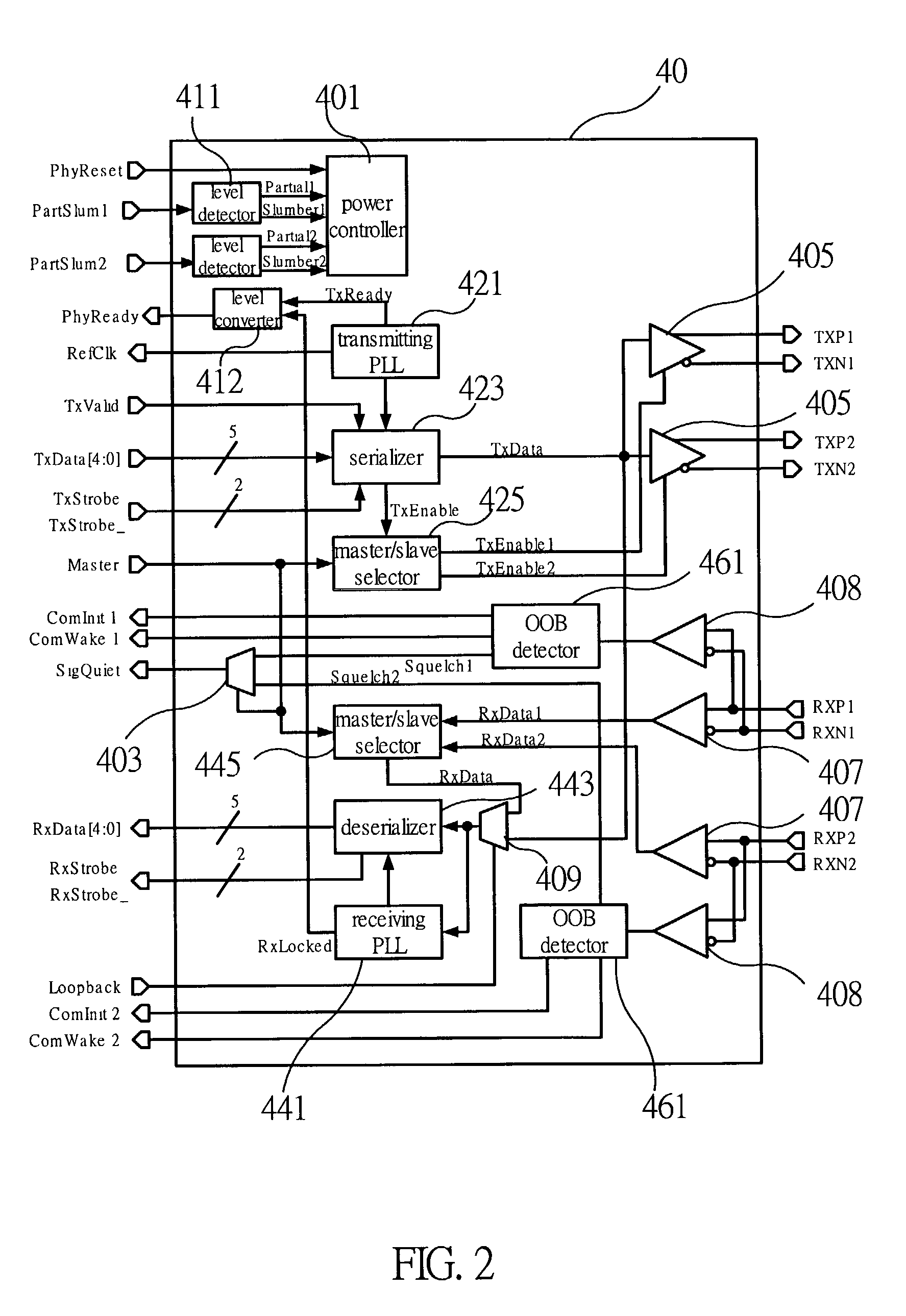

Circuit and signal encoding method for reducing the number of serial ATA external PHY signals

InactiveUS7020834B2Reduce in quantityMinimize the numberError preventionTransmission systemsControl signalData signal

A Circuit for reducing the number of serial ATA external PHY signals includes: a serializer / deserializer, connected to a storage medium controller through a set of parallel signal transmitting lines and a set of parallel signal receiving lines, so as to convert signals between parallel and serial specifications; a phase locked loop, connected to the serializer / deserializer so as to generate a clock signal required for data signal transmission; at least one pair of transmitter and receiver, each connected to the serializer / deserializer, each transmitter able to transmit the serial data signal from the serializer through a set of serial signal transmitting lines to a serial ATA device, and each receiver able to receive the serial data from the serial ATA device through a set of serial signal receiving lines to the deserializer; and at least one OOB signal detector, each connected to the corresponding receiving lines, so as to detect the out of band signals from the serial ATA device. The Circuit also employs in certain applications a signal encoding approach for reducing the number of serial ATA external PHY signals, wherein an encoder and a decoder are employed to encode control signals and status signals into special data codes transmitted between a serial ATA external PHY and a storage medium controller, so as to minimize the number of interface signals.

Owner:VIA TECH INC

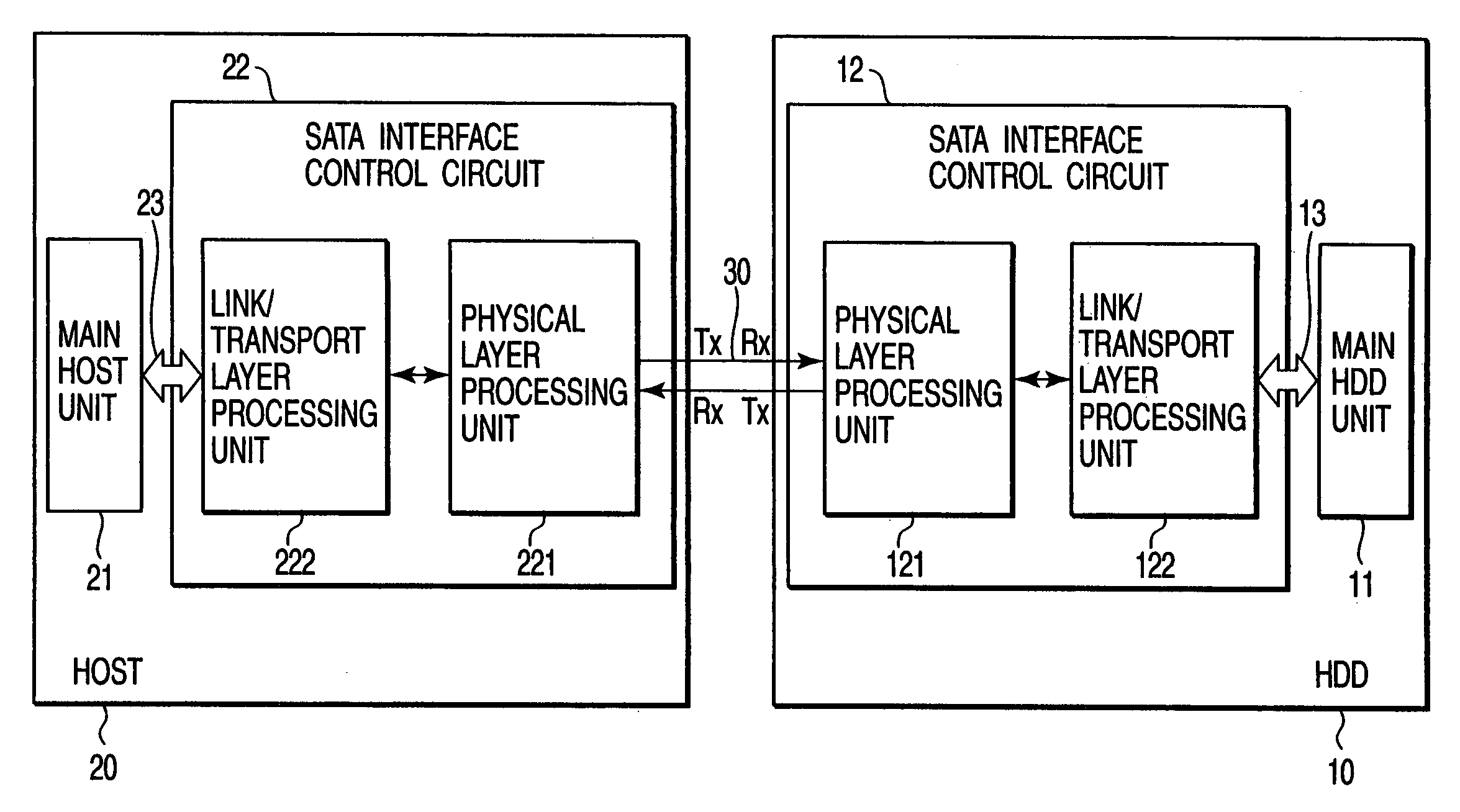

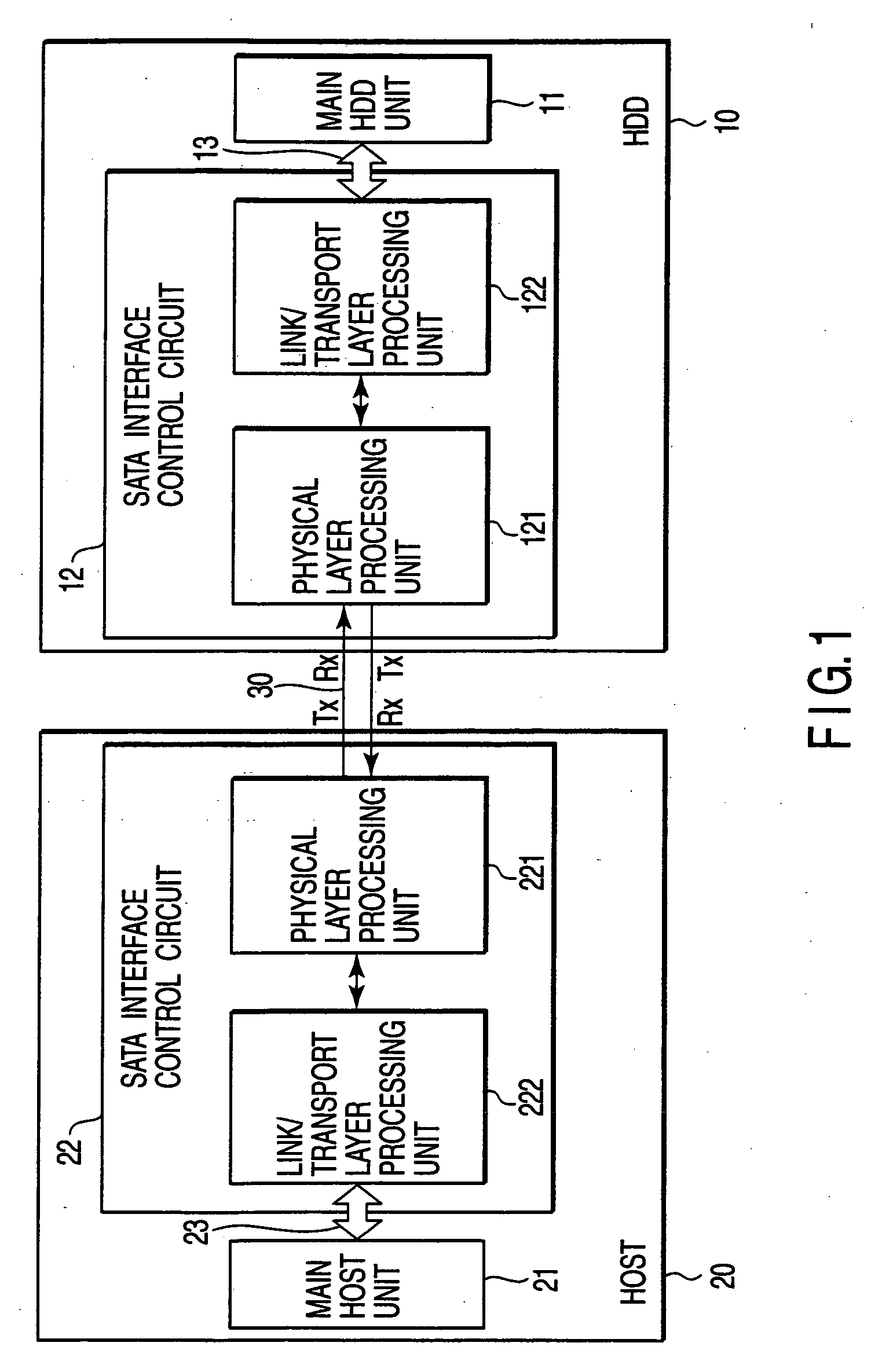

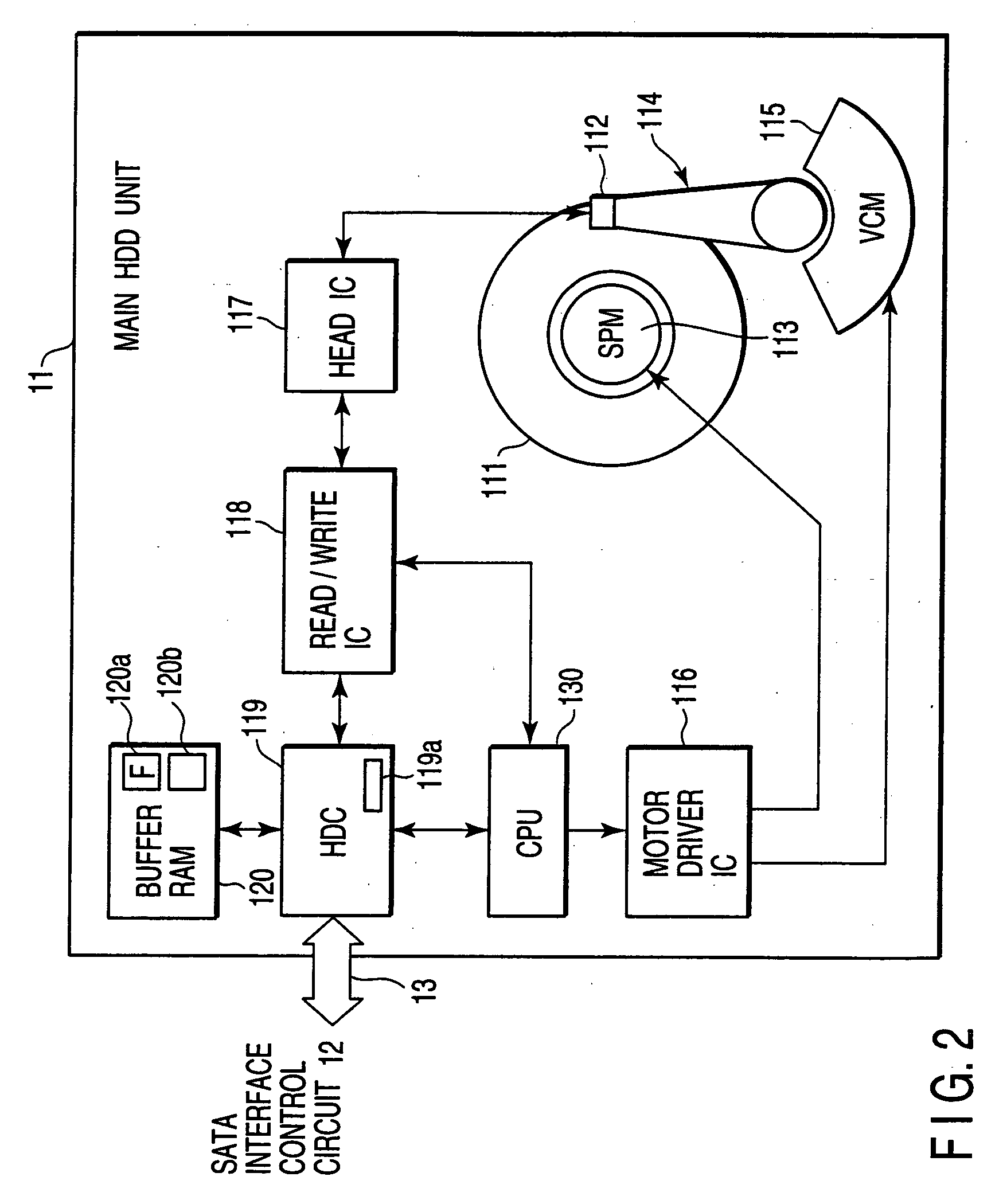

Apparatus and method for saving power in a disk drive with a serial ATA interface connected to a host via a serial ATA bus

ActiveUS7328356B2Reduce power consumptionUtilizing power saving modeEnergy efficient ICTInput/output to record carriersComputer scienceSerial ATA

In an electronic device with a serial ATA interface, upon detection of the issue or reception of a preset command, a confirmation device, such as a CPU, confirms the completion of execution of the command. Upon confirming the completion of execution of the command, a controller, which may also be the CPU, controls shifting of the serial ATA interface to a power saving mode.

Owner:KK TOSHIBA

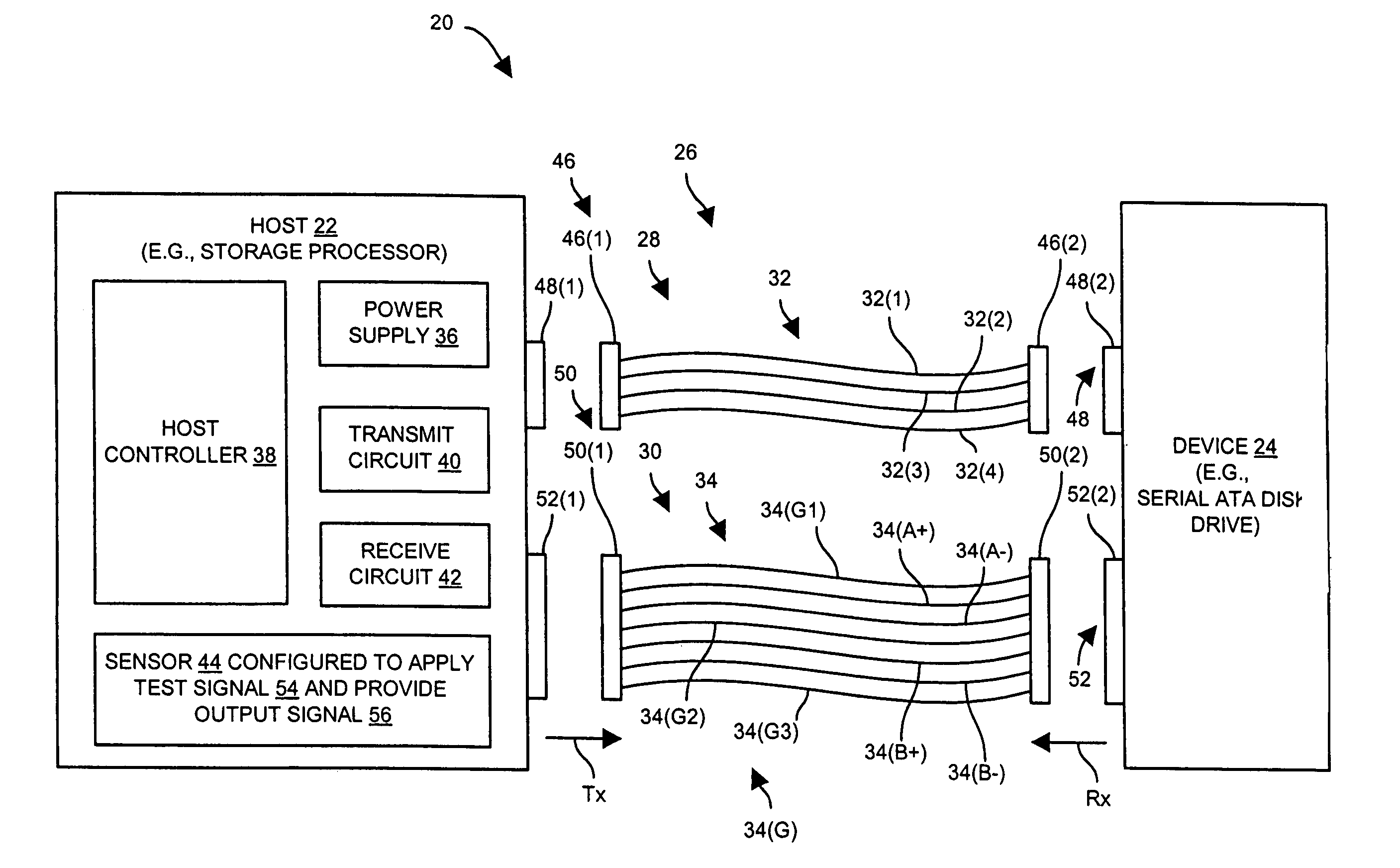

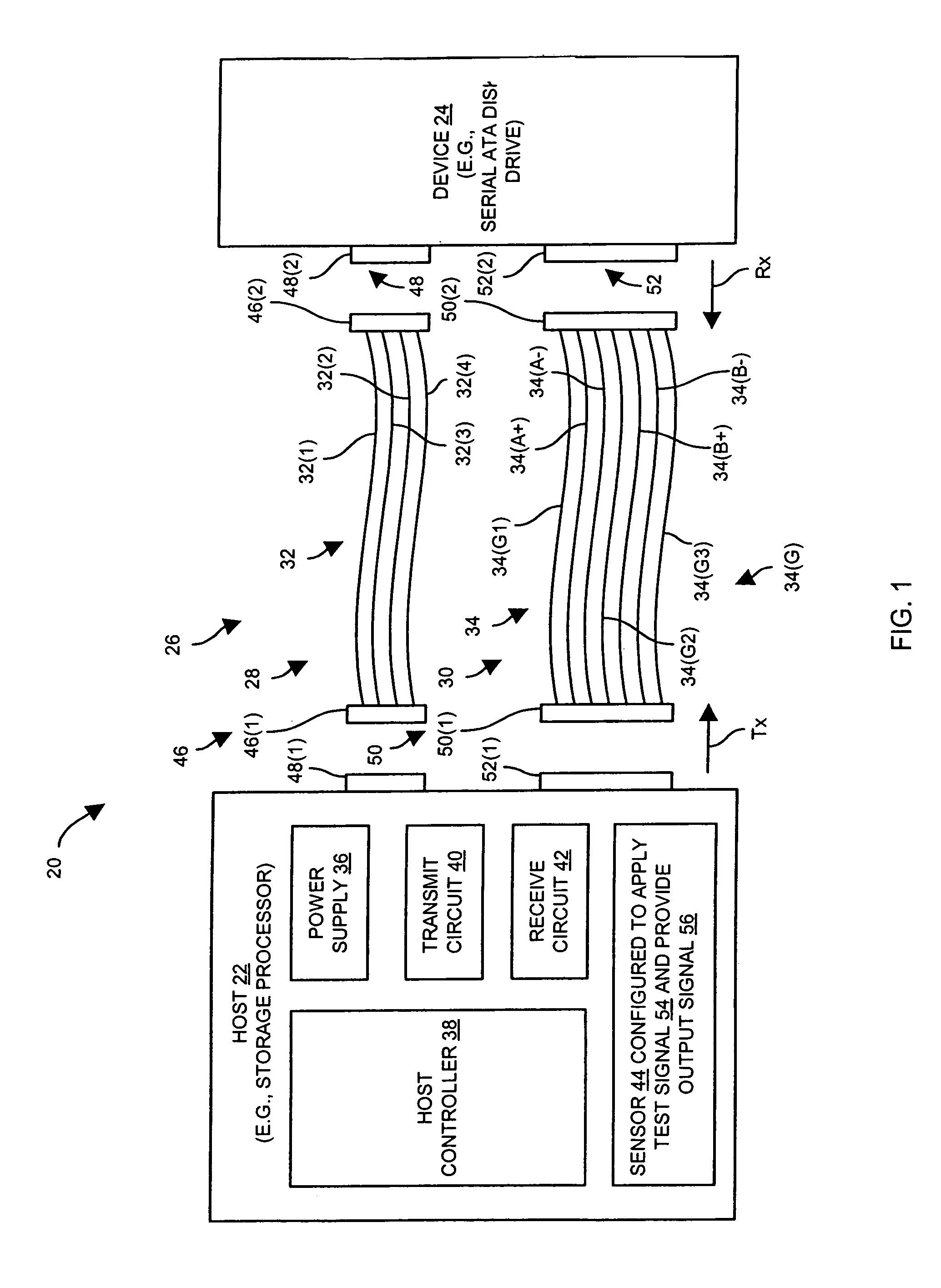

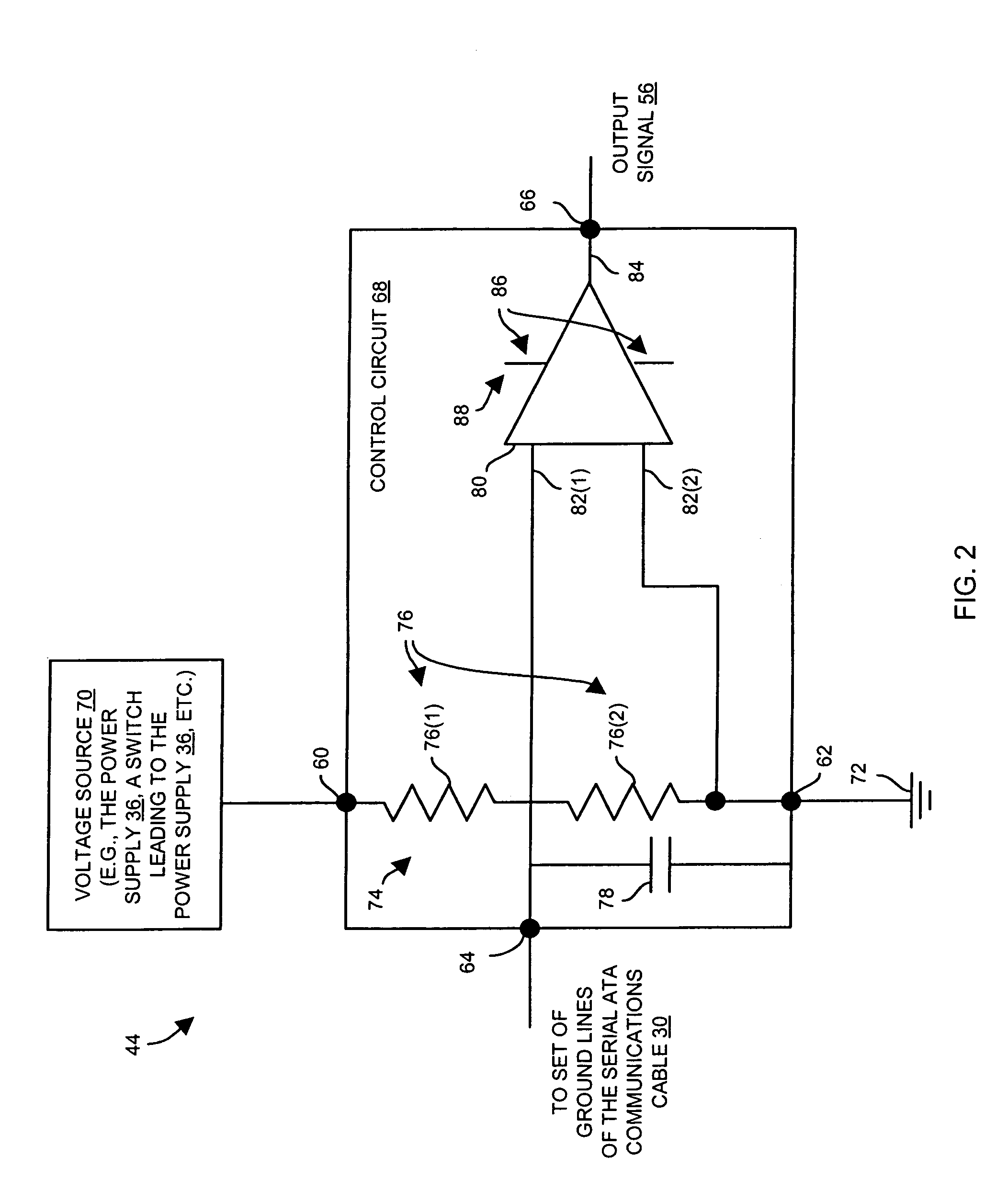

Methods and apparatus for indicating whether a device is connected to a serial ATA communications cable

ActiveUS7072995B1Guaranteed uptimeAvoid flowDigital data processing detailsHardware monitoringCommunications systemEngineering

A Serial ATA communications system has a host, a device, and a Serial ATA communications cable that connects the host to the device. The Serial ATA communications cable includes (i) a pair of transmit lines configured to carry a differential mode transmit signal, (ii) a pair of receive lines configured to carry a differential mode receive signal, and (iii) a set of ground lines. The host includes a transmit circuit configured to connect to the pair of transmit lines of the Serial ATA communications cable, a receive circuit configured to connect to the pair of receive lines of the Serial ATA communications cable, and a sensor. The sensor is configured to provide an output signal indicating whether a Serial ATA device is connected to the Serial ATA communications cable in response to a test signal applied to the set of ground lines.

Owner:EMC IP HLDG CO LLC

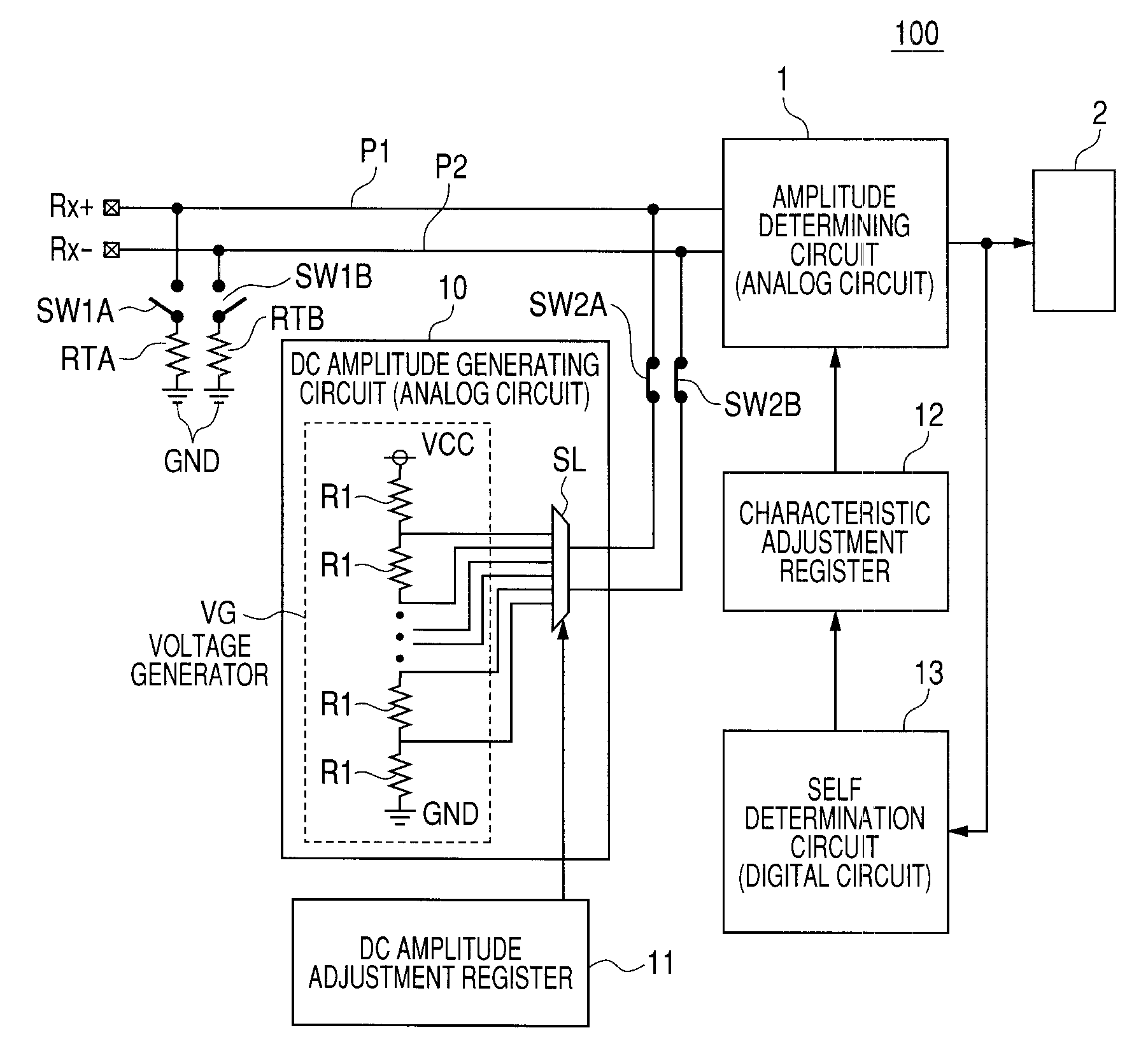

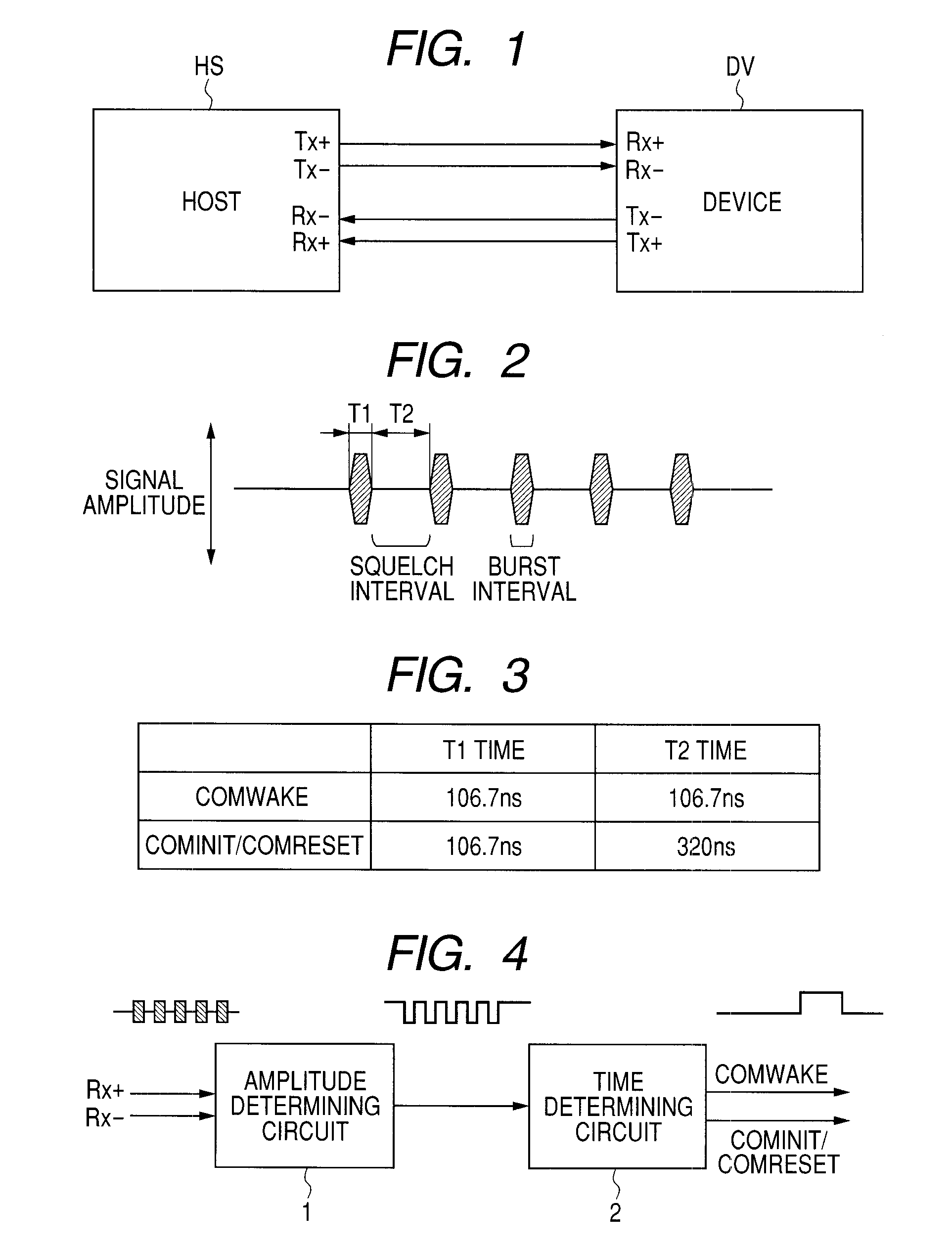

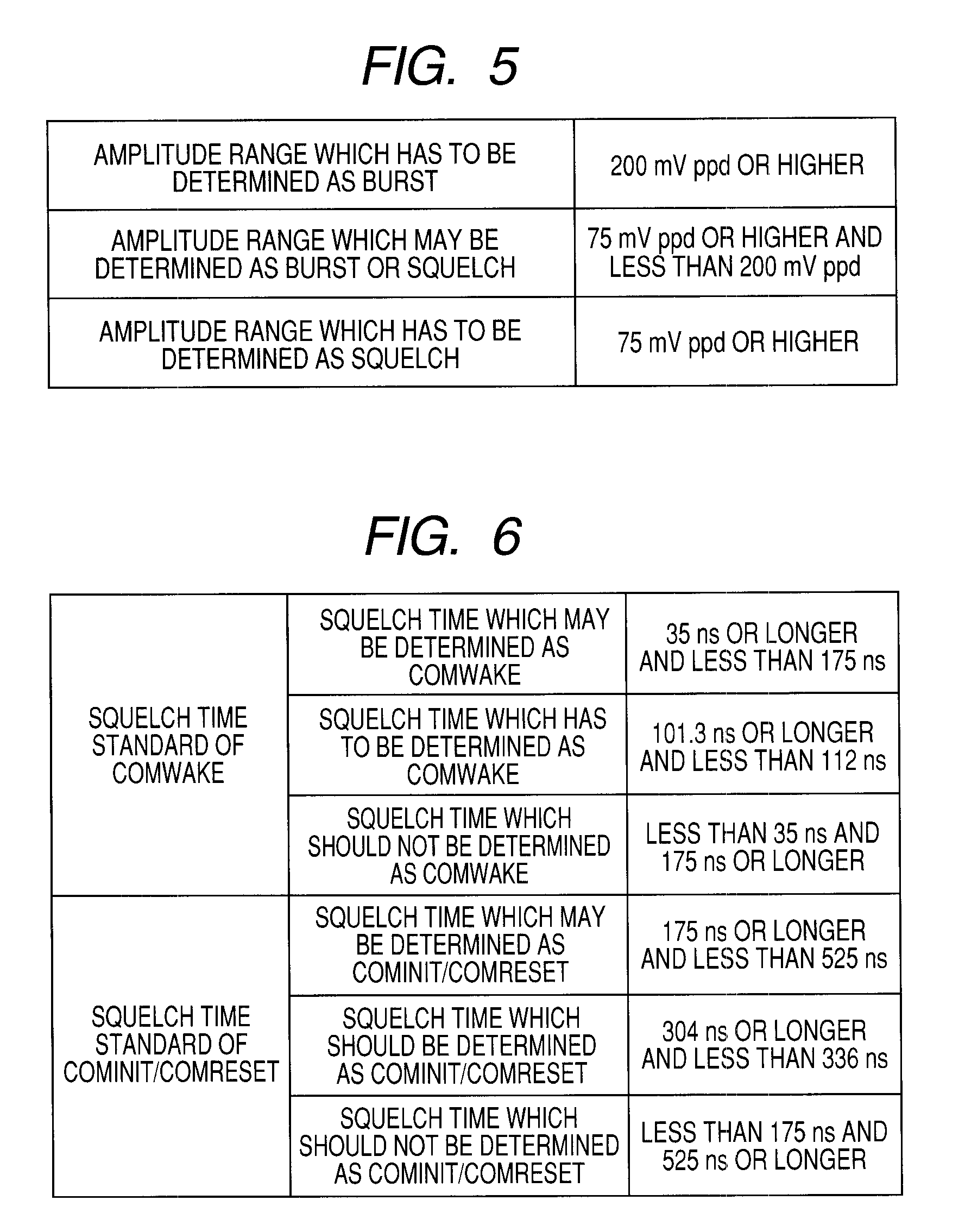

Oob (out of band) detection circuit and serial ata system

InactiveUS20090146721A1Accurate signal determinationInhibit deteriorationElectronic circuit testingGain controlProcessor registerSquelch

The present invention provides an OOB detection circuit capable of making accurate signal determination even in the case where a characteristic fluctuation occurs in an analog circuit, thereby preventing deterioration in the yield of a product. To an amplitude determining circuit, a characteristic adjustment register for changing setting of an amplitude threshold adjustment mechanism for distinguishing a burst and a squelch from each other provided for the amplitude determining circuit is coupled. The characteristic adjustment register is controlled by a self determination circuit. An output of the amplitude determination circuit is supplied to a time determining circuit and also to the self determination circuit. On the basis of the output of the amplitude determining circuit, the self determination circuit controls the characteristic adjustment register.

Owner:RENESAS ELECTRONICS CORP

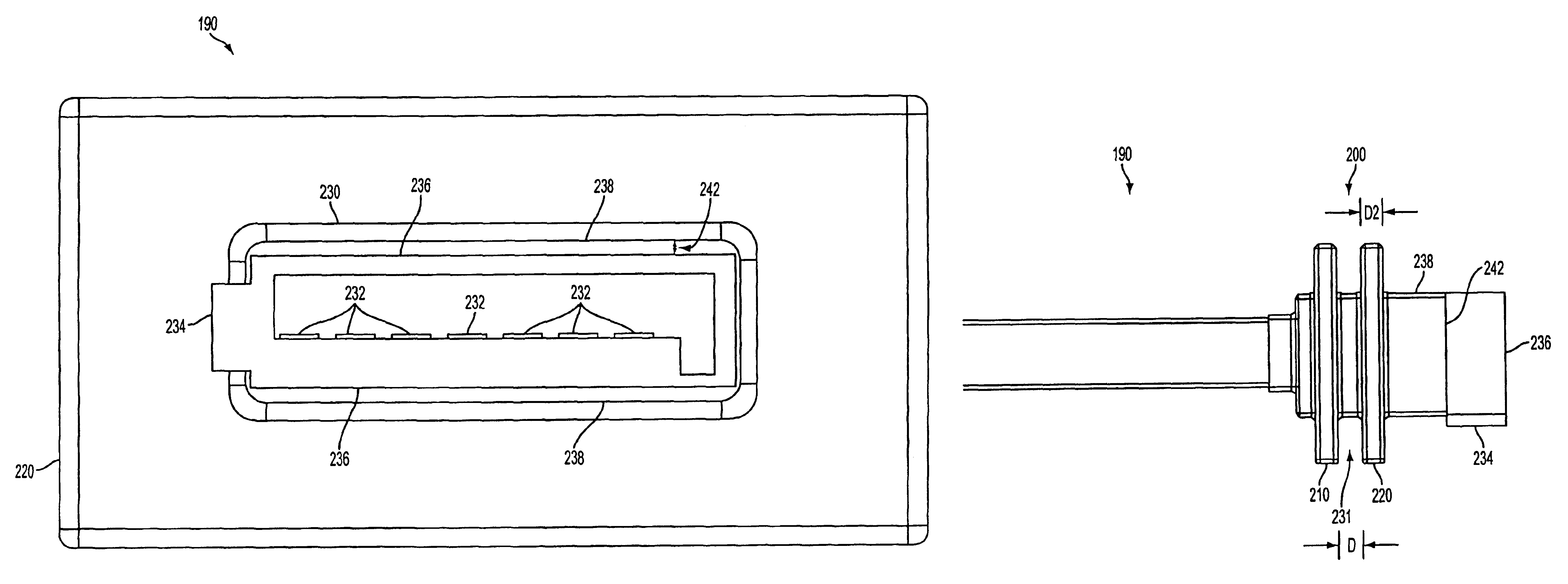

Method and apparatus for connecting serial ATA storage components

InactiveUS6843674B1Low costLimited maintenanceSubstation/switching arrangement detailsIncorrect coupling preventionEngineeringSerial ATA

A method for connecting to an SATA storage component includes a chassis having an interior and an exterior, and a wall portion provided with an opening. An SATA compatible connector, provided with a first restraining flange and a second restraining flange spaced from the first restraining flange, is inserted into the opening in the wall portion, wherein an interior surface of the first restraining flange faces a first surface of the wall portion and an interior surface of the second restraining flange faces a second surface of the wall portion. An SATA storage component is then inserted into the chassis such that it connects with the SATA compatible connector, whereby the first and second flange allows the SATA compatible connector to float in a limited fashion within the opening.

Owner:LATTICE SEMICON CORP

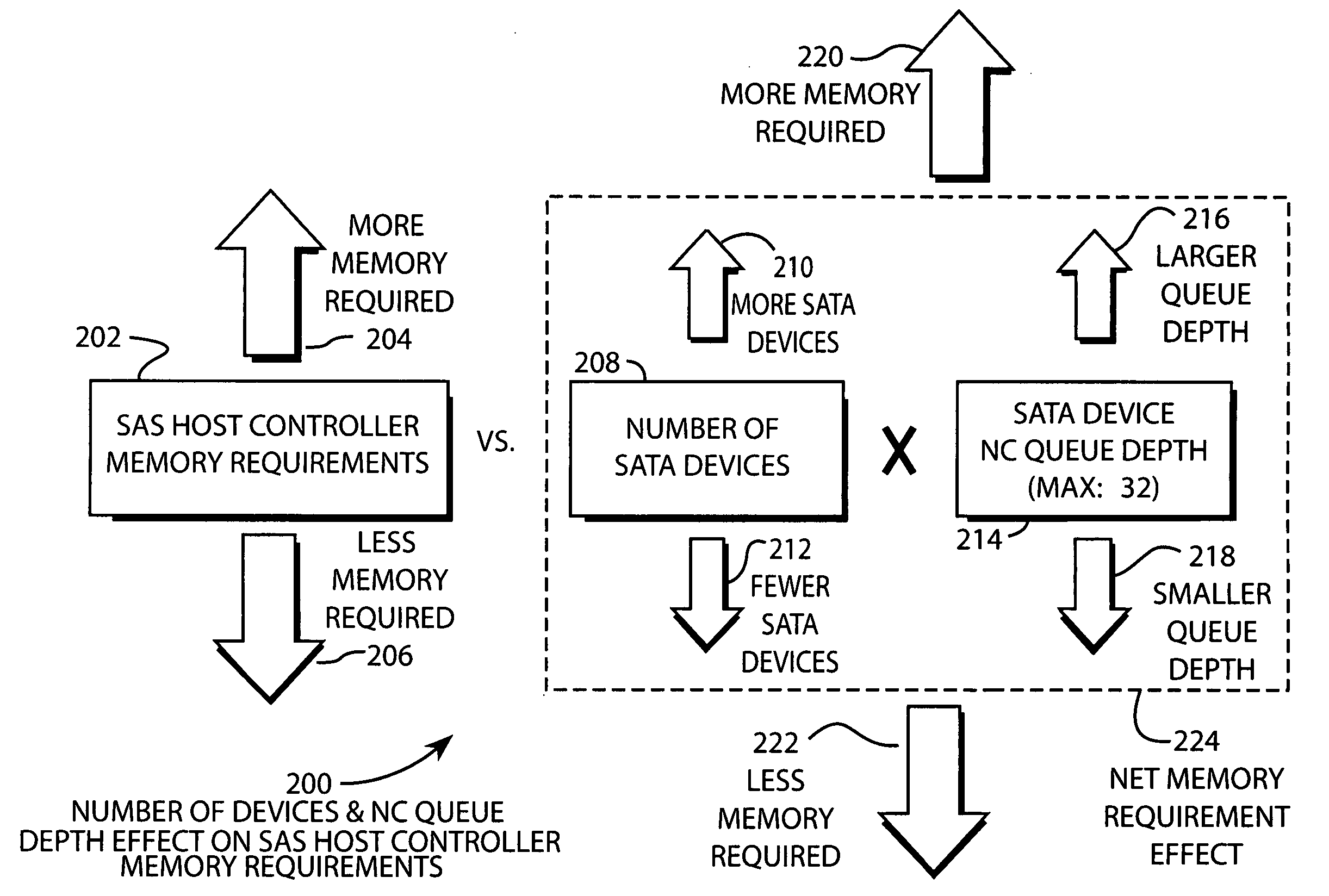

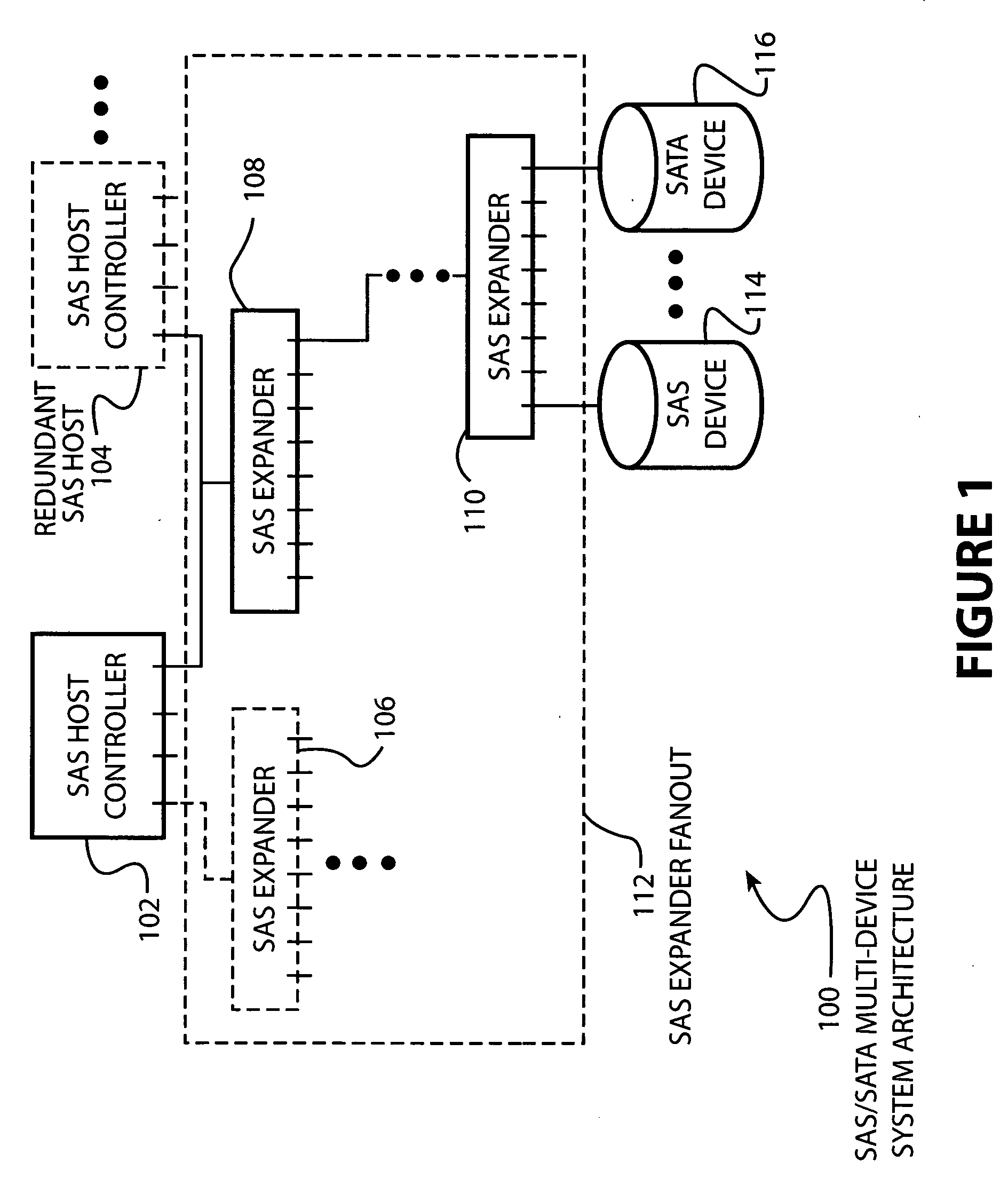

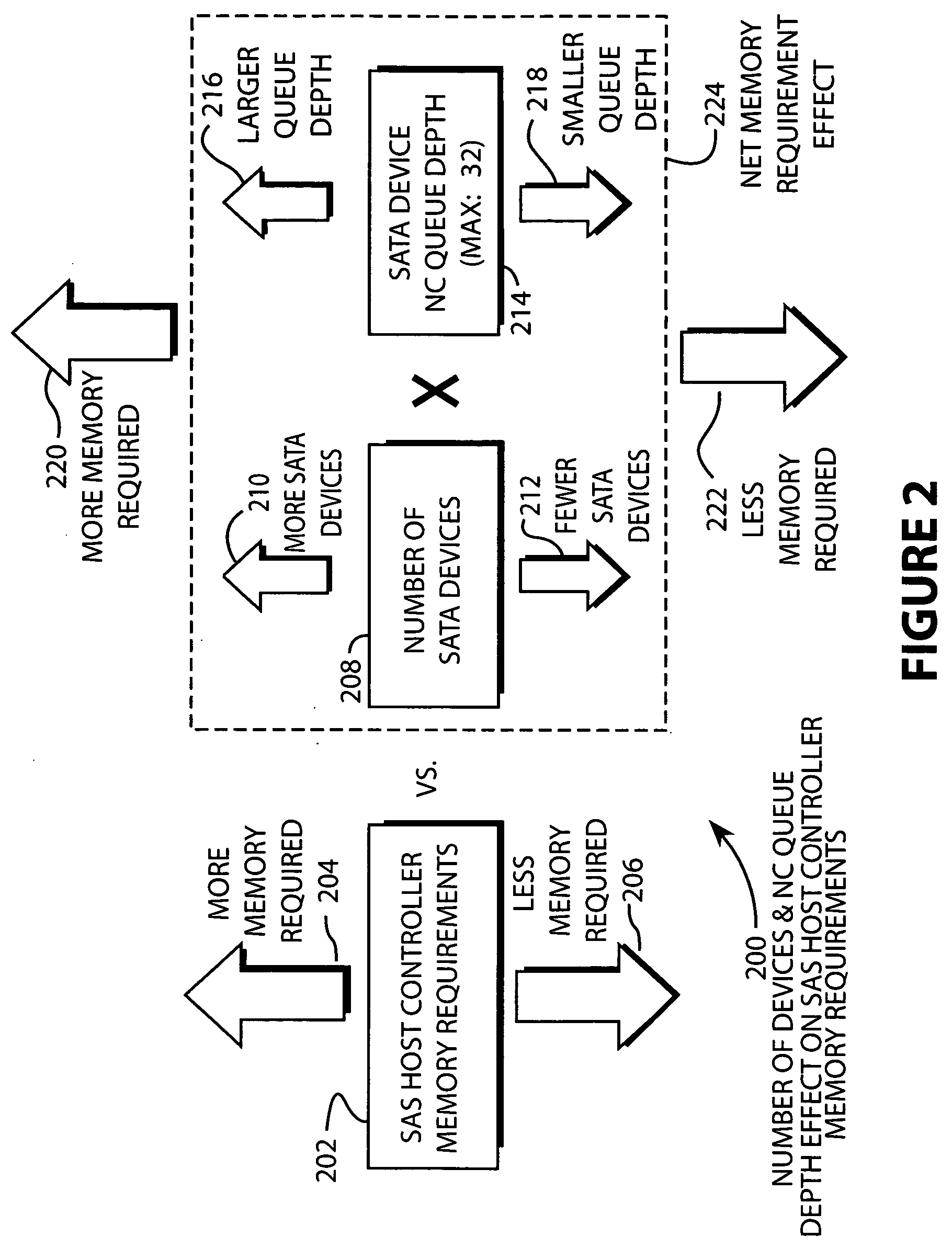

Circuit and method to provide configuration of serial ATA queue depth versus number of devices

InactiveUS20060041691A1Energy efficient ICTEnergy efficient computingTerminal equipmentMaster controller

Disclosed is a system using a SAS host controller and SAS expanders to control multiple SATA end devices where the memory contained on the SAS host controller is fixed to ease the cost and power consumption of the SAS host controller device, but where there is an expanded ability to support additional SATA end devices by configuring the allowed native command queue depth to be smaller for each SATA end device, thus allowing more SATA end devices to be supported by a single SAS host controller. An embodiment of the invention has three possible preset configuration states: thirty-two SATA end devices with a native command queue depth of thirty-two; sixty-four SATA end devices with a native command queue depth of sixteen; and one-hundred-twenty-eight SATA end devices with a native command queue depth of eight.

Owner:AVAGO TECH INT SALES PTE LTD

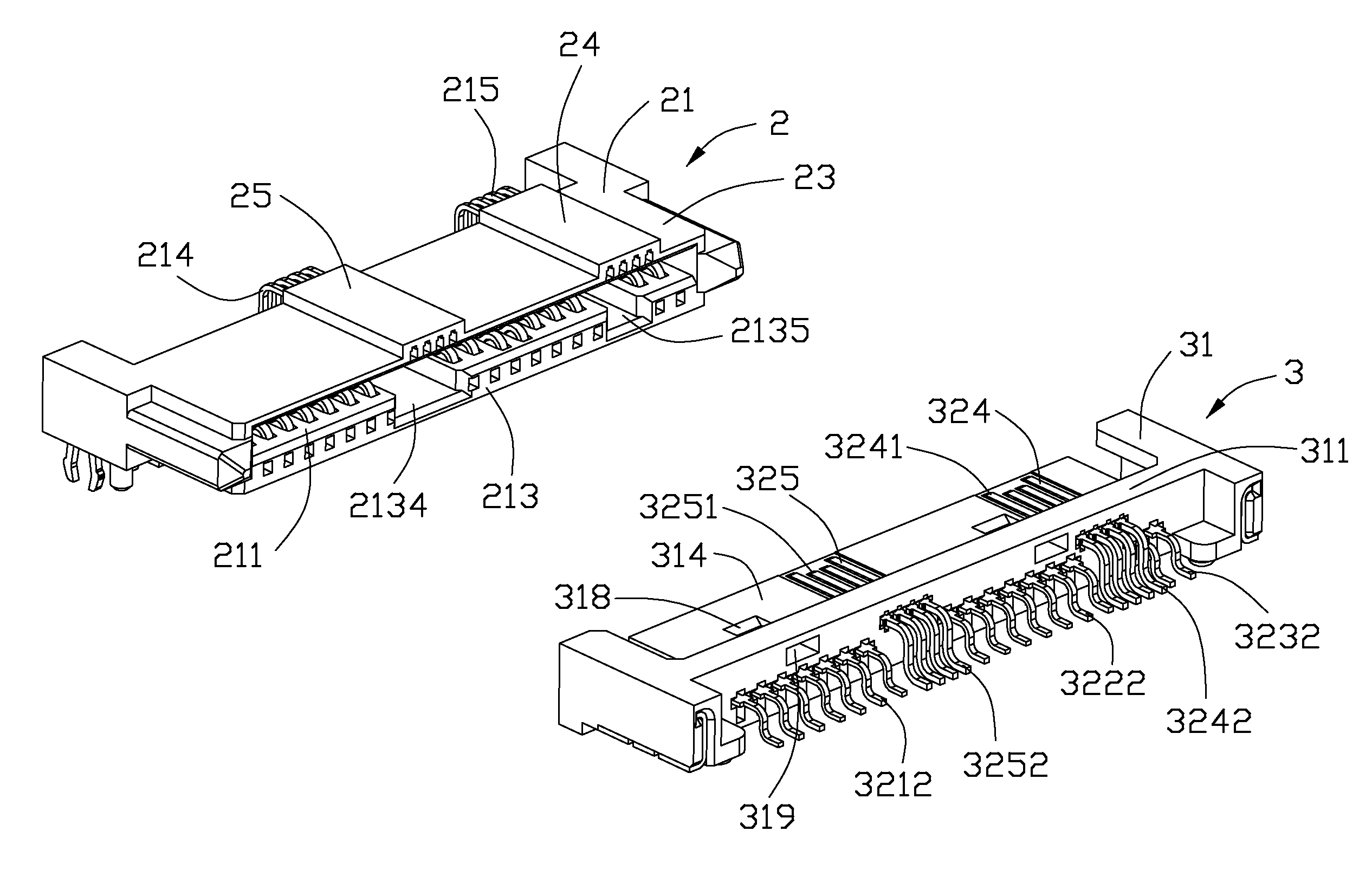

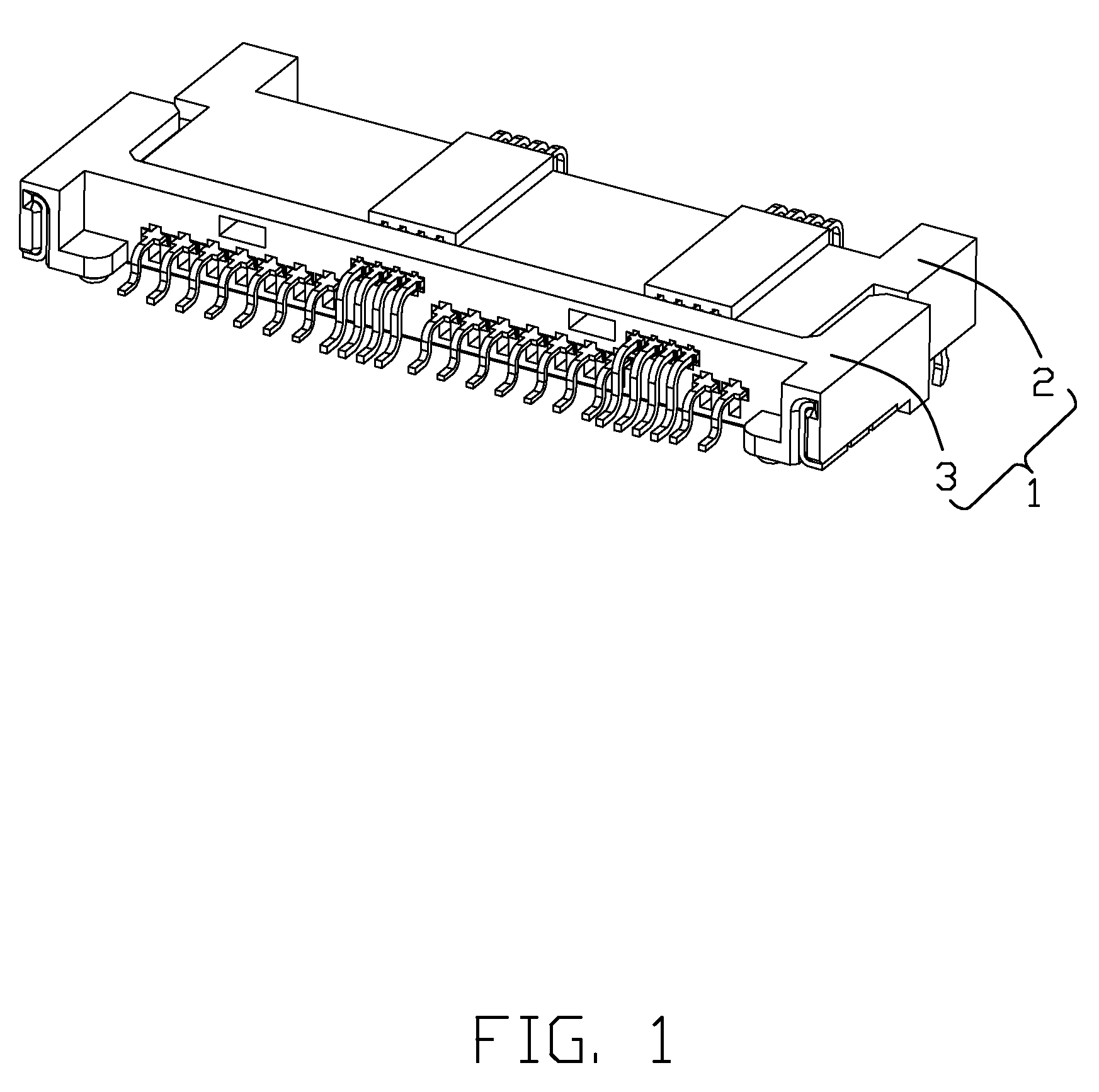

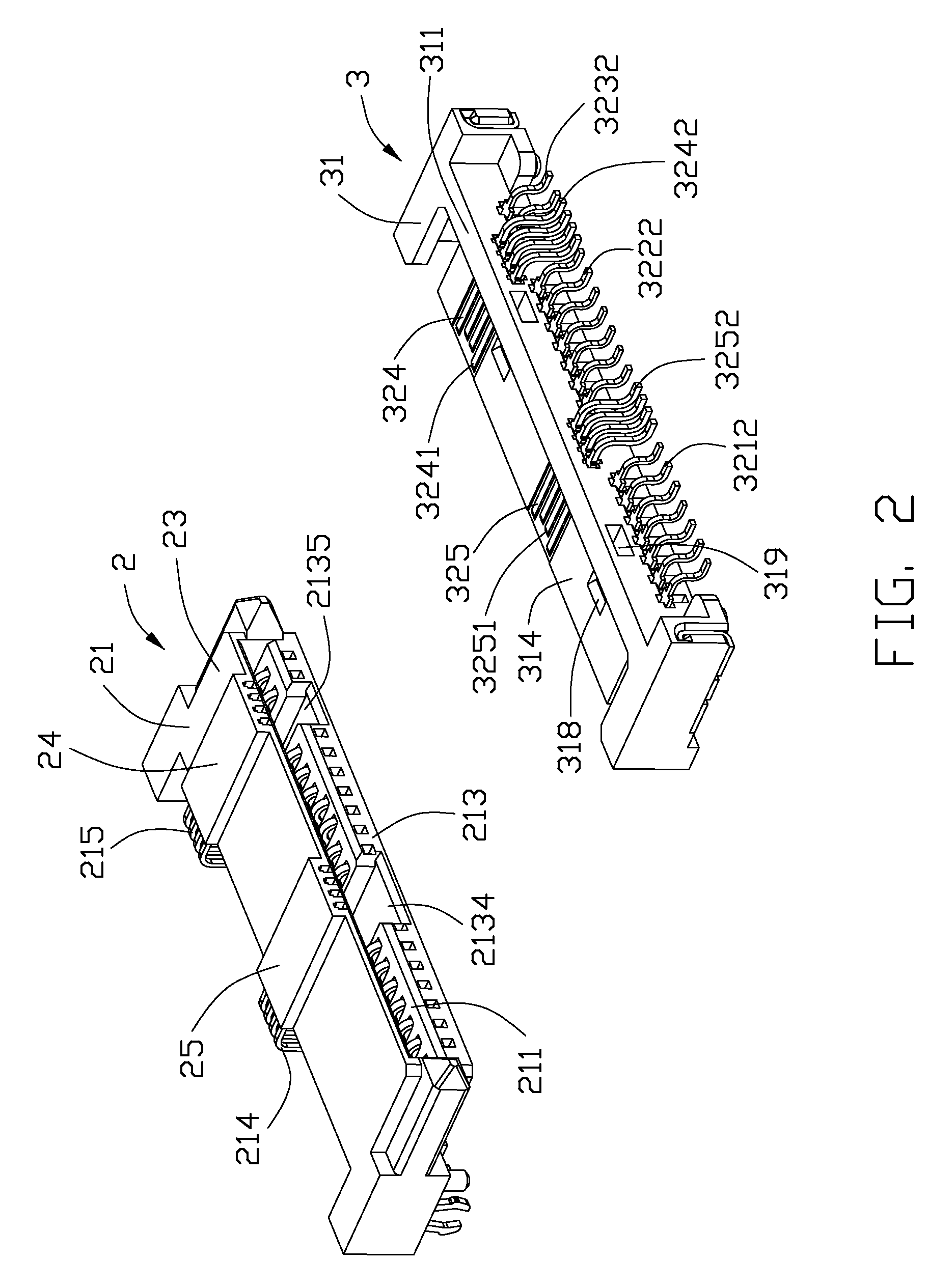

Electrical connector with two grooves dividing contacts

InactiveUS7909652B2Increase transfer speedElectric discharge tubesTwo-part coupling devicesElectricityMating connection

An electrical connector (2, 3) provides an interface compatible with an internal micro Serial ATA connector. The electrical connector (2, 3) includes an insulated housing (21, 31), a first number of contacts (221, 222, 223, 321, 322, 323) assembled to the insulated housing (21, 31); and a second number of contacts (224, 225, 324, 325) assembled to the insulated housing (21, 31). The first number of contacts (221, 222, 223, 321, 322, 323) constitute a power segment and a signal segment compatible with the internal micro Serial ATA connector. The second number of contacts (224, 225, 324, 325) is used for mating with a new type of mating connector (3, 2) when higher transfer speed is needed.

Owner:HON HAI PRECISION IND CO LTD

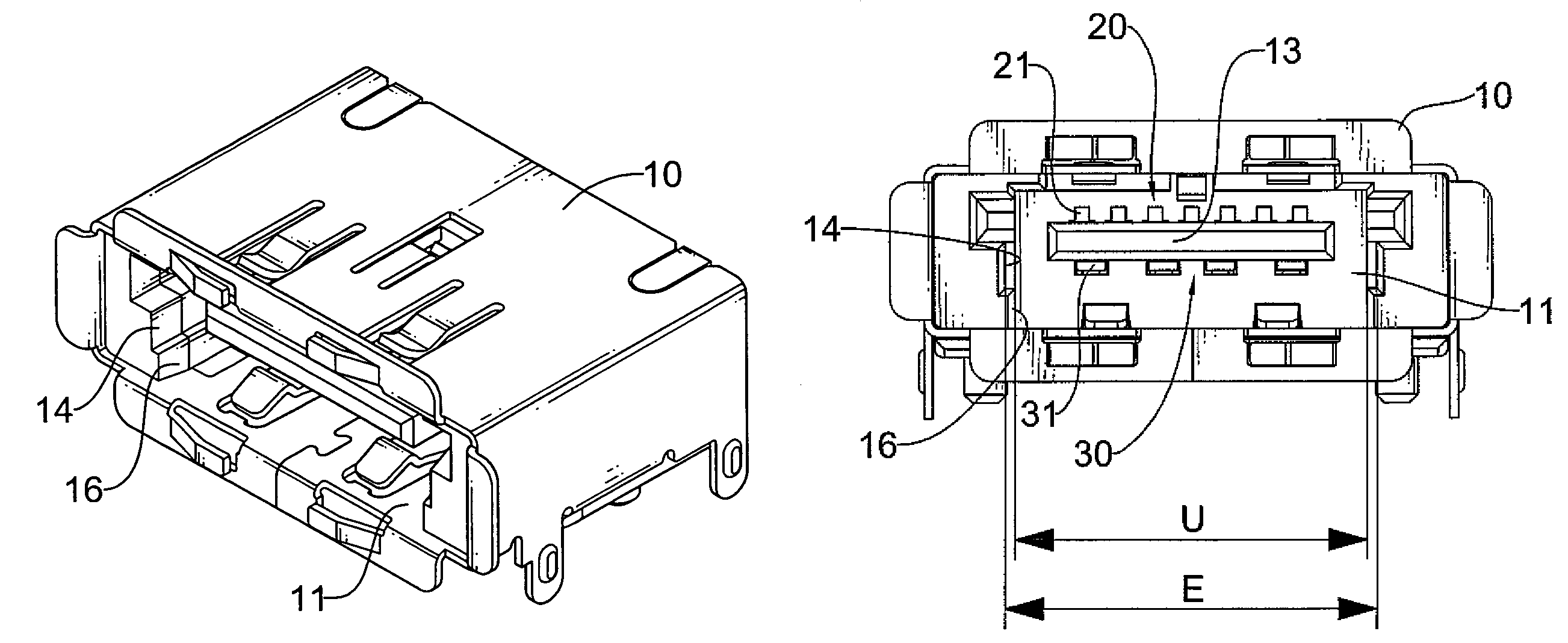

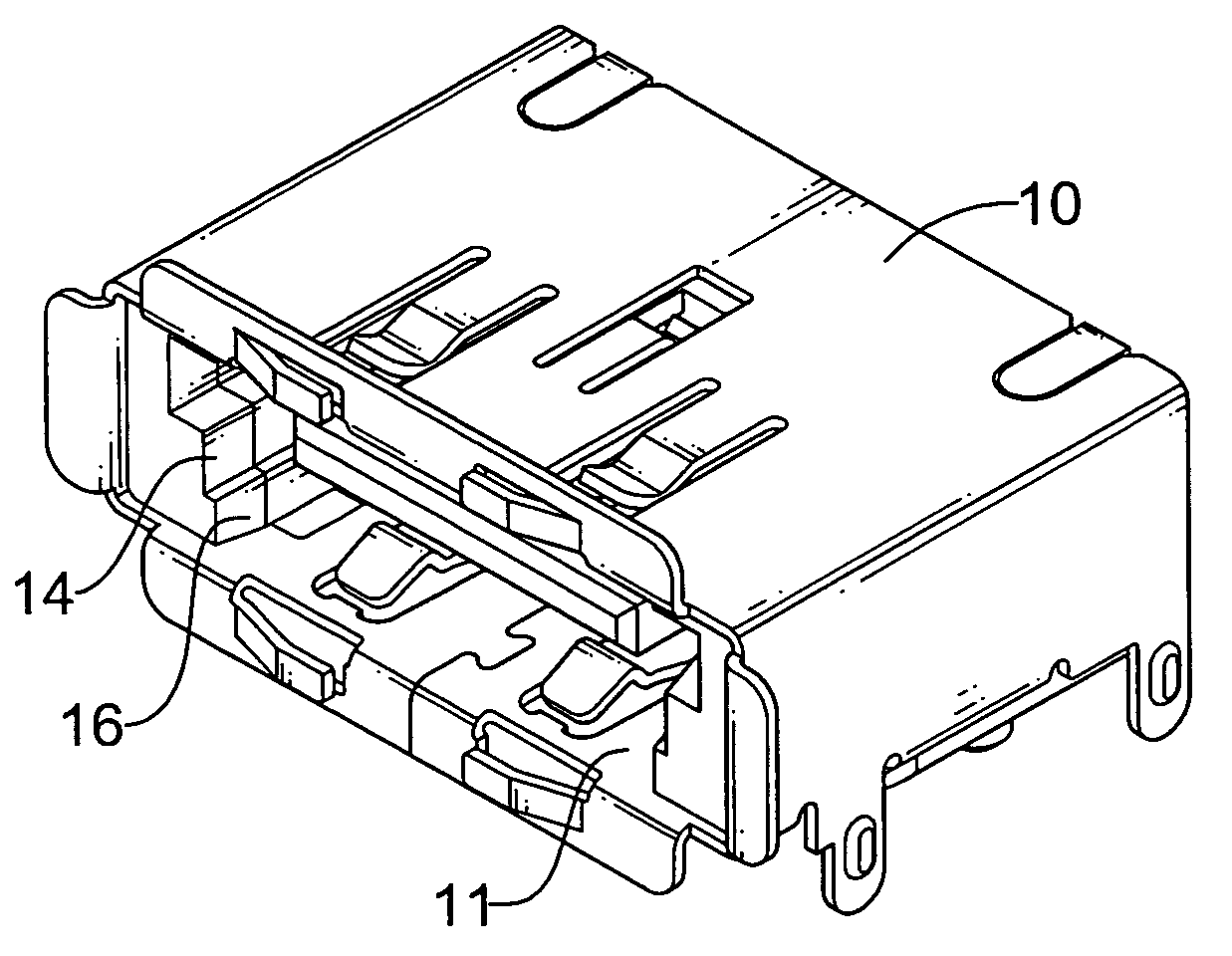

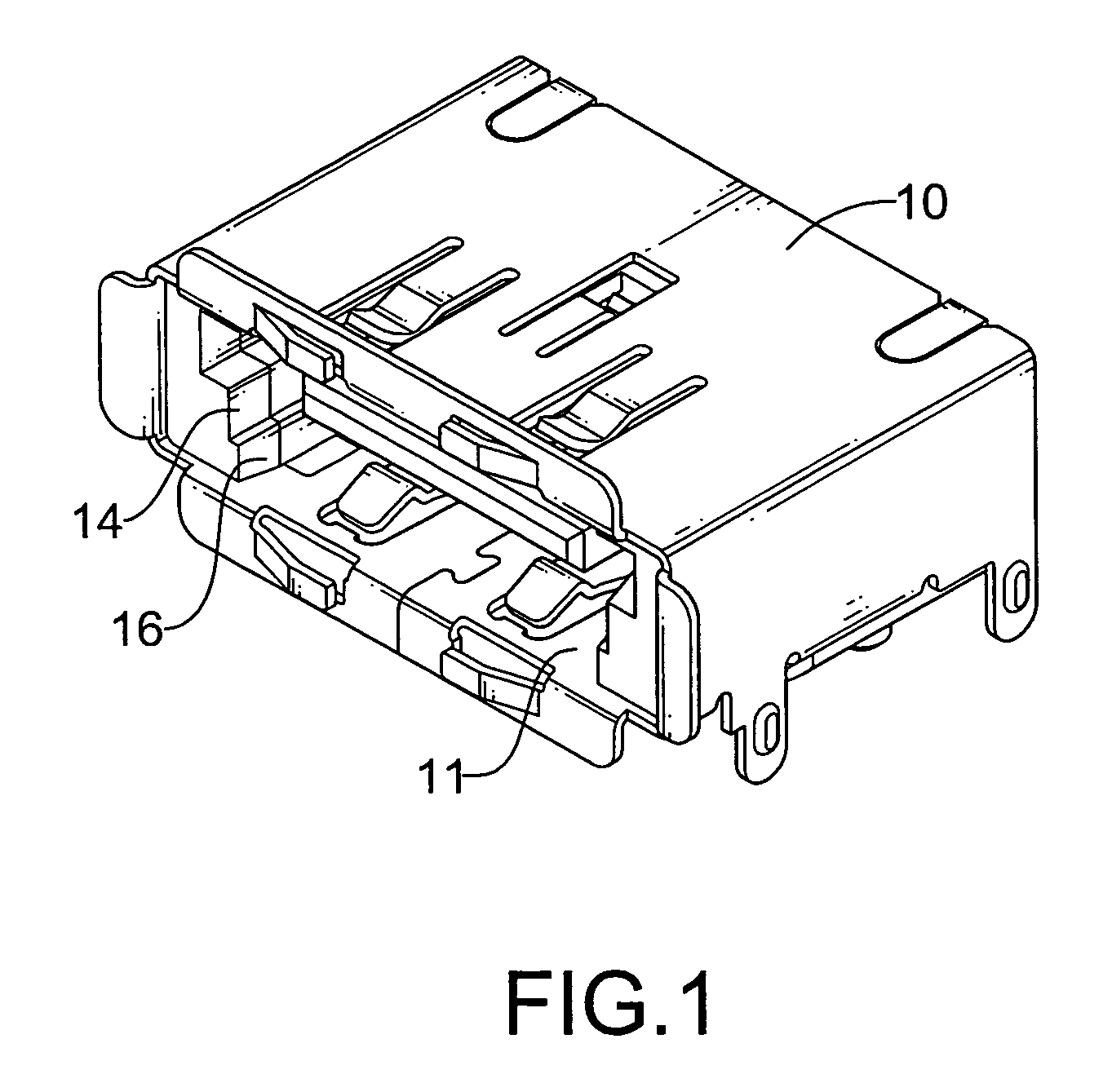

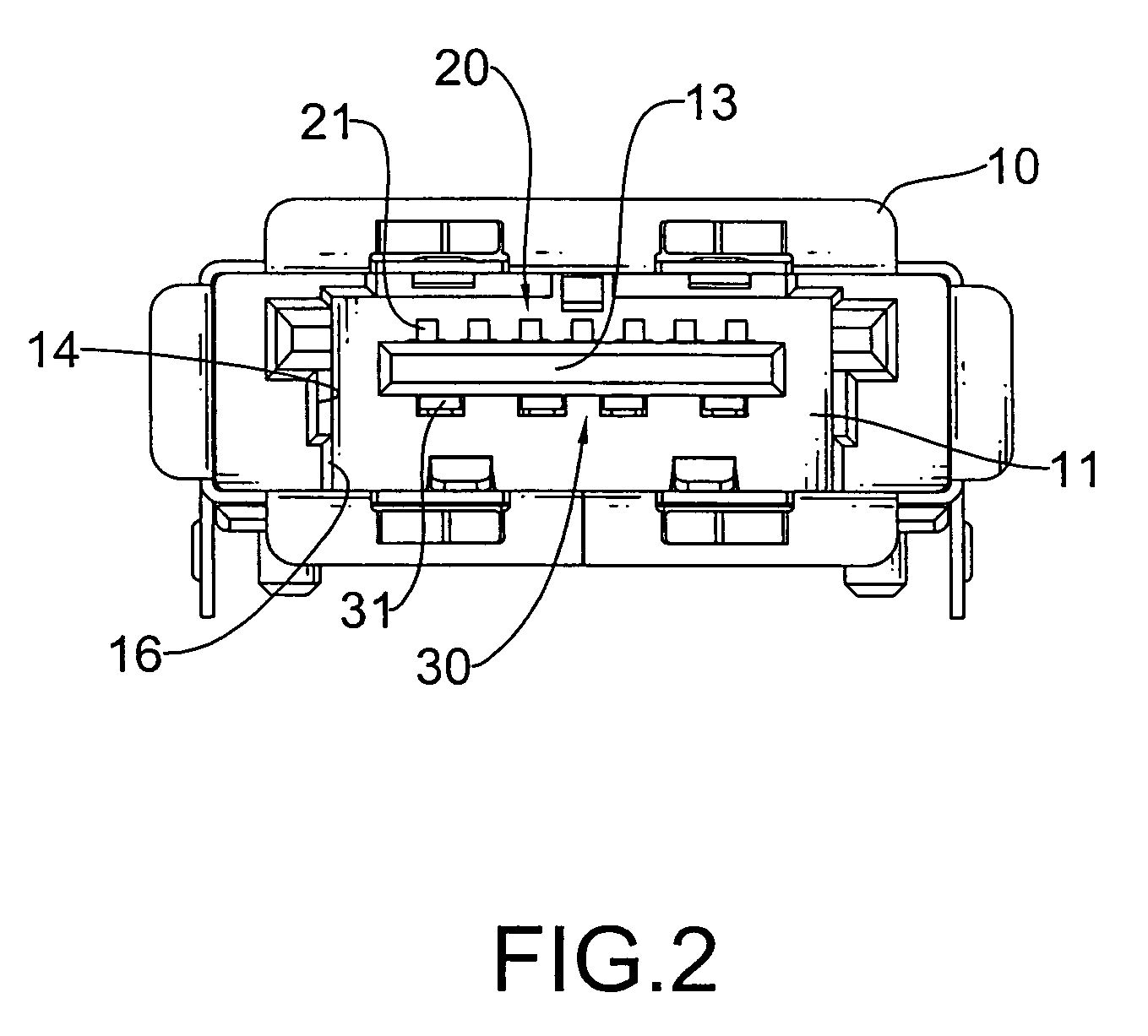

Connector socket for esata and USB plugs

ActiveUS20070173121A1Two-part coupling devicesCoupling protective earth/shielding arrangementsEngineeringUSB

A connector socket for external serial ATA (eSATA) and universal serial bud (USB) plugs has a casing, an eSATA contact set and a USB contact set. The casing has a cavity defined in the casing, an inner rear surface and a contact seat formed on and extending forward from the inner rear surface. The eSATA contact set is mounted on the contact seat and has multiple eSATA contacts being conductive and mounted on the contact seat. The USB contact set is mounted on the contact seat opposite to the eSATA contact set and has multiple USB contacts being conductive and mounted on the contact seat. The connector socket having the single contact seat is compact.

Owner:TAIWAN ELECTRONICS

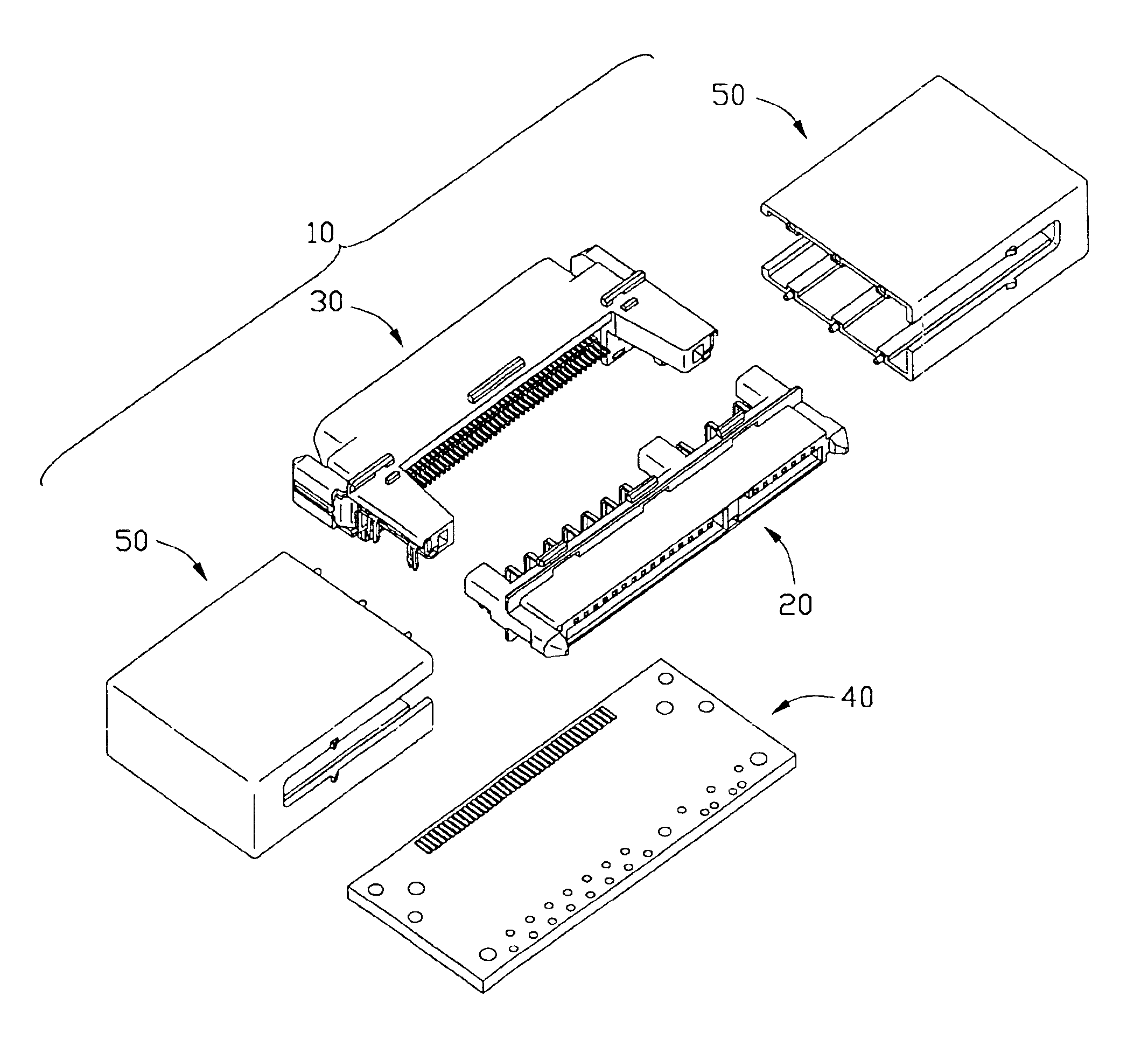

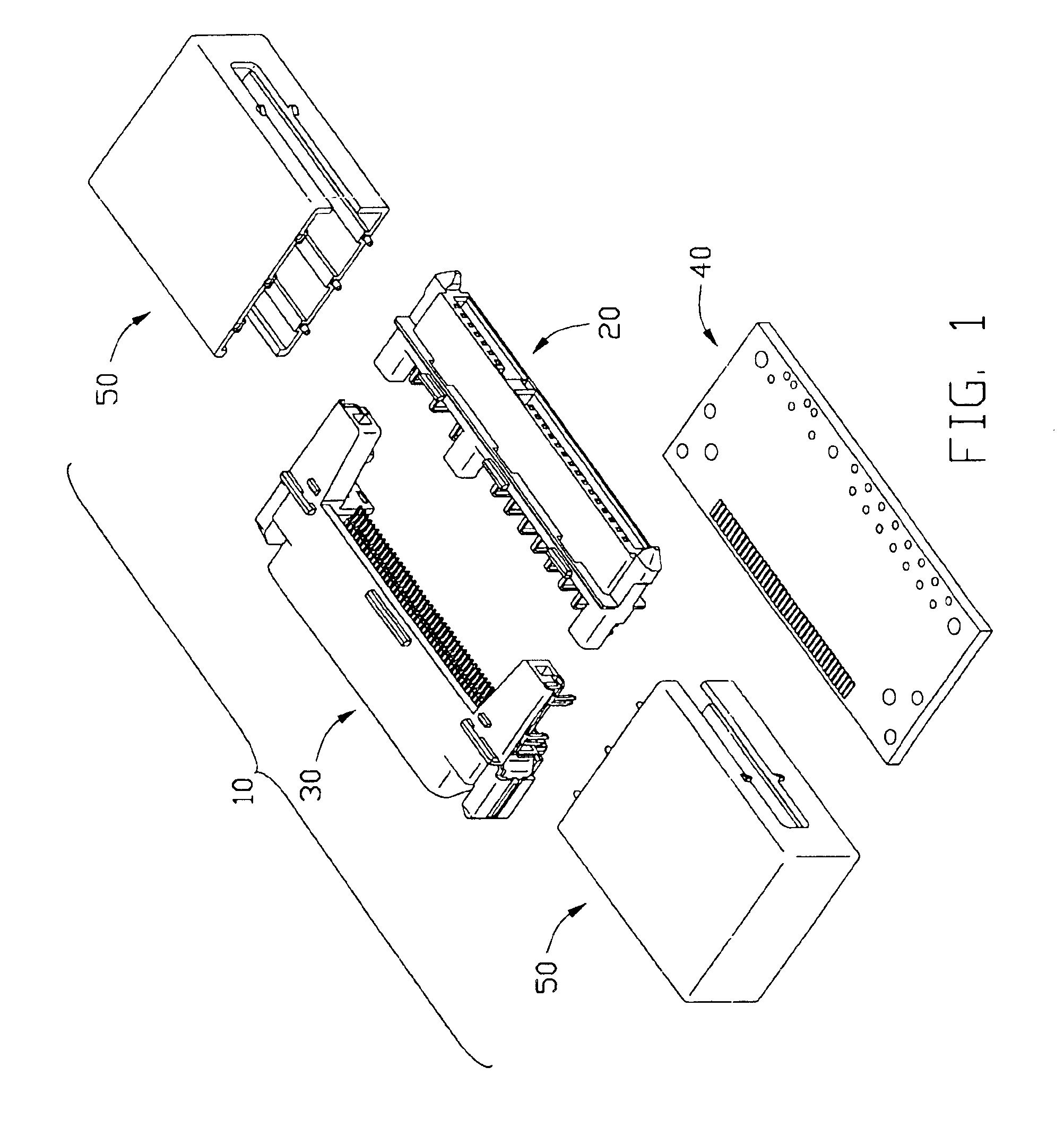

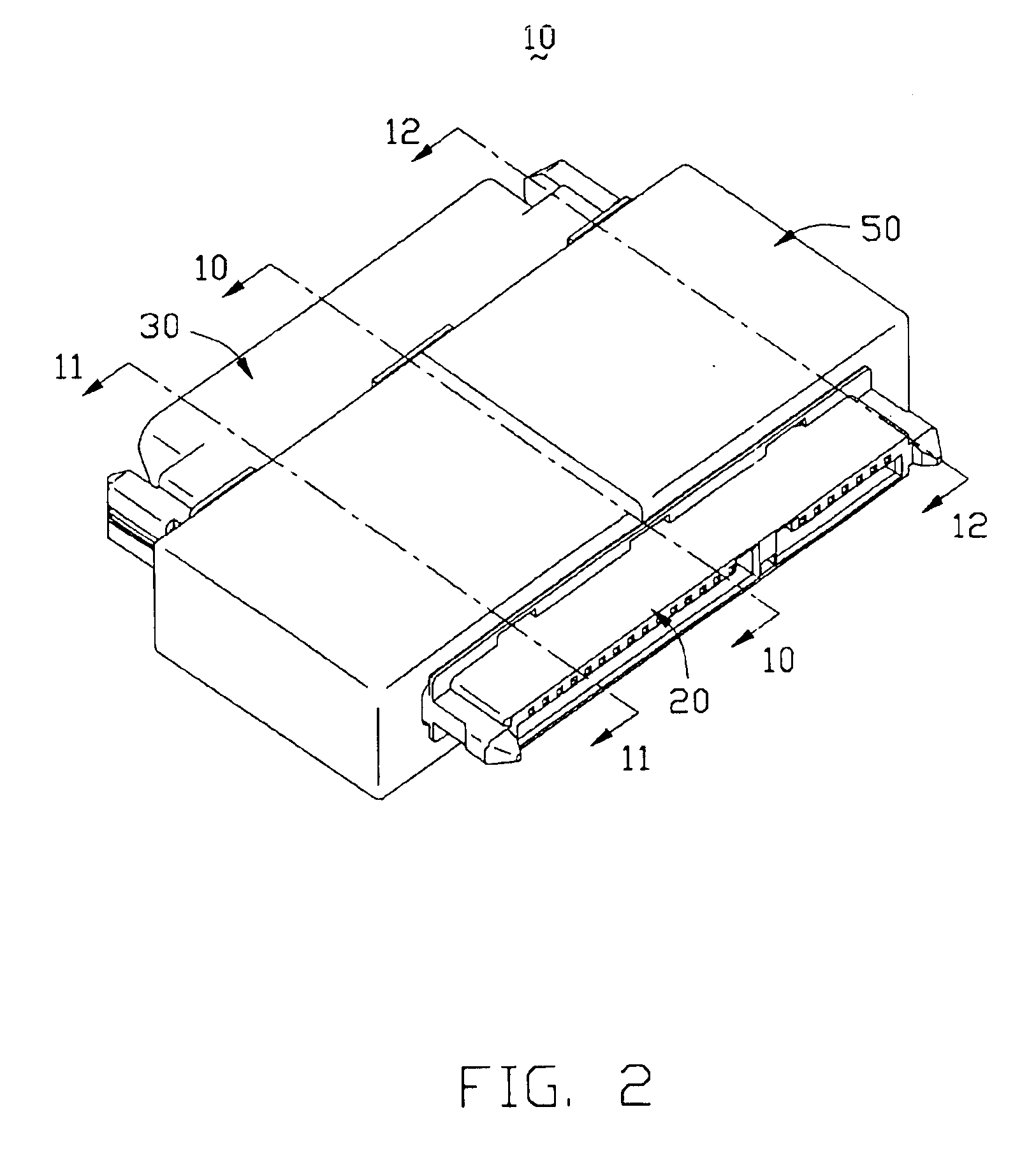

Electrical adapter

InactiveUS6887108B2Electric discharge tubesCoupling device detailsEngineeringSingle Connector Attachment

An electrical adapter (10) includes a serial advanced technology attachment (serial ATA) receptacle connector (20), a single connector attachment 2 (SCA2) plug connector (30), a printed circuit board (40) and a pair of covers (50). The serial ATA receptacle connector and the SCA2 plug connector are respectively electrically and mechanically connected to the printed circuit board. The printed circuit board performs the functions of signal transmission and conversion between the serial ATA receptacle connector and the SCA2 plug connector. The pair of covers are assembled to the subassembly of the serial ATA receptacle connector, the SCA2 plug connector and the printed circuit board, and finally combined with each other to fasten the electrical adapter. The electrical adapter interconnects the SCA2 interface with the serial ATA interface.

Owner:HON HAI PRECISION IND CO LTD

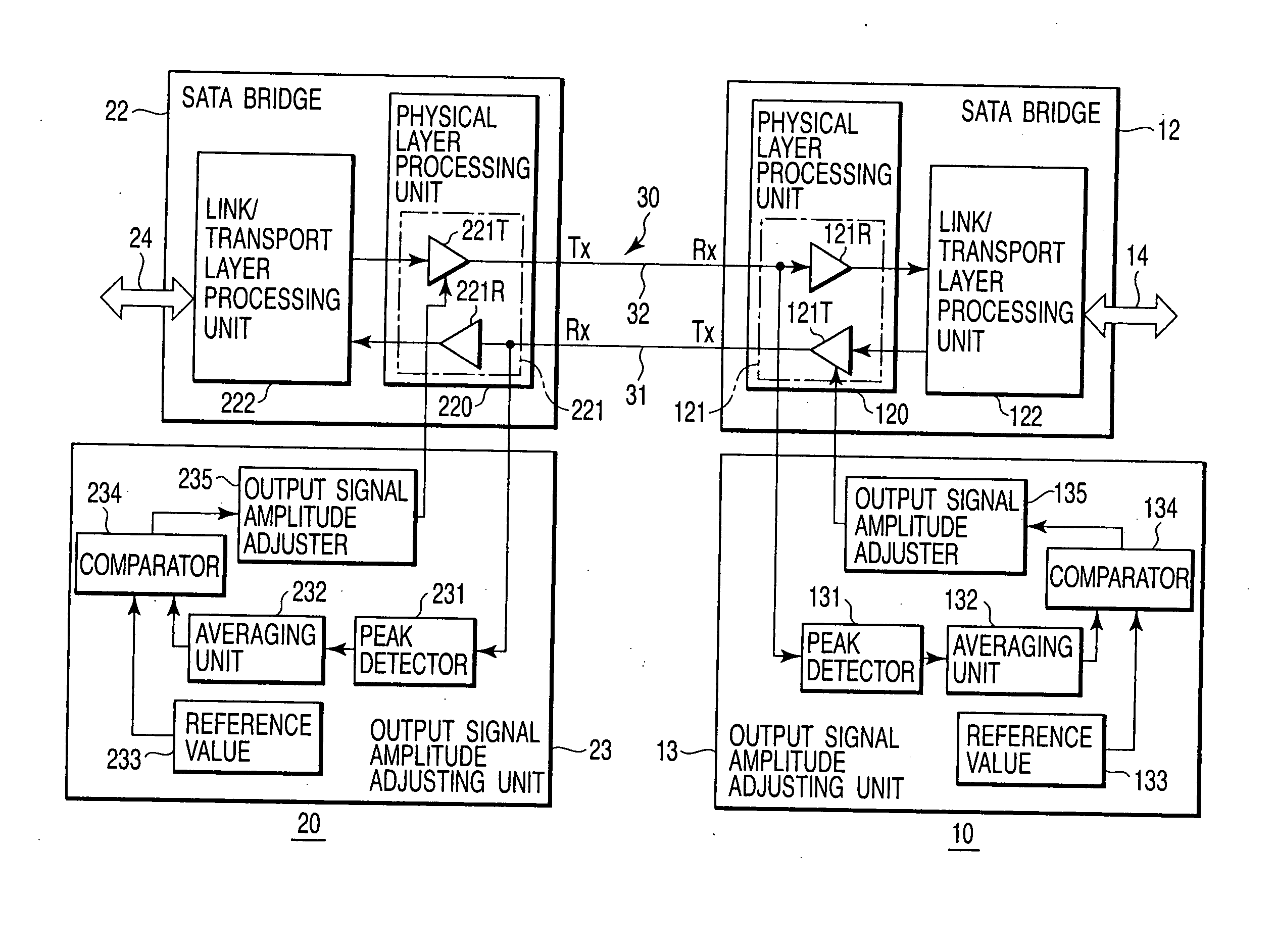

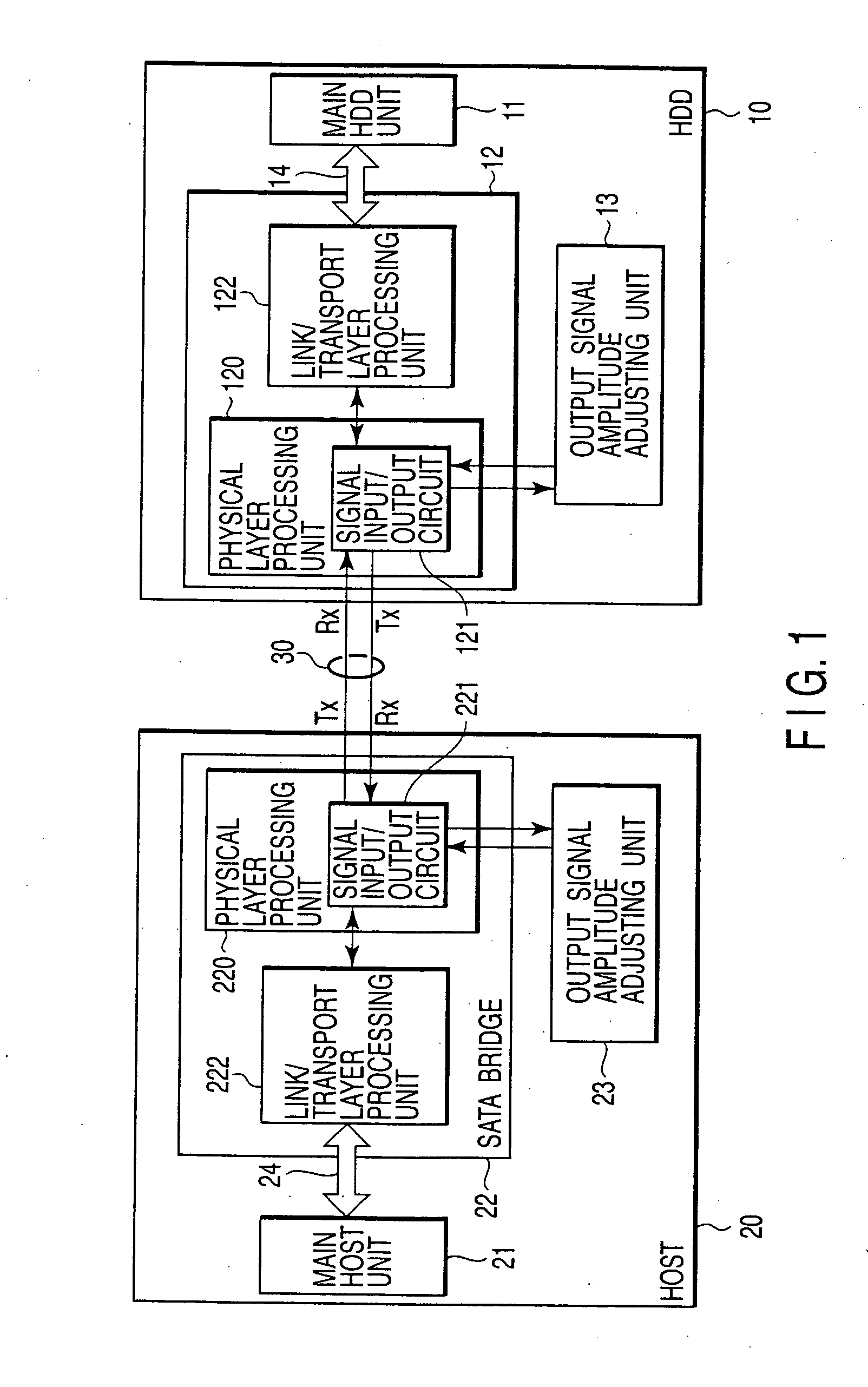

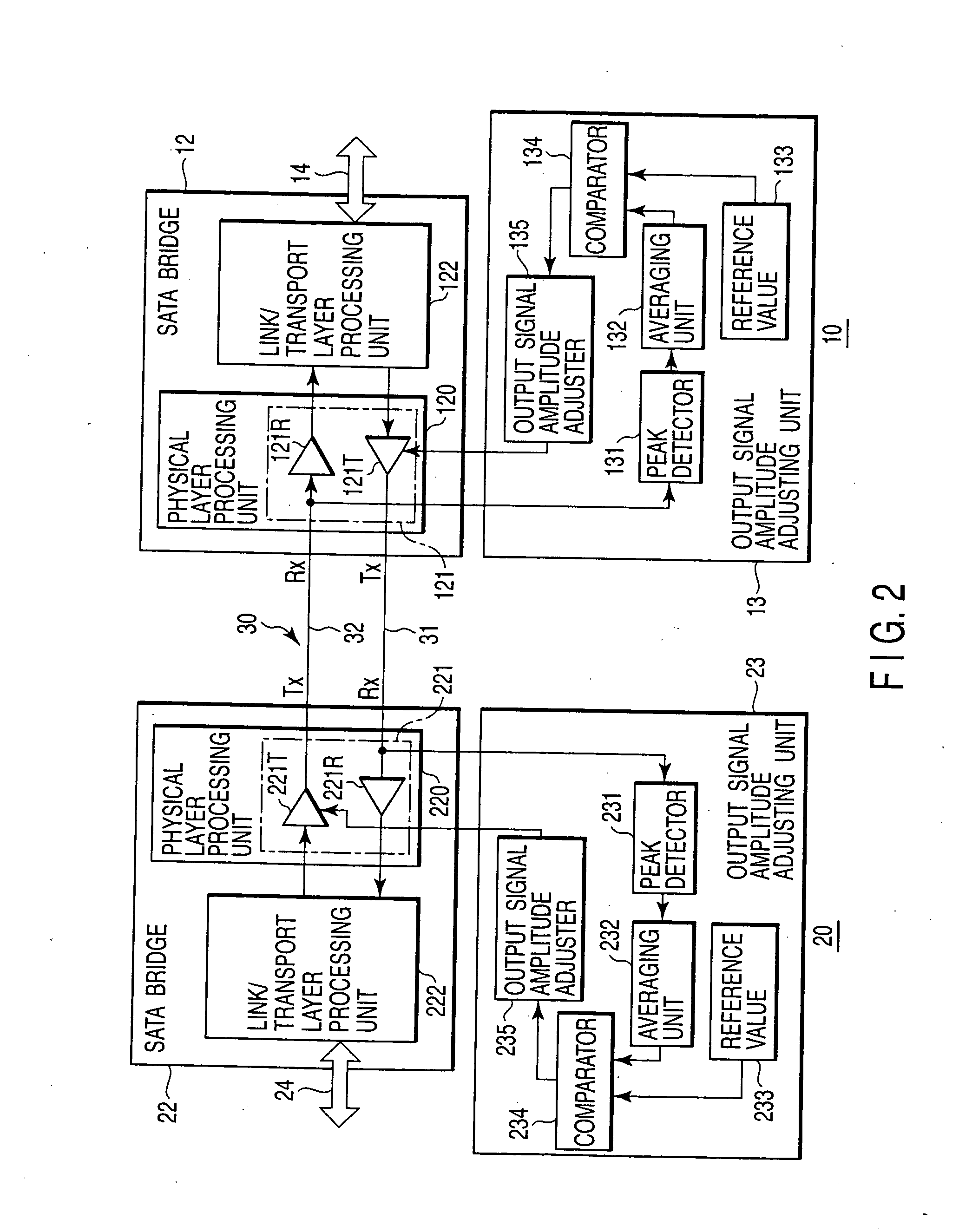

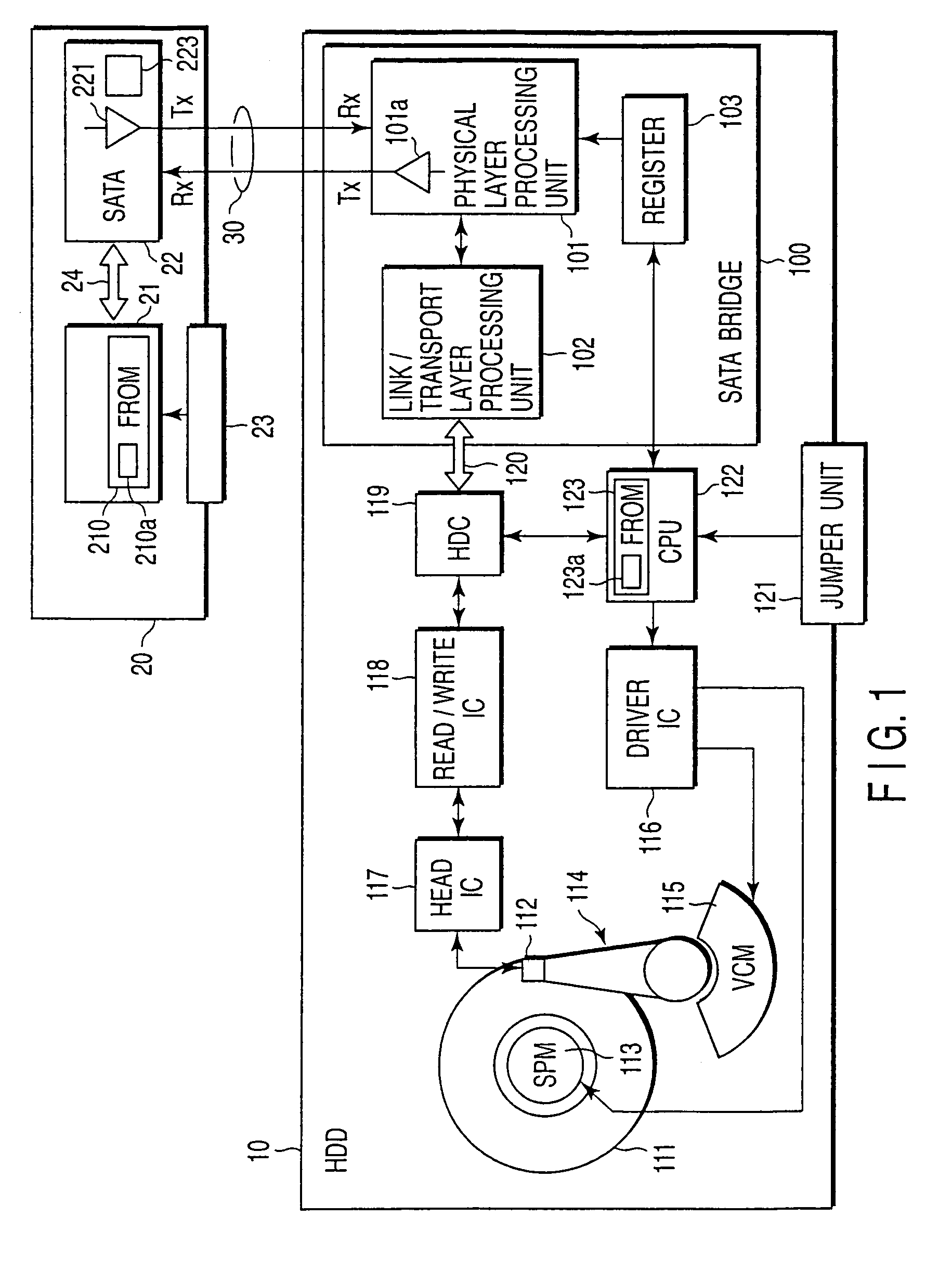

Electronic device with serial ATA interface and signal amplitude automatic adjustment method

InactiveUS20050024083A1Realize automatic adjustmentReliability increasing modificationsTransmission control/equlisationData signalComputer science

An amplitude detector incorporated in an electronic device with a serial ATA interface detects the amplitude of a serial data signal input to an I / O circuit via a SATA bus. An averaging unit averages the detection results of the amplitude detector. A comparator compares the resultant average with an expected input signal amplitude. Based on the comparison result, an amplitude adjuster adjusts the amplitude of a serial data signal when this signal is output from the I / O circuit. Adjustment is performed such that when the serial data signal output from the I / O circuit is input to another electronic device via the SATA bus, it has an amplitude at least approximately equal to the expected input signal amplitude. In other embodiments, the invention utilizes an amplitude detector, comparator and adjuster and employs a step-by-step adjustment of the electronic device with another similarly equipped electronic device.

Owner:KK TOSHIBA

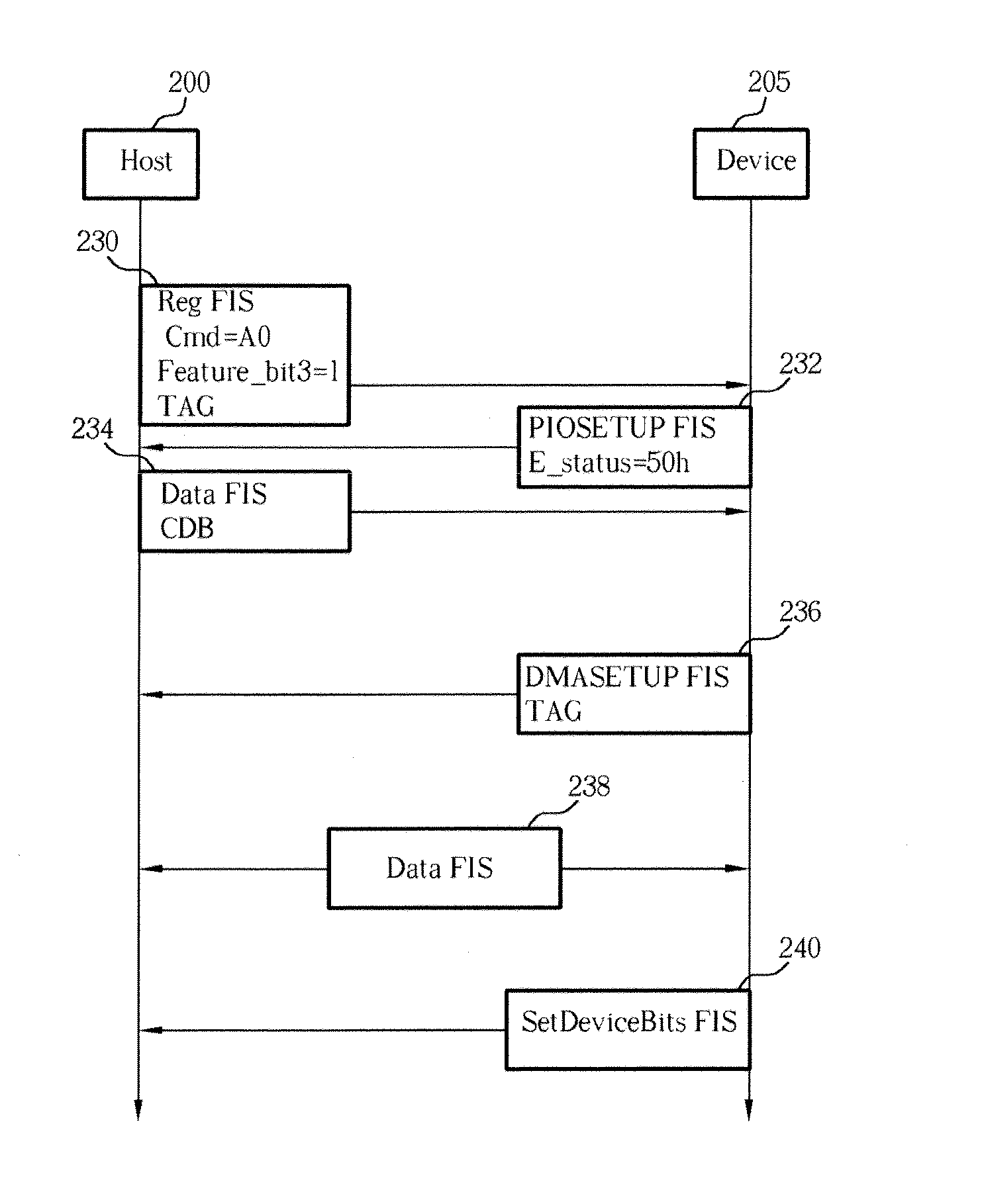

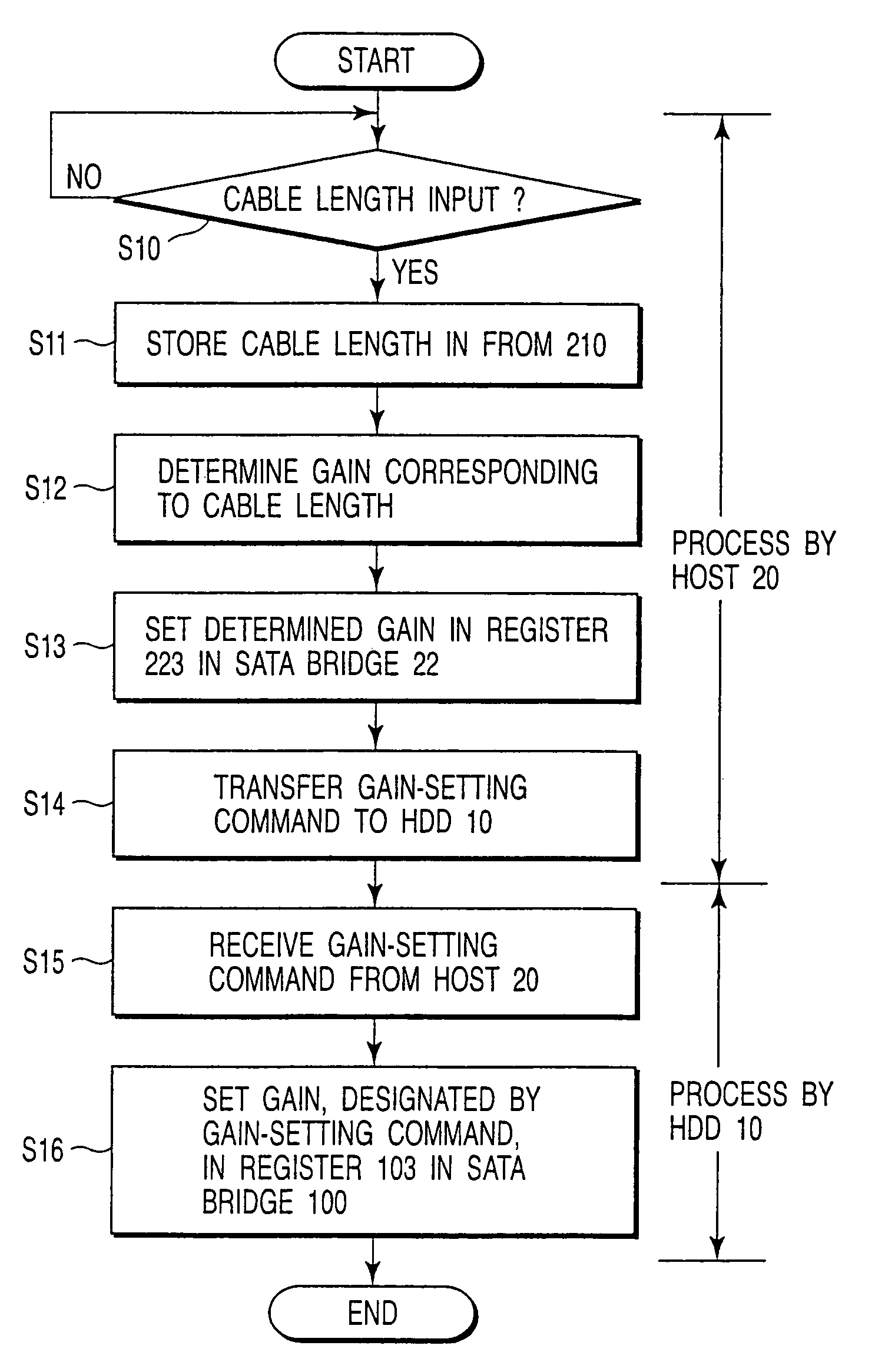

Method for Processing Command via SATA Interface

Methods for performing ATAPI NCQ and ATAPI normal command are provided. The method involves receiving a predefined packet comprising essential information regarding a host command, the predefined packet received from a Serial ATA interface that is coupled to a host, wherein the essential information further indicates whether the command is a NCQ command; executing the command; and sending a completion packet to the host over the Serial ATA interface for indicating that the command was executed.

Owner:MEDIATEK INC

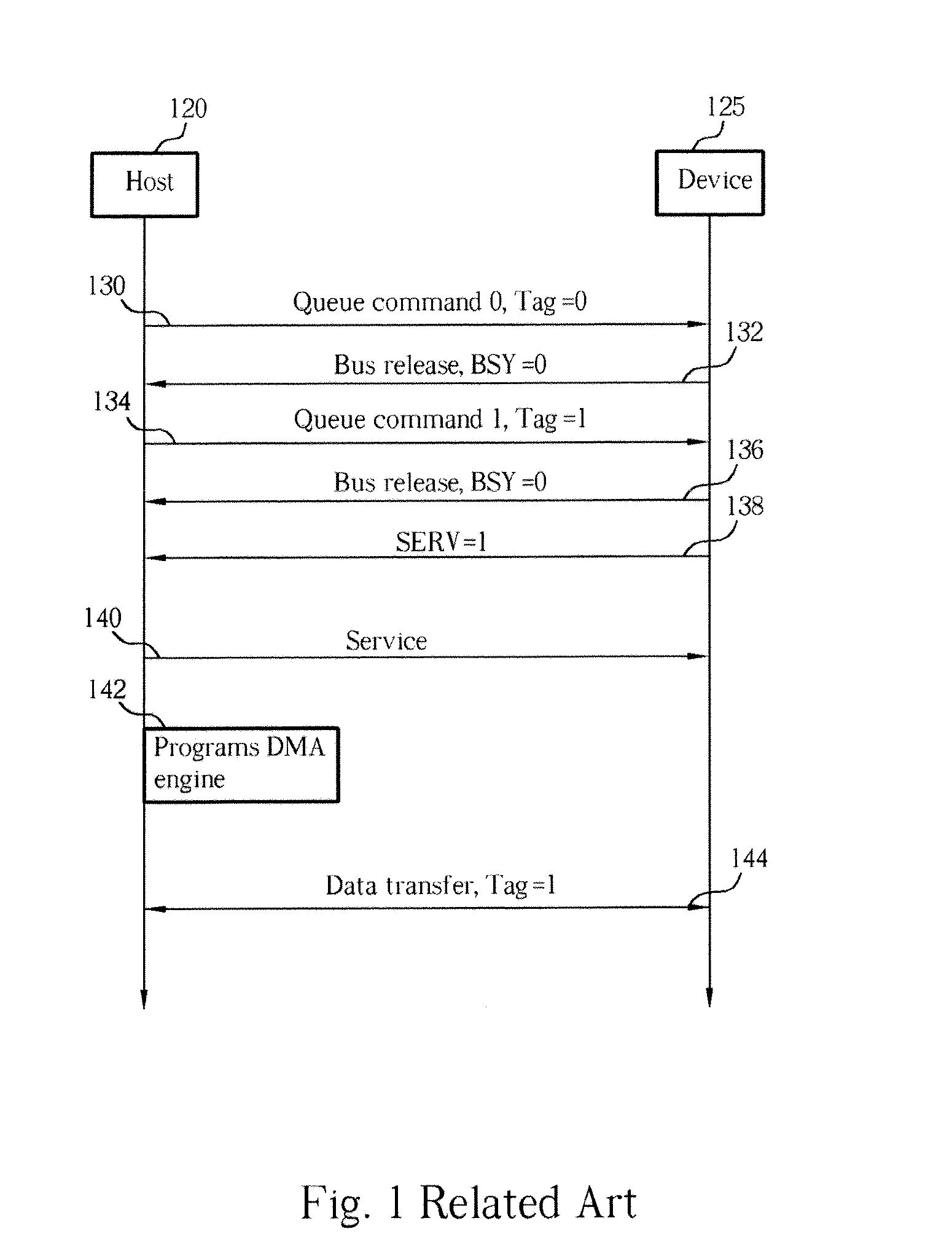

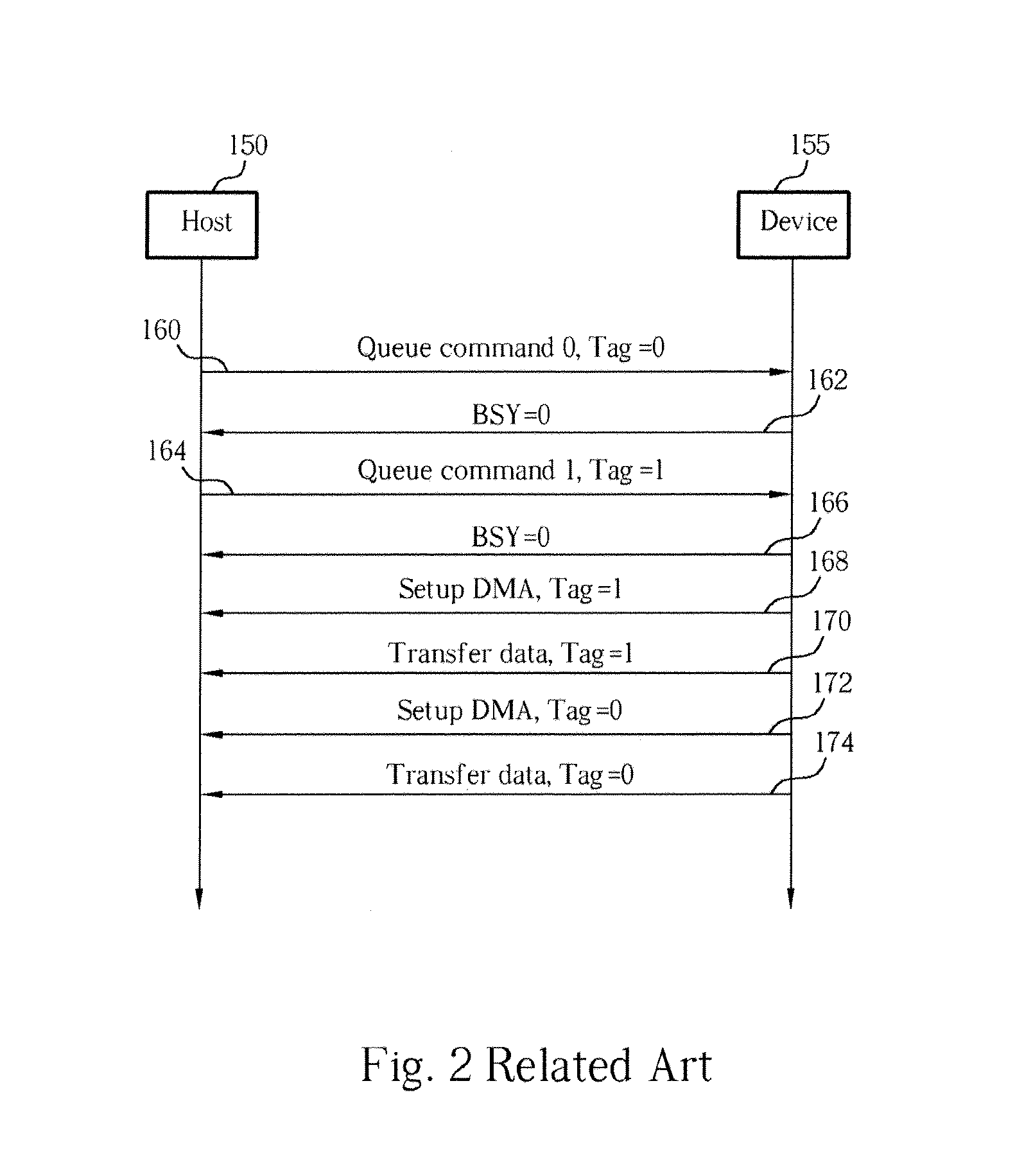

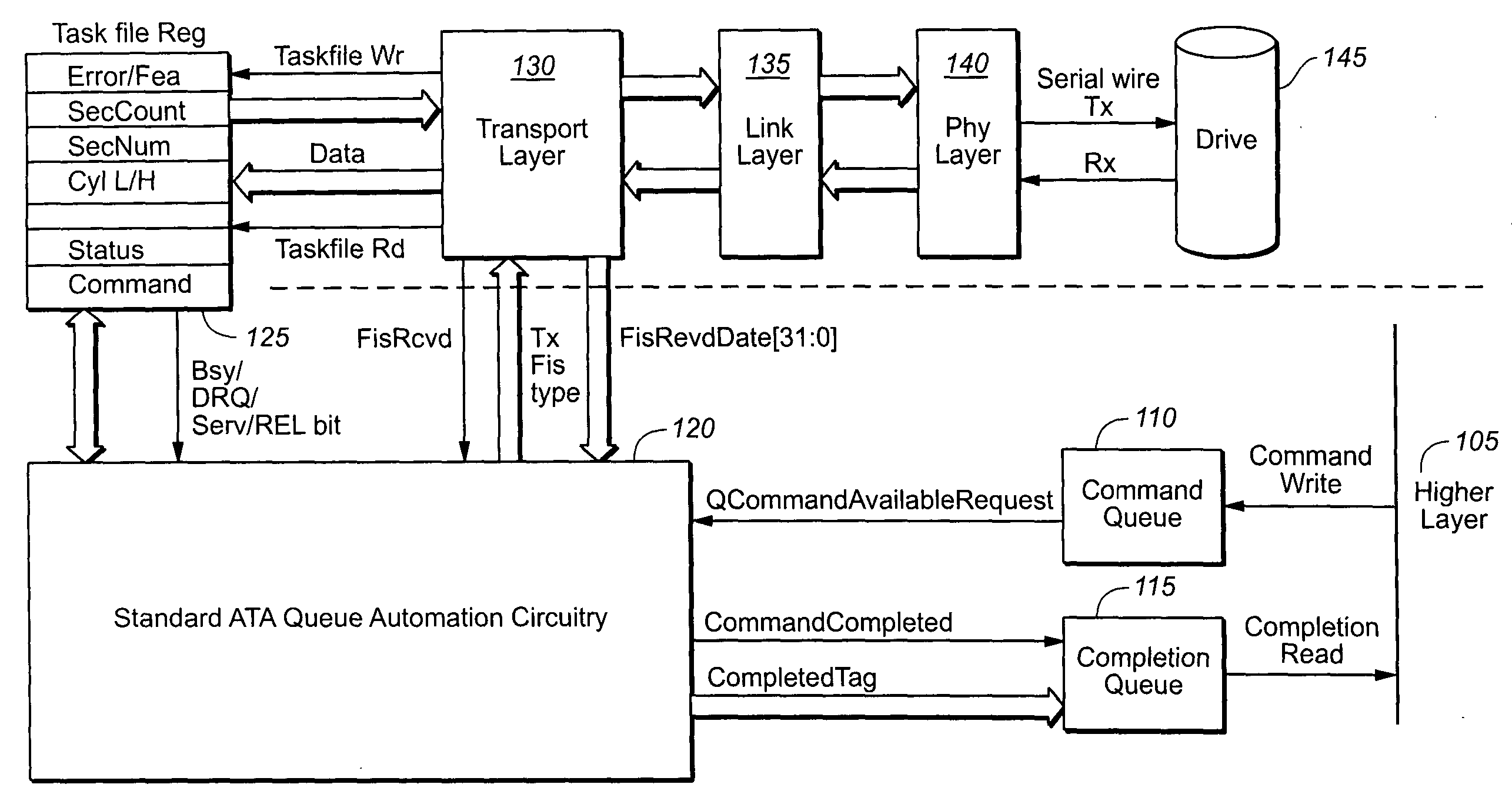

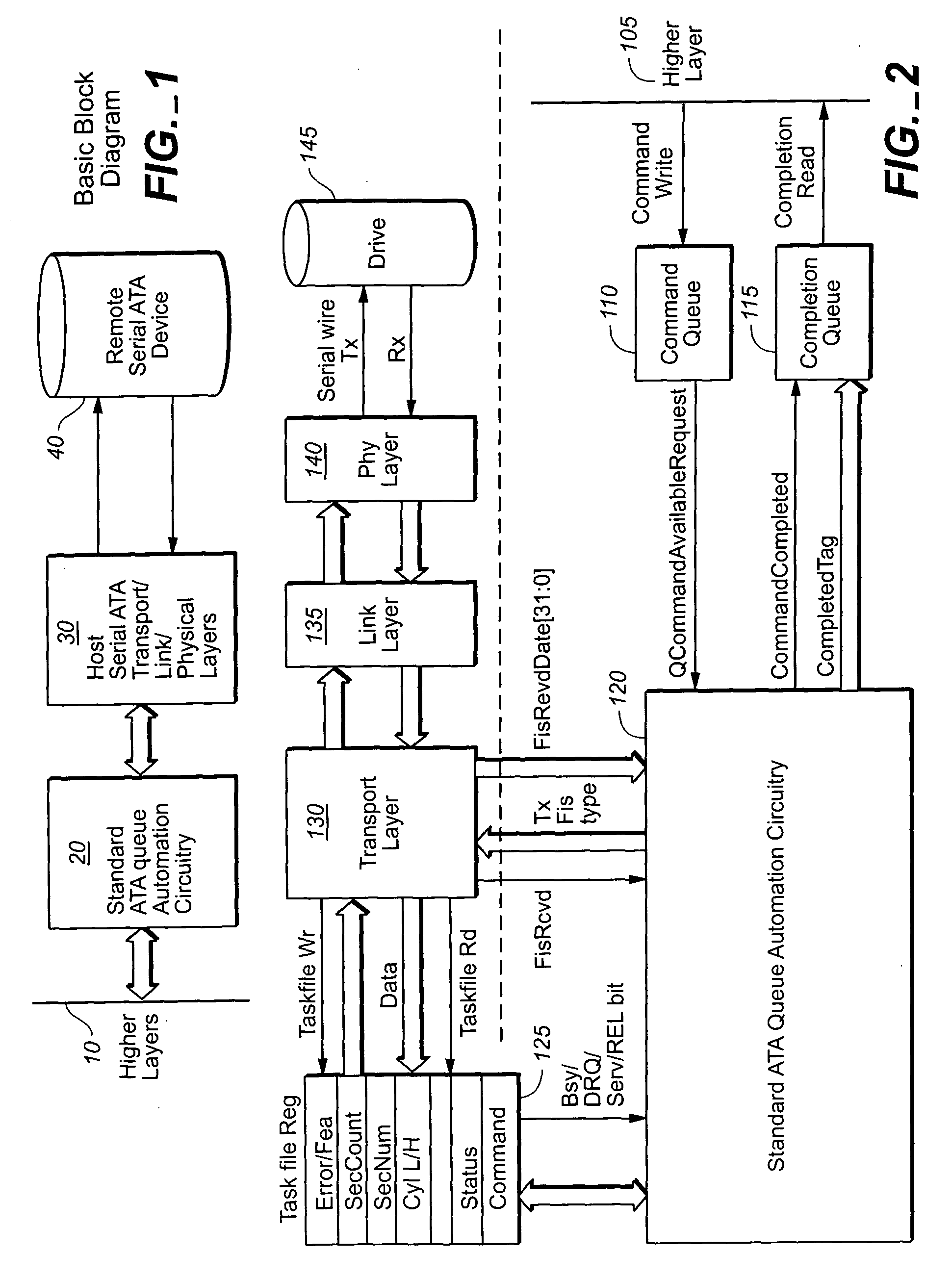

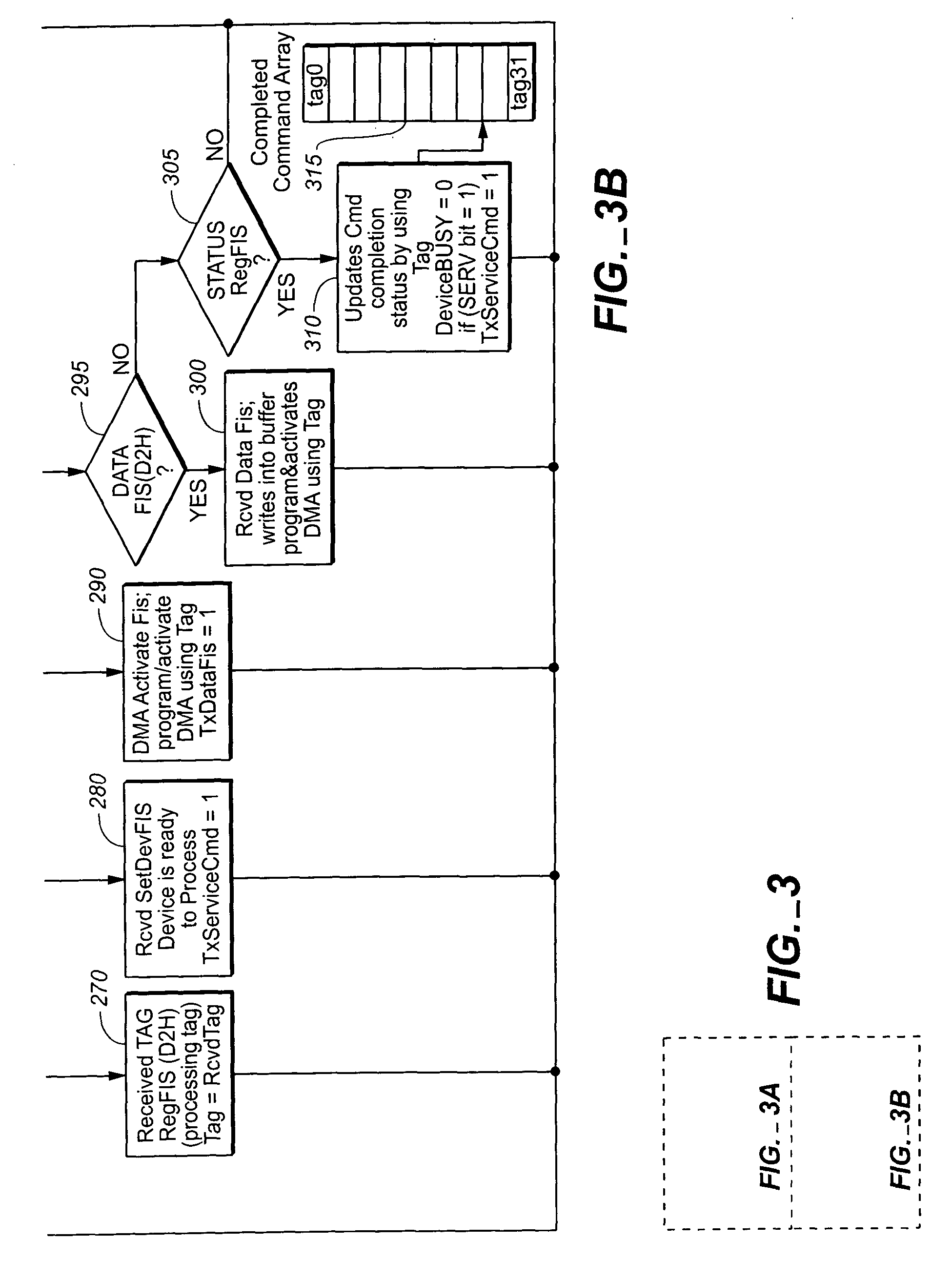

Standard ATA queuing automation in serial ATA interface

InactiveUS20050027894A1Reduces handshaking processing timeImprove performanceDigital computer detailsTime-division multiplexTransport layerData transmission

A method and circuit for enhancing the performance in a serial ATA interface uses a standard ATA queue automation circuitry that handles all the transmit / receive frame information structure (FIS) operations for ATA queue commands without interrupting the higher-level software and associated hardware, firmware, and drivers. If the standard ATA queue automation circuitry and command queues are not provided, then every FIS operation will interrupt the higher layer application program. The standard ATA queuing automation circuit preprocesses higher layer commands to write into the task file registers before initiating the transport layer for an FIS transmission and provides information regarding the success or failure of a command. Commands to be executed and completion command queues are preferably used to improve the performance further. These queues may be implemented within the higher layers, as part of the standard ATA queuing automation circuit, or as software, firmware, and / or hardware functionally located between the standard ATA queuing automation circuit and the higher layers. The standard ATA queue automation circuitry provides information to program the DMA controller and activates the DMA automatically for the data transfer.

Owner:AVAGO TECH INT SALES PTE LTD

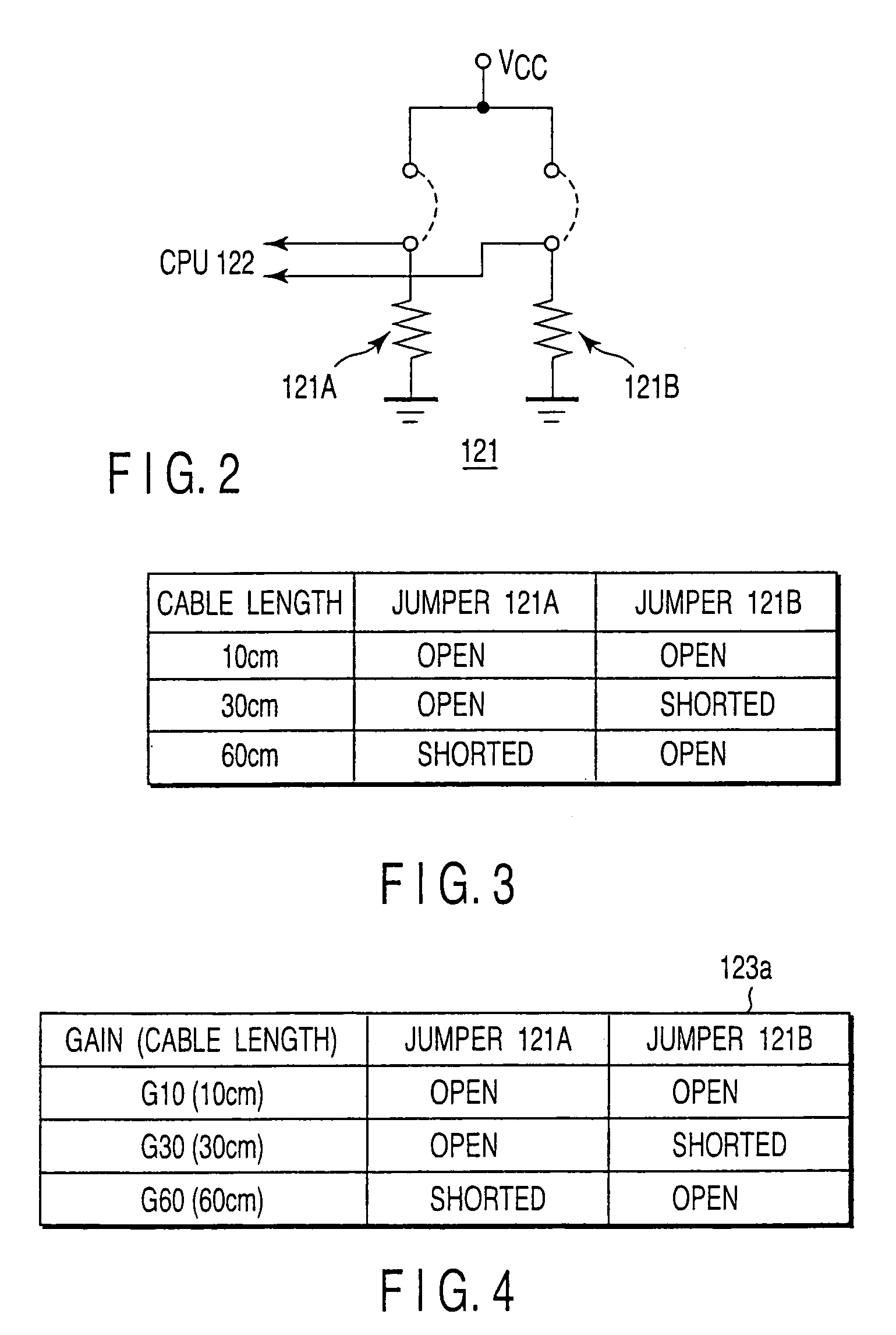

Electronic device with serial ATA interface and signal amplitude adjusting method

InactiveUS7133956B2Reliability increasing modificationsInput/output to record carriersData signalInterface standard

The CPU of an electronic device generates a parameter for determining the amplitude of a serial data signal when it is output from an output device to a serial ATA bus. The parameter indicates a value that is needed to make the amplitude of the received serial data signal fall within a range, stipulated in serial ATA interface standards, when another electronic device receives the serial data signal. The parameter is generated in accordance with the cable length of the serial ATA bus designated by a cable length designation unit. The other electronic device is connected to the serial ATA bus.

Owner:KK TOSHIBA

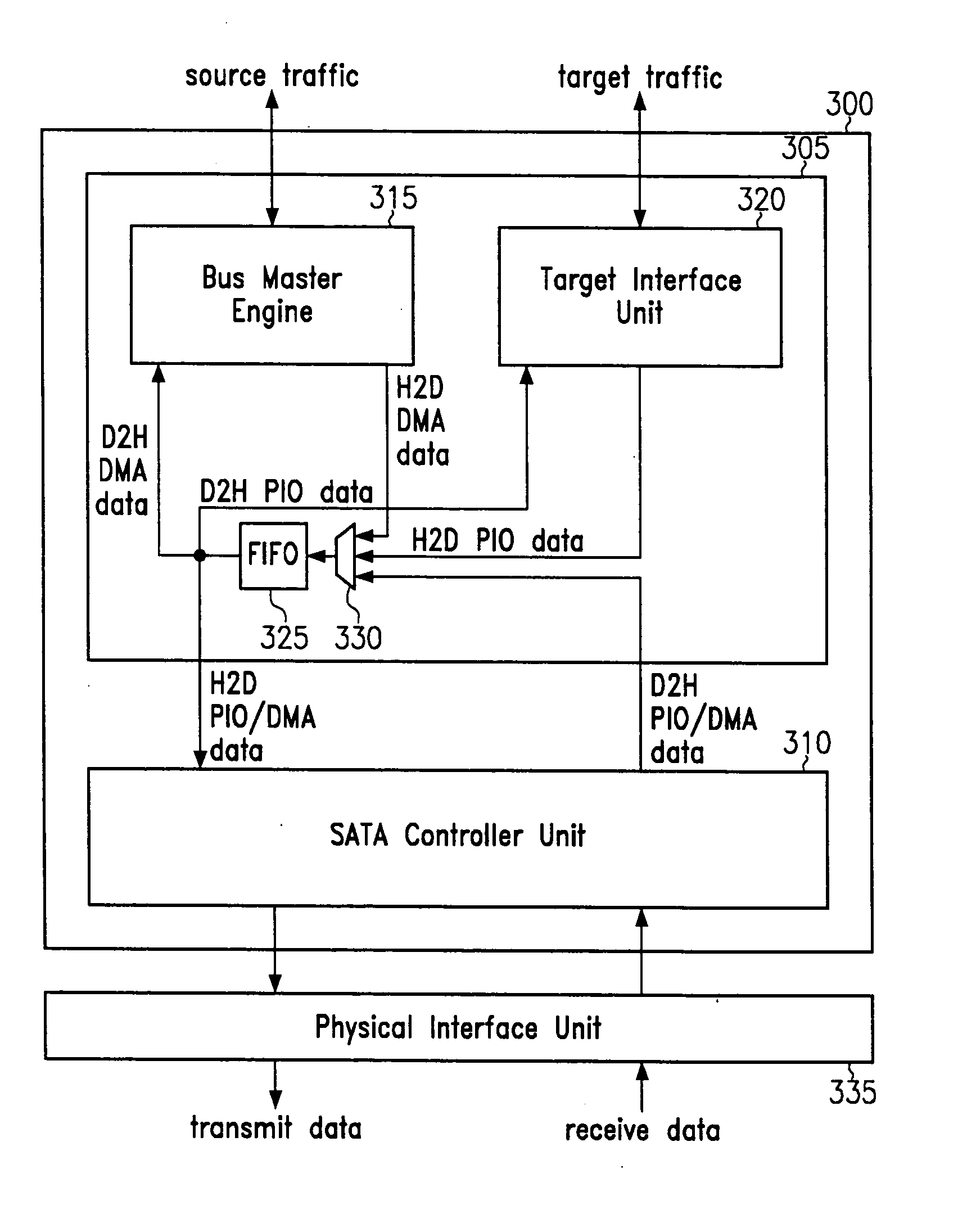

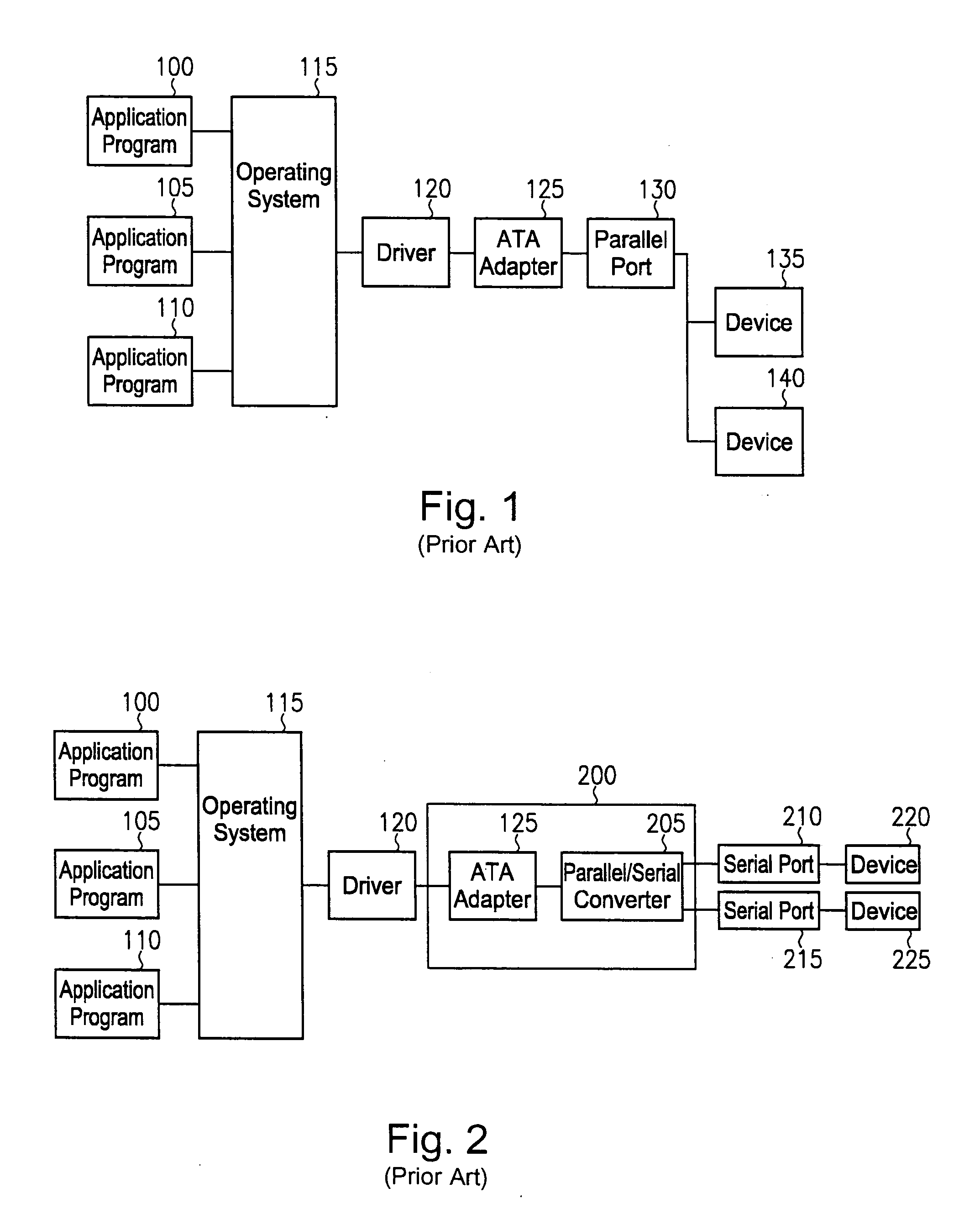

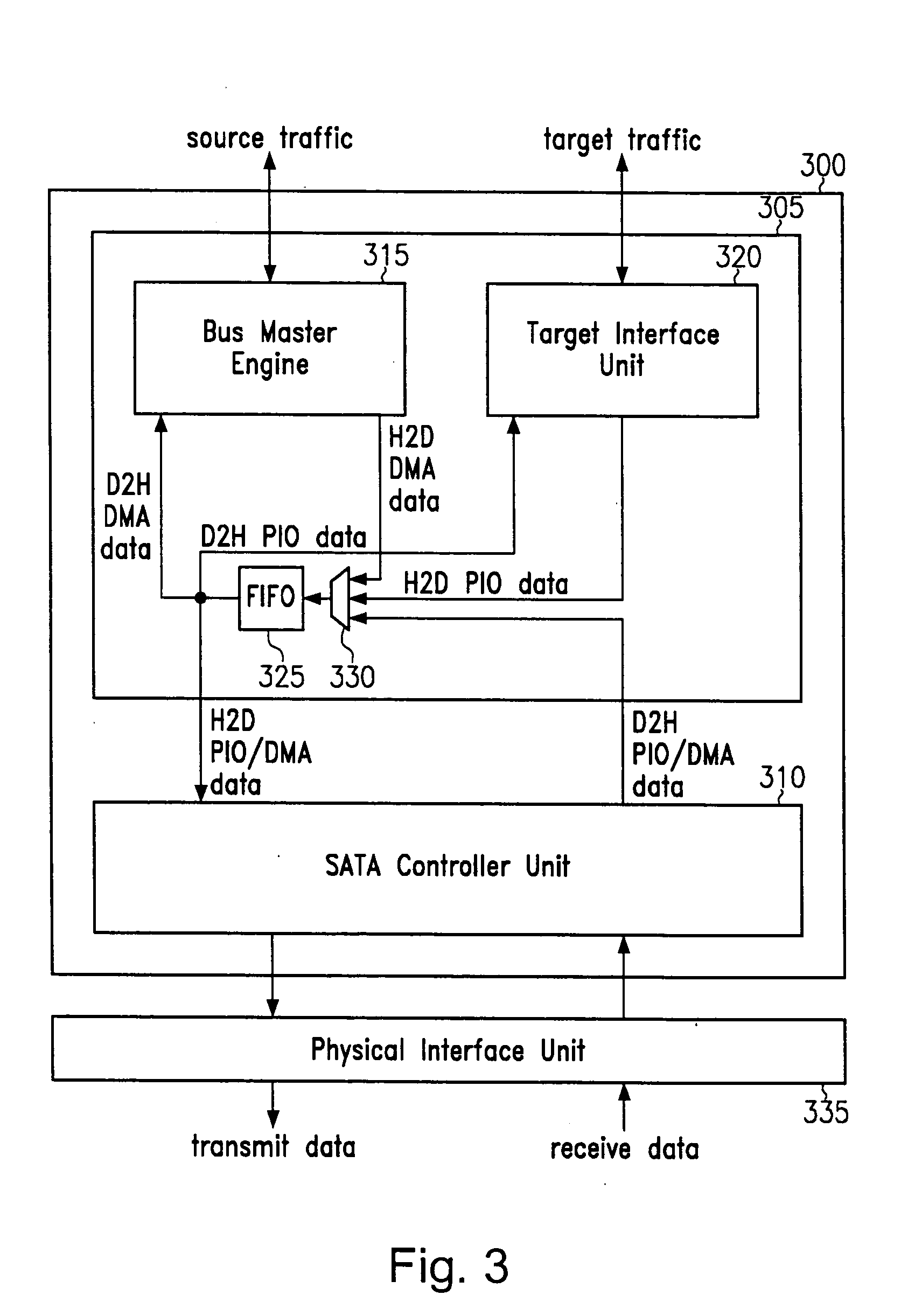

Buffer sharing in host controller

InactiveUS20050120150A1High densityImprove efficiencyInput/output to record carriersData conversionData streamDirect memory access

A storage device host controller such as an SATA (Serial ATA) host controller and a corresponding method are provided for performing host-to-device and device-to-host communications in a PIO (Programmed I / O) data transfer mode and a DMA (Direct Memory Access) data transfer mode. The host controller comprises a buffer unit for buffering data and a data stream selection unit for selecting a data stream for submission to the buffer unit. The data stream selection unit is connected to receive at any one time at least one of a host-to-device data stream in the PIO data transfer mode, a host-to-device data stream in the DMA data transfer mode, a device-to-host data stream in the PIO data transfer mode, and a device-to-host data stream in the DMA data transfer mode, and select from the received data streams the data stream to be submitted to the buffer unit.

Owner:GLOBALFOUNDRIES INC