Patents

Literature

185 results about "Host adapter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer hardware, a host controller, host adapter, or host bus adapter (HBA) connects a computer, which acts as the host system, to other network and storage devices. The terms are primarily used to refer to devices for connecting SCSI, Fibre Channel and SATA devices. Devices for connecting to IDE, Ethernet, FireWire, USB and other systems may also be called host adapters.

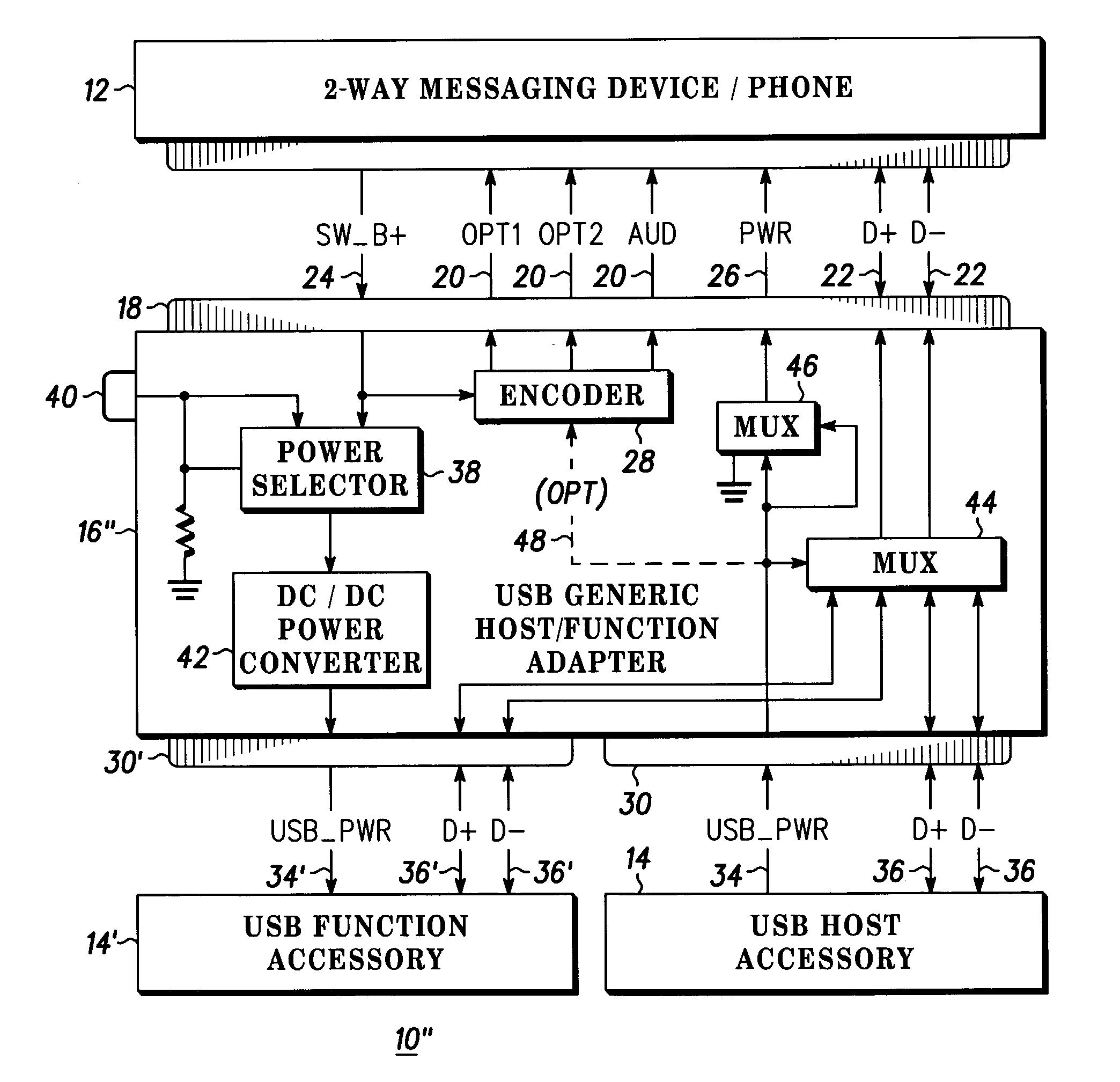

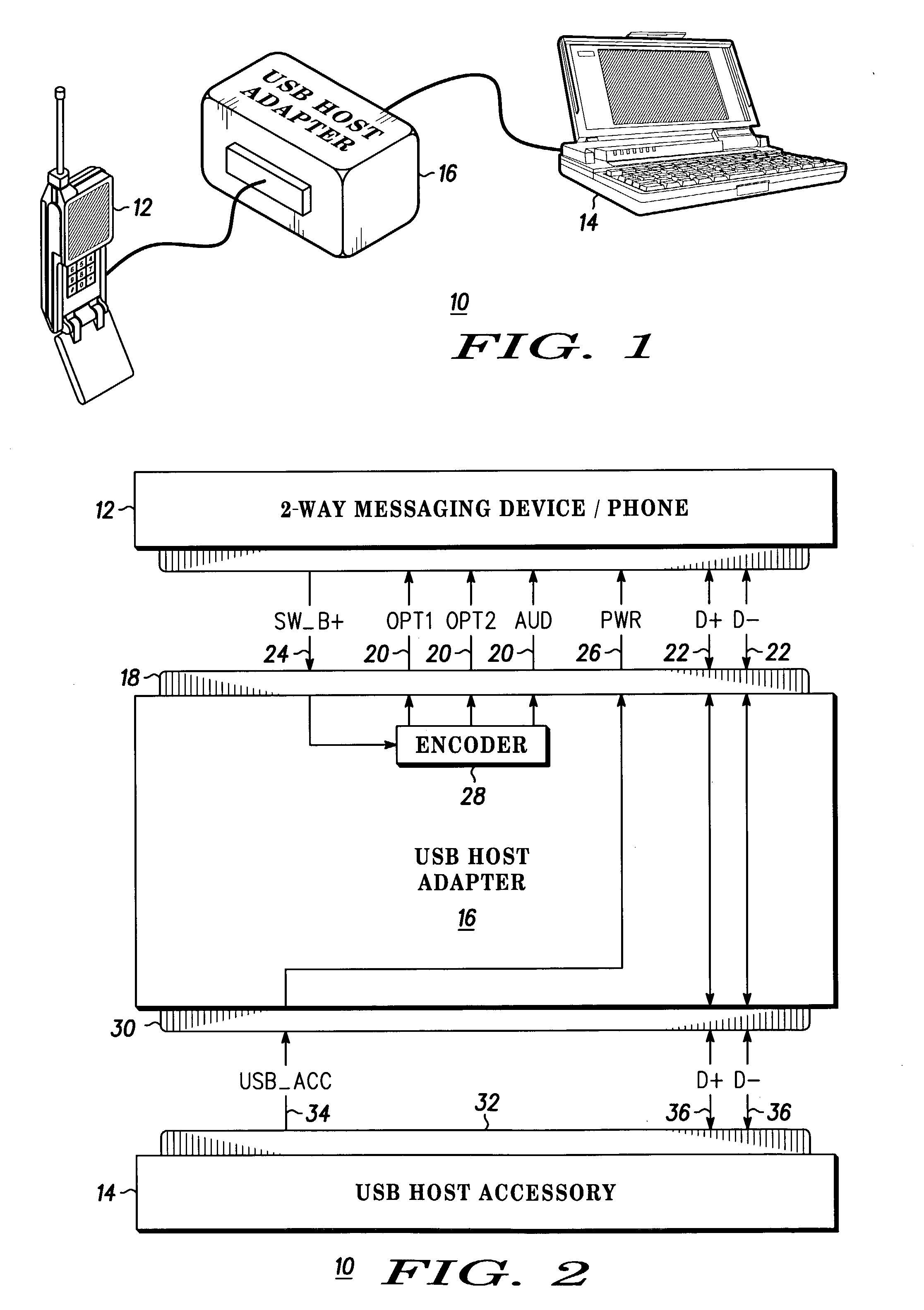

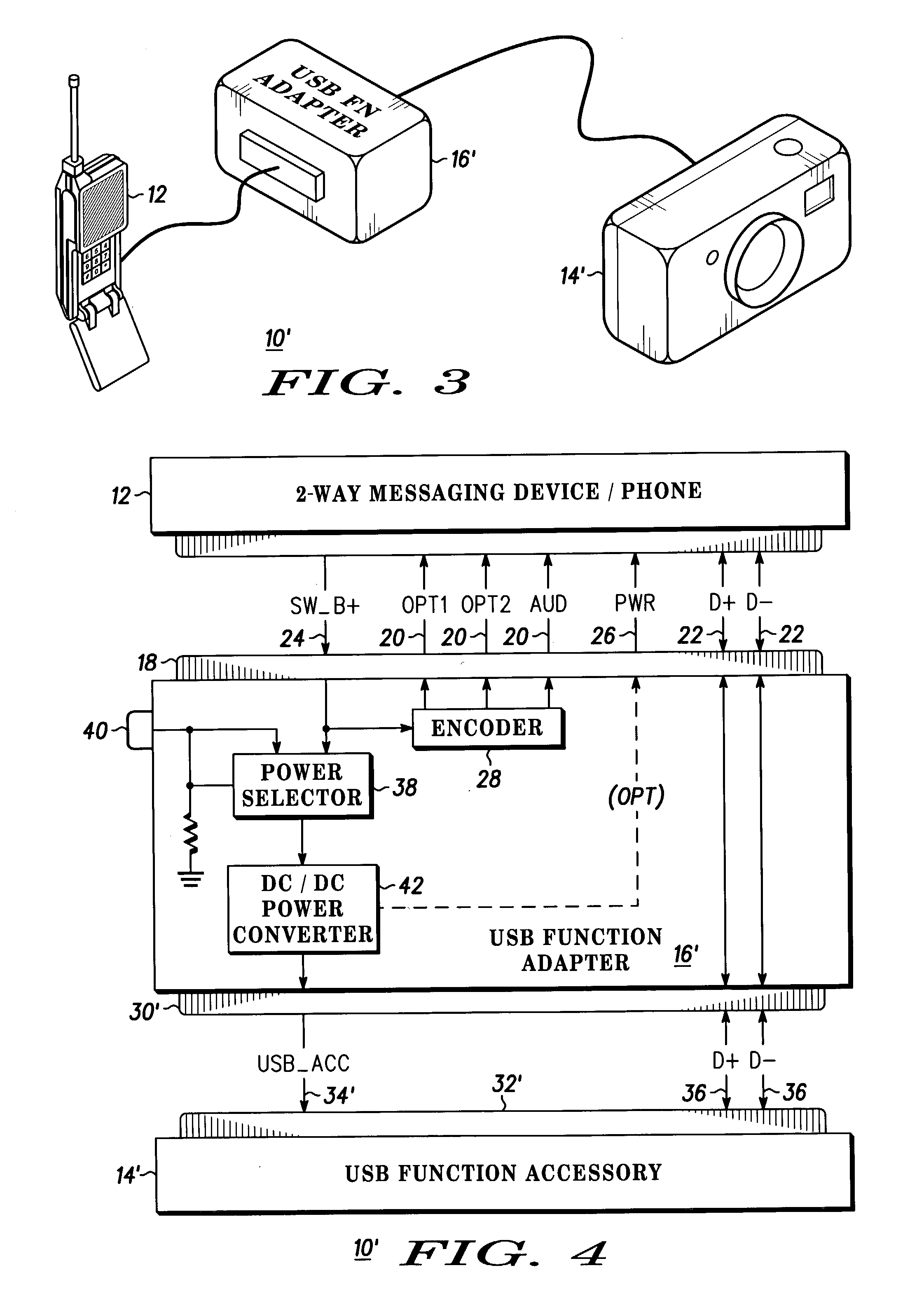

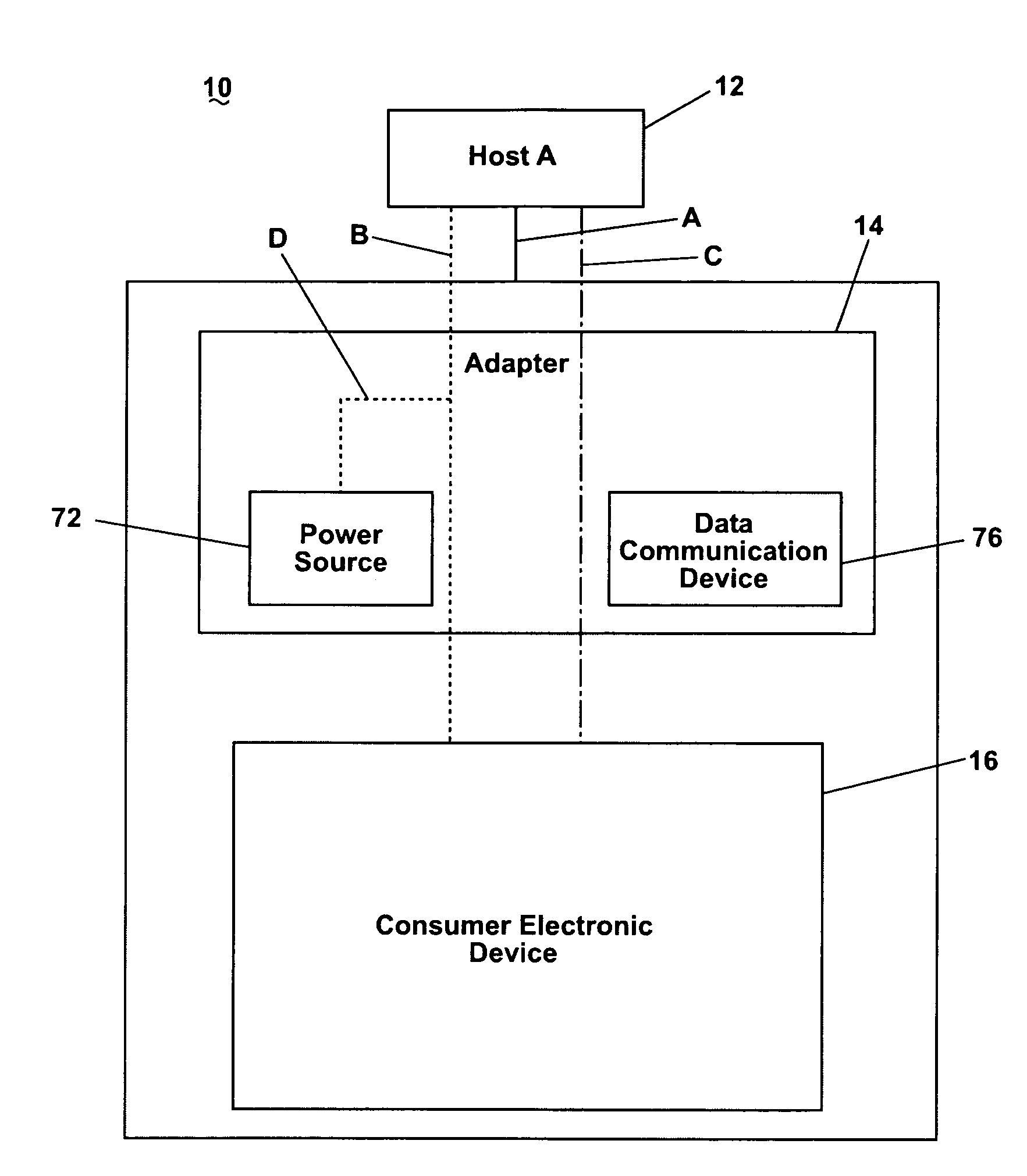

USB accessory adaptor

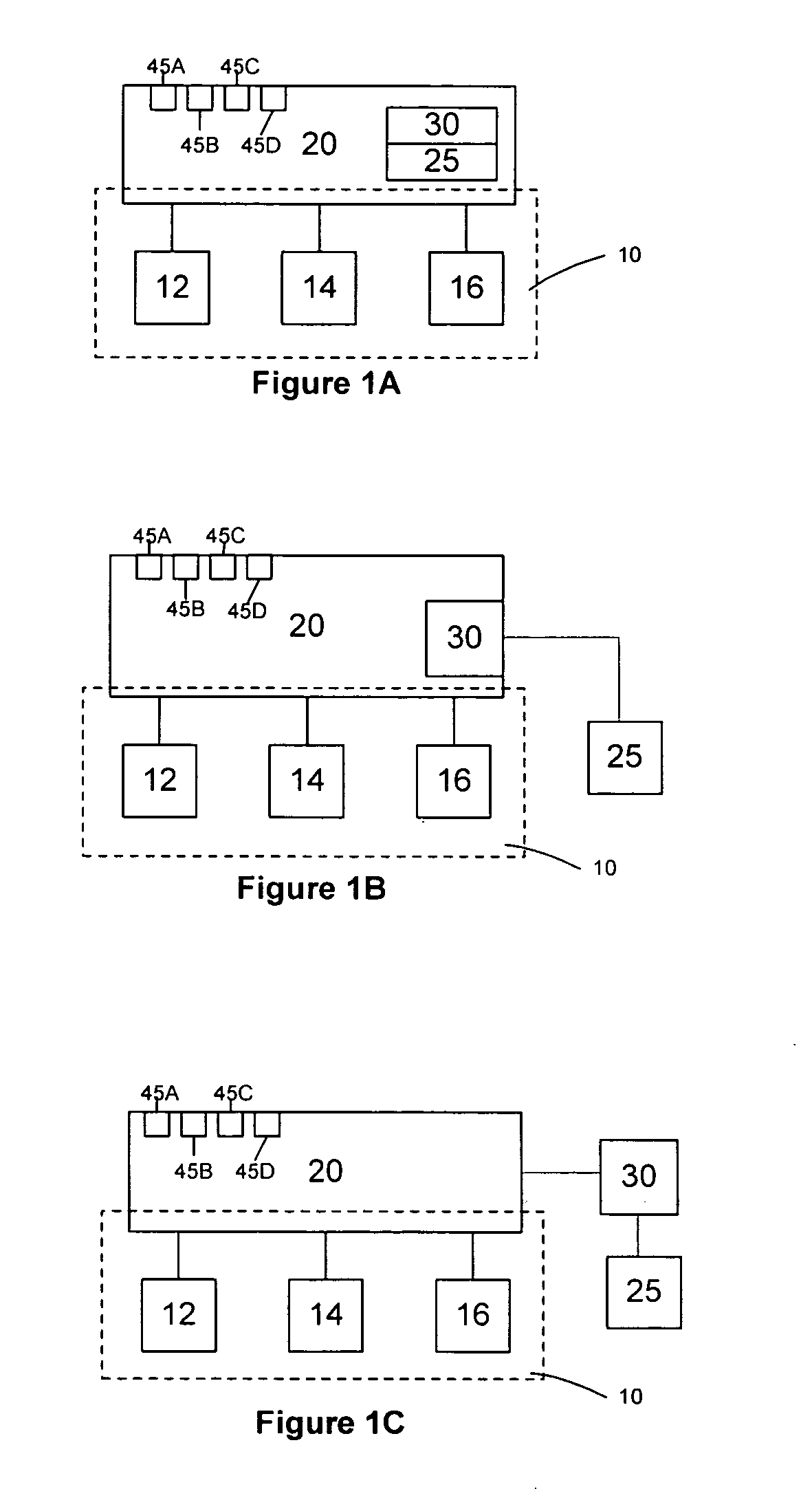

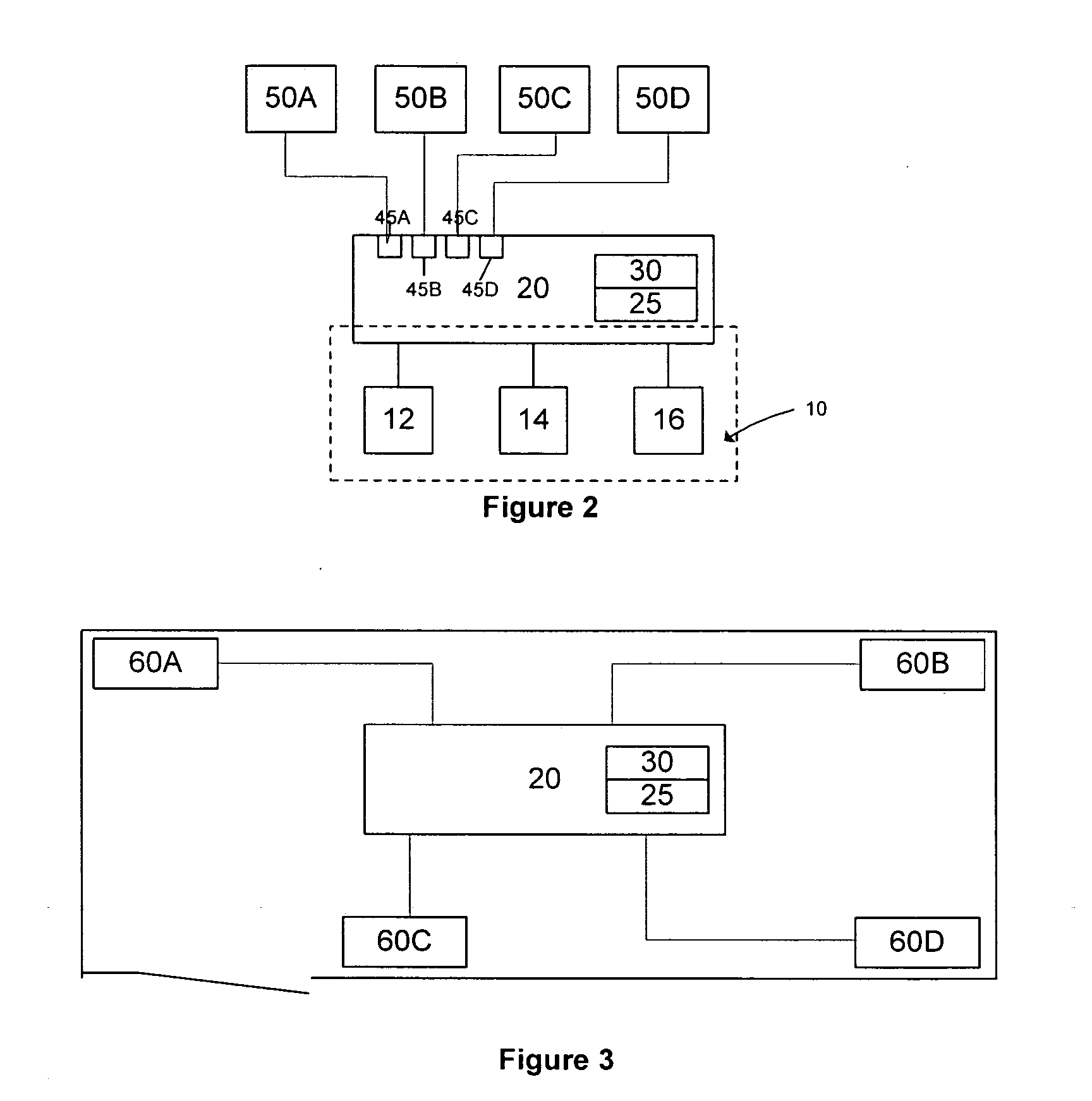

A Universal Serial Bus (USB) adaptor (16, 16', 16''), compatible with standard USB connectors, provides a simplified interface between a portable communications device (12) and a USB accessory (14, 14''). An encoder (28) provides an operating state to the portable communications device (12), enabling the portable communications device (12) to perform as either a USB host or a USB function accessory. A function adaptor (16') selects its DC power source and is capable of providing DC power to a function accessory (14'). The host adaptor (16) can obtain DC power from a host accessory (14), according to USB standards.

Owner:MOTOROLA INC

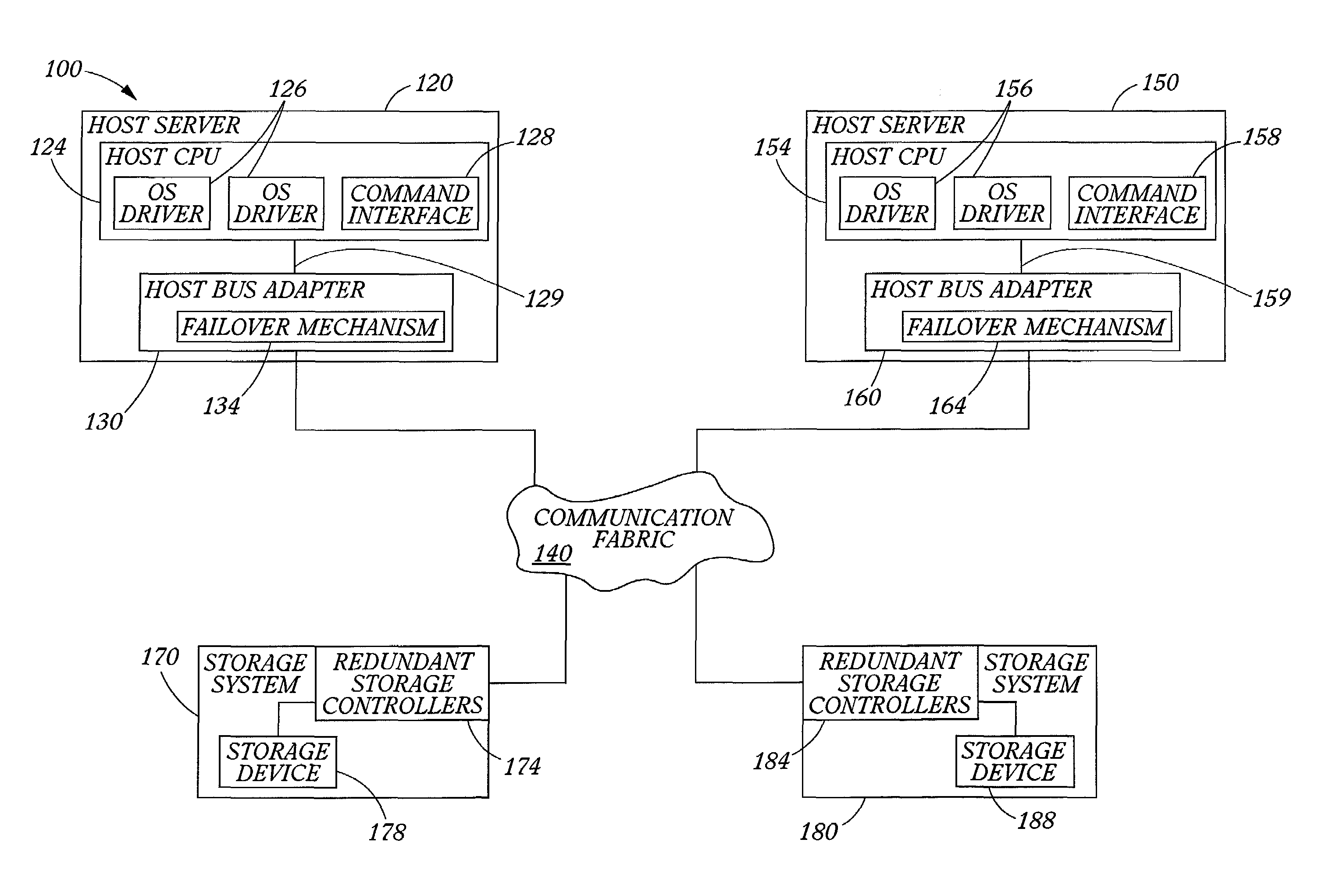

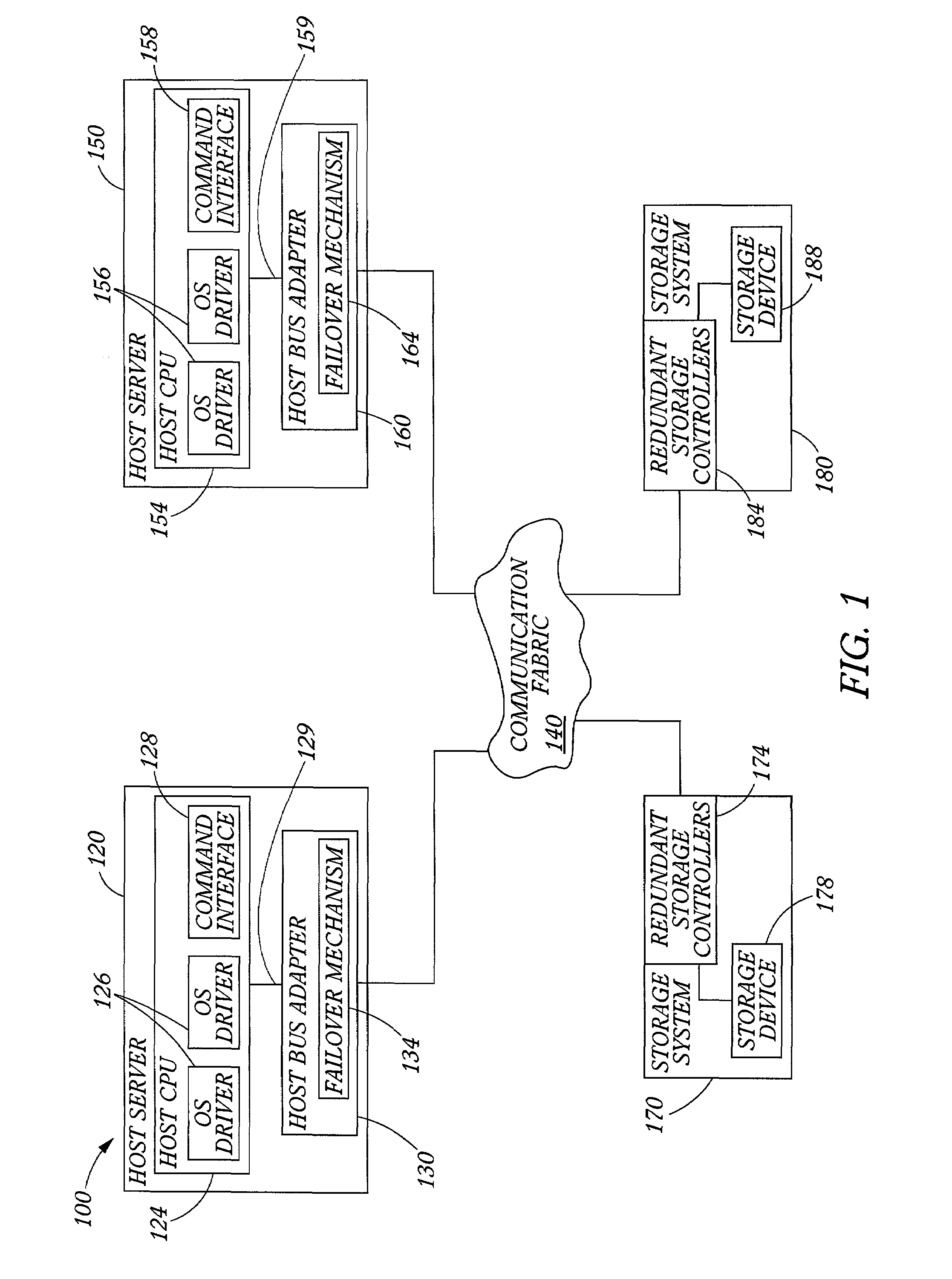

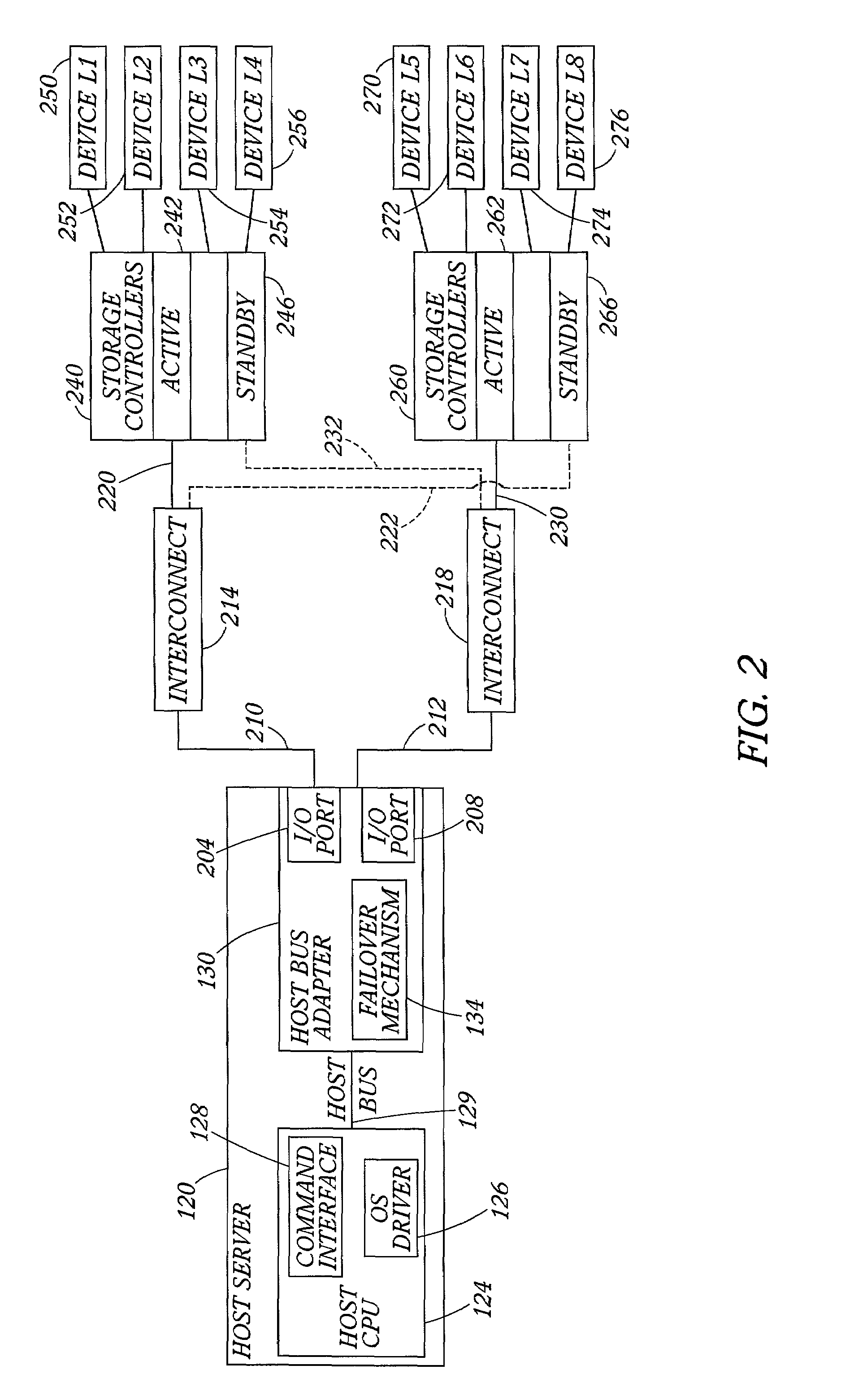

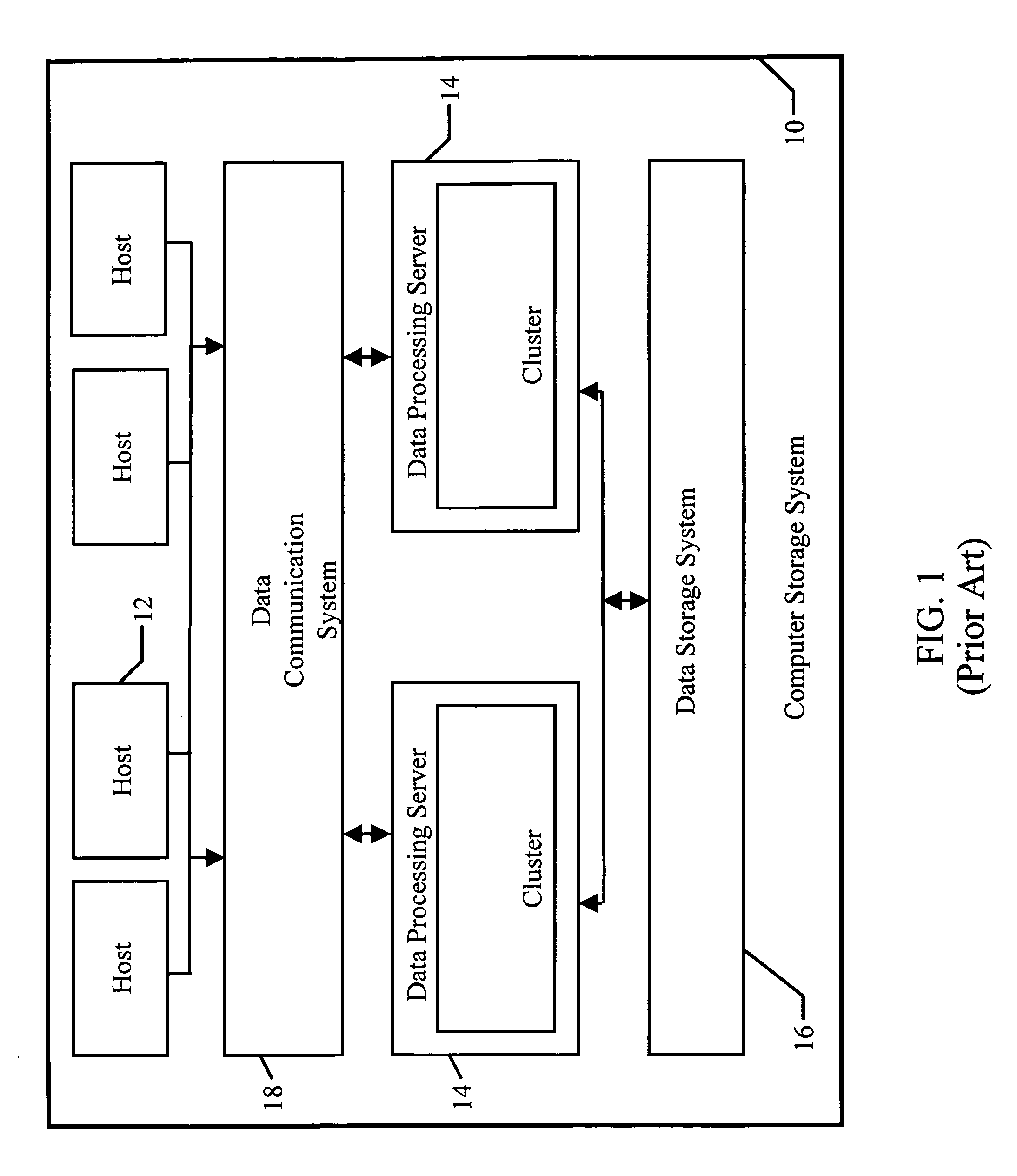

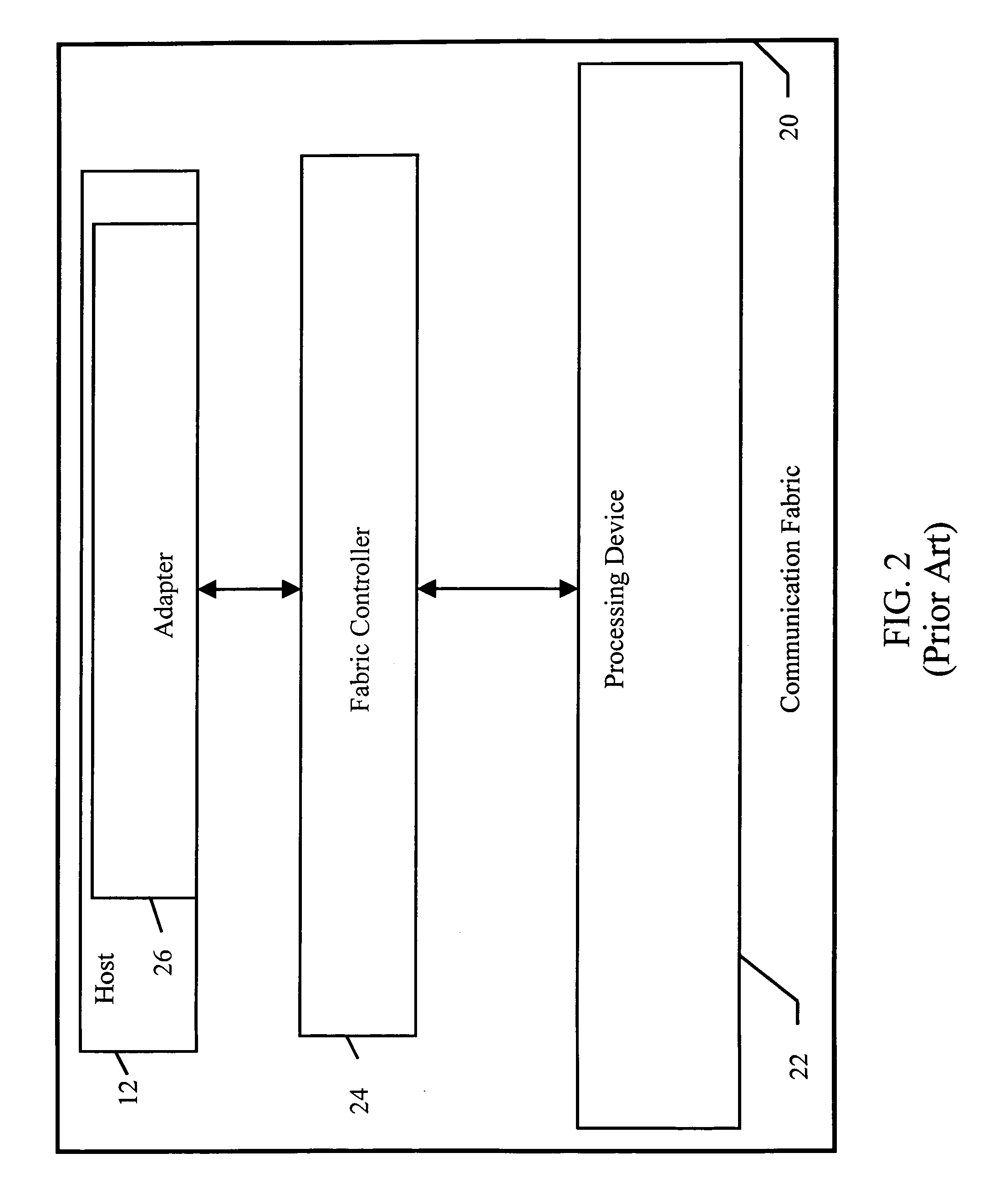

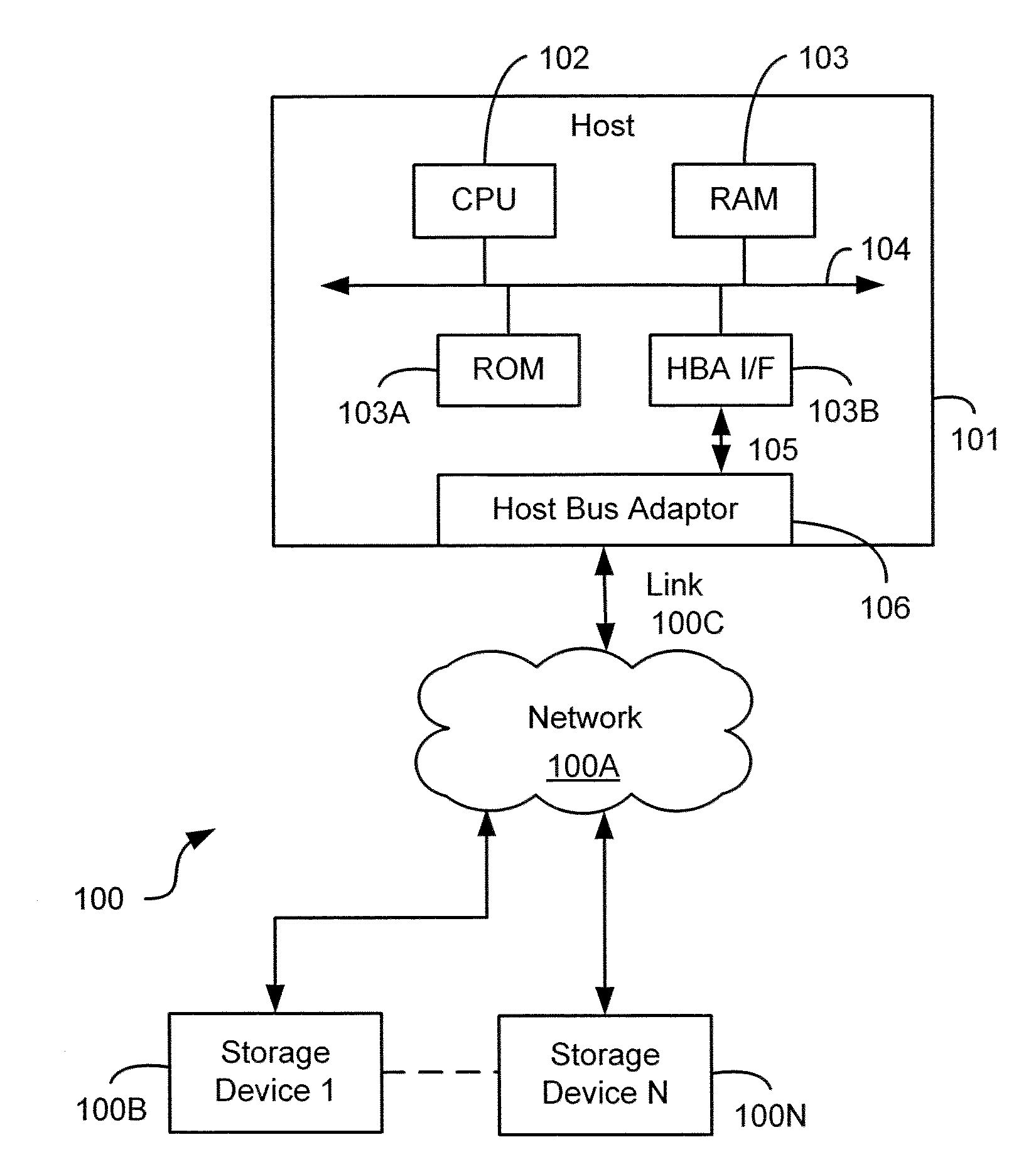

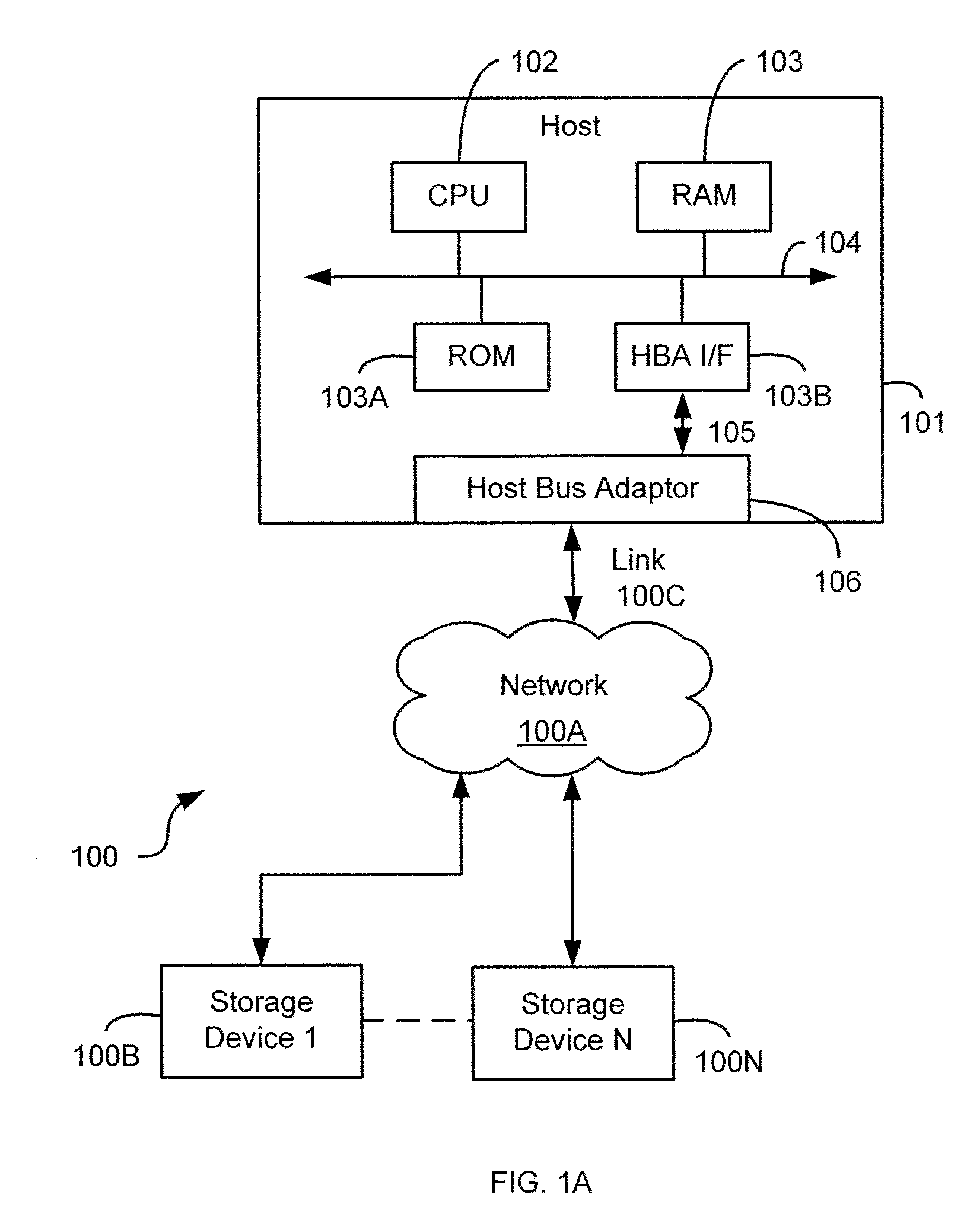

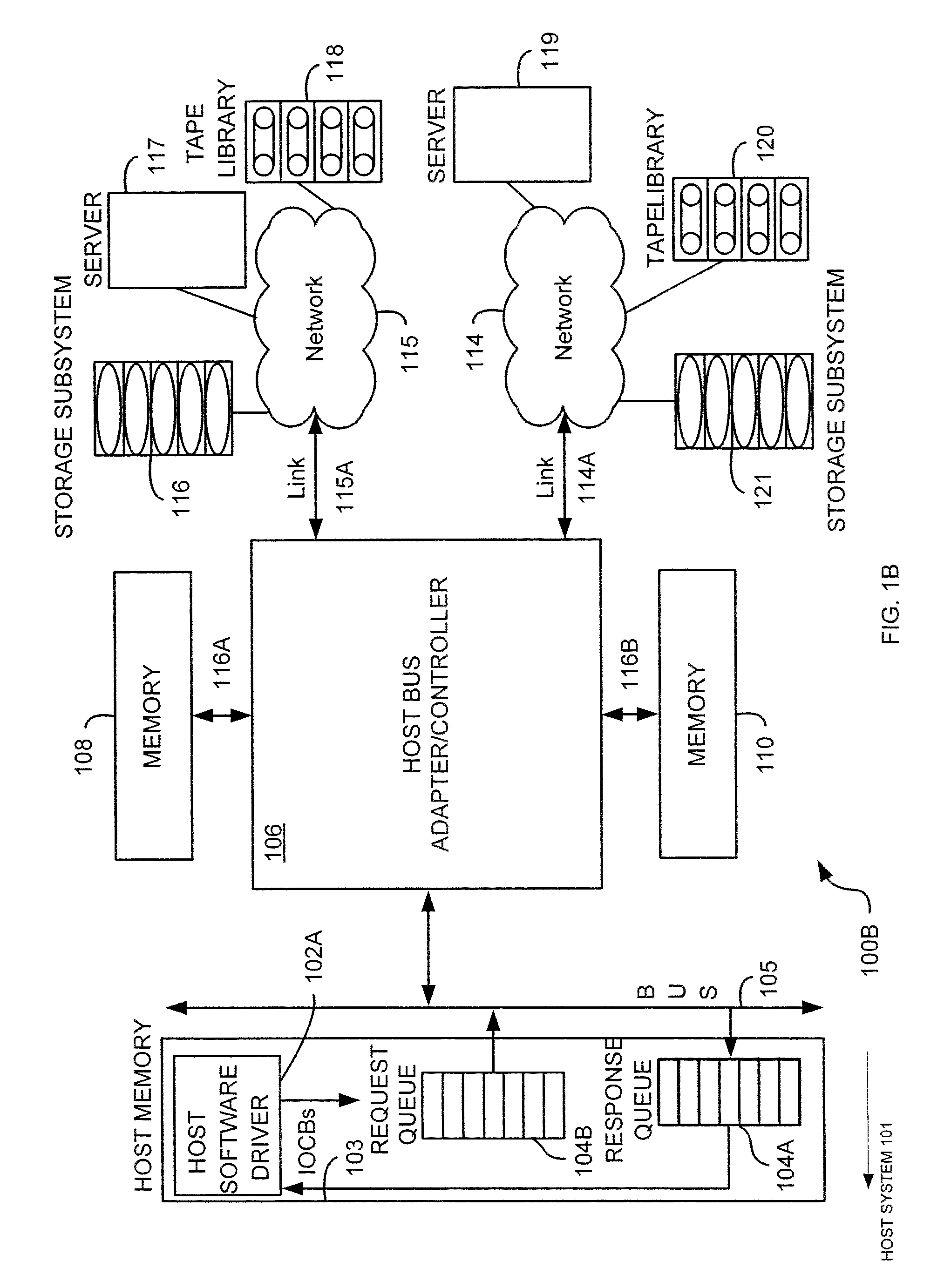

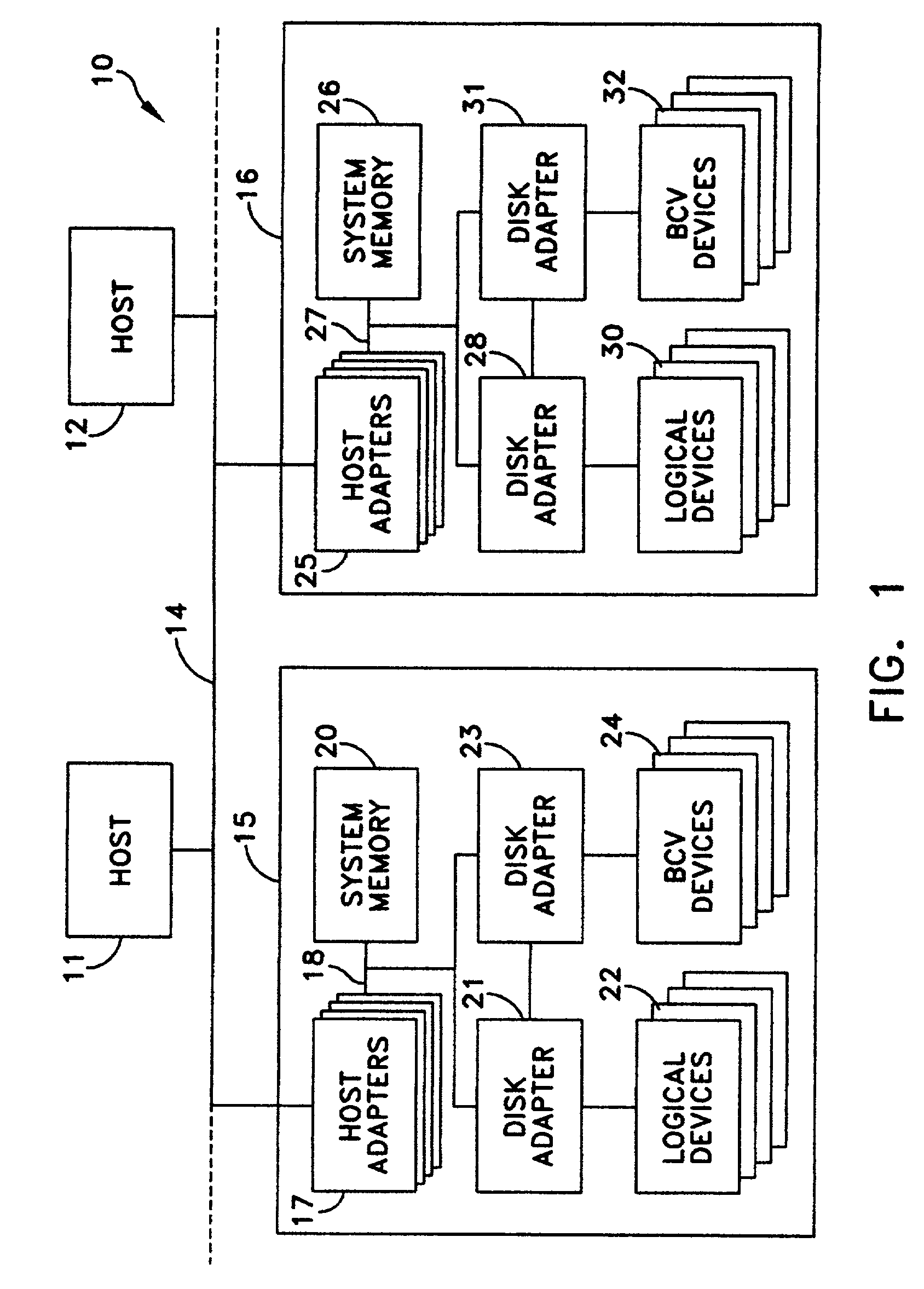

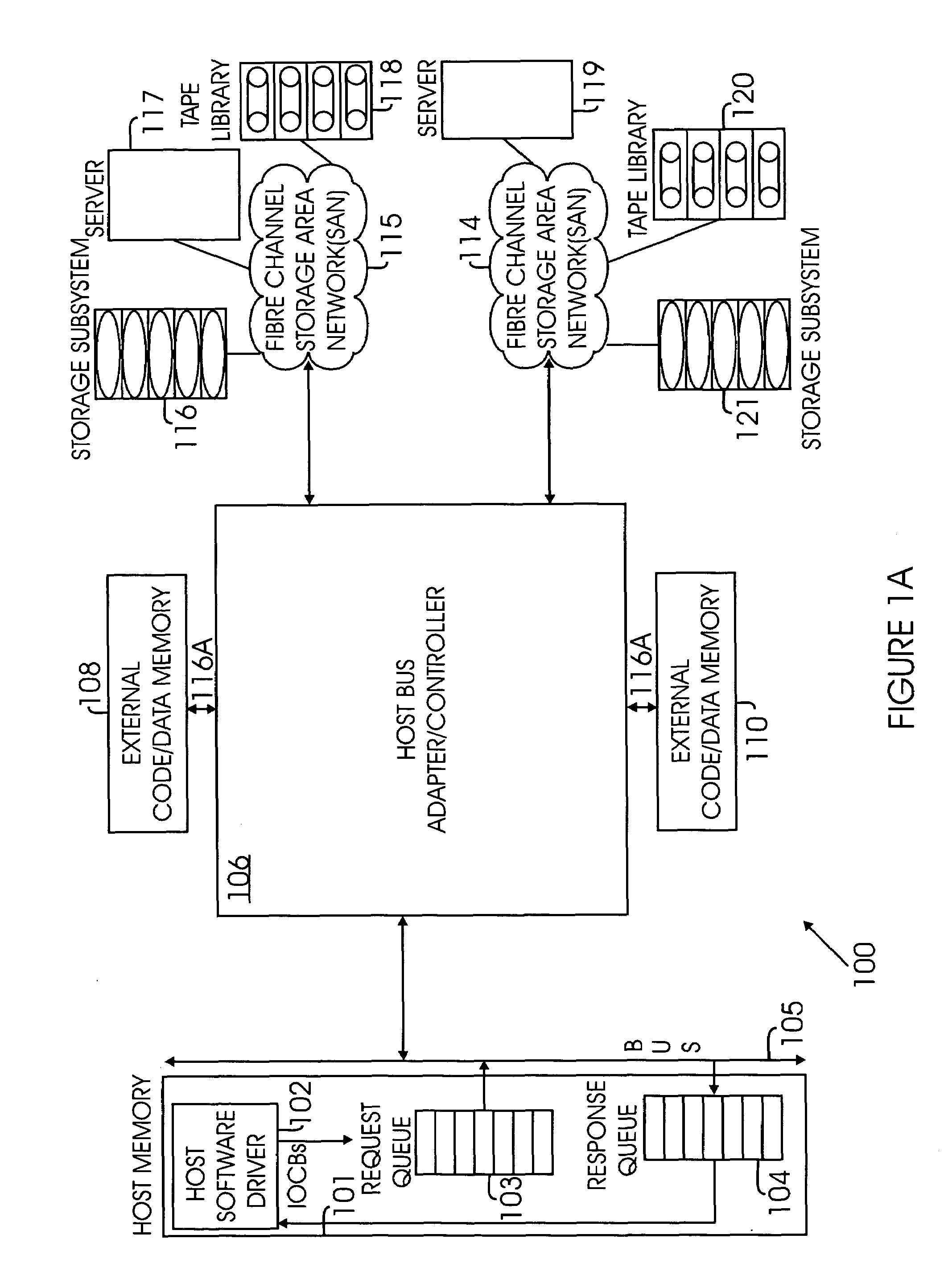

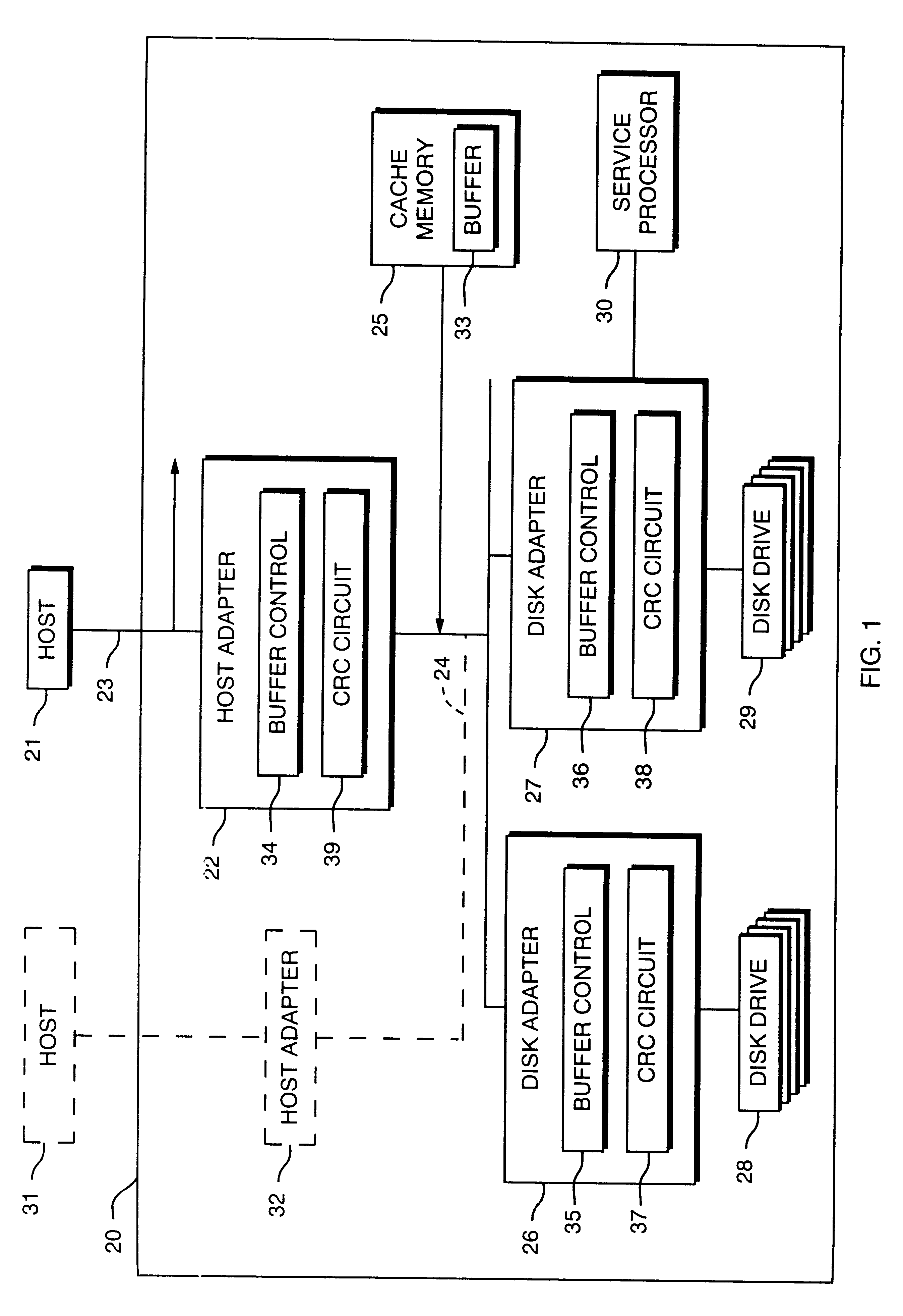

Data storage network with host transparent failover controlled by host bus adapter

ActiveUS7111084B2Facilitates consistent failbackFacilitates failover processingTransmissionRedundant hardware error correctionHard disc driveFailover

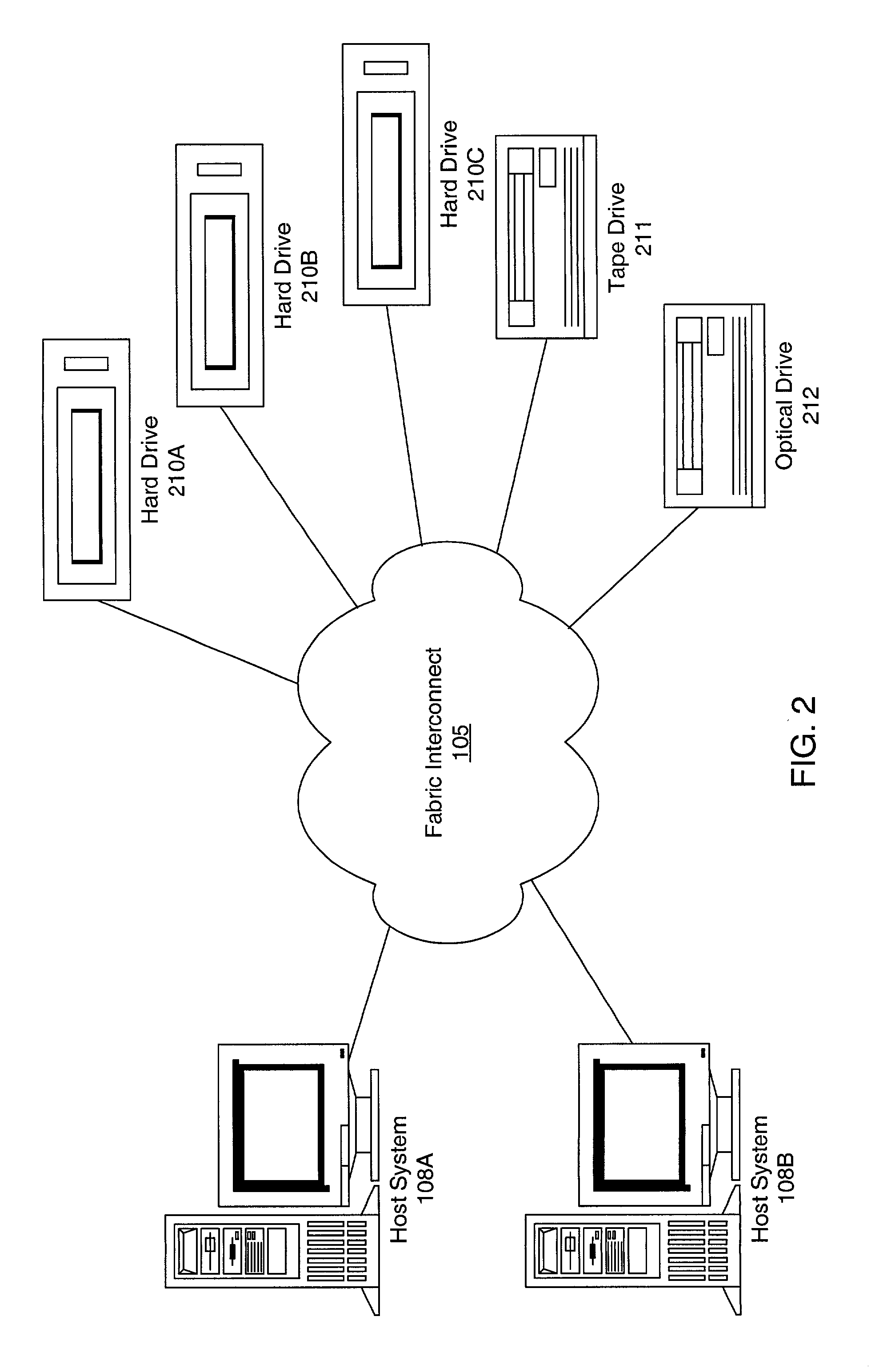

A method and host bus adapter for controlling failover and failback processes within a redundant data storage system. The method is carried out by a failover mechanism in a host bus adapter linked to a host server. The system includes a communication fabric providing data paths to pairs of redundant storage controllers managing access to storage devices (such as hard disk drives arranged as RAID). The method includes operating the host bus adapter to detect a failover condition and in response, to match the failover condition to a particular failover action. The failover conditions and corresponding actions are stored in a well-defined rule set accessed by the host bus adapter. The method continues with performing with the host bus adapter the matched failover action. The method is transparent to the host computer device, as the host is not required to participate in the failover processes.

Owner:VALTRUS INNOVATIONS LTD +1

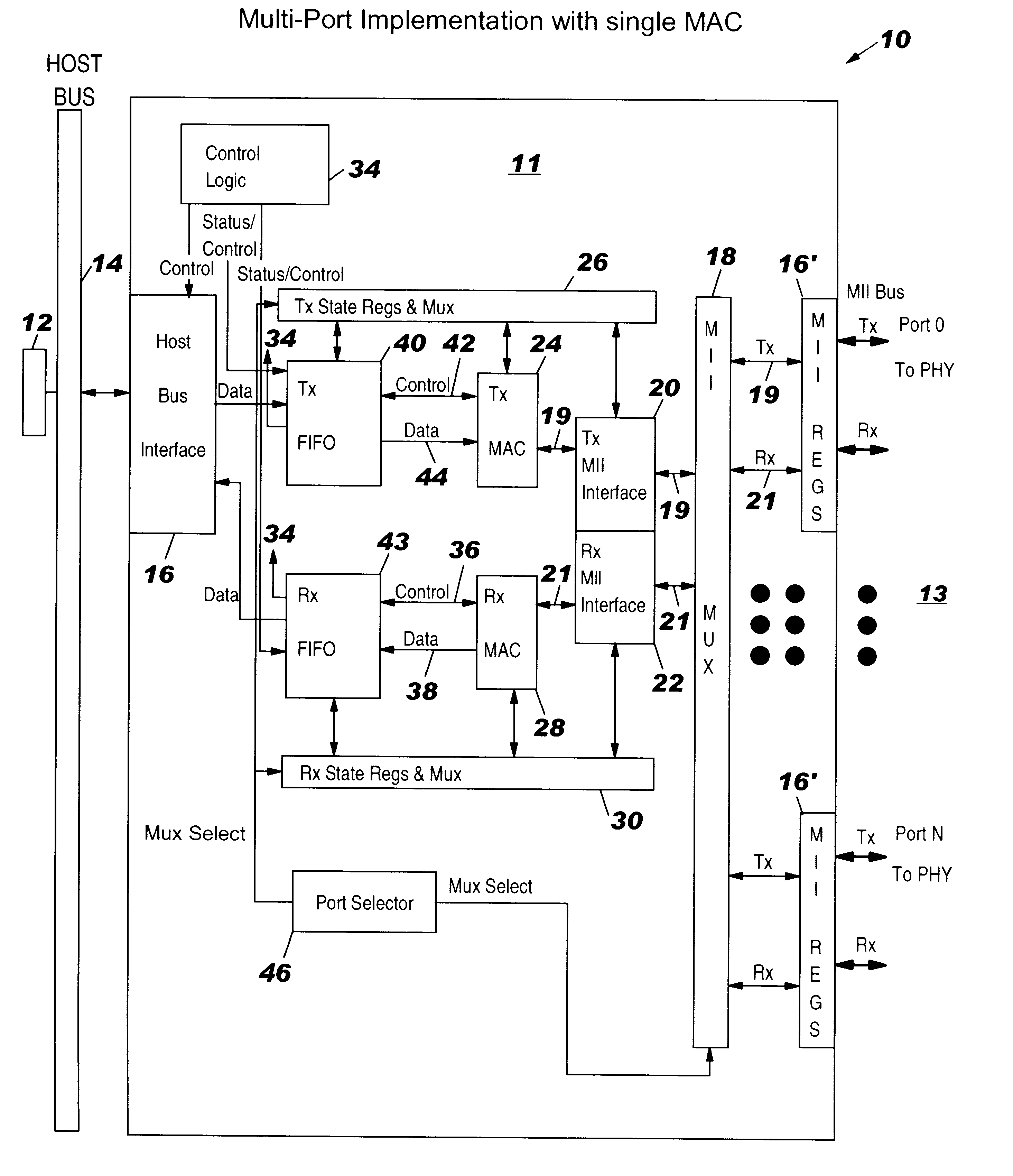

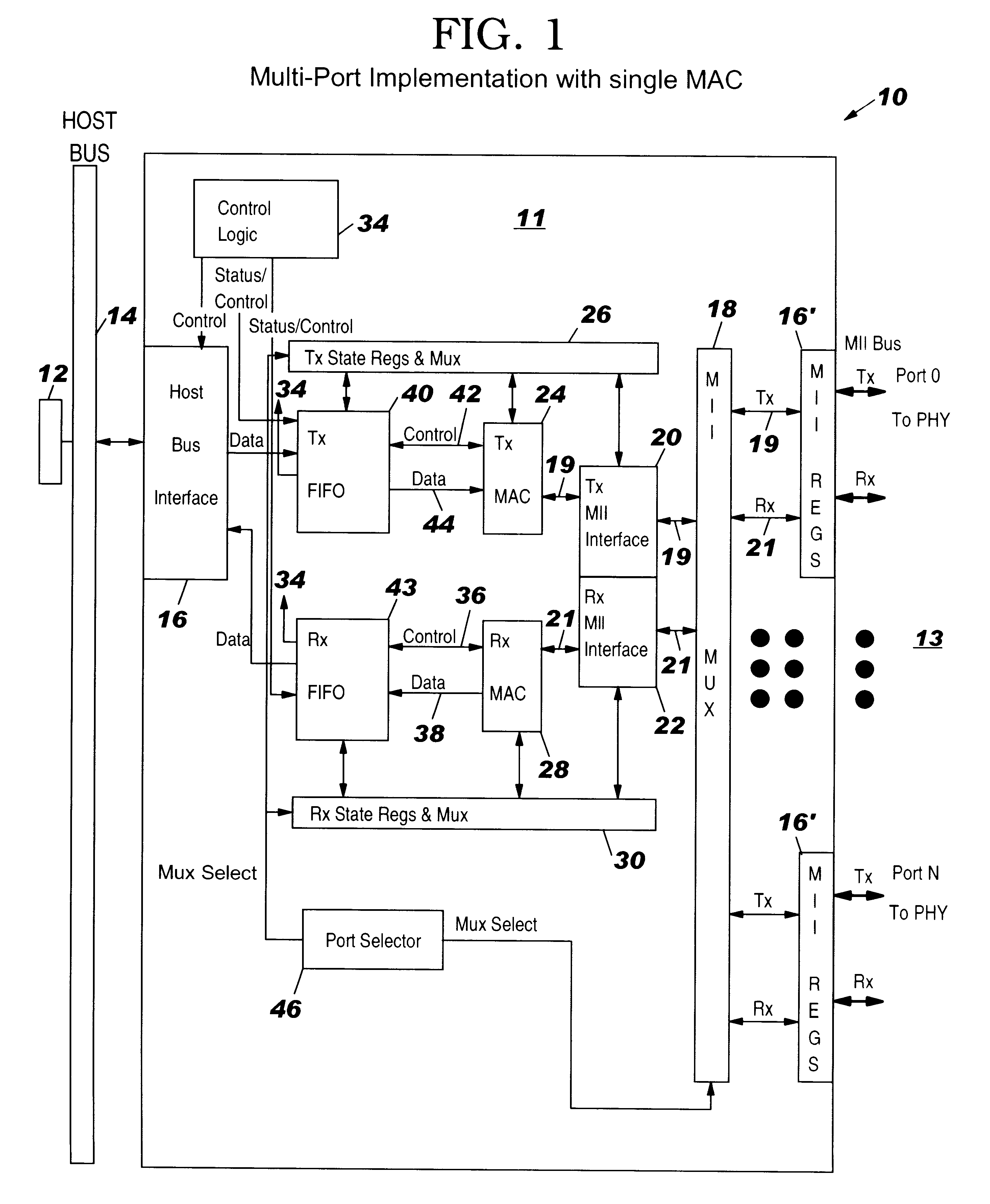

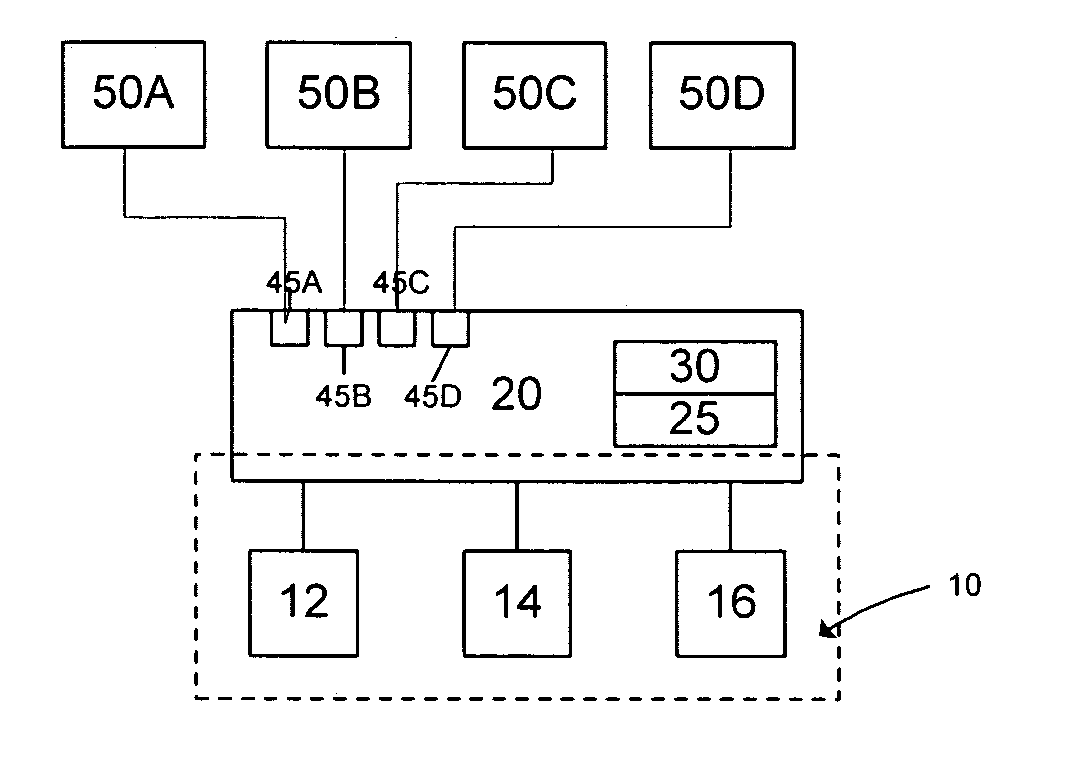

Architecture for a multi-port adapter with a single media access control (MAC)

InactiveUS6373848B1Data switching by path configurationStore-and-forward switching systemsBus interfaceMulti port

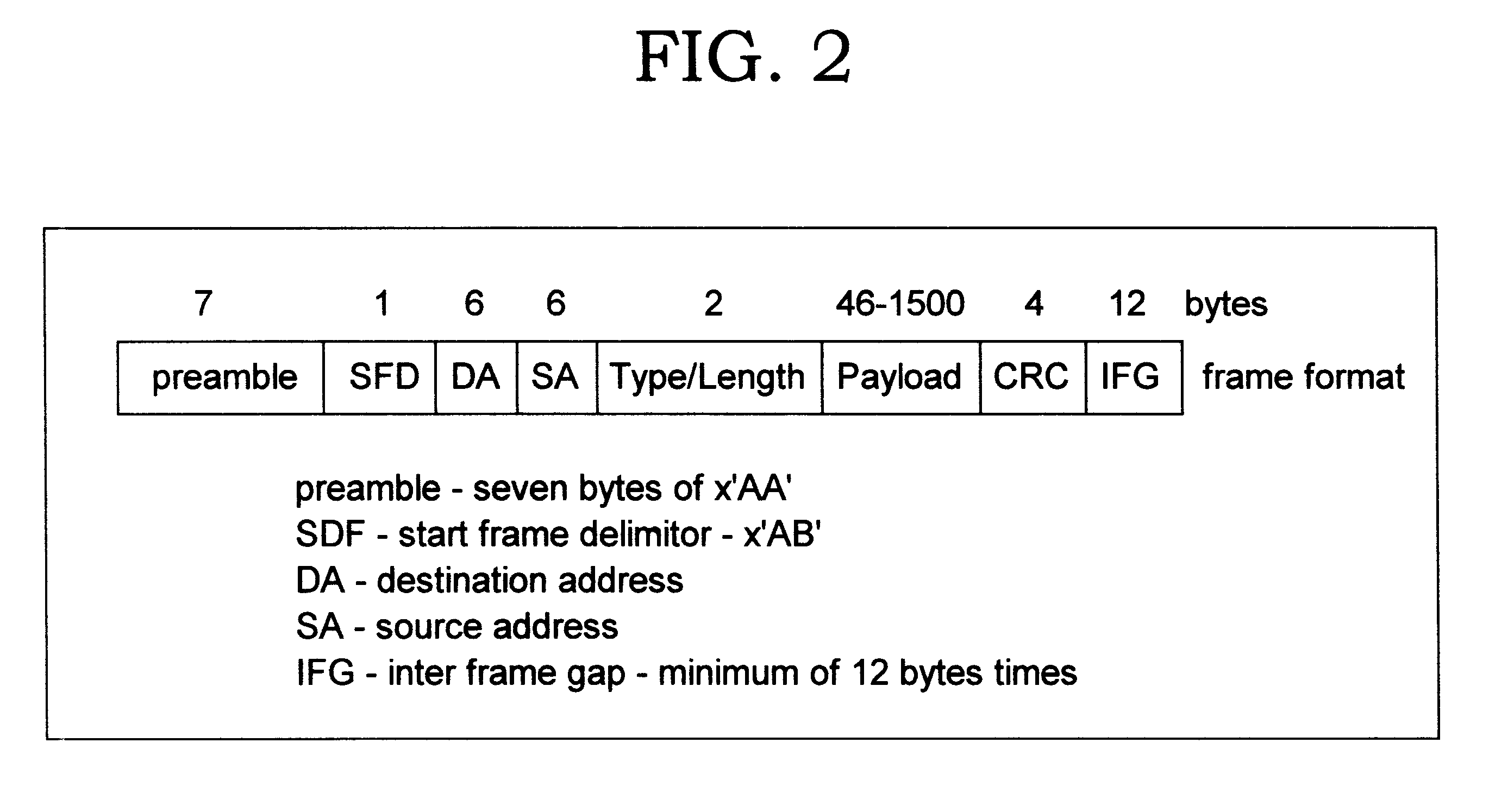

A multi-port adapter having a single MAC chip has reduced logic circuits for transferring data between a host system and a TDM communication system. The MAC chip includes a transmit MAC and a receive MAC, each coupled at one end to a port multiplexer through an interface and at the other end to respective storage registers. The port multiplexer is coupled to the Physical Layer of each port. Transmit and receive state registers track the state of each port in the transfer of data in the transmit and receive directions. The storage registers are coupled through a host bus interface to a host bus and to the host system. Control logic is coupled to the storage register to control the transfer of data between the system and the storage registers. A port selector coupled between the multiplexer and the transmit and receive state registers selects ports for transfer of data in succession. On each chip clock cycle, the port selector selects a state machine register to determine the state of the MACs for processing the data and a section of the FIFO's to write or read data for the selected port. At the end of the cycle, the state registers are set and stay set until selected again. The process repeats for each port in a cyclic manner. Once data is accumulated in the receive storage register, control logic reads the data of the host bus. Once space is available in the transmit storage register, the control logic writes data from the host system to the transmit storage register.

Owner:IBM CORP

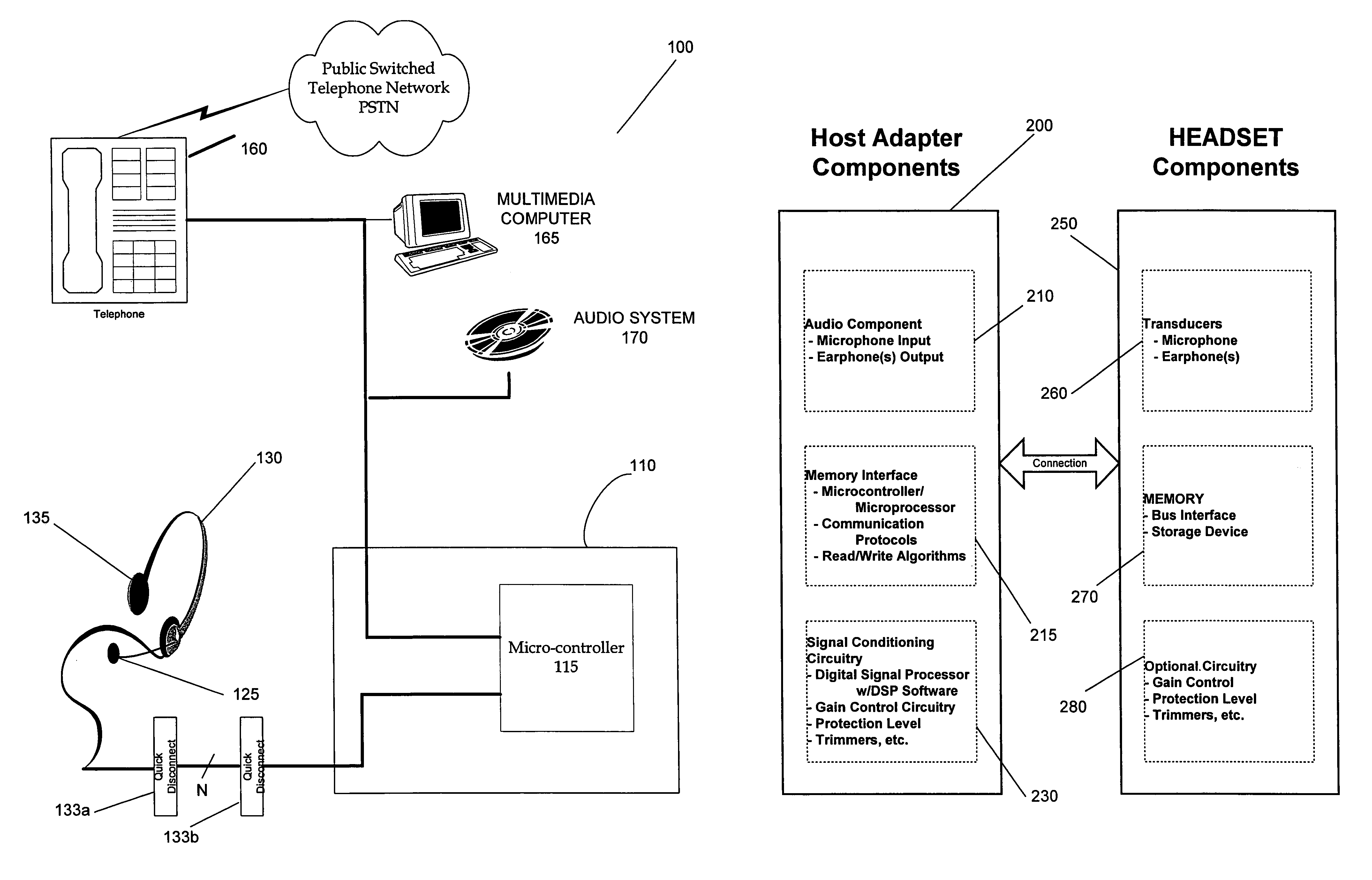

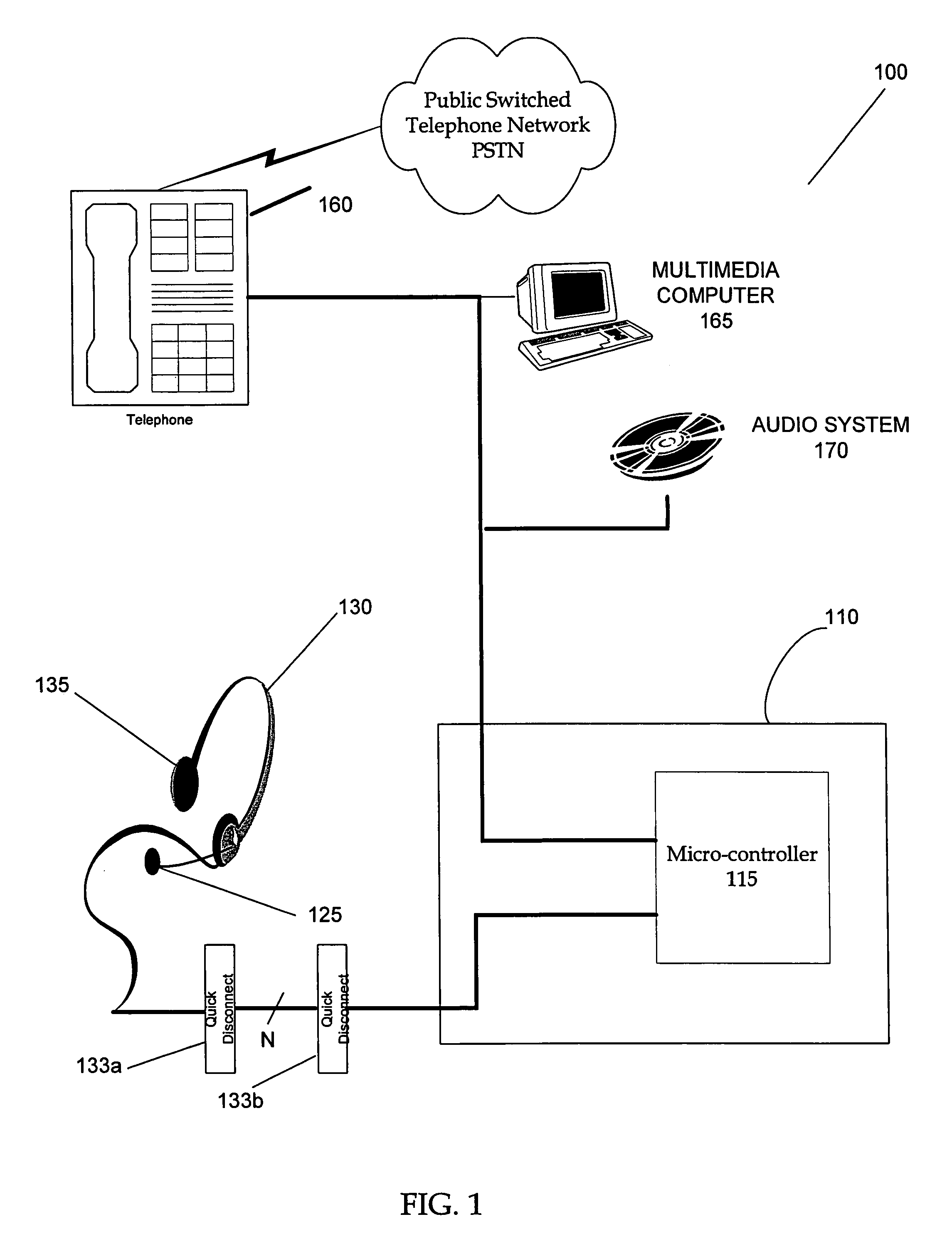

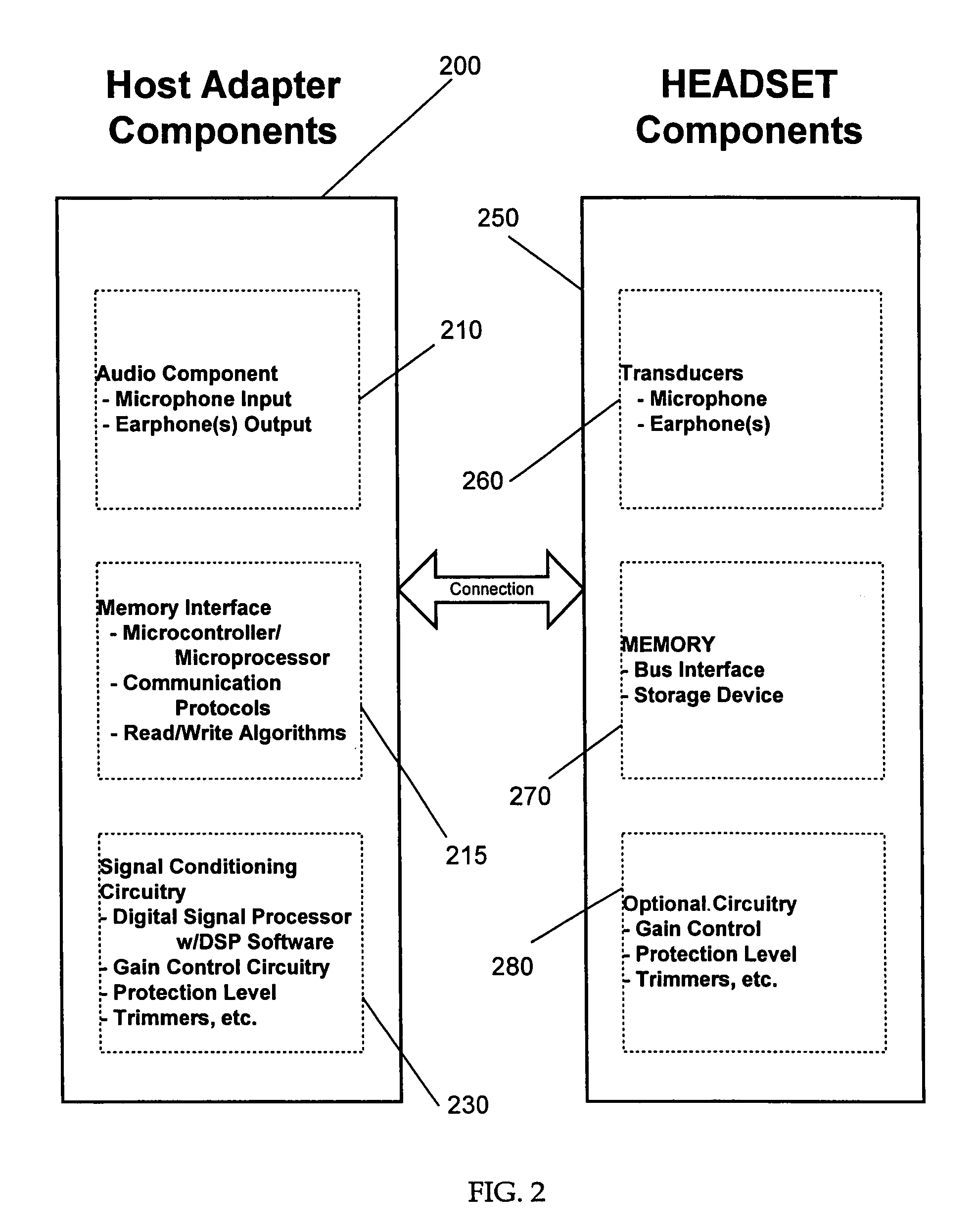

Headset with memory

InactiveUS7283635B1Streamline productionFacilitate future serviceMicrophonesLoudspeakersHeadphonesModel Number

A headset having a built-in memory to store parameter settings relating to headset performance characteristics such as headphone(s) and / or microphone performance characteristics. The performance characteristics can be measured during headset production and stored in the memory. A host adapter may communicate with the headset through a serial communications port of the headset. The host adapter may read the headset performance characteristics and adjust signals transmitted to and received from the headset in accordance thereto. When the headset is used in a system, the system parameters can be manually set and stored in the headset memory. When the headset is used again in the same system, the system parameters can be read from the memory and automatically set. The memory may also store product history information of the headset such as production date, serial and model numbers, and / or any service history.

Owner:PLANTRONICS

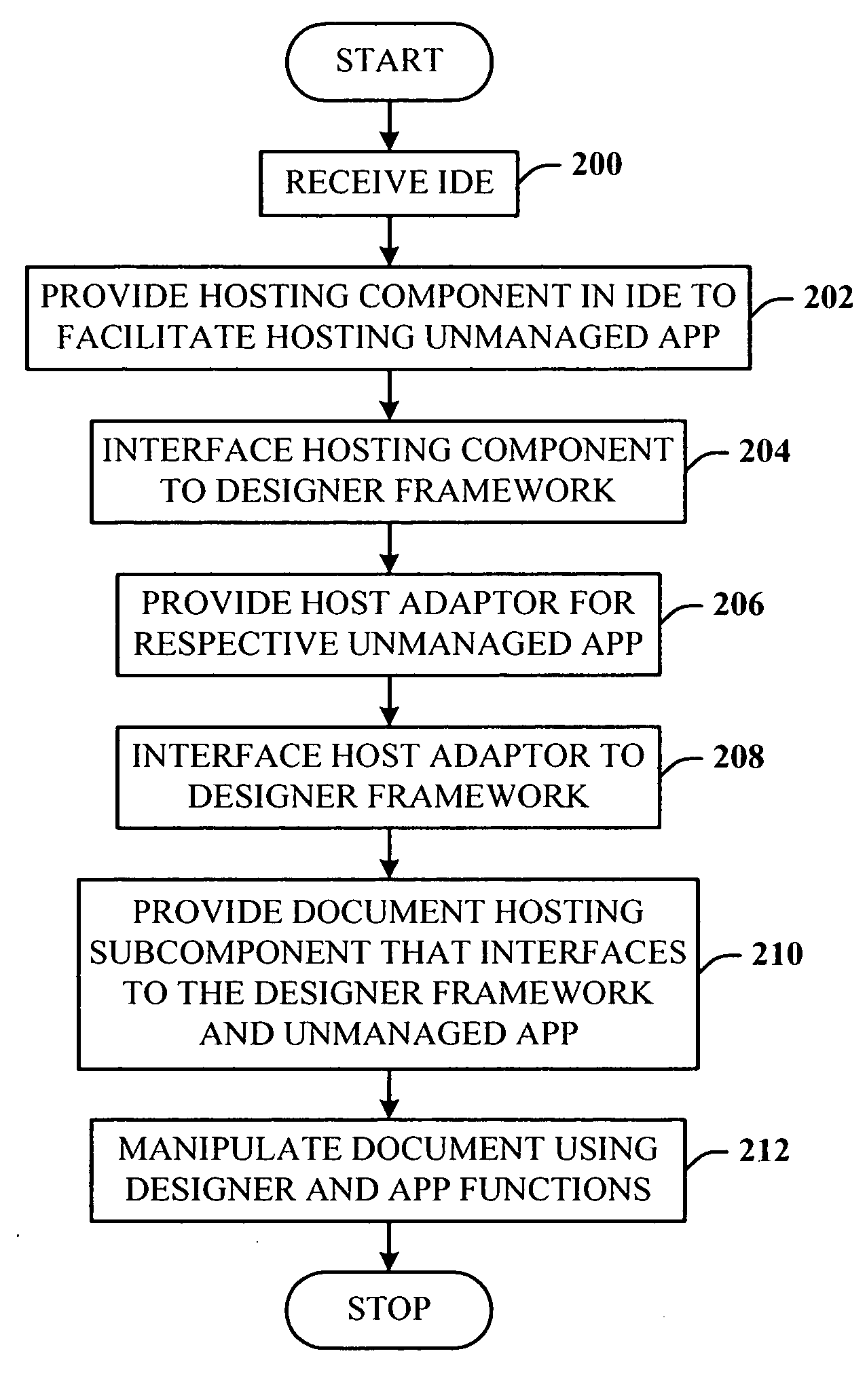

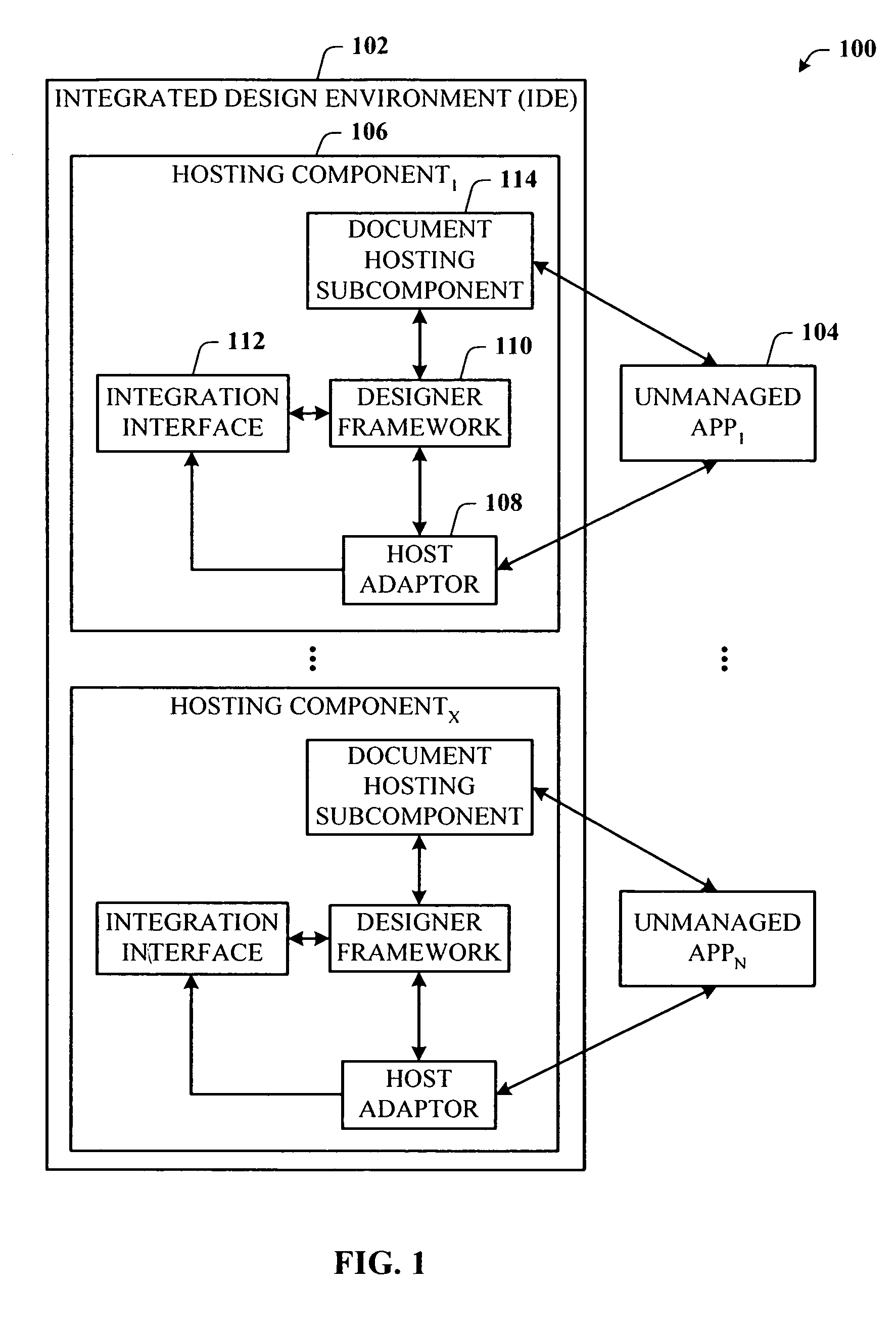

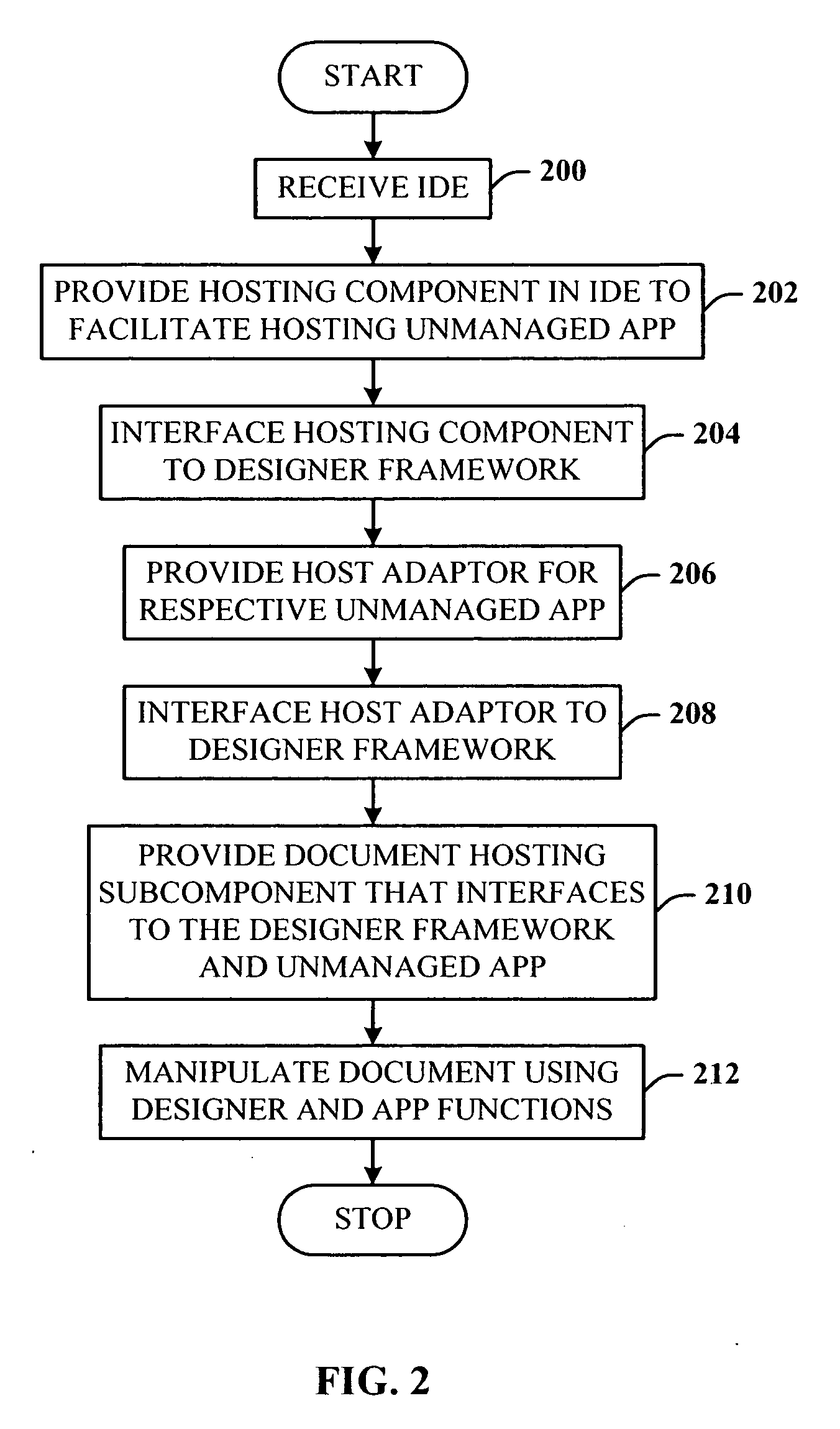

Hosted application as a designer in an integrated development environment

Architecture that integrates an unmanaged application as a hosted application into a design environment in a coherent yet usable manner such that the developer can use the hosted application's native functionality yet leverage rich productivity features provided by the IDE. The IDE includes a hosting component that comprises an application adaptor for providing an interface from the unmanaged application to the IDE. The IDE further includes a designer framework that provides user access to designer capabilities of the IDE. The host adaptor interfaces to the designer framework either directly and / or through an integration interface. Thus, the developer / user can then access the native functionality of the unmanaged application as well as the IDE functionality. This provides rich integration between the development environment and the hosted application, the end result of which is the designer interacting with the IDE.

Owner:MICROSOFT TECH LICENSING LLC

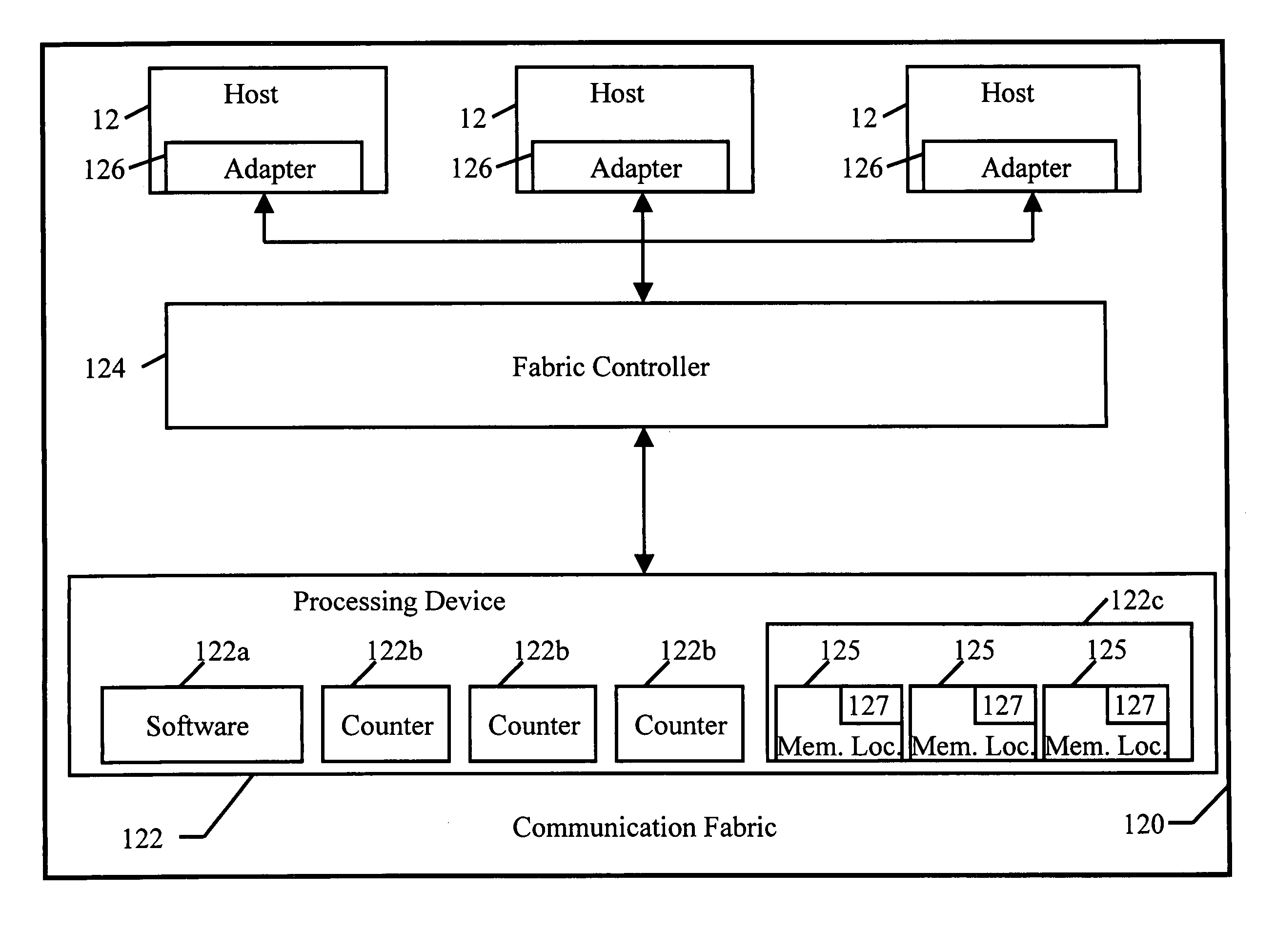

Dynamic threshold scaling in a communication system

A computer system including an error recovery system establishes error threshold inversely proportional to the number of a like kind of system resources, such as host adapters. When a host adapter is initialized or deactivated, a software subcomponent of a processing device calculates a new threshold number and writes it to a memory location associated with each host adapter. When a number of errors exceeds the threshold number, the host adapter is reset, quiesced for repair, or fenced for replacement.

Owner:IBM CORP

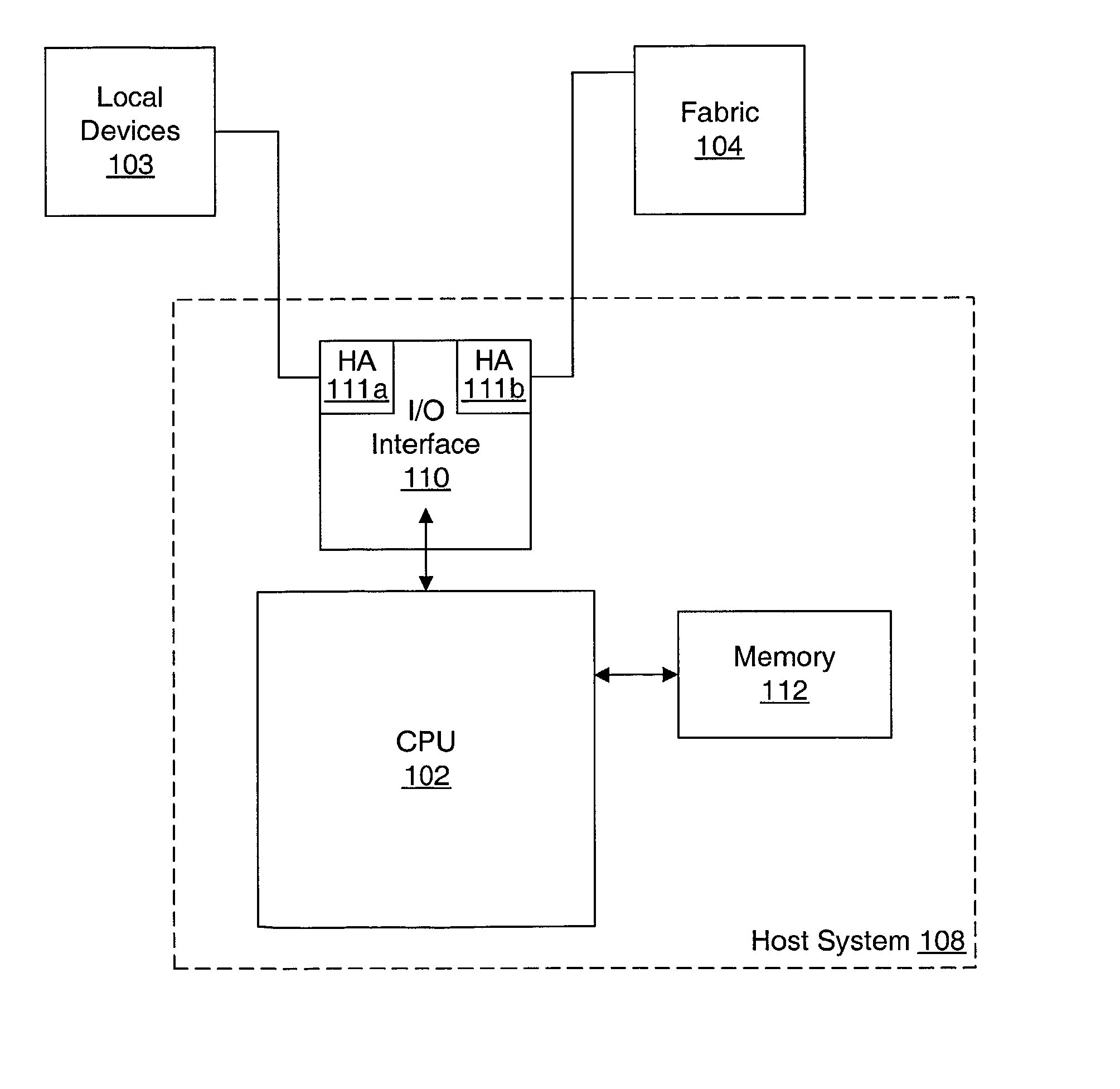

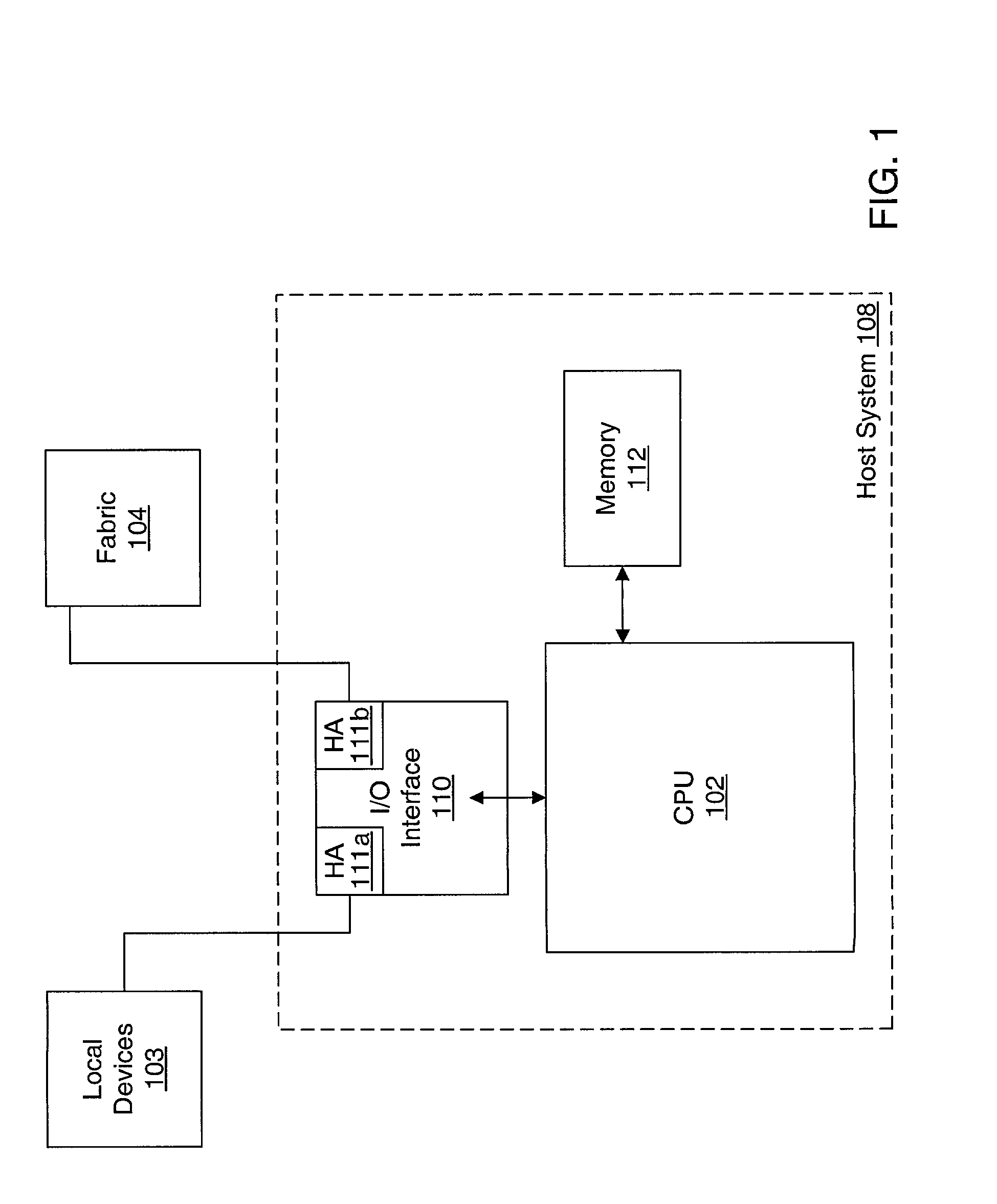

Maintaining fabric device configuration through dynamic reconfiguration

A fabric-attached device configuration for a host system may be managed in regard to fabric state changes for a host system connected to a fabric. An event may be received indicating a fabric state change for one or more host adapter ports. In response to the event, the host system's fabric device configuration may be dynamically changed. Dynamically changing the host system's fabric device configuration may include bringing online or taking offline one or more fabric devices for the one or more host adapter ports for the host system. In some embodiments, a configuration file may be stored specifying an action to be taken for various types of events. Upon receiving indicating a fabric state change, the configuration file may be accessed to determine the fabric device configuration action to be taken for the type of fabric state change indicated by the event.

Owner:SUN MICROSYSTEMS INC

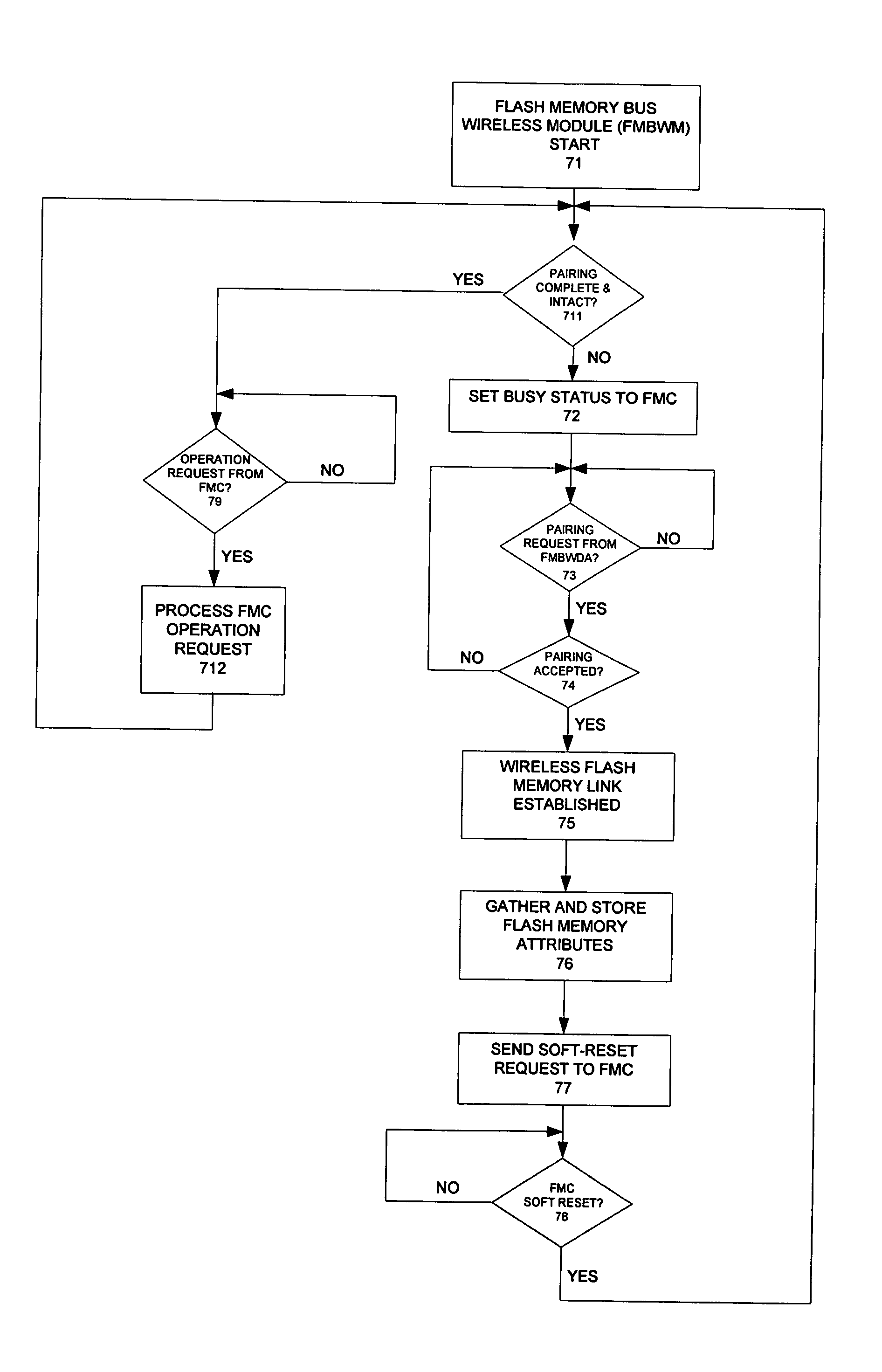

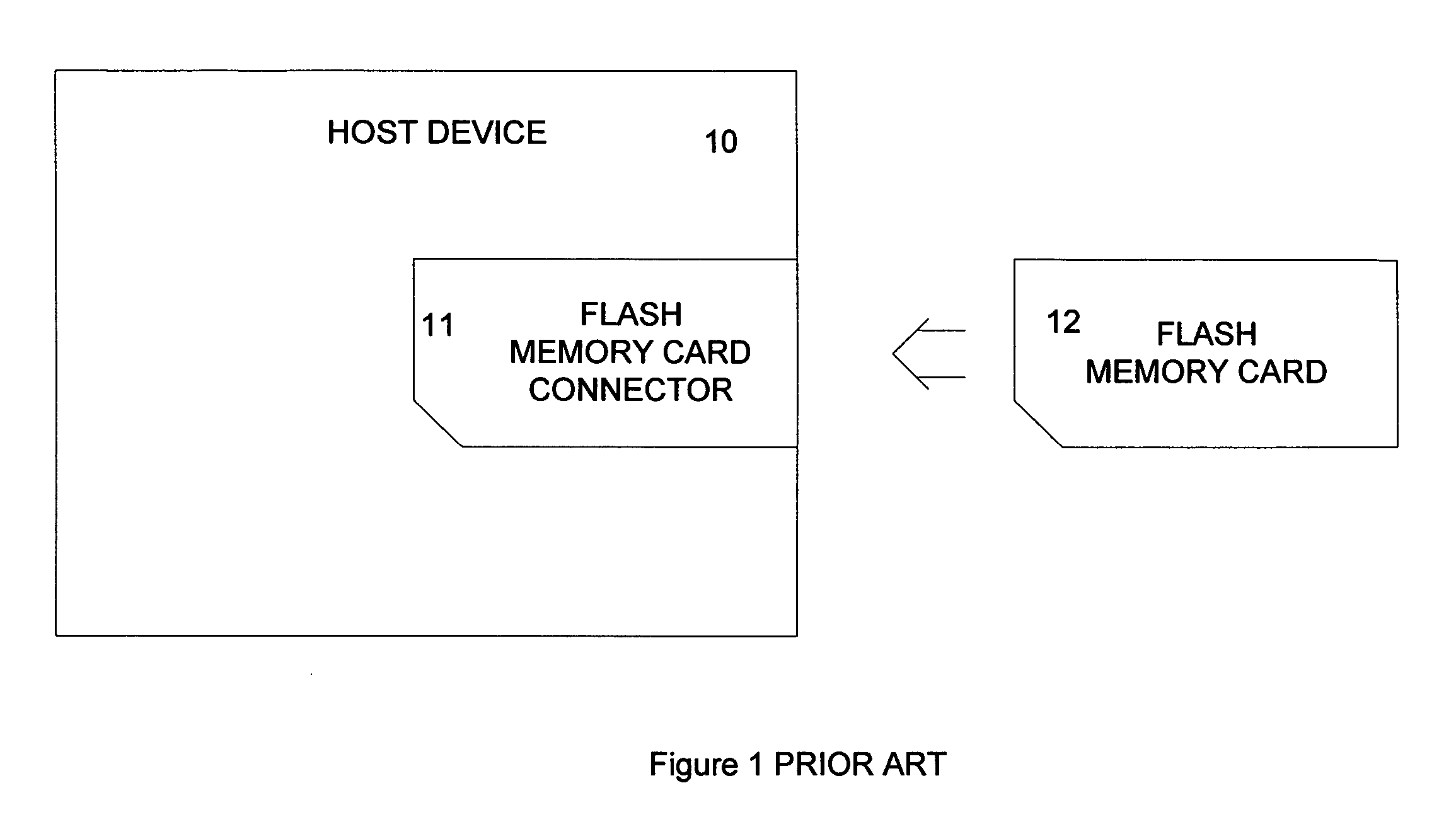

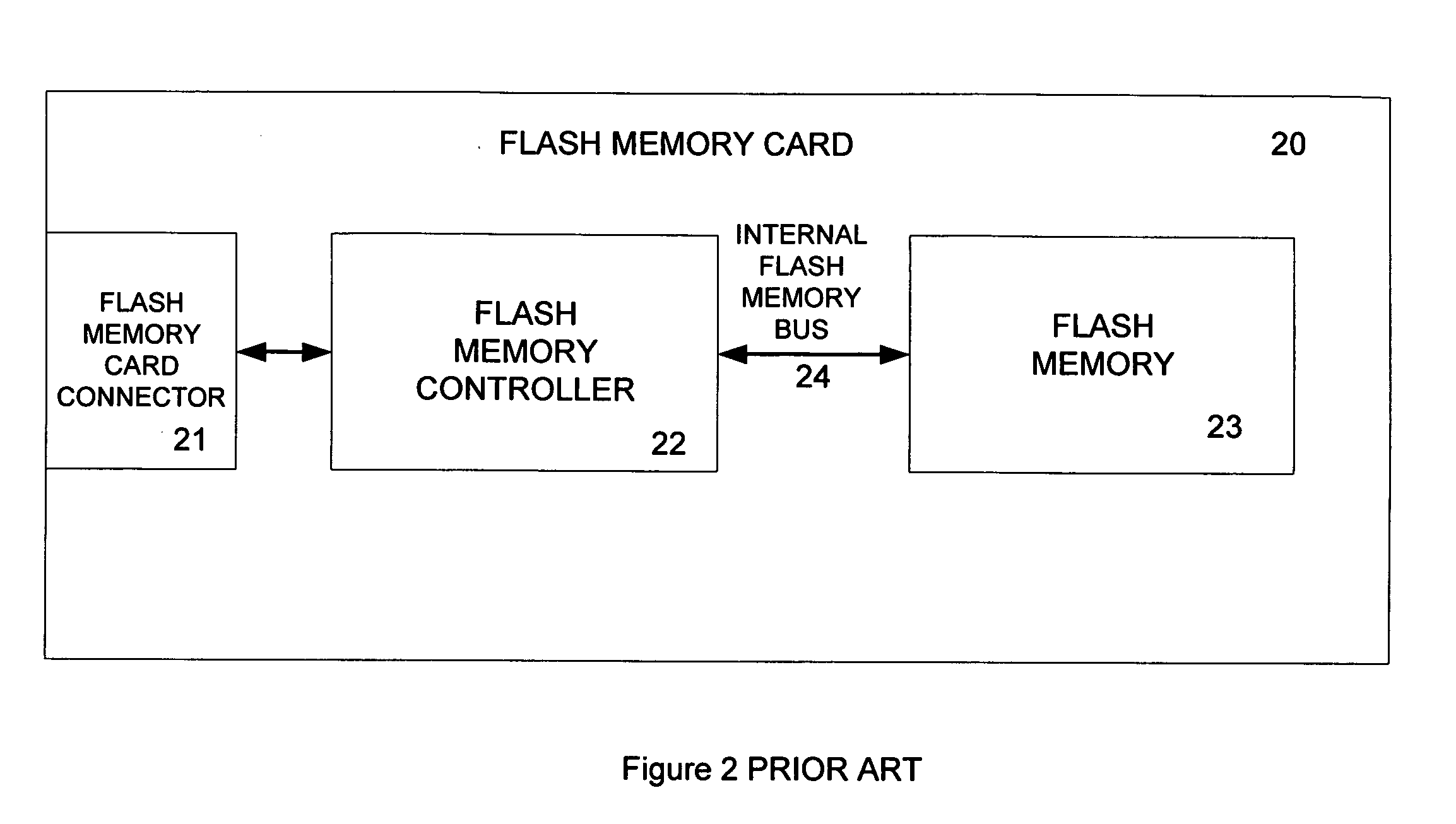

Wireless flash memory card expansion system

ActiveUS20070239929A1Multiple digital computer combinationsMemory systemsMemory busFlash memory controller

A Flash memory card system is disclosed. The Flash memory card system comprises a Flash memory wireless host adapter and a Flash memory bus wireless device. The Flash memory wireless host adapter comprises a Flash memory card connector and a Flash memory controller coupled to the Flash memory card connector. The Flash-52 memory card signals are converted to standard Flash memory internal bus signals by the Flash memory controller. The host adapter further comprises a Flash memory wireless module coupled to the Flash memory controller for receiving and transmitting the standard Flash memory bus signals wirelessly. The Flash-51 memory bus wireless device comprises a Flash memory bus wireless device adapter coupled to a Flash memory. The device adapter is paired to the wireless module for receiving and transmitting the standard Flash memory bus signals wirelessly. A host device storage capacity utilizing the Flash memory card system is expanded.

Owner:KINGSTON DIGITAL CO LTD

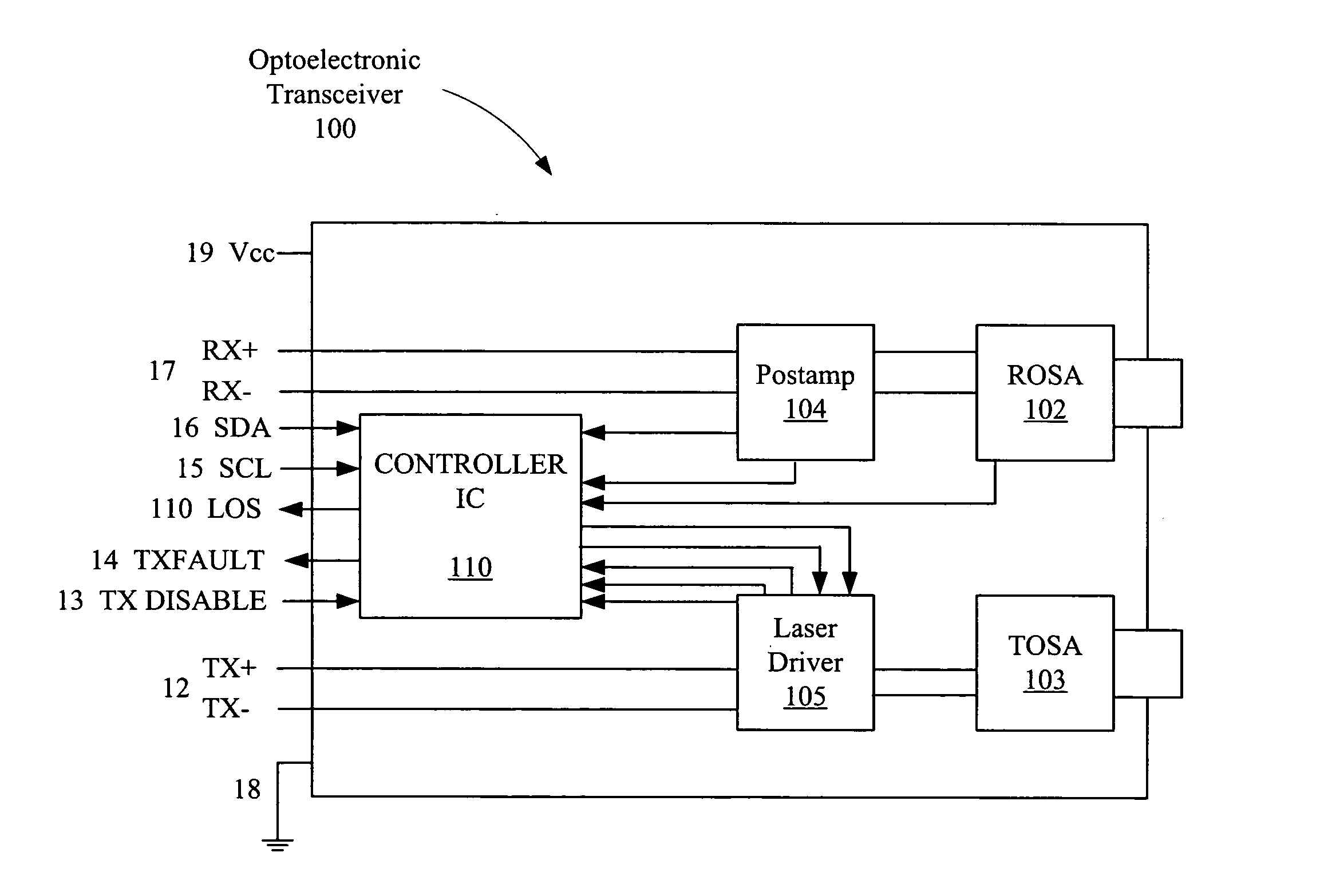

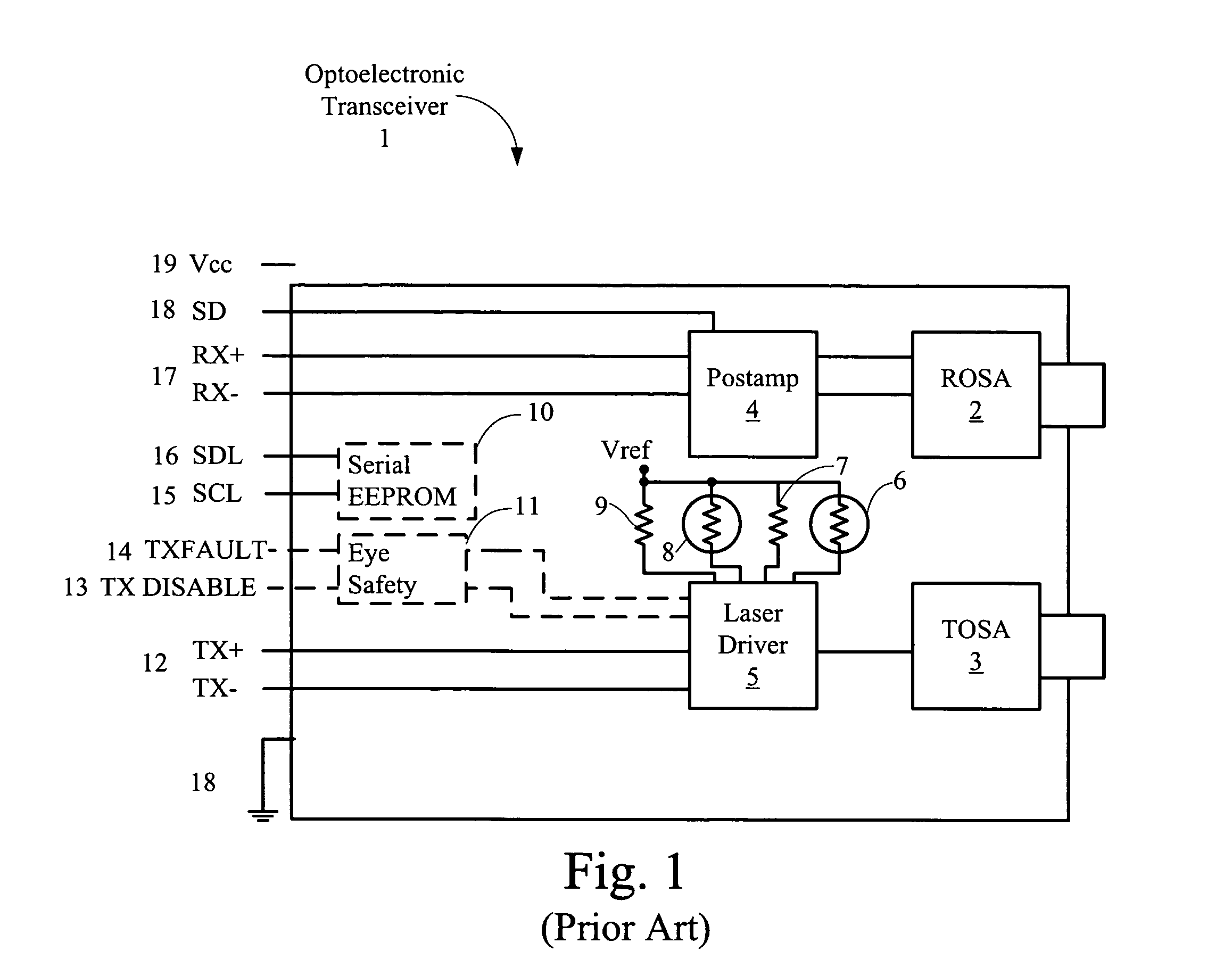

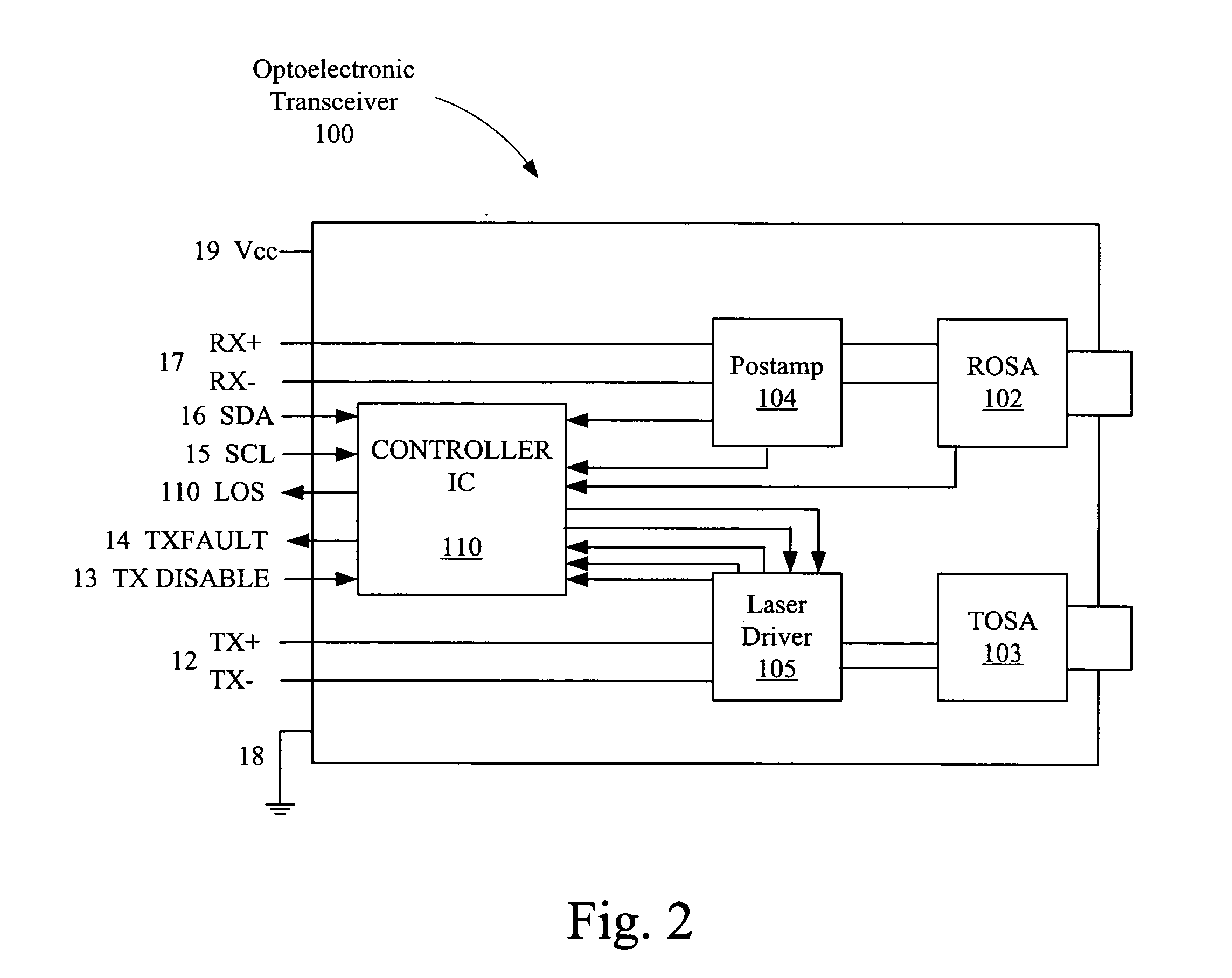

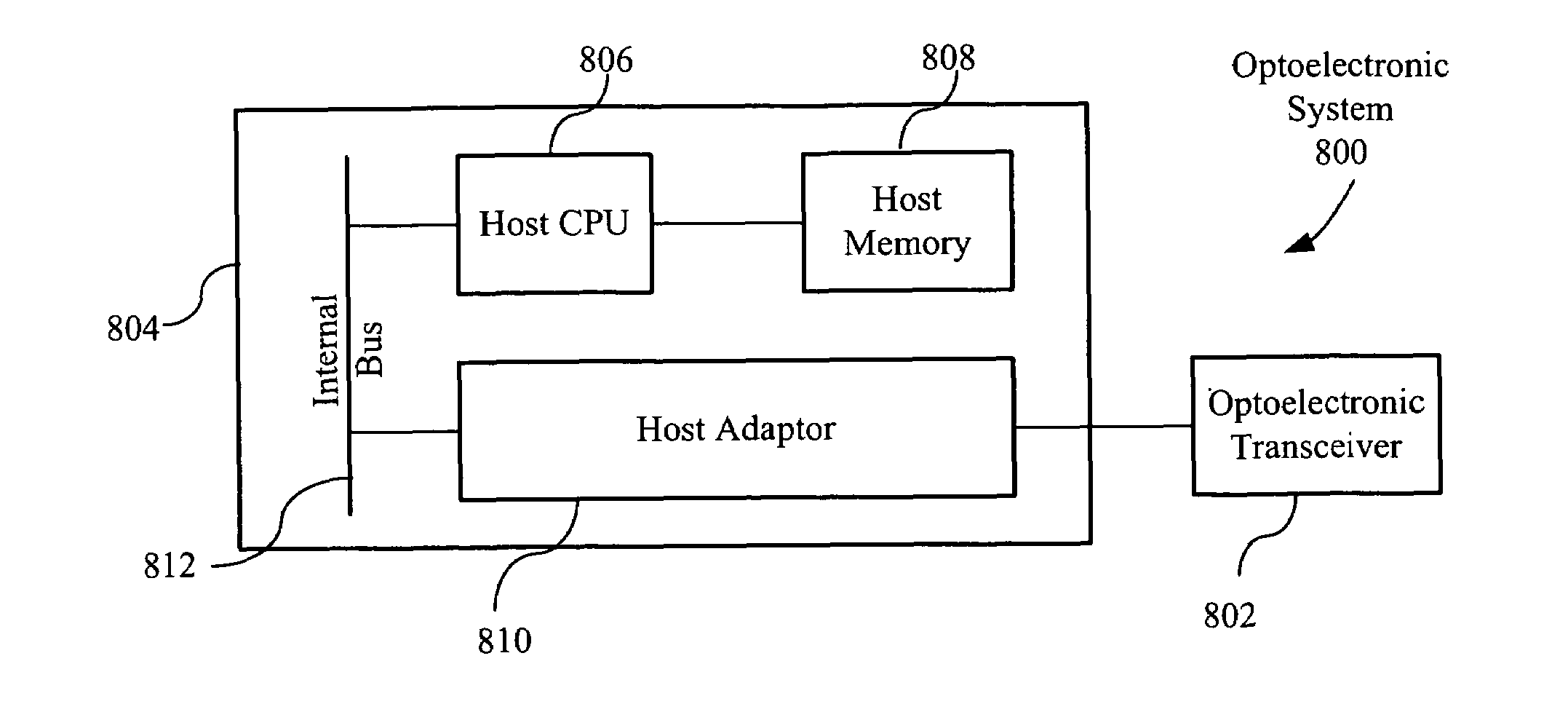

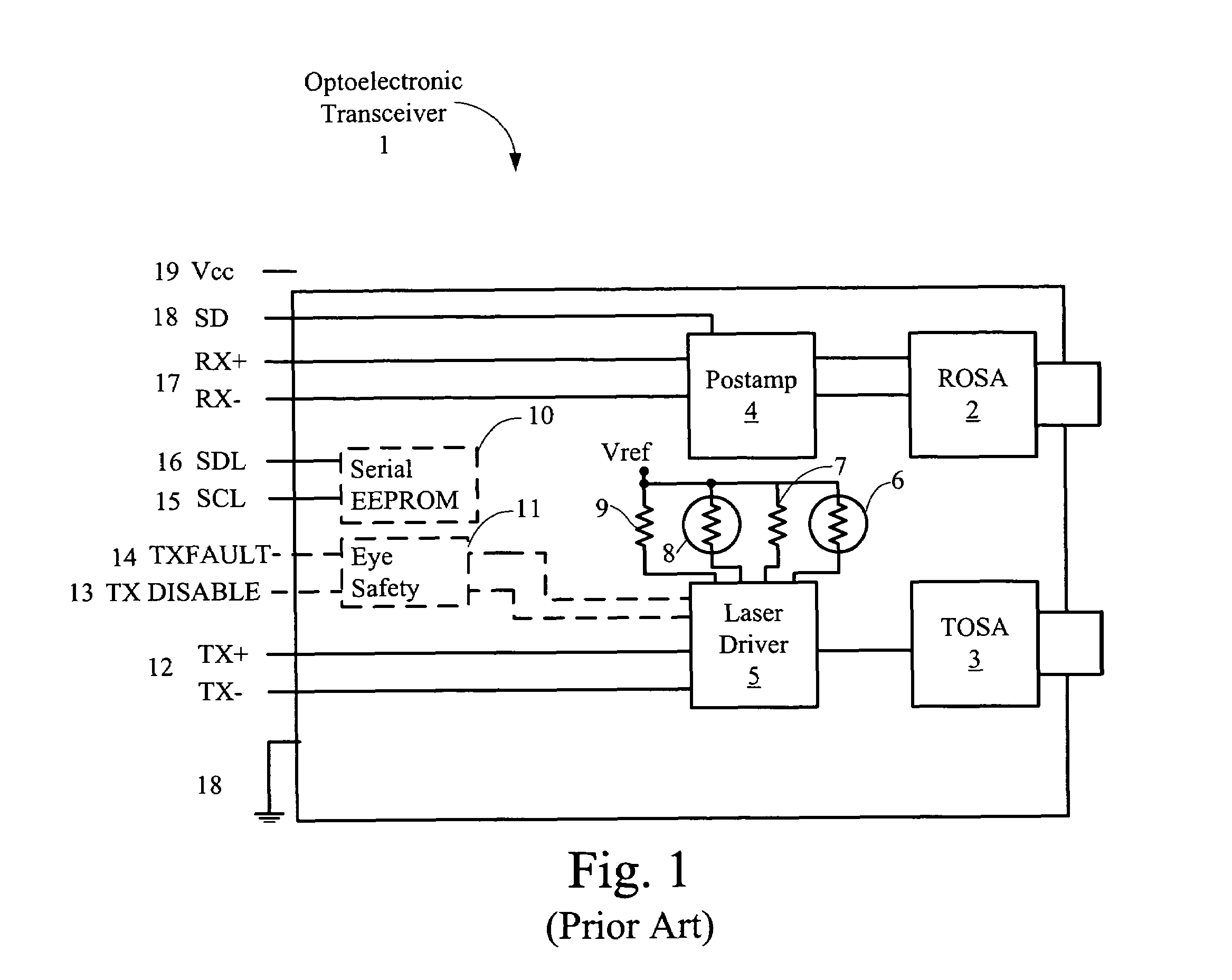

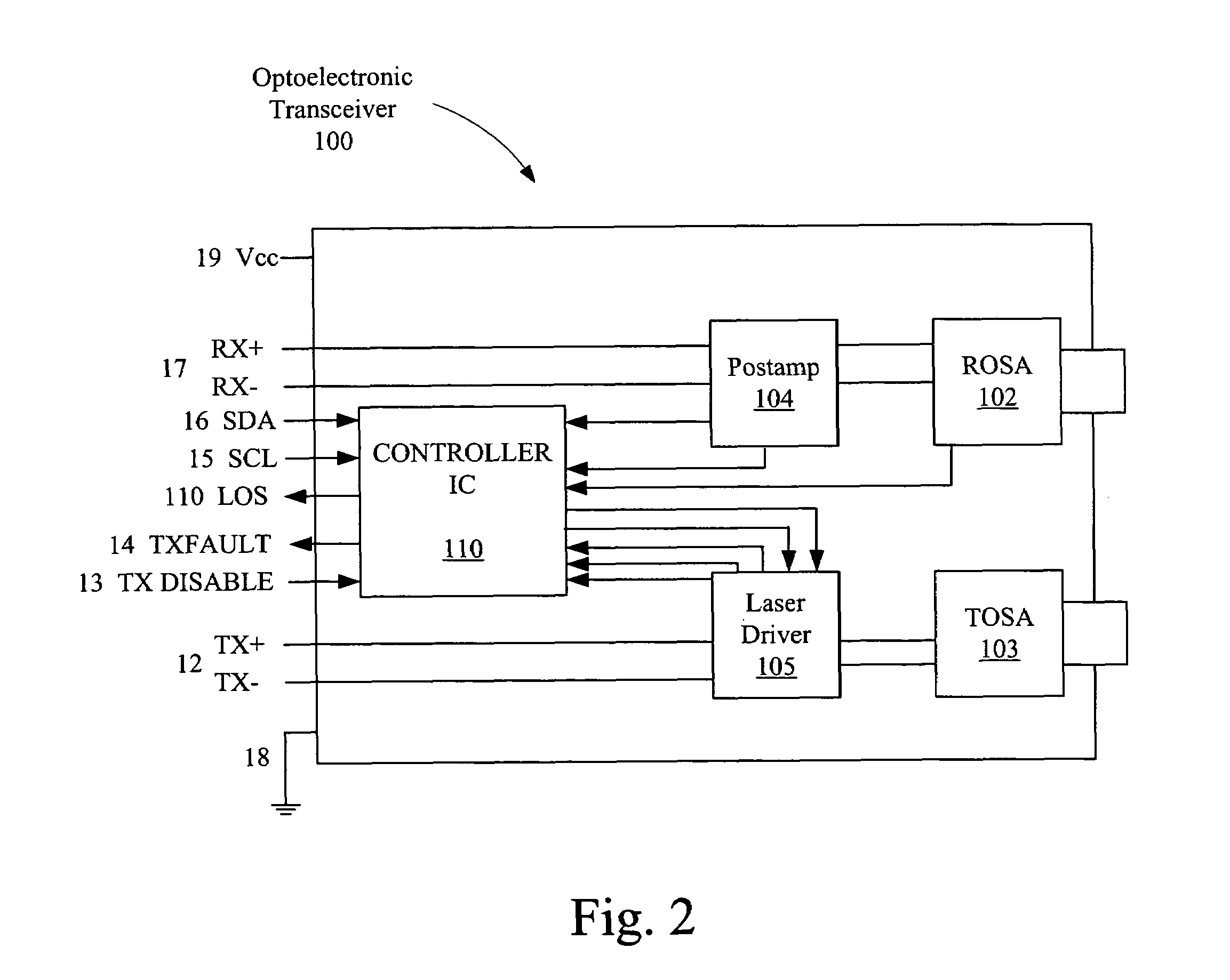

Optical transceiver and host adapter with memory mapped monitoring circuitry

InactiveUS20050031352A1Electromagnetic transmittersElectromagnetic transceiversTransceiverMemory map

A host adaptor is configured to monitor operation of an optoelectronic transceiver. The host adapter includes a transceiver interface, memory, comparison logic and a host interface. The transceiver interface receives from the optoelectronic transceiver digital values corresponding to operating conditions of the optoelectronic transceiver. The memory includes one or more memory arrays for storing information related to the optoelectronic transceiver, including the digital values received from the optoelectronic transceiver. The comparison logic is configured to compare the digital values with limit values to generate flag values, wherein the flag values are stored in predefined flag storage locations within the memory during operation of the optoelectronic transceiver. The host interface enables a host device to read from host specified locations within the memory, including the predefined flag storage locations, in accordance with commands received from the host device.

Owner:II VI DELAWARE INC

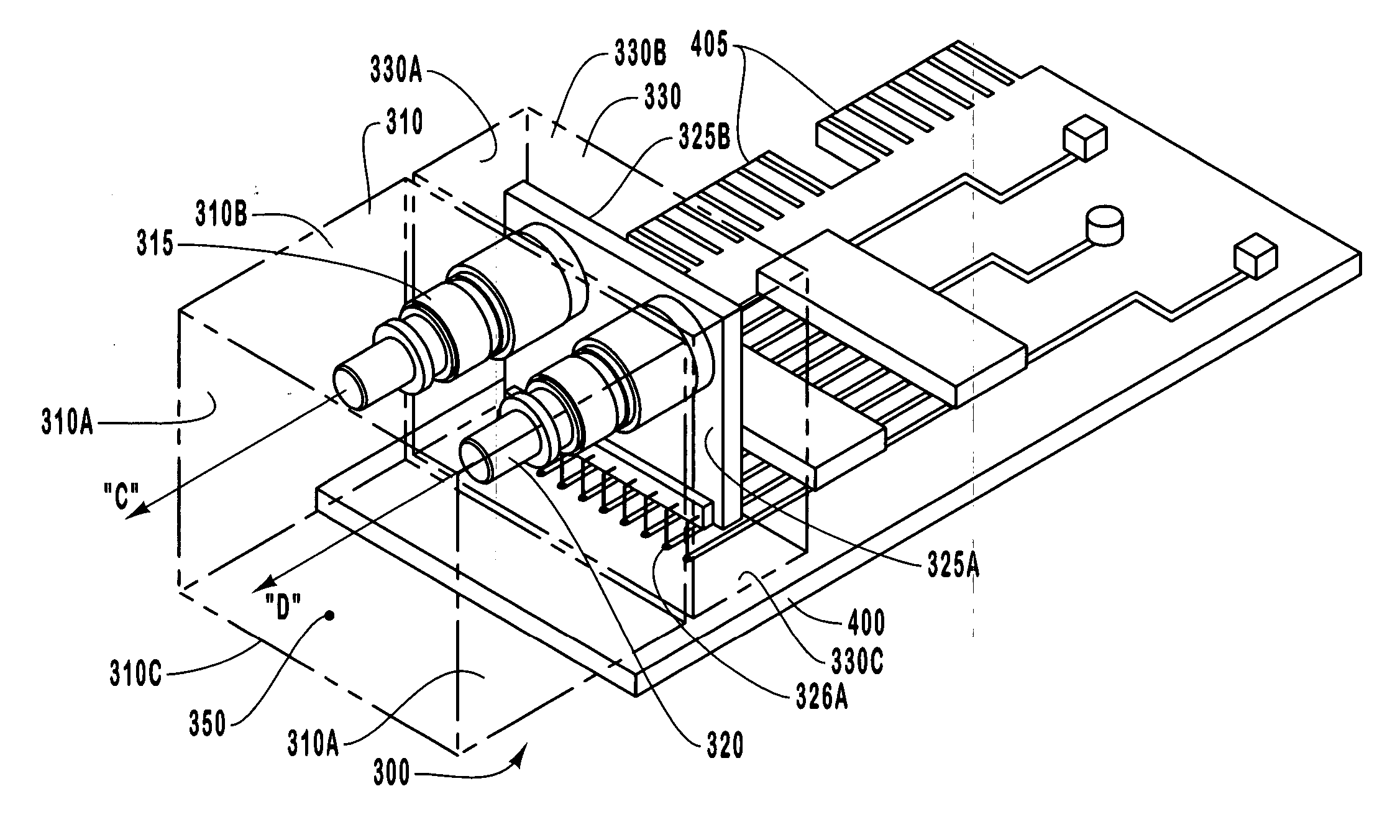

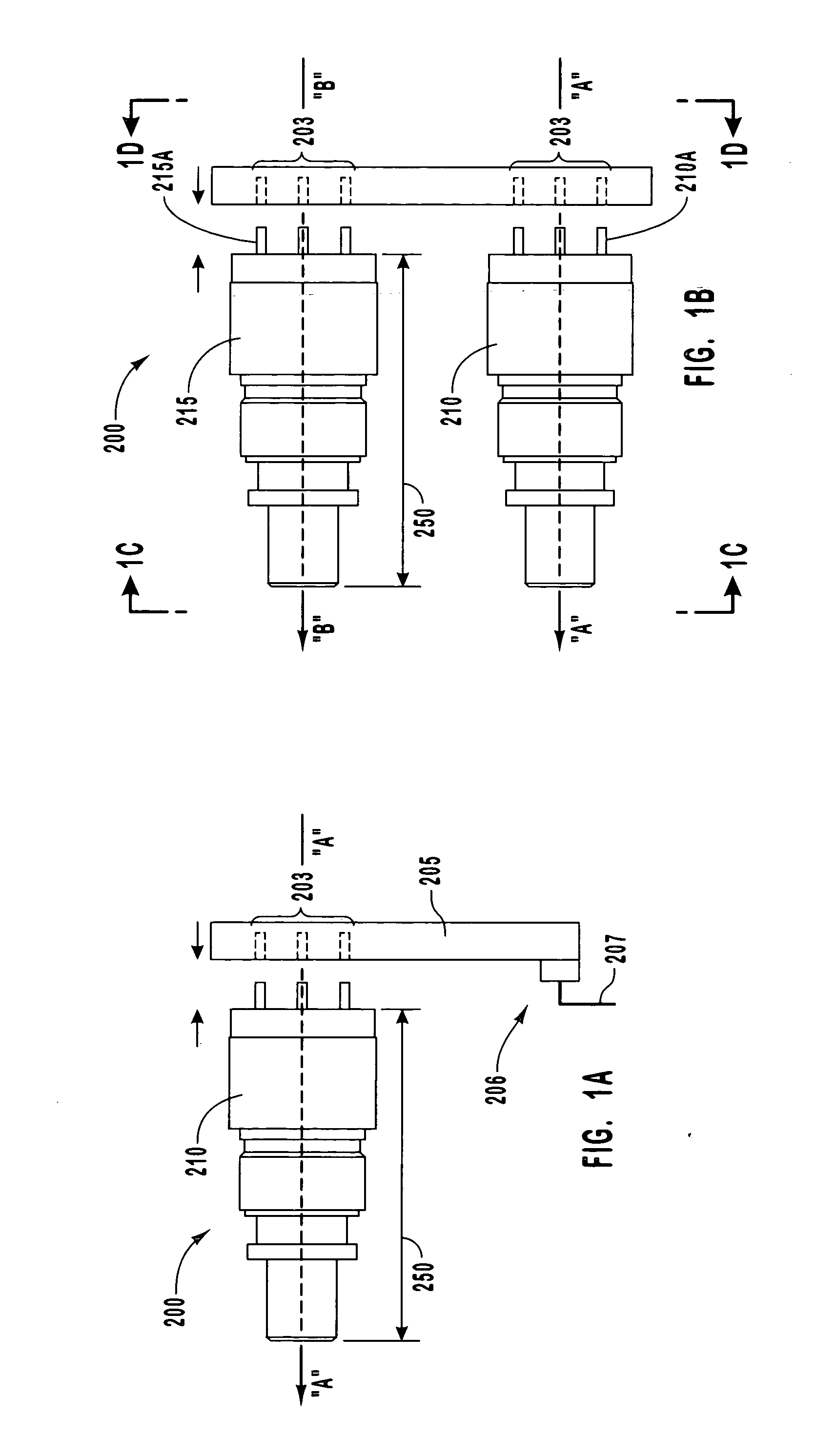

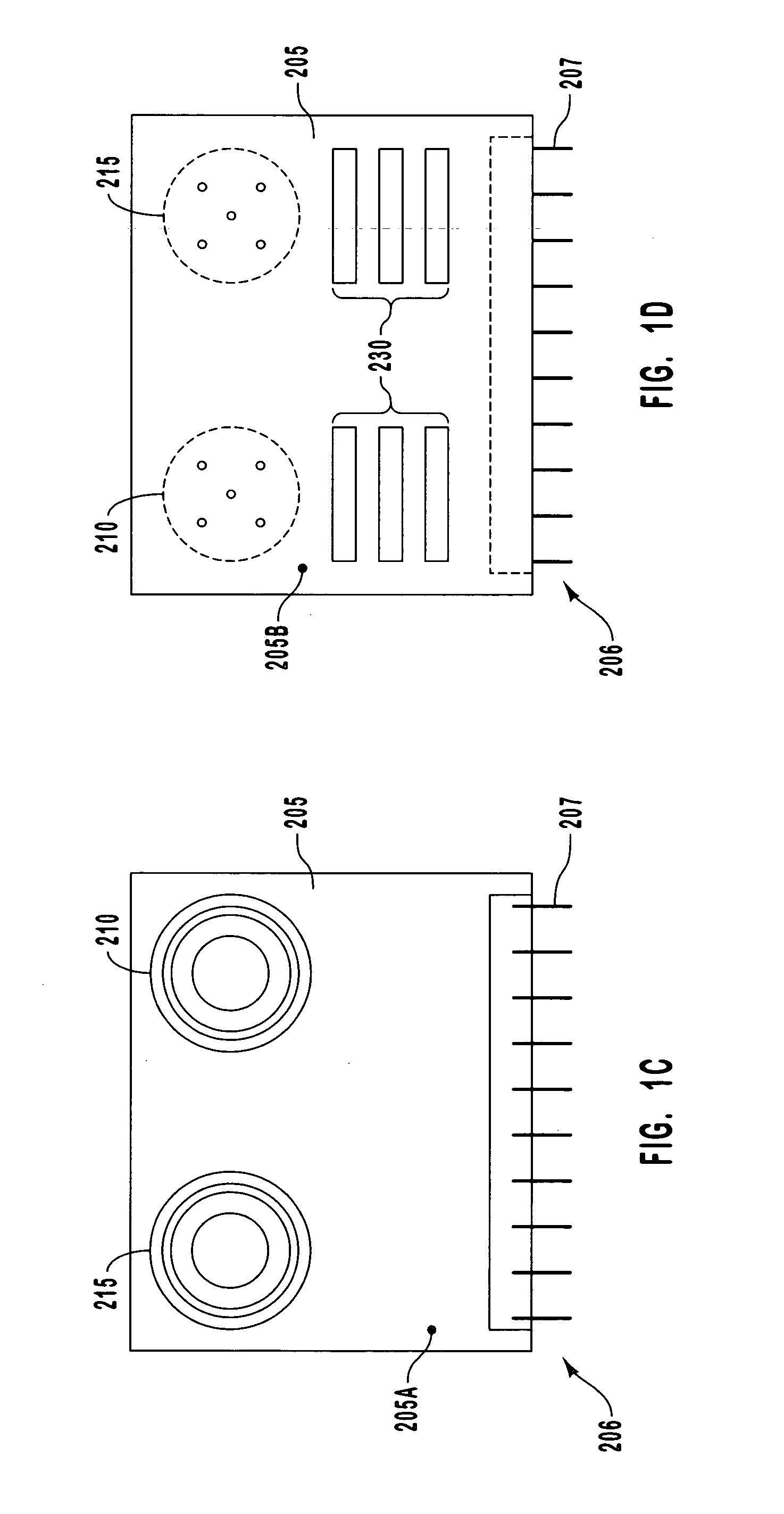

Compact optical transceivers for host bus adapters

InactiveUS20050105915A1Less board spaceFunction increasePrinted circuit assemblingPrinted circuit aspectsTransceiverEngineering

An optical transceiver is provided that includes a transceiver substrate arranged substantially perpendicular to longitudinal axes respectively defined by a transmit optical subassembly and receive optical subassembly. The transceiver substrate is configured to electrically and physically connect to the transmit optical subassembly and the receive optical subassembly, and includes a connector configured and arranged to interface with a host bus adapter. The combination of the host bus adapter and optical transceiver is sized and configured to be received within a standard slot of a host system, such as a PCI or PCMCIA slot. In this way, one or more optical connections are integrated within the host device or system.

Owner:II VI DELAWARE INC

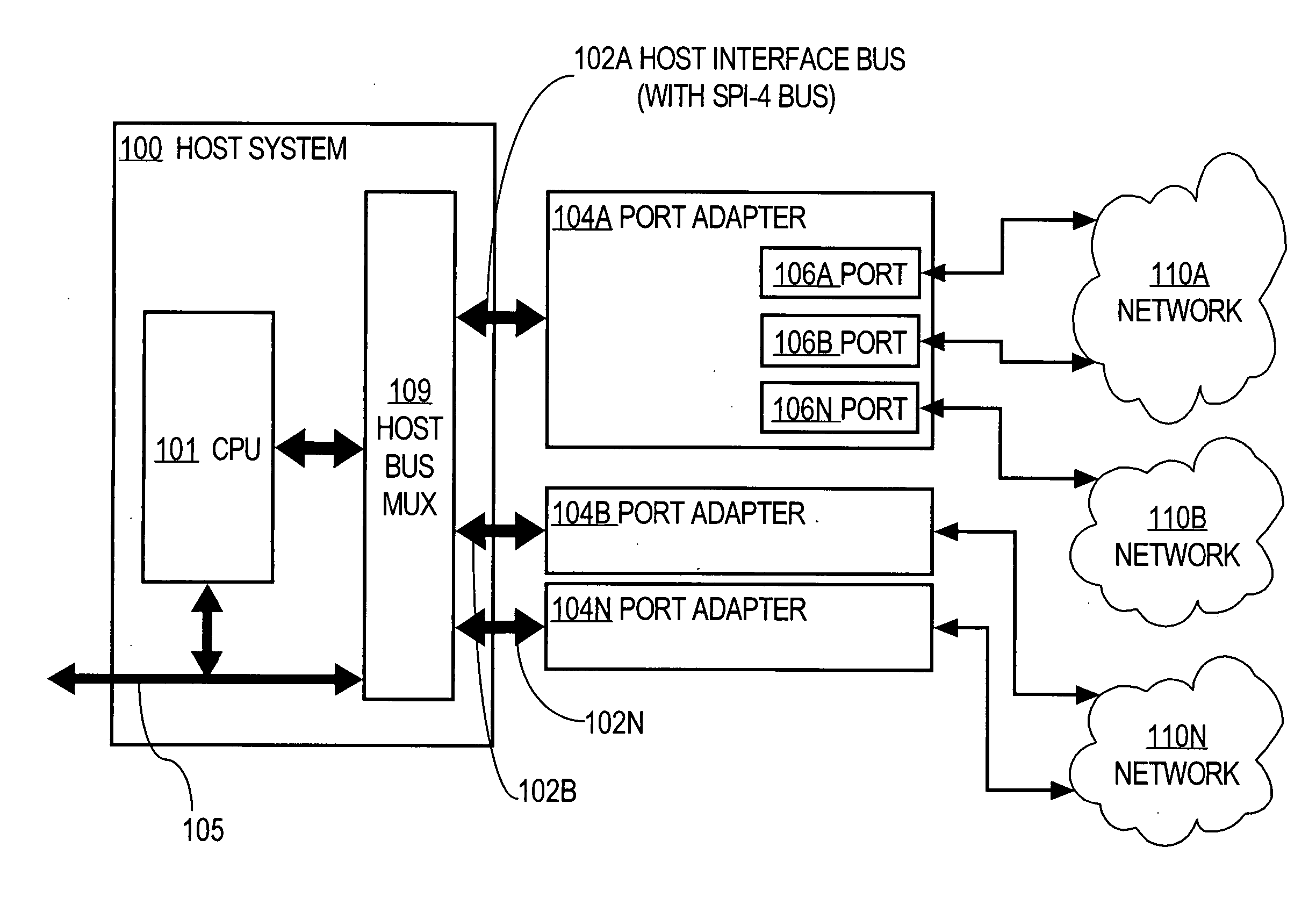

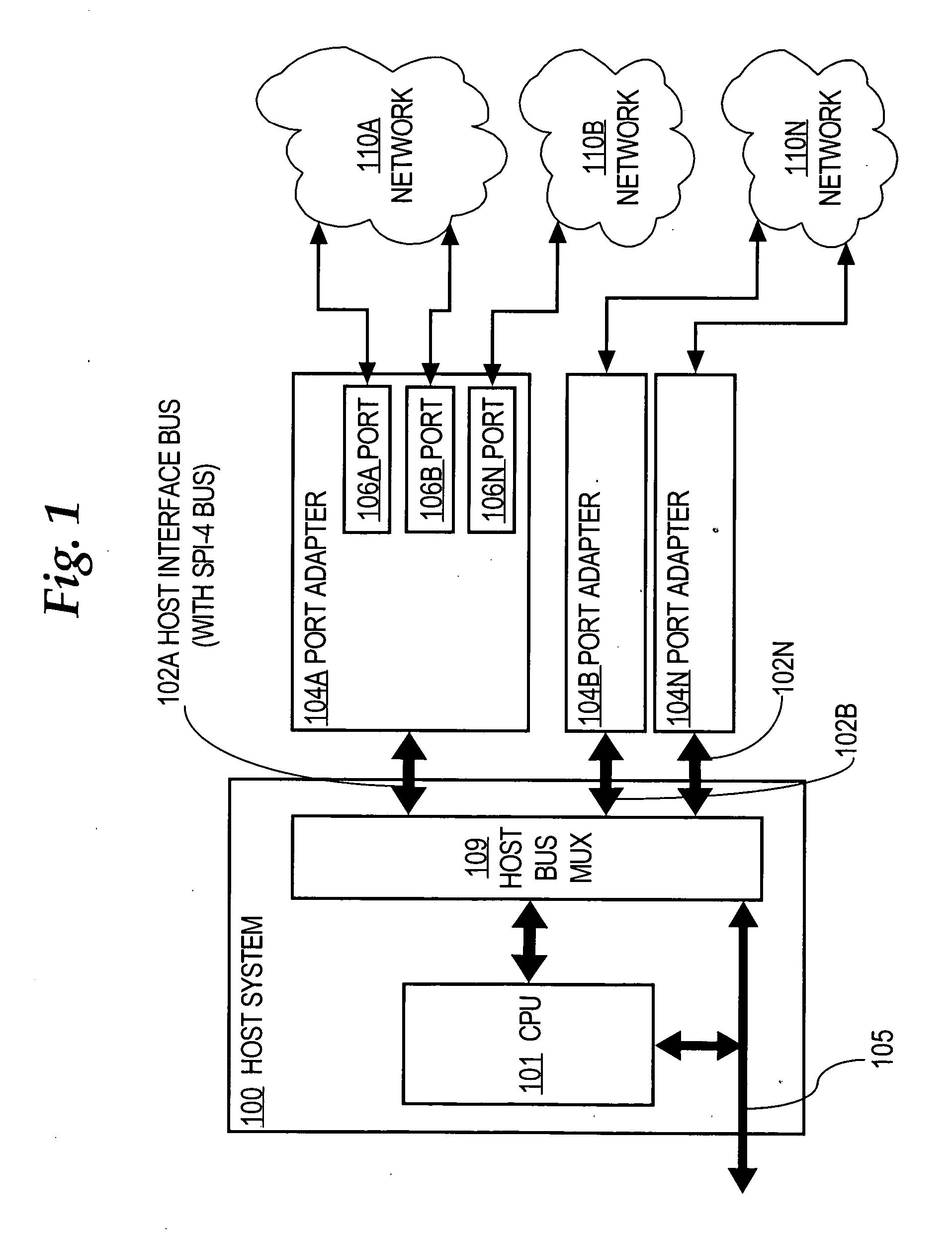

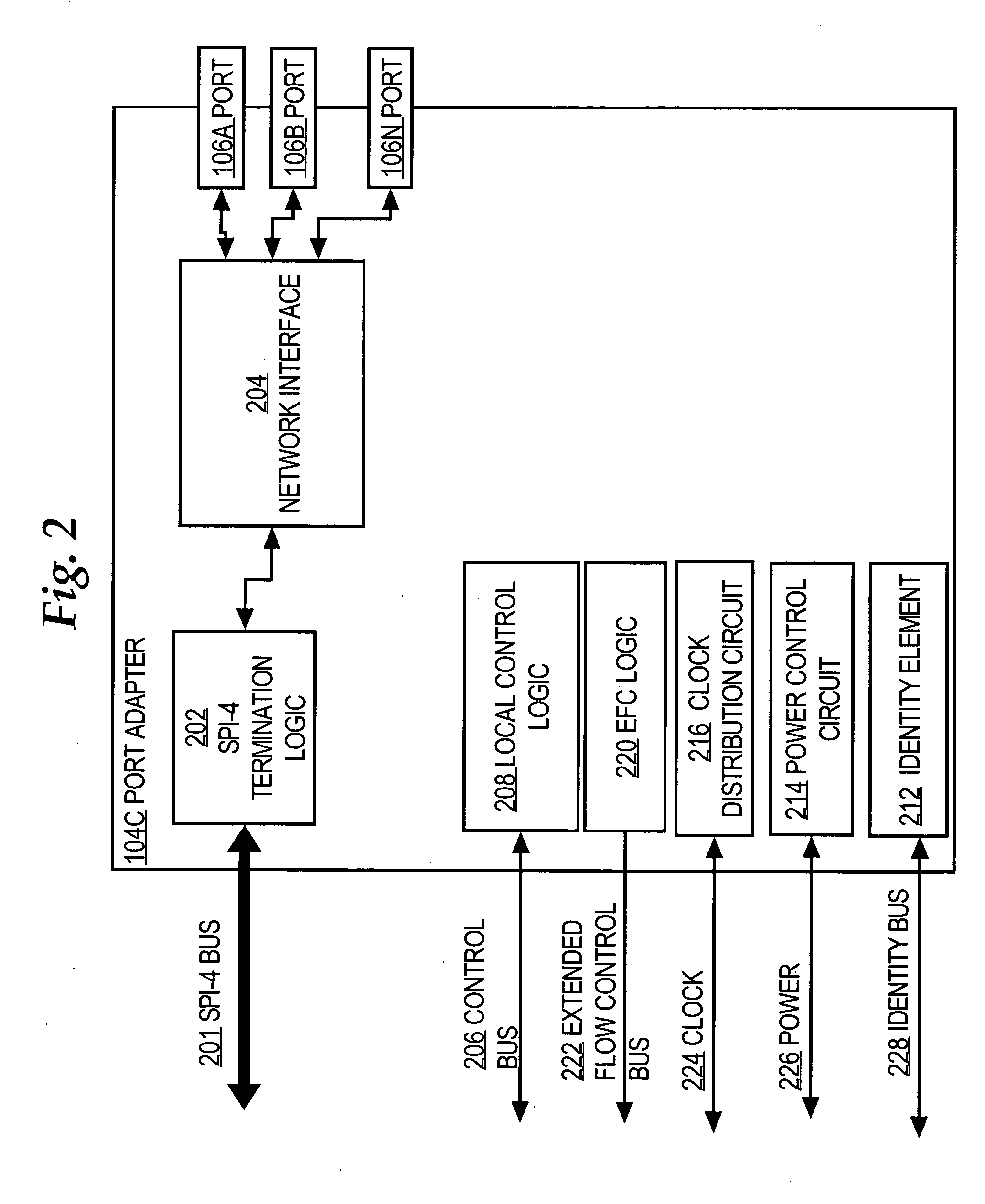

Port adapter for high-bandwidth bus

InactiveUS20050149651A1Prevent potentially high currentPrevent corruptionTime-division multiplexData switching by path configurationHigh bandwidthBandwidth requirement

Owner:CISCO TECH INC

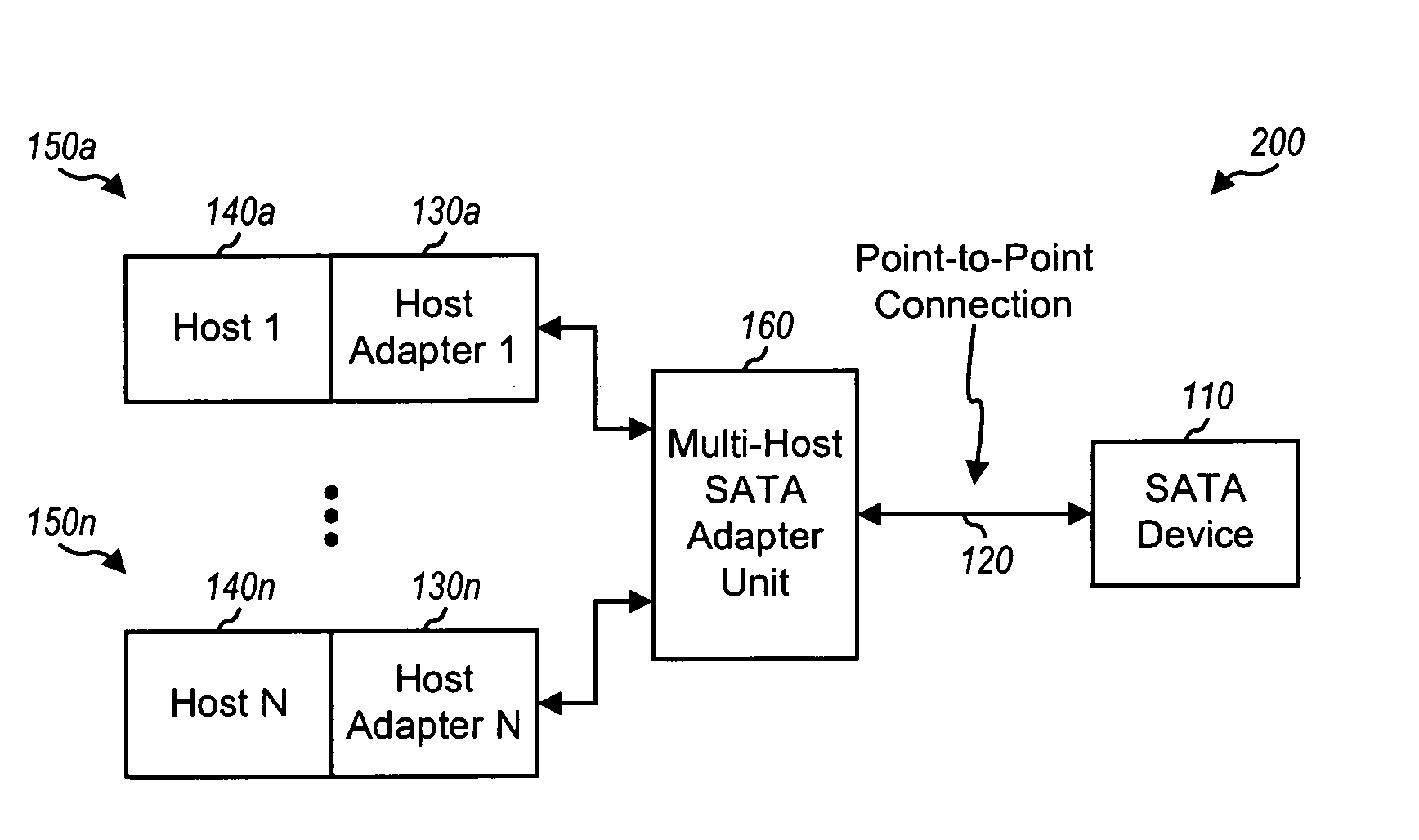

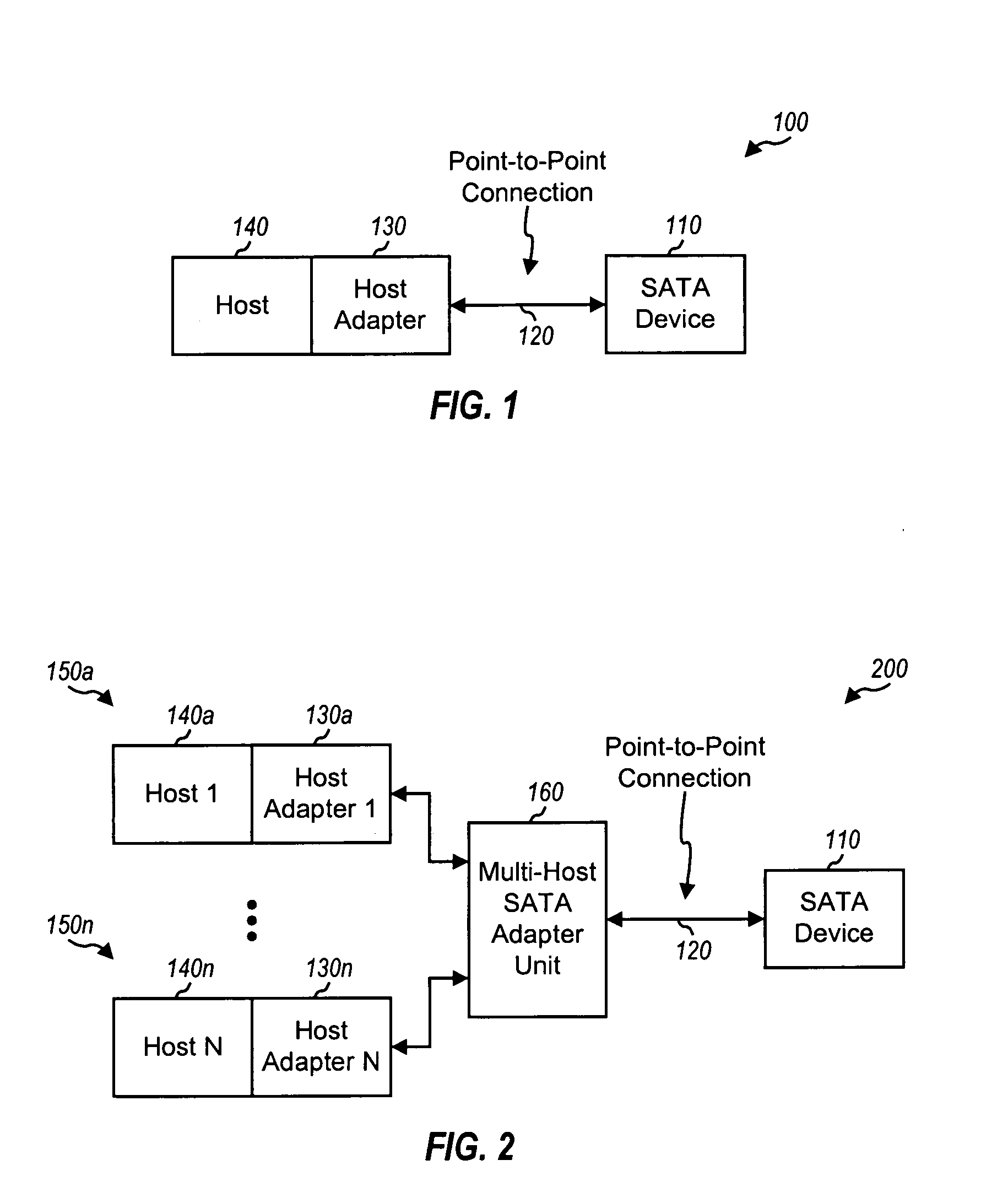

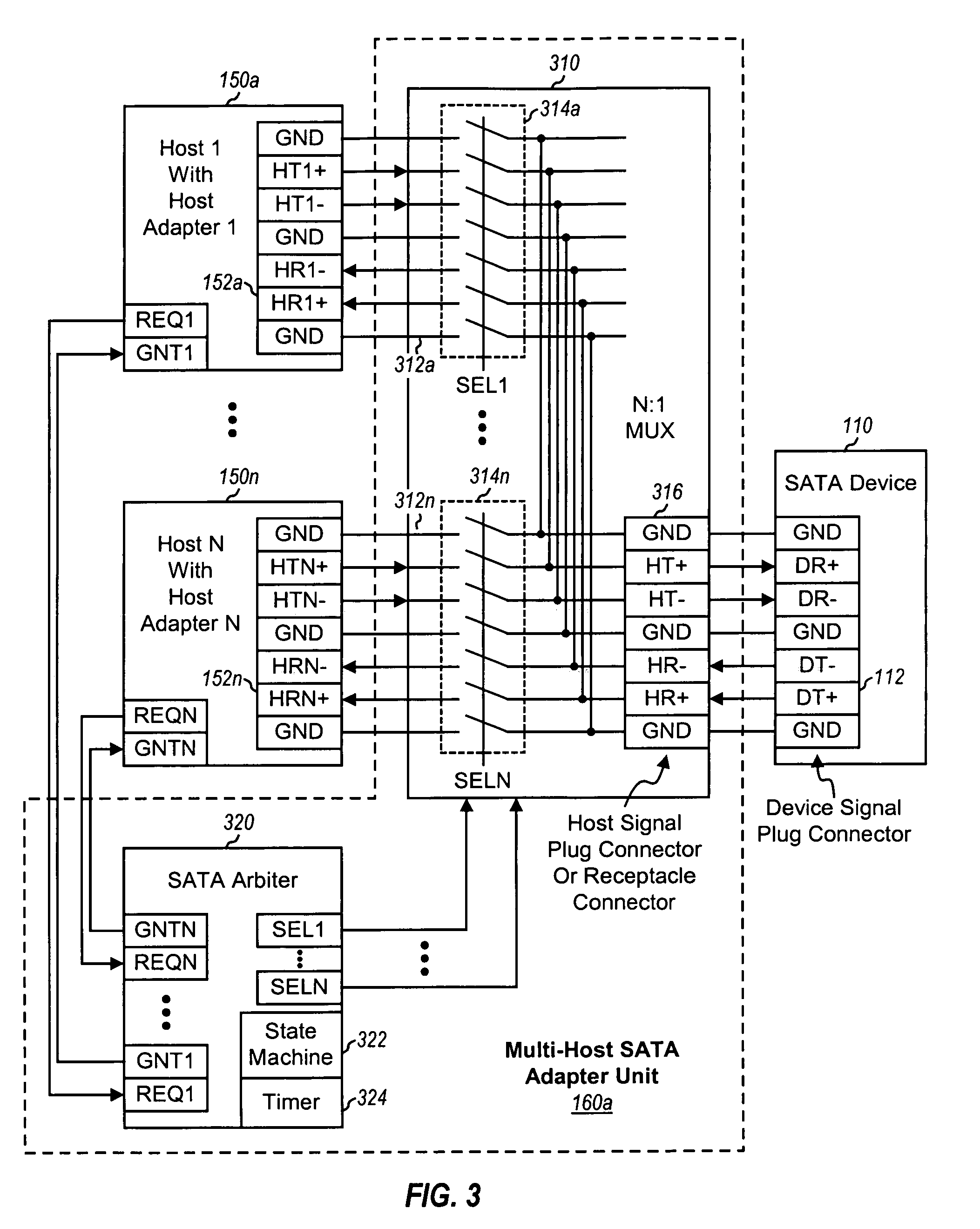

Method and apparatus for supporting access of a serial ATA storage device by multiple hosts with separate host adapters

An adapter unit operative to support access of an SATA storage device by a plurality of hosts associated with separate host adapters. The adapter unit includes a multiplexer coupled to an arbiter. The multiplexer receives a plurality of sets of communication signals, one signal set for each host adapter. The multiplexer then selects one of the signal sets based on a control signal and couples the selected signal set to its output. The arbiter receives requests from the hosts to access the SATA storage device, selects a particular requesting host, and provides the control signal indicative of the specific host granted access. The host adapter for the granted host and the SATA storage device are placed in a PHY READY power management state, prior to a read or write access, and are placed in a PARTIAL power management state after the read or write access.

Owner:RESILIENT

Method and system for quality of service in host bus adapters

Method and system for an adapter coupled to a network via a network link is provided. The method includes using a first selectable mode and a second selectable mode to provide quality of service to a plurality of applications executed by one or more computing system. In the first selectable mode, the quality of service is based on allocating bandwidth of the network link and dynamically adjusting an initial priority assigned to a plurality of queues, each queue being associated with an application from among a plurality of applications. In the second selectable mode, the quality of service is based on a user assigning a priority to each of the plurality of applications and the adapter determines a number of input / output (I / O) requests it needs to process within a duration and then transfers information based on the determined number of I / O requests and the assigned priority.

Owner:MARVELL ASIA PTE LTD

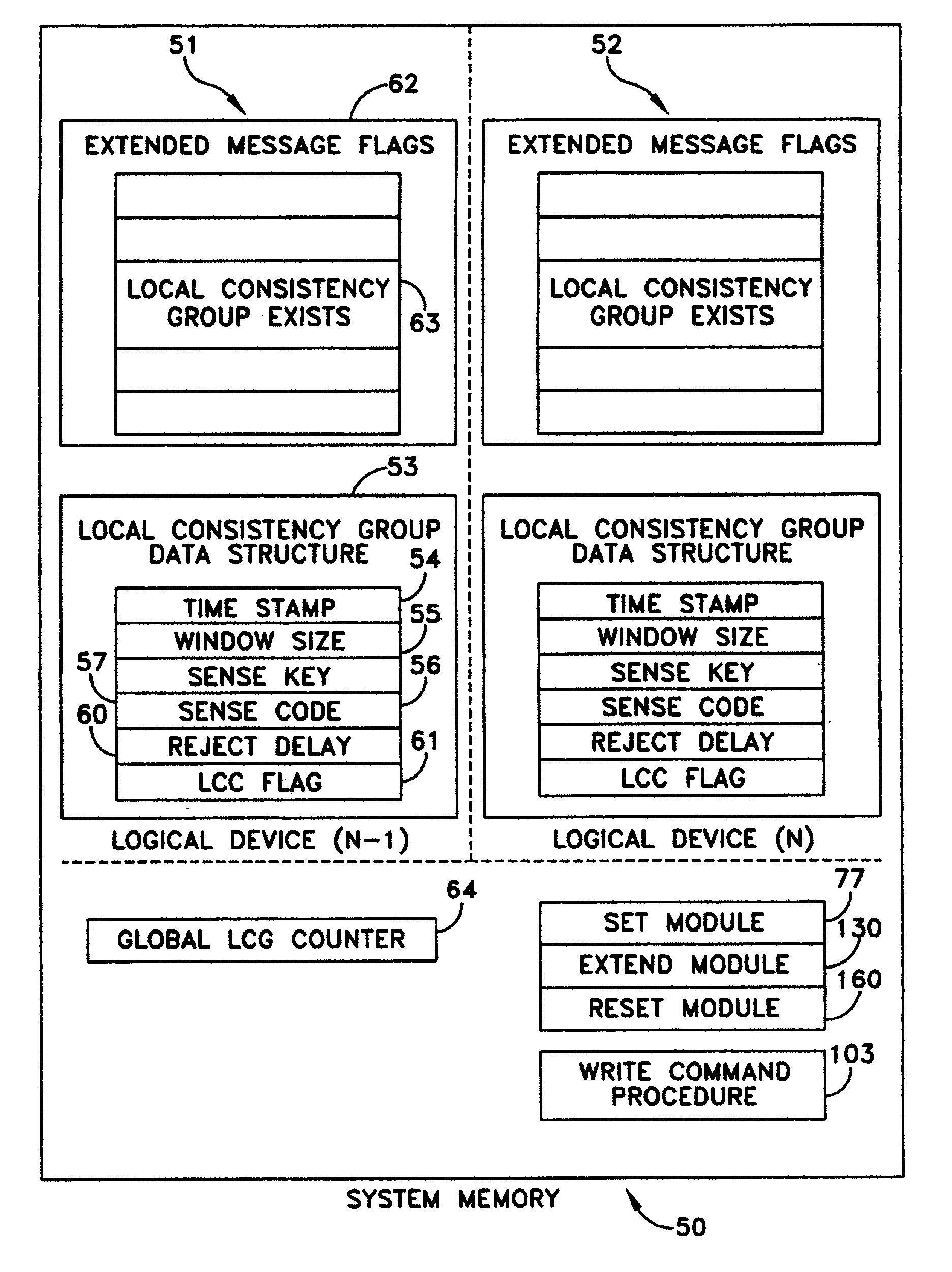

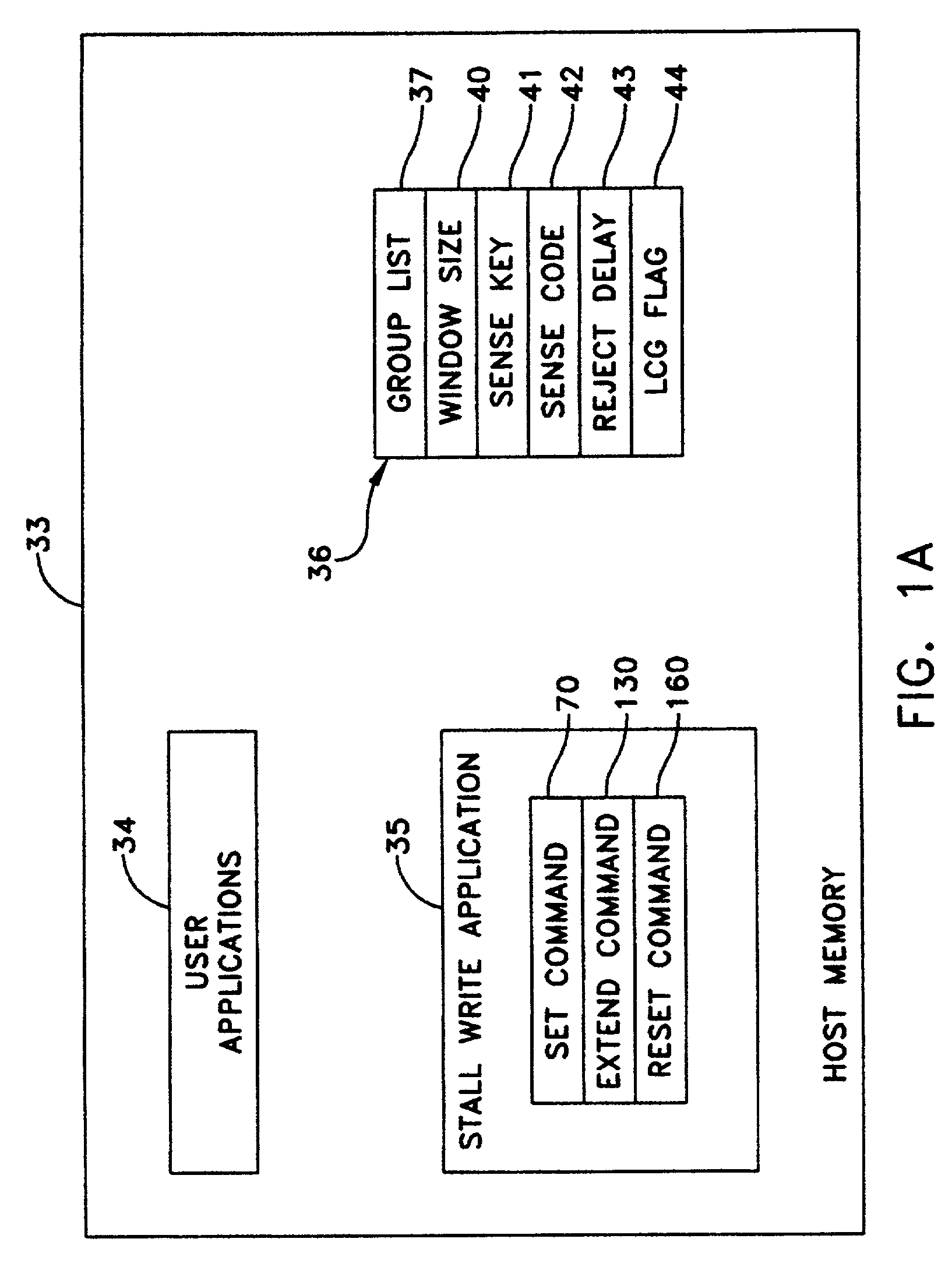

Method and apparatus for enhancing operations in disk array storage devices

InactiveUS20030204692A1Minimal impactConsistent dataInput/output to record carriersUnauthorized memory use protectionEngineeringDisk array

A method and apparatus for assuring data consistency during certain operations involving dependent input / output sequences. During such operations a stall application blocks write operations to specified logical devices in a local consistency group while allowing read operations to all devices and write operations to non-specified logical devices. When a write command is directed to a logical device in local consistency group, the host adapter associated with the logical device returns a message to the host that initiates a write command retry. Retries generally continue until a write command is successful.

Owner:EMC IP HLDG CO LLC

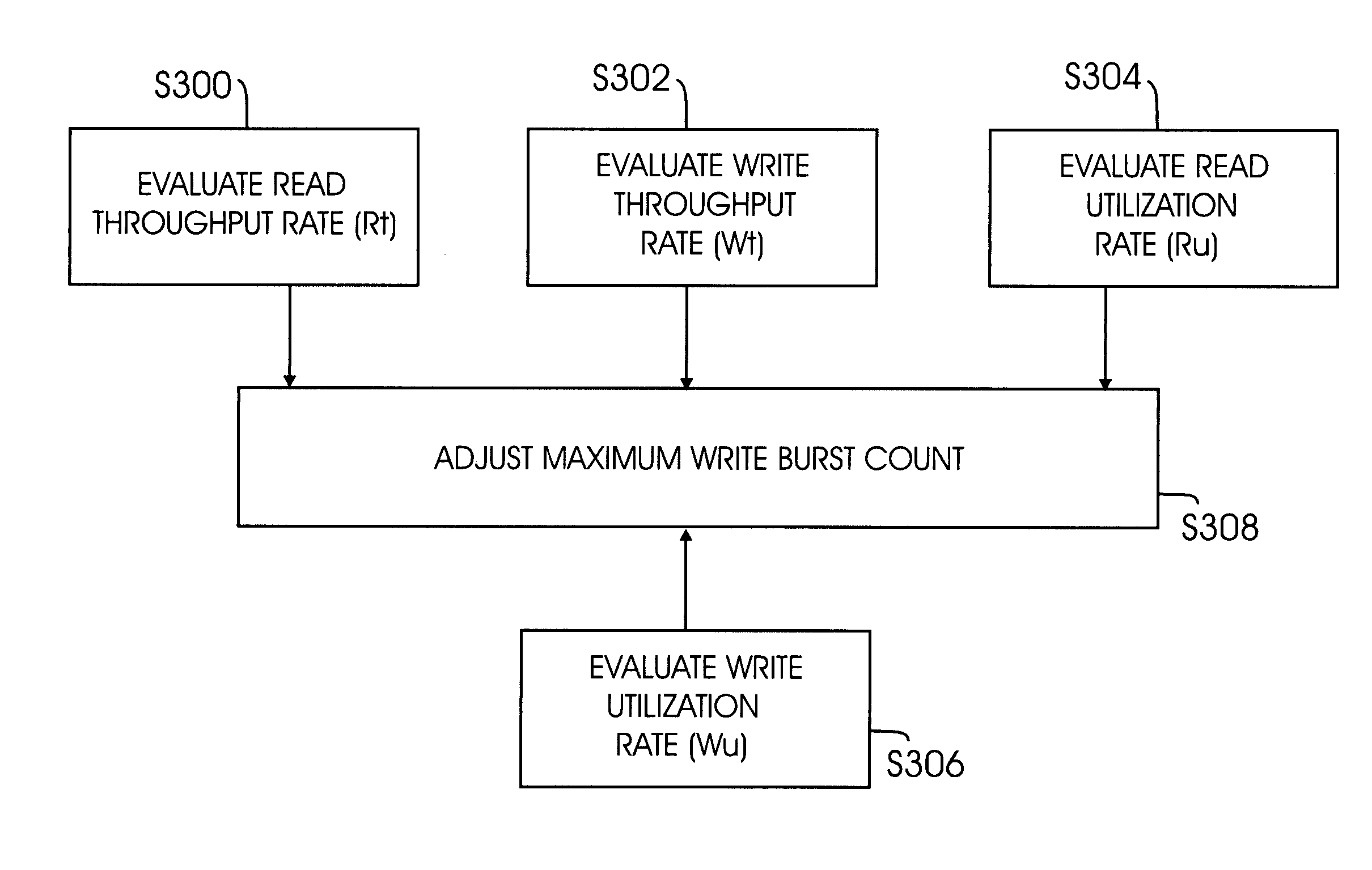

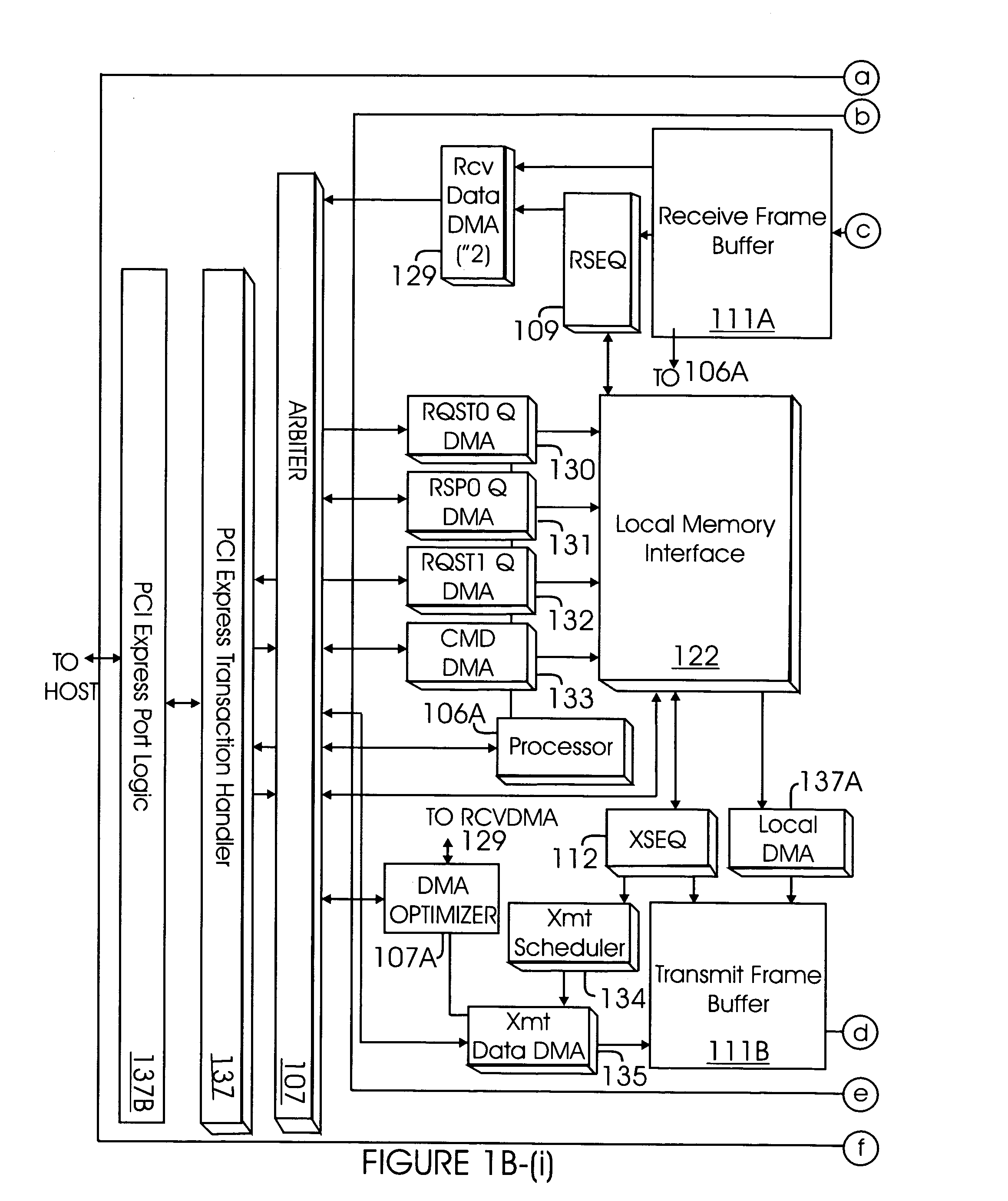

Method and system for DMA optimization in host bus adapters

InactiveUS7398335B2Optimize the writing processAdjustable performanceMultiple digital computer combinationsInput/output processes for data processingMaximum burst sizeBurst count

Method and system for optimizing DMA request processing is provided. The system includes a HBA that uses a dynamic DMA maximum write burst count sizing to optimize processing of write and read requests, wherein the HBA includes a DMA optimizer module that selects a certain write burst size to adjust performance when read and write DMA requests are being utilized. The DMA optimizer module can toggle between write and read request priority based on a maximum write request burst size. A shorter maximum write burst size provides more opportunity to issue read requests and a larger maximum burst size provides a better write request performance. The method includes, evaluating a read request throughput rate; evaluating a write request throughput rate; evaluating a read request utilization rate; evaluating a write request utilization rate; and adjusting a maximum write burst size.

Owner:MARVELL ASIA PTE LTD

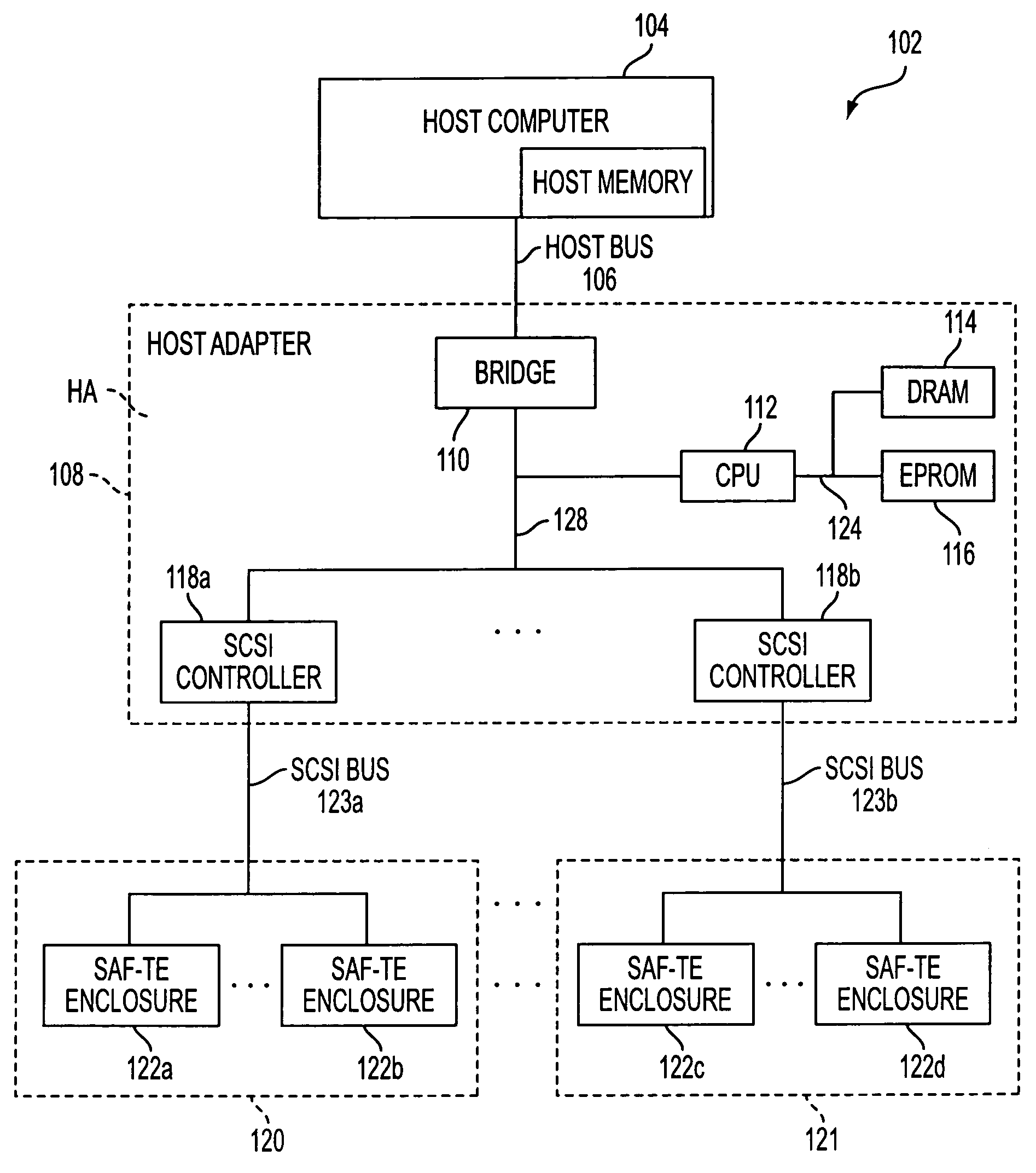

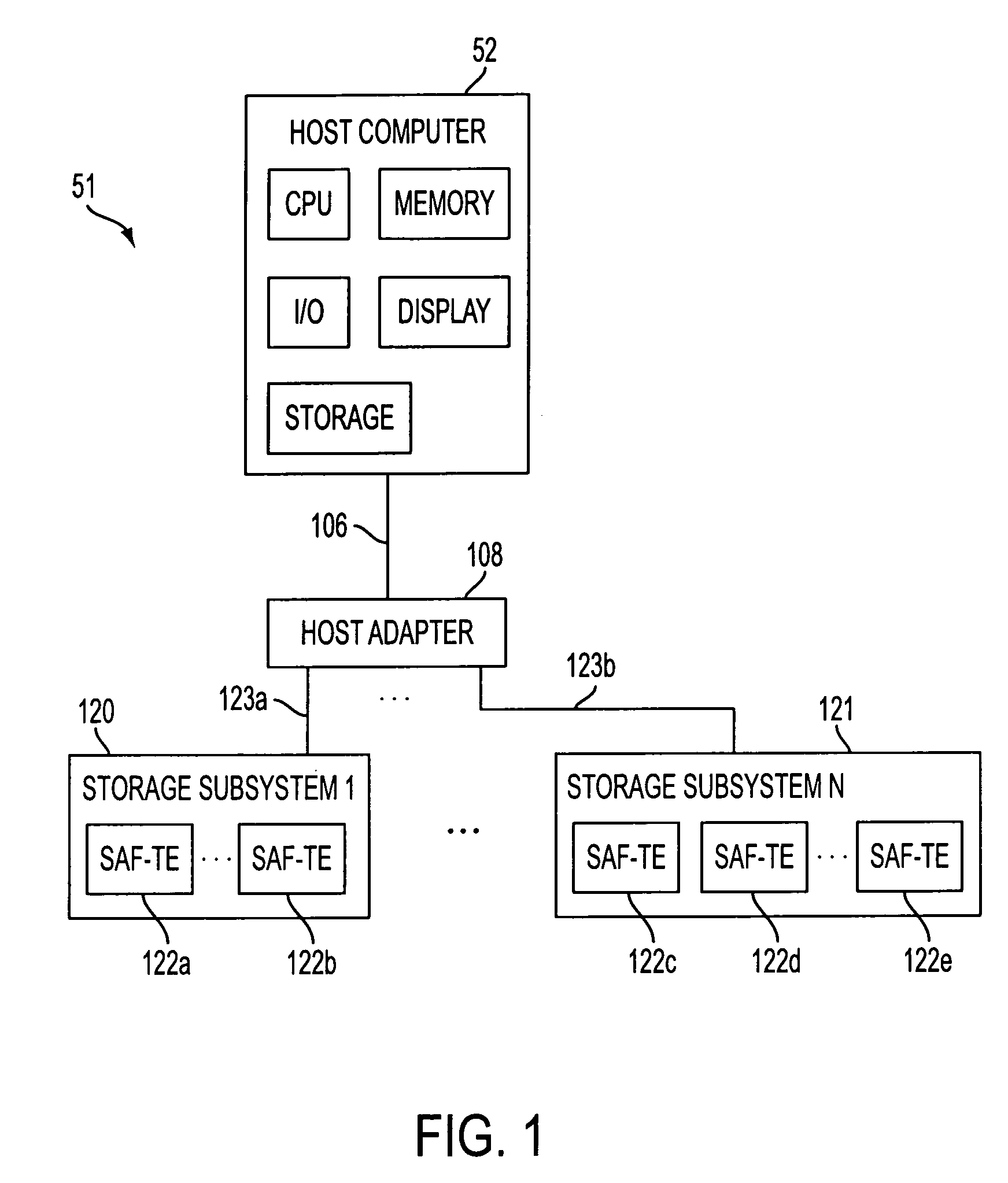

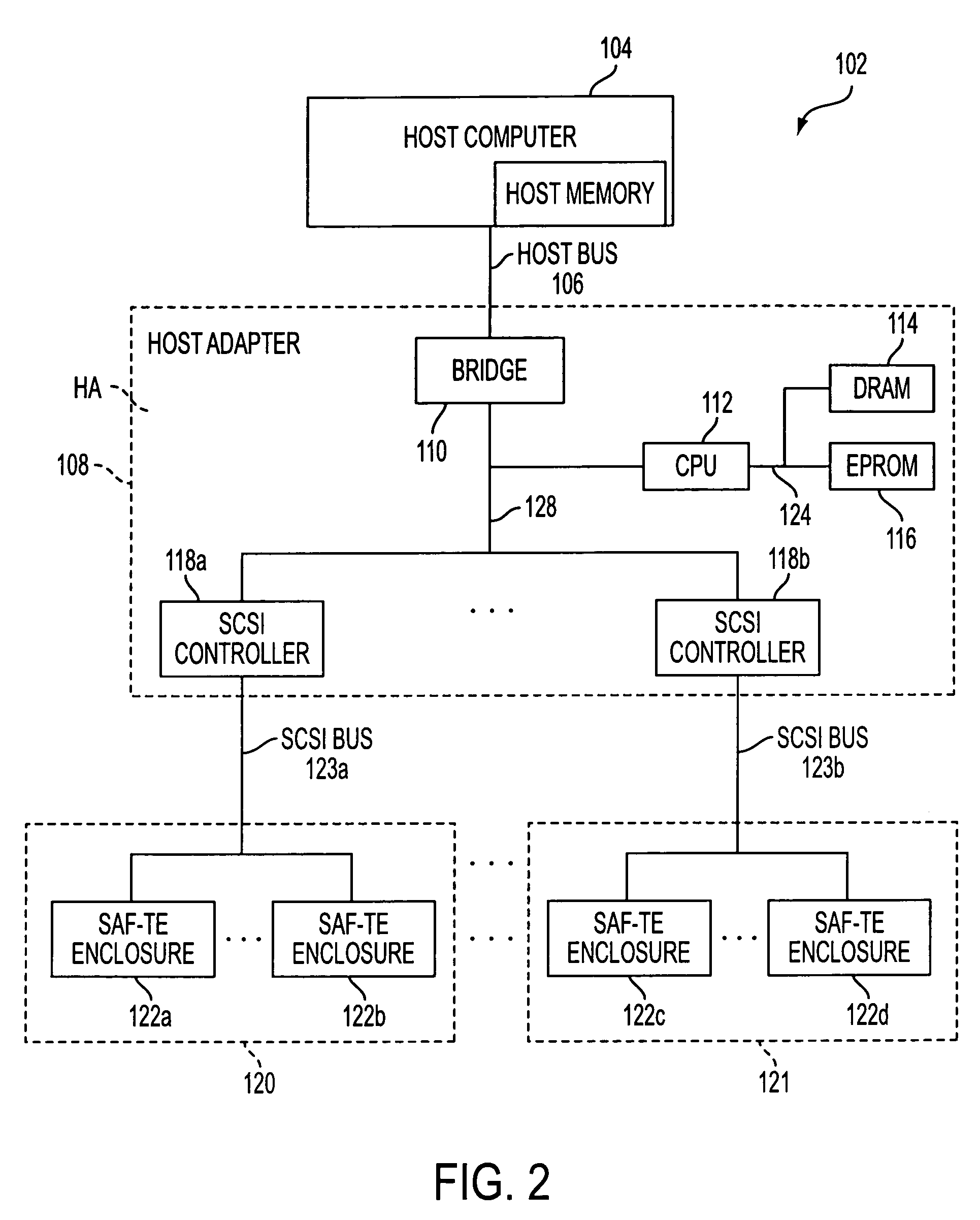

Method and structure for efficiently retrieving status for SCSI accessed fault-tolerant enclosure (SAF-TE) systems

InactiveUS7013336B1Hardware monitoringMultiple digital computer combinationsSCSITagged Command Queuing

A method for determining a change in the SAF-TE enclosure status and a change in the SAF-TE device slot status, each with a single issuance of one new command, replacing countless re-issuance of similar commands. Use is made of a common disconnection / reconnection capability as well as a tagged command queuing technique, such that multiple types of status changes in a SAF-TE enclosure are concurrently determined. Since each of the new commands described here is initiated by the host adapter, the host adapter is prepared for receiving asynchronously a changed status from the reconnecting target device such as a SEP whenever it becomes available, without resorting to use of a complex SCSI protocol known as “asynchronous event notification.” Status fields in the data packets transferred by the commands introduced in this invention may be the same as those in conventional systems, and so the inventive commands are a natural extension to conventional systems and may be adapted while maintaining compatibility with existing hardware and protocols. Removes stringent SEP response time requirements and causes negligible host system performance impact independent of how many SAF-TE enclosures are attached to the host adapter. Provides for use of an optional convenience timer for the SAF-TE Processor (SEP) device to check in with its current status before a status change occurs. Maintains backward compatibility by detection of an absence of the “tagged command queuing” indicator in inquiry data from the SEP device with implementations that do not support the inventive commands. Computer software and firmware implementations are provided.

Owner:TWITTER INC

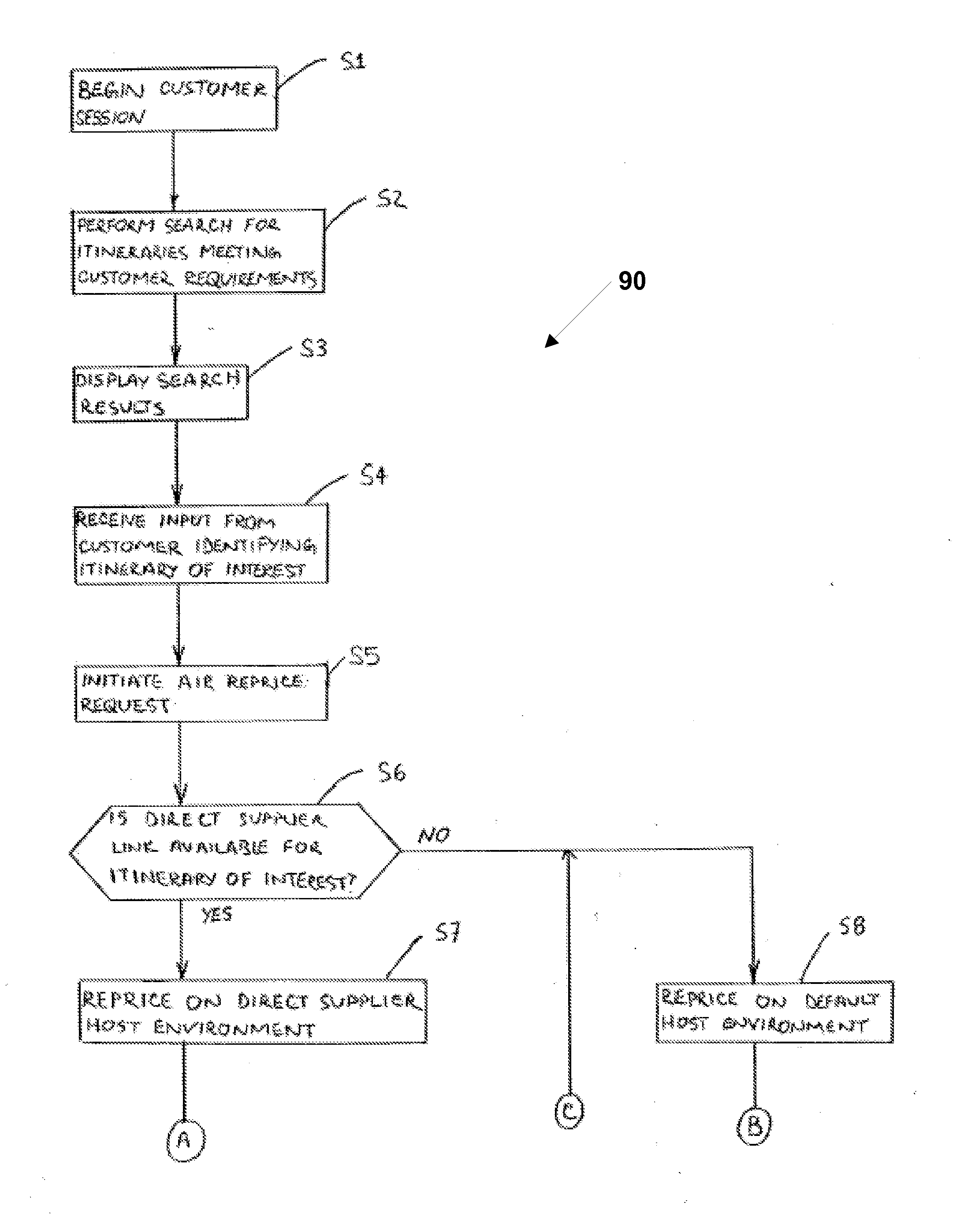

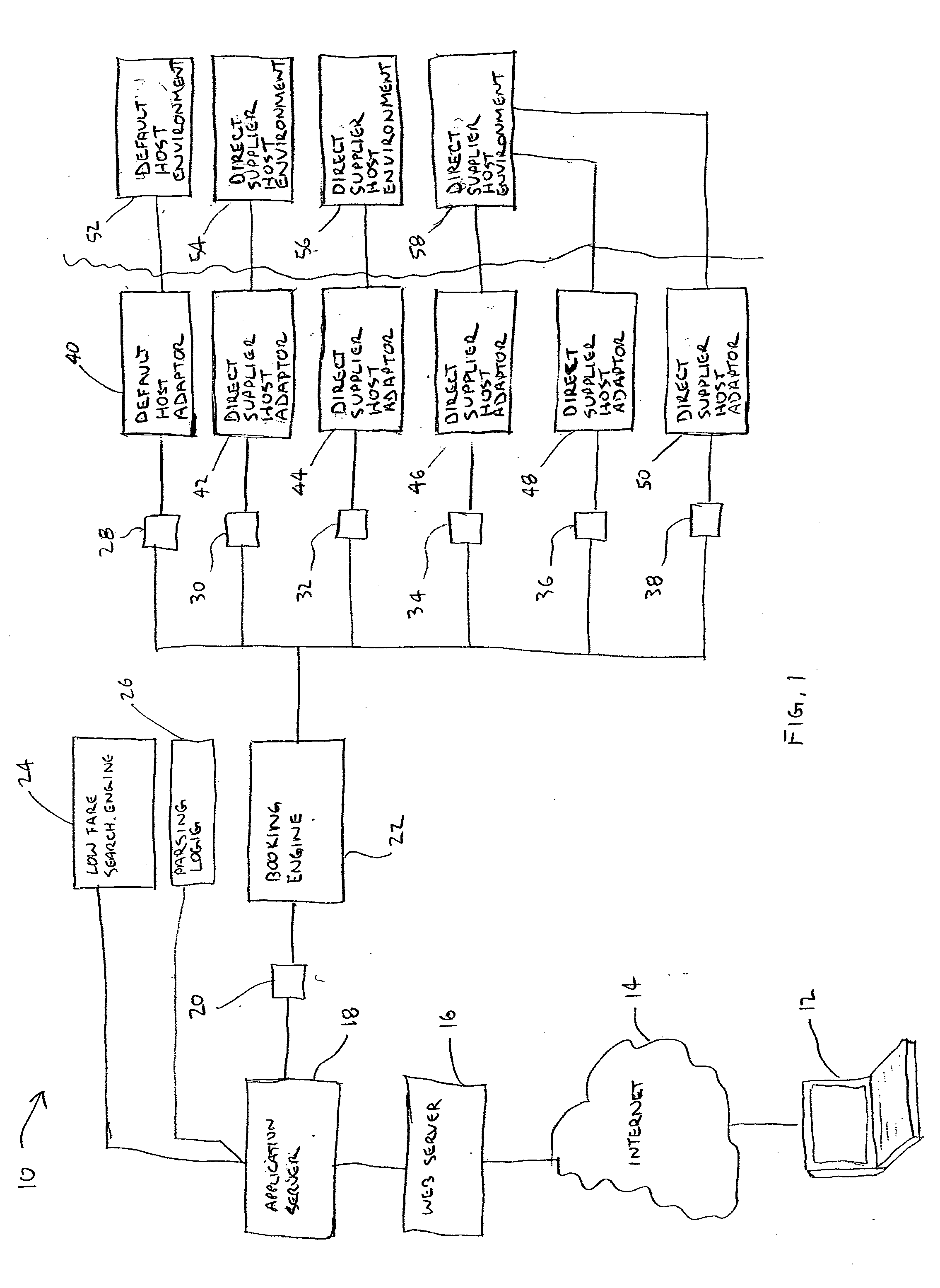

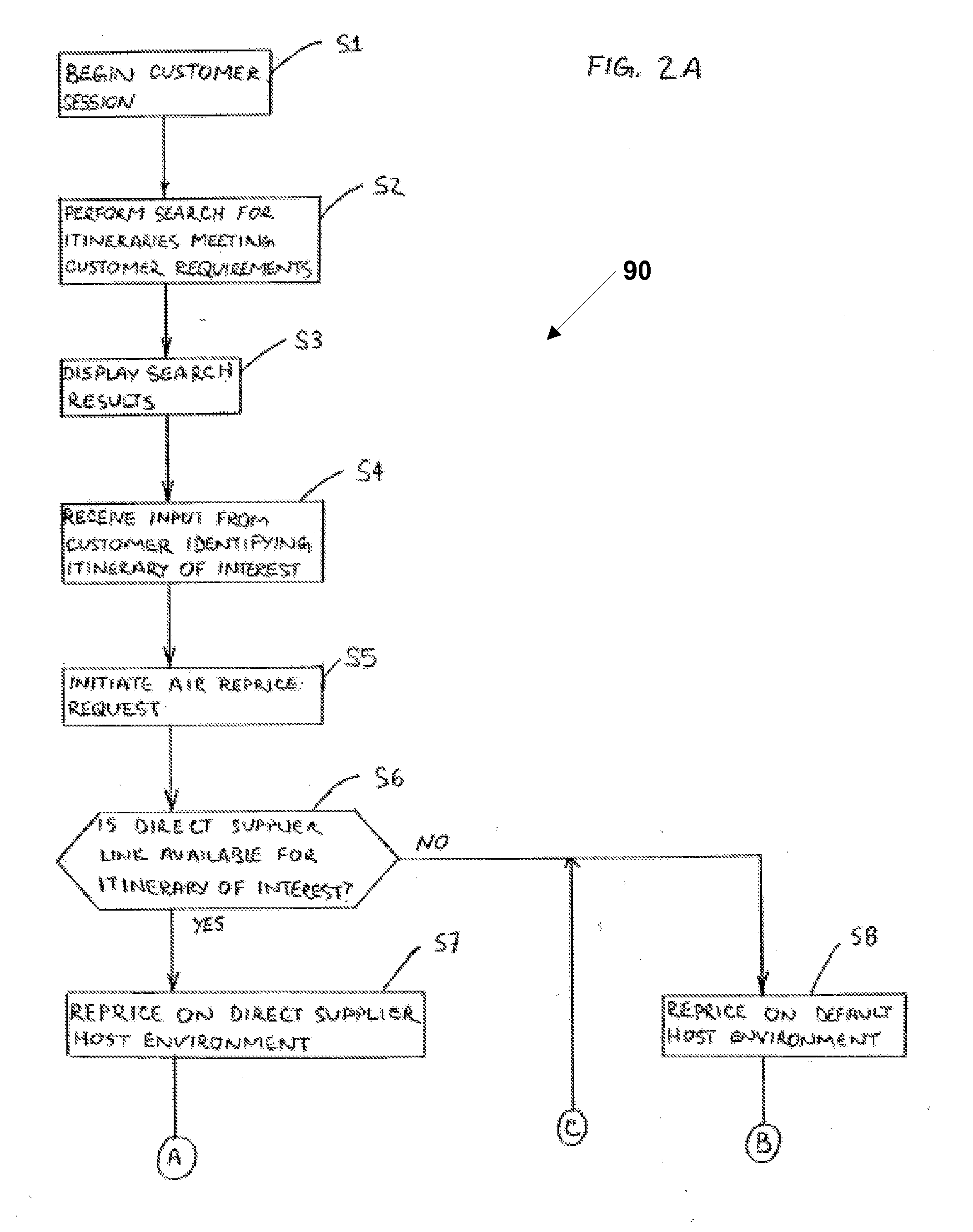

Booking engine for booking airline tickets on multiple host environments

A system and method of booking an itinerary on at least one of a multiplicity of host environments include a plurality of host adaptor modules. Each host adaptor module is configured to interact with one of the plurality of host ticketing environments. A booking engine is provided for receiving commands related to booking the air travel itinerary and determining an appropriate host ticketing environment for processing the commands based on a number of predefined criteria. When the booking engine receives a command it forwards the command to a first host adaptor module which is associated with first host ticketing environment selected by the booking engine for processing the command. The host adaptor module receives the command and issues the command to said first host ticketing environment. The first host adaptor module in turn receives a response from the first host ticketing environment and determines whether the response comports with an expected response. If the response does not comport with the expected response, the booking engine identifies a second appropriate host environment for processing the command and forwards the command to a second host adaptor module associated with the second host ticketing environment. The second host adaptor module then issues the command to the second host ticketing environment.

Owner:ORBITZ

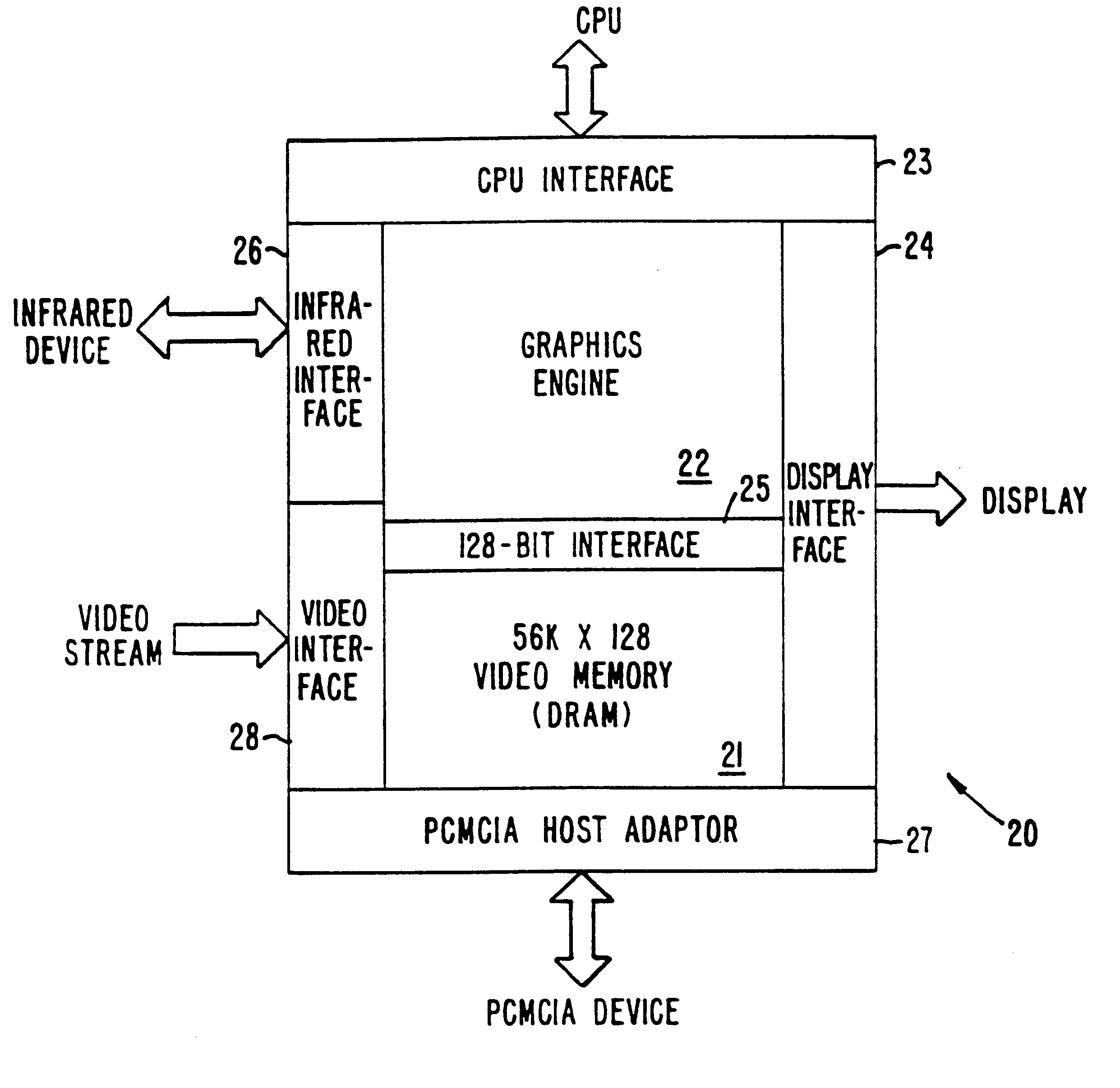

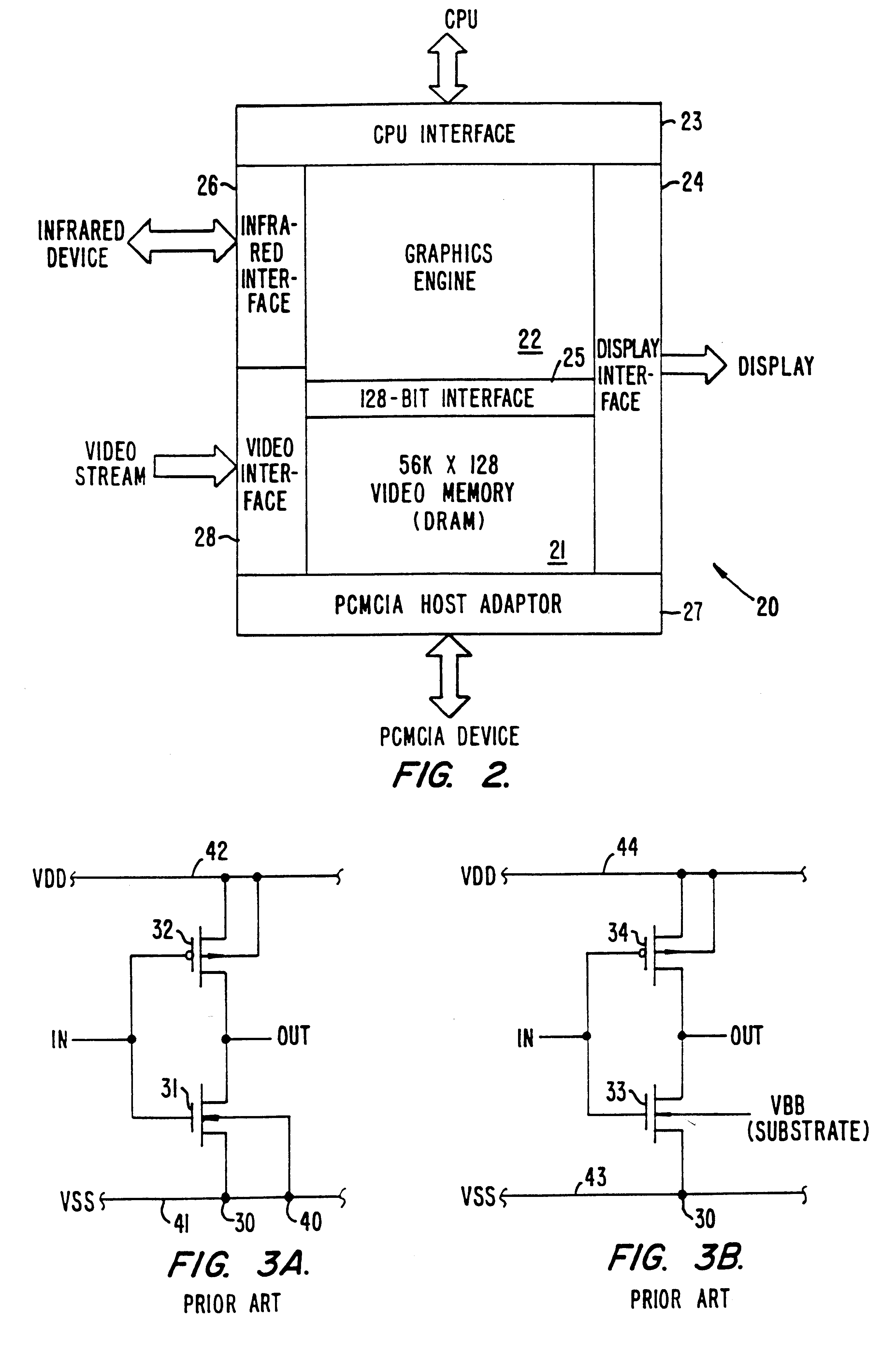

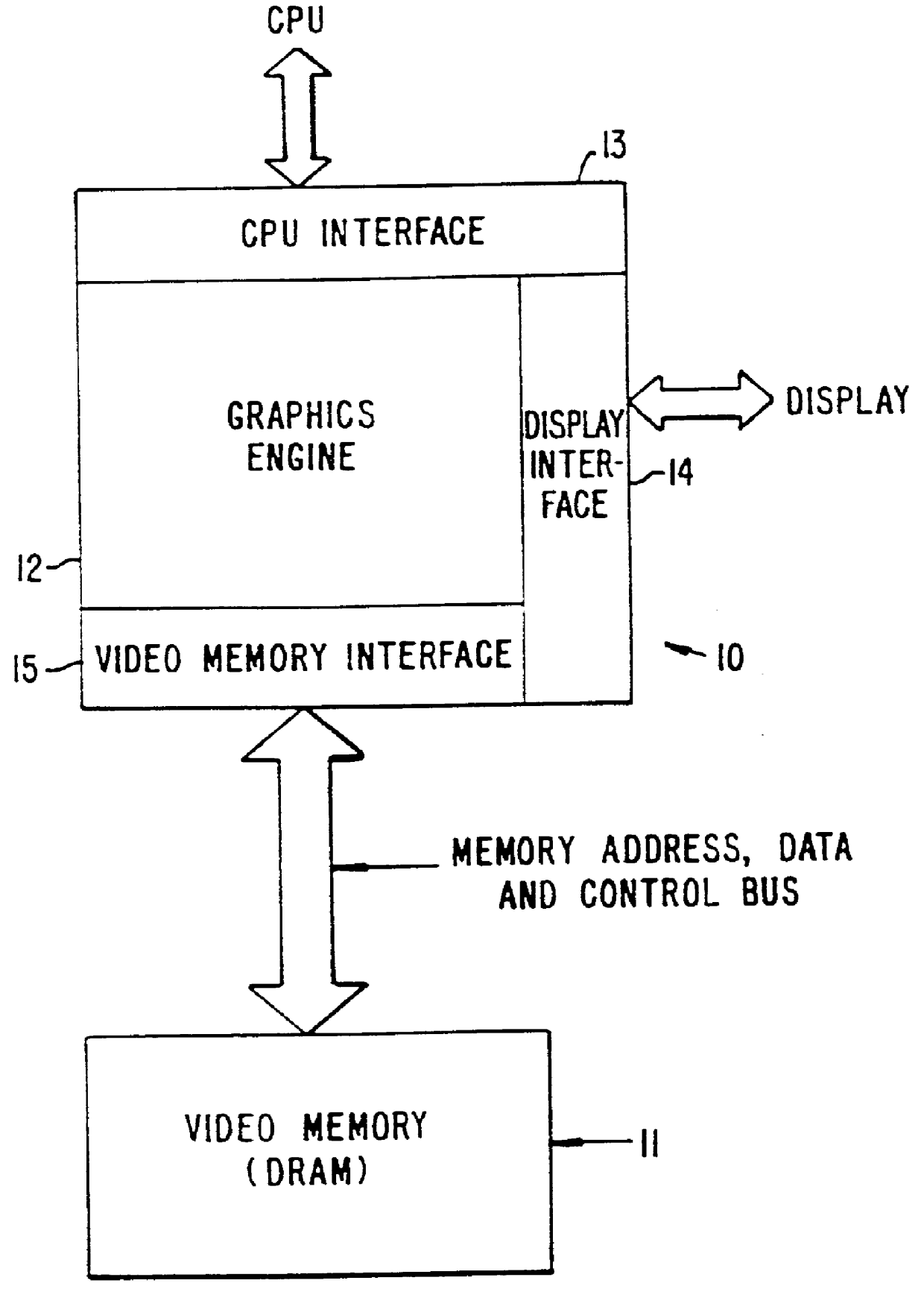

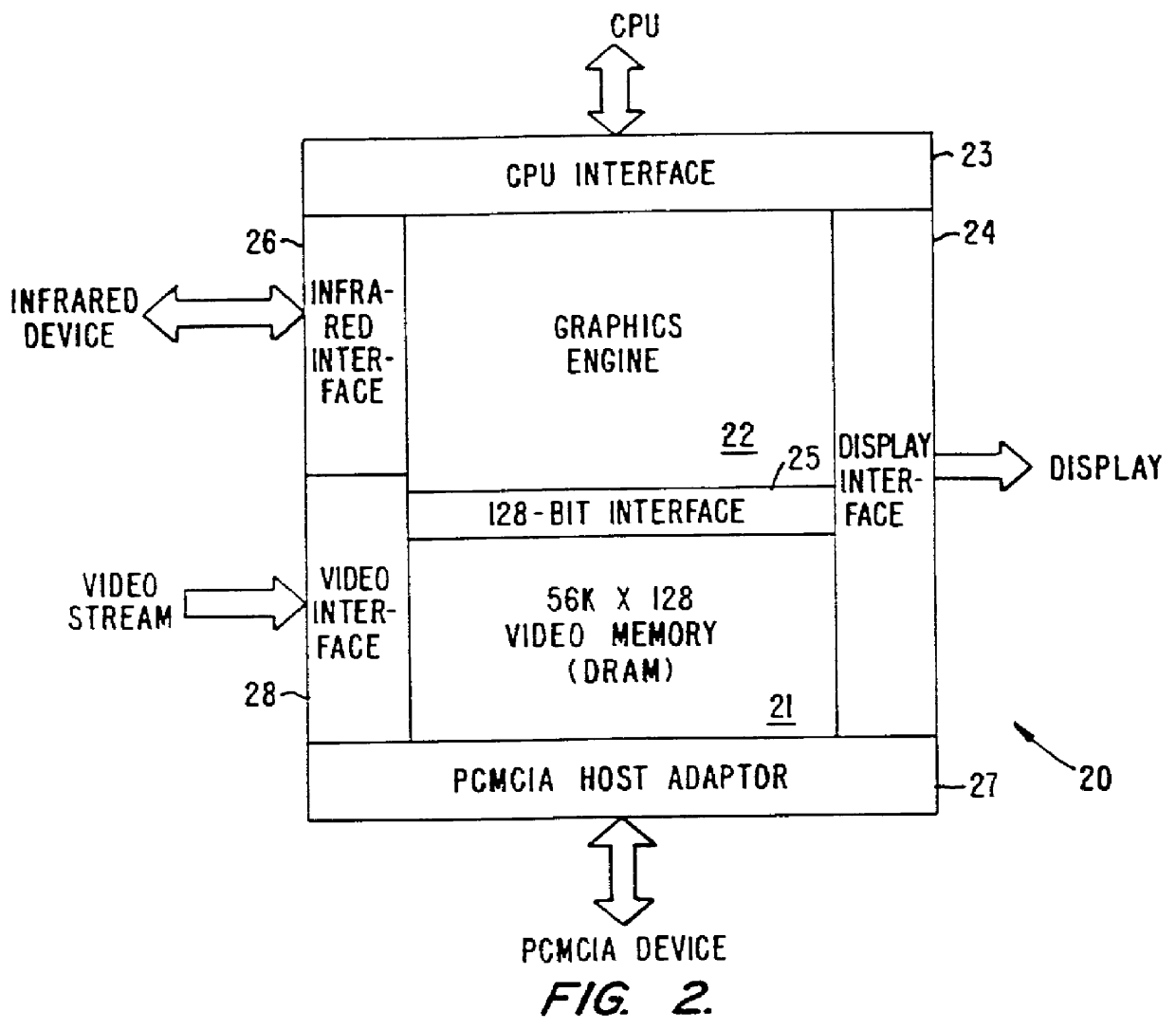

Graphics controller integrated circuit without memory interface

InactiveUS6356497B1Input/output to record carriersCathode-ray tube indicatorsVideo memoryInternal memory

A CMOS integrated circuit that comprises a graphics controller system that consists of a graphics engine and video memory together with some interface blocks, a PCMCIA host adapter, an infrared interface for generating video images on a LCD or CRT display unit, and a video stream interface for receiving video signals. Since the video memory is integrated on the same integrated circuit as the graphics controller, no package pins are required for the memory interface. The pins thus saved are used to provide access to an on-chip PCMCIA host adapter. The internal memory interface is 128 bits wide. Simultaneous performance improvement and power dissipation reduction is achieved because of the wide memory interface and the elimination of the large parasitic capacitances associated with a package pin connection.

Owner:INTELLECTUAL VENTURES I LLC

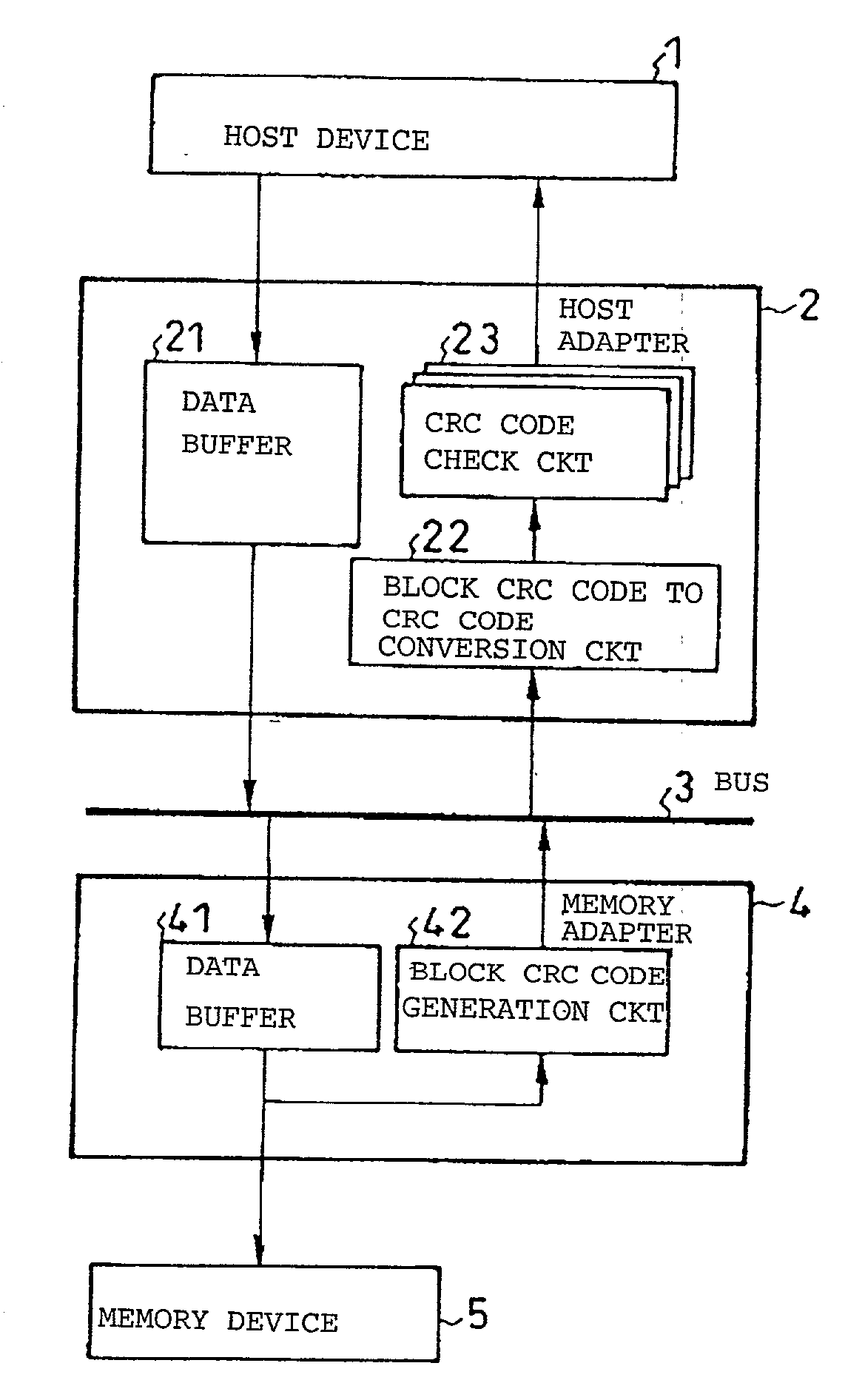

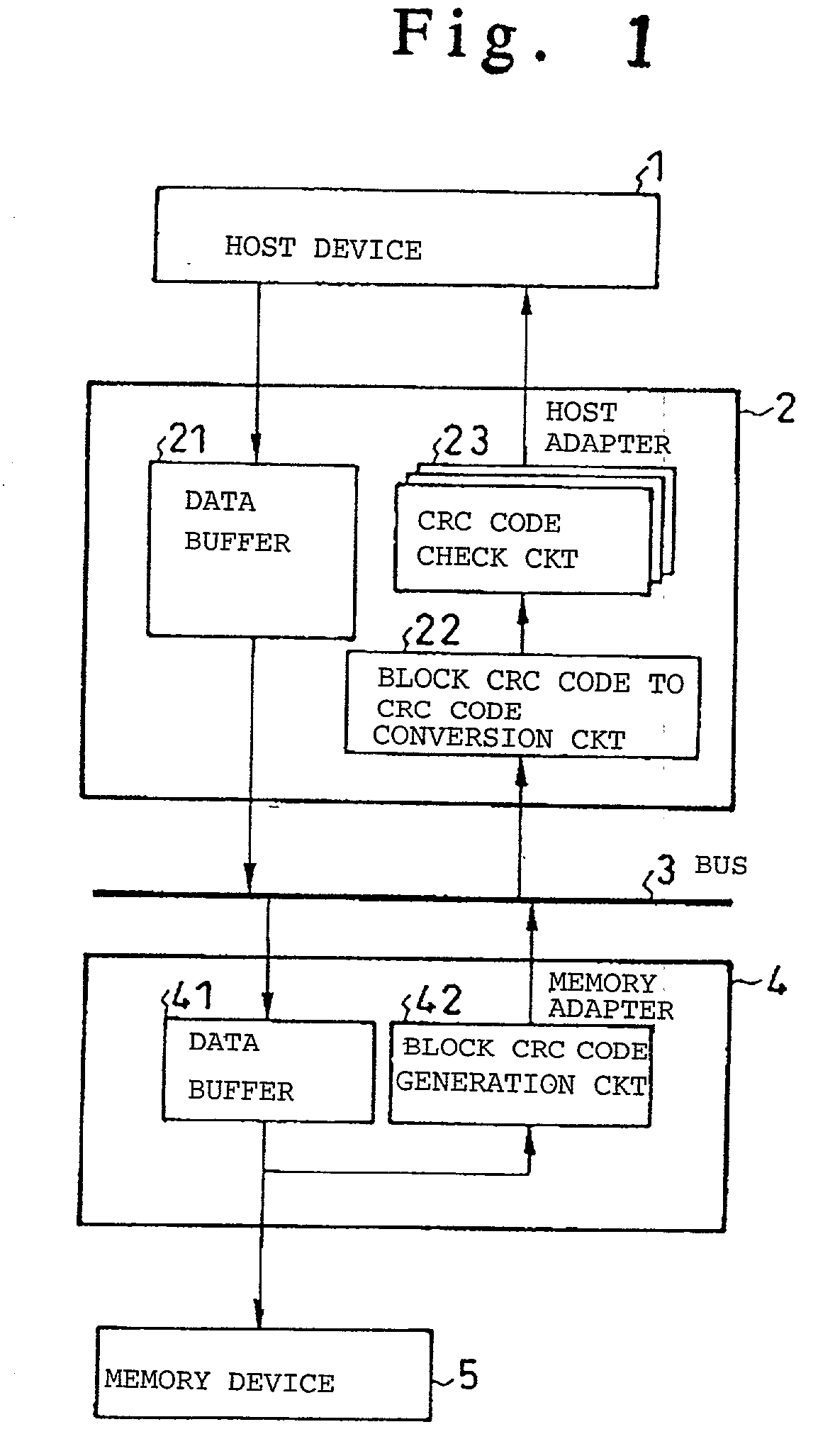

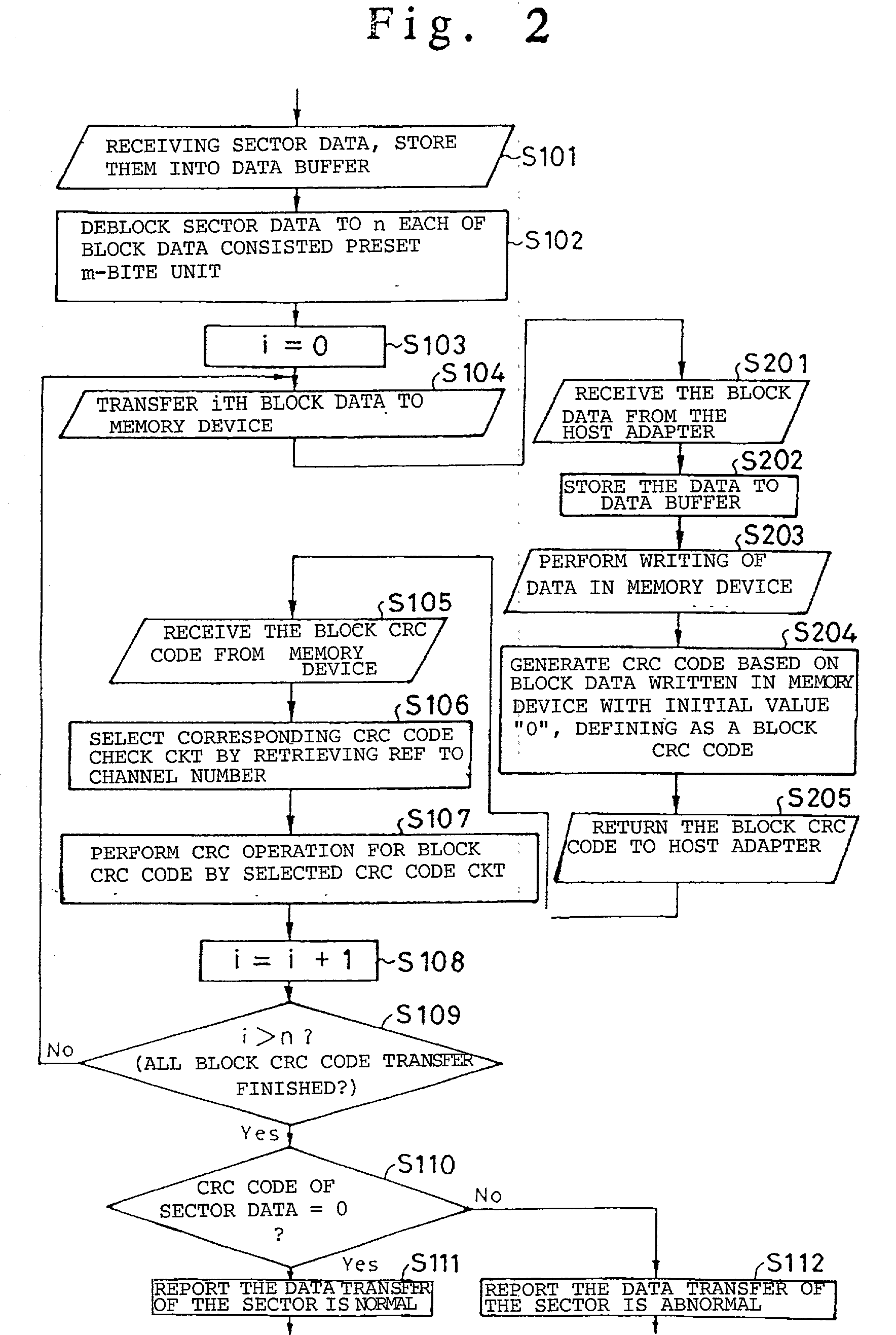

Data transfer system

A device is disclosed that allows a host device that is the source of data transfer to detect whether or not data have been correctly written to a memory device without interfering with the effective data transfer. When the host device issues a request to write sector data, a host adapter deblocks the sector data into data blocks and transfers the data in data block units to a memory adapter. The memory adapter not only memory-writes the data blocks to a memory device, but also generates block CRC code from the data blocks and returns the code as a write reply to the host adapter. The host adapter receives the block CRC code, carries out a CRC operation to reconstruct CRC code of complete sector data, performs a correspondence check with the CRC code of the original sector data, and reports the check results to the host device.

Owner:NEC CORP

Graphics controller integrated circuit without memory interface pins and associated power dissipation

InactiveUS6041010AInput/output to record carriersCathode-ray tube indicatorsInternal memoryVideo memory

A CMOS integrated circuit that comprises a graphics controller system that consists of a graphics engine and video memory together with some interface blocks, a PCMCIA host adapter, an infrared interface for generating video images on a LCD or CRT display unit, and a video stream interface for receiving video signals. Since the video memory is integrated on the same integrated circuit as the graphics controller, no package pins are required for the memory interface. The pins thus saved are used to provide access to an on-chip PCMCIA host adapter. The internal memory interface is 128 bits wide. Simultaneous performance improvement and power dissipation reduction is achieved because of the wide memory interface and the elimination of the large parasitic capacitances associated with a package pin connection.

Owner:INTELLECTUAL VENTURES I LLC

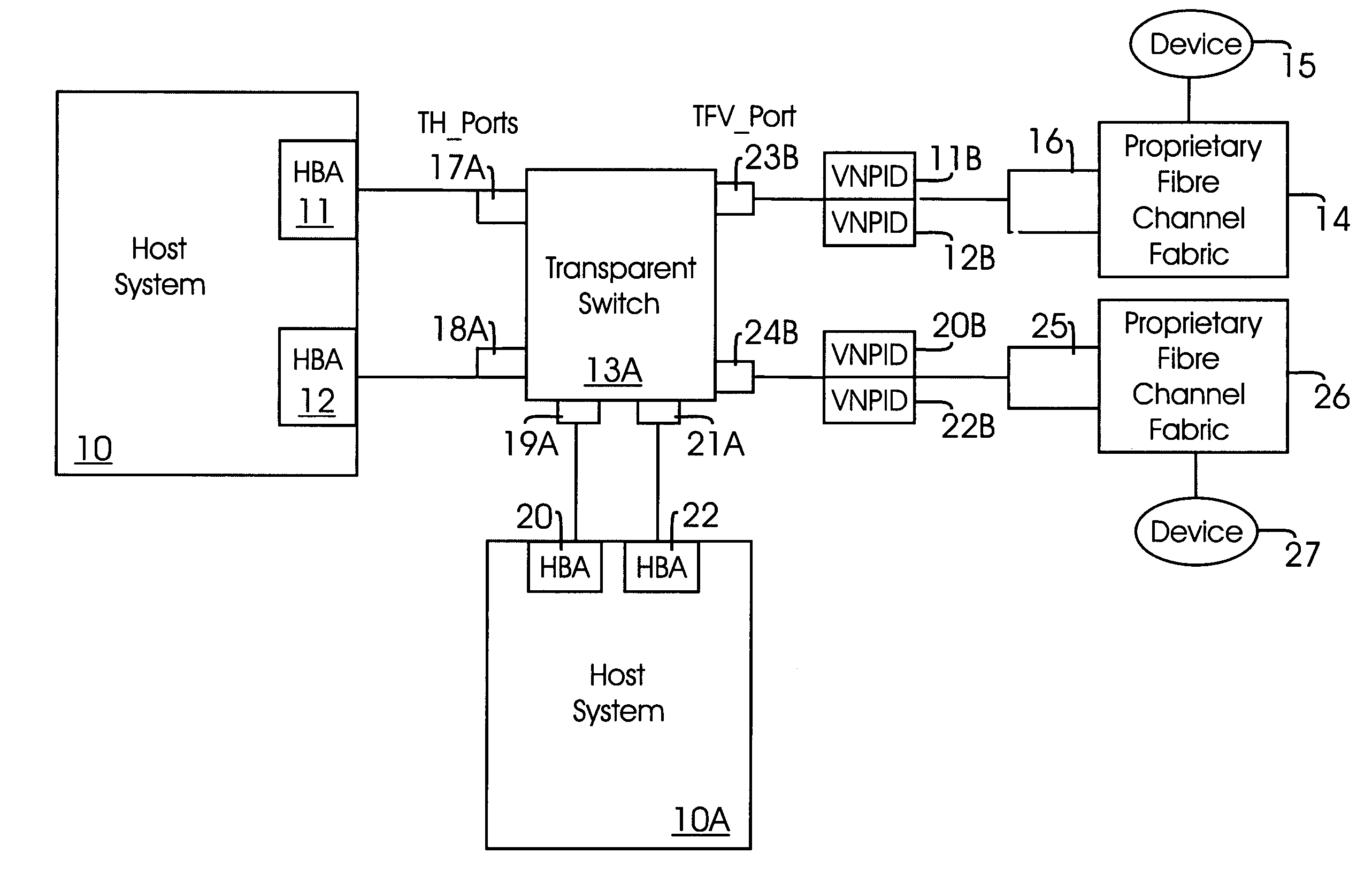

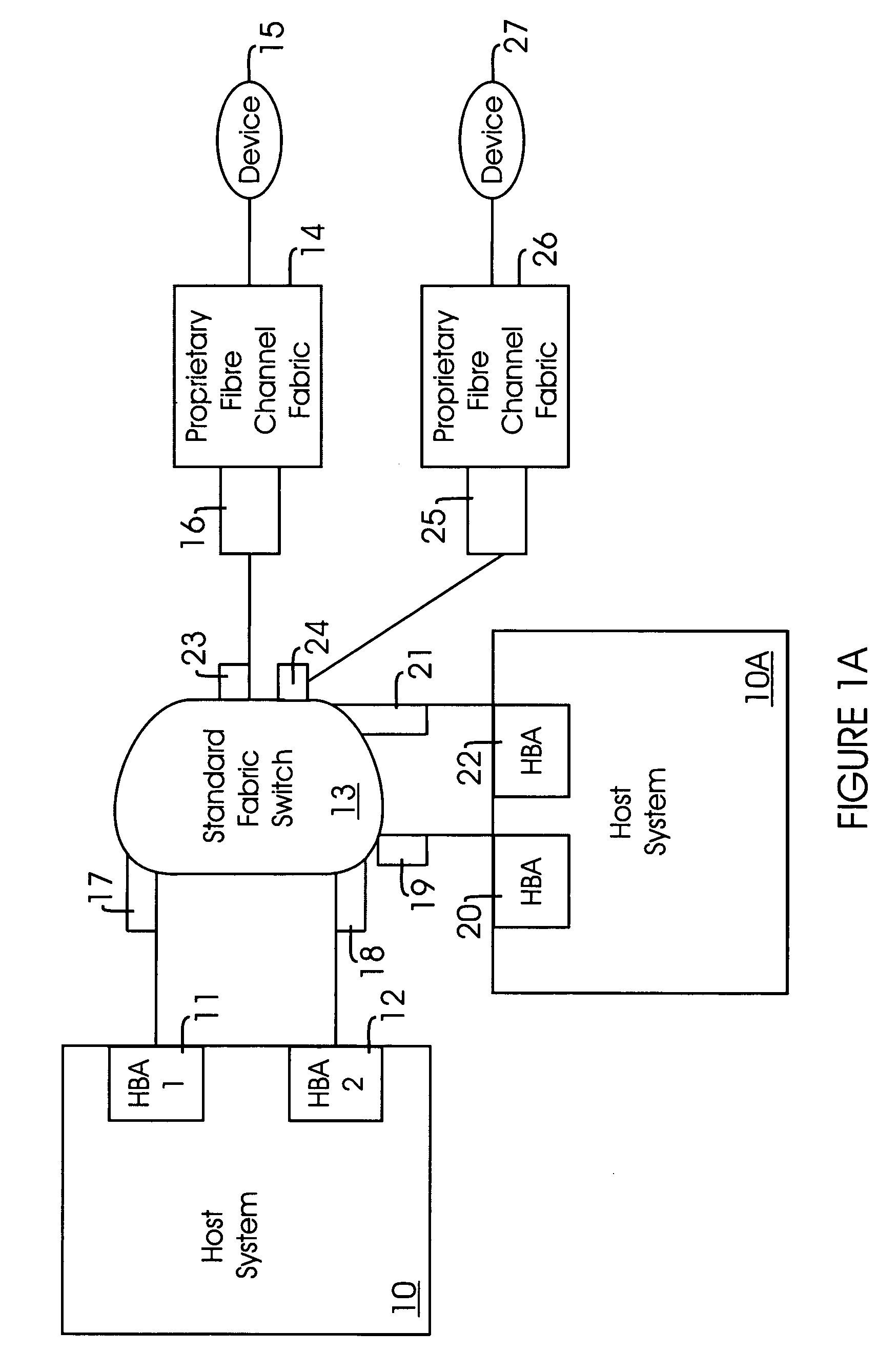

Fibre channel transparent switch for mixed switch fabrics

InactiveUS7340167B2Data switching by path configurationMultiple digital computer combinationsFiberFibre Channel switch

A method and a Fibre Channel switch element are provided that allows communication between a host system and a target device attached to a proprietary switch fabric in a network. The Fibre Channel switch element includes a first port that communicates with the target device through the proprietary switch fabric by logging on behalf of the host system so that the proprietary switch behaves as if it was directly communicating with the host system; and a second port that communicates with the host system and collects host bus adapter (“HBA”) identification information, wherein the HBA identification information is used to map the first port to the second port so that when the host system communicates with the target device the Fibre Channel switch element is transparent to the proprietary switch fabric.

Owner:MARVELL ASIA PTE LTD

Optical transceiver and host adapter with memory mapped monitoring circuitry

A host adaptor is configured to monitor operation of an optoelectronic transceiver. The host adapter includes a transceiver interface, memory, comparison logic and a host interface. The transceiver interface receives from the optoelectronic transceiver digital values corresponding to operating conditions of the optoelectronic transceiver. The memory includes one or more memory arrays for storing information related to the optoelectronic transceiver, including the digital values received from the optoelectronic transceiver. The comparison logic is configured to compare the digital values with limit values to generate flag values, wherein the flag values are stored in predefined flag storage locations within the memory during operation of the optoelectronic transceiver. The host interface enables a host device to read from host specified locations within the memory, including the predefined flag storage locations, in accordance with commands received from the host device.

Owner:II VI DELAWARE INC

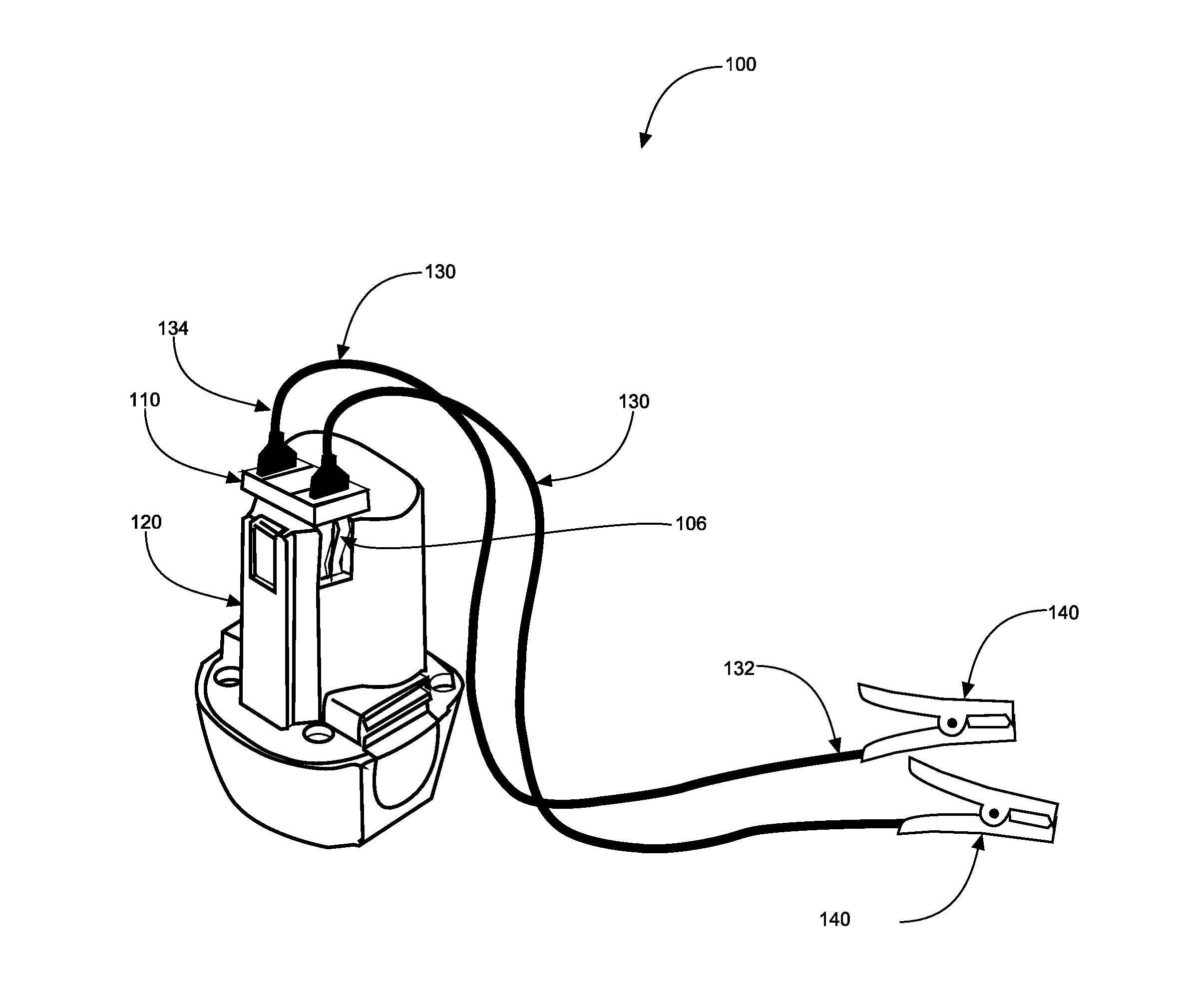

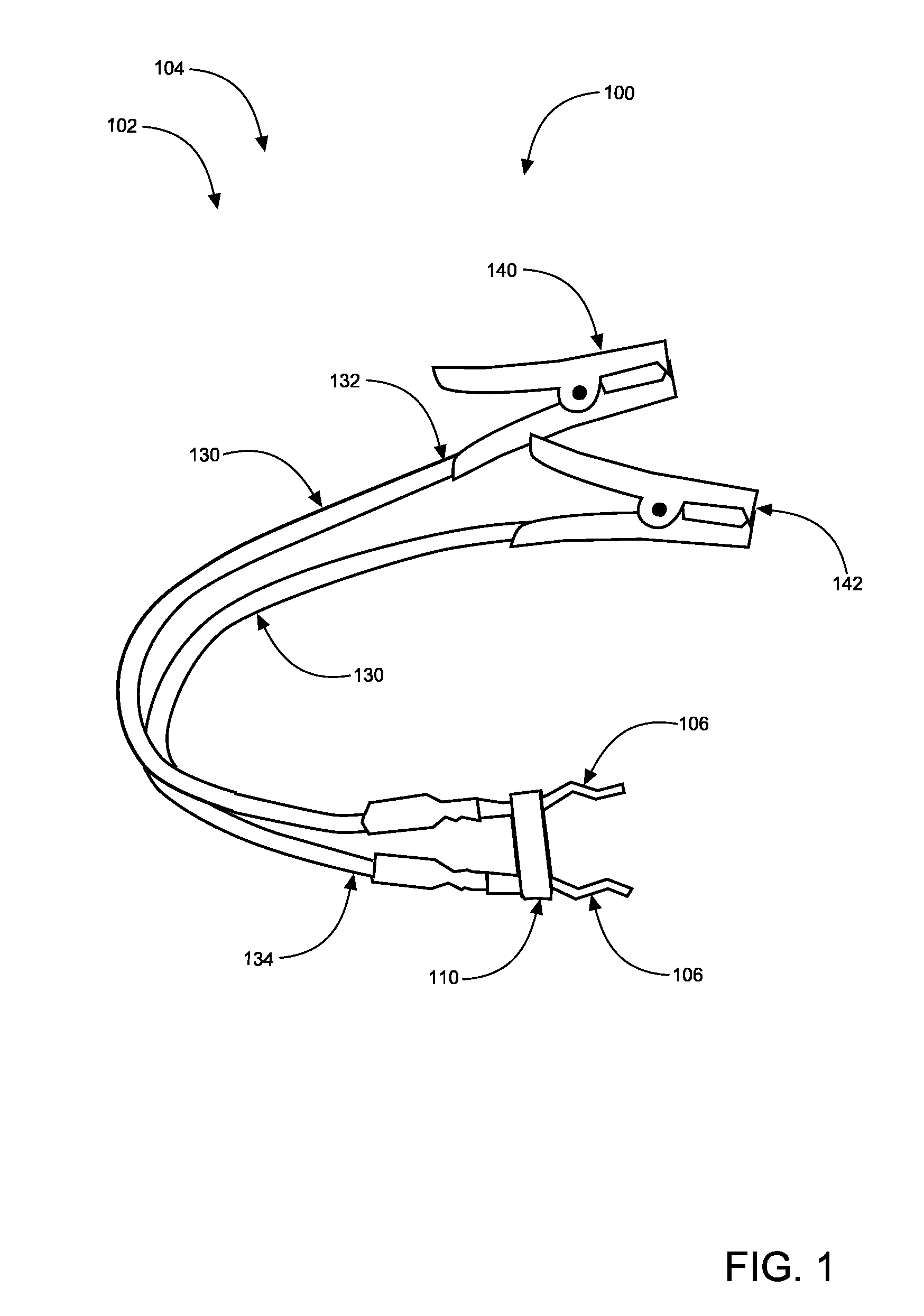

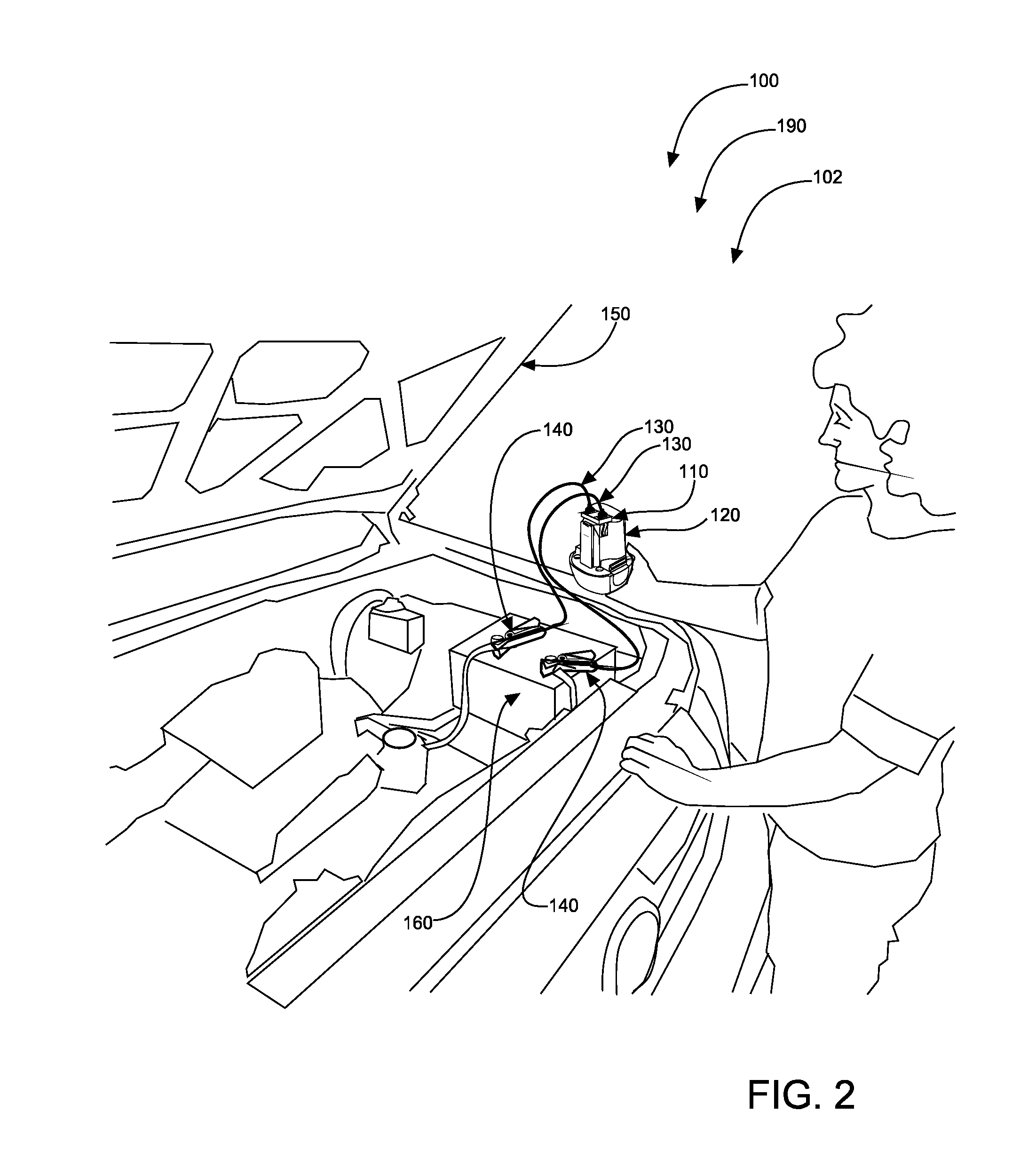

Jump start adapter

InactiveUS20120091944A1Low costEasily discriminatedBatteries circuit arrangementsElectric devicesElectrical batteryRechargeable cell

An apparatus for providing a low cost, quick, and convenient automobile jump starting system and method. The jump start system comprises an adapter suitable to receive at least one hand held power tool battery. The adapter in certain embodiments comprises conductive metallic spring clips for making electrical connection(s) between the tool battery and the adapter. The adapter further comprises a plurality of connectible gauge wires (serving as booster cables) each having biasing connectors (alligator clips). The distal ends of the gauge wire(s) may be removably connectible to the adapter or may be rigidly fixed to the adapter. The Jump Start Adapter System may also be removably connected to the vehicle battery using biasing connectors or may be hard wired to the vehicle electrical system eliminating the need for biasing connectors. The proximate end(s) of the connectible gauge wire(s) comprise the biasing connectors for making connection to the dead battery of the vehicle when using a free-standing jump start adapter system. One of the connectible gauge wires is a red color-coded eight-gauge wire serving as a positive cable and the other connectible gauge wires is a black color-coded eight-gauge wire serving as a negative cable. The Jump Start Adapter system of the present invention allows individuals to jump-start various types of vehicle engines using a rechargeable battery from a power tool battery.

Owner:ROGERS CHAD

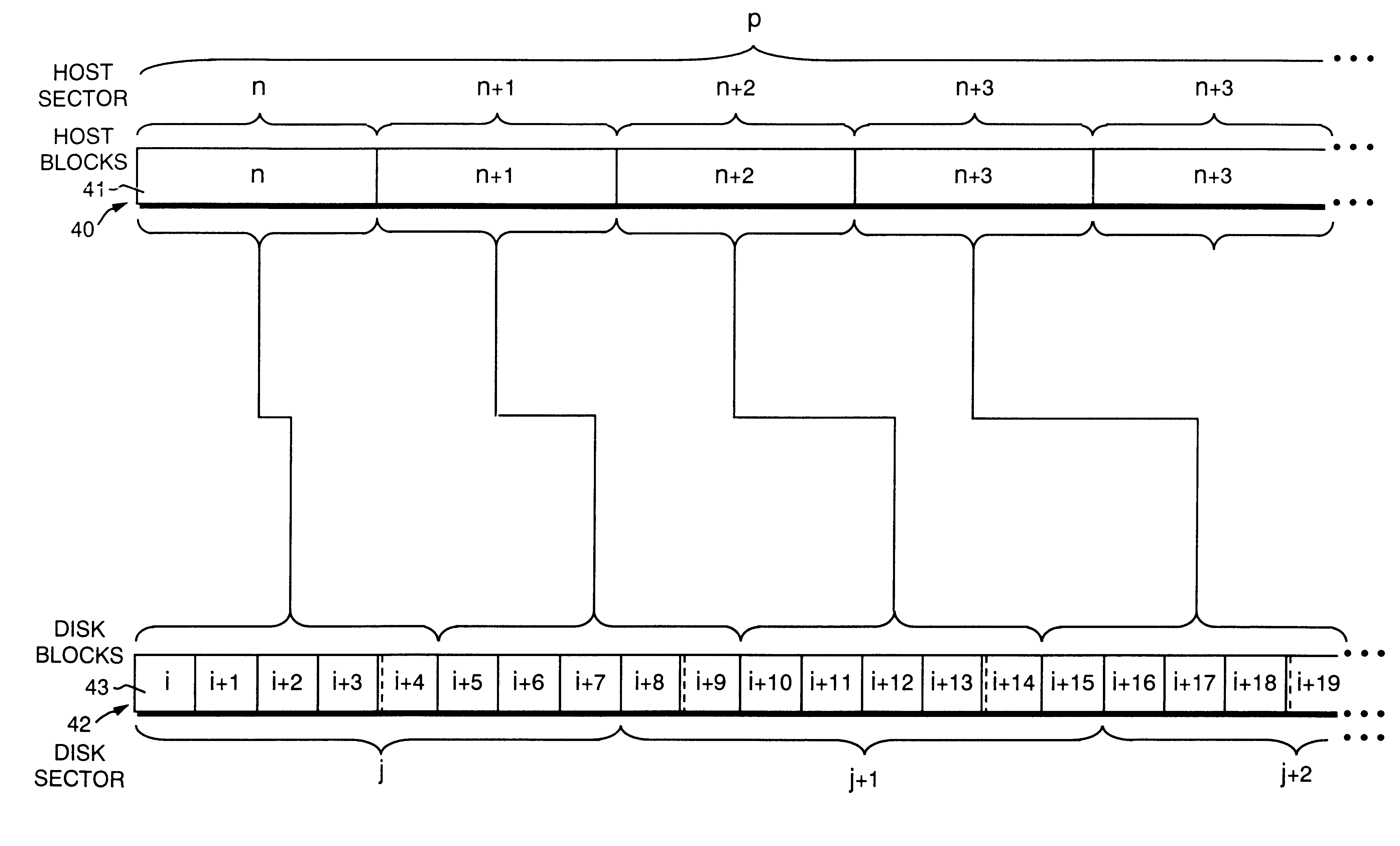

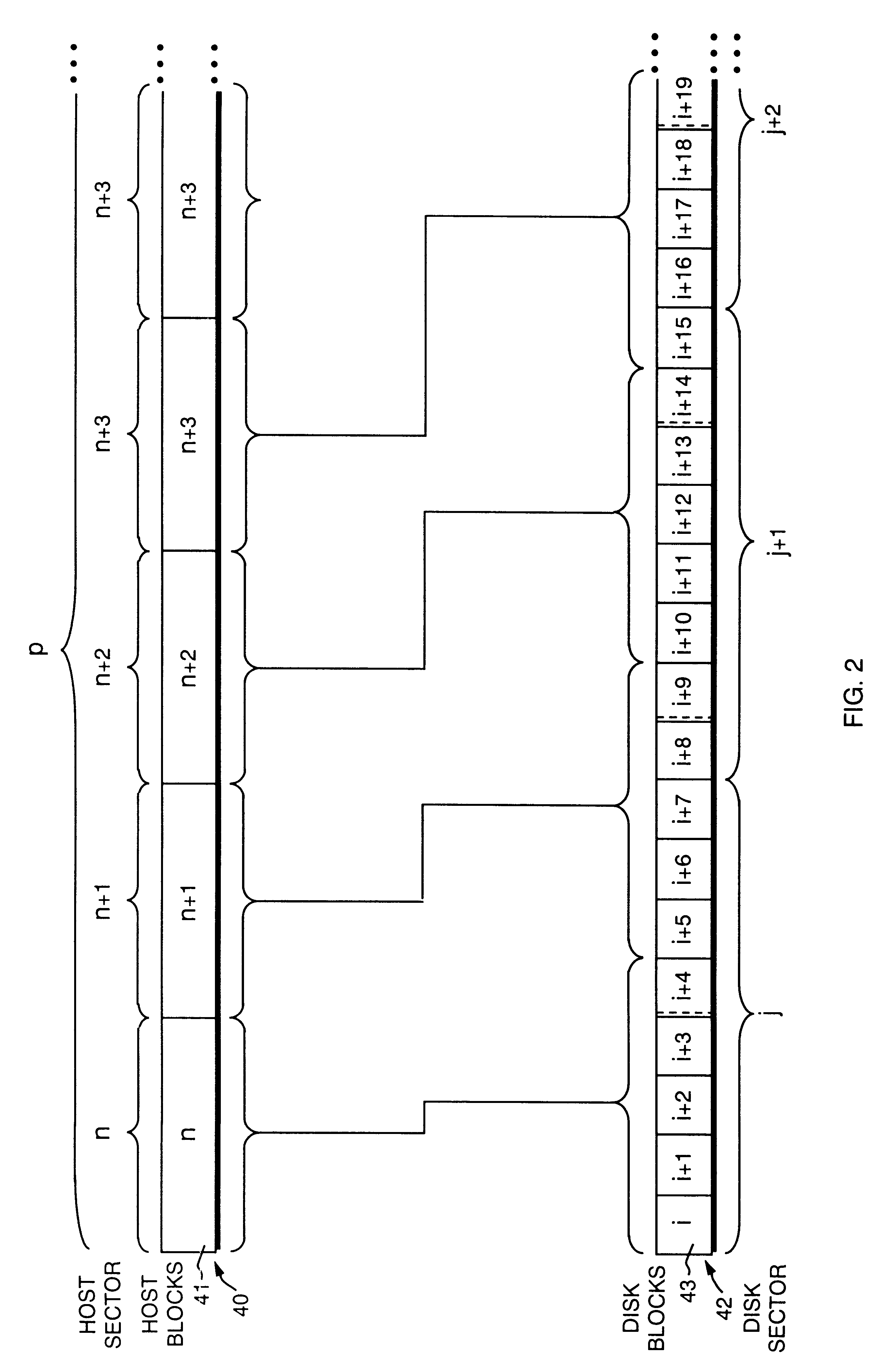

Magnetic disk storage for storing data in disk block size from fixed length of host block in non-integer multiple of the disk block size

InactiveUS6324604B1Input/output to record carriersRecord information storageMagnetic storageComputer science

A method and apparatus for enabling a magnetic disk storage device that stores data according to a first data structure characterized by a fixed-length disk block size to respond to input / output requests from a host that define data according to a different data structure characterized by a different fixed-length host block size. A host adapter transfers requests and data between the host and a cache memory in the magnetic disk storage device as host blocks. A disk adapter transfers requests and data between the cache memory and magnetic disks as disk blocks. CRC data and a sector number are appended to each host block in a set of disk blocks.

Owner:EMC IP HLDG CO LLC

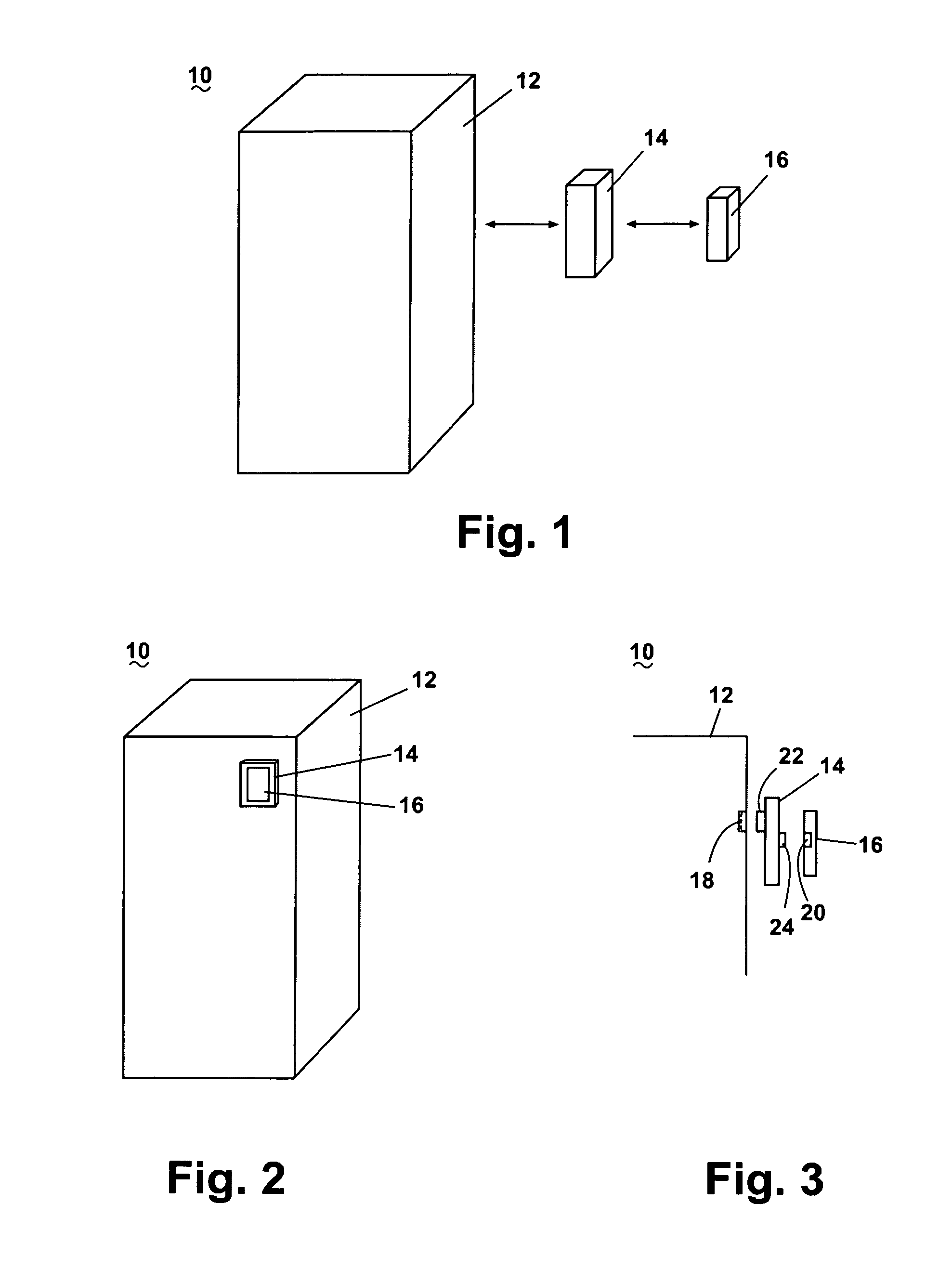

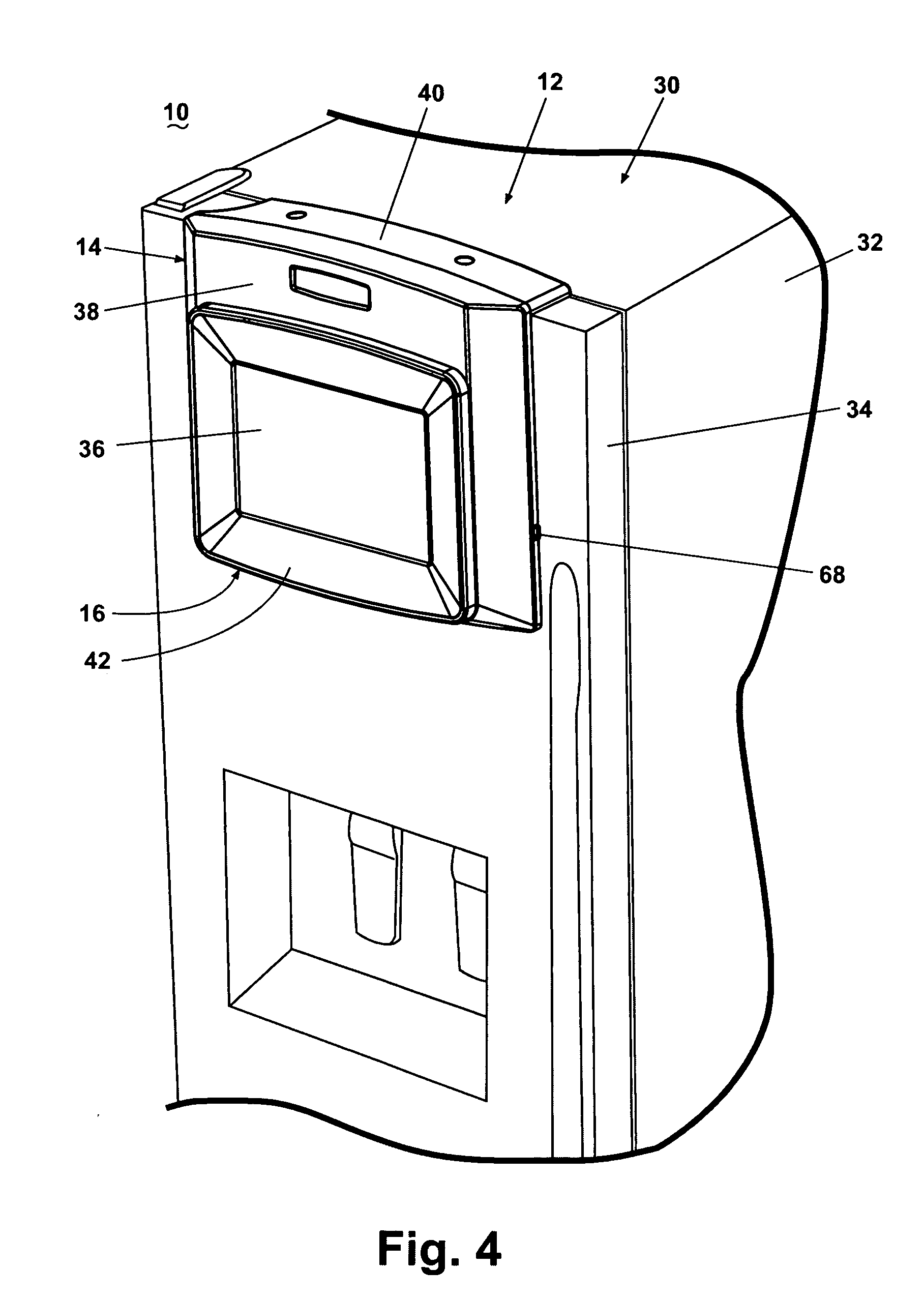

Adapter with an access panel for an electronic device

InactiveUS20080287009A1Digital data processing detailsTwo-part coupling devicesEmbedded systemElectronic equipment

An adapter for removably coupling an electronic device to a host and a modular system of the host, adapter and electronic device. The adapter comprises a main body, a first interface capable of coupling with the appliance, a cavity in the main body receiving the electronic device, a second interface within the cavity coupling with the electronic device; and an access panel removably mounted to the main body to selectively close the opening of the cavity.

Owner:WHIRLPOOL CORP

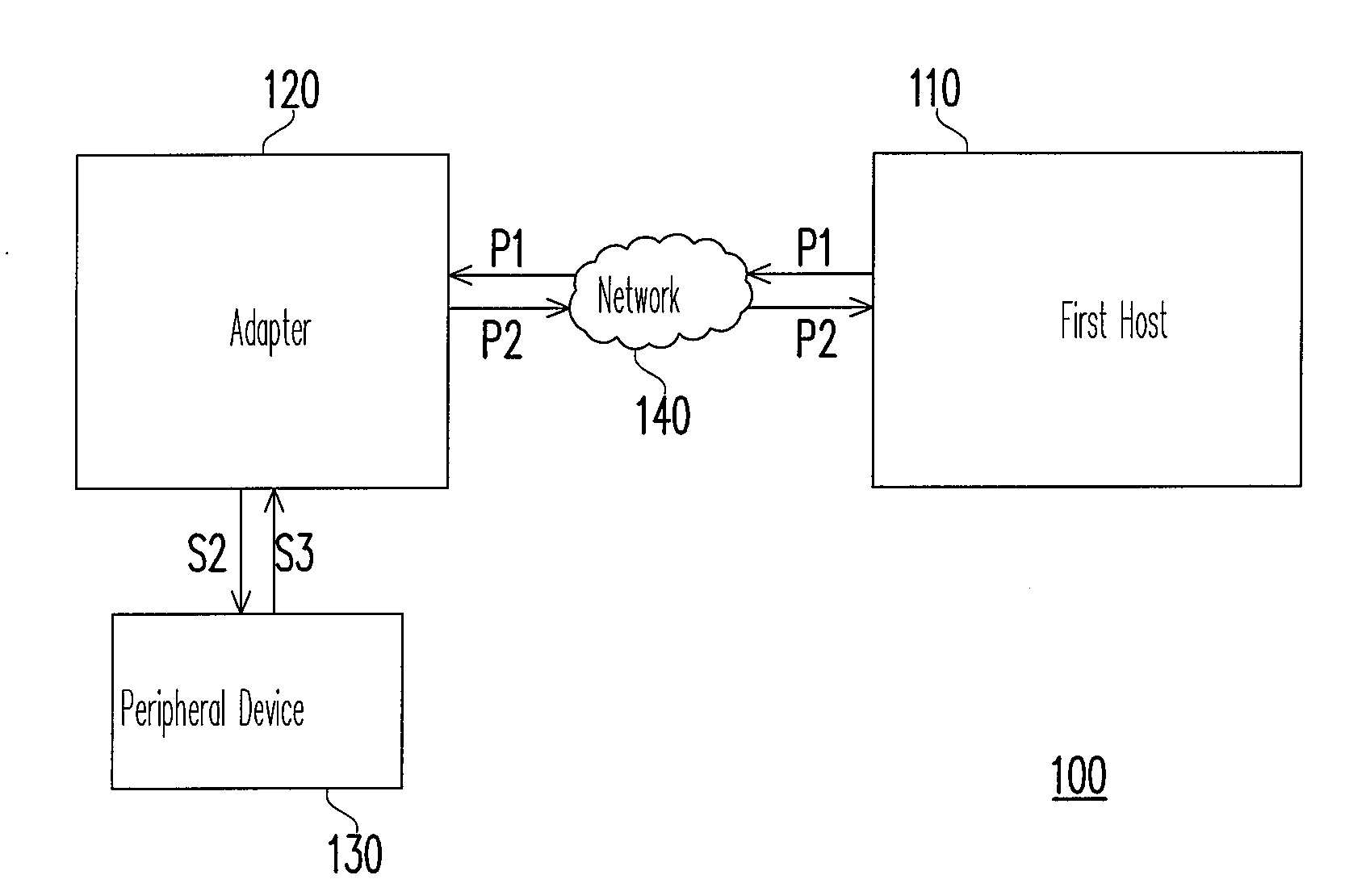

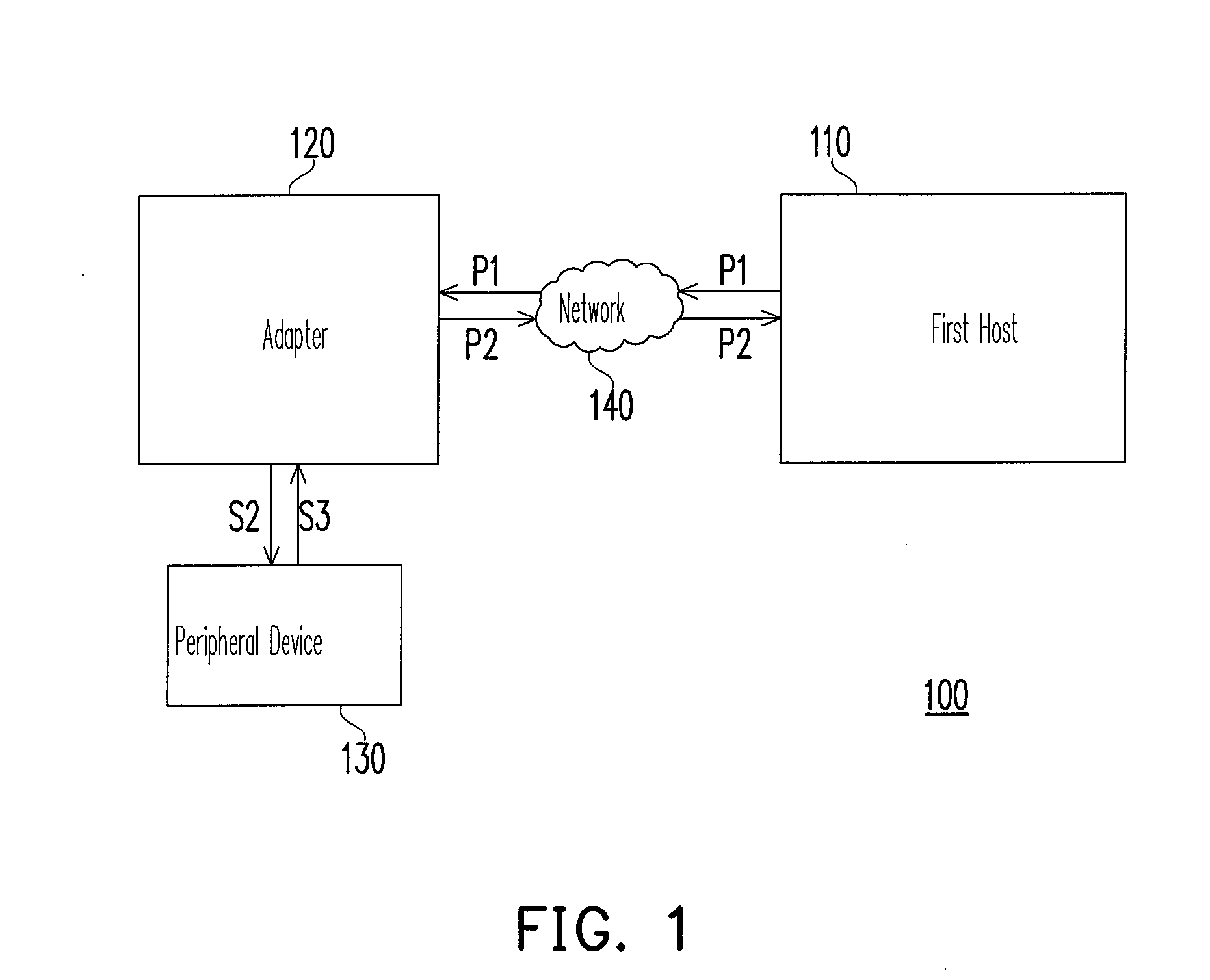

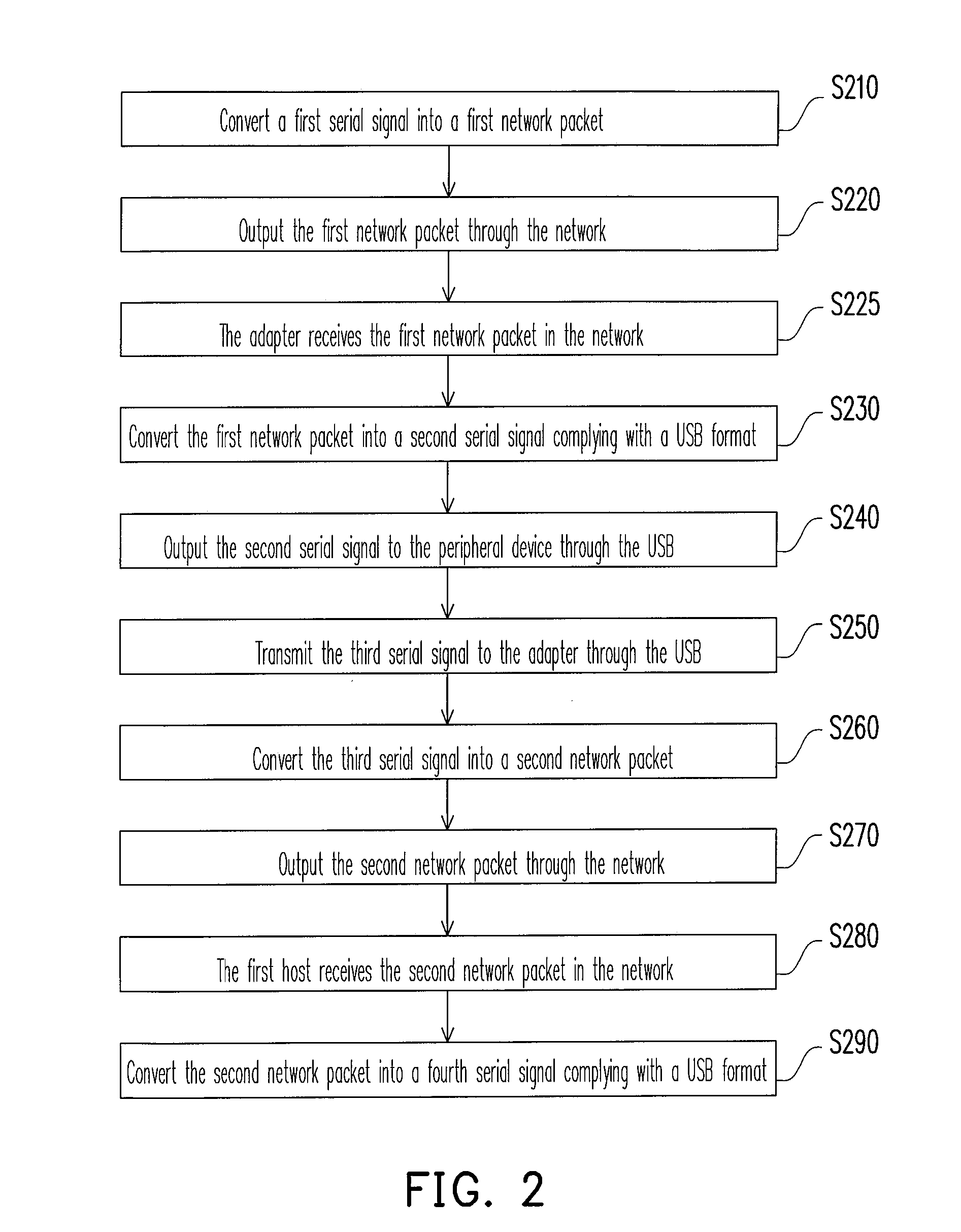

Remote control system and method thereof

InactiveUS20080282011A1Easy to useFirmly connectedElectric digital data processingNetwork packetRemote control

A remote control system and a method thereof are provided. The remote control system includes a first host, an adapter, and a peripheral device. The first host converts a first serial signal into a first network packet, and then outputs the first network packet through a network. The adapter is connected to the network to receive the first network packet, and then converts the first network packet into a second serial signal complying with a universal serial bus (USB) format. The peripheral device is coupled to the adapter through the USB, and receives the second serial signal, so that the user can control the peripheral device at a remote site through the network.

Owner:ARCADYAN

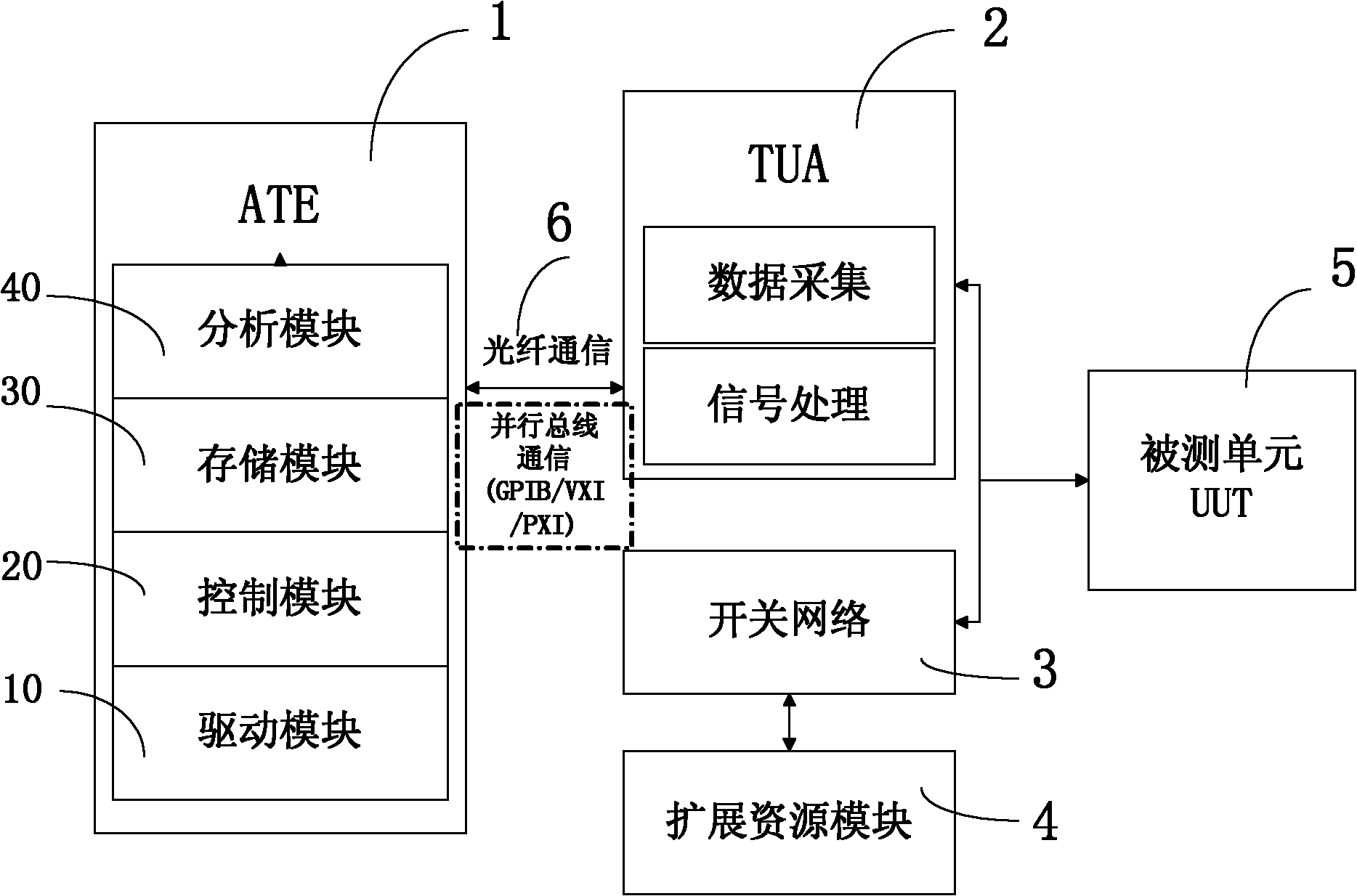

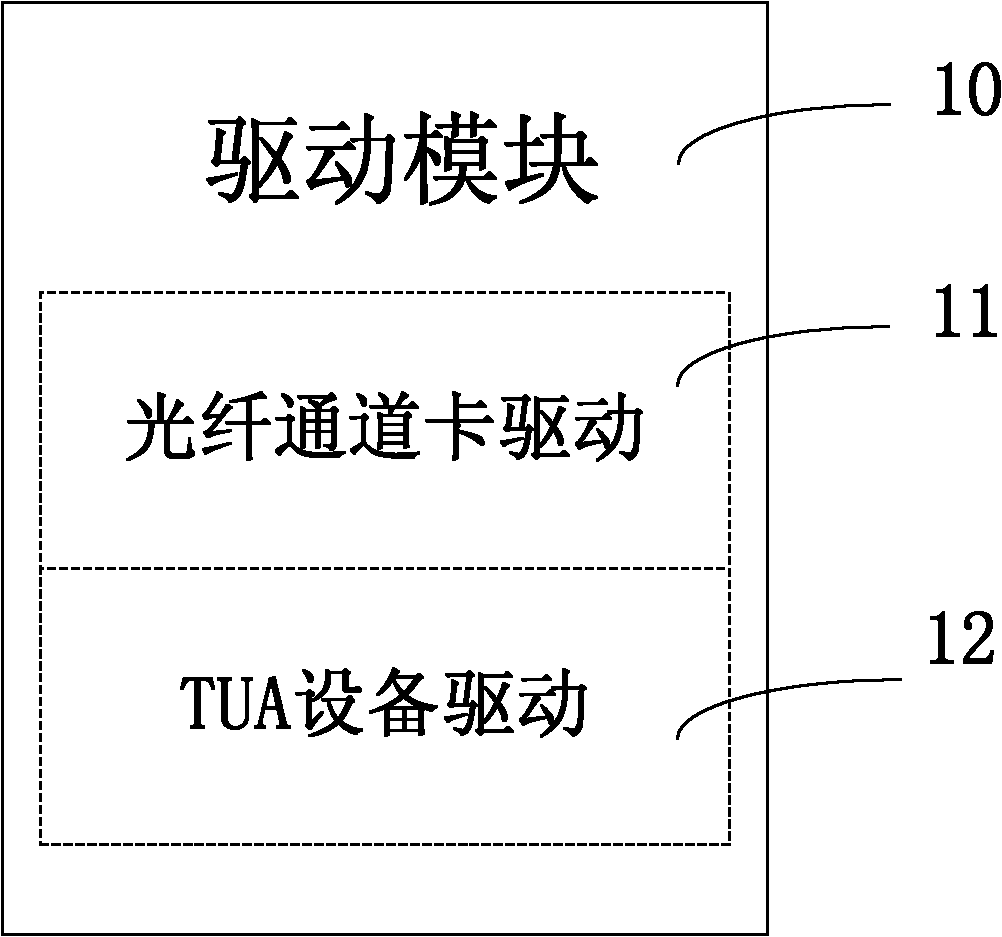

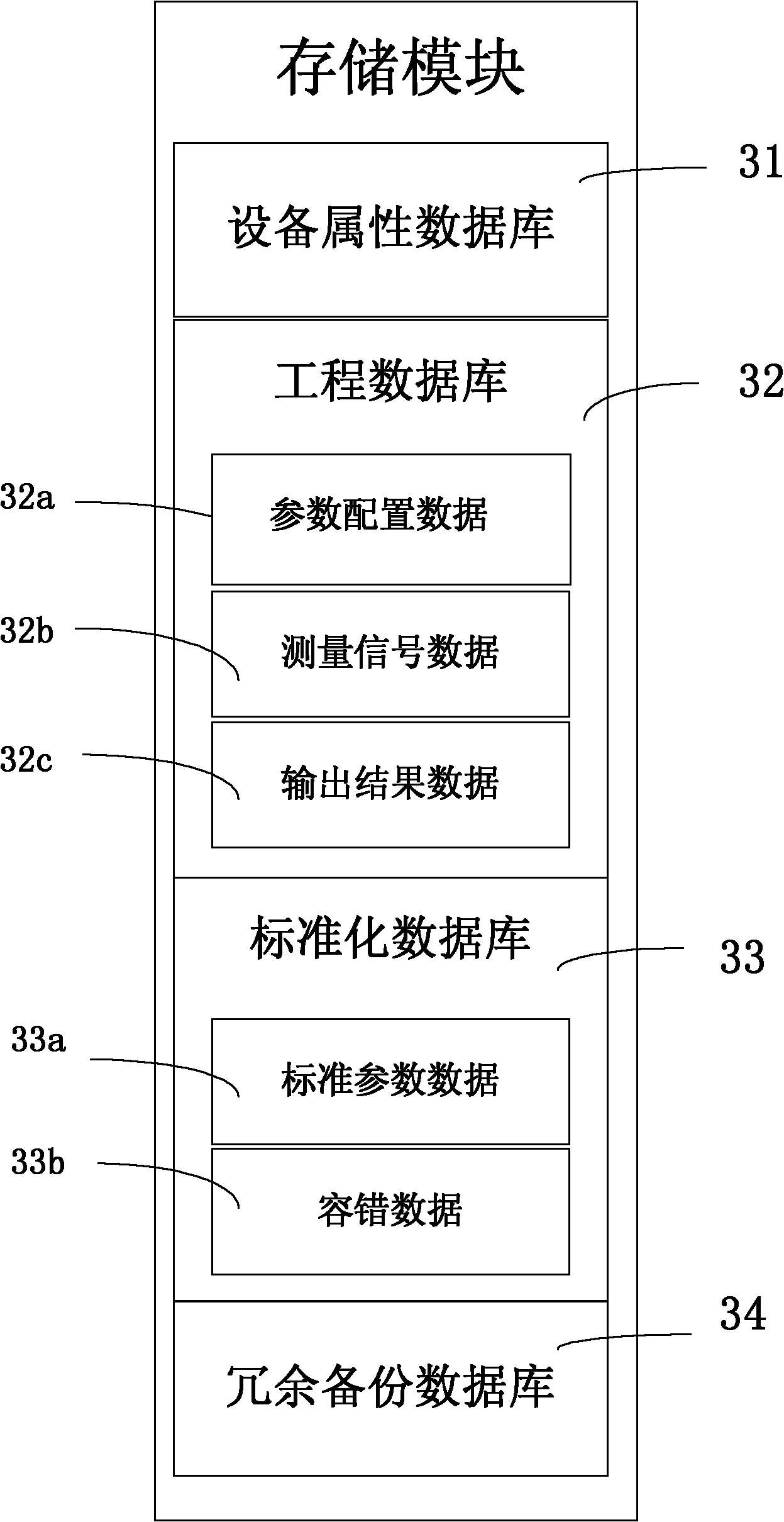

Fiber channel-based general automatic test system

InactiveCN102035673AIntegrity guaranteedGuaranteed reliabilityTime-division multiplexData switching networksFiberTransmission protocol

The invention discloses a fiber channel-based general automatic test system, and belongs to the field of automatic test. The system comprises an automatic test system and an automatic test system network. The test system consists of automatic test equipment, a test adapter, a switching network, an extended resource module and a tested unit; and detection and analysis of the tested unit are realized together. The test system network consists of a local automatic test system and a non-local automatic test system network and realizes networked test system function. The system makes full use of two properties of a fiber channel, namely input / output (I / O) channel technology and network technology. The high-speed storage performance of the I / O channel technology is used as an internal communication protocol of the automatic test system, the network performance is used as a transmission protocol of the test system network, the structure of the traditional automatic test system is accommodated under the condition that the system construction is not changed, and good compatibility is realized.

Owner:BEIHANG UNIV

Biometric authentication system and method for providing access to a KVM system

InactiveUS20050149738A1Digital data processing detailsUser identity/authority verificationBiometric dataMulti user environment

The present invention relates to a system and method for providing a user access to at least one host computer through a Keyboard, Video, and Mouse (KVM) switch based upon biometric authentication of the user. In one embodiment, a method is provided for permitting a user to access a KVM switch based upon biometric data associated with a user in a single user station environment and a multiple user environment. In another embodiment, a system is provided for permitting a user to access a KVM system in a single and / or multiple user environment based upon biometric data associated with the user. The system further provides for direct coupling of host computers to the KVM switch and / or utilizing host adapters to couple a host computer to an input station. The system is scalable by communicatively coupling a fabric which may include associations with host computers or additional fabrics to the host adapters in order to provide a user a logical connection to a wide assortment of host computers.

Owner:VIDEO PRODS

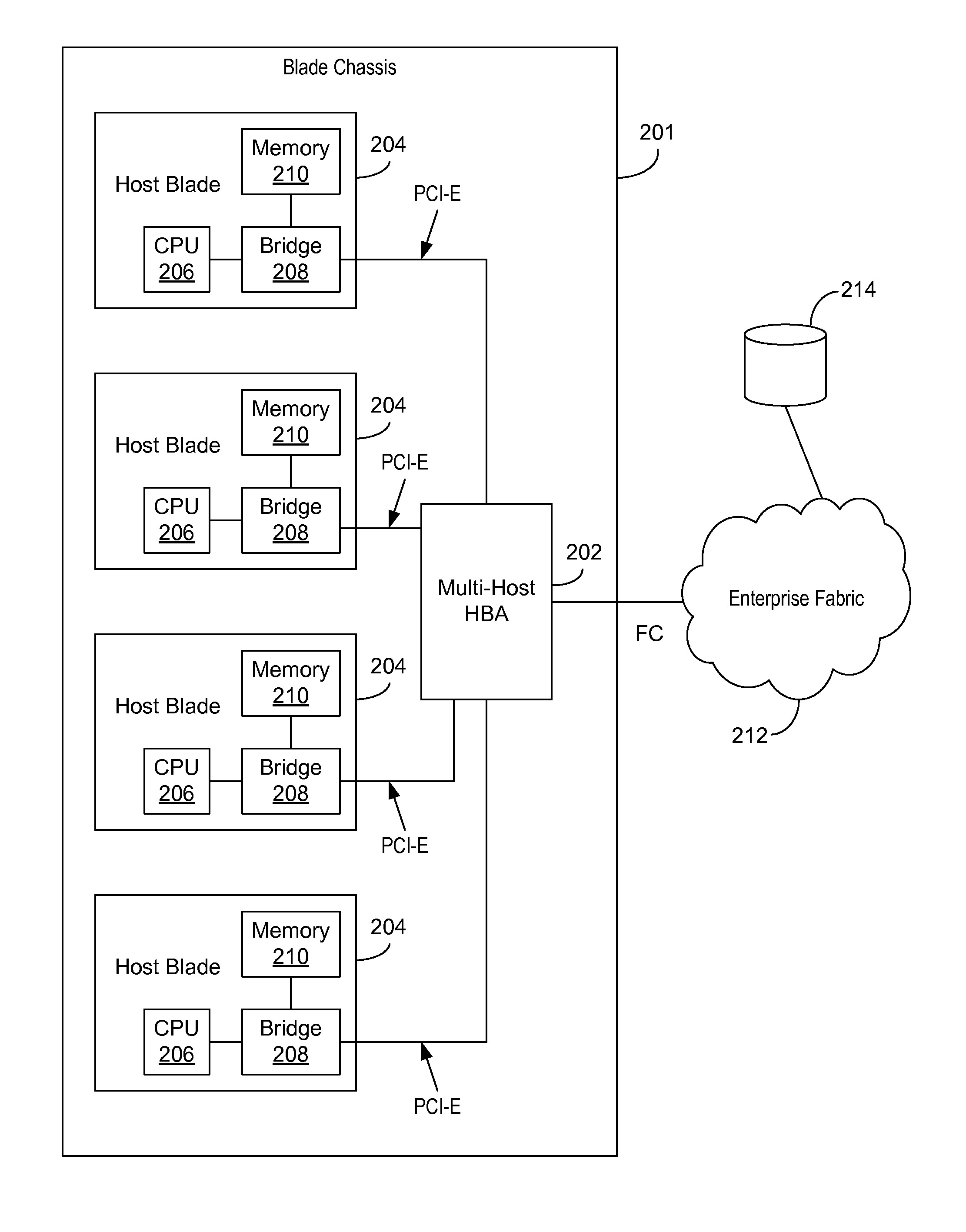

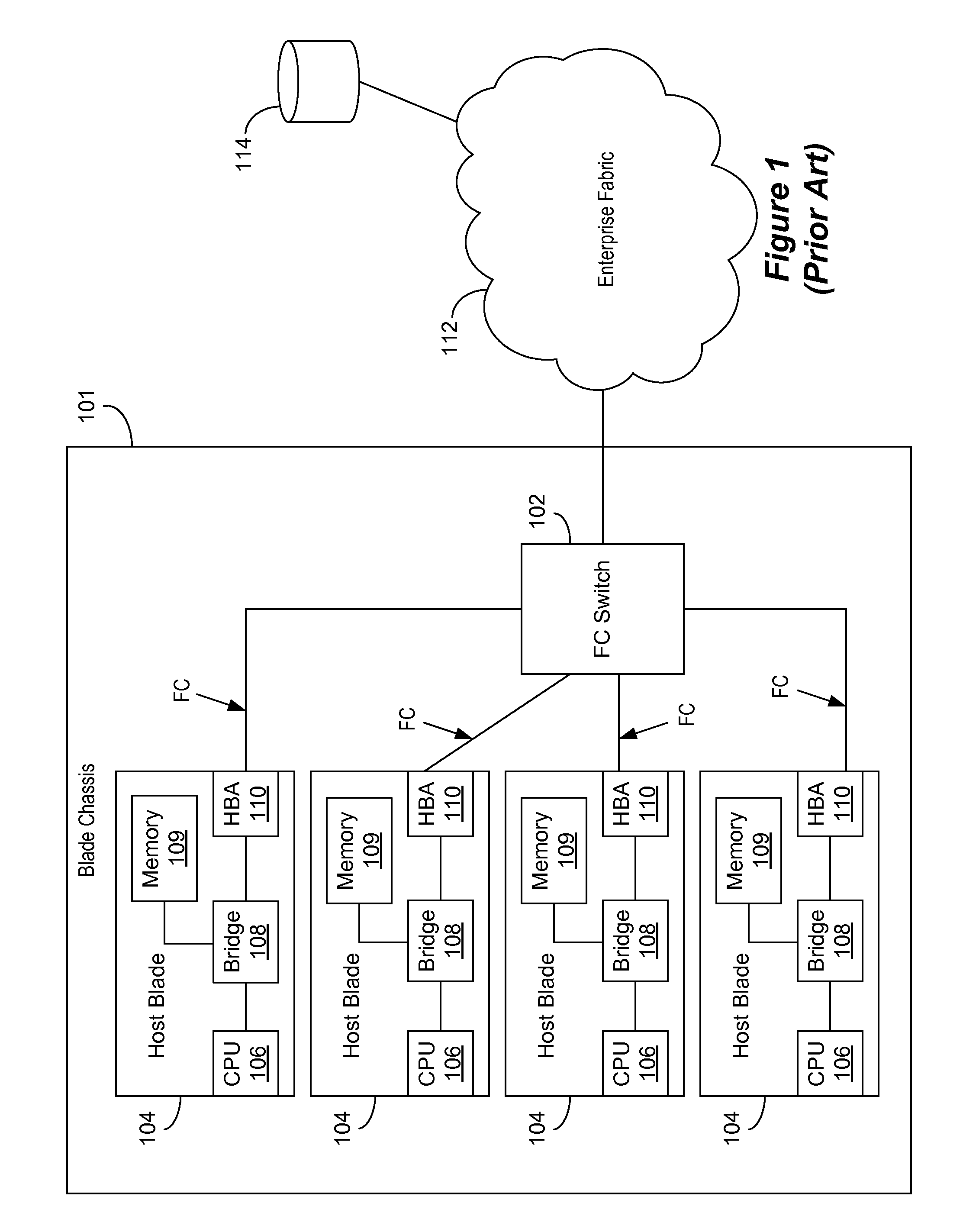

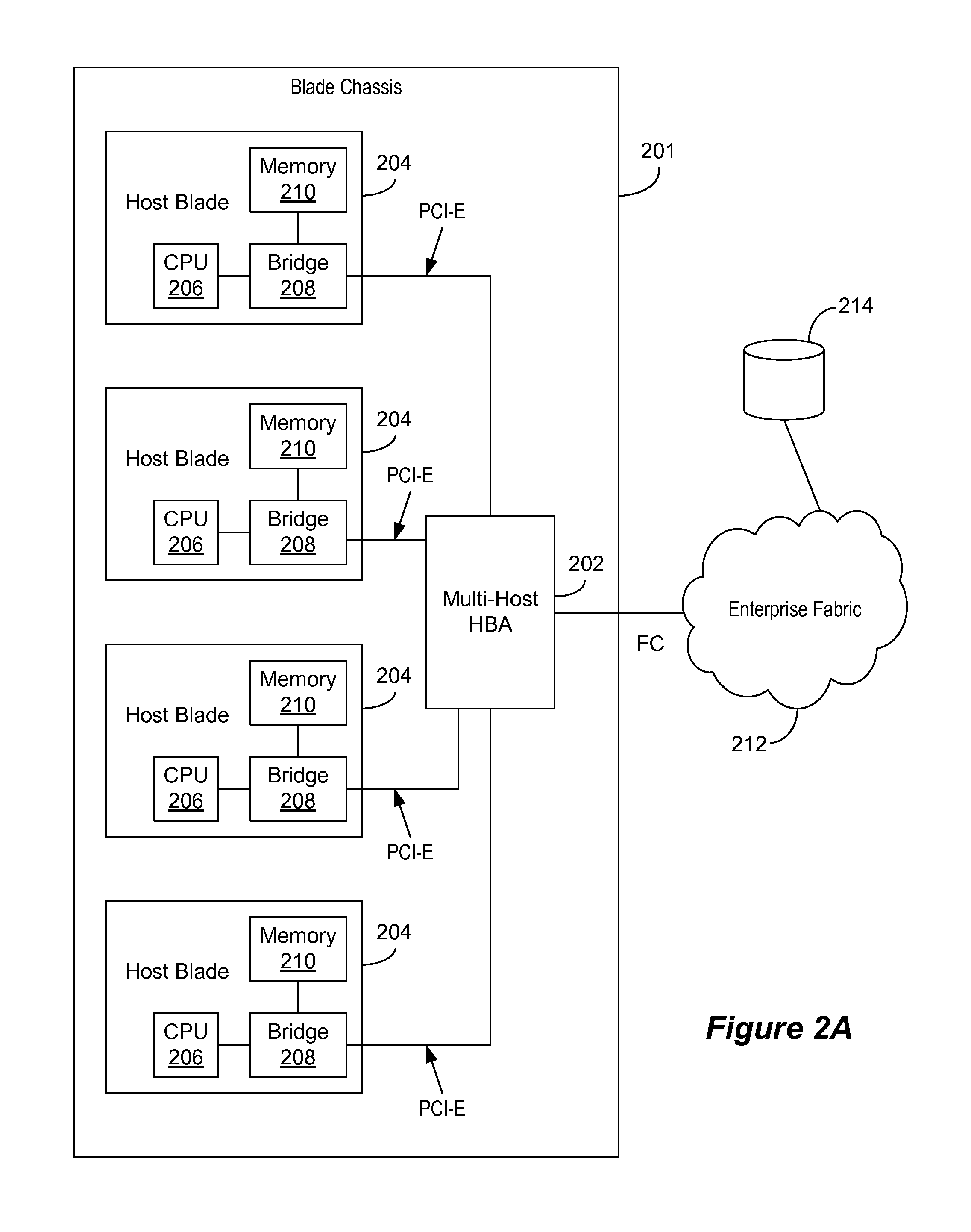

Host bus adapter with multiple hosts

ActiveUS20090106470A1Multiple digital computer combinationsComponent plug-in assemblagesOn boardFibre Channel

A multi-host host bus adapter (HBA) can be connected to multiple host devices to allow the multiple host devices to communicate on a SAN fabric. More specifically, the multi-host HBA provides an interface for multiple SAN hosts without necessitating an HBA on each host, eliminating the need for an on-board HBA on each SAN host. The multi-host HBA interfaces to memory in each SAN host to which it is connected using PCI-Express (or a similar protocol), and communicates with other devices on the SAN fabric using Fibre Channel ports. The multi-host HBA communicates by receiving a command from a connected host, forwarding the command to a processor in the multi-host HBA, and sending the command to a device on a SAN. When the multi-host HBA receives a response from the device on the SAN, the multi-host HBA associates the response with the process and sends the response to the host.

Owner:AVAGO TECH INT SALES PTE LTD

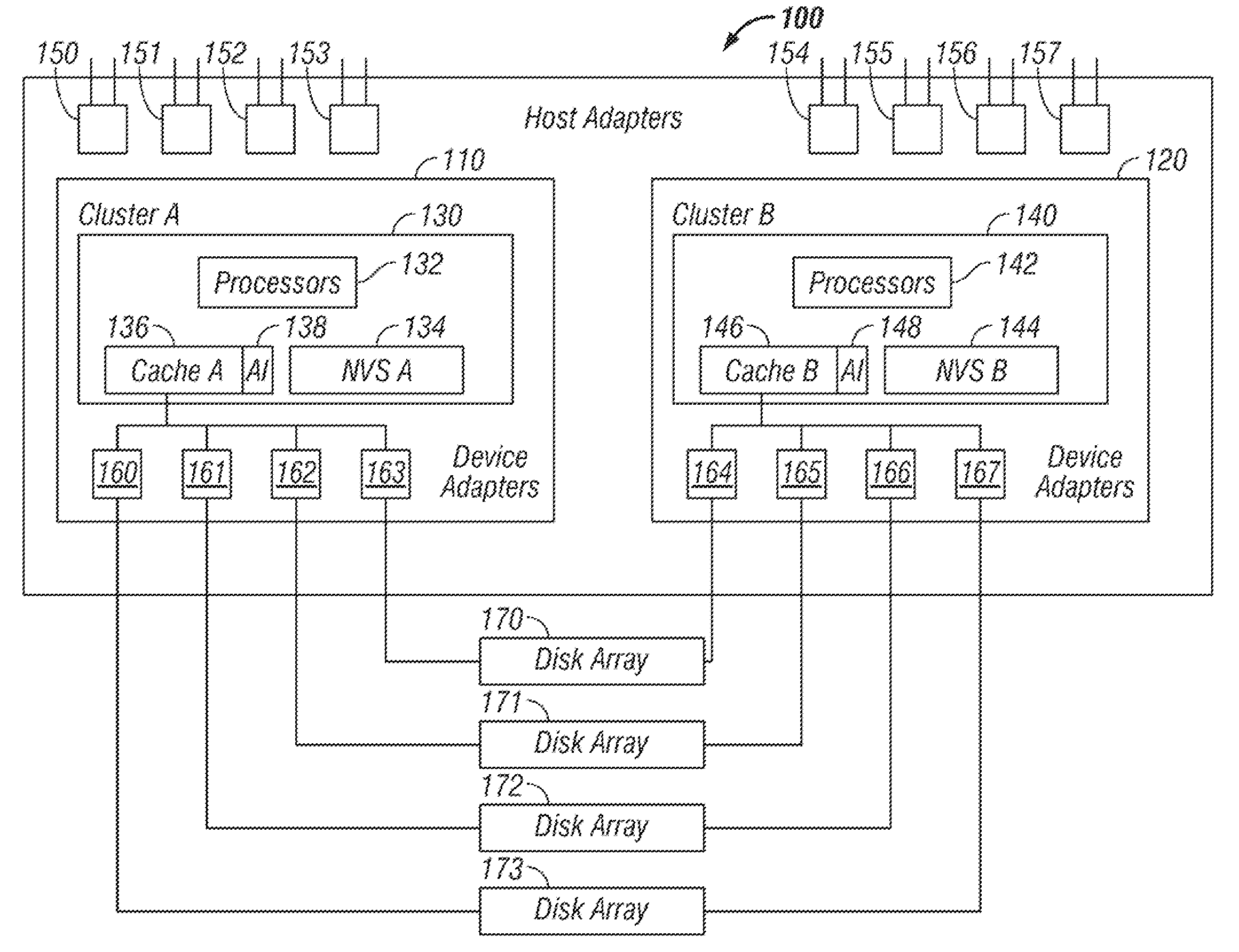

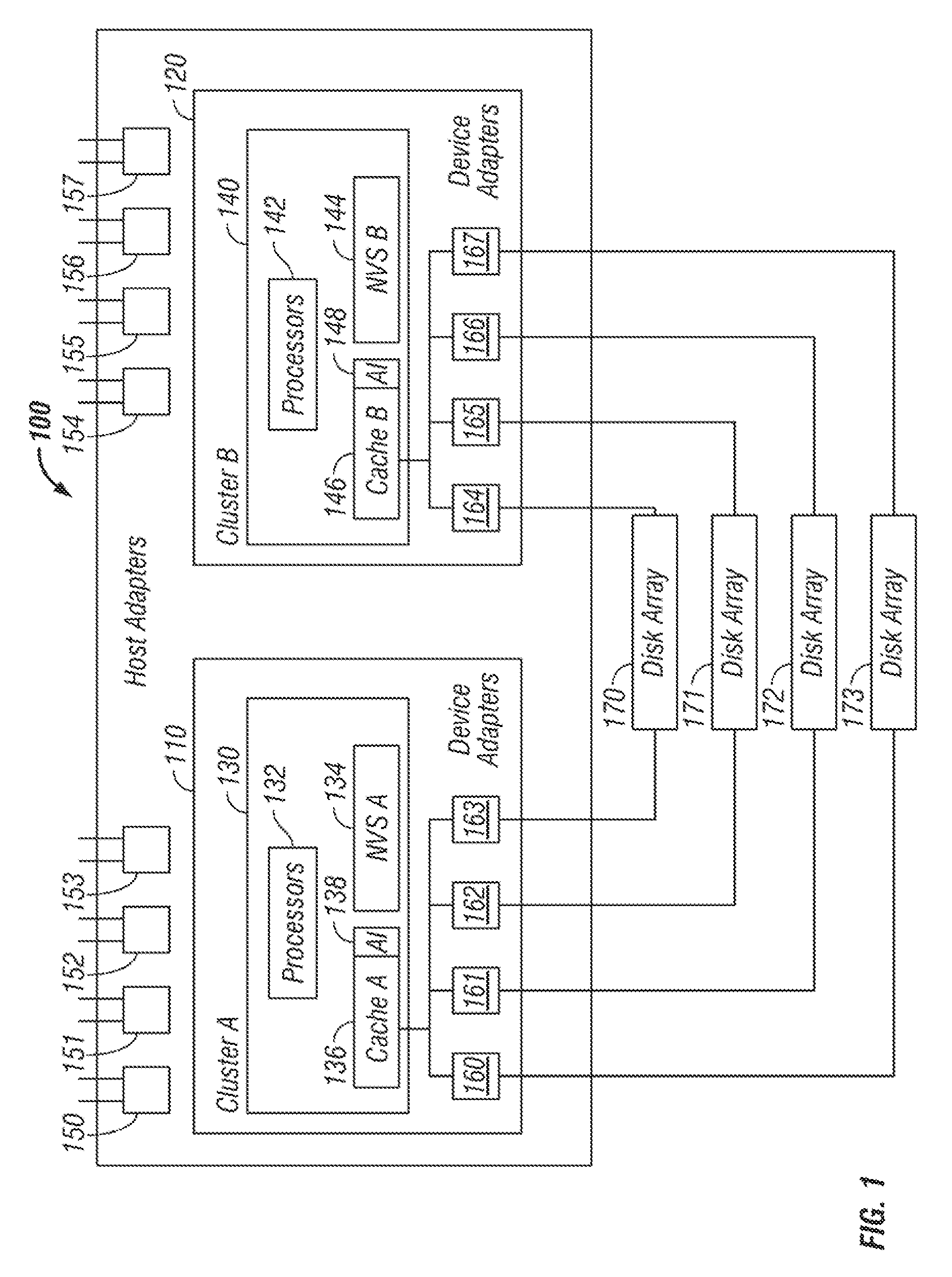

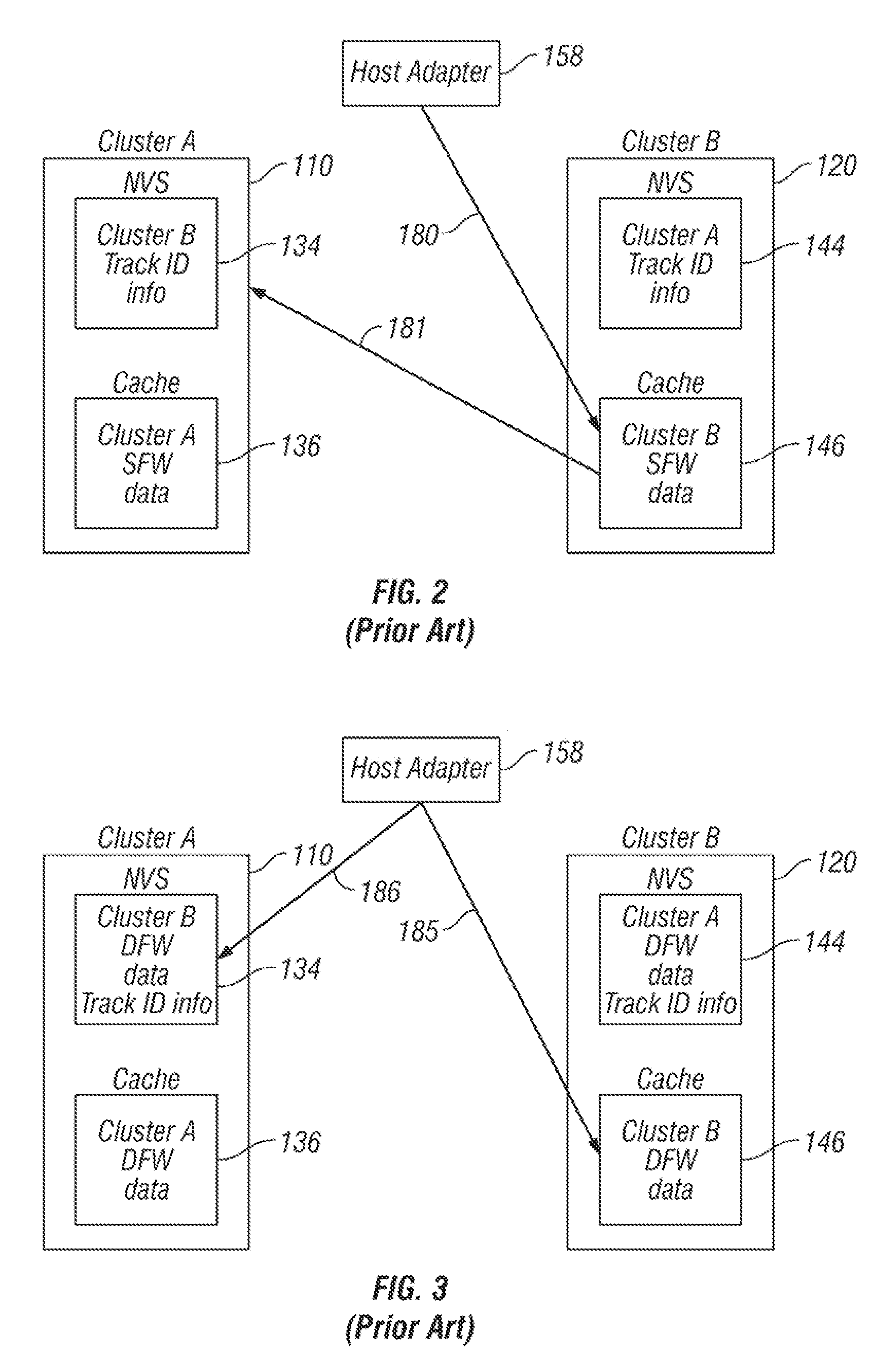

Preservation of cache data following failover

InactiveUS20080201523A1Memory adressing/allocation/relocationDigital computer detailsFailoverData storing

In a data storage subsystem with disk storage and a pair of clusters, one set of DASD fast write data is in cache of one cluster and in non-volatile data storage of the other. In response to a failover of one of the pair of clusters to a local cluster, the local cluster converts the DASD fast write data in local cache to converted fast write data to prioritize the converted data for destaging to disk storage. In response to failure to destage, the local cluster allocates local non-volatile storage tracks and emulates a host adapter to store the converted fast write data by the local non-volatile storage, reconverting the converted fast write data of the non-volatile storage to local DASD fast write data stored in the local non-volatile storage and stored in the local cache storage.

Owner:IBM CORP