Patents

Literature

507results about How to "Reduced pin count" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

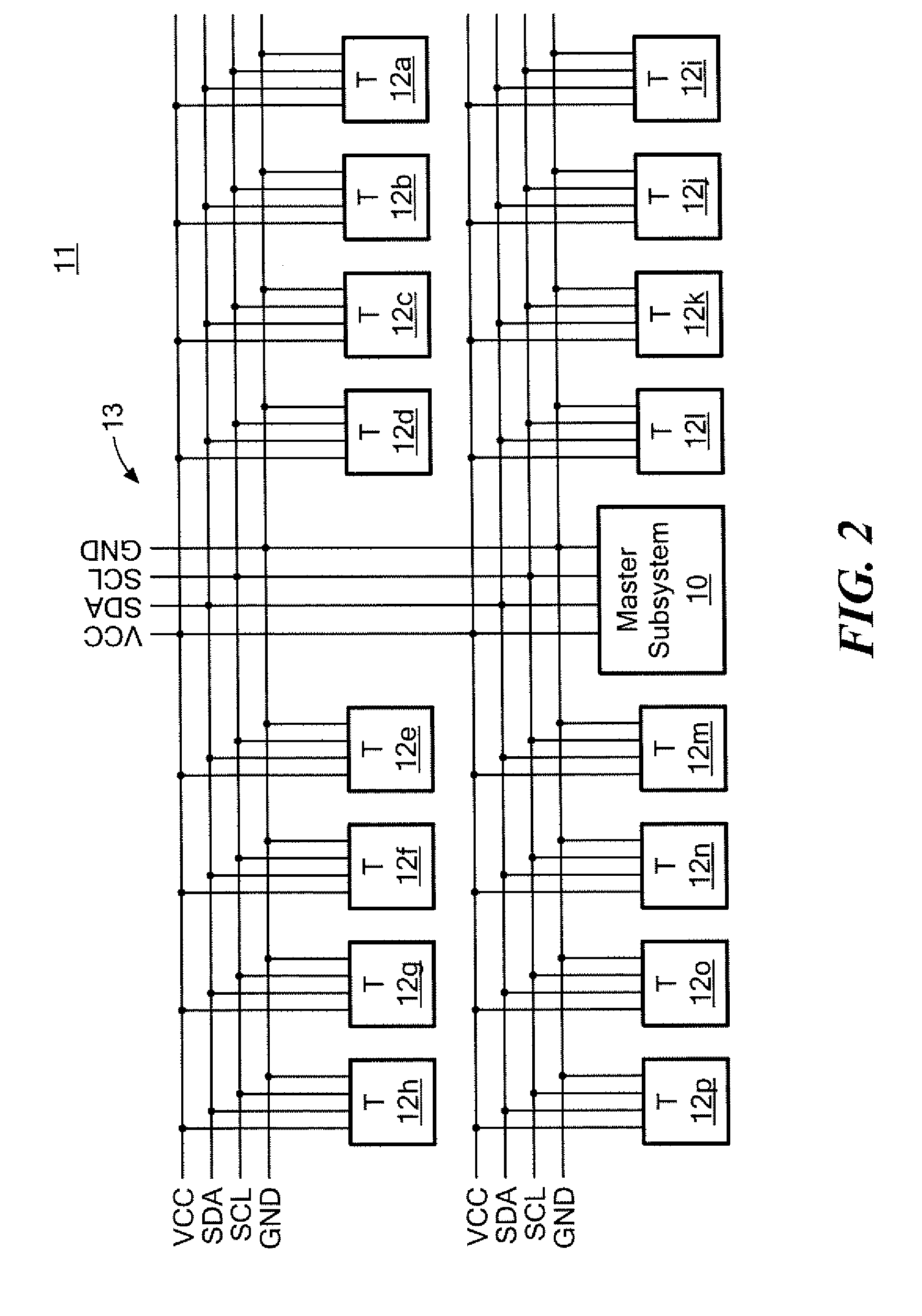

Reducing the number of power and ground pins required to drive address signals to memory modules

InactiveUS20060039205A1Reduced pin countReduce in quantityEnergy efficient ICTDigital storageChip selectEngineering

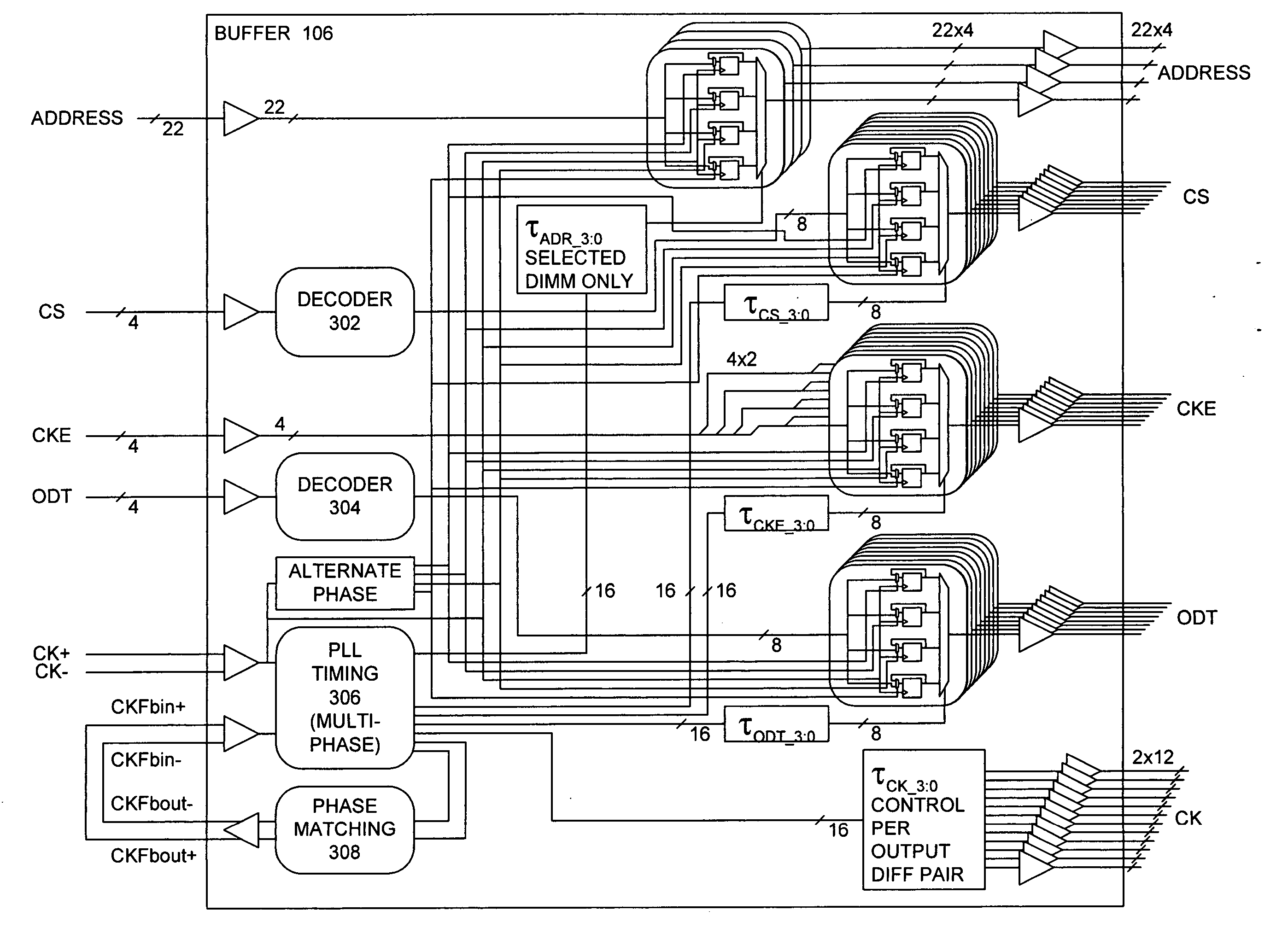

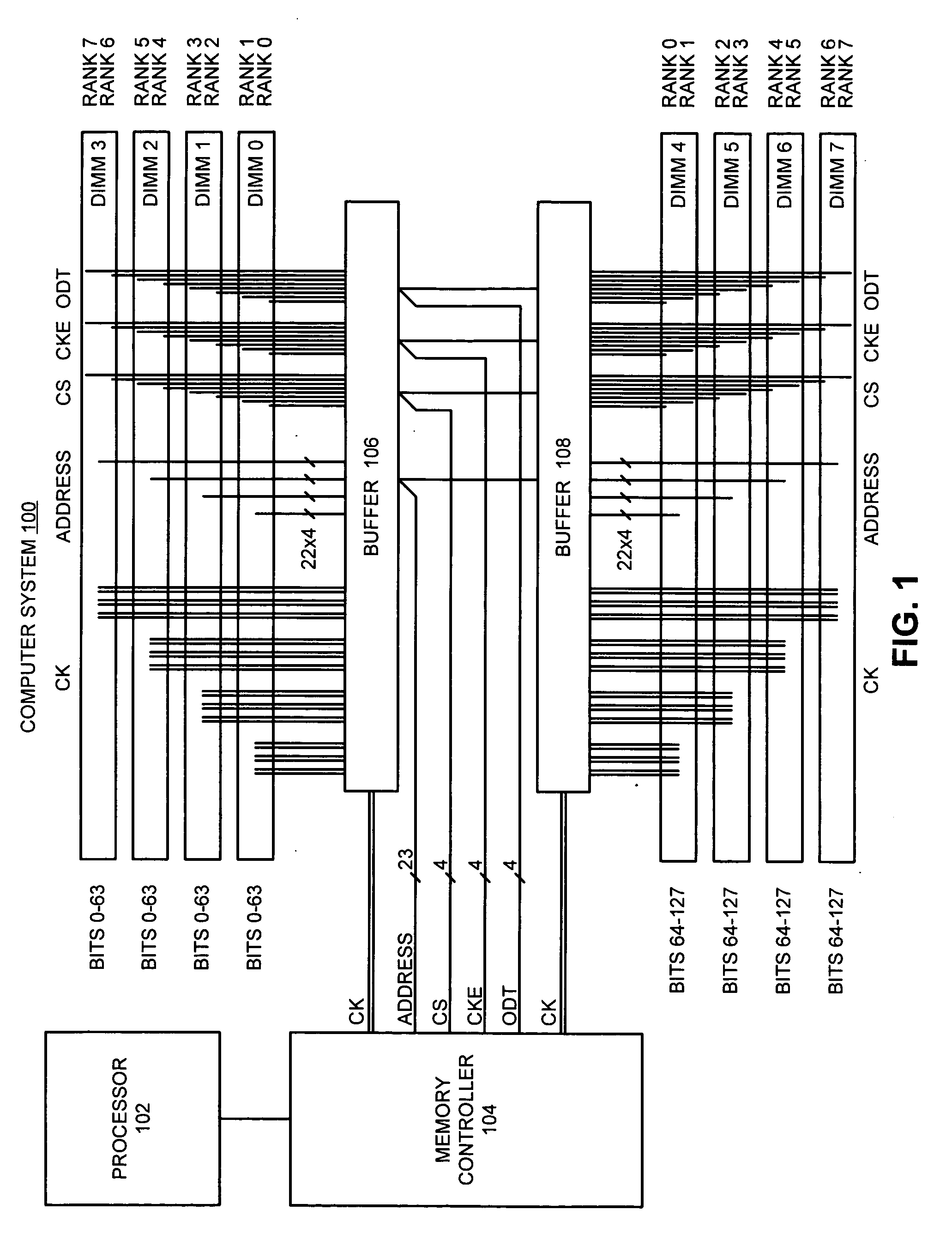

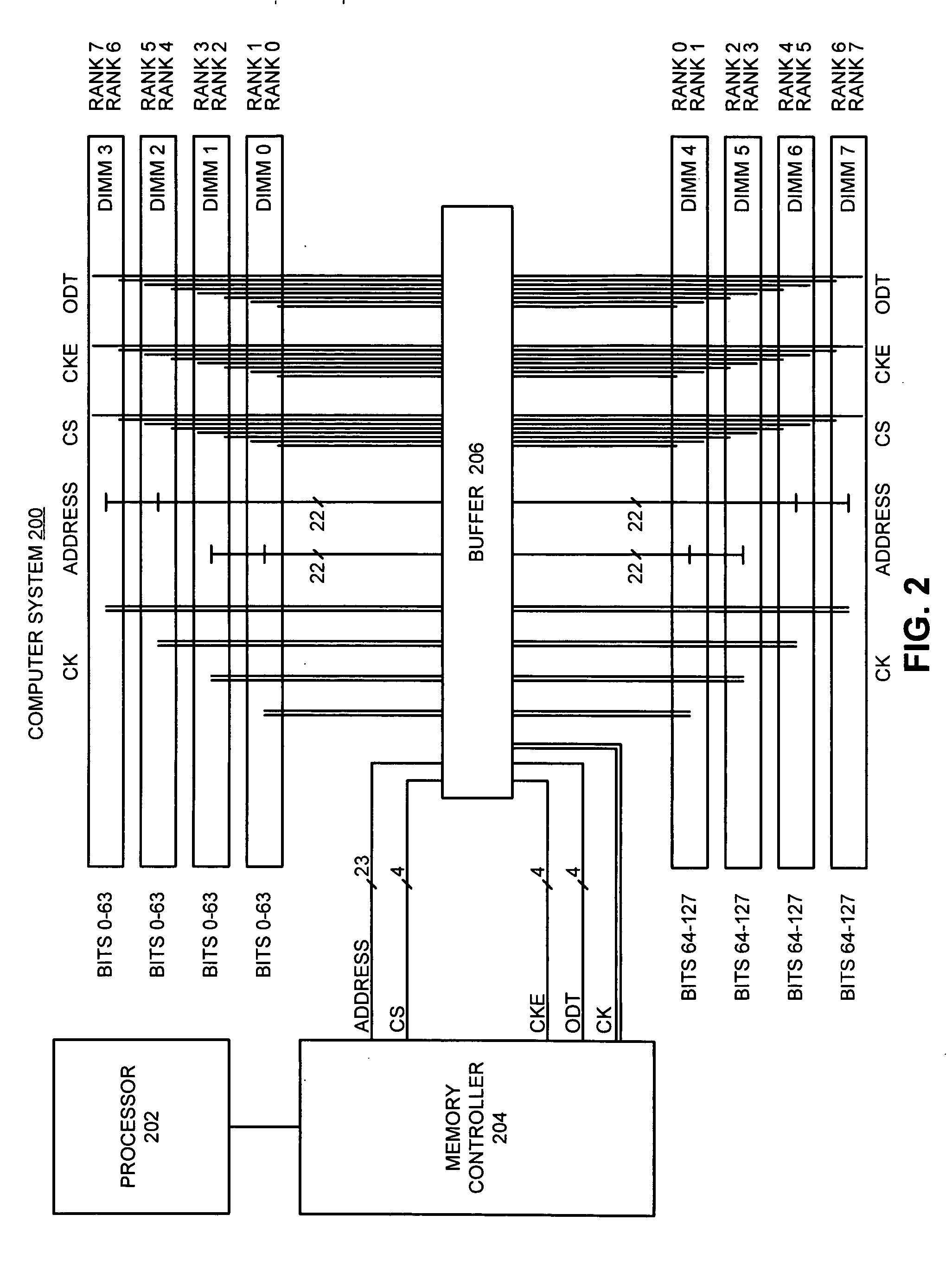

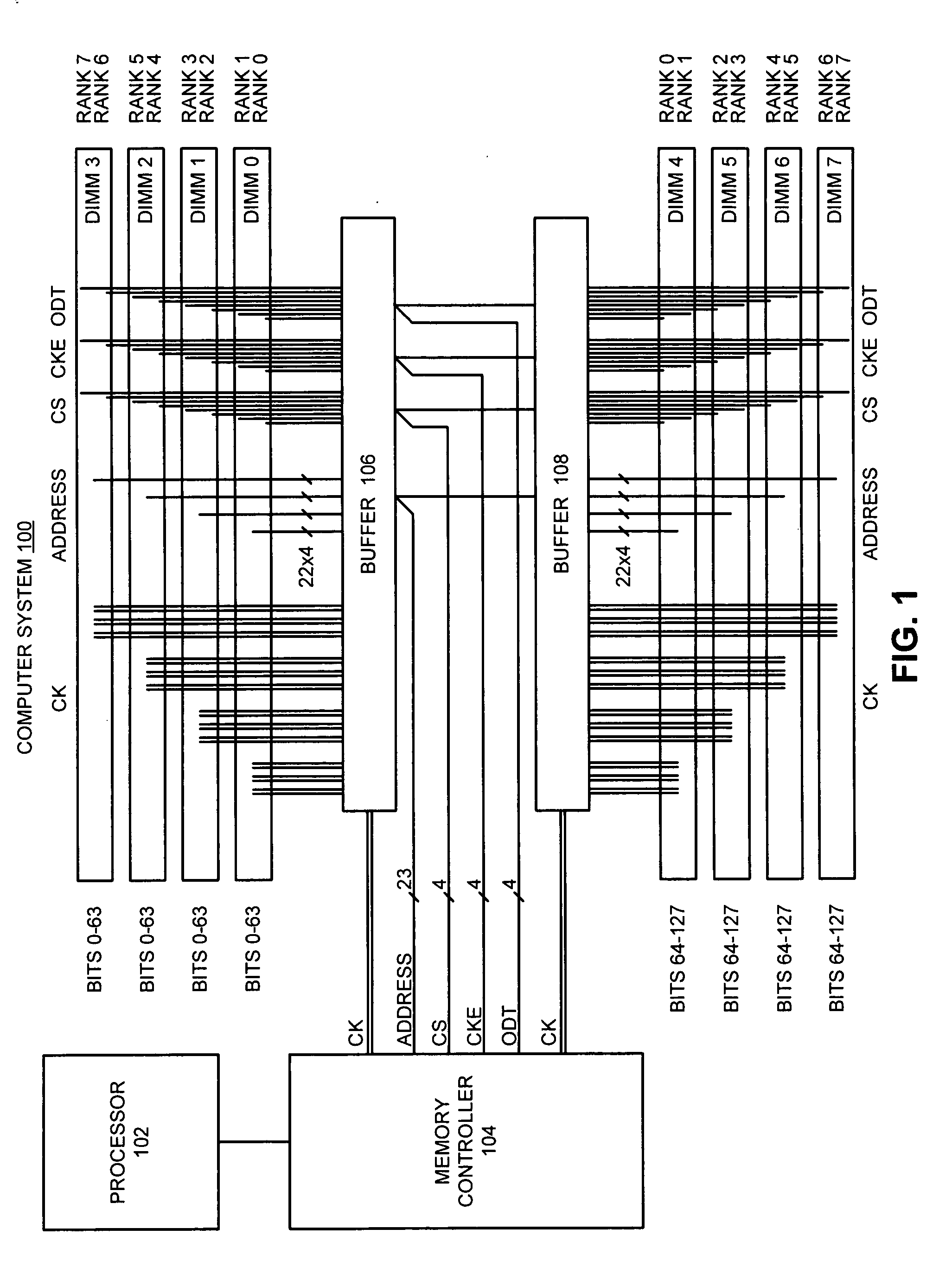

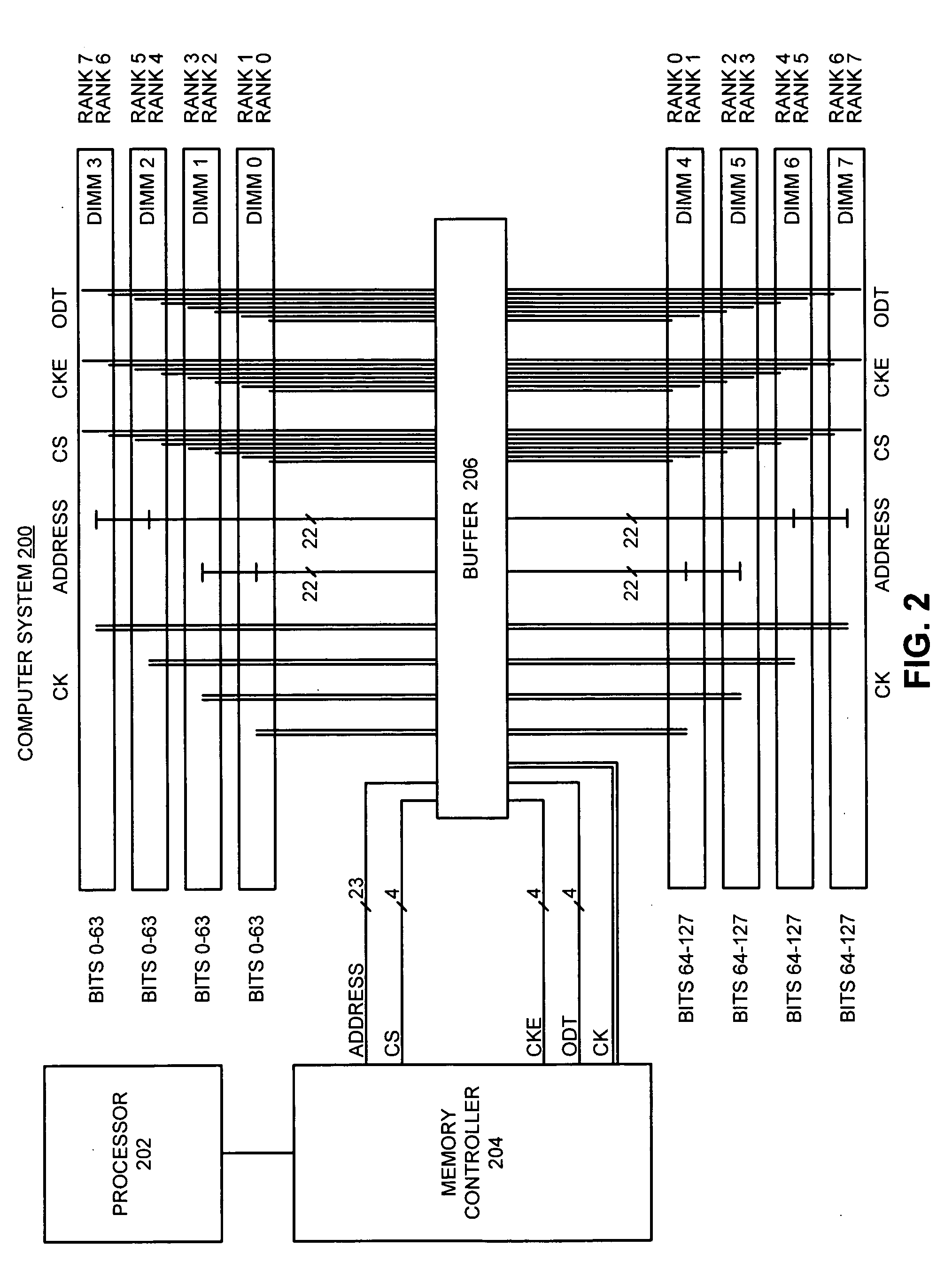

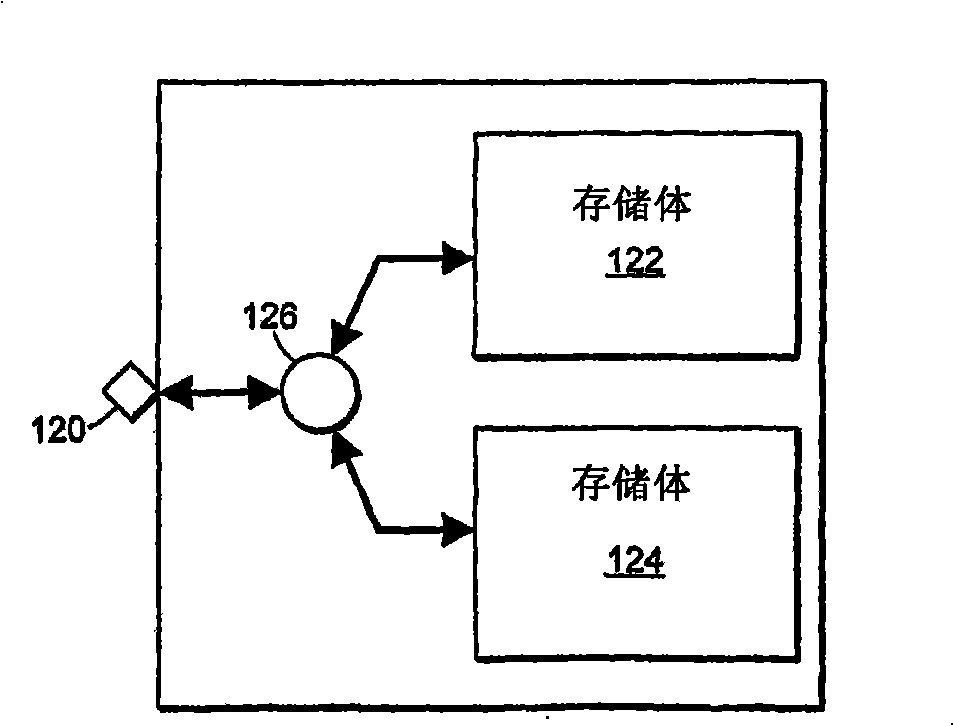

One embodiment of the present invention provides a system that reduces the number of power and ground pins required to drive address signals to system memory. During operation, the system receives address signals associated with a memory operation from a memory controller, wherein the address signals are received at a buffer chip, which is external the memory controller. The system also receives chip select signals associated with the memory operation at the buffer chip. Next, the system uses the chip select signals to identify an active subset of memory modules in the system memory, which are active during the memory operation. The system then uses address drivers on the buffer chip to drive the address signals only to the active subset of memory modules, and not to other memory modules in the system memory. In this way, the buffer chip requires fewer power and ground pins for the address drivers because the address signals are only driven to the active subset of memory modules, instead of being driven to all memory modules in the system memory.

Owner:APPLE INC

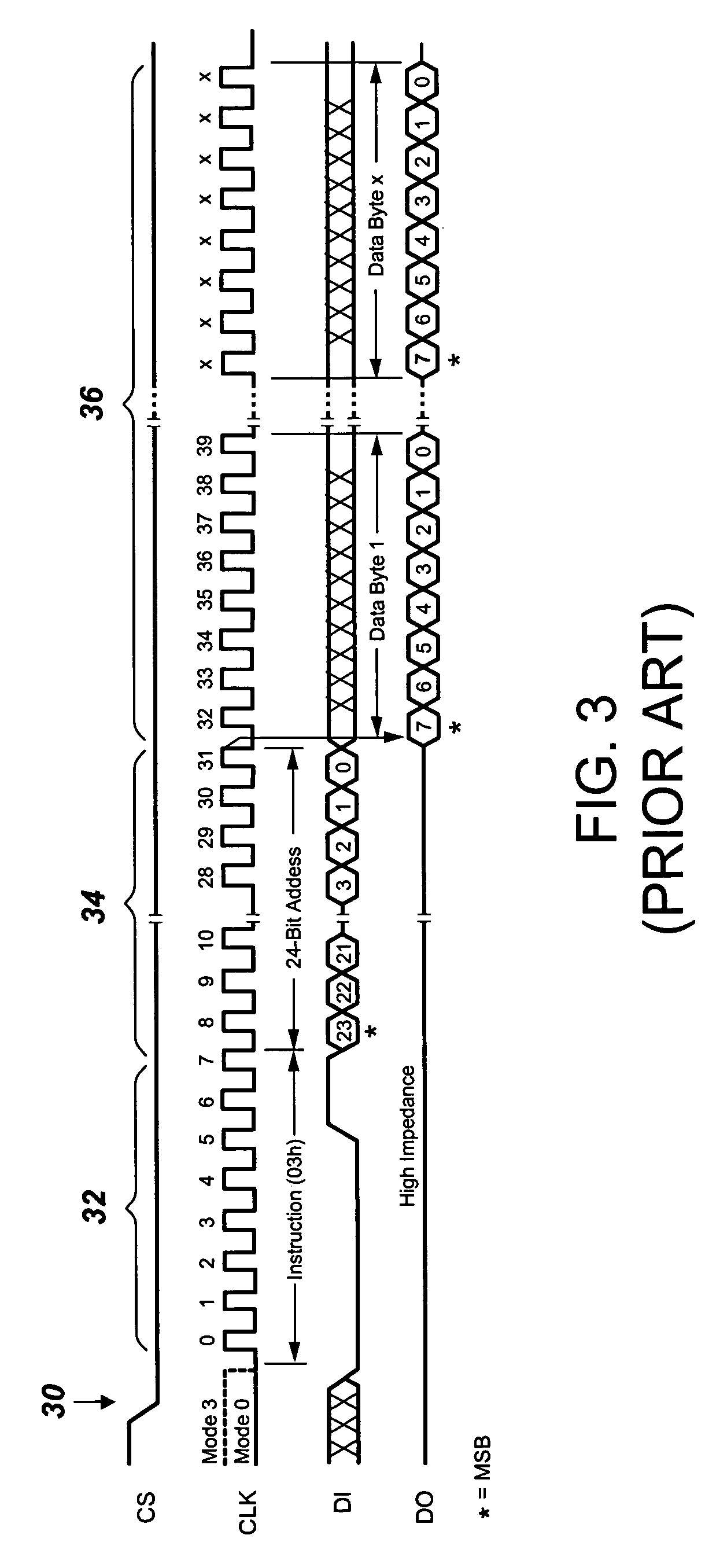

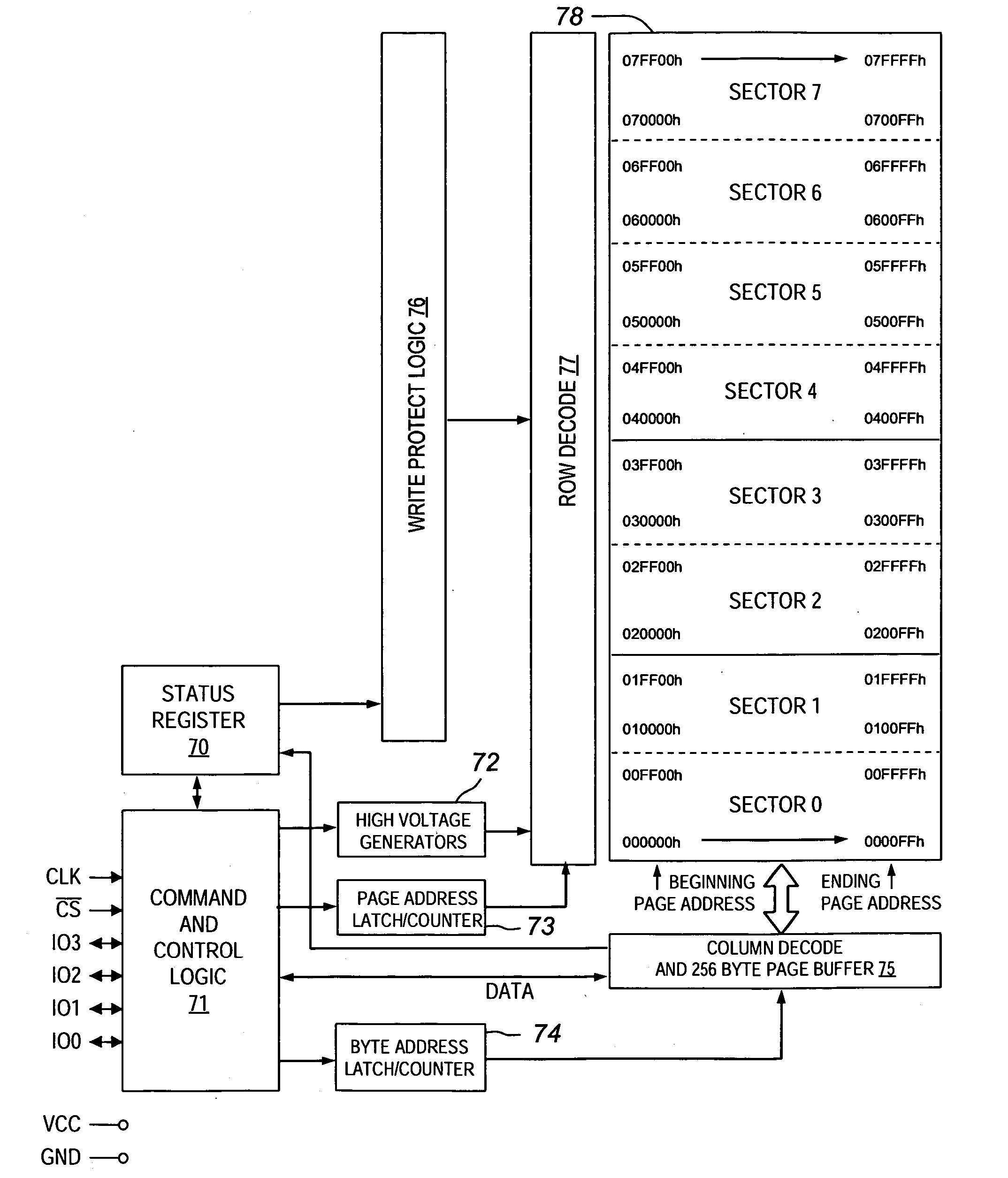

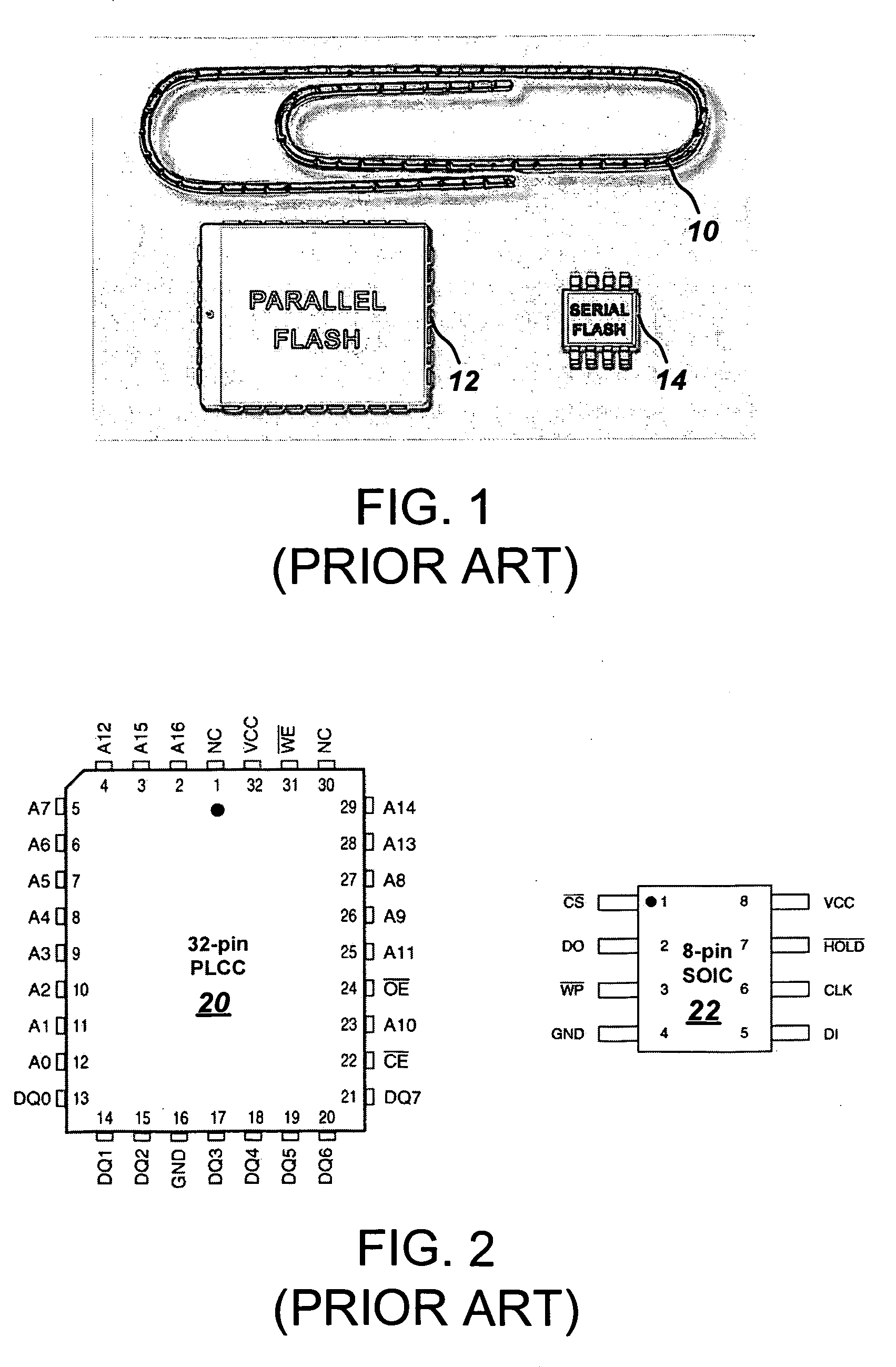

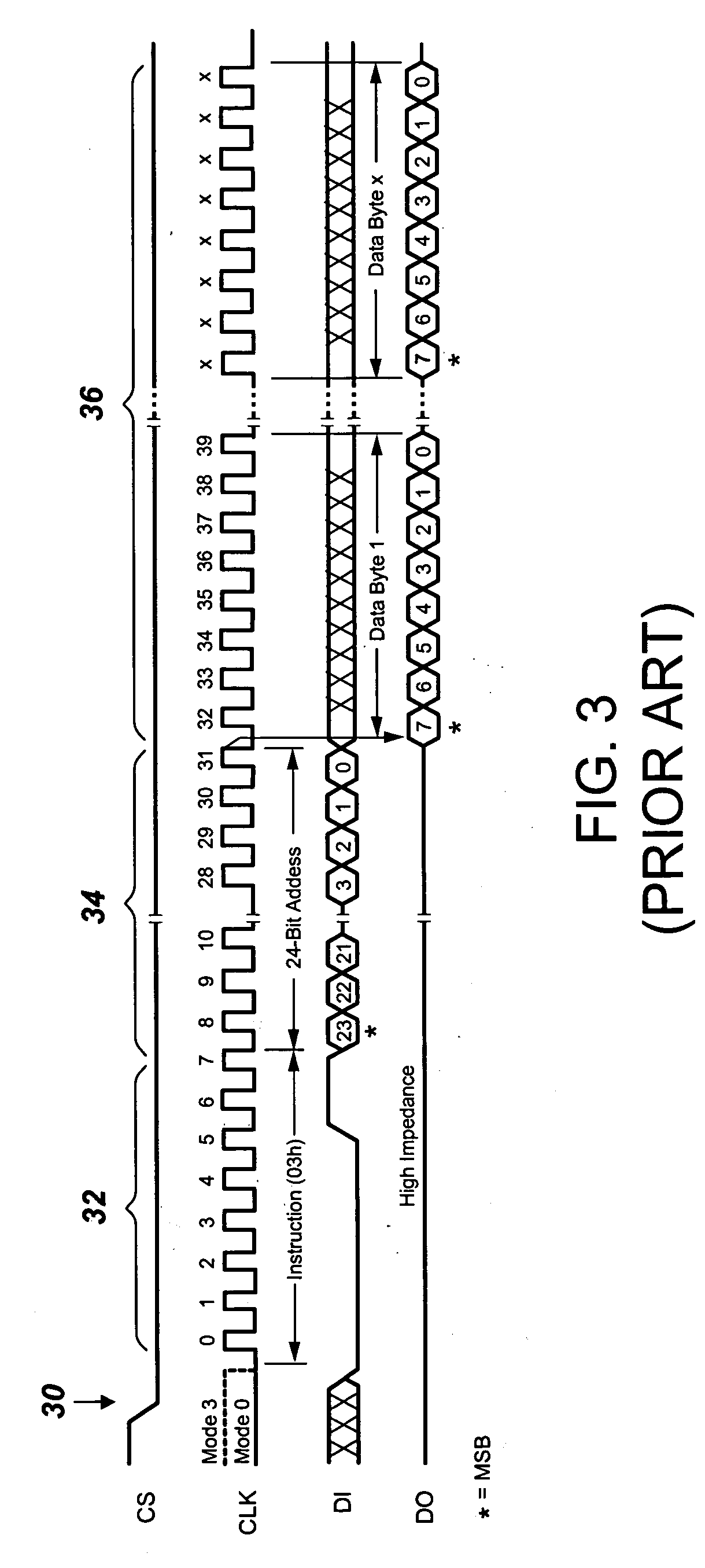

Serial flash semiconductor memory

ActiveUS7558900B2Reduced pin countImprove rendering capabilitiesRead-only memoriesDigital storageData transmissionLow Pin Count

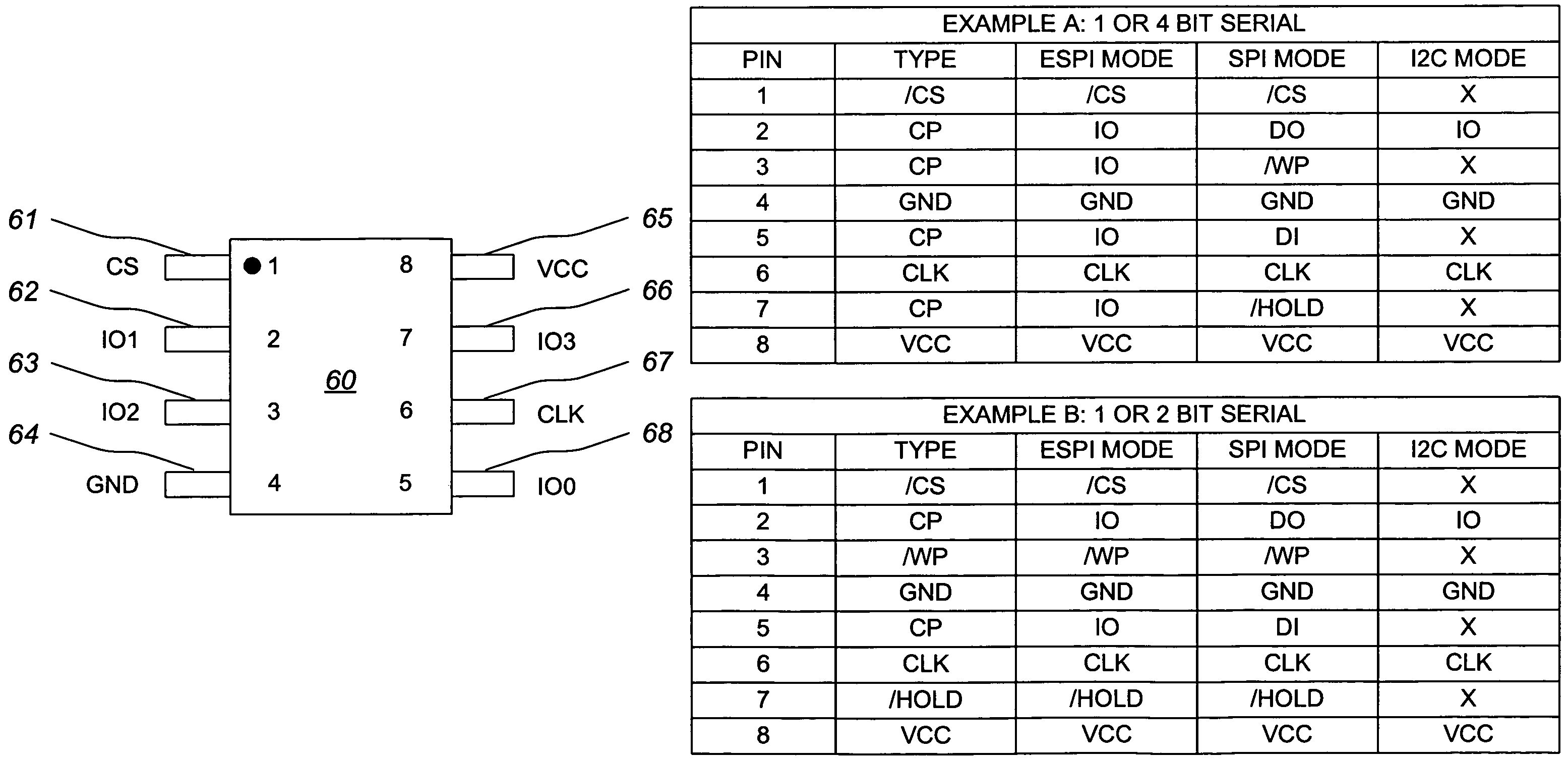

A serial flash memory is provided with multiple configurable pins, at least one of which is selectively configurable for use in either single-bit serial data transfers or multiple-bit serial data transfers. In single-bit serial mode, data transfer is bit-by-bit through a pin. In multiple-bit serial mode, a number of sequential bits are transferred at a time through respective pins. The serial flash memory may have 16 or fewer pins, and even 8 or fewer pins, so that low pin count packaging such as the 8-pin or 16-pin SOIC package and the 8-contact MLP / QFN / SON package may be used. The availability of the single-bit serial type protocol enables compatibility with a number of existing systems, while the availability of the multiple-bit serial type protocol enables the serial flash memory to provide data transfer rates, in systems that can support them, that are significantly faster than available with standard serial flash memories.

Owner:WINBOND ELECTRONICS CORP

Serial flash semiconductor memory

ActiveUS20060067123A1Low pin-countIncrease capacityRead-only memoriesDigital storageData transmissionSemiconductor memory

A serial flash memory is provided with multiple configurable pins, at least one of which is selectively configurable for use in either single-bit serial data transfers or multiple-bit serial data transfers. In single-bit serial mode, data transfer is bit-by-bit through a pin. In multiple-bit serial mode, a number of sequential bits are transferred at a time through respective pins. The serial flash memory may have 16 or fewer pins, and even 8 or fewer pins, so that low pin count packaging such as the 8-pin or 16-pin SOIC package and the 8-contact MLP / QFN / SON package may be used. The availability of the single-bit serial type protocol enables compatibility with a number of existing systems, while the availability of the multiple-bit serial type protocol enables the serial flash memory to provide data transfer rates, in systems that can support them, that are significantly faster than available with standard serial flash memories.

Owner:WINBOND ELECTRONICS CORP

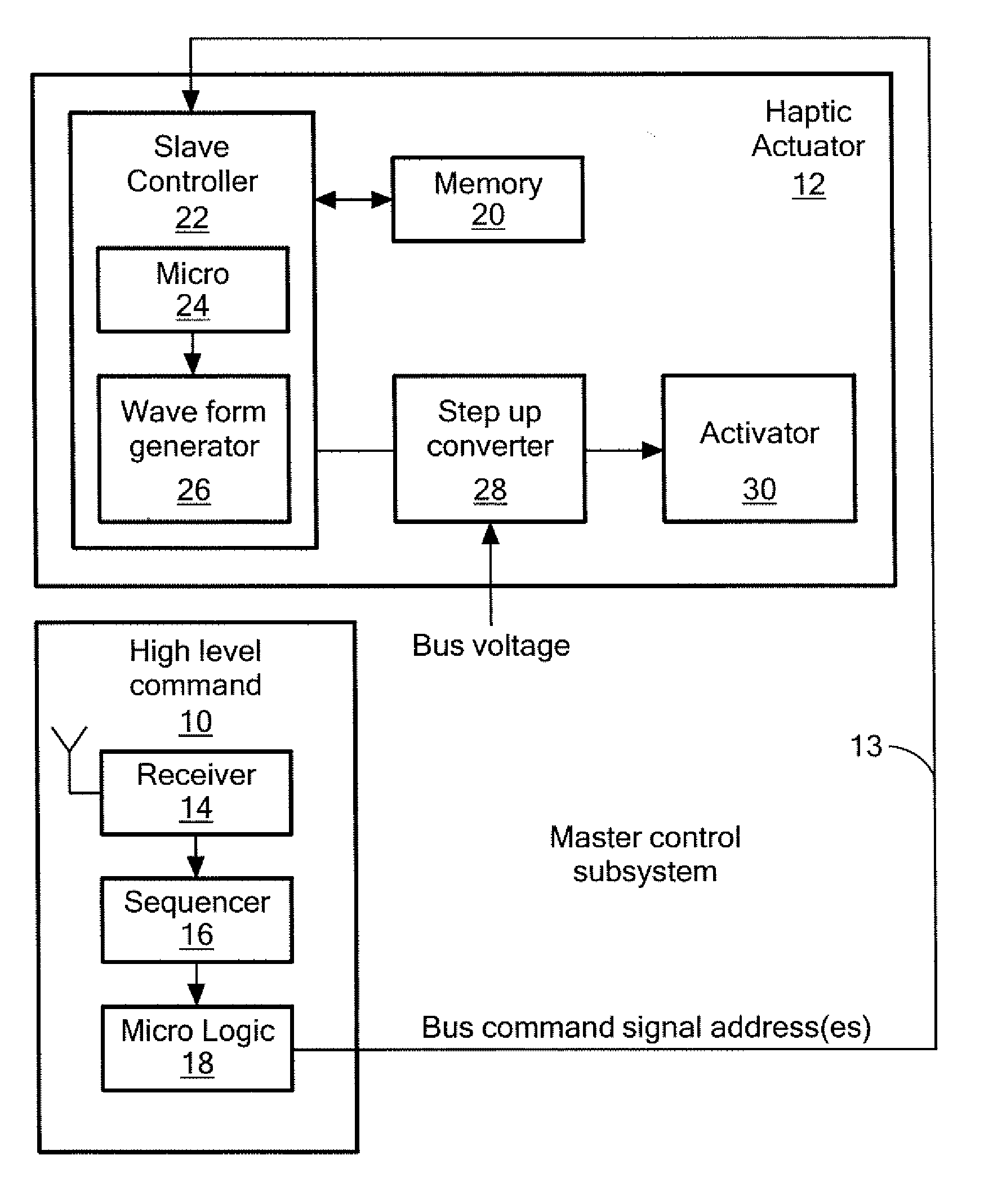

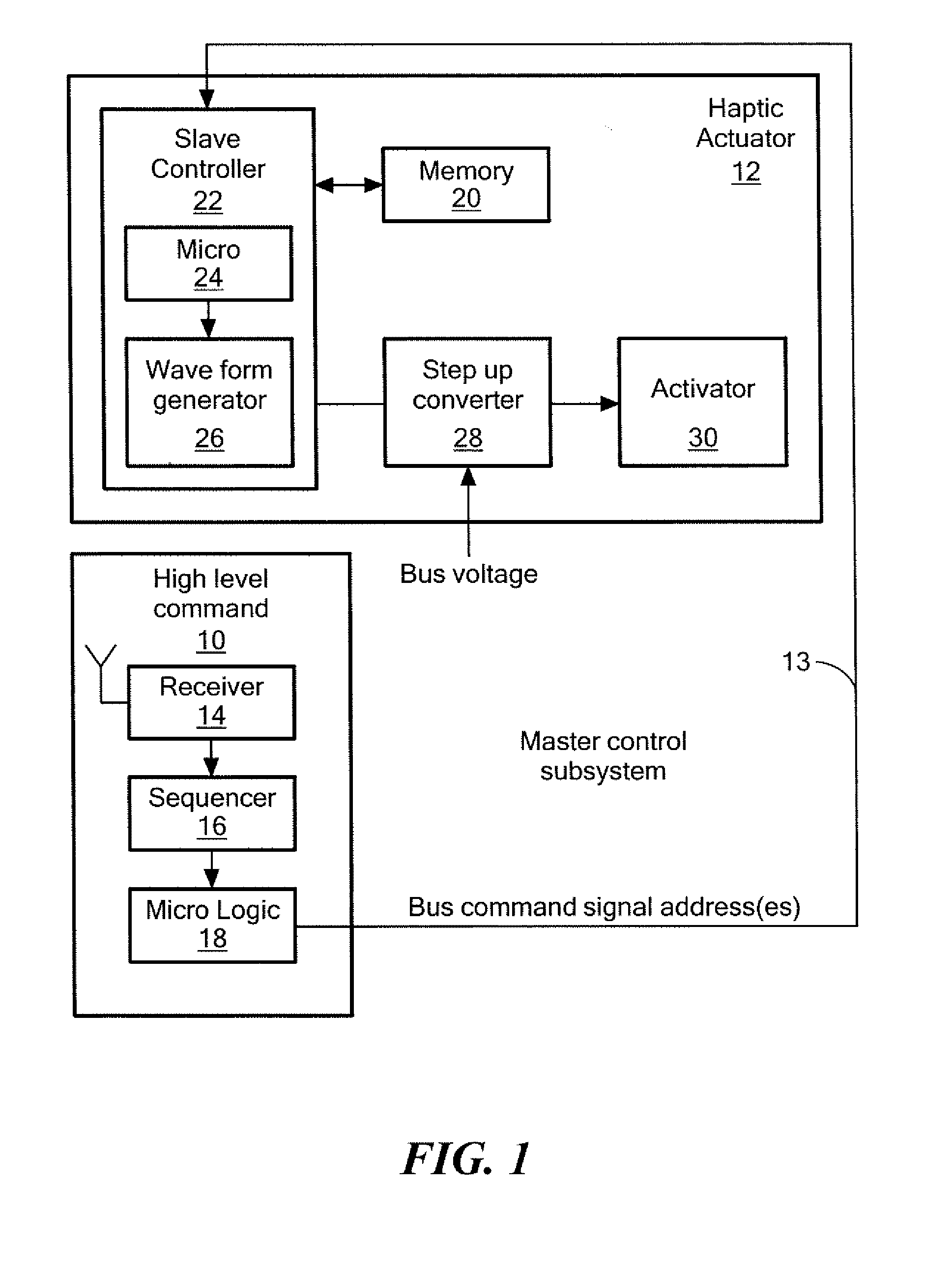

Bussed haptic actuator system and method

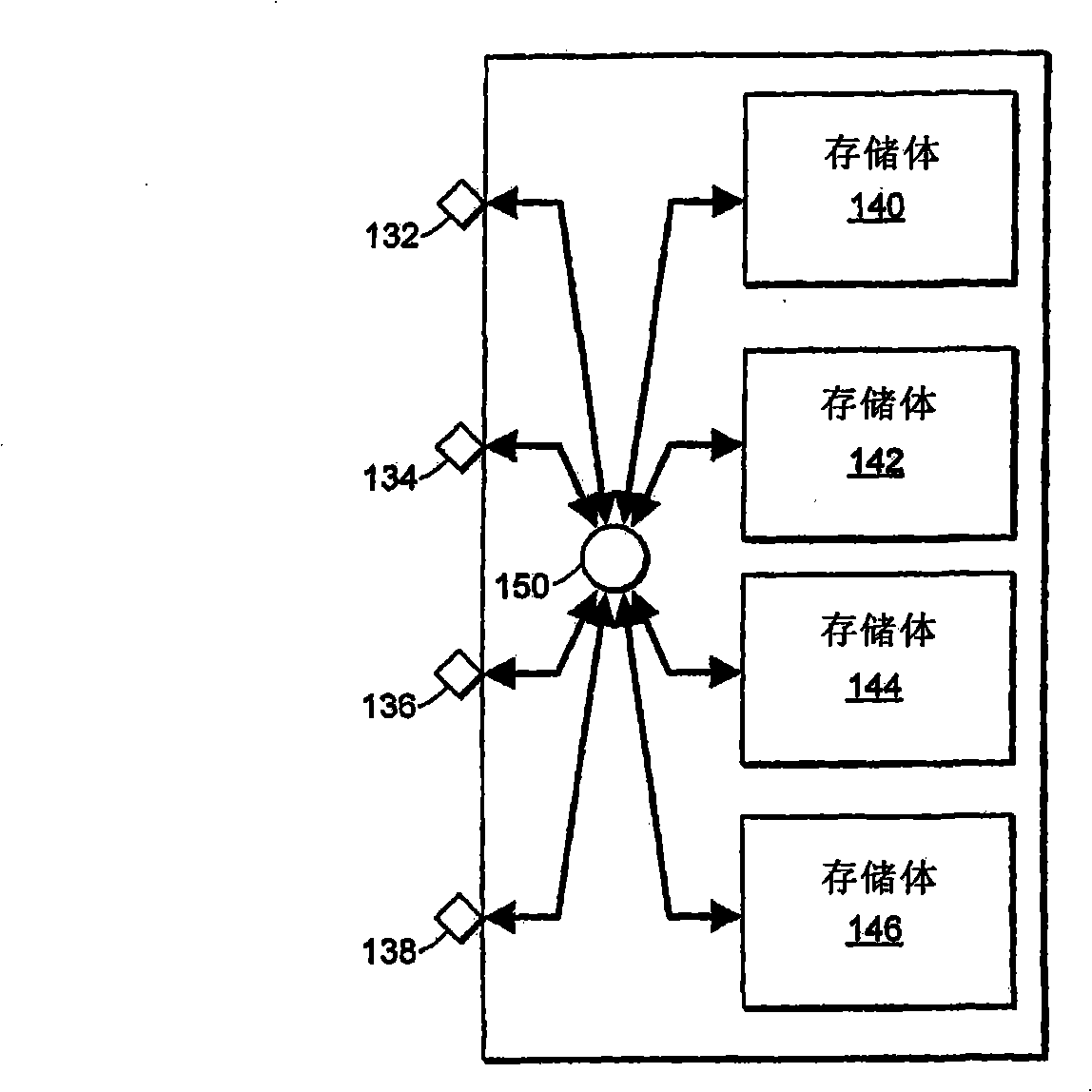

ActiveUS20150227204A1Reduced pin countReduce the numberInput/output for user-computer interactionDigital data processing detailsActuatorControl theory

A bussed haptic actuator system includes a plurality of haptic actuators and a master control subsystem. Each haptic actuator includes a memory with an address storable therein and a slave controller subsystem configured to control the actuator in response to a received command signal. The master control subsystem is connected via a bus to the plurality of haptic actuators. The master control subsystem includes sequencer configured to determine which of the plurality of haptic actuators are to be activated and logic configured to provide, on the bus, a command signal including one or more addresses corresponding to haptic actuators to be activated as determined by the sequencer.

Owner:MIDE TECH

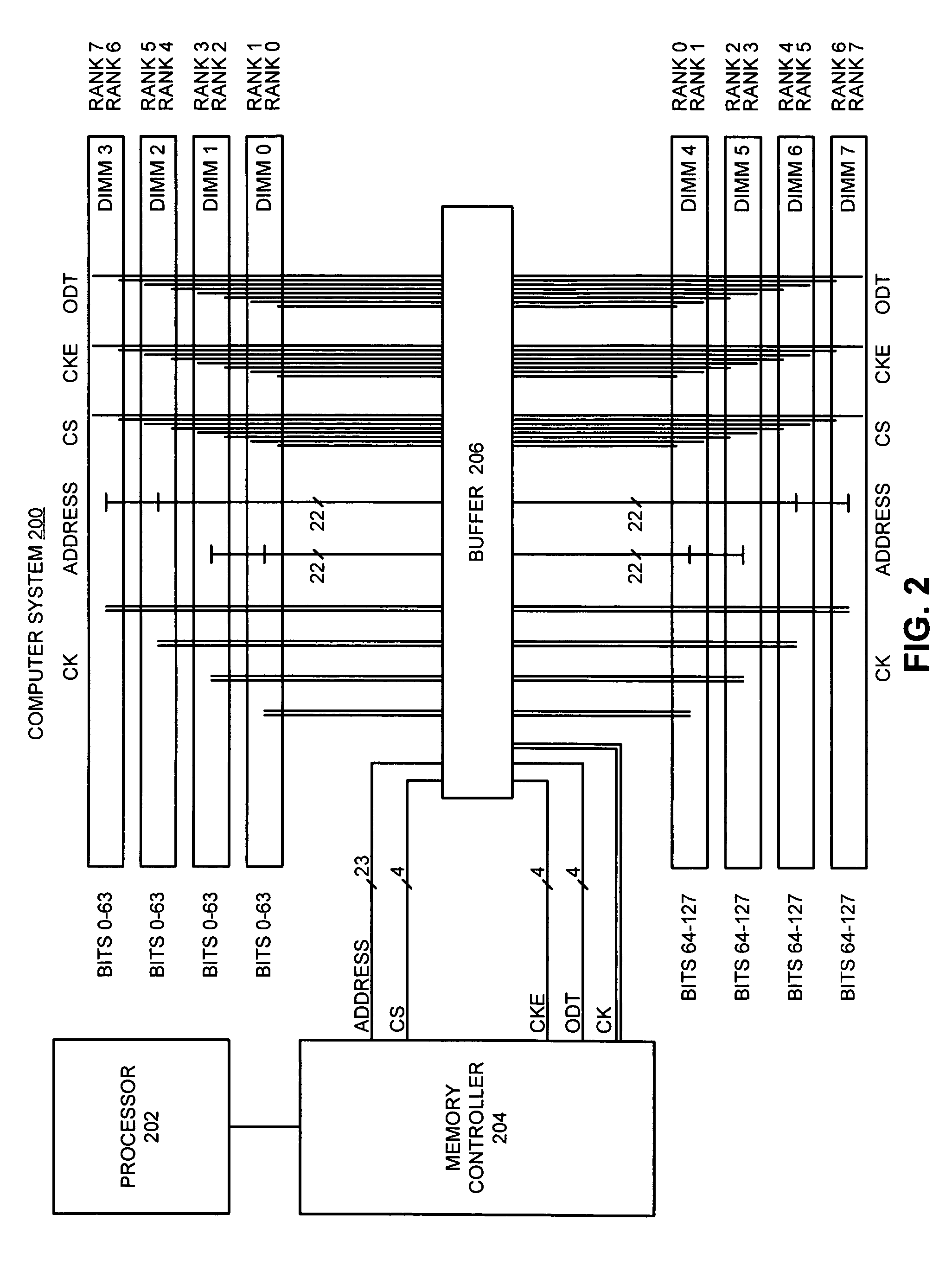

Method and apparatus for encoding memory control signals to reduce pin count

InactiveUS20060039204A1Reduced pin countReduce in quantityDigital storageMemory systemsSignal onControl signal

One embodiment of the present invention provides a system that uses encoded memory control signals to reduce pin count on chips that generate and drive memory control signals. During operation, the system receives encoded memory control signals from a memory controller, wherein the memory control signals were encoded to reduce the number of memory control signals, and wherein the encoded memory control signals are received at a buffer chip, which is external to the memory controller. Next, the system decodes the encoded memory control signals on the buffer chip to restore the memory control signals, and then drives the memory control signals from the buffer chip to corresponding memory modules in the system memory. By transferring the memory control signals in encoded form from the memory controller to the buffer chip, fewer pins are required on both the memory controller chip and the buffer chip.

Owner:APPLE INC

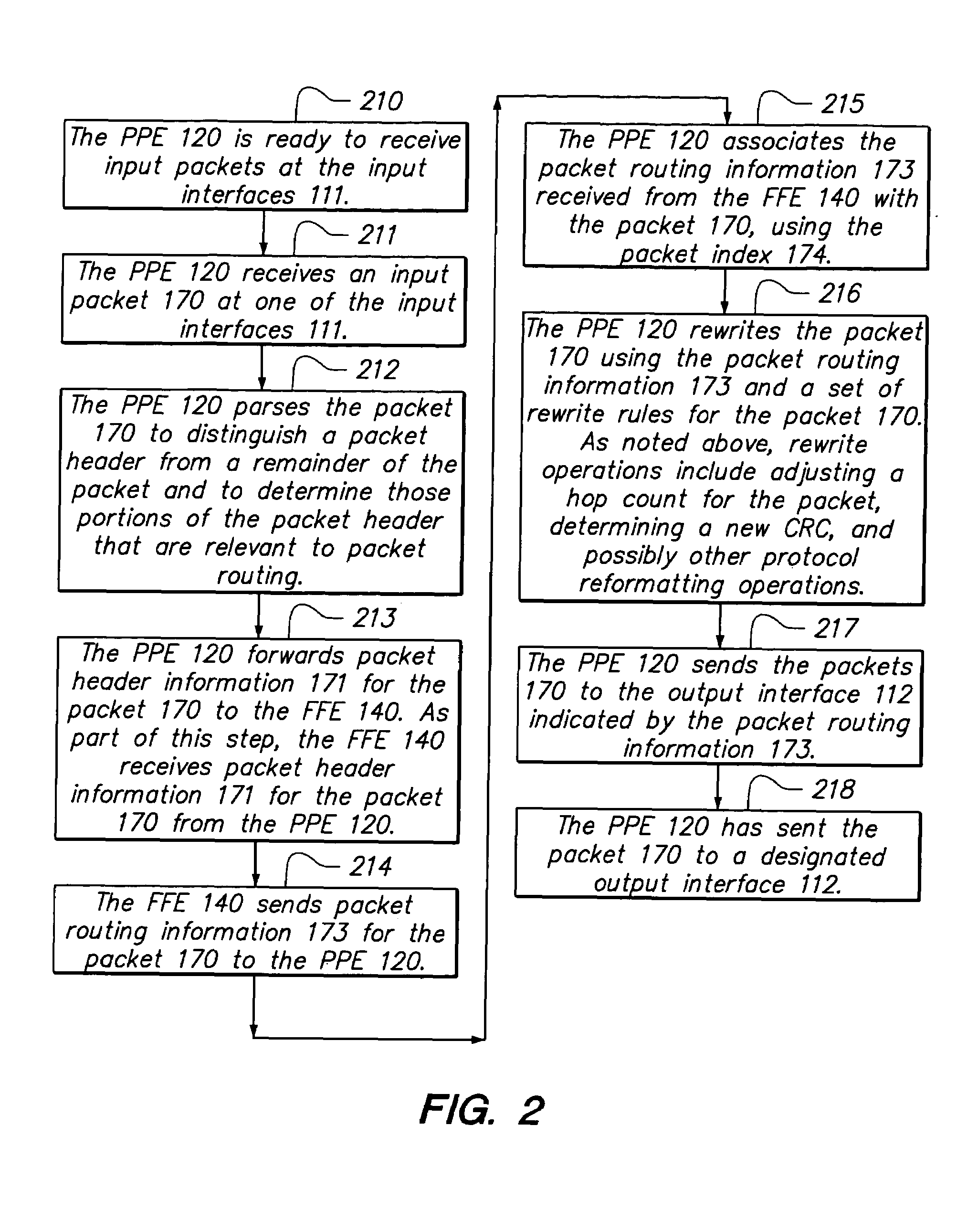

Packet processing engine architecture

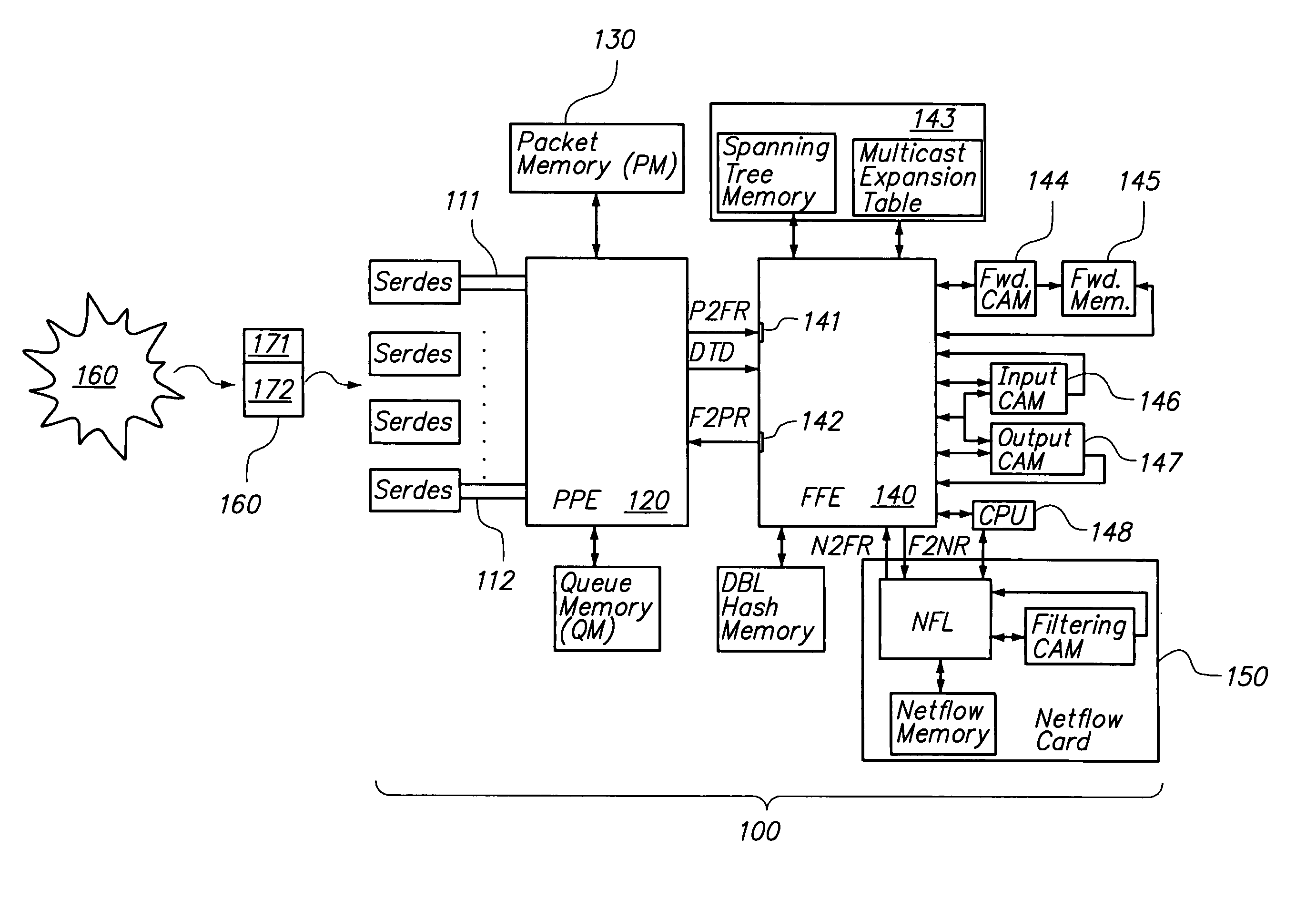

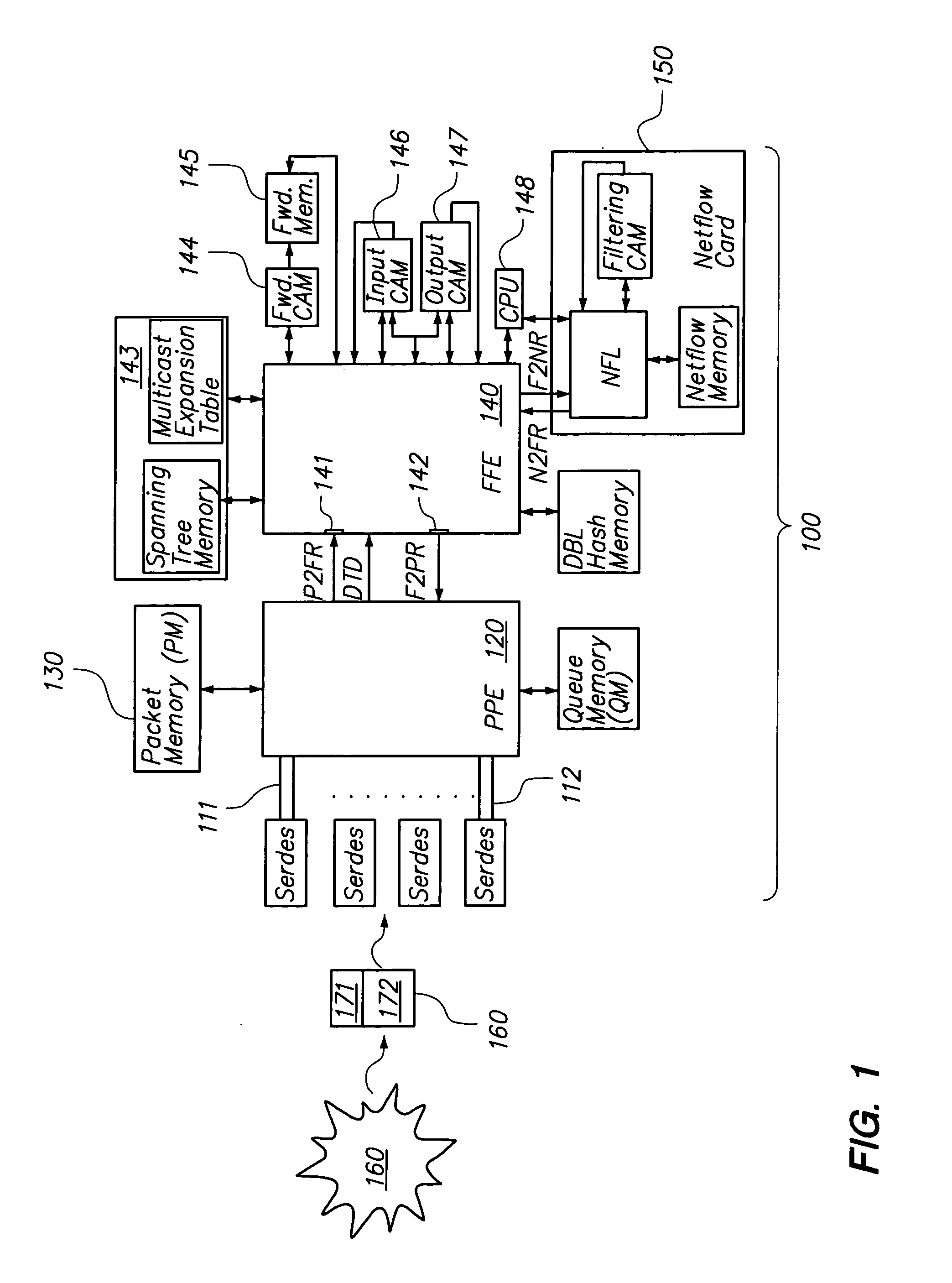

InactiveUS7218632B1Reduce data volumeReduced pin countData switching by path configurationPacket routingPacket processing

The invention provides a method and system for packet processing, in which a router (or switch) is capable of quickly processing incoming packets, thus performing level 2, 3, and 4 routing and additional services, in real time. A system includes a packet processing engine (PPE), having elements for receiving packets, distinguishing header and payload information for those packets, outsourcing router decision-making to additional hardware resources such as a fast forwarding engine (FFE), and forwarding those packets. The PPE is synchronized to the FFE, so that the PPE can send and the FFE can receive packets at each one of a sequence of constant-duration time quanta. Similarly, the PPE can receive and the FFE can send packet routing information at each one of a sequence of similar time quanta. The PPE and the FFE have separate hardware so that their functions can be performed in parallel without contention for operating resources.

Owner:CISCO TECH INC

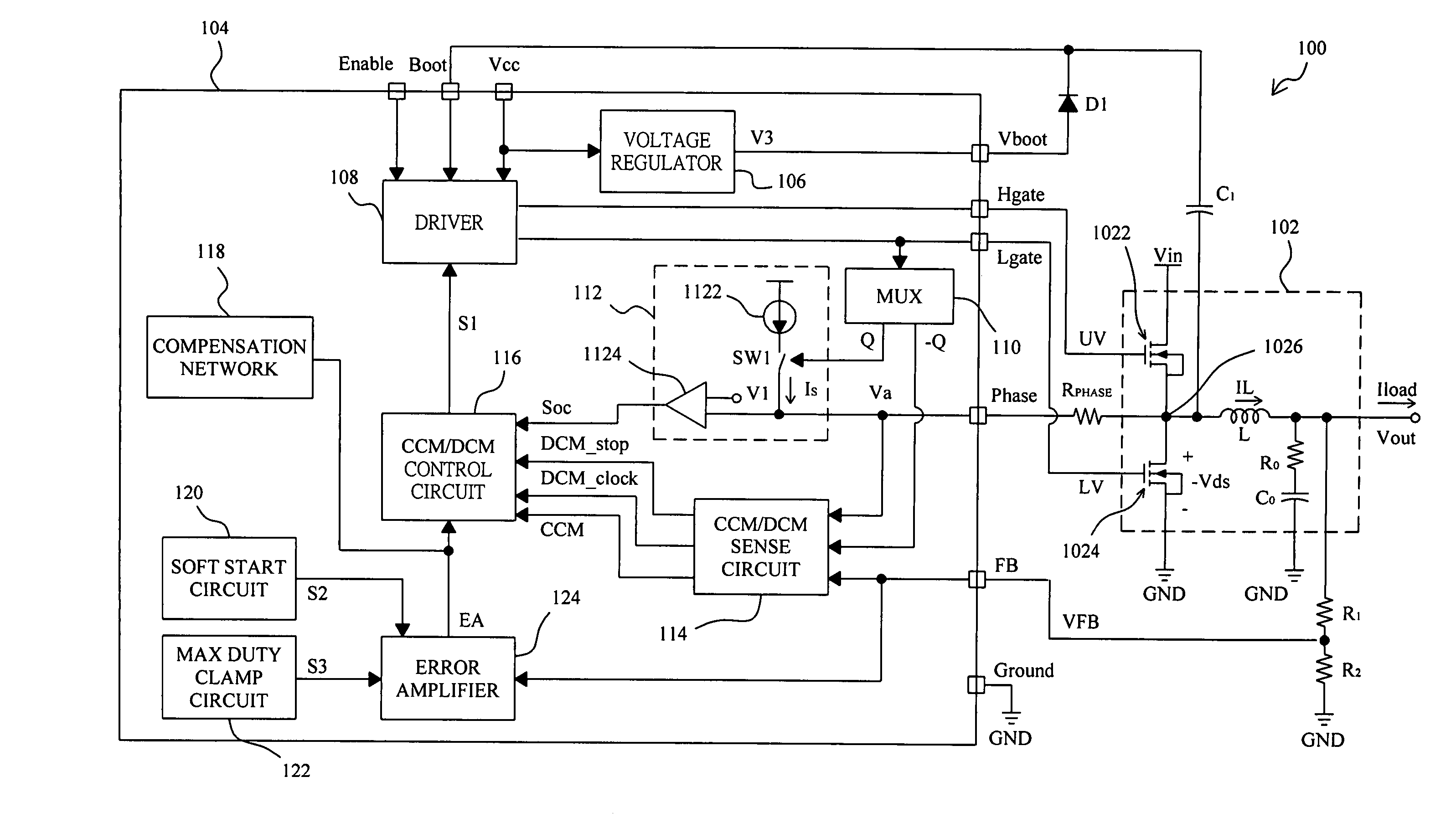

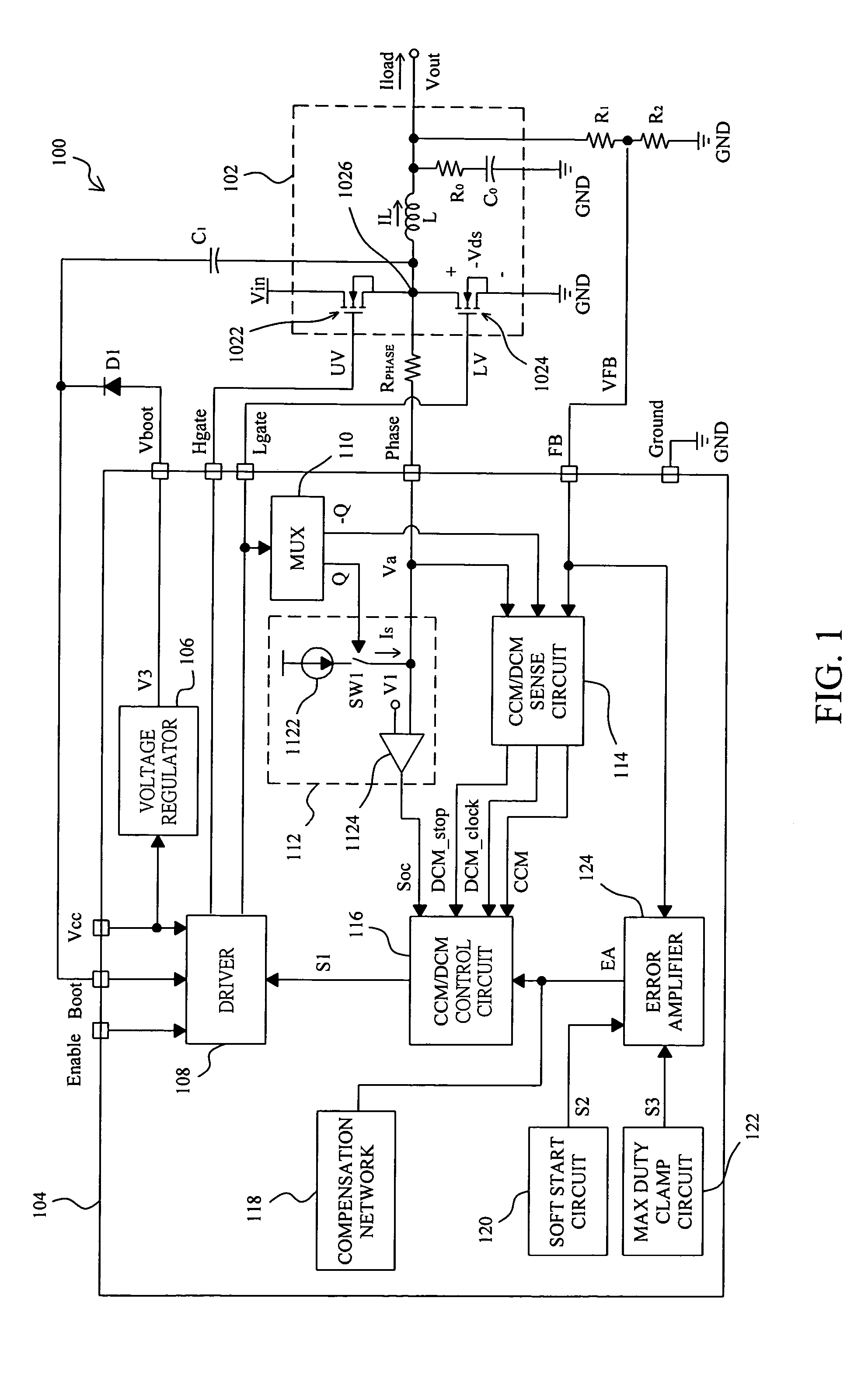

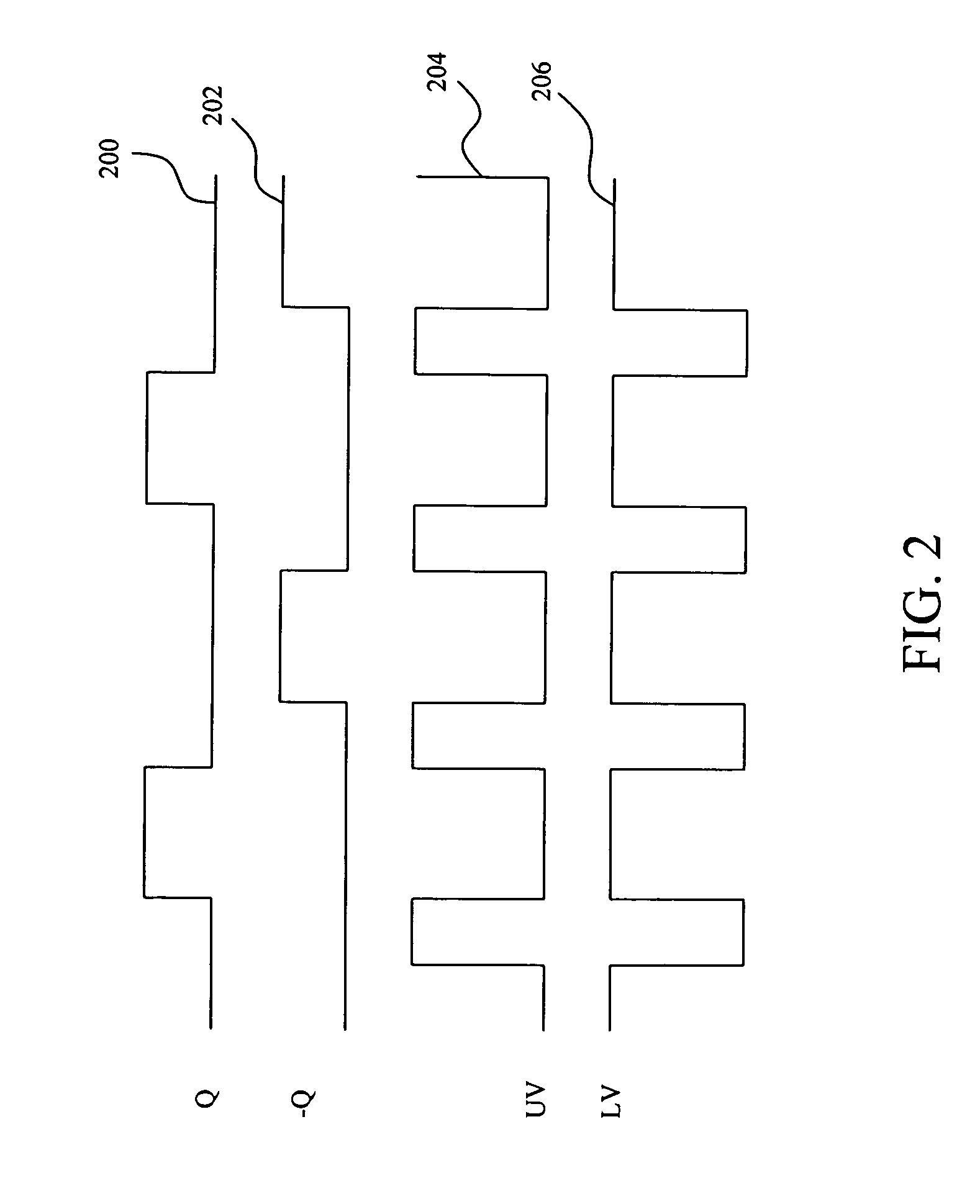

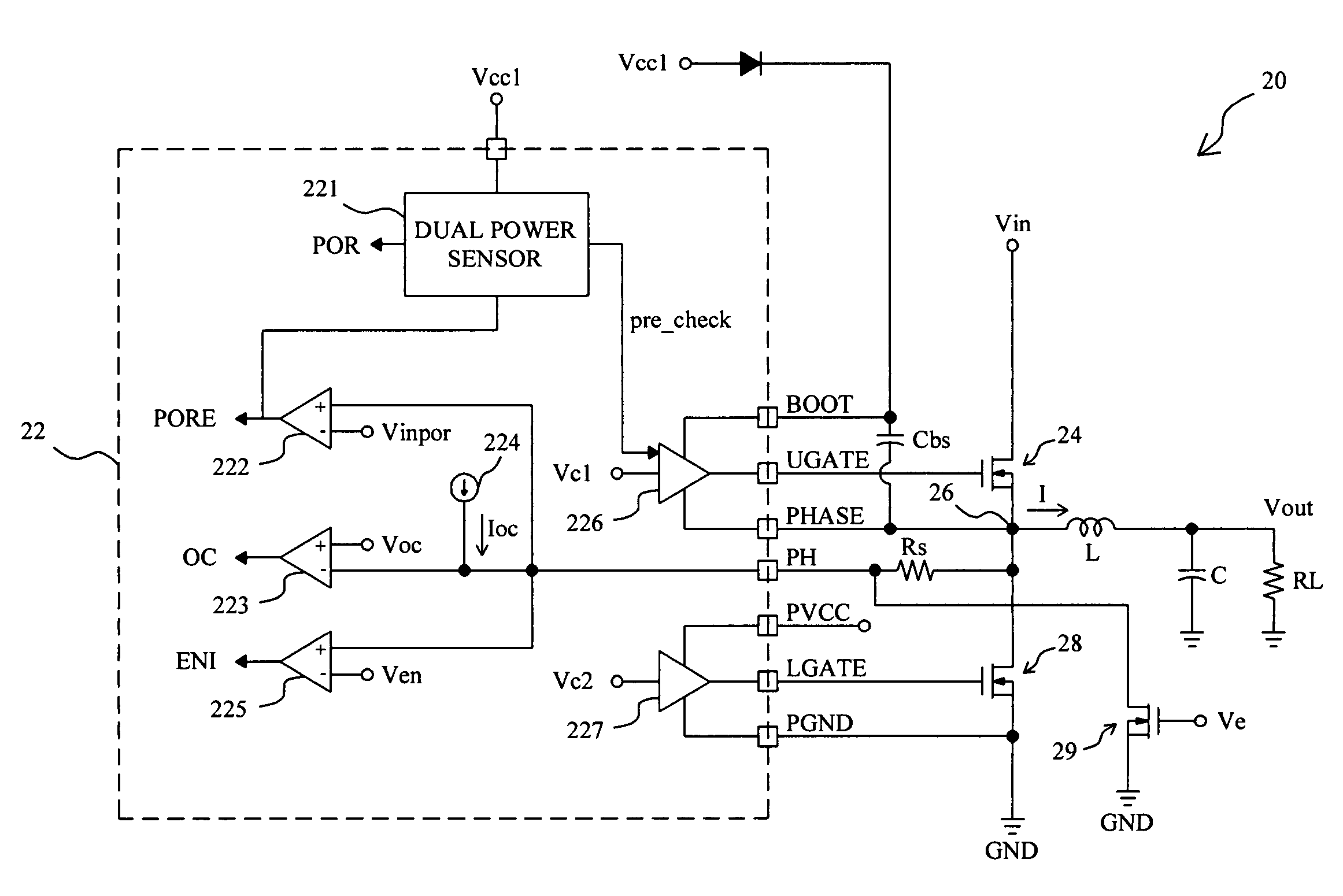

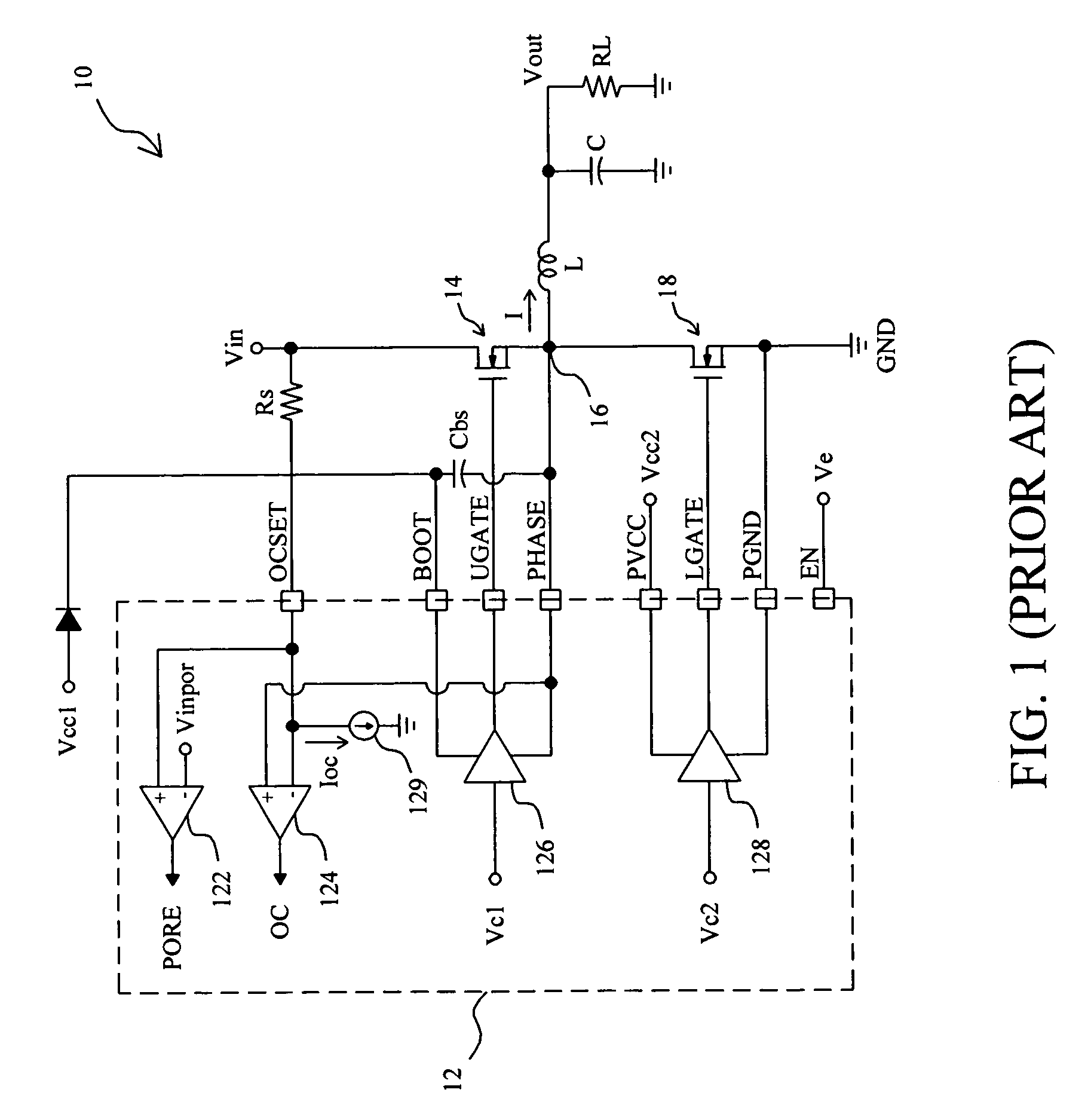

Controller in a voltage mode buck converter for implementing a mode-switch function and an over-current protection by a multifunction pin and method thereof

ActiveUS7098632B2Reduced pin countReduce in quantityEmergency protective circuit arrangementsDc-dc conversionControl signalBuck converter

In a voltage mode buck converter having a pair of switches connected in series by a phase node to be switched by a pair of drive signals generated from a first control signal, a phase resistor is connected between a multifunction pin and the phase node, and a controller generates a second control signal and a third control signal from the second drive signal to sense the voltage on the multifunction pin respectively to generate an over-current signal and a CCM mode switch signal to switch the converter between a CCM mode and a DCM mode.

Owner:ANPEC ELECTRONICS CORPORATION

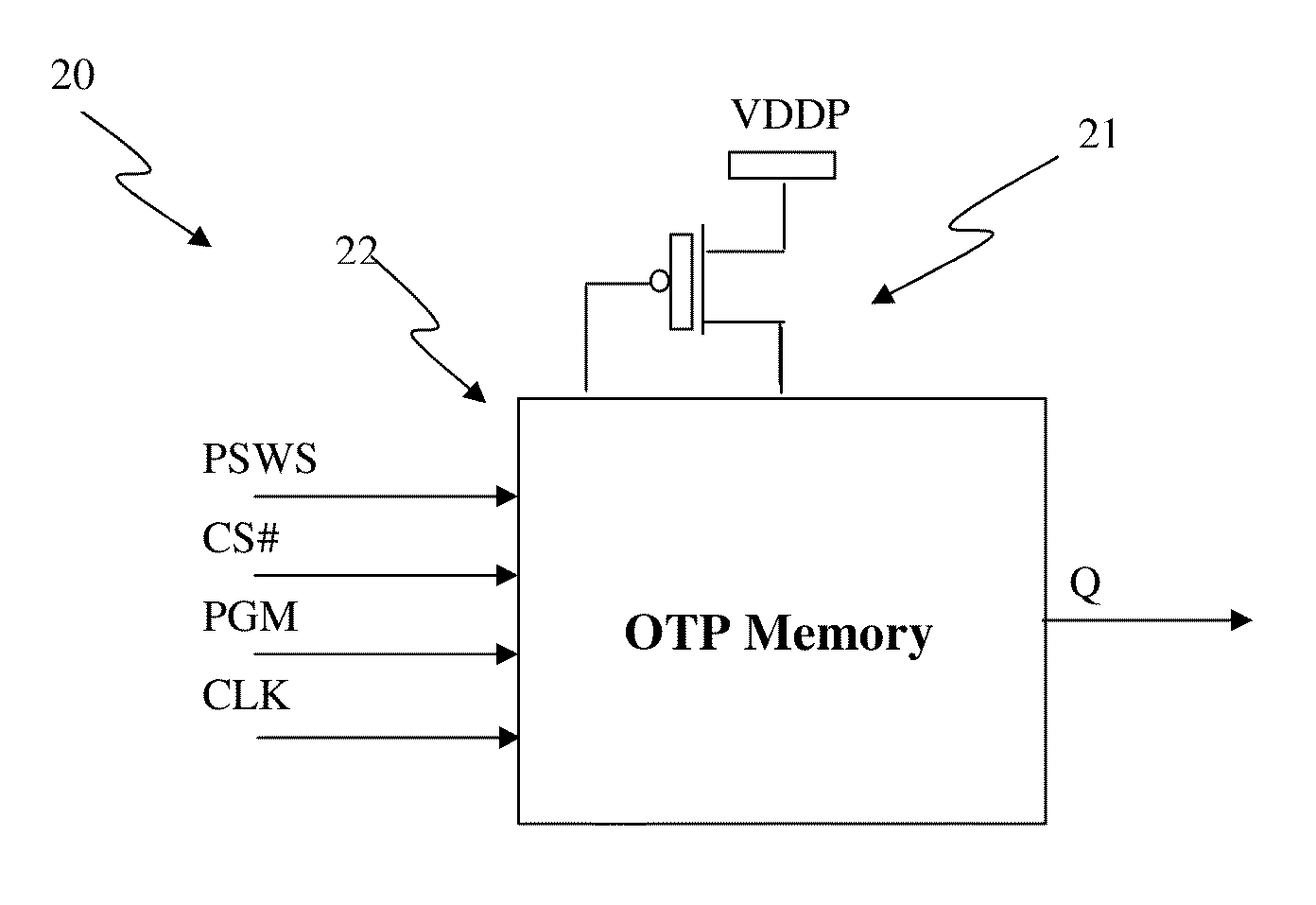

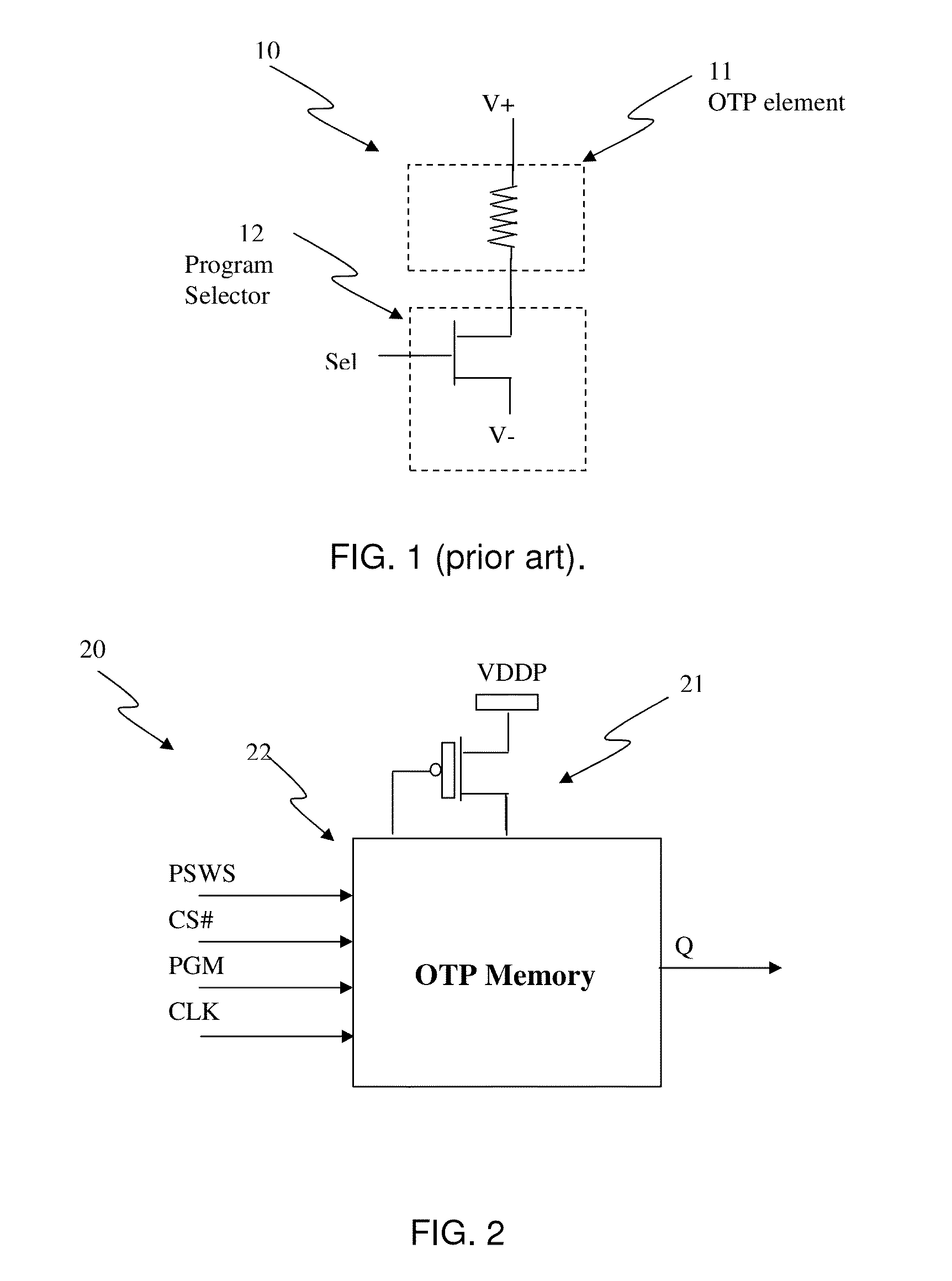

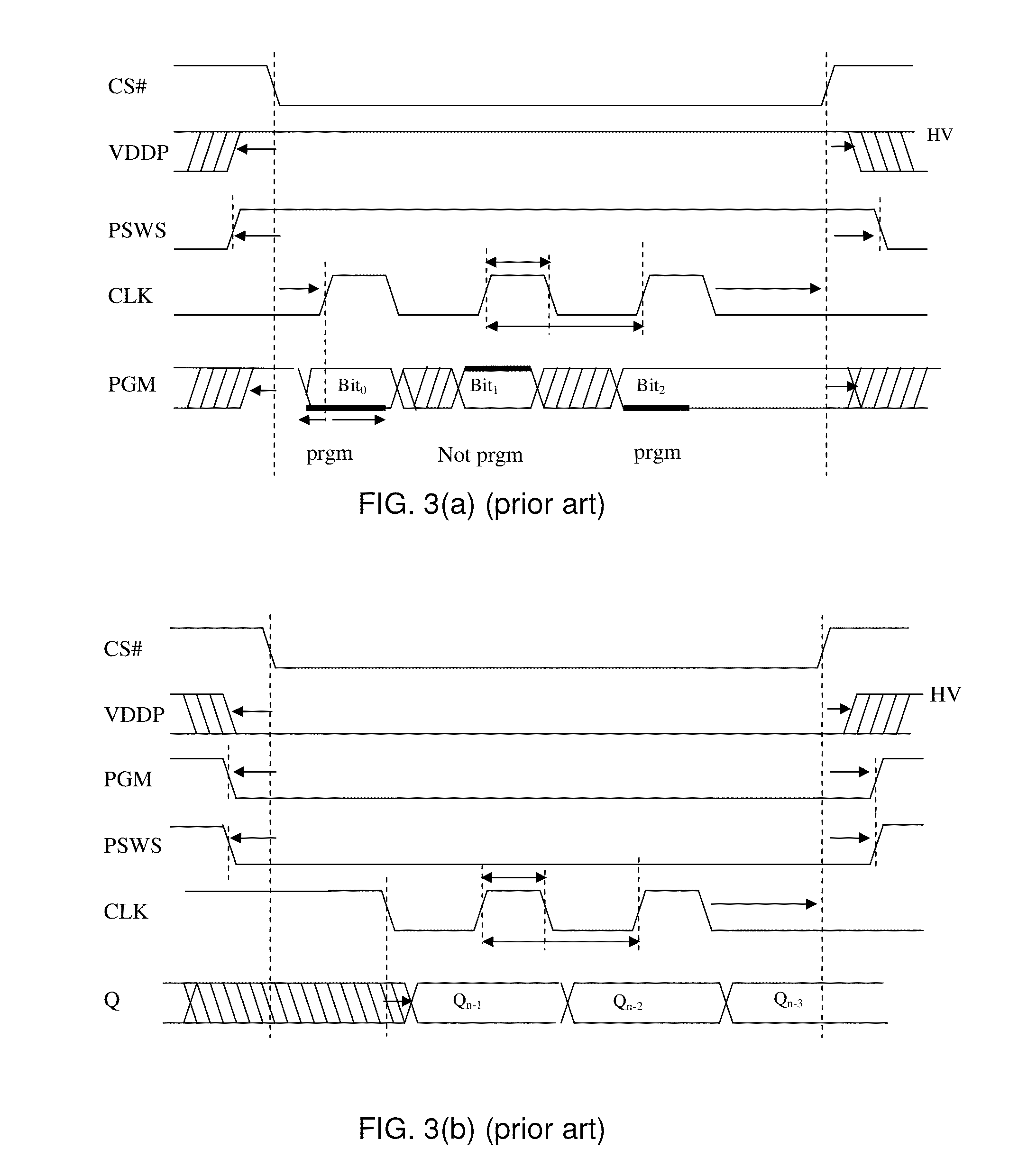

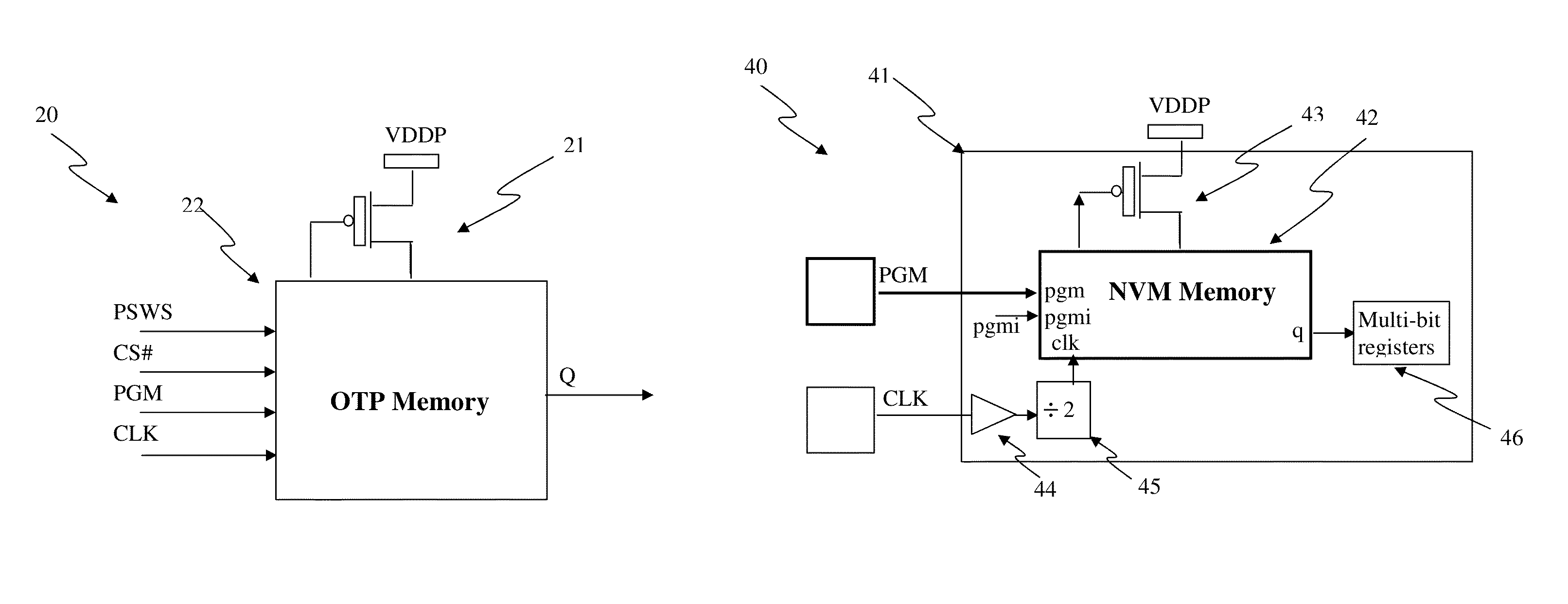

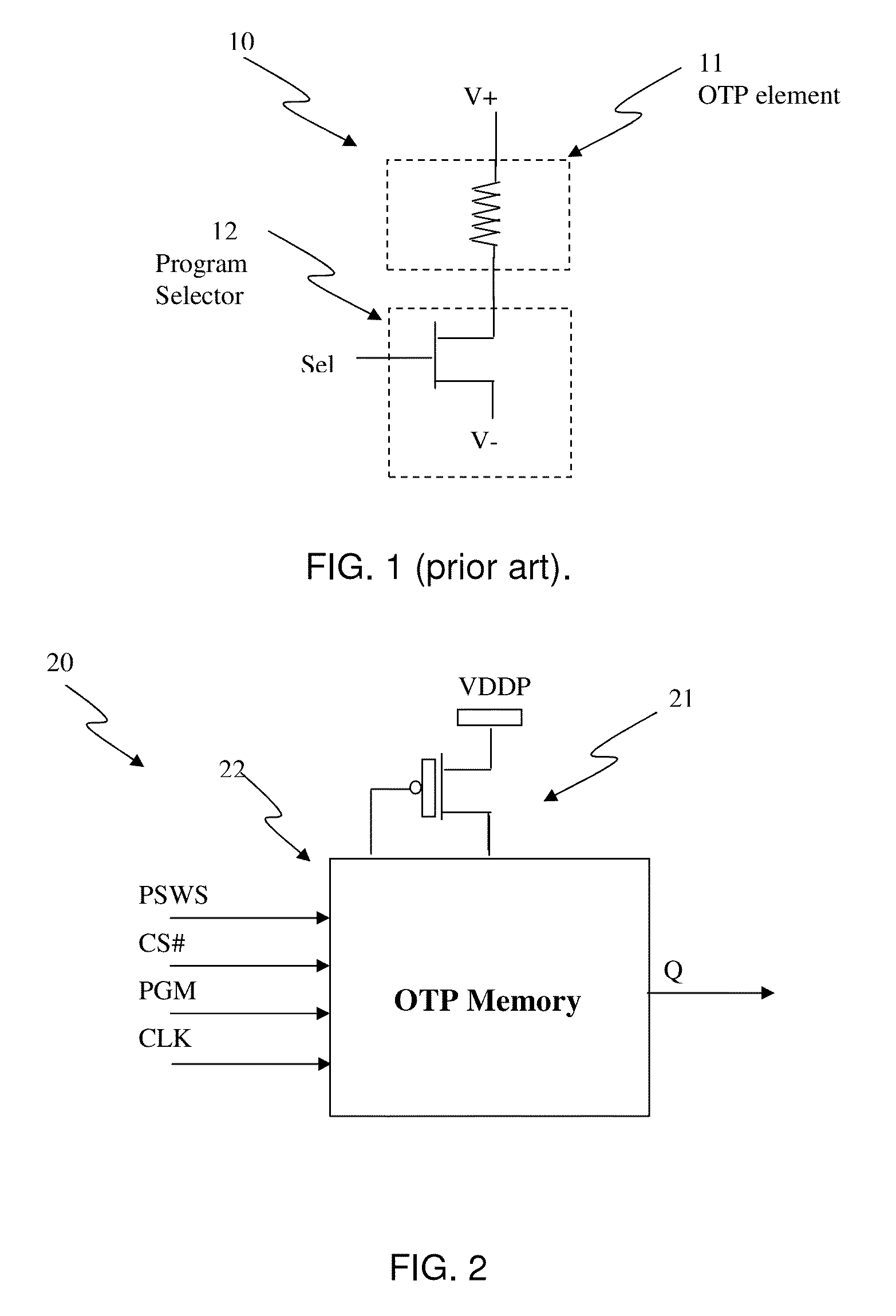

Low-Pin-Count Non-Volatile Memory Interface for 3D IC

ActiveUS20150009743A1Reduce number of pinReduce numberRead-only memoriesDigital storageIntegrated circuitNon-volatile memory

A low-pin-count non-volatile (NVM) memory to be provided in an integrated circuit for a 3D IC to repair defects, trim devices, or adjust parameters is presented here. At least one die in a 3D IC can be built with at least one low-pin-count OTP memory. The low-pin-count OTP memory can be built with a serial interface such as I2C-like or SPI-like of interface. The pins of the low-pin-count OTP in at least one dies can be coupled together to have only one set of low-pin-count bus for external access. With proper device ID, each dies in a 3D IC can be accessed individually for soft programming, programming, erasing, or reading. This technique can improve the manufacture yield, device, circuit, or logic performance or to store configuration parameters for customization after 3D IC are built.

Owner:ATTOPSEMI TECH CO LTD

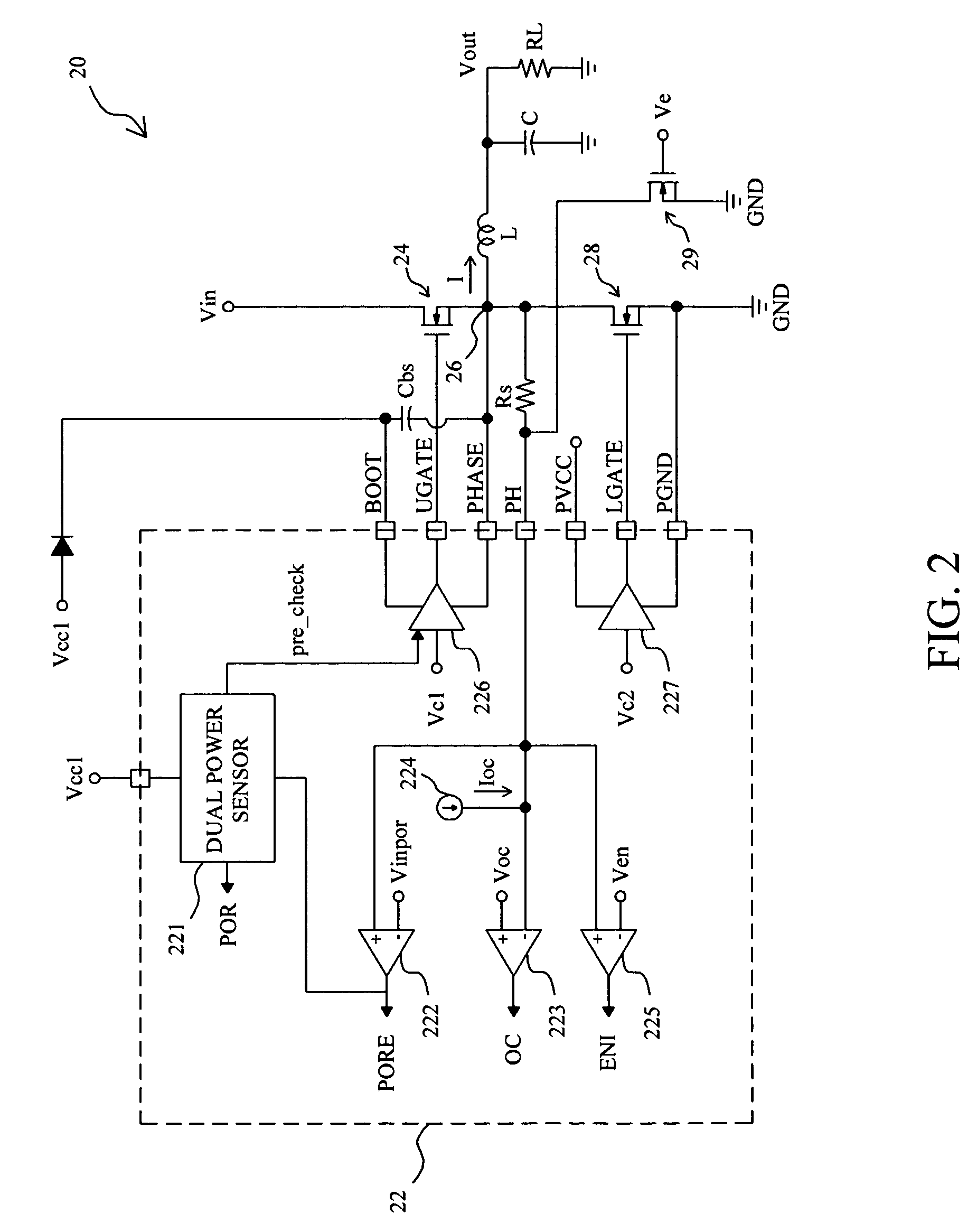

Circuit and method for implementing a multi-function pin on a PWM controller chip in a voltage converter

ActiveUS7233131B2Low costReduced pin countConversion with intermediate conversion to dcDc-dc conversionVoltage converterEngineering

For a PWM controller chip in a voltage converter to switch a pair of high side and low side switches connected with a phase node therebetween, a circuit comprises a sense resistor connected between a multi-function pin on the PWM controller chip and the phase node, and an enable arrangement, a power sensing arrangement, and an over-current protection arrangement to detect the voltage on the multi-function pin for accomplishing enable function, power sensing, and over-current protection, respectively.

Owner:RICHTEK TECH

Low-pin-count non-volatile memory interface for 3D IC

ActiveUS9019791B2Easily integrated into integrated circuitReduce areaRead-only memoriesDigital storageLow Pin CountNon-volatile memory

A low-pin-count non-volatile (NVM) memory to be provided in an integrated circuit for a 3D IC to repair defects, trim devices, or adjust parameters is presented here. At least one die in a 3D IC can be built with at least one low-pin-count OTP memory. The low-pin-count OTP memory can be built with a serial interface such as I2C-like or SPI-like of interface. The pins of the low-pin-count OTP in at least one dies can be coupled together to have only one set of low-pin-count bus for external access. With proper device ID, each dies in a 3D IC can be accessed individually for soft programming, programming, erasing, or reading. This technique can improve the manufacture yield, device, circuit, or logic performance or to store configuration parameters for customization after 3D IC are built.

Owner:ATTOPSEMI TECH CO LTD

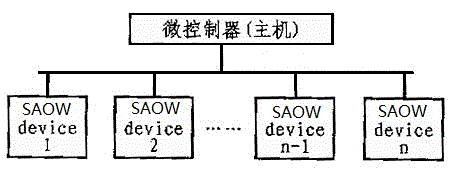

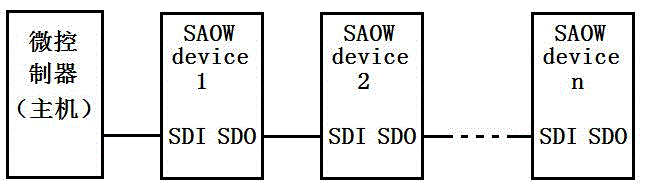

Implement method for high speed single bus communication

ActiveCN104811273ALarge tolerance rangeSimple interfaceBus networksTransmission format adaptationBaudData information

The invention relates to an implement method for high speed single bus communication. Data double-way transmission is performed on basis of an SDI signal line, the SDI signal line is connected with a host and a slave, the host sends signals through the SDI signal line, the slave is automatically adapted to receiving rate and starting and stopping of communication according to the received signals so that a self adaption one wire (SAOW) host-slave structure is formed, data information is transmitted by means of a command frame structure in terms of the data double-way transmission, and a command frame comprises a frame header, a slave address, a register address, data length, data and a frame tail. By means of the implement method for high speed single bus communication, one-bus double-way communication can be achieved, two communication parties are not required to use fixed baud rate, the baud rate can be changed whenever possible, and the method can be applied to occasions with unstable working frequency.

Owner:FUZHOU UNIVERSITY

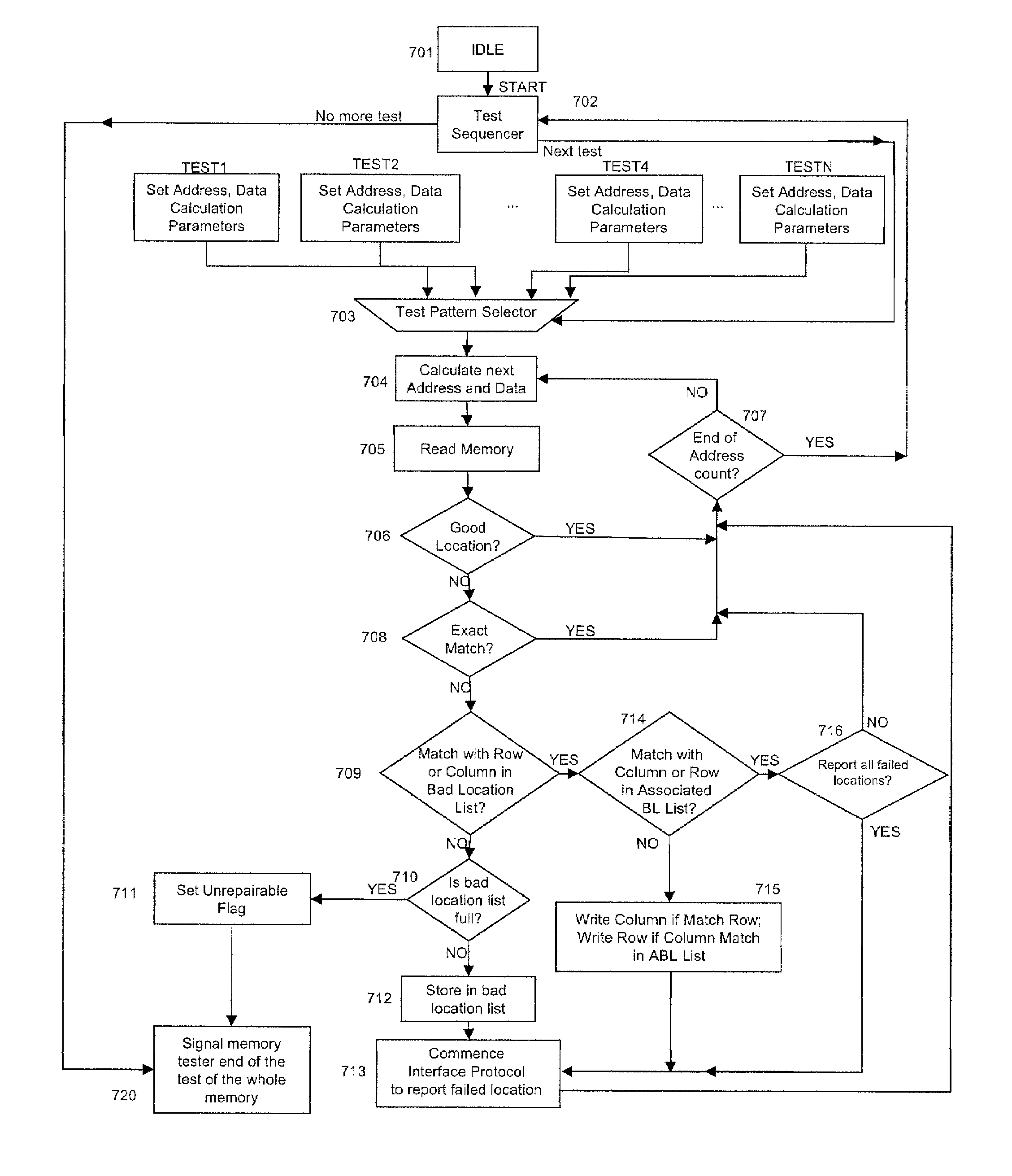

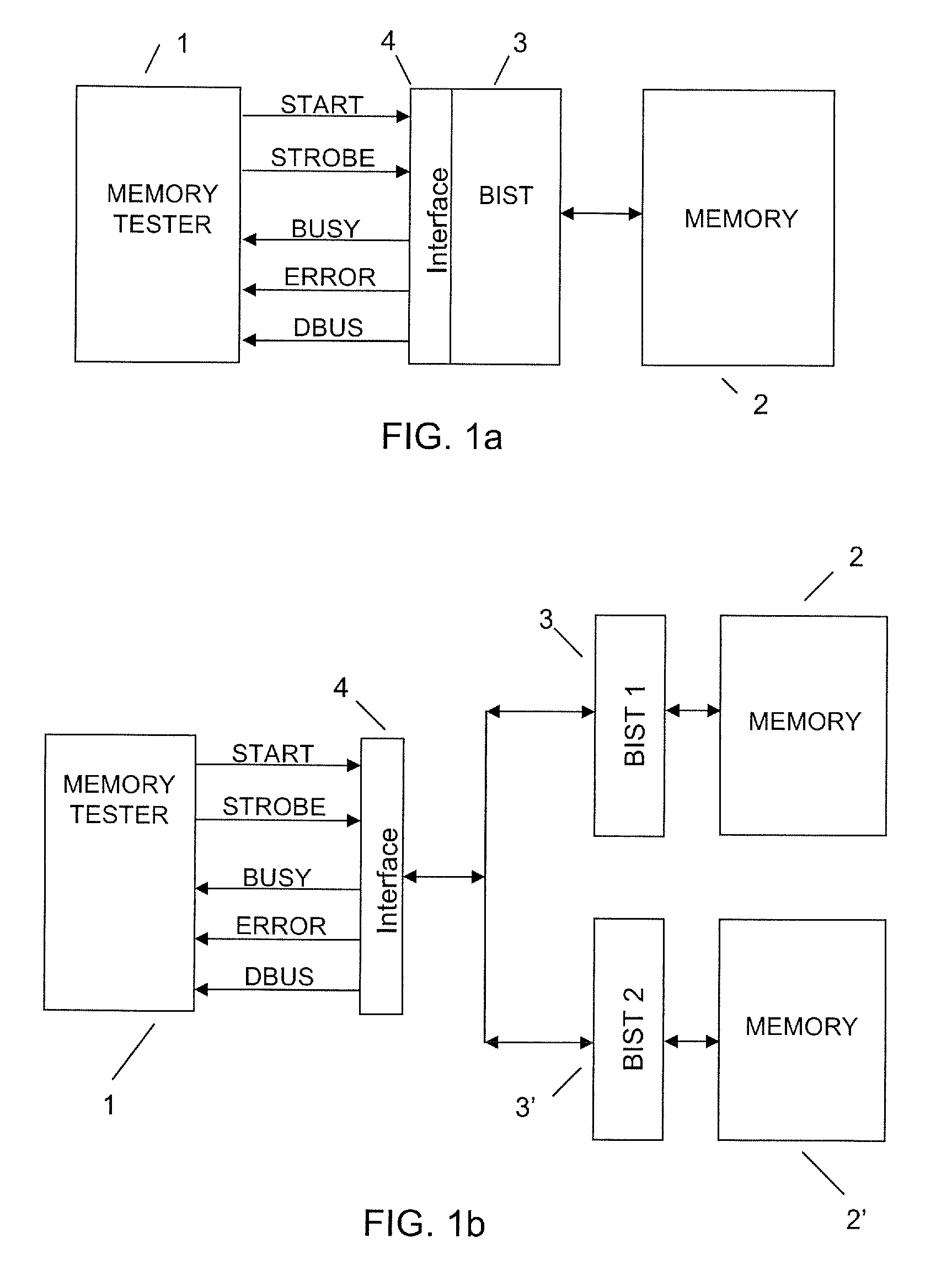

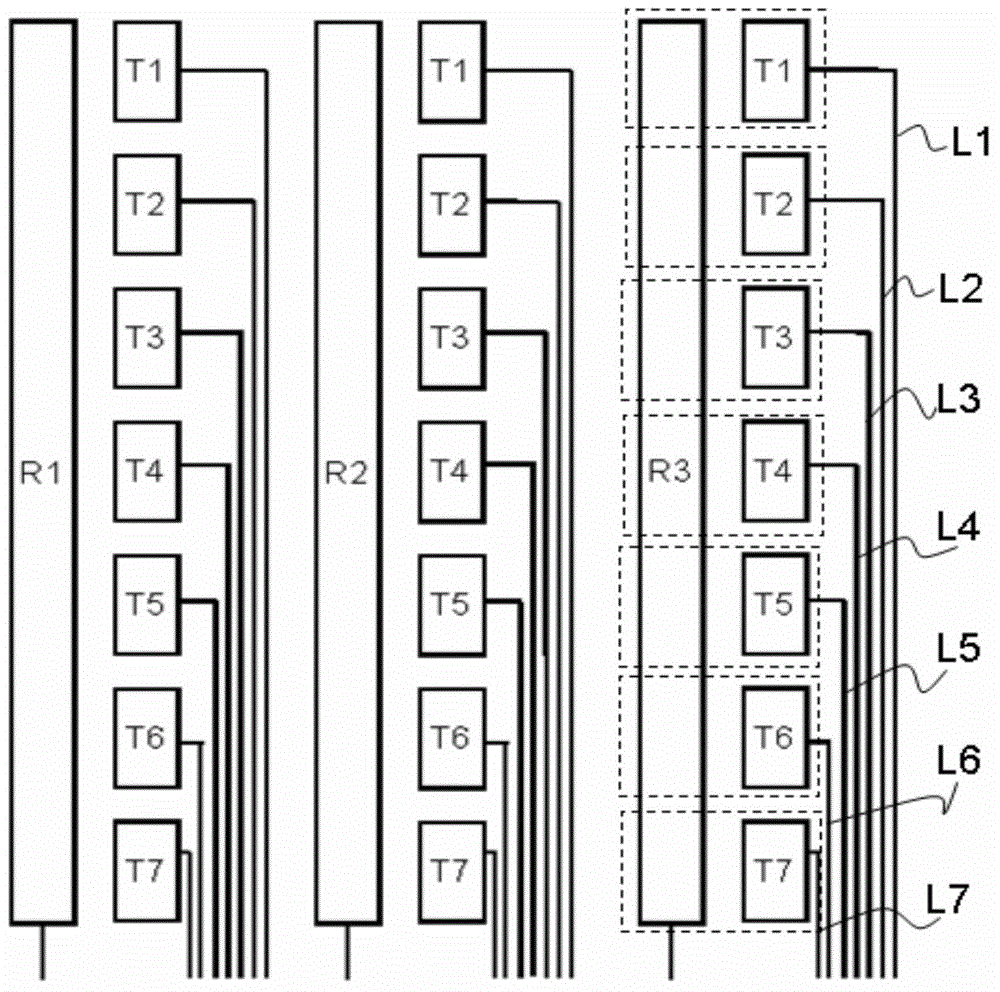

Method and system for memory testing and test data reporting during memory testing

ActiveUS7734966B1Reduced pin countNarrow interfaceElectronic circuit testingError detection/correctionAnalysis dataHigh memory

The present invention provides a method and system for improving memory testing efficiency, raising the speed of memory testing, detecting memory failures occurring at the memory operating frequency, and reducing data reported for redundancy repair analysis. The memory testing system includes a first memory tester extracting failed memory location information from the memory at a higher memory operating frequency, an external memory tester receiving failed memory location information at a lower memory tester frequency, and an interface between the first memory tester and the external memory tester. The memory testing method uses data strobes at the memory tester frequency to clock out failed memory location information obtained at the higher memory operating frequency. In addition, the inventive method reports only enough information to the external memory tester for it to determine row, column and single bit failures repairable with the available redundant resources. The present invention further provides a redundant resource allocation system, which uses a bad location list and an associated bad location list to classify failed memory locations according to a predetermined priority sequence, and allocates redundant resources to repair the failed memory locations according to the priority sequence.

Owner:MARVELL ASIA PTE LTD

Touch control structure, touch screen and touch display device

InactiveCN103941936AIncreased touch resolutionReduced pin countInput/output processes for data processingElectricityDisplay device

The invention provides a touch control structure which is characterized in that the touch control structure comprises multiple rows of driving electrodes, multiple rows of induction electrodes, multiple rows of drive signal pins and multiple induction signal pins, wherein each row of the driving electrodes comprises multiple driving electrodes, each row of the induction electrodes comprises multiple induction electrodes, the induction electrodes in each row of the induction electrodes are divided into multiple groups, and the multiple rows of the induction electrodes and the multiple rows of the driving electrodes are arranged at intervals; the driving electrodes in each row of the driving electrodes are correspondingly and electrically connected with driving signal ends one to one; the induction electrodes in one group are electrically connected with the different induction signal pins, one induction electrode in every group is electrically connected with the same induction signal pin, and one driving electrode corresponds to one group of induction electrodes.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

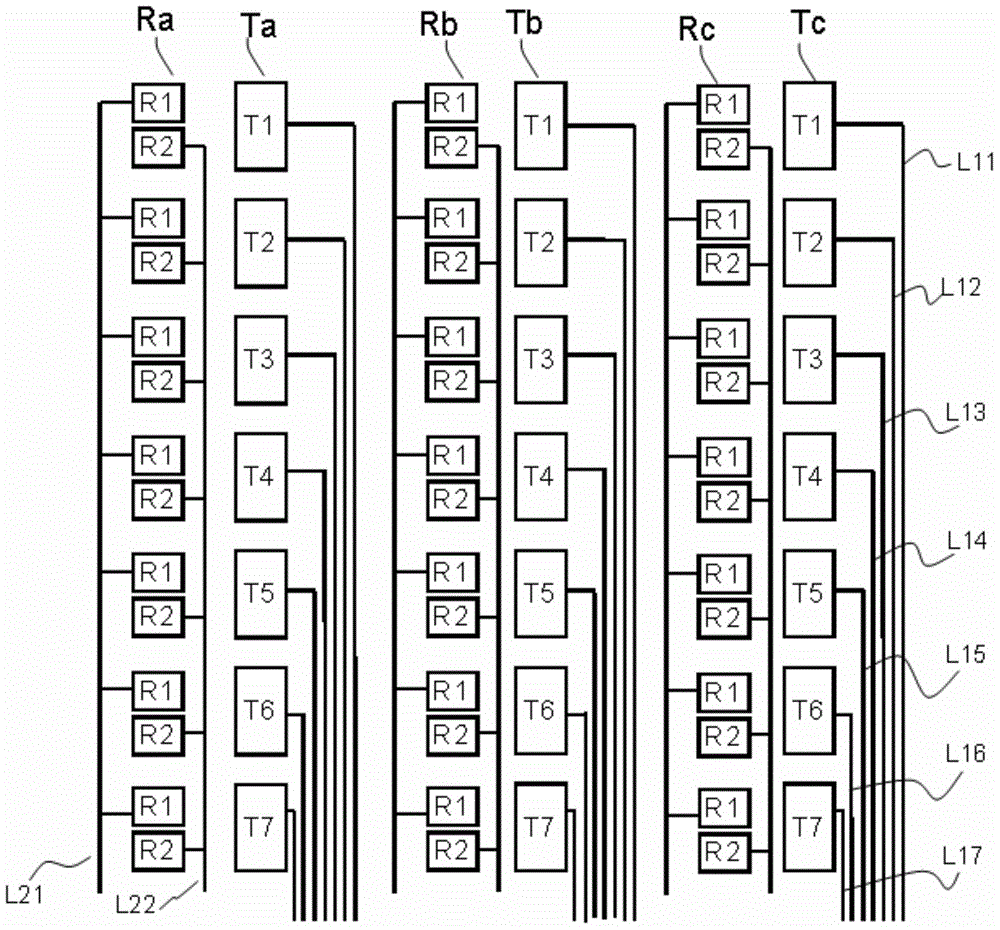

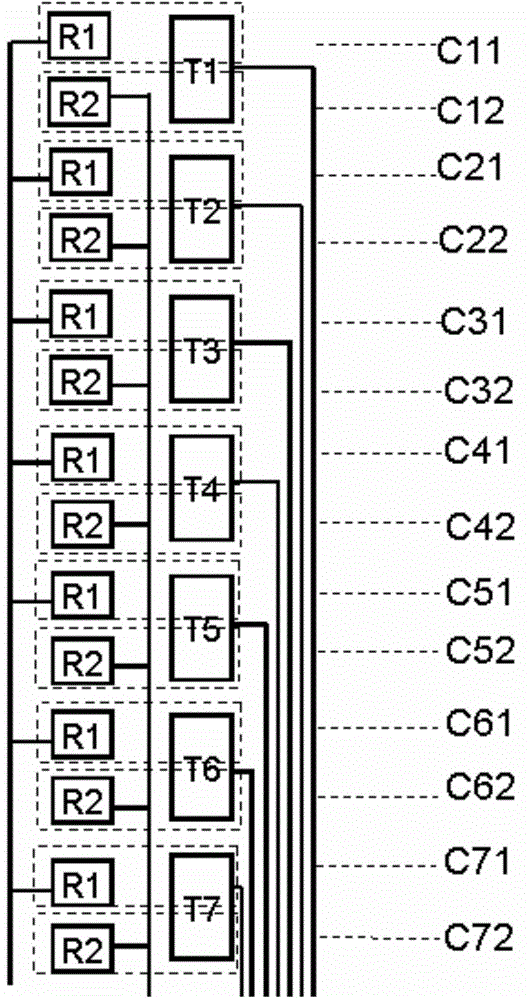

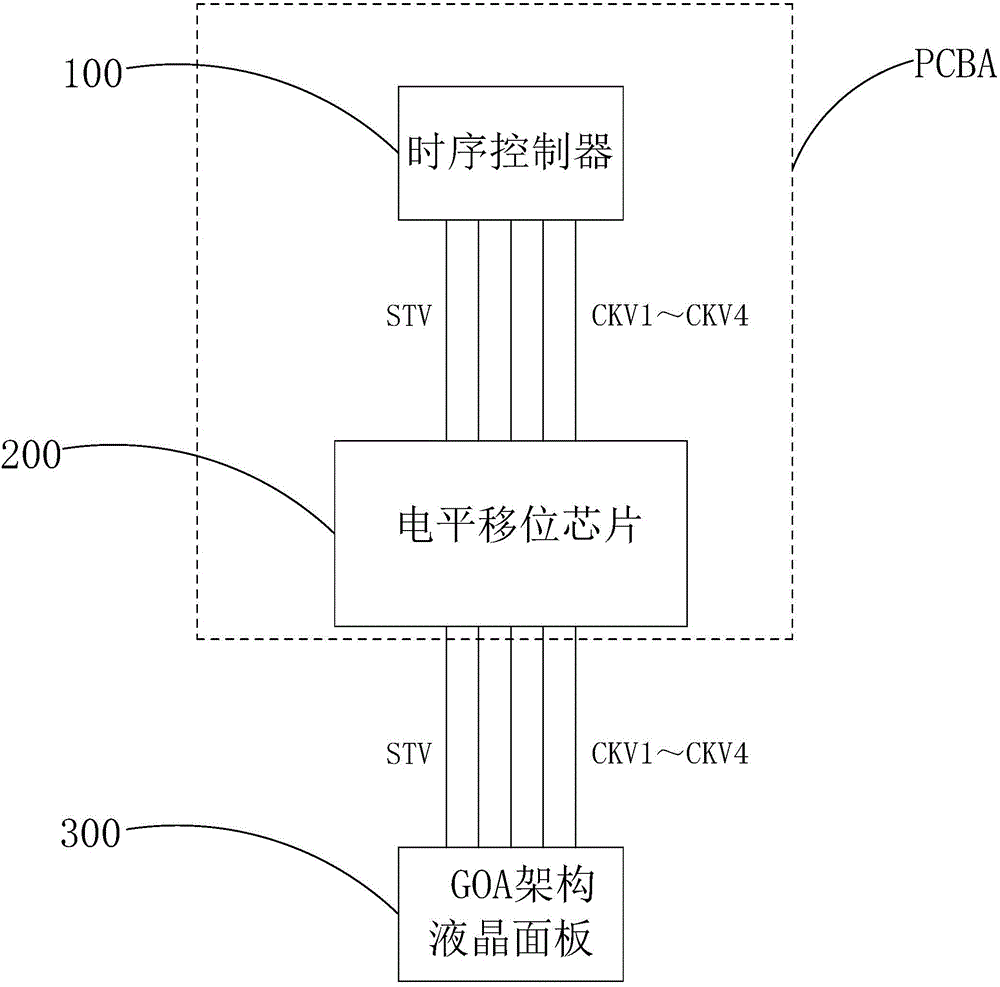

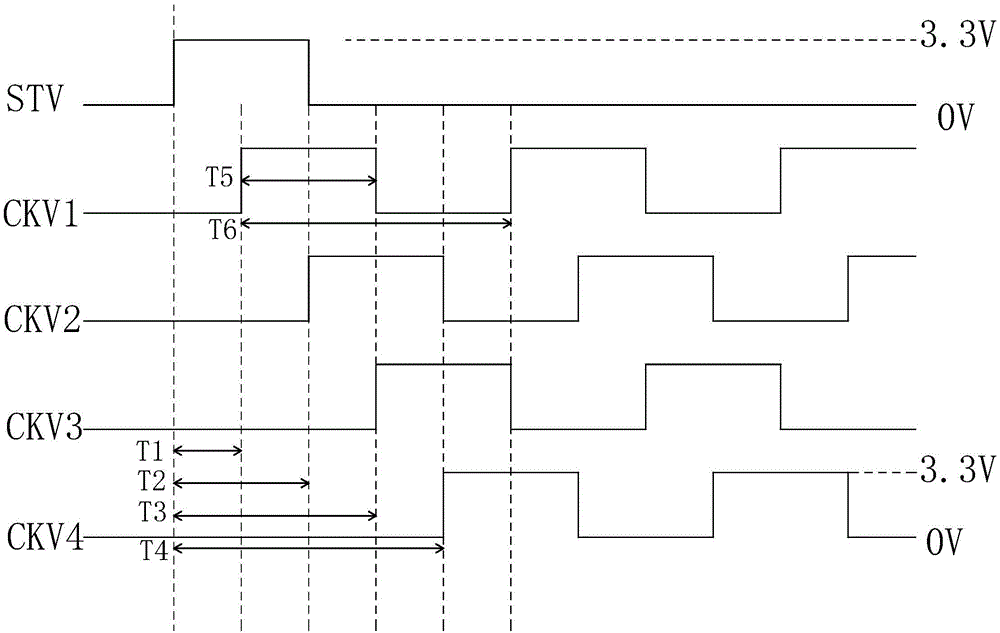

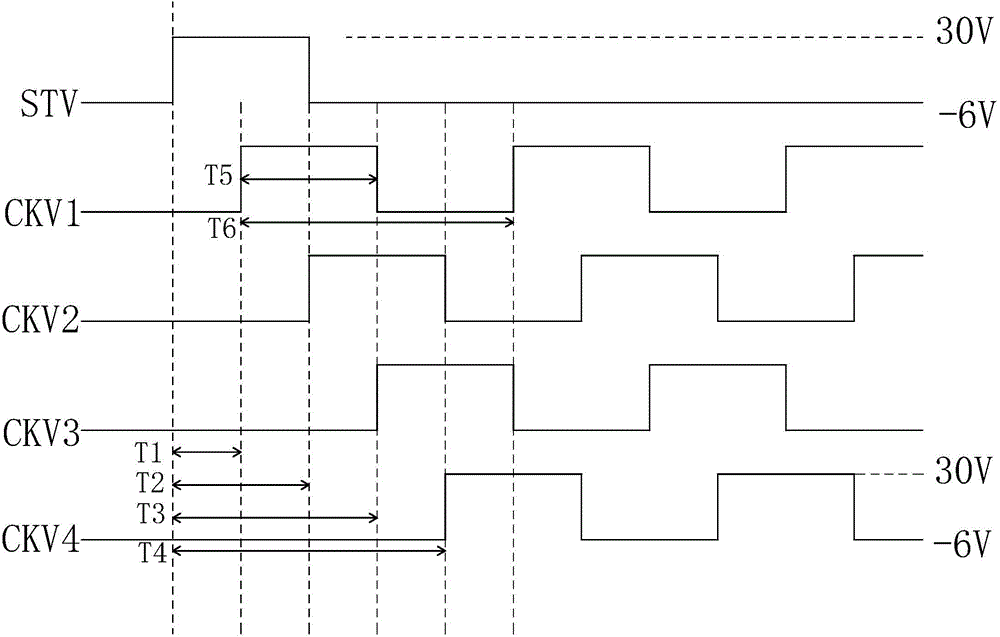

Level shifting circuit and method for GOA-framework liquid crystal panel

ActiveCN104680991AReduced package numberReduced pin countStatic indicating devicesLevel shiftingComputer module

The invention provides a level shifting circuit and method for a GOA-framework liquid crystal panel. A delay calculation and registration module (201) is arranged inside a level shifting chip (20); a time sequence controller (10) is in communication connection with the level shifting chip (20) through a start signal line (30) and an IIC bus (40); the time sequence controller (10) performs initialized assignment (T1-Tn) on the delay calculation and registration module (201) through the IIC bus (40), and sends a start signal (STV) to the level shifting chip (20) through the start signal line (30); with the start signal (STV) as a reference, the level shifting chip (20) triggers to output at least four groups of time sequence signals (CKV1-CKVn) according to the initialized assignment (T1-Tn) in the delay calculation and registration module, and boosts the start signal (STV) and the voltages of at least four groups of time sequence signals (CKV1-CKVn)) so as to drive the GOA-framework liquid crystal panel (50), so that more time sequence signals are generated at the relatively low cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

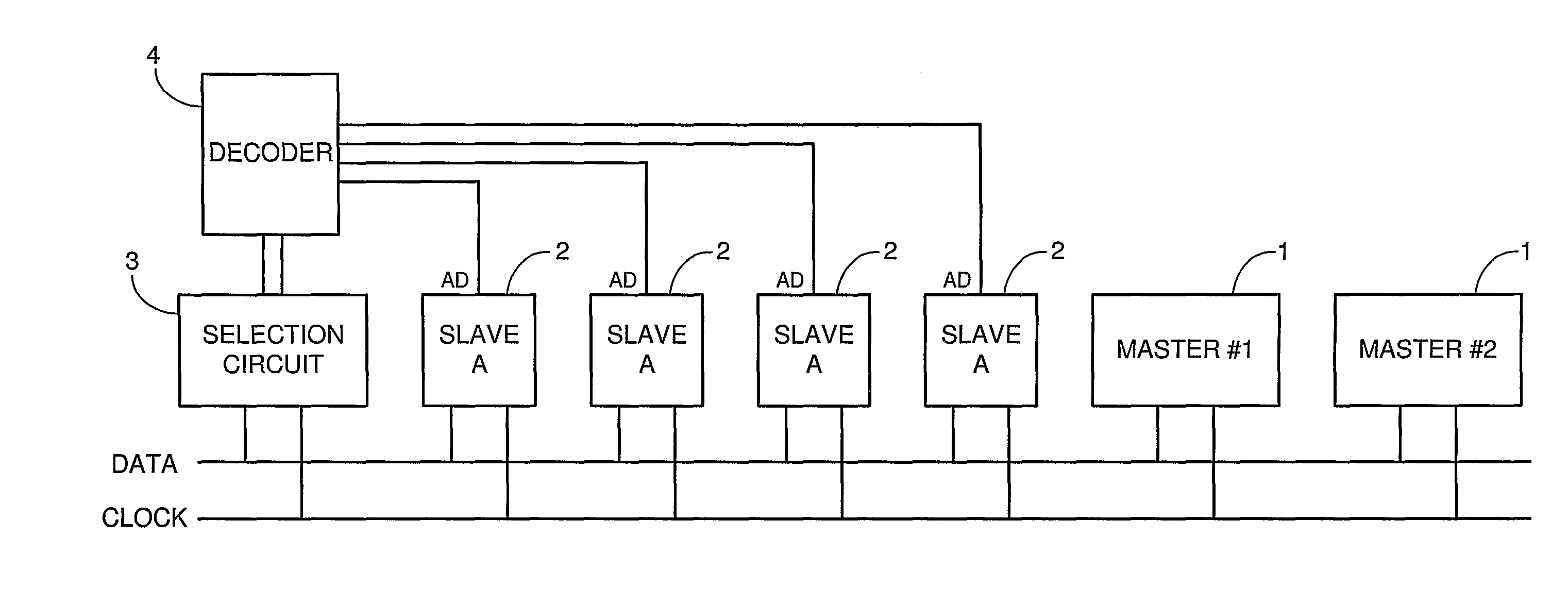

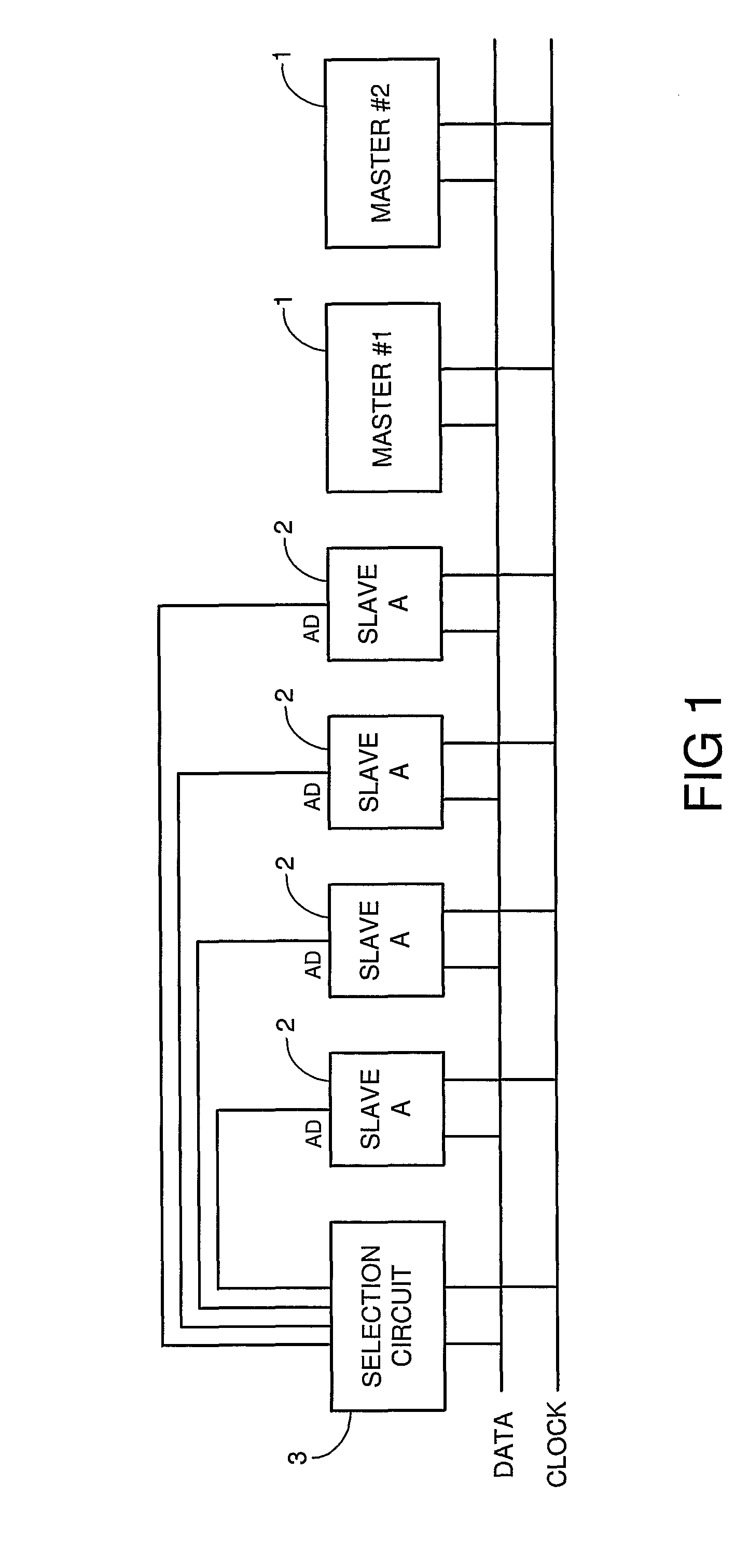

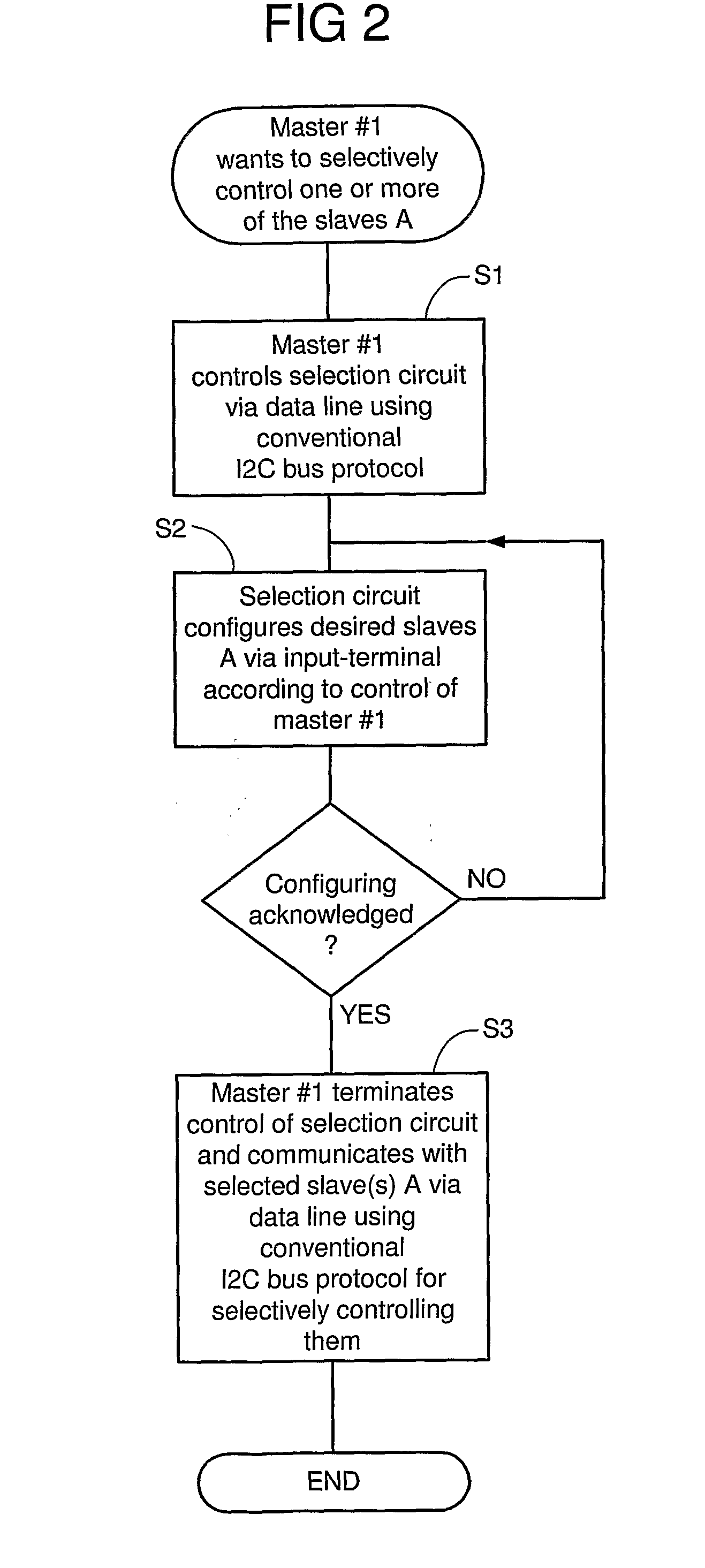

Bus System for Selectively Controlling a Plurality of Identical Slave Circuits Connected to the Bus and Method Therefore

InactiveUS20080270654A1Avoid disadvantagesSimple and cost efficient structureElectric digital data processingEmbedded systemData lines

A bus system (BS) for selectively controlling a plurality of identical slave circuits (slave A) comprises a bus (B) having a clock line (CLOCK) and at least one data line (DATA). The bus system (BS) includes at least one master circuit (1) and a plurality of slave circuits (2) with a group of identical slave circuits (slave A) connected to said bus (B). Each of the identical slave circuits (slave A) comprises an input-terminal (AD). The bus system (BS) further includes a selection circuit (3) connected to said bus (B), said selection circuit (3) is connected to each of said input-terminals (AD) for configuring at least one of the identical slave circuits (slave A) to be addressable by a master circuit (1) via said at least one data line (DATA).

Owner:NXP BV

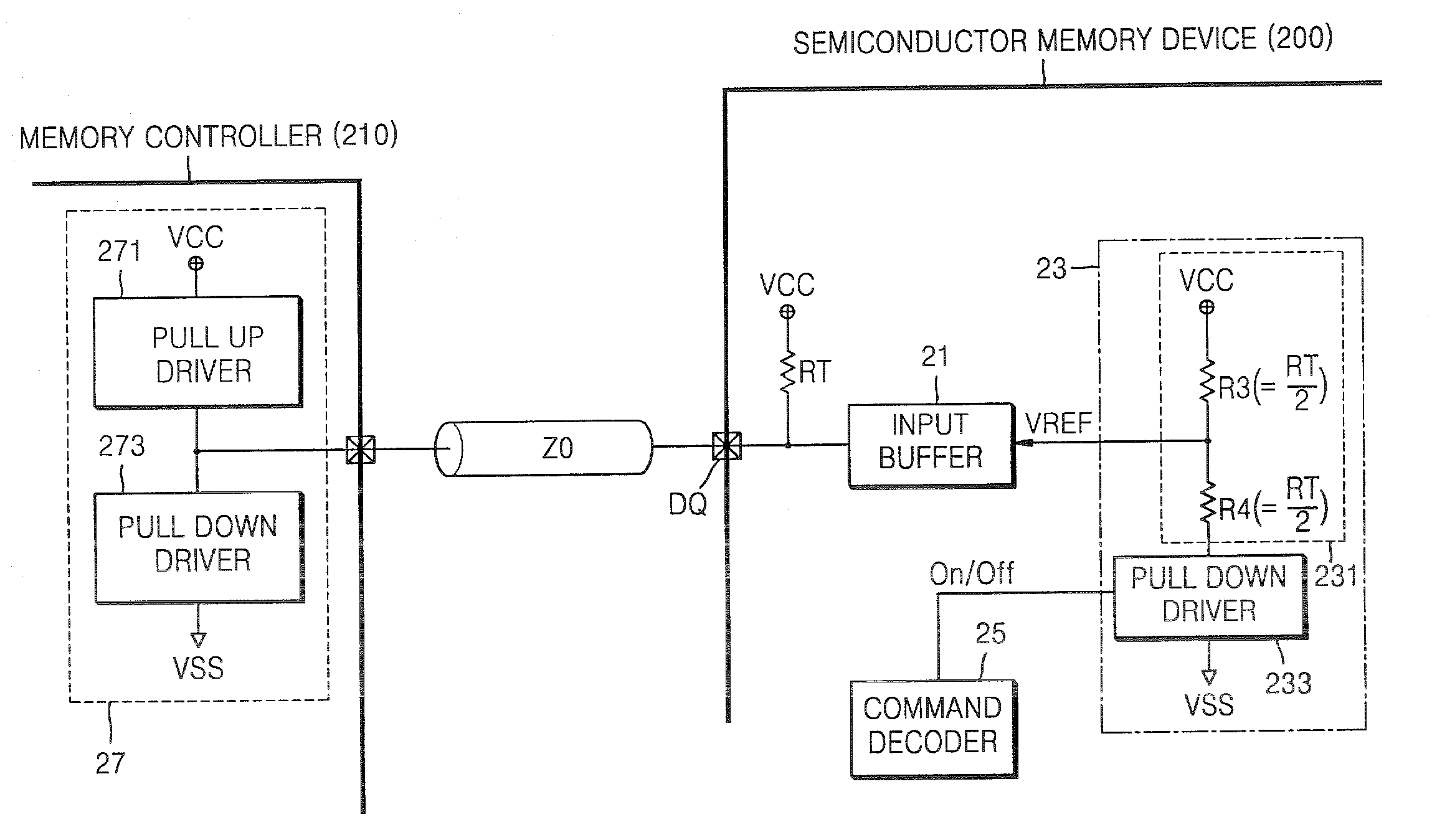

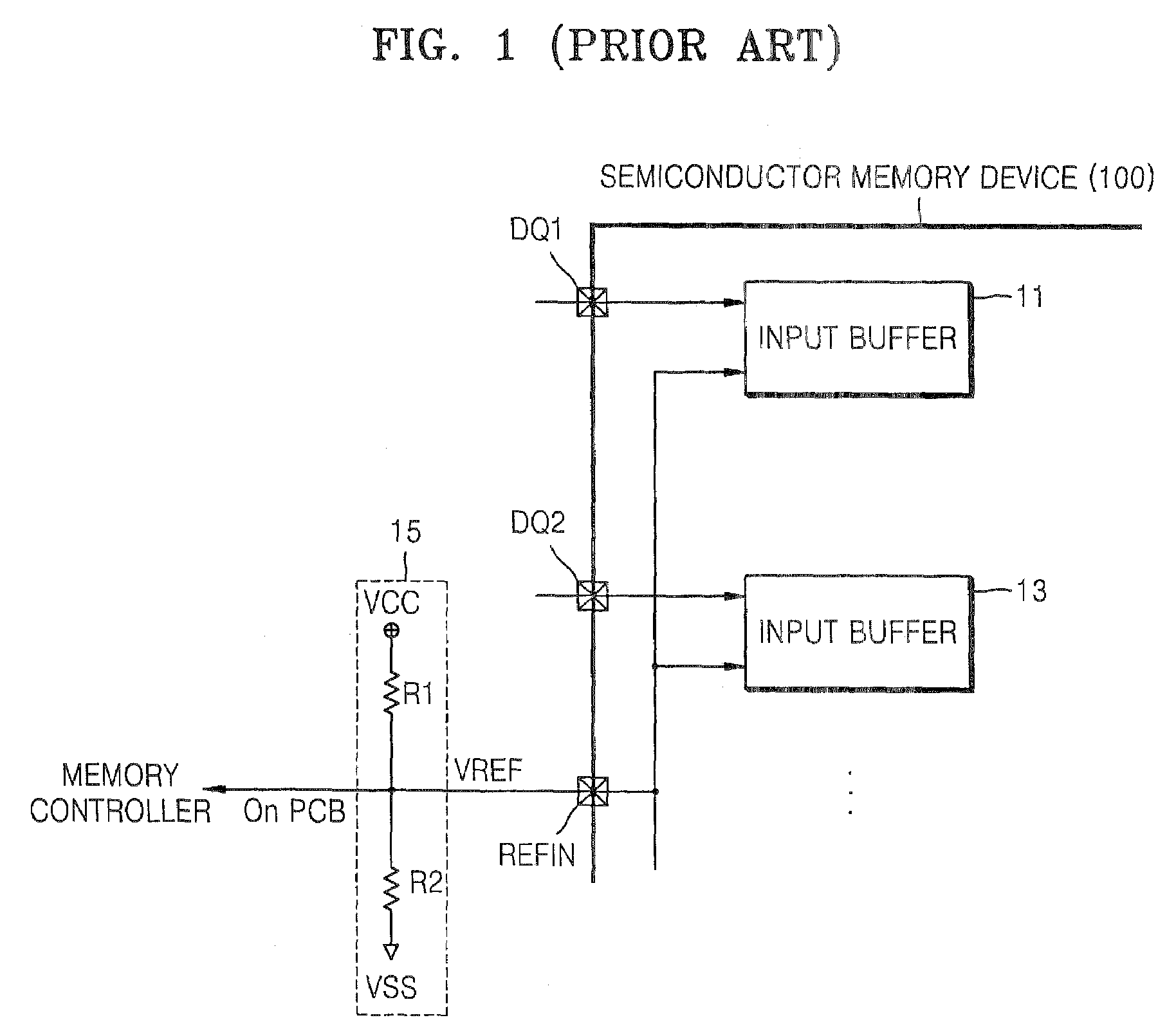

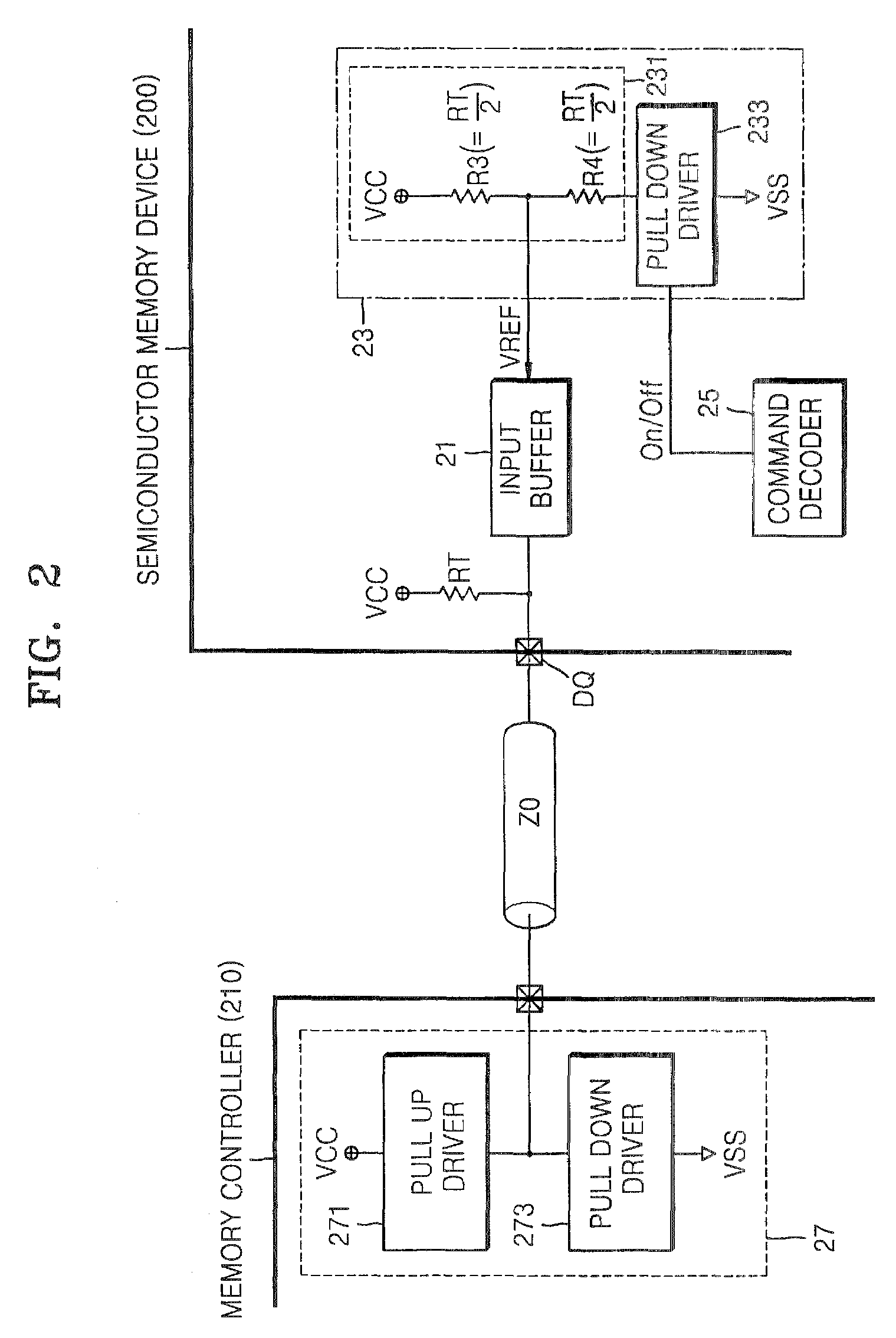

Internal reference voltage generating circuit for reducing standby current and semiconductor memory device including the same

InactiveUS7515487B2Reduced pin countReliability increasing modificationsElectronic switchingDividing circuitsEngineering

An internal reference voltage generating circuit that reduces a standby current and the number of pins of a semiconductor memory device, in which a reference voltage is provided to an input buffer that receives a signal through an input to which an on die transmitor resistor is connected, includes: a voltage dividing circuit outputting the reference voltage by a power voltage; a pull down driver connected to an end of the voltage dividing circuit; and a calibration control circuit comparing a voltage level of the input and a voltage level of an end of the voltage dividing circuit, and controlling the on resistor value of the pull down driver according to a result of the comparison. The internal reference voltage generating circuit is operated while the memory controller inputs a signal into a mode register set (MRS) to enable the internal reference voltage generating circuit and the output signal of the MRS is activated.

Owner:SAMSUNG ELECTRONICS CO LTD

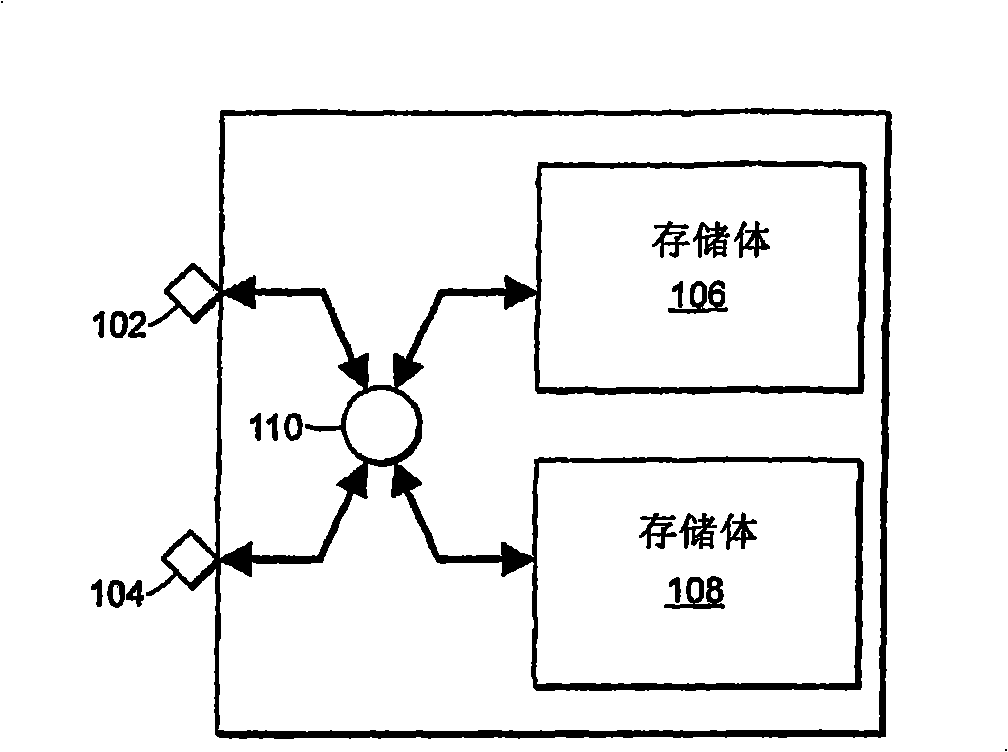

Multiple independent serial link memory

An apparatus, system, and method for controlling data transfer between a serial data link interface and memory banks in a semiconductor memory is disclosed. In one example, a flash memory device with multiple serial data links and multiple memory banks, where the links are independent of the banks, is disclosed. The flash memory devices may be cascaded in a daisy-chain configuration using echo signal lines to serially communicate between memory devices. In addition, a virtual multiple link configuration is described wherein a single link is used to emulate multiple links.

Owner:CONVERSANT INTPROP MANAGEMENT INC

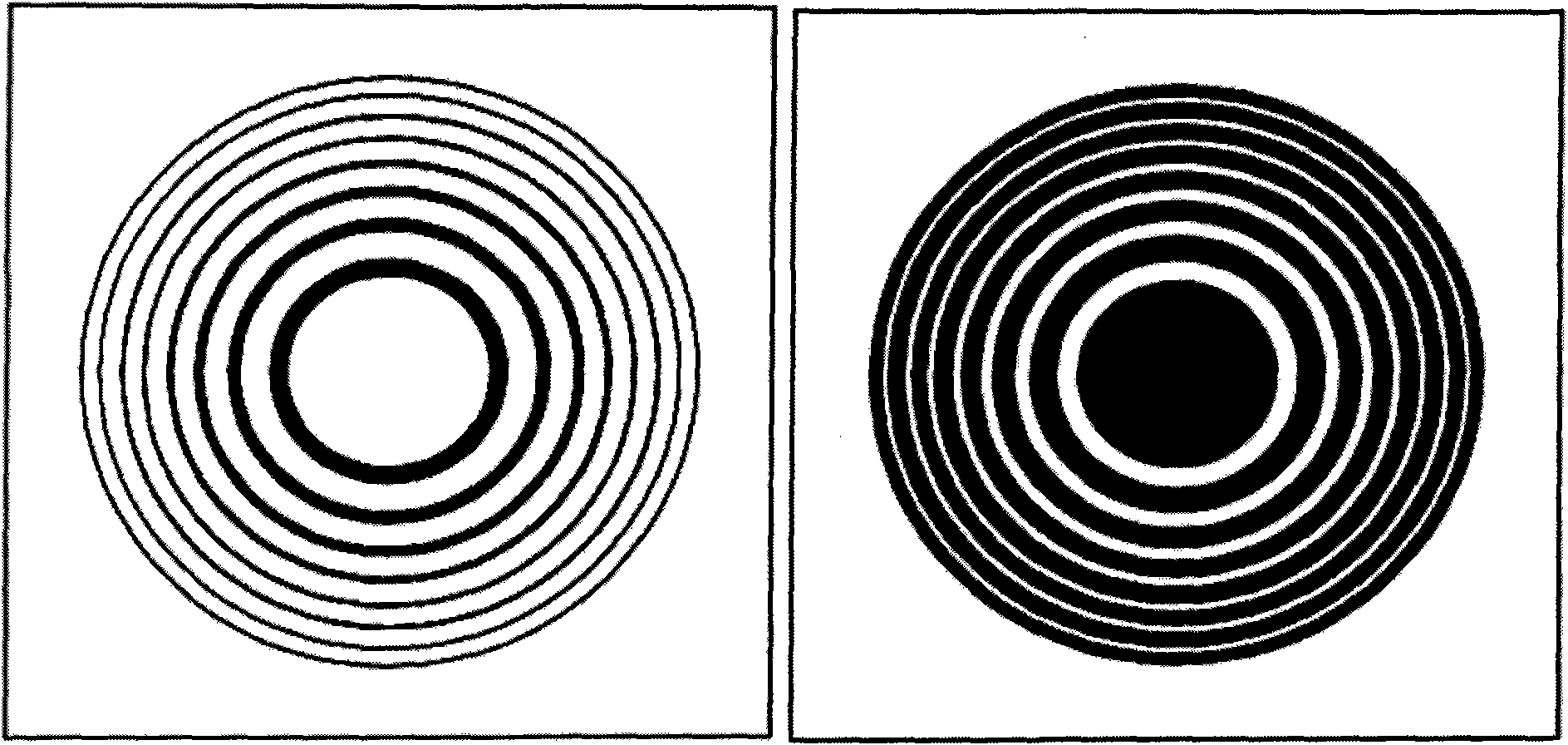

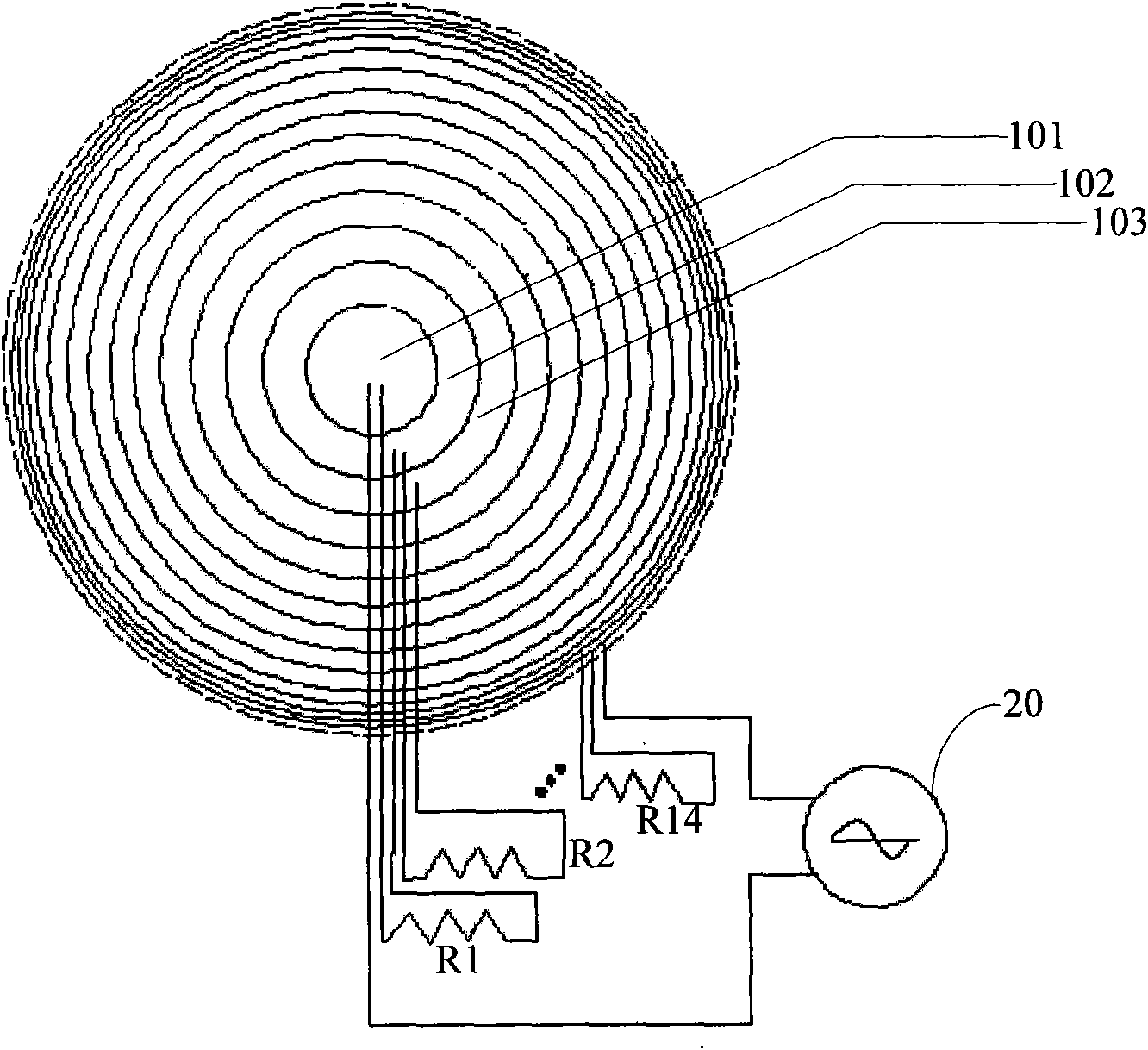

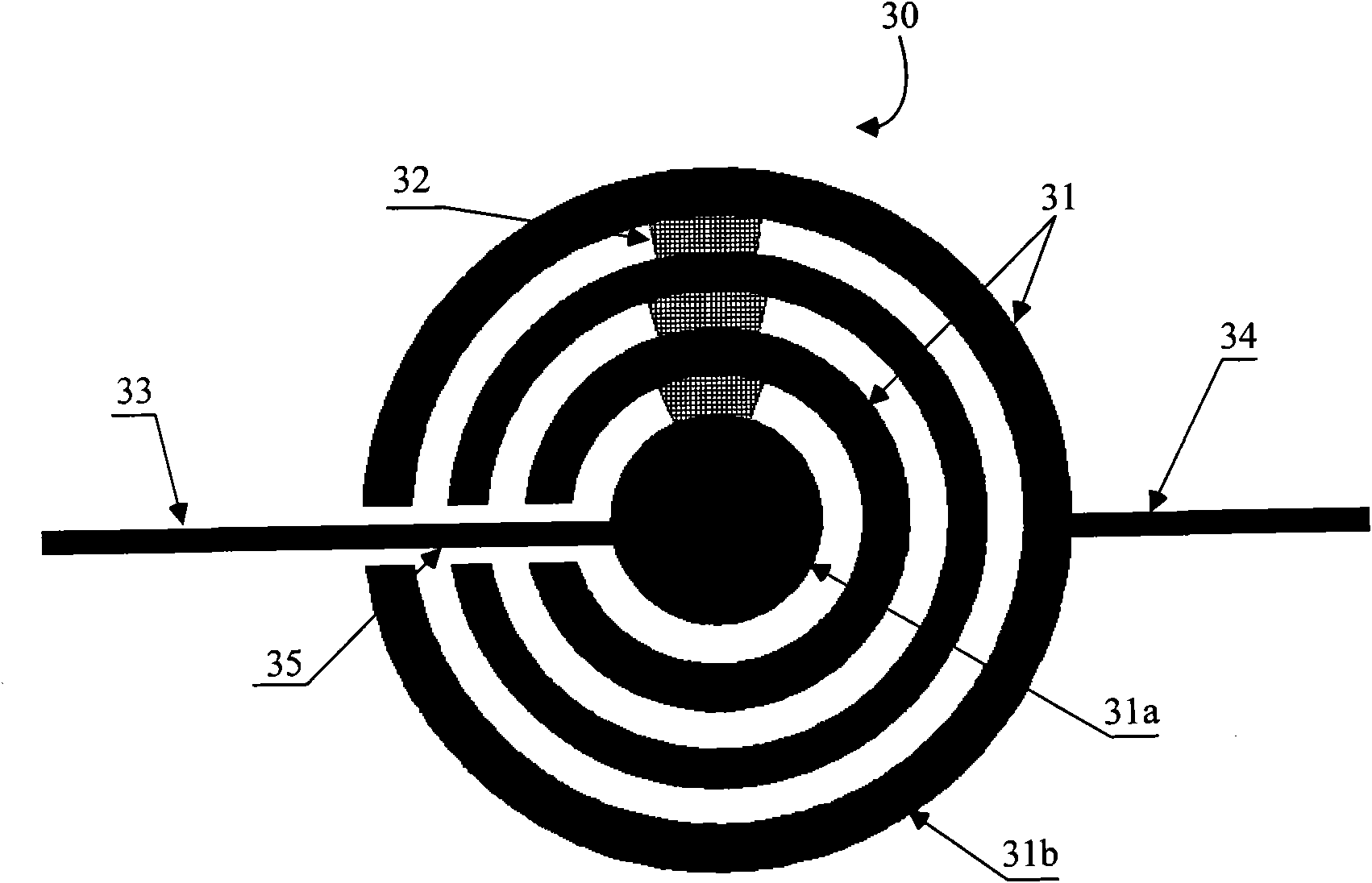

Liquid-crystal zoom lens and electronic device

The invention applies to the field of liquid-crystal lenses, and provides a liquid-crystal zoom lens and an electronic device. By connecting conductive media between every two adjacent annular waveband electrodes of transparent electrodes of a substrate and extracting the electrodes through gap channels of the annular waveband electrodes, the invention greatly reduces the number of pins required by a step electric field, is simple in control, reduces the interference in the step electric field, and reduces space area occupied by the substrate.

Owner:BYD CO LTD

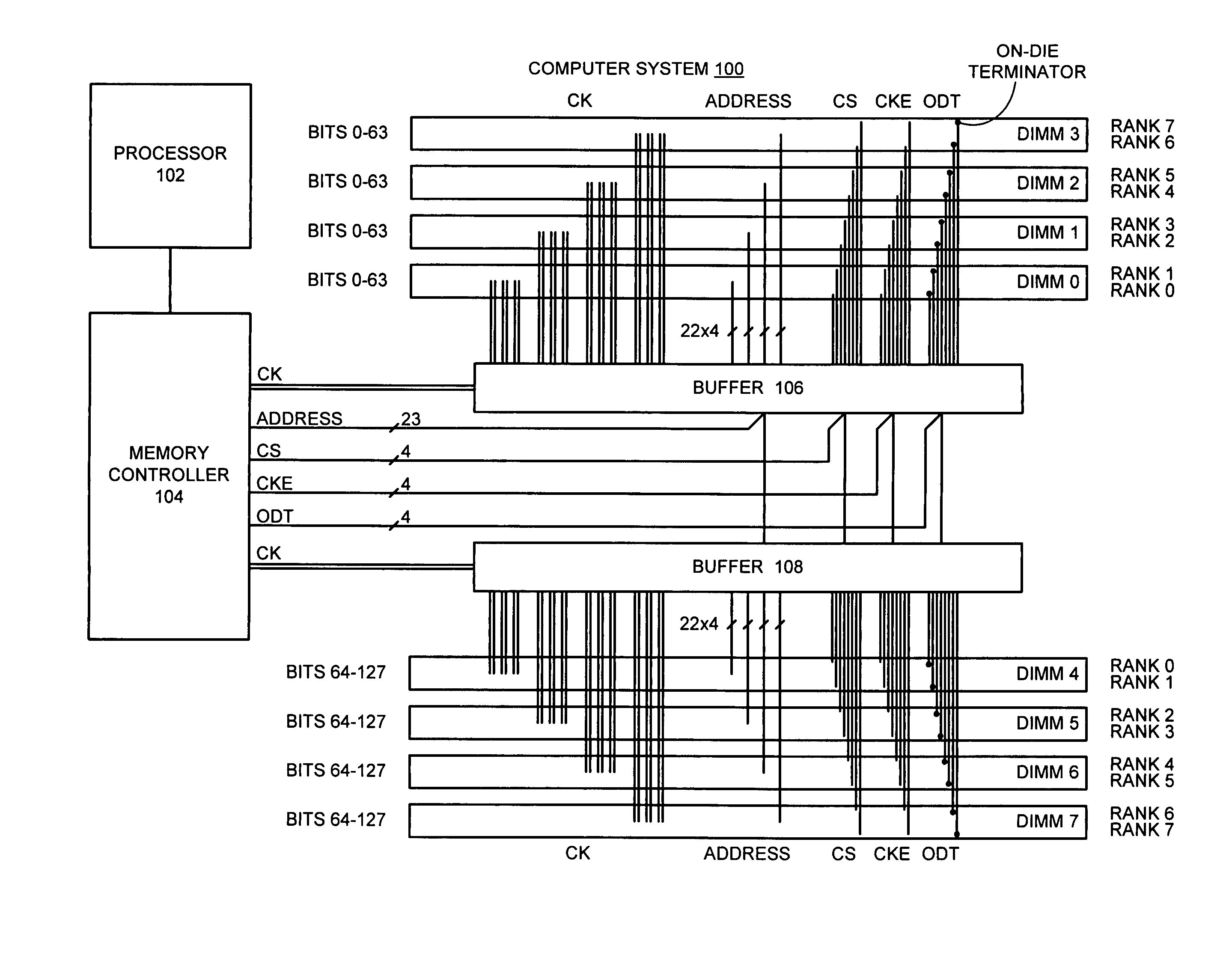

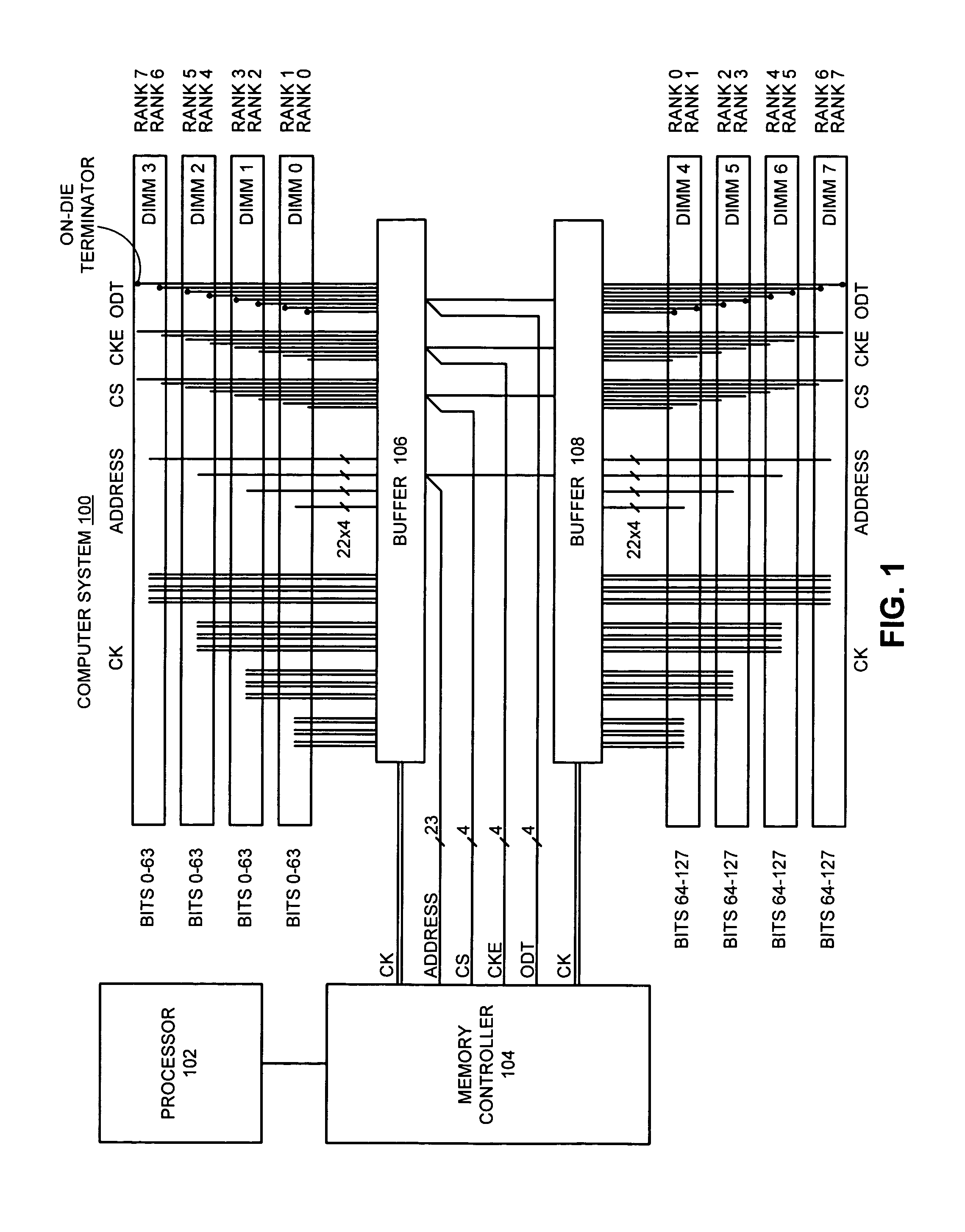

Reducing the number of power and ground pins required to drive address signals to memory modules

InactiveUS7289383B2Reduced pin countReduce in quantityEnergy efficient ICTDigital storageComputer moduleChip select

One embodiment of the present invention provides a system that reduces the number of power and ground pins required to drive address signals to system memory. During operation, the system receives address signals associated with a memory operation from a memory controller, wherein the address signals are received at a buffer chip, which is external the memory controller. The system also receives chip select signals associated with the memory operation at the buffer chip. Next, the system uses the chip select signals to identify an active subset of memory modules in the system memory, which are active during the memory operation. The system then uses address drivers on the buffer chip to drive the address signals only to the active subset of memory modules, and not to other memory modules in the system memory. In this way, the buffer chip requires fewer power and ground pins for the address drivers because the address signals are only driven to the active subset of memory modules, instead of being driven to all memory modules in the system memory.

Owner:APPLE INC

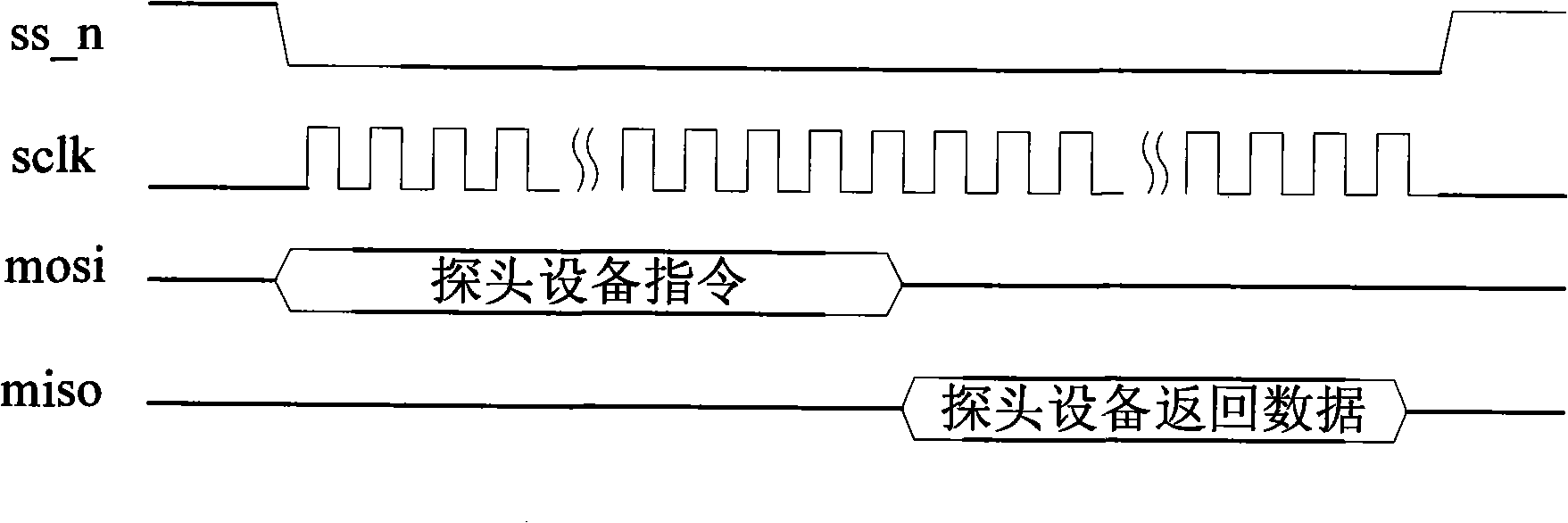

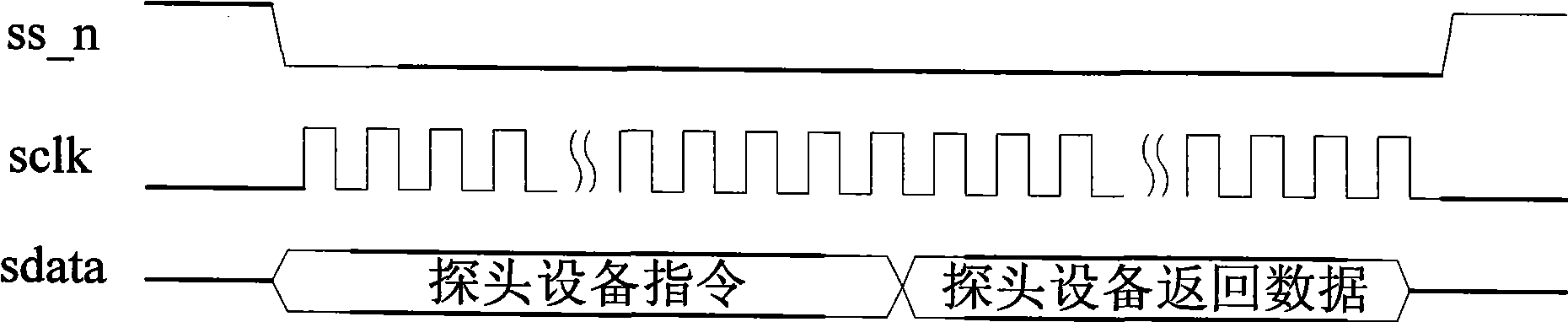

Communicated method, communication system and communication routing device based on SPI bus

ActiveCN101582823AReduced pin countImplement access operationsBus networksEmbedded systemEngineering

The invention discloses a communication method based on an SPI bus, comprising the following steps: providing selection signals of slave equipment through a data line of main equipment; determining the selected slave equipment according to the selection signals; carrying out accessing operation on the selected slave equipment through the main equipment; providing selection signals of a controlled electric unit through the data line of the main equipment; selecting the controlled electric unit according to the selection signals, and generating an open / close control command of the controlled electric unit; sending the control command to the controlled electric unit to control actions of the controlled electric unit. The invention also discloses a communication system based the on the SPI bus and a communication routing device used for the communication system. SPI main equipment provides the selection signals through the data line, and determines a selected operation object according to treatment of the signals, therefore, the accessing operation of the main equipment on the slave equipment can be realized only needing the SPI bus of 3 line or 4 line and without arranging more pins on a host end to descend any other control signals.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD +1

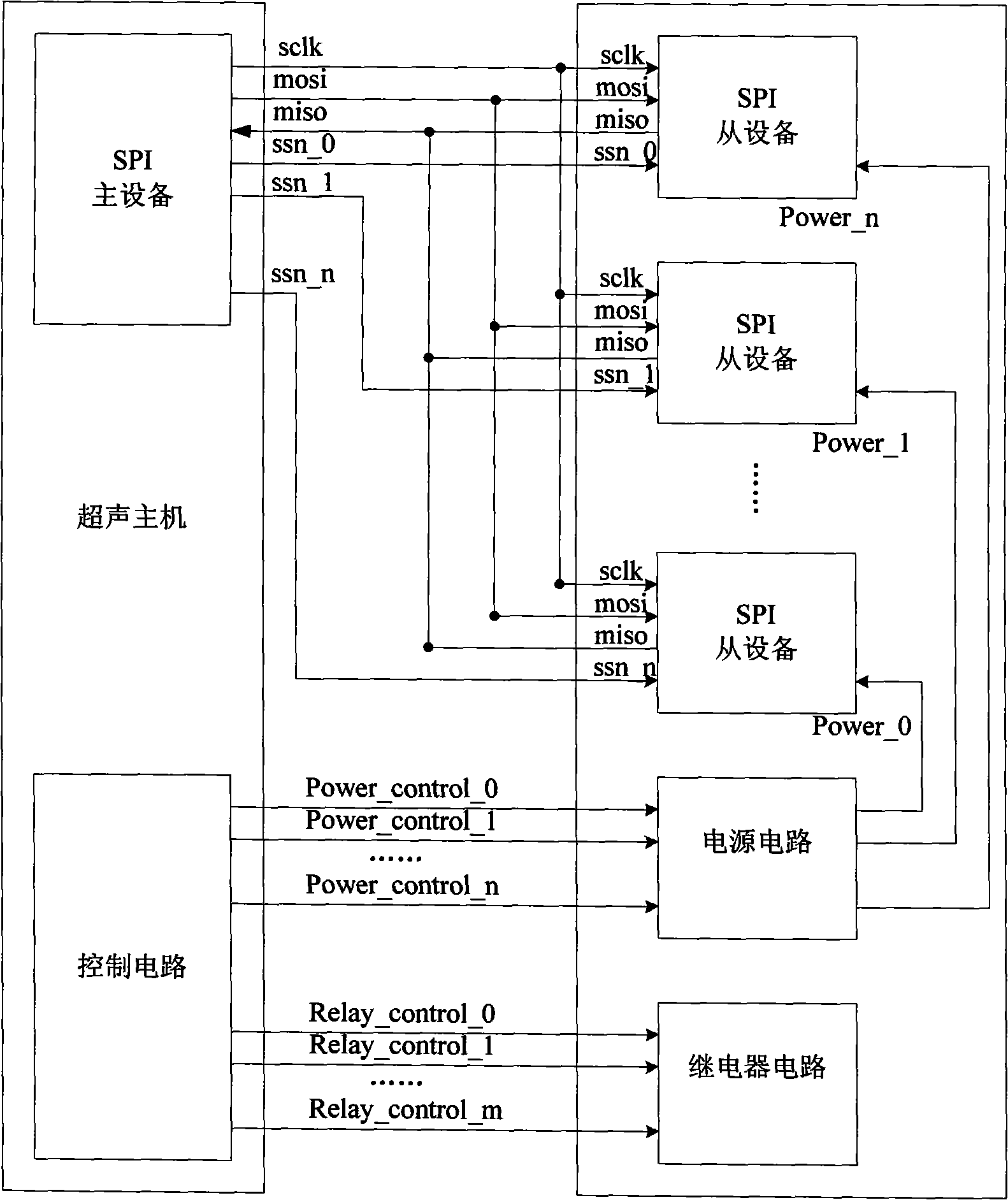

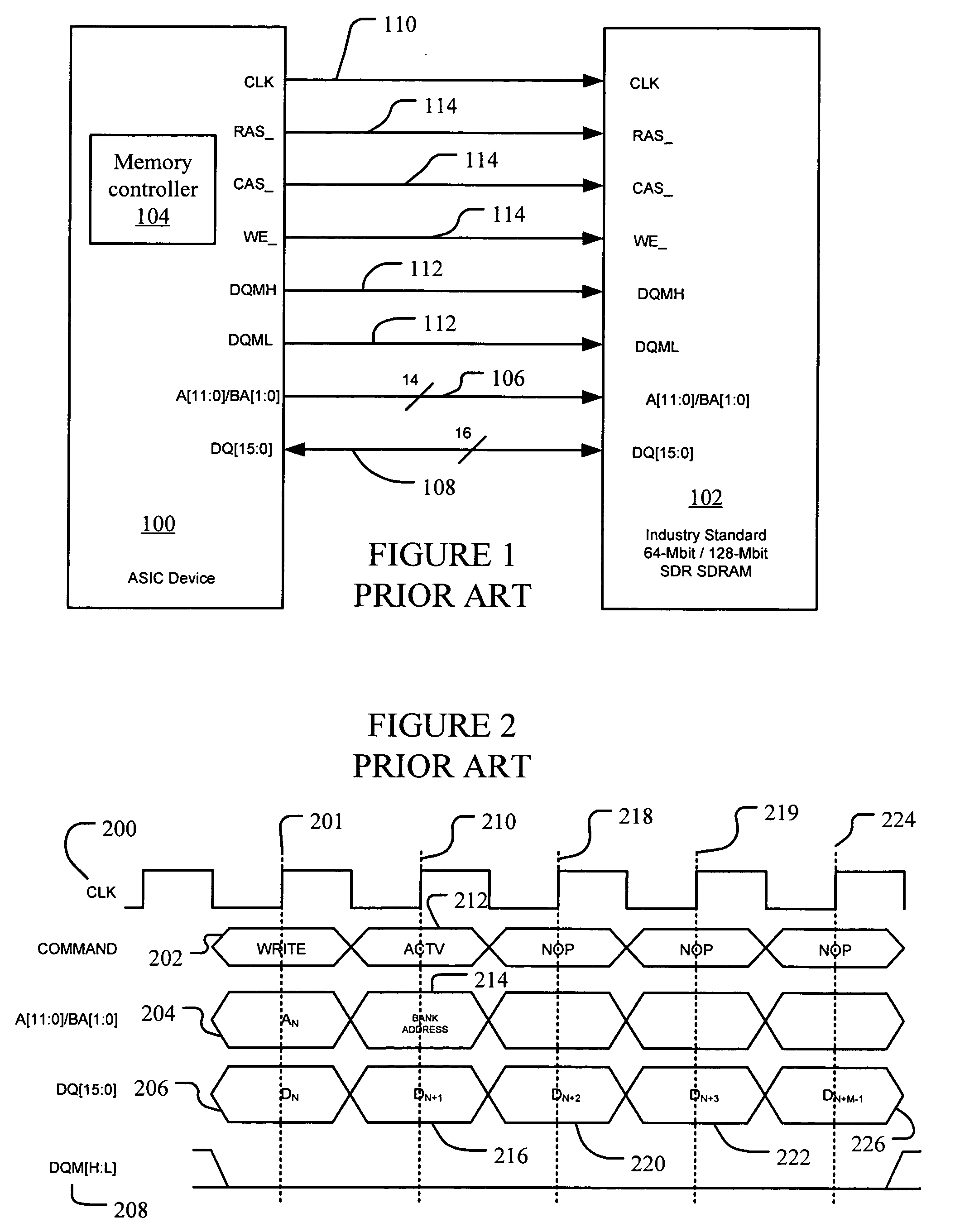

Method and system for reducing pin count in an integrated circuit when interfacing to a memory

InactiveUS20060041713A1Reduce number of pinReduce numberStatic storageMemory systemsEmbedded systemIntegrated circuit

The invention provides a system and method for reducing pin count in an integrated circuit (IC) when interfacing to a synchronous dynamic random access memory (SDRAM). The SDRAM has a plurality of address lines and a plurality of data lines. The method includes connecting together the plurality of data lines and the plurality of address lines. The IC interfaces to the SDRAM through the connected plurality of address lines and the plurality of data lines.

Owner:AVAGO TECH INT SALES PTE LTD

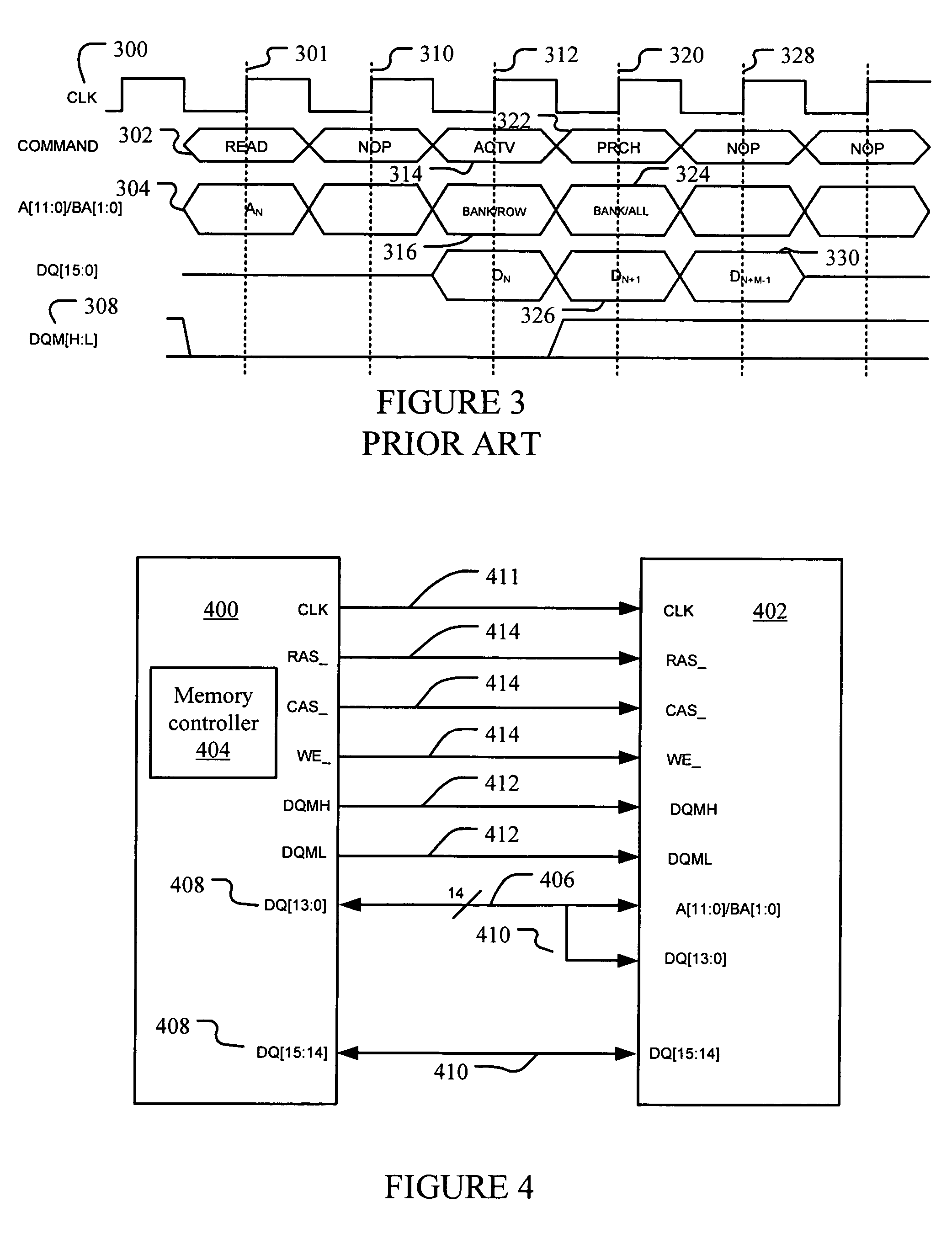

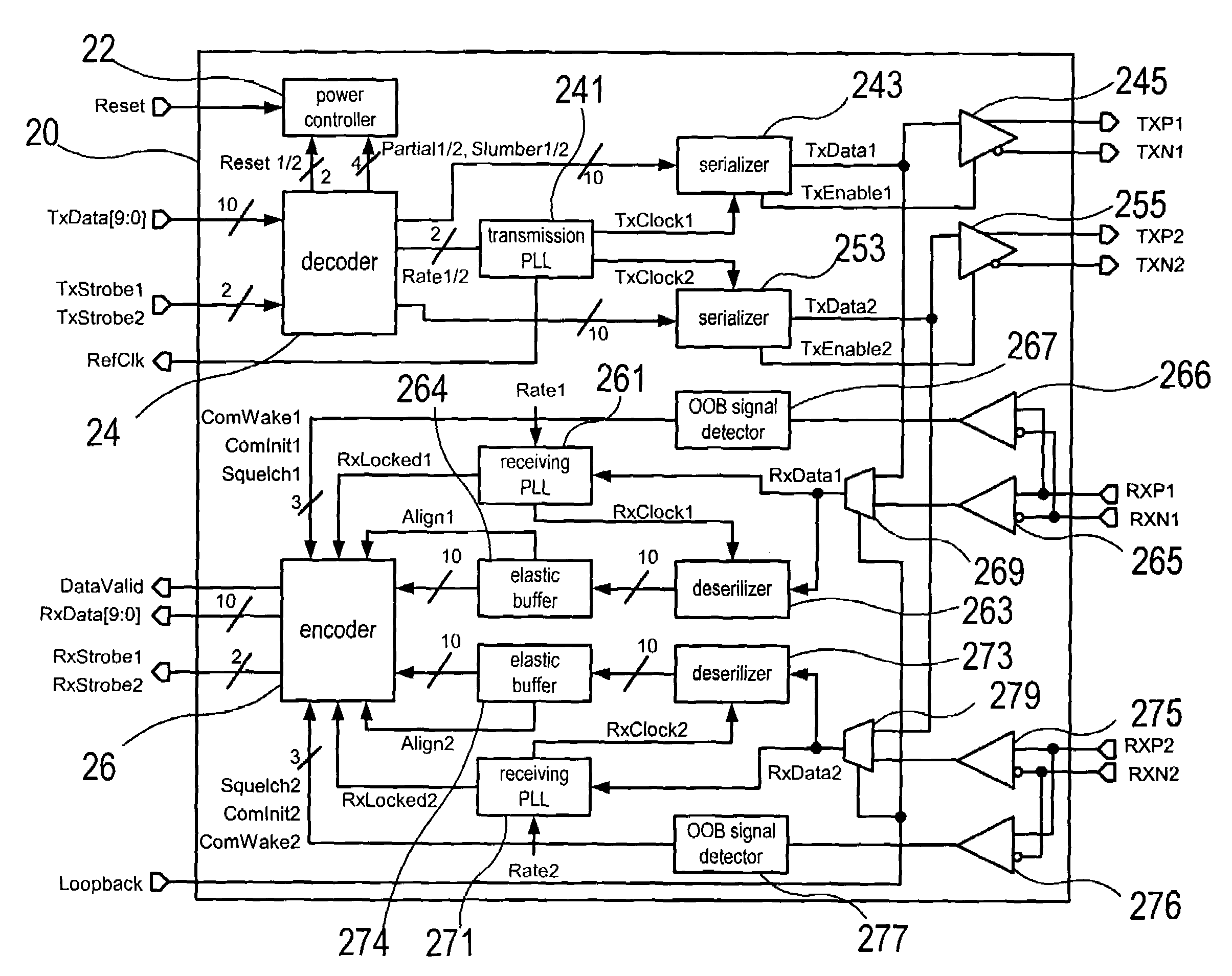

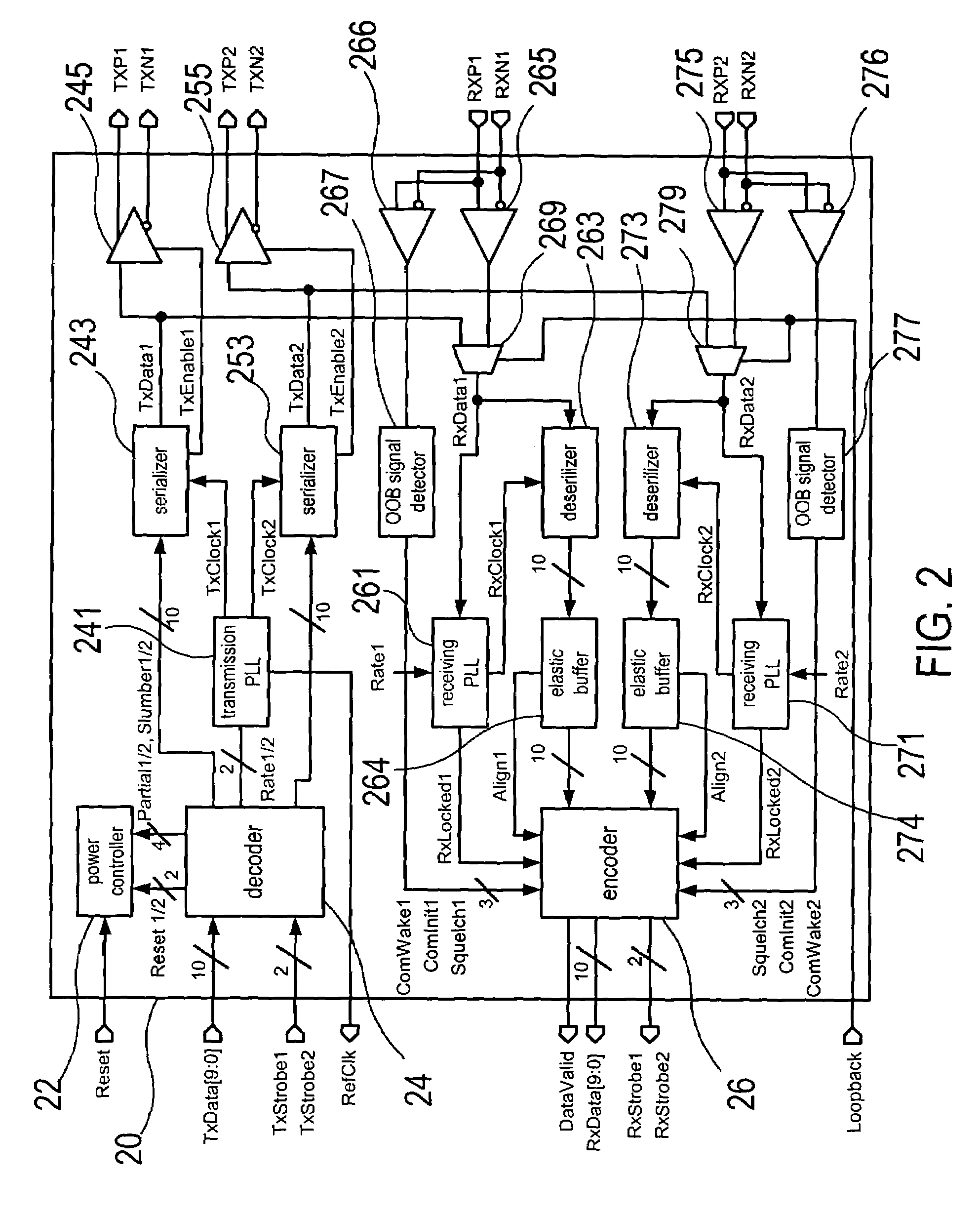

Circuit structure and signal encoding method for a serial ATA external physical layer

ActiveUS7251280B2Reduced pin countReduce in quantityInput/output to record carriersGenerating/distributing signalsControl signalSignal encoding

A circuit structure and signal encoding method for a serial ATA external physical layer is provided. The circuit structure and signal encoding method thereof is capable of reducing the number of interface signals of a serial ATA external physical layer, essentially comprising a decoder / encoder, a serializer / deserializer, a phase locked loop, at least one transmitter, at least one receiver, and at least one OOB signal detector, encoding various control signals and various status signals, required for the connection between the decoder / encoder and a storage medium controller, into data signals using signals other than a data conversion requirement of 8 bits and 10 bits, by the decoder / encoder, in order for greatly reducing the number of interface signals required for the connection between the external physical layer and a main control chip.

Owner:VIA TECH INC

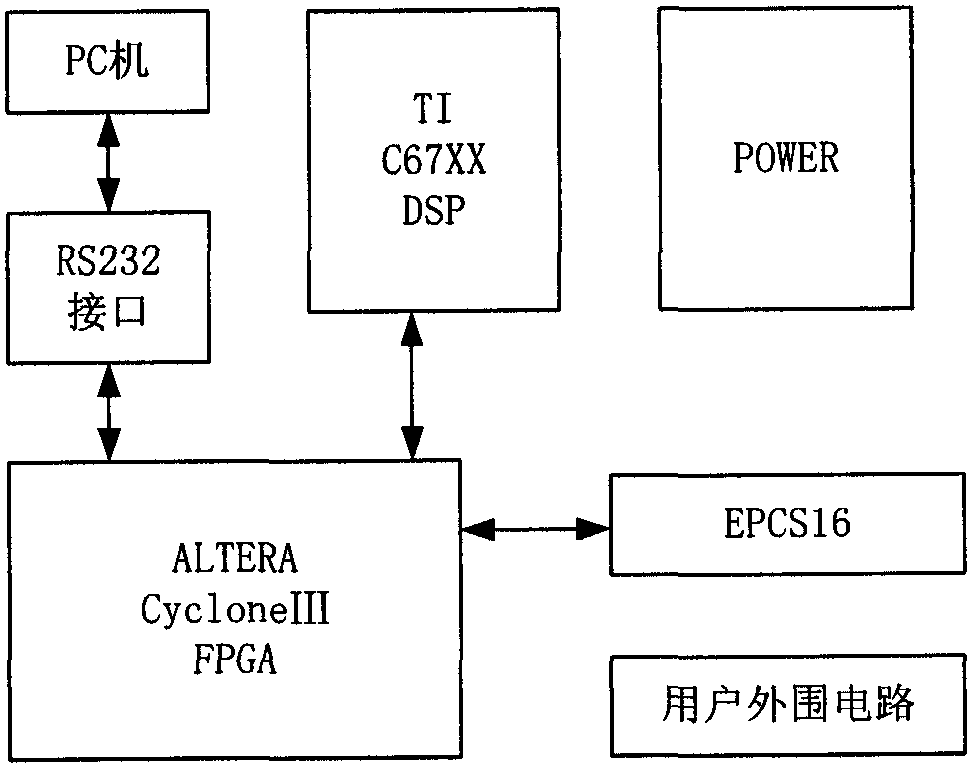

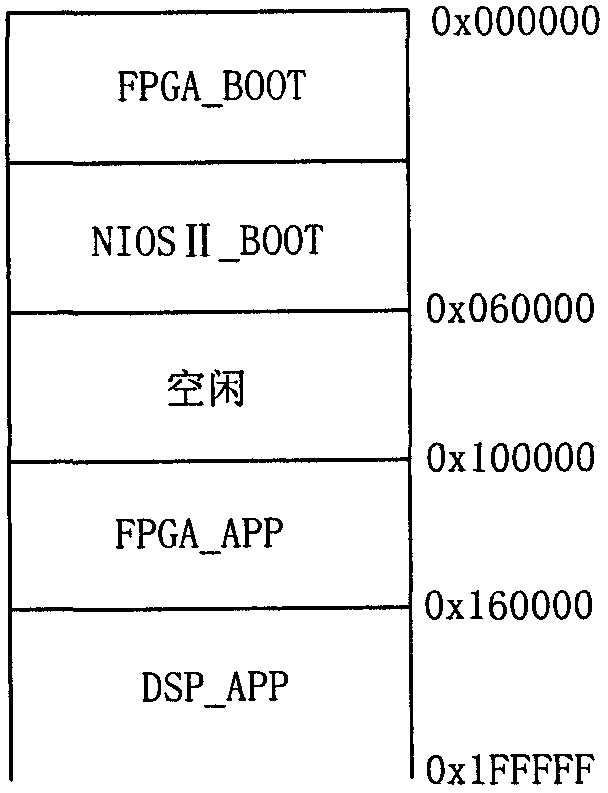

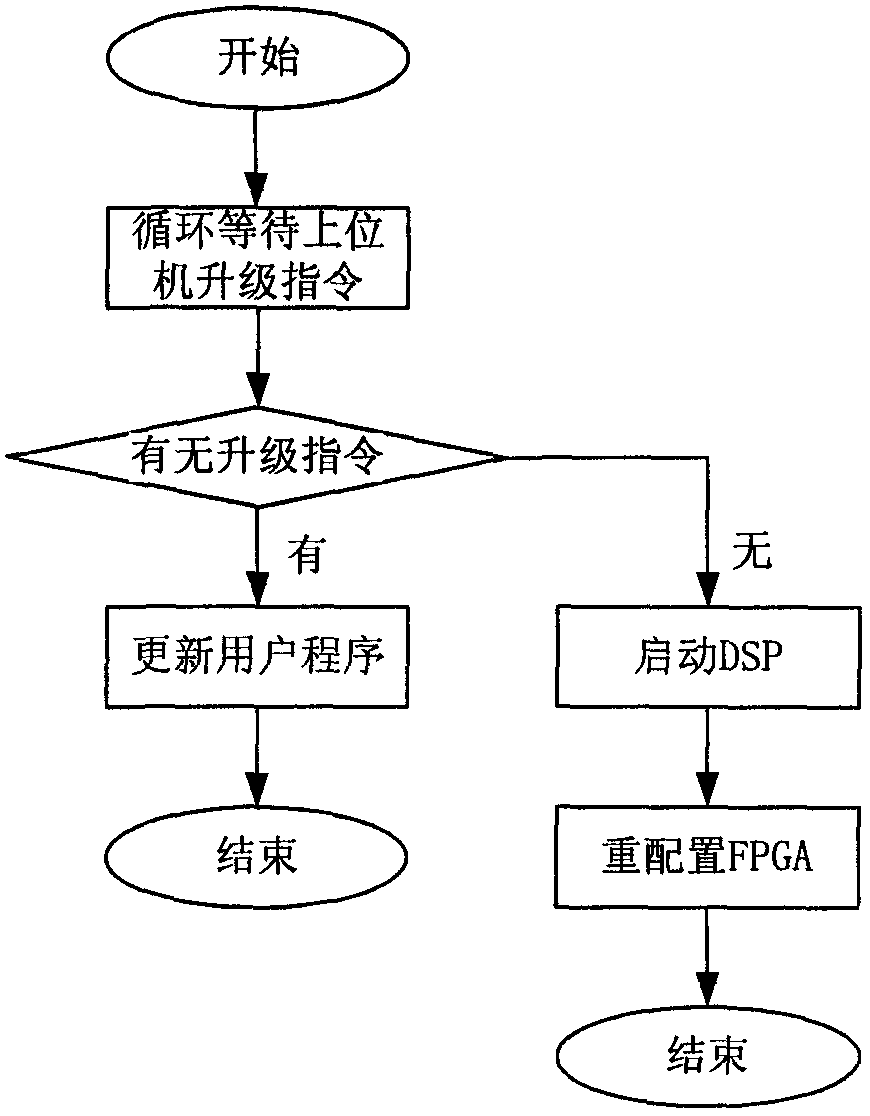

Program updating method for FPGA (Field Programmable Gate Array)/DSP (Digital Signal Processor) embedded system

ActiveCN103019779AOvercome limitationsReduce volumeProgram loading/initiatingControl systemStructure of Management Information

A program updating method for an FPGA (Field Programmable Gate Array) / DSP (Digital Signal Processor) embedded system, based on a special active serial figuration chip EPCS (Electronic Propulsion Control System), builds communication with an upper computer through an embedded soft-core processor NIOS (National Institute of Open Schooling) II so as to control and finish updating of FPGA hardware figuration data and DSP application program data of users. Compared with the traditional embedded system with an FPGA / DSP+FLASH structure, the method reduces the board level PCB wiring complexity and the system volume, and satisfies requirements for updating the FPGA hardware figuration data and the DSP application program data when a JTAG (Joint Test Action Group) interface is invisible after this kind of products are assembled.

Owner:BEIJING RES INST OF TELEMETRY +1

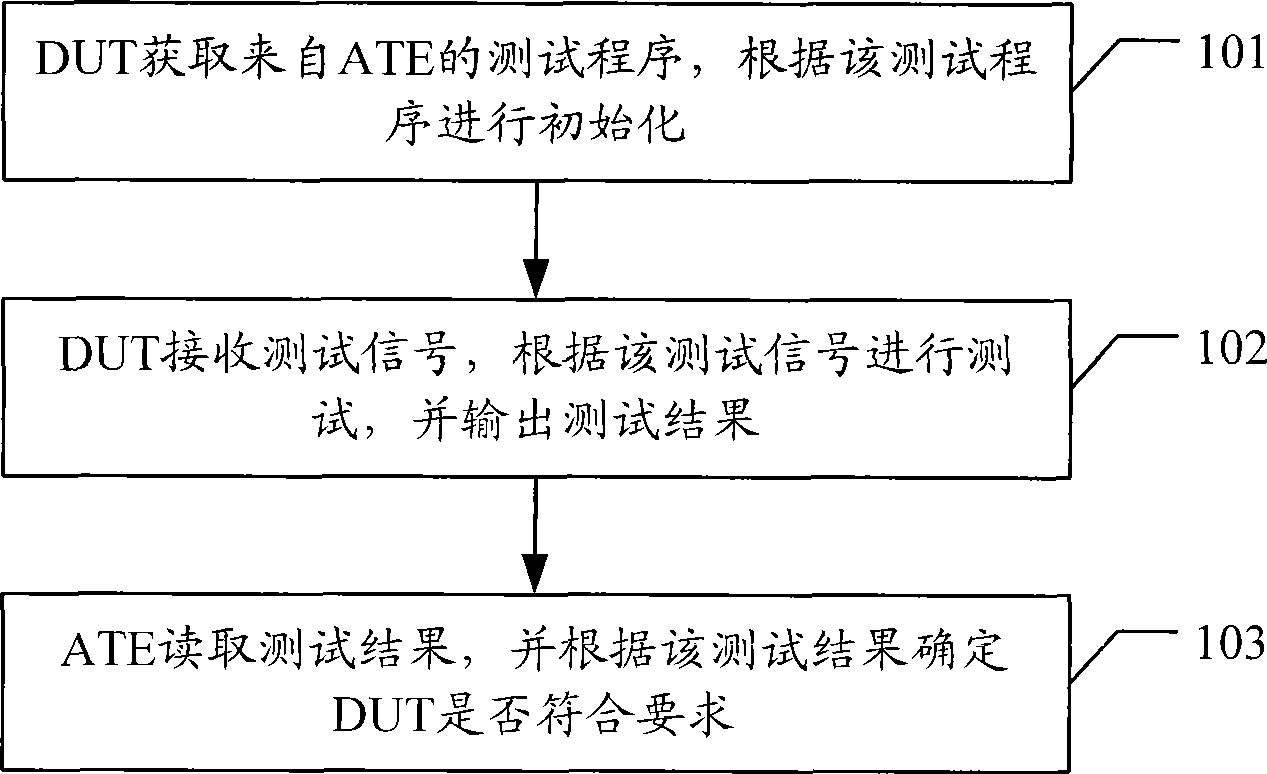

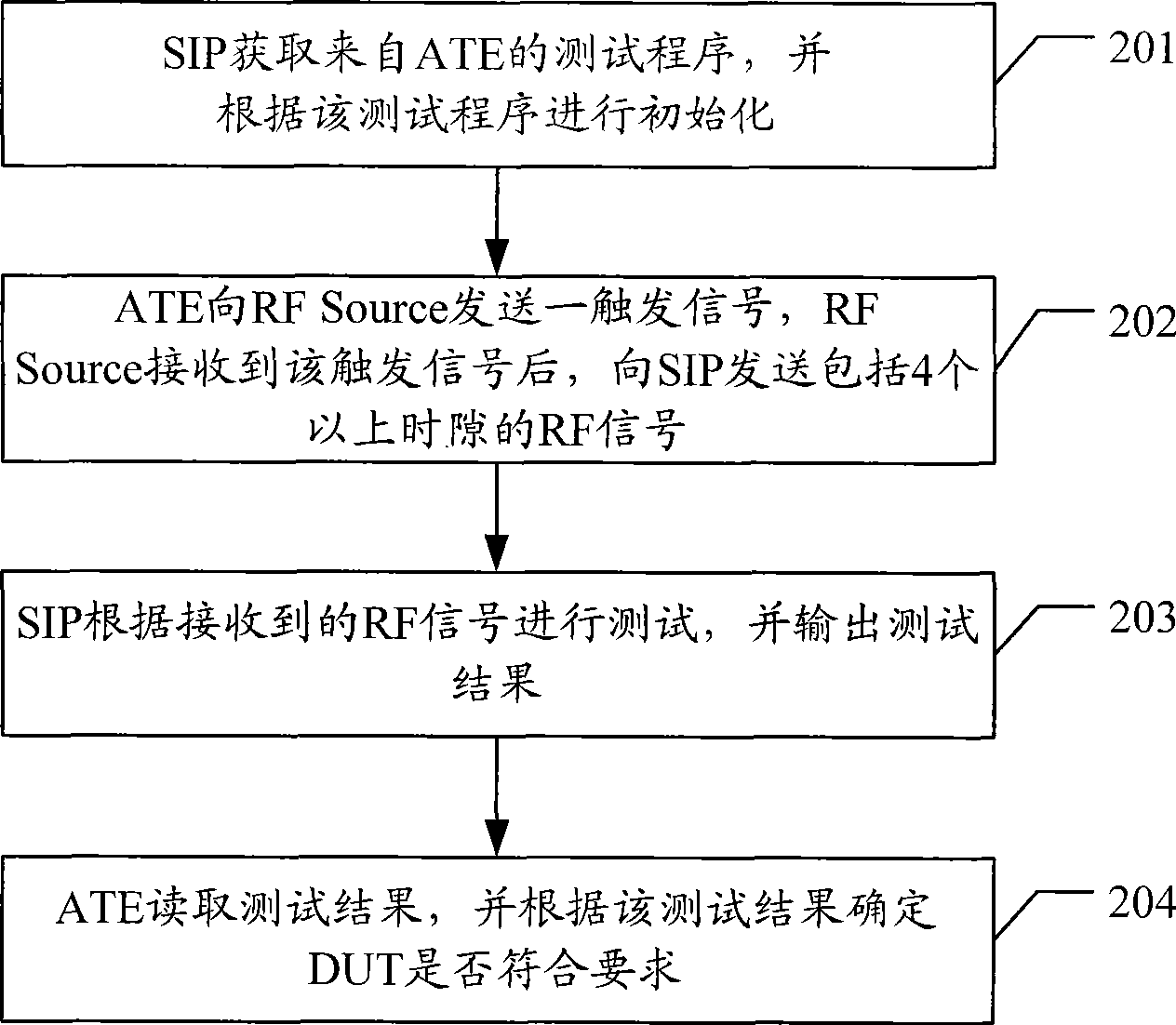

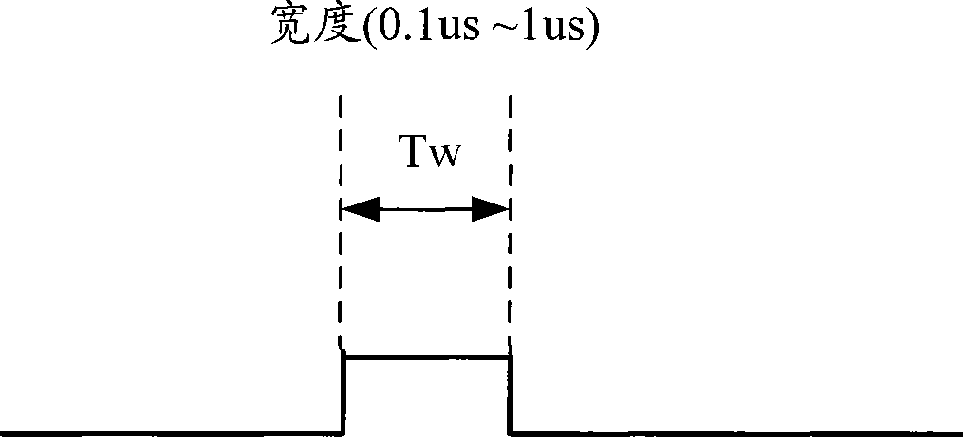

Test method and system

InactiveCN101464491AEasy to implementReduced pin countElectronic circuit testingFault coverageAutomatic test equipment

The invention discloses a testing method which comprises the following steps: acquiring the testing procedure from automatic test equipment (ATE) by using a device under test (DUT) and initializing according to the testing procedure; receiving test signals by using the DUT, and testing according the test signals, and outputting test results; and reading the test results by using the ATE and determining whether the DUT conforms to the requirements according to the test results. The invention simultaneously discloses a testing system. By applying the method and the system, the test cost can be reduced, the fault coverage can be improved, and the invention can be implemented easily.

Owner:新奇点智能科技集团有限公司

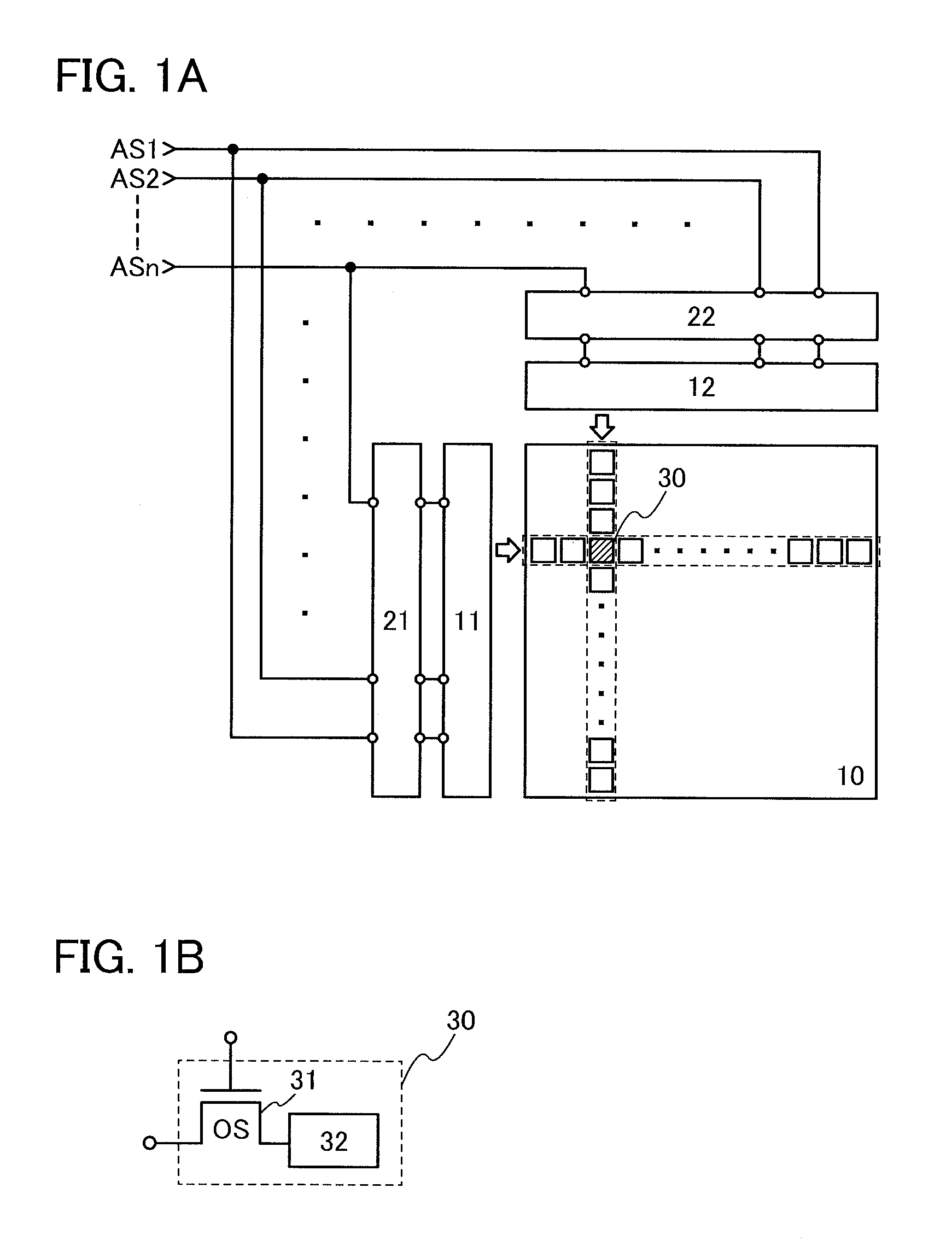

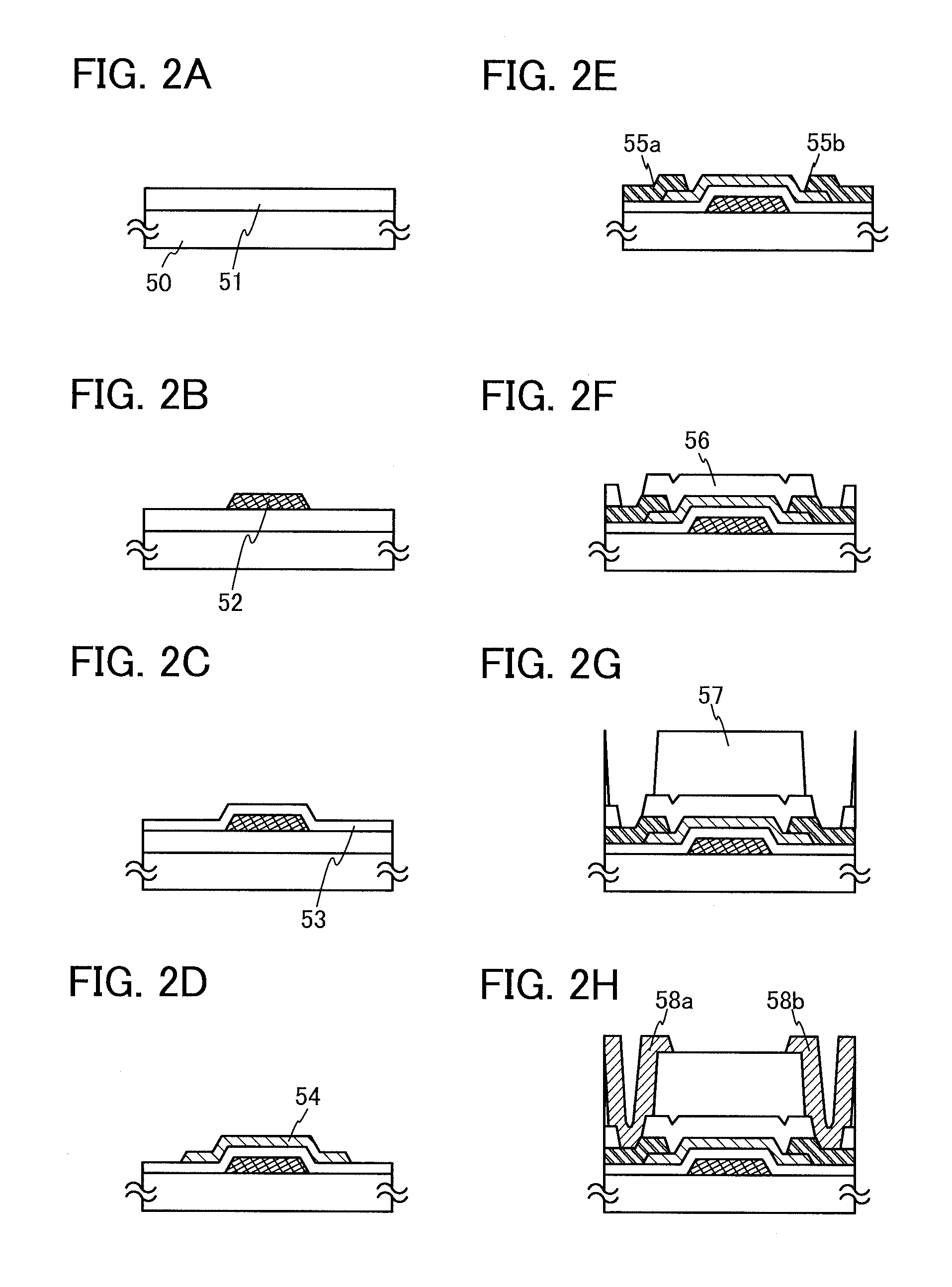

Active display device and driving method thereof

InactiveCN101826300AReduce in quantityLow costStatic indicating devicesDisplay deviceElectrical polarity

An active display device comprises a sub-pixel array and a sub-pixel array driving circuit; all of the sub-pixels of the same column in the sub-pixel array are connected with the same data line, each data line is connected with and located between two adjacent columns of sub-pixels, two columns of sub-pixels are arranged between two adjacent data lines; each line of sub-pixels correspond to two scanning lines, the sub-pixels of odd-numbered columns in the same line are connected to one of the scanning lines, the sub-pixels of even-numbered columns in the same line are connected to the other one of the scanning lines, and the sub-pixels connected with each data line are disposed in the same line. When driving, the sub-pixels of odd-numbered columns in the same line are controlled by one scanning line, and the sub-pixels of even-numbered columns in the same line are controlled by the other scanning line. The number of the scanning lines is decreased by half compared with the traditional organic display device, the column inversion and the point inversion of the polarity of the sub-pixel array can be realized, and thereby improving the process yield, reducing the cost and improving the display effect while realizing the high fining.

Owner:SHANTOU GOWORLD DISPLAY (PLANT II) CO LTD

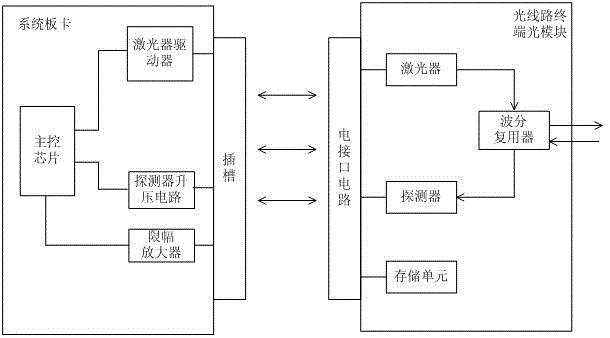

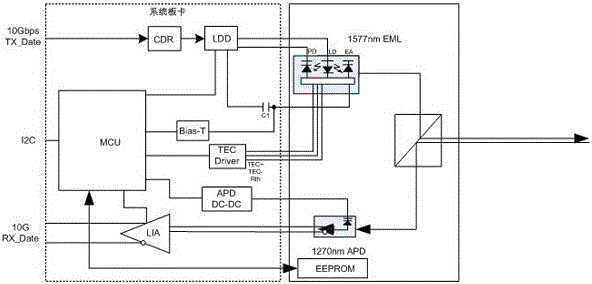

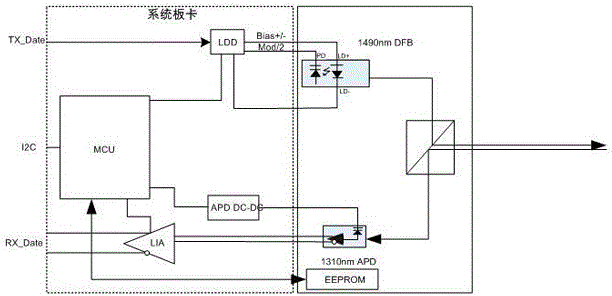

Optical module and optical line terminal device

InactiveCN106059673AReduce volumeHigh densityCoupling light guidesFibre transmissionElectricityOptical Module

The invention discloses an optical module and an optical line terminal device. The optical module includes: a housing, a circuit board, an optical assembly and a storage unit. The optical assembly is in electrical connection to the circuit board and is intended for generating an optical signal based on an electrical signal; or is intended for converting the received optical signal to an electrical signal; the storage unit is in electrical connection to the circuit board, and is intended for storing the working parameters of the optical assembly; the circuit board, the optical assembly and the storage unit are packaged inside the housing, and the circuit board is provided with an electrical interface thereon, and the electrical interface have pins which are in one by one corresponding connection to a driving end of the optical assembly and a data transmission base pin of the storage unit. When the optical module works, the working parameters of the optical assembly are transmitted to an external master control chip through the electrical interface, and the external master control chip configures an external drive circuit on the basis of the working parameters of the optical assembly, and the external drive circuit drives the optical assembly through the electrical interface. The optical module only packages the optical assembly and the storage unit and is conductive to the reduction of the volume of the optical module.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

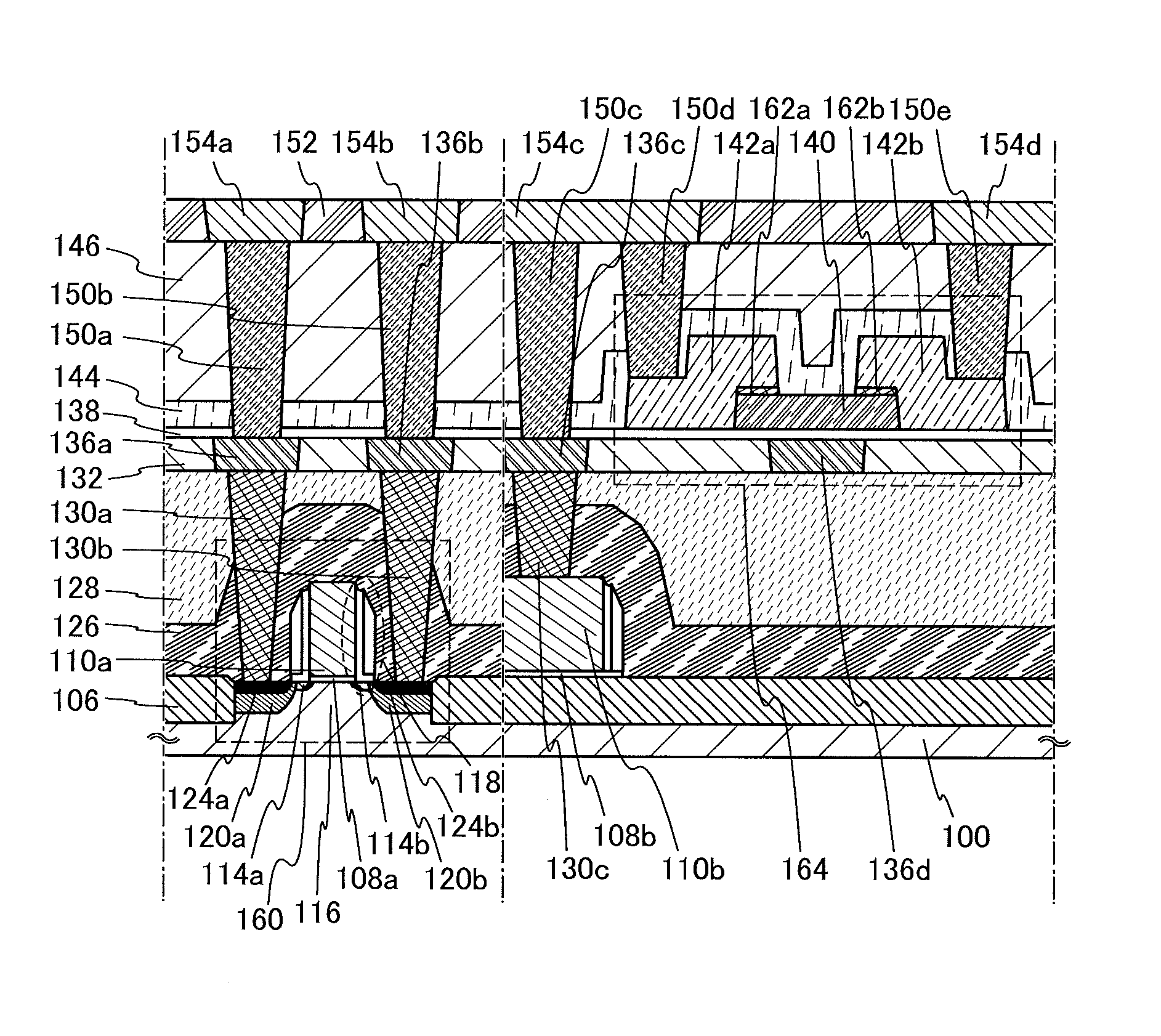

Semiconductor device

ActiveUS8582349B2Constant potentialAccurate dataSolid-state devicesRead-only memoriesNODALPower semiconductor device

An object is to provide a semiconductor device which includes a memory cell capable of holding accurate data even when the data is multilevel data. The semiconductor device includes a memory cell holding data in a node to which one of a source and a drain of a transistor whose channel region is formed from an oxide semiconductor. Note that the value of off-state current (leakage current) of the transistor is extremely small. Thus, after being set to have a predetermined value, the potential of the node can be kept constant or substantially constant by turning the transistor off. In this manner, accurate data can be stored in the memory cell.

Owner:SEMICON ENERGY LAB CO LTD

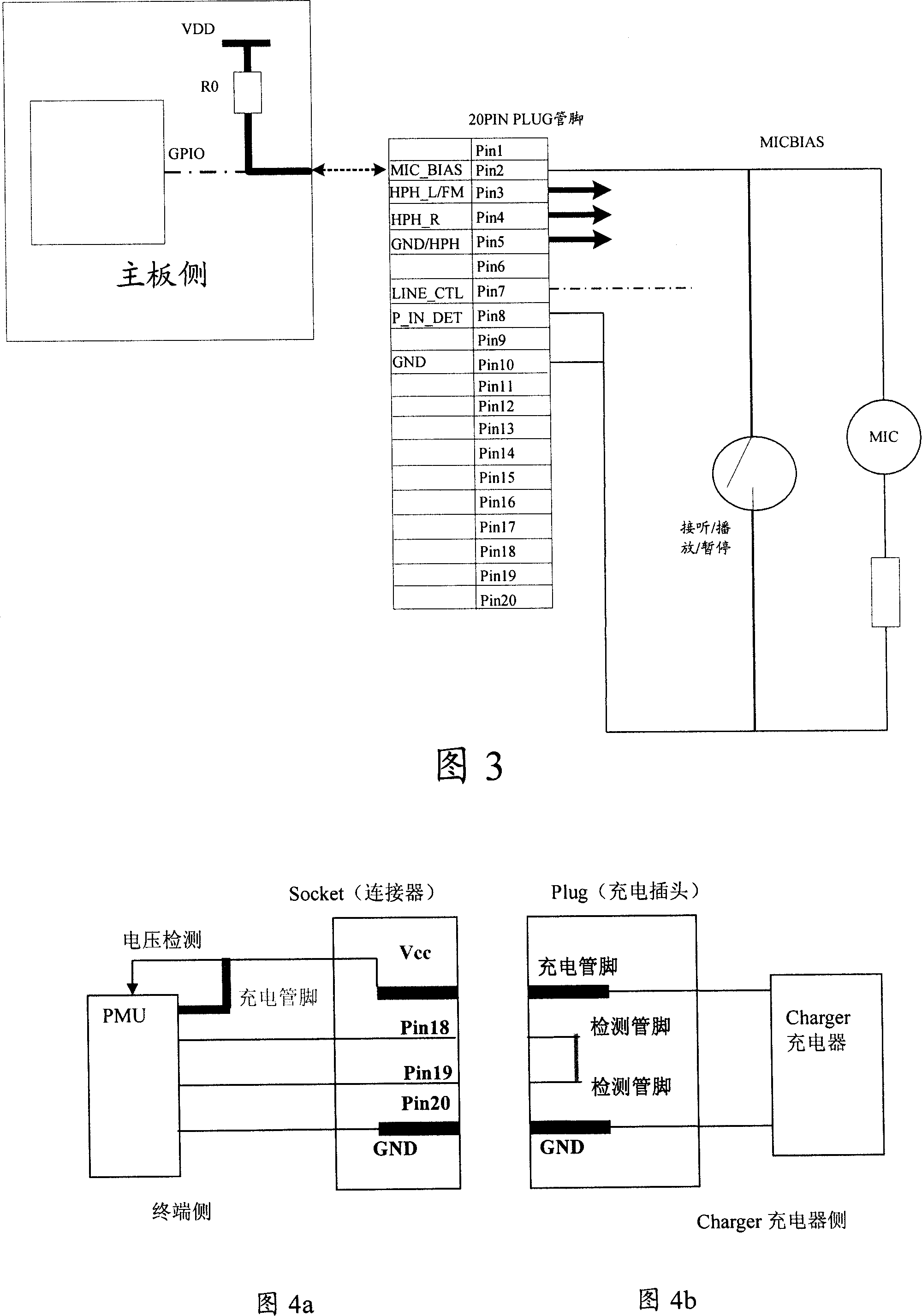

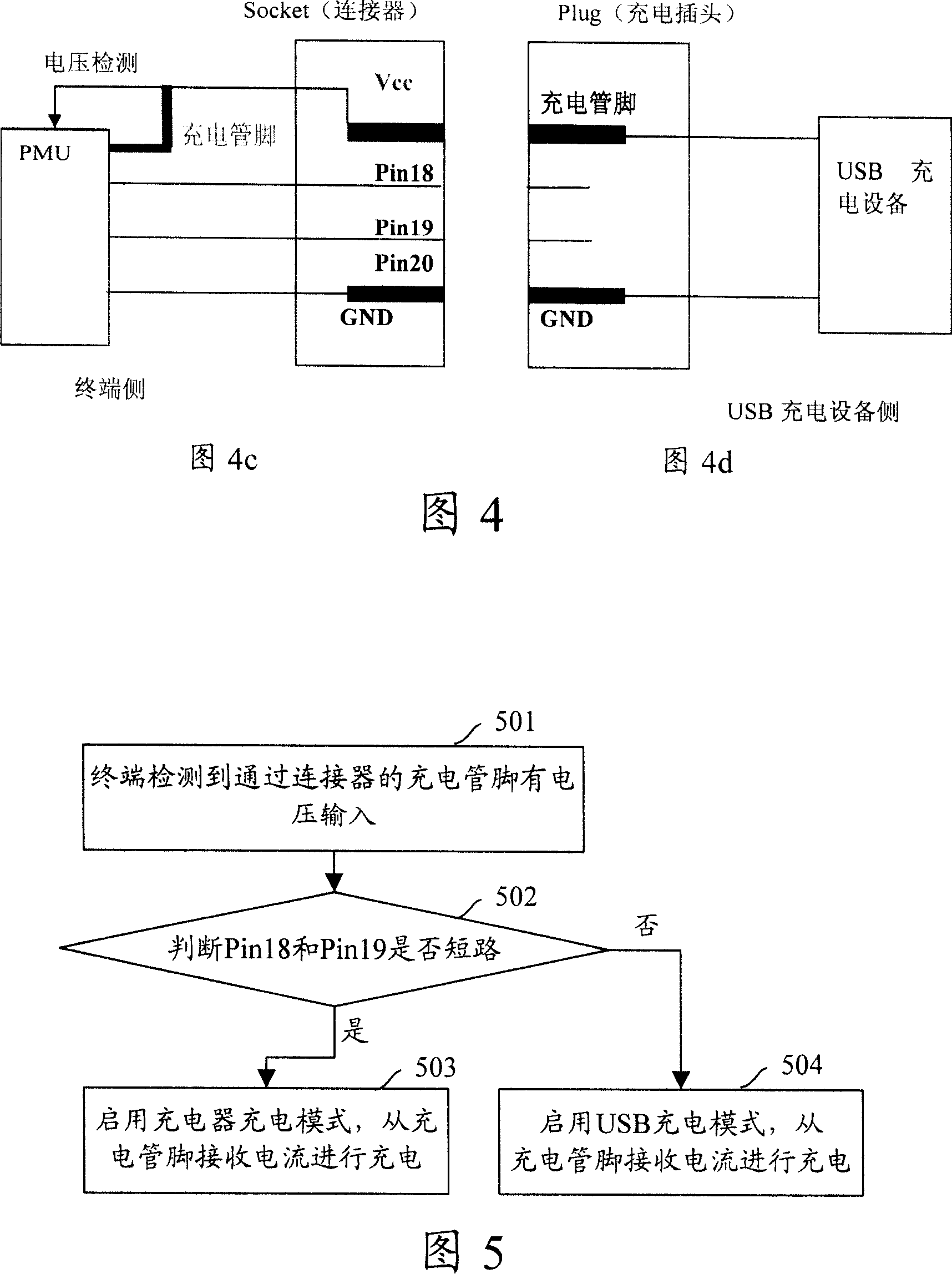

Terminal equipment, connector, charger and charging method

ActiveCN101022278AReduced pin countReduce volumeSecondary cells charging/dischargingTransmissionSupply managementTerminal equipment

A terminal device consists of power supply management module PMU and connector with a charge pin and two detection pins. It is featured as starting up charge mode of charger to receive current from charge pin for carrying out charge when voltage input on said charge pin is detected by PMU module and two said detection pins are short-circuit, starting up charge mode of universal serial bus USB to receive current from said charge pin for carrying out charge when voltage input on said charge pin is detected and two said detection pins are not short-circuited.

Owner:HUAWEI TECH CO LTD

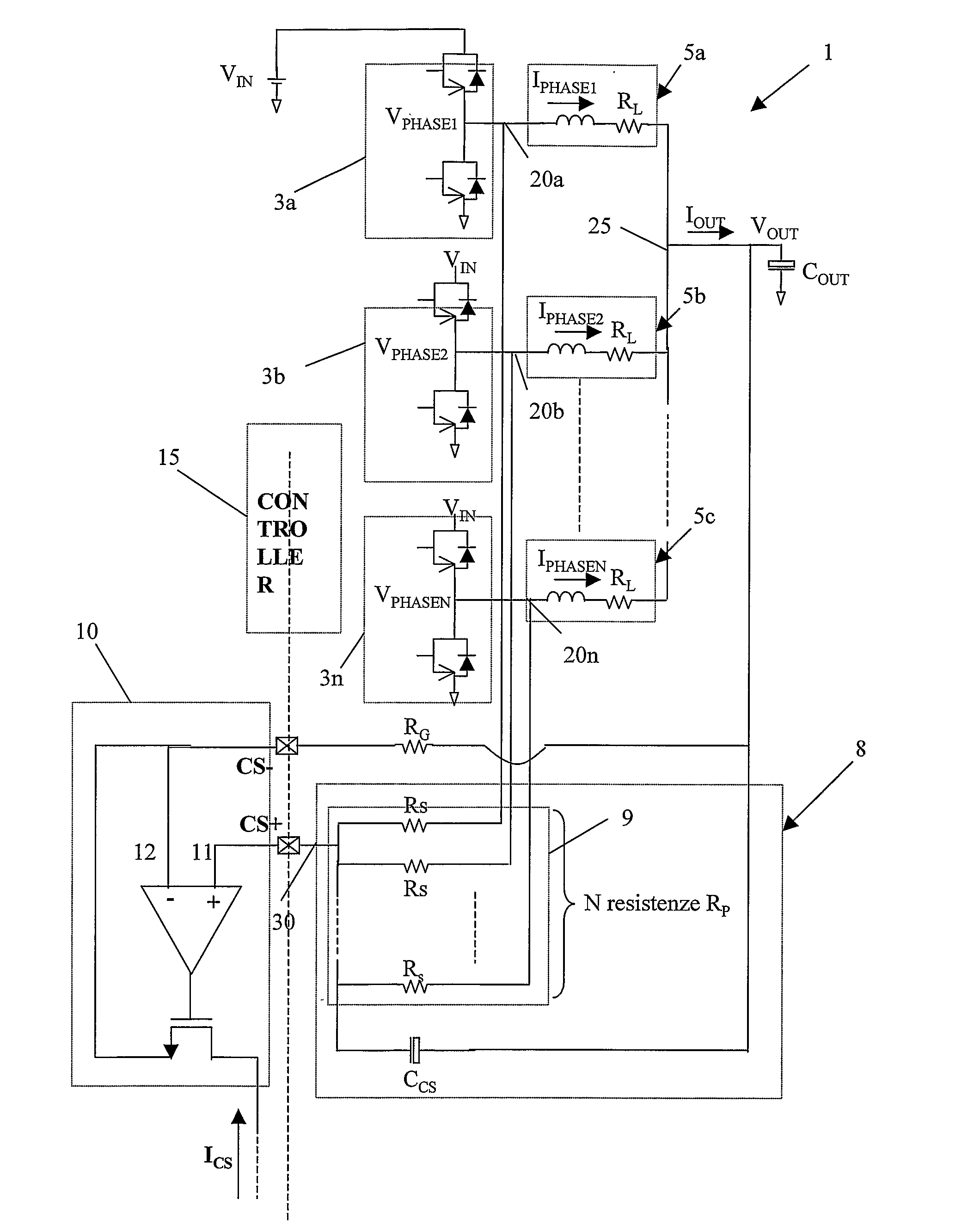

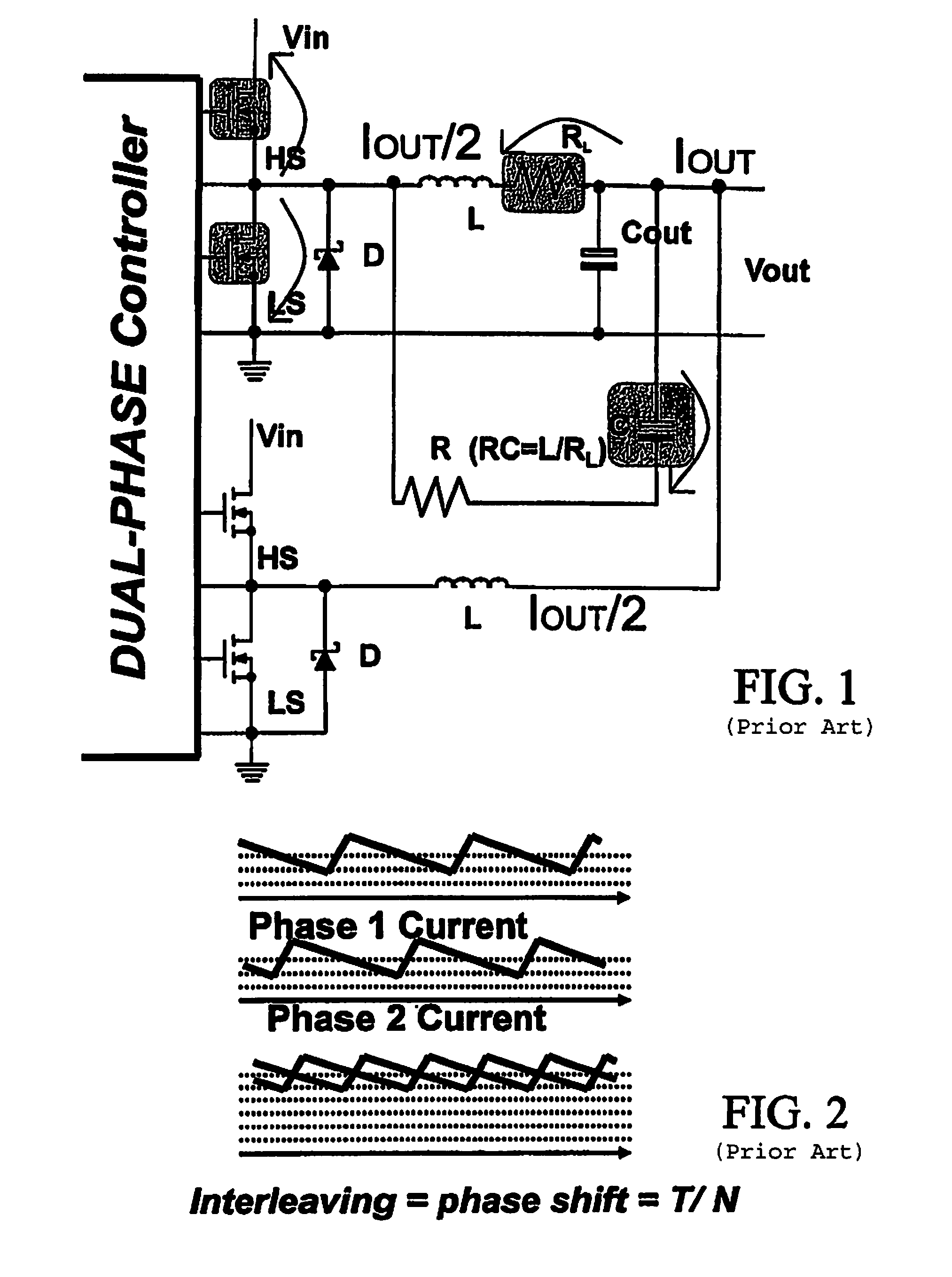

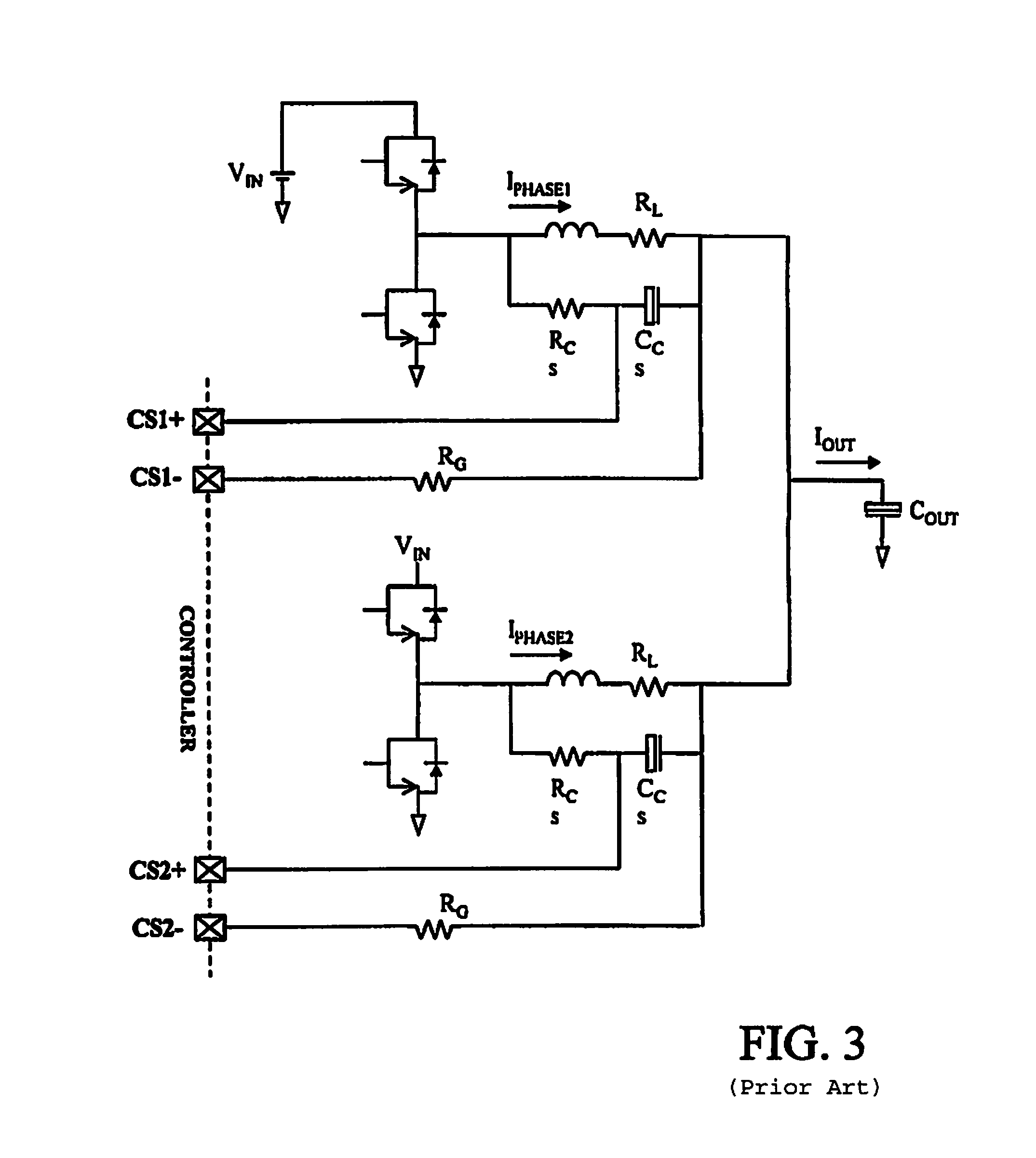

Multi-Phase Voltage Regulator

ActiveUS20080169797A1Reduce and minimize useReduce number of pinDc-dc conversionElectric variable regulationVoltage regulationEngineering

A multiphase voltage regulator provides a voltage to an output terminal. The voltage regulator includes N parallel switches providing respective current phases that are added together to generate a total current for a general load coupled to the output terminal. The voltage regulator also includes N inductive circuits. Each inductive circuit is between an output node of a respective switch and the output terminal. A sense circuit adds the voltages in each of the output nodes of the N switches. An amplifier circuit has an input receiving the added voltage, and outputs a current proportional to the total current. A controller with two pins reads the total current. The two pins are connected to the inputs of the amplifier.

Owner:STMICROELECTRONICS SRL

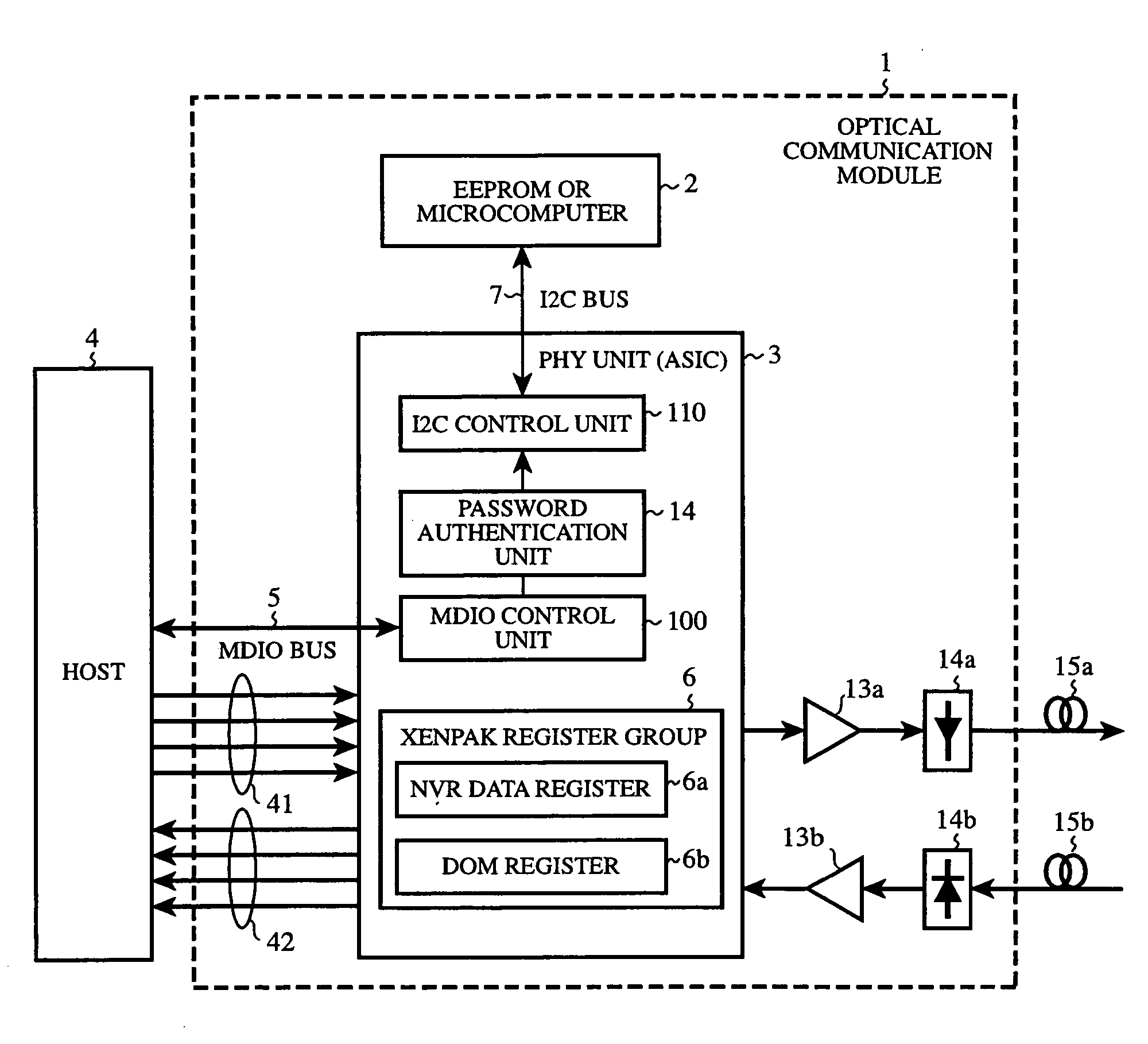

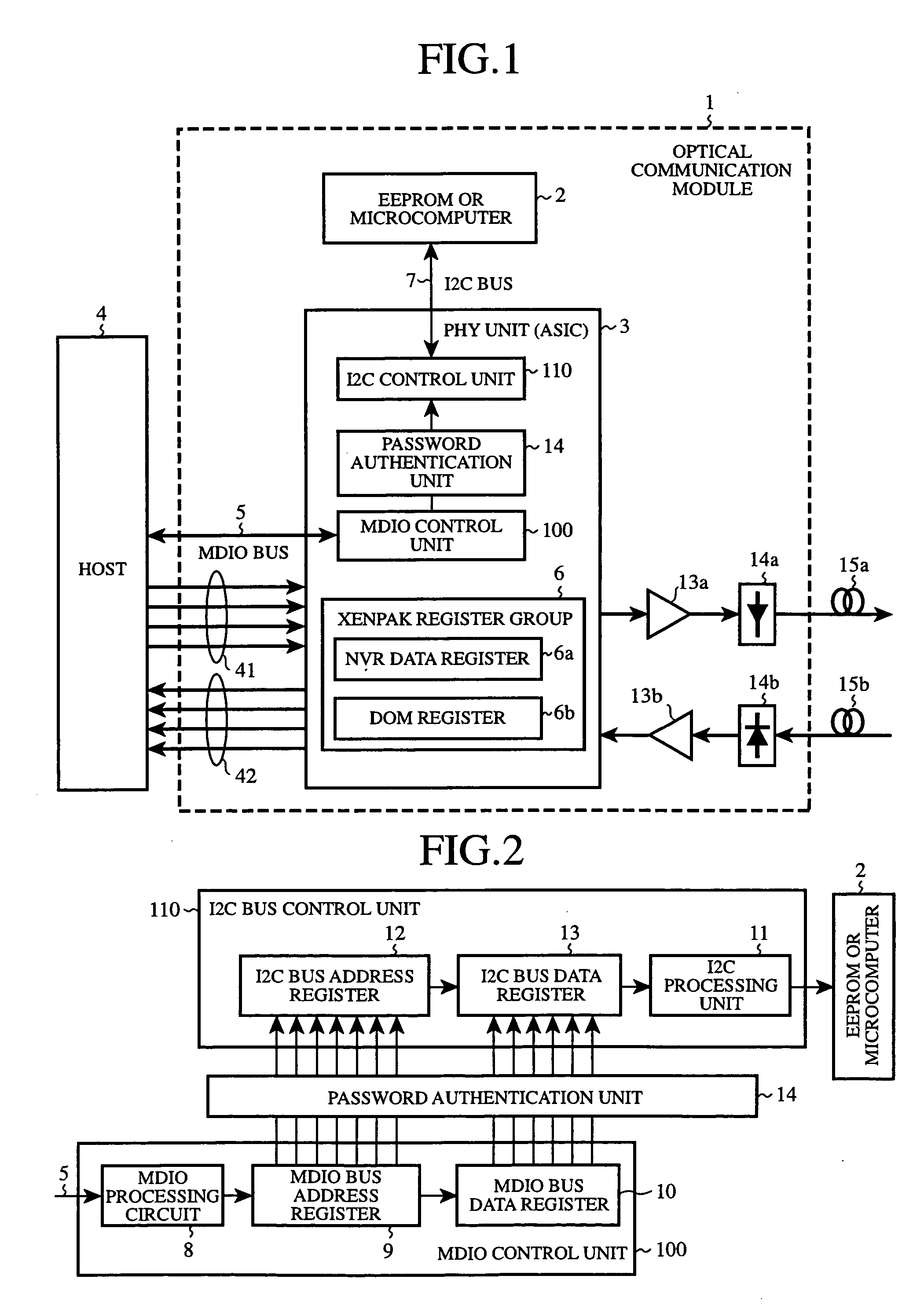

Optical communication module

InactiveUS20060069822A1Reduced pin countEasy to useElectromagnetic transmittersElectromagnetic receiversMicrocomputerPhysical layer

An optical communication module includes a physical-layer unit having a first control unit for receiving a write destination address and NVR data from a host via a serial bus, and for carrying out serial / parallel conversion of the received write destination address and NVR data, and storing them in registers of the first control unit, respectively, and a second control unit for copying the stored write destination address and NVR data to corresponding registers of the second control unit, respectively, and for carrying out parallel / serial conversion of the write destination address and NVR data which are copied to the registers of the second control unit, respectively, and sending them to either an EEPROM or a flash memory of a microcomputer, as well as a write command, via another serial bus to write the NVR data into either the EEPROM or the flash memory of the microcomputer.

Owner:MITSUBISHI ELECTRIC CORP