Patents

Literature

351results about How to "Improve semiconductor device performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

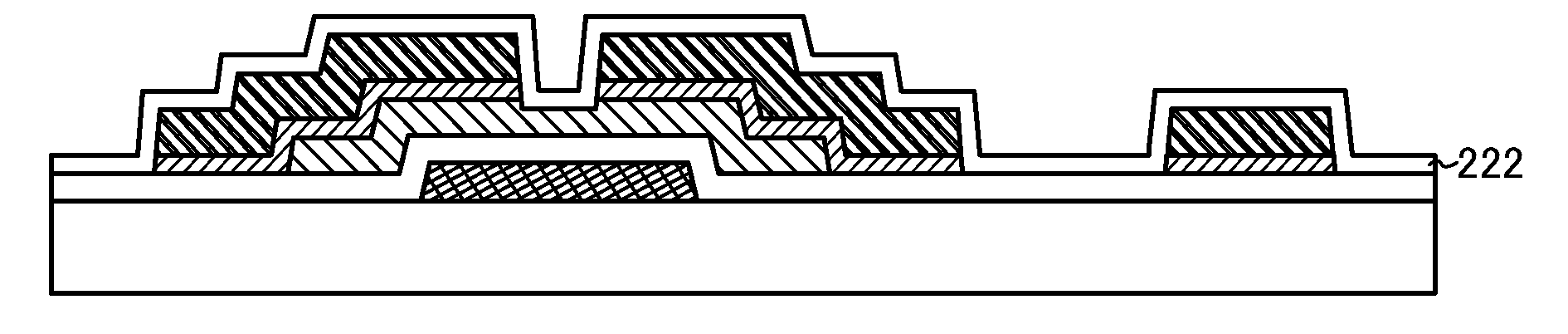

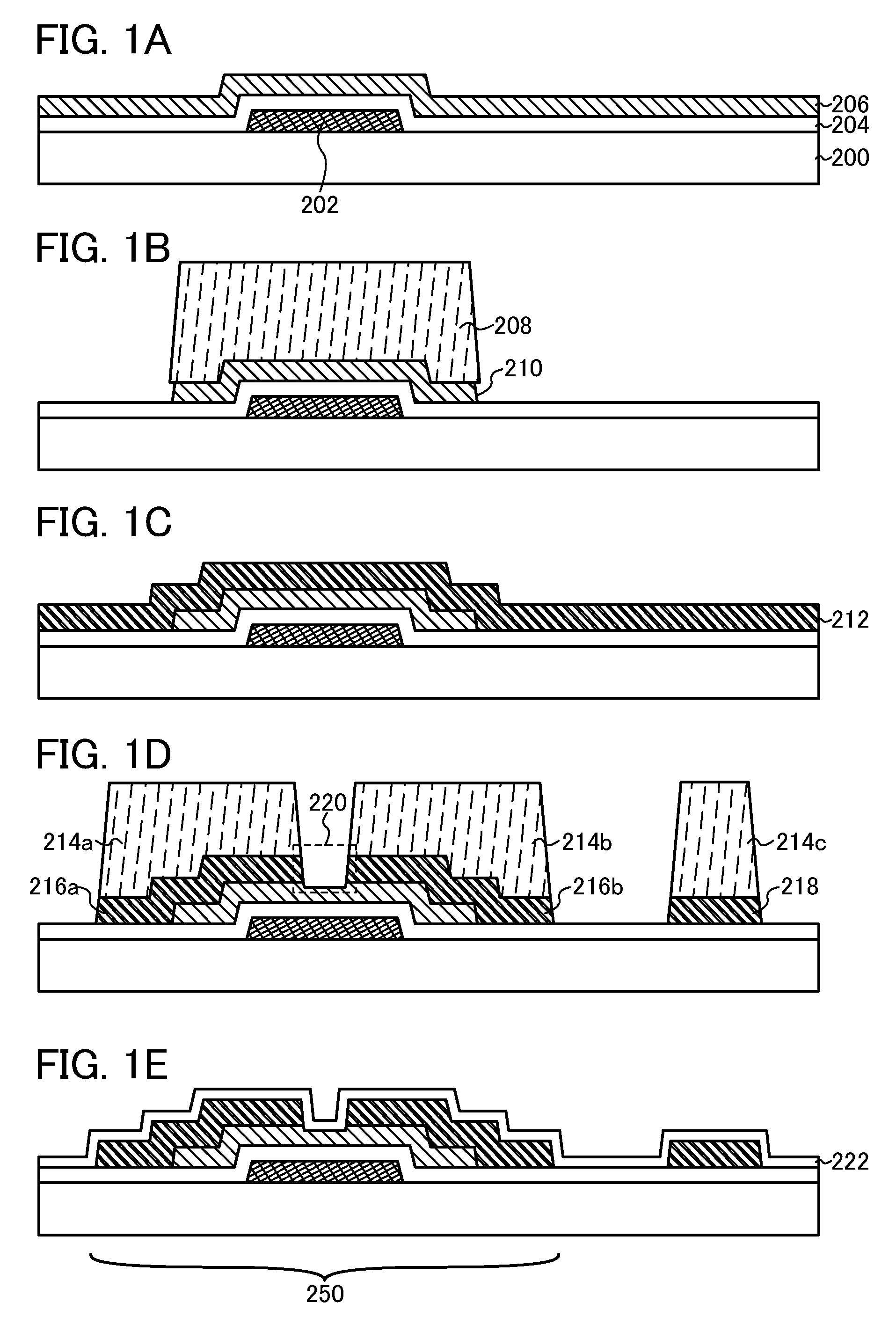

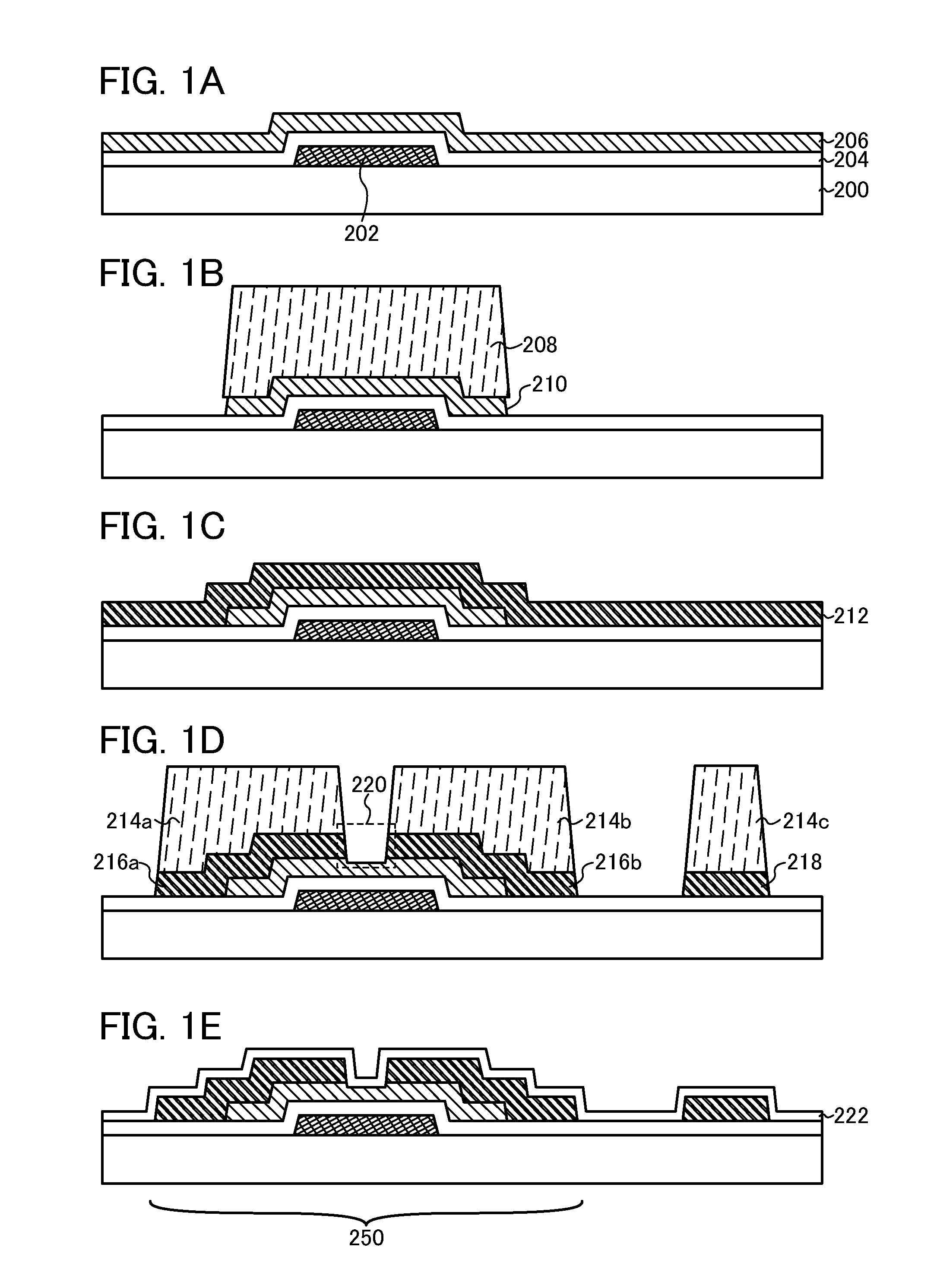

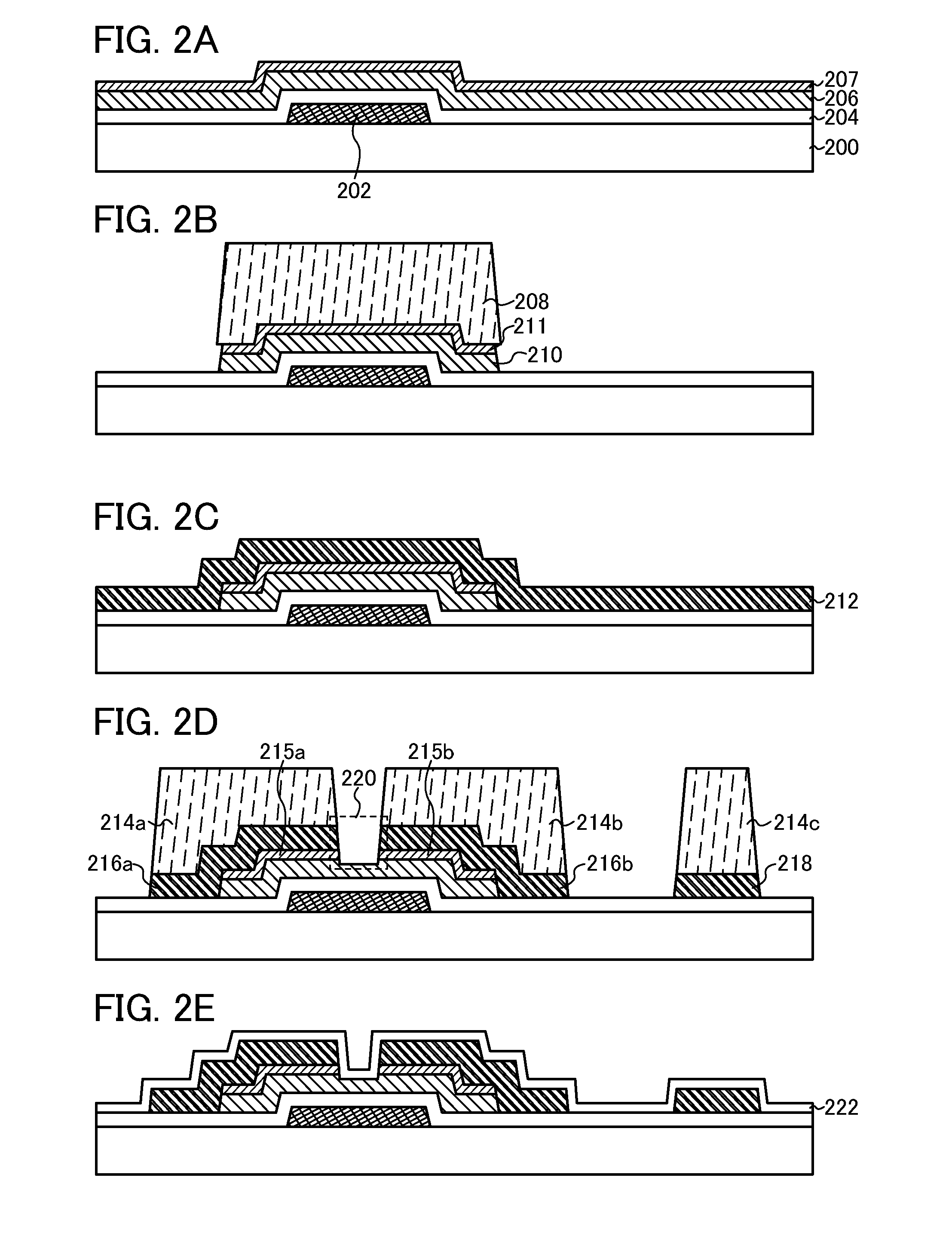

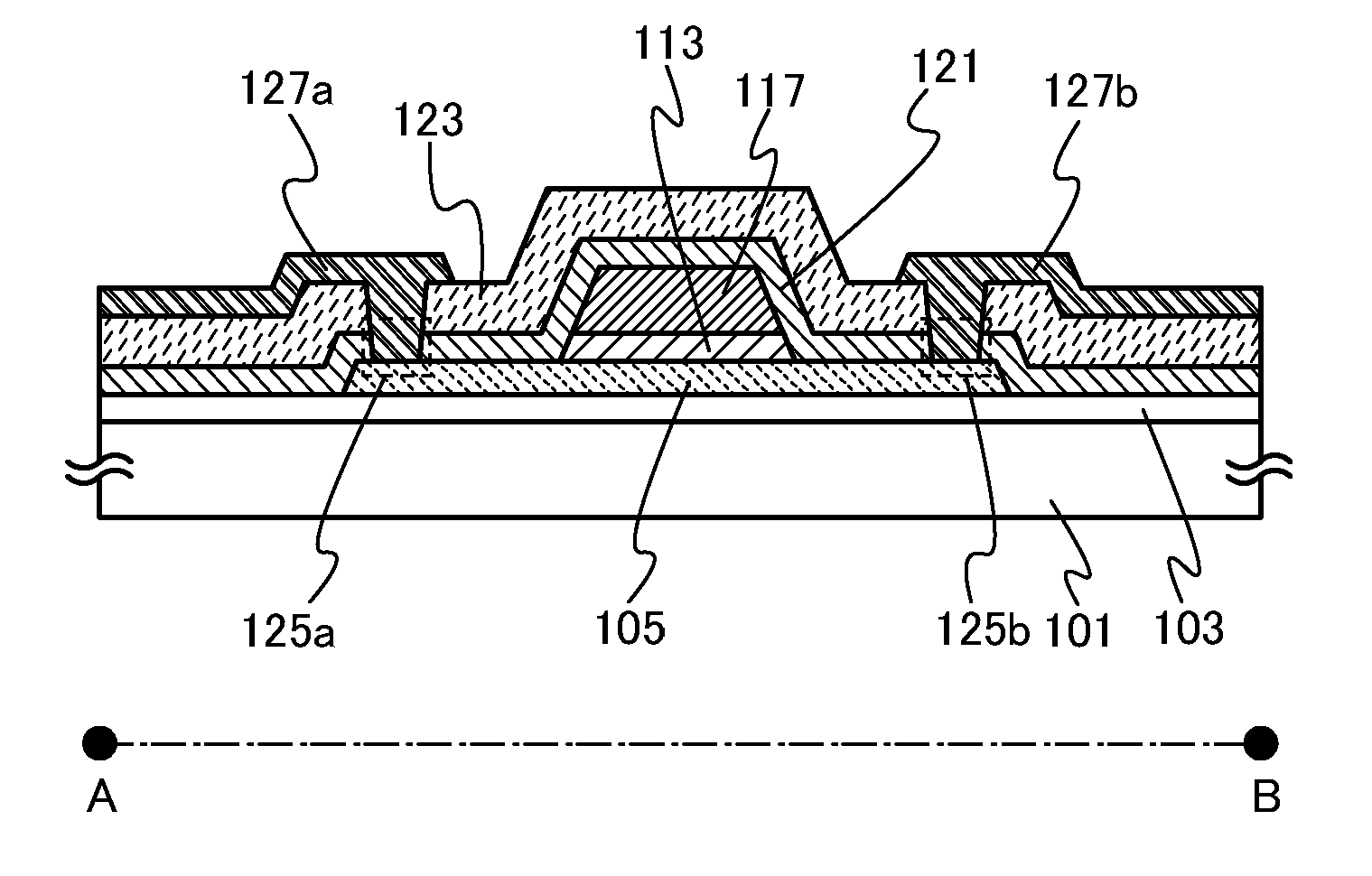

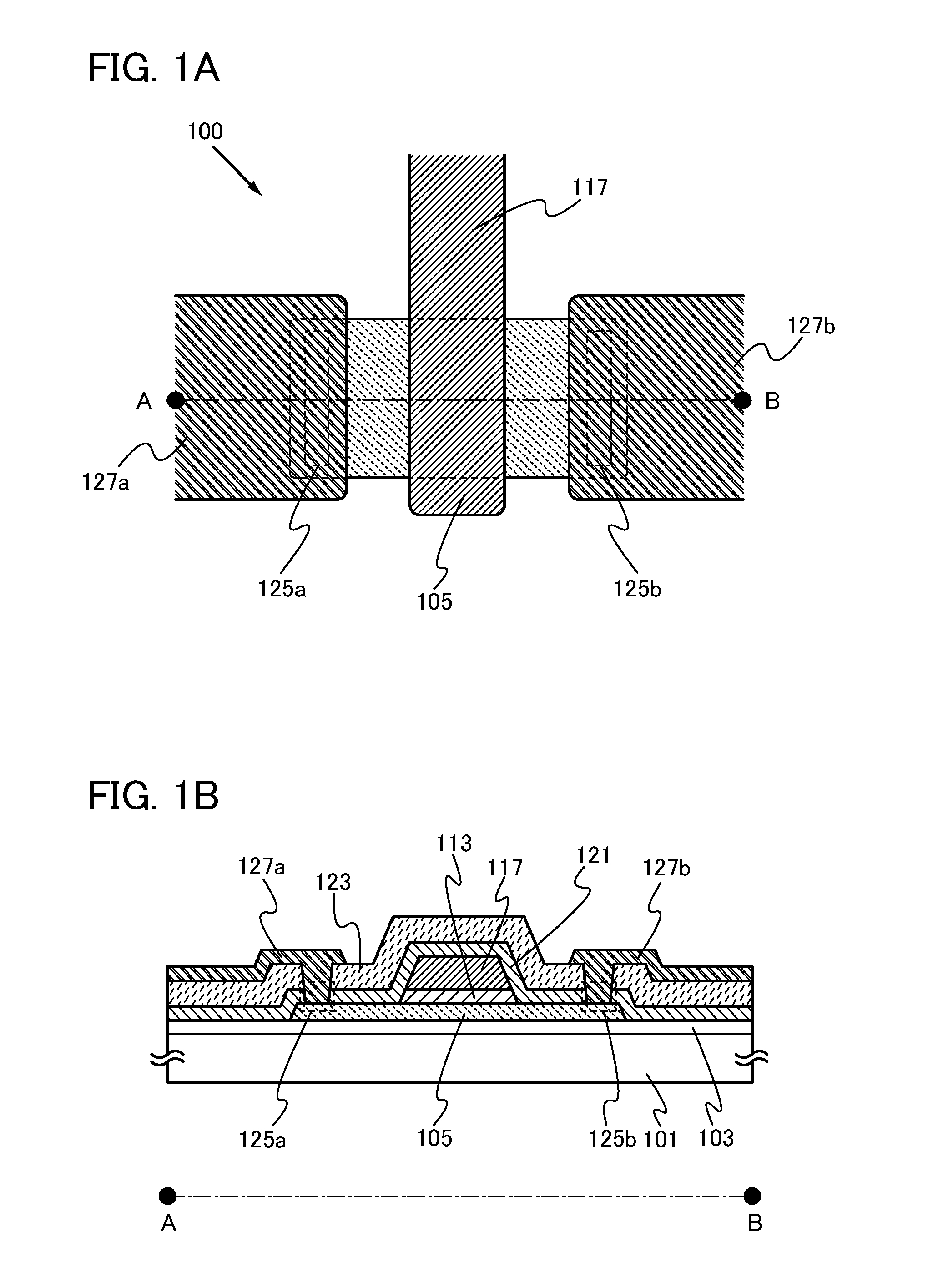

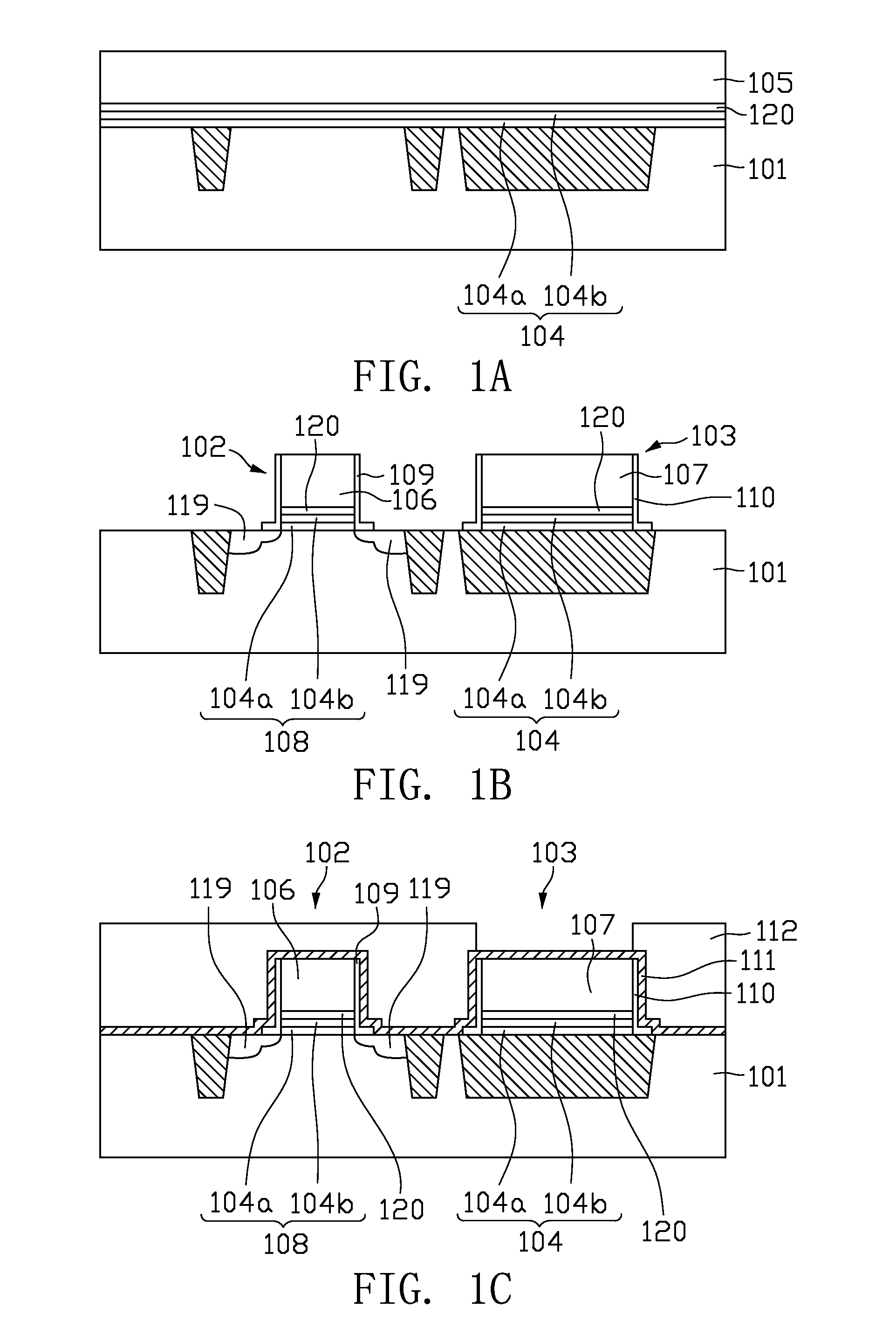

Method for manufacturing semiconductor device

ActiveUS20110117698A1Low costSemiconductor device can be miniaturizedStatic indicating devicesSolid-state devicesPower semiconductor deviceDry etching

An object is to establish a processing technique in manufacture of a semiconductor device in which an oxide semiconductor is used. A gate electrode is formed over a substrate, a gate insulating layer is formed over the gate electrode, an oxide semiconductor layer is formed over the gate insulating layer, the oxide semiconductor layer is processed by wet etching to form an island-shaped oxide semiconductor layer, a conductive layer is formed to cover the island-shaped oxide semiconductor layer, the conductive layer is processed by dry etching to form a source electrode, and a drain electrode and part of the island-shaped oxide semiconductor layer is removed by dry etching to form a recessed portion in the island-shaped oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

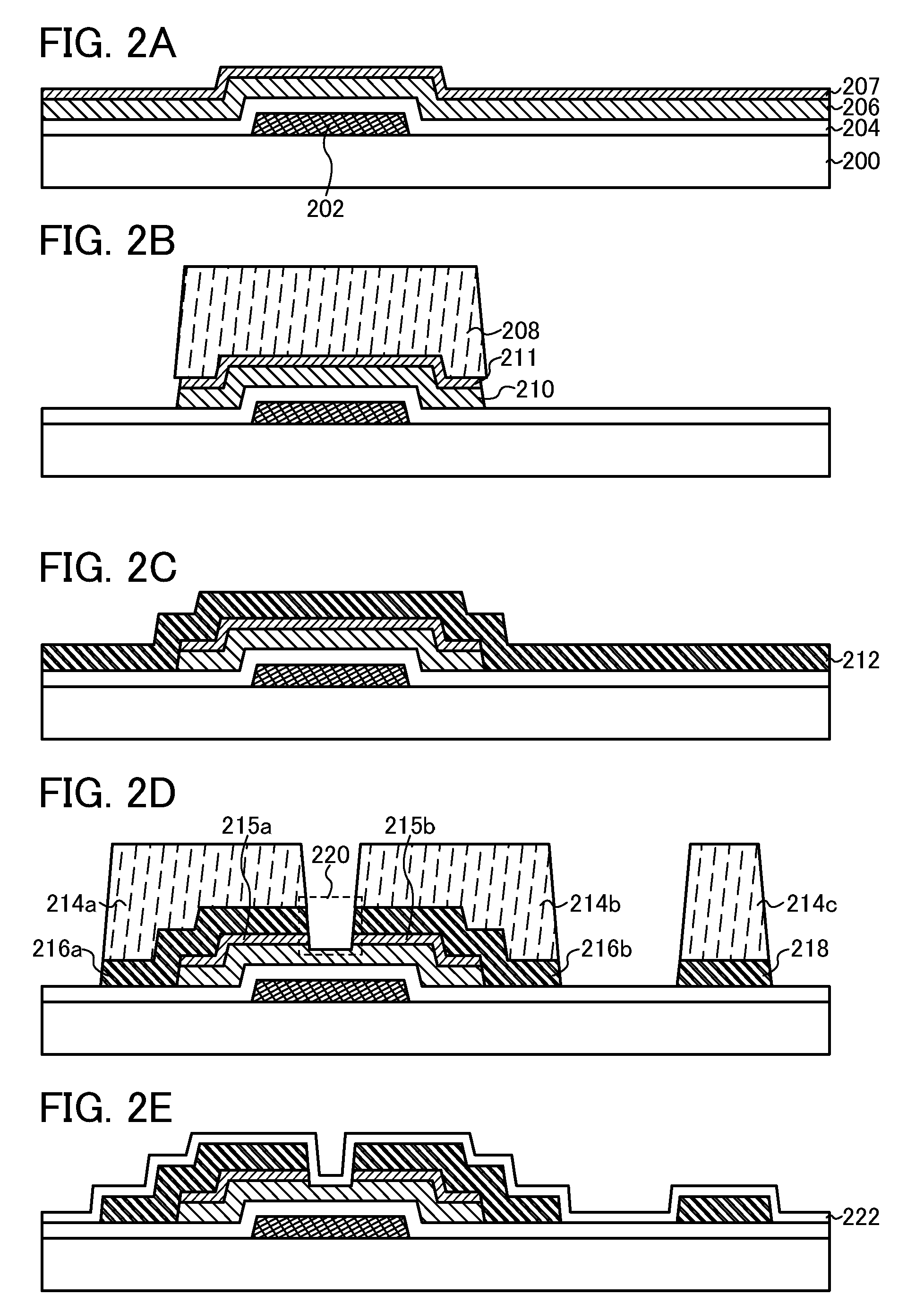

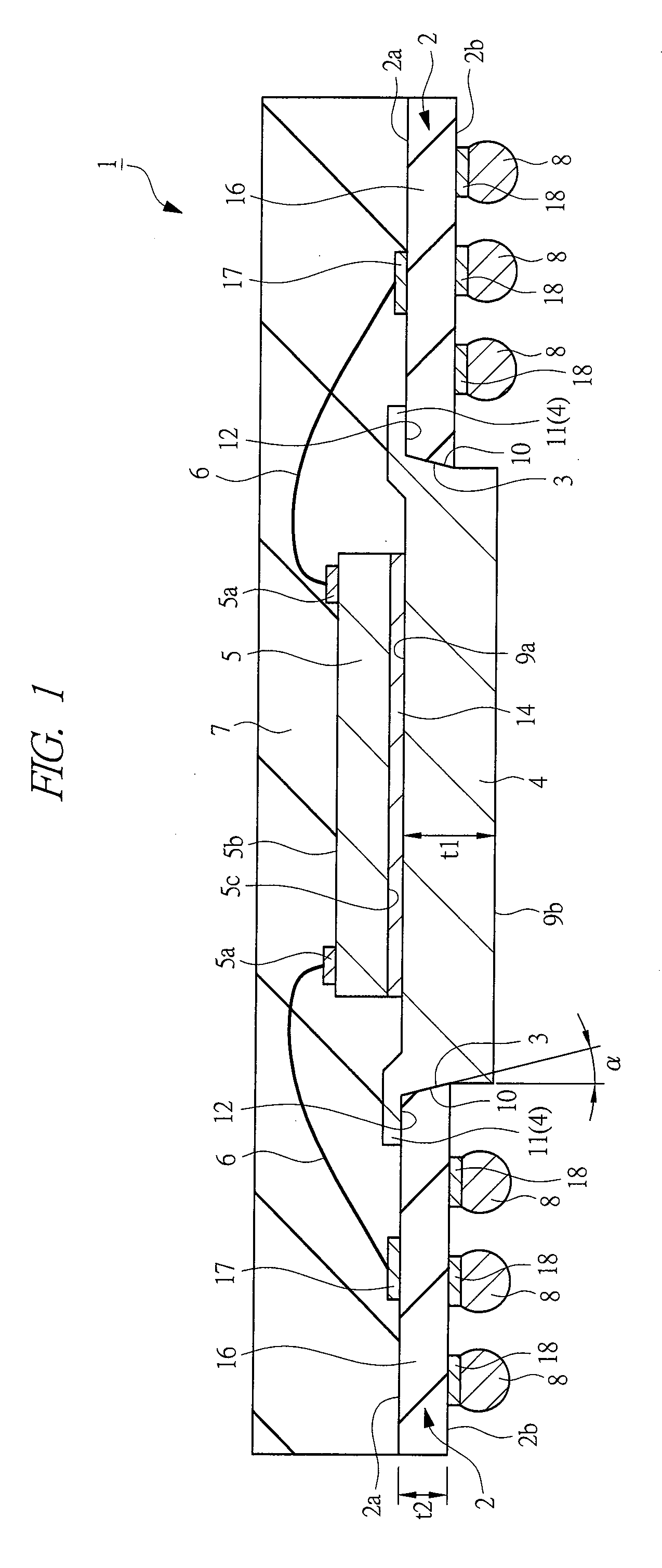

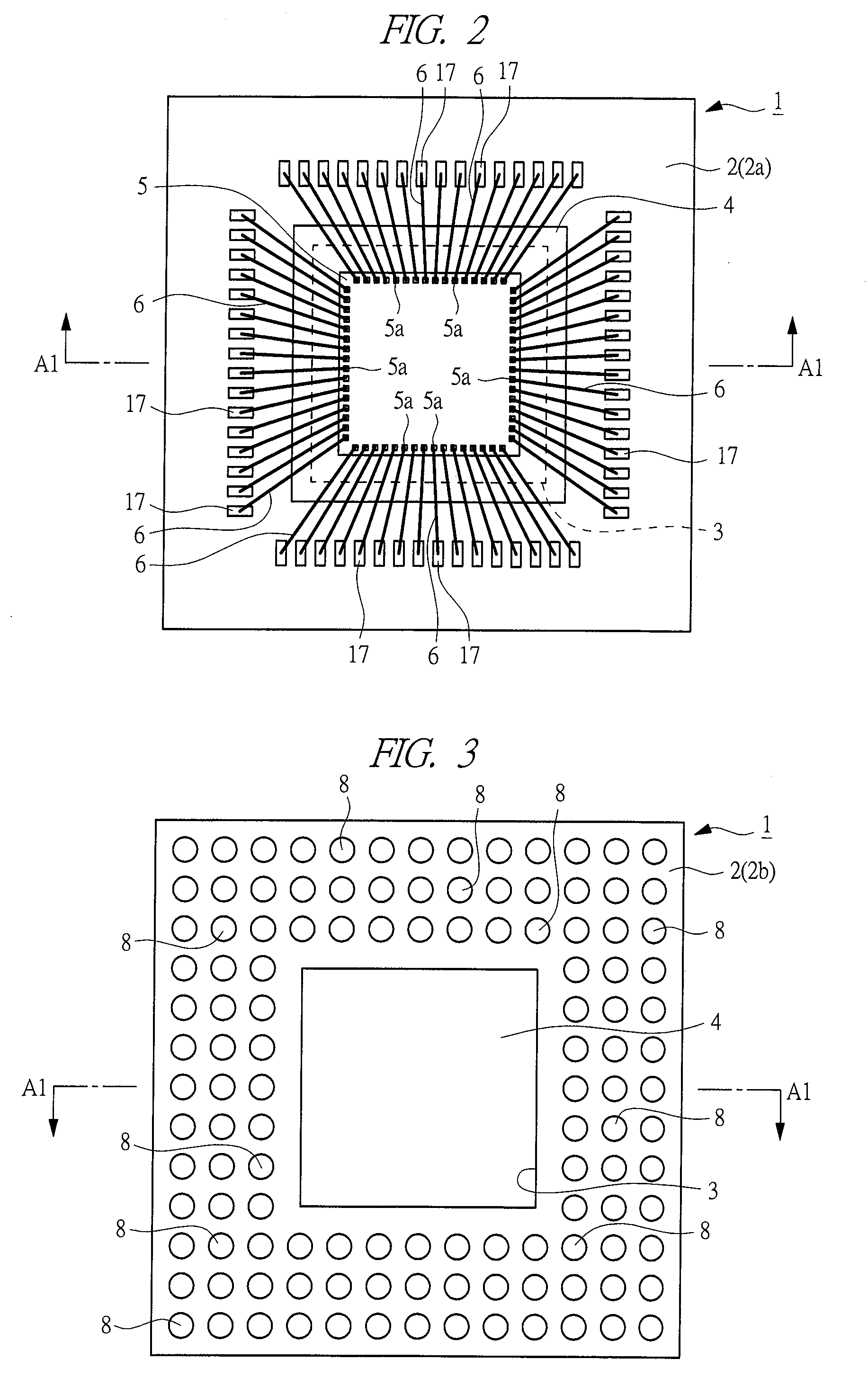

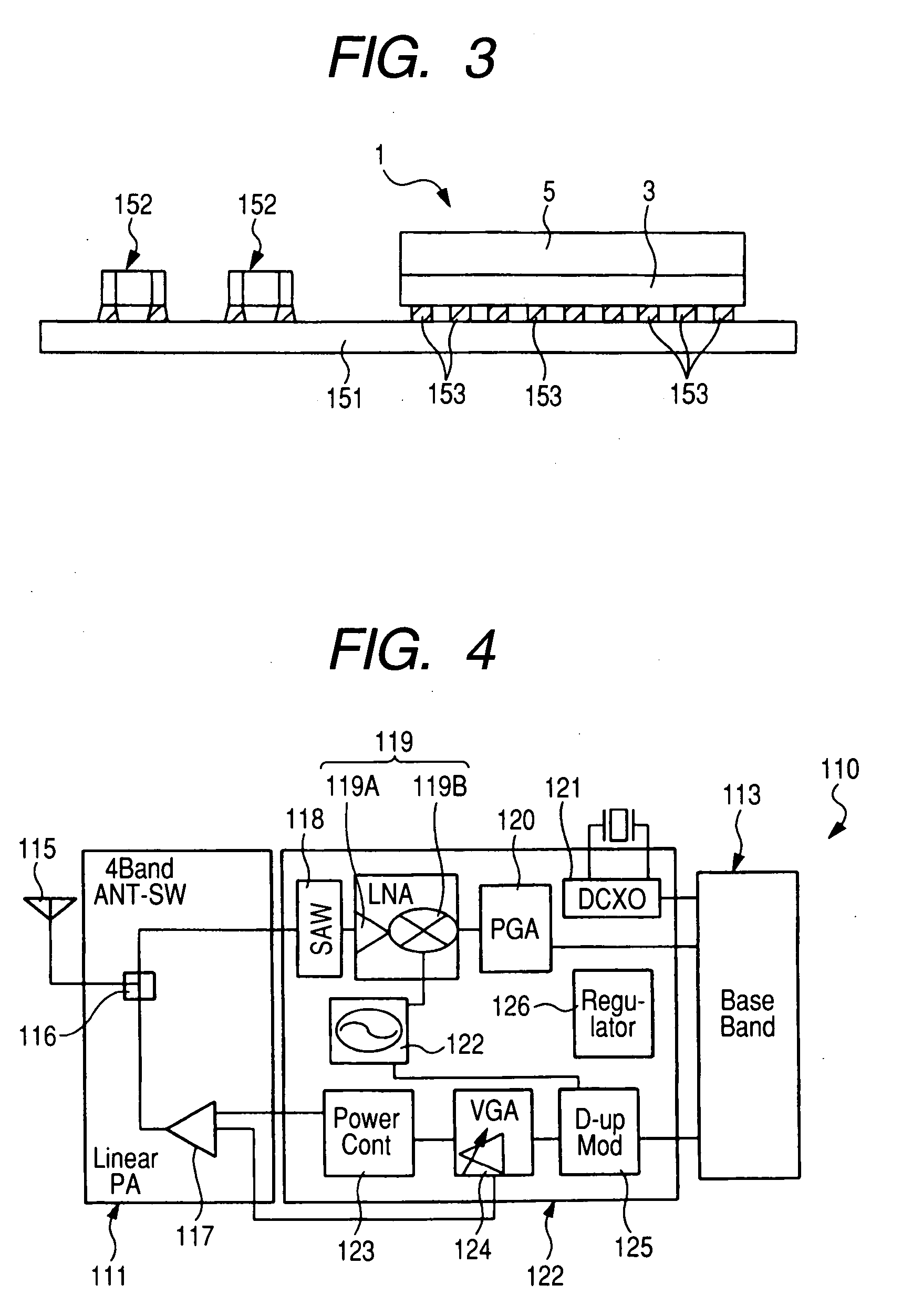

Semiconductor device and manufacturing method of the same

ActiveUS20090309213A1Improve cooling effectImprove manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A semiconductor chip is mounted on a heat sink disposed inside a through-hole of a wiring board, electrodes of the semiconductor chip and connecting terminals of the wiring board are connected by bonding wires, a sealing resin is formed to cover the semiconductor chip and the bonding wires, and solder balls are formed on the lower surface of the wiring board, thereby constituting the semiconductor device. The heat sink is thicker than the wiring board. The heat sink has a protruded portion protruding to outside from the side surface of the heat sink, the protruded portion is located on the upper surface of the wiring board outside the through-hole, and the lower surface of the protruded portion contacts to the upper surface of the wiring board. When the semiconductor device is manufactured, the heat sink is inserted from the upper surface side of the wiring board.

Owner:RENESAS ELECTRONICS CORP

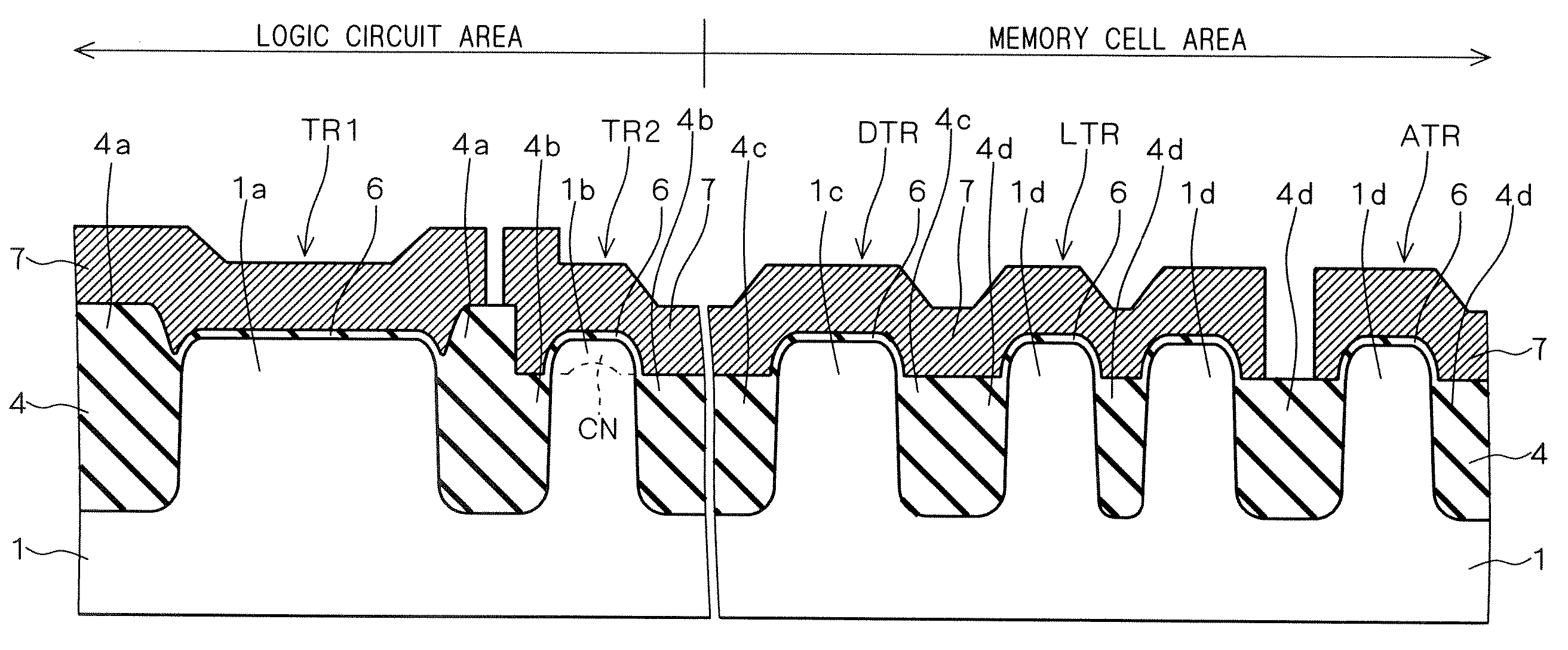

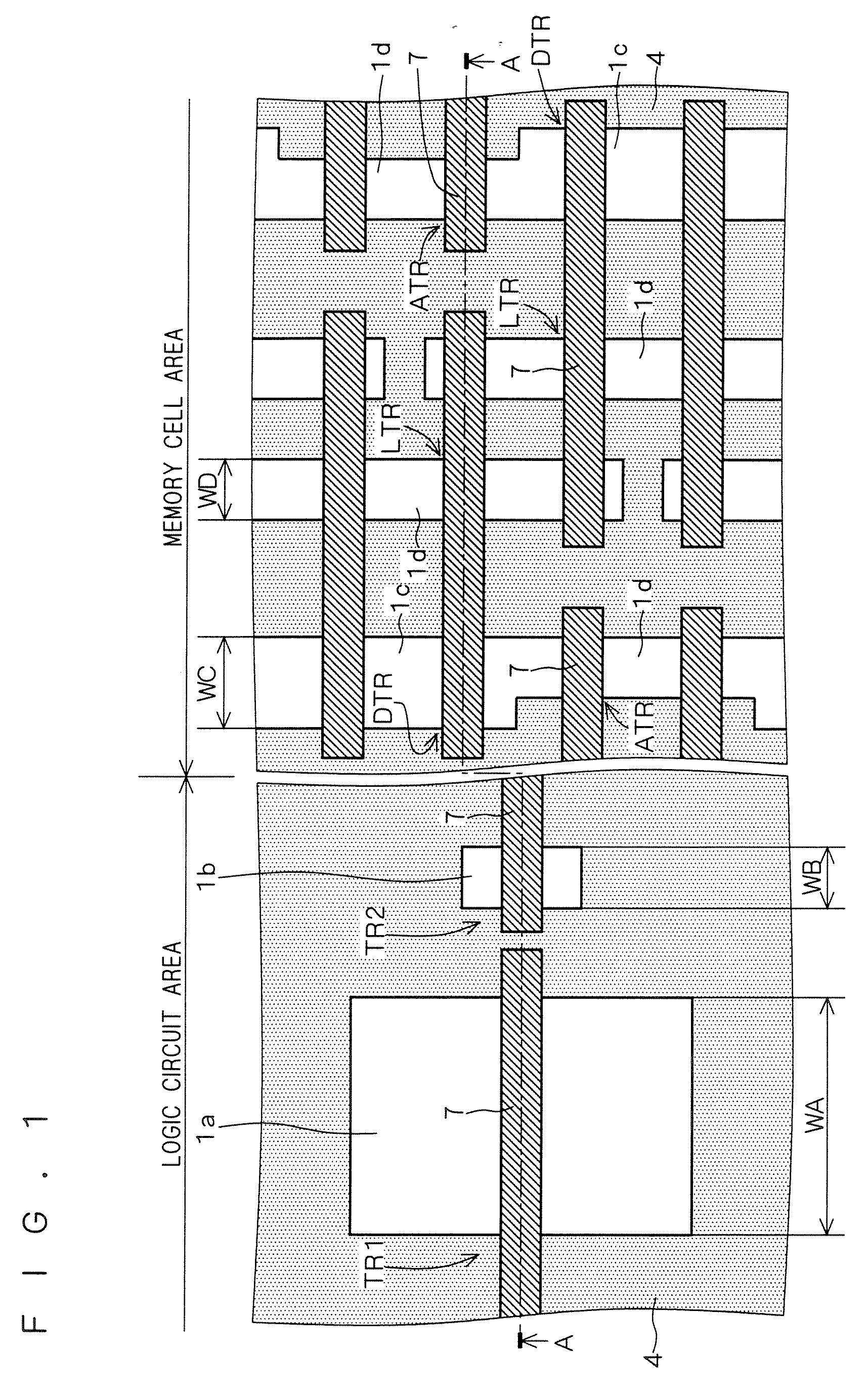

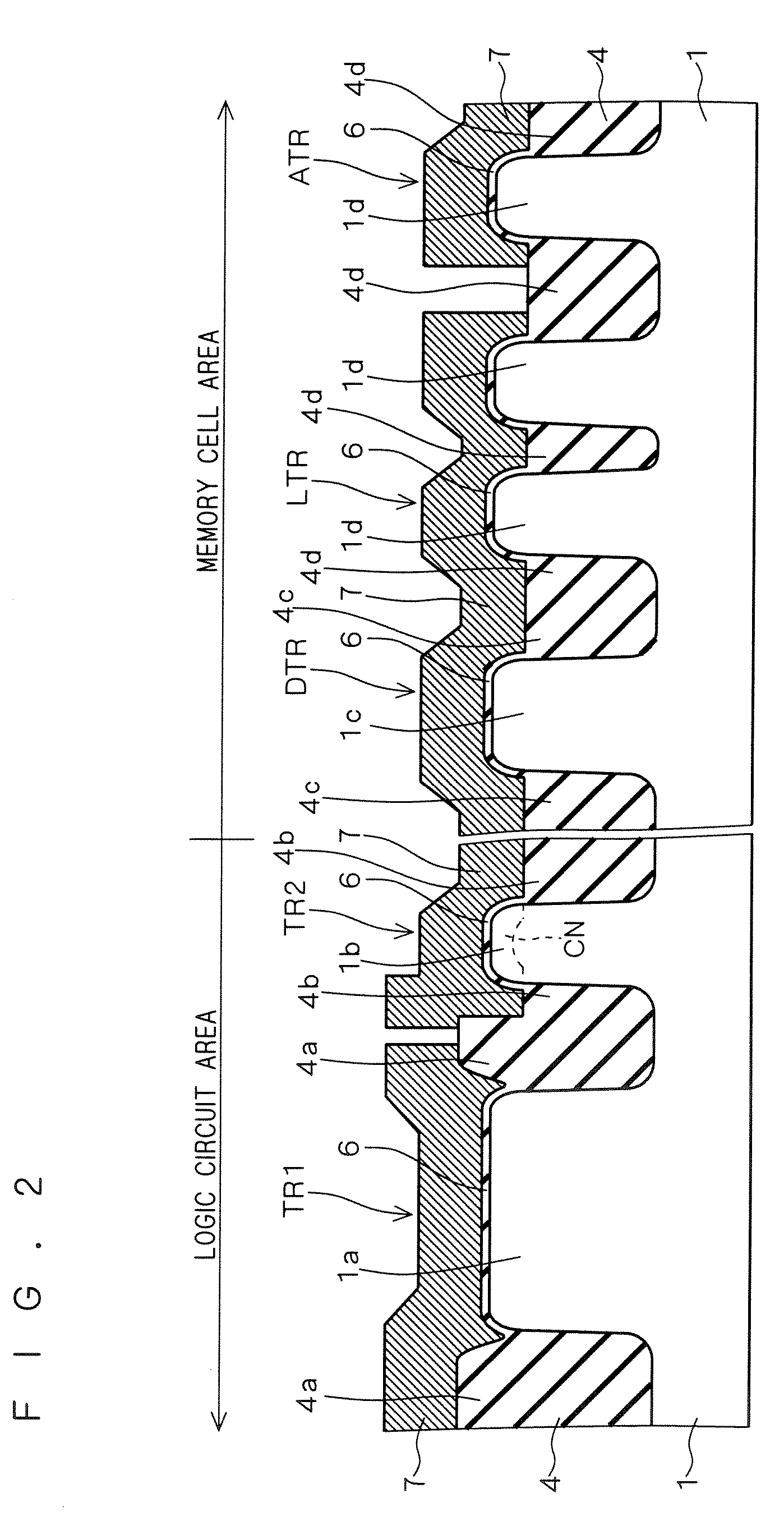

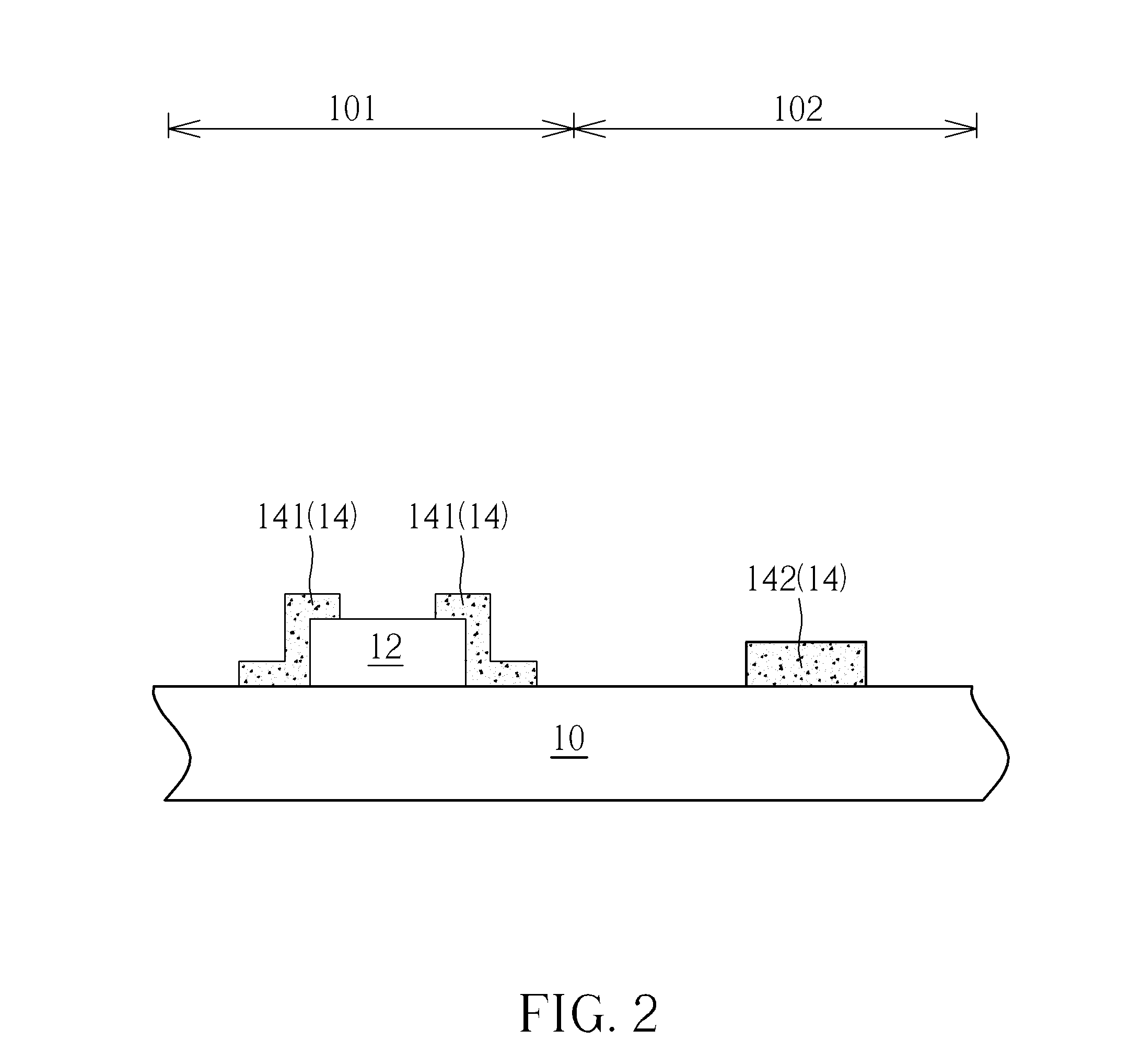

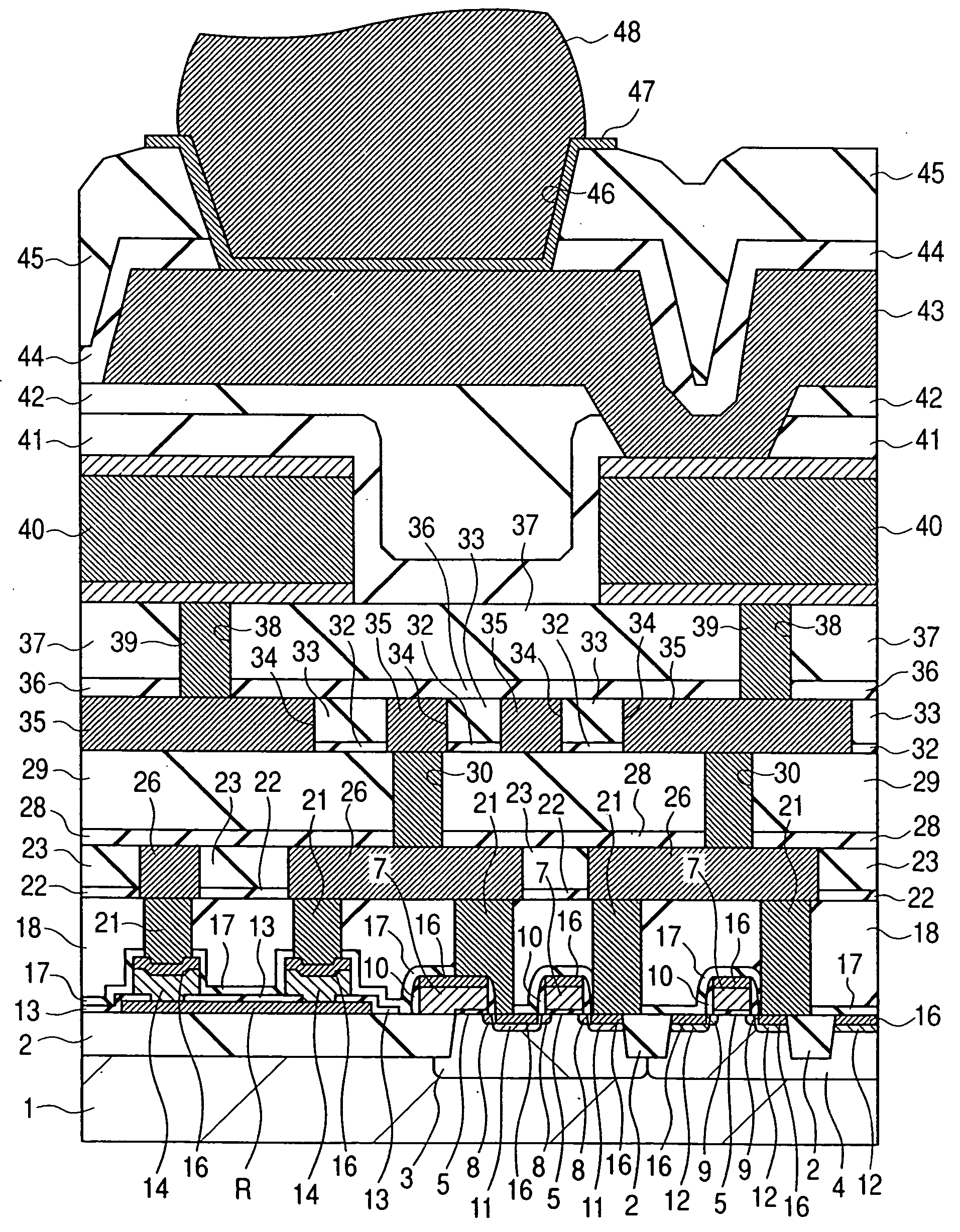

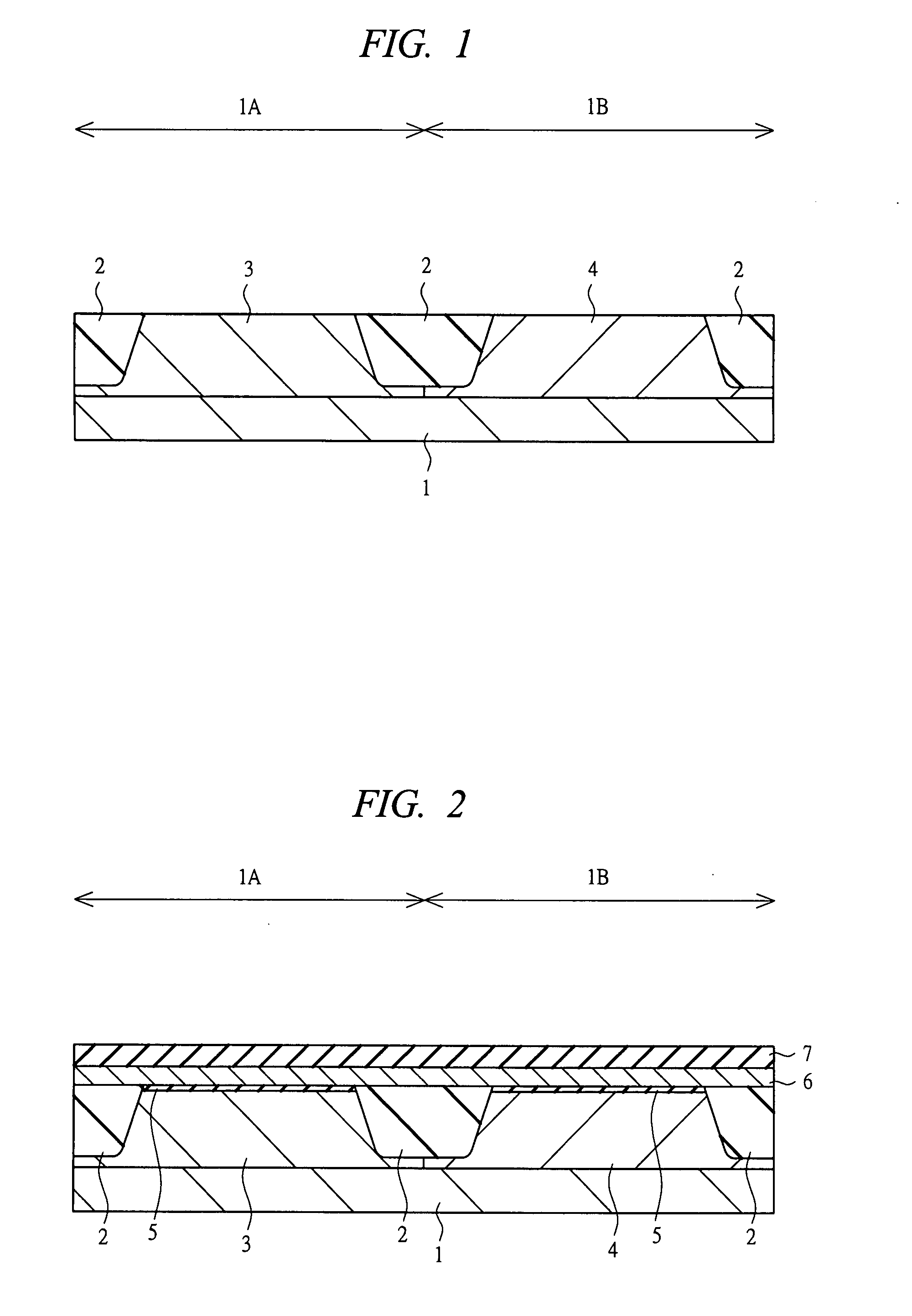

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20060214212A1Improve semiconductor device performanceImprove featuresTransistorSolid-state devicesDevice materialSemiconductor

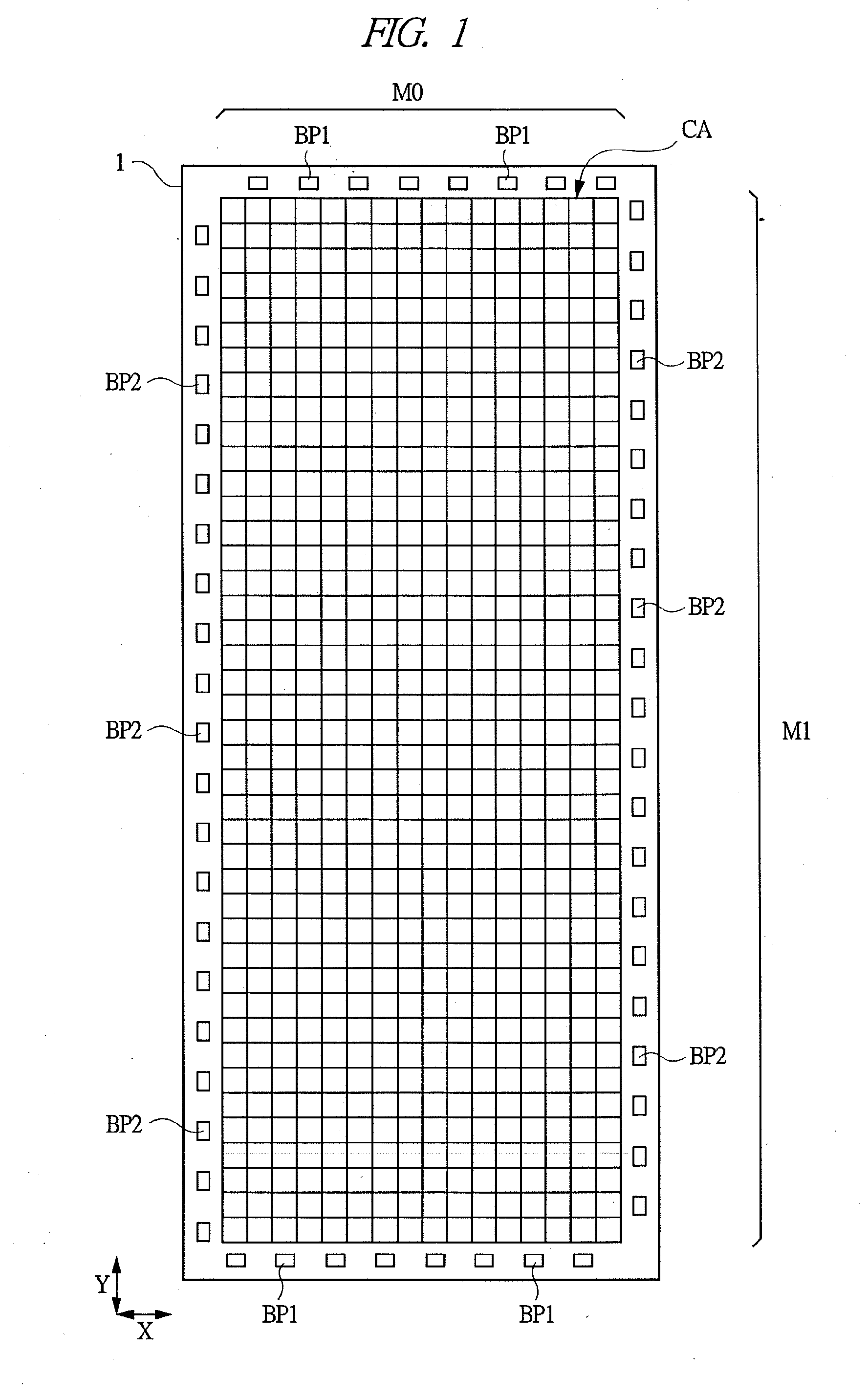

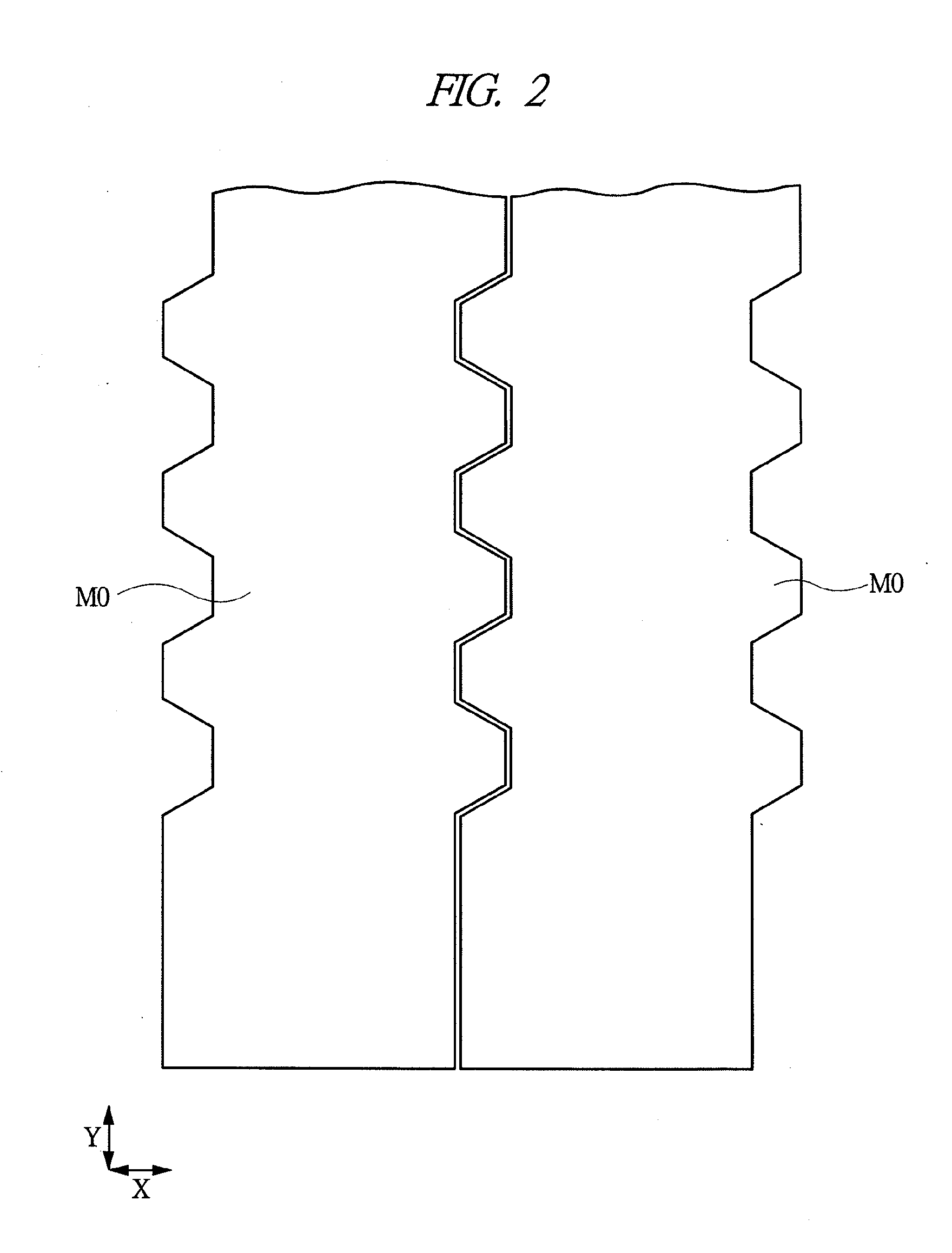

First active region and second and third active regions are defined in a semiconductor substrate within a memory cell area and a logic circuit area, respectively. First to third MOS transistors are formed in the first to third active regions, respectively. As viewed from above, the length of the first and second active regions along the gate width is not greater than the length of the third active region along the gate width. In the isolation insulation film, the upper surface of a peripheral portion provided around the first active region is positioned below the upper surface thereof, and the upper surface of a peripheral portion provided around the second active region is positioned below the upper surface thereof. A gate electrode is formed on the upper surfaces of the first to third active regions and the side surfaces of the first and second active regions.

Owner:RENESAS TECH CORP

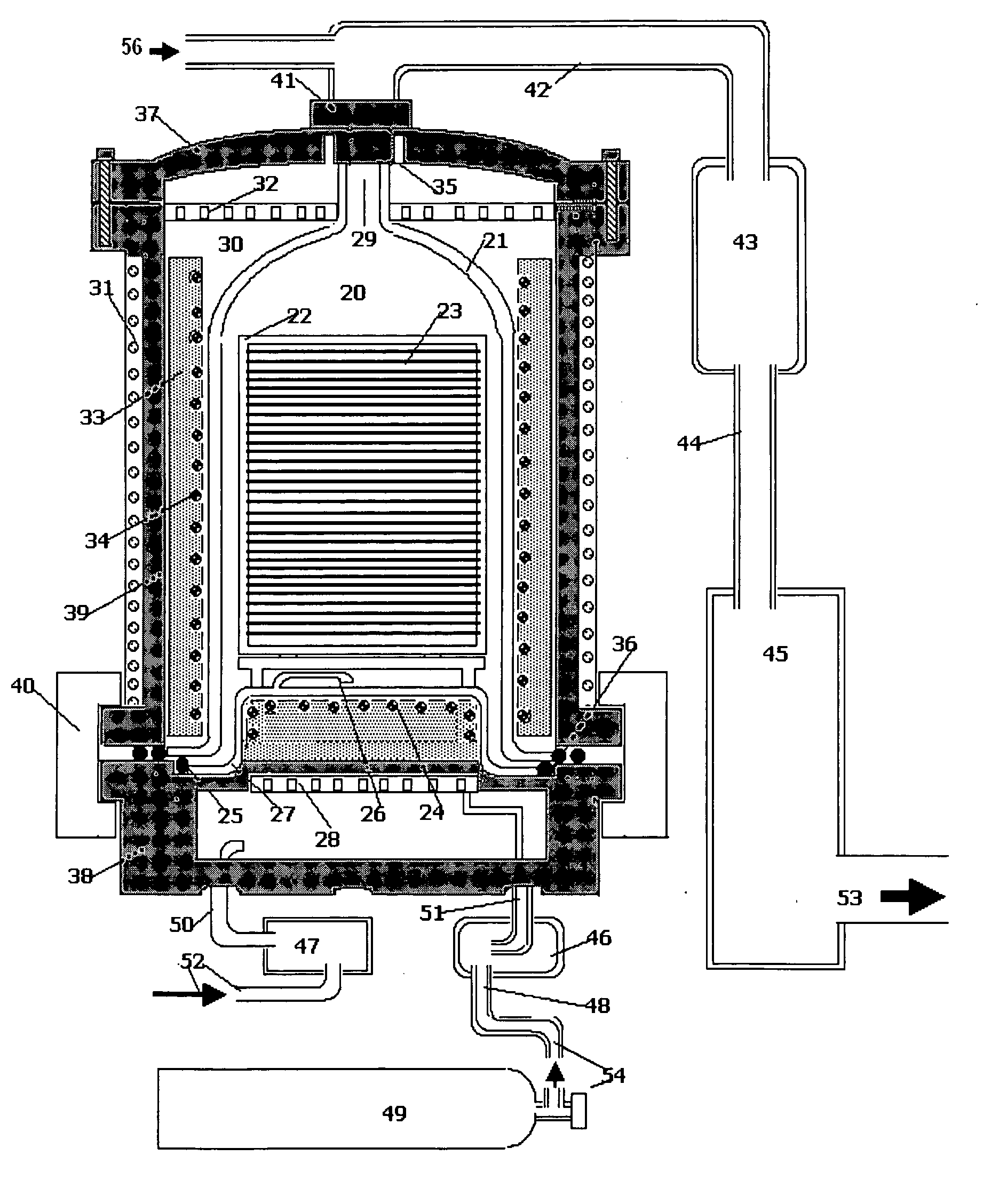

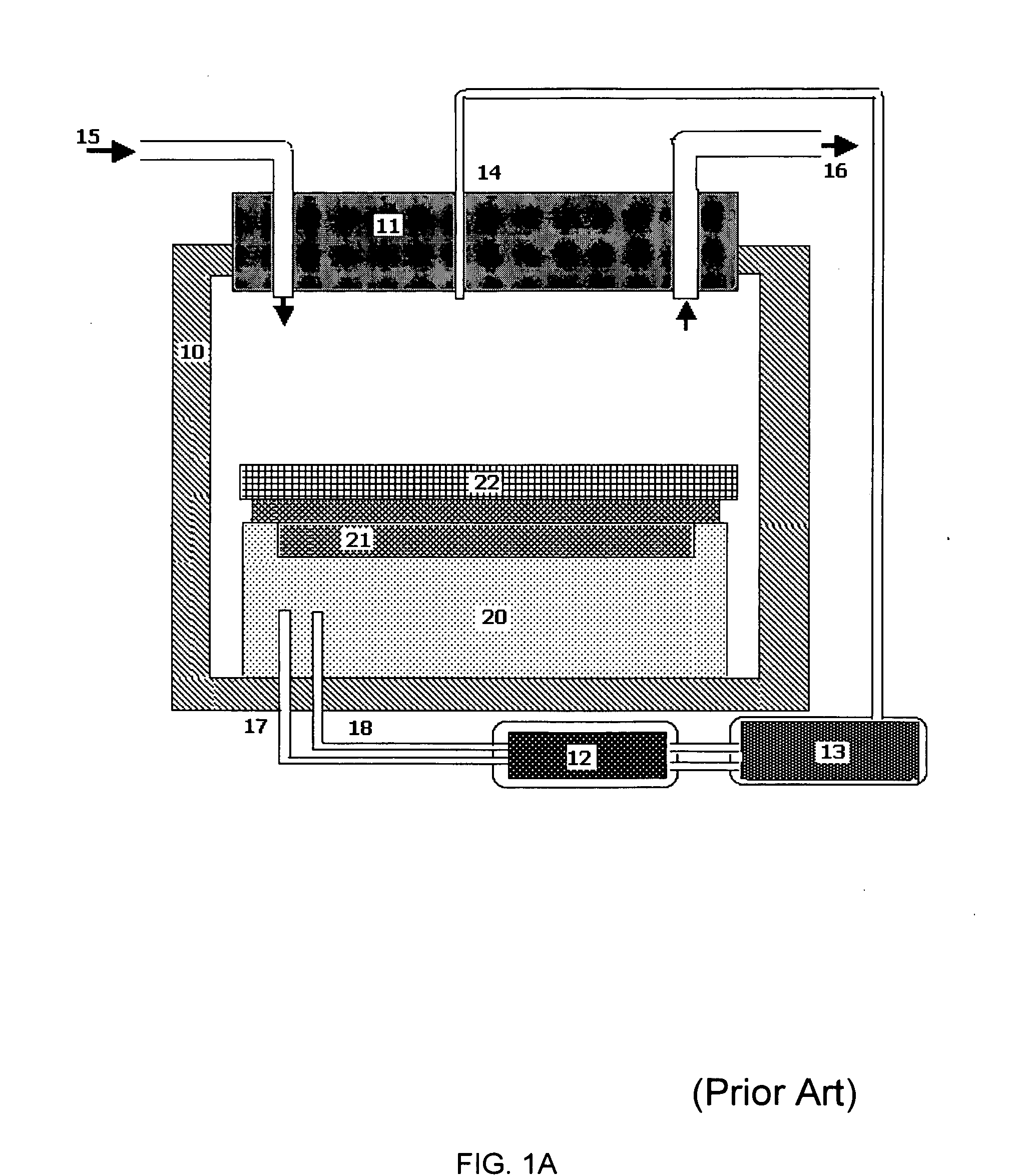

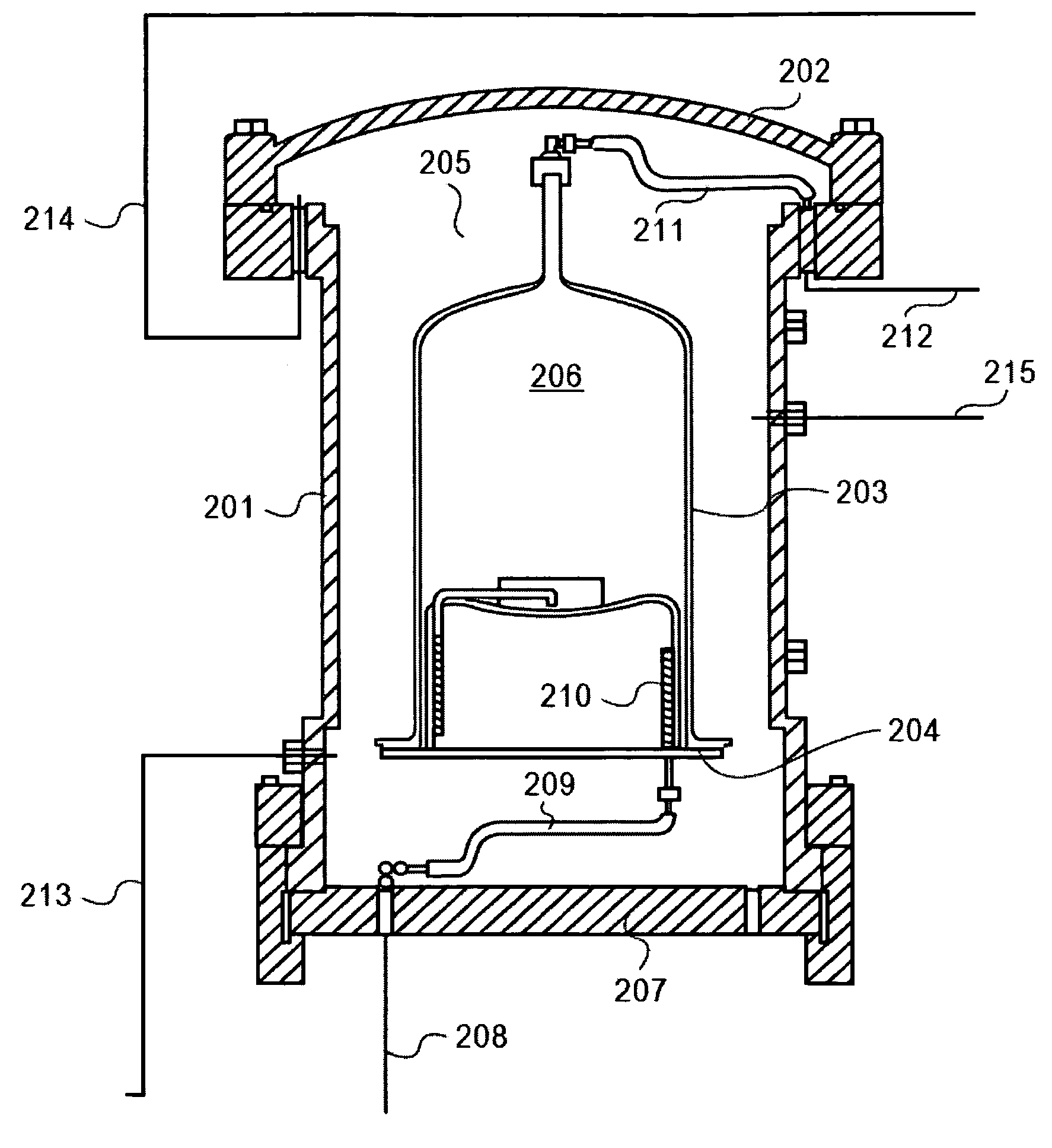

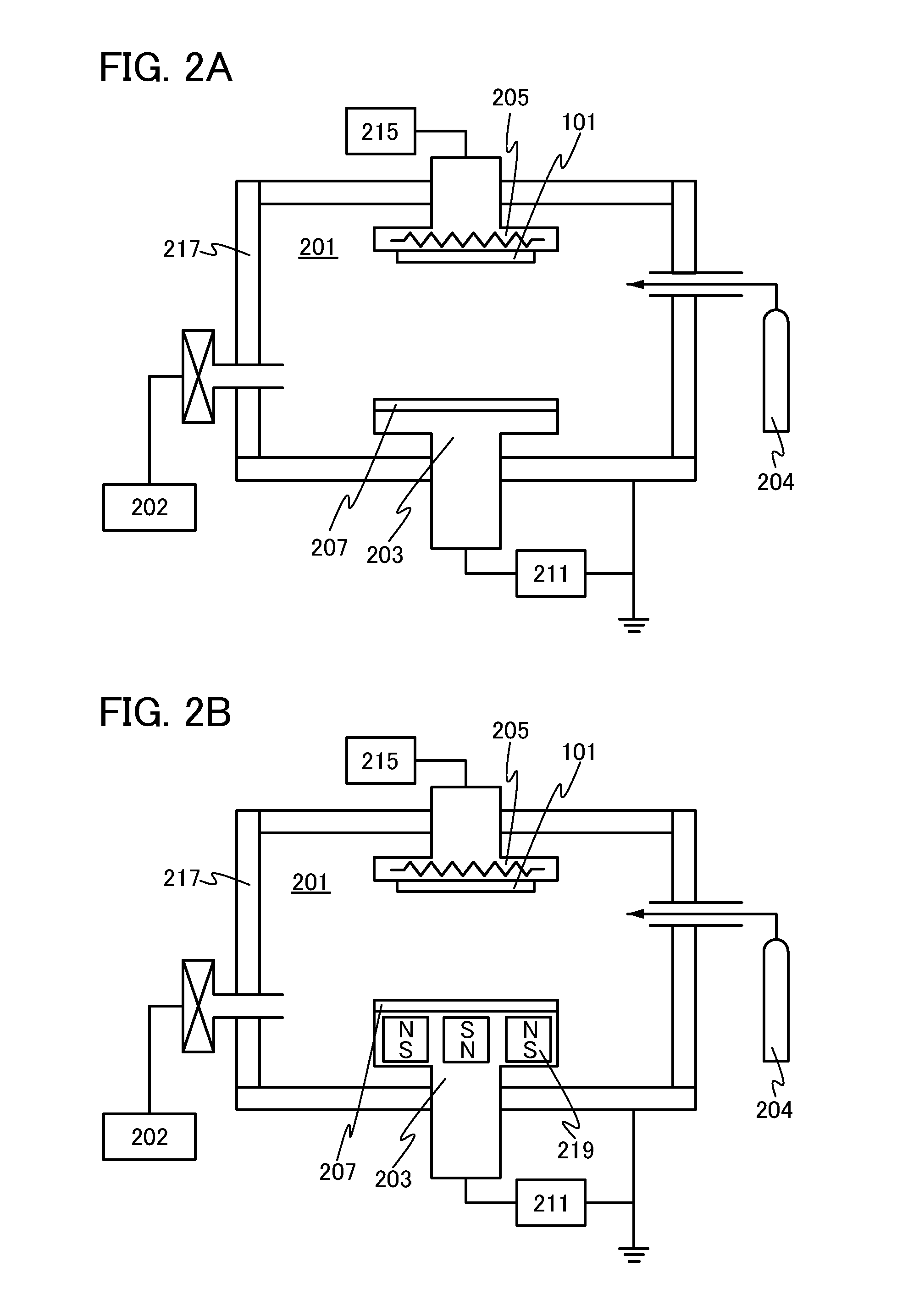

Methods and apparatuses for high pressure gas annealing

InactiveUS20070187386A1Improve device performanceIncrease device 's lifetimeSemiconductor/solid-state device testing/measurementSolid-state devicesForming gasGate dielectric

Novel methods and apparatuses for annealing semiconductor devices in a high pressure gas environment. According to an embodiment, the annealing vessel has a dual chamber structure, and potentially toxic, flammable, or otherwise reactive gas is confined in an inner chamber which is protected by pressures of inert gas contained in the outer chamber. The incoming gas delivery system and exhaust gas venting system are likewise protected by various methods. Embodiments of the present invention can be used, for example, for high-K gate dielectric anneal, post metallization sintering anneal, and forming gas anneal in the semiconductor manufacturing process.

Owner:PSMC

Semiconductor device and method of manufacturing the same

ActiveUS20100155940A1Improve semiconductor device performanceWithout deteriorating productivitySemiconductor/solid-state device detailsSolid-state devicesProduction rateSemiconductor chip

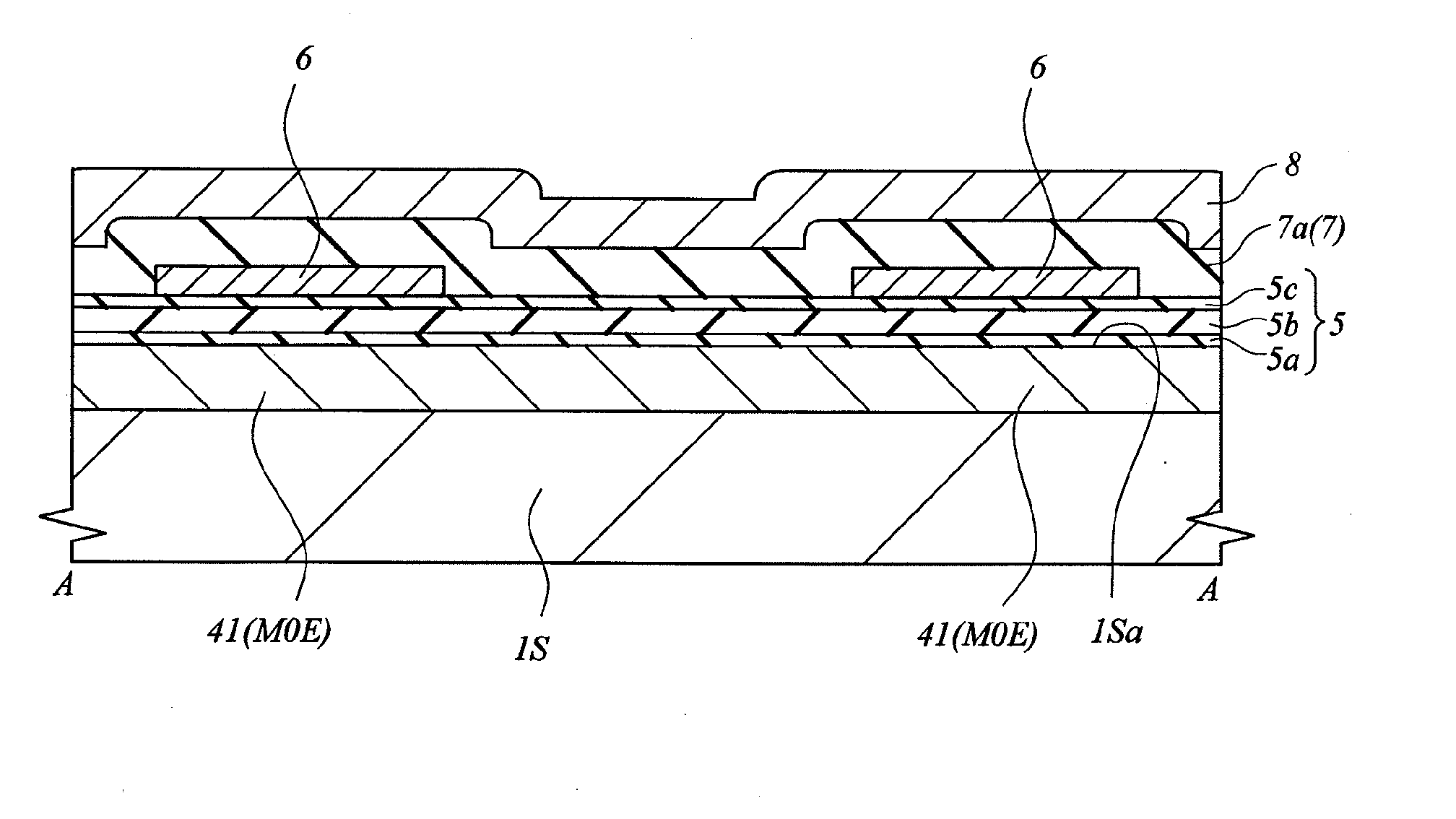

In a semiconductor device in which a plurality of semiconductor chips are stacked, performance is enhanced without deteriorating productivity. The semiconductor device has a plurality of elements, an interlayer insulating film, a pad, and a bump electrode electrically connected with the pad sequentially formed on a main surface of a silicon substrate and has a back-surface electrode formed on a back surface of the silicon substrate and electrically connected with the bump electrode. The bump electrode has a protruding portion penetrating through the pad and protruding toward the silicon substrate side. The back-surface electrode is formed so as to reach the protruding portion of the bump electrode from the back surface side of the silicon substrate toward the main surface side and to cover the inside of a back-surface-electrode hole portion which does not reach the pad, so that the back-surface electrode is electrically connected with the bump electrode.

Owner:TESSERA ADVANCED TECH

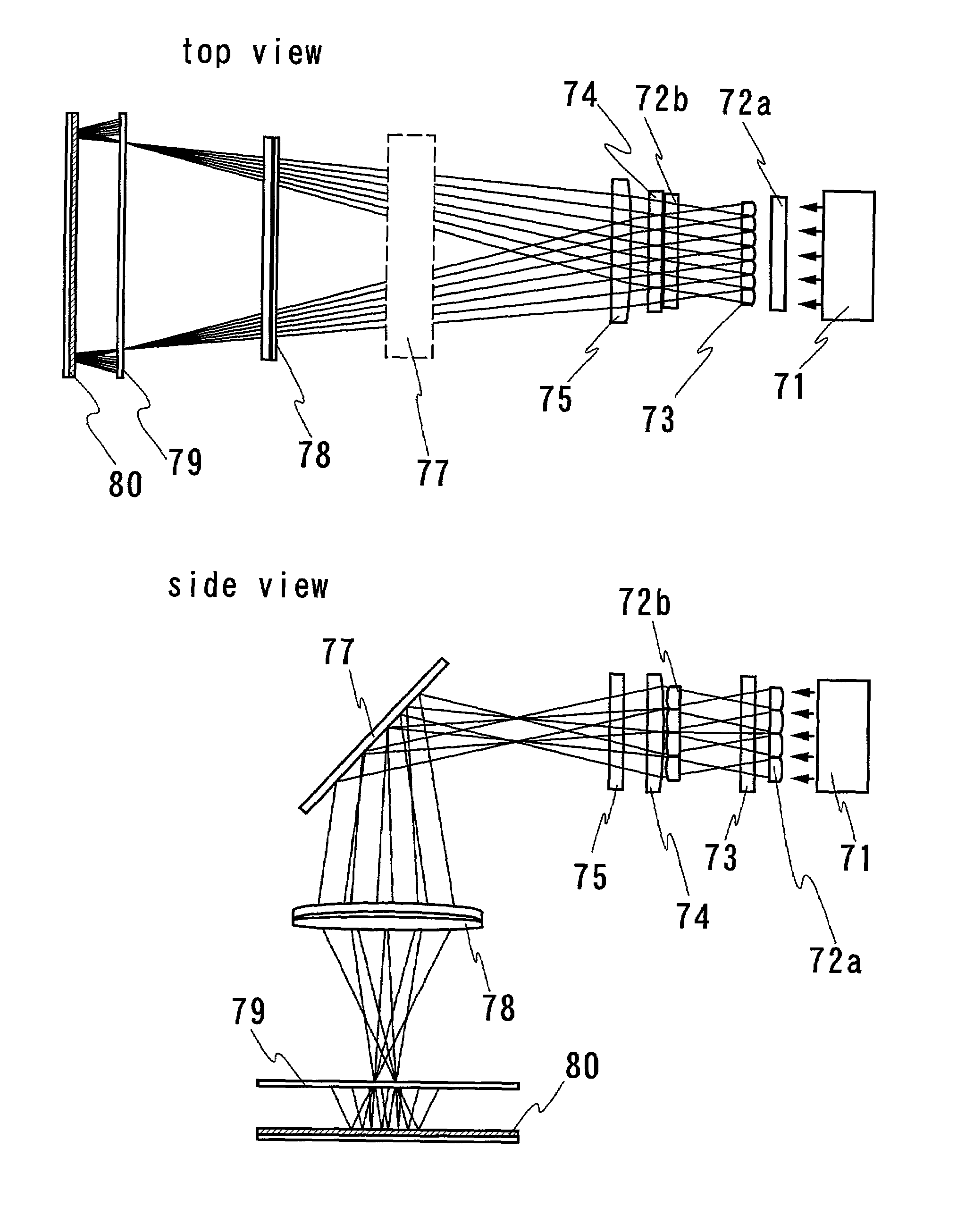

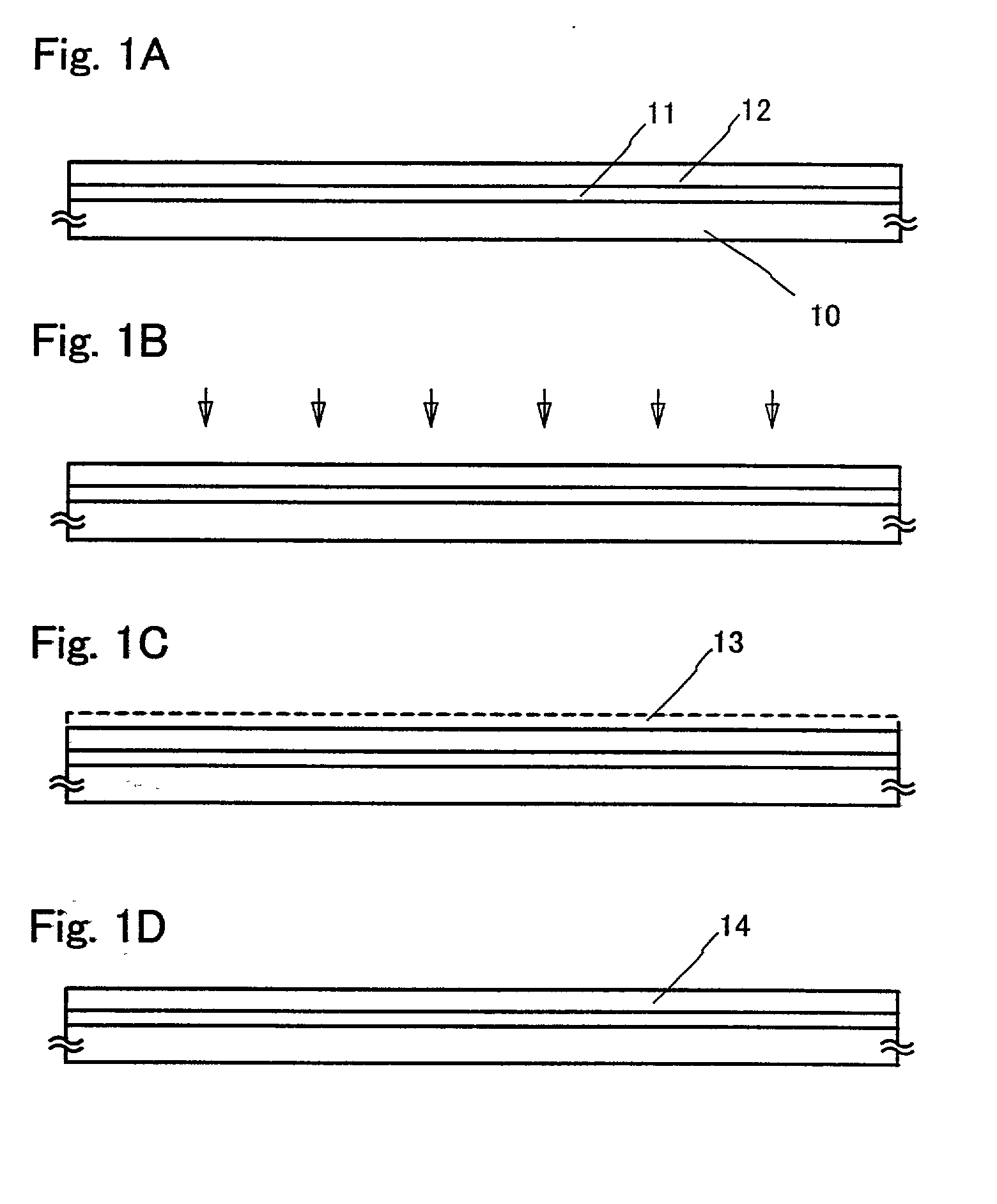

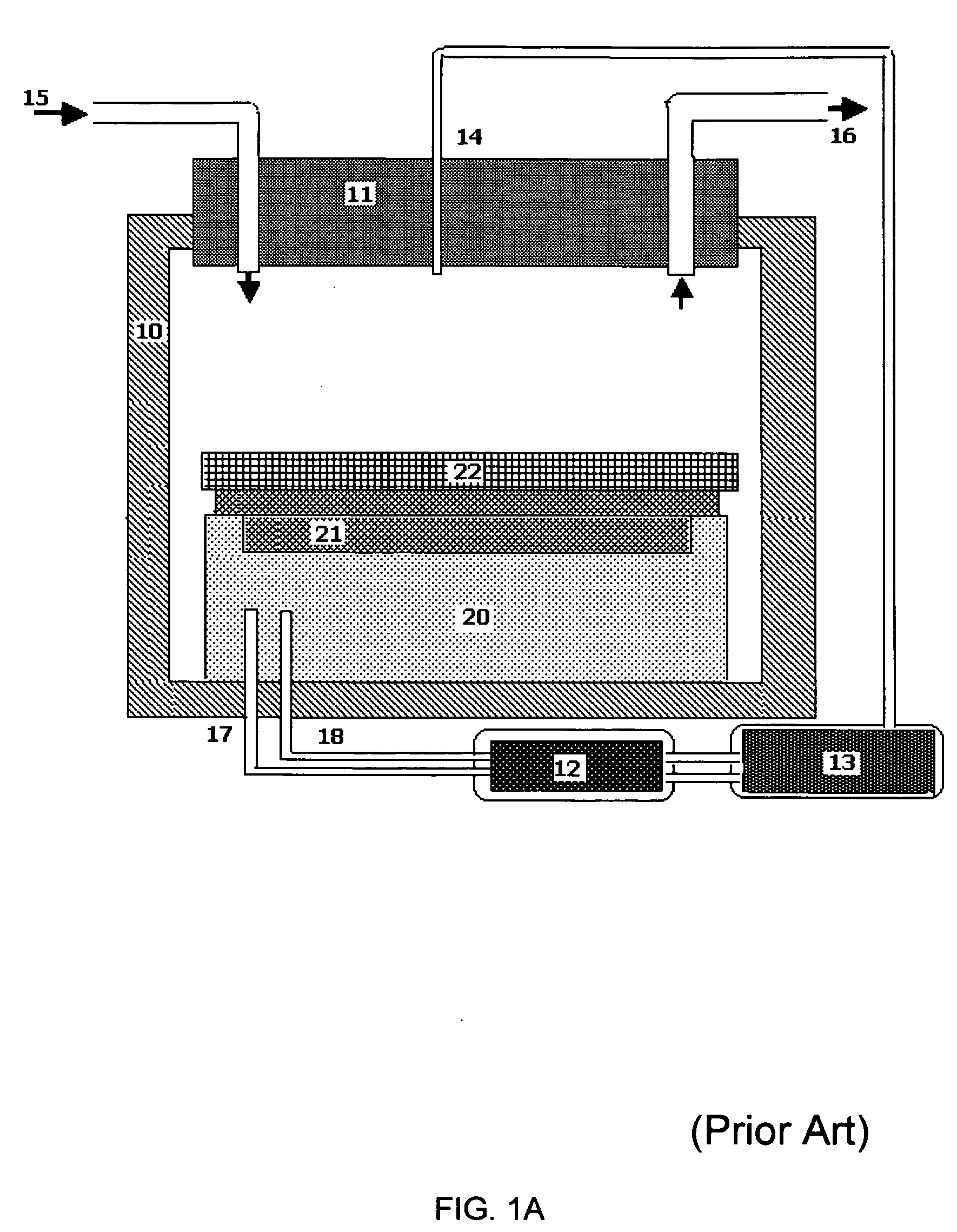

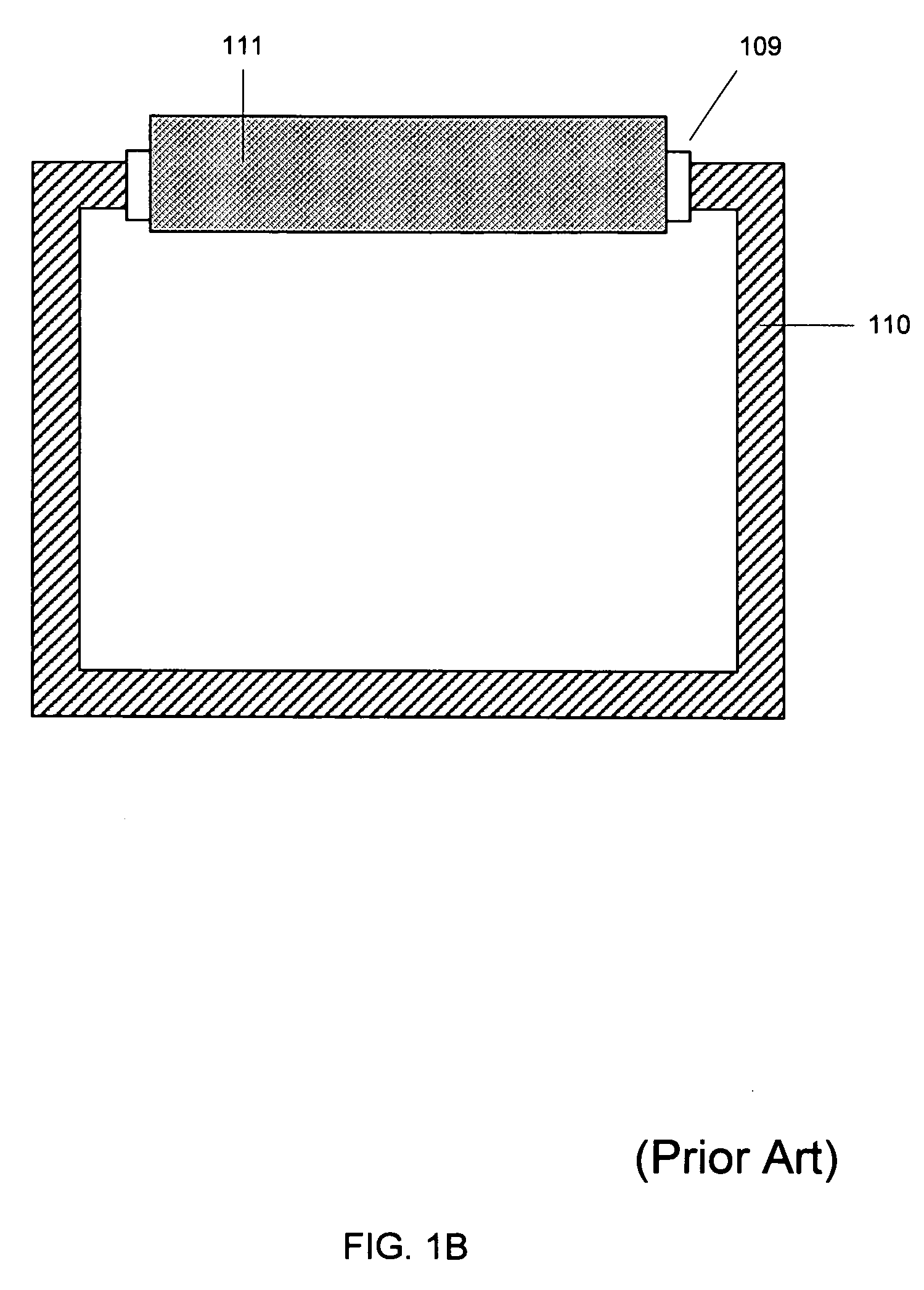

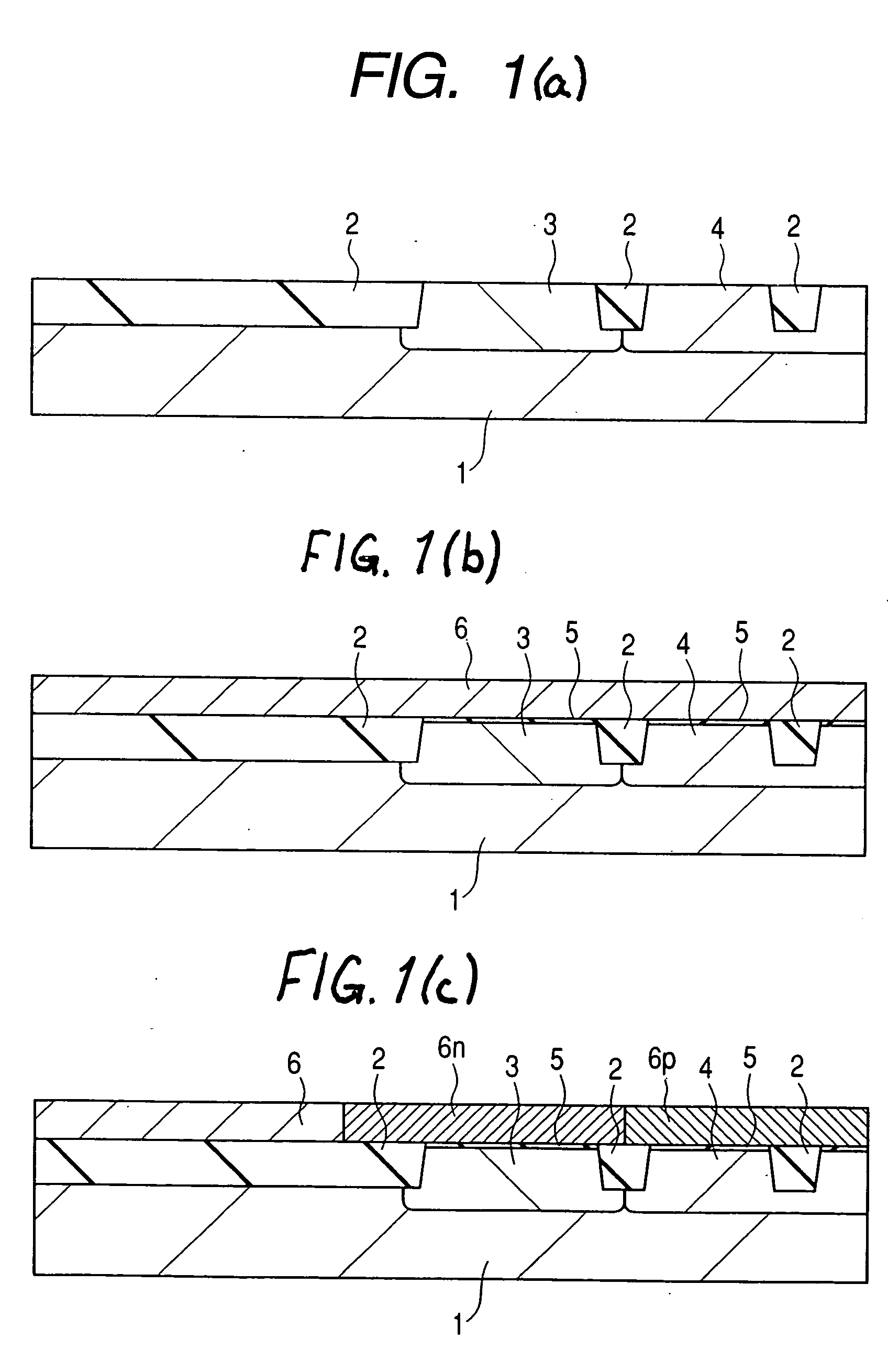

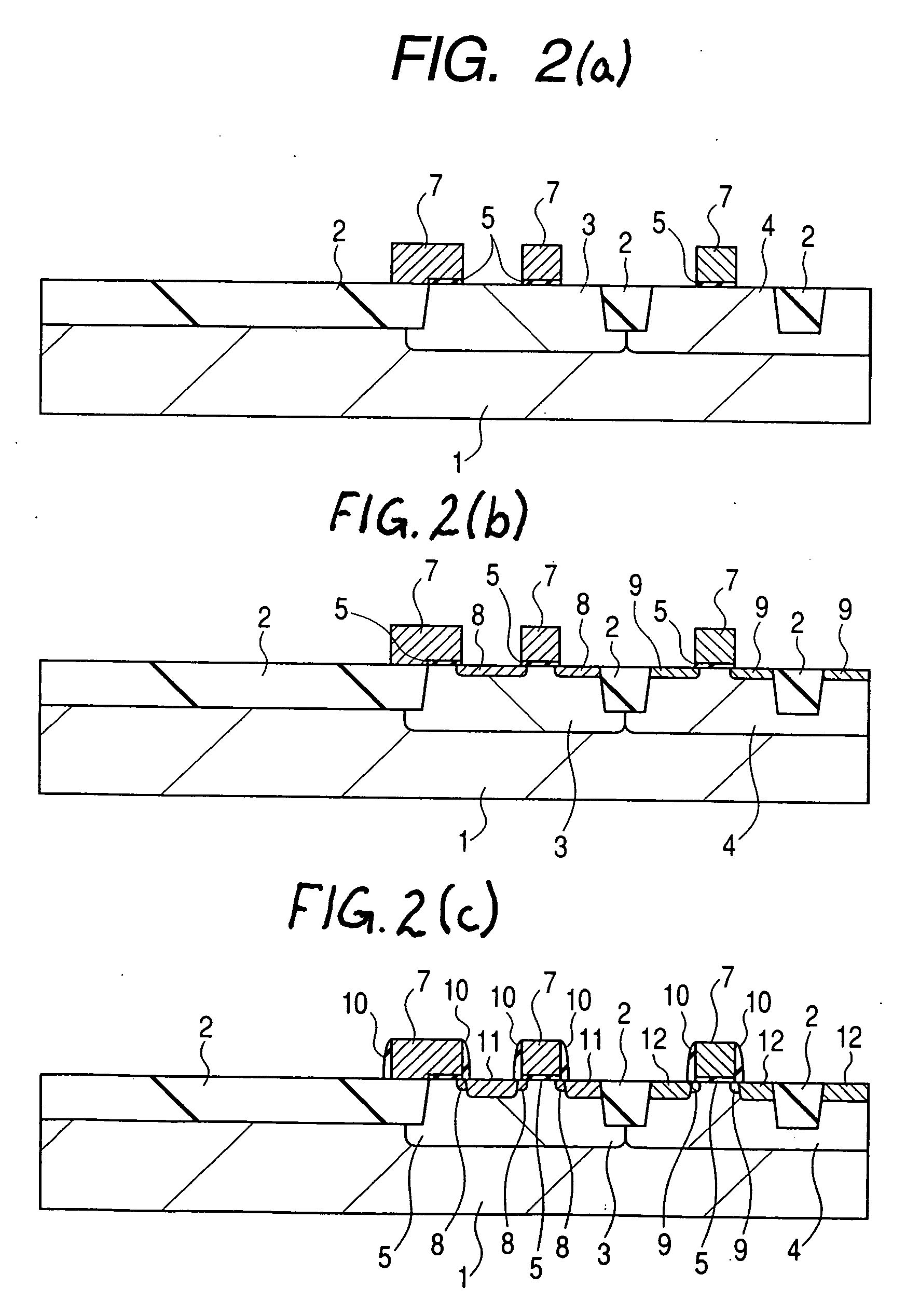

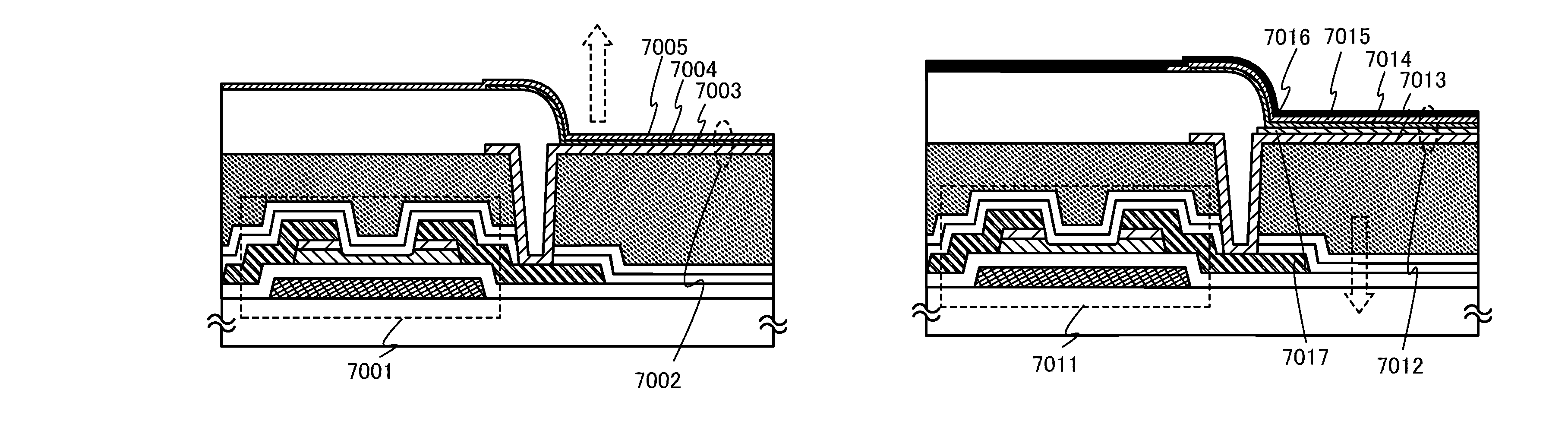

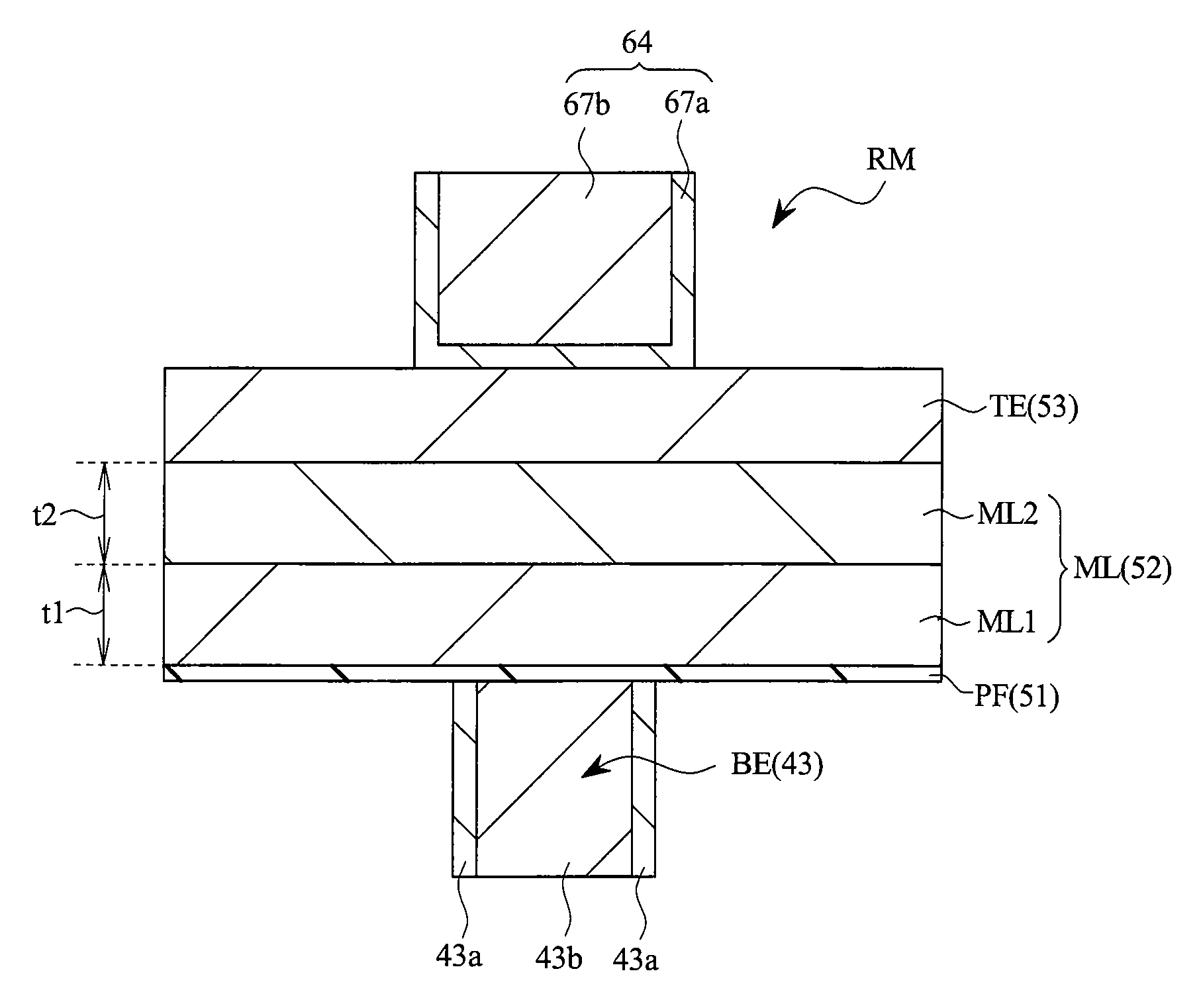

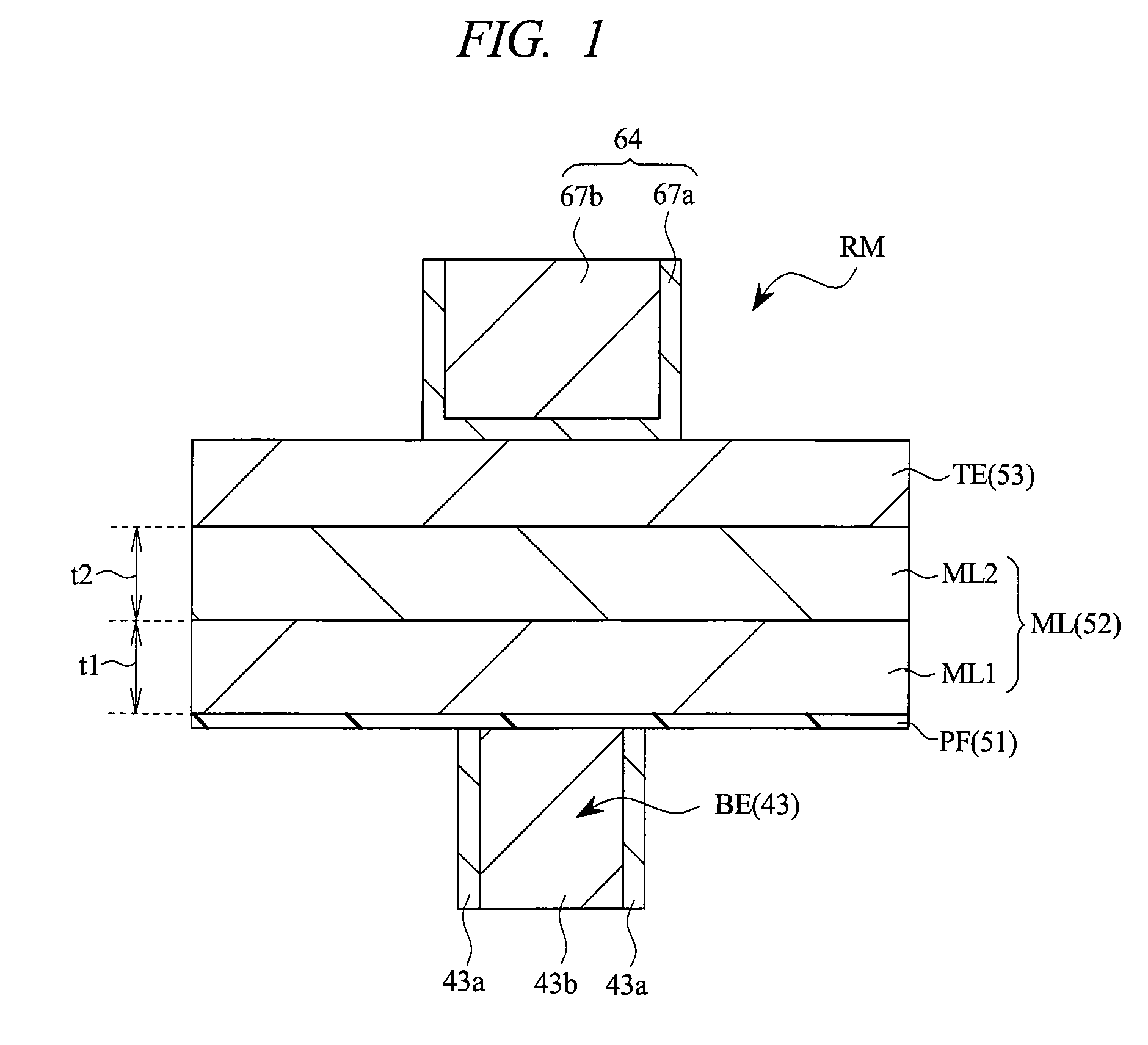

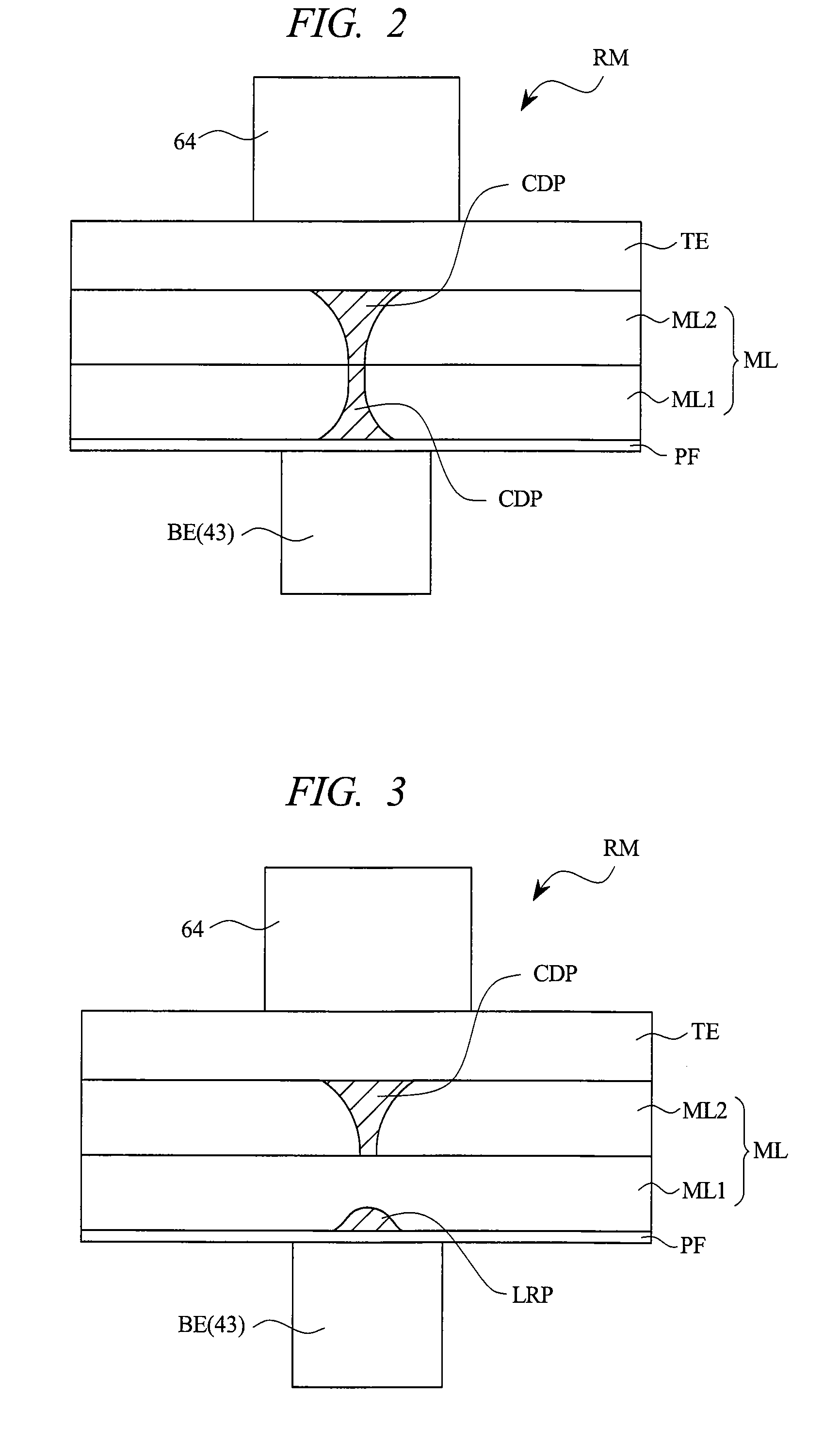

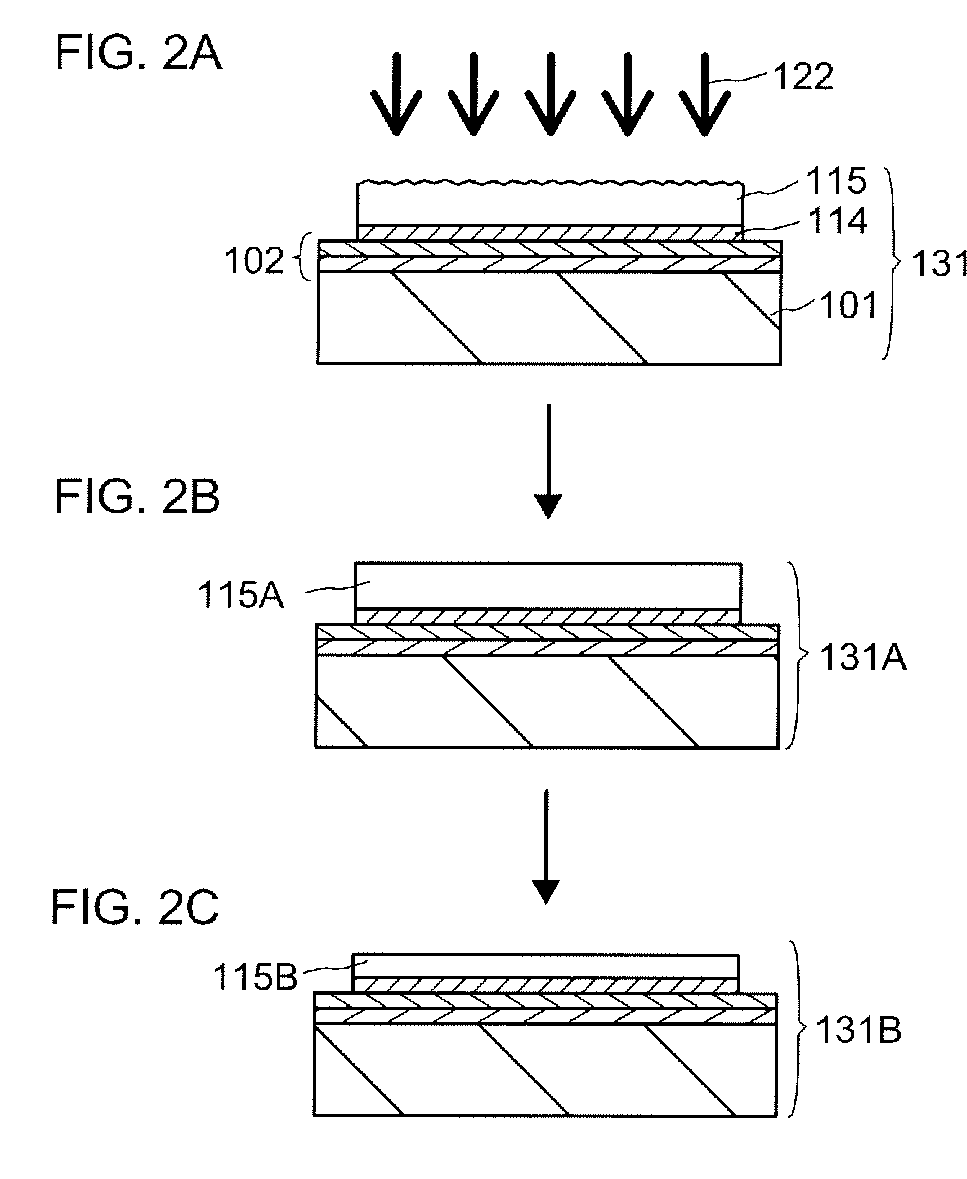

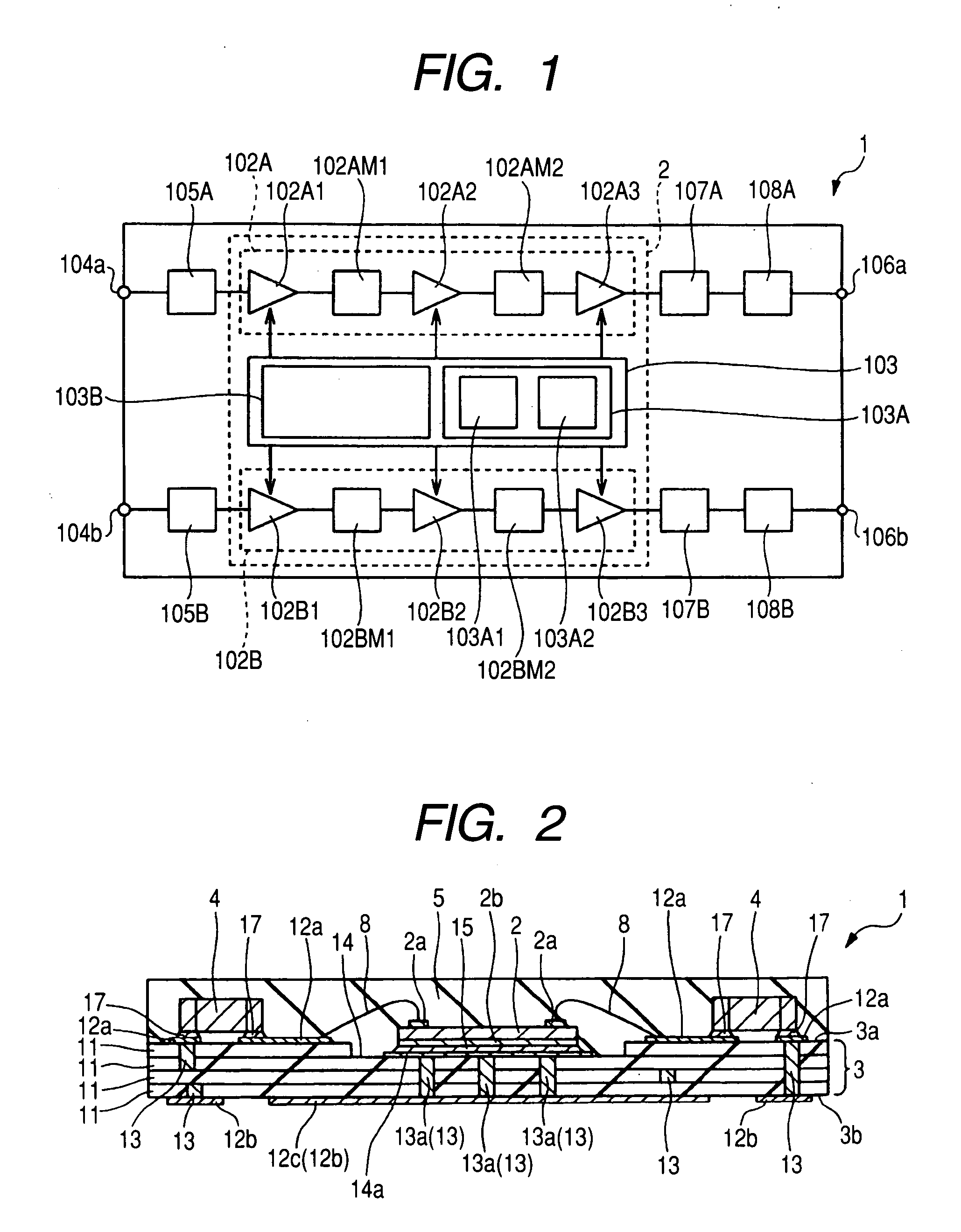

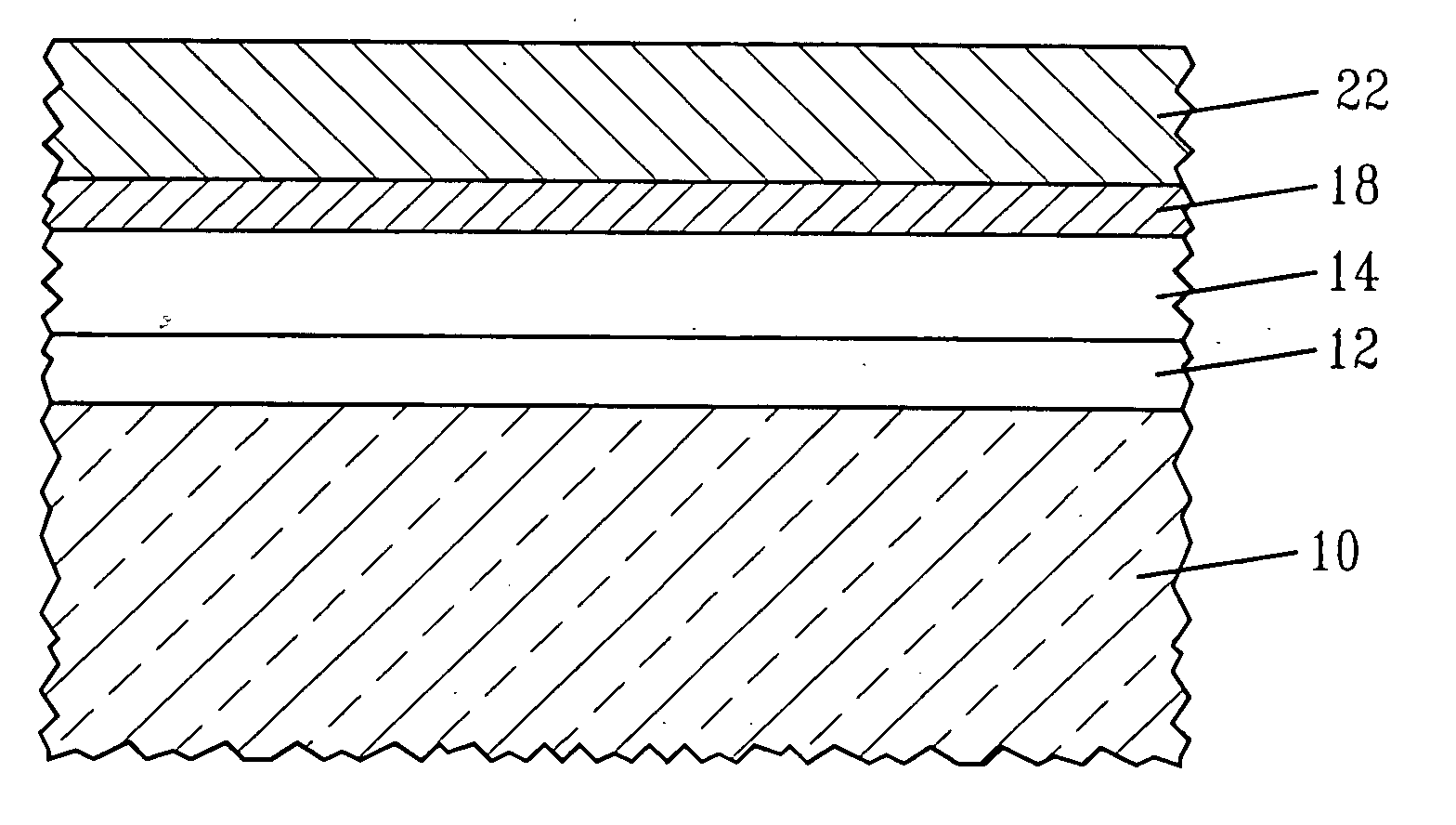

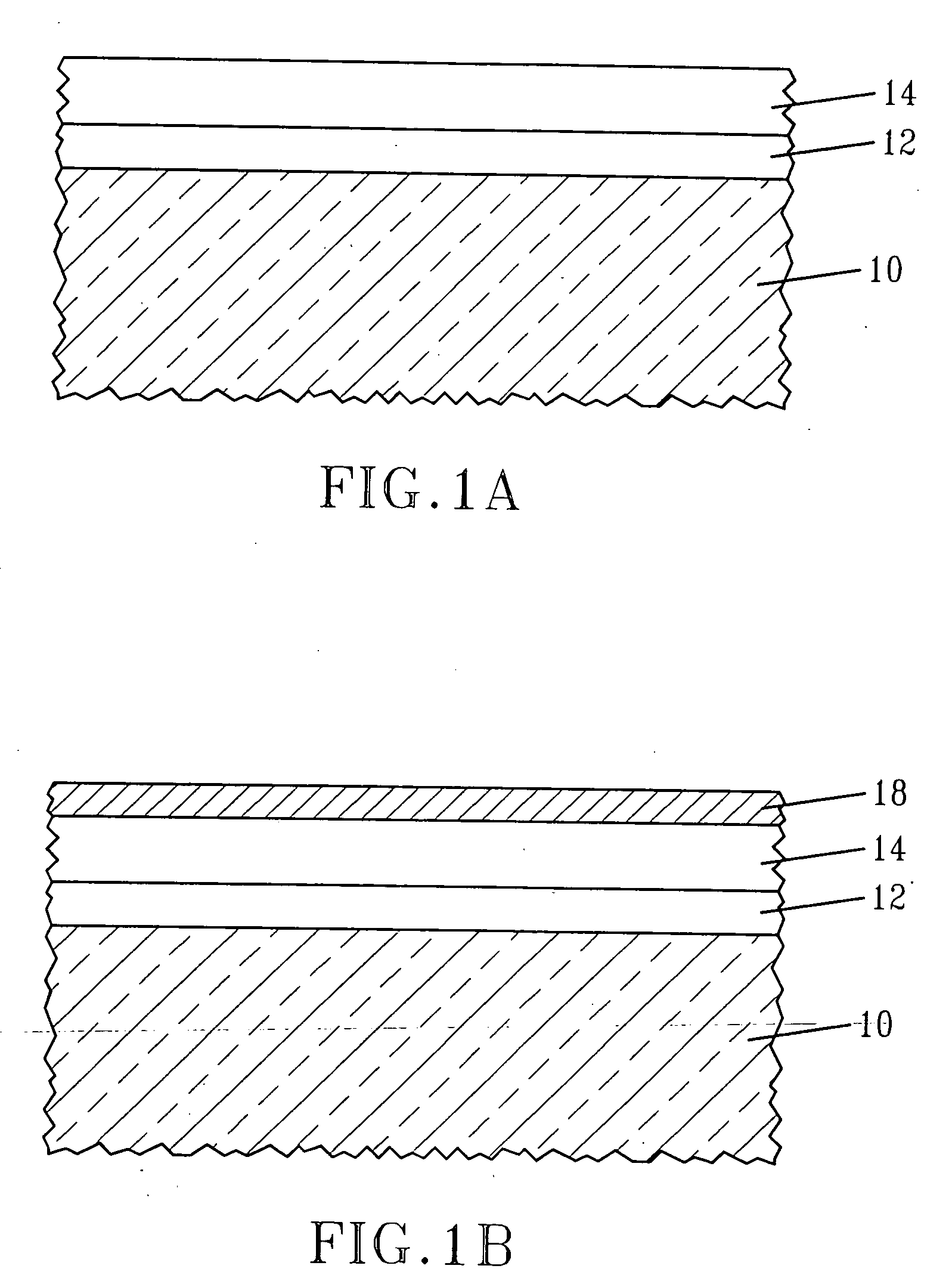

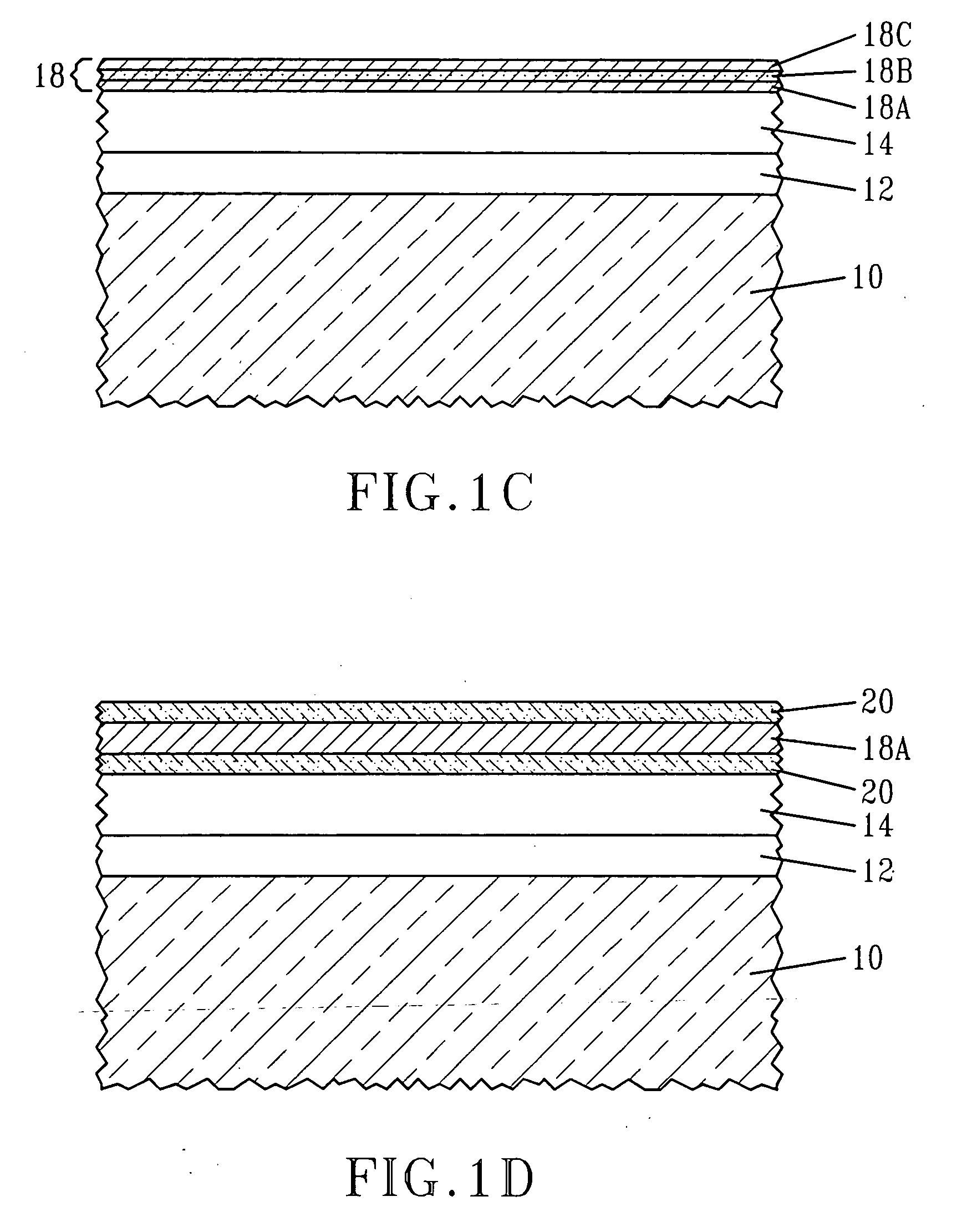

Laser irradiation method and method of manufacturing a semiconductor device

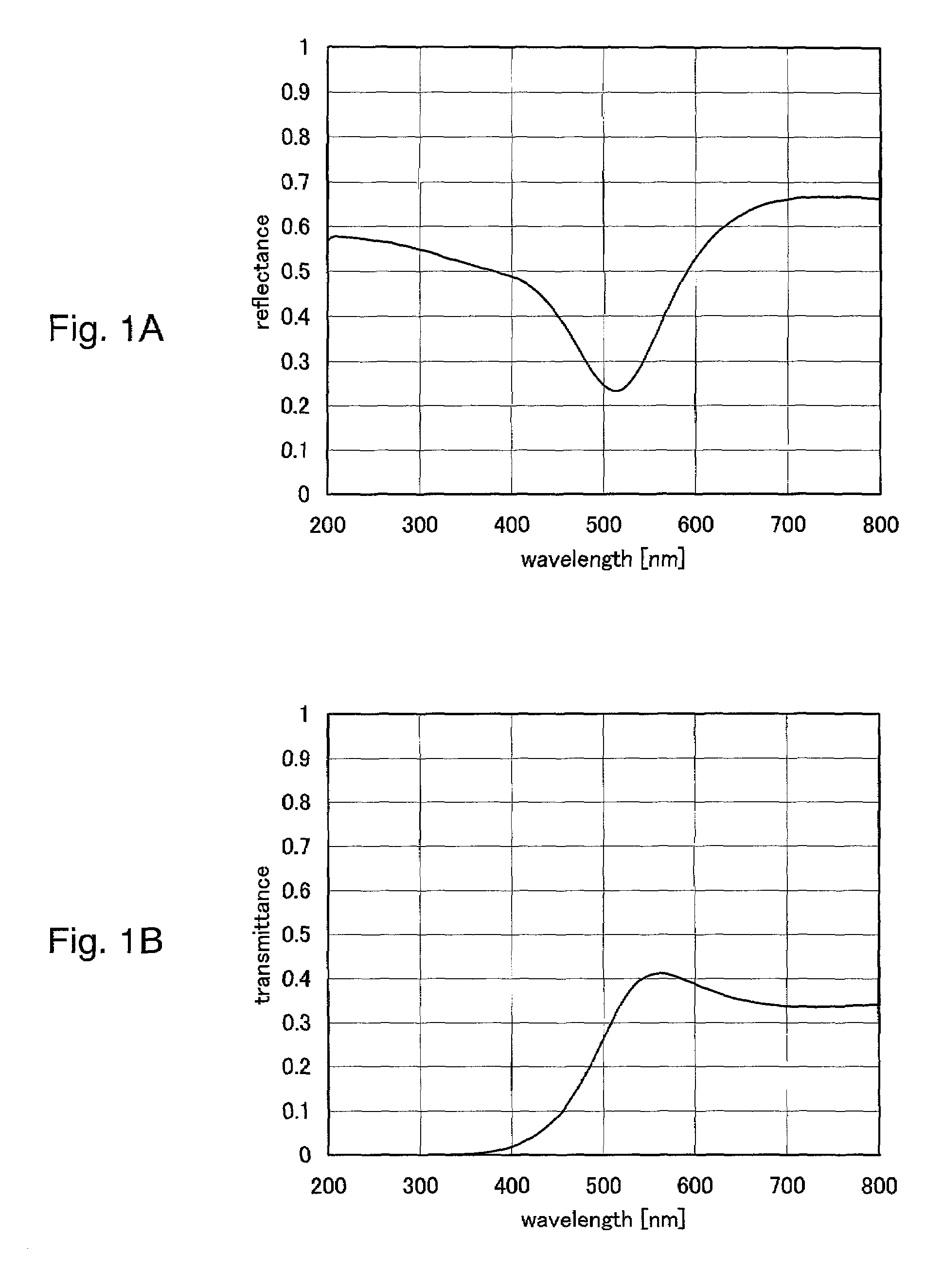

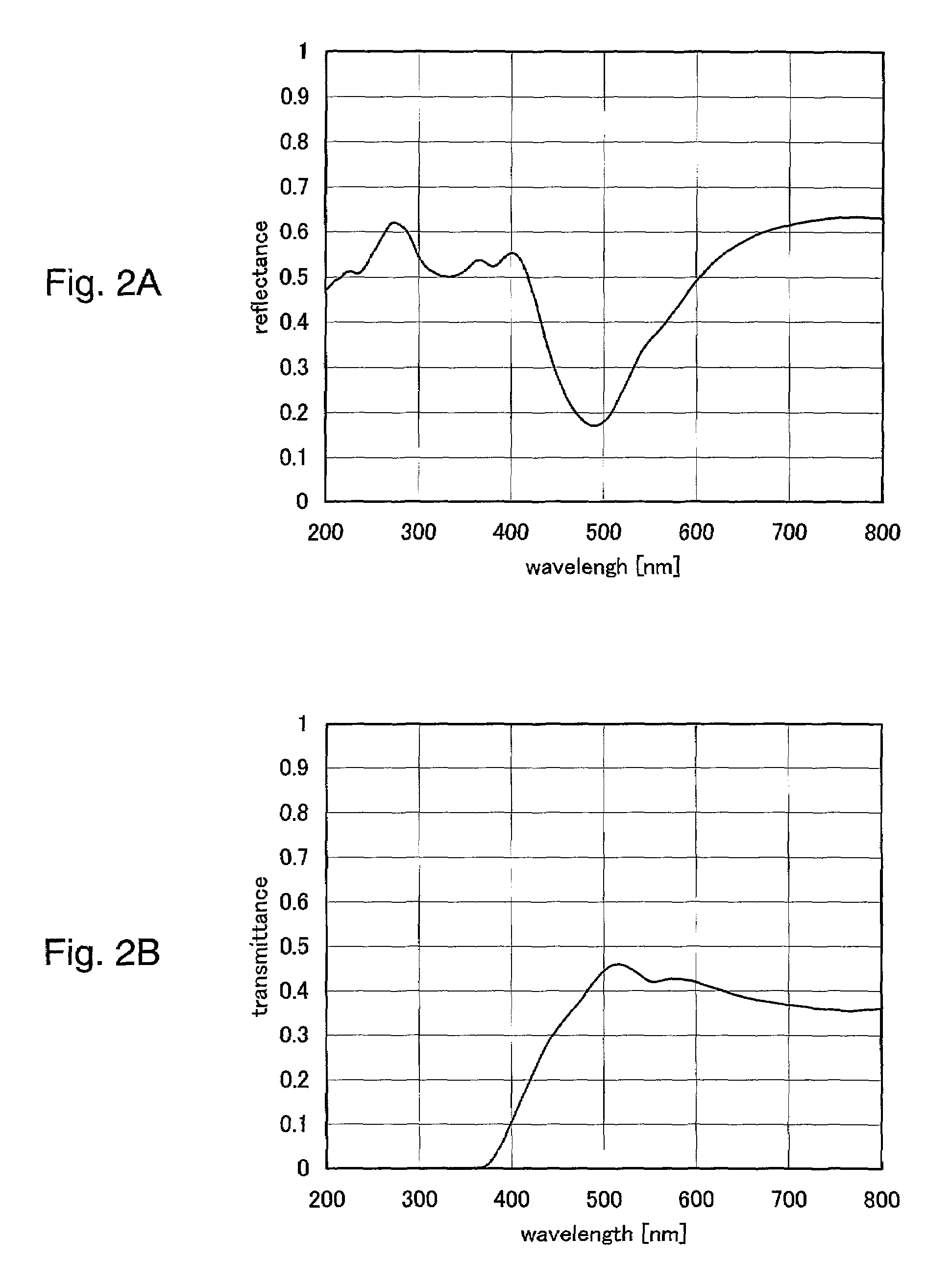

InactiveUS7217605B2Improve mobilityImprove semiconductor device performanceFrom solid stateSolid-state devicesLight beamReflective layer

A crystalline semiconductor film having crystal grains of large grain size or crystal grains in which the position and the size are controlled is formed to manufacture a TFT, whereby a semiconductor device that enables a high-speed operation is realized. First, a reflecting member is provided on a rear surface side of a substrate on which a semiconductor film is formed (semiconductor film substrate). When a front surface side of the semiconductor film substrate is irradiated with a laser beam that penetrates the semiconductor film substrate, the laser beam is reflected by the reflecting member to irradiate the semiconductor film from the rear surface side. With this method, an effective energy density is raised in the semiconductor film, and an output time is made long. Thus, the cooling rate of the semiconductor film is made gentle and crystal grains of large grain size are formed. Further, the front surface side of the semiconductor film substrate is irradiated with the laser beam by using a substrate on which a reflecting layer is partially formed as the reflecting member, whereby the semiconductor film is partially irradiated with the laser beam from the rear surface side. Thus, a temperature distribution is generated in the semiconductor film, and the location where a lateral growth is generated and the lateral direction can be controlled. Therefore, the crystal grains of large grain size can be obtained.

Owner:SEMICON ENERGY LAB CO LTD

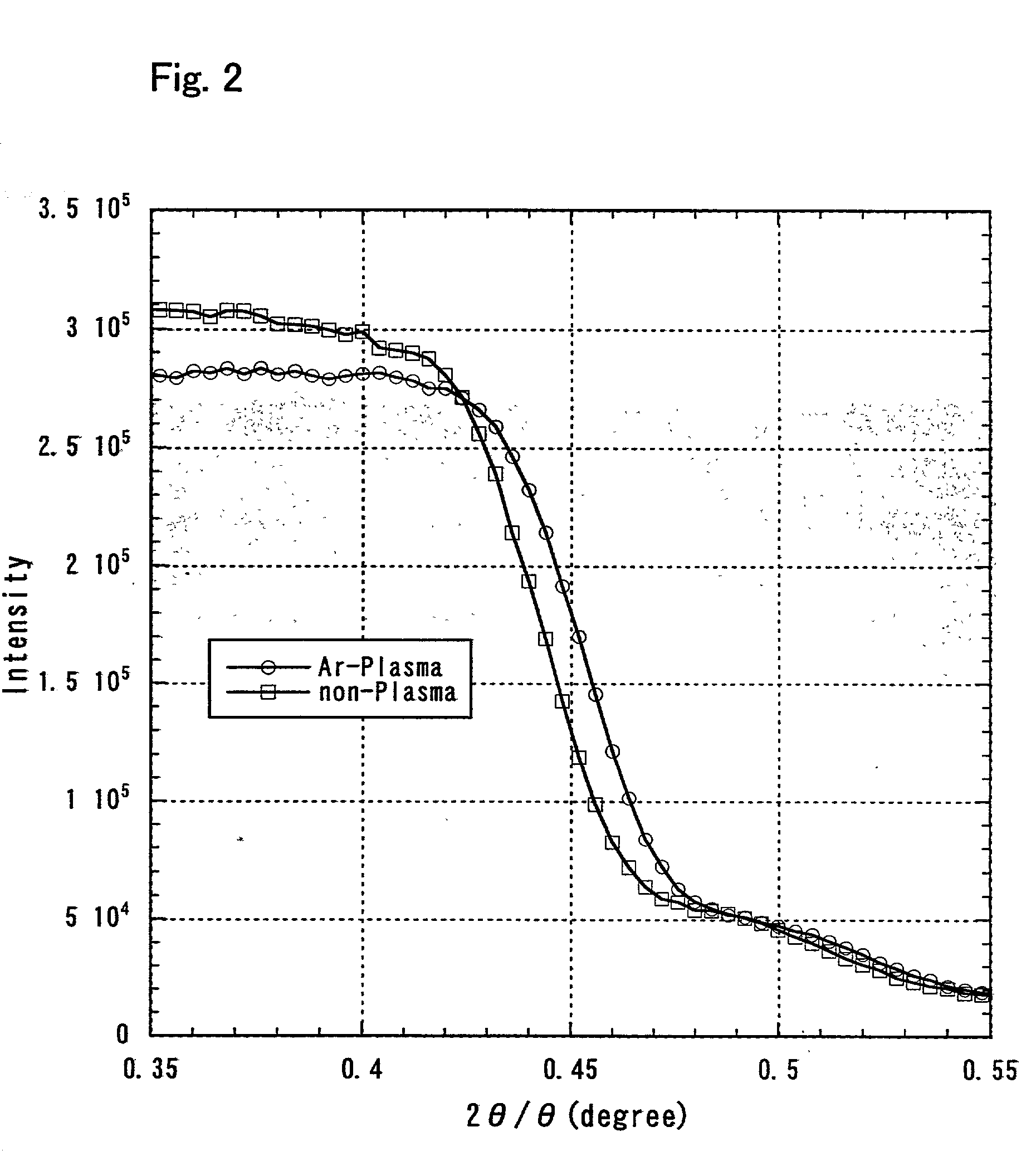

Method of manufacturing a semiconductor device

InactiveUS20020155706A1High densityChemical potential of the semiconductor film is increasedTransistorSolid-state devicesAtmospheric airNitrogen

The number of grains in active regions of devices can be made uniform by making the grains of crystalline semiconductor films, obtained by thermal crystallization using a metal element, smaller. The present invention is characterized in that a semiconductor film is exposed within an atmosphere in which a gas, having as its main constituent one or a plurality of members from the group consisting of inert gas elements, nitrogen, and ammonia, is processed into a plasma, and then thermal crystallization using a metal element is performed. The concentration of crystal nuclei1 generated is thus increased, making the grain size smaller, by performing these processes. Heat treatment may also be performed, of course, after exposing the semiconductor film, to which the metal element is added, to an atmosphere in which a gas, having as its main constituent one or a plurality of members from the group consisting of inert gas elements, nitrogen, and ammonia, is processed into a plasma.

Owner:SEMICON ENERGY LAB CO LTD

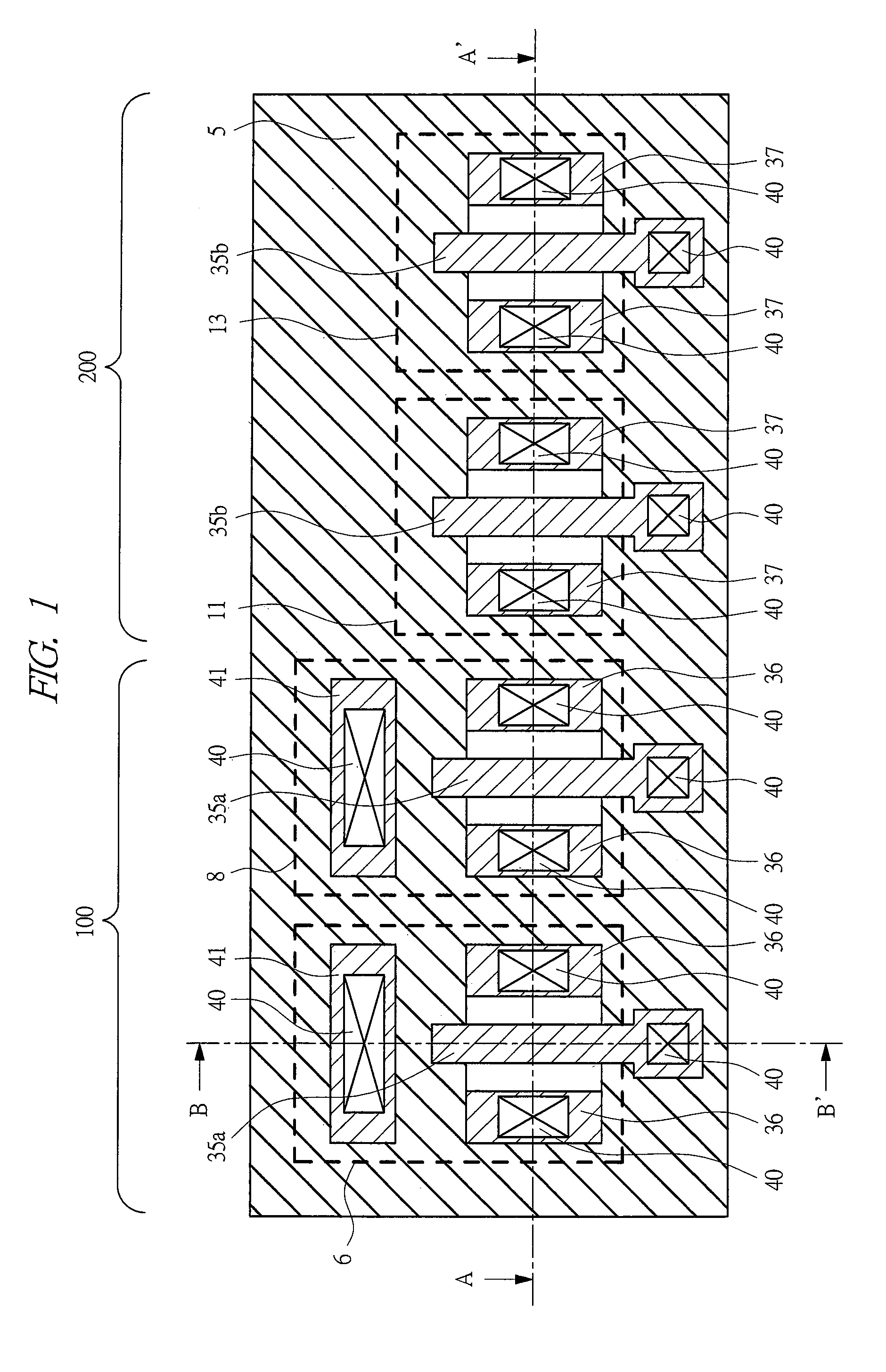

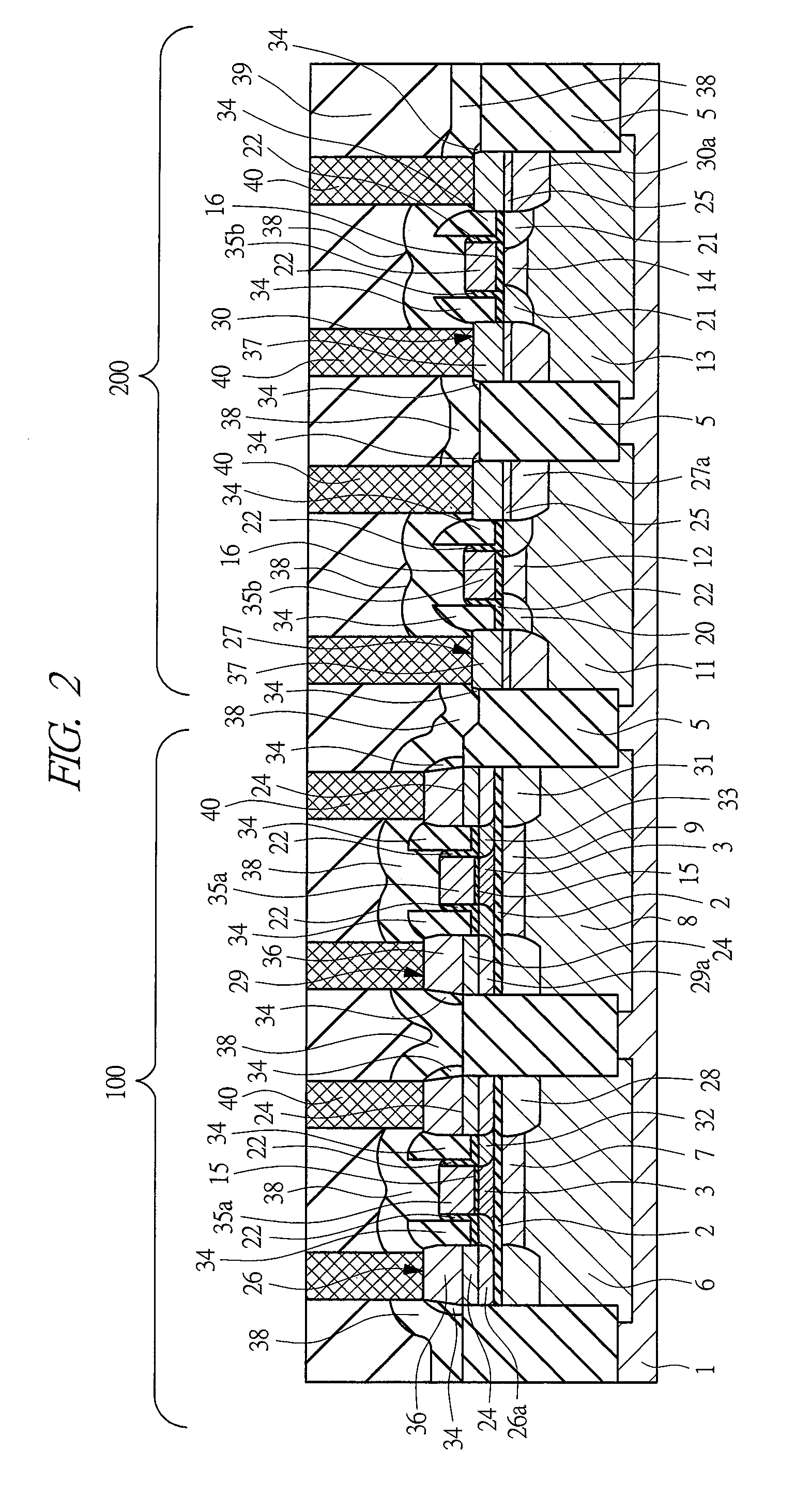

Semiconductor device and method of manufacturing the same

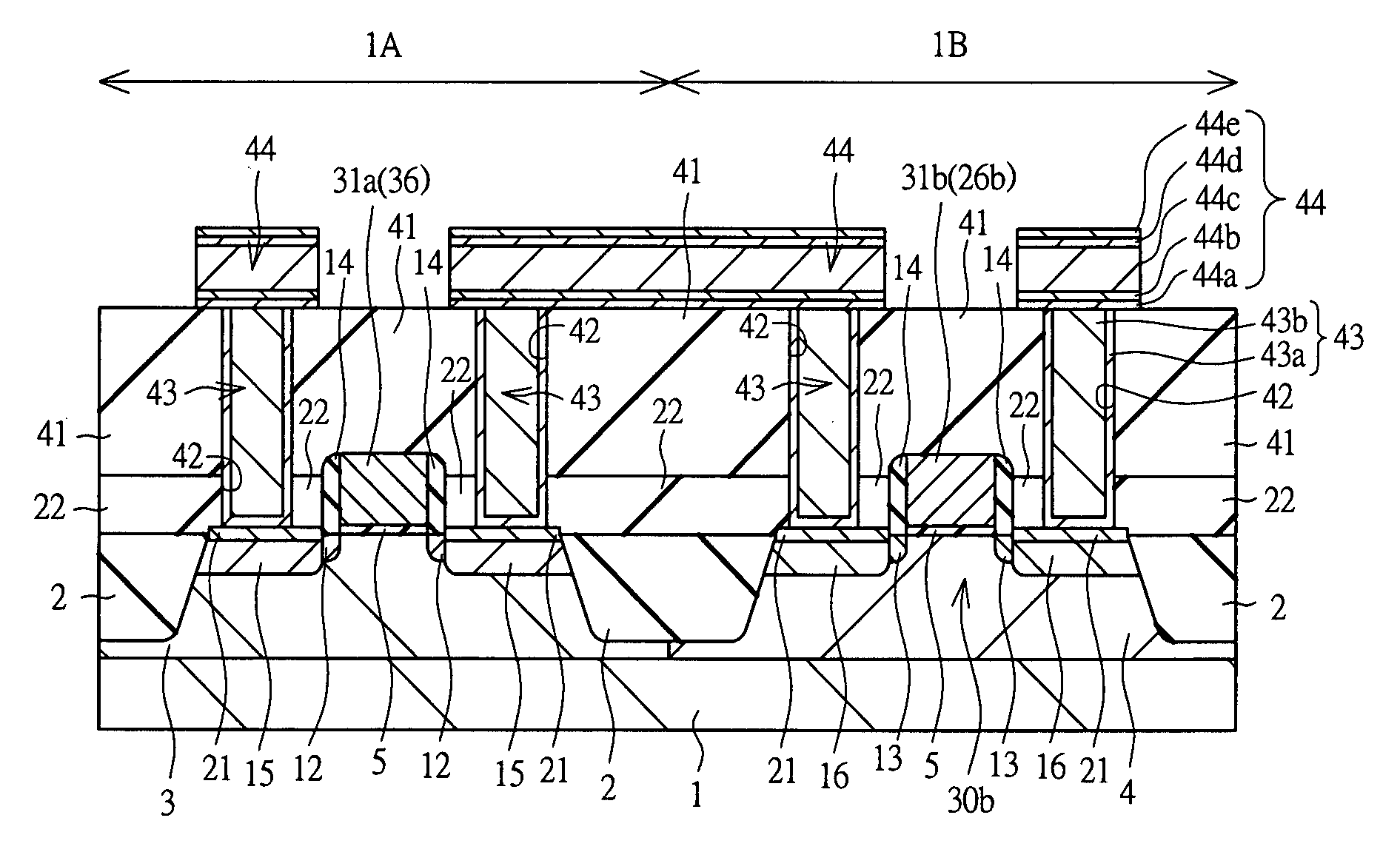

InactiveUS20090096036A1Easy to integrateImprove semiconductor device performanceTransistorSolid-state devicesGate insulatorSemiconductor

There is provided an SOI-MISFET including: an SOI layer; a gate electrode provided on the SOI layer interposing a gate insulator; and a first elevated layer provided higher in height from the SOI layer than the gate electrode at both sidewall sides of the gate electrode on the SOI layer so as to constitute a source and drain. Further, there is also provided a bulk-MISFET including: a gate electrode provided on a silicon substrate interposing a gate insulator thicker than the gate insulator of the SOI MISFET; and a second elevated layer configuring a source and drain provided on a semiconductor substrate at both sidewalls of the gate electrode. A the first elevated layer is thicker than the elevated layer, and the whole of the gate electrodes, part of the source and drain of the SOI-MISFET, and part of the source and drain of the bulk-MISFET are silicided.

Owner:RENESAS ELECTRONICS CORP

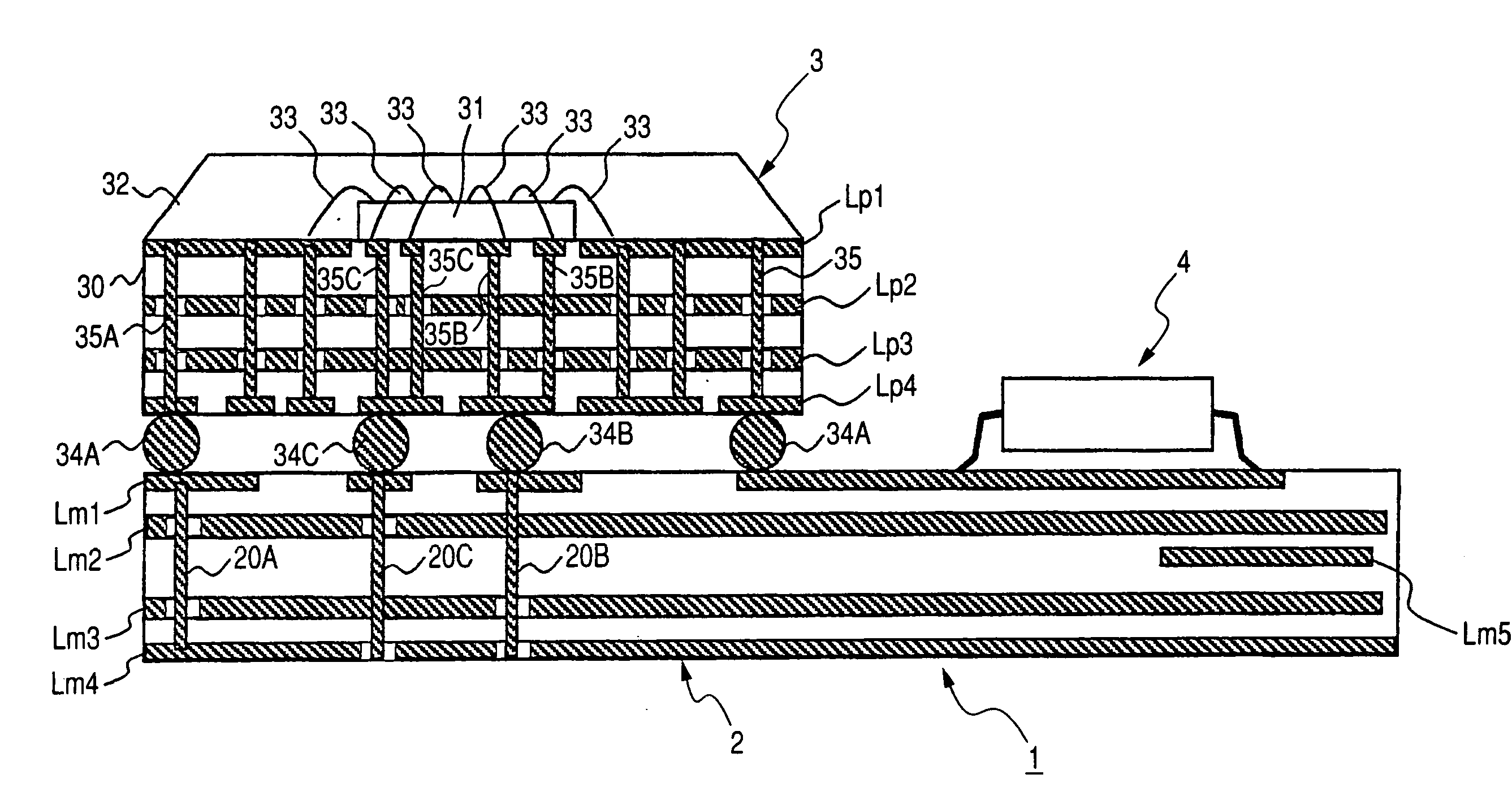

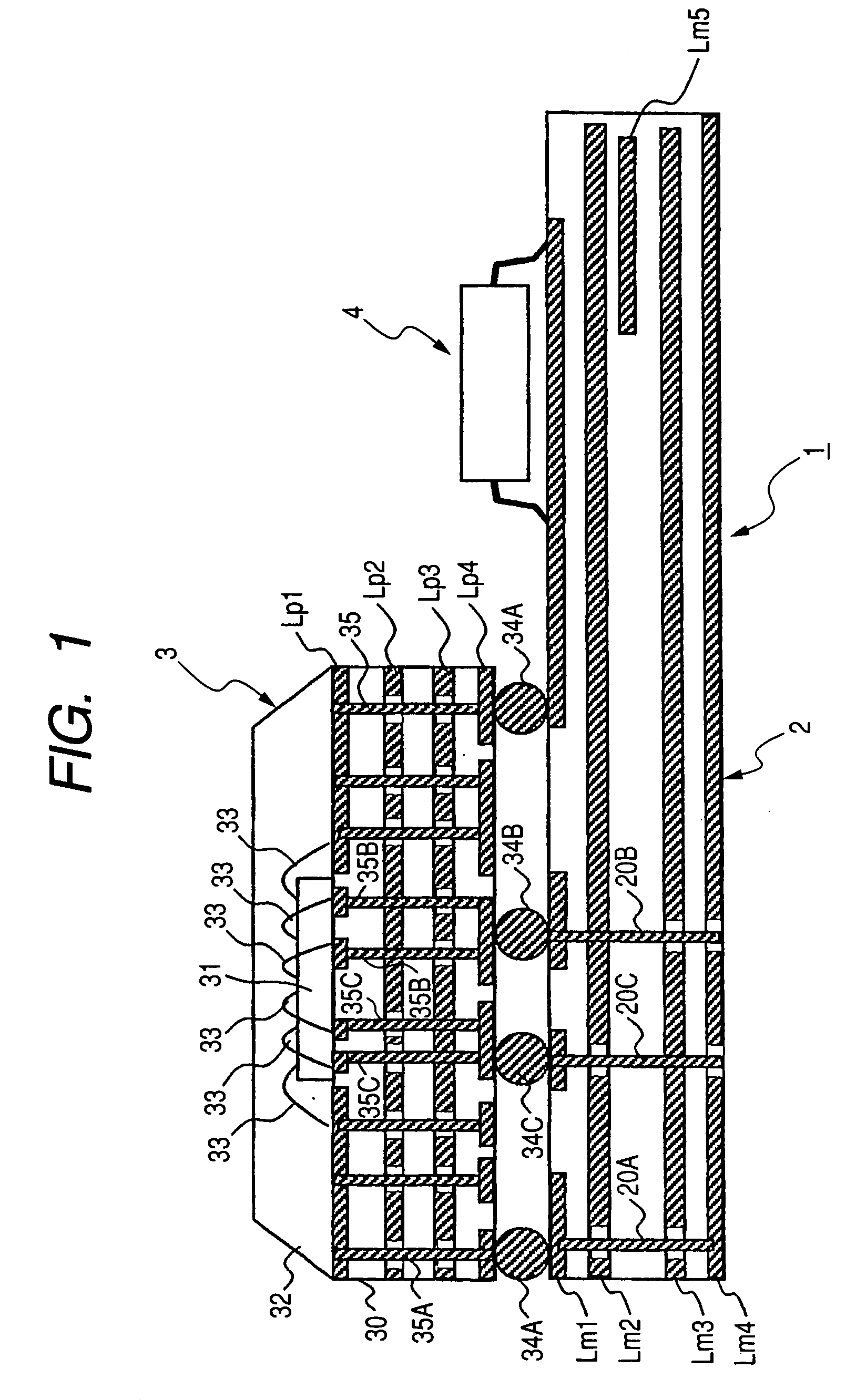

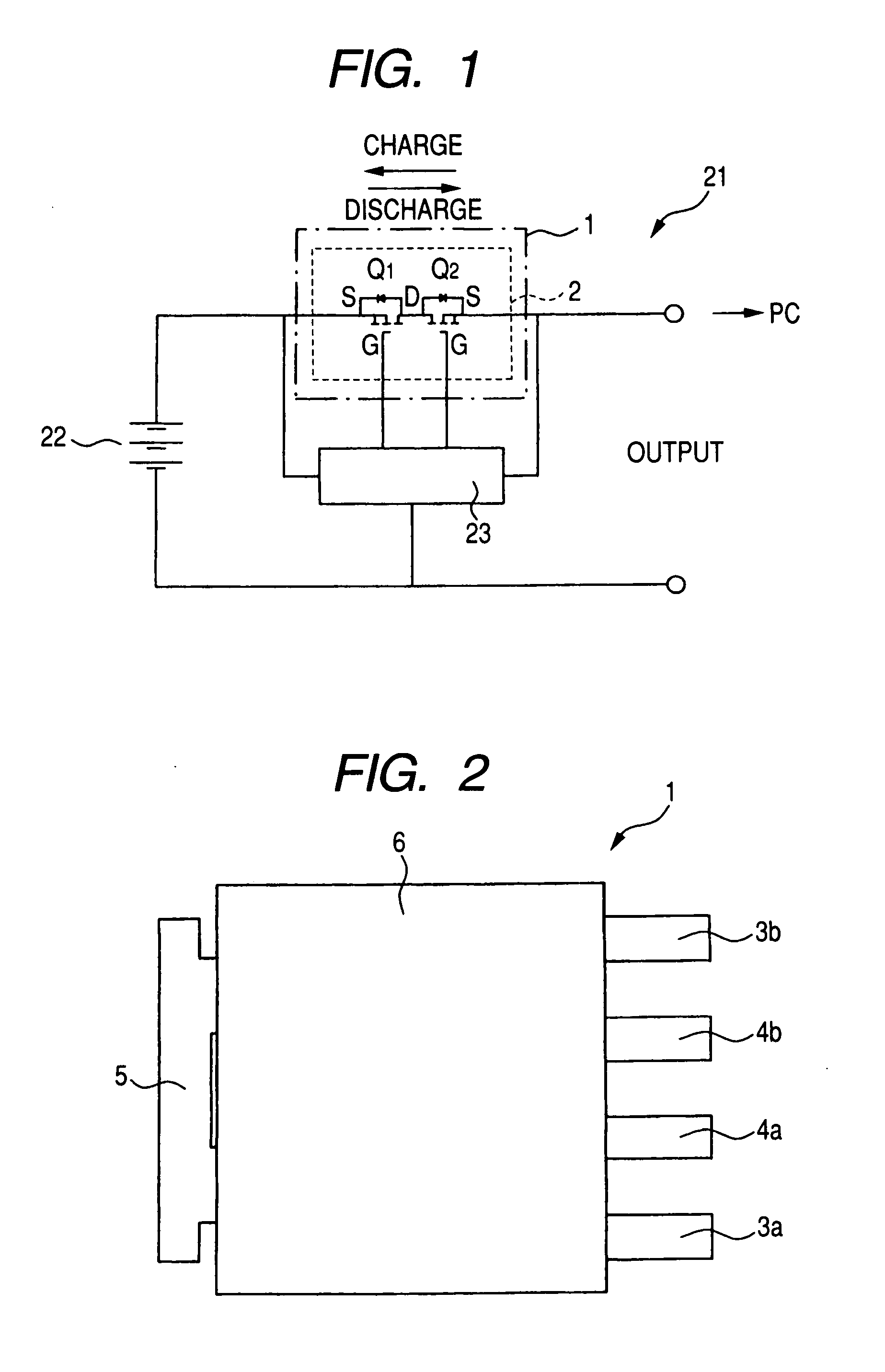

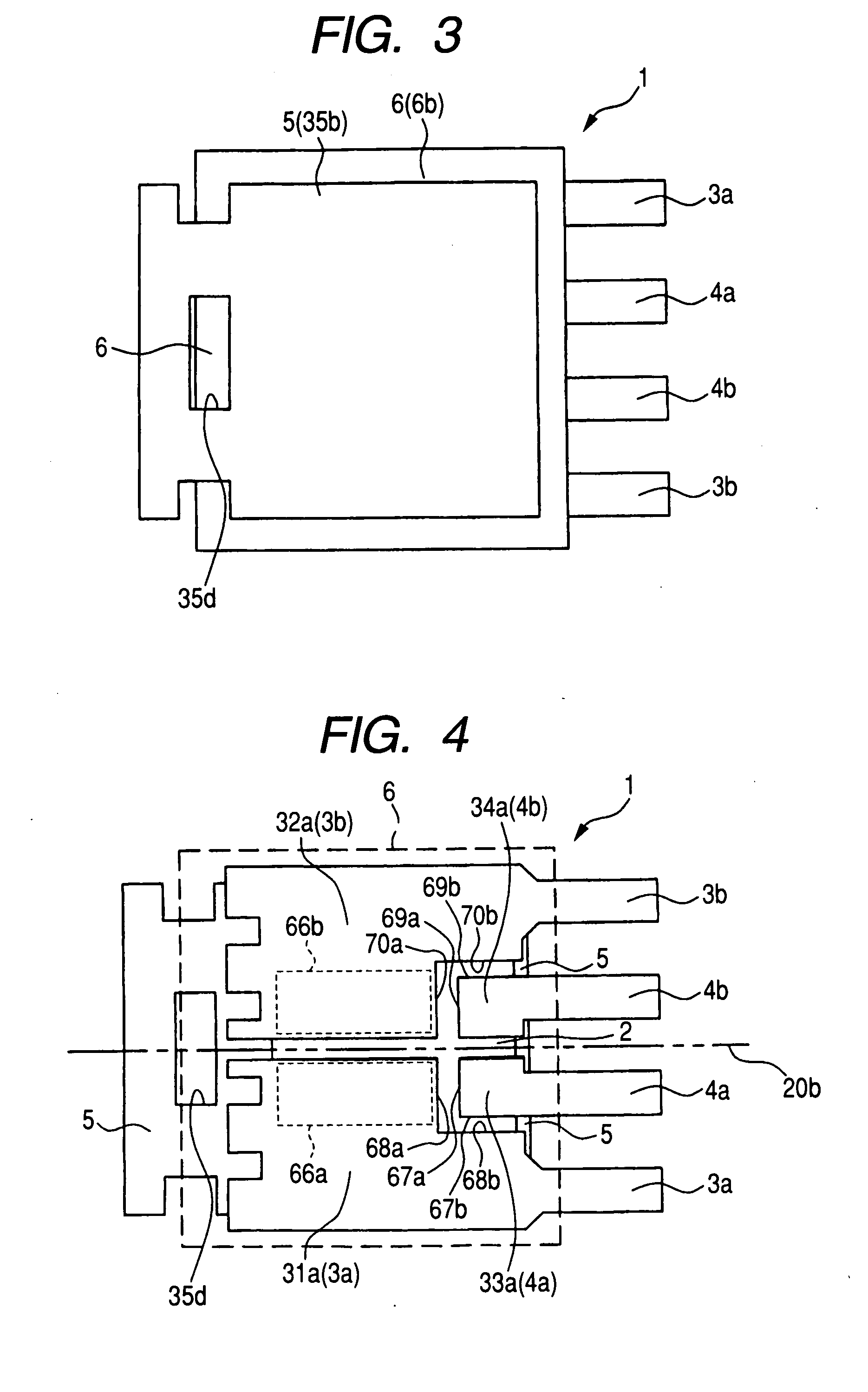

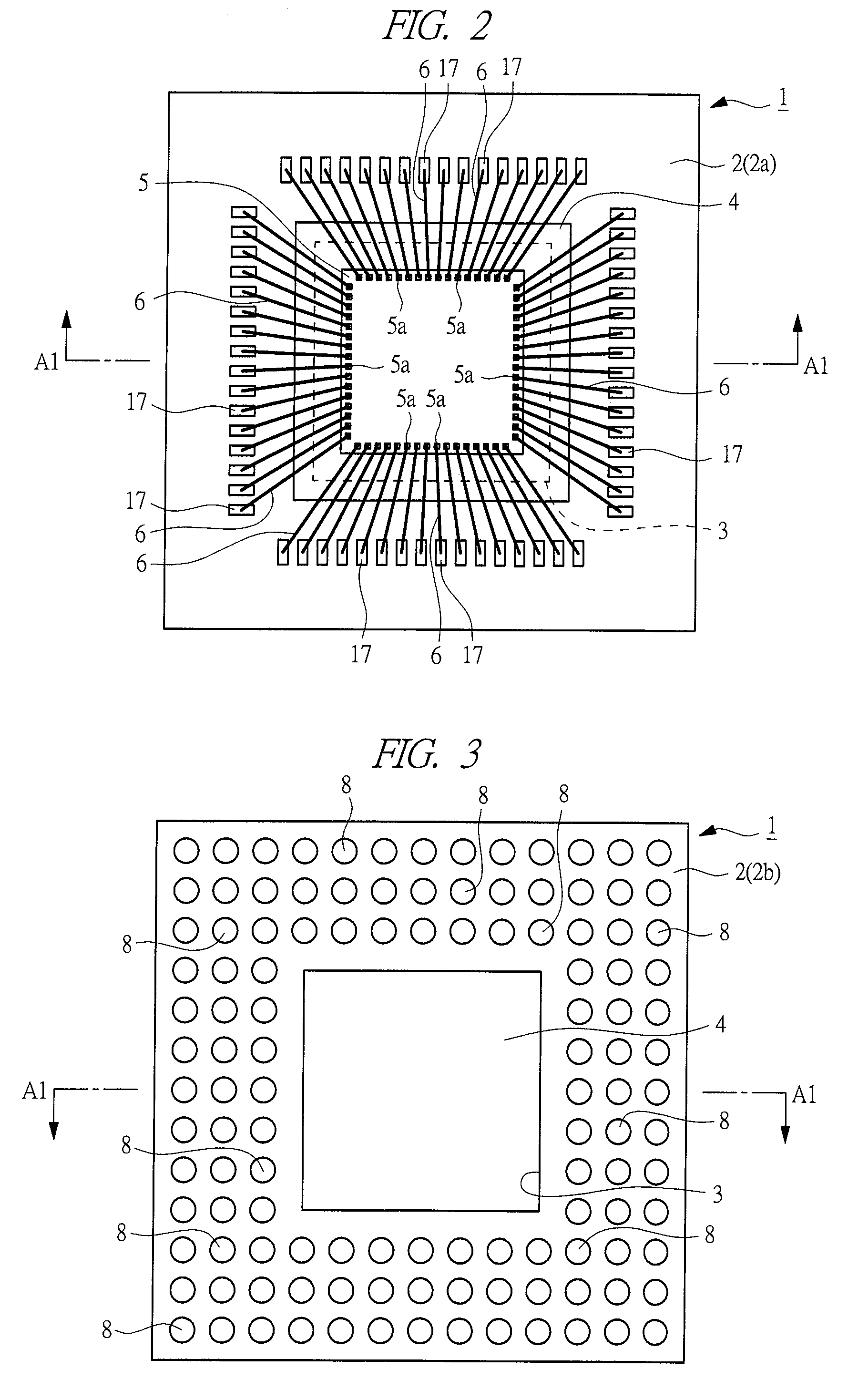

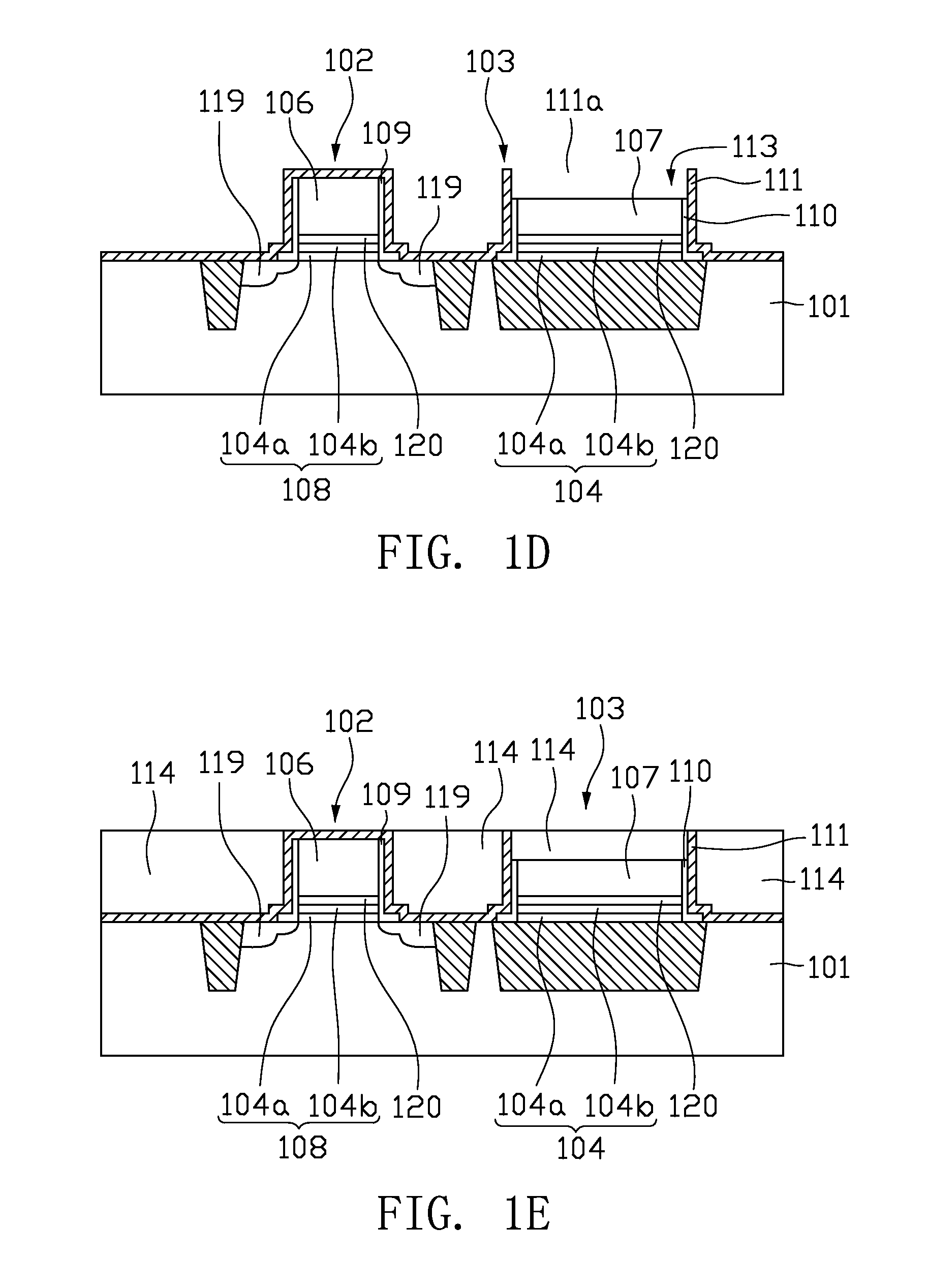

Electronic circuit, a semiconductor device and a mounting substrate

InactiveUS20070194433A1Improve conversion accuracyPrevent switching noiseFinal product manufactureCross-talk/noise/interference reductionDevice materialSemiconductor chip

An electronic circuit includes a first semiconductor device (4) and a second semiconductor device (3) on a mounting substrate. The mounting substrate includes a plurality of mounting substrate lines (201 to 204) which are connected in common with external terminals of a plurality of bits of the first semiconductor device and external terminals of a plurality of bits of the second semiconductor device for every bit. The mounting substrate lines have lengths thereof from the external terminals of the first semiconductor device to the external terminals of the second semiconductor device made unequal for respective bits. Assembling lines (361 to 364) which reach connecting electrodes of a semiconductor chip from the external terminals of the second semiconductor device have made lengths thereof unequal for respective bits. Here, the unequal lengths of the mounting substrate lines have a relationship which offsets the unequal lengths of the assembling lines. According to such a constitution, it is unnecessary to set lengths between the external terminals of the second semiconductor device and the connecting electrodes of the semiconductor chip equal.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and electroluminescent device and method of making the same

ActiveUS20130015448A1Simplify manufacturing processReduce resistanceTransistorSolid-state devicesPower semiconductor deviceSemiconductor device modeling

A semiconductor device, disposed on a substrate, includes a first channel layer, a patterned doped layer, a gate insulating layer, a conducting gate electrode, a second channel layer, a first electrode and a second electrode, and a third electrode and a fourth electrode. The first channel layer is disposed on the substrate and in a first region. The patterned doped layer includes a doped gate electrode disposed in a second region, and two contact electrodes electrically connected to two sides of the first channel layer, respectively. The conducting gate electrode is disposed on the gate insulating layer in the first region. The second channel layer is disposed on the gate insulating layer in the second region. The first electrode and the second electrode are electrically connected to the contact electrodes, respectively. The third electrode and the fourth electrode are electrically connected to two sides of the second channel layer, respectively.

Owner:AU OPTRONICS CORP

Method and apparatuses for high pressure gas annealing

ActiveUS20090148965A1Reduce in quantityImprove device performanceSemiconductor/solid-state device testing/measurementSolid-state devicesGate dielectricForming gas

Novel methods and apparatuses for annealing semiconductor devices in a high pressure gas environment. According to an embodiment, the annealing vessel has a dual chamber structure, and potentially toxic, flammable, or otherwise reactive gas is confined in an inner chamber which is protected by pressures of inert gas contained in the outer chamber. The incoming gas delivery system and exhaust gas venting system are likewise protected by various methods. Embodiments of the present invention can be used, for example, for high-K gate dielectric anneal, post metallization sintering anneal, and forming gas anneal in the semiconductor manufacturing process.

Owner:HPSP CO LTD

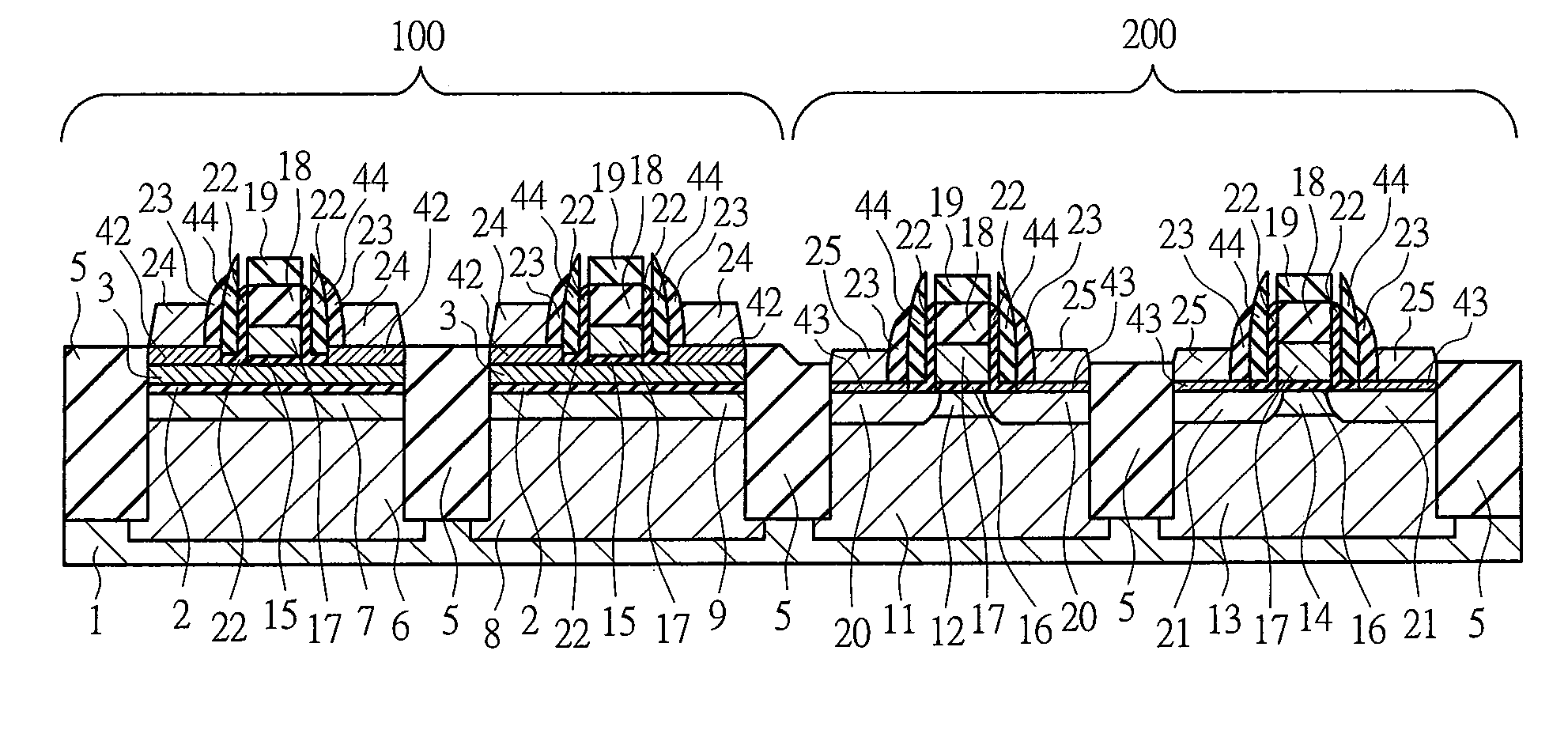

Semiconductor integrated circuit device and process for manufacturing the same

InactiveUS20050020021A1Image degradationLess fluctuationTransistorSolid-state devicesDevice materialHydrogen content

In the manufacture of a semiconductor device having a high-performance and high-reliability, a silicon nitride film 17 for self alignment, which film is formed to cover the gate electrode of a MISFET, is formed at a substrate temperature of 400° C. or greater by plasma CVD using a raw material gas including monosilane and nitrogen. A silicon nitride film 44 constituting a passivation film is formed at a substrate temperature of about 350° C. by plasma CVD using a raw material gas including monosilane, ammonia and nitrogen. The hydrogen content contained in the silicon nitride film 17 is smaller than that contained in the silicon nitride film 44, making it possible to suppress hydrogen release from the silicon nitride film 17.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device

InactiveUS20060263988A1Substrate wiring resistant is increasedImprove the immunityTransistorSemiconductor/solid-state device detailsDevice materialSemiconductor chip

Two vertical-type power MISFETs are formed over a semiconductor chip, a common drain electrode formed over a back surface of the semiconductor chip is electrically connected with a drain terminal via a conductive bonding material, source electrodes and gate electrodes formed over a surface of the semiconductor chip are respectively electrically connected with source terminals and gate terminals via bump electrodes, and these components are sealed by a resin sealing portion. The exposed portions of the gate terminals are arranged inside the resin sealing portion, and the exposed portions of the source terminals are arranged outside the resin sealing portion. The source terminals extend over the surface of the semiconductor chip and are connected with the source electrodes which are uniformly arranged over regions of the surface of the semiconductor chip except for gate electrode forming regions and the vicinities of these regions via the bump electrodes.

Owner:RENESAS ELECTRONICS CORP

Method for manufacturing semiconductor device

ActiveUS7915075B2Low costSemiconductor device can be miniaturizedStatic indicating devicesSolid-state devicesDry etchingSemiconductor

An object is to establish a processing technique in manufacture of a semiconductor device in which an oxide semiconductor is used. A gate electrode is formed over a substrate, a gate insulating layer is formed over the gate electrode, an oxide semiconductor layer is formed over the gate insulating layer, the oxide semiconductor layer is processed by wet etching to form an island-shaped oxide semiconductor layer, a conductive layer is formed to cover the island-shaped oxide semiconductor layer, the conductive layer is processed by dry etching to form a source electrode, and a drain electrode and part of the island-shaped oxide semiconductor layer is removed by dry etching to form a recessed portion in the island-shaped oxide semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

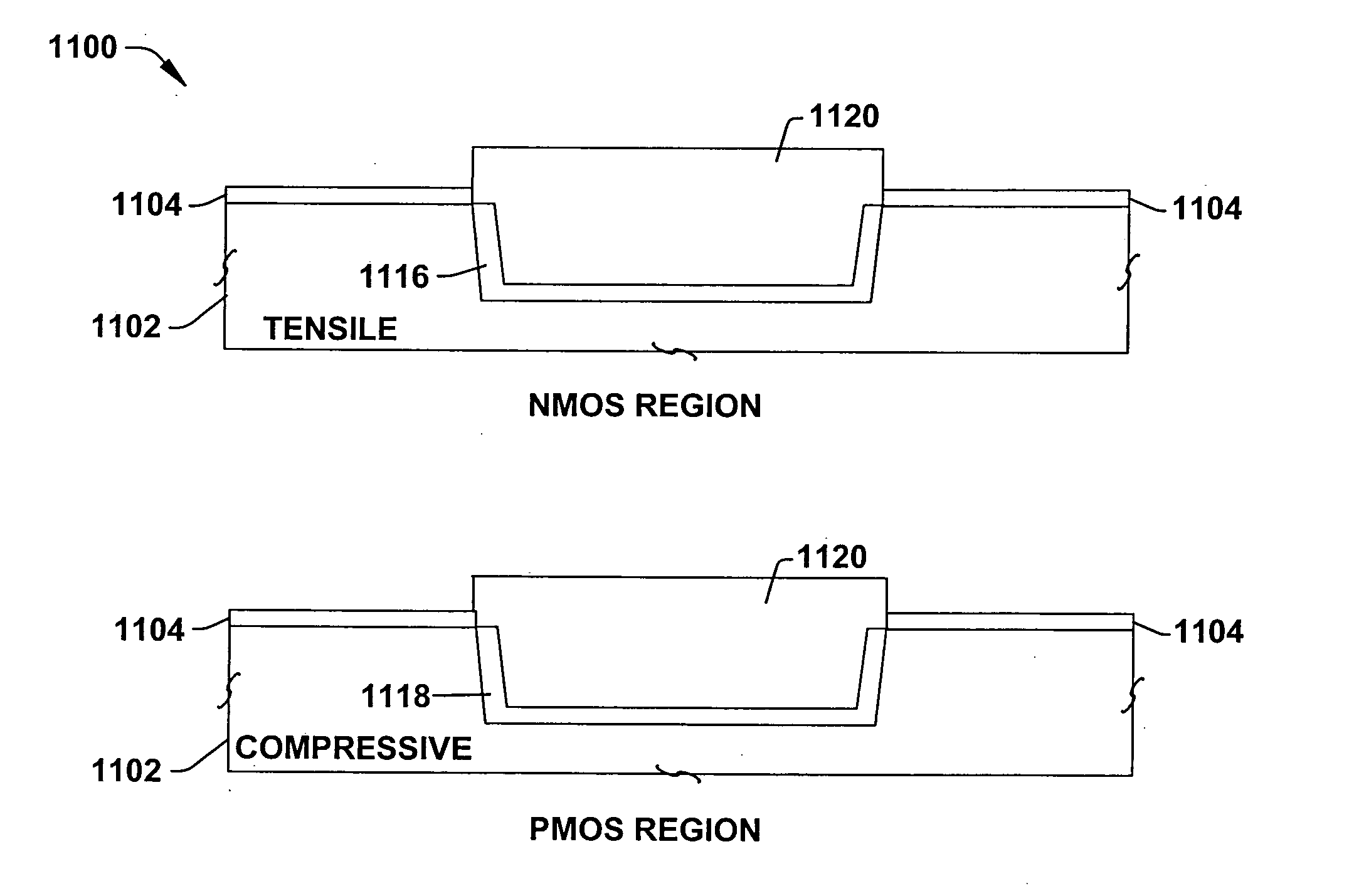

Strain modulation employing process techniques for CMOS technologies

ActiveUS20070015347A1Improve performancePerformance degradationSemiconductor/solid-state device manufacturingFermentationPhysicsCMOS

A method forms a semiconductor device comprising a modifiable strain inducing layer. A semiconductor body is provided. First and second regions of the semiconductor body are identified. A modifiable tensile strain inducing layer is formed over the device within the first and second regions. A mask is then formed that exposes the second region and covers the first region. A material is selected for a modification implant and the selected material is implanted into the second region thereby converting a portion of the modifiable tensile strain inducing layer into a compressive strain inducing layer within the PMOS region.

Owner:TEXAS INSTR INC

Semiconductor device

InactiveUS20090039336A1Improve semiconductor device performancePerformance of a semiconductor device capable of storing information can be improvedSolid-state devicesDigital storageDevice materialLanthanide

The performance of a semiconductor device capable of storing information is improved. A memory layer of a memory element is formed by a first layer at a bottom electrode side and a second layer at a top electrode side. The first layer contains 20-70 atom % of at least one element of a first element group of Cu, Ag, Au, Al, Zn, and Cd, contains 3-40 atom % of at least one element of a second element group of V, Nb, Ta, Cr, Mo, W, Ti, Zr, Hf, Fe, Co, Ni, Pt, Pd, Rh, Ir, Ru, Os, and lanthanoid elements, and contains 20-60 atom % of at least one element of a third element group of S, Se, and Te. The second layer contains 5-50 atom % of at least one element of the first element group, 10-50 atom % of at least one element of the second element group, and 30-70 atom % of oxygen.

Owner:HITACHI LTD

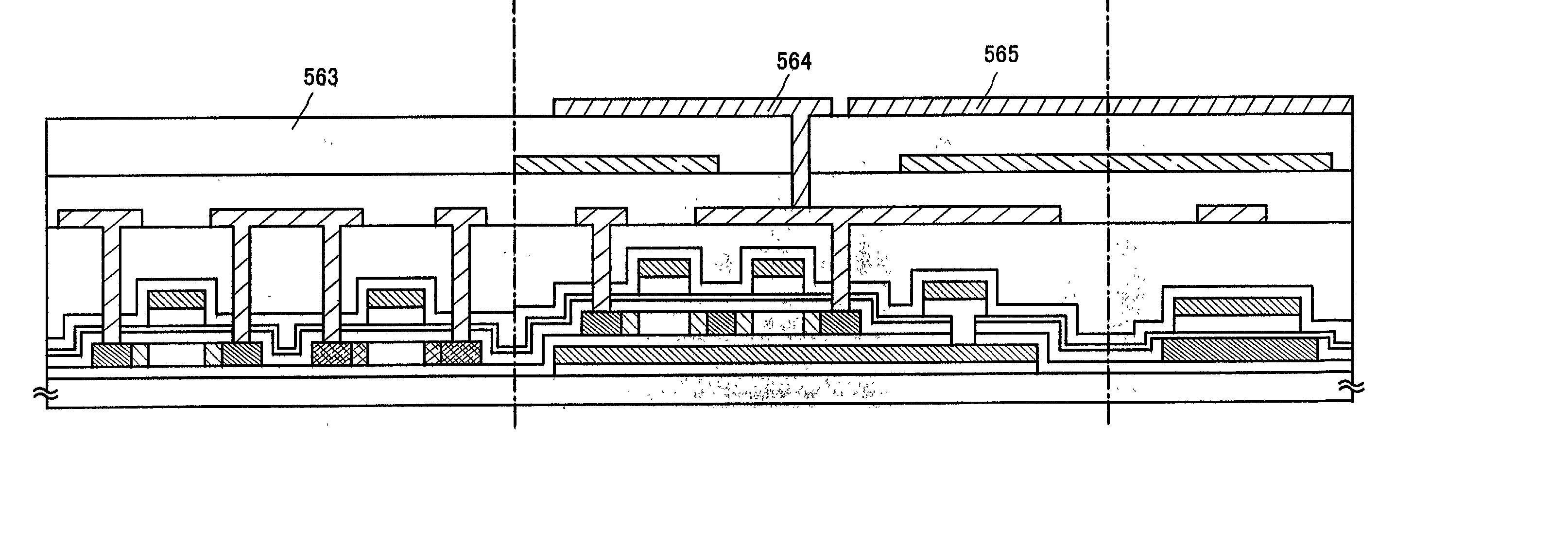

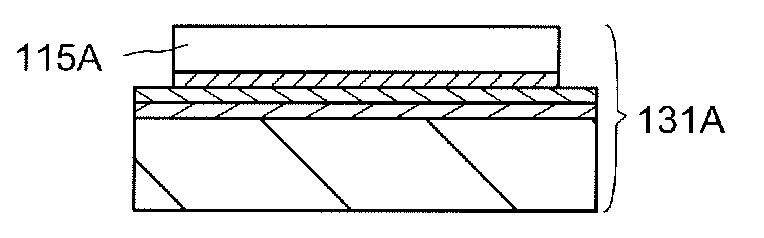

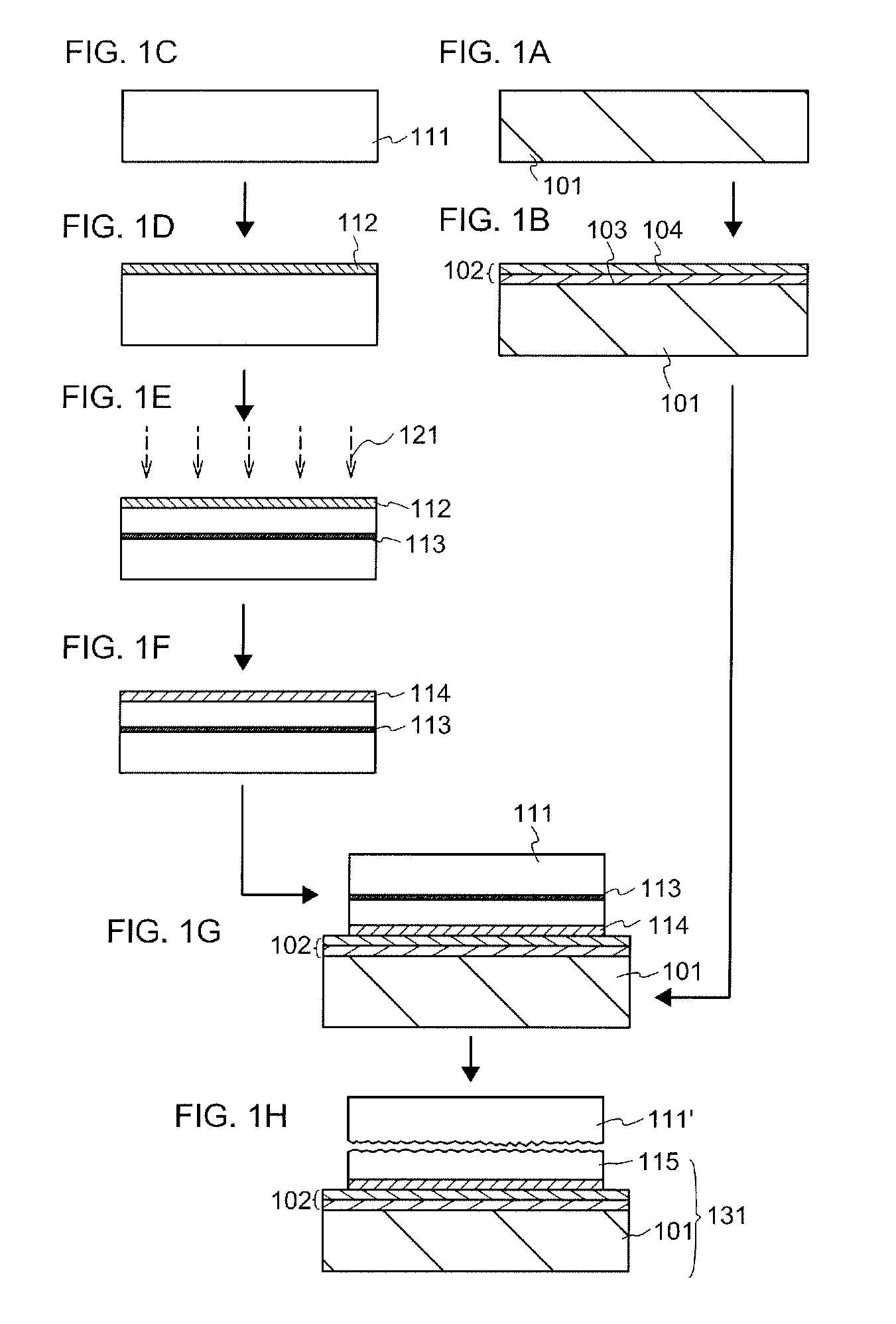

Method for manufacturing semiconductor device, and semiconductor device and electronic device

InactiveUS20090117716A1Surface unevenness and defect be reduceHigh performanceSemiconductor/solid-state device manufacturingIrradiation laserSemiconductor components

To provide a high-performance semiconductor device using an SOI substrate in which a substrate having low heat resistance is used as a base substrate, to provide a high-performance semiconductor device without performing mechanical polishing, and to provide an electronic device using the semiconductor device, planarity of a semiconductor layer is improved and defects in the semiconductor layer are reduced by laser beam irradiation. Accordingly, a high-performance semiconductor device can be provided without performing mechanical polishing. In addition, a semiconductor device is manufactured using a region having the most excellent characteristics in a region irradiated with the laser beam. Specifically, instead of the semiconductor layer in a region which is irradiated with the edge portion of the laser beam, the semiconductor layer in a region which is irradiated with portions of the laser beam except the edge portion is used as a semiconductor element. Accordingly, performance of the semiconductor device can be greatly improved. Moreover, an excellent electronic device can be provided.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device, method for manufacturing semiconductor device, and method for forming oxide film

InactiveUS20130228775A1High carrier mobilityHigh currentTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

One embodiment of the present invention is a semiconductor device at least including an oxide semiconductor film, a gate insulating film in contact with the oxide semiconductor film, and a gate electrode overlapping with the oxide semiconductor film with the gate insulating film therebetween. The oxide semiconductor film has a spin density lower than 9.3×1016 spins / cm3 and a carrier density lower than 1×1015 / cm3. The spin density is calculated from a peak of a signal detected at a g value (g) of around 1.93 by electron spin resonance spectroscopy. The oxide semiconductor film is formed by a sputtering method while bias power is supplied to the substrate side and self-bias voltage is controlled, and then subjected to heat treatment.

Owner:SEMICON ENERGY LAB CO LTD

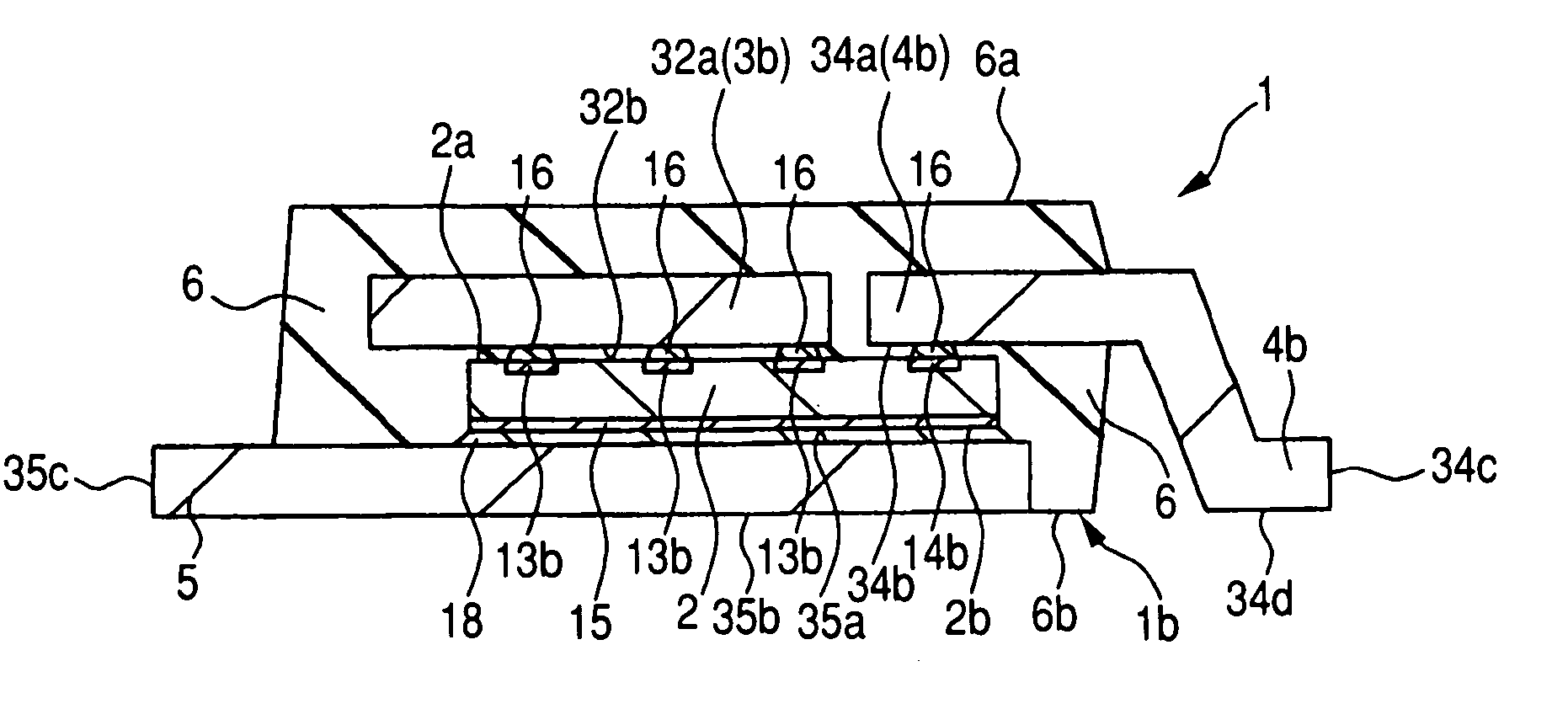

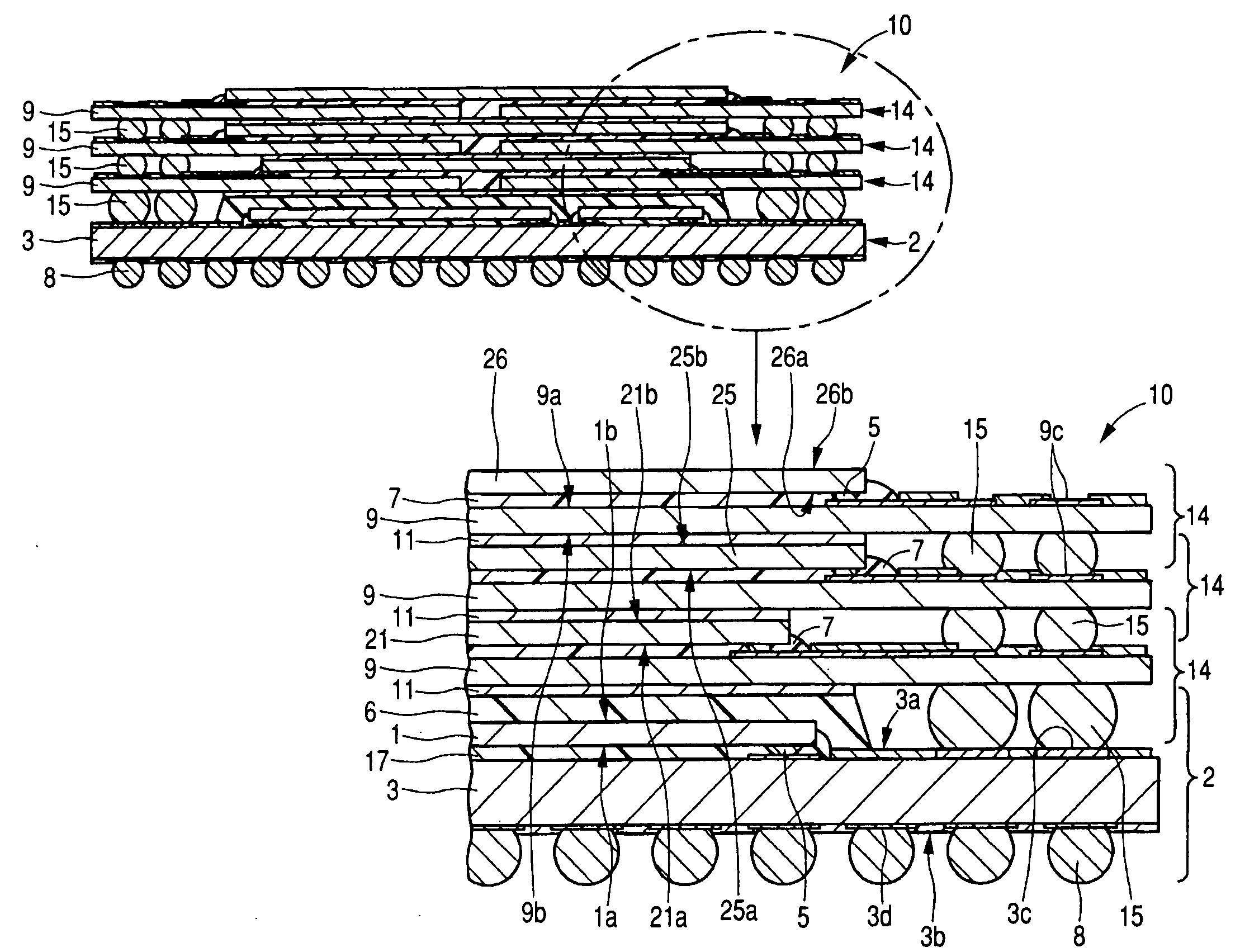

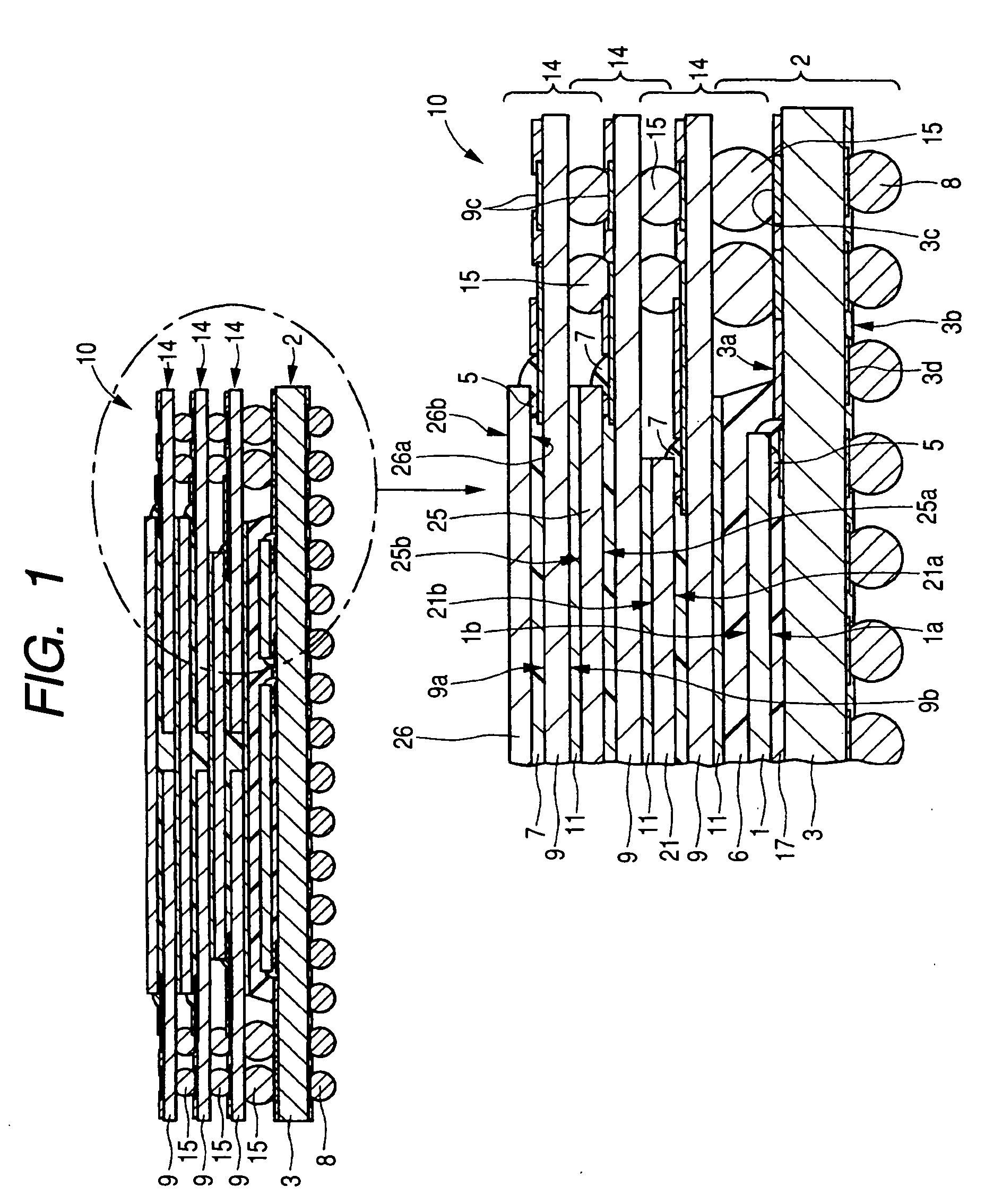

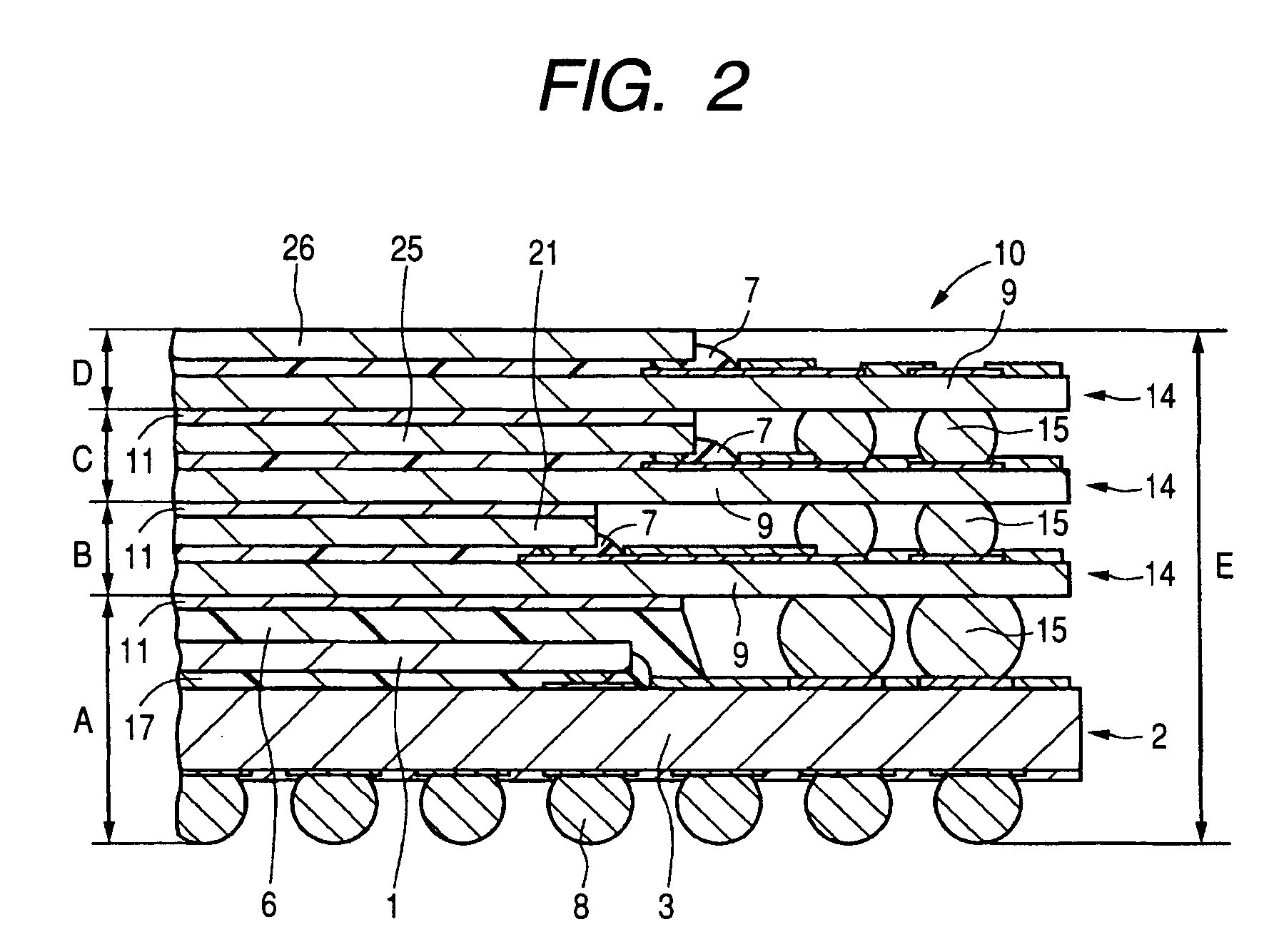

Semiconductor device and a method of manufacturing the same

InactiveUS20070096287A1Improve packaging effectIncrease heat radiationSemiconductor/solid-state device detailsSolid-state devicesDevice materialMagnetic tape

Packaging performance of a semiconductor device is improved. A semiconductor device has a package substrate having a base material formed of resin; a semiconductor chip mounted on a main surface of the package substrate; a tape substrates being stacked on the package substrate in several stages, and electrically connected to a substrate at a lower stage via a plurality of solder balls; a second-stage chip, third-stage chip, and fourth-stage chip mounted on the tape substrates at respective stages; and a plurality of solder balls provided on a back surface of the package substrate; wherein a sealing body, which resin-seals the semiconductor chip and is formed by resin molding, is formed on a main surface of a package substrate disposed at the lowest stage, and the sealing body is disposed between the package substrate at the lowest stage and the tape substrate stacked thereon.

Owner:RENESAS TECH CORP

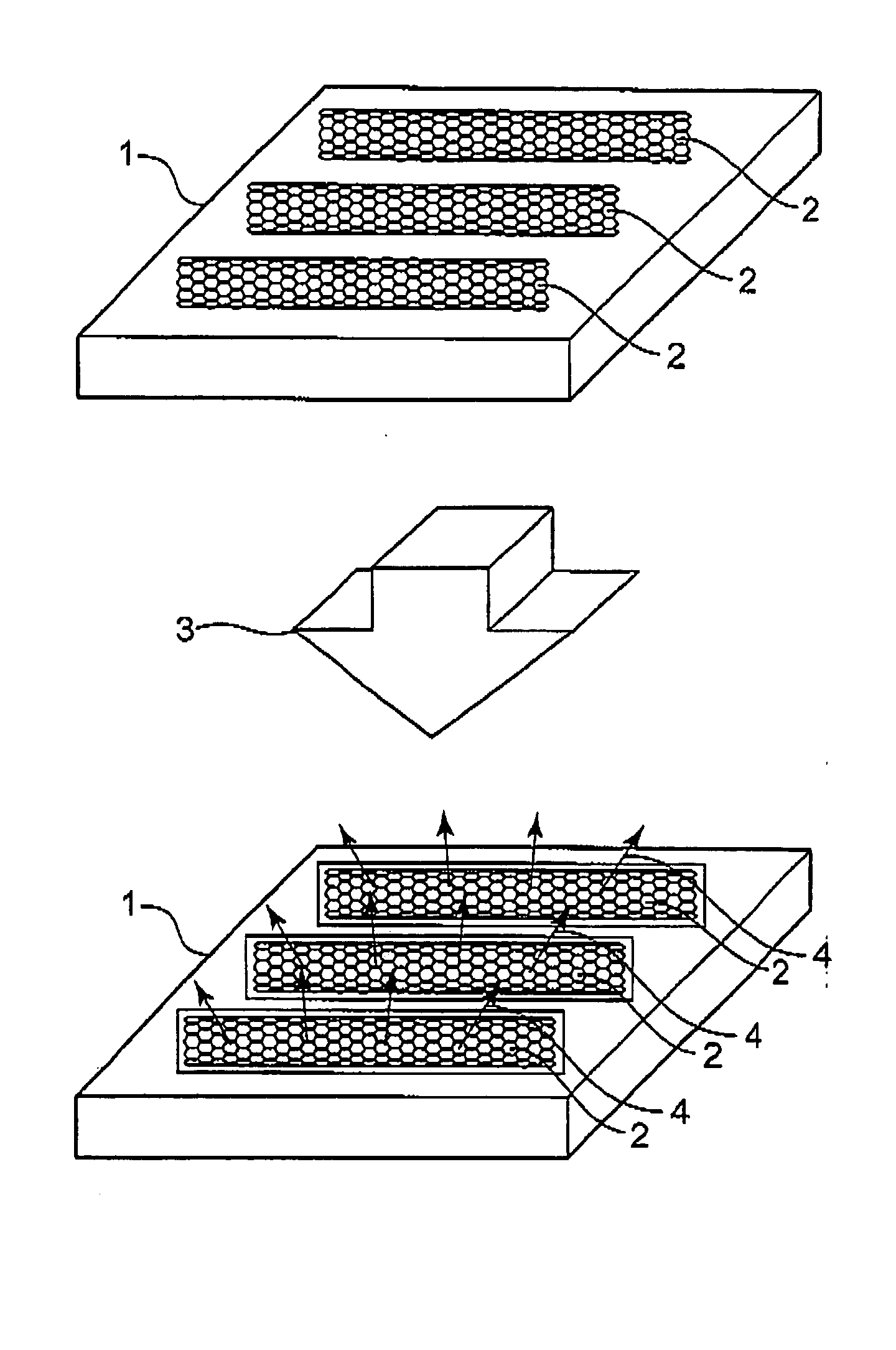

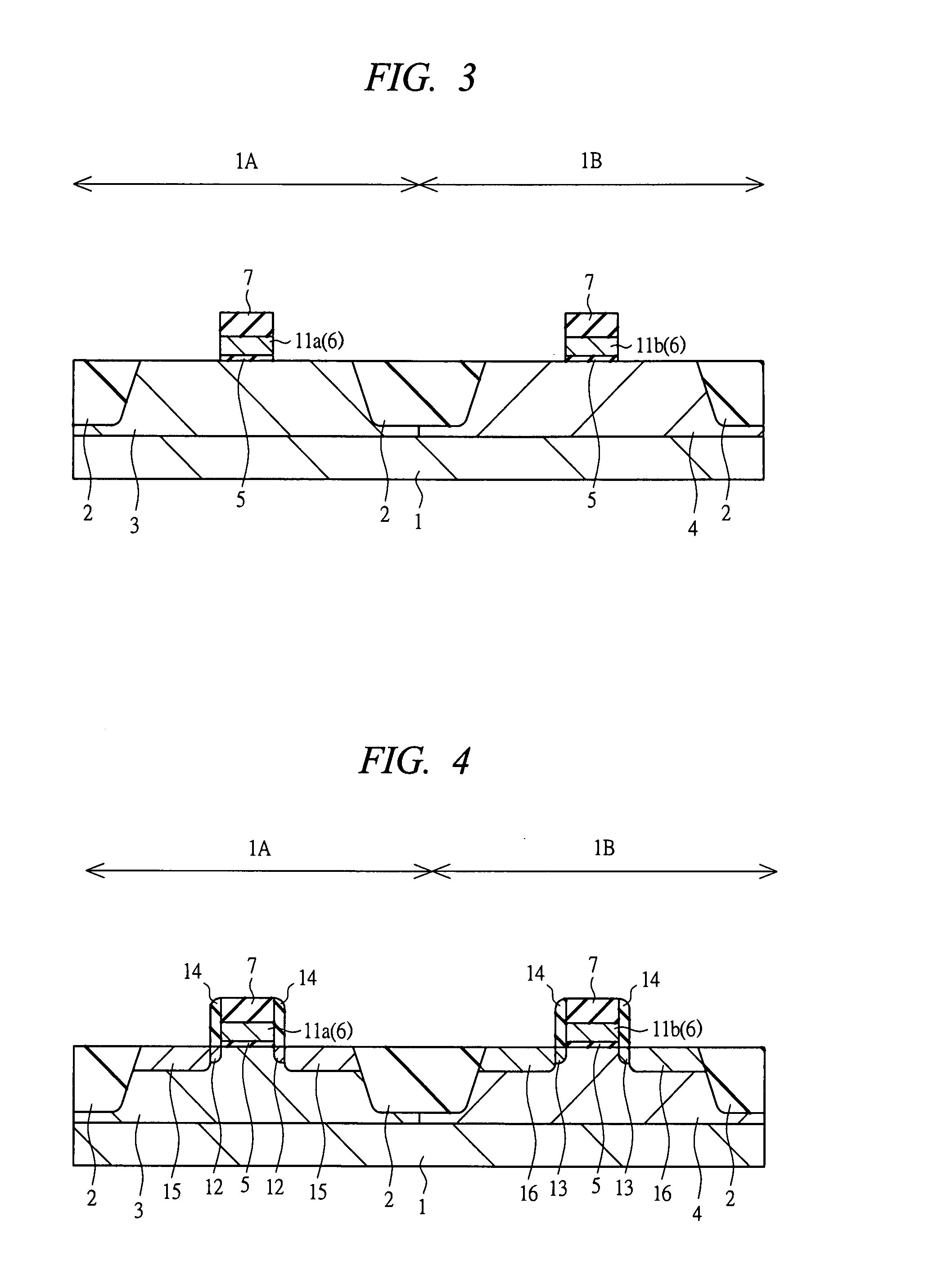

Semiconductor device and method of manufacturing the same

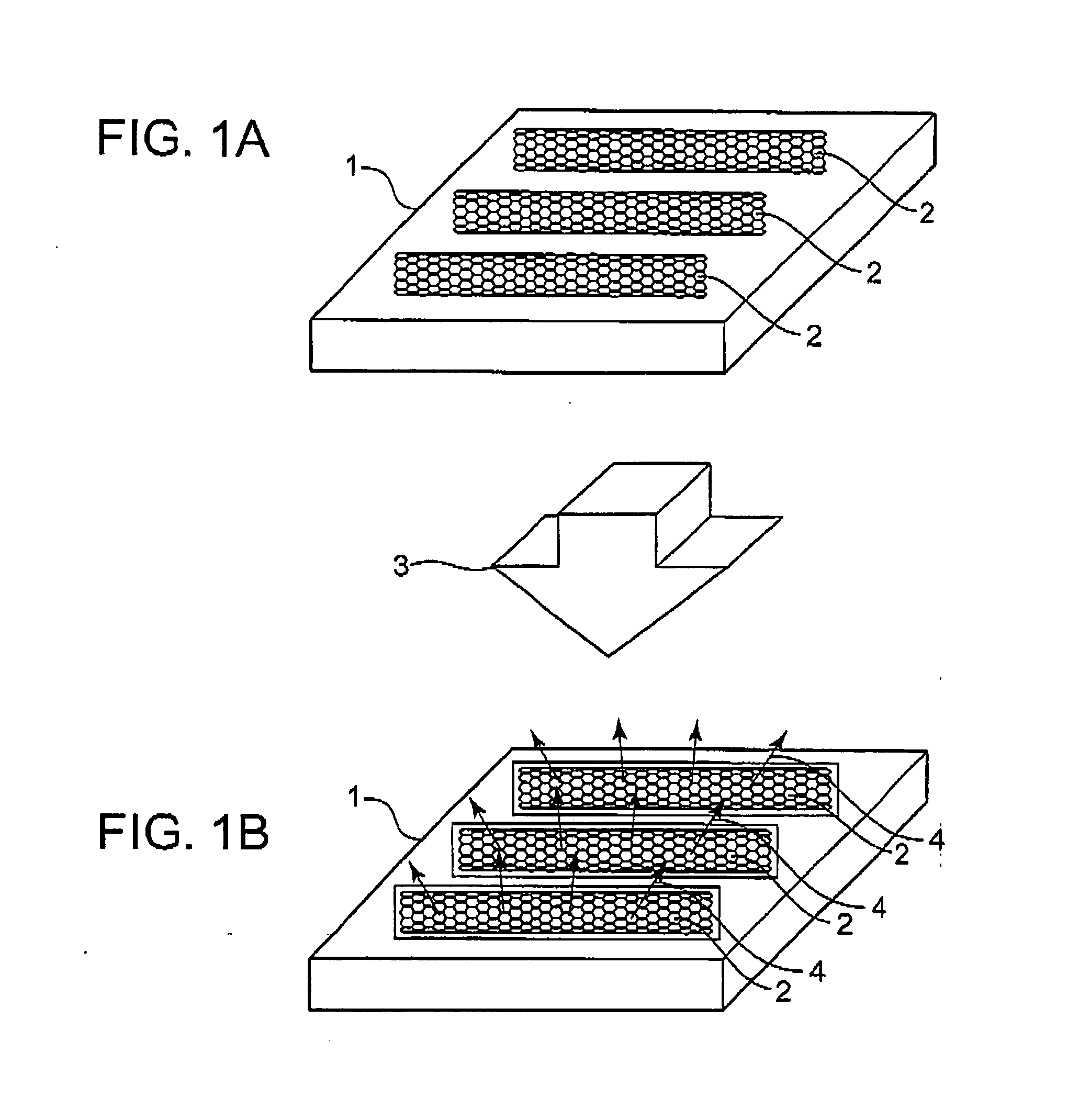

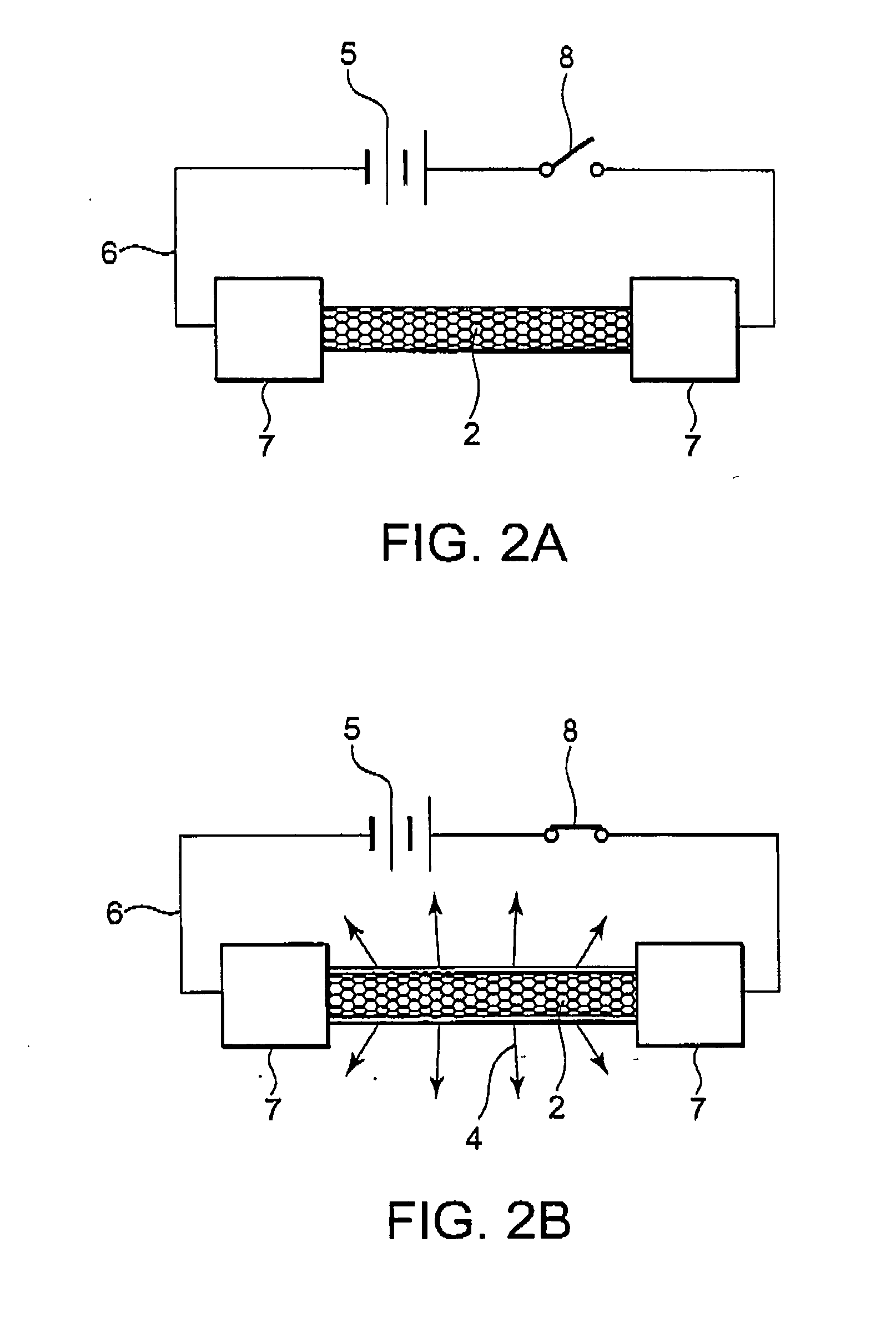

InactiveUS20070161213A1Improve semiconductor device performanceNanoinformaticsSolid-state devicesNanowireChemical reaction

A self-aligned / self-limited processing is carried out on a nanowire material typified by a carbon nanotube or on the vicinity of the nanowire material alone in the following manner. External energy is applied to the nanowire material. Joule heat, light, or a thermoelectron is thereby locally formed and acts as minute energy. The minute energy causes a chemical reaction of an externally added raw material and causes the conversion of a property of the nanowire material.

Owner:NEC CORP

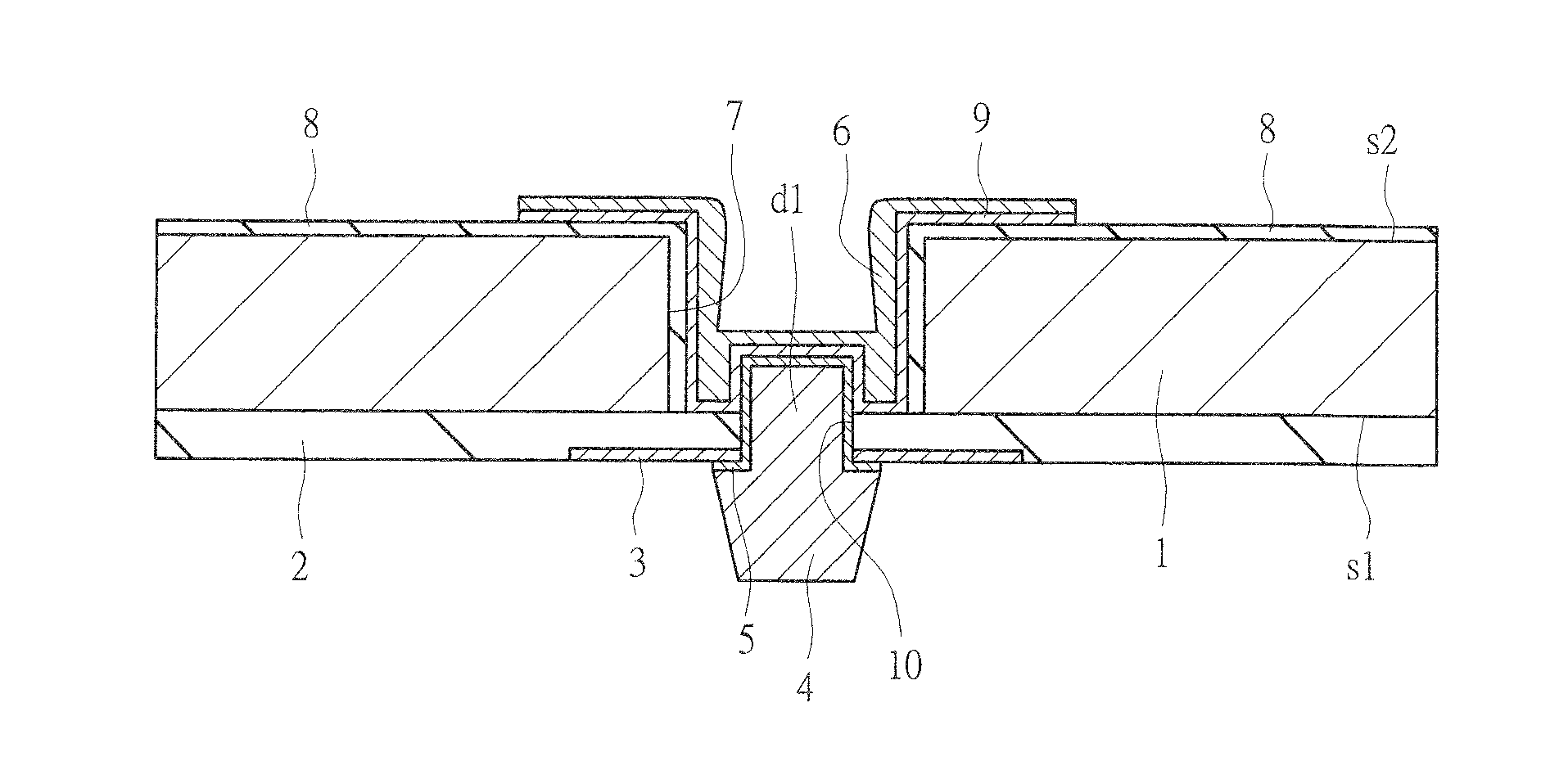

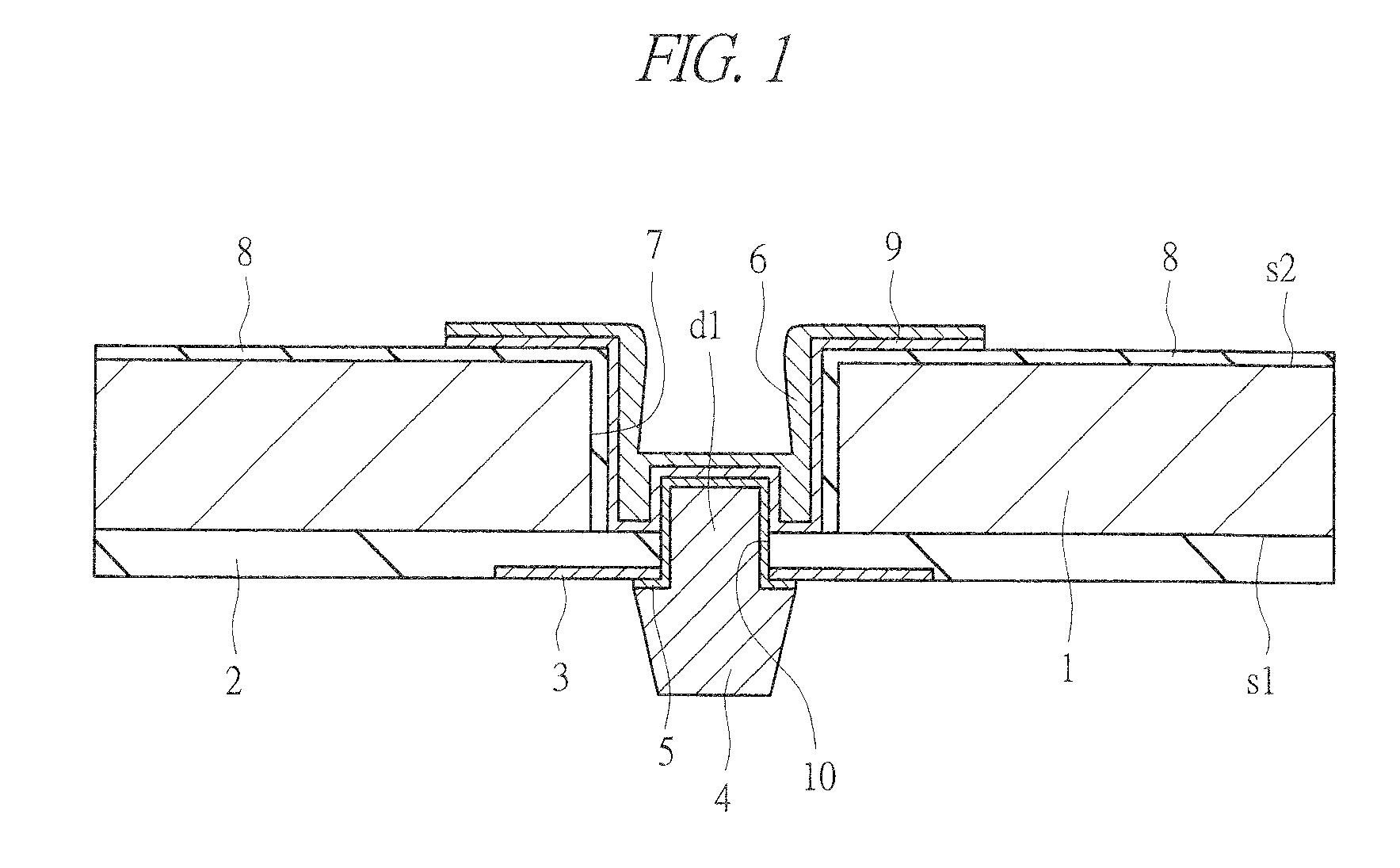

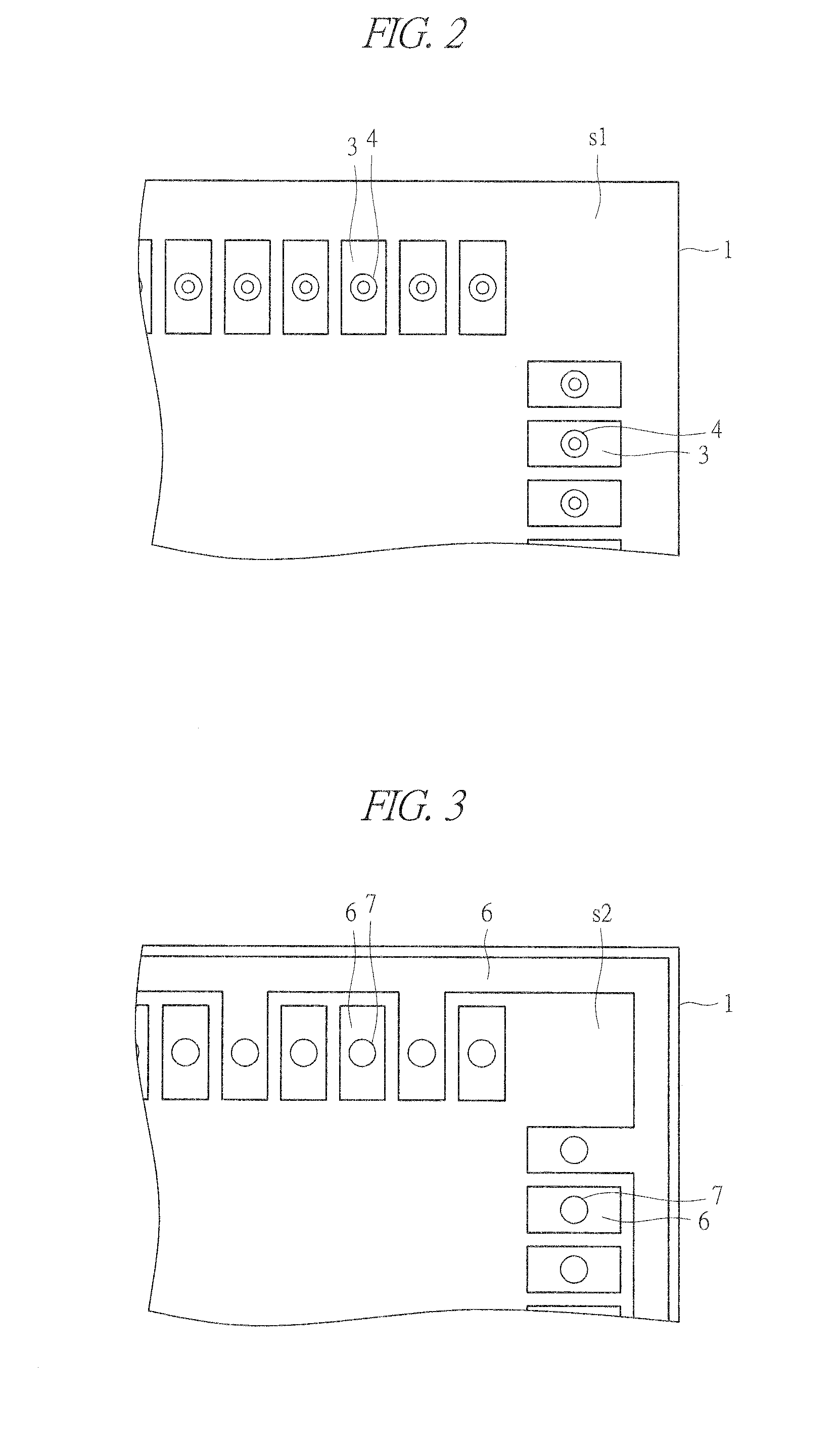

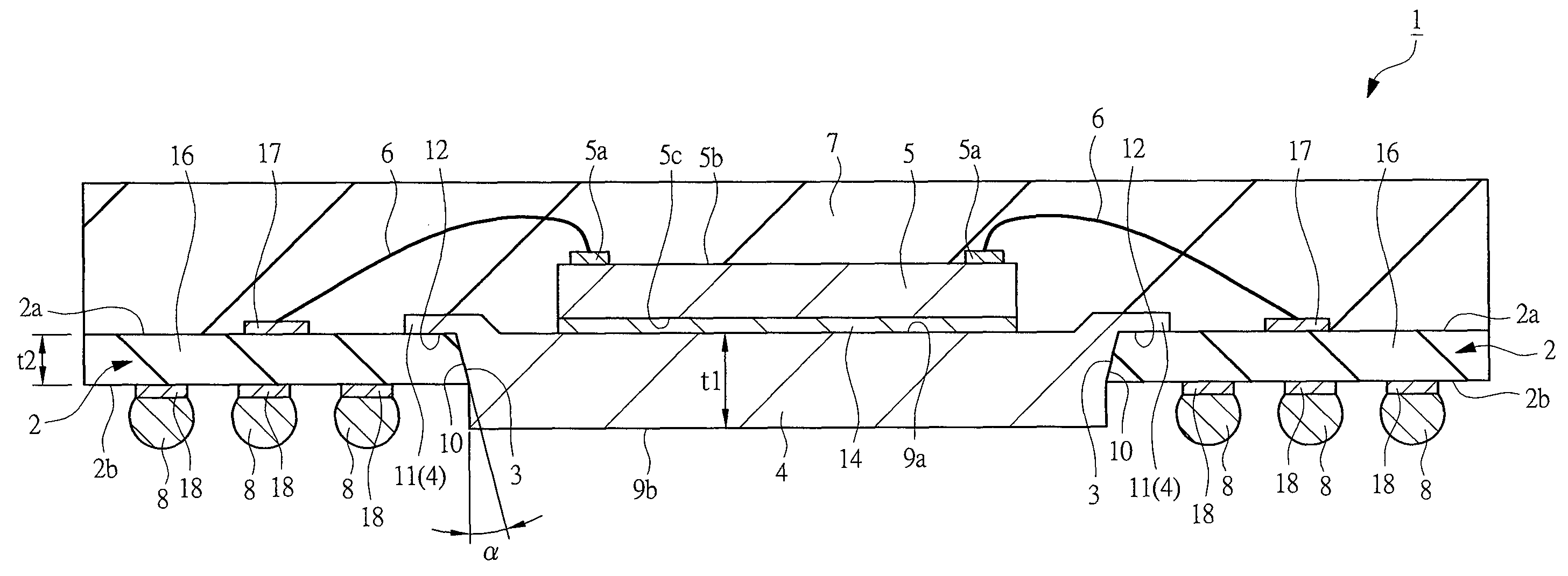

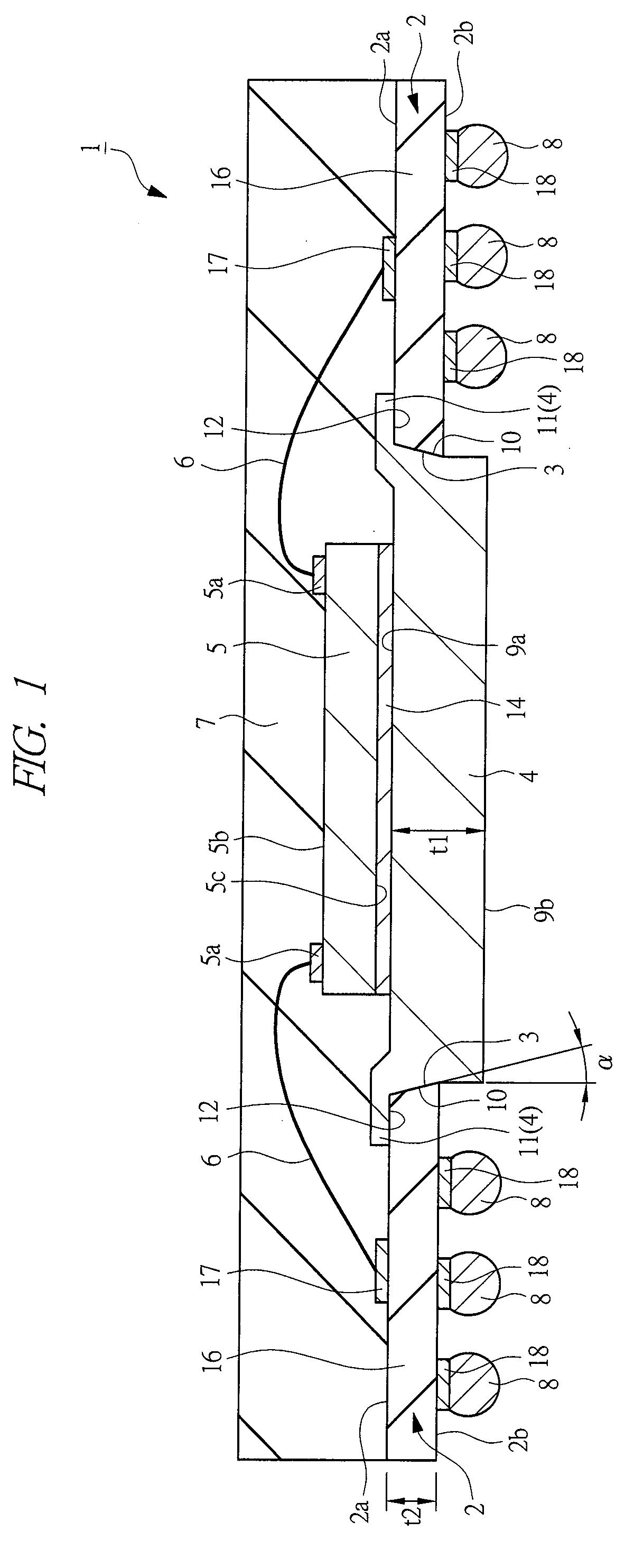

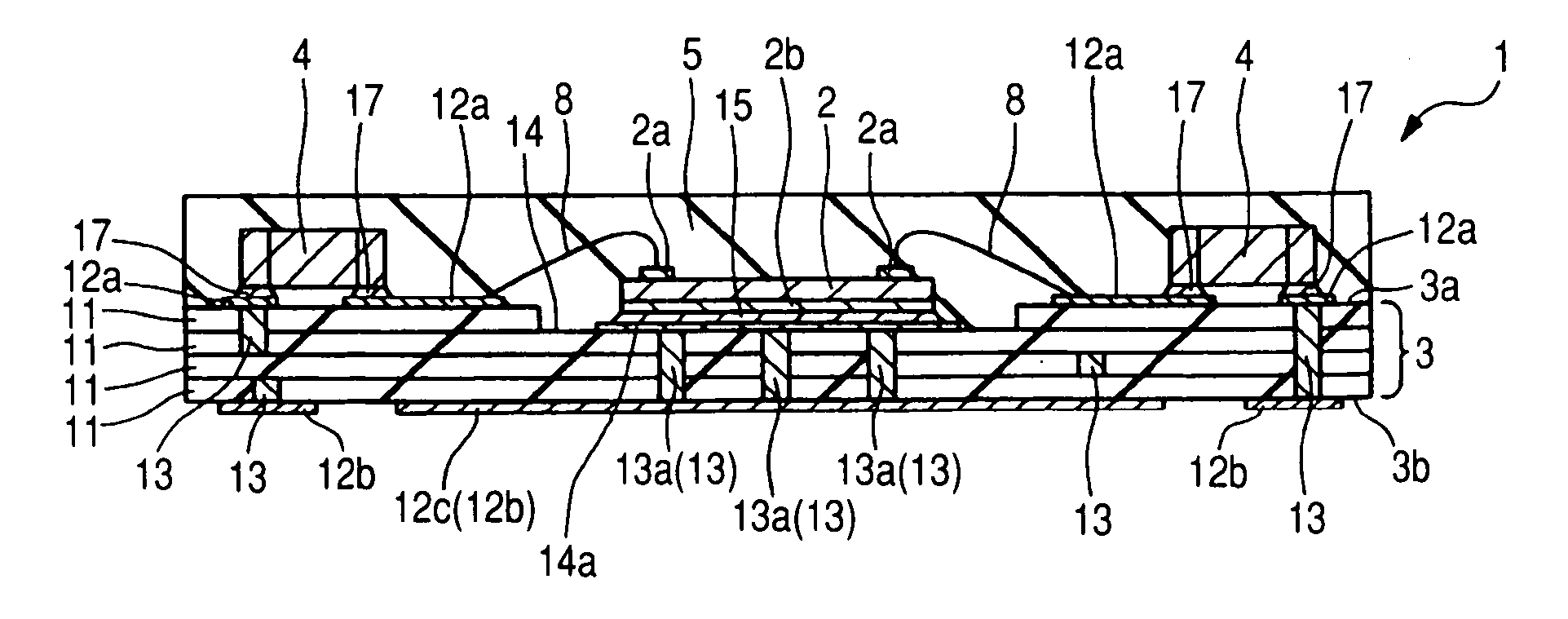

Semiconductor device mounted on heat sink having protruded periphery

ActiveUS7923826B2Improve semiconductor device performanceHigh calorific valueSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A semiconductor chip is mounted on a heat sink disposed inside a through-hole of a wiring board, electrodes of the semiconductor chip and connecting terminals of the wiring board are connected by bonding wires, a sealing resin is formed to cover the semiconductor chip and the bonding wires, and solder balls are formed on the lower surface of the wiring board, thereby constituting the semiconductor device. The heat sink is thicker than the wiring board. The heat sink has a protruded portion protruding to outside from the side surface of the heat sink, the protruded portion is located on the upper surface of the wiring board outside the through-hole, and the lower surface of the protruded portion contacts to the upper surface of the wiring board. When the semiconductor device is manufactured, the heat sink is inserted from the upper surface side of the wiring board.

Owner:RENESAS ELECTRONICS CORP

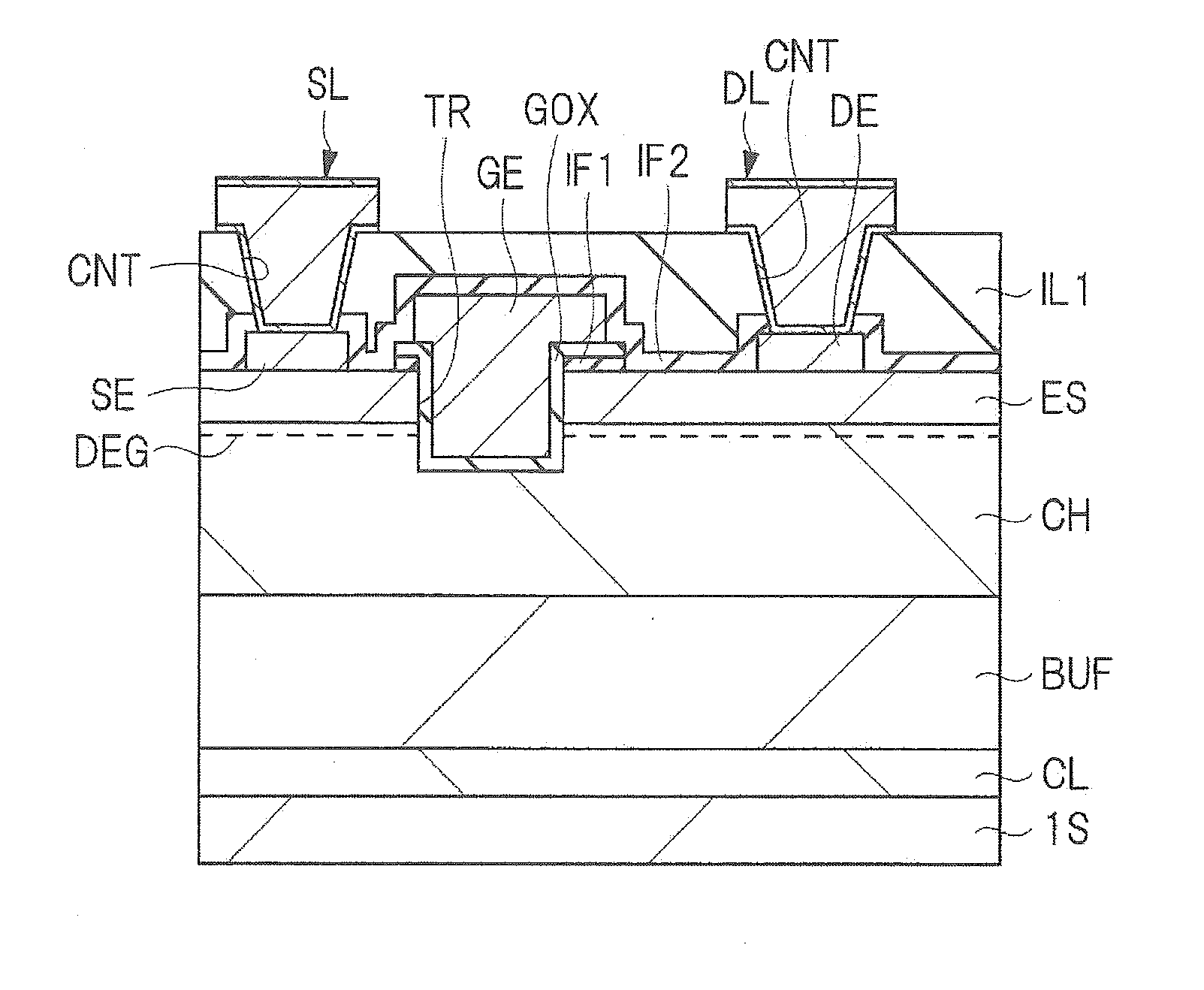

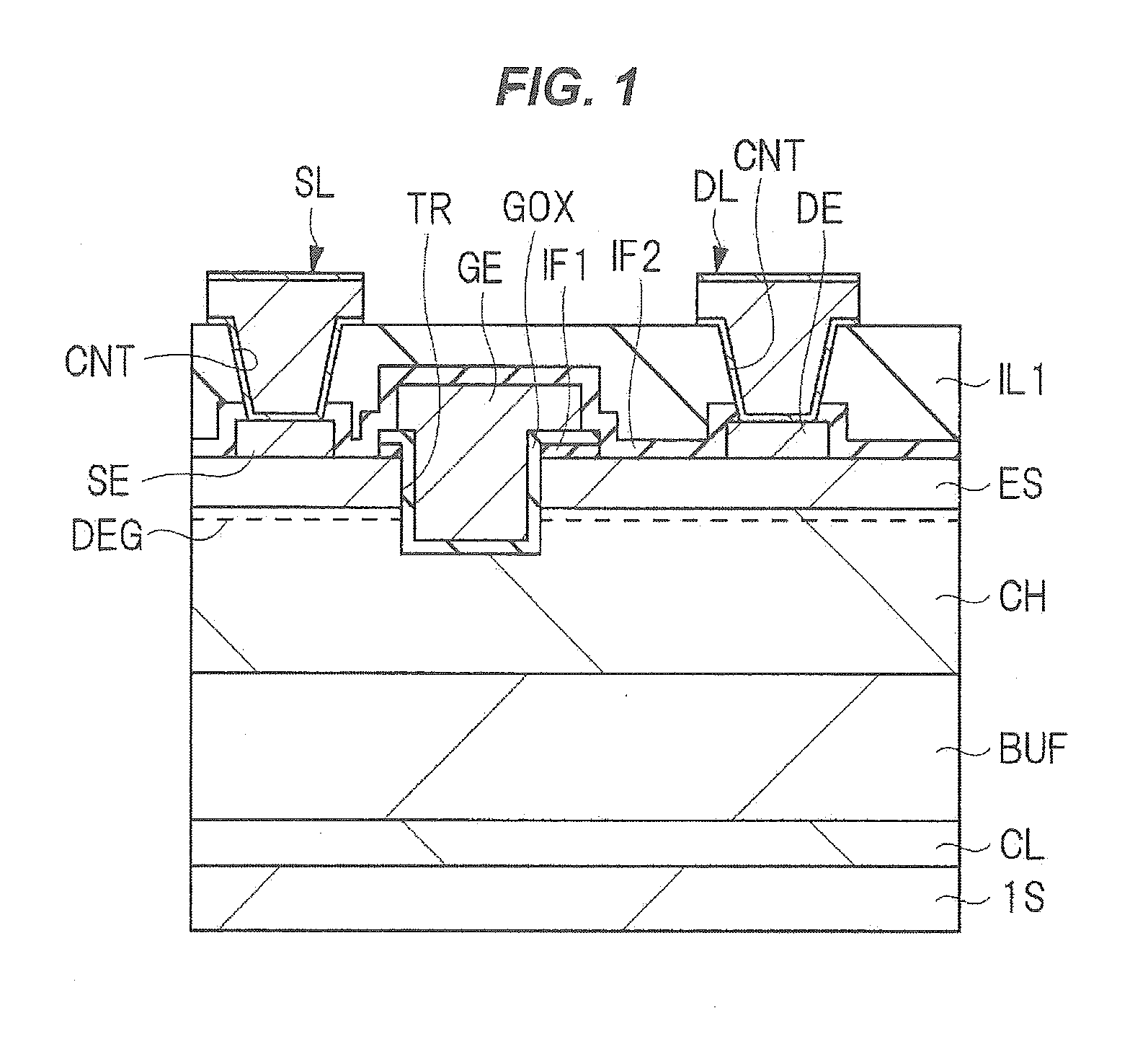

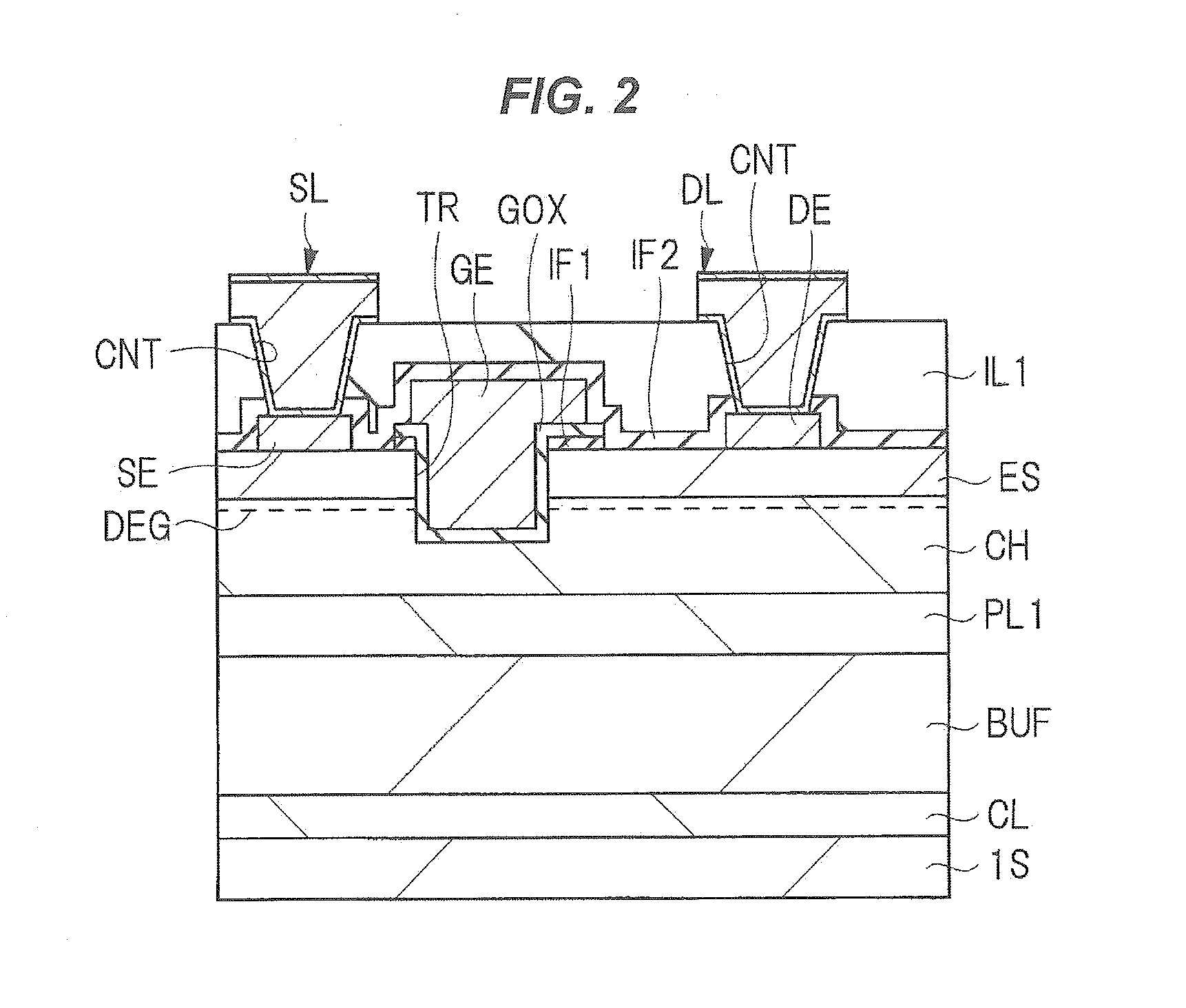

Semiconductor device

ActiveUS20140264274A1Improve semiconductor device performanceHigh activation rateSemiconductor devicesDevice materialNitride semiconductors

To improve performance of a semiconductor device. For example, on the assumption that a superlattice layer is inserted between a buffer layer and a channel layer, a concentration of acceptors introduced into nitride semiconductor layers forming a part of the superlattice layer is higher than a concentration of acceptors introduced into nitride semiconductor layers forming the other part of the superlattice layer. That is, the concentration of acceptors introduced into the nitride semiconductor layers having a small band gap is higher than the concentration of acceptors introduced into the nitride semiconductor layers having a large band gap.

Owner:RENESAS ELECTRONICS CORP

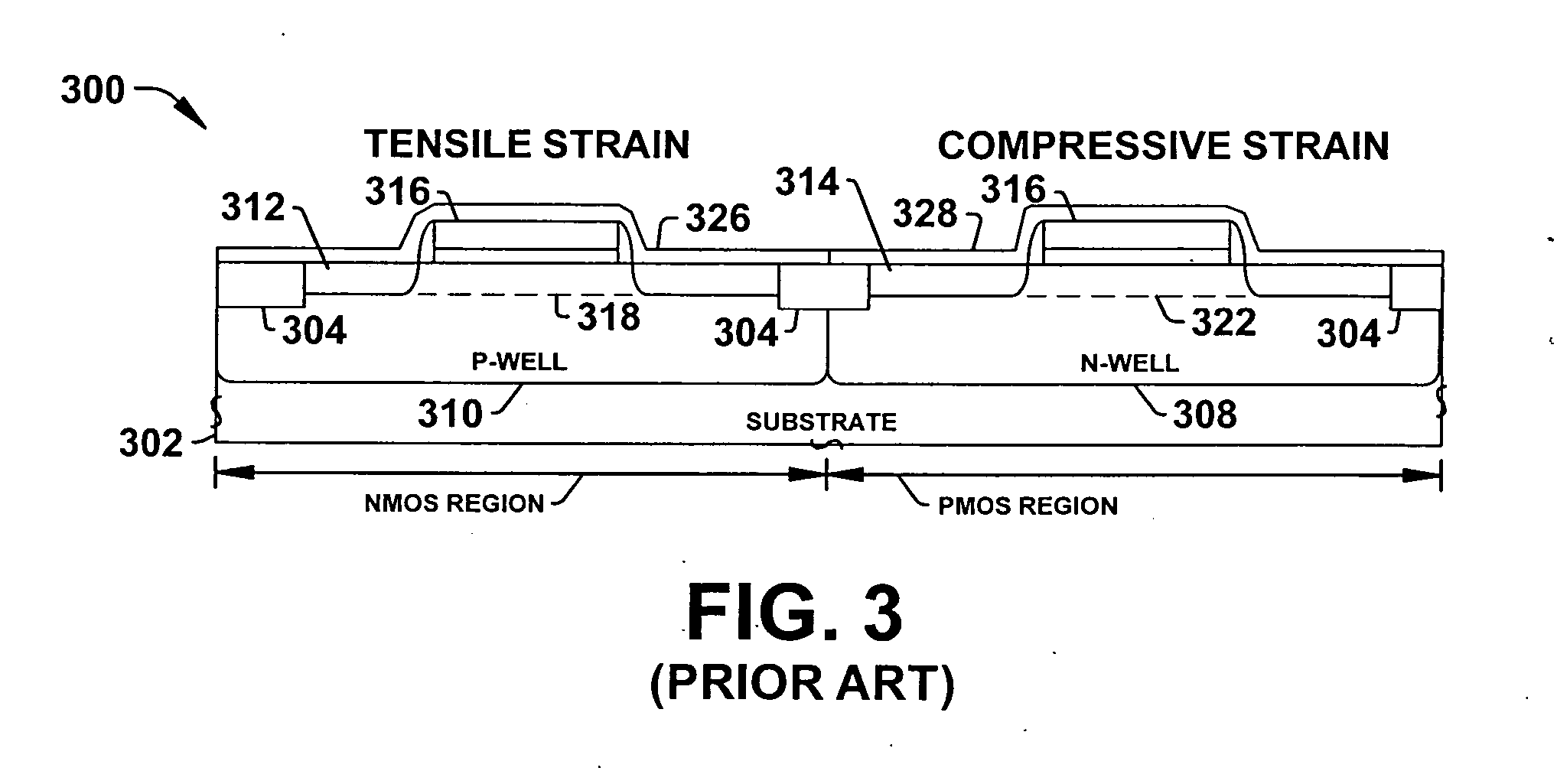

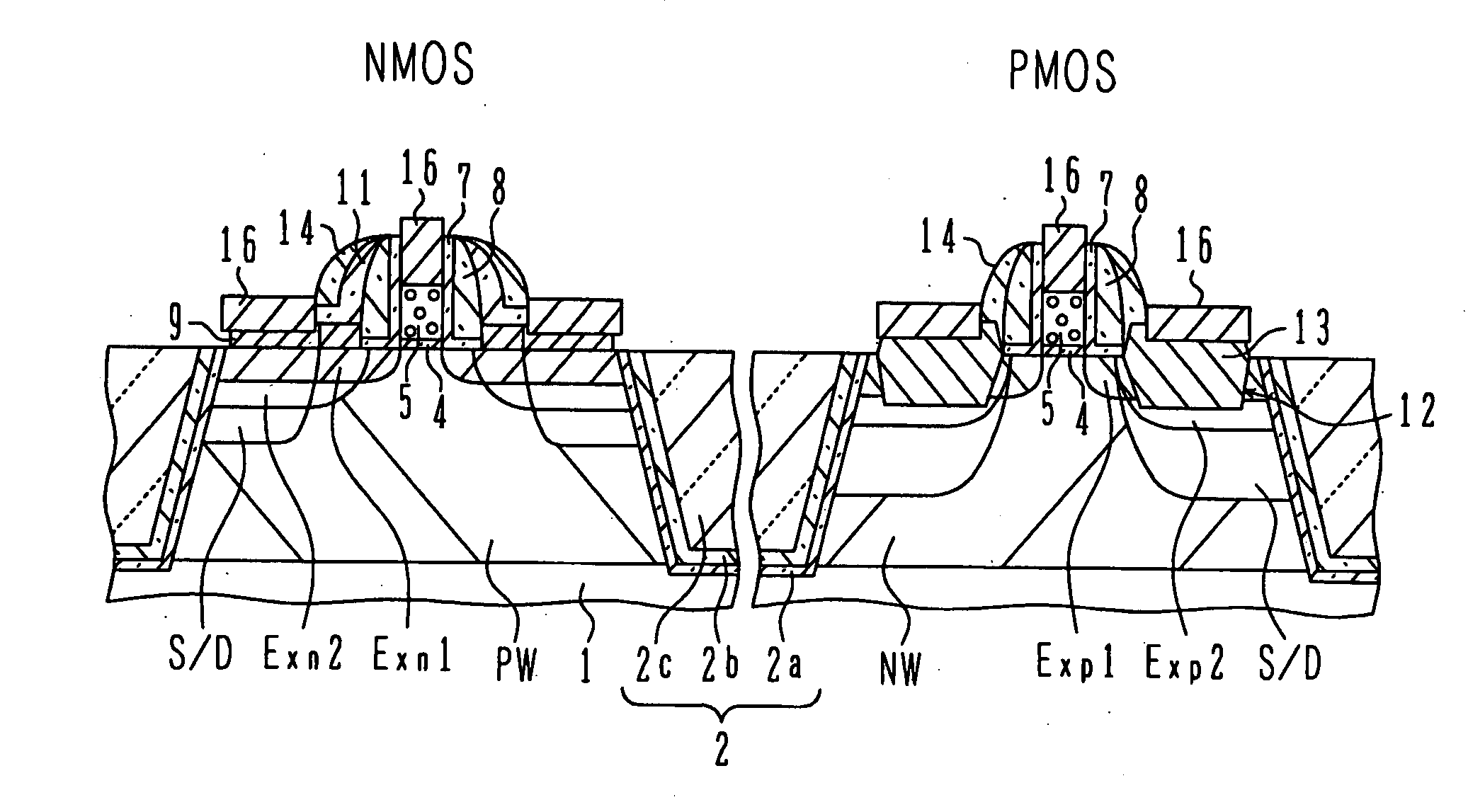

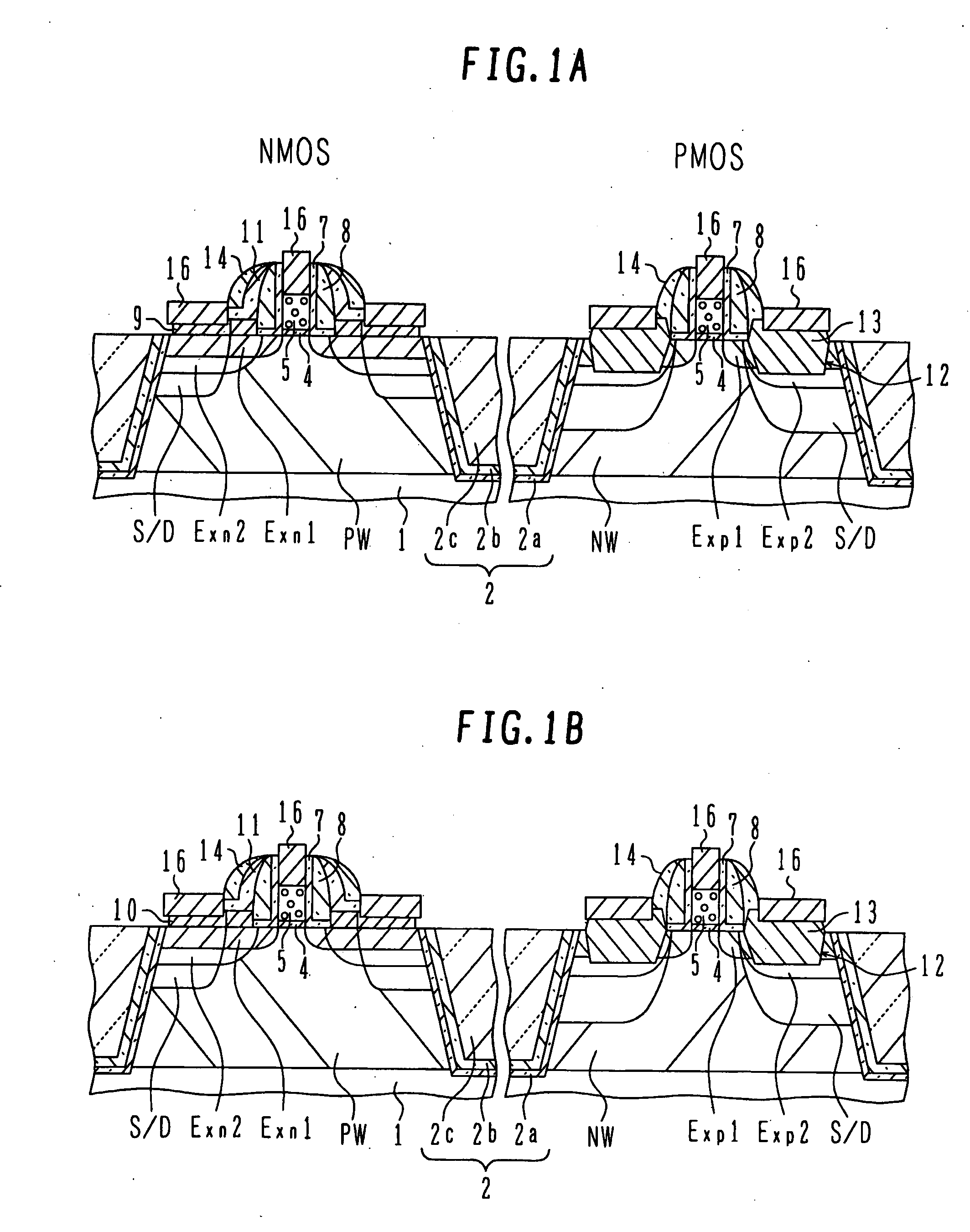

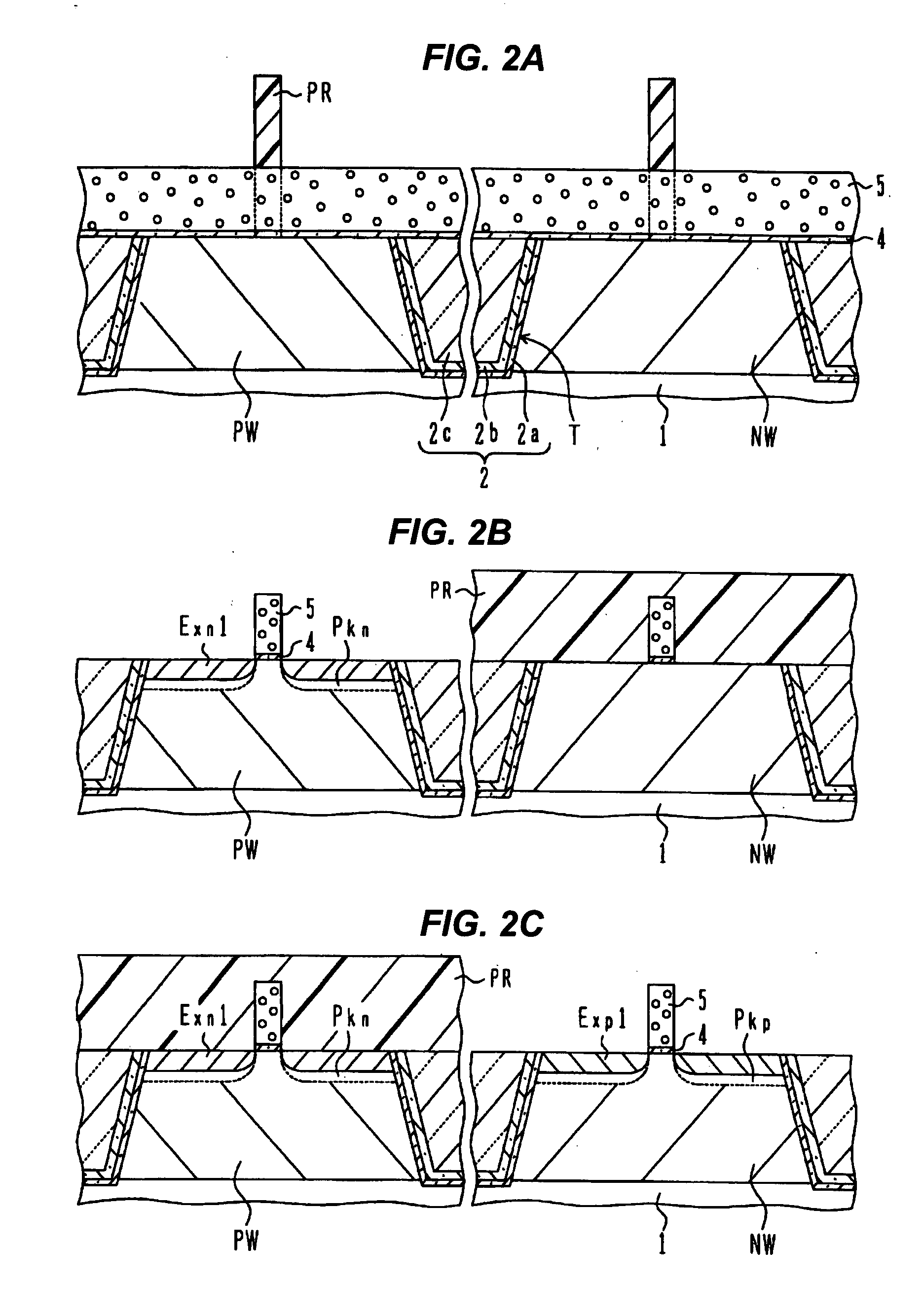

Semiconductor device and its manufacture method

ActiveUS20080099846A1Simple manufacturing processRemissionTransistorSolid-state devicesCMOSSemiconductor

A semiconductor device has a first MOS transistor formed on first active region of the first conductivity type, having first gate electrode structure, first source / drain regions, recesses formed in the first source / drain regions, and semiconductor buried regions buried and grown on the recesses for applying stress to the channel under the first gate electrode structure, and a second MOS transistor formed on second active region of the second conductivity type, having second gate electrode structure, second source / drain regions, and semiconductor epitaxial layers formed on the second source / drain regions without forming recesses and preferably applying stress to the channel under the second gate electrode structure. In a CMOS device, performance can be improved by utilizing stress and manufacture processes can be simplified.

Owner:FUJITSU SEMICON LTD

Semiconductor device and fabrication method thereof

ActiveUS20130087861A1Improve semiconductor device performanceTransistorSolid-state devicesDevice materialEngineering

A semiconductor device comprises a metal gate electrode, a passive device and a hard mask layer. The passive device has a poly-silicon element layer. The hard mask layer is disposed on the metal gate electrode and the passive electrode and has a first opening and a second opening substantially coplanar with each other, wherein the metal gate electrode and the poly-silicon element layer are respectively exposed via the first opening and the second opening; and there is a distance between the first opening and the metal gate electrode substantially less than the distance between the second opening and the poly-silicon element layer.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor device and manufacturing method of the same

InactiveUS20060057793A1Improve semiconductor device performanceImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingMetal silicideEngineering

The invention improves the performance of a semiconductor device. A metal silicide film is formed by a silicide process on a gate electrode and an n+-type source region of an LDMOSFET, and no such metal silicide film is formed on an n−-type offset drain region, an n-type offset drain region, and an n+-type drain region. A side wall spacer comprising a silicon film is formed via an insulating film on the side wall of the gate electrode over the drain side thereof, and a field plate electrode is formed by this side wall spacer. The field plate electrode does not extend above the gate electrode, and a metal silicide film is formed over the entire upper surface of the gate electrode in the silicide process.

Owner:RENESAS ELECTRONICS CORP

Introduction of metal impurity to change workfunction of conductive electrodes

ActiveUS20070173008A1Improve semiconductor device performanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureMetallic materials

Semiconductor structures, such as, for example, field effect transistors (FETs) and / or metal-oxide-semiconductor capacitor (MOSCAPs), are provided in which the workfunction of a conductive electrode stack is changed by introducing metal impurities into a metal-containing material layer which, together with a conductive electrode, is present in the electrode stack. The choice of metal impurities depends on whether the electrode is to have an n-type workfunction or a p-type workfunction. The present invention also provides a method of fabricating such semiconductor structures. The introduction of metal impurities can be achieved by codeposition of a layer containing both a metal-containing material and workfunction altering metal impurities, forming a stack in which a layer of metal impurities is present between layers of a metal-containing material, or by forming a material layer including the metal impurities above and / or below a metal-containing material and then heating the structure so that the metal impurities are introduced into the metal-containing material.

Owner:GLOBALFOUNDRIES US INC

Semiconductor device

ActiveUS20080283945A1Improve semiconductor device performanceImprove breakdown voltageMaterial analysis using sonic/ultrasonic/infrasonic wavesPiezoelectric/electrostriction/magnetostriction machinesSilicon nitrideEngineering

A lower electrode is formed over a semiconductor substrate via an insulator film, first and second insulator films are formed to cover the lower electrode, an upper electrode is formed over the second insulator film, third to fifth insulator films are formed to cover the upper electrode and a void is formed between the first and second insulator films between the lower and upper electrodes. An ultrasonic transducer comprises the lower electrode, the first insulator film, the void, the second insulator film and the upper electrode. A portion of the first insulator film contacting with the lower electrode is made of silicon oxide, a portion of the second insulator film contacting with the upper electrode is made of silicon oxide and the first or second insulator film includes a silicon nitride film positioned between the upper and lower electrodes and not in contact with the upper and lower electrodes.

Owner:HITACHI LTD

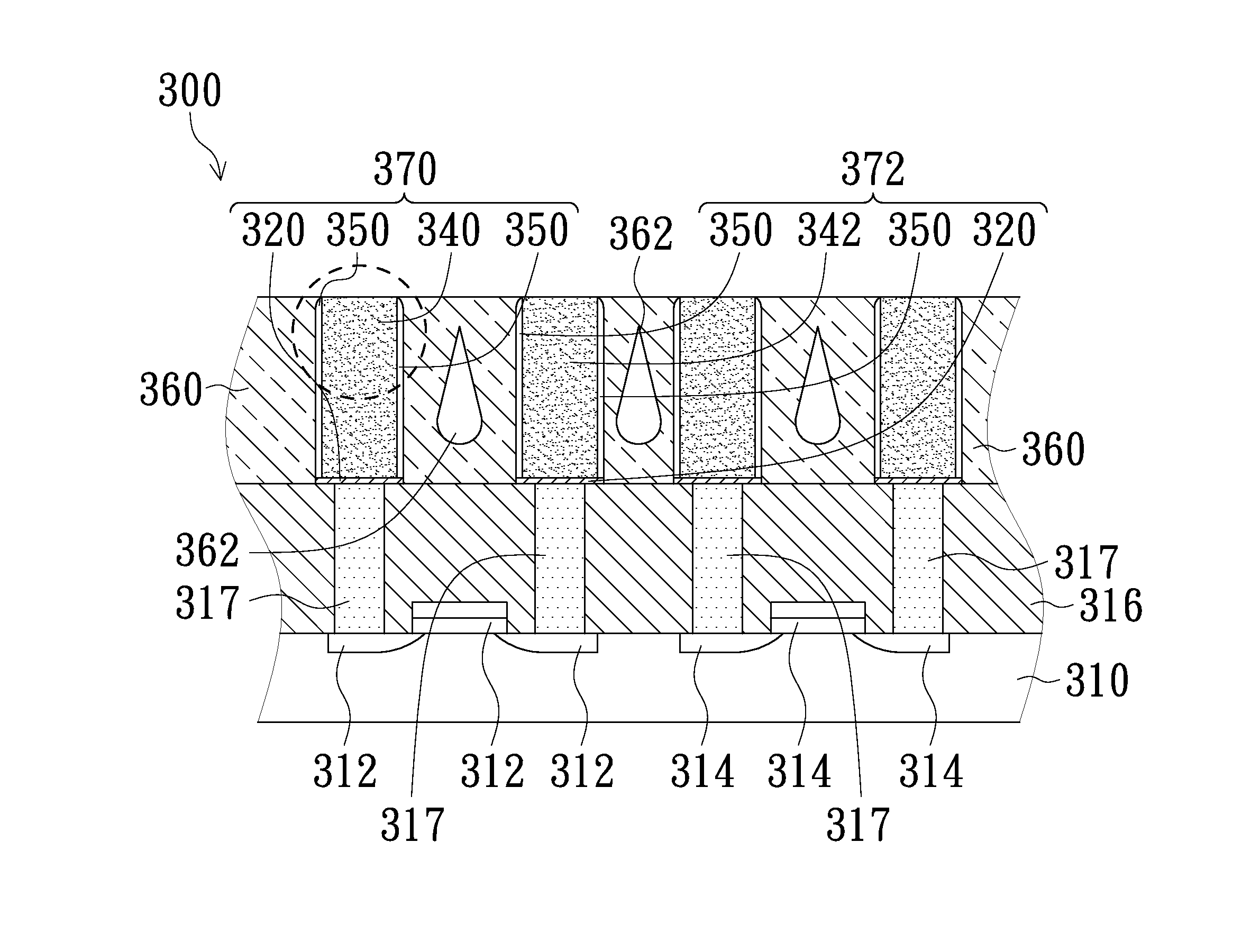

Manufacturing method of semiconductor device and semiconductor device

InactiveUS20070221970A1Increase the number ofIncrease manufacturing costTransistorSemiconductor/solid-state device manufacturingSalicideMetal silicide

In a manufacturing process of a semiconductor device having a CMISFET, first, a silicon film and a first metal film made of a first metal are reacted with each other through heat treatment, thereby forming a gate electrode of a p-channel type MISFET and a dummy gate electrode of an n-channel type MISFET, which are formed of metal silicide. Subsequently, an insulating film is formed so as to cover the gate electrode but expose the dummy electrode, and then, a metal film formed of a second metal having a work function lower than that of the first metal. The metal film contacts with the dummy gate but not with the gate electrode due to the insulating film interposing therebetween. Thereafter, through heat treatment, the dummy gate electrode and the metal film are reacted with each other to form a gate electrode of the n-channel type MISFET.

Owner:RENESAS TECH CORP

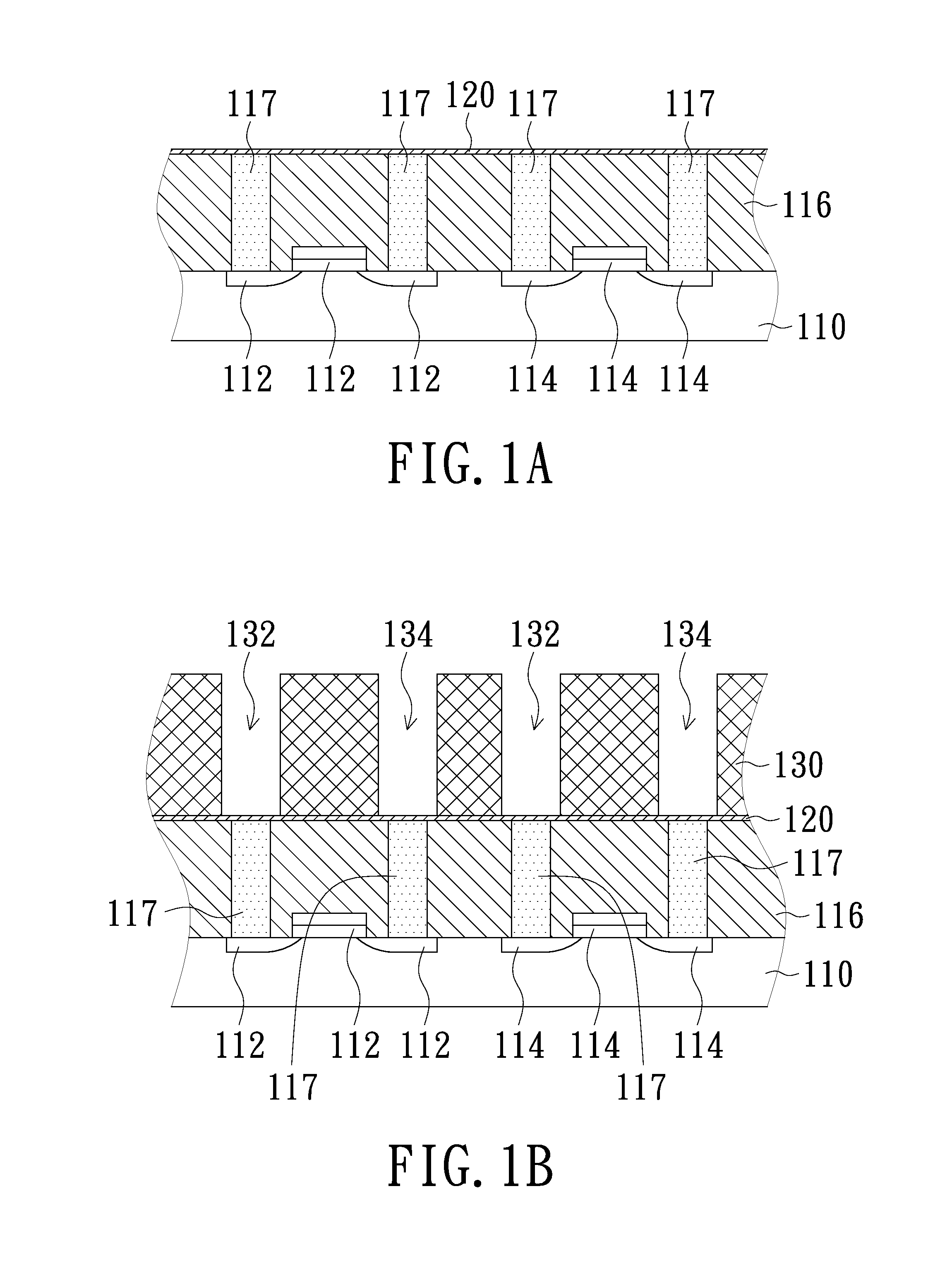

Manufacturing method for metal line

InactiveUS20140073128A1Reduce parasitic capacitanceImprove electrical performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialMetallic materials

A method for manufacturing metal lines in a semiconductor device is provided. The method includes steps of: providing a substrate; forming a first barrier layer on the substrate; forming a sacrificial layer on the first barrier layer; forming an opening penetrating through the sacrificial layer to expose a portion of the first barrier layer; depositing a metal material on the exposed first barrier layer to form a metal line in the opening; removing the sacrificial layer and forming a second barrier layer over the resulting structure; etching the second barrier layer and the first barrier layer while remaining a barrier spacer on a sidewall of the metal line; and forming an insulating layer on the substrate and the barrier spacer. A semiconductor device having the metal lines produced by the method is also provided.

Owner:NAT APPLIED RES LAB

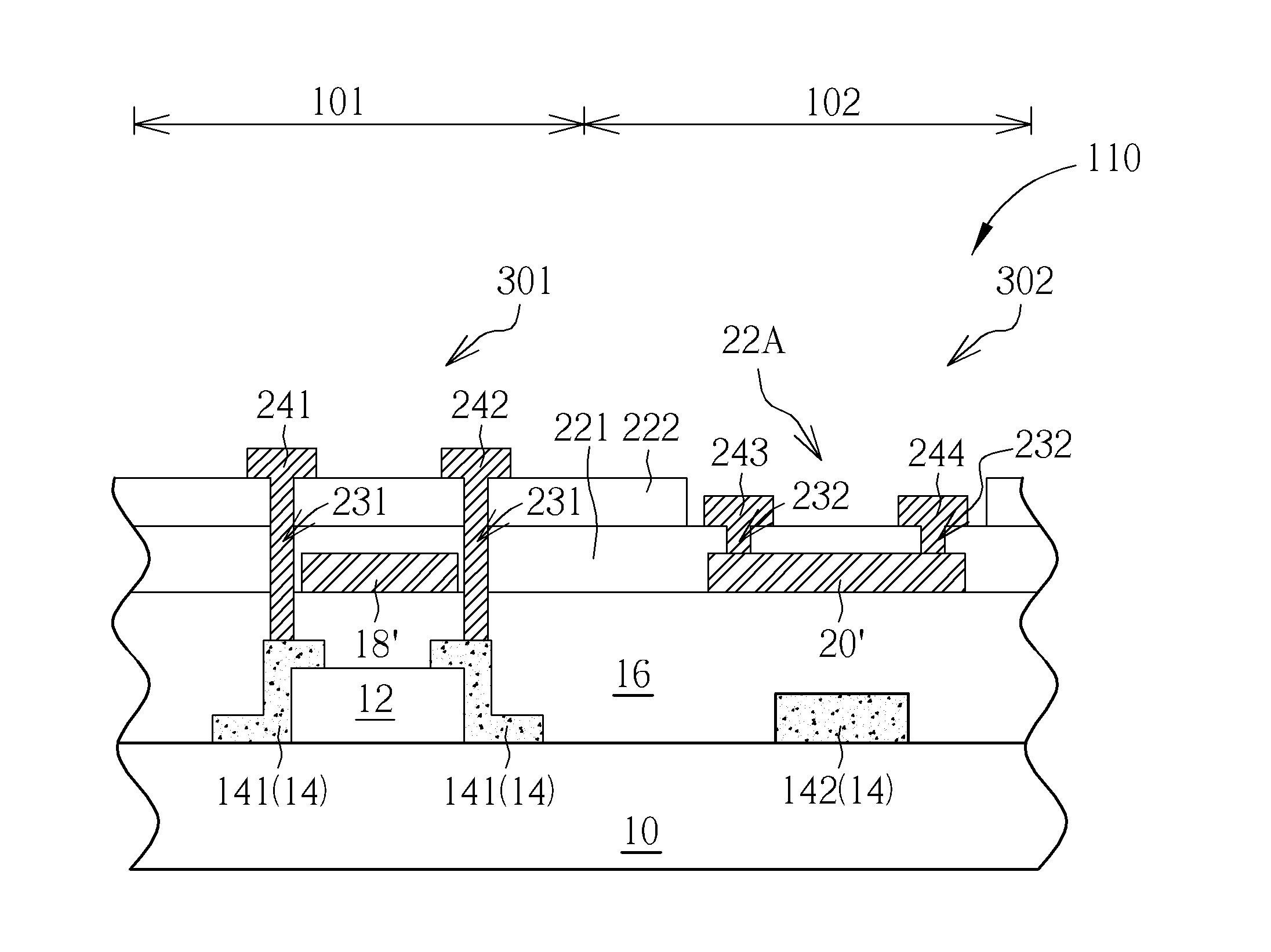

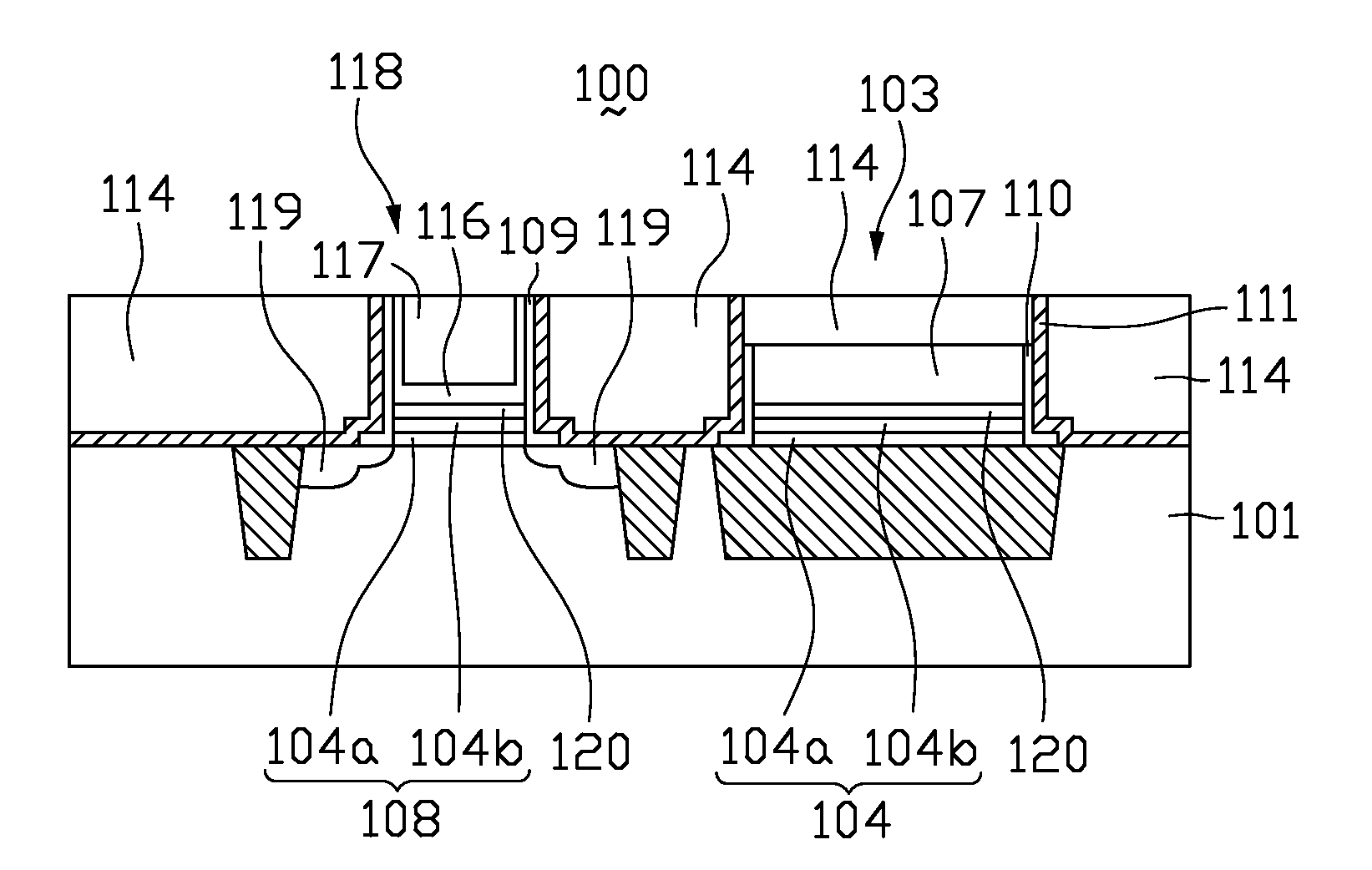

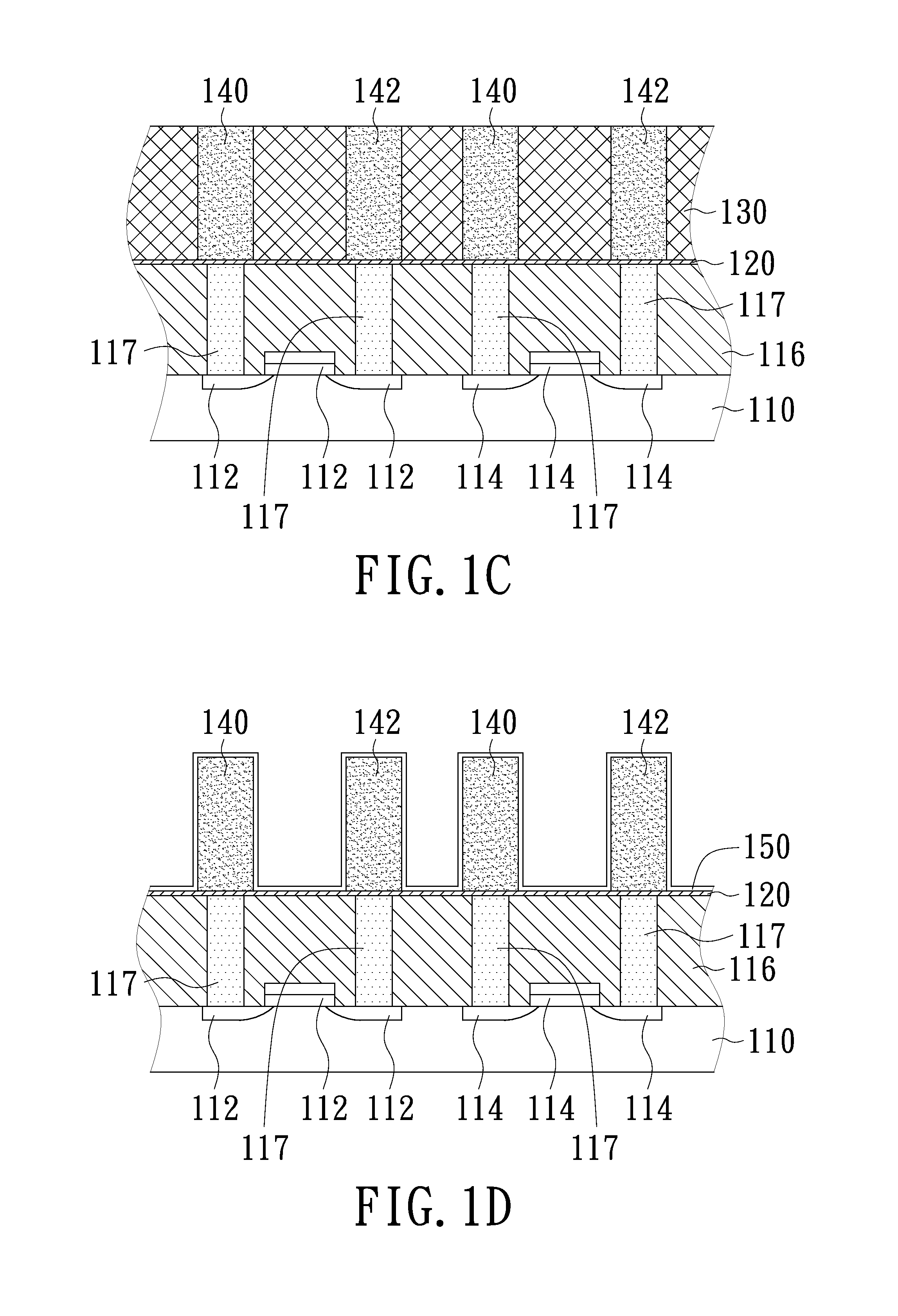

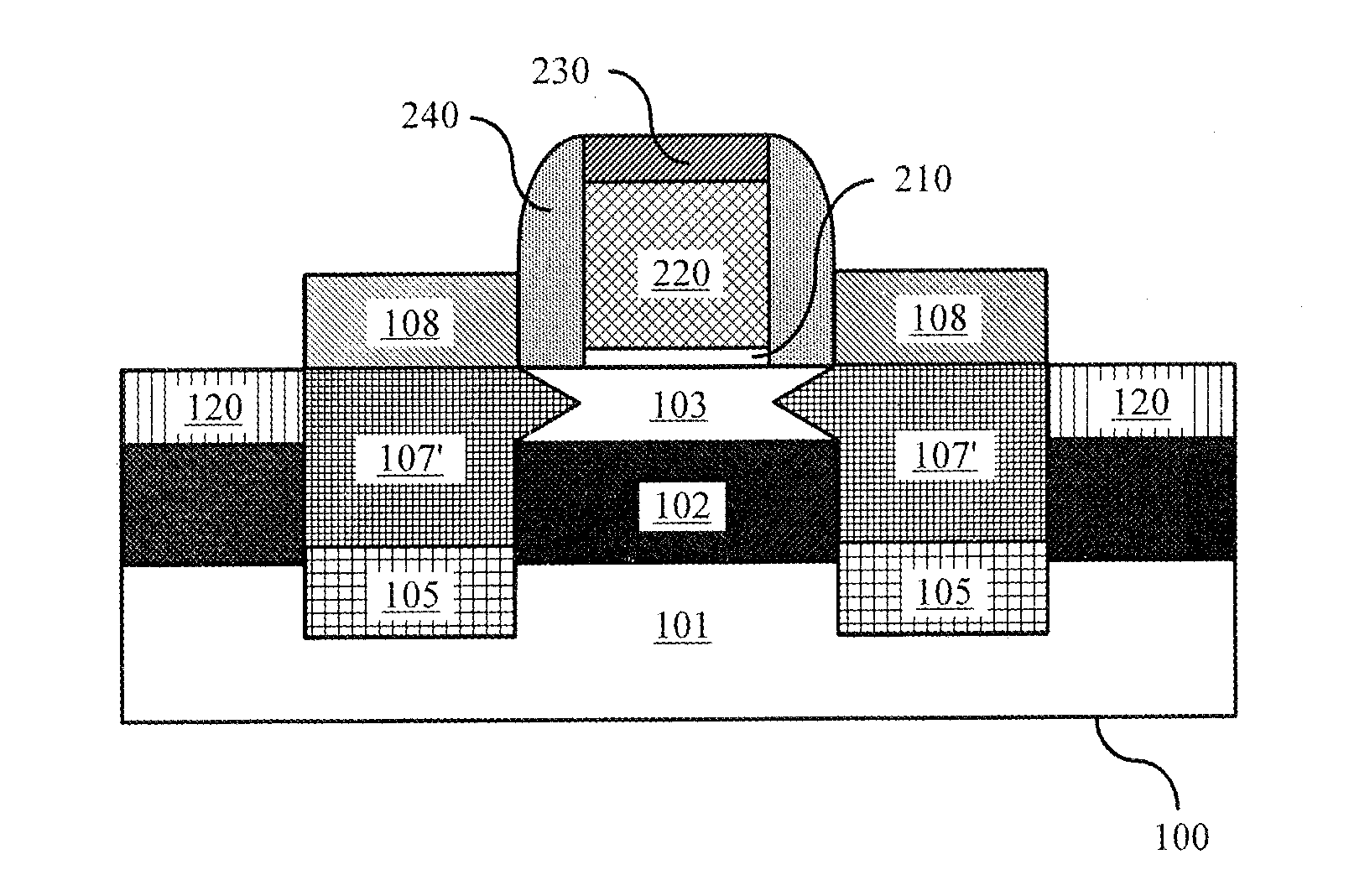

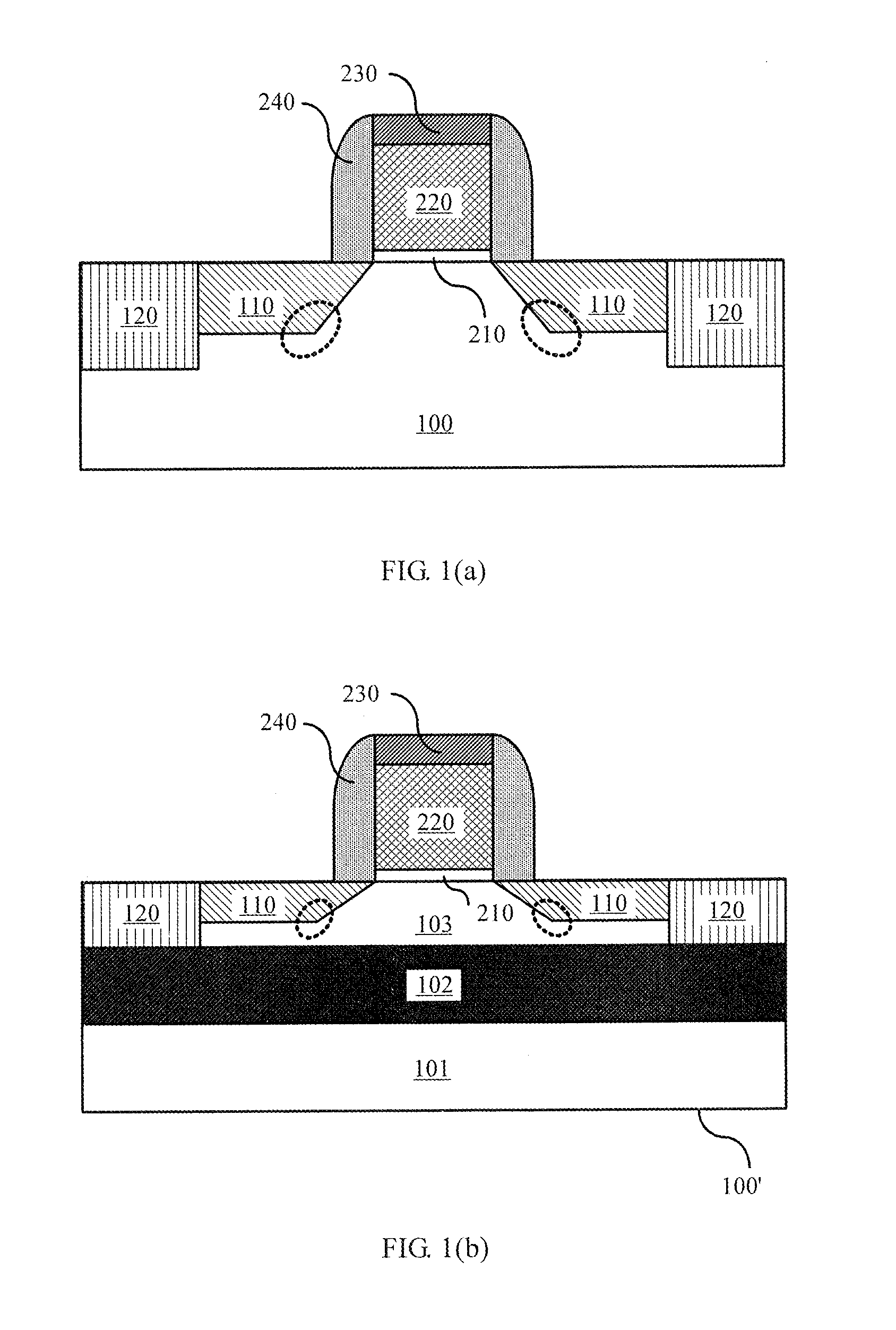

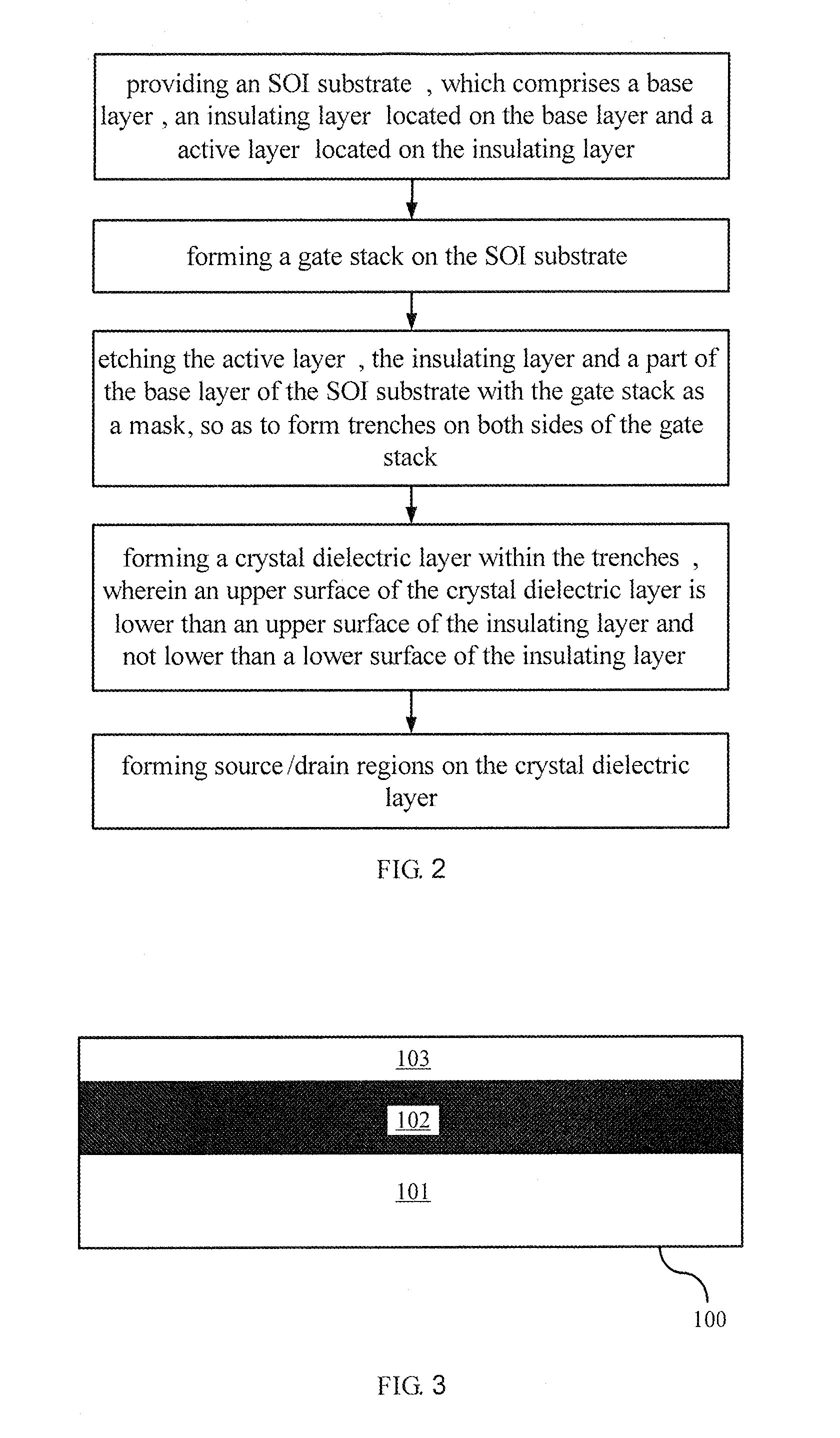

Semiconductor Device And Method For Manufacturing The Same

ActiveUS20150228735A1Reduce contact resistanceElimination pathwaySemiconductor/solid-state device manufacturingSemiconductor devicesGate stackSoi substrate

The present invention provides a method for manufacturing a semiconductor device, which comprises: providing an SOI substrate, which comprises a base layer, an insulating layer located on the base layer and a active layer located on the insulating layer; forming a gate stack on the SOI substrate; etching the active layer, the insulating layer and a part of the base layer of the SOI substrate with the gate stack as a mask, so as to form trenches on both sides of the gate stack; forming a crystal dielectric layer within the trenches, wherein the upper surface of the crystal dielectric layer is lower than the upper surface of the insulating layer and not lower than the lower surface of the insulating layer; and forming source / drain regions on the crystal dielectric layer. The present invention further provides a semiconductor device. The present invention is capable of eliminating pathway for leakage current between source / drain regions and SOI substrate at the meantime of reducing contact resistance at source / drain regions.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI