Semiconductor device and method of manufacturing the same

a semiconductor and field-effect transistor technology, applied in the direction of semiconductor devices, transistors, electrical appliances, etc., to achieve the effect of higher integration and higher performance of a semiconductor devi

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

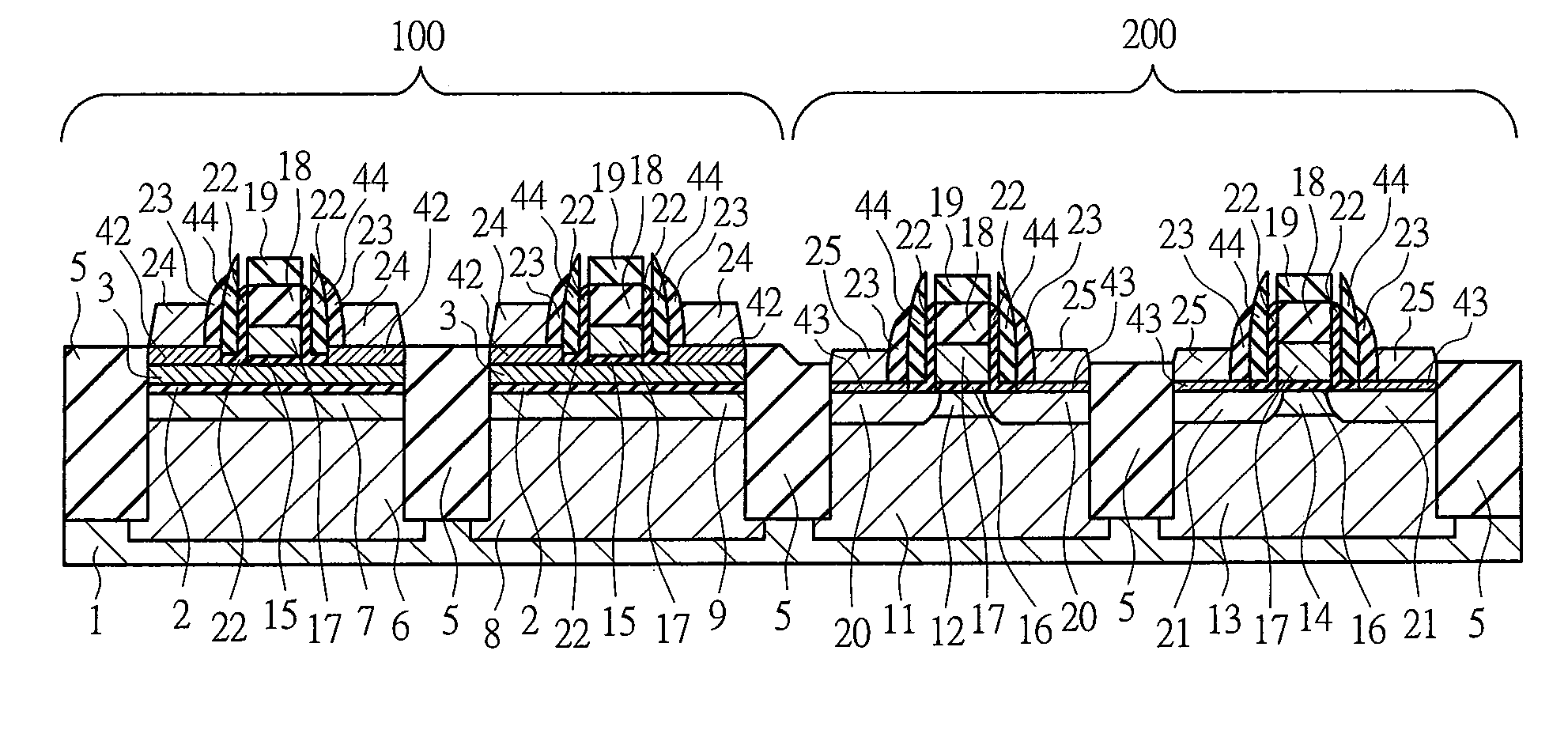

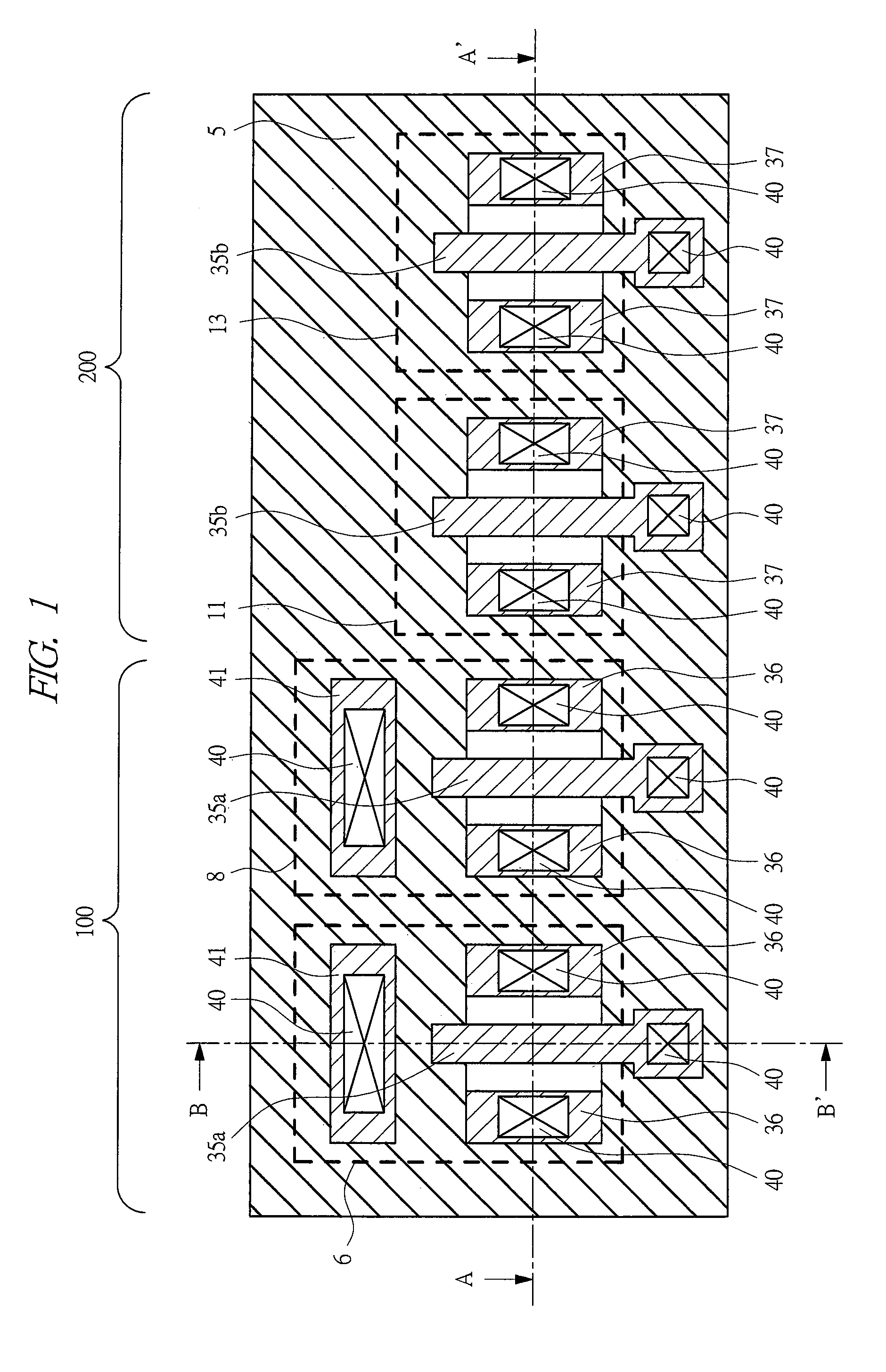

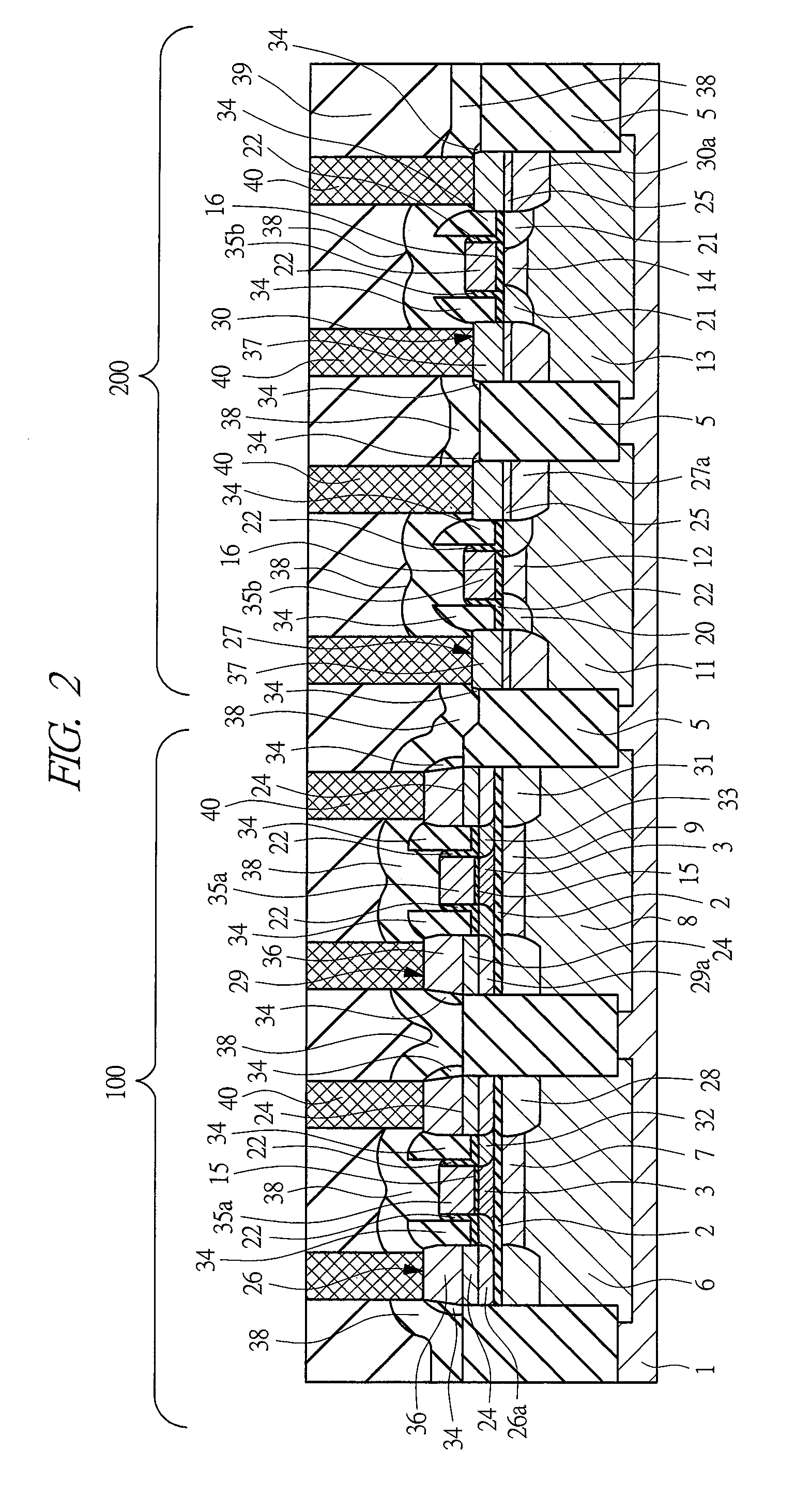

[0059]In FIGS. 1 to 3, a semiconductor device according to an embodiment of the present invention is shown. FIG. 1 is a planar view of main parts, FIG. 2 is a cross-sectional view of main parts taken along the line A-A′ of FIG. 1, and FIG. 3 is a cross-sectional view of main parts taken along the line B-B′ of FIG. 1. In the planar view of FIG. 1, to facilitate visualization, illustrations of part of members such as an insulating film (insulator) are omitted.

[0060]The semiconductor device of the present embodiment includes: an SOI-MISFET having a gate electrode 35a that is fully silicided and an elevated source and drain structure inside an SOI region 100 of a silicon substrate 1; and a bulk-MISFET (high-breakdown voltage MISFET) having a gate electrode 35b that is fully silicided and an elevated source and drain structure inside a bulk region 200 on the silicon substrate 1 that is exposed by removing an SOI layer 3 and a buried insulating layer 2.

[0061]In this manner, the semiconduc...

second embodiment

[0117]A plan view of main parts of a semiconductor device according to a second embodiment of the present invention is, for example, FIG. 1, and a cross-sectional view of main parts of a semiconductor substrate taken along the line A-A′ of FIG. 1 at this time is FIG. 24.

[0118]While the elevated layers of the SOI-MISFET and the bulk-MISFET have been formed by the single selective epitaxial growth process in the first embodiment, in the second embodiment, the selective epitaxial growth process is performed twice, thereby forming first and second elevated layers for the SOI-MISFET and the bulk-MISFET, respectively. This point is different from the first embodiment.

[0119]In the SOI-MISFET according to the second embodiment, a first elevated layer (lowermost layer) 42 is formed directly below the sidewalls 34 at both sides of the gate. Hence, the diffusion layers 26 and 29 are provided such that the two layers have a distance from the gate electrode 35a, the uppermost elevated layers 24 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More