Patents

Literature

199results about How to "Good semiconductor performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

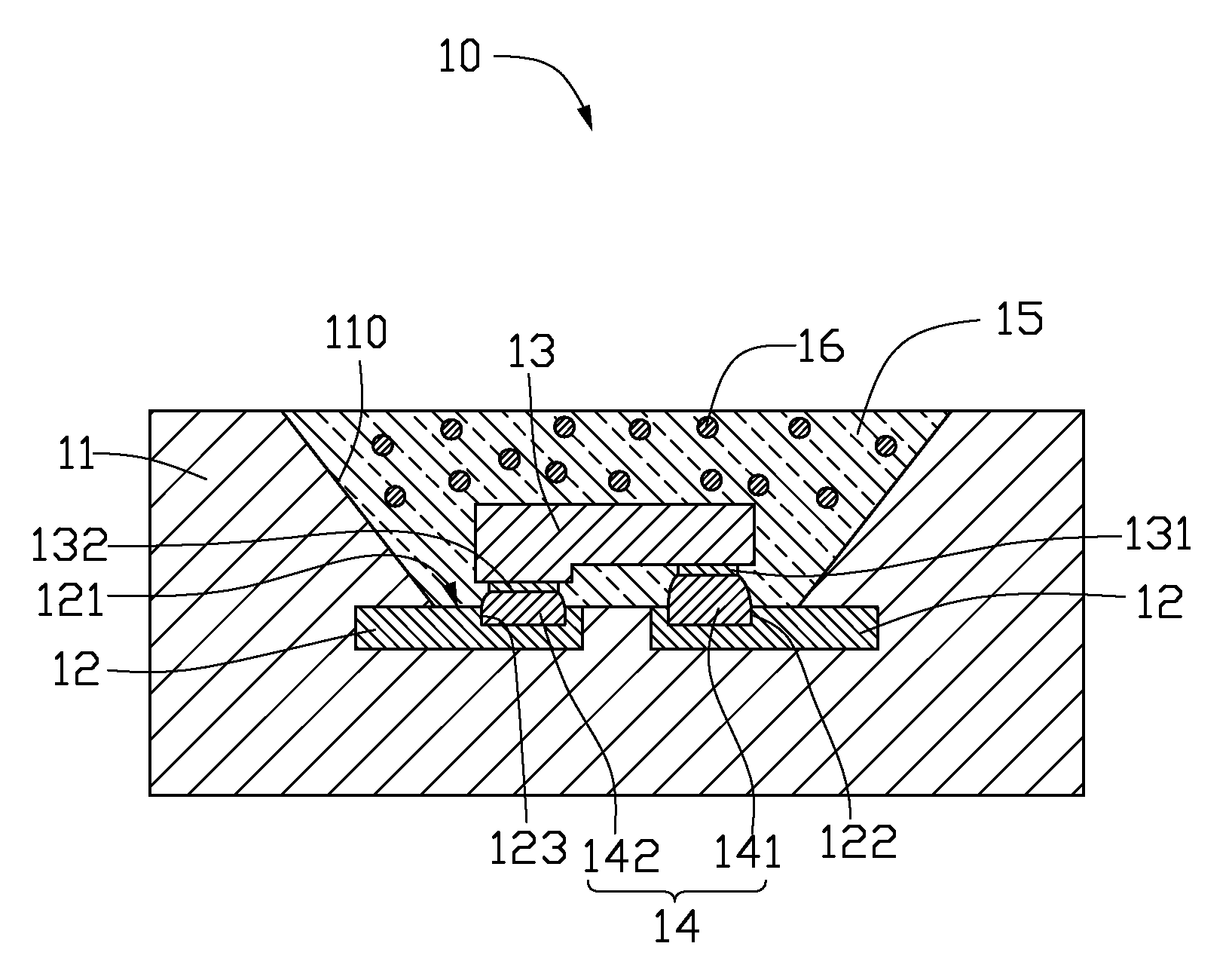

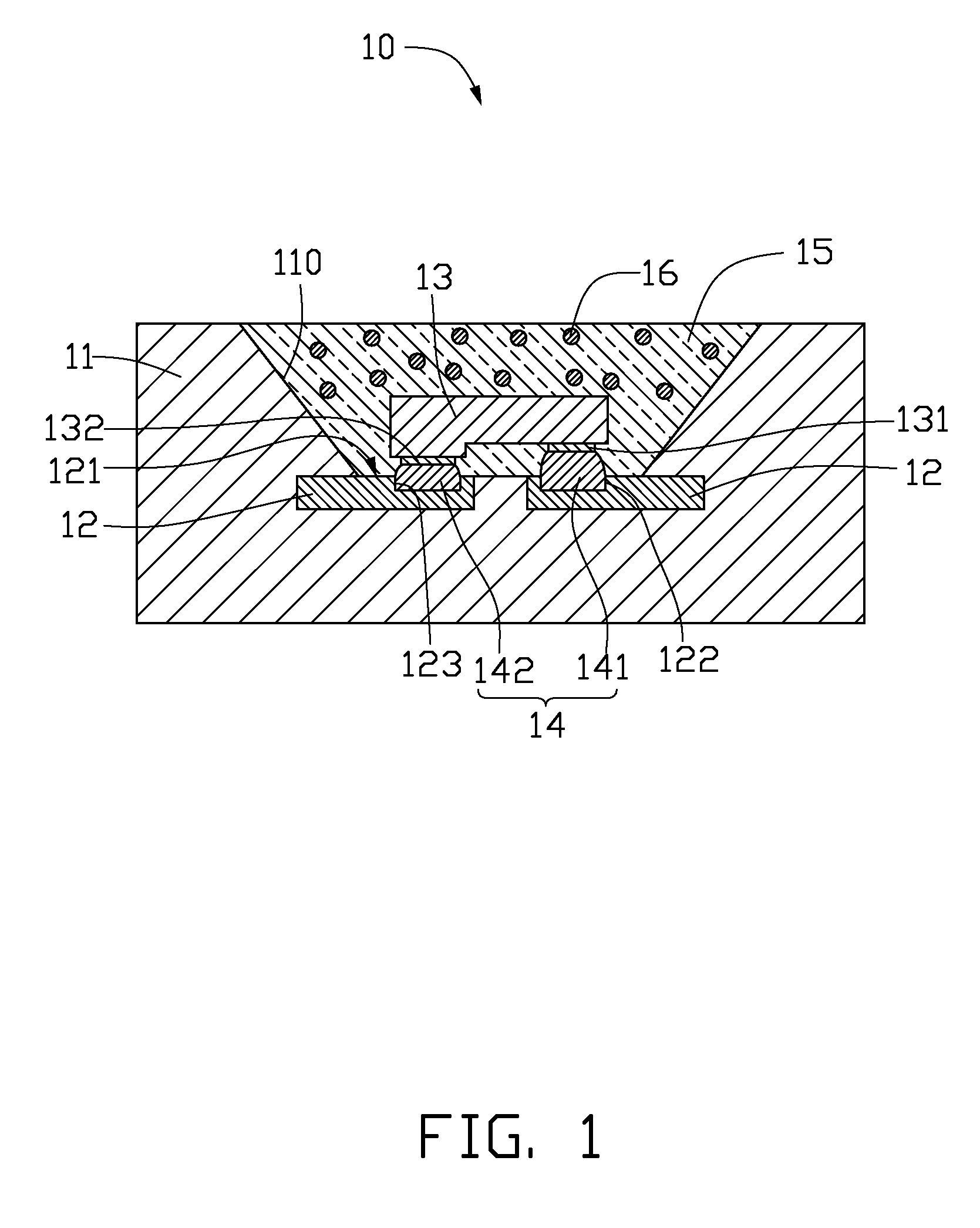

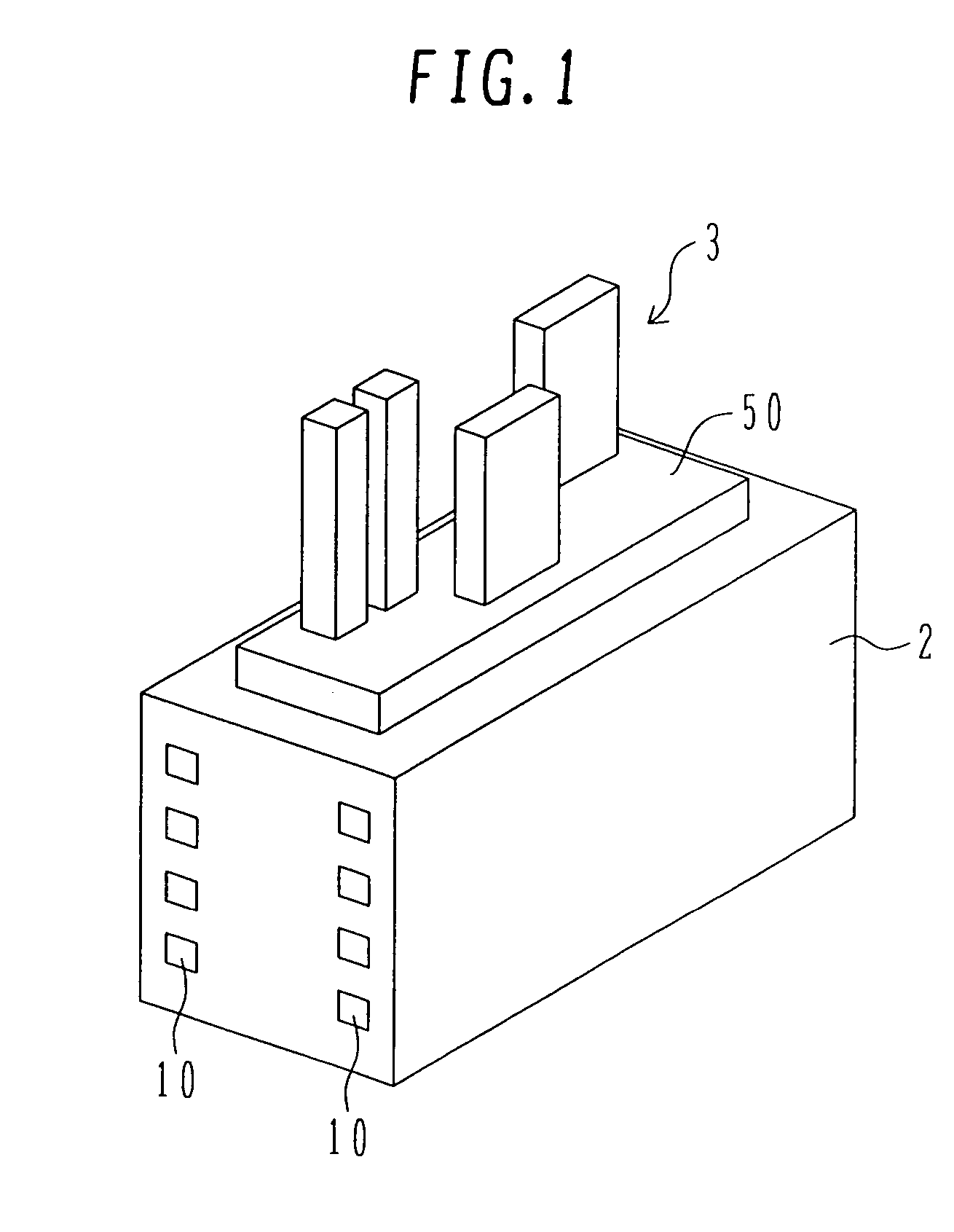

Flip-chip light emitting diode and method for fabricating the same

InactiveUS20090321778A1Small sizeLower impedanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringFlip chip

A flip-chip light emitting diode includes a substrate, an LED chip and a plurality of conductive bumps. The substrate has at least one recess defined in the surface of the substrate, and at least a part of the conductive bumps is embedded the at least one recess. The LED chip is mounted on a surface of the substrate by a flip-chip mounting process. The conductive bumps are sandwiched between the substrate and the LED chip to bond and electrically connect the LED chip to the substrate.

Owner:ADVANCED OPTOELECTRONICS TECH

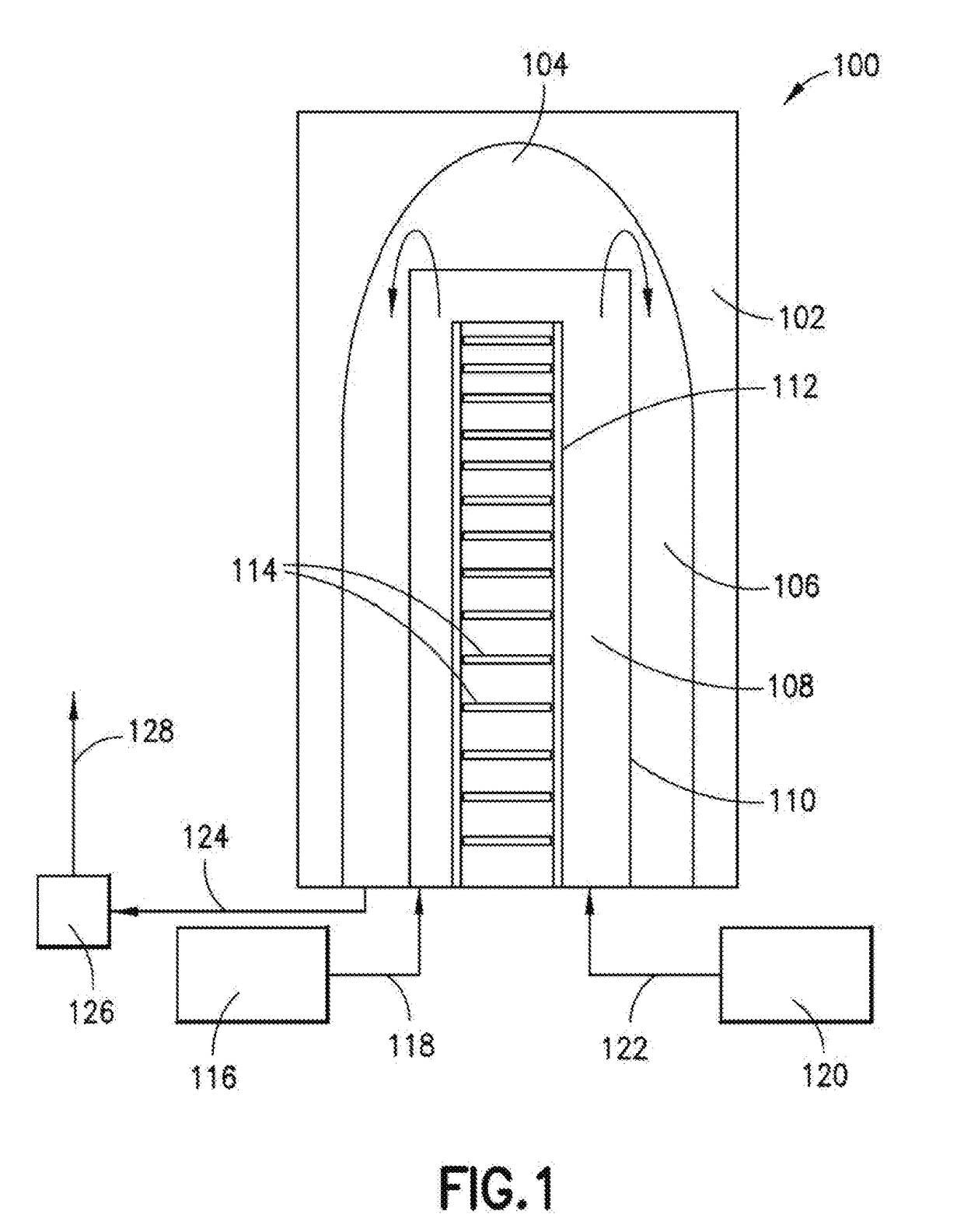

Coatings for enhancement of properties and performance of substrate articles and apparatus

PendingUS20180044800A1Avoid reactionGood semiconductor performanceSemi-permeable membranesVacuum evaporation coatingCoated surfaceReactive gas

Coatings applicable to a variety of substrate articles, structures, materials, and equipment are described. In various applications, the substrate includes metal surface susceptible to formation of oxide, nitride, fluoride, or chloride of such metal thereon, wherein the metal surface is configured to be contacted in use with gas, solid, or liquid that is reactive therewith to form a reaction product that is deleterious to the substrate article, structure, material, or equipment. The metal surface is coated with a protective coating preventing reaction of the coated surface with the reactive gas, and / or otherwise improving the electrical, chemical, thermal, or structural properties of the substrate article or equipment. Various methods of coating the metal surface are described, and for selecting the coating material that is utilized.

Owner:ENTEGRIS INC

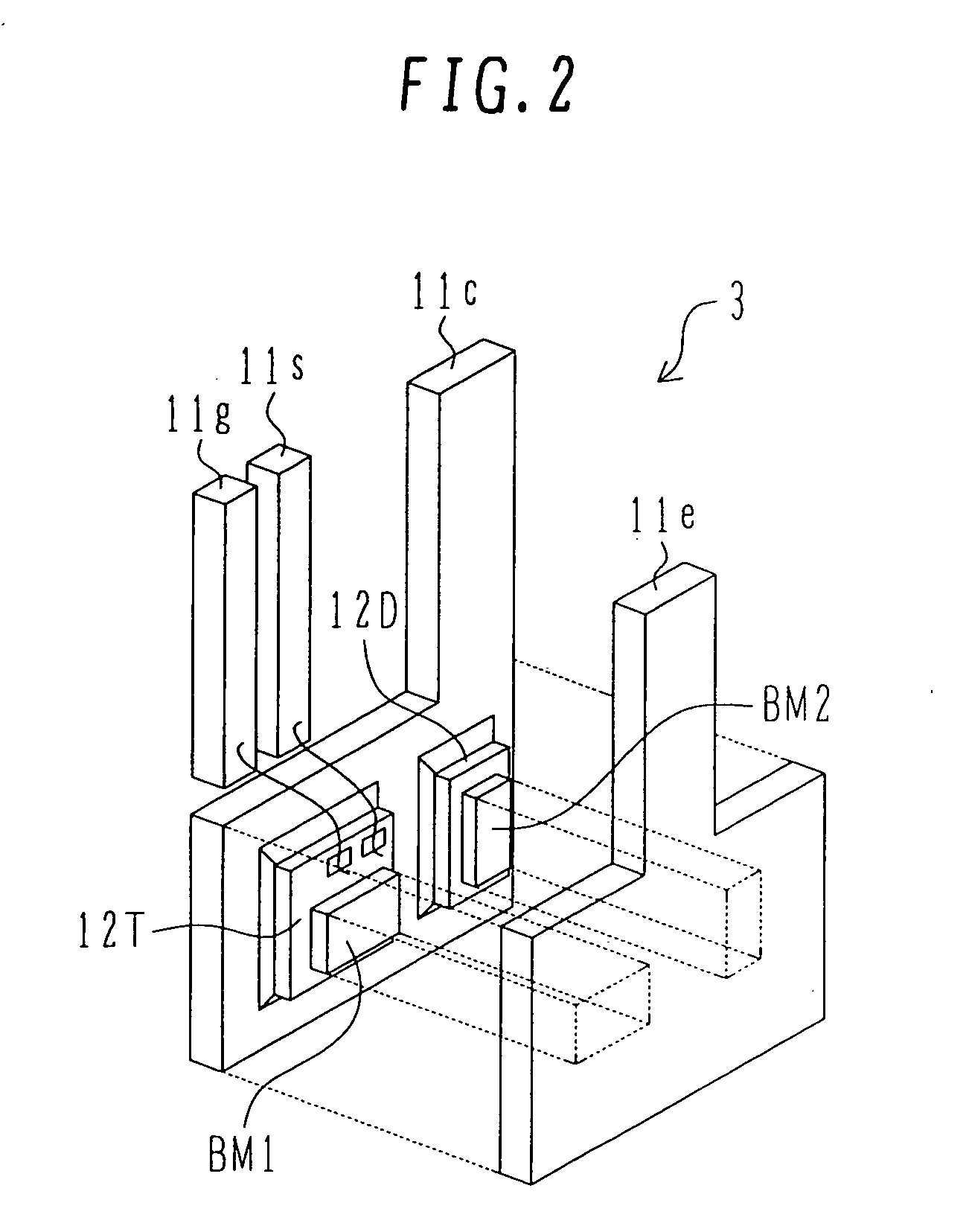

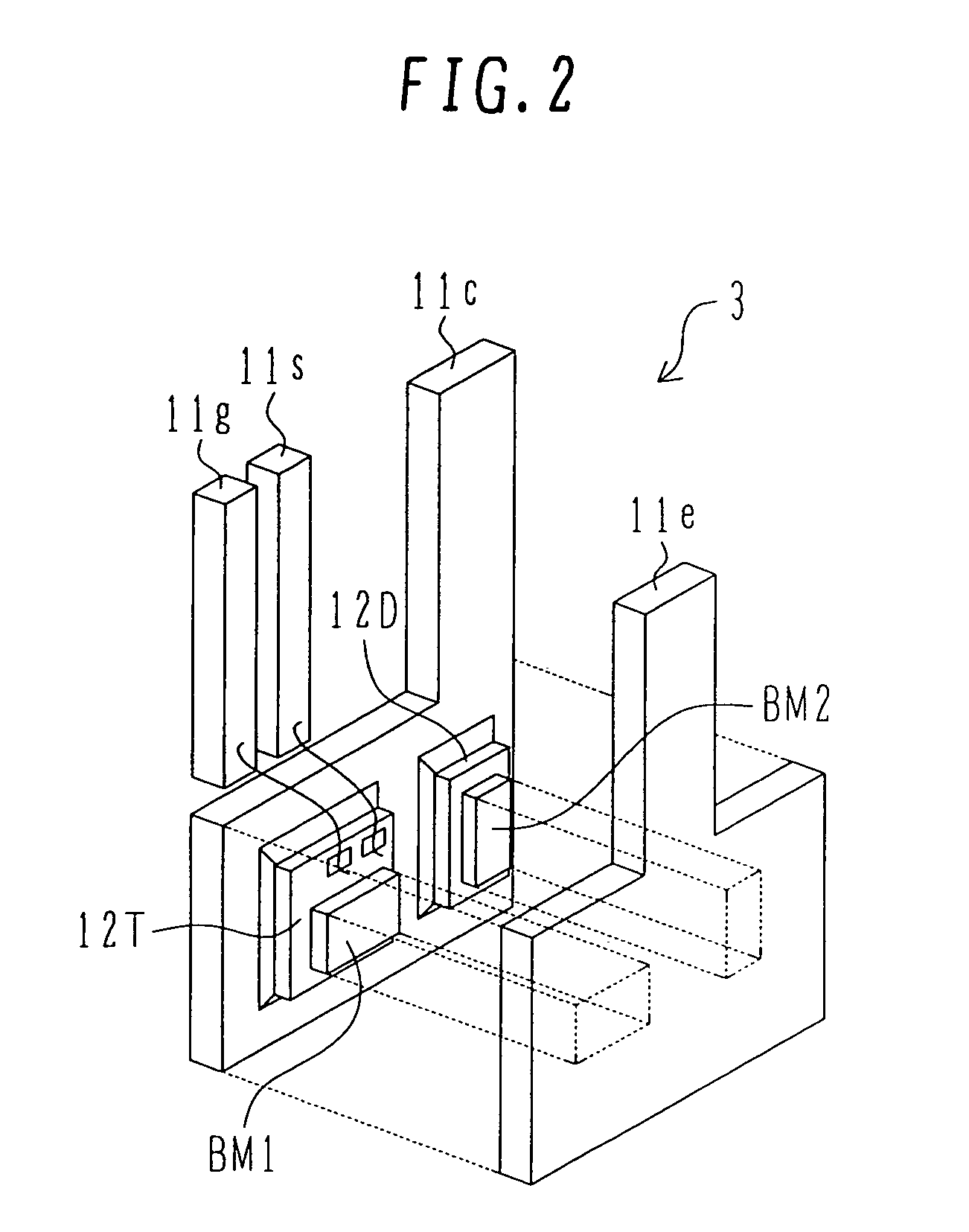

Semiconductor unit, and power conversion system and on-vehicle electrical system using the same

InactiveUS20070096278A1Improve insulation performanceReduce thermal resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectric power

A semiconductor device includes a semiconductor chip and leads electrically connected to the electrodes of the semiconductor chip. A hollow radiator base houses the semiconductor device which is molded with high-thermal-conductivity resin having an electrical insulating property. The radiator base has a cooling-medium channel therein or radiating fins on the outside. Alternatively, the radiator base is housed in a second radiator base.

Owner:HITACHI LTD

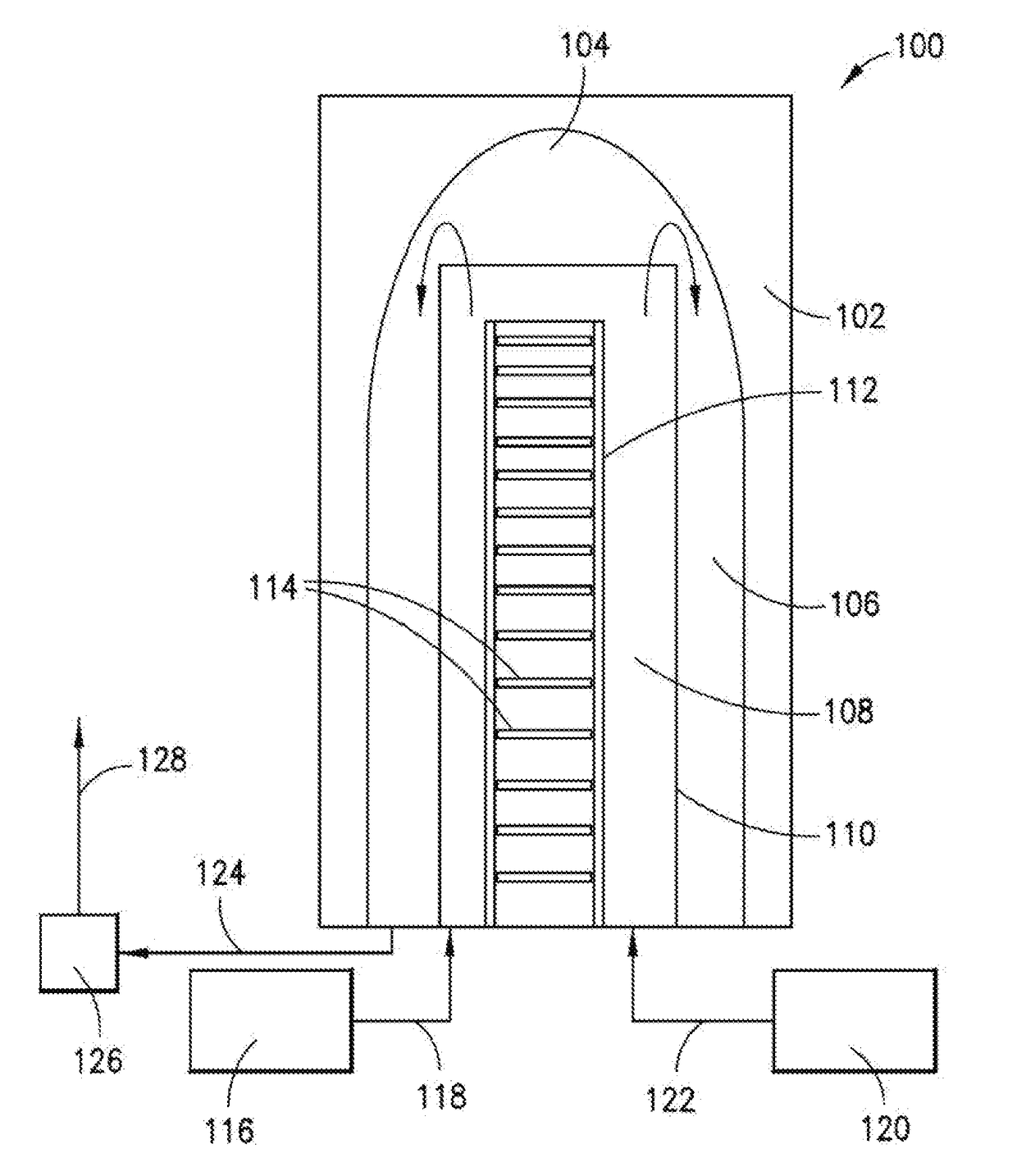

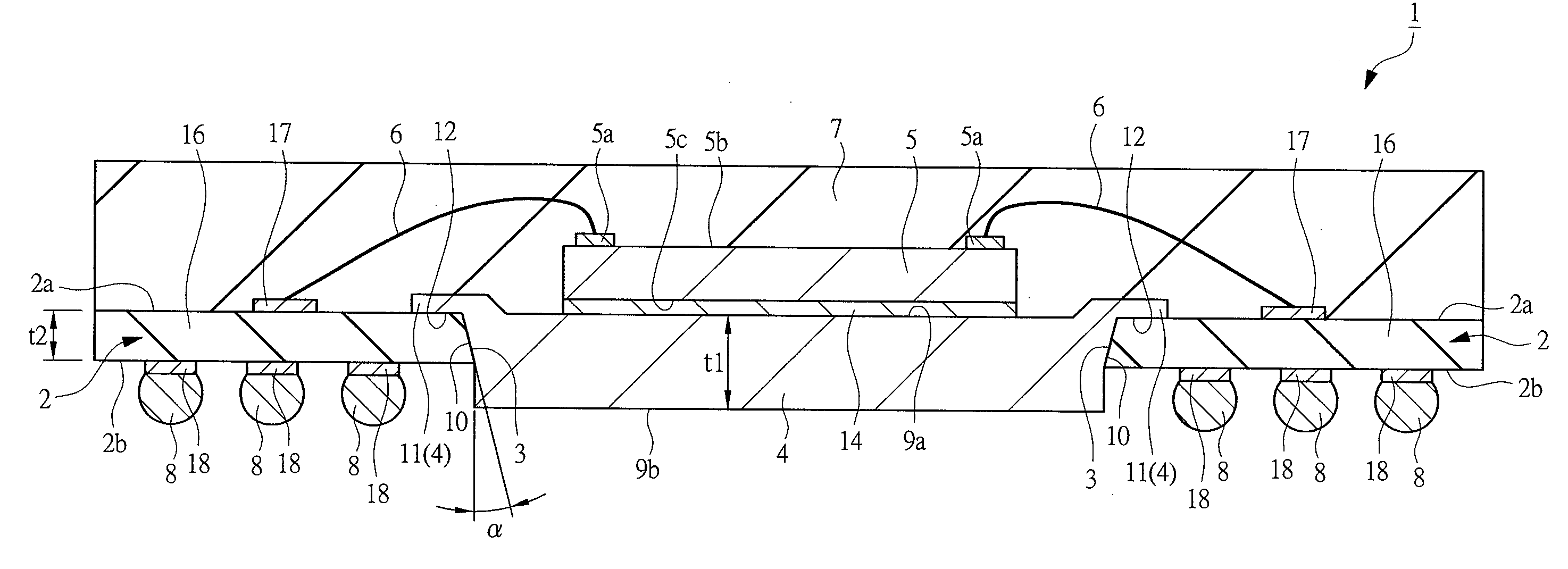

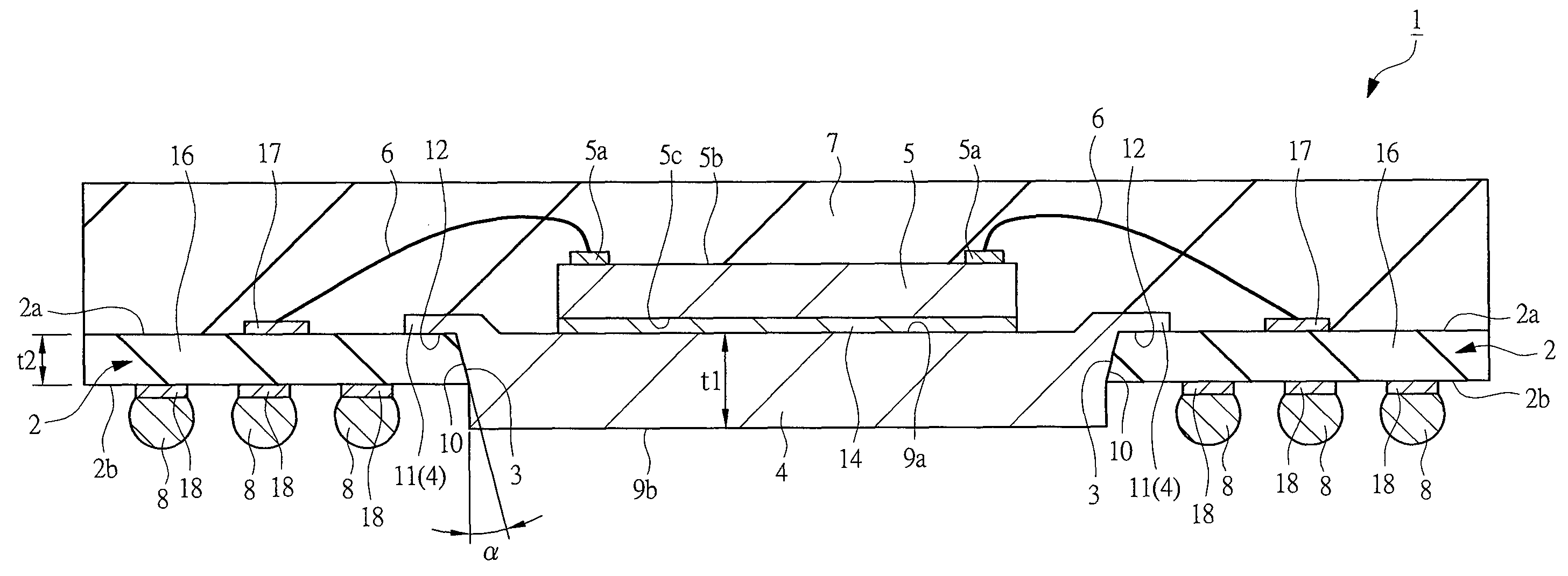

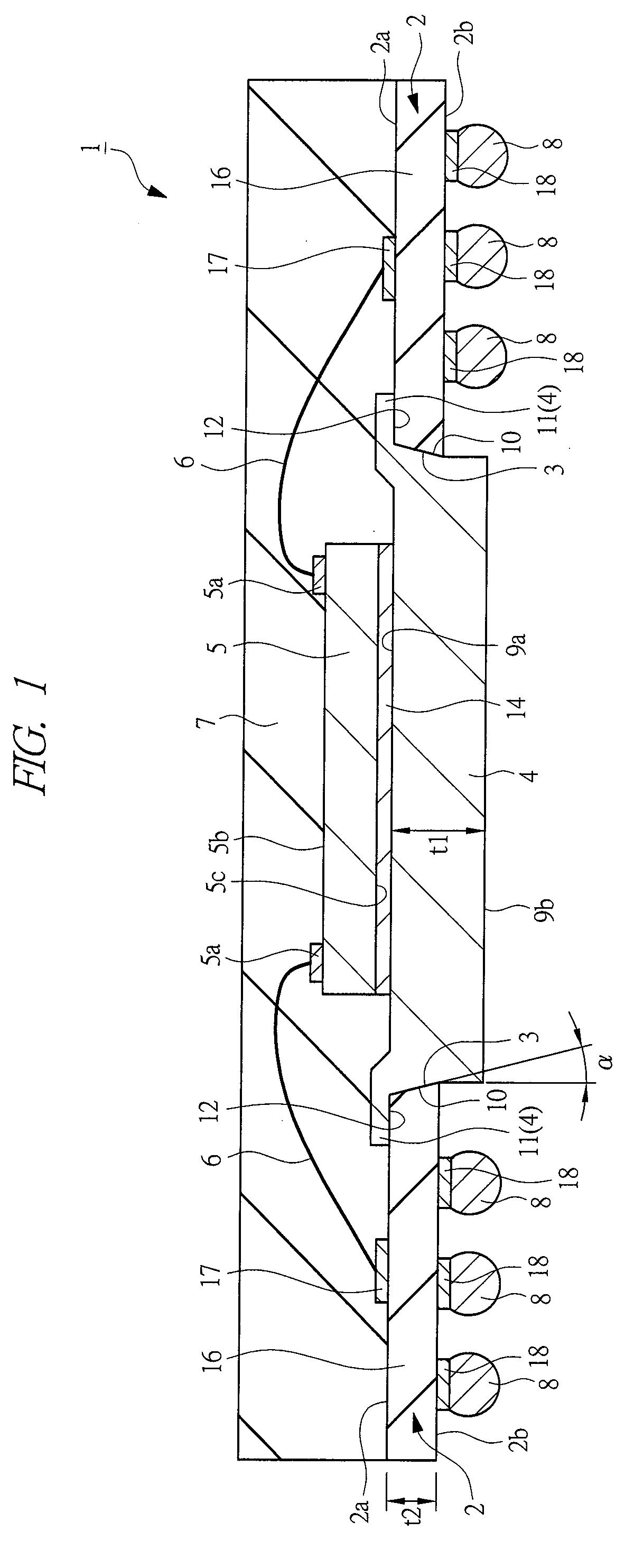

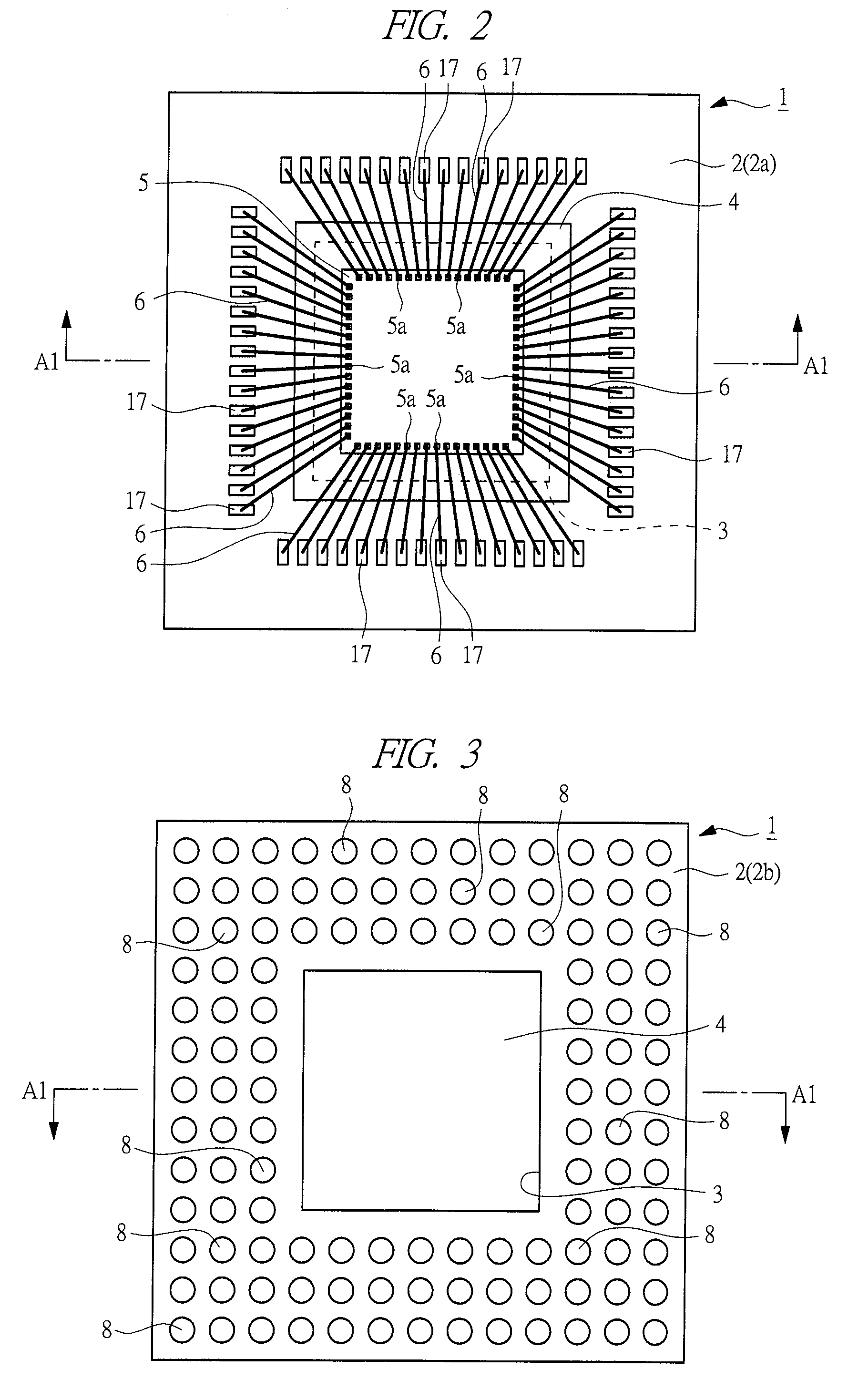

Semiconductor device and manufacturing method of the same

ActiveUS20090309213A1Improve cooling effectImprove manufacturing yieldSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSolder ball

A semiconductor chip is mounted on a heat sink disposed inside a through-hole of a wiring board, electrodes of the semiconductor chip and connecting terminals of the wiring board are connected by bonding wires, a sealing resin is formed to cover the semiconductor chip and the bonding wires, and solder balls are formed on the lower surface of the wiring board, thereby constituting the semiconductor device. The heat sink is thicker than the wiring board. The heat sink has a protruded portion protruding to outside from the side surface of the heat sink, the protruded portion is located on the upper surface of the wiring board outside the through-hole, and the lower surface of the protruded portion contacts to the upper surface of the wiring board. When the semiconductor device is manufactured, the heat sink is inserted from the upper surface side of the wiring board.

Owner:RENESAS ELECTRONICS CORP

Coating composition

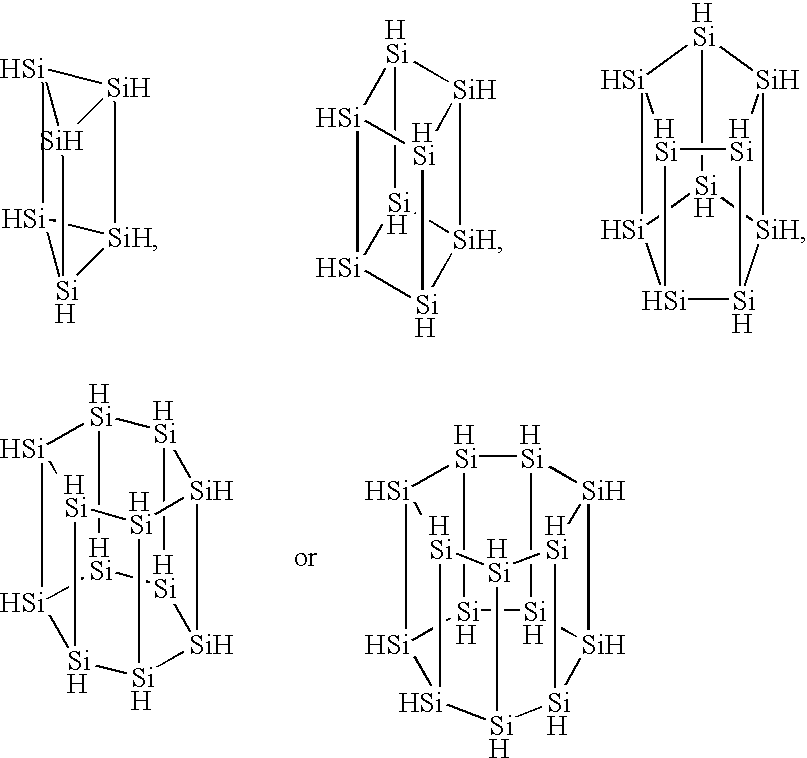

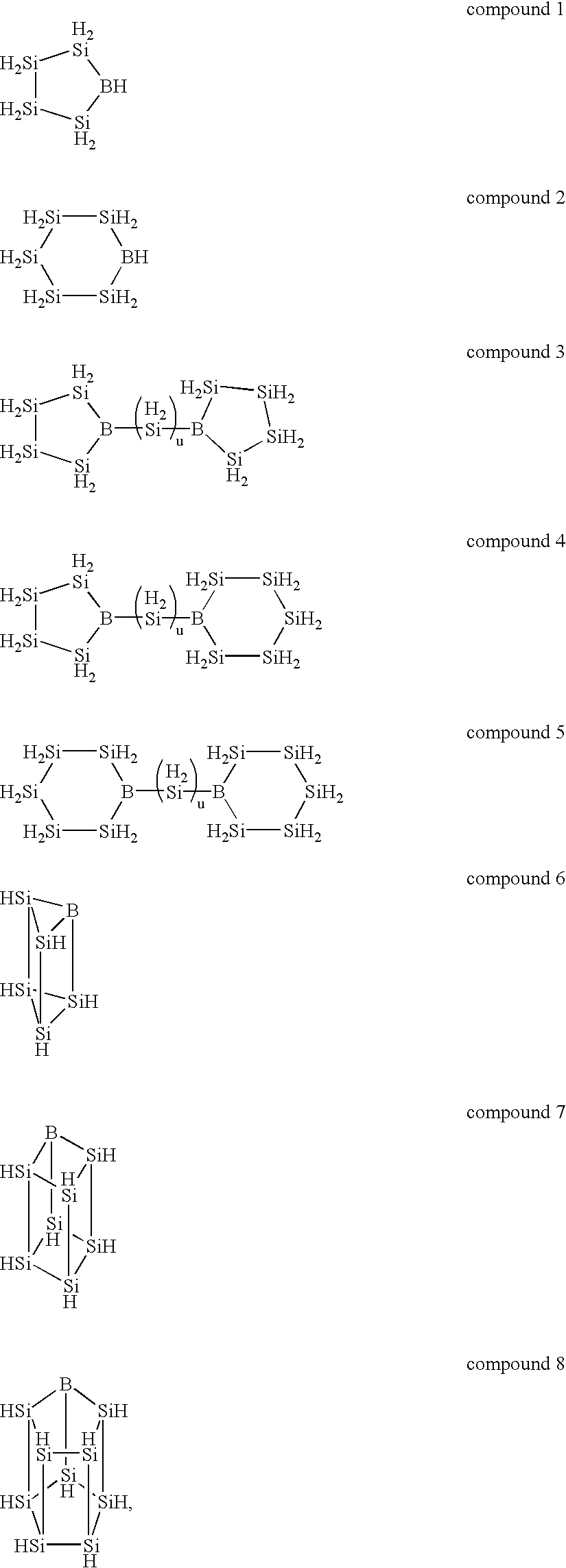

InactiveUS6527847B1Good semiconductor performanceLow costSilicon halogen compoundsSilicon hydridesSolventBoron atom

A coating composition comprising a silicon compound represented by the following formula (1):wherein X1 is a hydrogen atom or a halogen atom, and n is an integer of 4 or more, on the proviso that n occurrences of X1 may be the same as or different from one another, or a modified silane compound represented by the following formula (2):wherein X2 is a hydrogen atom or a halogen atom, Y is a boron atom or a phosphorus atom, n is an integer of 3 or more, l is an integer of 1 or more, and m is an integer of n to 2n+3, on the proviso that m occurrences of X2 may be the same as or different from one another, and solvent thereof. This coating composition is suitably used in the production of a device for forming a silicon film or a boron- or phosphorous-doped silicon film on a substrate having a large area.

Owner:JSR CORPORATIOON

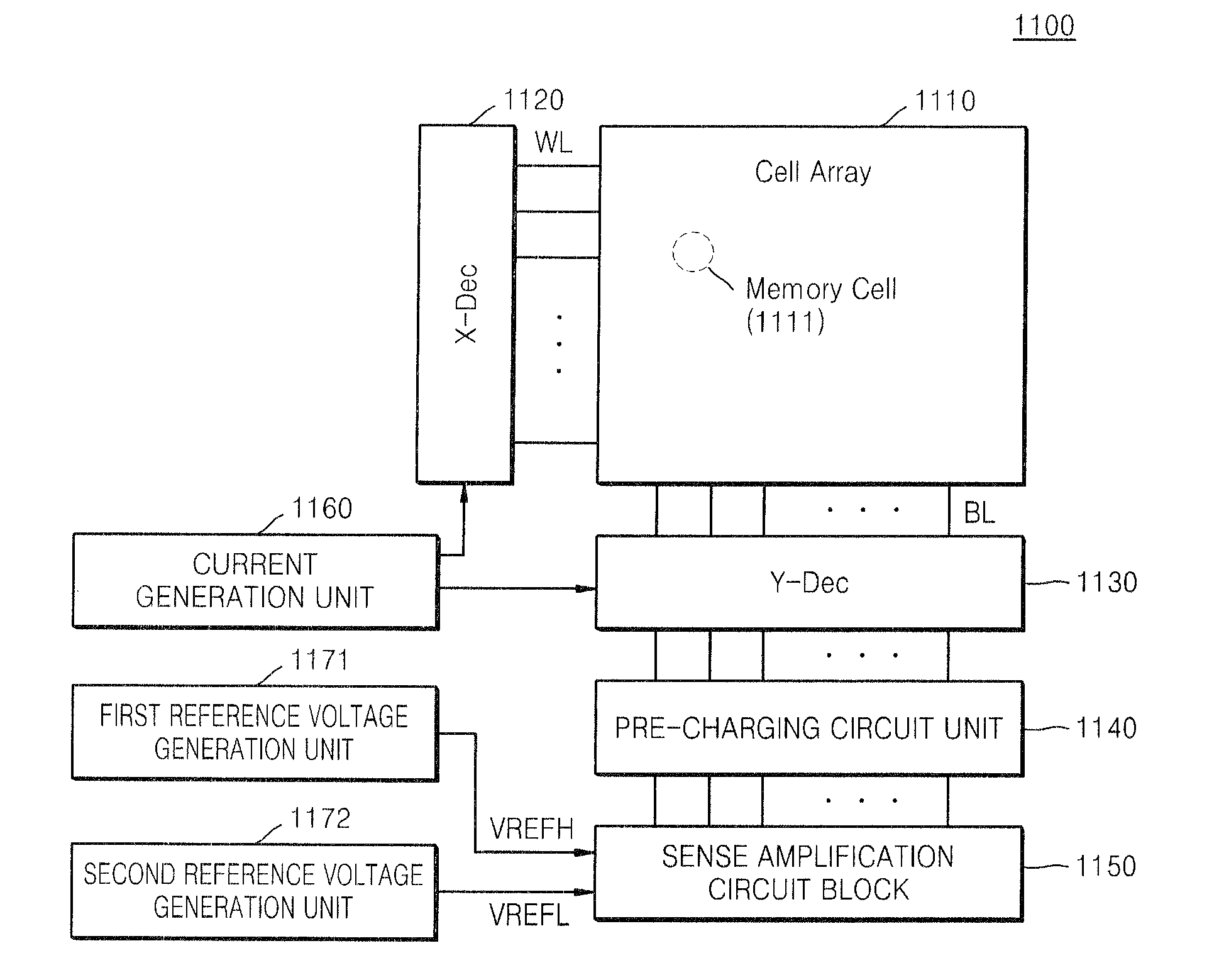

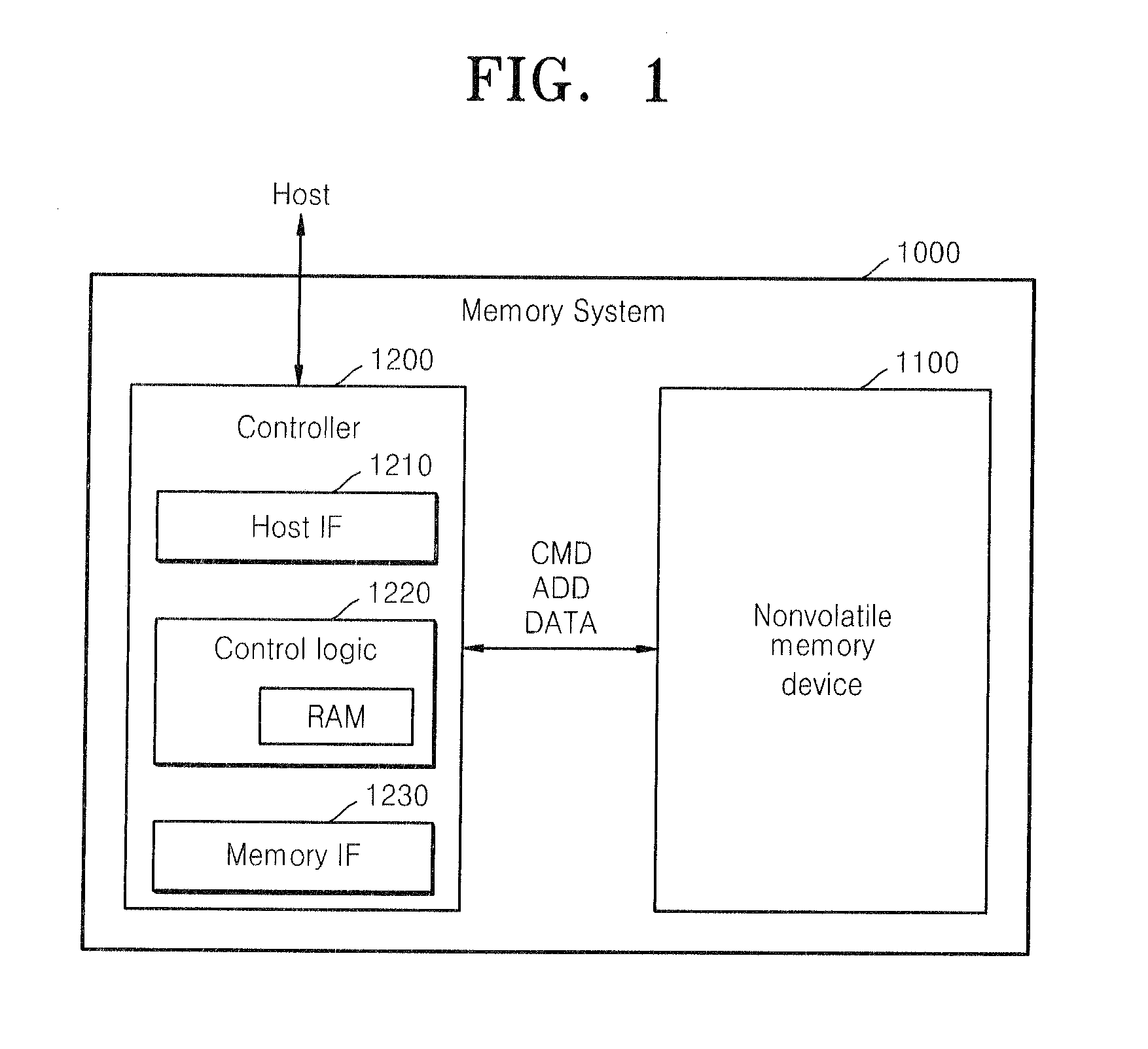

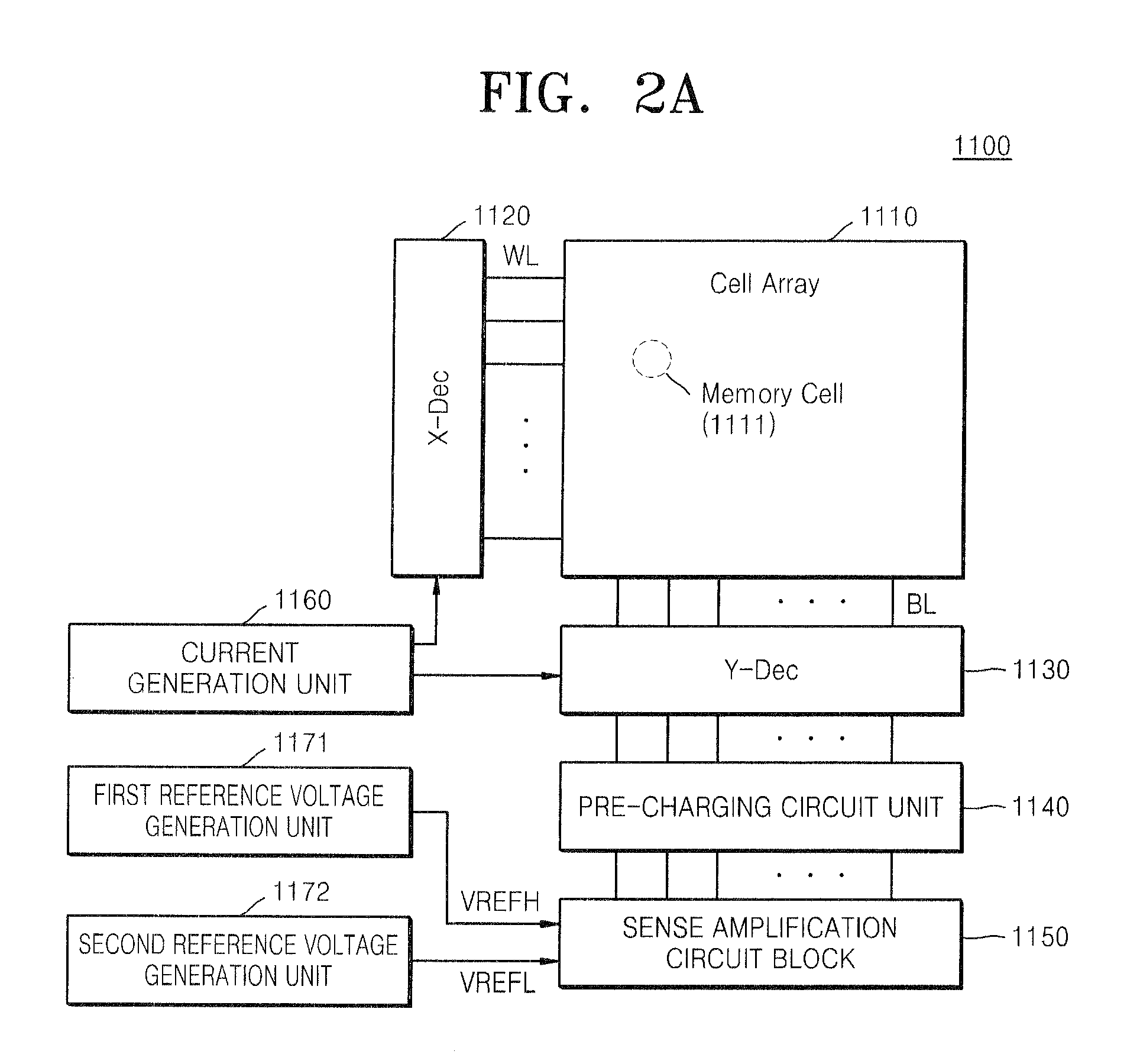

Data read circuit, a non-volatile memory device having the same, and a method of reading data from the non-volatile memory device

ActiveUS20130051114A1Improve performanceGood semiconductor performanceDigital storageVoltage referenceHemt circuits

A non-volatile memory device including a cell array, which includes a plurality of memory cells, and a sense amplification circuit. The sense amplification circuit is configured to receive a data voltage of a memory cell, a first reference voltage and a second reference voltage during a data read operation of the memory cell, generate differential output signals based on a voltage level difference between the data voltage and the first and second reference voltages, and output the differential output signals as data read from the memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

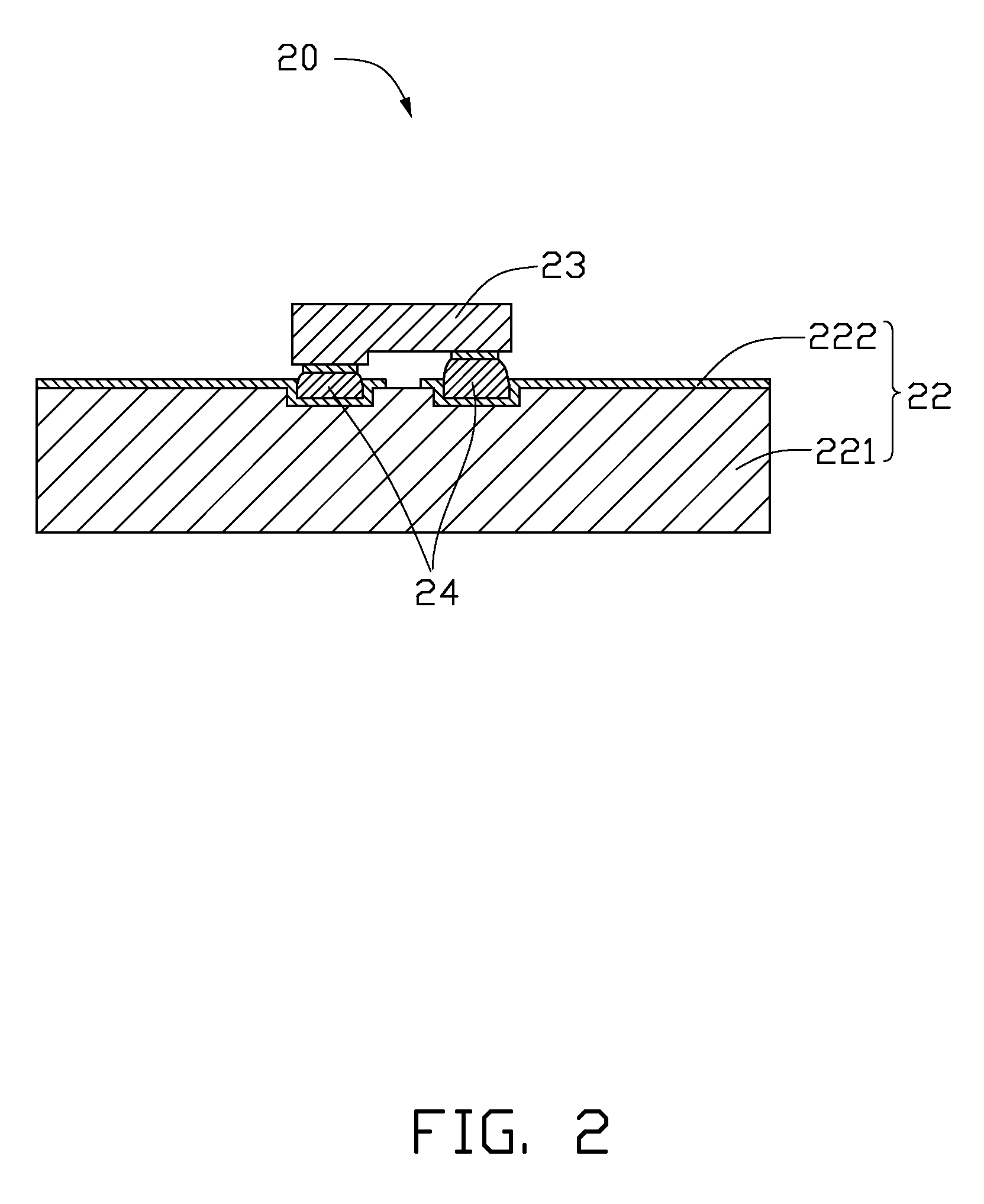

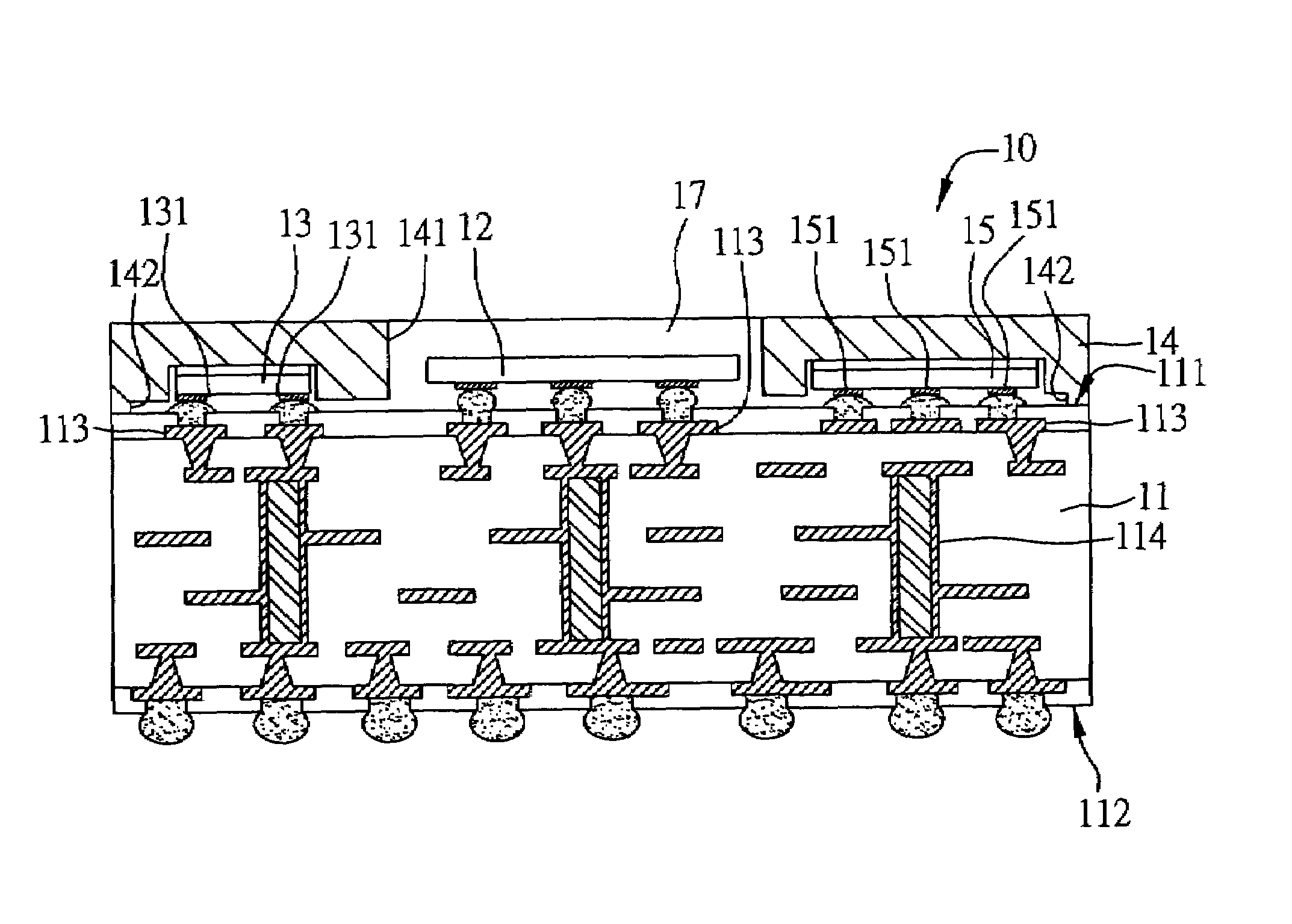

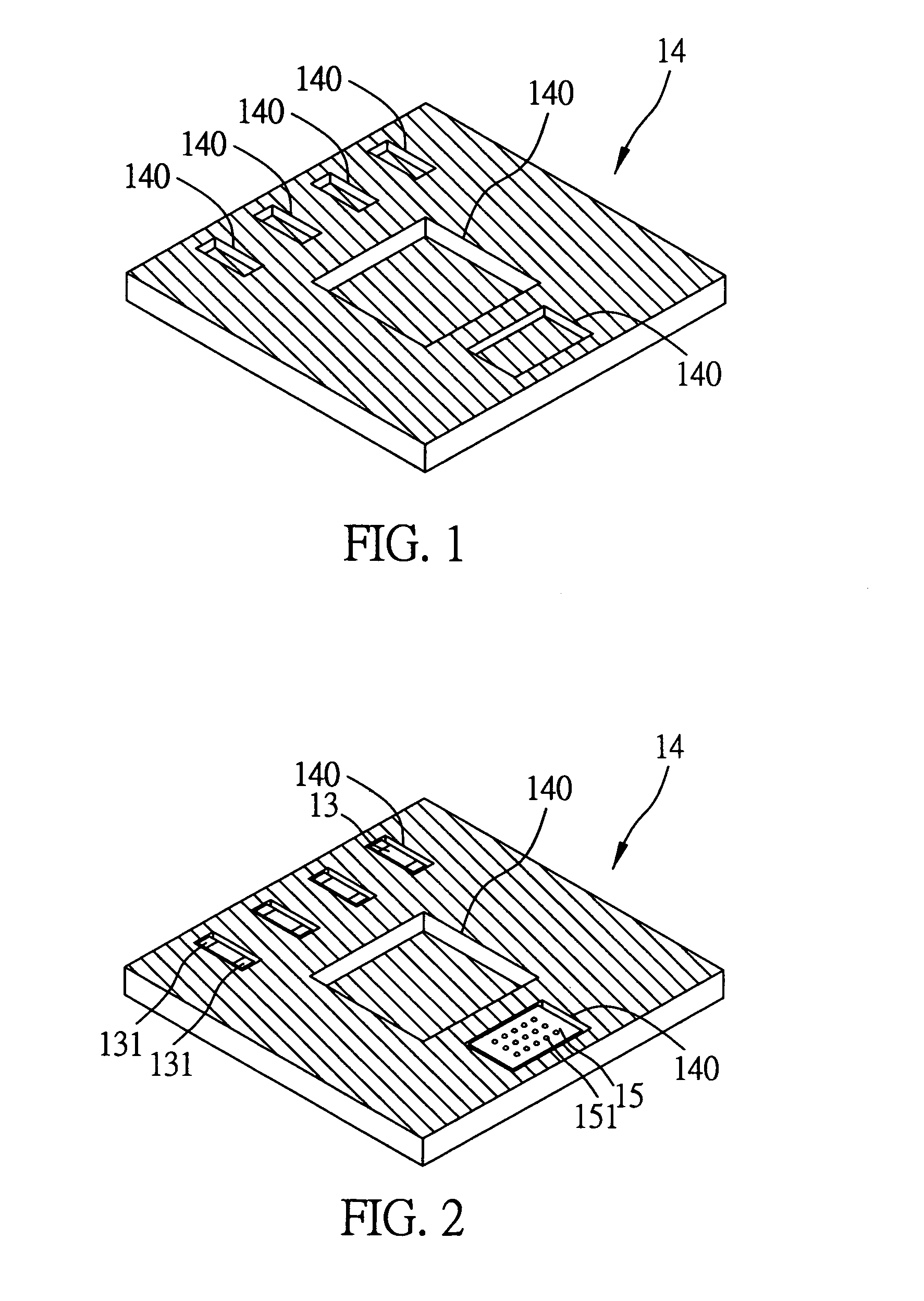

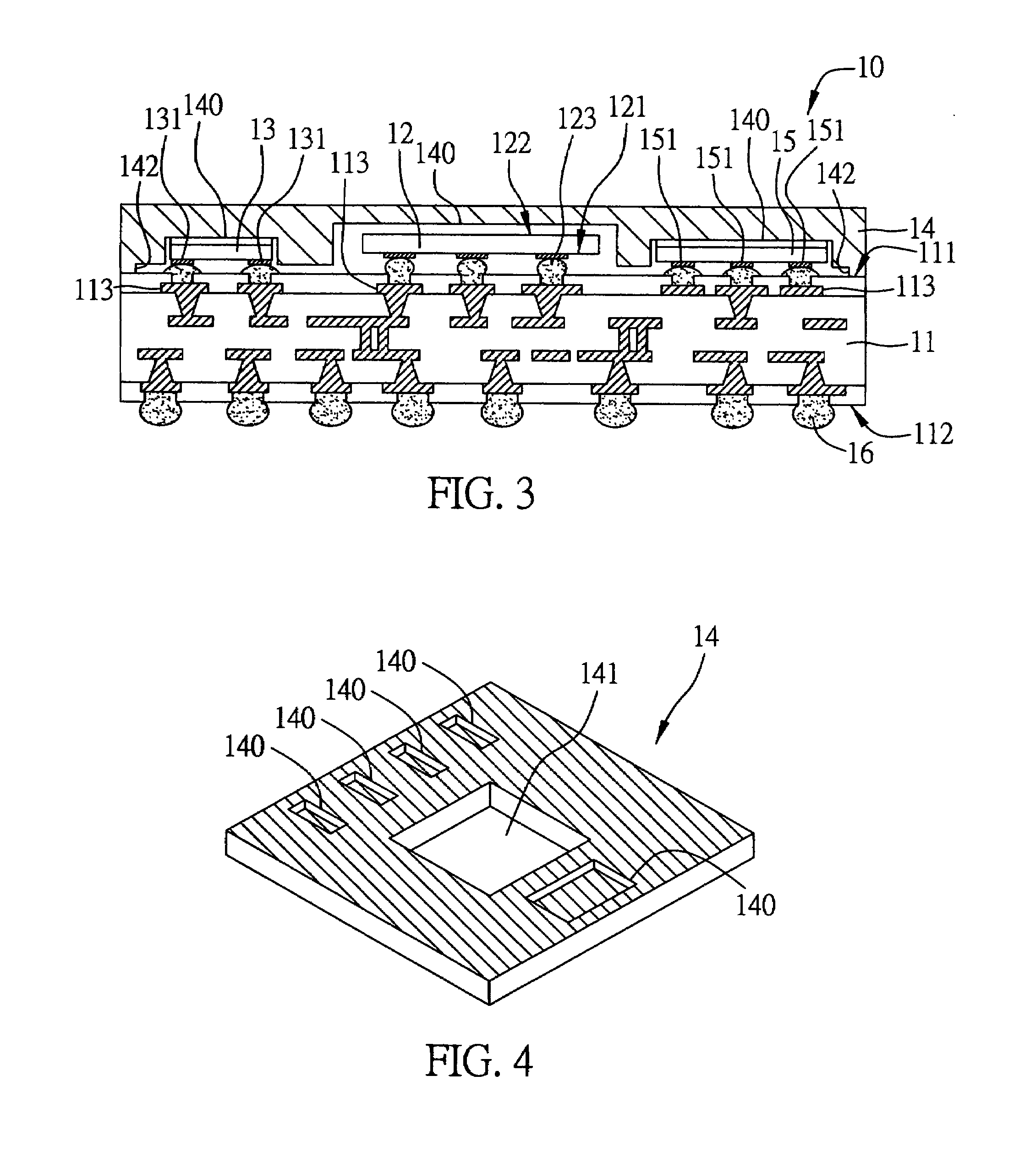

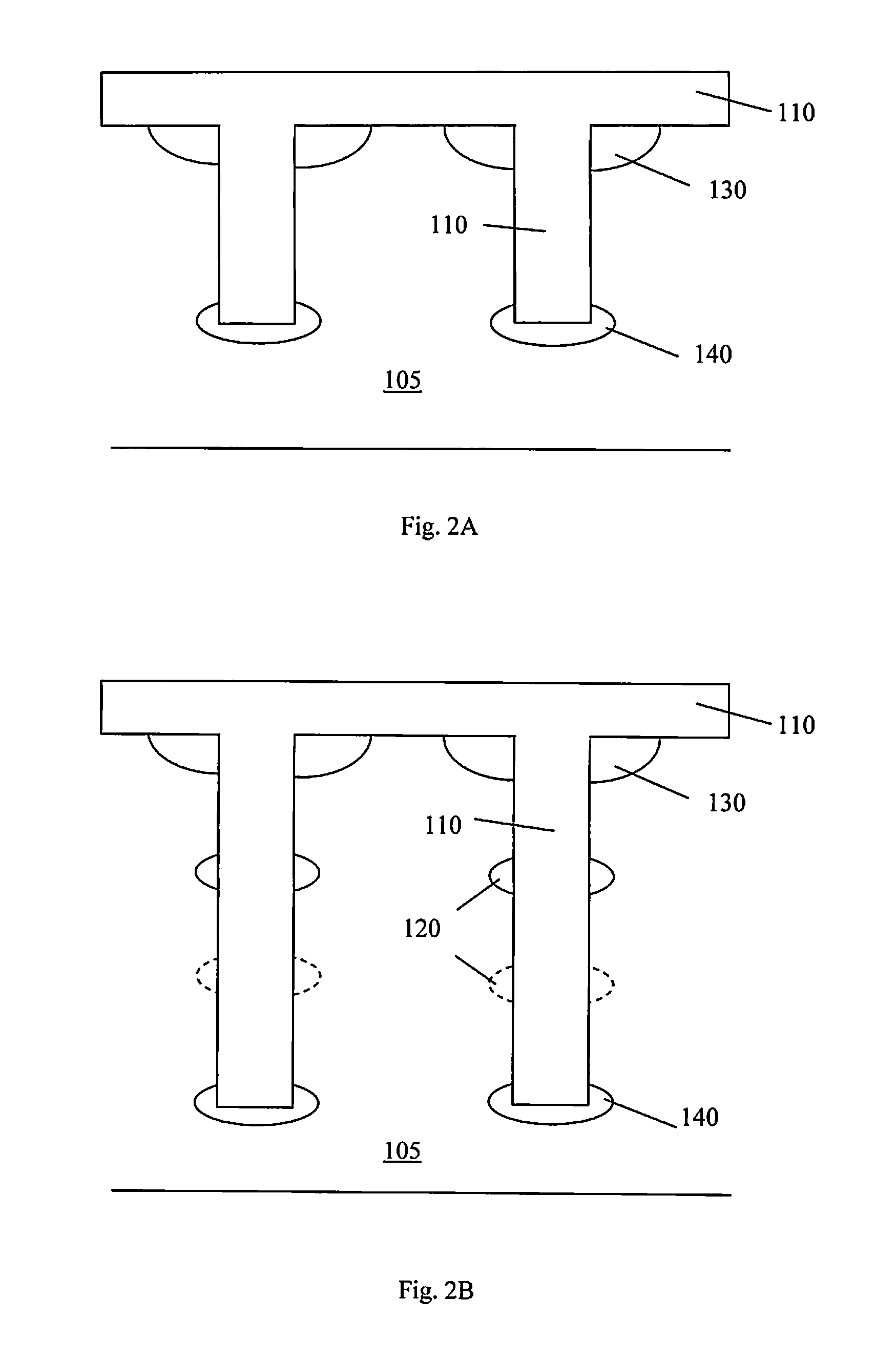

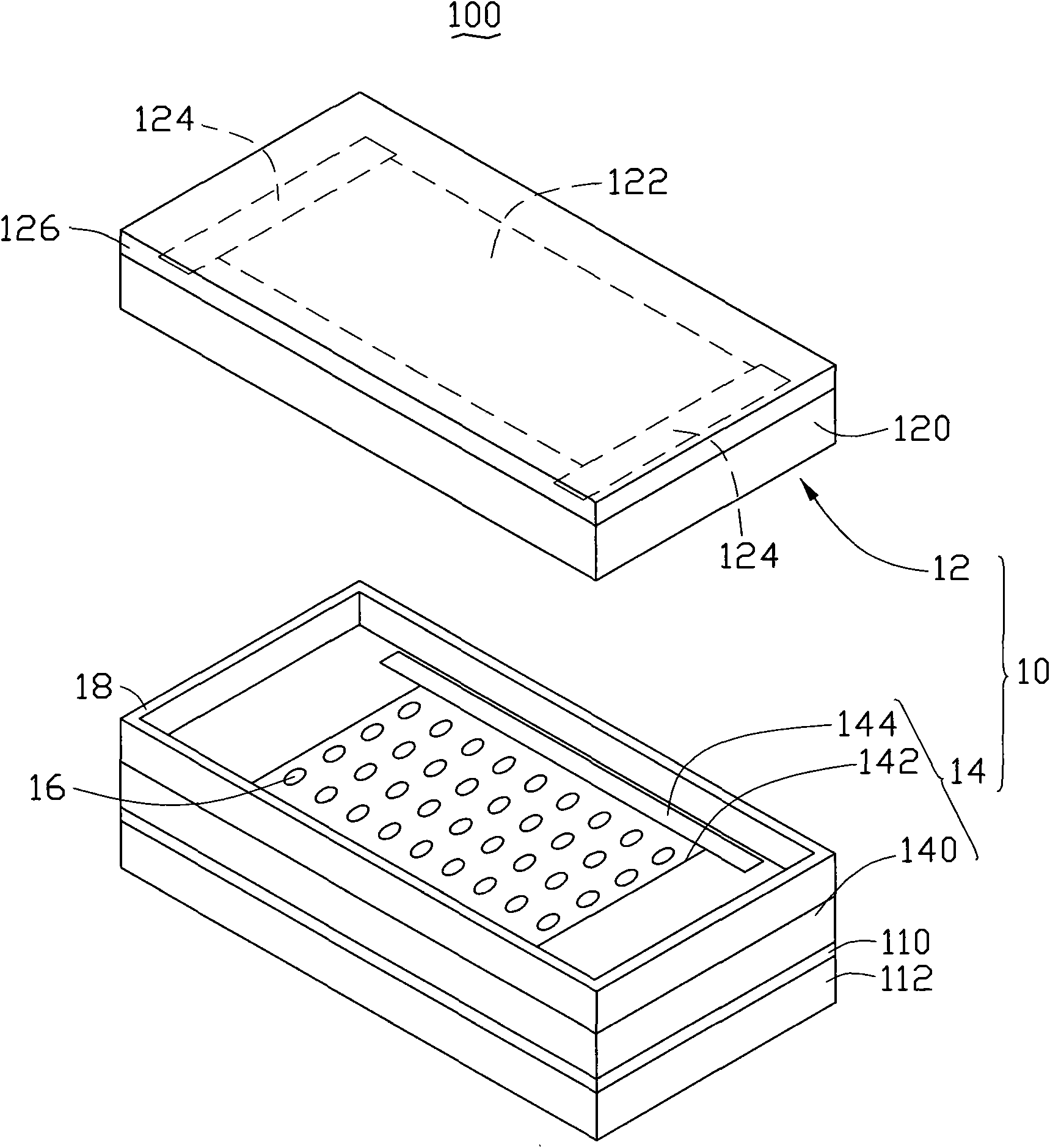

Heat sink structure with embedded electronic components for semiconductor package

ActiveUS7050304B2Good semiconductor performanceImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

A heat sink structure with embedded electronic components is proposed, wherein a plurality of recessed cavities are formed on a heat sink for embedding the electronic components and receiving at least one semiconductor chip therein. This arrangement enhances electric performance of a semiconductor package with the above heat sink structure and improves heat dissipating efficiency of the semiconductor package.

Owner:PHOENIX PRECISION TECH CORP

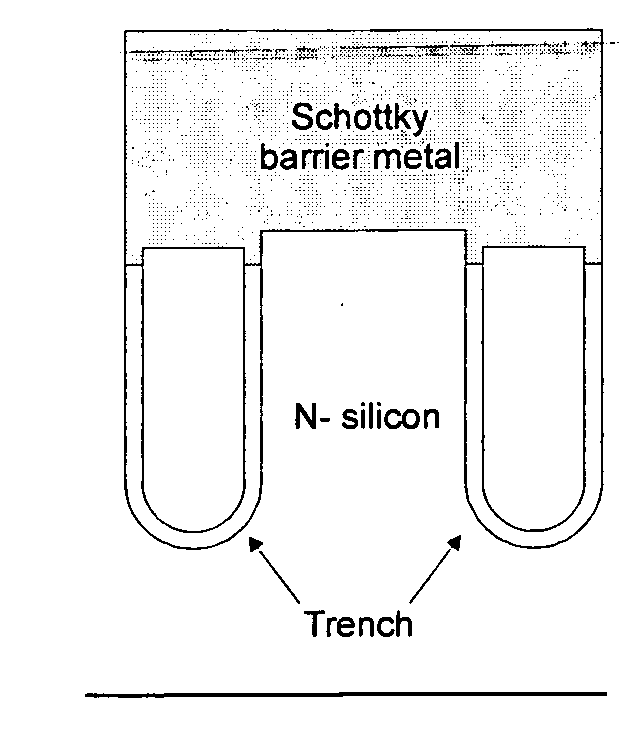

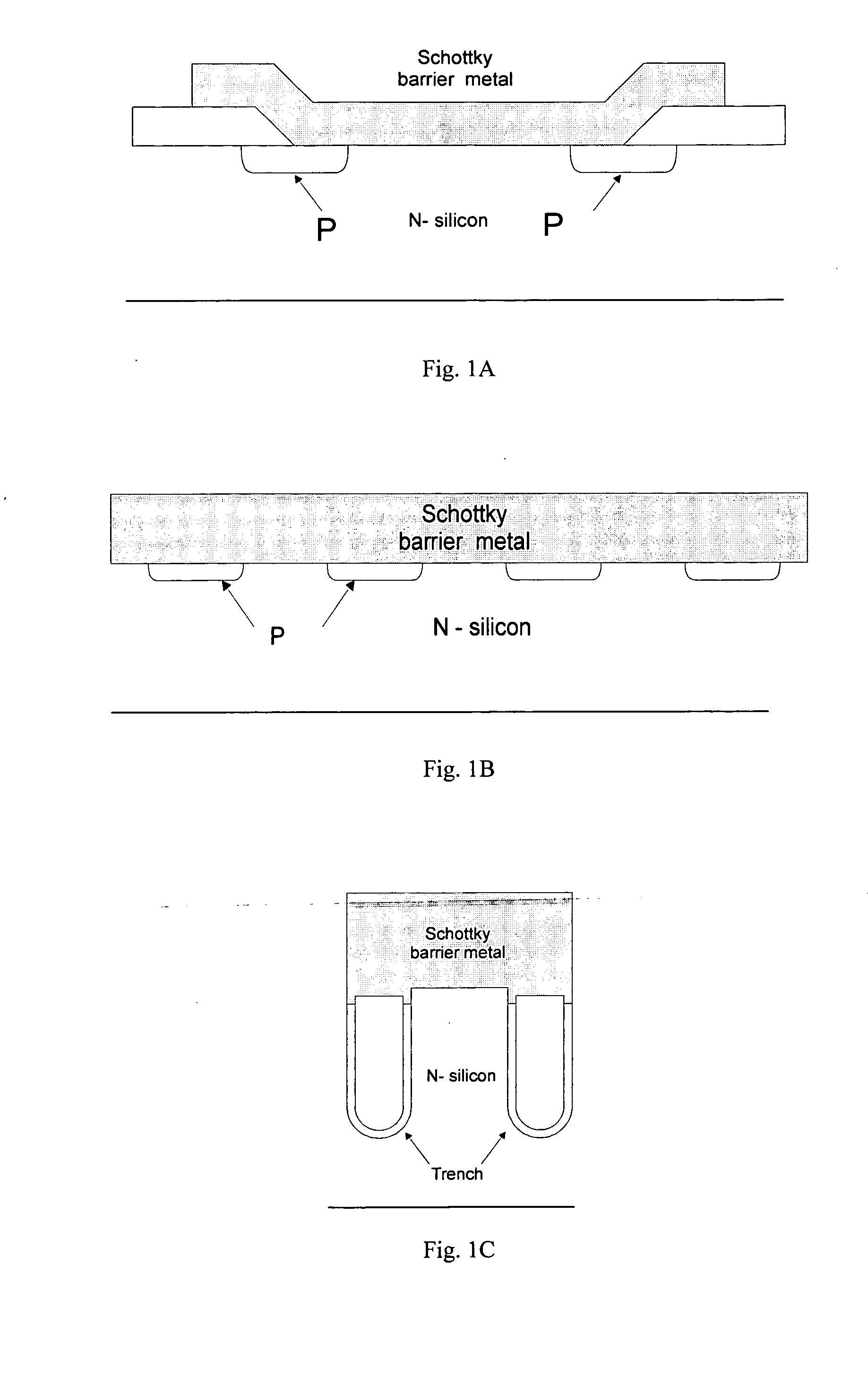

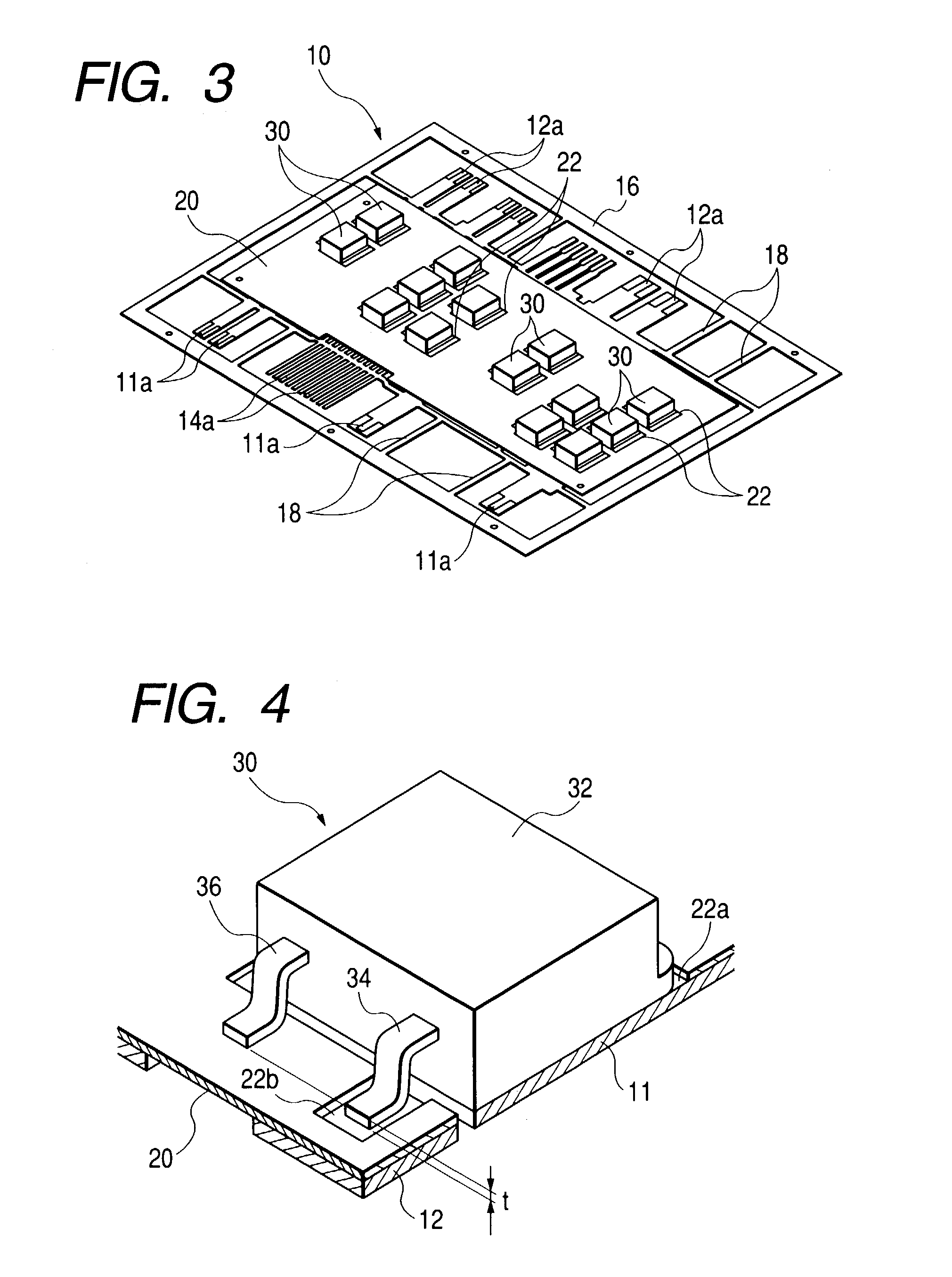

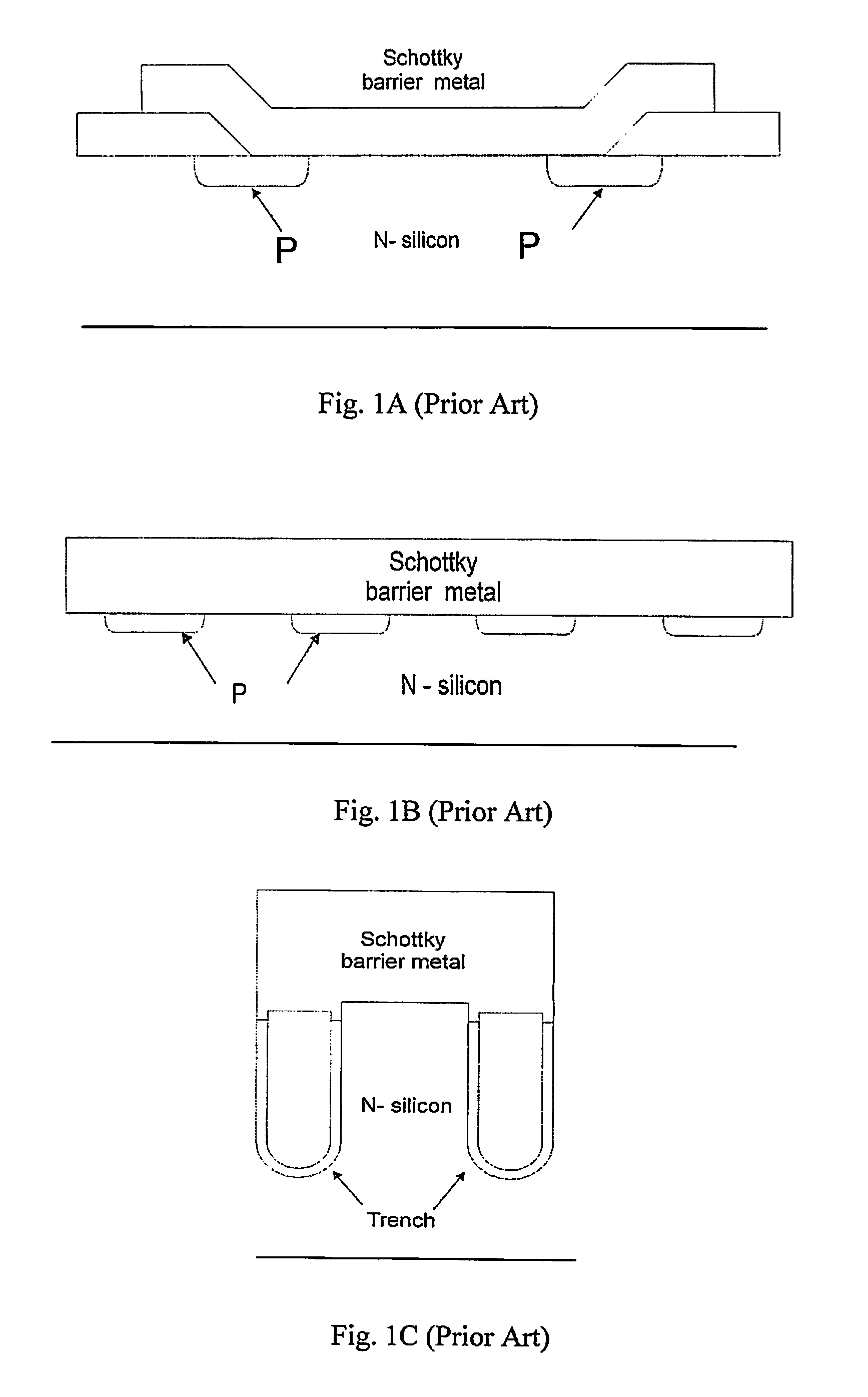

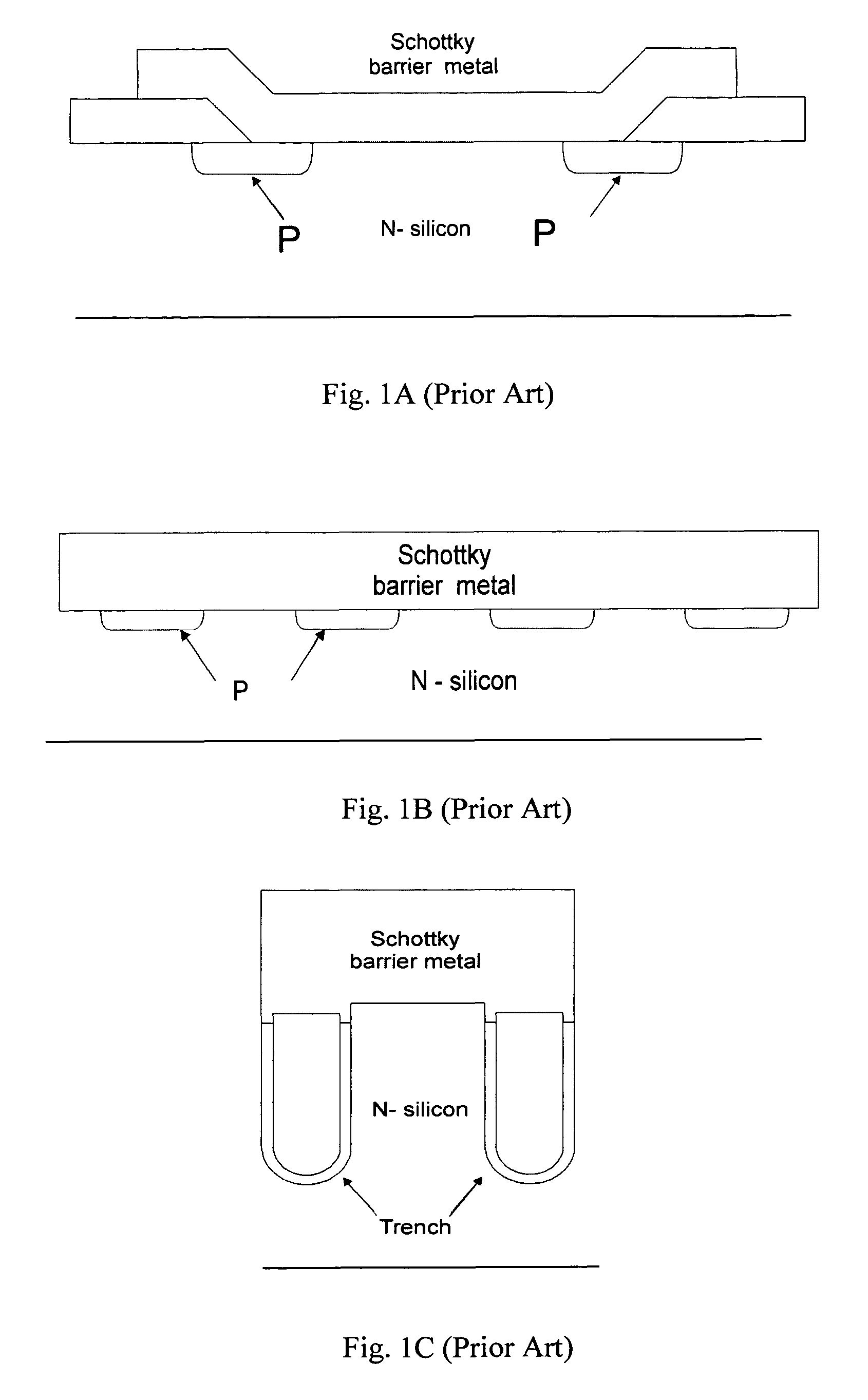

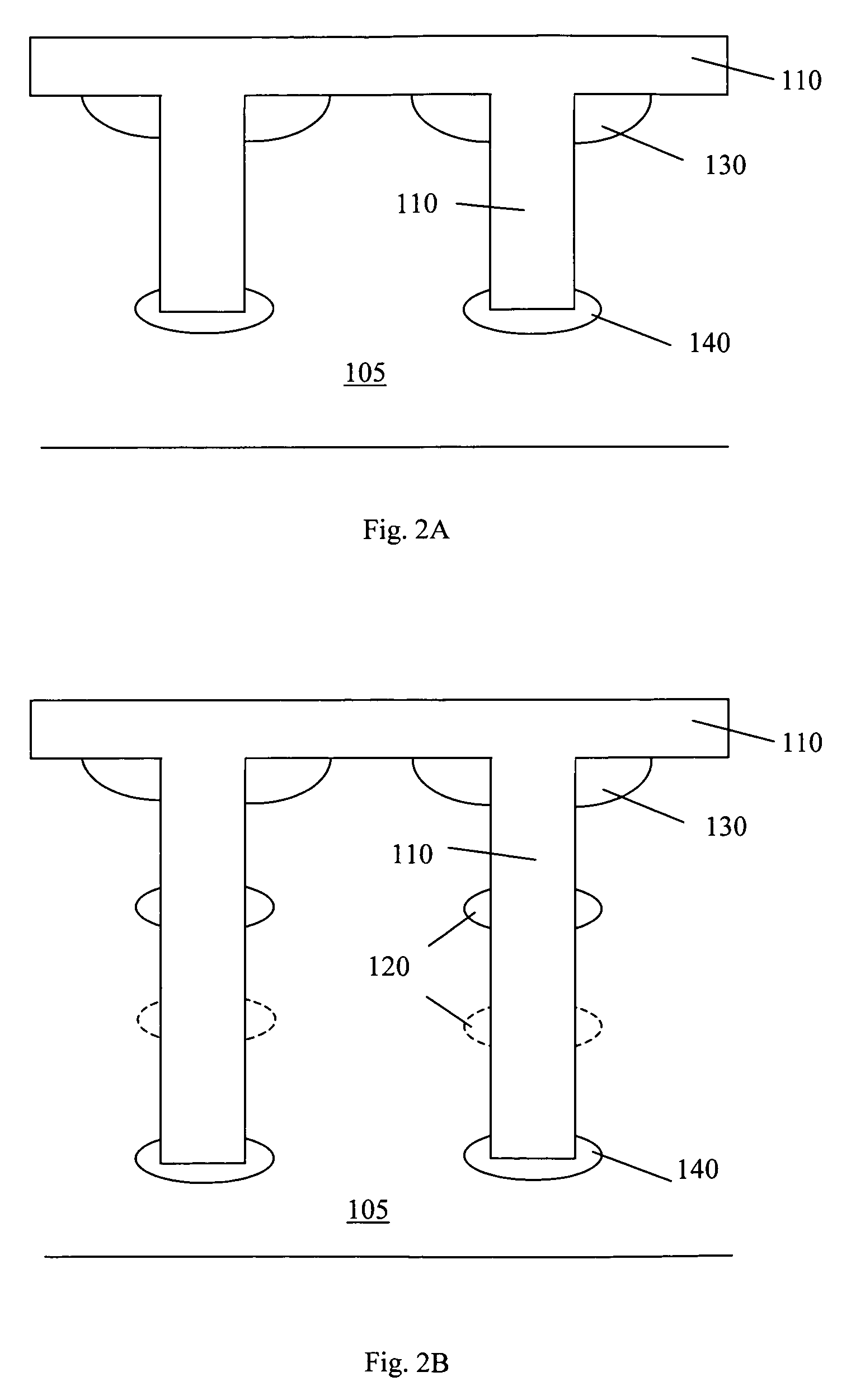

Trench junction barrier controlled Schottky

ActiveUS20070034901A1Silicon area utilization is greatly improvedEliminate requirementsTransistorSolid-state devicesDopantSemiconductor

A Schottky diode includes at least a trenched opened in a semiconductor substrate doped with a dopant of a first conductivity type wherein the trench is filled with a Schottky junction barrier metal. The Schottky diode further includes one or more dopant region of a second conductivity type surrounding sidewalls of the trench distributed along the depth of the trench for shielding a reverse leakage current through the sidewalls of the trench. The Schottky diode further includes a bottom-doped region of the second conductivity type surrounding a bottom surface of the trench and a top-doped region of the second conductivity type surrounding a top portion of the sidewalls of the trench. In a preferred embodiment, the first conductivity type is a N-type conductivity type and the middle-depth dopant region comprising a P-dopant region.

Owner:ALPHA & OMEGA SEMICON LTD

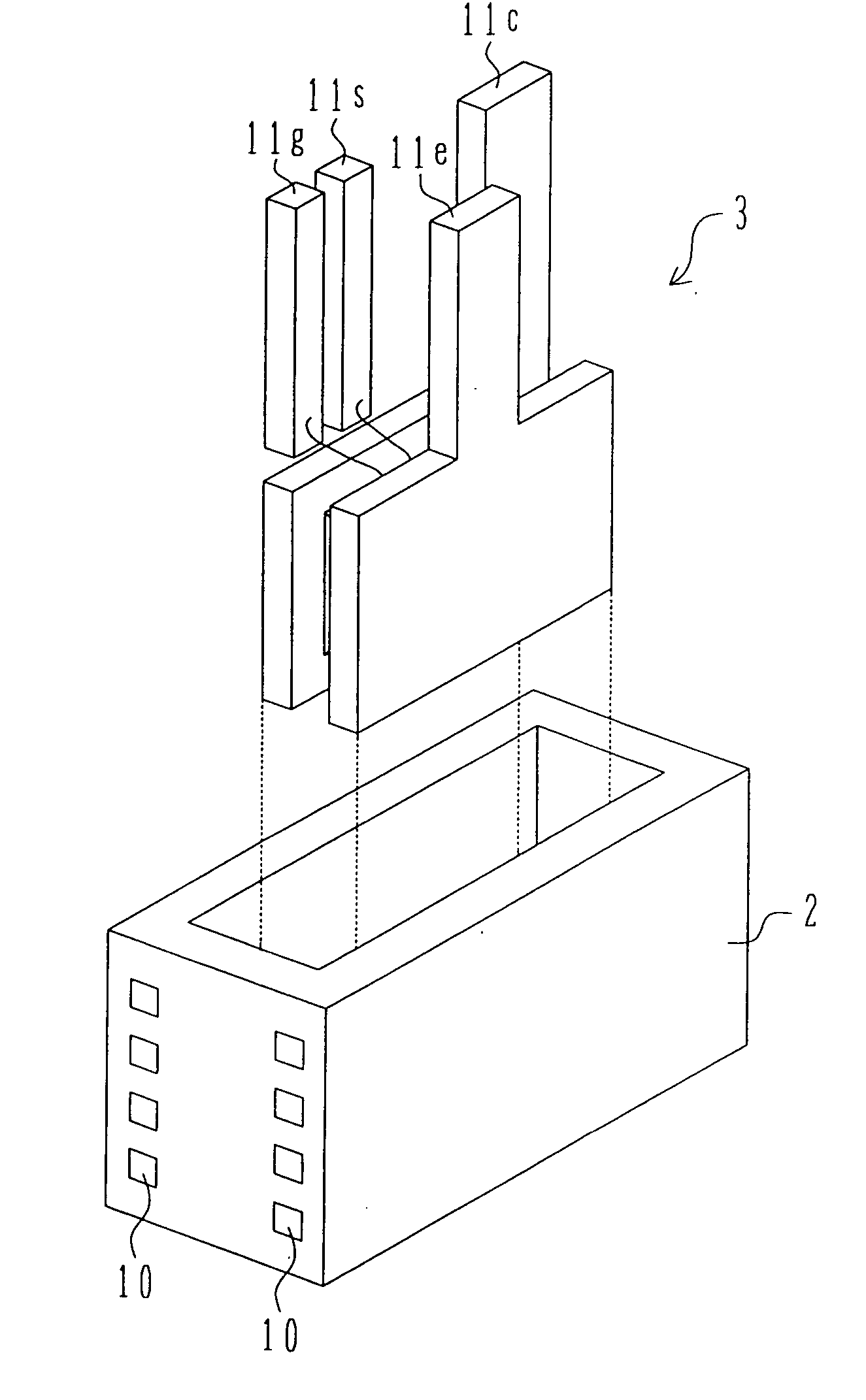

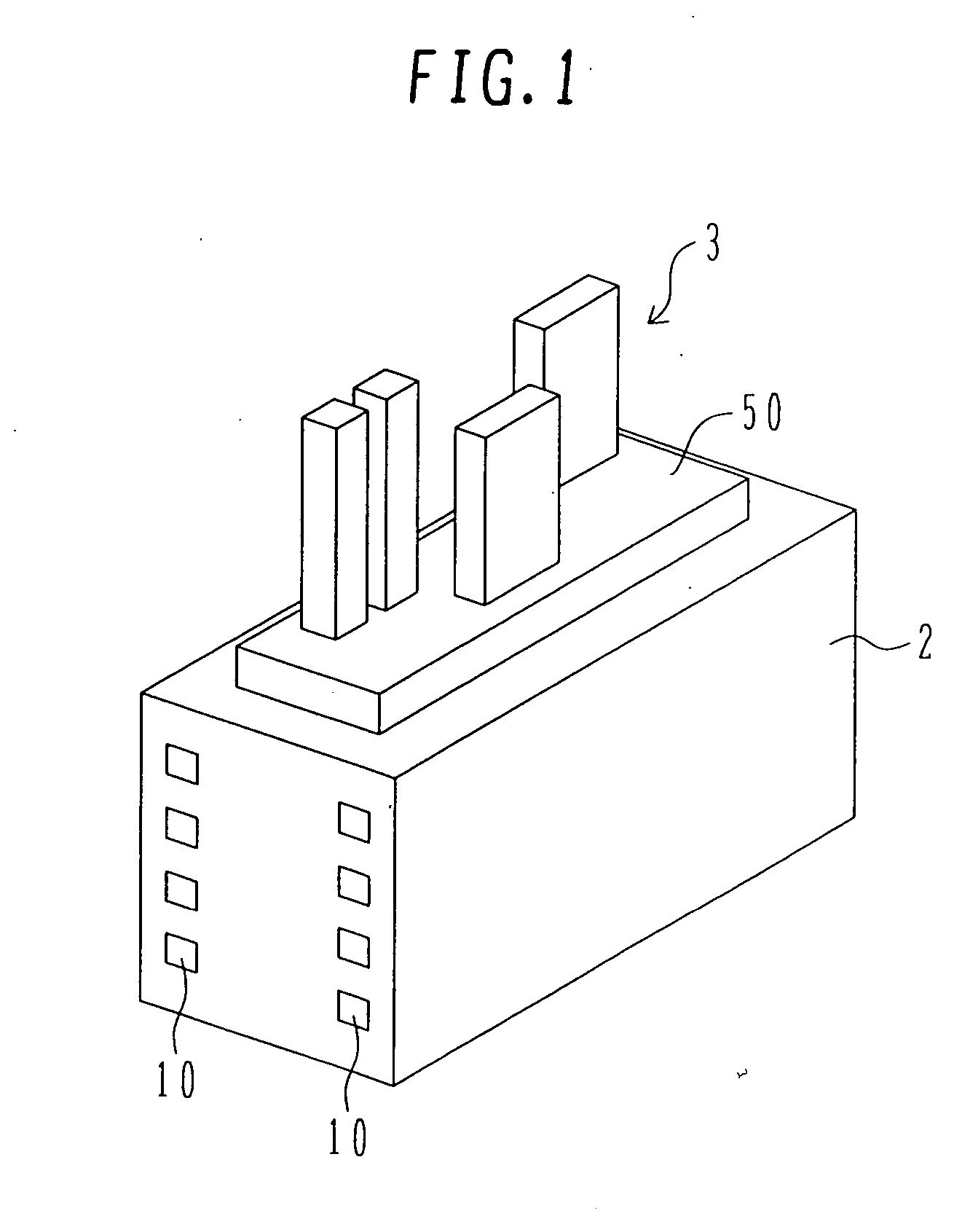

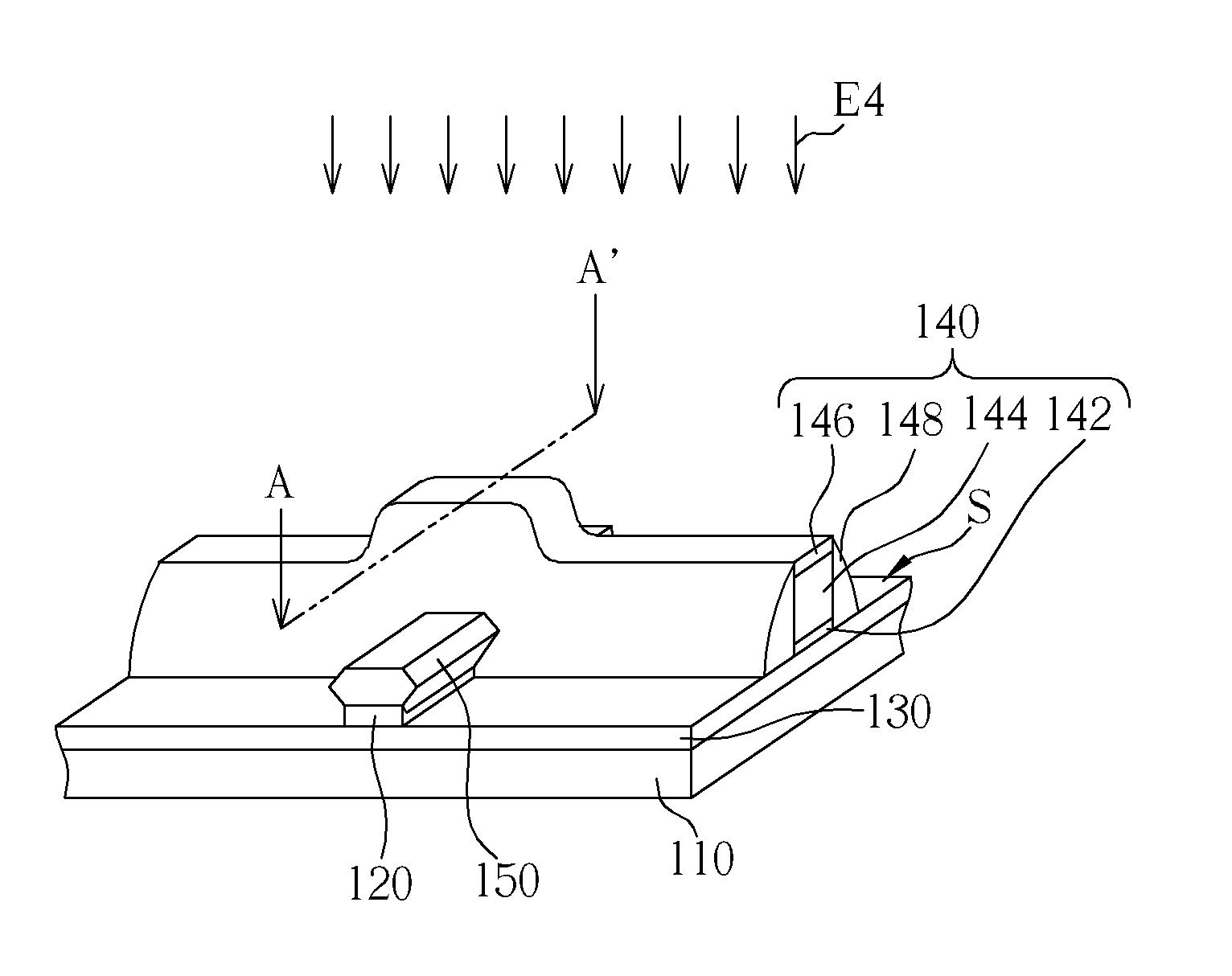

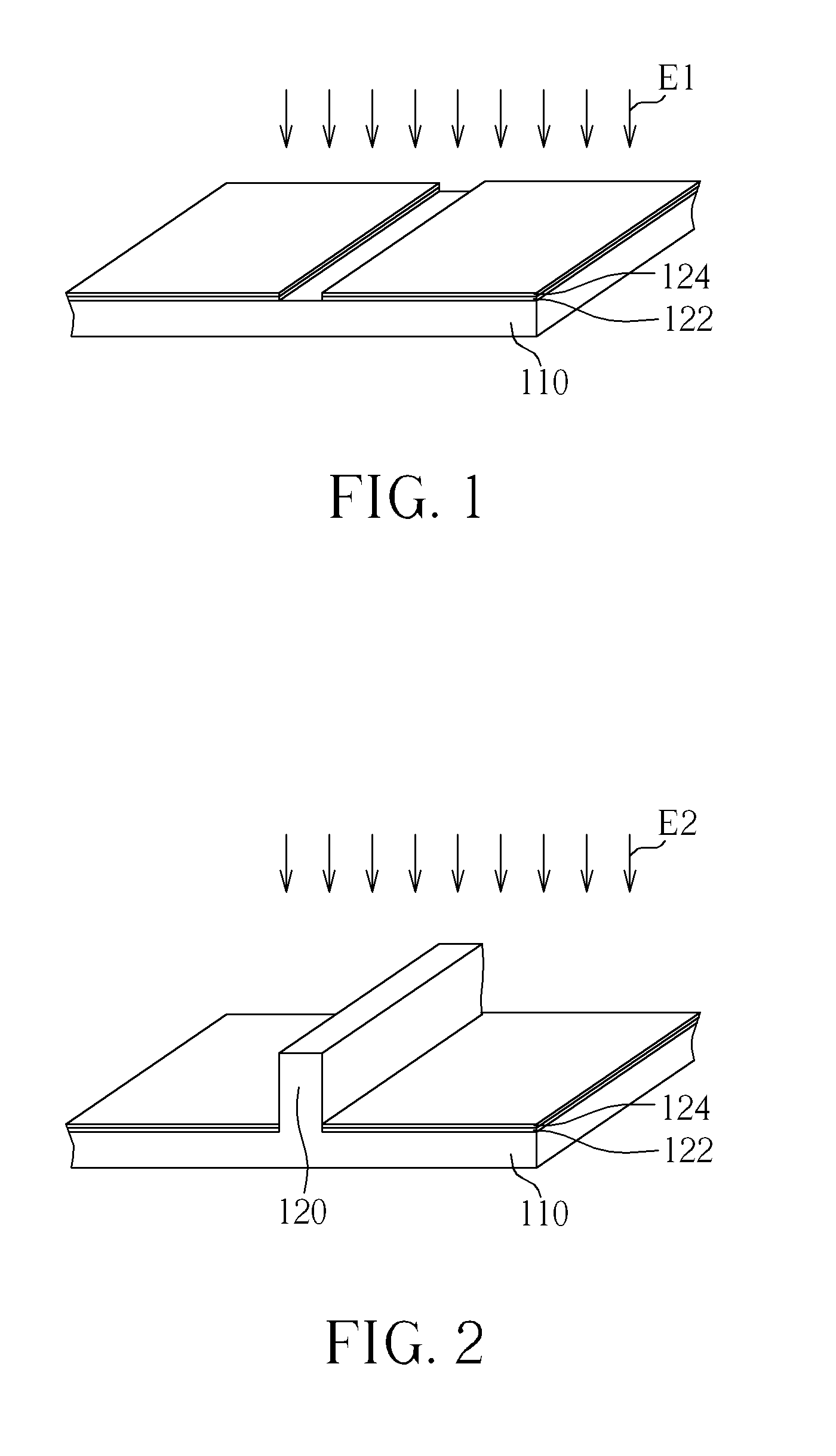

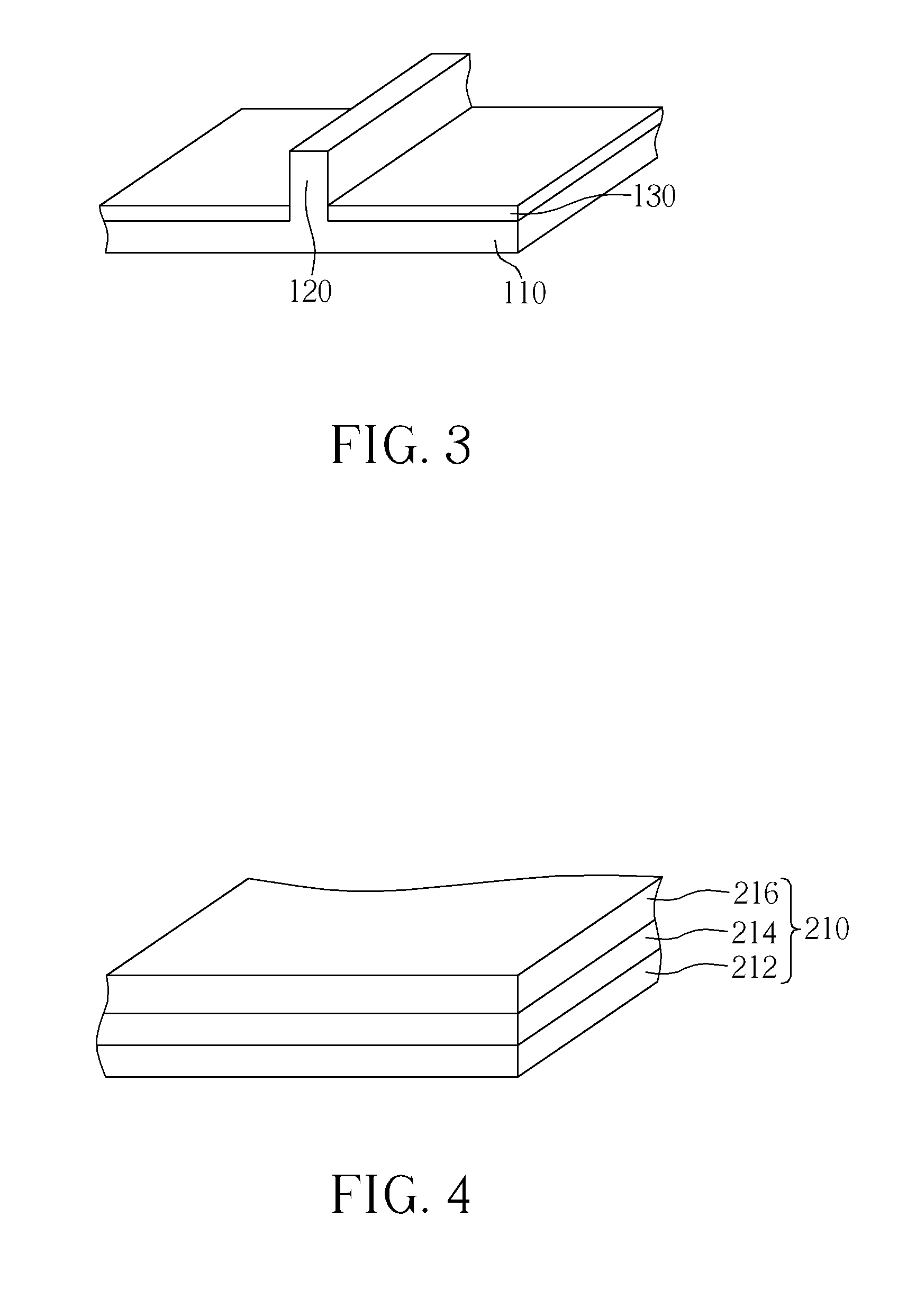

Semiconductor process

ActiveUS20130052778A1Easy to disassembleHigh carrier mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor packageEngineering

A semiconductor process includes the following steps. A substrate is provided. At least a fin-shaped structure is formed on the substrate. An oxide layer is formed on the substrate without the fin-shaped structure being formed thereon. A gate is formed to cover a part of the oxide layer and a part of the fin-shaped structure. An etching process is performed to etch a part of the fin-shaped structure beside the gate, therefore at least a recess is formed in the fin-shaped structure. An epitaxial process is performed to form an epitaxial layer in the recess, wherein the epitaxial layer has a hexagon-shaped profile structure.

Owner:UNITED MICROELECTRONICS CORP

Semiconductor unit, and power conversion system and on-vehicle electrical system using the same

InactiveUS7504720B2Higher-reliability systemsImprove vehicle mountabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectric power

A semiconductor device includes a semiconductor chip and leads electrically connected to the electrodes of the semiconductor chip. A hollow radiator base houses the semiconductor device which is molded with high-thermal-conductivity resin having an electrical insulating property. The radiator base has a cooling-medium channel therein or radiating fins on the outside. Alternatively, the radiator base is housed in a second radiator base.

Owner:HITACHI LTD

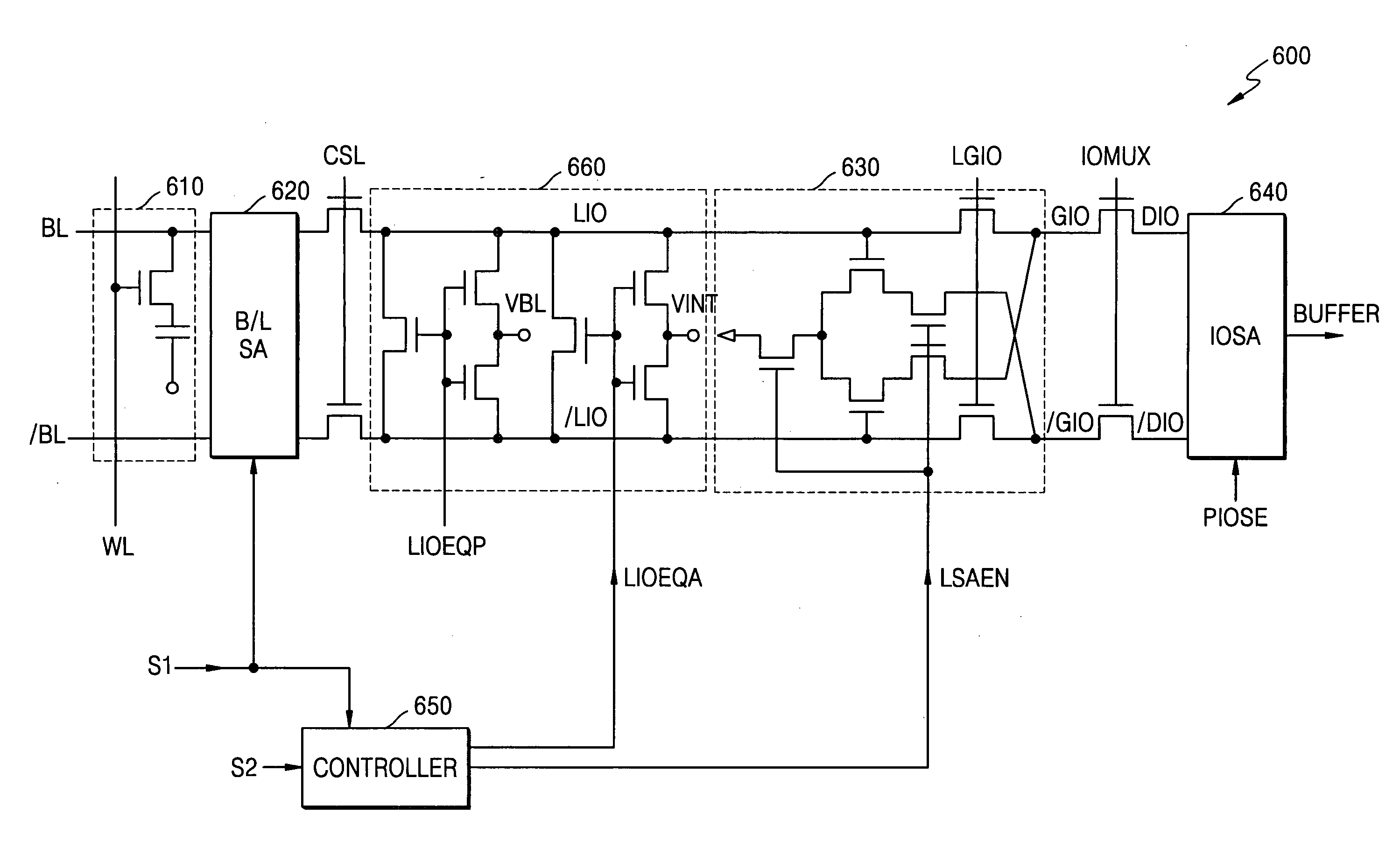

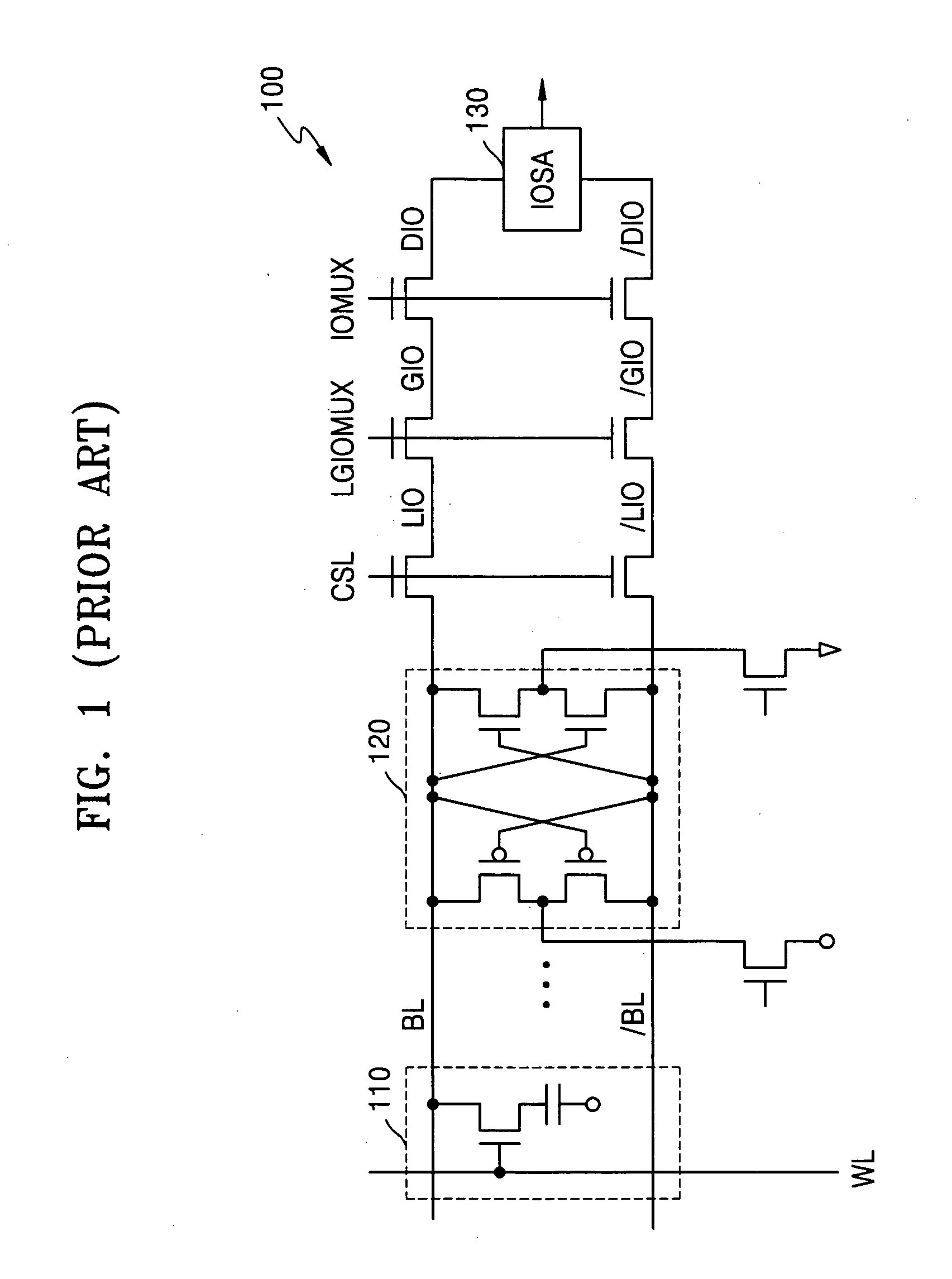

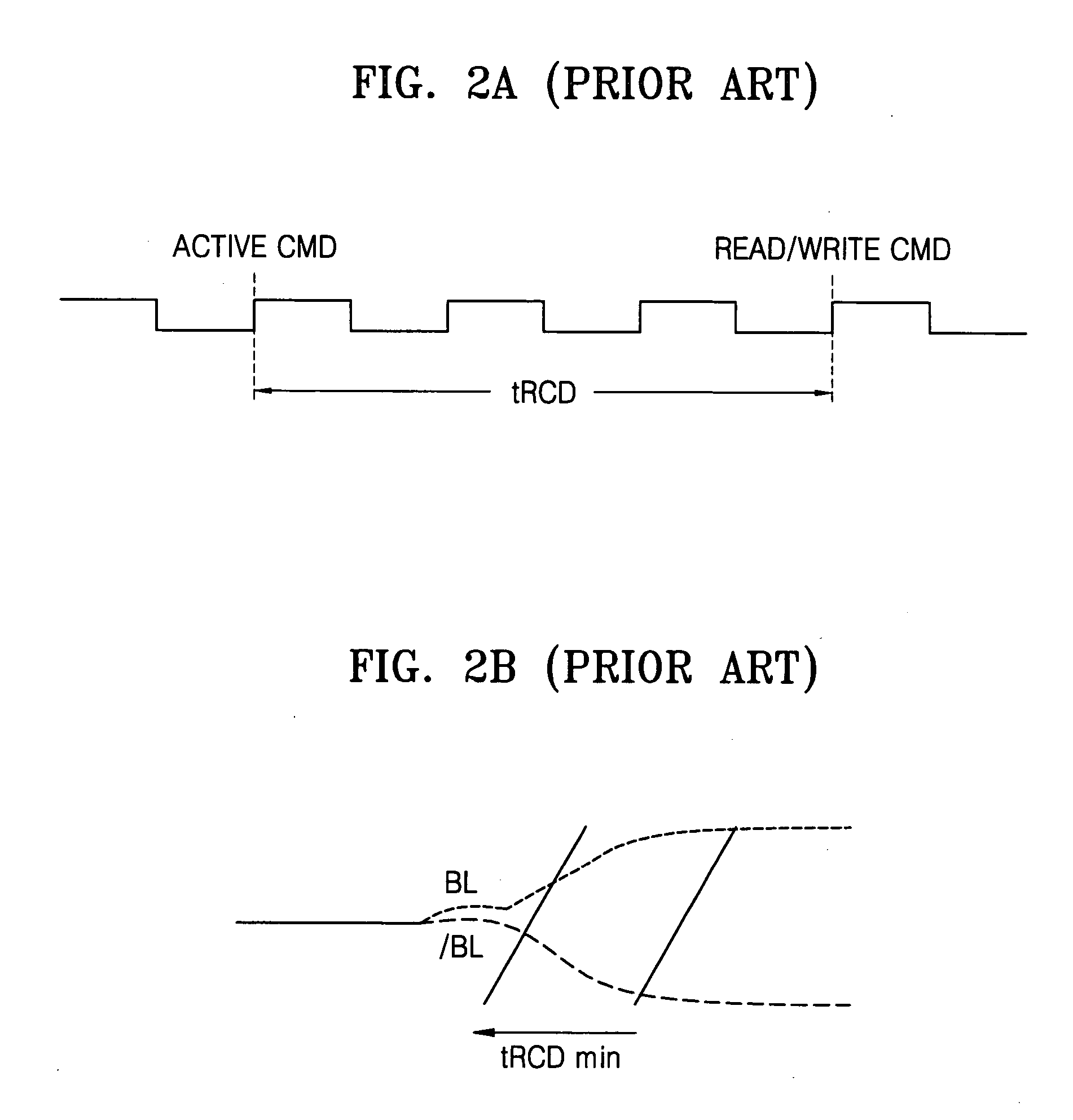

Semiconductor memory device having local sense amplifier with on/off control

InactiveUS20060028888A1Increase the tRCD parameterGood semiconductor performanceDigital storageBit lineAudio power amplifier

A semiconductor memory device includes a plurality of memory cell array blocks, a bit line sense amplifier, a local sense amplifier that can be controlled to be turned on or off, a data sense amplifier, and a controller. The controller activates a local sense control signal for a predetermined duration in response to first and second signals. The first signal is a bit line sense enable signal that activates the bit line sense amplifier, and the local sense amplifier is activated for a predetermined duration after the bit line sense enable signal is activated. The second signal is activated or deactivated in phase with a column selection line signal that connects a pair of bit lines and a pair of local input / output lines. Accordingly, it is possible to turn on or off the local sense amplifier according to operating conditions, thereby increasing a tRCD parameter and reducing the consumption of current. The operating speed of the semiconductor memory device can be improved by combining the local sense amplifier with a current type data sense amplifier that does not require precharging and equalization during a read operation.

Owner:SAMSUNG ELECTRONICS CO LTD

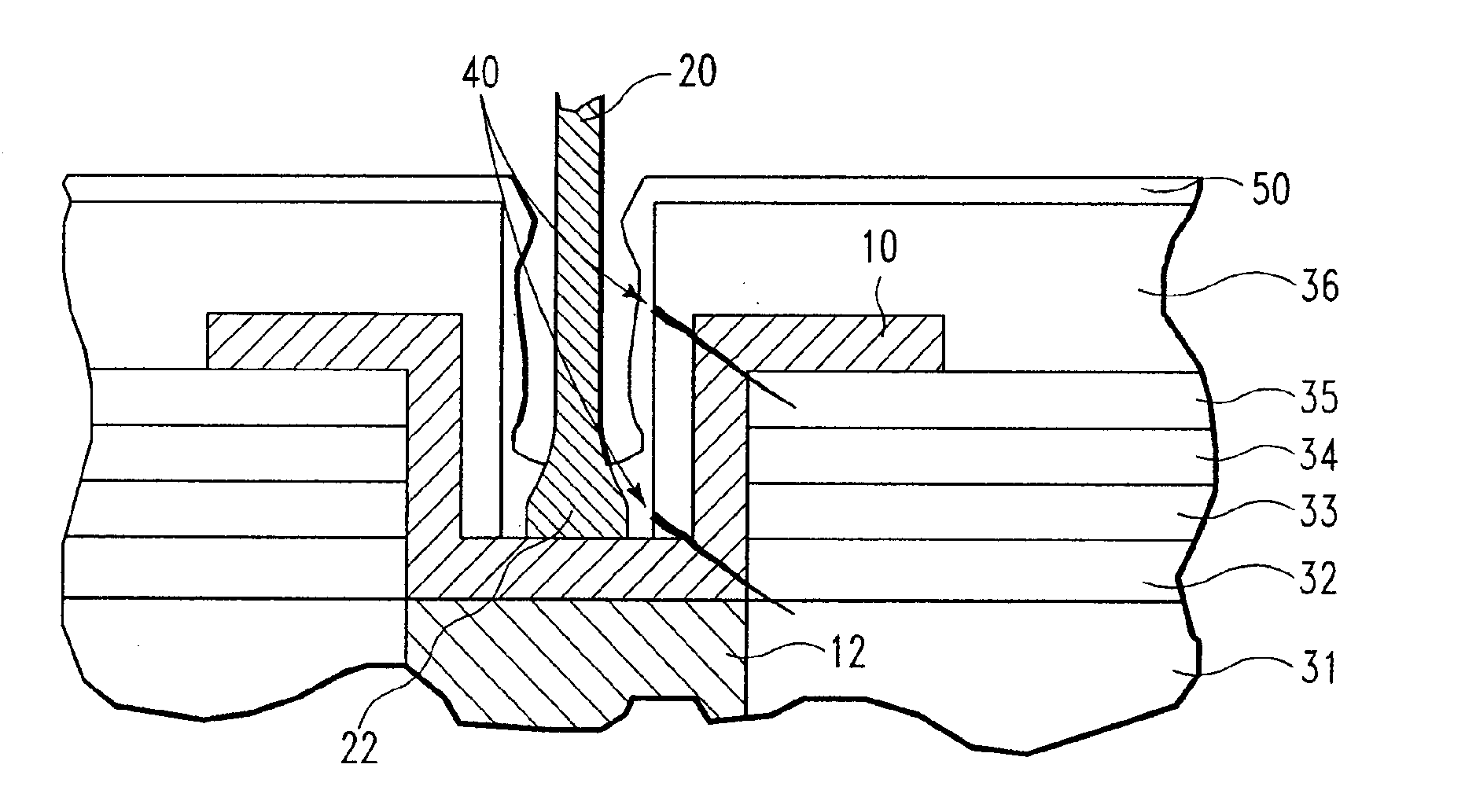

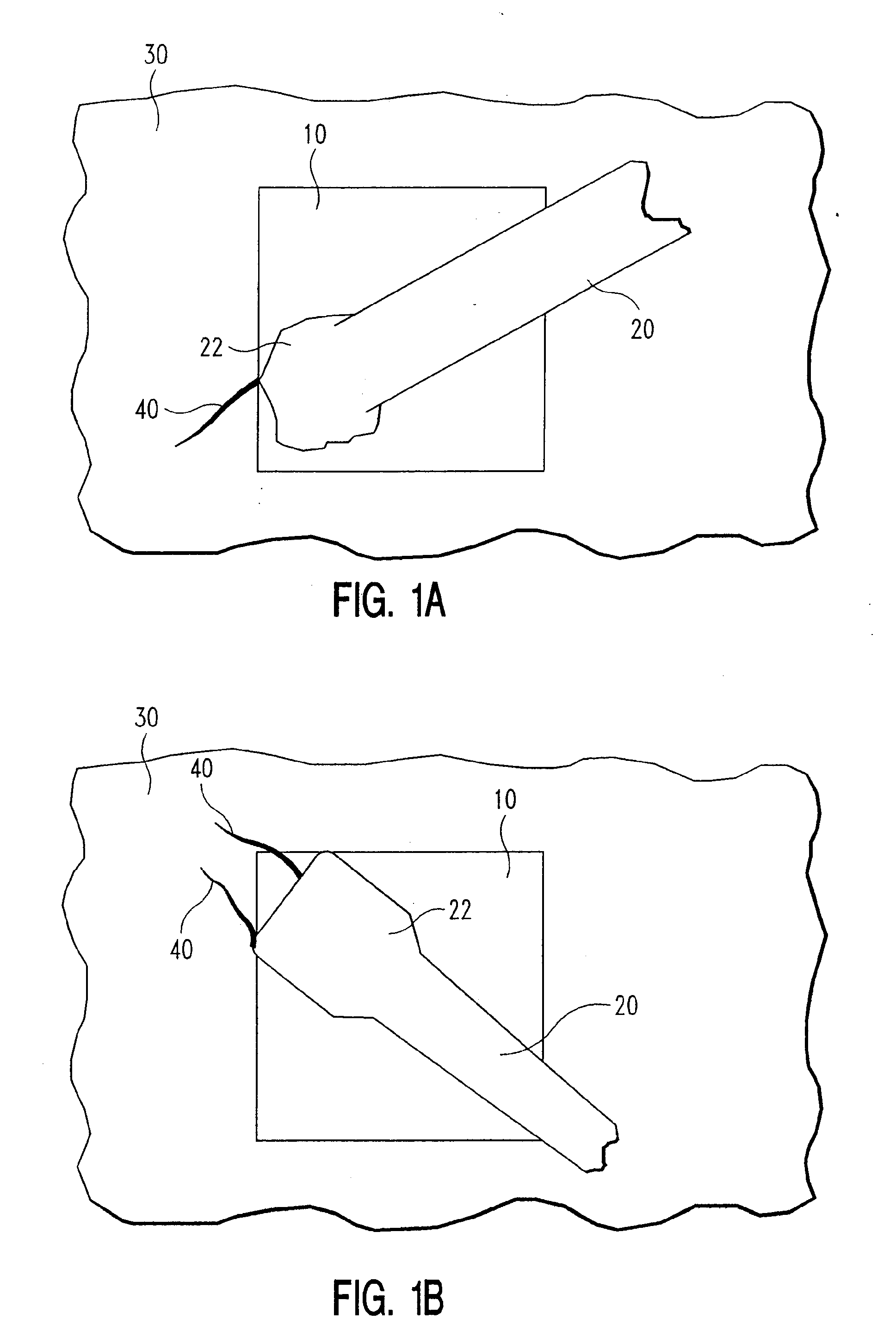

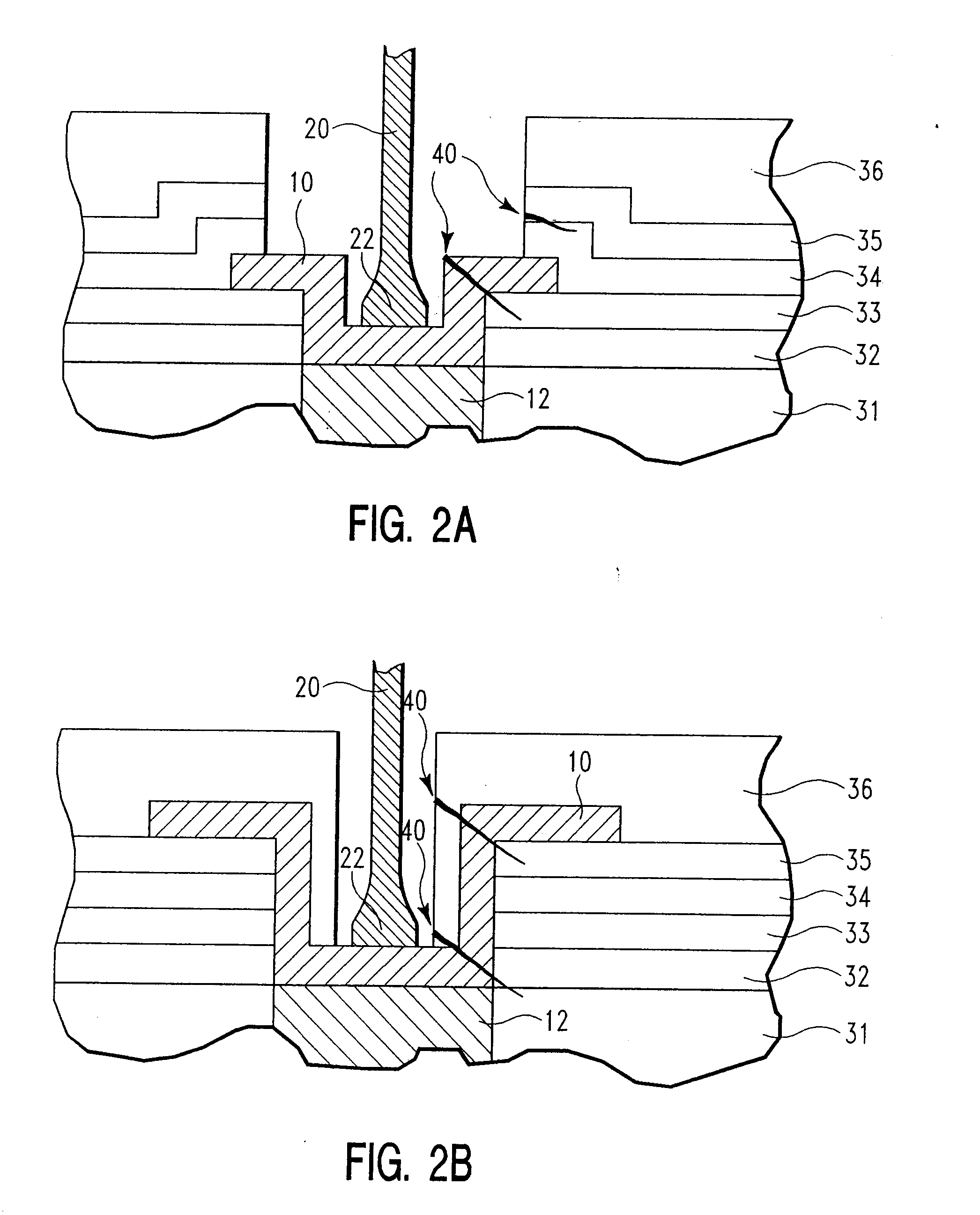

Semiconductor device mounted on heat sink having protruded periphery

ActiveUS7923826B2Improve semiconductor device performanceHigh calorific valueSemiconductor/solid-state device detailsSolid-state devicesSolder ballSemiconductor chip

A semiconductor chip is mounted on a heat sink disposed inside a through-hole of a wiring board, electrodes of the semiconductor chip and connecting terminals of the wiring board are connected by bonding wires, a sealing resin is formed to cover the semiconductor chip and the bonding wires, and solder balls are formed on the lower surface of the wiring board, thereby constituting the semiconductor device. The heat sink is thicker than the wiring board. The heat sink has a protruded portion protruding to outside from the side surface of the heat sink, the protruded portion is located on the upper surface of the wiring board outside the through-hole, and the lower surface of the protruded portion contacts to the upper surface of the wiring board. When the semiconductor device is manufactured, the heat sink is inserted from the upper surface side of the wiring board.

Owner:RENESAS ELECTRONICS CORP

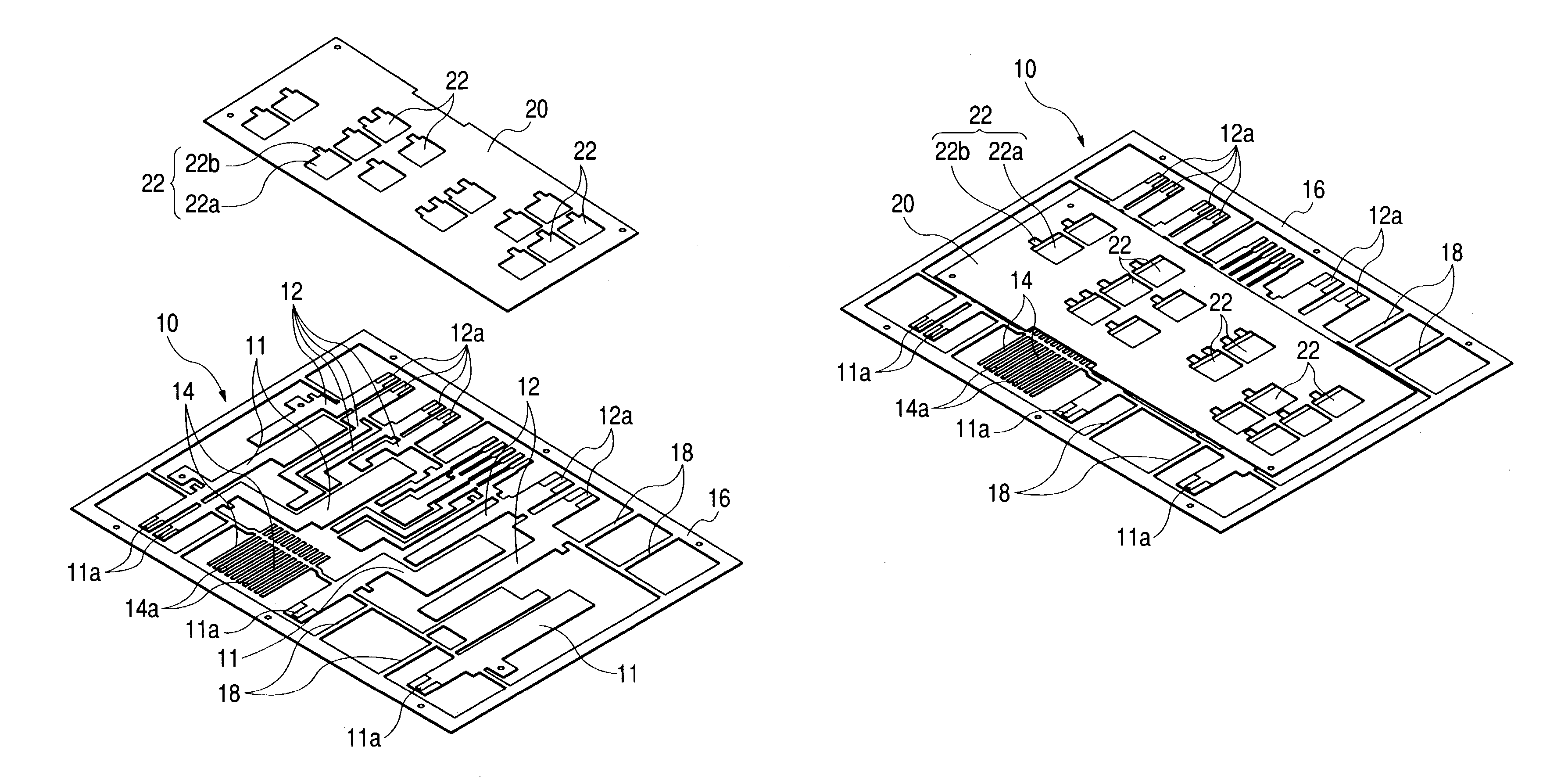

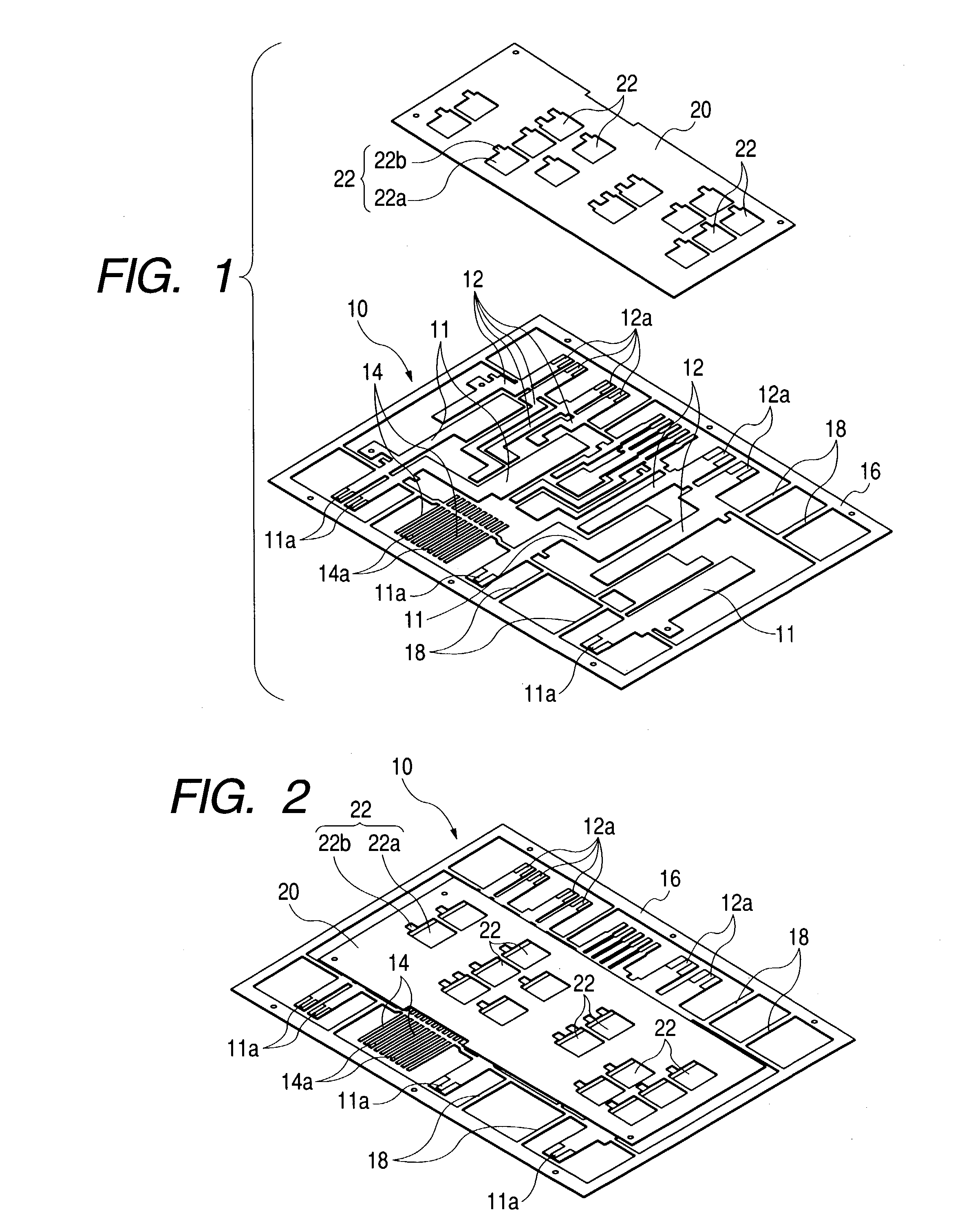

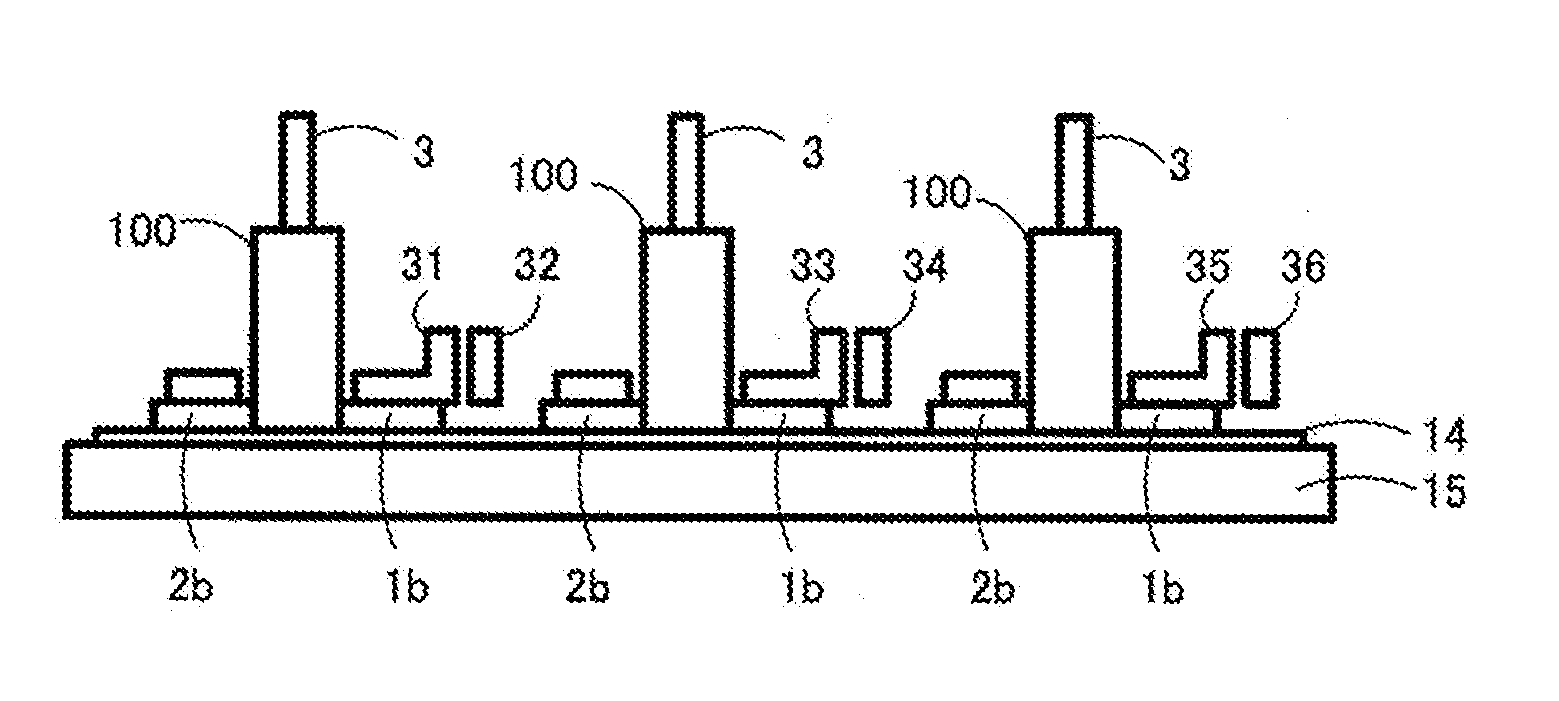

Circuit-constituting unit and method of producing the same

InactiveUS7167377B2Simple structureReduce constructionElectrically conductive connectionsPrinted circuit aspectsControl circuitPower circuits

A circuit-constituting unit forming a distribution circuit or the like in a vehicle. The circuit-constituting unit includes a plurality of bus bars for constituting a power circuit; a semiconductor switching device provided in the power circuit; and a control circuit board. The bus bars are bonded to a surface of the control circuit board such that the bus bars are arranged to be generally coplanar with each other. The semiconductor switching device is mounted on both of the corresponding bus bars and the control circuit board. An opening may be formed through the control circuit board. In this case, one of terminals of the semiconductor switching device may be connected to a surface of the control circuit board facing away from the surface to which the bus bars are bonded. The other terminals may be connected respectively to the bus bar through the opening.

Owner:AUTONETWORKS TECH LTD +2

Trench junction barrier controlled schottky

ActiveUS20140332882A1Silicon area utilization is greatly improvedEliminate requirementsSemiconductor/solid-state device manufacturingDiodeDopantSchottky barrier

A method for manufacturing a Schottky diode comprising steps of 1) providing a region with a dopant of a second conductivity type opposite to a first conductivity type to form a top doped region in a semiconductor substrate of said first conductivity type; 2) providing a trench through the top doped region to a predetermined depth and providing a dopant of the second conductivity type to form a bottom dopant region of the second conductivity type; and 3) lining a Schottky barrier metal layer on a sidewall of the trench at least extending from a bottom of the top doped region to a top of the bottom doped region.

Owner:ALPHA & OMEGA SEMICON INC

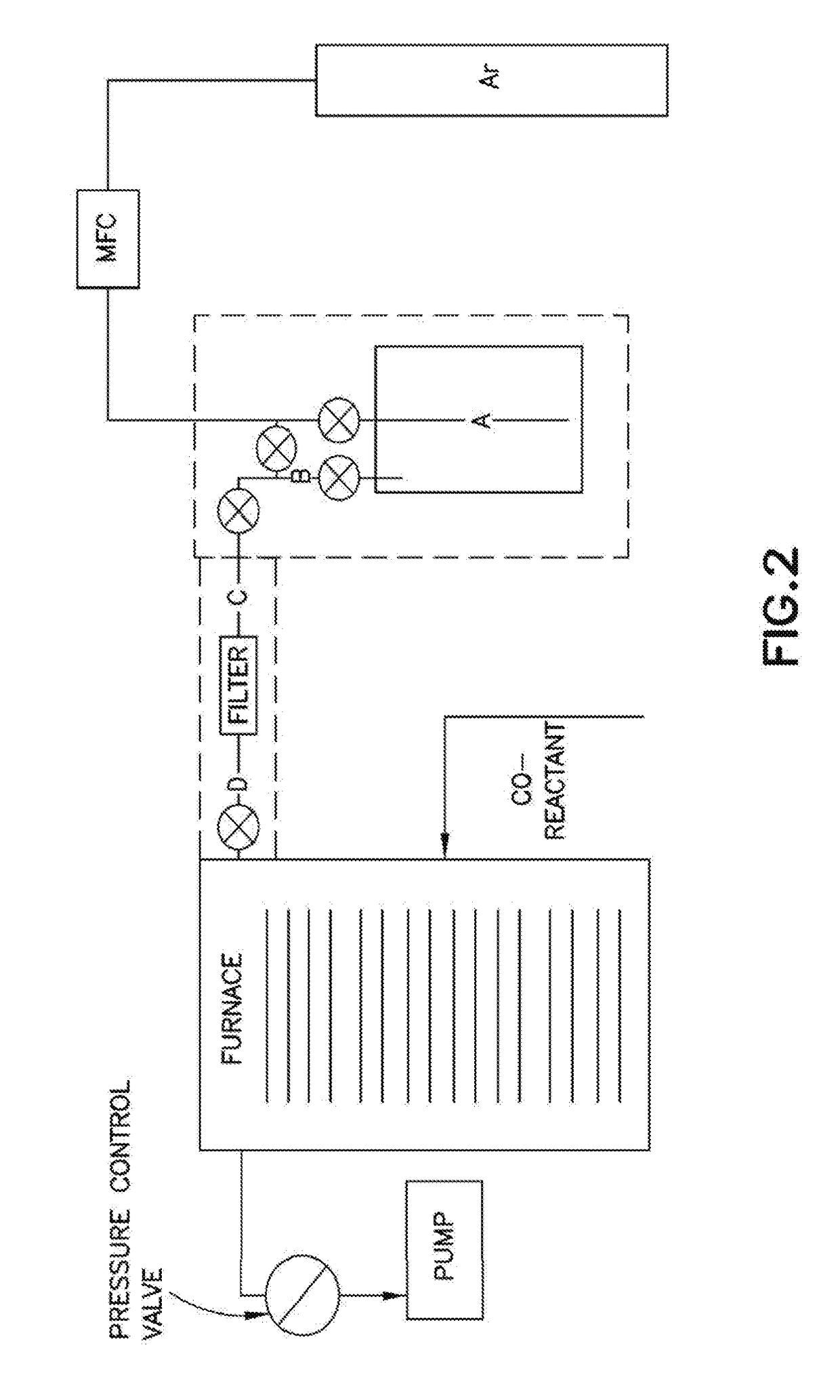

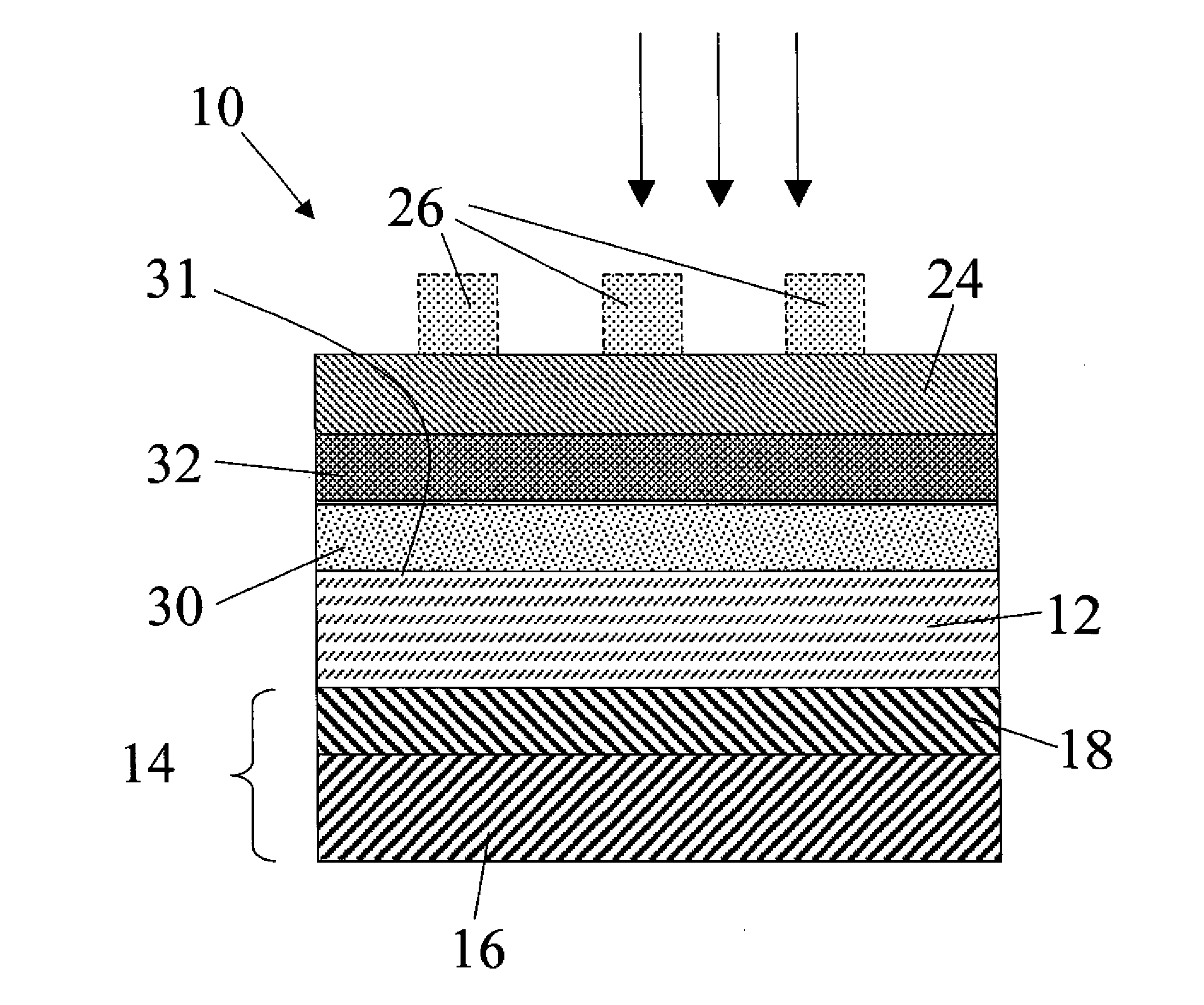

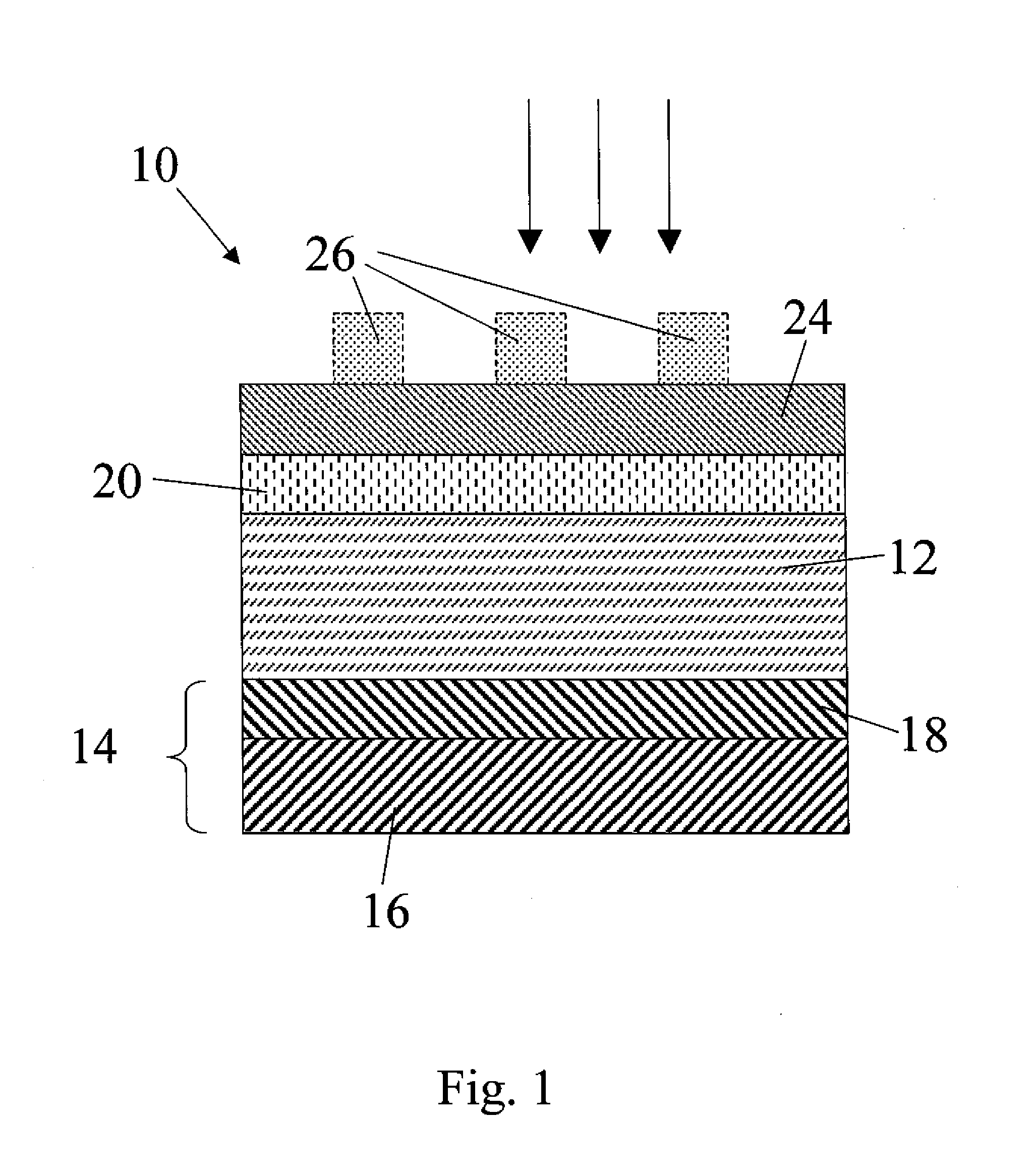

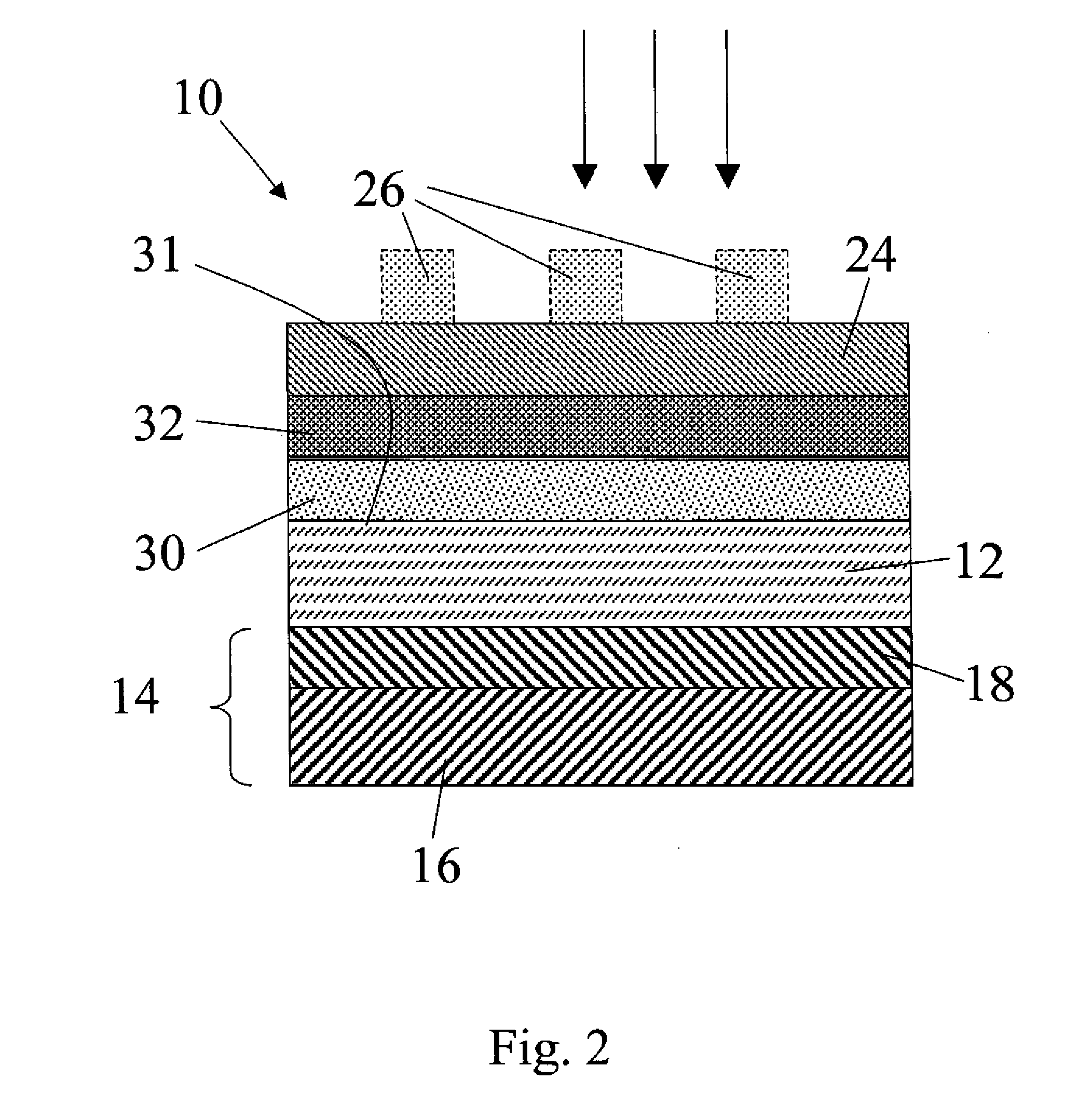

Group iib/va semiconductors suitable for use in photovoltaic devices

InactiveUS20110309477A1Good semiconductor performanceImprove electronic performanceSemiconductor/solid-state device manufacturingPhotovoltaic energy generationDopantSemiconductor materials

The present invention relates to devices, particularly photovoltaic devices, incorporating Group IIB / VA semiconductors such phosphides, arsenides, and / or antimonides of one or more of Zn and / or Cd. In particular, the present invention relates to methodologies, resultant products, and precursors thereof in which electronic performance of the semiconductor material is improved by causing the Group IIB / VA semiconductor material to react with at least one metal-containing species (hereinafter co-reactive species) that is sufficiently co-reactive with at least one Group VA species incorporated into the Group IIB / VA semiconductor as a lattice substituent (recognizing that the same and / or another Group VA species also optionally may be incorporated into the Group IIB / VA semiconductor in other ways, e.g., as a dopant or the like).

Owner:CALIFORNIA INST OF TECH +1

Trench junction barrier controlled Schottky device with top and bottom doped regions for enhancing forward current in a vertical direction

ActiveUS7737522B2Improve utilizationEliminate requirementsTransistorSolid-state devicesDopantN type conductivity

A Schottky diode includes at least a trenched opened in a semiconductor substrate doped with a dopant of a first conductivity type wherein the trench is filled with a Schottky junction barrier metal. The Schottky diode further includes one or more dopant region of a second conductivity type surrounding sidewalls of the trench distributed along the depth of the trench for shielding a reverse leakage current through the sidewalls of the trench. The Schottky diode further includes a bottom-doped region of the second conductivity type surrounding a bottom surface of the trench and a top-doped region of the second conductivity type surrounding a top portion of the sidewalls of the trench. In a preferred embodiment, the first conductivity type is a N-type conductivity type and the middle-depth dopant region comprising a P-dopant region.

Owner:ALPHA & OMEGA SEMICON LTD

Nano grade transition metal oxidation catalyst and its preparing method and use

InactiveCN1714936AHigh activityEnhanced anti-toxicityCatalyst carriersCatalyst activation/preparationMischmetalGranularity

The present invention is efficient oxidizing catalyst for organic waste water treating and its preparation process and application. The carrier prepared with composite powder of Ti, Si, Al and RE oxide and in the average granularity smaller than 100 nm is loaded with at least two kinds of transition metal to prepare the catalyst. The catalyst contains TiO2-SiO2-Al2O3 65-85 wt%, RE oxide 5-15 wt%, and transition oxide 5-30 wt%. The preparation process of the catalyst includes preparing carrier powder with the carrier components and through precipitation, homogenization, ageing, filtering, washing, pulping, dispersing, fluidizing at supercritical condition to eliminate water and activating; forming the carrier, soaking, fluidizing and drying, and activating to obtain the catalyst. The catalyst is used in acid organic waste water treatment and has COD degrading rate higher than 95 %, ammonia nitrogen oxidizing conversion rate higher than 99 % and chroma eliminating rate higher than 95 %.

Owner:CNPC JILIN CHEM GROUP CORP

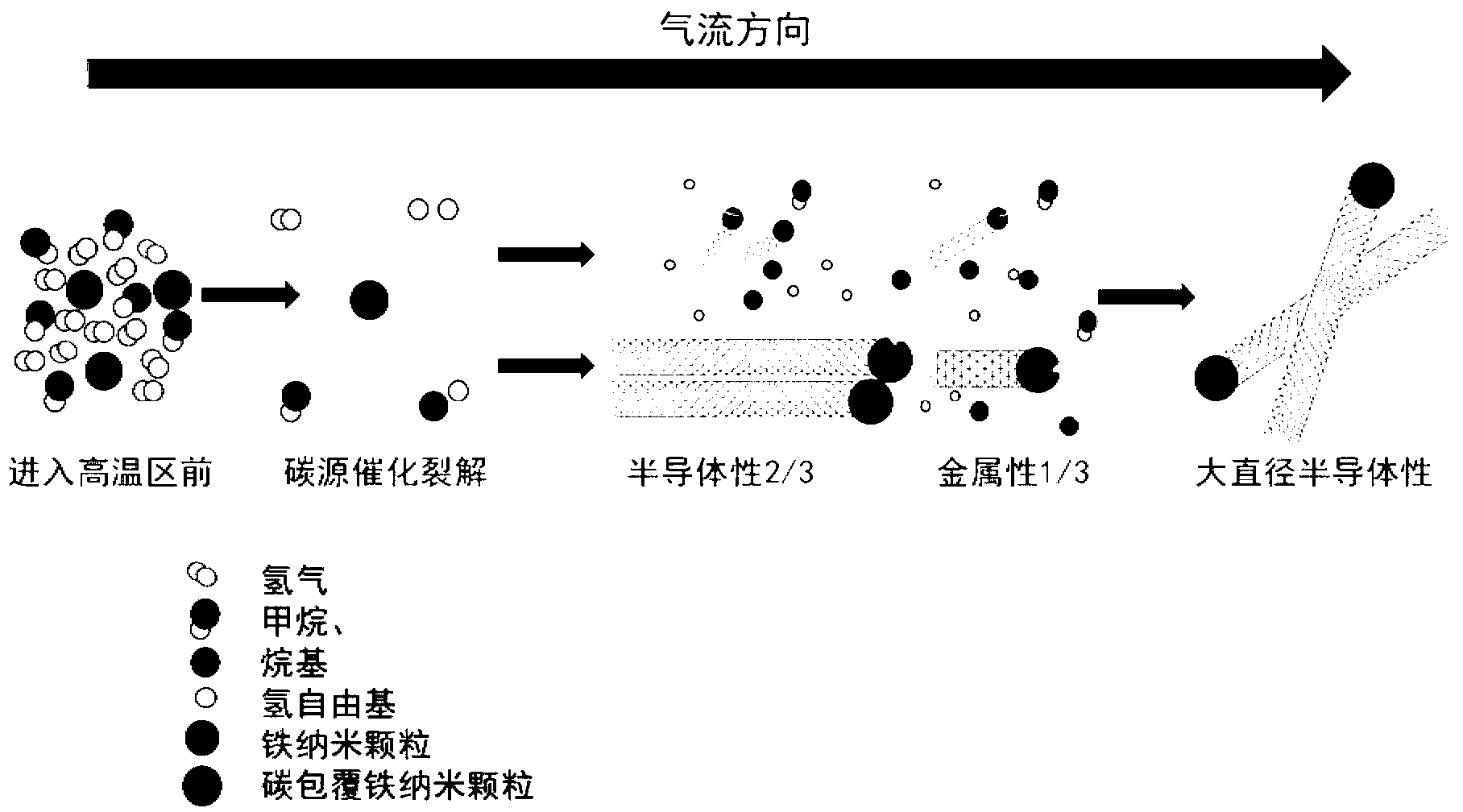

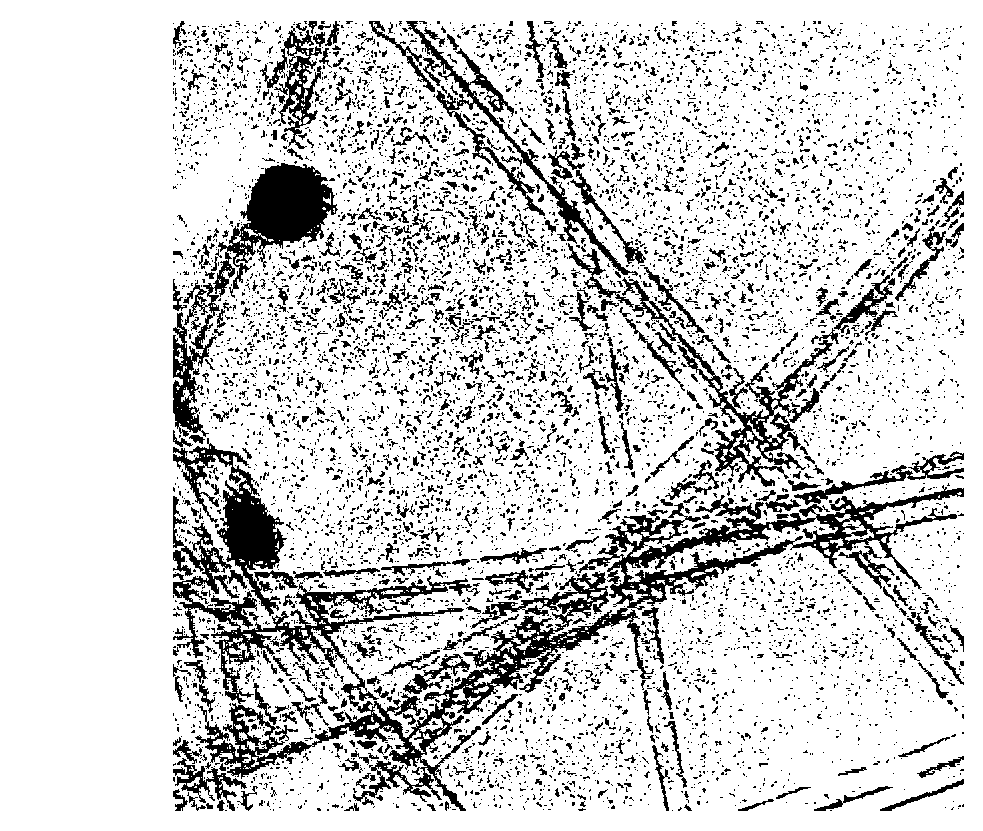

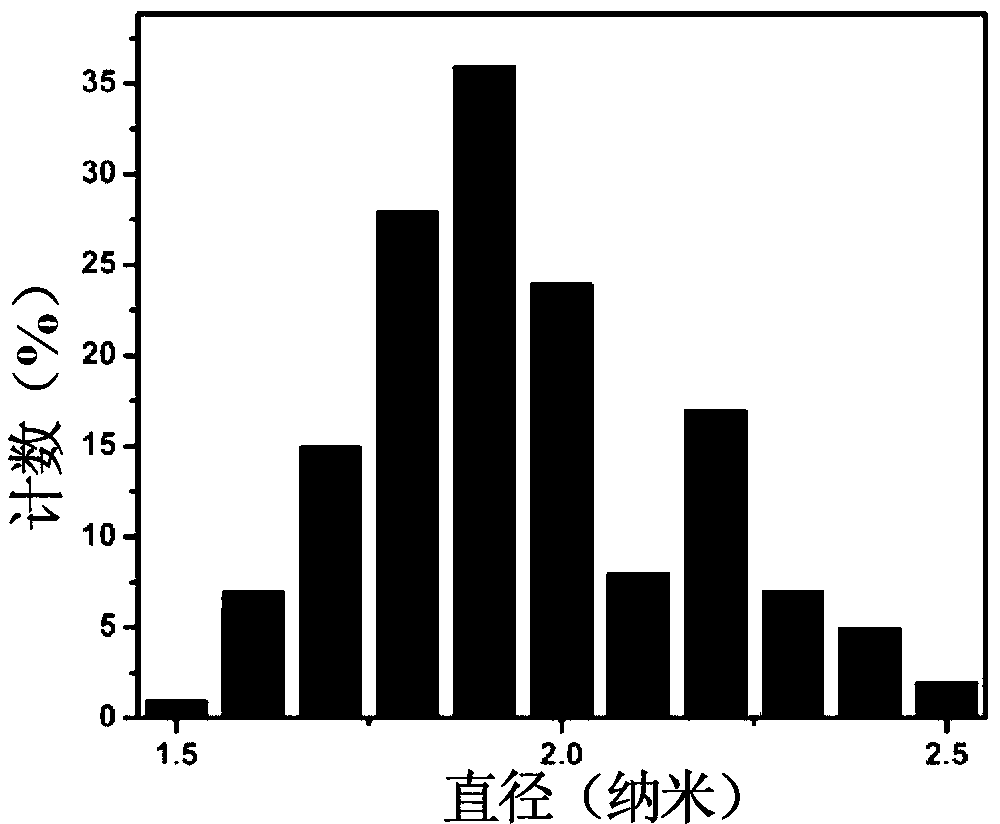

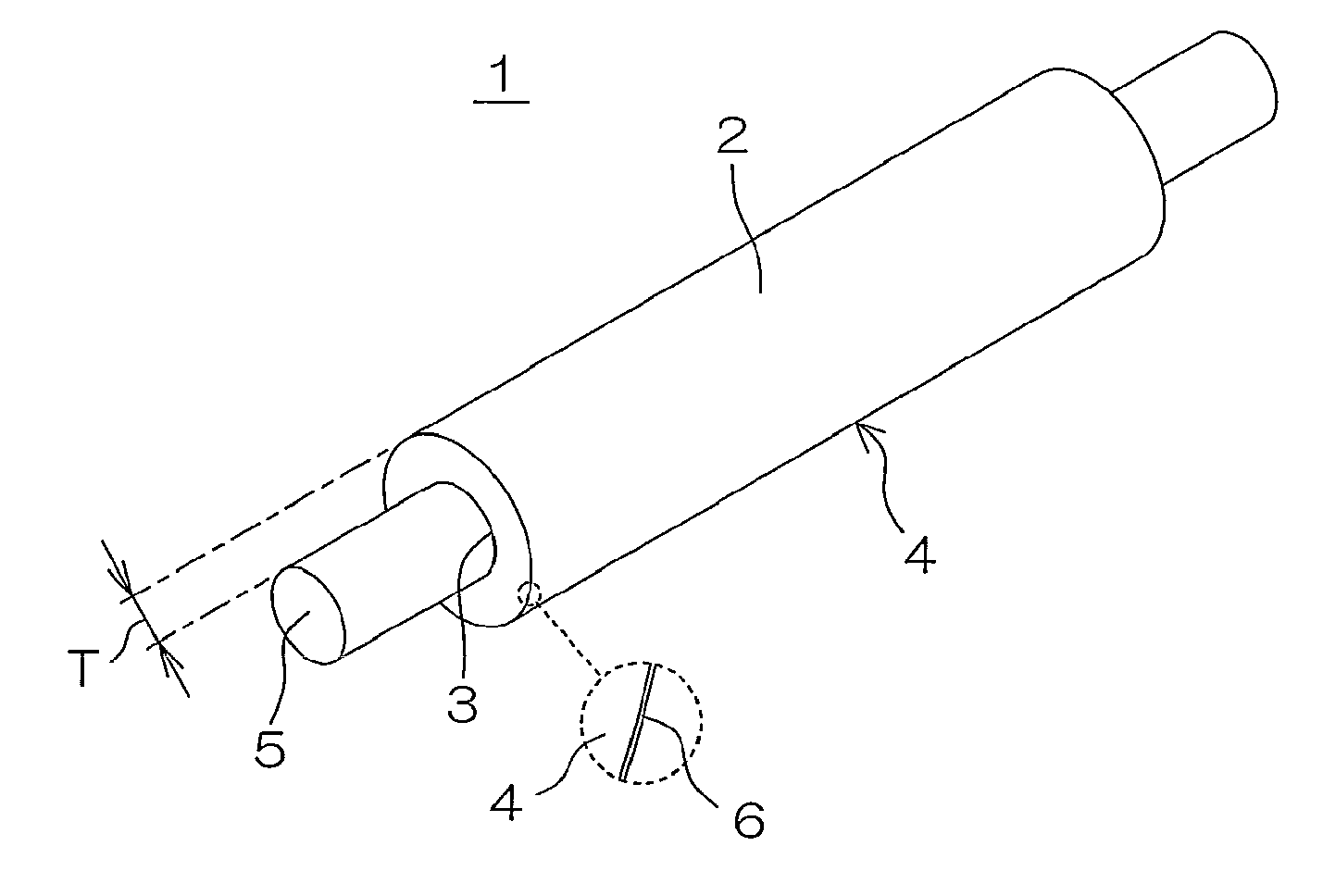

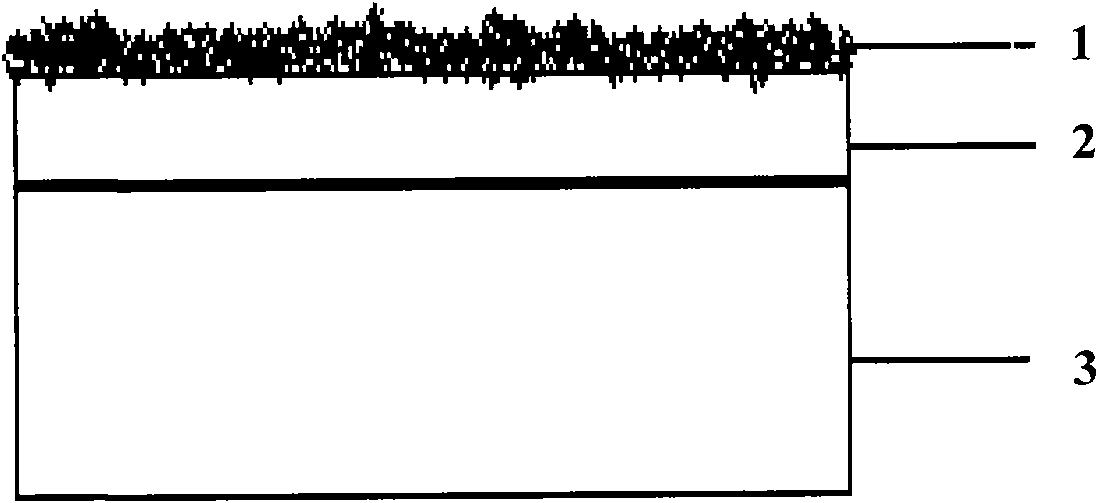

Method for growing high-quality semiconductor single-walled carbon nanotube through in-situ weak hydrogen etching

ActiveCN103011130AQuality improvementGood semiconductor performanceCarbon nanotubesNanotechnologyHydrogenSulfur

The invention relates to the field of fabrication of a high-quality semiconductor single-walled carbon nanotube, in particular to a method for directly growing the high-quality semiconductor single-walled carbon nanotube through in-situ weak hydrogen etching. A metallic and small-diameter single-walled carbon nanotube can be etched in situ at a certain reaction temperature by regulating and optimizing a flow of carrier gas, namely hydrogen and under the conditions of taking dicyclopentadienyl iron as a catalyst precursor, sulfur powder as a growth promoter and organic low-carbon hydrocarbon as a carbon source; and the high-quality semiconductor-superior single-walled carbon nanotube is finally obtained. The content of the semiconductor single-walled carbon nanotube is greater than or equal to 91wt%, the diameter distribution is between 1.5nm and 2.5nm, and the highest concentrated oxidation temperature reaches 800 DEG. With the adoption of the method, the massive, fast and low-cost controlled growth of the semiconductor single-walled carbon nanotube with the narrower diameter distribution and the high quality is realized, and the problems such as serious damages to a sample due to a strong etching agent, complexity of a fabrication process, low output and high cost during a selective fabrication course of a conduction-superior single-walled carbon nanotube can be effectively solved.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

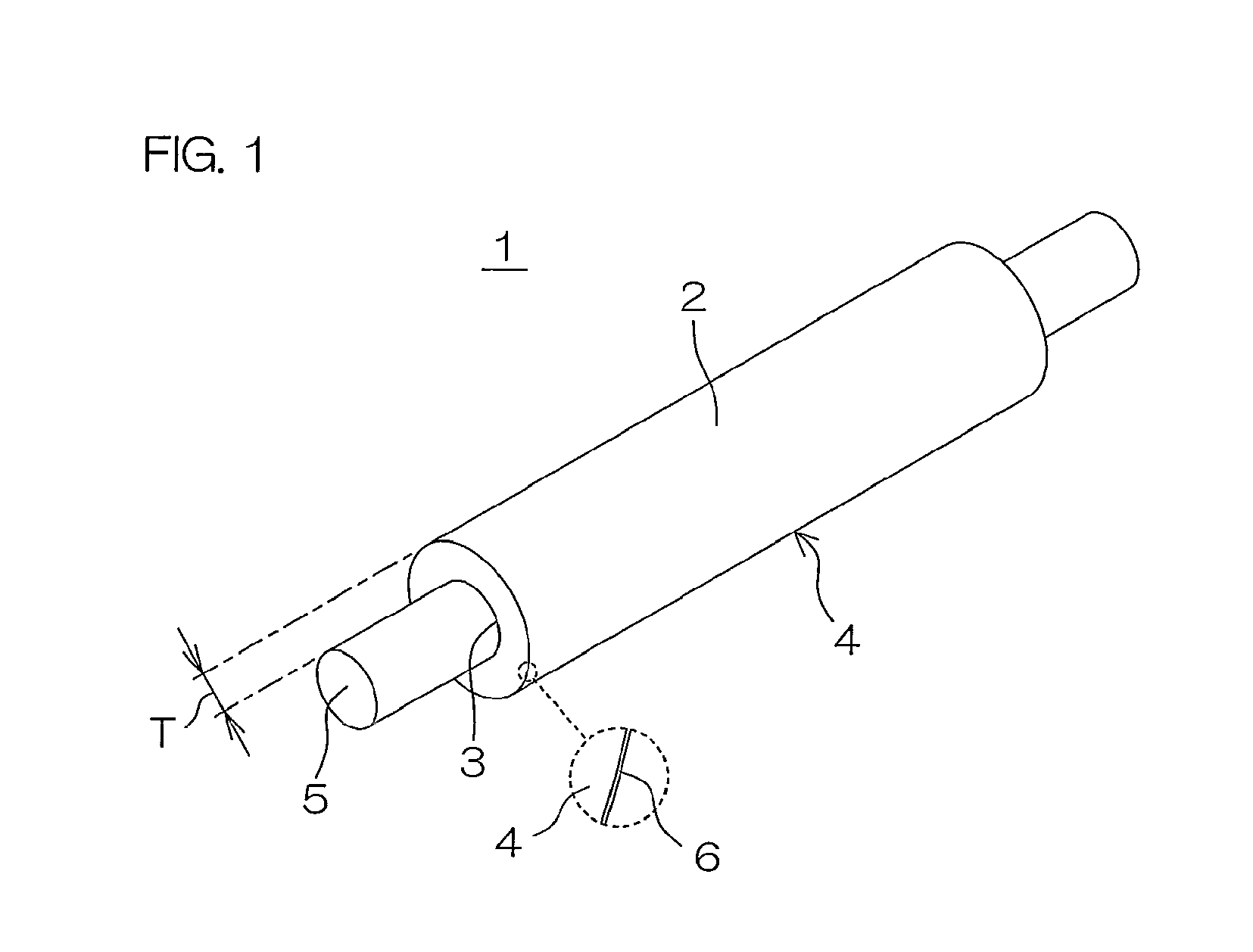

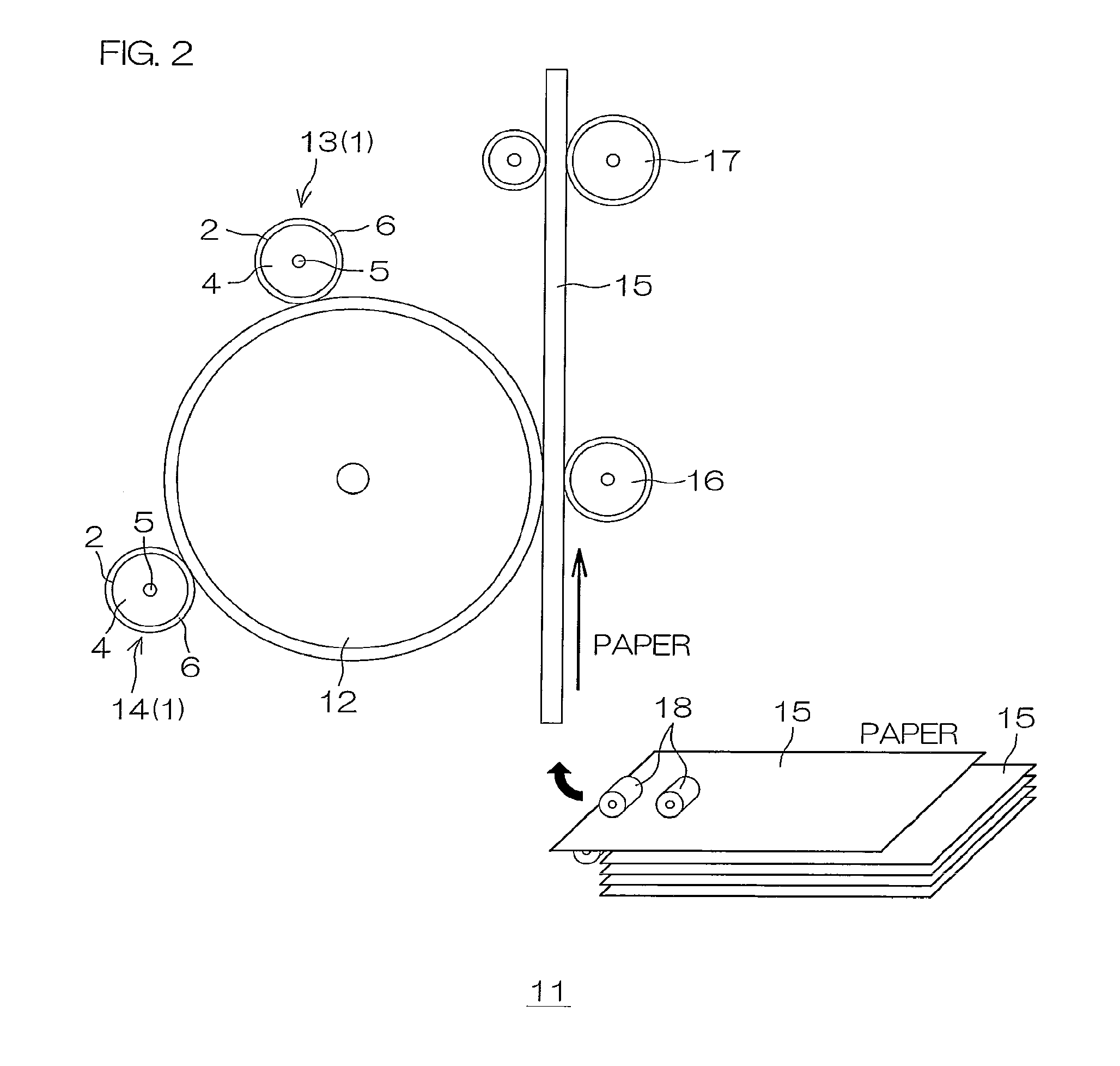

Semiconductive roller, charging roller and electrophotographic apparatus

ActiveUS20110281703A1Avoid stainsGood semiconductor performanceLiquid surface applicatorsShaft and bearingsPolymer scienceThiourea

The semiconductive roller according to the present invention includes: a roller body having an outer peripheral surface made of a semiconductive rubber composition; and an oxide film covering the outer peripheral surface of the roller body, while the semiconductive rubber composition contains a base polymer and a crosslinking component for crosslinking the base polymer, the base polymer is a mixture of a bicopolymer E containing epichlorohydrin and nitrile-butadiene rubber N, the mass ratio E / N of the bicopolymer E and the nitrile-butadiene rubber N in the mixture is 50 / 50 to 80 / 20, and the crosslinking component includes a thiourea-based crosslinking component for crosslinking the bicopolymer E and a sulfur-based vulcanizing component for vulcanizing the nitrile-butadiene rubber N.

Owner:SUMITOMO RUBBER IND LTD

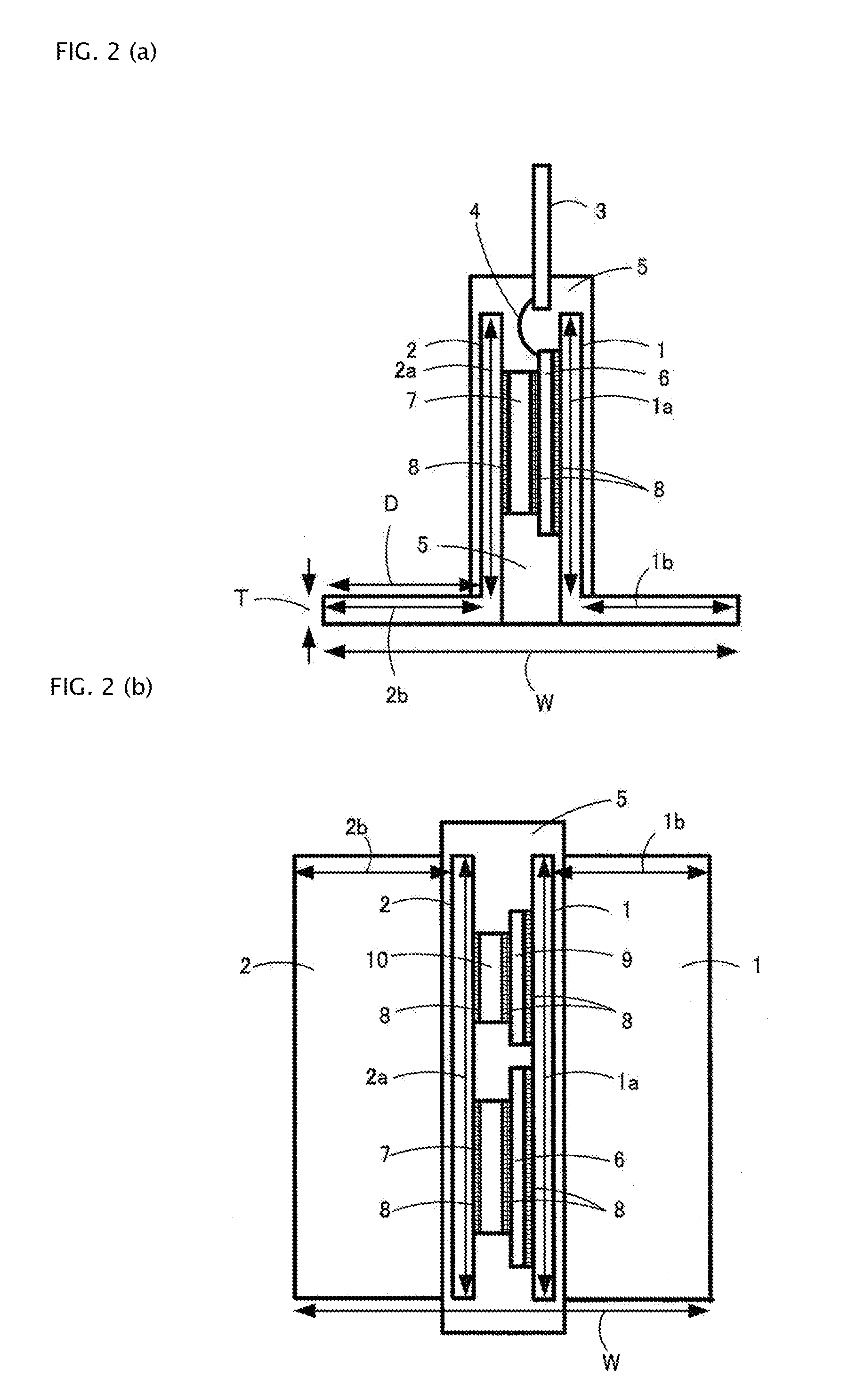

Semiconductor unit and semiconductor apparatus using same

InactiveUS20110278643A1Small sizeImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectrically conductive

A semiconductor unit of certain aspects of the invention includes electrically conductive plates in the shape of the letter L, each consisting of a horizontally disposed leg portion and a vertically disposed flat body portion that is perpendicular to a cooling plate adhered to the bottom of the semiconductor unit. A pair of the vertically disposed flat body portions sandwiches a semiconductor chip. Owing to this construction, the heat generated in the semiconductor chip can be conducted away through the both surfaces of the chip, thus improving cooling performance. Since the heat is conducted away through the leg portions of the L-shaped electrically conductive plates a projected planar area occupied by the cooling plate required for cooling the semiconductor unit is reduced. Therefore, the size of the semiconductor unit can be reduced.

Owner:FUJI ELECTRIC CO LTD

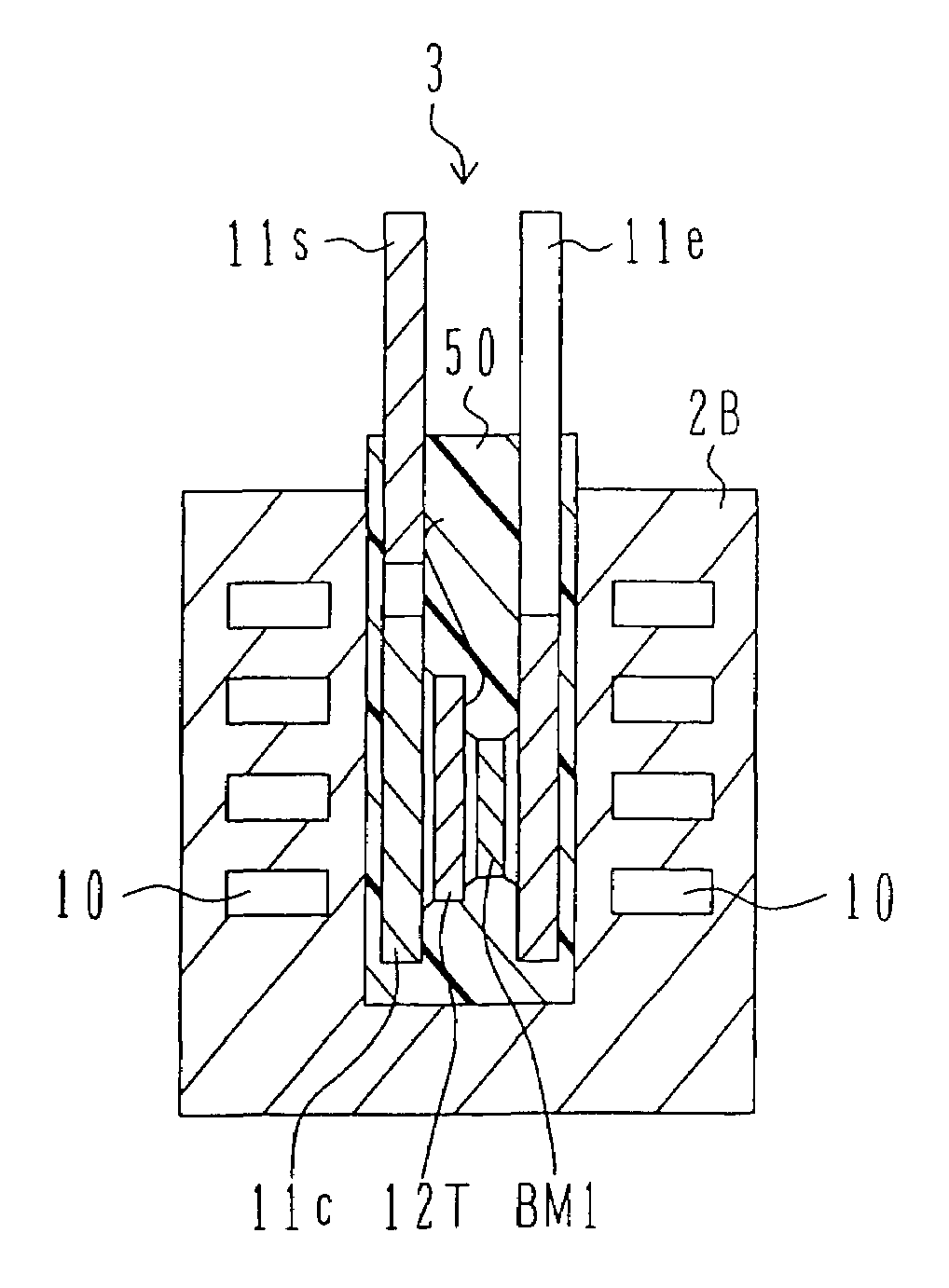

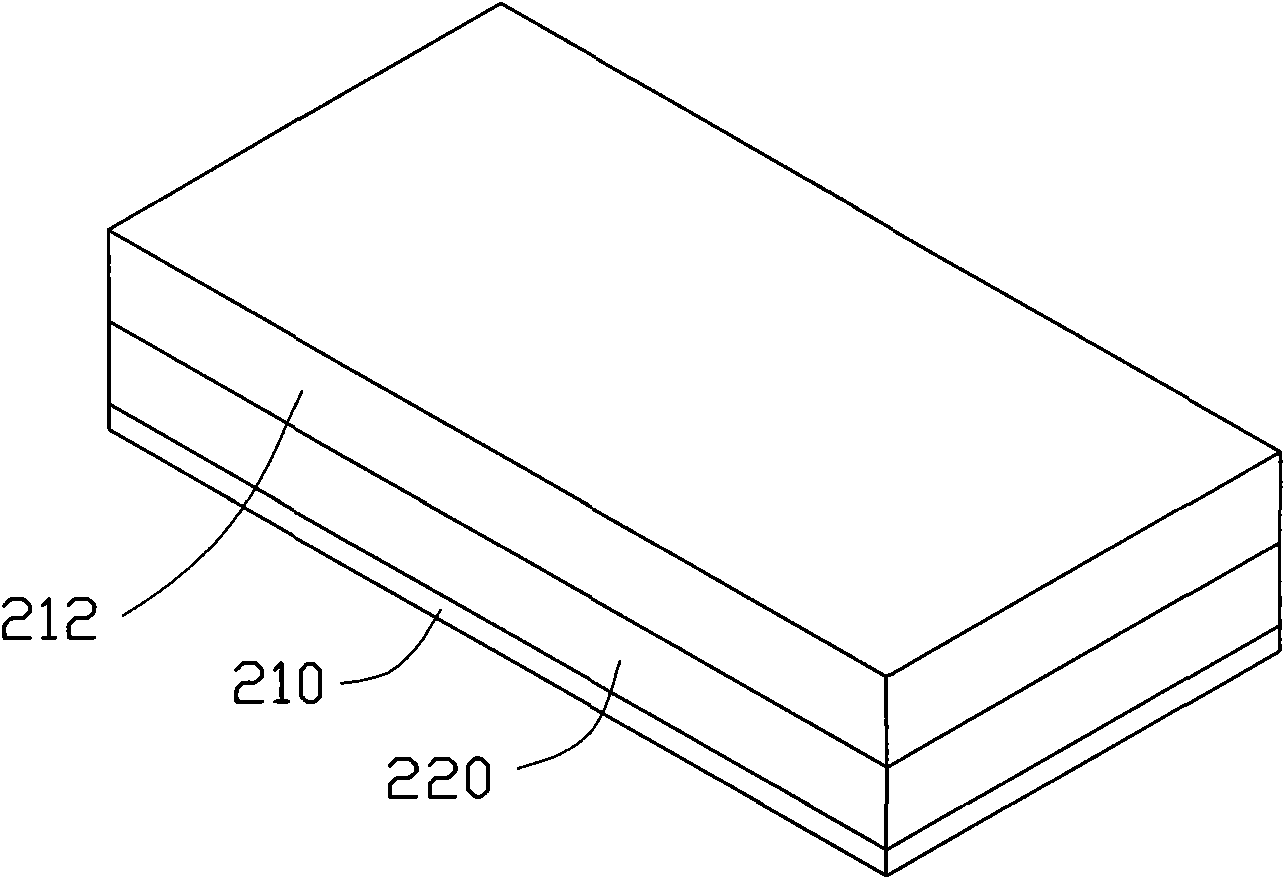

Method and structure to enhance temperature/humidity/bias performance of semiconductor devices by surface modification

InactiveUS20050116357A1Good semiconductor performanceLow cost methodSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipApplication specific

A method is disclosed of repairing wirebond damage on semiconductor chips such as high speed semiconductor microprocessors, application specific integrated circuits (ASICs), and other high speed integrated circuit devices, particularly devices using low-k dielectric materials. The method involves surface modification using reactive liquids. In a preferred embodiment, the method comprises applying a silicon-containing liquid reagent precursor such as TEOS to the surface of the chip and allowing the liquid reagent to react with moisture to form a solid dielectric plug or film (50) to produce a barrier against moisture ingress, thereby enhancing the temperature / humidity / bias (THB) performance of such semiconductor devices.

Owner:GLOBALFOUNDRIES INC

Thienothiophene quinone-type organic photoelectric material, its preparation method and application

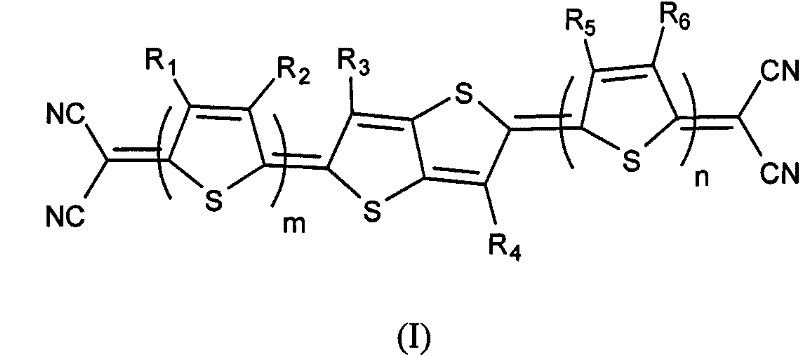

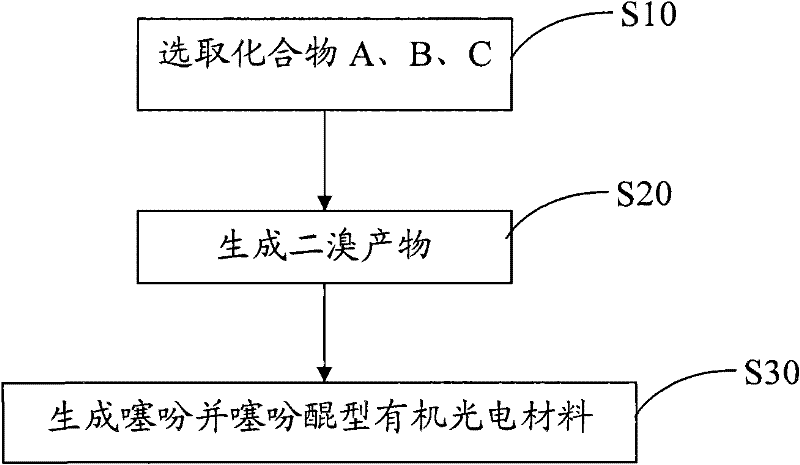

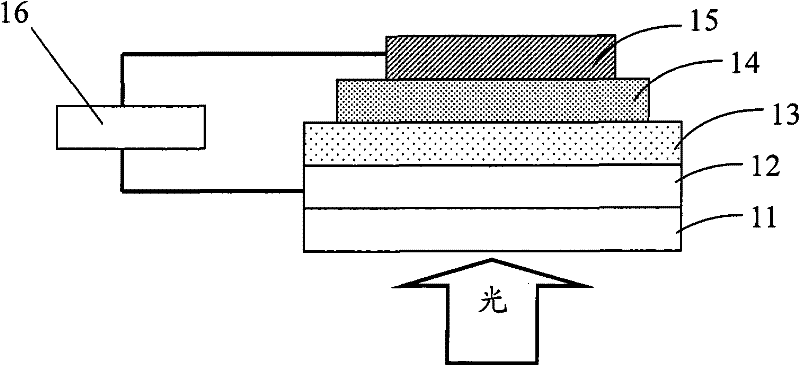

InactiveCN102276801AModerate bandgapImprove photoelectric conversion efficiencyLaser active region structureSolid-state devicesSpectral responseThermal stability

The invention relates to the technical field of organic materials and provides a thienothiophene quinoid organic photoelectric material. The material is a compound which is shown as a structural formula (I); in the formula, R1, R2, R3, R4, R5 and R6 are selected from H, C1-C20 alkyl group or C1-C20 alkoxyl group; and m and n are integers of 0-10. The invention also provides a preparation method and application of the thienothiophene quinoid organic photoelectric material. Since the thienothiophene quinoid organic photoelectric material has a quinoid thiophene ring and a cyano group, wider spectral response is guaranteed, the photoelectric conversion efficiency of the material is increased, and better thermal stability and environmental stability are shown.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +1

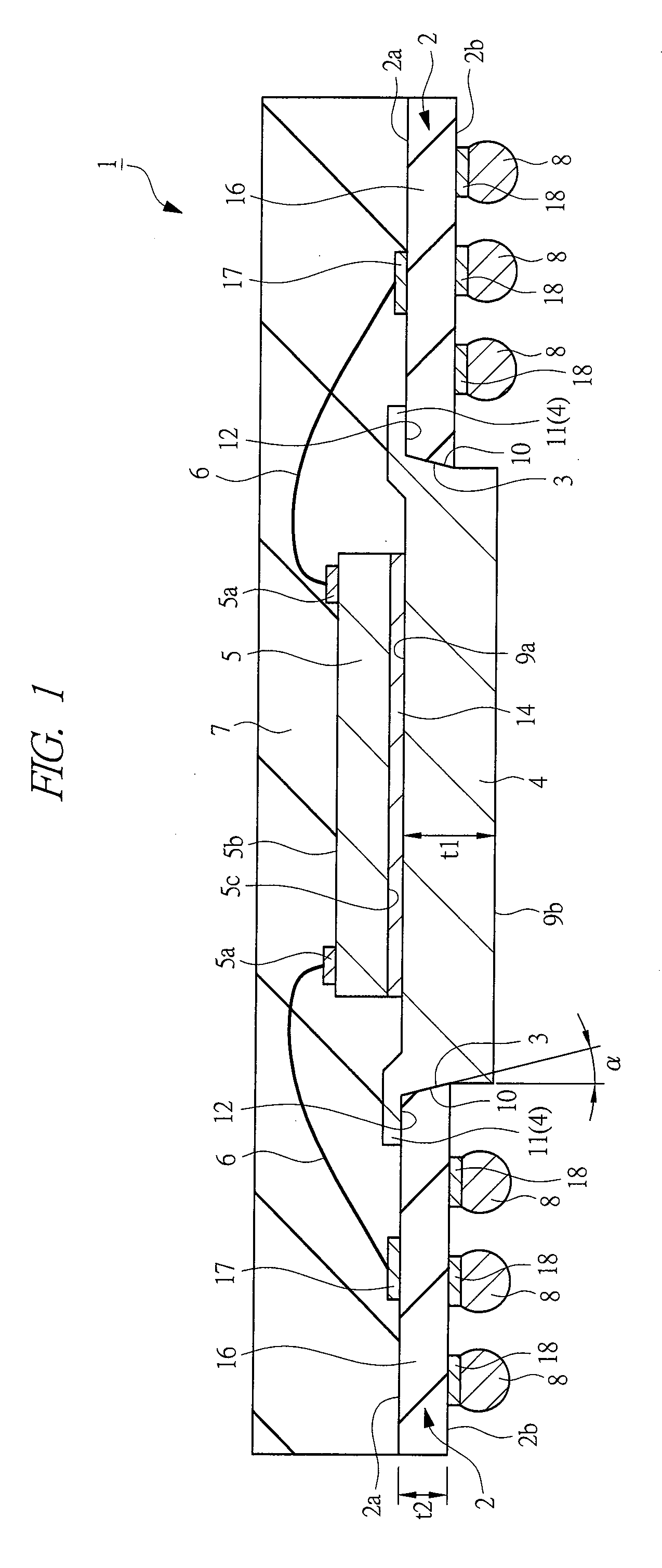

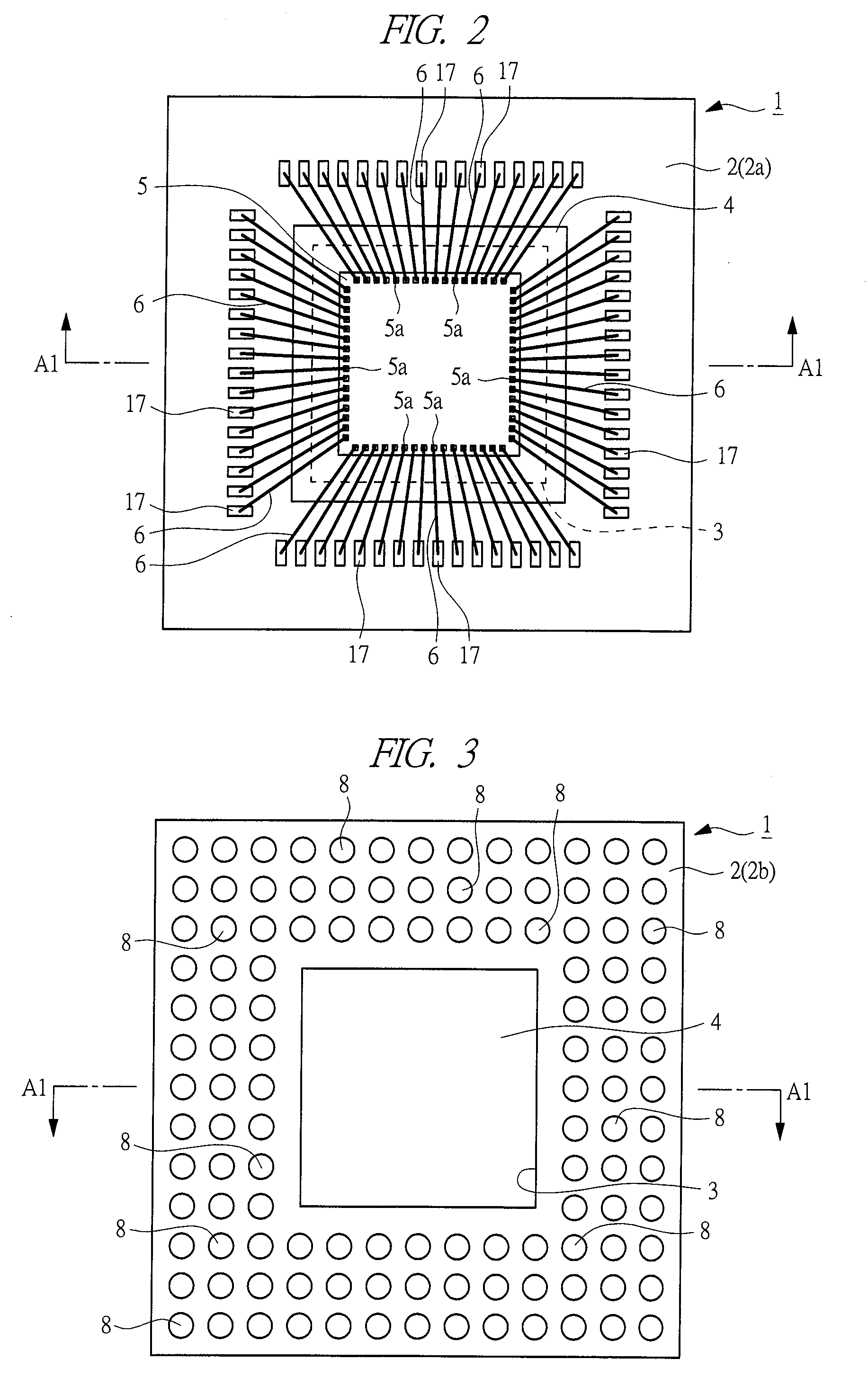

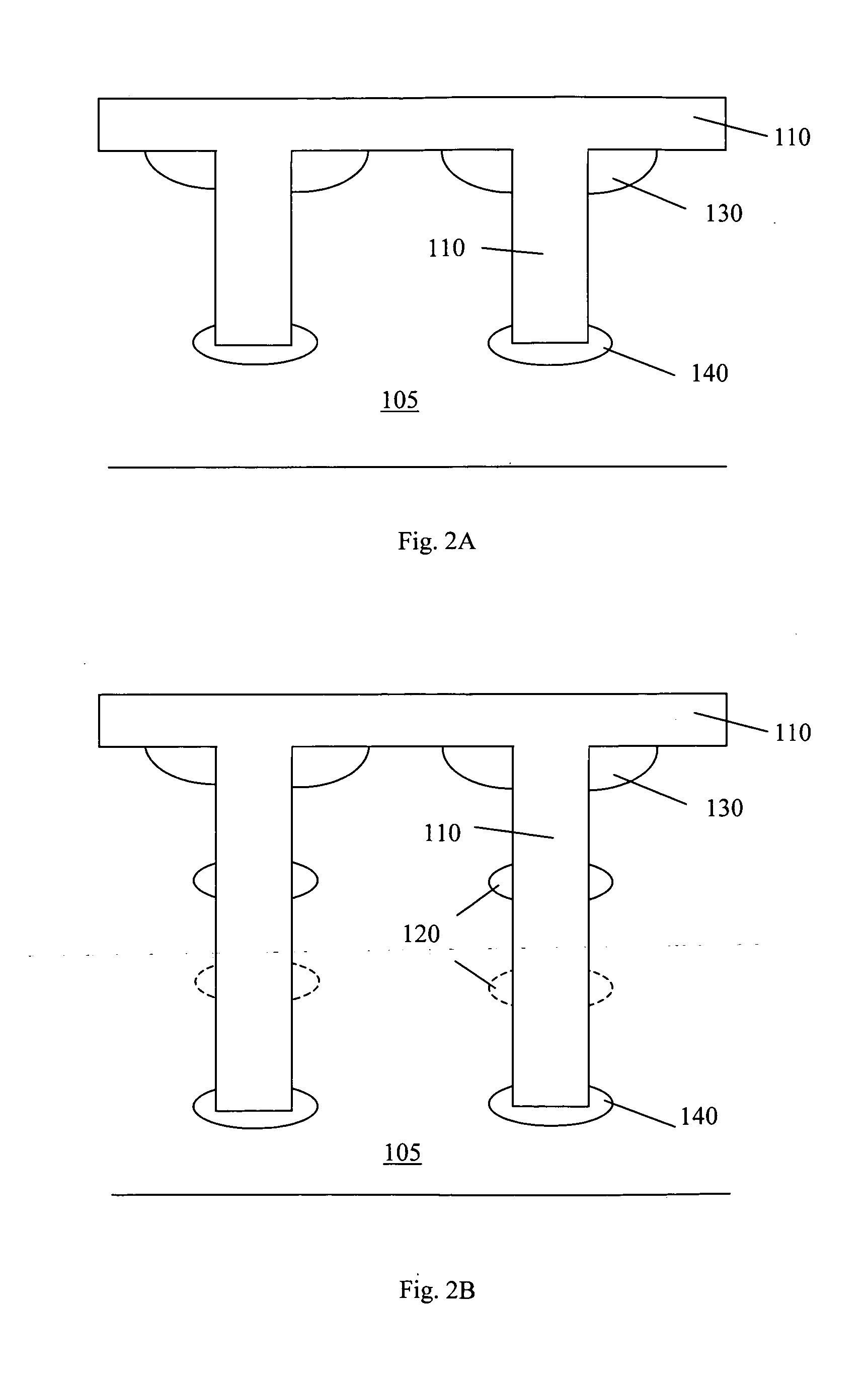

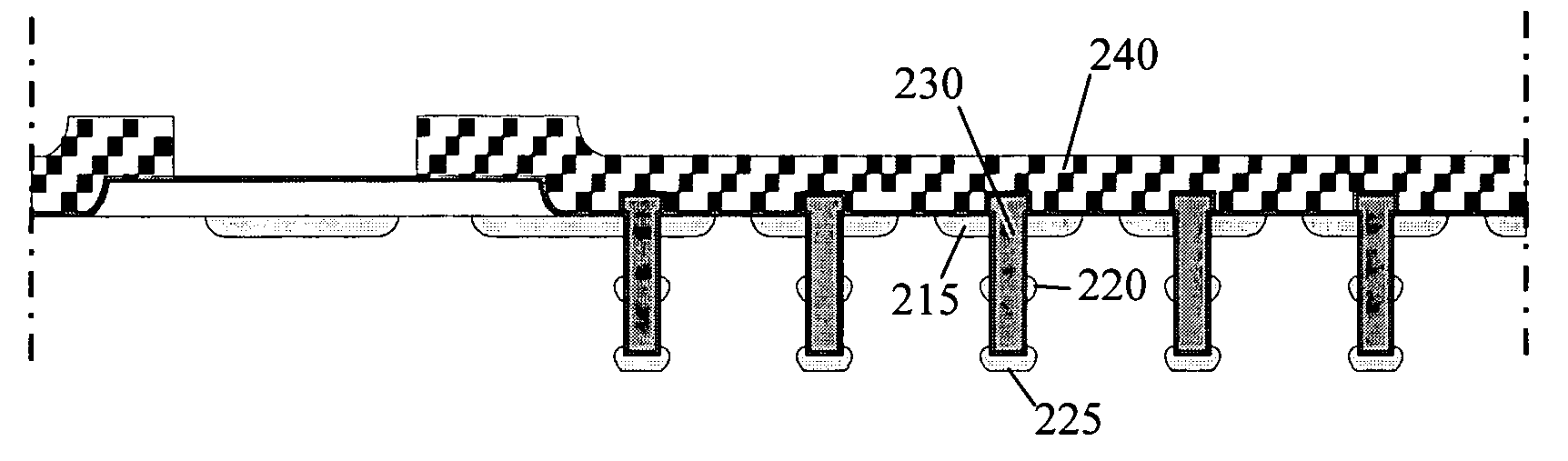

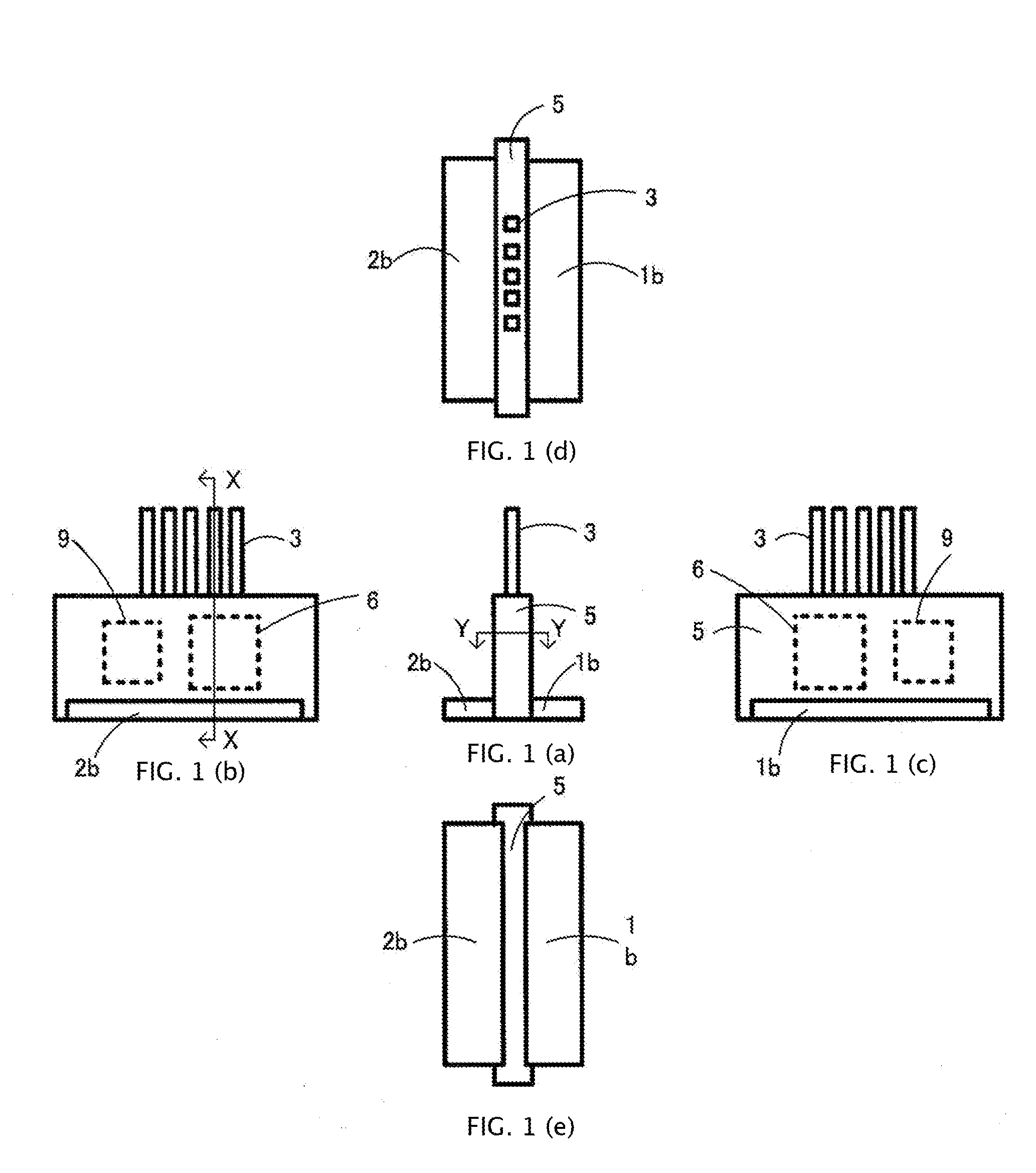

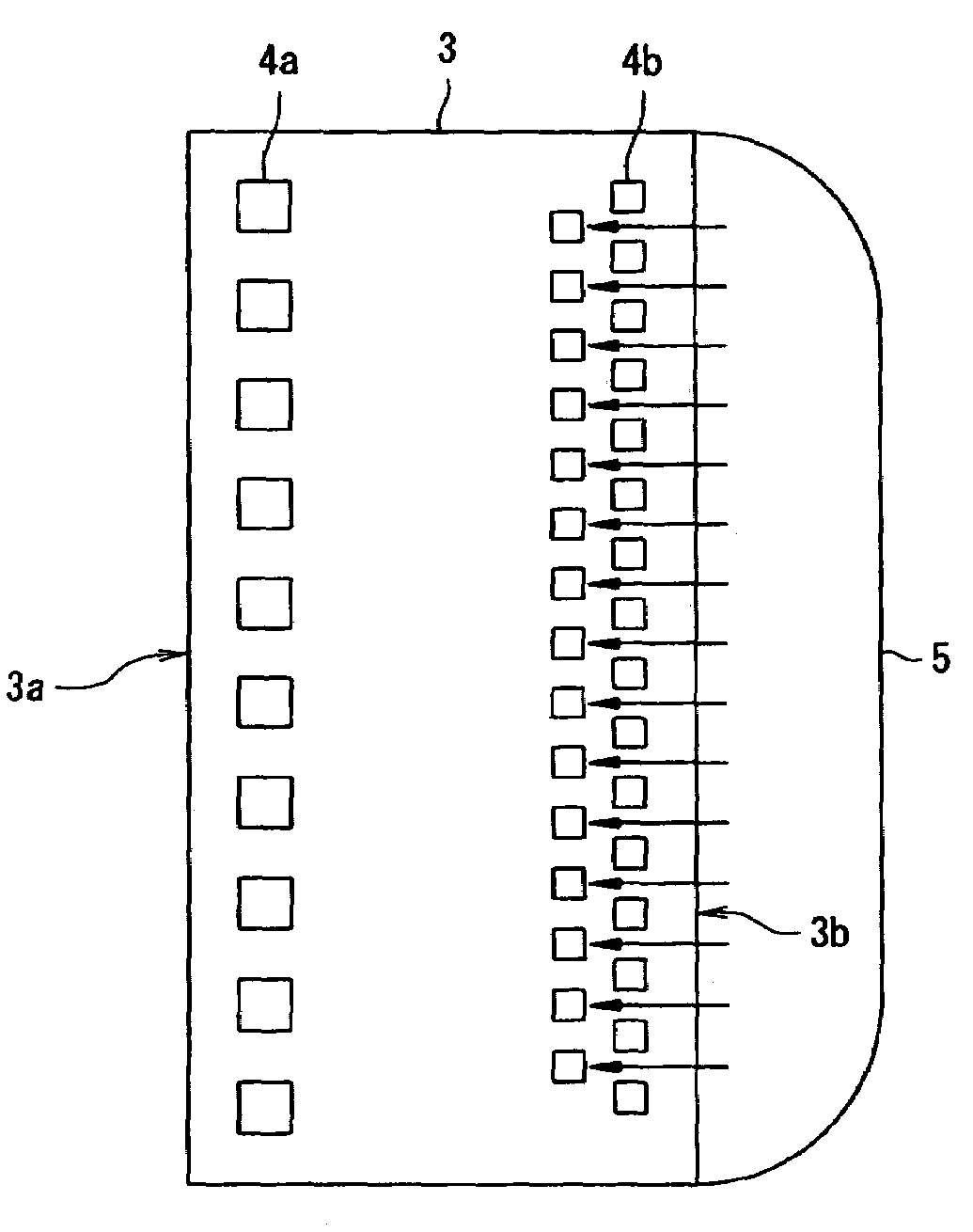

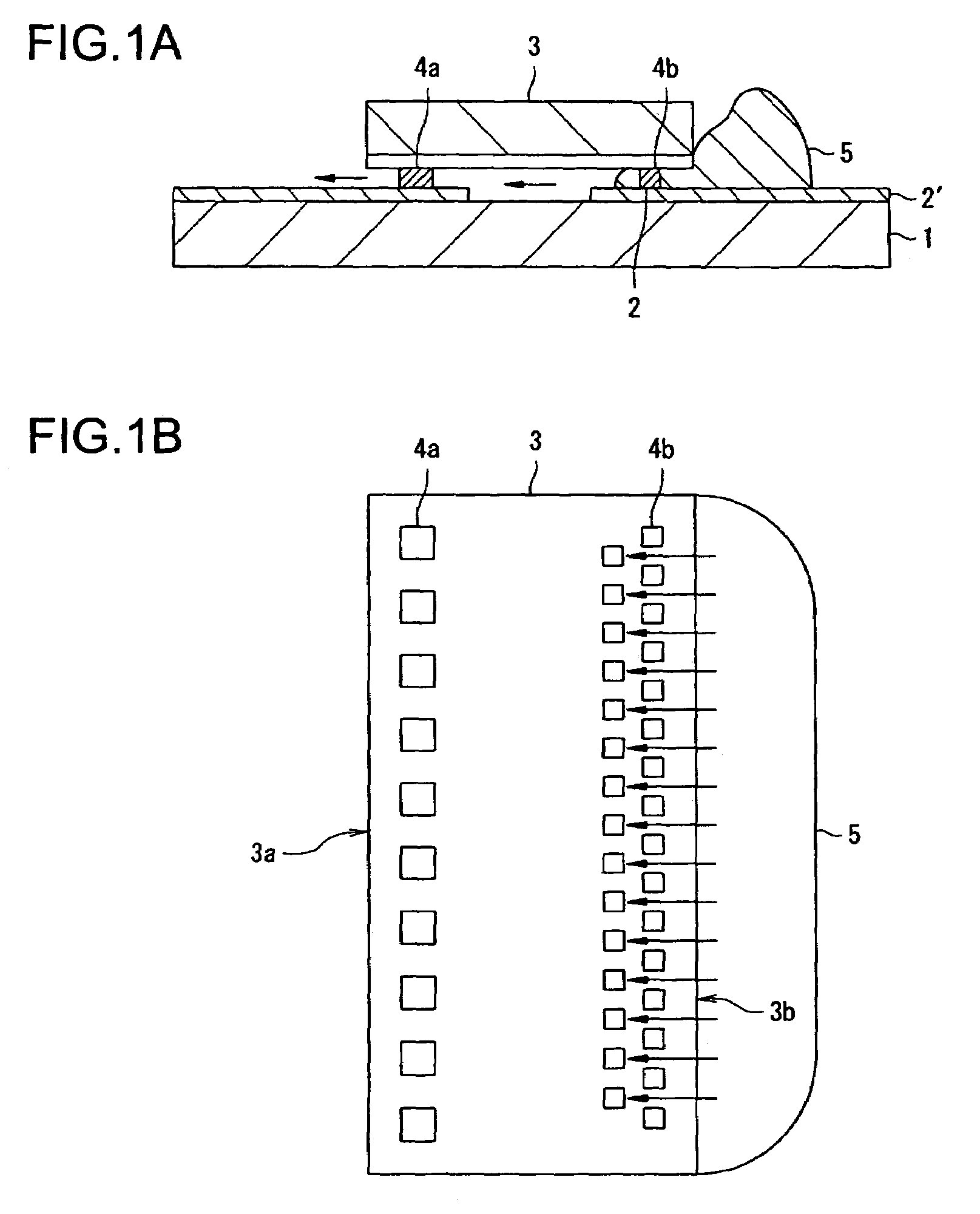

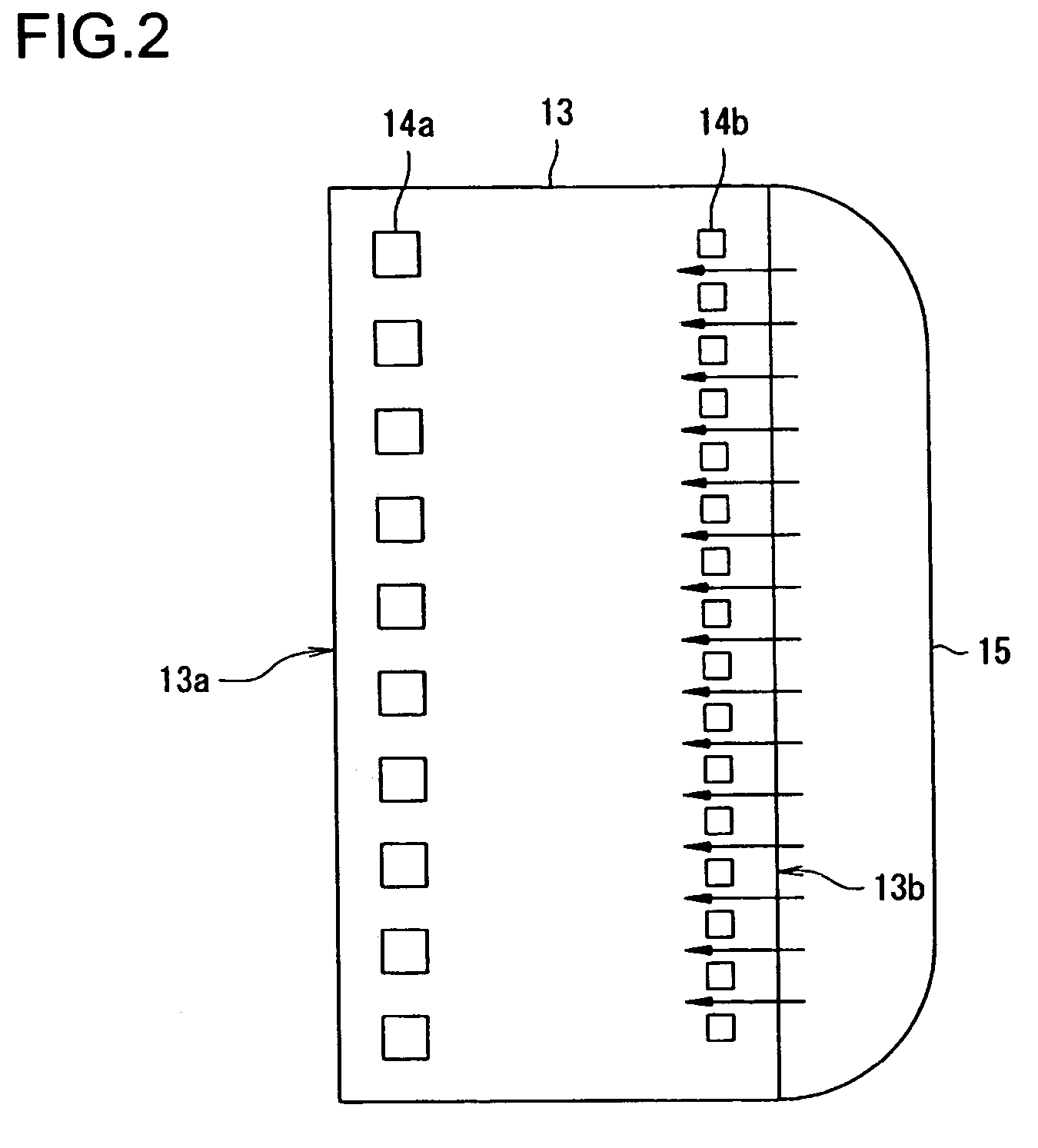

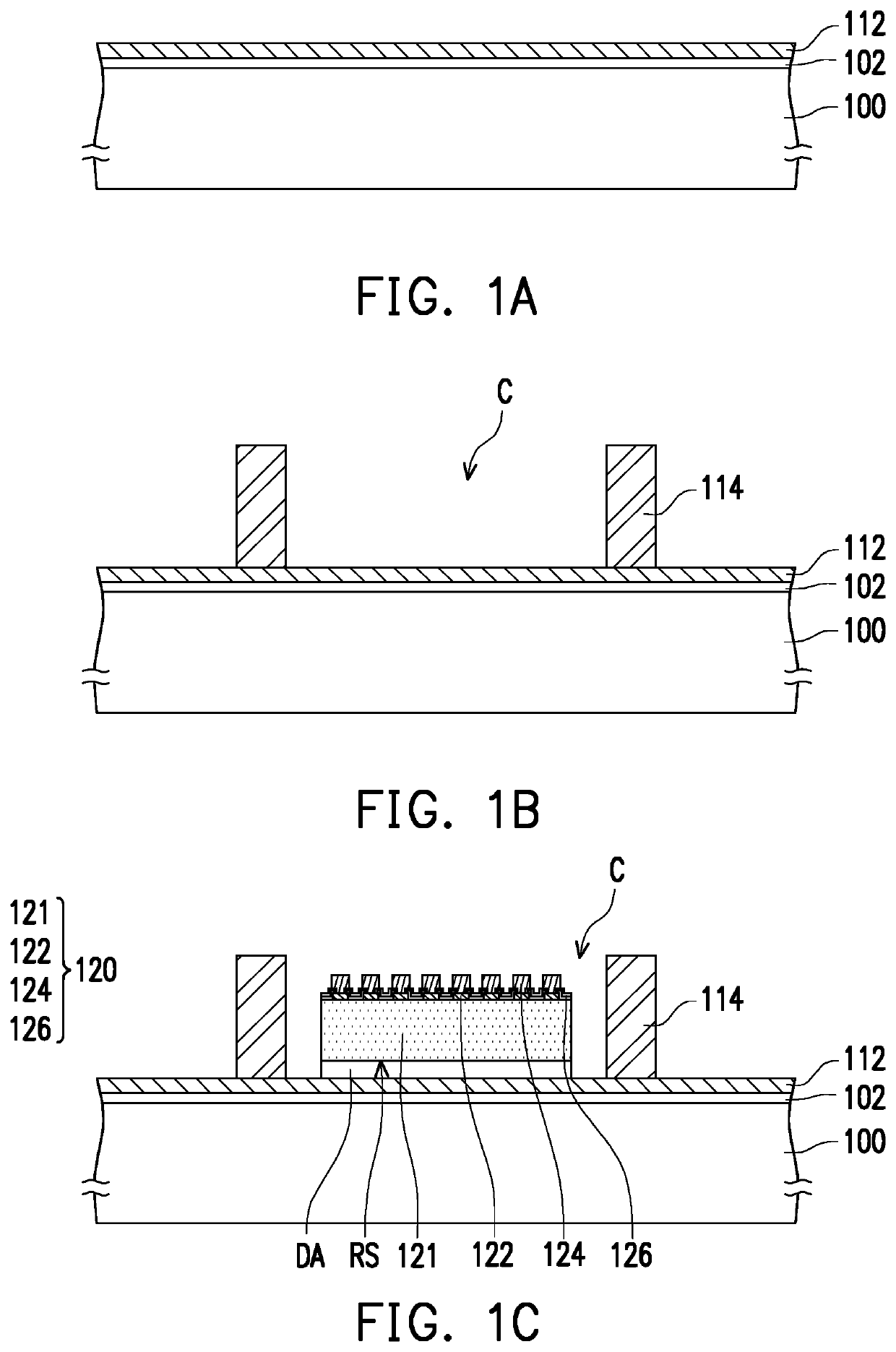

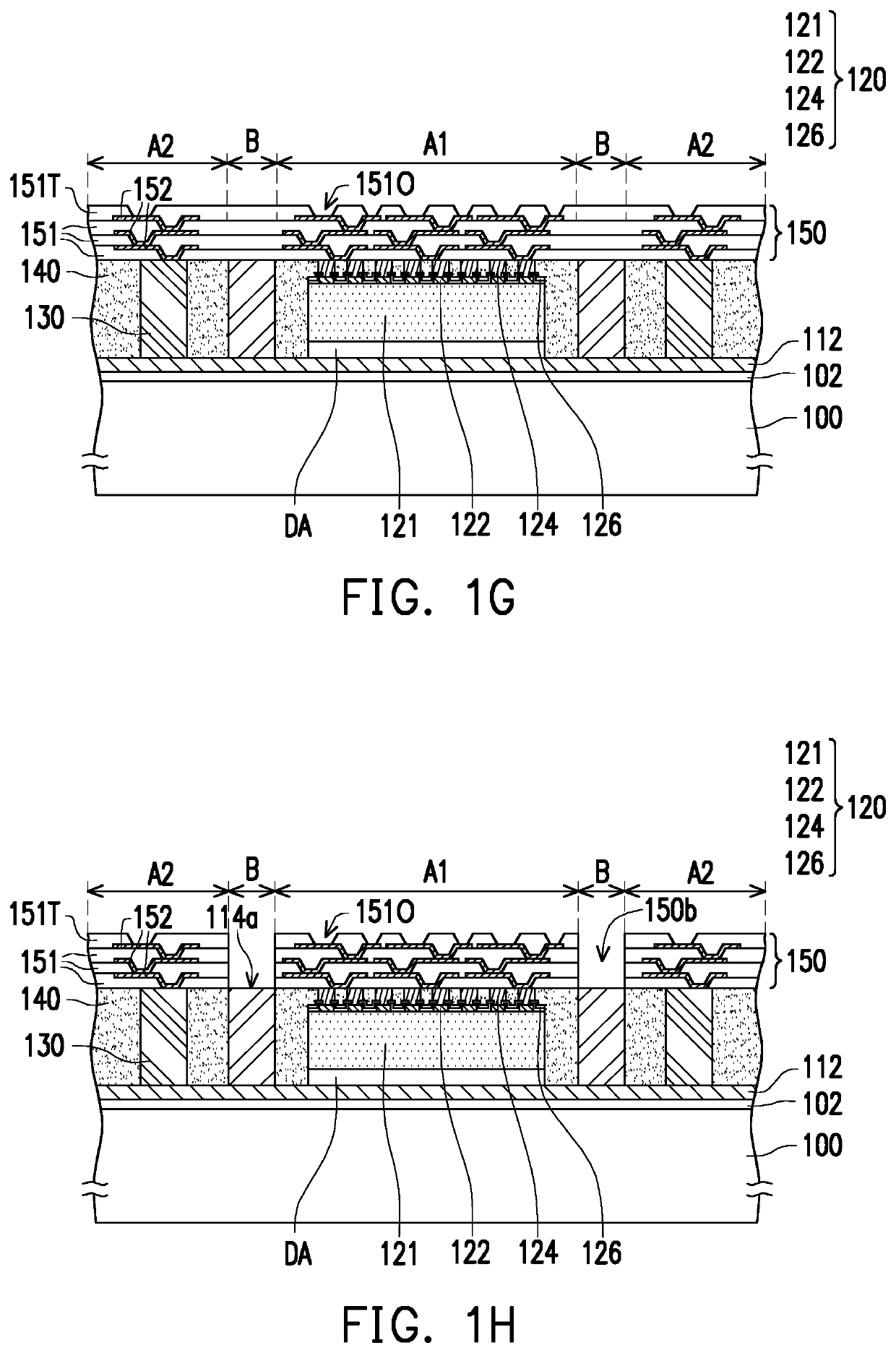

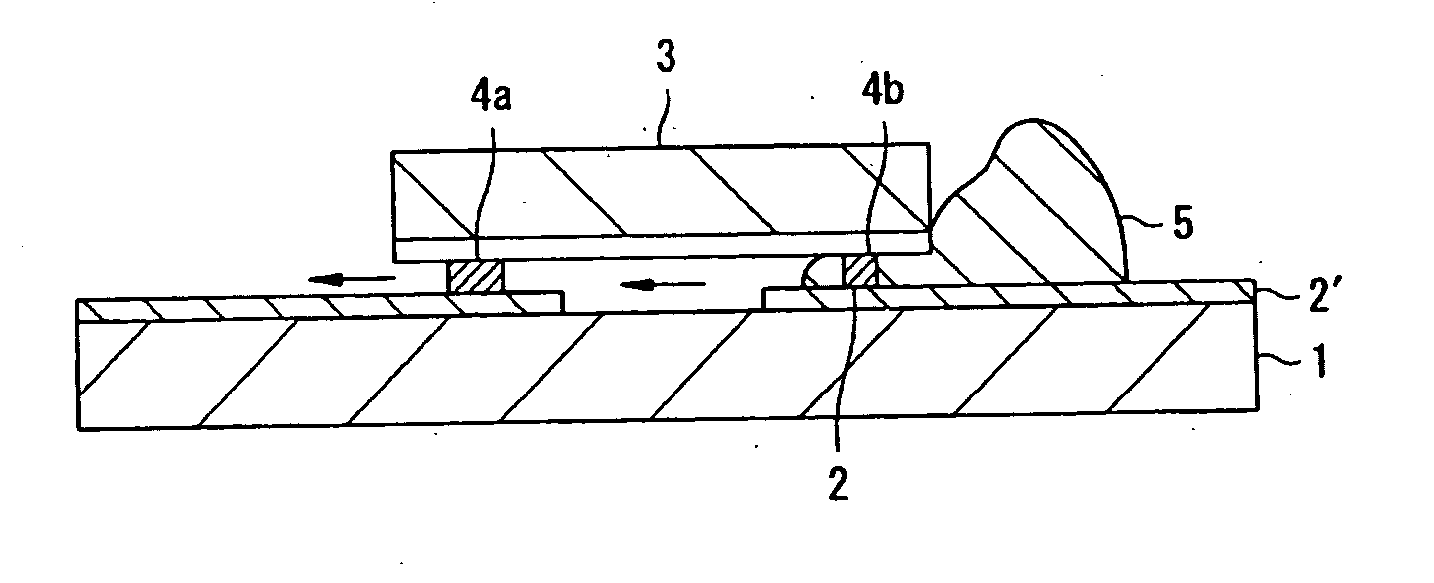

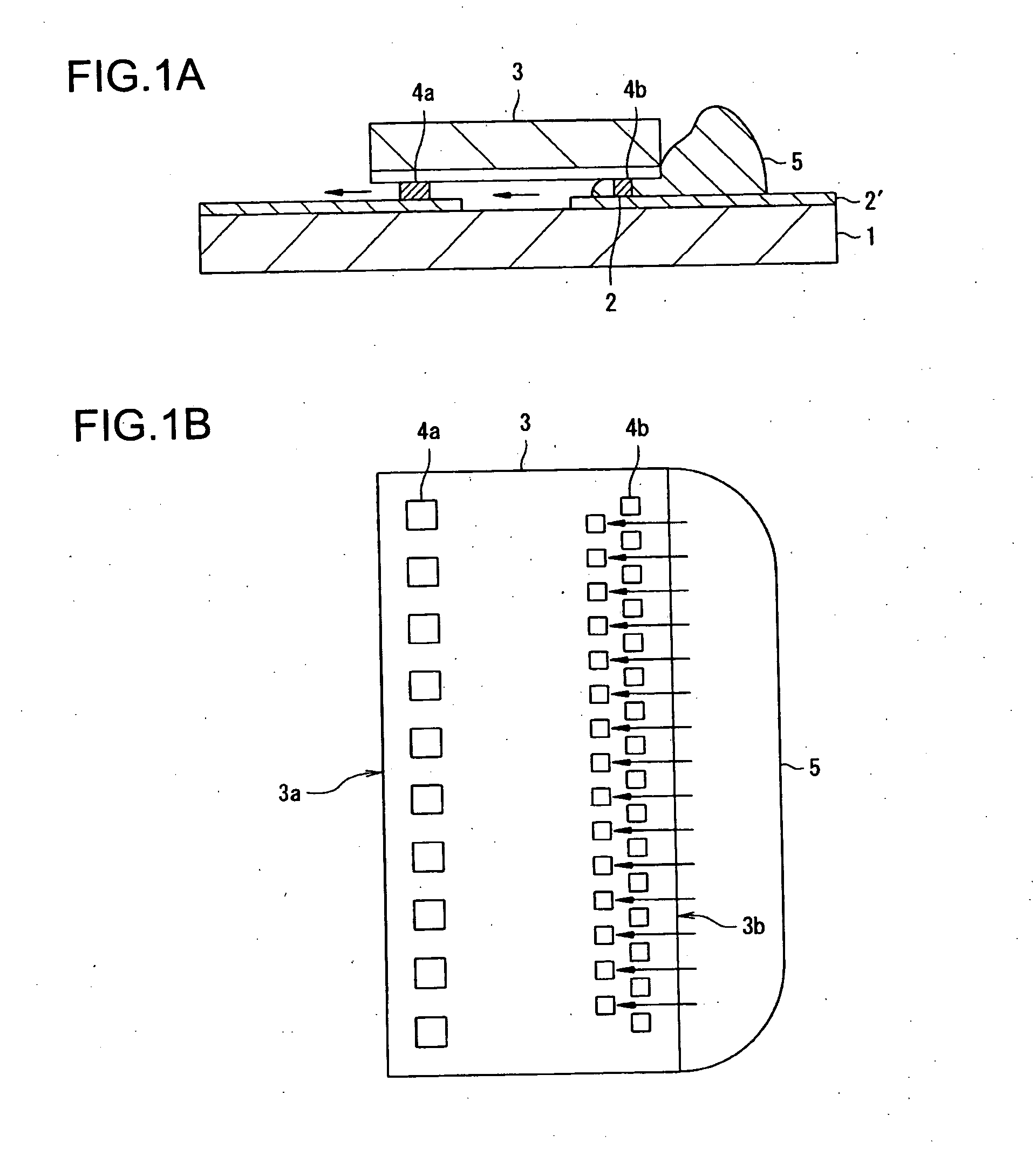

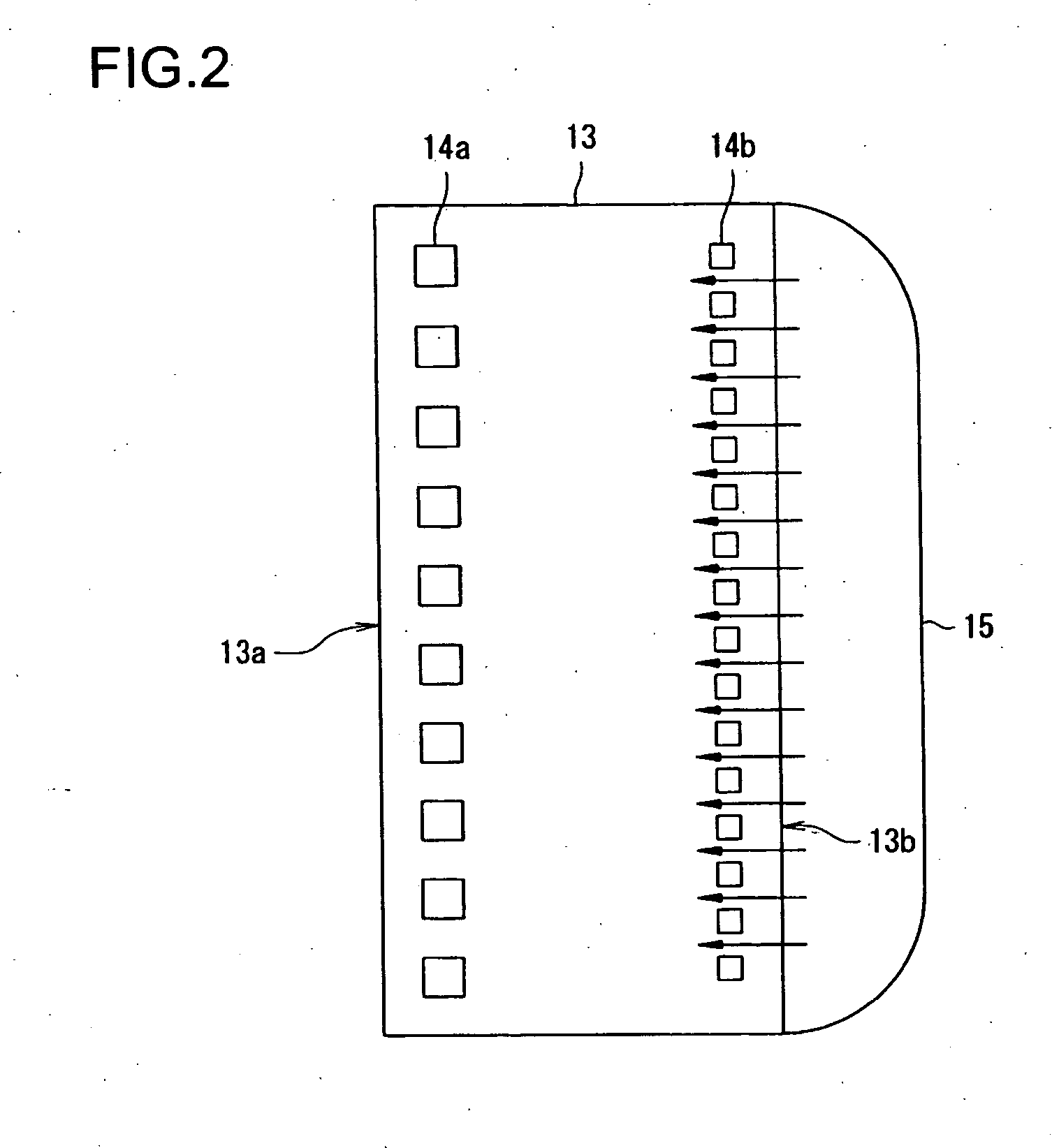

Manufacturing method of semiconductor device, including differently spaced bump electrode arrays

ActiveUS7144758B2InhibitionWithout increasing complex and laborious handling in manufacturing processesSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

First bump electrodes are arrayed in a straight line along a first side of a semiconductor chip. Second bump electrodes are more narrowly arrayed in a zigzag arrangement along a second side of the chip. By carrying out an injection of a sealing resin from the second side on which the second bump electrodes are arrayed, a surface of the semiconductor chip that is subjected to face-down mounting on a film substrate is sealed.

Owner:SEIKO EPSON CORP

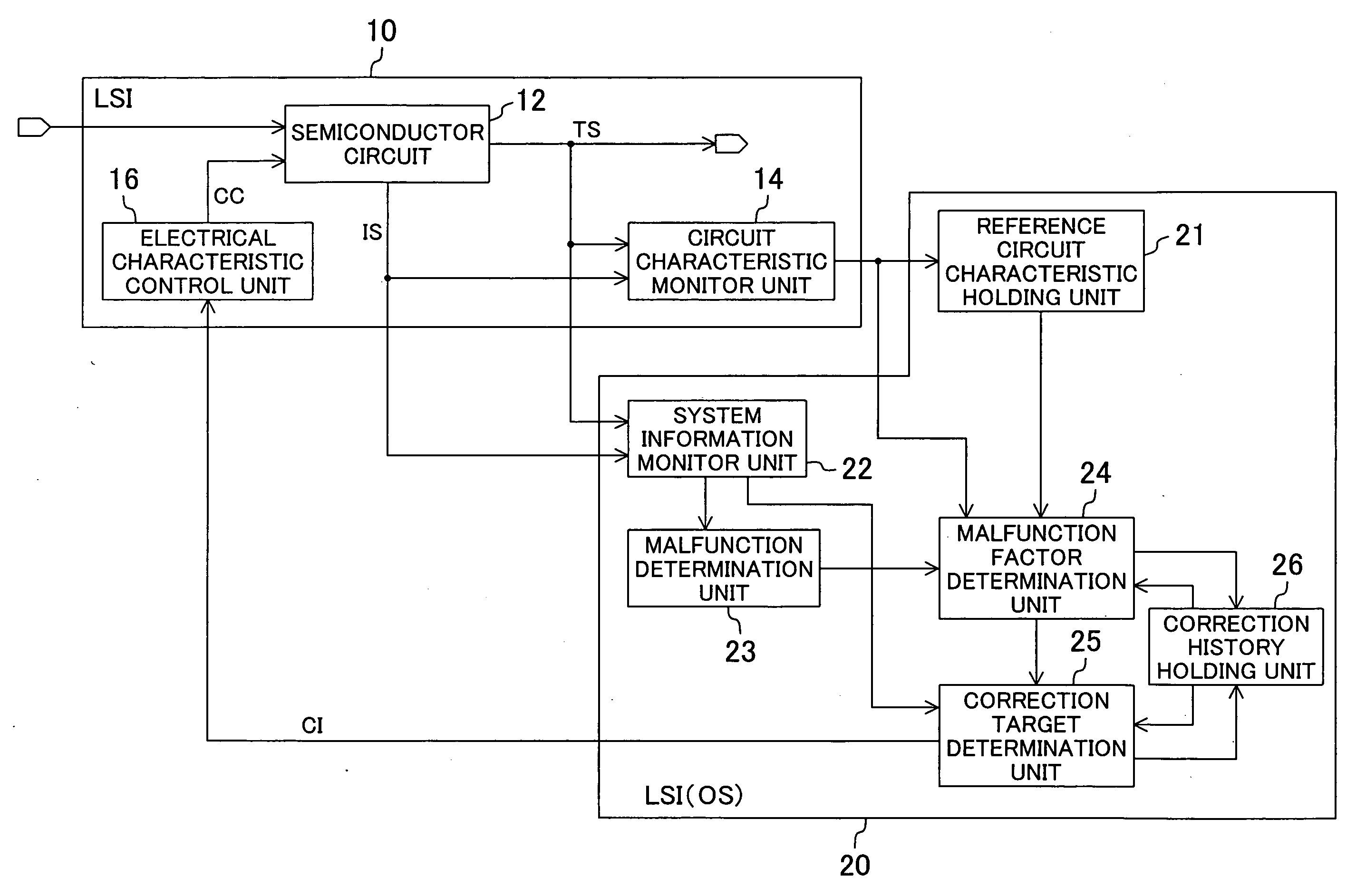

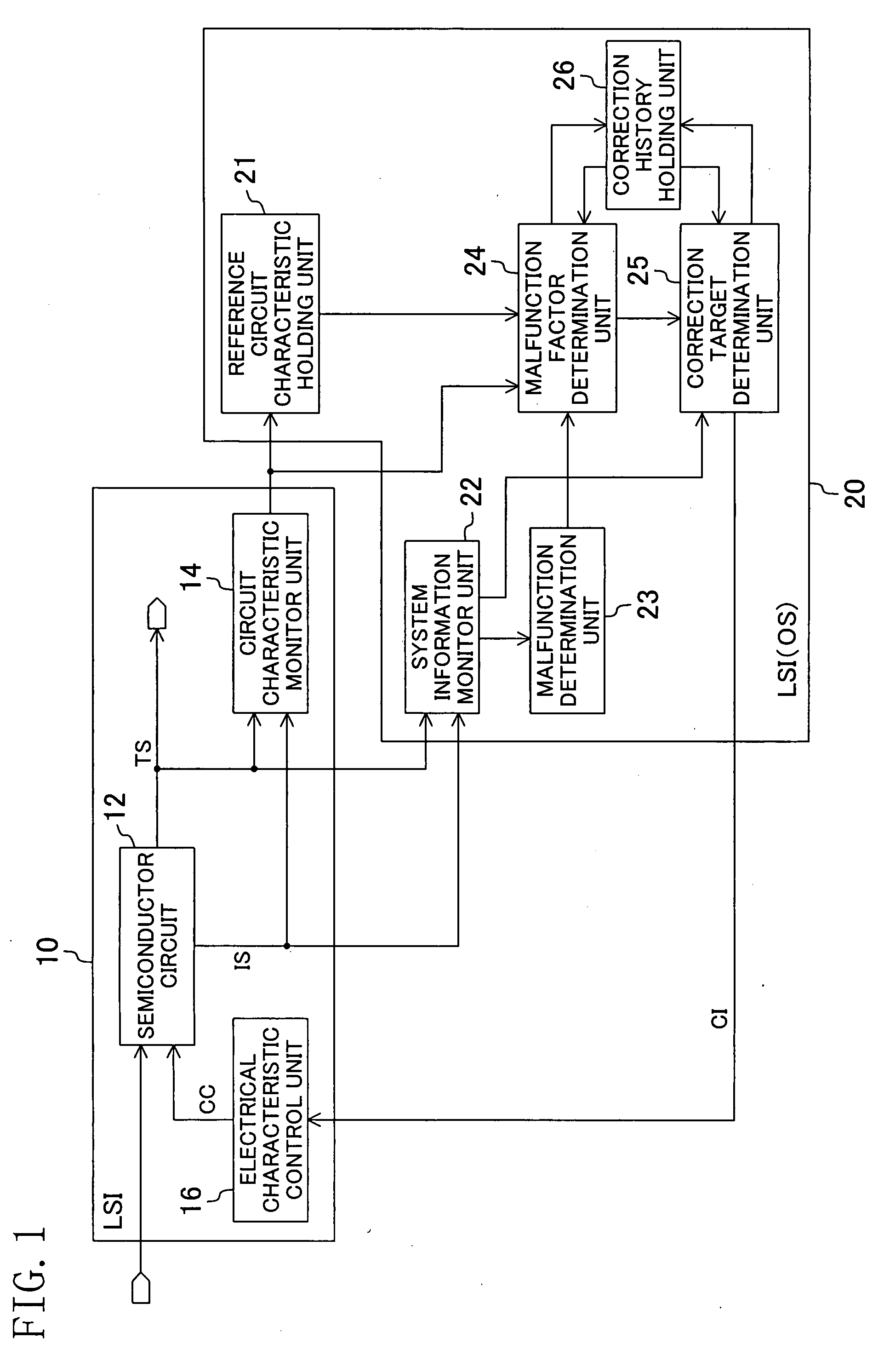

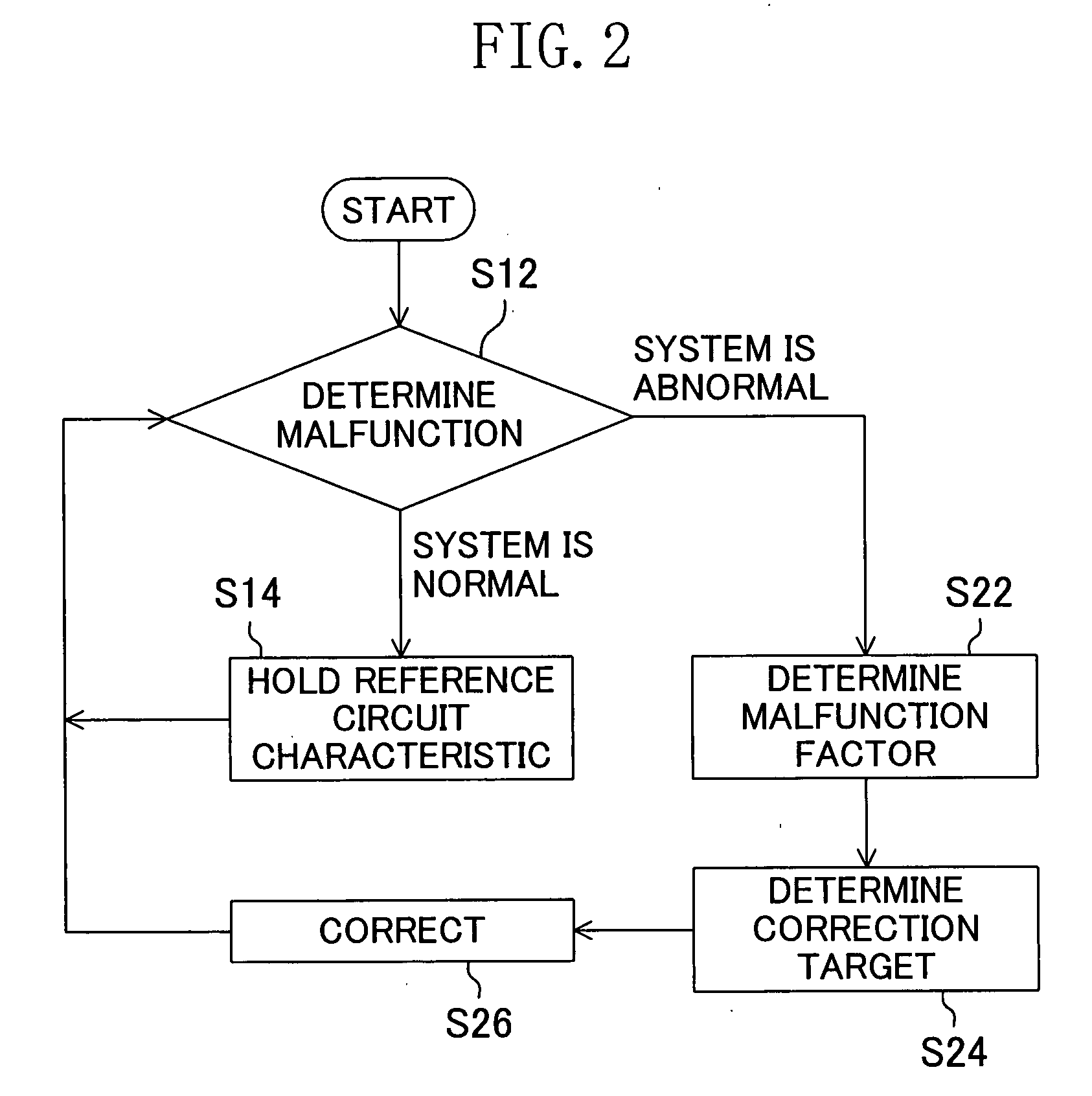

Semiconductor integrated circuit system, semiconductor integrated circuit, operating system, and control method for semiconductor integrated circuit

ActiveUS20070255992A1Good semiconductor performanceImprove performanceElectronic circuit testingError detection/correctionOperational systemEngineering

A semiconductor integrated circuit system has a control target circuit executing a program, a system information monitor unit for outputting system information indicating a state of the control target circuit, a circuit characteristic monitor unit for determining a circuit characteristic of the control target circuit and outputting the circuit characteristic as circuit characteristic information, a malfunction determination unit for determining whether or not the control target circuit is normally operating based on the system information, a reference circuit characteristic holding unit for holding the circuit characteristic information as reference circuit characteristic information when the control target circuit is normally operating, a malfunction factor determination unit for determining a malfunction factor based on the circuit characteristic information and on the reference circuit characteristic information when the control target circuit is not normally operating, and a correction target determination unit for determining a correction target in the control target circuit.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

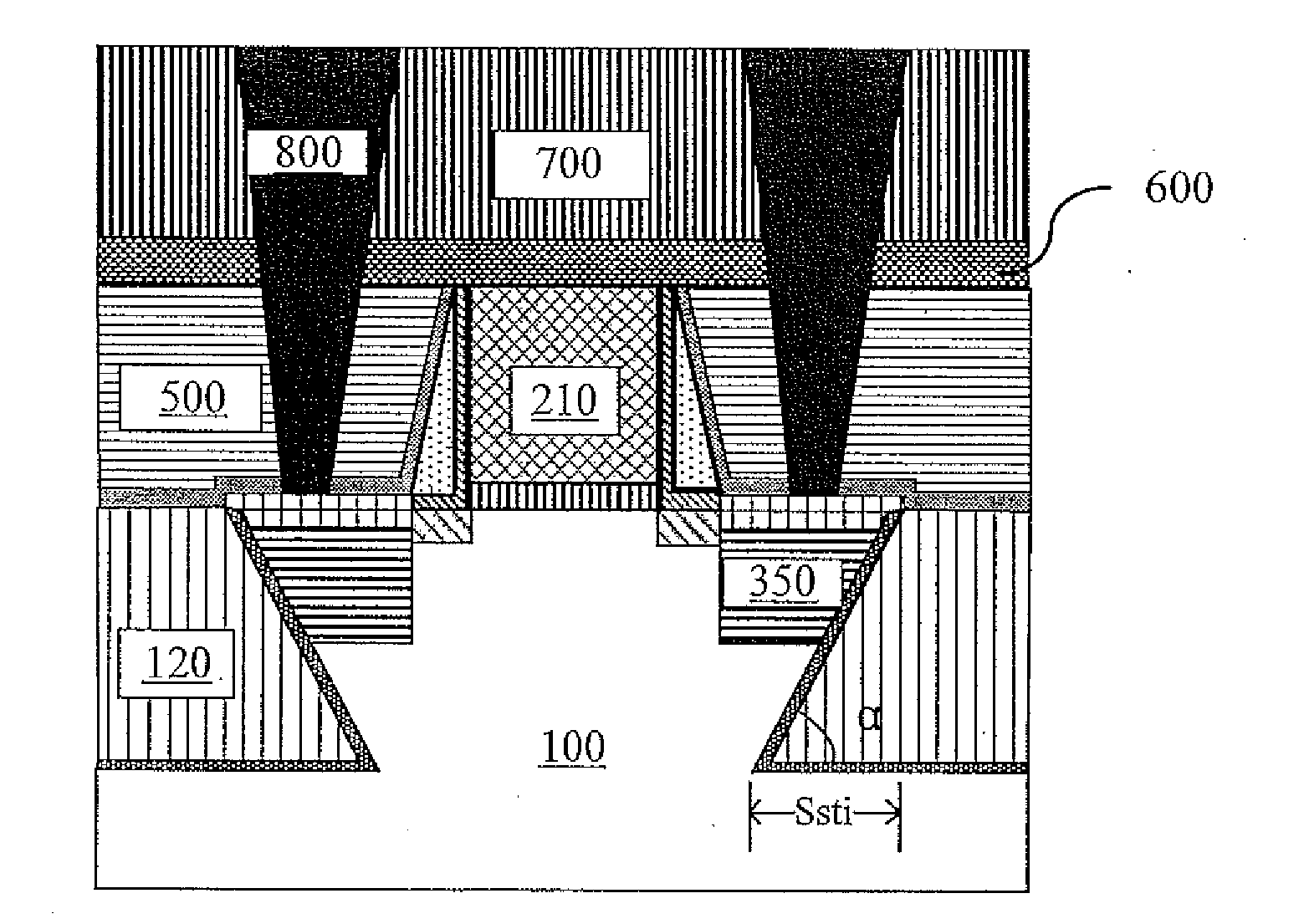

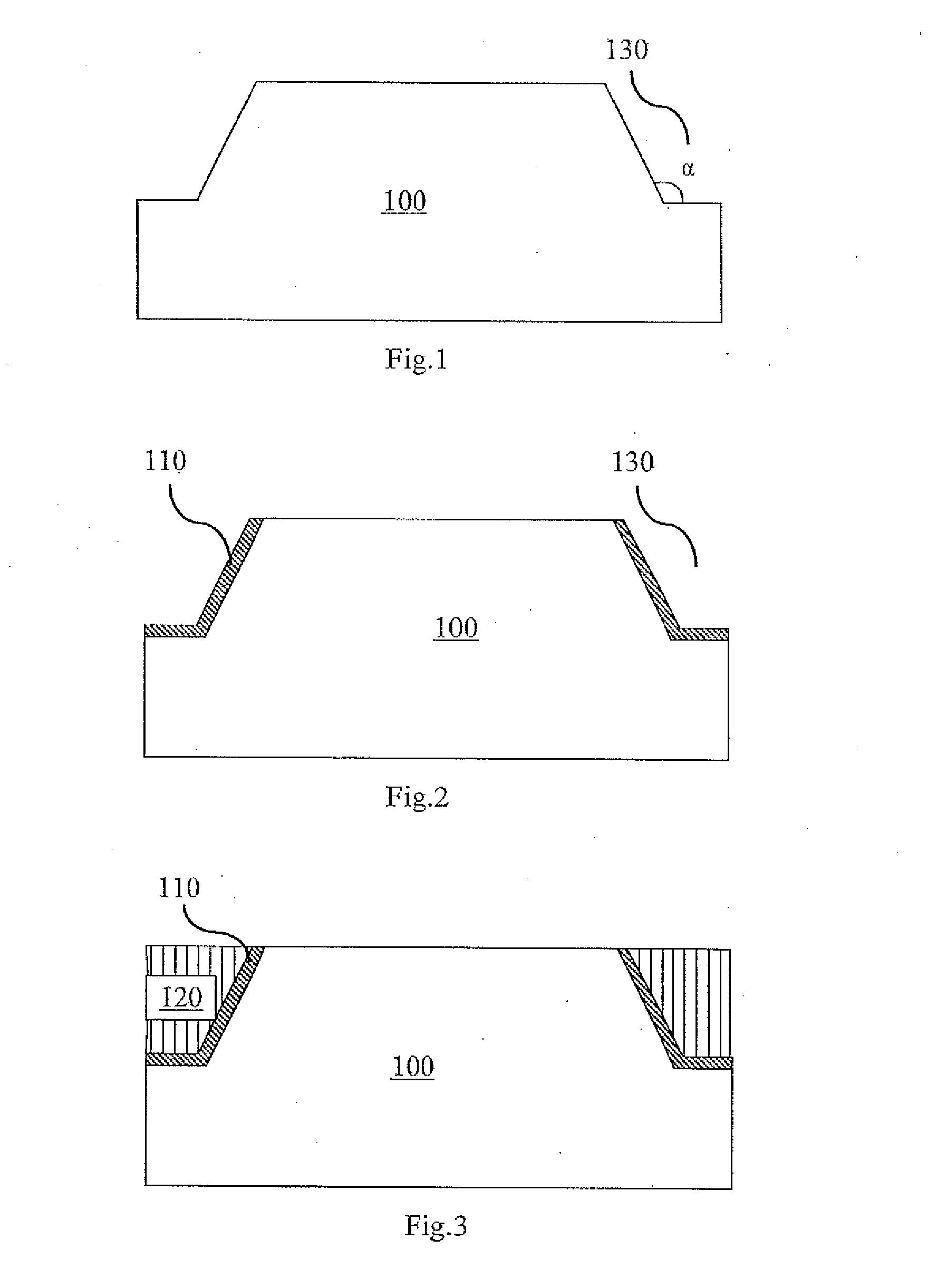

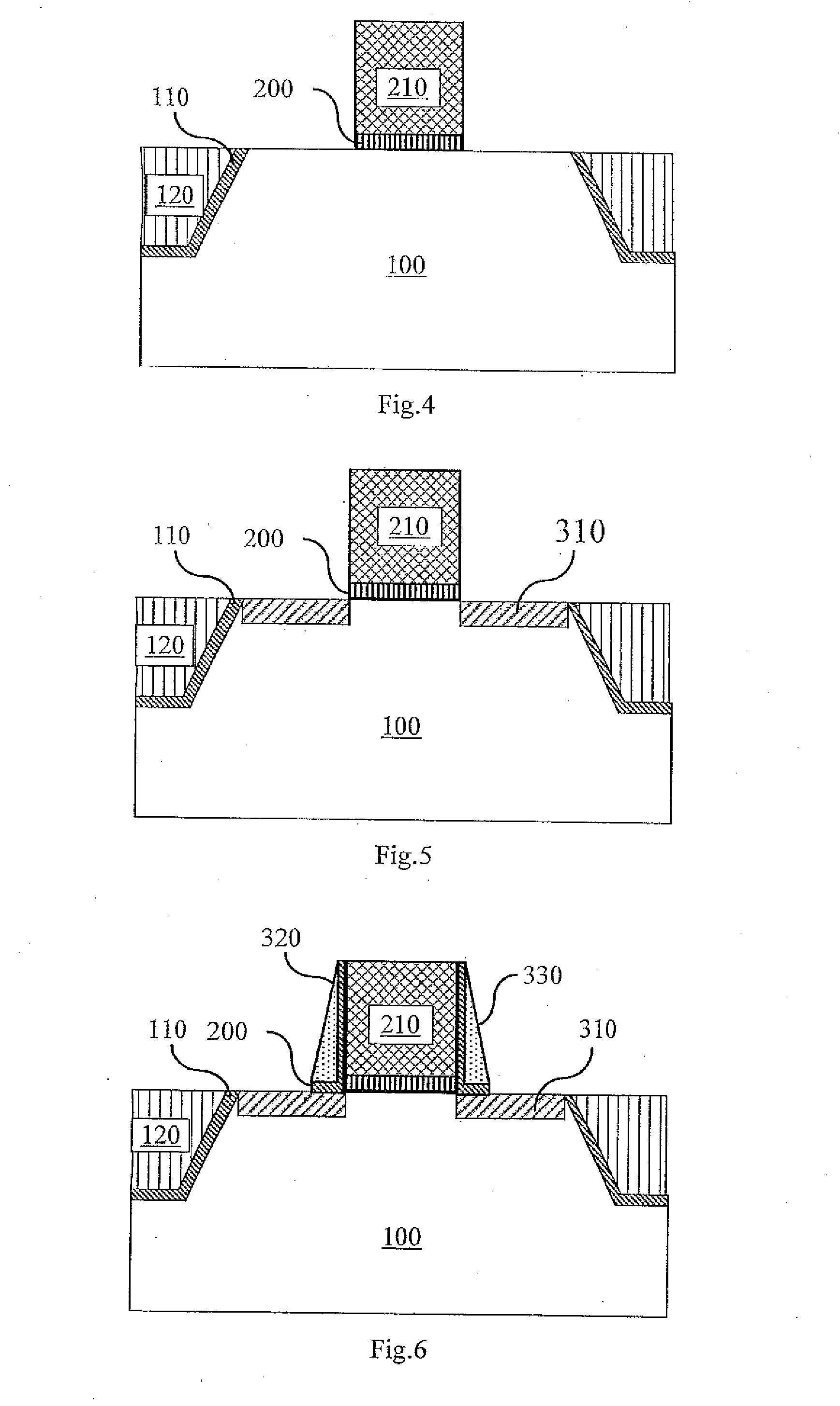

Semiconductor structure and method for manufacturing the same

InactiveUS20140231923A1Improve device performanceImprove impactTransistorSemiconductor/solid-state device manufacturingGate dielectricSemiconductor structure

The present invention provides a semiconductor structure, comprising: a substrate; a gate stack located on the substrate and comprising at least a gate dielectric layer and a gate electrode layer; source / drain regions, located in the substrate on both sides of the gate stack; an STI structure, located in the substrate on both sides of the source / drain regions, wherein the cross-section of the STI structure is trapezoidal, Sigma-shaped or inverted trapezoidal depending on the type of the semiconductor structure. Correspondingly, the present invention further to provides a method of manufacturing the semiconductor structure. In the present invention, STI structures having different shapes can be combined with different stress fillers to apply tensile stress or compressive stress laterally to the channel, which will produce a positive impact on the electron mobility of NMOS and the hole mobility of PMOS and increase the channel current of the device, thereby effectively improving the performance of the semiconductor structure.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

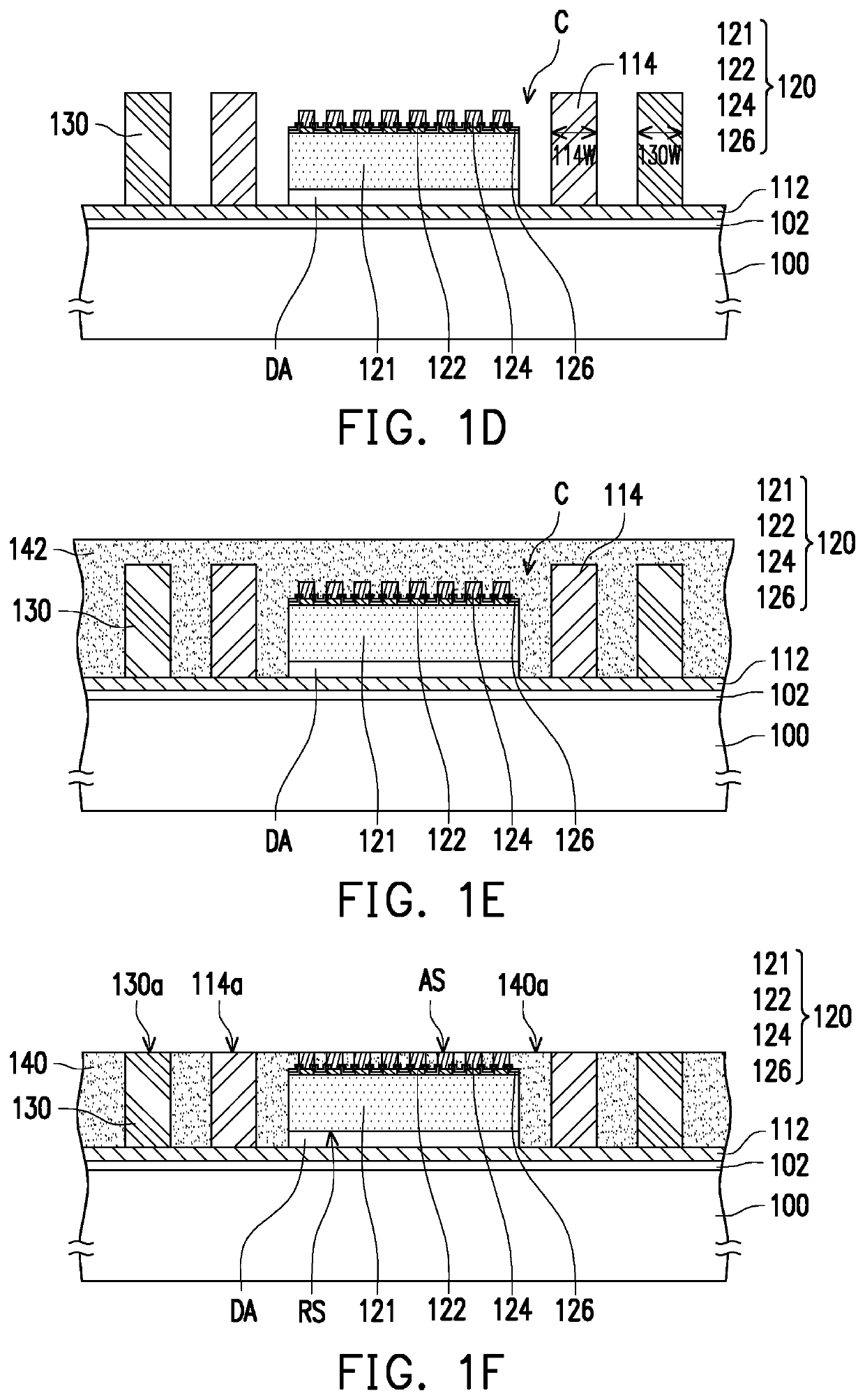

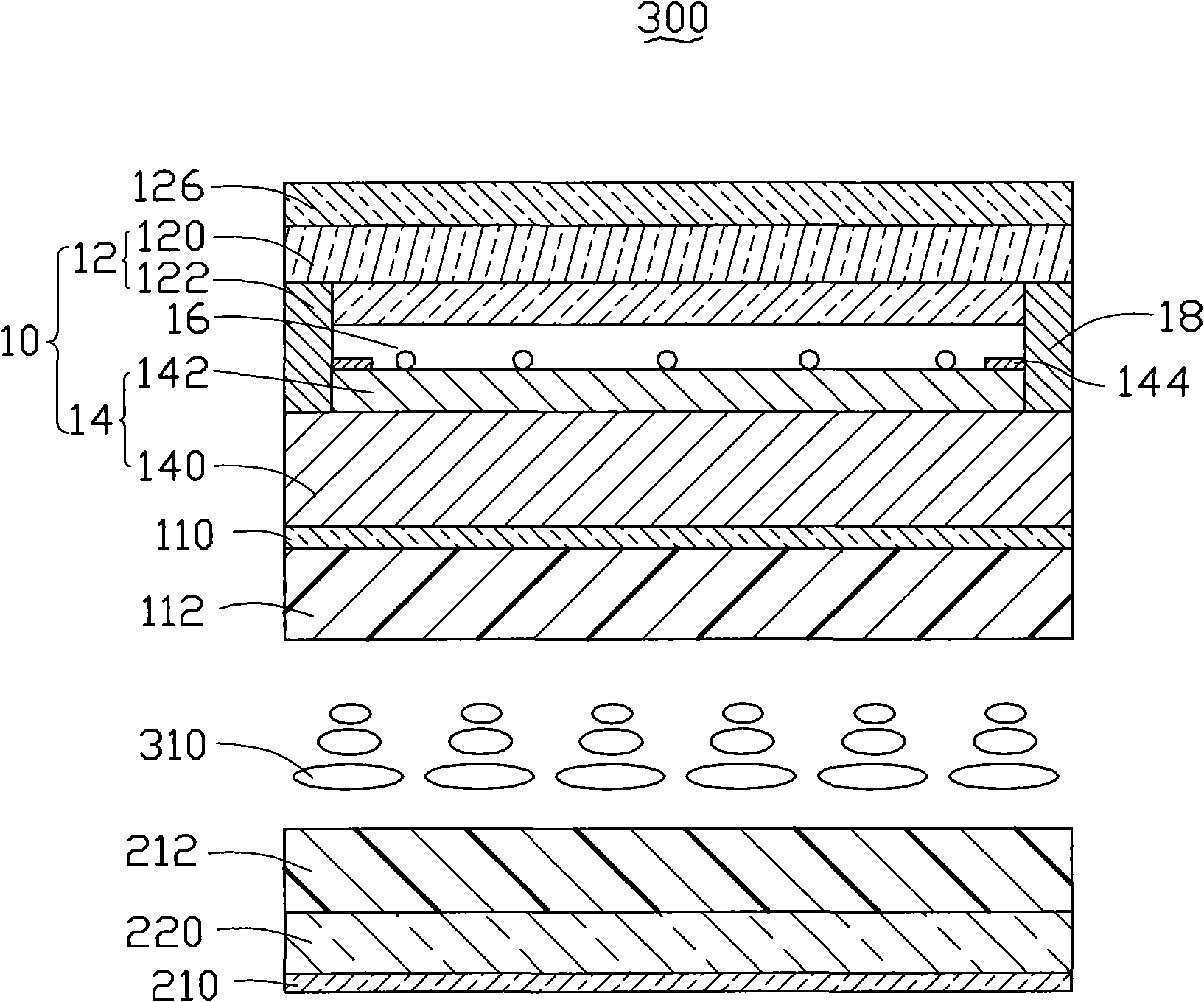

Semiconductor package and manufacturing method thereof

ActiveUS20200013721A1Effective coolingReduce electromagnetic interferenceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical connection

A semiconductor package and a manufacturing method thereof are provided. The semiconductor package includes a conductive casing, a semiconductor die, a conductive connector, an insulating encapsulant, a redistribution structure, and a first conductive terminal. The conductive casing has a cavity. The semiconductor die is disposed in the cavity of the conductive casing. The conductive connector is disposed on a periphery of the conductive casing. The insulating encapsulant encapsulates the conductive connector, the semiconductor die and the cavity. The redistribution structure is formed on the insulating encapsulant and is electrically connected to the conductive connector and the semiconductor die. The first conductive terminal is disposed in openings of the redistribution structure and is physically in contact with a portion of the conductive casing.

Owner:POWERTECH TECHNOLOGY

Touch LCD screen

ActiveCN101620328AIncreased durabilityHigh transparencyStatic indicating devicesSolid-state devicesLiquid-crystal displayCarbon nanotube

The invention discloses a touch LCD screen, which comprises an upper substrate, a lower substrate, and a liquid crystal layer, wherein the upper substrate comprises a touch screen; the lower substrate and the upper substrate are oppositely arranged; the lower substrate comprises a thin film transistor panel; the liquid crystal layer is arranged between the upper substrate and the lower substrate; a conducting layer of the touch screen comprises a first carbon nanotube layer; and a semiconductor layer of a thin film transistor on the thin film transistor panel comprises a second carbon nanotube layer.

Owner:TSINGHUA UNIV +1

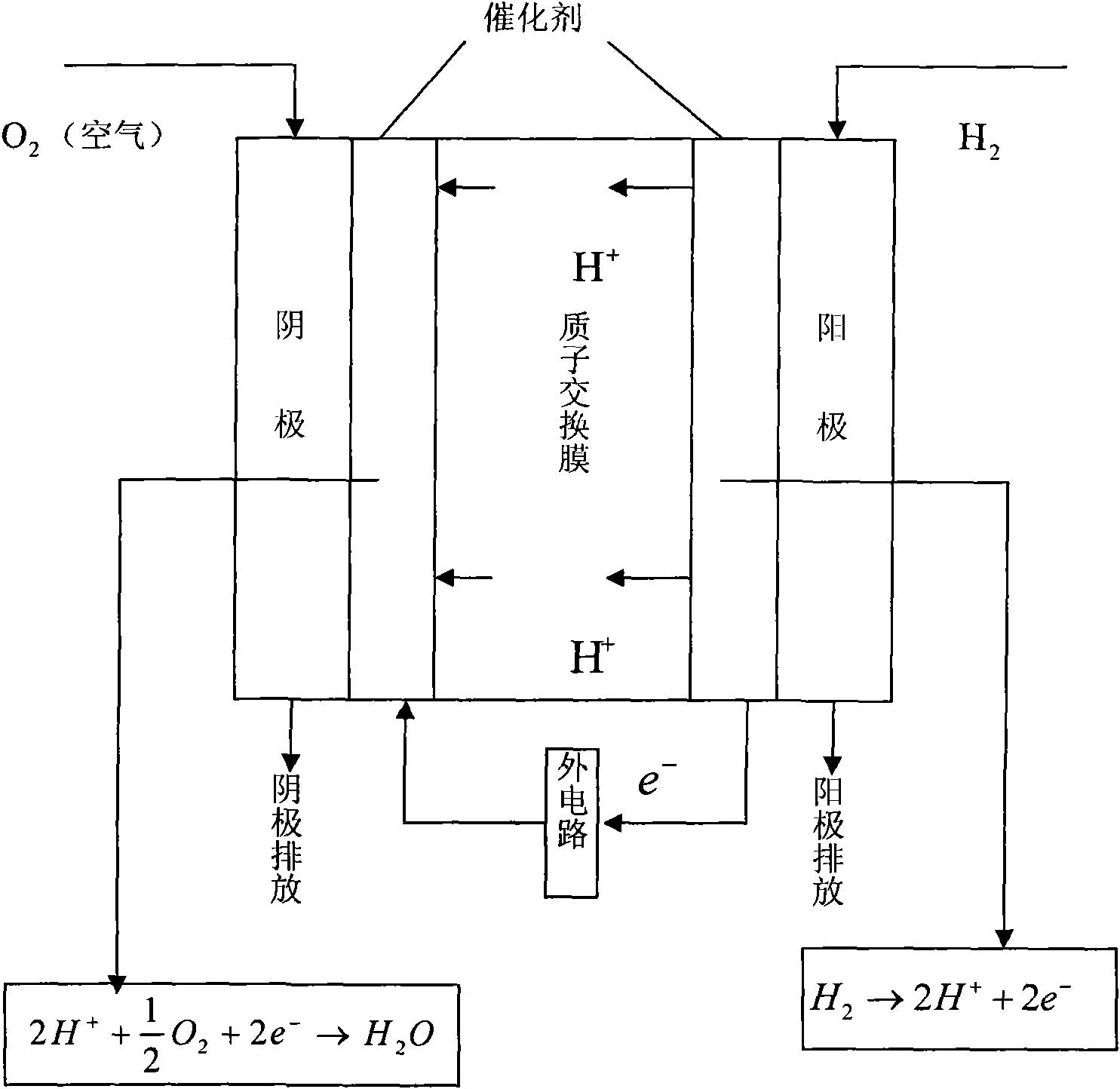

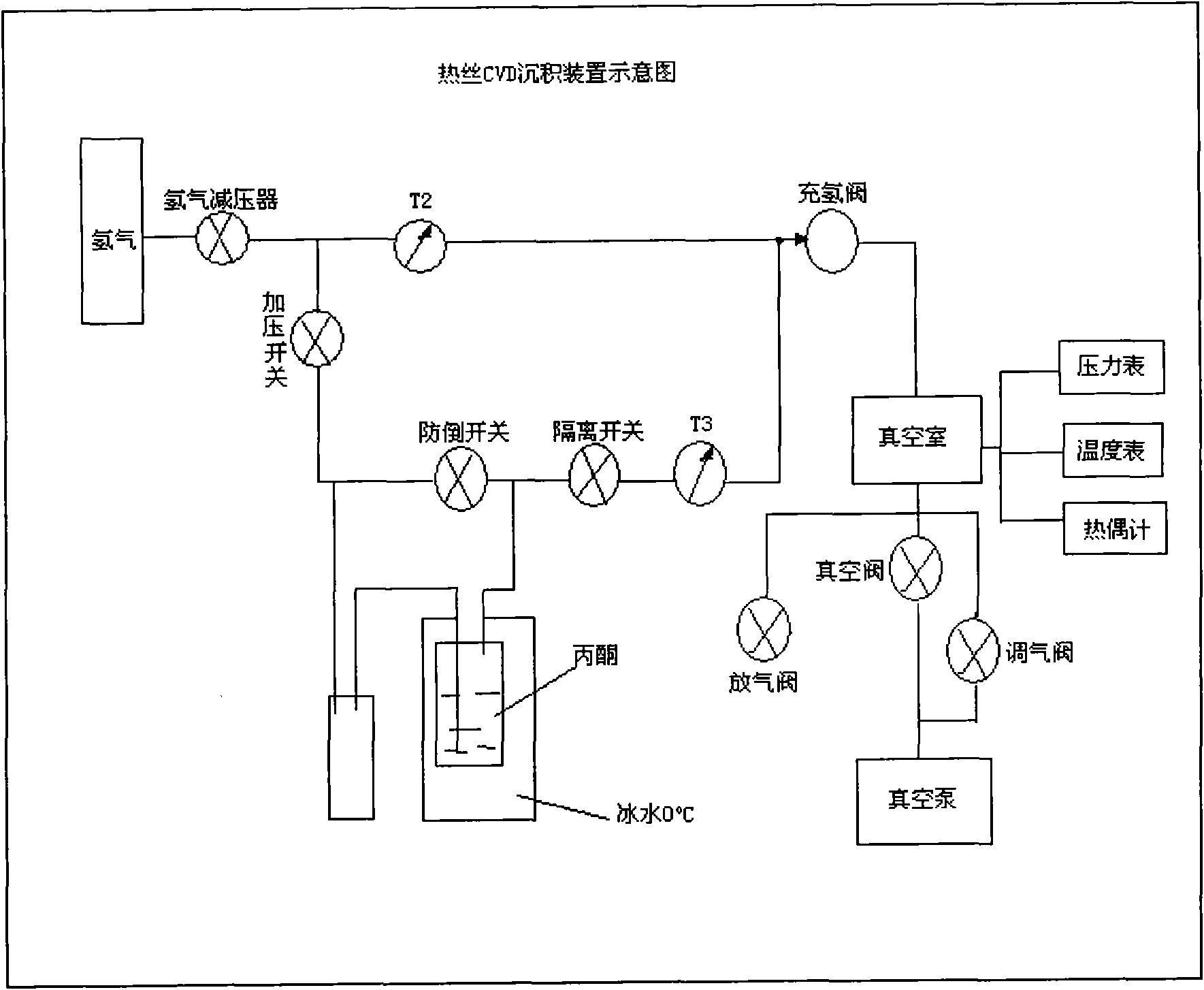

Boron-doping diamond film modification-based PEMFC (Proton Exchange Membrane Fuel Cell) bipolar plate and preparation method thereof

InactiveCN102074708AAccelerated corrosionImprove conductivityCell electrodesSputteringHeat conducting

The invention discloses a boron-doping diamond film modification-based PEMFC (Proton Exchange Membrane Fuel Cell) bipolar plate and a preparation method thereof, belonging to the field of batteries. In the boron-doping diamond film modification-based PEMFC bipolar plate, after a stainless steel plate is subjected to surface pretreatment, a layer of TI film is sputtered on the stainless steel plate by using magnetron sputtering; a boron-doping diamond film is deposited on the TI film by using heat wire CVD (Chemical Vapor Deposition) equipment; and a diamond film and TI film compounded modification layer is formed on the surface of stainless steel. The stainless steel plate treated by the method has high corrosion resistance and a favorable conductive and heat-conducting property; and according to the stainless steel plate, the battery ratio power can be greatly improved and the PEMFC can achieve the aims of prolonging the service life and reducing the weight, the volume and the cost.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

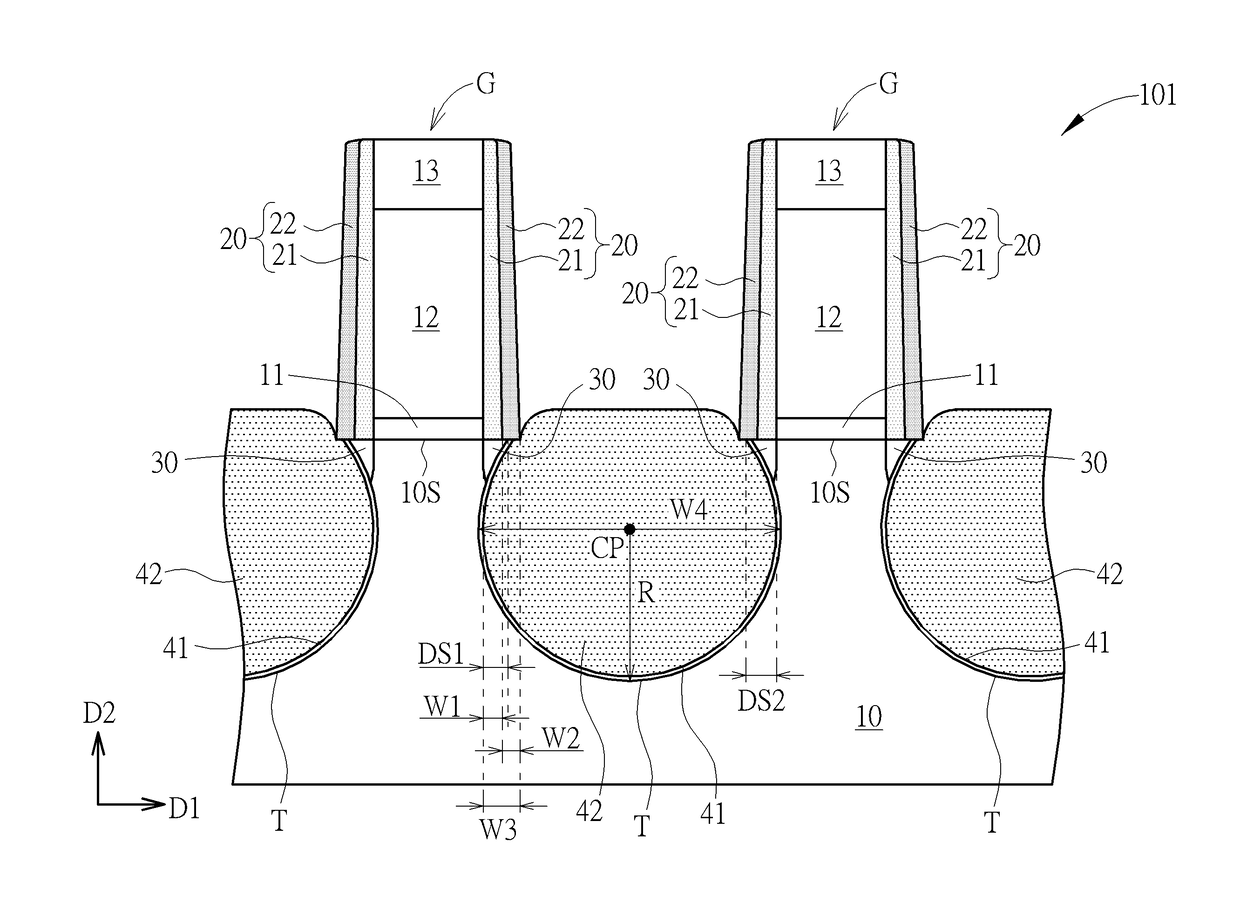

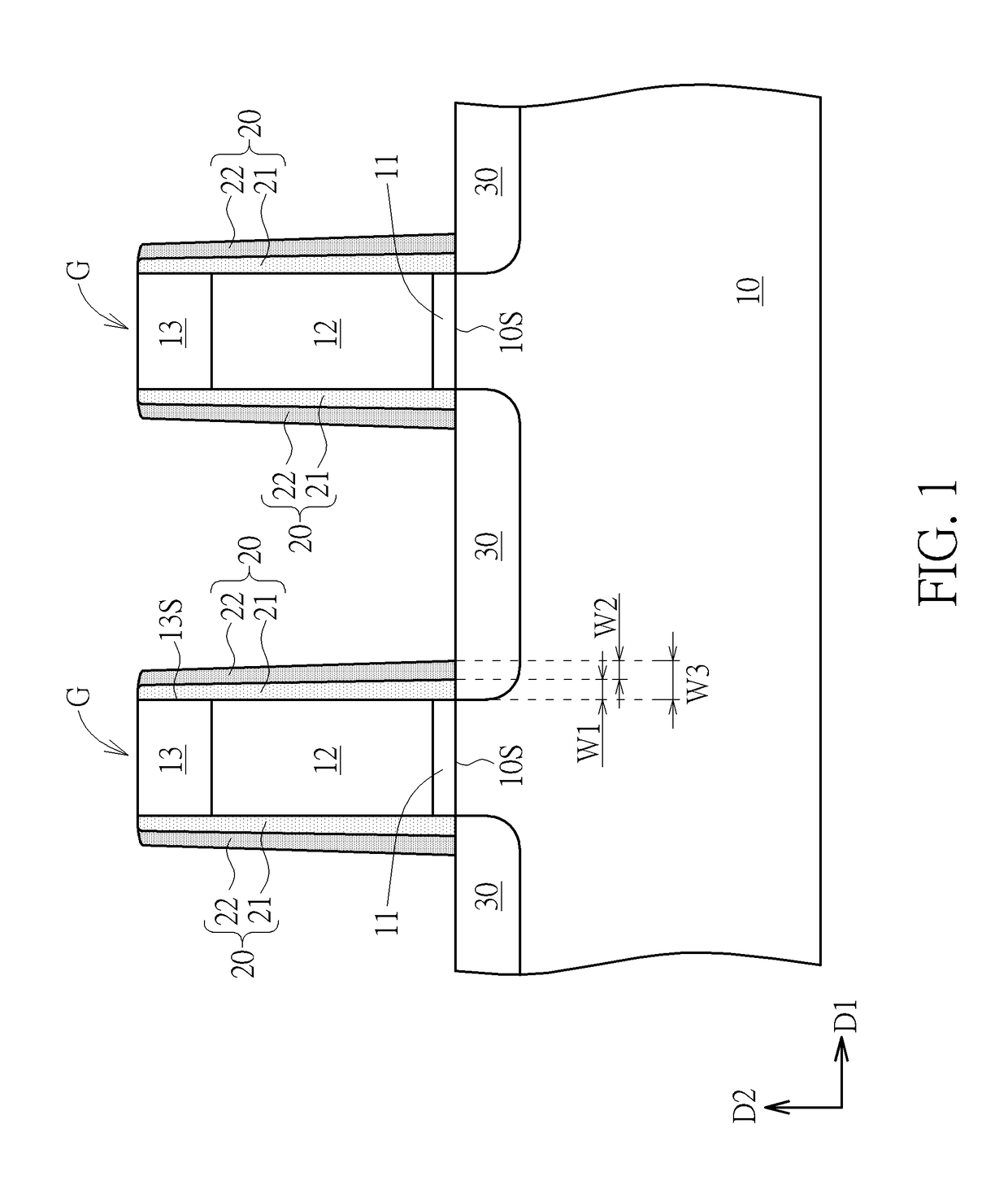

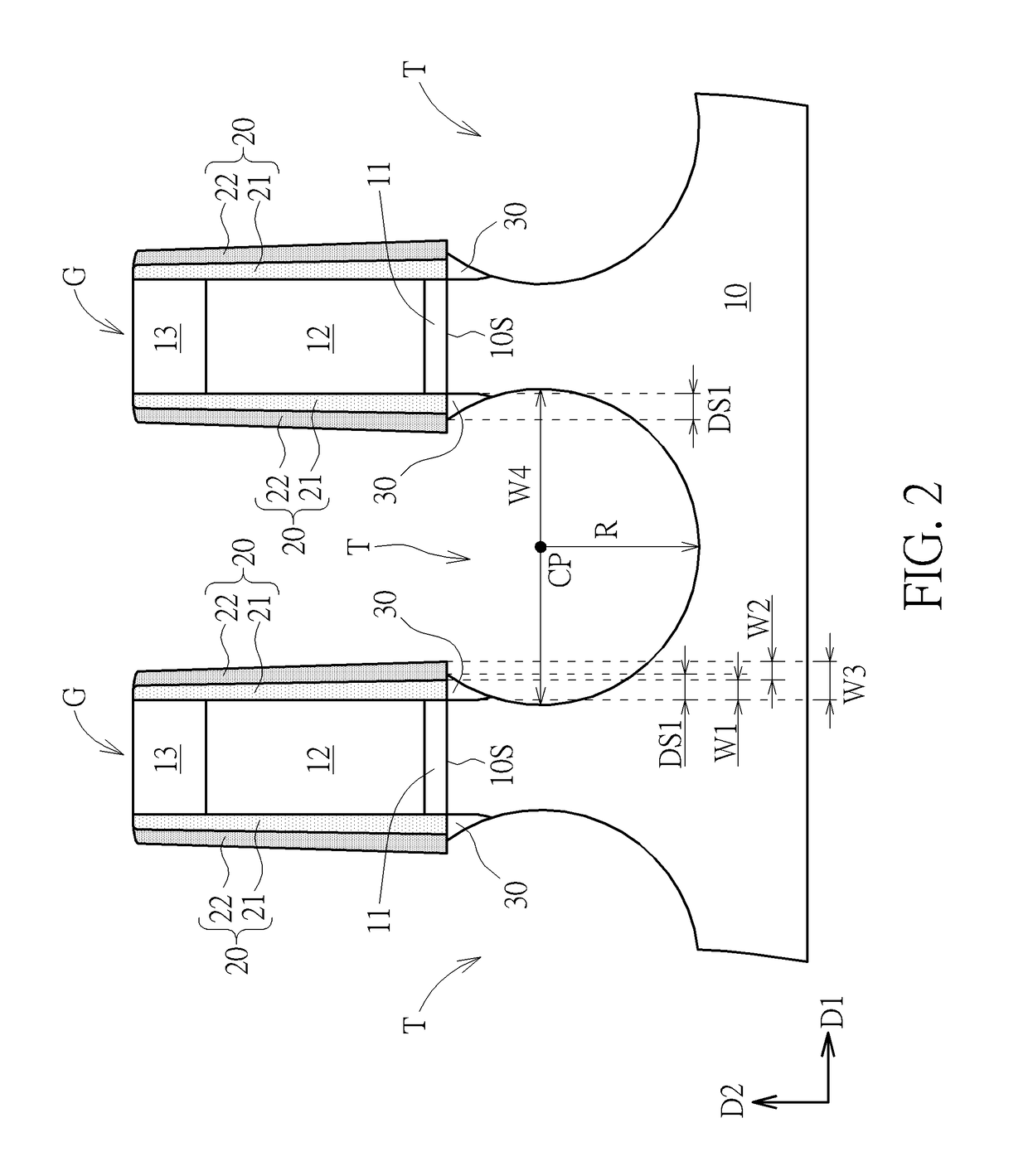

Semiconductor device

ActiveUS20170098708A1Reduce widthDistanceTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device includes a substrate, a gate structure, a sidewall spacer, and an epitaxial layer. The gate structure is disposed on the substrate, and the substrate has at least one recess disposed adjacent to the gate structure. The sidewall spacer is disposed on at least two sides of the gate structure. The sidewall spacer includes a first spacer layer and a second spacer layer, and the first spacer layer is disposed between the gate structure and the second spacer layer. The epitaxial layer is disposed in the recess, and the recess is a circular shaped recess. A distance between an upmost part of the recess and the gate structure is less than a width of the sidewall spacer.

Owner:UNITED MICROELECTRONICS CORP

Manufacturing method of semiconductor device, manufacturing method of electronic device

ActiveUS20050009240A1Increase resin injection pressureInhibitionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

First bump electrodes are arrayed in a straight line along a first side of a semiconductor chip. Second bump electrodes are more narrowly arrayed in a zigzag arrangement along a second side of the chip. By carrying out an injection of a sealing resin from the second side on which the second bump electrodes are arrayed, a surface of the semiconductor chip that is subjected to face-down mounting on a film substrate is sealed.

Owner:SEIKO EPSON CORP