Patents

Literature

161 results about "N type conductivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

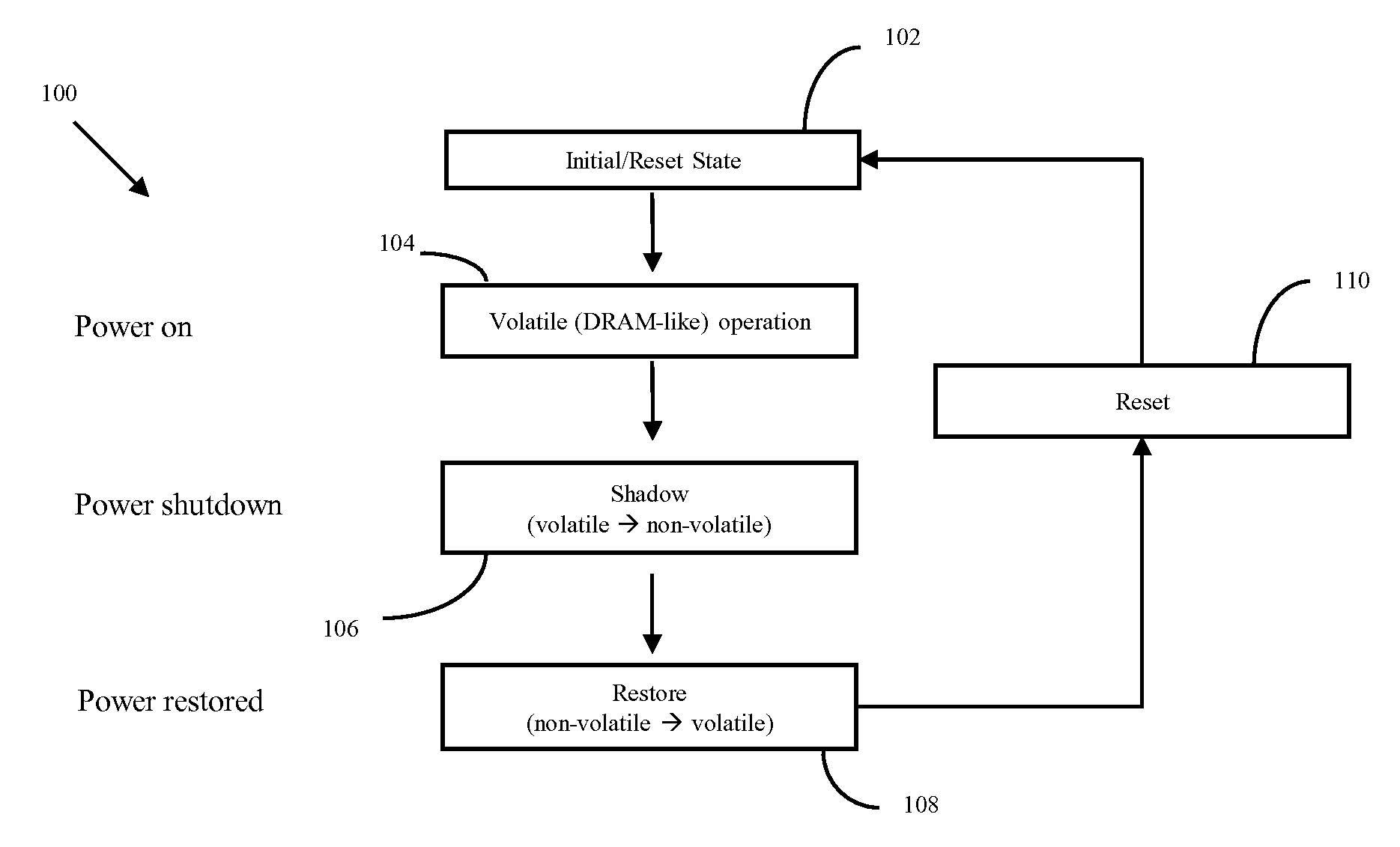

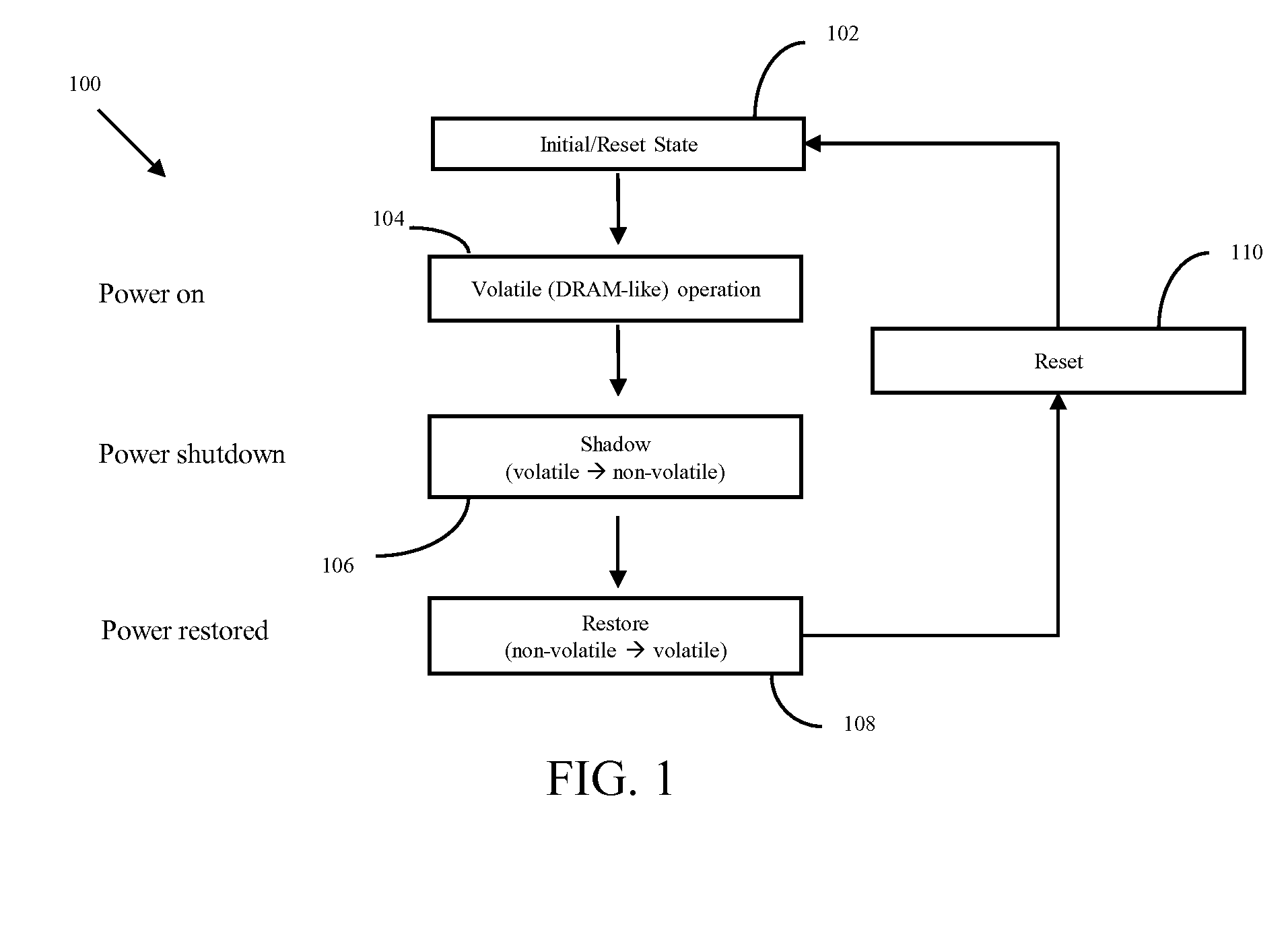

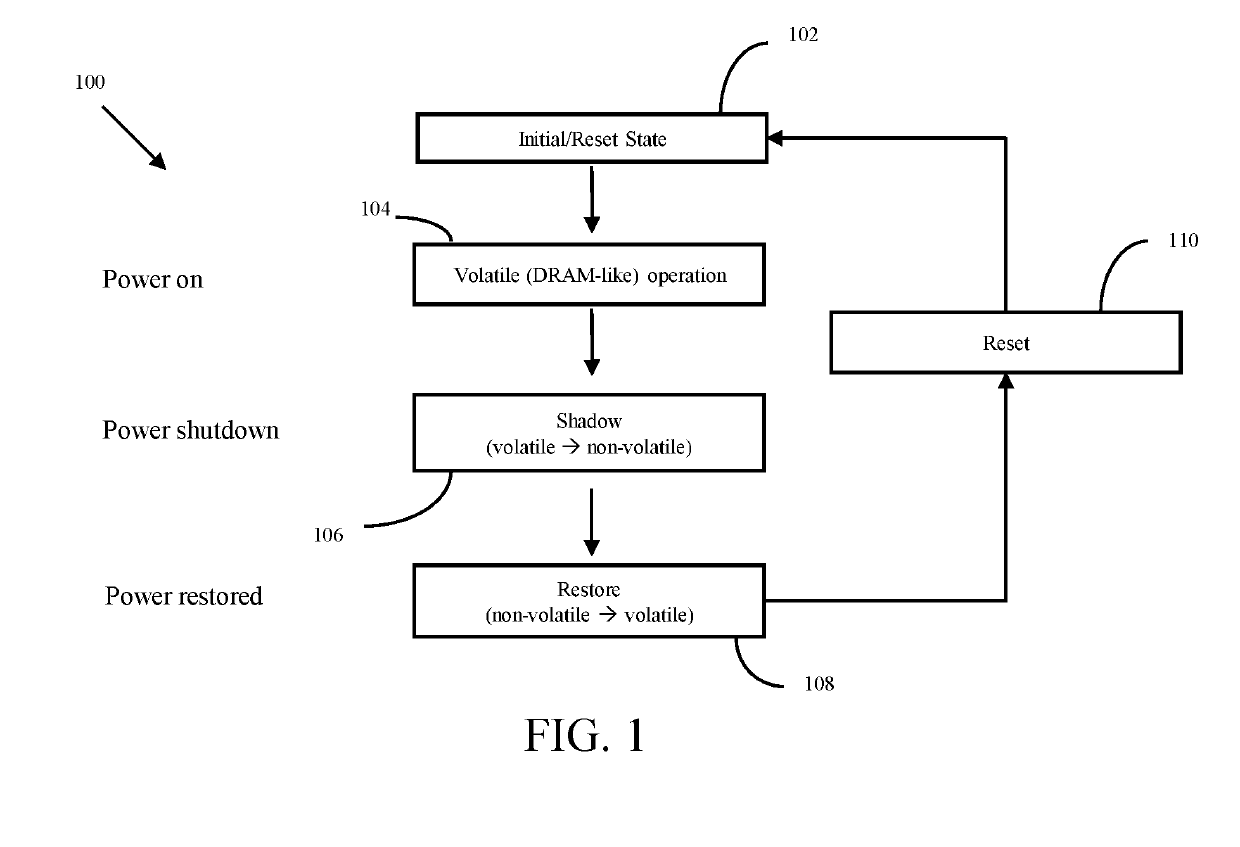

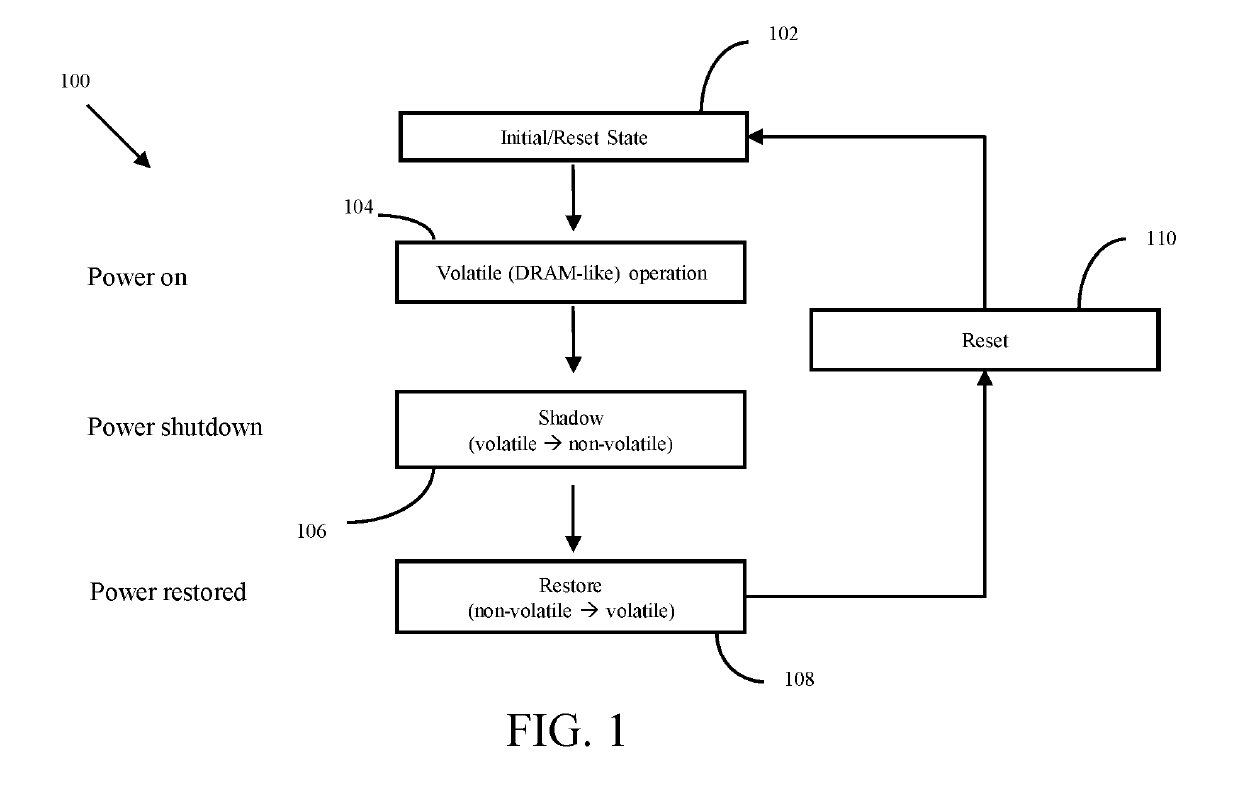

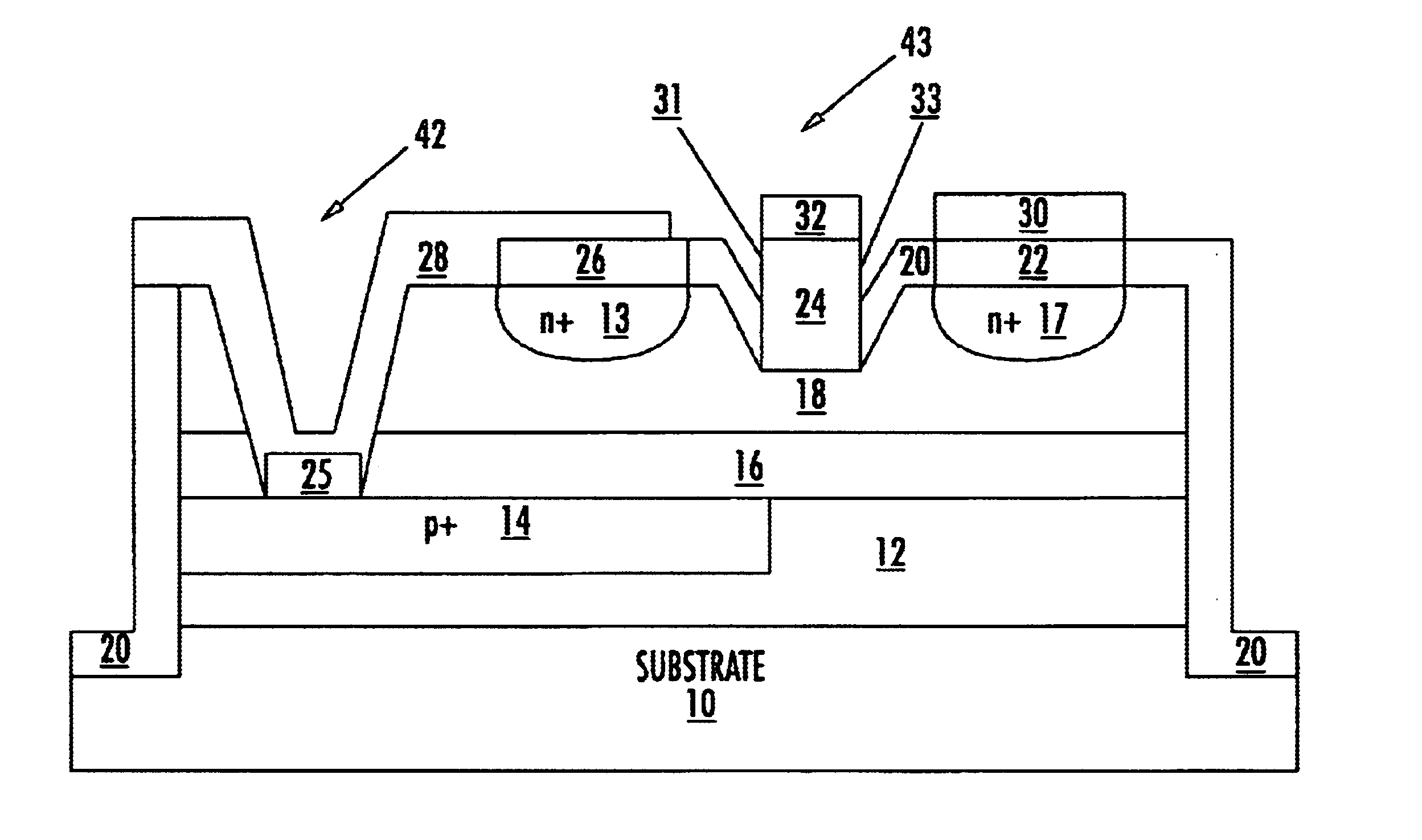

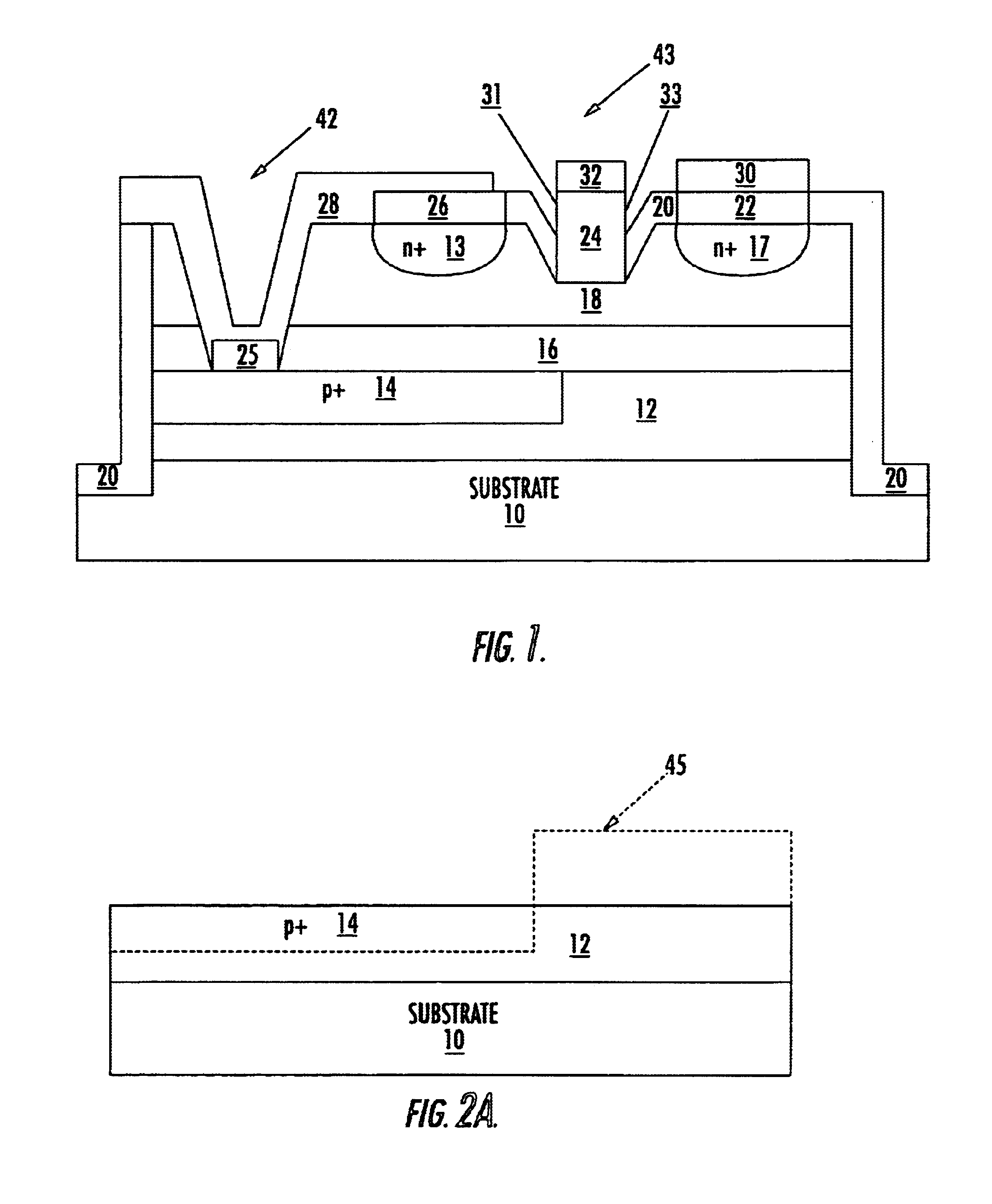

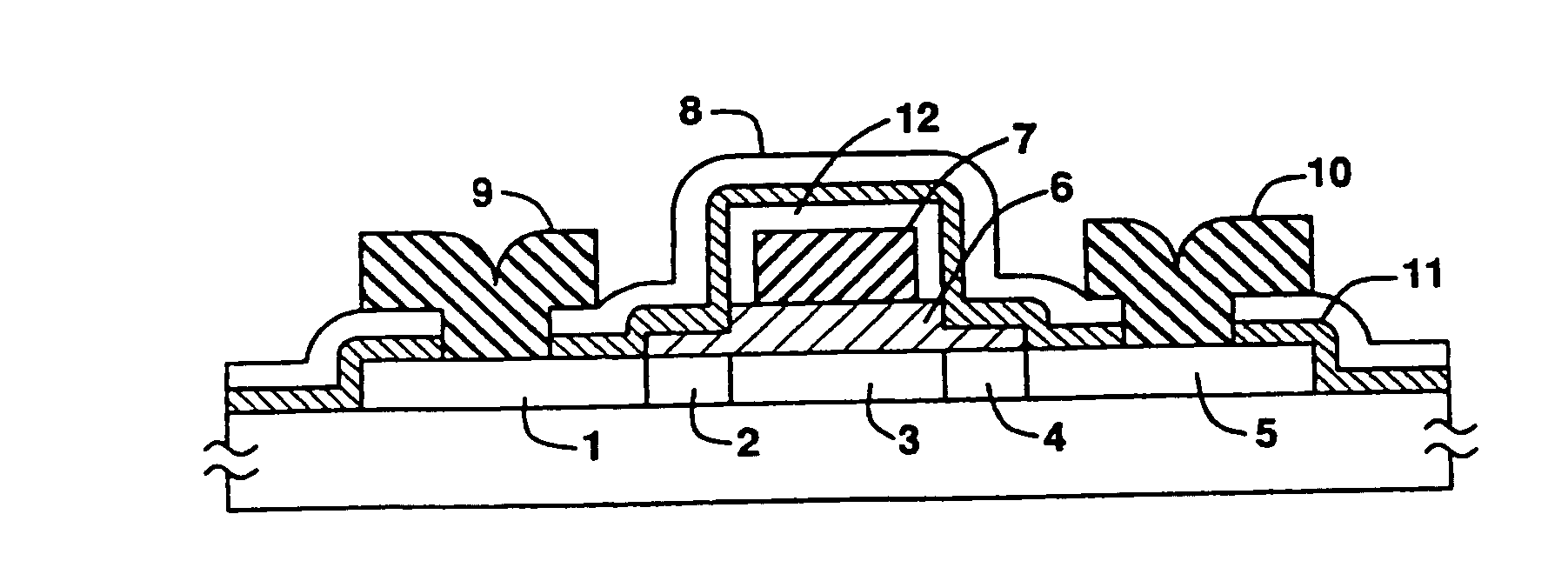

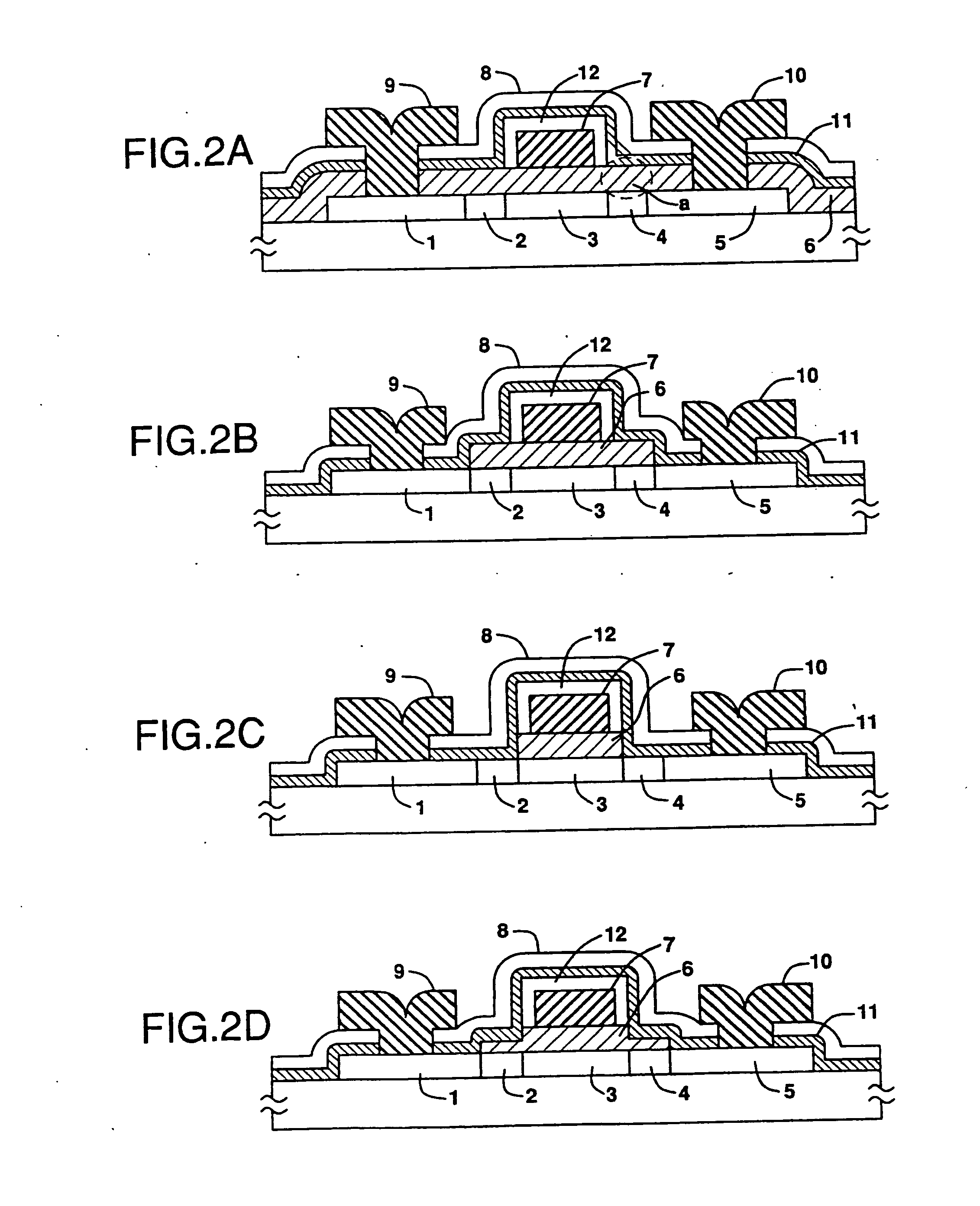

Memory cells, memory cell arrays, methods of using and methods of making

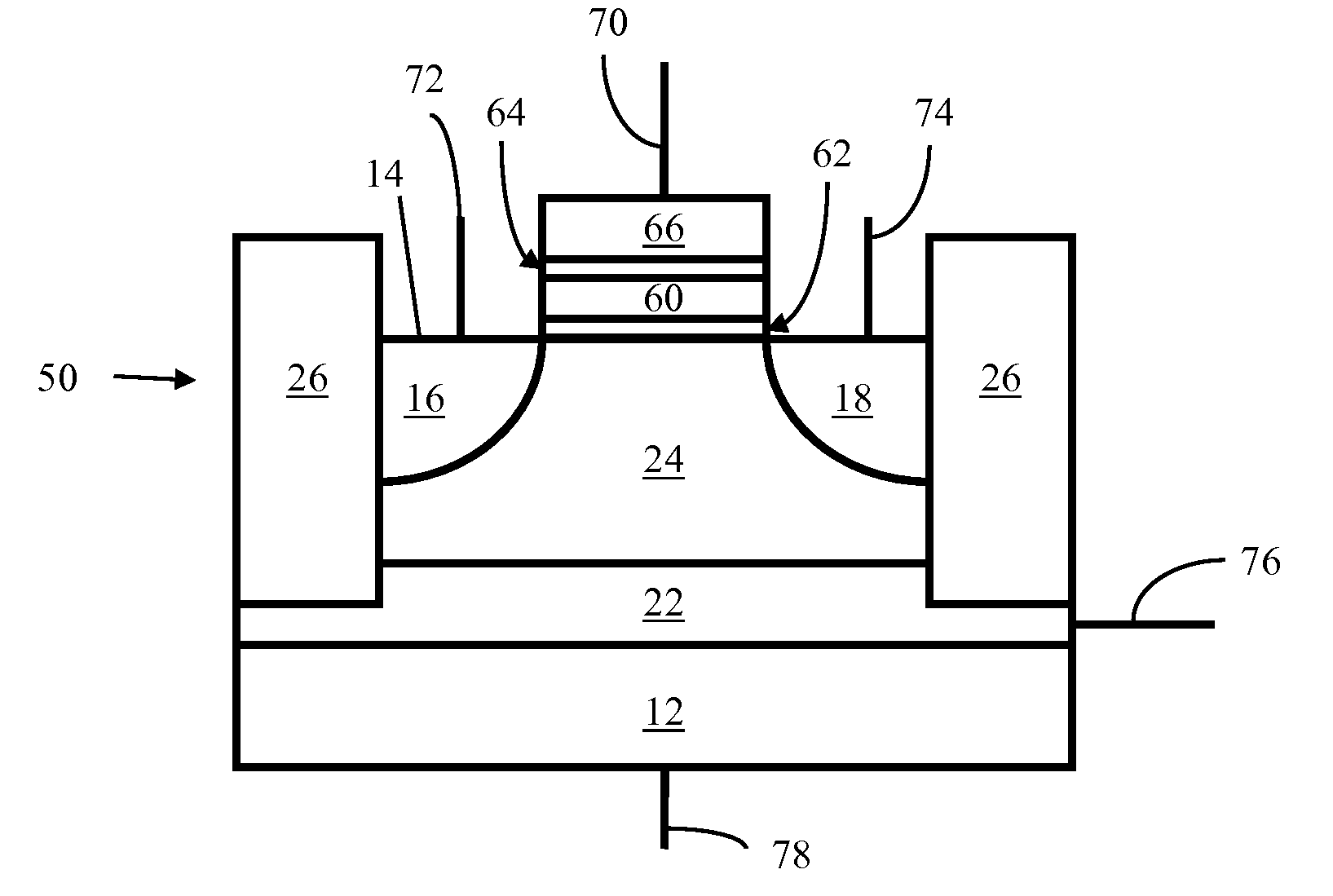

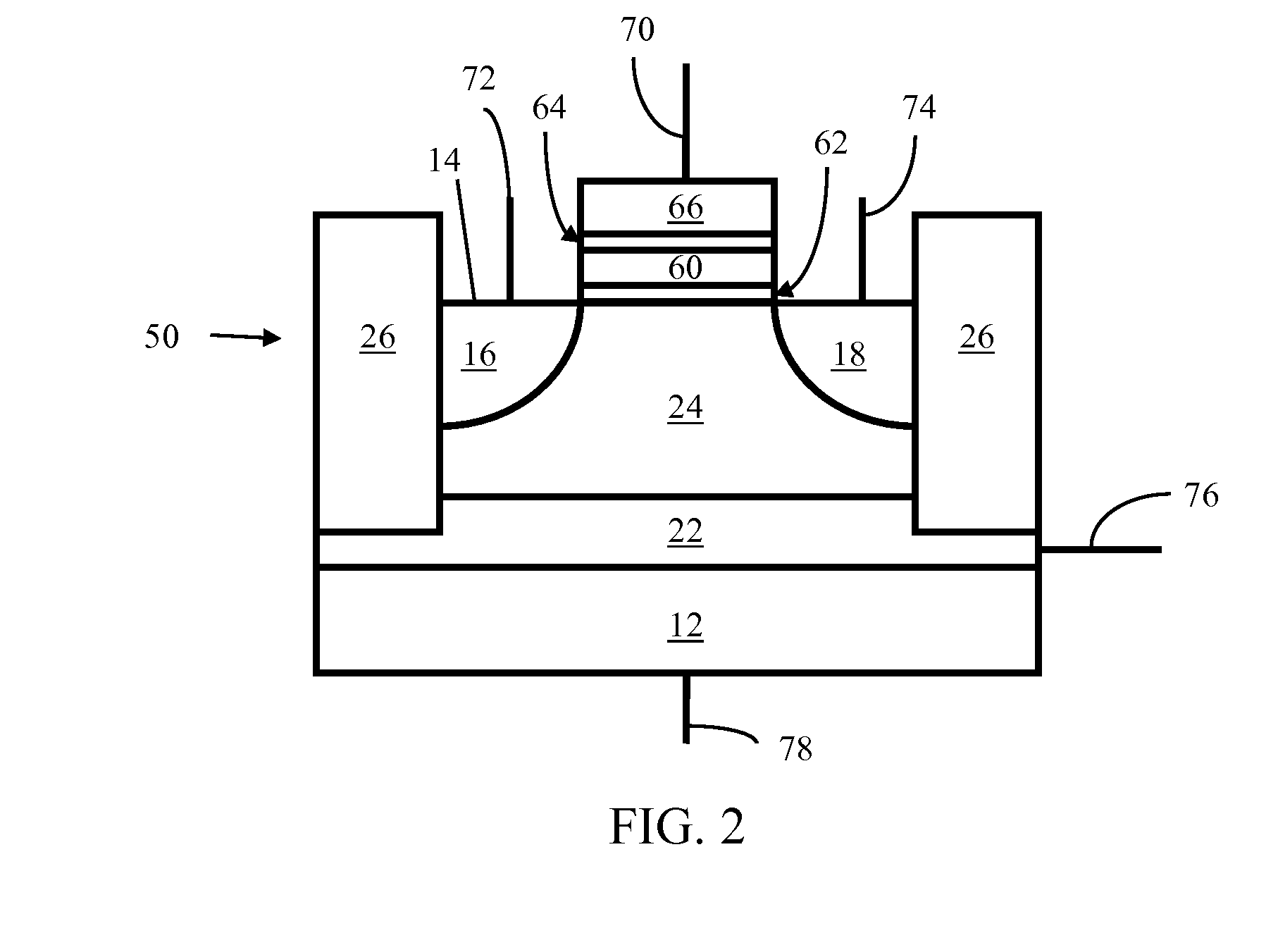

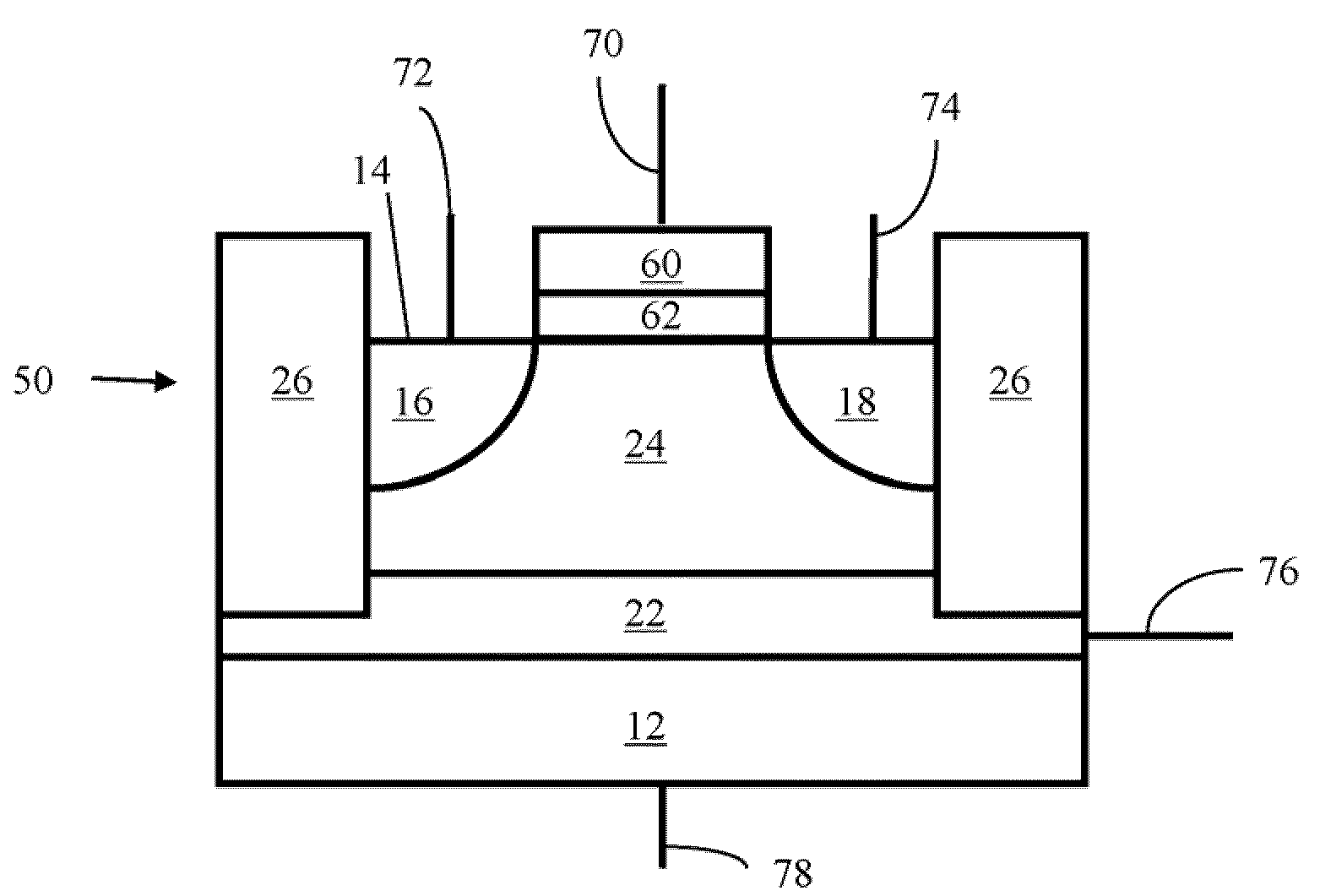

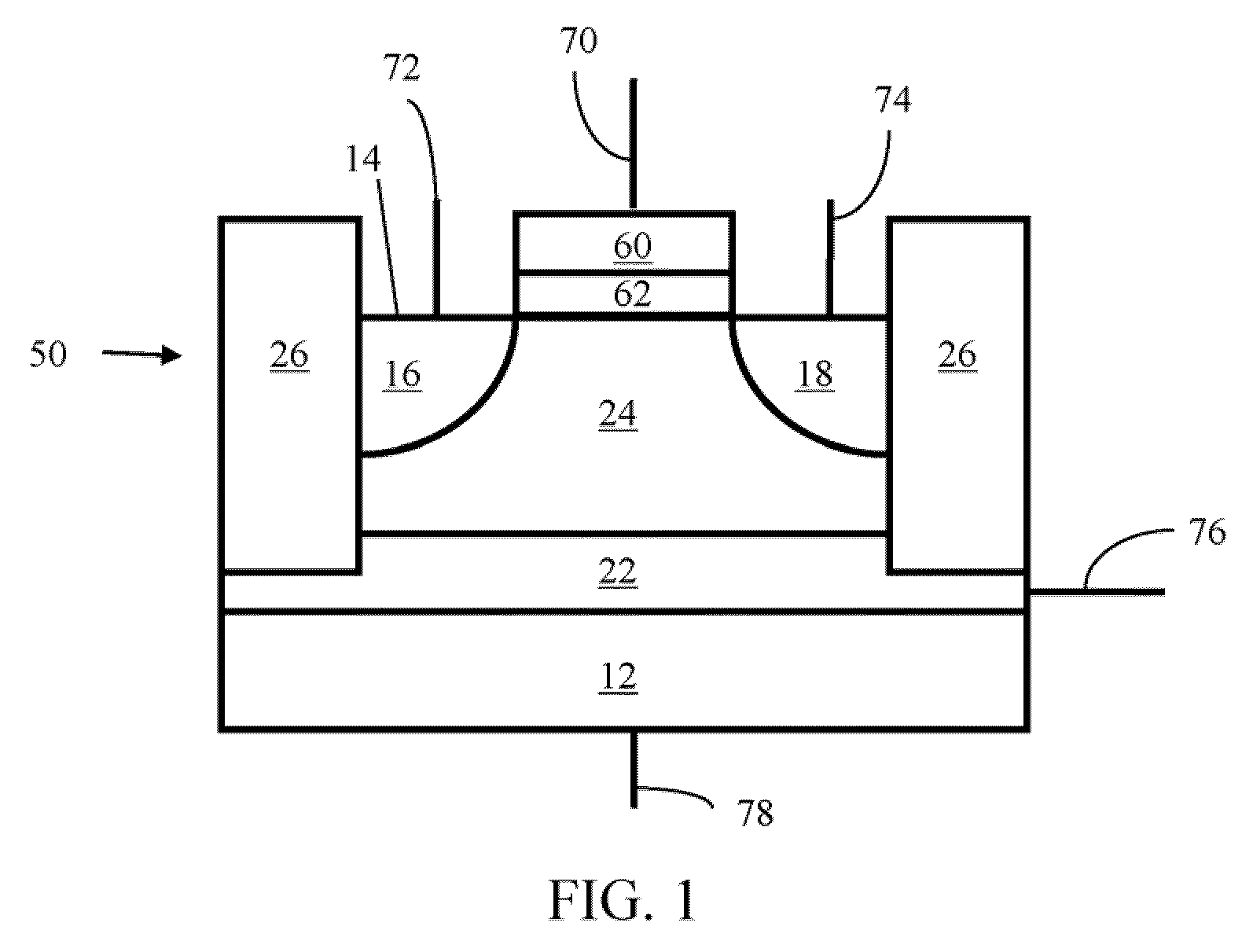

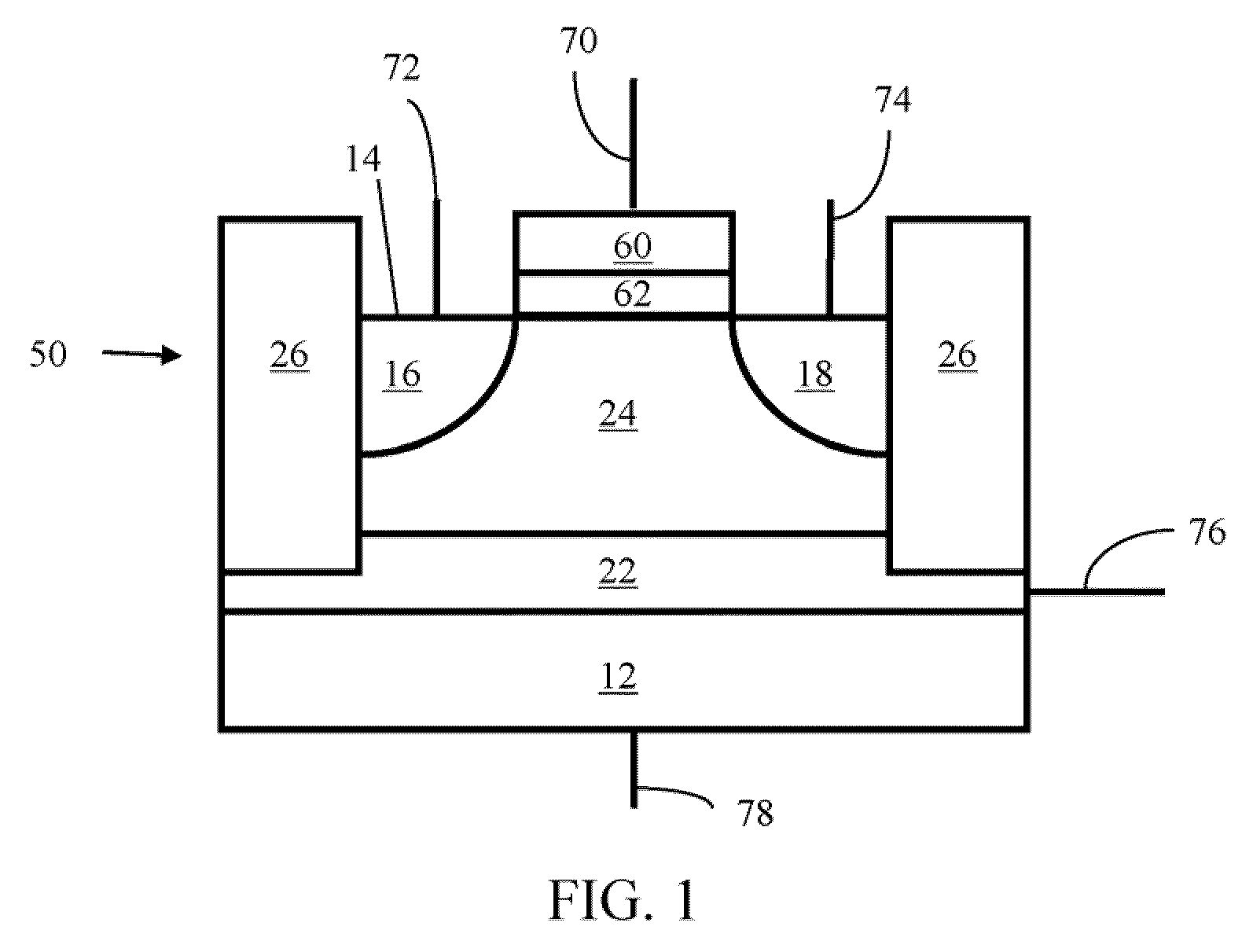

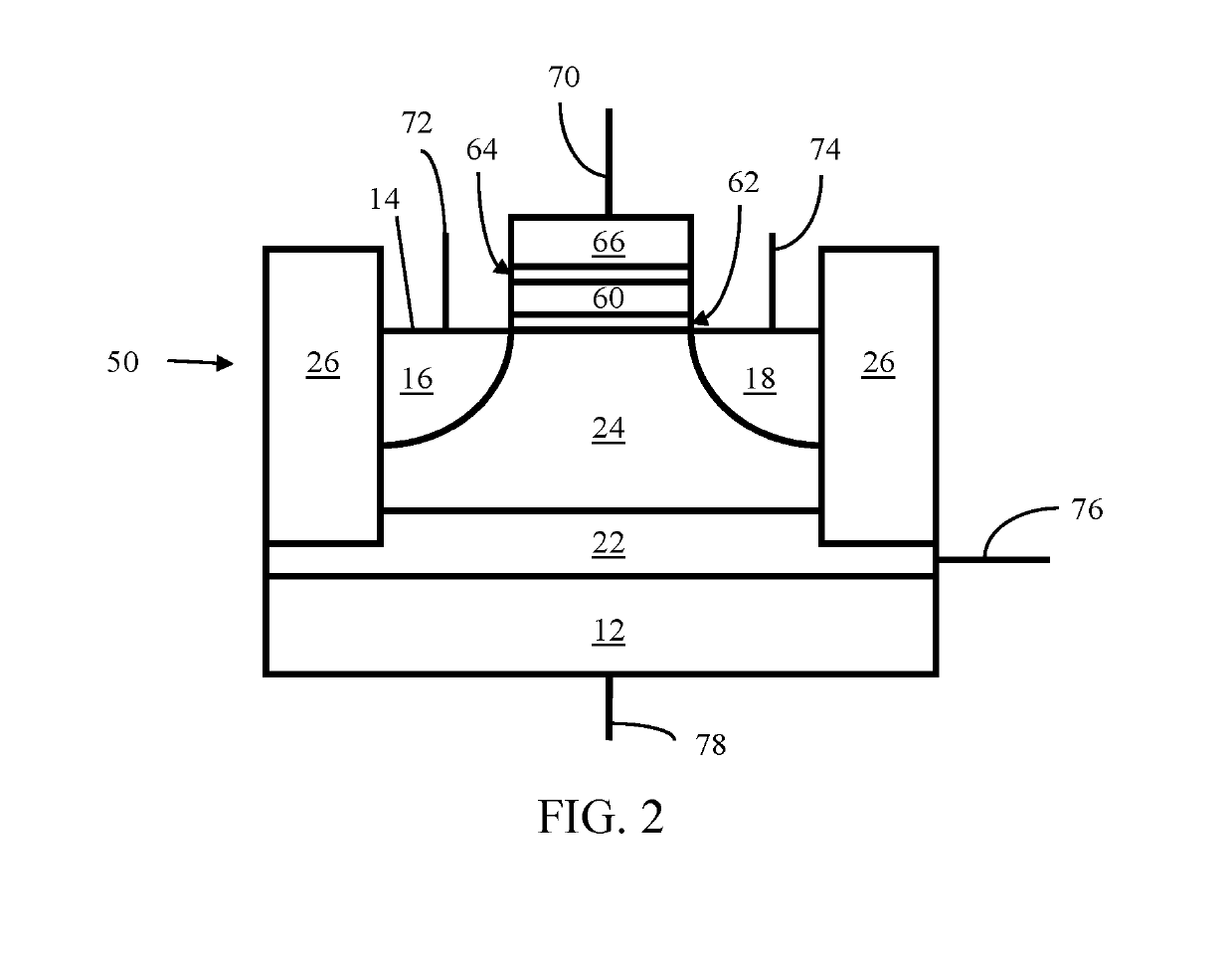

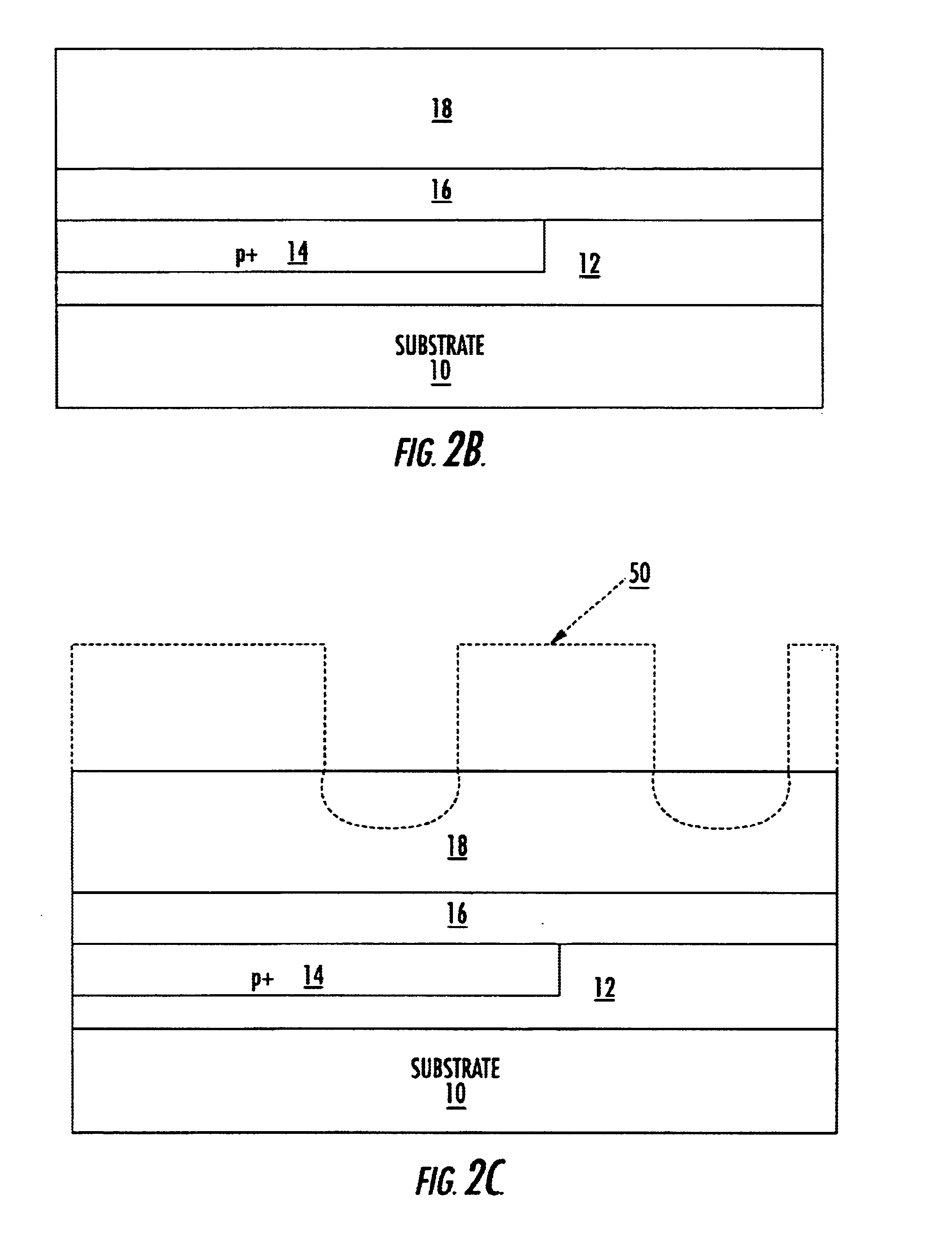

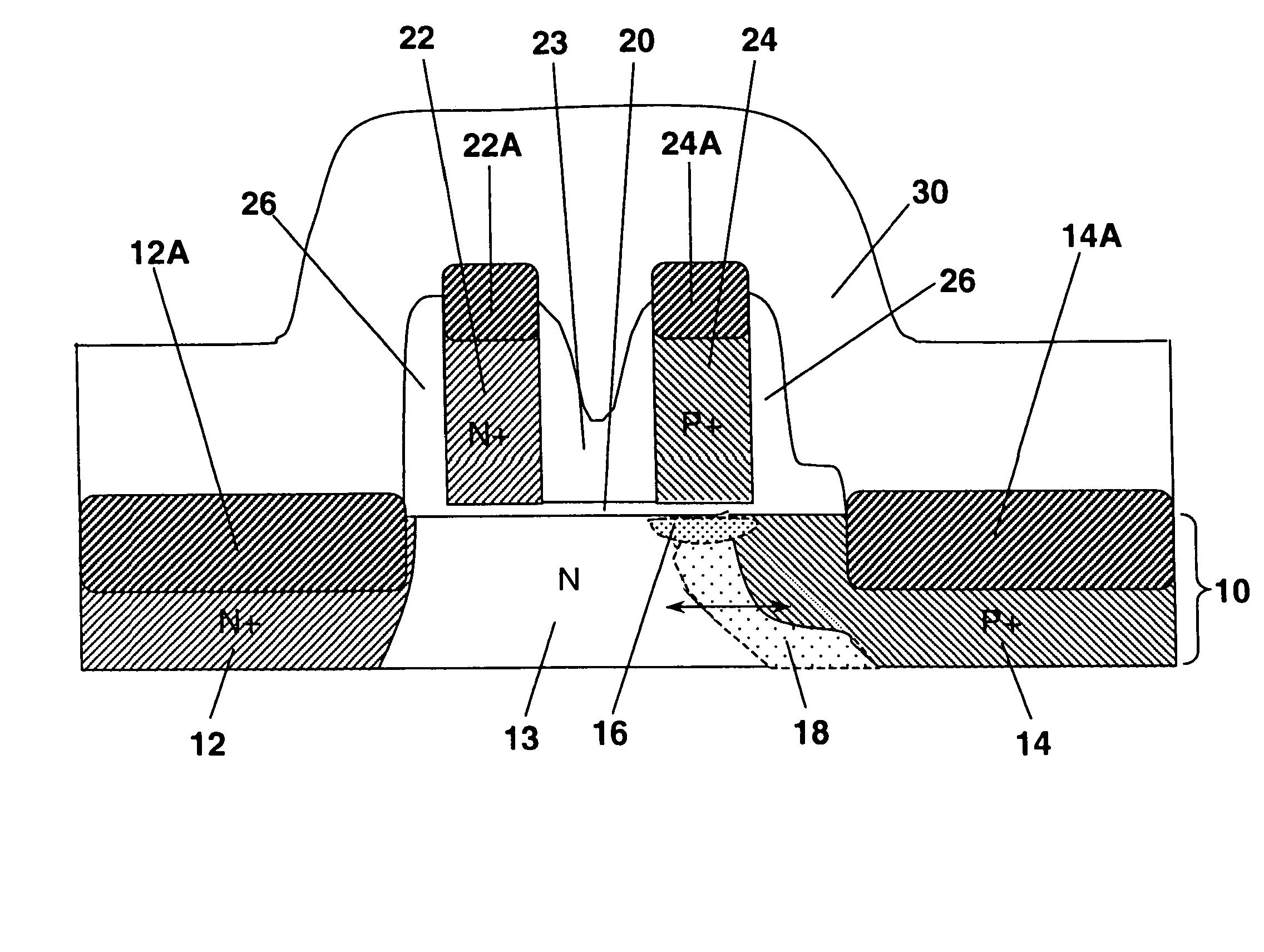

A semiconductor memory cell and arrays of memory cells are provided In at least one embodiment, a memory cell includes a substrate having a top surface, the substrate having a first conductivity type selected from a p-type conductivity type and an n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type, the first region being formed in the substrate and exposed at the top surface; a second region having the second conductivity type, the second region being formed in the substrate, spaced apart from the first region and exposed at the top surface; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; a gate positioned between the first and second regions and above the top surface; and a nonvolatile memory configured to store data upon transfer from the body region.

Owner:ZENO SEMICON

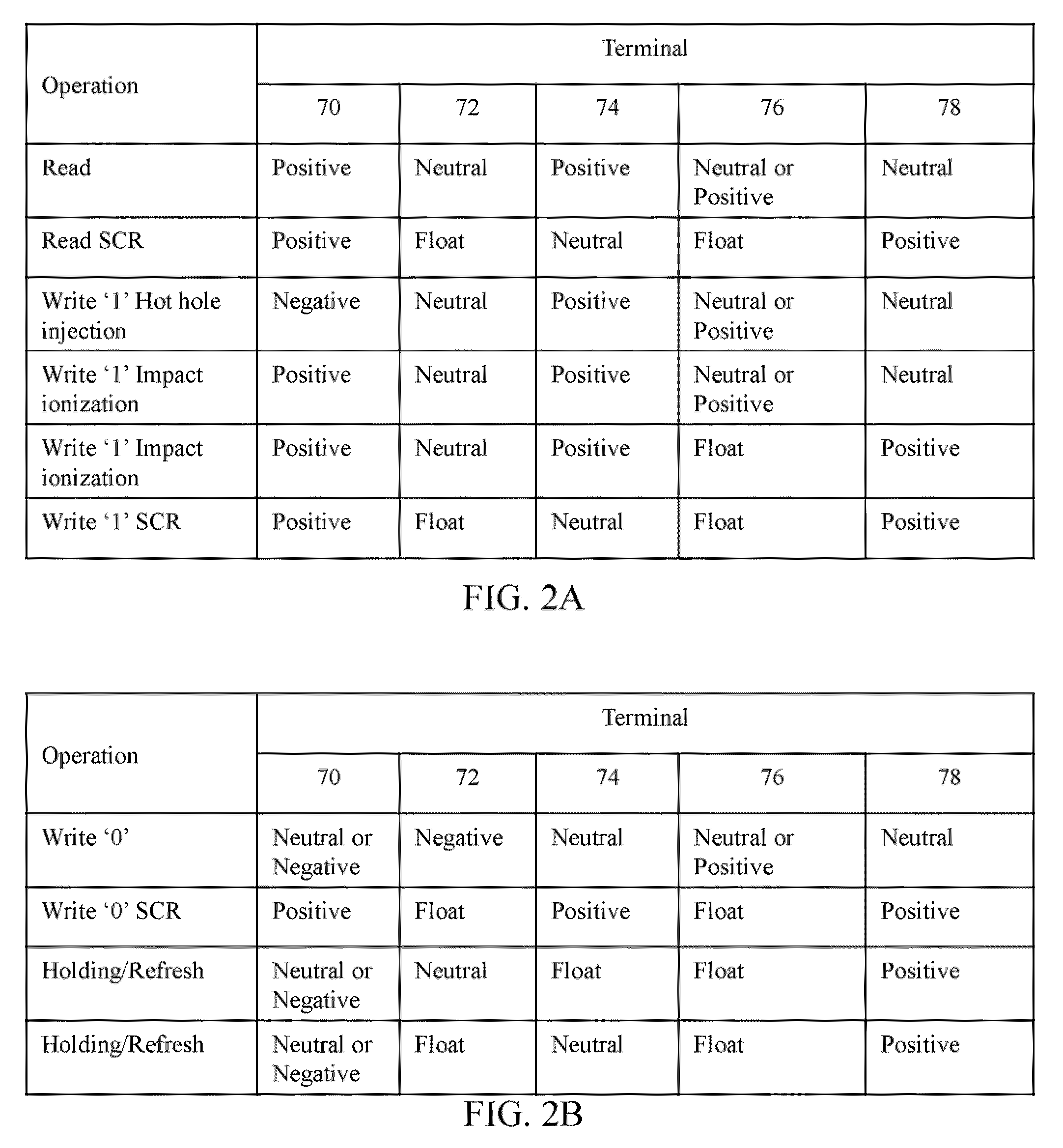

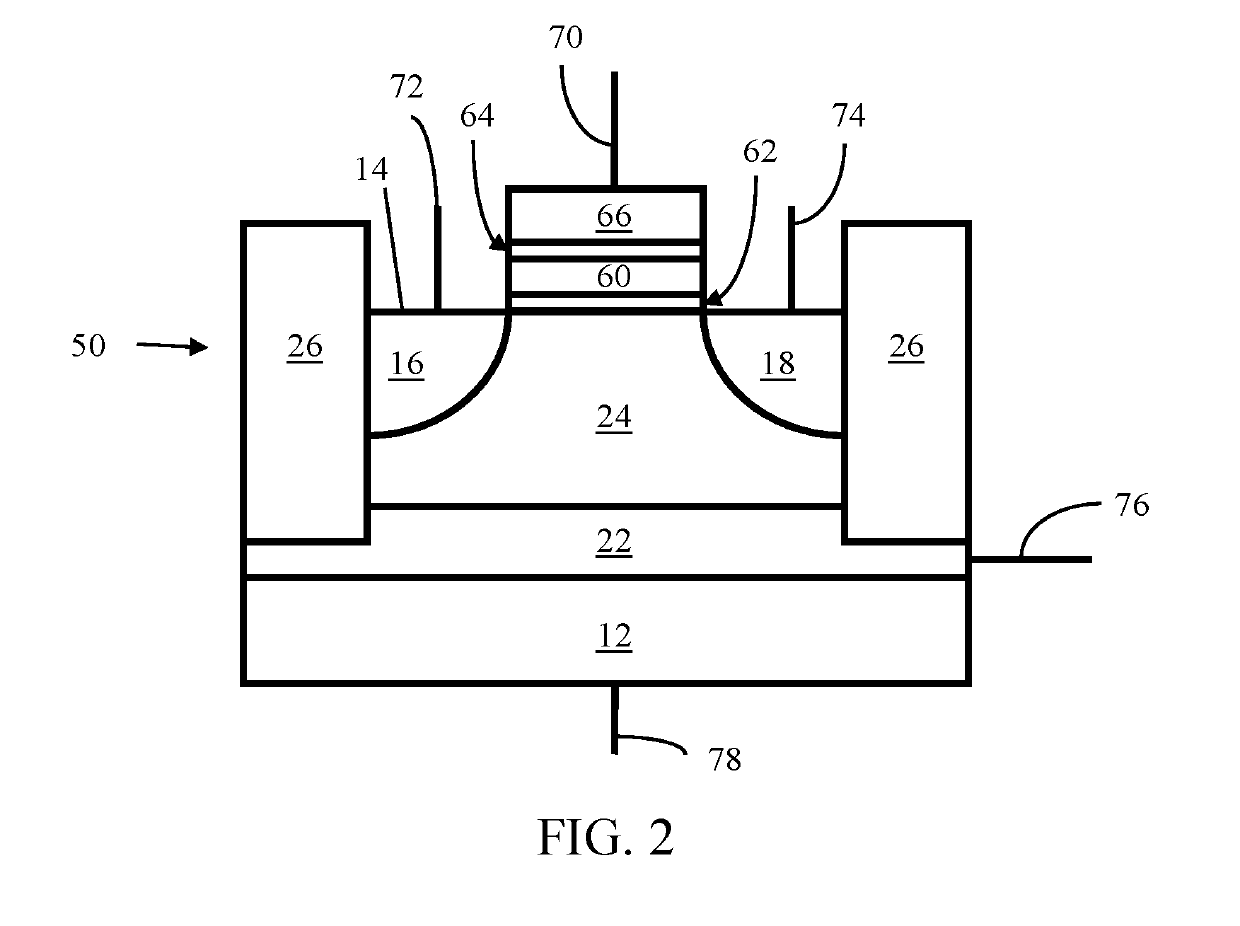

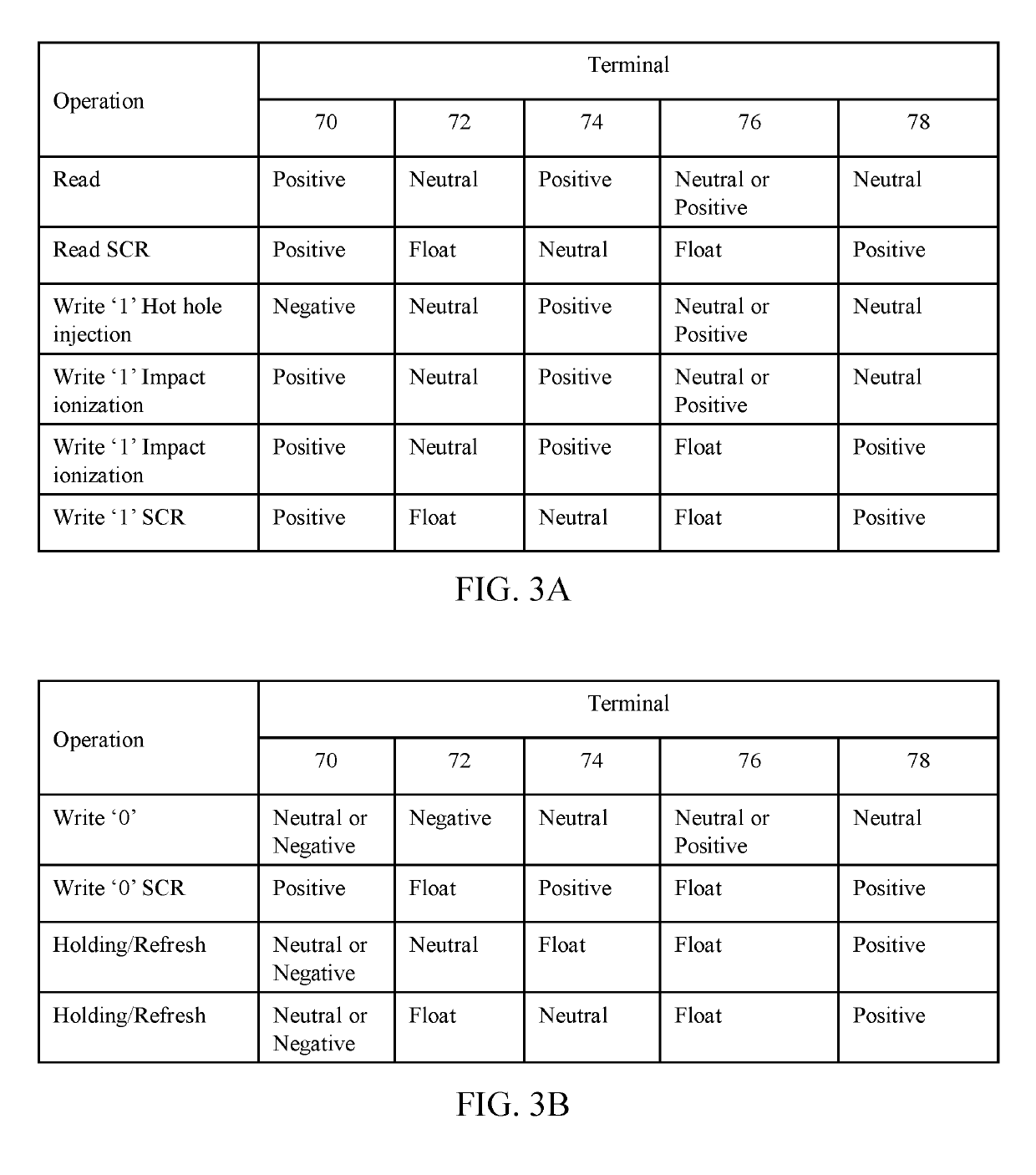

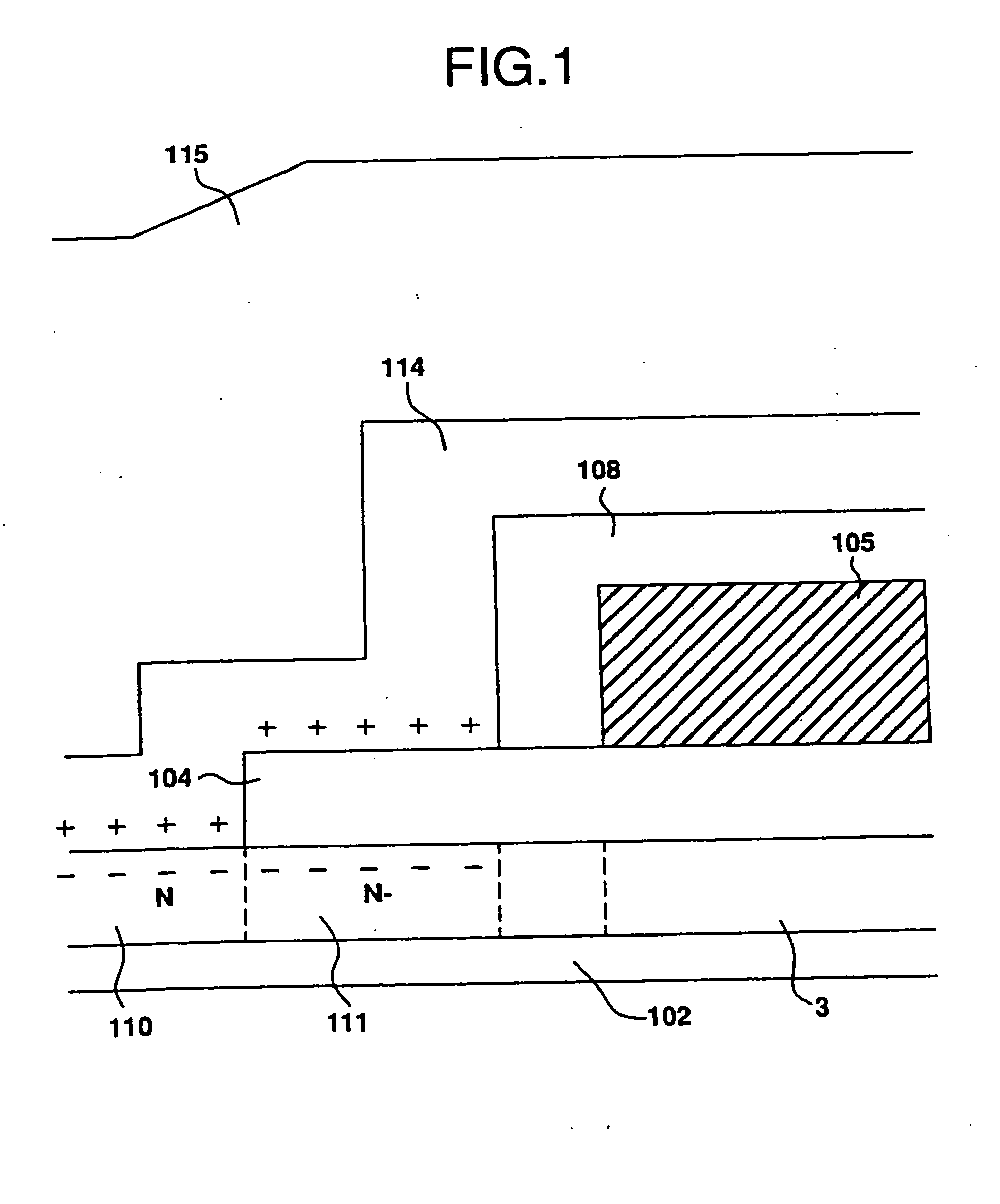

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

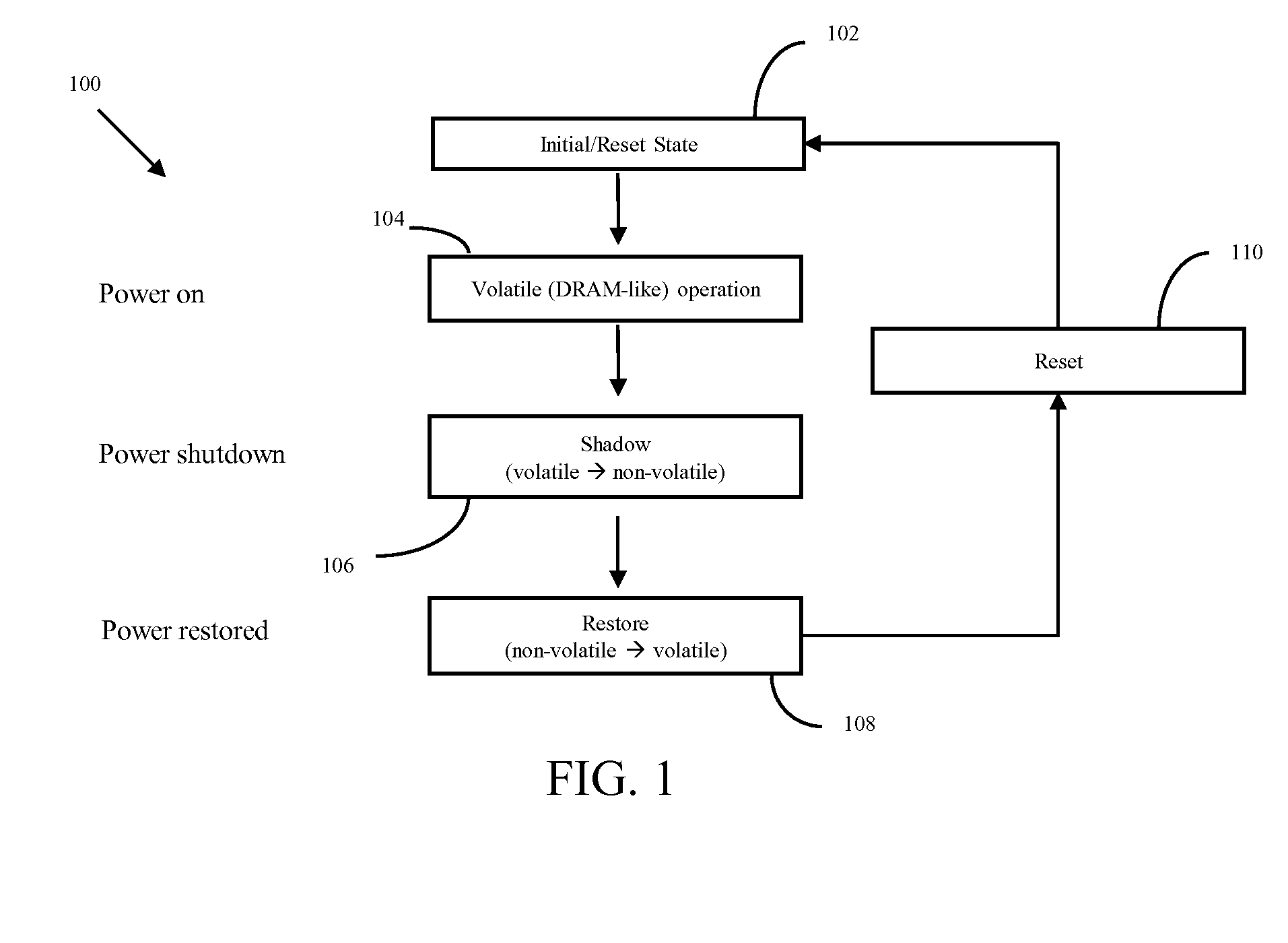

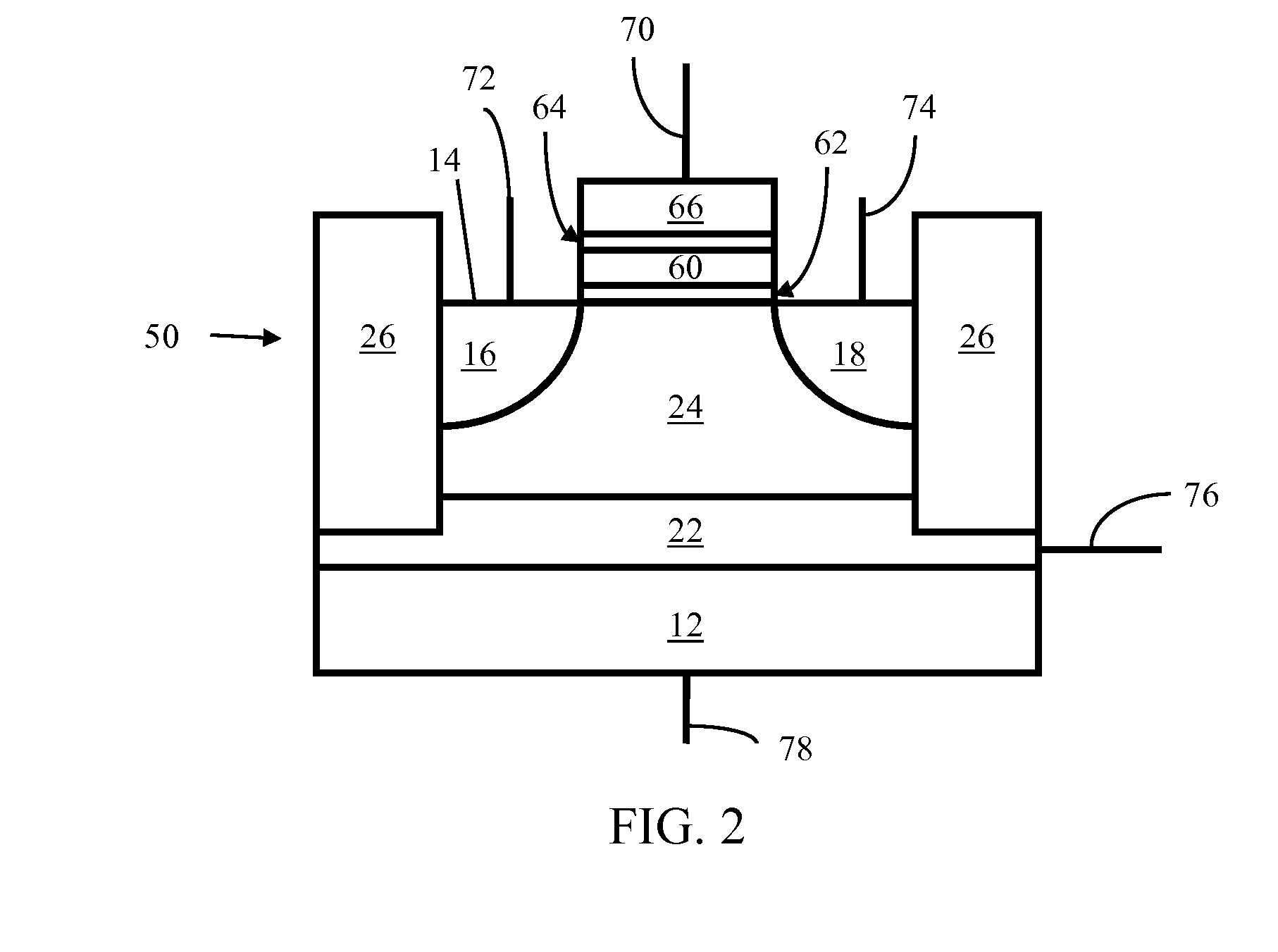

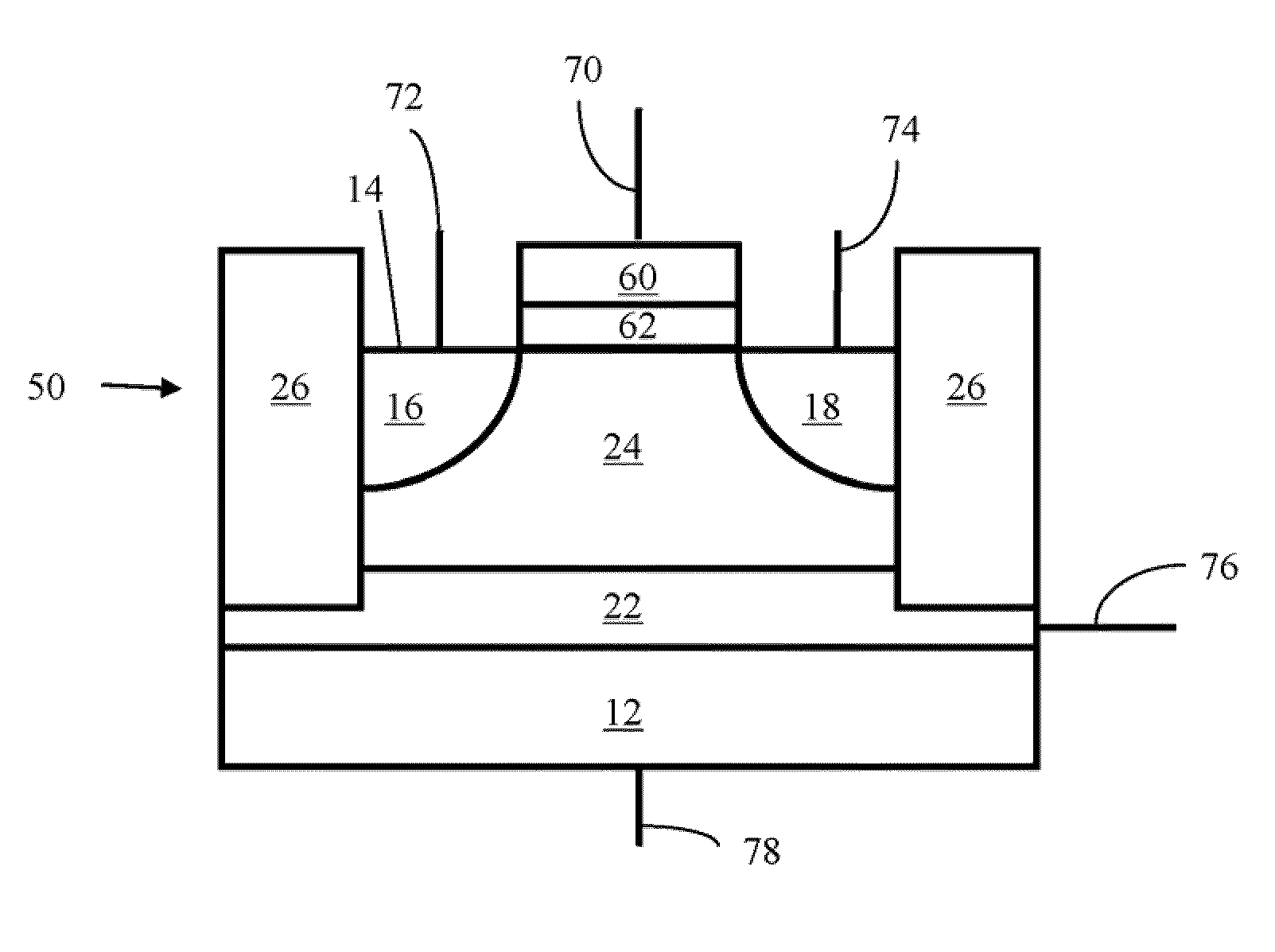

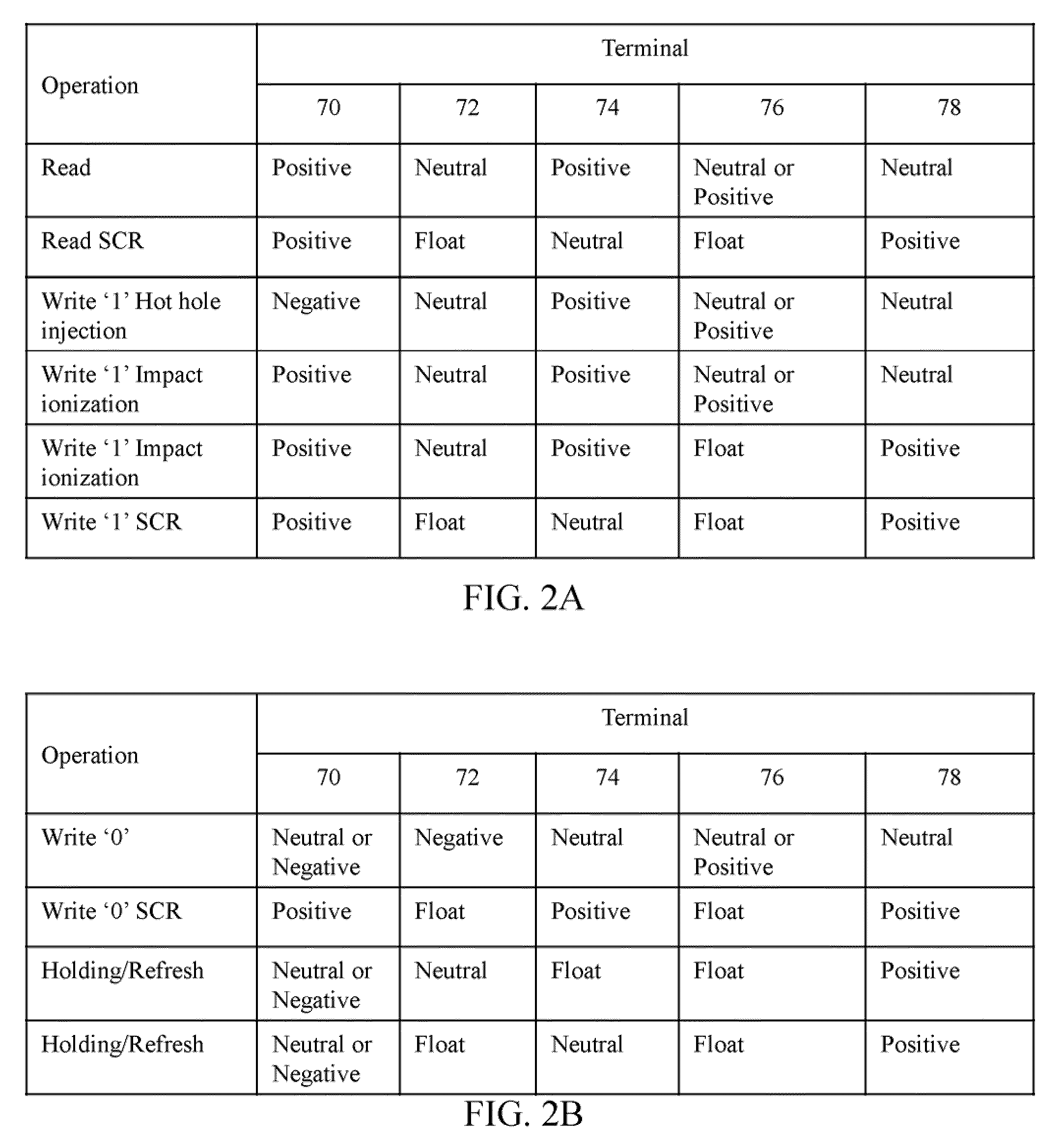

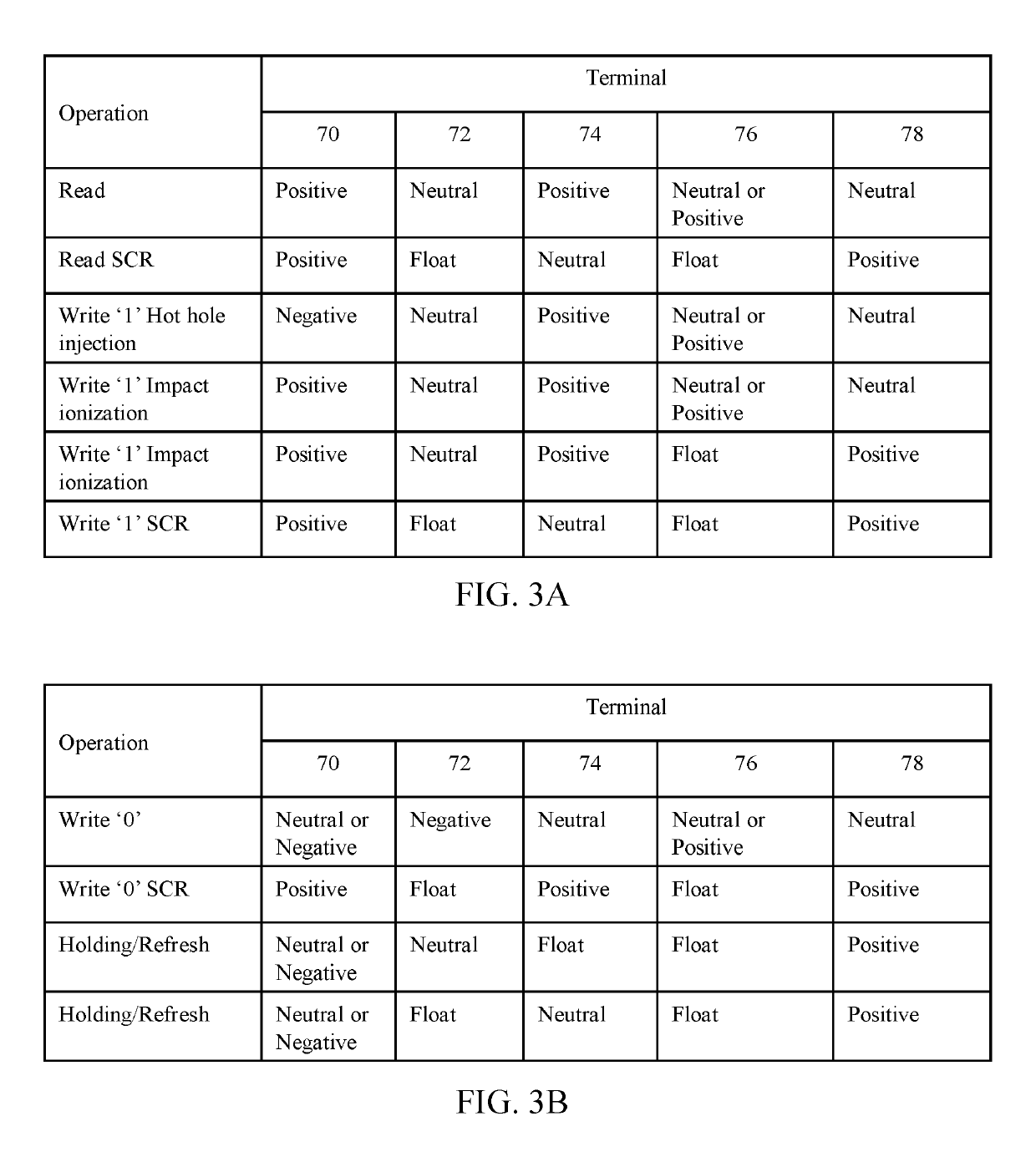

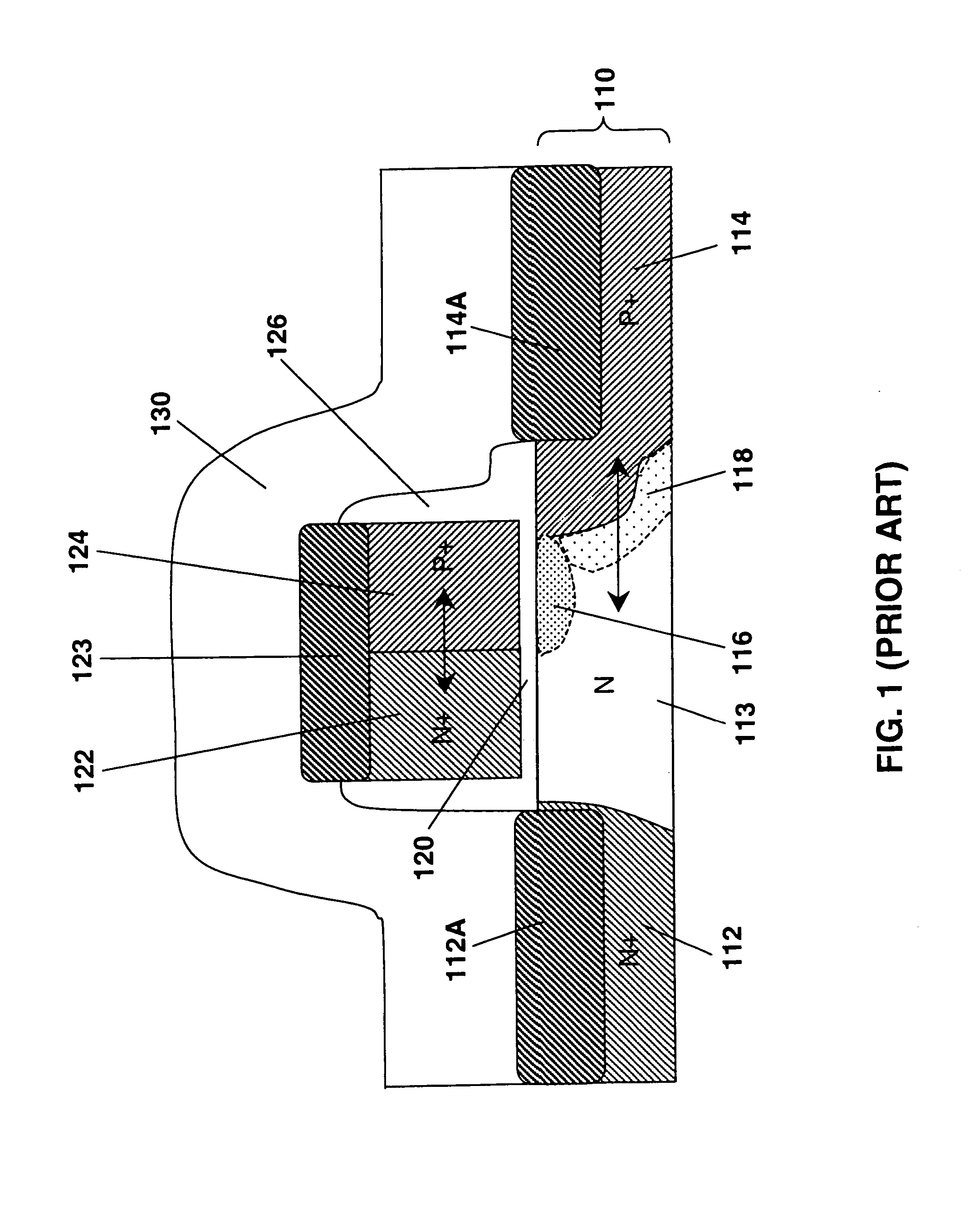

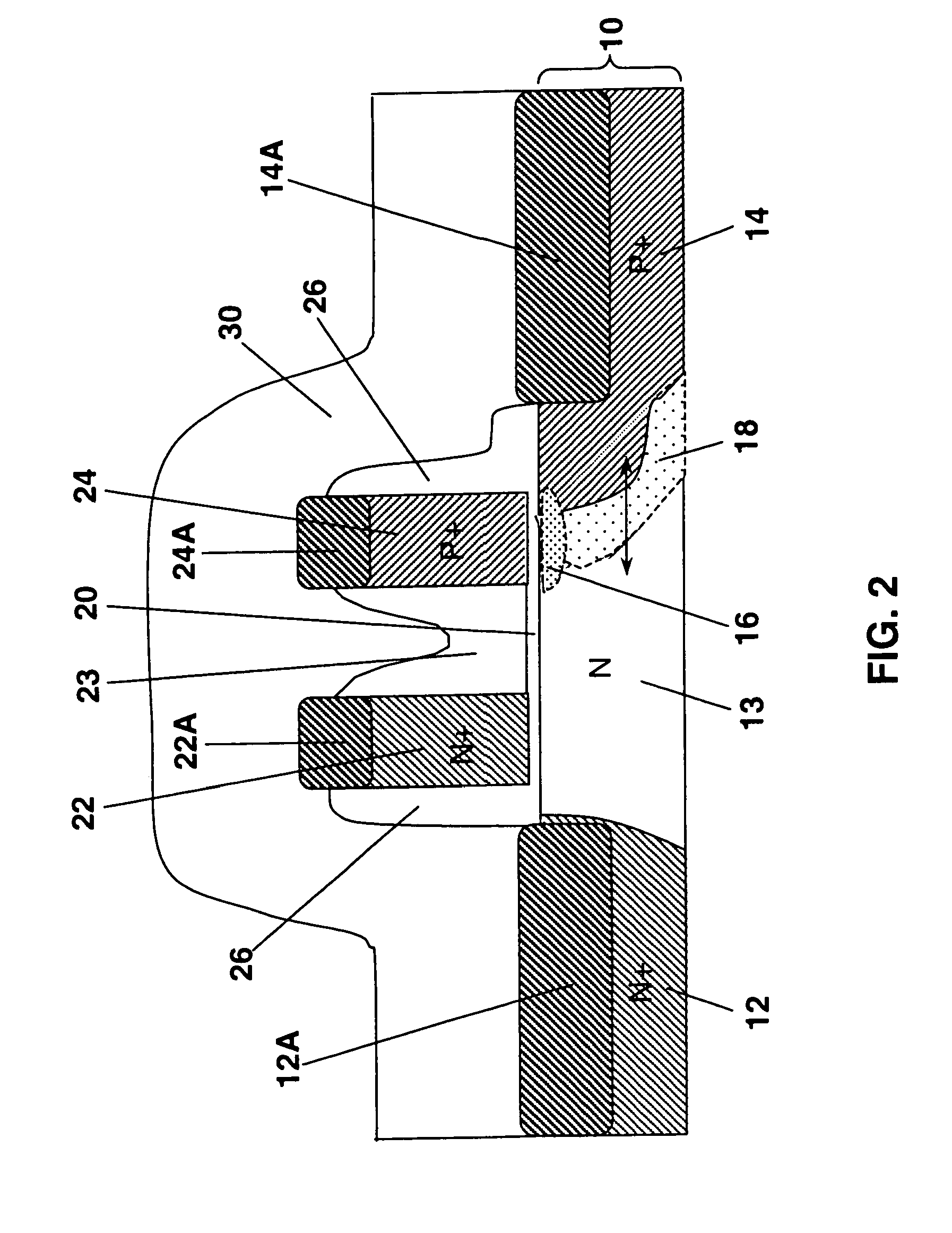

Methods of operating semiconductor memory devices with floating body transistors, using a silicon controlled rectifier principle are provided, as are semiconductor memory devices for performing such operations. A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region. The memory cell is configured to store a first data state which corresponds to a first charge in the body region in a first configuration, and a second data state which corresponds to a second charge in the body region in a second configuration. The method includes: providing the memory cell storing one of the first and second data states; and applying a positive voltage to a substrate terminal connected to the substrate beneath the buried layer, wherein when the body region is in the first state, the body region turns on a silicon controlled rectifier device of the cell and current flows through the device to maintain configuration of the memory cell in the first memory state, and wherein when the memory cell is in the second state, the body region does not turn on the silicon controlled rectifier device, current does not flow, and a blocking operation results, causing the body to maintain the second memory state.

Owner:ZENO SEMICON

Memory cells, memory cell arrays, methods of using and methods of making

A semiconductor memory cell and arrays of memory cells are provided In at least one embodiment, a memory cell includes a substrate having a top surface, the substrate having a first conductivity type selected from a p-type conductivity type and an n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type, the first region being formed in the substrate and exposed at the top surface; a second region having the second conductivity type, the second region being formed in the substrate, spaced apart from the first region and exposed at the top surface; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; a gate positioned between the first and second regions and above the top surface; and a nonvolatile memory configured to store data upon transfer from the body region.

Owner:ZENO SEMICON

Method of operating semiconductor memory device with floating body transistor using silicon controlled rectifier principle

A method of maintaining the data state of a semiconductor dynamic random access memory cell is provided, wherein the memory cell comprises a substrate being made of a material having a first conductivity type selected from p-type conductivity type and n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type; a second region having the second conductivity type, the second region being spaced apart from the first region; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; and a gate positioned between the first and second regions and adjacent the body region.

Owner:ZENO SEMICON

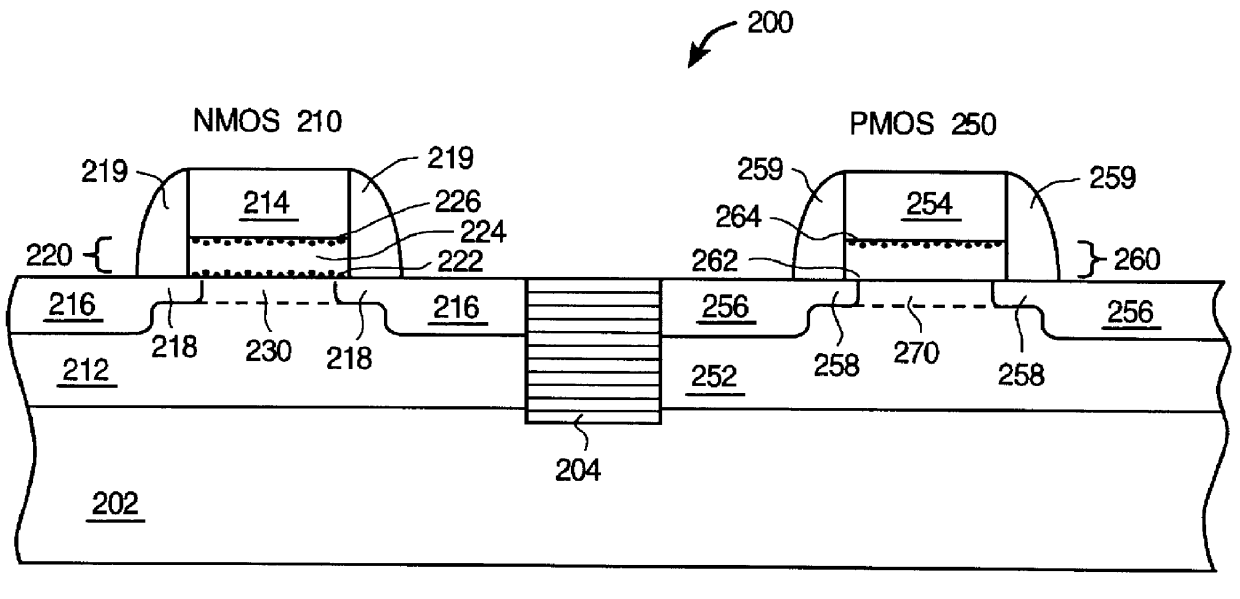

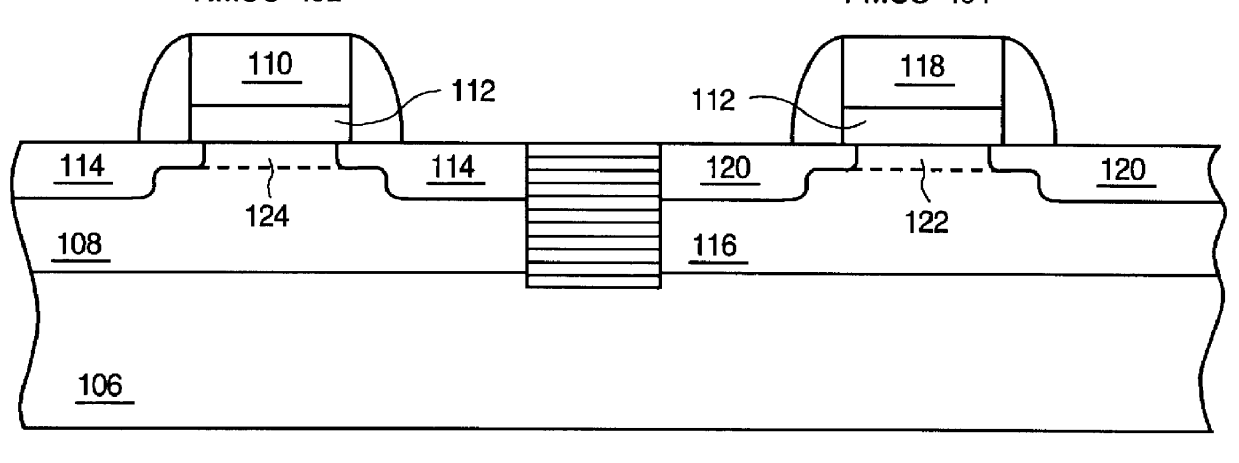

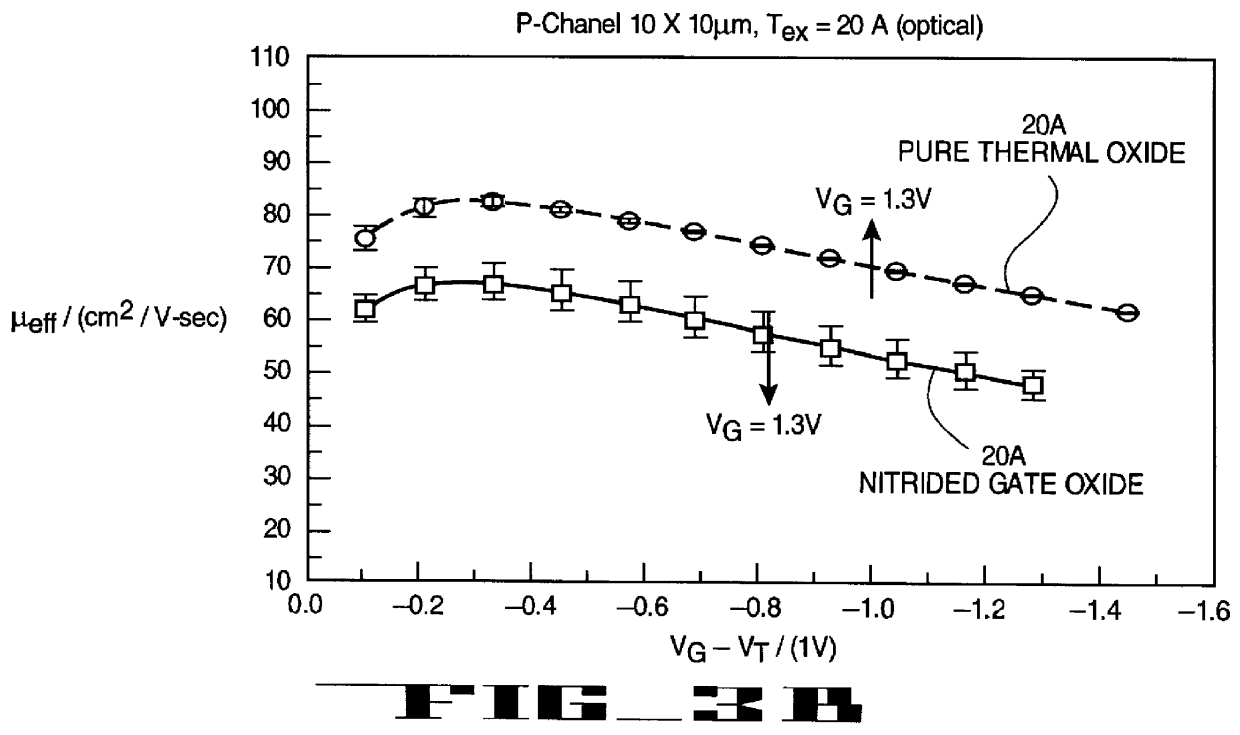

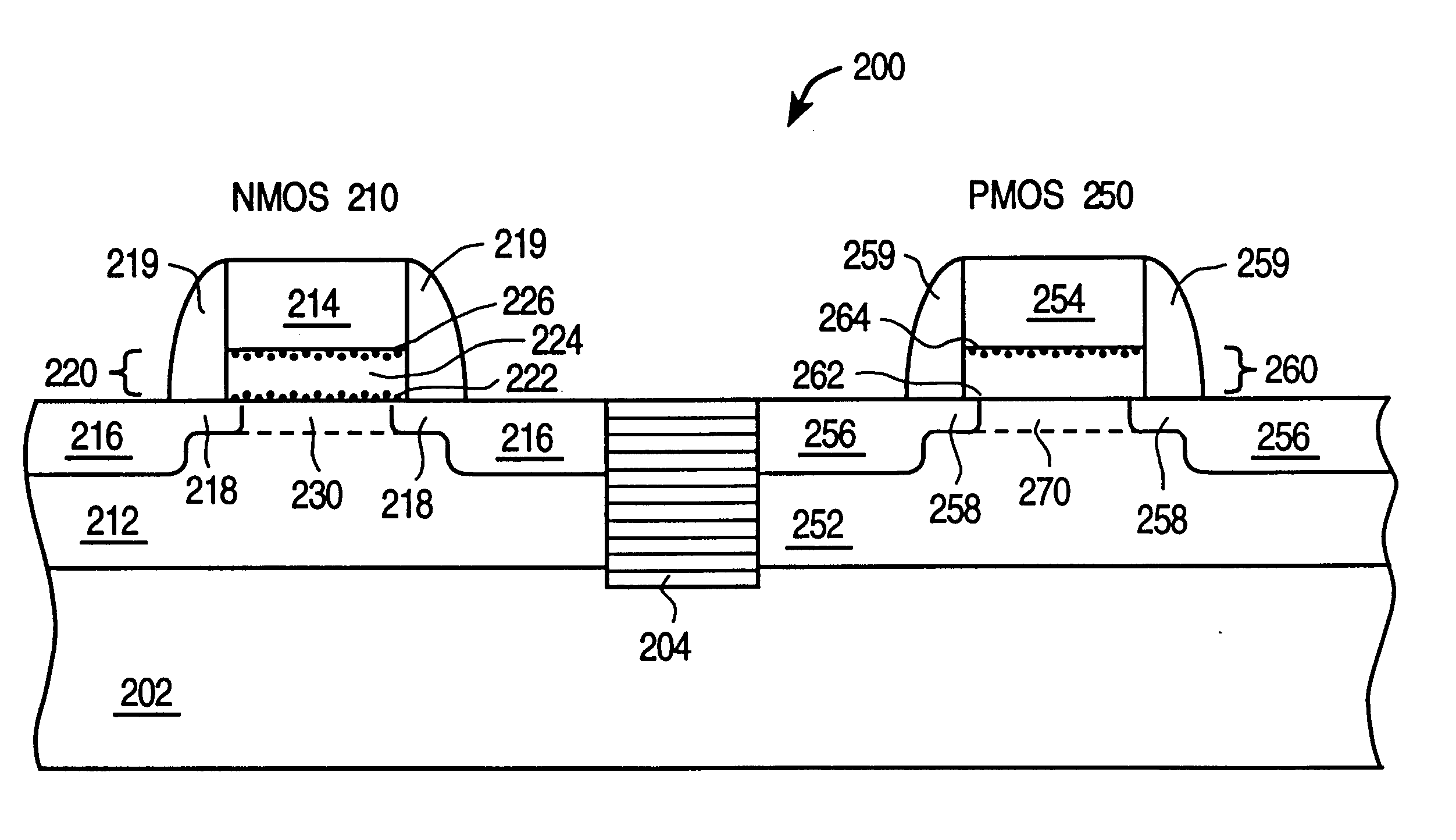

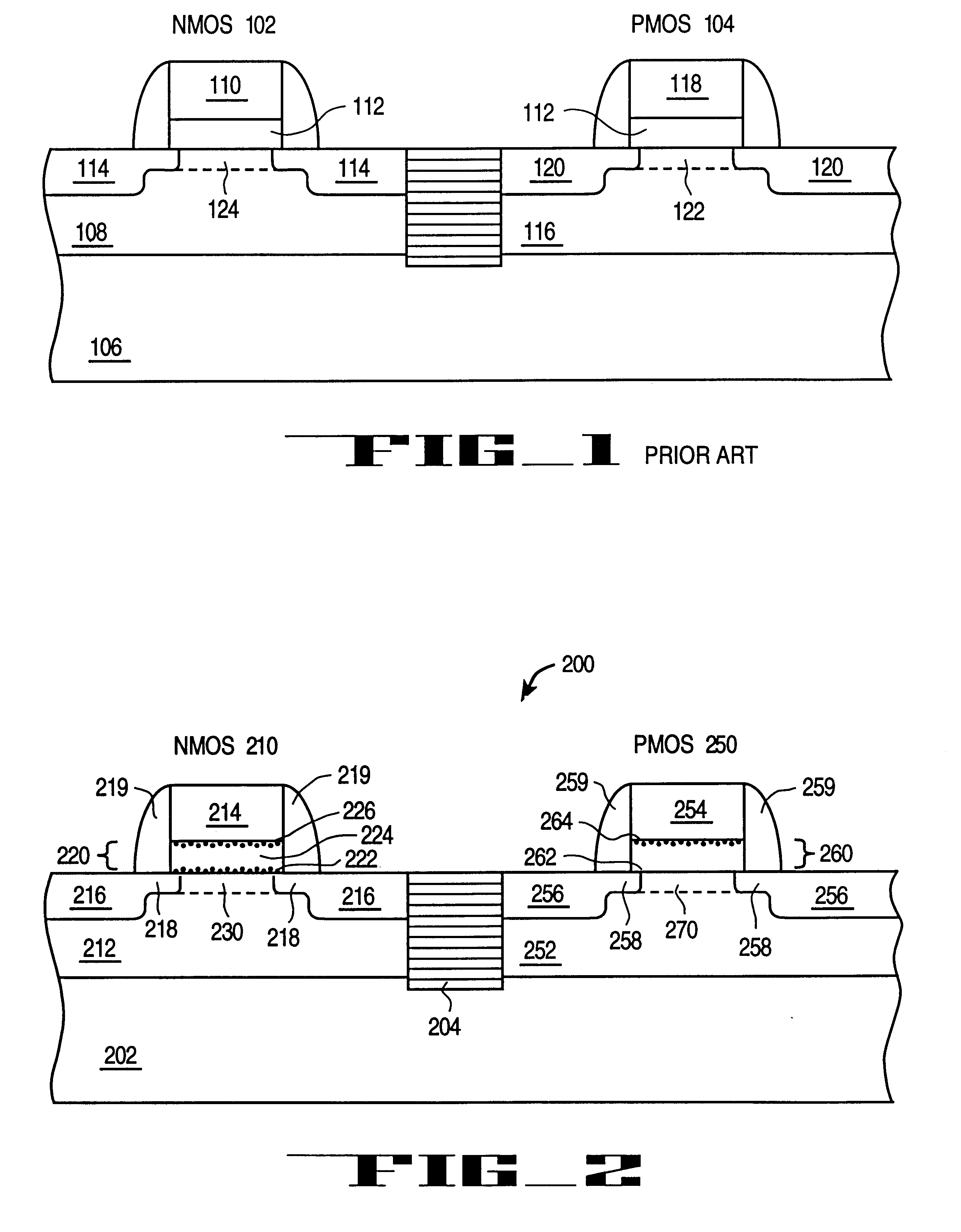

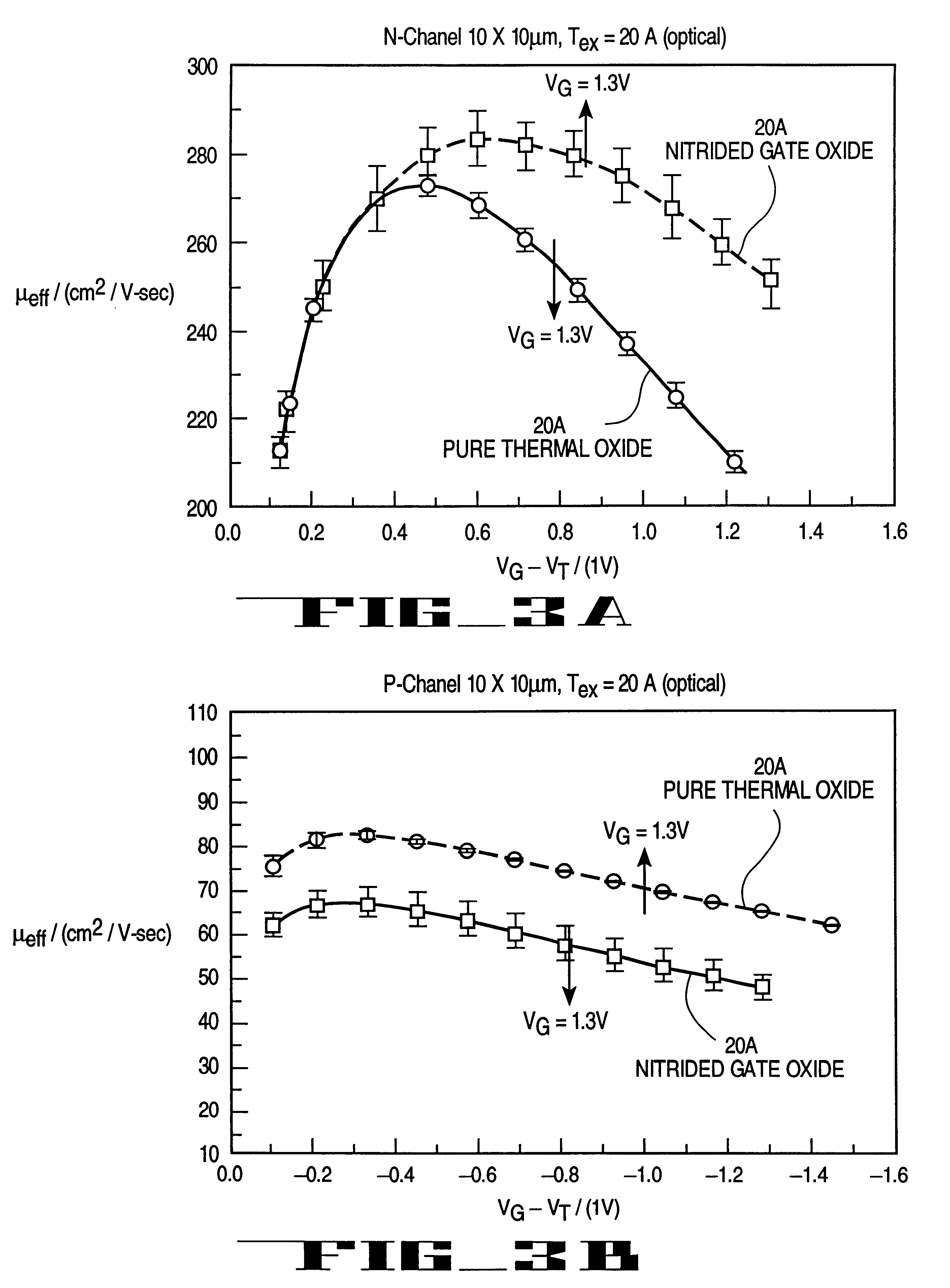

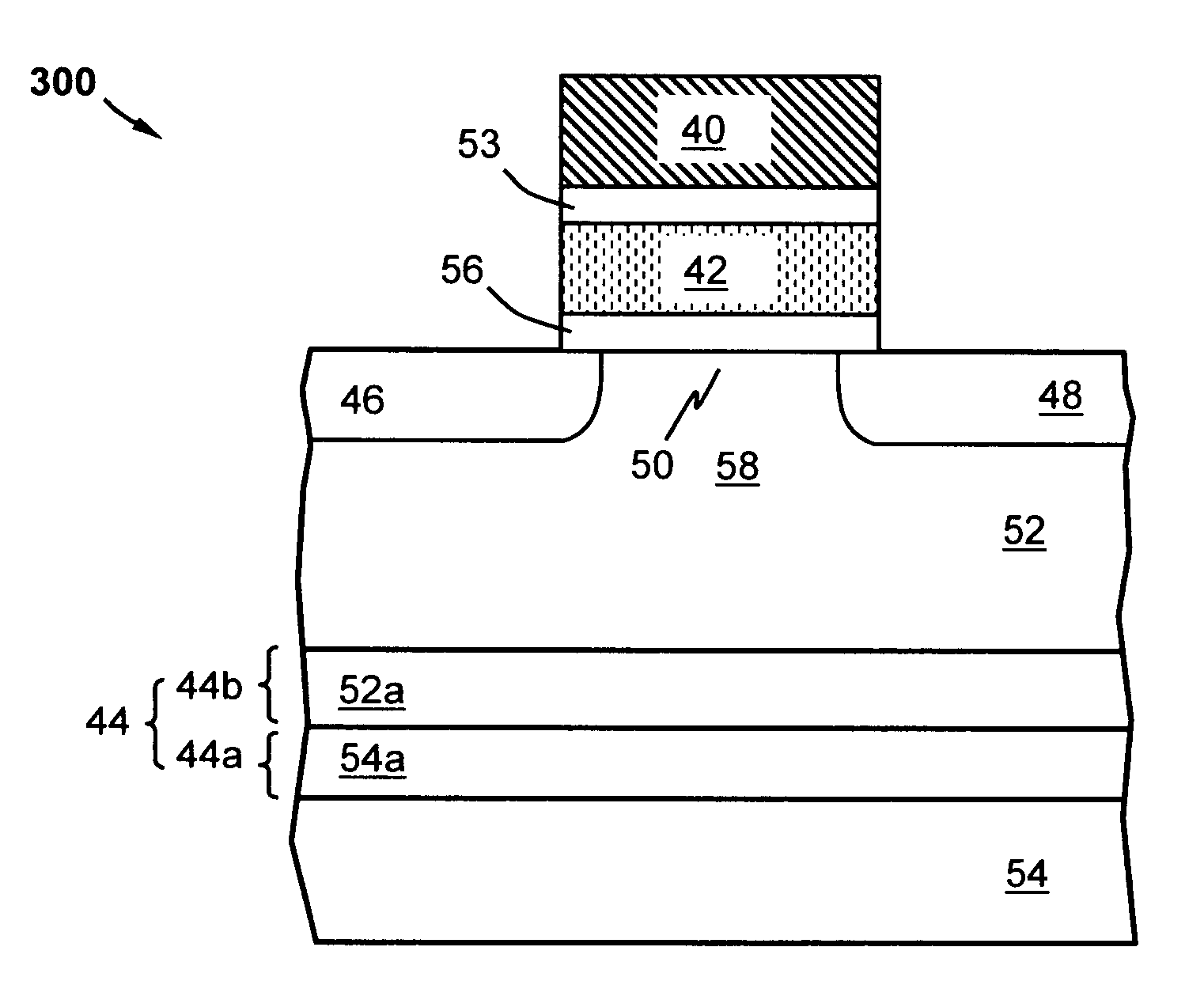

CMOS integrated circuit having PMOS and NMOS devices with different gate dielectric layers

A CMOS integrated circuit having a PMOS and NMOS device with different gate dielectric layers. According to the present invention, an NMOS transistor is formed on a p-type conductivity region of a semiconductor substrate. The NMOS transistor has first gate dielectric layer formed on the p-type conductivity region. A PMOS transistor is formed on a n-type conductivity region of the semiconductor substrate. The PMOS transistor has a second gate dielectric layer wherein the second gate dielectric layer has a different composition than the first gate dielectric layer.

Owner:INTEL CORP

CMOS integrated circuit having PMOS and NMOS devices with different gate dielectric layers

Owner:INTEL CORP

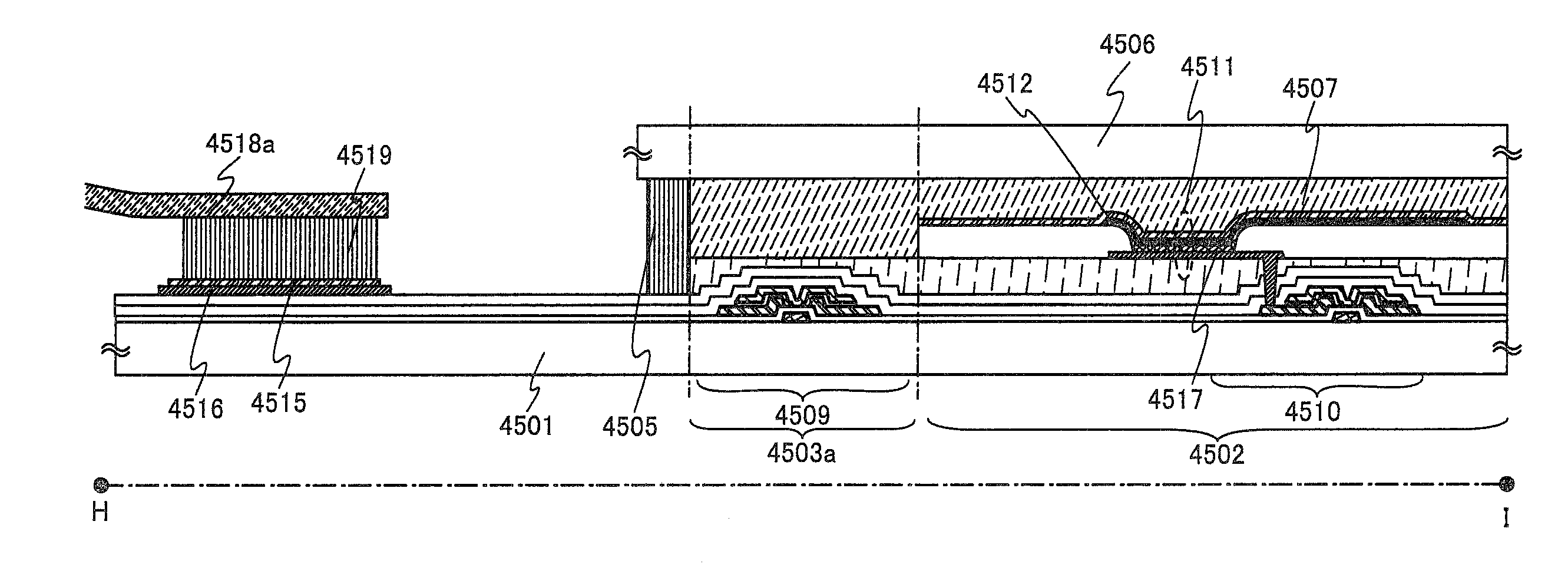

Method for manufacturing semiconductor device

ActiveUS8343817B2Increase the number ofDecrease productivitySolid-state devicesSemiconductor/solid-state device manufacturingResistN type conductivity

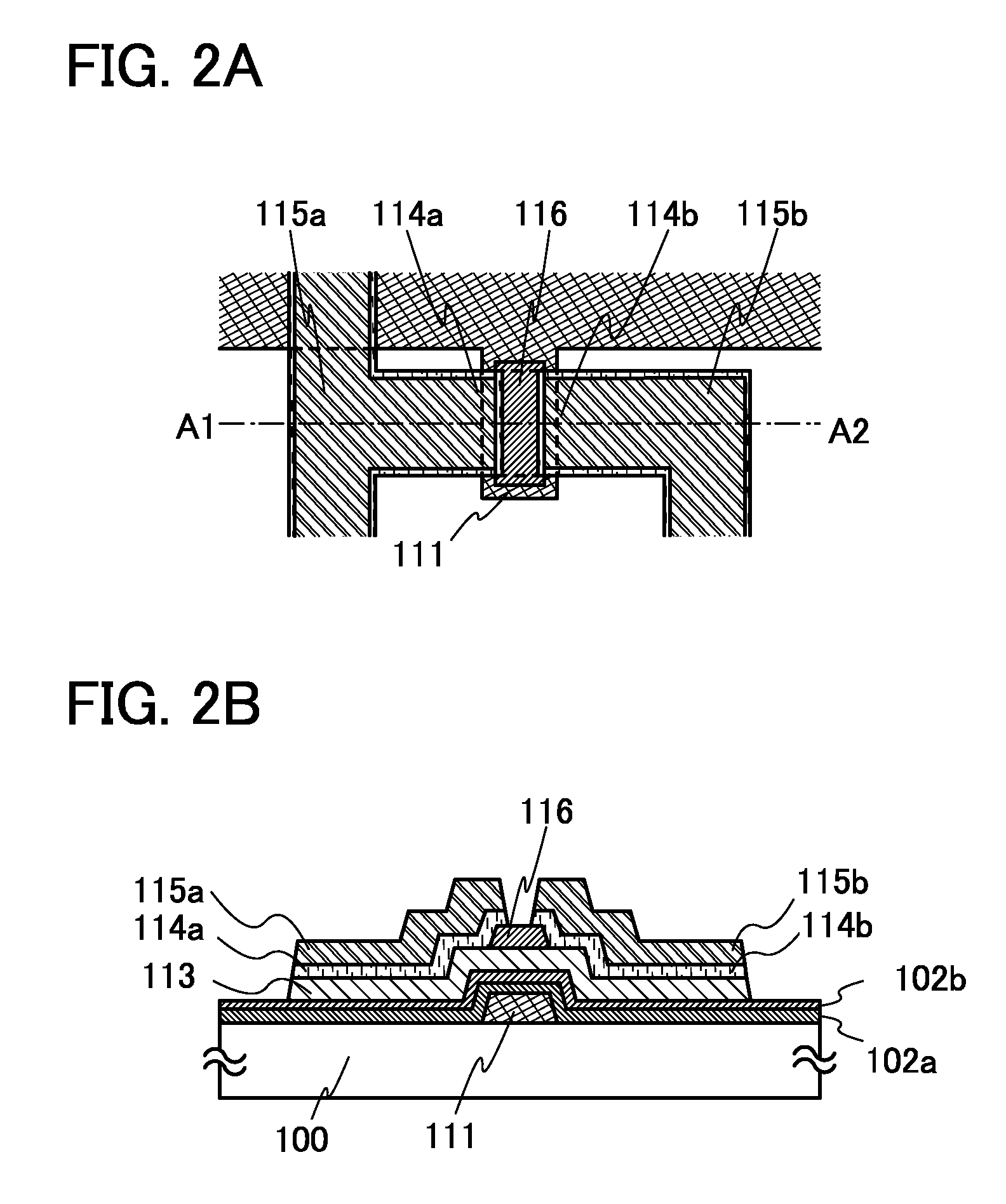

To provide a method by which a semiconductor device including a thin film transistor with excellent electric characteristics and high reliability is manufactured with a small number of steps. After a channel protective layer is formed over an oxide semiconductor film containing In, Ga, and Zn, a film having n-type conductivity and a conductive film are formed, and a resist mask is formed over the conductive film. The conductive film, the film having n-type conductivity, and the oxide semiconductor film containing In, Ga, and Zn are etched using the channel protective layer and gate insulating films as etching stoppers with the resist mask, so that source and drain electrode layers, a buffer layer, and a semiconductor layer are formed.

Owner:SEMICON ENERGY LAB CO LTD

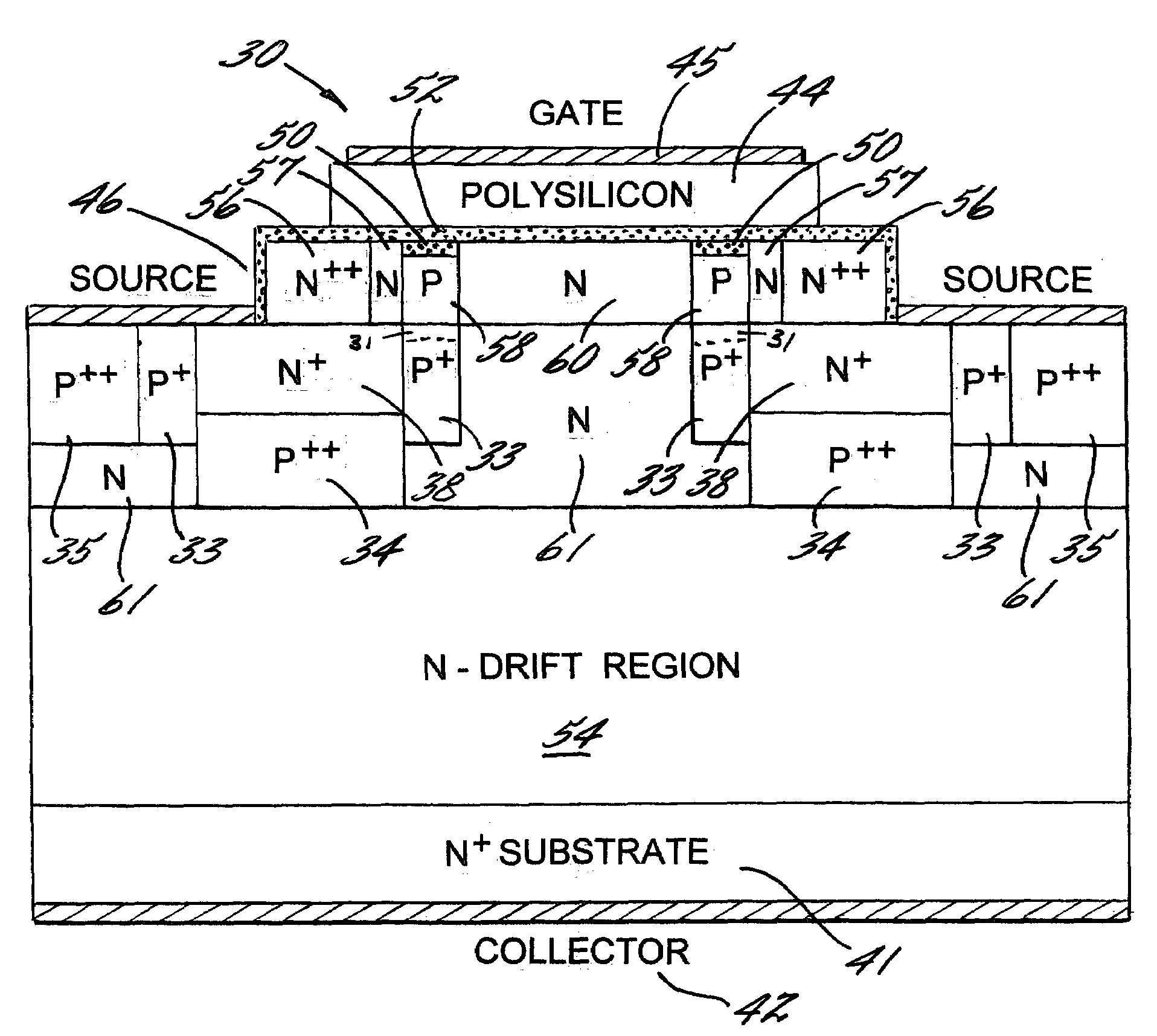

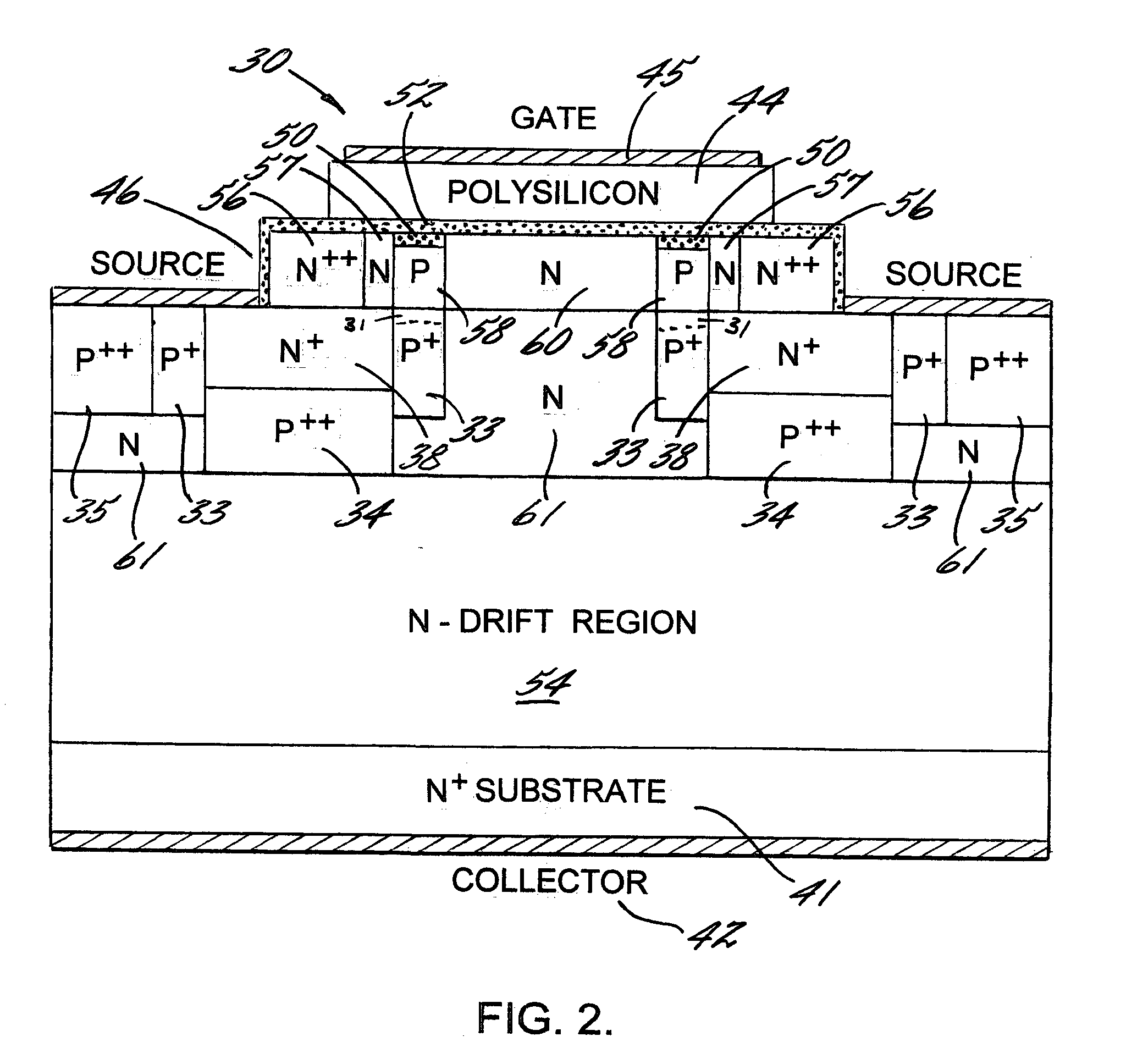

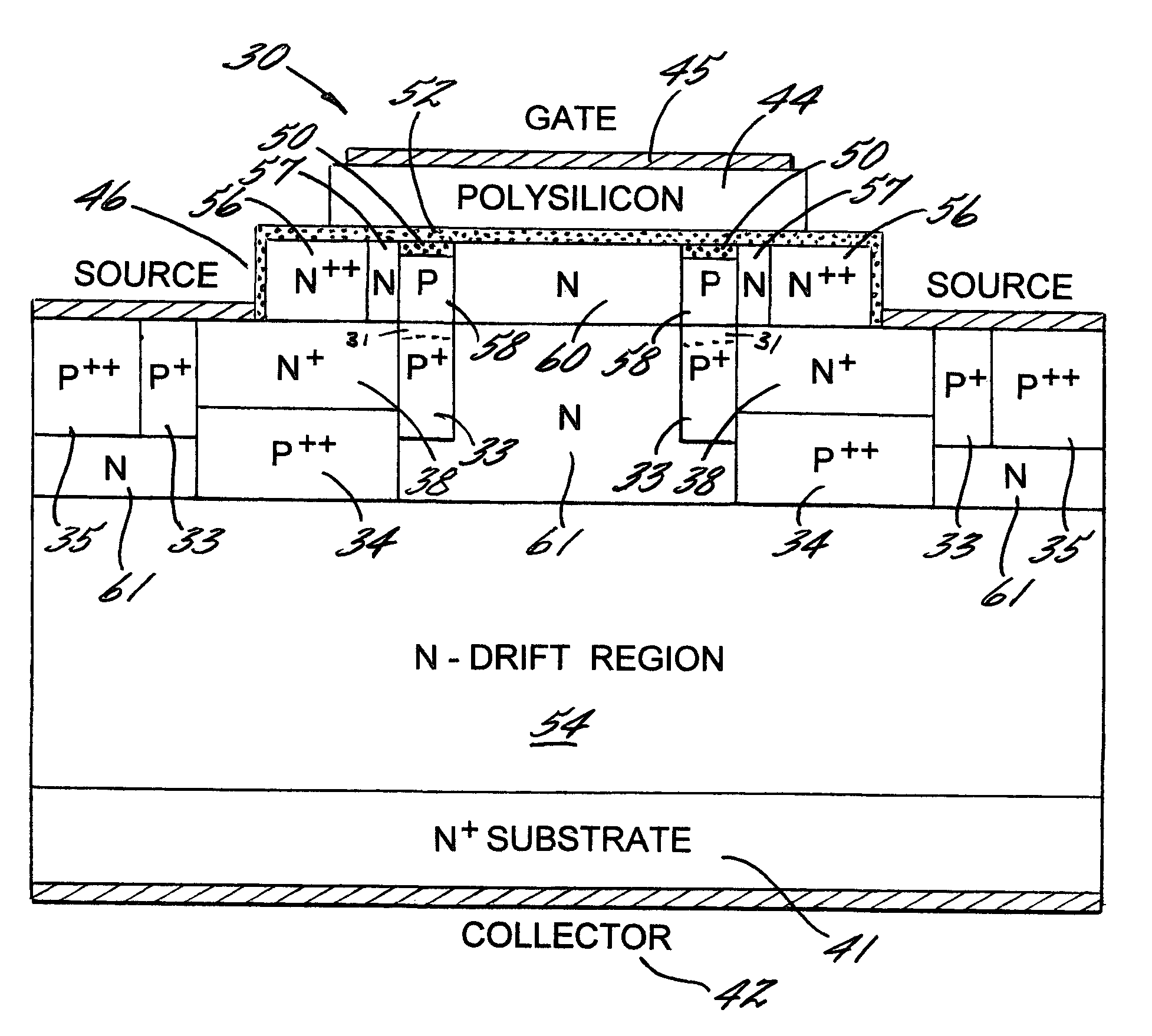

Semiconductor transistor with p type re-grown channel layer

ActiveUS20090189228A1Easy to controlTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

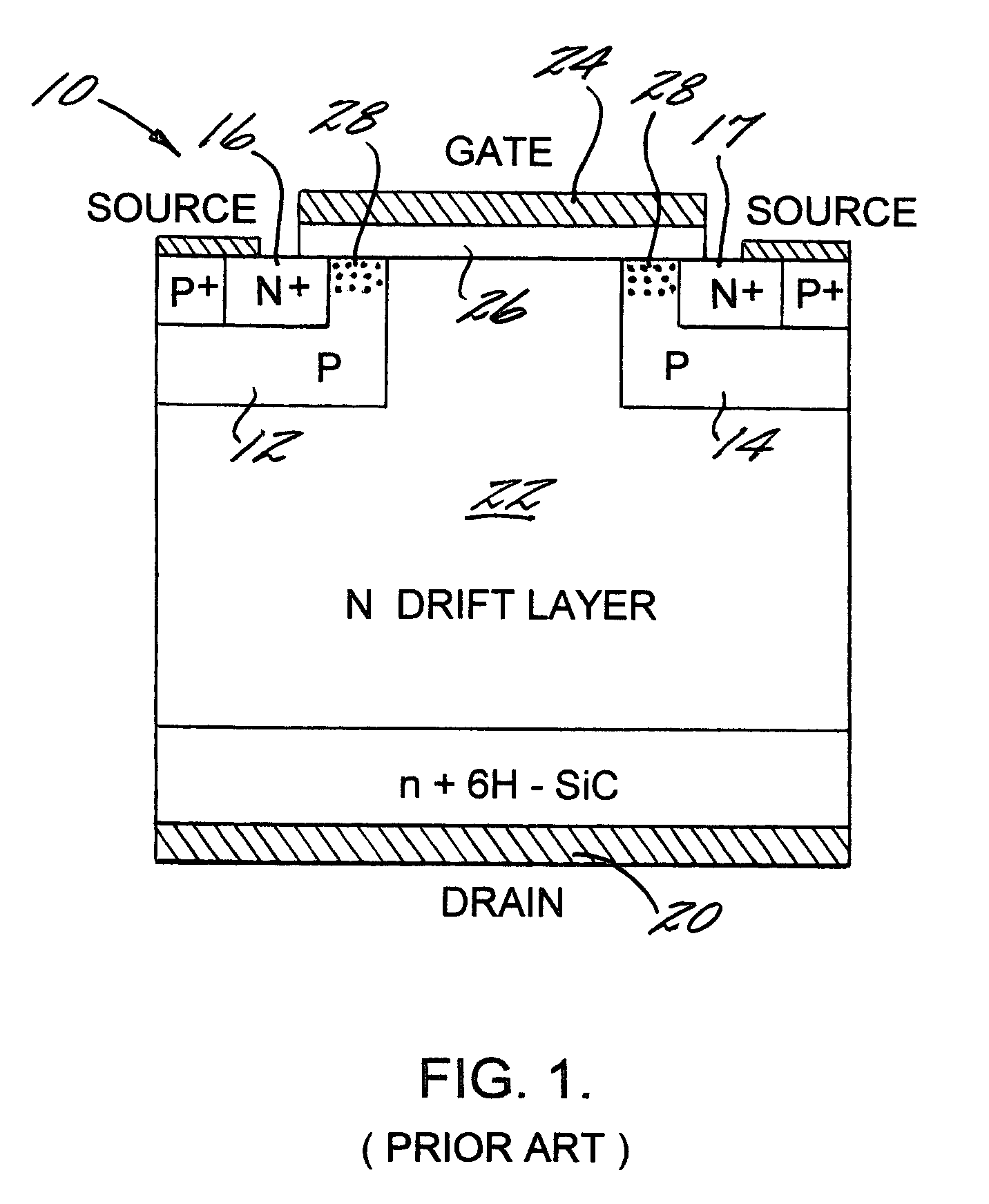

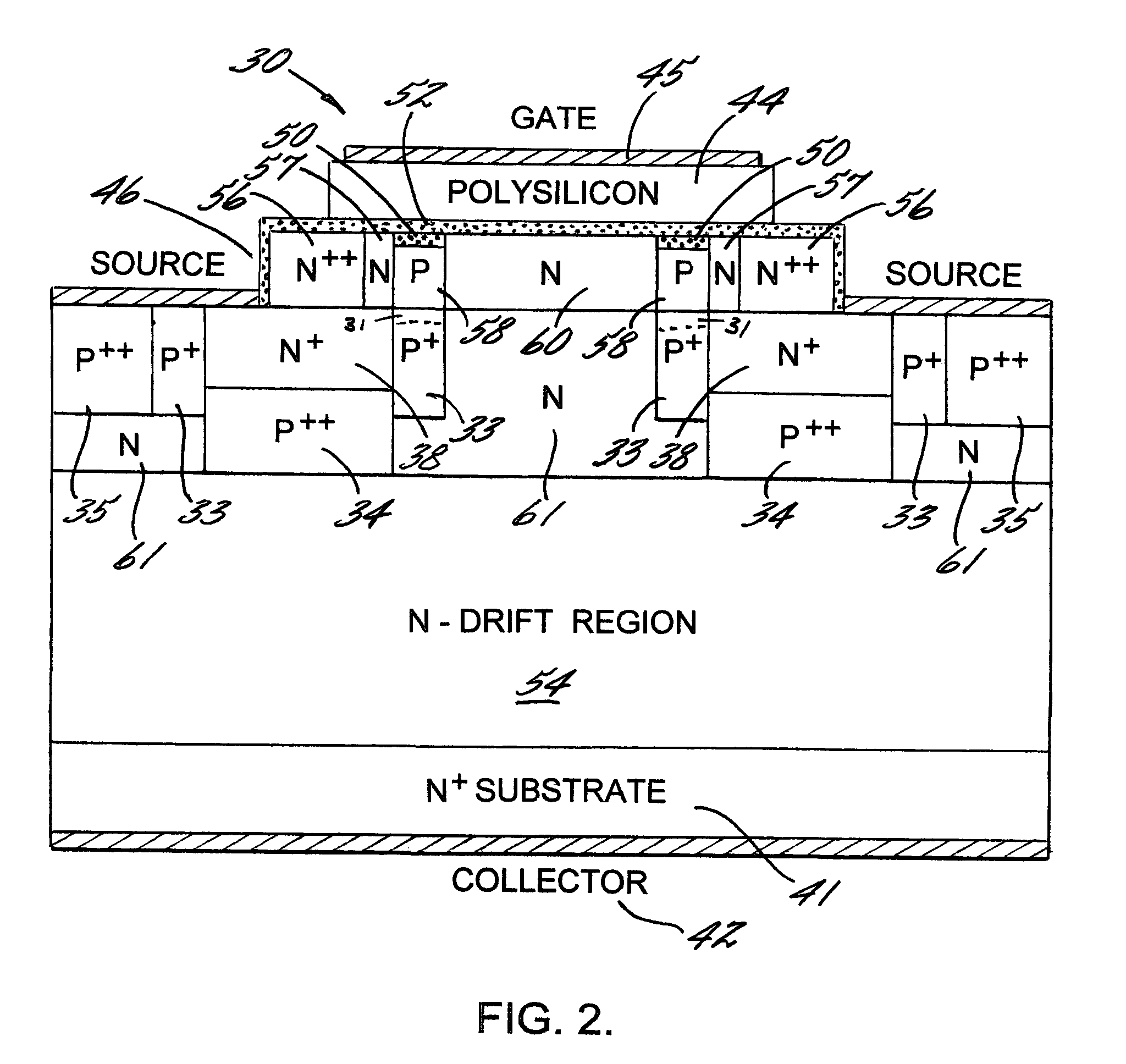

The invention is a device for controlling conduction across a semiconductor body with a P type channel layer between active semiconductor regions of the device and the controlling gate contact. The device, often a MOSFET or an IGBT, includes at least one source, well, and drift region. The P type channel layer may be divided into sections, or divided regions, that have been doped to exhibit N type conductivity. By dividing the channel layer into regions of different conductivity, the channel layer allows better control over the threshold voltage that regulates current through the device. Accordingly, one of the divided regions in the channel layer is a threshold voltage regulating region. The threshold-voltage regulating region maintains its original P type conductivity and is available in the transistor for a gate voltage to invert a conductive zone therein. The conductive zone becomes the voltage regulated conductive channel within the device.

Owner:WOLFSPEED INC

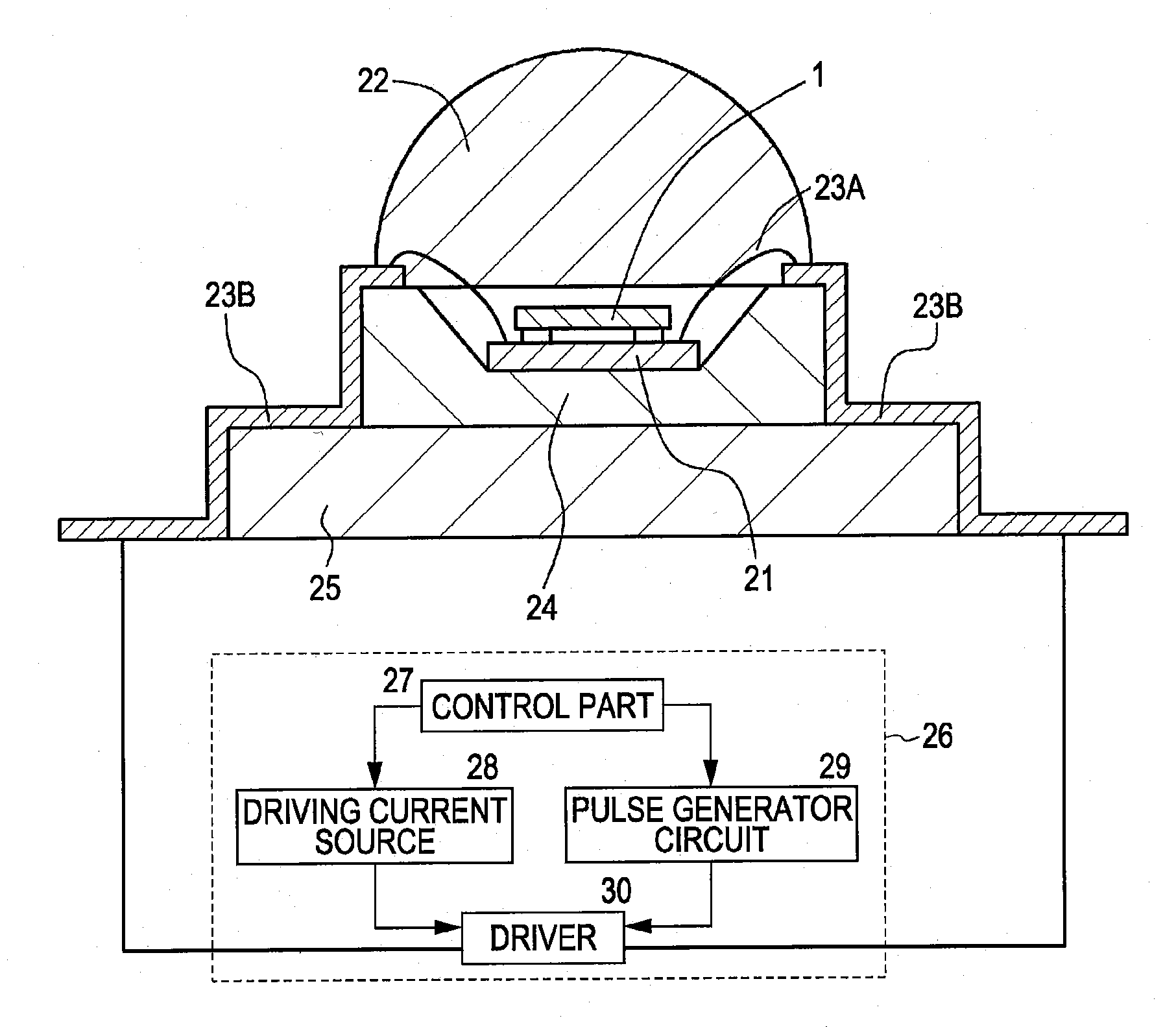

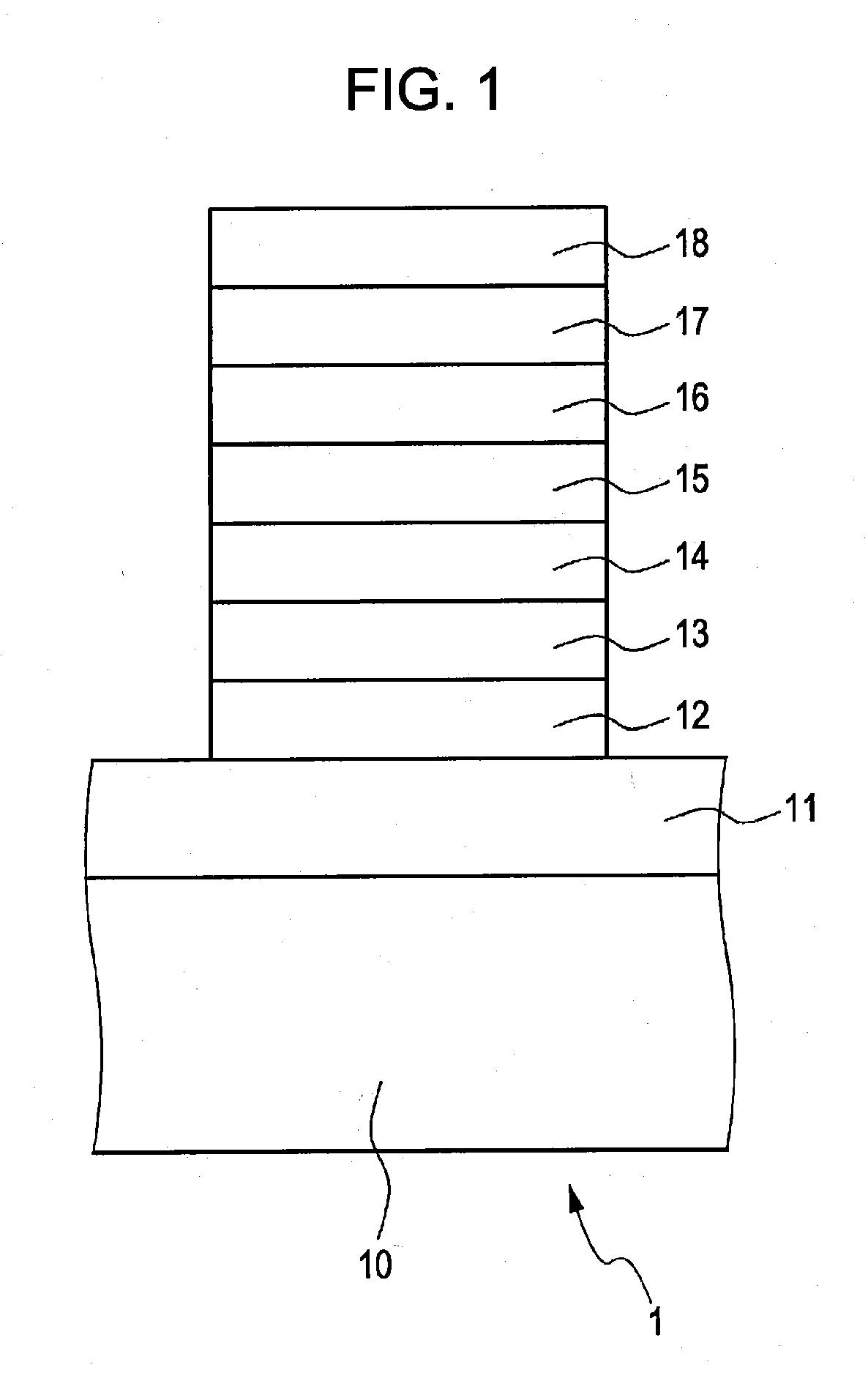

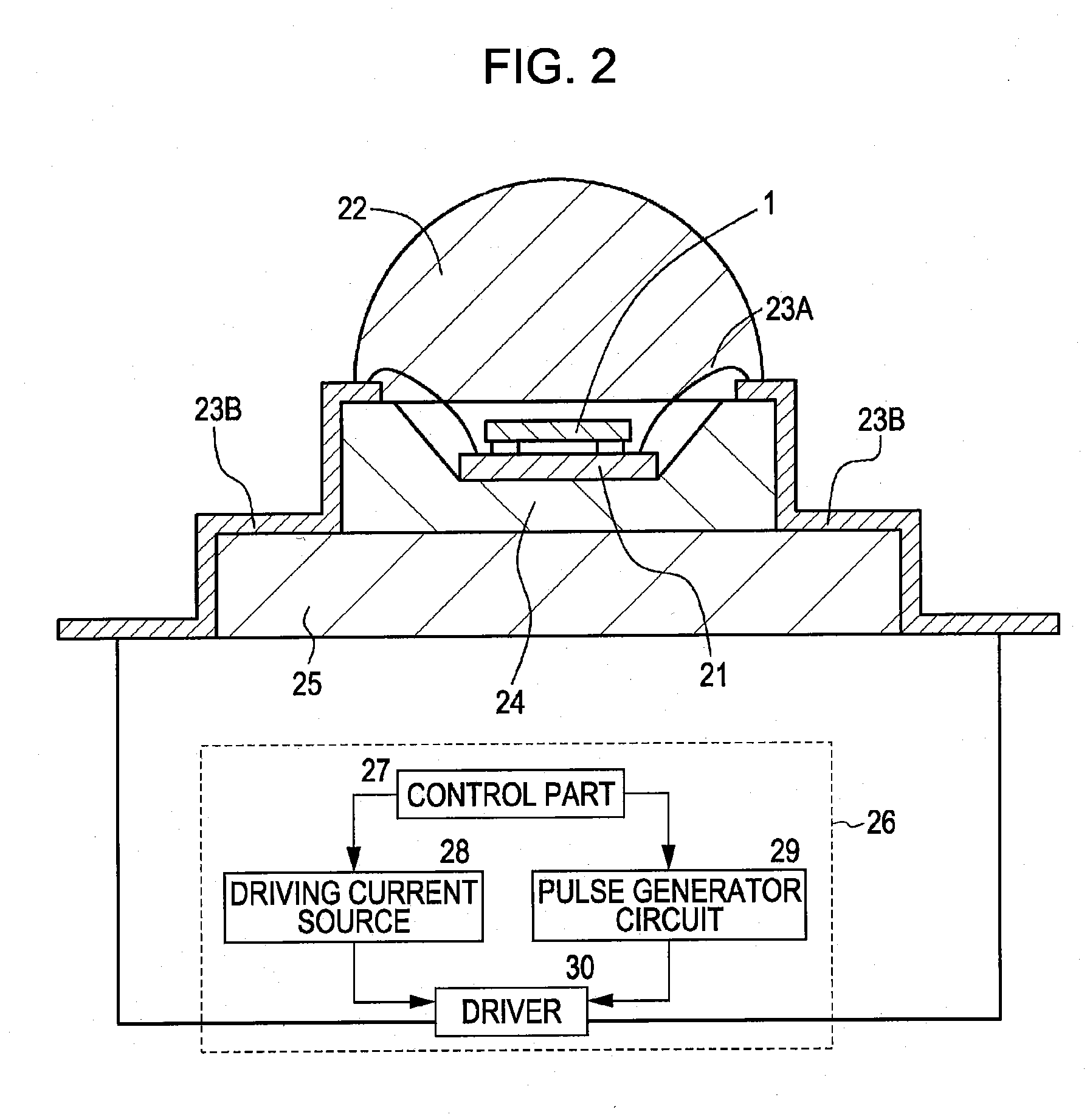

Gan-Based Semiconductor Light-Emitting Device, Light Illuminator, Image Display Planar Light Source Device, and Liquid Crystal Display Assembly

ActiveUS20070284564A1Suppress large shift of emission wavelengthIncrease in operating current densitySolid-state devicesNanoopticsLiquid-crystal displayQuantum well

A GaN-based semiconductor light-emitting device includes (A) a first GaN-based compound semiconductor layer 13 having n-type conductivity, (B) an active layer 15 having a multi-quantum well structure including well layers and barrier layers for separating between the well layers, and (C) a second GaN-based compound semiconductor layer 17 having p-type conductivity. The well layers are disposed in the active layer 15 so as to satisfy the relation d1<d2 wherein d1 is the well layer density on the first GaN-based compound semiconductor layer side in the active layer and d2 is the well layer density on the second GaN-based compound semiconductor layer side.

Owner:SONY SEMICON SOLUTIONS CORP

Memory cells, memory cell arrays, methods of using and methods of making

A semiconductor memory cell and arrays of memory cells are provided In at least one embodiment, a memory cell includes a substrate having a top surface, the substrate having a first conductivity type selected from a p-type conductivity type and an n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type, the first region being formed in the substrate and exposed at the top surface; a second region having the second conductivity type, the second region being formed in the substrate, spaced apart from the first region and exposed at the top surface; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; a gate positioned between the first and second regions and above the top surface; and a nonvolatile memory configured to store data upon transfer from the body region.

Owner:ZENO SEMICON

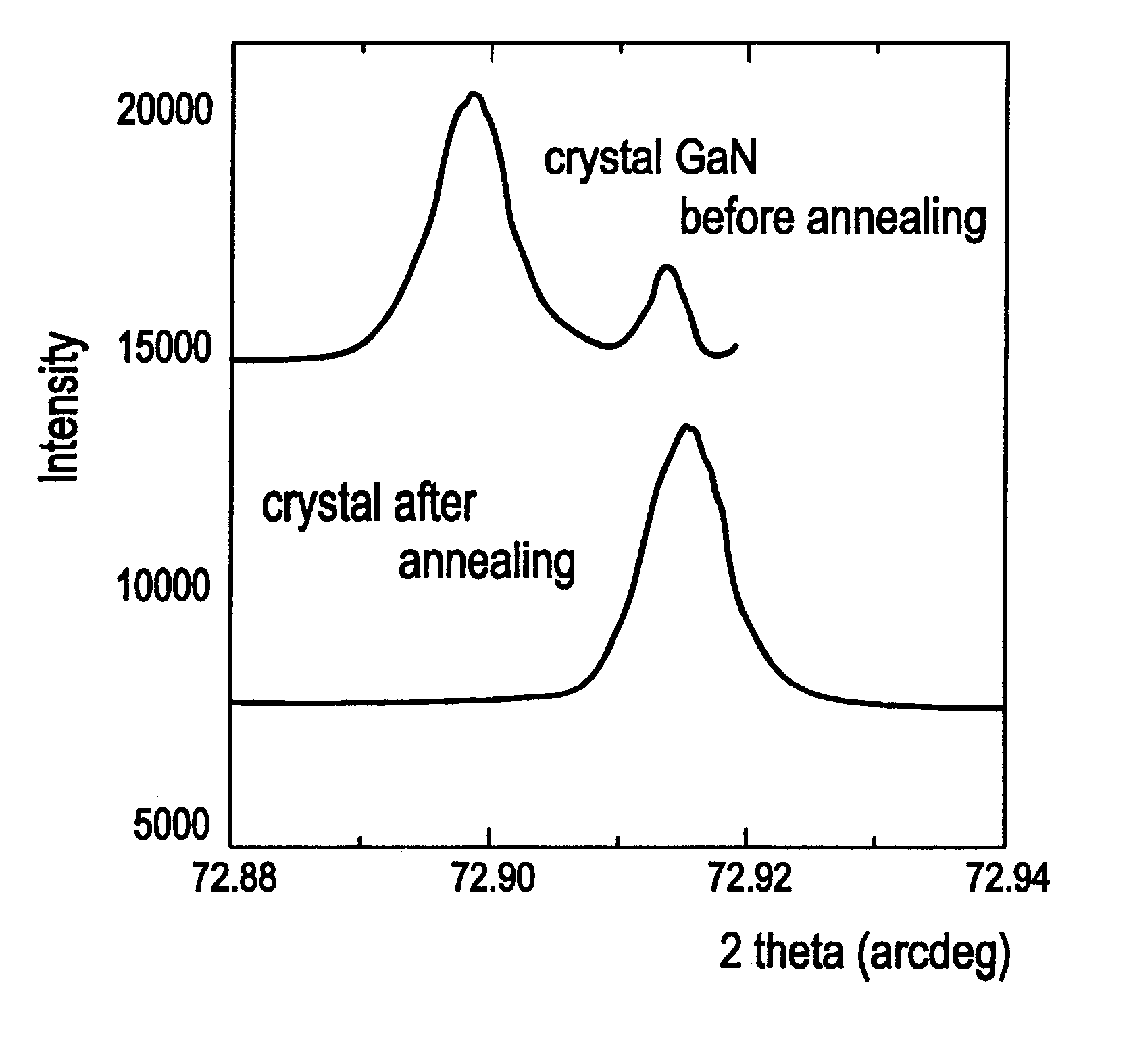

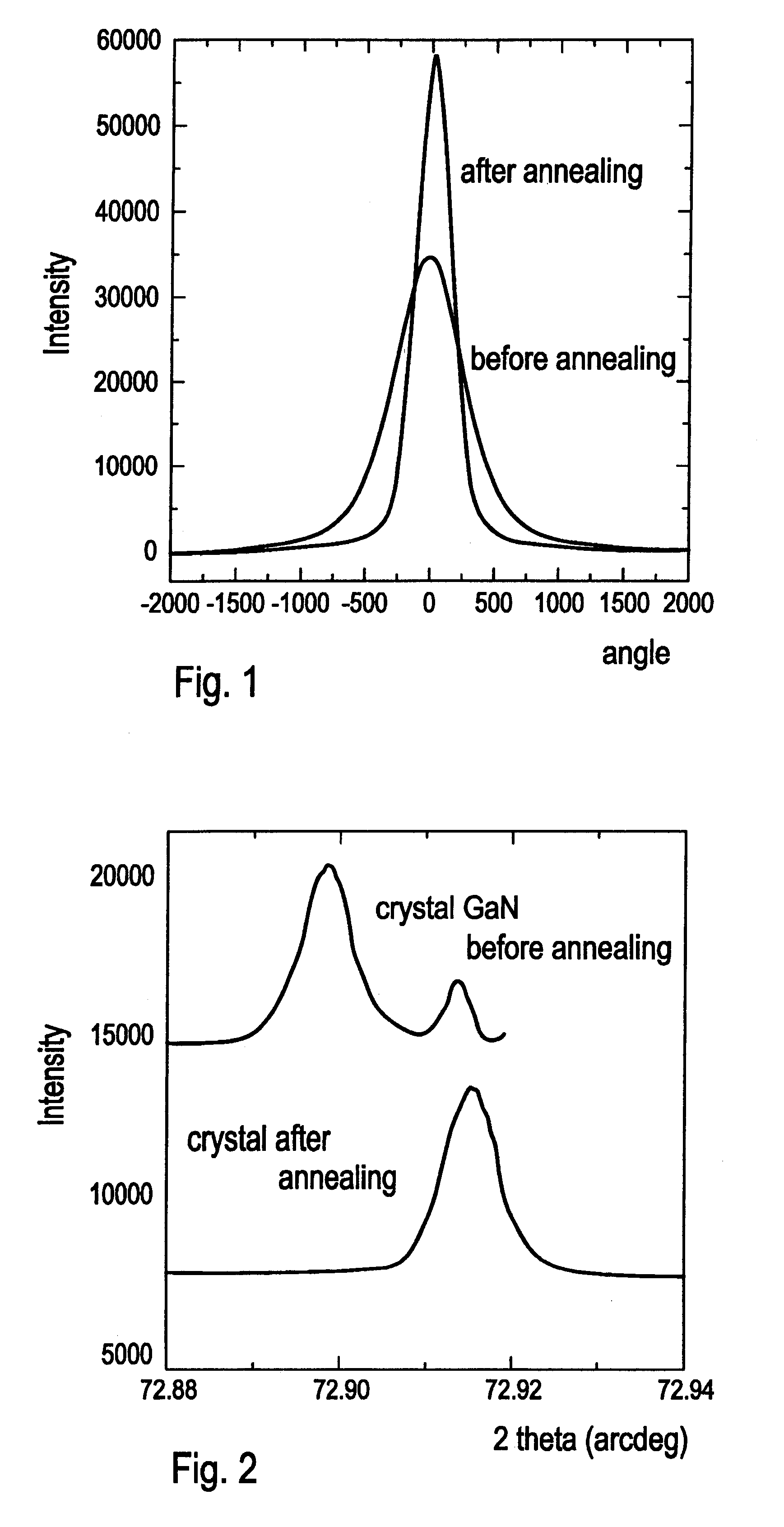

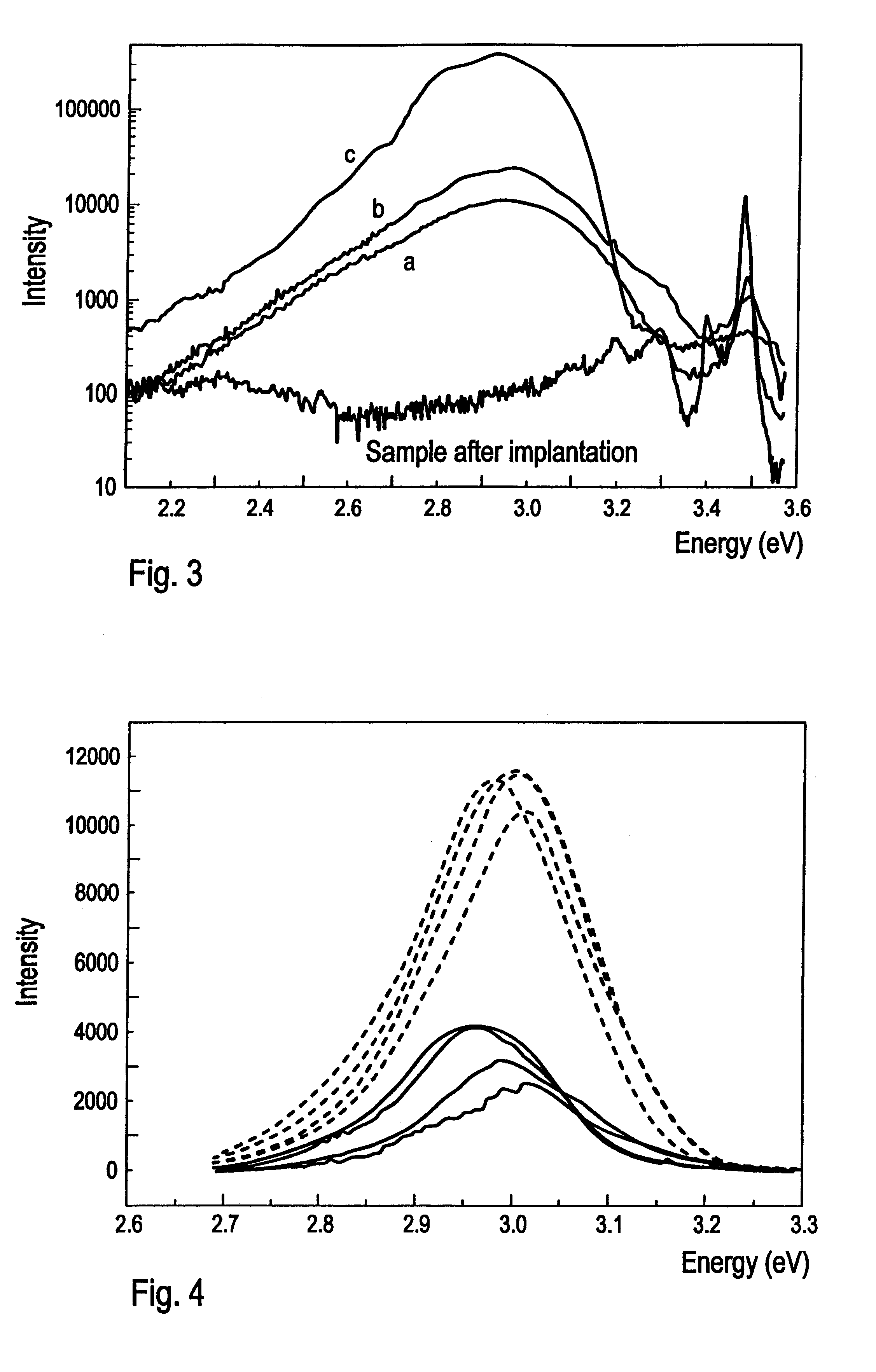

Method of fabrication of semiconducting compounds of nitrides A3B5 of P-and N-type electric conductivity

InactiveUS6329215B1Low resistivityIncrease intensityPolycrystalline material growthLaser detailsHigh power lasersHigh pressure

The subject of the Invention is the method of fabrication of nitride semiconductor A3B5 such as GaN, AlN, InN or their solid solutions, characterized by p- or n-type conductivity, high intensity of emitted light and high structural quality. The semiconductors obtained by this method are applied in the construction of light emitting devices, light detectors and electric current amplifiers such as for example: highly efficient blue and green light diodes, laser diodes and high power lasers, ultraviolet detectors and high temperature field transistors. The method according to the Invention is characterized by the fact that the homoepitaxial or heteroepitaxial layers of nitride semiconductors A3B5 are deposited on the conductive substrate after the introductory processing or isolating substrate, and after that the so prepared structures are located in high pressure diffusional chamber filled with the one or multi-component gas, compressed to pressure in the range 1000-20000 bar, and annealed in the temperature 1000-1800 ° C. in the prescribed time in the presence of the dopant from the external and / or internal source.

Owner:INST WYSOKICH CISNIEN POLSKIEJ AKADI NAUK

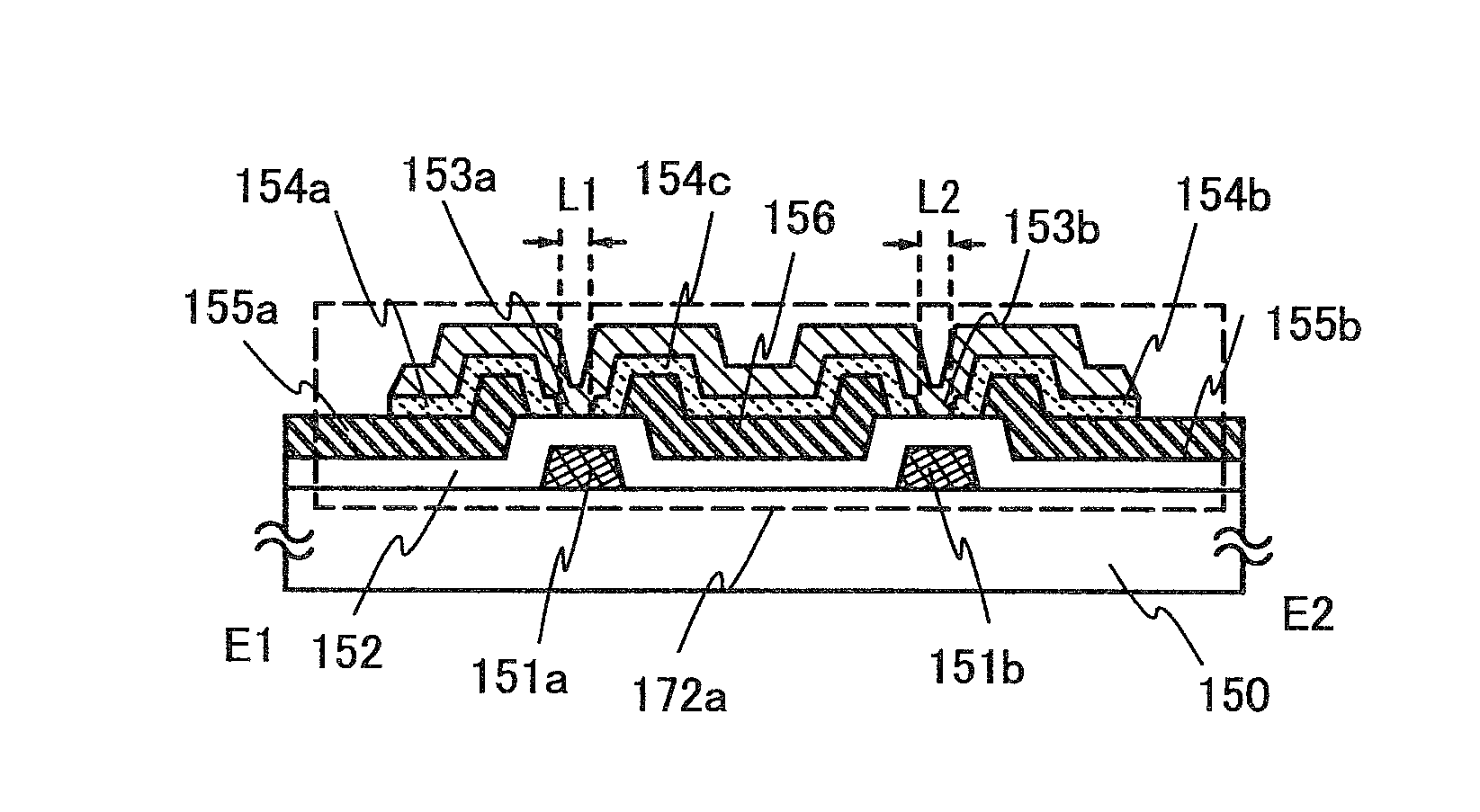

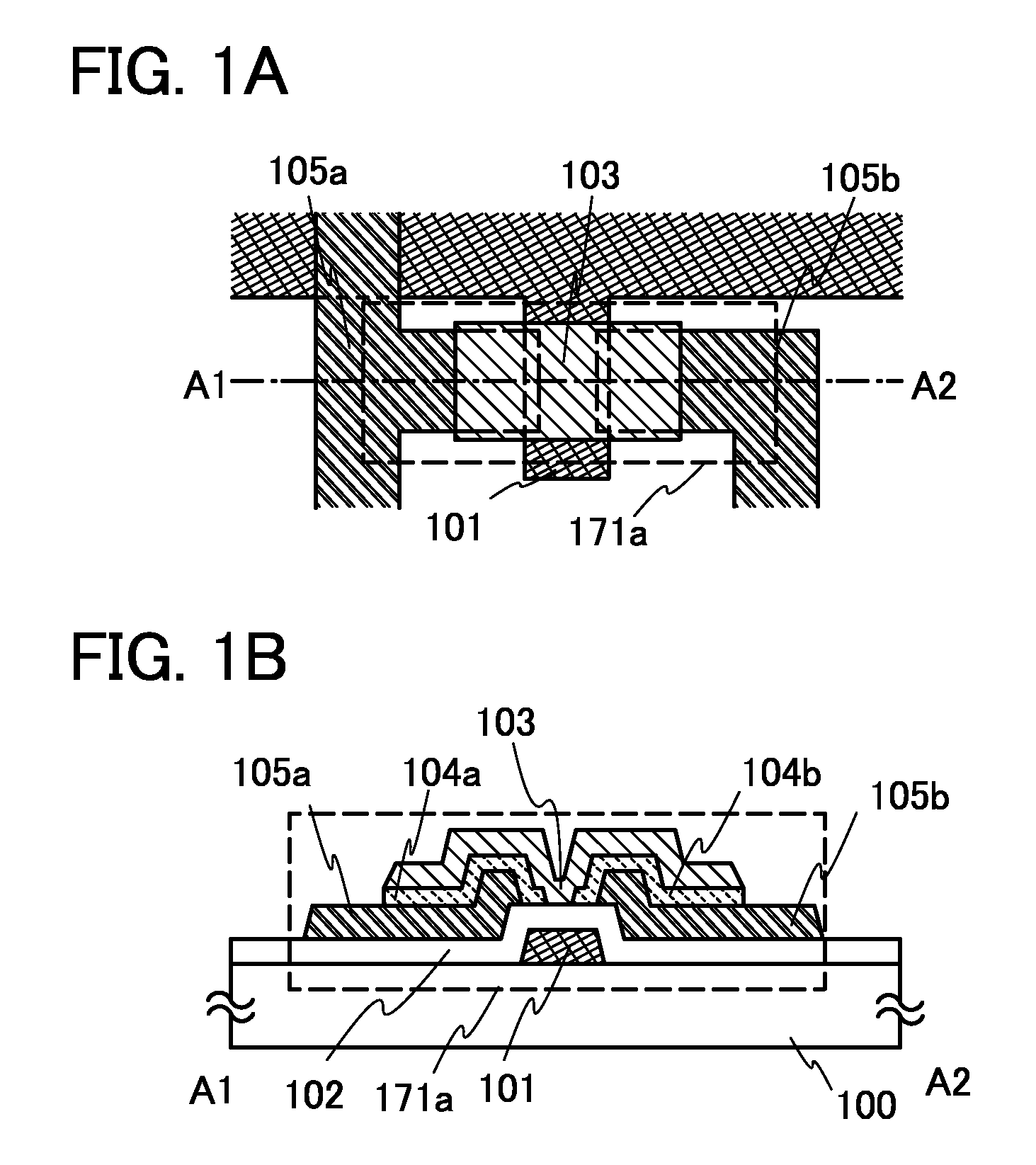

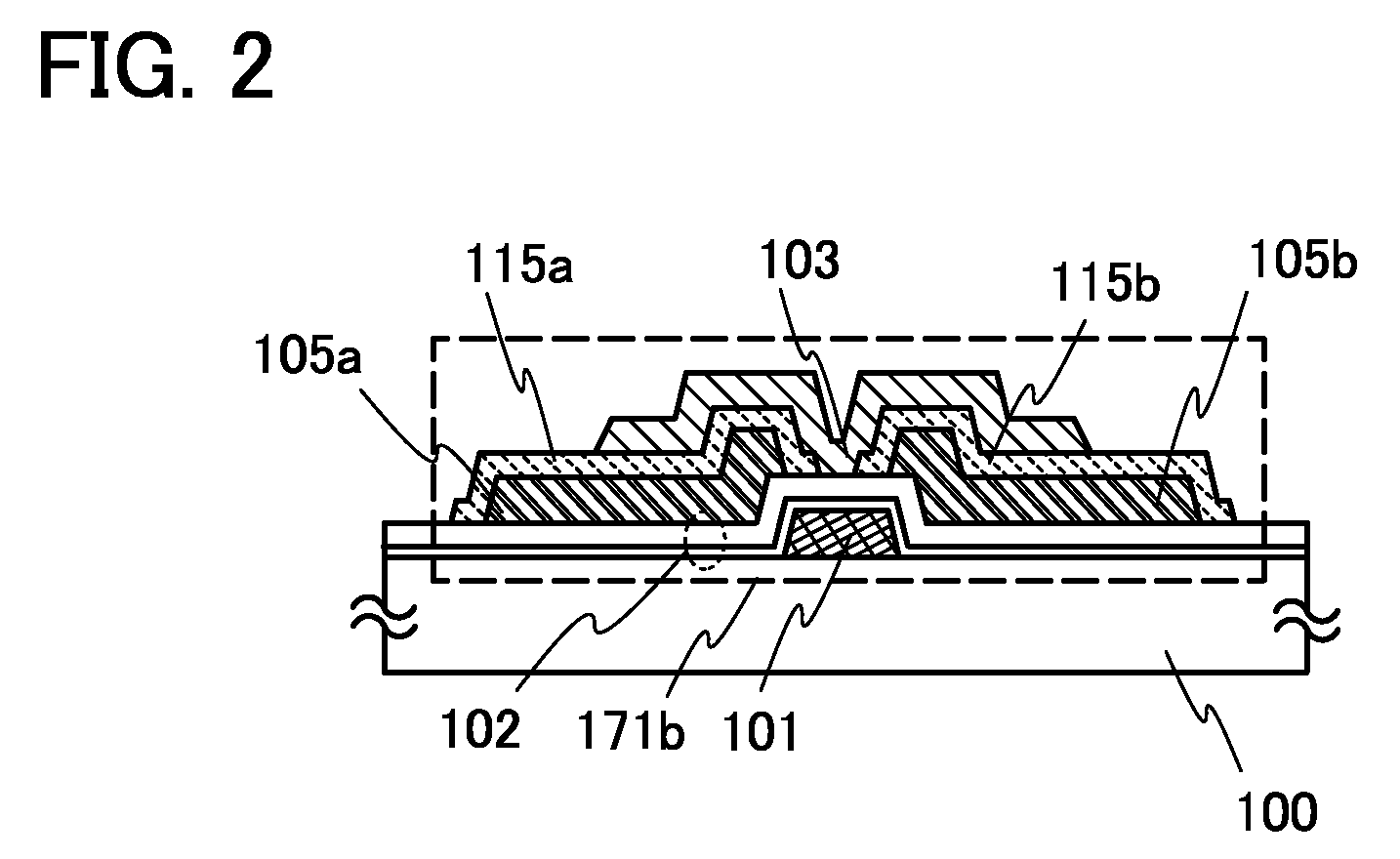

Semiconductor device and manufacturing method thereof

InactiveUS8030663B2Contact resistanceReduce contact resistanceSolid-state devicesSemiconductor/solid-state device manufacturingIndiumN type conductivity

A semiconductor device including thin film transistors having high electrical properties and reliability is proposed. Further, a method for manufacturing the semiconductor devices with mass productivity is proposed. The semiconductor device includes a thin film transistor which includes a gate electrode layer, a gate insulating layer over the gate electrode layer, a source electrode layer and a drain electrode layer over the gate insulating layer, a buffer layer over the source electrode layer and the drain electrode layer, and a semiconductor layer over the buffer layer. A part of the semiconductor layer overlapping with the gate electrode layer is over and in contact with the gate insulating layer and is provided between the source electrode layer and the drain electrode layer. The semiconductor layer is an oxide semiconductor layer containing indium, gallium, and zinc. The buffer layer contains a metal oxide having n-type conductivity. The semiconductor layer and the source and drain electrode layers are electrically connected to each other through the buffer layer.

Owner:SEMICON ENERGY LAB CO LTD

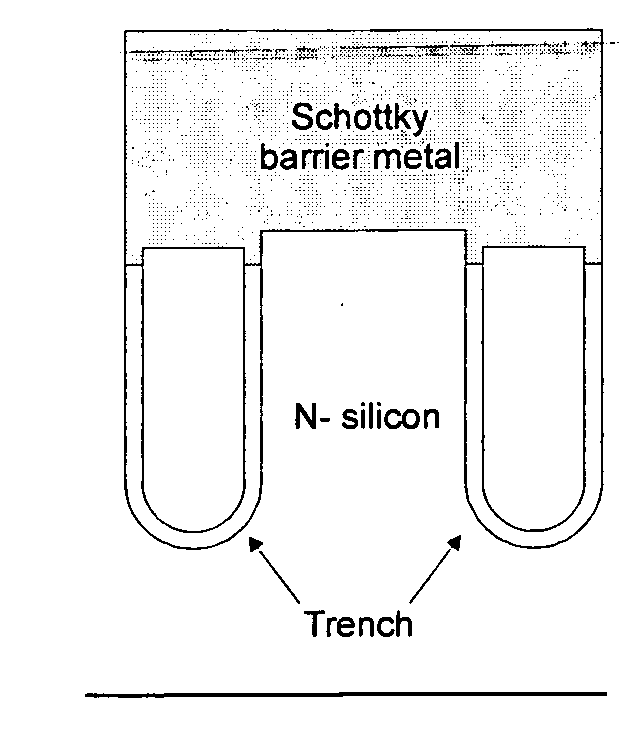

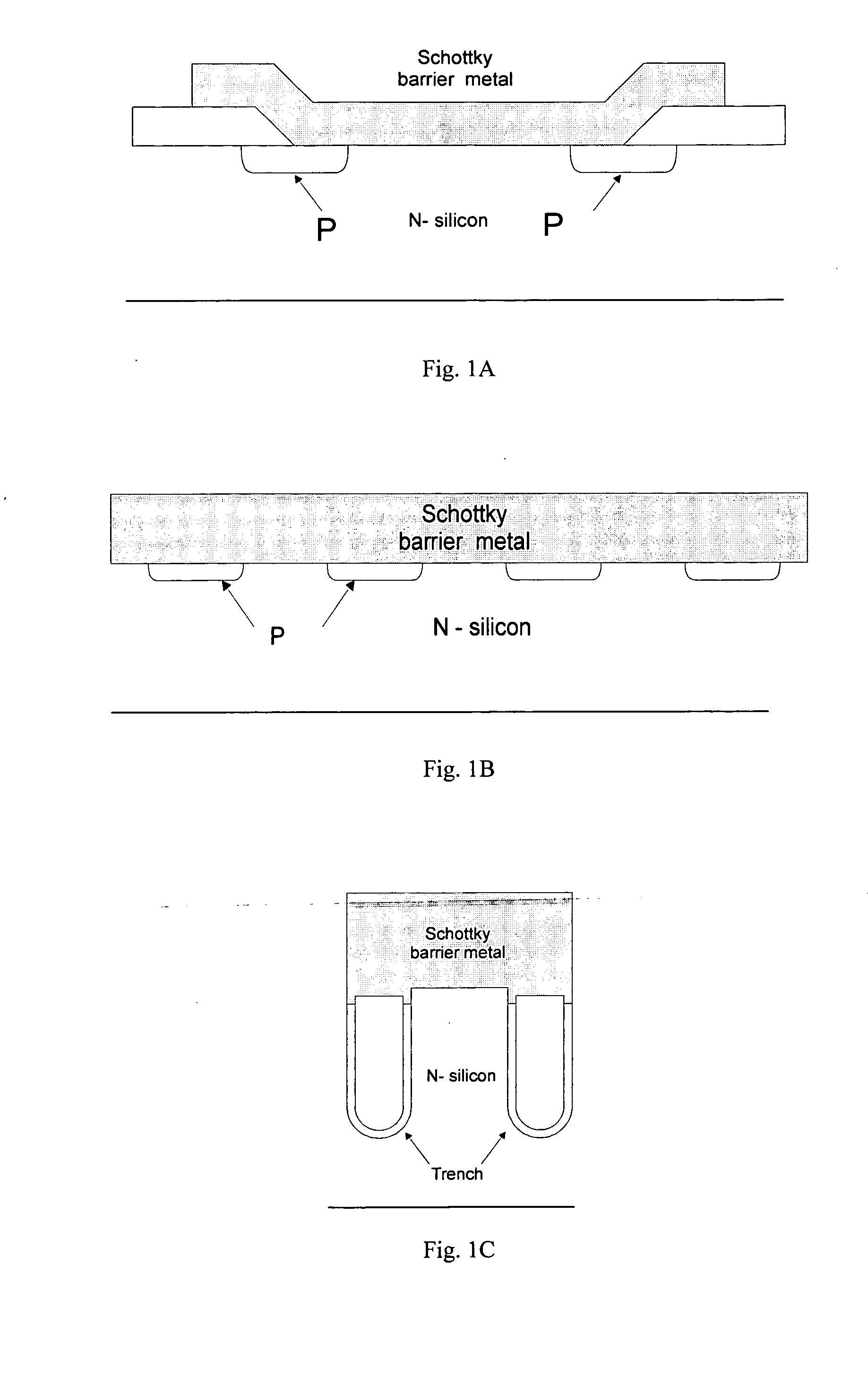

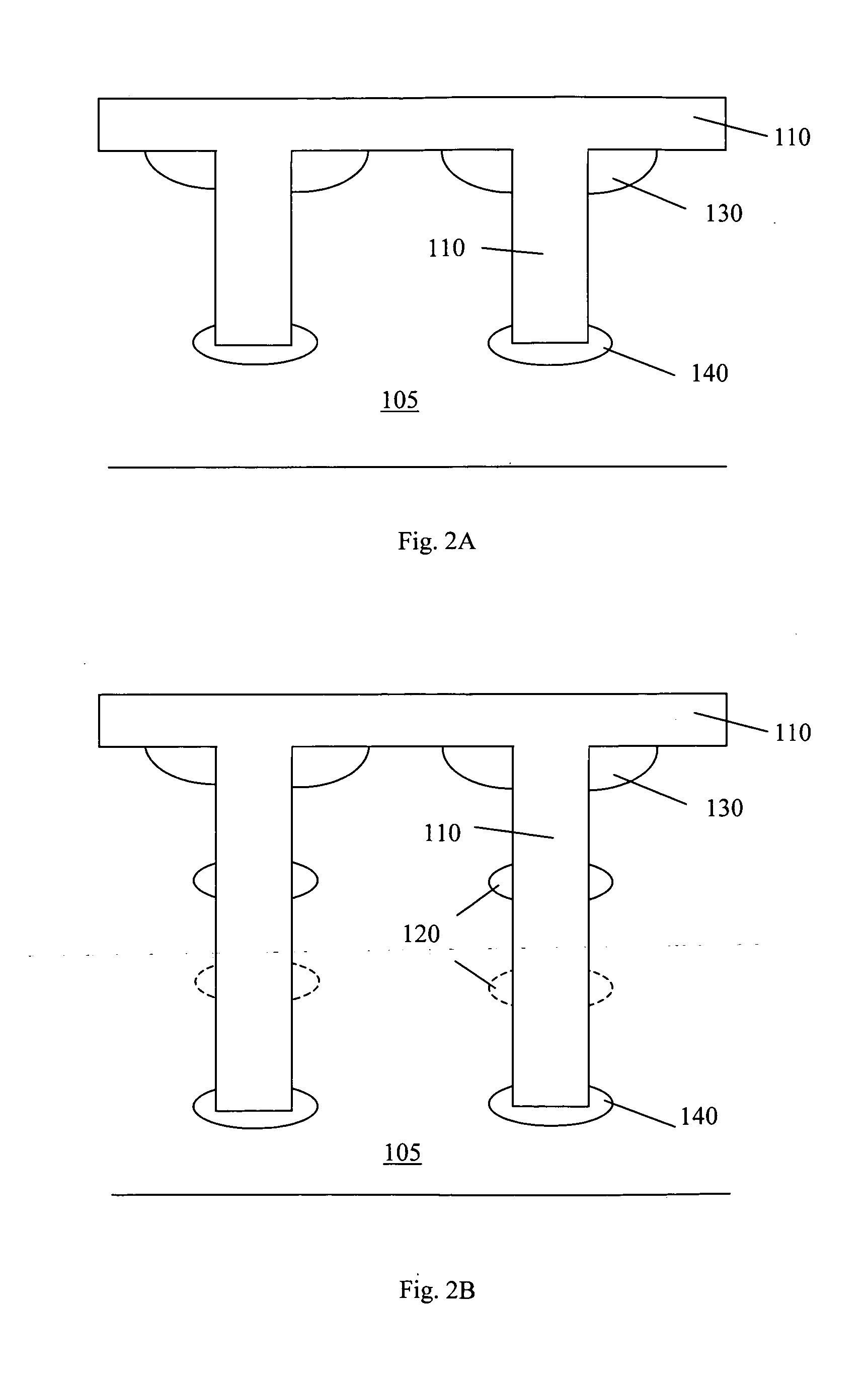

Trench junction barrier controlled Schottky

ActiveUS20070034901A1Silicon area utilization is greatly improvedEliminate requirementsTransistorSolid-state devicesDopantSemiconductor

A Schottky diode includes at least a trenched opened in a semiconductor substrate doped with a dopant of a first conductivity type wherein the trench is filled with a Schottky junction barrier metal. The Schottky diode further includes one or more dopant region of a second conductivity type surrounding sidewalls of the trench distributed along the depth of the trench for shielding a reverse leakage current through the sidewalls of the trench. The Schottky diode further includes a bottom-doped region of the second conductivity type surrounding a bottom surface of the trench and a top-doped region of the second conductivity type surrounding a top portion of the sidewalls of the trench. In a preferred embodiment, the first conductivity type is a N-type conductivity type and the middle-depth dopant region comprising a P-dopant region.

Owner:ALPHA & OMEGA SEMICON LTD

Memory cells, memory cell arrays, methods of using and methods of making

A semiconductor memory cell and arrays of memory cells are provided In at least one embodiment, a memory cell includes a substrate having a top surface, the substrate having a first conductivity type selected from a p-type conductivity type and an n-type conductivity type; a first region having a second conductivity type selected from the p-type and n-type conductivity types, the second conductivity type being different from the first conductivity type, the first region being formed in the substrate and exposed at the top surface; a second region having the second conductivity type, the second region being formed in the substrate, spaced apart from the first region and exposed at the top surface; a buried layer in the substrate below the first and second regions, spaced apart from the first and second regions and having the second conductivity type; a body region formed between the first and second regions and the buried layer, the body region having the first conductivity type; a gate positioned between the first and second regions and above the top surface; and a nonvolatile memory configured to store data upon transfer from the body region.

Owner:ZENO SEMICON

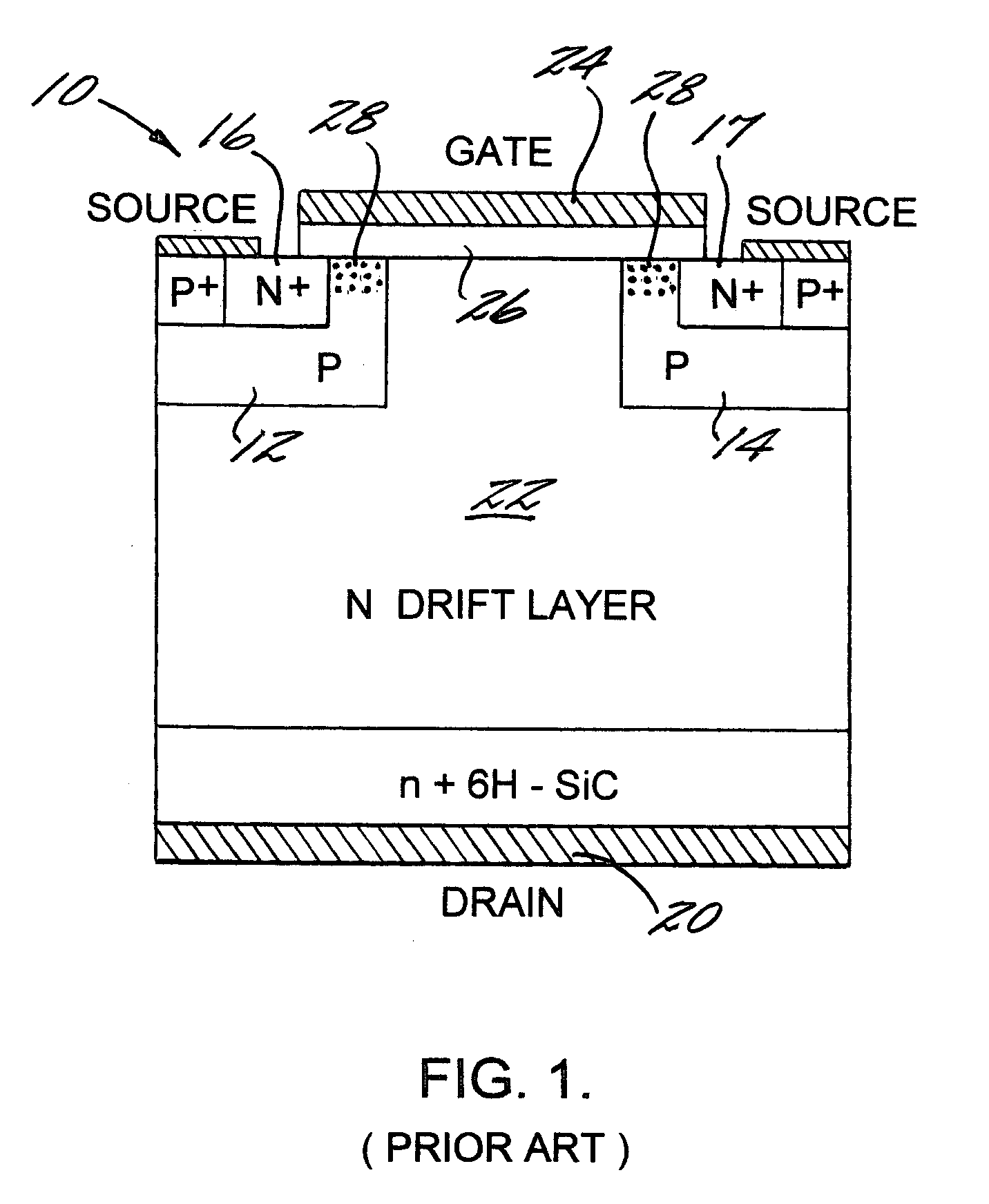

Transistors having buried p-type layers beneath the source region

InactiveUS6956239B2Semiconductor/solid-state device manufacturingSemiconductor devicesMESFETEngineering

The present invention provides a unit cell of a metal-semiconductor field-effect transistor (MESFET). The unit cell of the MESFET includes a source, a drain and a gate. The gate is disposed between the source and the drain and on an n-type conductivity channel layer. A p-type conductivity region is provided beneath the source and has an end that extends towards the drain. The p-type conductivity region is spaced apart from the n-type conductivity channel region and is electrically coupled to the source.

Owner:CREE INC

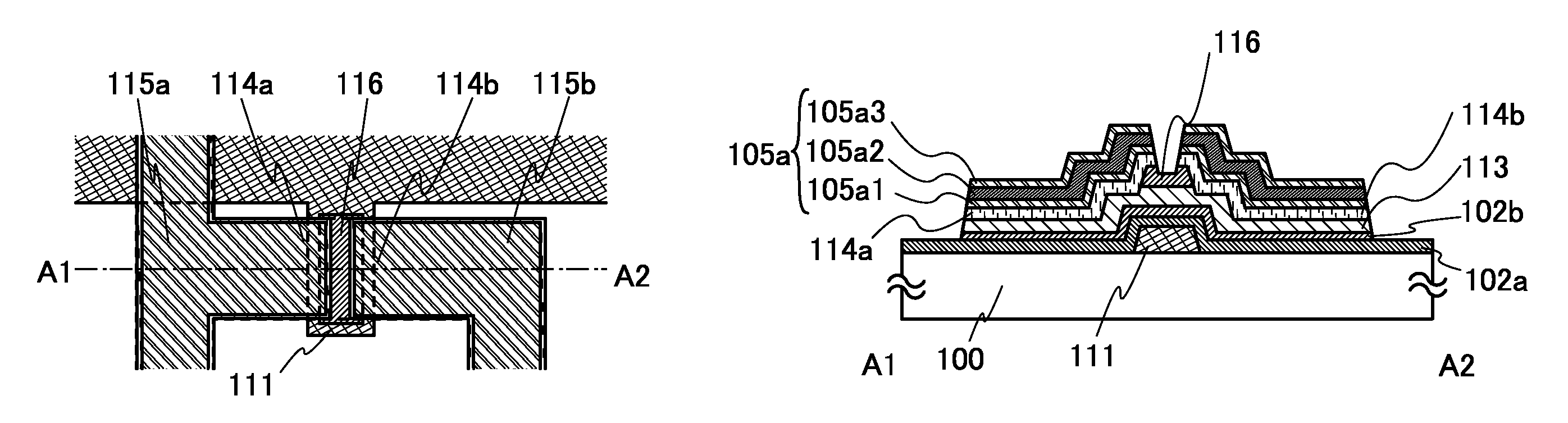

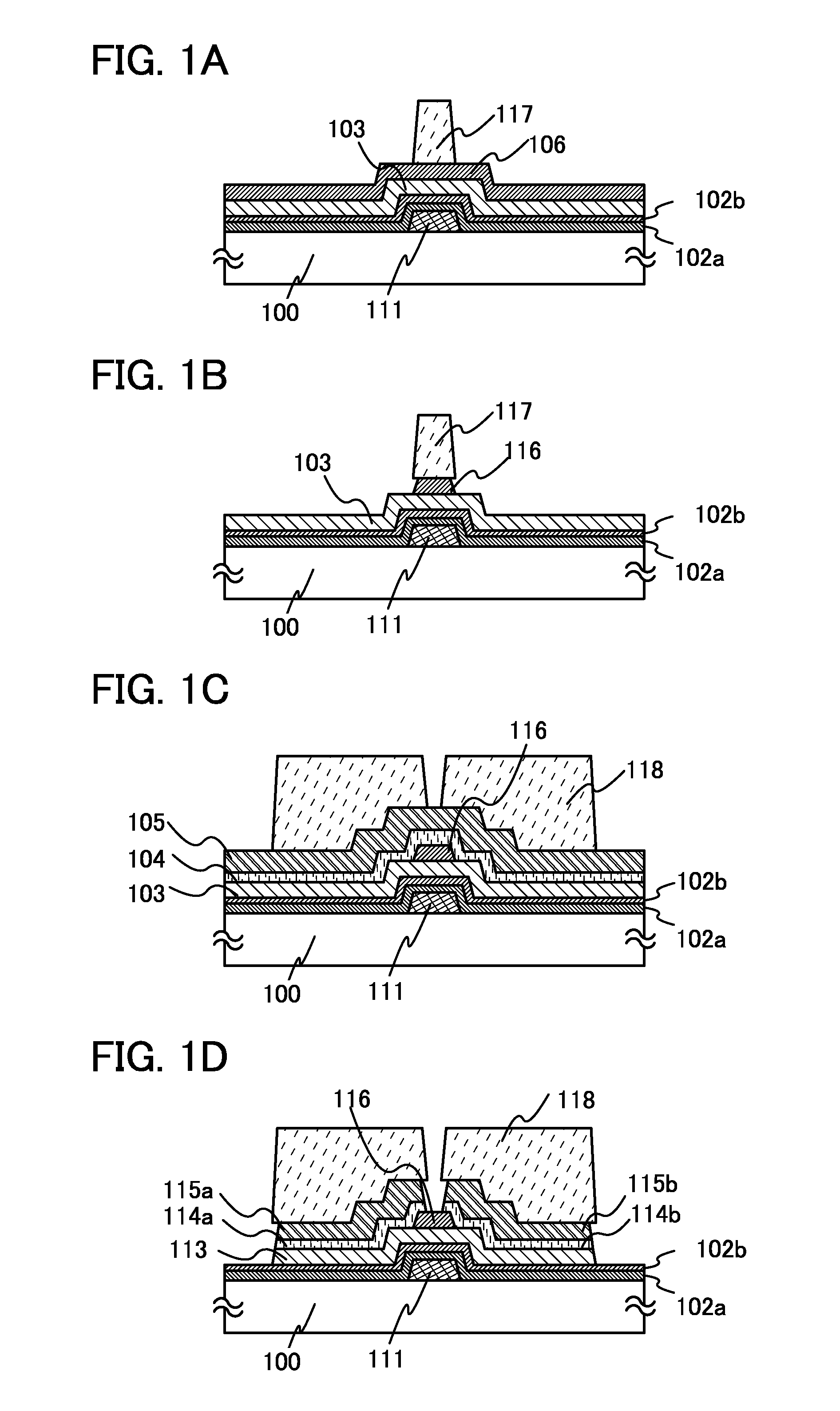

Semiconductor device and manufacturing method thereof

ActiveUS20100032666A1Small amount of photocurrentReduce parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingProduction rateIndium

A semiconductor device including thin film transistors having high electrical properties and reliability is proposed. Further, a method for manufacturing the semiconductor devices with mass productivity is proposed. The semiconductor device includes a thin film transistor which includes a gate electrode layer, a gate insulating layer over the gate electrode layer, a source electrode layer and a drain electrode layer over the gate insulating layer, a buffer layer over the source electrode layer and the drain electrode layer, and a semiconductor layer over the buffer layer. A part of the semiconductor layer overlapping with the gate electrode layer is over and in contact with the gate insulating layer and is provided between the source electrode layer and the drain electrode layer. The semiconductor layer is an oxide semiconductor layer containing indium, gallium, and zinc. The buffer layer contains a metal oxide having n-type conductivity. The semiconductor layer and the source and drain electrode layers are electrically connected to each other through the buffer layer.

Owner:SEMICON ENERGY LAB CO LTD

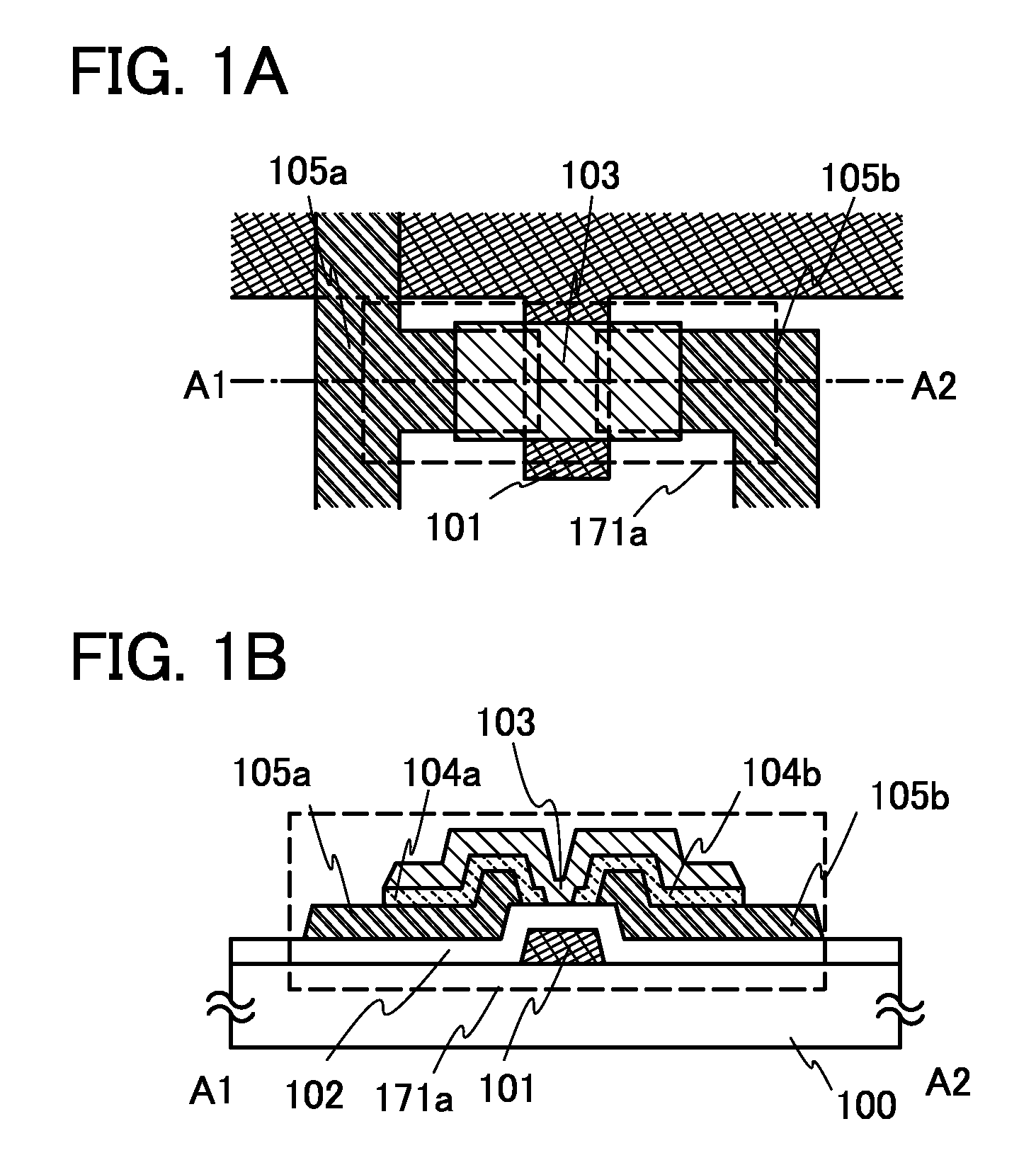

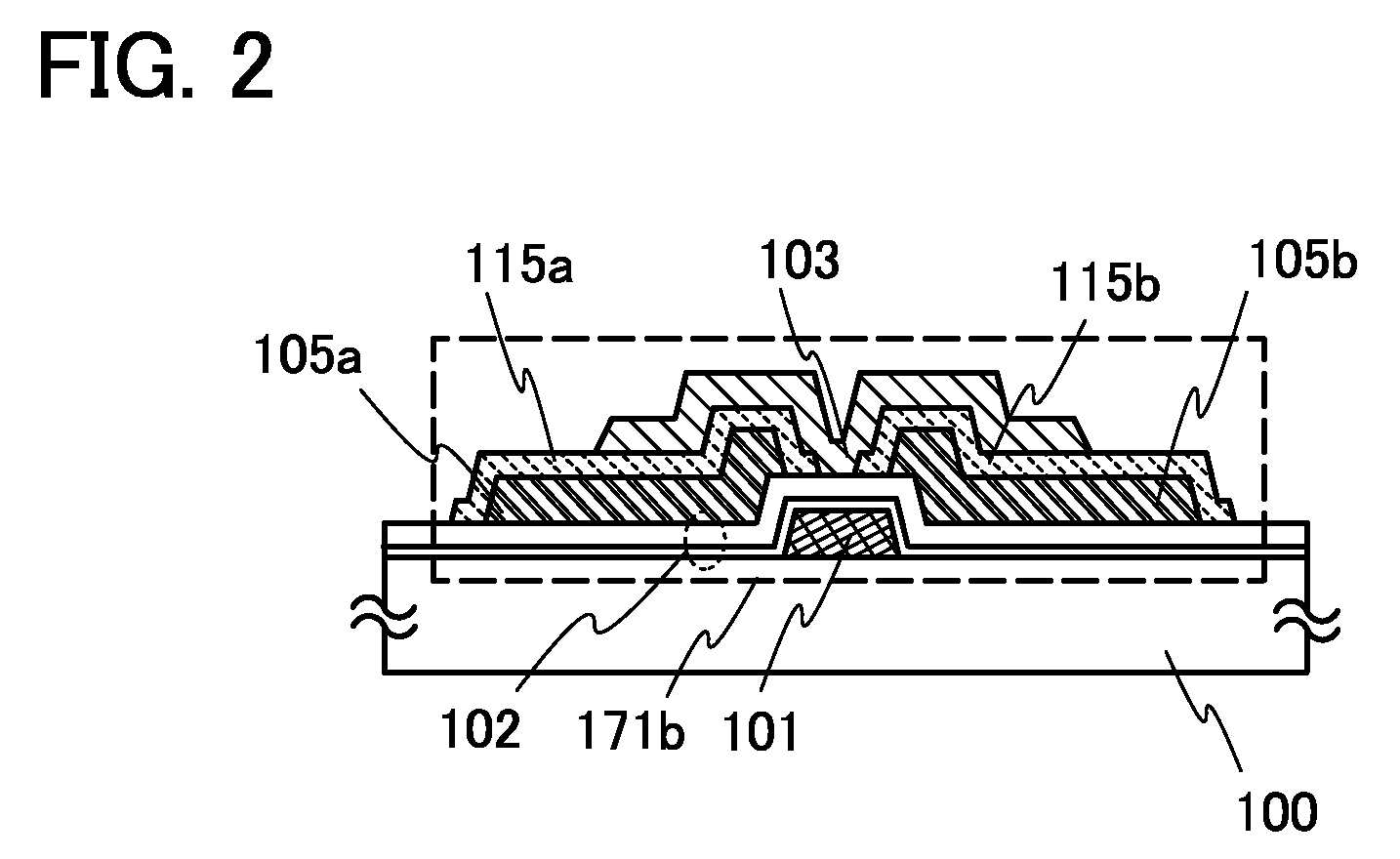

Semiconductor device and a method for manufacturing the same

InactiveUS20070096224A1Quality improvementHigh yieldTransistorSolid-state devicesElectrical resistance and conductanceDevice material

A thin film transistor of the present invention has an active layer including at least source, drain and channel regions formed on an insulating surface. A high resistivity region is formed between the channel region and each of the source and drain regions. A film capable of trapping positive charges therein is provided on at least the high resistivity region so that N-type conductivity is induced in the high resistivity region. Accordingly, the reliability of N-channel type TFT against hot electrons can be improved.

Owner:SEMICON ENERGY LAB CO LTD

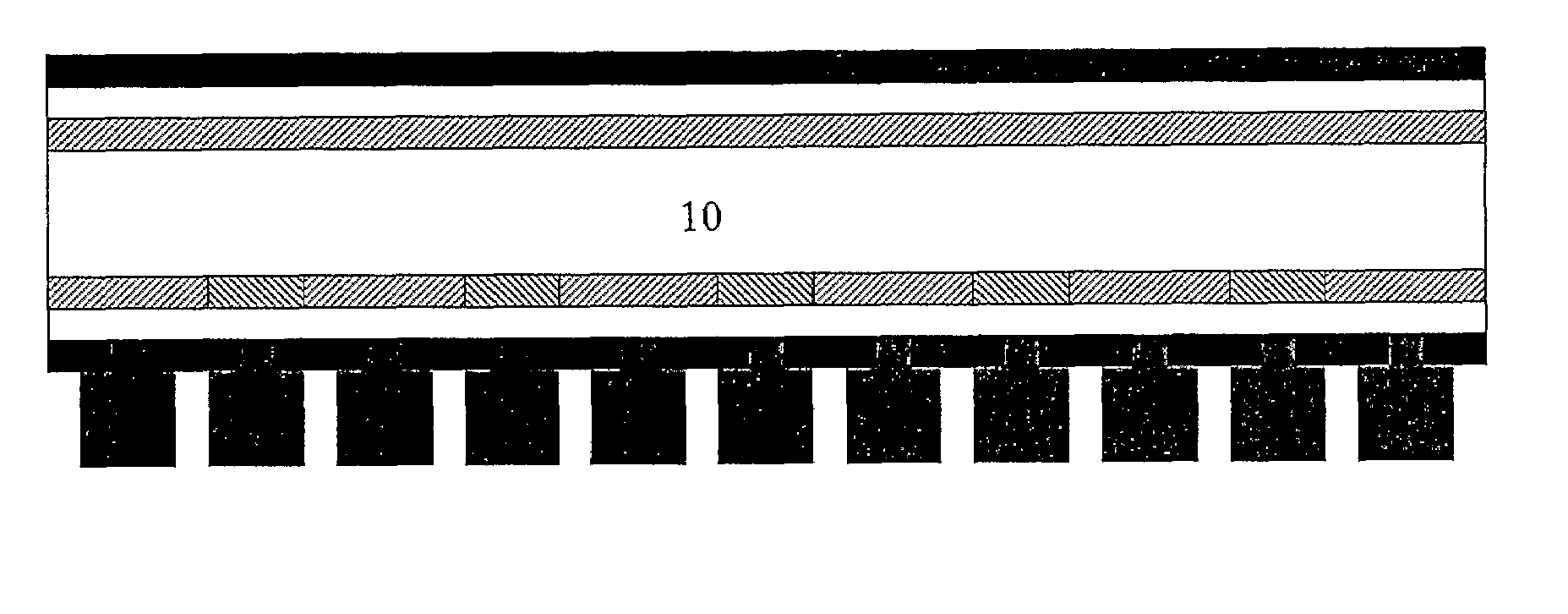

Back contacted solar cell

InactiveUS20100032011A1Cost-effective manufacturing methodHigh energy conversion rateSemiconductor/solid-state device manufacturingPhotovoltaic energy generationSilicon solar cellN type conductivity

This invention relates to a cost effective method of producing a back contacted silicon solar cell and the cell made by the method, where the method comprises applying a silicon substrate, wafer or thin film, doped on the back side with alternating P-type and N-type conductivity in an interdigitated pattern and optionally a layer of either P- or N-type on the front side of the wafer, depositing one or more surface passivation layers on both sides of the substrate, creating openings in the surface passivation layers on the back side of the substrate, depositing a metallic layer covering the entire back side and which fills the openings in the surface passivation layers, and creating openings in the deposited metallic layer such that electric insulated contacts with the doped regions on the back side of the substrate is obtained.

Owner:RENEWABLE ENERGY CORP LTD

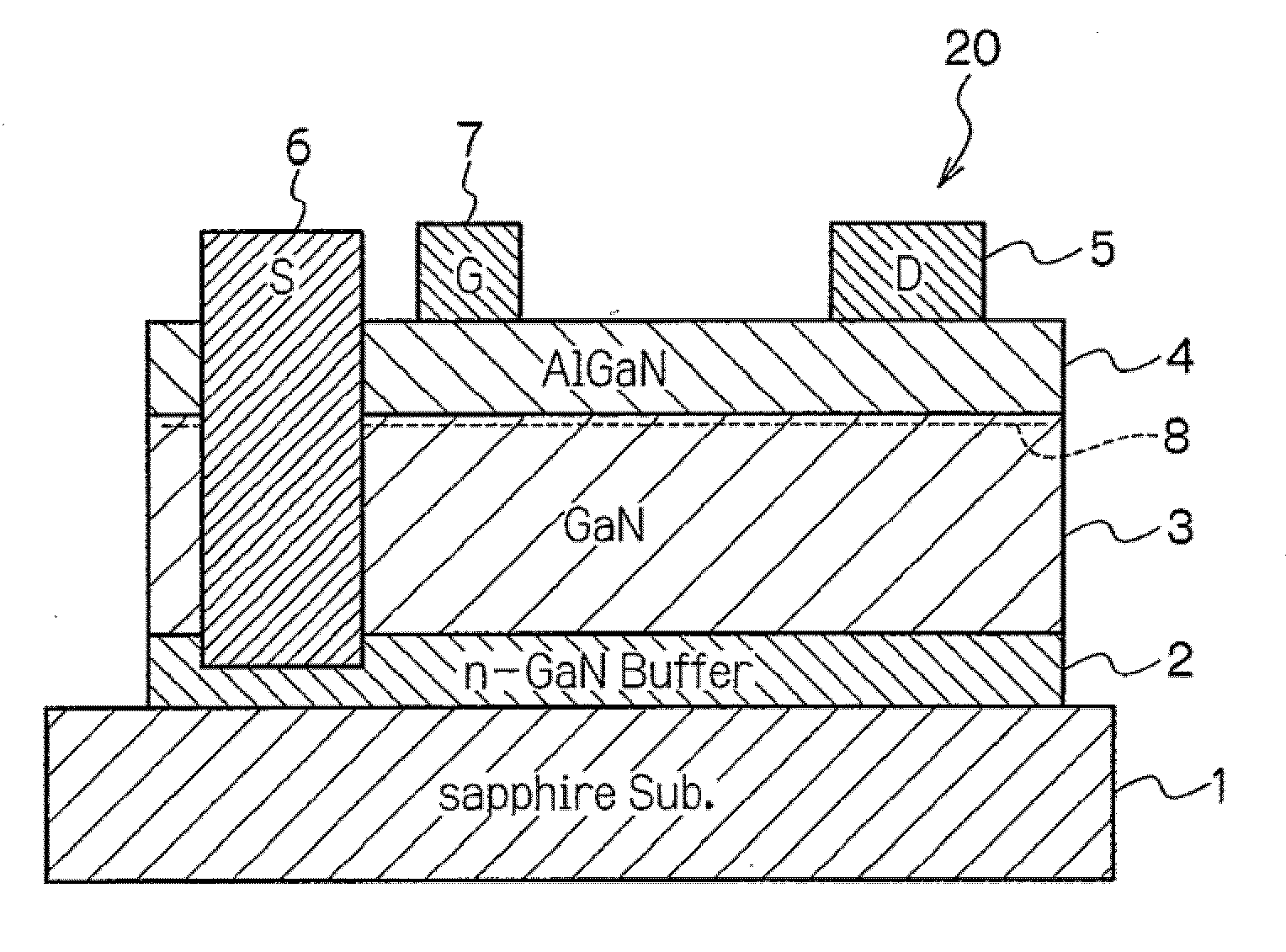

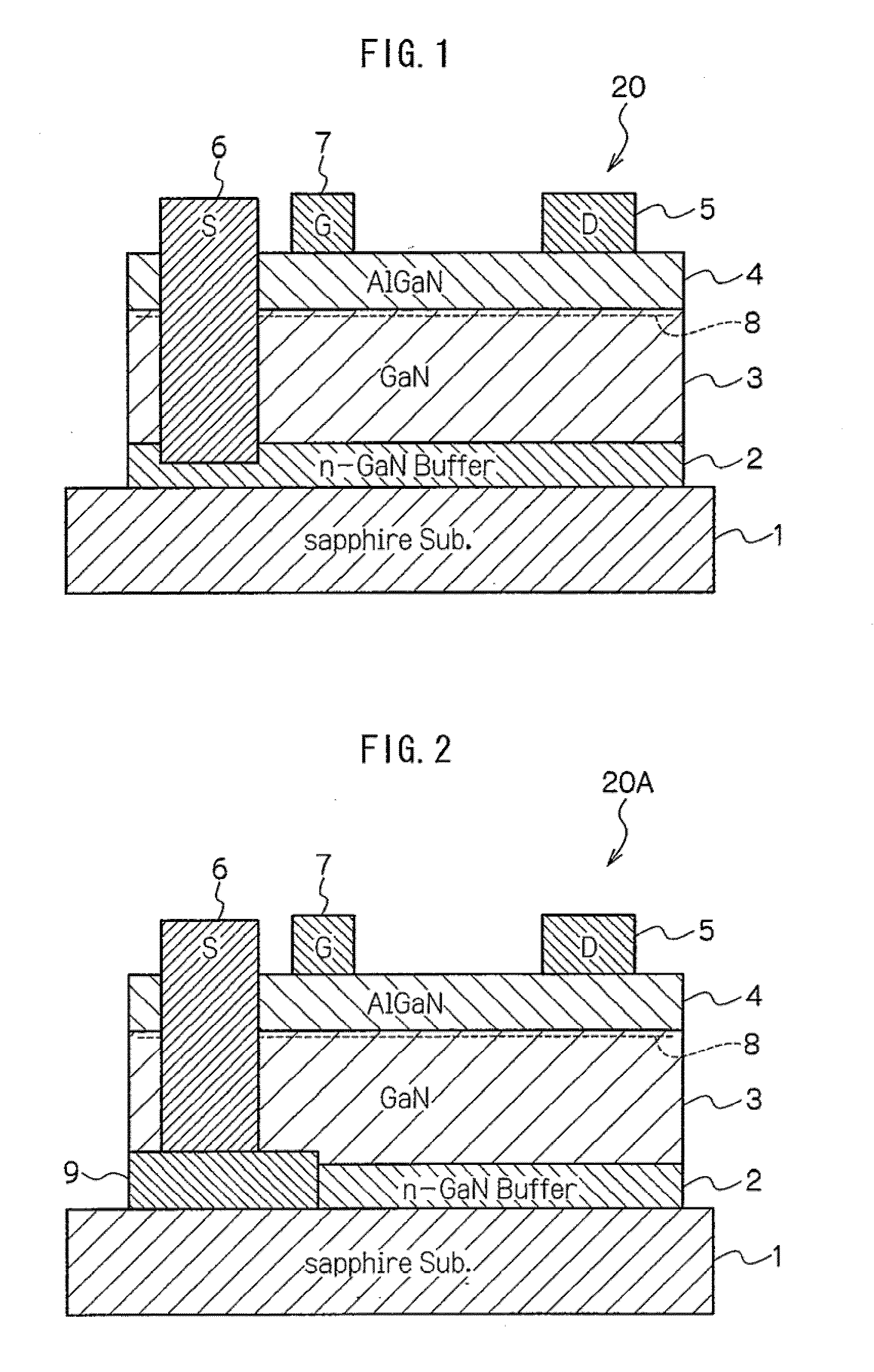

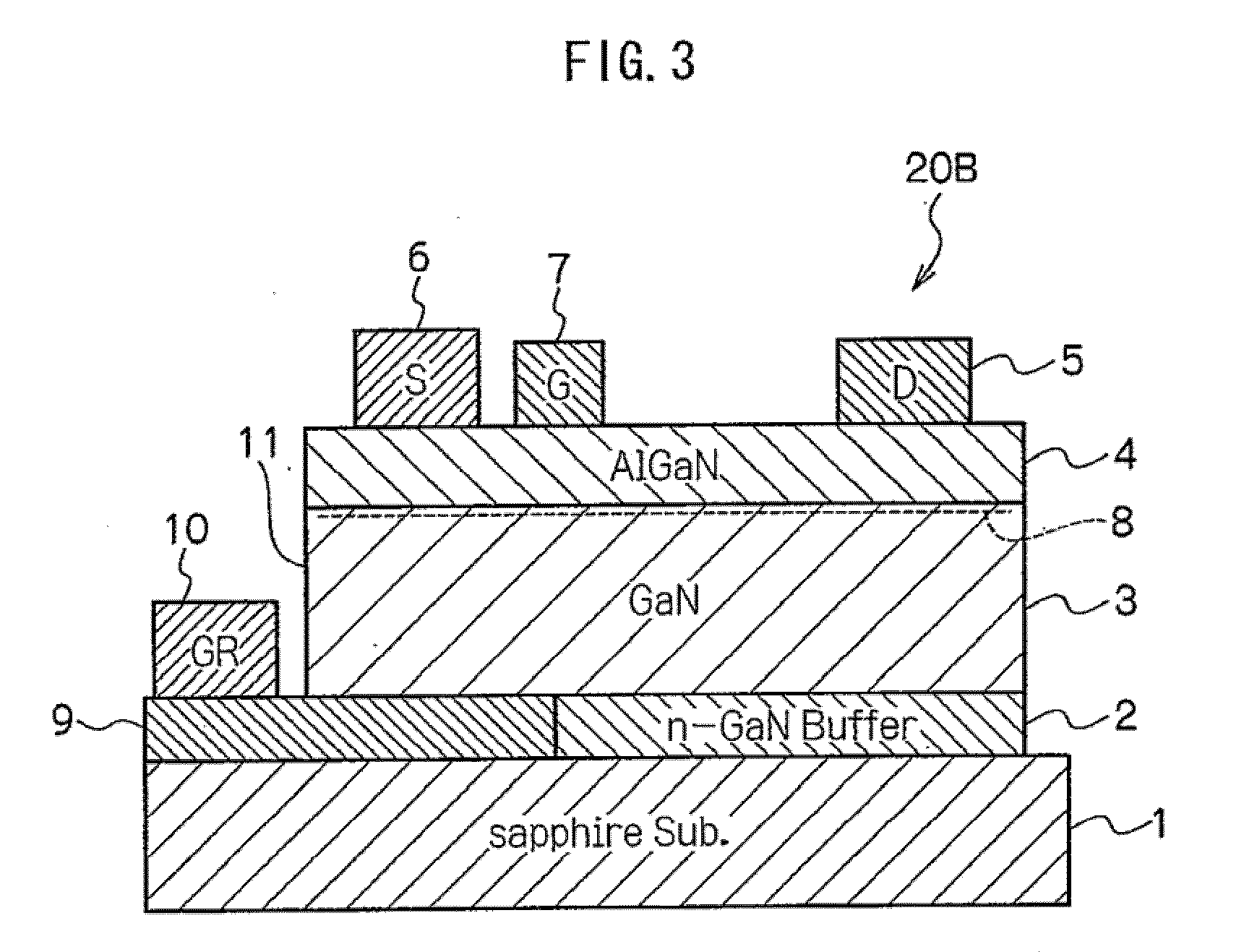

GaN-BASED SEMICONDUCTOR ELEMENT

ActiveUS20100032683A1Suppress crashSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactN type conductivity

The GaN-based semiconductor element 20 of the present invention comprises the buffer layer 2 formed on the sapphire (0001) substrate 1, the channel layer 3 comprised of the undoped GaN layer, and the electron supply layer 4 comprised of the undoped AlGaN layer. The buffer layer 2 is comprised of the n-GaN layer having n-type conductivity. The configuration is adopted as the structure to be able to control the electric potential of the buffer layer 2, wherein the source electrode 6 is implanted into the epitaxial layer (the channel layer 3 and the electron supply layer 4) to be formed on the buffer layer 2, and it is extended to the depth reaching the buffer layer 2 for ohmic contacting to the buffer layer 2. It is able to fix the electric potential of the buffer layer 2 comprised of the n-GaN layer for being equal to that of the source electrode 6 because the source electrode 6 is ohmic contacted to the buffer layer 2.

Owner:FURUKAWA ELECTRIC CO LTD

Improved CMOS diodes with dual gate conductors, and methods for forming the same

InactiveUS20070252212A1Reduce variationSemiconductor/solid-state device detailsSolid-state devicesCMOSElectrical conductor

The present invention provides an improved CMOS diode structure with dual gate conductors. Specifically, a substrate comprising a first n-doped region and a second p-doped region is formed. A third region of either n-type or p-type conductivity is located between the first and second regions. A first gate conductor of n-type conductivity and a second gate conductor of p-type conductivity are located over the substrate and adjacent to the first and second regions, respectively. Further, the second gate conductor is spaced apart and isolated from the first gate conductor by a dielectric isolation structure. An accumulation region with an underlying depletion region can be formed in such a diode structure between the third region and the second or the first region, and such an accumulation region preferably has a width that is positively correlated with that of the second or the first gate conductor.

Owner:GLOBALFOUNDRIES INC

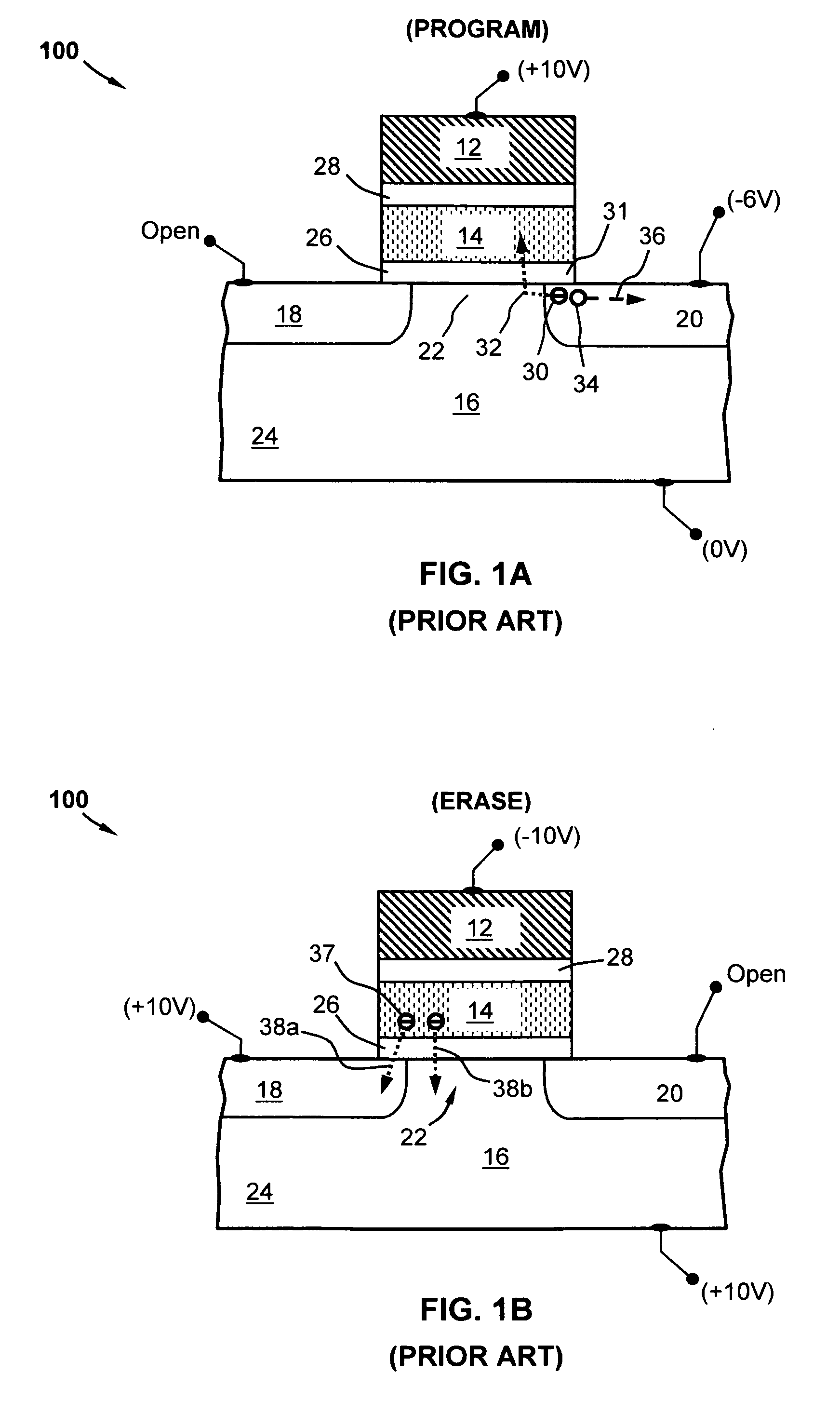

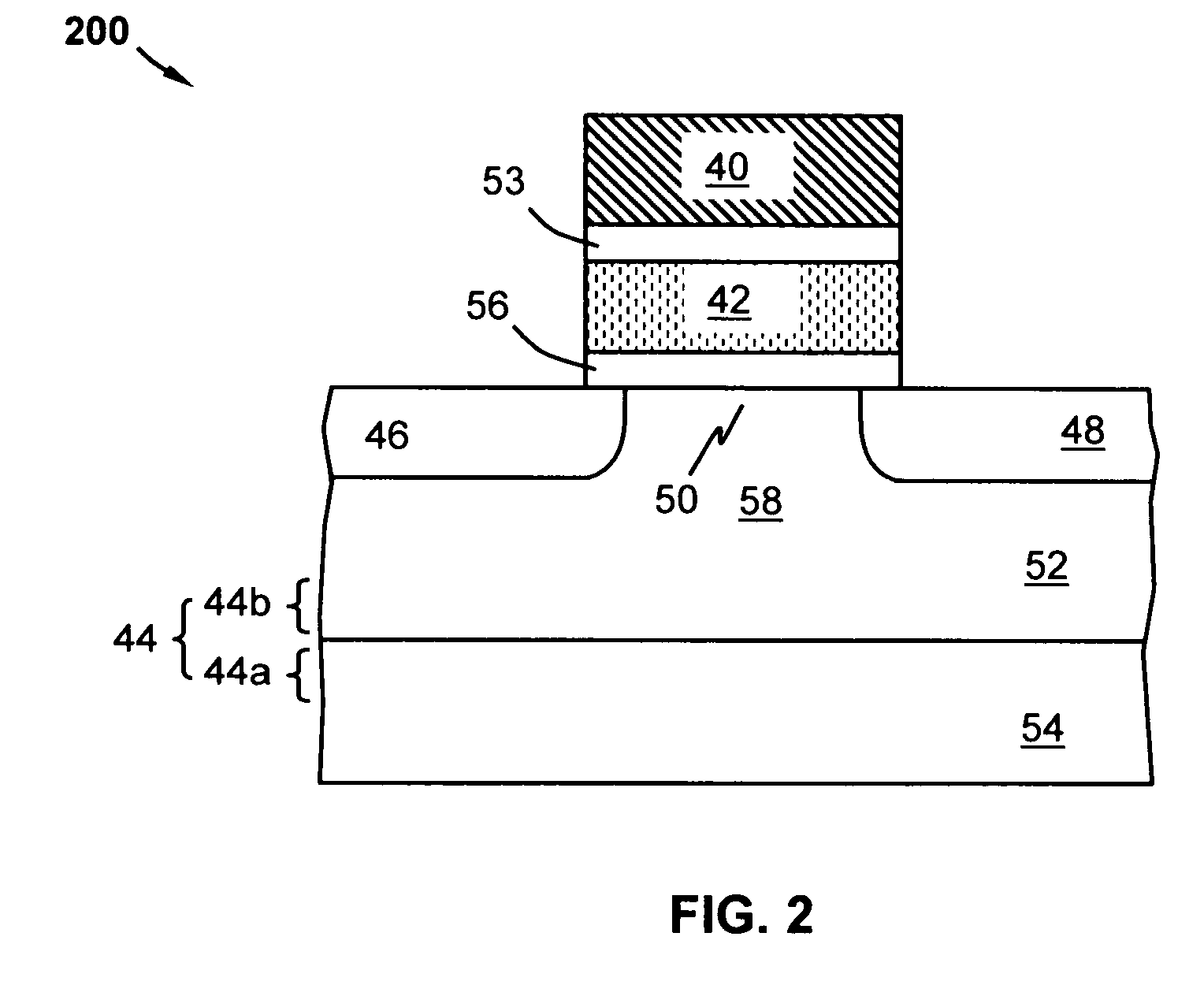

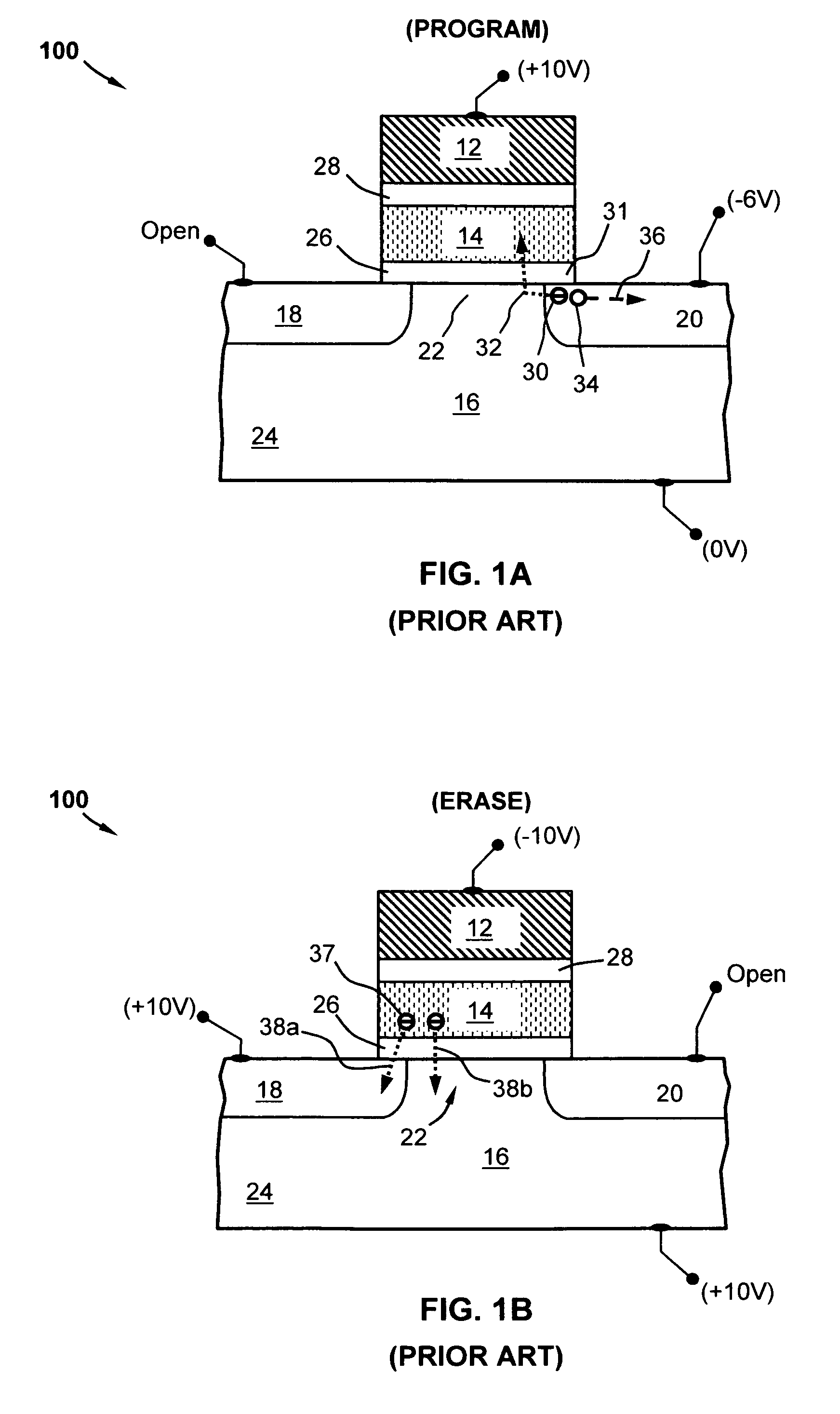

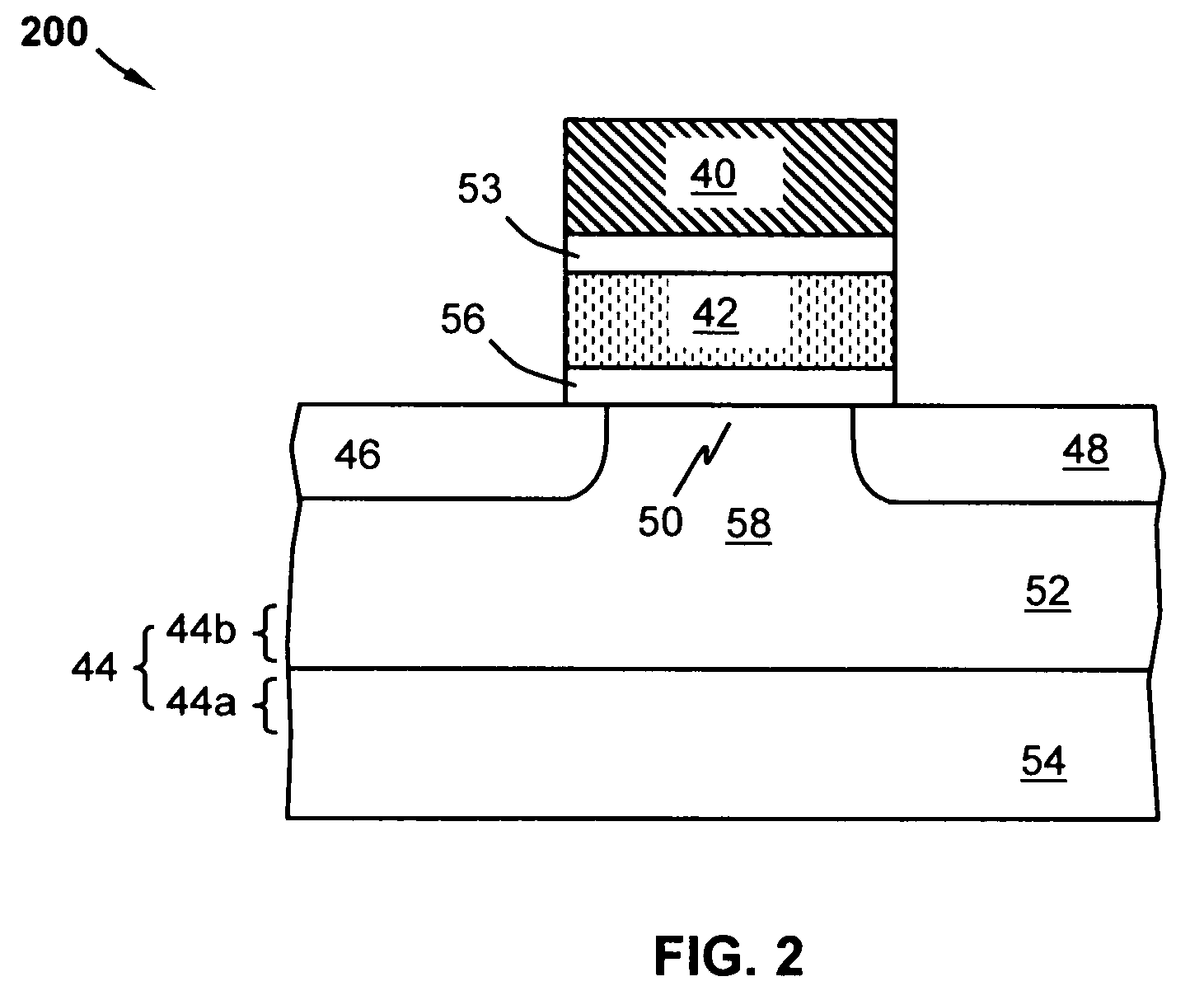

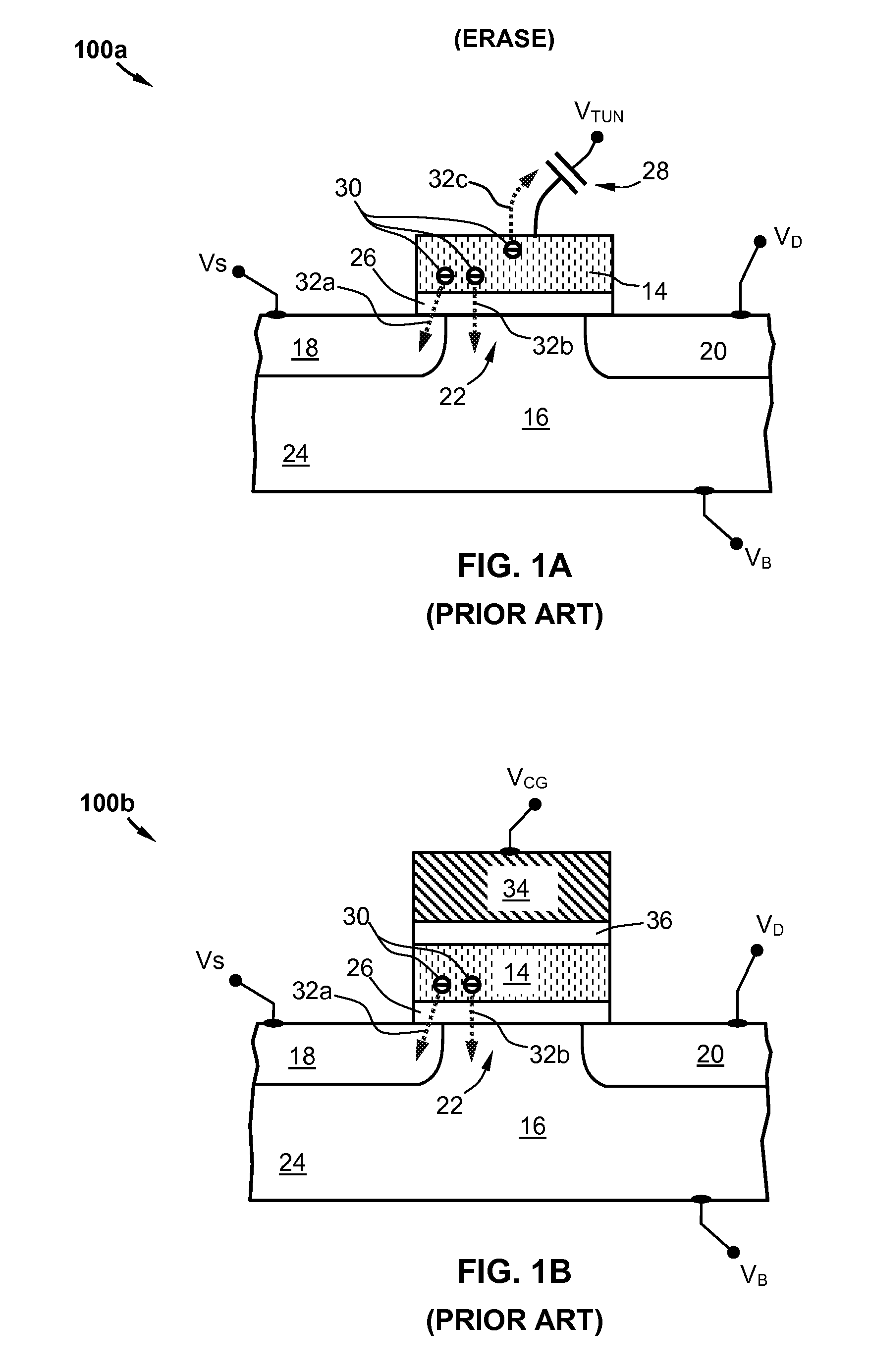

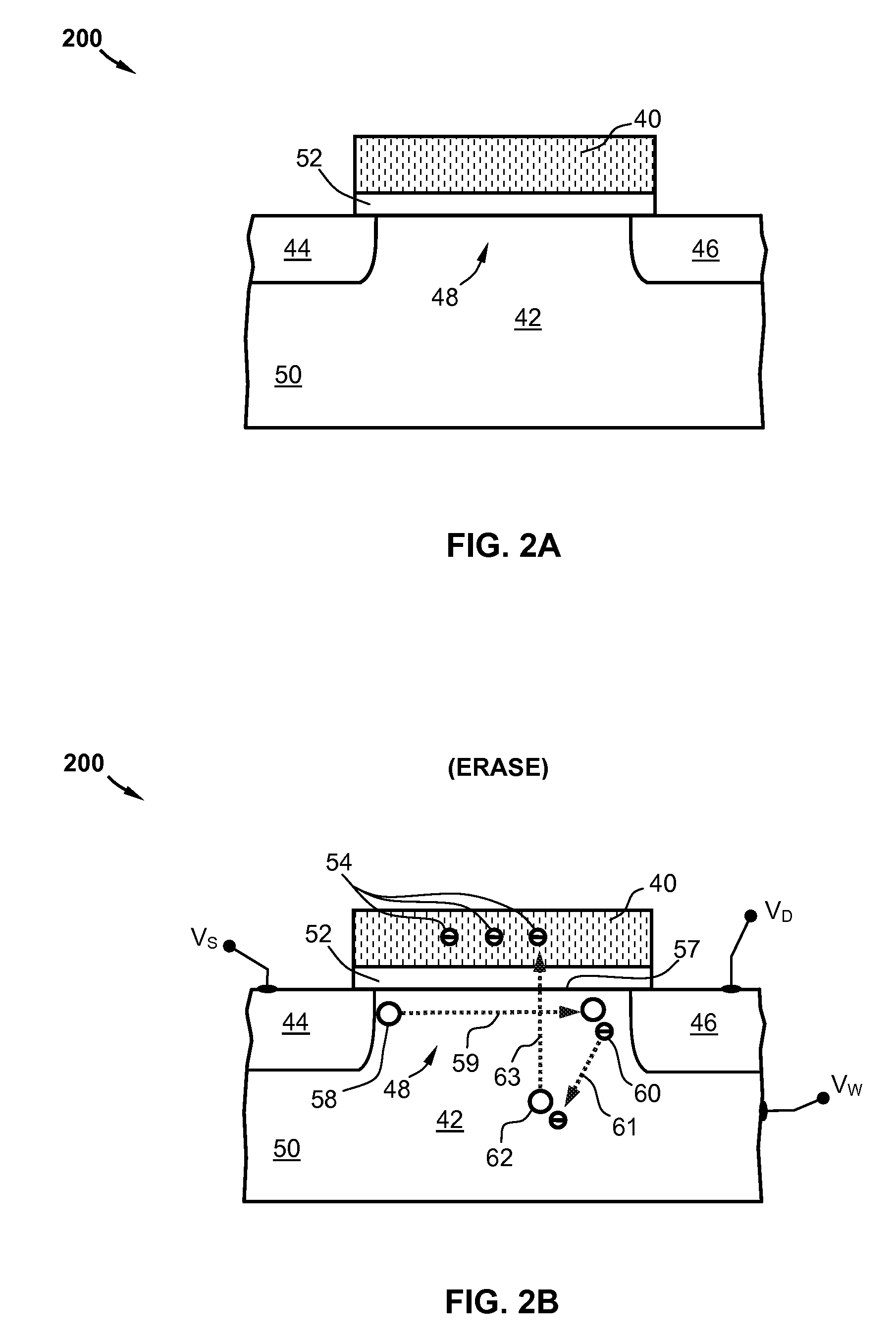

P-channel electrically alterable non-volatile memory cell

A nonvolatile memory cell is provided. The memory cell comprises a storage transistor and an injector in a semiconductor substrate of a p-type conductivity. The injector comprises a first region of the p-type conductivity and a second region of an n-type conductivity. The storage transistor comprises a source, a drain, a channel, a charge storage region, and a control gate. The source and the drain have the p-type conductivity and are formed in a well of the n-type conductivity in the substrate with the channel of the well defined therebetween. The charge storage region is disposed over and insulated from the channel by a first insulator. The control gate is disposed over and insulated from the charge storage region by a second insulator. Further provided are methods operating the memory cell, including means for injecting electrons from the channel through the first insulator onto the charge storage region and means for injecting holes from the injector through the well through the channel through the first insulator onto the charge storage region.

Owner:MARVELL INT LTD

P-channel electrically alterable non-volatile memory cell

Owner:MARVELL INT LTD

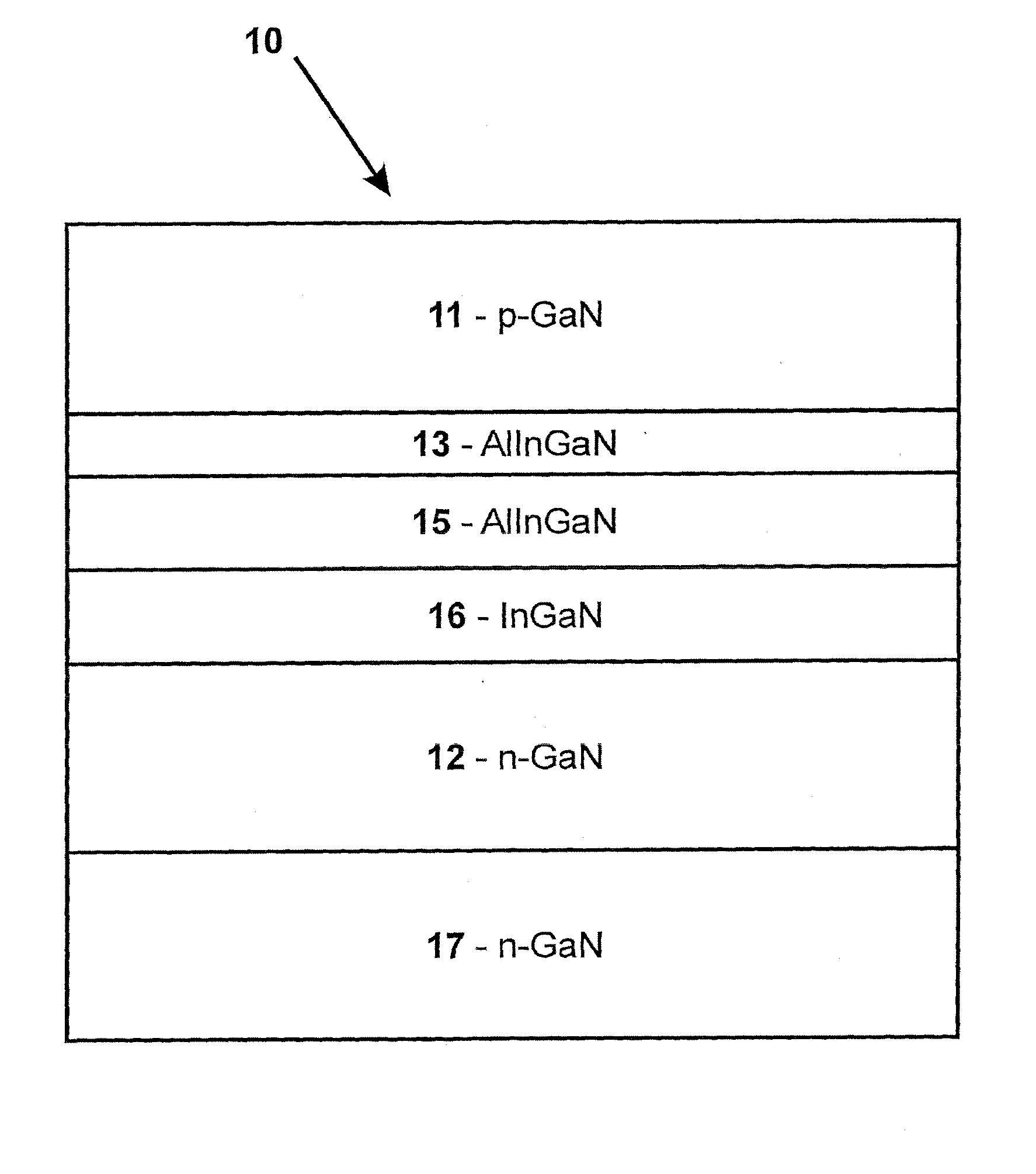

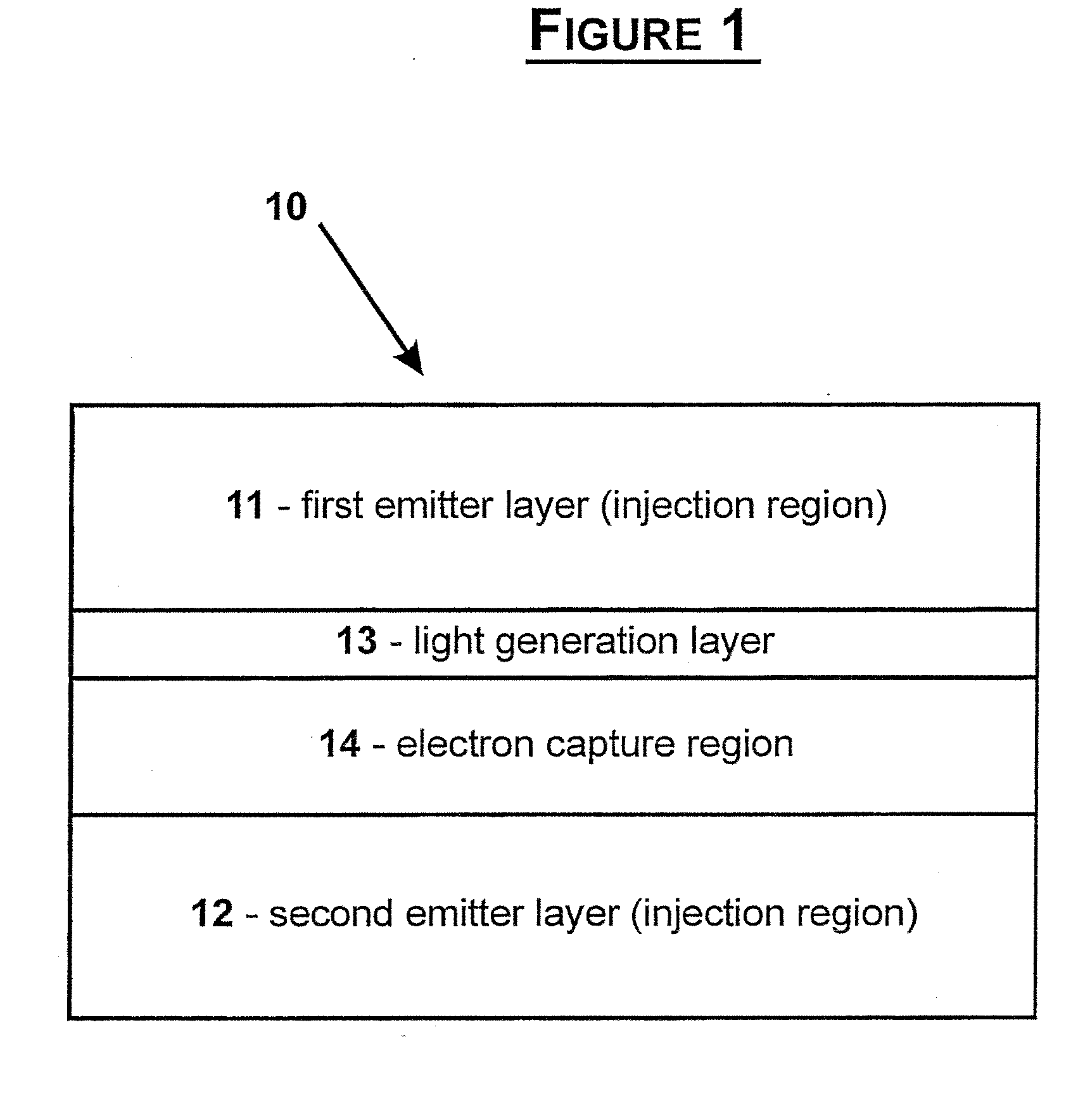

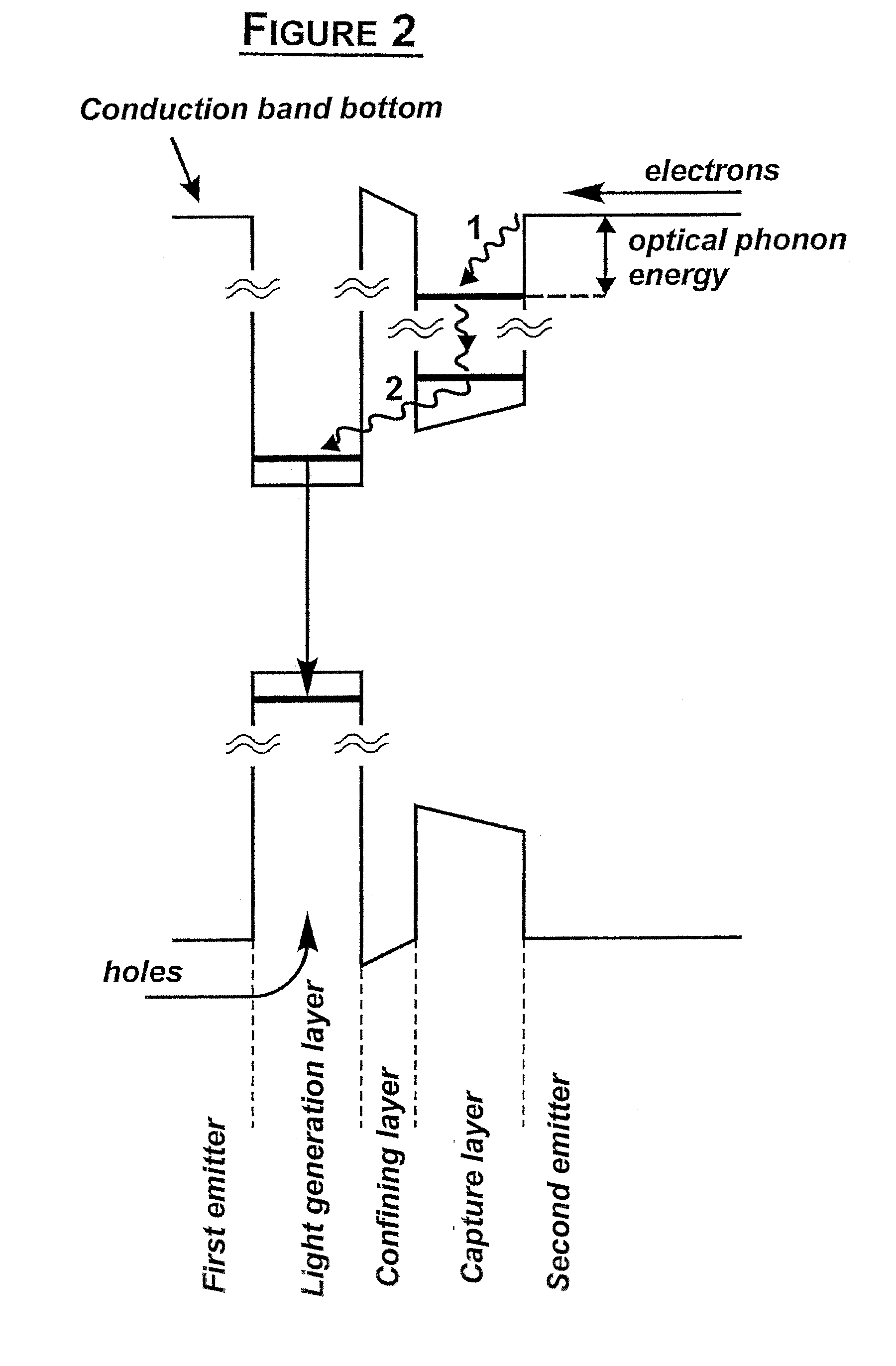

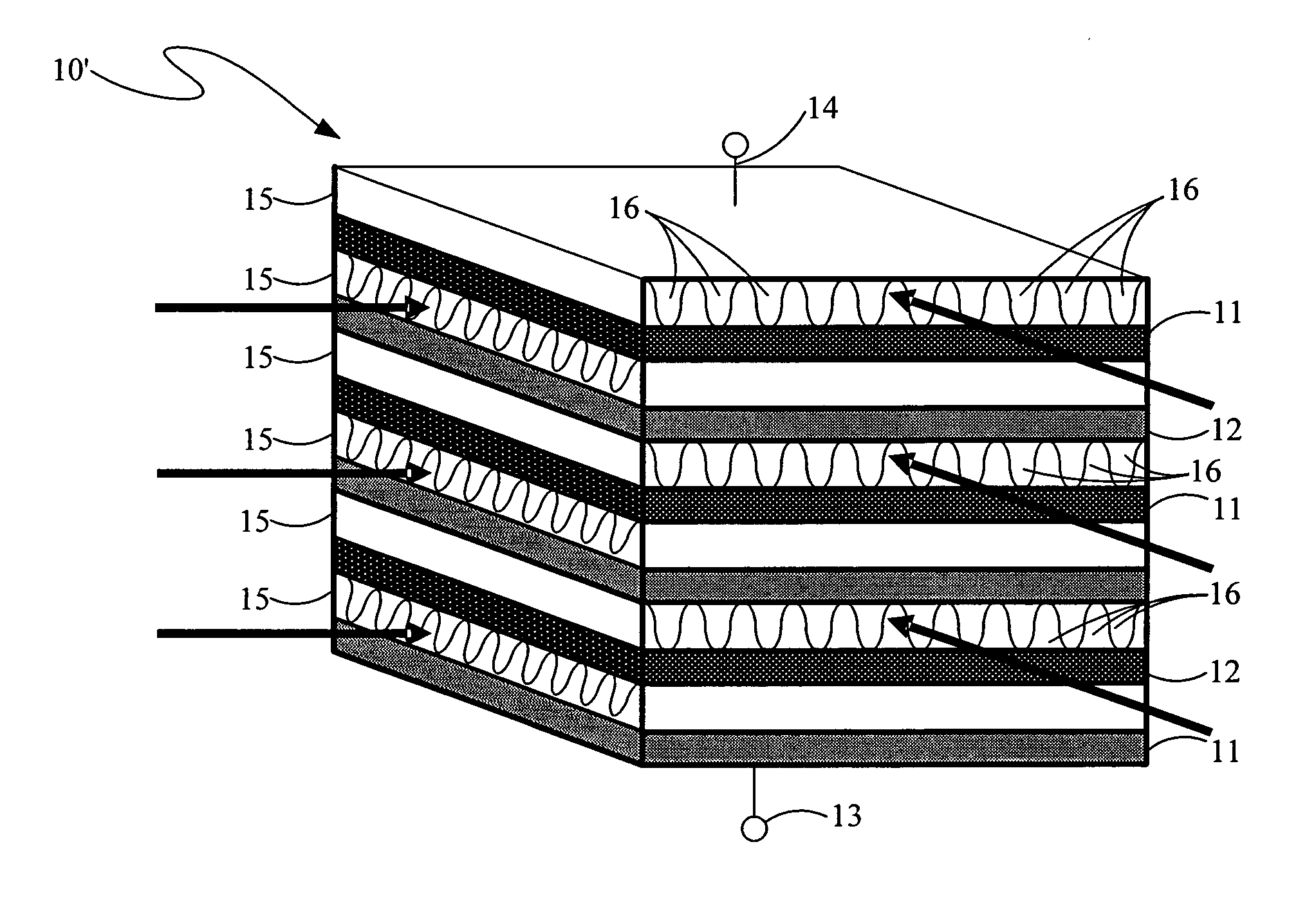

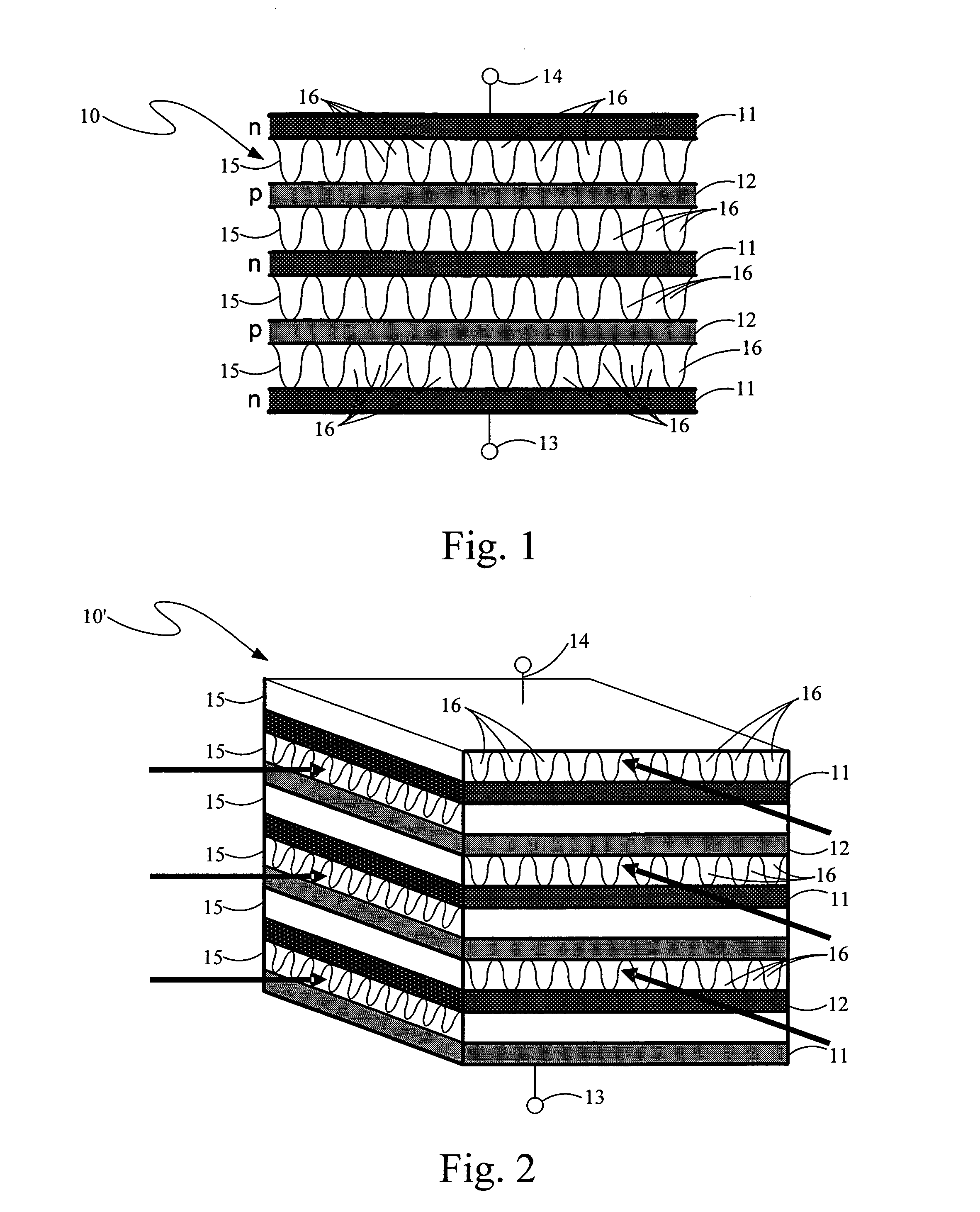

Semiconductor Heterostructure

InactiveUS20080283818A1Enhanced total light generating capabilityEmission rate can be suppressedNanoopticsSemiconductor devicesSemiconductor heterostructuresConduction band

A strained semiconductor heterostructure (10) comprises an injection region comprising a first emitter layer (11) having p-type conductivity and a second emitter layer (12) having n-type conductivity, and a light generation layer (13) positioned between the first emitter layer (11) and the second emitter layer (12). An electron capture region (14) is positioned between the light generation layer (13) and the second emitter layer (12), said electron capture region comprising a capture layer (16) adjacent to the second emitter layer, and a confining layer (15) adjacent to said electron capture layer. According to the present invention, the widths and materials of the confining and capture layers (15, 16) are selected to provide energy difference between one of localized energy levels for electrons in the capture layer (16) and the conduction band bottom of the second emitter layer (12) equal to the energy of the optical phonon.

Owner:OPTOGAN OY

Semiconductor transistor with P type re-grown channel layer

ActiveUS7795691B2Easy to controlTransistorSemiconductor/solid-state device manufacturingMOSFETVoltage regulation

Owner:WOLFSPEED INC

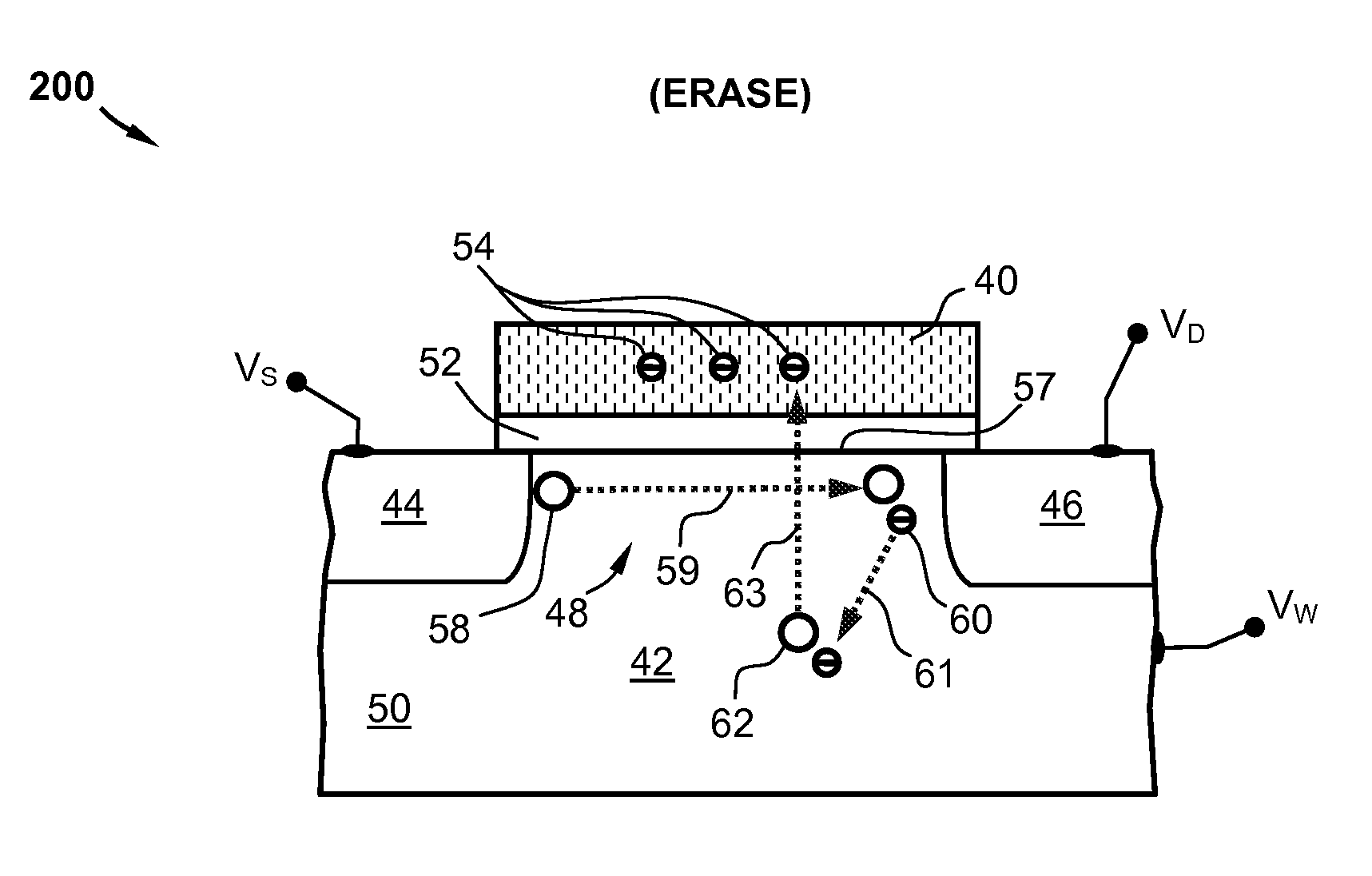

Electrically alterable non-volatile memory cells and arrays

Nonvolatile memory cells and array are provided. The memory cell comprises a body, a source, a drain, and a charge storage region. The body comprises an n-type conductivity and is formed in a well of the n-type conductivity. The source and the drain have p-type conductivity and are formed in the well with a channel of the body defined therebetween. The charge storage region is disposed over and insulated from the channel by a channel insulator. Each cell further comprises a bias setting having a source voltage applied to the source, a well voltage applied to the well, and a drain voltage applied to the drain. A bias configuration for an erase operation of the memory cell is further provided, wherein the source voltage is sufficiently more negative with respect to the well voltage and is sufficiently more positive with respect to the drain voltage to inject hot holes onto the charge storage region. The cells can be arranged in row and column to form memory arrays and memory device.

Owner:WANG CHIH HSIN

Polycrystalline silicon material for solar power generation and silicon wafer for solar power generation

InactiveUS20060249200A1Inexpensively and stably obtainFinal product manufactureChemical vapor deposition coatingHydrogenSilanes

A polycrystalline silicon material for solar power generation is polycrystalline silicon obtained by supplying a raw material silane gas to a red-hot silicon seed rod in a sealed reactor at high temperature to thereby thermally decompose or hydrogen-reduce the raw material silane gas. The polycrystalline silicon has a p-type or n-type conductivity, a resistivity of 3 to 500 Ωcm, and a lifetime of 2 to 500 μsec and is used for manufacturing a silicon wafer for solar power generation.

Owner:SUNRIC +1

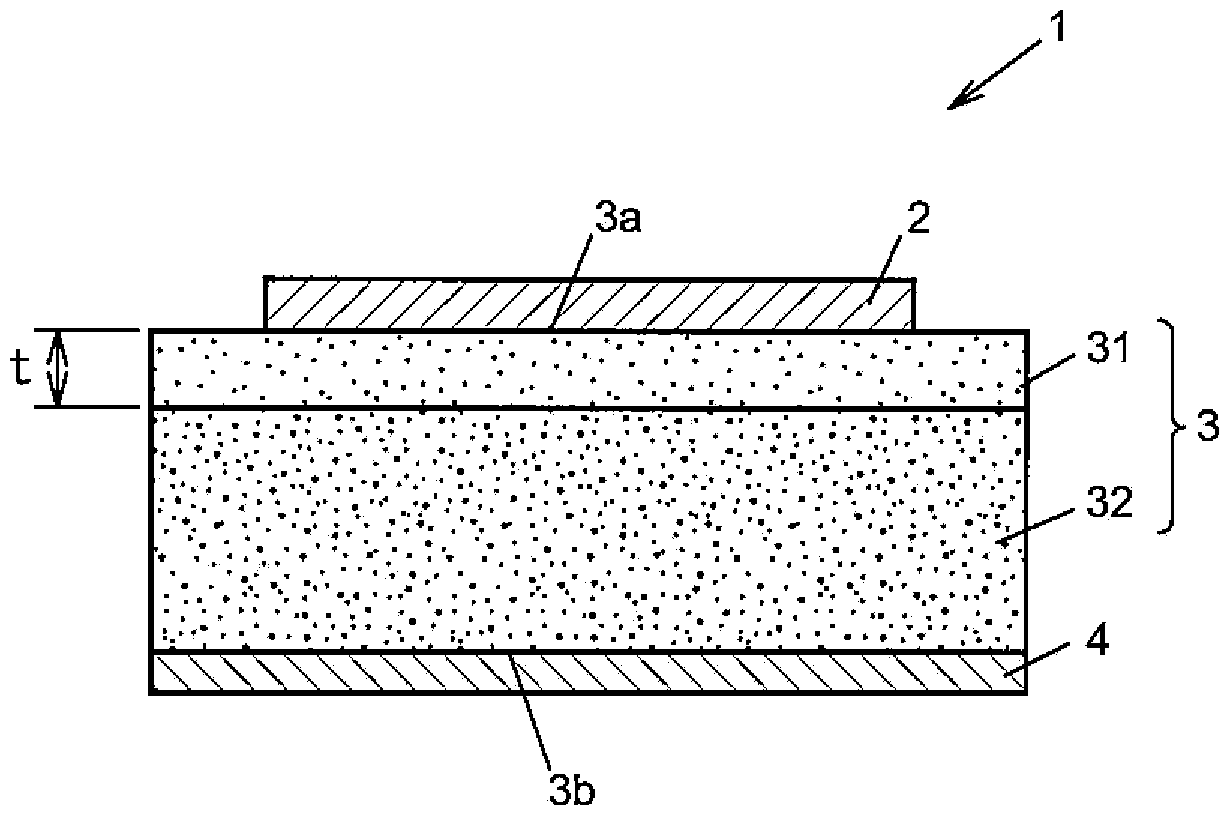

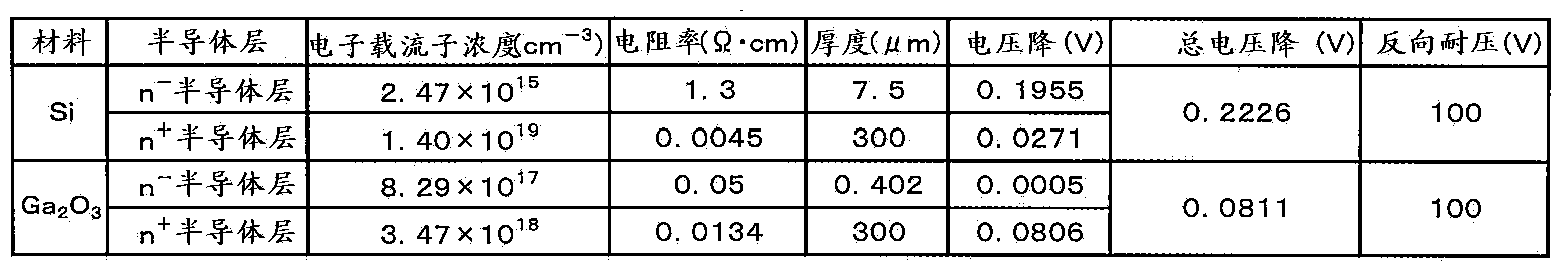

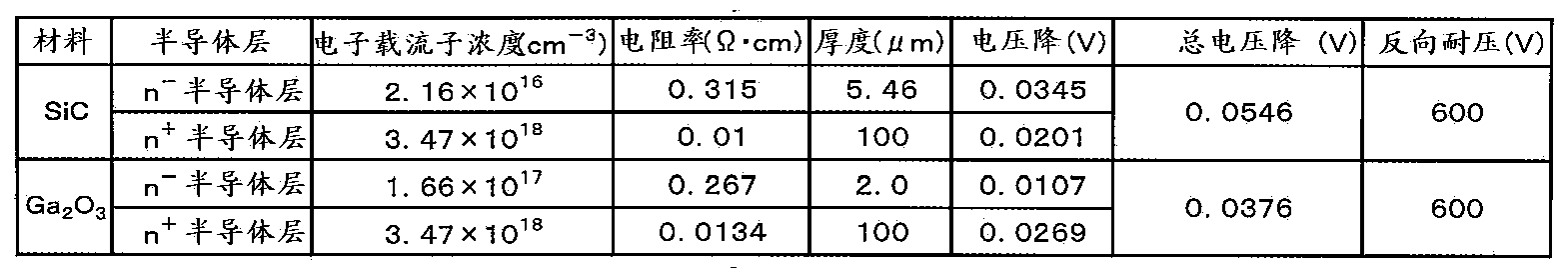

Schottky barrier diode

ActiveCN103918082AIncrease forward voltageIncrease contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCharge carrier

Provided is a Schottky barrier diode that is capable of preventing an increase in a forward voltage and an increase in a contact resistance with an ohmic electrode layer even when a reverse withstand voltage is increased. The Schottky barrier diode (1) is provided with: an n-type semiconductor layer (3) comprising Ga2O3-based compound semiconductors with n-type conductivity; and a Schottky electrode layer (2) which is in Schottky-contact with the n-type semiconductor layer (3). An n--type semiconductor layer (31), which has a relatively low electron carrier concentration and is brought into Schottky-contact with the Schottky electrode layer (2), and an n+ semiconductor layer (32), which has a higher electron carrier concentration than the n-semiconductor layer (31), are formed in the n-type semiconductor layer (3).

Owner:TAMURA KK

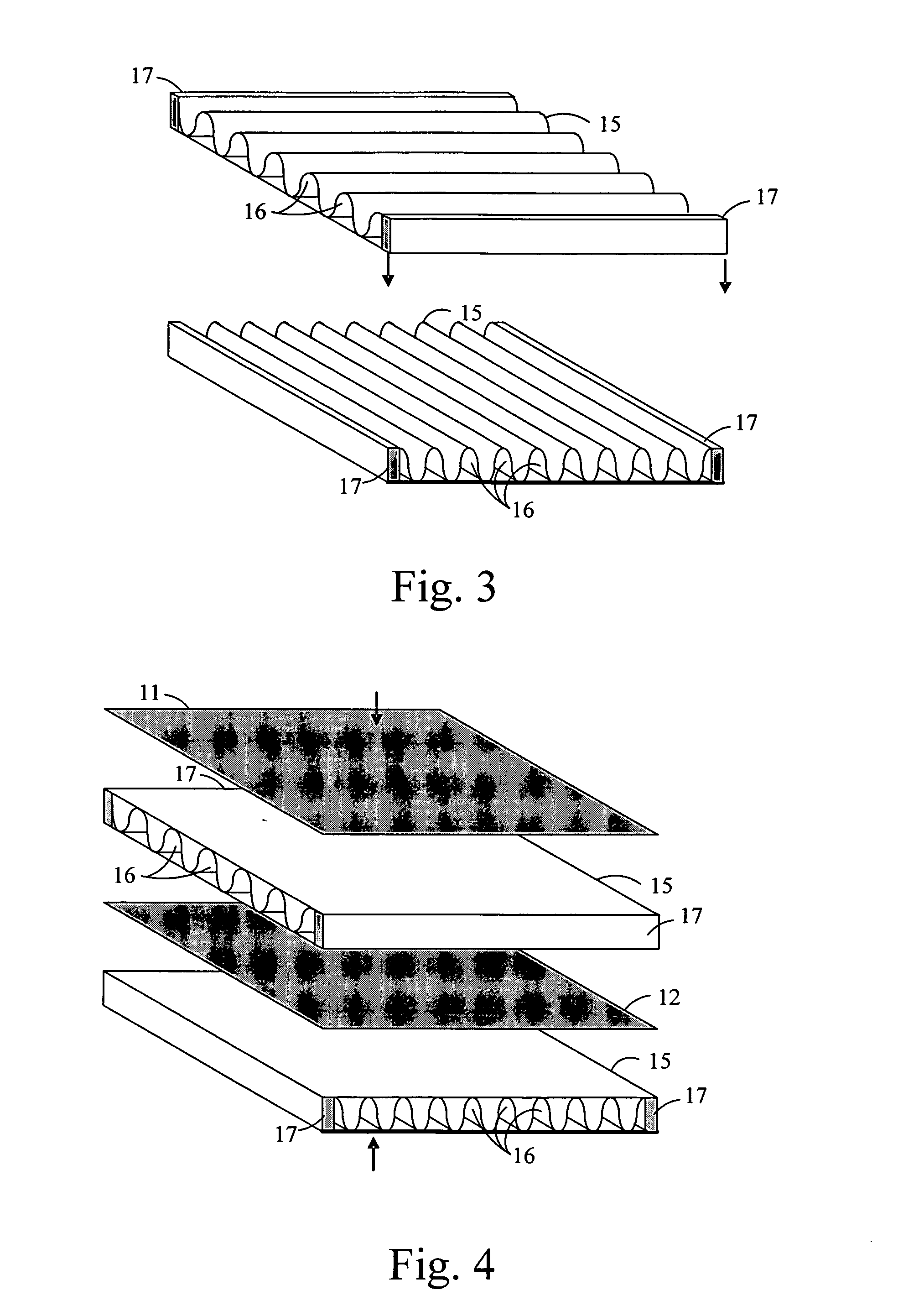

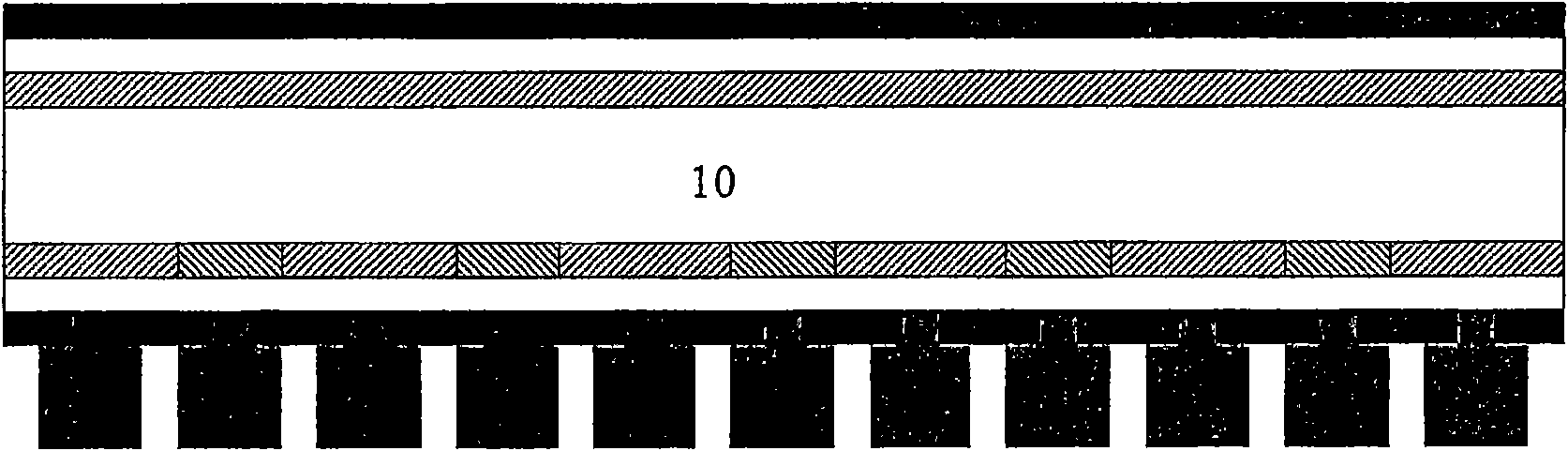

Thermoelectric heat exchanger

InactiveUS20080083447A1Selective conversionThermoelectric device with peltier/seeback effectThermoelectric materialsThermal energy

A thermoelectric effects materials based energy transduction device, for selectively providing conversions between electrical and thermal energies having interleaved n-type conductivity material layers having thermoelectric effects properties and a first plurality of p-type conductivity material layers each having thermoelectric effects properties. There is a first plurality of passageway structures each being thermally conductive and each having passageways therethrough extending between two sides thereof with such a passageway structure from this first plurality thereof positioned between members of each overlapped pair of succeeding layers.

Owner:RAYTHEON TECH CORP

Back contacted solar cell

InactiveCN101622717AHigh energy conversion ratePhotovoltaic energy generationSemiconductor devicesSilicon solar cellN type conductivity

This invention relates to a cost effective method of producing a back contacted silicon solar cell and the cell made by the method, where the method comprises applying a silicon substrate, wafer or thin film, doped on the back side with alternating P-type and N-type conductivity in an interdigitated pattern and optionally a layer of either P- or N-type on the front side of the wafer, depositing one or more surface passivation layers on both sides of the substrate, creating openings in the surface passivation layers on the back side of the substrate, depositing a metallic layer covering the entire back side and which fills the openings in the surface passivation layers, and creating openings in the deposited metallic layer such that electric insulated contacts with the doped regions on the back side of the substrate is obtained.

Owner:RENEWABLE ENERGY CORP LTD

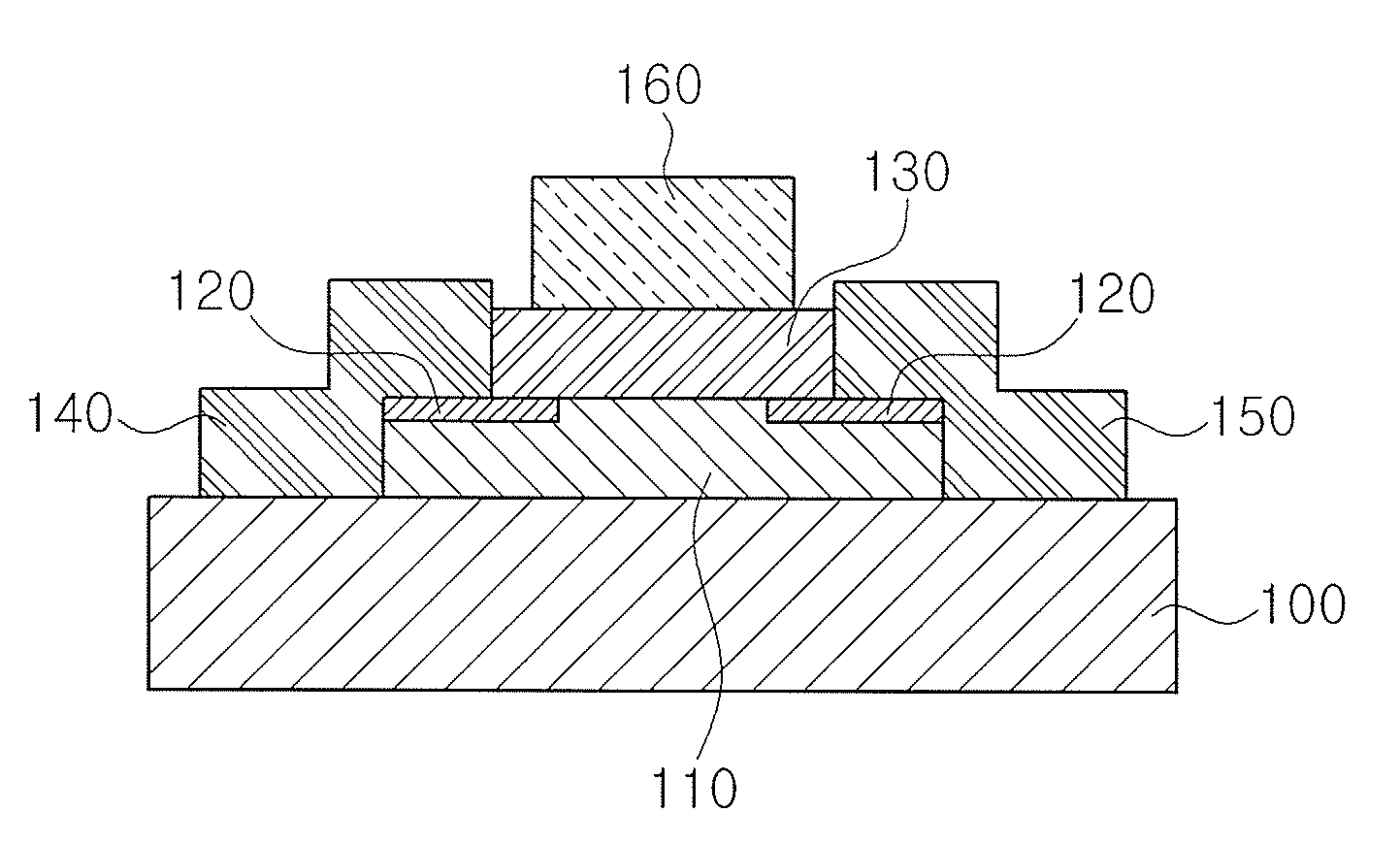

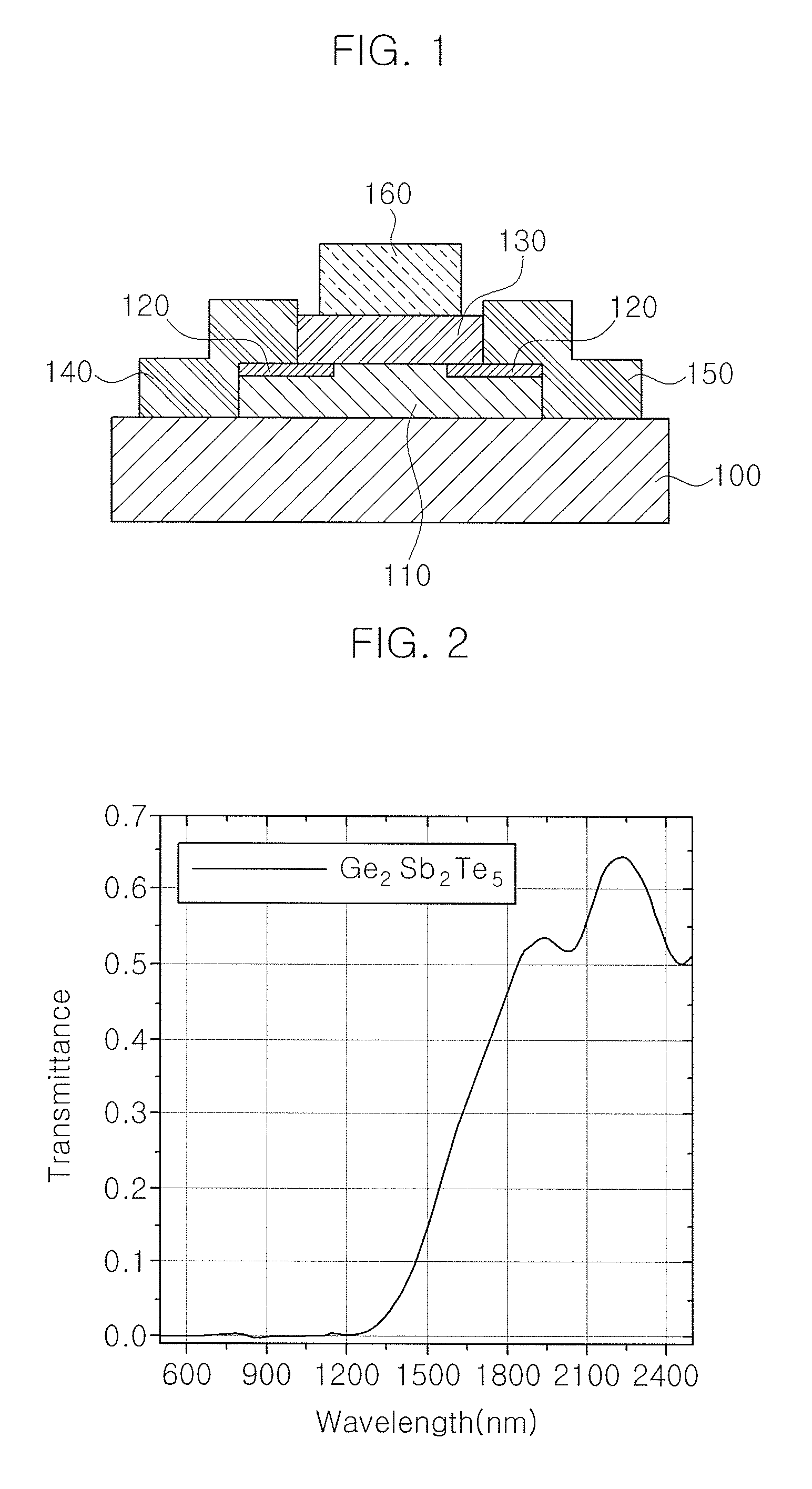

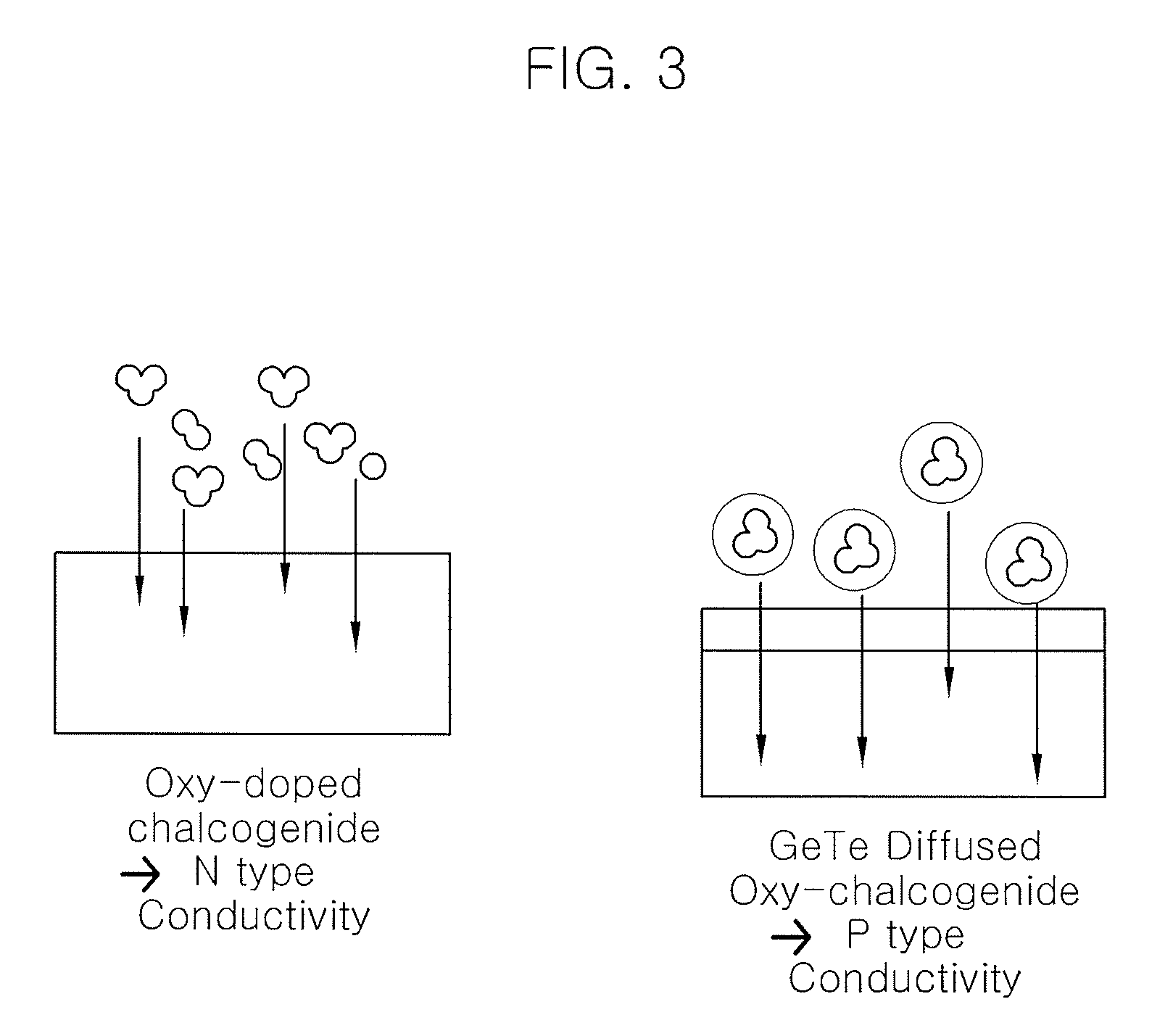

Method for manufacturing n-type and p-type chalcogenide material, doped homojunction chalcogenide thin film transistor and method of fabricating the same

InactiveUS20090146141A1Low costLow-cost implementationTransistorSemiconductor/solid-state device manufacturingAlloyN type conductivity

The present invention provides a doped homojunction chalcogenide thin film transistor and a method of fabricating the same, comprising forming an N-type chalcogenide layer constituting a channel layer on a substrate, forming and patterning a diffusion prevention layer on the upper part of the N-type chalcogenide layer, and forming a P-type chalcogenide layer constituting source and drain regions by depositing and diffusing Te alloy on the N-type chalcogenide layer. With the present invention, a thin film transistor can be fabricated using chalcogenide material having N-type conductivity and chalcogenide material having P-type conductivity.

Owner:ELECTRONICS & TELECOMM RES INST