Patents

Literature

157 results about "Semiconductor heterostructures" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semiconductor heterostructures. Structures consisting of two different semiconductor materials in junction contact, with unique electrical or electrooptical characteristics. A heterojunction is a junction in a single crystal between two dissimilar semiconductors.

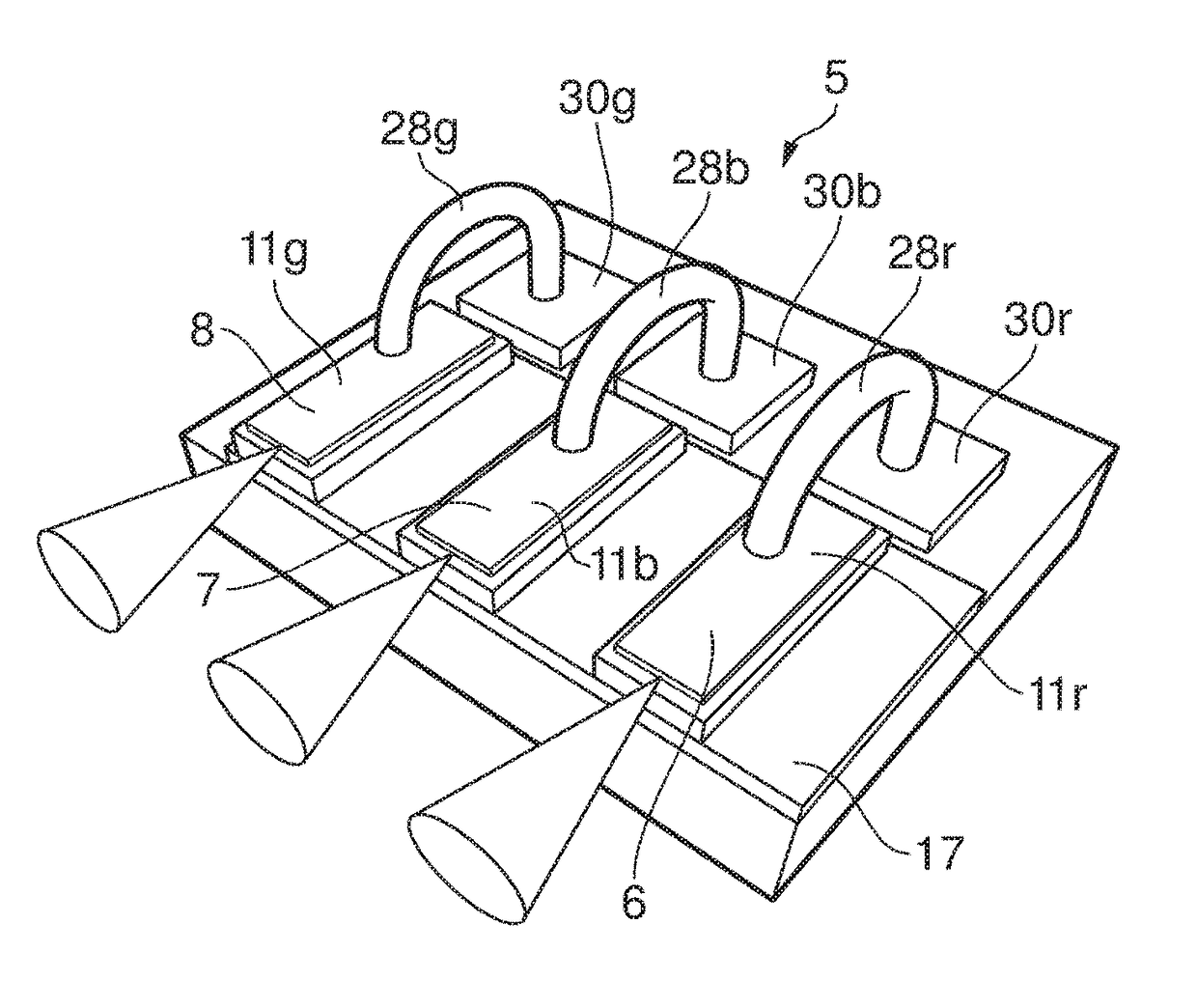

Broadband light emitting device

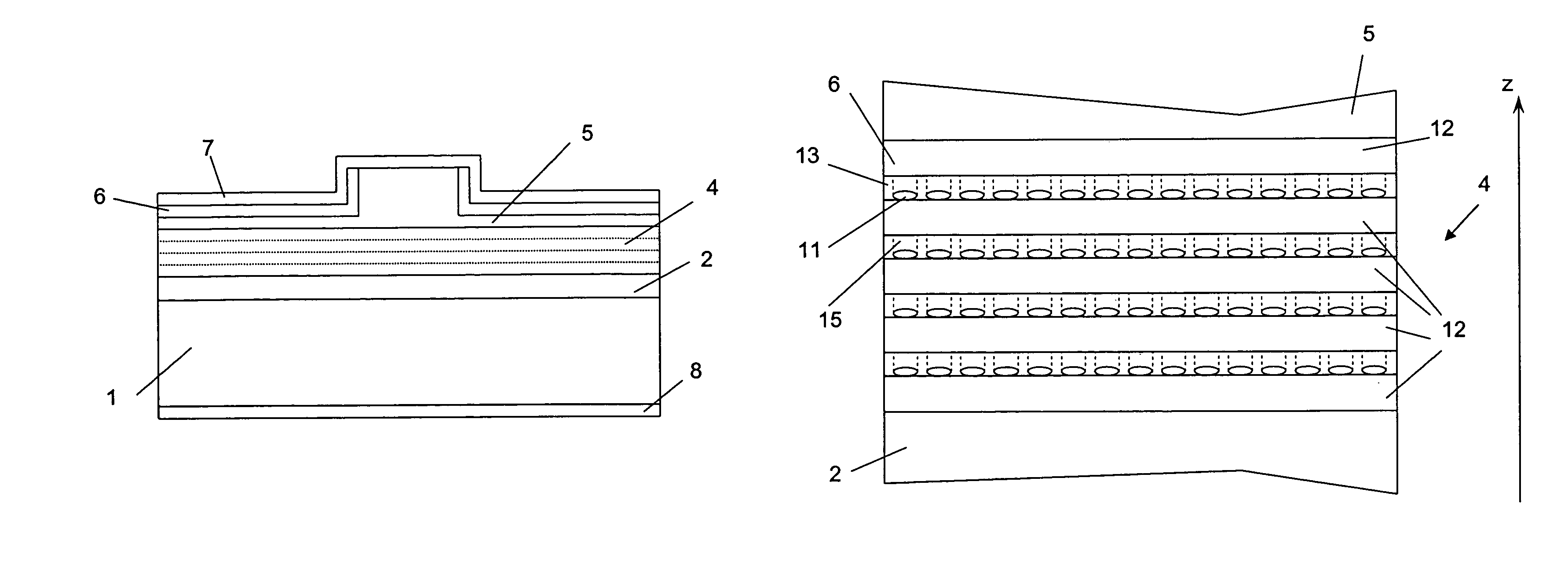

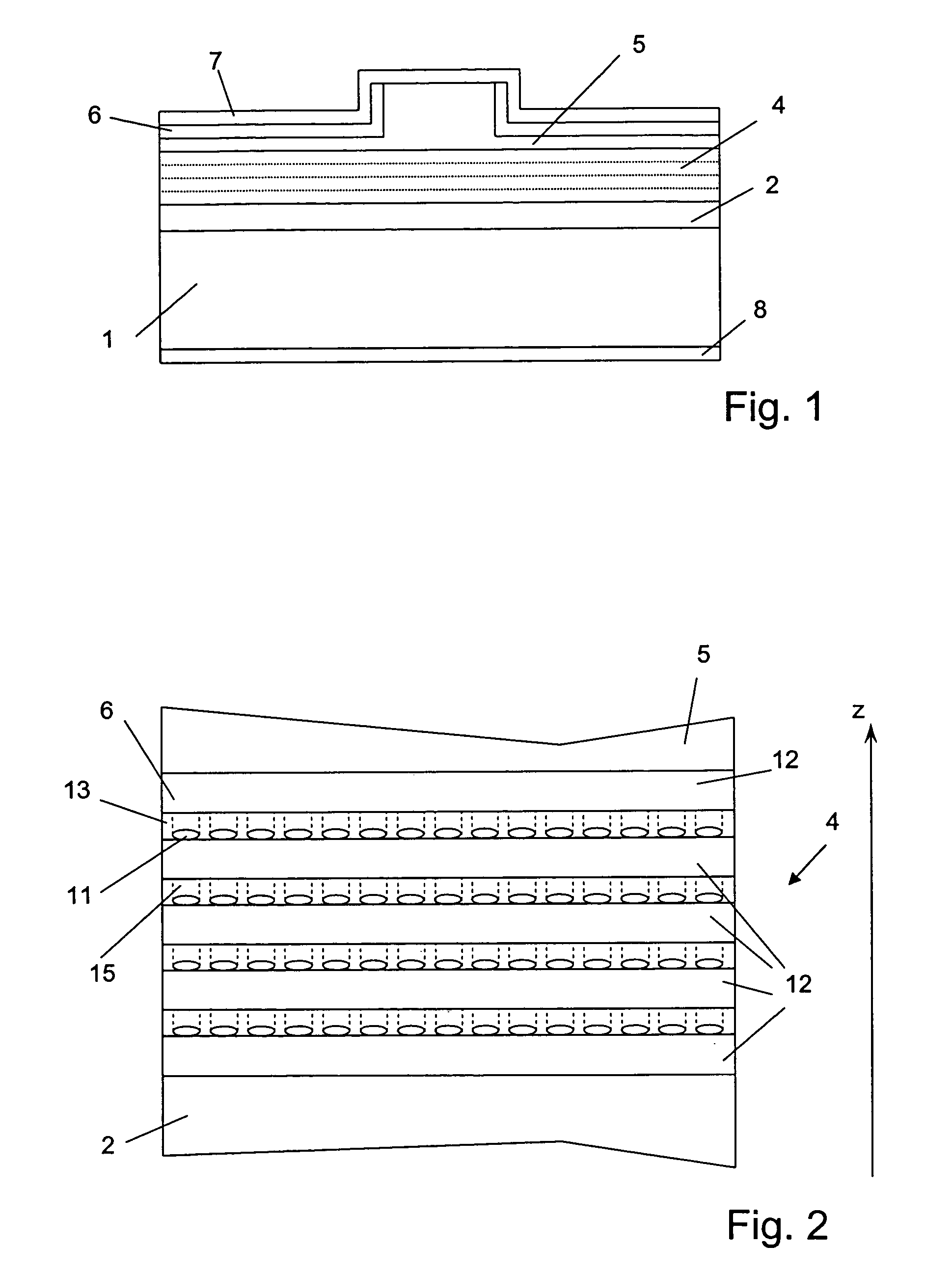

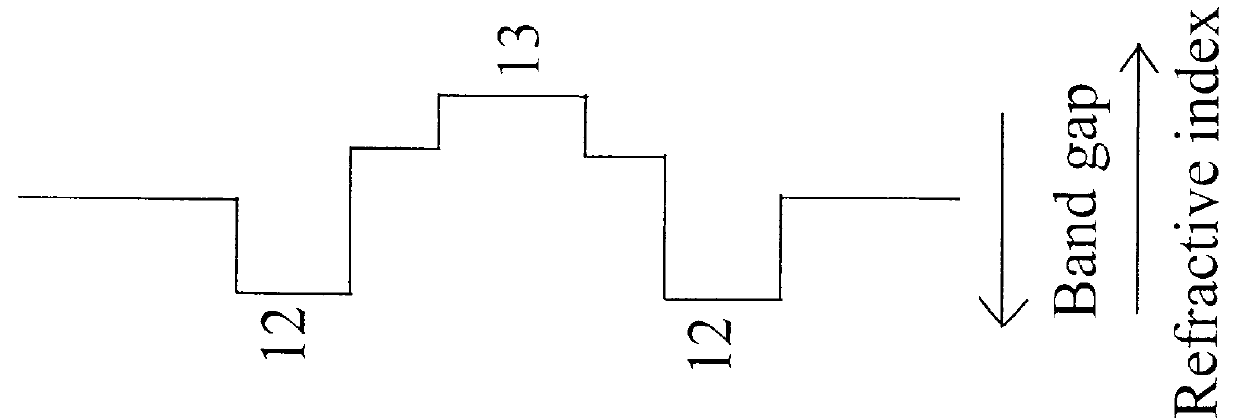

ActiveUS7019325B2Increase heightBroad emission spectrumLaser detailsLaser optical resonator constructionStimulated emissionP–n junction

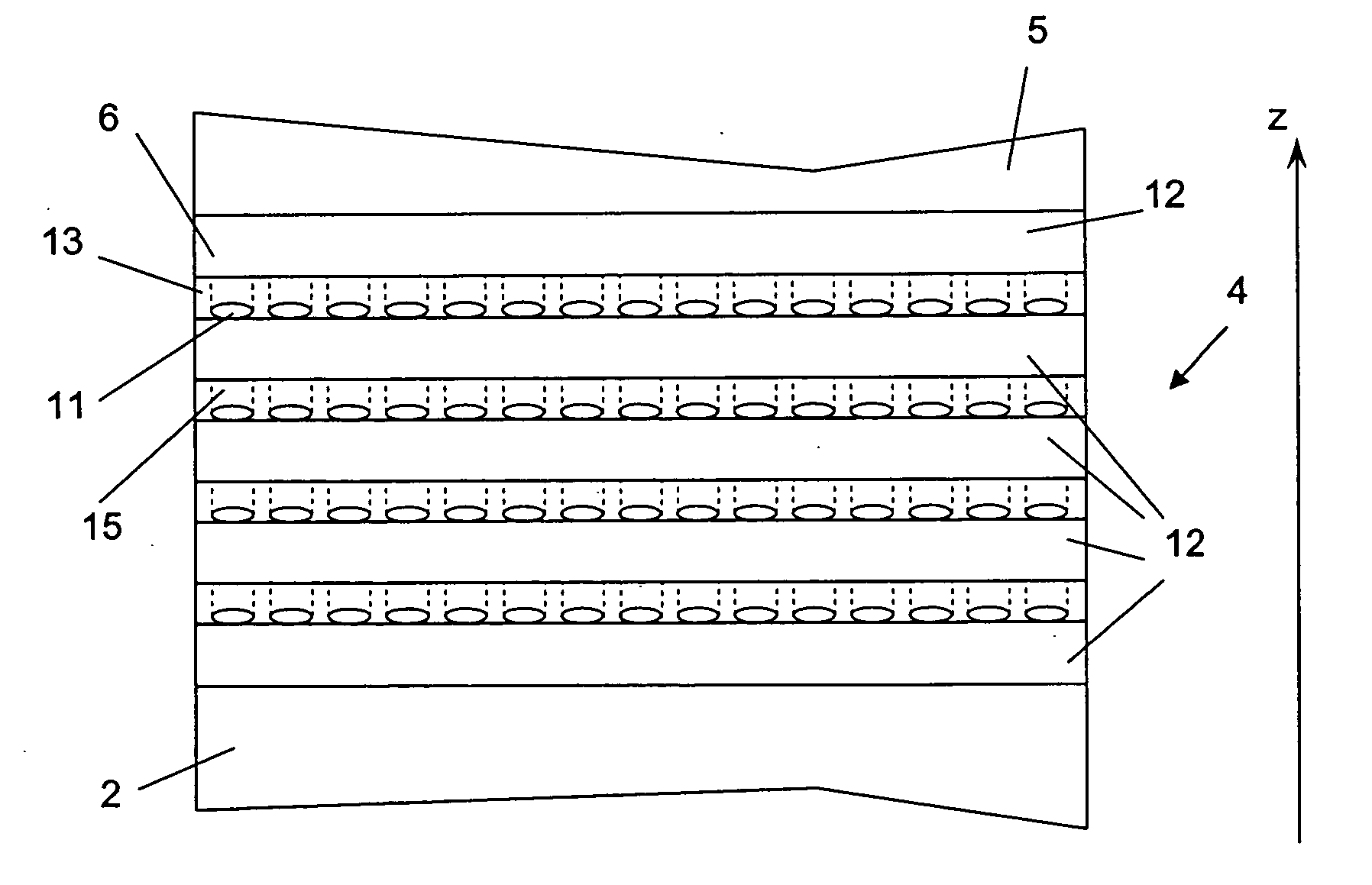

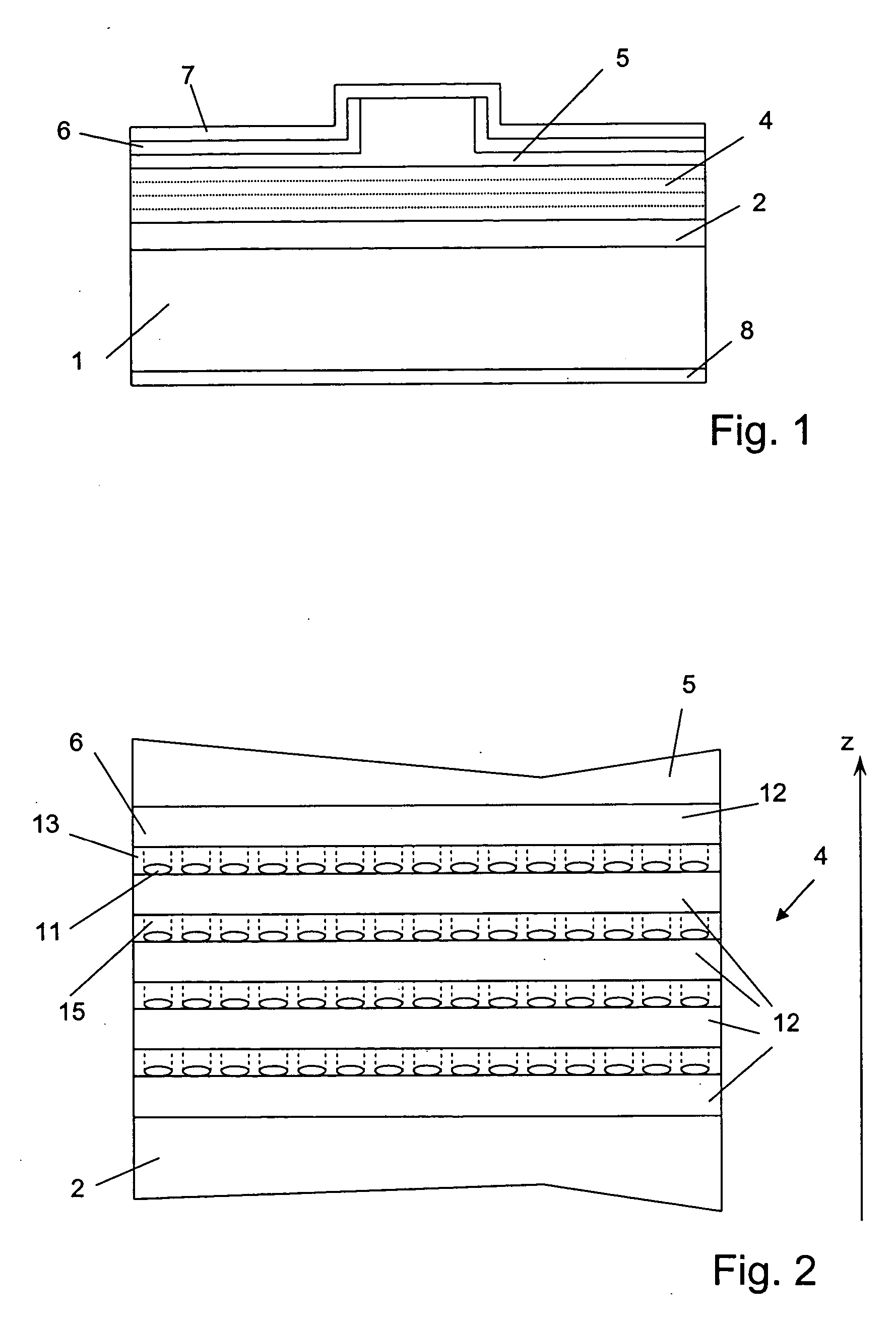

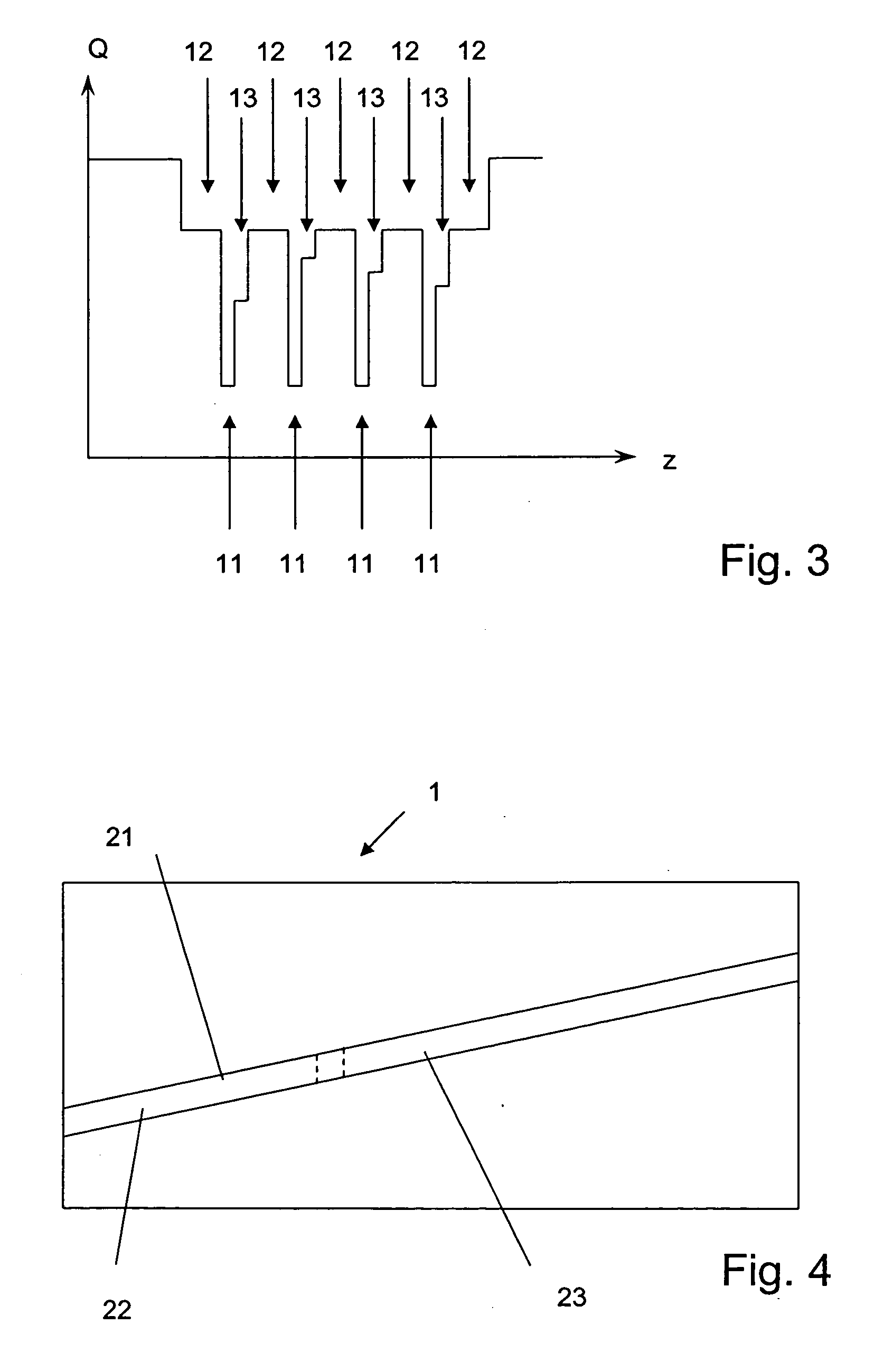

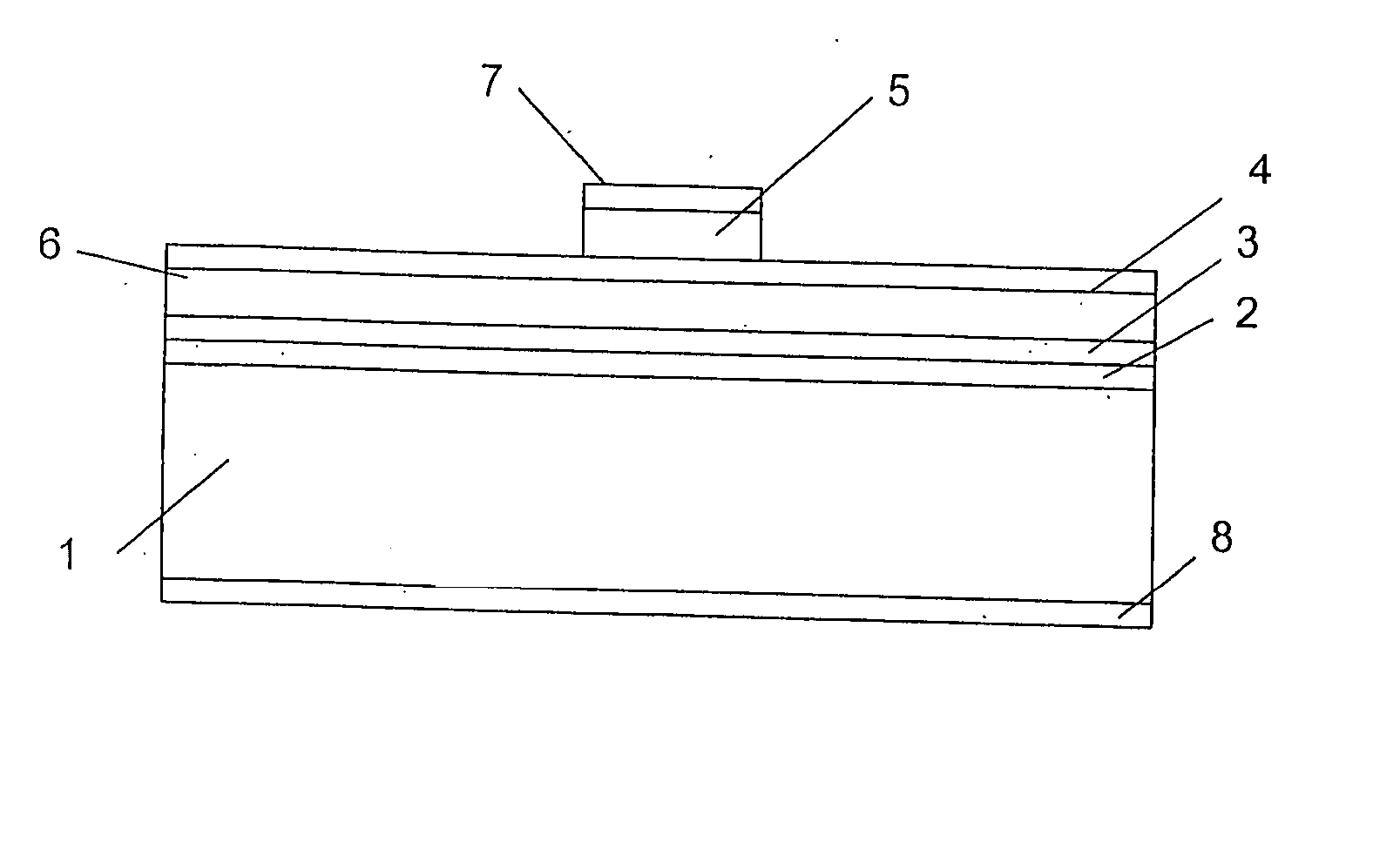

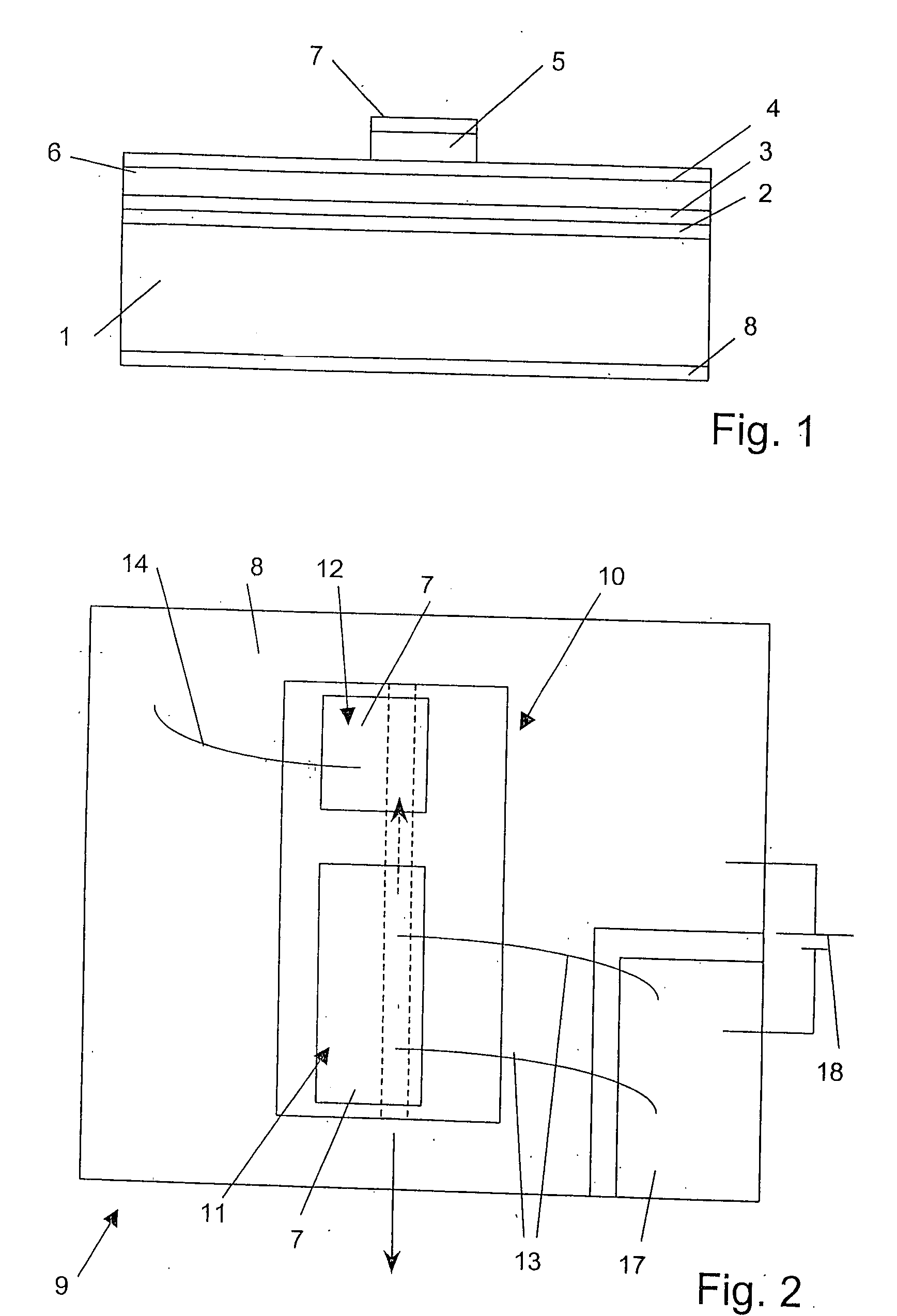

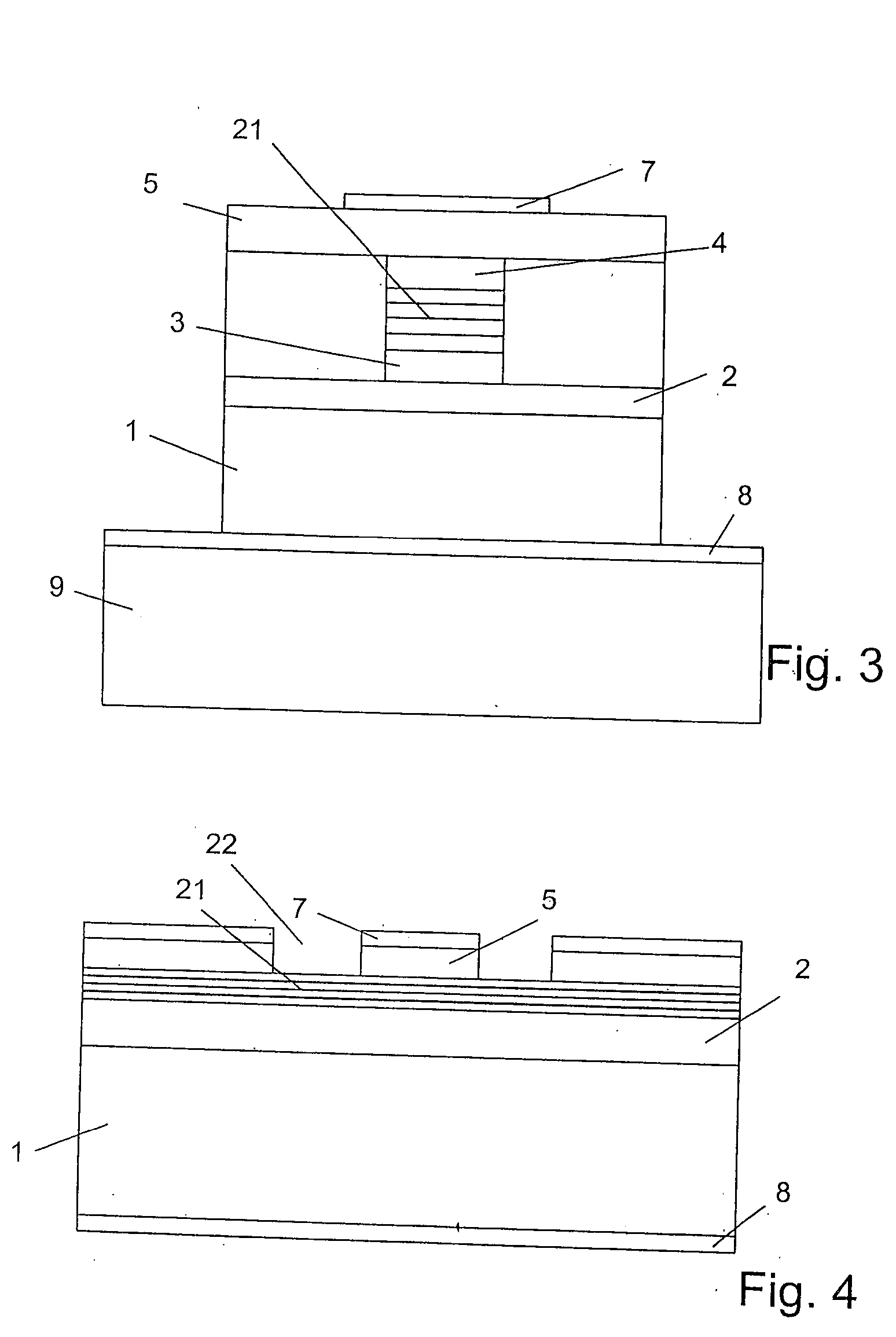

The invention concerns a superluminescent light emitting diode (SLED) comprising a semiconductor heterostructure forming a PN junction and a waveguide. The semiconductor heterostructure includes a gain region with a contact means for biasing the PN junction so as to produce light emission including stimulated emission from an active zone of the gain region, and in the active zone a plurality of quantum dot layers, each quantum dot layer made up of a plurality of quantum dots and a plurality of adjoining layers, each adjoining layer adjacent to one of said quantum dot layers. The material composition or a deposition parameter of at least two adjoining layers is different. This ensures an enhanced emission spectral width.

Owner:EXALOS

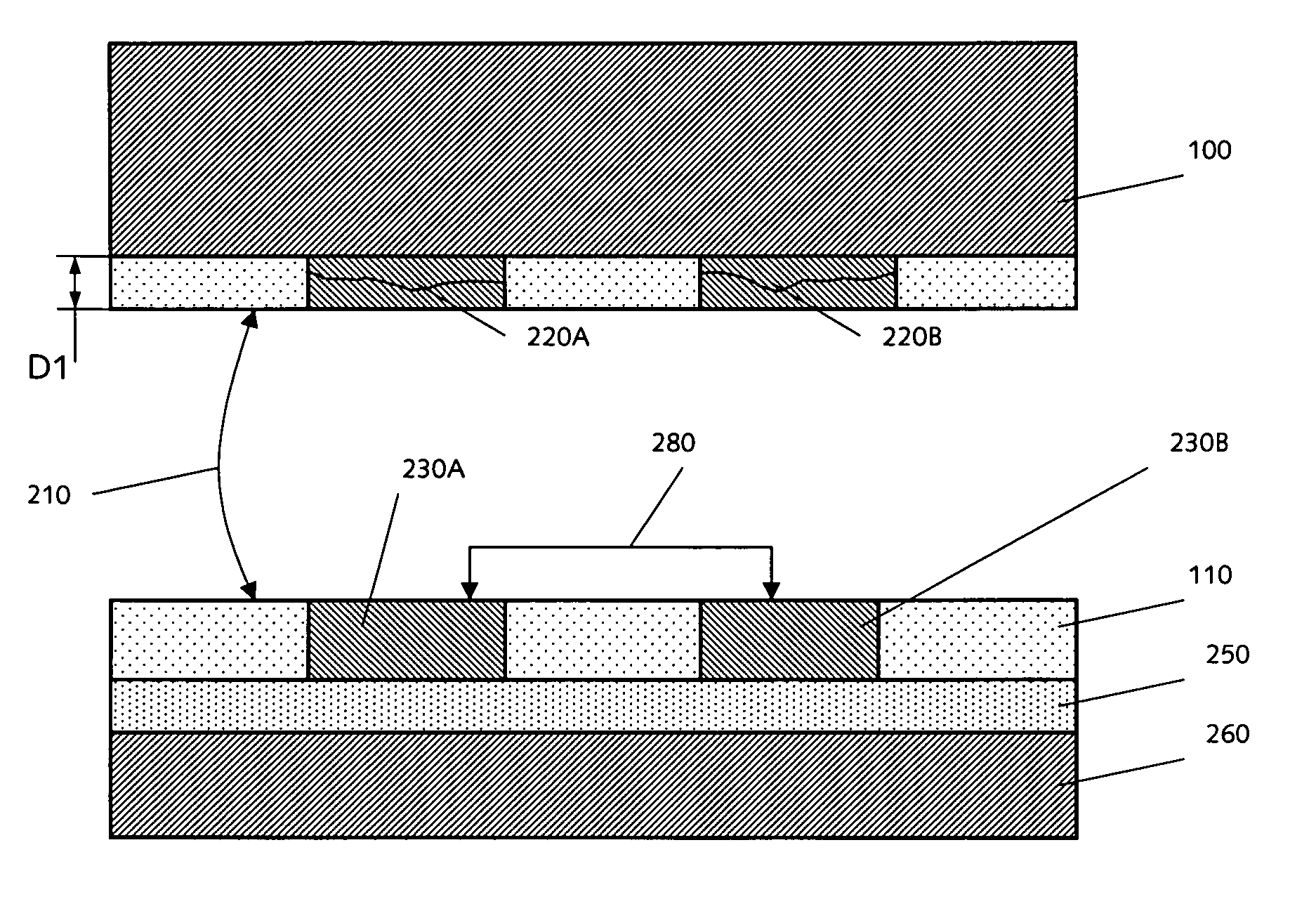

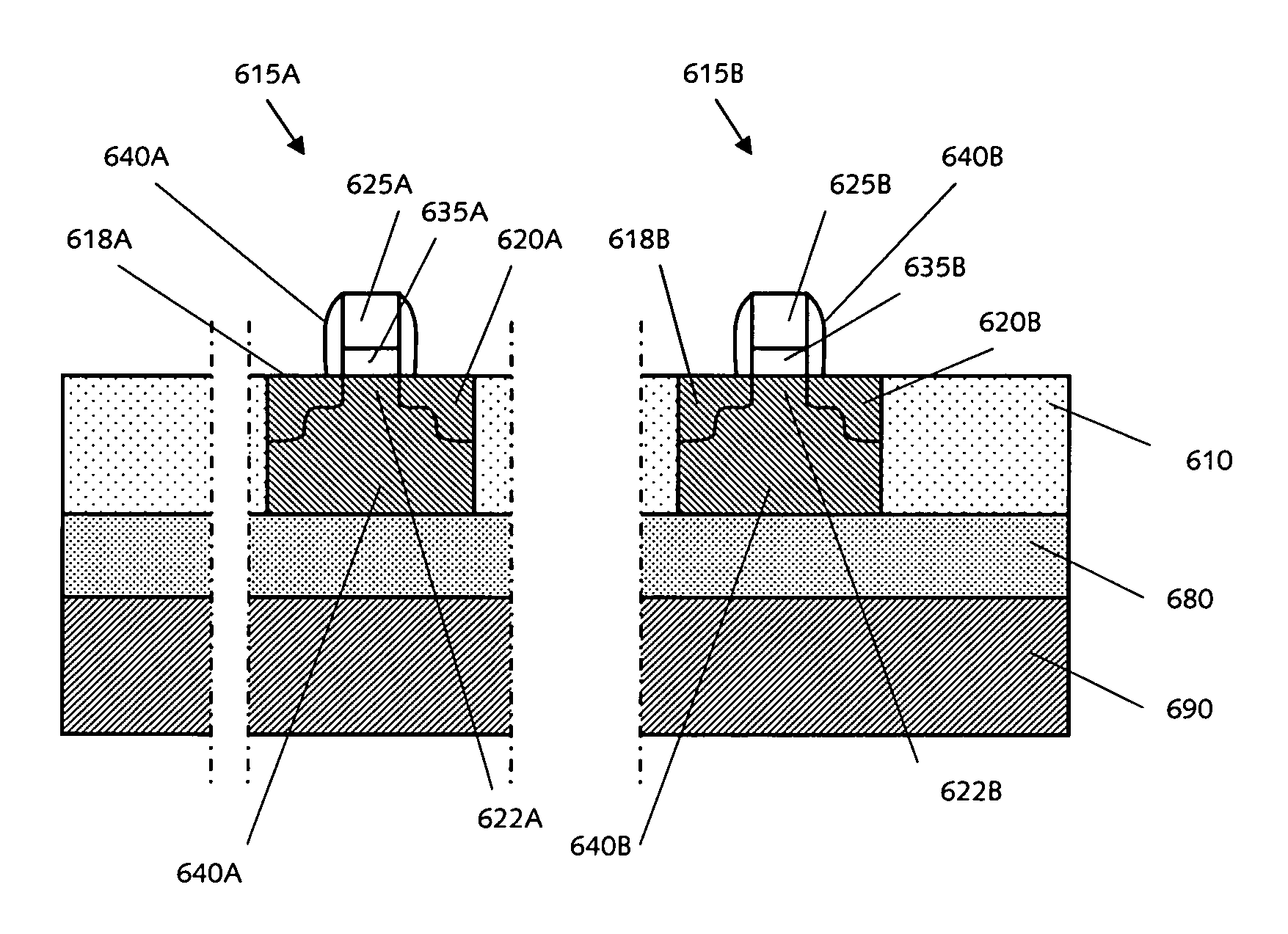

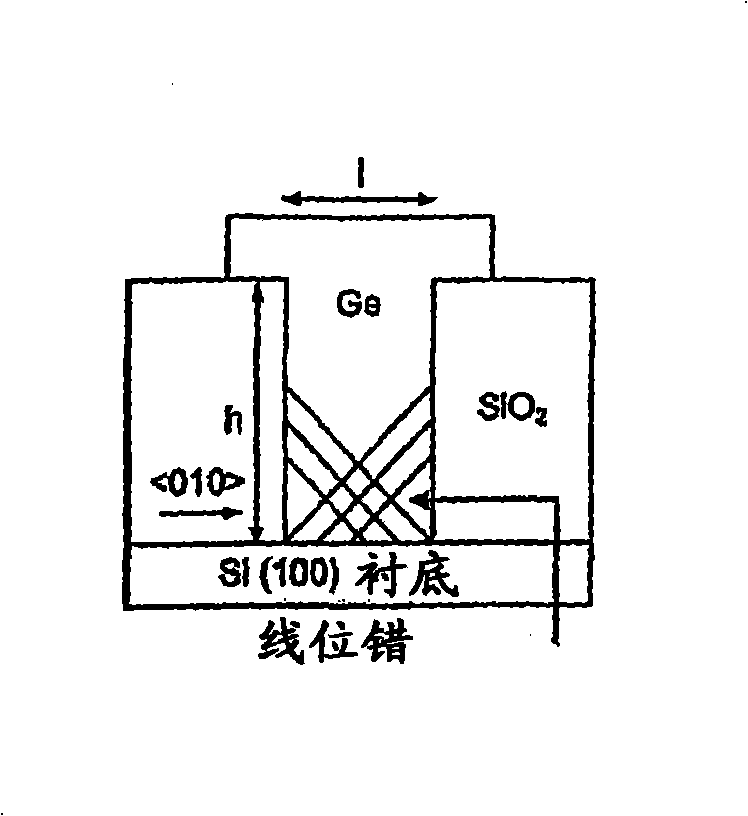

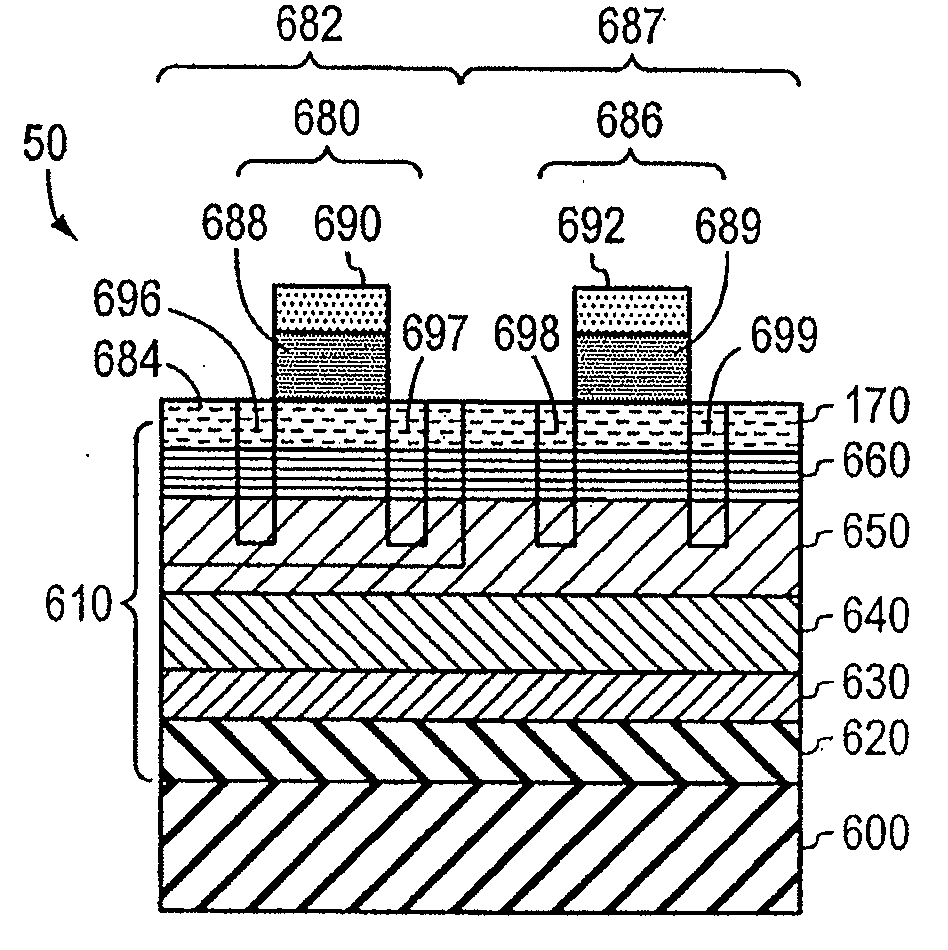

Methods for integrating lattice-mismatched semiconductor structure on insulators

InactiveUS20070054467A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsSemiconductor structure

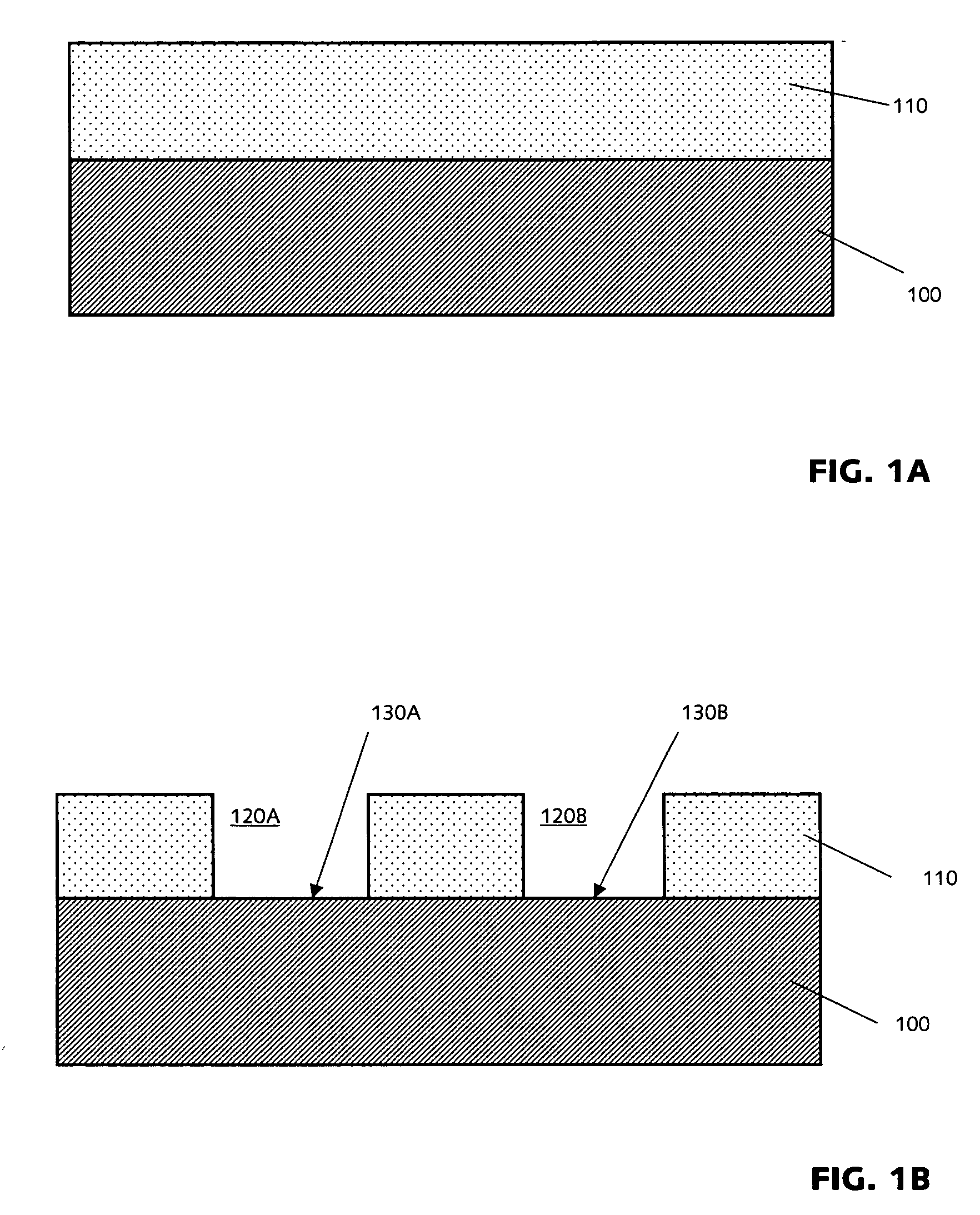

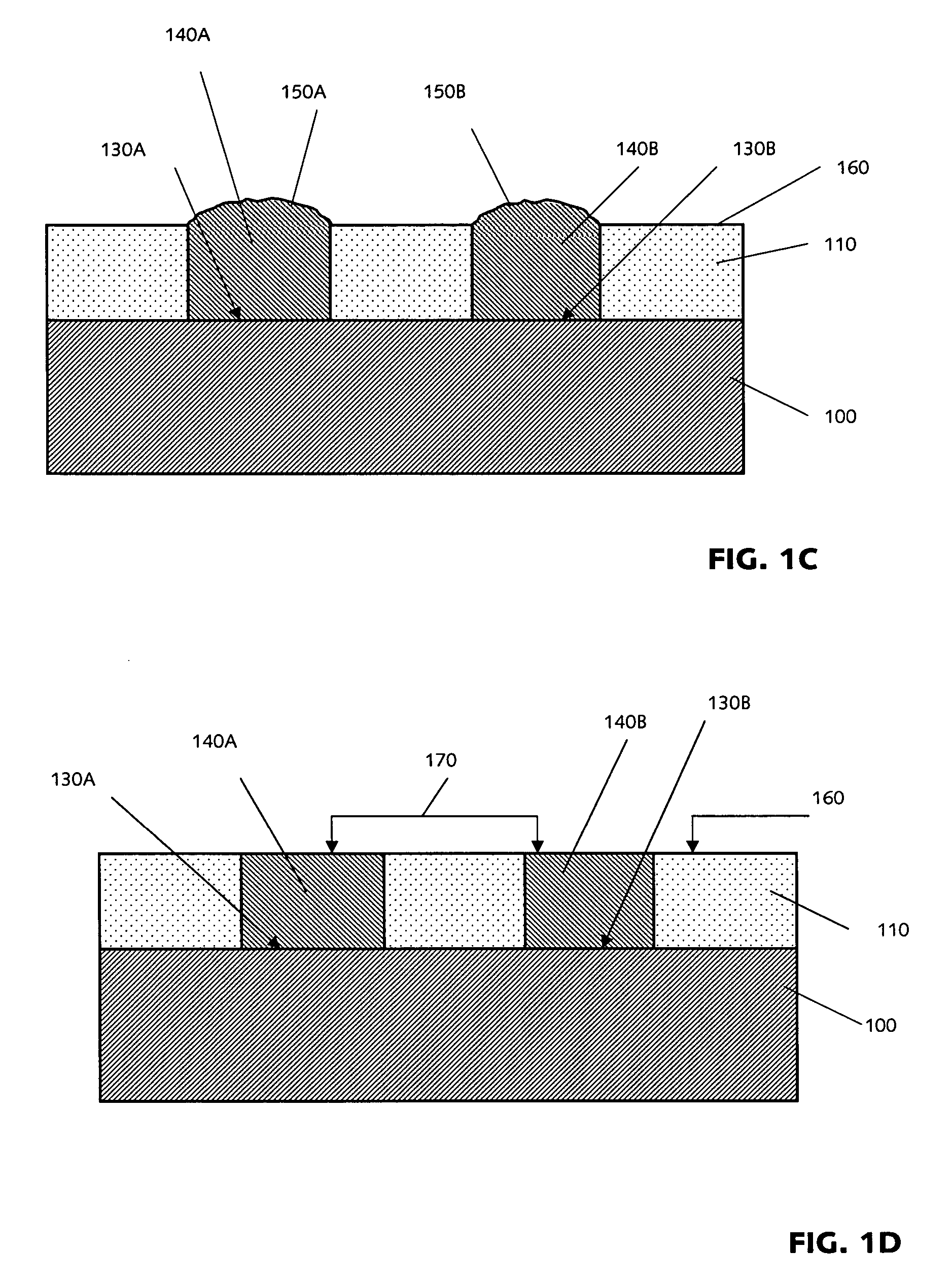

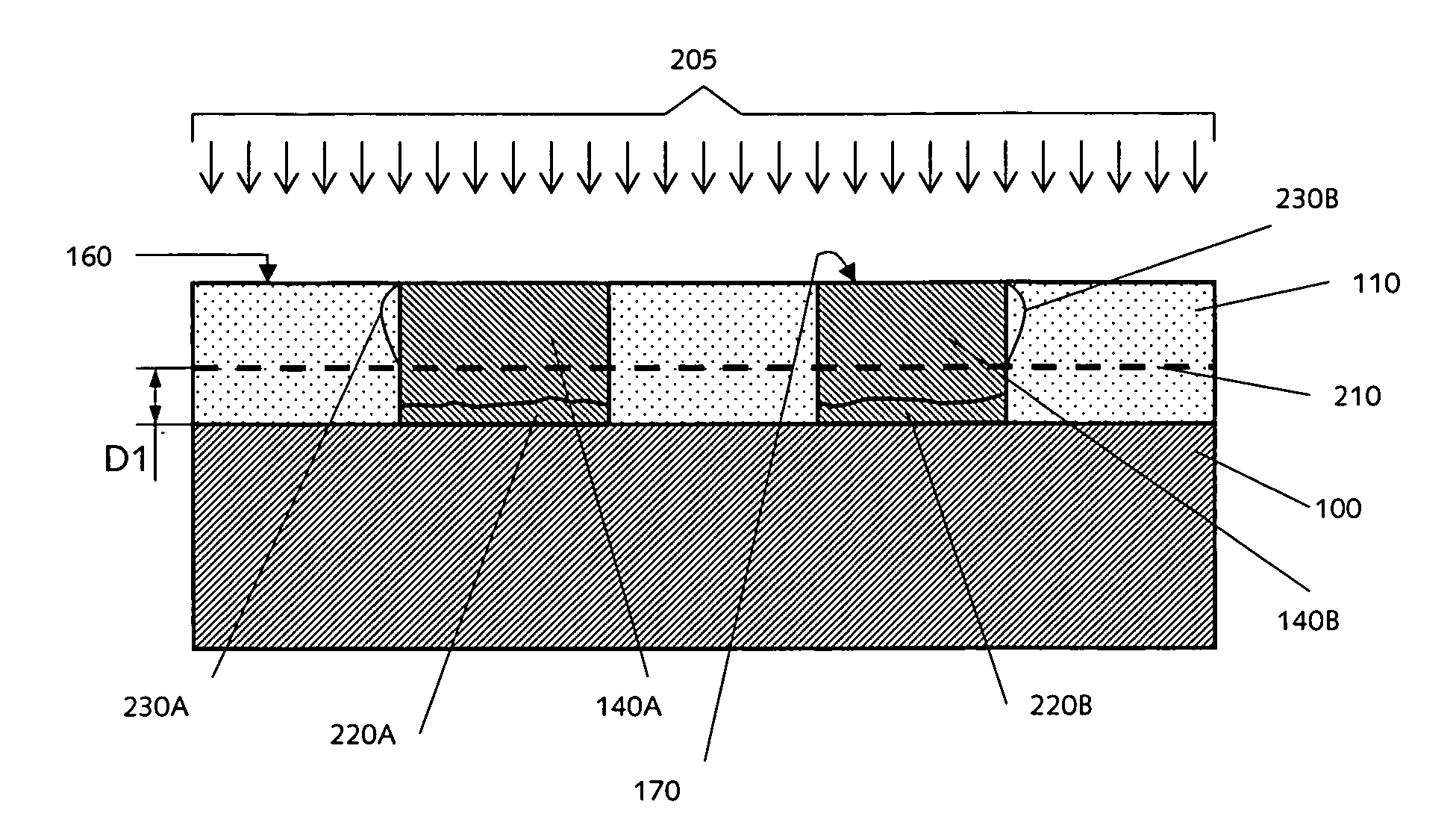

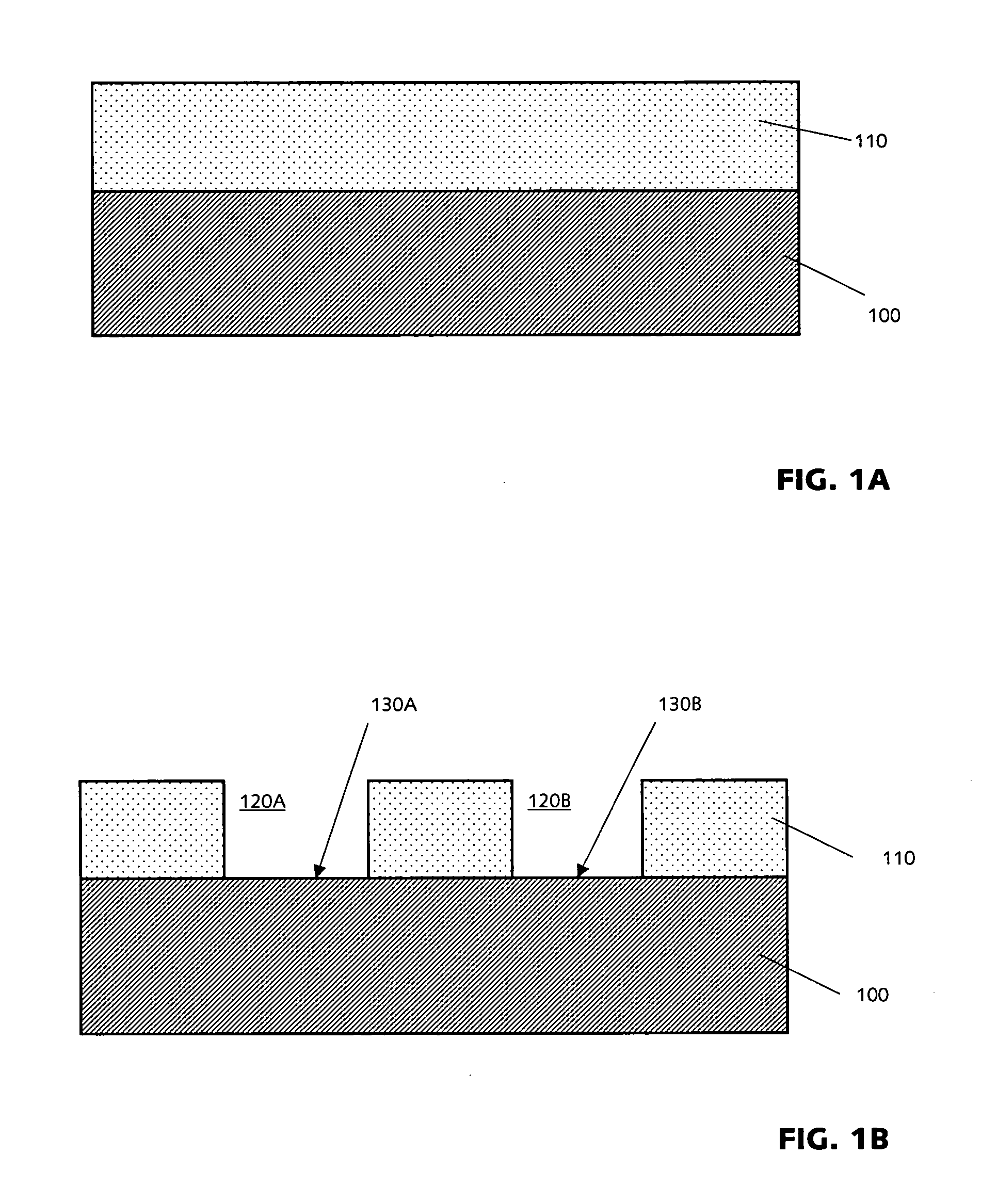

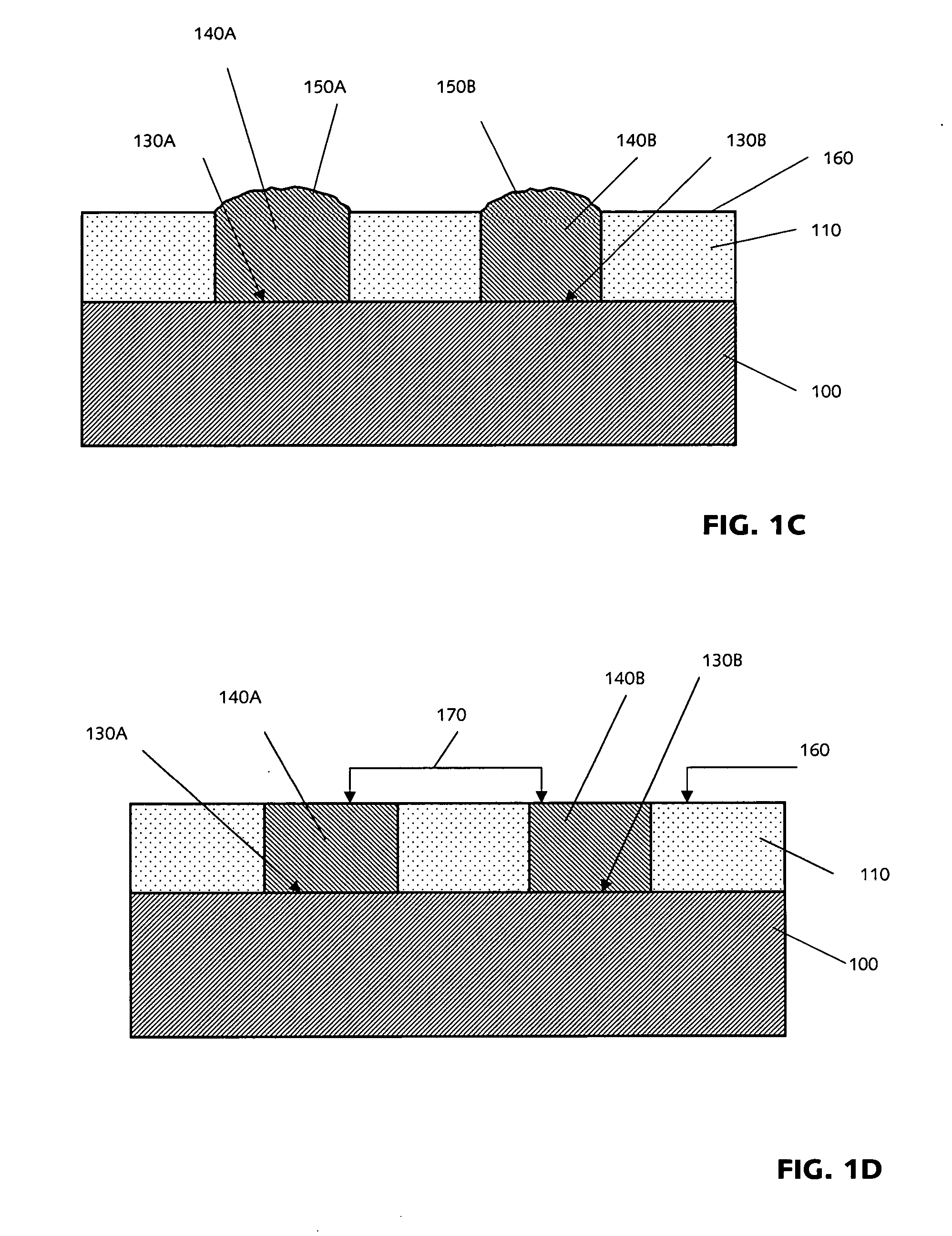

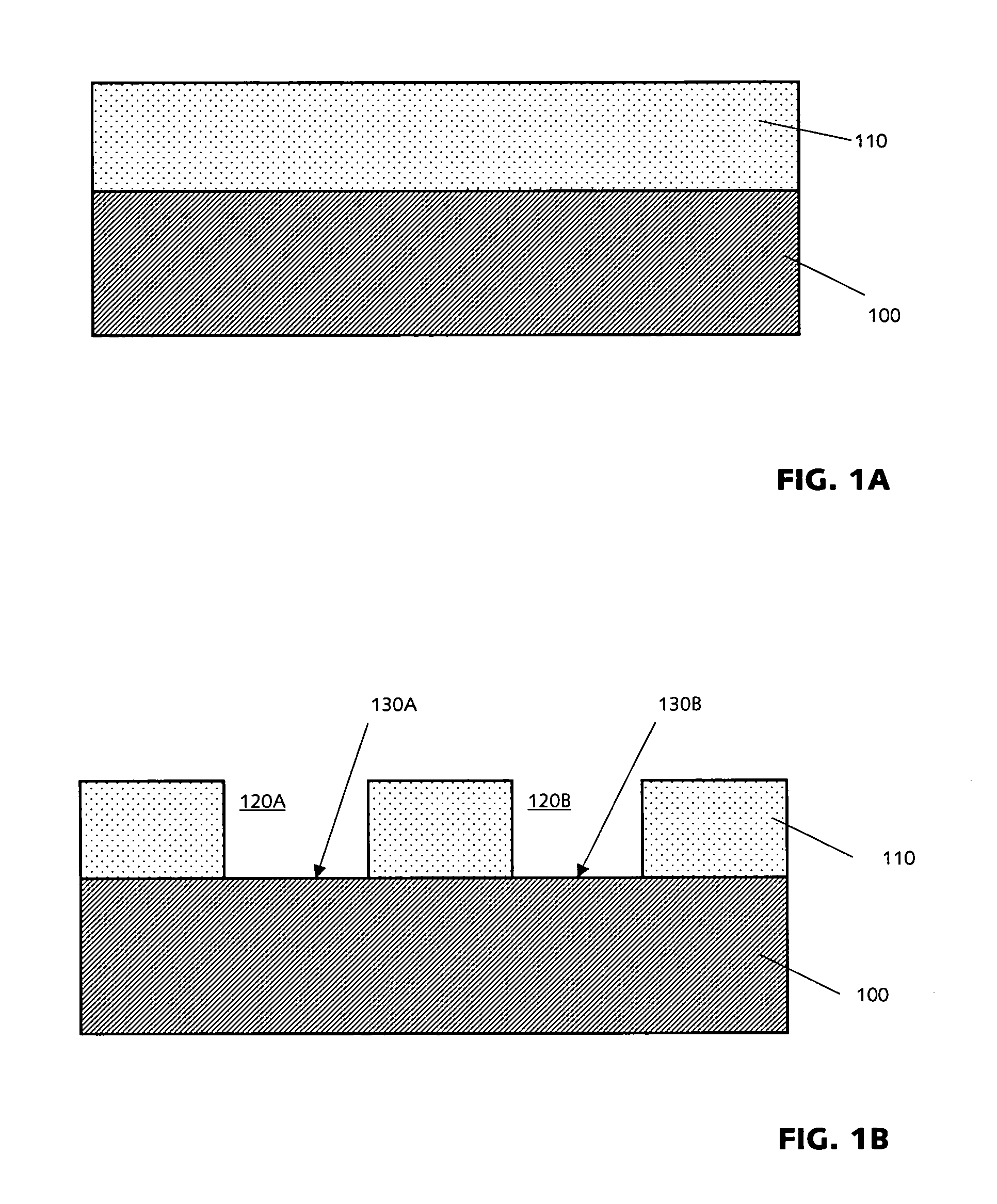

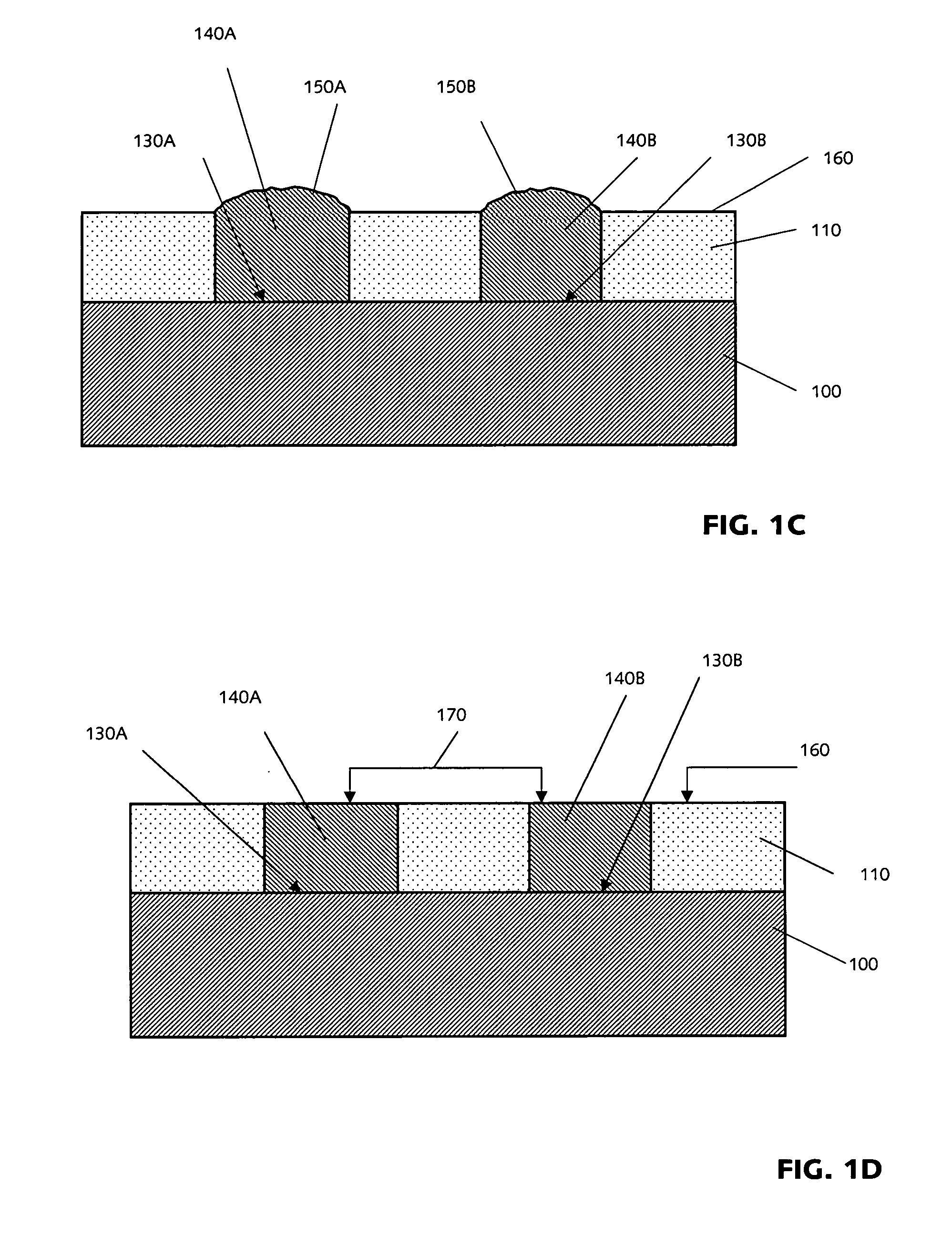

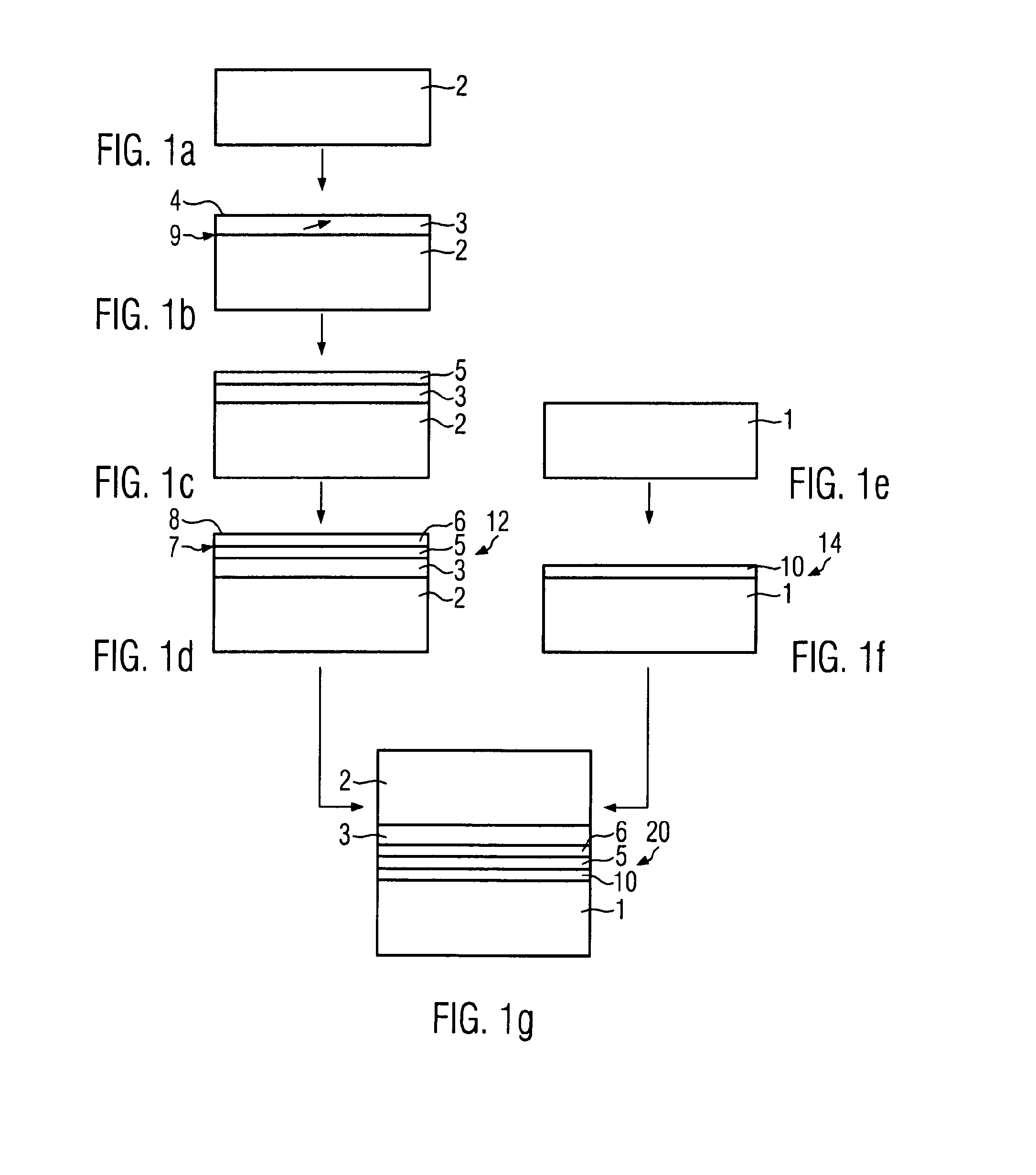

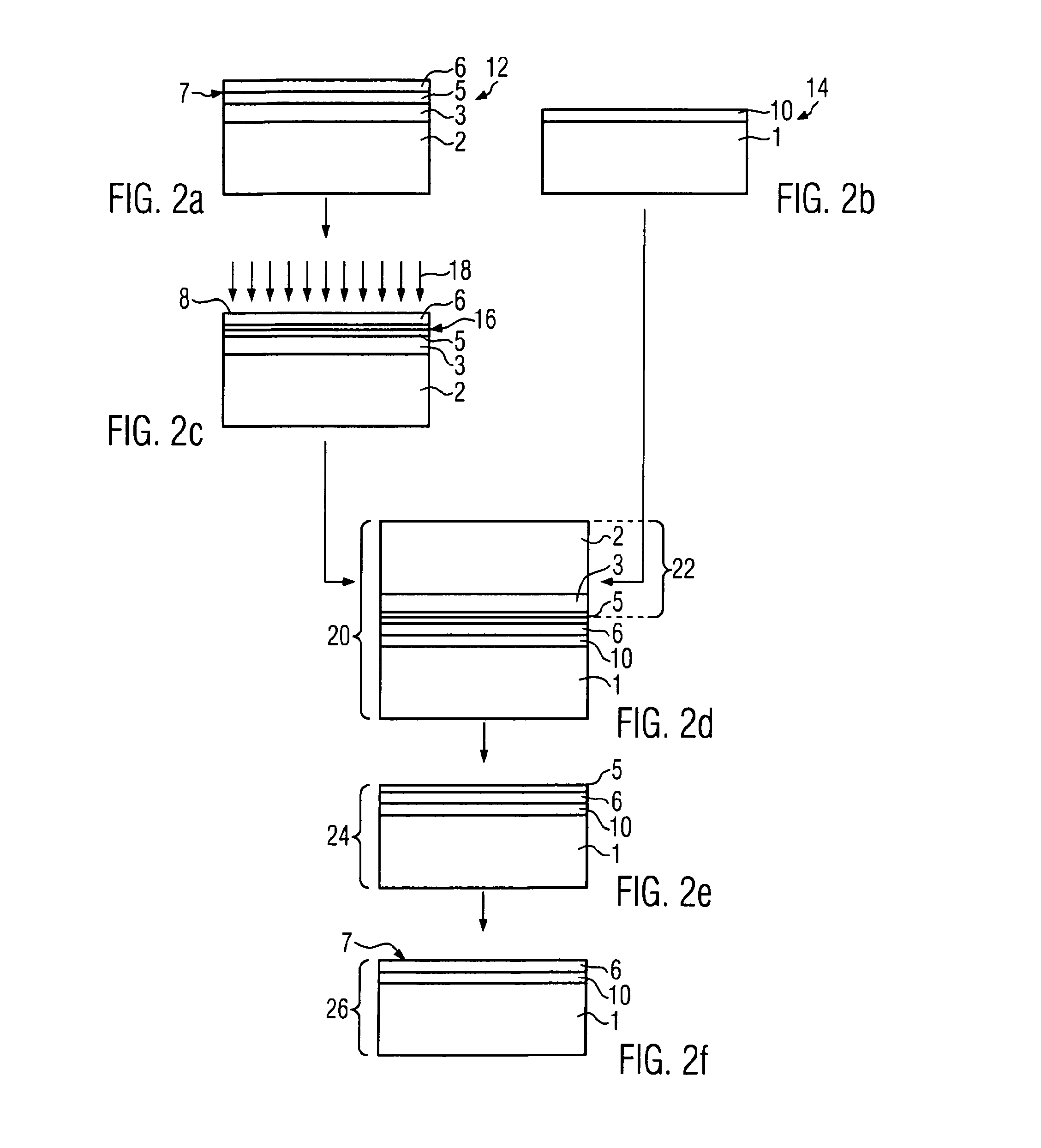

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:AMBERWAVE SYST

Lattice-mismatched semiconductor structures on insulators

ActiveUS20070054465A1Improve functionalityImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingThreading dislocationsLattice mismatch

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

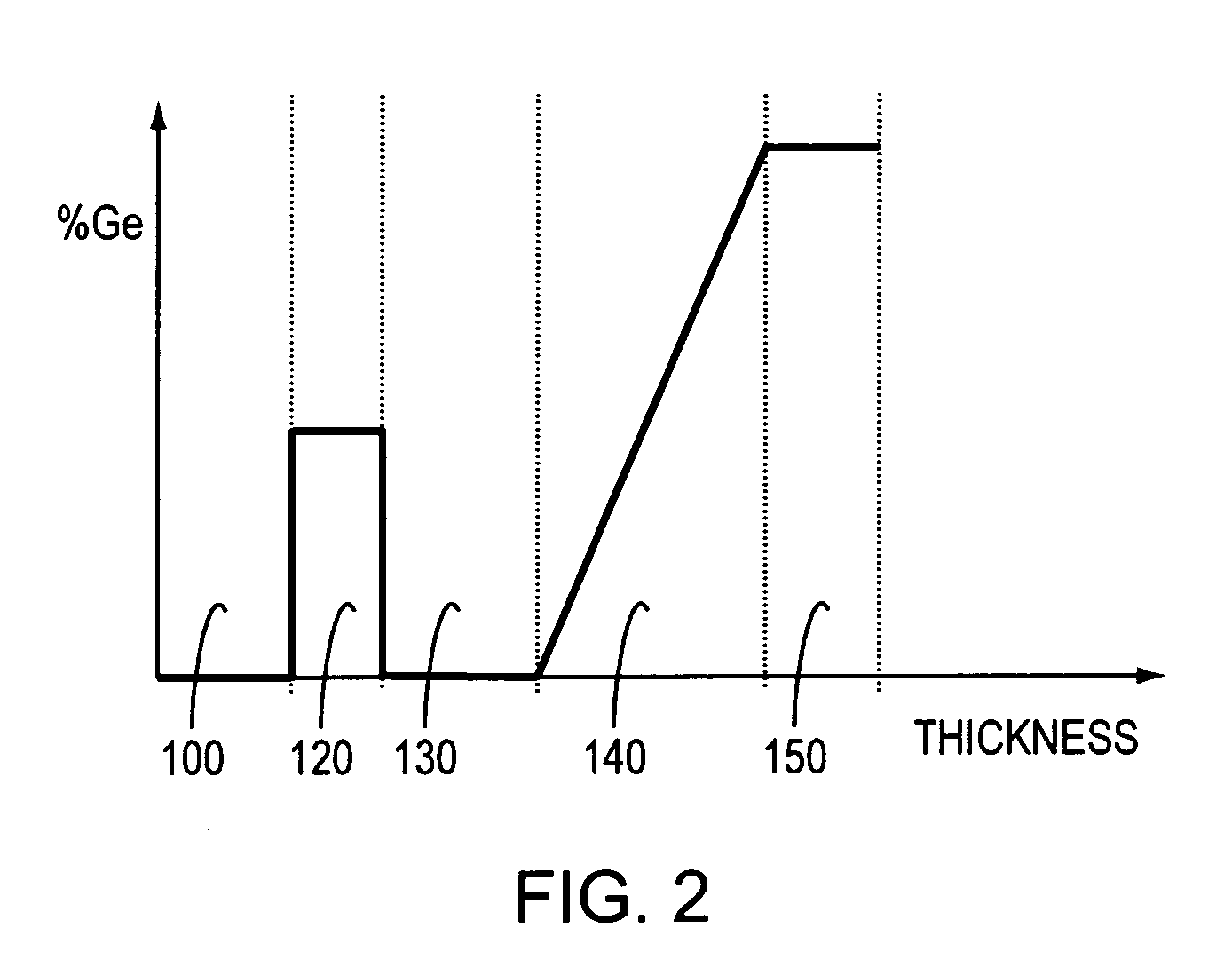

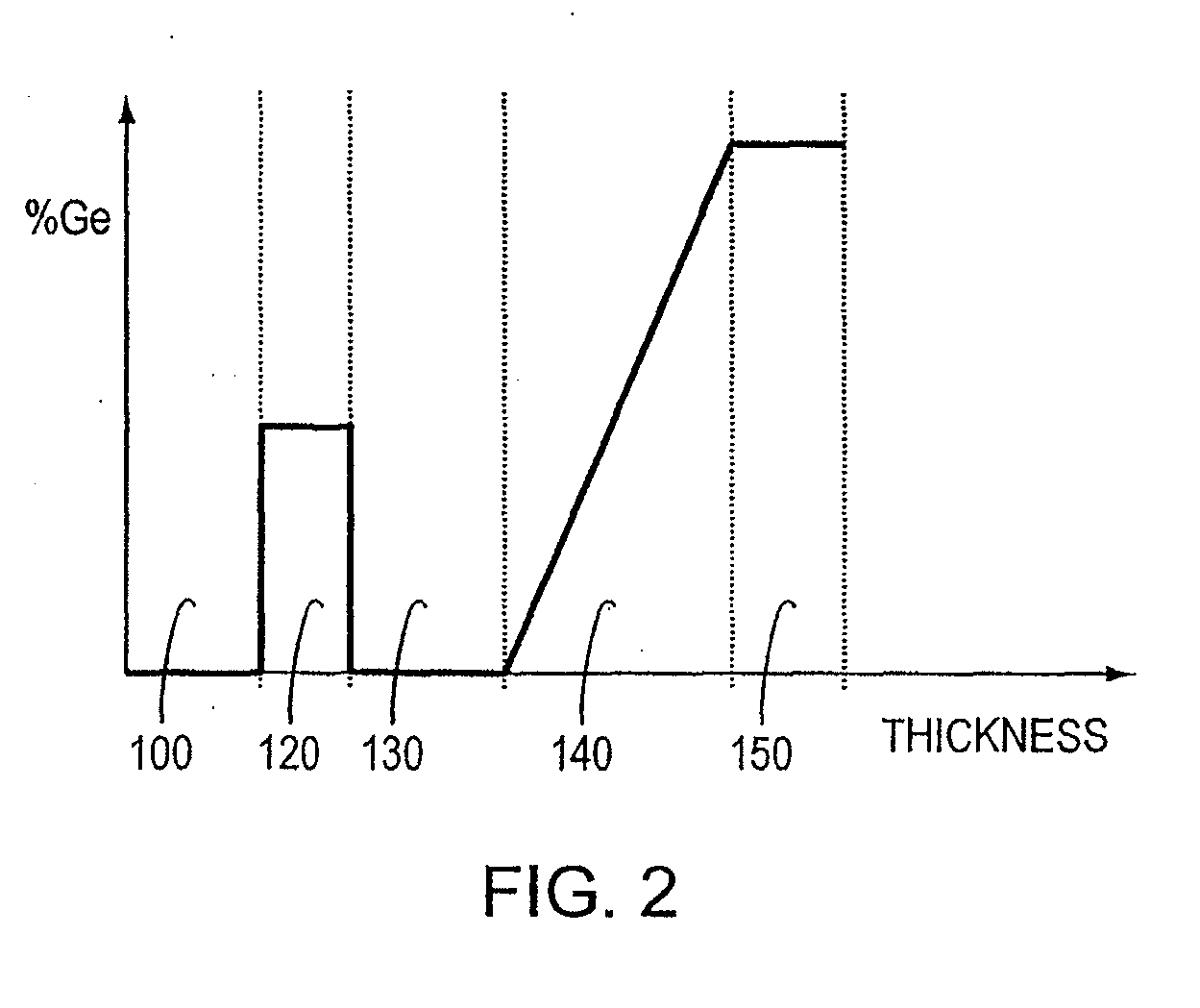

Semiconductor heterostructures and related methods

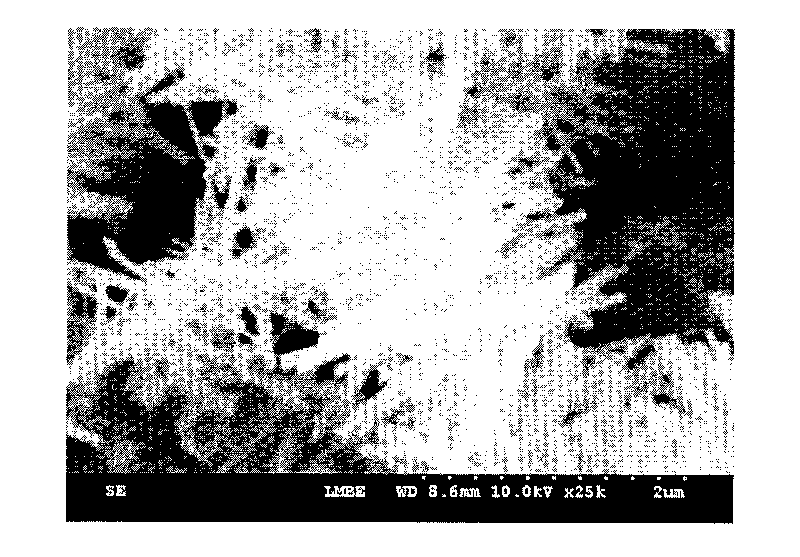

InactiveUS7049627B2Overcome limitationsImprove manufacturabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsInter layer

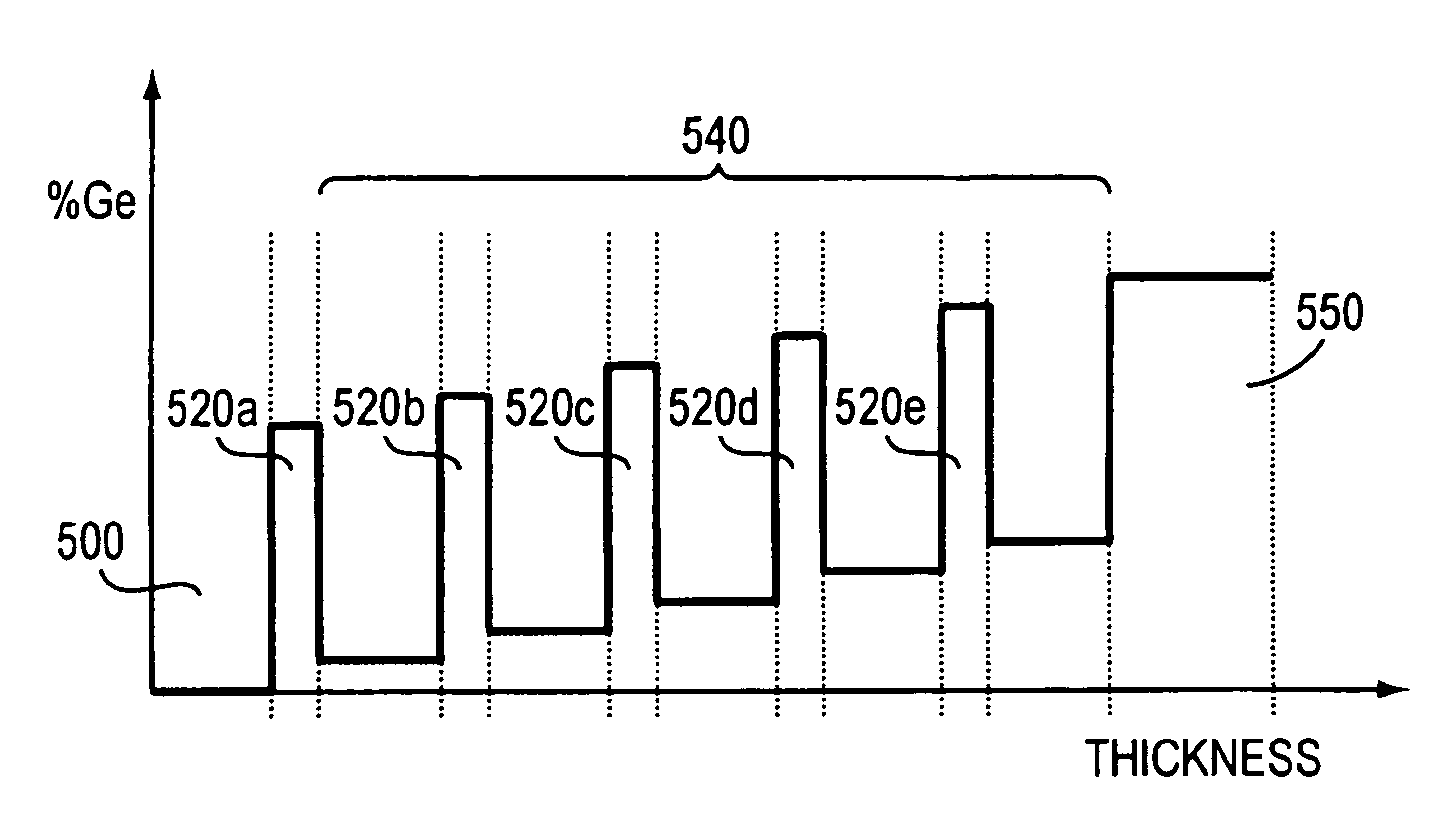

Dislocation pile-ups in compositionally graded semiconductor layers are reduced or eliminated, thereby leading to increased semiconductor device yield and manufacturability. This is accomplished by introducing a semiconductor layer having a plurality of threading dislocations distributed substantially uniformly across its surface as a starting layer and / or at least one intermediate layer during growth and relaxation of the compositionally graded layer. The semiconductor layer may include a seed layer disposed proximal to the surface of the semiconductor layer and having the threading dislocations uniformly distributed therein.

Owner:TAIWAN SEMICON MFG CO LTD

Methods of fabricating semiconductor heterostructures

InactiveUS20060009012A1Overcome limitationsImprove manufacturabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsDevice material

Dislocation pile-ups in compositionally graded semiconductor layers are reduced or eliminated, thereby leading to increased semiconductor device yield and manufacturability. This is accomplished by introducing a semiconductor layer having a plurality of threading dislocations distributed substantially uniformly across its surface as a starting layer and / or at least one intermediate layer during growth and relaxation of the compositionally graded layer. The semiconductor layer may include a seed layer disposed proximal to the surface of the semiconductor layer and having the threading dislocations uniformly distributed therein.

Owner:TAIWAN SEMICON MFG CO LTD

Lattice-mismatched semiconductor structures on insulators

ActiveUS7638842B2Functionality and performance improvementsLower channel resistanceSemiconductor/solid-state device detailsSolid-state devicesThreading dislocationsSemiconductor structure

Monolithic lattice-mismatched semiconductor heterostructures are fabricated by bonding patterned substrates with alternative active-area materials formed thereon to a rigid dielectric platform and then removing the highly-defective interface areas along with the underlying substrates to produce alternative active-area regions disposed over the insulator and substantially exhausted of misfit and threading dislocations.

Owner:TAIWAN SEMICON MFG CO LTD

Light emitting heterostructure

ActiveUS6943377B2Easy to optimizeLaser detailsLaser optical resonator constructionSemiconductor heterostructuresNitride

An improved light emitting heterostructure. In particular, a nitride-based light emitting heterostructure is provided that includes a light generating structure and a distributed semiconductor heterostructure Bragg reflector structure formed above the light generating structure. In operation, the light generating structure generates light, a portion of which is reflected by the distributed semiconductor heterostructure Bragg reflector structure, thereby increasing the total amount of light that can be emitted from the heterostructure.

Owner:SENSOR ELECTRONICS TECH

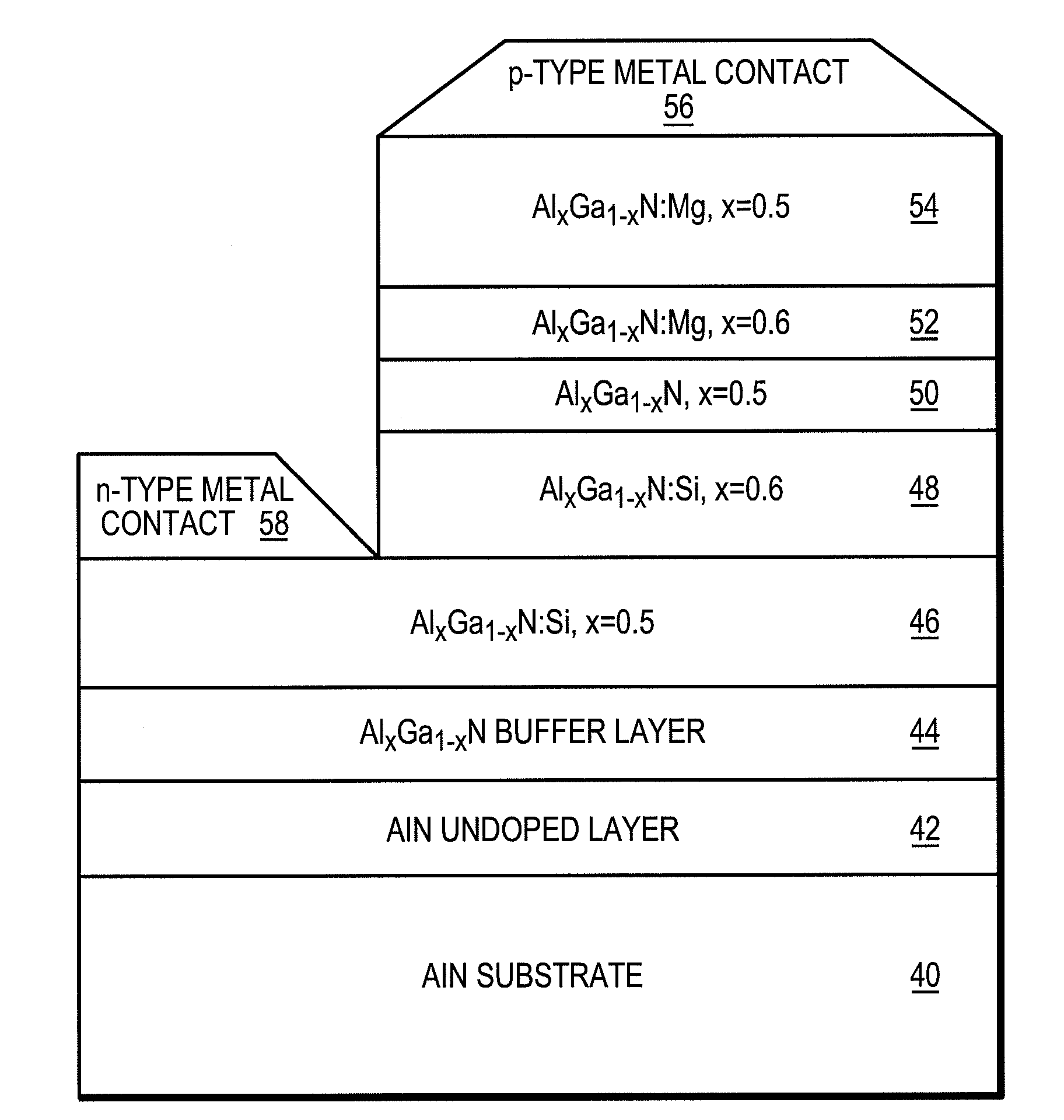

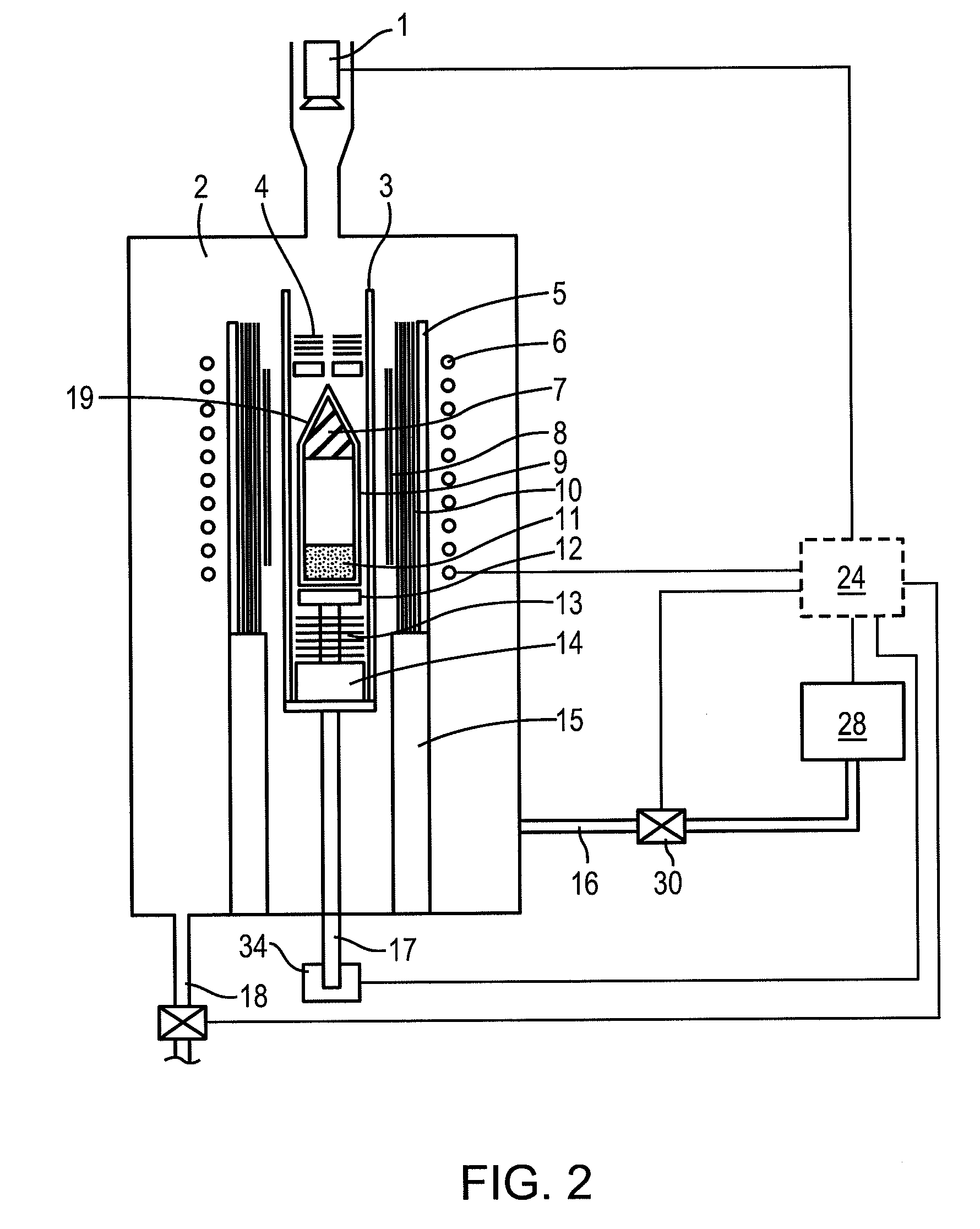

Nitride semiconductor heterostructures and related methods

InactiveUS20090283028A1Easy to manufactureGood chemical compatibilityFrom gel statePolycrystalline material growthSemiconductor structureSemiconductor heterostructures

Semiconductor structures and devices based thereon include an aluminum nitride single-crystal substrate and at least one layer epitaxially grown thereover. The epitaxial layer may comprise at least one of AlN, GaN, InN, or any binary or tertiary alloy combination thereof, and have an average dislocation density within the semiconductor heterostructure is less than about 106 cm−2.

Owner:CRYSTAL

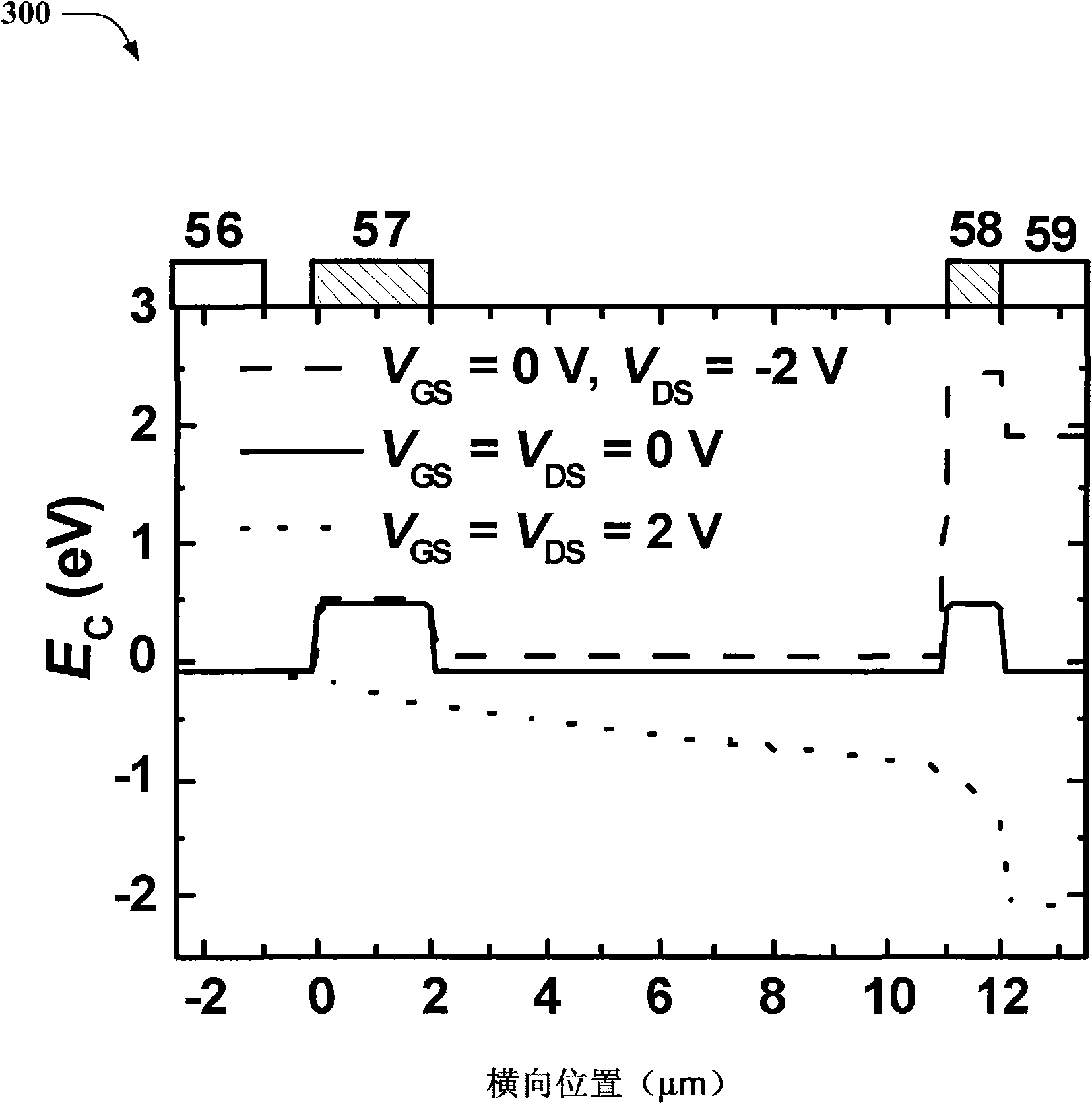

Transistor device and method

ActiveUS20090134939A1Semiconductor/solid-state device manufacturingFrequency-independant attenuatorsSemiconductor heterostructuresEngineering

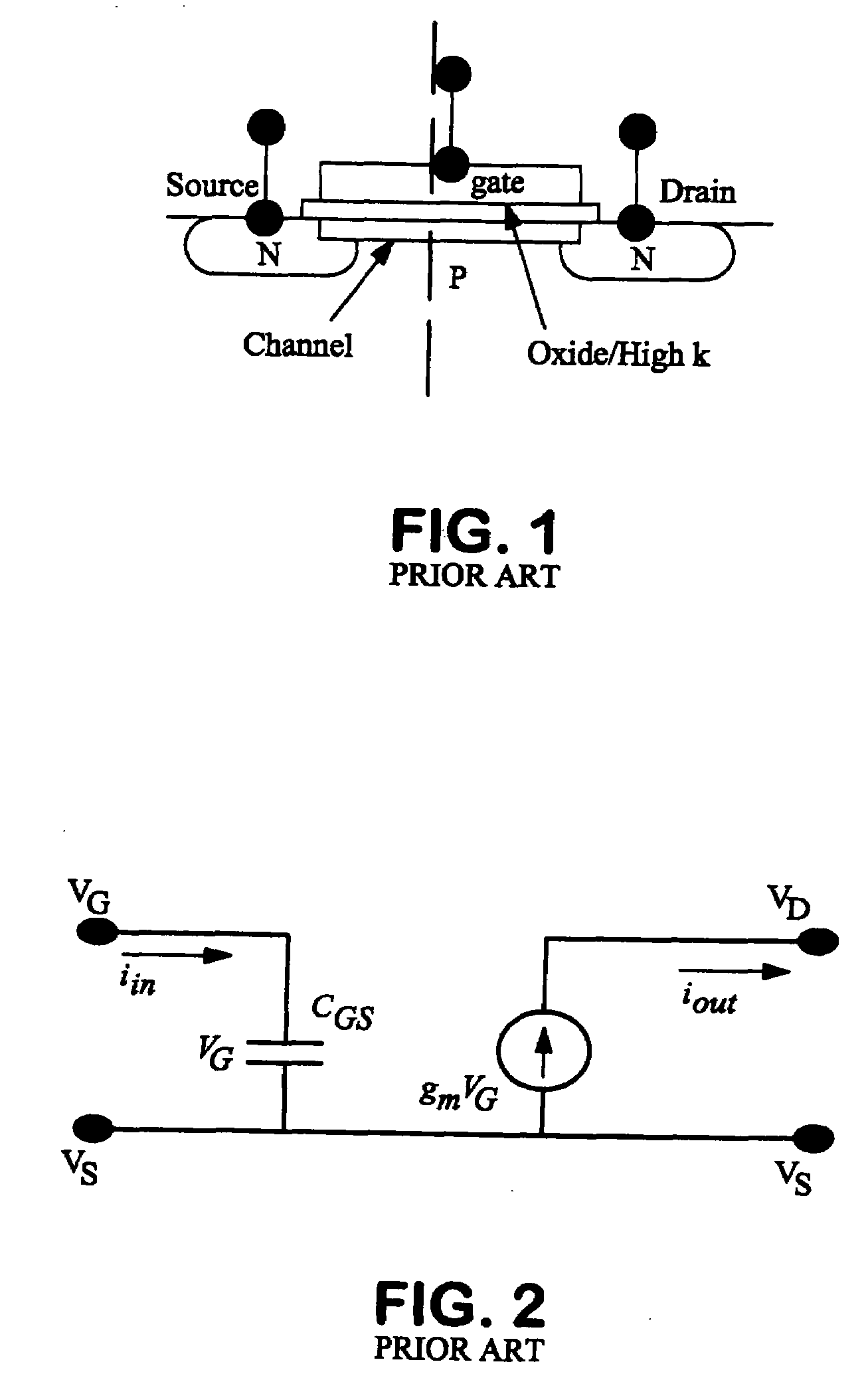

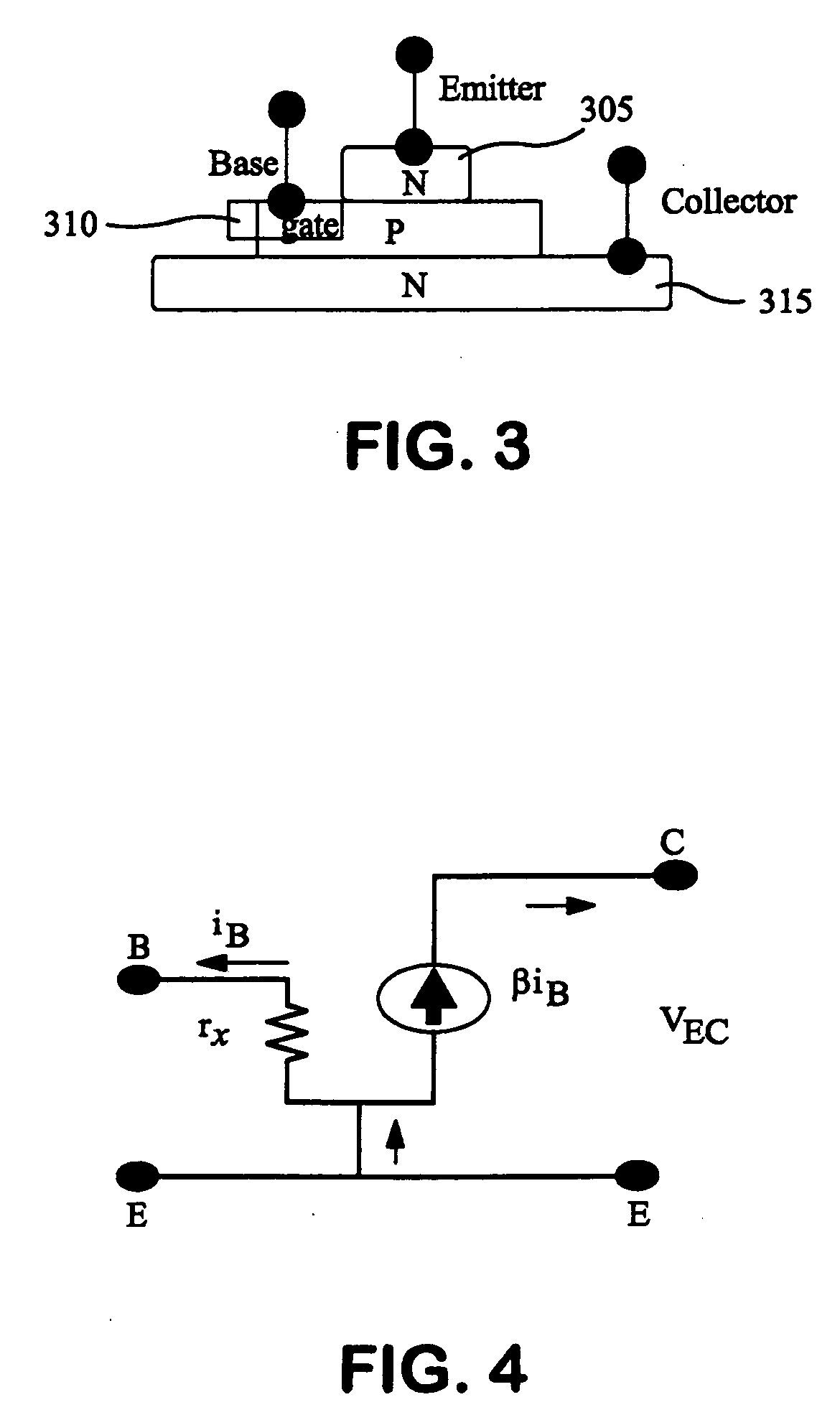

A field-effect transistor device, including: a semiconductor heterostructure comprising, in a vertically stacked configuration, a semiconductor gate layer between semiconductor source and drain layers, the layers being separated by heterosteps; the gate layer having a thickness of less than about 100 Angstroms; and source, gate, and drain electrodes respectively coupled with said source, gate, and drain layers. Separation of the gate by heterosteps, rather than an oxide layer, has very substantial advantages.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

Nitride semiconductor heterostructures and related methods

InactiveUS7638346B2Easy to manufactureReduce dislocationFrom gel statePolycrystalline material growthSemiconductor structureSemiconductor heterostructures

Owner:CRYSTAL

Lattice-mismatched semiconductor structures with reduced dislocation defect densities related methods for device fabrication

ActiveCN101300663ASemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDevice material

Fabrication of monolithic lattice-mismatched semiconductor heterostructures with limited area regions having upper portions substantially exhausted of threading dislocations, as well as fabrication of semiconductor devices based on such lattice-mismatched heterostructures.

Owner:TAIWAN SEMICON MFG CO LTD

Broadband light emitting device

ActiveUS20050279989A1Increase heightBroad emission spectrumLaser detailsLaser optical resonator constructionStimulated emissionP–n junction

The invention concerns a superluminescent light emitting diode (SLED) comprising a semiconductor heterostructure forming a PN junction and a waveguide. The semiconductor heterostructure includes a gain region with a contact means for biasing the PN junction so as to produce light emission including stimulated emission from an active zone of the gain region, and in the active zone a plurality of quantum dot layers, each quantum dot layer made up of a plurality of quantum dots and a plurality of adjoining layers, each adjoining layer adjacent to one of said quantum dot layers. The material composition or a deposition parameter of at least two adjoining layers is different. This ensures an enhanced emission spectral width.

Owner:EXALOS

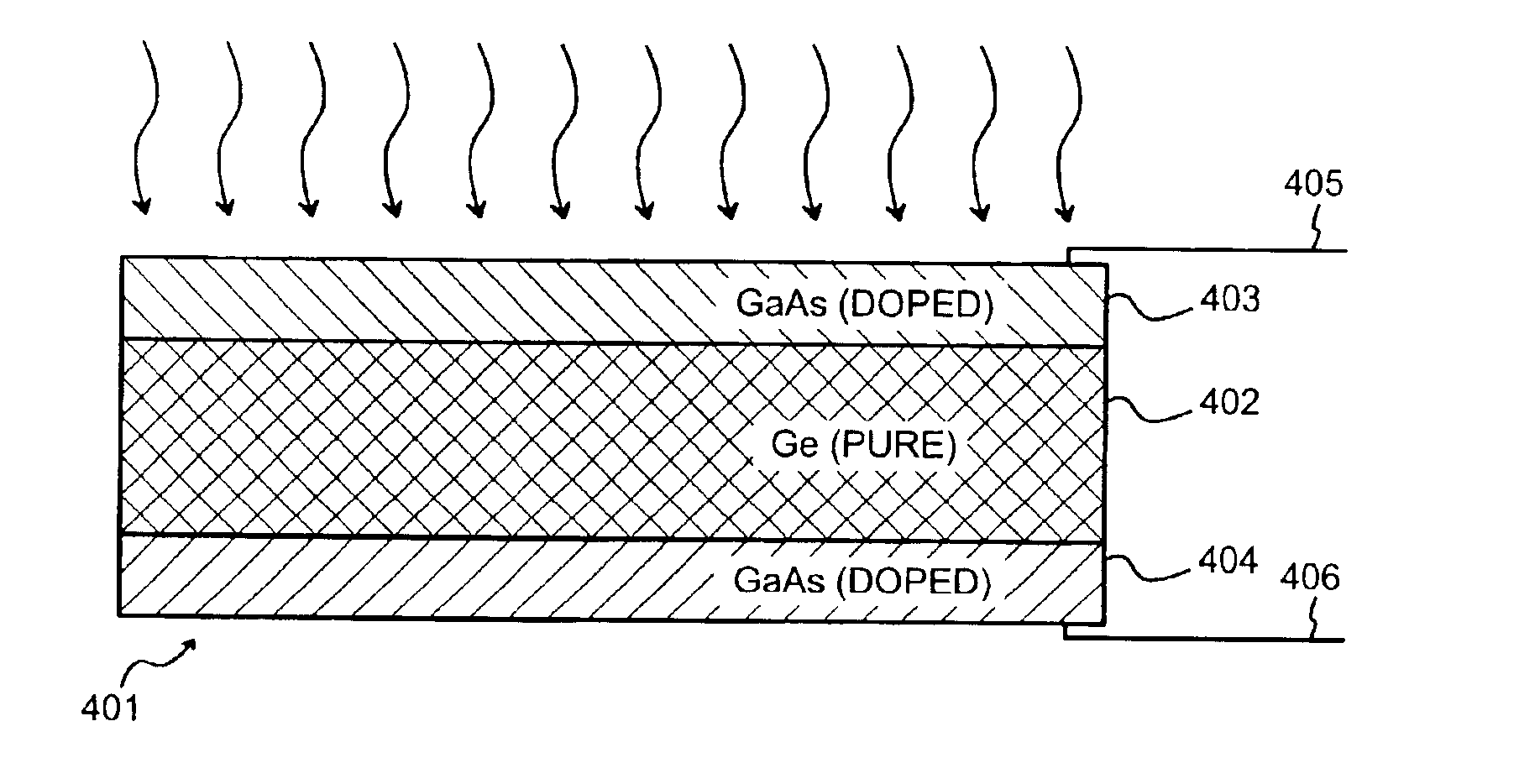

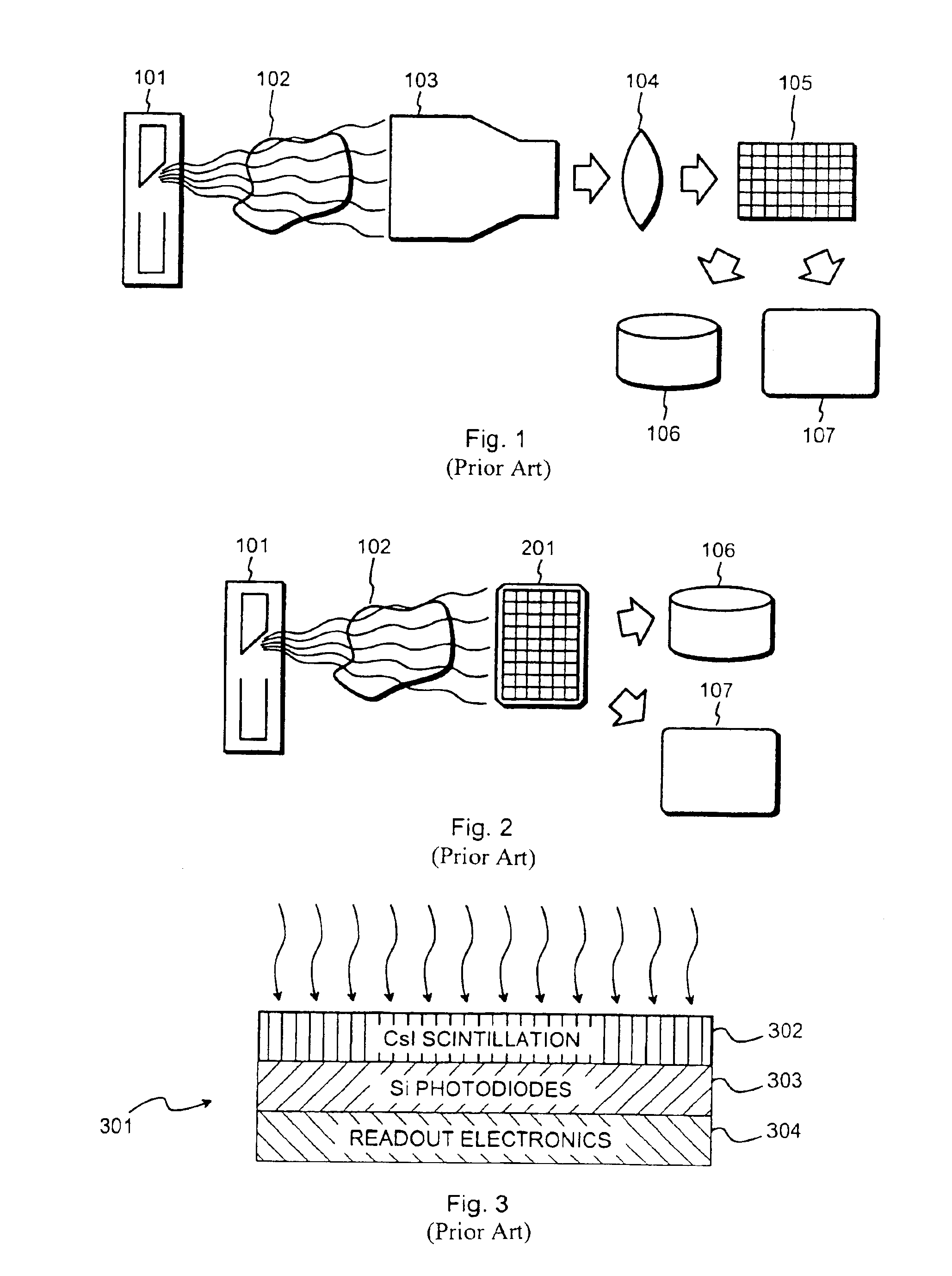

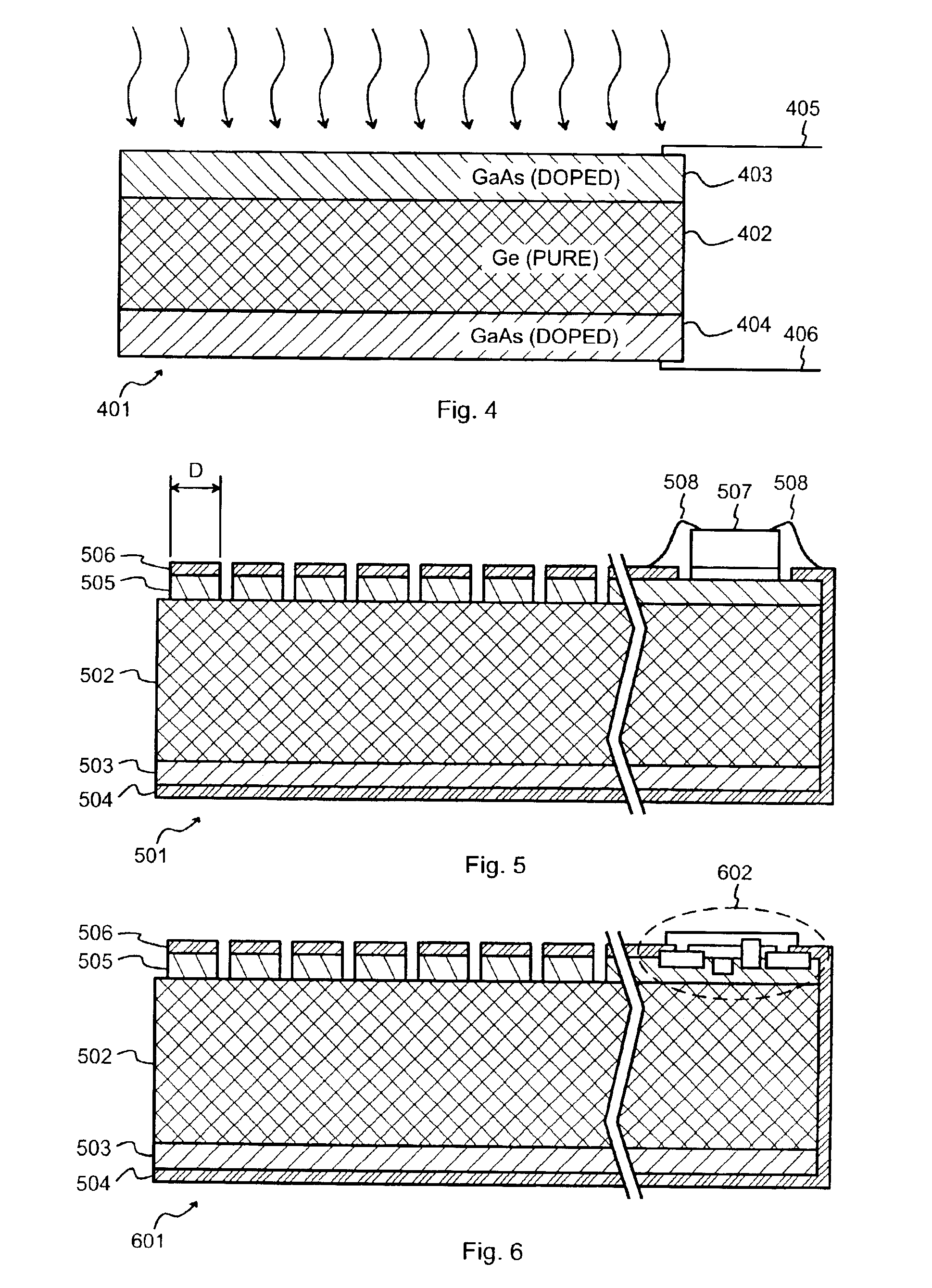

Imaging X-ray detector based on direct conversion

InactiveUS6933503B2Easy to produceImprove efficiencyTelevision system detailsSolid-state devicesSemiconductor heterostructuresGallium arsenide

Owner:OXFORD INSTUMENTS ANALYTICAL LIMITED +1

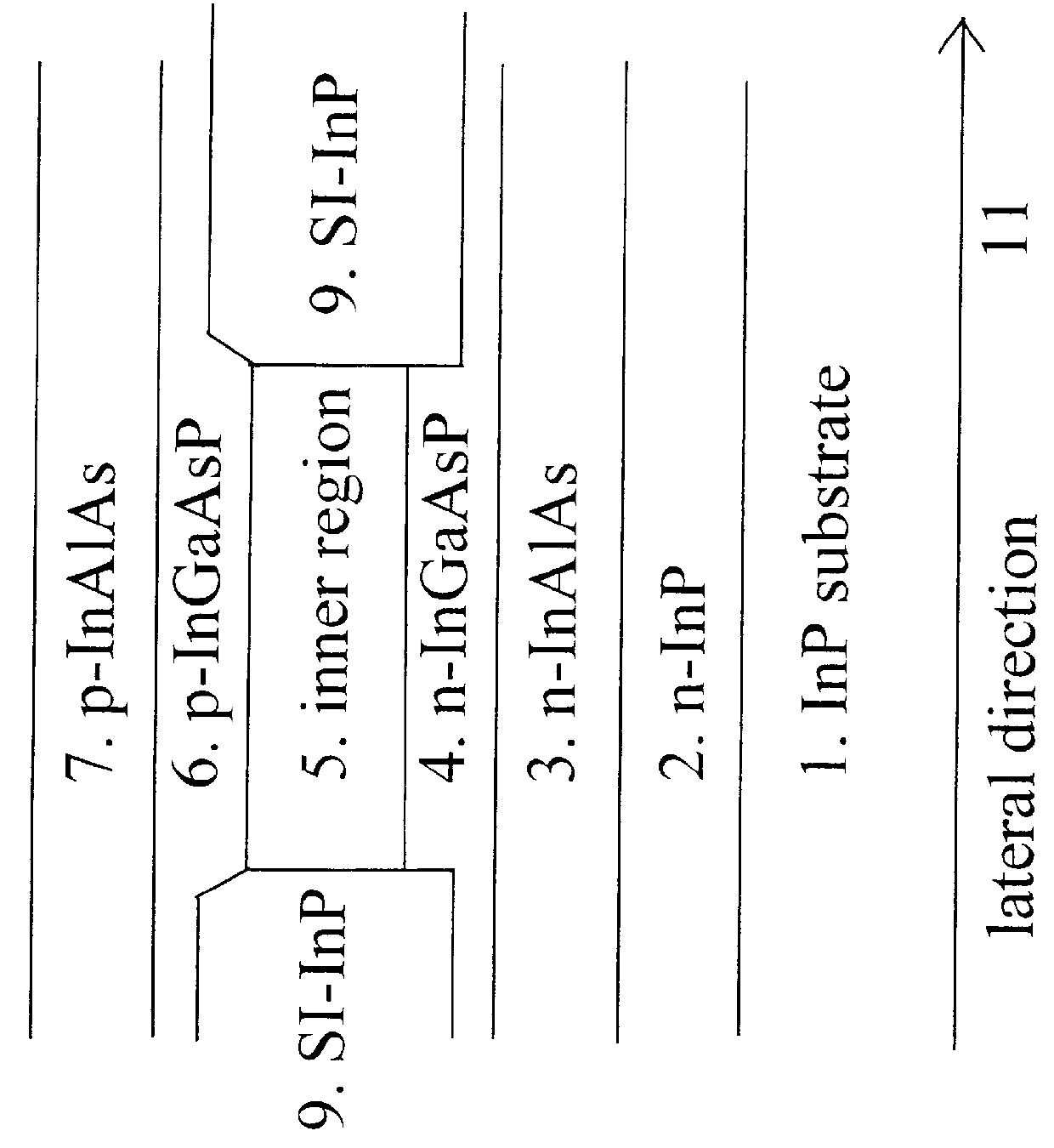

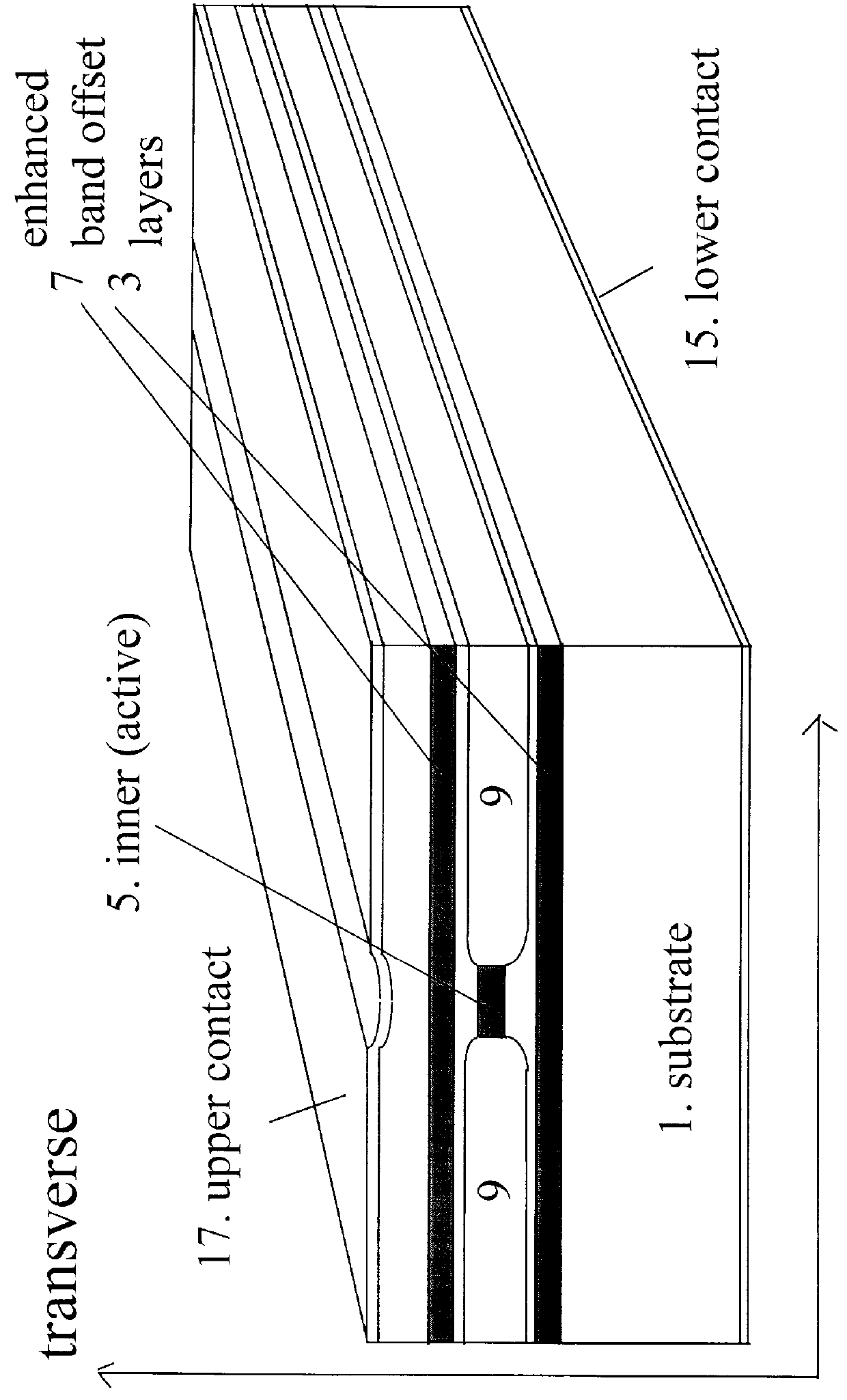

Buried heterostructure with aluminum-free active layer and method of making same

InactiveUS6011811AAvoid contactEasy to controlOptical wave guidanceLaser detailsEtchingSemiconductor heterostructures

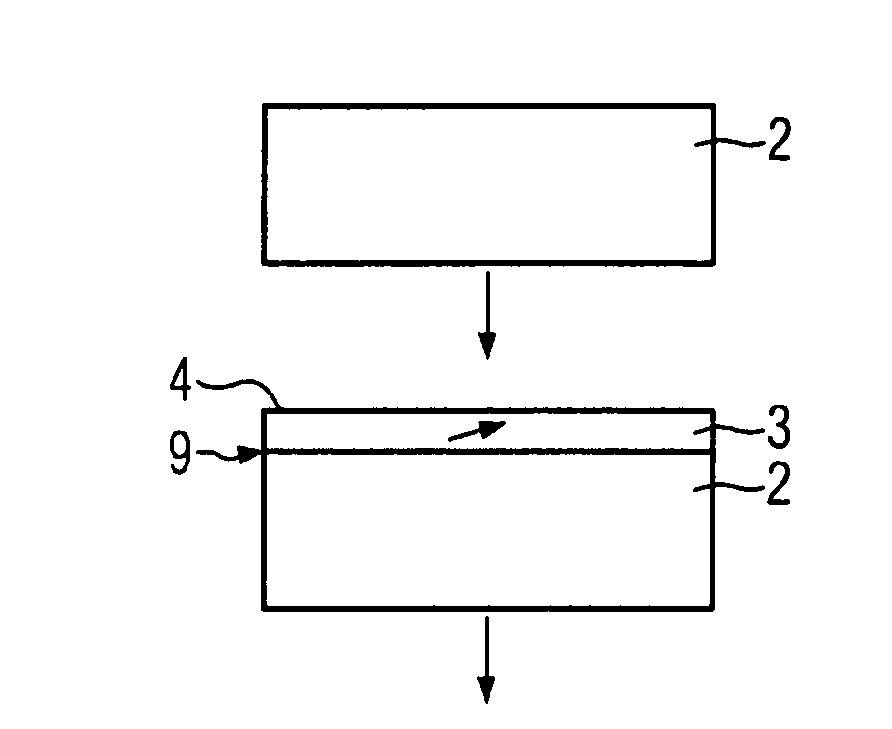

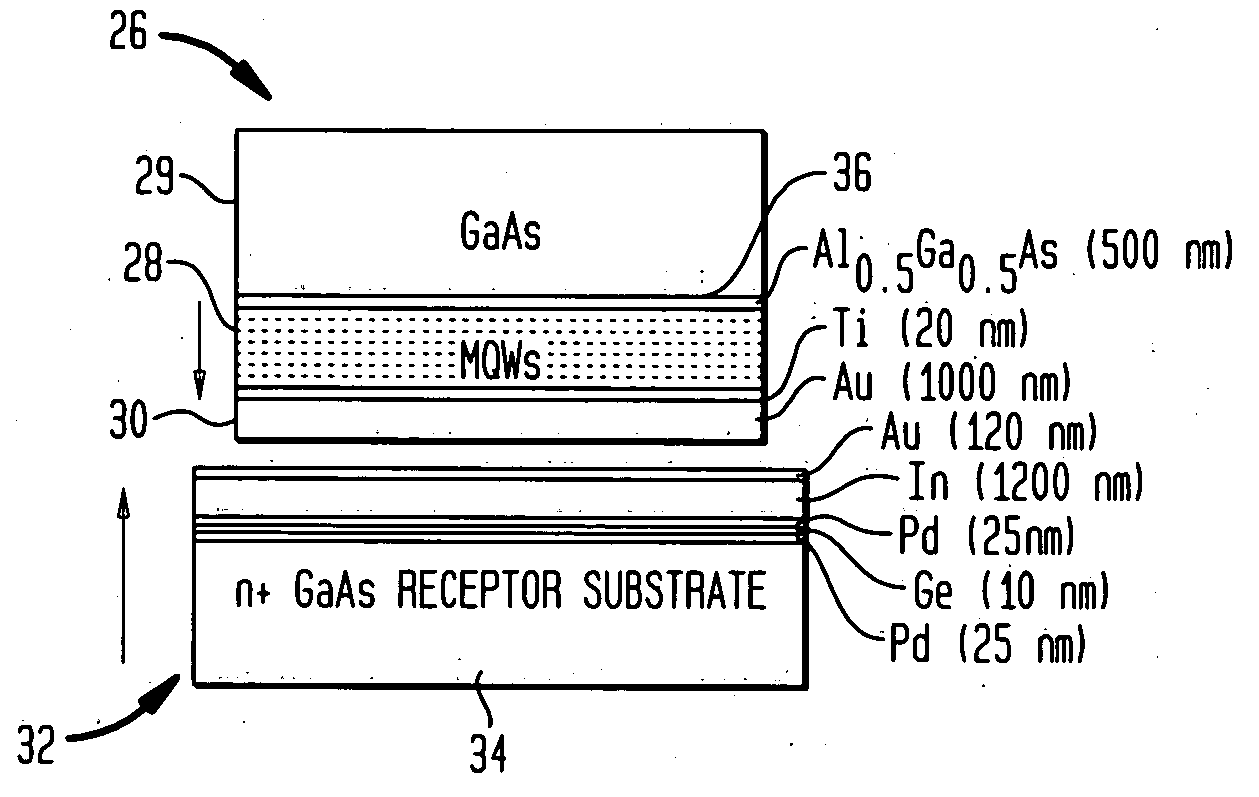

An epitaxially grown semiconductor heterostructure has an inner region (5) which is substantially laterally confined by confinement regions (9) and has enhanced transverse confinement by enhanced transverse confinement layers (3, 7). The latter layers are not exposed outside the growth chamber during processing, by stopping the etching for producing the lateral confinement, above the lower enhanced transverse confinement layer (3) and growing such an upper layer (7) after making the lateral confinement regions (9). The structure is intended to be used in particular having the inner region act as an active laser region, for instance in InP-based 1.3 mu m wavelength lasers. Then the simultaneous lateral confinement, enhanced transverse confinement and exposure protection enables simultaneously a low threshold current, a small temperature sensitivity and reliable, long life operation. The enhanced transverse confinement layers (3, 7) could comprise aluminium protected from oxidation during processing. Such a laser will then be protected from a declined reliability.

Owner:TELEFON AB LM ERICSSON (PUBL)

Transistors and rectifiers utilizing hybrid electrodes and methods of fabricating the same

ActiveCN101969071ATransistorSemiconductor/solid-state device manufacturingSemiconductor heterostructuresActive layer

The invention provides transistors and rectifiers utilizing hybrid electrodes and methods of fabricating the same. A heterostructure semiconductor transistor can include a III-N-type semiconductor heterostructure including a barrier layer overlying an active layer and a hybrid electrode region including a hybrid drain electrode region. Further, a heterostructure semiconductor rectifier can include a III-N-type semiconductor heterostructure and a hybrid electrode region including a hybrid cathode electrode region. Furthermore, the hybrid electrode region of the transistor and rectifier can include permanently trapped charge located under a Schottky contact of the hybrid electrode region.

Owner:THE HONG KONG UNIV OF SCI & TECH

Making method for IV-VI semiconductor single crystal film and the heterogeneous structure

InactiveCN101106092AQuality improvementPrecise and controllable thicknessSemiconductor/solid-state device manufacturingFrom condensed vaporsBeam sourceUltra-high vacuum

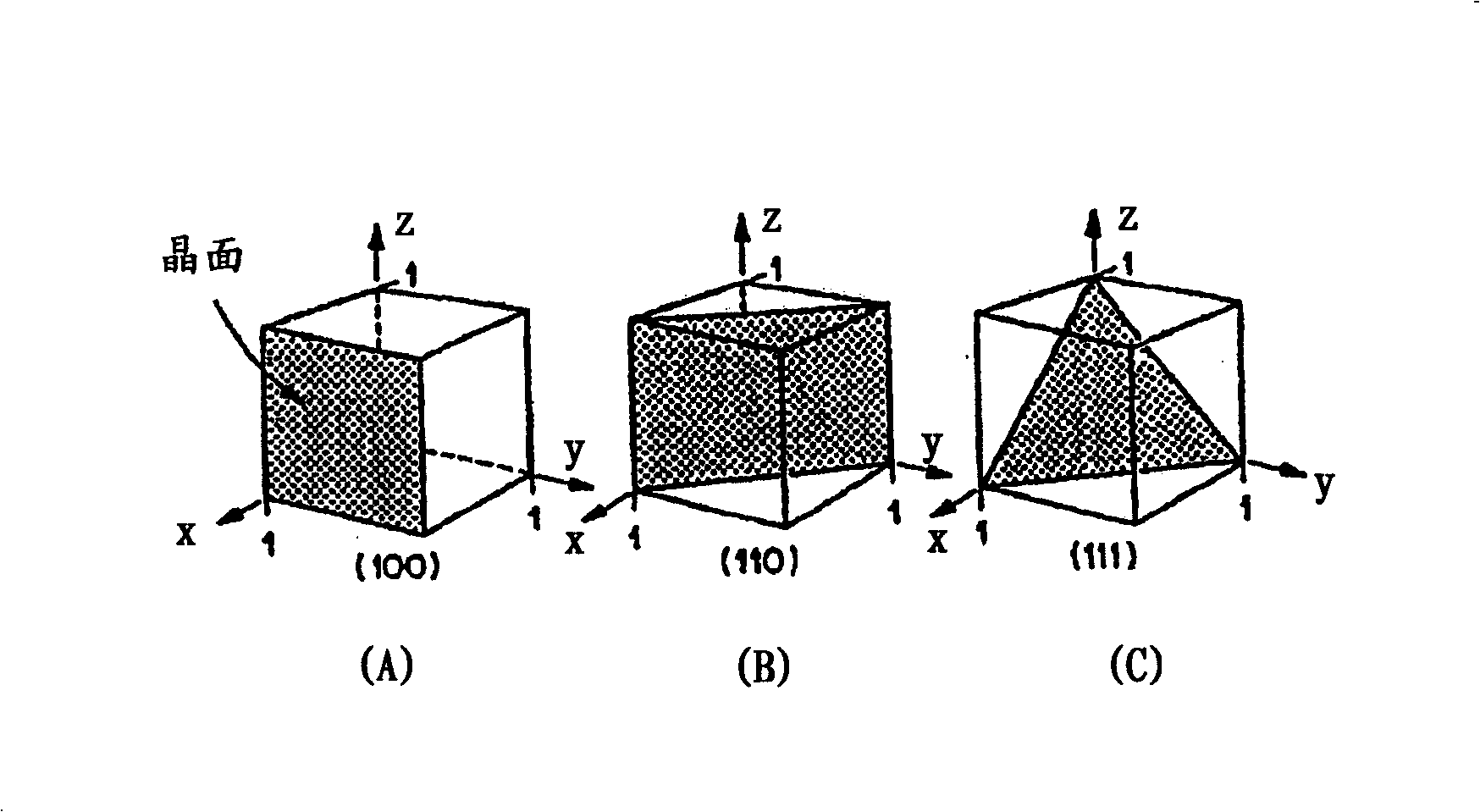

The invention discloses a method to produce IV-VI semiconductor single-crystal thin film and the hetero-structure thereof. Under the condition of accurately controlled ultra-high vacuum, IV-VI atom and molecular beams vaporized from a beam source furnace encounter a clean single-crystal liner surface with good crystal surface orientation, and atom and molecular reaching the surface of the liner form high-quality single-crystal thin film after processes such as attachment, transition, and crystallization on the surface of liner. Through the accurate control of growth conditions, such as beam runoff and linear temperature, extended IV-VI compounds grow on the surface of linear by a molecular layer and a molecular layer. The method can grow IV-VI semiconductor hetero-structures, including quantum-well and super-lattice. The production cost is low, and the quality is high.

Owner:ZHEJIANG UNIV

Semiconductor heterostructure diodes

ActiveCN102308390AOther obvious featuresObvious purposeTransistorDiodeSemiconductor materialsOhmic contact

Planar Schottky diodes for which the semiconductor material includes a heterojunction which induces a 2DEG in at least one of the semiconductor layers. A metal anode contact is on top of the upper semiconductor layer and forms a Schottky contact with that layer. A metal cathode contact is connected to the 2DEG, forming an ohmic contact with the layer containing the 2DEG.

Owner:TRANSPHORM INC

Semiconductor heterostructure and method for forming same

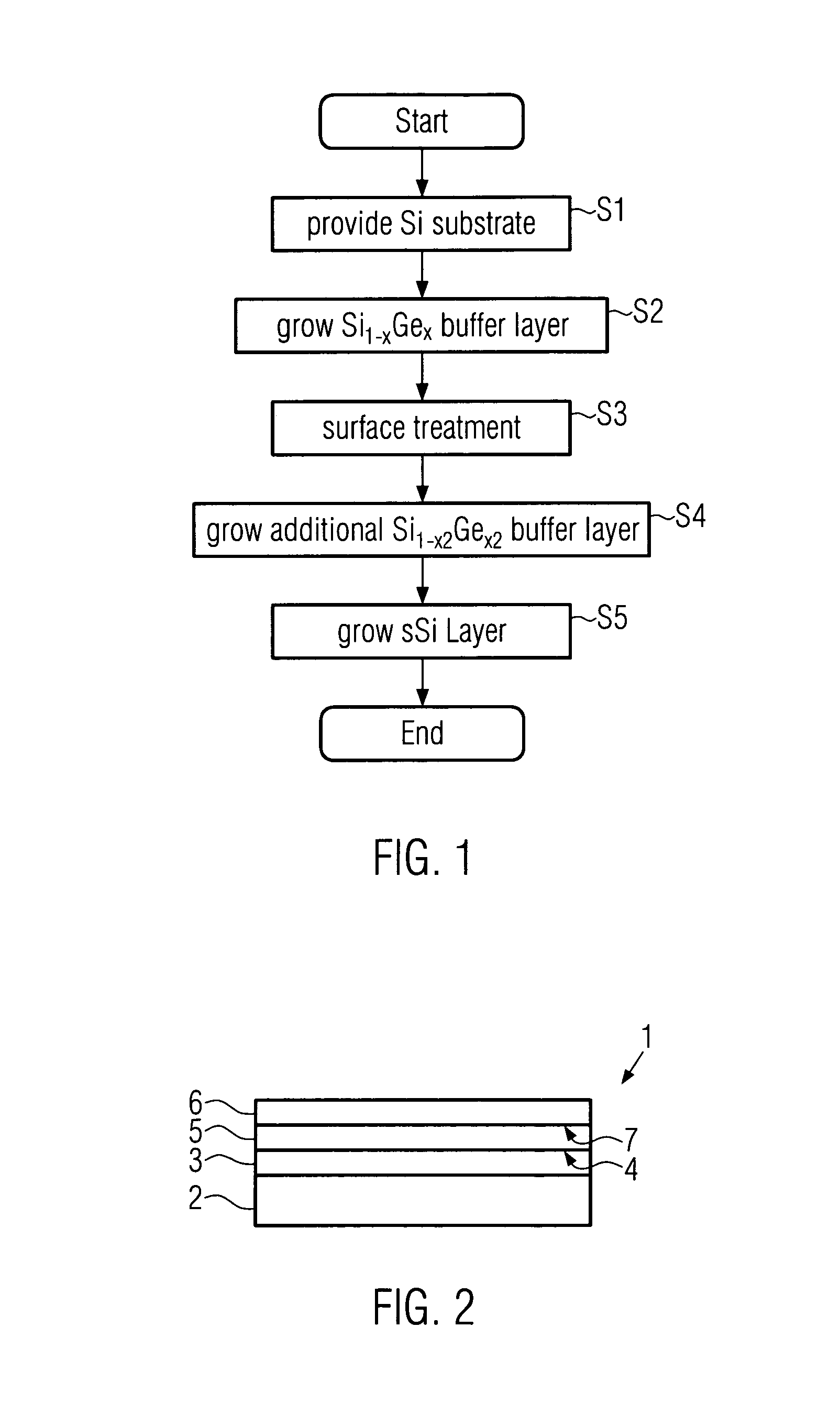

ActiveUS20070051975A1Surface roughness propertyReduce surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesIn planeSurface roughness

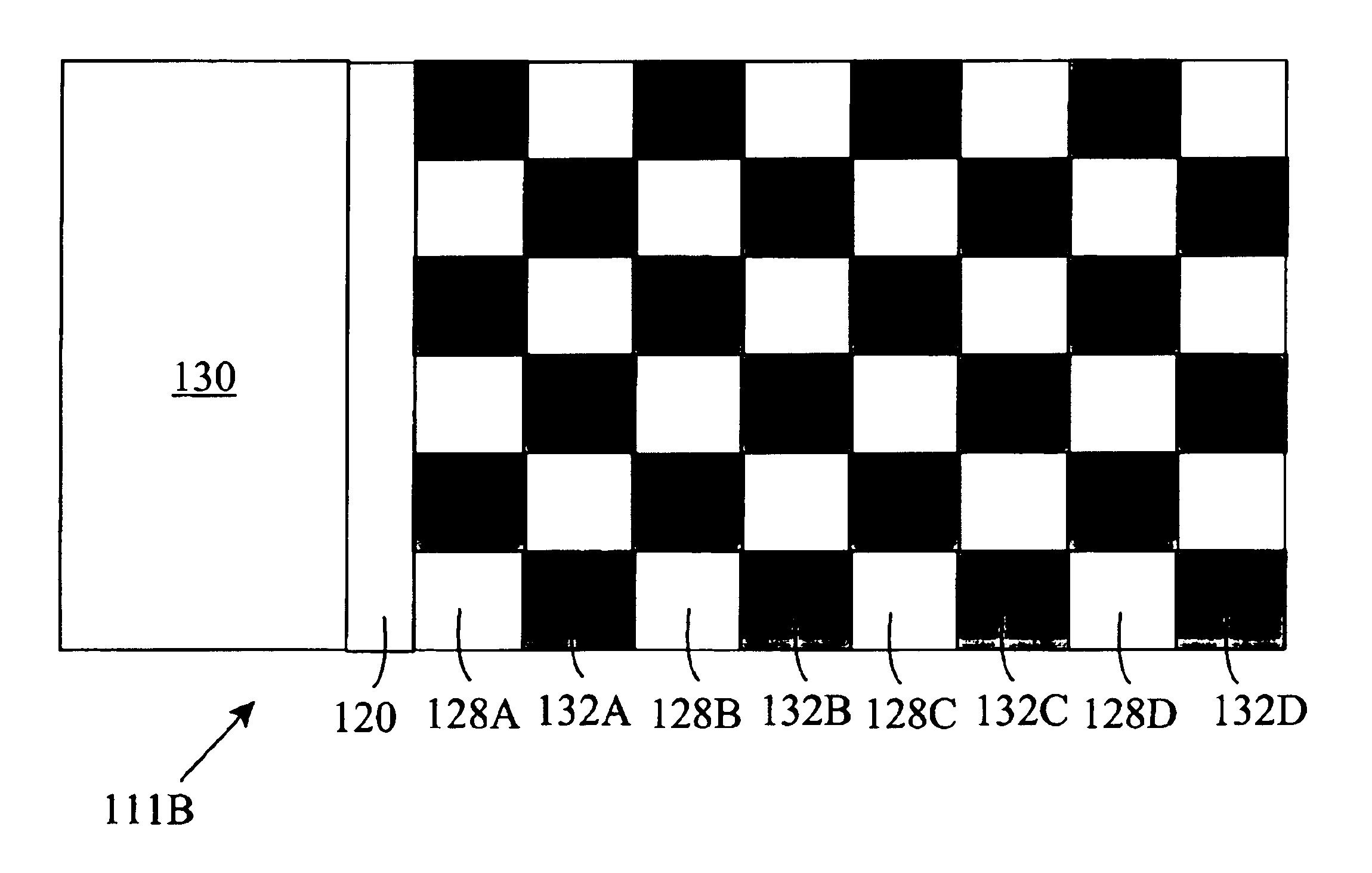

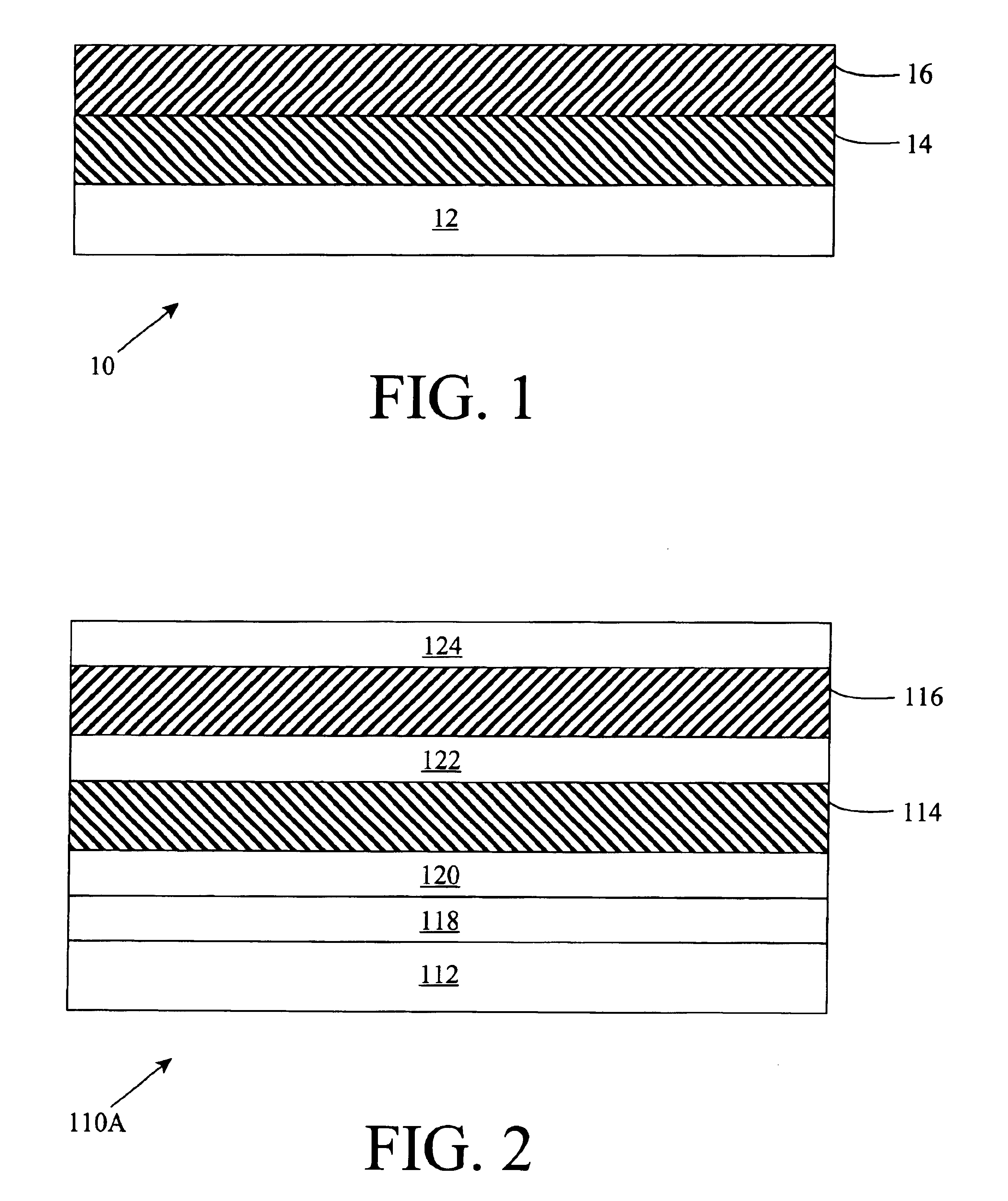

The invention relates to a method for forming a semiconductor heterostructure by providing a substrate with a first in-plane lattice parameter a1, providing a buffer layer with a second in-plane lattice parameter a2 and providing a top layer over the buffer layer. In order to improve the surface roughness of the semiconductor heterostructure, an additional layer is provided in between the buffer layer and the top layer, wherein the additional layer has a third in-plane lattice parameter a3 which is in between the first and second lattice parameters.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

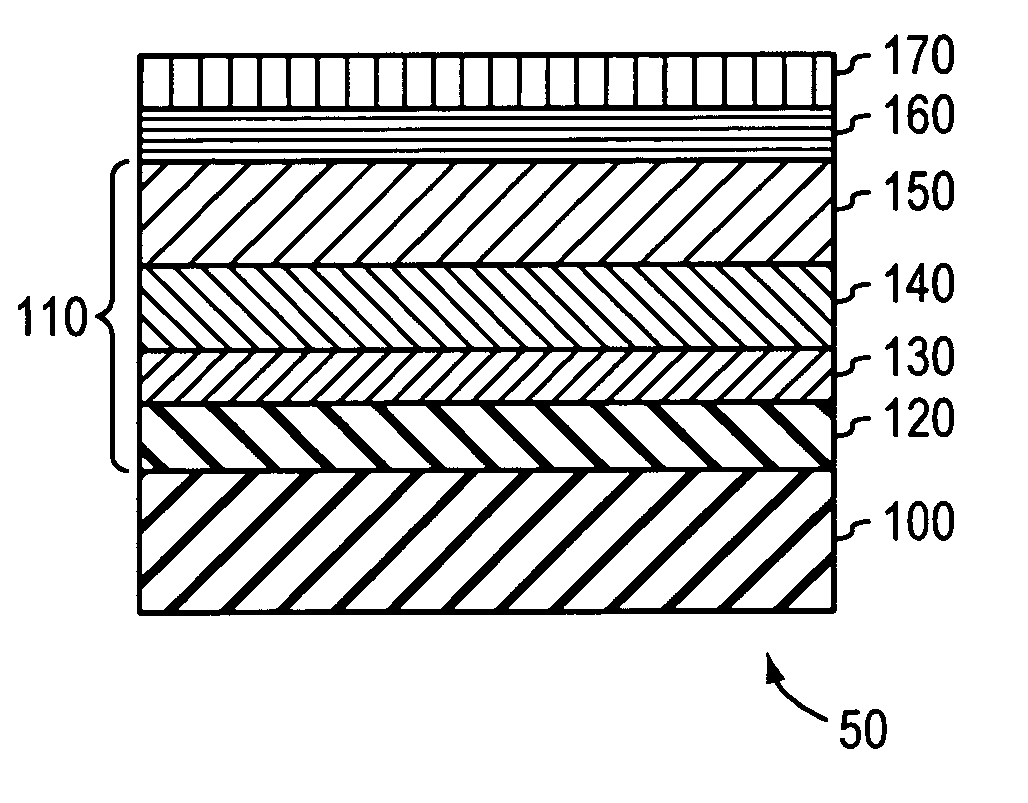

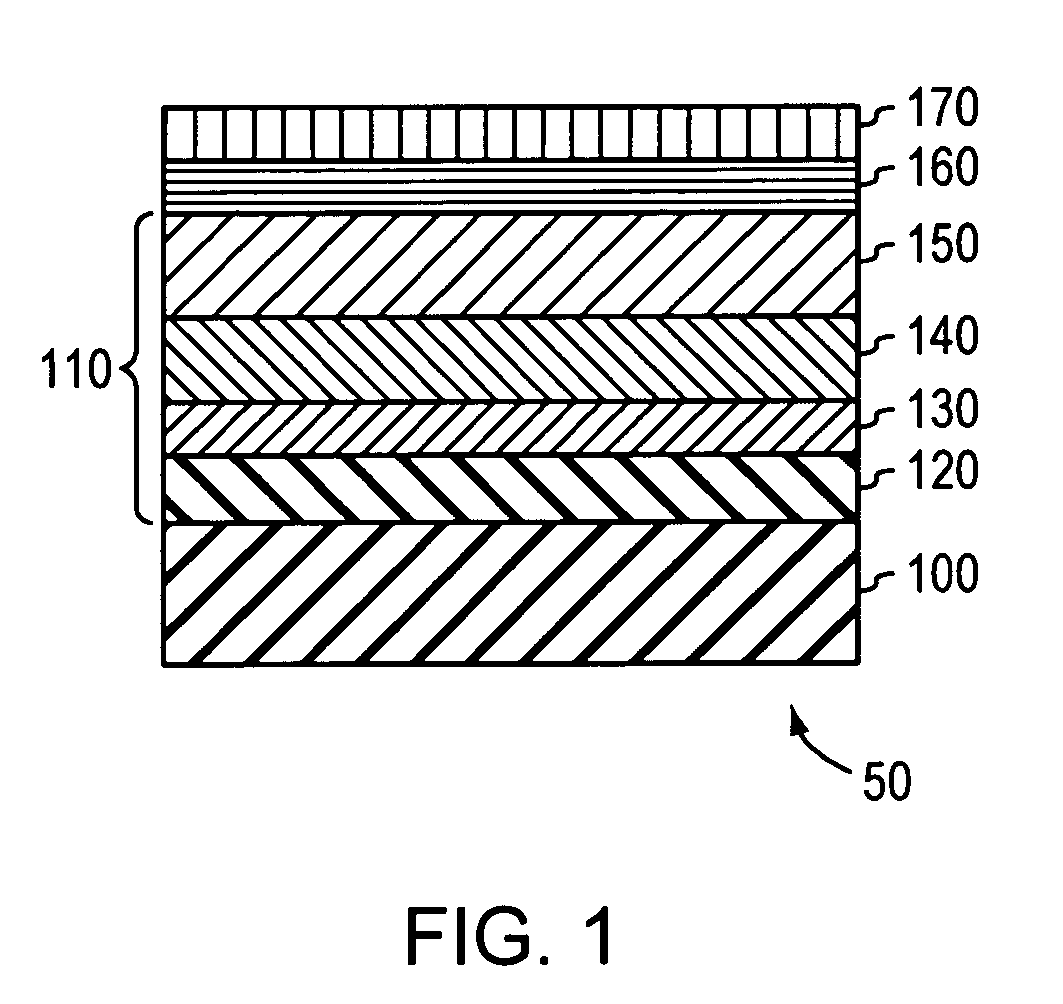

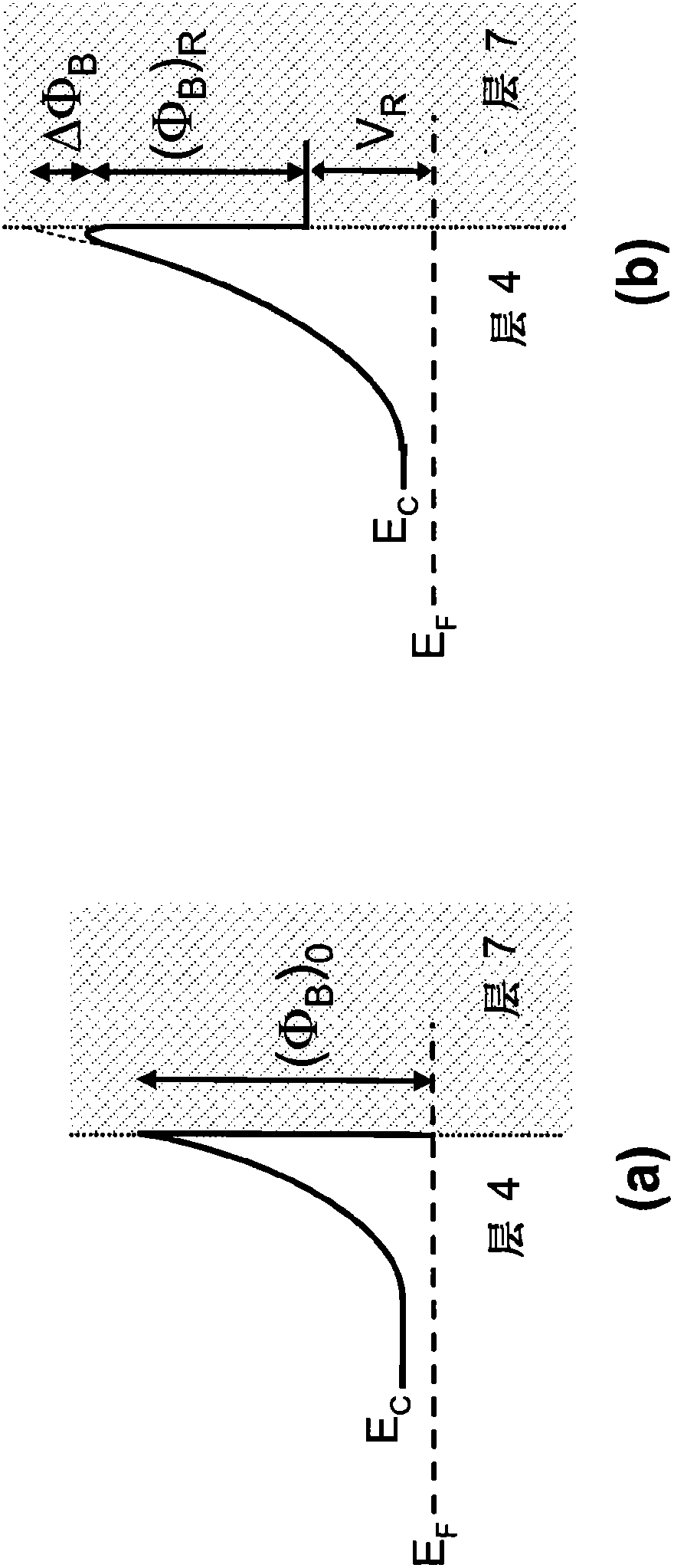

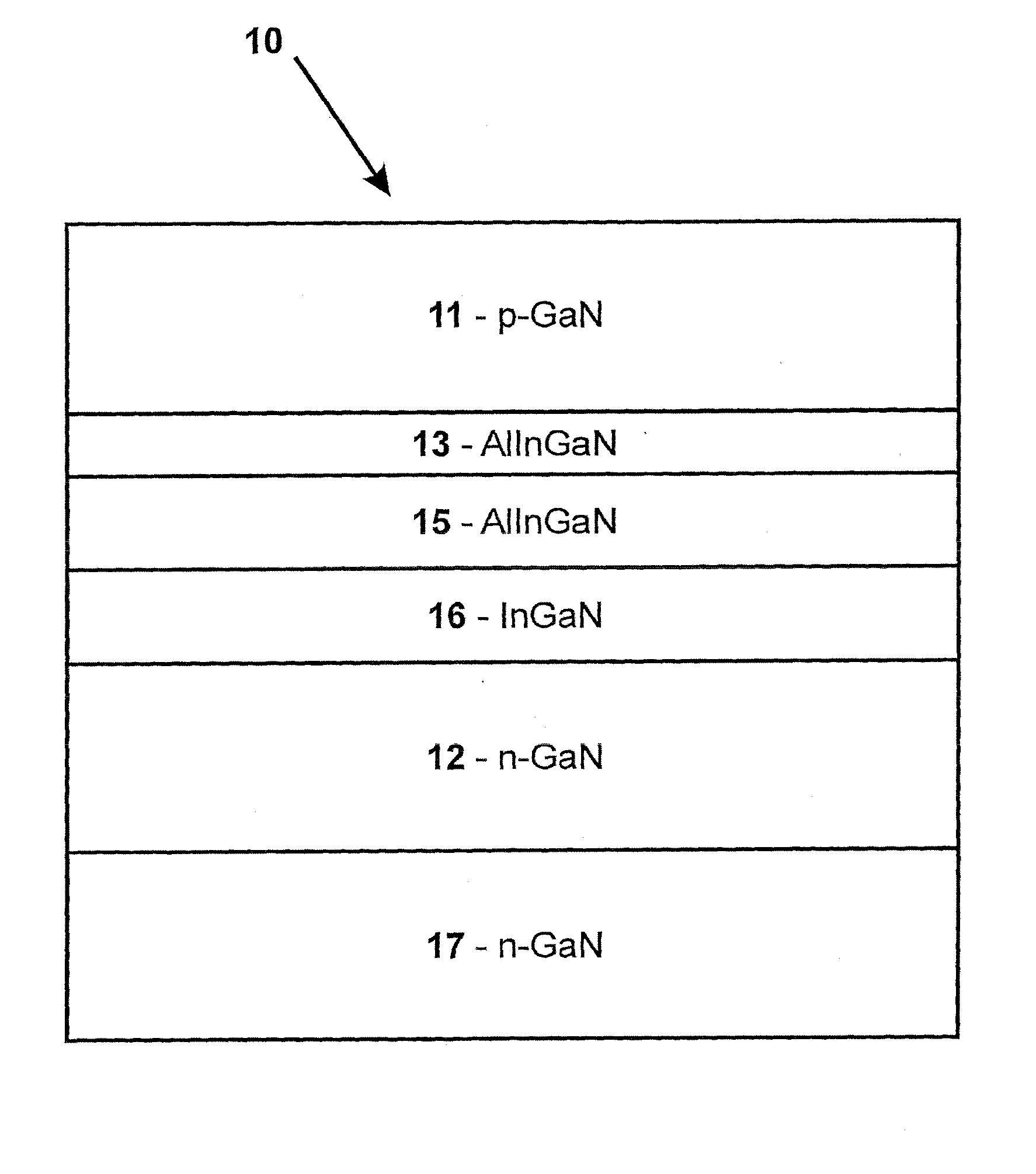

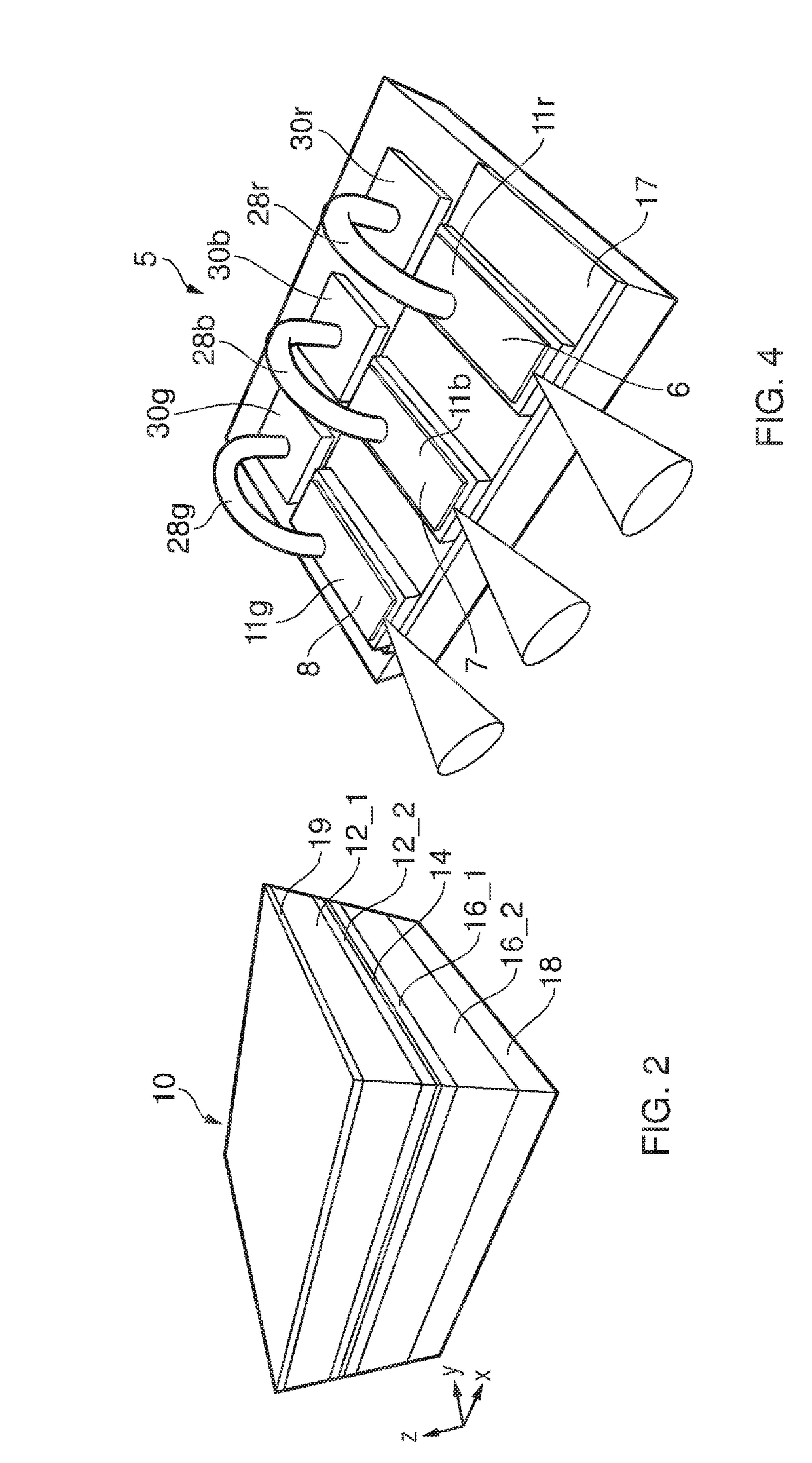

Semiconductor Heterostructure

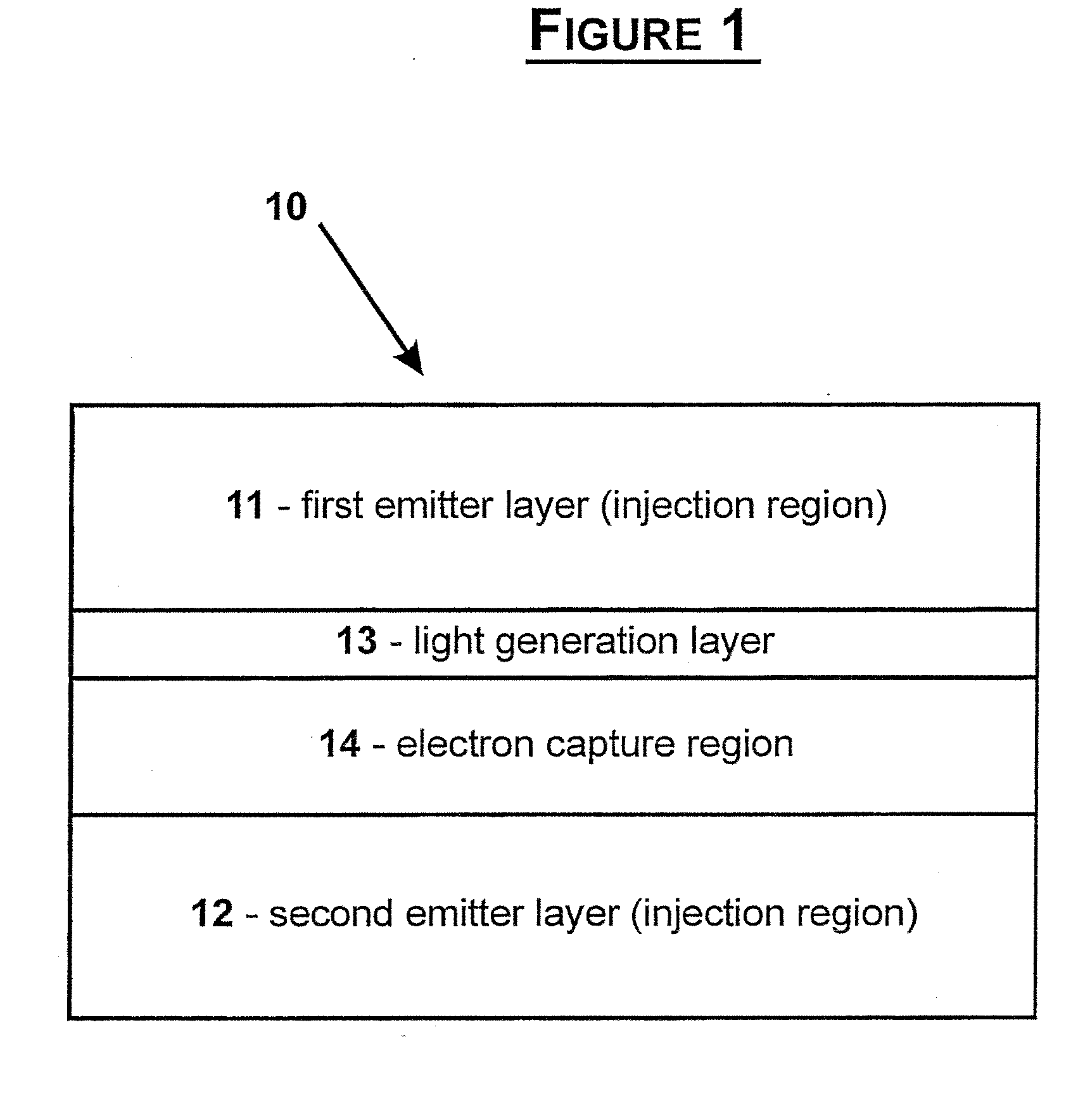

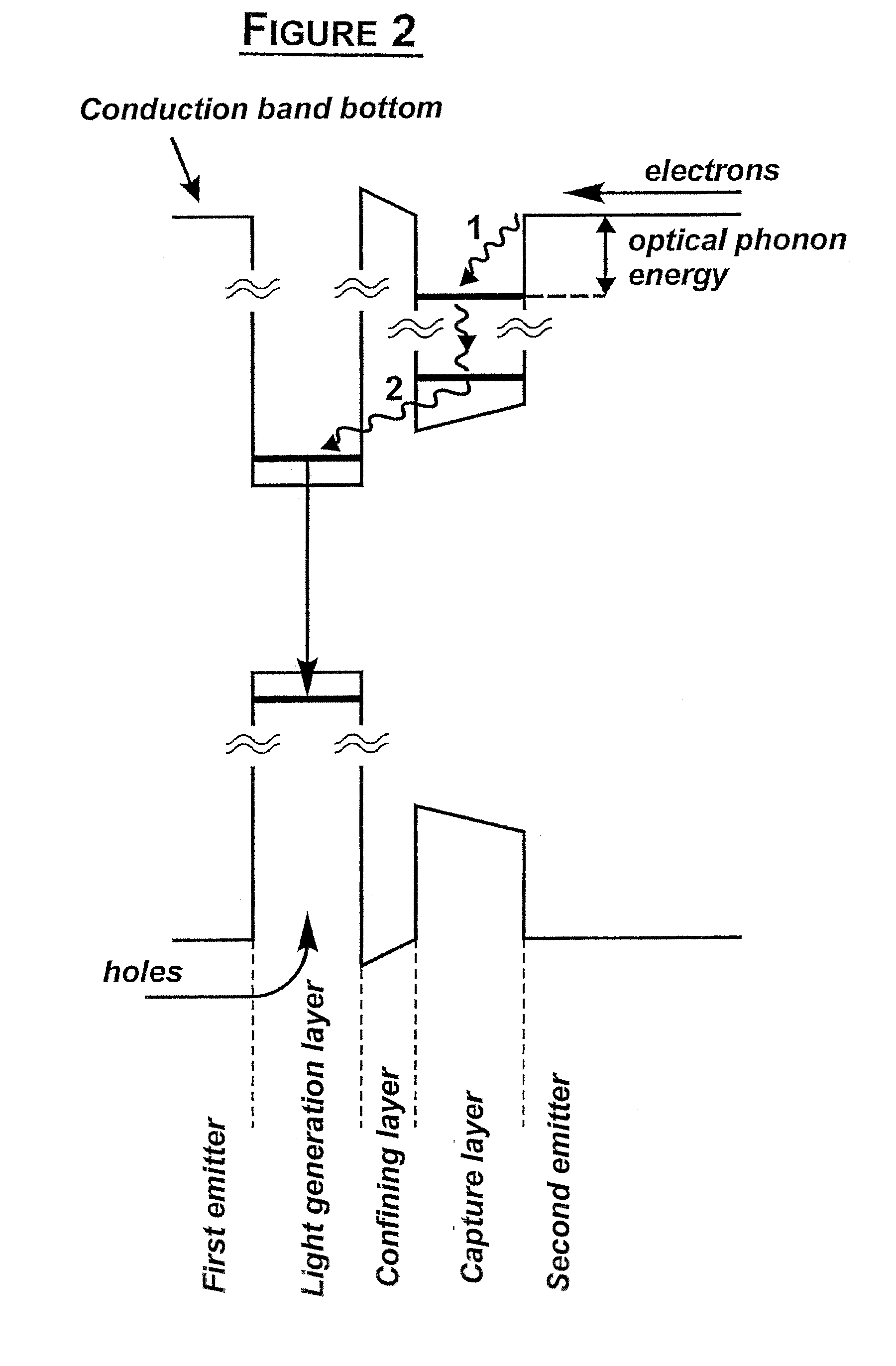

InactiveUS20080283818A1Enhanced total light generating capabilityEmission rate can be suppressedNanoopticsSemiconductor devicesSemiconductor heterostructuresConduction band

A strained semiconductor heterostructure (10) comprises an injection region comprising a first emitter layer (11) having p-type conductivity and a second emitter layer (12) having n-type conductivity, and a light generation layer (13) positioned between the first emitter layer (11) and the second emitter layer (12). An electron capture region (14) is positioned between the light generation layer (13) and the second emitter layer (12), said electron capture region comprising a capture layer (16) adjacent to the second emitter layer, and a confining layer (15) adjacent to said electron capture layer. According to the present invention, the widths and materials of the confining and capture layers (15, 16) are selected to provide energy difference between one of localized energy levels for electrons in the capture layer (16) and the conduction band bottom of the second emitter layer (12) equal to the energy of the optical phonon.

Owner:OPTOGAN OY

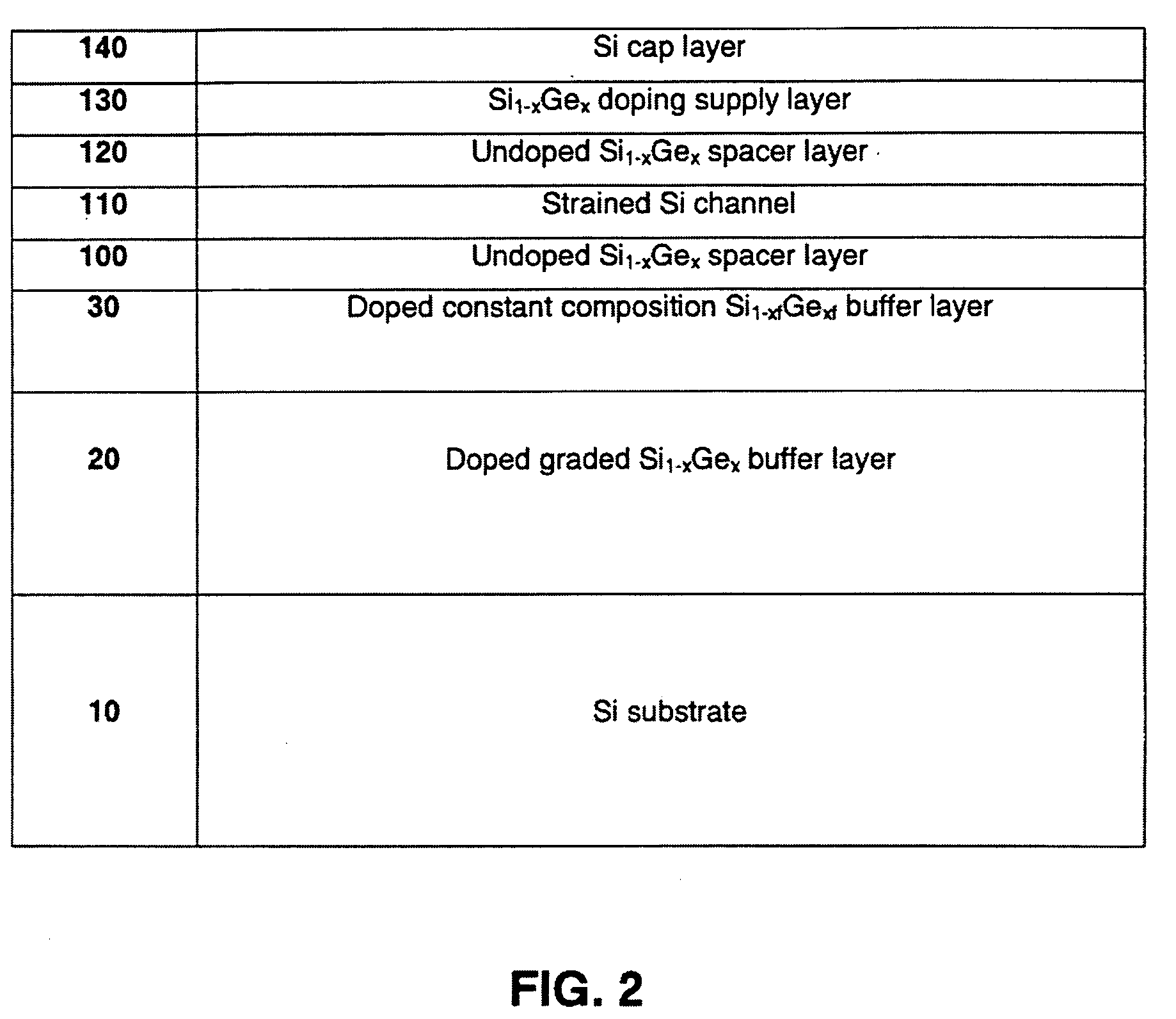

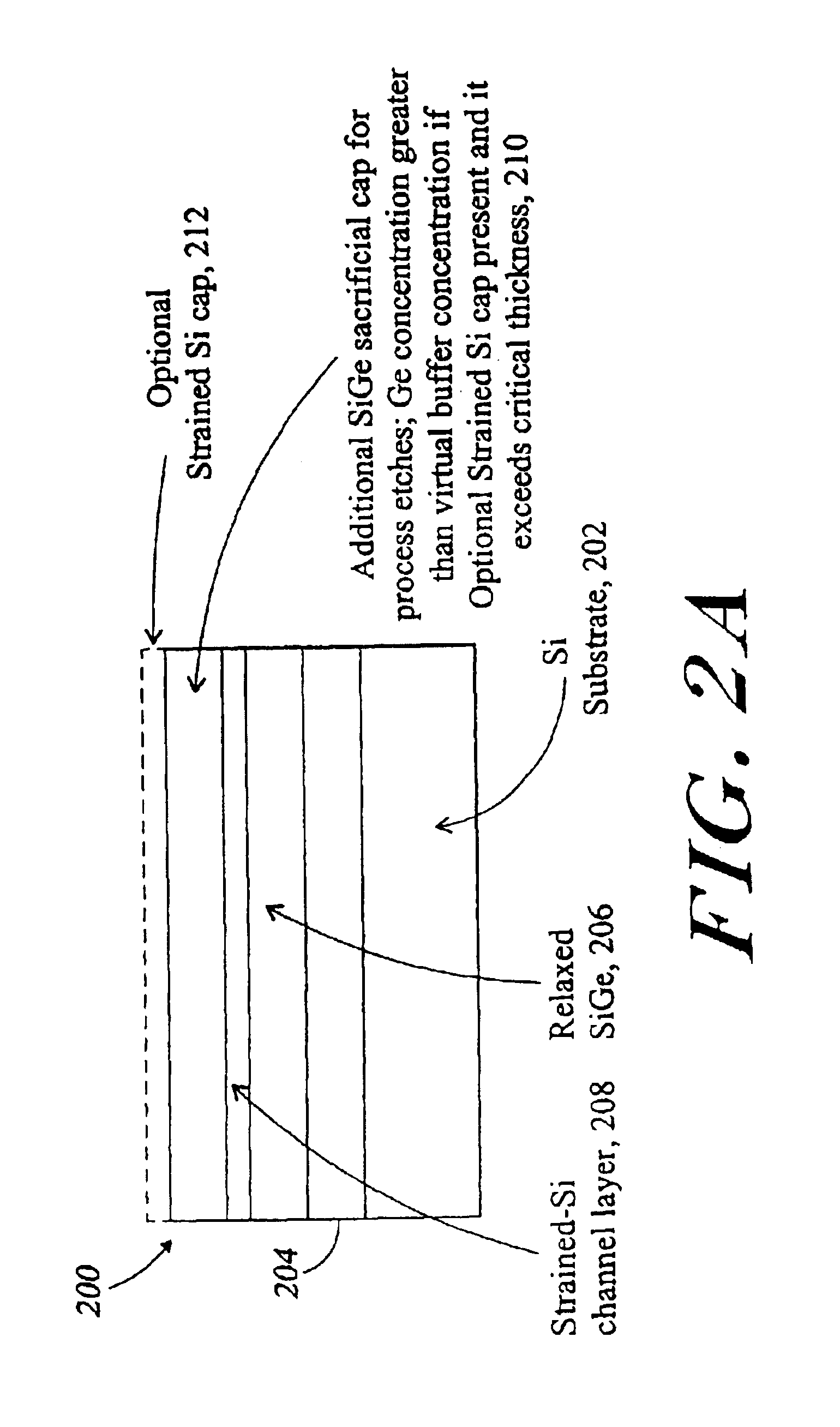

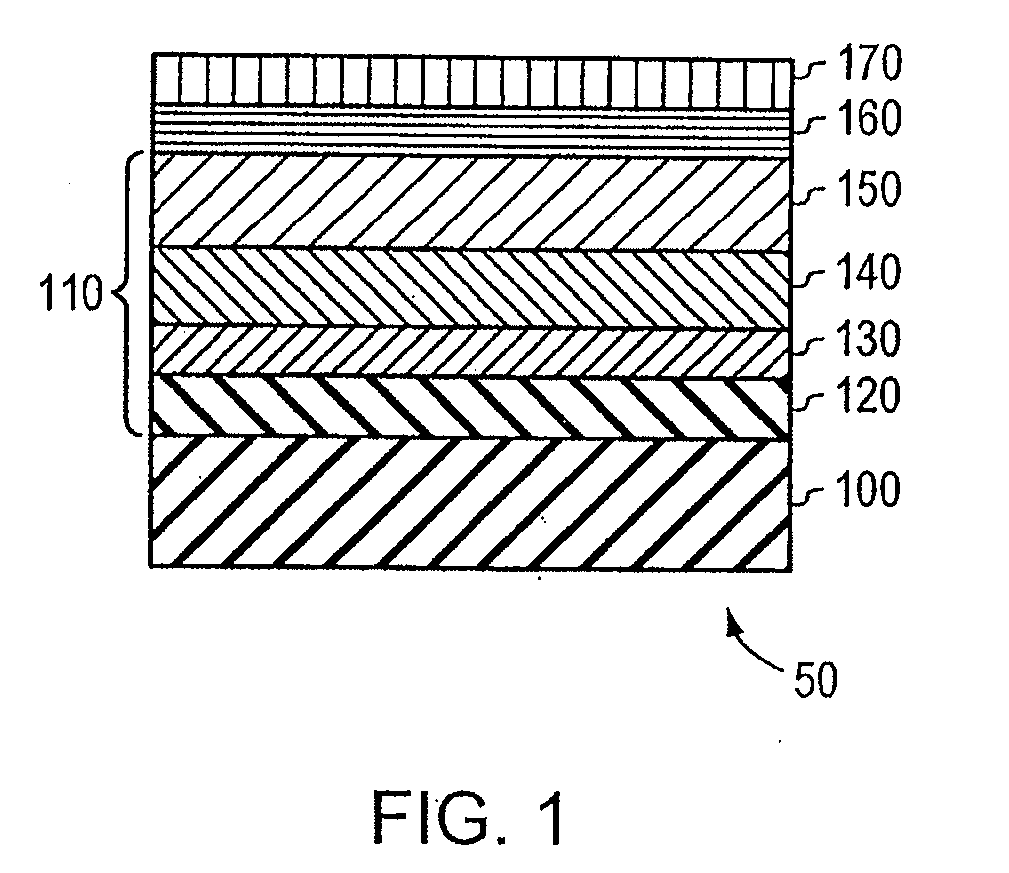

Fabrication of MOS-gated strained-Si and SiGe buried channel field effect transistors

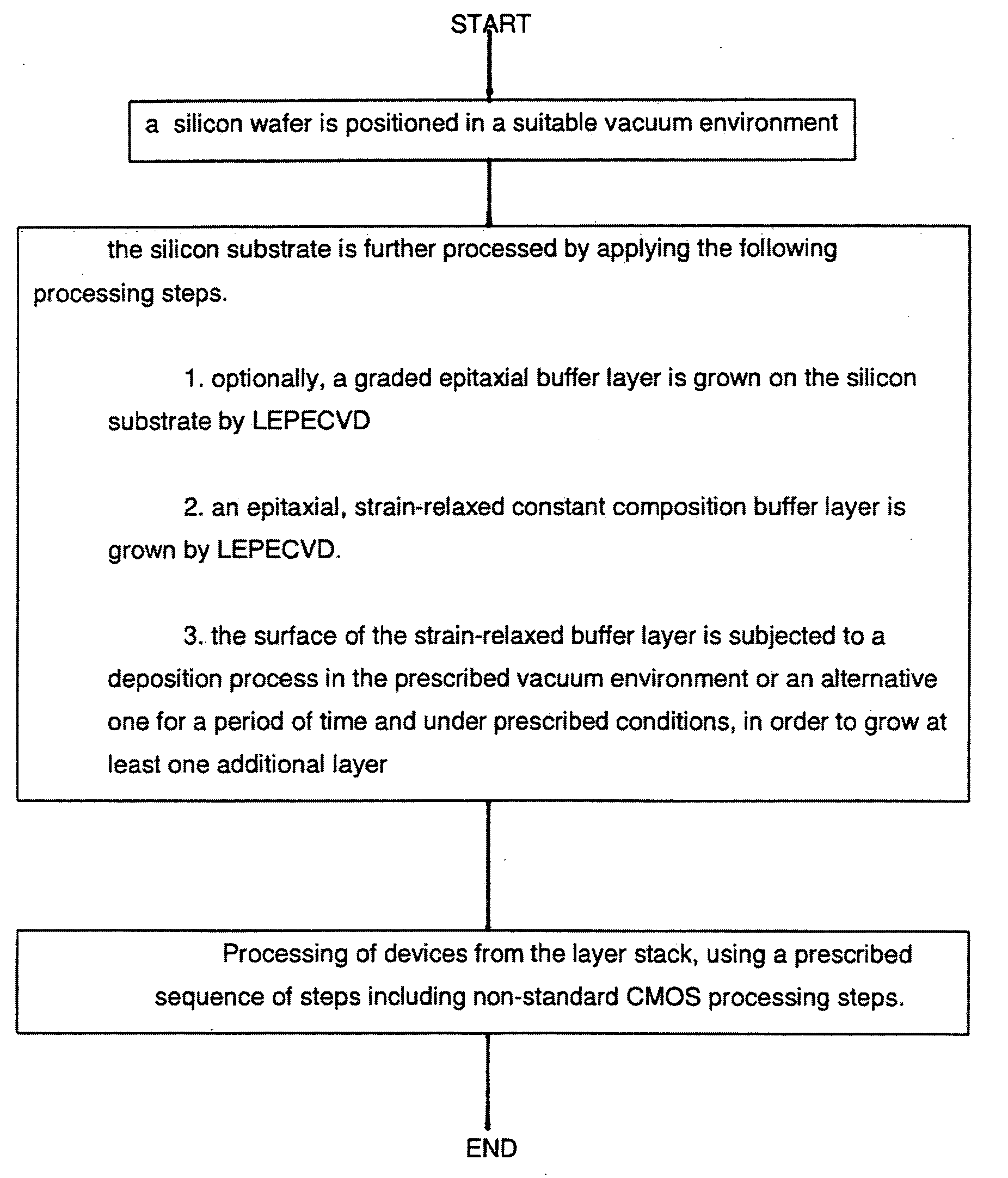

InactiveUS20060157732A1Quick upgradeSemiconductor/solid-state device manufacturingSemiconductor devicesConstant compositionSemiconductor heterostructures

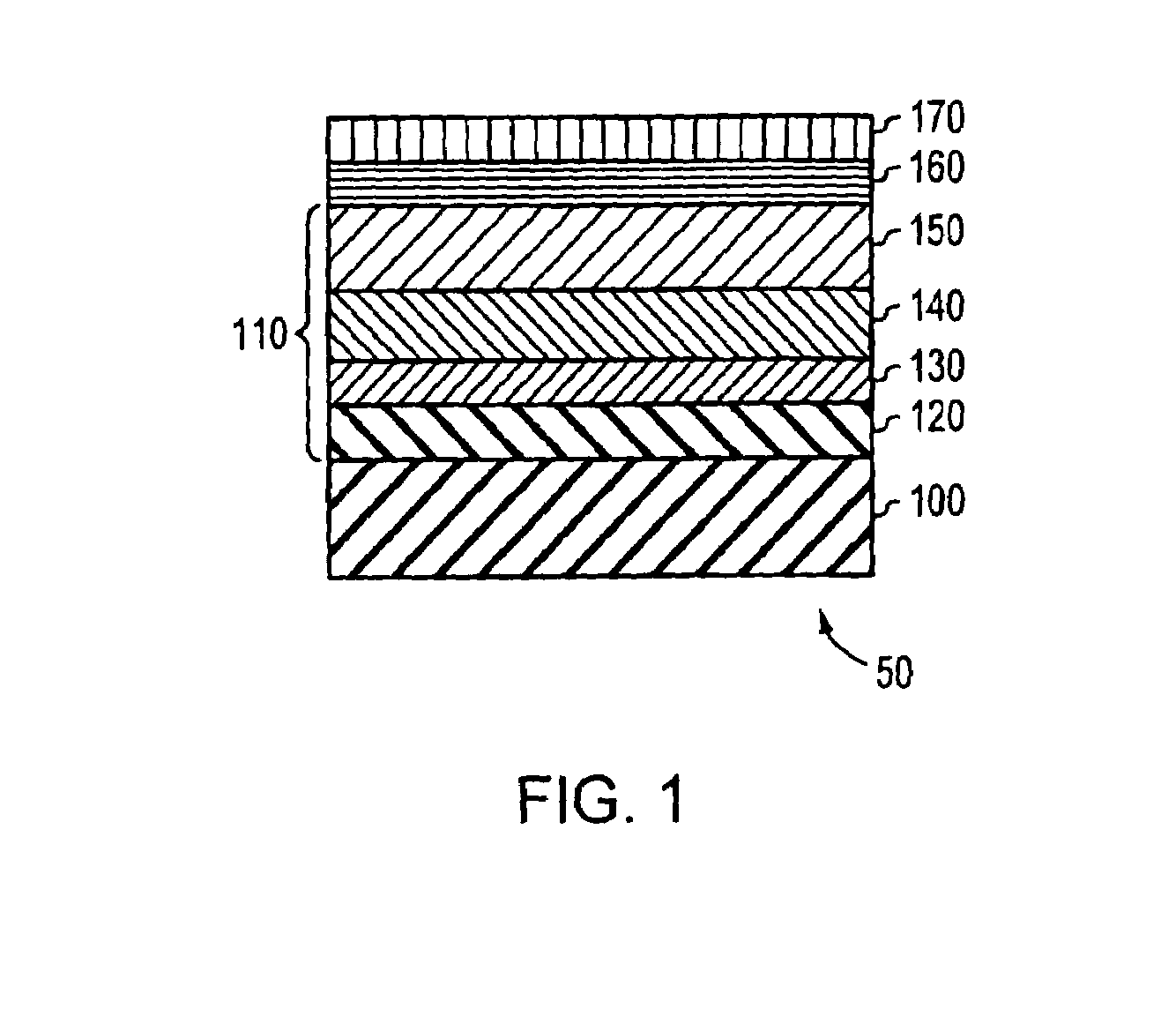

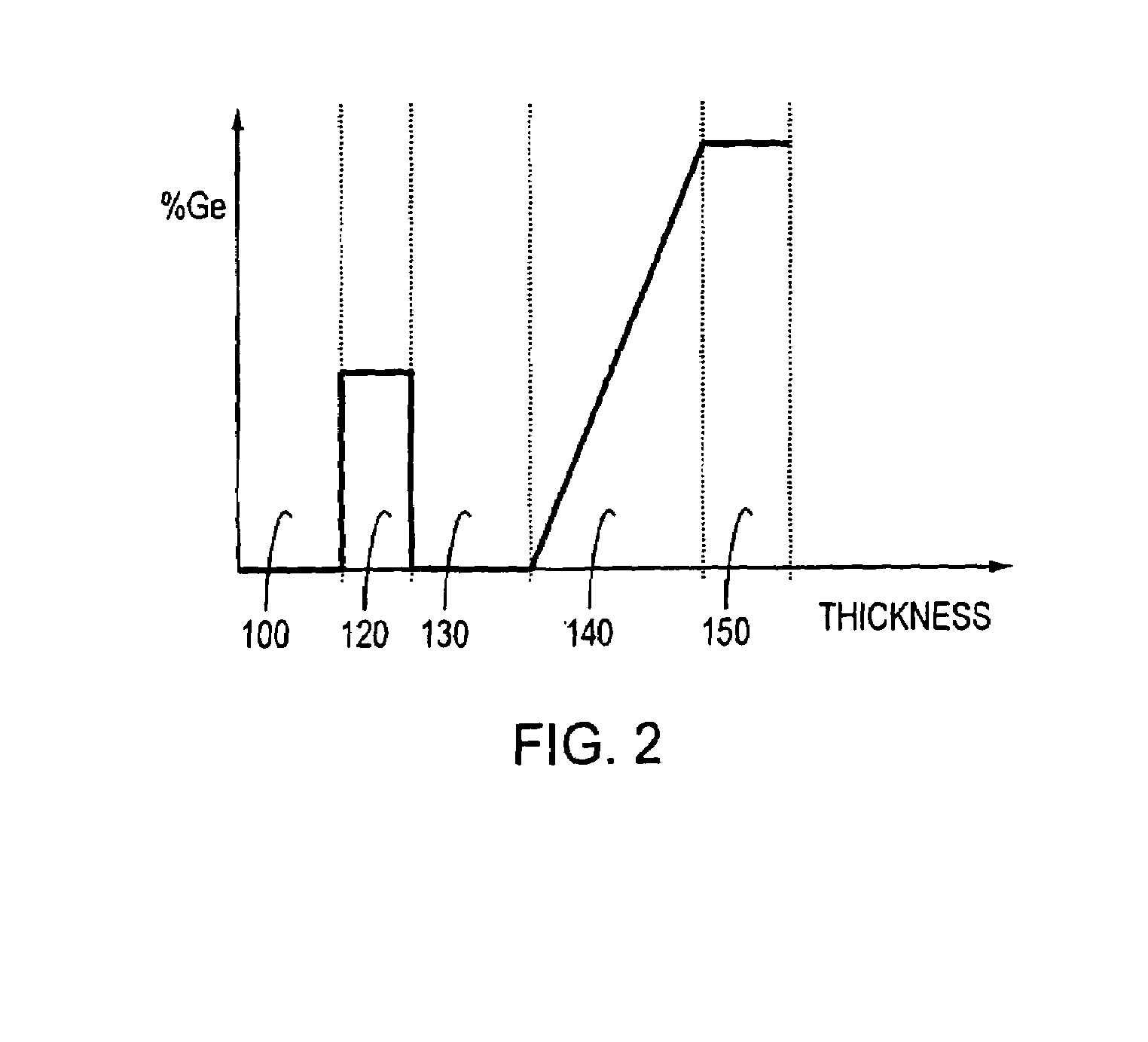

A method of fabricating semiconductor heterostructures including the steps of: (a) positioning a silicon wafer in a suitable environment and (b) processing the silicon substrate by applying several processing steps. A first optional processing step includes growing a graded buffer layer on a silicon substrate by low-energy plasma-enhanced chemical vapor deposition (LEPECVD). A second processing step includes growing a constant composition buffer layer by LEPECVD. A third processing step includes subjecting the surface of the strain-relaxed buffer layer to a deposition process for a period of time and under prescribed conditions, in order to grow at least one additional layer. Subsequently, devices may be processed from the grown layer stack by using a prescribed sequence of steps including non-standard CMOS processes.

Owner:EPISPEED

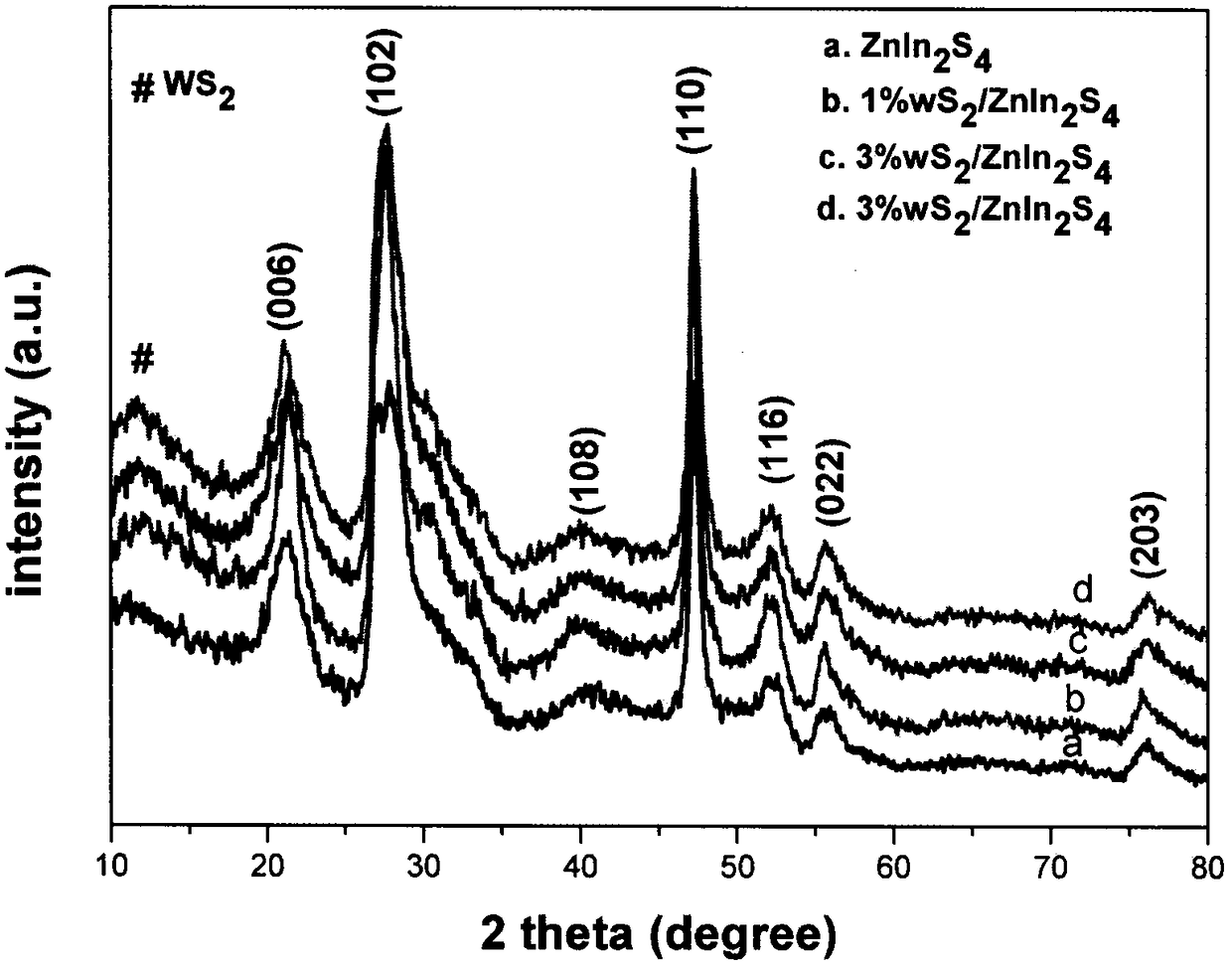

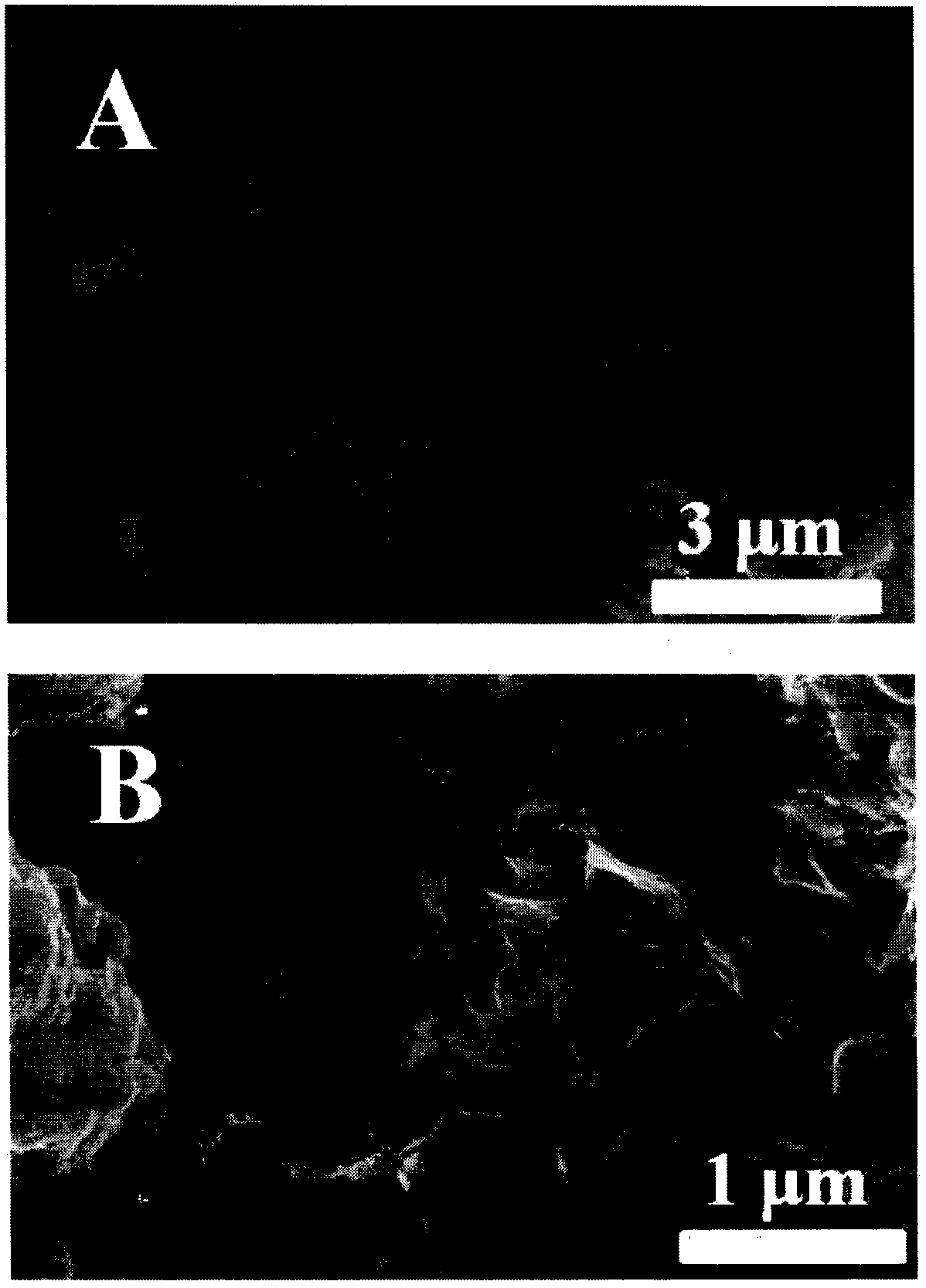

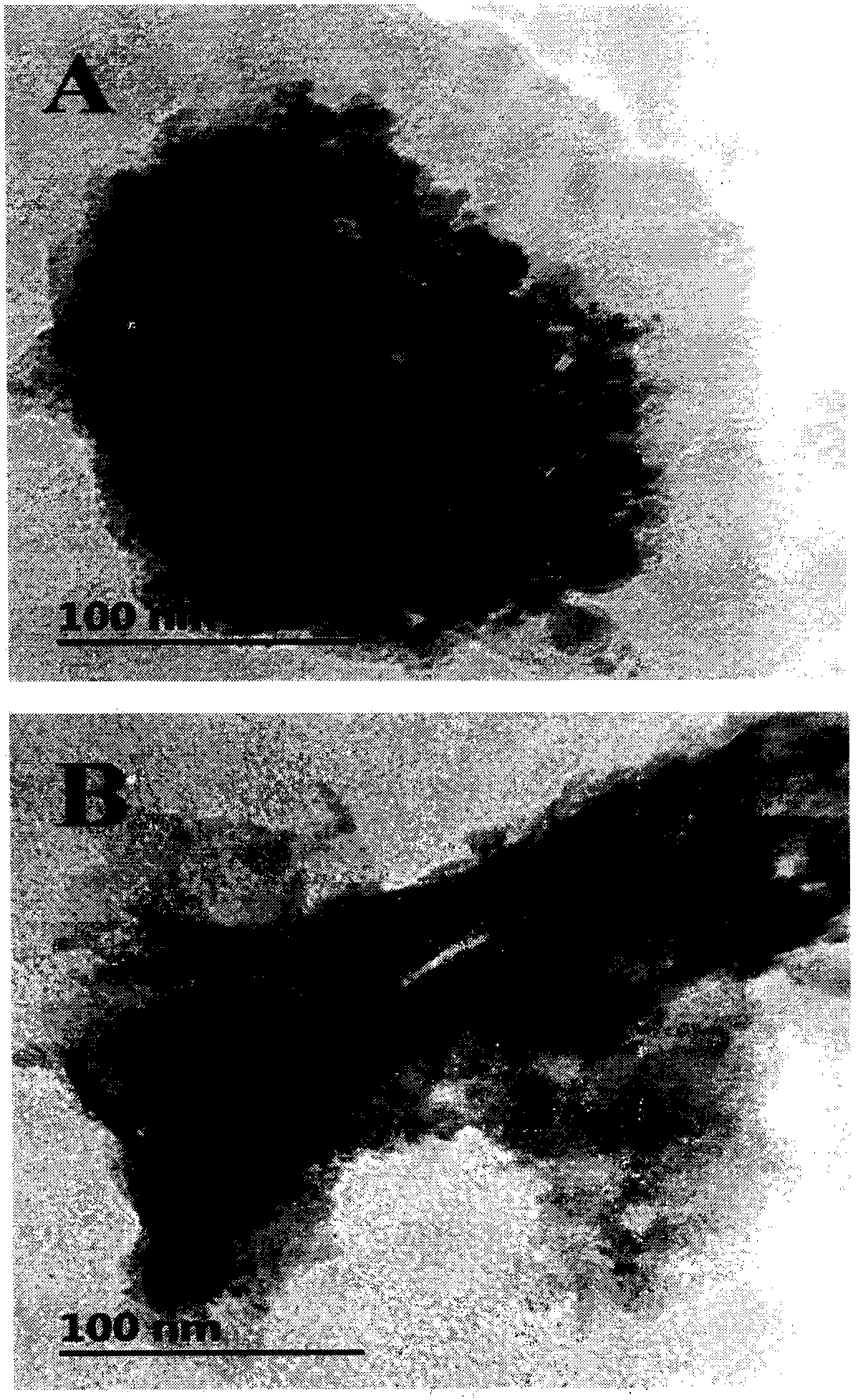

WS2/ZnIn2S4 composite visible light catalyst and preparation method thereof

InactiveCN108479810AImprove bindingEasy to separatePhysical/chemical process catalystsElectrodesSemiconductor heterostructuresPhotochemistry

The invention belongs to the technical field of semiconductor photocatalysis, and particularly relates to a WS2 / ZnIn2S4 composite visible light catalyst and a preparation method thereof. The inventionprovides a WS2 / ZnIn2S4 composite visible light catalyst and a preparation method thereof. The preparation method is characterized in that a WS2 nano sheet used as a promoter is tightly combined withZnIn2S4 particles through a hydrothermal reaction, thereby forming the WS2 / ZnIn2S4 composite visible light catalyst. Compared with a pure ZnIn2S4 photocatalyst, the prepared WS2 / ZnIn2S4 composite visible light catalyst can effectively promote separation of photogenerated charges and reduce combination of photogenerated electrons and holes due to the formation of a semiconductor heterostructure, sothat the photocatalytic hydrogen production performance can be greatly improved. The WS2 / ZnIn2S4 composite visible light catalyst and the preparation method thereof which are provided by the invention provide a new idea and a new way for design and development of a novel efficient visible light catalyst.

Owner:CHINA JILIANG UNIV

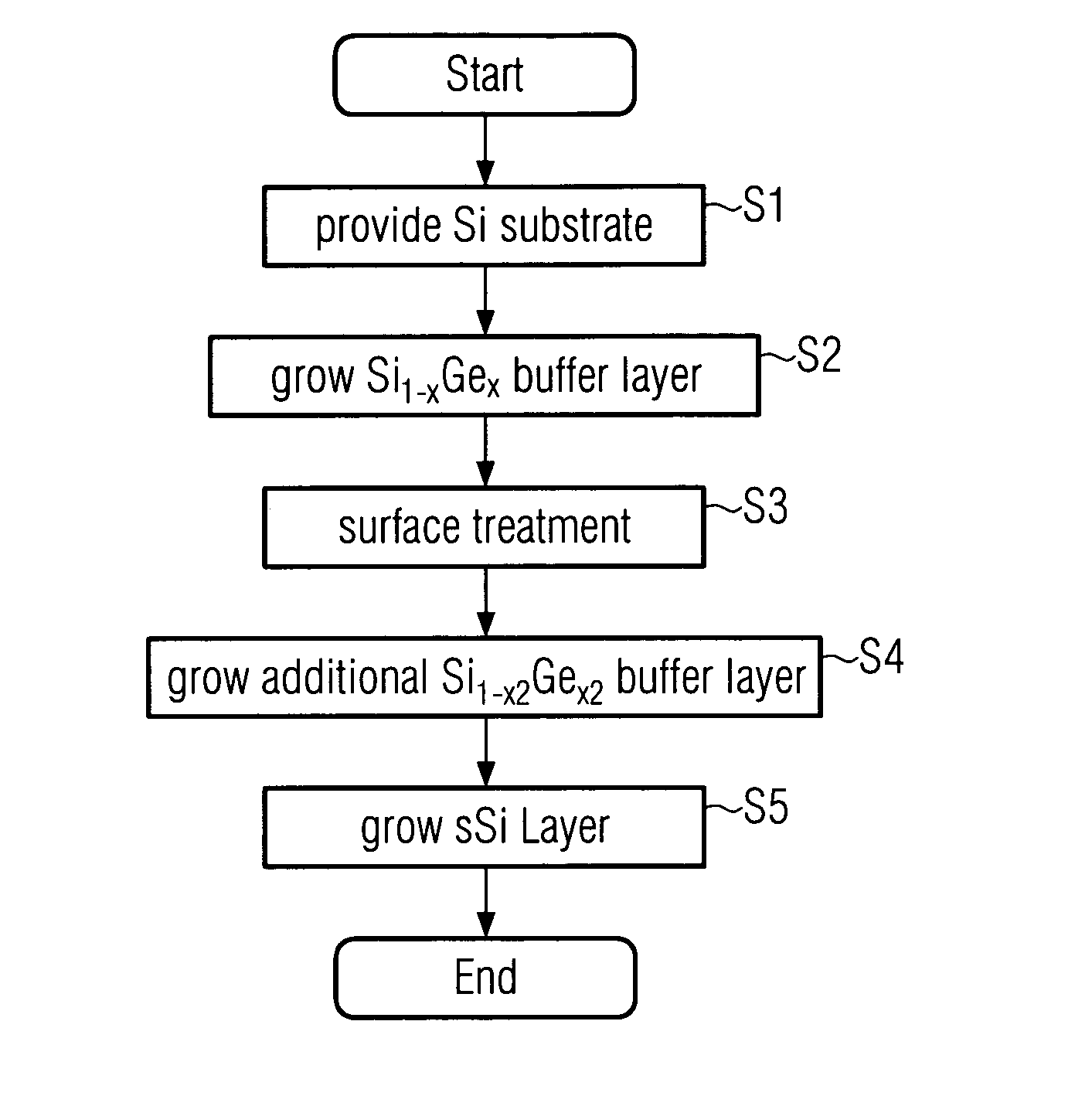

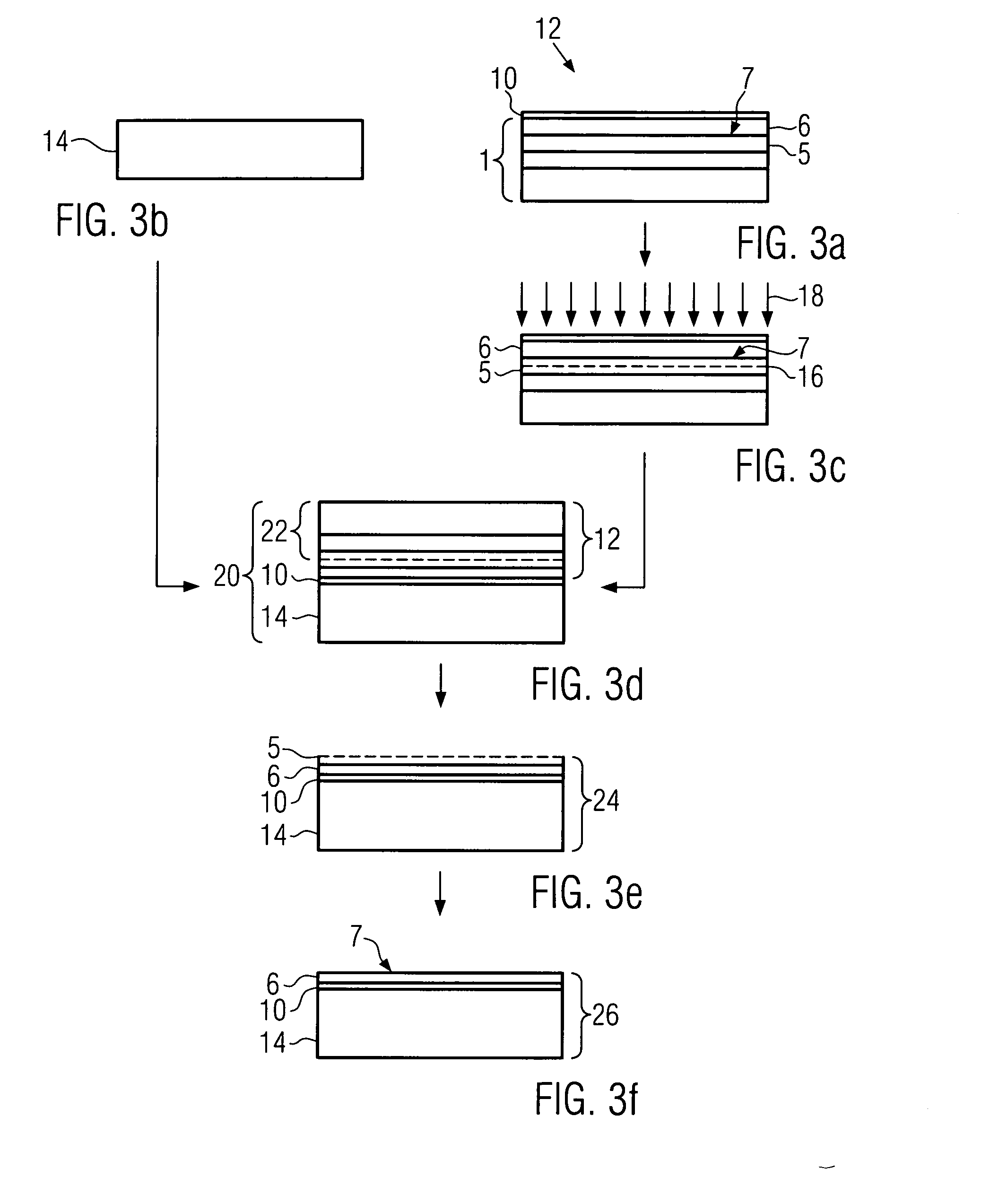

Method of manufacturing a semiconductor heterostructure

ActiveUS7459374B2Reduce surface roughnessReduce heat loadSemiconductor/solid-state device manufacturingNanotechnologyIn planeSemiconductor materials

A method for manufacturing a semiconductor heterostructure by first manufacturing a donor wafer having a first substrate with a first in-plane lattice parameter, a spatially graded buffer layer having a second in-plane lattice parameter, and a strained smoothing layer of a semiconductor material having a third in-plane lattice parameter which has a value between that of the first and second lattice parameters. A top layer is formed on the ungraded layer a top layer of a semiconductor material having a top surface, optionally with a superficial layer present on the top surface and having a thickness that is equal to or smaller than 10 nanometers. Next, a handle wafer of a second substrate having an insulator layer thereon is bonded with the donor wafer in such way that (a) the insulator layer of the handle wafer is bonded directly onto the top surface of the top layer of the donor wafer, or (b) the insulator layer of the handle wafer is bonded onto the superficial layer.

Owner:SOITEC SA

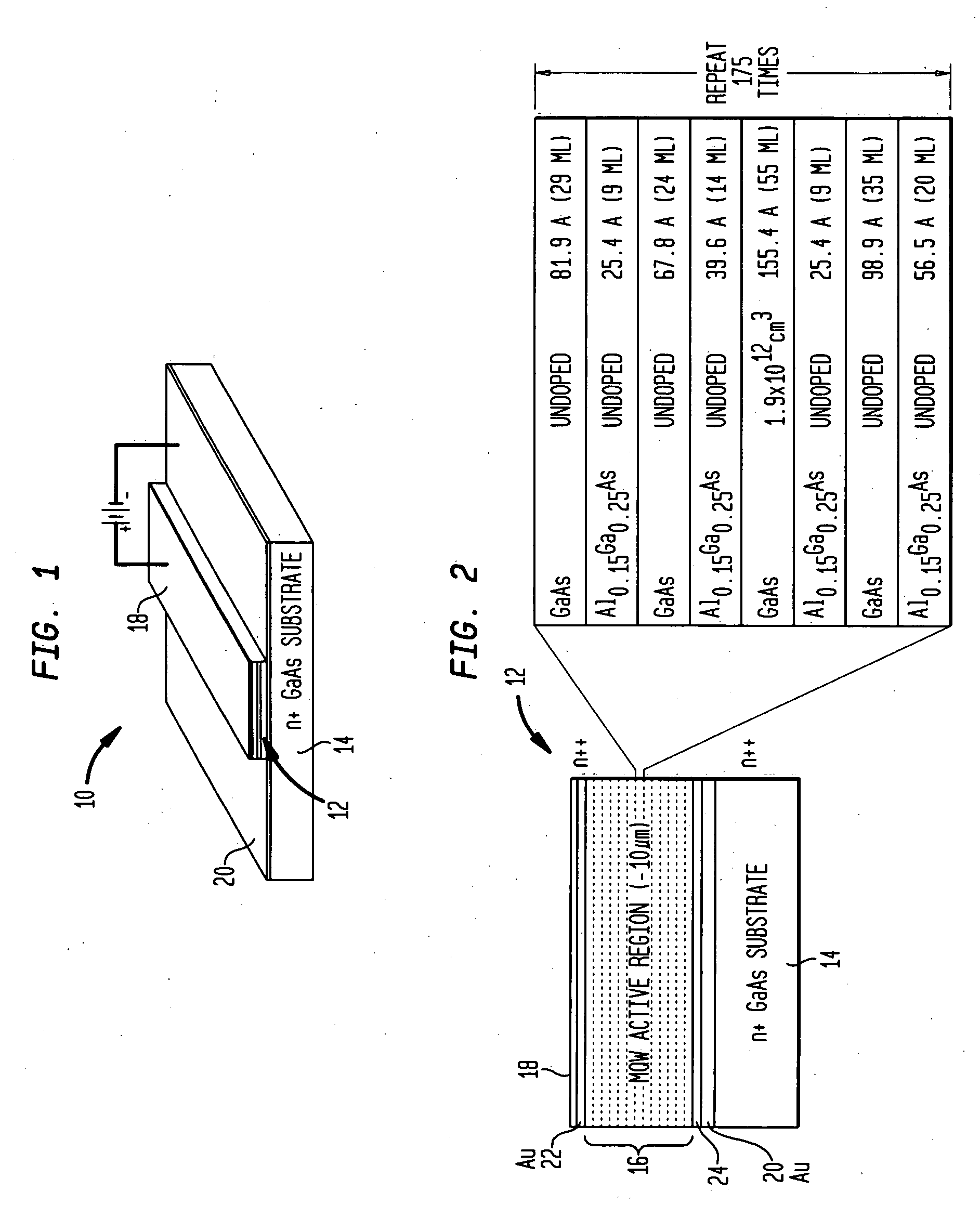

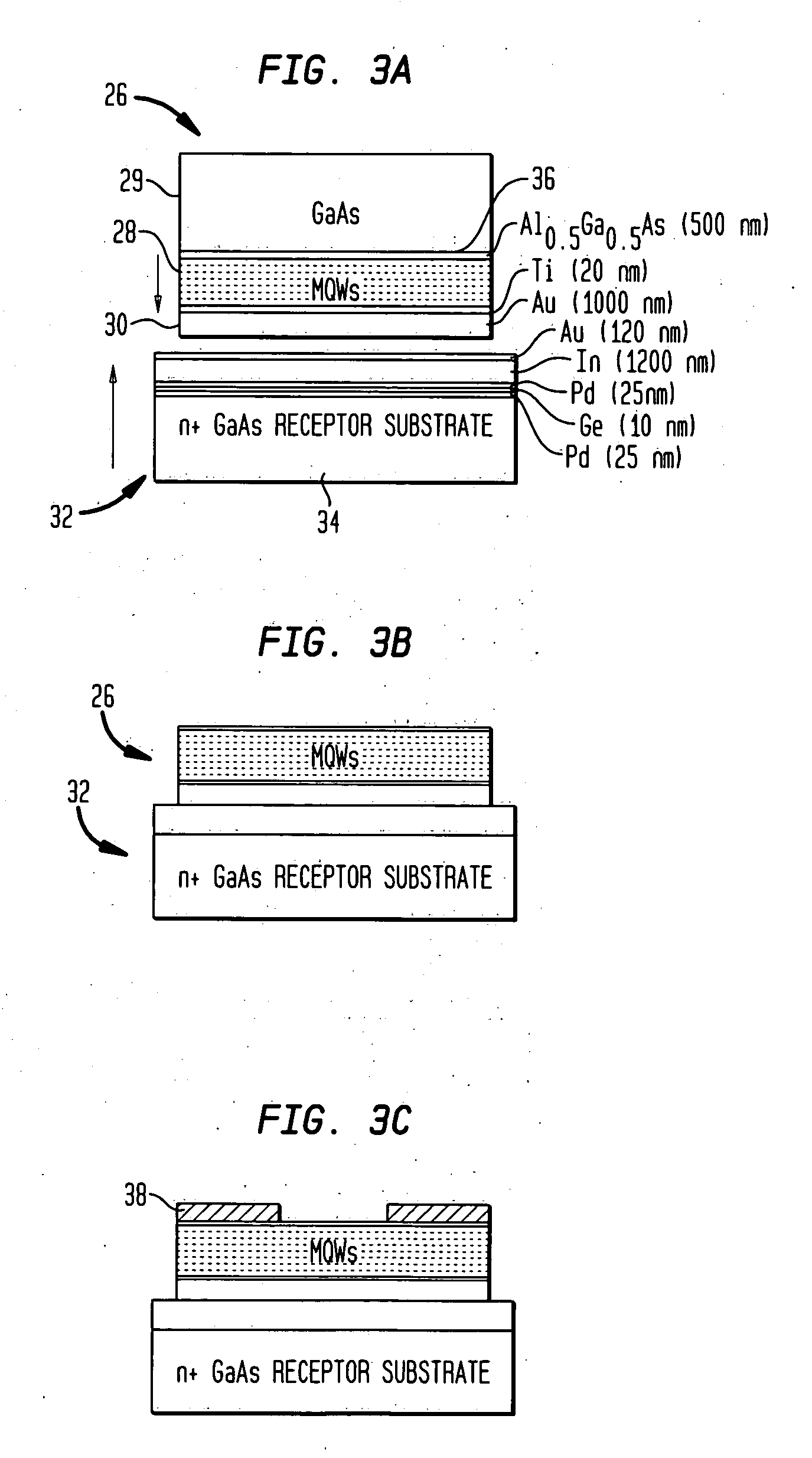

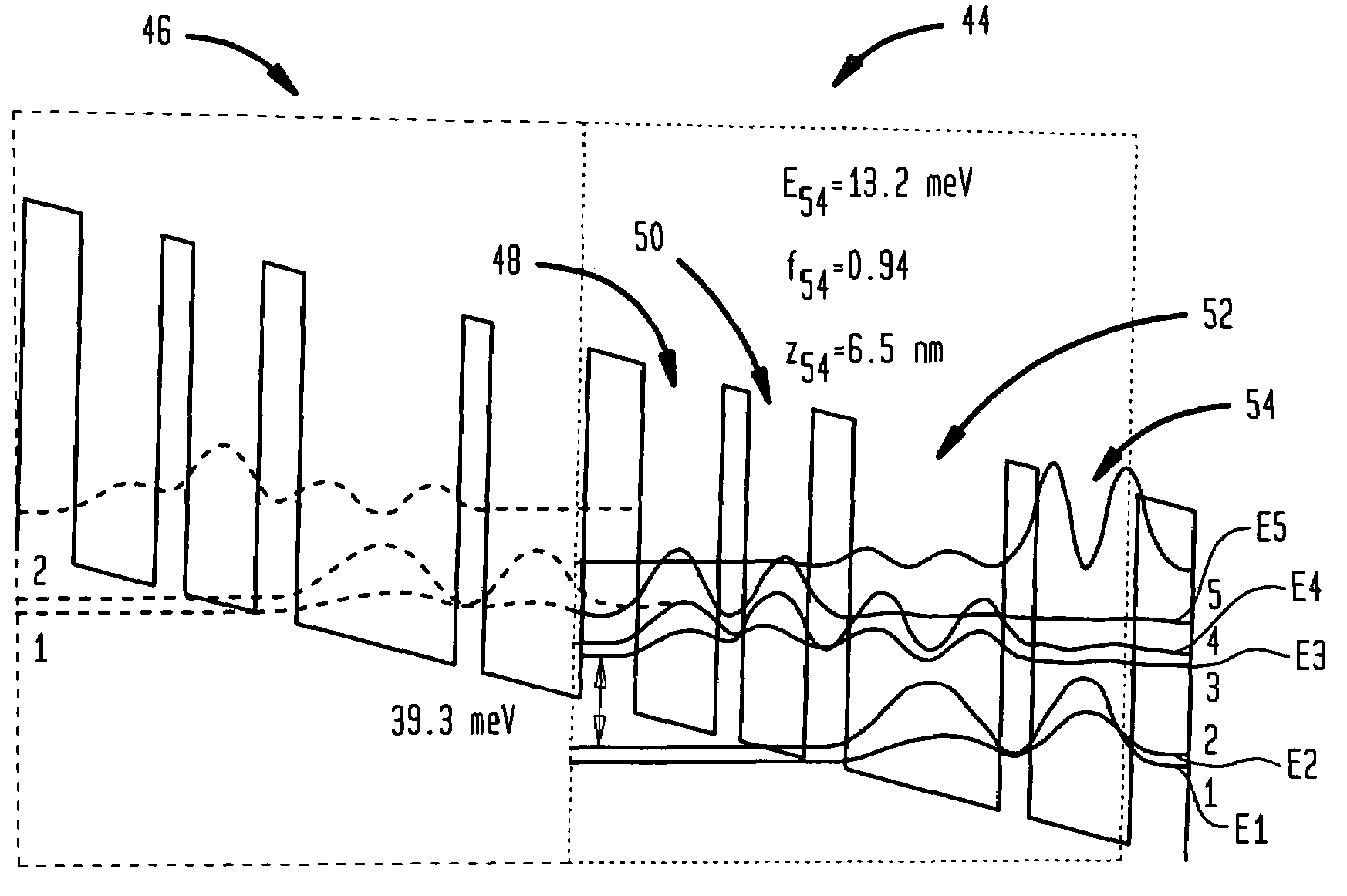

Terahertz lasers and amplifiers based on resonant optical phonon scattering to achieve population inversion

ActiveUS20050058168A1Highly selective and very fast depopulationPromote generationOptical wave guidanceLaser using scattering effectsAudio power amplifierQuantum well

The present invention provides quantum cascade lasers and amplifier that operate in a frequency range of about 1 Terahertz to about 10 Terahertz. In one aspect, a quantum cascade laser of the invention includes a semiconductor heterostructure that provides a plurality of lasing modules connected in series. Each lasing module includes a plurality of quantum well structure that collectively generate at least an upper lasing state, a lower lasing state, and a relaxation state such that the upper and the lower lasing states are separated by an energy corresponding to an optical frequency in a range of about 1 to about 10 Terahertz. The lower lasing state is selectively depopulated via resonant LO-phonon scattering of electrons into the relaxation state.

Owner:MASSACHUSETTS INST OF TECH

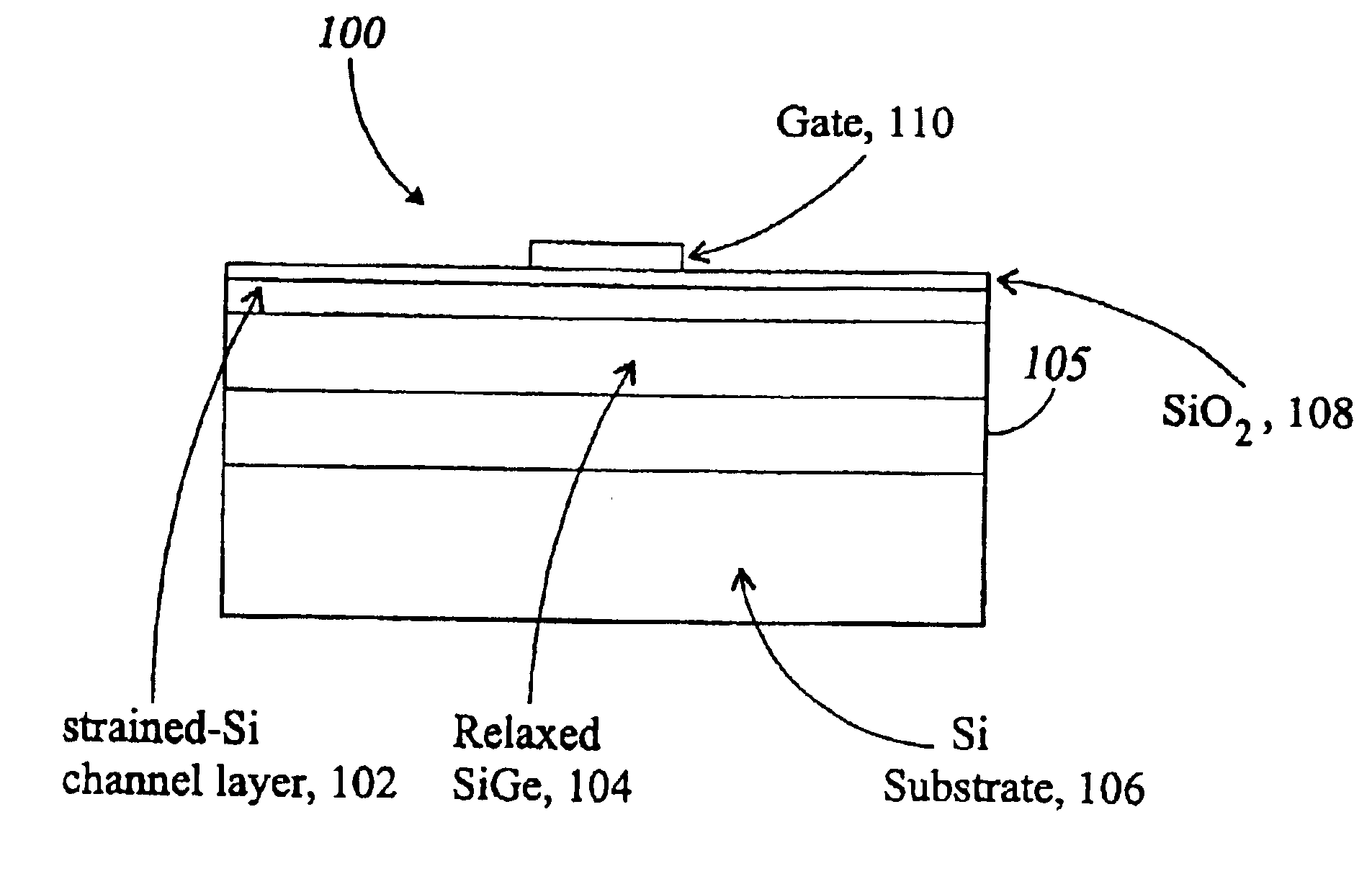

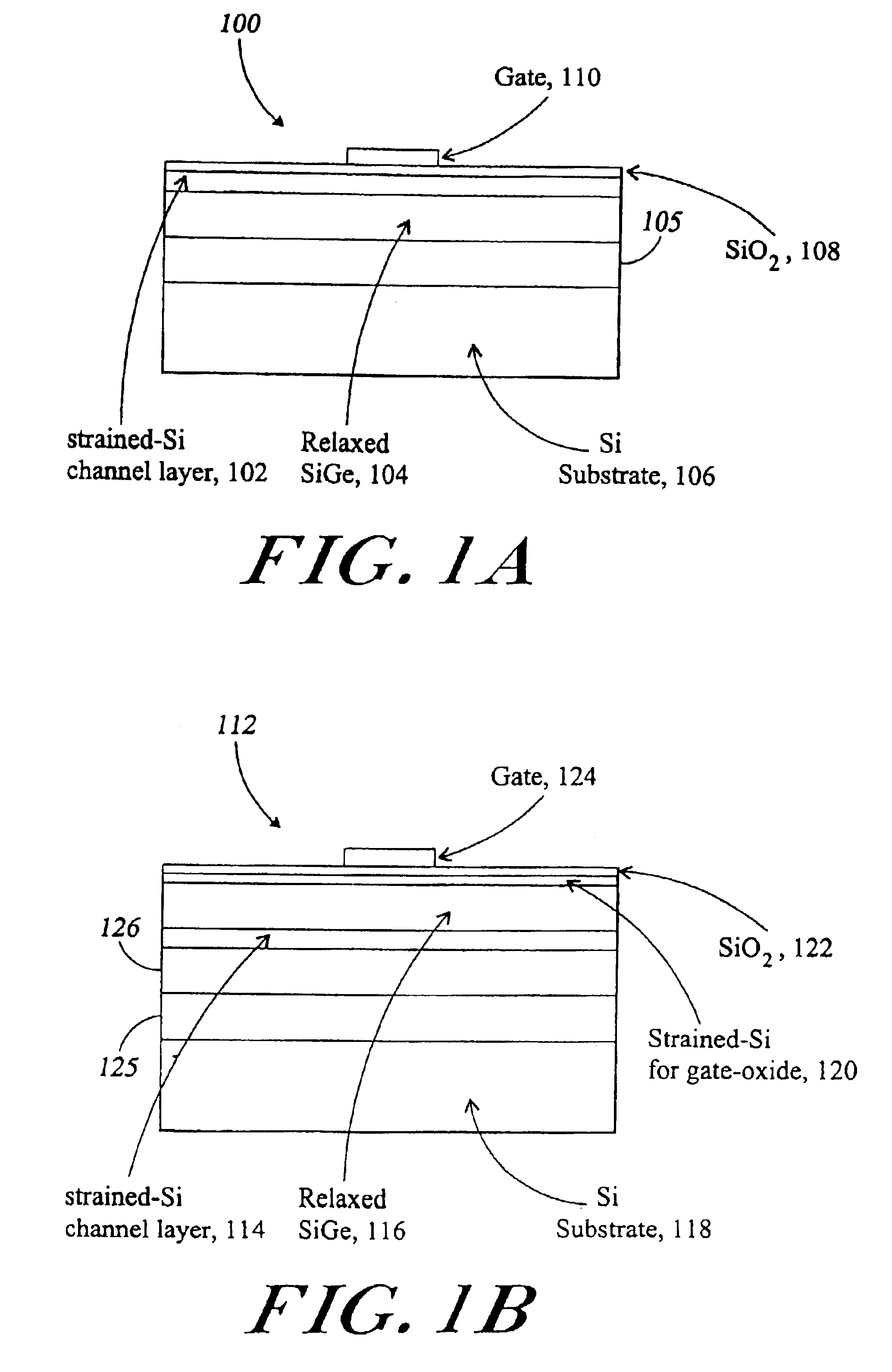

Gate technology for strained surface channel and strained buried channel MOSFET devices

InactiveUS6846715B2Solid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

A method of fabricating a semiconductor device including providing a semiconductor heterostructure, the heterostructure having a relaxed Si1−xGex layer on a substrate, a strained channel layer on the relaxed Si1−xGex layer, and a Si1−yGey layer; removing the Si1−yGey layer; and providing a dielectric layer. The dielectric layer includes a gate dielectric of a MISFET. In alternative embodiments, the heterostructure includes a SiGe spacer layer and a Si layer.

Owner:TAIWAN SEMICON MFG CO LTD

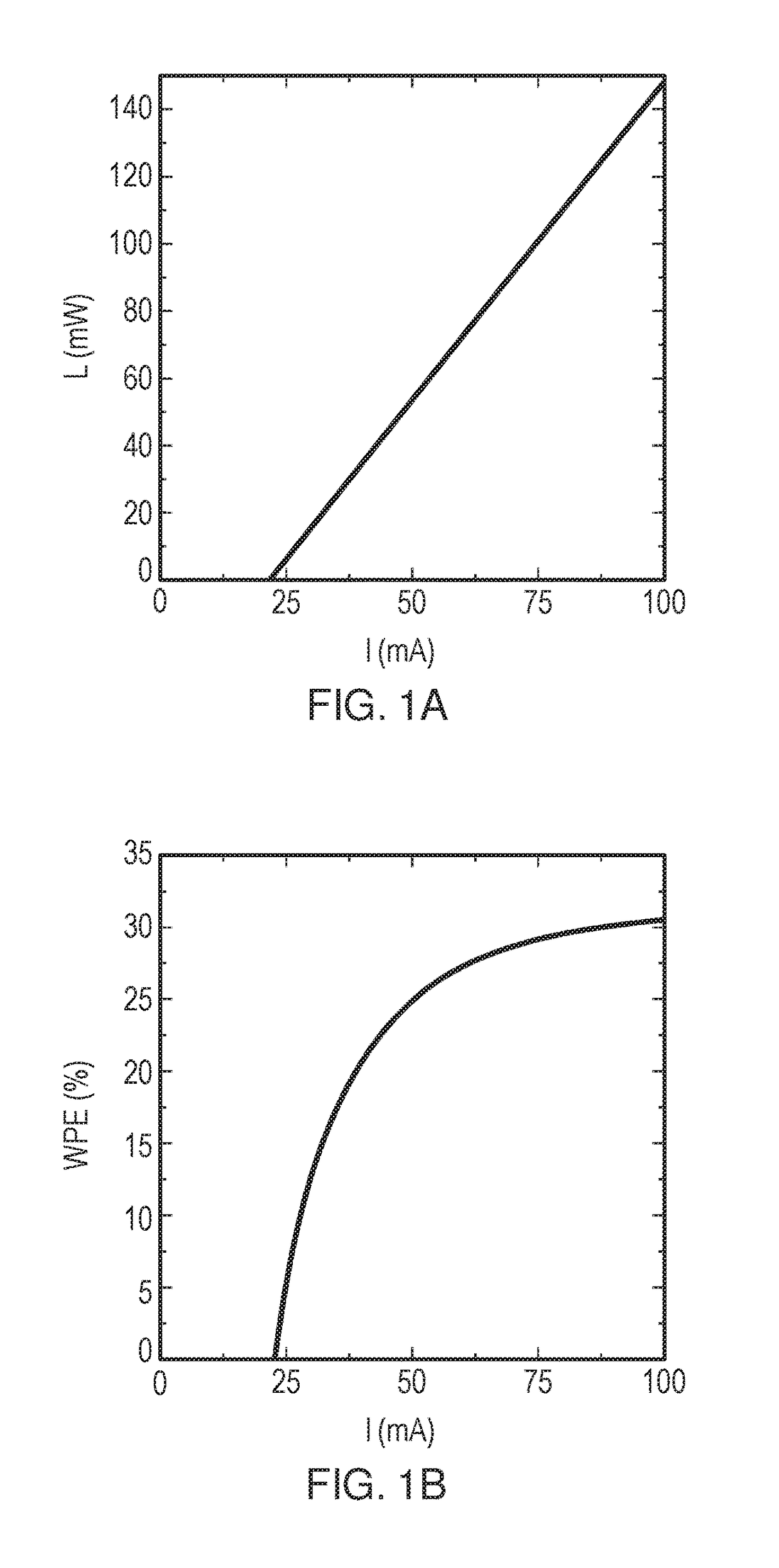

Low Power Edge-Emitting Laser Diode and Laser Diode Module

ActiveUS20180083422A1Stable light power levelImprove output power stabilityOptical wave guidanceSemiconductor laser arrangementsBack reflectorSemiconductor heterostructures

A low power, side-emitting semiconductor laser diode is provided. The laser diode is formed from a semiconductor heterostructure having an active layer sandwiched between an n-type layer and a p-type layer, wherein the active layer forms a gain medium of width W. Front and back reflectors of reflectivity Rf and Rb are arranged on opposing side facets of the semiconductor heterostructure part to form a cavity of length L containing at least a part of the active layer which thus forms the gain medium for the laser diode, the gain medium having an internal loss αi. To achieve stable, low power operation close to threshold, the laser diode is configured with the following parameter combination: width W: 1 μm≦W≦2 μm; cavity length L: 100 μm≦L≦600 μm; internal loss αi: 0 cm−1αi≦30 cm−1; back reflectivity Rb: 100≧Rb≧80%; and front reflectivity Rf: 100≧Rf≧60%.

Owner:EXALOS

Semiconductor heterostructures having reduced dislocation pile-ups and related methods

InactiveUS20080079024A1Overcome limitationsImprove manufacturabilityPolycrystalline material growthSemiconductor/solid-state device manufacturingThreading dislocationsInter layer

Dislocation pile-ups in compositionally graded semiconductor layers are reduced or eliminated, thereby leading to increased semiconductor device yield and manufacturability. This is accomplished by introducing a semiconductor layer having a plurality of threading dislocations distributed substantially uniformly across its surface as a starting layer and / or at least one intermediate layer during growth and relaxation of the compositionally graded layer. The semiconductor layer may include a seed layer disposed proximal to the surface of the semiconductor layer and having the threading dislocations uniformly distributed therein.

Owner:TAIWAN SEMICON MFG CO LTD

Terahertz lasers and amplifiers based on resonant optical phonon scattering to achieve population inversion

ActiveUS7158545B2Promote generationHigh selectivityOptical wave guidanceLaser using scattering effectsAudio power amplifierOptical frequencies

The present invention provides quantum cascade lasers and amplifier that operate in a frequency range of about 1 Terahertz to about 10 Terahertz. In one aspect, a quantum cascade laser of the invention includes a semiconductor heterostructure that provides a plurality of lasing modules connected in series. Each lasing module includes a plurality of quantum well structure that collectively generate at least an upper lasing state, a lower lasing state, and a relaxation state such that the upper and the lower lasing states are separated by an energy corresponding to an optical frequency in a range of about 1 to about 10 Terahertz. The lower lasing state is selectively depopulated via resonant LO-phonon scattering of electrons into the relaxation state.

Owner:MASSACHUSETTS INST OF TECH

Heterostructure photoanode for dye-sensitized solar cell and manufacturing method thereof

InactiveCN101728083AImprove photoelectric conversion efficiencyFacilitate transmissionLight-sensitive devicesFinal product manufactureFiberDye absorption

The invention discloses a heterostructure photoanode for a dye-sensitized solar cell, comprising conductive glass and a dye absorption layer coated on the conductive glass. The dye absorption layer is a TiO2-semiconductor heterostructure film, wherein a primary structure is TiO2 nano-fiber or / and TiO2 nano-tubes, and a secondary structure is at least one of semiconductor nano-particles, semiconductor nao-rods and semiconductor nano-wires constructed by semiconductor nano-fiber or / and semiconductor nano-tubes, namely that 1-D heterostructure nano-material as the dye absorption layer of the photoanode of a dye-sensitized solar cell. The combination of the structural characteristics of 1-D nano-size and the polarization property of galvanic couple formed by TiO2 / semiconductor composite system interface can enhance the transmission and the separation of electric charges and improve the electronic transmission efficiency; meanwhile, a huge specific surface area can effectively improve the amount of dye absorption and the light utilization efficiency and further improve the photoelectric transformation efficiency of the dye-sensitized solar cell by 10 percent.

Owner:DALIAN FISHERIES UNIVERSITY

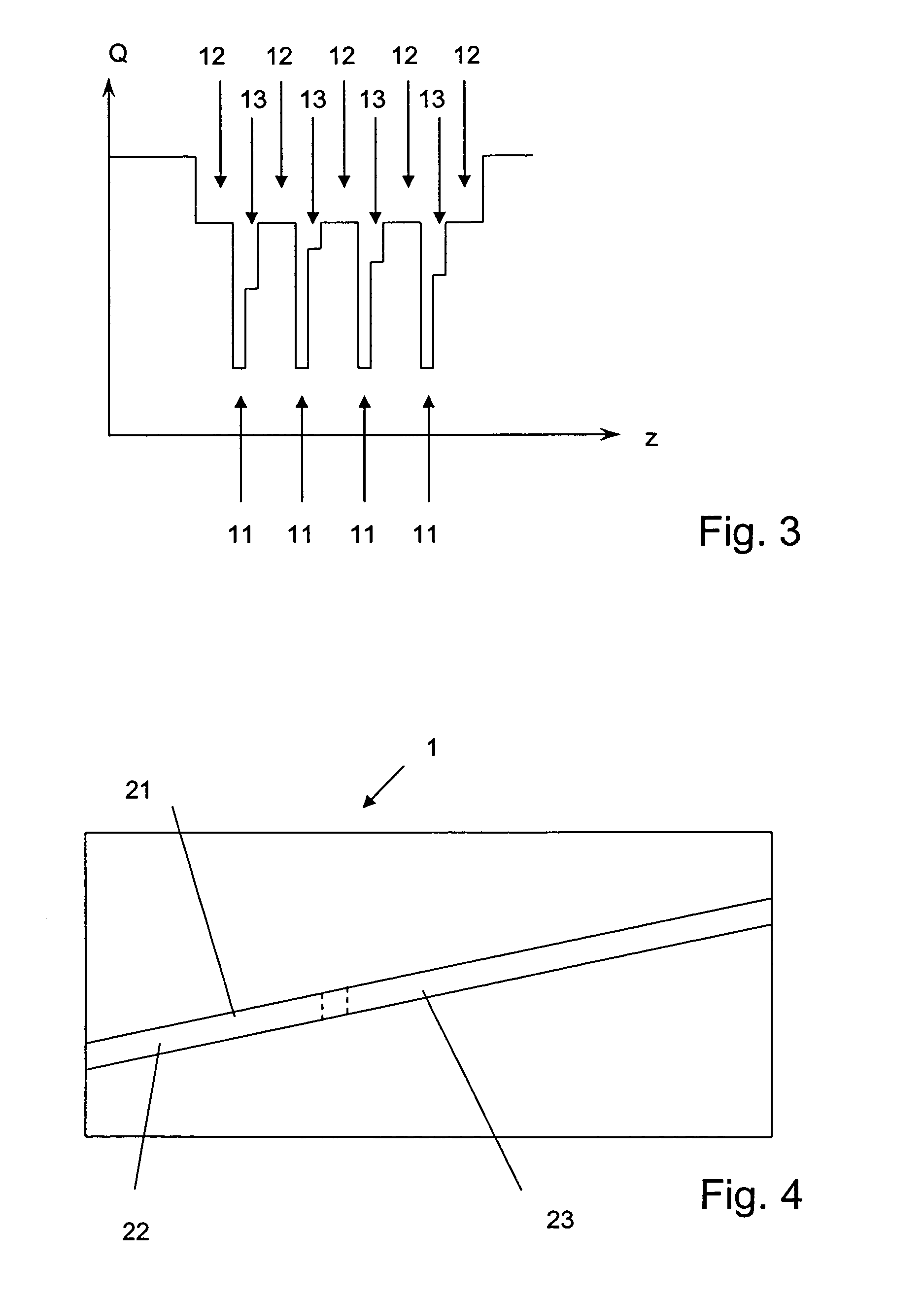

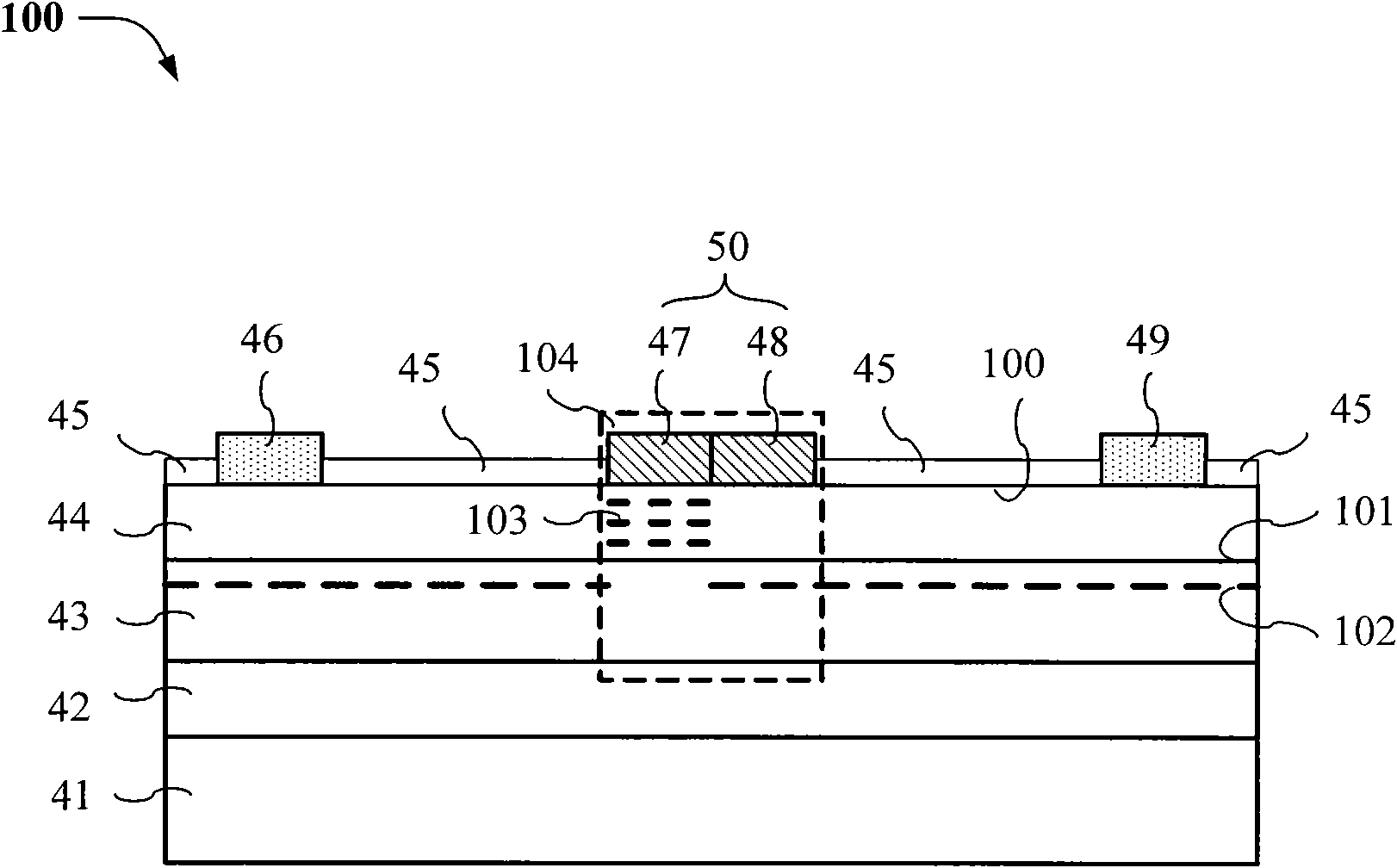

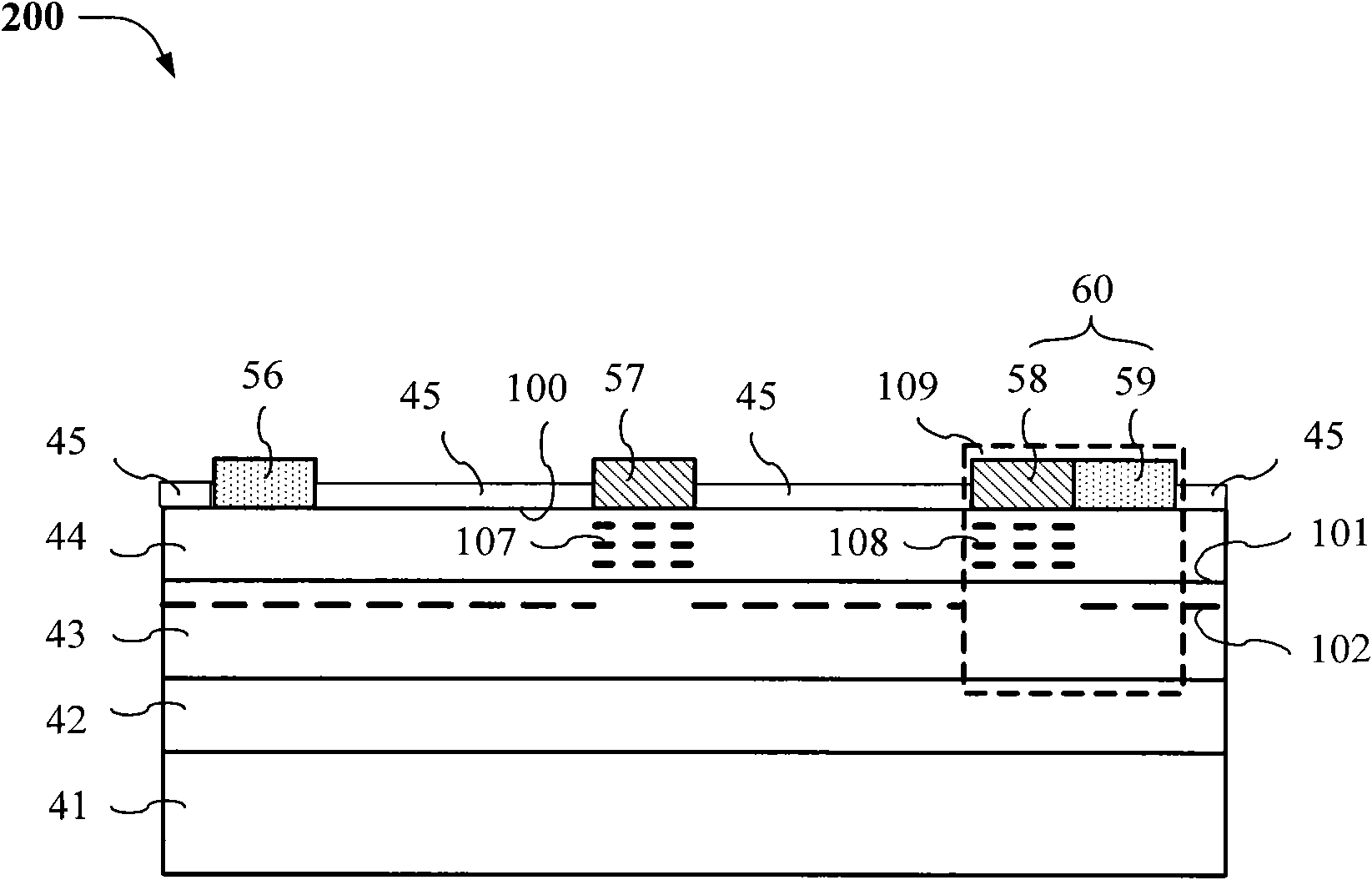

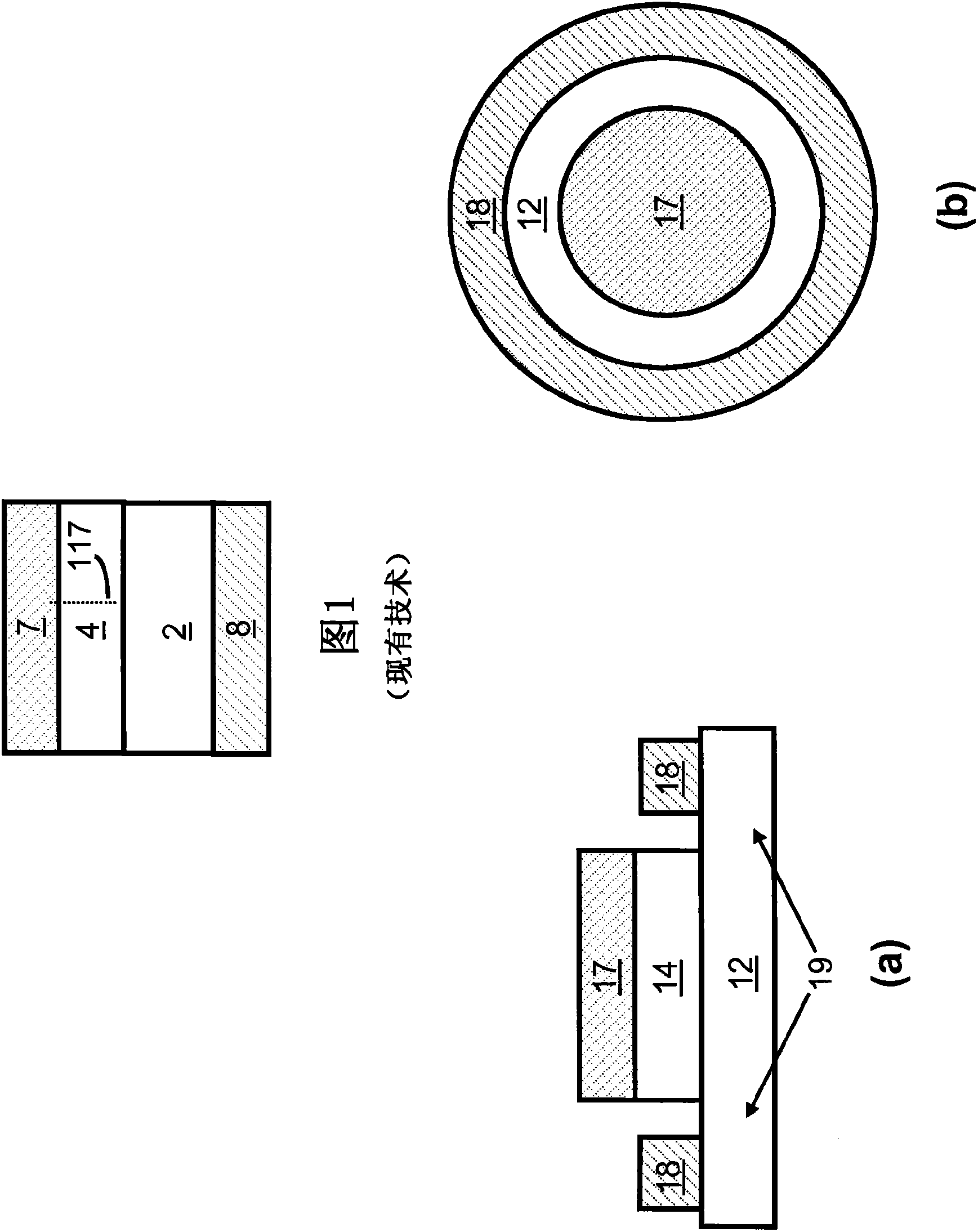

sled

ActiveUS20050161685A1Reduce manufacturing costIncrease output strengthSemiconductor/solid-state device detailsSolid-state devicesCharge carrierLight beam

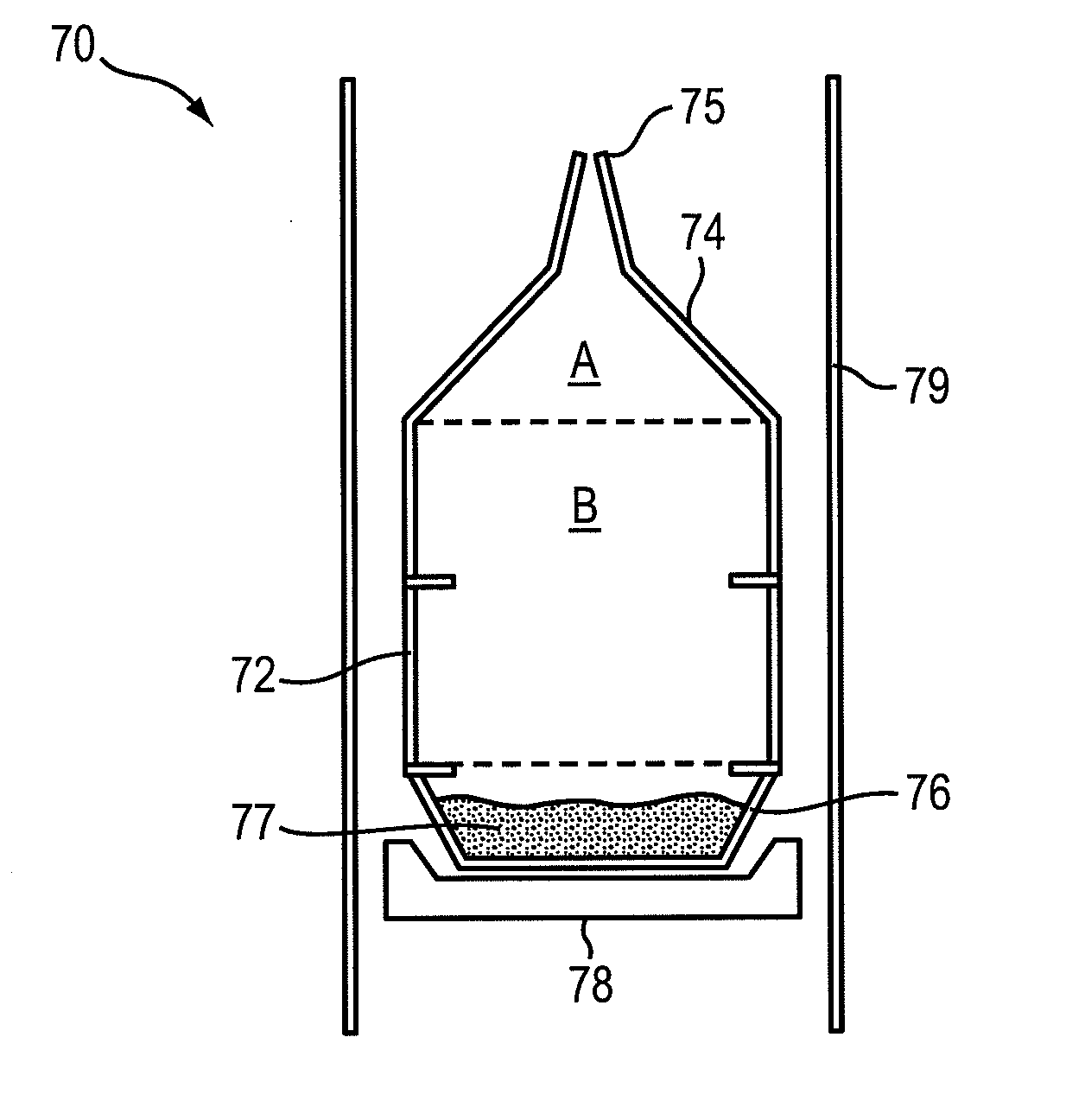

A non-lasing superluminescent light emitting diode (SLED) comprises a semiconductor heterostructure forming a PN junction and a waveguide defining an optical beam path. The heterostructure includes a gain region and an absorber region in series with the gain region in the optical beam path. A voltage is applied to the PN junction in the gain region by first contact means, so that light emission from the active region and along the optical beam path is produced. According to the invention, second contact means are provided, contacting the PN junction in the absorber region and operable to remove charge carriers generated by absorption in the absorber region. The second contact means are not connected to a voltage source, but to a charge carrier reservoir such as a metal surface. According to a preferred embodiment, the two end facets of the waveguide are perpendicular to the optical beam path.

Owner:EXALOS

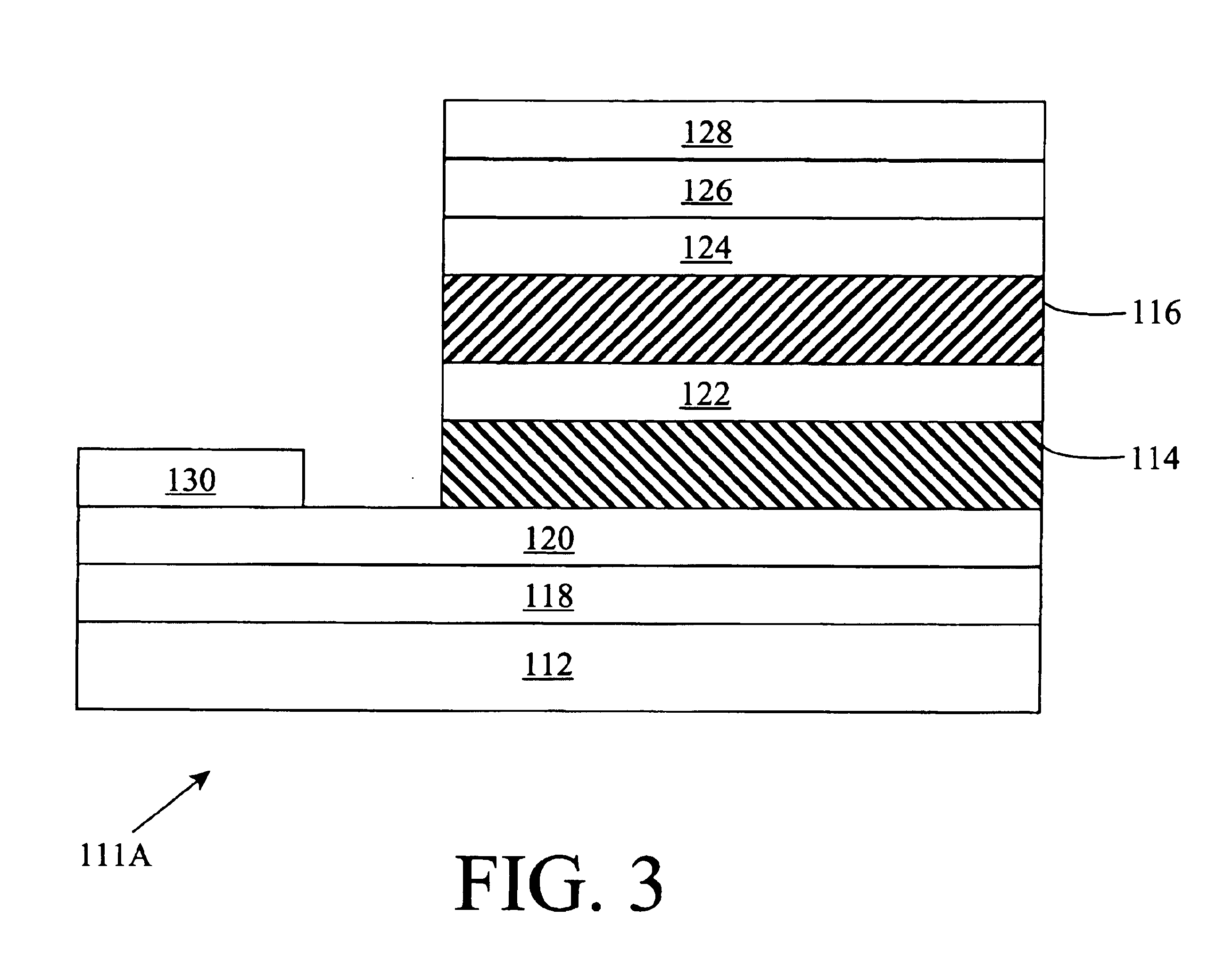

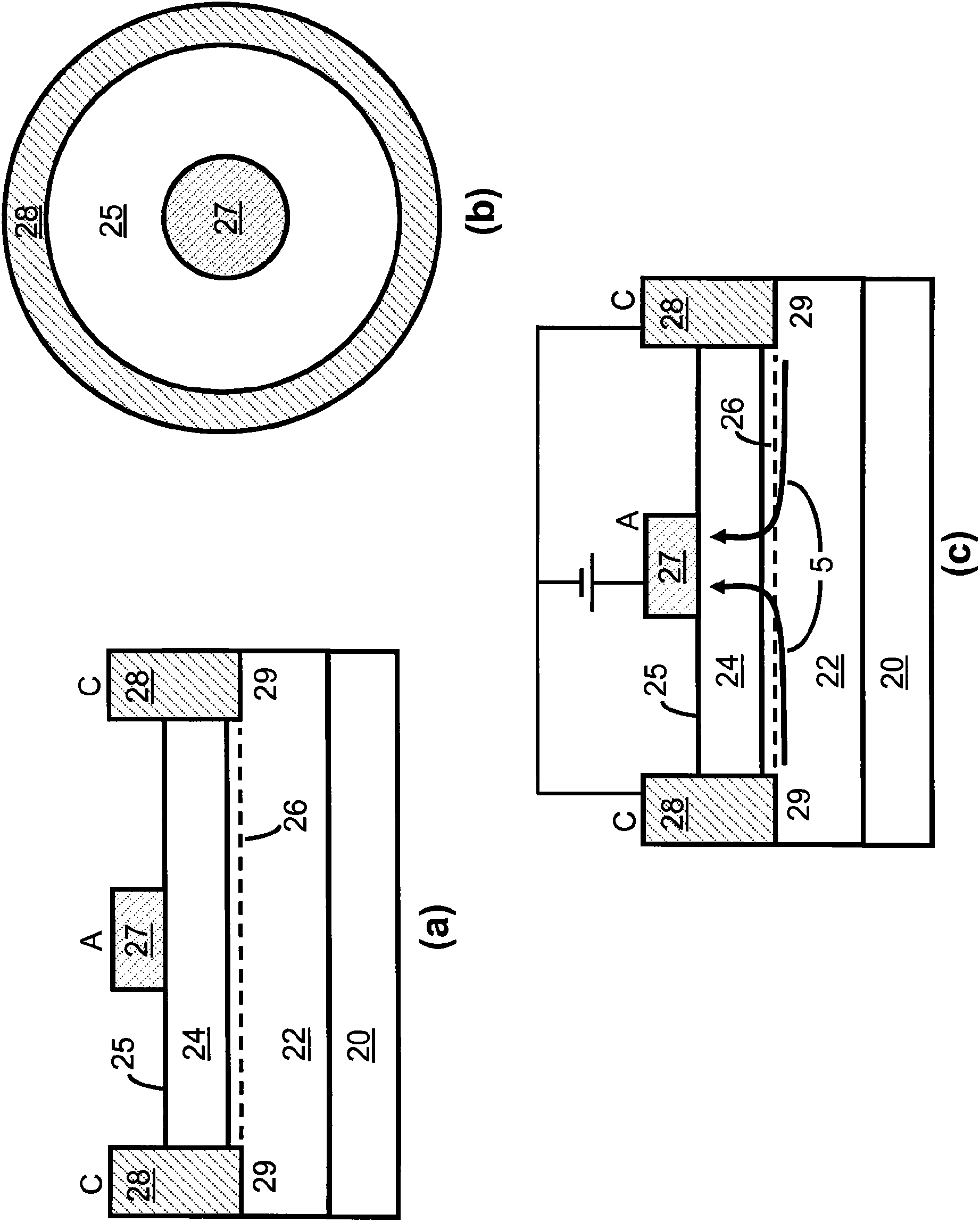

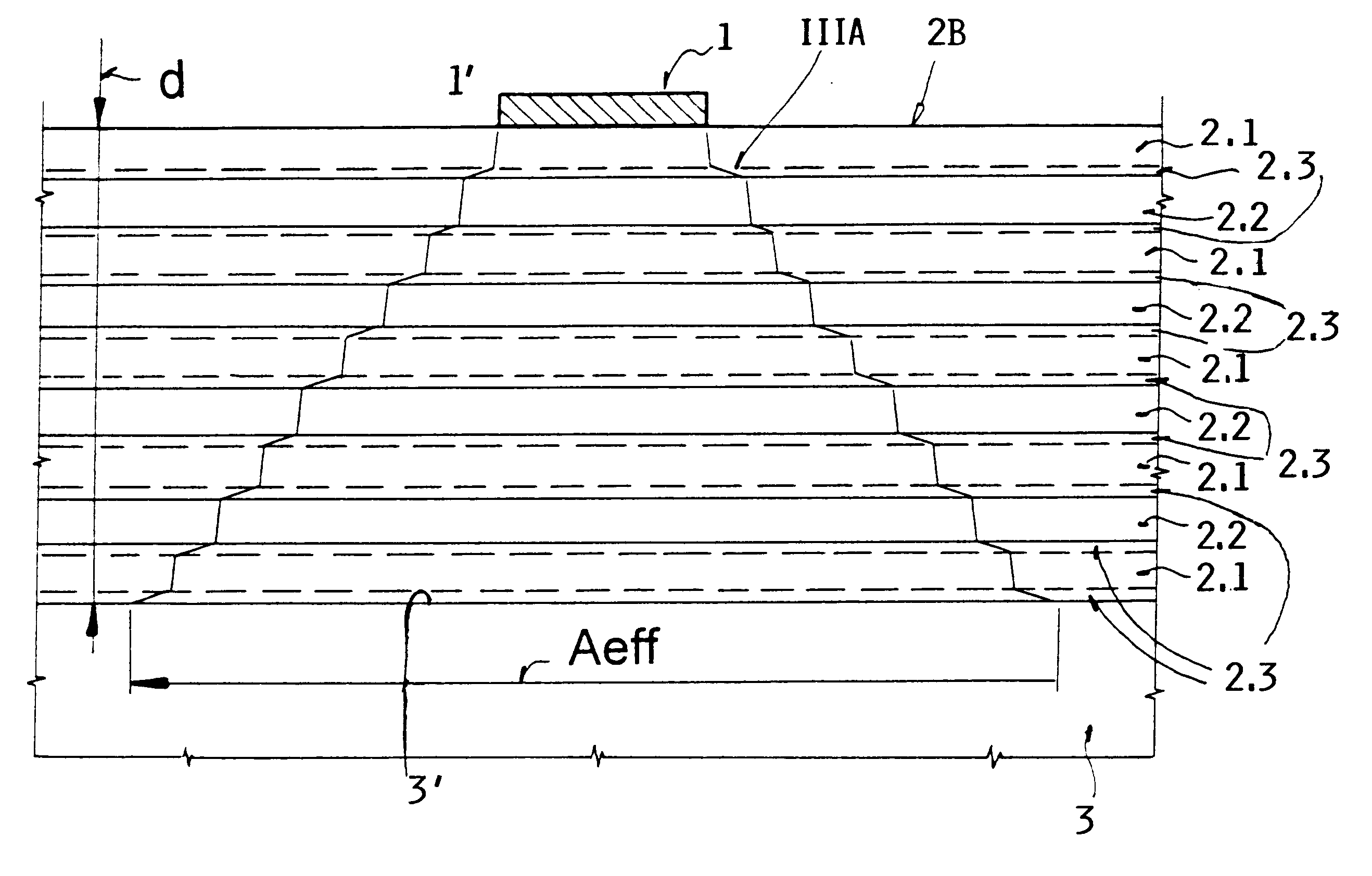

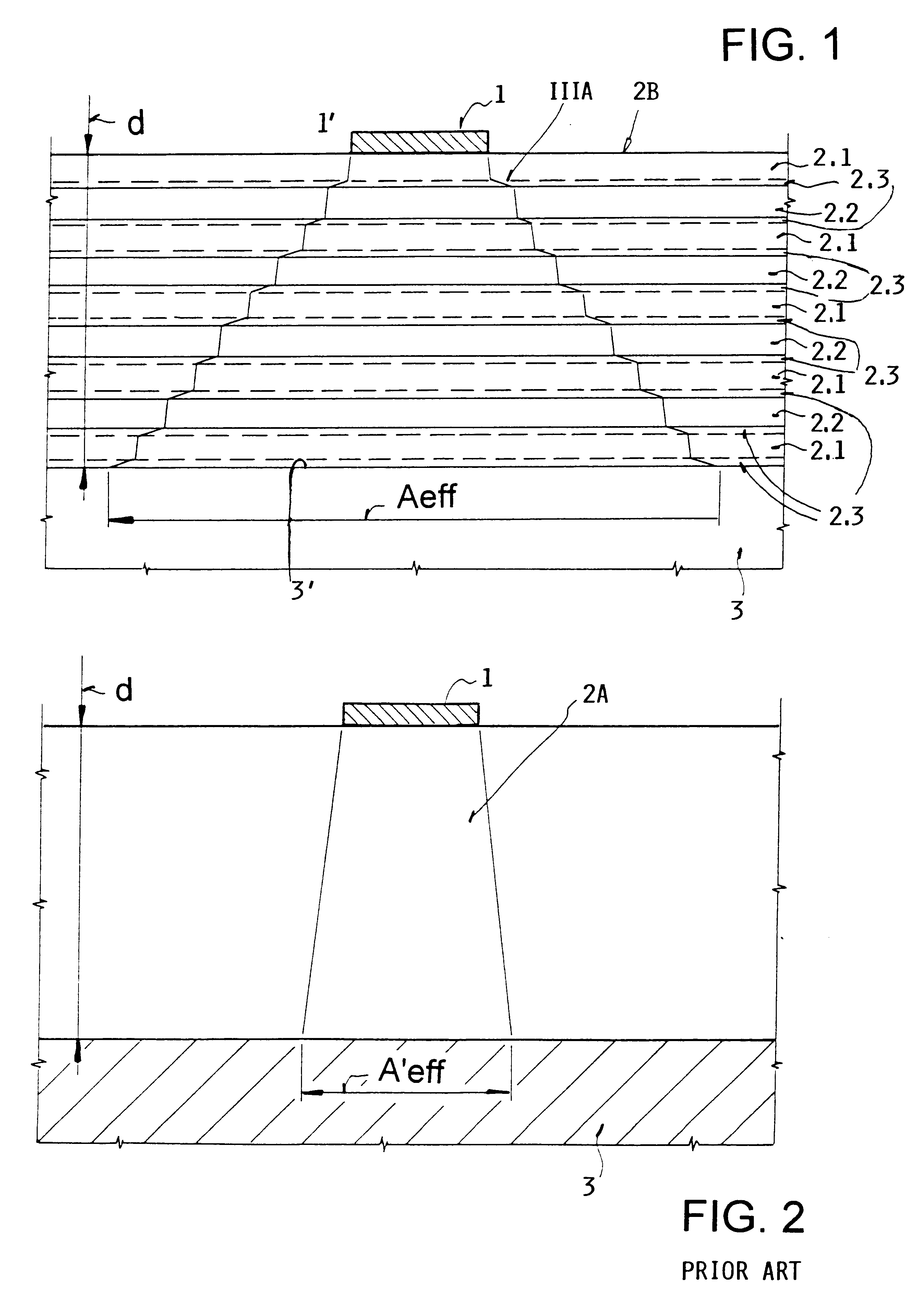

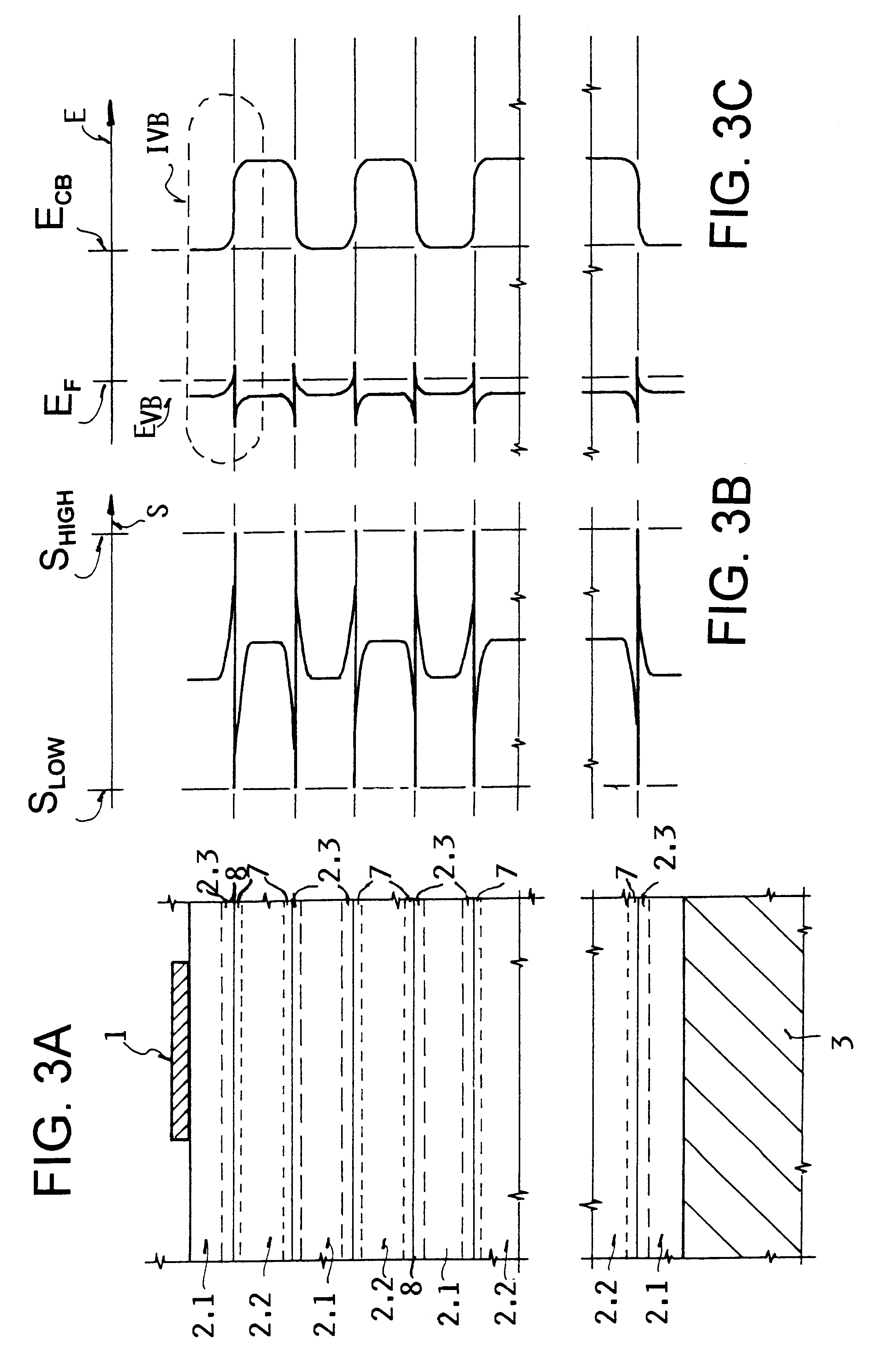

Layered semiconductor structure for lateral current spreading, and light emitting diode including such a current spreading structure

In order to achieve lateral current spreading between a current injecting or current collecting surface of an electrode and an active surface of an active region in a semiconductor device such as a light emitting diode, a layered semiconductor heterostructure is arranged between the electrode and the active surface. The heterostructure includes at least two semiconductor layers forming a heterojunction therebetween, whereby the semiconductor layers are composed of different semiconductor materials or different compositional proportions of the same compound semiconductor. An enrichment region for the majority charge carriers is formed in one of the layers adjacent the heterojunction, and a majority charge carrier energy band discontinuity exists at the heterojunction. Each enrichment region provides a strong lateral current spreading effect, such that a stacked arrangement of plural heterojunction layer pairs brings about a strong step-wise lateral current spreading. The light output and efficiency of a light emitting diode is substantially improved by incorporating such a current spreading heterostructure.

Owner:VISHAY SEMICON