Lattice-mismatched semiconductor structures with reduced dislocation defect densities related methods for device fabrication

A lattice mismatch, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

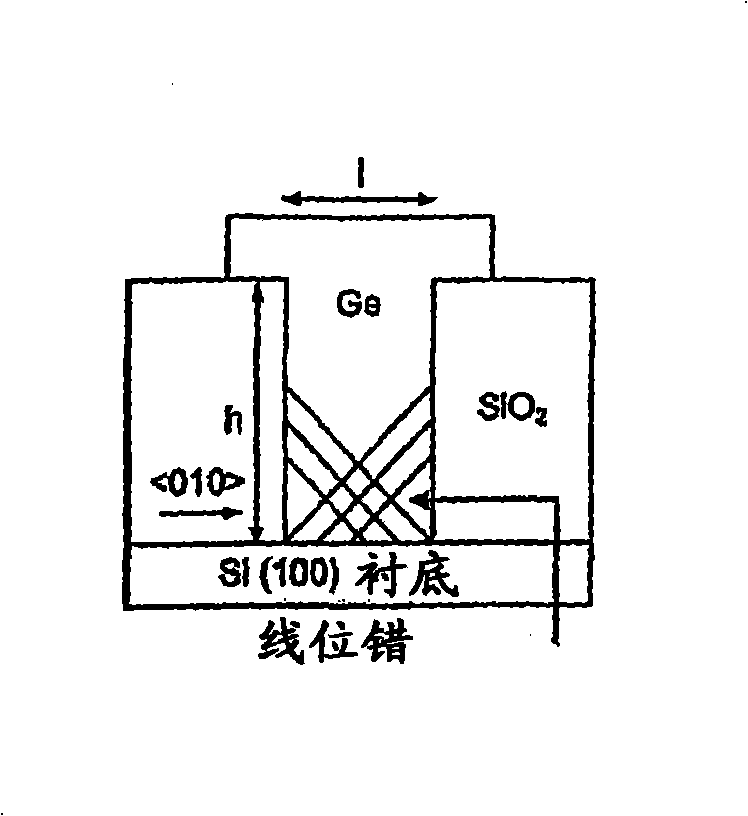

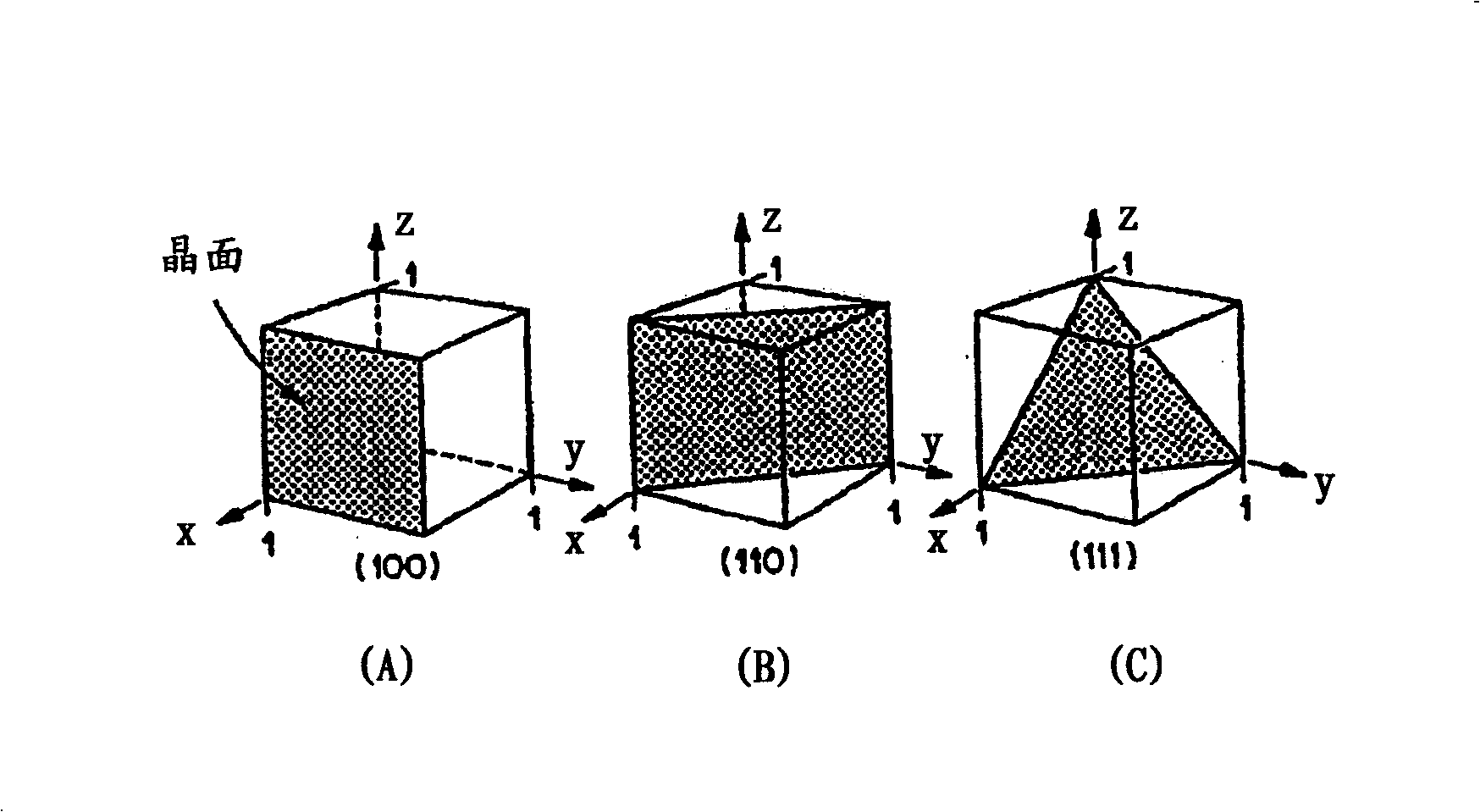

[0046] According to various embodiments of the invention, the present invention is concerned with the fabrication of monolithic lattice-mismatched semiconductor heterostructures with limited area regions of the upper surface substantially depleted of line dislocations and other dislocation defects , and the fabrication of semiconductor devices based on such lattice-mismatched heterostructures.

[0047] Silicon (Si) is considered to be the most common semiconductor used in the electronics industry today. Most of the silicon used to form wafers is formed from single crystal silicon. Silicon wafers are used as substrates on which CMOS devices are formed. A silicon wafer also refers to a semiconductor substrate or a semiconductor wafer. However, although described in connection with silicon wafers, substrates comprising or consisting essentially of other semiconductor materials are also contemplated without departing from the spirit and scope of the present invention.

[0048] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com