Patents

Literature

656 results about "Gigabit Ethernet" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer networking, Gigabit Ethernet (GbE or 1 GigE) is the various technologies for transmitting Ethernet frames at a rate of a gigabit per second (1,000,000,000 bits per second), as defined by the IEEE 802.3ab standard. It came into use beginning in 1999, gradually supplanting Fast Ethernet in wired local networks, as a result of being considerably faster. The cables and equipment are very similar to previous standards and have been very common and economical since 2010.

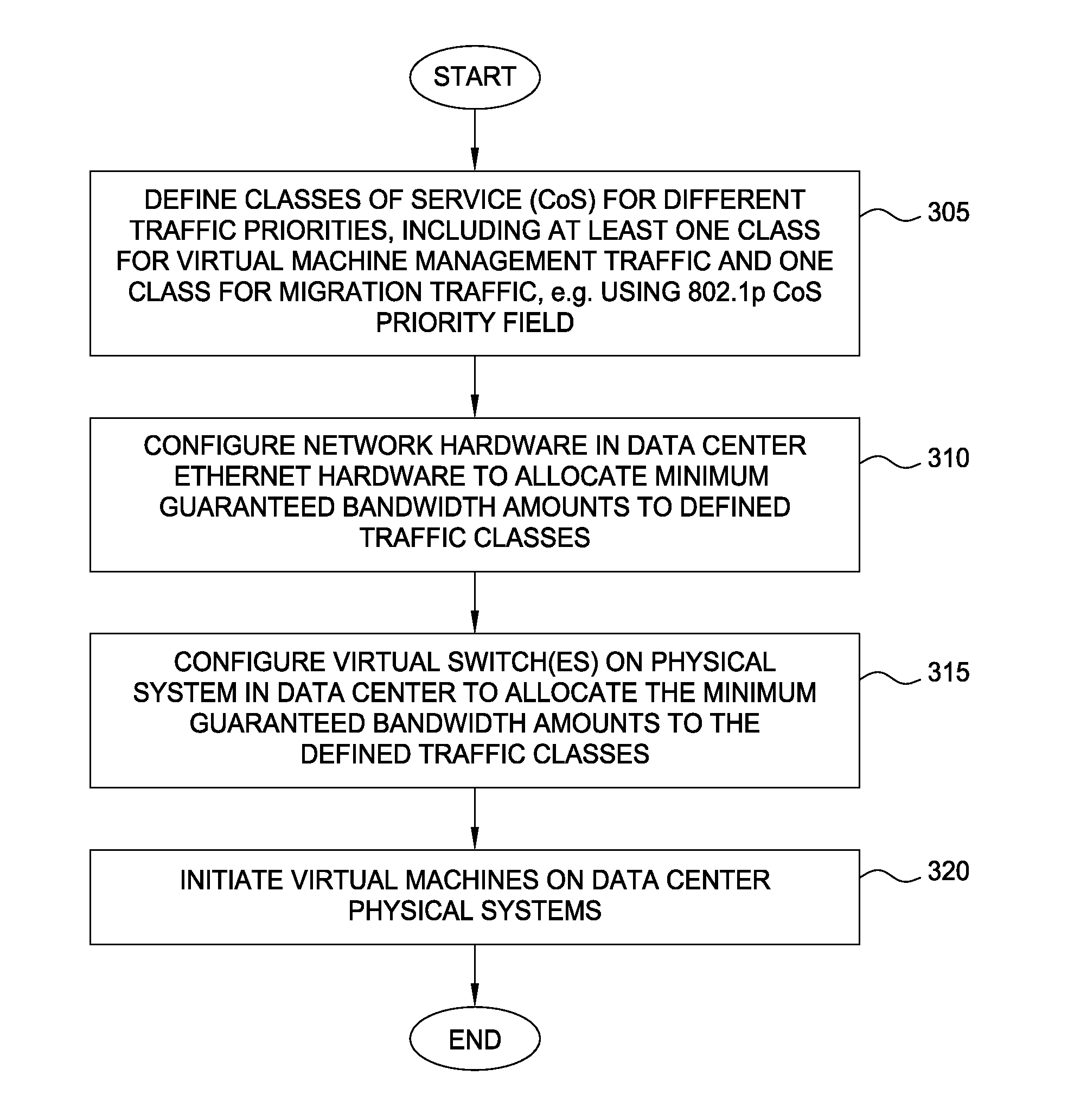

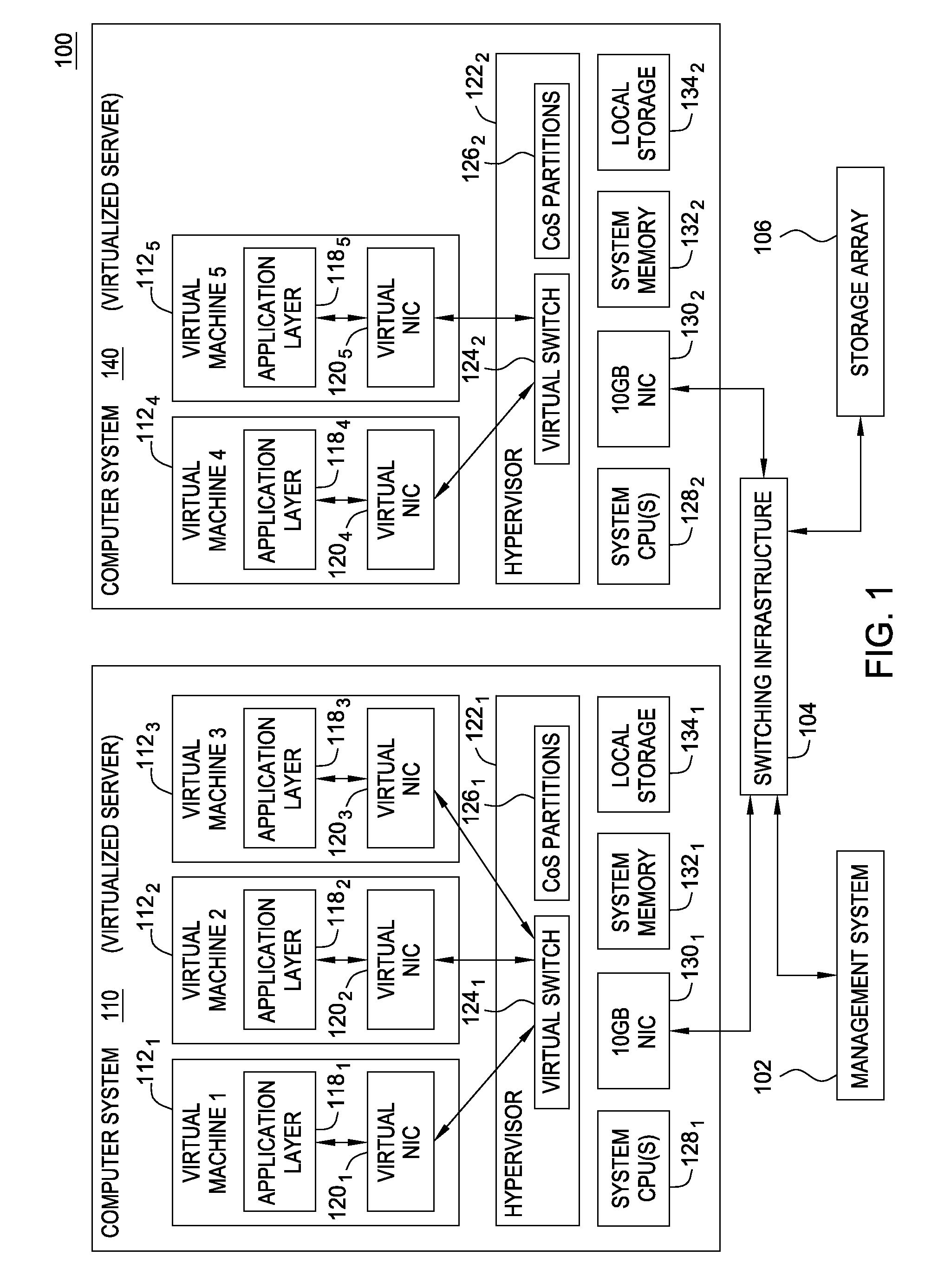

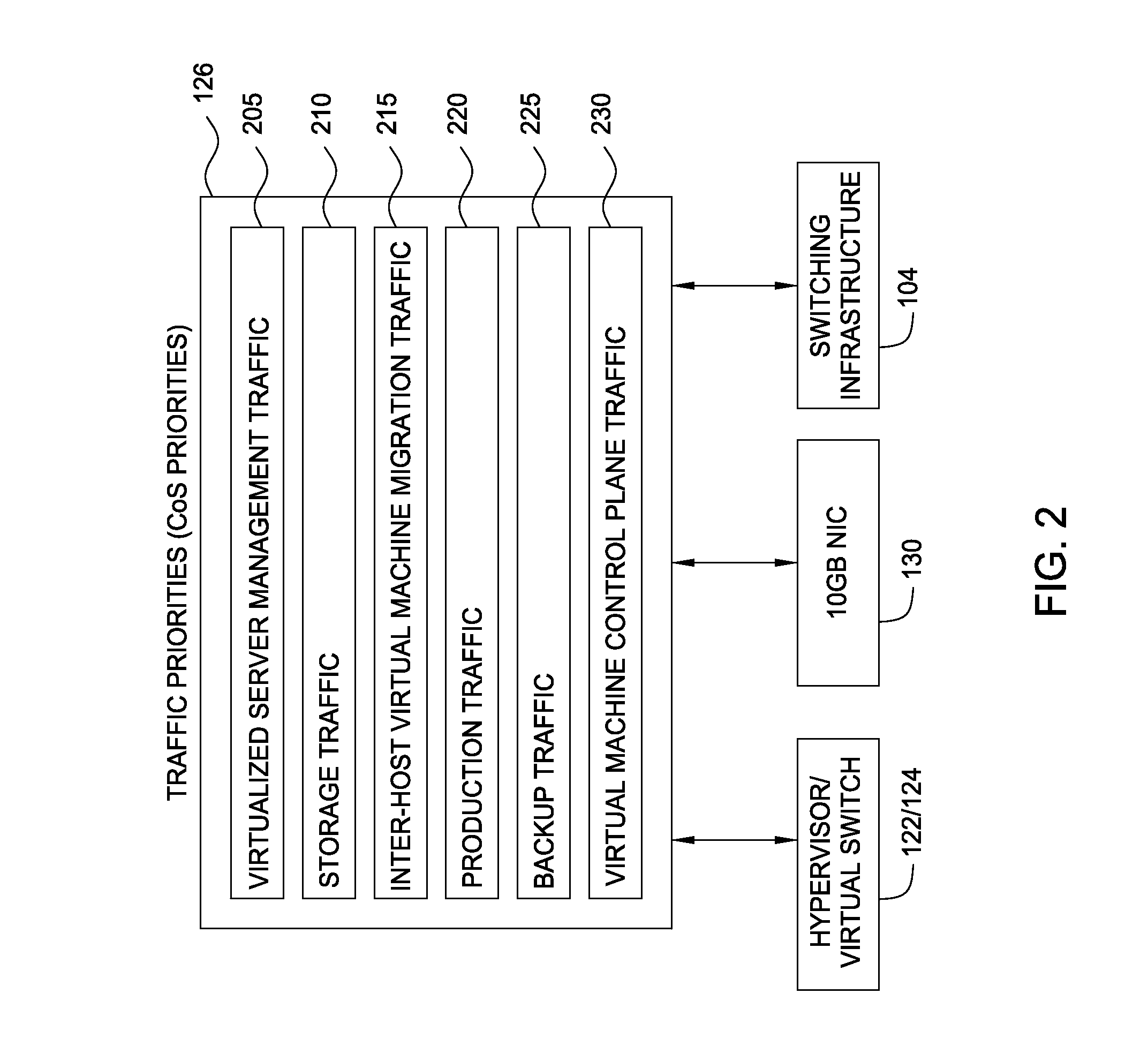

Network consolidation for virtualized servers

Techniques are disclosed for virtualized server kernel and virtual networks consolidation. The network consolidation allows a data center to migrate from an infrastructure that uses multiple dedicated gigabit Ethernet Network Adapters to manage system virtualization and migration to an infrastructure using consolidated, redundant, 10 gigabit Ethernet adapters. Different priority classes may be defined for different classes of network traffic such as hypervisor management traffic, inter-host virtual machine migration traffic, virtual machine production traffic, virtualized switching control plane traffic, etc. Further, an enhanced transmission standard may be used to specify a minimum bandwidth guarantee for certain traffic classes. Thus, the hypervisor management and inter-host virtual machine migration traffic may be transmitted, even the presence of congestion.

Owner:CISCO TECH INC

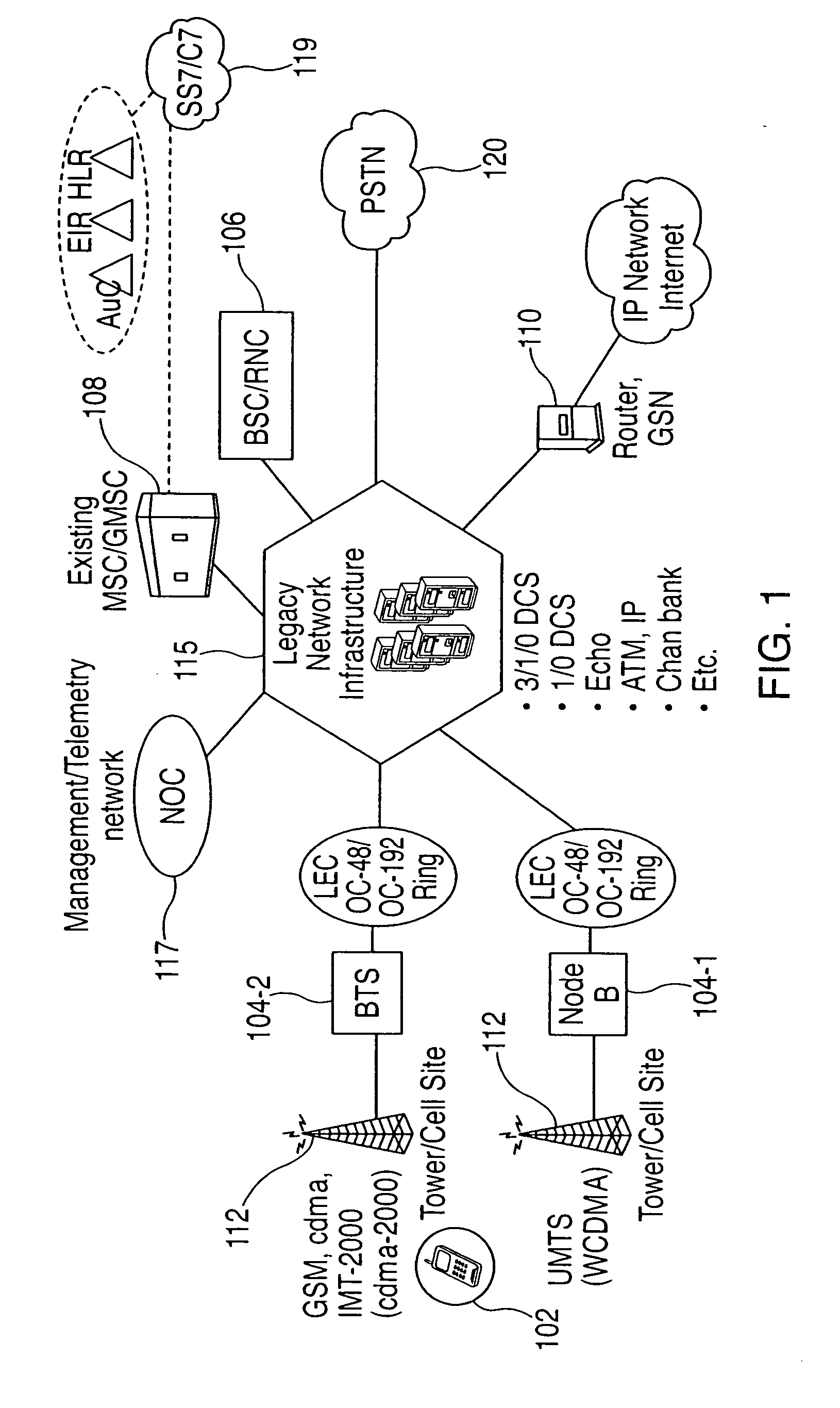

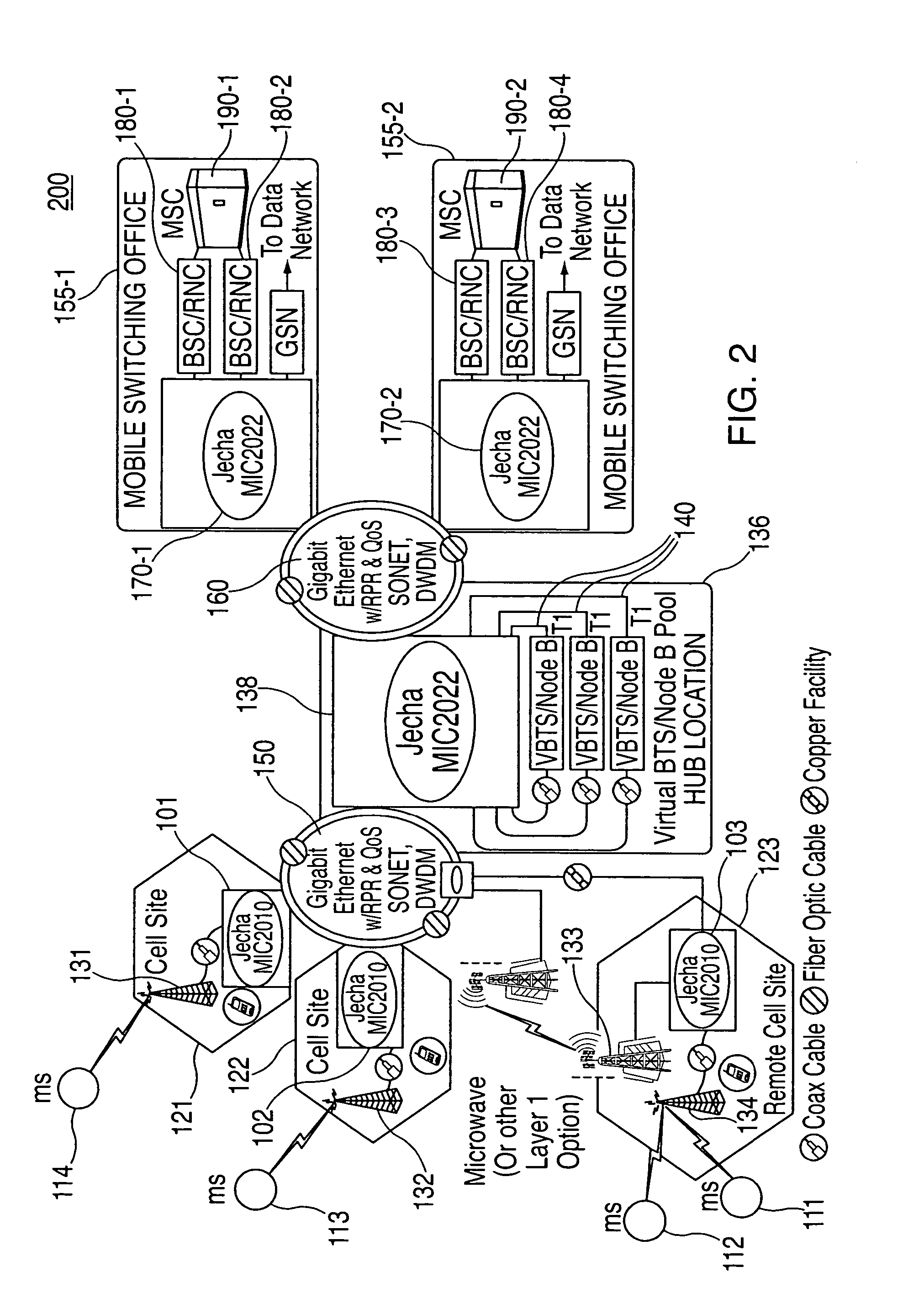

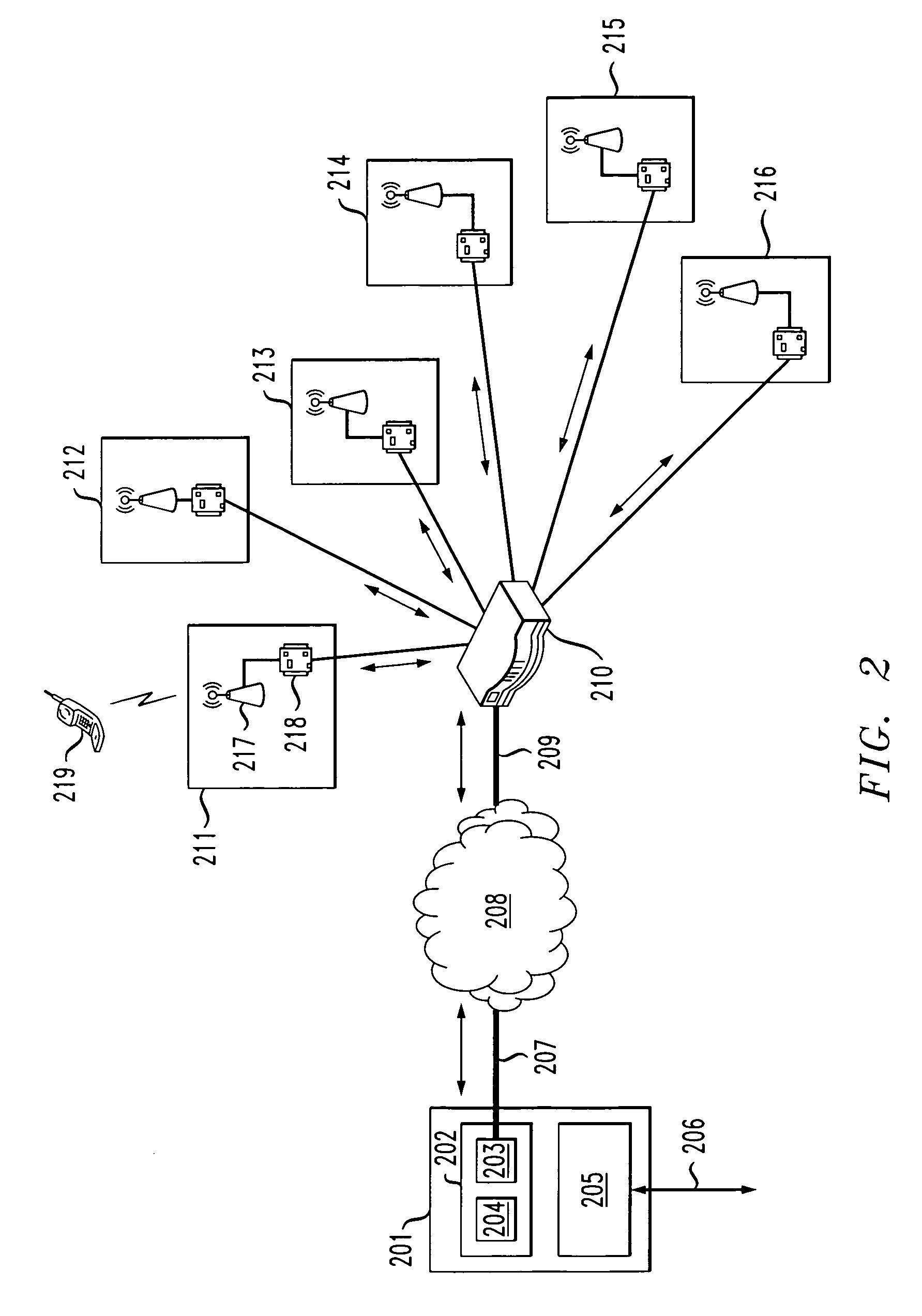

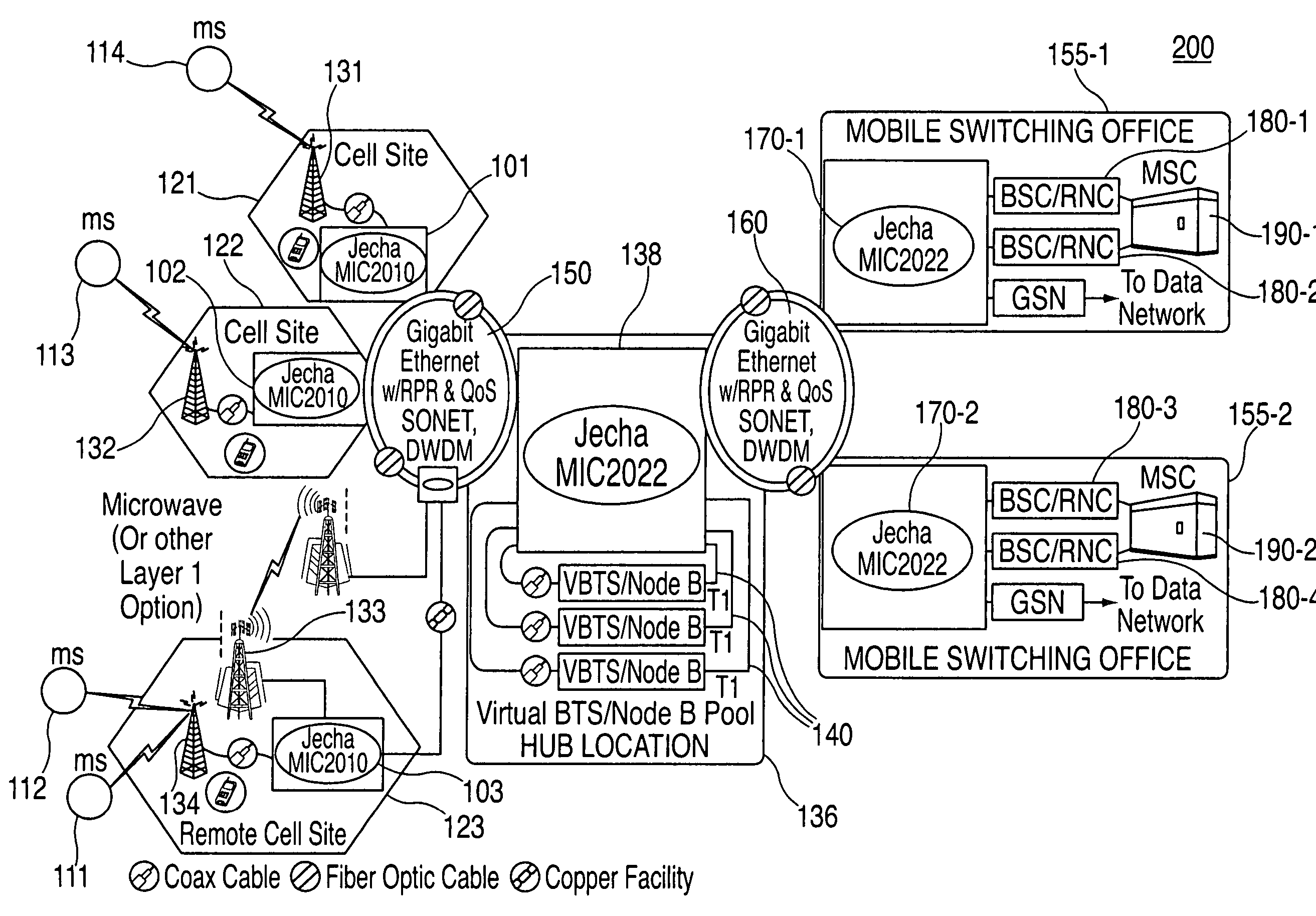

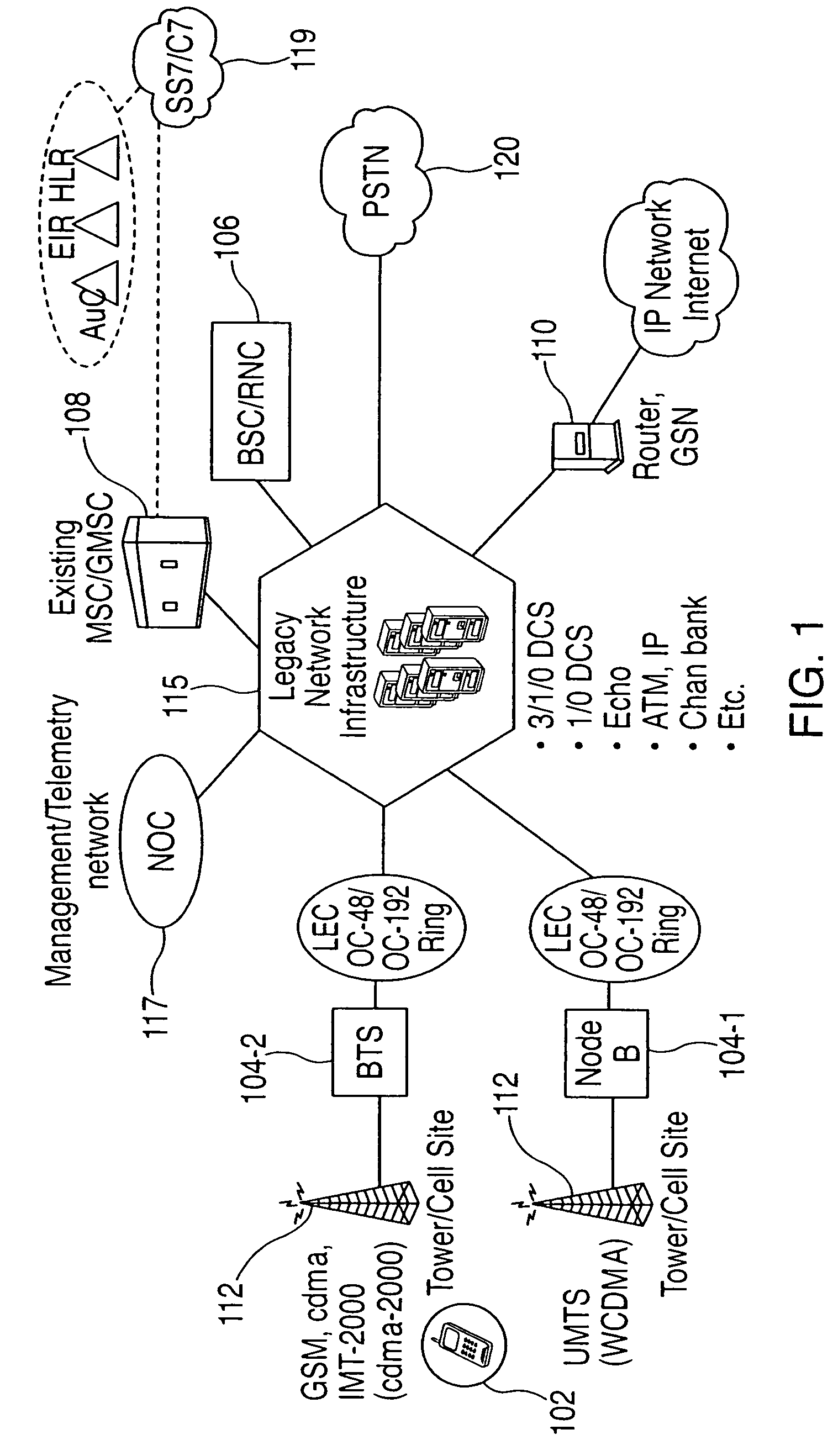

System and method for optimizing network capacity in a cellular wireless network

InactiveUS20050007993A1Easy to adaptNetwork traffic/resource managementPower distribution line transmissionQuality of serviceFiber

Owner:CHAMBERS MAHDI +1

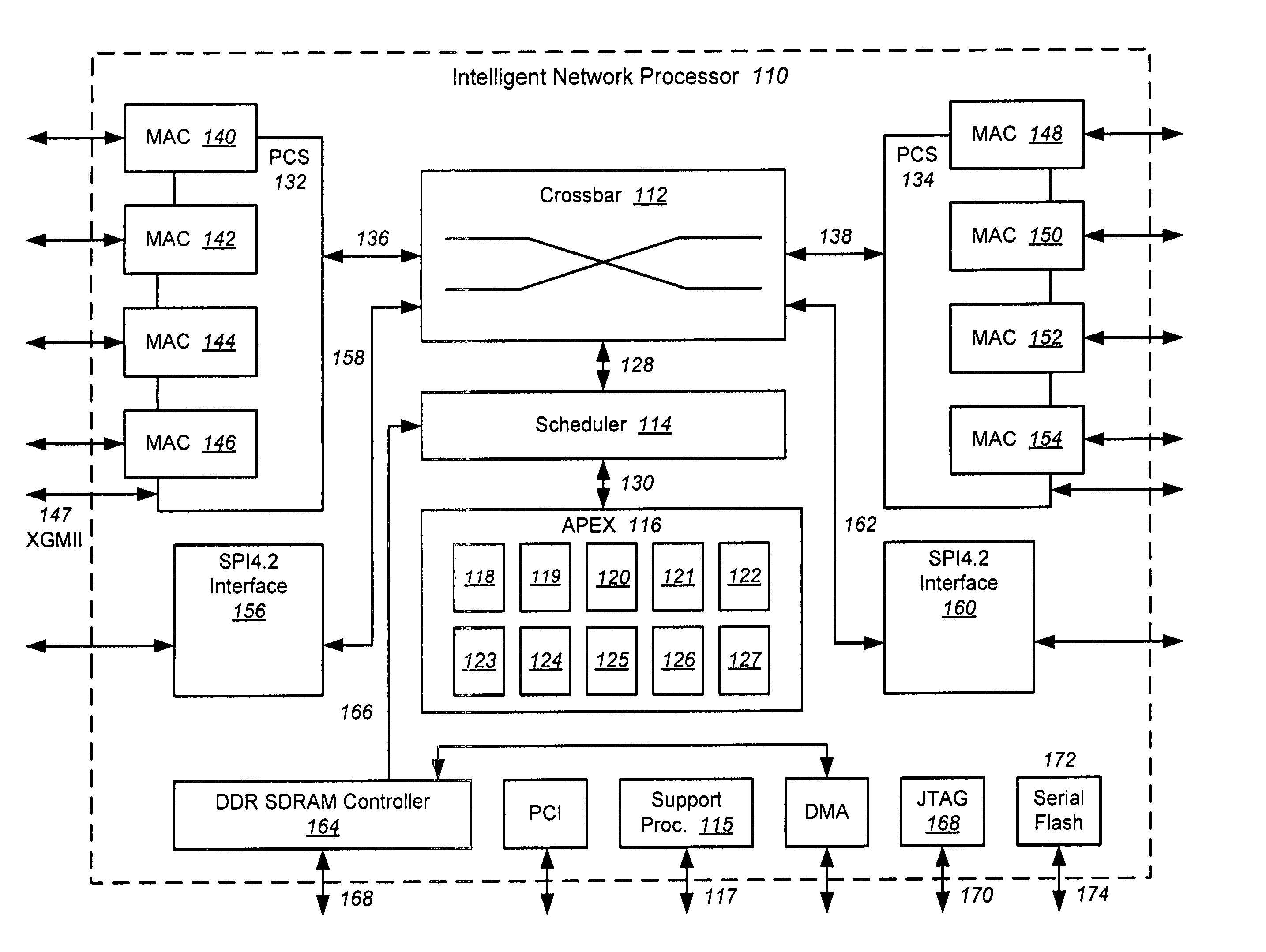

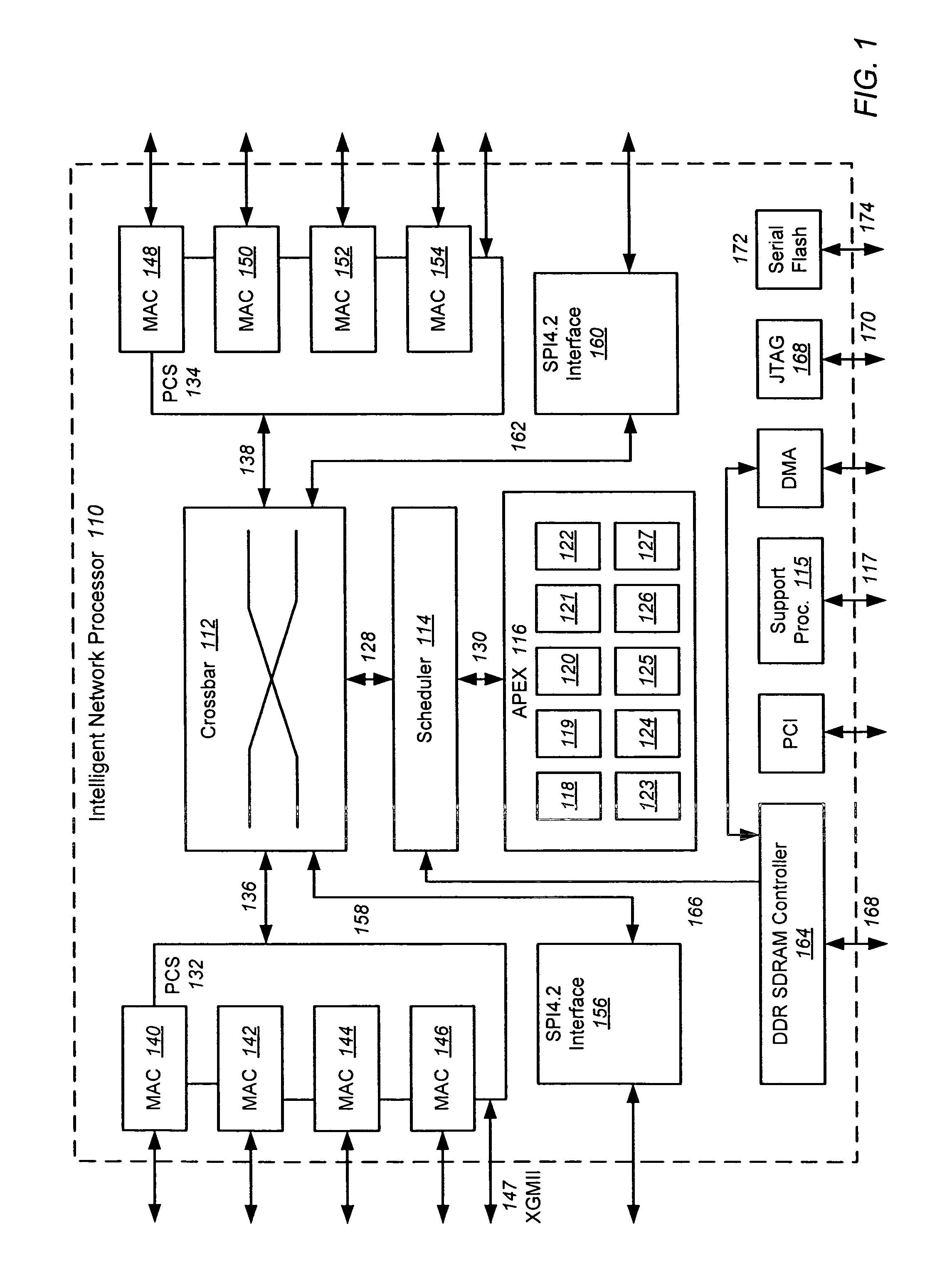

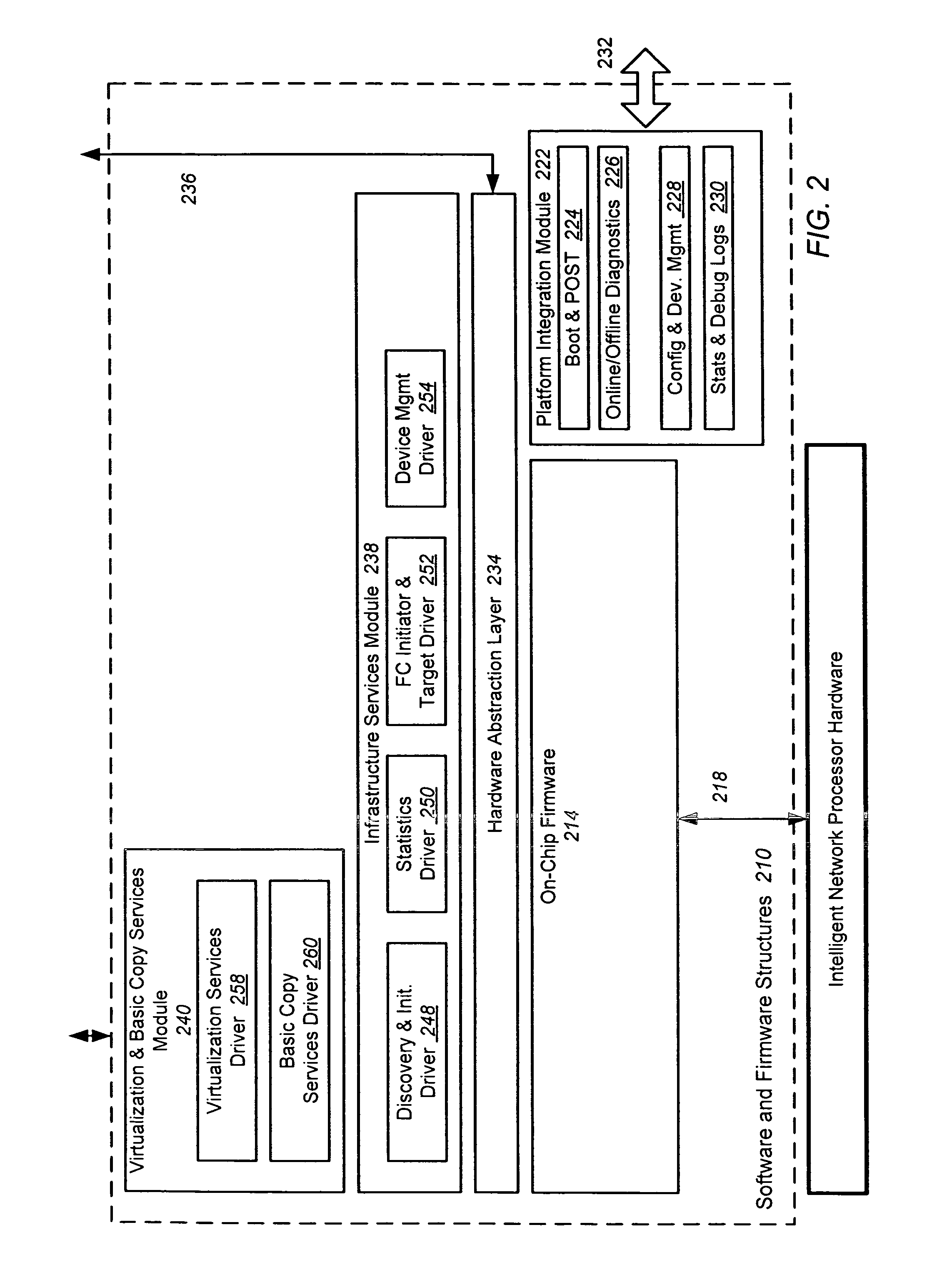

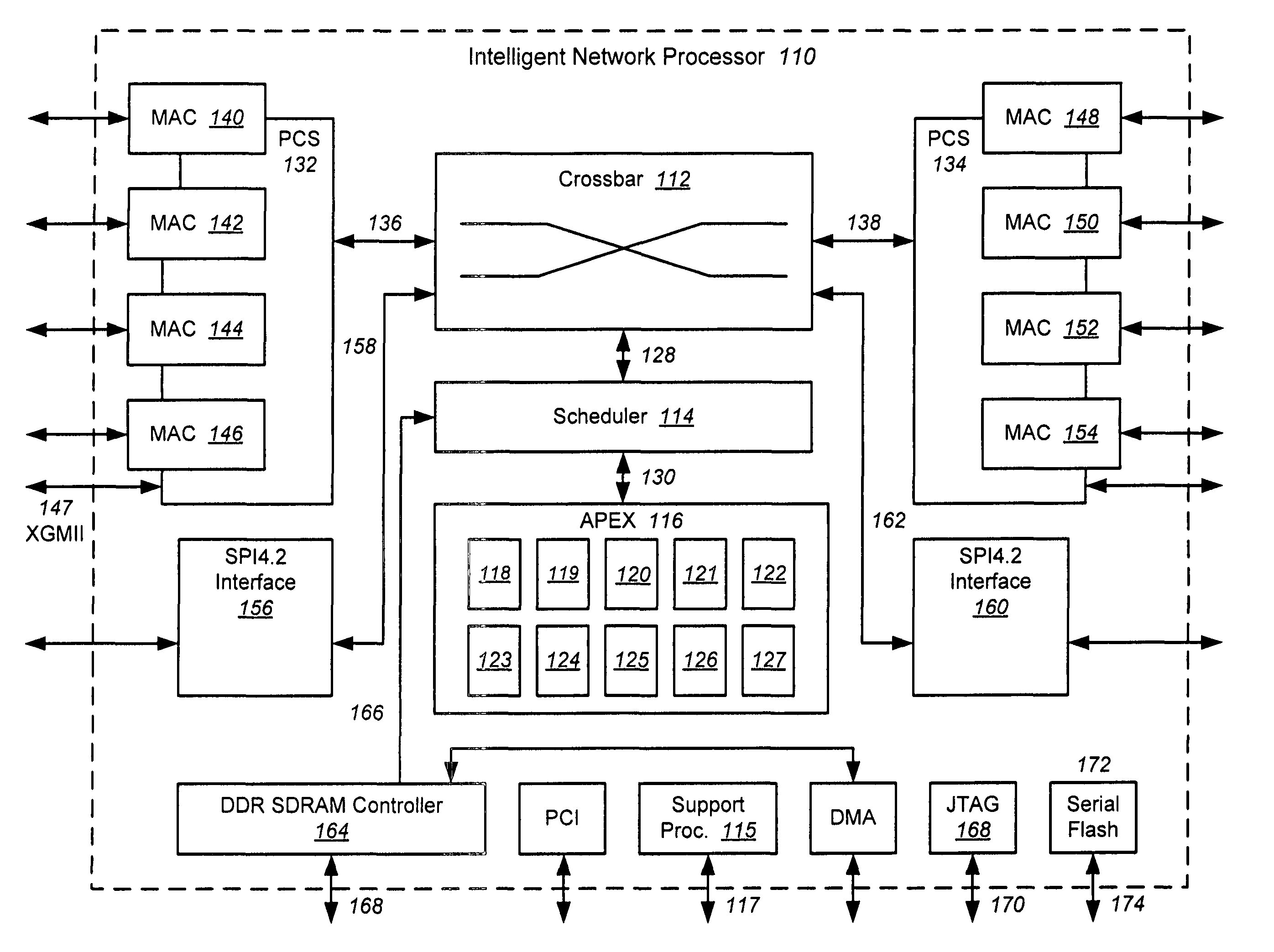

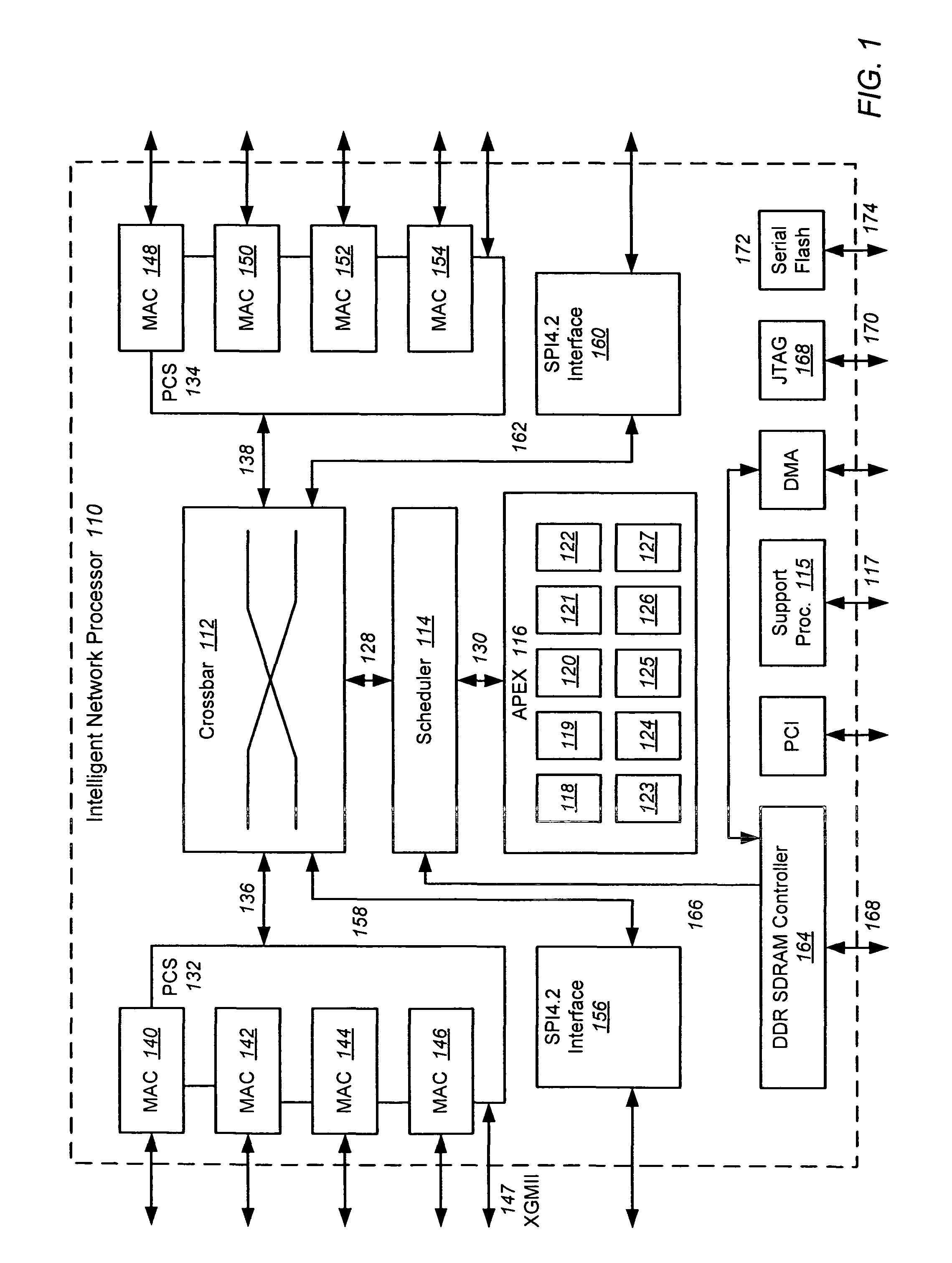

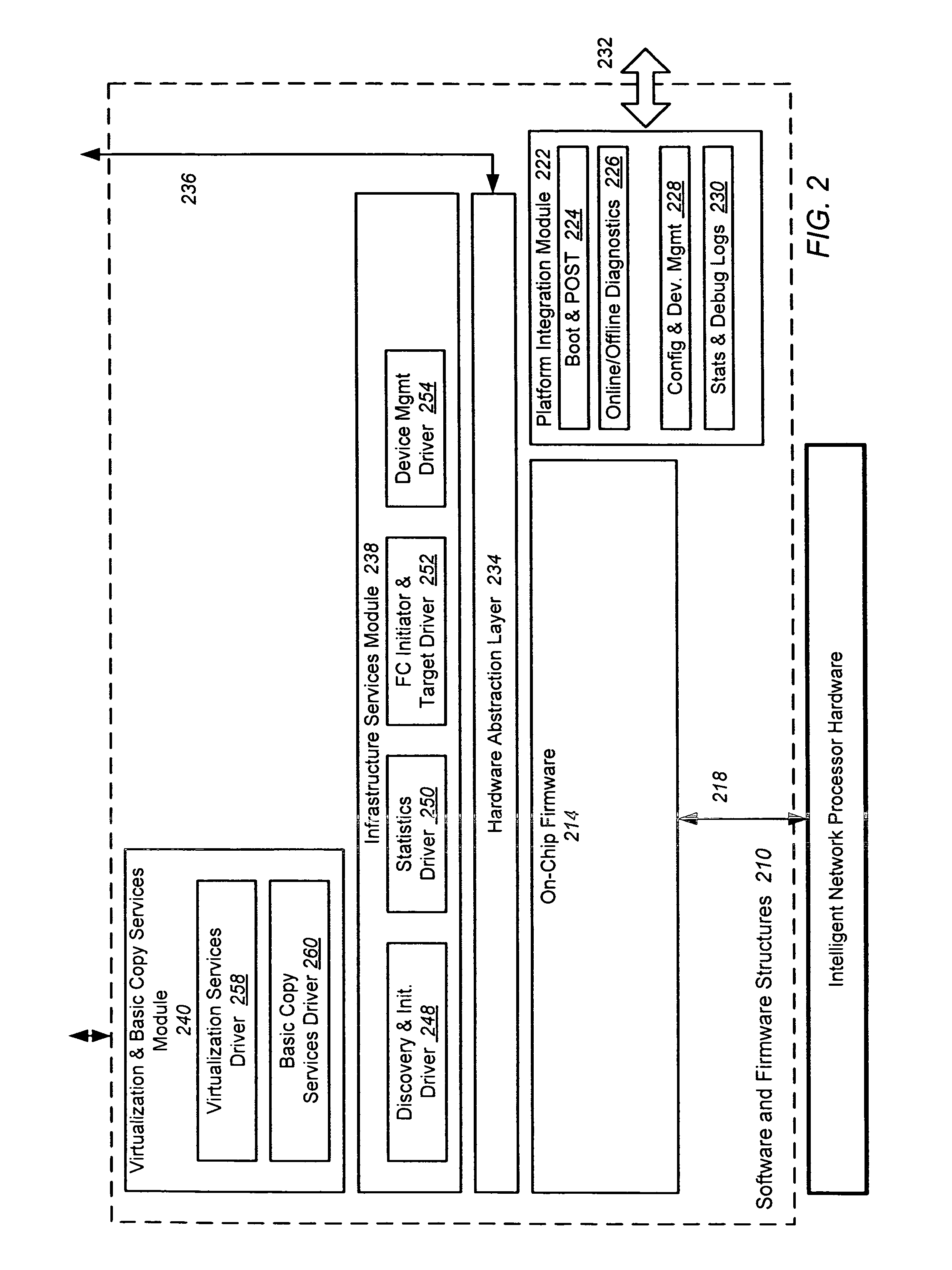

Intelligent network processor and method of using intelligent network processor

ActiveUS20070266179A1Efficient accessImprove creditMultiple digital computer combinationsData switching networksIntelligent NetworkPCI Express

An intelligent network processor is disclosed that provides a PCI express (PCIe) host bus adapter with firmware selectable hardware capabilities and firmware enabled emulation of capabilities not supported by hardware. Support for Fibre Channel (FC) and Gigabit Ethernet (GbE) protocols are provided through the same fabric ports, including multiple port trunking for both protocols. On chip protocol conversion is provided for switching and routing between FC and GbE ports. Switching using the same crossbar module is provided for both FC and GbE protocols. The crossbar module is coupled to directly access external DDR memory so that messages from FC, GbE, and PCIe interfaces may be switched directly to the DDR memory.

Owner:EMULEX COMM CORP

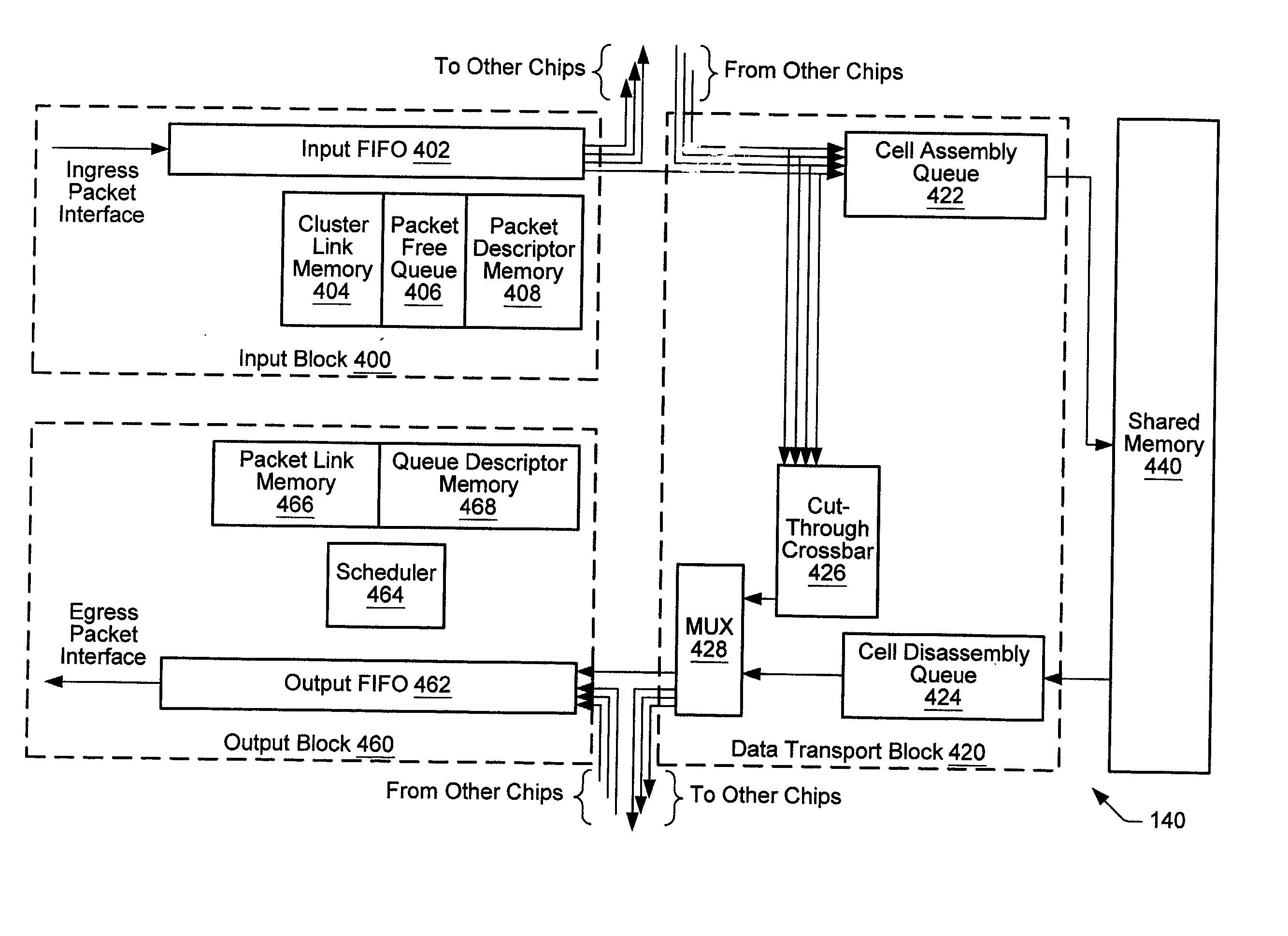

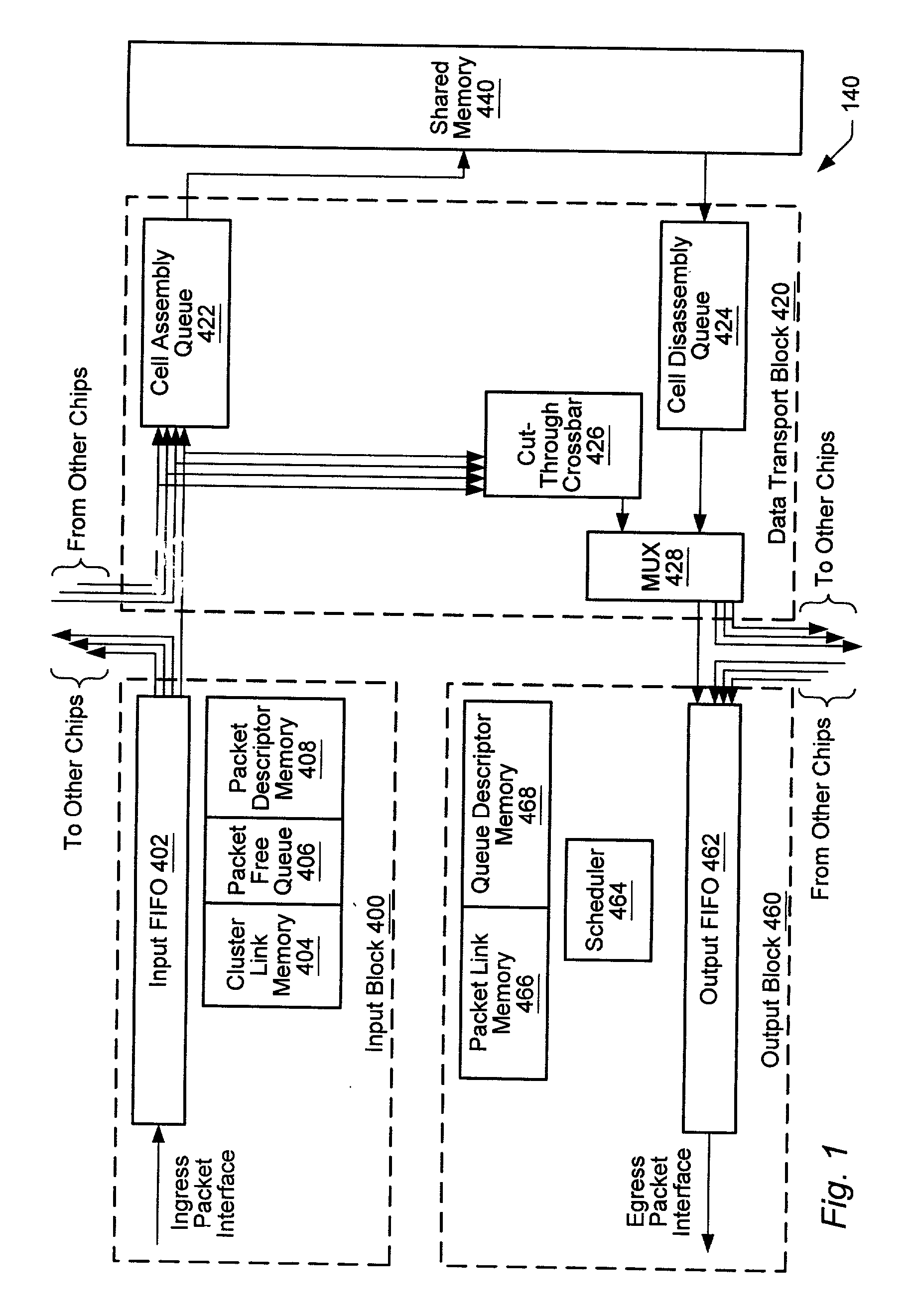

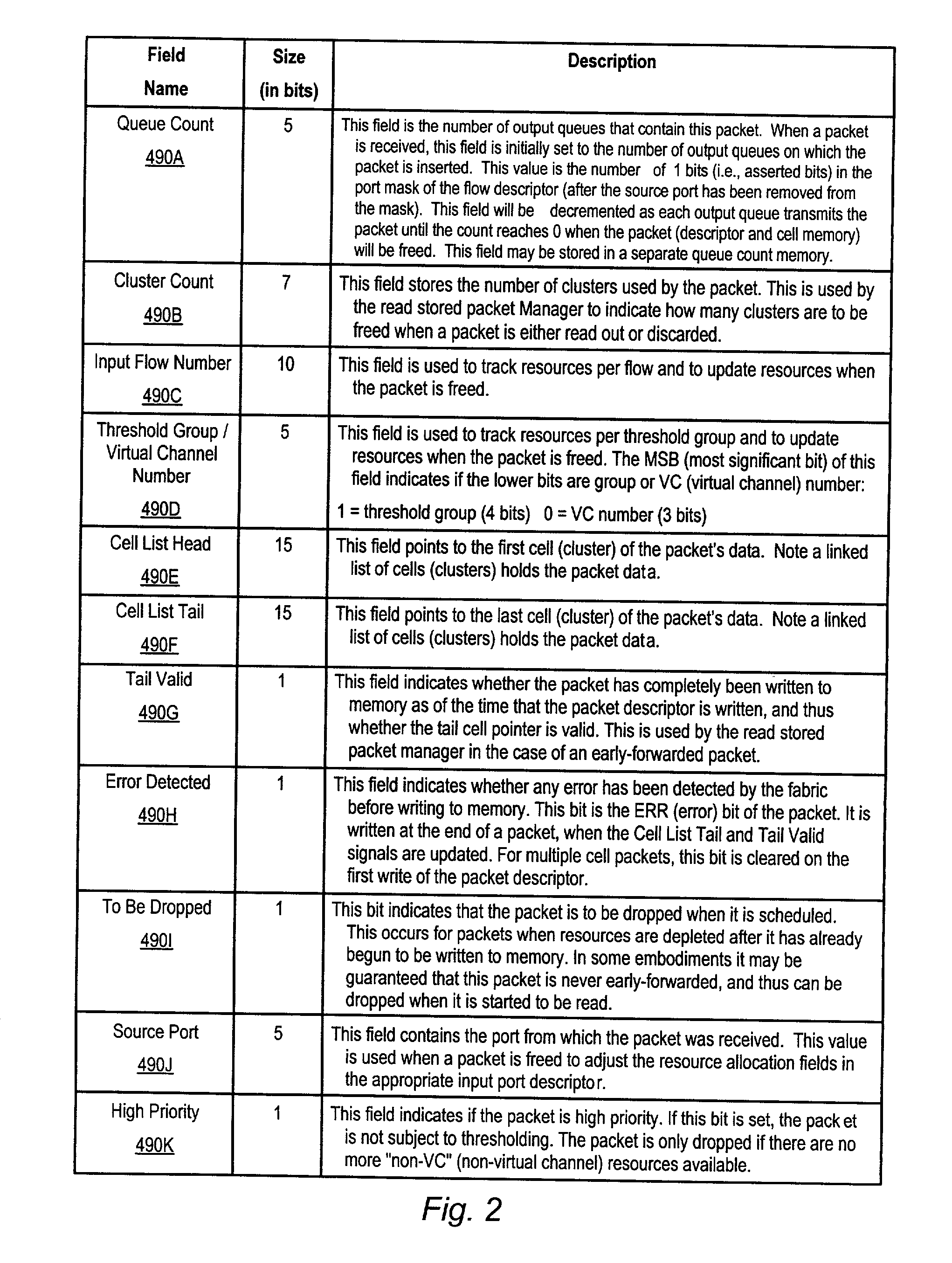

Virtual channels in a network switch

A system and method providing virtual channels with credit-based flow control on links between network switches. A network switch may include multiple input ports, multiple output ports, and a shared random access memory coupled to the input ports and output ports by data transport logic. Two network switches may go through a login procedure to determine if virtual channels may be established on a link. A credit initialization procedure may be performed to establish the number of credits available to the virtual channels. Credit-based packet flow may then begin on the link. A credit synchronization procedure may be performed to prevent the loss of credits due to errors. On detecting certain error conditions, a virtual channel may be deactivated. In one embodiment, the link is a Gigabit Ethernet link, and the packets are Gigabit Ethernet packets. The packets may encapsulate storage format (e.g. Fiber Channel) frames.

Owner:NISHAN SYST

Method and apparatus for cellular communication over data networks

InactiveUS20050157675A1Increase possible numberReduce in quantityNetwork traffic/resource managementNetwork topologiesModem deviceOperating energy

Owner:LUCENT TECH INC

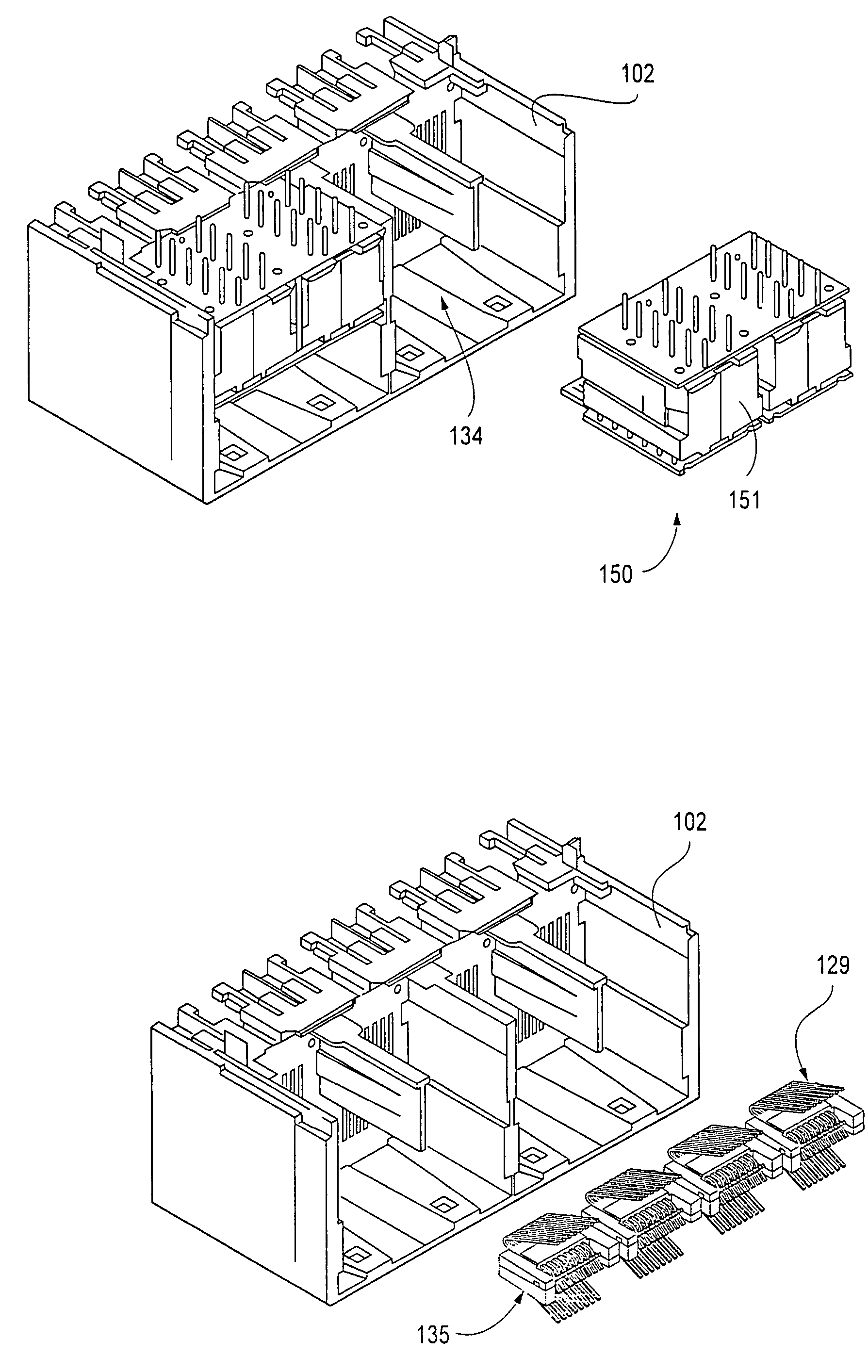

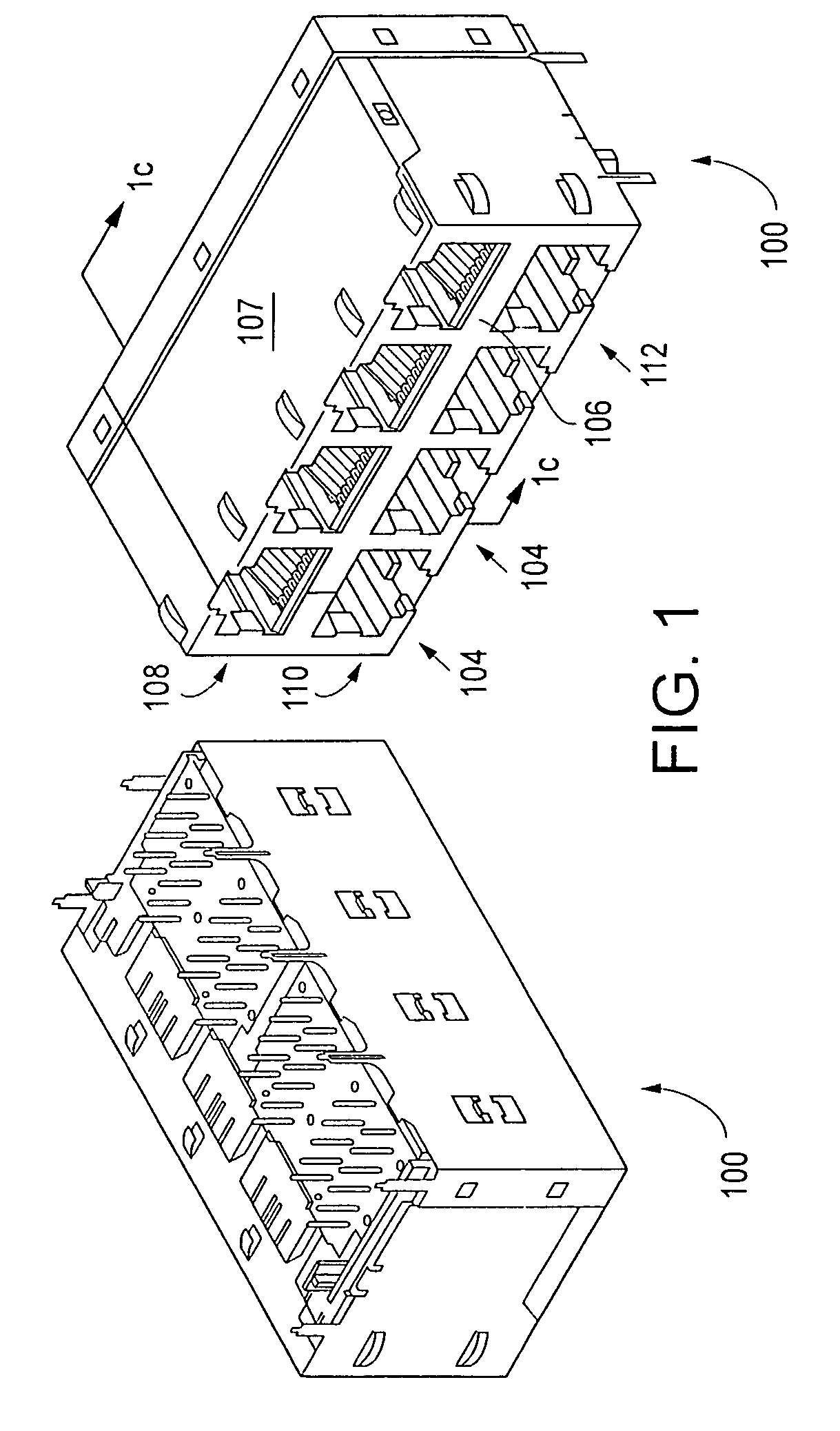

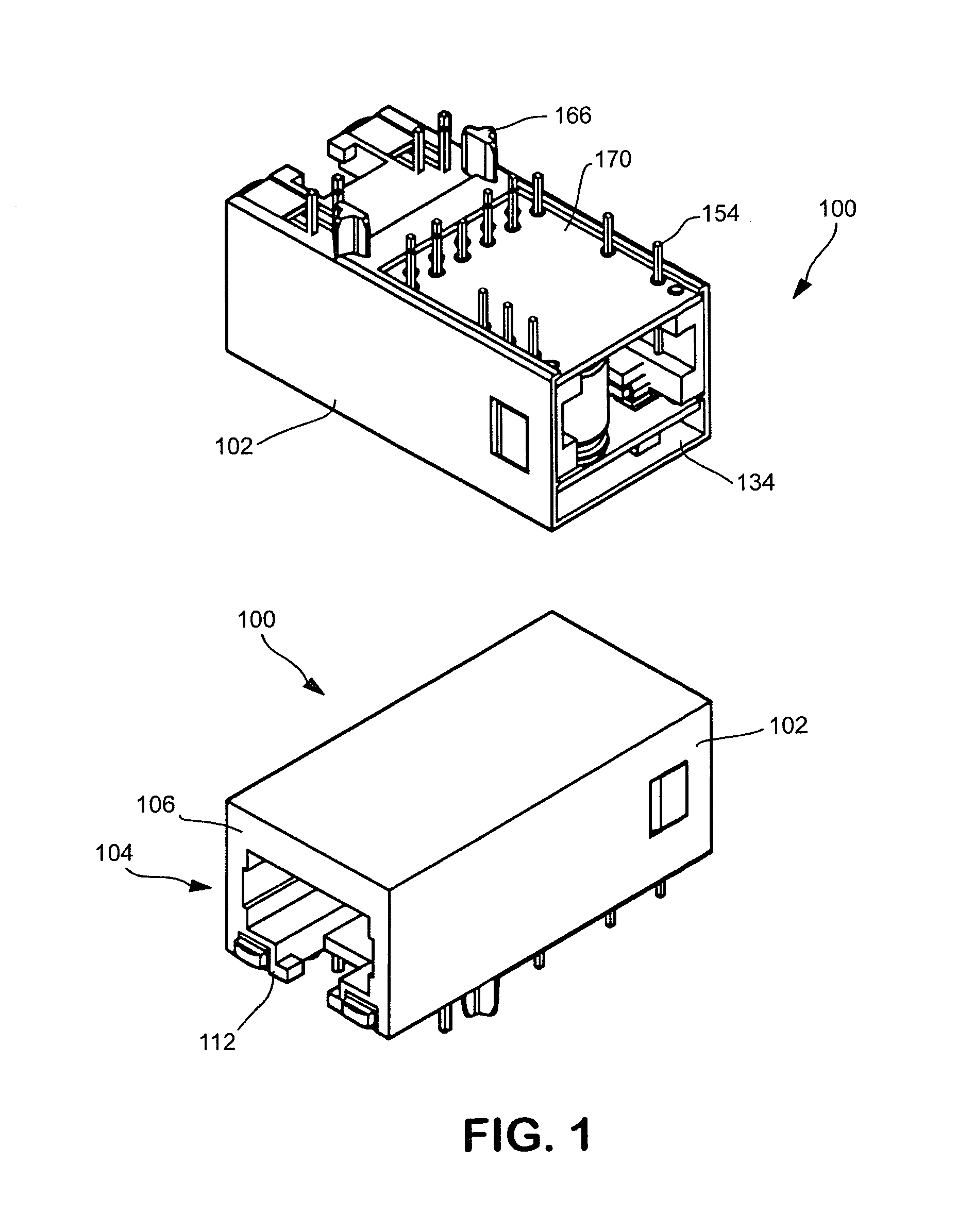

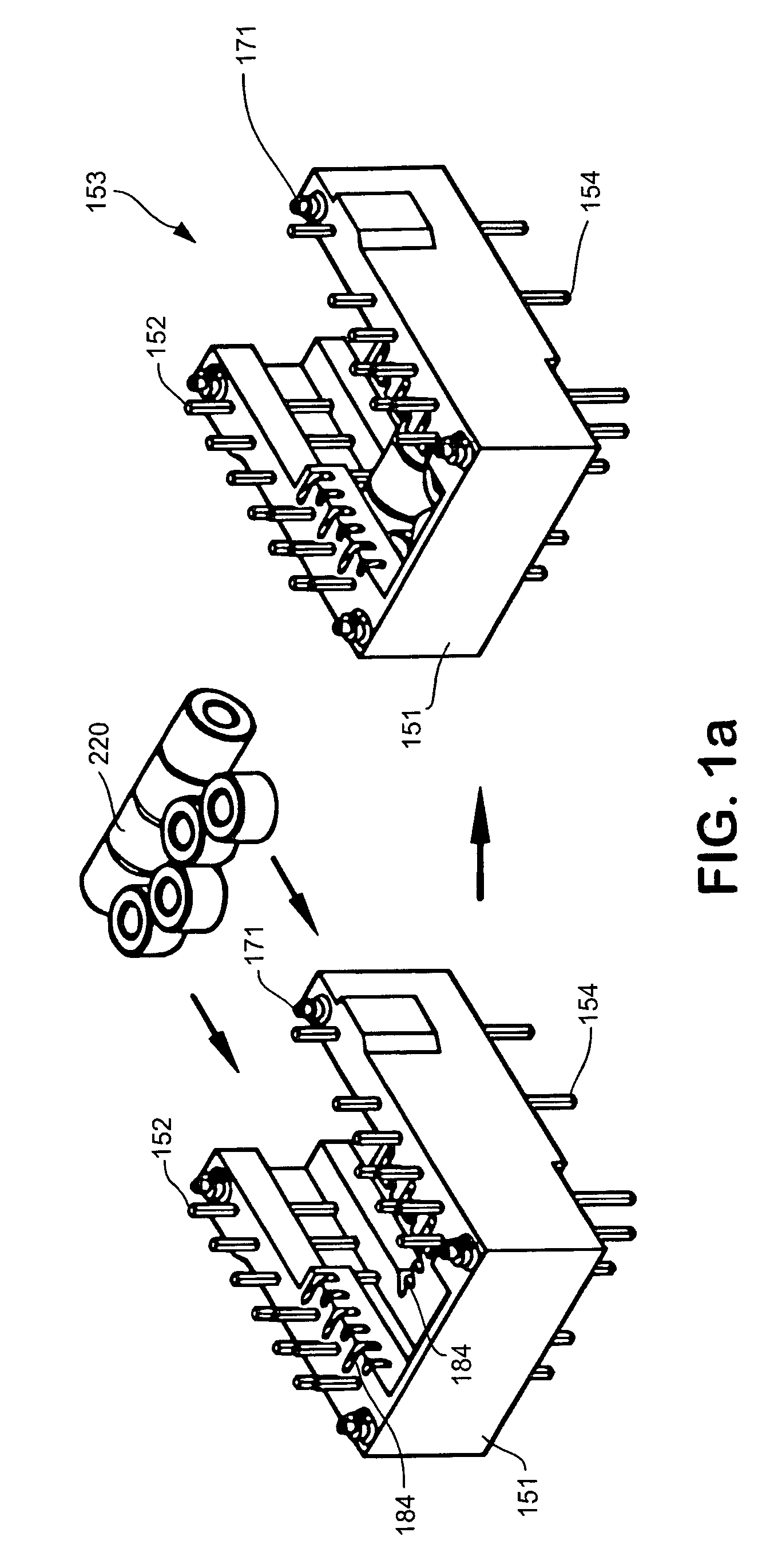

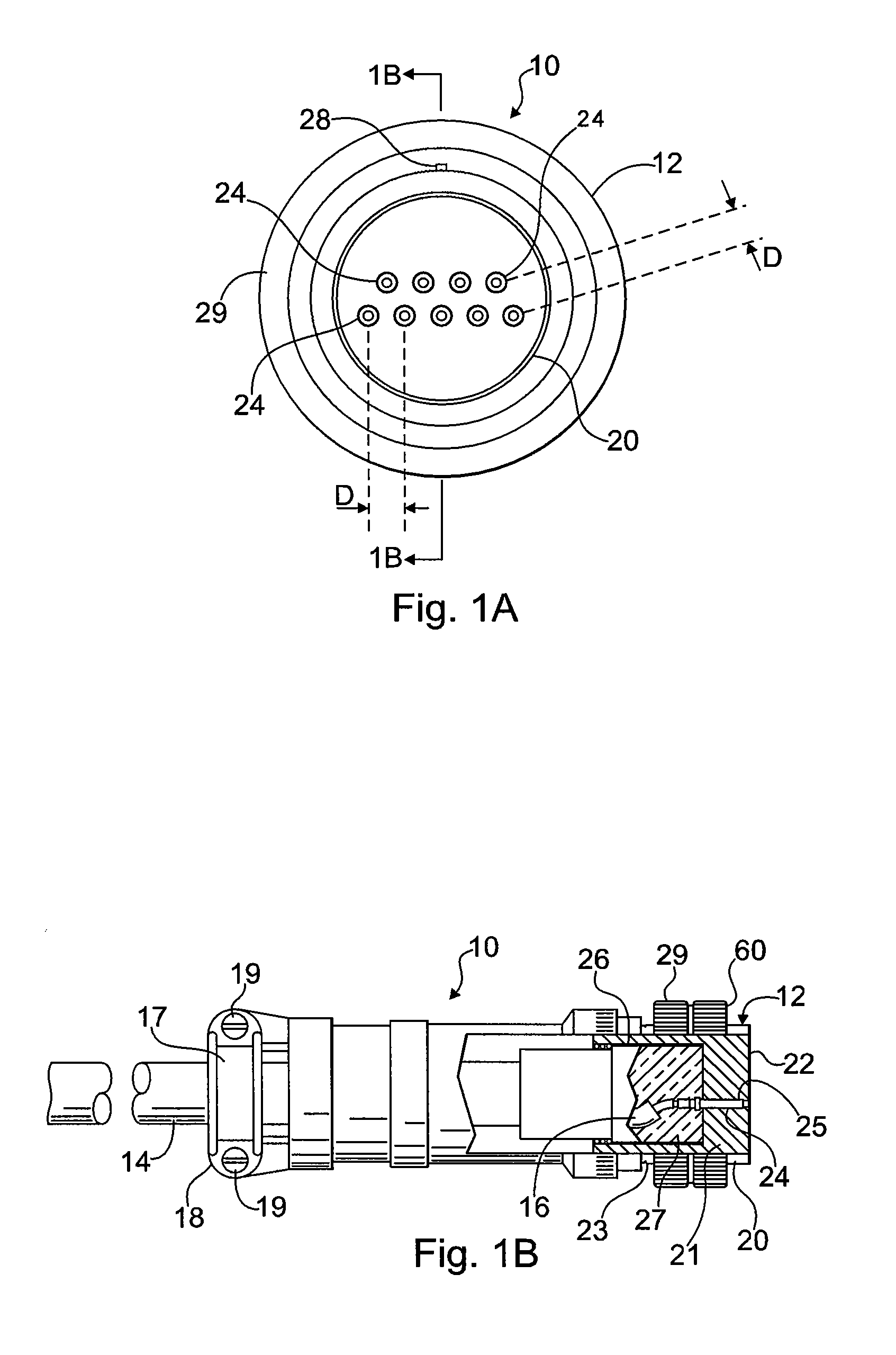

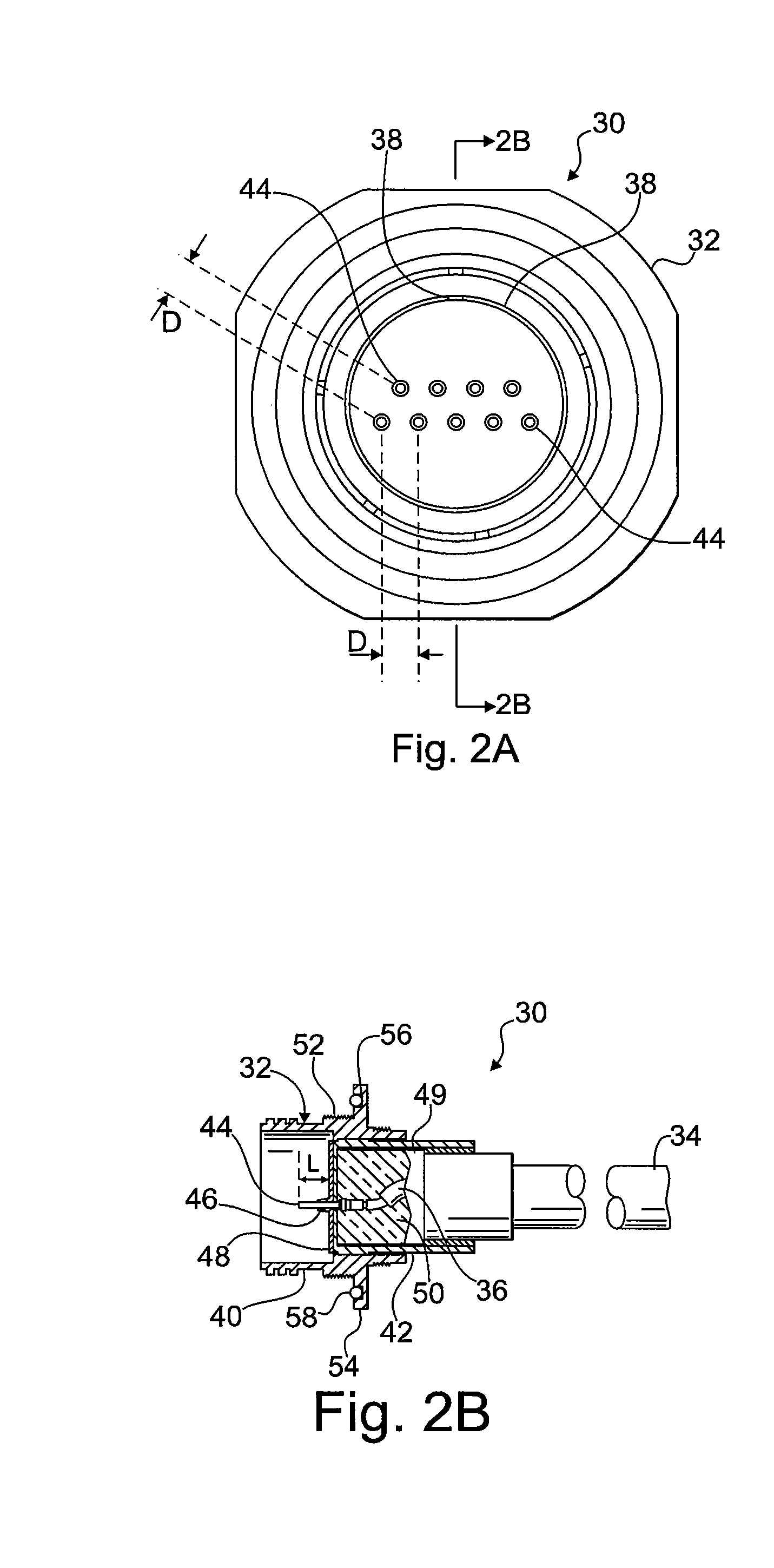

Universal connector assembly and method of manufacturing

ActiveUS7241181B2Coupling for high frequencyTwo-part coupling devicesElectrical conductorTransformer

An advanced modular plug connector assembly incorporating an insert assembly disposed in the rear portion of the connector housing. In one embodiment, the connector has a plurality of ports in multi-row configuration, and the insert assembly includes a substrate adapted to receive one or more electronic components such as choke coils, transformers, or other signal conditioning elements or magnetics. The substrate also interfaces with the conductors of two modular ports of the connector, and is removable from the housing such that an insert assembly of a different electronics or terminal configuration can be substituted therefor. In this fashion, the connector can be configured to a plurality of different standards (e.g., Gigabit Ethernet and 10 / 100). In yet another embodiment, the connector assembly comprises a plurality of light sources (e.g., LEDs) received within the housing. Methods for manufacturing the aforementioned embodiments are also disclosed.

Owner:PULSE ELECTRONICS

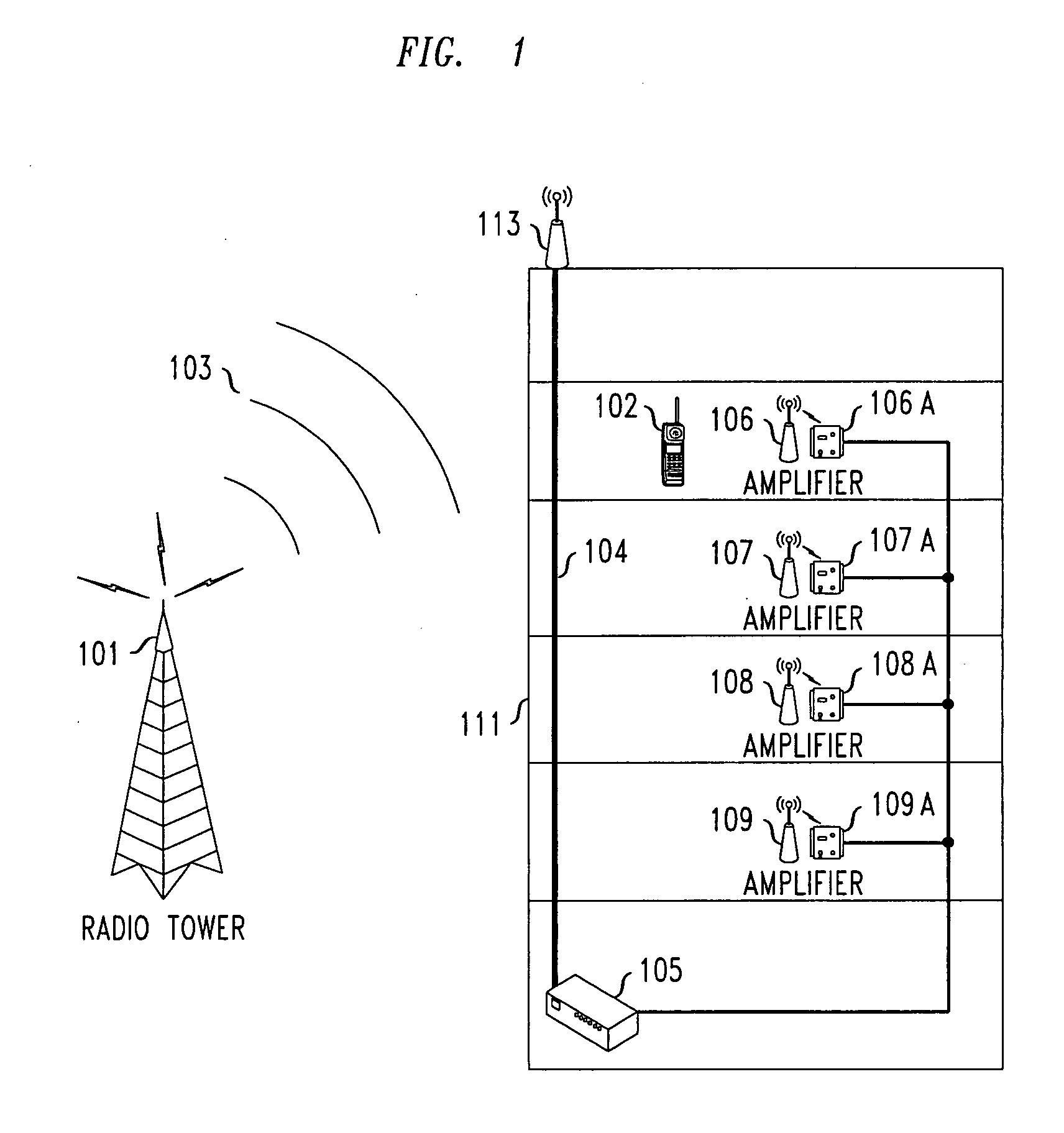

Method and apparatus for cellular communication over data networks

InactiveUS20060209752A1Increase possible numberReduce in quantityNetwork traffic/resource managementNetwork topologiesModem deviceOperating energy

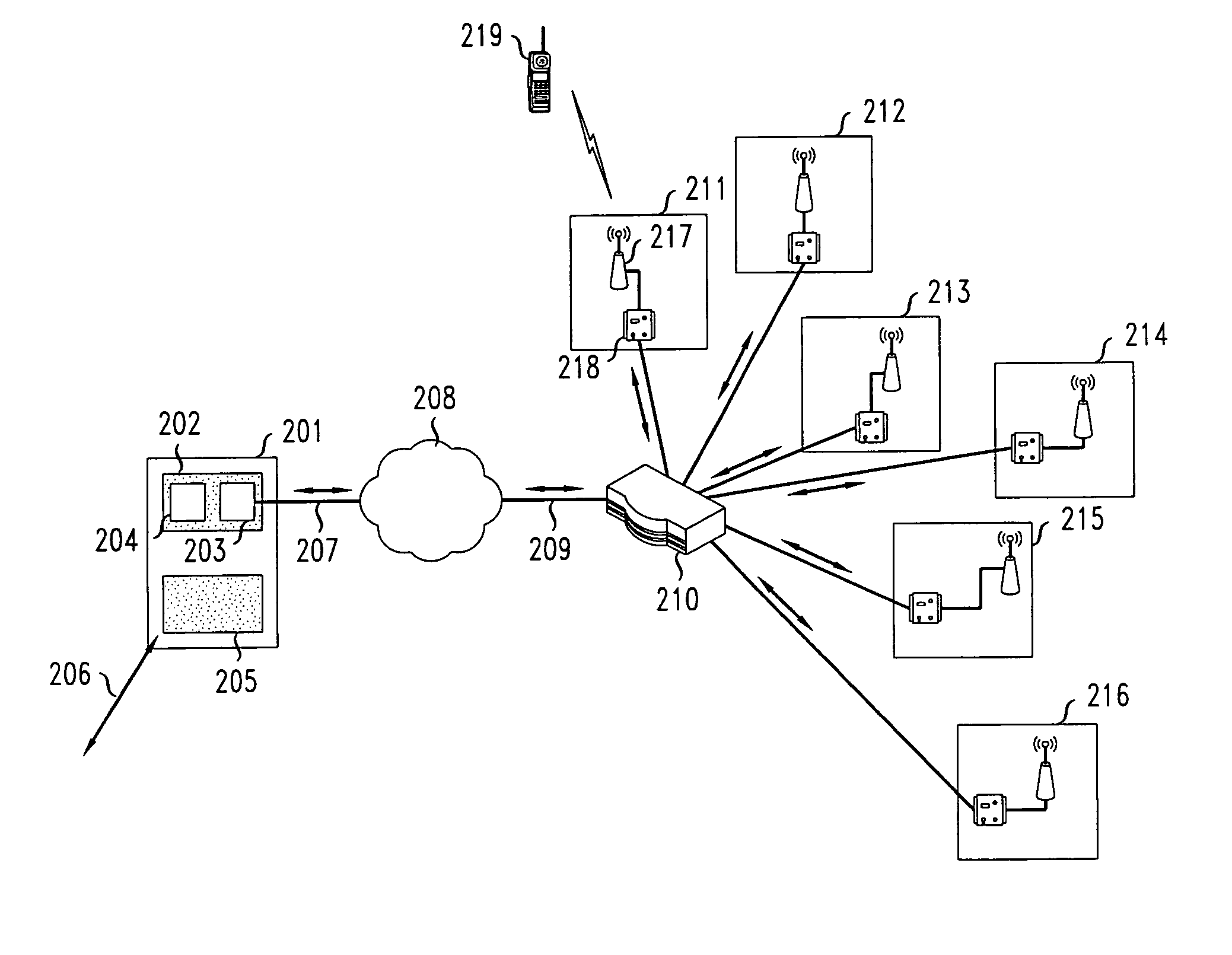

Cellular signals or other wireless signals / messages are introduced into a building or to an outside location by transmitting packets corresponding to those signals over a data network and low cost cables to designated locations within the data network. Once the designated packets containing the signals reach the destination, they are then broadcast over the air to a terminal capable of receiving the wireless message. In a first embodiment, an in-building gigabit Ethernet network, such as that currently existing presently in many buildings, is used to distribute radio signals indoors. Instead of transmitting the radio signals over the air from a repeater connected to a base station, coded baseband signals generated by the coding processor (e.g., a CDMA Modem Unit) in the base station are packetized and sent over the Ethernet network to radio processing equipment and antennas distributed throughout the building. The radio processing equipment strips the packet headers from the baseband signal packets so those signals can be broadcast via the antennas to one or more mobile terminals. Additionally, hard handoff is employable upon entering a building using specifically configured pilot signals.

Owner:WSOU INVESTMENTS LLC +1

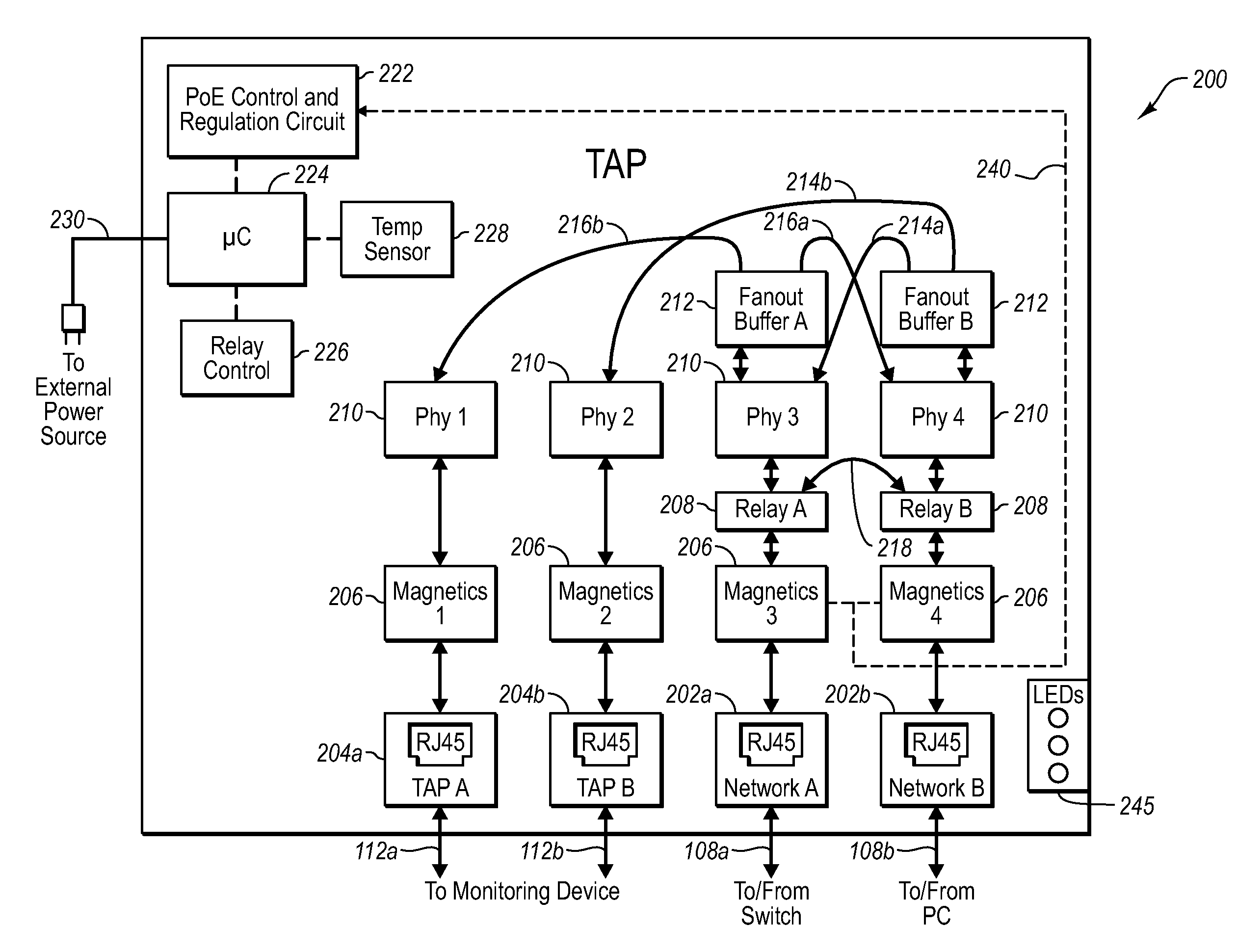

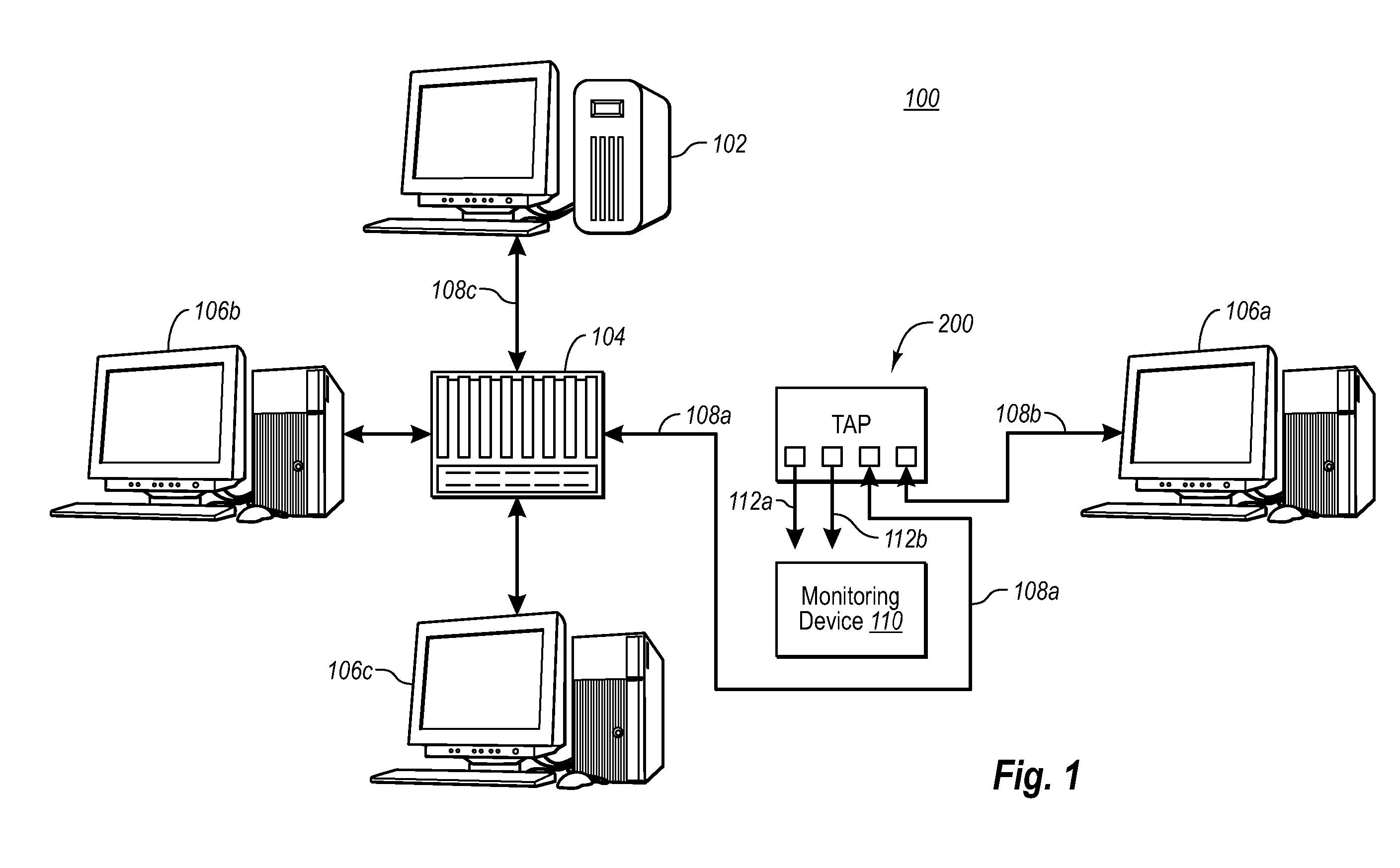

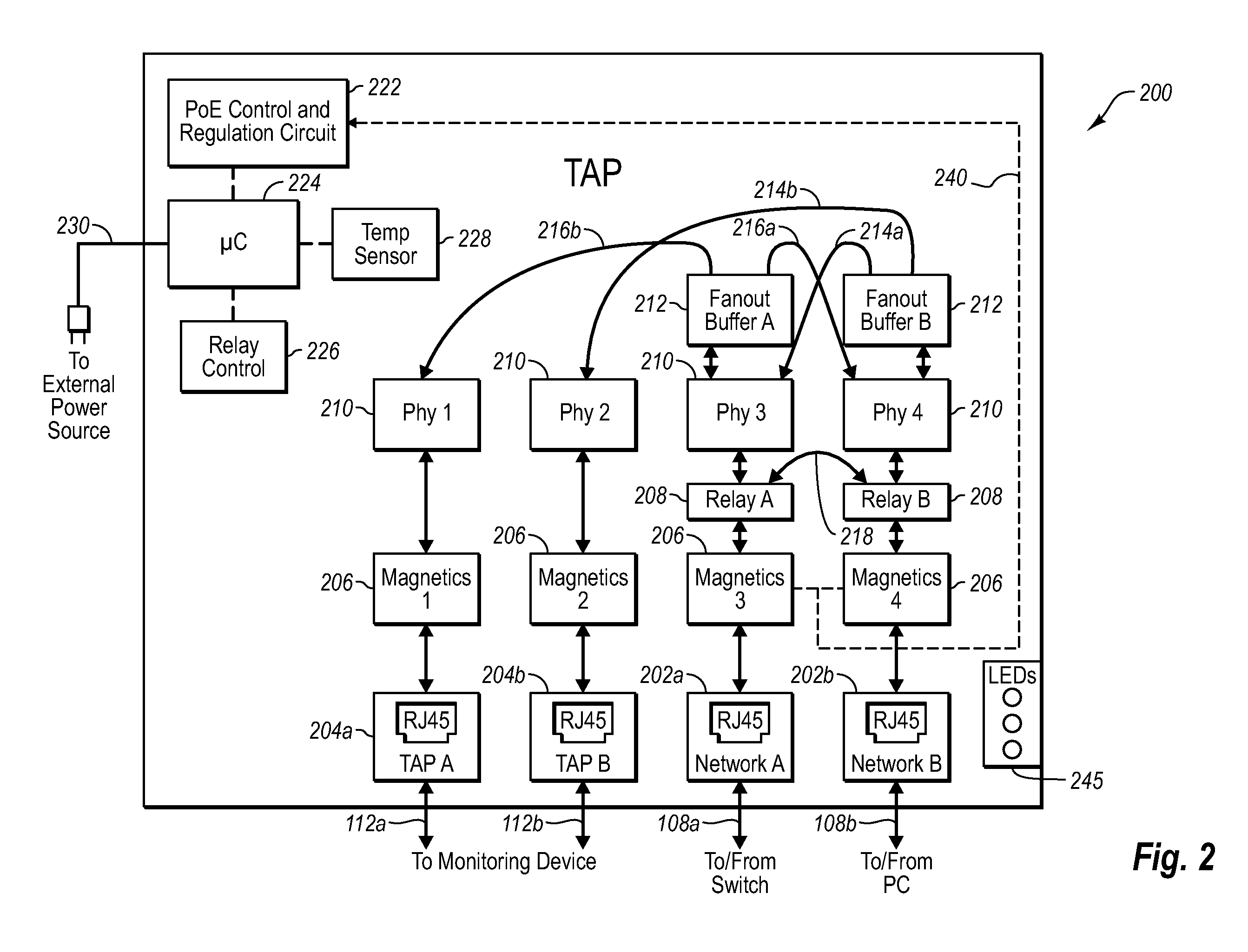

Network tap device powered by power over ethernet

ActiveUS20070081553A1Improve reliabilityImprove operationMechanical power/torque controlLevel controlNetwork tapMonitor equipment

A network tap device that is configured for operation in a copper Gigabit Ethernet communications network using a power-over-Ethernet (“POE”) electrical supply is disclosed. In one embodiment, a network tap device powered by a POE supply is disclosed, comprising first and second network ports that are configured with receptacles for receiving communication cables. The communication cables are configured to carry both data signals and the POE supply to and from the network tap device. The network tap device further includes first and second tap ports that connect with additional communication cables to a monitoring device. The network tap device also includes control and regulation circuitry that is configured to receive the POE supply from the communication cables via the network ports and to enable components of the network tap device to be operated by the POE supply.

Owner:VIAVI SOLUTIONS INC

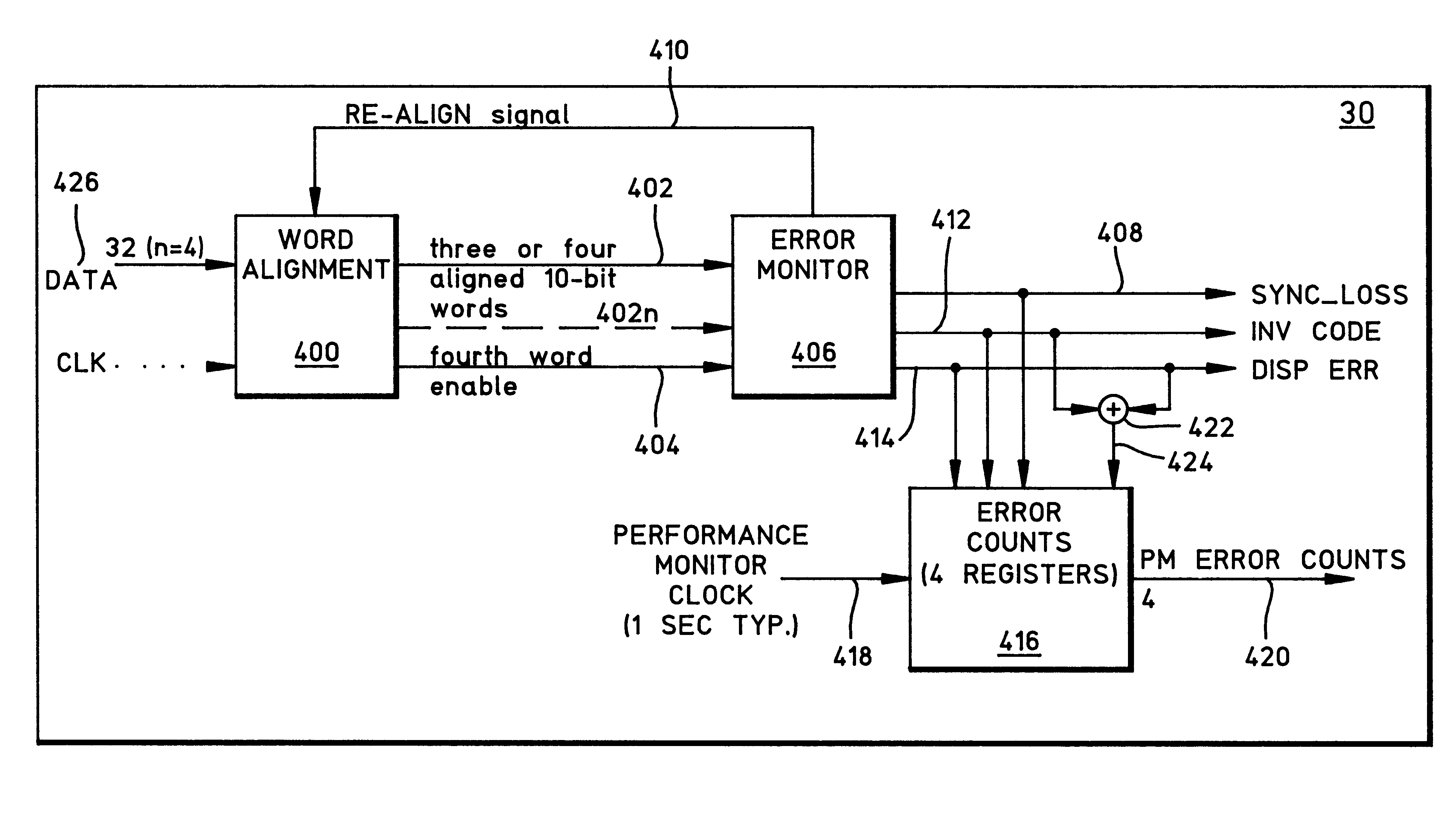

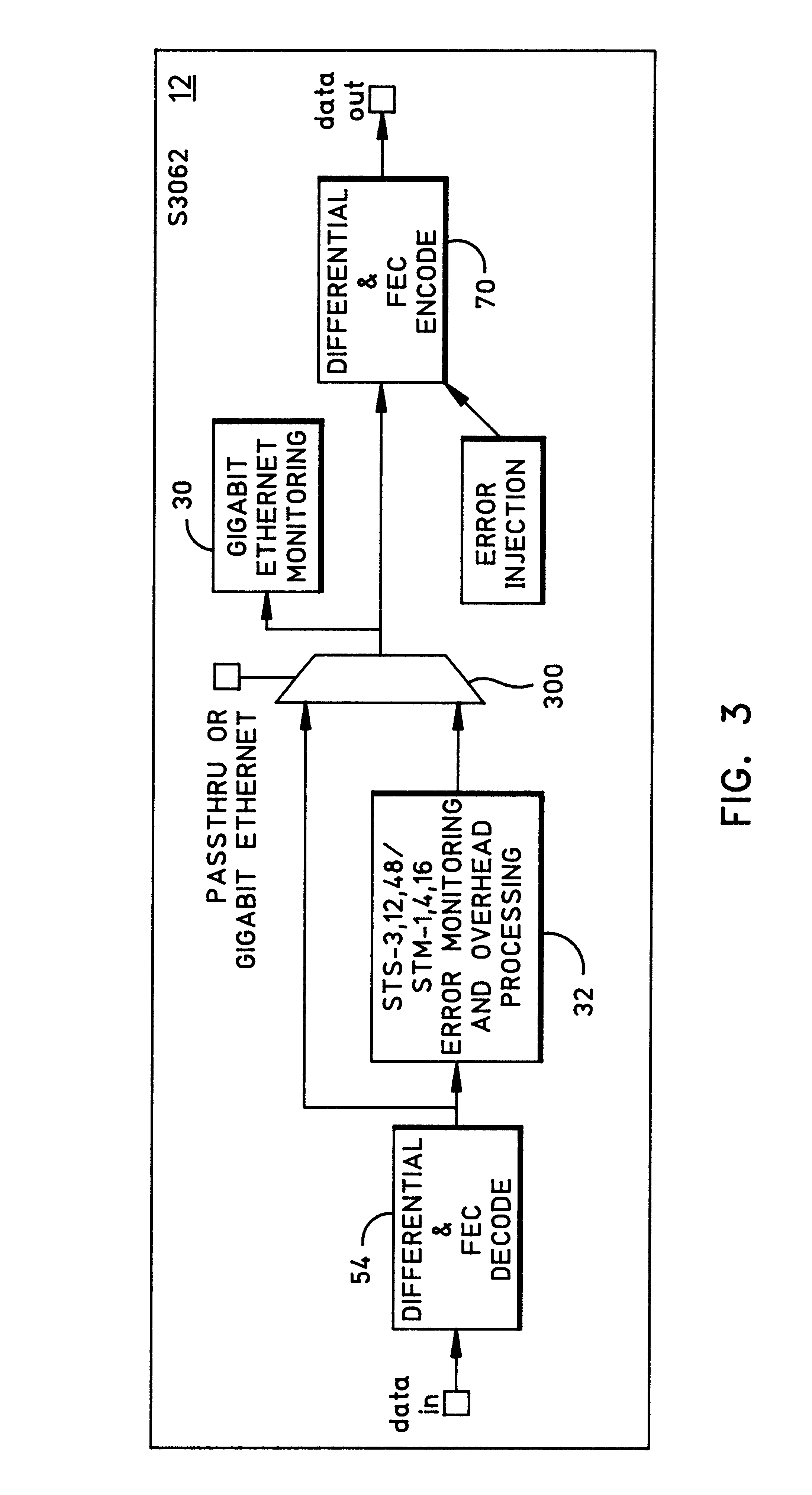

Gigabit ethernet performance monitoring

A method for analyzing Gigabit Ethernet (GBE) and fiber channel protocol communications is provided which provides a more detailed understanding of the errors, than that provided under the IEEE 802.3z standard. The method creates an additional parity error signal which is not specified under the IEEE 802.3z standard. The parity error signals and IEEE 802.3z invalid code word signals are used to provide an analysis of whether the underlying communication errors are a result of 8B / 10B coding word errors or running disparity errors. A system and apparatus to monitor performance in accordance with the above-mentioned method is also provided.

Owner:QUALCOMM INC

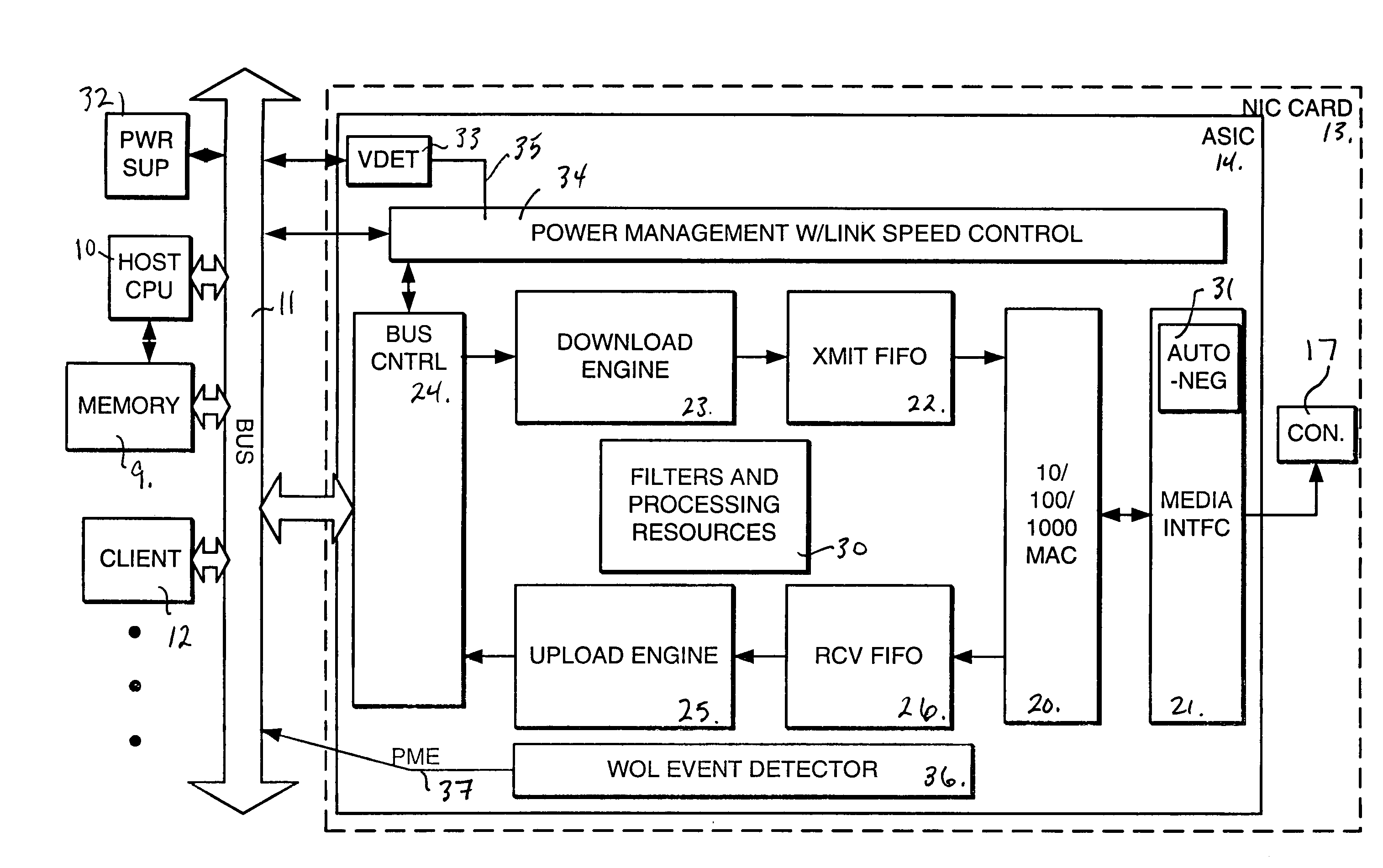

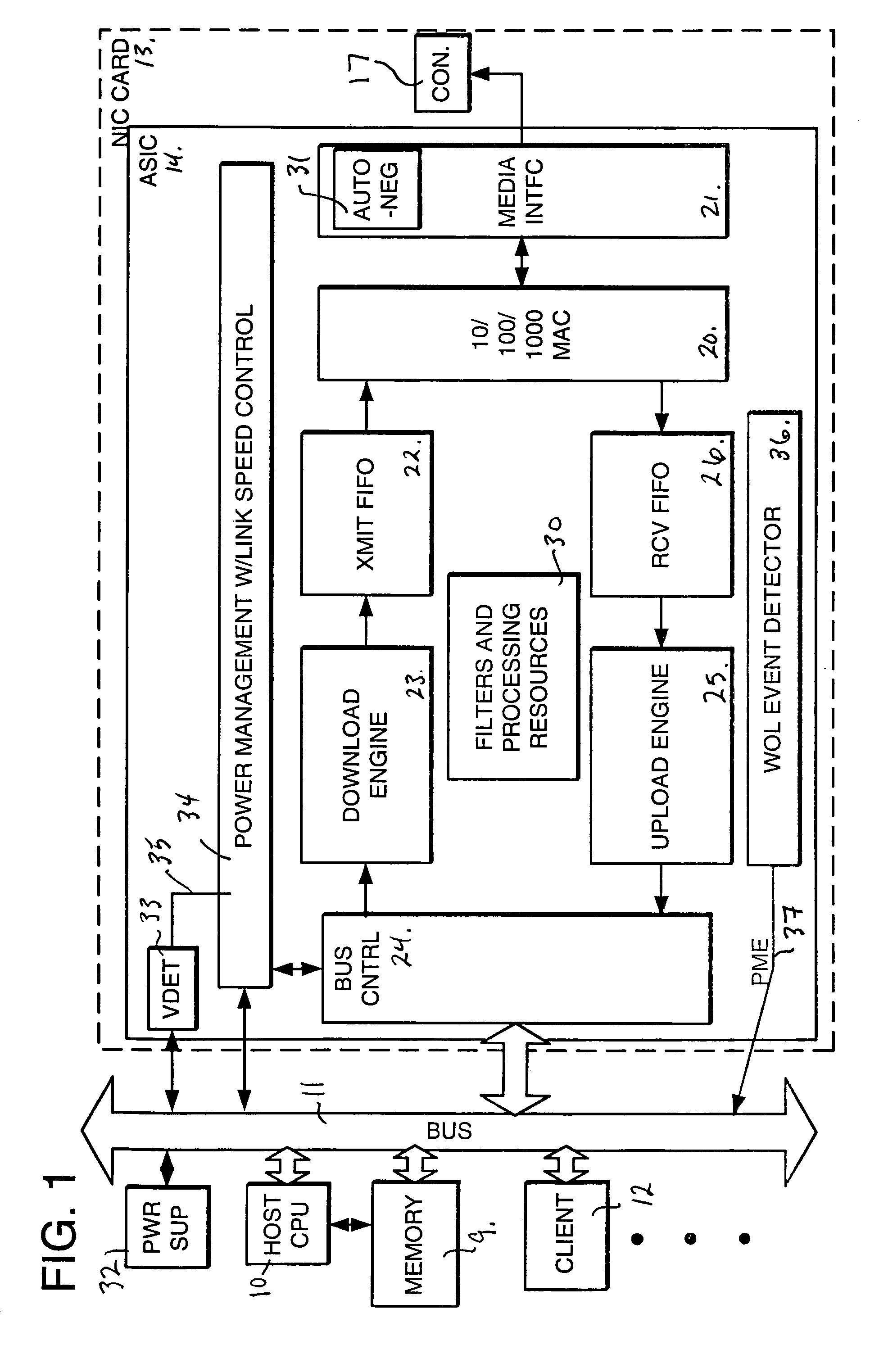

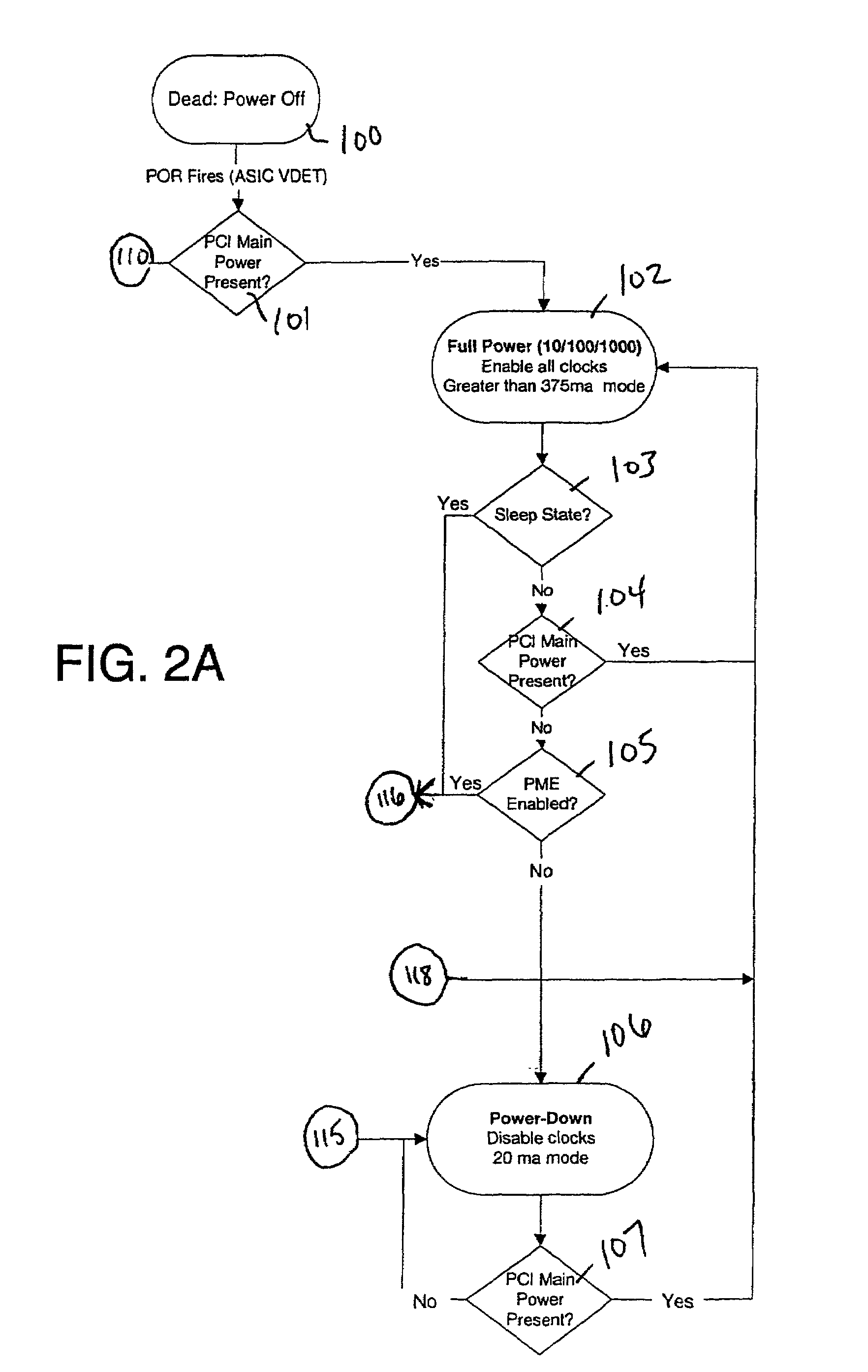

Method and system for power management in a gigabit Ethernet chip

InactiveUS20050097378A1Set clearEnergy efficient ICTPower managementControl registerFinite-state machine

Aspects of the invention for managing power in a single chip device may comprise, an internal finite state machine that, while in a communicating state, determines from within the single chip device whether a power management status is set and / or whether a first power management event is received. If the power management status is set, the finite state machine may transition from the communicating state to a power management event sent state. If the first power management event is received, the finite state machine may transition from the communicating state to a non-communicating state. The first power management event may be a turn off power management event. Furthermore, in instances where the power management status is set, it may be cleared, thereby causing the finite state machine to transition back to the communicating state. One or more power management control registers may be utilized for indicating power management status.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

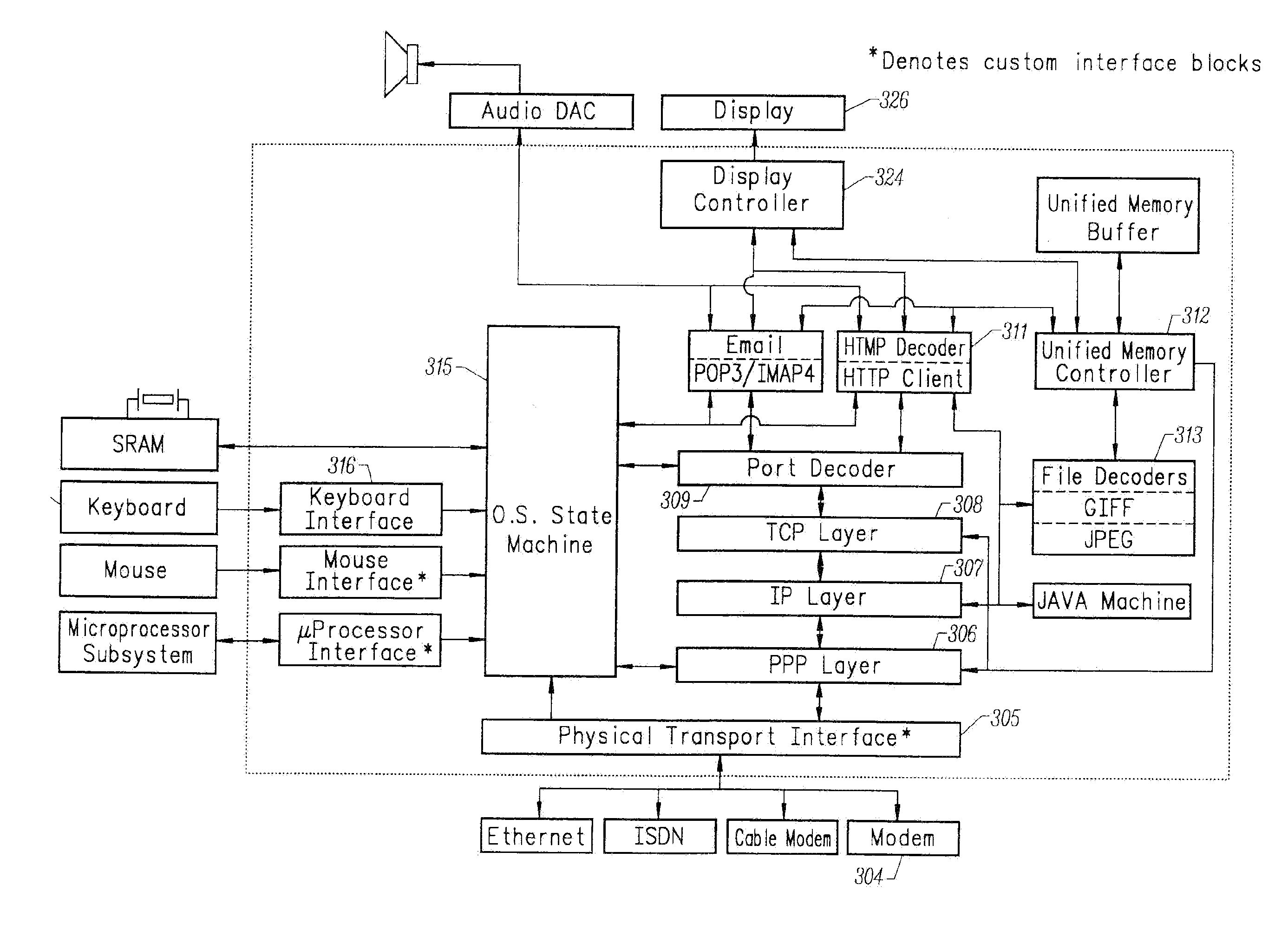

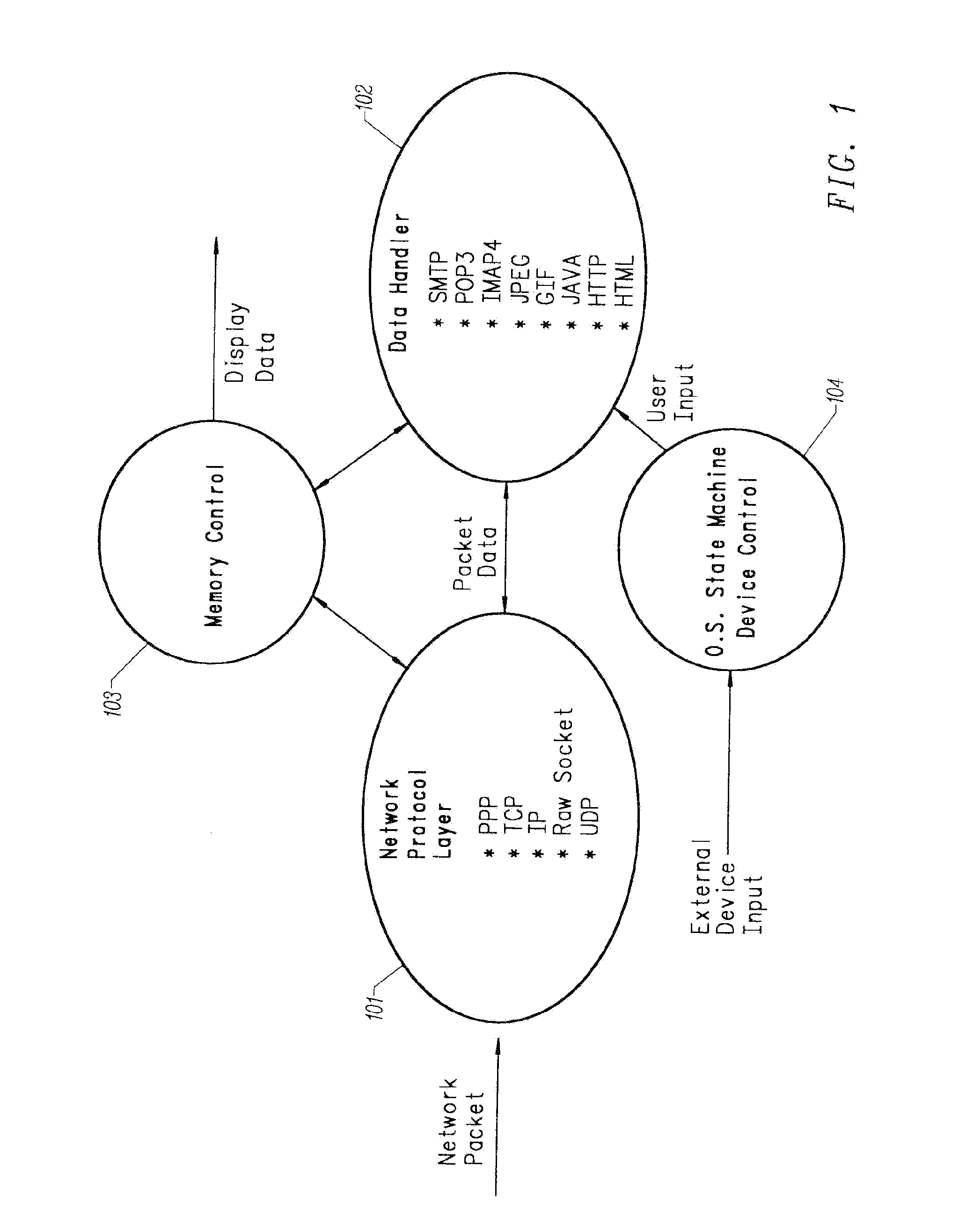

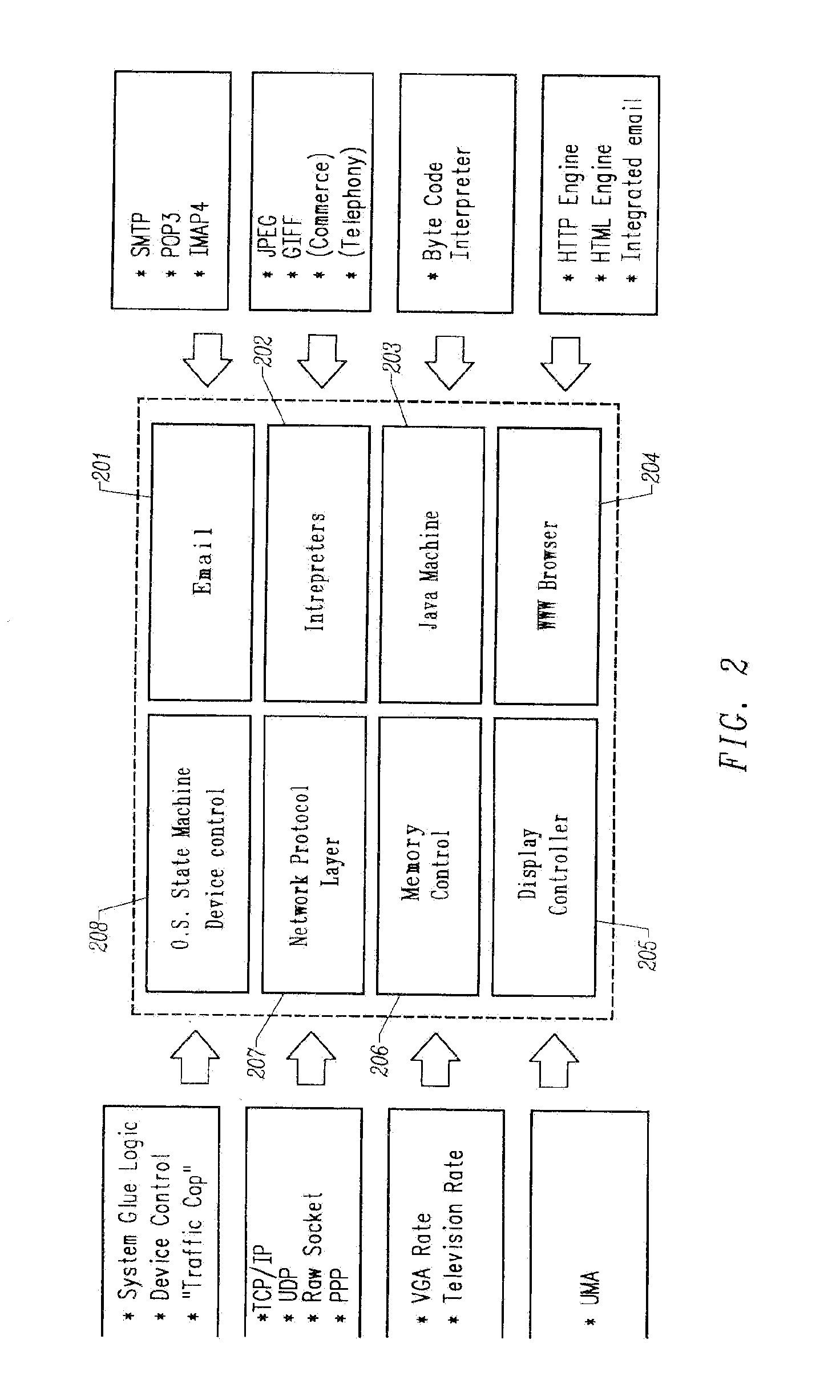

Gigabit Ethernet Adapter

InactiveUS20070253430A1Fast communication speedCompact solutionWide area networksRaw socketSmall form factor

A gigabit Ethernet adapter provides a provides a low-cost, low-power, easily manufacturable, small form-factor network access module which has a low memory demand and provides a highly efficient protocol decode. The invention comprises a hardware-integrated system that both decodes multiple network protocols byte-streaming manner concurrently and processes packet data in one pass, thereby reducing system memory and form factor requirements, while also eliminating software CPU overhead. A preferred embodiment of the invention comprises a plurality of protocol state machines that decode network protocols such as TCP, IP, User Datagram Protocol (UDP), PPP, Raw Socket, RARP, ICMP, IGMP, iSCSI, RDMA, and FCIP concurrently as each byte is received. Each protocol handler parses, interprets, and strips header information immediately from the packet, requiring no intermediate memory. The invention provides an internet tuner core, peripherals, and external interfaces. A network stack processes, generates and receives network packets. An internal programmable processor controls the network stack and handles any other types of ICMP packets, IGMP packets, or packets corresponding to other protocols not supported directly by dedicated hardware. A virtual memory manager is implemented in optimized, hardwired logic. The virtual memory manager allows the use of a virtual number of network connections which is limited only by the amount of internal and external memory available.

Owner:NVIDIA CORP

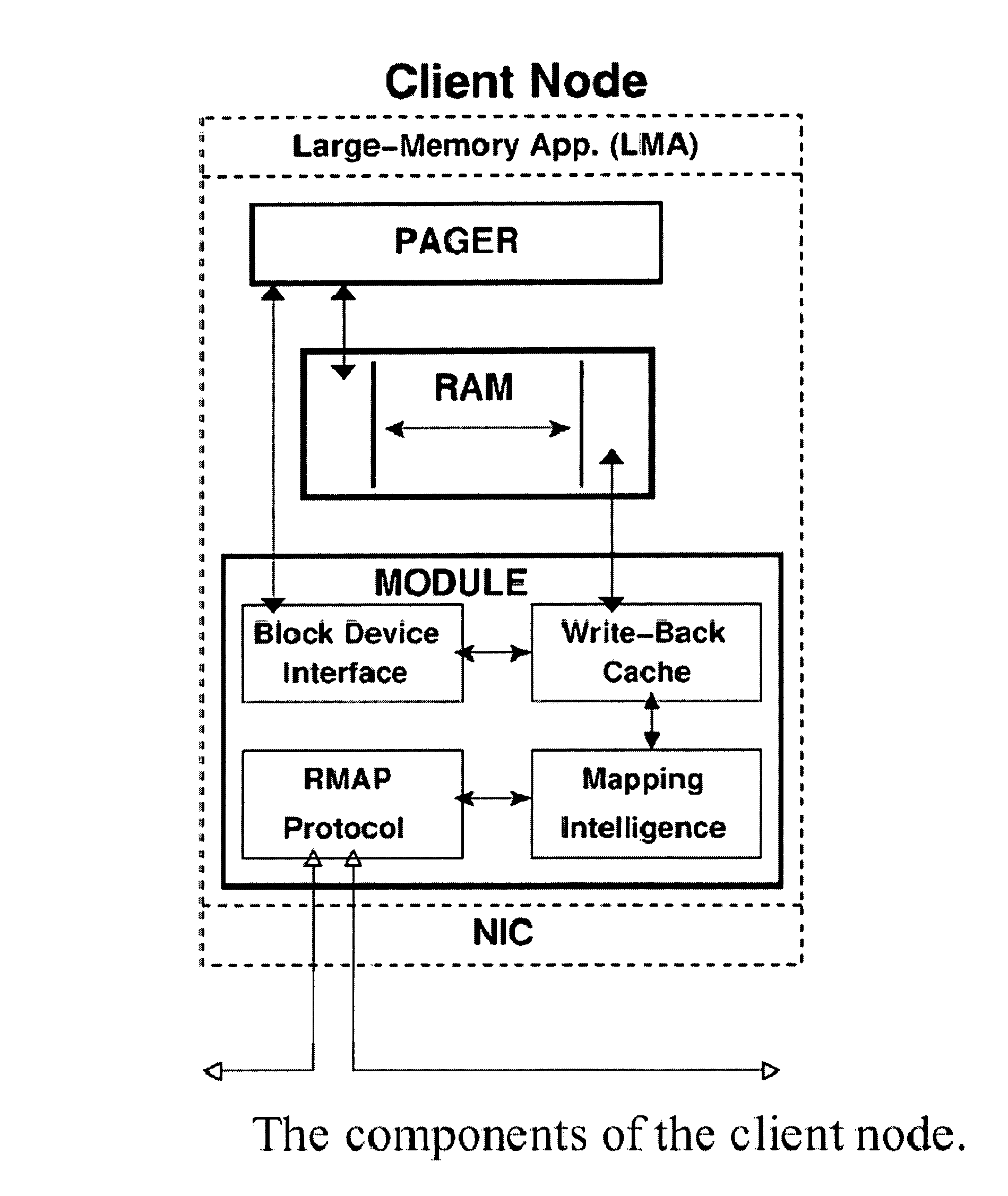

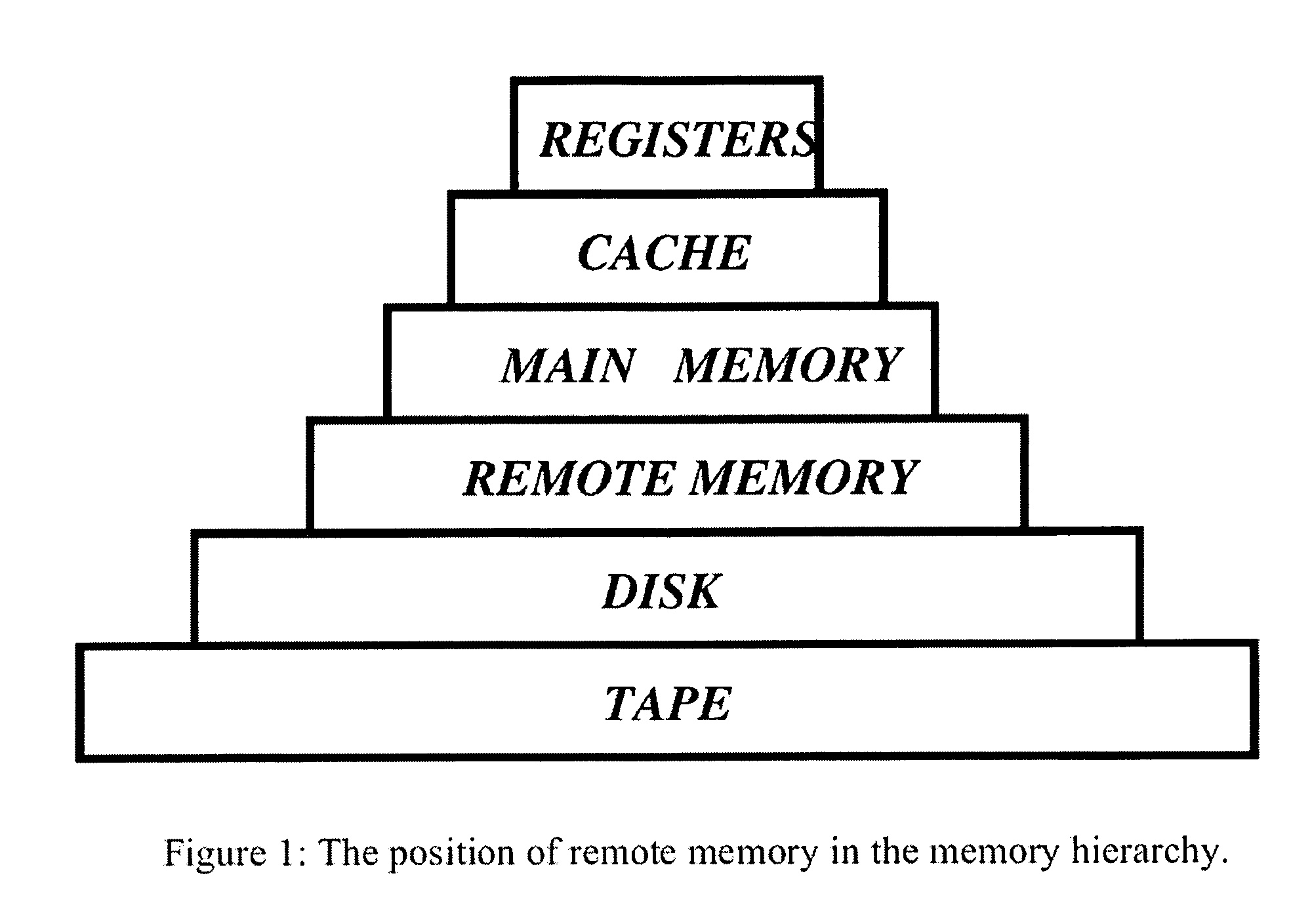

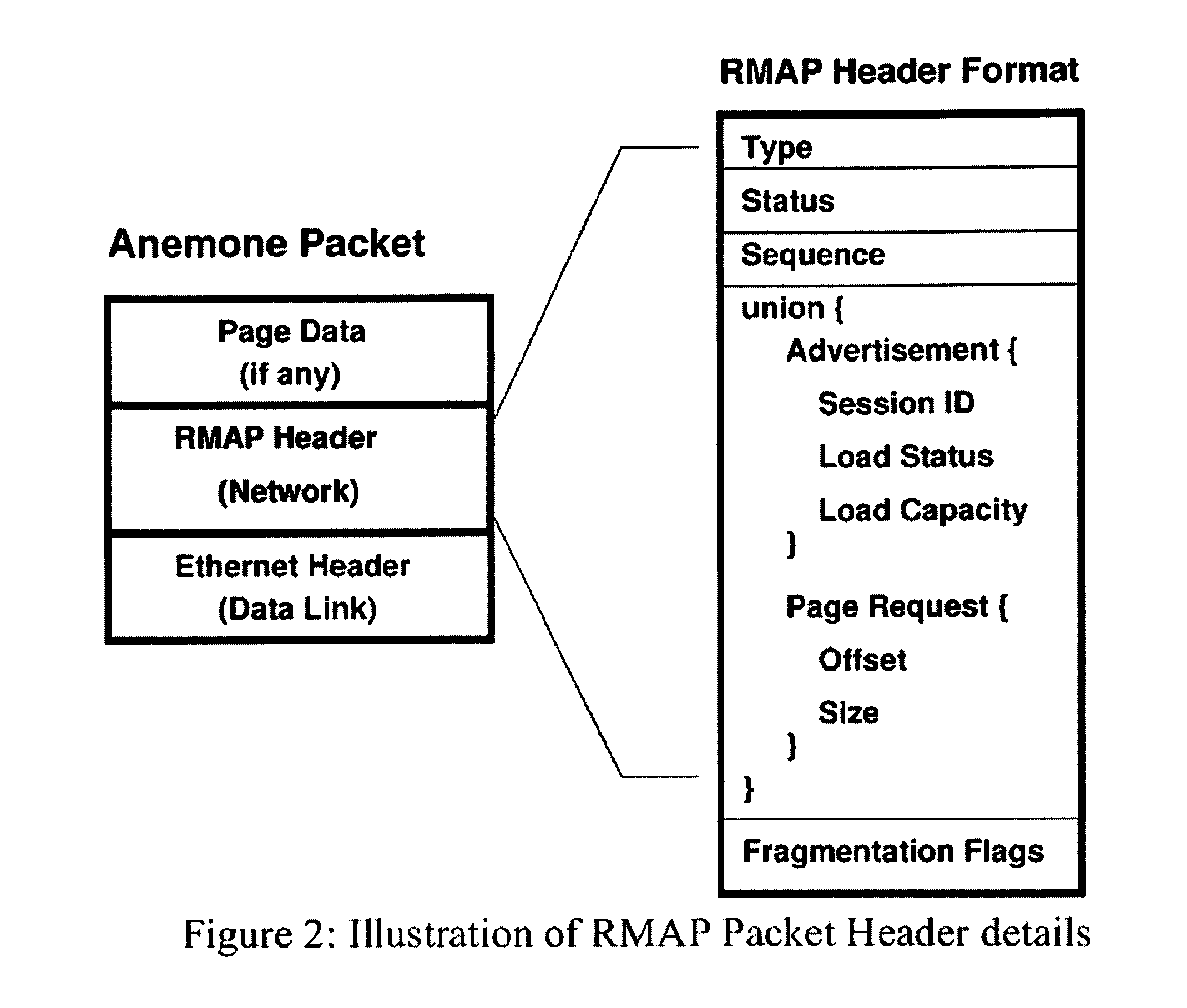

Distributed adaptive network memory engine

ActiveUS7917599B1Processing speedLower latencyMultiple digital computer combinationsTransmissionMass storageOperational system

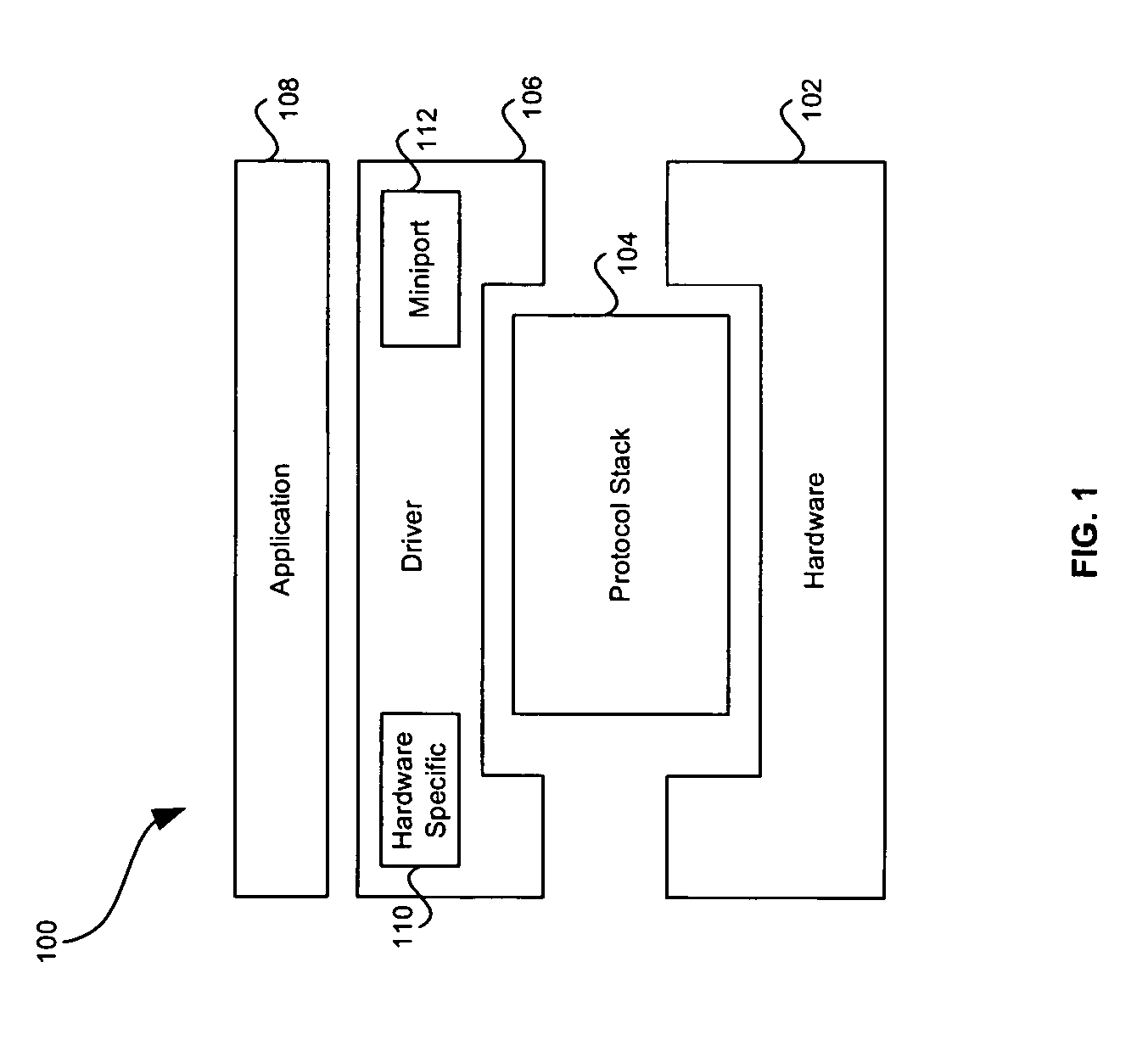

Memory demands of large-memory applications continue to remain one step ahead of the improvements in DRAM capacities of commodity systems. Performance of such applications degrades rapidly once the system hits the physical memory limit and starts paging to the local disk. A distributed network-based virtual memory scheme is provided which treats remote memory as another level in the memory hierarchy between very fast local memory and very slow local disks. Performance over gigabit Ethernet shows significant performance gains over local disk. Large memory applications may access potentially unlimited network memory resources without requiring any application or operating system code modifications, relinkling or recompilation. A preferred embodiment employs kernel-level driver software.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

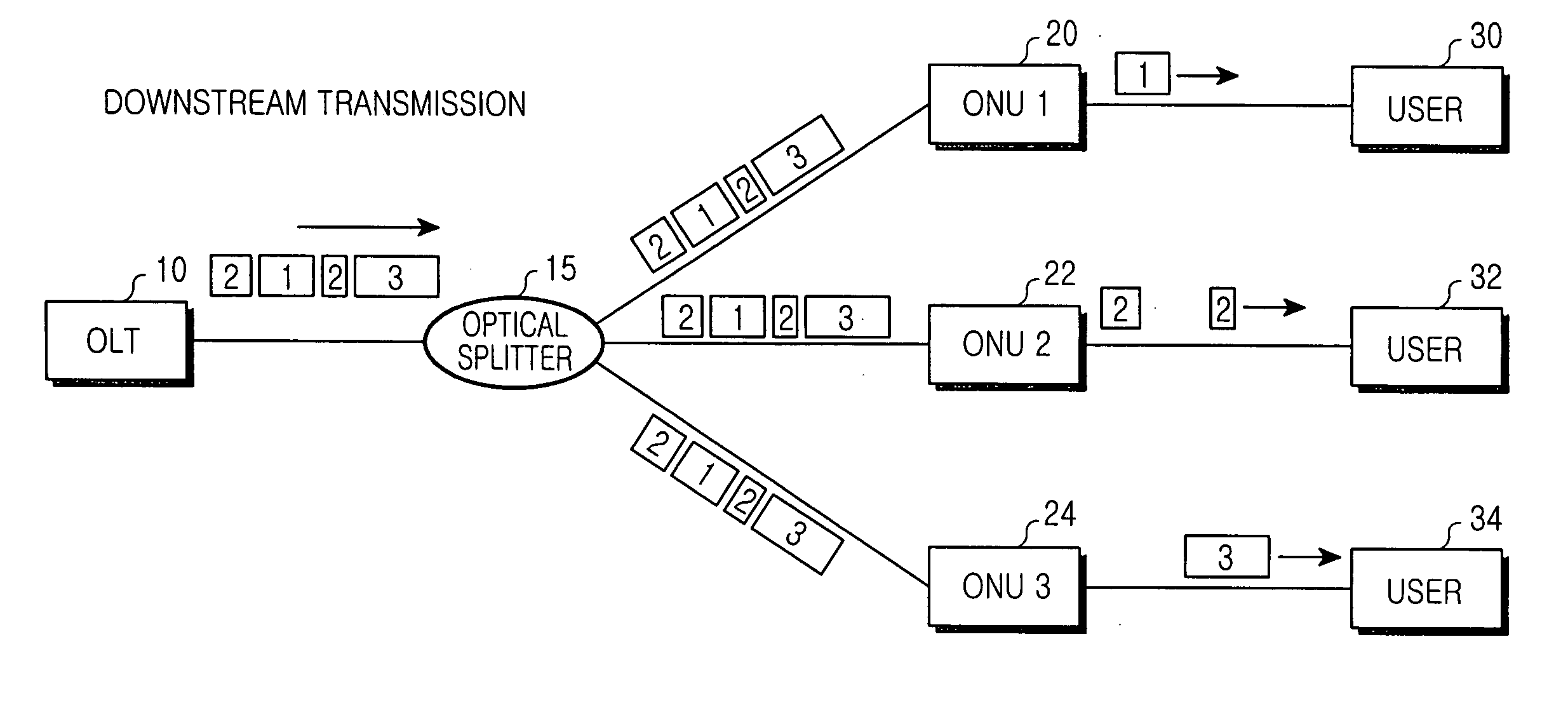

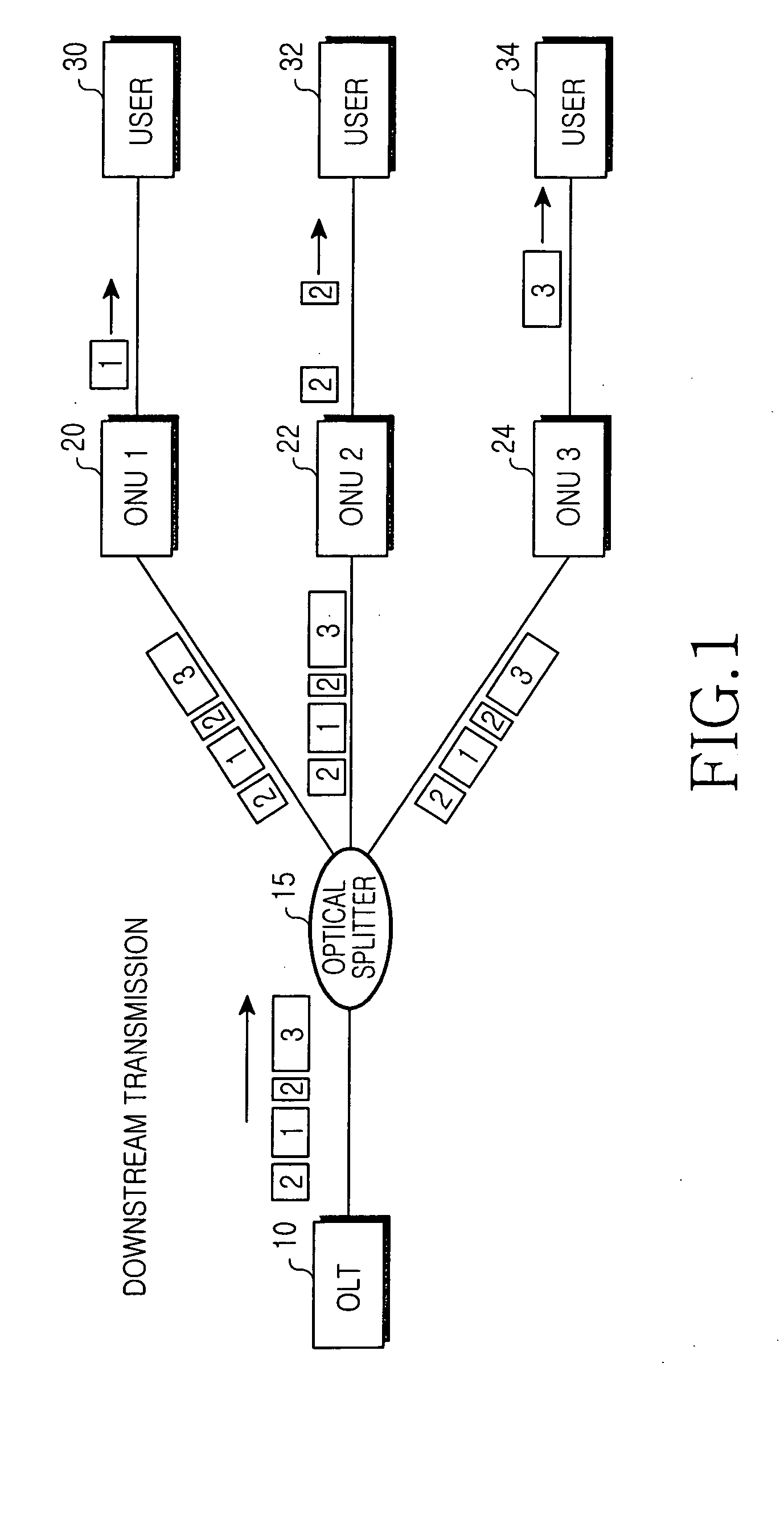

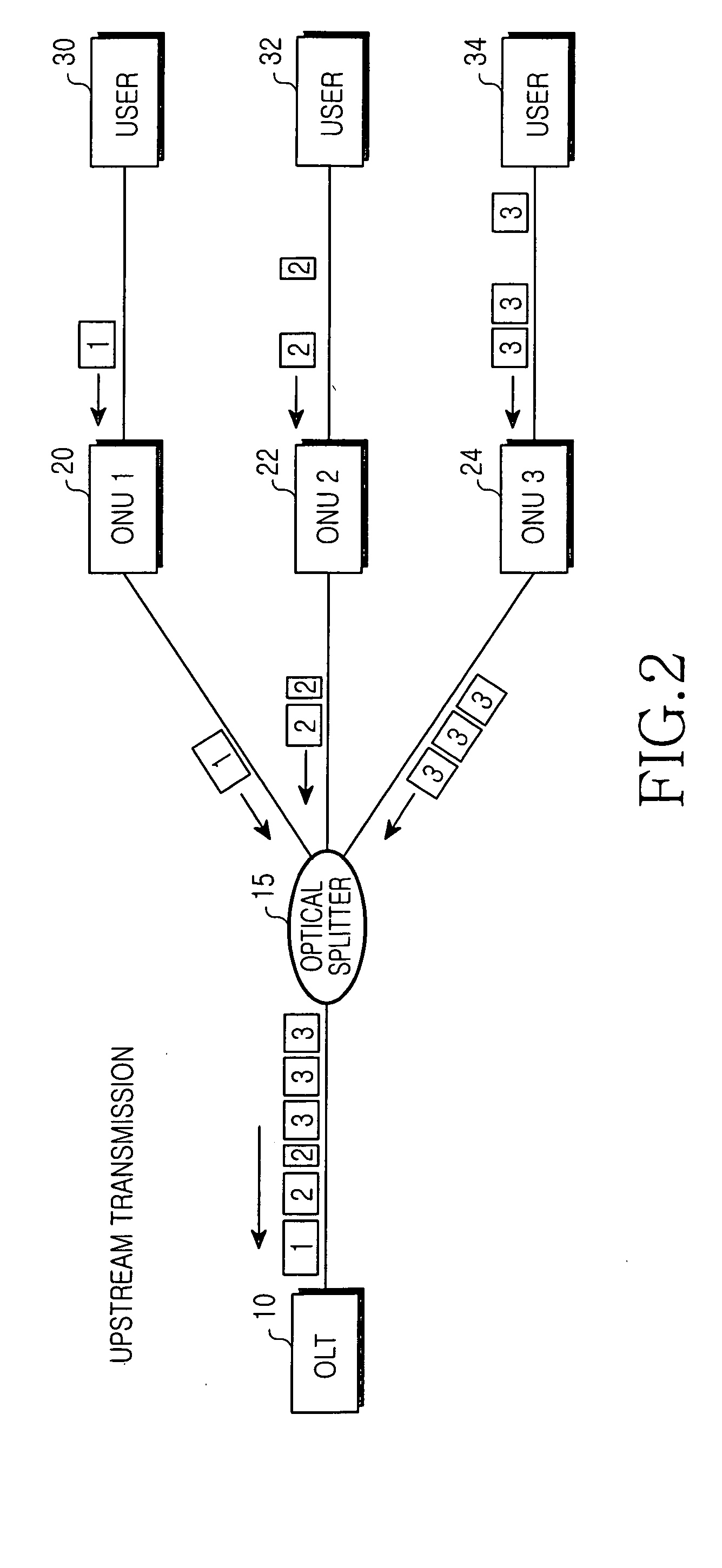

Optical line terminal for managing link status of optical network units and gigabit ethernet passive optical network employing same

InactiveUS20050158048A1Precise managementAccurately discriminate and manageTime-division multiplexFibre transmissionData signalOptical line termination

A system and method for managing link status in Gigabit Ethernet passive optical network (GE-PON) units (ONUs) is disclosed. The GE-PON comprises one or more ONUs allocated data transmission periods, respectively. Each of the ONUs sends a report signal and a data signal in a corresponding one of the allocated data transmission periods. The report signal contains a signal to request allocation of a bandwidth for data signal transmission in a next window period. The GE-PON further comprises an optical splitter having its one side connected with the ONUs and its other side connected with at least one optical communication channel. The optical splitter switches an input signal to a desired destination. The GE-PON further comprises an optical line terminal (OLT) for determining whether the report signal is received, identifying a specific one of the ONUs having sent the report signal when the report signal is received, determining whether the data signal is received from the specific ONU in a specific one of the data transmission periods allocated to the specific ONU, and discriminating and managing a link status of the specific ONU in accordance with the determination made.

Owner:SAMSUNG ELECTRONICS CO LTD

System and method for virtualizing PCIe devices

ActiveUS7743197B2Efficient accessImprove creditMultiple digital computer combinationsData switching networksCrossbar switchIntelligent Network

An intelligent network processor is disclosed that provides a PCI express (PCIe) host bus adapter with firmware selectable hardware capabilities and firmware enabled emulation of capabilities not supported by hardware. Support for Fibre Channel (FC) and Gigabit Ethernet (GbE) protocols are provided through the same fabric ports, including multiple port trunking for both protocols. On chip protocol conversion is provided for switching and routing between FC and GbE ports. Switching using the same crossbar module is provided for both FC and GbE protocols. The crossbar module is coupled to directly access external DDR memory so that messages from FC, GbE, and PCIe interfaces may be switched directly to the DDR memory.

Owner:EMULEX COMM CORP

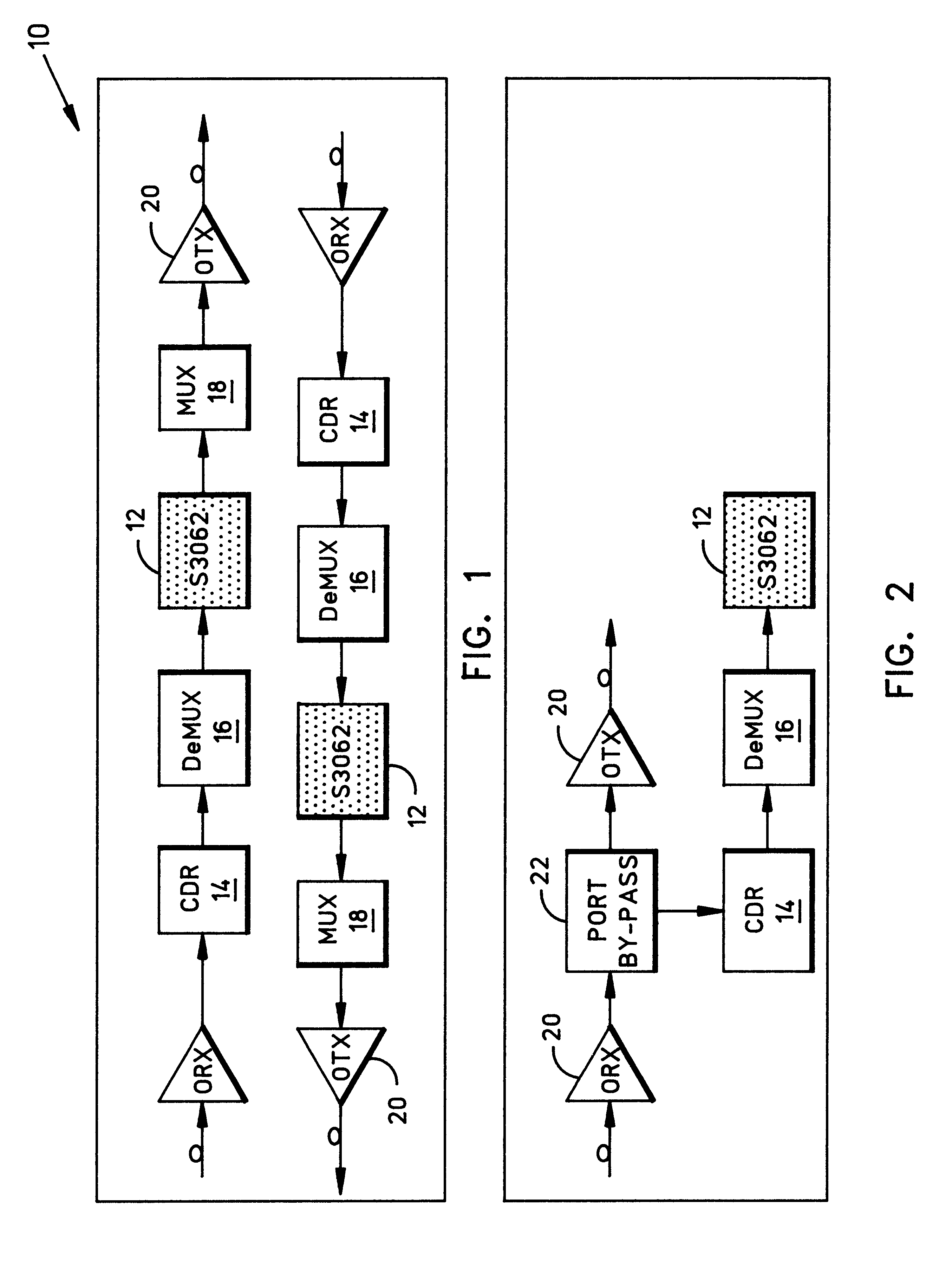

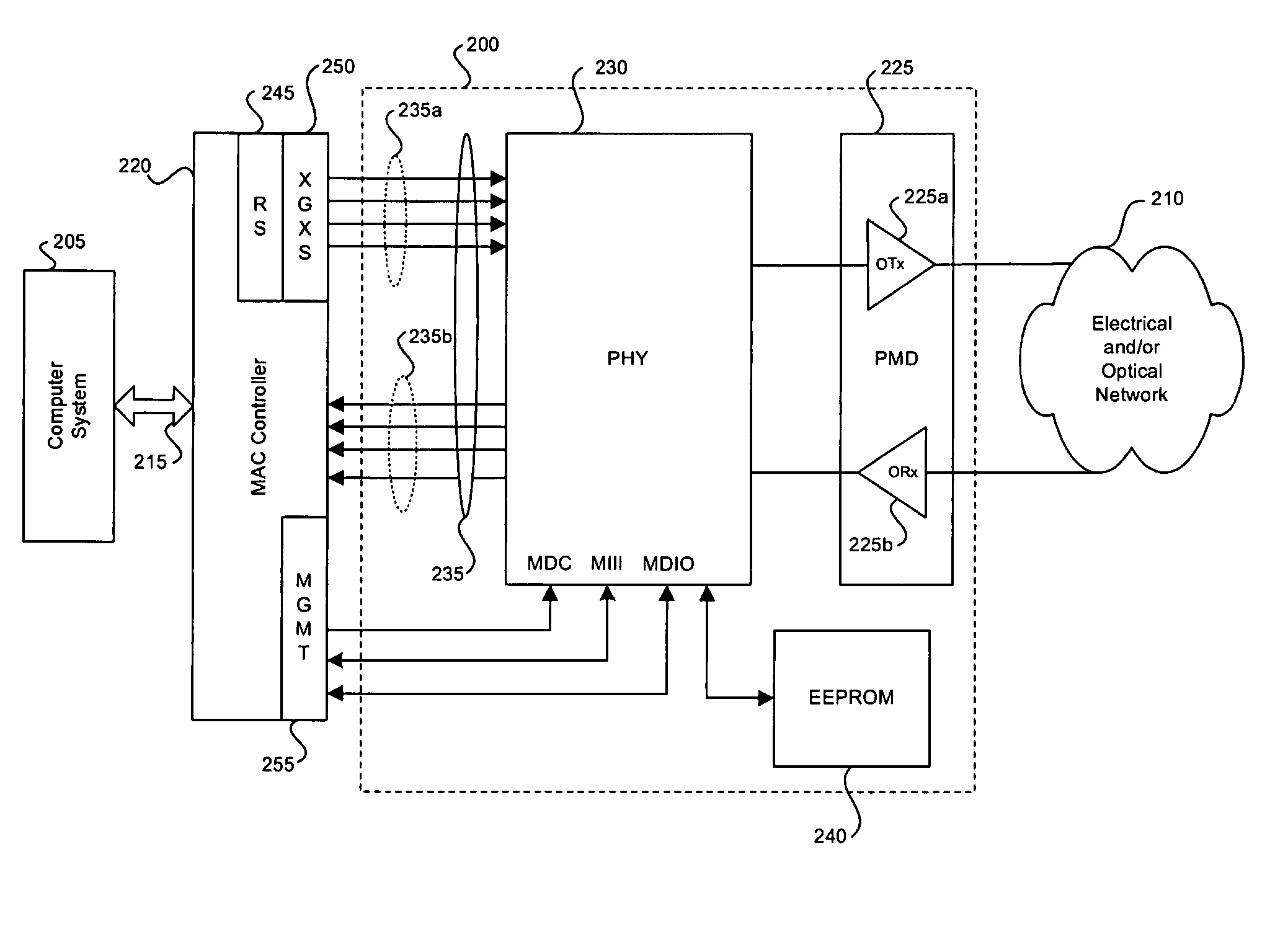

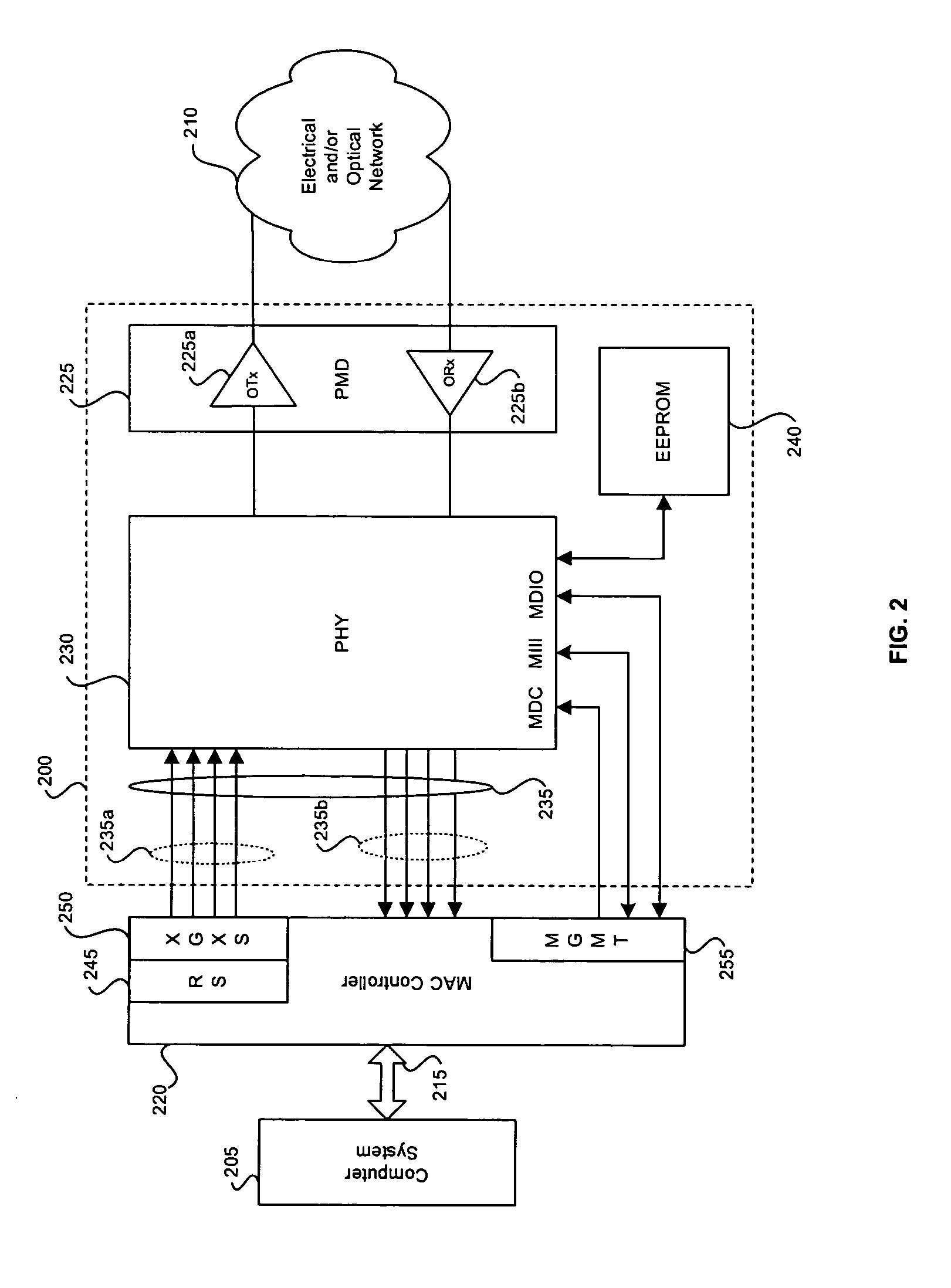

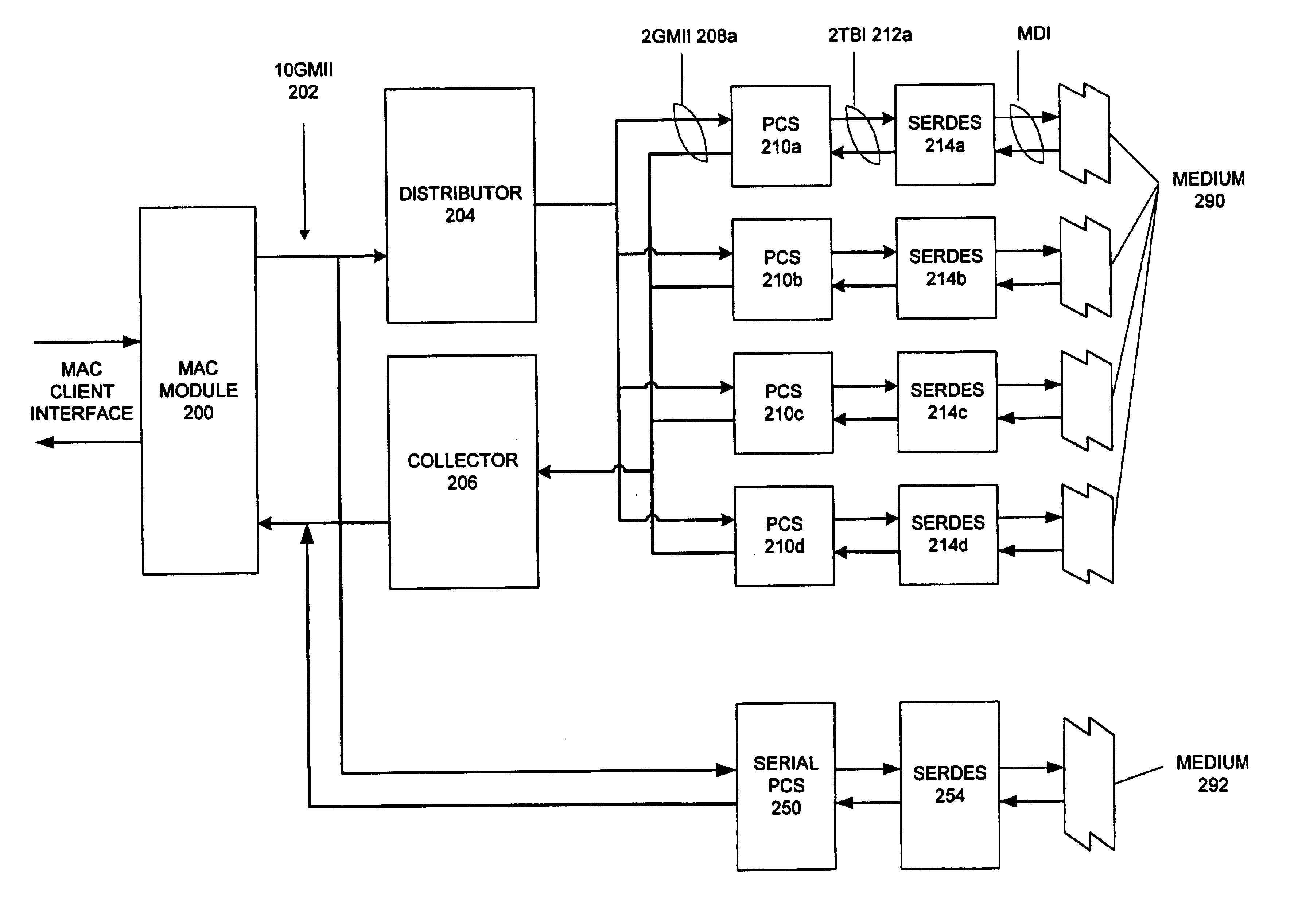

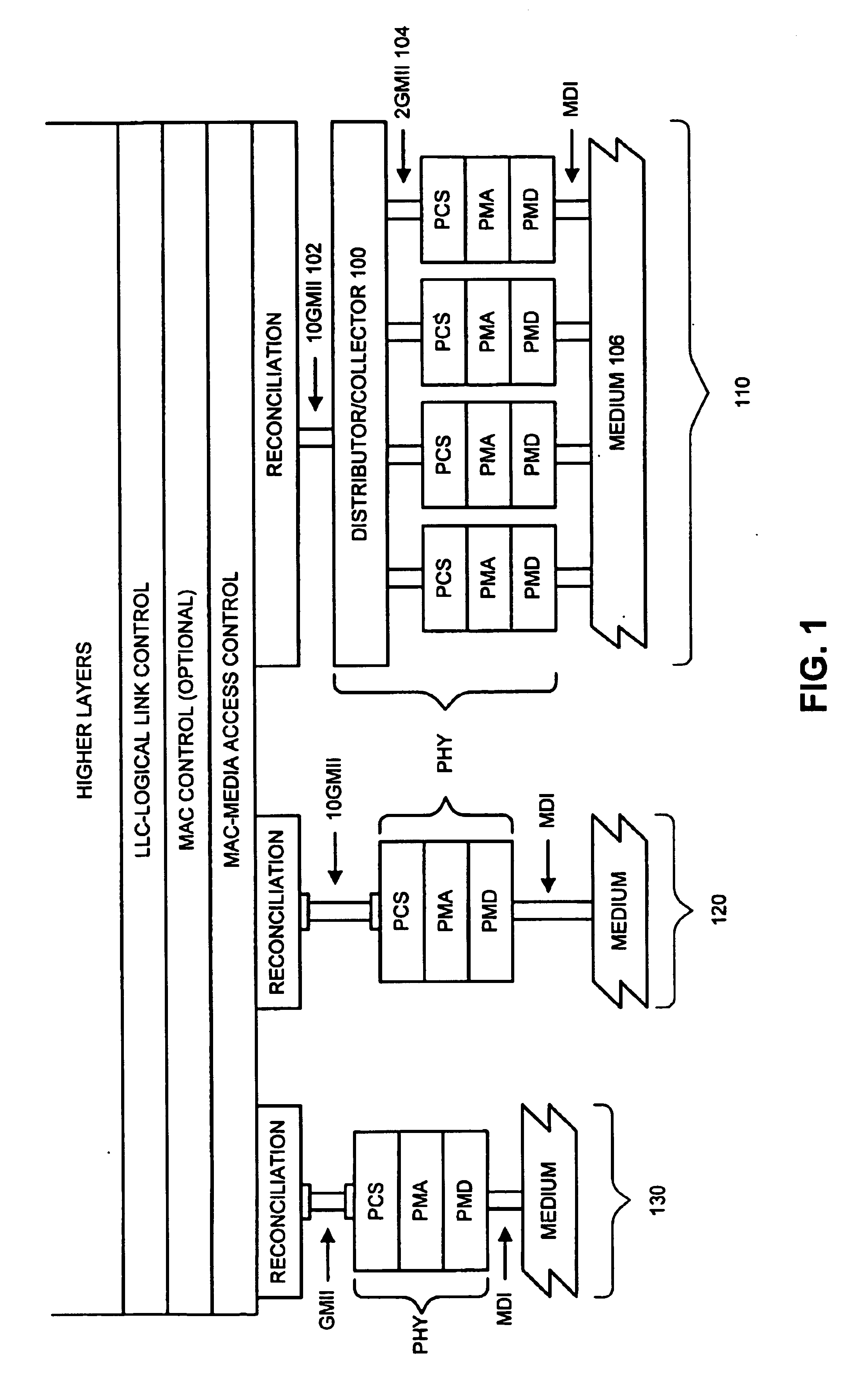

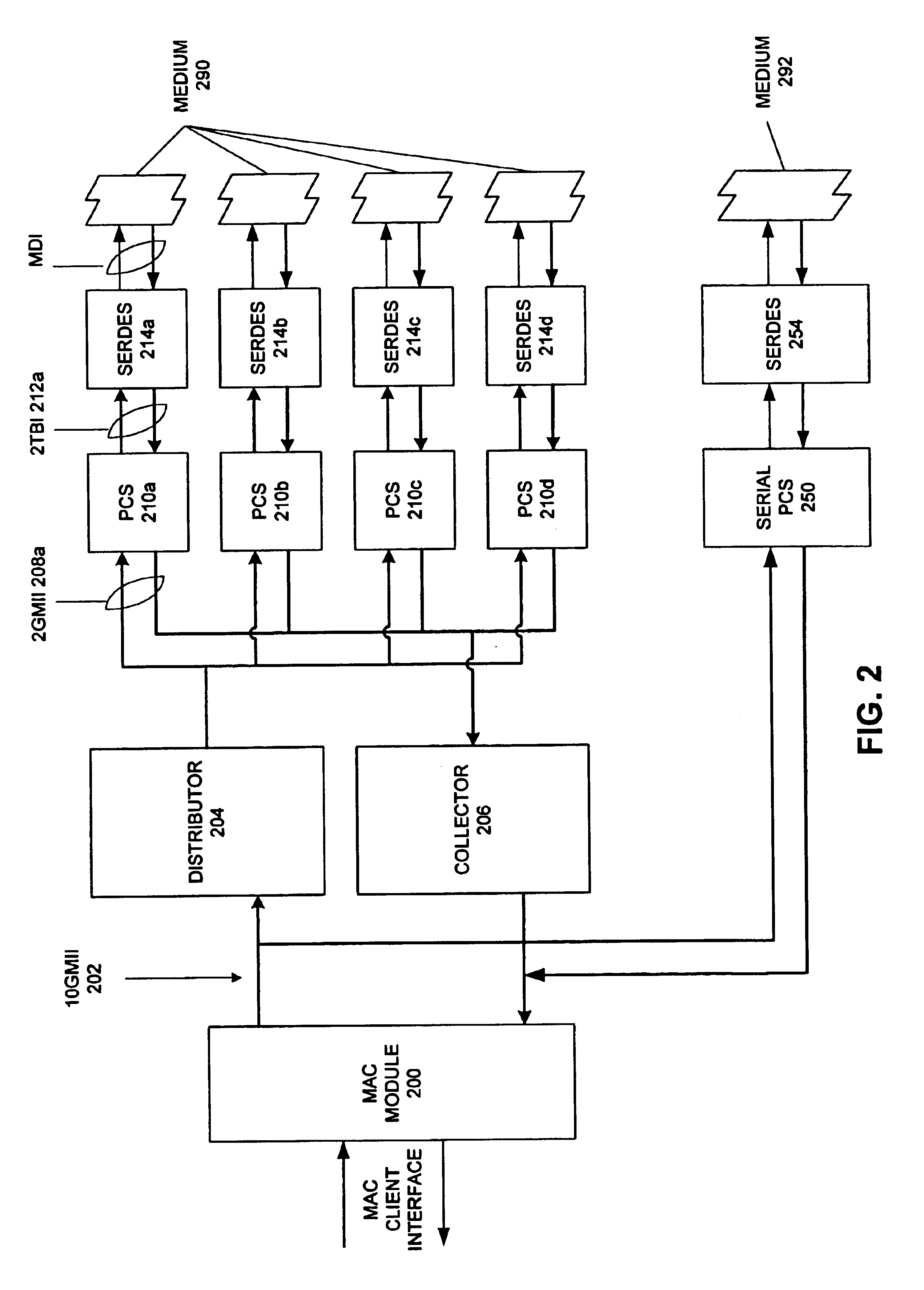

Method and apparatus for a multi-gigabit ethernet architecture

InactiveUS6873630B1Communication speed be lowerTime-division multiplexNetwork connectionsMultiplexingPropagation delay

An Ethernet architecture is provided for connecting a computer system or other network entity to a dedicated Ethernet network medium. The network interface enables the transmission and receipt of data by striping individual Ethernet frames across a plurality of logical channels and may thus operate at substantially the sum of the individual channel rates. Each channel may be conveyed by a separate conductor (e.g., in a bundle) or the channels may be carried simultaneously on a shared medium (e.g., an electrical or optical conductor that employs a form of multiplexing). On a sending station, a distributor within the sender's network interface receives Ethernet frames (e.g., from a MAC) and distributes frame bytes in a round-robin fashion on the plurality of channels. Each “mini-frame” is separately framed and encoded for transmission across its channel. On a receiving station, the receiver's network interface includes a collector for collecting the multiple mini-frames (e.g., after decoding) and reconstructing the frame's byte stream (e.g., for transfer to the receiver's MAC). The first and last bytes of each frame and mini-frame are marked for ease of recognition. Multiple unique idle symbols may be employed for transmission during inter-packet gaps to facilitate the collector's synchronization of the multiple channels and / or enhance error detection. A maximum channel skew is specified, and each received channel may be buffered with an elasticity that is proportional to the maximum skew so that significant propagation delay may be encountered between channels without disrupting communications.

Owner:ORACLE INT CORP

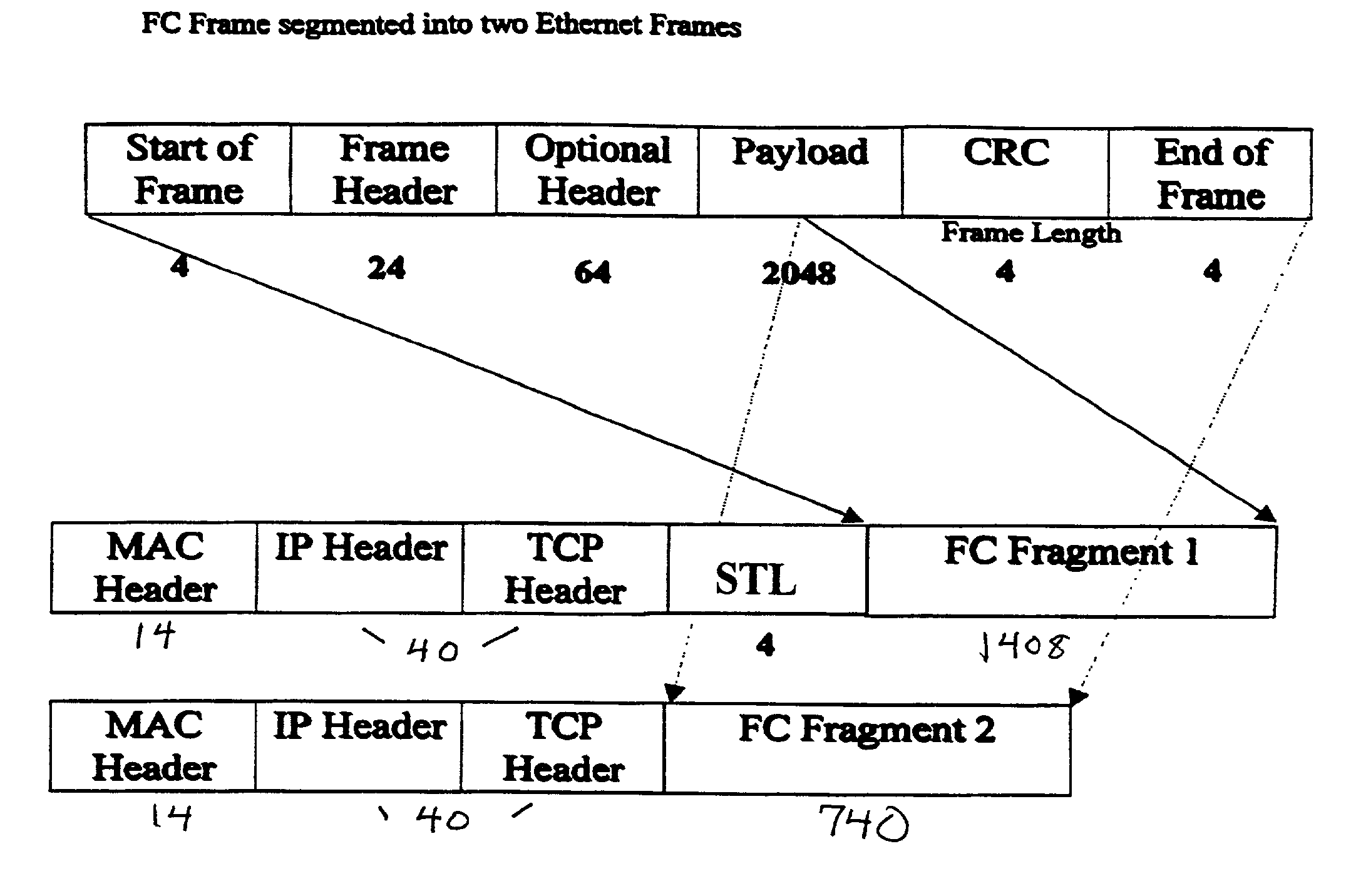

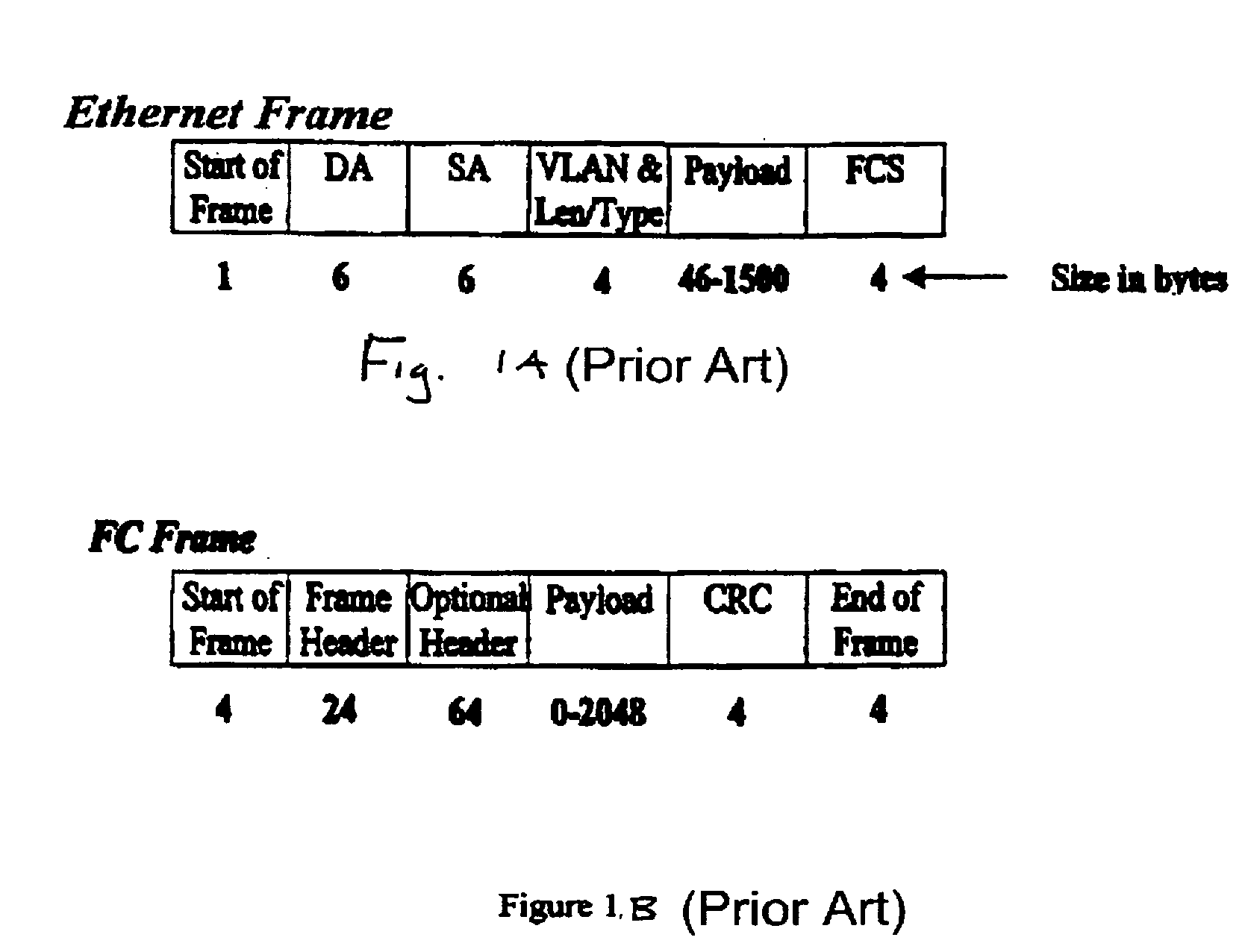

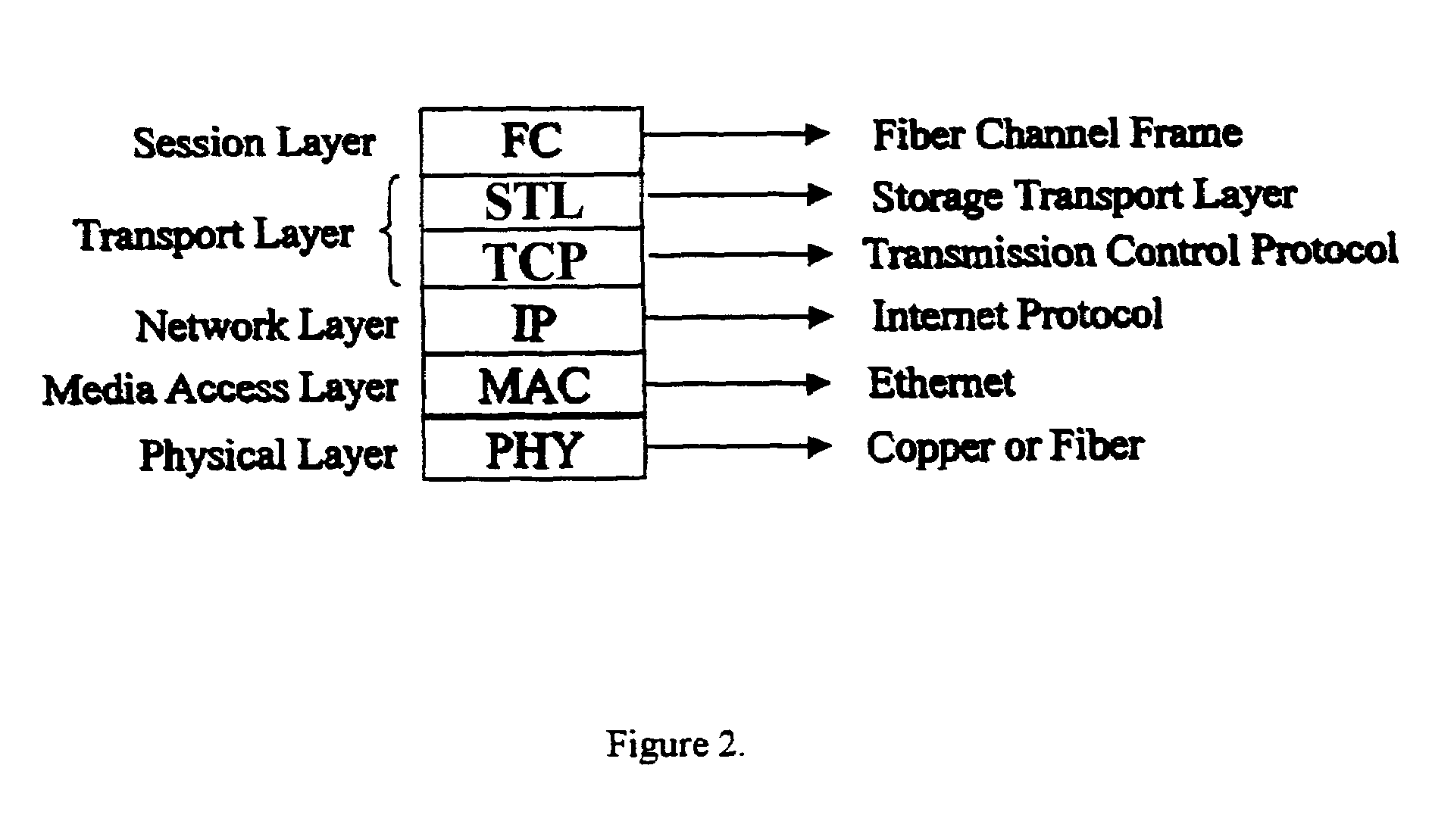

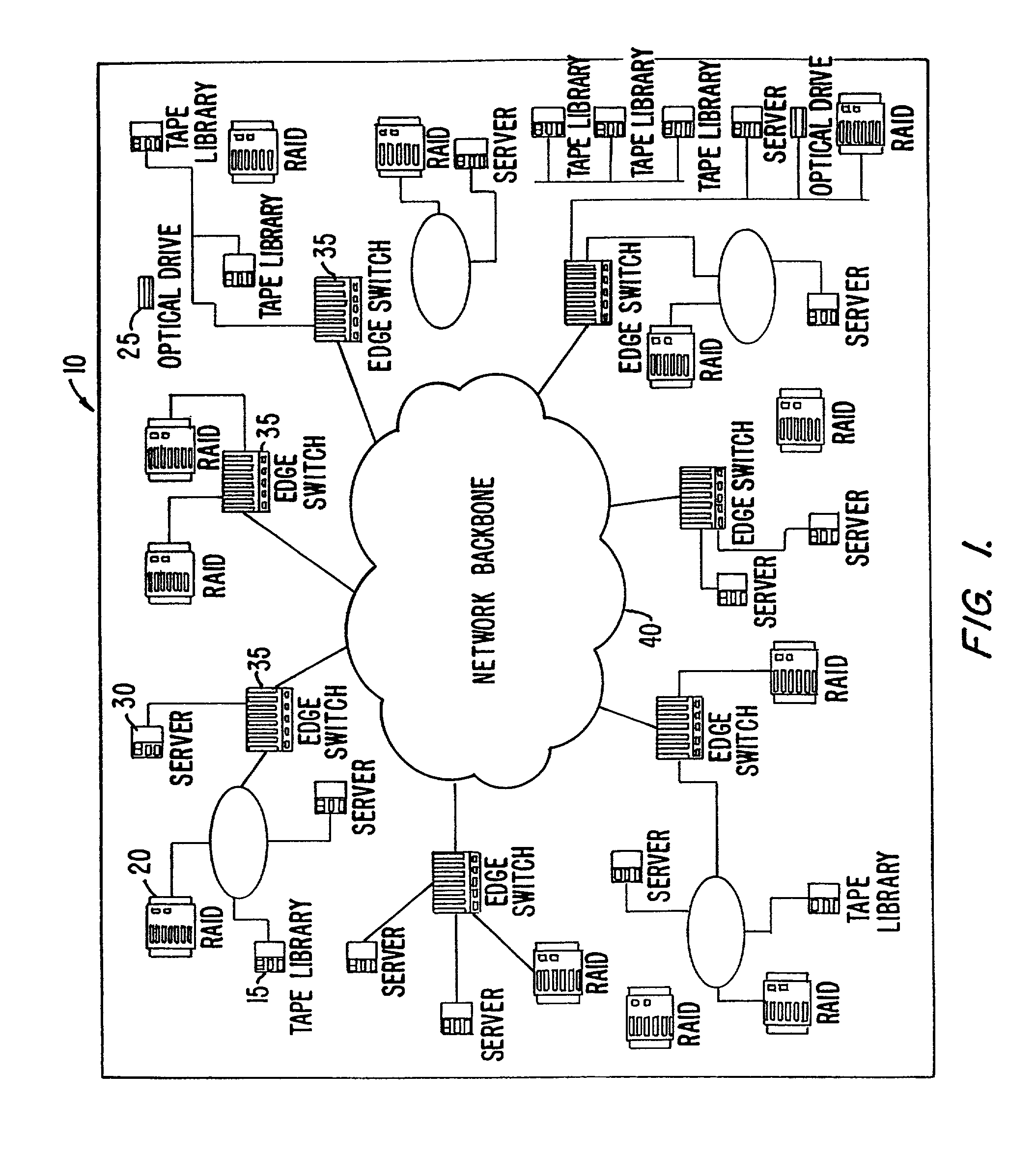

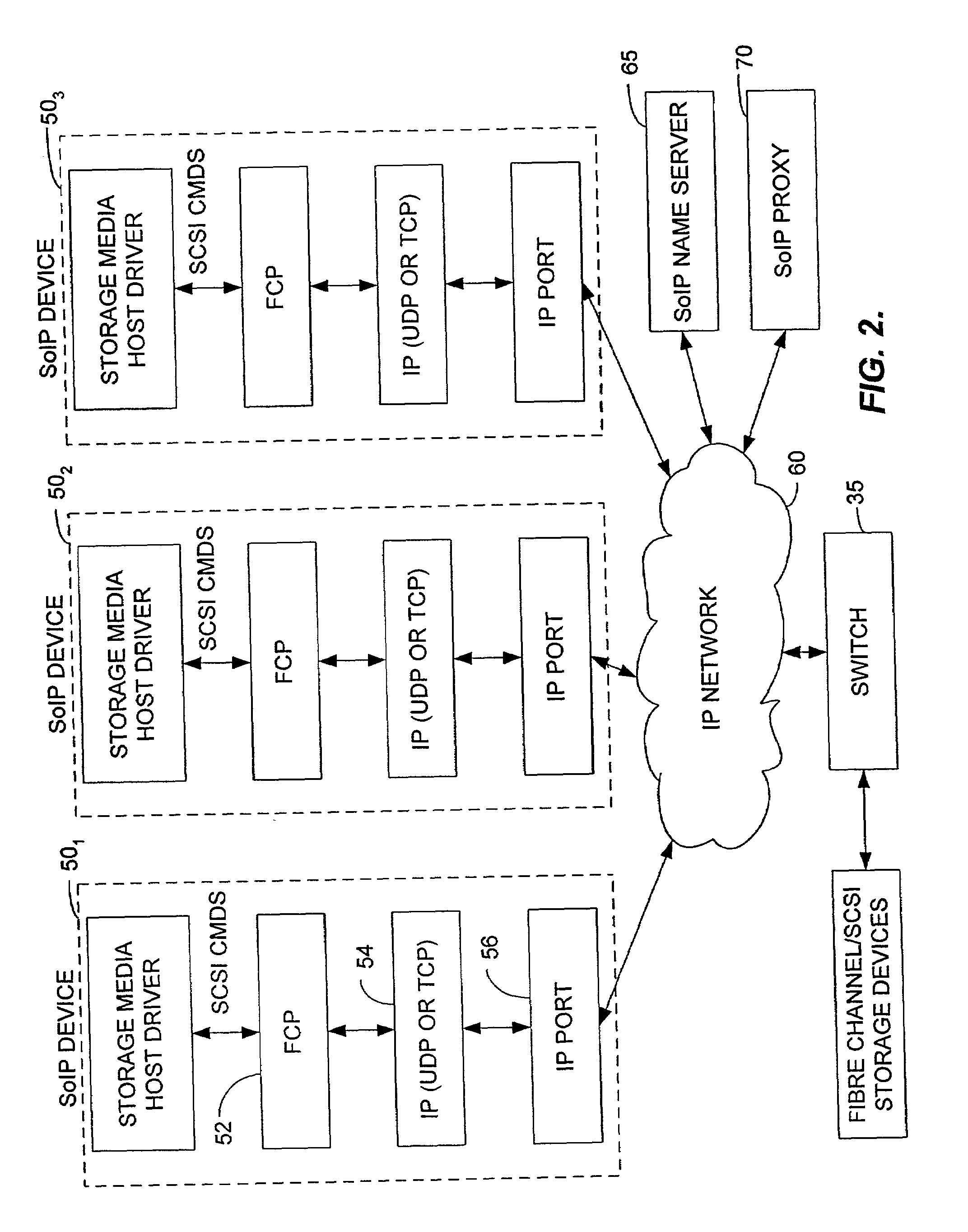

Protocol stack for linking storage area networks over an existing LAN, MAN, or WAN

InactiveUS7020715B2High bandwidthLow-latency and reliableTime-division multiplexData switching by path configurationTelecommunicationsHigh bandwidth

The present invention provides for a method and protocol for high bandwidth, low-latency and reliable transfer of variable length FC Frames over the Gigabit Ethernet.

Owner:AVAGO TECH INT SALES PTE LTD

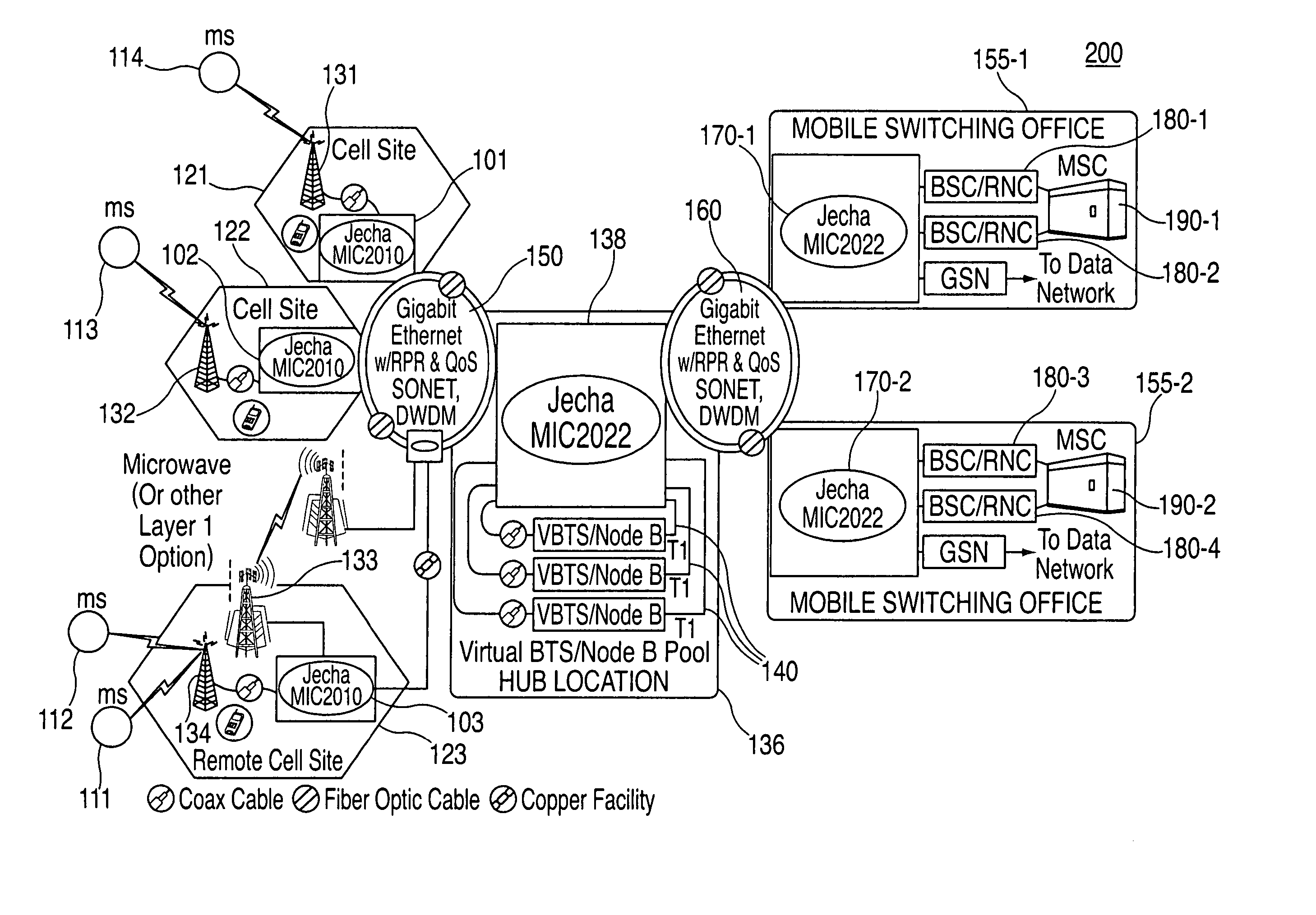

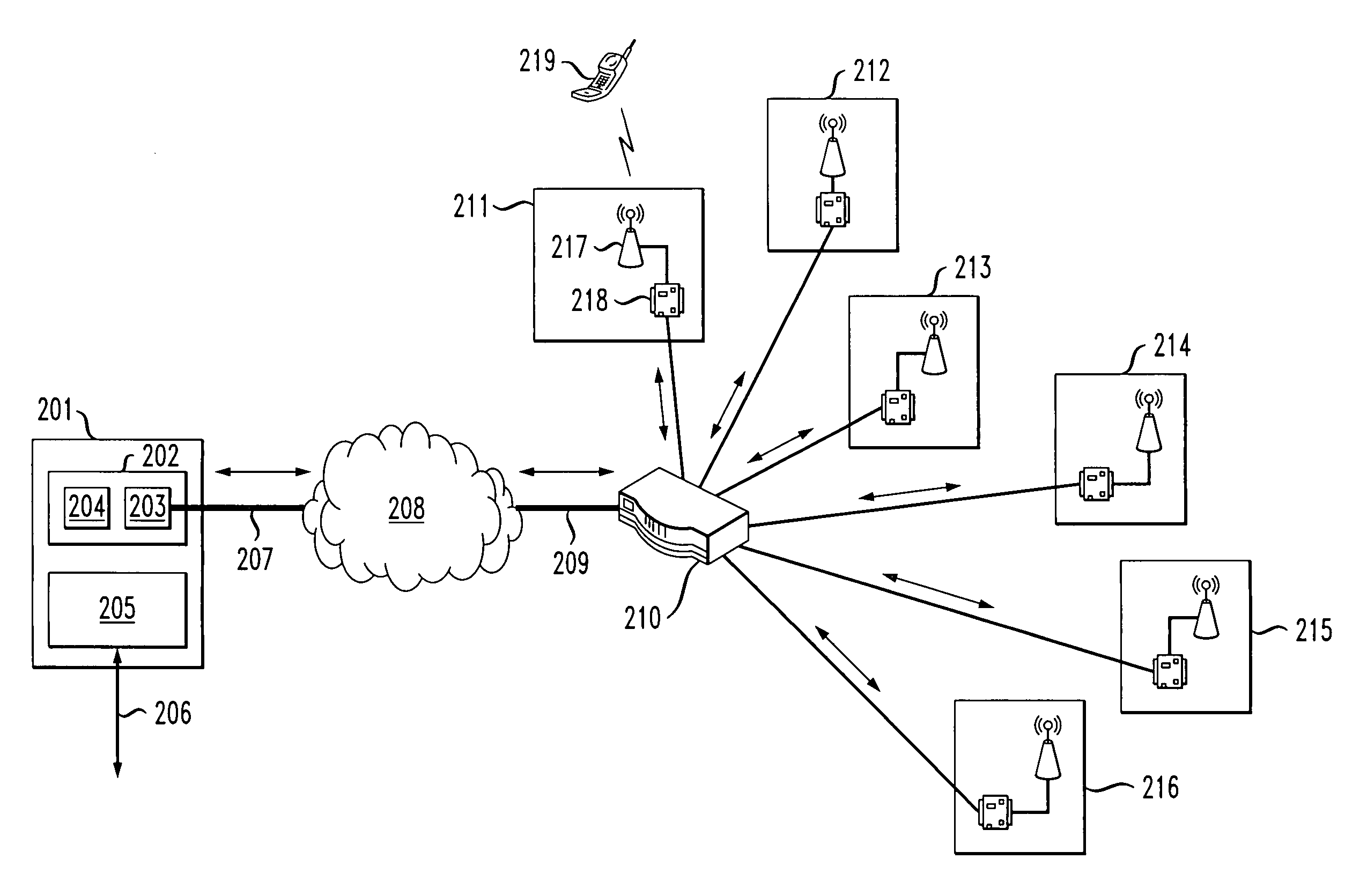

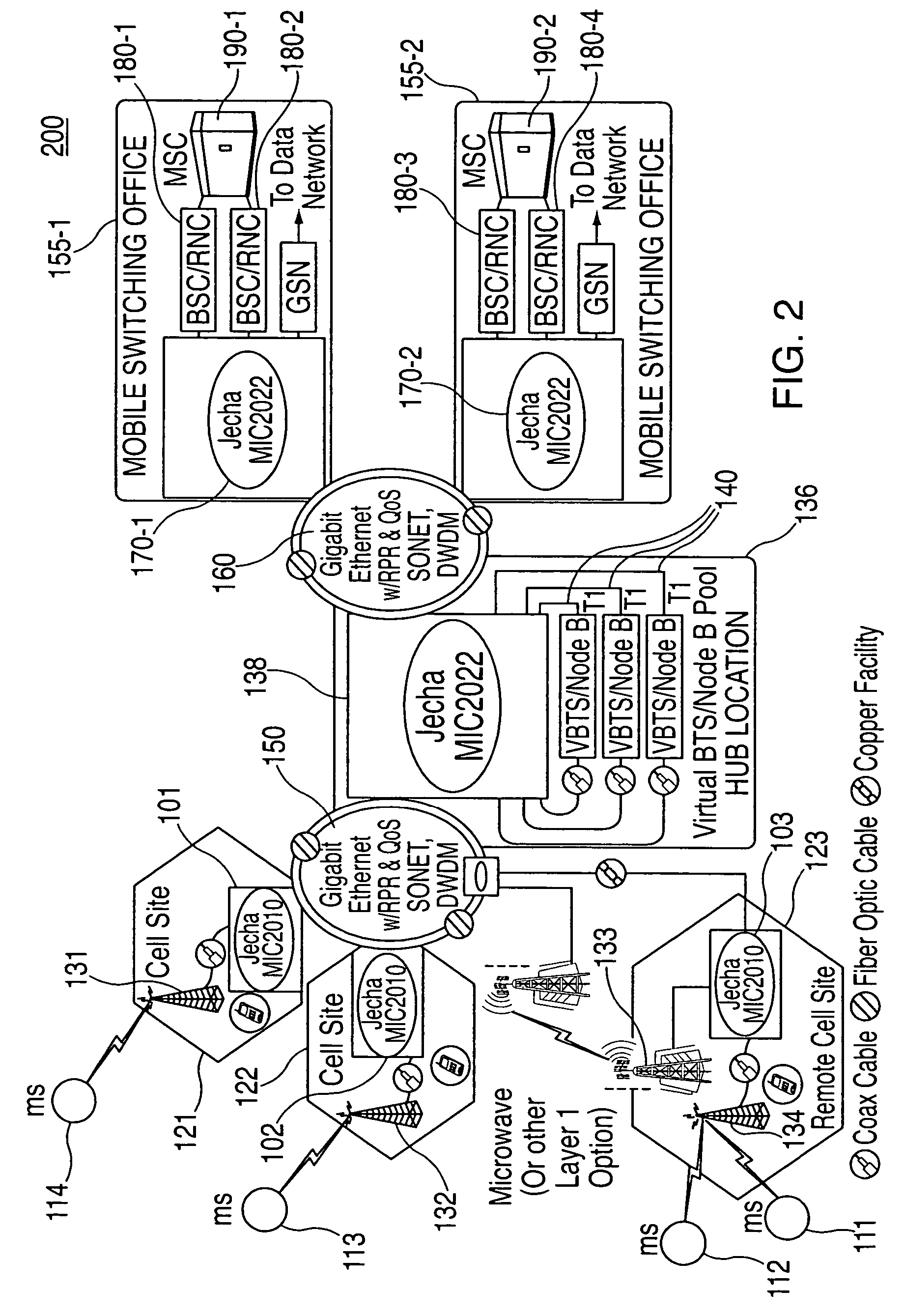

System and method for optimizing network capacity in a cellular wireless network

InactiveUS7573862B2Improve efficiencyReduce operating costsNetwork traffic/resource managementPower distribution line transmissionQuality of serviceFiber

A system and method is disclosed for increasing the efficiency of a cellular communication network, reduce ongoing operating costs and increase revenue. According to one aspect, a method is disclosed for increasing the efficiency of a cellular communication network whereby network capacity in the radio access network (RAN) and baseband processing for wireless connections are dynamically adjusted to automatically provision sufficient bandwidth and baseband processing capacity in response to changes in the network. The method is further extended by implementing policy management which allows wireless carriers to develop and implement network based policies to automatically increase or decrease the amount of processing resources and network bandwidth required from any cell site, hub or mobile switching office. According to another aspect, network efficiency is enhanced by utilizing a novel cellular network infrastructure. RF signals from cell site antennas of various technology types are demodulated, digital bit information is extracted from the RF signals, processed, and groomed into Gigabit Ethernet / Resilient Packet Ring (GigE / RPR) or Ethernet over copper traffic flows using specific Quality of Service (QoS) priorities. The GigE / RPR traffic flows are routed to hub sites or mobile switching offices, at which point the packetized information is extracted and converted to RF signals that are equivalent to the signals that were received at the antenna. The RF signals are sent over coaxial cable to a network hub including a pool of Base Transceiver Stations (BTSs) (or Node Bs). The hub is coupled to one or more mobile switching offices via a second fiber optic ring.

Owner:CHAMBERS MAHDI +1

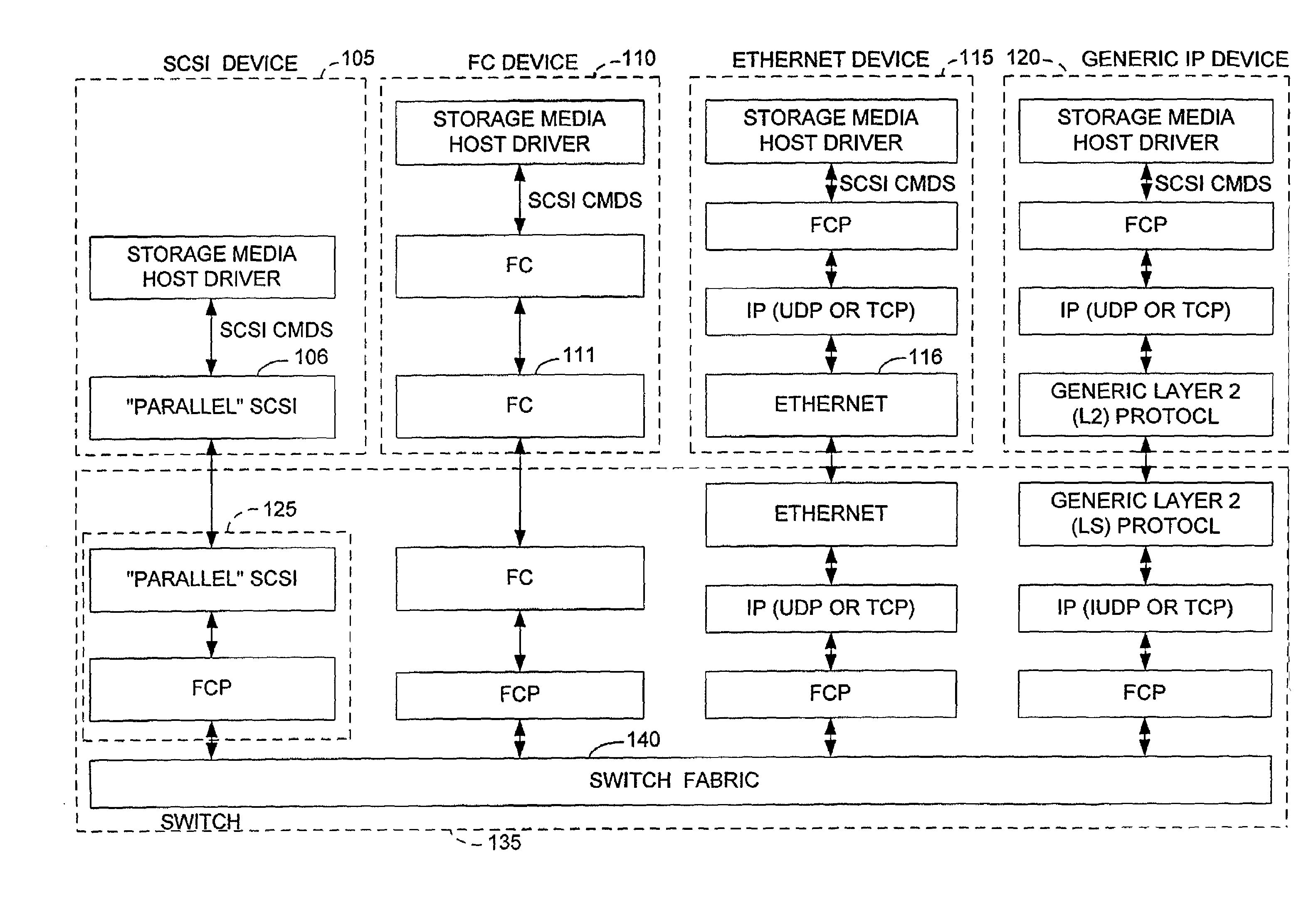

Method and apparatus for transferring data between IP network devices and SCSI and fibre channel devices over an IP network

InactiveUS7197047B2Good conditionFast transferAnswer-back mechanismsTime-division multiplexSCSIFibre Channel

A method and apparatus for transferring data between IP devices (including, but not limited to, Gigabit Ethernet devices) and SCSI or Fibre Channel devices. The device interfaces may be either SCSI, Fibre Channel or IP interfaces such as Gigabit Ethernet. Data is switched between SCSI and IP, Fibre Channel and IP, or between SCSI and Fibre Channel. Data can also be switched from SCSI to SCSI, IP to IP and FC to FC. The port interfaces provide the conversion from the input frame format to an internal frame format, which can be routed within the apparatus. The amount of processing performed by each port interface is dependent on the interface type. The processing capabilities of the present invention permit rapid transfer of information packets between multiple interfaces at latency levels meeting the stringent requirements for storage protocols. The configuration control can be applied to each port on a switch and, in turn, each switch on the network, via an SNMP or Web-based interface, providing a flexible, programmable control for the apparatus.

Owner:AVAGO TECH INT SALES PTE LTD

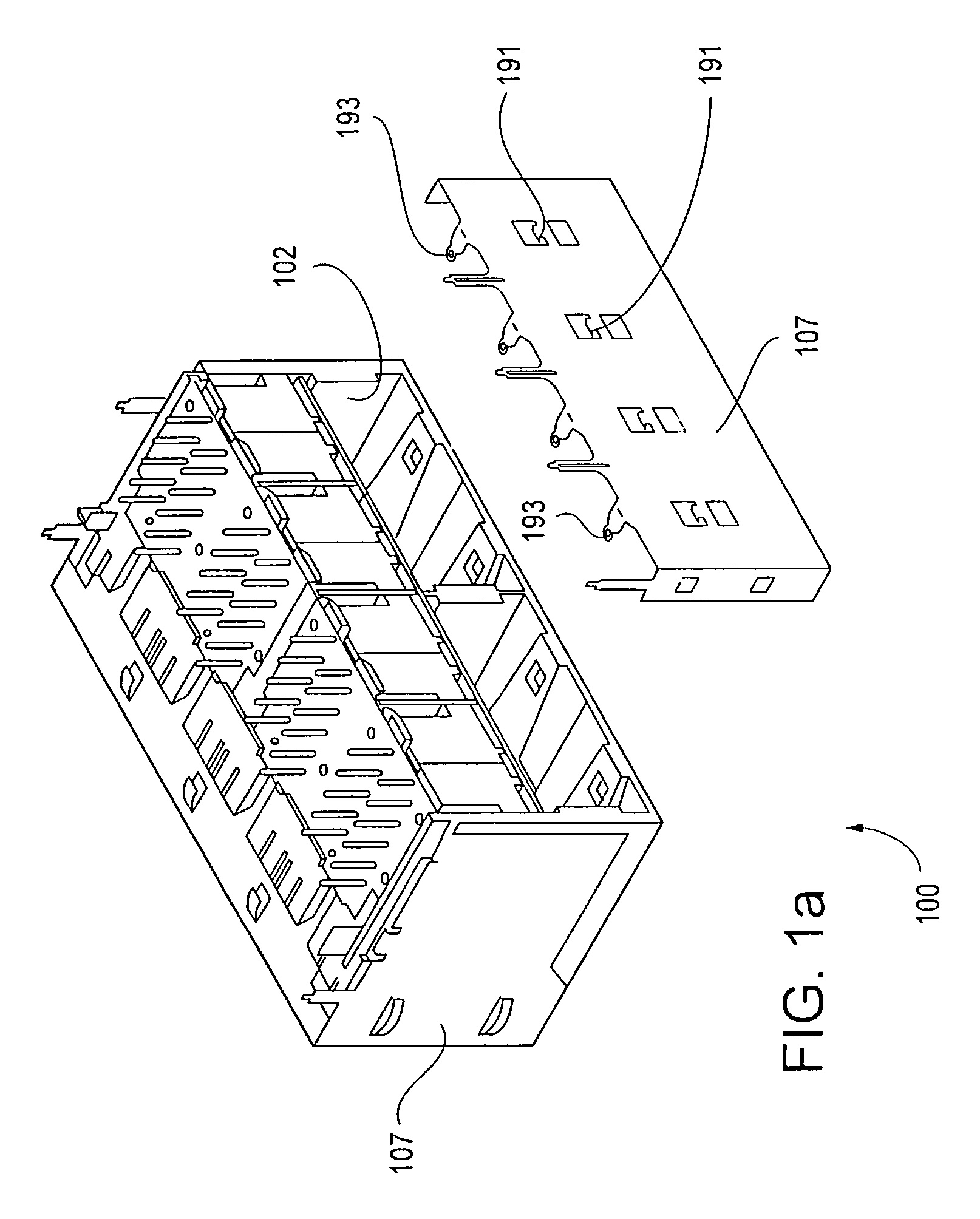

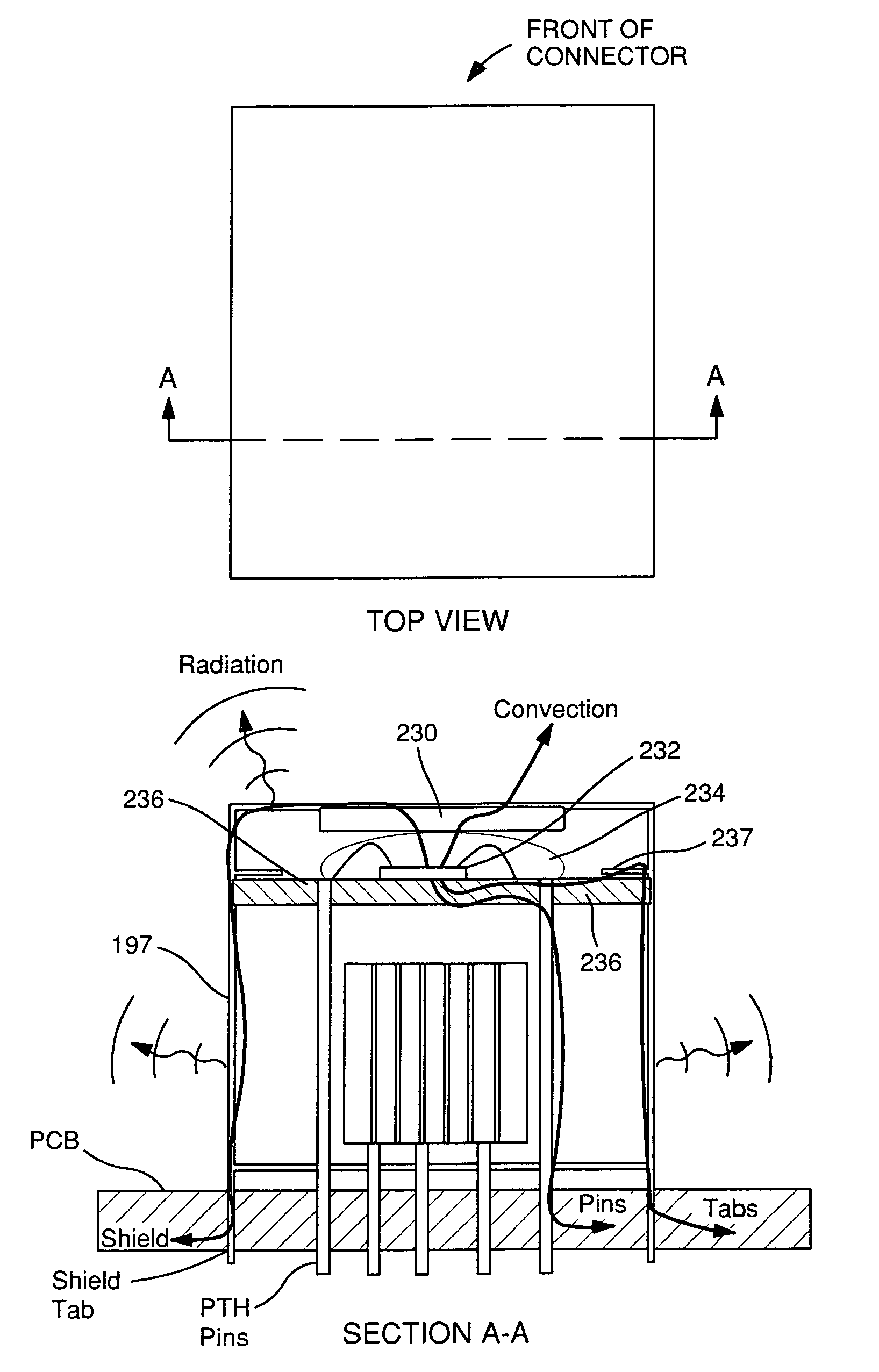

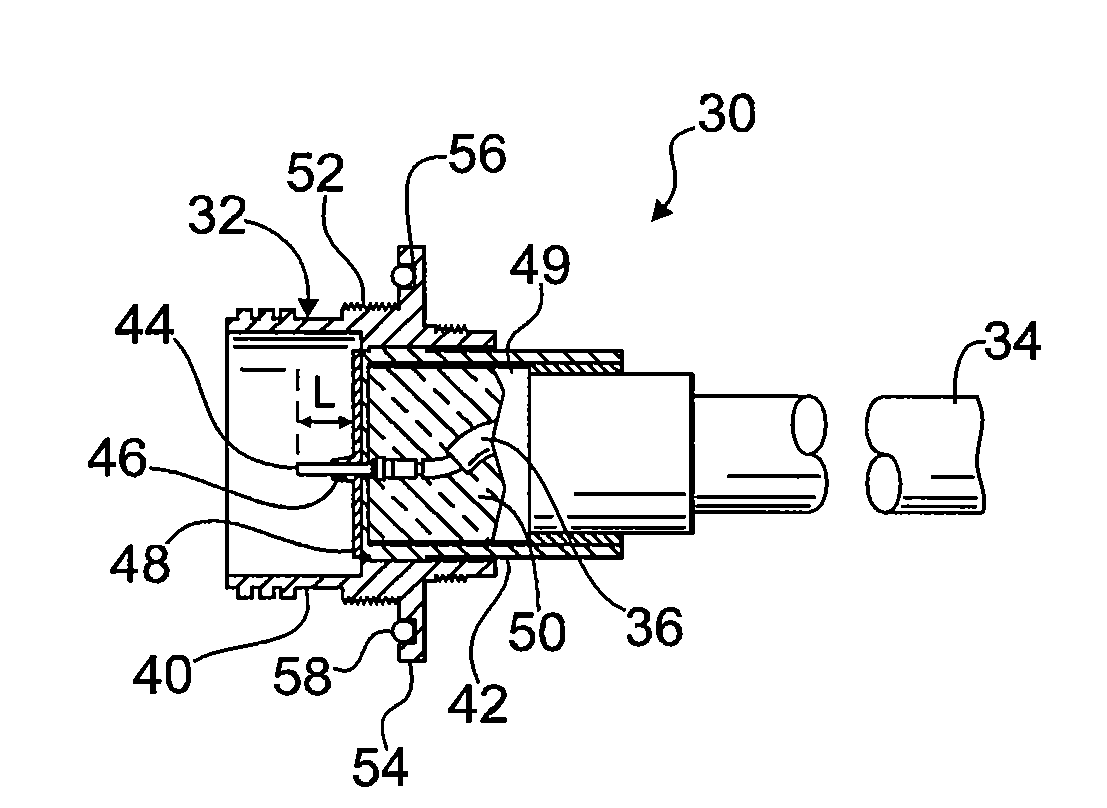

Power-enabled connector assembly with heat dissipation apparatus and method of manufacturing

InactiveUS7524206B2Improve handlingNetwork connectorsTwo-part coupling devicesSignal conditioningEngineering

An advanced connector assembly enabled to receive and distribute power signals. In one embodiment, the connector comprises a single port modular jack, and incorporates an insert assembly disposed in the rear portion of the connector housing. The insert assembly includes first and second substrates and a cavity adapted to receive one or more electronic or signal conditioning components. Heat removal features are also utilized within the jack to effectively dissipate heat produced by the electronic or signal conditioning components. The insert assembly is also optionally made removable from the jack housing such that an insert assembly of a different electronics or terminal configuration can be substituted therefor. In this fashion, the connector can be configured to a plurality of different standards (e.g., Gigabit Ethernet, 10 / 100, etc.). Methods for manufacturing the aforementioned embodiments are also disclosed.

Owner:PULSE ELECTRONICS

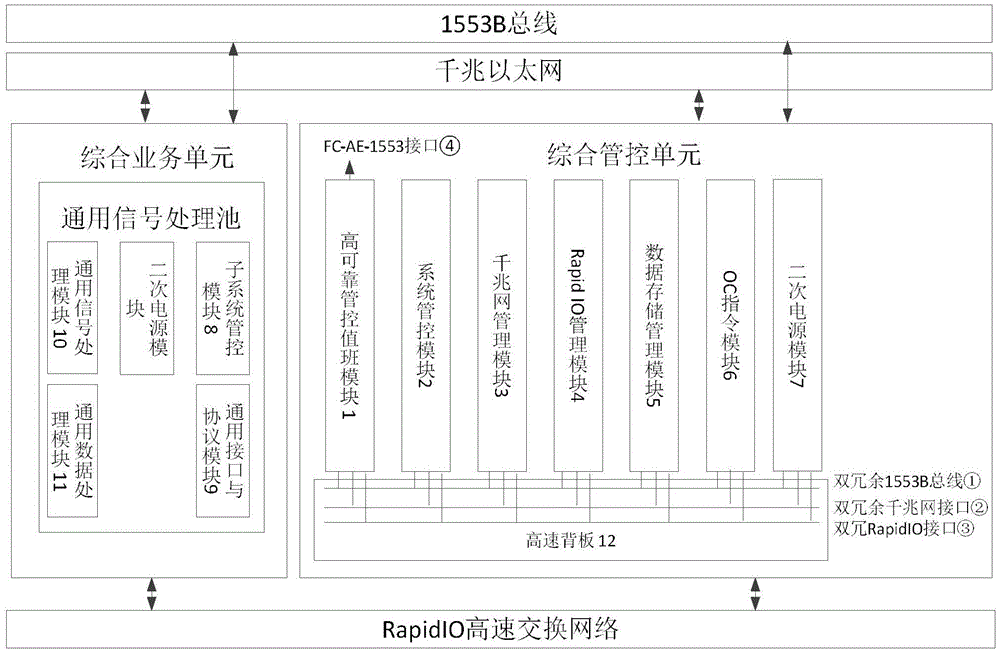

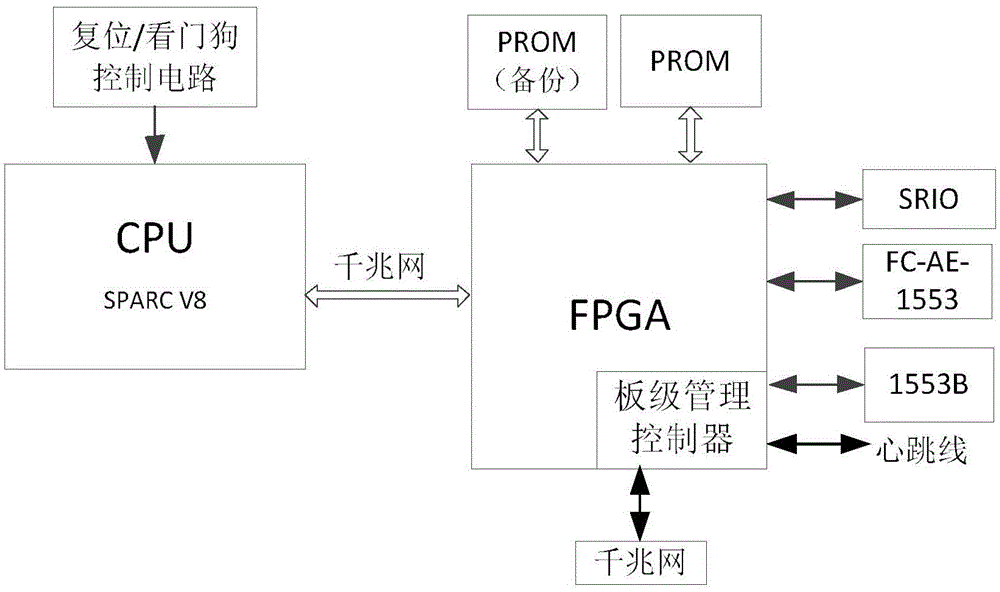

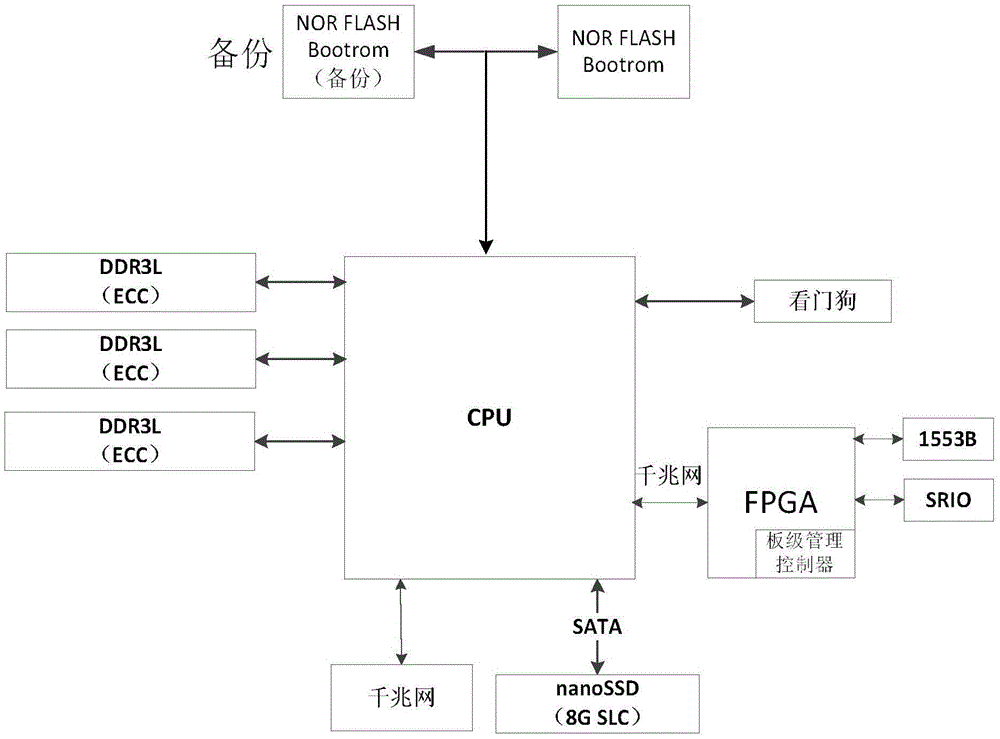

Satellite-borne electronic equipment comprehensive management and control system

ActiveCN105549460AAvoid complexityHighly integratedProgramme controlComputer controlRemote controlControl system

The invention discloses a satellite-borne electronic equipment comprehensive management and control system and aims to provides the satellite-borne electronic equipment comprehensive management and control system which is high in integration, stable and reliable and capable of reducing a device number and redundant remote measurement and remote control interfaces. According to the technical field, each module in a comprehensive management and control unite and a comprehensive service unit is connected to a 1553B bus through a board-level management controller in the module so as to carry out data monitoring and instruction data transmission; by means of a J599 type connector, the comprehensive service unit realizes external gigabit Ethernet data communication among units and management and control data isolation and interaction; the comprehensive management and control unite receives platform remote control, time and attitude information and sends remote measurement and data transmission data through a management and control duty module; and the comprehensive management and control unite is configured to X1 or X4 mode through a Rapid IO management module, and a Rapid IO network topological structure in the unit is configured to a single satellite or double mode through the Rapid IO management module.

Owner:10TH RES INST OF CETC

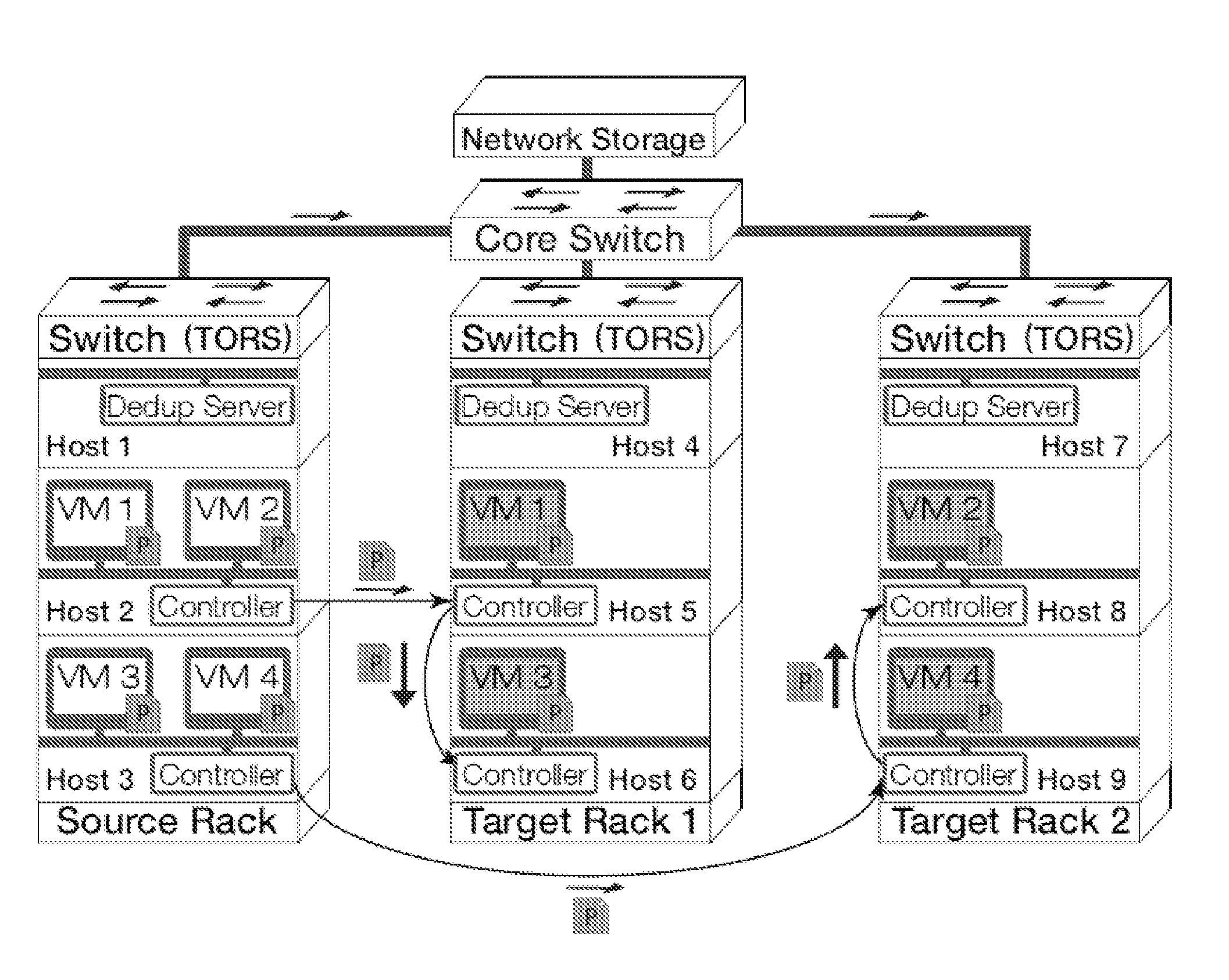

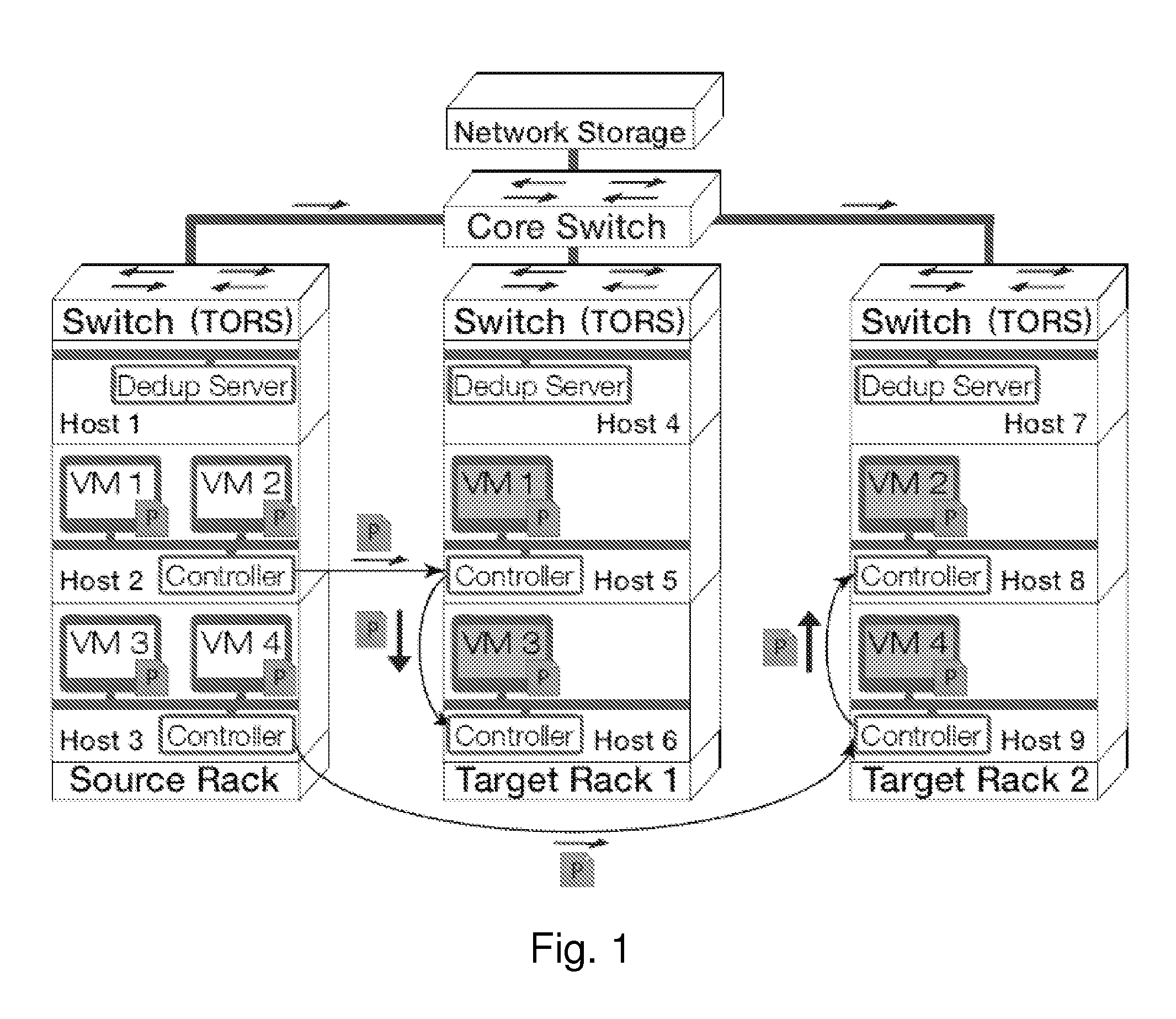

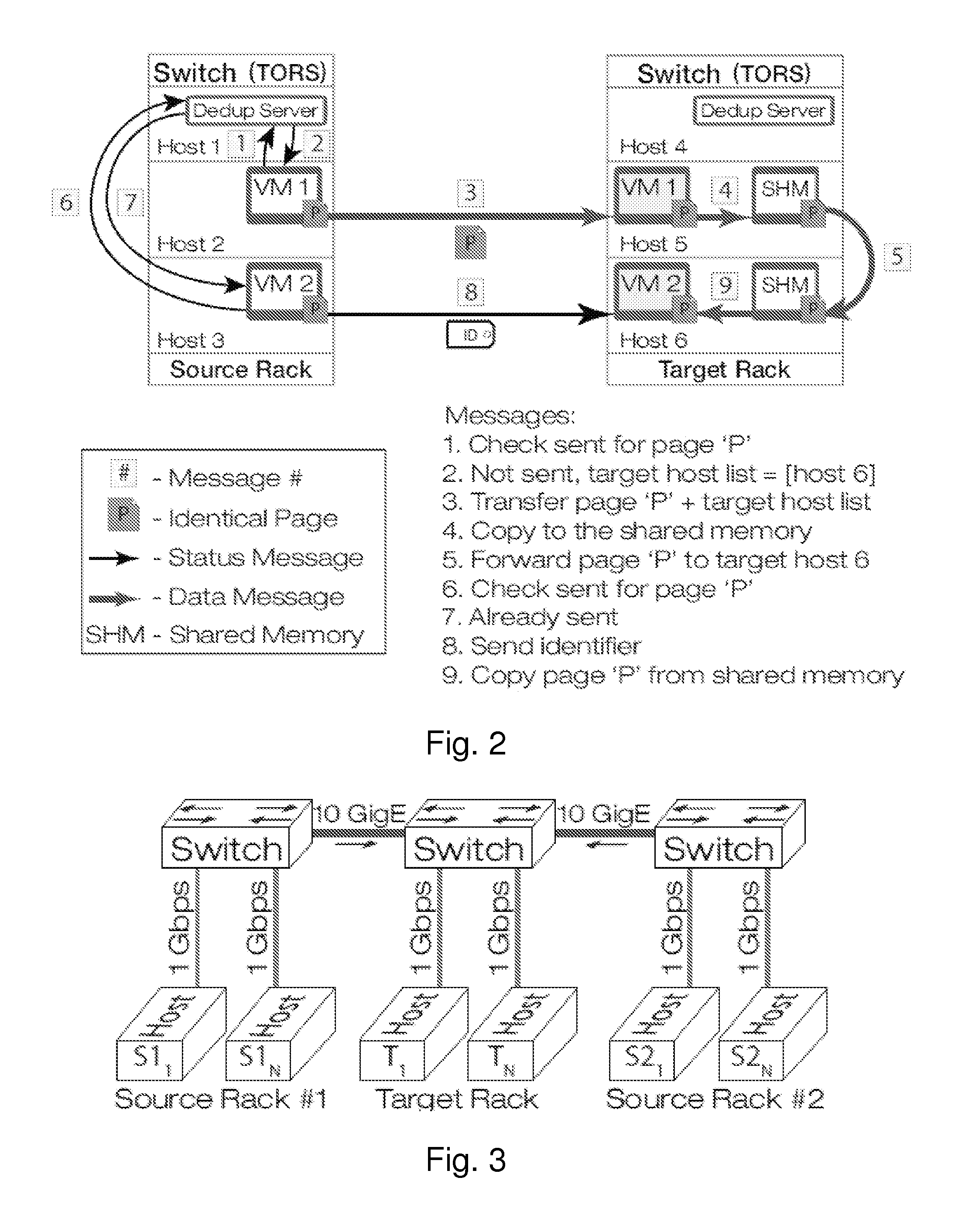

Gang migration of virtual machines using cluster-wide deduplication

ActiveUS20150324236A1Prevent race conditionReduce network overheadInput/output to record carriersResource allocationInternet trafficEngineering

Gang migration refers to the simultaneous live migration of multiple Virtual Machines (VMs) from one set of physical machines to another in response to events such as load spikes and imminent failures. Gang migration generates a large volume of network traffic and can overload the core network links and switches in a datacenter. In this paper, we present an approach to reduce the network overhead of gang migration using global deduplication (GMGD). GMGD identifies and eliminates the retransmission of duplicate memory pages among VMs running on multiple physical machines in the cluster. The design, implementation and evaluation of a GMGD prototype is described using QEMU / KVM VMs. Evaluations on a 30-node Gigabit Ethernet cluster having 10 GigE core links shows that GMGD can reduce the network traffic on core links by up to 65% and the total migration time of VMs by up to 42% when compared to the default migration technique in QEMU / KVM. Furthermore, GMGD has a smaller adverse performance impact on network-bound applications.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

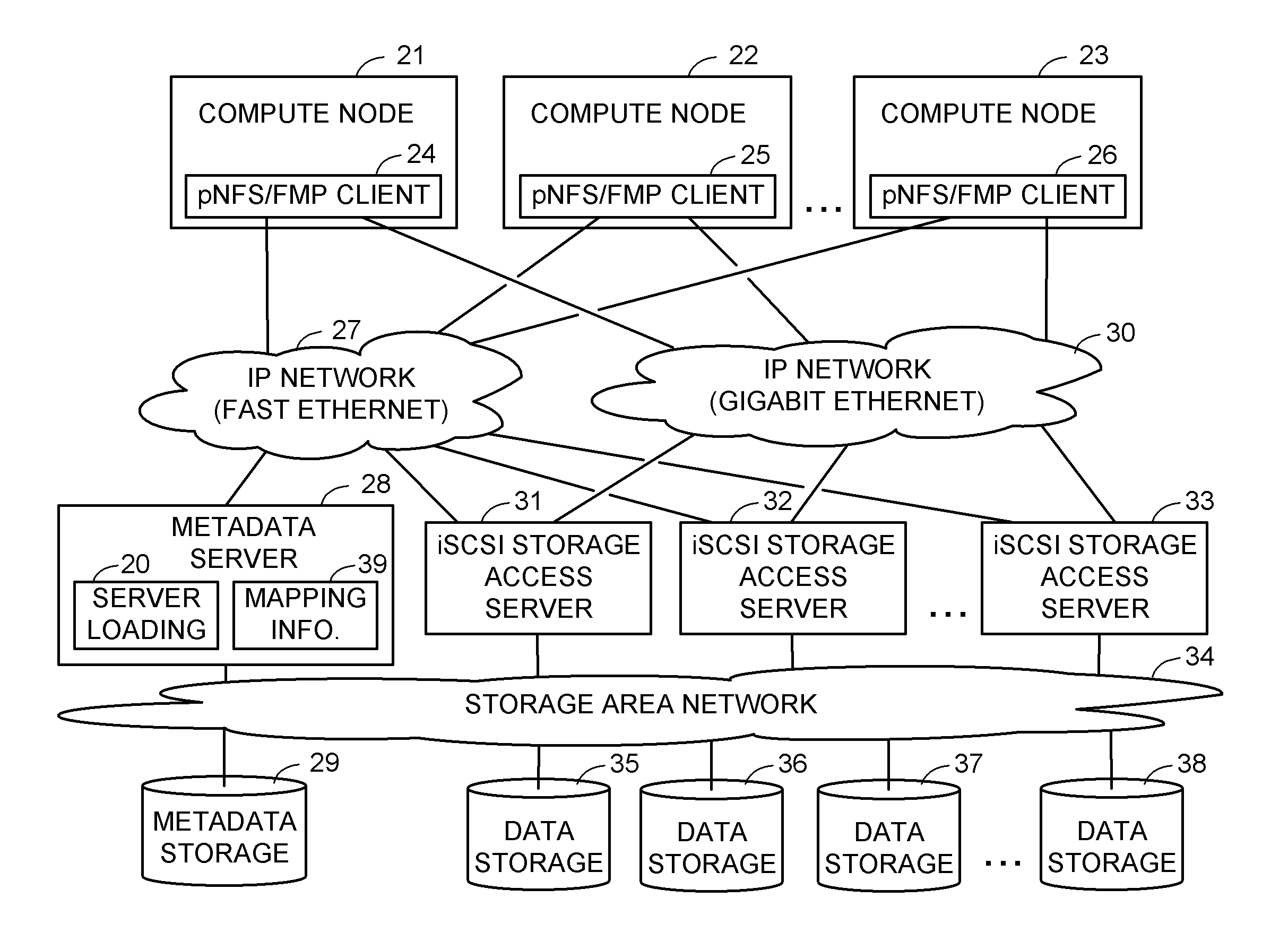

Asymmetric data storage system for high performance and grid computing

ActiveUS8589550B1Easy accessEnsure load balanceDigital computer detailsSpecial data processing applicationsData processing systemData treatment

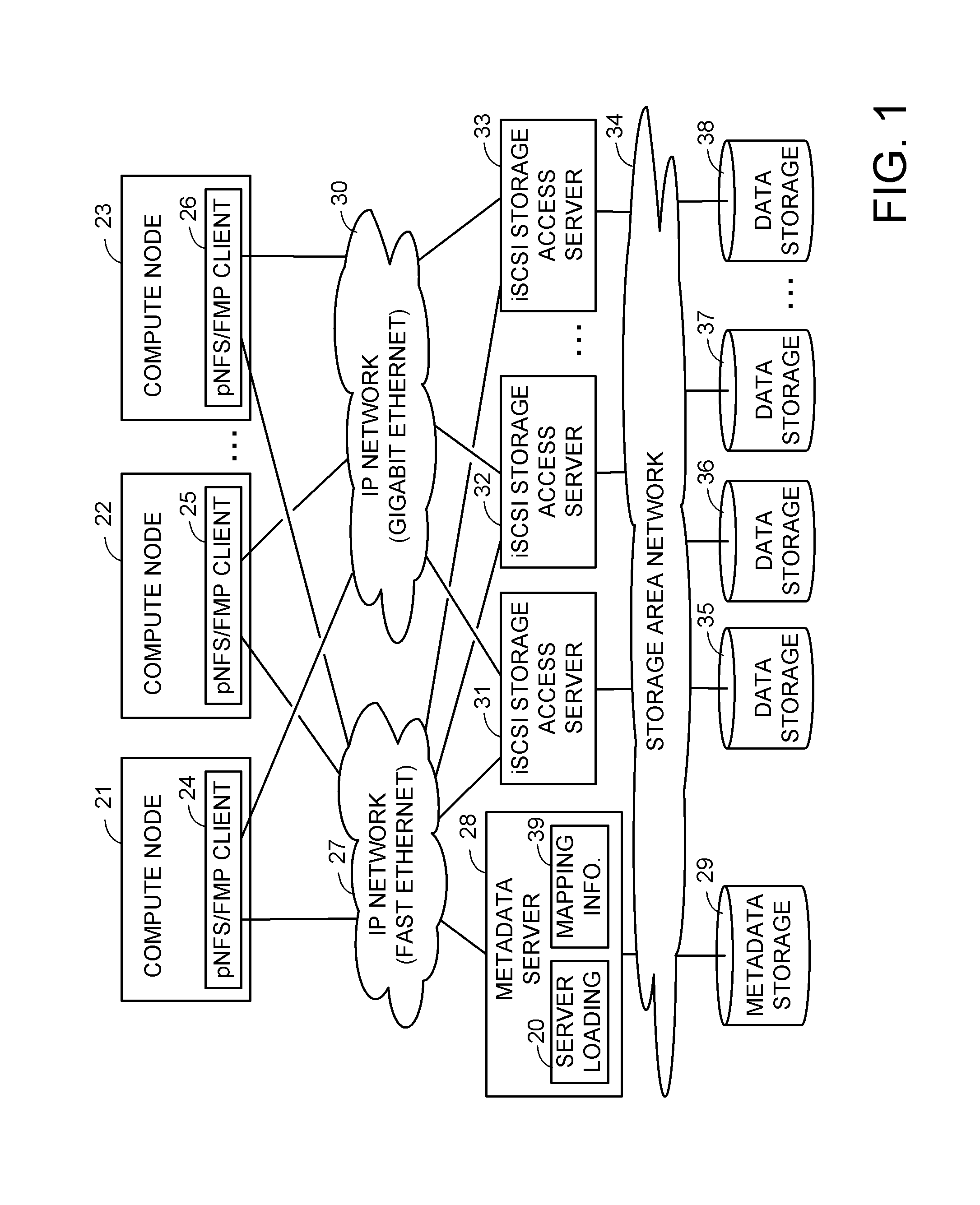

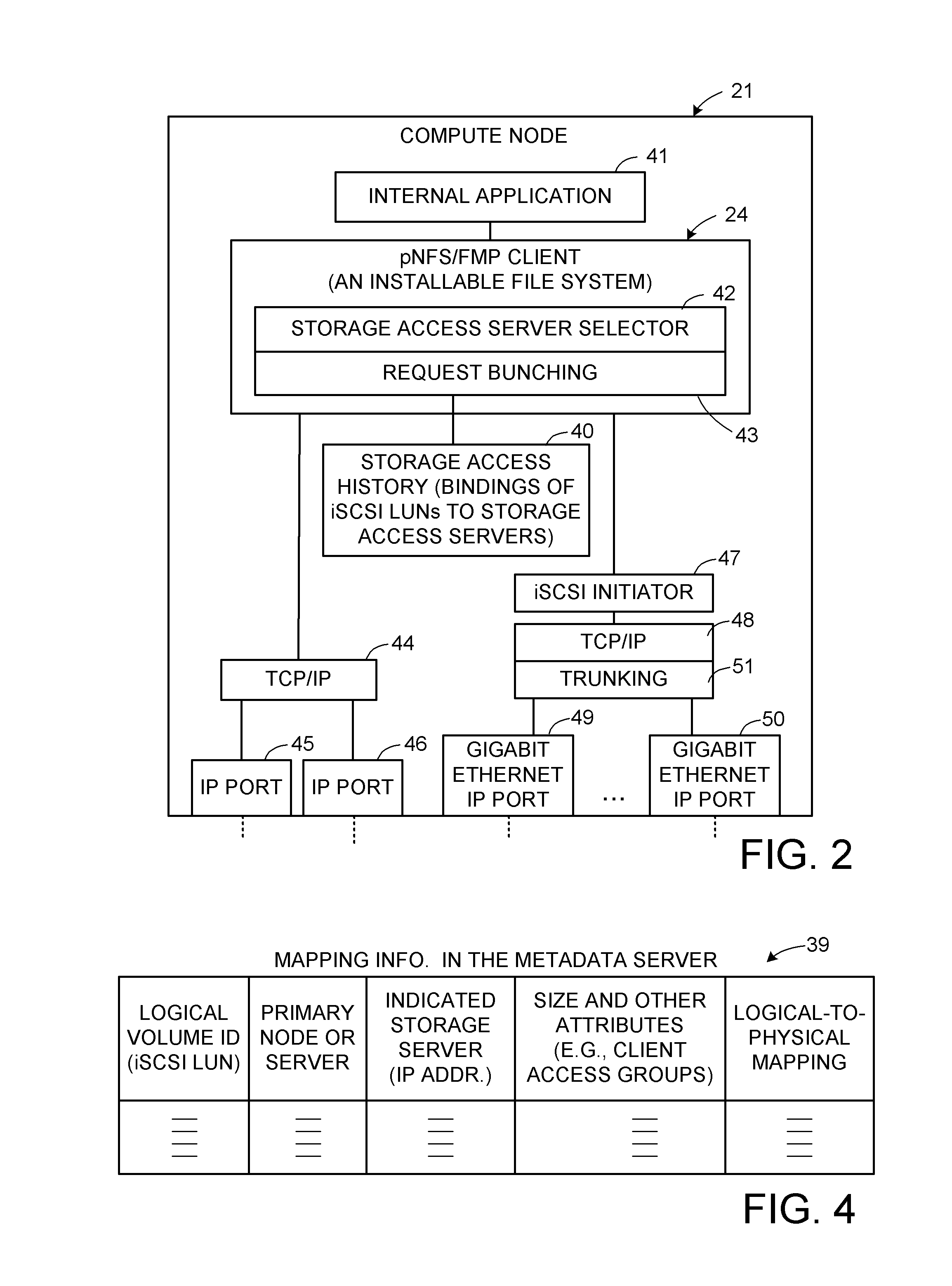

A data processing system includes compute nodes, at least one metadata server, iSCSI storage access servers, and data storage devices. The metadata server services requests from the compute nodes for file mapping information identifying iSCSI LUNs and logical blocks of file data. The storage access servers service iSCSI I / O requests from the compute nodes, and report server loading to the metadata server. A Gigabit Ethernet IP network transfers read and write data between the compute nodes and the storage access servers. The storage access servers are linked to the data storage devices for parallel access to iSCSI LUNs of the file data in the data storage devices. The metadata server is programmed for server load balancing by indicating to the compute nodes respective ones of the storage access servers that should be used for access to the iSCSI LUNs.

Owner:EMC IP HLDG CO LLC

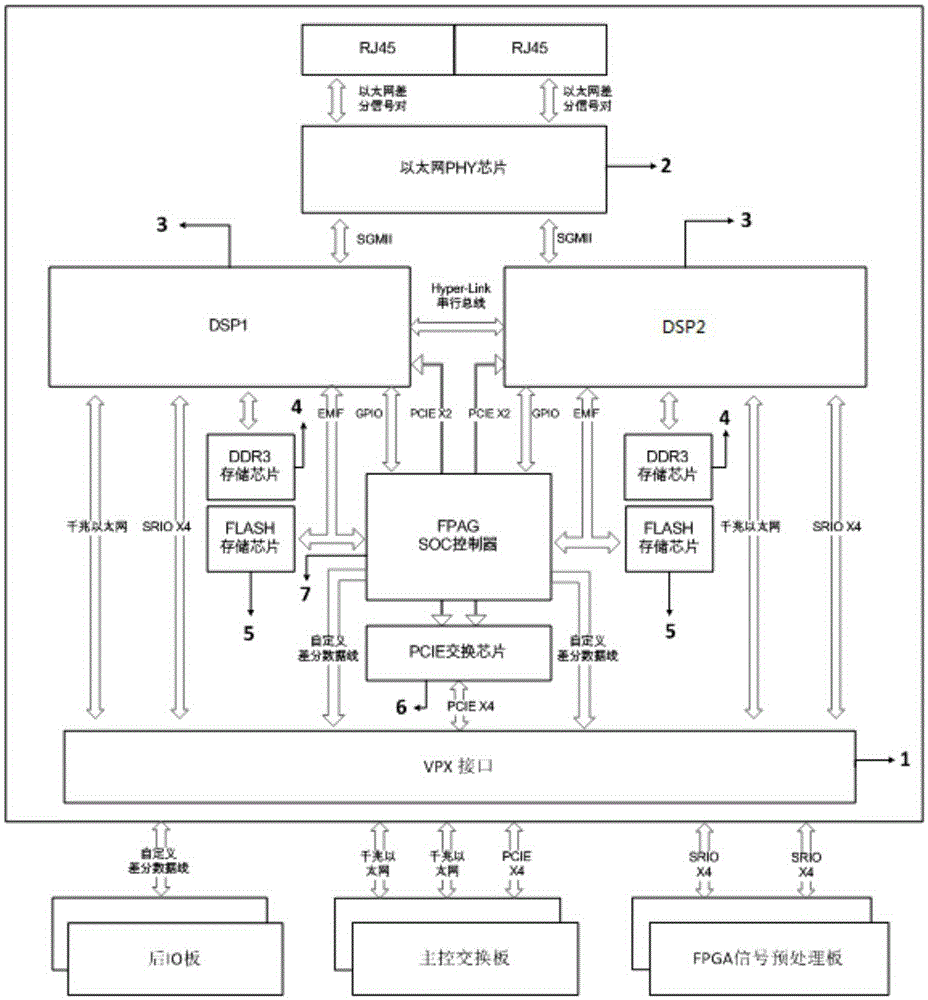

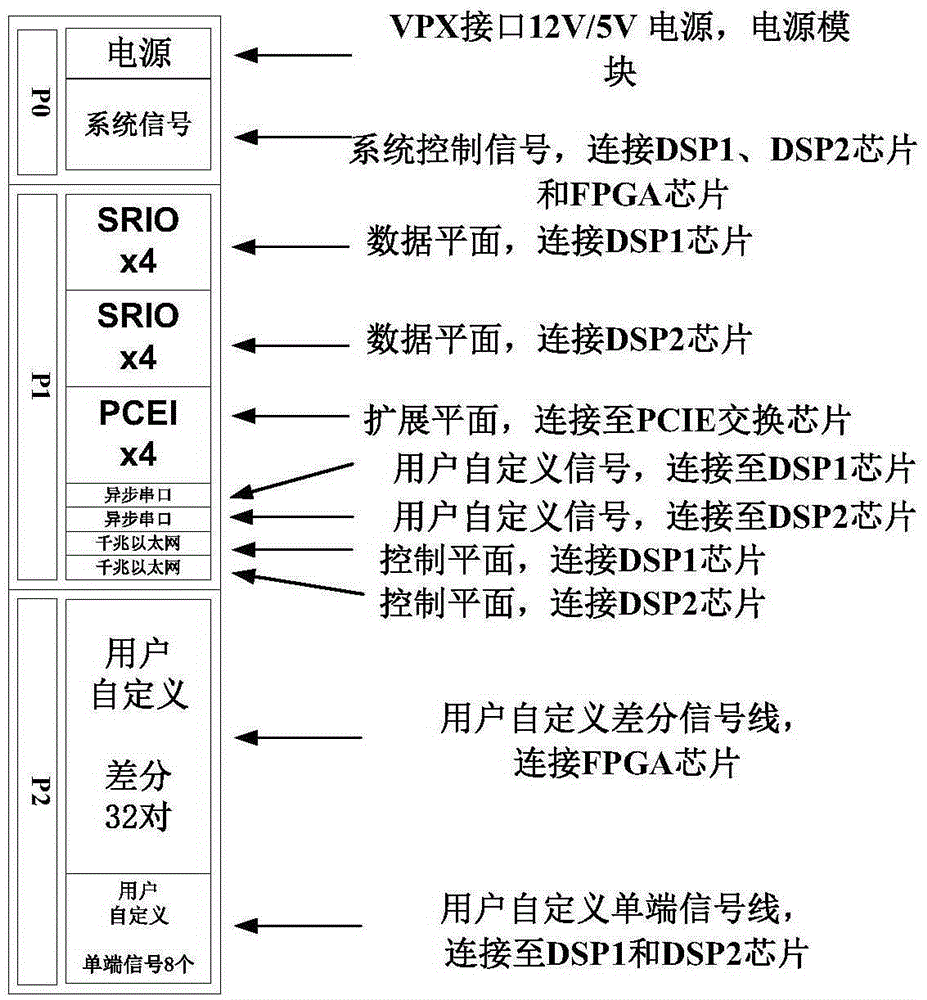

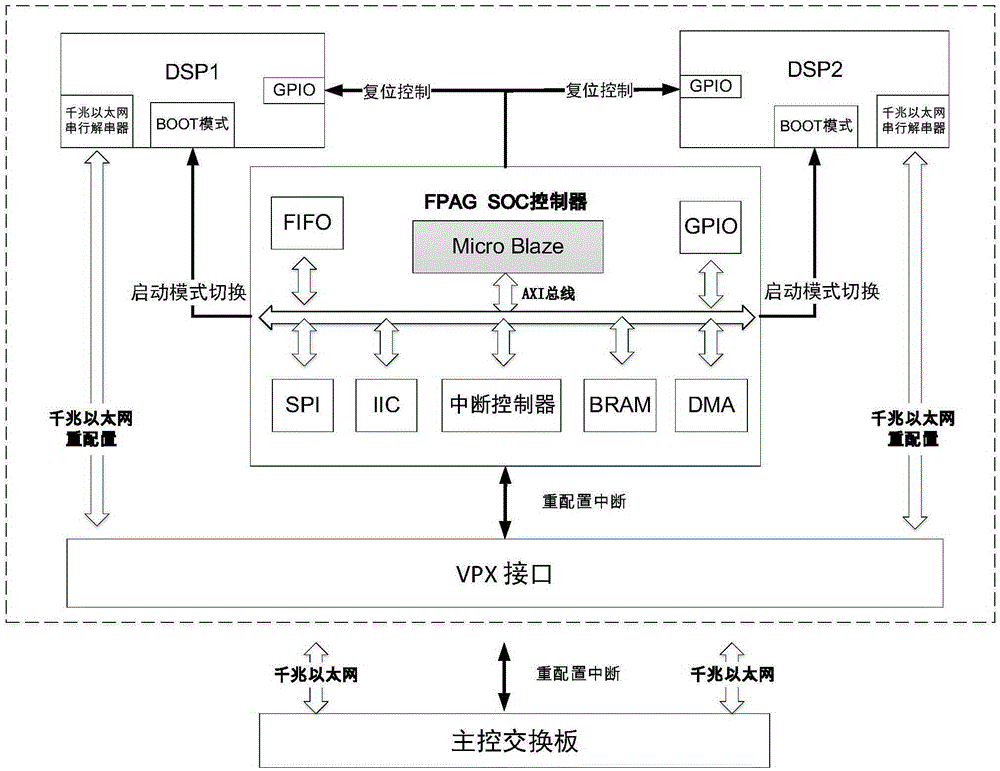

VPX parallel DSP signal processing board card based on SoC online reconstruction

InactiveCN105279133AIncrease flexibilityImprove real-time performanceDigital computer detailsElectric digital data processingDigital signal processingData signal

The invention discloses a VPX parallel DSP (Digital Signal Processing) board card based on SoC (System on a Chip) online reconstruction. An FPGA (Field Programmable Gate Array) chip is used as a board stage SoC controller; and two DSP chips are used as core operation chips of a DSP board card. During the practical configuration of the DSP chips, the FPGA chip used as the SoC controller can complete the dynamic re-configuration of work code by GE (Gigabit Ethernet) through the hardware resetting on the DSP and the switching on the starting mode; and the flexibility and the real-time performance during the DSP are greatly improved. The DSP chips receive two kinds of high-speed serial bus signals of SRIO (Serial Rapid Input Output) X4 and the GE transmitted through a VPX interface, repacking the transferred PCIE (Peripheral Component Interface Express) X2 high-speed serial bus signal through a PCIE exchange chip, and receives a data signal to be processed and a control instruction; or the DSP chips receive the GE protocol signal of a peripheral component through an RJ45 net port.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

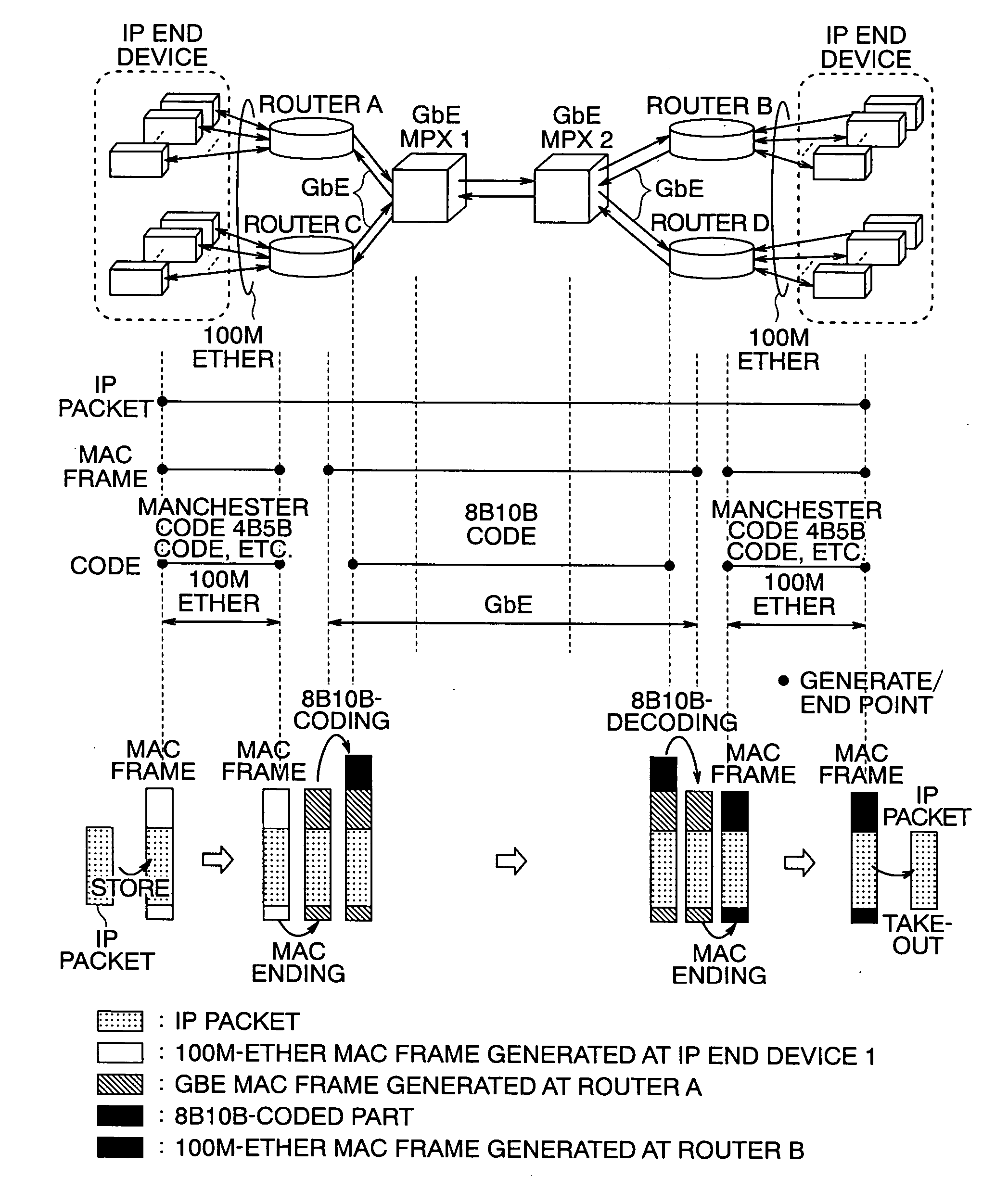

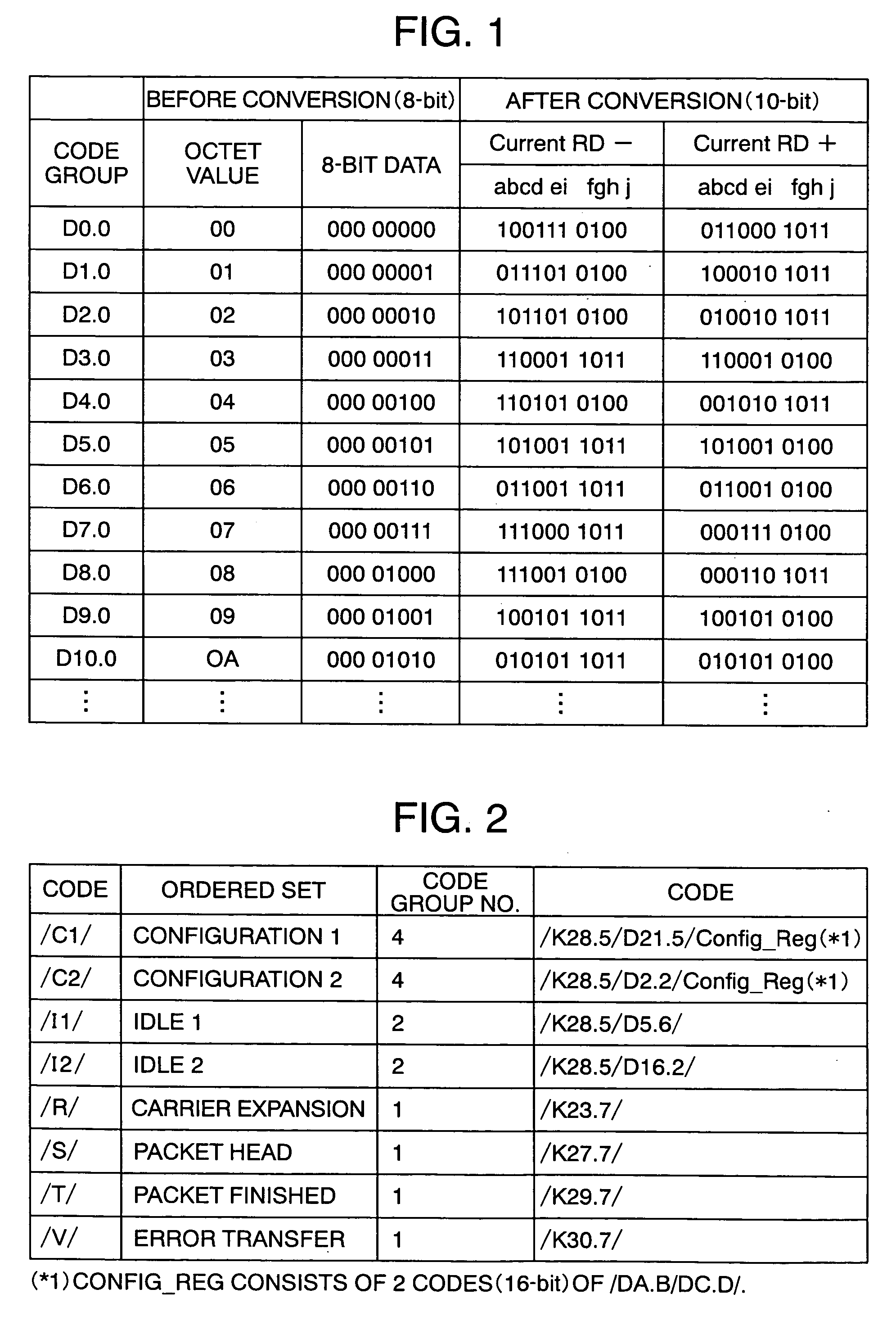

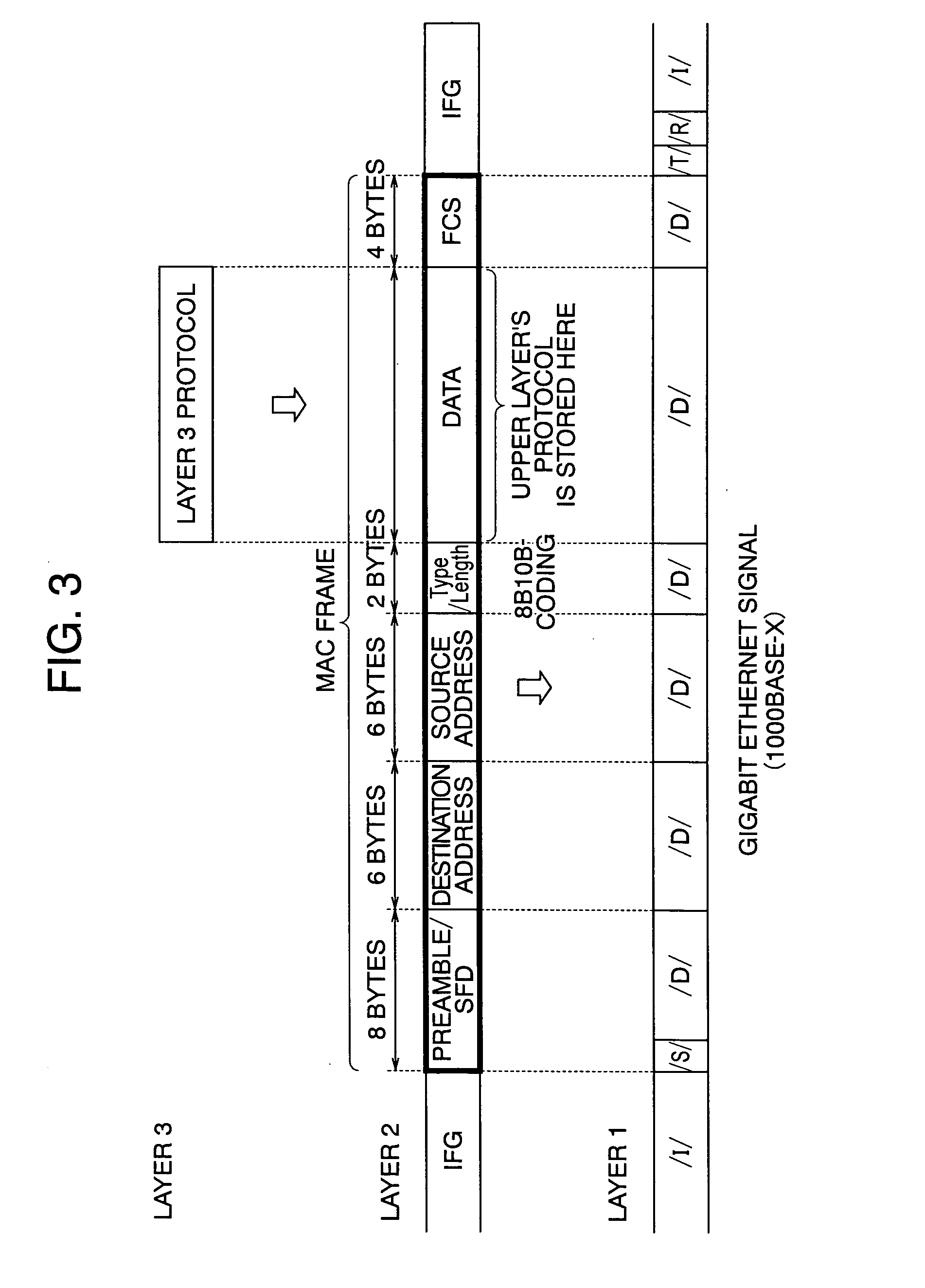

Transmission apparatus

InactiveUS20070116055A1Avoid it happening againTime-division multiplexBaseband systemsMultiplexingUser device

A transmission apparatus is disclosed, which performs positive / negative stuffing with 8-bit / 10-bit (8B / 10B) codes being kept intact while retaining the normality of 8B / 10B codes and the continuity of running disparity (RD) without termination of 8B / 10B codes of a plurality of Gigabit Ethernet (GbE) signals received. The apparatus then executes multiplexing and separation after synchronization of the plurality of signals, thereby achieving the “transparent” transport of management information which is contained in the 8B10B codes between user devices.

Owner:HITACHI LTD

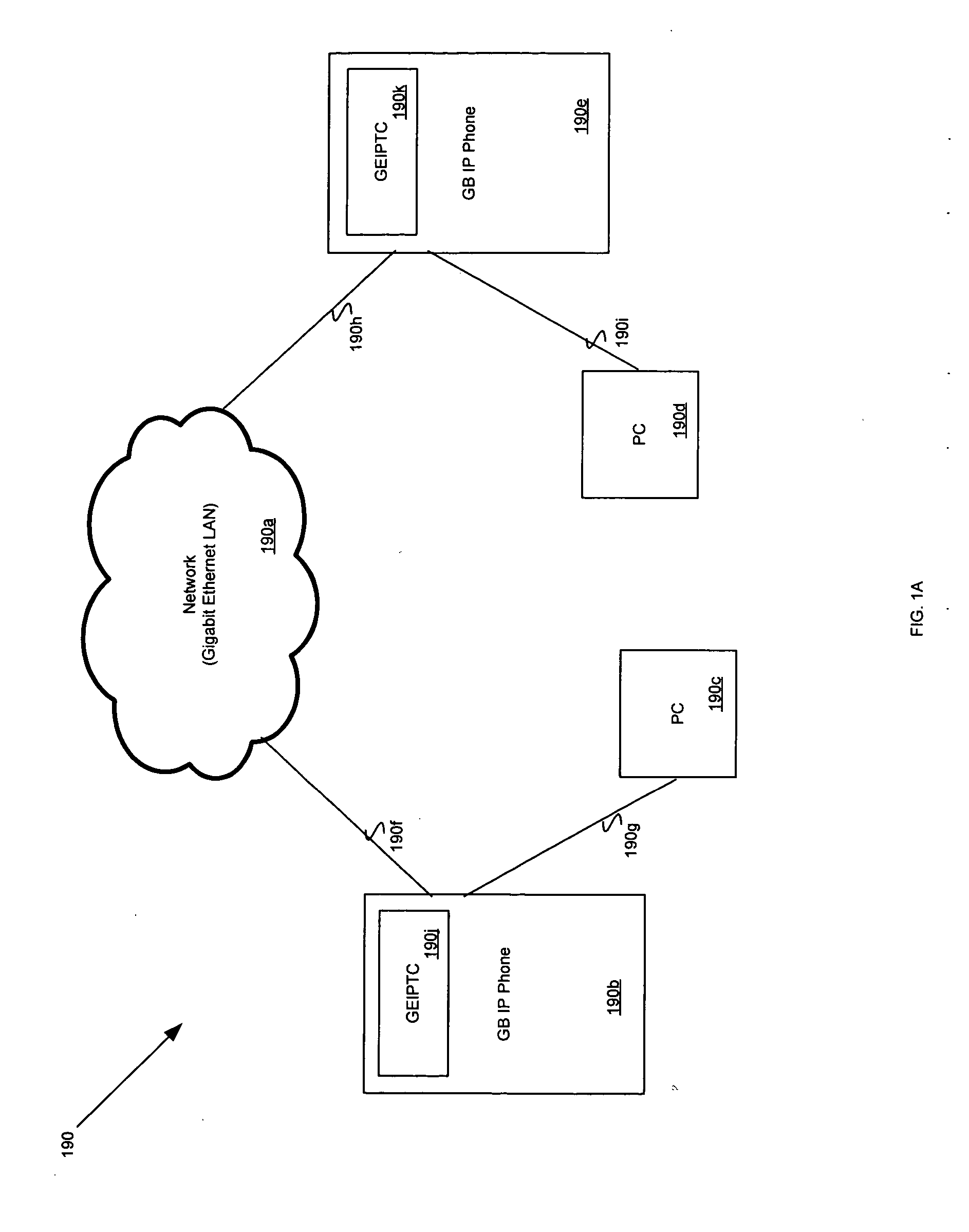

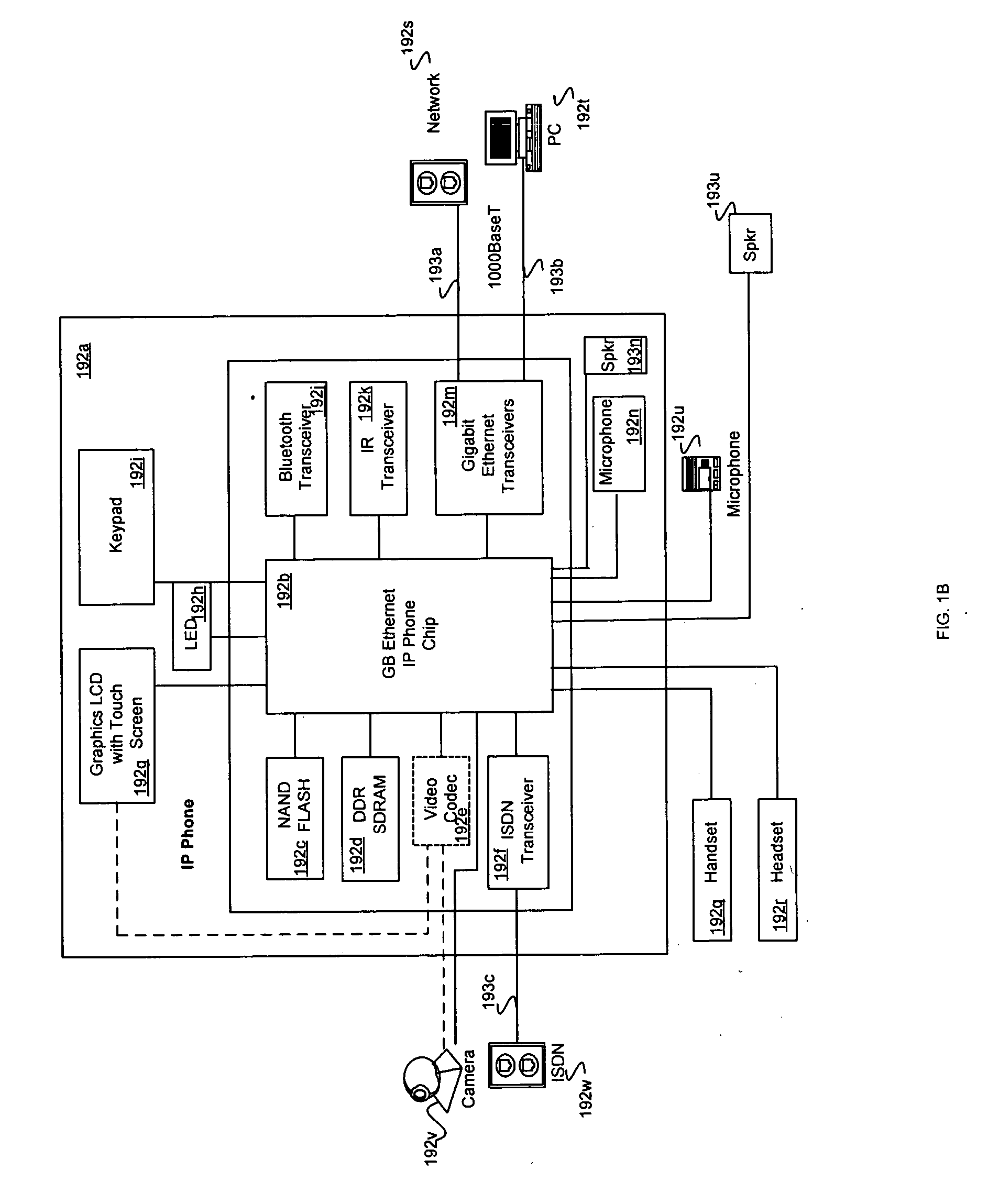

Method and system for a gigabit Ethernet IP telephone chip with no DSP core, which uses a RISC core with instruction extensions to support voice processing

InactiveUS20060013218A1Time-division multiplexData switching by path configurationNetwork dataVoice data

Methods and systems for processing data are disclosed and may comprise receiving packetized data comprising voice data and network data via an Ethernet switch integrated within a single gigabit Ethernet IP phone chip. The received packetized data may be processed via a single main processor core integrated within the single gigabit Ethernet IP phone chip. The single main processor core may comprise circuitry that is controlled by an instruction set for handling processing of the voice data for a plurality of voice channels without the use of a separate DSP. It may be determined whether data to be processed by the single main processor core is voice data or network data. If the data to be processed by the single main processor core is voice data, at least one modified instruction may be selected from the modified instruction set for processing the voice data.

Owner:AVAGO TECH INT SALES PTE LTD

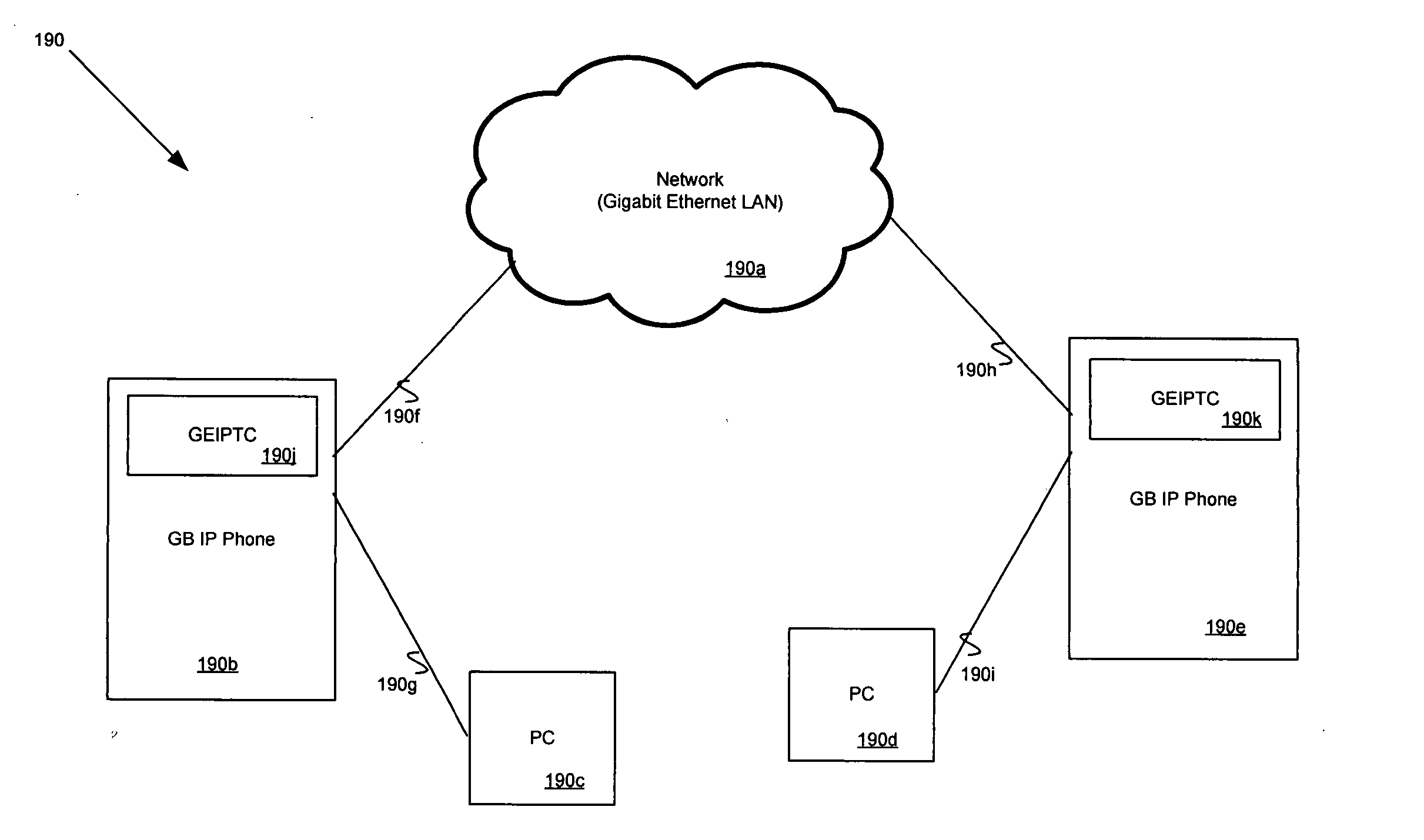

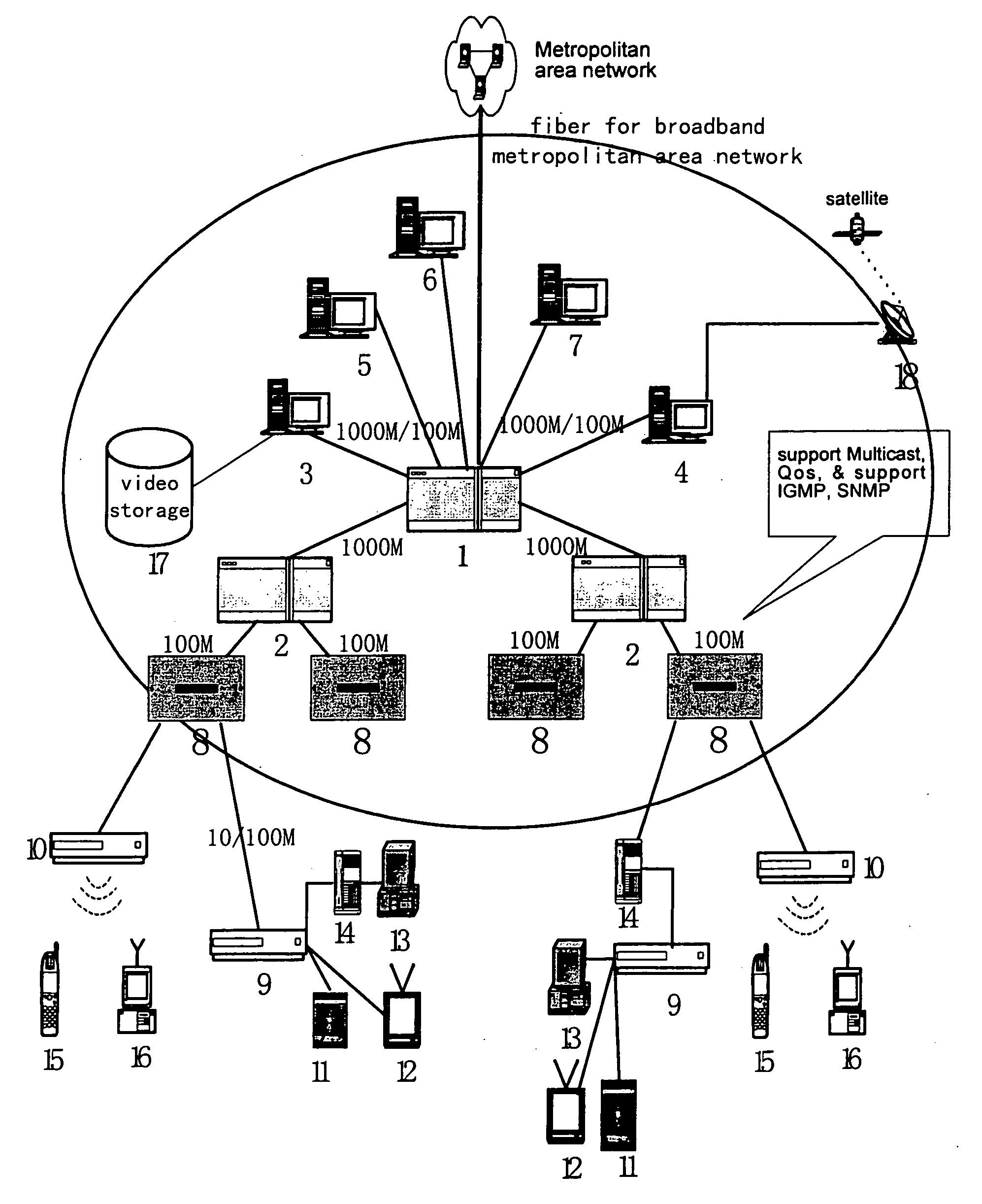

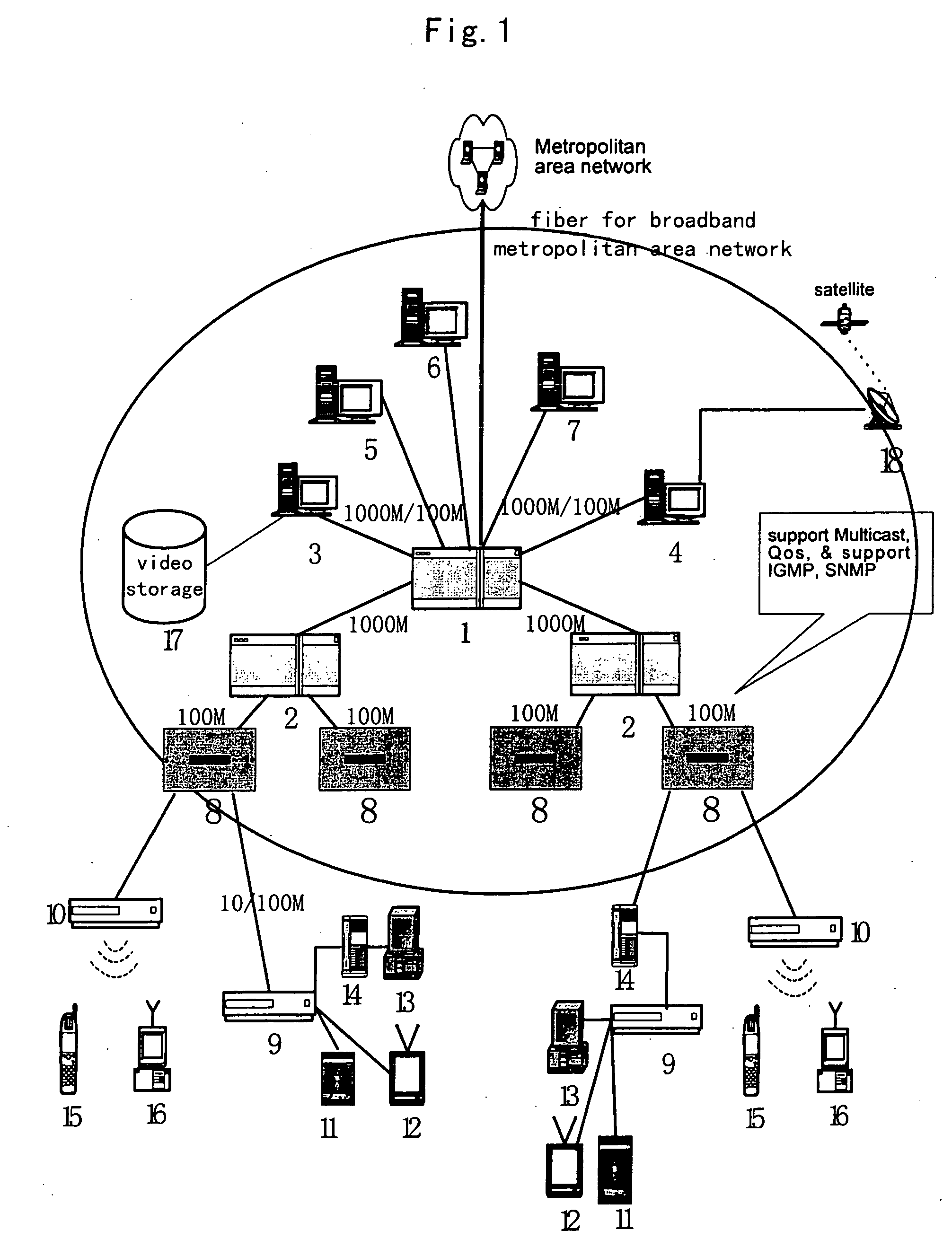

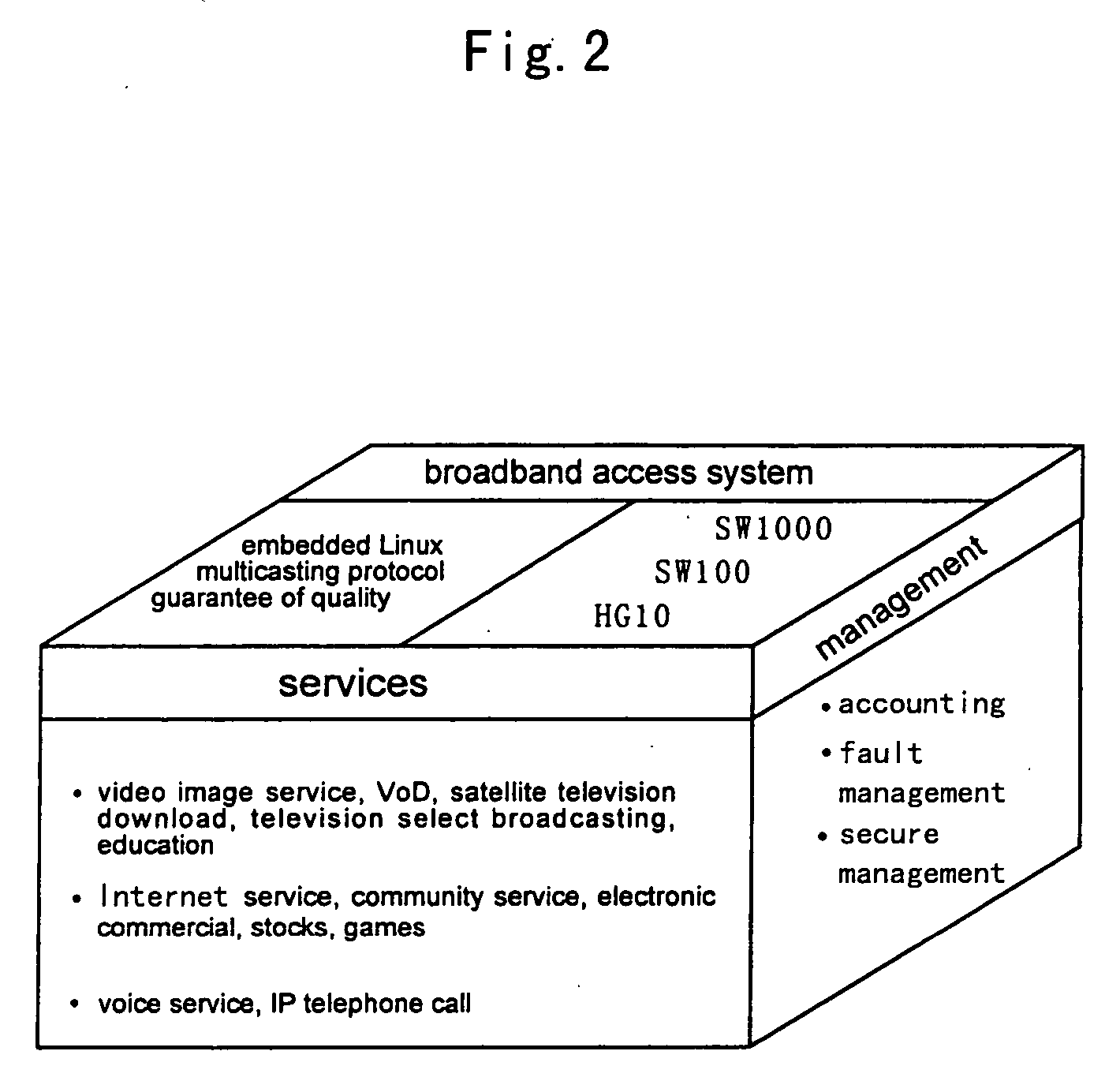

Community network system with broadband integrated services

InactiveUS20060190627A1Broadband local area networksMultiple digital computer combinationsNetwork managementInformation security

Owner:WU ZHIMEI +4

Waterproof gigabit ethernet connector

InactiveUS20090233475A1Electrically conductive connectionsIncorrect coupling preventionGigabitBody positions

A mateable pair of Ethernet connector assemblies for propagating data at Gigabit rates is disclosed. The pair of electrical connector assemblies includes a male Ethernet plug and a female Ethernet receptacle. The male Ethernet plug includes a substantially cylindrical hollow-body shell, an insulator body positioned within the shell, and a plurality of cylindrical pins positioned within respective apertures formed in the insulator body. One end of each pin extends beyond the mating surface of the insulator body for insertion into a respective socket of the female receptacle. The female Ethernet receptacle includes a substantially cylindrical hollow-body shell, an insulator body positioned within the receptacle shell, and a plurality of hollow-body cylindrical sockets positioned within respective apertures formed in the receptacle insulator body. One end of each socket is substantially flush with a mating surface of the receptacle insulator body for receiving a pin of the male Ethernet plug.

Owner:AMETEK INC

High speed network interface with automatic power management with auto-negotiation

ActiveUS7577857B1Avoid physical damageEnergy efficient ICTVolume/mass flow measurementLow speedNetwork media

A computer system comprises host processor and a network interface, wherein the host processor includes resources supporting a full power mode, a lower power mode and a power down mode, as seen in standard system bus specifications such as PCI and InfiniBand. The network interface includes a medium interface unit coupled to network media supporting a least high speed protocol, such as a Gigabit Ethernet or high-speed InfiniBand, and a lower speed protocol, such as one of 10 Mb and 100 Mb Ethernet or a lower speed InfiniBand. Power management circuitry forces the medium interface unit to the lower speed protocol in response to an event signaling entry of the lower power mode. In the lower power mode, the network interface consumes less than the specified power when executing the lower speed protocol, and consumes greater than the specified power when executing the high speed protocol. Logic in the network interface operates in the lower power mode, and uses the lower speed protocol to detect a pattern in incoming packets. In response to the detection of said pattern, the logic issues a reset signal to the host processor. Thus, the network interface operates as a wake-up device in the lower power mode, using the lower speed protocol.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

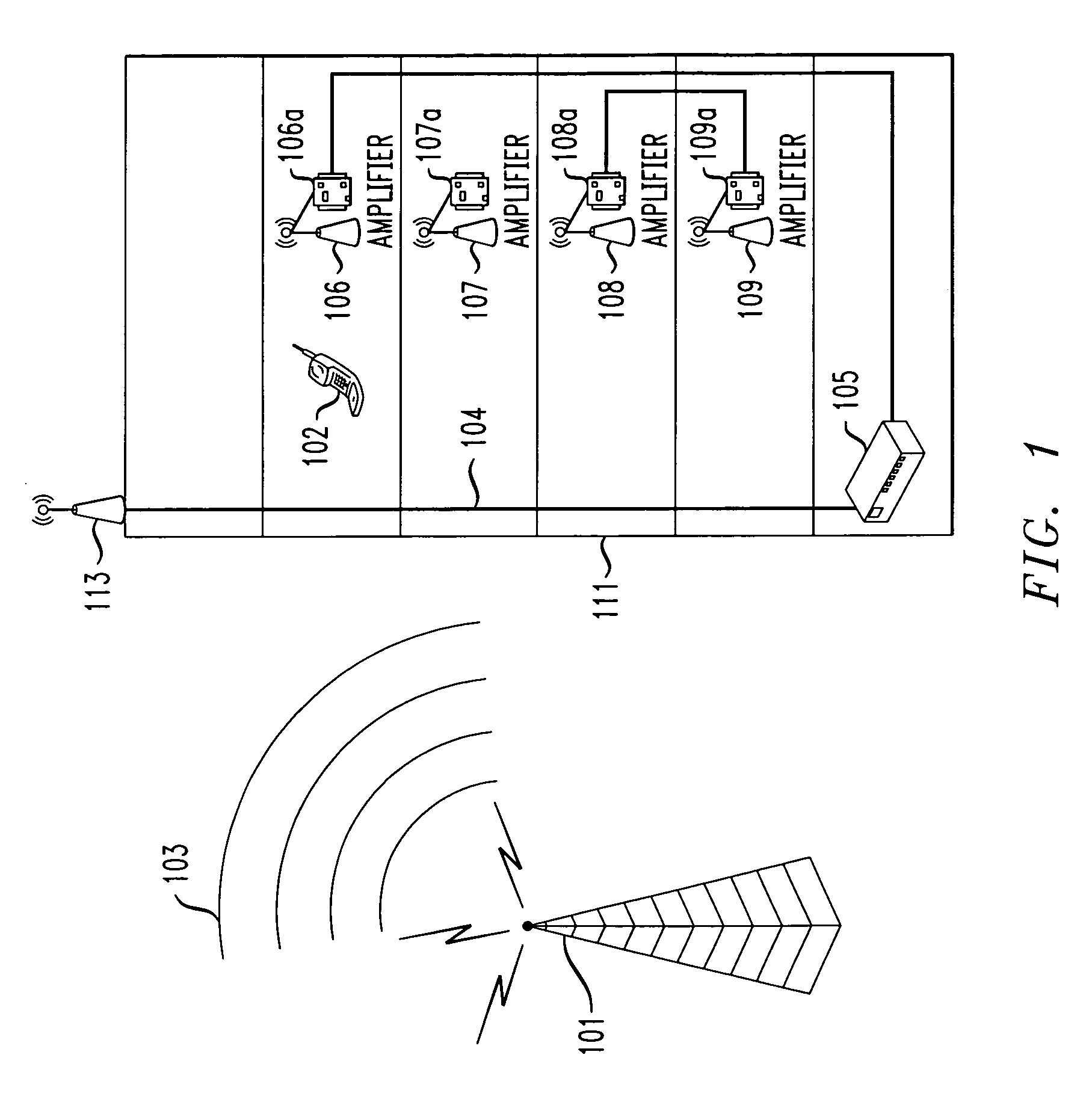

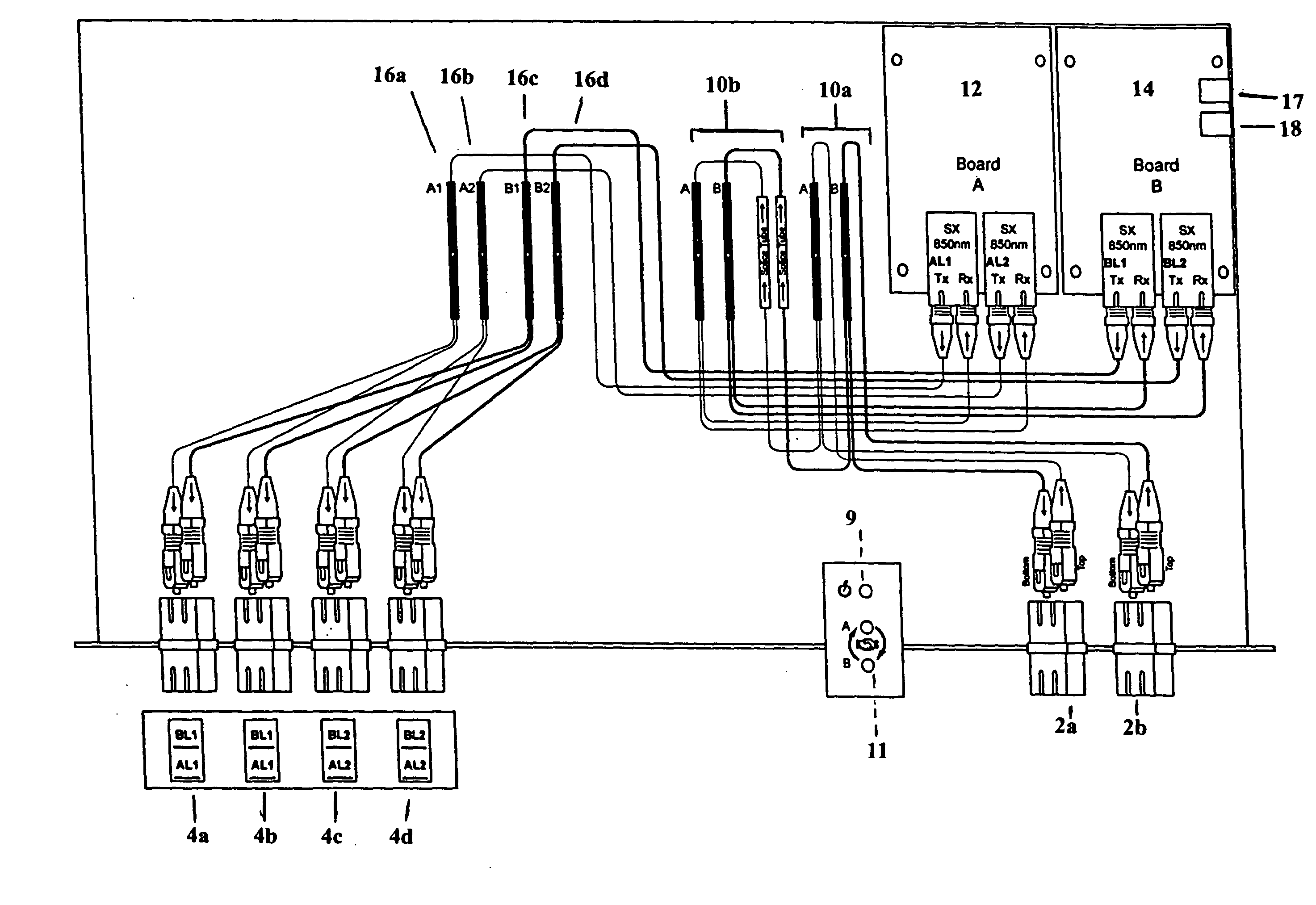

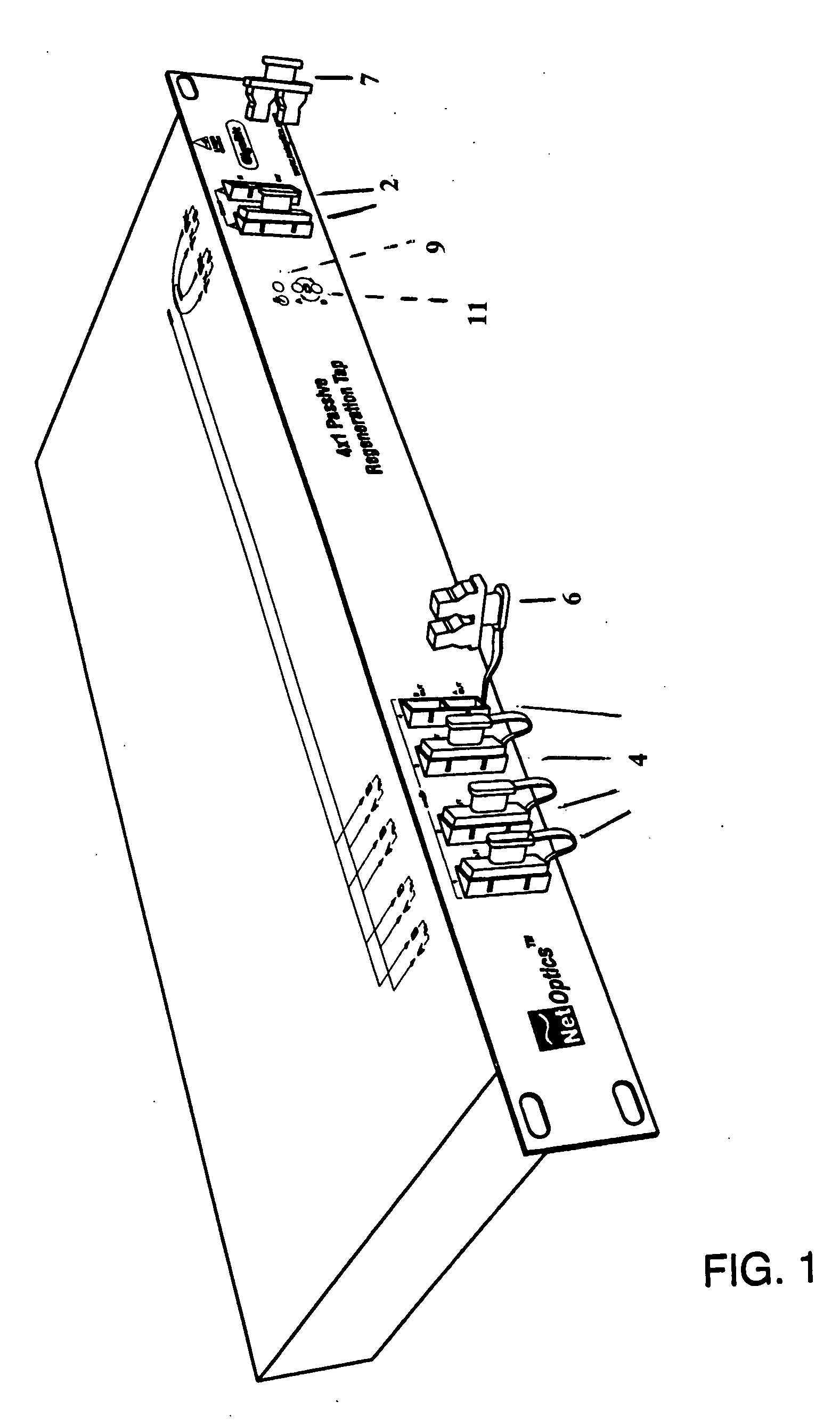

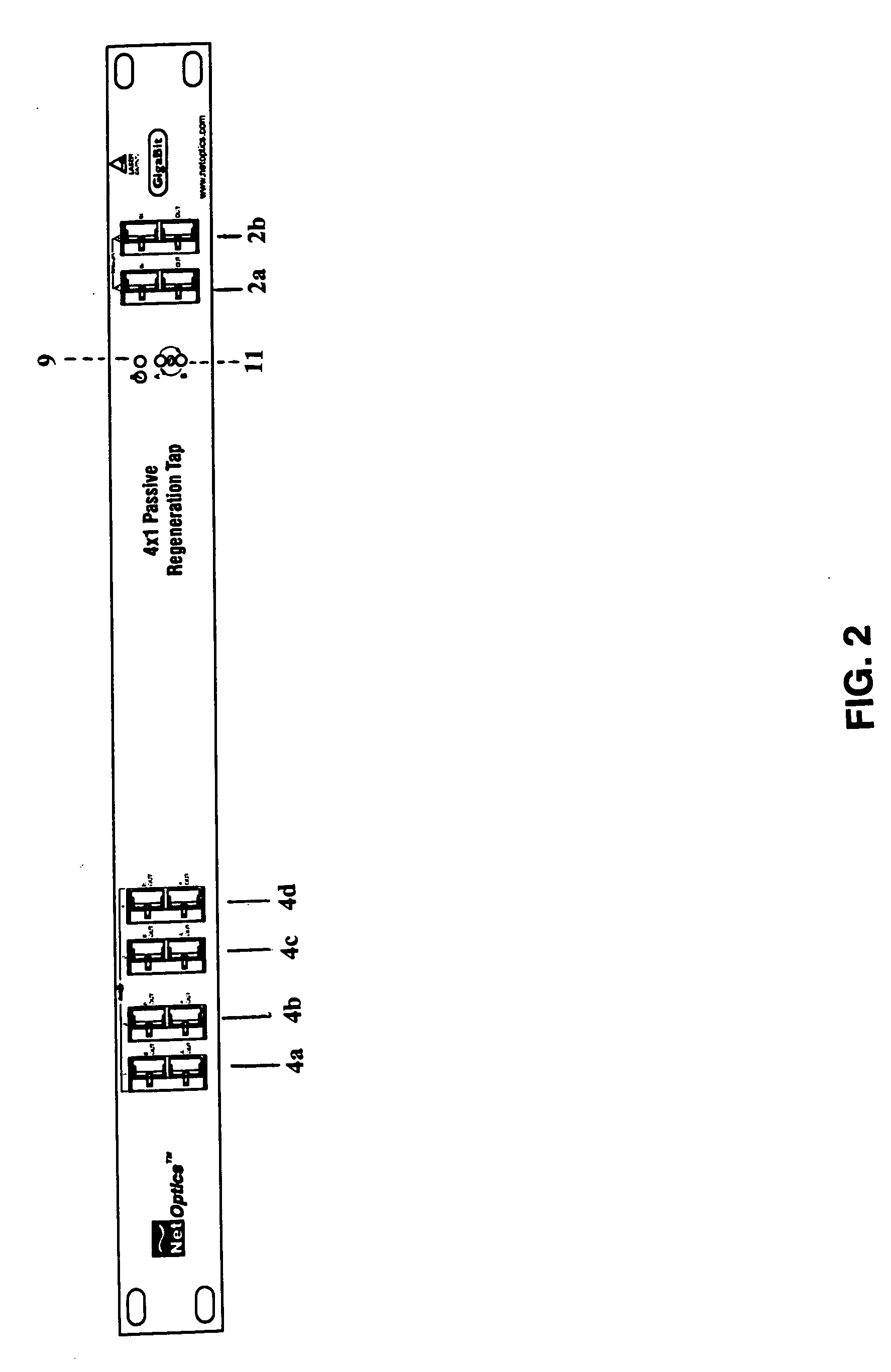

Multiple and parallel access network tap for gigabit internet lans

ActiveUS20050071711A1Avoid interferenceUndesired interferenceError preventionTransmission systemsTransmission protocolThe Internet

A single-usage network tap monitors network information flow over a particular connection. Instead of requiring a tap for each analytical device, by incorporating elements that regenerate, spread, and coordinate the timing of the signal, multiple, simultaneous, and parallel analytical devices can monitor a particular network connection through one tap, It incorporates four amplifiers preferably manufactured on the same IC die with high-impedance input terminals connected directly to the two conductors of a gigabit Ethernet local area network digital transmission line so as not to load or otherwise upset its impedance or other parameters. The output terminals of the operational amplifiers are connected to and match the input impedance of the digital transmission protocol Gigabit analyzer. The gain of the operational amplifiers is arranged so as to replicate at the input of the analyzer the signals appearing on the Gigabit local area network transmission line with uninterruptible power supply.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

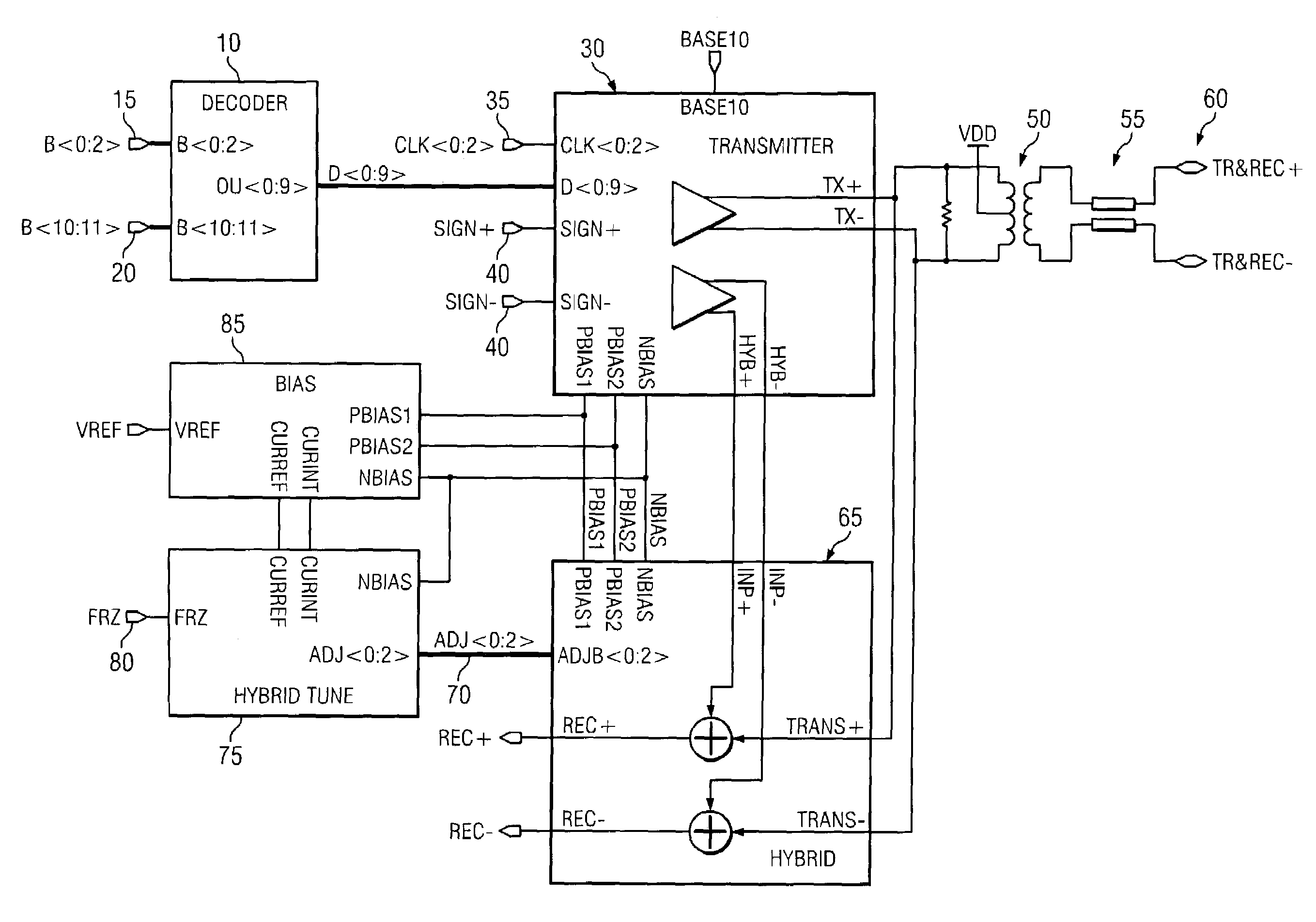

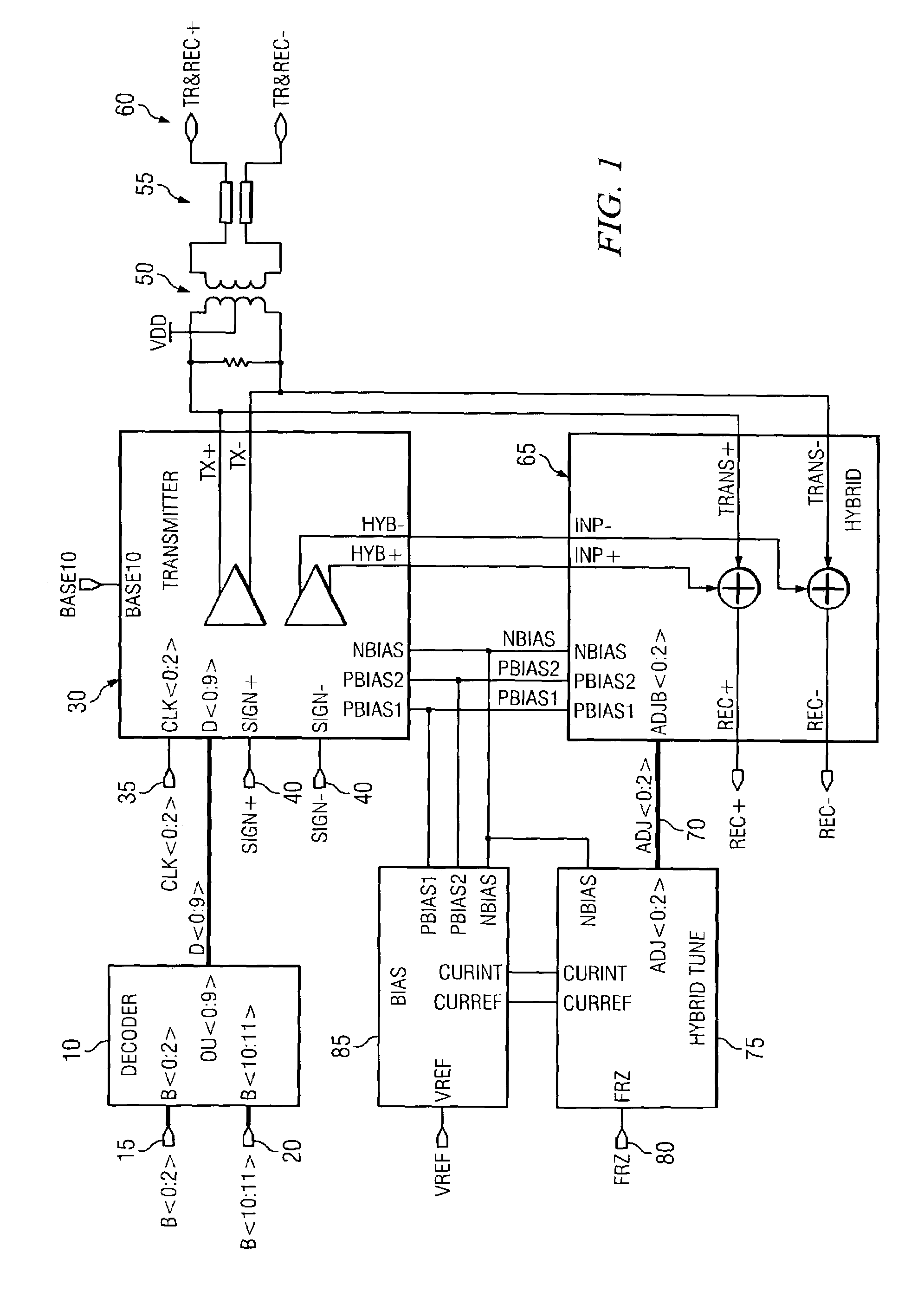

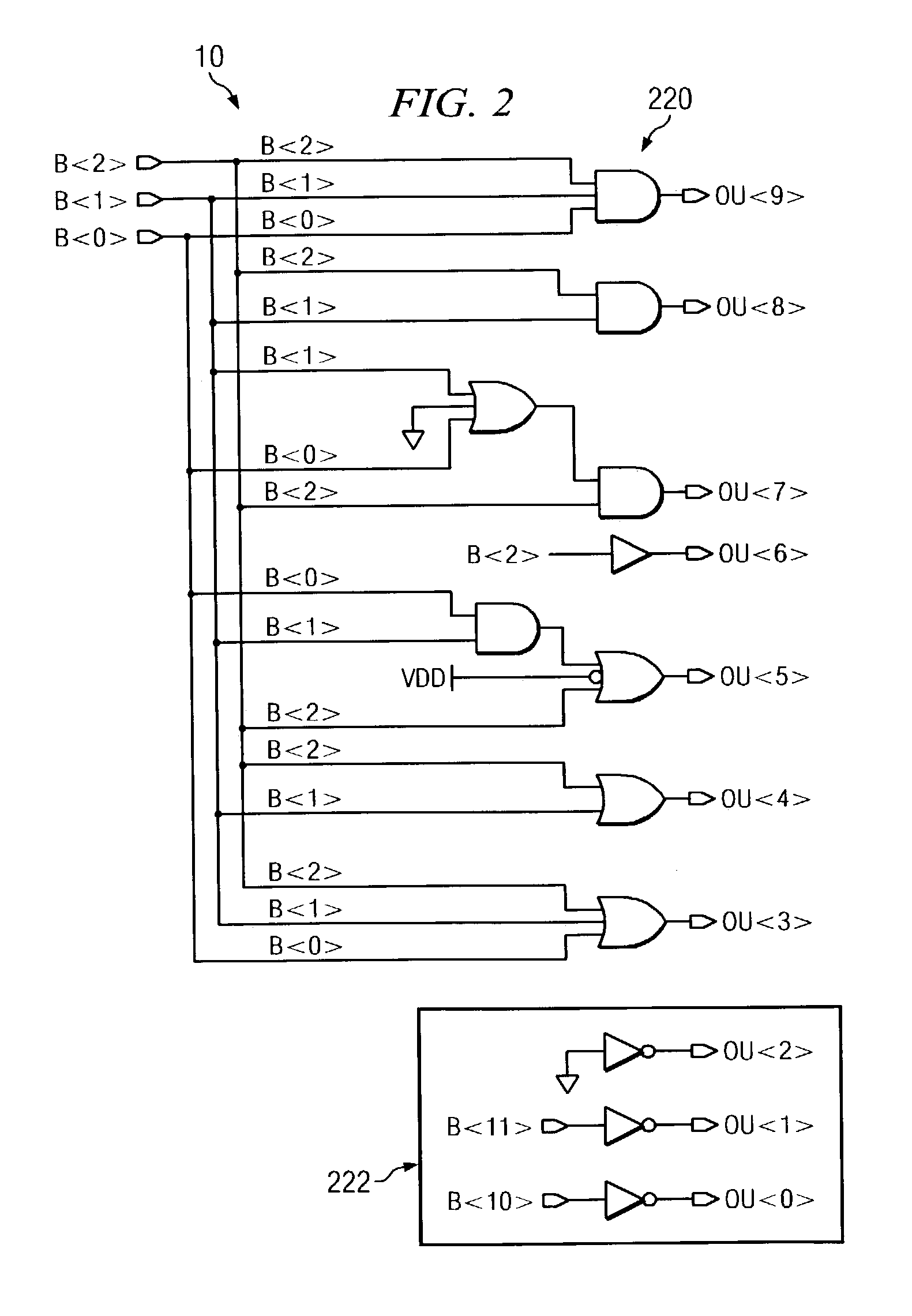

Gigabit ethernet line driver and hybrid architecture

ActiveUS7176823B2Electric signal transmission systemsDigital-analogue convertorsTransmitter power outputEngineering

A gigabit ethernet line driver includes a transmitter having both transmitter and active hybrid outputs. The transmitter consists of a plurality of transmitter clusters each connected to both the transmitter and active hybrid outputs. Each transmitter cluster includes a plurality of transmitter cells consisting of a driver cell and digital to analog converter connected to driver cell. A hybrid circuit connects between the transmitter outputs and receiver inputs for separating a receiver signal from the transmitter signal responsive to a tuning signal.

Owner:STMICROELECTRONICS SRL