Patents

Literature

119 results about "10 Gigabit Ethernet" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

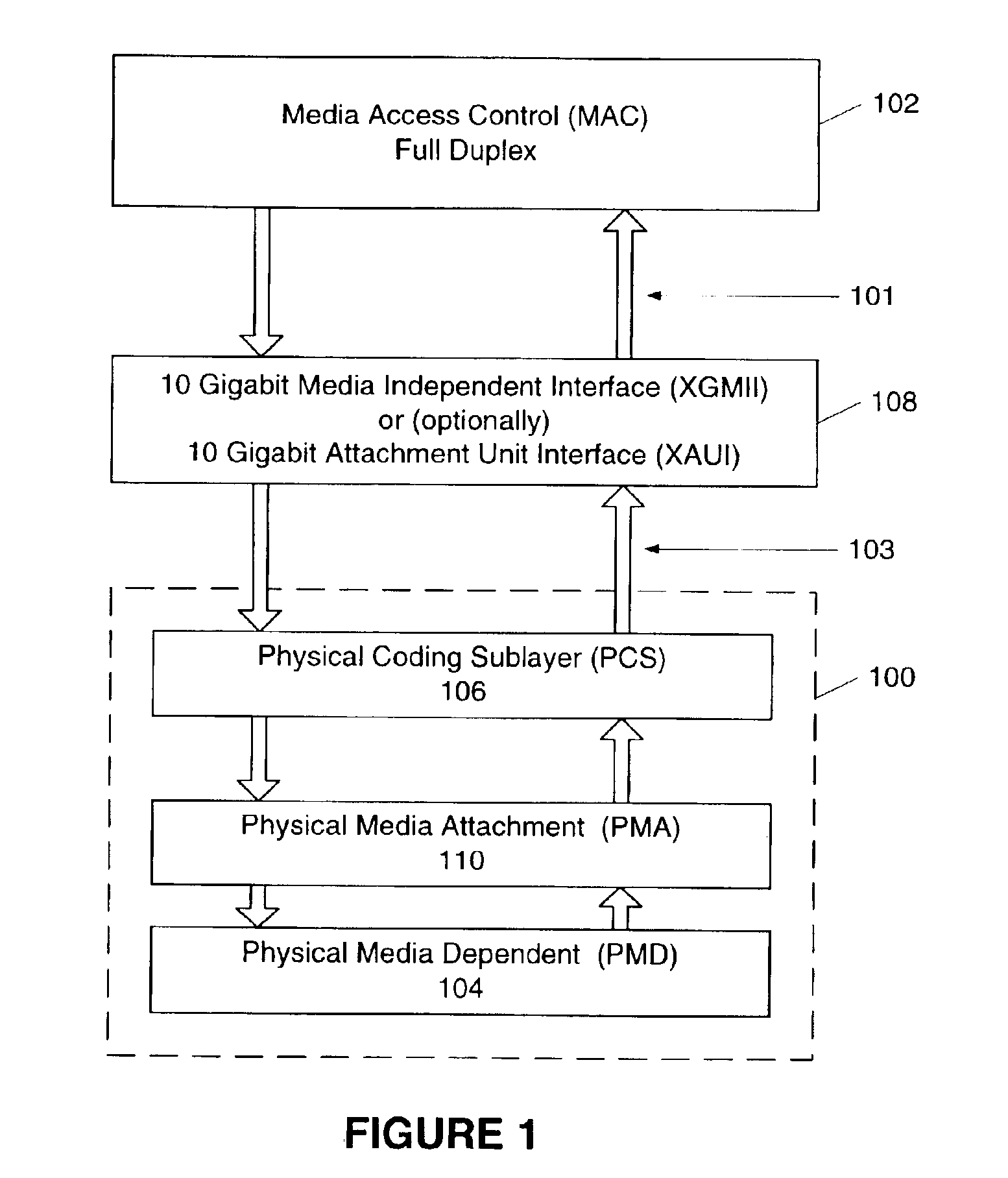

10 Gigabit Ethernet (10GE, 10GbE, or 10 GigE) is a group of computer networking technologies for transmitting Ethernet frames at a rate of 10 gigabits per second. It was first defined by the IEEE 802.3ae-2002 standard. Unlike previous Ethernet standards, 10 Gigabit Ethernet defines only full-duplex point-to-point links which are generally connected by network switches; shared-medium CSMA/CD operation has not been carried over from the previous generations Ethernet standards so half-duplex operation and repeater hubs do not exist in 10GbE.

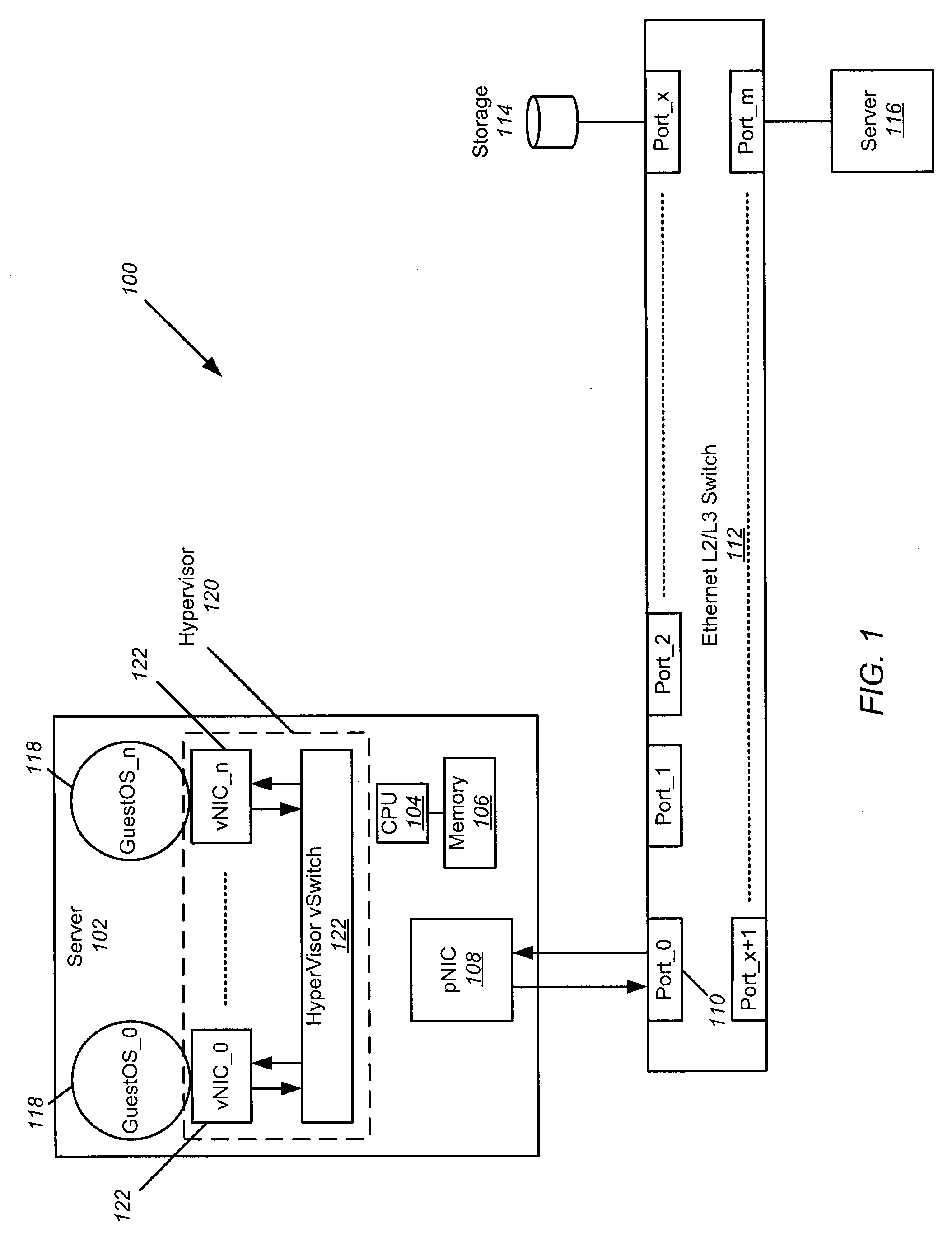

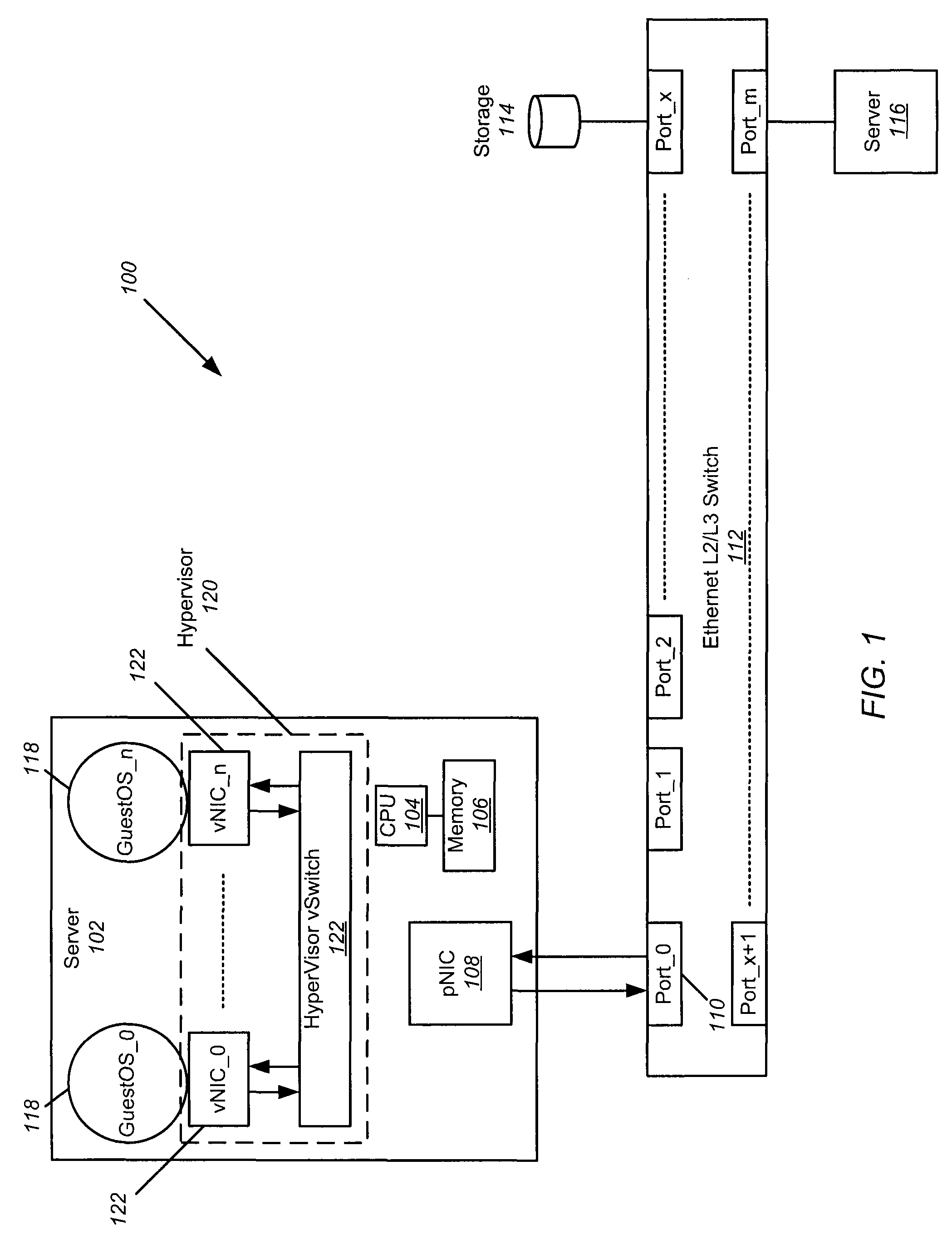

Network consolidation for virtualized servers

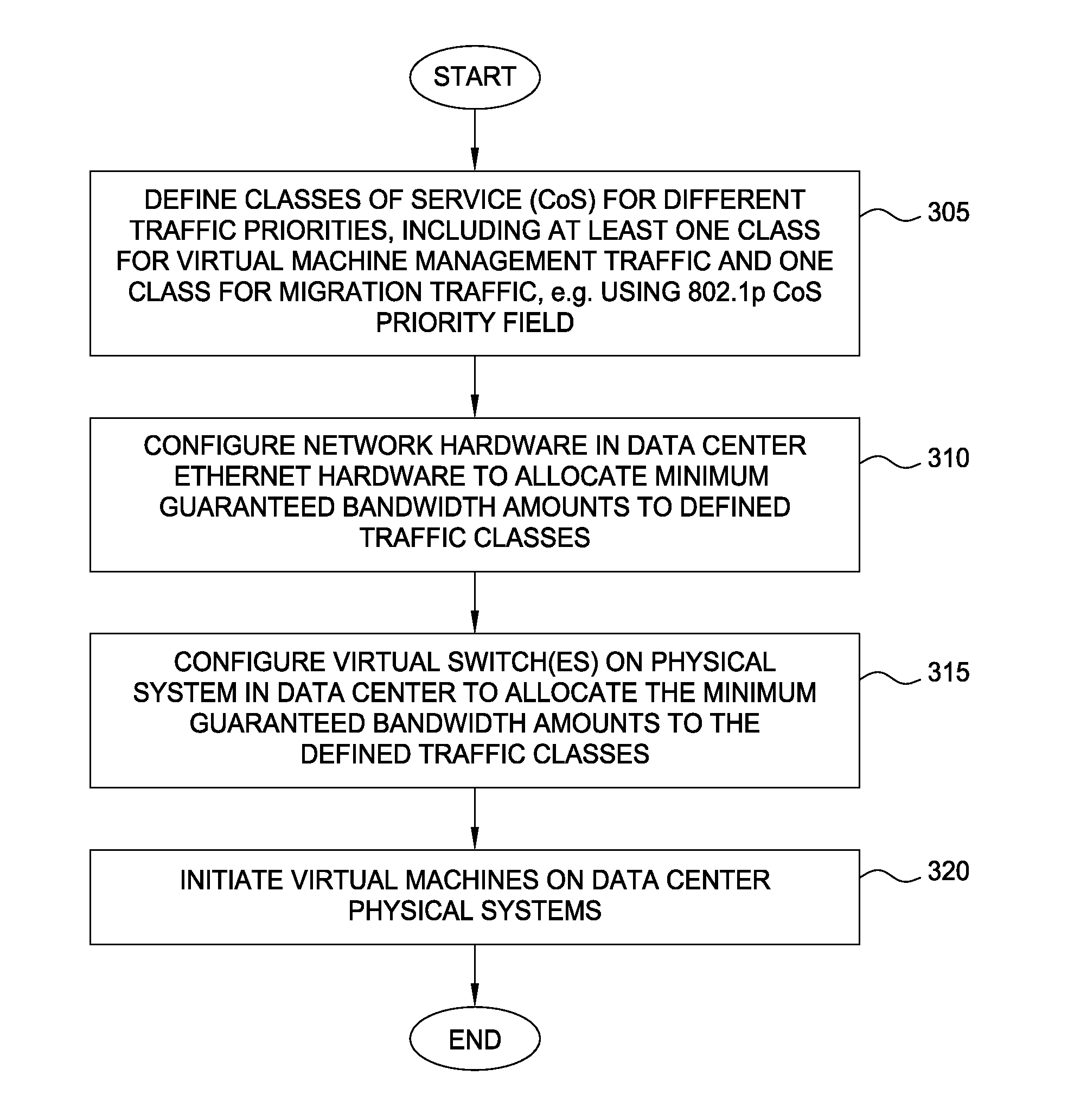

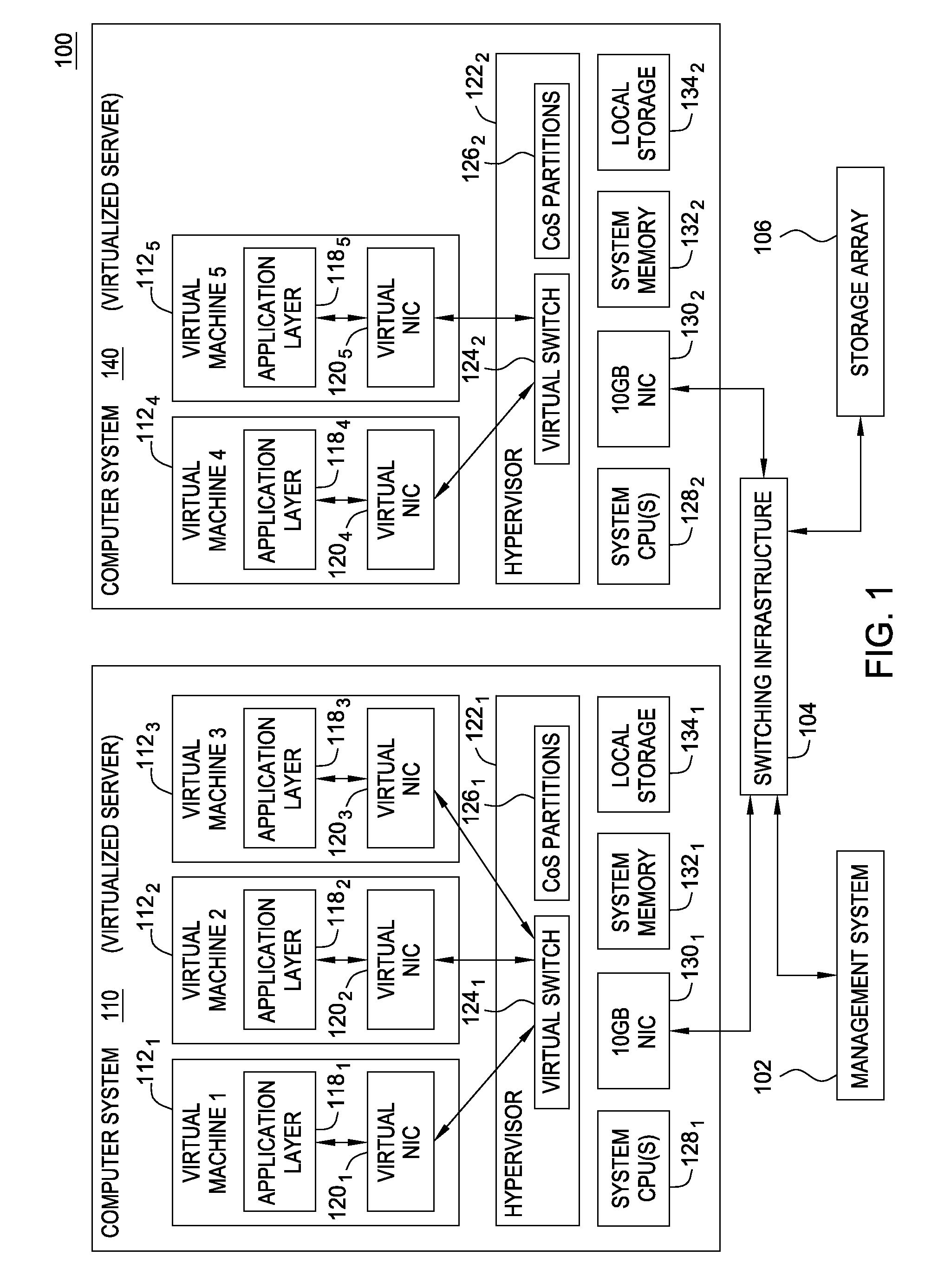

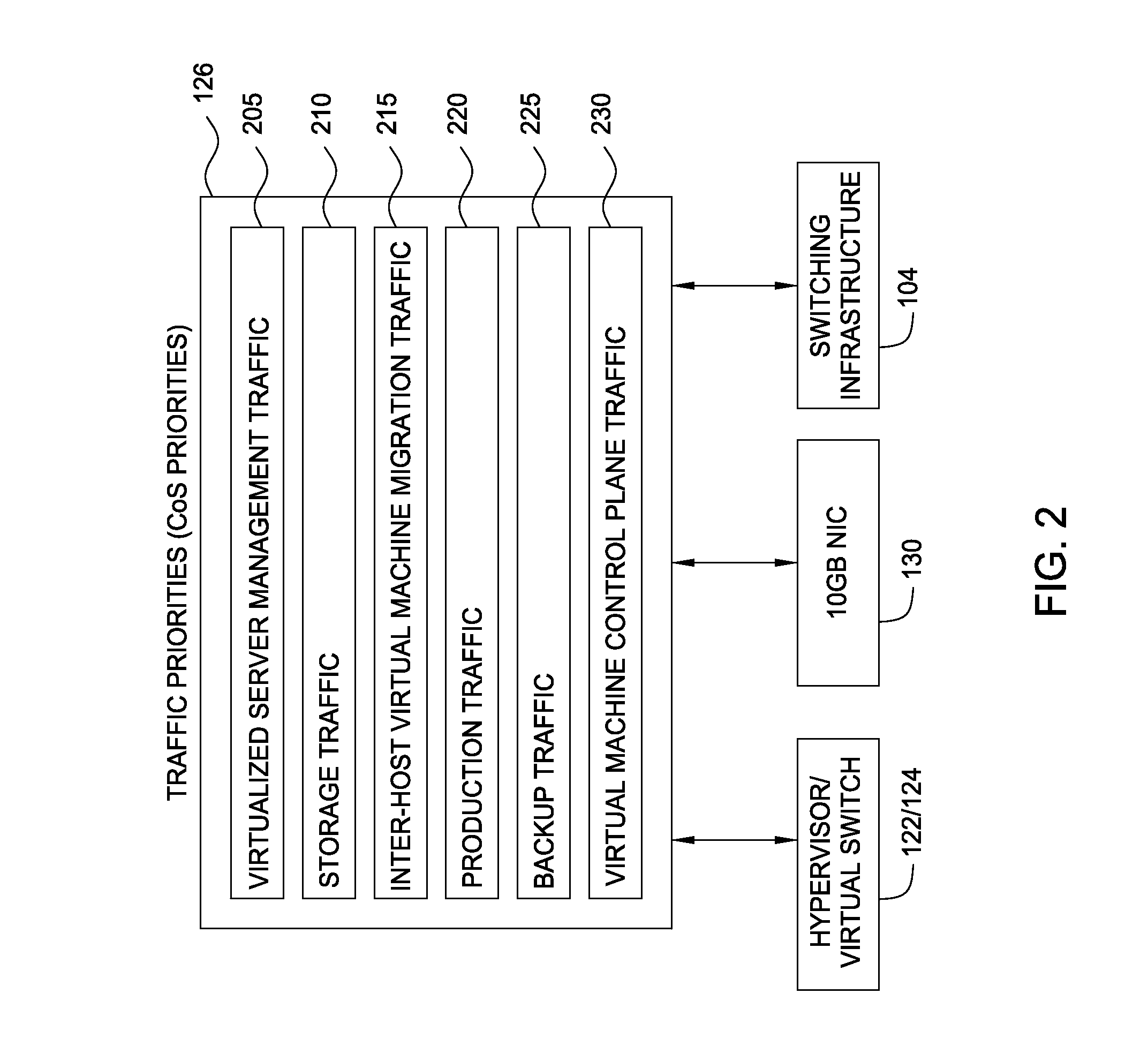

Techniques are disclosed for virtualized server kernel and virtual networks consolidation. The network consolidation allows a data center to migrate from an infrastructure that uses multiple dedicated gigabit Ethernet Network Adapters to manage system virtualization and migration to an infrastructure using consolidated, redundant, 10 gigabit Ethernet adapters. Different priority classes may be defined for different classes of network traffic such as hypervisor management traffic, inter-host virtual machine migration traffic, virtual machine production traffic, virtualized switching control plane traffic, etc. Further, an enhanced transmission standard may be used to specify a minimum bandwidth guarantee for certain traffic classes. Thus, the hypervisor management and inter-host virtual machine migration traffic may be transmitted, even the presence of congestion.

Owner:CISCO TECH INC

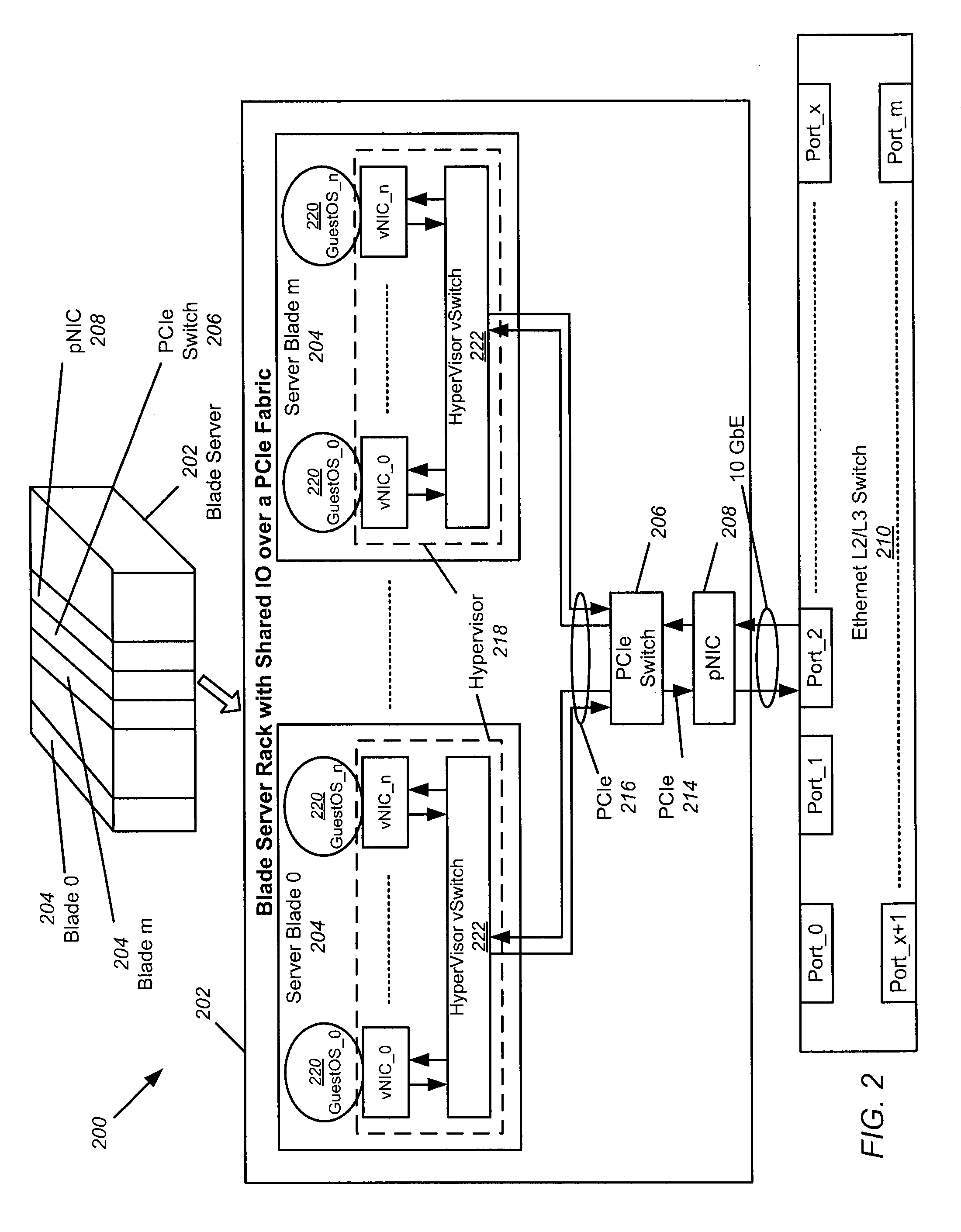

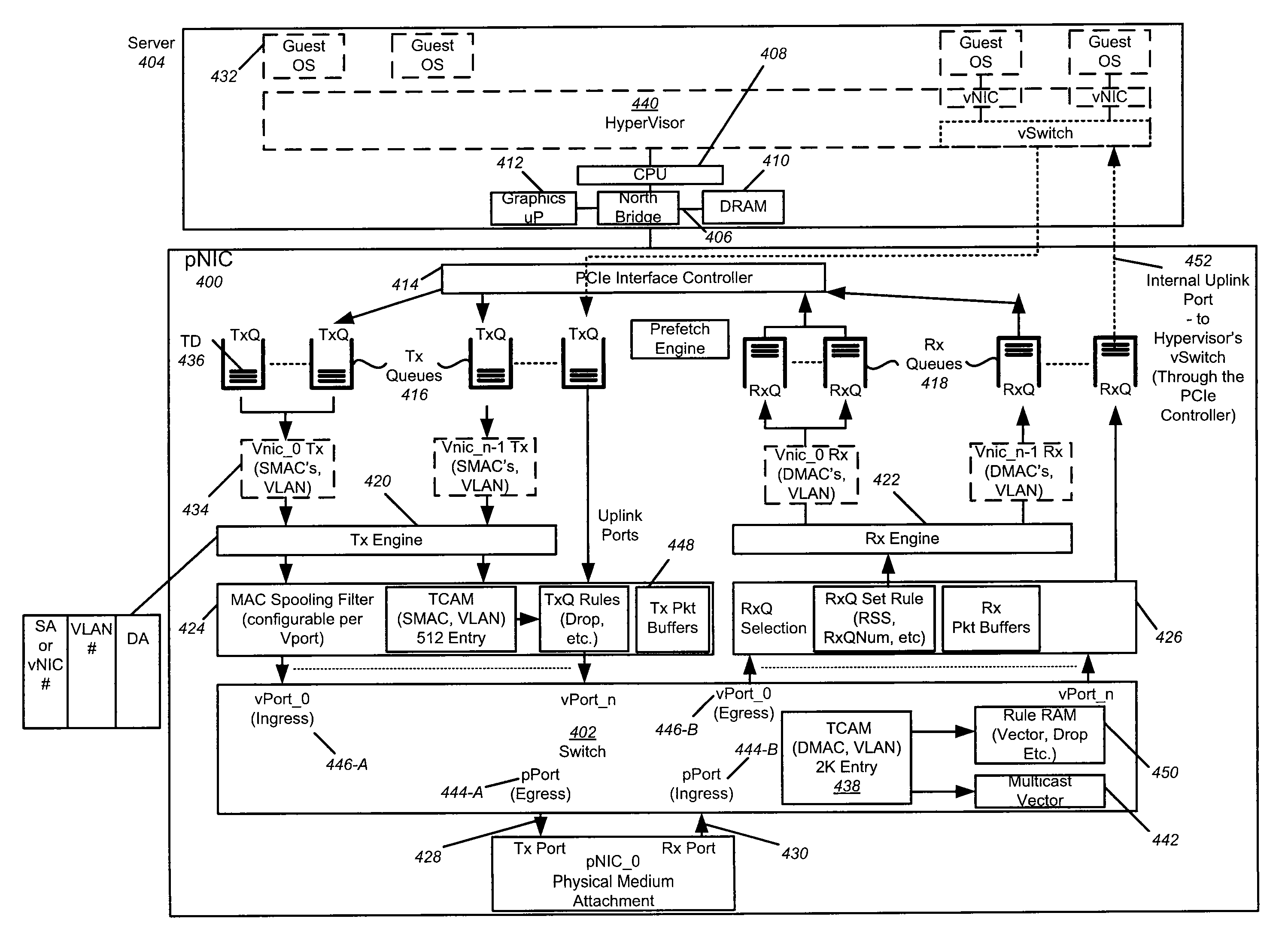

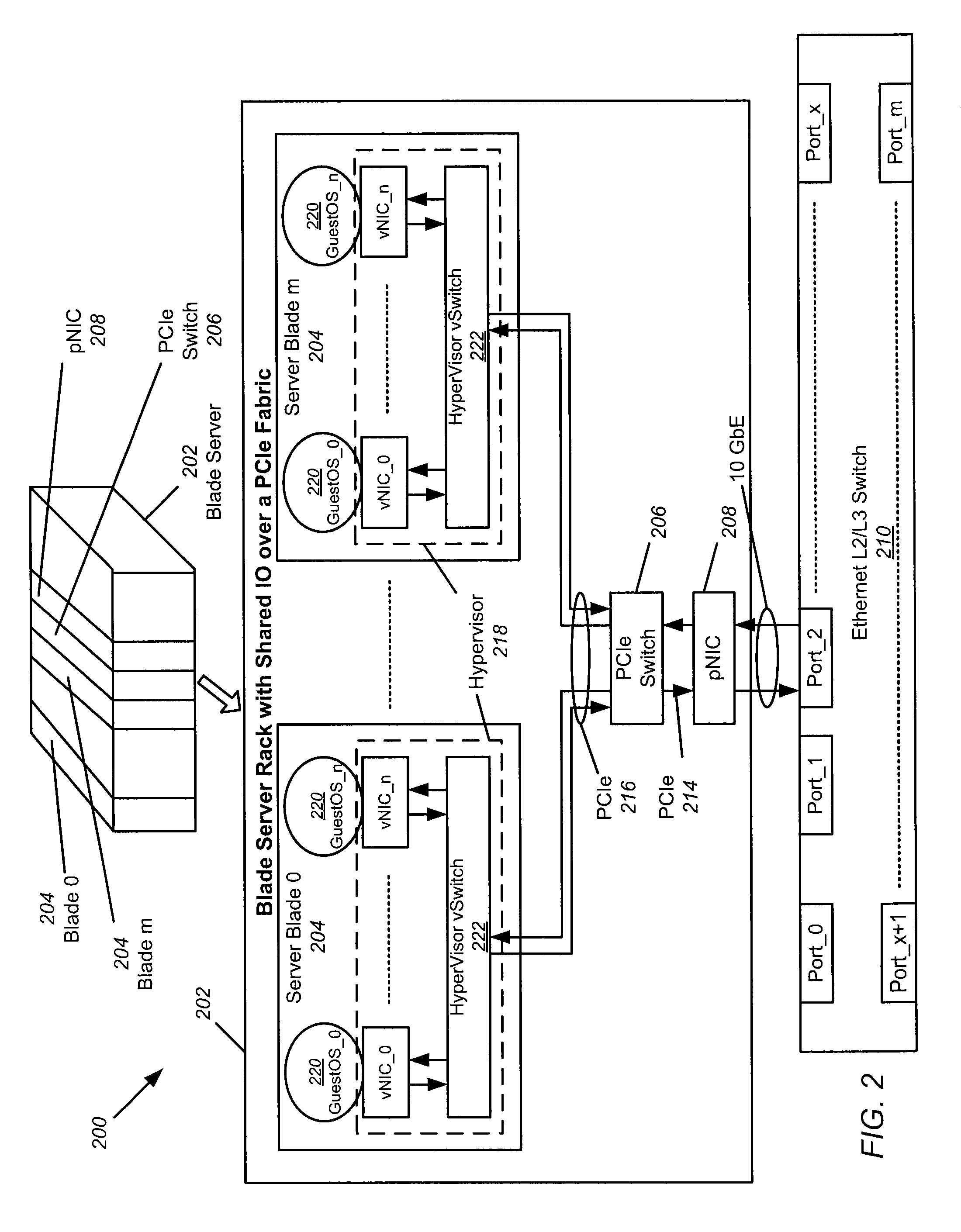

Hardware Switch for Hypervisors and Blade Servers

ActiveUS20100014526A1Quick switchData switching by path configurationMemory systemsFiber10 Gigabit Ethernet

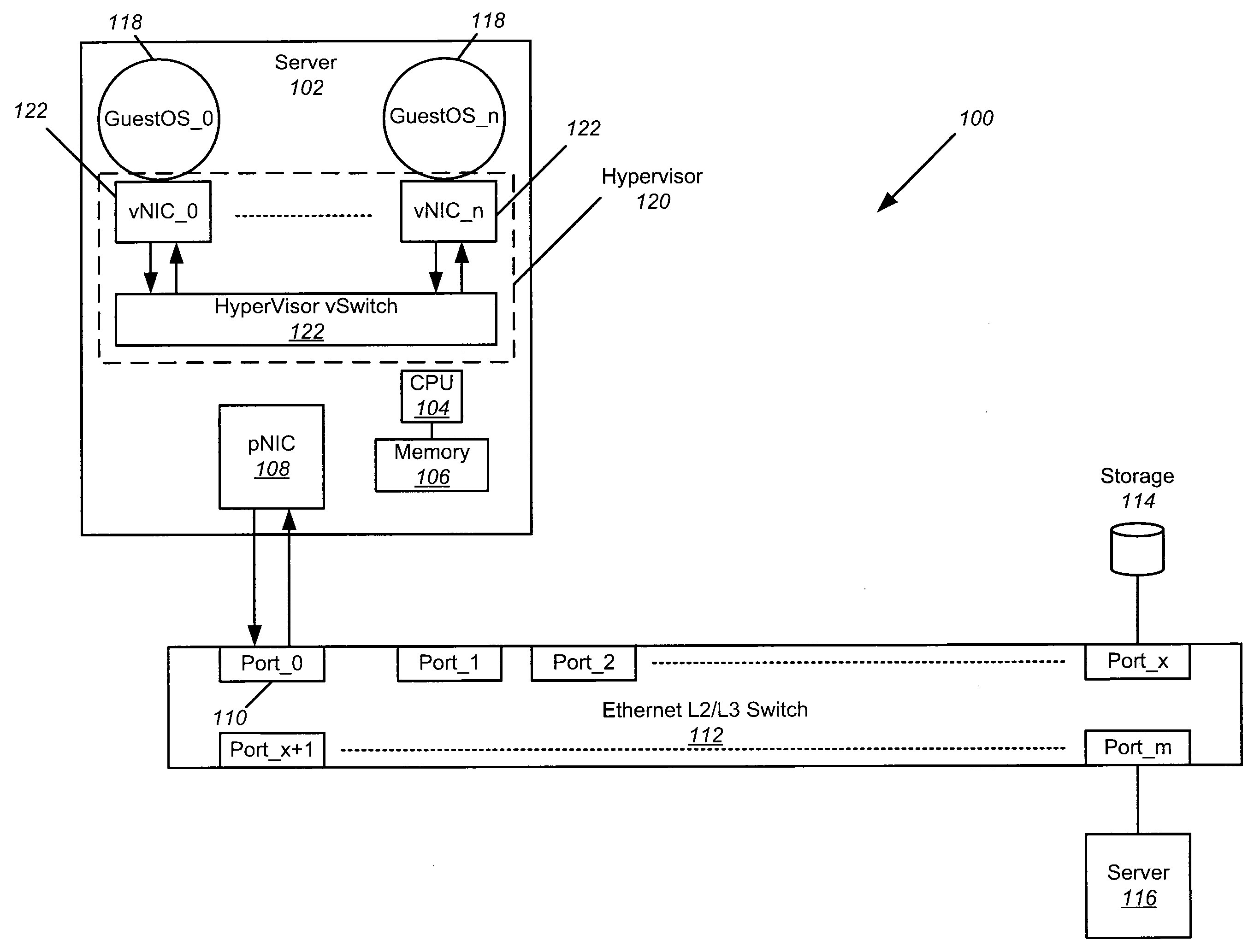

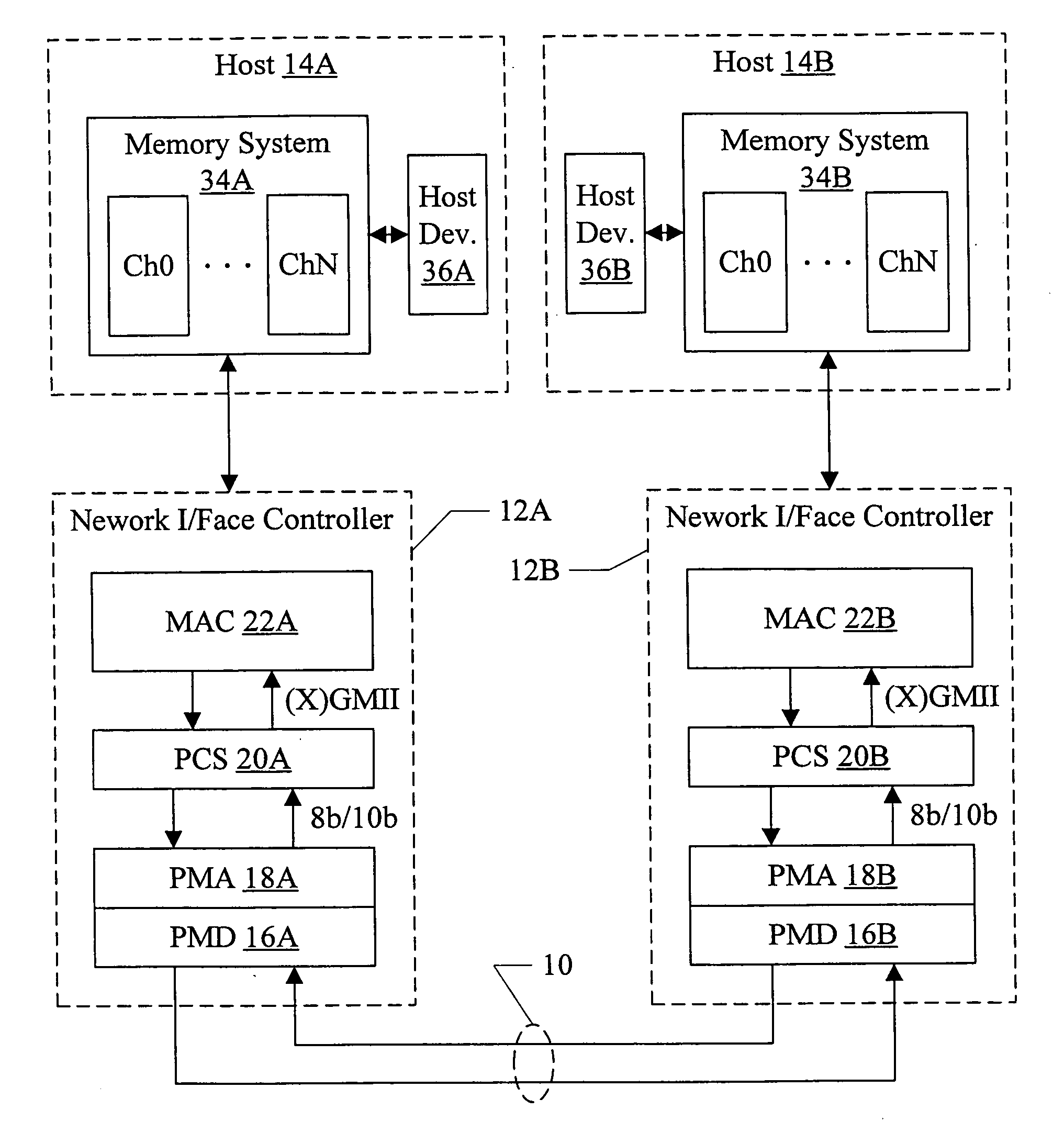

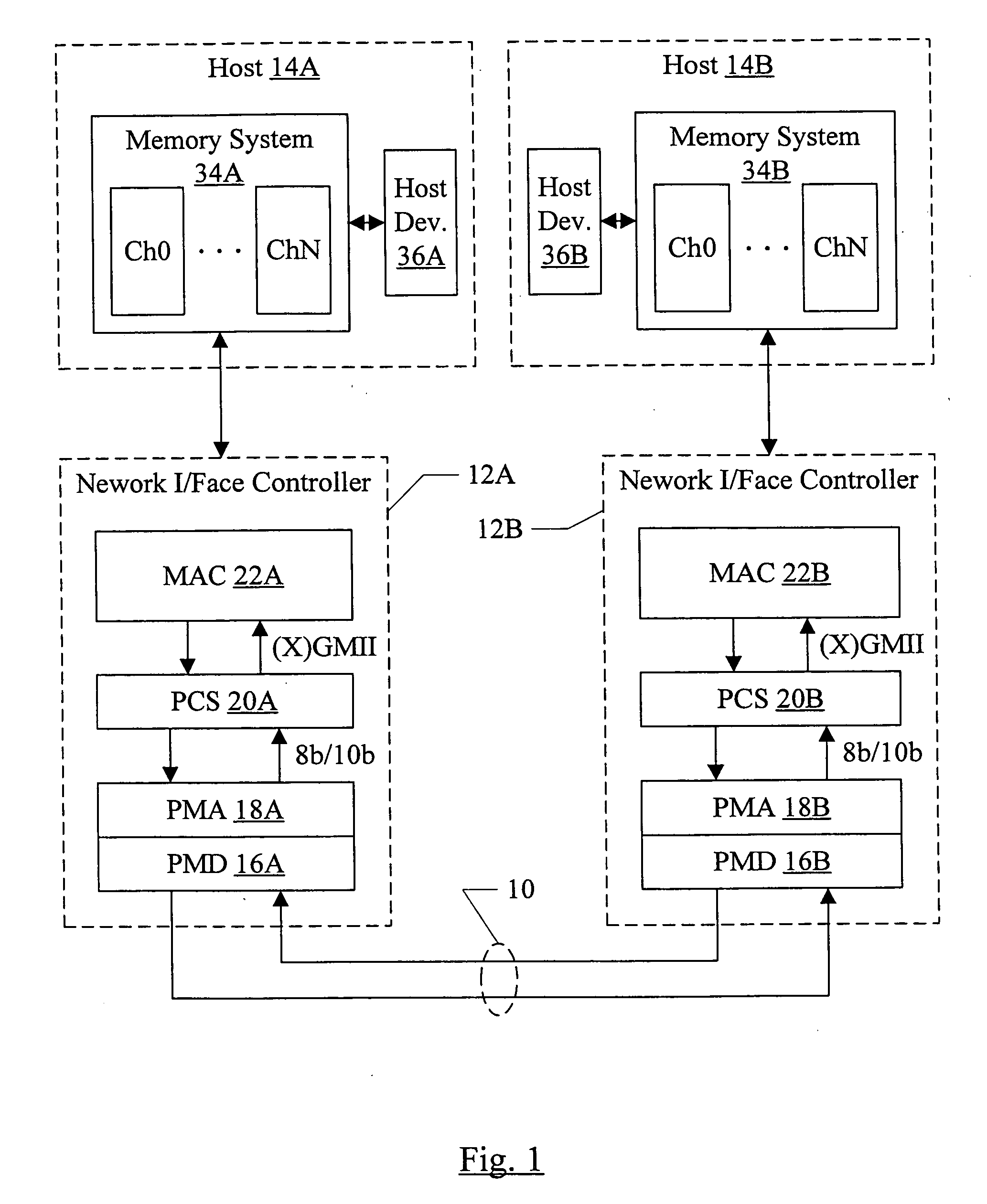

A hardware switch for use with hypervisors and blade servers is disclosed. The hardware switch enables switching to occur between different guest OSs running in the same server, or between different servers in a multi-root IOV system, or between different guest OSs running in the same server in single-root IOV systems. Whether embedded in a host bus adapter (HBA), converged network adapter (CNA), network interface card (NIC) or other similar device, the hardware switch can provide fast switching with access to and sharing of at least one external network port such as a Fibre Channel (FC) port, 10 Gigabit Ethernet (10 GbE) port, FC over Ethernet (FCOE) port, or other similar port. The hardware switch can be utilized when no hypervisor is present or when one or more servers have hypervisors, because it allows for switching (e.g. Ethernet switching) between the OSs on a single hypervisor.

Owner:AVAGO TECH INT SALES PTE LTD

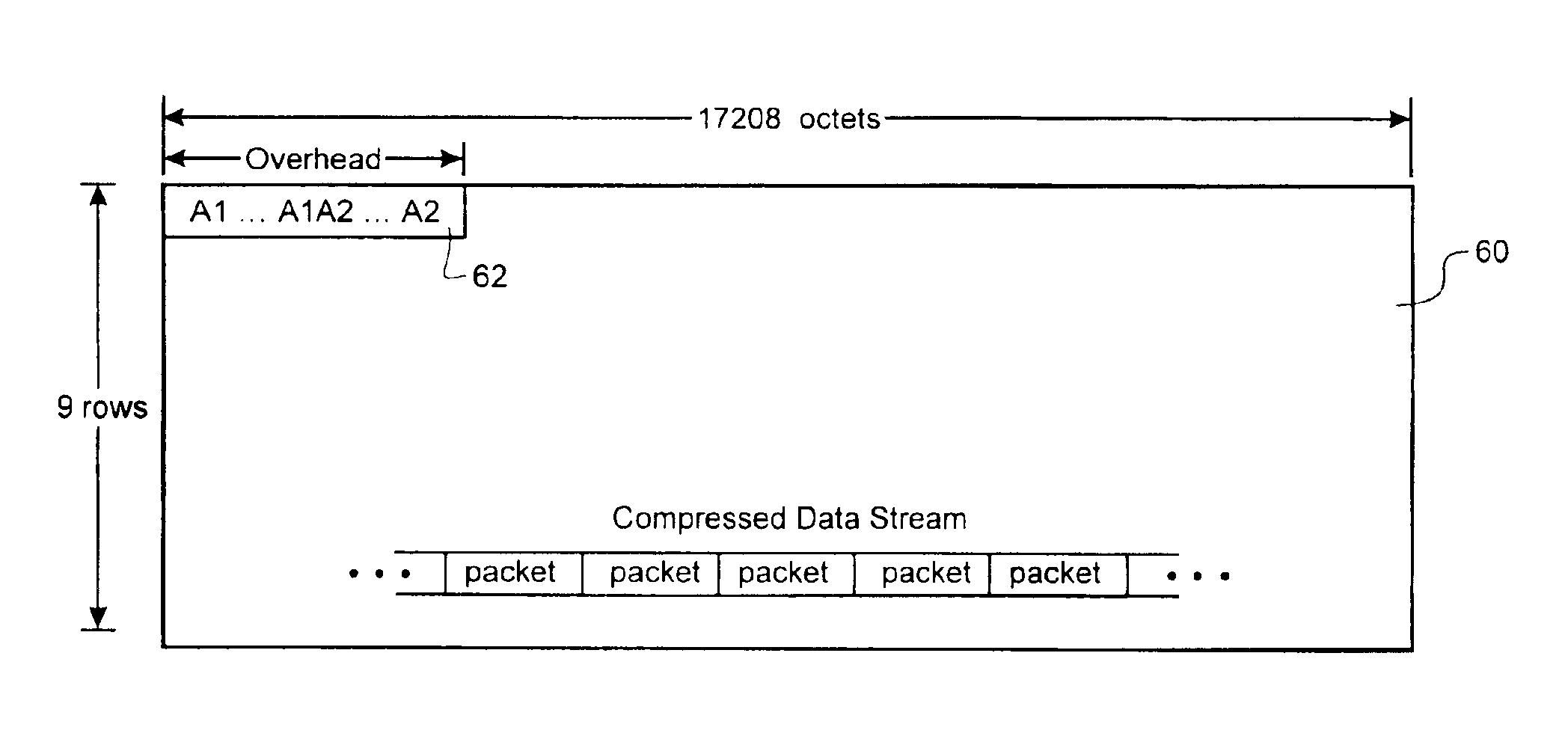

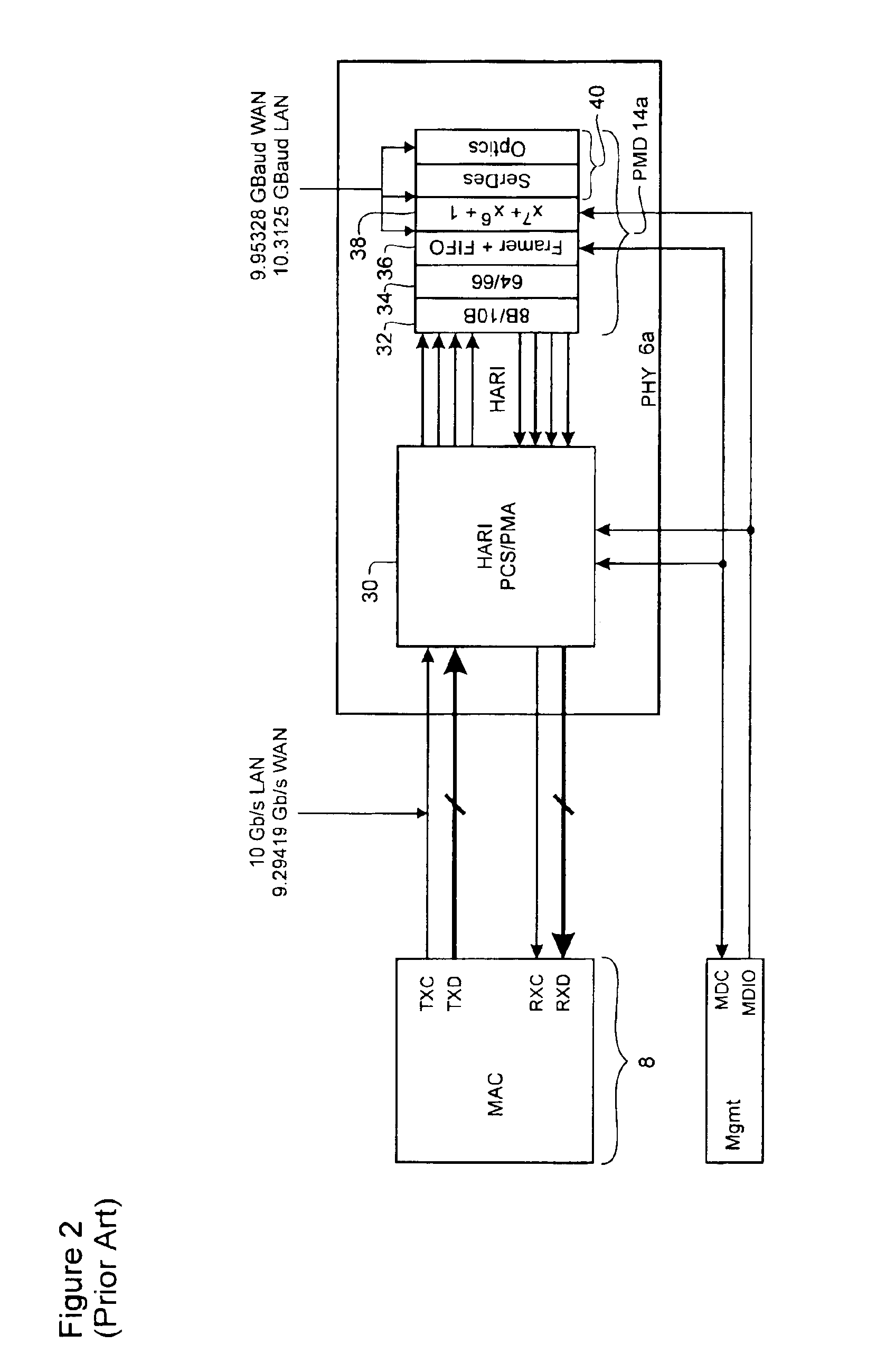

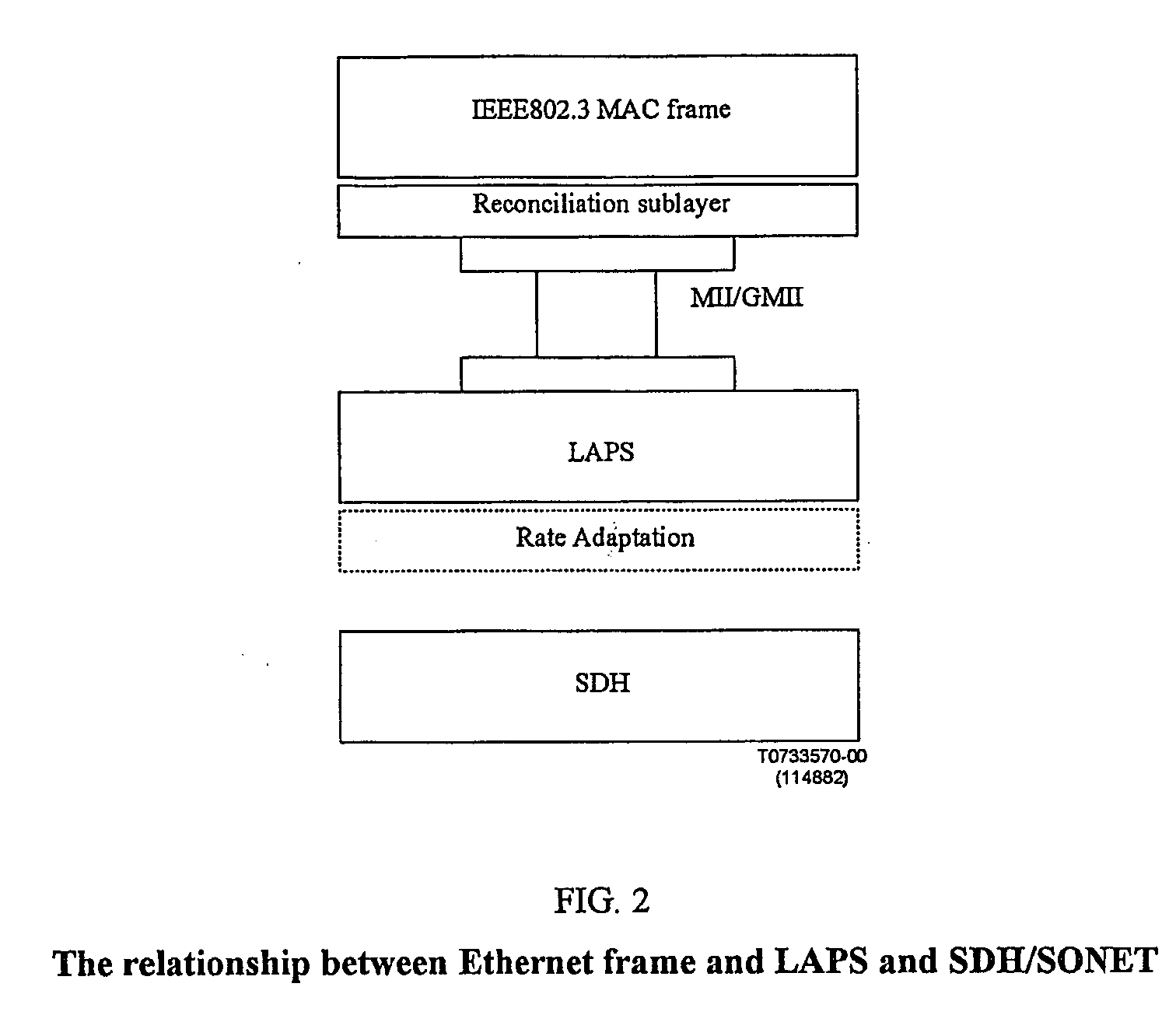

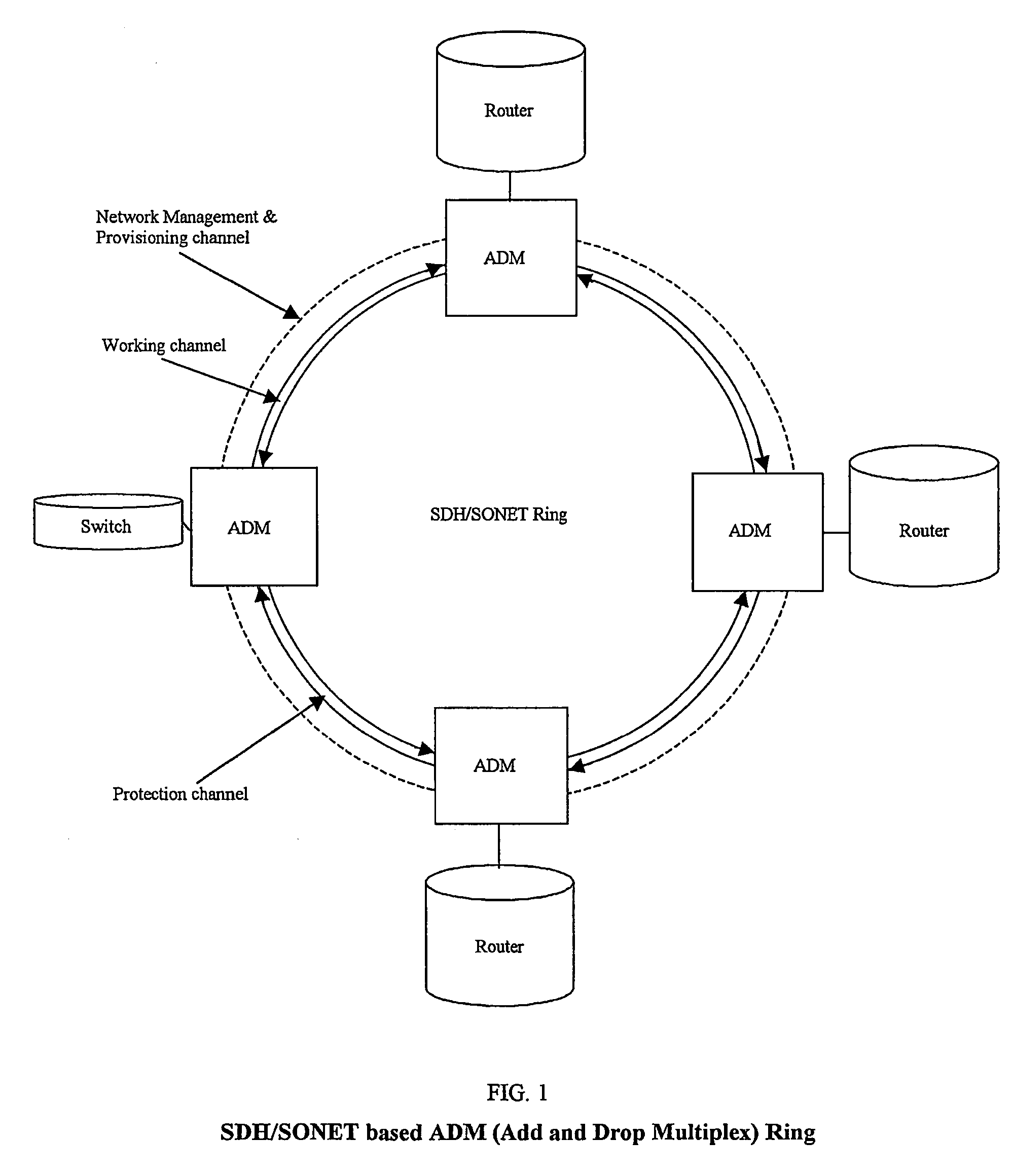

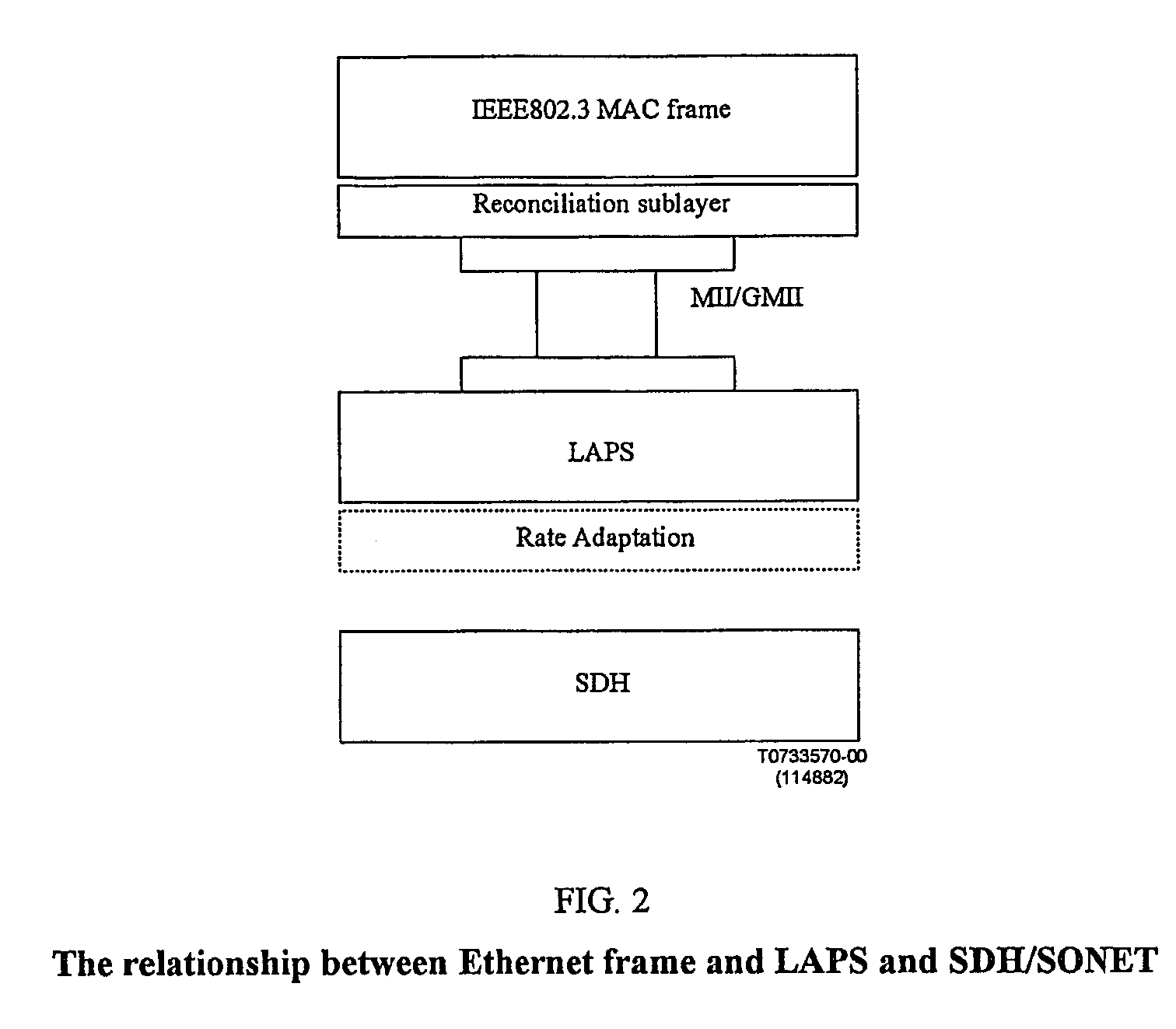

10 Gigabit ethernet mappings for a common LAN/WAN PMD interface with a simple universal physical medium dependent interface

An Ethernet mapping enables high speed Ethernet data streams having a data rate of 10 Gb / s to be transported across a synchronous packet switched network fabric having a standard SONET OC-192 line rate of 9.953280 Gbaud. The 10 Gb / s Ethernet data stream is compressed by removing interframe gaps between successive MAC frames to produce a compressed data stream, which is then mapped to a synchronous container. The synchronous container is then launched across the synchronous packet switched network fabric at a standard SONET OC-192 line rate of 9.953280 Gbaud. The synchronous container is preferably provided as a stripped STS-192c frame having only A1 and A2 octets of the Transport Overhead (TOH). The compressed data stream is mapped directly to the synchronous container, starting at the first octet following the A1 and A2 octets, without first being inserted into a conventional STS-192c SPE, so that most of the space normally used for TOH and Path overhead (POH) within a conventional STS-192c frame is freed-up for carrying the compressed data stream. At a receiving interface, the compressed data stream is extracted from received synchronous containers and decompressed, by insertion of interframe gaps between successive MAC frames, to generate a recovered 10 Gb / s Ethernet data stream. The starting bit of each successive MAC frame can be identified by examination of the length field of the immediately previous MAC frame.

Owner:CIENA

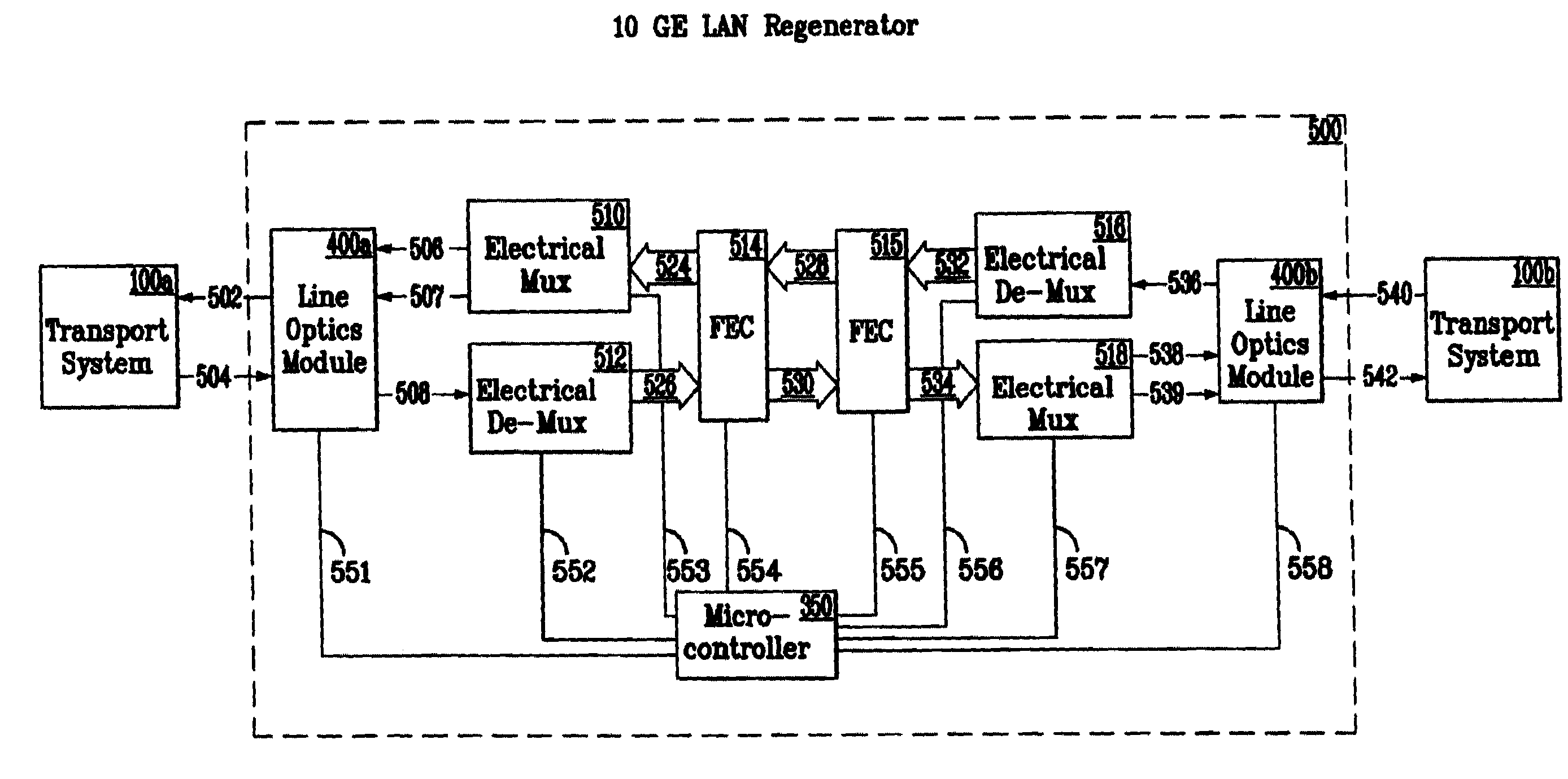

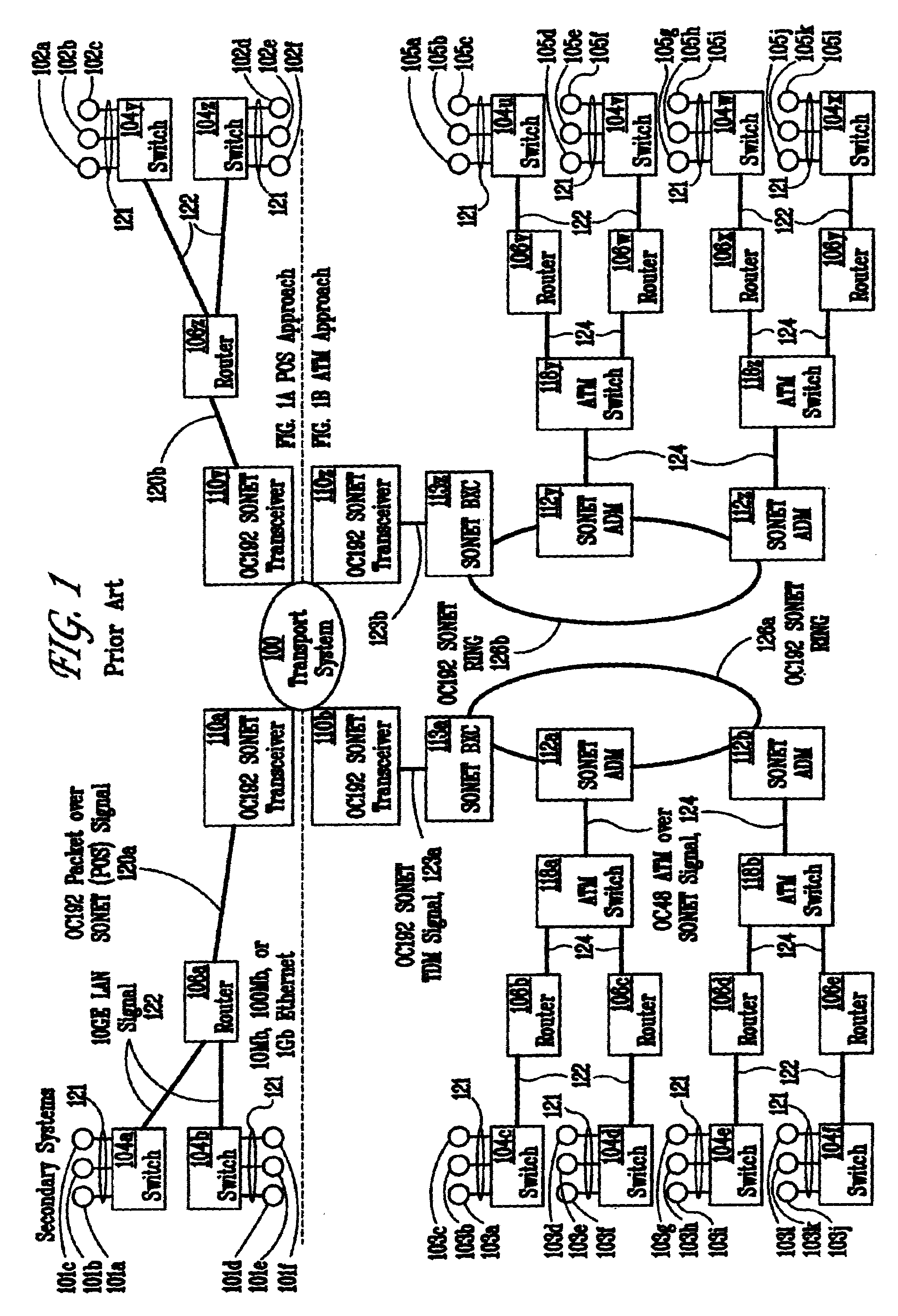

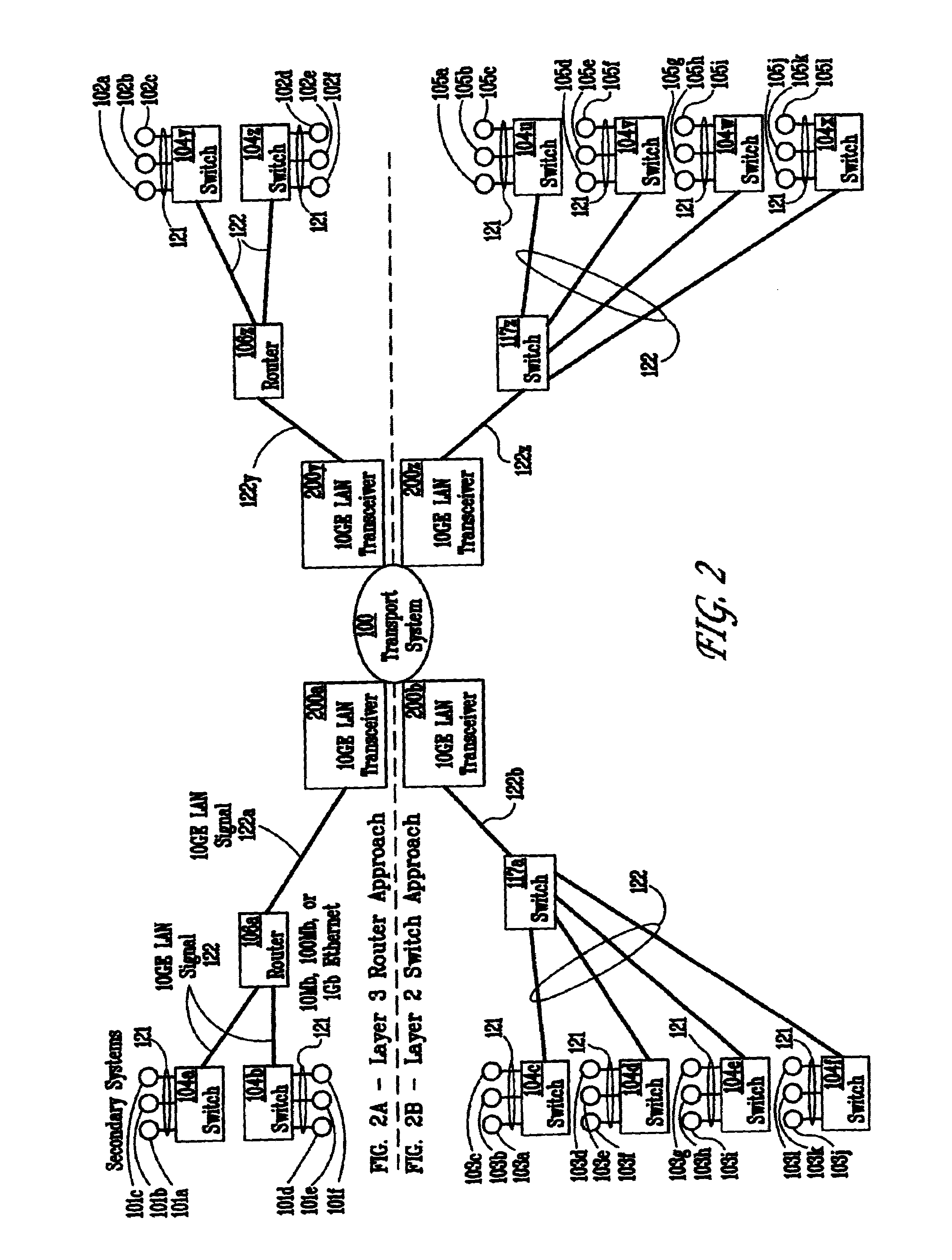

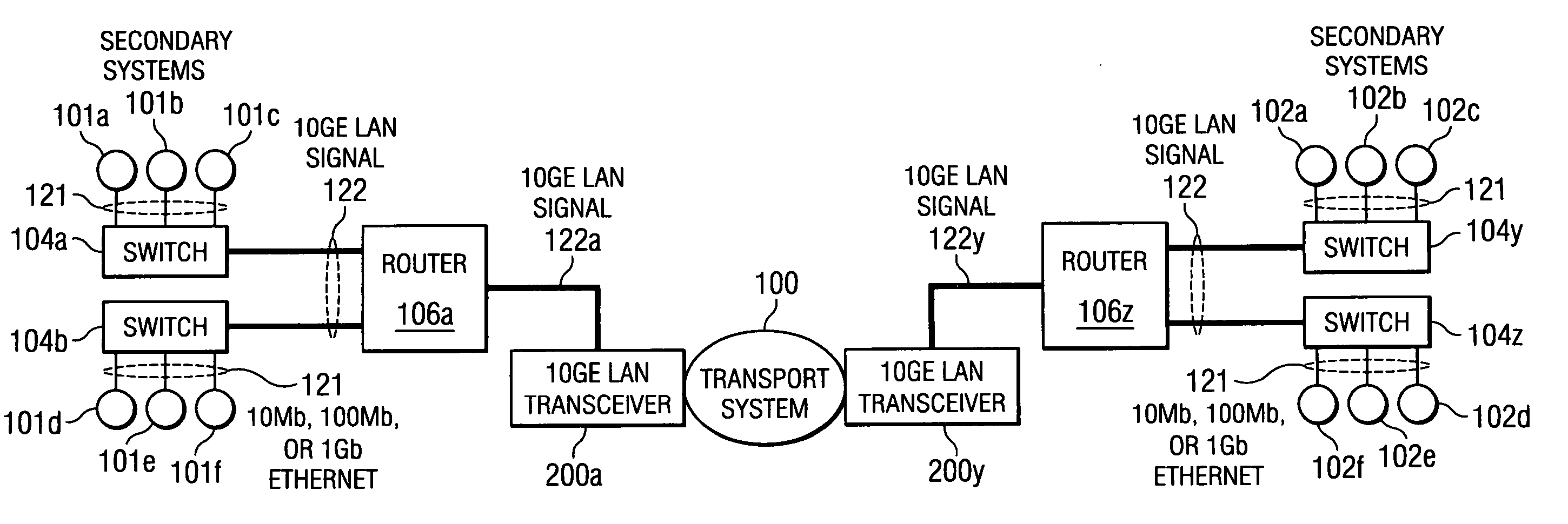

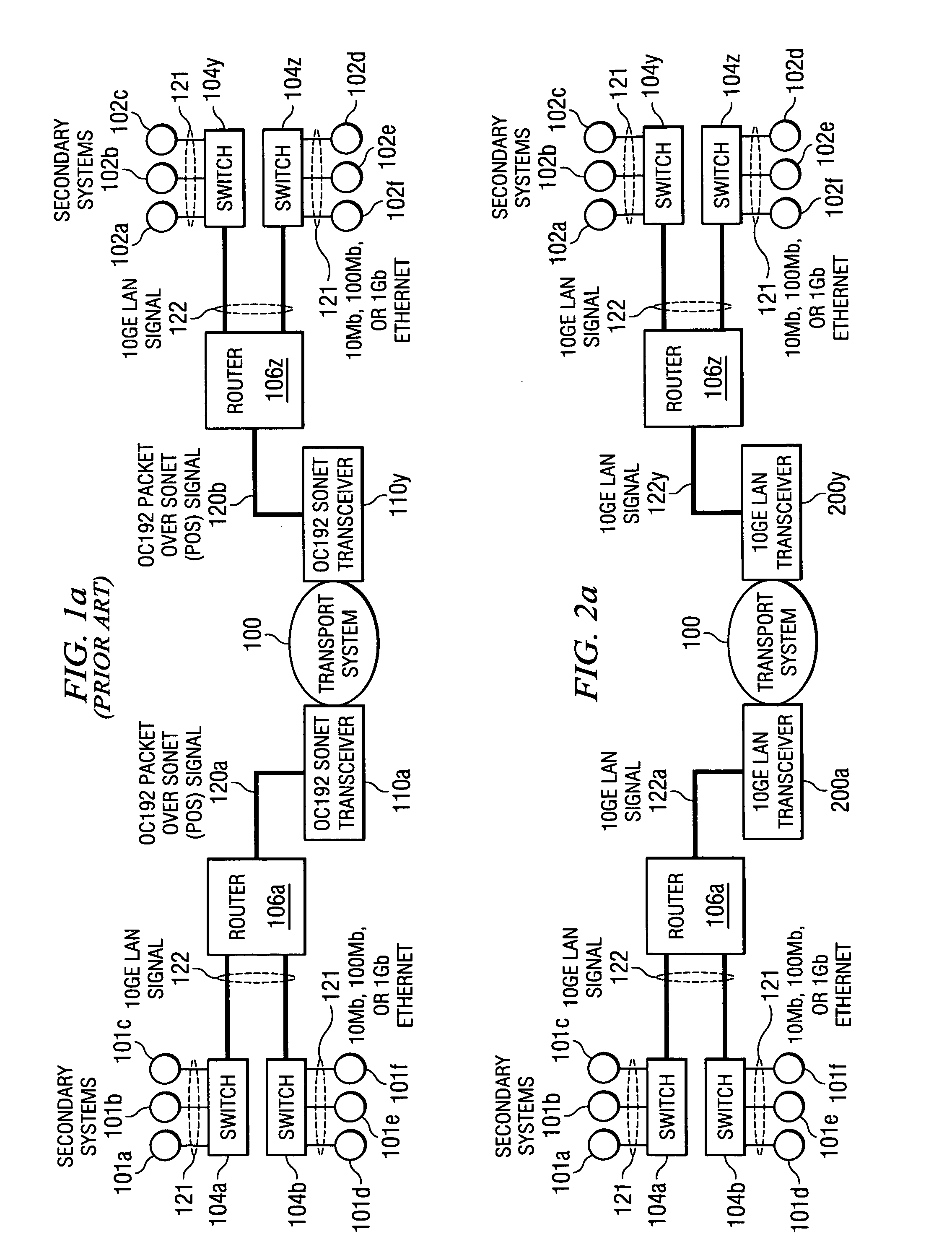

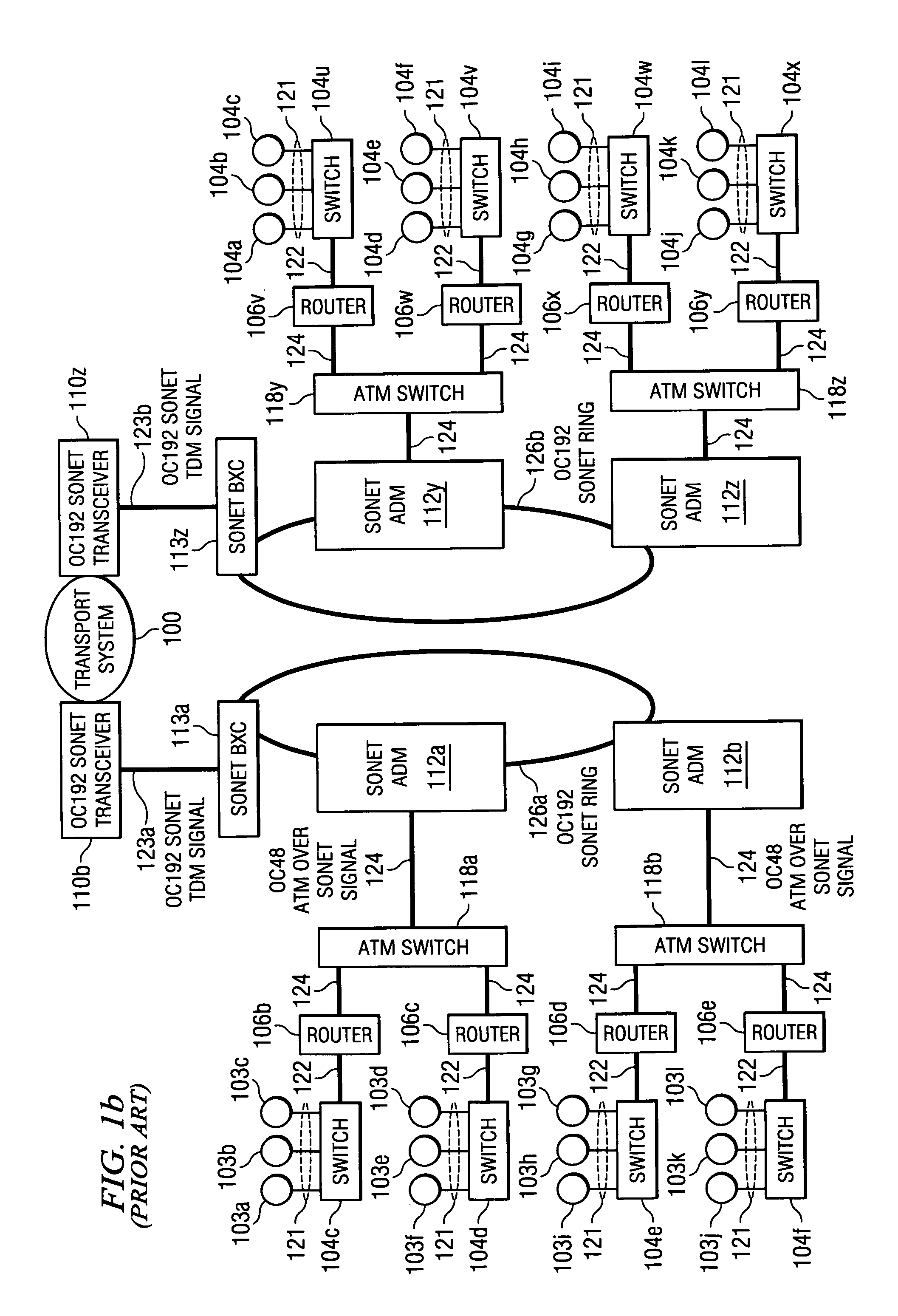

Apparatus and method for transmitting 10 Gigabit Ethernet LAN signals over a transport system

InactiveUS7164692B2Easy to operateEasy to useTime-division multiplexElectromagnetic network arrangementsTransport systemTransceiver

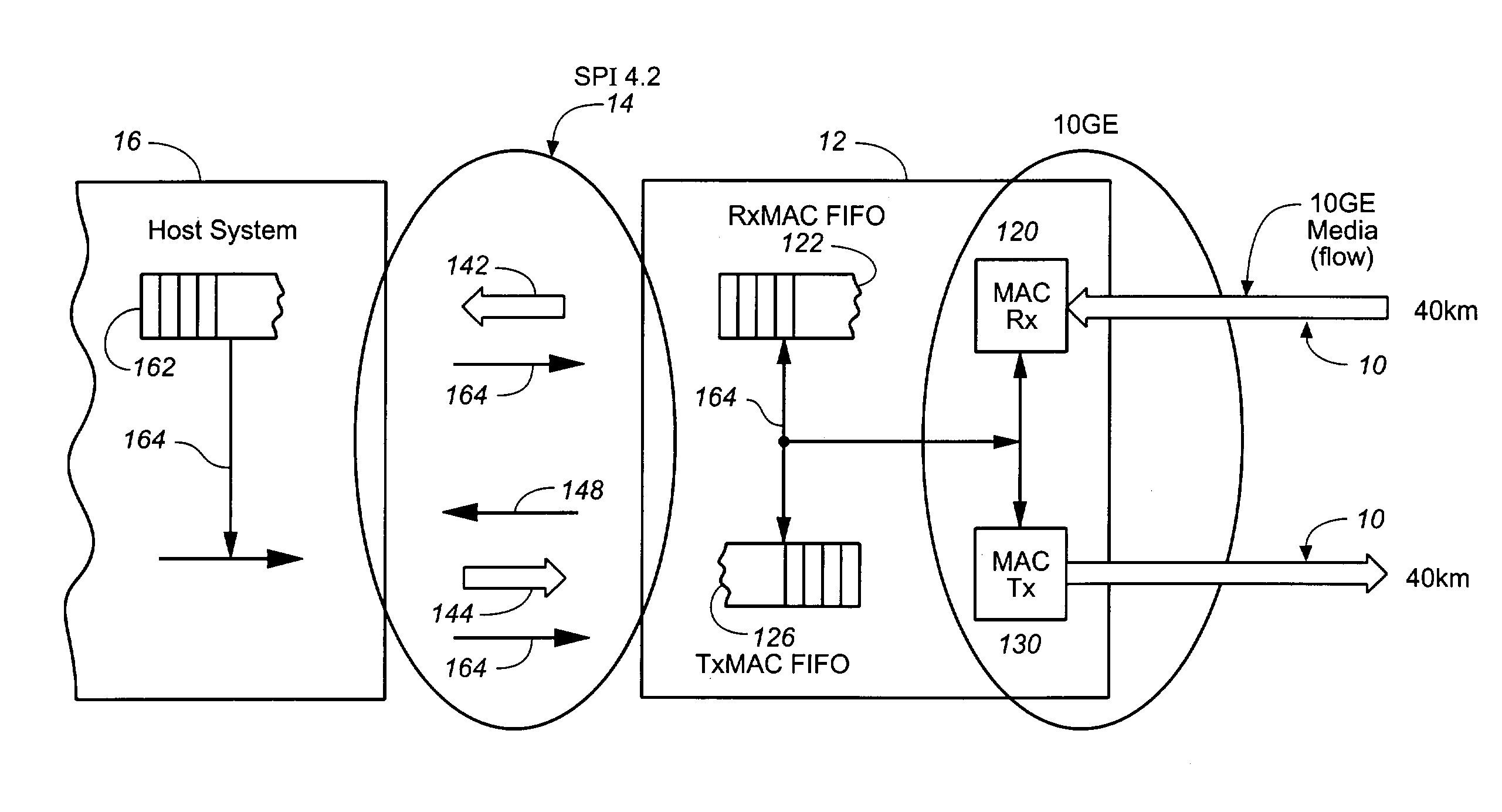

A computer system and method for transmitting 10 Gigabit Ethernet (10GE) LAN signals over transport systems. Standard 10GE LAN signals are generated in any client IEEE 802.3 10GE LAN compliant interface. A transceiver receives the client 10GE LAN signal in the LAN format. The client 10GE LAN signals are not converted to a SONET transmission format at any time before reaching the transceiver. The transceiver then converts the client 10GE LAN signal to an internal electrical 10GE LAN signal before re-clocking the internal electrical LAN signal. The re-clocked internal electrical 10GE LAN signal is then re-modulated into a second 10GE LAN signal. The second 10GE LAN signal is then transmitted to a transport system.

Owner:WINTERSPRING DIGITAL LLC

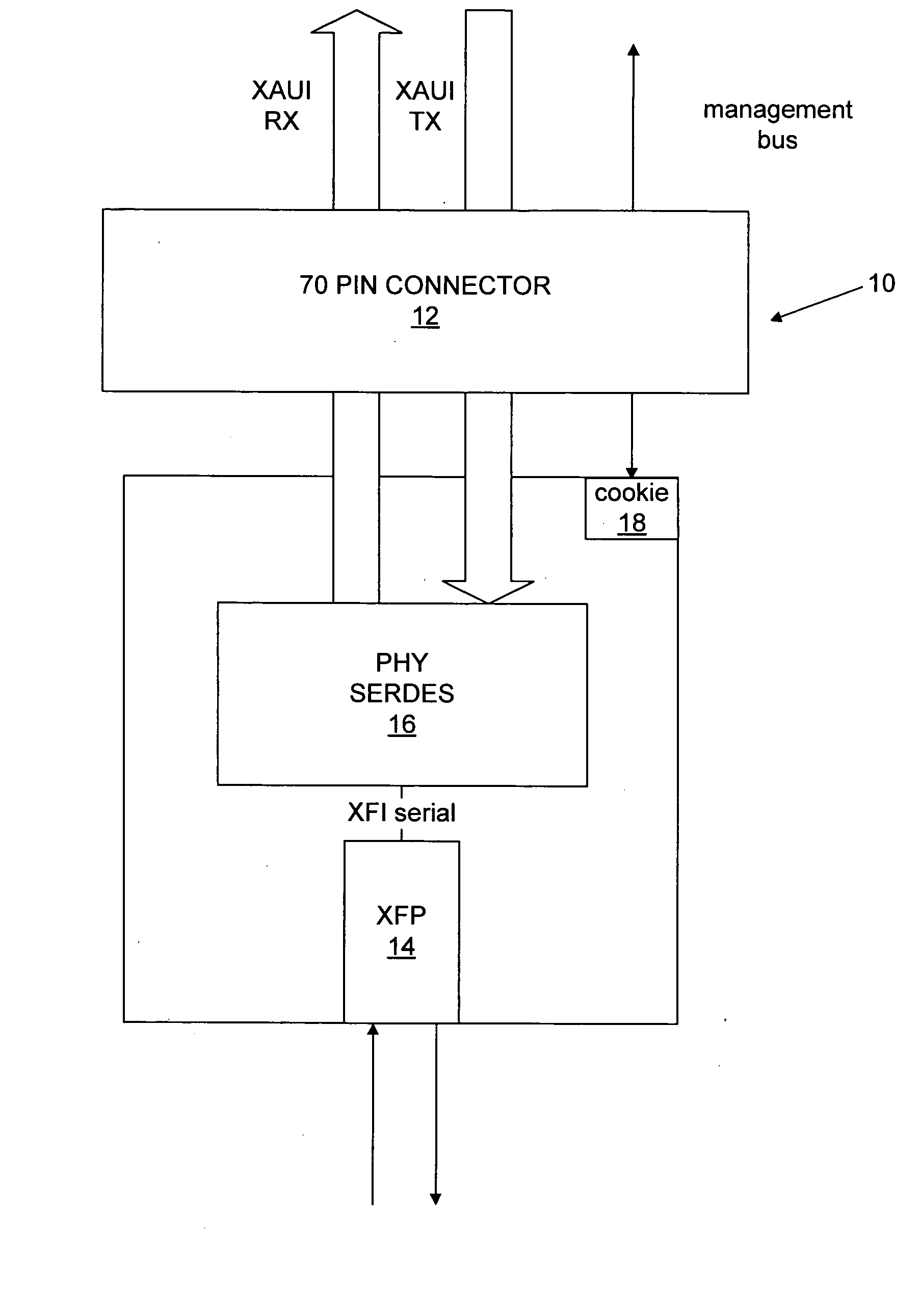

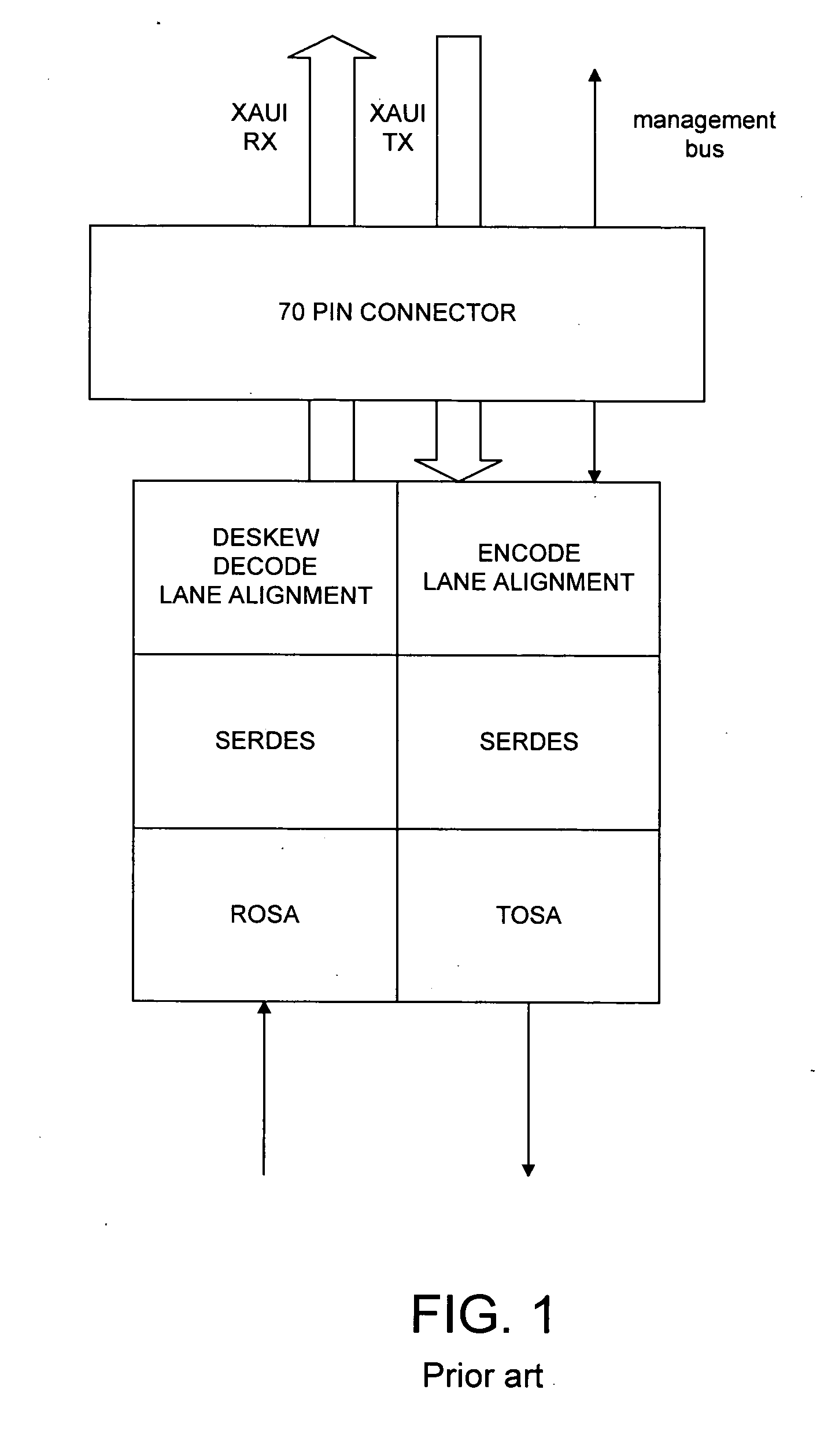

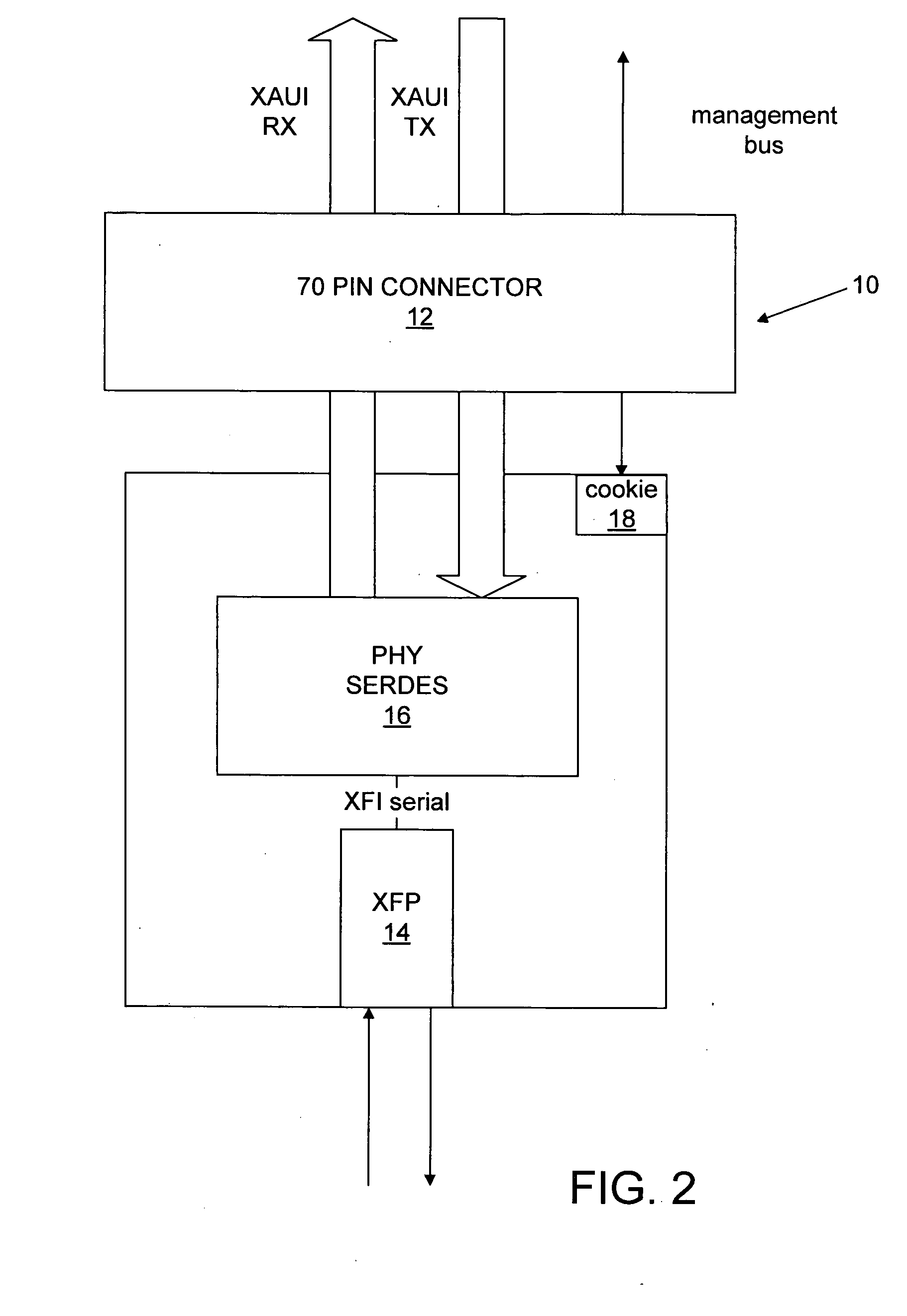

Carrier card converter for 10 gigabit ethernet slots

ActiveUS20060216958A1Avoid the needCoupling device connectionsElectric discharge tubes10 Gigabit EthernetCarrier signal

A carrier module is physically compatible with a XENPAK / X2 10 GE slot and includes a socket for accepting a non-XENPAK / X2 module and interface circuitry for providing appropriate signals to a XENPAK / X2 70-pin connector on an interior side of the carrier module. The carrier module includes a cookie, accessible by host software, identifying the type of carrier module and non-XENPAK / X2 module accepted by the carrier card.

Owner:CISCO TECH INC

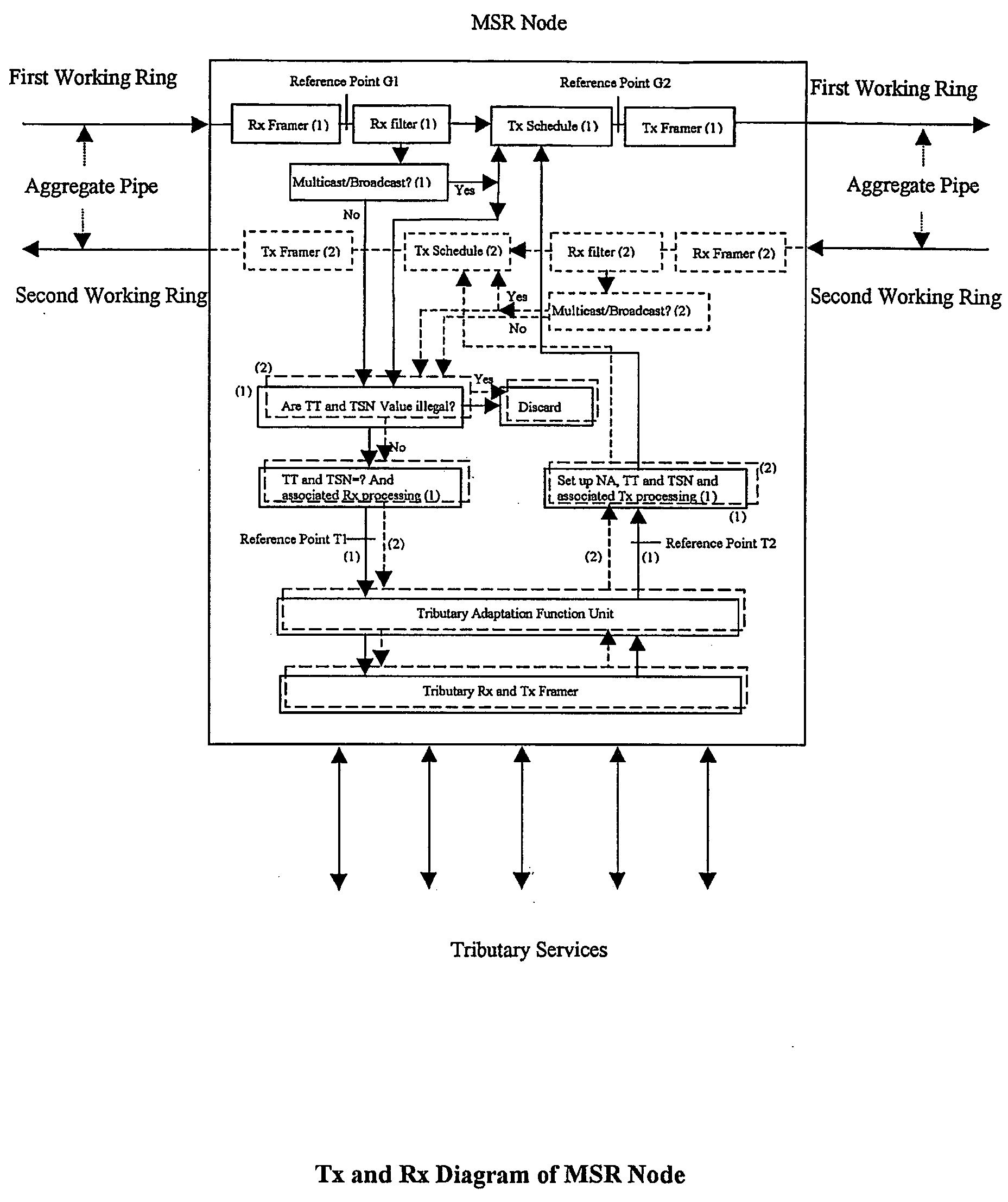

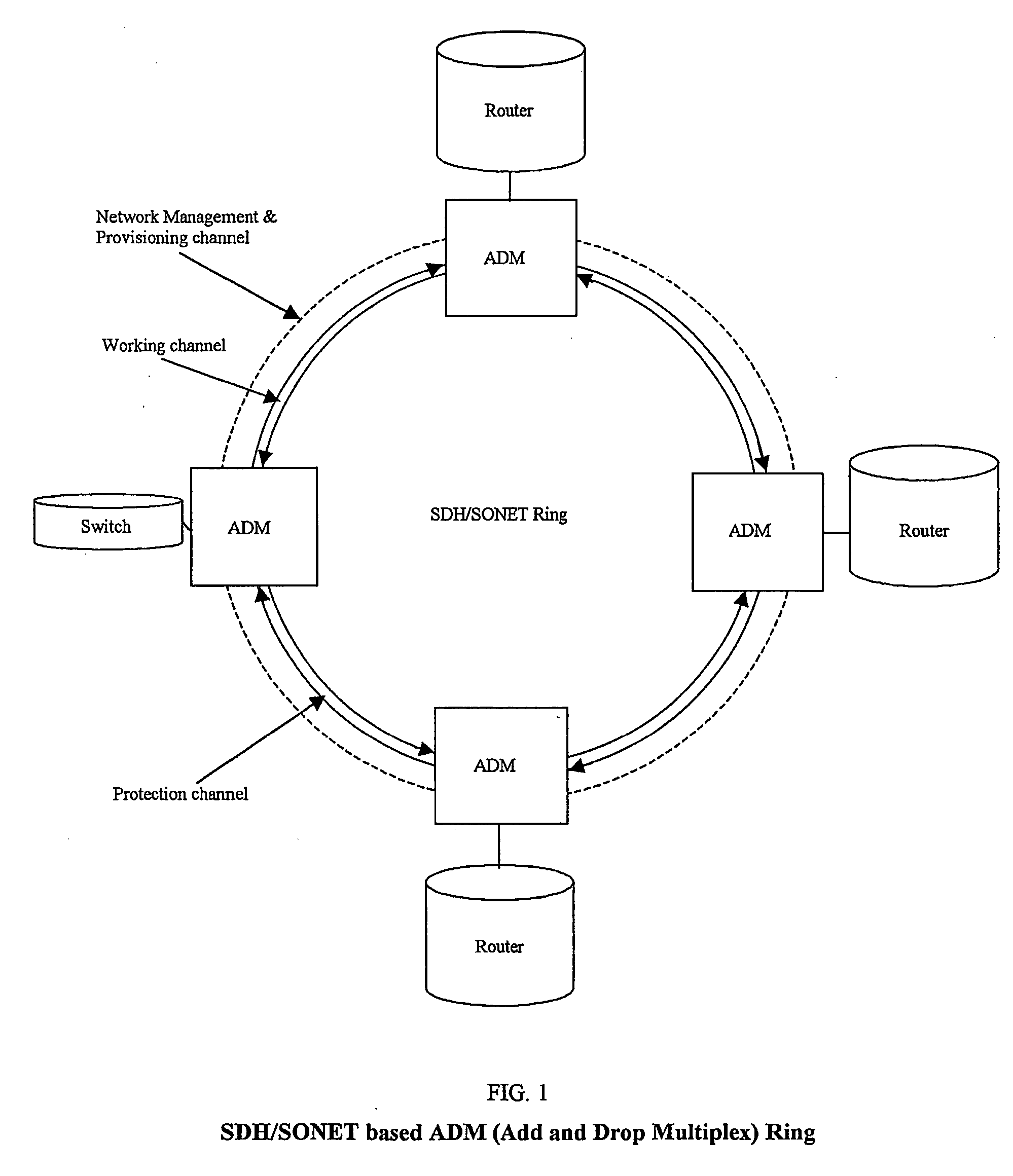

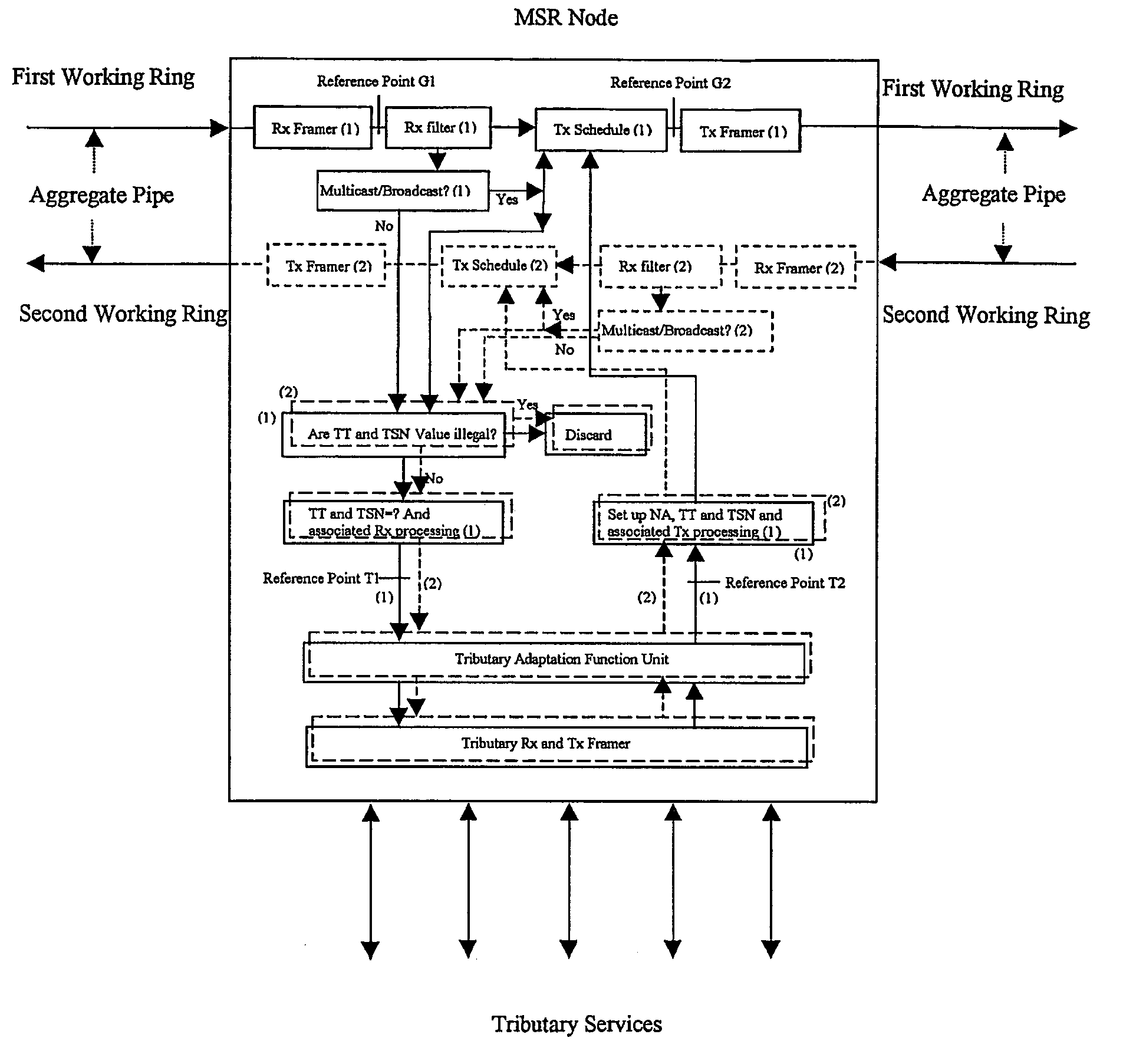

Resilient multiple service ring

A data transmission apparatus and method used in resilient multiple service ring, including a first working ring and a second working ring, for transmitting data between physical layer side device and network layer device or other upper layer facilities, such as carrier class node equipments, core and edge routers, switch devices, IP based network accessing equipments, line cards, and interfacing units used in high rates or low rates, e.g. Ethernet, Gigabit Ethernet, 10 Gigabit, Ethernet, DVB (MPEG1, MPEG2, MPEG4 and MPEG7), ATM, Packet over SDH / SONET transmissions, other MSR, RPR for adapting IP and various tributaries (Ethernet,) directly to SDH / SONET or simplified SDH / SONET, or Gigabit Ethernet, 10 Gigabit Ethernet, or other physical layer devices.

Owner:FENGHUO COMM SCI & TECH CO LTD

Apparatus and method for transmitting 10 Gigabit Ethernet LAN signals over a transport system

InactiveUS20060002419A1Easy to operateEasy to useTime-division multiplexElectromagnetic network arrangements10 Gigabit EthernetTransceiver

A computer system and method for transmitting 10 Gigabit Ethernet (10GE) LAN signals over transport systems. Standard 10GE LAN signals are generated in any client IEEE 802.3 10GE LAN compliant interface. A transceiver receives the client 10GE LAN signal in the LAN format. The client 10GE LAN signals are not converted to a SONET transmission format at any time before reaching the transceiver. The transceiver then converts the client 10GE LAN signal to an internal electrical 10GE LAN signal before re-clocking the internal electrical LAN signal. The re-clocked internal electrical 10GE LAN signal is then re-modulated into a second 10GE LAN signal. The second 10GE LAN signal is then transmitted to a transport system.

Owner:WINTERSPRING DIGITAL LLC +1

Hardware switch for hypervisors and blade servers

ActiveUS7983257B2Quick switchData switching by path configurationMemory systemsFiber10 Gigabit Ethernet

A hardware switch for use with hypervisors and blade servers is disclosed. The hardware switch enables switching to occur between different guest OSs running in the same server, or between different servers in a multi-root IOV system, or between different guest OSs running in the same server in single-root IOV systems. Whether embedded in a host bus adapter (HBA), converged network adapter (CNA), network interface card (NIC) or other similar device, the hardware switch can provide fast switching with access to and sharing of at least one external network port such as a Fibre Channel (FC) port, 10 Gigabit Ethernet (10 GbE) port, FC over Ethernet (FCoE) port, or other similar port. The hardware switch can be utilized when no hypervisor is present or when one or more servers have hypervisors, because it allows for switching (e.g. Ethernet switching) between the OSs on a single hypervisor.

Owner:AVAGO TECH INT SALES PTE LTD

Flow control enhancement

ActiveUS7379422B2Error preventionFrequency-division multiplex detailsControl flow10 Gigabit Ethernet

A networking / communication chip having a receiving buffer or FIFO whereby it receives data from a data source across a network and transfers the data to a host system. The memory in the host system acts as a logical extension of the receiving buffer in the chip; in this way, the host system controls the flow of data from the source, rather than the control flow being based on the capacity of the receiving buffer in the networking / communication chip. The networking / communication chip may be a controller, such as a 10 Gigabit Ethernet controller, wherein data received from the source in one protocol is transformed to a second protocol input to the host. If either or both the networking / communication chip or the host system is / are made of FPGAs, it / they can be reprogrammed to disable the flow control in the networking / communication chip and enable flow control in the host system. Data flow is enhanced because memory in the host system typically is much larger than memory in the networking / communication chip.

Owner:AVAGO TECH INT SALES PTE LTD

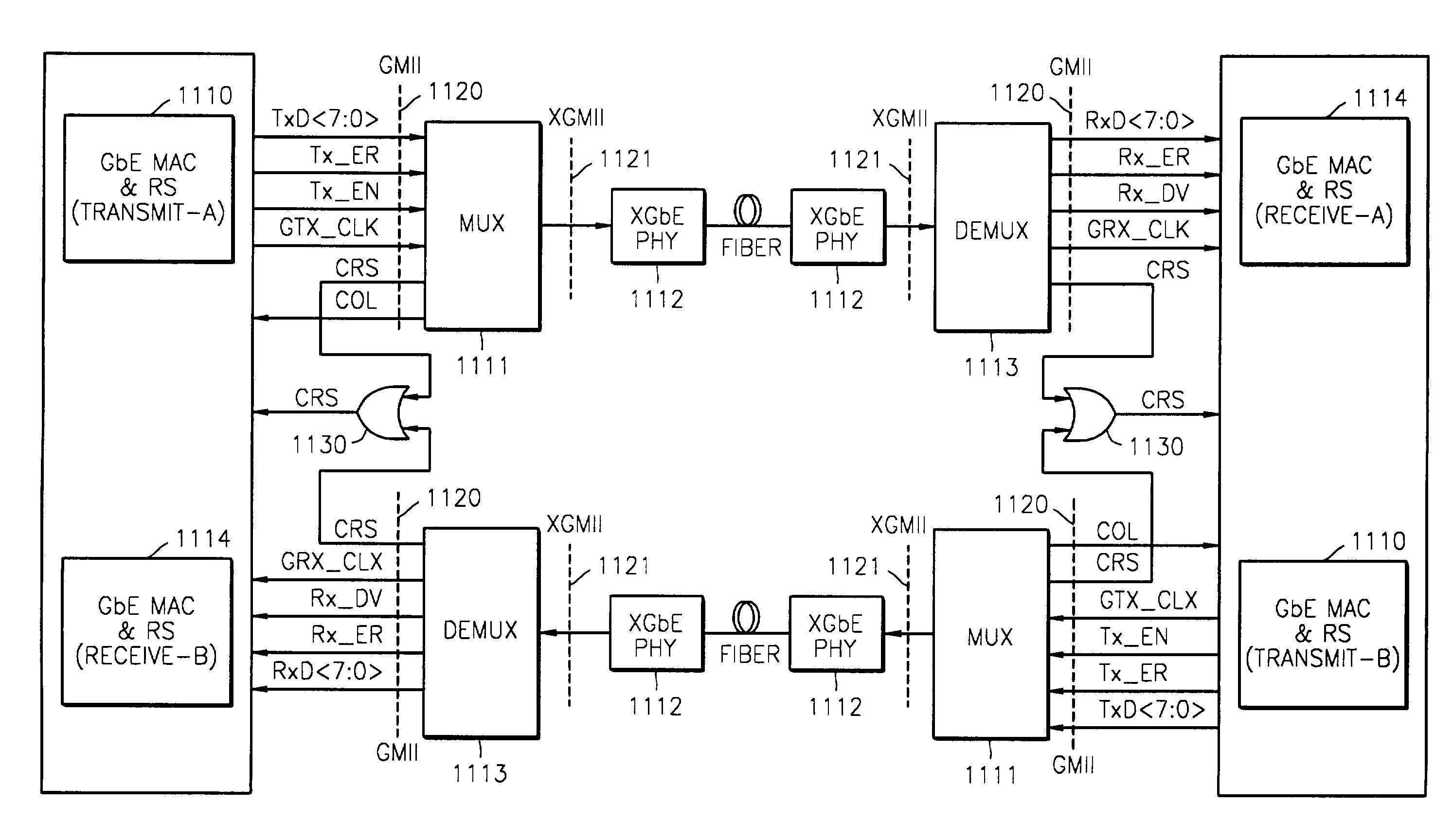

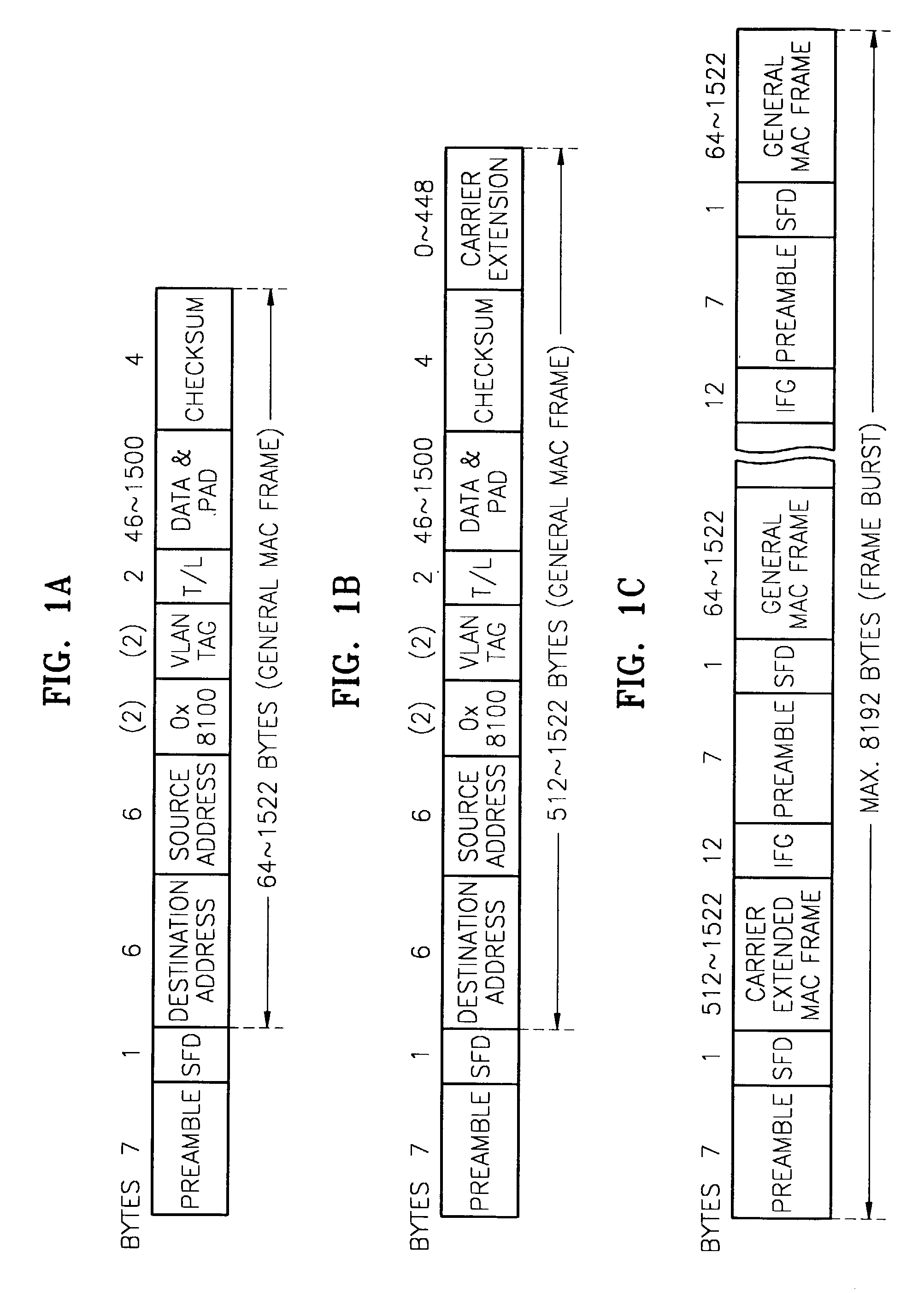

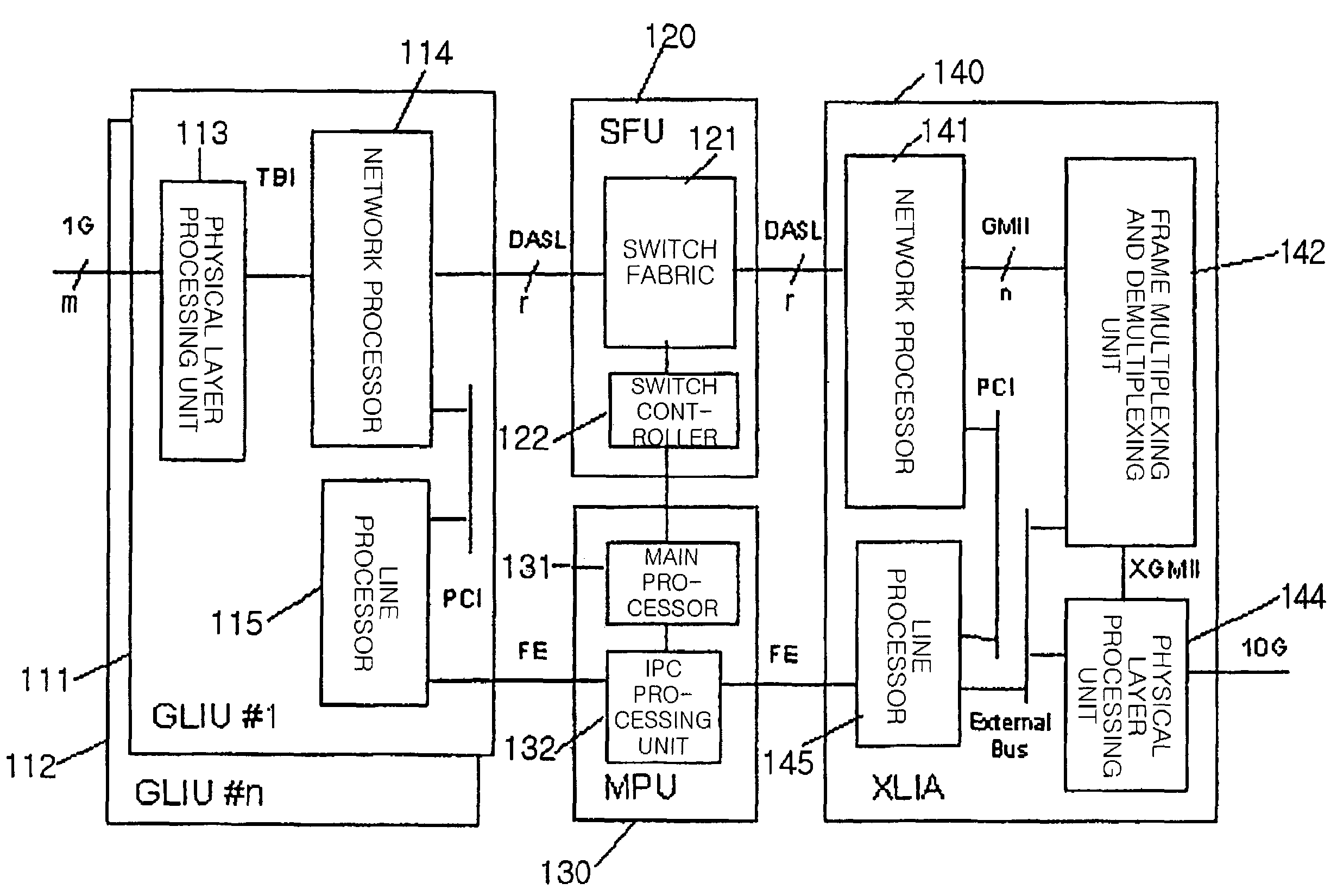

Ethernet switching apparatus and method using frame multiplexing and demultiplexing

InactiveUS7260120B2Increase the scope of applicationMaximize efficiencyError preventionTransmission systemsMultiplexing10 Gigabit Ethernet

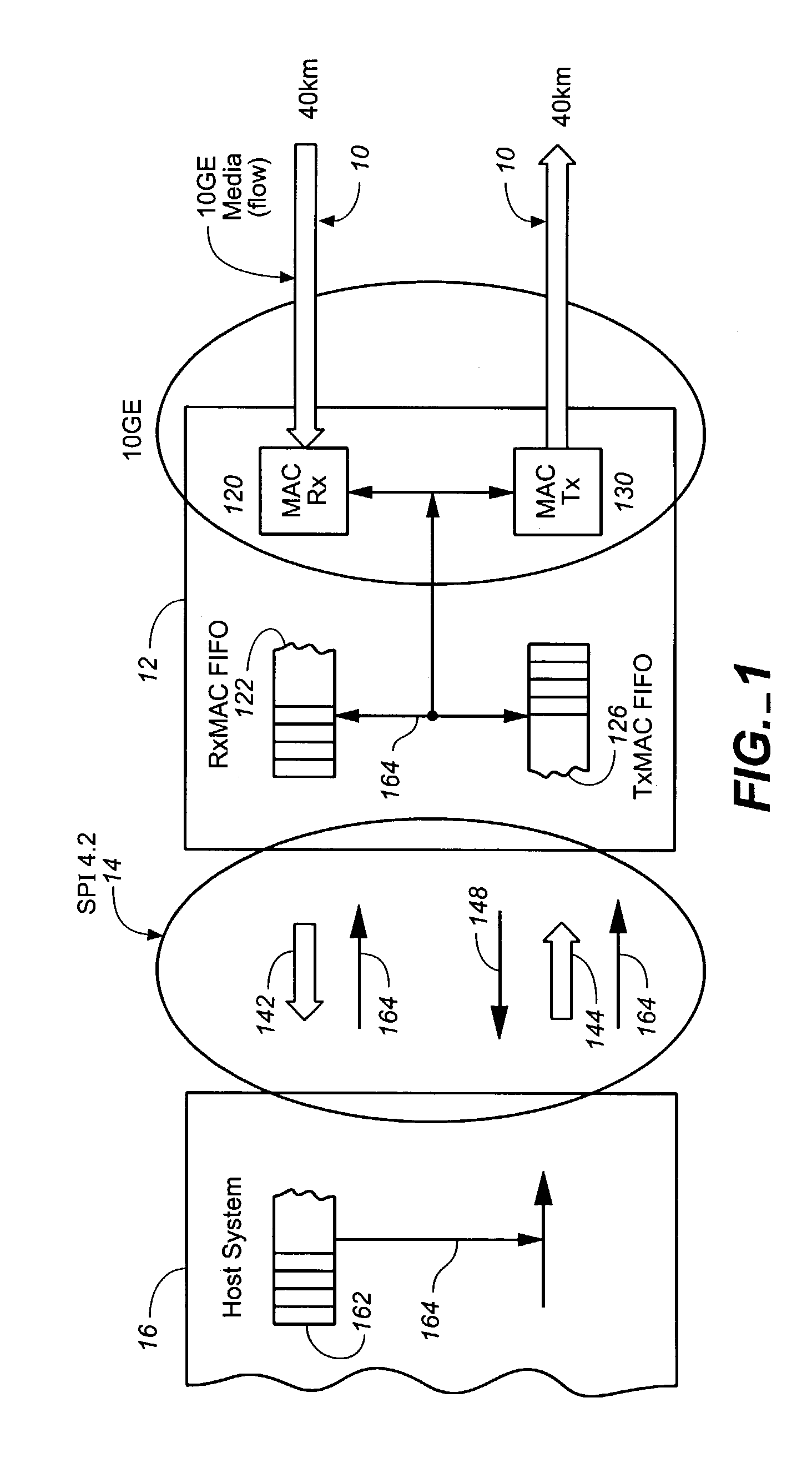

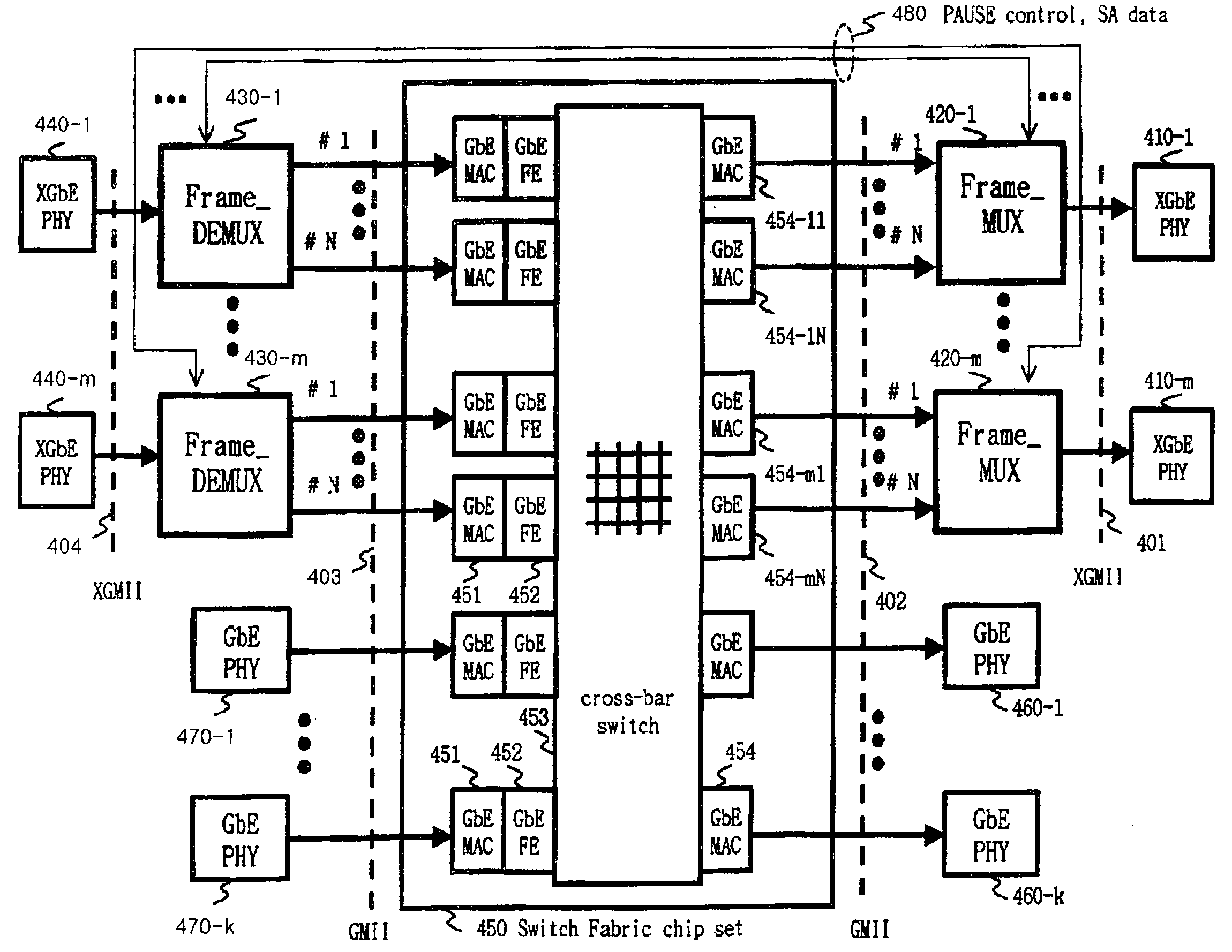

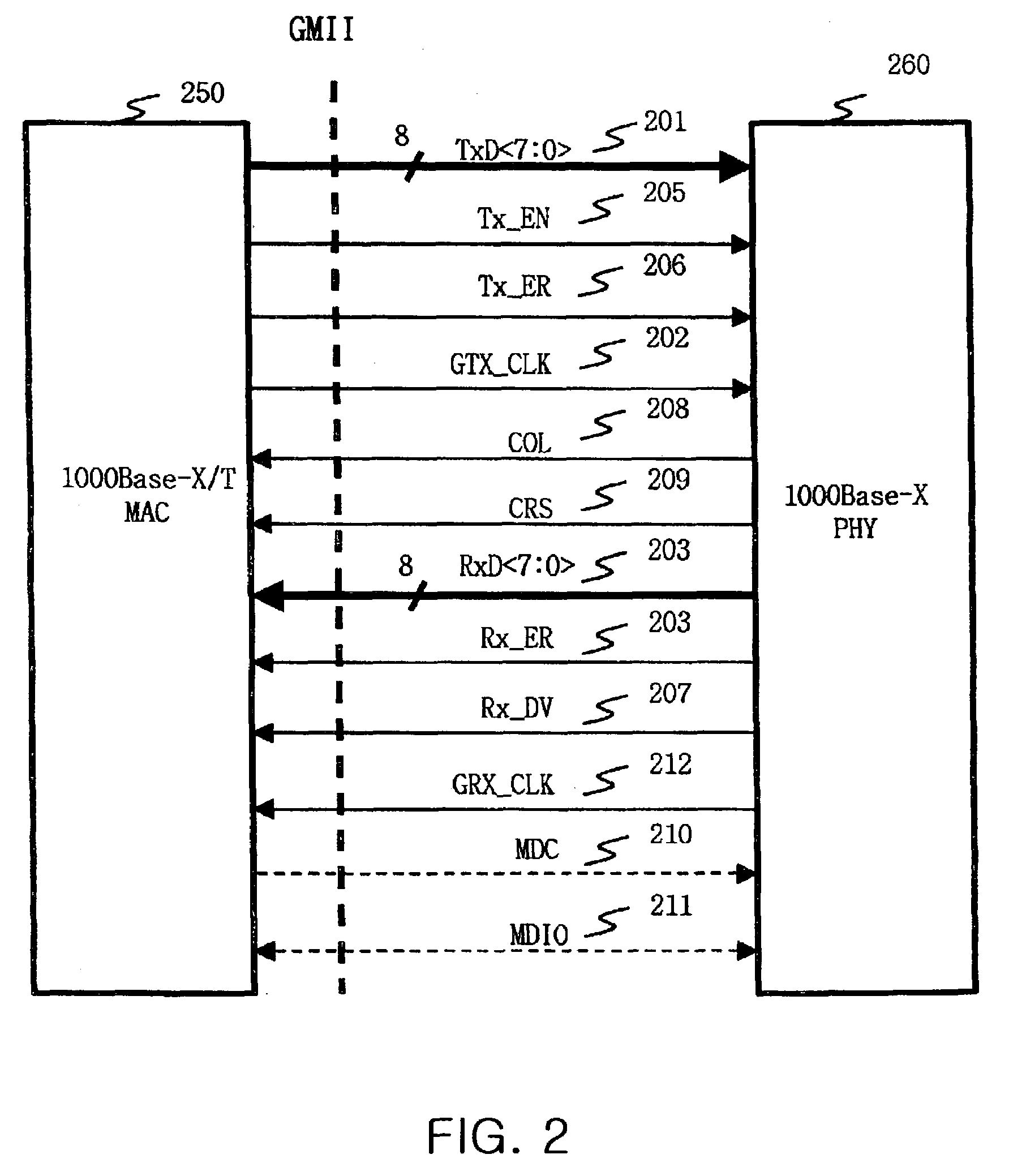

The present invention provides an Ethernet switching apparatus using frame multiplexing and demultiplexing. The Ethernet switching apparatus has a plurality of frame demultiplexers, a plurality of frame multiplexers and a switch fabric chip set. The frame demultiplexers convert at least one 10 gigabits Ethernet frame into a plurality of gigabit Ethernet frames. The frame multiplexers convert a plurality of gigabit Ethernet frames into at least one 10 gigabits Ethernet frame. The switch fabric chip set is provided with input and output interfaces using the GMII, and is connected to the frame demultiplexers and the frame multiplexers in the GMII format. The switch fabric chip set outputs frames through an arbitrary usable one of a plurality of GMII ports connected to a corresponding frame multiplexer if the frames are transmitted to the corresponding frame multiplexer.

Owner:ELECTRONICS & TELECOMM RES INST

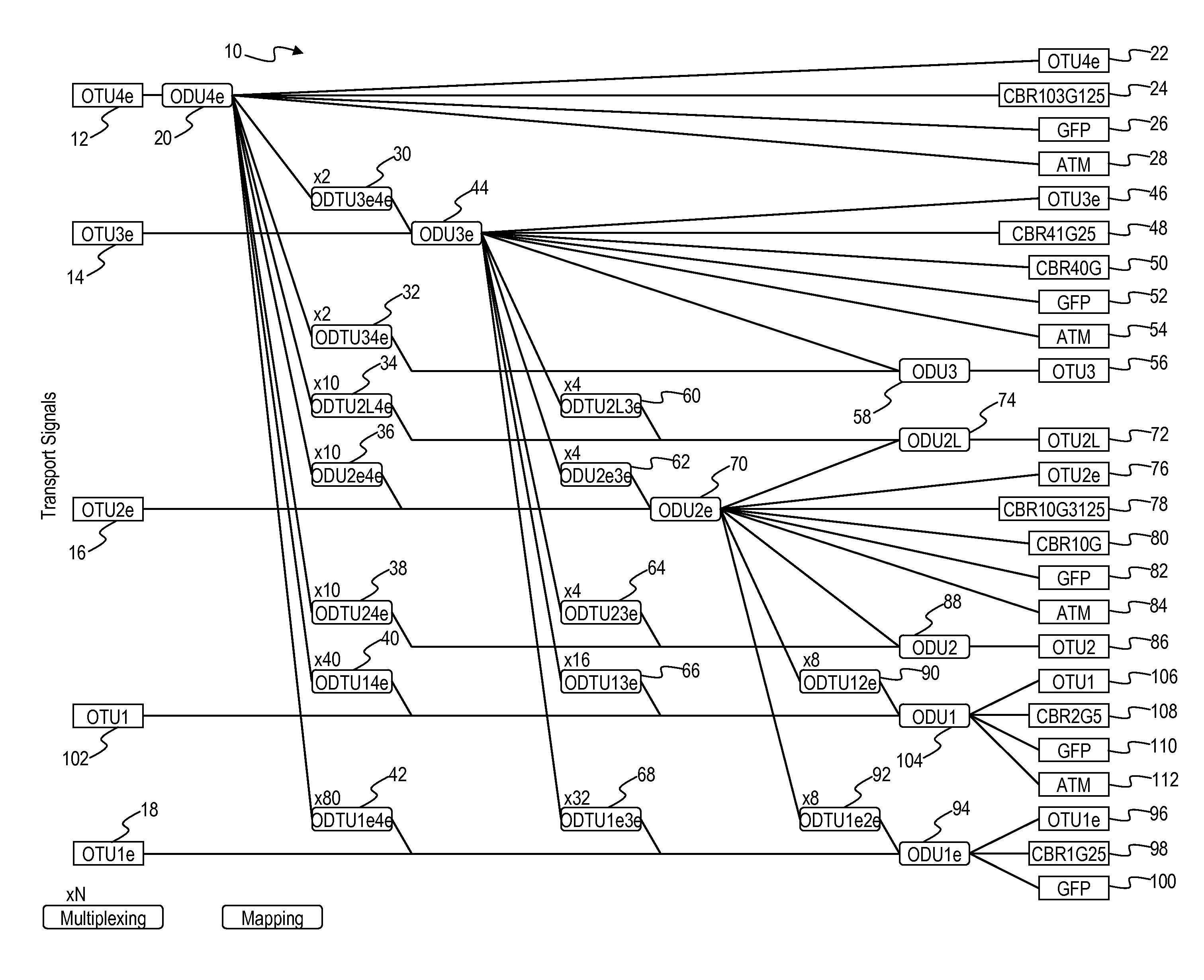

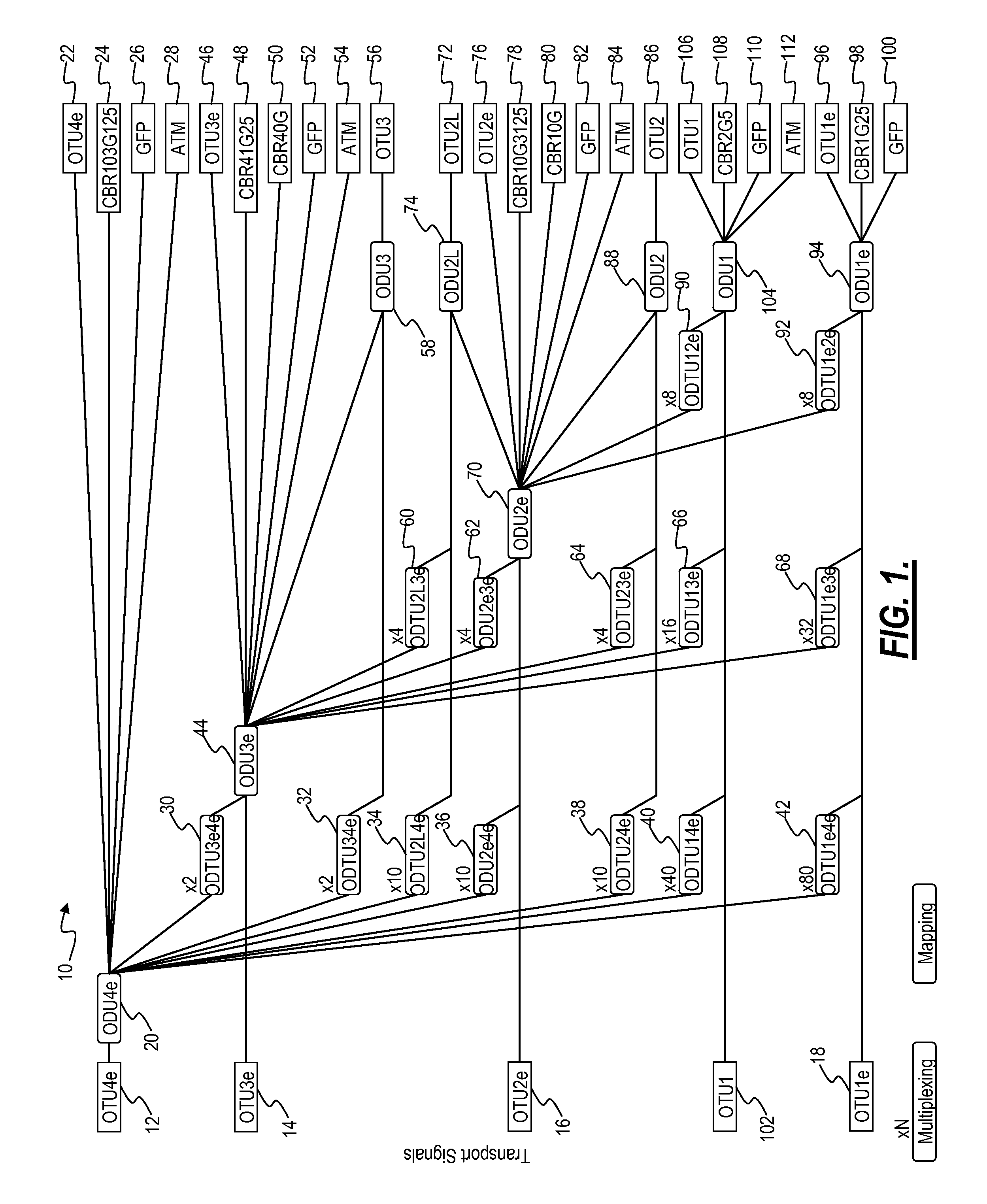

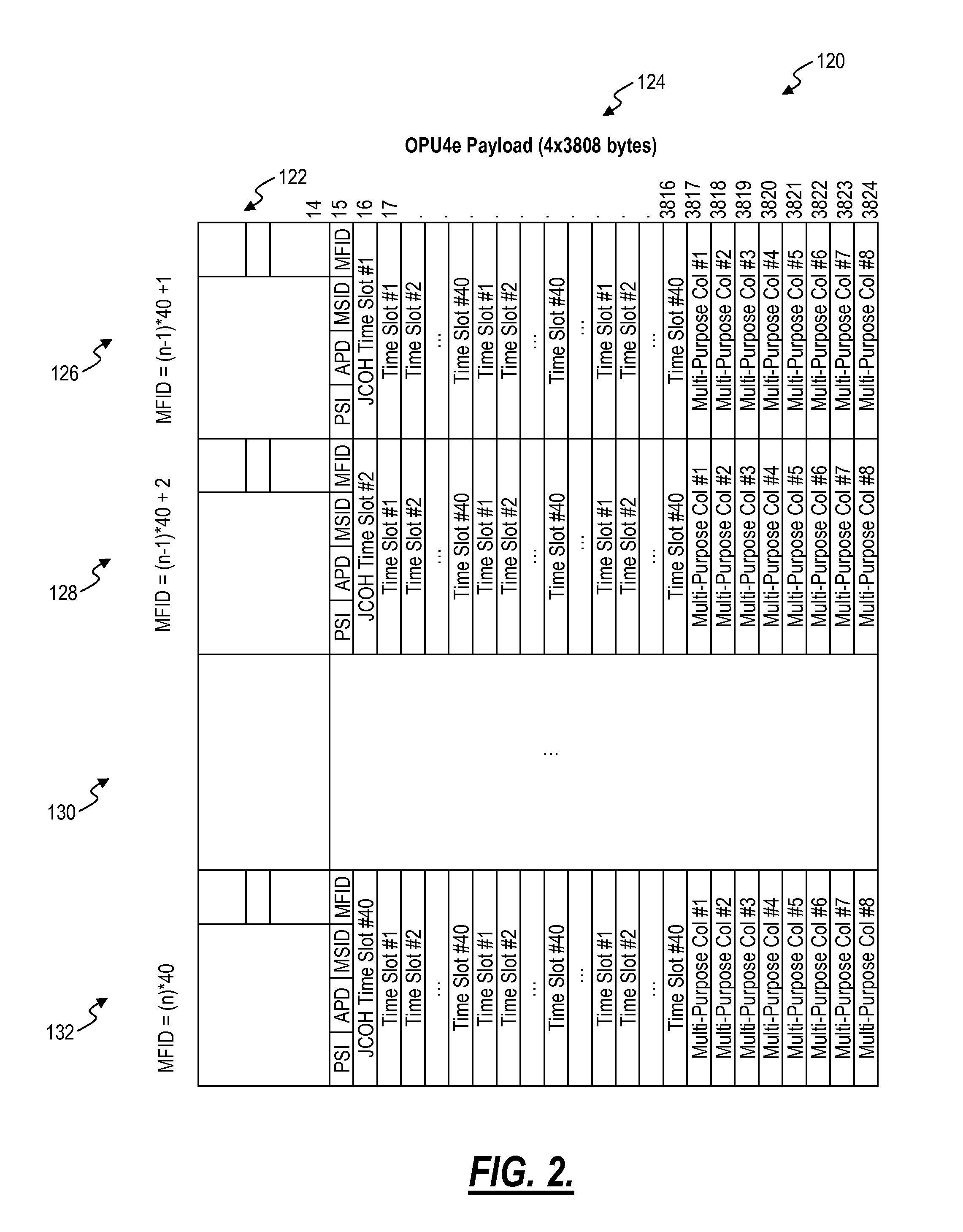

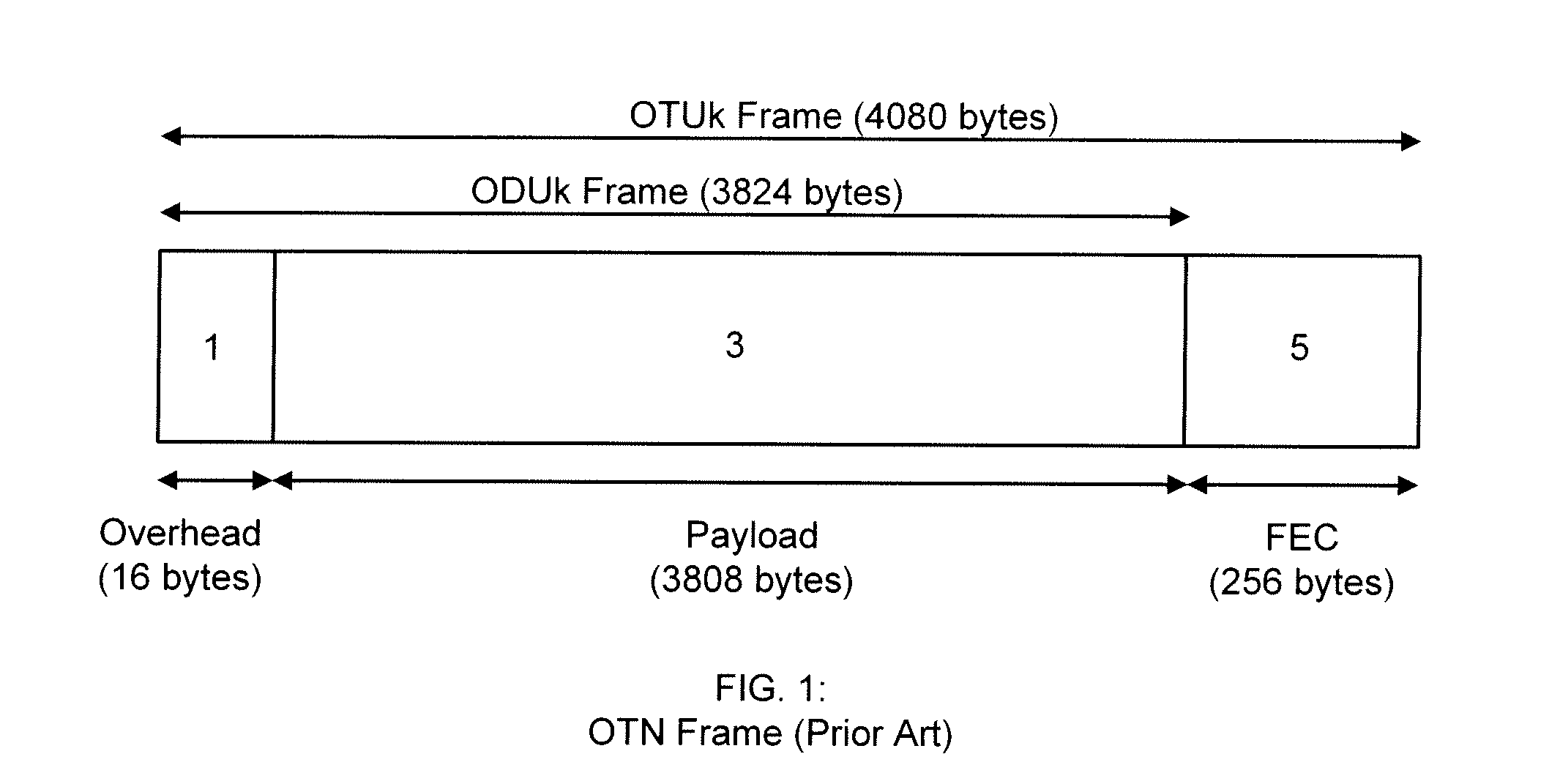

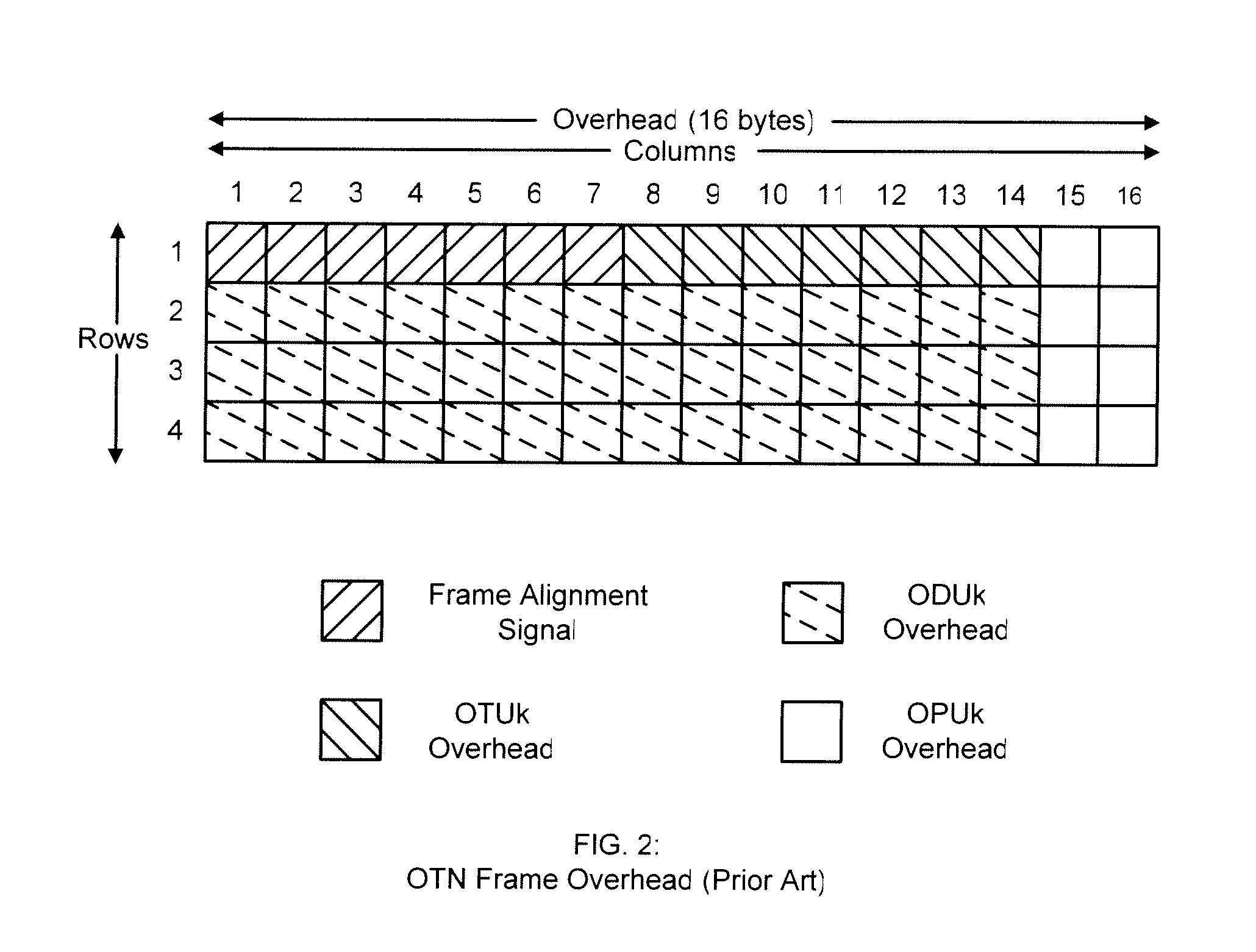

Optical transport network hierarchy for full transparent transport of datacom and telecom signals

ActiveUS20080279553A1Increase ratingsIncreased payload capacityTime-division multiplexOptical multiplexMultiplexingHigh rate

The present invention provides an Optical Transport Network (OTN) hierarchy that supports full transparency for both Ethernet and Telecom signals. The present invention defines new rates and mapping / multiplexing methods to adapt transparent 10 Gigabit Ethernet (10 GBE) (255 / 238 and 255 / 237) and 10 Gigabit Fibre Chanel (10 GFC) (255 / 237) to Optical Channel Transport Unit-3 (OTU3) at a higher rate. Additionally, the present invention defines new rates and mapping / multiplexing methods to adapt future transparent 100 GBE into an Optical Channel Transport Unit-4-extended (OTU4e) which is an OTU4 at a higher rate to support full transparency.

Owner:CIENA

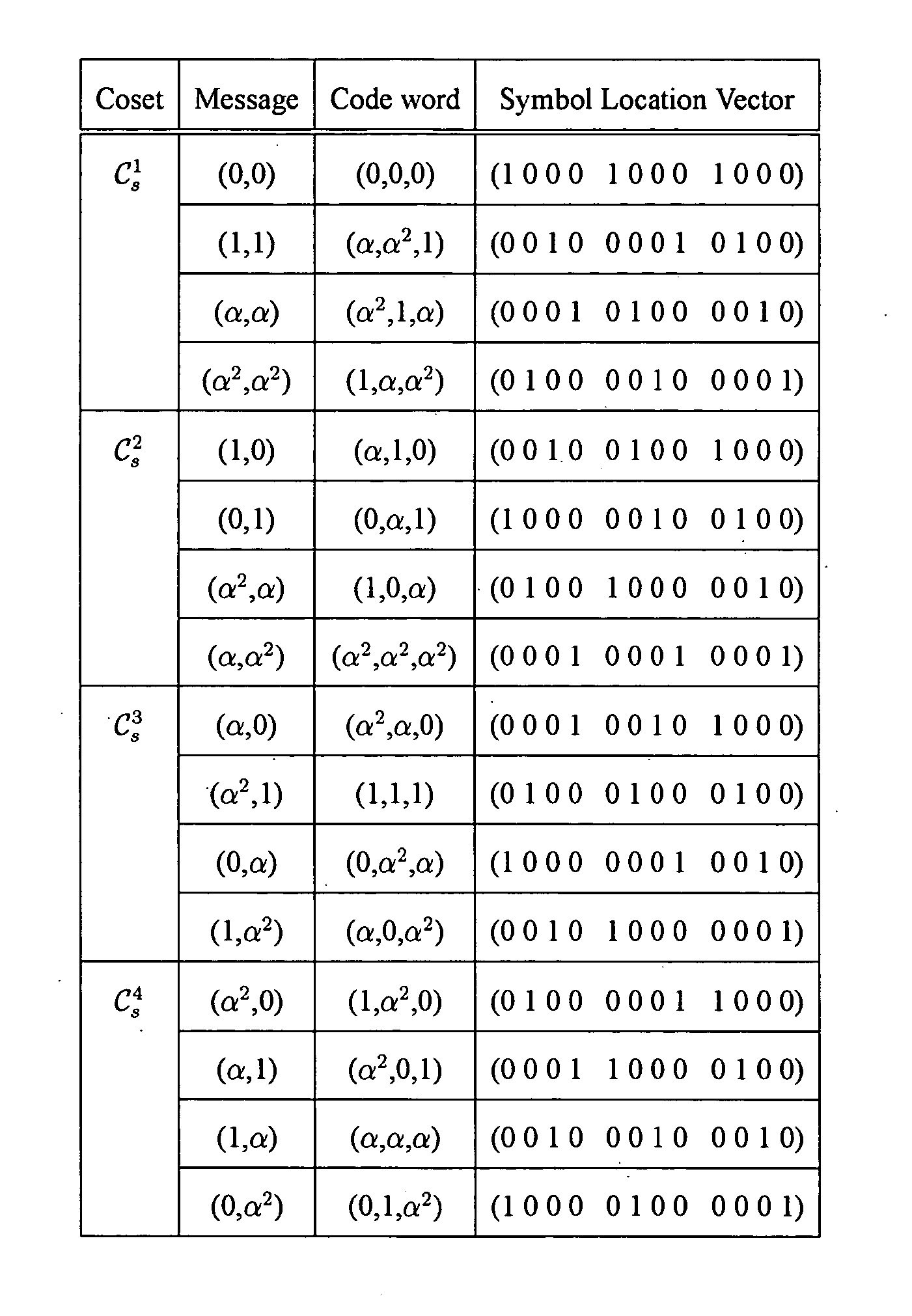

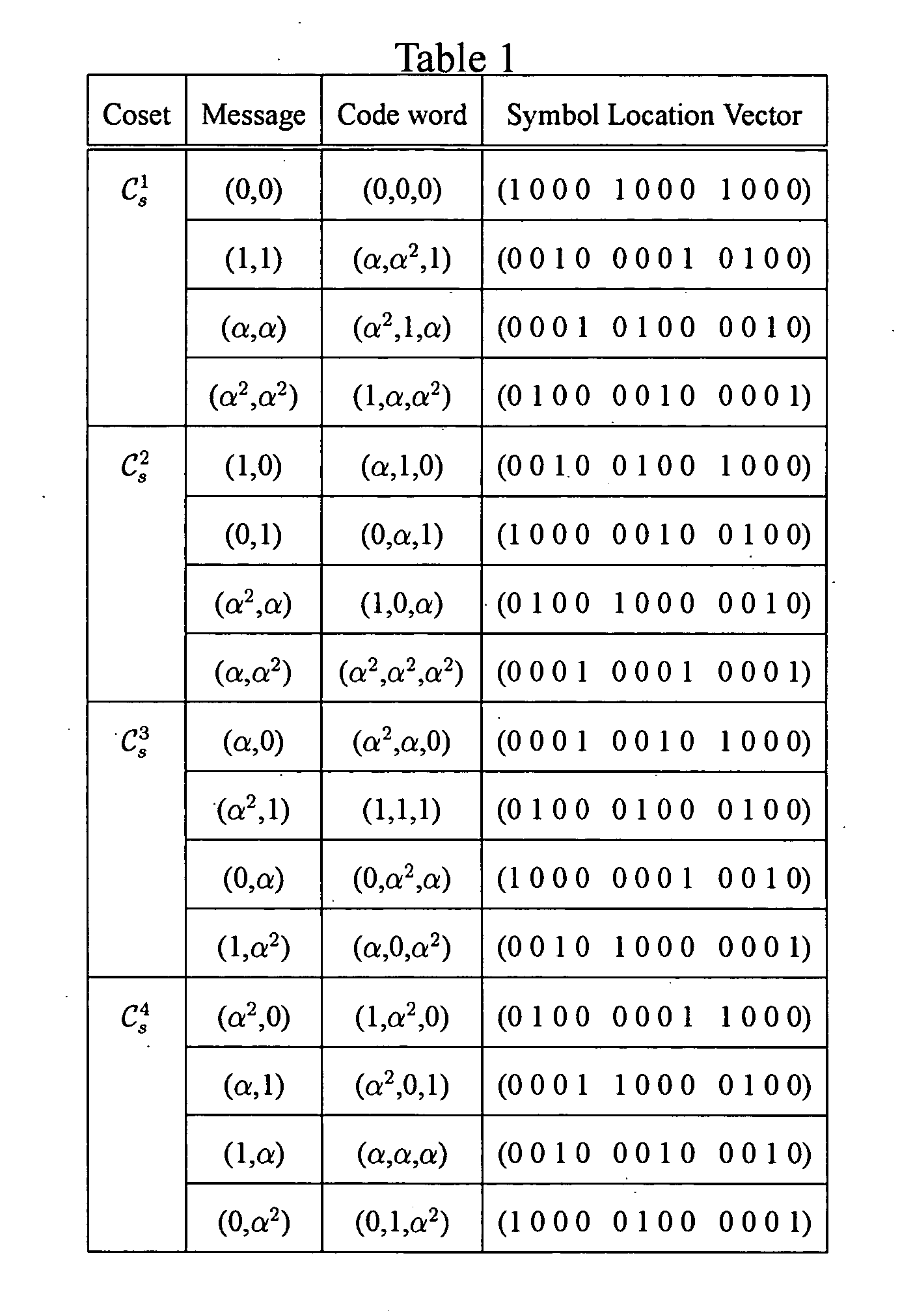

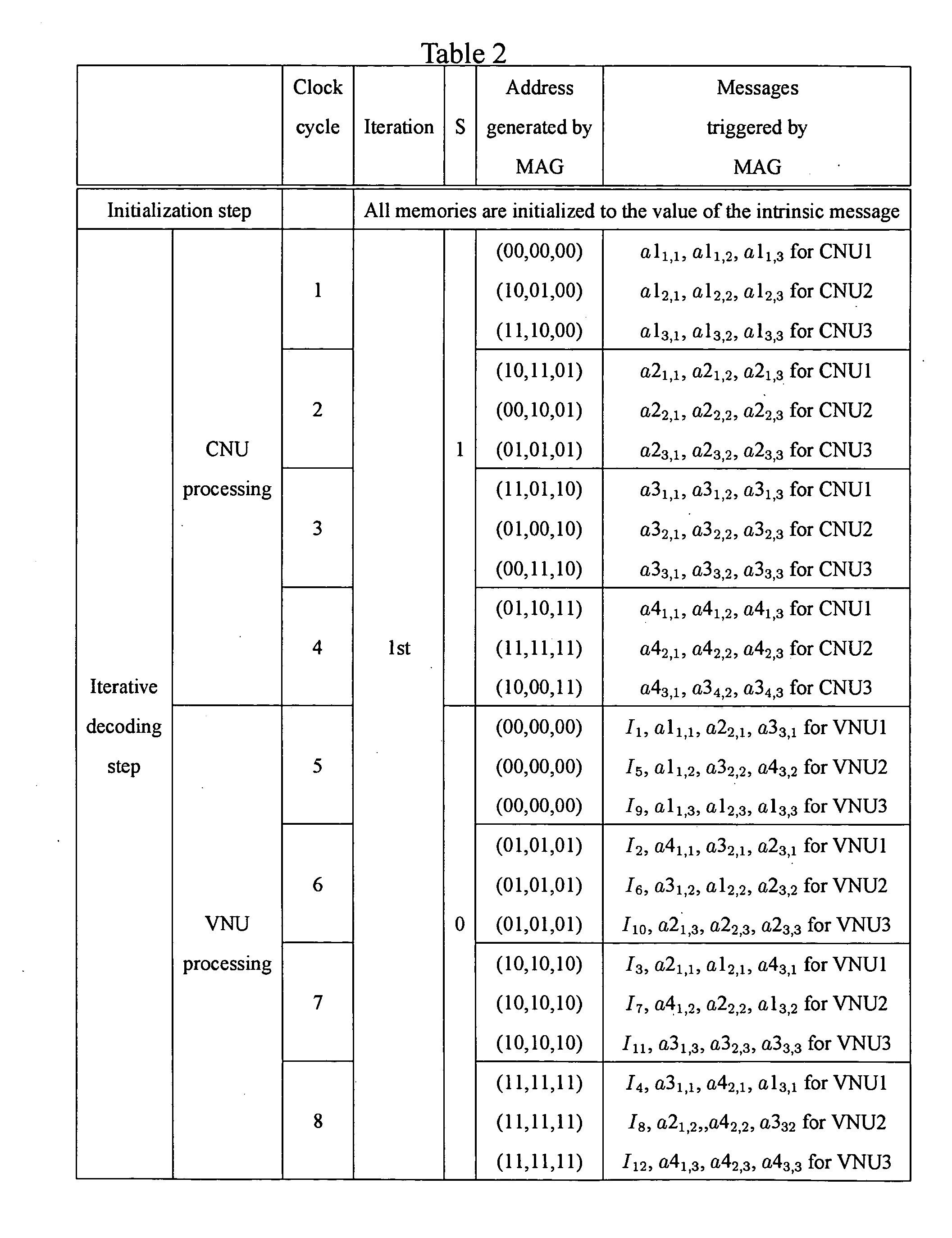

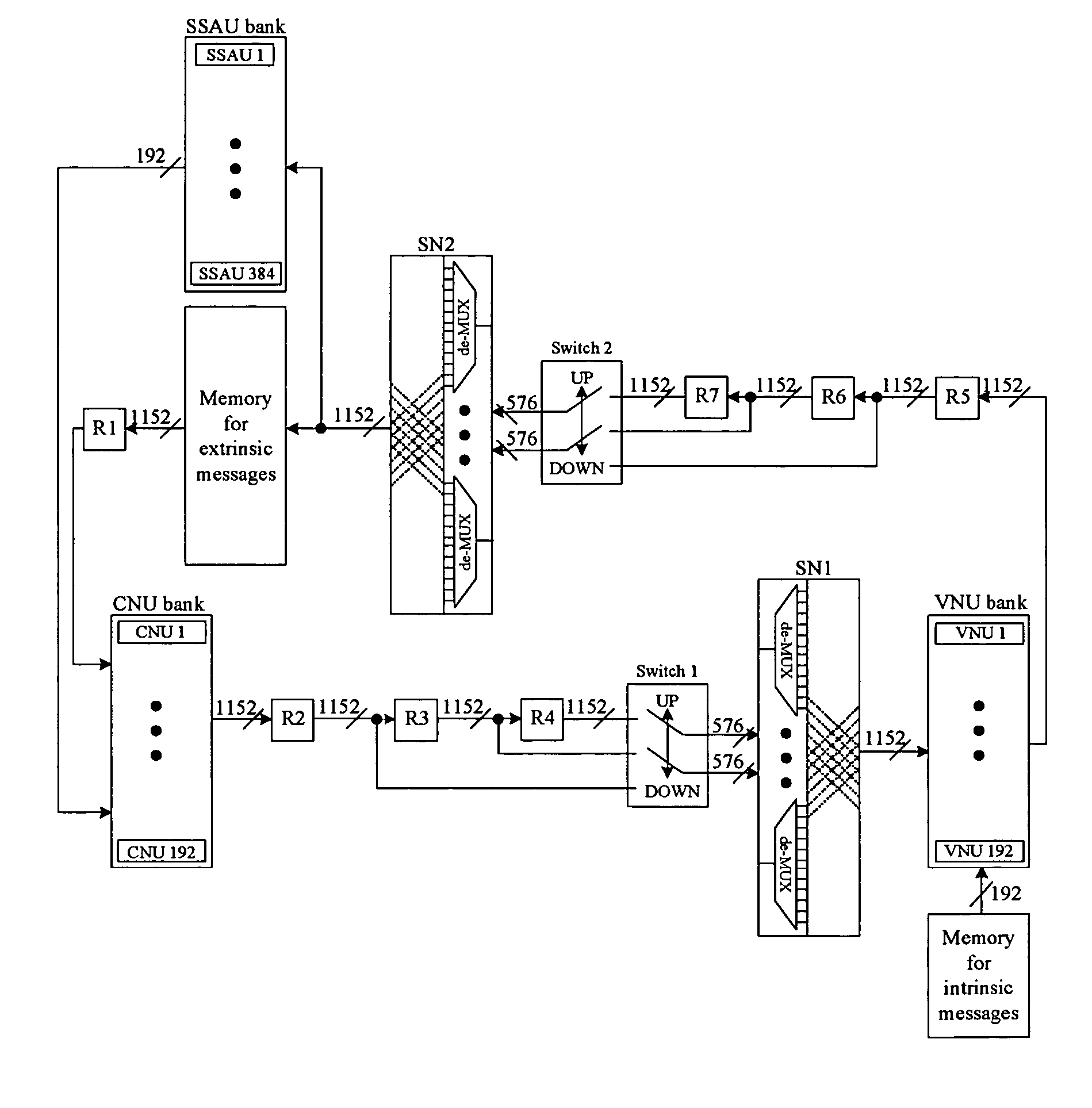

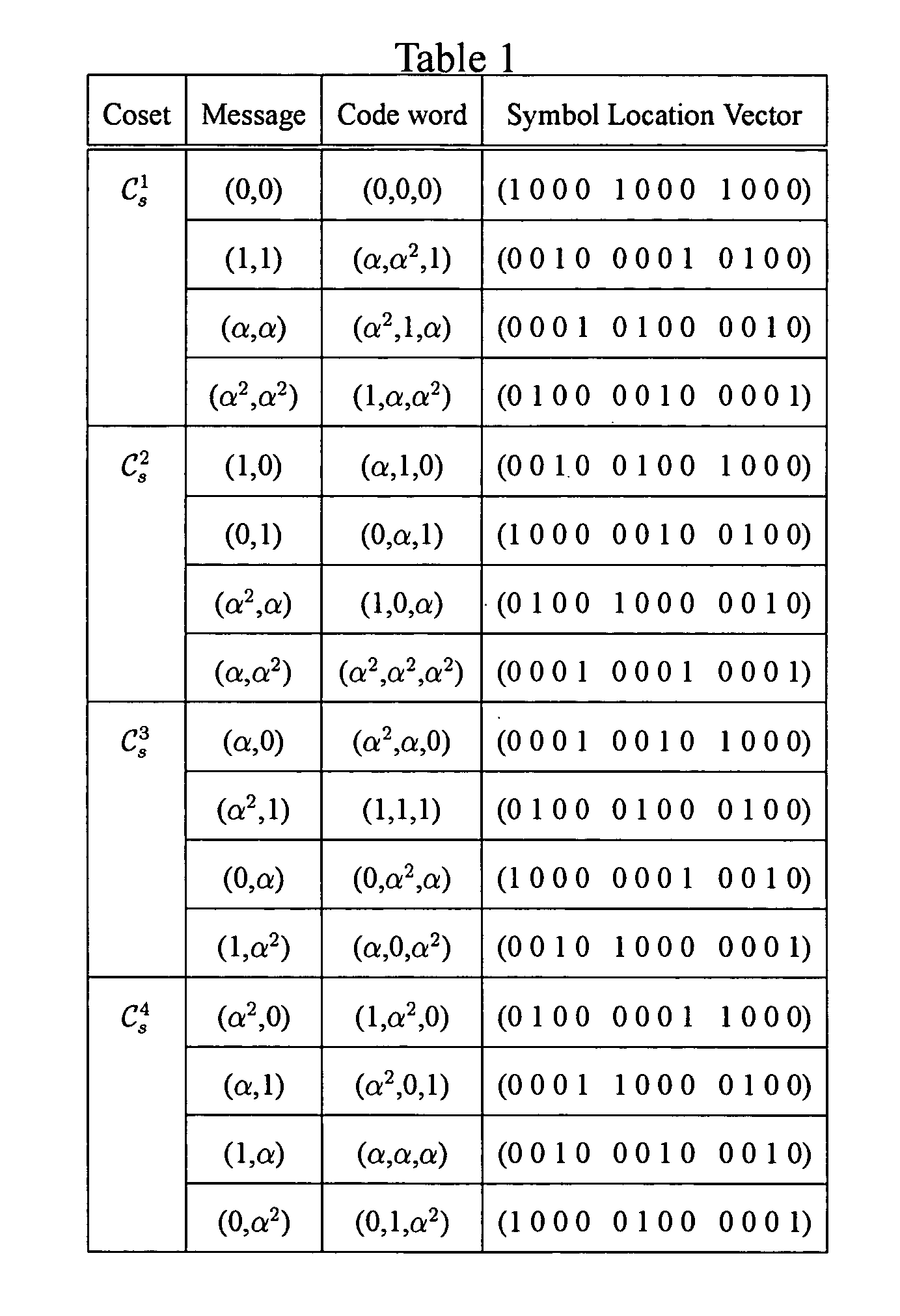

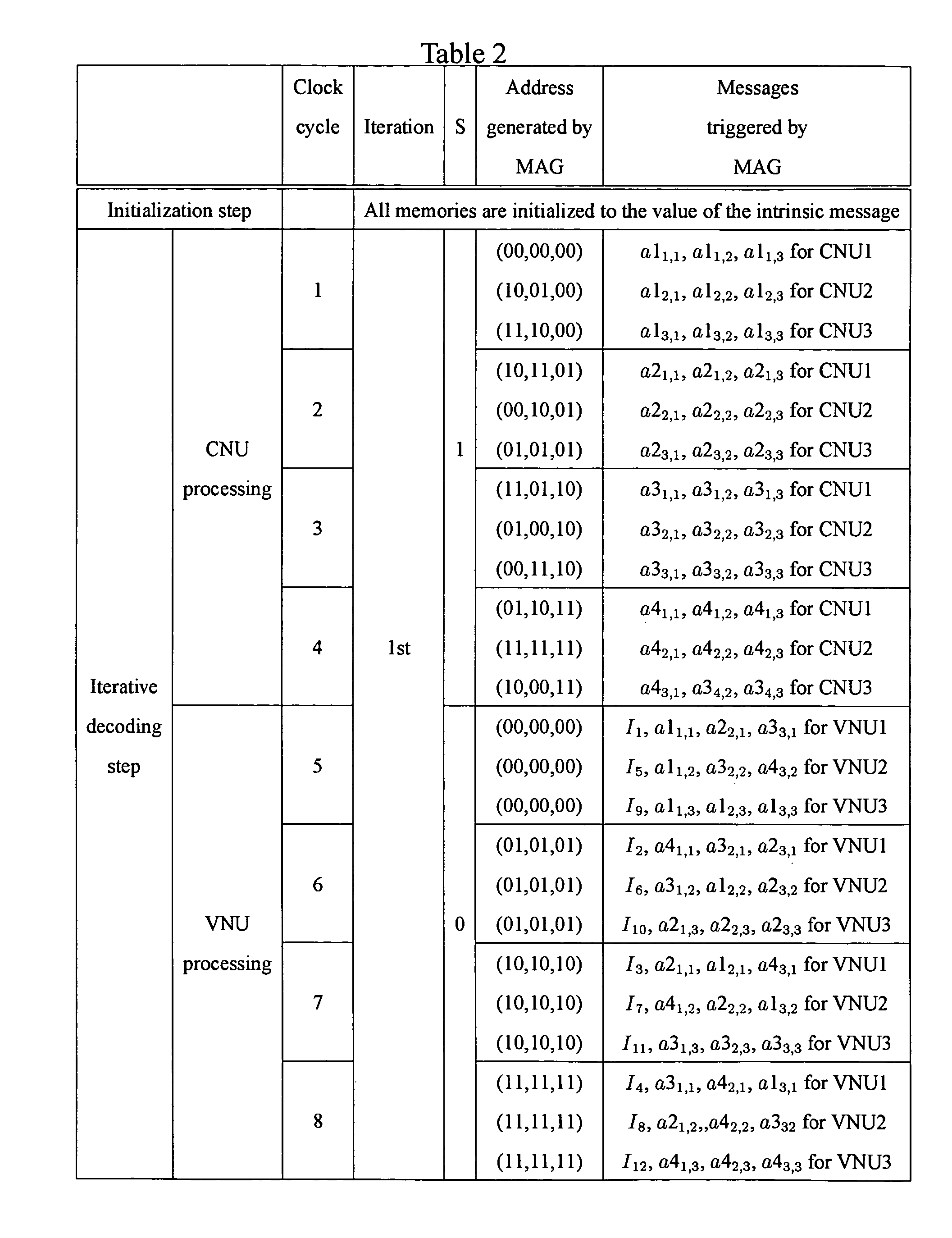

System and method for designing RS-based LDPC code decoder

InactiveUS20070033484A1Low costImprove decoding throughputData representation error detection/correctionCode conversionMemory addressComputer architecture

A memory address generation method and circuit architecture for time-multiplexed RS-based LDPC code decoder is presented. The method is developed for non quasi-cyclic RS-based LDPC code decoder implementation. A circuit for the memory address generation method achieves low area. High throughput time-multiplexed RS-based LDPC code decoder design models and circuit architectures are presented. The decoder models are specifically developed for 10BASE-T (10-Gigabit Ethernet Transceiver Over Copper) system. These time-multiplexed architectures enable higher throughput with lower area.

Owner:PARHI KESHAB K

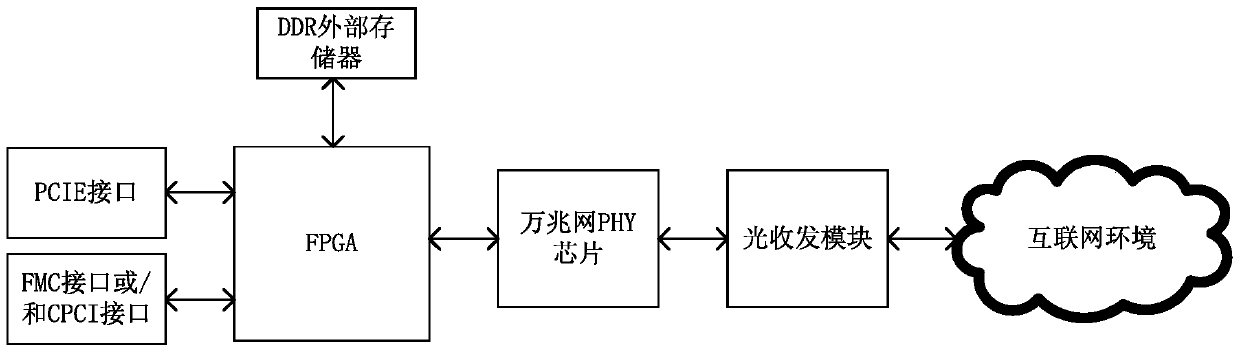

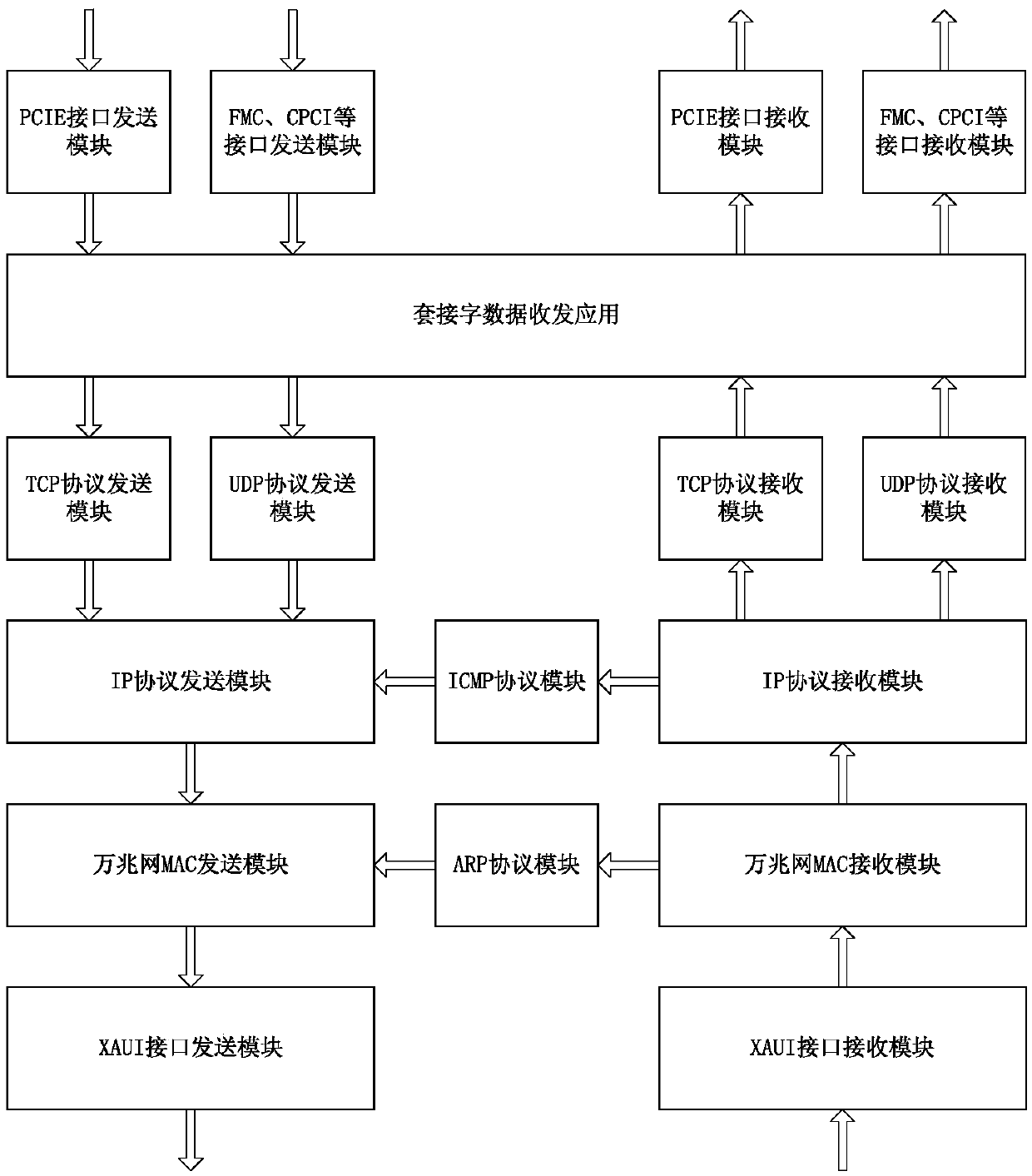

10-gigabit Ethernet TCP offload engine (TOE) system realized based on FPGA

ActiveCN105516191AAvoid homeostasisImprove the status quo of high loadTransmissionTransceiverNetworked Transport of RTCM via Internet Protocol

The invention discloses a 10-gigabit Ethernet TCP offload engine (TOE) system realized based on an FPGA, comprising the FPGA for realizing a TCP / IP protocol stack and a 10-gigabit Ethernet MAC layer, a 10-gigabit Ethernet PHY chip connected with the FPGA, a 10G optical transceiver module connected with the FPGA and used for serving as a 10-gigabit Ethernet transmission medium, and a DDR external memory connected with the FPGA and used for data caching. The FPGA is creatively adopted to realize the TCP / IP protocol stack, replacing a soft TCP / IP protocol stack realized by a conventional way of using a processor and an operation system with a hardware manner. According to the system, the processing speed of the TCP / IP protocol stack is effectively increased, the smoothness and balance of 10-gigabit Ethernet transmission are realized, and most importantly, computer application and network protocol separation is realized.

Owner:CHENGDU ZHIXUN LIANCHUANG TECH

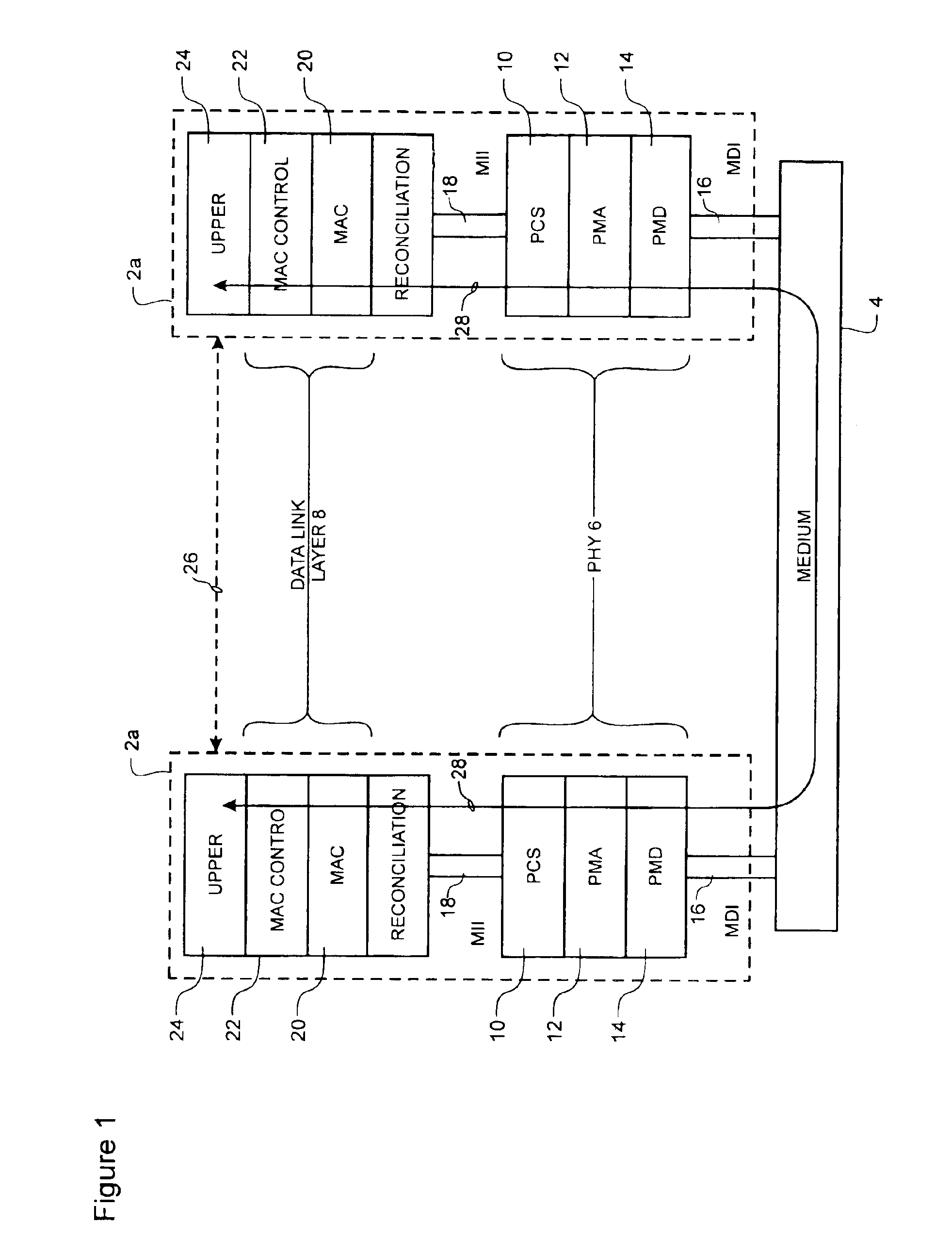

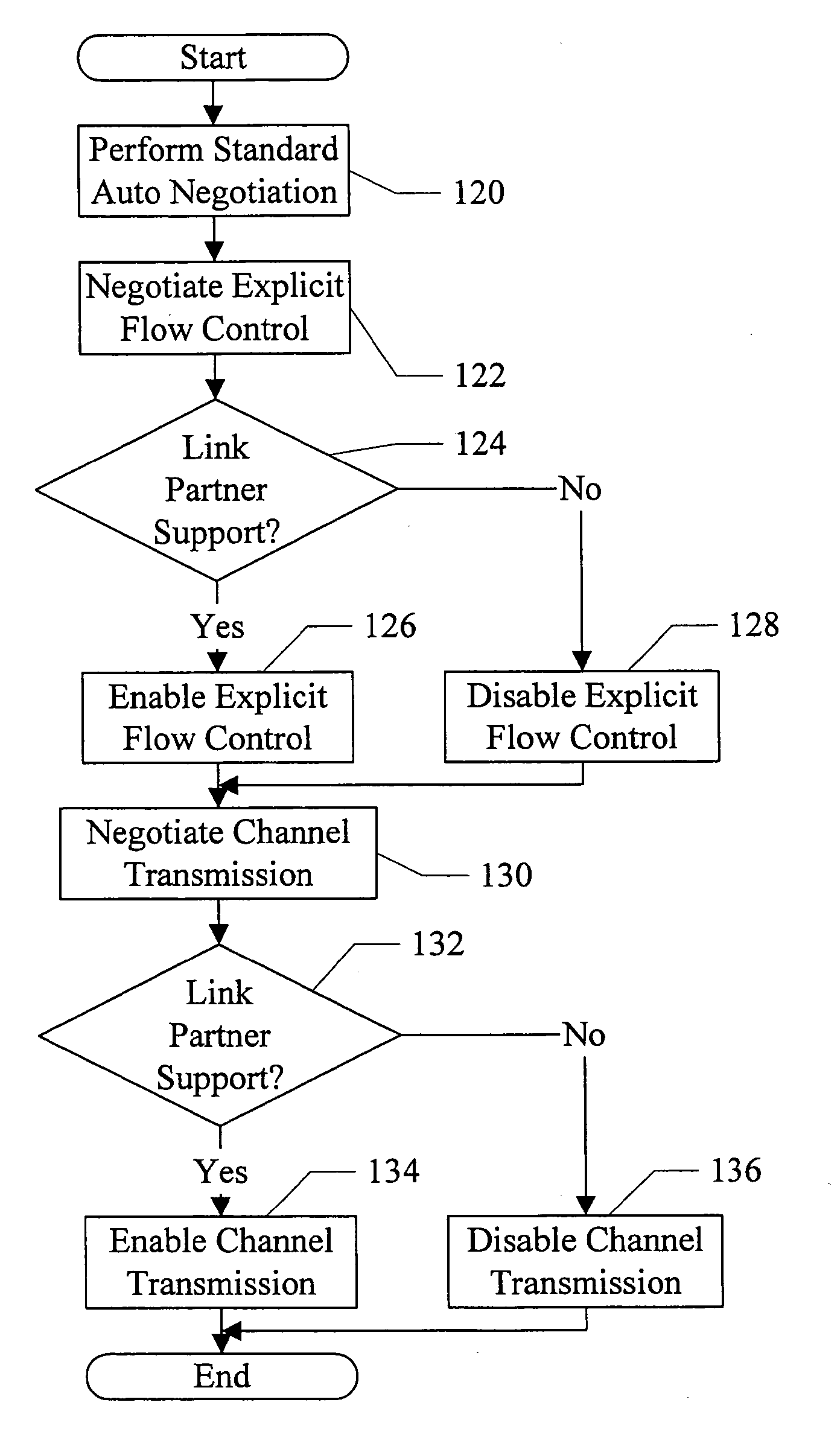

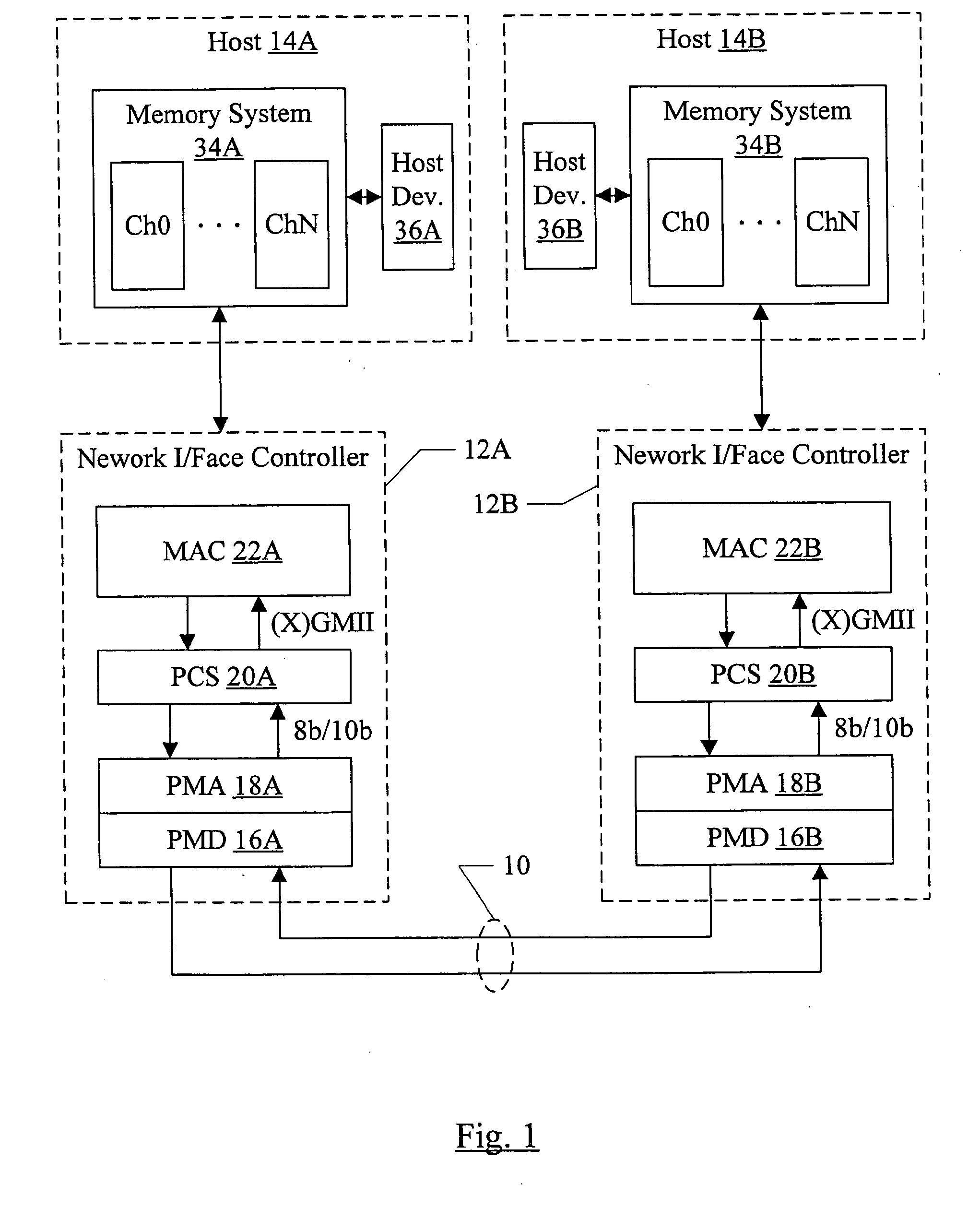

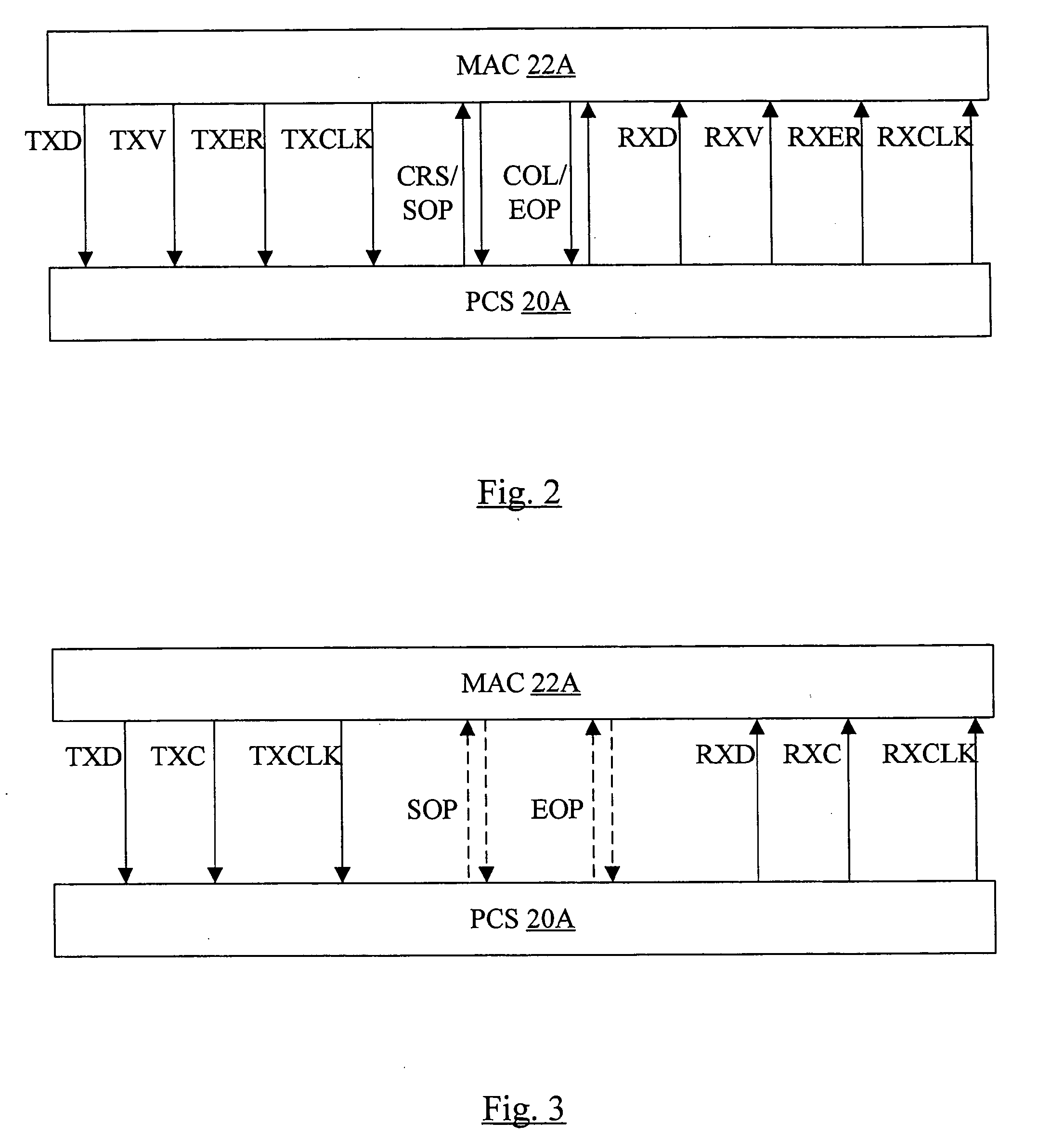

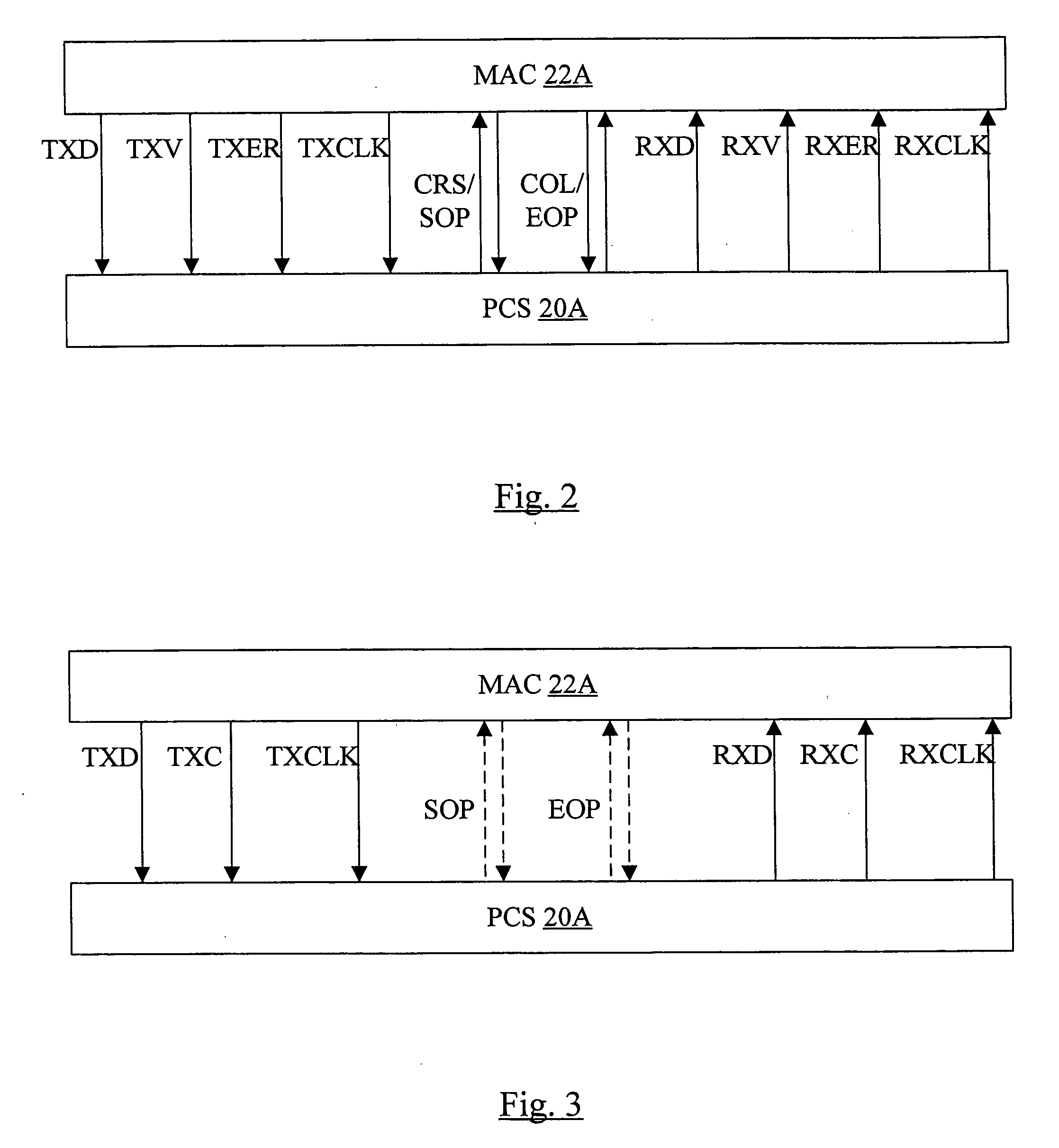

Explicit Flow Control in a Gigabit/10 Gigabit Ethernet System

InactiveUS20100188980A1Error preventionFrequency-division multiplex detailsTraffic capacity10 Gigabit Ethernet

In one embodiment, a system comprises a communication medium; a first controller coupled to the communication medium; and a second controller coupled to the communication medium. The first controller is configured to interrupt transmission of a packet on the communication medium to the second controller subsequent to transmission of a first portion of the packet. The first controller is configured to transmit at least one control symbol on the communication medium in response to interrupting transmission of the packet, and wherein the first controller is configured to continue transmission of the packet with a second portion of the packet. The controller(s) may include, in some embodiments, a media access controller and a physical coding sublayer.

Owner:DESAI SHAILENDRA S +1

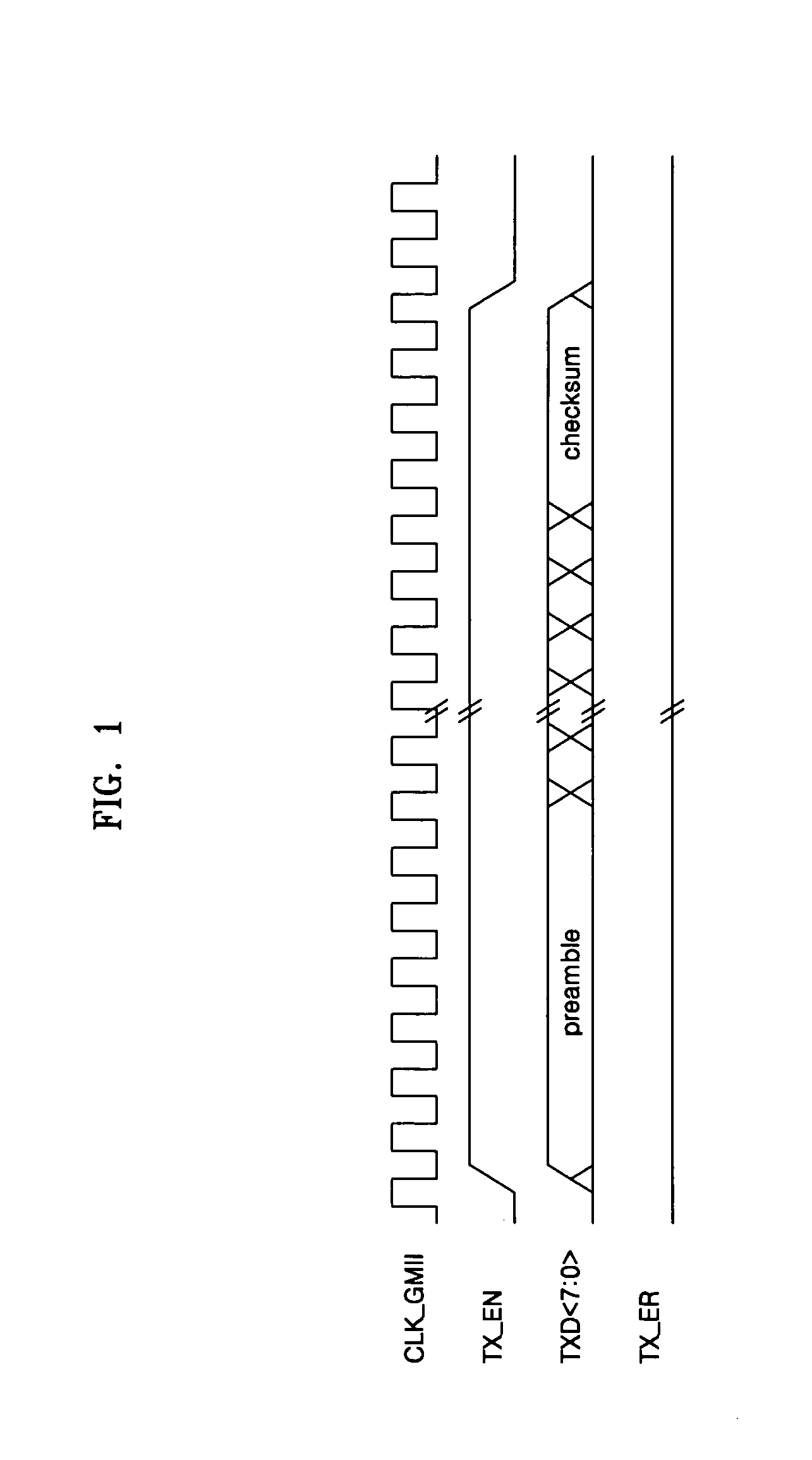

Method and apparatus for multiplexing and demultiplexing variable-length packets

InactiveUS7230957B2Low costMaximize efficiencyEnergy efficient ICTTime-division multiplexComputer hardwareMultiplexing

Provided are a method and apparatus for multiplexing and demultiplexing variable-length high-speed packets. According to the method and apparatus, a plurality of one-gigabit Ethernet frames are multiplexed into a single 10-gigabit Ethernet frame and the single 10-gigabit Ethernet frame is demultiplexed into the plurality of one-gigabit Ethernet frames. In order to process variable-length high-speed packets, packet multiplexing instead of simple TDM is used and a larger input bandwidth than an output bandwidth is used, so that a statistical multiplex effect is accomplished. In addition, standard interface is used for input and output interface, so existing universal chips can be used.

Owner:ELECTRONICS & TELECOMM RES INST

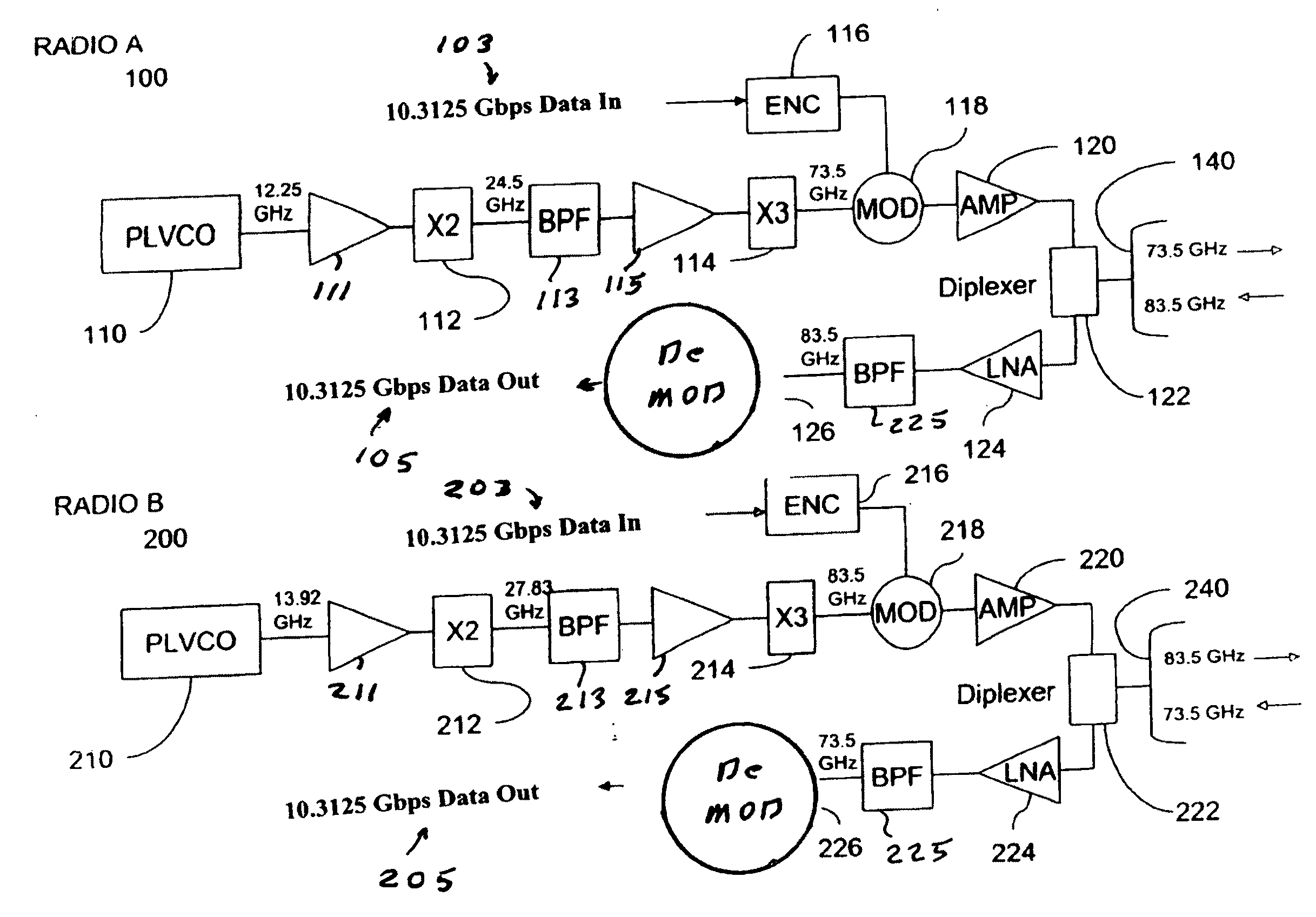

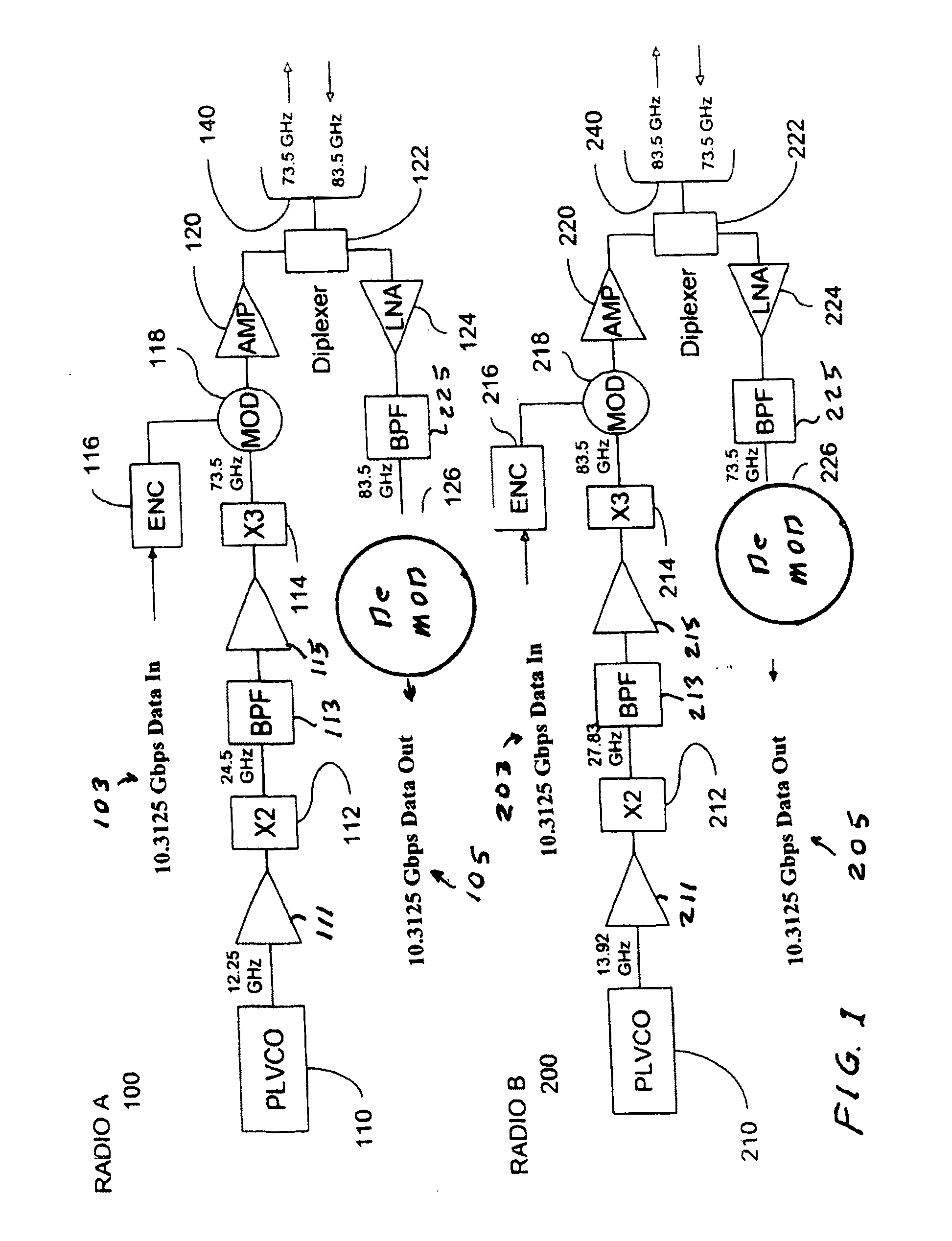

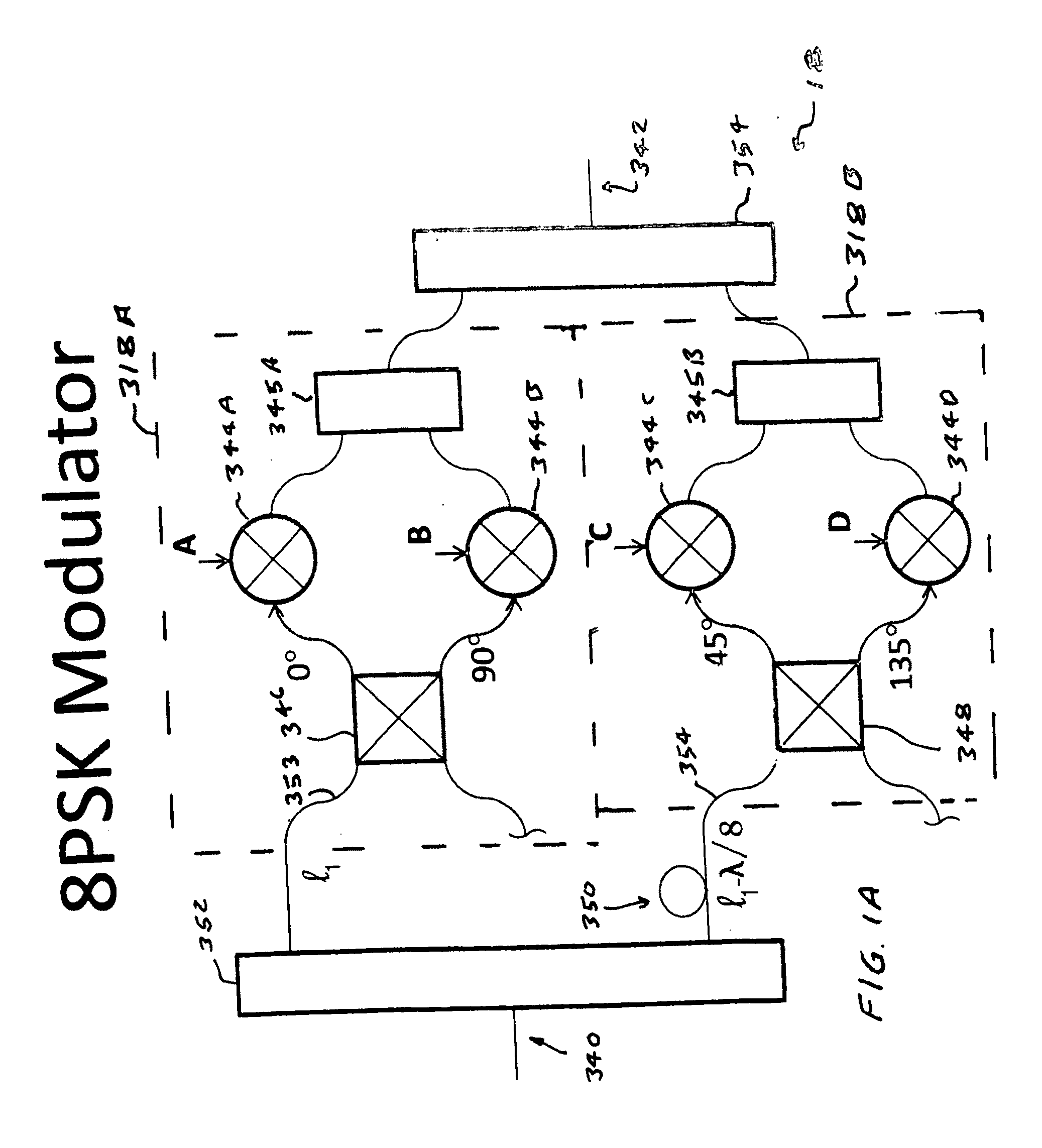

High data rate milllimeter wave radio

InactiveUS20110075713A1Phase-modulated carrier systemsDuplex signal operationPhase shifted10 Gigabit Ethernet

A high data rate millimeter wave radio adapted to receive an binary input data at an input data rate in excess of 3.5 Gbps and to transmit at a transmit data rate in excess of 3.5 Gbps utilizing encoded three-bit data symbols on a millimeter carrier wave at a millimeter wave nominal carrier frequency, defining a carrier wavelength and period, in excess of 70 GHz with differential phase-shift keying utilizing eight separate phase shifts. Preferred embodiments of the invention can support many of the high data rate standards including the following group of protocols or standards: SONET OC-96 (4.976 Gbps); 4xGig-E (5.00 Gbps); 5xGig-E (6.25 Gbps); OBSAI RP3-01 (6.144 Gbps); 6xGig-E (7.50 Gbps); Fibre Channel 8GFC (8.5 Gbps); SONET OC-192 (9.952 Gbps); Fibre Channel 10GFC Serial (10.52 Gbps) and 10 GigaBit Ethernet.

Owner:TREX ENTERPRISES CORP

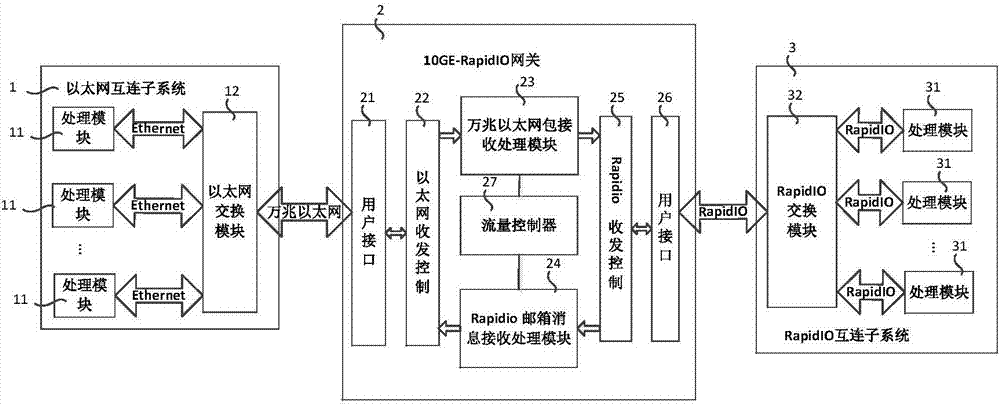

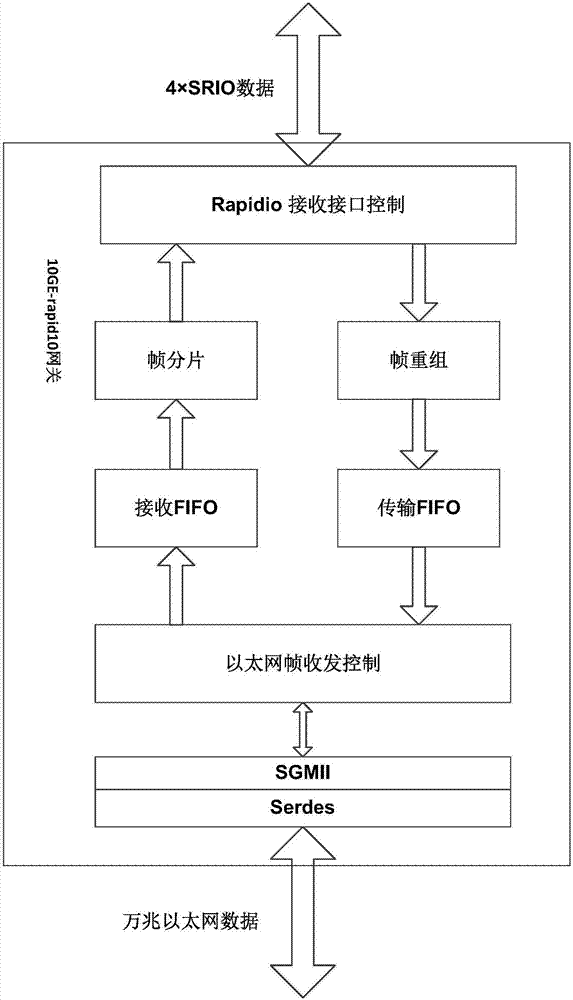

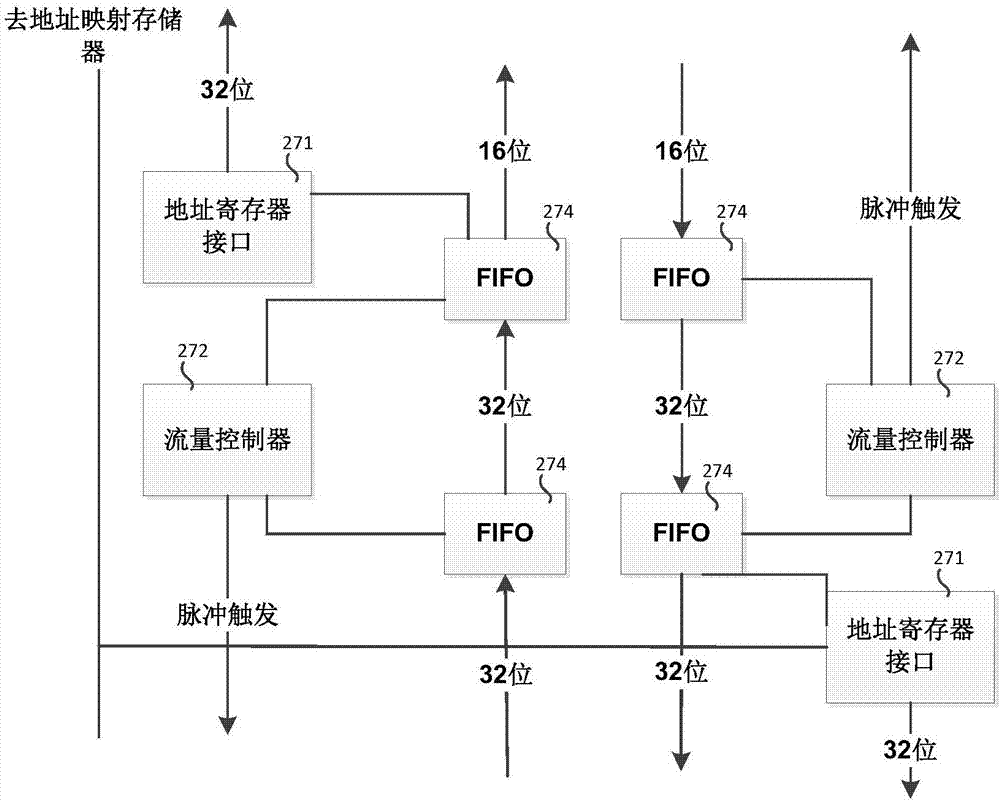

High-speed data exchange system between 10-gigabit Ethernet and RapidIO protocol based on FPGA

The invention discloses a high-speed data exchange system between a 10-gigabit Ethernet and a RapidIO protocol based on an FPGA. A RapidIO gateway splits an Ethernet packet into RapidIO bus mailbox messages. Processing modules in an Ethernet interconnection sub-system are connected through an Ethernet exchange module. The Ethernet interconnection sub-system is externally connected with a RapidIO exchange module through the RapidIO gateway and then carries out data interaction with the processing modules in a RapidIO interconnection sub-system through the RapidIO exchange module. An IP network data packet and a RapidIO protocol data packet are mutually converted in the RapidIO gateway. A RapidIO mailbox message receiving and processing module is used for receiving the RapidIO messages and converting the messages into the Ethernet packet. A 10-gigabit Ethernet packet receiving and processing module is used for receiving the Ethernet packet and converts the Ethernet packet into the RapidIO messages.

Owner:BEIJING INST OF COMP TECH & APPL

Explicit flow control in Gigabit/10 Gigabit Ethernet system

In one embodiment, a system comprises a communication medium; a first controller coupled to the communication medium; and a second controller coupled to the communication medium. The first controller is configured to interrupt transmission of a packet on the communication medium to the second controller subsequent to transmission of a first portion of the packet. The first controller is configured to transmit at least one control symbol on the communication medium in response to interrupting transmission of the packet, and wherein the first controller is configured to continue transmission of the packet with a second portion of the packet. The controller(s) may include, in some embodiments, a media access controller and a physical coding sublayer.

Owner:APPLE INC

Resilient multiple service ring

A data transmission apparatus and method used in resilient multiple service ring, including a first working ring and a second working ring, for transmitting data between physical layer side device and network layer device or other upper layer facilities, such as carrier class node equipments, core and edge routers, switch devices, IP based network accessing equipments, line cards, and interfacing units used in high rates or low rates, e.g. Ethernet, Gigabit Ethernet, 10 Gigabit, Ethernet, DVB (MPEG1, MPEG2, MPEG4 and MPEG7), ATM, Packet over SDH / SONET transmissions, other MSR, RPR for adapting IP and various tributaries (Ethernet,) directly to SDH / SONET or simplified SDH / SONET, or Gigabit Ethernet, 10 Gigabit Ethernet, or other physical layer devices.

Owner:FENGHUO COMM SCI & TECH CO LTD

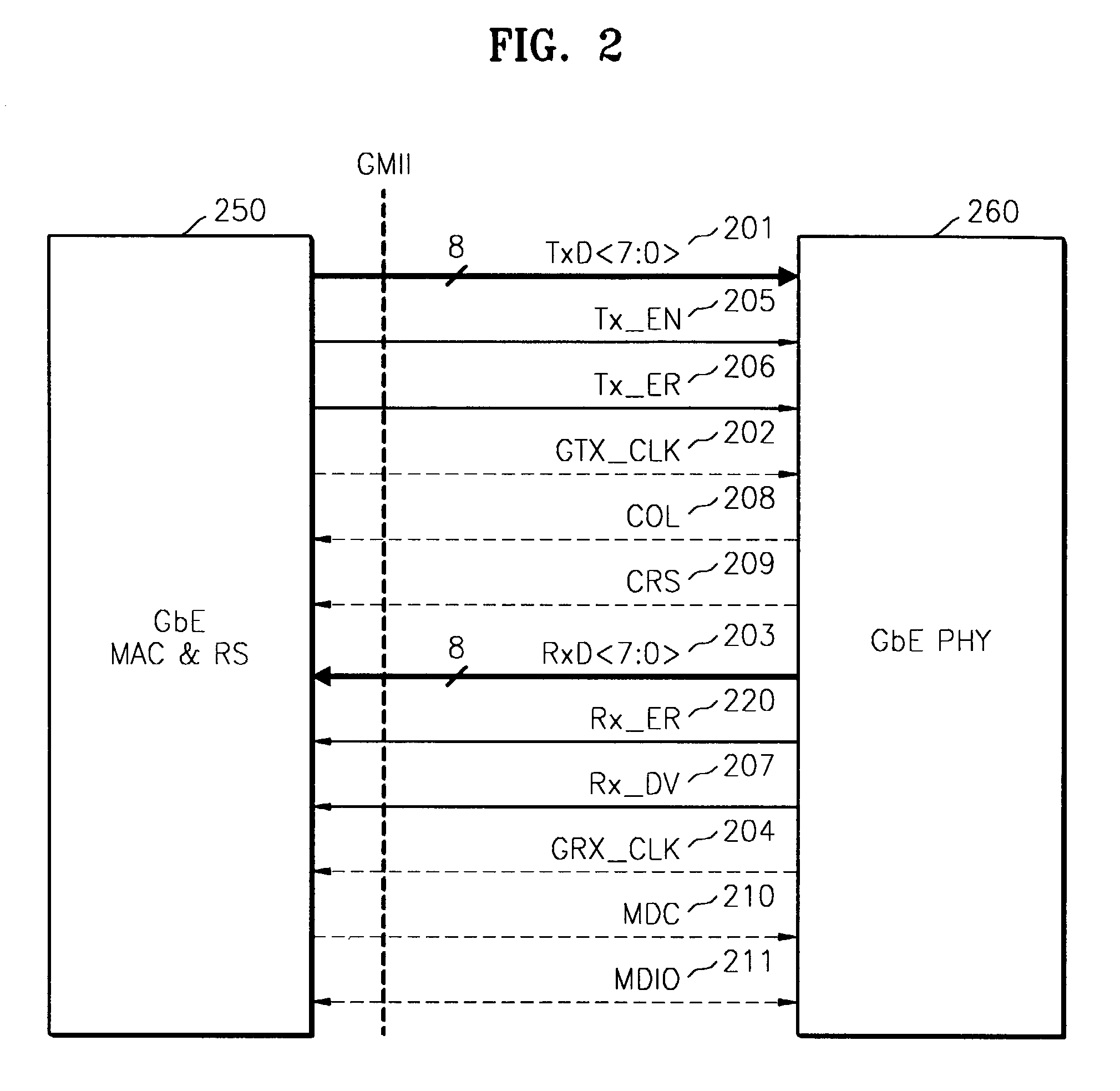

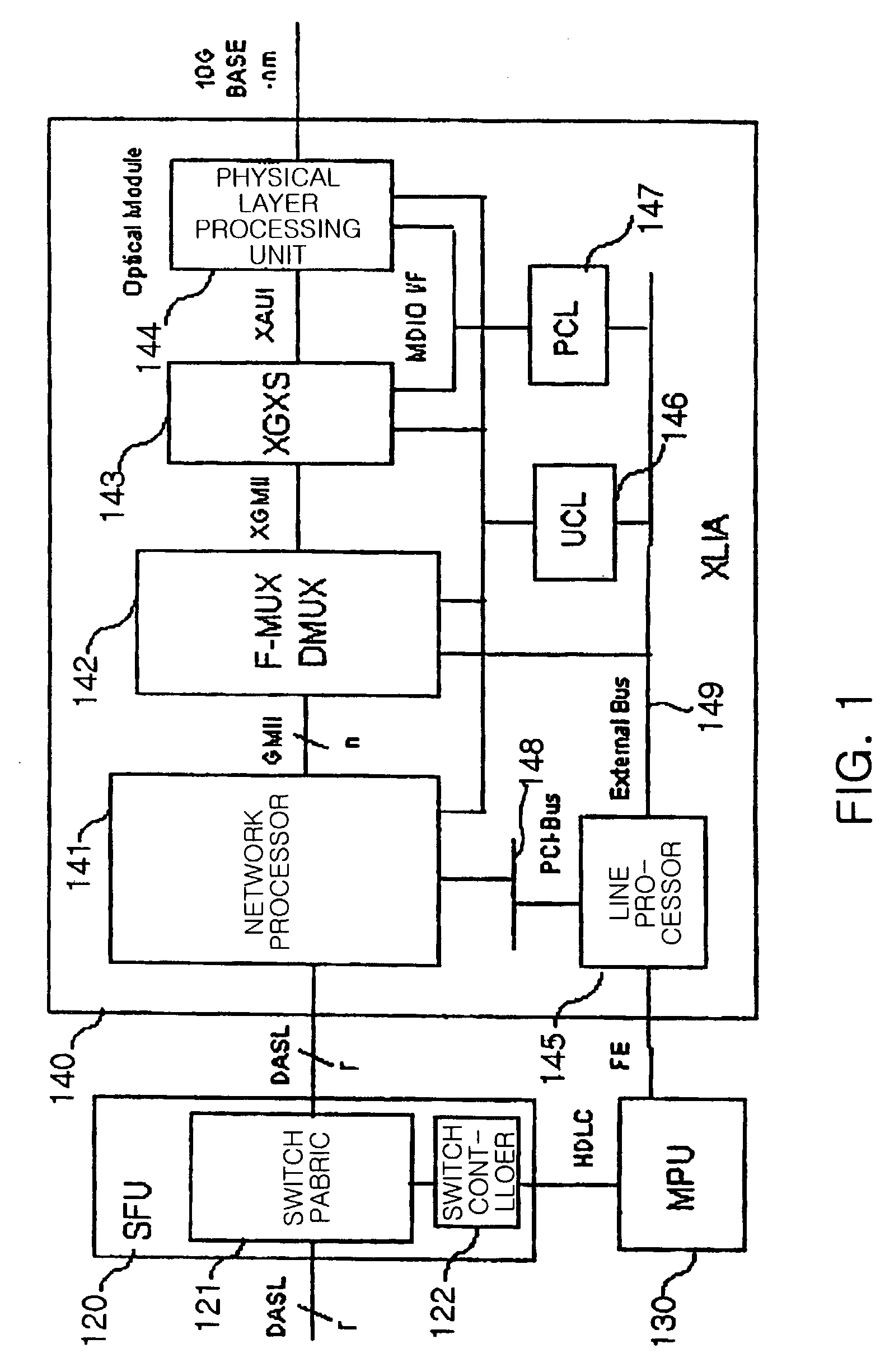

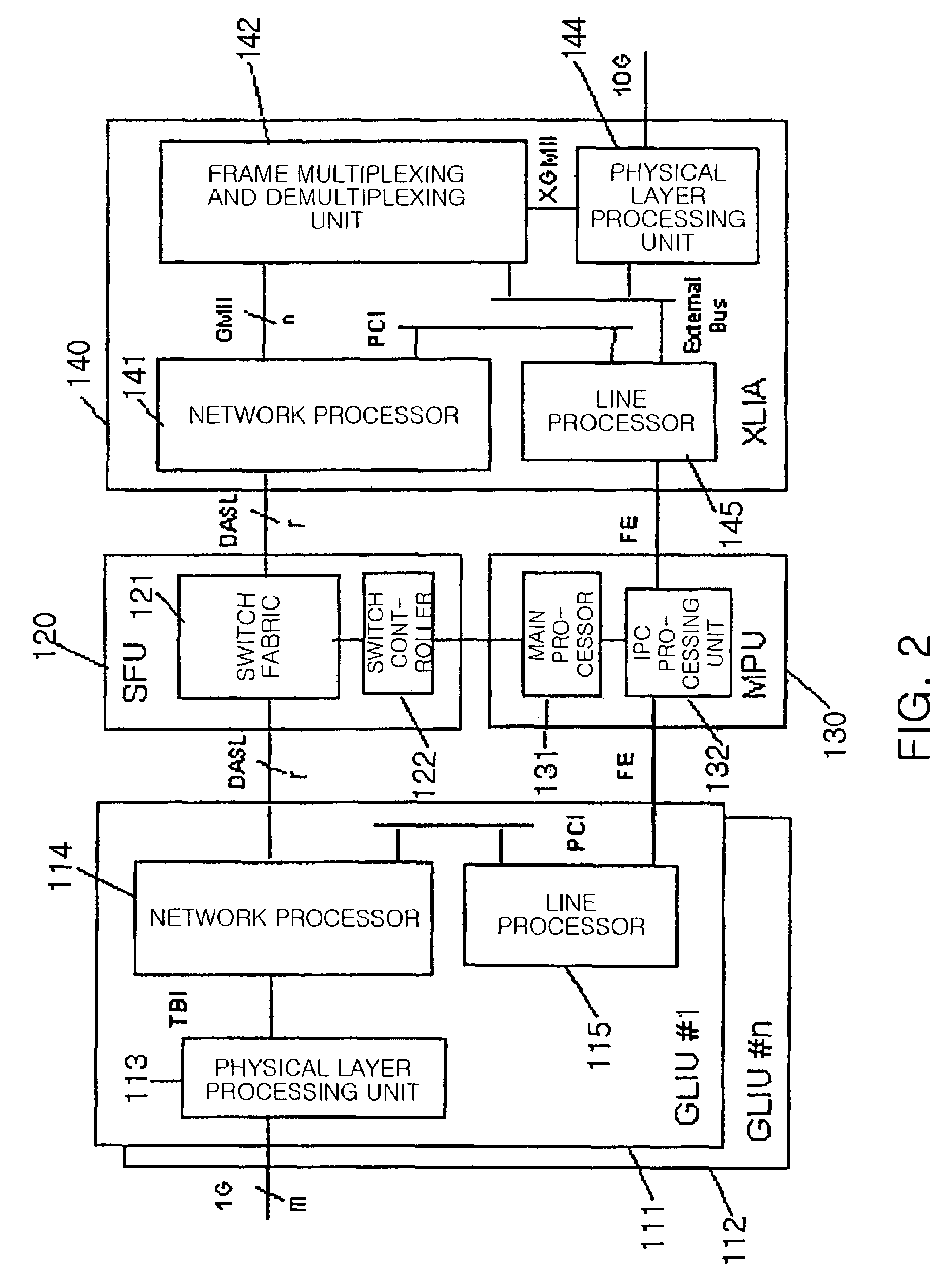

10-gigabit Ethernet line interface apparatus and method of controlling the same

InactiveUS7394825B2Avoid lostImprove performanceTime-division multiplexData switching by path configurationMultiplexing10 Gigabit Ethernet

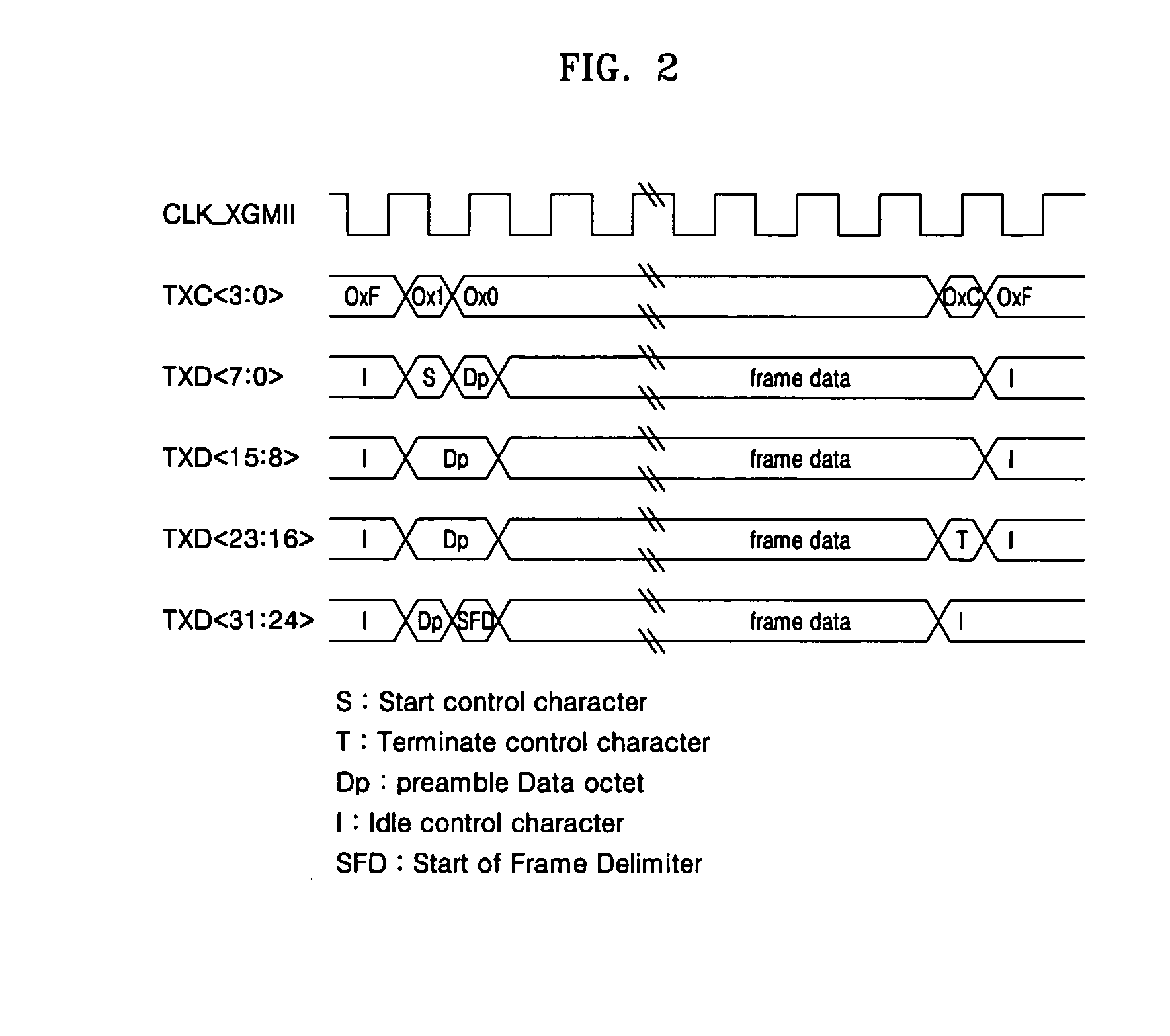

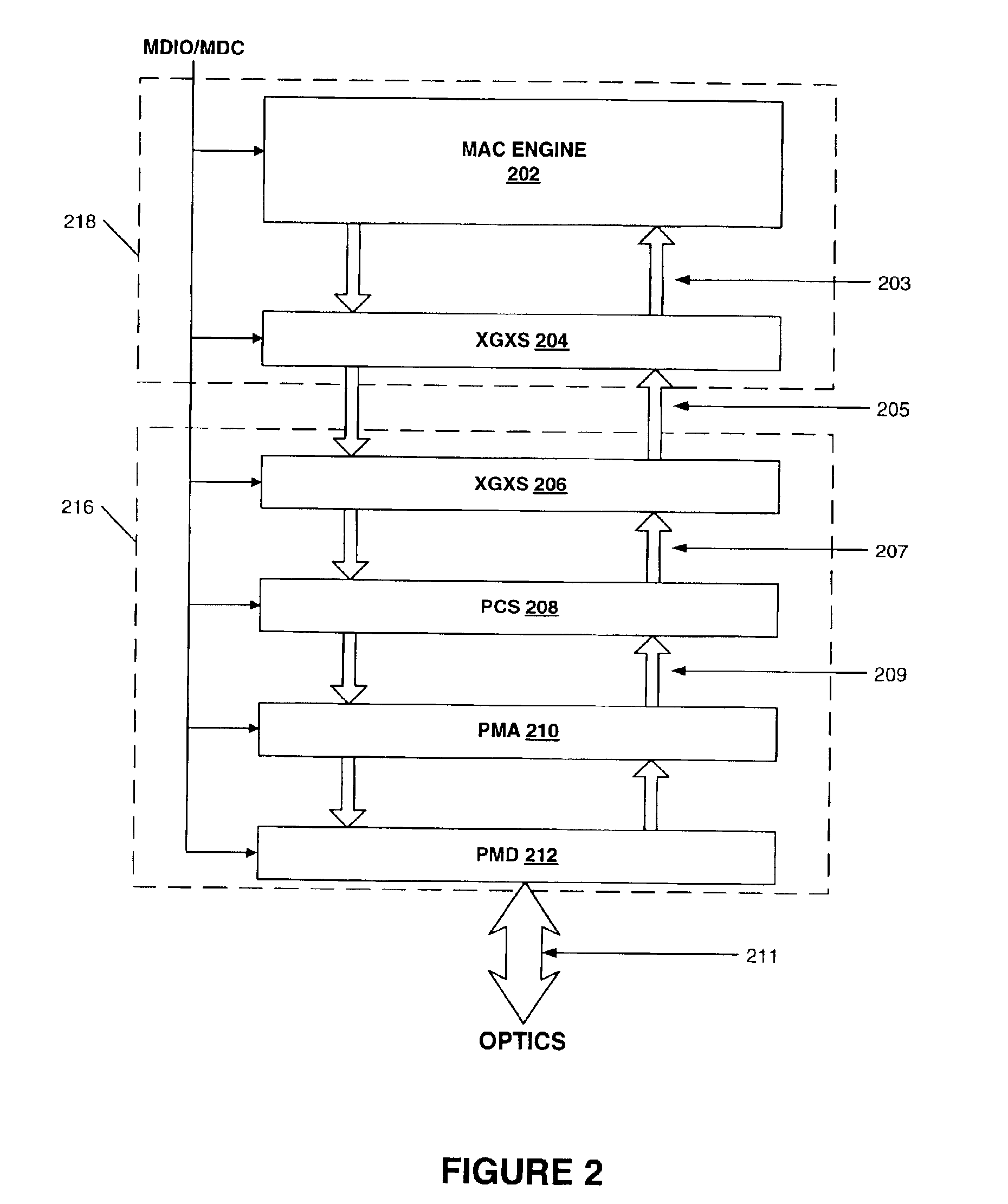

Disclosed herein is a 10-gigabit Ethernet line interface apparatus and method of controlling the same. The apparatus has N network processors, a frame multiplexing and demultiplexing block, a 10-gigabit extender sublayer processing block, a 10-gigabit Ethernet physical layer processing block, a 10-gigabit physical layer control logic, a line interface control logic, and a line processor. The N network processors are connected to the switch fabric unit. The frame multiplexing and demultiplexing block provides GMII and XGMII between the N network processors and a 10-gigabit extender sublayer processing block. The present invention can improve transmission speed and packet processing performance of a physical layer to a 10 Gbps level while maintaining basic frame standards of a 1-gigabit Ethernet switch apparatus.

Owner:ELECTRONICS & TELECOMM RES INST

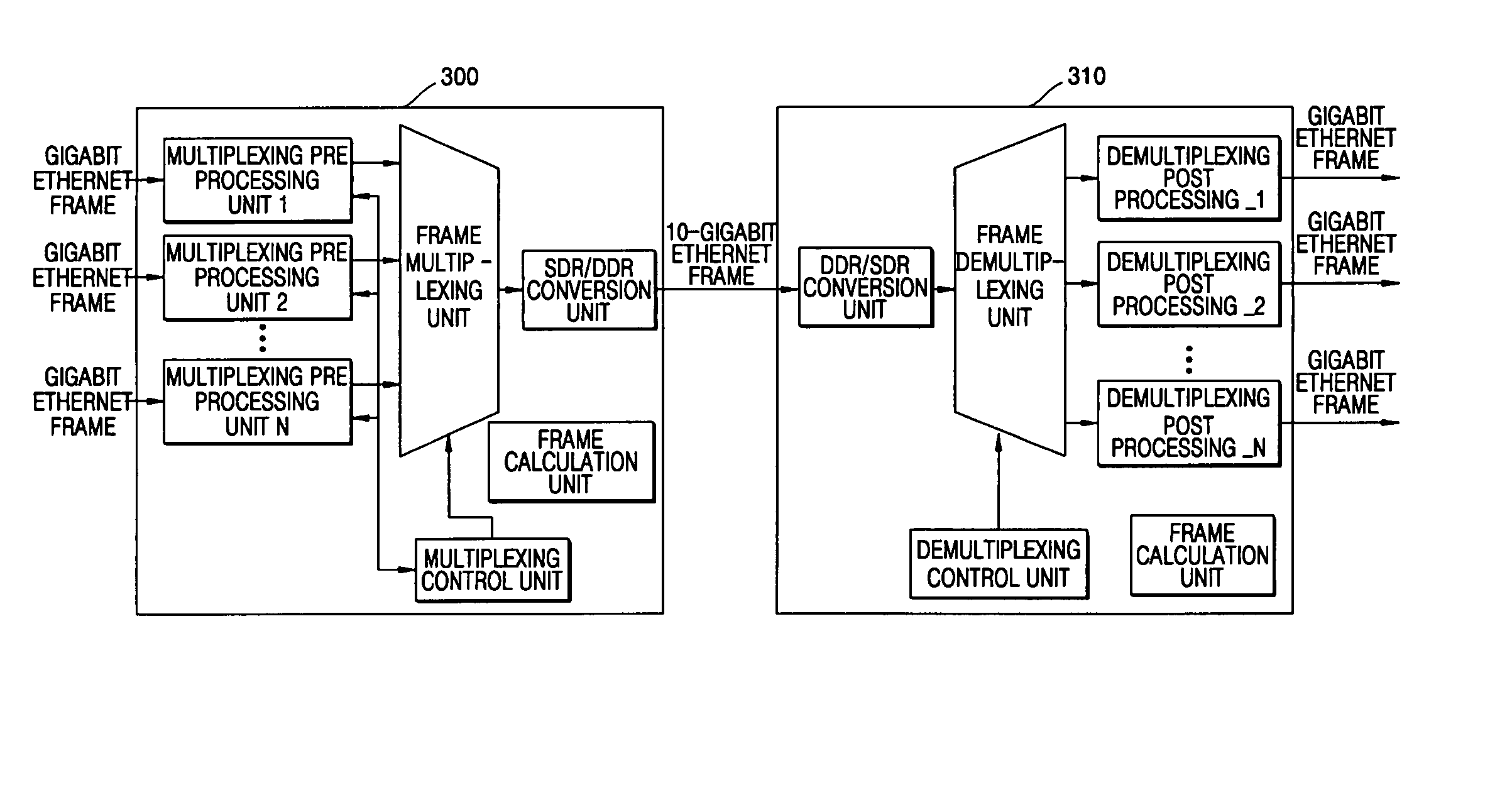

Apparatus for multiplexing Gigabit Ethernet frame and apparatus for demultiplexing 10-Gigabit Ethernet frame

InactiveUS20050135434A1Special service provision for substationTime-division multiplex10 Gigabit EthernetControl signal

Provided are an apparatus for multiplexing Gigabit Ethernet frames and an apparatus for demultiplexing 10-Gigabit Ethernet frames. The apparatus for multiplexing Gigabit Ethernet frames includes at least one pre-processing unit, a multiplexing unit, an SDR / DDR conversion unit, and a control unit. The at least one pre-processing unit receives Gigabit Ethernet frames, converts the Gigabit Ethernet frames into 10-Gigabit Ethernet frames, and outputs the 10-Gigabit Ethernet frames. The multiplexing unit receives the 10-Gigabit Ethernet frames, time division multiplexes the 10-Gigabit Ethernet frames in frame units, and outputs the time division multiplexed 10-Gigabit Ethernet frames as first data. The SDR / DDR conversion unit, which converts the first data into second data having two 32-bit bus structures and outputs the second data. The control unit outputs a first control signal in response to an output request of the pre-processing unit.

Owner:ELECTRONICS & TELECOMM RES INST

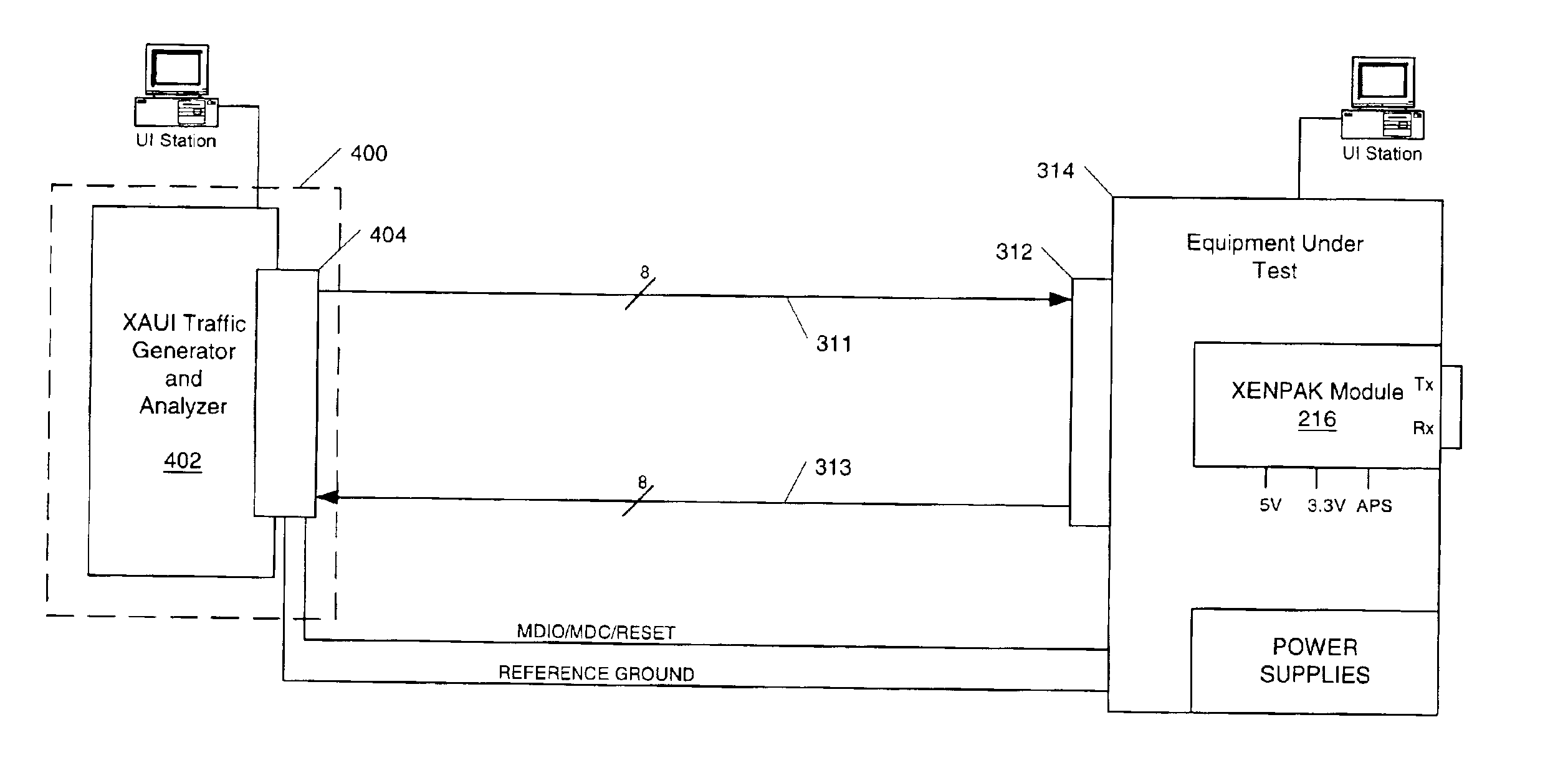

Xaui extender card

InactiveUS6880078B2Reliable and efficient and cost-effectiveEfficient measurementError detection/correctionStructural/machines measurementCapacitance10 Gigabit Ethernet

Access to the XAUI lanes of a 10 Gigabit Ethernet device is provided when needed for testing of the XAUI electrical interface. Access is provided by extending the XAUI interface contained in a XENPAK interface connector. An embodiment of the present invention uses an extension of the XENPAK connector to generate and receive XAUI signals thus making it possible for any device with a XENPAK connector to become a XUAI tester with minimal components between the test equipment and the device under test. The reduction of components (only an AC-Coupling capacitor resides between the XENPAK connector and the SMA connector) results in significant reduction in insertion loss and signal degradation. Also, the availability of any device with a XENPAK interface as a XAUI tester eliminates any requirement for specialized test equipments. The XAUI Extender card fits in the slot in the test equipment that would normally house the XENPAK module. Thus, no special connector is required to configure a device as a test equipment of the present invention.

Owner:SPIRENT COMM

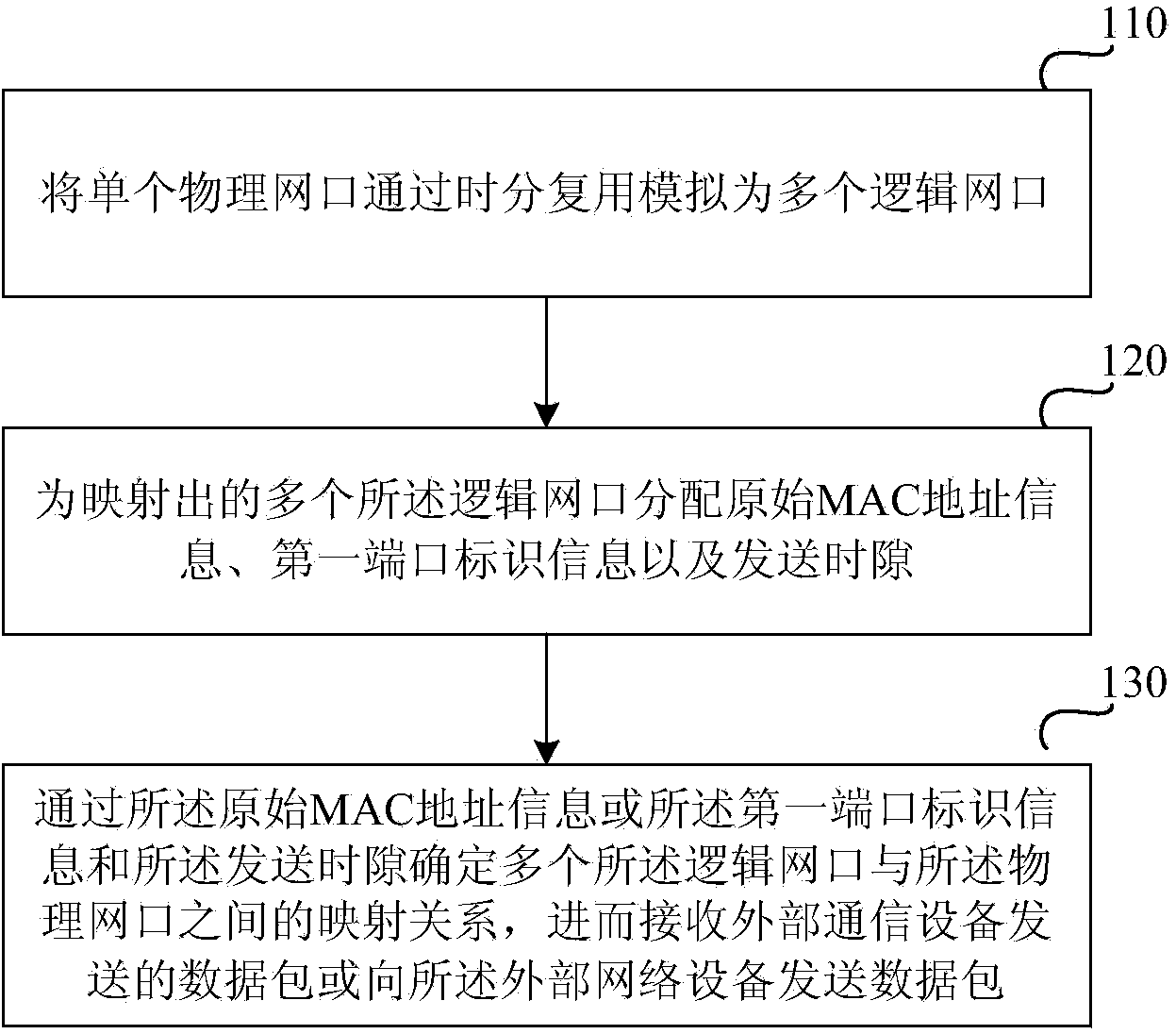

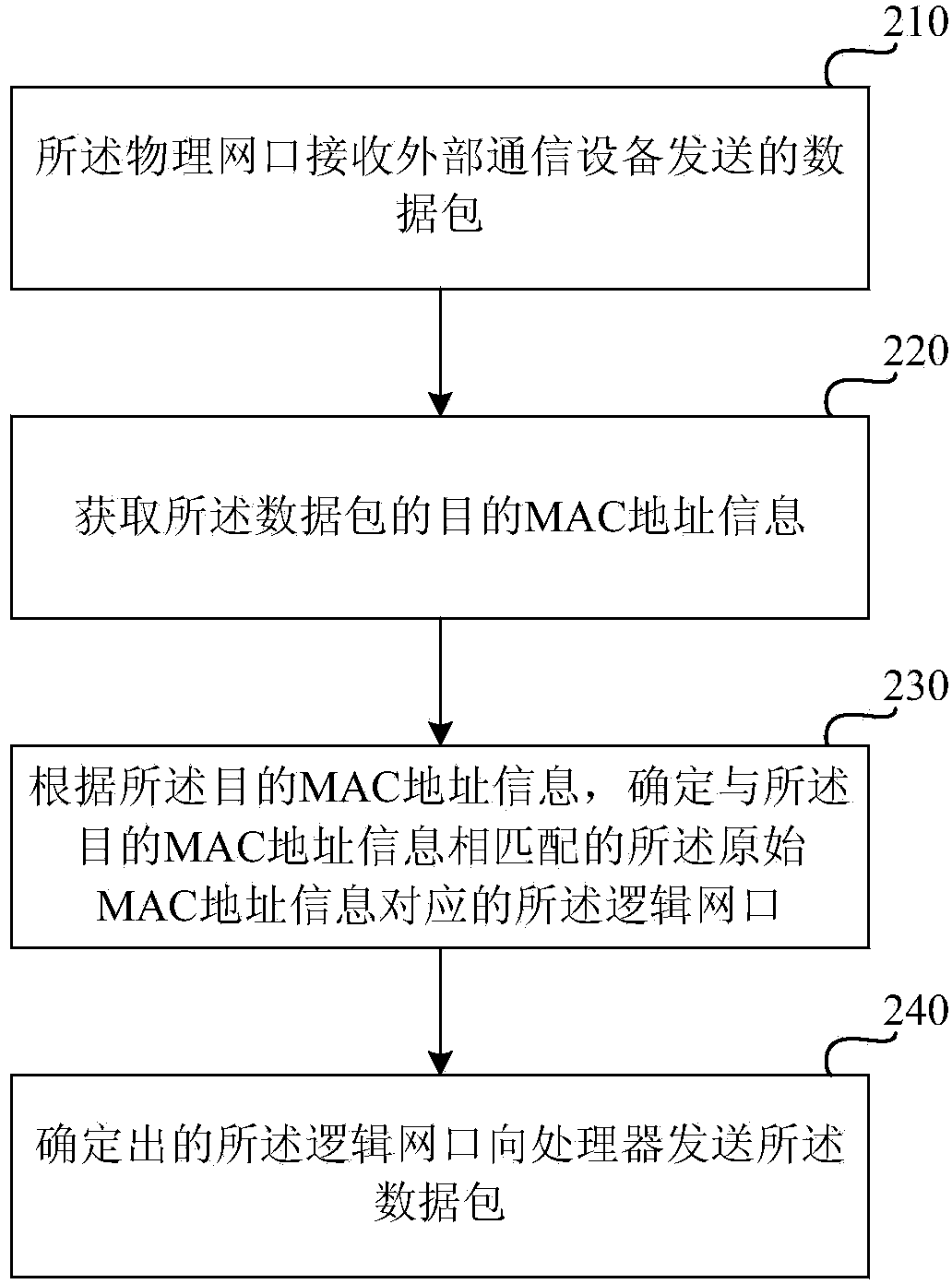

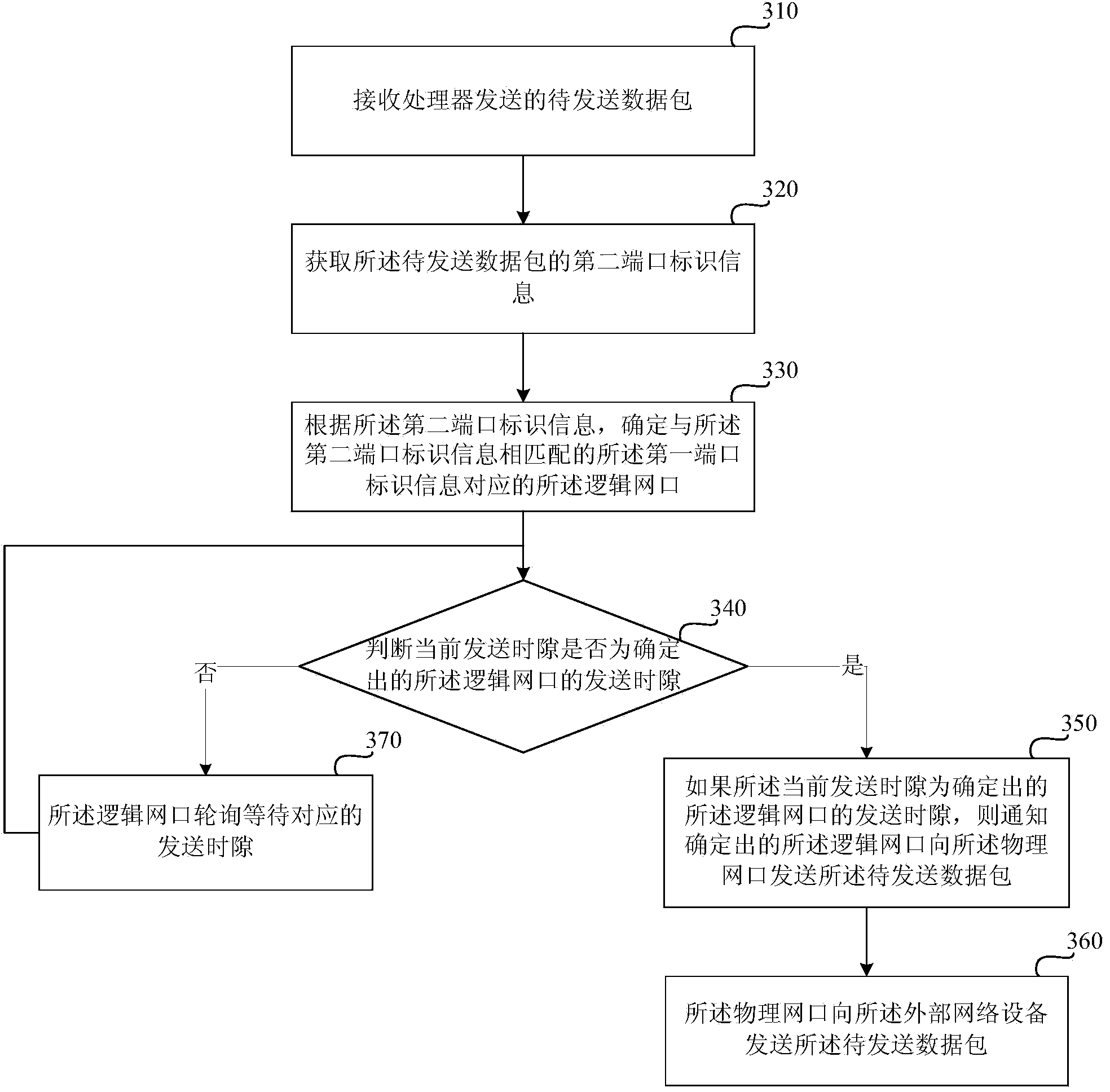

Mapping method and device for simulating single physical network port into multiple logical network ports

InactiveCN103533090AImplementation supportSolve the problem of not being able to receive through a single physical network portTransmission10 Gigabit EthernetNetwork packet

The embodiment of the invention relates to a mapping method and a device for simulating a single physical network port into multiple logical network ports. The method comprises the steps of simulating and mapping the single physical network port into the logical network ports through time division multiplexing, assigning original MAC (Media Access Control) address information, first port identification information and a transmission time slot to the mapped logical network ports, determining a mapping relationship between the logical network ports and the physical network port through the original MAC address information or the first port identification information and the transmission time slot, and further receiving a data packet transmitted by external communication equipment or transmitting the data packet to external network equipment. The method and the device solve the bottle neck that the high-speed data packet cannot be received or transmitted through the single physical network port in the prior art, and realize the support of the single physical network port to the high-speed 10-gigabit Ethernet.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI +1

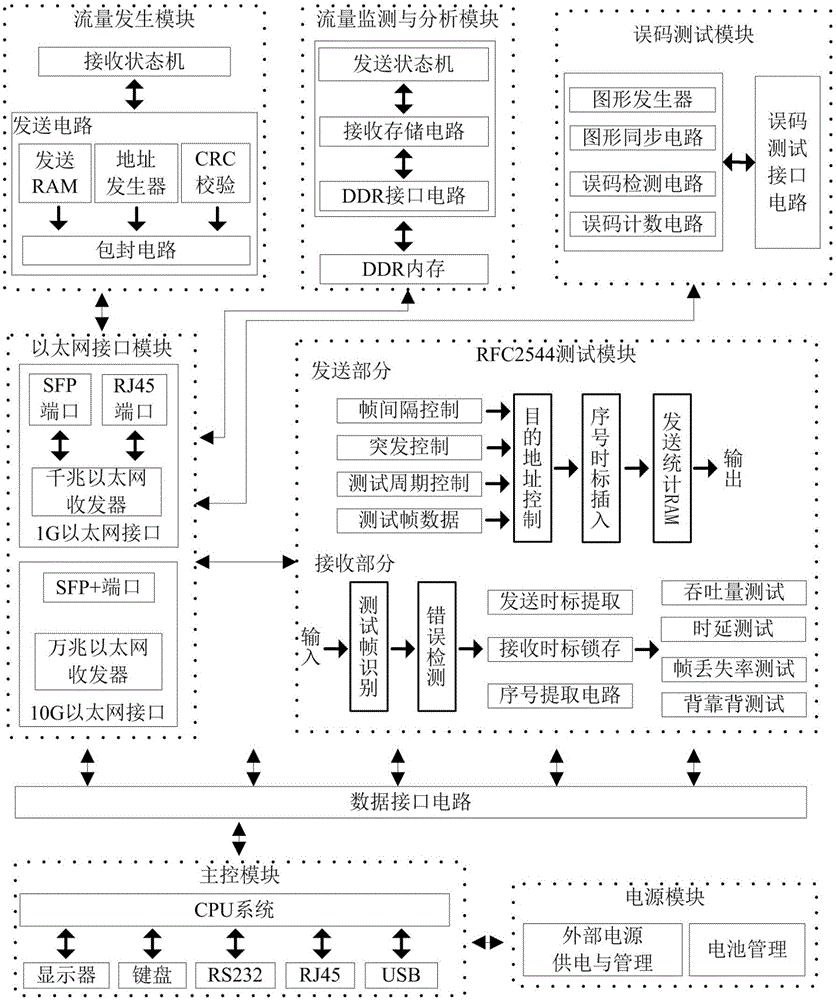

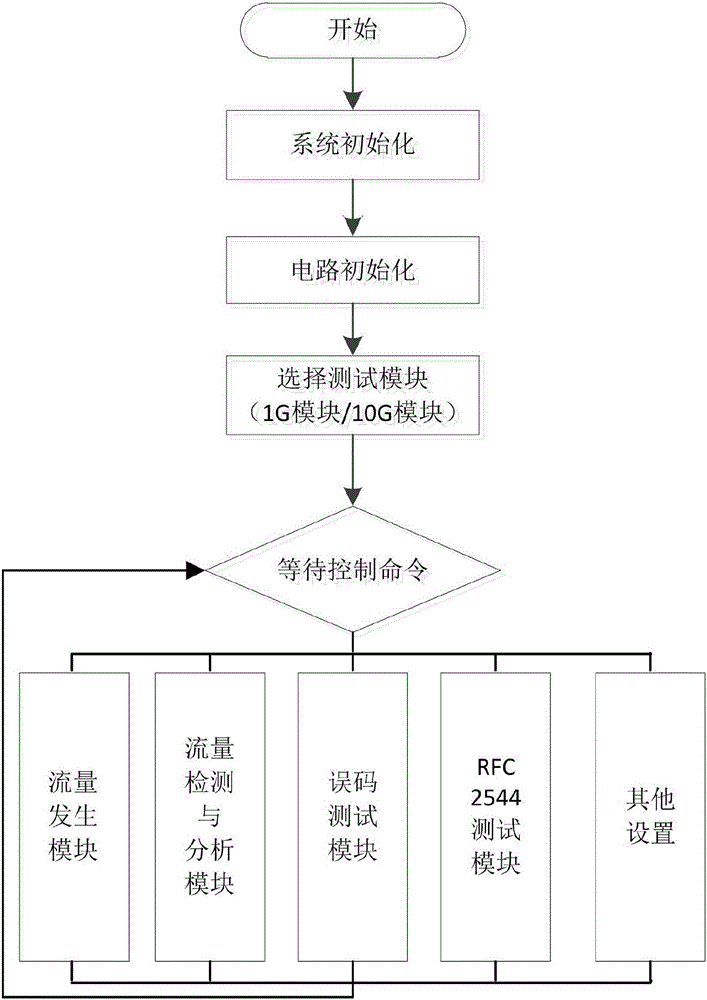

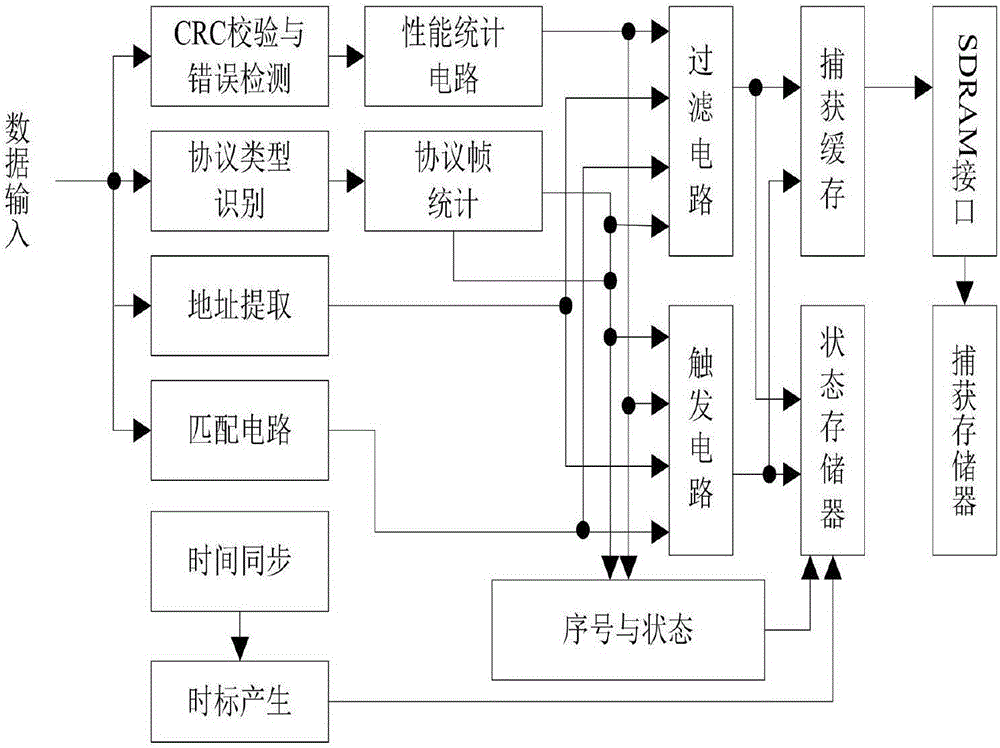

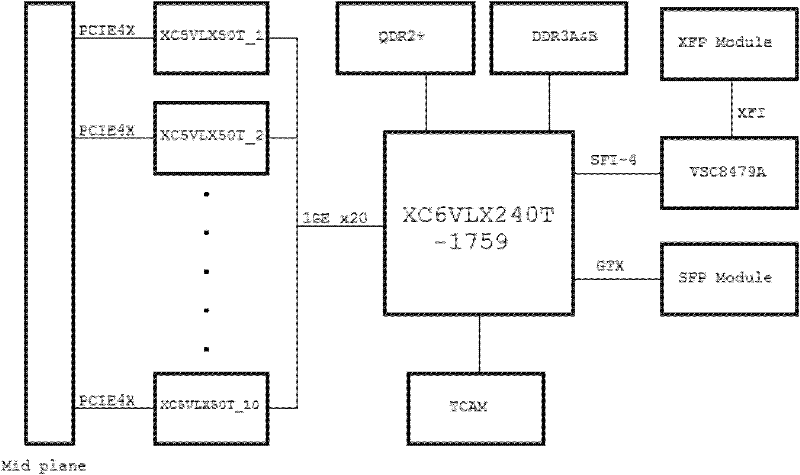

10-gigabit Ethernet tester

ActiveCN106375161AHighly integratedReduce volumeData switching networksPacket loss10 Gigabit Ethernet

The invention provides a 10-gigabit Ethernet tester. 10Mbps / 100Mbps / 1000Mbps / 10Gbps Ethernet test ports are integrated, Ethernet test in the rate from 10Mbps to 10Gbps is supported, and the tester has functions of testing and monitoring network performances including time delay, packet loss ratio, throughput, back-to-back as well as functions as flow generation, collection, analysis and calculation and error code test. The tester is of a handheld structure, and an internal battery supplies power. The tester is capable of remote control, so that a test staff can implement test when in a remote position. According to the schemes, the problems that different test modules are designed independently, the circuit scale is too large, power consumption is too high and the test modules cannot be integrated in handheld equipment are solved, and functions of service generation, data collection, error code test and RFC2544 test needed for the different test modules are integrated in a control circuit.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

Data distribution platform of blade server

ActiveCN102244662AImplement processing distributionData switching networks10 Gigabit EthernetDistribution function

The invention provides a data distribution platform of a blade server. The data distribution platform comprises a main control module, a blade control module, a middle plate, a 10-gigabit Ethernet module and a gigabit Ethernet module, wherein the 10-gigabit Ethernet module and the gigabit Ethernet module transmit signals to the main control module; the main control module processes and forwards the signals to the blade control module; and the blade control module transmits the signals to blades through the middle plate. By utilizing the data distribution platform, data processing and distribution functions are realized so that the data received from gigabit Ethernet and 10-gigabit Ethernet can be screened and distributed to the blades only by one data distribution plate.

Owner:曙光信息系统(辽宁)有限公司

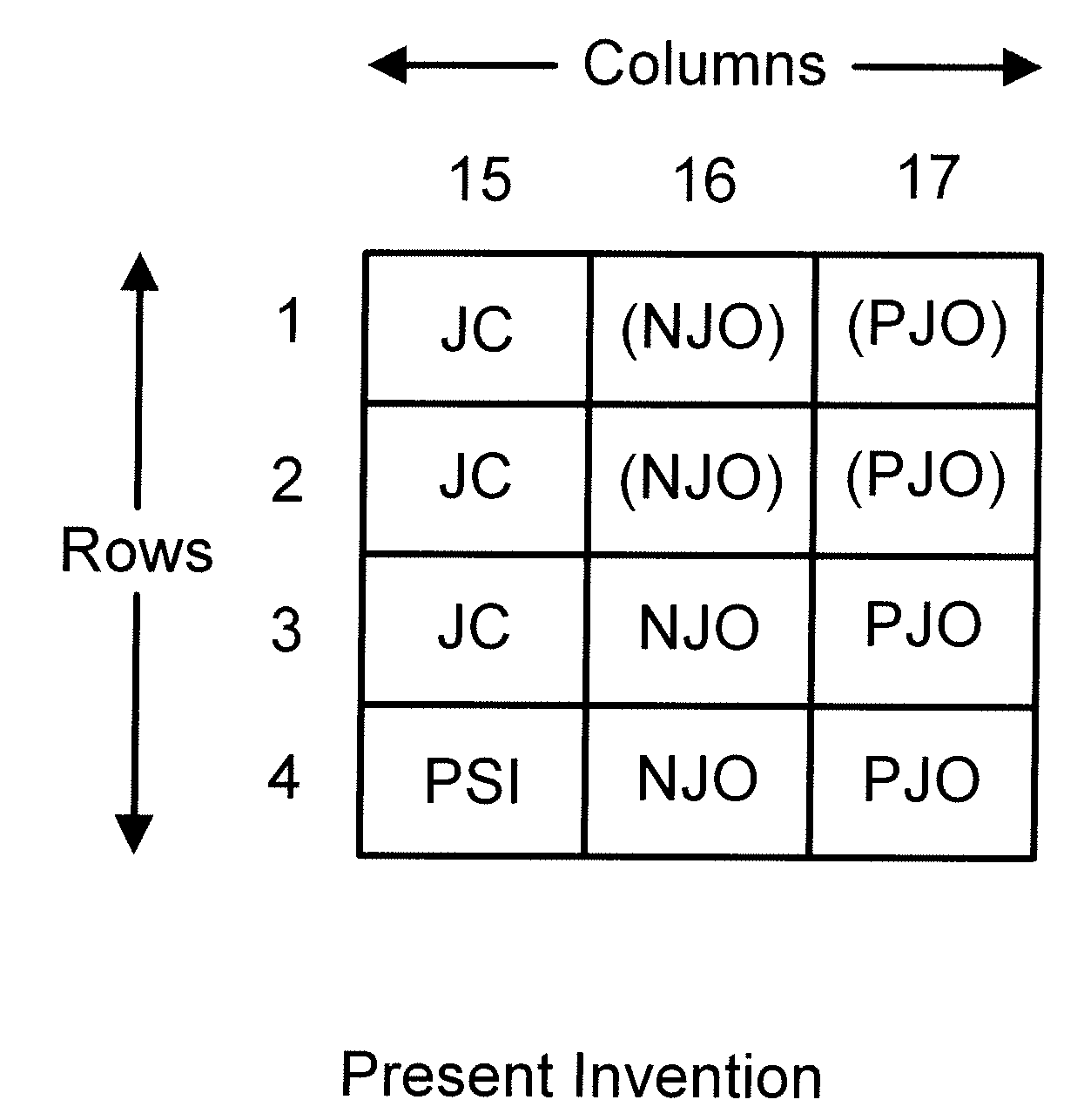

Method of mapping OPUke into OTN frames

The present invention discloses a method of mapping Optical Payload Unit (OPU) k (k=1, 2, 3 or any positive integer) Ethernet signals (E) into Optical Transport Network (OTN) frames for 10 Gigabit Ethernet (10 GbE) Local Area Network Physical Layer (LAN PHY), wherein OPUk Overhead (OH) is altered by the relocation of Justification Control (JC) bytes, from the standardized ITU-T G.709 locations, into the novel locations of rows 1-3 of column 15. This allows for rows 1-4 of column 16 to be available for any type of Justification Overhead (JOH), such as four Negative Justification Opportunity (NJO) byte locations. Four NJO byte locations, combined with four Positive Justification Opportunity (PJO) byte locations in rows 1-4 of column 17, provides for up to nine justification state choices to be determined by the JC bytes. In addition, the ability to add or remove a plurality of two, three or fours bytes from OTN Payload can double, triple, or quadruple the standardized maximum bit rate tolerance of ±65 parts per million (ppm).

Owner:ALTERA CANADA

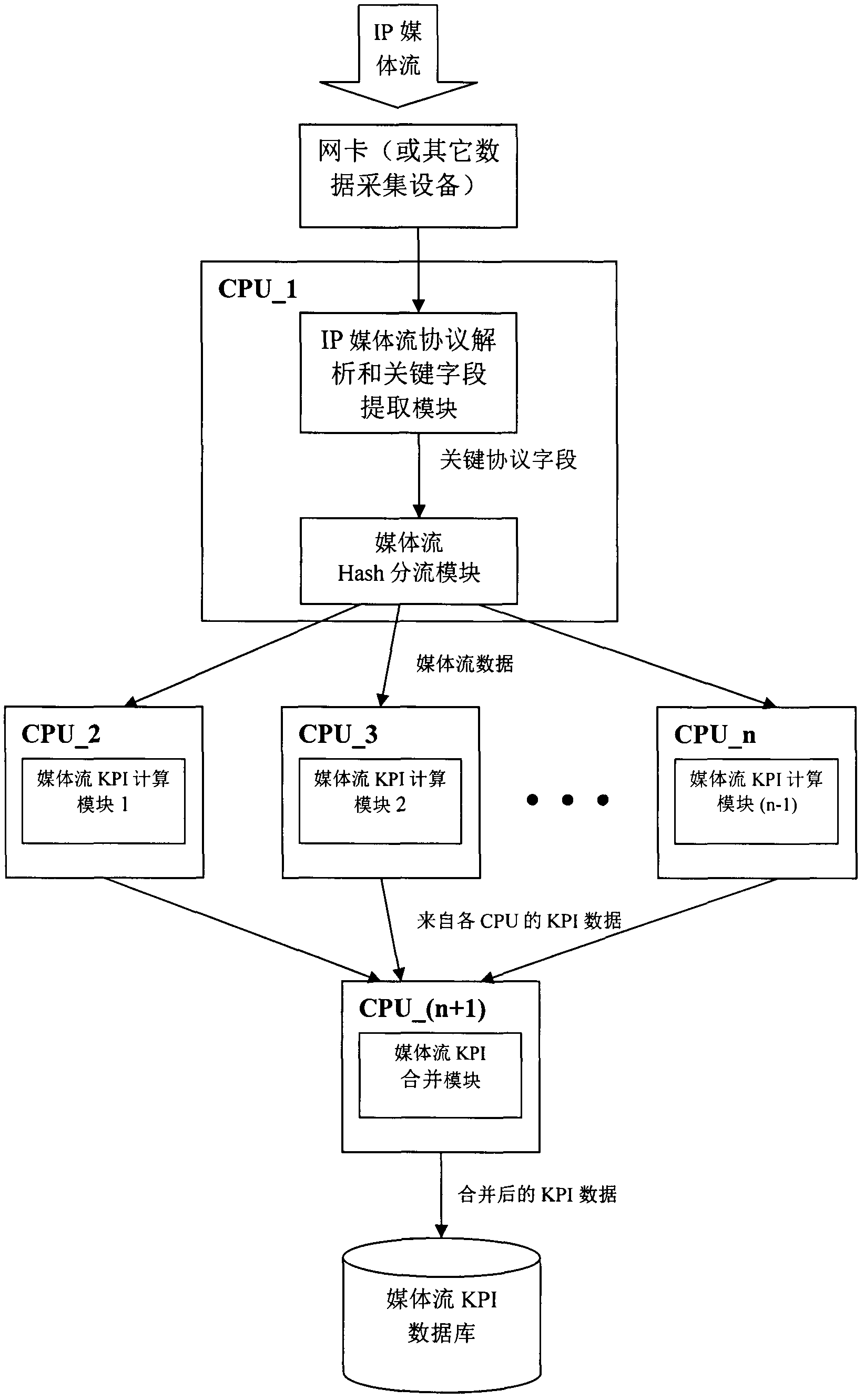

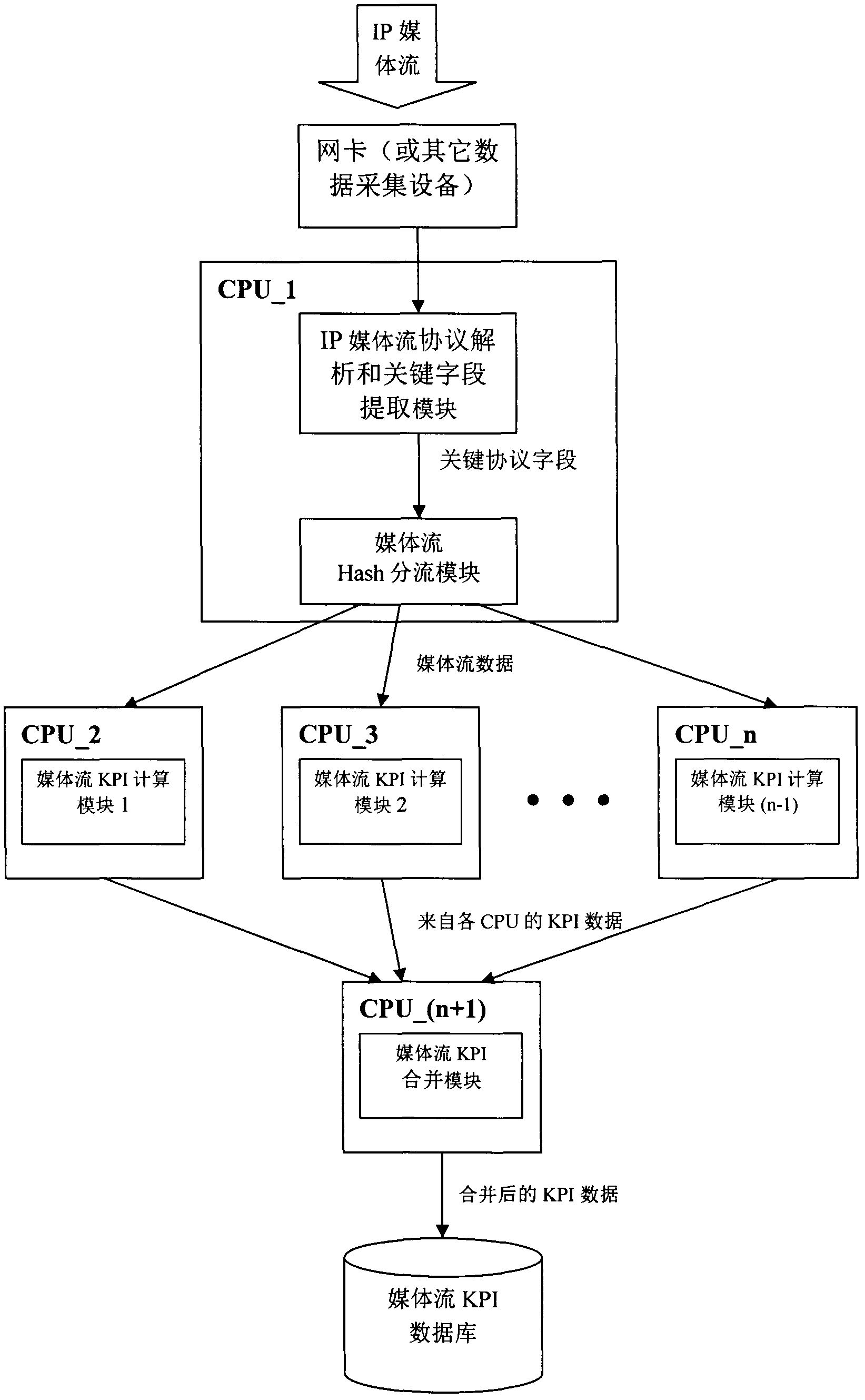

Method and system for monitoring high-performance IP (Internet Protocol) media stream

The invention discloses a method and a system for monitoring high-performance IP (Internet Protocol) media stream. The method comprises the following steps of: for the media streams on a high-load Ethernet link, according to an IP key field, allocating different media streams to a plurality of CPUs (Central Processing Units) by a Hash algorithm to perform multi-thread KPI (Key Performance Indicator) statistics; and then, combining the KPI data generated by each CPU, thereby forming the KPI statistic result of all the media streams on the whole link. The method and the system can execute real-time VoIP (Voice over Internet Protocol) and IPTV (Internet Protocol Television) media stream quality of service (QoS) and quality of experience (QoE) parameter statistics on a Gigabit / 10 Gigabit Ethernet interface, thereby reducing the cost of the monitoring system.

Owner:DEKSCOM TECH

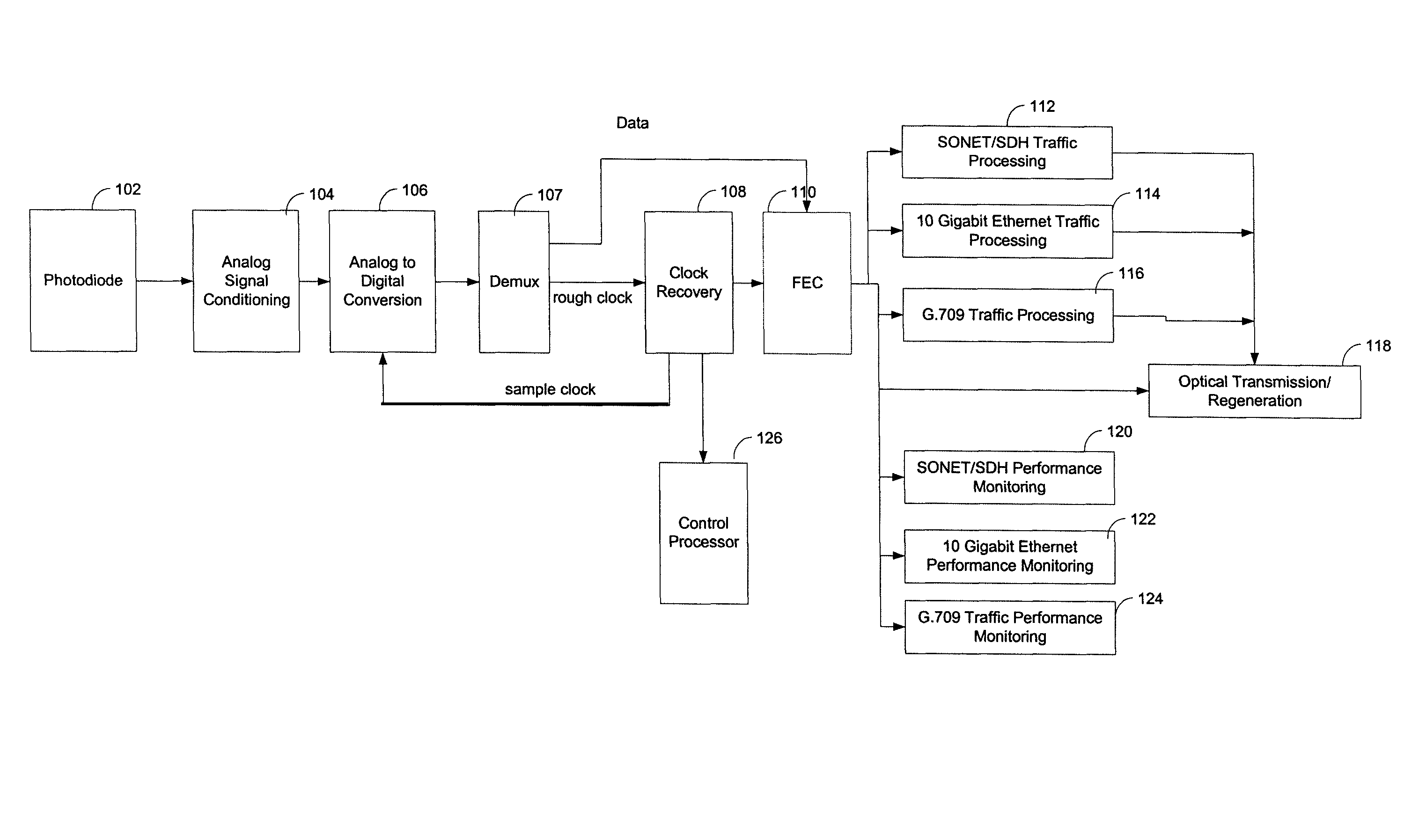

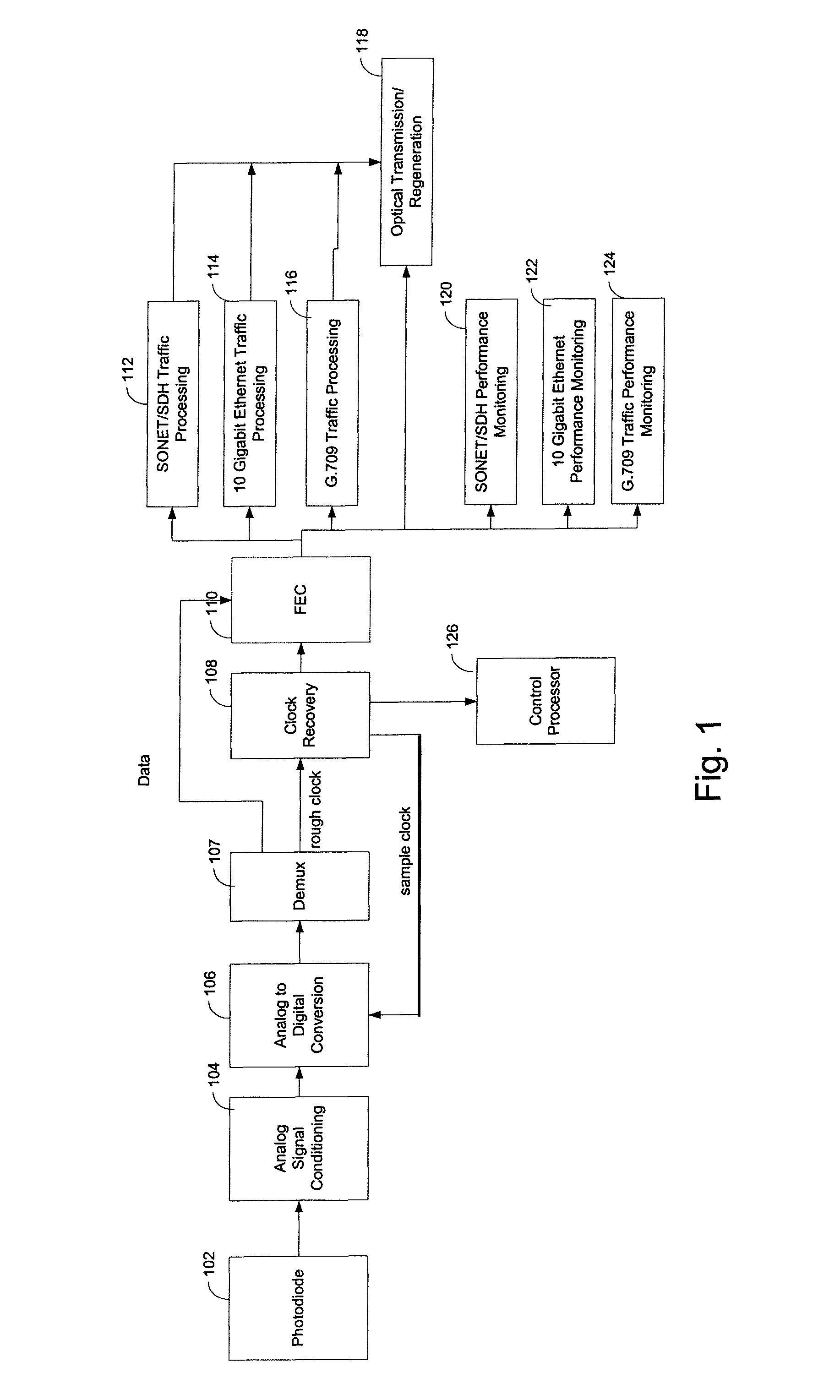

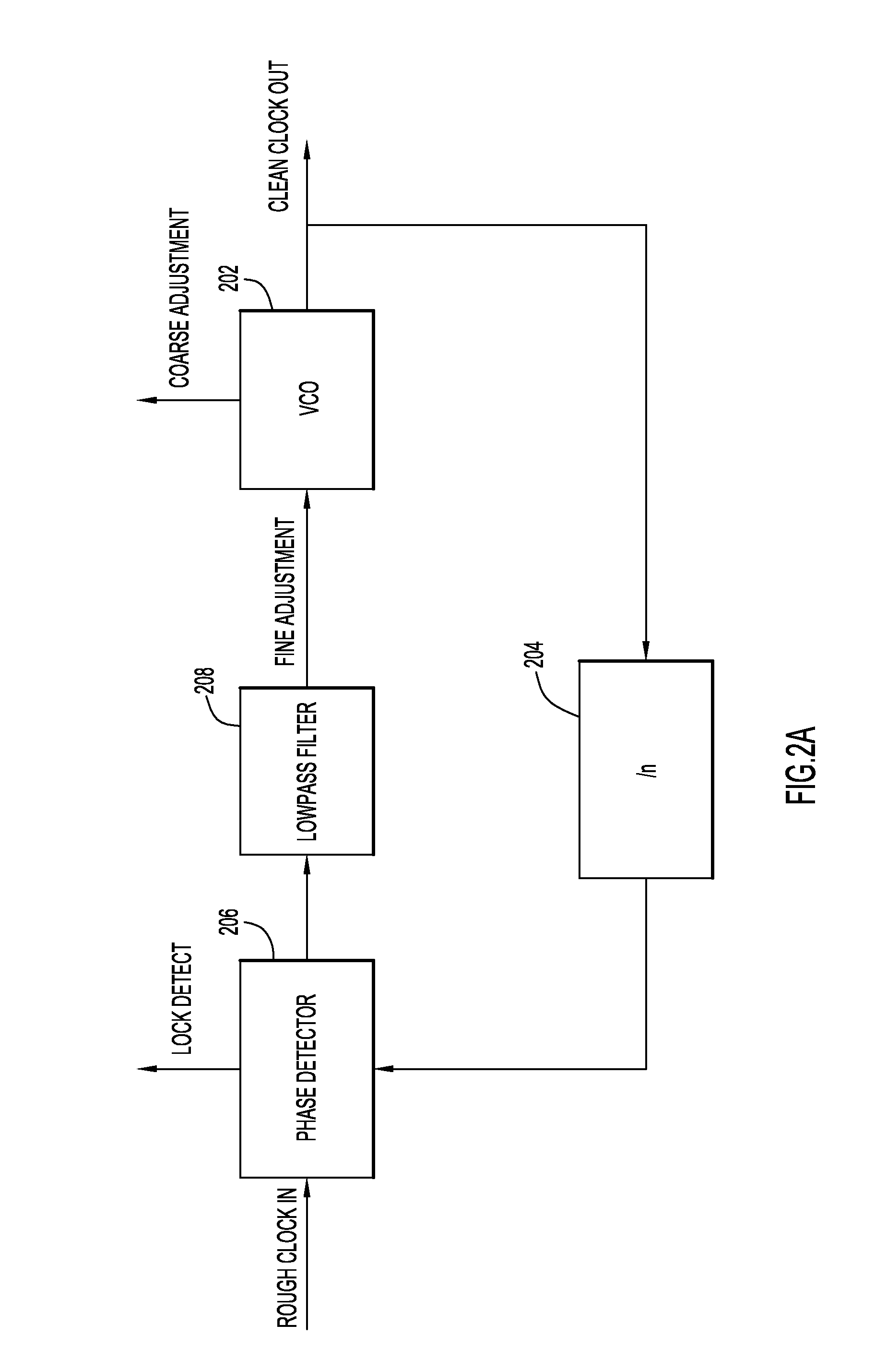

Automatic selection of the performance monitoring based on client type

InactiveUS7751726B1Appropriately processedEase of configurationPulse automatic controlTime-division multiplex10 Gigabit EthernetData rate

Systems and methods for operating transponders that automatically accommodate multiple received signal types. The different signal types may include different clients such as, e.g., SONET / SDH, G.709, 10 Gigabit Ethernet, etc. as well as different data rates. A transponder can automatically detect the client signal type and data rate and respond by processing the received signal appropriately, notifying a control processor, and invoking an appropriate performance monitoring method. This maximizes the network operator's flexibility and ease of configuration.

Owner:CISCO TECH INC

System and method for designing RS-based LDPC code decoder

InactiveUS7716553B2Low costImprove decoding throughputData representation error detection/correctionCode conversionMemory addressComputer architecture

Owner:PARHI KESHAB K

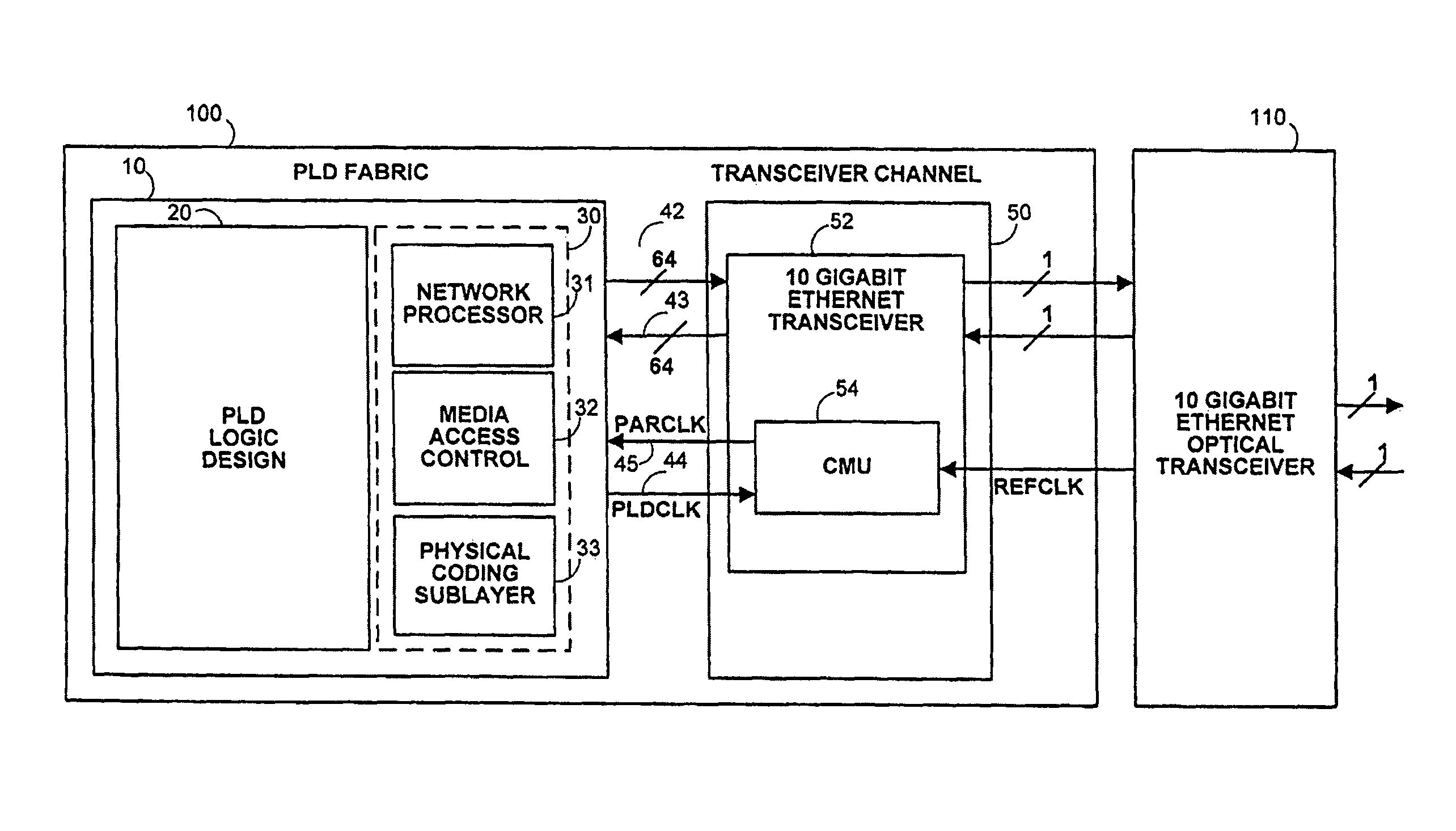

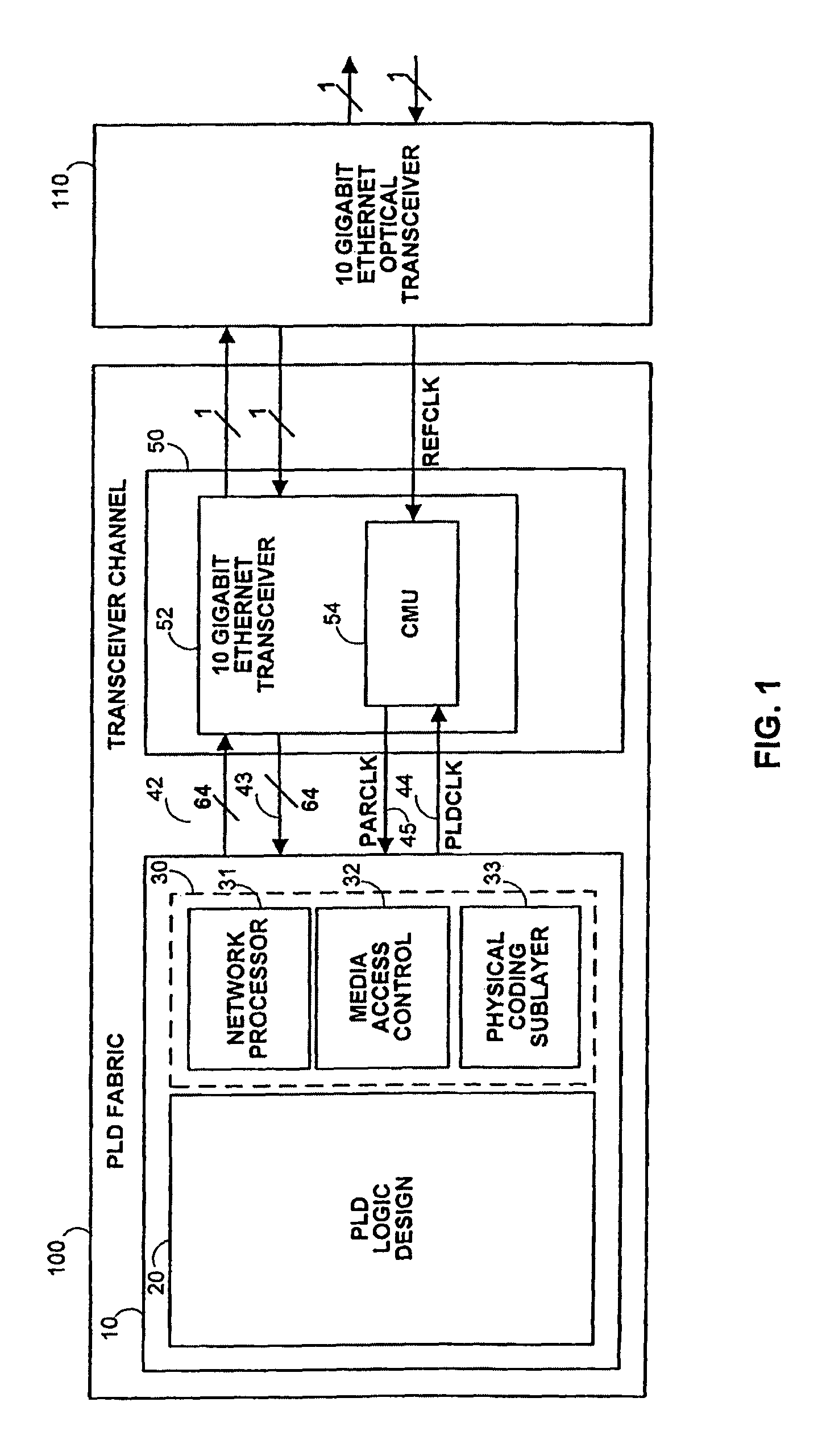

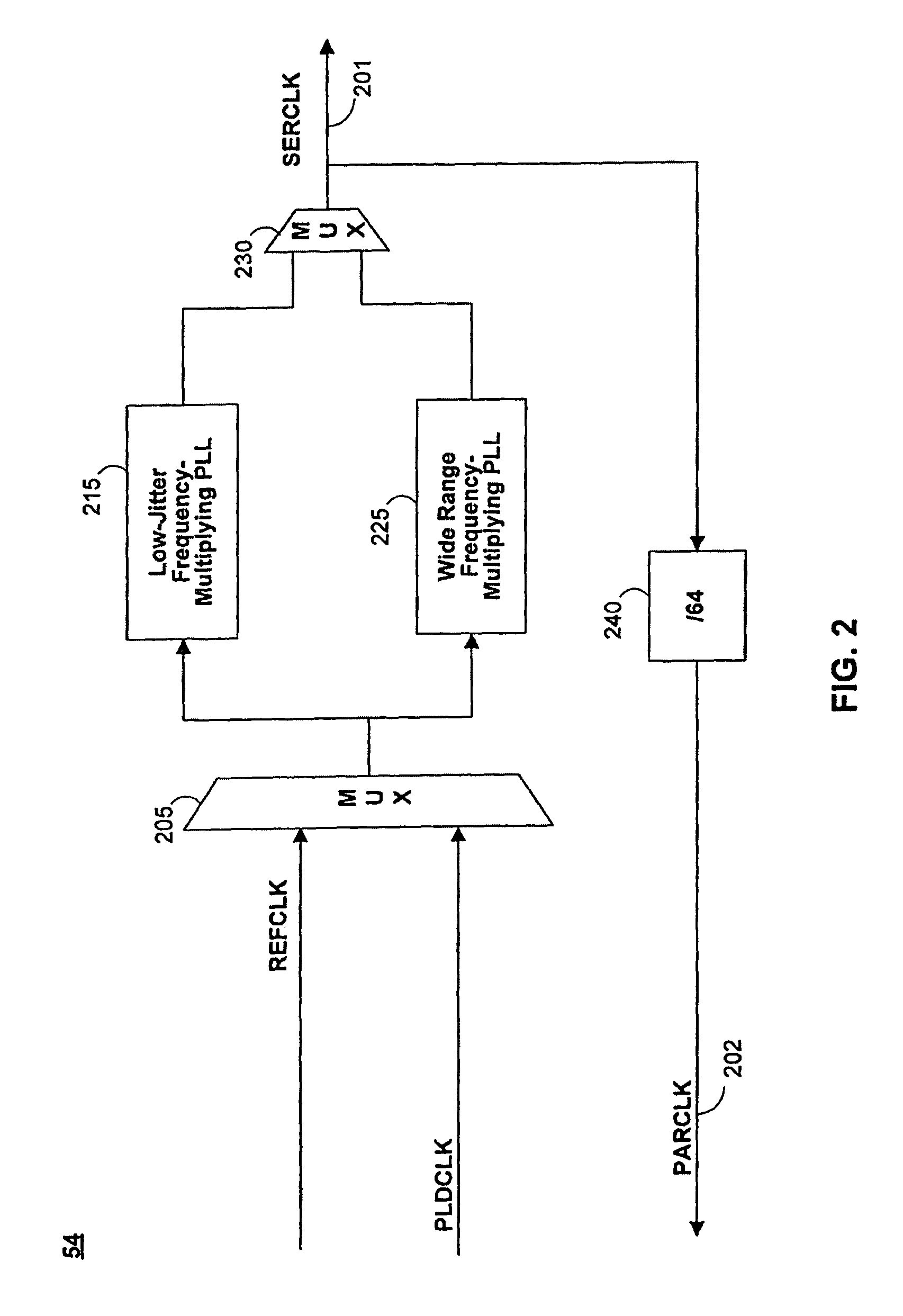

PLD architecture optimized for 10G Ethernet physical layer solution

An integrated circuit (e.g., a programmable integrated circuit such as a programmable microcontroller, a programmable logic device, etc.) includes programmable circuitry and 10 Gigabit Ethernet (10 GbE) transceiver circuitry. The programmable circuitry and the transceiver circuitry may be configured to implement the physical (PHY) layer of the 10 GbE networking specification. This integrated circuit may then be coupled to an optical transceiver module in order to transmit and receive 10 GbE optical signals. The transceiver circuitry and interface circuitry that connects the transceiver circuitry with the programmable circuitry may be hard-wired or partially hard-wired.

Owner:ALTERA CORP