Patents

Literature

222 results about "RapidIO" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The RapidIO architecture is a high-performance packet-switched interconnect technology. RapidIO supports messaging, read/write and cache coherency semantics. RapidIO fabrics guarantee in-order packet delivery, enabling power- and area- efficient protocol implementation in hardware. Based on industry-standard electrical specifications such as those for Ethernet, RapidIO can be used as a chip-to-chip, board-to-board, and chassis-to-chassis interconnect. The protocol is marketed as: RapidIO - the unified fabric for Performance Critical Computing, and is used in many applications such as Data Center & HPC, Communications Infrastructure, Industrial Automation and Military & Aerospace that are constrained by at least one of size, weight, and power (SWaP).

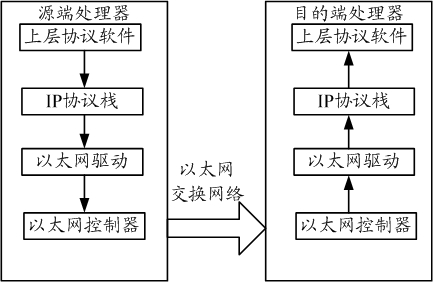

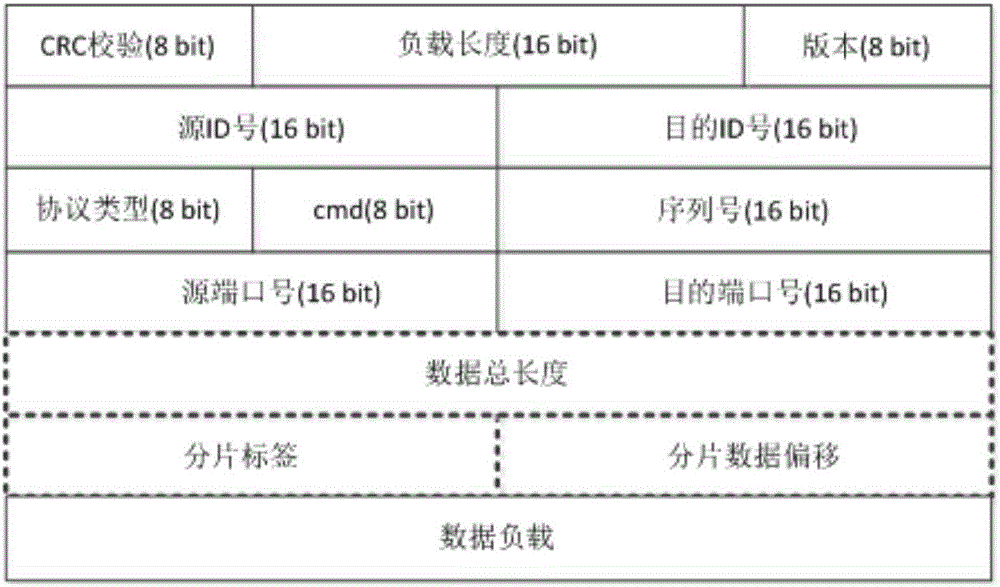

Data transmission method and equipment

InactiveCN102035751AIncrease transfer rateReliable transmissionError preventionData switching networksComputer hardwareReliable transmission

The invention discloses a data transmission method and data transmission equipment. The method comprises that: when a data packet to be transmitted is determined to be fragmented according to the dimension information of the data packet to be transmitted, an internet protocol (IP) protocol stack fragments the data packet to be transmitted; and the IP protocol stack calls a rapid input / output (RapidIO) driver to transmit the processed fragmented data. In the method, by fragmenting the data packet to be transmitted through the IP protocol stack and transmitting the processed fragmented data through the RapidIO driver, the transmission rate can be improved; the RapidIO message transmission process is responsive transmission and belongs to reliable transmission; and if link congestion occurs, the data can finally reach an opposite terminal.

Owner:DATANG MOBILE COMM EQUIP CO LTD

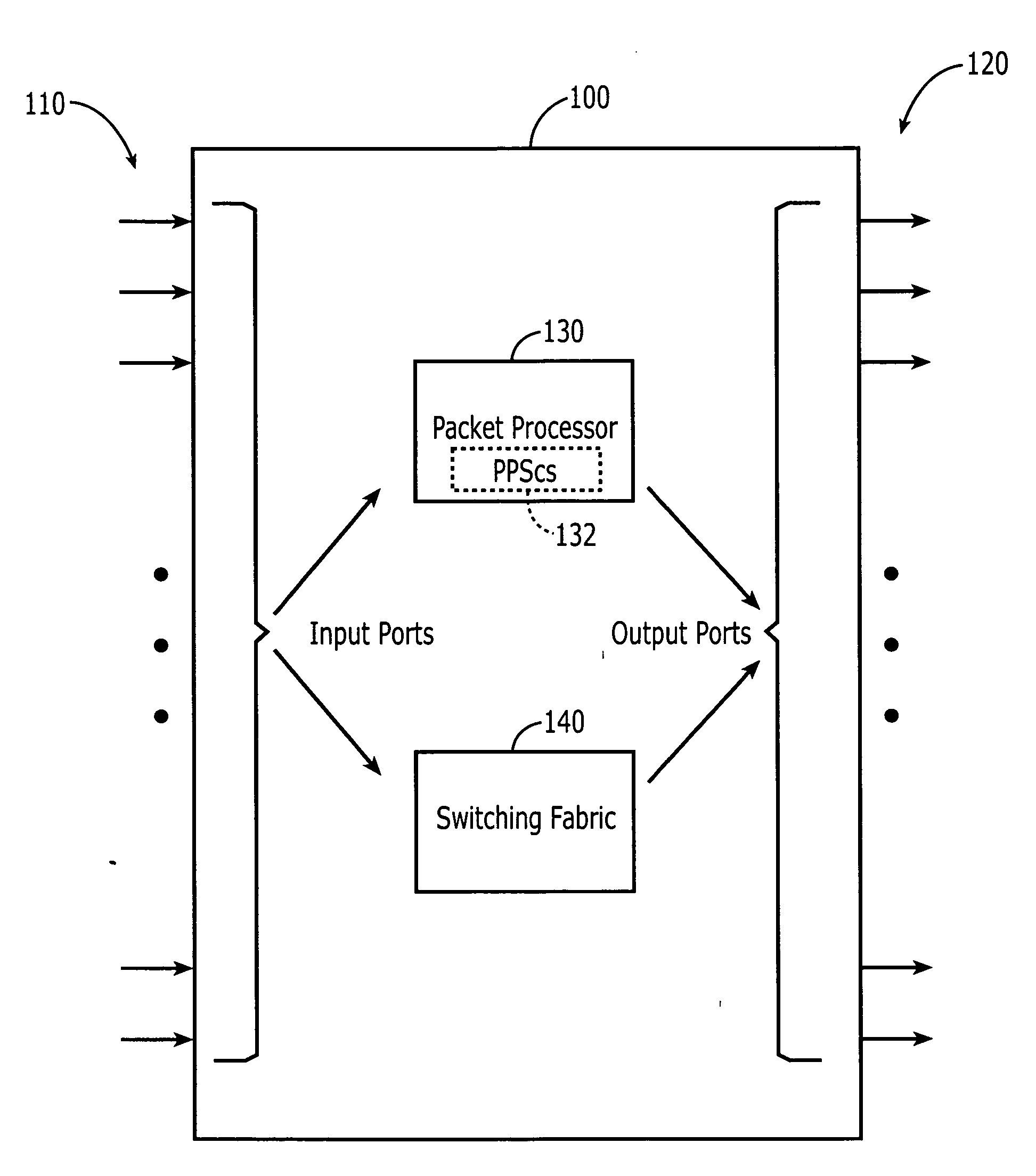

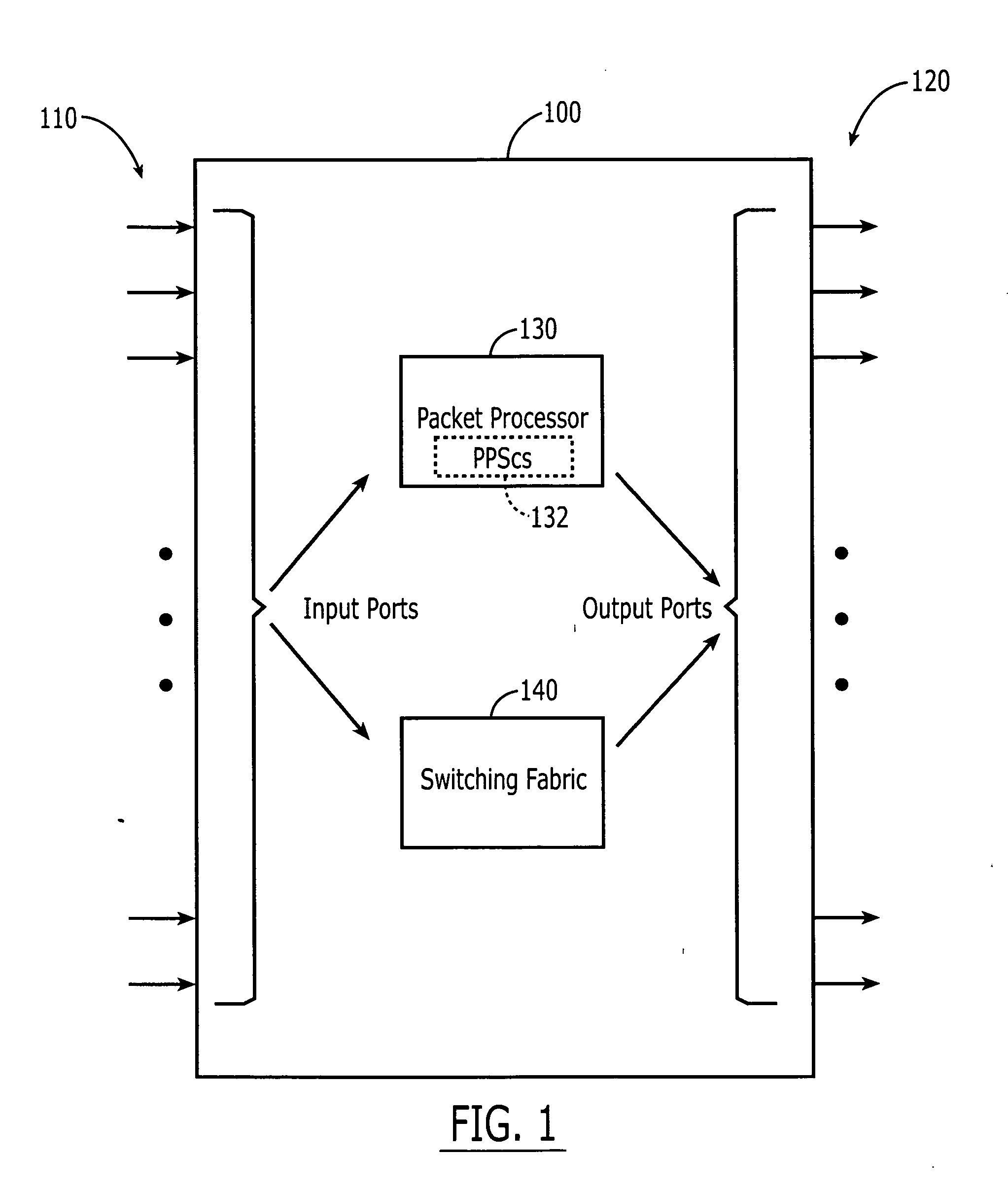

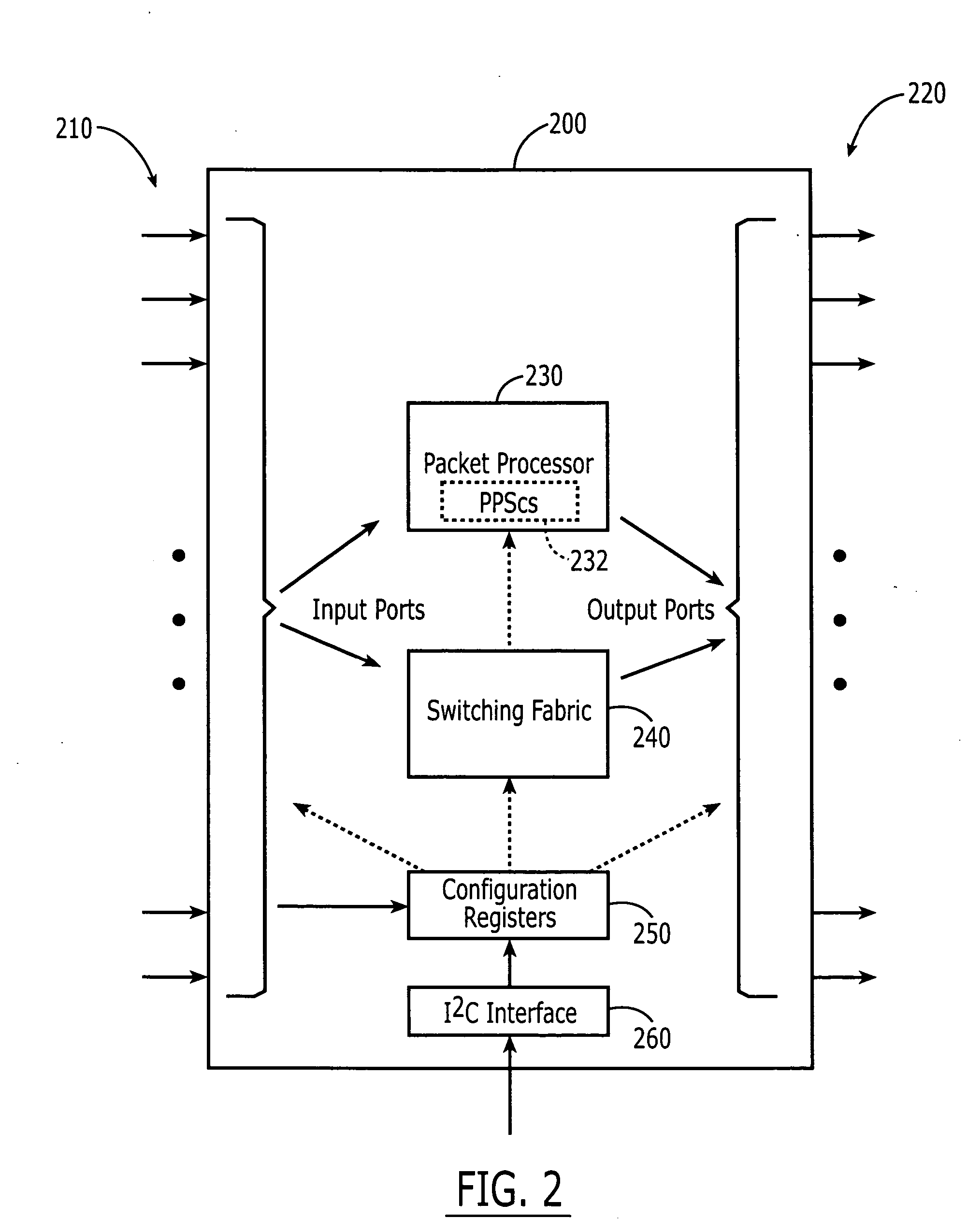

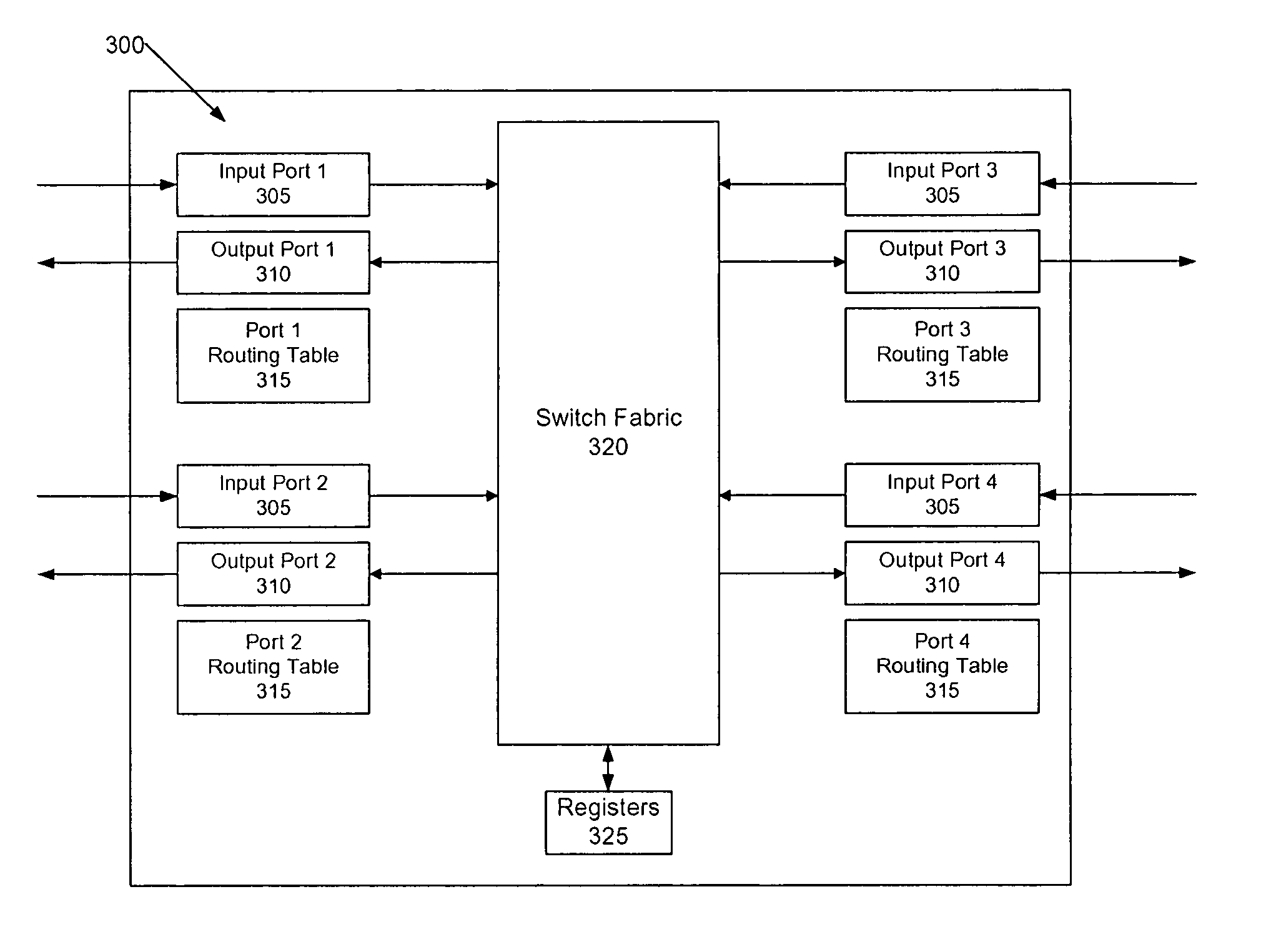

Packet processing switch and methods of operation thereof

ActiveUS20060248377A1Error detection/correctionData switching networksComputer scienceIntegrated circuit

A packet switching integrated circuit chip is configured to receive packets, e.g., RapidIO™-compliant packets, from a plurality of external sources, and selectively passes data in the received packets to a plurality of external recipients. The chip is configured to pass first received packets without modification and to terminate second received packets and preprocess payloads thereof to produce new packets. The chip may be configured to perform signal sample processing operations on the second received packets, such as bit extension, bit truncation, bit reordering and / or bit arithmetic operations. The chip may be further configured to manage the first and second received packets based on destination addresses in the received packets.

Owner:INTEGRATED DEVICE TECH INC

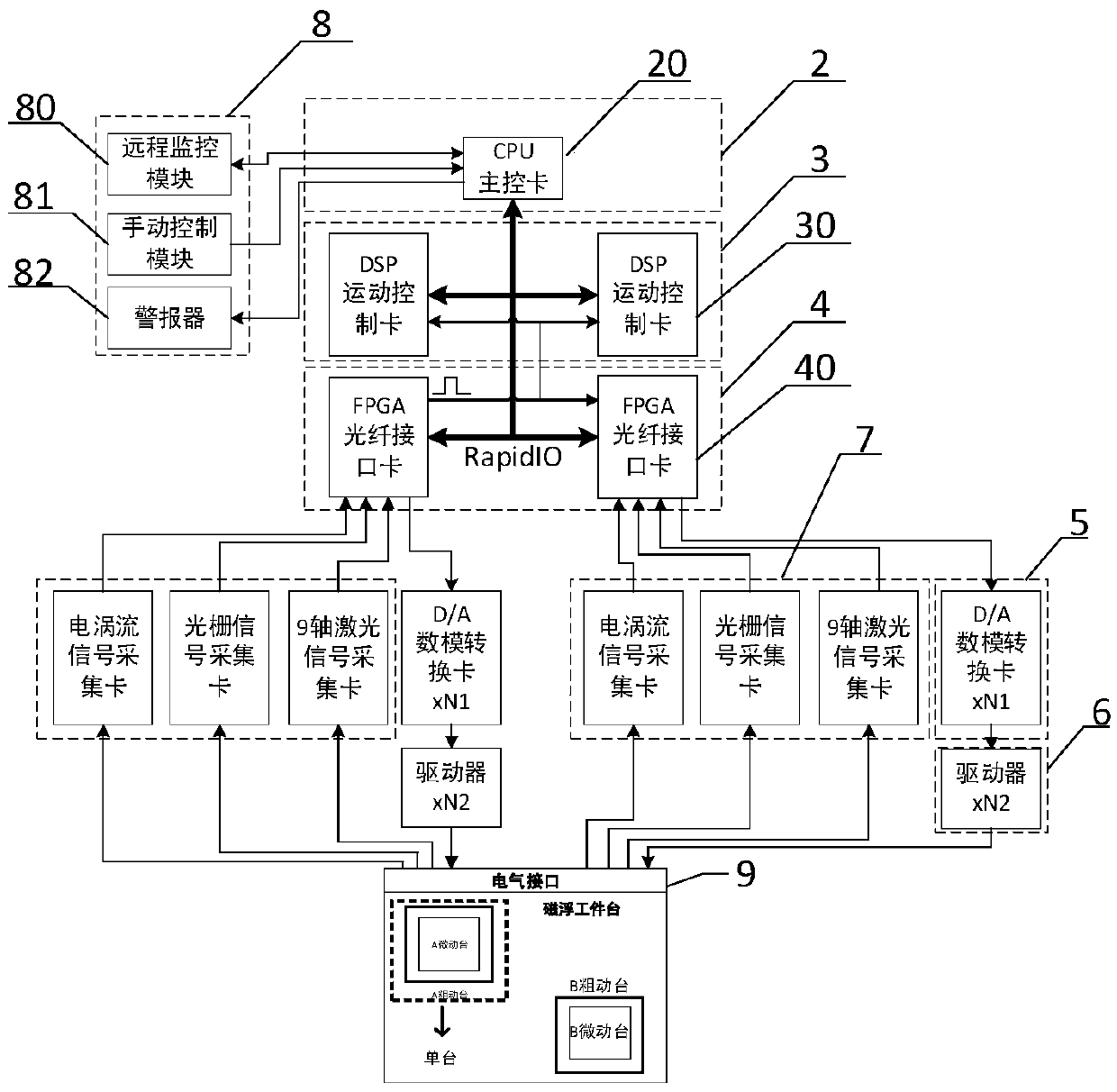

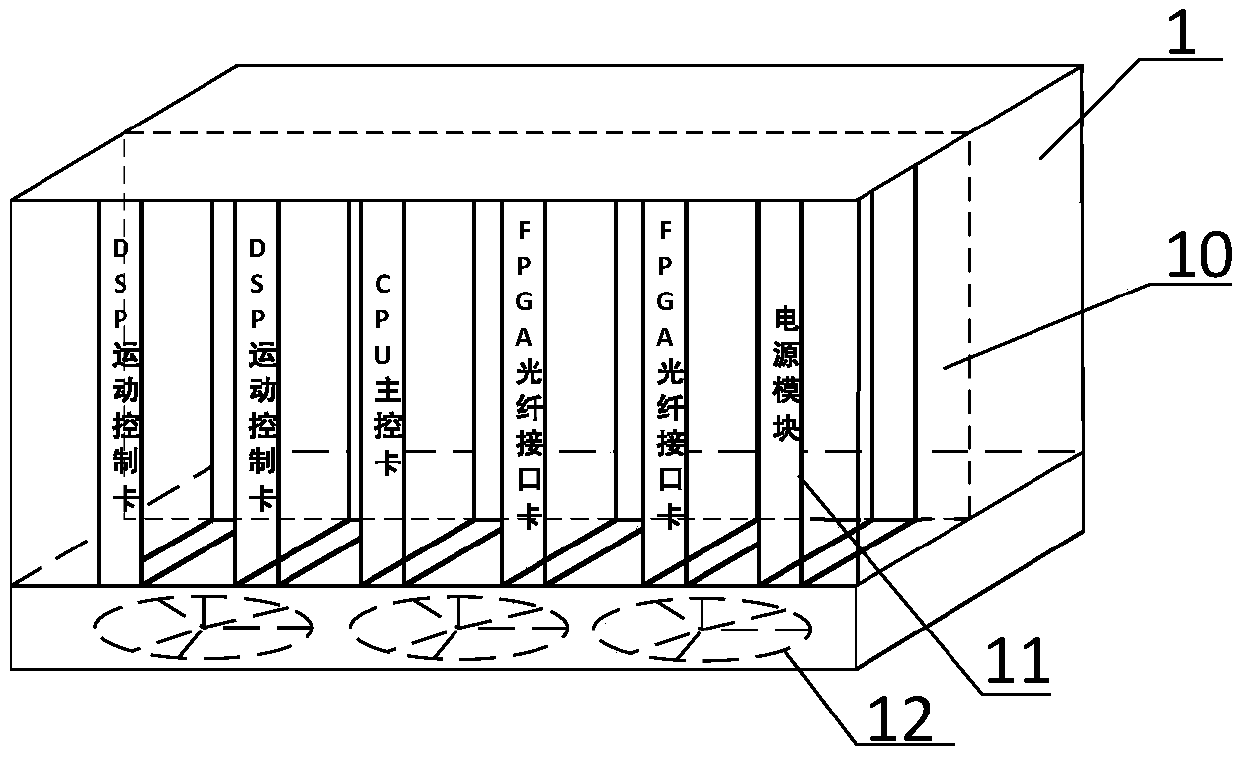

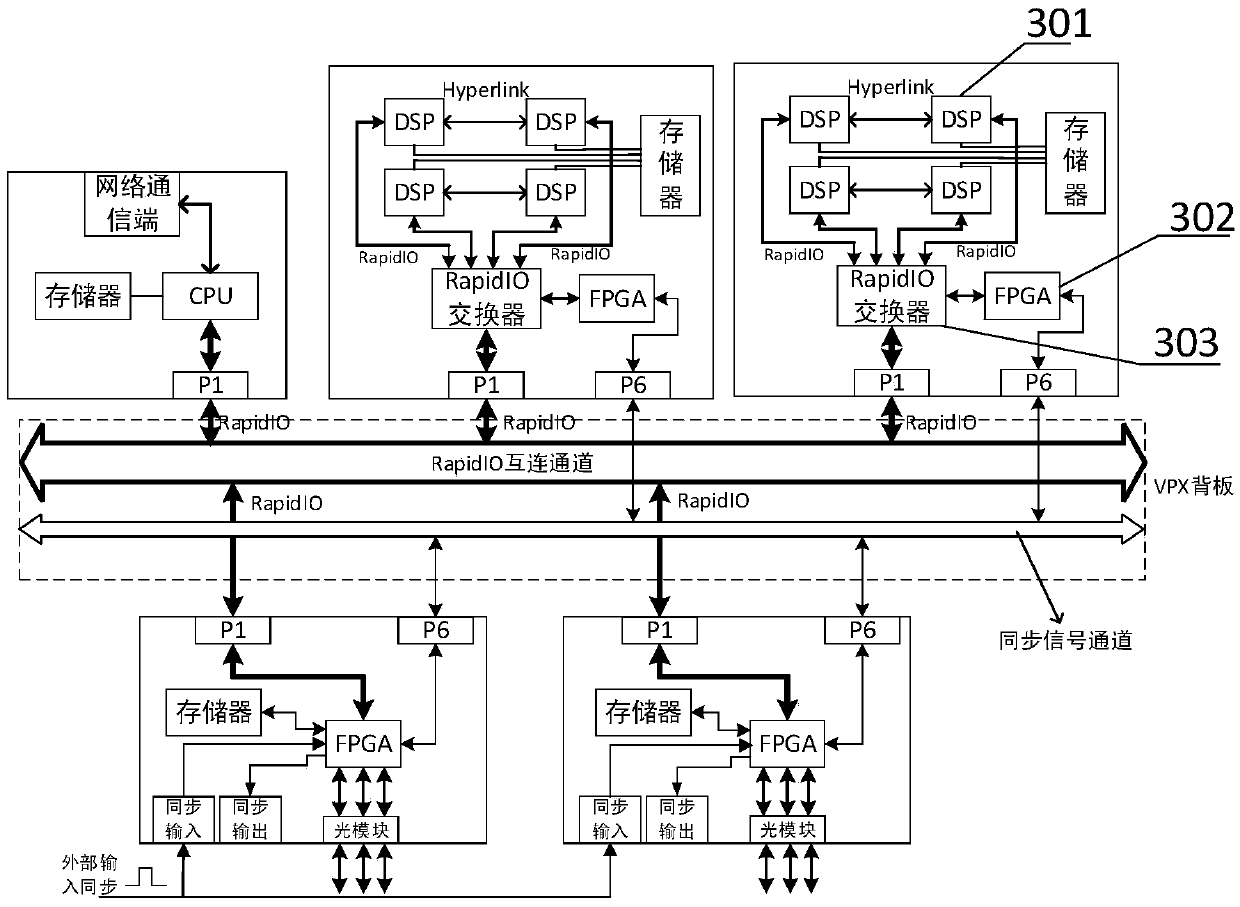

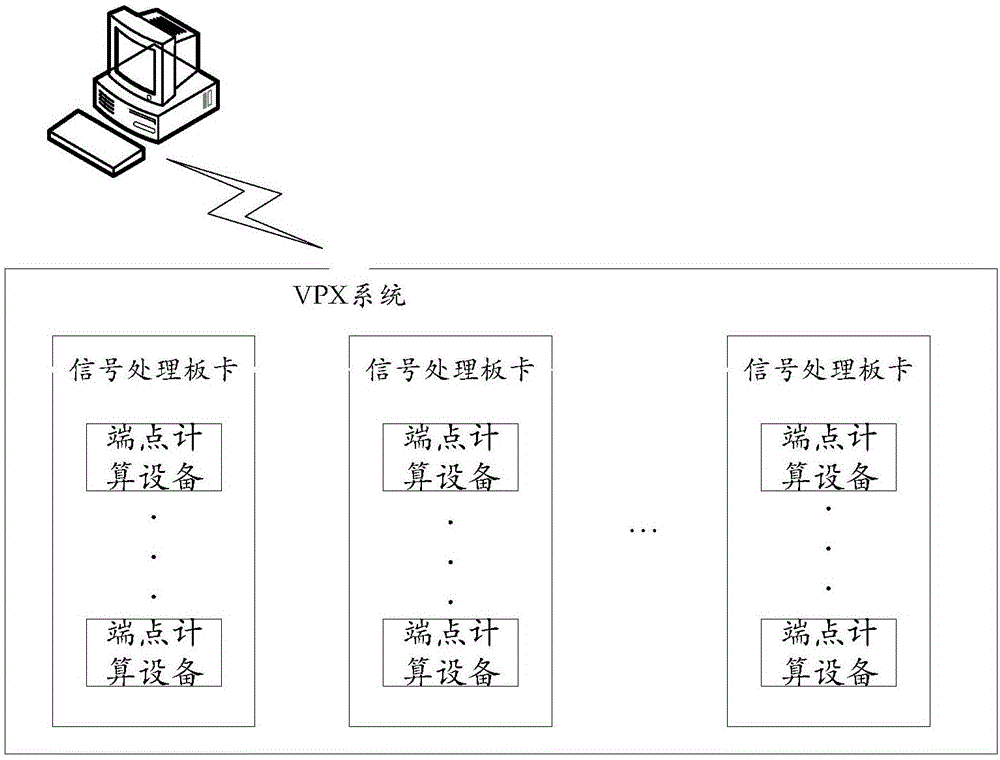

VPX bus-based workpiece bench synchronous motion control system and method

ActiveCN105511502AHigh speed transmissionFlexible Interconnect ArchitectureControl using feedbackPhotomechanical exposure apparatusMechanical equipmentMotor Drive Unit

The invention relates to a VPX bus-based workpiece bench synchronous motion control system and method and belongs to the semiconductor precision mechanical equipment motion control system technical field. The motion control system includes a VPX bus chassis, a CPU main control unit, a motion control unit, an optical fiber interface unit, a power amplifier unit, a motor driving unit, a measuring unit and a man-machine interaction unit. The VPX bus-based workpiece bench synchronous motion control system of the invention can be suitable for different platforms with a large number of motor shafts, a large quantity of information, complicated control algorithms and the like. According to the control system, high-speed interconnection of a plurality of processors of the system can be realized through a RapidIO bus architecture; feedback data calculation can be completed in real time and fast through the multi-core DSP motion control unit; and communication of various paths of data can be realized through the optical fiber interface unit. Compared with the prior art, the control system not only can load complex control algorithms, but also has a flexible network topological structure, high real-time performance, high-speed data transmission ability and powerful data processing ability.

Owner:TSINGHUA UNIV +1

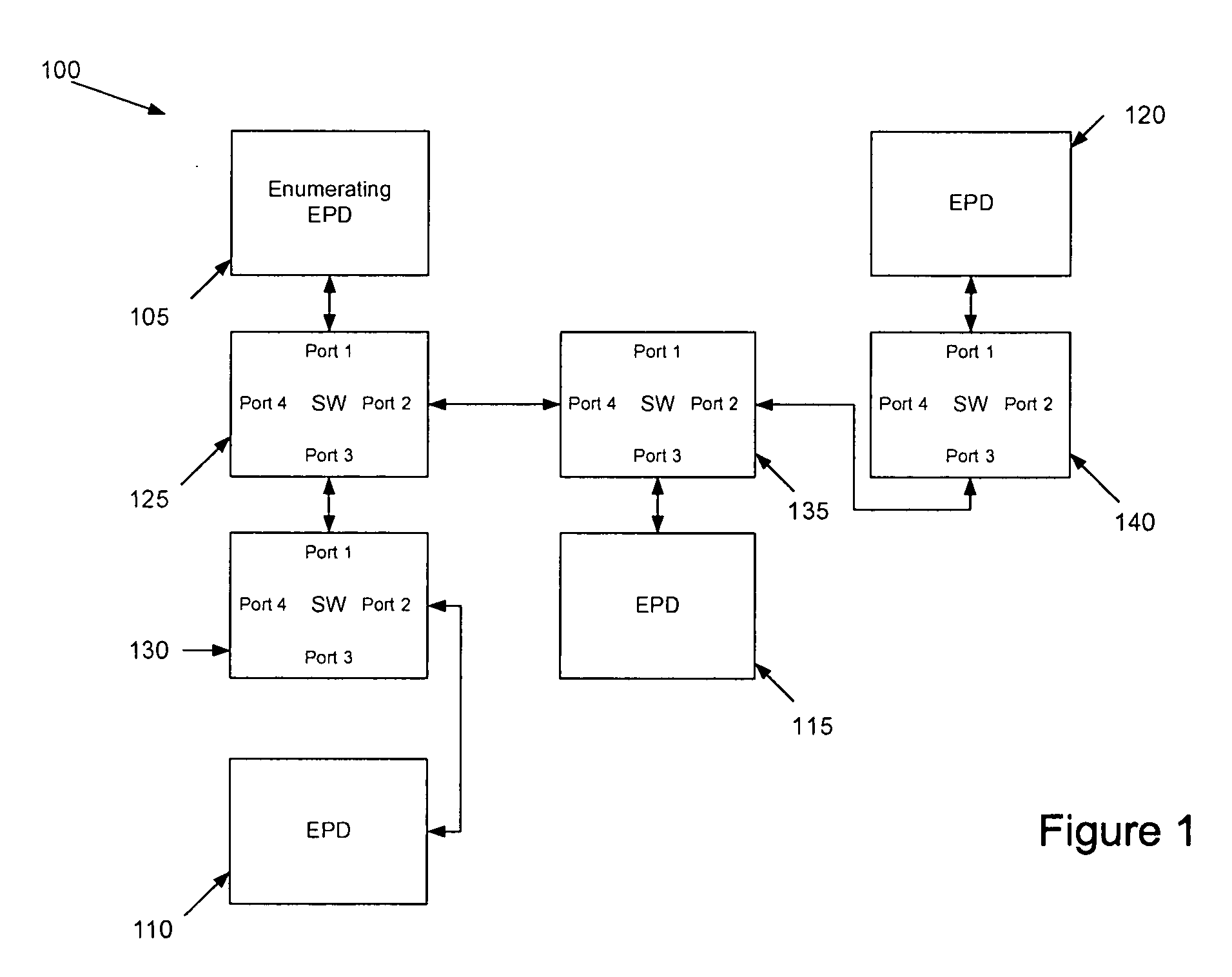

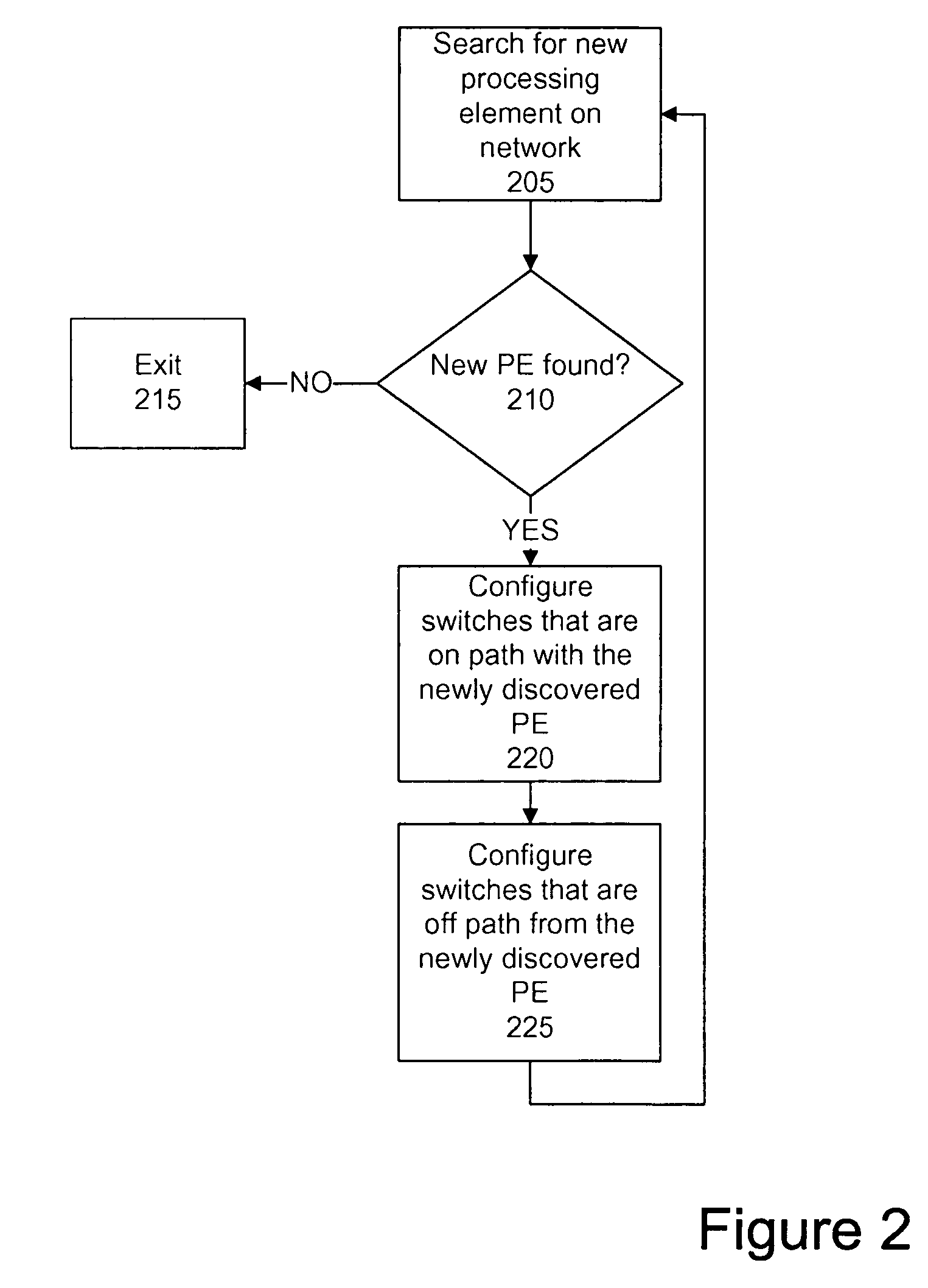

System for configuring switches in a network

ActiveUS20070097881A1Data switching by path configurationNetwork connectionsProcessing elementEmbedded system

A network is set forth that comprises a plurality of multiple port switches, a plurality of endpoint devices connected to the ports of the plurality of switches, and an enumerating endpoint device that is connected to at least one of the multiple port switches. The enumerating endpoint device configures the routing through the multiple port switches based on whether the multiple port switch is on path with respect to a newly discovered processing element or off path with respect to the newly discovered processing element. Each off path switch may be configured so that communication packets destined for the new processing element are routed through the port of the off path switch that the off path switch uses for communications with the enumerating endpoint device. Each on path switch may be configured so that communication packets destined for the newly discovered processing element are routed through the port of the on path switch at which the enumerating endpoint device discovered the new processing element. In one example, the network is implemented as a RapidIO network.

Owner:BLACKBERRY LTD

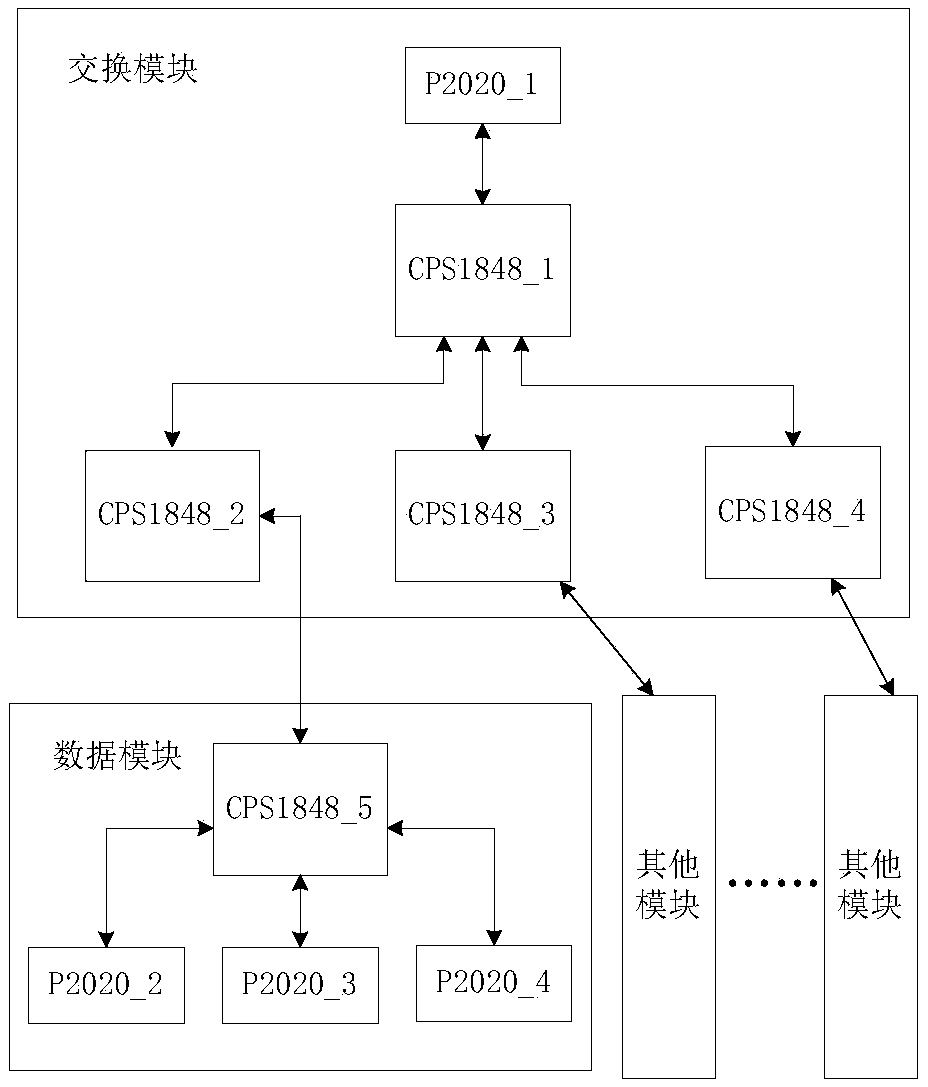

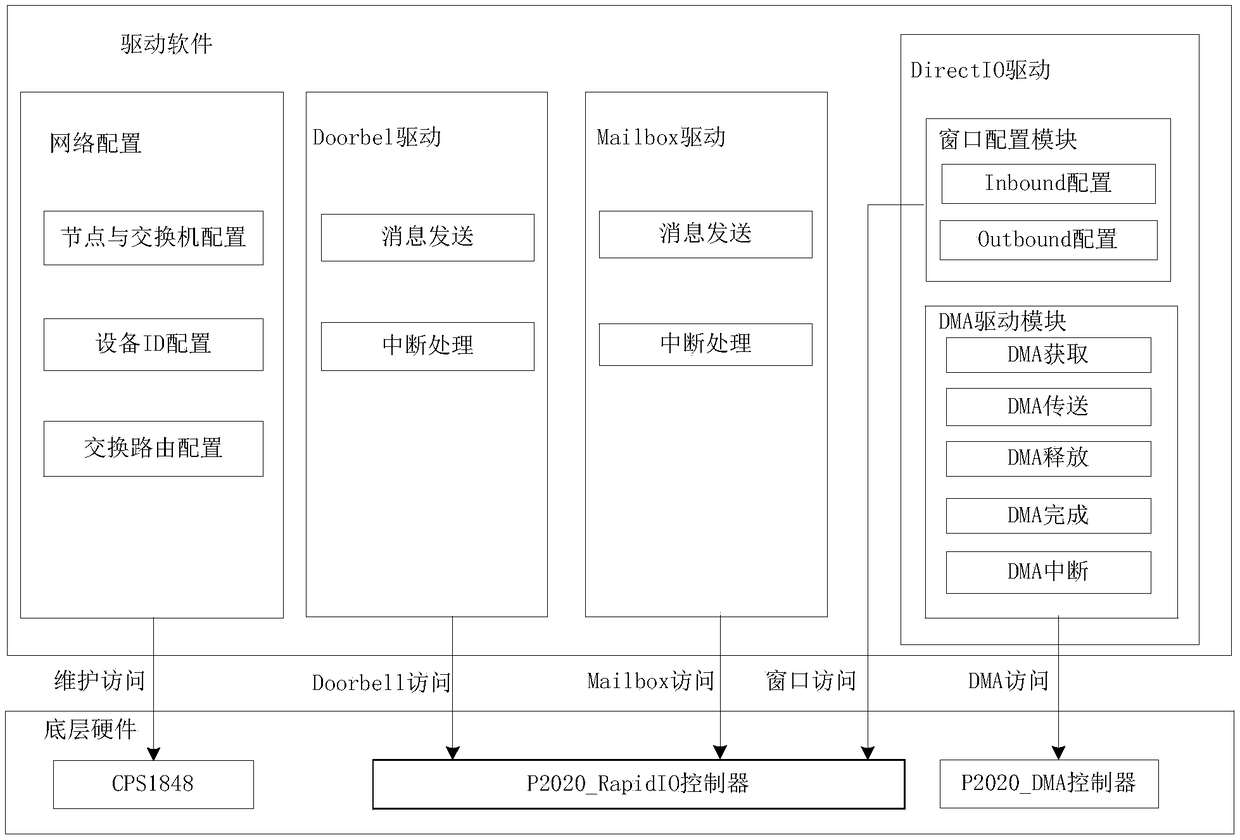

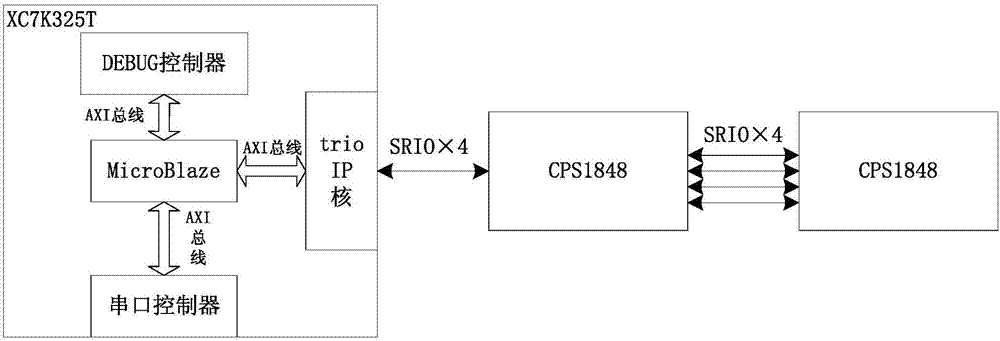

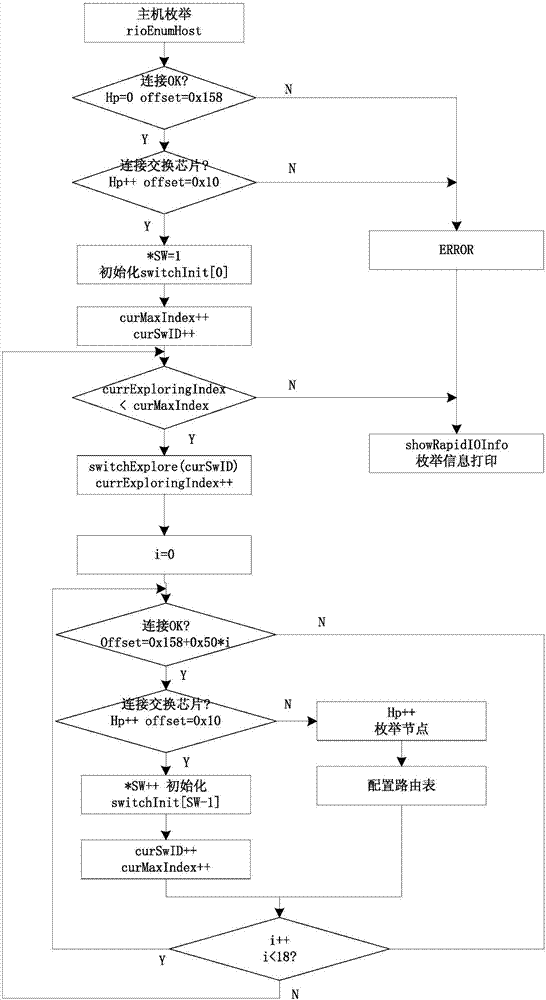

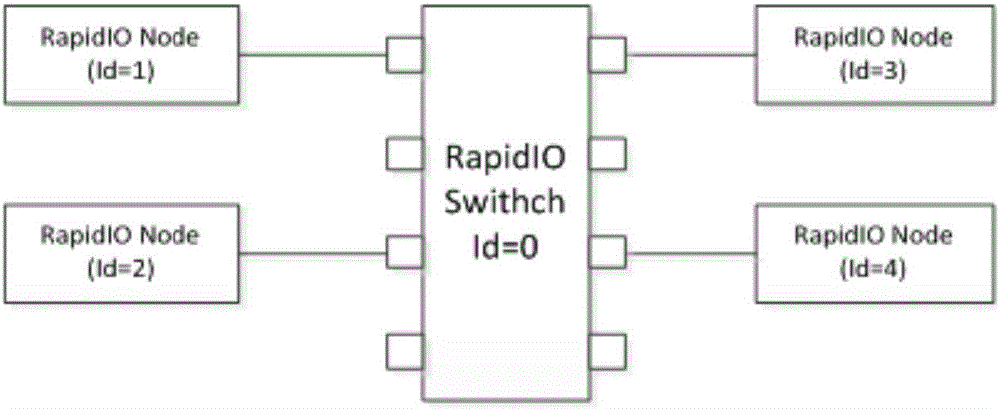

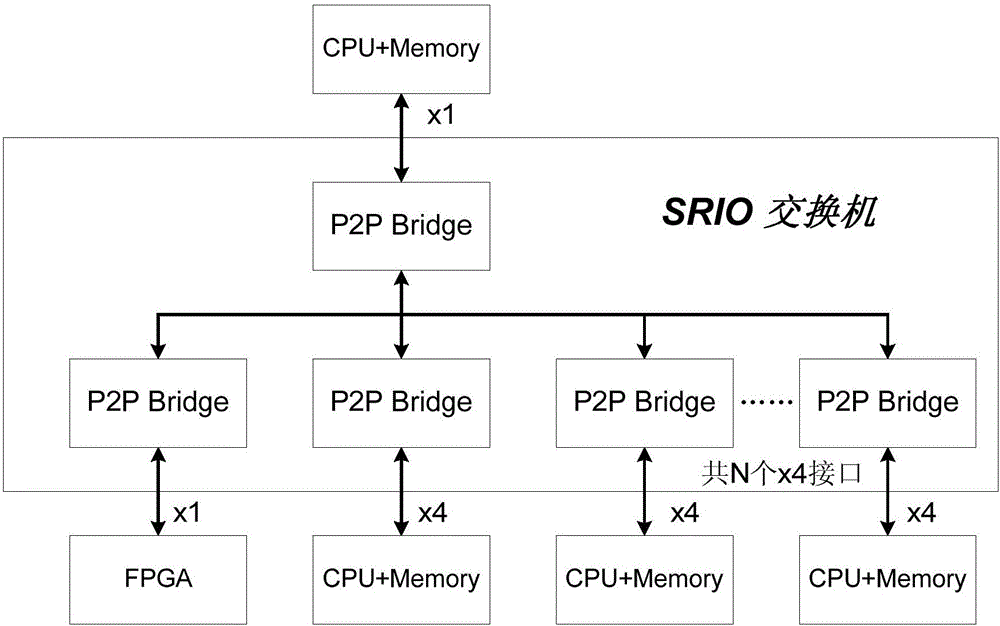

Rapid IO switching network

The invention discloses a rapid IO switching network, which is composed of a plurality of P2020 processing chips as nodes and a plurality of CPS1848 switching chips as switches. As the master node, the P2020 processor uses DFS algorithm to search the whole network topology in the initialization process, Enumerate all RapidIO devices in the network, get the number of nodes and switches and the connection relationship between the devices, on this basis, dynamically configure the routing table to complete the network initialization configuration. Each terminal node in RapidIO network realizes thehigh-speed data communication among Doorbell, Mailbox and DirectIO nodes by configuring its own registers. The invention realizes the function of RapidIO networking communication, and provides support for wide application of RapidIO bus in modern avionics system.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

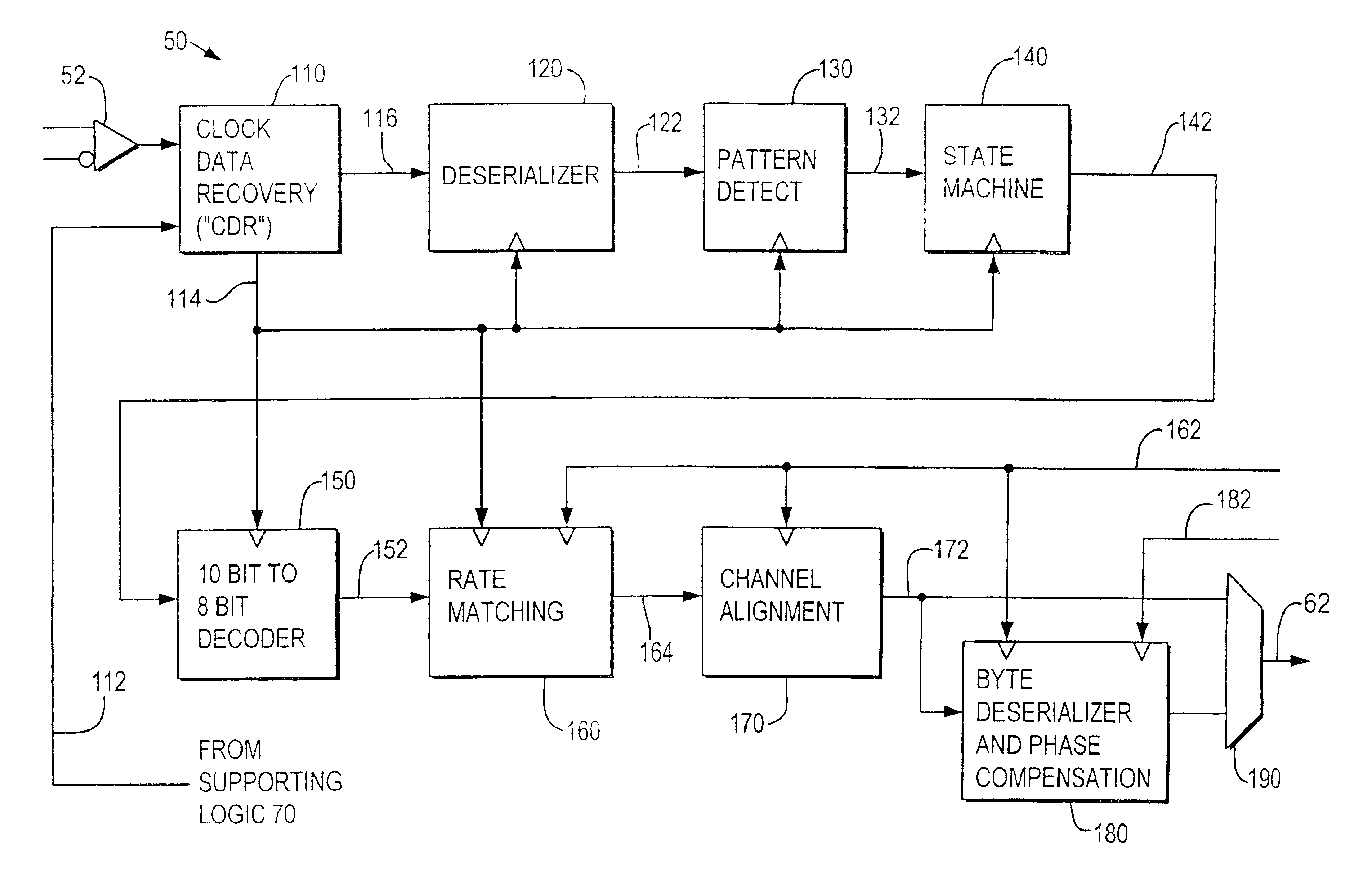

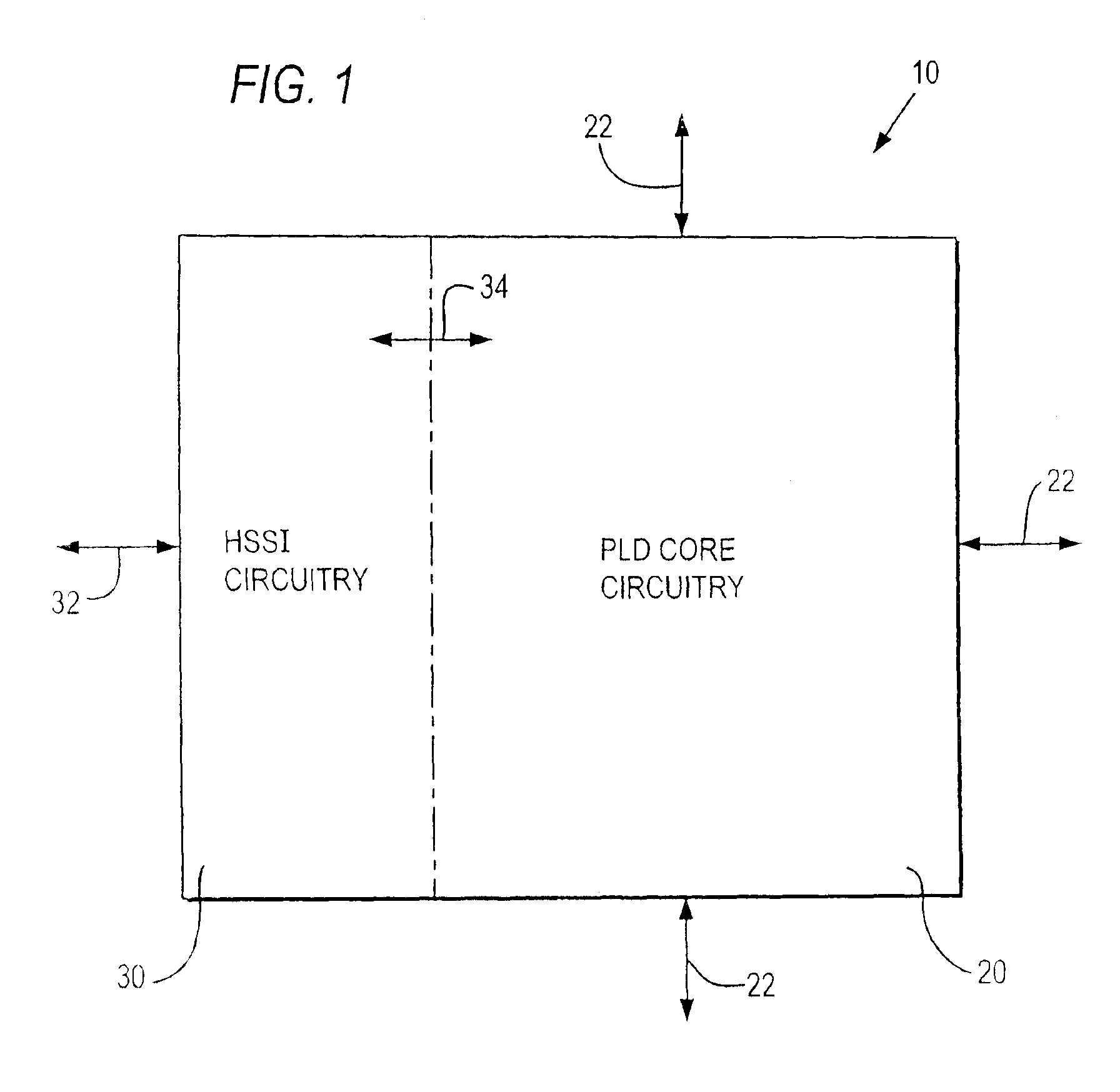

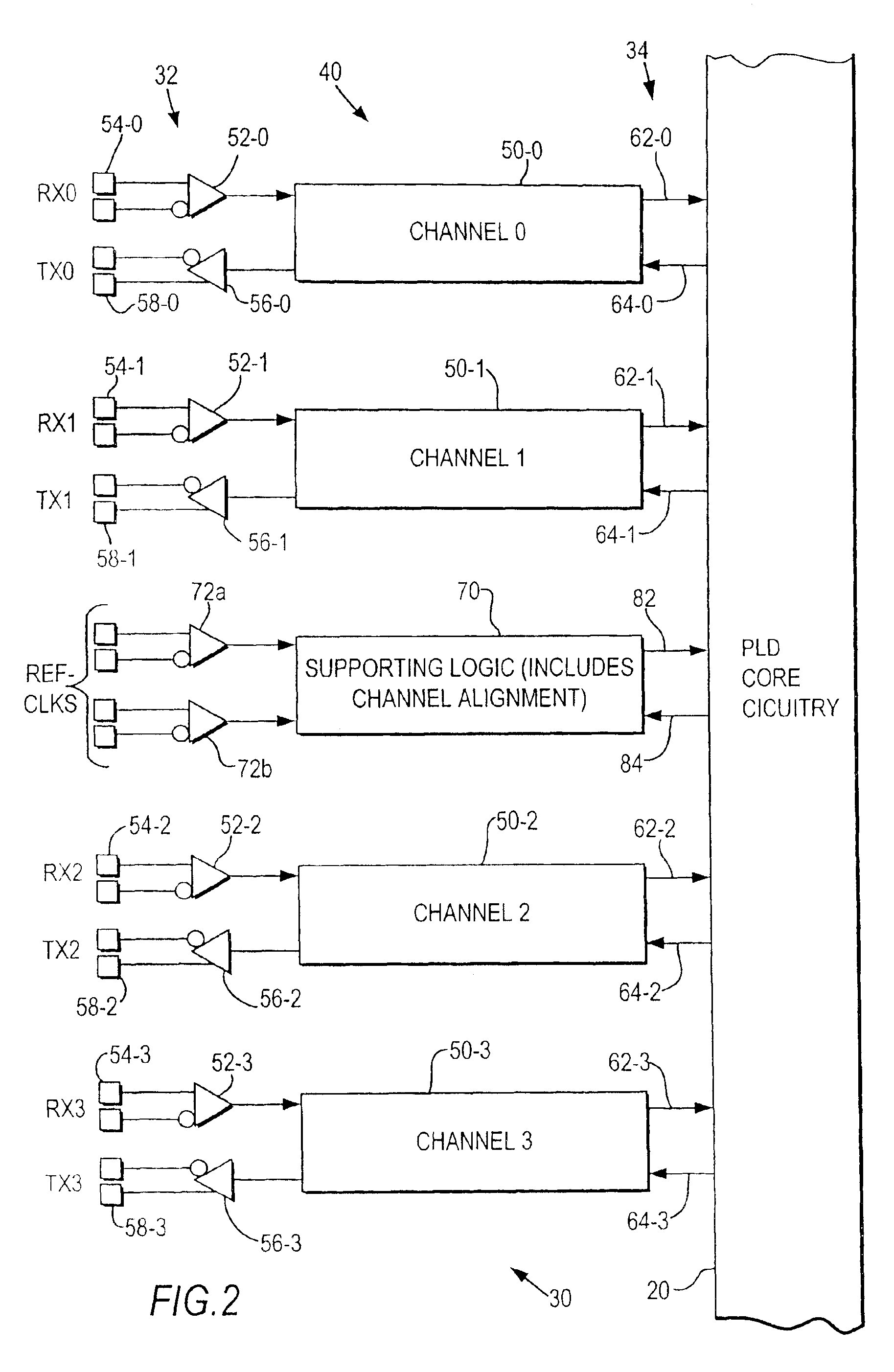

Programmable logic device with high speed serial interface circuitry

InactiveUS6911841B2Logic circuits using elementary logic circuit componentsComputation using denominational number representationXAUIProgrammable logic device

A programmable logic device (“PLD”) includes high speed serial interface (“HSSI”) circuitry that can support several high speed serial (“HSS”) standards. Examples of the standards that can be supported are XAUI, InfiniBand, 1G Ethernet, FibreChannel, and Serial RapidIO. The HSSI circuitry may be partly programmable to support these various standards. In some cases control may come from the associated PLD core circuitry. Also in some cases some of the interface functions may be performed in the PLD core circuitry.

Owner:ALTERA CORP

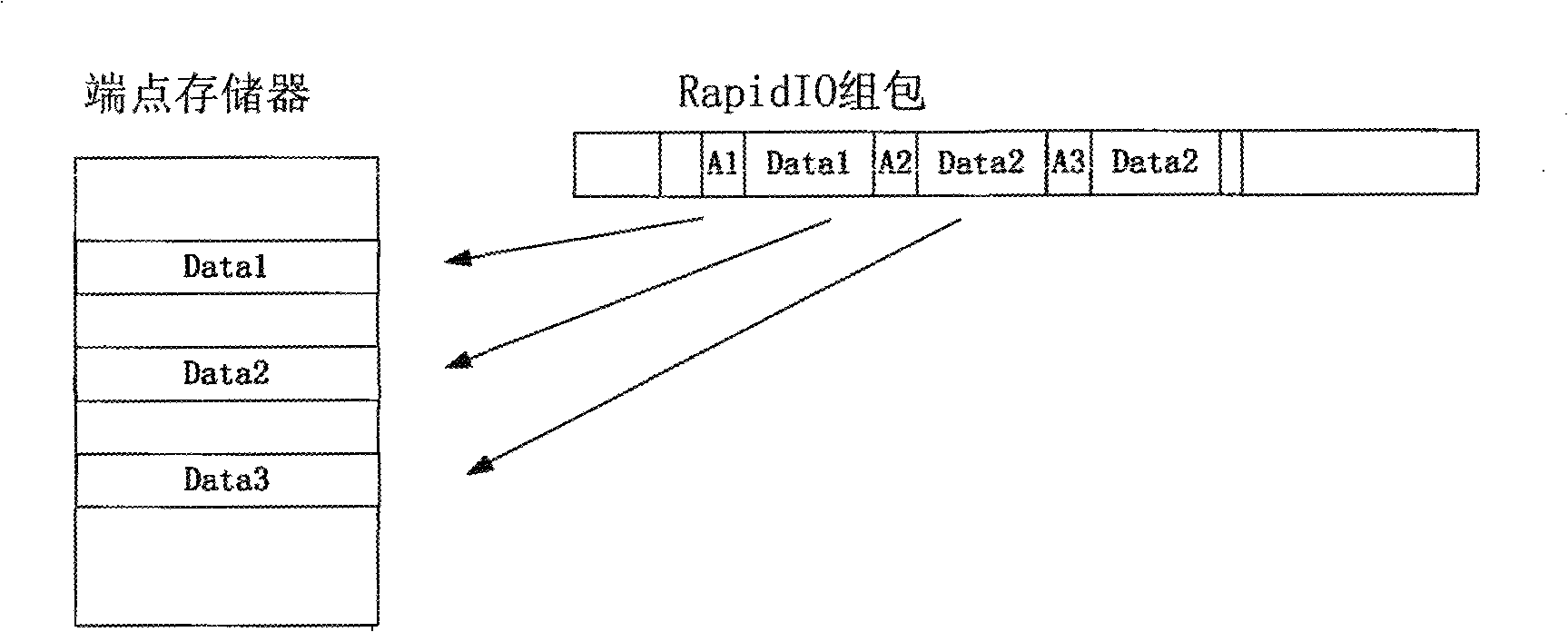

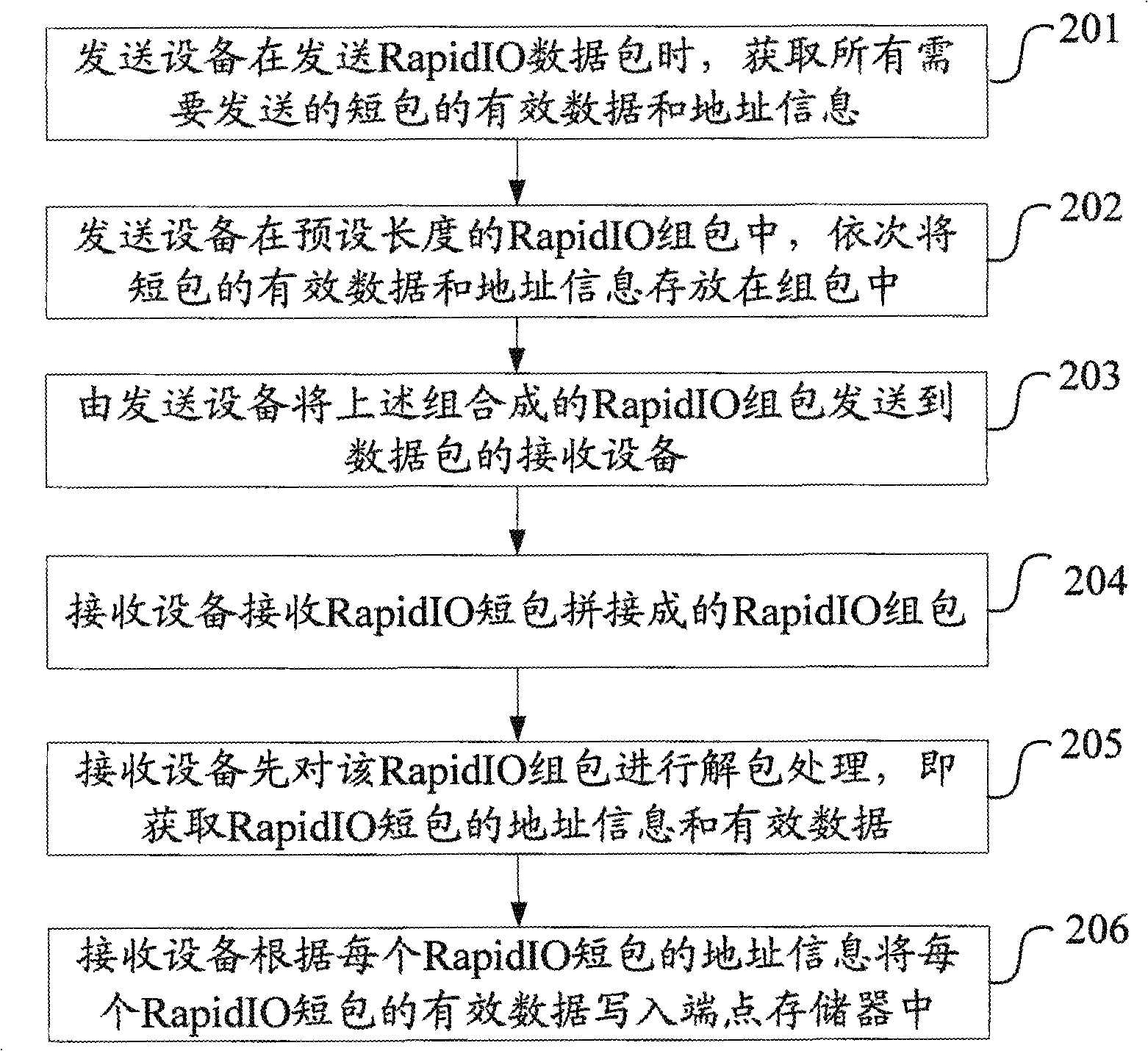

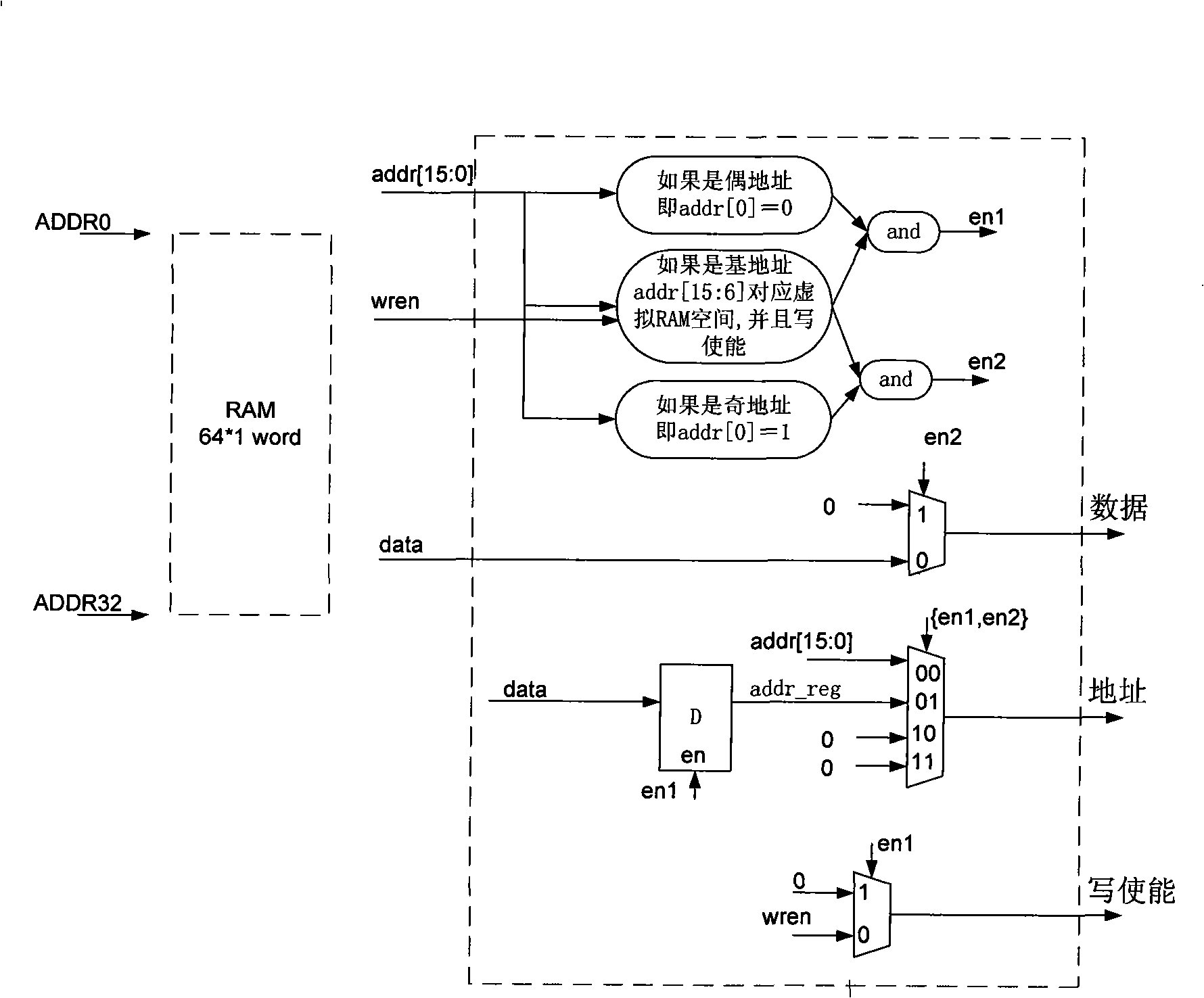

Method for data packet transmission based on RapidIO, device and system

ActiveCN101515841AReduce transmission delayImprove bandwidth utilizationError preventionData switching networksData informationTransmission delay

The invention discloses a method for data packet transmission based on RapidIO, a device and a system, belonging to the communication technical field. The method comprises steps: a RapidIO grouping packet transmitted by a transmitting apparatus is received, the valid data of the grouping packet comprises the data information of at least two RapidIO short packets which are stored in a seamless way; the data information of the RapidIO short packets in the RapidIO grouping packet is acquired; the RapidIO short packets are stored in an endpoint memory according to the data information of the RapidIO short packets. A receiving device comprises a receiving module, an acquisition module and a storage module; the transmitting apparatus comprises the acquisition module, a combination module and a sending module. The system comprises the transmitting apparatus and the receiving device. The embodiment of the invention causes a plurality of RapidIO short packets to make up the RapidIO grouping packet for transmitting, can effectively shorten the transmission delay of most of RapidIO short packets, and increases the bandwidth utilization factor of the system and further the performance of the system.

Owner:HUAWEI TECH CO LTD

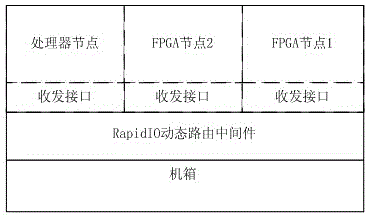

Data dynamic routing system and method based on RapidIO message mode

ActiveCN104363169AImprove scalabilityData communication has no effectData switching networksClient agentResource virtualization

The invention provides a data dynamic routing system and method based on a RapidIO message mode. A subscription and publication mechanism is adopted, an application component declares the required subscription or publication data type through a client agent, and a service agent instead of the application component itself decides where the data come and go. The system and method are mainly characterized in that information is irrelevant to a device address and is identified based on content, data subscription or publication can be achieved simply by identifying the data type, and a source address and a target address are not needed. Increase and decrease of the number of communication devices do not affect the operation of the system. Therefore, by the adoption of the data dynamic routing method based on the subscription and publication mechanism, middleware used for processing resource virtualization is obtained and located between the application component and hardware, a data receiving and sending interface provided by the middleware is called by an application program based on a total exchange RapidIO network, and then transparent data transmission between two nodes is achieved.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

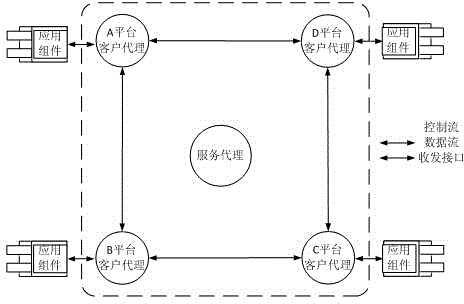

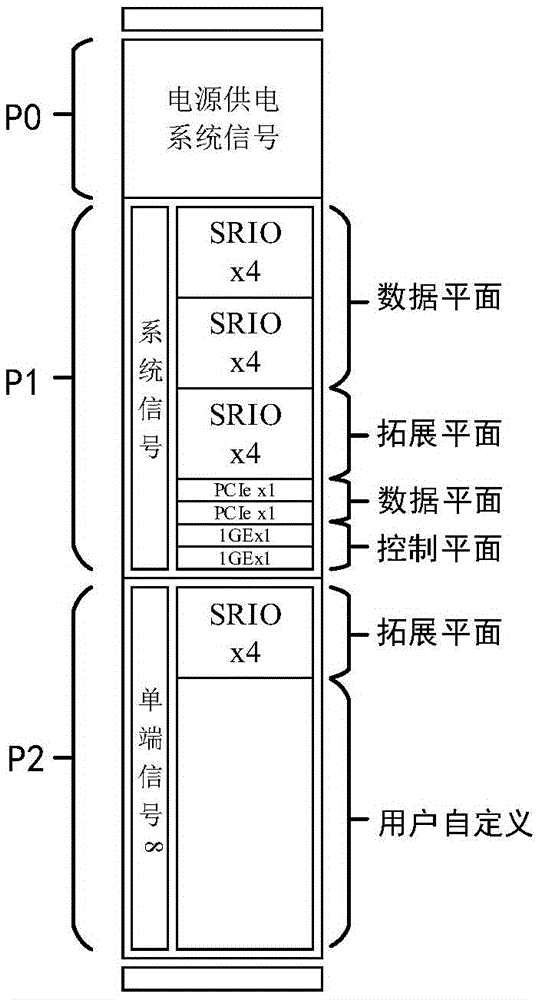

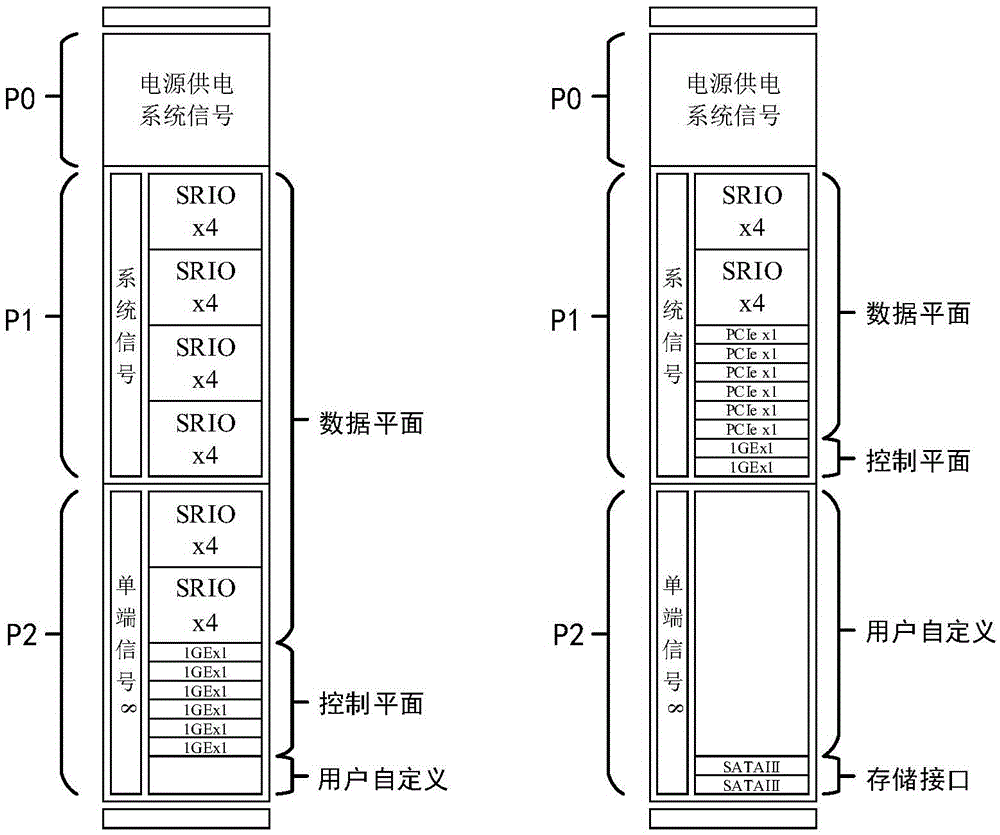

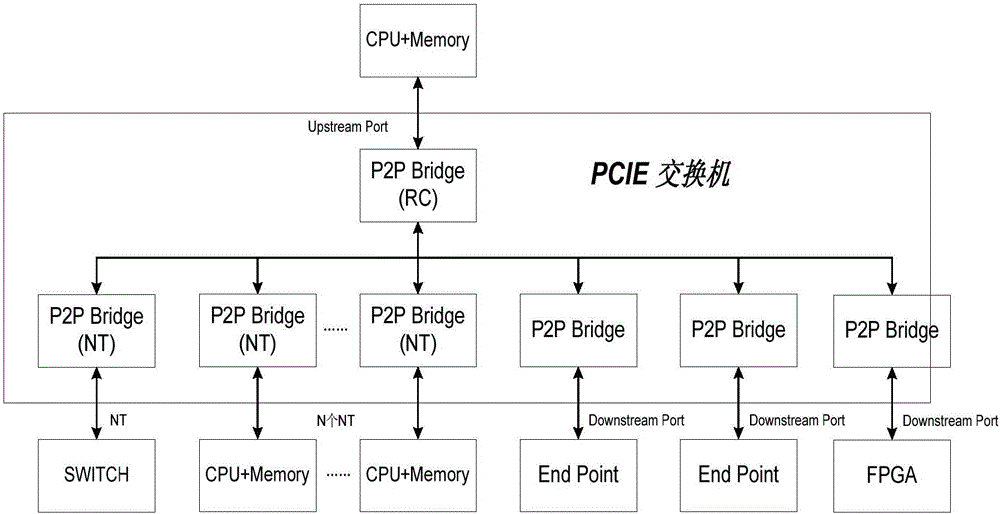

Adaptive variable redundancy 3U signal processing backboard based on VPX bus

InactiveCN105607694AImplement hot backupImprove good performanceDigital data processing detailsComputer scienceEthernet

The invention discloses an adaptive variable redundancy 3U signal processing backboard based on a VPX bus. Through two paths of SRIO (Serial RapidIO)x4 and two paths of PCIe (Peripheral Component Interface Express)x1, the dual redundancy point-to-point interconnection of high-speed data is realized; through two paths of 1GE (1GB Ethernet)x1, the dual redundancy point-to-point interconnection of a control command is realized; and through two paths of SRIOx4 and two paths of 1GEx1, data interaction between two master control switching boards is realized so as to realize the hot backup of the whole system. The whole signal processing backboard topology framework can expand the amount and the type of board cards supported by the backboard according to a current signal processing task, and therefore, the backboard exhibits good expansibility and flexibility, and can adapt to the tendency of current aerospace field development.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

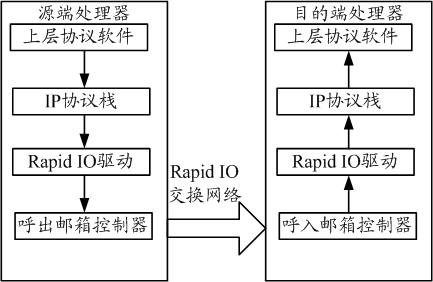

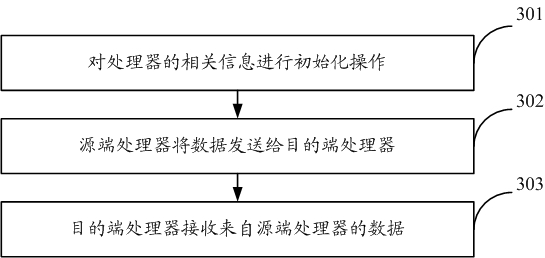

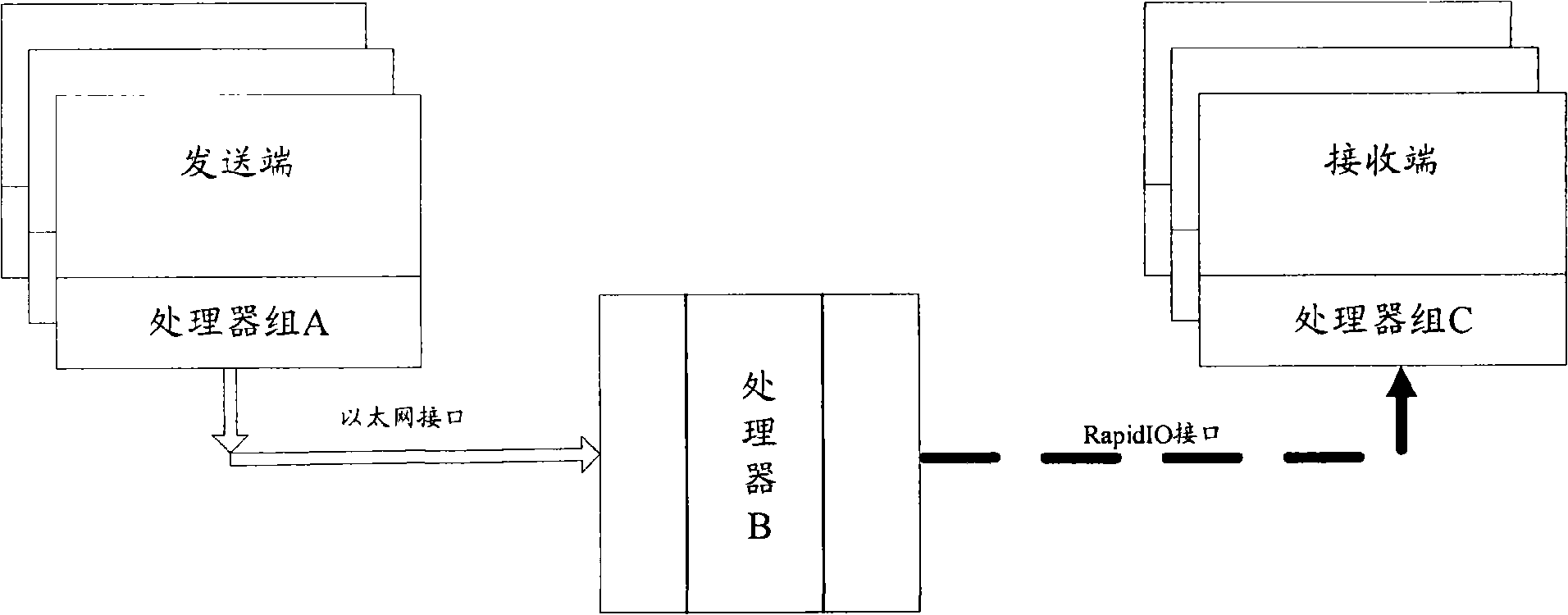

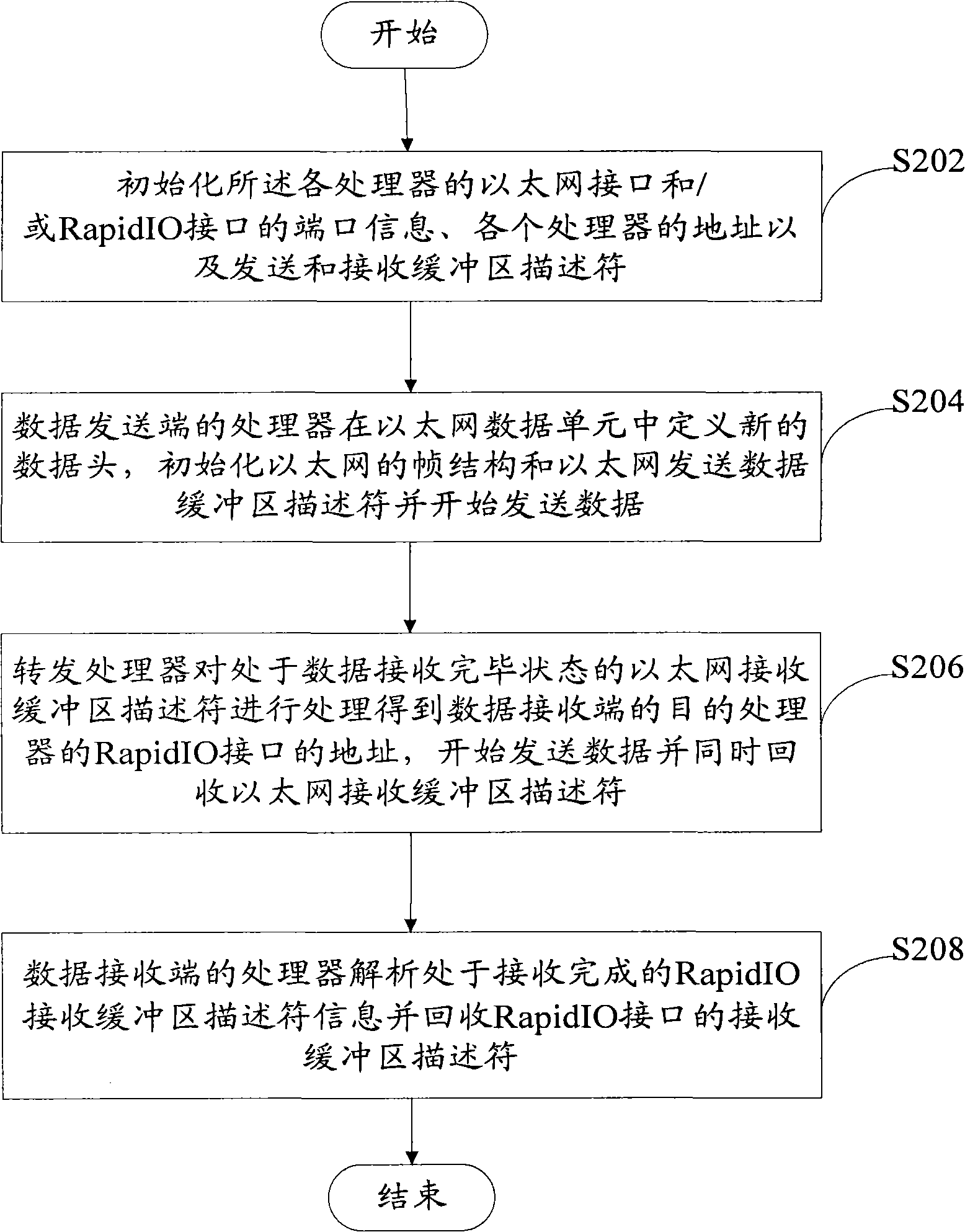

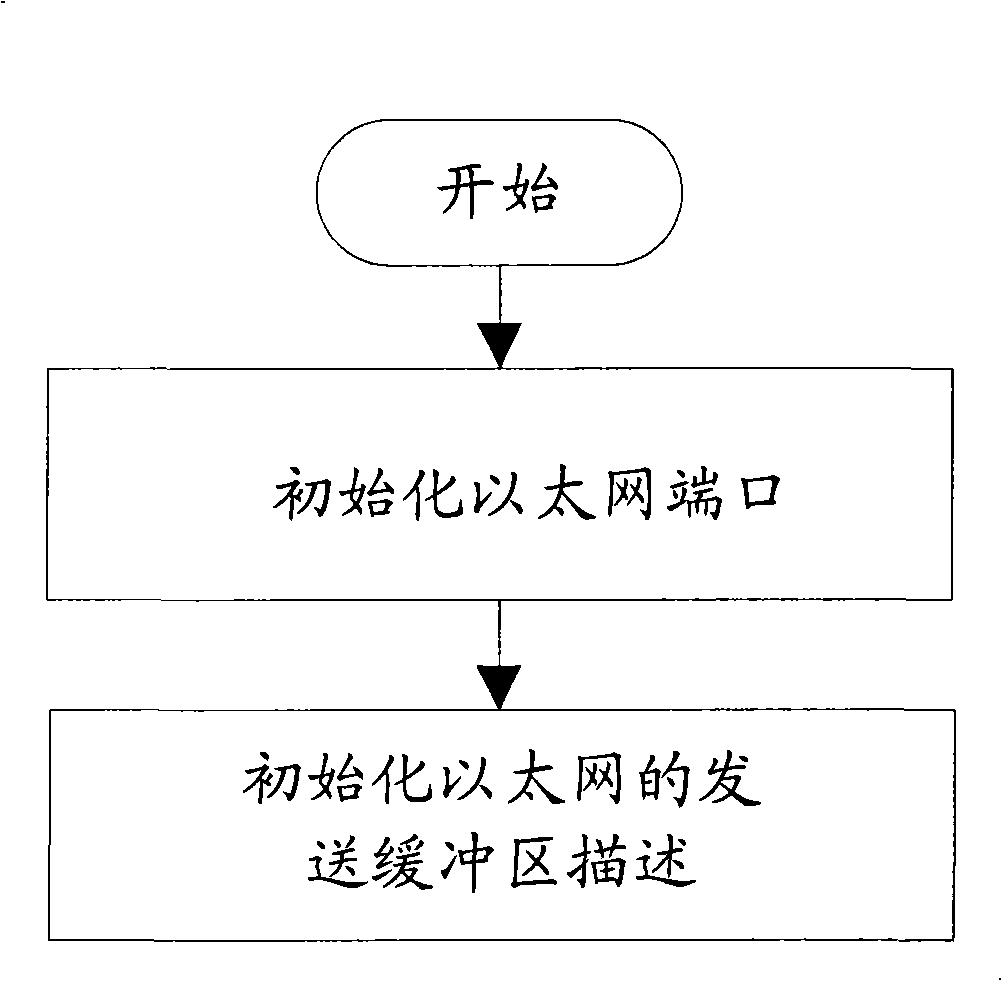

Data transmission method

InactiveCN101335667AReduce latencyReduce processing loadData switching by path configurationEthernetData transmission systems

The invention discloses a data transmission method which includes the steps that: S202, the topology structure of each processor in a data transmission system is determined, the port information of an Ethernet interface and / or a RapidIO interface of each processor, the address of each processor as well as a sending buffer zone descriptor and a receiving buffer zone descriptor of each processor are initialized. S204, the processor at a data sending end defines a new data head in an Ethernet data unit, the frame structure of Ethernet and a data sending buffer zone descriptor of the Ethernet are initialized and data sending is started. S206, a forwarding processor in the data transmission system receives the data coming from the data sending end and processes the receiving buffer zone descriptor of the Ethernet, which is in the state that data receiving is completed, to obtain the address of the RapidIO interface of a purpose processor at a data receiving end, the data sending is started and the receiving buffer zone descriptor of the Ethernet is recycled simultaneously. S208, the processor at the data receiving end analyzes information of the RapidIO receiving buffer zone descriptor in the state that the data receiving is completed, and recycles the receiving buffer zone descriptor of the RapidIO interface.

Owner:ZTE CORP

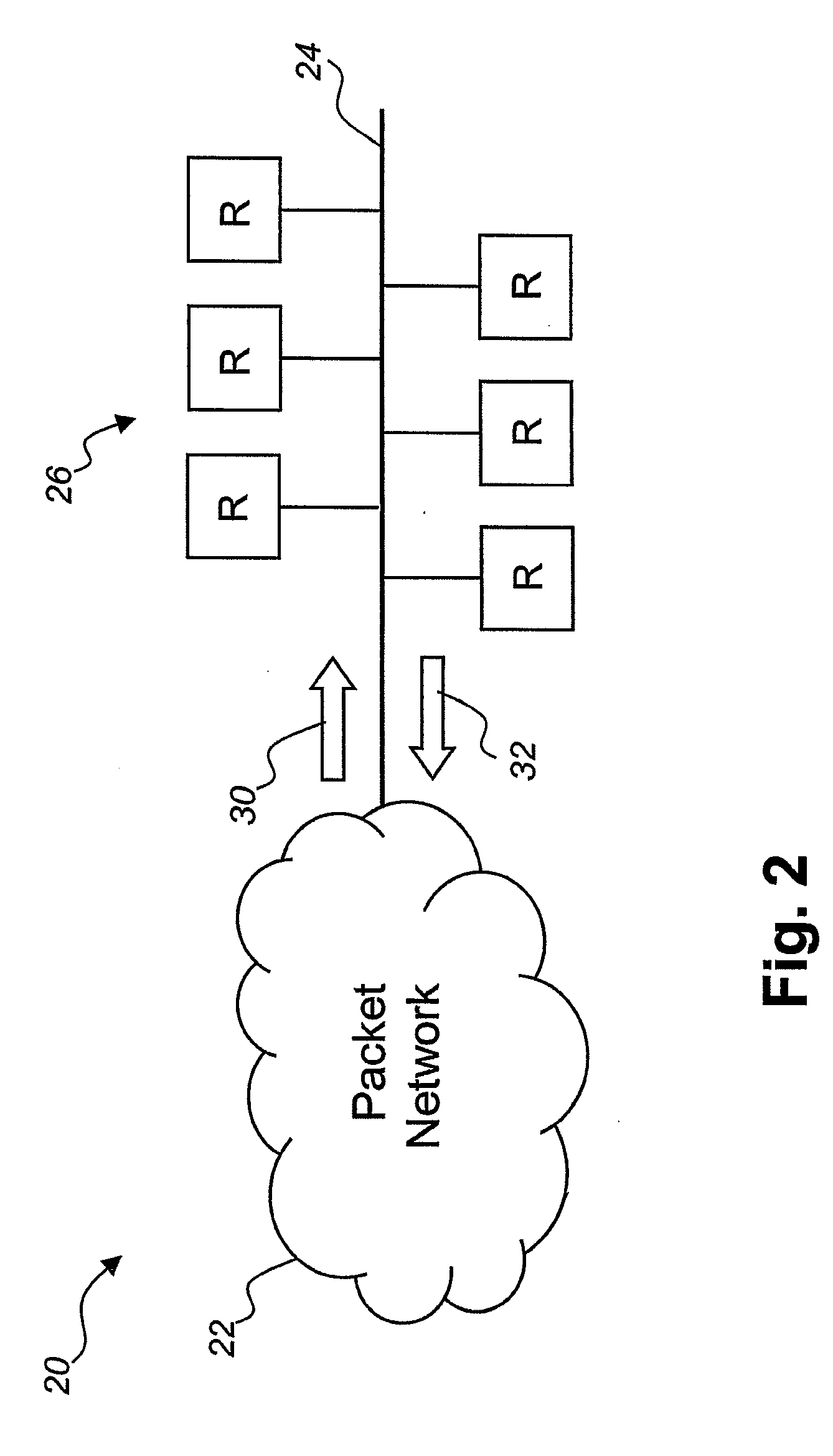

Data Communications Network

InactiveUS20090262732A1Reliable deliveryNetwork traffic/resource managementData switching by path configurationNetwork packetRapidIO

In a system comprising a first subsystem having a first plurality of nodes connected through an interconnect providing unreliably delivery (URD) of packets and a second subsystem having a second plurality of nodes connected through a packet-based interconnect offering reliable delivery of packets, a method of communicating comprising the step of transporting in both the first and second subsystem, a common packet format. The URD and packet interconnects conform with a standard. The standard is Serial RapidIO. The first subsystem places a Serial RapidIO idle sequence after each packet. The first subsystem places the Serial RapidIO idle sequence after a Multicast Event Control Symbol (MECS).

Owner:IDT CANADA

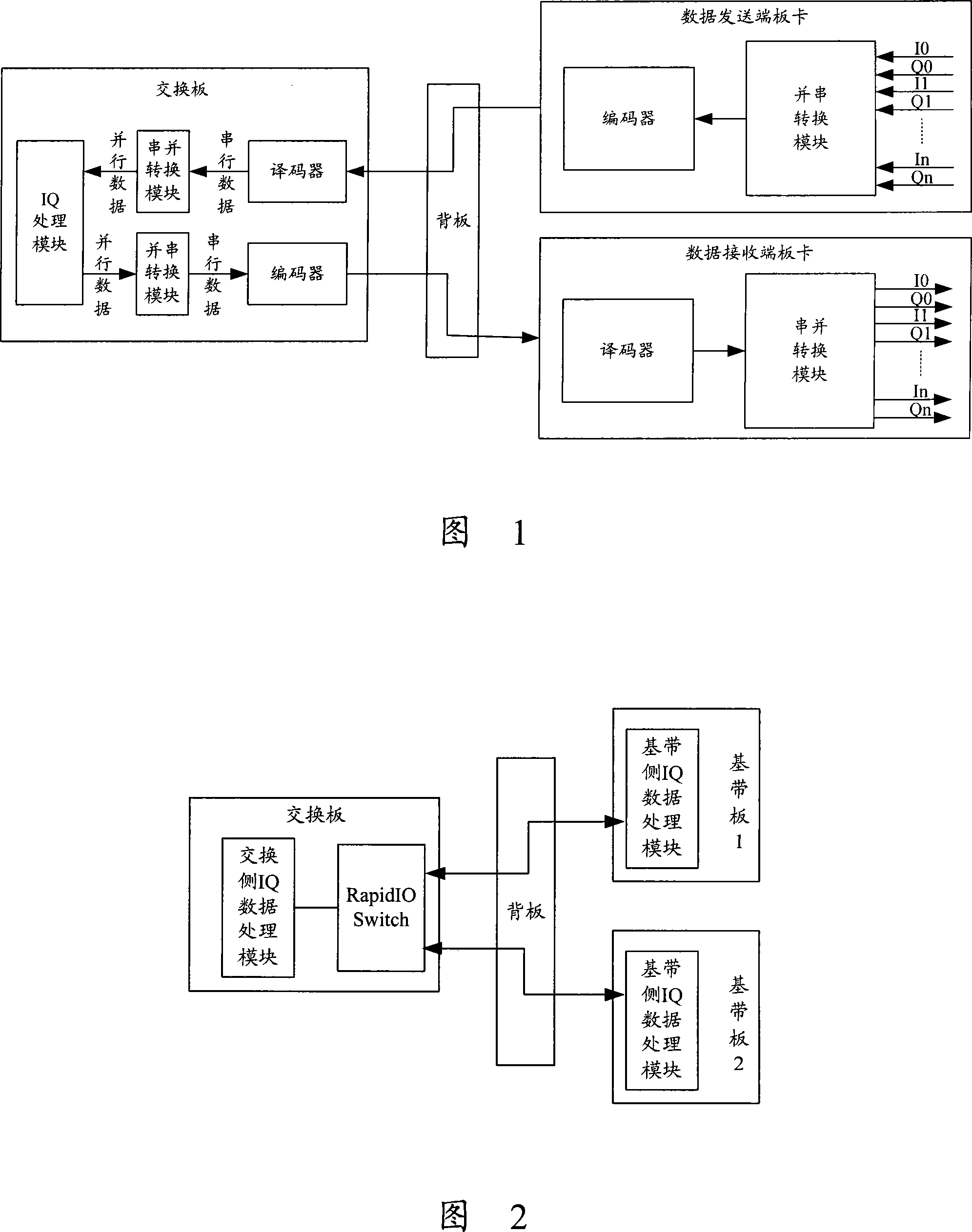

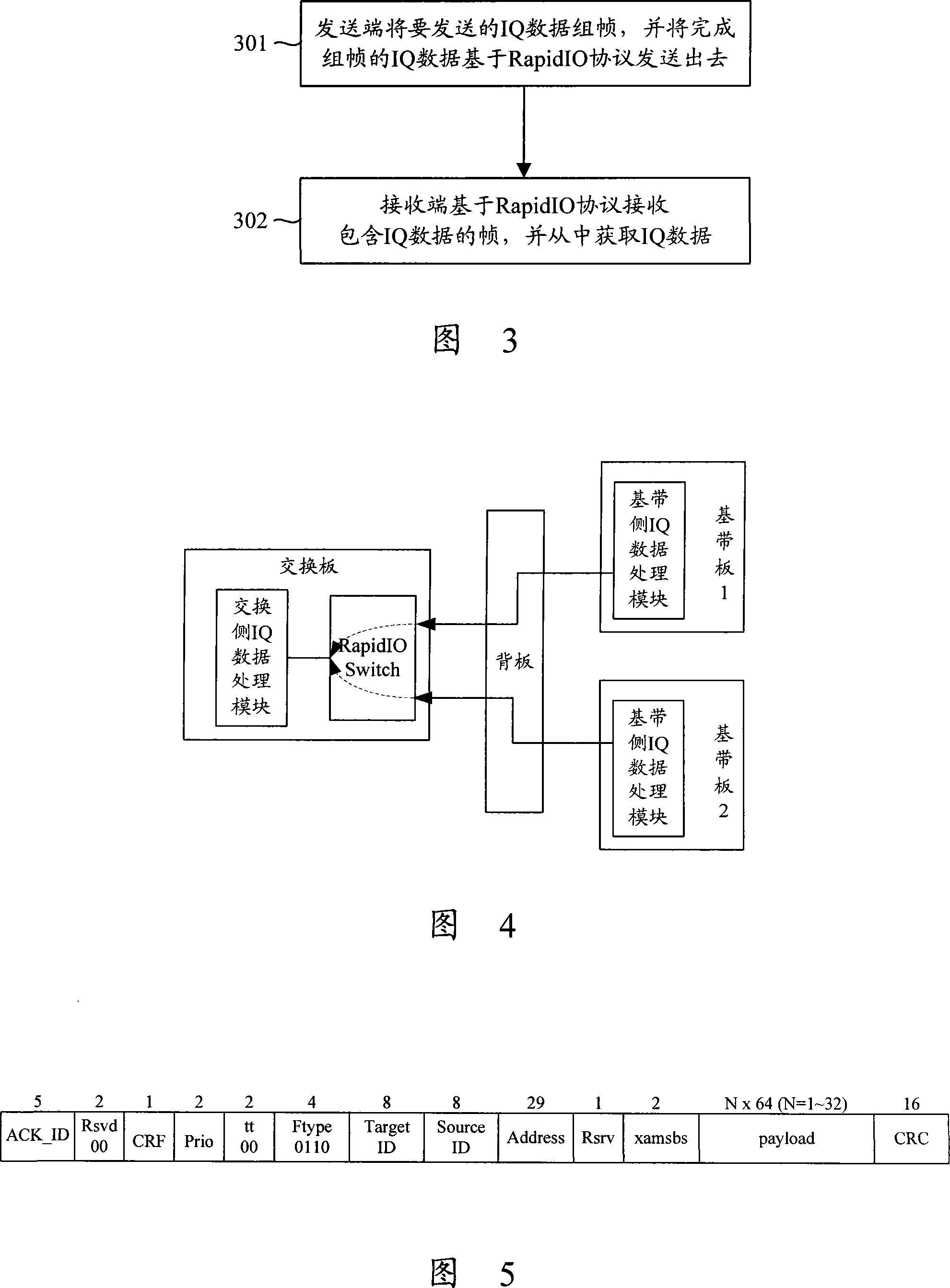

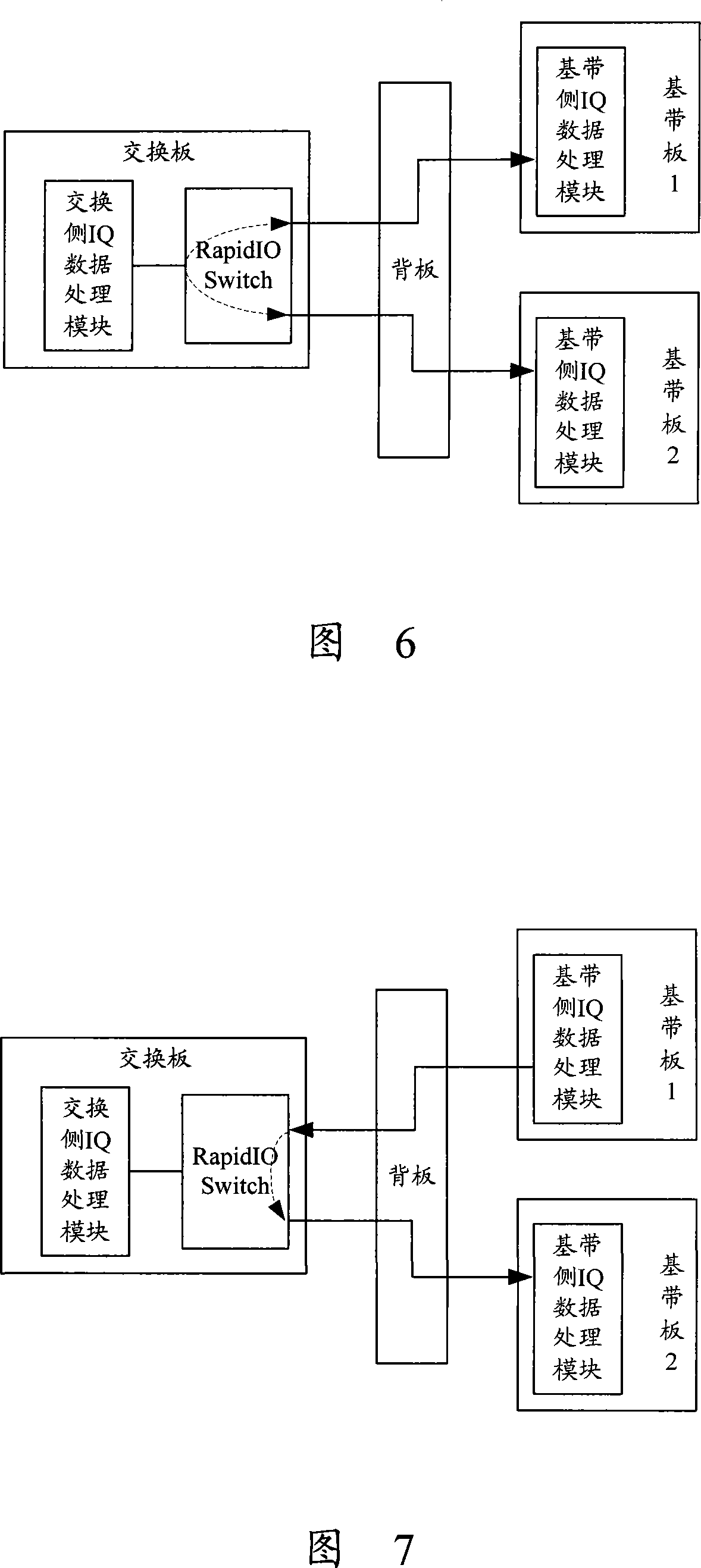

IQ data transmission apparatus and method

The invention discloses an IQ data transmission device method, which comprises framing the IQ data to be transmitted by a transmitting terminal, and transmitting the IQ data frame based on RapidIO protocol; and receiving the frame including the IQ data by a receiving terminal based on RapidIO protocol and acquiring IQ data therefrom. Obviously, since the IQ data to be transmitted by the transmitting terminal is framed and transmitted based on RapidIO protocol, the receiving terminal can receive the frame including the IQ data based on RapidIO protocol and acquire IQ data therefrom. Therefore, the current IQ data conversion operation in a parallel period is obviated, thereby to effectively obviate the waste of logic resources. Besides, complex operation is not needed to be executed to IQ data of different formants in the transmission process between the transmitting terminal and the receiving terminal. Accordingly, the invention can be commonly used for a mobile communication system of different formats.

Owner:ZTE CORP

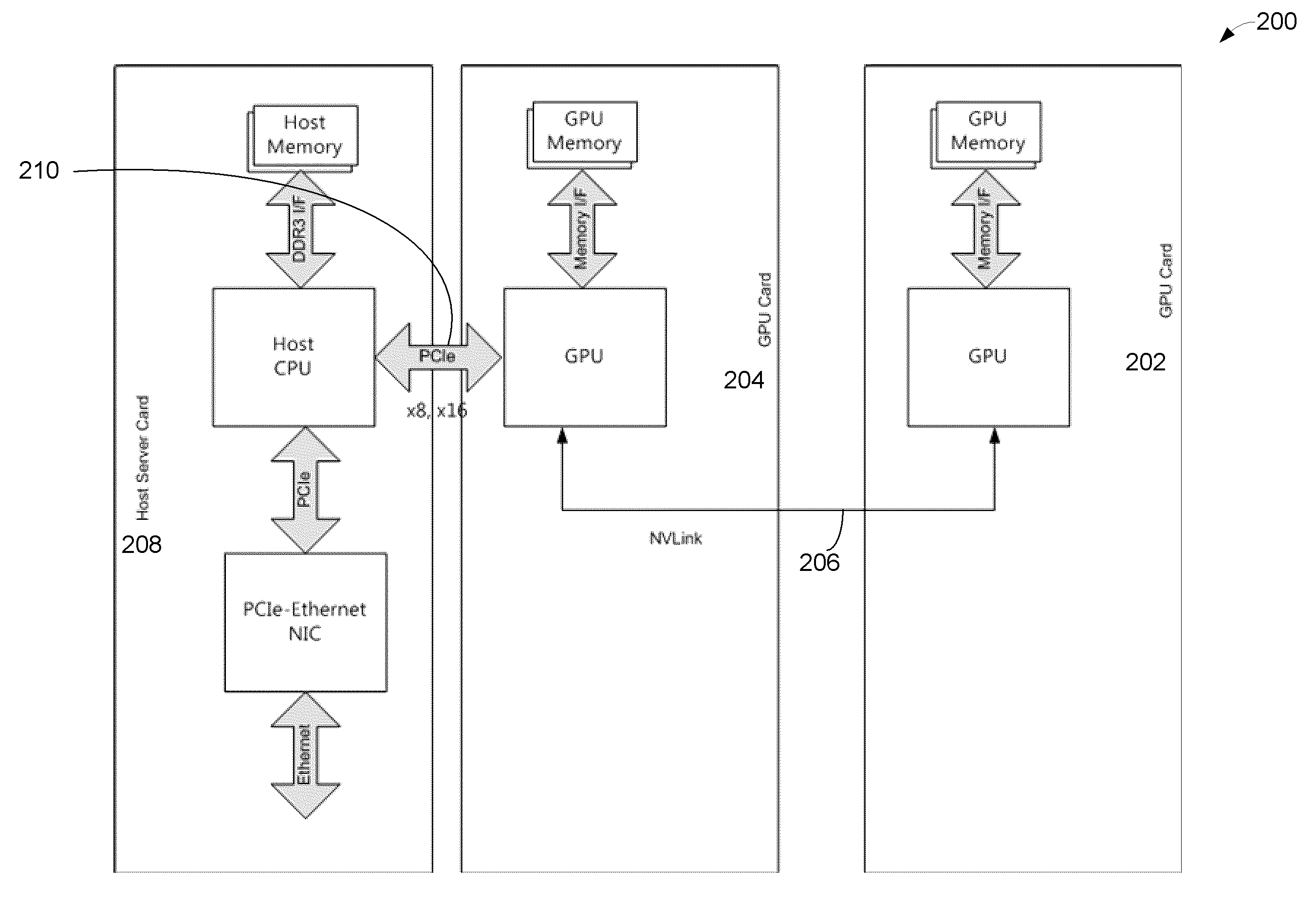

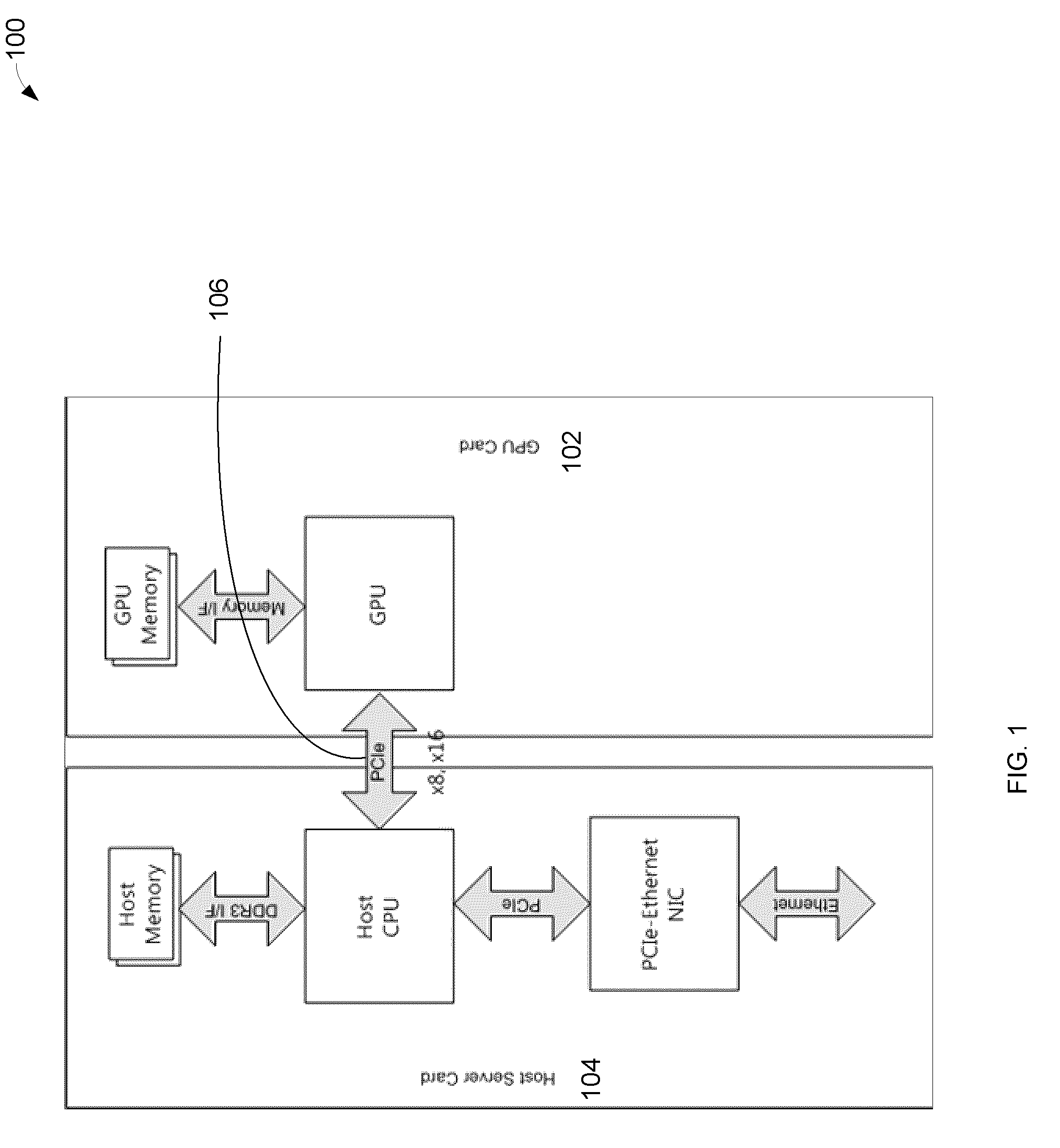

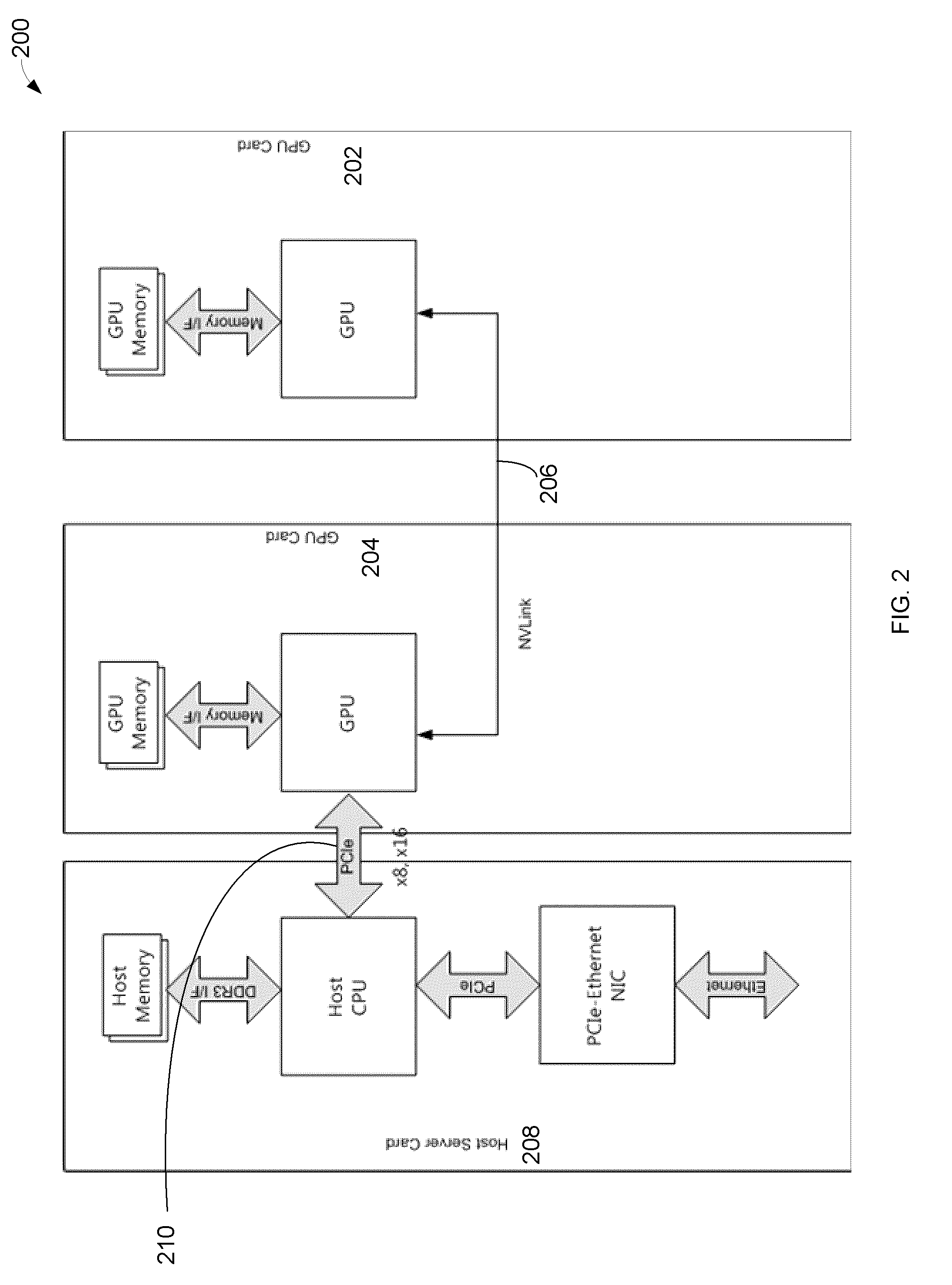

Methods and Apparatus for IO, Processing and Memory Bandwidth Optimization for Analytics Systems

InactiveUS20160292115A1Processor architectures/configurationEnergy efficient computingParallel computingMemory bandwidth

Methods and Apparatus for IO, Processing and Memory Bandwidth Optimization for Analytics Systems has been disclosed. In one implementation a plurality of cards each having one or more GPU+CPU are interconnected via RapidIO.

Owner:INTEGRATED DEVICE TECH INC

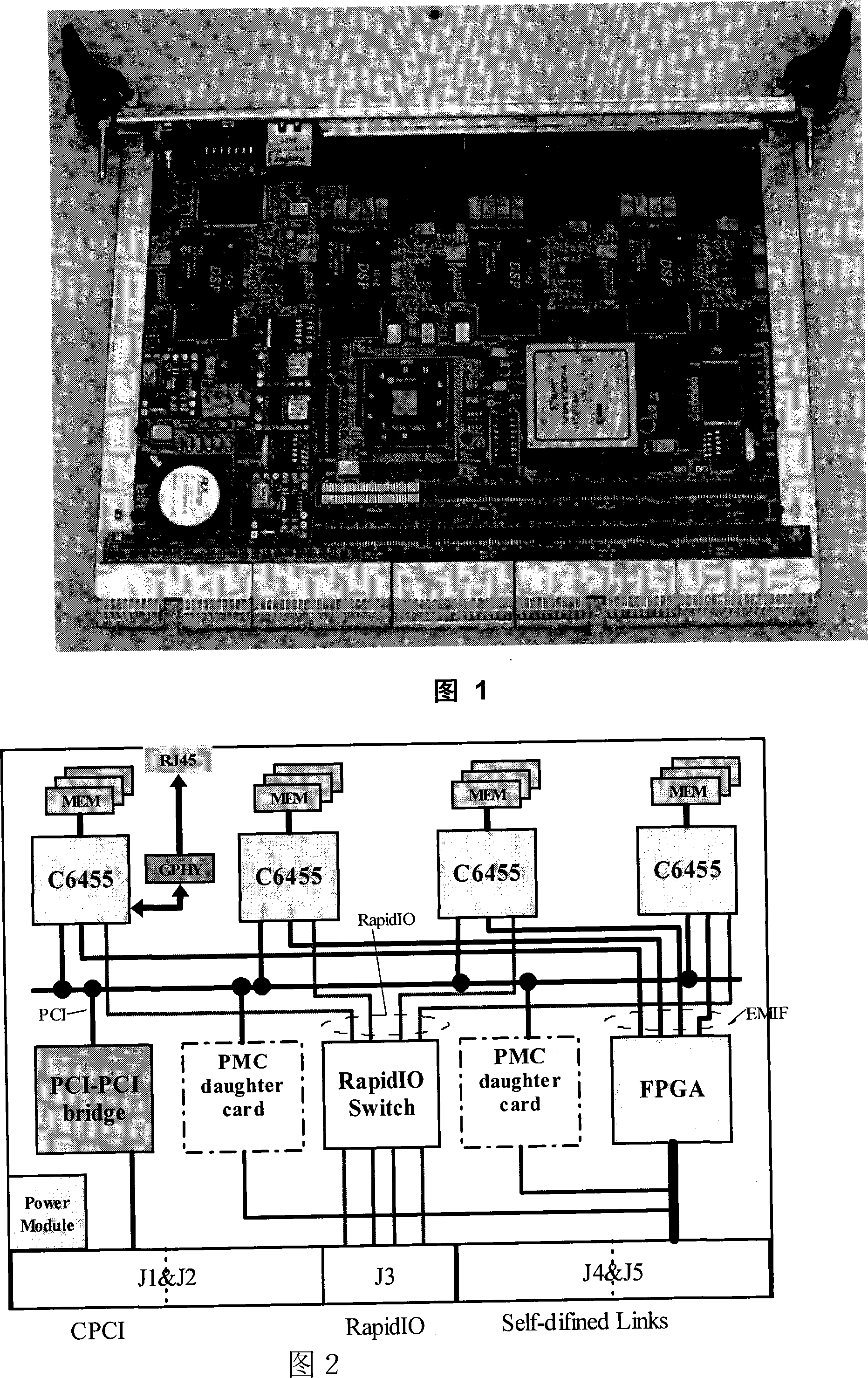

Scalable DSPEED-DSP_Q6455 signal processing board based on switcher

InactiveCN101102197AEasy to handleLarge storage capacityData switching detailsData switching by path configurationExtensibilityThe Internet

The card thereof comprises seven power modules, four processing nodes, a chipset for interconnecting said processing nodes and a gigabit Ethernet port. The communication protocol comprises PCI protocol, serial RapidIO protocol and gigabit Ethernet protocol. The board type is cPCI standard board type. The working platform is an engineering control computer platform. The method for constructing internet is: based on the switch mode under serial RapidIO protocol, based on the sync transmission mode of FPGA, based on cPCI protocol bus mode, and based on gigabit Ethernet mode. The invention can be used in radar signal process, image process and base station.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

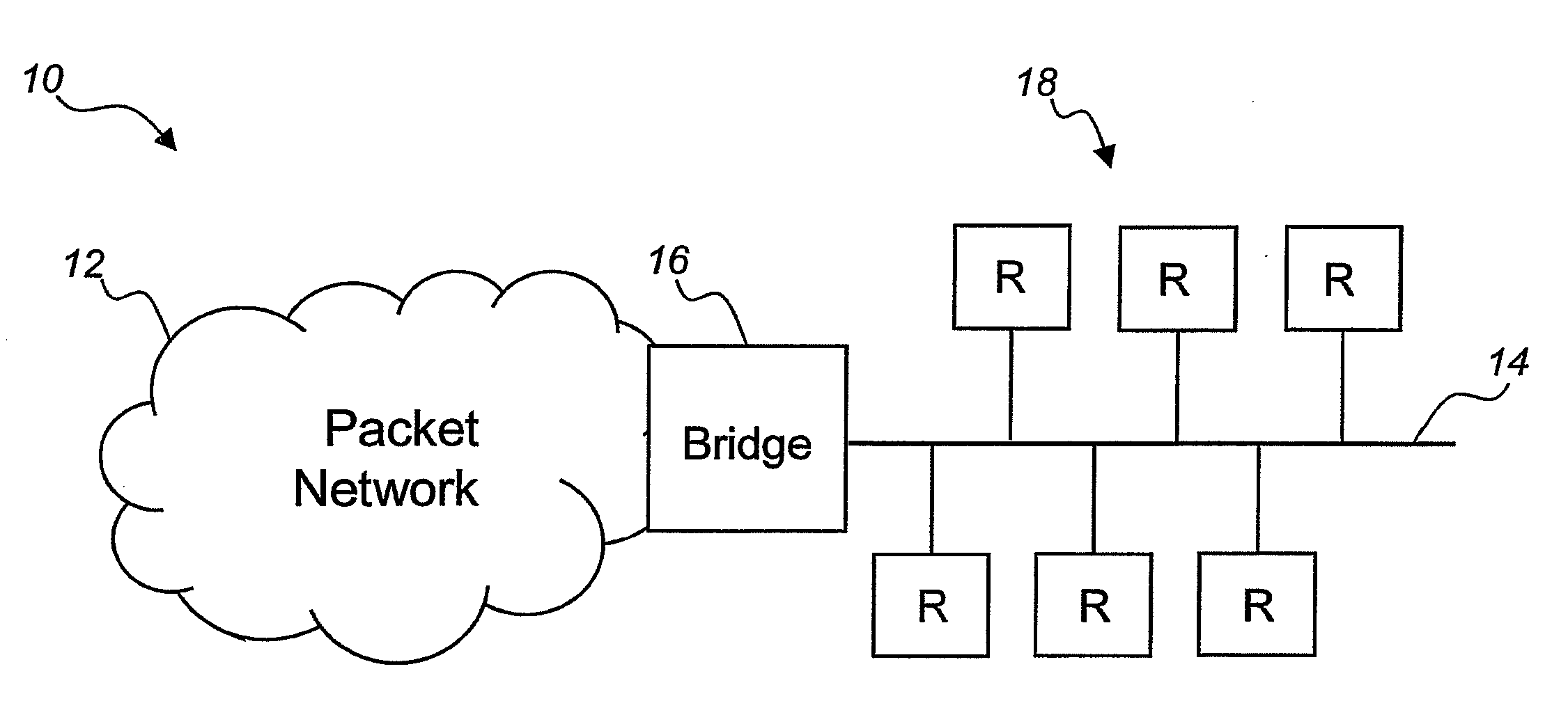

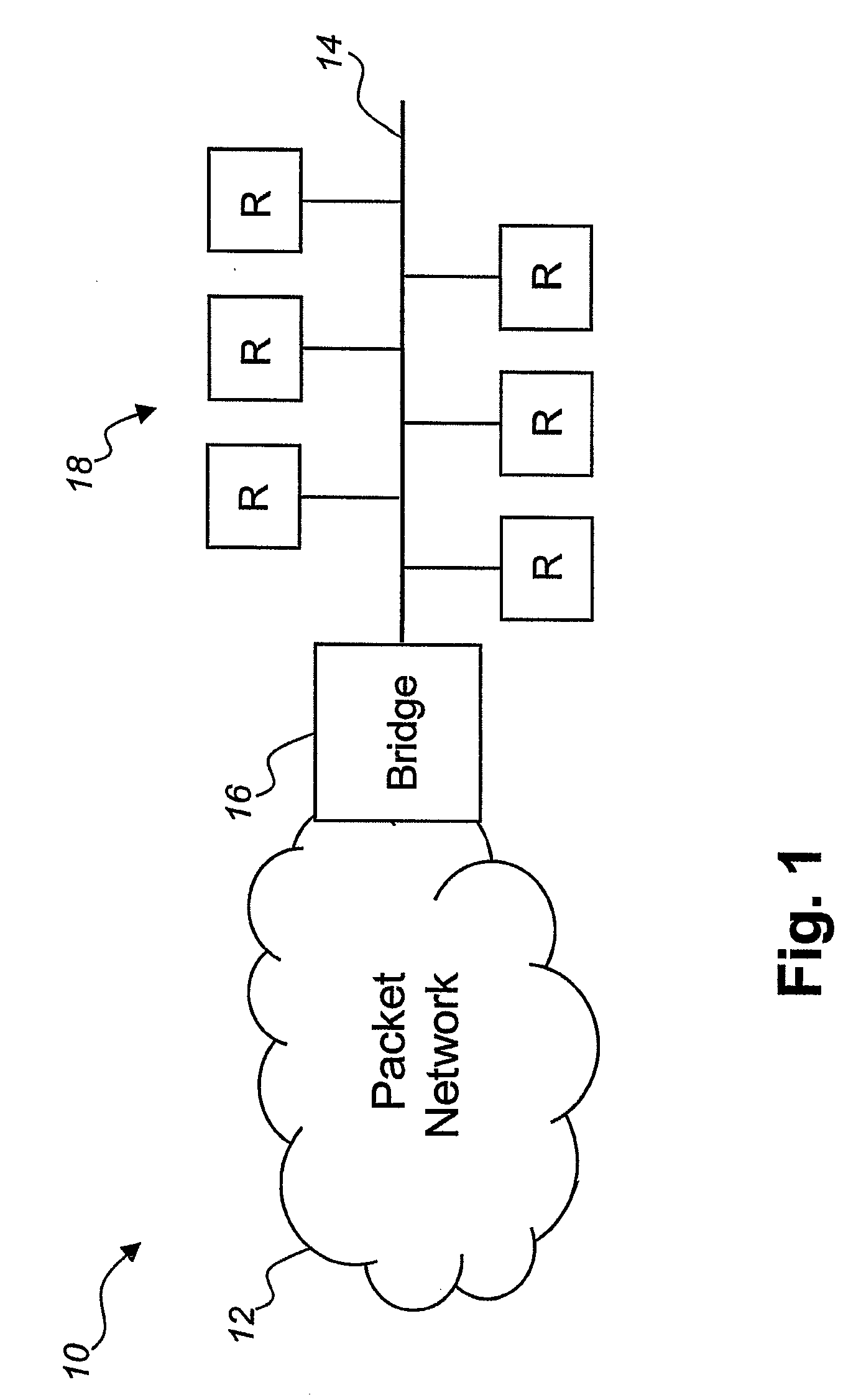

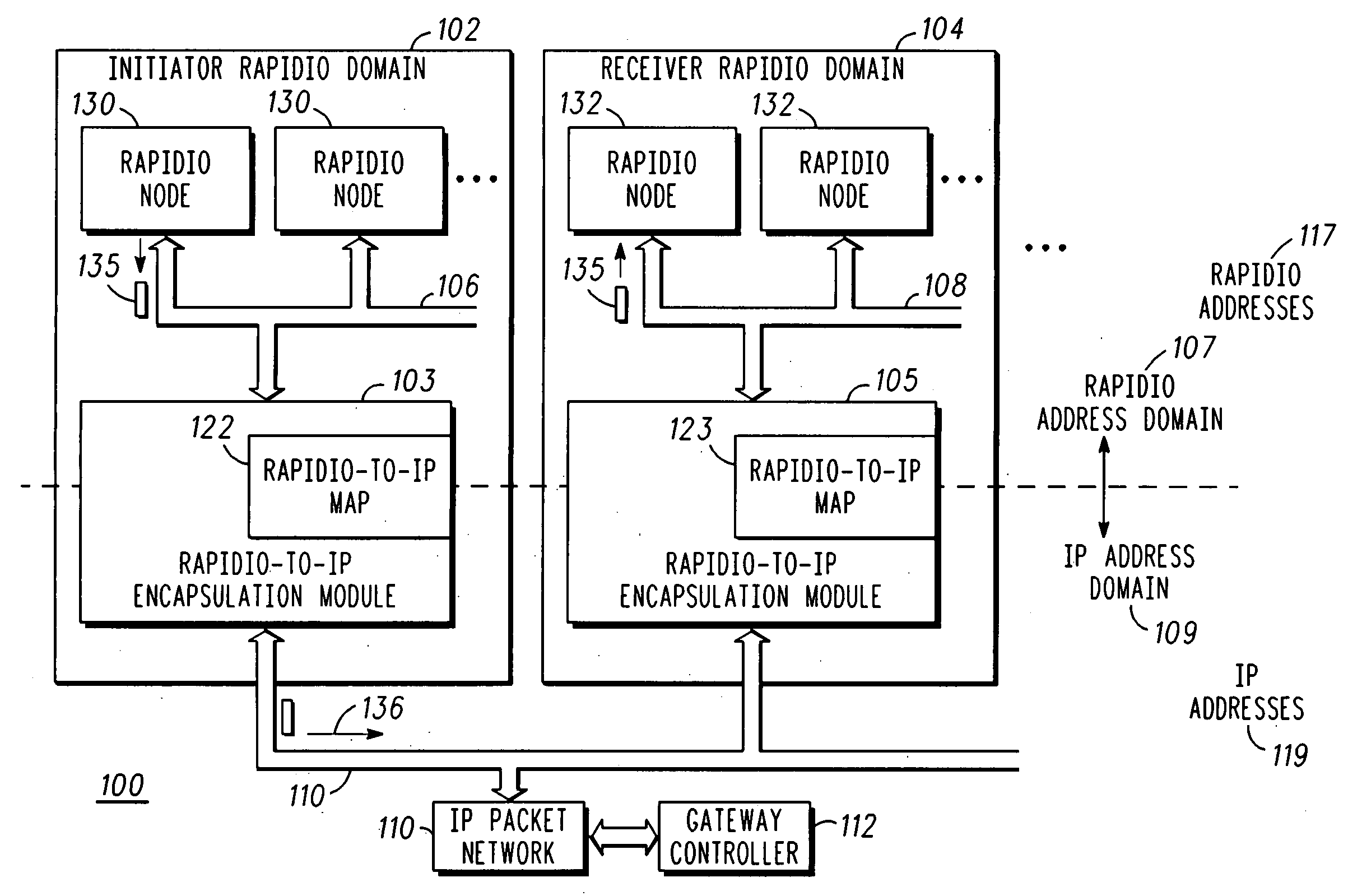

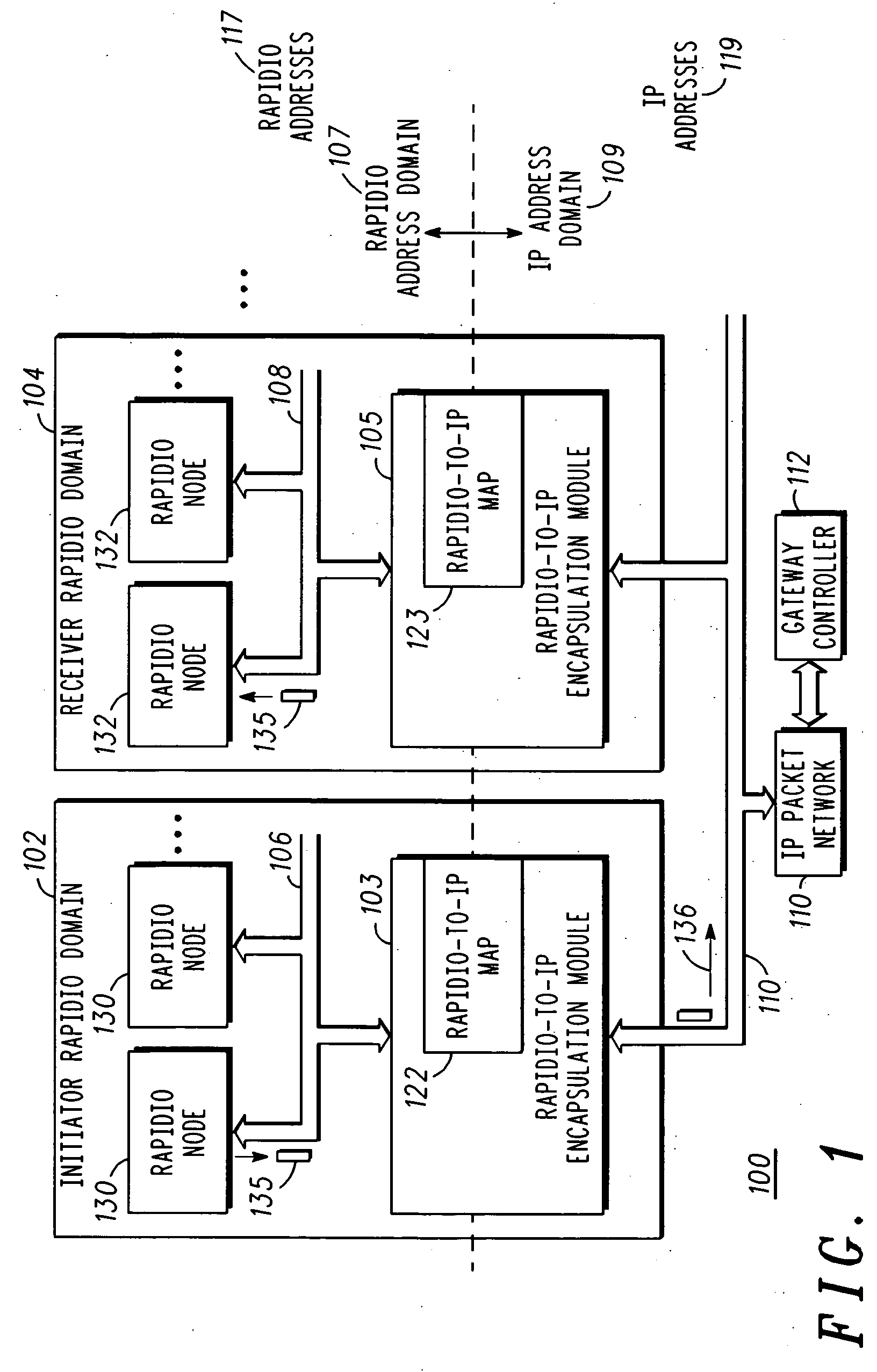

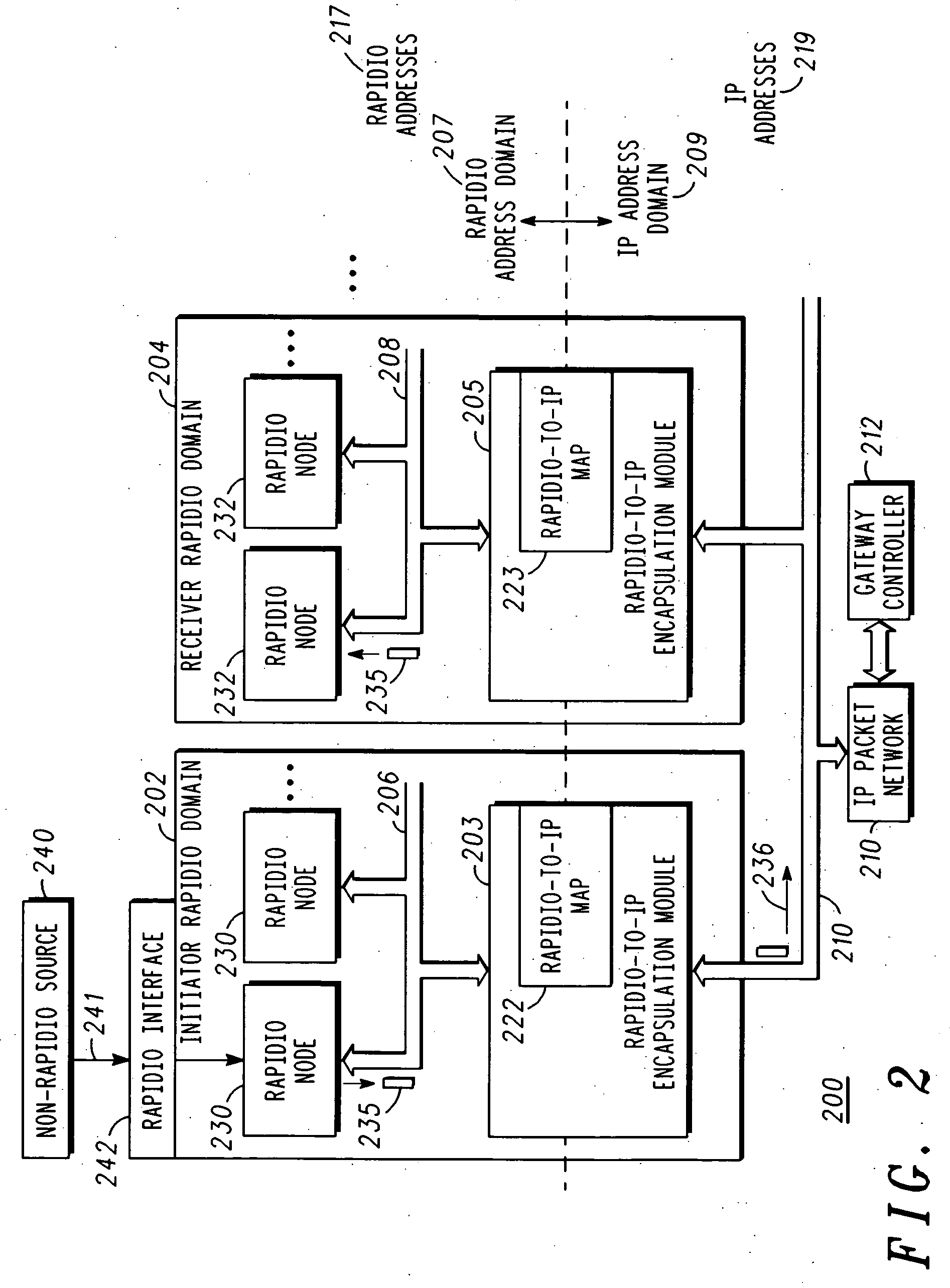

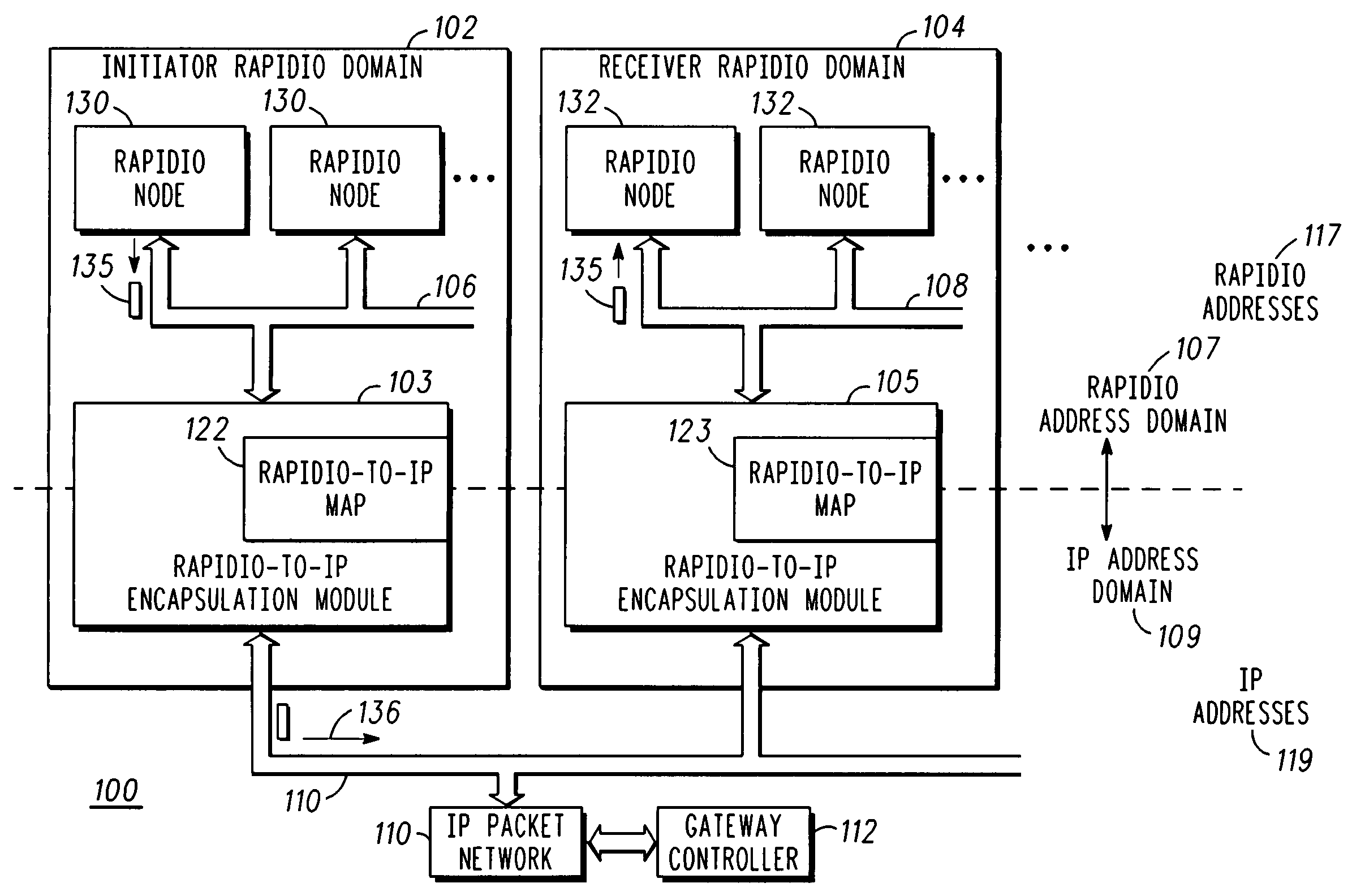

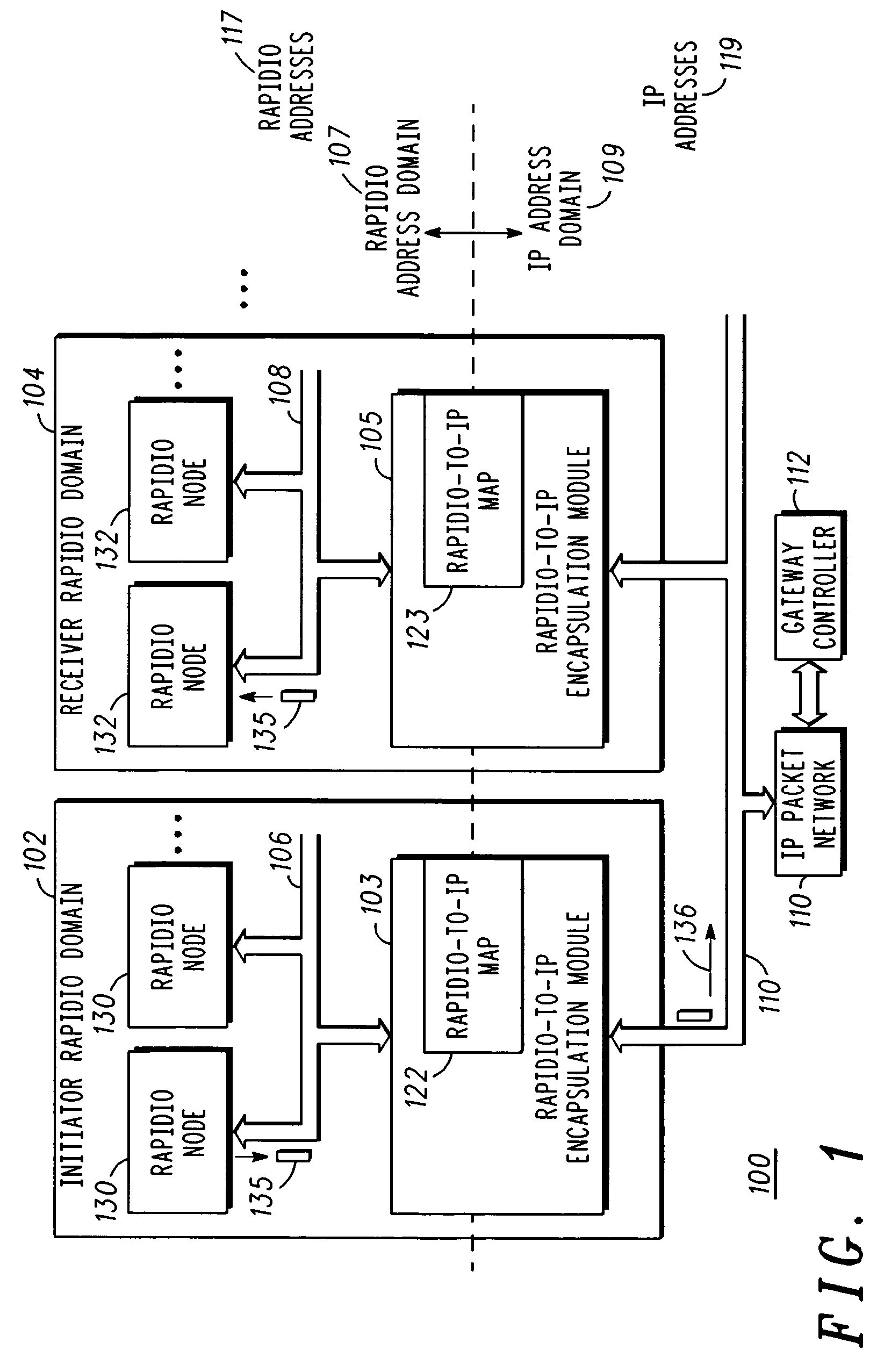

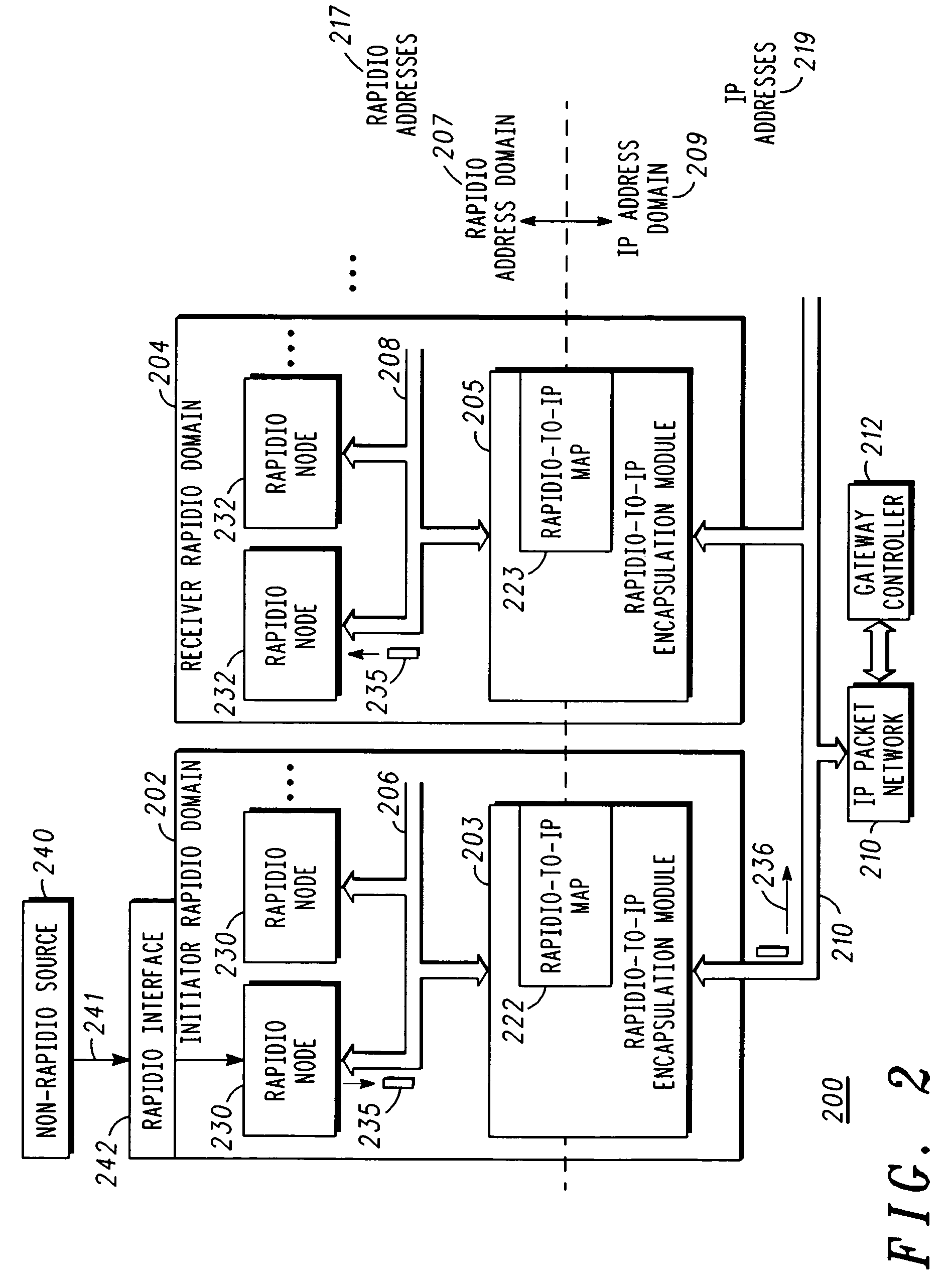

Method of transporting a RapidIO packet over an IP packet network

ActiveUS20060109845A1Time-division multiplexData switching by path configurationIp addressReal-time computing

A method of transporting a RapidIO packet (135) from an initiator RapidIO domain (102) over an IP packet network (110) to a receiver RapidIO domain (104) can include the initiator RapidIO domain creating the RapidIO packet and reading a destination domain ID (483) of the RapidIO packet, where the destination domain ID corresponds to the receiver RapidIO domain. The destination domain ID is mapped to a receiver RapidIO domain IP address (473). The RapidIO packet is encapsulated in an IP packet (436) and the IP packet is communicated to the receiver RapidIO domain over the IP packet network.

Owner:SMART EMBEDDED COMPUTING INC

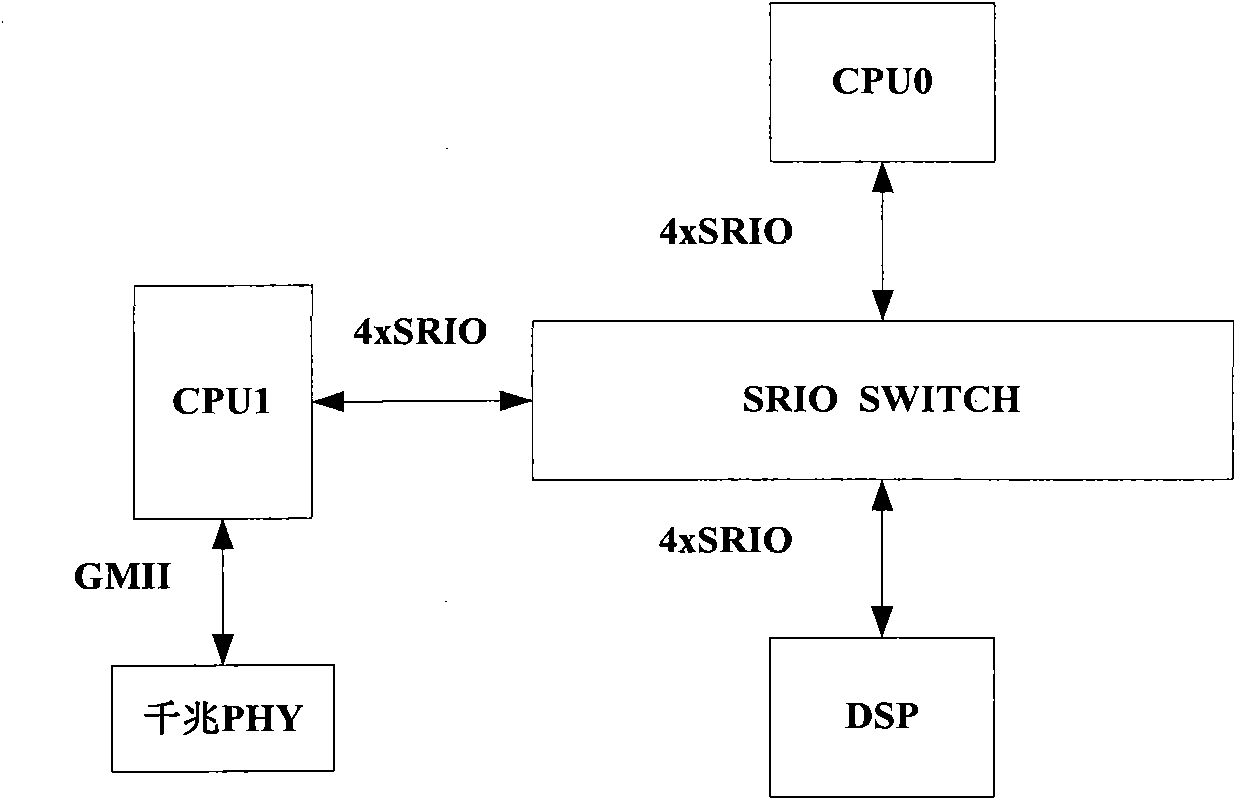

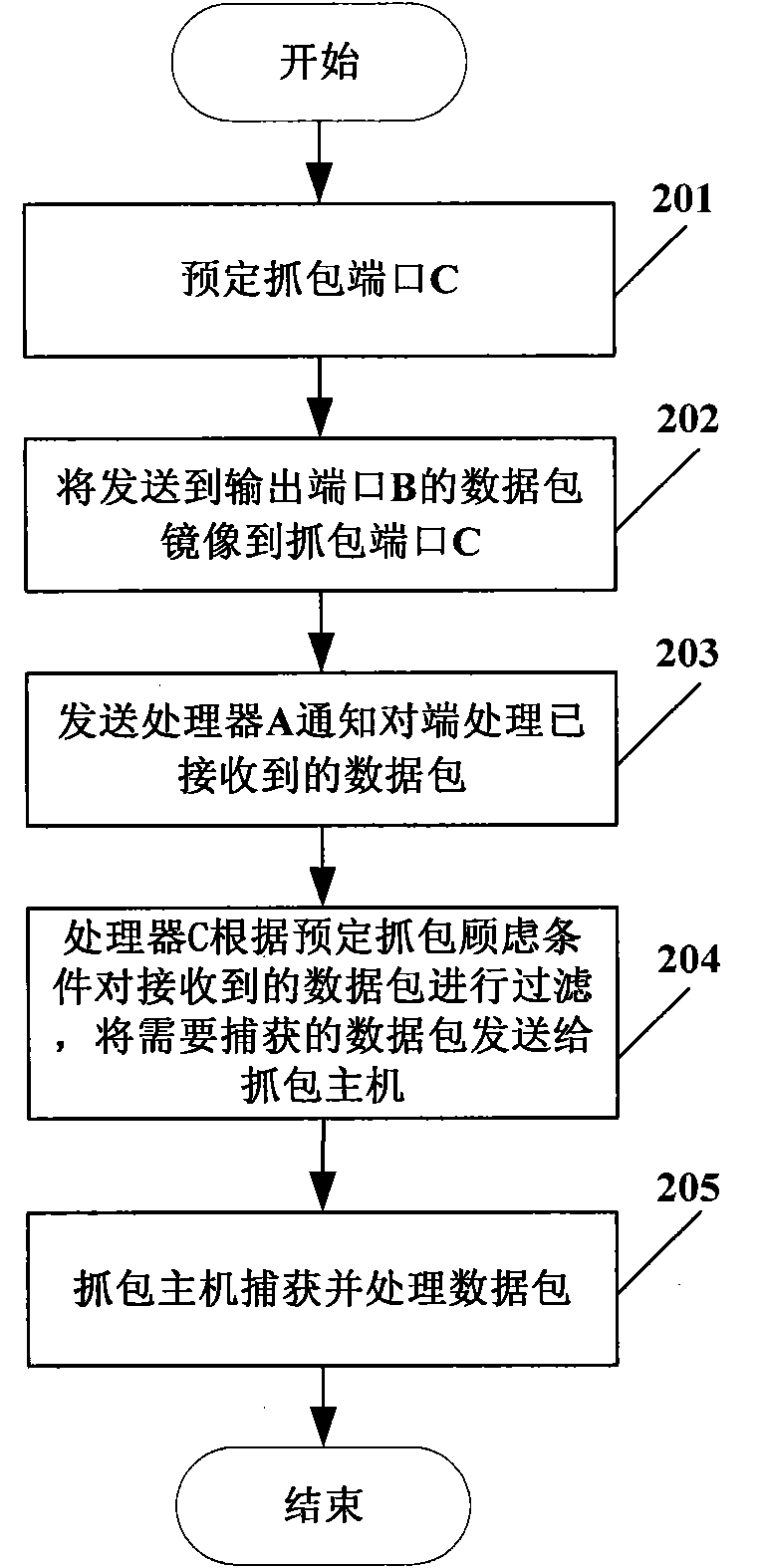

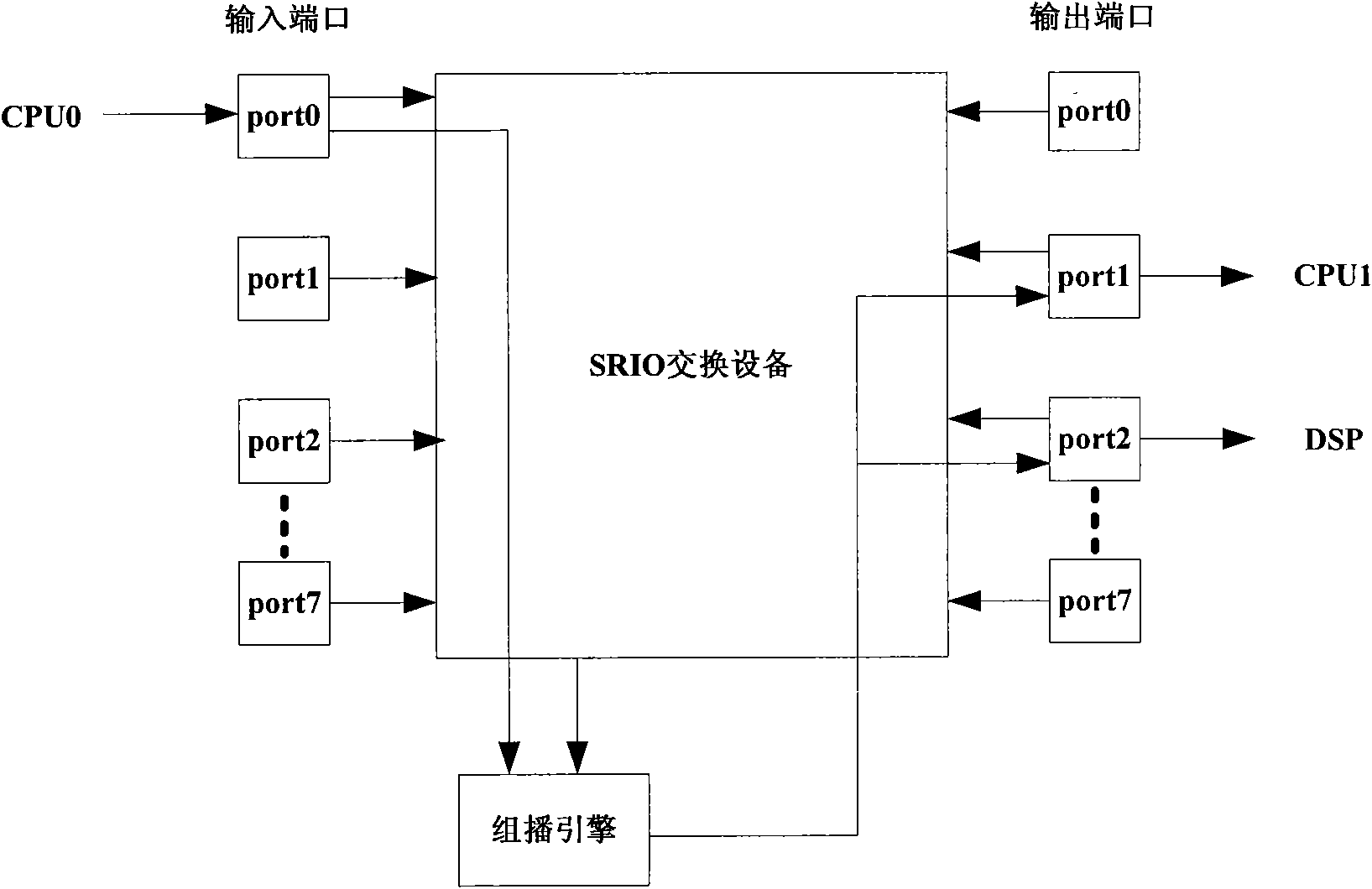

Packet sniffing method and device in high-speed interconnection system

InactiveCN102055653AFast and efficient packet capture functionData switching networksPort mirroringRapidIO

The invention discloses a packet sniffing method and device in a high-speed interconnection system. In the invention, an output port of SRIO (Serial RapidIO) exchange equipment, i.e. high-speed interconnection equipment, is preset to be a packet sniffing port, and when a sending processor needs to send a packet to a target processor, the method comprises the following steps of: mirroring the packet required to be sent to the target processor to a processor connected with a packet sniffing port by the sending processor; filtering the received packet by the processor connected with the packet sniffing port according to a preset packet sniffing filtering condition; and sending the packet required to be captured to a preset packet sniffing host for analyzing. The invention realizes a quick and high-efficiency packet sniffing function in a port mirroring mode on the basis of not influencing the efficiency of the sending processor and the receiving processor.

Owner:ZTE CORP

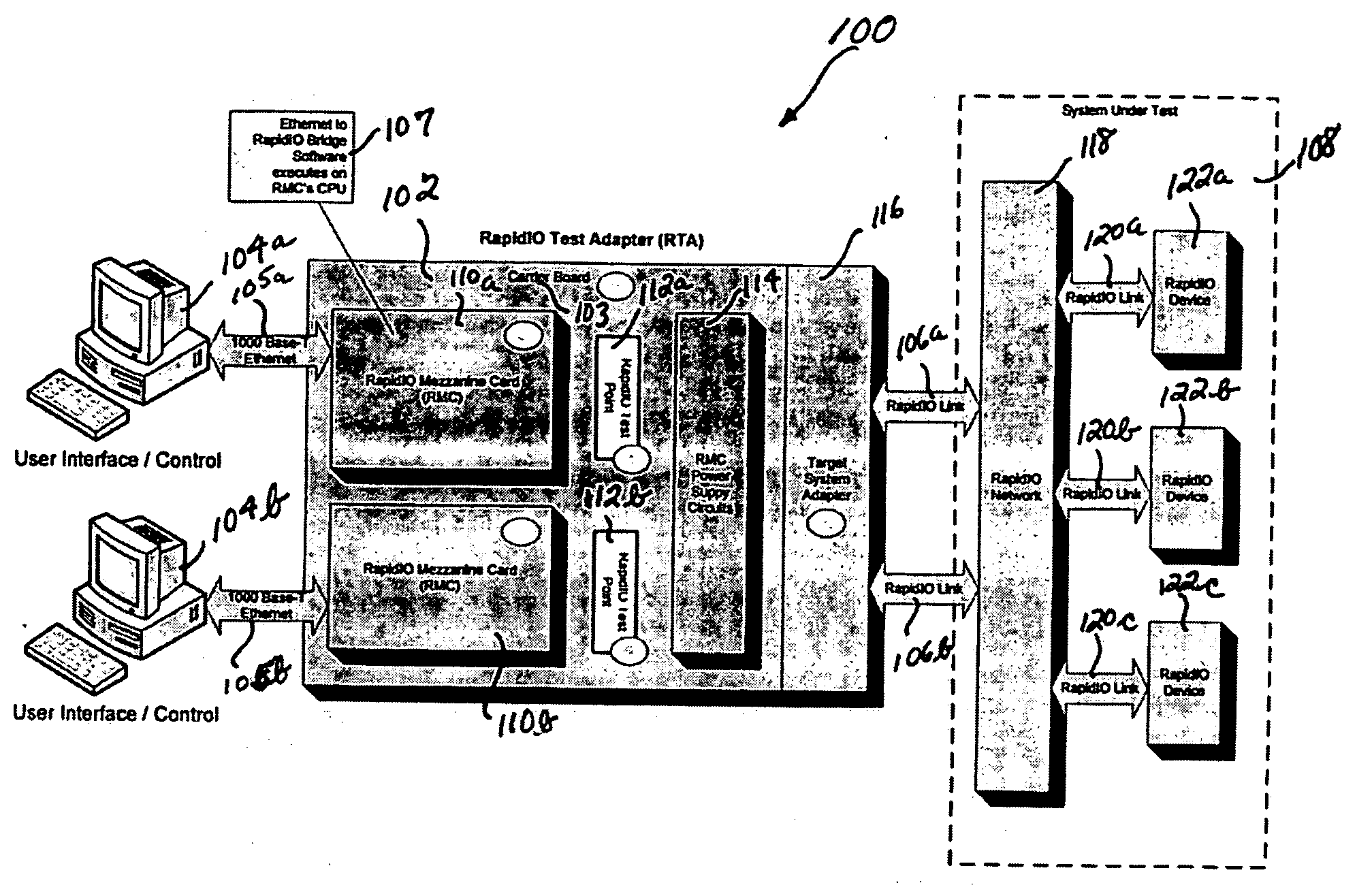

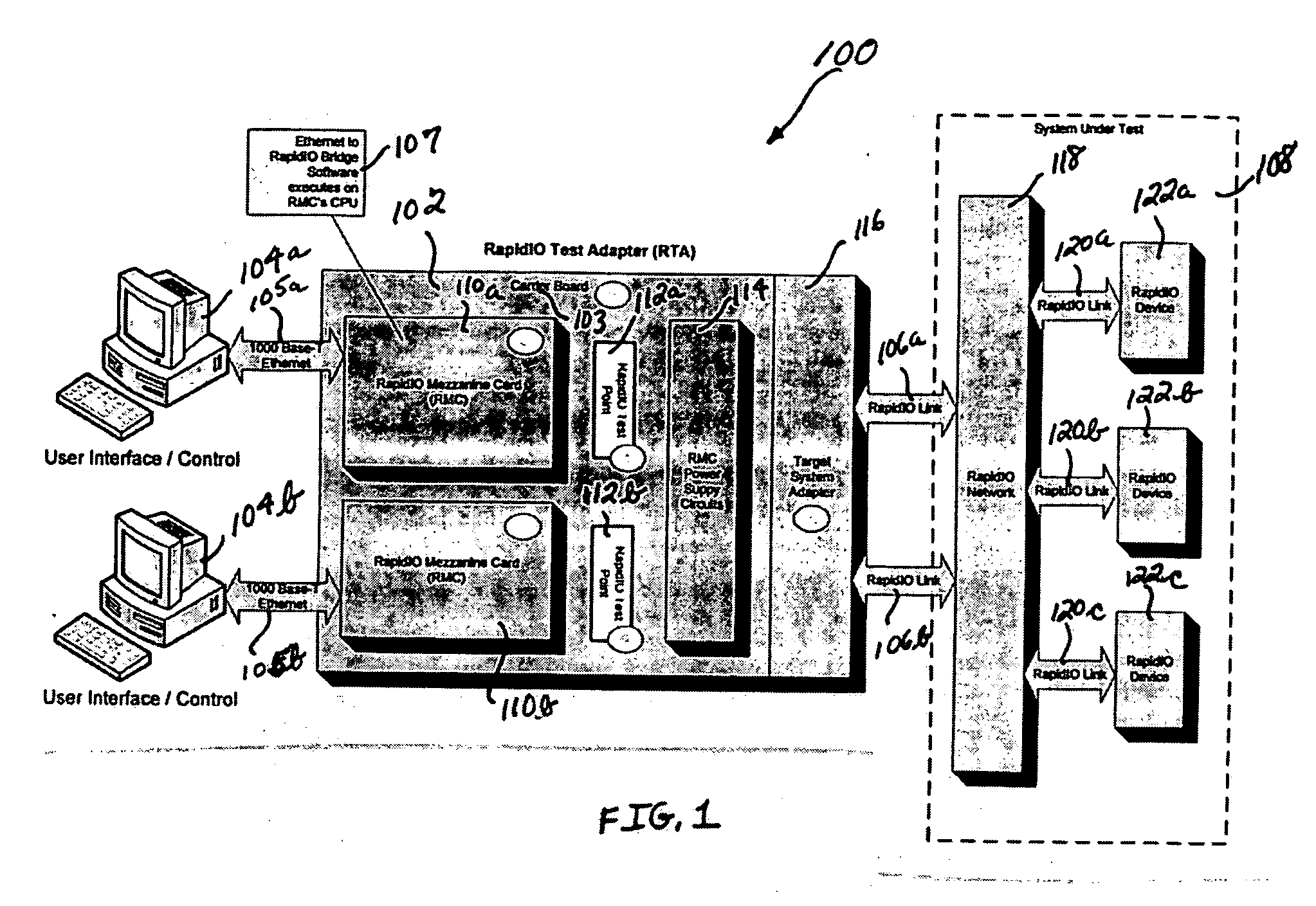

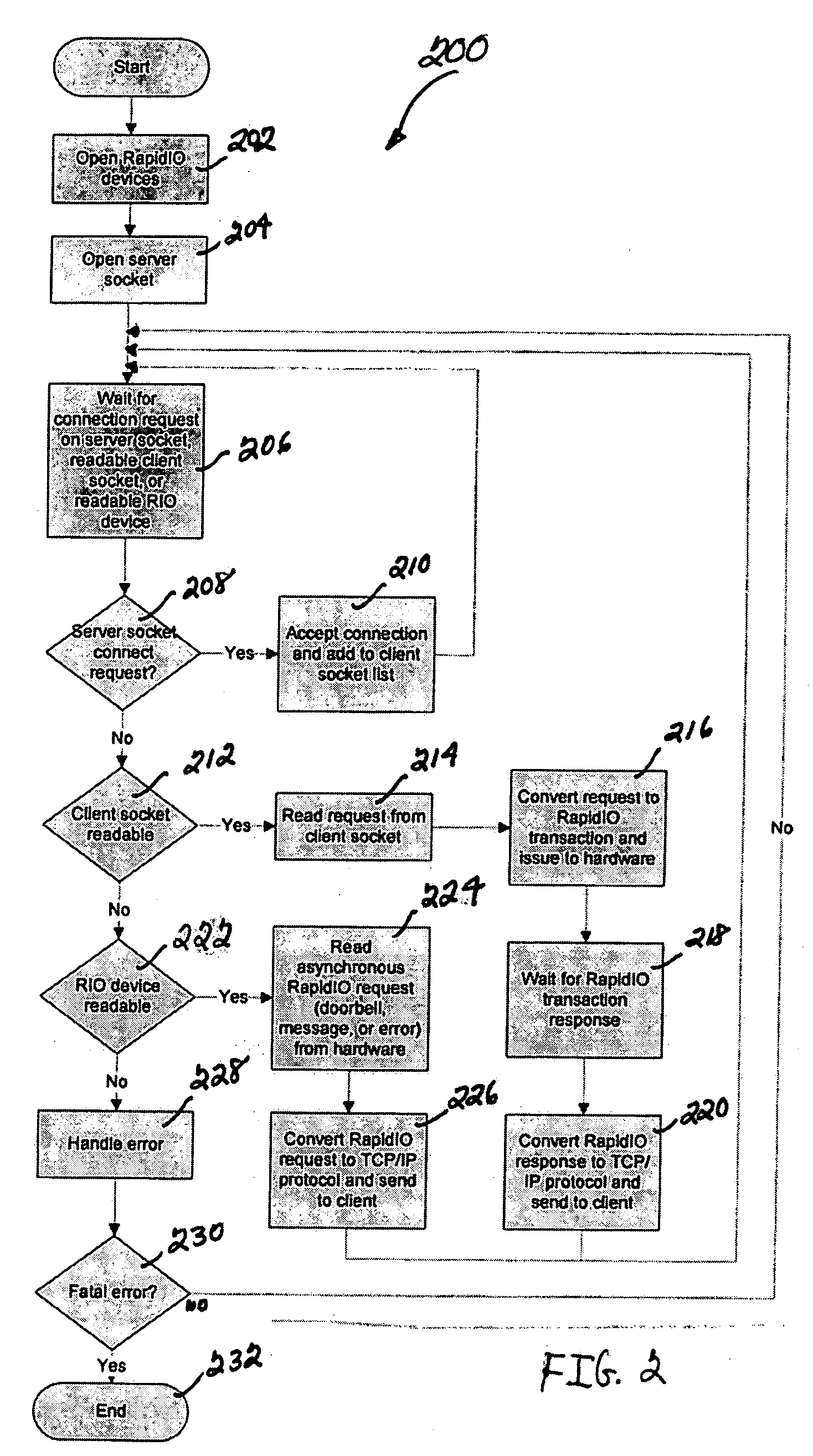

System and method to facilitate testing of rapidio components

InactiveUS20070104219A1Easy accessEasy to testError detection/correctionTime-division multiplexComputer hardwareSoftware architecture

A system and method are disclosed for sending and receiving RapidIO traffic to / from a RapidIO system, network or device, independent of the system, network or device. For example, a RapidIO test adapter (RTA) system is disclosed that facilitates the accessing and testing of an embedded system or device with a RapidIO interface, RapidIO network switch, and / or an entire RapidIO network. The RTA system provides a “known good” RapidIO endpoint and can issue and receive RapidIO transaction requests and responses. Also, the RTA system provides a hardware and software architecture that facilitates the programming of external systems so as to allow them to exercise control over the issuance and reception of RapidIO transaction requests and responses, without needing detailed knowledge of the RapidIO protocol or hardware used to implement the RapidIO endpoint involved. Also, the RTA system provides a plurality of independent RapidIO endpoints, which can support a wide variety of test cases without the need for additional RapidIO devices. As such, the RTA system provides physical test points on each RapidIO interface that can be used to connect an embedded system or device to RapidIO protocol analyzer hardware. Furthermore, the RTA system allows a user to manually initiate RapidIO transactions via a web-based user interface, and also uses a simple TCP / IP protocol which an external host can use to send / receive RapidIO transactions, thereby reducing the time required to program custom tests. Also, the RTA system enables RapidIO operations to be initiated by embedded software that can provide human-to-machine and machine-to-machine interfaces suitable for performing both static and dynamic tests.

Owner:HONEYWELL INT INC

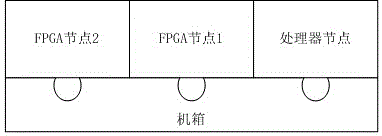

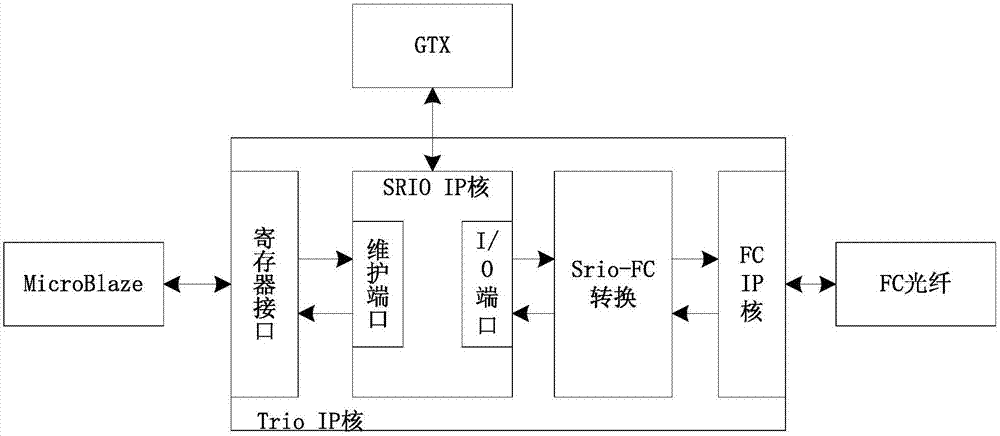

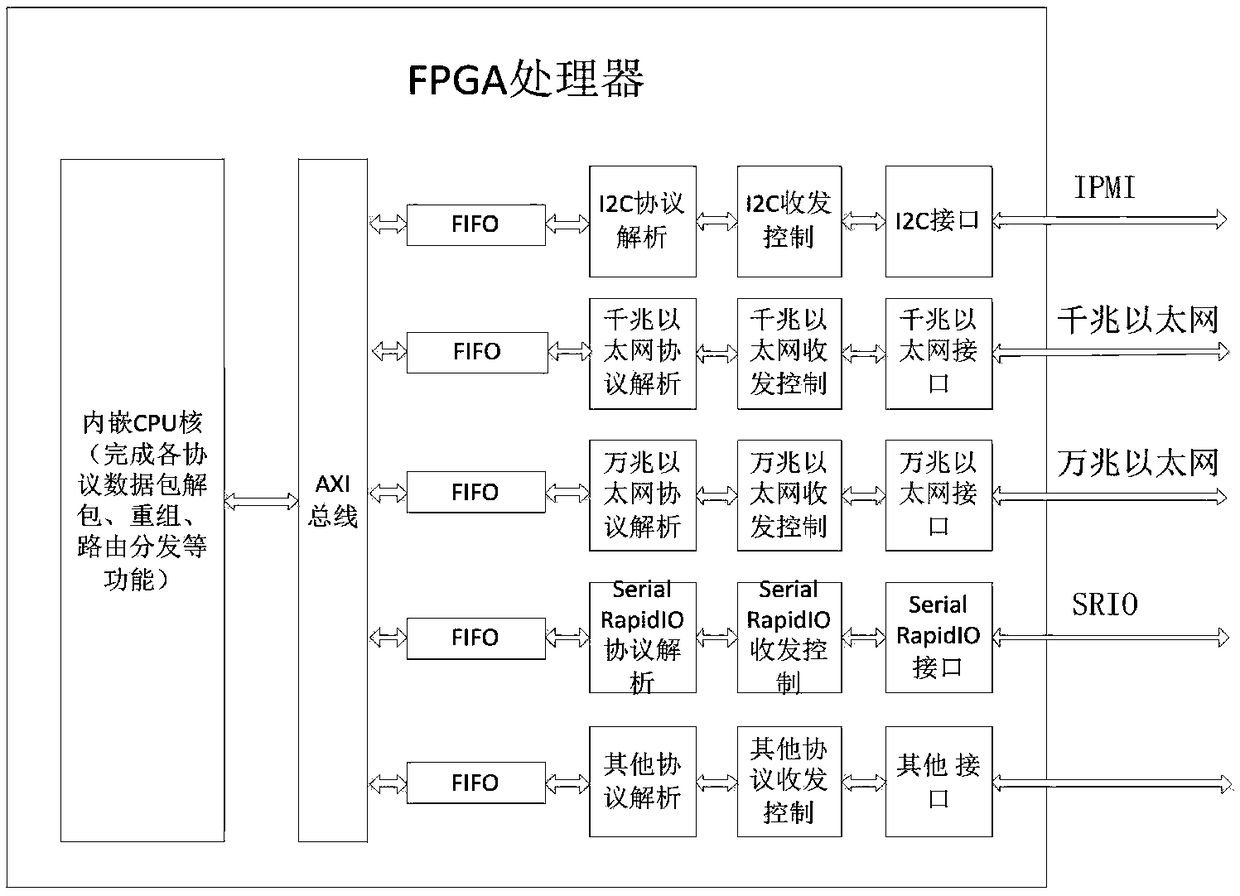

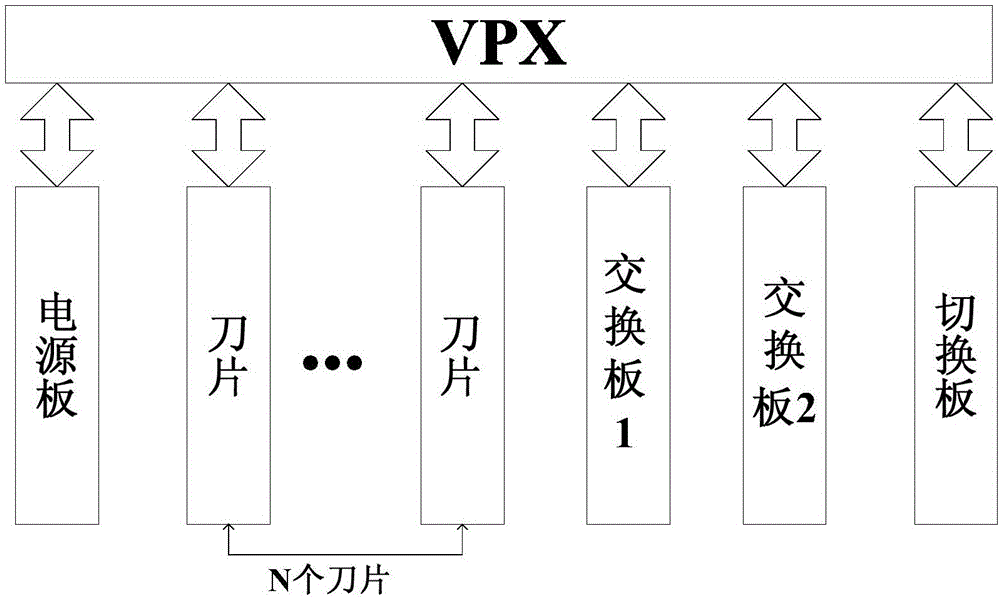

RapidIO network switching method for VPX switching board

The invention relates to a rapidIO network switching method for a VPX switching board. On an FPGA chip of the VPX cabinet switching board, based on an SOPC architecture, a self-defined IP core is invented, a rapidIO-FC conversion function and an interface between a rapidIO maintenance port and a CPU soft core are integrated, and under the hardware architecture, SDK software is adopted to complete rapidIO driving and a network enumeration algorithm, and bandwidth allocation and hot pluggable management functions are realized.

Owner:THE 724TH RES INST OF CHINA SHIPBUILDING IND

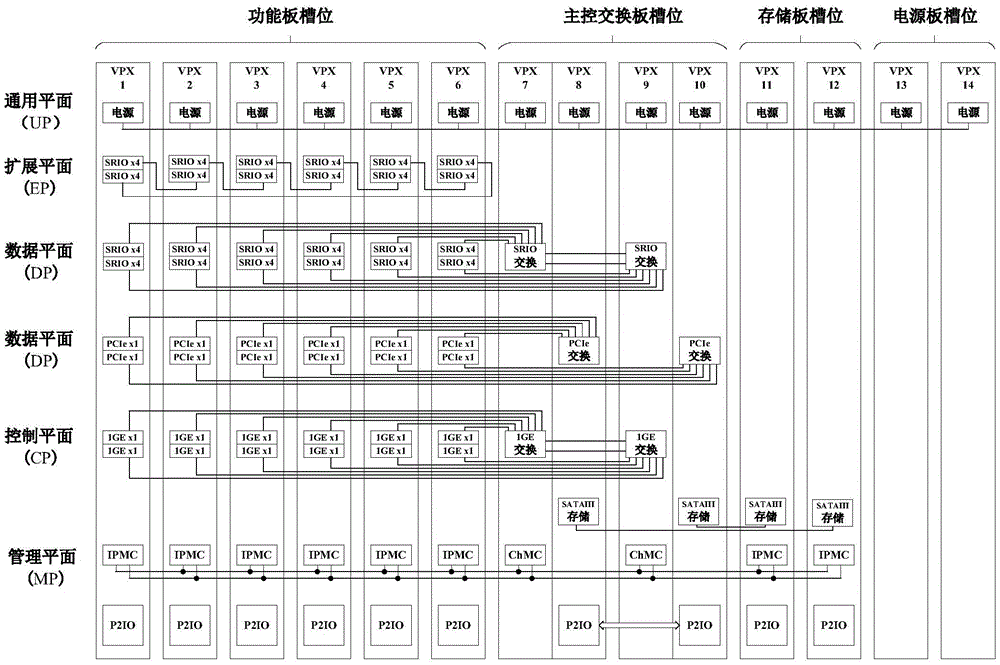

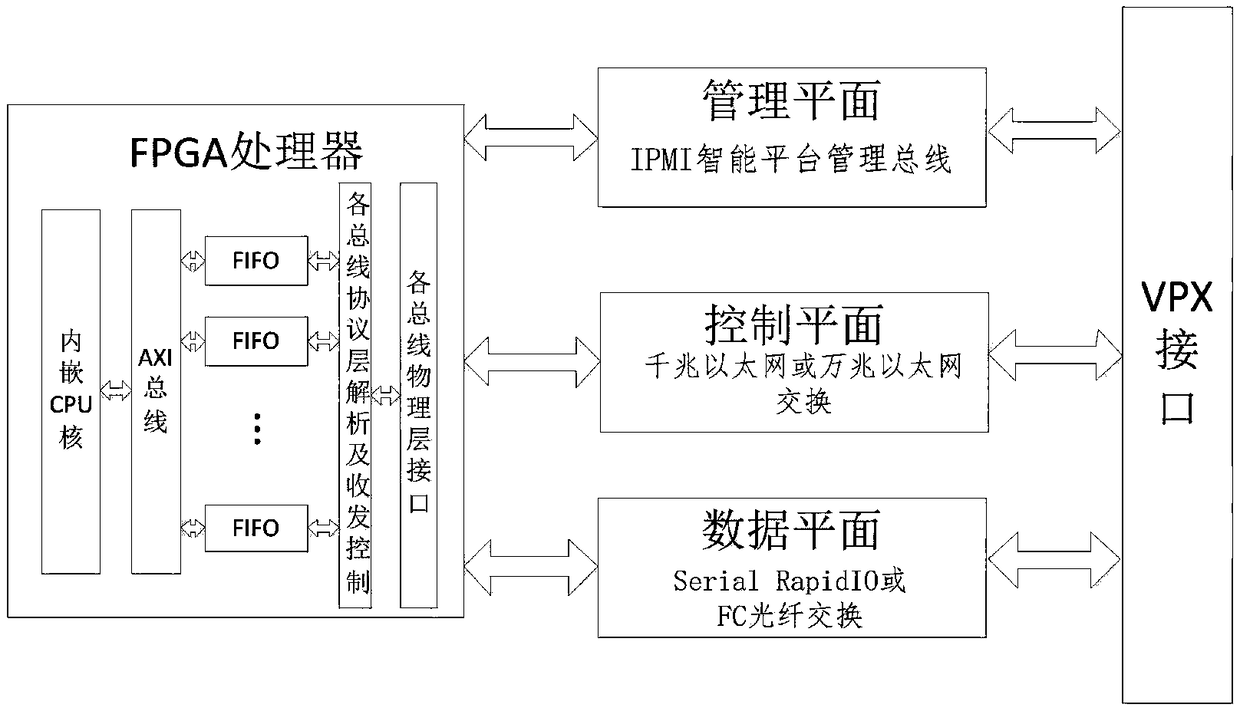

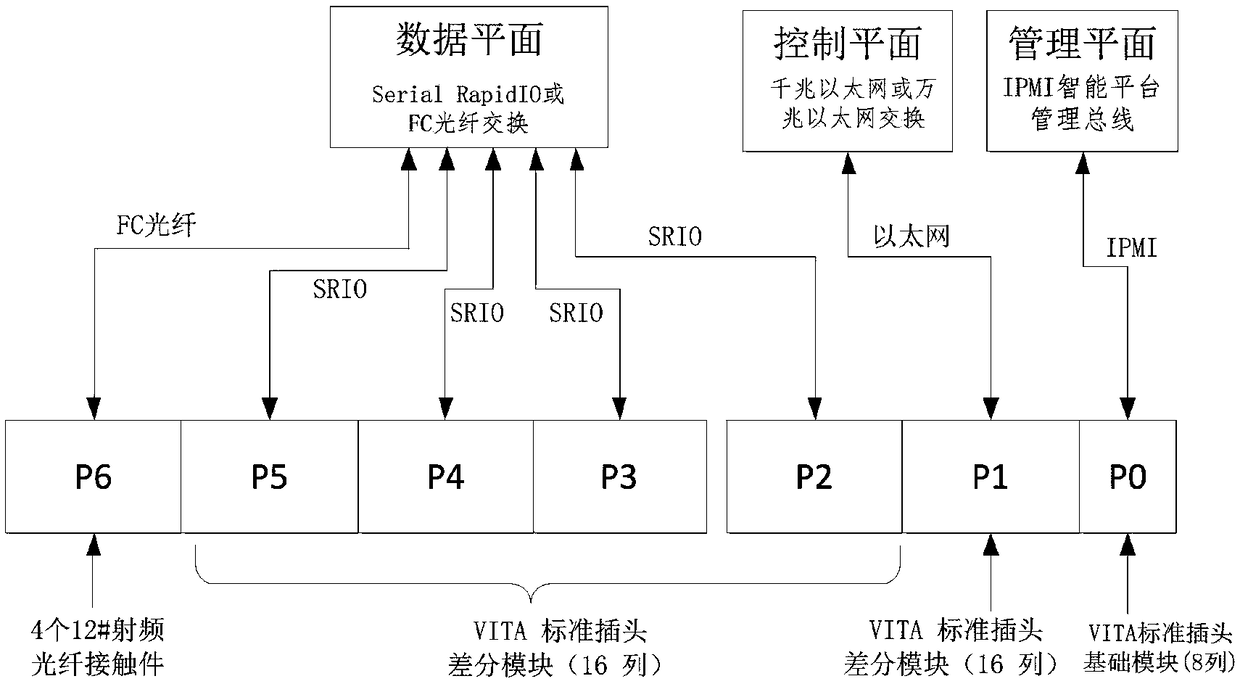

Multiple plane loose coupling high-bandwidth data exchange system

ActiveCN109120624AImplementing Loosely Coupled DesignsFulfill exchange needsFibre transmissionData switching networksSystems designData platform

The present invention relates to a multiple plane loose coupling high-bandwidth data exchange system, and relates to the technical field of electronic systems. In a complex electronic system, the datatransmission exchange mainly comprises a management platform, a control platform and a data platform, the exchange system is designed and three platforms are planned, the management platform employsan IPMI intelligent platform to manage a bus technology, the control platform employs a gigabit Ethernet or gigabit Ethernet bus exchange technology, the data platform employs Serial RapidIO or FC fiber transmission exchange technology to achieve the high bandwidth data exchange in the same plane, and the maximum bandwidth of the data plane is 825 gigabits; and technologies such as protocol analysis and conversion among different planes are employed to achieve loose coupling design among multiple planes. The multiple plane loose coupling high-bandwidth data exchange system achieves exchange demands of big data high bandwidth exchange demand in the same plane of the complex electronic system and achieves data protocol conversion and transmission control of the loose coupling structure amongdifferent planes.

Owner:BEIJING INST OF COMP TECH & APPL

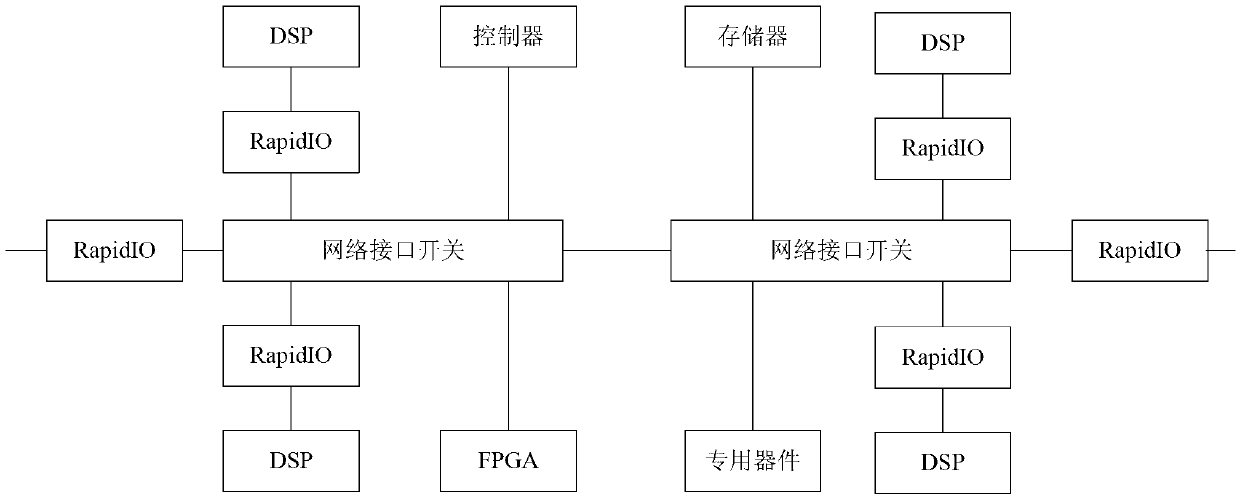

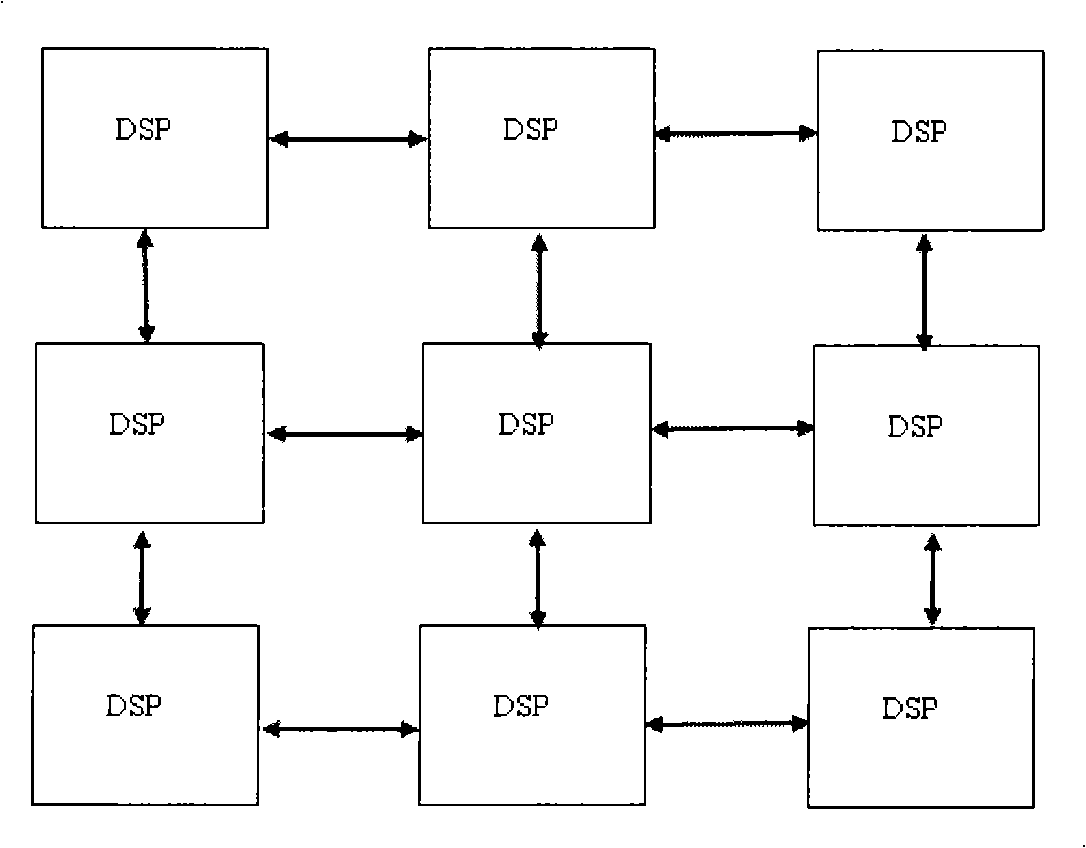

Interconnection method among cores of multi-core processor

InactiveCN103106173AThe method of interconnection is convenientEasy to implementMultiple digital computer combinationsData switching networksComputer architecturePhysical layer

The invention relates to an interconnection method among cores of a multi-core processor, and is used for realizing interconnection among inner cores chips of the multi-core processor. The multi-core processor includes m chips and each chip includes n inner cores, wherein m and n are integers. According to the interconnection method among cores of the multi-core processor, a m*n mesh interconnection topological structure based on a RapidIO physical layer protocol is formed among the chips, the interconnection topological structure comprises RapidIO cores corresponding to the chips one-to-one and network interface switches connected with each RapidIO core, and the chips form a serial bus through the RapidIO cores and network interface switches. The interconnection method among cores of the multi-core processor is convenient to realize, easy to be used for integration on chip level and ideal in using effect.

Owner:SUZHOU R&D CENT OF NO 214 RES INST OF CHINA NORTH IND GRP

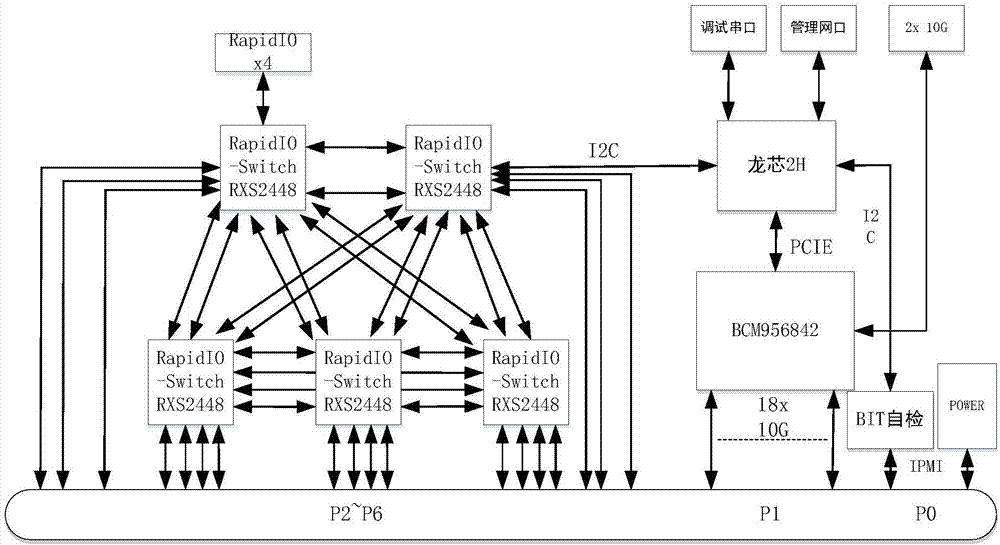

10-gigabit Ethernet switching and RAPIDIO switching fusion plate based on domestic CPU

InactiveCN106936735AImprove reinforcement effectEasy to manageData switching networks10 Gigabit EthernetEmbedded system

The invention relates to the technical field of RapidIO switching and network switching, and in particular relates to a 10-gigabit Ethernet switching and RAPIDIO switching fusion plate based on a domestic CPU. The 10-gigabit Ethernet switching and RAPIDIO switching fusion plate structurally comprises a mainboard and a backplane; a domestic Godson CPU is arranged on the mainboard; the domestic Godson CPU configures a RapidIO data switching chip through an I2C bus, and configures an Ethernet switching chip through a PCIE bus; the mainboard is connected to a power supply through a VPX connector of the backplane; and the mainboard externally provides 18 4X RapidIO interfaces and 18 10-gigabit Ethernet SerDes interfaces through the backplane, and is in cascade connection with the backplane through the VPX connector. By means of the 10-gigabit Ethernet switching and RAPIDIO switching fusion plate based on the domestic CPU disclosed by the invention, the domestic Godson can be used as the CPU; and thus, the purposes of satisfying 10-gigabit Ethernet switching and also satisfying RapidIO switching can be achieved.

Owner:JINAN INSPUR HIGH TECH TECH DEV CO LTD

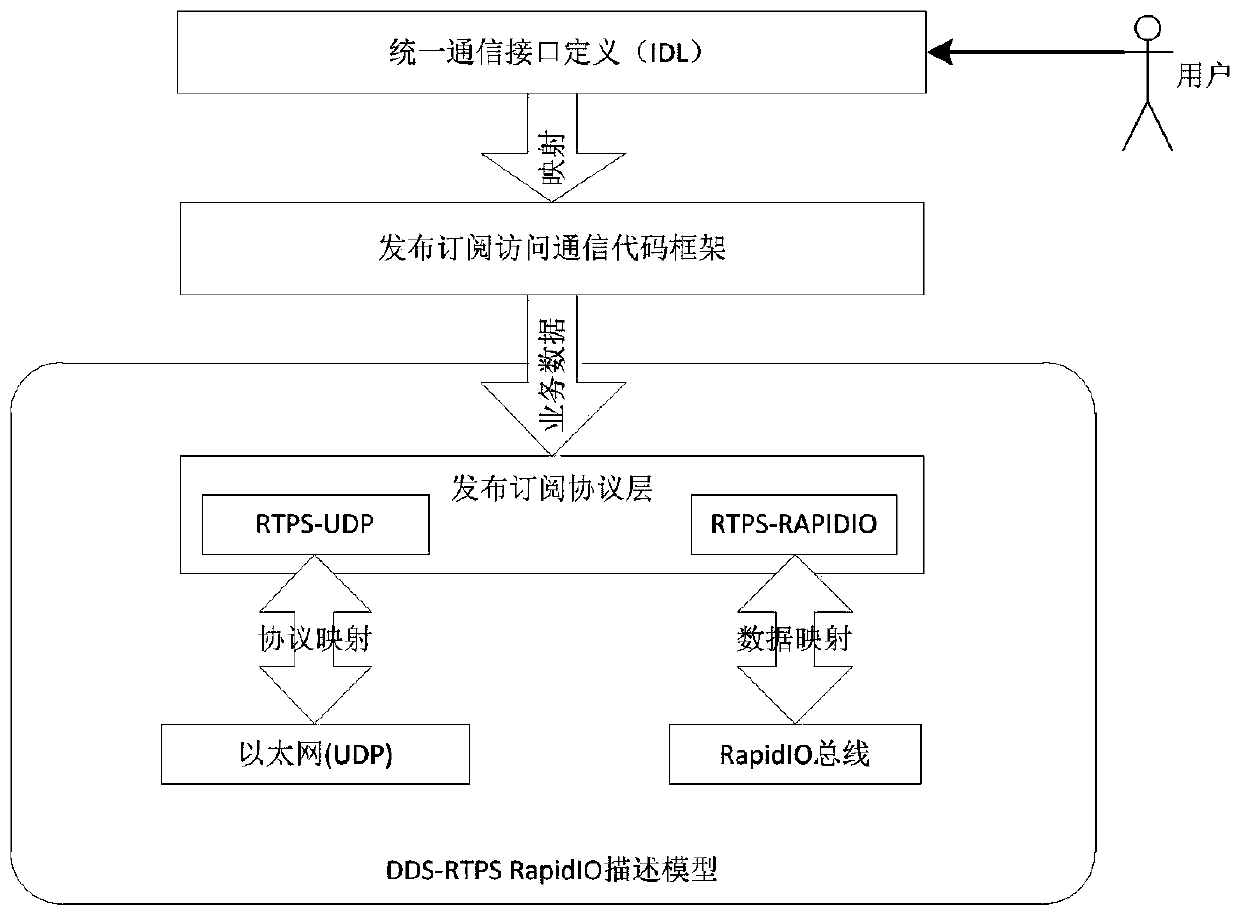

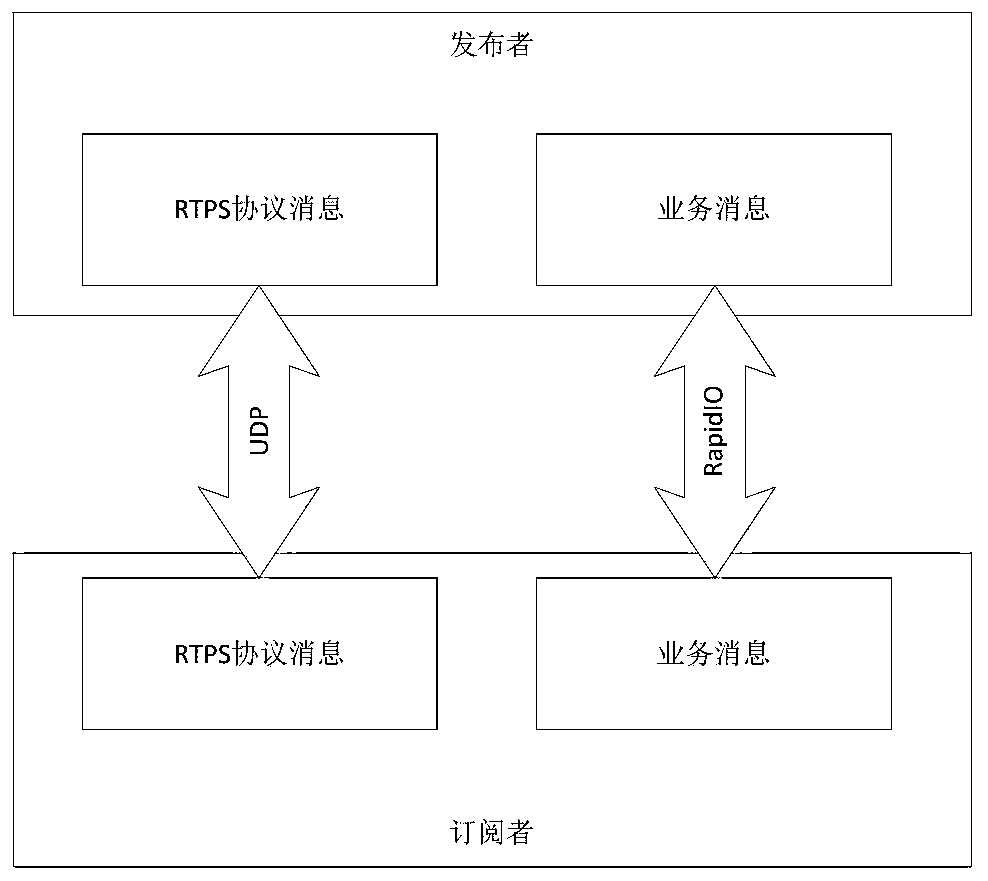

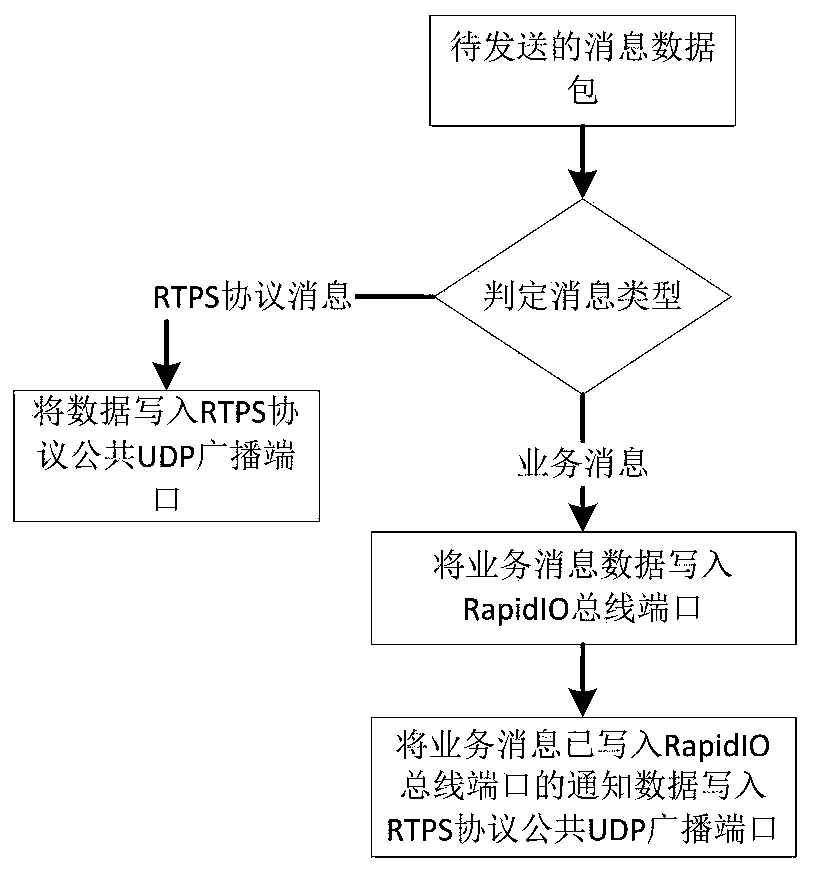

Method and system for integrating RapidIO transmission by DDS communication middleware

ActiveCN111400228AEfficient real-time distributionImprove communication efficiencyTransmissionElectric digital data processingData packElectronic information

The invention provides a method and a system for integrating RapidIO transmission by DDS communication middleware. The method comprises the following steps: a new model creation step, a RapidIO description model of a DDS-RTPS protocol is provided based on the DDS-RTPS protocol, and the brand-new RapidIO-based data transceiving model of the DDS-RTPS protocol is provided by utilizing the characteristics of UDP broadcasting, efficient UDP small data packet transmission and efficient RapidIO large data packet transmission. According to the invention, a DDS communication model of task electronic information system data based on a RapidIO underlying communication mechanism is realized, interfaces are uniformly accessed, efficient real-time distribution is realized, a uniform communication soft bus is provided for applications in the task electronic information system, and the communication efficiency and portability of the applications are effectively improved.

Owner:EAST CHINA INST OF COMPUTING TECH

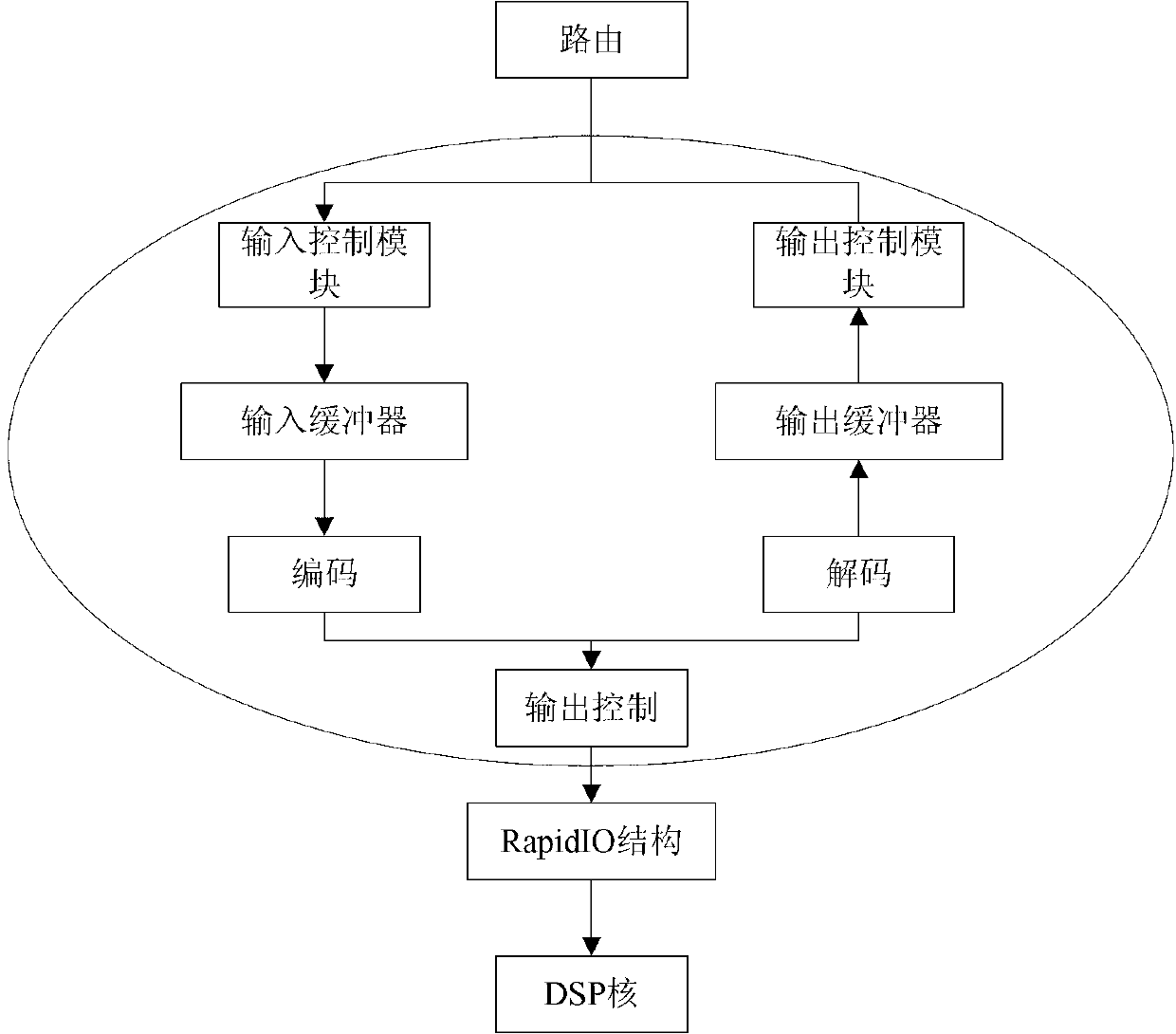

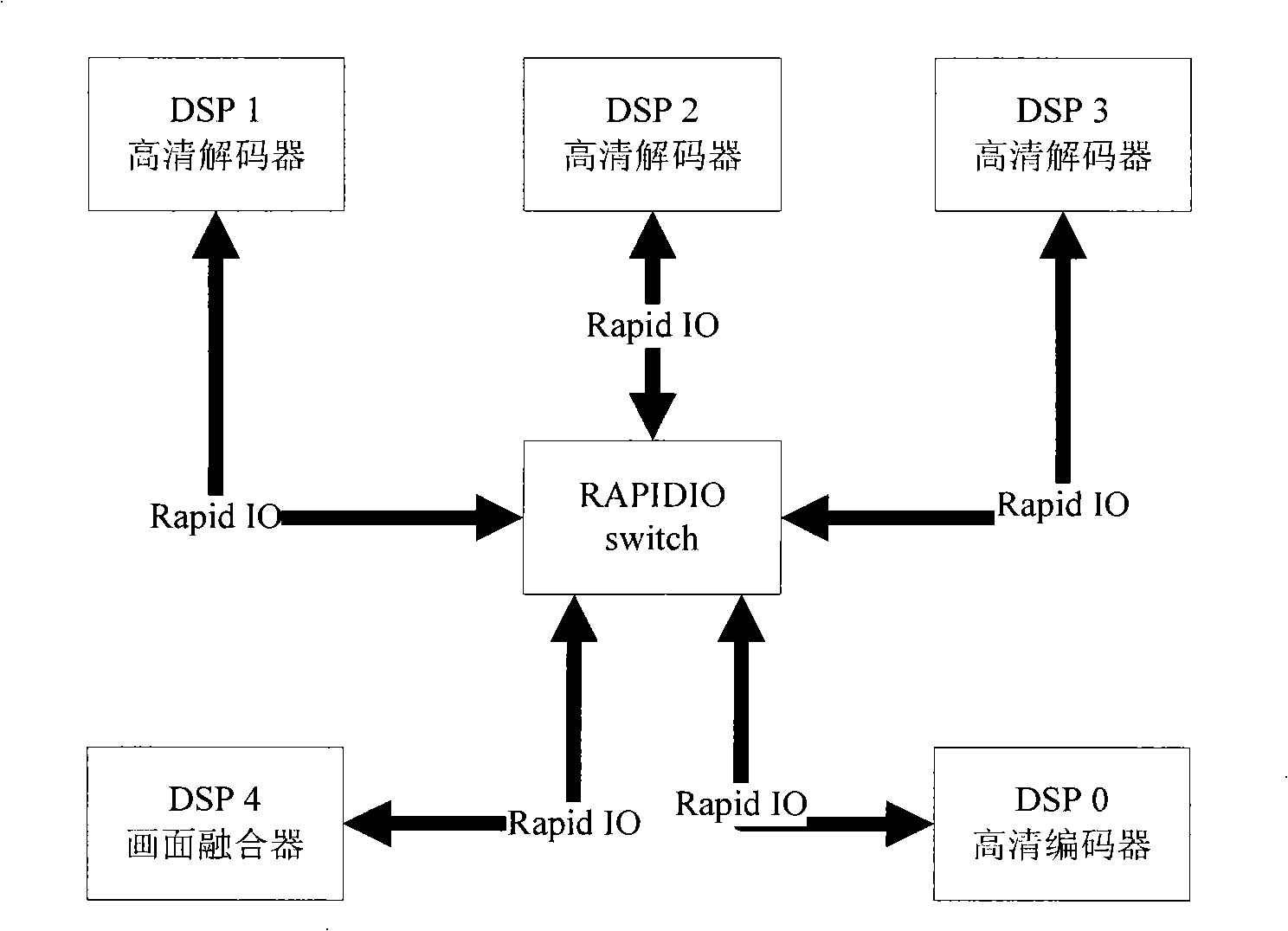

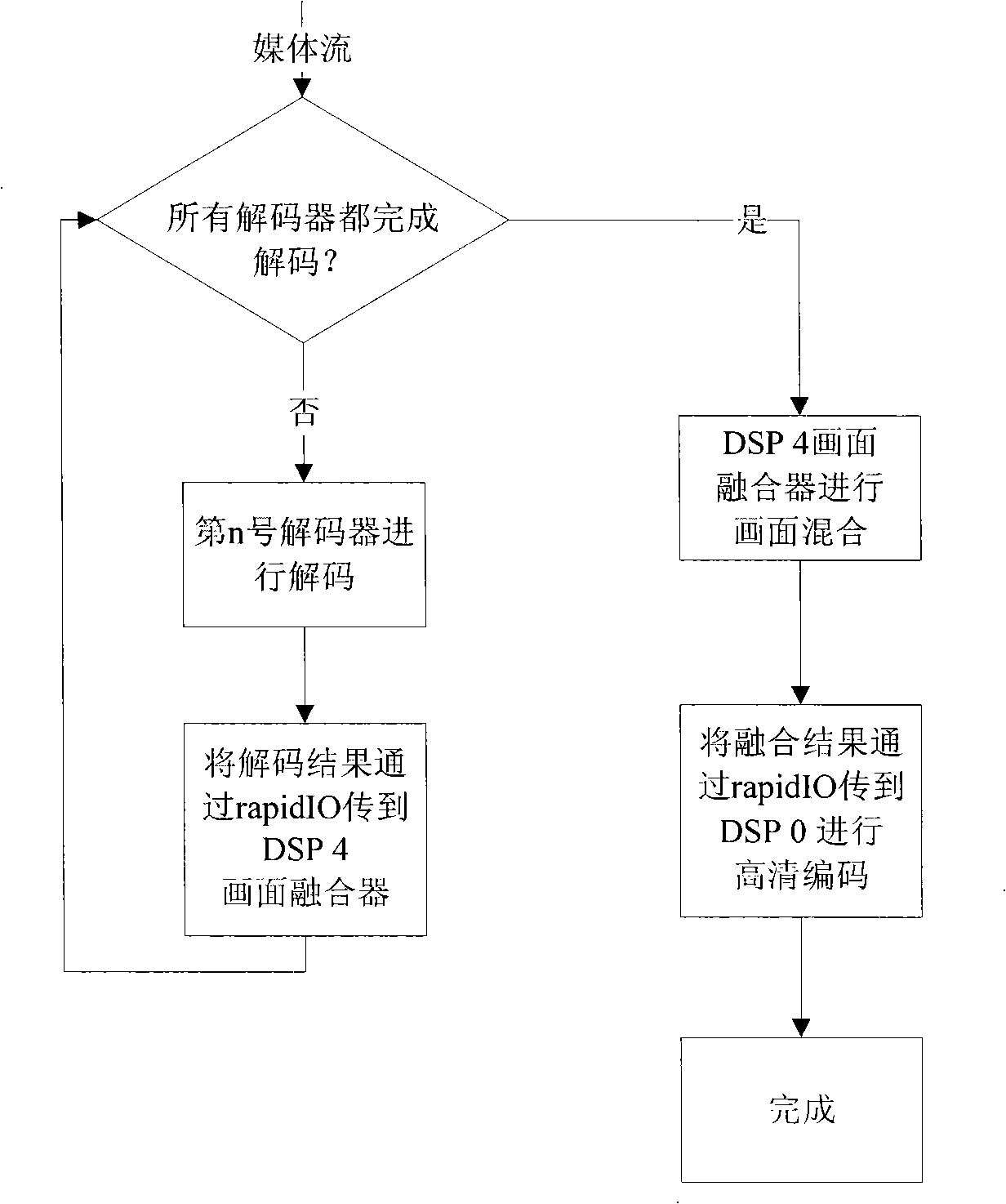

Method and system for processing multicore DSP array medium based on RapidIO interconnection

InactiveCN101282477AImprove processing densityGuaranteed feasibilityTelevision systemsDigital video signal modificationLow delayHandling system

The invention relates to a multi-core DSP array media processing system based on RapidIO interconnection and method thereof. Three more multi-core DSP are serially interconnected by RapidIO and are packaged inside a chip, communications between the cores are realized by employing high-speed bus and shared memory; the media processing method is: transmitting high-definition media processing streams respectively to multiple DSP high-definition decoders for decoding; transmitting the result to another multi-core DSP image synthesizer through RapidIO, and inputting the processed signal to the multi-core DSP high-definition encoders for encoding. RapidIO switching technology is employed by the invention, which can respectively provide a low-delay data switching path with maximum transmission speed of 10Gbps between each DSP chip, which ensures feasibility of pipeline processing and greatly improves processing density for a signal DSP, which can real-time distribute processing task effectively according to processing load of each DSP kernel.

Owner:AVONACO COMM SYST SUZHOU

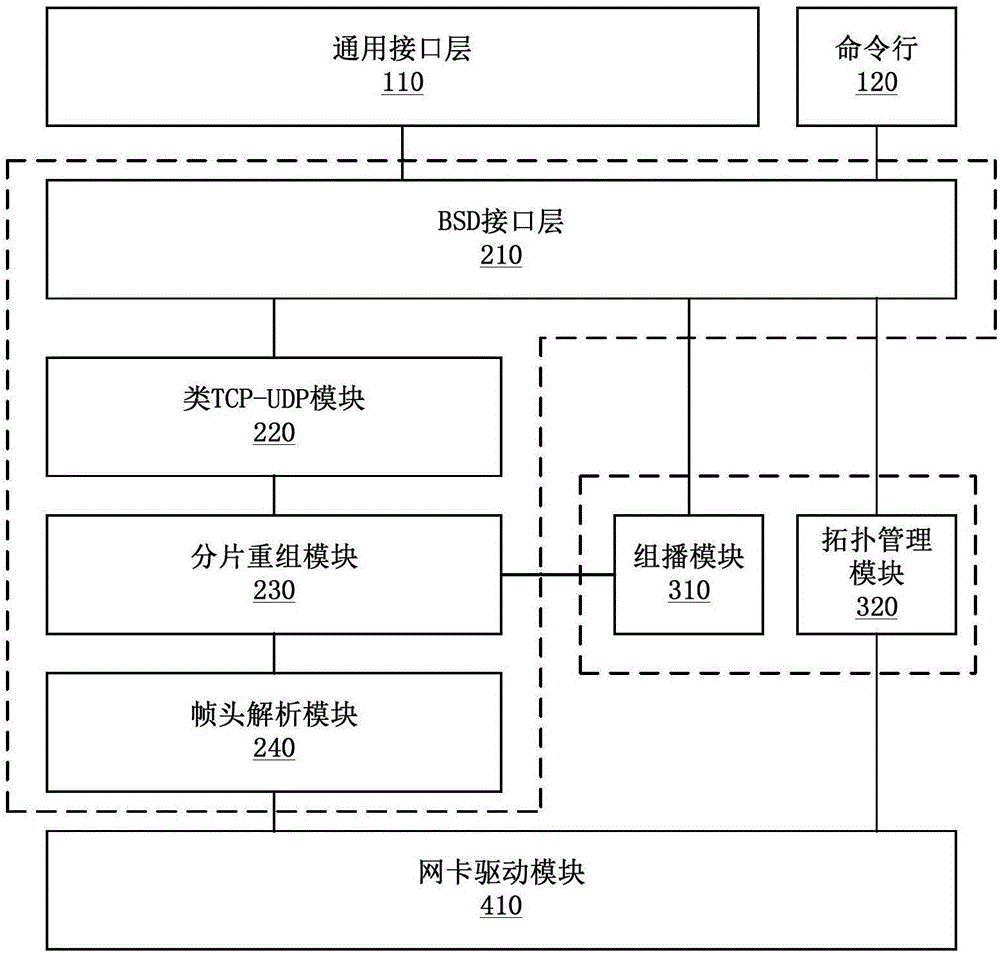

System and method for implementing RapidIO network universal socket

The invention provides a system and method for implementing a RapidIO network universal socket. The system comprises a universal interface layer, a command line and a BSD interface layer, wherein an application layer uses a socket interface for carrying out RapidIO network communication; a user views and configures equipment, a topological relationship and protocol stack parameters of a RapidIO network; and a new RapidIO network protocol stack is created by utilizing a kernel function provided by the BSD interface layer. According to the system and the method which are provided by the invention, a set of TCP / UDP-like programming interfaces is provided for a user, an application protocol based on data streaming and a datagram is implemented, direct I / O communication and message transmission are used as network drivers, and high-speed communication is implemented.

Owner:NO 32 RES INST OF CHINA ELECTRONICS TECH GRP

Method of transporting a RapidIO packet over an IP packet network

ActiveUS7620047B2Time-division multiplexData switching by path configurationIp addressNetwork packet

A method of transporting a RapidIO packet (135) from an initiator RapidIO domain (102) over an IP packet network (110) to a receiver RapidIO domain (104) can include the initiator RapidIO domain creating the RapidIO packet and reading a destination domain ID (483) of the RapidIO packet, where the destination domain ID corresponds to the receiver RapidIO domain. The destination domain ID is mapped to a receiver RapidIO domain IP address (473). The RapidIO packet is encapsulated in an IP packet (436) and the IP packet is communicated to the receiver RapidIO domain over the IP packet network.

Owner:SMART EMBEDDED COMPUTING INC

B code time synchronization method based on VPX architecture

InactiveCN106788950ARadio-controlled time-piecesSynchronising arrangementData synchronizationSystem time

The invention relates to a B code time synchronization method based on VPX architecture, and belongs to the technical field of accurate timing. The VPX architecture comprises a power board, an exchange board and a plurality of blade motherboards, and accurate synchronization and timing between blades are the premise of realizing the load balance of the system. Receiving and timekeeping circuits of a B code are implemented on an FPGA of the exchange board, and the FPGA can decode information indicating the second, minute, hour, date, month and year from the input B code. Meanwhile, the FPGA connects a PCIE interface to a PCIE switching chip of the exchange board, and the port is used as an EP. The CPU of the exchange board is used as a RC of a PCIE switching network, and the blades are set as an NT mode. When each NT (blade) requires time synchronization, the current time is required from the EP by an NT port of a PICE bus, and the extracted time is the system time after the time synchronization. Meanwhile, a serial RapidIO interface is reserved in the RPGA, and a RapidIO switch is used as redundancy backup of the B code system. By adoption of the B code time synchronization method, the time synchronization precision can reach a microsecond level, and thus has a very good application prospect in a VPX system.

Owner:TIANJIN JINHANG COMP TECH RES INST

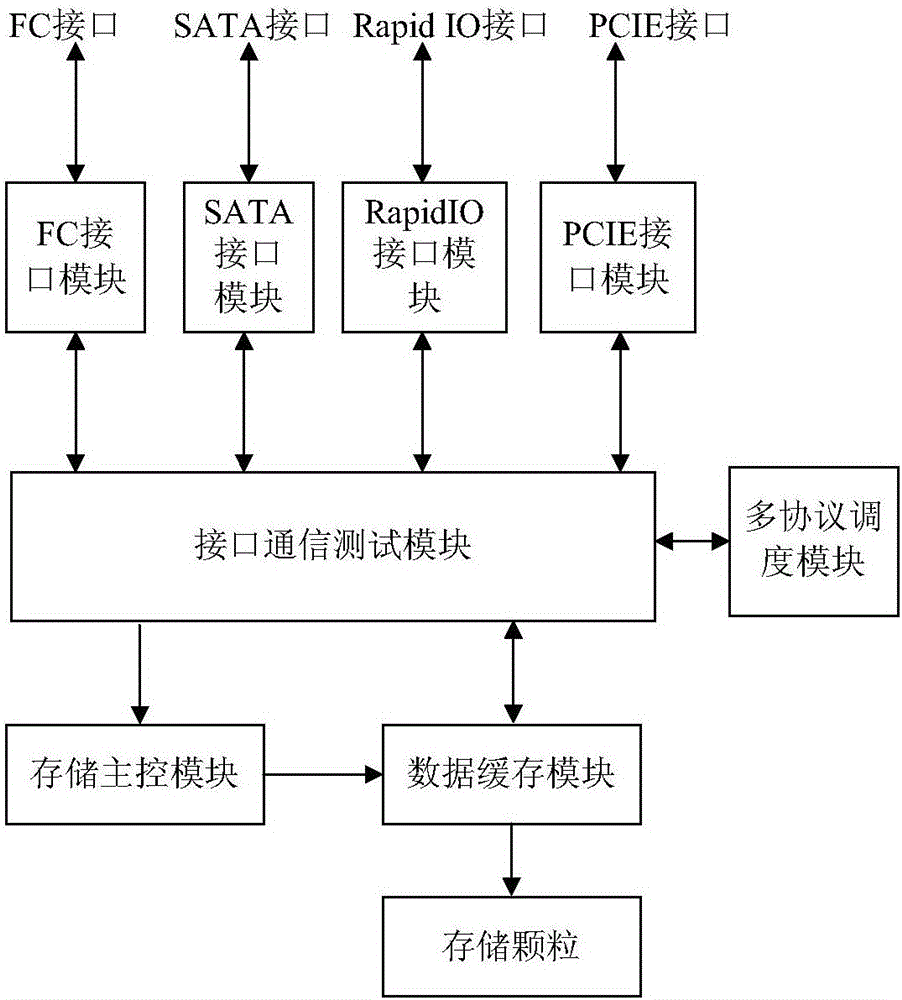

Solid state hard disk with multiple protocol interfaces

InactiveCN106681945ARealize communicationElectric digital data processingState of artFlexible scheduling

The invention belongs to the technical field of storage, and particularly relates to a solid state hard disk with multiple protocol interfaces. Compared with a prior art, the invention provides the solid state hard disk system with multichannel and multiple protocol interfaces. The solid state hard disk system is provided with an SATA protocol interface, a PCIE interface, a RapidIO interface, an FC interface and the like, and communication of the main equipment with different interfaces can be achieved through flexible scheduling and interfaces among multiple main equipment without using a protocol handover interface.

Owner:TIANJIN JINHANG COMP TECH RES INST

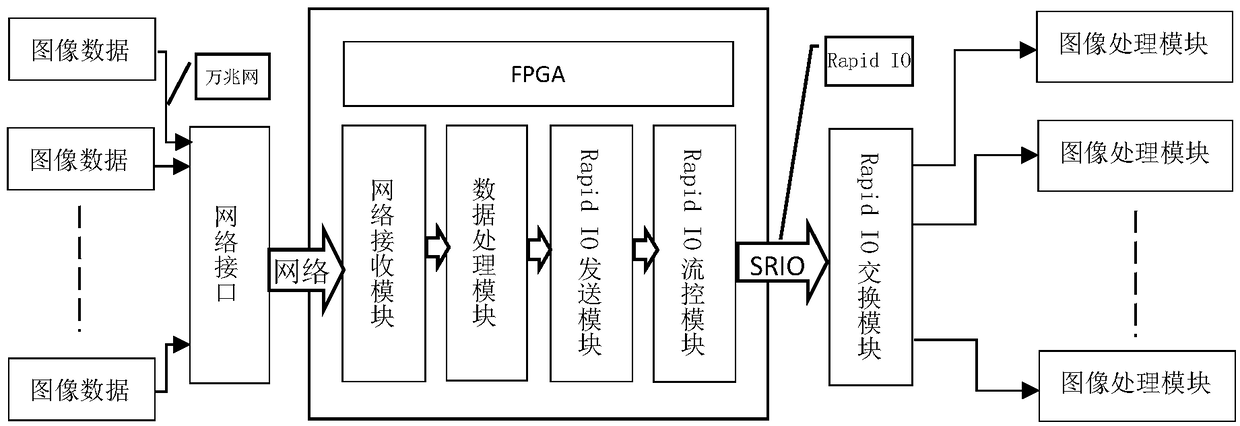

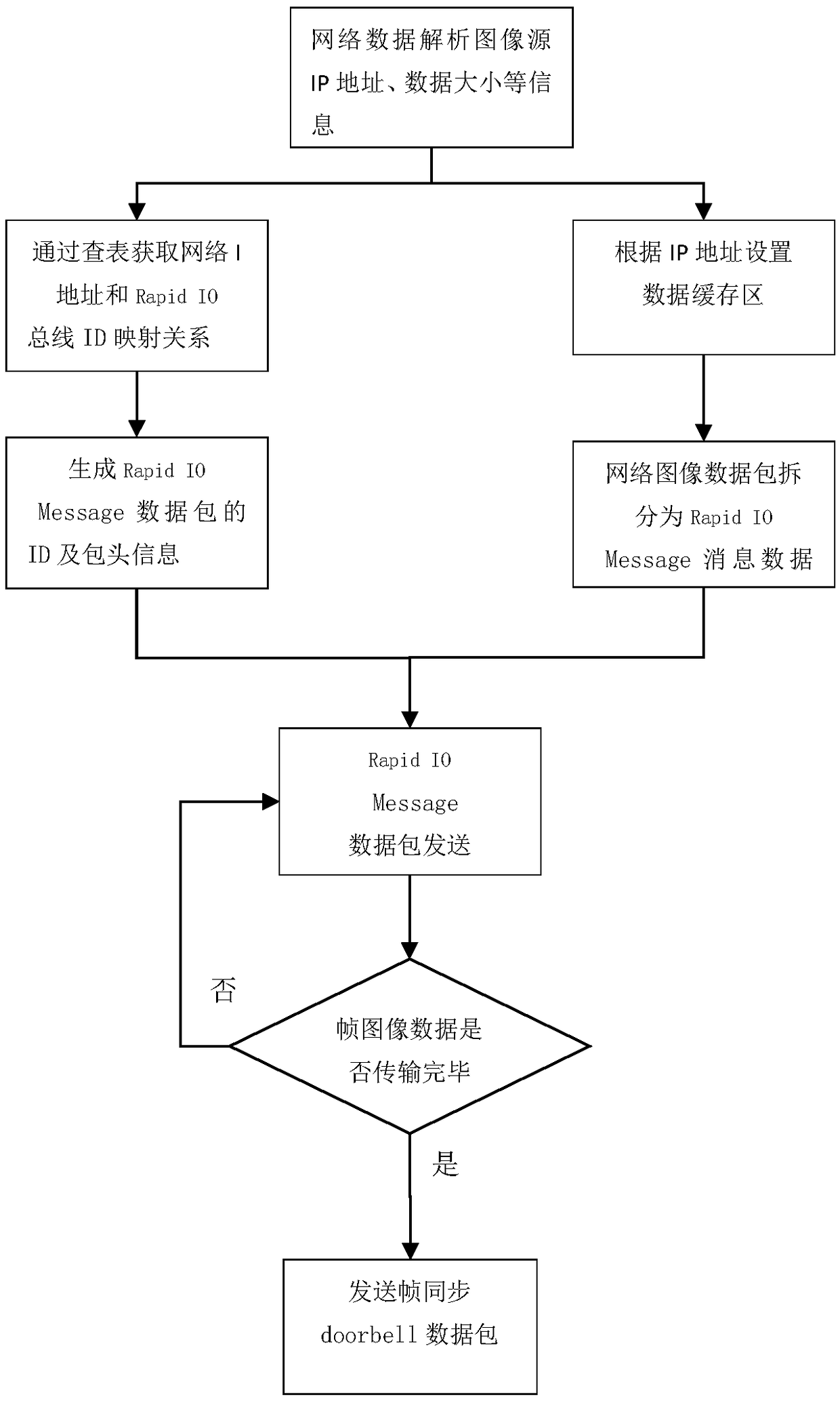

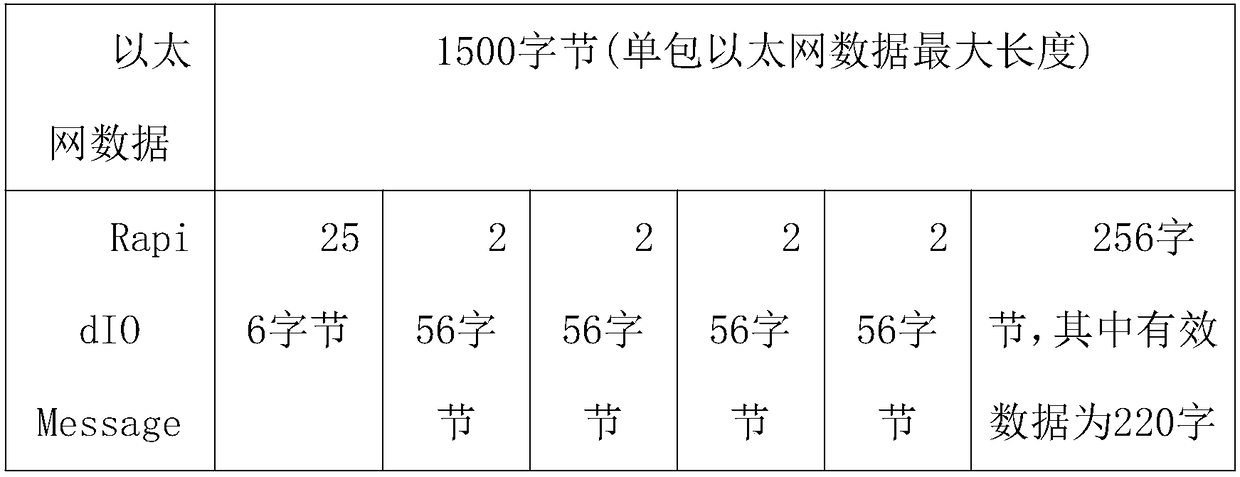

FPGA-based 10-gigabit fiber Ethernet to RapidIO multi-channel image transmission processing system

InactiveCN109510973AHigh-speed deliveryRealize data conversion and transmissionTelevision system detailsOptical transmission adaptations10 Gigabit EthernetOptical Module

The invention belongs to the field of data conversion, and particularly relates to an FPGA-based 10-gigabit fiber Ethernet to RapidIO multi-channel image transmission processing system. The system comprises a network interface, an FPGA and a RapidIO switching module, wherein the FPGA comprises a network receiving module, a data processing module, a RapidIO transmitting module and a RapidIO trafficcontrol module. According to the FPGA-based 10-gigabit fiber Ethernet to RapidIO multi-channel image transmission processing system, long-distance transmission of large-capacity multi-channel imagesis implemented by using the fiber 10-gigabit Ethernet, a gigabit optical module is connected to the FPGA for high-speed conversion between a network protocol and a RapidIO protocol, and image data isforwarded to each node by a RapidIO bus to realize data conversion and transmission of the multi-channel large-capacity image data 10-gigabit fiber Ethernet and the RapidIO high-speed serial bus inside the embedded system, so that the remote image data is conveniently and reliably transmitted to an image processing board in the system at a high speed.

Owner:SOUTH WEST INST OF TECHN PHYSICS

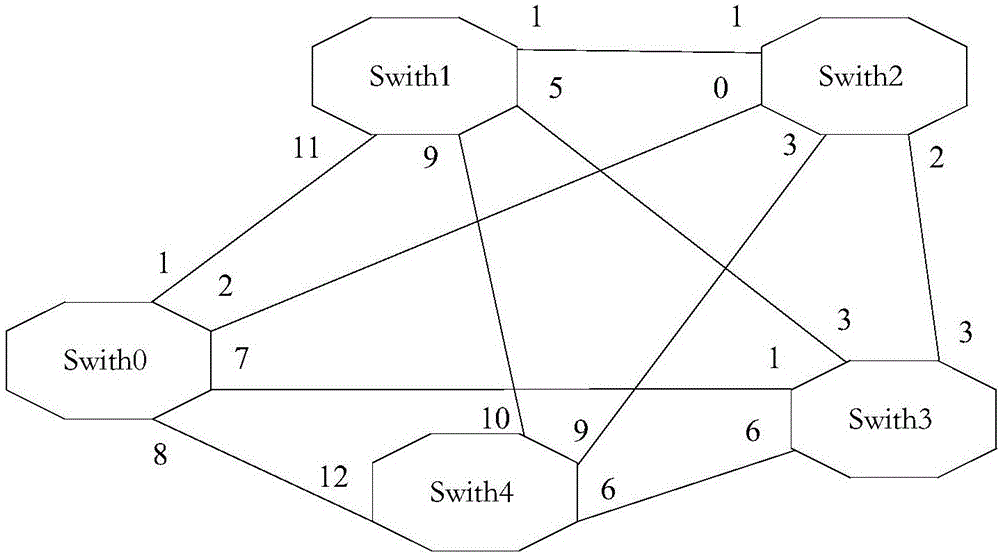

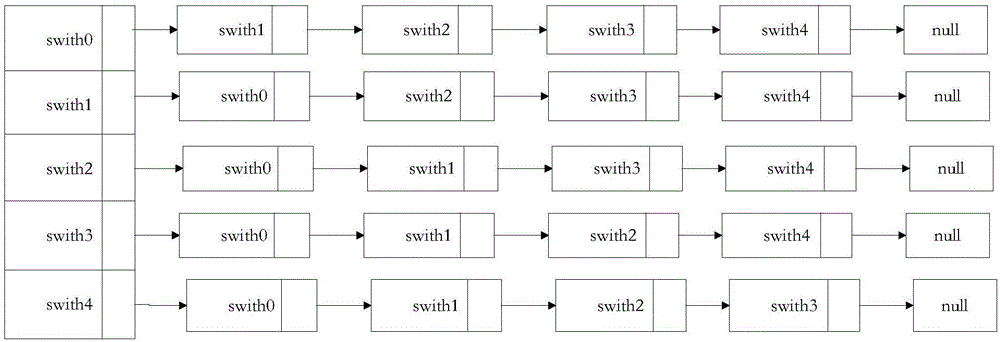

RapidIO route configuration method and device based on VPX system

ActiveCN106789161AAccurate calculationImprove accuracyData switching networksElectric digital data processingRouting modelStructure of Management Information

The invention relates to a RapidIO route configuration device and a RapidIO route configuration method based on a VPX system. The device comprises an upper computer and a VPX system, wherein a node in a RapidIO network of the VPX system serves as a RapidIO main node; the upper computer is used for building a corresponding RapidIO route model according to the network topological structure of the VPX system, and also used for traversing the whole RapidIO route model, computing an optimal path between any two RapidIO nodes in the model according to path weights, forming a route configuration table and transmitting the route configuration table to the RapidIO main node in the VPX system; and the RapidIO main node is used for performing route configuration on the whole RapidIO network of the VPX system according to the route configuration table.According to the device and the method provided by the invention, the upper computer is responsible for computing the route configuration table of the RapidIO network, and then configuration is performed by the RapidIO main node in the VPX system; compared with a traditional single-point configuration method, the method provided by the invention is significantly improved in configuration speed and configuration accuracy via cooperative configuration of the upper computer and the RapidIO main node.

Owner:BEIJING INST OF RADIO MEASUREMENT

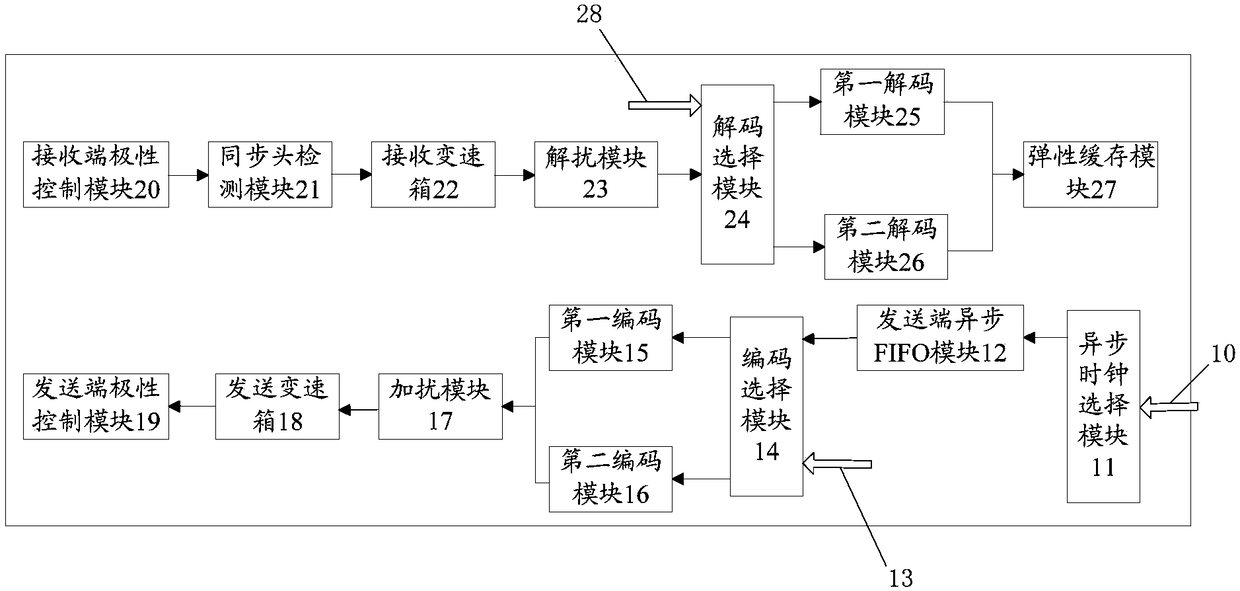

Dual protocol multiplexing chip and dual protocol multiplexing method

InactiveCN108521430AReduce use costSave logic resourcesTransmissionMultiplexingNetwork communication

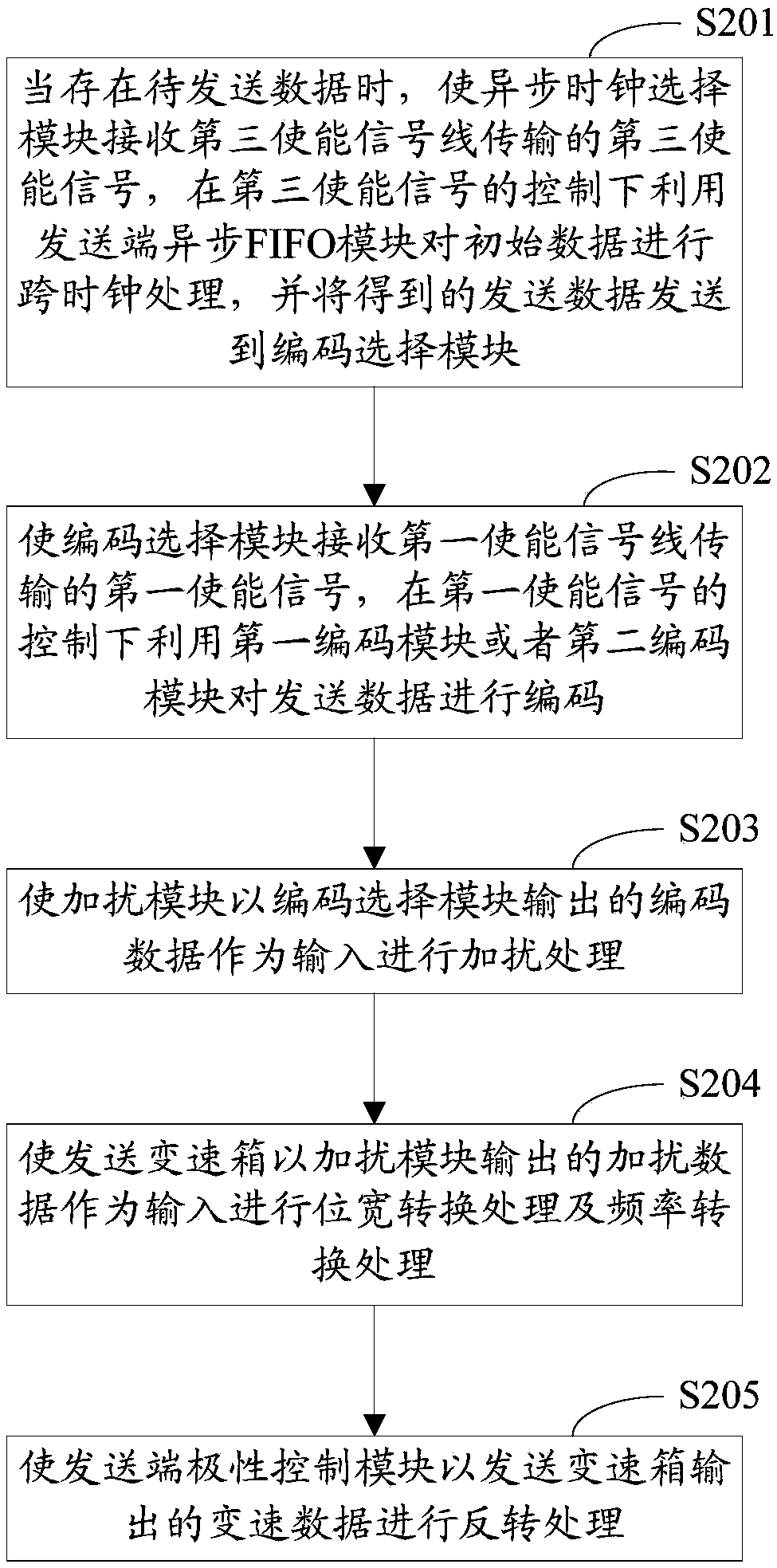

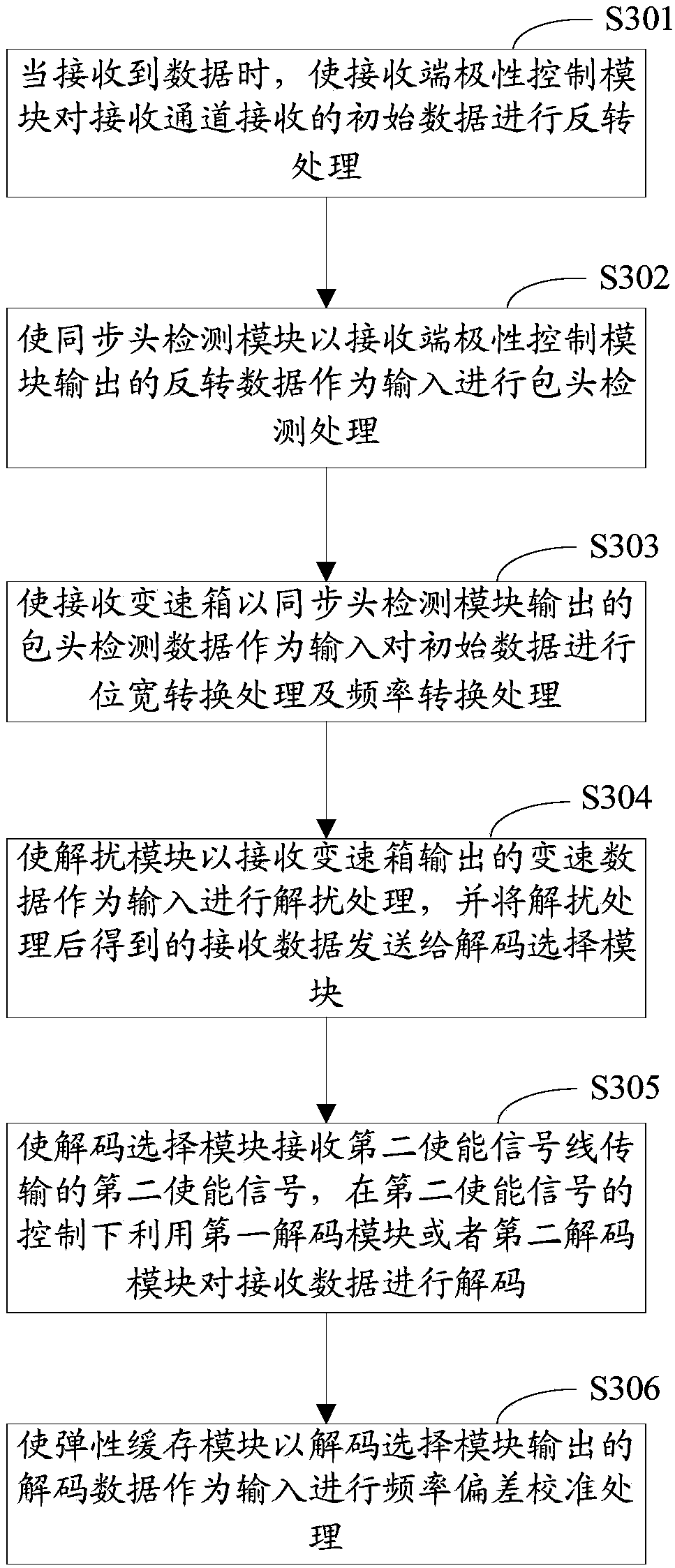

The invention provides a dual protocol multiplexing chip and a dual protocol multiplexing method, and belongs to the technical field of network communication, wherein the dual protocol multiplexing chip comprises a first encoding module supporting a 16G Fiber Channel PCS protocol, a second encoding module supporting a 10.3125G Serial RapidIO PCS protocol, an encoding selection module respectivelyconnected to the first encoding module and the first second encoding module, a first decoding module supporting the 16G Fiber Channel PCS protocol, a second decoding module supporting the 10.3125G Serial RapidIO PCS protocol, and a decoding selection module respectively connected to the first decoding module and the second decoding module; and the encoding selection module is connected with a first enabling signal line, and the decoding selection module is connected with a second enabling signal line. According to the dual protocol multiplexing chip and the dual protocol multiplexing method provided by the embodiment of the present invention, transmission of the data packaged according to the 16G Fiber Channel PCS protocol and the 10.3125G Serial RapidIO PCS protocol is achieved in the same architecture, thereby saving a large amount of logic resources and reducing the cost of using the chip.

Owner:TIANJIN CHIP SEA INNOVATION TECH CO LTD +1