Rapid IO switching network

A technology of switching networks and switches, applied in the field of airborne computers, to achieve the effects of high bandwidth, high reliable data transmission performance, and low delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described in detail below with reference to the drawings and embodiments.

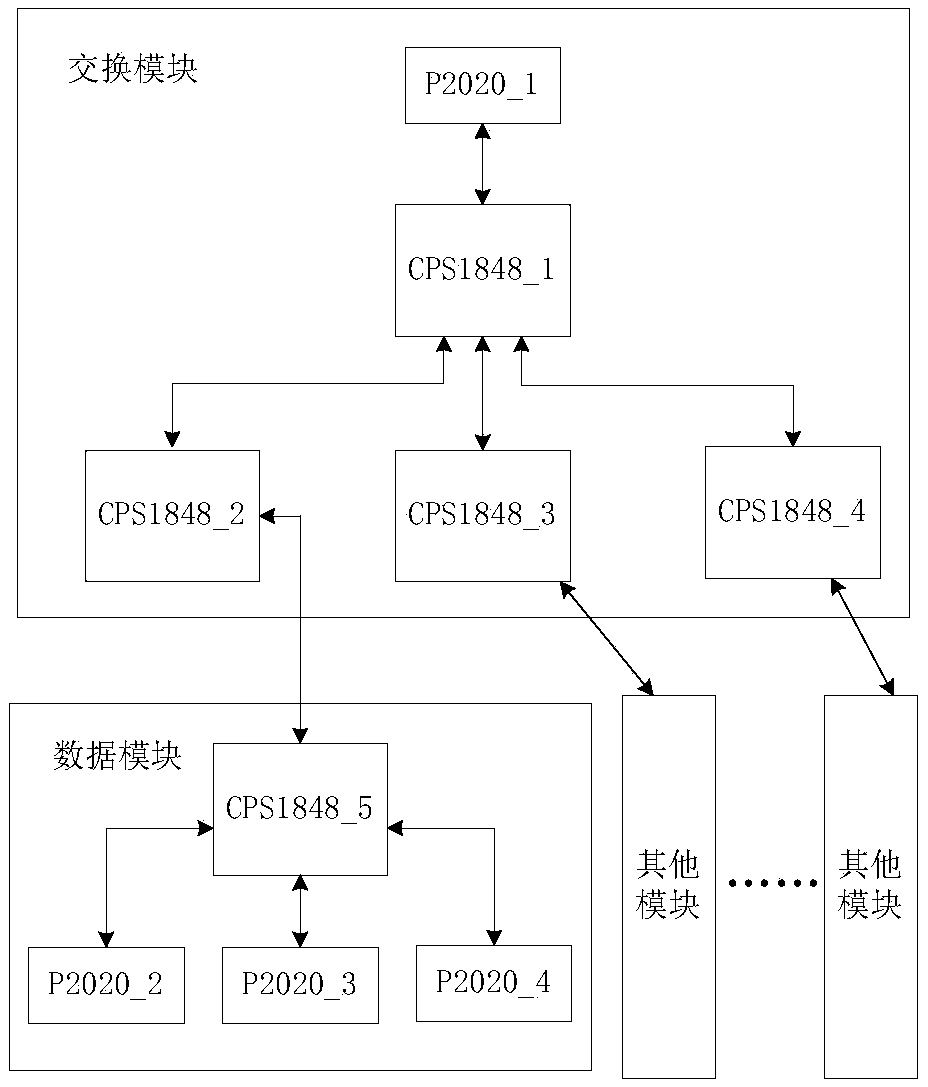

[0043] A RapidIO switching network provided by this embodiment, for its hardware structure, see figure 1 As shown, the RapidIO switching network includes multiple nodes and multiple switches. The nodes are P2020 processing chips, and the switches are CPS1848 switch chips. Multiple nodes are connected by switches to form a RapidIO network to realize high-speed data communication between multiple nodes.

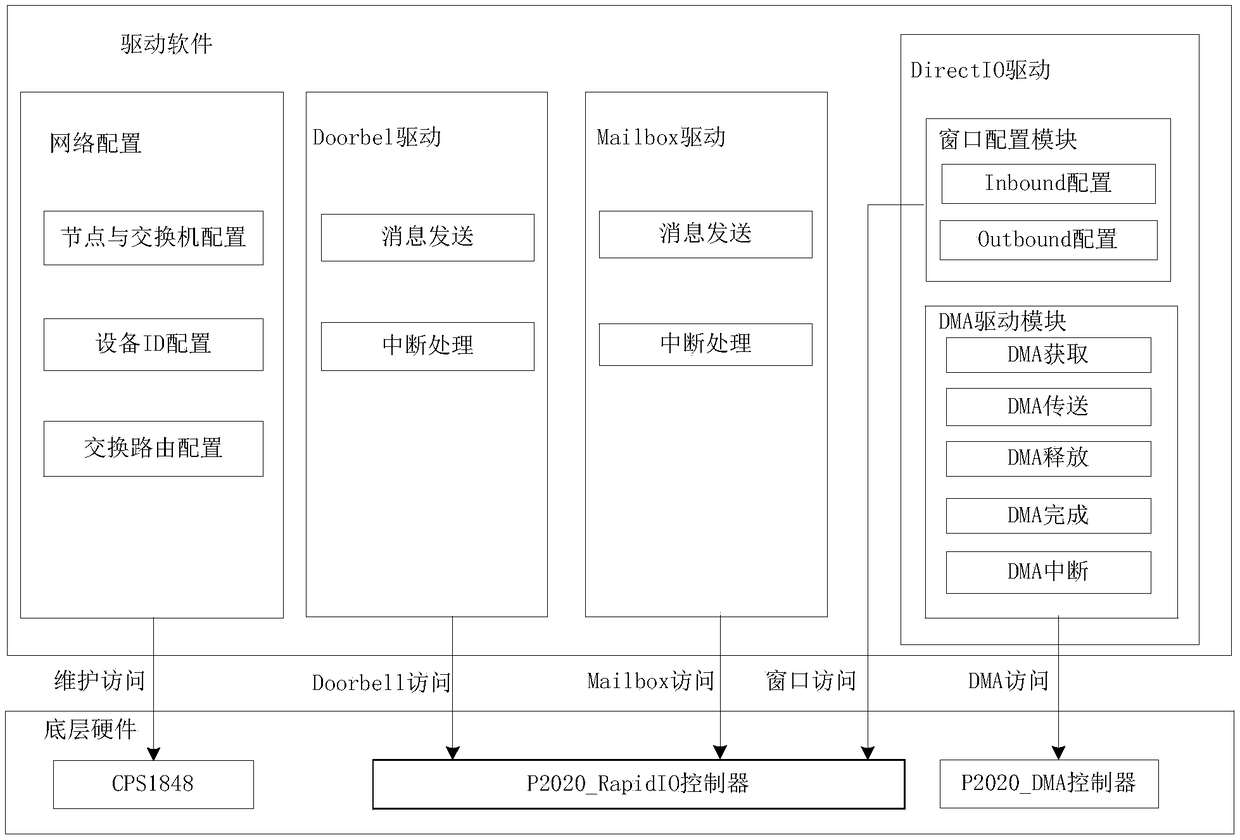

[0044] RapidIO switching network driver software includes RapidIO network configuration function, Doorbell doorbell interrupt function, Mailbox data transmission function and DirectIO data transmission function. Its relationship with the underlying hardware is as figure 2 Shown:

[0045] 1. RapidIO network configuration

[0046] The RapidIO network configuration includes the configuration of each P2020 processing chip and CPS1848 switch.

[0047] The RapidIO network...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More