Method and system for processing multicore DSP array medium based on RapidIO interconnection

A processing system, multi-core technology, applied in the fields of electrical digital data processing, television, instruments, etc., can solve problems such as insufficient bus bandwidth, achieve the effect of improving processing density and ensuring feasibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

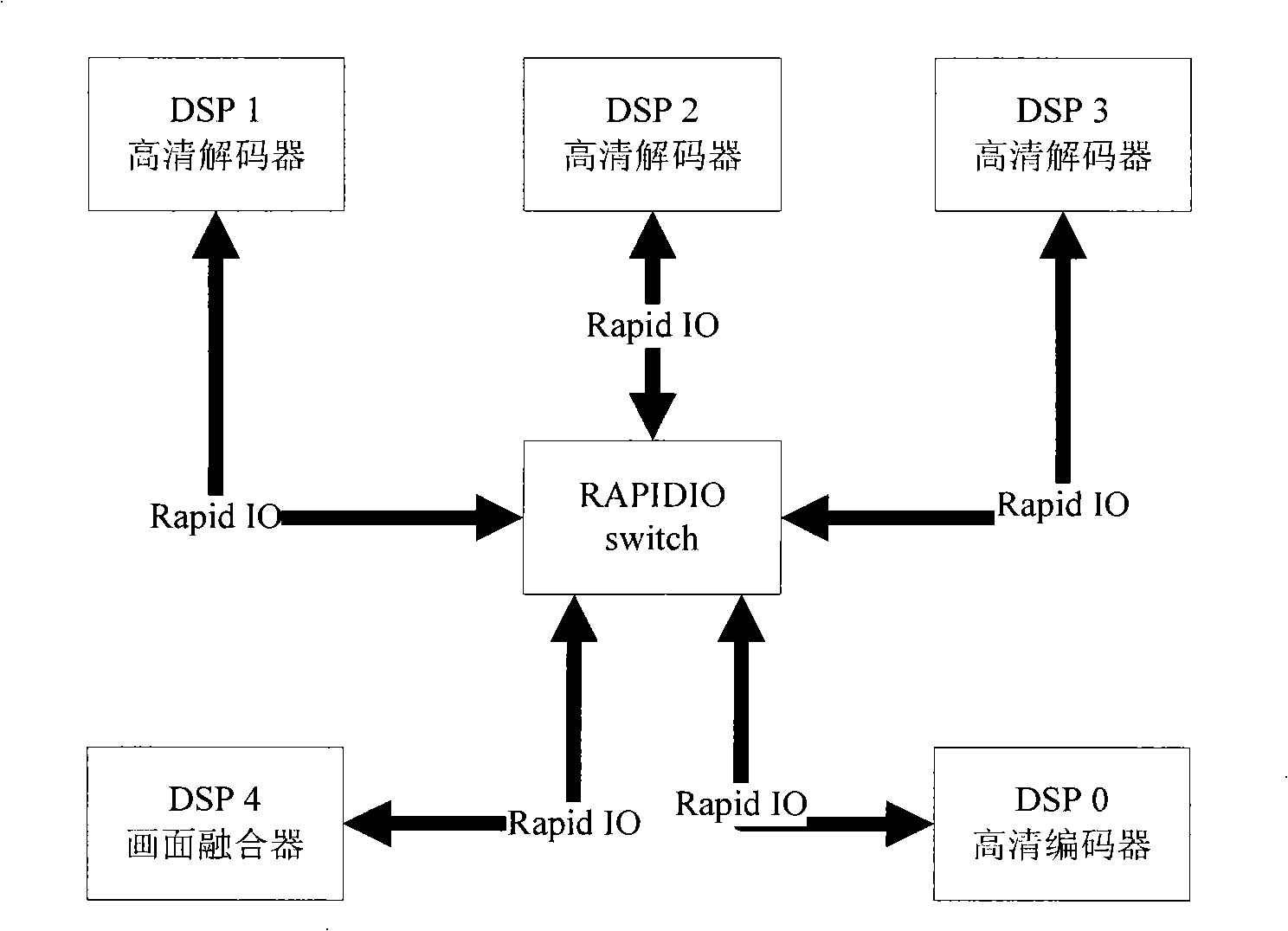

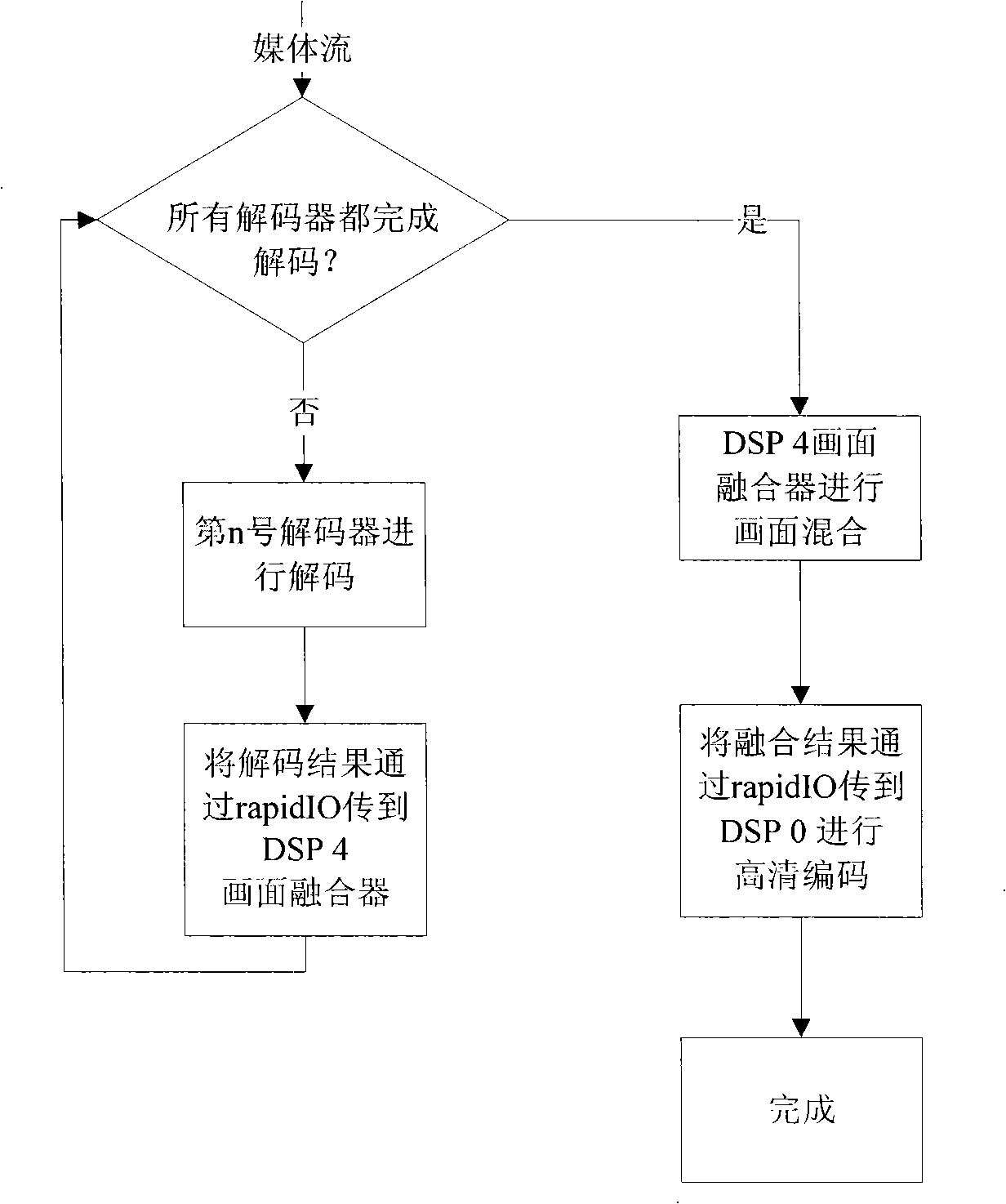

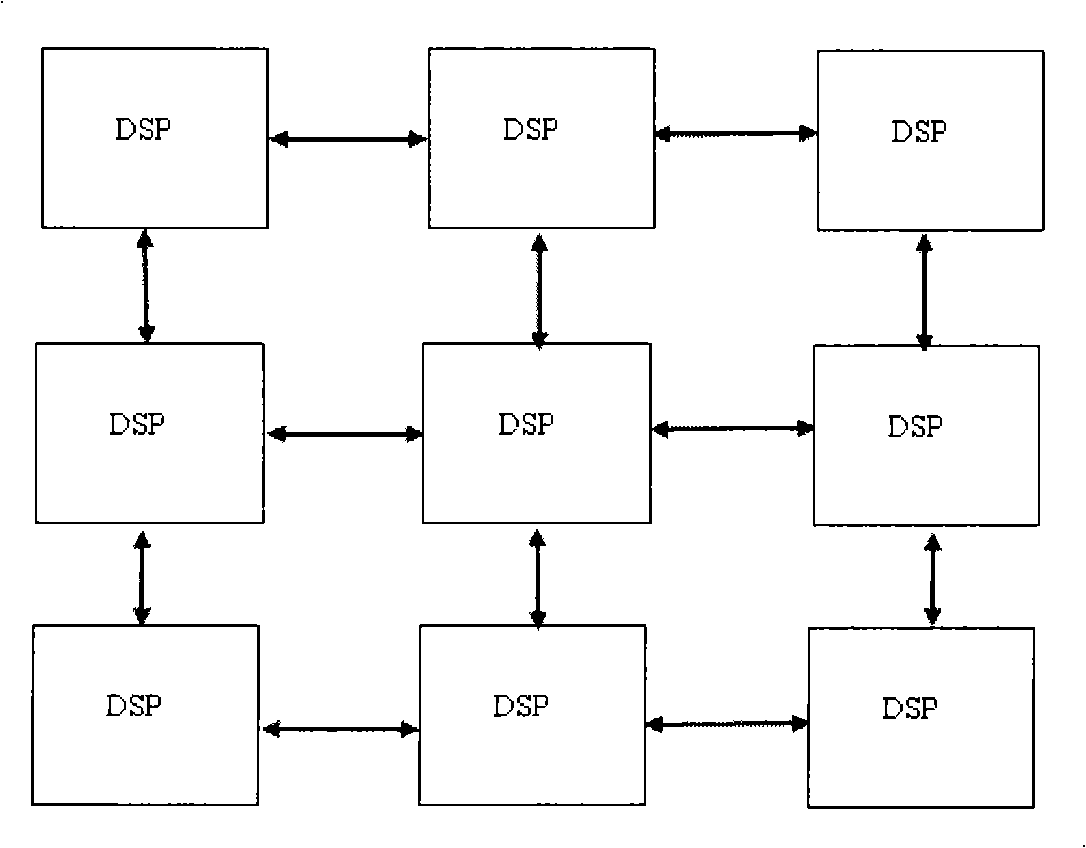

[0017] See attached figure 1 , which is a schematic diagram of the multi-core DSP star topology based on RapidIO interconnection in this embodiment; five multi-core DSPs are connected in a star shape through the RapidIO Switch. Among the multi-core DSPs, one is a high-definition encoder, one is a picture fuser, and three For HD codec. In this embodiment, five DSP cores are packaged in one chip, and the cores communicate through a high-speed bus and a shared memory. Each DSP core runs independently at a frequency up to 1GHz, which greatly improves the processing density of a single DSP chip while reducing power consumption and area.

[0018] For complex video processing, such as H.264 encoding of 1280x720, a single DSP core cannot handle it. With the technical solution of the present invention, these complex video applications can be processed in a pipelined manner, and each DSP chip only undertakes processing a certain For example: video decoding or picture synthesis, a vide...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More