A signal processing system with dual processing nodes based on arria10 FPGA

A signal processing and processing node technology, applied in the field of signal processing, can solve the problems of high data processing density, large storage capacity and high transmission rate interconnection characteristics of signal processing systems, etc., and achieve fast transmission rate, large storage capacity, external Interconnect flexible effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in detail below with reference to the accompanying drawings and examples.

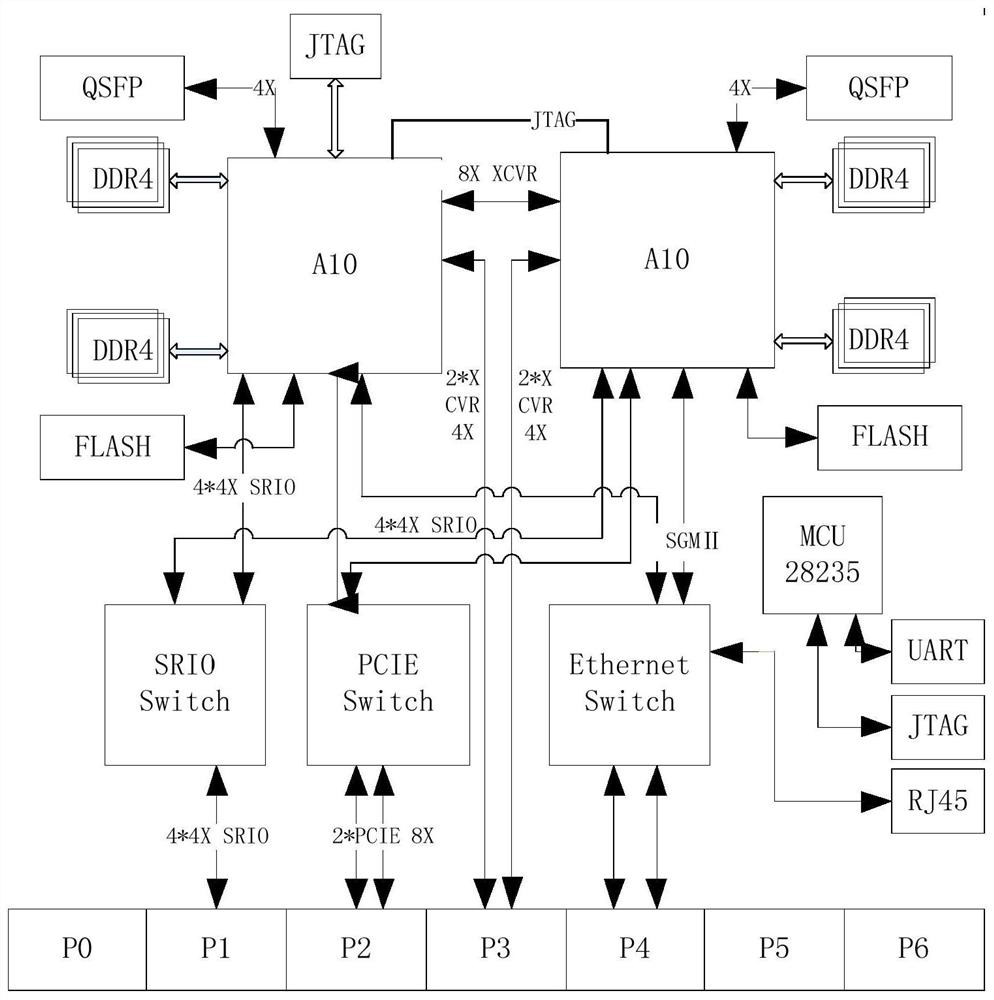

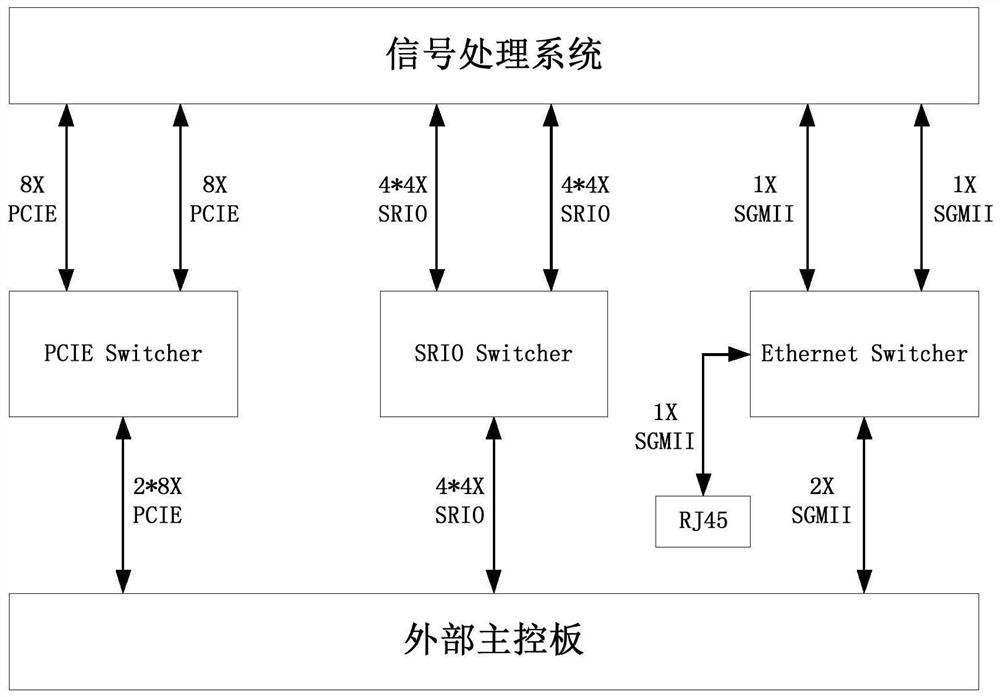

[0028] The present invention provides a signal processing system based on Arria10 FPGA's dual processing nodes, its specific structure is as follows figure 1 As shown, the signal processing system includes two identical processing nodes.

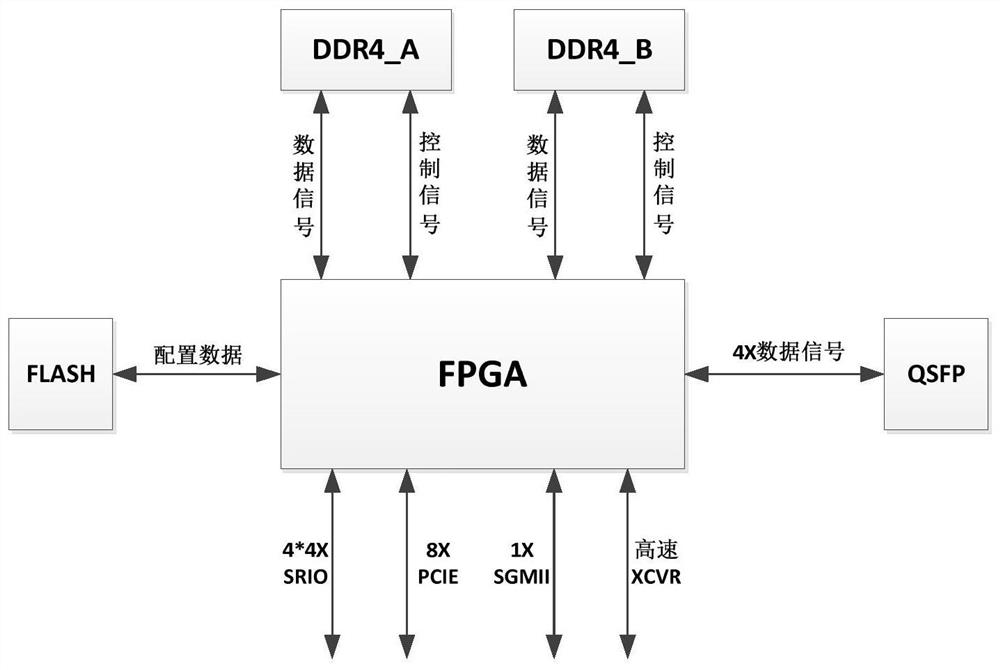

[0029] Each processing node is composed of an FPGA chip and a fourth-generation double-rate synchronous dynamic random access memory DDR4 and QSFP optical module connected to the FPGA chip; the FPGA chips of the two processing nodes are connected through 8 pairs of high-speed XCVR buses.

[0030] The total processing capacity of two FPGAs can reach 30GFLOPs, and the maximum capacity of a single board is 16GB DDR4. Each FPGA is connected with two DDR4 controllers for data transmission and storage. Each controller controls a 4GB DDR4 bus, and the DDR4 controller supports the highest The clock frequency is 1200MHz, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More