Scalable DSPEED-DSP_Q6455 signal processing board based on switcher

A signal processing board, TMS320C6455 technology, applied in the field of multi-DSP boards, can solve problems such as poor interconnectivity of multi-DSP, and achieve the effects of flexible and diverse interface forms, large data transmission bandwidth, and strong processing capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

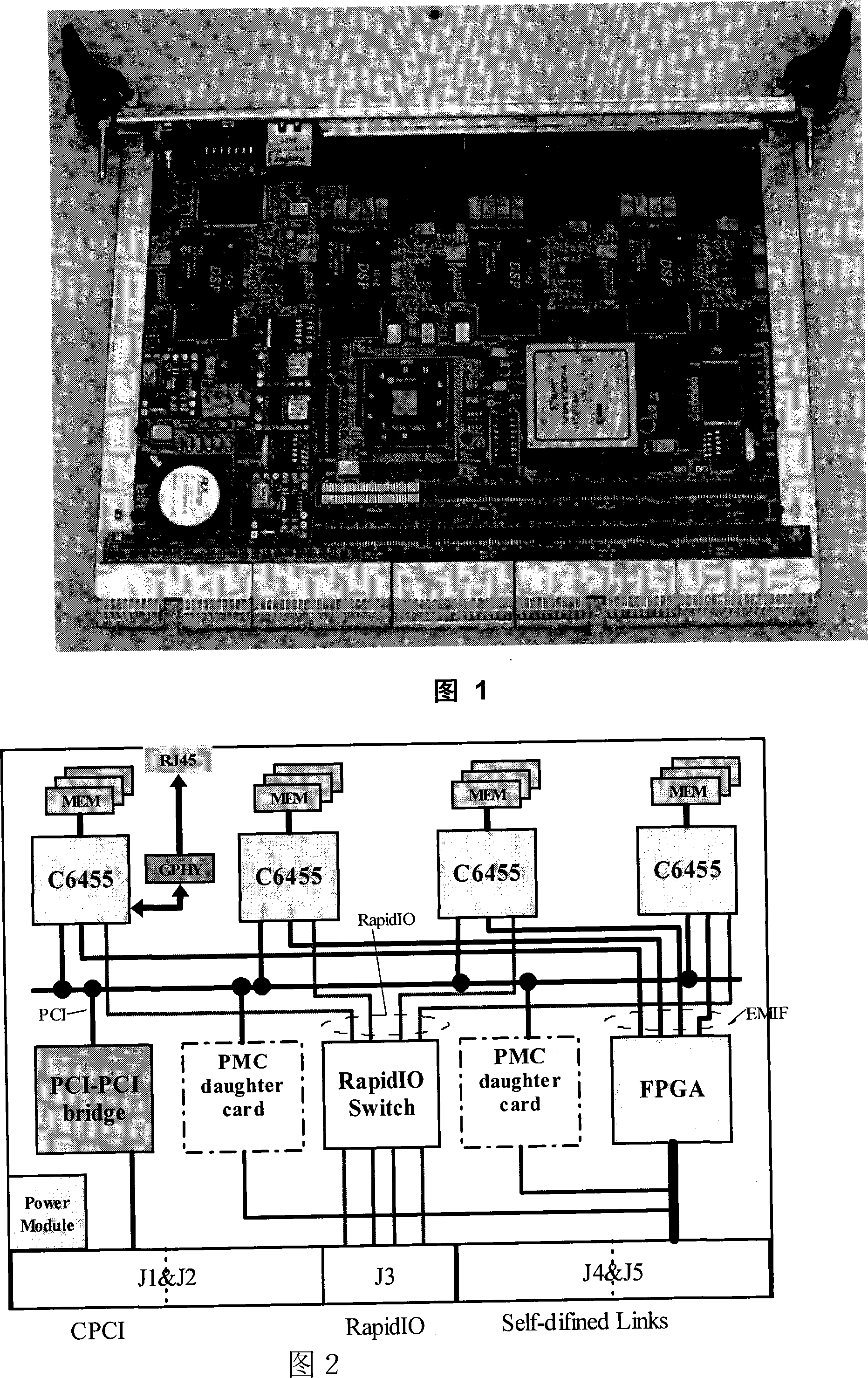

[0014] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

[0015] The power supply part of this board is composed of seven power modules, they are: two PTH05000WAH, two PHT08T220, one LT1764-3.3, one LT1764-2.5 and one UC385TDKTTT-ADJ. There are a total of four TMS320C6455 DSP chips on the whole board. When four DSPs work in parallel, they have a peak processing capability of 4×8000MIPS. There is a 512MB DDRII-SDAM chipset on the DDRII-SDRAM controller interface of each TMS320C6455. The DDRII-SDAM chipset consists of two pieces of MT47H128M16HG-37E. The storage capacity of DRII-SDRAM on the whole board is 2GB, and the access speed of each DSP to the DDRII-SDAM chipset can reach 2GBps. There are 4MB of Flash (one S29AL032D70TAI00 chip) and 8MB of SBSRAM memory (two CY7C1441AV33-133AXC chips) on the EMIFA interface of each DSP. As shown in Figure 1 and Figure 2.

[0016] There are three interconnecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More