Patents

Literature

2653results about How to "Reduce processing load" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

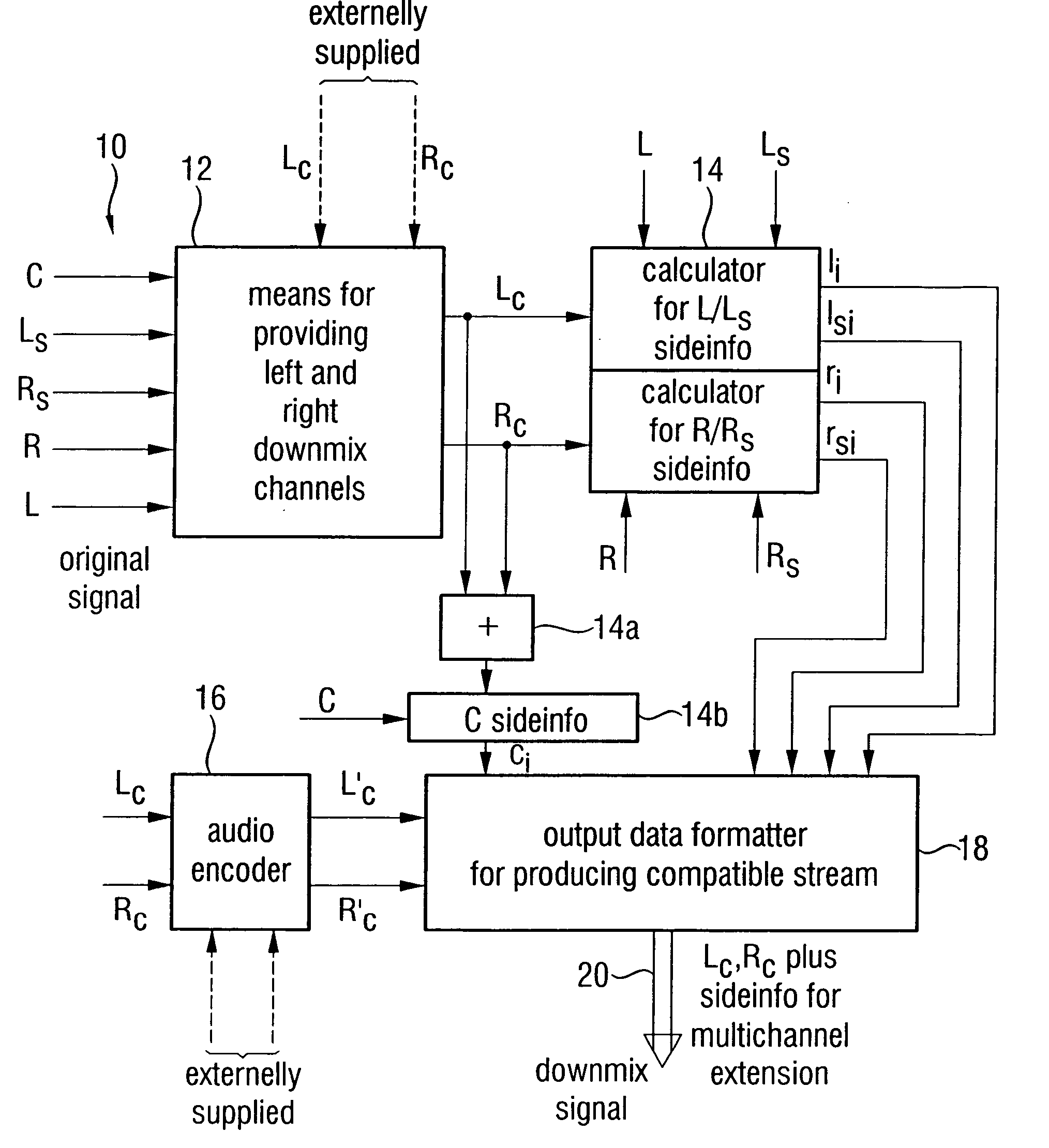

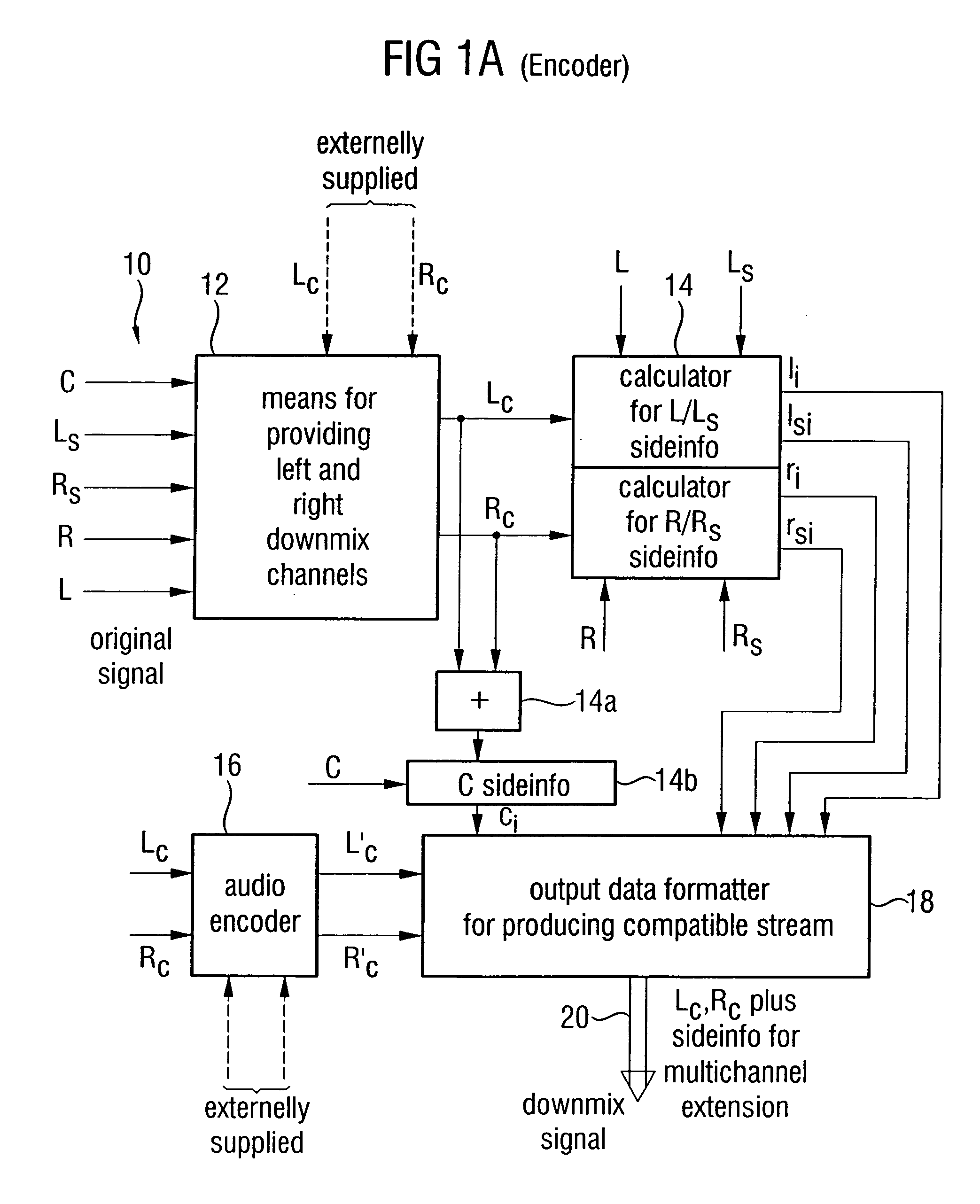

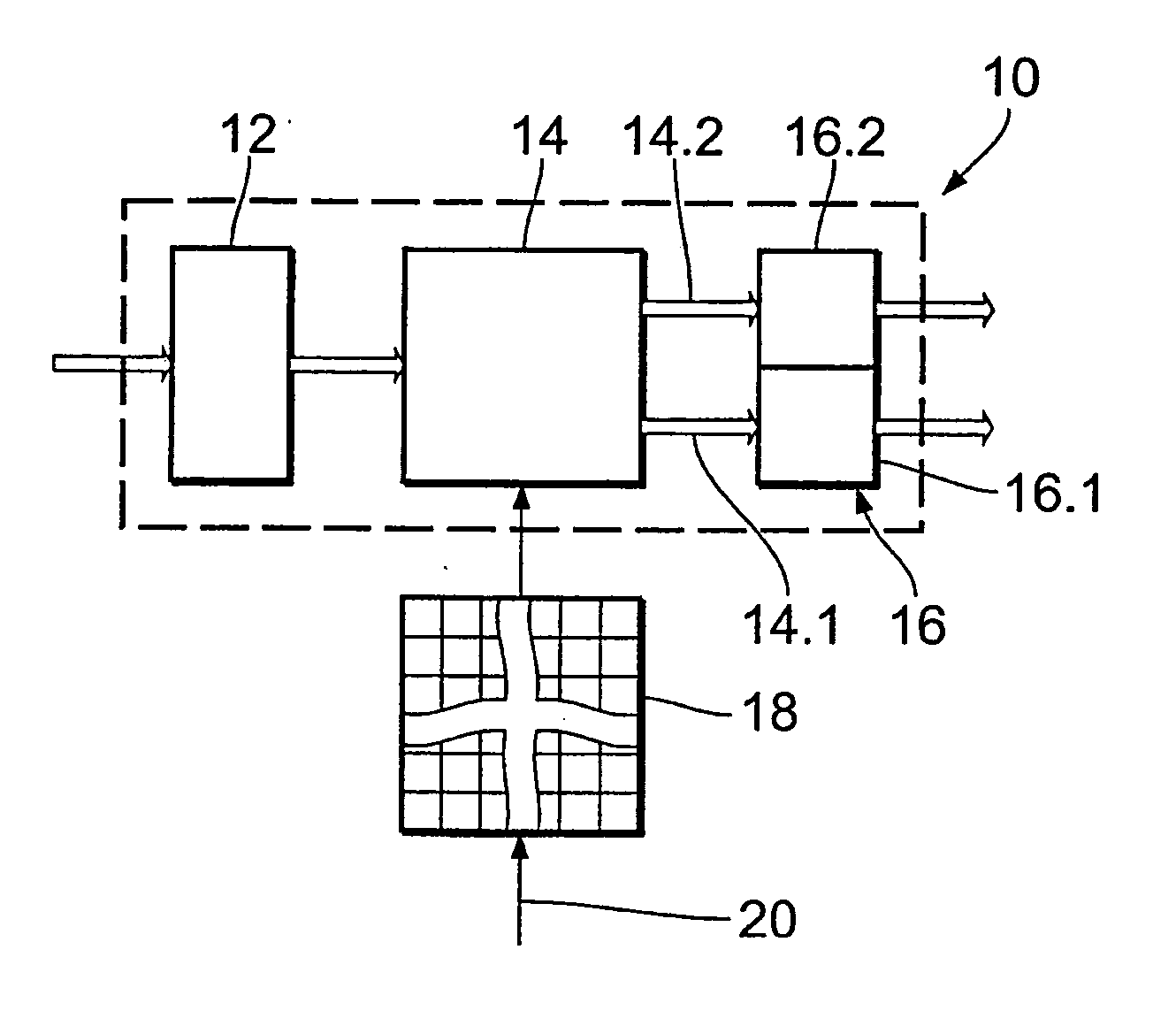

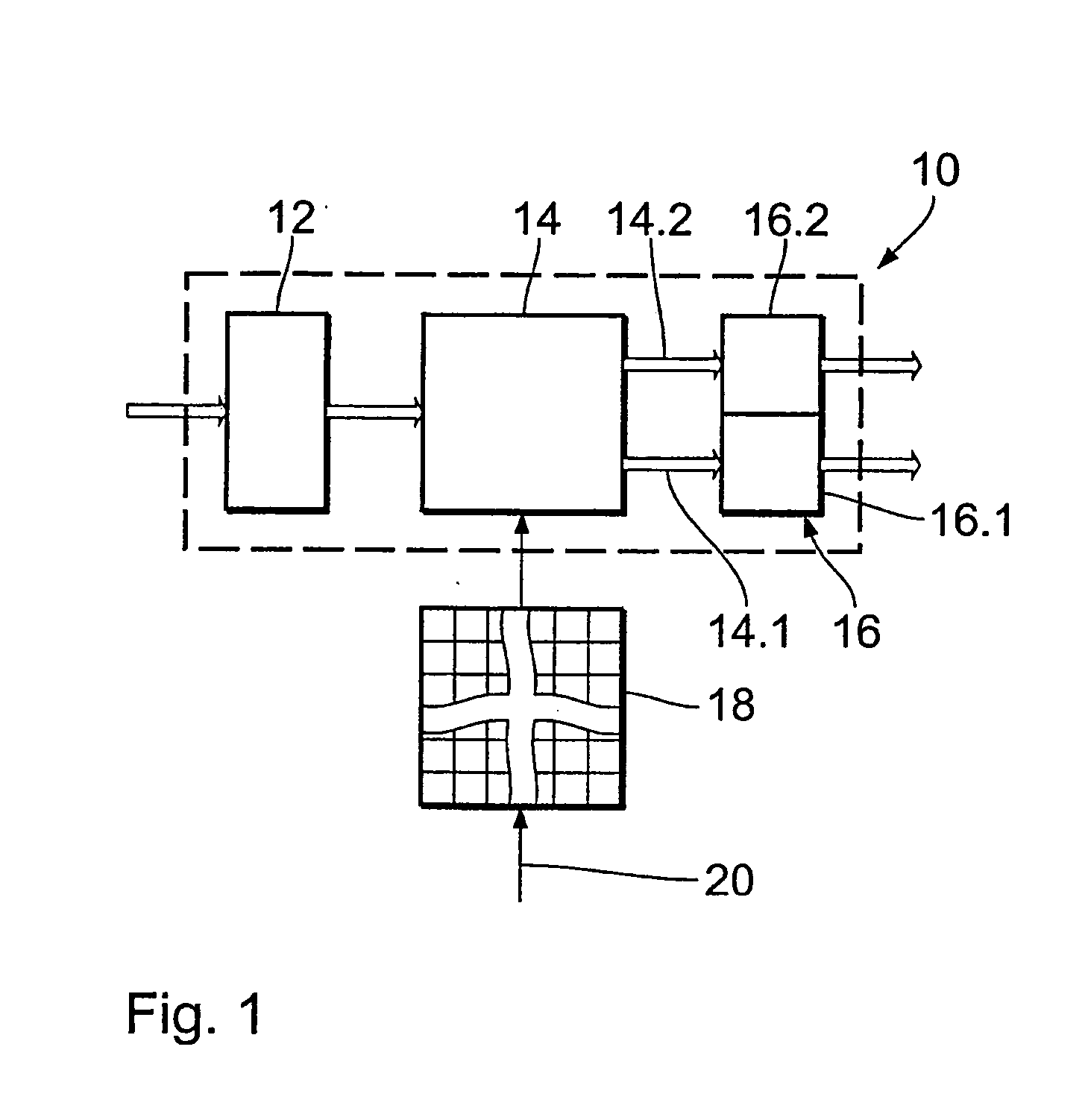

Apparatus and method for constructing a multi-channel output signal or for generating a downmix signal

ActiveUS20050157883A1High scaleReduce processing loadSpeech analysisTransmissionSide informationEngineering

The apparatus for constructing a multi-channel output signal using an input signal and parametric side information, the input signal including the first input channel and the second input channel derived from an original multi-channel signal, and the parametric side information describing interrelations between channels of the multi-channel original signal uses base channels for synthesizing first and second output channels on one side of an assumed listener position, which are different from each other. The base channels are different from each other because of a coherence measure. Coherence between the base channels (for example the left and the left surround reconstructed channel) is reduced by calculating a base channel for one of those channels by a combination of the input channels, the combination being determined by the coherence measure. Thus, a high subjective quality of the reconstruction can be obtained because of an approximated original front / back coherence.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

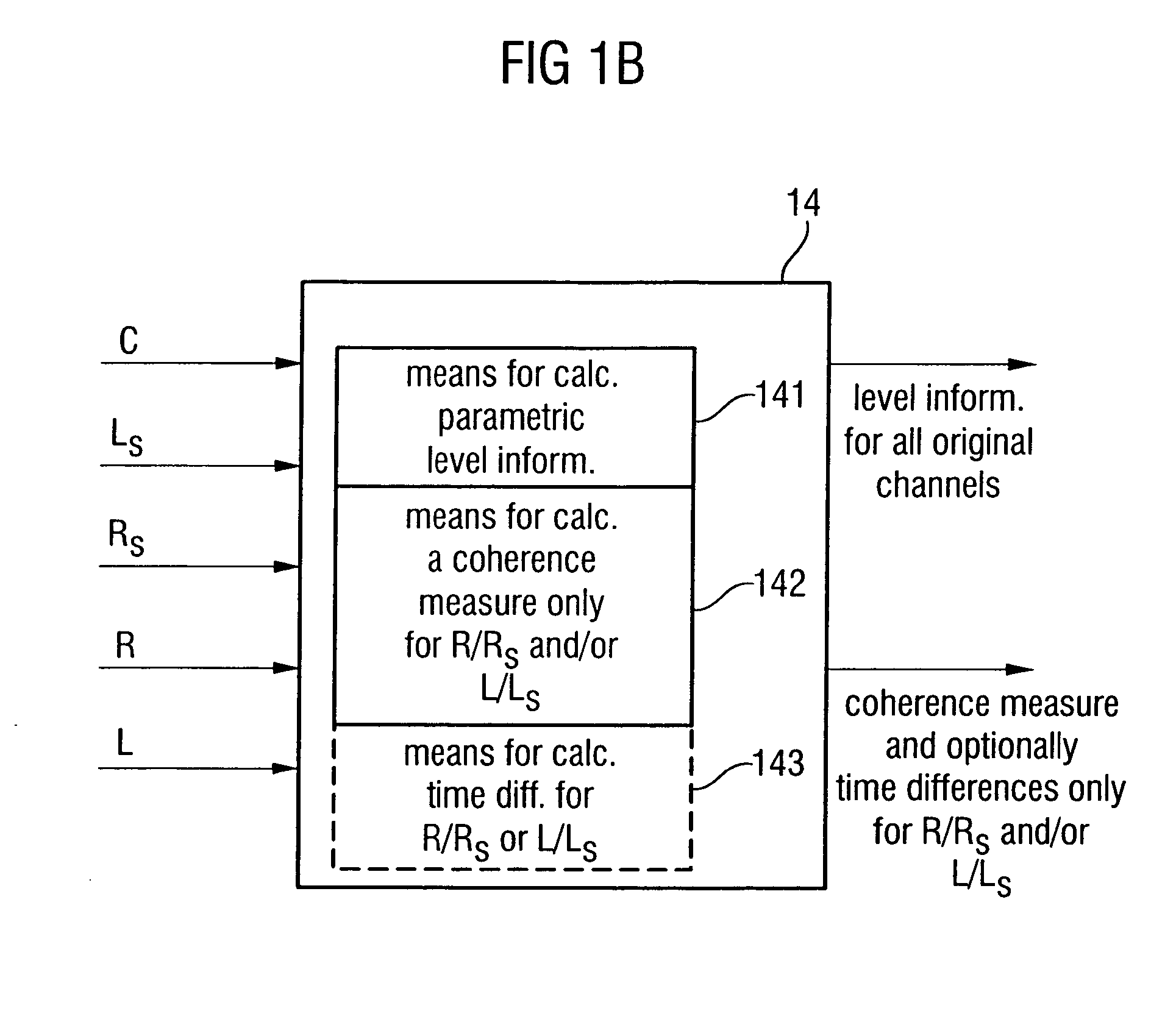

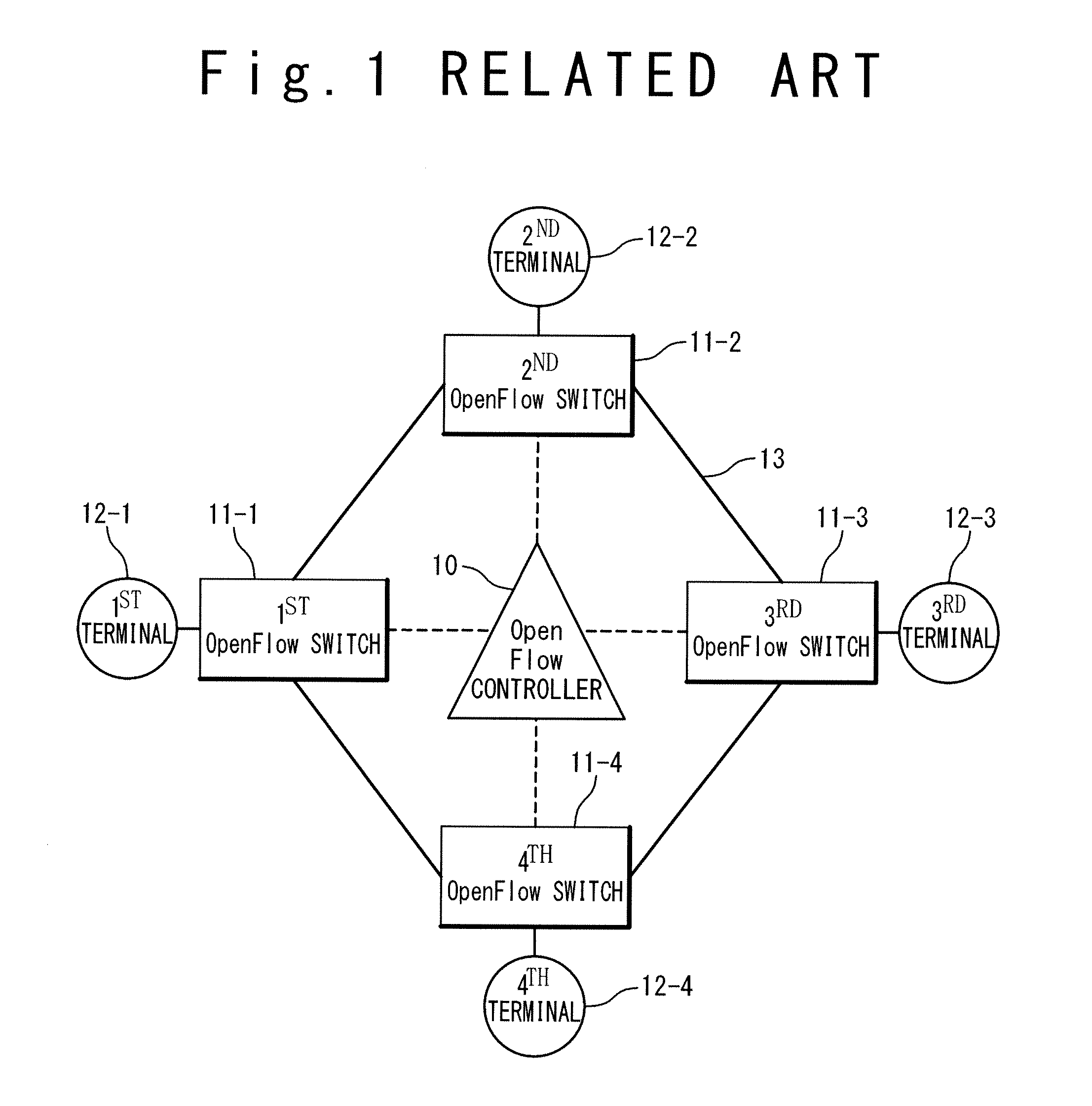

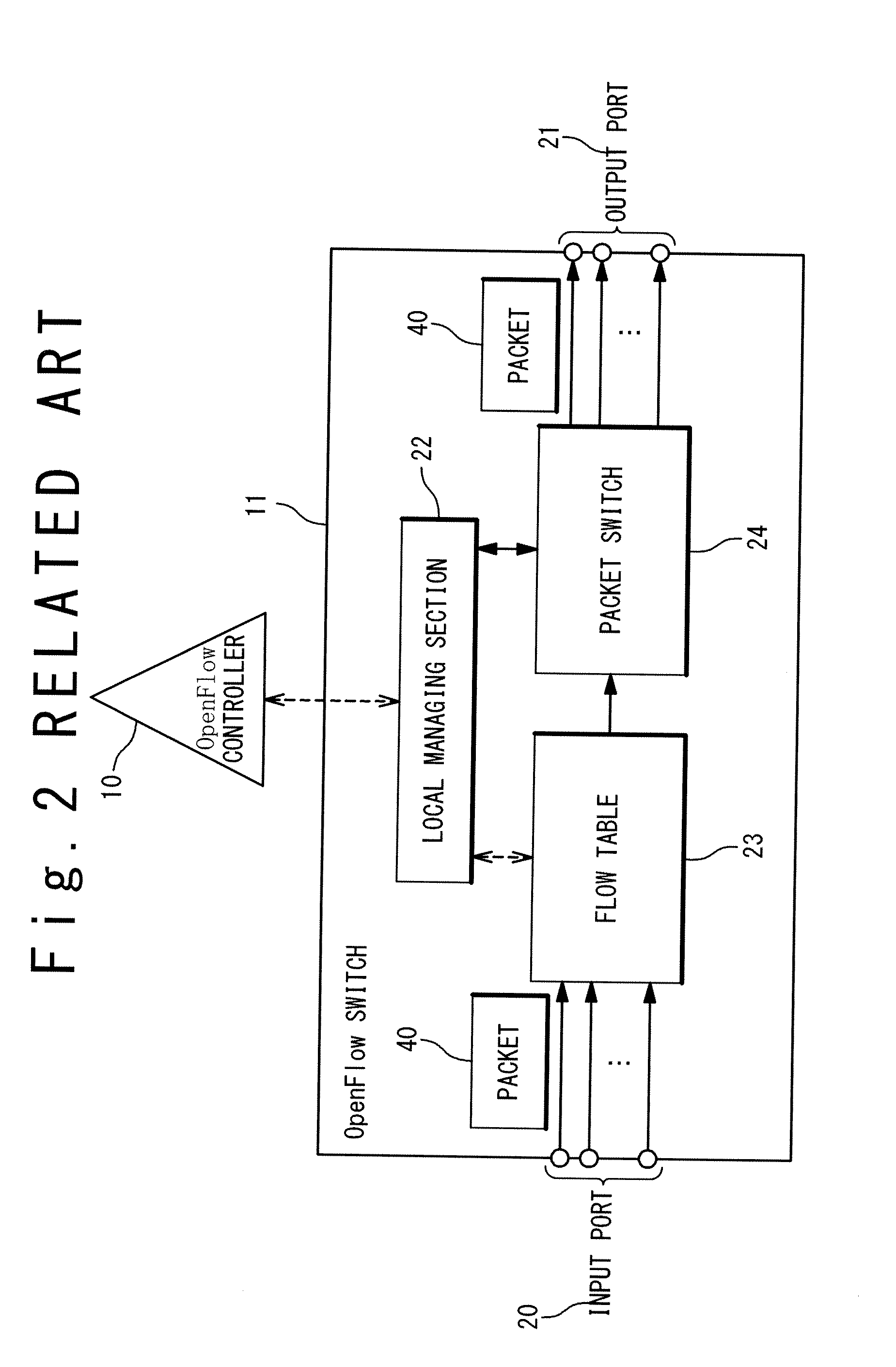

OpenFlow COMMUNICATION SYSTEM AND OpenFlow COMMUNICATION METHOD

InactiveUS20110261825A1Reduce processing loadShorten the timeDigital computer detailsData switching by path configurationCommunications systemOpenFlow

An OpenFlow switch controls transmission and reception of a packet according to a flow entry. Each of the flow entries contains a matching condition showing a communication flow of the packet and an action showing processing on the packet. An OpenFlow controller generates a registration flow entry which is stored in a flow table of a specific OpenFlow switch arranged on a route of the communication flow. An encapsulated packet is generated by relating the registration flow entry and an ordinary packet. The specific OpenFlow switch extracts the registration flow entry from the encapsulated packet in response to the reception of the encapsulated packet to produce a new flow entry and executes the action shown in the new flow entry.

Owner:NEC CORP

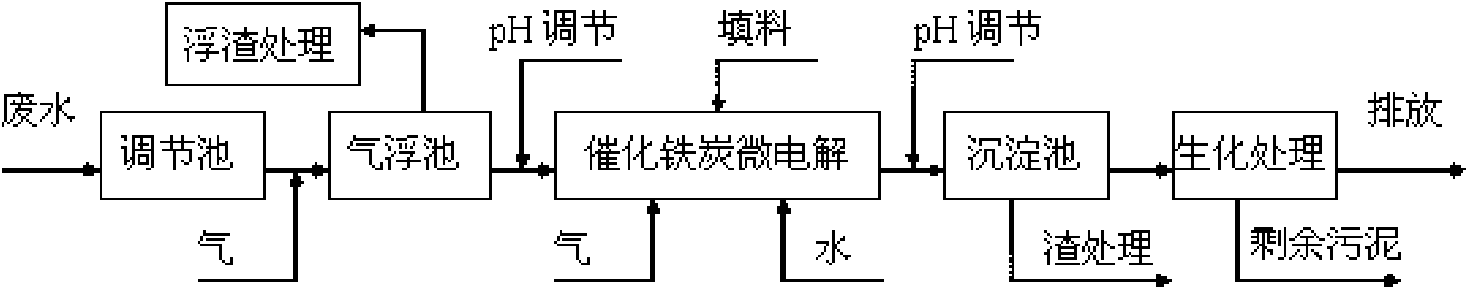

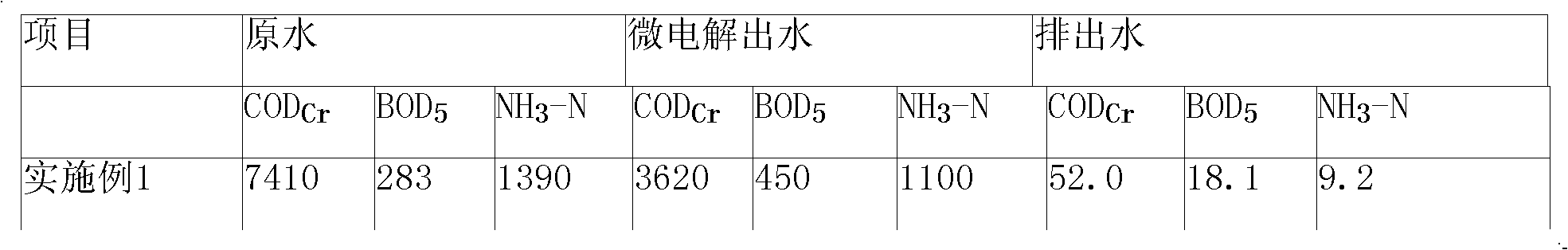

Catalysis and micro-electrolysis combined technology for high-concentration refractory organic wastewater

InactiveCN101665311AReduce processing loadEasy to handleTreatment with aerobic and anaerobic processesMultistage water/sewage treatmentHigh concentrationElectrolysis

The invention relates to a catalysis and micro-electrolysis combined technology for high-concentration refractory organic wastewater; the organic wastewater is collected to an adjusting tank and enters an air floatation tank for air floatation treatment to remove part of the organic matters after the adjustment of water volume and water quality; the scruff is collected or recovered; the wastewatergoes through Ph adjustment and then enters a catalytic iron-carbon and micro-electrolysis unit to improve the biochemical quality; the effluent goes through Ph adjustment and then enters a sedimentation tank; the effluent of the sedimentation tank adopts anoxic-aerobic biochemistry treatment to remove the organic matters and ammonia nitrogen and then is emitted after reaching the standard; and the filler of the catalytic iron-carbon and micro-electrolysis unit comprises iron, carbon and a catalyst, wherein the mass ratio of the iron, carbon and catalyst is 1: (0.3-1.5): (0.01-0.5). The invention can effectively improve the micro-electrolysis electrochemical reaction efficiency and the degrading capability to the organic matters, and reduce the wastewater treatment cost with convenient technological operation.

Owner:CENT SOUTH UNIV

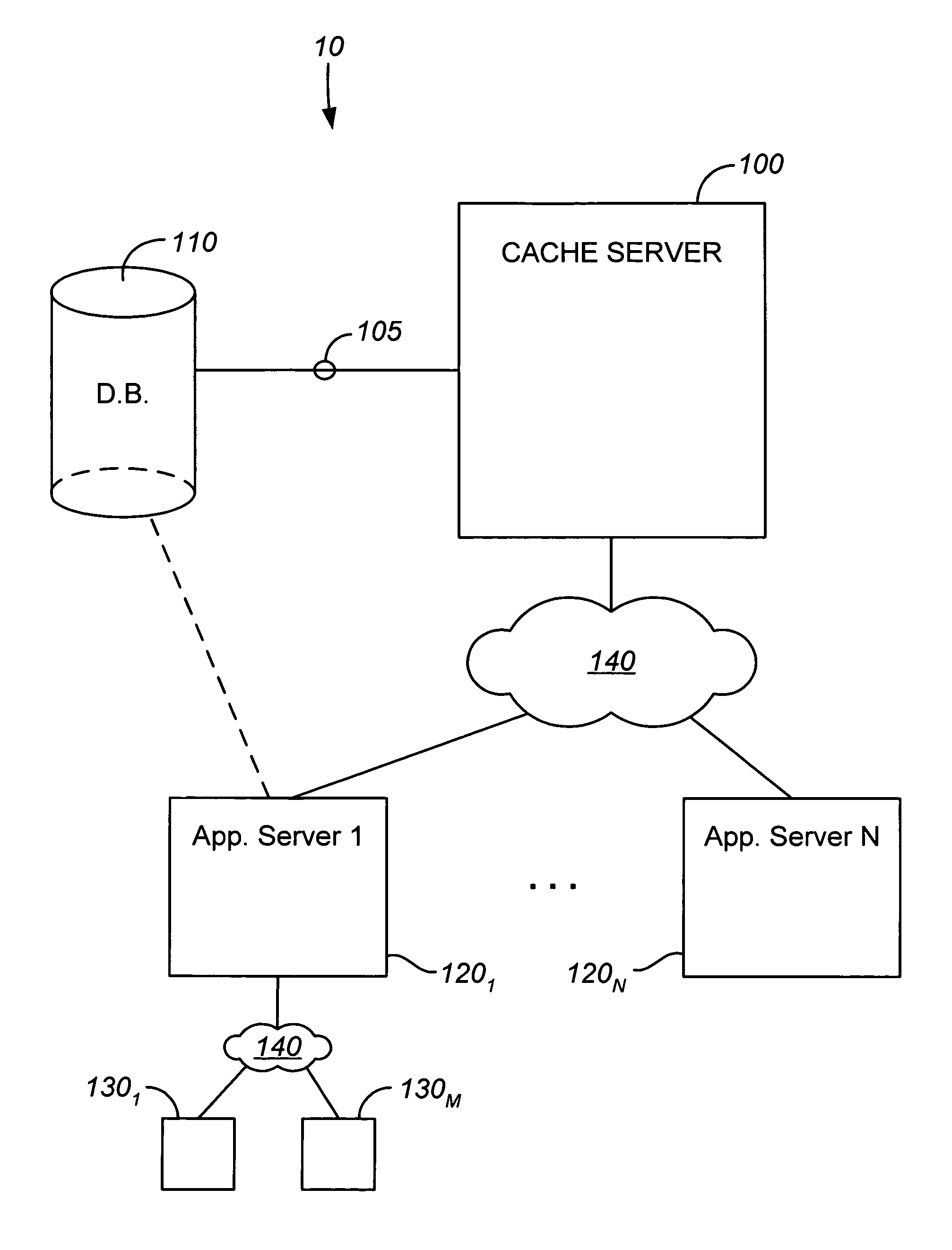

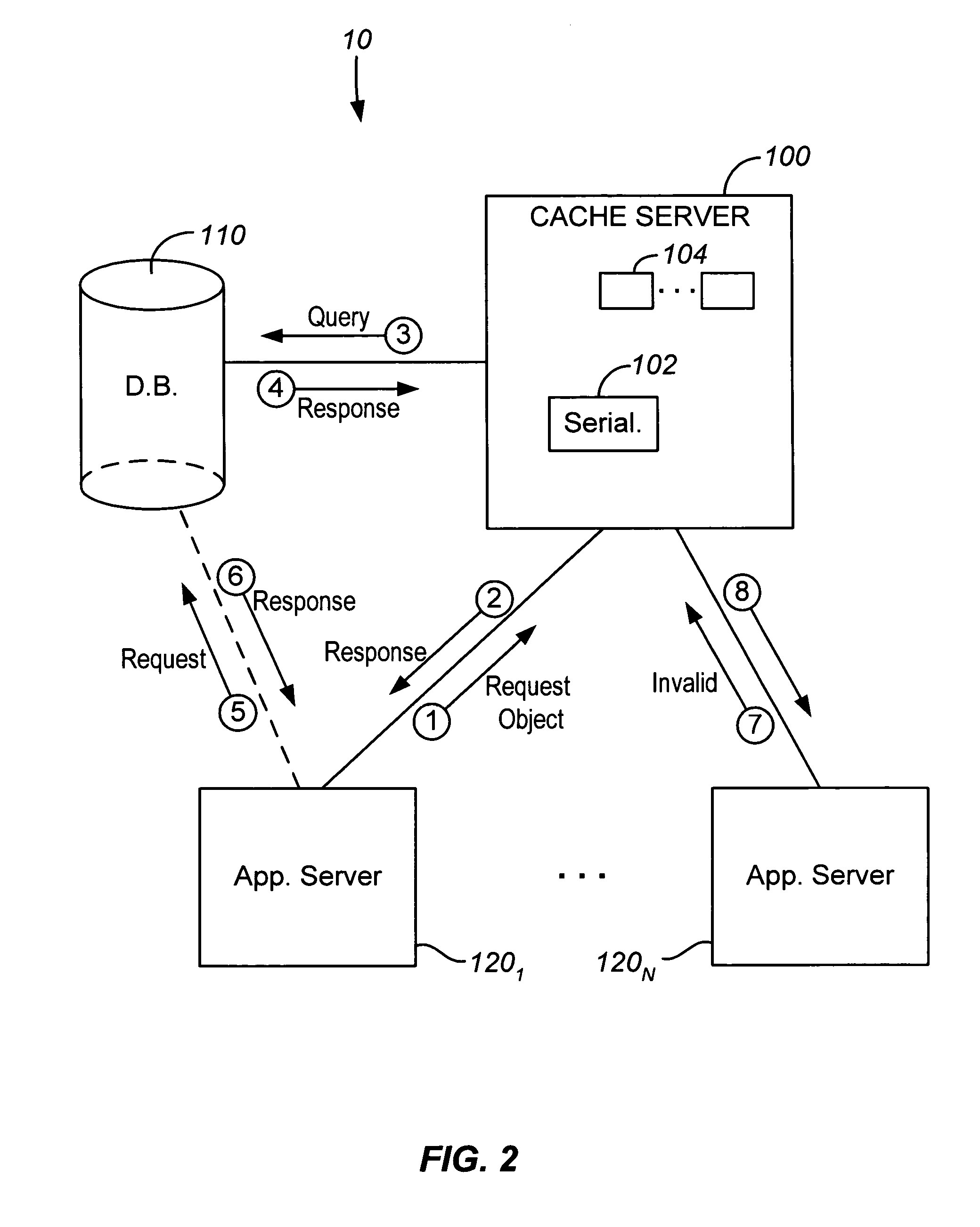

Java object cache server for databases

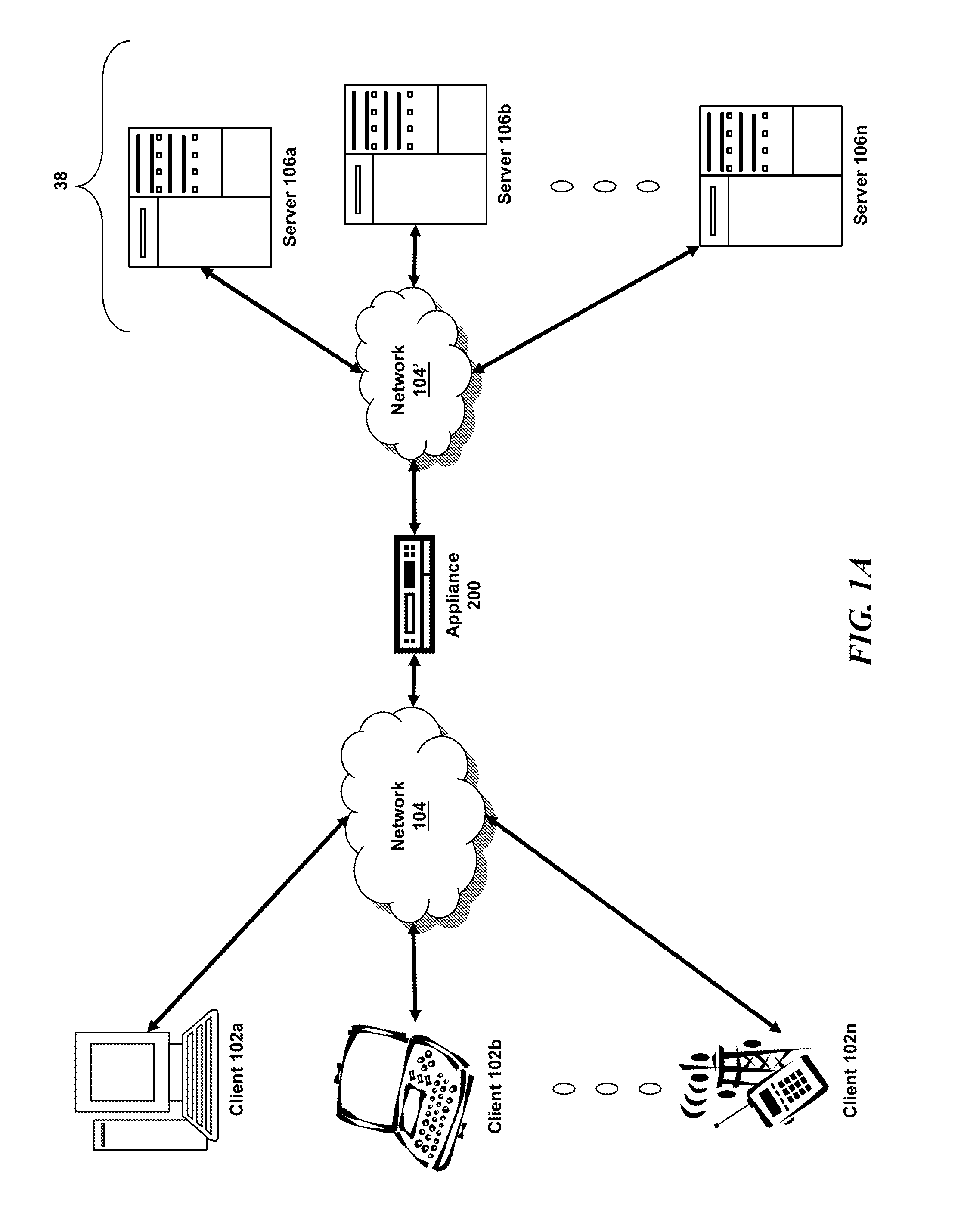

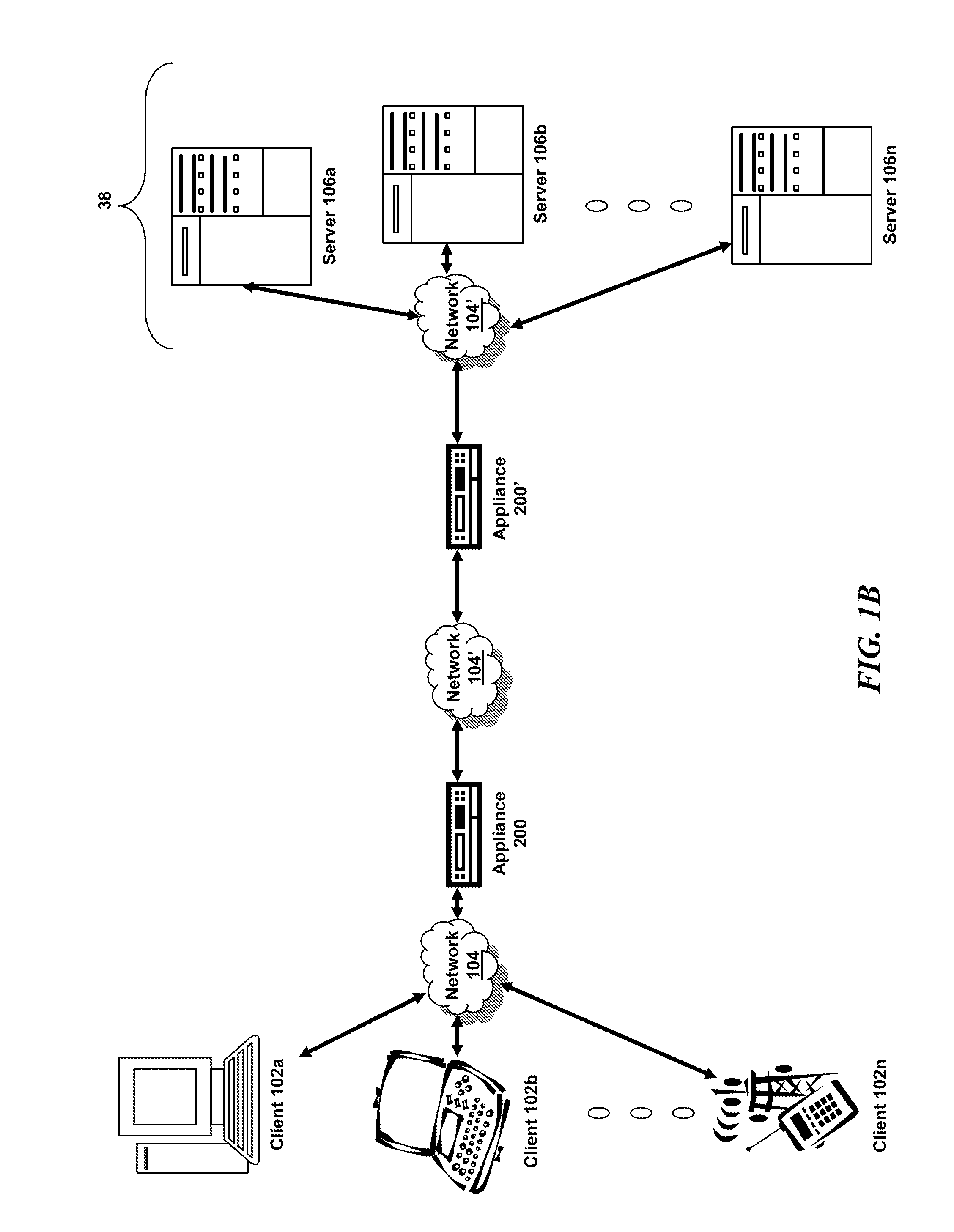

ActiveUS7209929B2Reduce loadReduce processing loadData processing applicationsDigital data processing detailsApplication serverCache server

A cache server is provided in a network for storing Java objects for retrieval by one or multiple application servers. Application server(s) are configured to request an object from the cache server, rather than requesting the Java object directly from a database, so as to reduce processing load on the database and free up database resources. Responsive to a request for a Java object from an application server, e.g., in an HTTP request, the cache server determines if the object is stored in memory and if so, serializes the requested object and sends the serialized object to the requesting server, e.g., in an HTTP response. The requesting server then deserializes the Java object. If the object is not stored in memory, the cache server instantiates the object (typically by requesting the object from the database), serializes the instantiated object and sends it to the requesting server. Cache coherency methods are also provided.

Owner:SALESFORCE COM INC

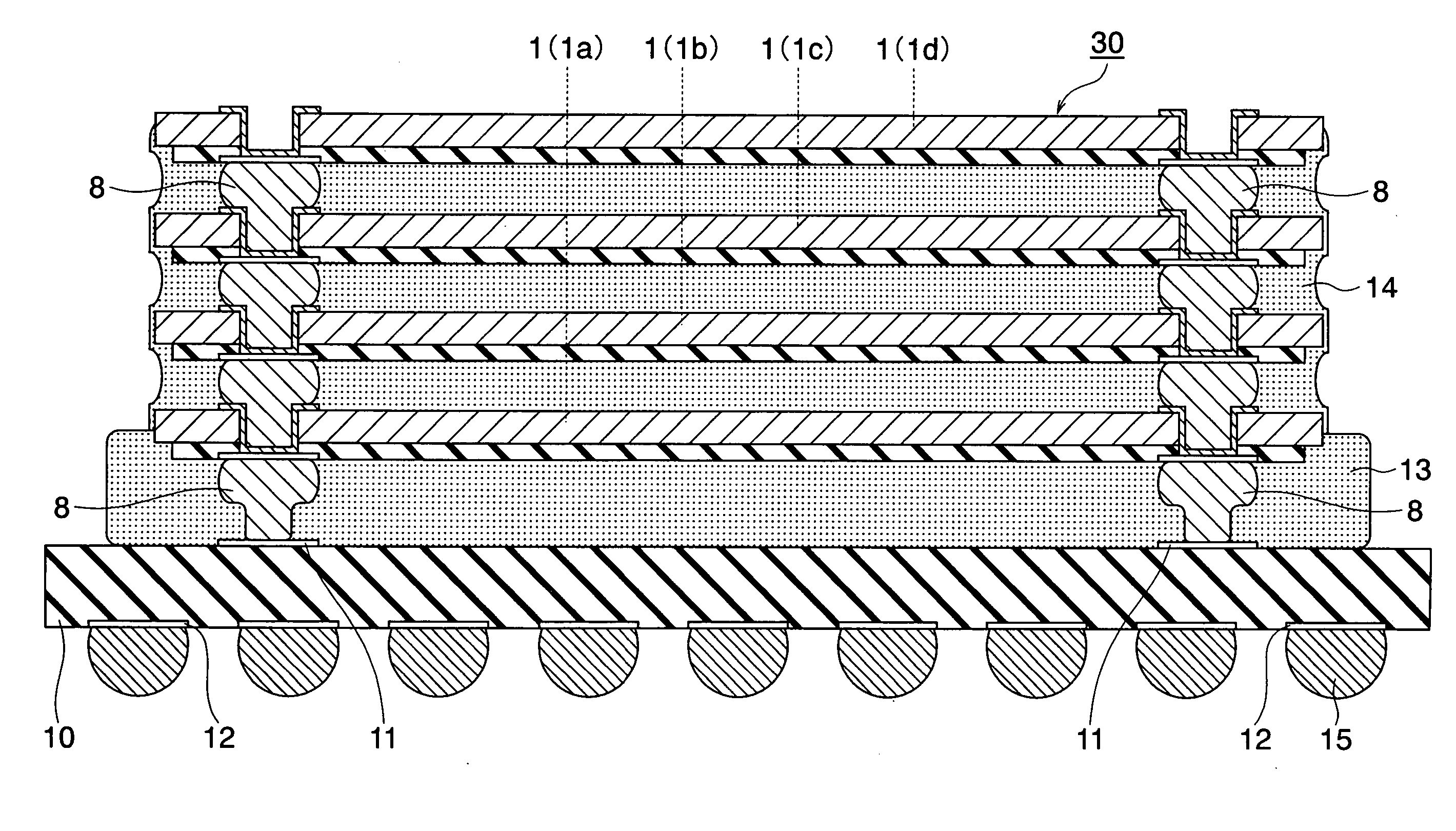

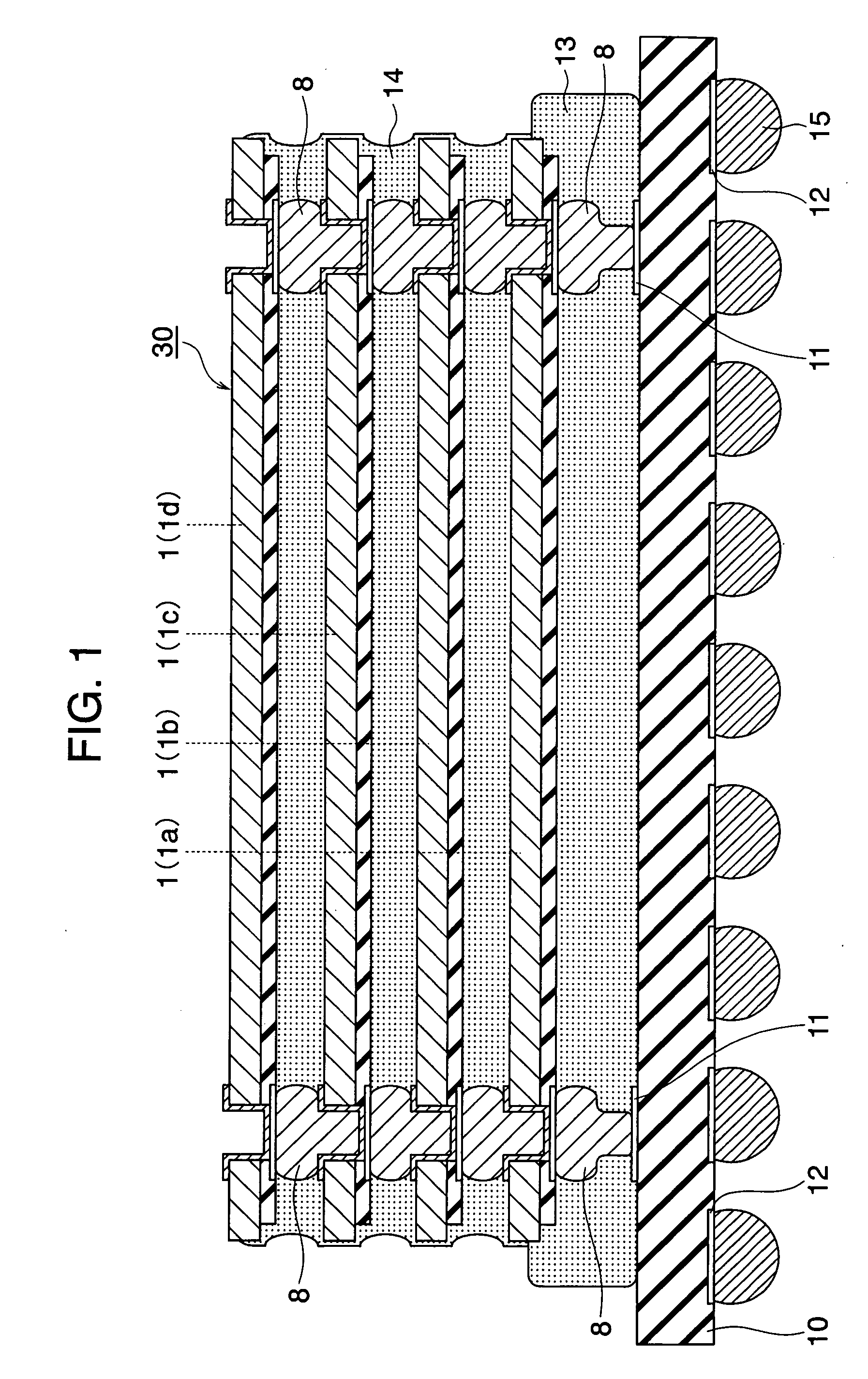

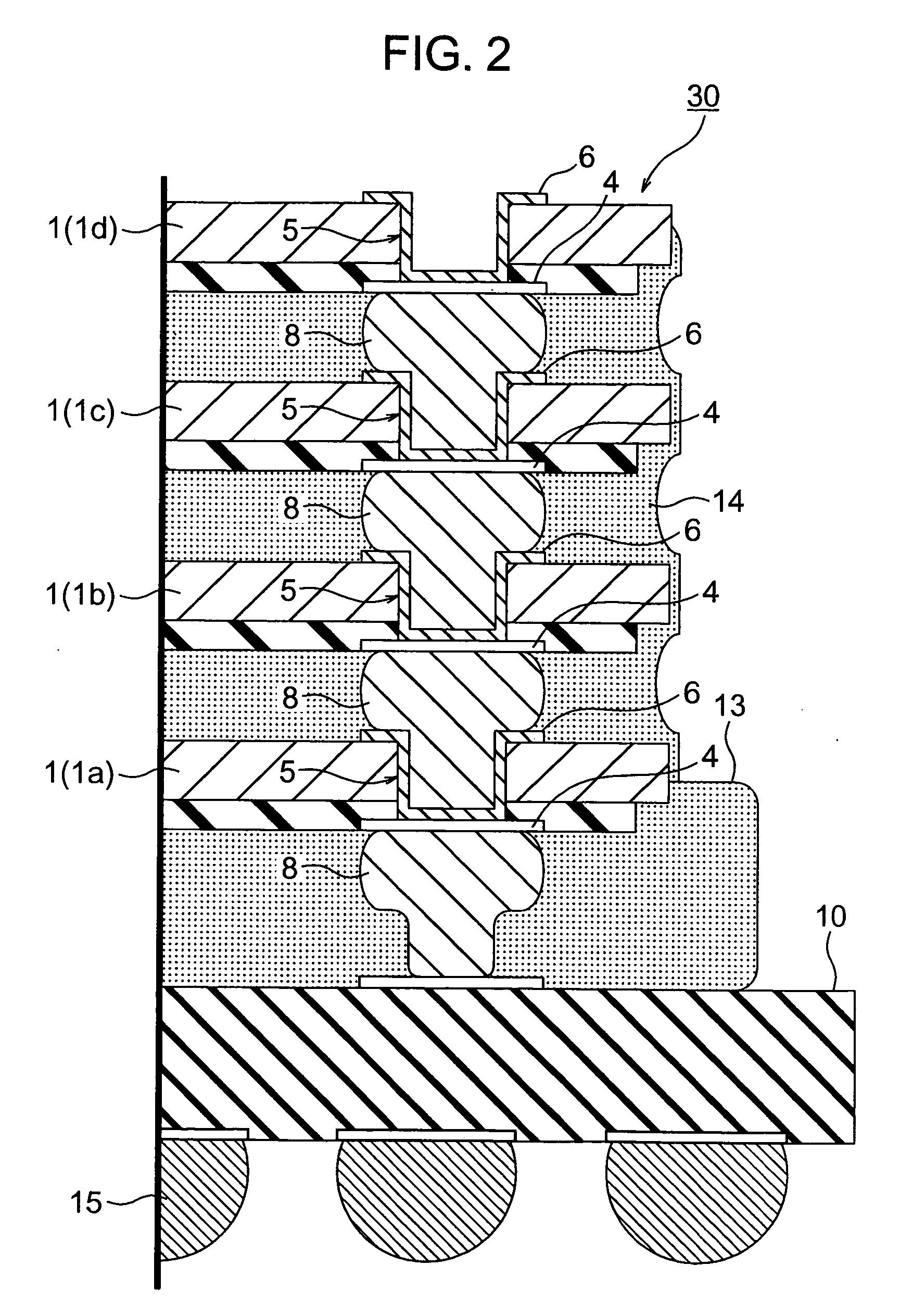

Semiconductor device and manufacturing process therefor

InactiveUS20050263869A1Improve reliabilityHigh practicabilitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologySurface layer

To provide a very-low-cost and short-TAT connection structure superior in connection reliability in accordance with a method for three-dimensionally connecting a plurality of semiconductor chips at a shortest wiring length by using a through-hole electrode in order to realize a compact, high-density, and high-function semiconductor system. The back of a semiconductor chip is decreased in thickness up to a predetermined thickness through back-grinding, a hole reaching a surface-layer electrode is formed at a back position corresponding to a device-side external electrode portion through dry etching, a metallic deposit is applied to the sidewall of the hole and the circumference of the back of the hole, a metallic bump (protruded electrode) of another semiconductor chip laminated on the upper side is deformation-injected into the through-hole by compression bonding, and the metallic bump is geometrically caulked and electrically connected to the inside of a through-hole formed in an LSI chip. It is possible to realize a unique connection structure having a high reliability in accordance with the caulking action using the plastic flow of a metallic bump in a very-low-cost short-TAT process and provide a three-dimensional inter-chip connection structure having a high practicability.

Owner:RENESAS TECH CORP

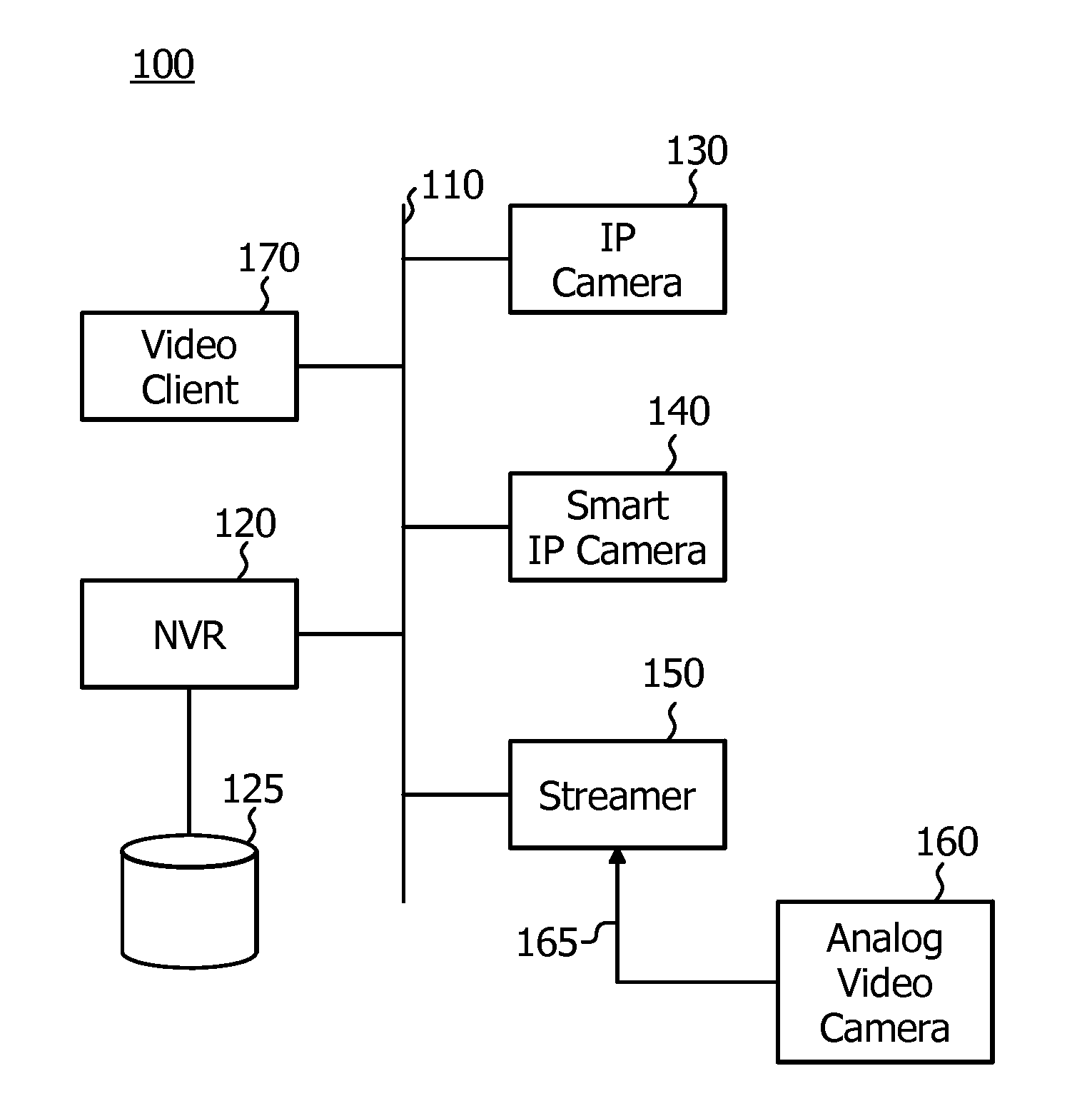

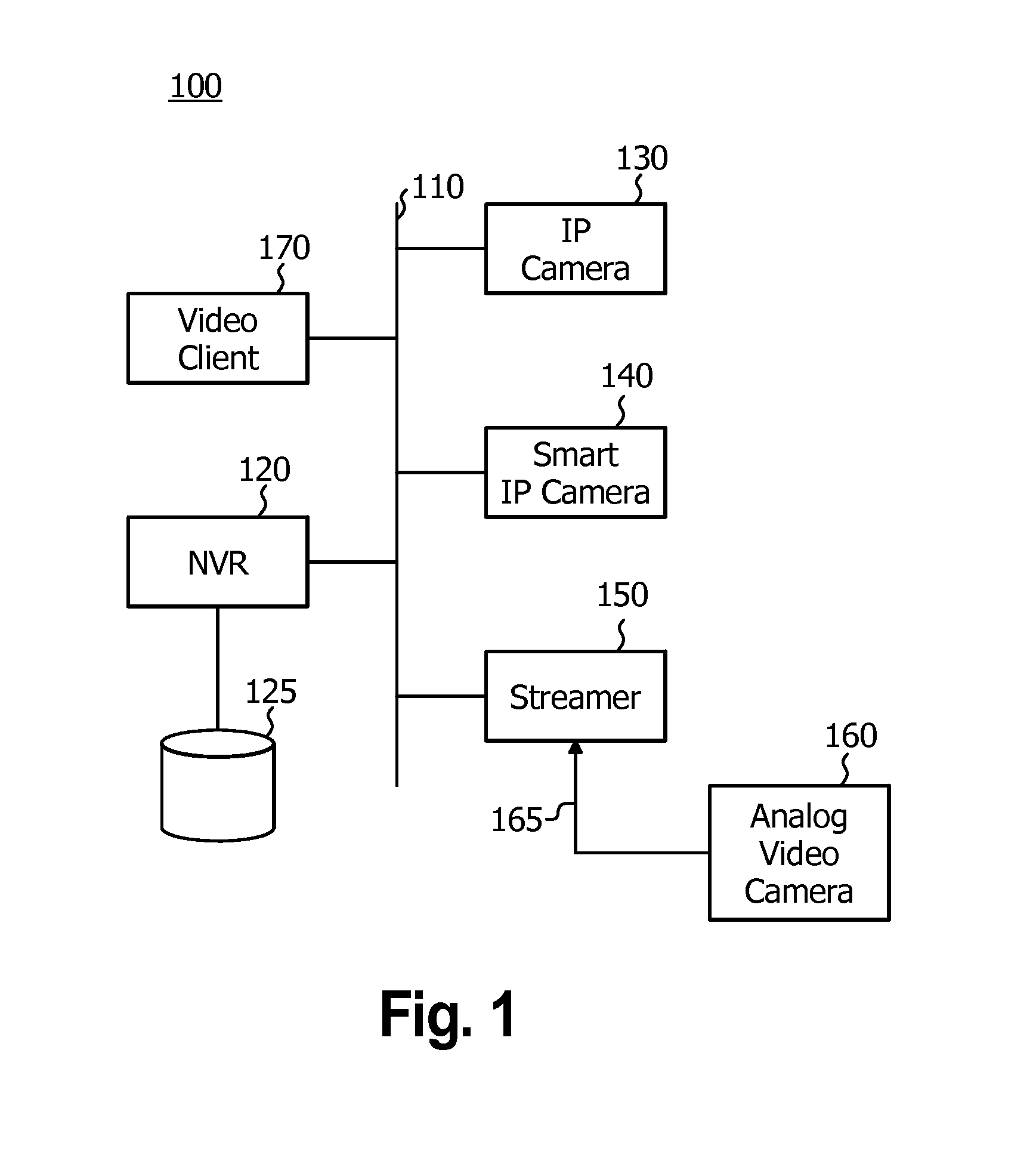

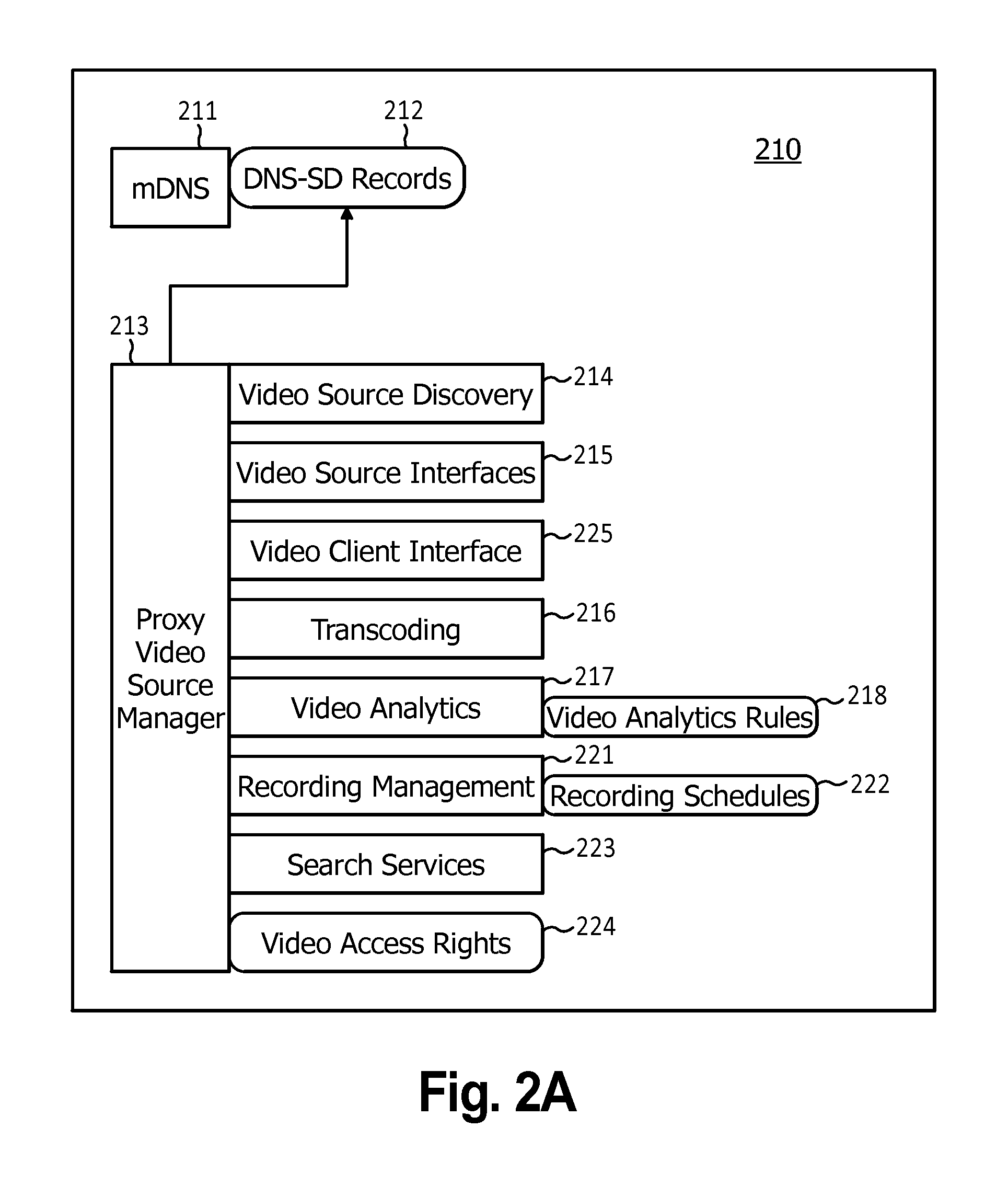

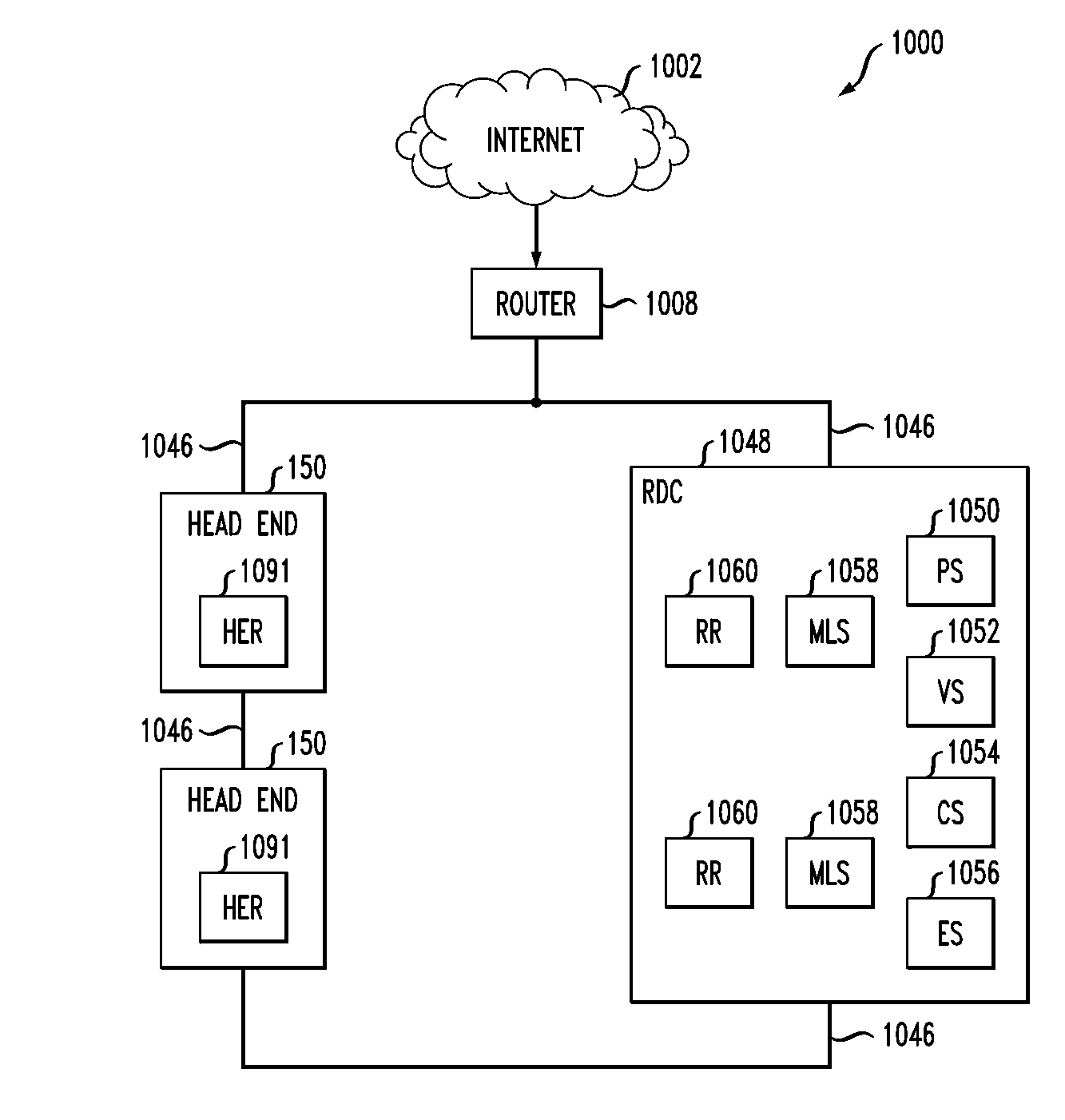

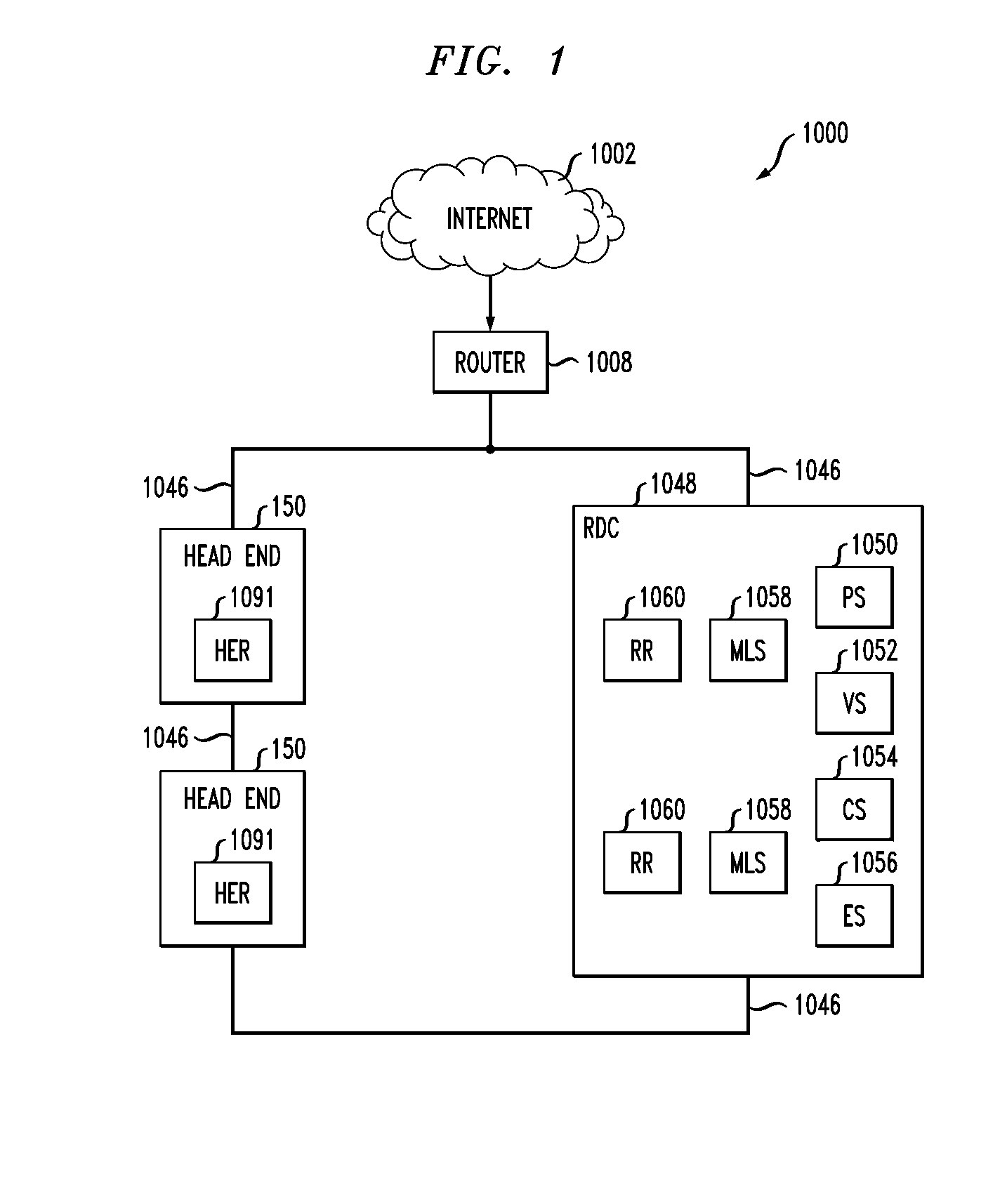

Proxy video server for video surveillance

InactiveUS20090031381A1Improve abilitiesSimplifying access to capabilityTwo-way working systemsTransmissionVideo monitoringClient-side

A proxy video server for managing video surveillance data in a network that includes at least one video source and client. The proxy video server includes a proxy video source manager for managing the video sources to appear as virtual smart video sources to video clients, a video client interface for receiving and interpreting requests from video clients and sending responses to video clients on behalf of the video sources, one or more video source interfaces for sending requests to a video source using a protocol specific to the video source and for receiving and interpreting responses from a video source using a protocol specific to the video source and a video analytics service function for providing video analytics as needed in order to present smart camera capabilities for each video source to any video client.

Owner:HONEYWELL INT INC

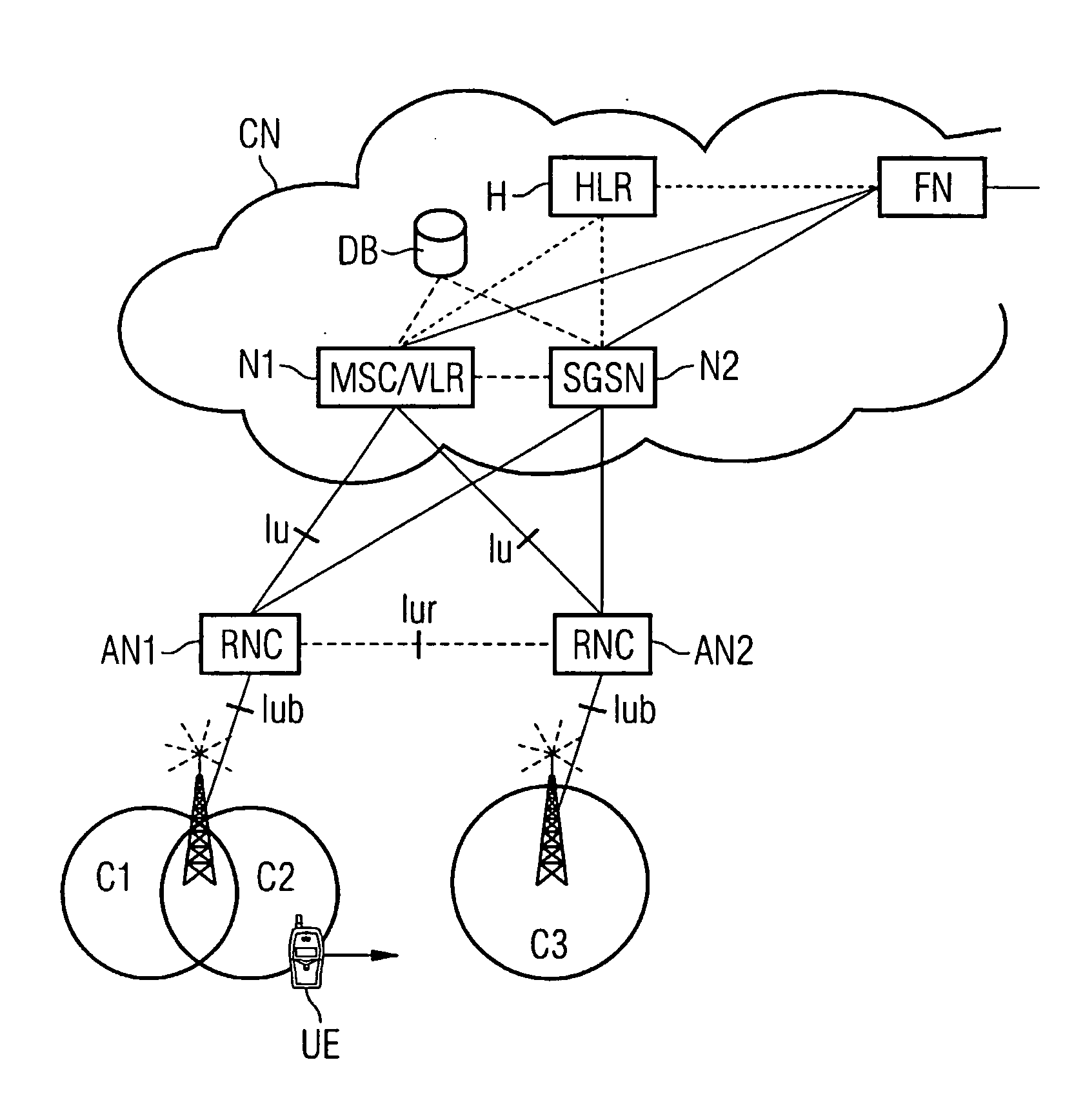

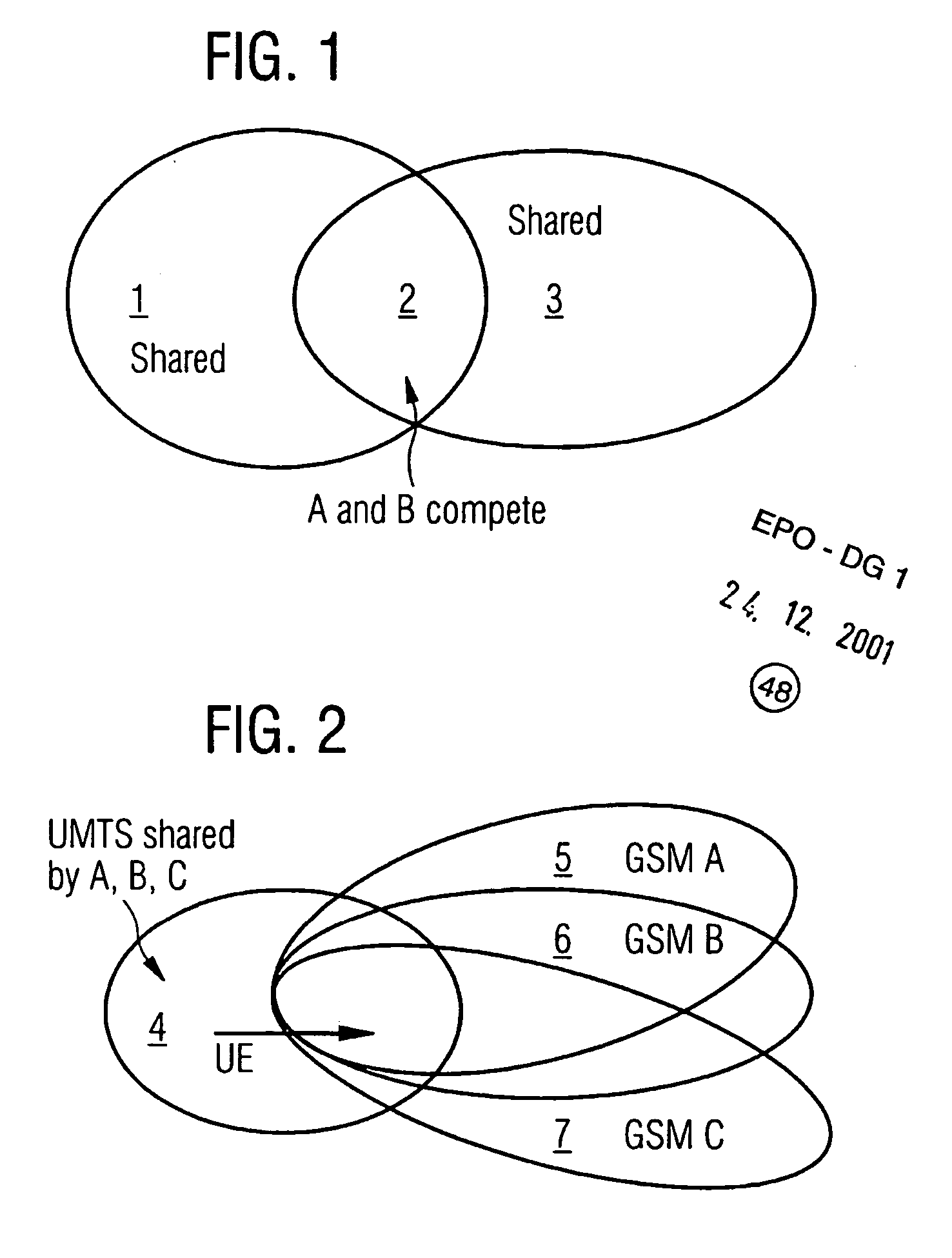

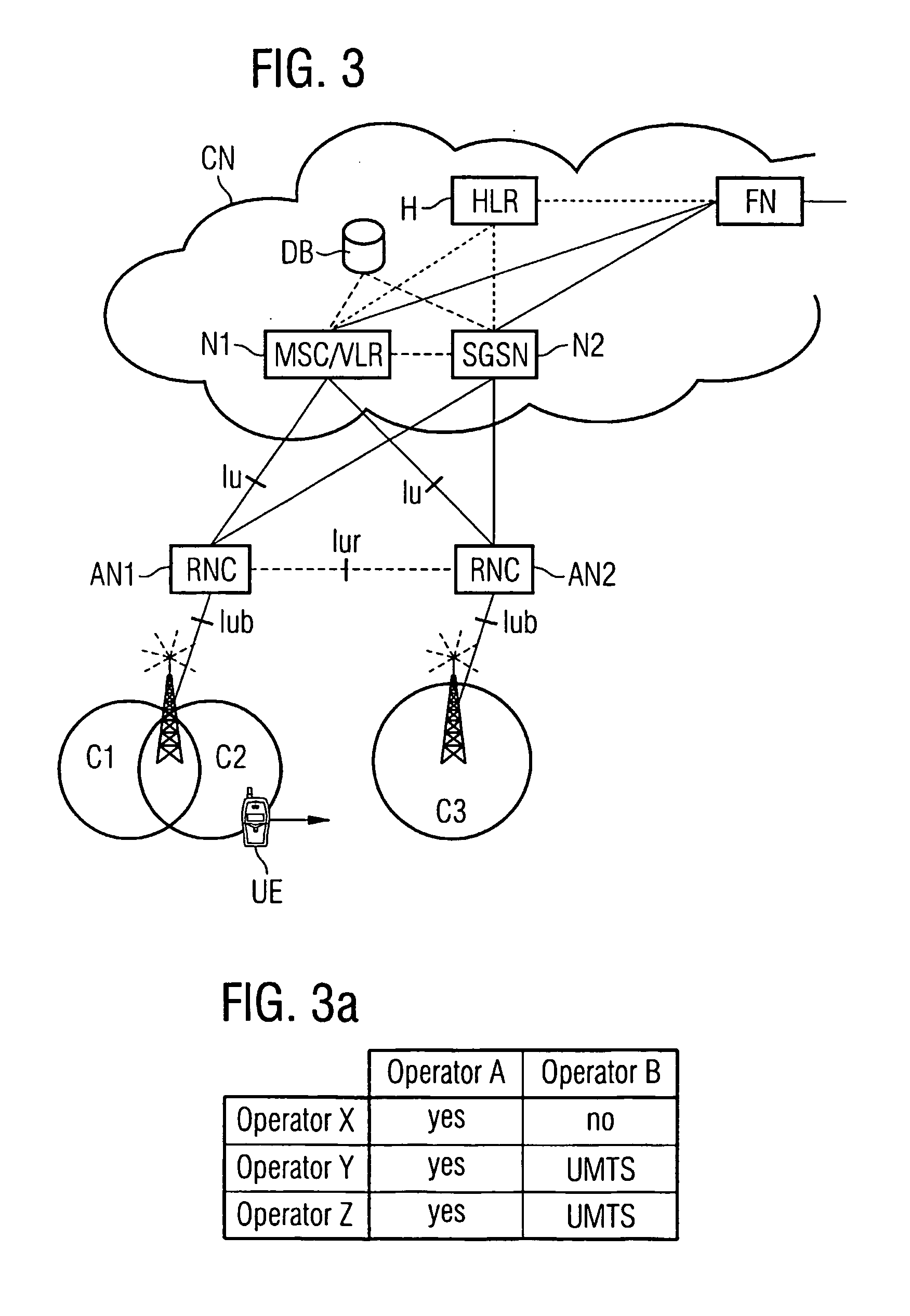

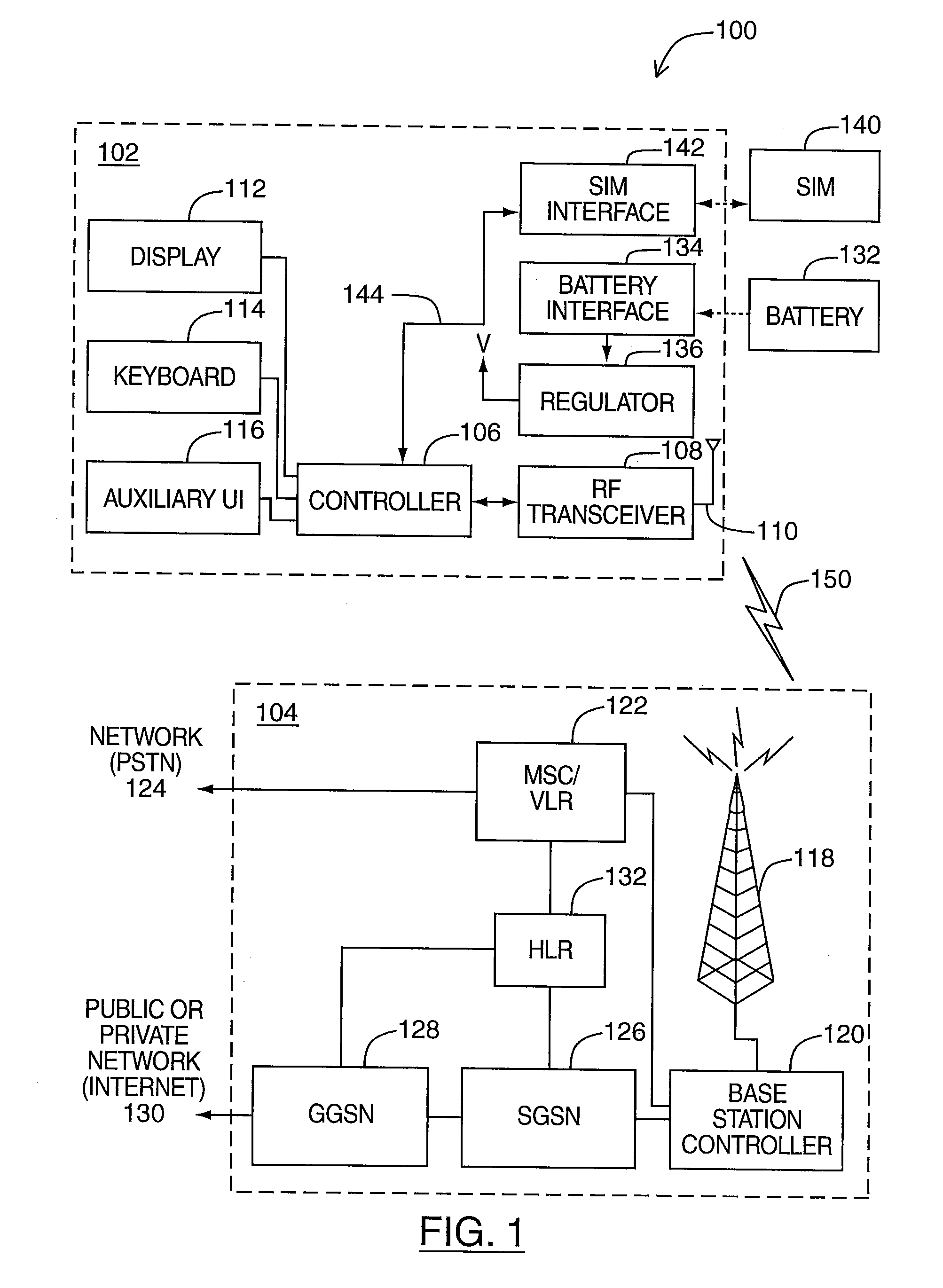

Method for determining whether to grant access of a user equipment to a radio access network

InactiveUS20040157600A1Easy to implementEfficient methodAssess restrictionRadio/inductive link selection arrangementsAccess networkCommunications system

The invention concerns a method for determining whether to grant access of a user equipment (UE) to a radio access network in a present position of the user equipment (UE) within a communications system. The communications system comprises a control node (N1, N2) handling services for the user equipment (UE) and an access node (AN1, AN2) controlling the access network. The method is initiated by receiving a request for service processing for the user equipment (UE) in the control node (N1, N2) with an identification of the user equipment (UE). A subscriber group information is determined for the user equipment (UE) according to the identification of the user equipment and sent to the access node (AN1, AN2). Furthermore, an area access information according to the present location of the user equipment (UE) is determined in the access node (AN1, AN2). The access granting of the user equipment (UE) to the radio access network is performed according to a logical combination of the subscriber group information and the area access information. A communication network, nodes and software programs embodying the invention are also described.

Owner:TELEFON AB LM ERICSSON (PUBL)

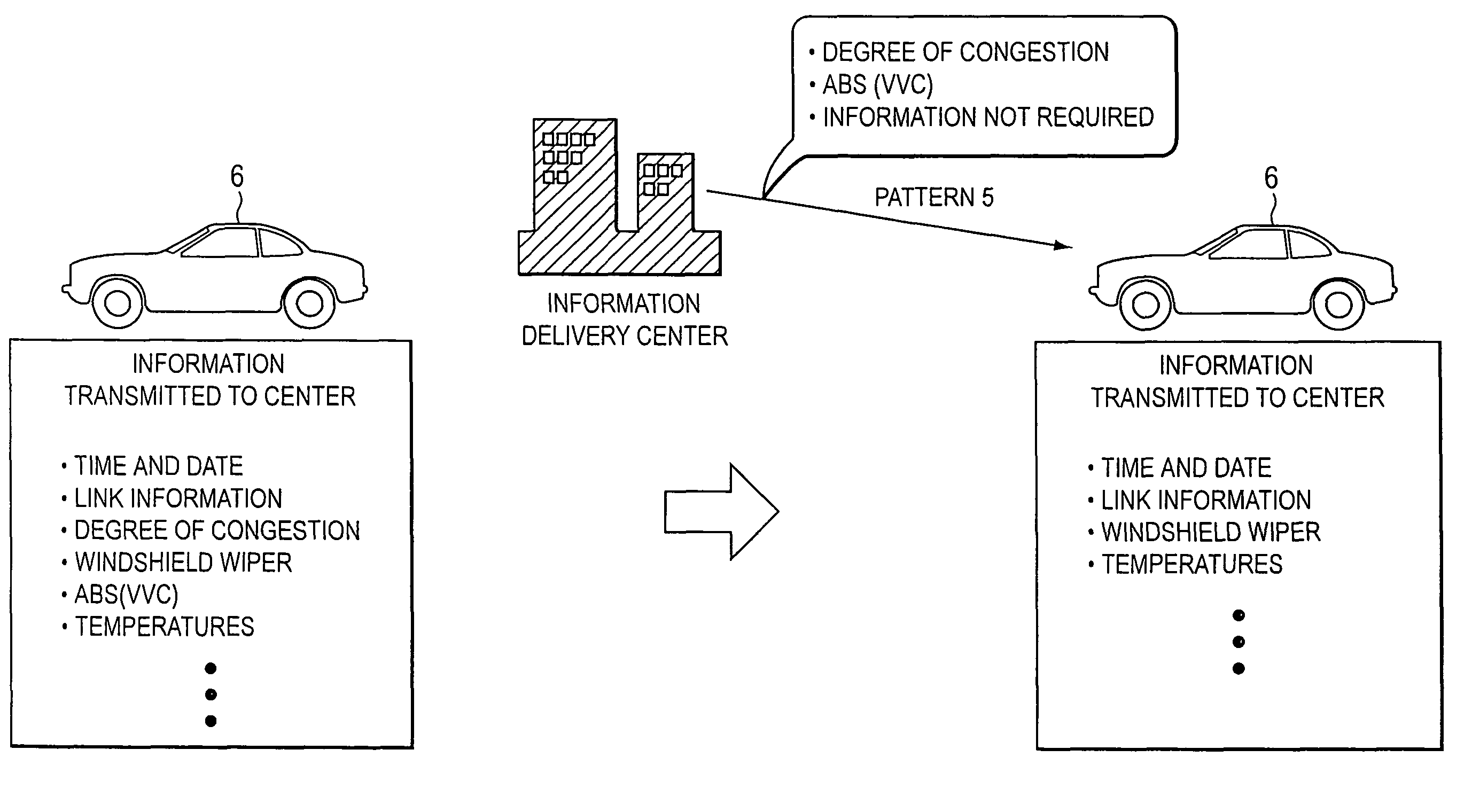

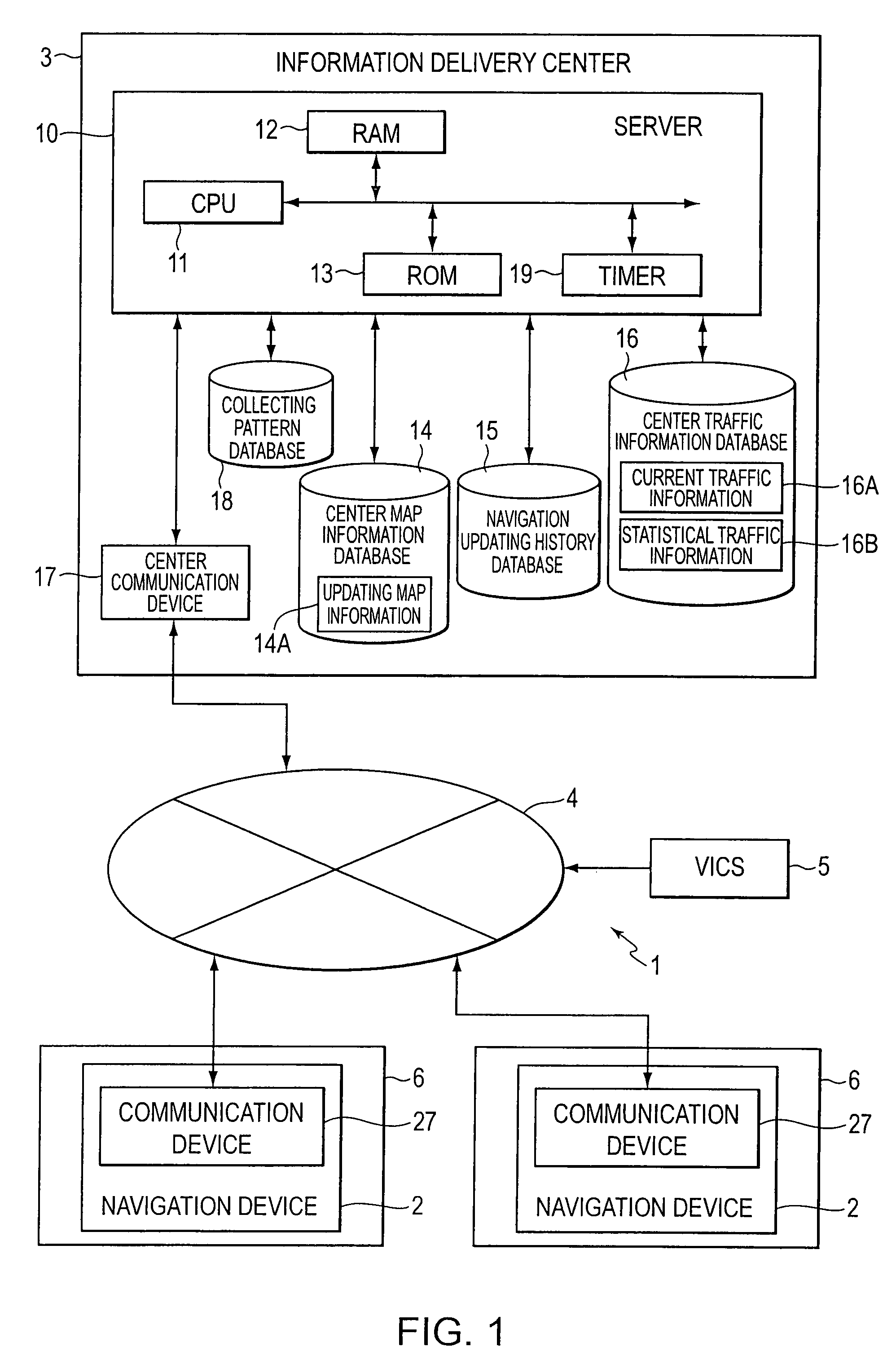

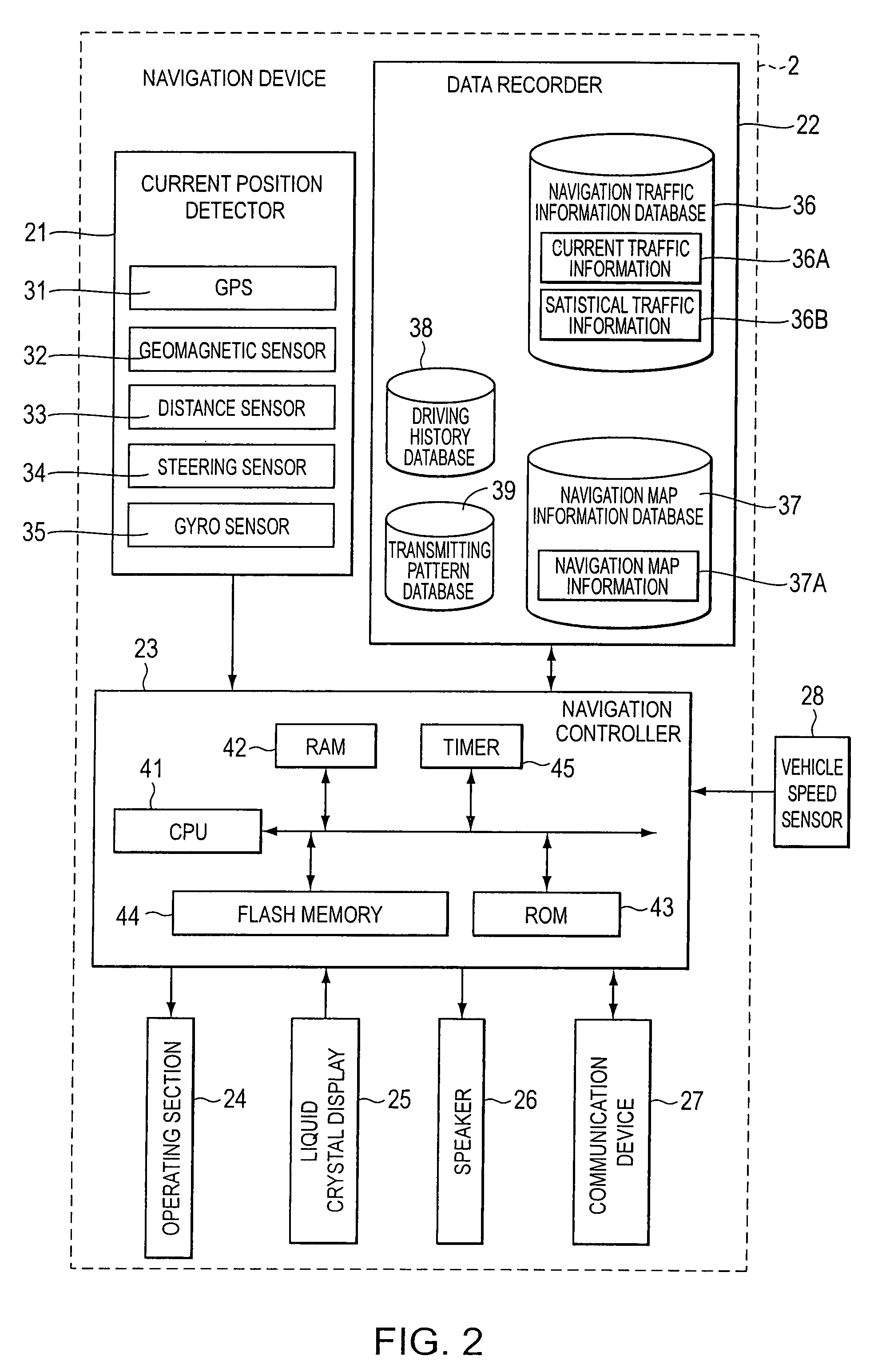

Navigation system

InactiveUS8364391B2High processing loadReduce communication costsAnalogue computers for vehiclesInstruments for road network navigationNavigation systemMarine navigation

A navigation system includes an information center and a navigation device installed in a probe vehicle. The information center stores limiting information for specifying a content of probe information in accordance with predefined factors, specifies a predefined factor corresponding to a navigation device, selects the limiting information based on the specified predefined factor, transmits the selected limiting information to the navigation device, and receives the corresponding probe information transmitted from a navigation device. The navigation device receives the limiting information from the information center, collects probe information, selects only the probe information specified by the received limiting information for transmission to the information center, and transmits the selected probe information to the information center.

Owner:AISIN AW CO LTD

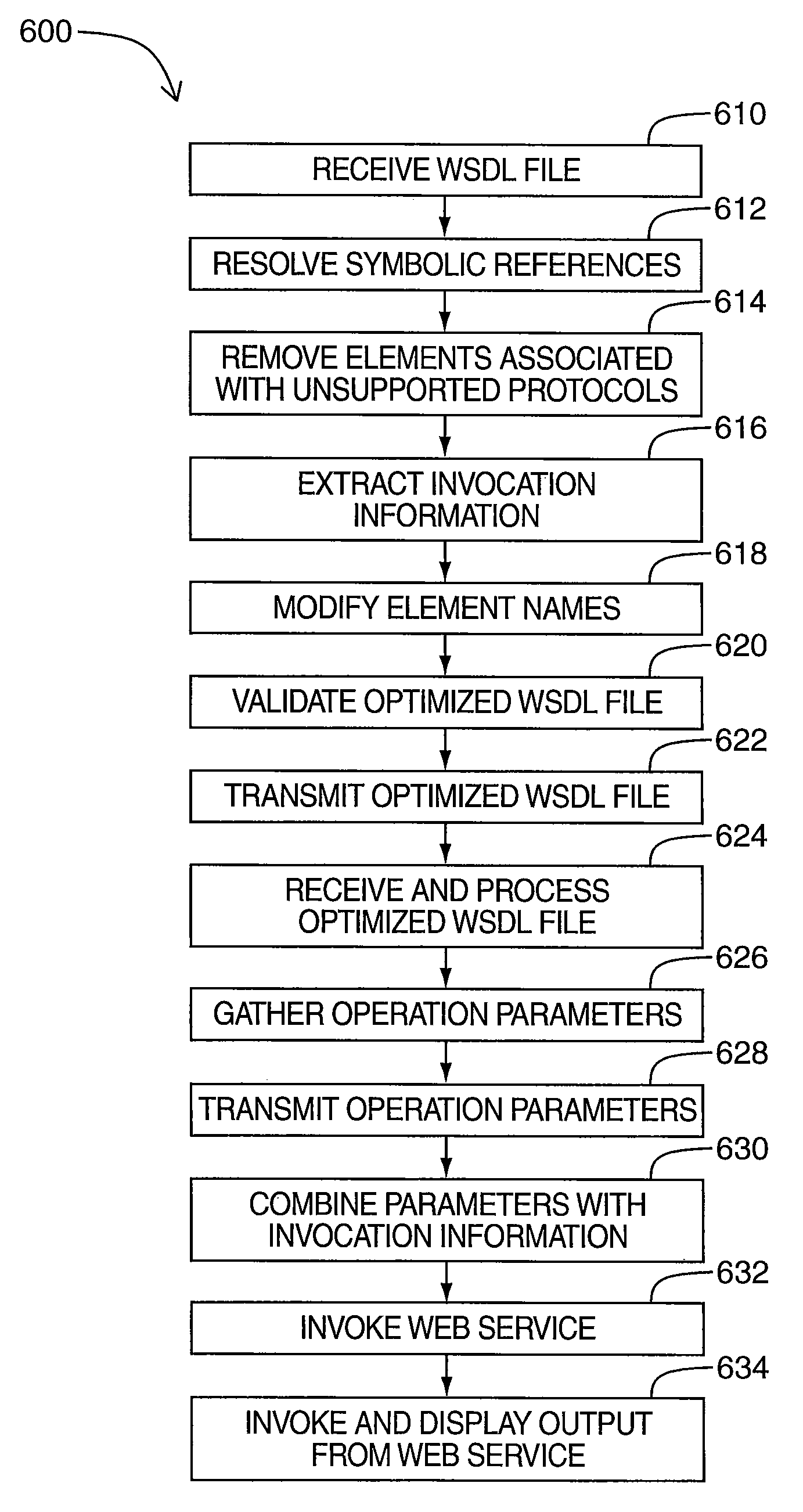

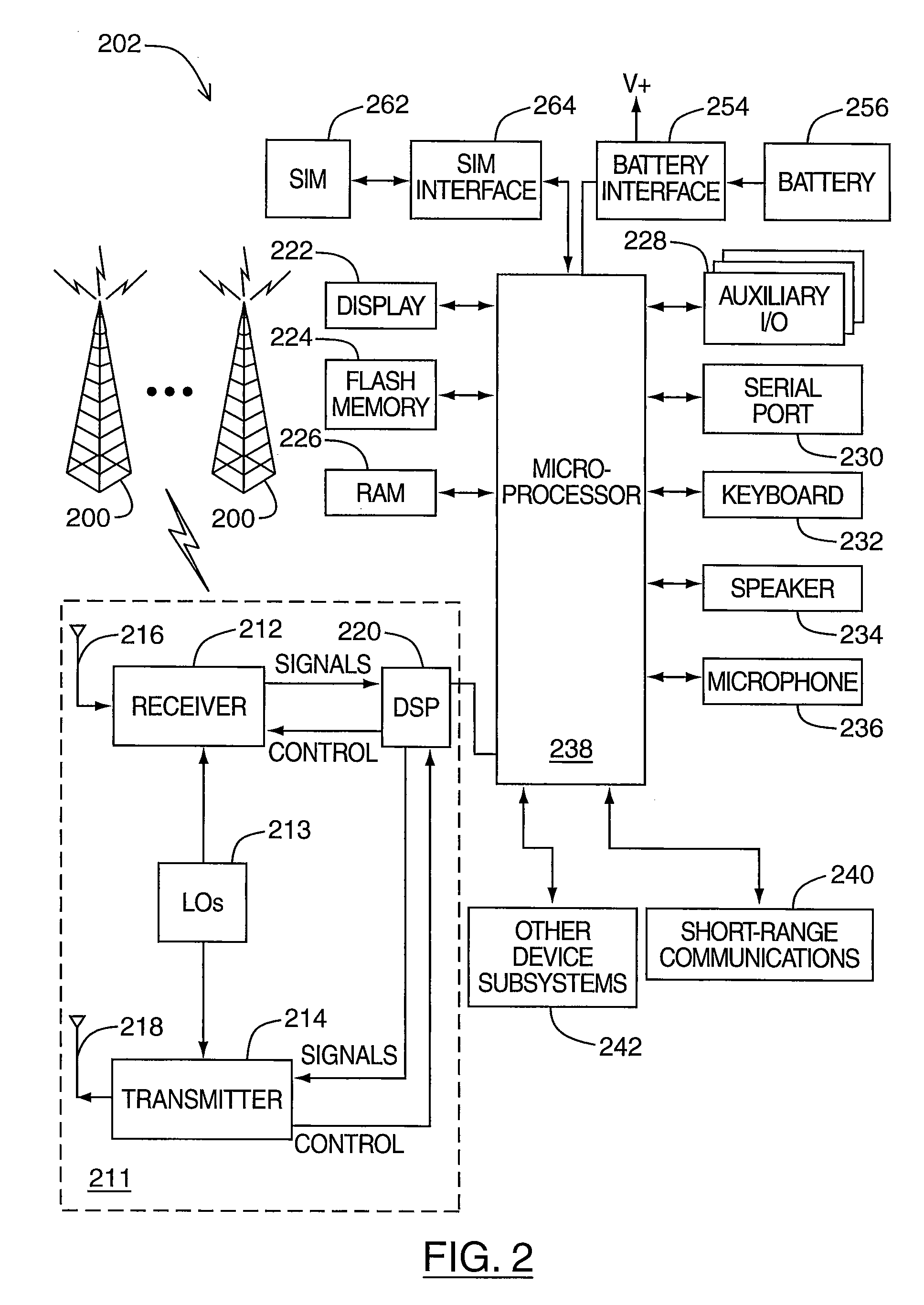

Apparatus and method for processing web service descriptions

ActiveUS7596622B2Facilitates invocation of web serviceReduce processing loadDigital data processing detailsMultiple digital computer combinationsWeb serviceMobile device

An apparatus and method for processing a web service description such that the web service description is adapted for use with mobile devices. A web services accelerator is adapted to receive a web service description that defines an interface to a web service, create at least one accelerator output file from the web service description, and transmit the at least one accelerator output file to a mobile device. Accelerator output files are used by the mobile device to invoke web services.

Owner:MALIKIE INNOVATIONS LTD

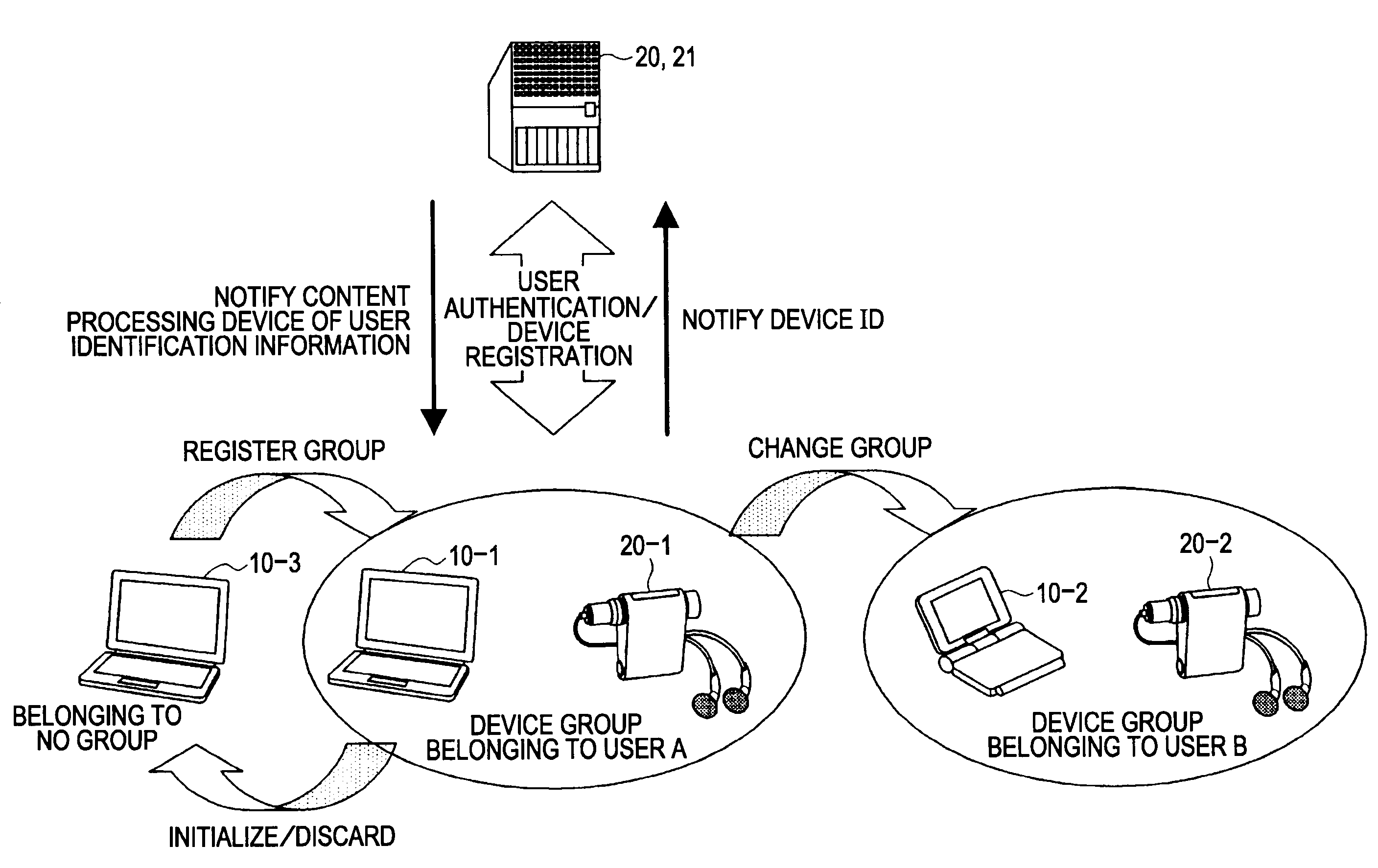

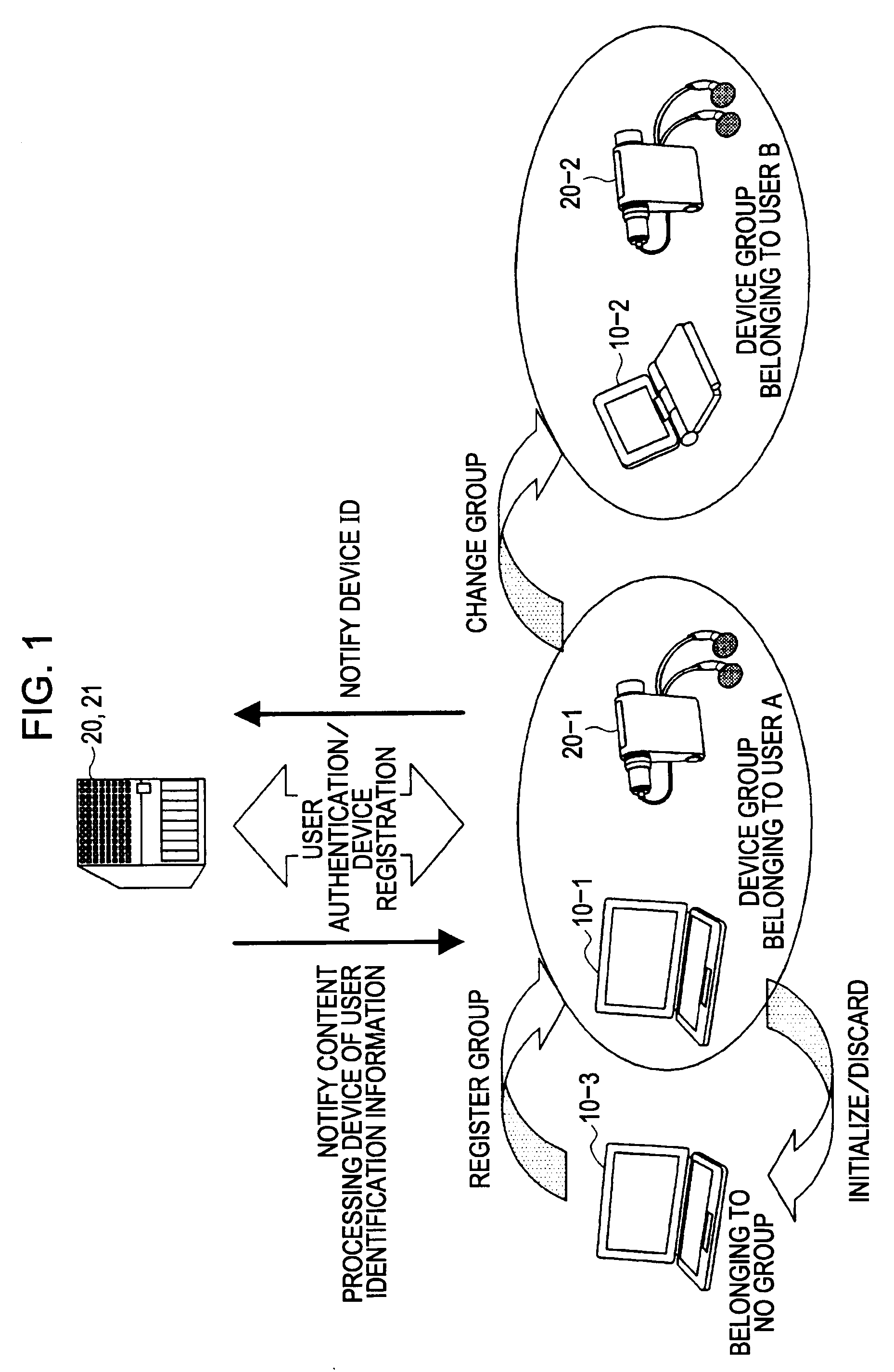

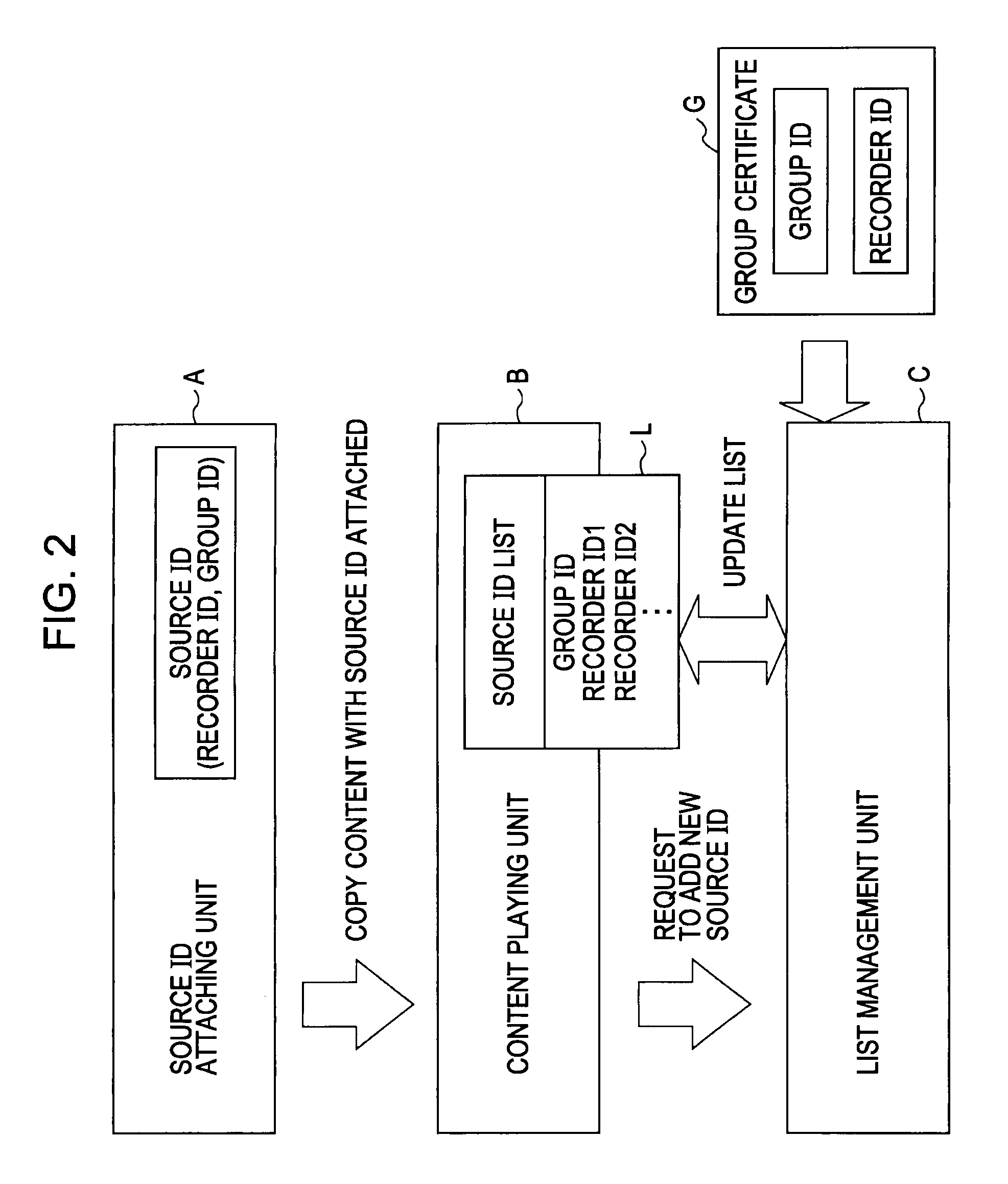

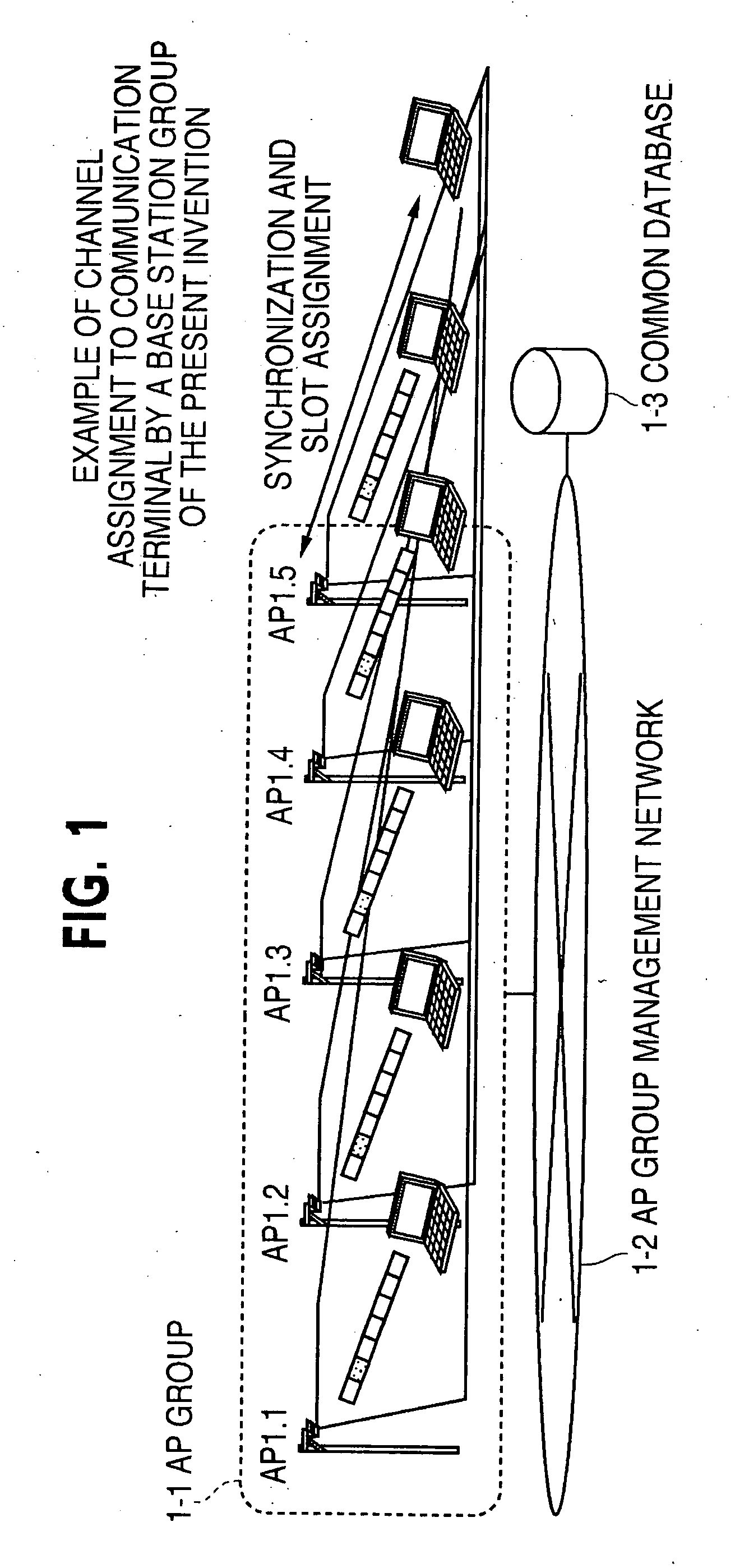

Group registration device, group registration release device, group registration method, license acquisition device, license acquisition method, time setting device, and time setting method

InactiveUS20090151006A1Simplify the registration processExecuted sufficientlyDigital data processing detailsUser identity/authority verificationDatabaseLicense

There is provided a group registration device or the like which is capable of simplifying registration processing to readily perform group registration while retaining secure registration processing.A group registration device 10 includes a registration request detecting unit, a session ID generating unit for generating a session ID, a registration request message sending unit, a registration reply message receiving unit, a verification unit 231 for verifying non-redundancy of a message, and a storage unit 241 for storing an ID list included in a registration reply message in a storage region so as to be associated with a group ID. Within the same registration session, the registration request message is sent once, the registration reply message is received once, and processing is restricted to sending of the registration request message and receiving of the registration reply message.

Owner:SONY CORP

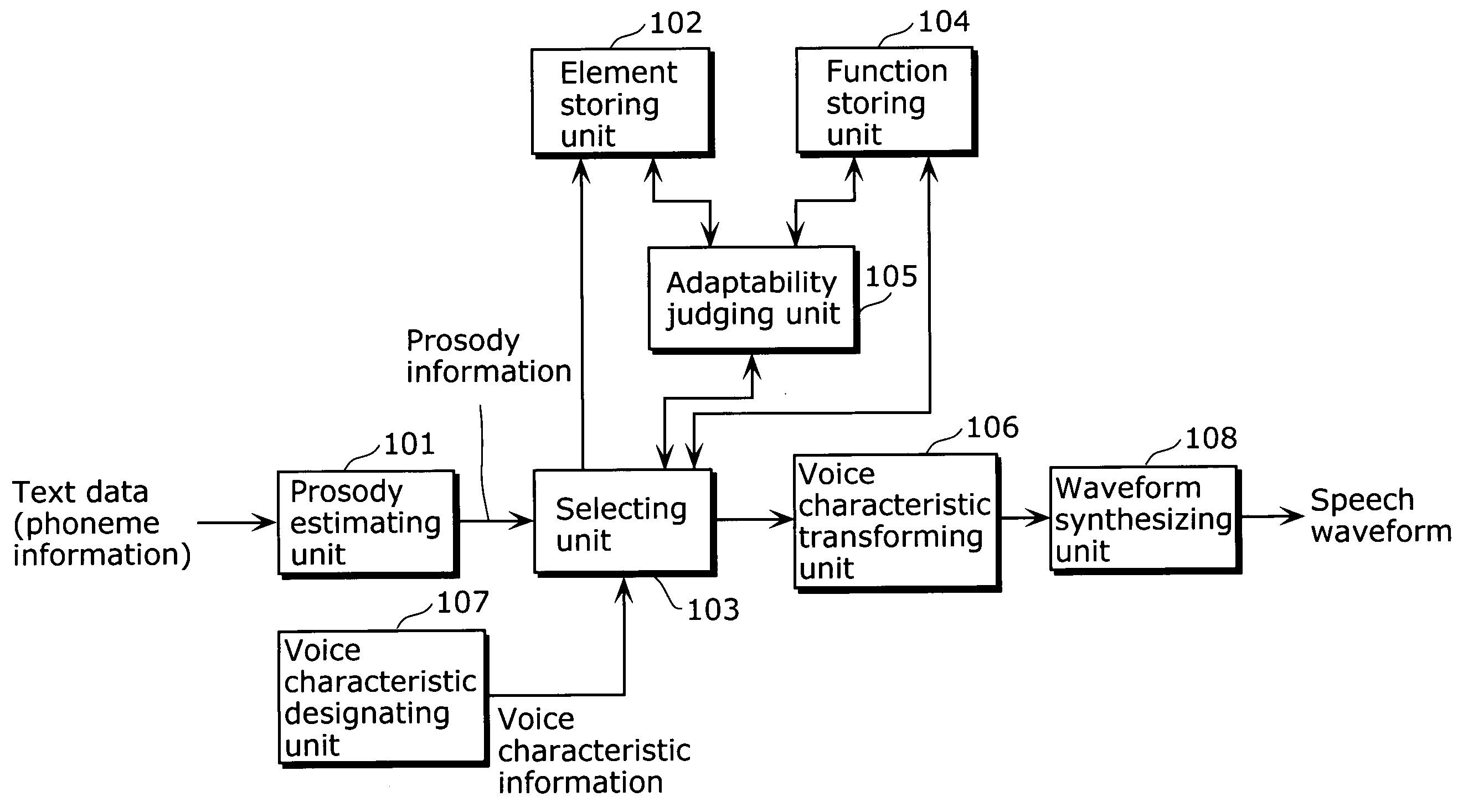

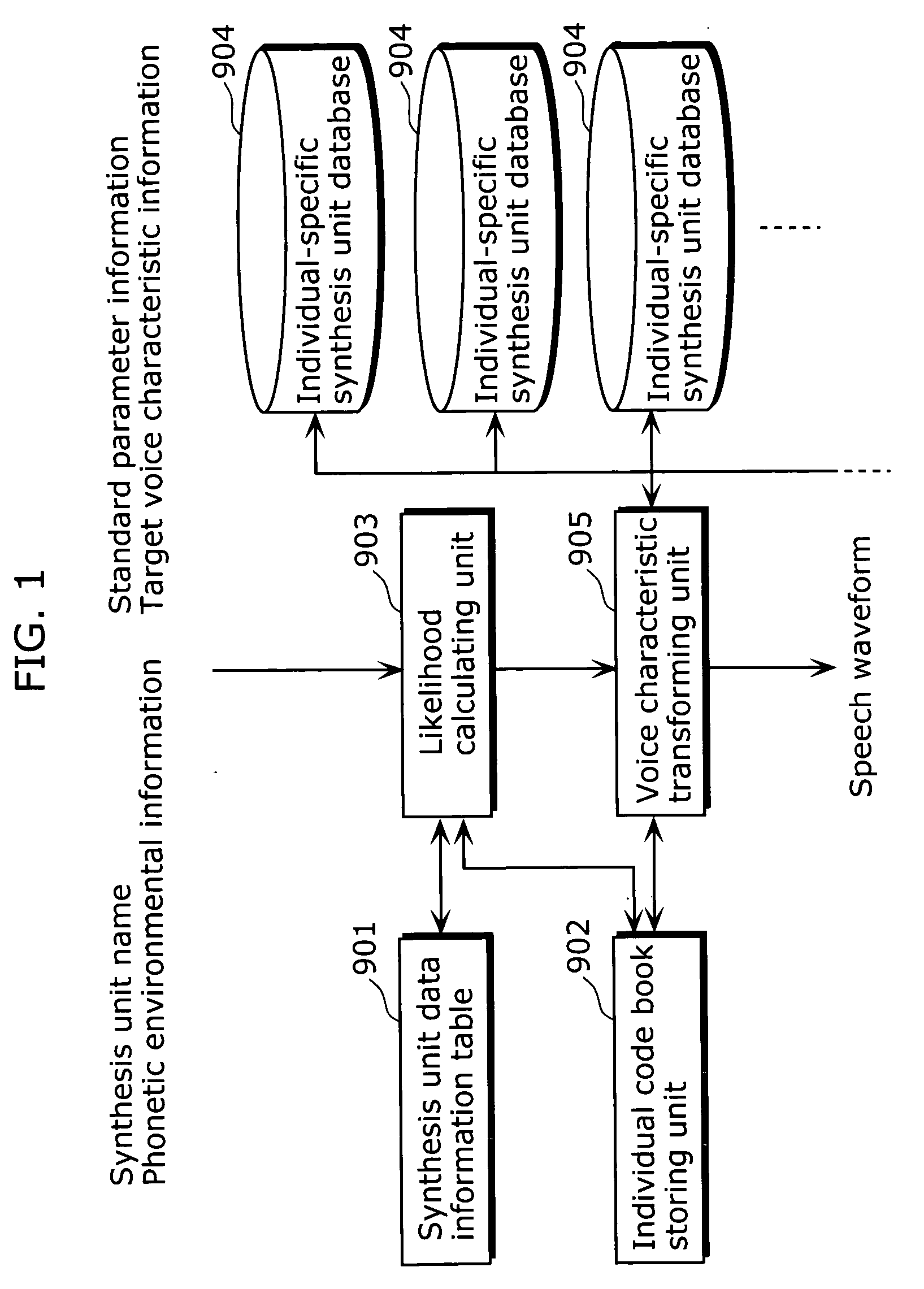

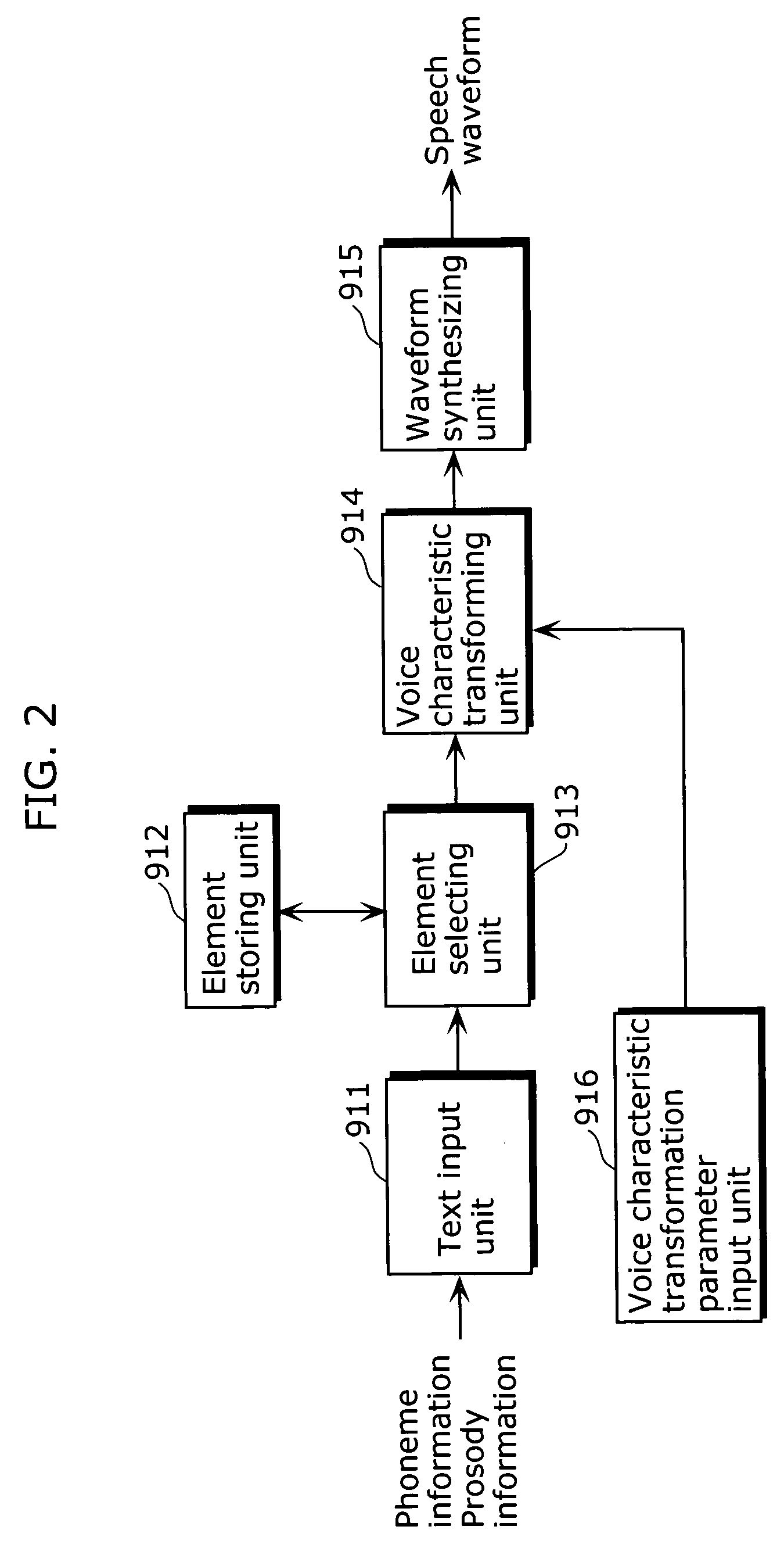

Speech synthesis apparatus and speech synthesis method

ActiveUS20060136213A1Appropriately transformedQuality improvementSpeech synthesisAcousticsSpeech synthesis

A speech synthesis apparatus which can appropriately transform a voice characteristic of a speech is provided. The speech synthesis apparatus includes an element storing unit in which speech elements are stored, a function storing unit in which transformation functions are stored, an adaptability judging unit which derives a degree of similarity by comparing a speech element stored in the element storing unit with an acoustic characteristic of the speech element used for generating a transformation function stored in the function storing unit, and a selecting unit and voice characteristic transforming unit which transforms, for each speech element stored in the element storing unit, based on the degree of similarity derived by the adaptability judging unit, a voice characteristic of the speech element by applying one of the transformation functions stored in the function storing unit.

Owner:PANASONIC INTELLECTUAL PROPERTY CORP OF AMERICA

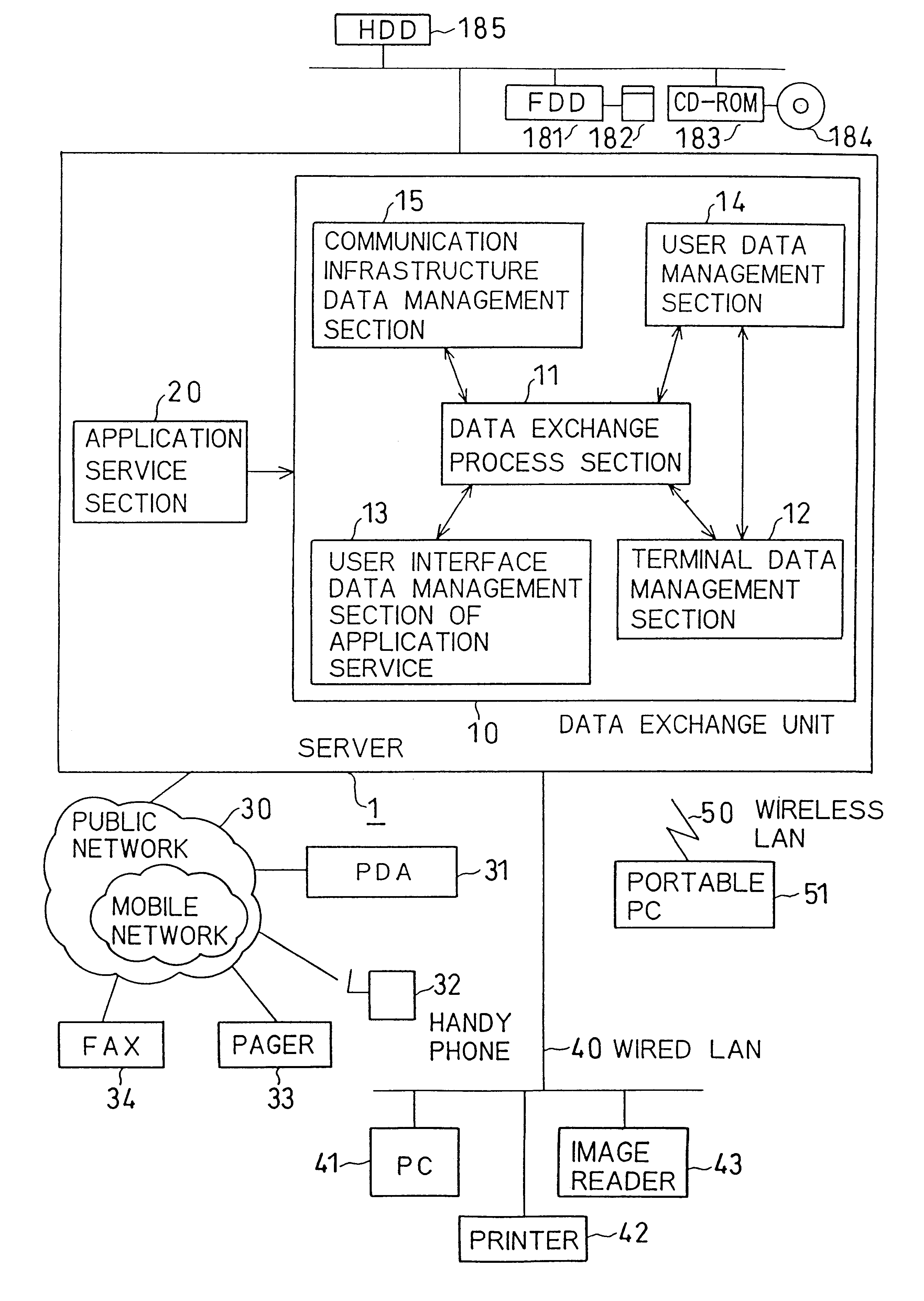

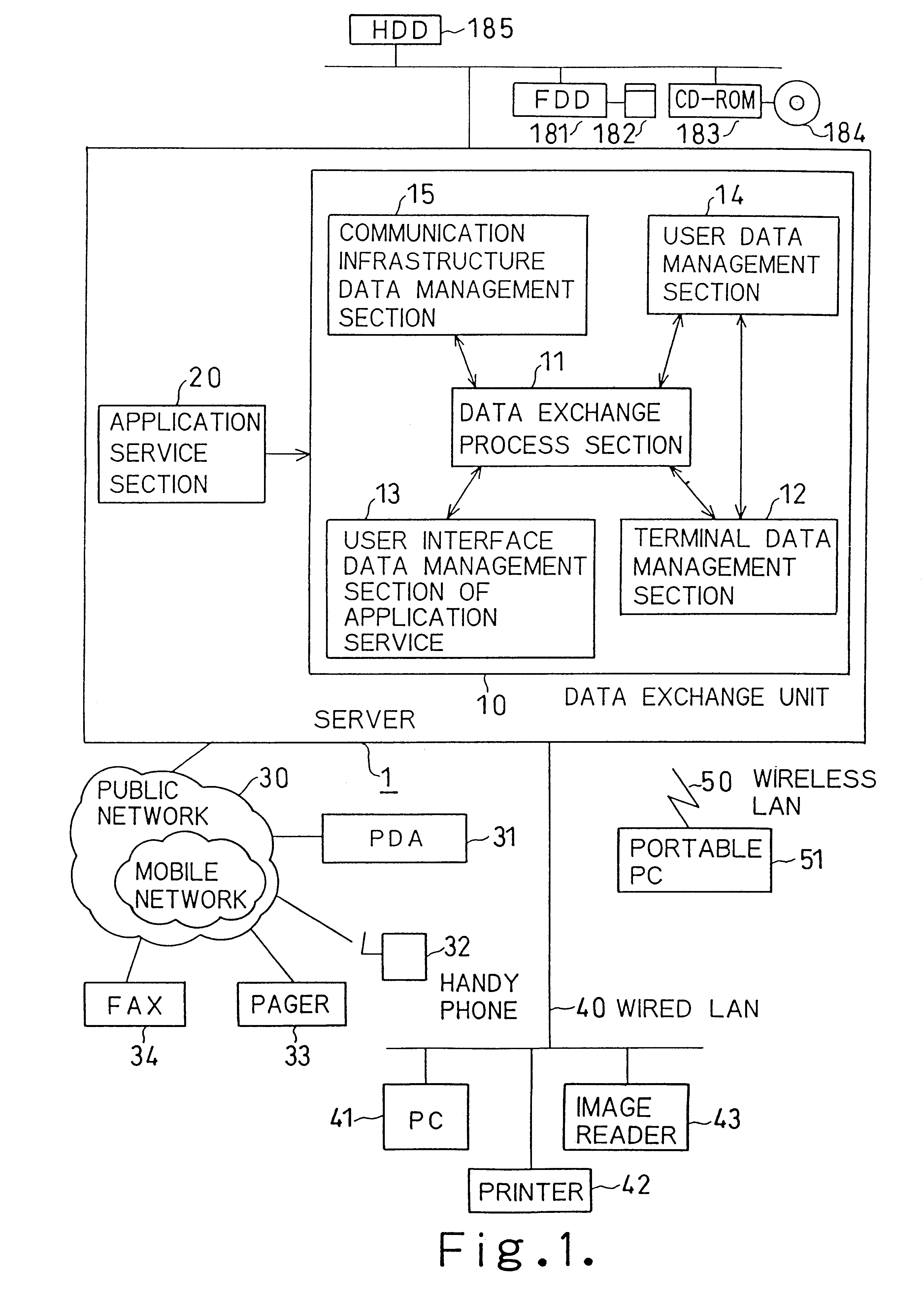

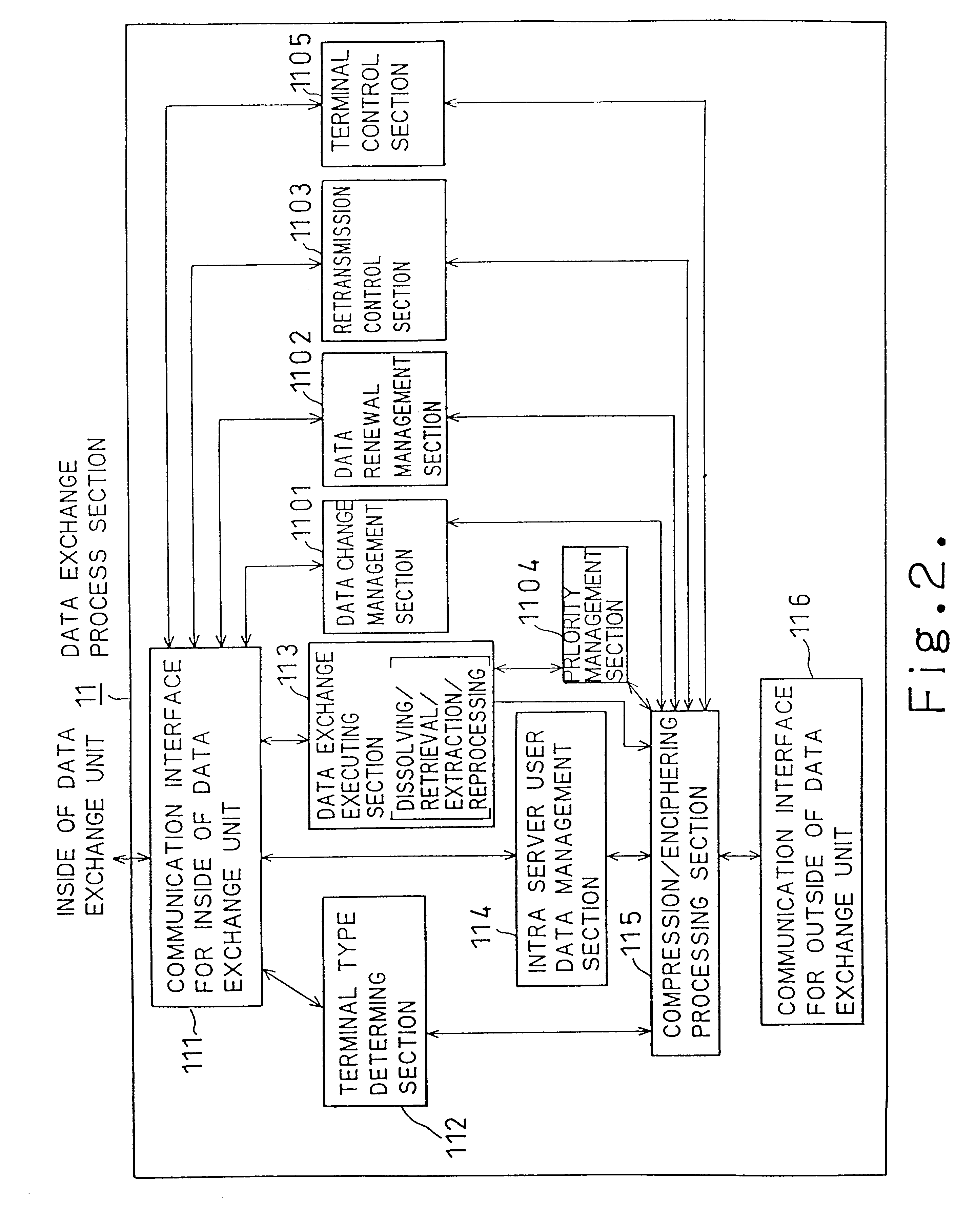

Distributed network computing system for data exchange/conversion between terminals

InactiveUS6195677B1Improve security featuresReduce data processingCharacter and pattern recognitionDigital data protectionService provisionTerminal equipment

A data exchange unit is arranged in a server. Service data provided as an application service is converted into a predetermined format on the basis of the attribute data of a terminal as a communication partner and is transmitted. With this processing, the application service can be provided while adjusting the relative difference in processing capability terminals. When the service data is converted into a predetermined format on the basis of the attribute of a communication network connected to the terminal and transmitted, the application service can be provided while adjusting the relative difference in communication capability among communication networks. Also, terminal equipment 51 is able to communicate with server computer while keeping the security function.

Owner:KK TOSHIBA

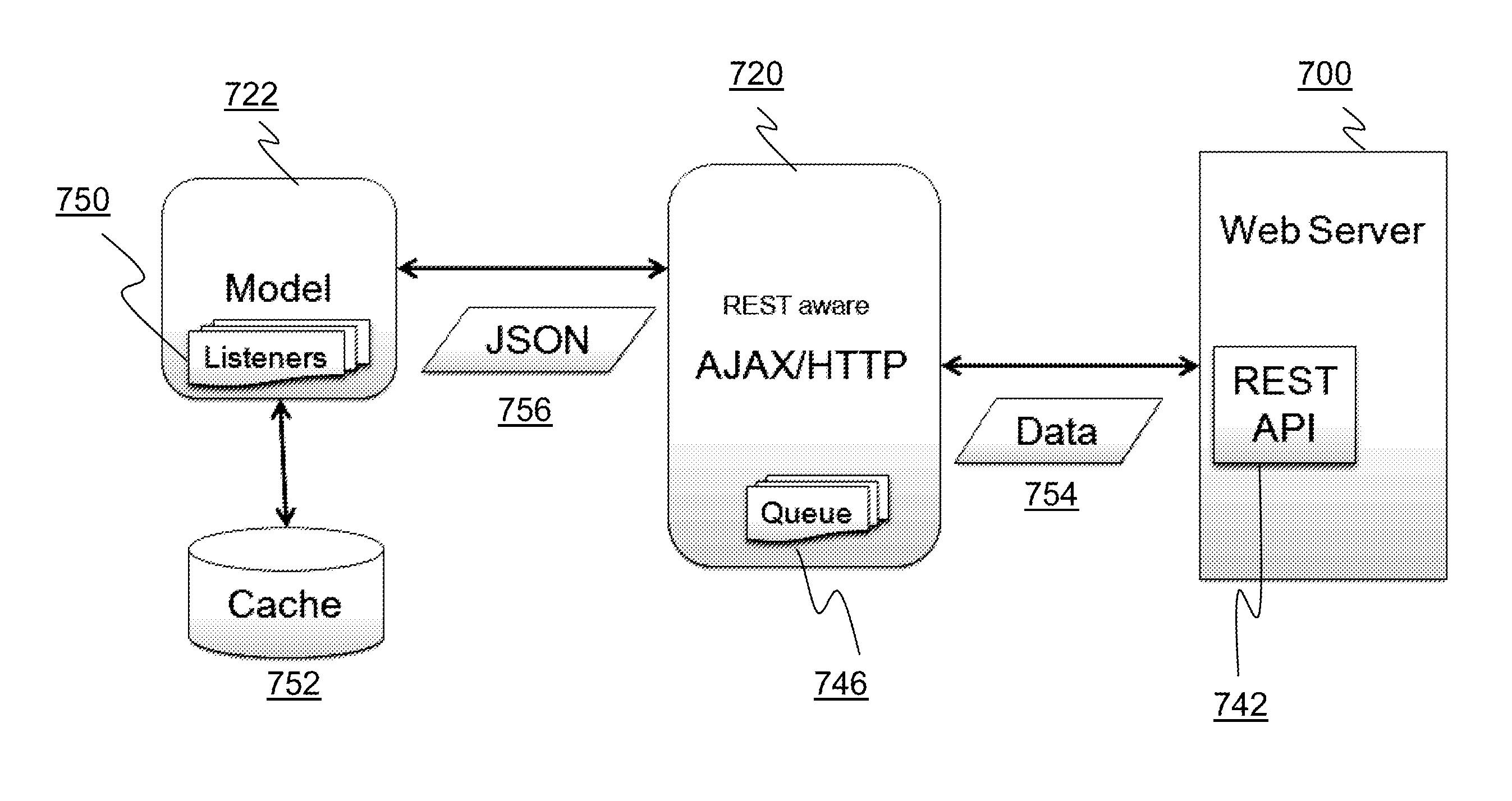

Systems and methods for providing user interfaces for management applications

ActiveUS20130246944A1Attenuation bandwidthReduce consumptionInterprogram communicationTransmissionExtensibilityRepresentational state transfer

The present application is directed towards systems and methods for providing user interfaces for management applications via a definition-based graphical user interface (GUI) framework for developing web based management applications for servers, intermediaries, routers, wide area network (WAN) accelerators, caches, switches, or any other type and form of computing device. The plug-in free framework reduces the server's resource consumption and bandwidth by making a full use of resources available on the client computing device or browser. A complete web application can be developed using JavaScript Object Notation (JSON) definitions along with a representational state transfer (REST) based application programming interface (API) efficiently using the framework, which may comprise light-weight pure JavaScript or similar executable code. In many embodiments, the framework may be layered in a model-view-controller (MVC) architecture easing resource consumption, maintenance and extensibility.

Owner:CITRIX SYST INC

Routing data packets in a compressed-header domain

InactiveUS20060075134A1Reduce loadReduce processing loadDigital computer detailsData switching networksData packReal-time computing

The invention concerns routing of data packets in a header-compressed domain. According to the method described, routing a data packet with a compressed header section and an uncompressed payload section comprises steps of receiving the data packet at an ingress interface, routing the data packet to an egress interface, and forwarding the data packet to the egress interface. According to this method, the compressed header section remains unchanged between the ingress interface and the egress interface. Various implementations of this method are described, including the use of the header compression context identifier (HCCID) by for routing the packets to the correct egress interface. Accordingly, a decompressor and a router are also disclosed.

Owner:NOKIA CORP

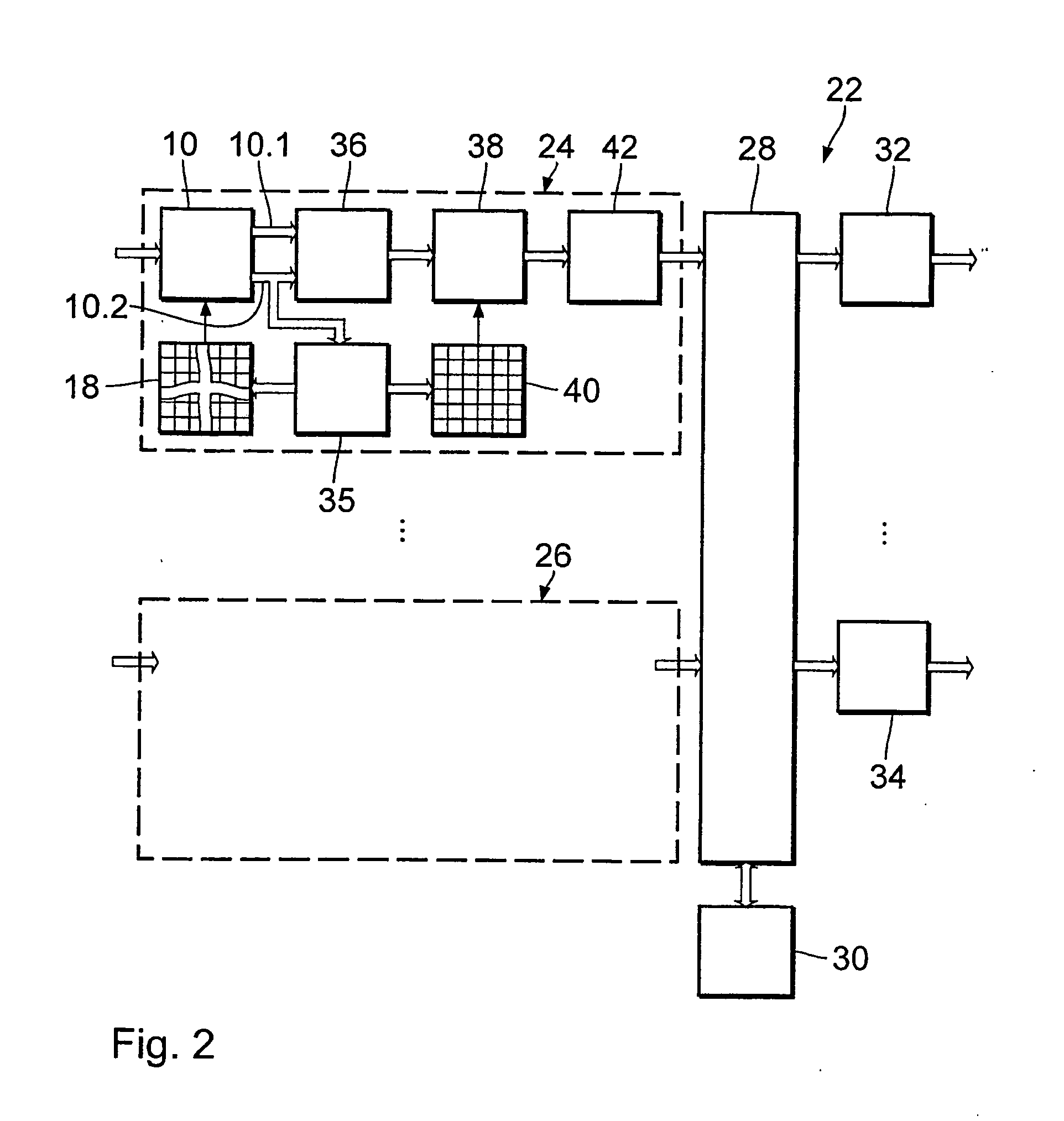

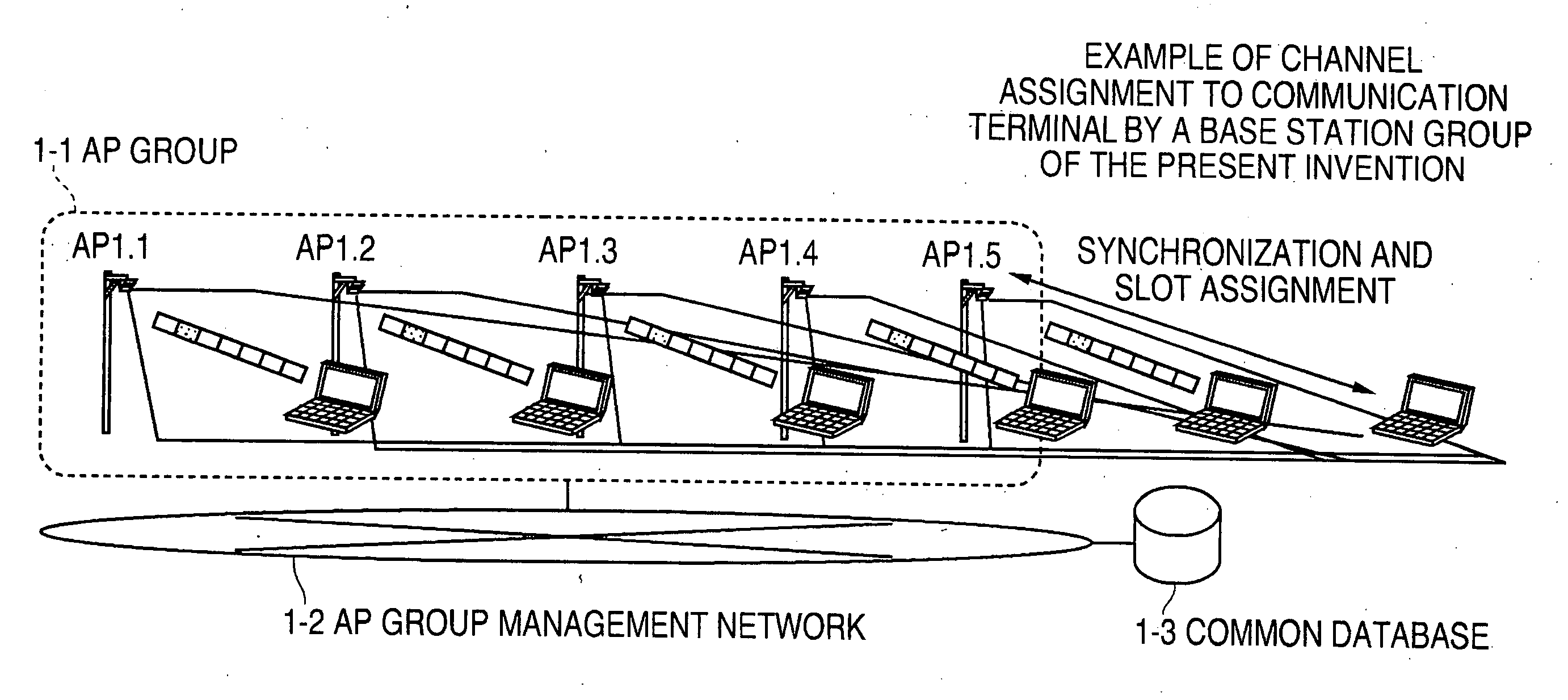

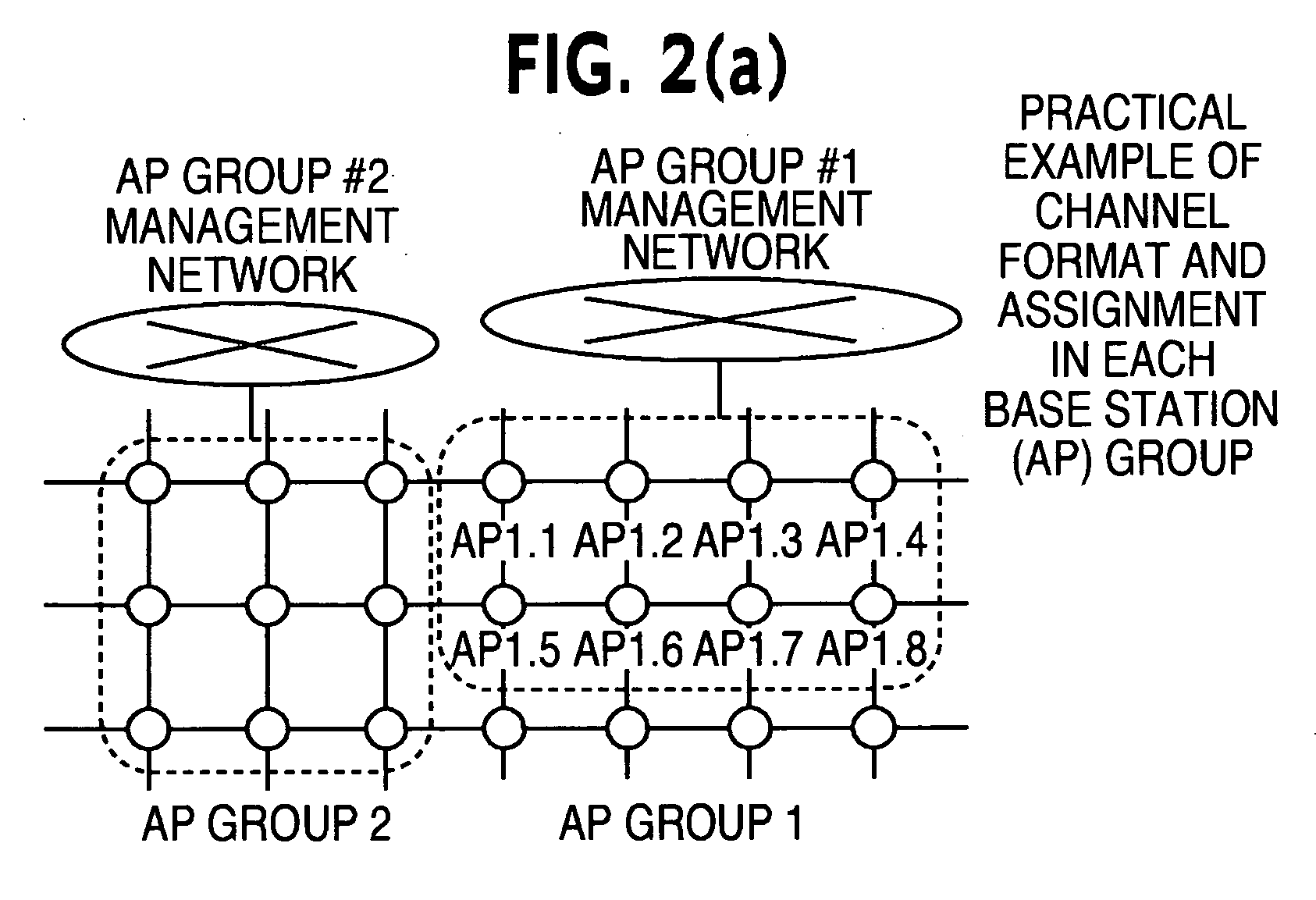

Channel assigning method and system for radio base station group

InactiveUS20070135150A1Quality improvementReduce processing loadNetwork topologiesConnection managementRadio Base StationAuthentication

To reduce the processing load such as channel assignment and an authentication process in a plurality of radio base stations and communication terminals, and quickly and efficiently assign channels to the communication channels. The channel assigning method by a radio base station group, includes determining assignment of a communication channel between a communication terminal entering a radio area of the radio station group and all radio base stations within the radio station group by a base station in the radio base station group. Channel assigning information common to the radio base station group is updated as to the determined communication channel and a communication channel is assigned to the communication terminal with reference to the channel assigning information by each radio base station in the radio base station group other than the radio base station.

Owner:FUJITSU LTD

Information transmission system, information sending device, information receiving device, information transmission method, information sending method, information receiving method and program product

ActiveUS20120328302A1Without increase loadReduce processing loadClose-range type systemsElectromagnetic receiversInformation transferInformation transmission

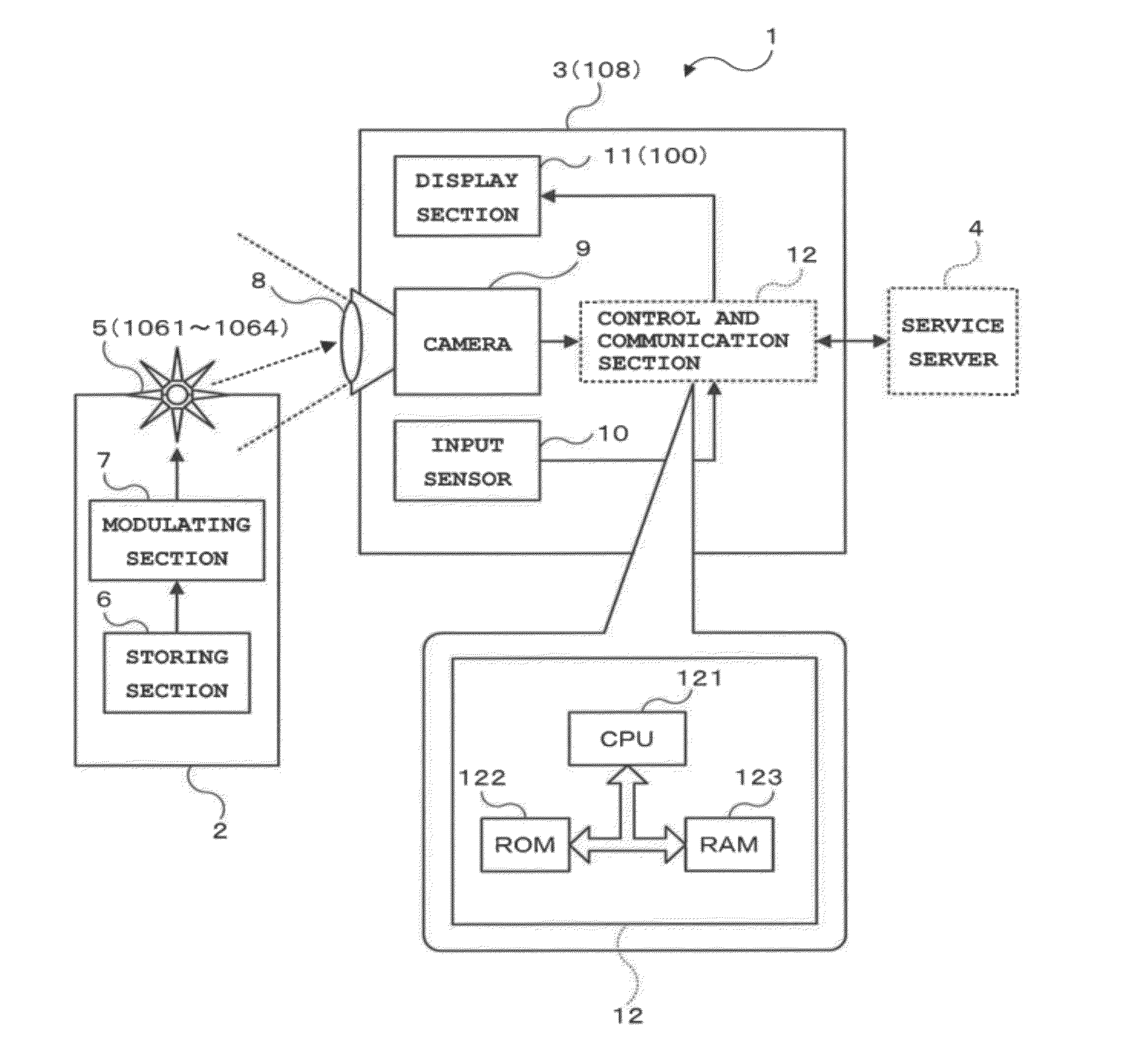

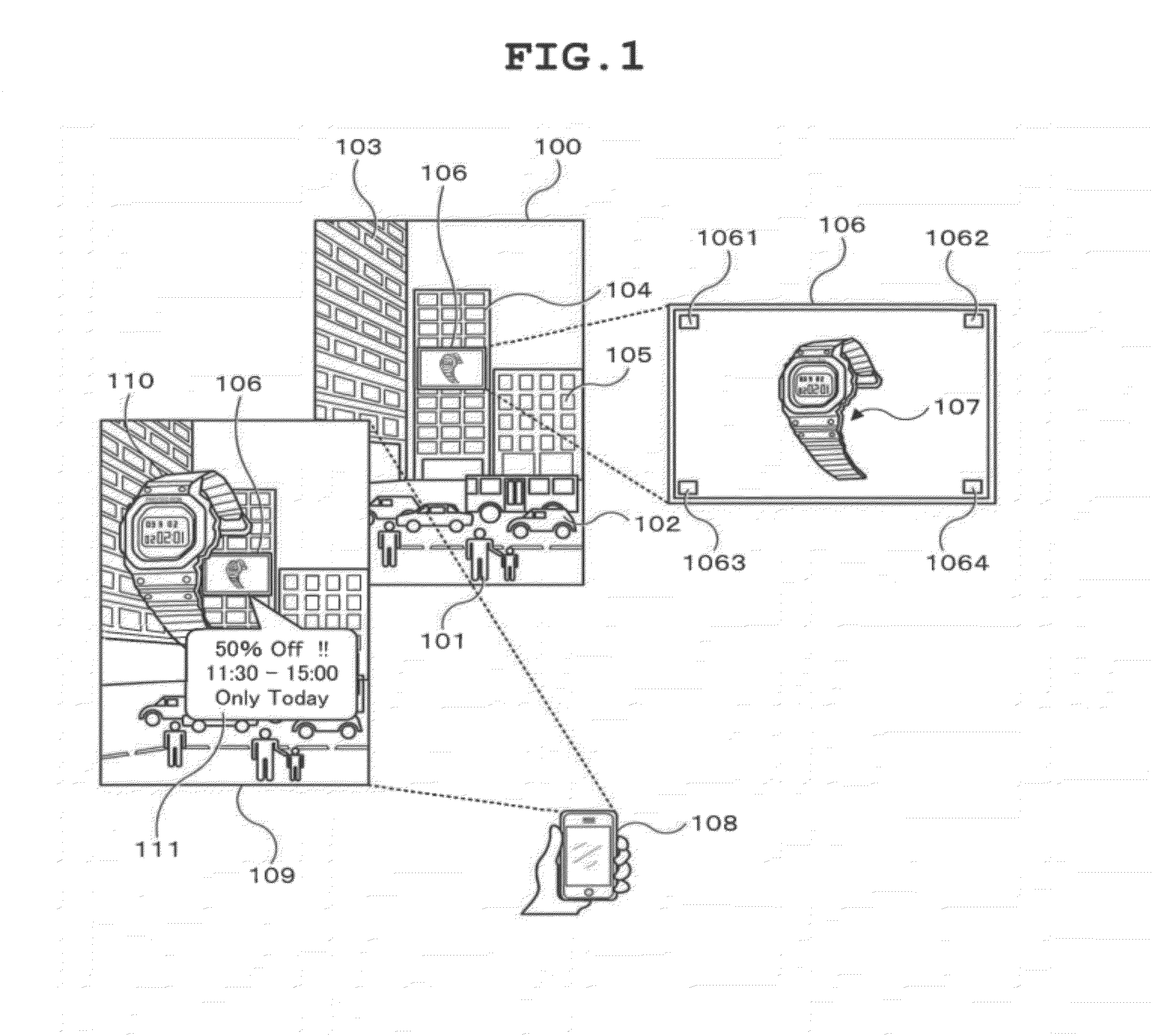

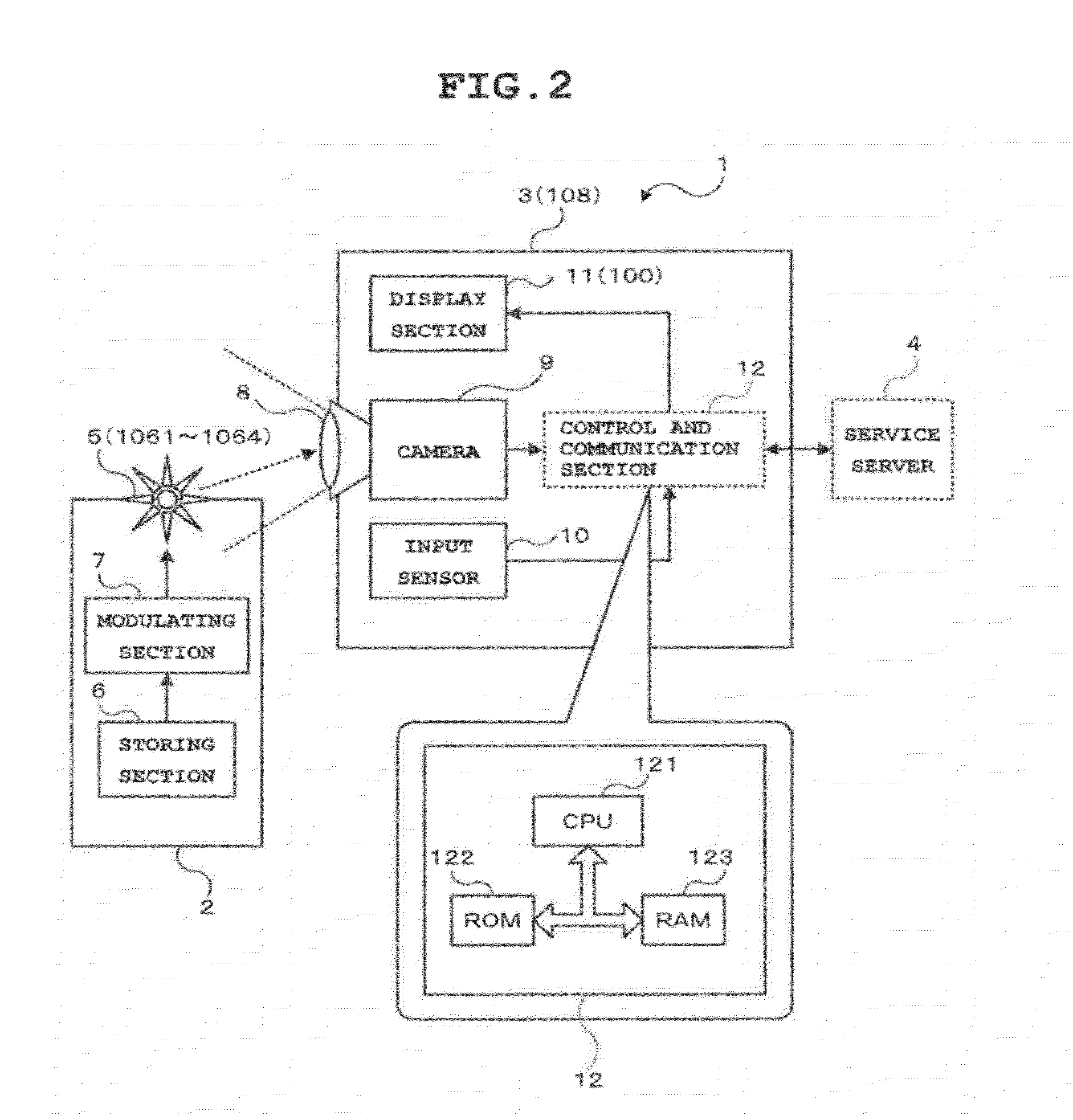

An information transmission system is constituted by: an information sending device including a light emitting section that emits light in a plurality of colors, a modulating section that modulates information to be transmitted into signals composed of changes in color, and a light emission control section that controls the light emitting section to emit light while changing color temporally based on the signals generated by the modulating section; and a receiving device including a camera that captures an image having color, and a control and communication section that detects a temporal color change of the light emitting section emitting light by light emission control by the information transmitting device, from images consecutively captured by the camera, decodes the detected color change into information, and outputs the generated information to a display section.

Owner:CASIO COMPUTER CO LTD

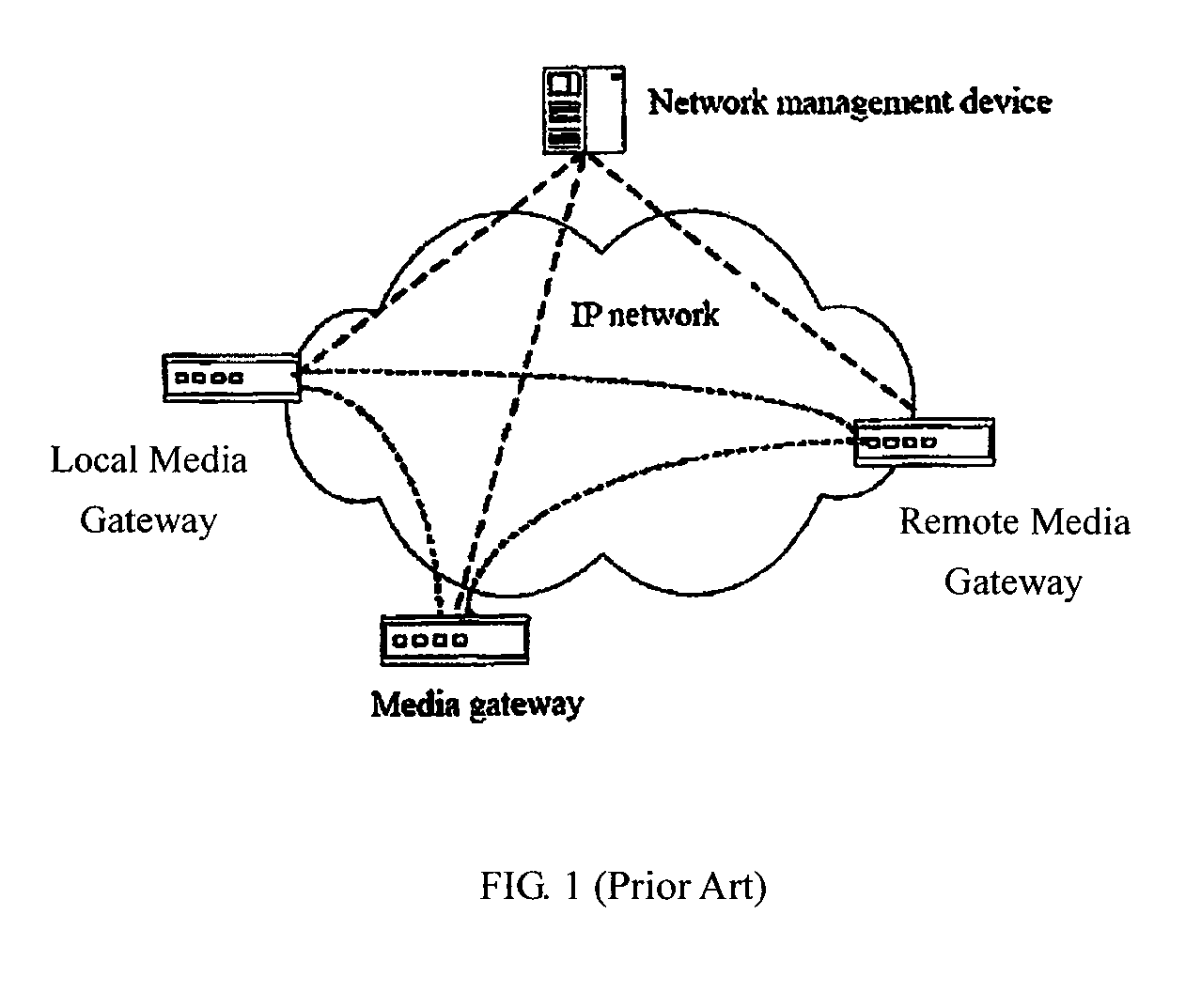

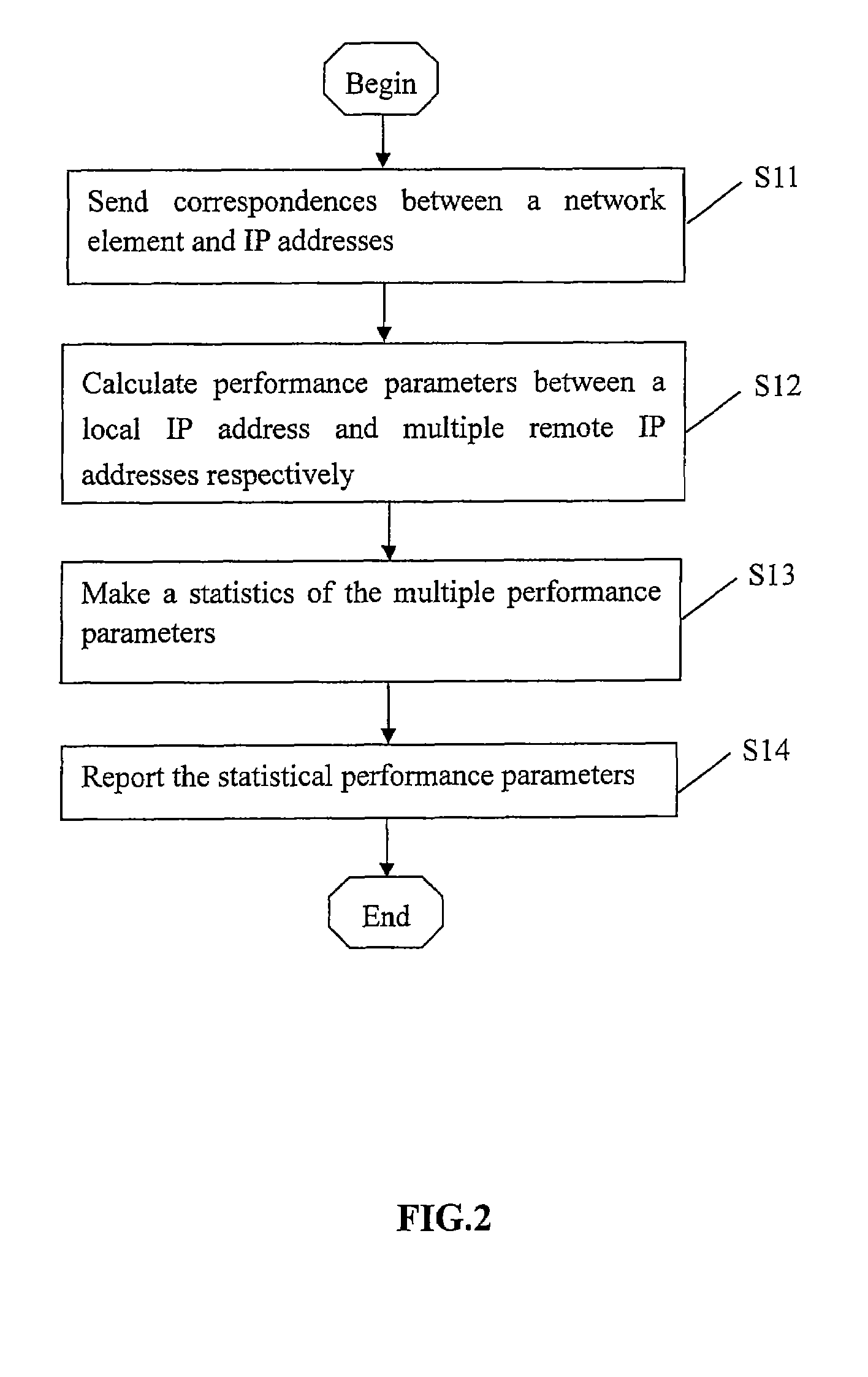

Method, device and system for monitoring network performance

ActiveUS7653005B2Save bandwidthReduce network loadError preventionTransmission systemsIp addressNetworked system

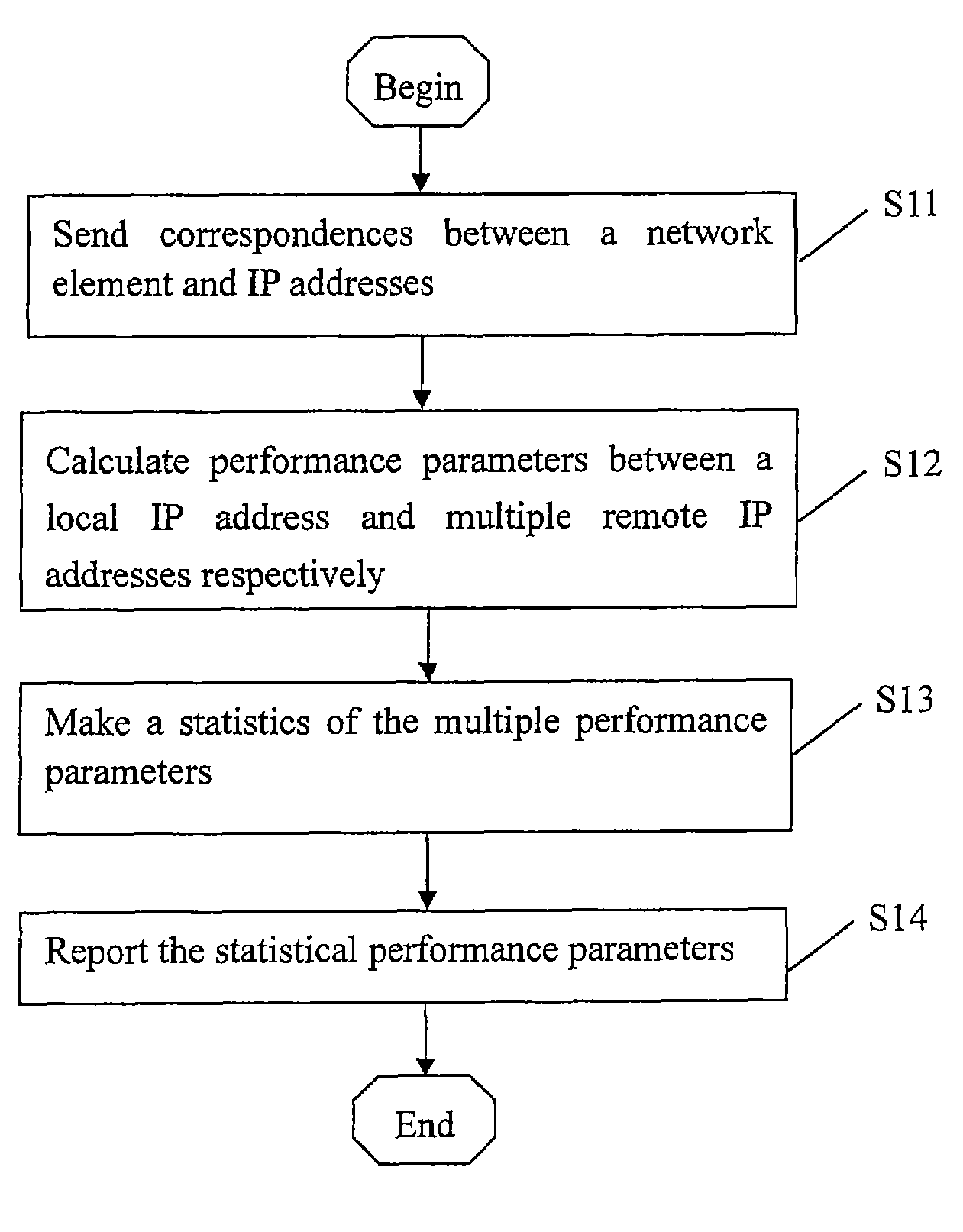

A method for monitoring network performance includes: sending correspondences between a remote network element and a plurality of IP addresses thereof from a network management device to a local network element; according to the correspondences, calculating performance parameters between the local IP address and the plurality of remote IP addresses respectively, by the local network element; making a statistics of the calculated performance parameters by the local network element. A network element for monitoring network performance, connected with a network management device and a remote network element, includes: a receiving unit, a performance parameter processing unit, a performance parameter statistics unit, and the transmitting unit. A network system for monitoring network performance is further provided. According to embodiments of this invention, the efficient measurement of network performance including IP QoS between each two MGWs of an IP network, RTP stream bandwidths, and the like, is realized, thus the message bandwidth of performance test can be saved and processing load of the network management device can be reduced.

Owner:HUAWEI TECH CO LTD

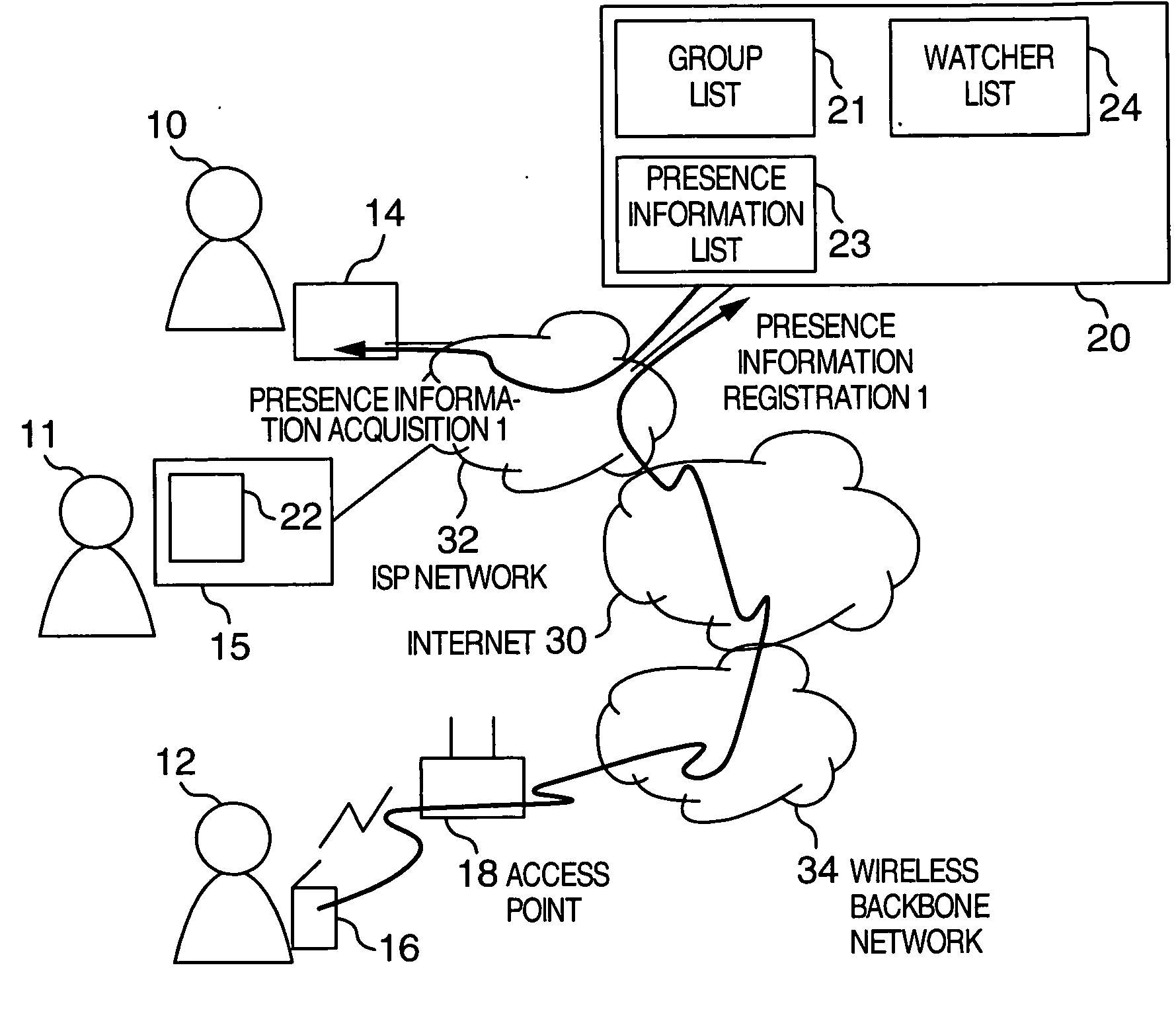

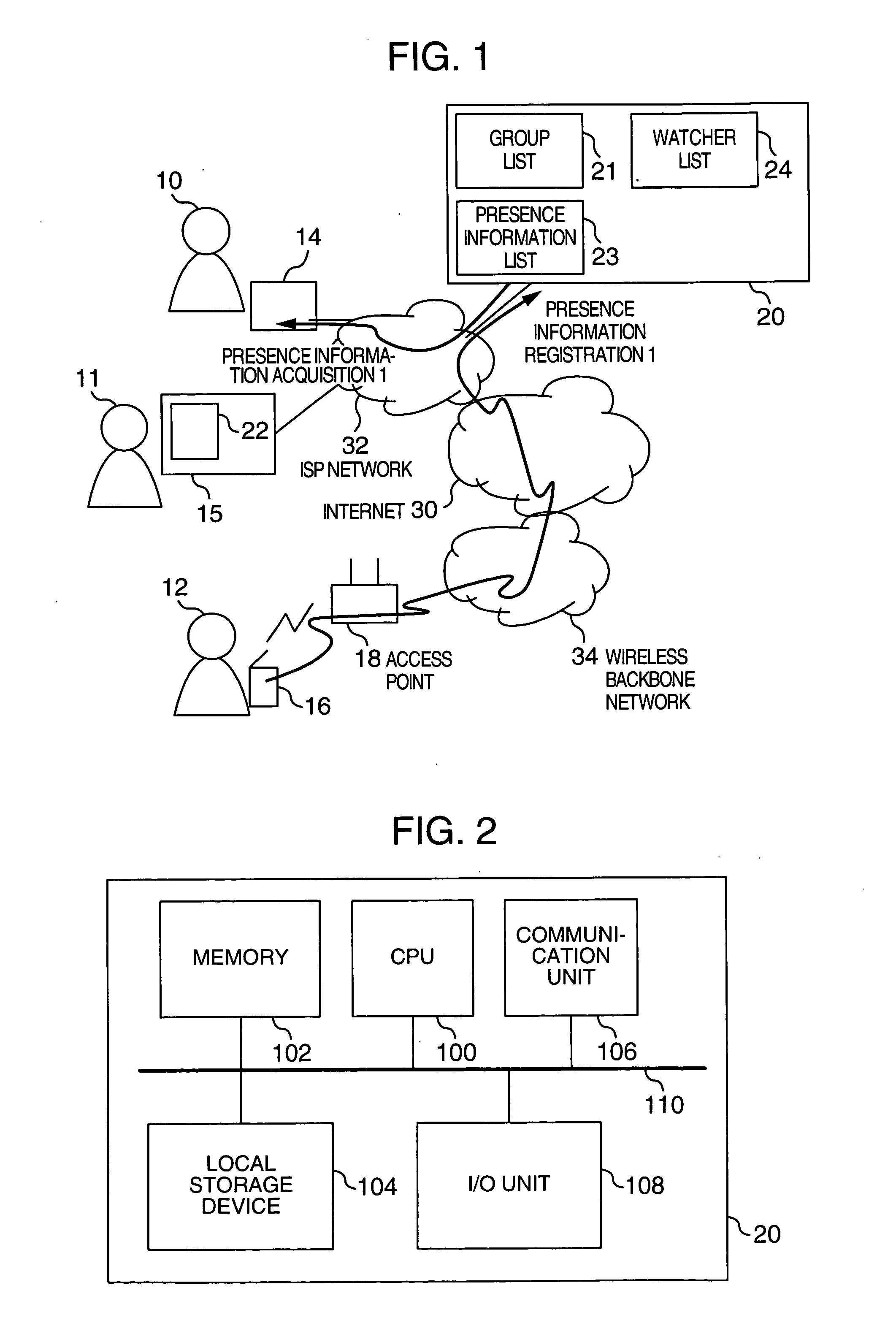

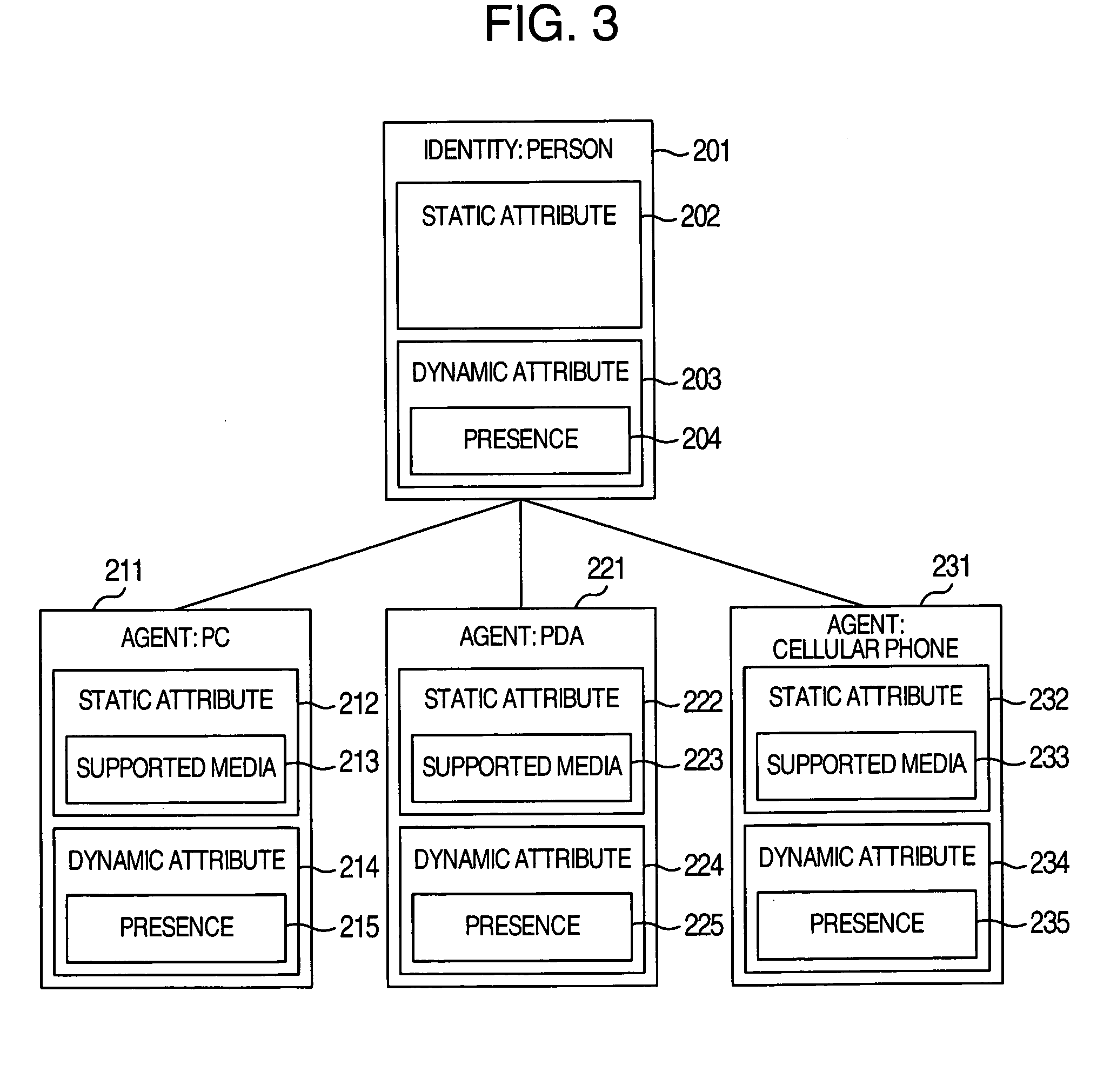

Presence data management method

InactiveUS20050154698A1Reduce data volumeEliminating redundant deliveryNetwork traffic/resource managementDigital data processing detailsData managementData type

The amount of data of presence information delivered from a presence server to a terminal is reduced by letting the presence server discard part of the presence information depending on communication measures and data type available to the terminal, by which the amount of data processed by the terminal is reduced. The presence server fetches terminal information stored therein based on terminal information contained in a presence inquiry request message from a user and thereby learns the type of data that can be processed by the terminal of the user. The presence server reconstructs the presence information of a referred user into information that can be processed by the terminal, and sends the information to the application of the terminal. By reducing the amount of presence data transmitted from the presence server to the terminal, the amount of data to be processed by the terminal can be cut down.

Owner:HITACHI LTD

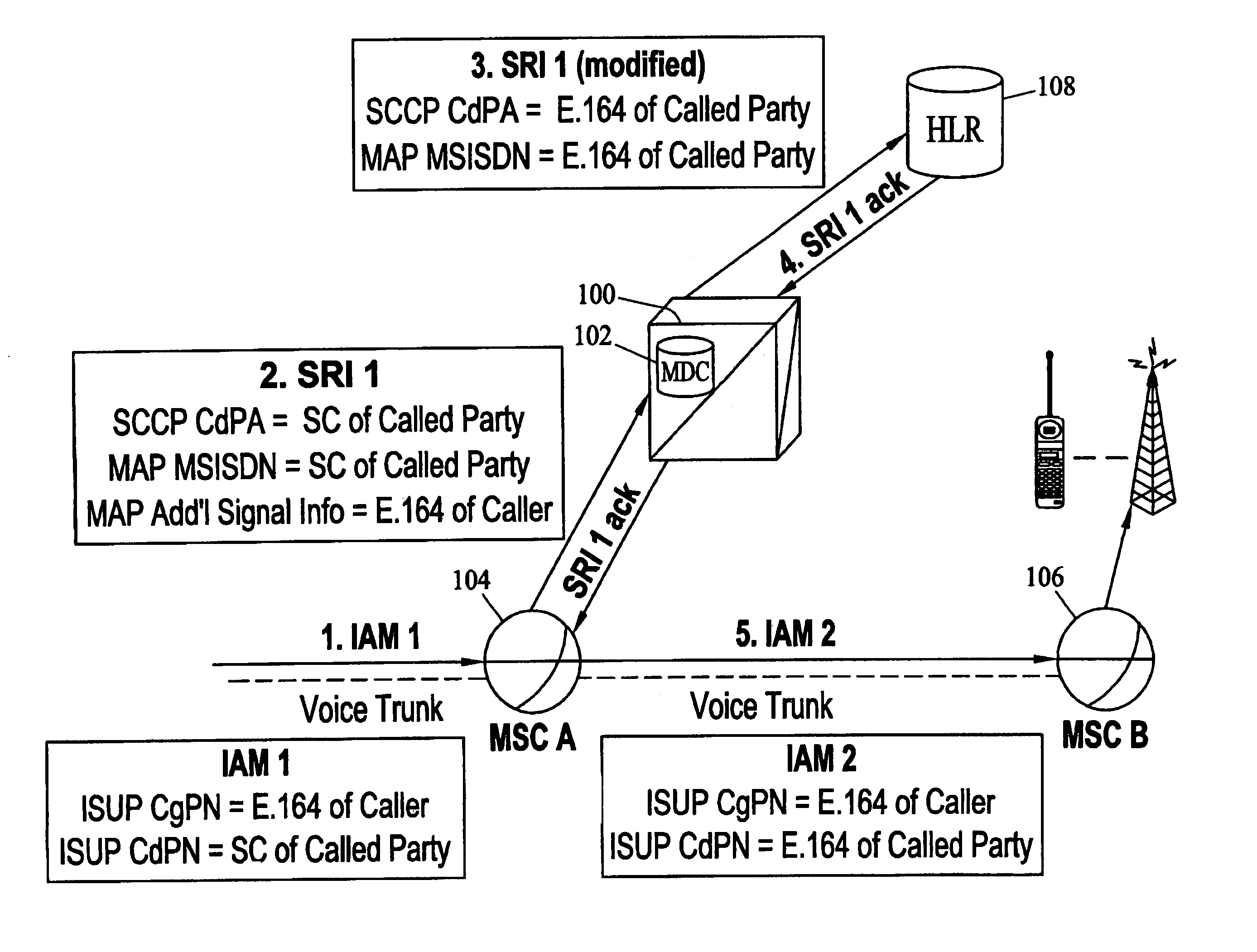

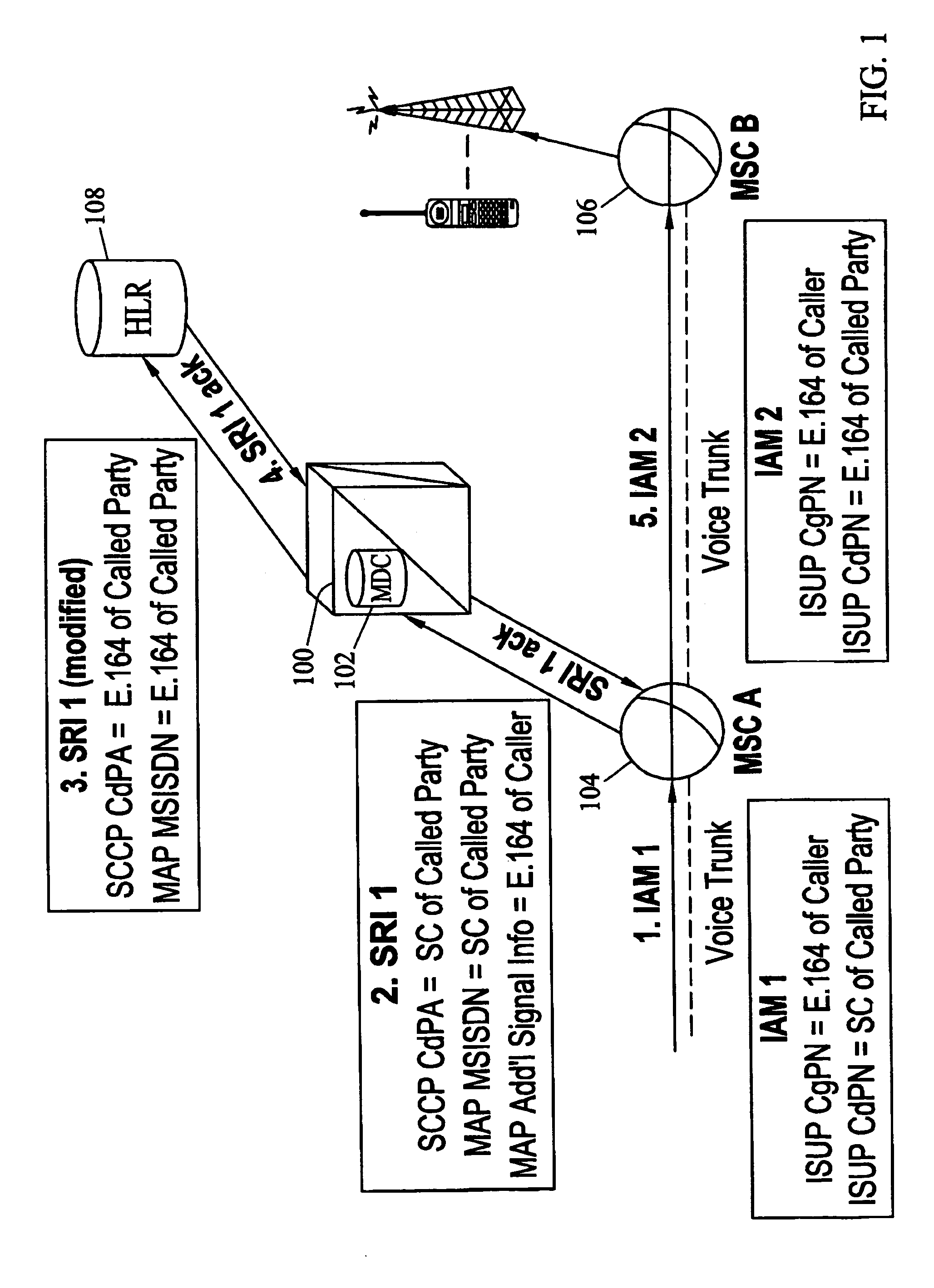

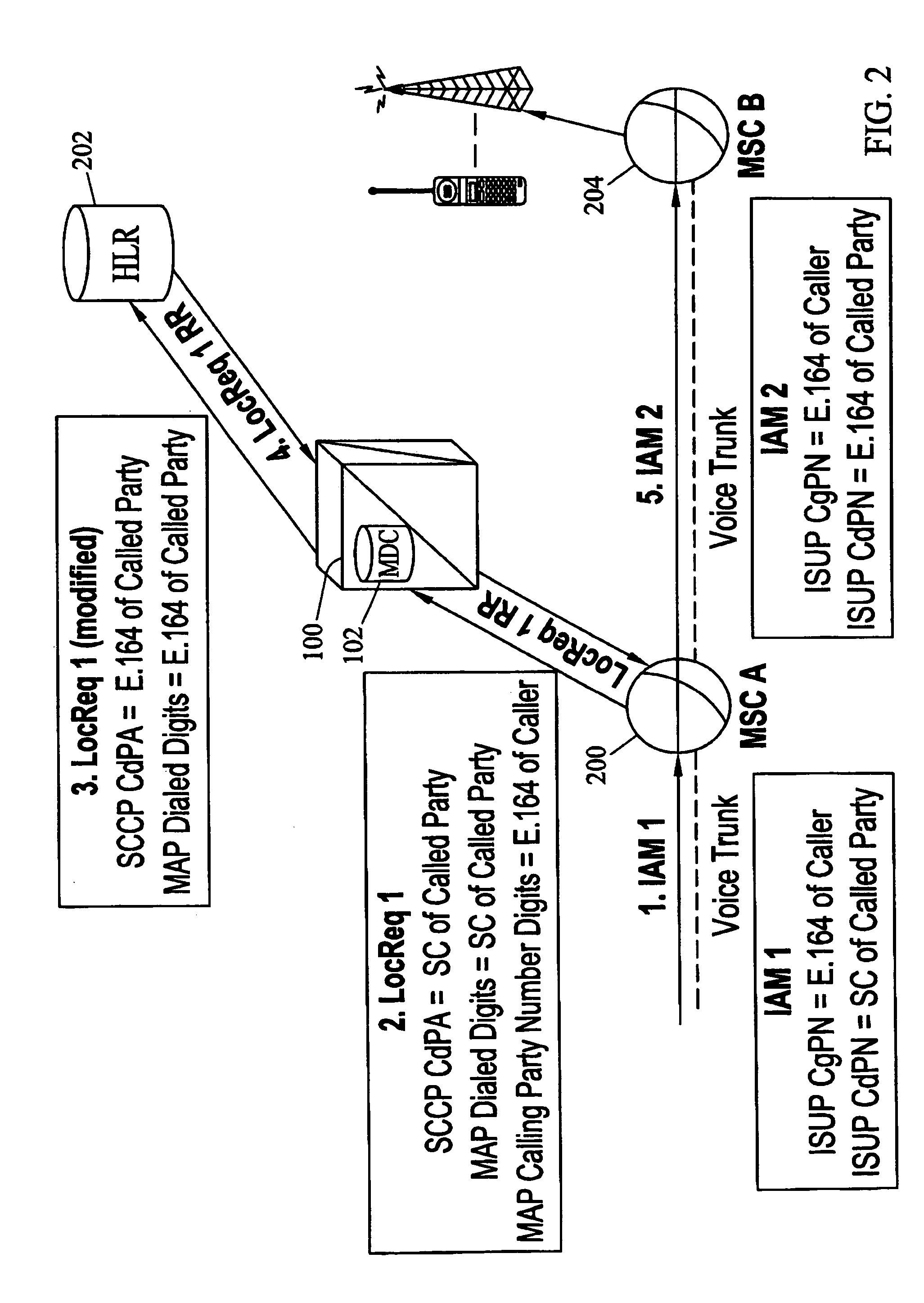

Methods and systems for triggerless mobile group dialing

ActiveUS7072678B2Improve customizabilityShorten call setup timeInterconnection arrangementsSpecial service for subscribersTelecommunications

Owner:TEKELEC GLOBAL INC

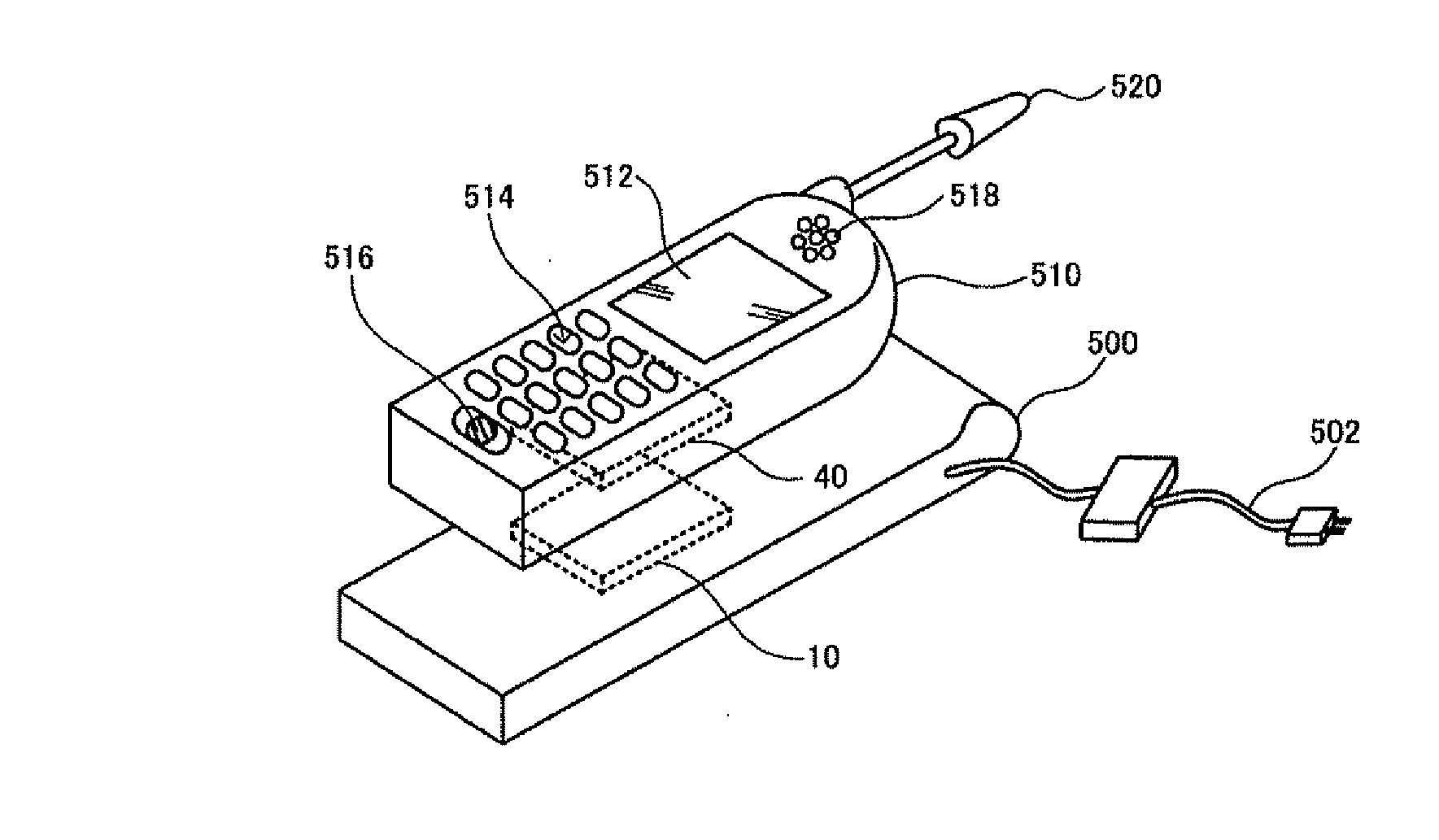

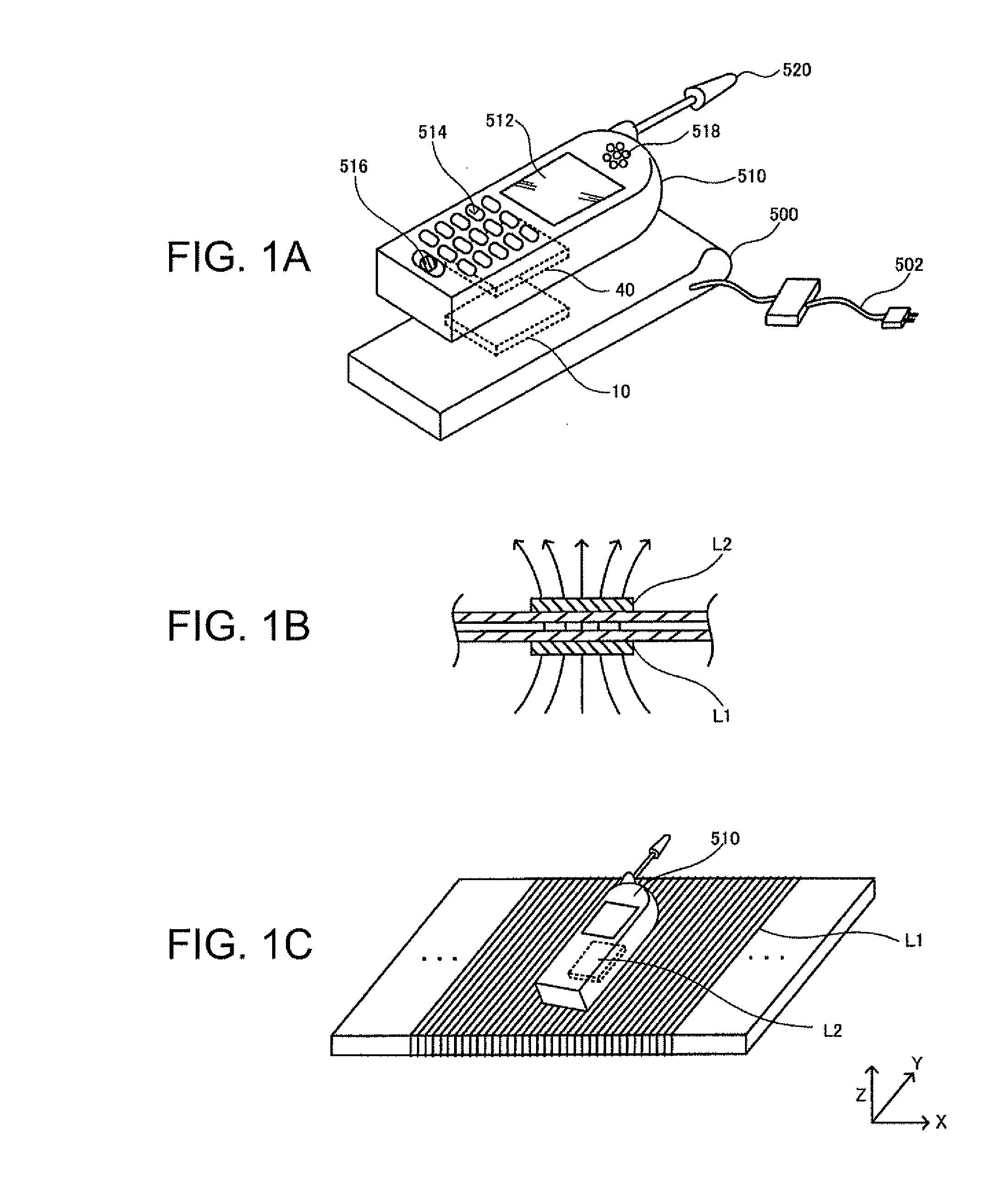

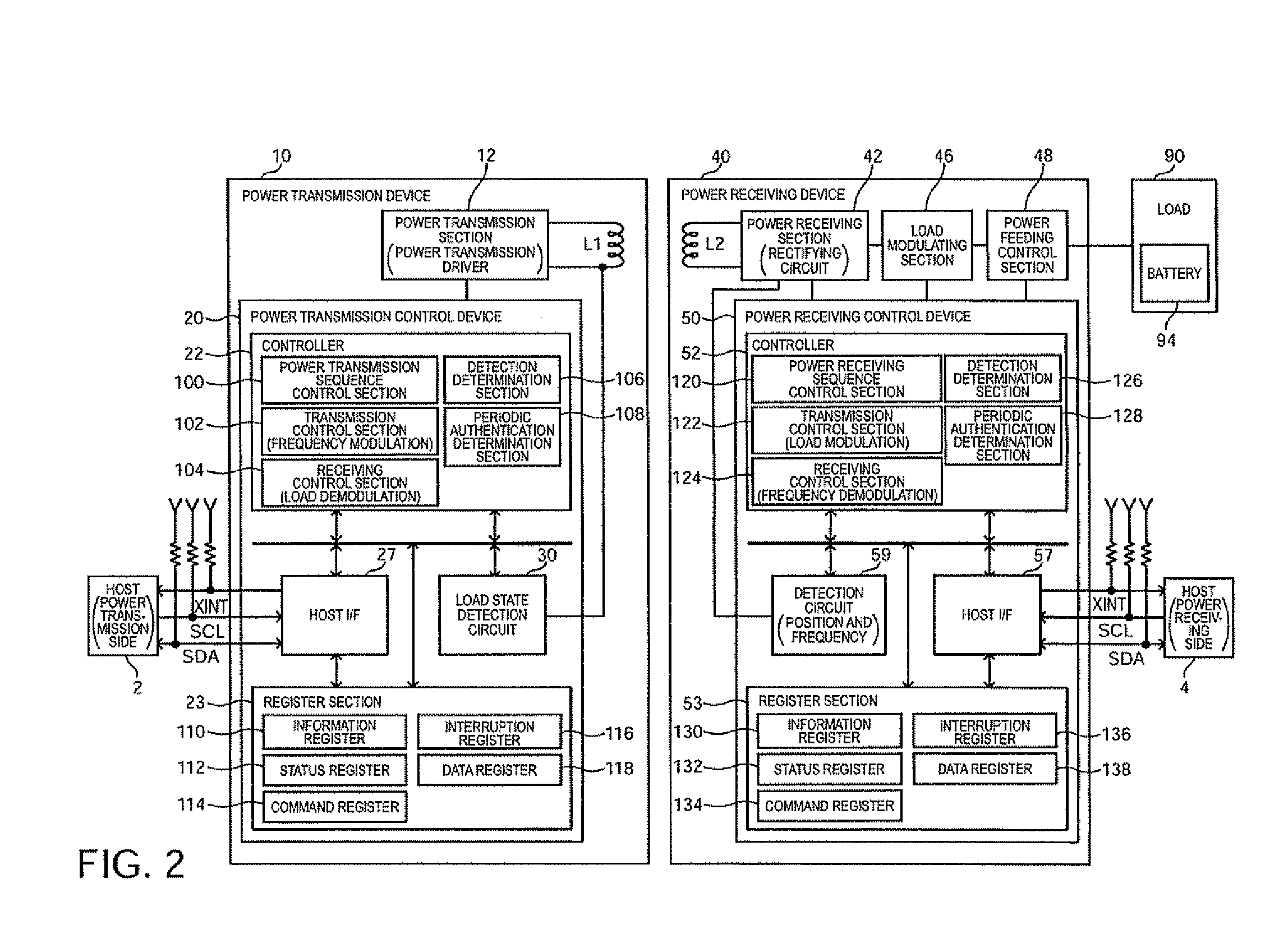

Power transmission control device, power transmission device, power receiving control device, power receiving device, and electronic apparatus

ActiveUS20100013319A1Efficient use ofReduce electricity loadVariable inductances/transformersSubstation equipmentElectricityElectric power transmission

There is provided a power transmission control device included in a power transmission device in a contactless power transmission system that transmits power from the power transmission device to a power receiving device by electromagnetically coupling a primary coil to a secondary coil to supply the power to a load of the power receiving device. The power transmission control device includes a controller controlling the power transmission control device, a host interface communicating with a power transmission-side host, and a register section accessible from the power transmission-side host via the host interface. The controller shifts into a communication mode that executes communication between the power transmission-side host and a power receiving-side host, when the power transmission-side host writes, via the host interface, a communication request command that requests the communication between the hosts in the register section. Then, the controller transmits the communication request command to the power receiving device.

Owner:138 EAST LCD ADVANCEMENTS LTD

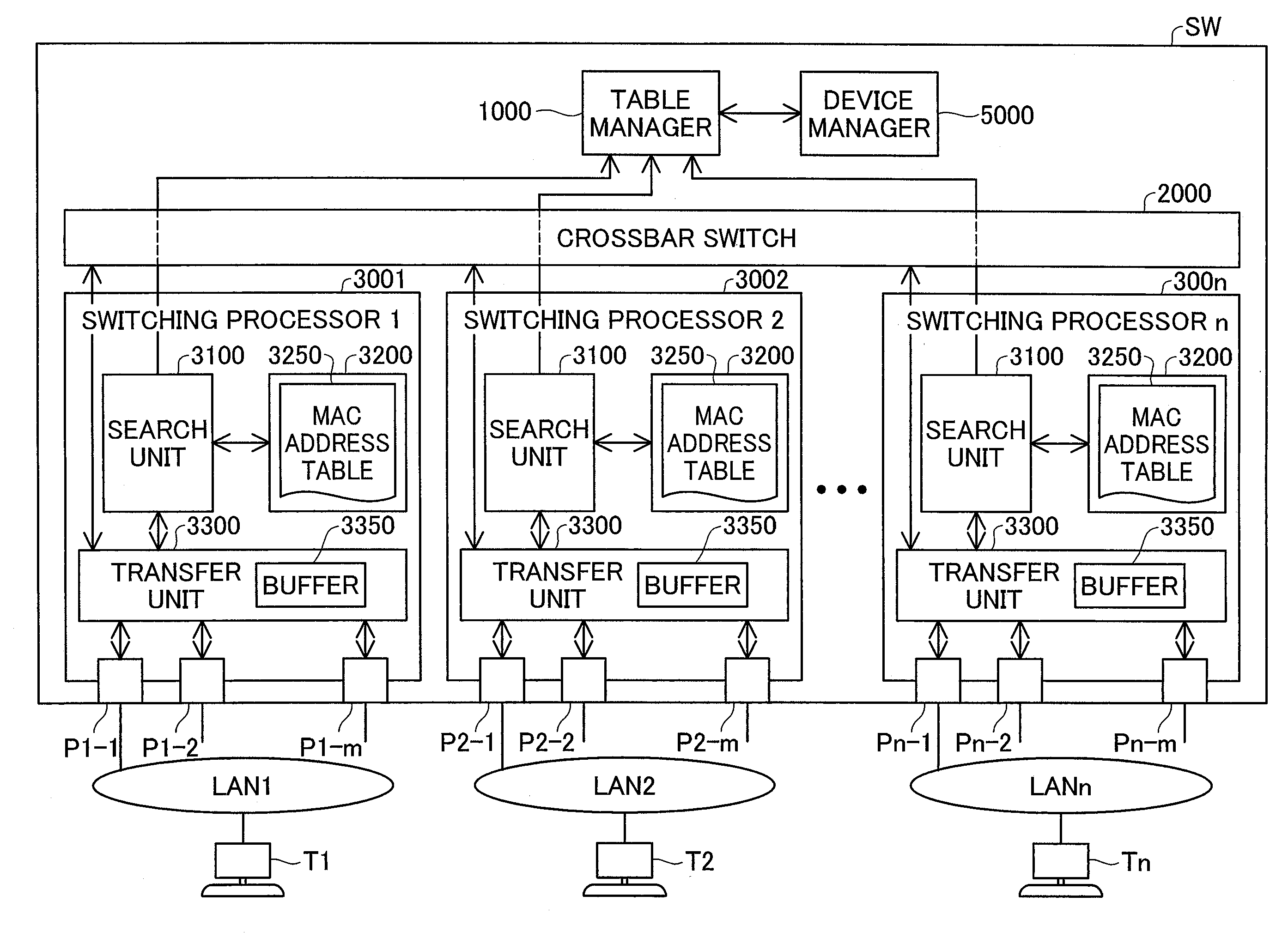

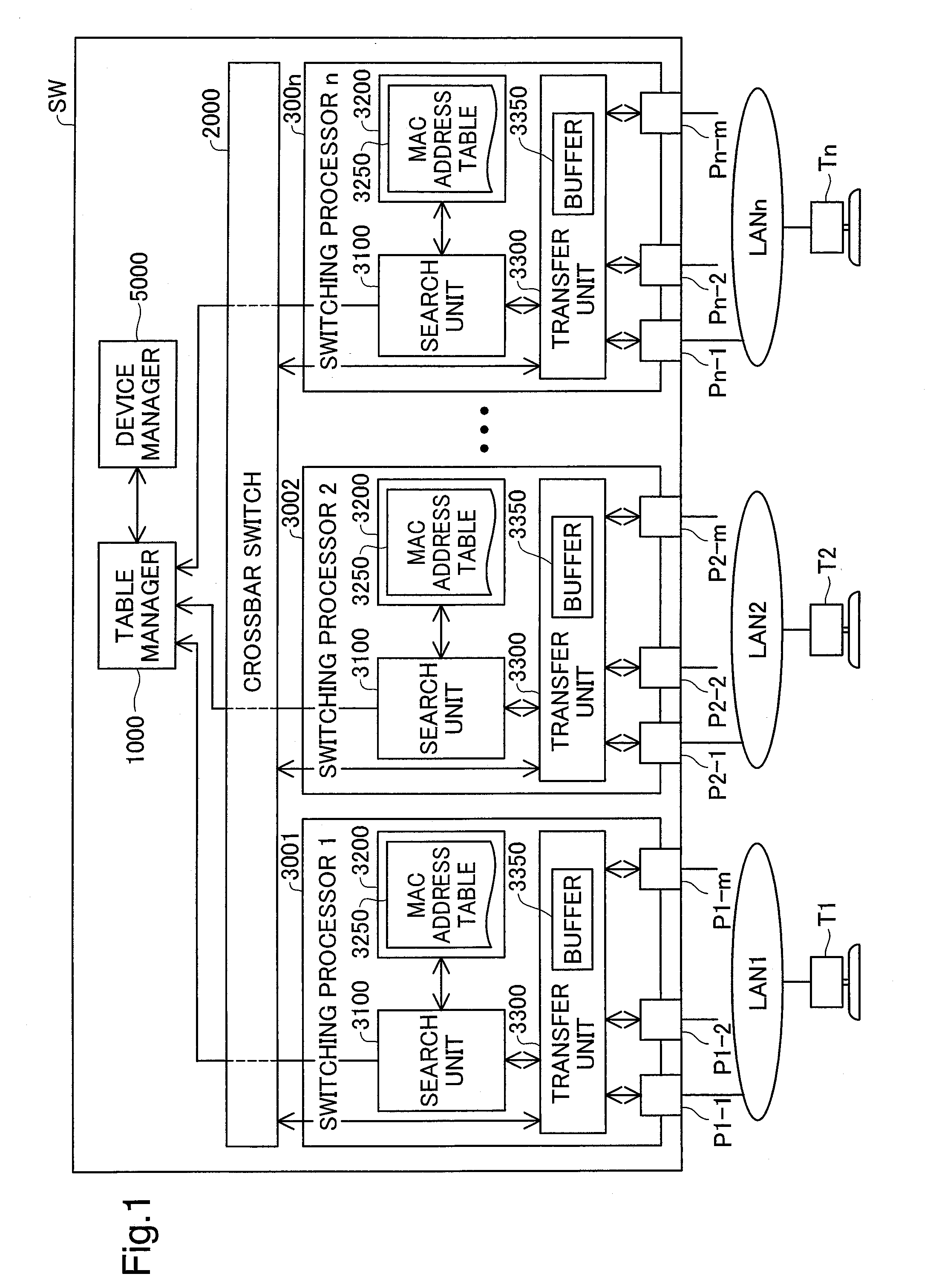

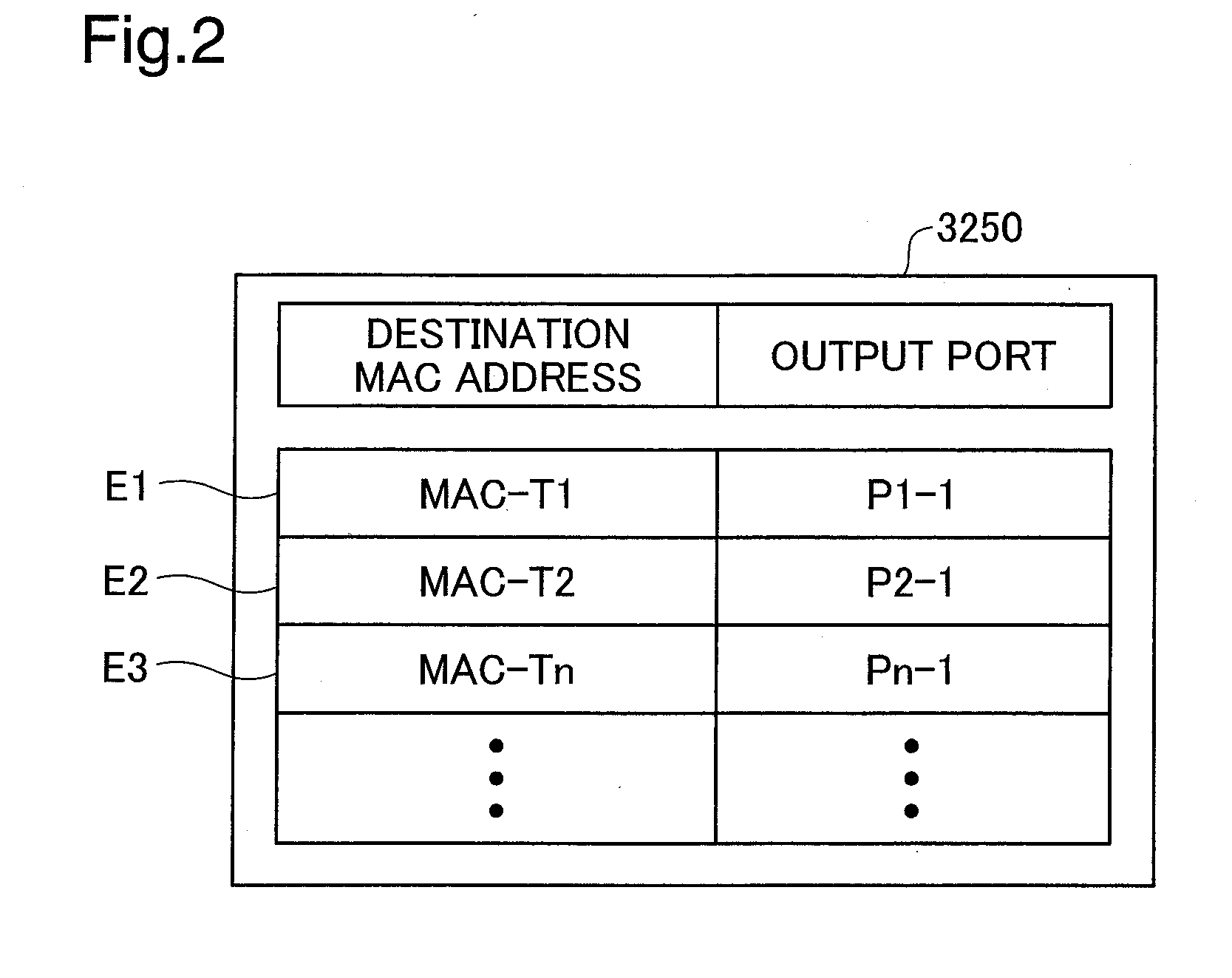

Network switching device and control method of network switching device

InactiveUS20080052487A1Effectively be standardizedReduce processing loadMemory adressing/allocation/relocationData switching by path configurationNetwork switchComputer engineering

A network switching device includes multiple ports, multiple switching processors, and a table manager. The switching processors respectively have an address table, a output port specification module, an update requirement determination module, and a table update module. The output port specification module refers to a destination address in received data and the address table and specifies a output port for sending the data among the multiple ports. The update requirement determination module determines requirement for update of the address table with regard to a source address in the data. The table manager has an update detail acquisition module and an update request module. Upon determination of the requirement for update of the address table, the update detail acquisition module obtains an update detail of the address table from one of the switching processors. The update request module sends an update request to the switching processors, based on the update detail.

Owner:ALAXALA NETWORKS

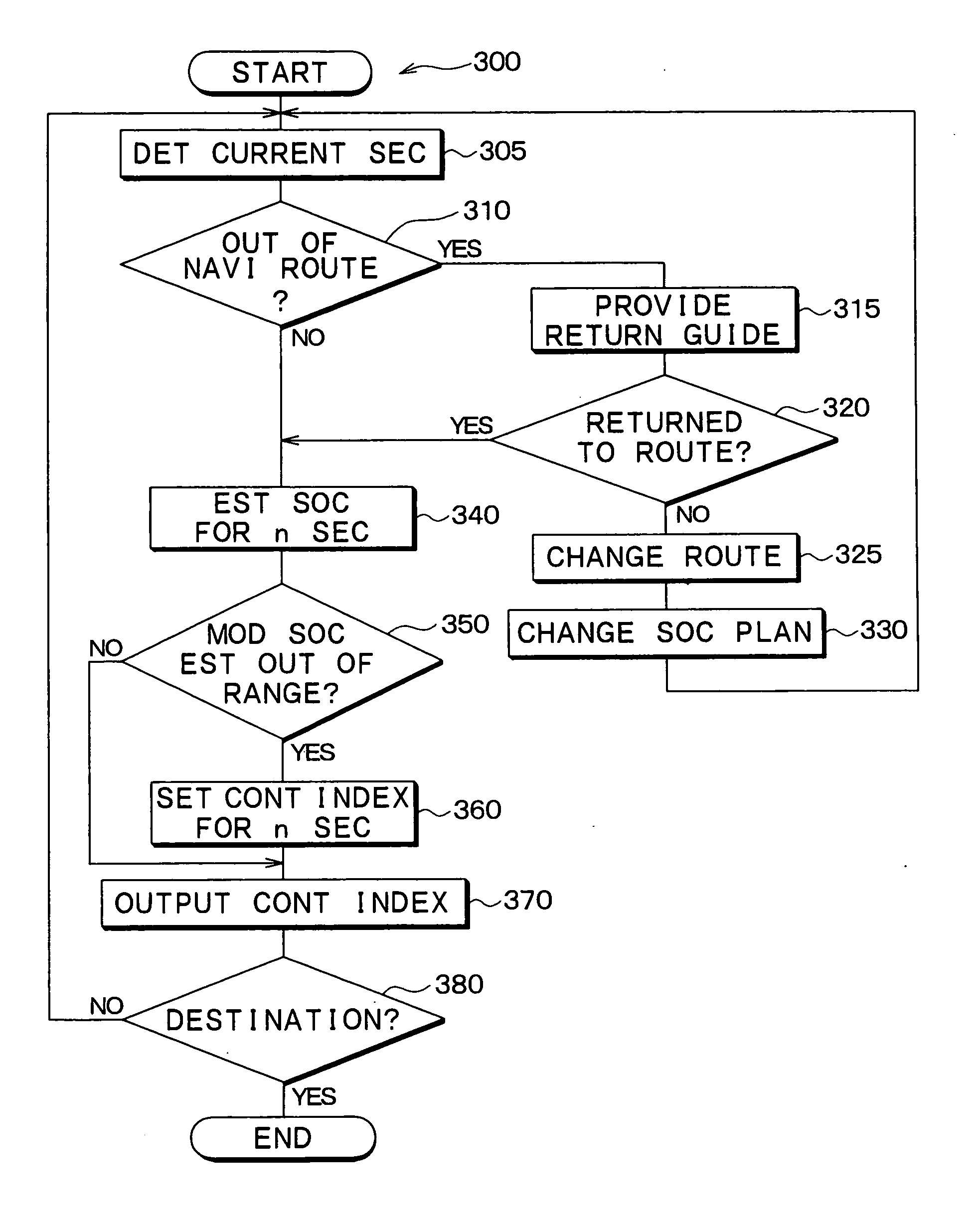

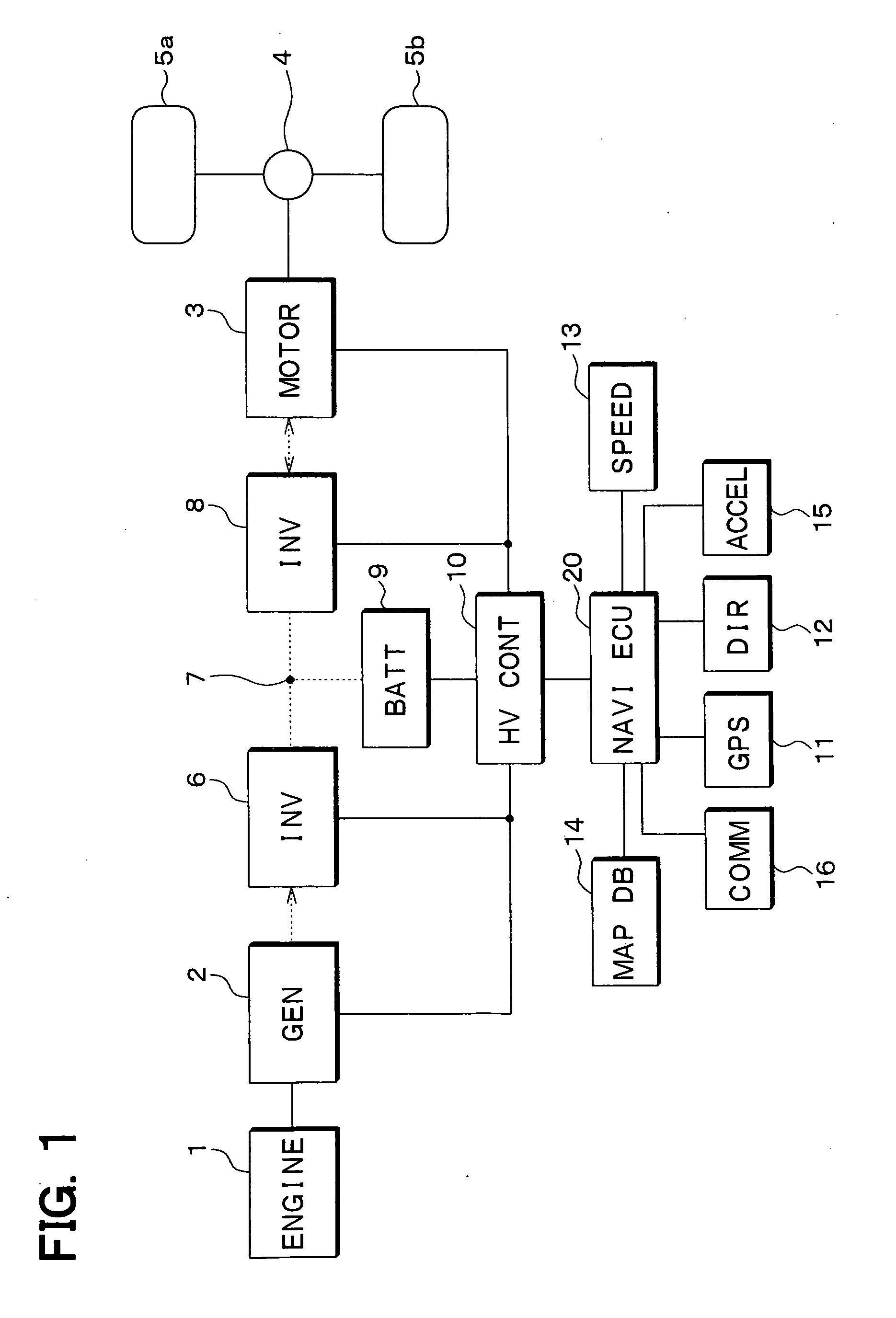

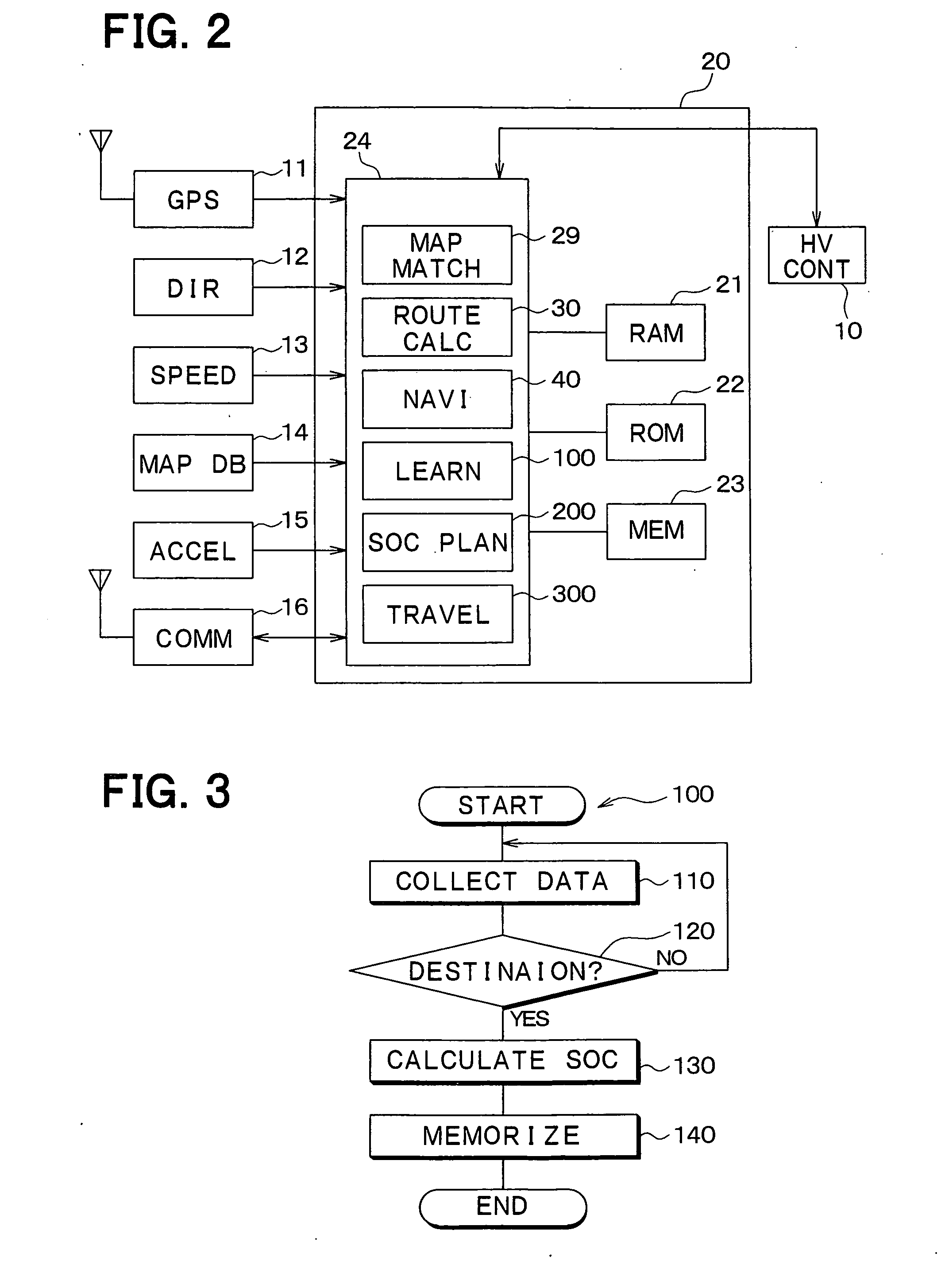

Charge planning apparatus

InactiveUS20100131139A1Reduce loadReduce changesLevel controlDigital data processing detailsProgram planningState of charge

A charge planning apparatus that formulates a control plan for controlling both of a motor and a generator in a hybrid vehicle performs a control plan re-formulation by changing a control index that provides a basis for state of charge (SOC) estimation, when a modification of the control plan based on a current SOC during the travel of the hybrid vehicle results in an excessive charging or discharging portion in a transition of the modified SOC estimation.

Owner:DENSO CORP

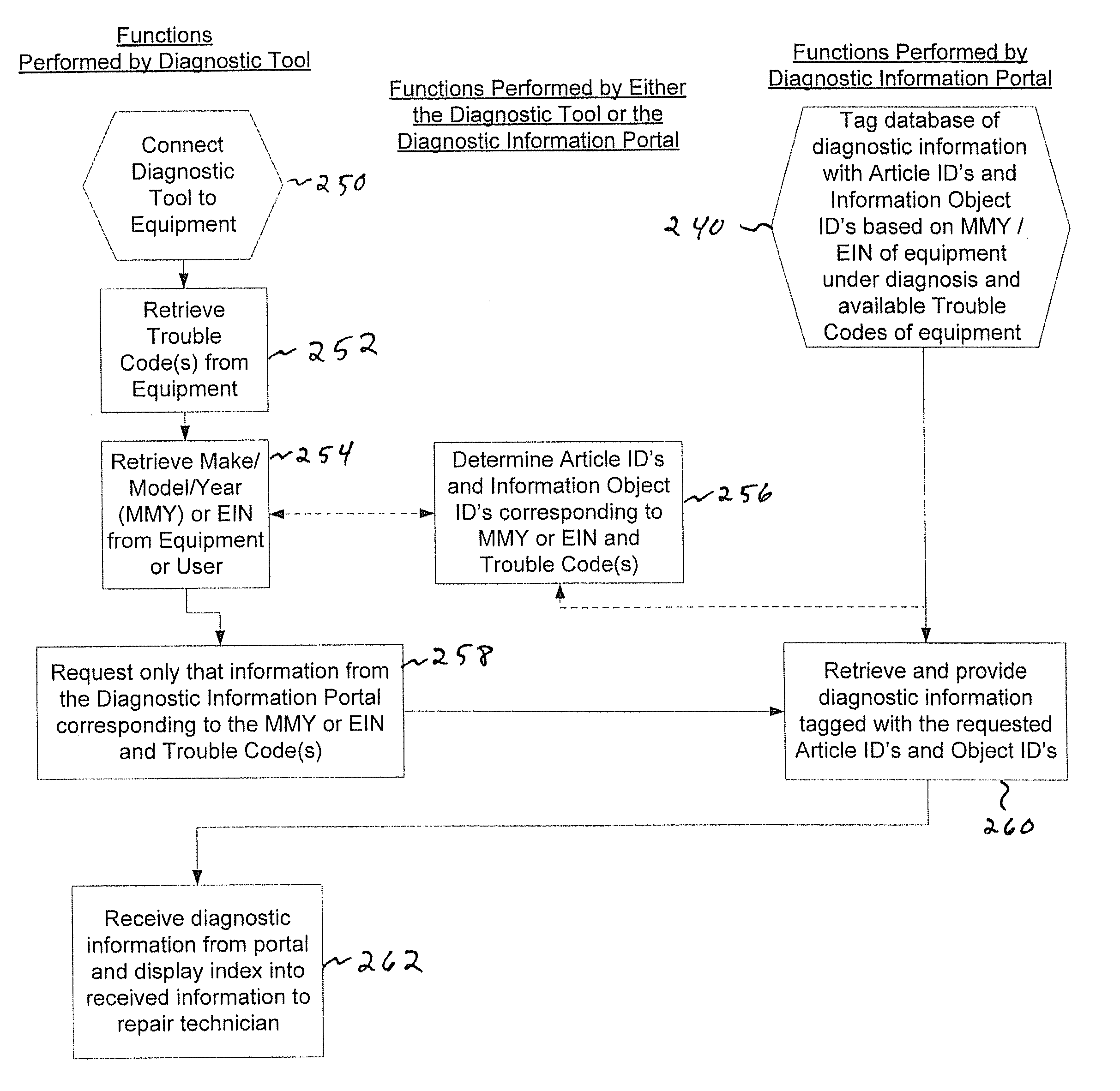

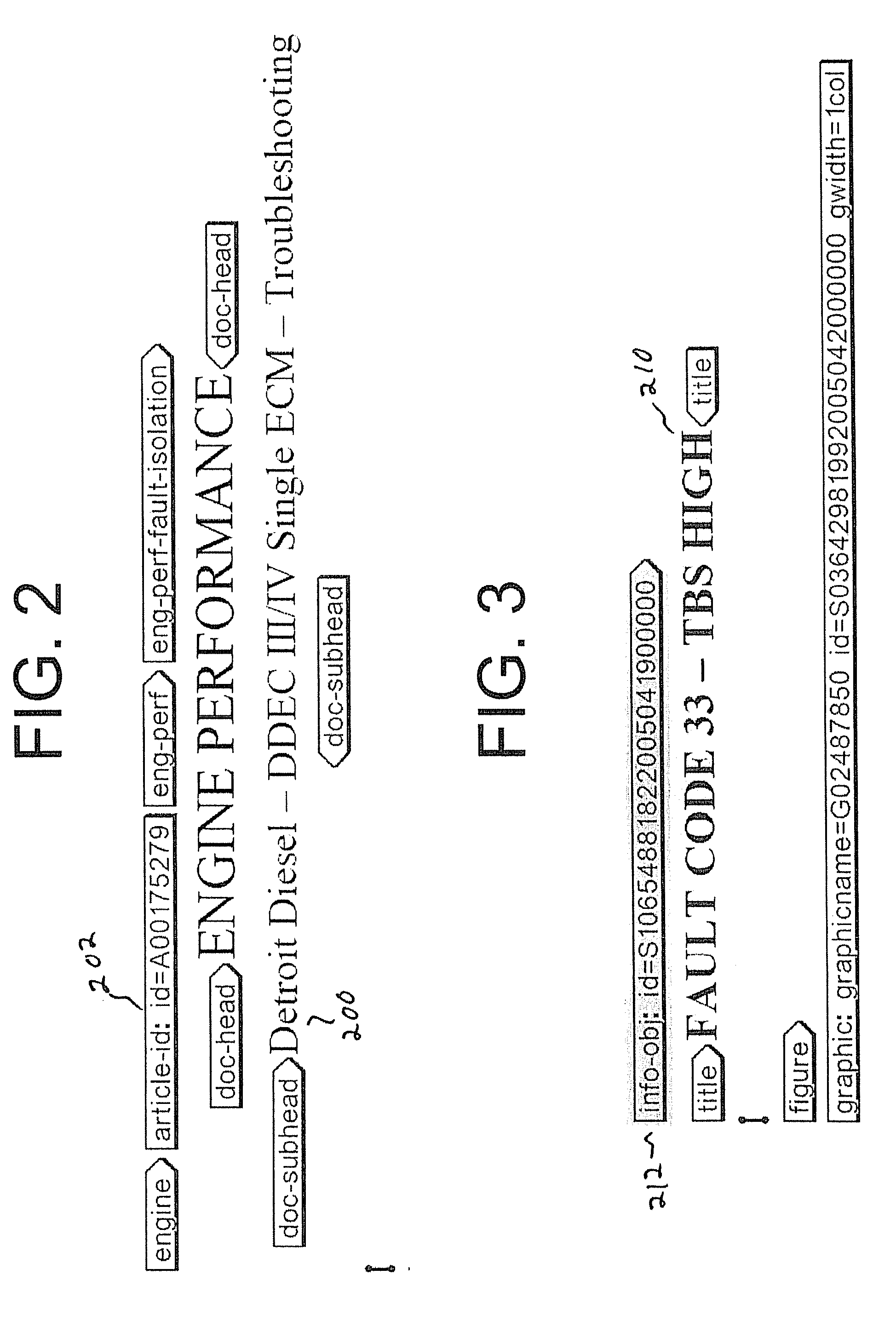

Method and System for Retrieving Diagnostic Information

ActiveUS20100138701A1Rapid diagnosisFast repairVehicle testingRegistering/indicating working of vehiclesDiagnostic informationComputer science

A system, method, and apparatus for retrieving trouble codes from an equipment under diagnosis and retrieving only relevant diagnostic information relative to the returned codes from one or more remote diagnostic libraries. An electronic diagnostic library contains diagnostic vehicle information tagged with trouble code identification ID's at a first location, and a diagnostic tool at a second location requests only relevant diagnostic information from the electronic library that is tagged with trouble code identification ID's corresponding to the retrieved trouble codes and information identifying the equipment under diagnosis. The diagnostic tool receives the specific diagnostic vehicle information at the first location and may store the specific vehicle information locally prior to displaying an index to the information to a repair technician.

Owner:MITCHELL REPAIR INFORMATION

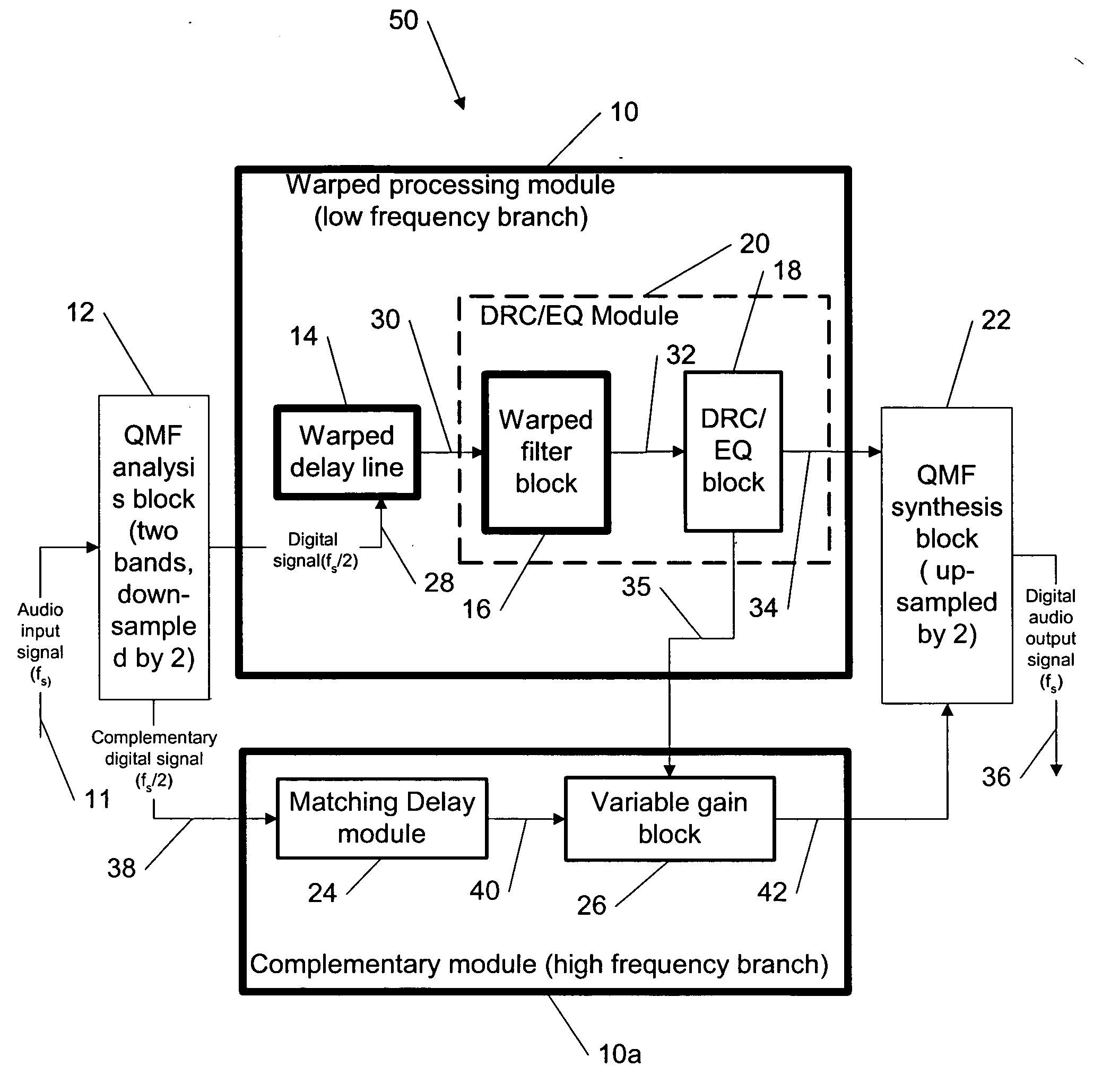

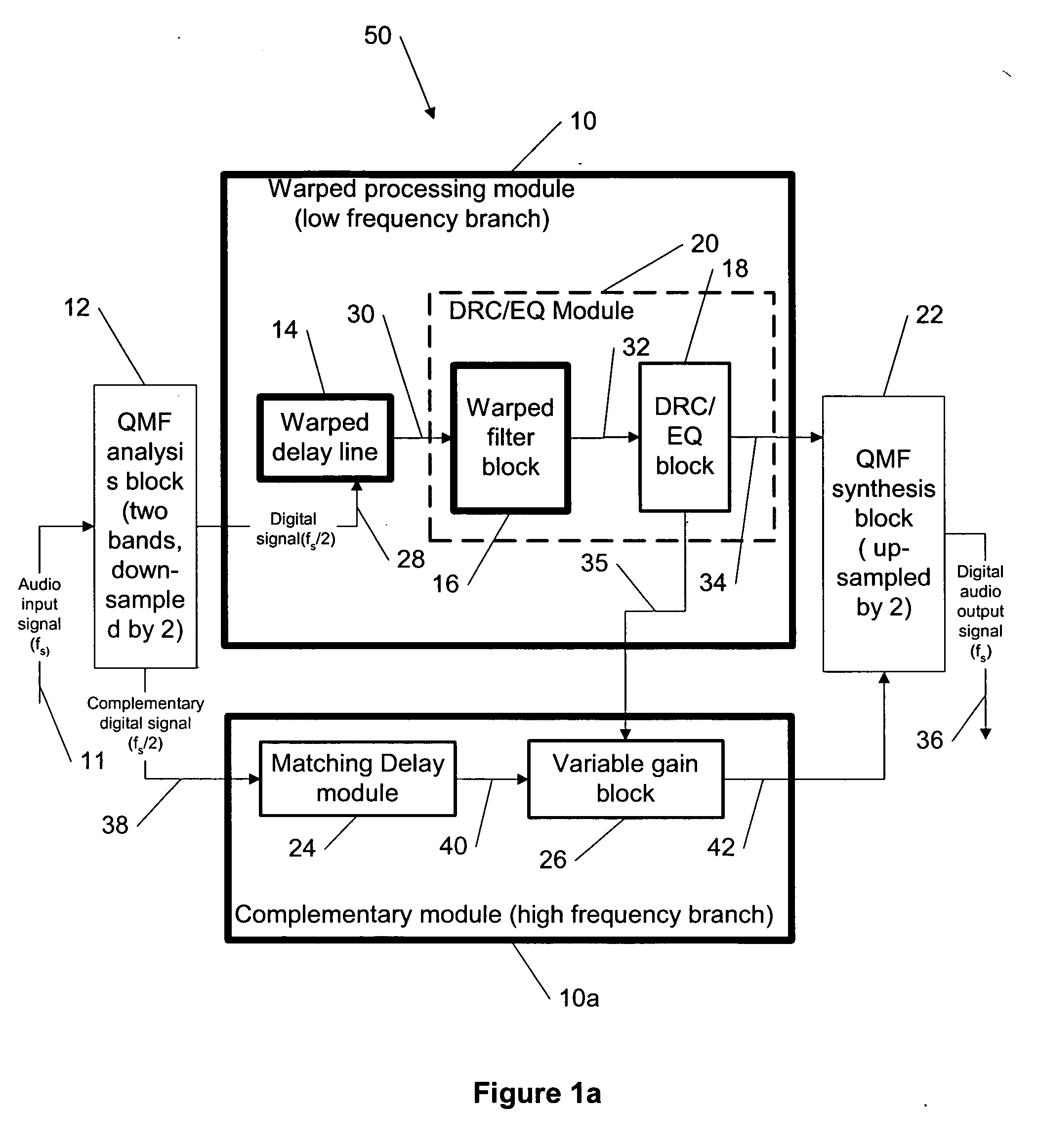

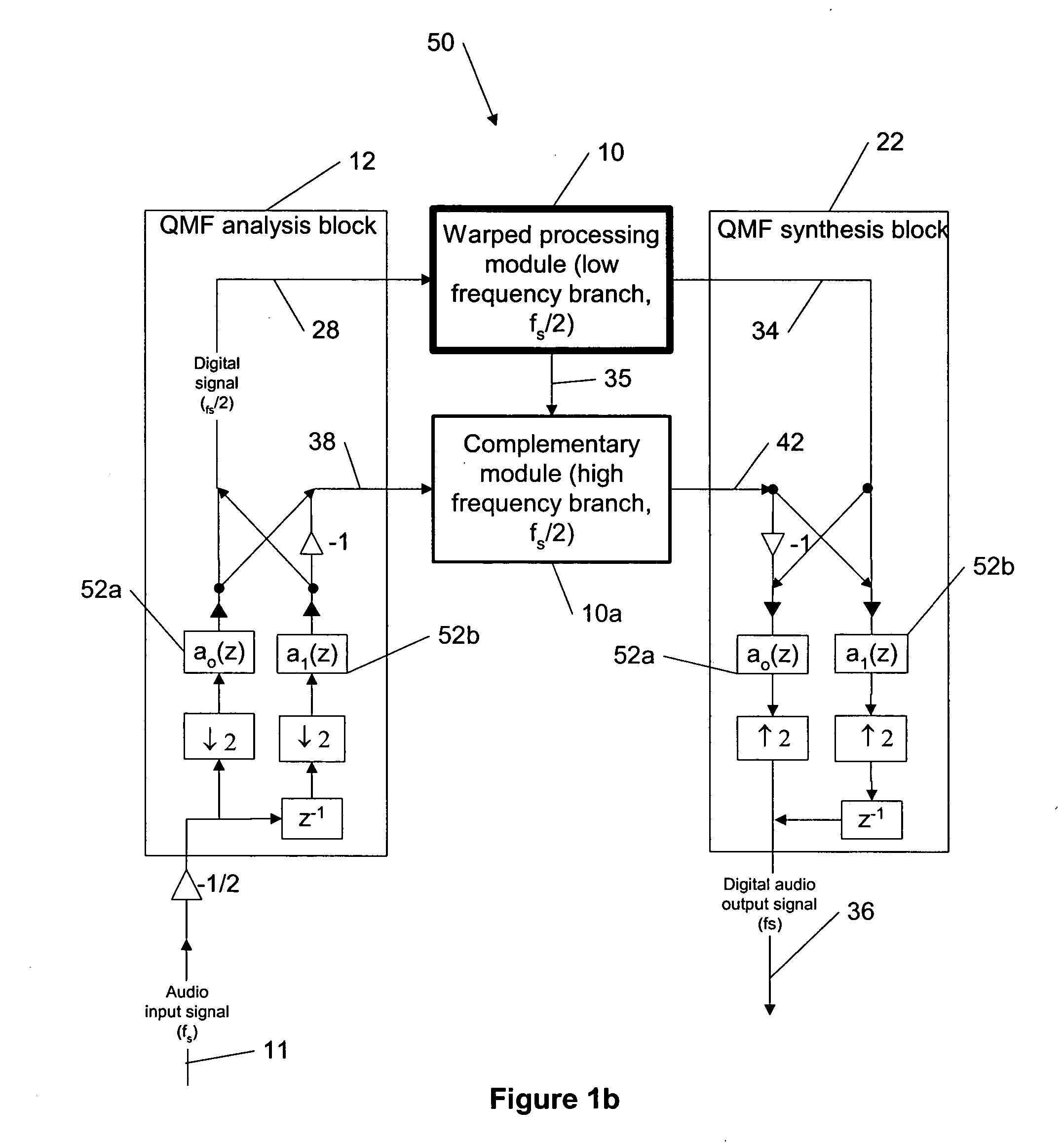

Dynamic range control and equalization of digital audio using warped processing

ActiveUS20050249272A1Reduce processing loadComputationally efficientMultiple-port networksDelay line applicationsFrequency bandLoudness

This invention describes a method for adjusting the loudness and the spectral content of digital audio signals in a real-time using warped spectral filtering. A warped processing module modifies a spectral content of a digital audio signal with a set of gains for a plurality of non-linearly-scaled frequency bands determined by a warping factor λ of a warped delay line. Warped delay line signals, generated by the warped delay line, are processed by a warped filter block containing multiple warped finite impulse response filters, e.g., Mth band filters, using individual warped spectral filtering in said plurality of the non-linearly-scaled frequency bands, which is followed by a conventional processing by a dynamic range control / equalization block. The present invention describes another innovation, that is embedding the warped processing module in a two-channel quadrature mirror filter (QMF) bank for improving processing efficiency at high sample rates.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

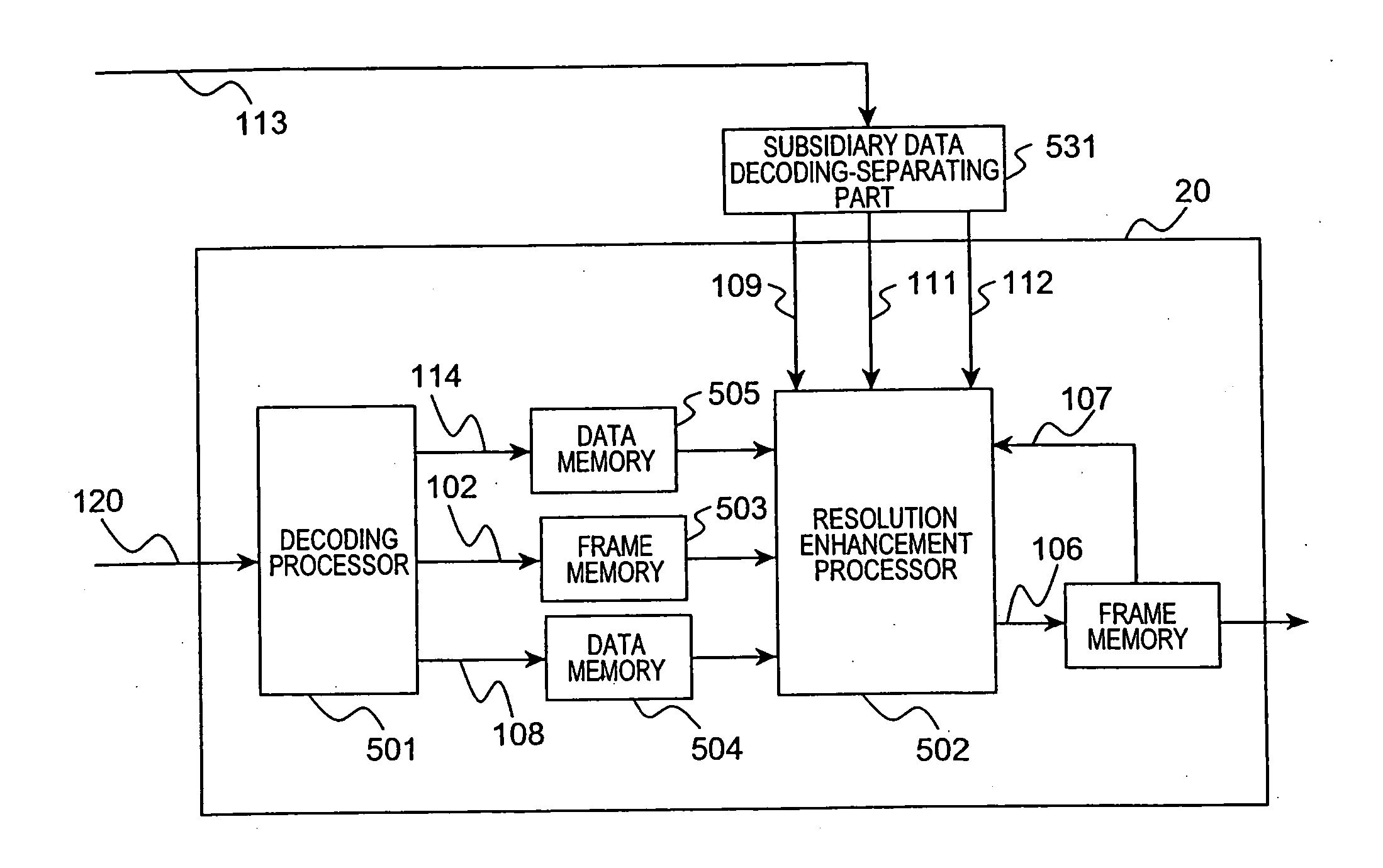

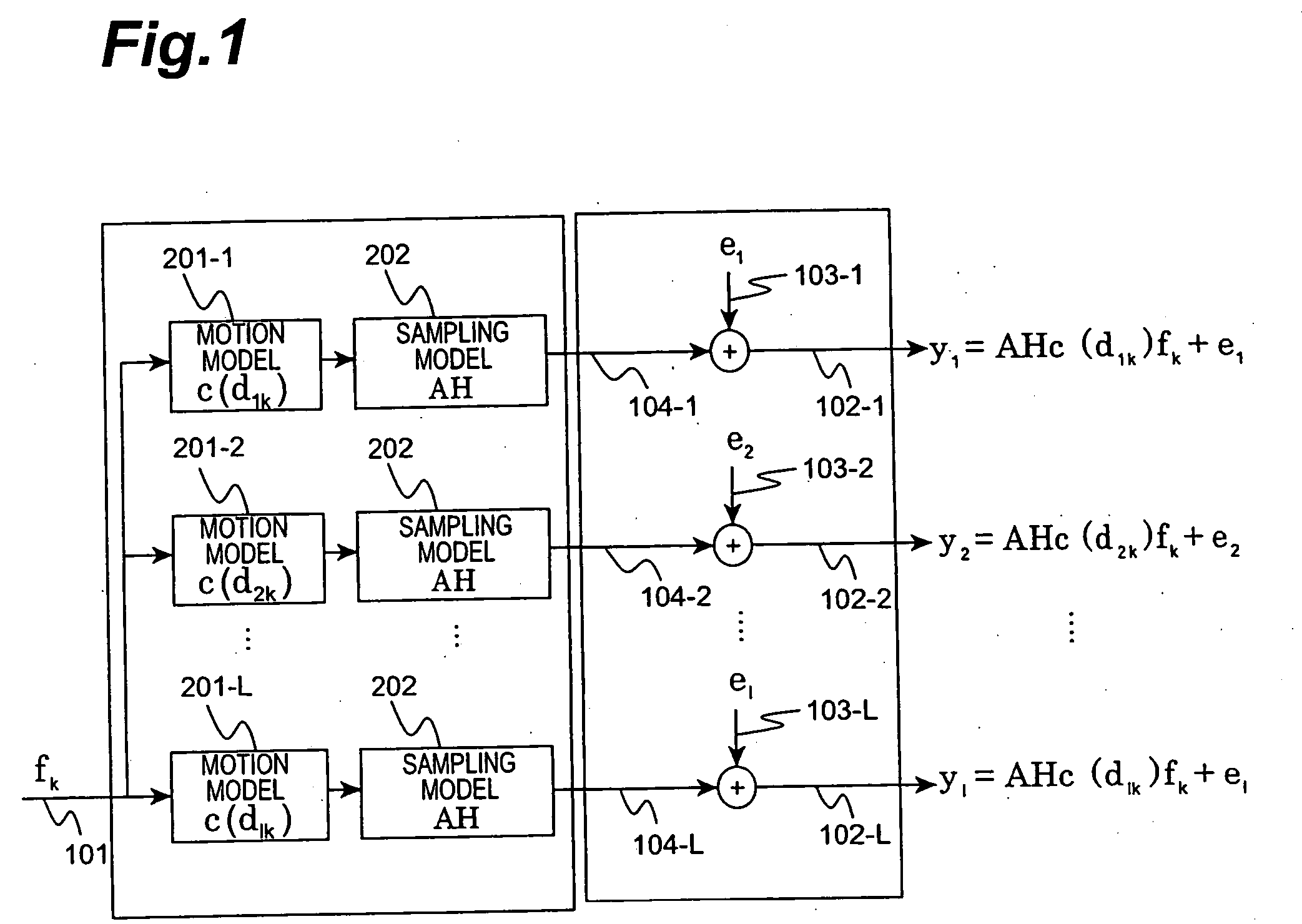

Image decoding apparatus, image decoding program, image decoding method, image encoding apparatus, image encoding program, and image encoding method

InactiveUS20060126952A1Improve accuracyComputational complexity is reducedImage enhancementImage analysisMotion vectorImage resolution

An image decoding apparatus has a video data decoder for receiving and decoding encoded video data to acquire a plurality of reconstructed images; a subsidiary data decoder for receiving and decoding subsidiary data to acquire subsidiary motion information; and a resolution enhancer for generating motion vectors representing time-space correspondences between the plurality of reconstructed images, based on the subsidiary motion information acquired by the subsidiary data decoder, and for generating a high-resolution image with a spatial resolution higher than that of the plurality of reconstructed images, using the generated motion vectors and the plurality of reconstructed images acquired by the video data decoder.

Owner:NTT DOCOMO INC

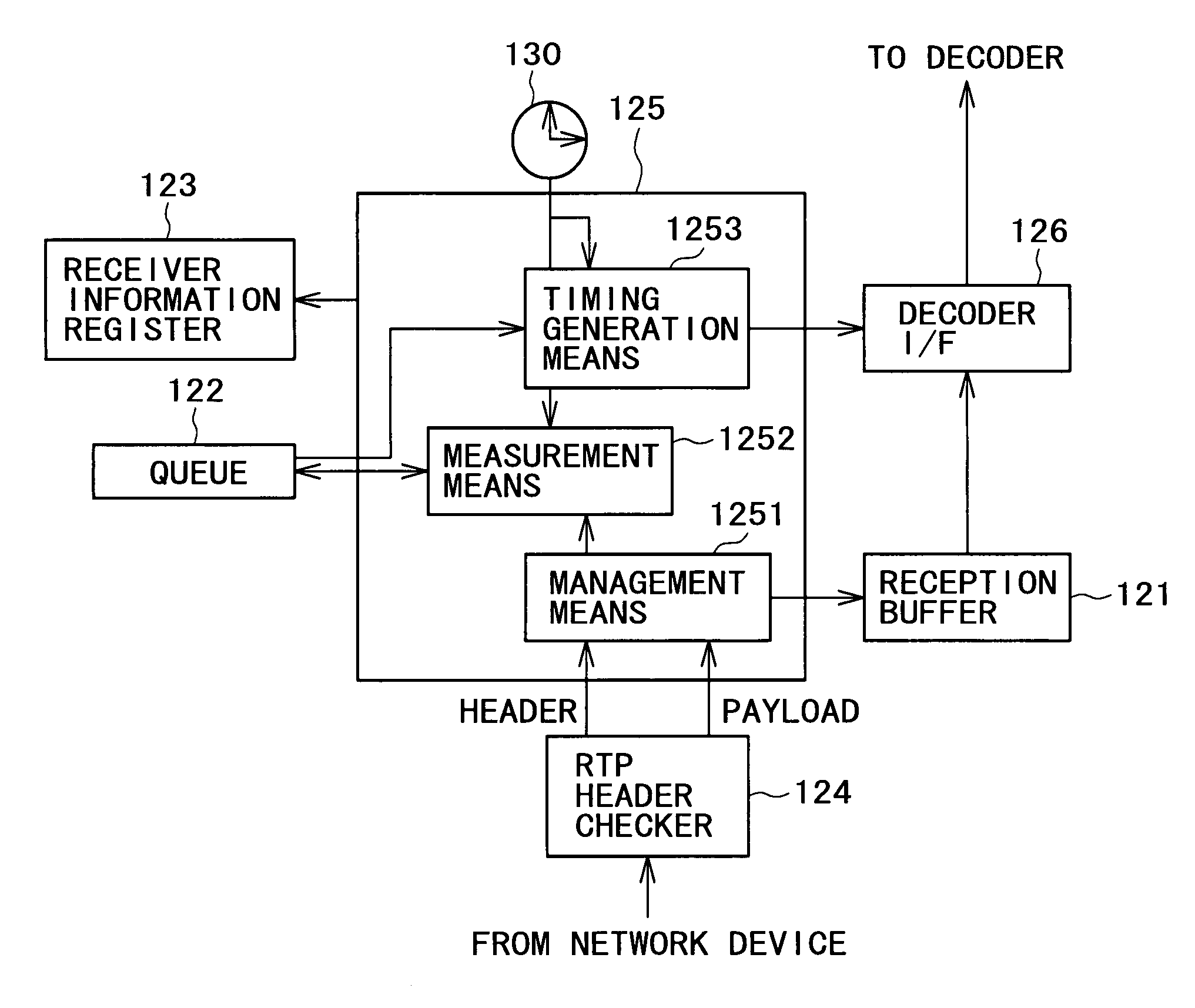

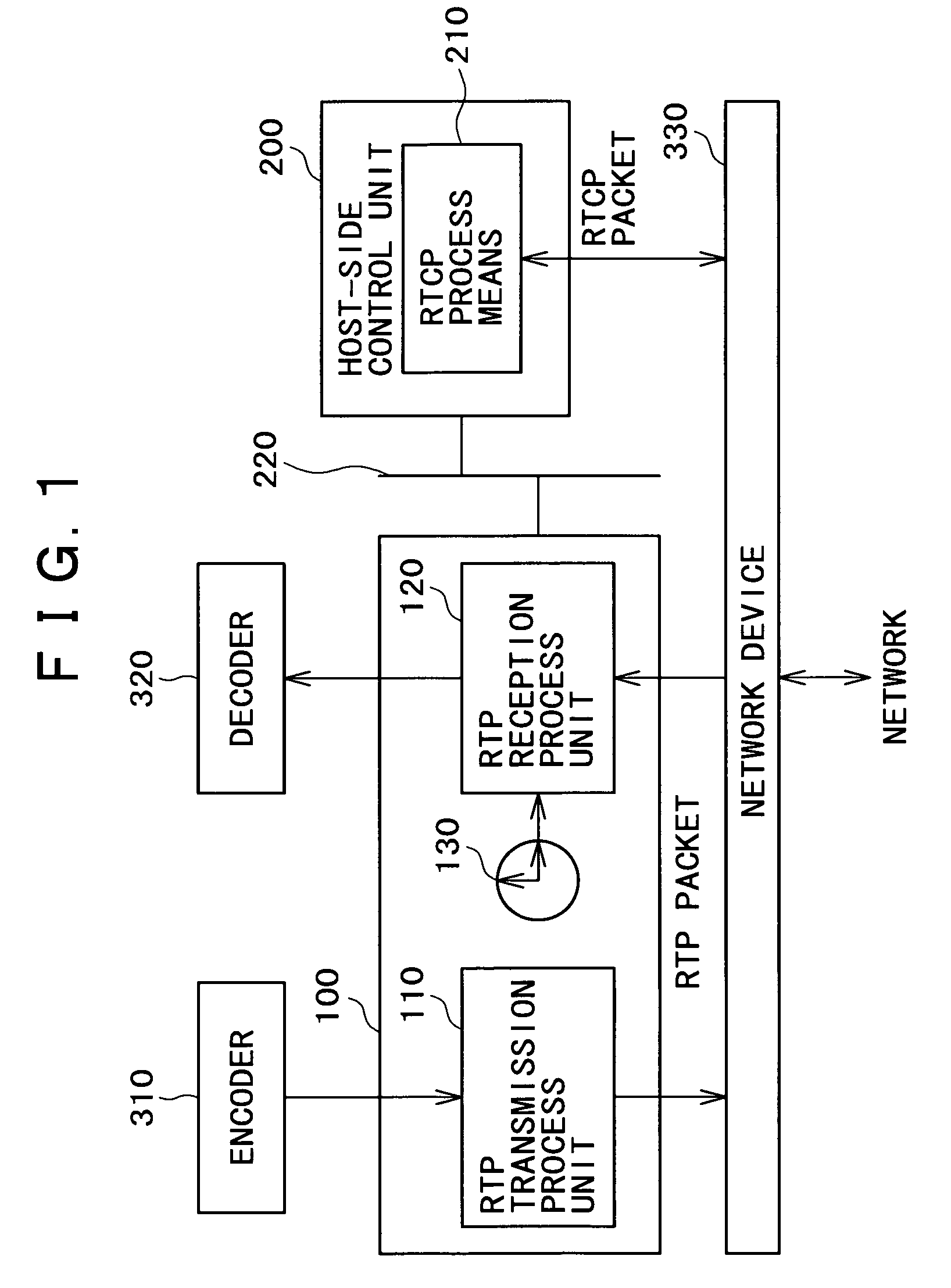

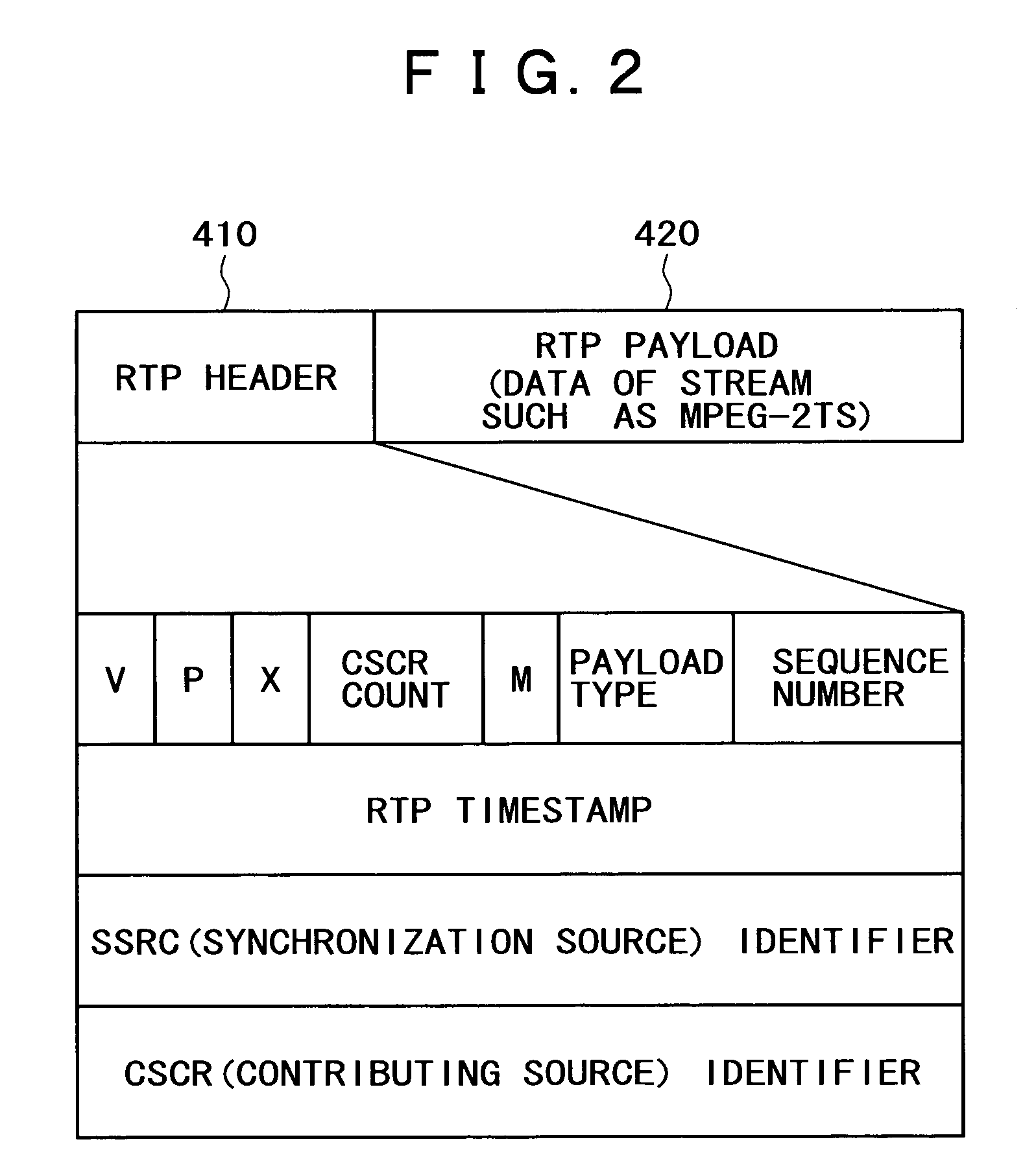

Communication apparatus, transmission apparatus and reception apparatus

InactiveUS7447164B2High streaming qualityReduce circuit sizeError preventionFrequency-division multiplex detailsMPEG transport streamControl unit

Upon reception of a transport stream of information data from an encoder, an RTP transmission process unit employed in an RTP process circuit is activated to packetize the transport stream in an RTP packet. A network device then outputs the resulting RTP packet to a network. At that time, sender information for the transmission is created and stored. On the other hand, an RTP reception process unit employed in the RTP process circuit depacketizes an RTP packet received from the network through the network device to obtain a transport stream and supplies the transport stream to a decoder. At that time, receiver information for the reception is created and stored. An RTCP process means employed in a control unit on the host side acquires the sender information and the receiver information through an internal bus and uses them to create an RTCP packet to be output to the network by way of the network device. As a result, the streaming quality can be assured independently of the state of the control unit on the host side.

Owner:SONY CORP

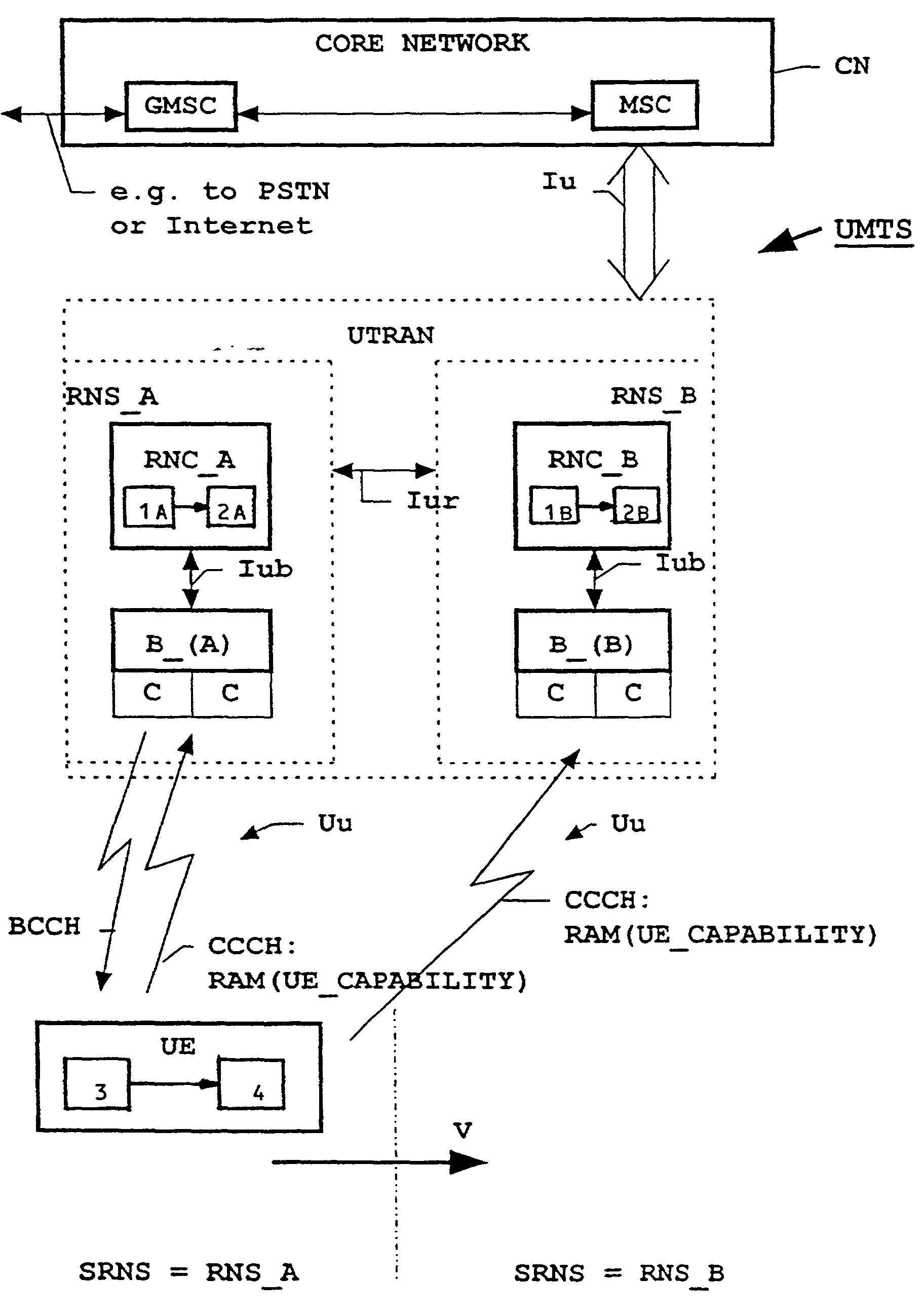

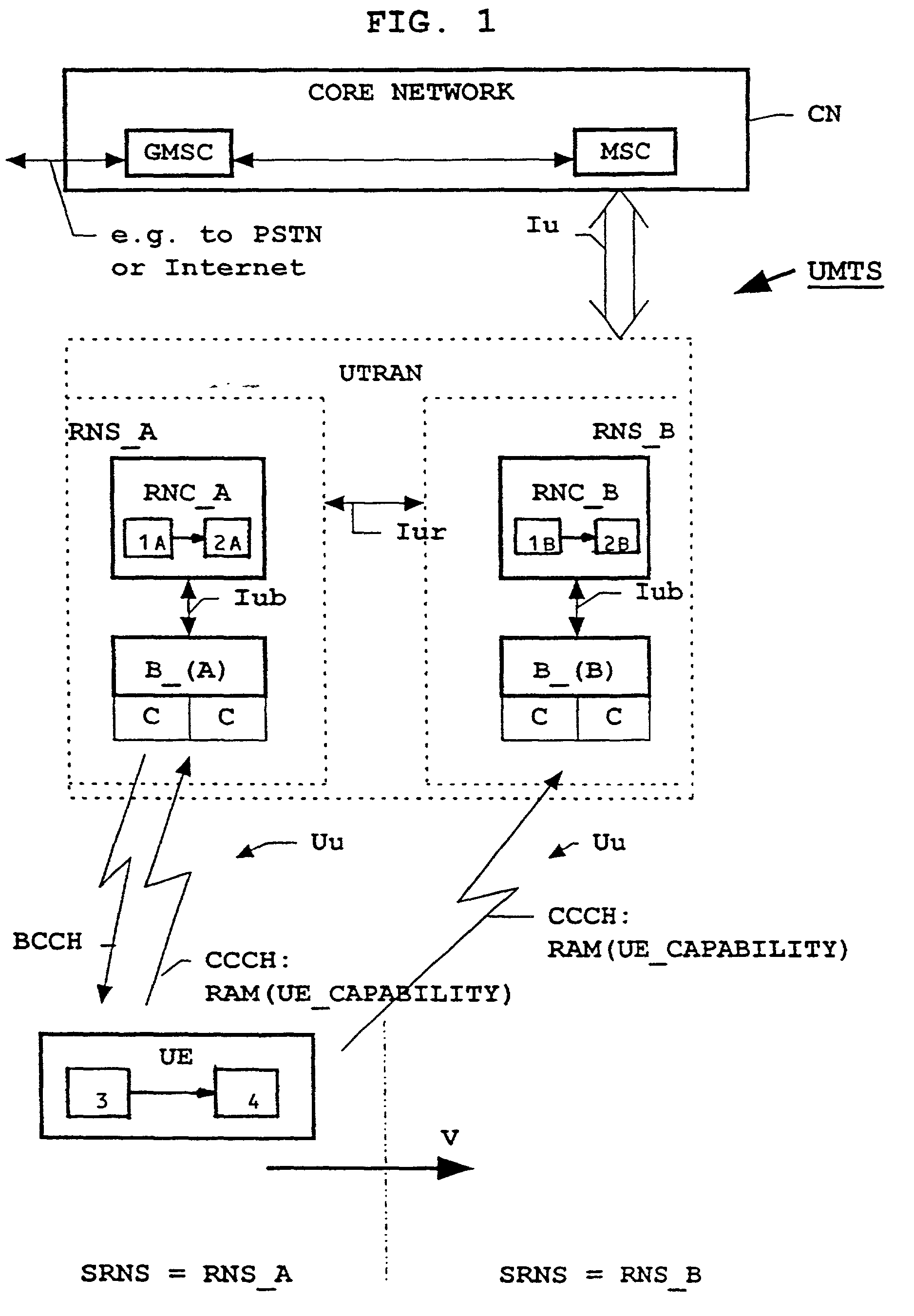

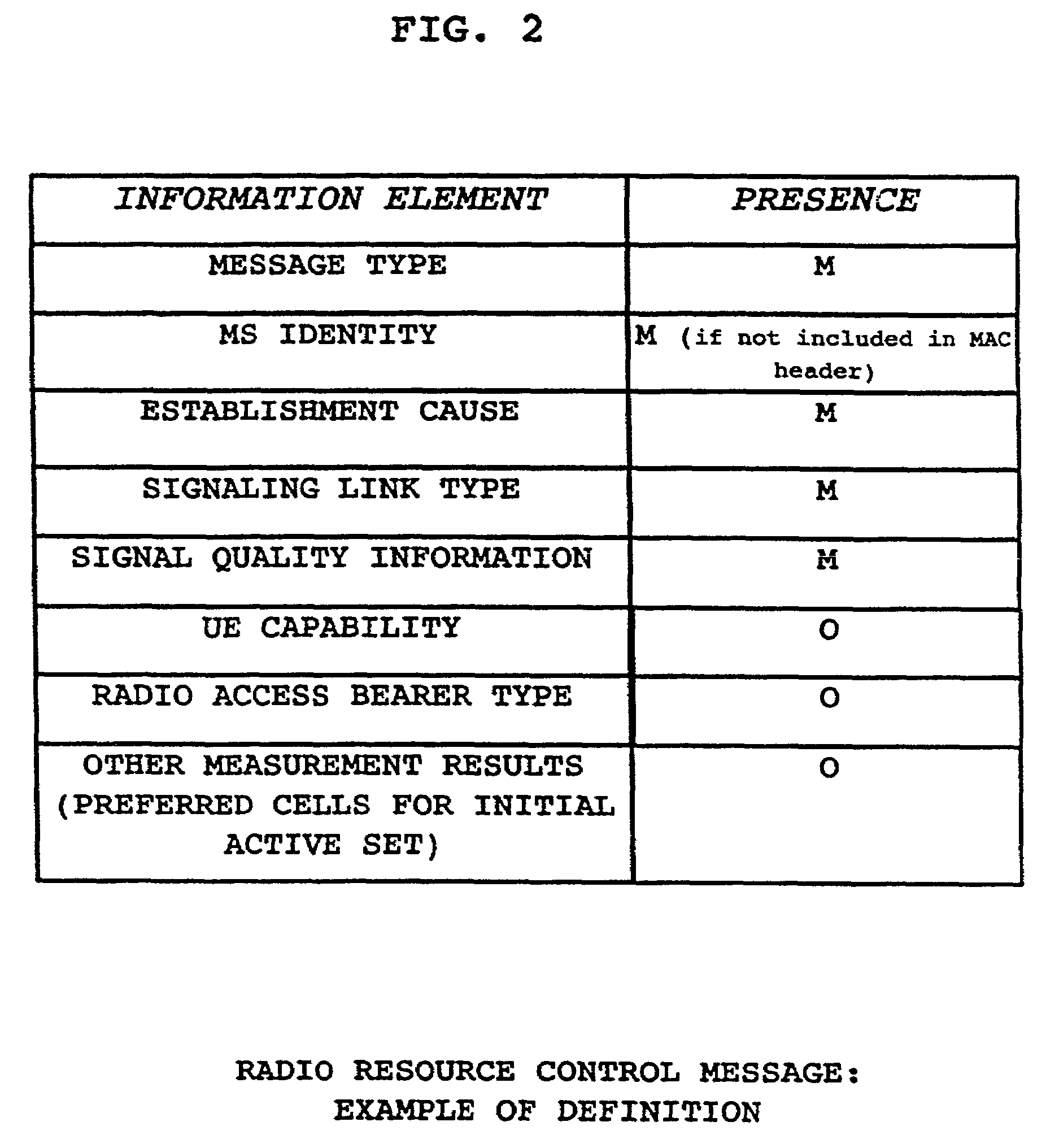

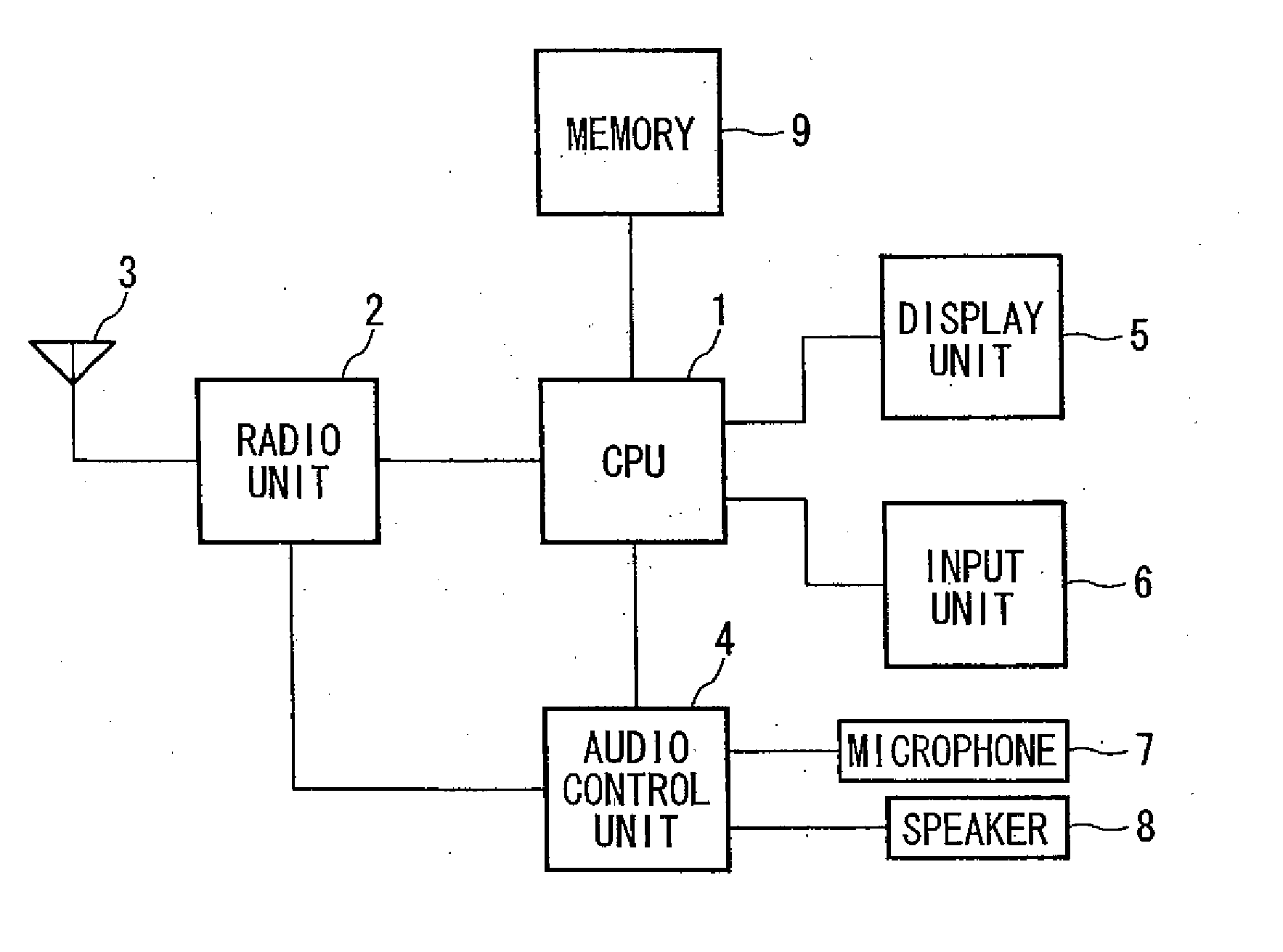

Method for establishing a communication link between a user equipment and a radio network

InactiveUS7433334B2Improve random access performanceFunction increaseTime-division multiplexRadio/inductive link selection arrangementsTelecommunications linkRadio networks

A method for improving the performance of random access when establishing a communication link between a user equipment (UE) and a radio network (UTRAN) the method includes transmitting a random access message (RAM) from the user equipment (UE) to the radio network (UTRAN), wherein the radio random access message (RAM) contains information describing a functional capability (UB_CAPABILITY) of the user equipment (UE). Thereby, the network knows the capabilities of the terminal as early as possible and can thus optimize all functions performed by the network to be in conformity with the terminal capabilities.

Owner:WSOU INVESTMENTS LLC

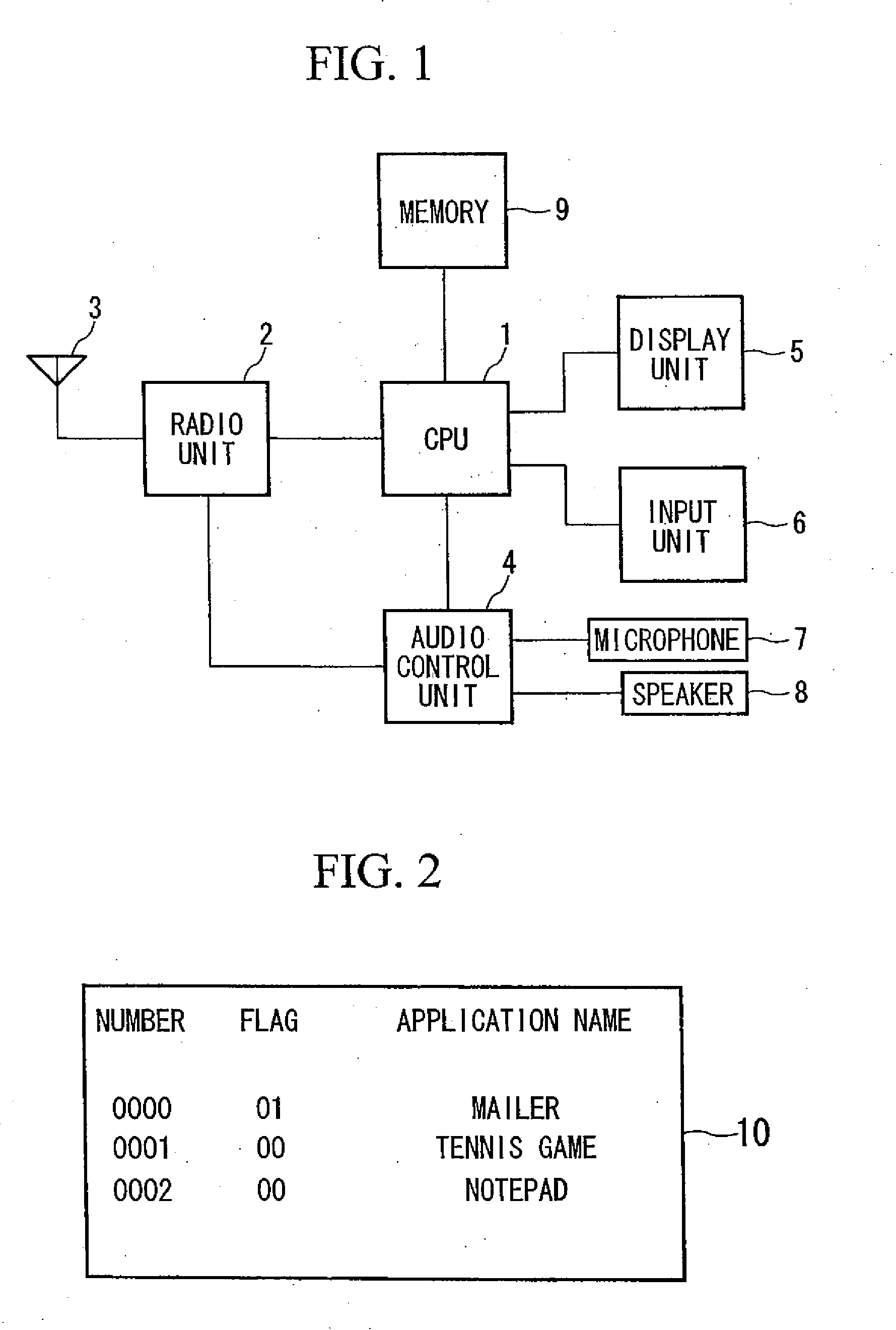

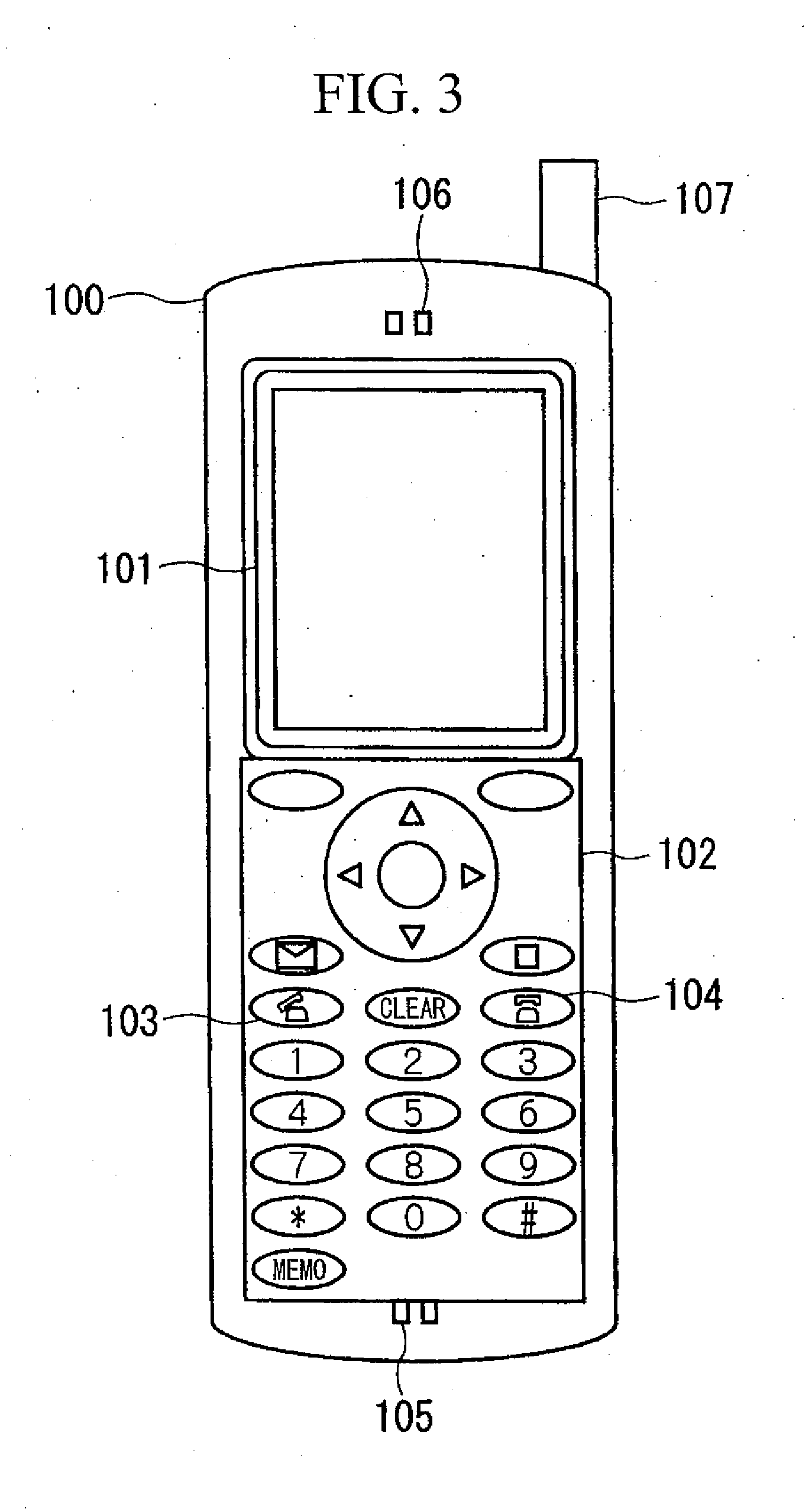

Mobile Terminal, Method for Controlling Mobile Telephone Terminal, and Mobile Telephone Terminal

InactiveUS20070225022A1Reduce processing loadIncrease speedStampsDollsTelephone terminalMultiple applications

Owner:KYOCERA CORP

Mechanism for establishing reputation in a network environment

ActiveUS8887238B2Reduce loadReduce processing loadDigital data processing detailsData switching by path configurationTraffic capacityNetwork address translation

Traffic is obtained from a plurality of internet protocol version six addresses within a plurality of internet protocol version six blocks; and a first indication of inappropriate traffic is obtained from a first one of the addresses. Responsive thereto, a reputation score for a first given one of the blocks, containing the first one of the internet protocol version six addresses, is incremented by a first predetermined amount; and a reputation score for an adjacent block is incremented by a second predetermined amount which is less than the first predetermined amount. Traffic from the plurality of internet protocol version six addresses within the plurality of internet protocol version six blocks is passed or blocked in accordance with a policy based on the incremented reputation scores for the first block and adjacent block. Techniques for internet protocol version four (individual and network address translation aspects) are also provided.

Owner:TIME WARNER CABLE ENTERPRISES LLC

Information access system information providing device information access device information providing mehtod and information acess method

ActiveUS20060095543A1Reduce processing loadEasy to handlePulse modulation television signal transmissionMetadata video data retrievalInformation accessInformation searching

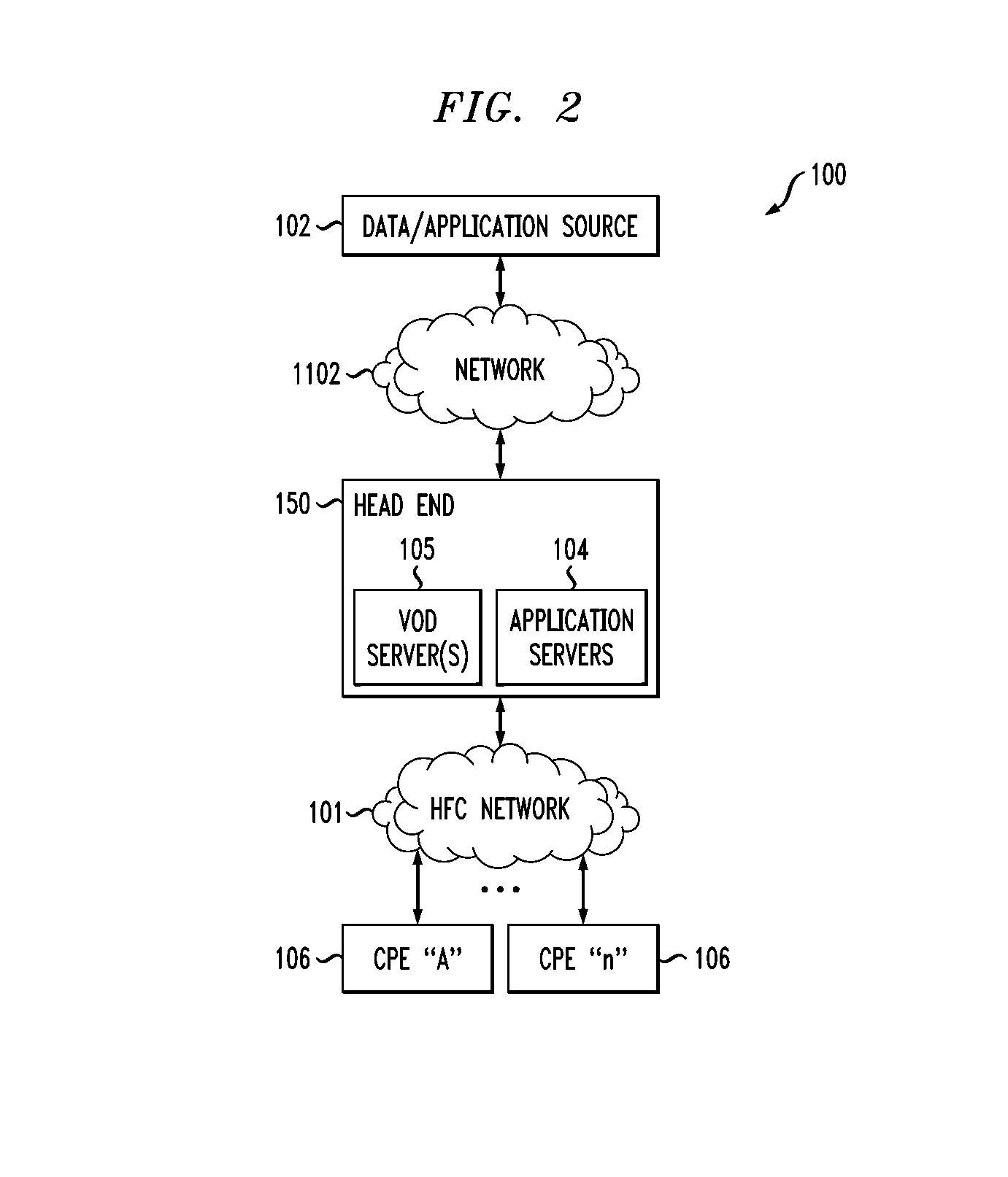

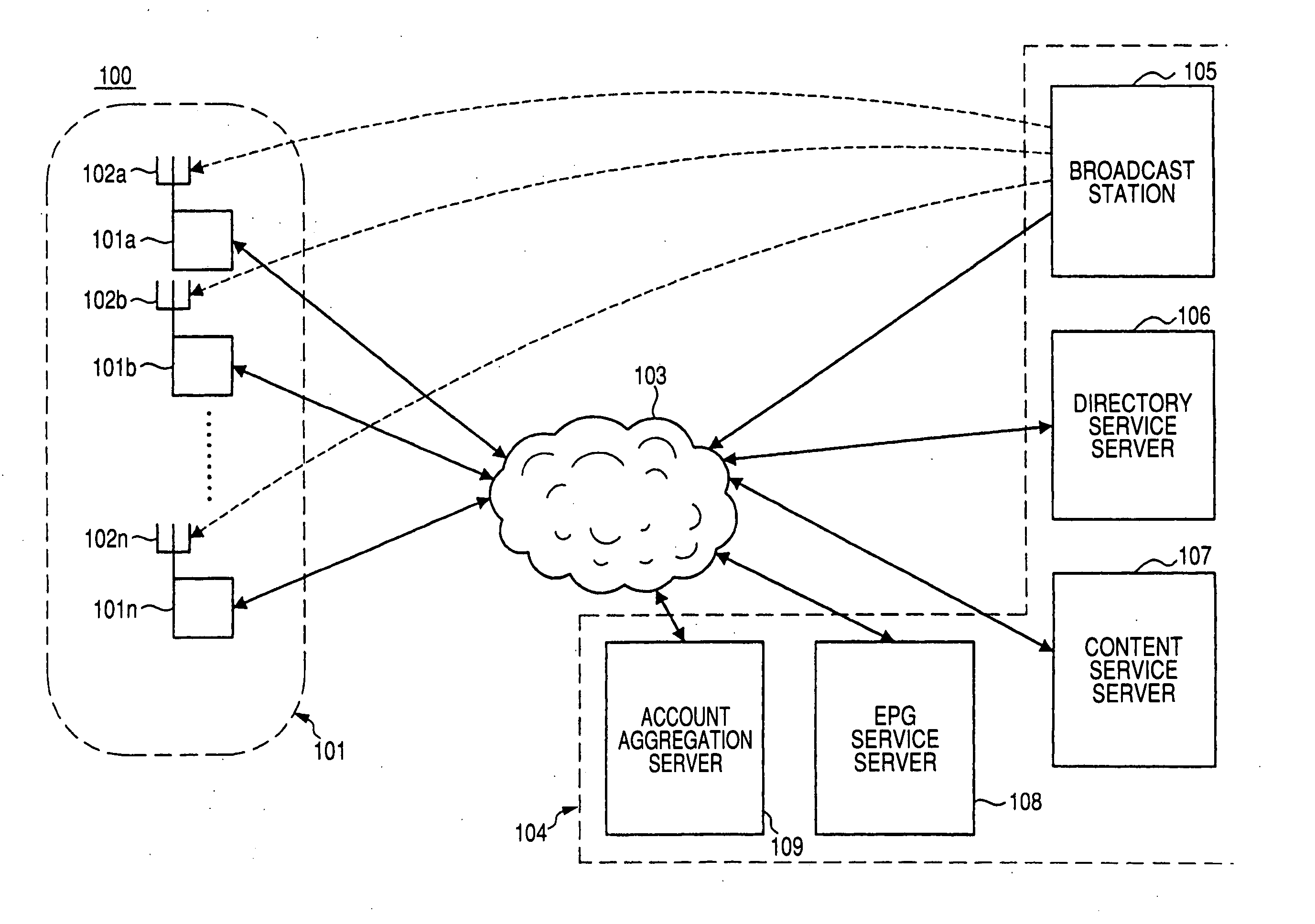

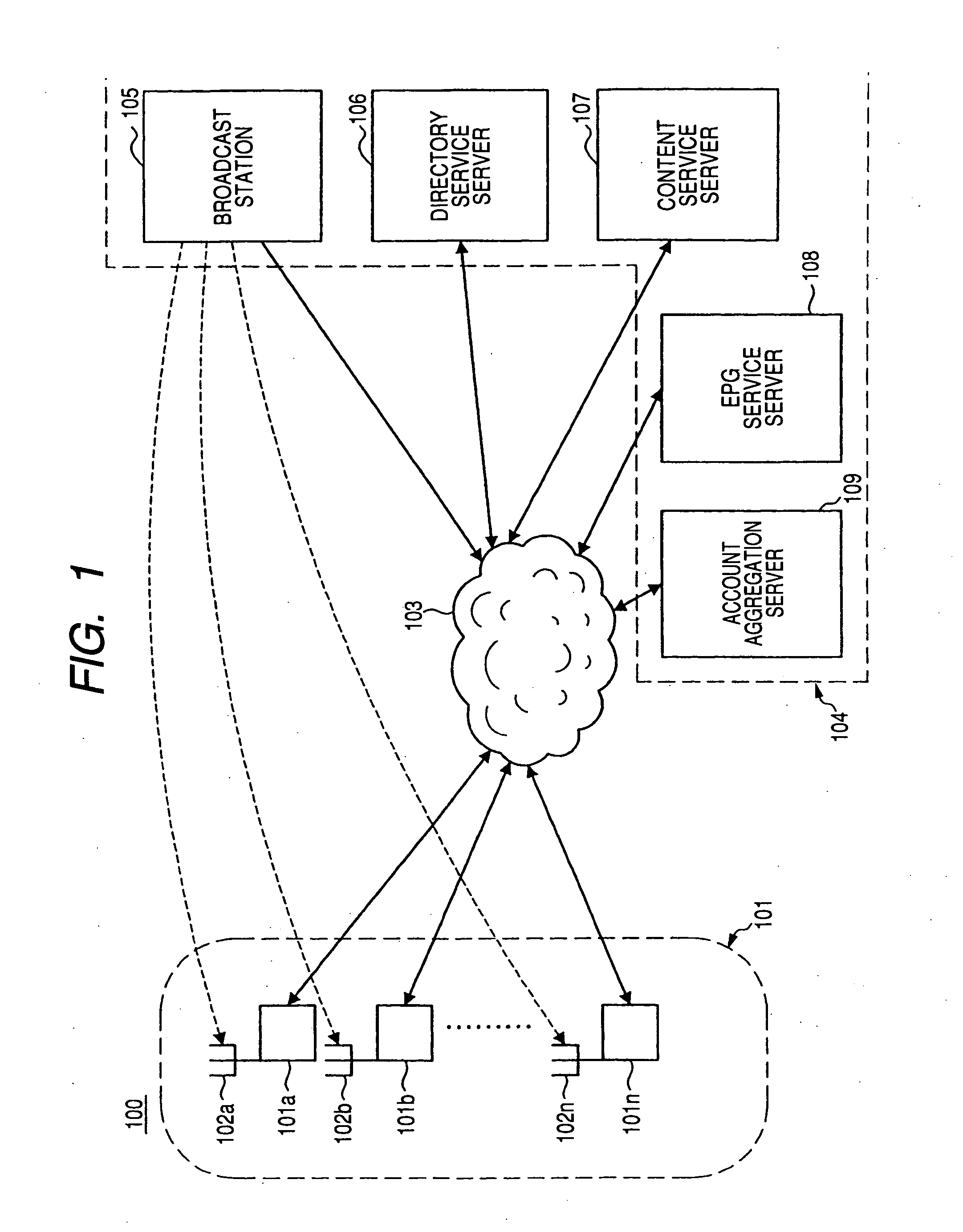

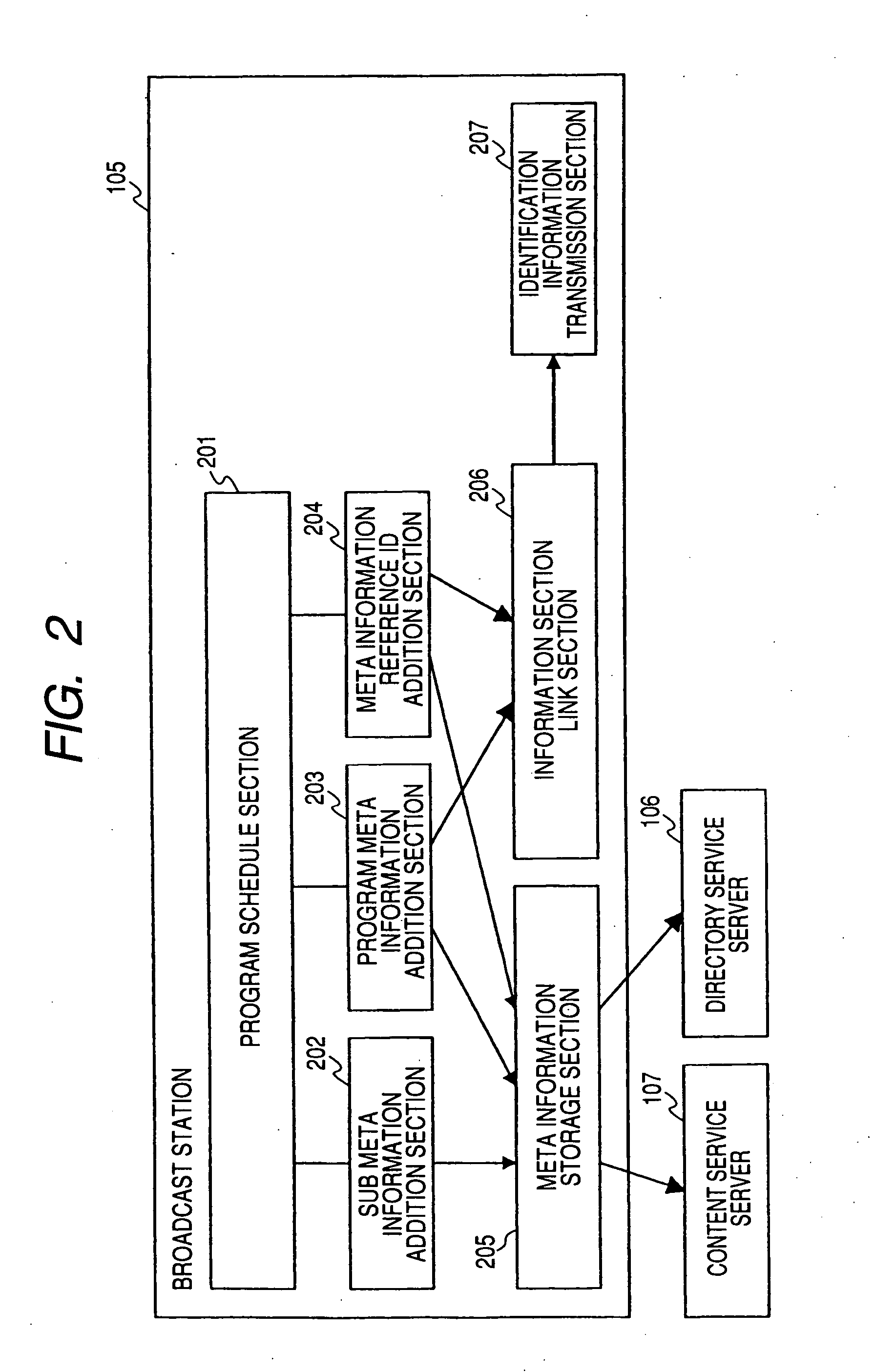

An information search system is provided. The information search system is capable of searching a target content based on meta information provided by a broadcast station, in which a reception device makes an inquiry toward a directory service server based on a meta information reference ID accompanying meta information coming from the broadcast station so that a meta information group is derived for reference by the meta information reference ID. Also, another inquiry is made toward a content service server based on address information or a keyword of the content included in sub meta information in the meta information group so as to perform a search for any desired content.

Owner:SATURN LICENSING LLC