Patents

Literature

459results about "Variable inductances/transformers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

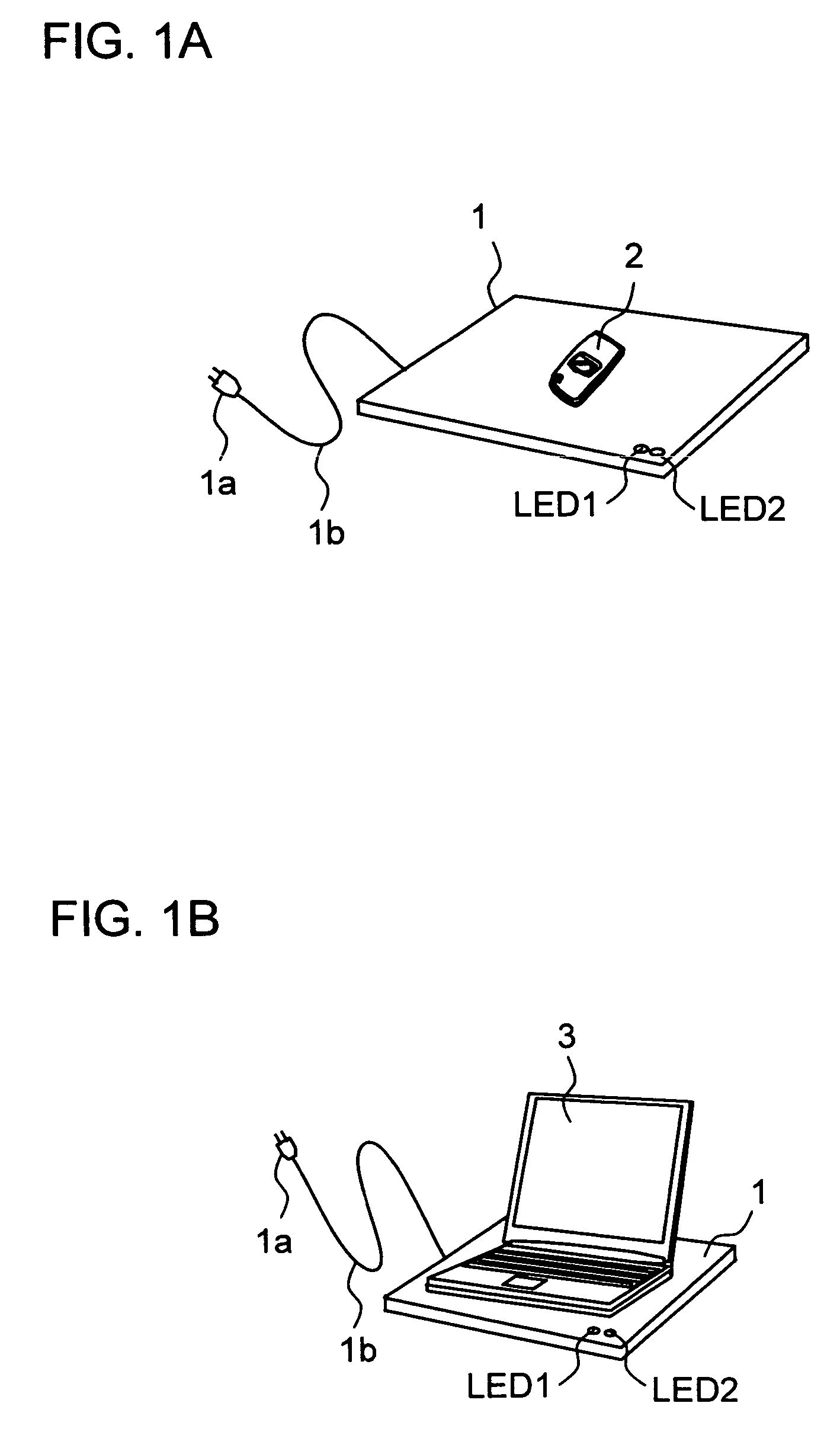

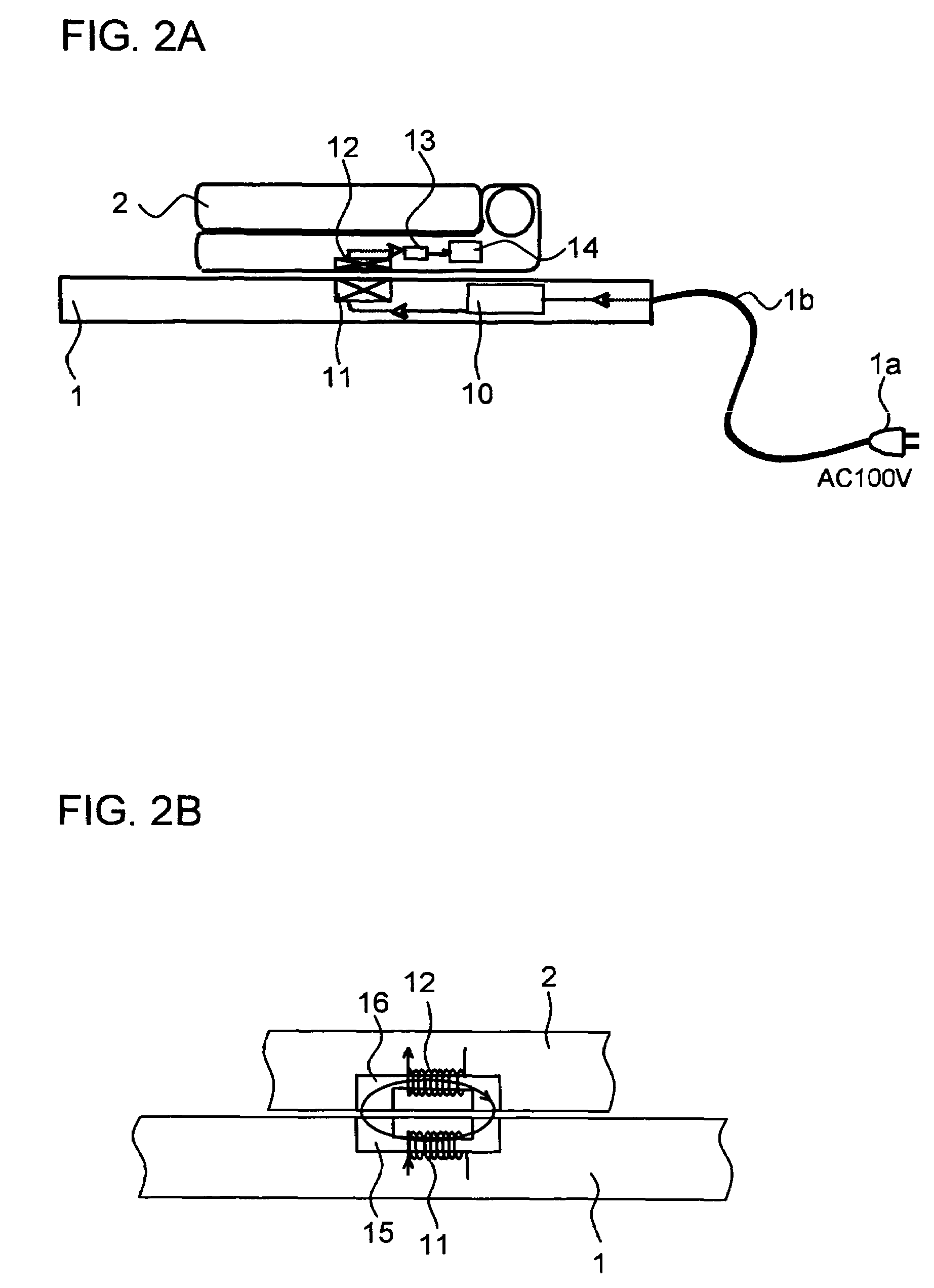

Power supply system

InactiveUS20050068019A1Save spaceDc network circuit arrangementsCircuit monitoring/indicationElectric forceElectricity

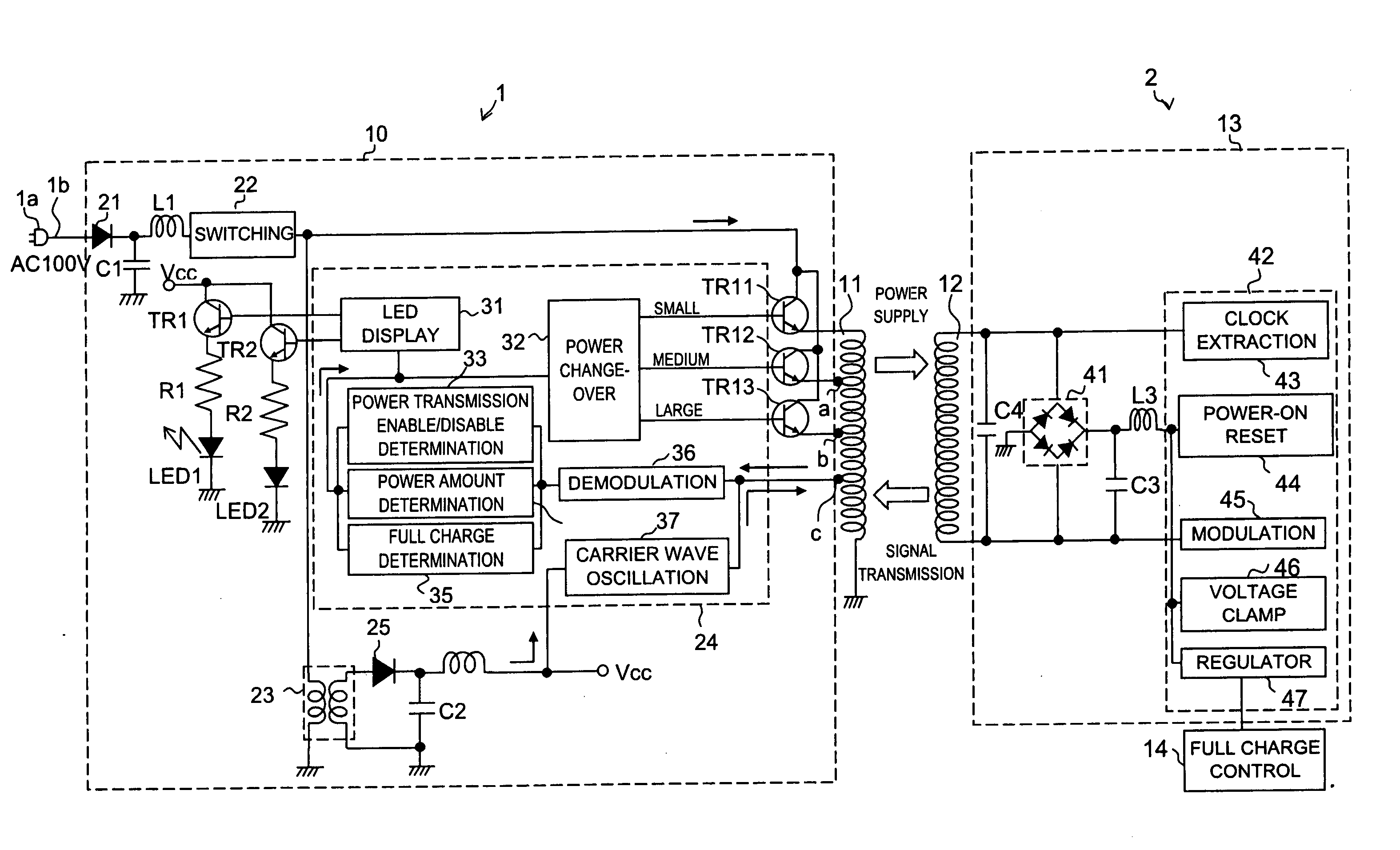

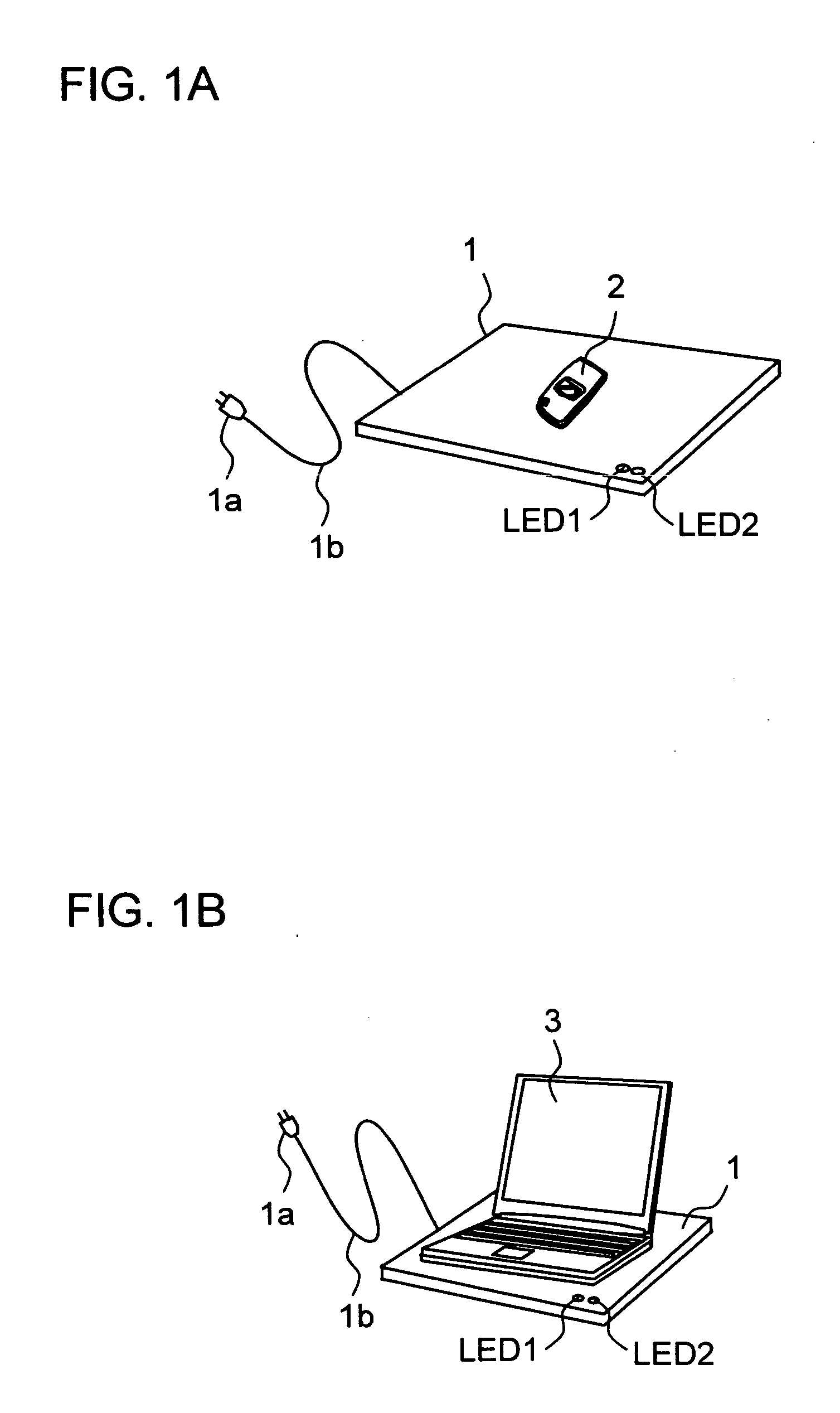

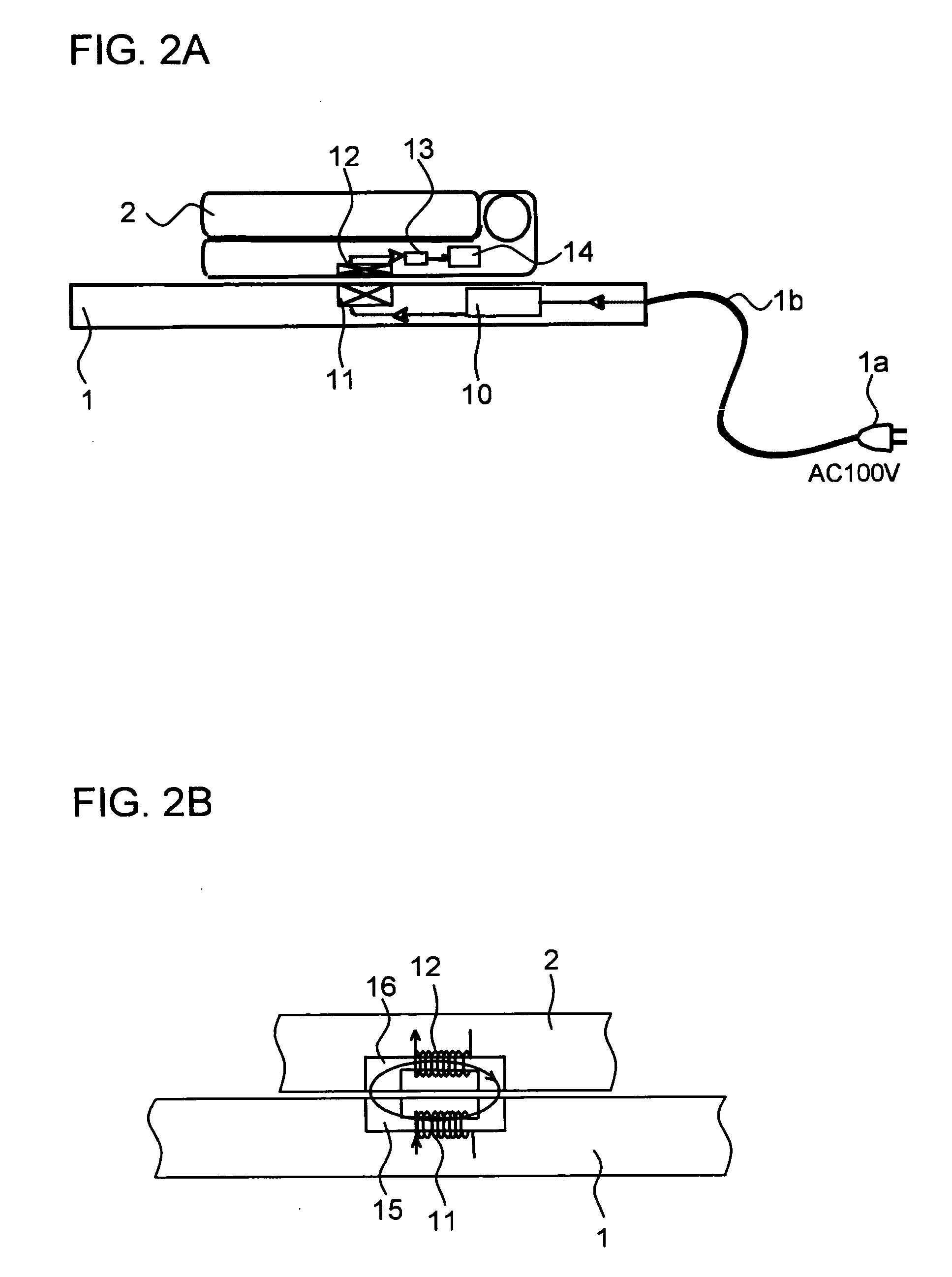

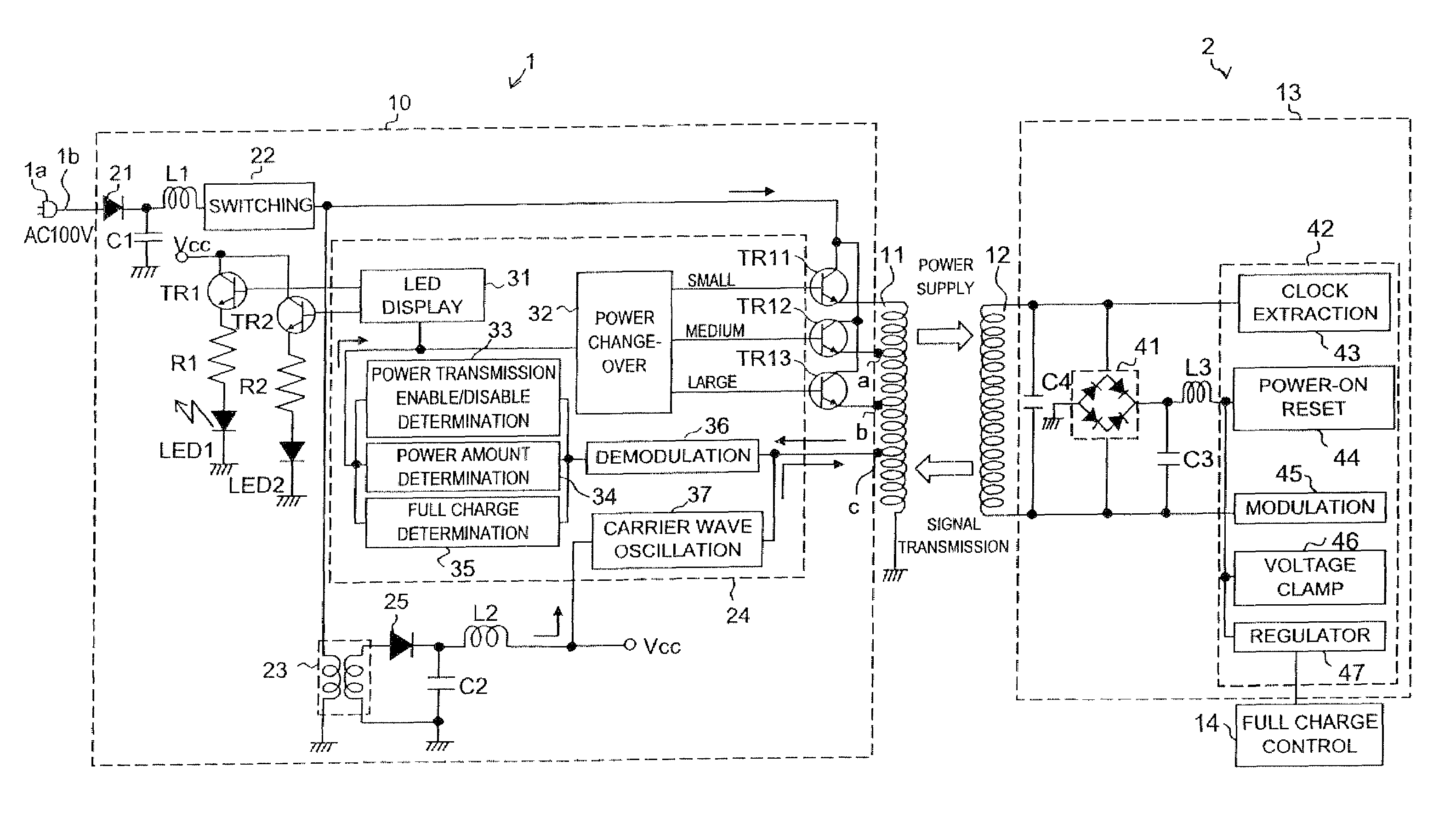

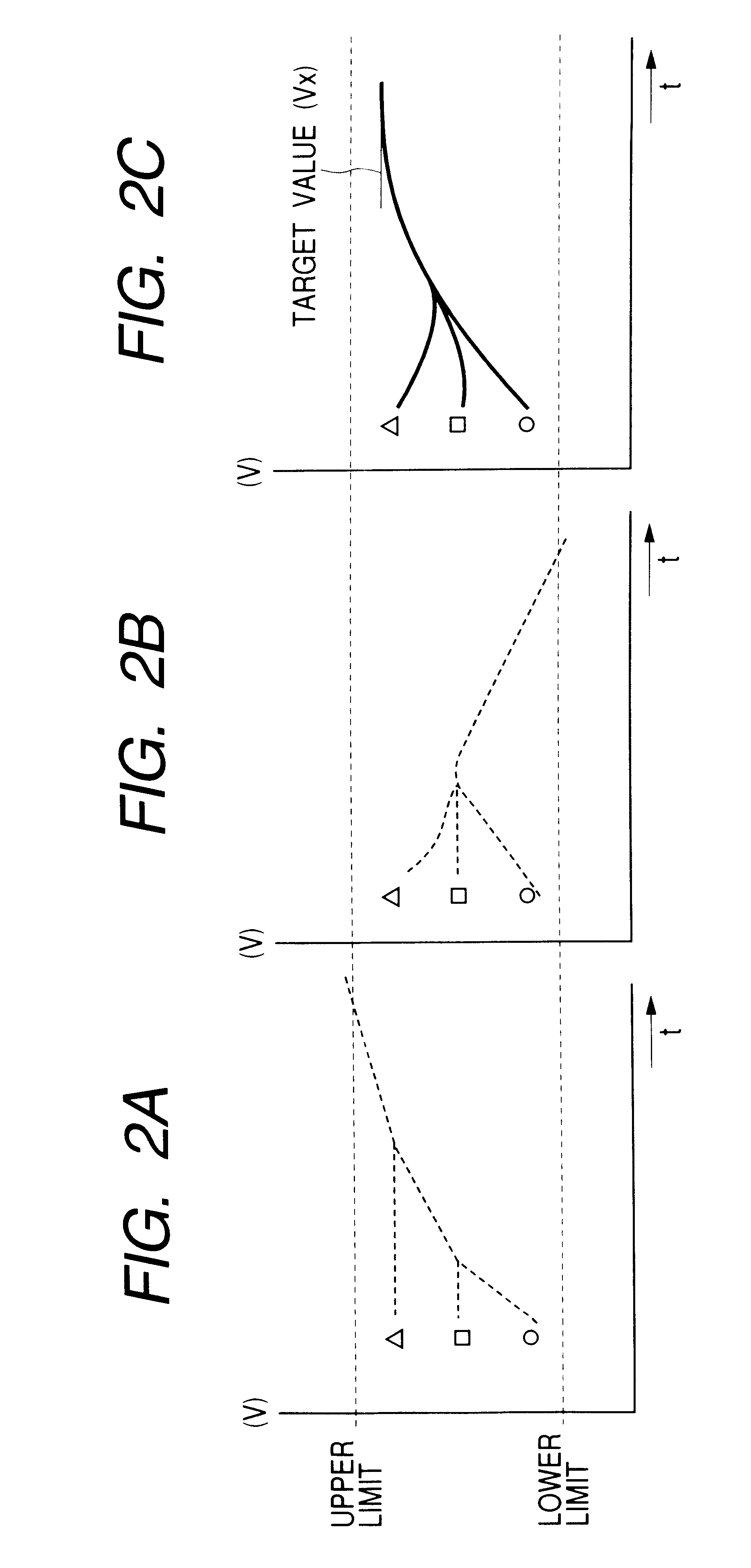

A power supply system according to the present invention comprises: a primary side coil; a power transmission apparatus having a primary side circuit for feeding a pulse voltage resulted from switching a DC voltage which is obtained by rectifying and smoothing a commercial power supply to the primary side coil; a secondary side coil magnetically coupled to the primary side coil; and power reception equipment having a secondary side circuit for rectifying and smoothing voltage induced across the secondary side coil, wherein there is provided a power adjusting section for adjusting a level of power to be transmitted according to power required by the power reception equipment. The power adjusting section has, in the primary side circuit, a carrier wave oscillation circuit for supplying a carrier wave to the primary side coil, a demodulation circuit for demodulating a modulated signal transmitted from the secondary circuit and received by the primary side coil, and a power change-over section for selecting a level of power to be transmitted according to an information signal from the power reception equipment and demodulated by the demodulation circuit. The power adjusting section has, in the secondary side circuit, a modulation circuit for modulating the carrier wave fed from the carrier wave oscillation circuit and received by the secondary side coil with the information signal from the power reception equipment and transmitting the modulated signal.

Owner:SHARP KK

Power supply system

InactiveUS7233137B2Save spaceCircuit monitoring/indicationVolume/mass flow measurementElectric power transmissionCarrier signal

A power supply system is provided, having: a primary side coil; a power transmission apparatus having a primary side circuit for feeding a pulse voltage resulted from switching a DC voltage which is obtained by rectifying and smoothing a commercial power supply to the primary side coil; a secondary side coil magnetically coupled to the primary side coil; and power reception equipment having a secondary side circuit for rectifying and smoothing voltage induced across the secondary side coil, wherein there is provided a power adjusting section for adjusting a level of power to be transmitted according to power required by the power reception equipment. The power adjusting section has, in the primary side circuit, a carrier wave oscillation circuit for supplying a carrier wave to the primary side coil, a demodulation circuit for demodulating a modulated signal transmitted from the secondary circuit and received by the primary side coil, and a power change-over section for selecting a level of power to be transmitted according to an information signal from the power reception equipment and demodulated by the demodulation circuit. The power adjusting section has, in the secondary side circuit, a modulation circuit for modulating the carrier wave fed from the carrier wave oscillation circuit and received by the secondary side coil with the information signal from the power reception equipment and transmitting the modulated signal.

Owner:SHARP KK

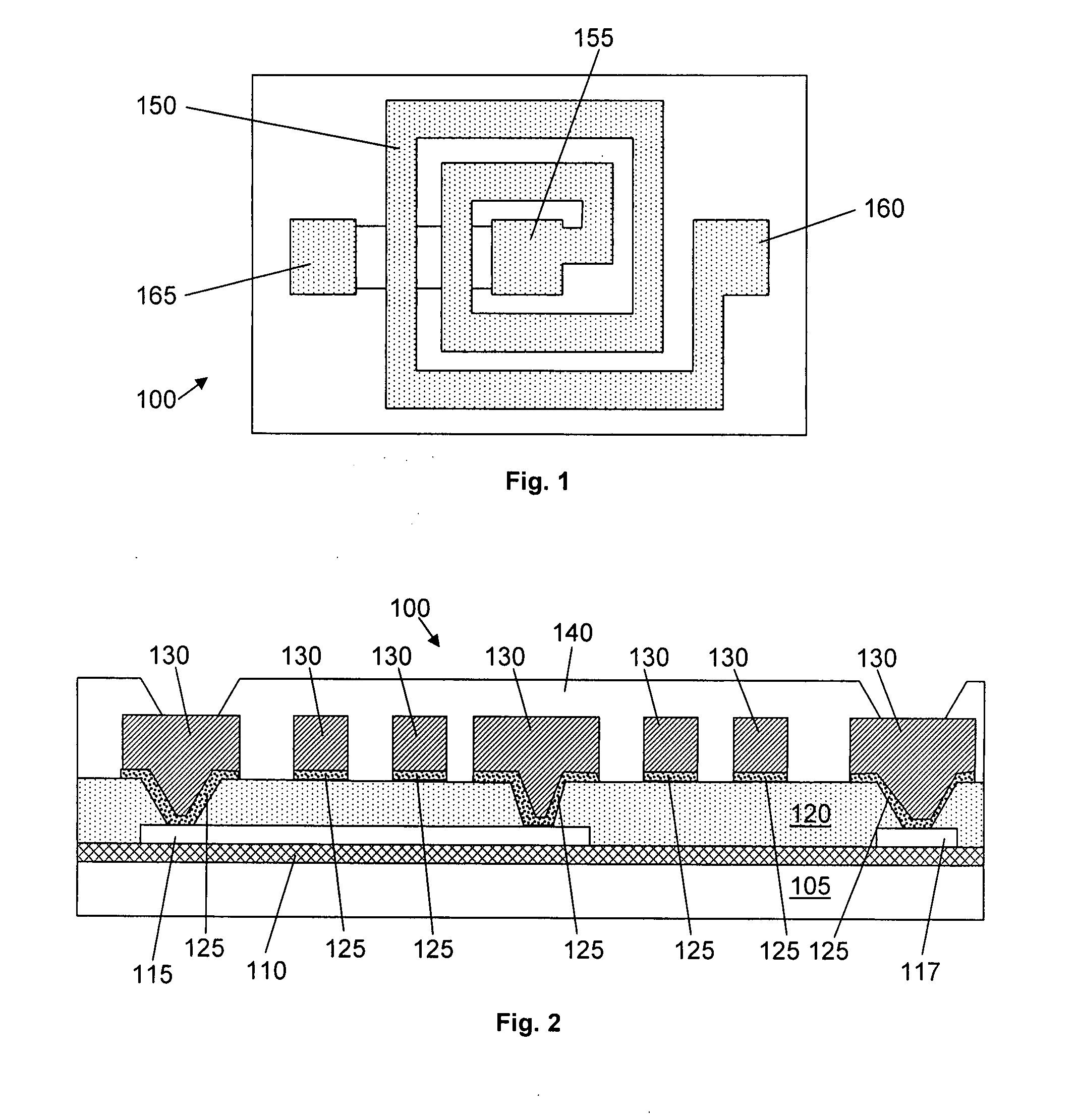

Method for fabricating a thin film inductor

InactiveUS6040226AClose toleranceSemiconductor/solid-state device detailsSolid-state devicesLithographic artistEngineering

A method is provided for the manufacture of precision electronic components such as resistors, inductors, and capacitors on a polymer or ceramic surface. The electronic components can be deposited and trimmed to precise or matched values without having precise depositions of all of the pre-patterned materials. Thin film electronic components are deposited on a surface, parameter values are measured or estimated, a correction offset file is generated, and the components are trimmed using adaptive lithography to a very close tolerance. A computer program can be used to enable the adjustment of electronic components by techniques such as changing the physical length of an inductor coil or resistor lead, or by changing a capacitor plate area.

Owner:GENERAL ELECTRIC CO

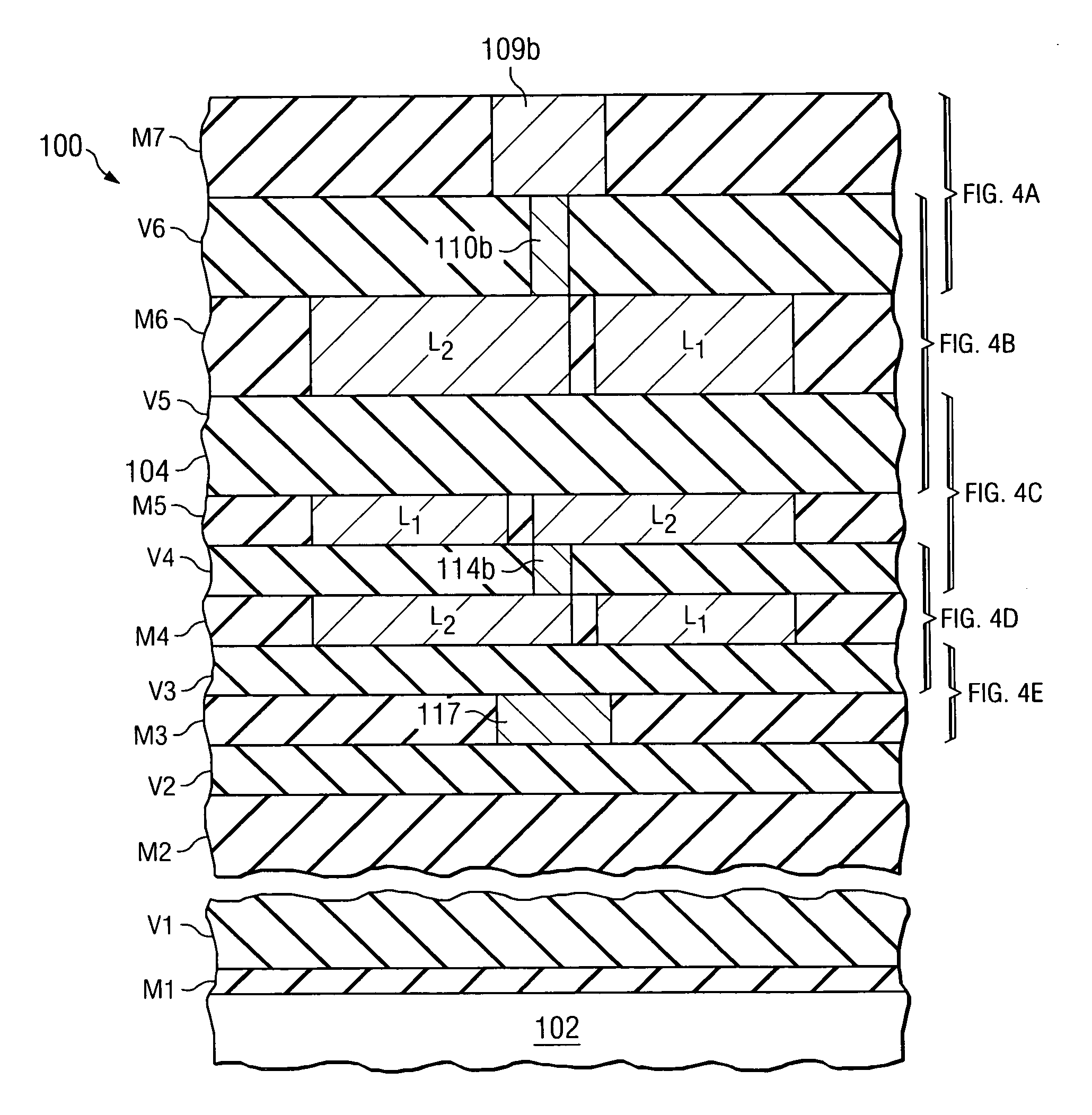

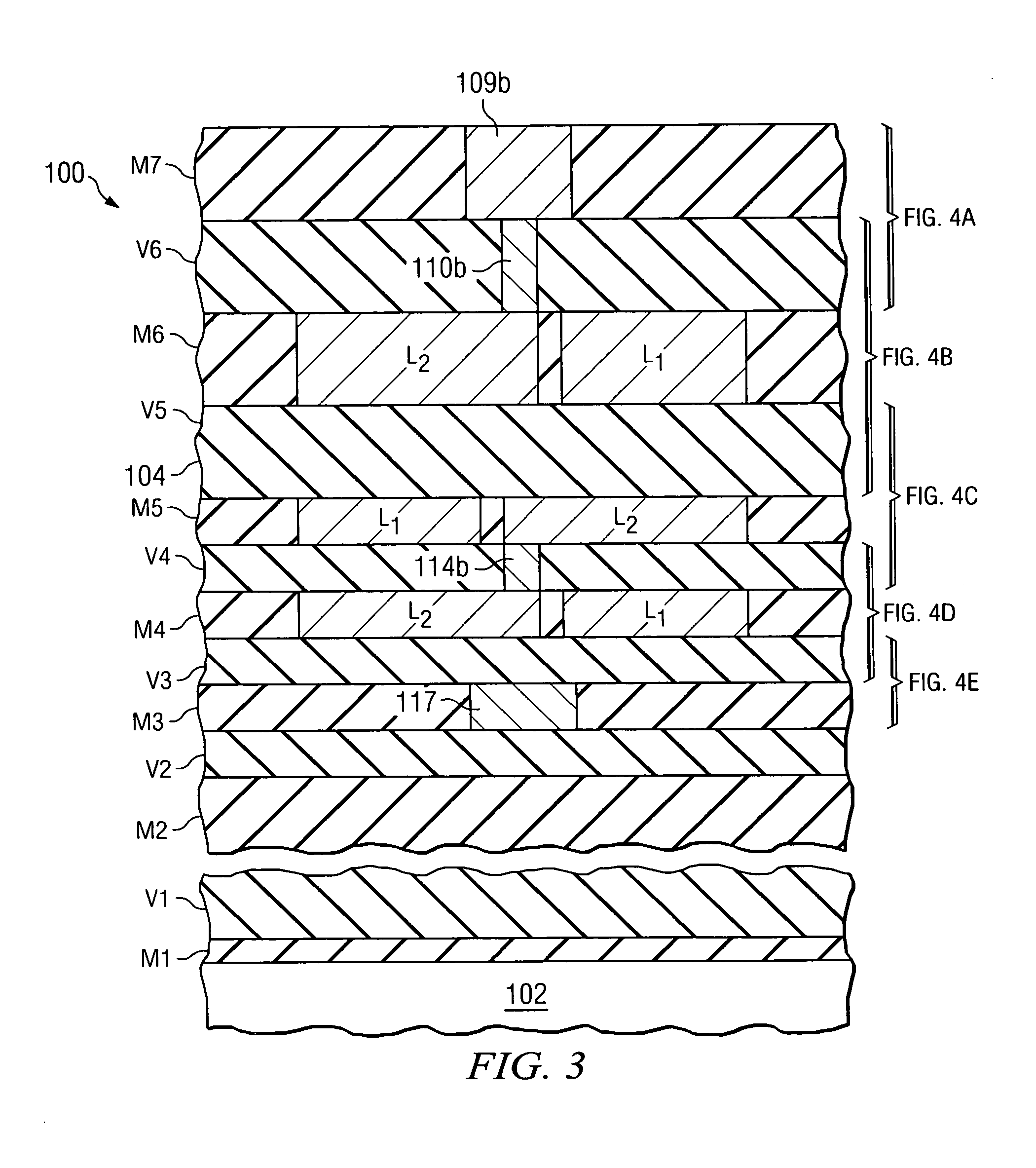

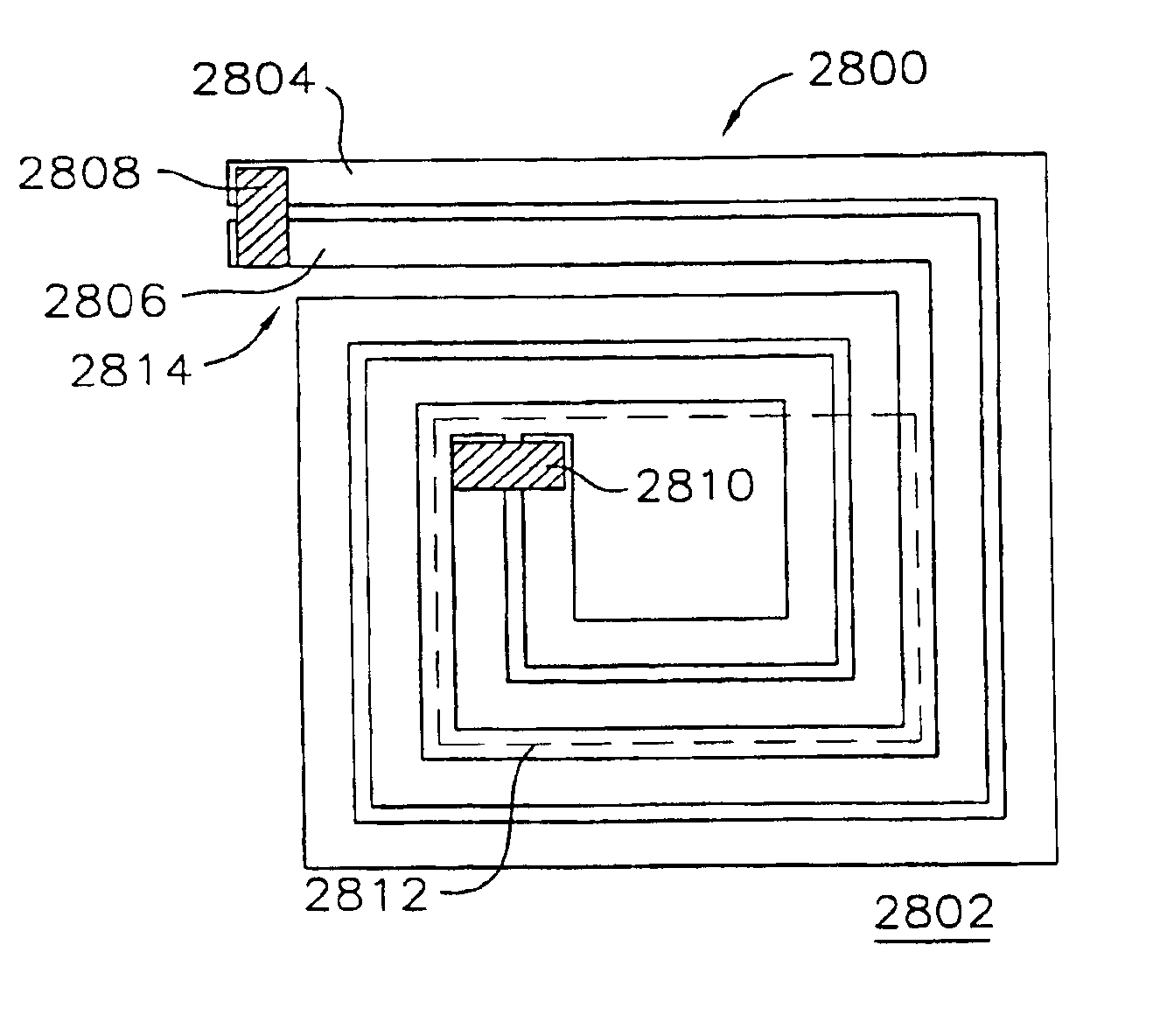

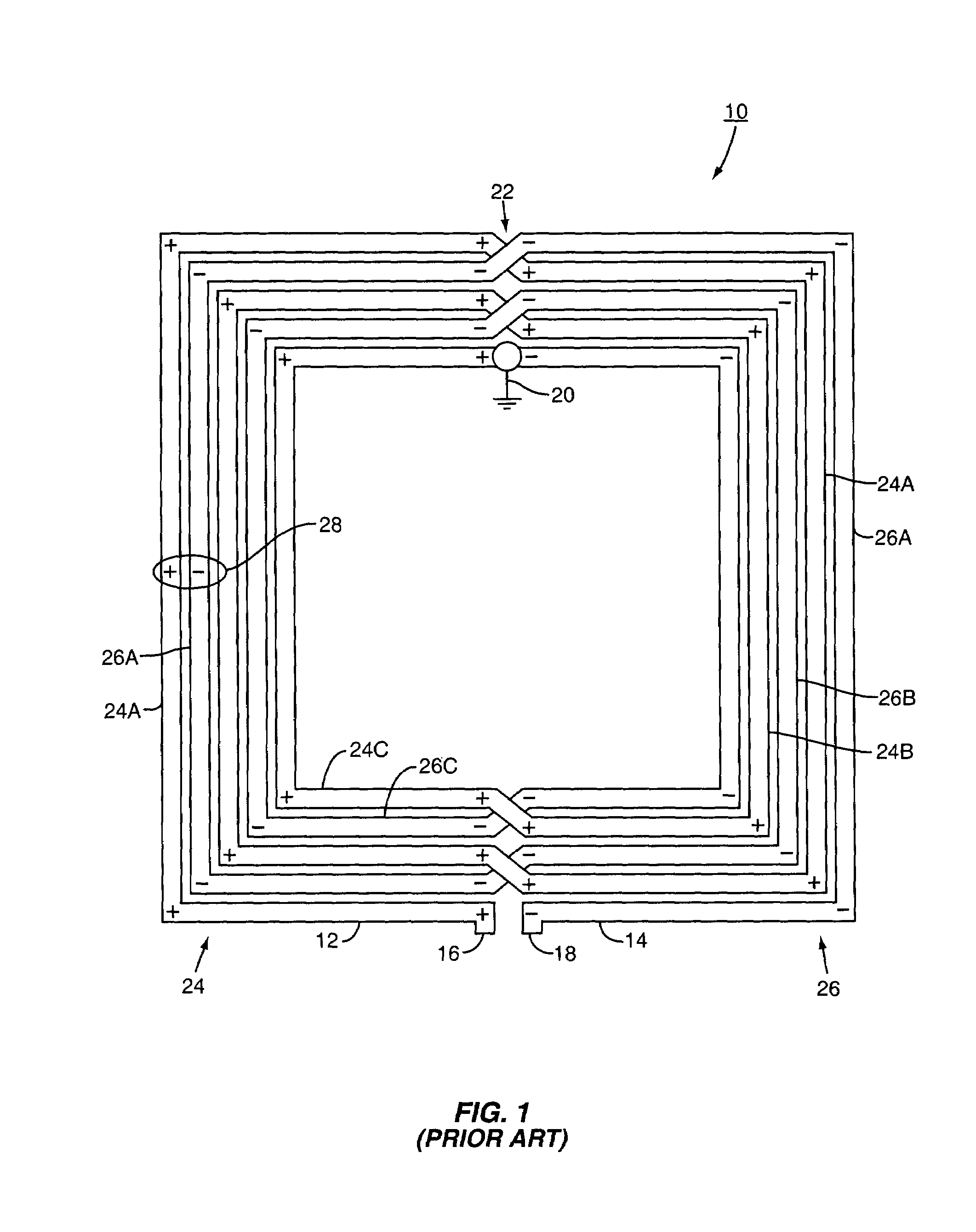

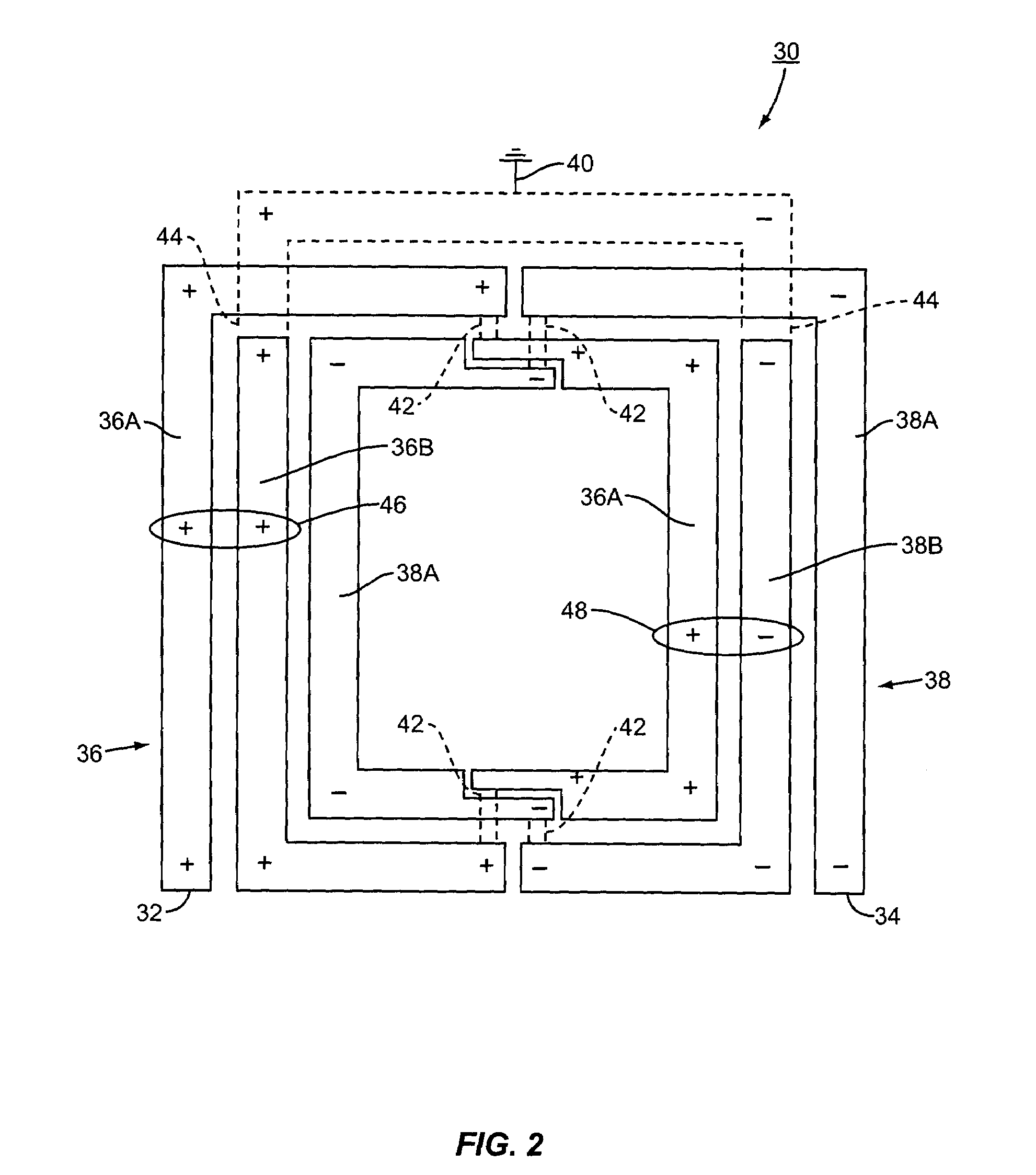

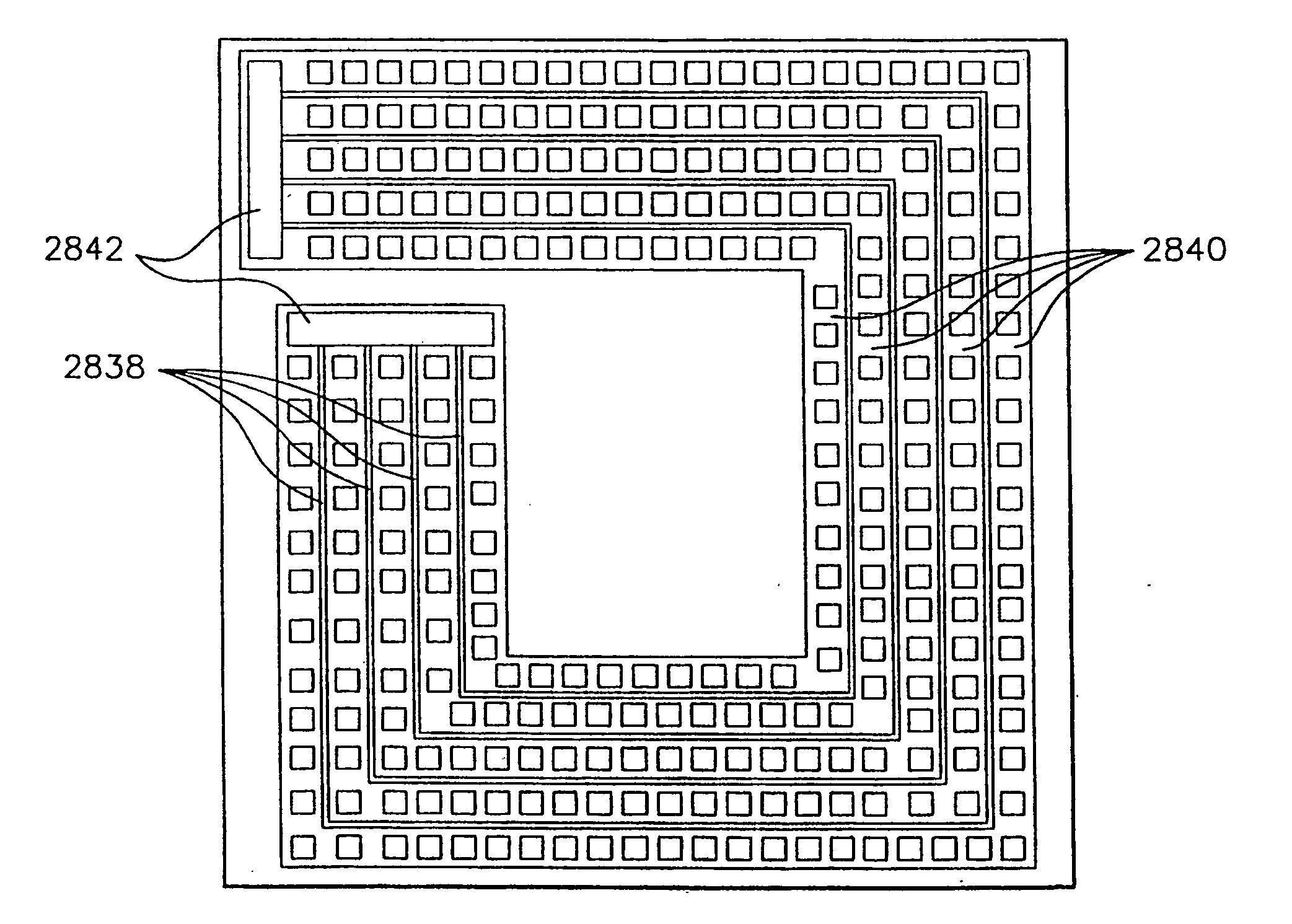

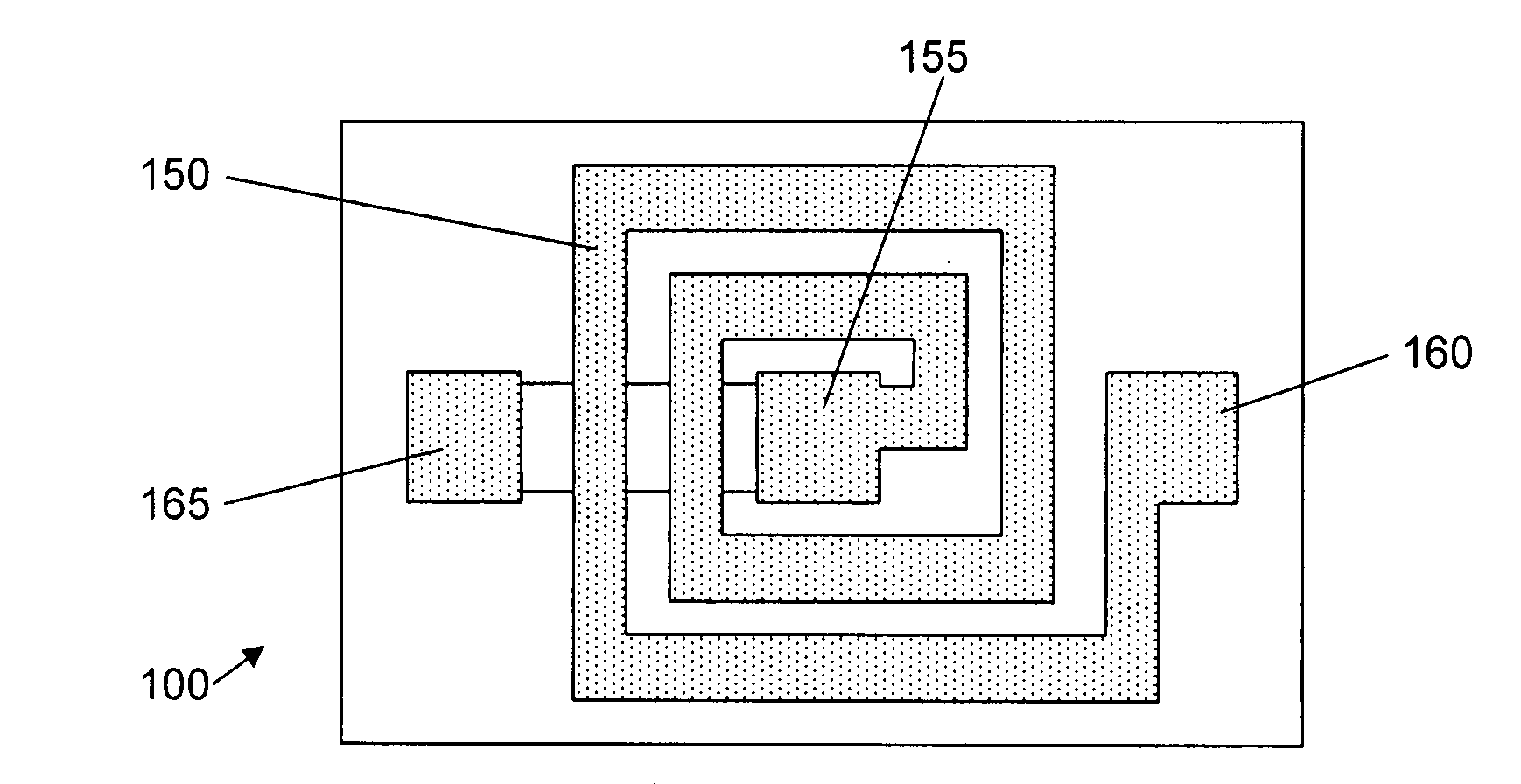

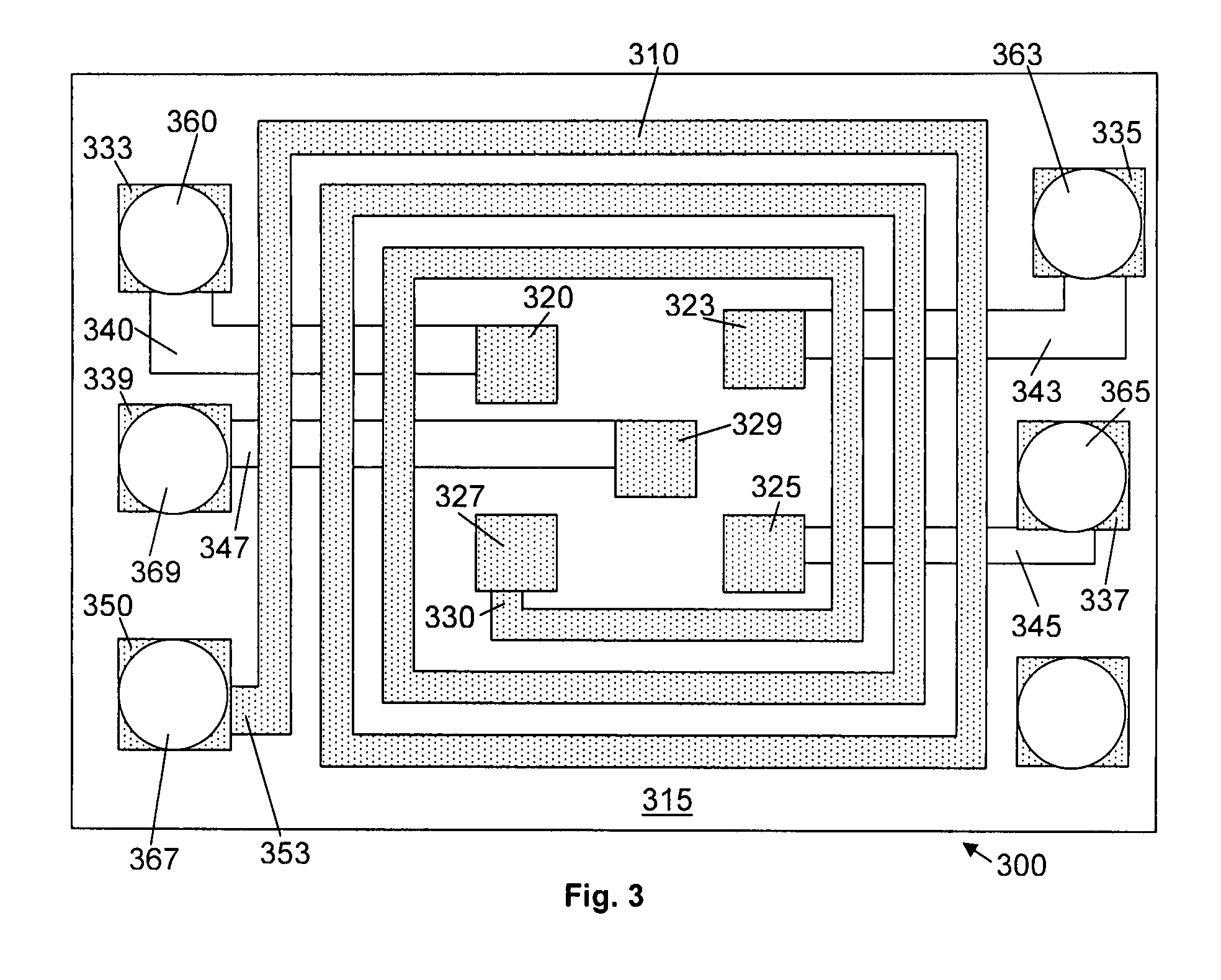

Integrated circuits with inductors in multiple conductive layers

ActiveUS20060284718A1Increase inductanceIncrease the number of windingsSemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsInductorEngineering

Two inductors formed in multiple layers of conductive layers of integrated circuits are disclosed. Symmetric portions of a first inductor and a second inductor are formed in two or more conductive layers. Portions of the first inductor in adjacent conductive layers are connected by vias, and portions of the second inductor in adjacent conductive layers are connected by vias. The first and second inductor portions form a substantially loop-shaped structure in each conductive layer. The first and second inductor vias may be positioned at the same position within the substantially loop-shaped inductor structure by alternating inner and outer radiuses, or the vias for the second inductor may be positioned opposite the vias for the first inductor within the substantially loop-shaped inductor structure, using notches in the first and second inductor portions.

Owner:INFINEON TECH AG

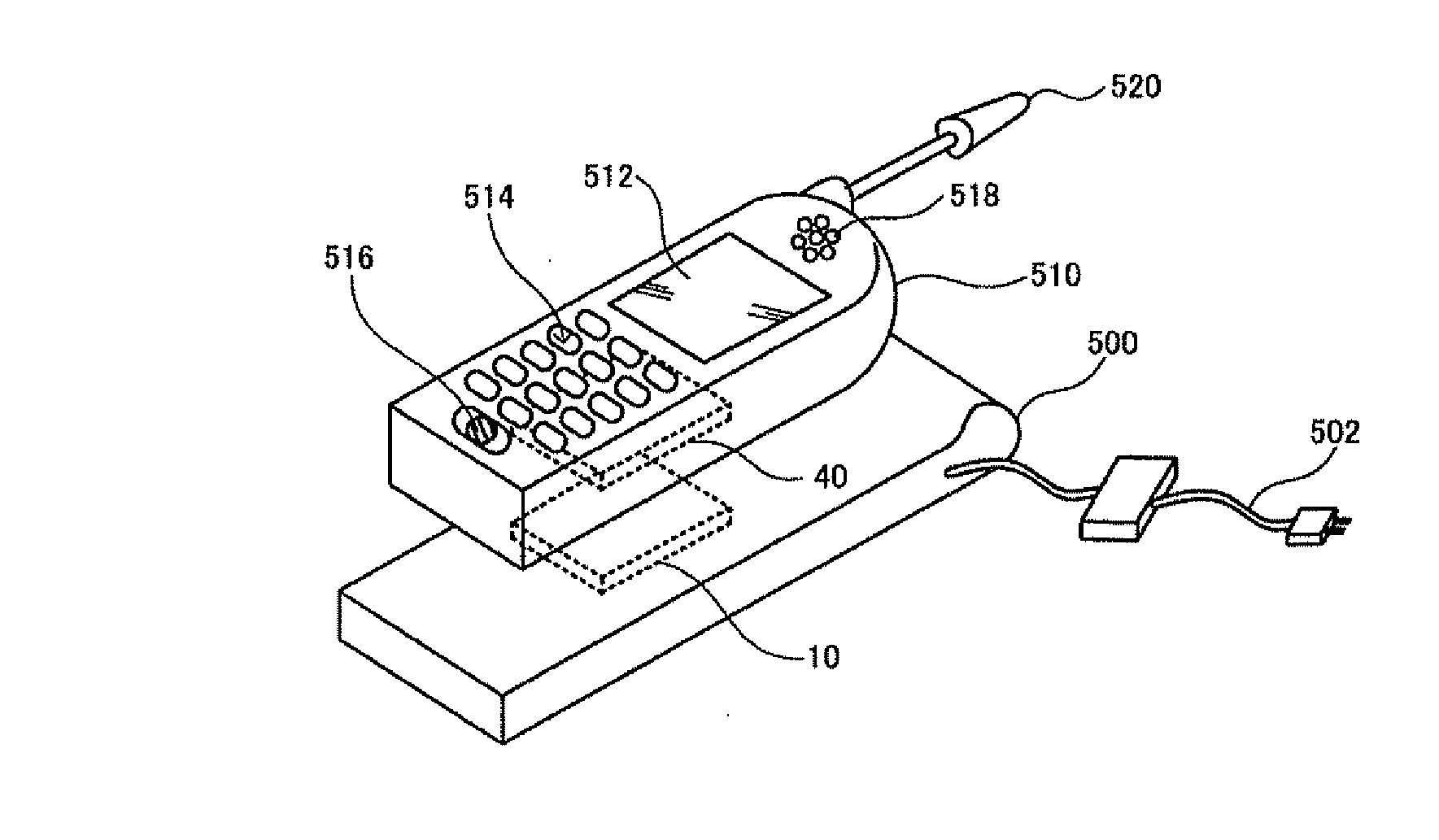

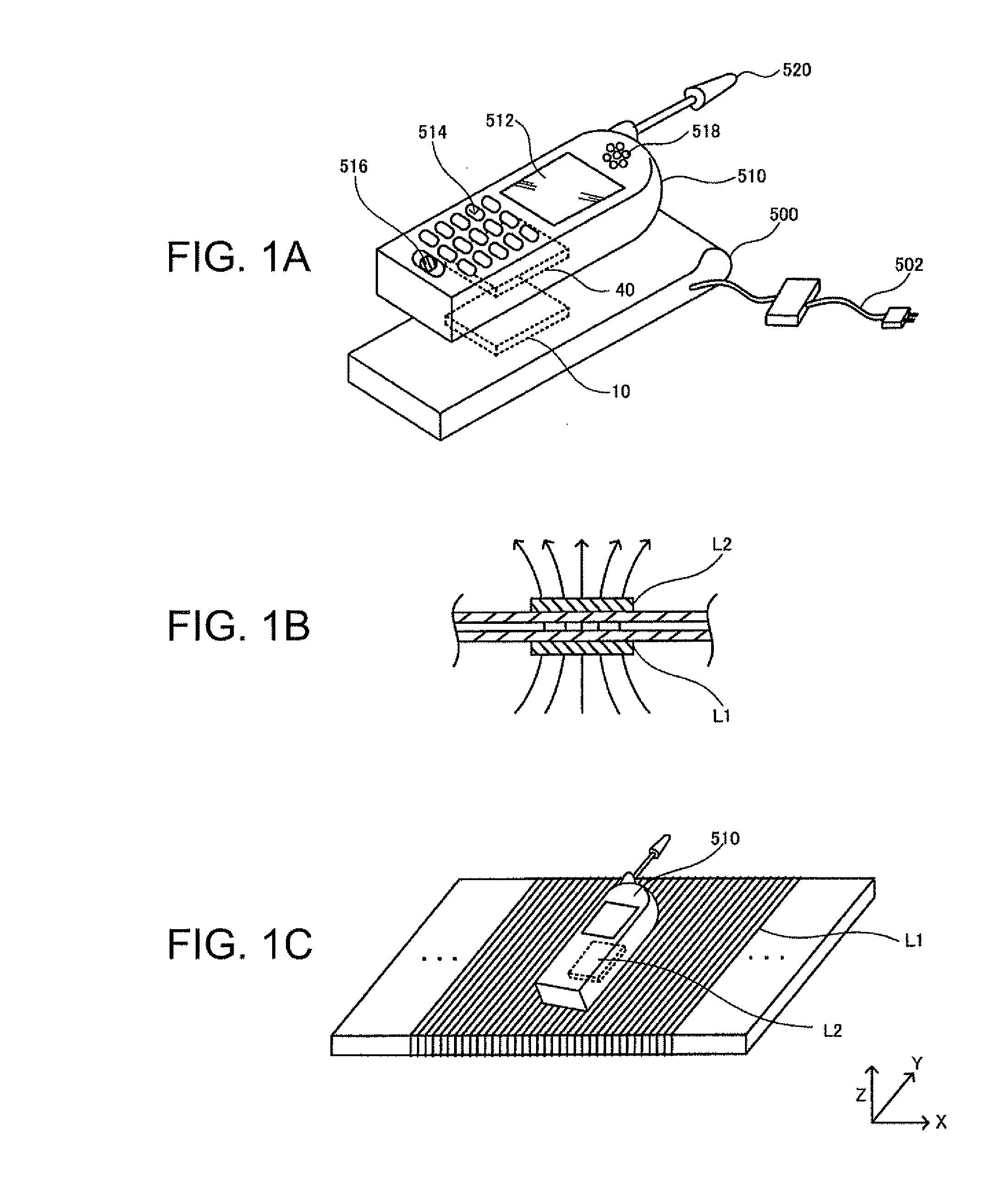

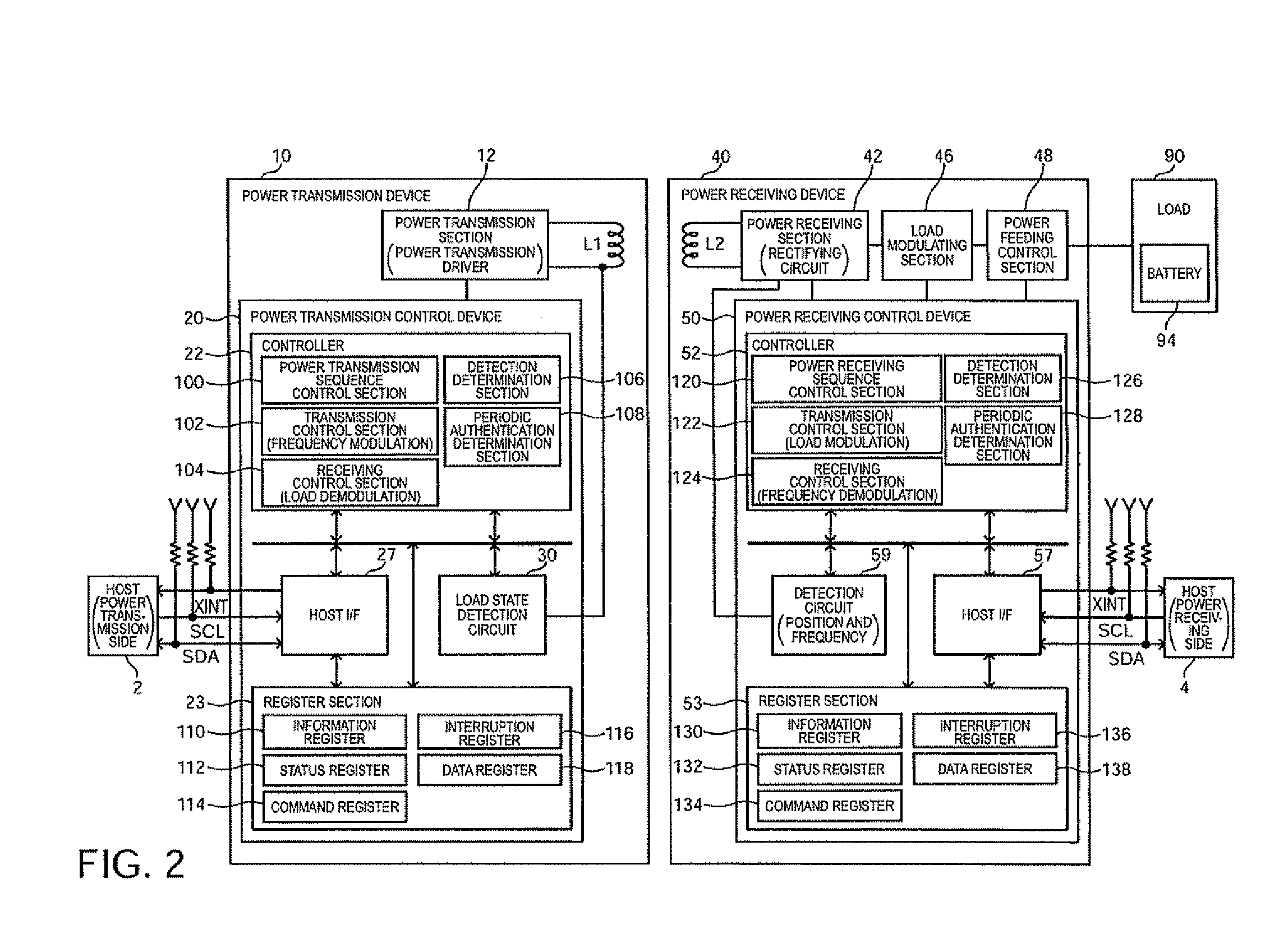

Power transmission control device, power transmission device, power receiving control device, power receiving device, and electronic apparatus

ActiveUS20100013319A1Efficient use ofReduce electricity loadVariable inductances/transformersSubstation equipmentElectricityElectric power transmission

There is provided a power transmission control device included in a power transmission device in a contactless power transmission system that transmits power from the power transmission device to a power receiving device by electromagnetically coupling a primary coil to a secondary coil to supply the power to a load of the power receiving device. The power transmission control device includes a controller controlling the power transmission control device, a host interface communicating with a power transmission-side host, and a register section accessible from the power transmission-side host via the host interface. The controller shifts into a communication mode that executes communication between the power transmission-side host and a power receiving-side host, when the power transmission-side host writes, via the host interface, a communication request command that requests the communication between the hosts in the register section. Then, the controller transmits the communication request command to the power receiving device.

Owner:138 EAST LCD ADVANCEMENTS LTD

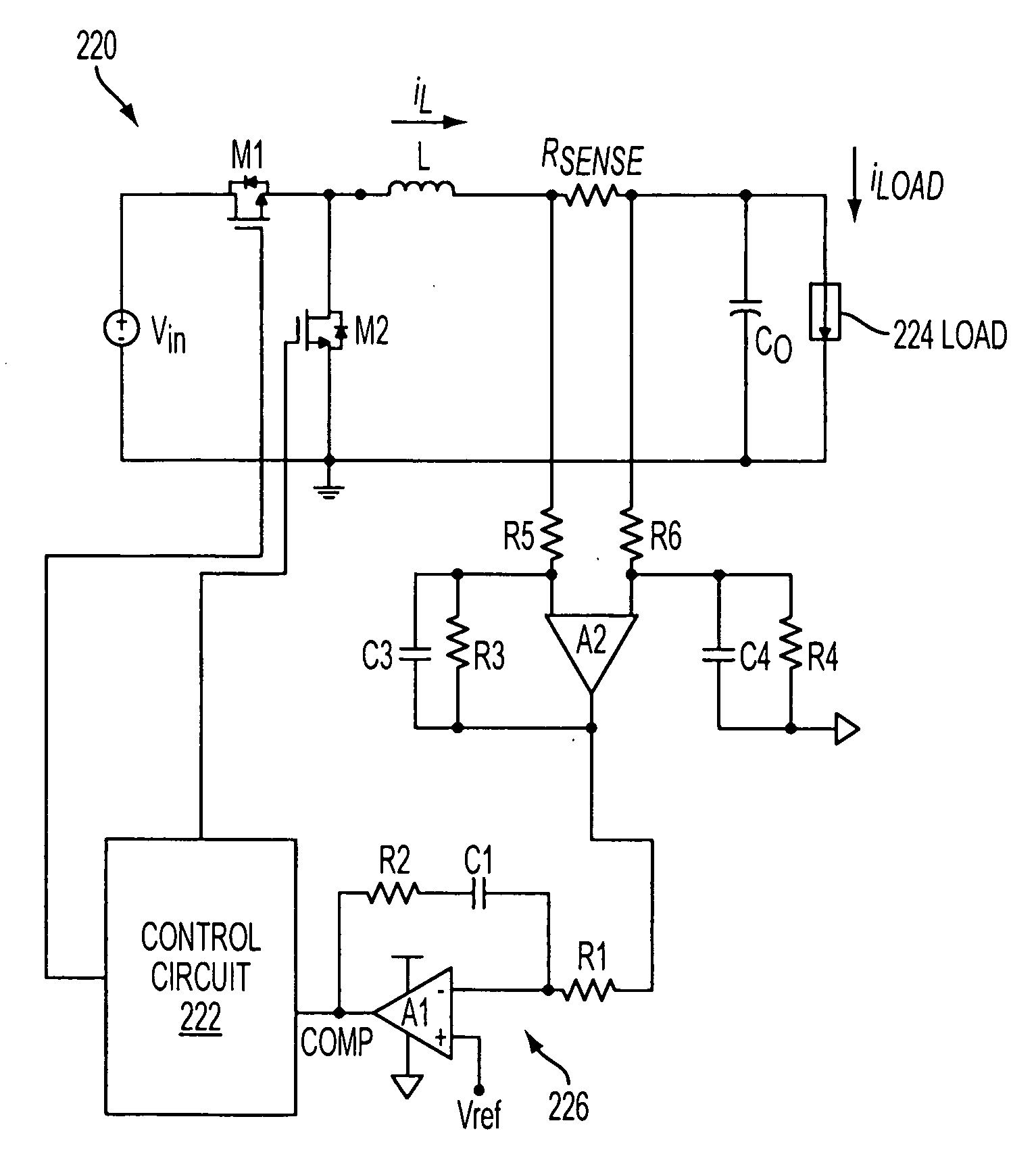

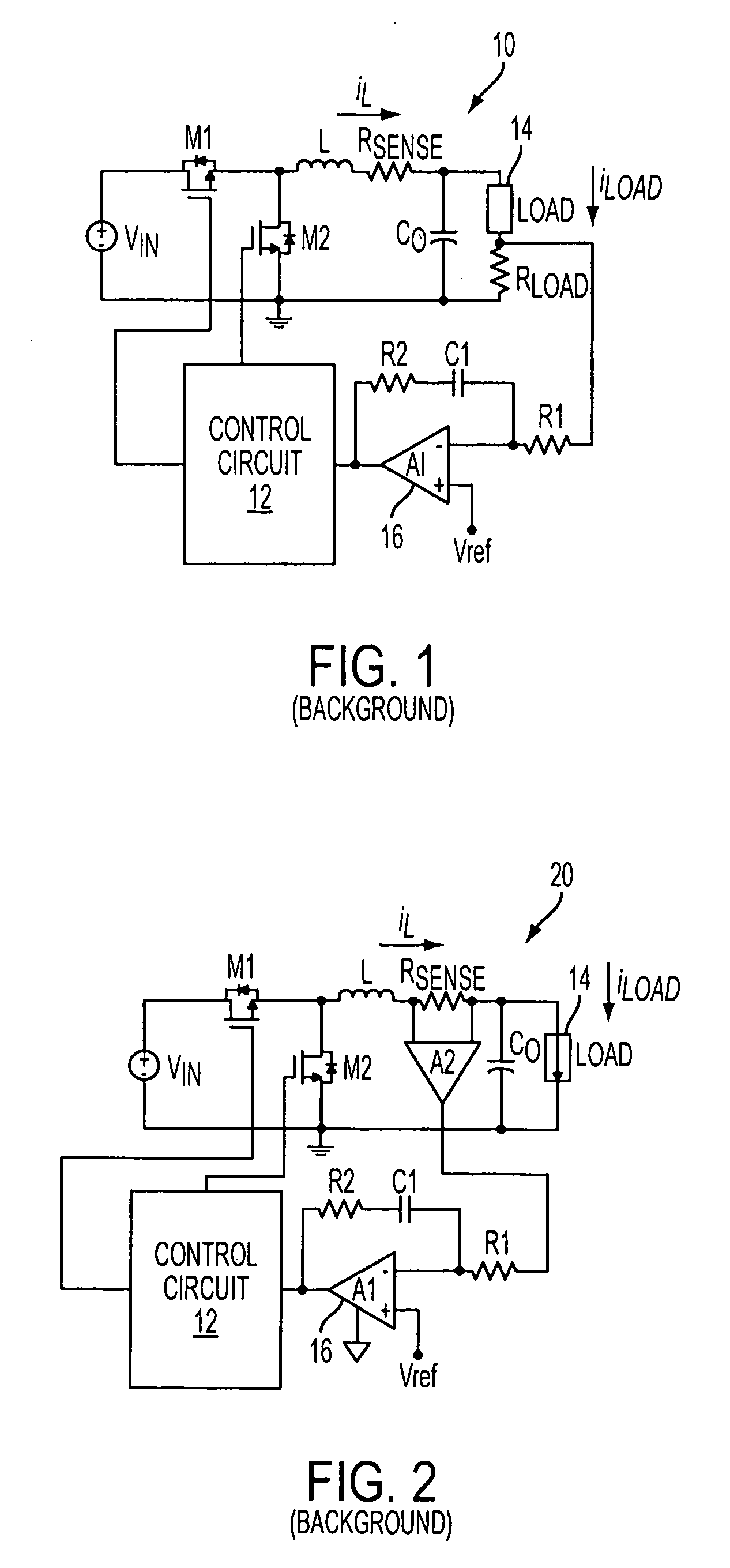

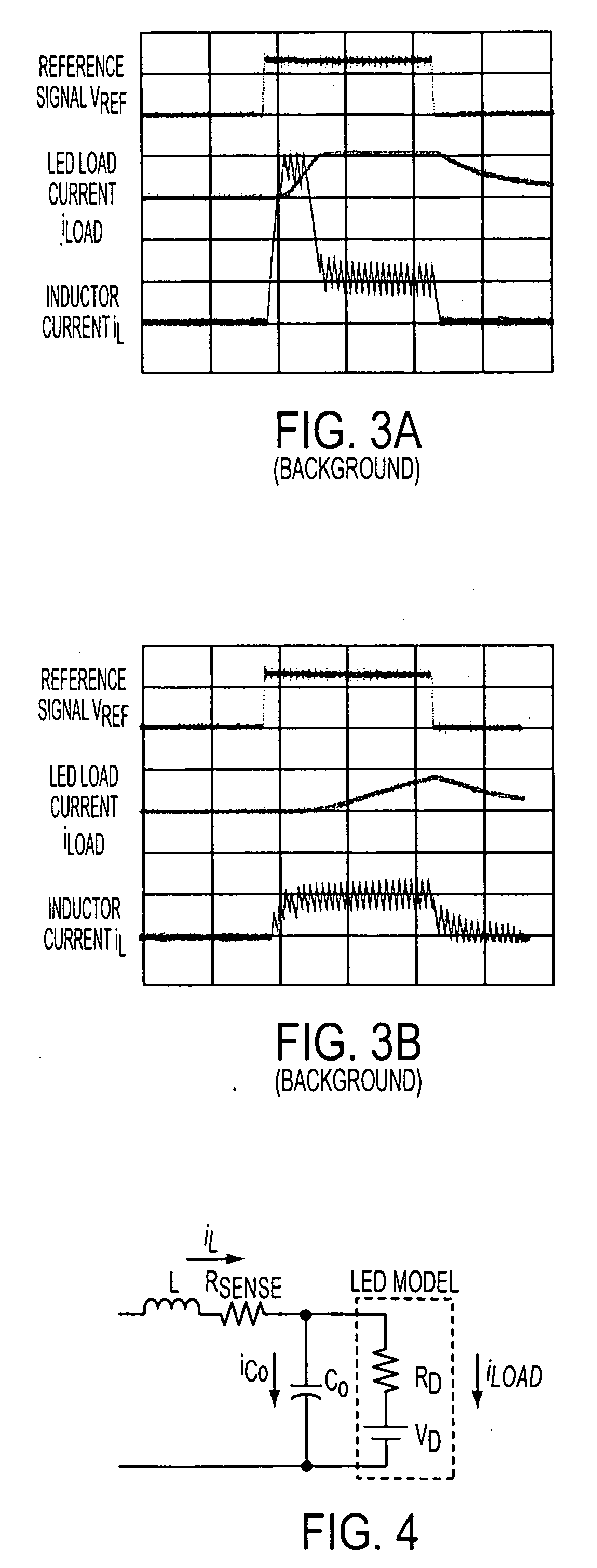

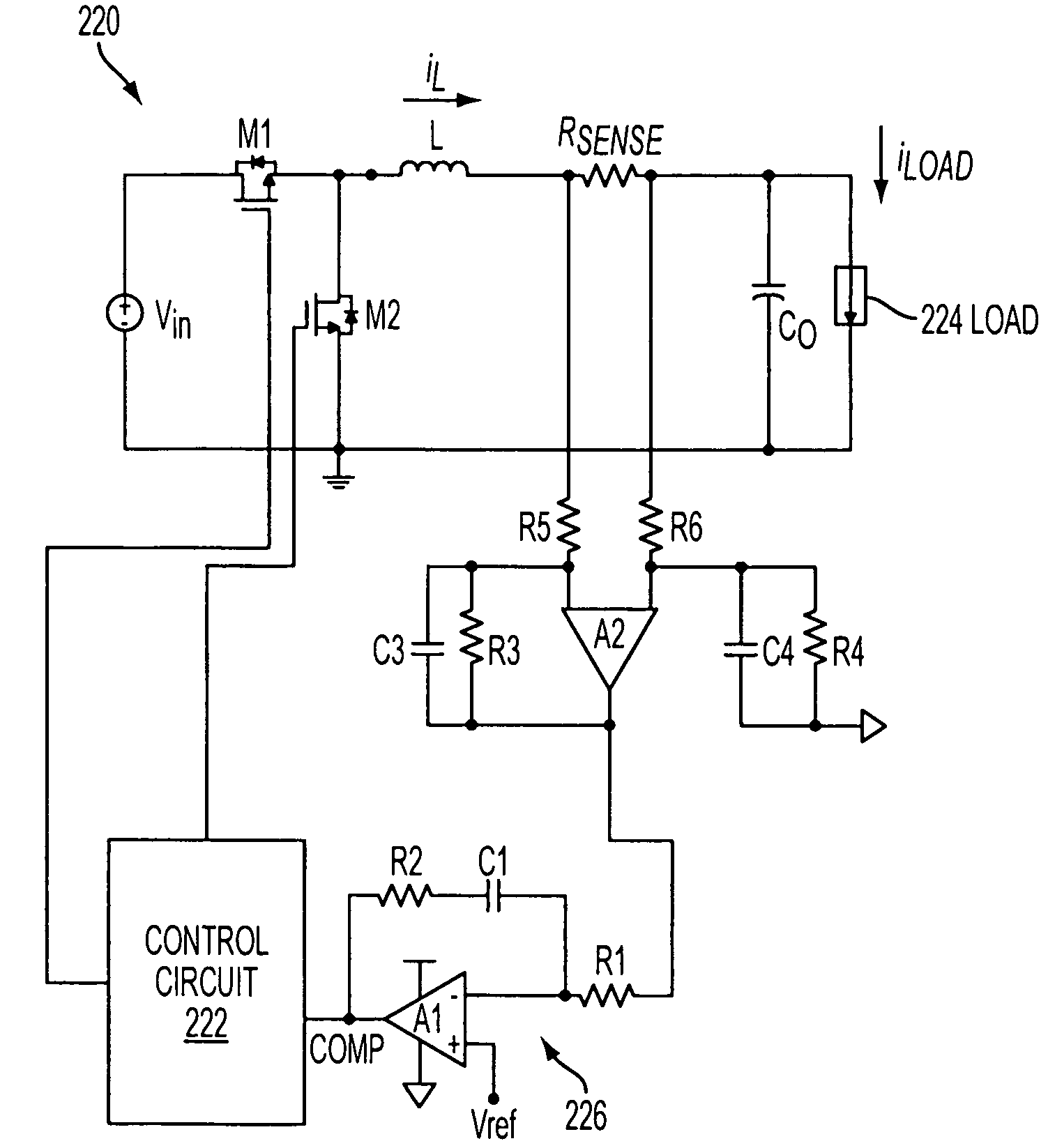

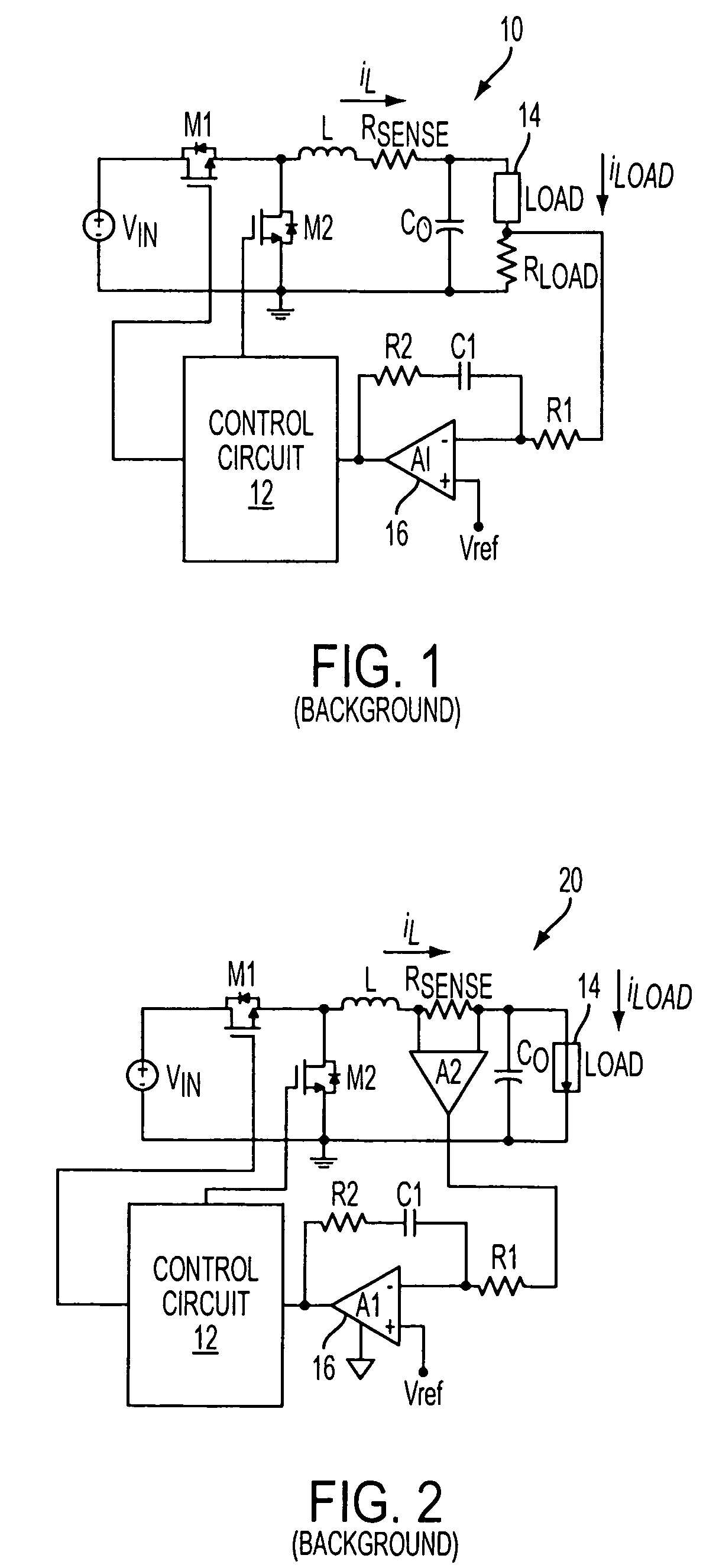

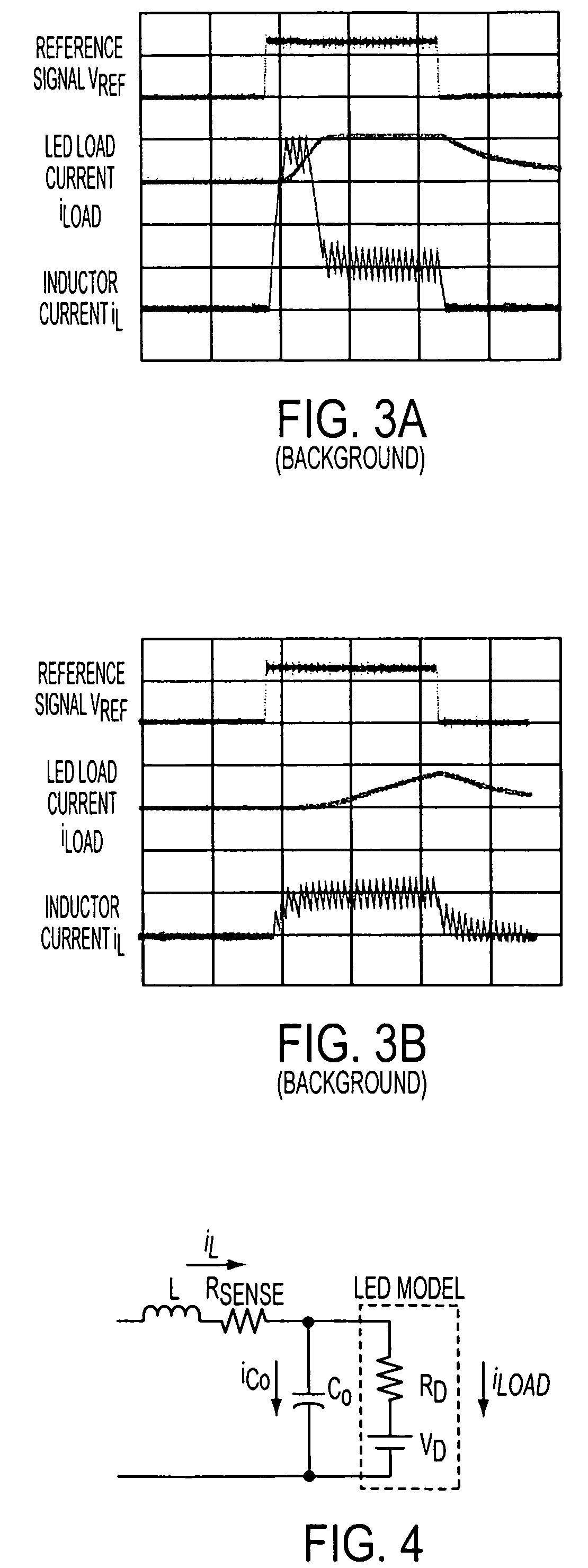

Current source with indirect load current signal extraction

A switching circuit for supplying current to a load has a switching element, an inductive element coupled to the switching element, and a load current extraction circuit responsive to current in the inductive element for producing a load current signal as a simulated current approximating current in the load.

Owner:ANALOG DEVICES INT UNLTD

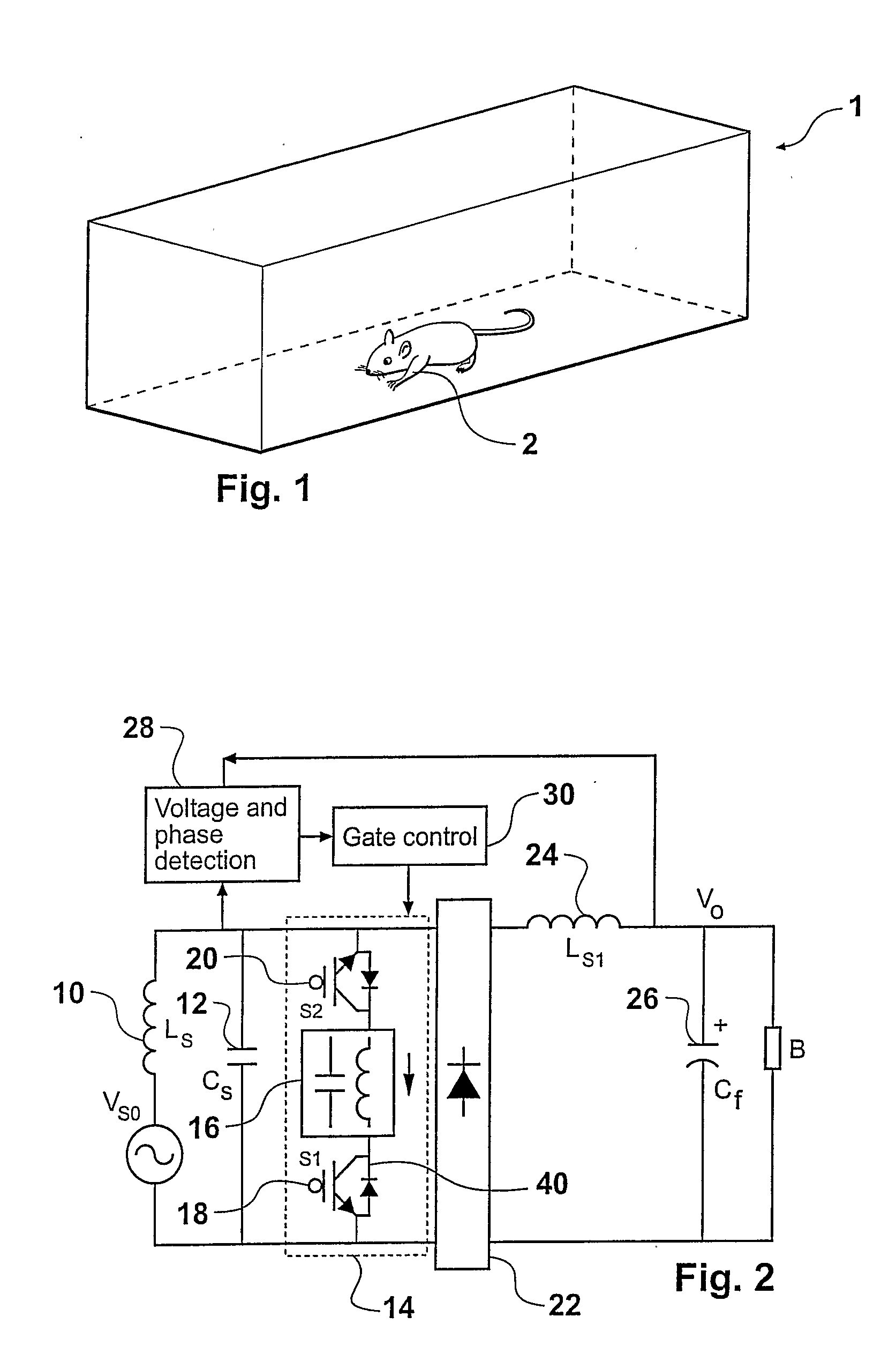

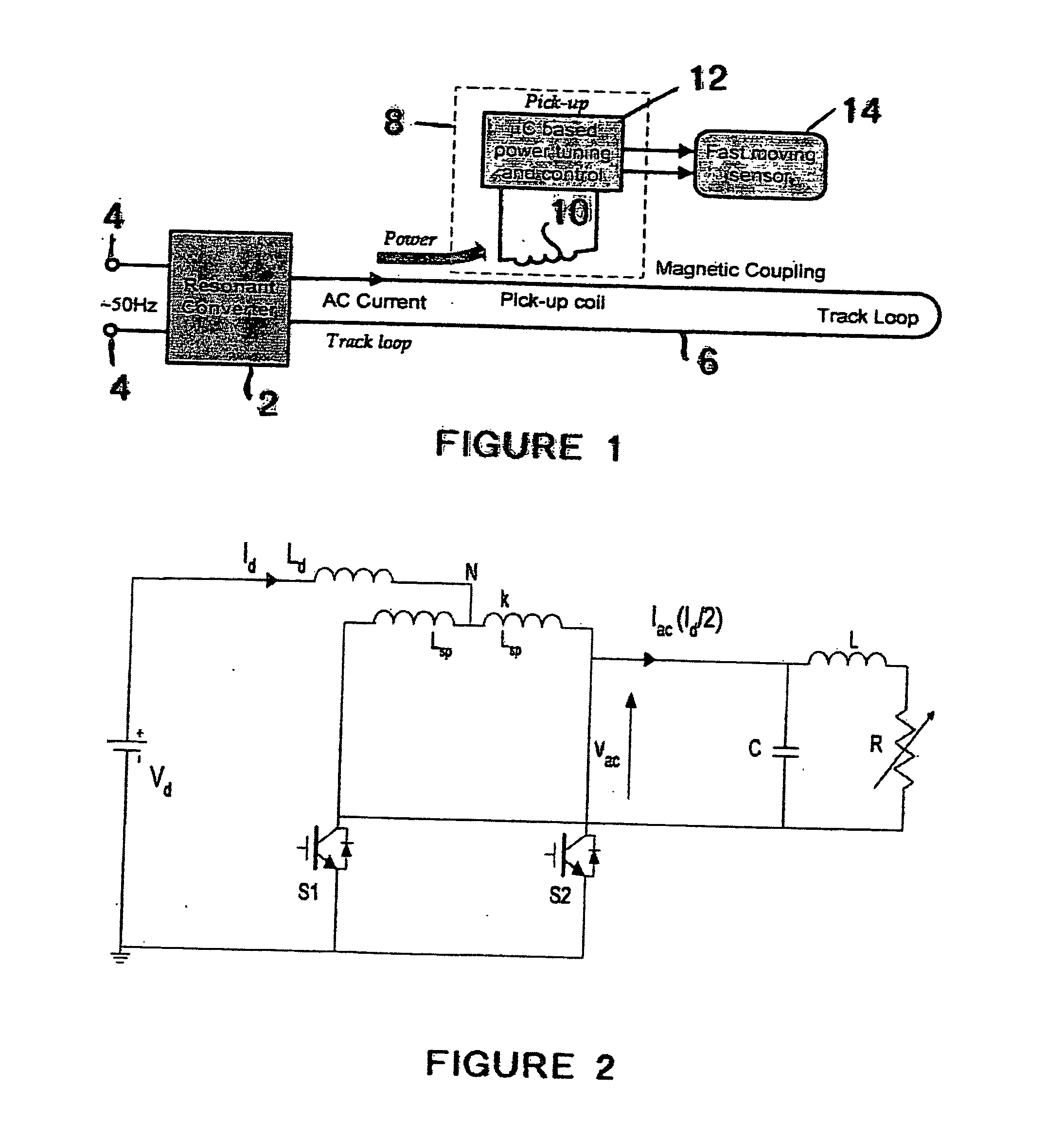

Inductively Powered Mobile Sensor System

ActiveUS20070296393A1Batteries circuit arrangementsElectromagnetic wave systemPower sensorEngineering

The present invention provides an inductively powered sensor system having a primary conductive path capable of being energized to provide an electromagnetic field in a defined space. An inductive power pick-up is associated with a sensor and is capable of receiving power from the field to supply the sensor. The system includes a first sensing unit to sense the power available to the pick-up and a control unit to increase or decrease the power available to the sensor dependant on the sensed power available. A method of inductively powering a sensor, an inductively powered sensor and an animal enclosure including one or more primary conductive path of an inductive power supply are also disclosed.

Owner:AUCKLAND UNISERVICES LTD

Power Converter Employing Regulators with a Coupled Inductor

A power converter includes a power train with a coupled inductor and a plurality of regulators, and method of forming and operating the same. In one embodiment, the power train includes a coupled inductor including a magnetic core with a common leg, a first leg and a second leg. The coupled inductor also includes a common winding formed around the common leg, and first and second windings. The first winding is formed around the first leg, and is electrically and magnetically coupled to the common winding. The second winding is formed around the second leg, and is electrically and magnetically coupled to the common winding. The power train also includes a first regulator including a first main switch coupled to the first winding and a second regulator including a second main switch coupled to the second winding.

Owner:MYPAQ HLDG LTD

Multi-track integrated spiral inductor

InactiveUS6885275B1Resonant circuit detailsSemiconductor/solid-state device detailsSpiral inductorEngineering

An integrated circuit inductor includes a spiral pattern disposed upon a substrate. The track of the spiral is divided into multiple tracks to form a multi-track inductor. The individual tracks are disposed side by side and in different layers. Tracks that are aligned vertically are coupled by feed throughs, or vias. Multiple vias are used along the length of each of the multiple tracks. Tracks disposed in the same layer are joined together at their beginning, and at their termination. A patterned shield is fabricated from conductive fingers of n+ salicided material that is separated by non conducting polysilicon that fills the gaps between the fingers. The conductive fingers are coupled together in groups, which are in turn tied to a single point ground. In tying the groups together, a gap in the conducting path is provided to prevent ground loop currents. The shield is disposed between the multi-track inductor and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

Current source with indirect load current signal extraction

A switching circuit for supplying current to a load has a switching element, an inductive element coupled to the switching element, and a load current extraction circuit responsive to current in the inductive element for producing a load current signal as a simulated current approximating current in the load.

Owner:ANALOG DEVICES INT UNLTD

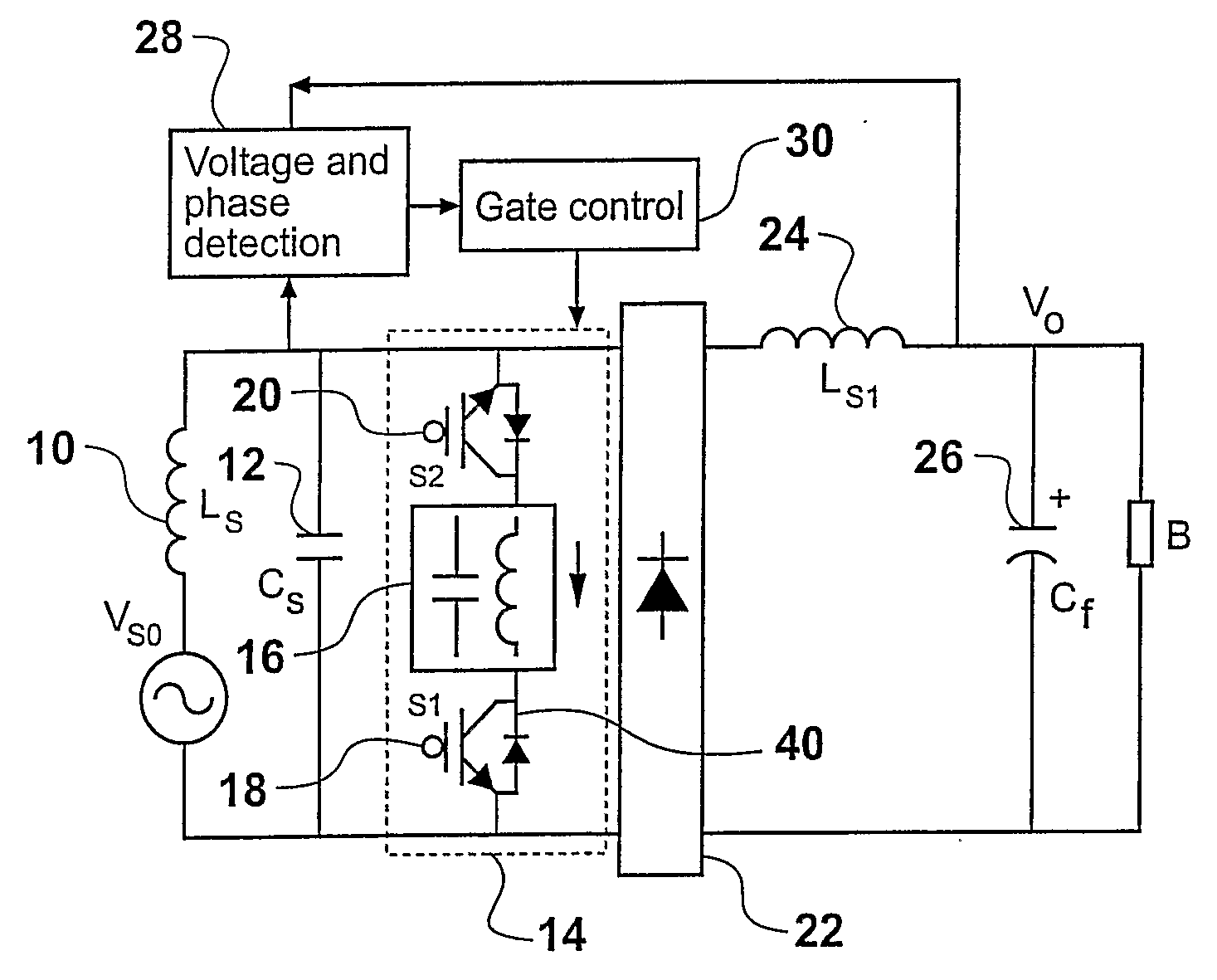

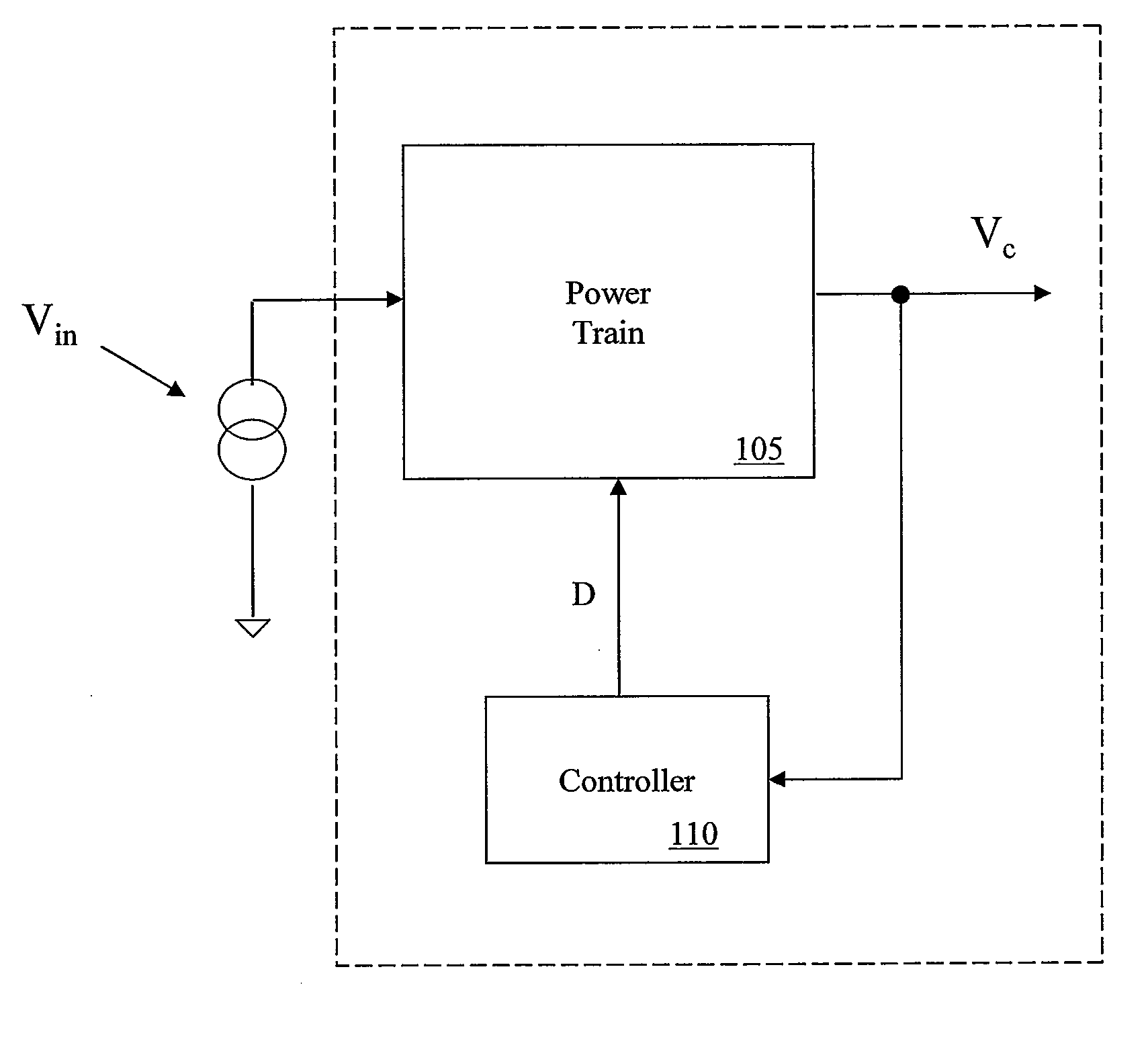

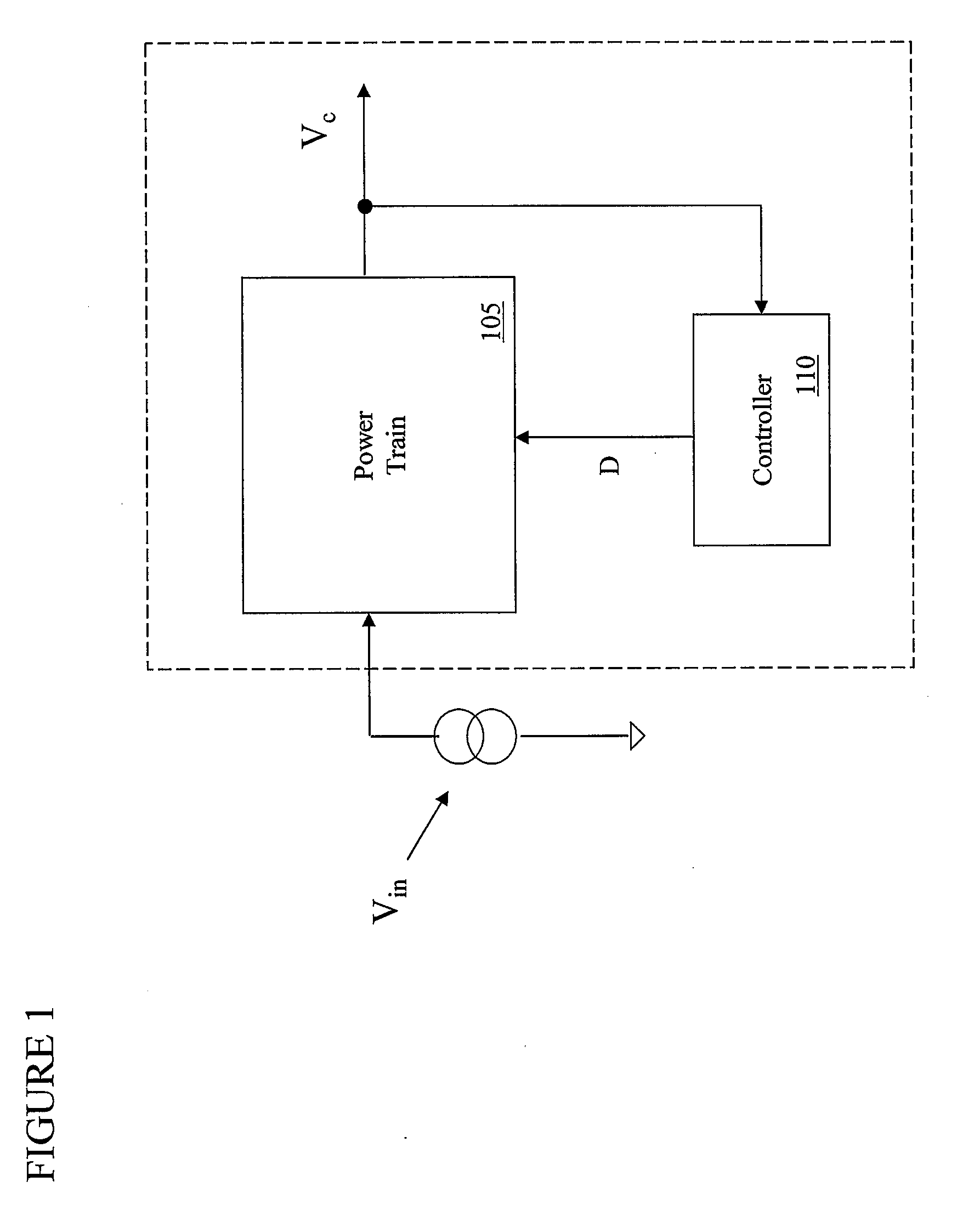

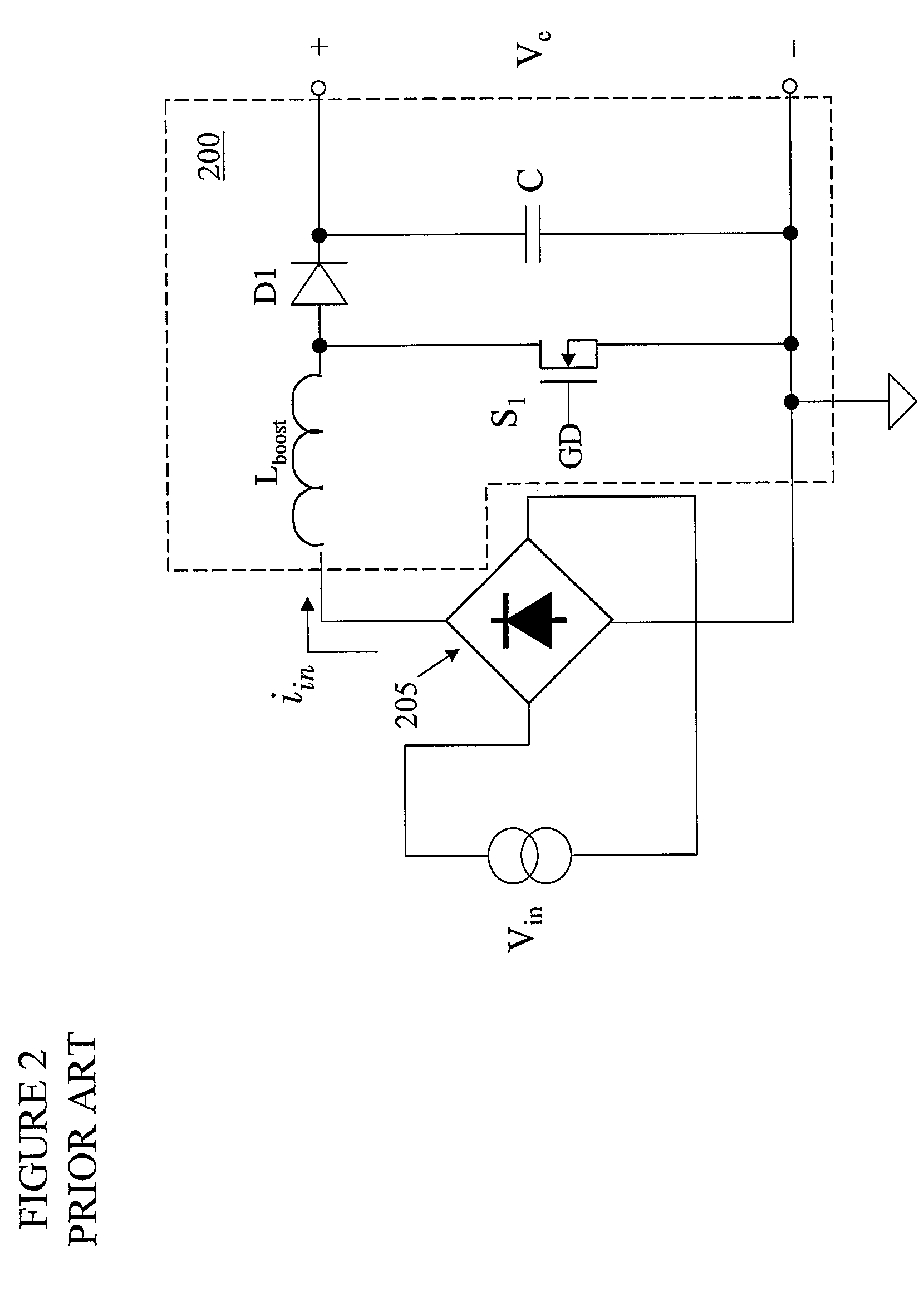

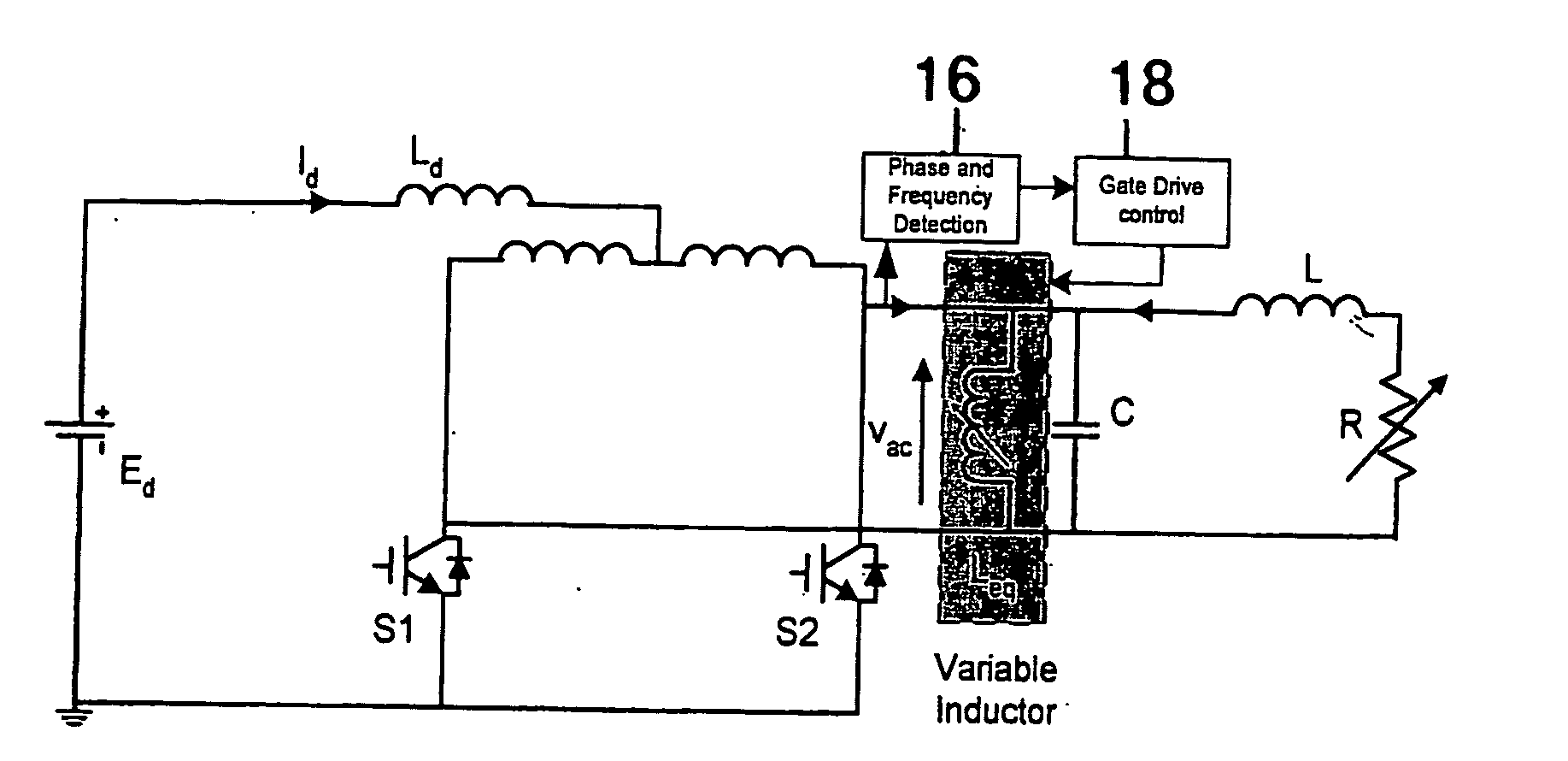

Frequency Controller Resonant Converter

ActiveUS20080211478A1Overcome disadvantagesEfficient power electronics conversionDc-dc conversionElectricityCapacitance

A resonant converter is provided which may be used for supplying power to the primary conductive path of an inductively coupled power transfer (ICPT) system. The converter includes a variable reactive element in the resonant circuit which may be controlled to vary the effective inductance or capacitance of the reactive element. The frequency of the converter is stabilised to a nominal value by sensing the frequency of the converter resonant circuit, comparing the sensed frequency with a nominal frequency and varying the effective inductance or capacitance of the variable reactive element to adjust the converter frequency toward the nominal frequency.

Owner:AUCKLAND UNISERVICES LTD

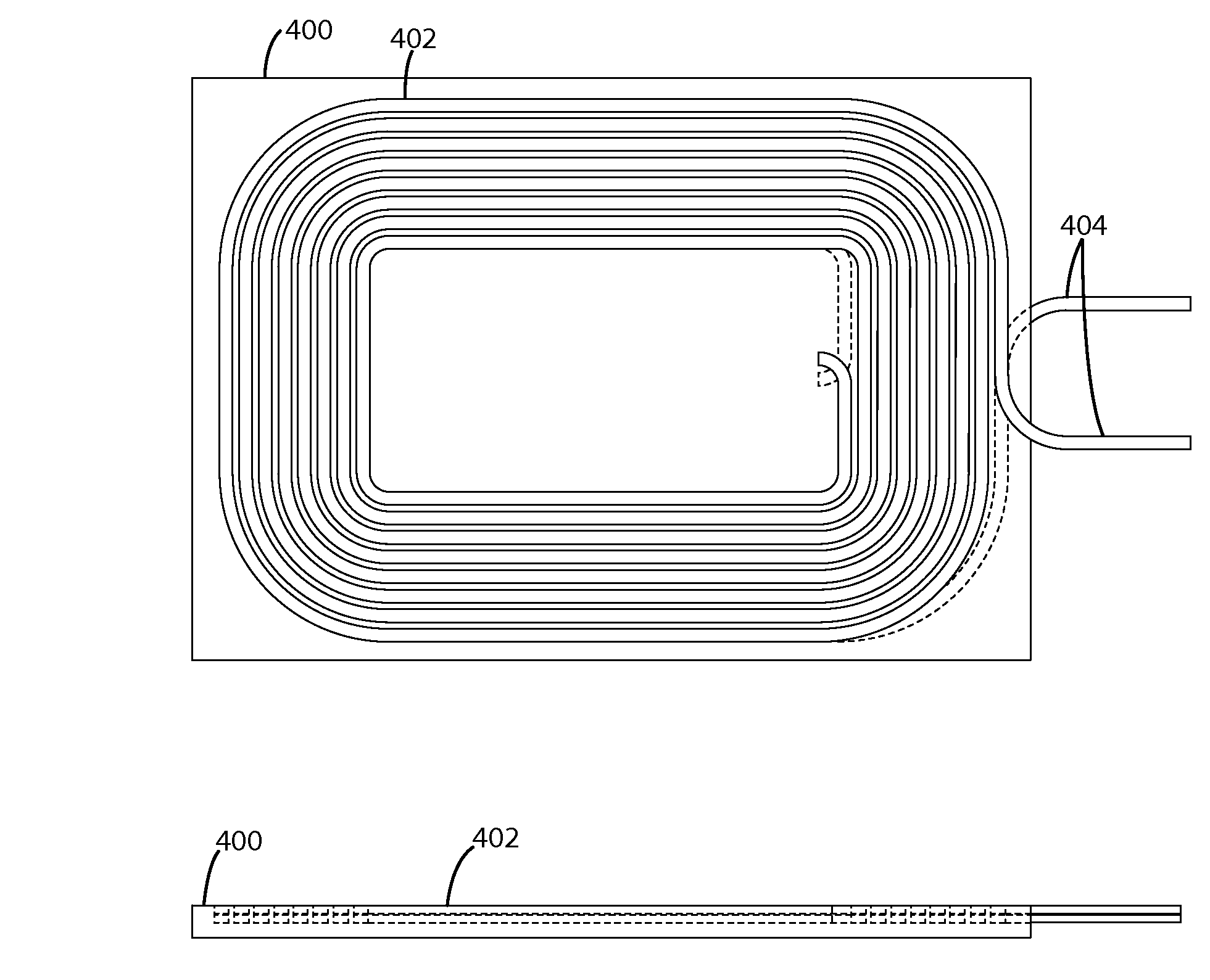

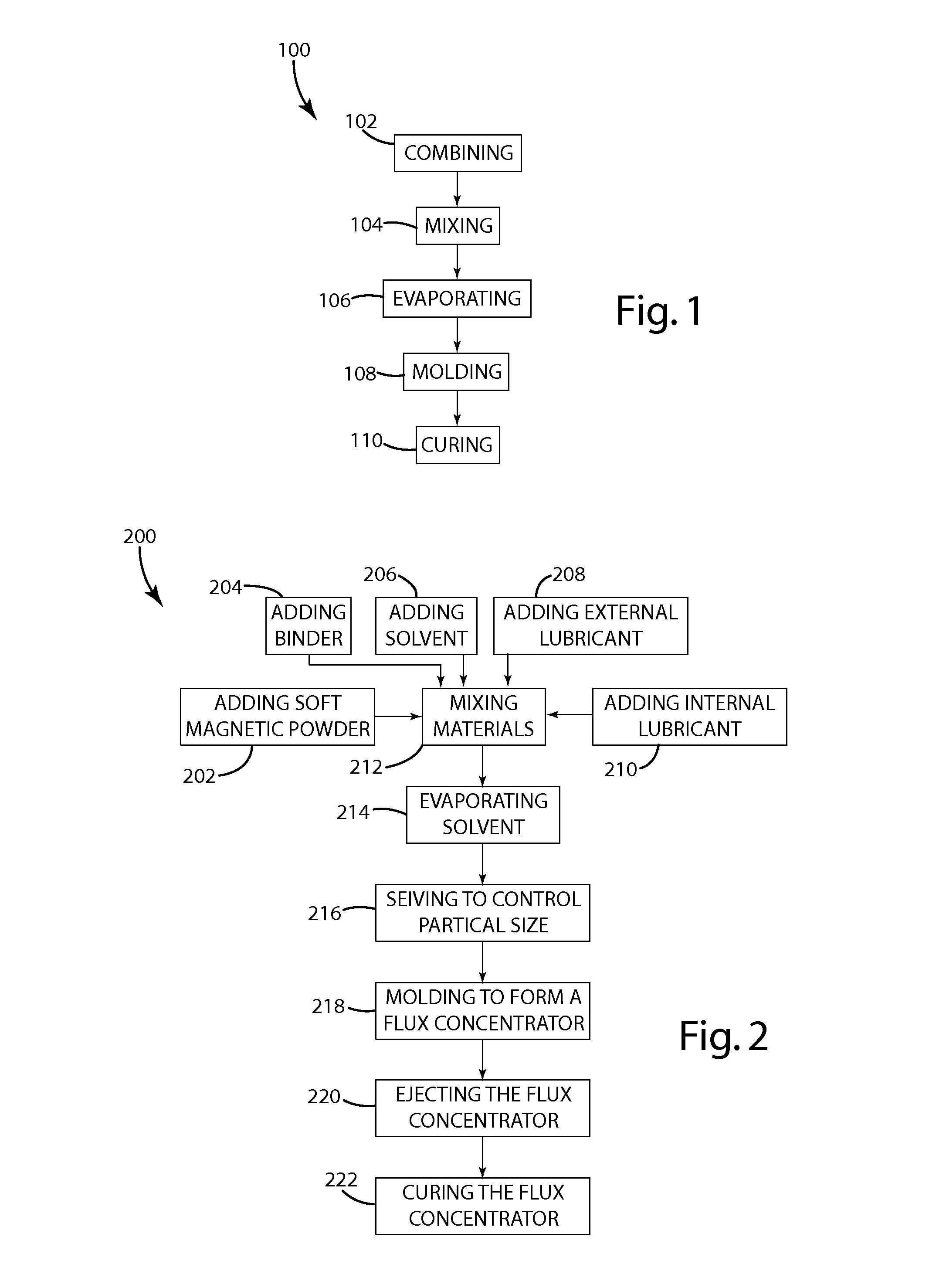

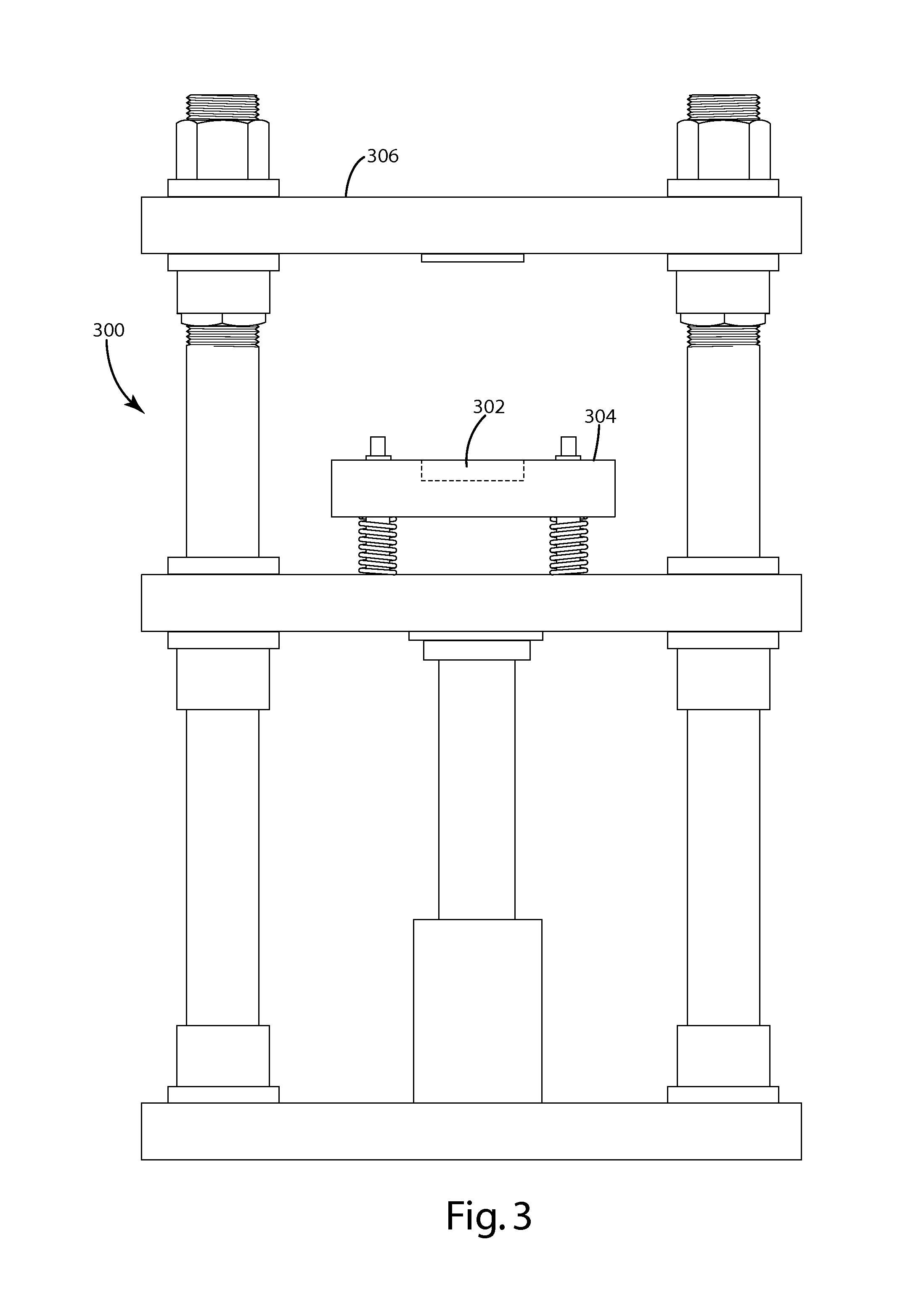

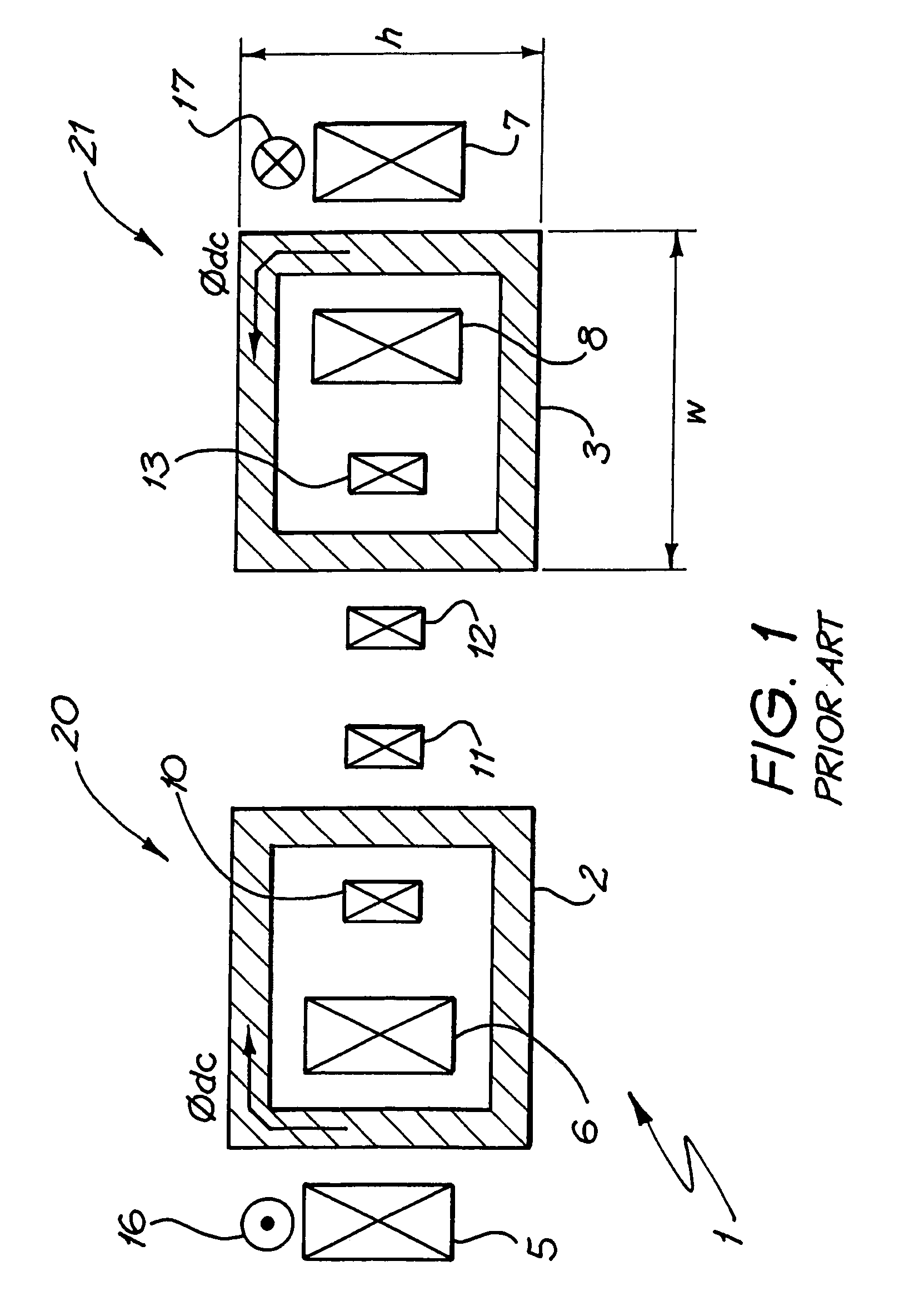

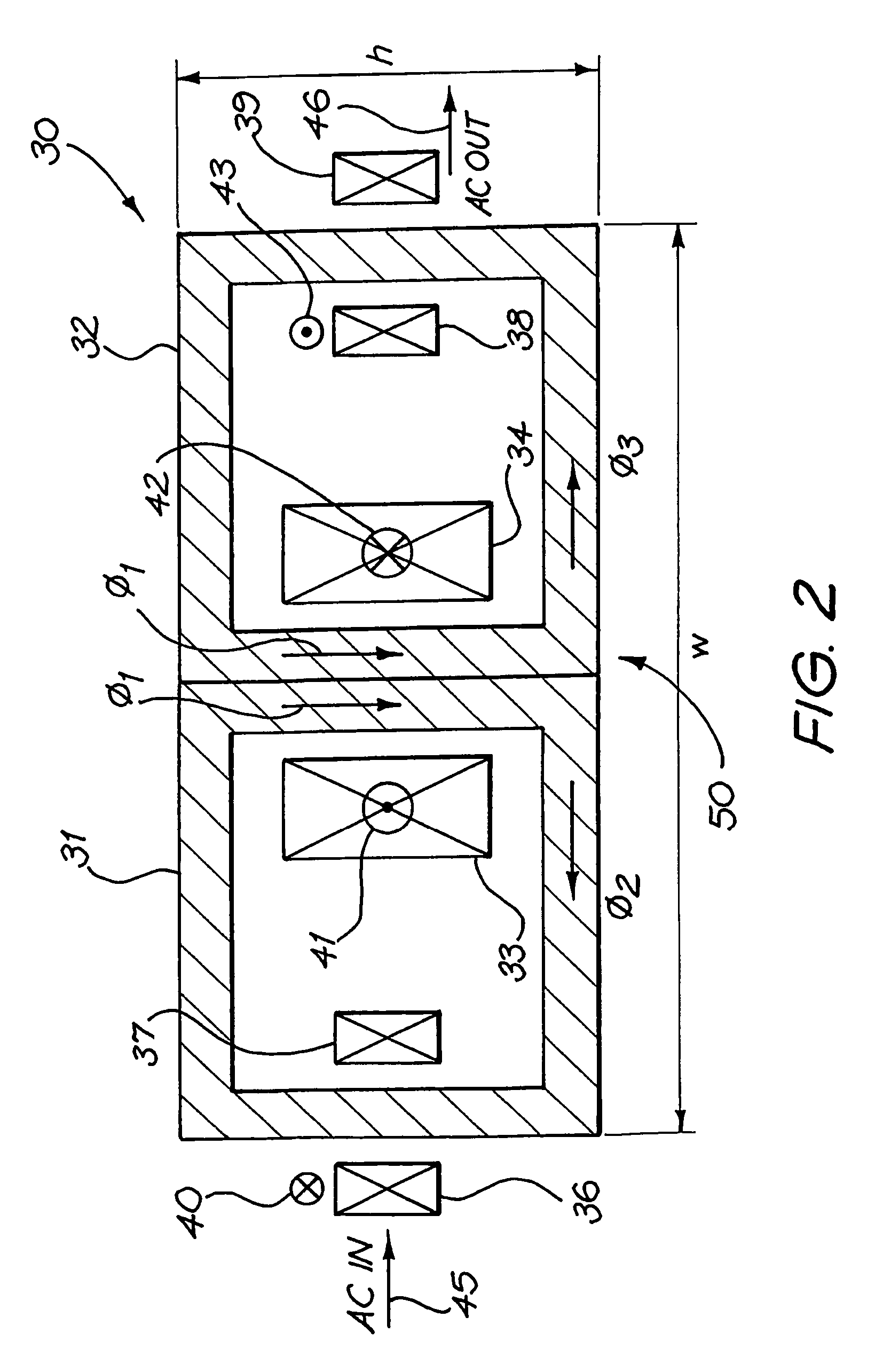

Flux concentrator and method of making a magnetic flux concentrator

ActiveUS8692639B2Fewer eddy currents formingSuitable characteristicTransformersTransformers/inductances coils/windings/connectionsSolventMagnetic flux

A flux concentrator and method for manufacturing a flux concentrator is provided. The method can include combining powdered soft magnetic material, a binder, a solvent, a internal lubricant; mixing the materials to create a mixture, evaporating the solvent from the mixture, molding the mixture to form a flux concentrator, and curing the flux concentrator. The flux concentrator may be laminated and broken into multiple pieces, which makes the flux concentrator more flexible. Breaking the flux concentrator does not significantly affect the magnetic properties. Since the permeability of the binder is very similar to that of air, adding tiny air gaps between the fractions is not significantly different than adding more binder.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

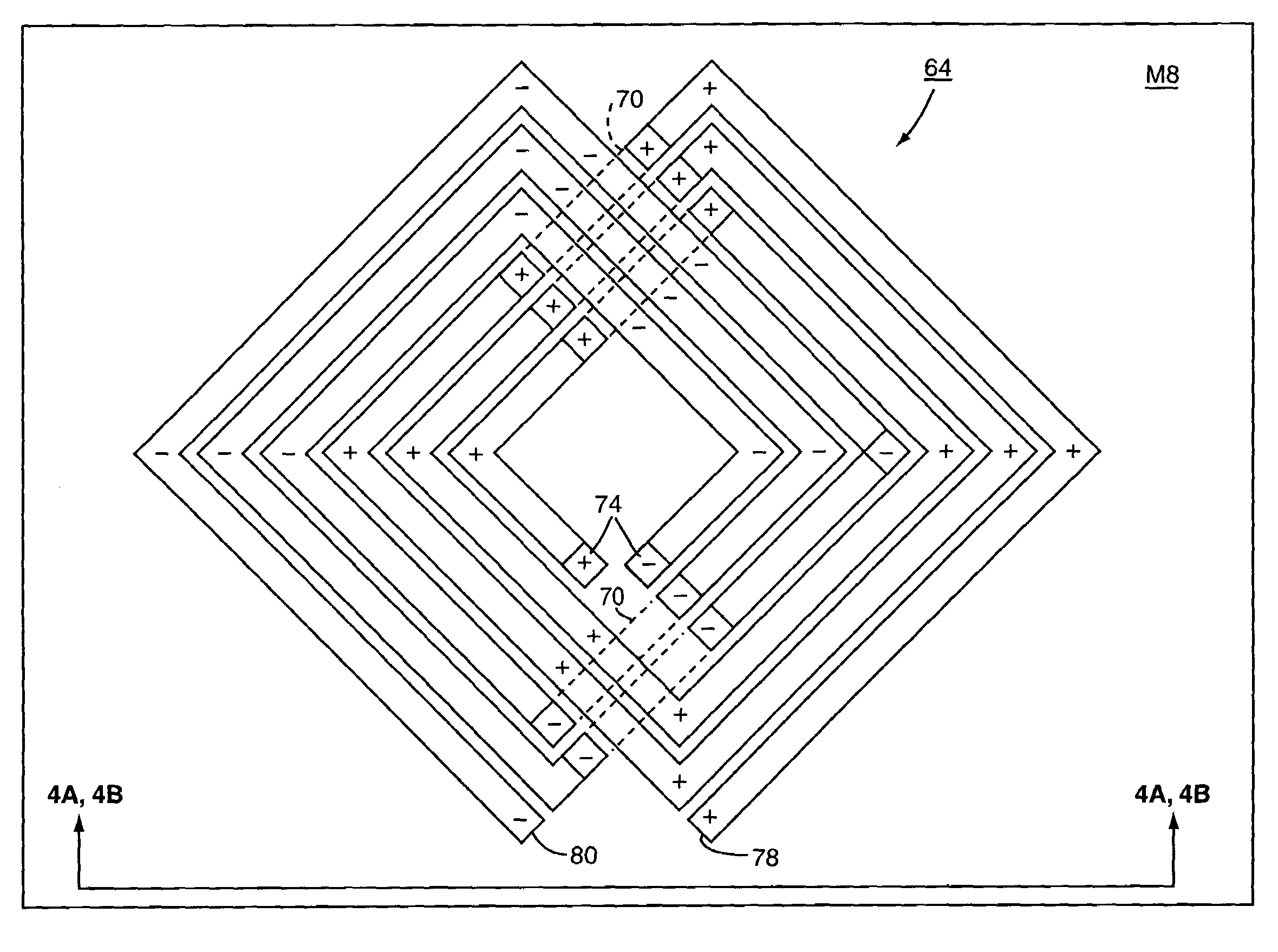

Differential inductor design for high self-resonance frequency

ActiveUS6972658B1Low effective capacitanceRaise the self-resonant frequencySemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

A differential inductor is formed from branch coils that are staggered with respect to one another rather than concentrically coiled within one another. Each coil is formed from conductive strips. The conductive strips with the largest voltage swings thereon are shielded from one another by conductive strips with lower voltage swings thereon. This shielding allows the effective capacitance of the differential inductor to be lowered, which in turn raises the range of frequencies at which the differential inductor can operate.

Owner:QORVO US INC

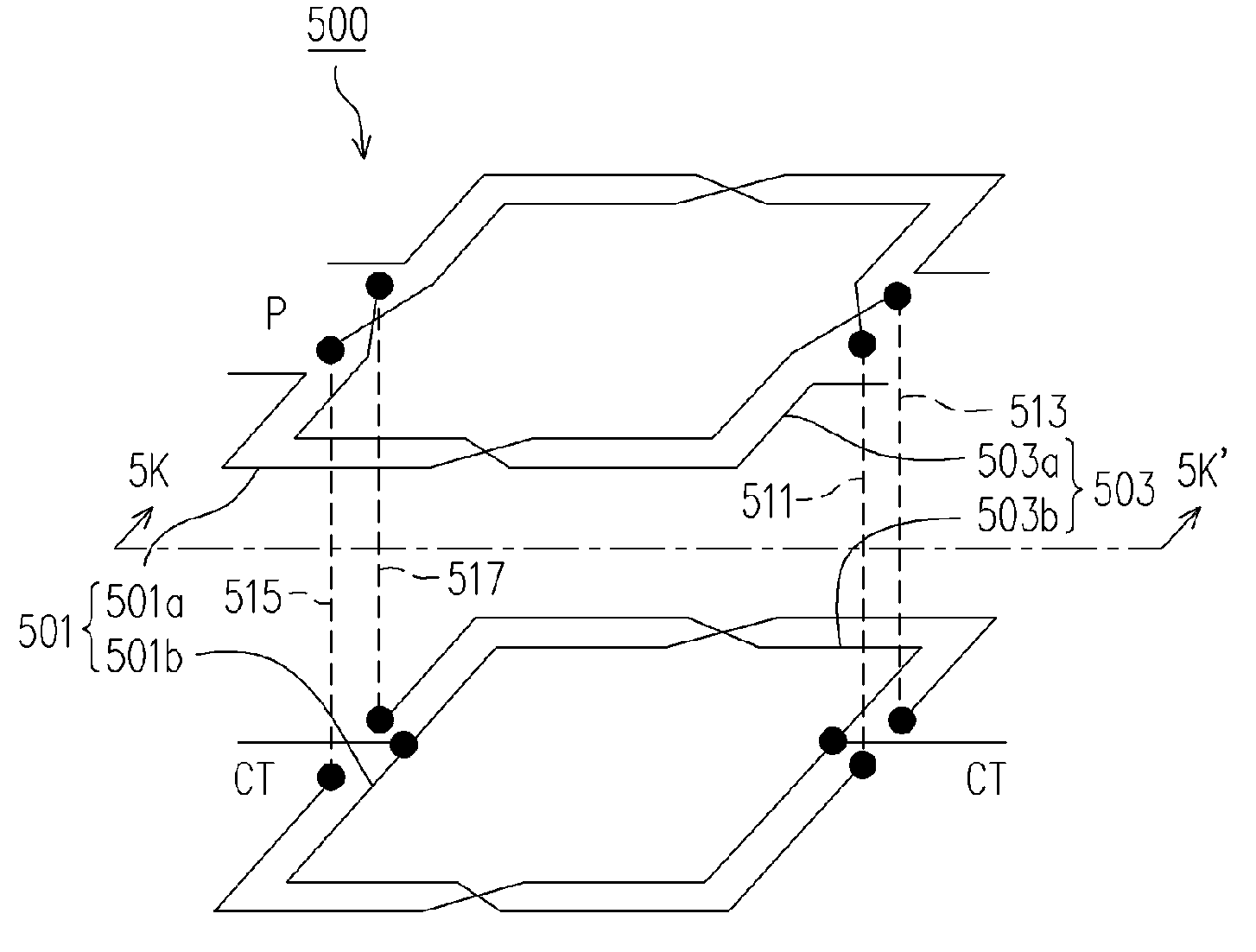

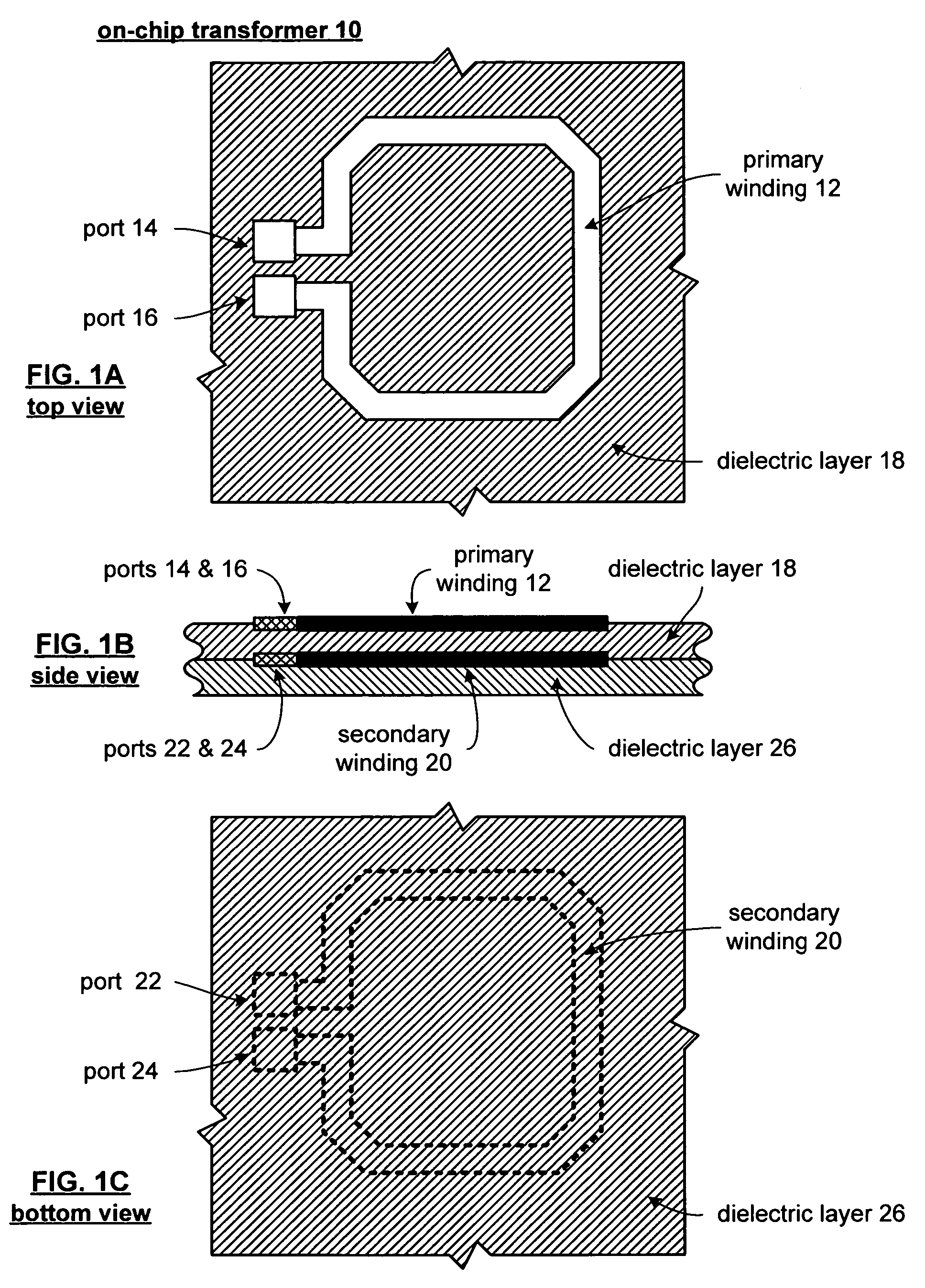

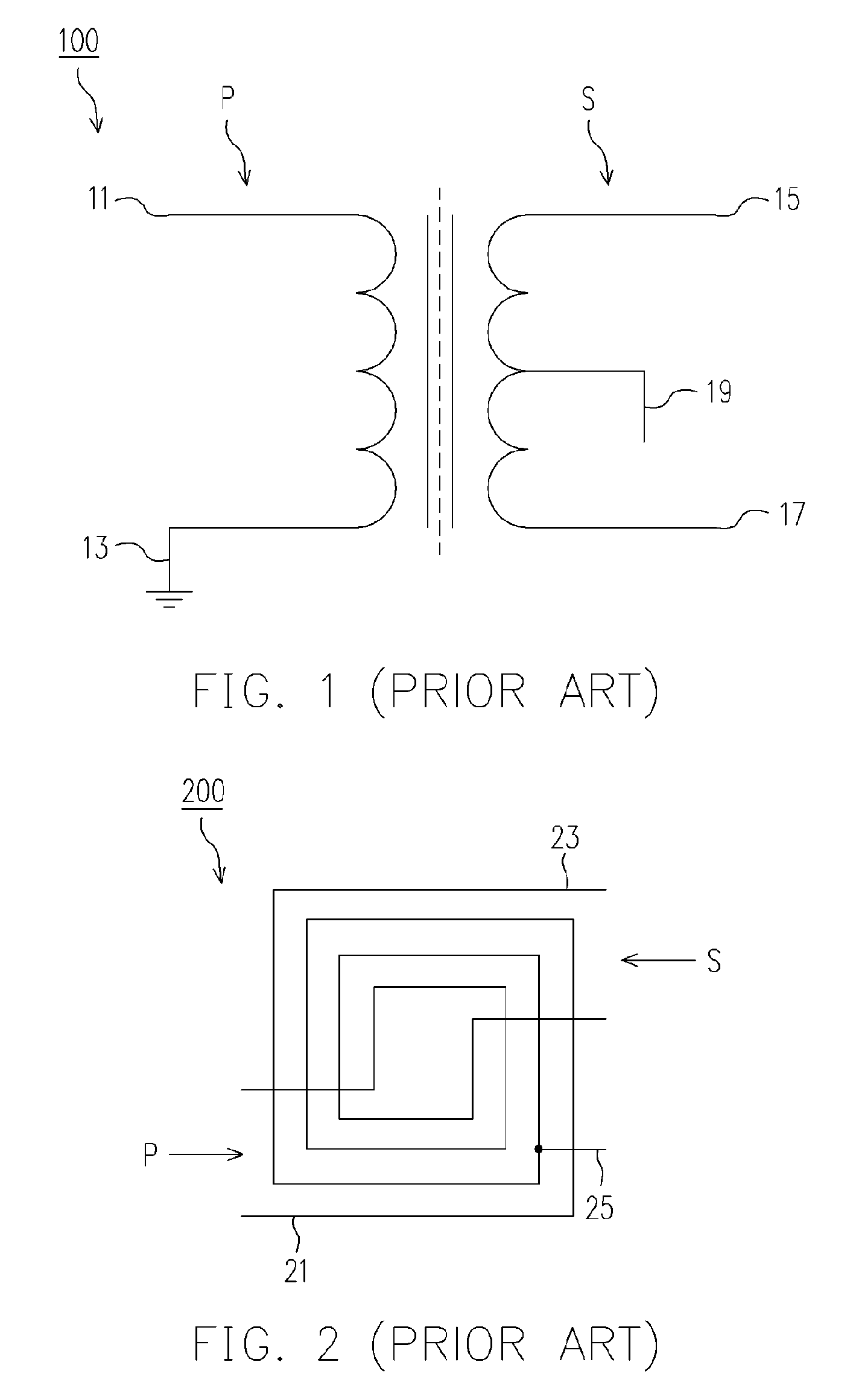

Integrated transformer with stack structure

ActiveUS7164339B2Precise positioningReduced insertion lossTransformers/inductances coils/windings/connectionsSolid-state devicesTransformerConductor Coil

An integrated transformer with a stack structure comprises a middle dielectric layer, a bottom dielectric layer, a first winding and a second winding. A portion of the first winding is disposed over a surface of the middle dielectric layer and the remaining portion of the first winding is disposed over a surface of the bottom dielectric layer. A portion of the second winding is disposed over the surface of the middle dielectric layer and the remaining portion of the second winding is disposed over the surface of the bottom dielectric layer. The second winding doesn't intersect with the first winding. The portions of the first and second windings over the surface of the middle dielectric layer connect with the remaining portions of the first and second windings over the surface of the bottom dielectric through via plugs.

Owner:WINBOND ELECTRONICS CORP

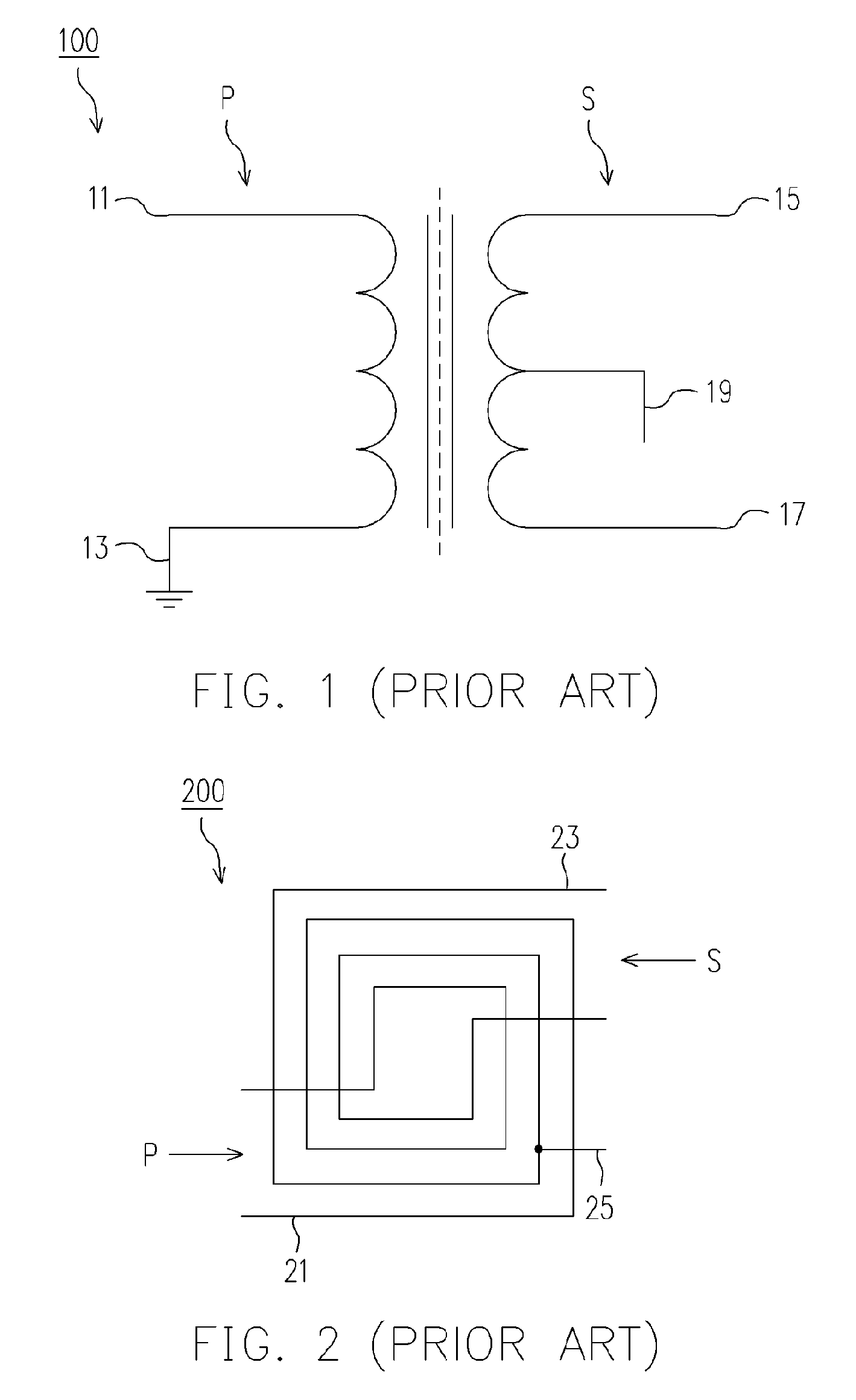

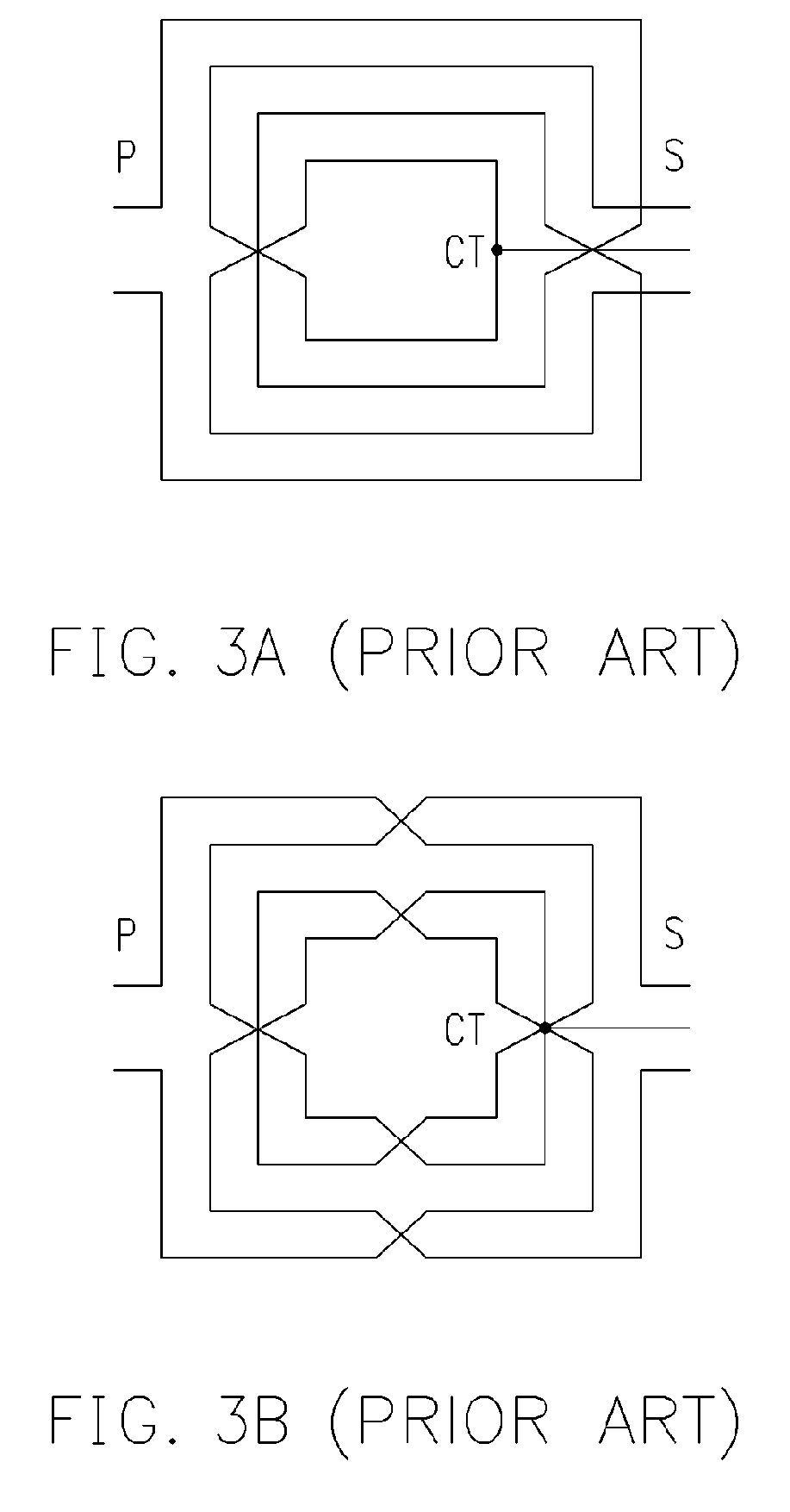

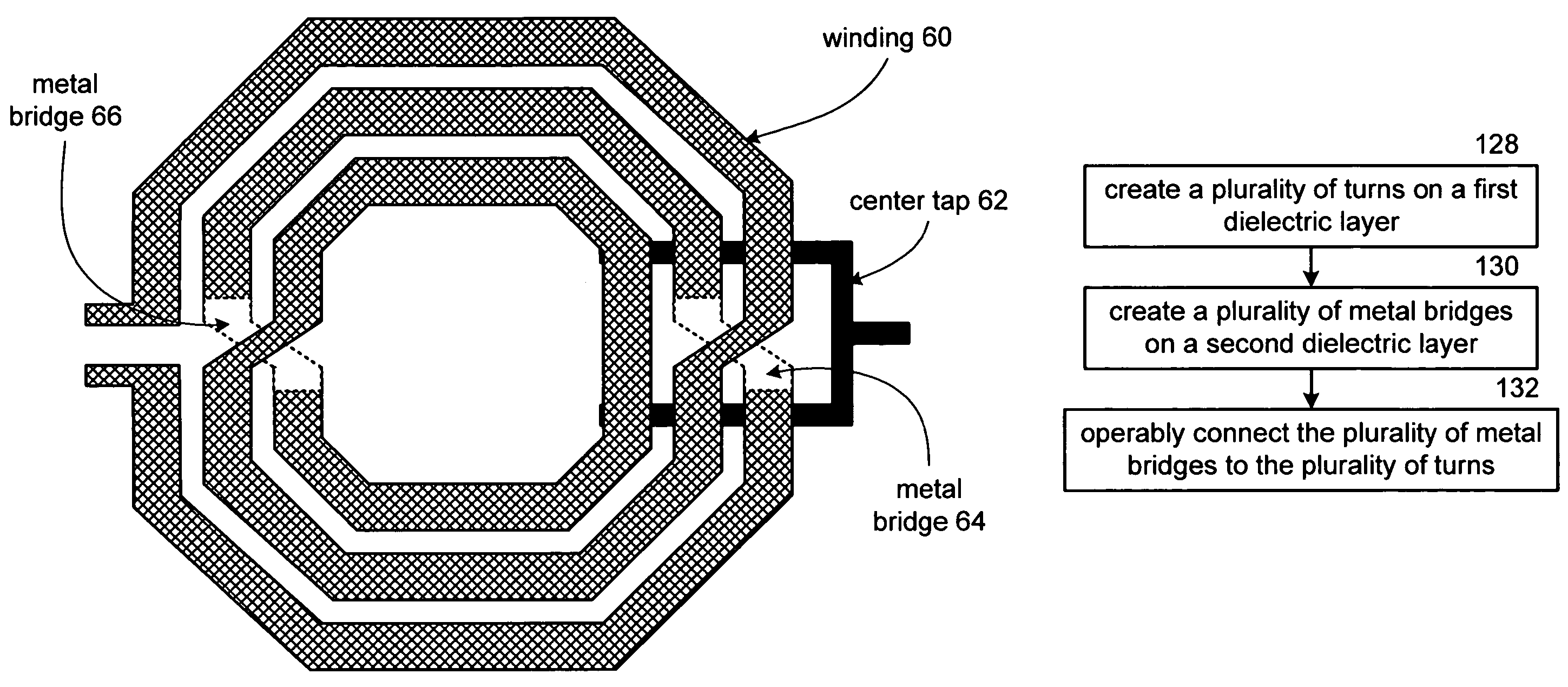

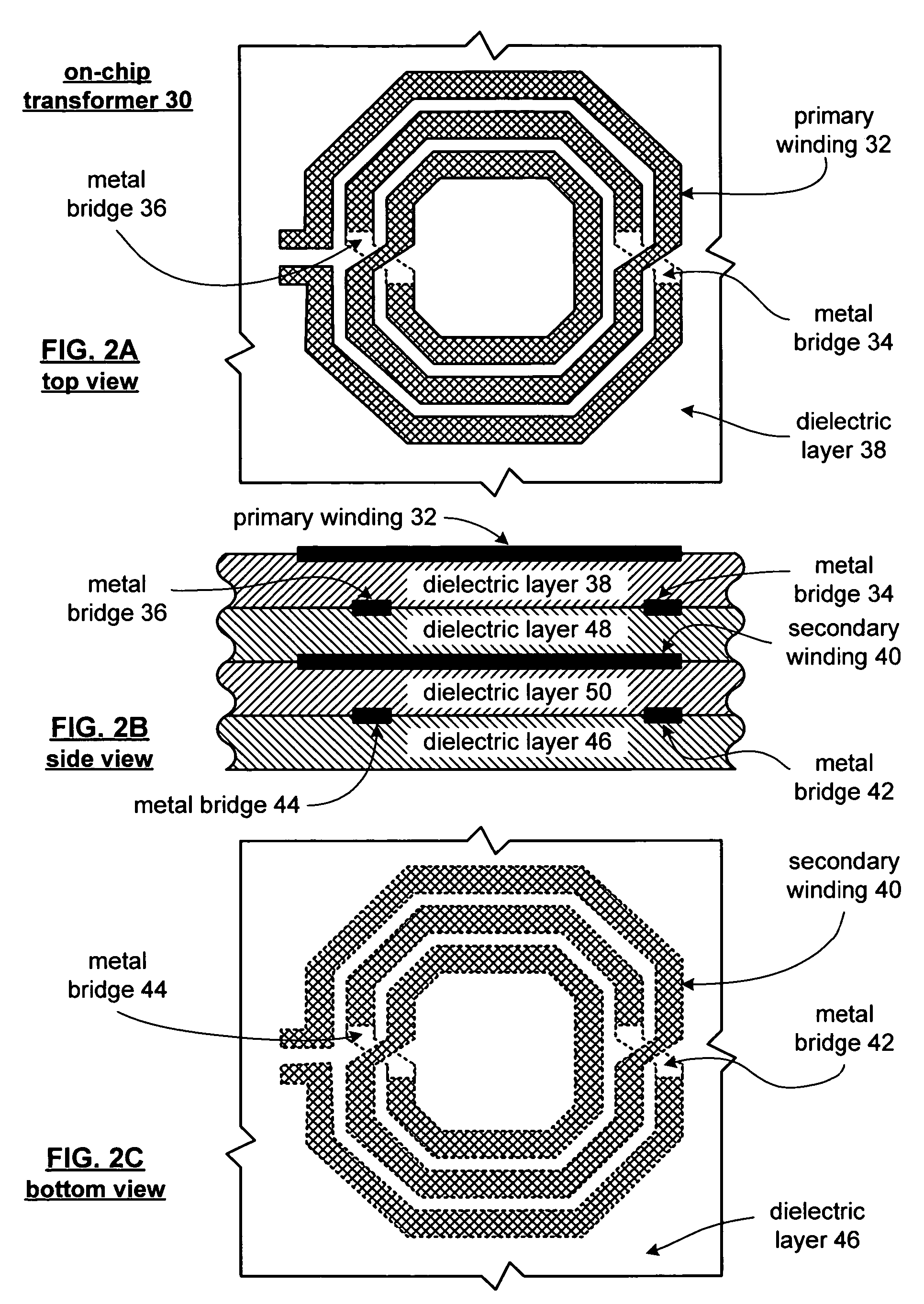

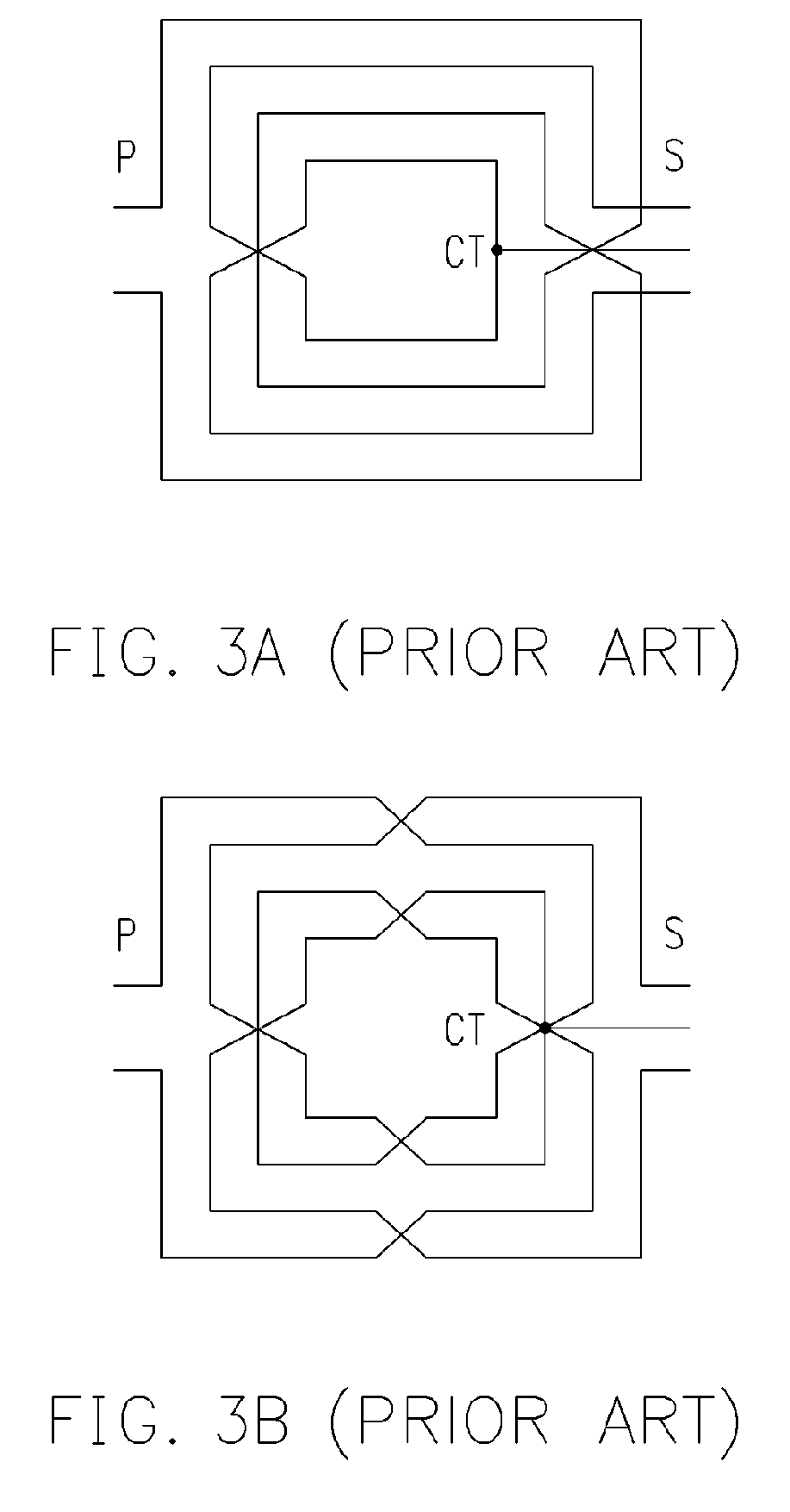

Method of manufacturing an on-chip transformer balun

A method of manufacturing an on-chip transformer balun includes creating, on a semiconductor substrate, a primary winding having at least one substantially symmetrical primary turn on a first dielectric layer and at least one metal bridge on a second layer. A secondary winding is created on the semiconductor substrate, the secondary winding having at least one substantially symmetrical secondary turn on a third dielectric layer and at least one metal bridge on a fourth dielectric layer. In an alternative embodiment, the primary winding has at least one first primary turn on a first dielectric layer and at least one second primary turn on a second dielectric layer and at least one via that operably connects the first primary turn to the second primary turn. The secondary winding has at least one first secondary turn on a third dielectric layer and at least one second secondary turn on a fourth dielectric layer.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

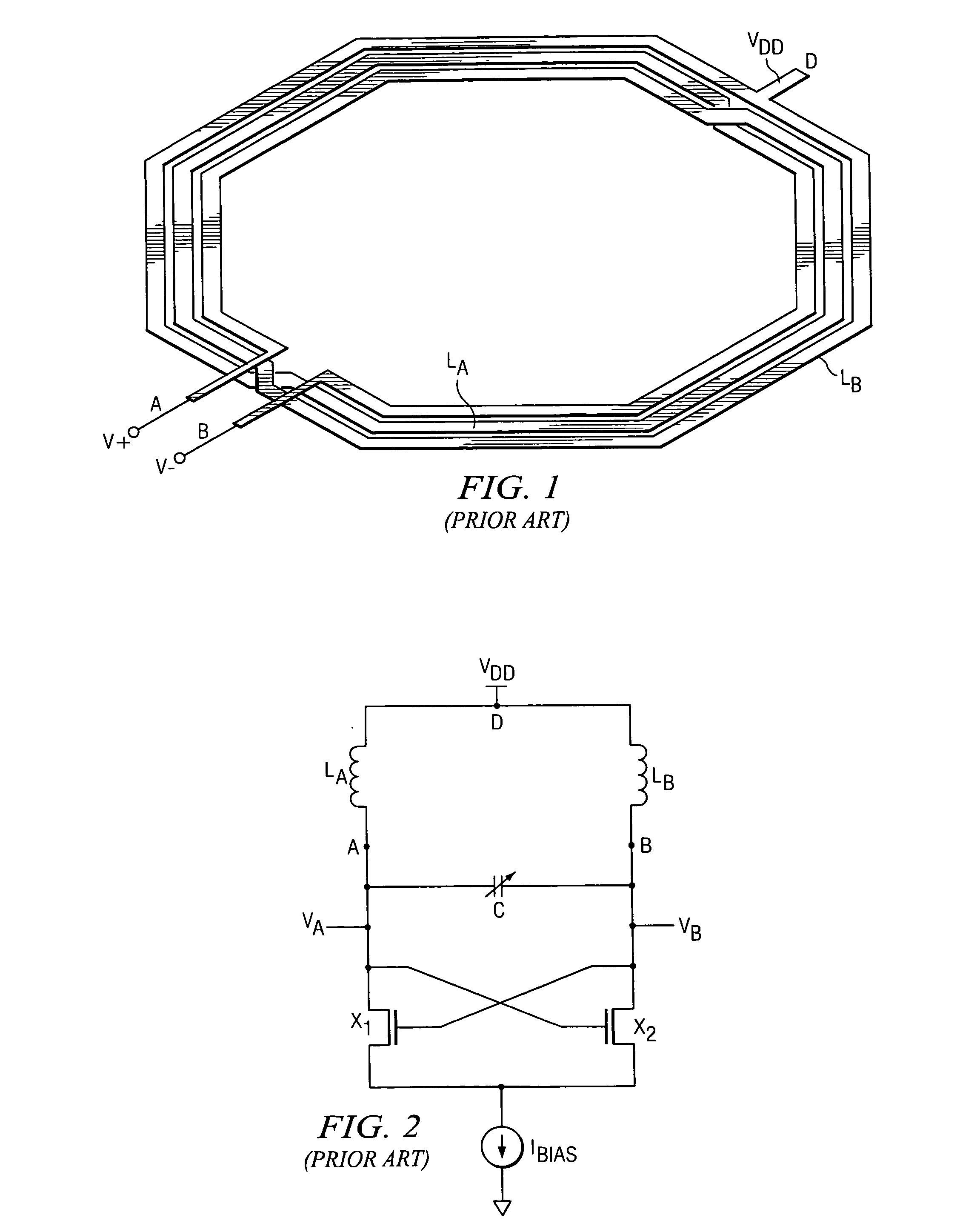

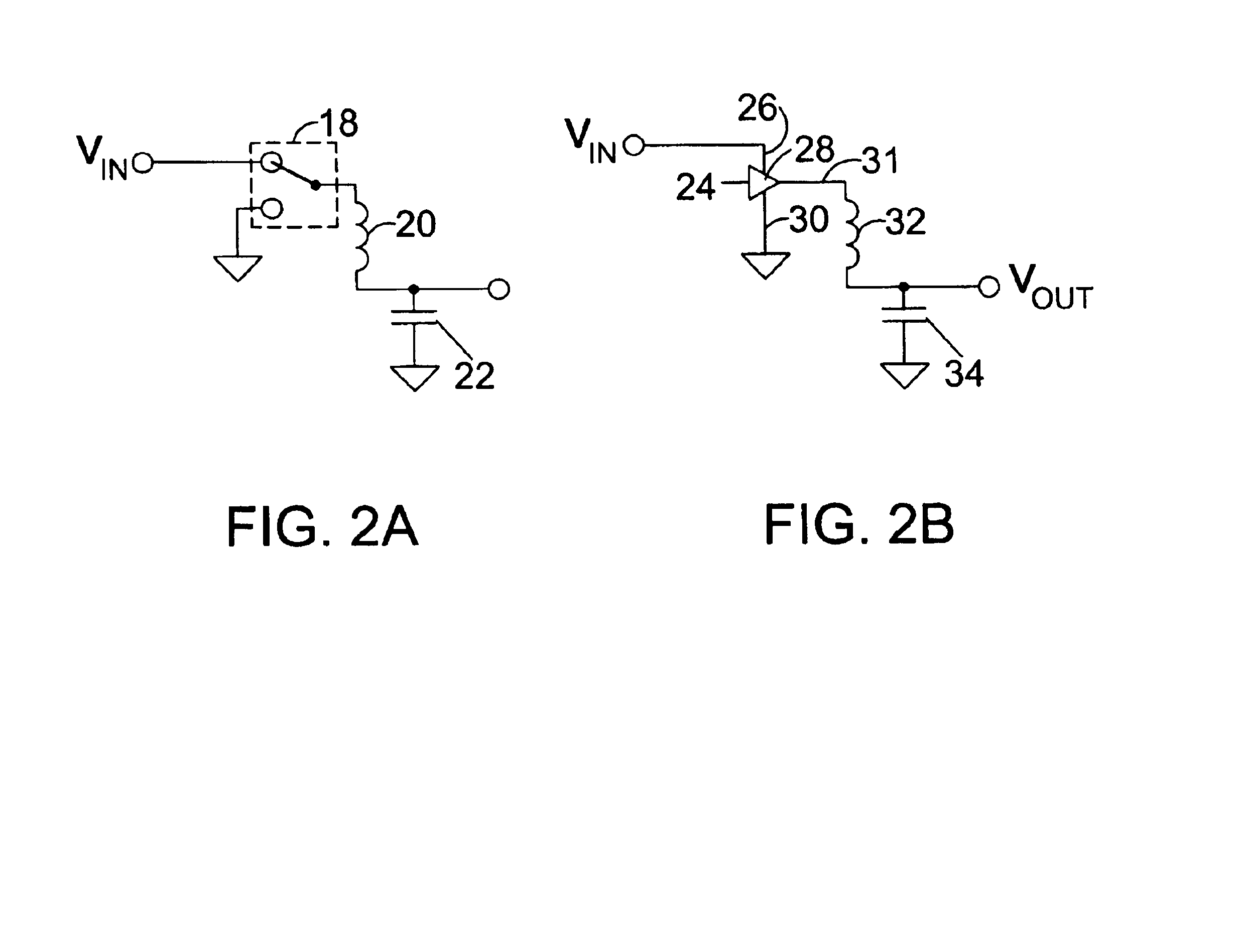

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS7019598B2Angle modulation by variable impedenceResonant circuit detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

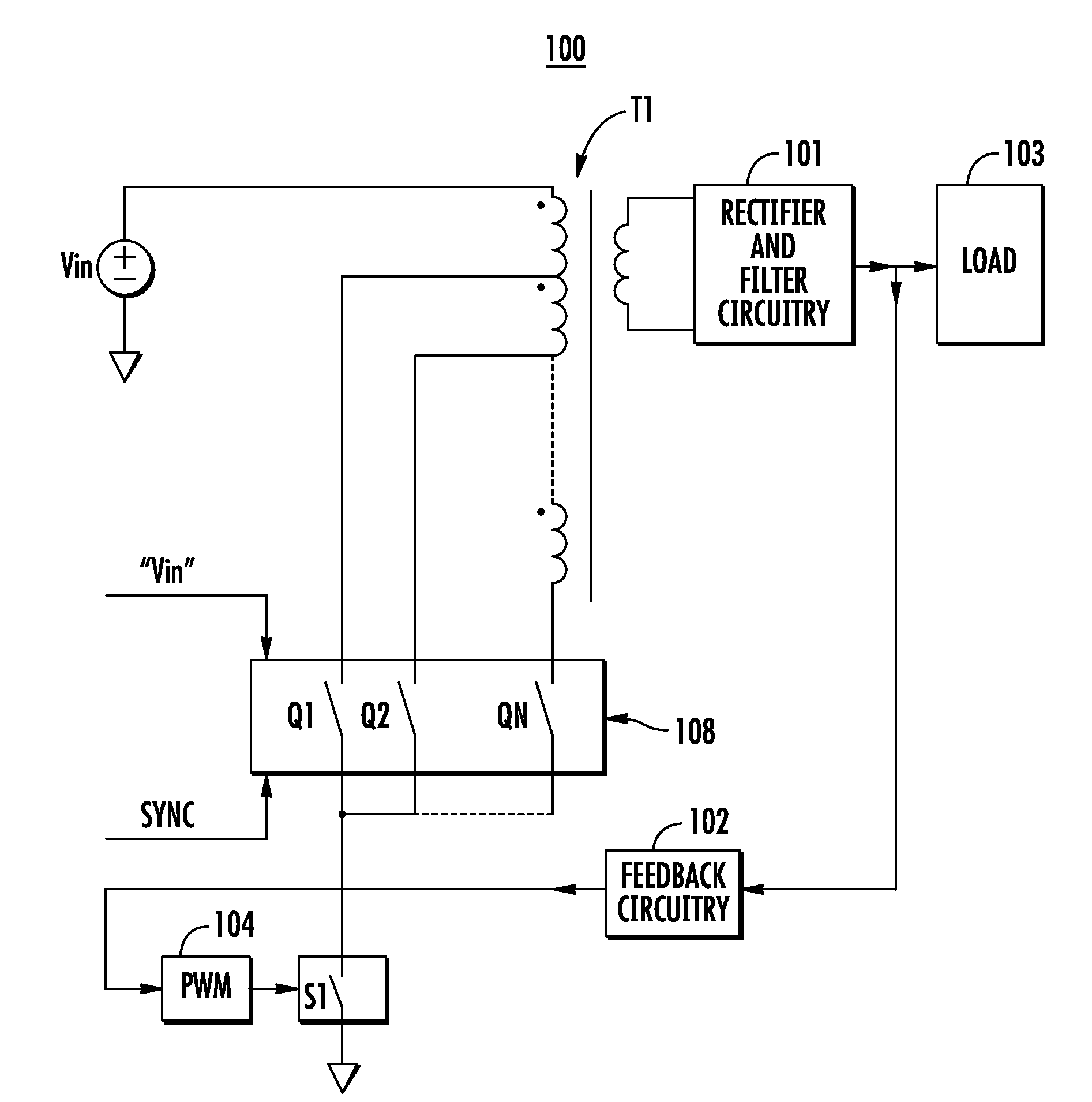

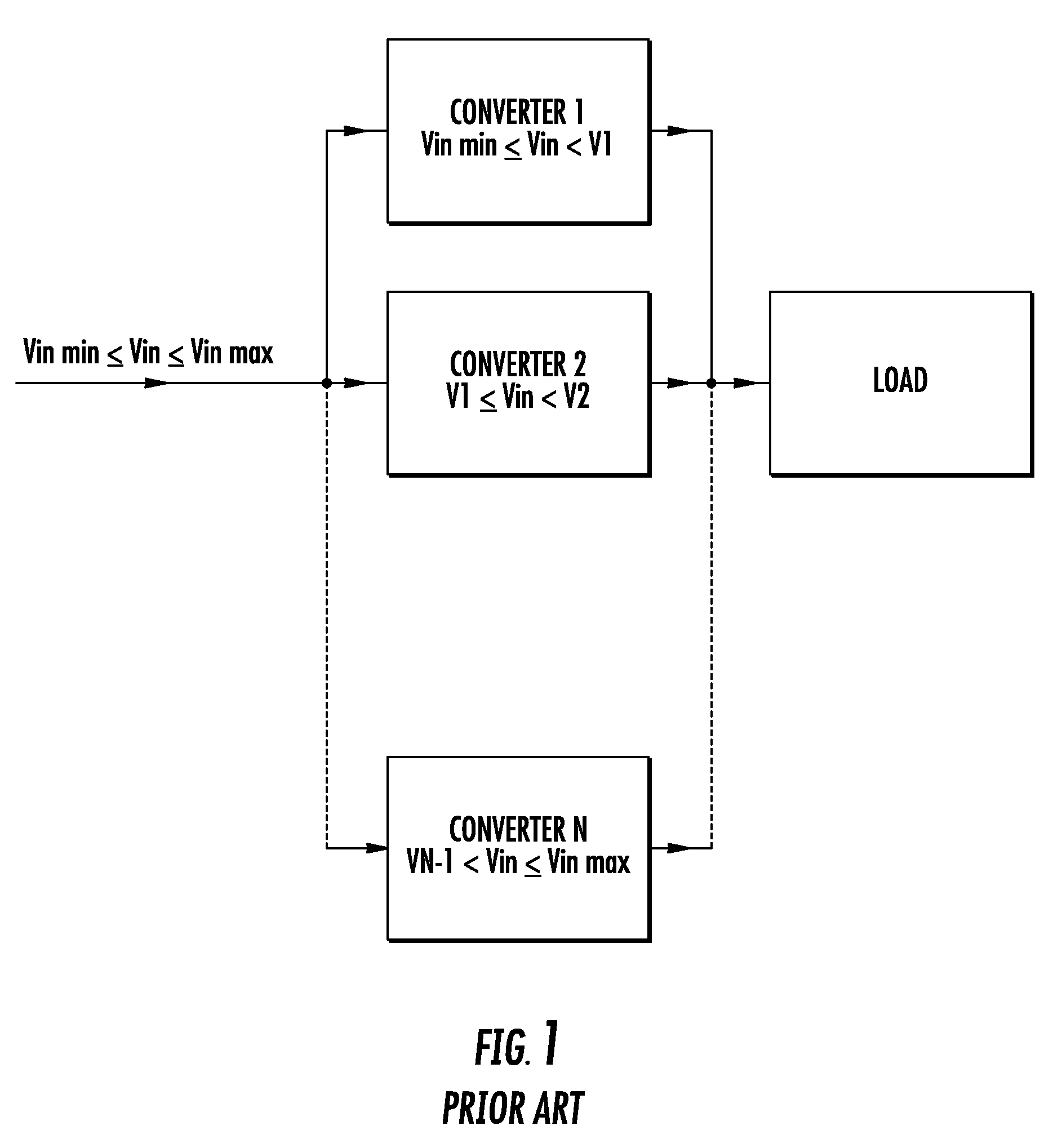

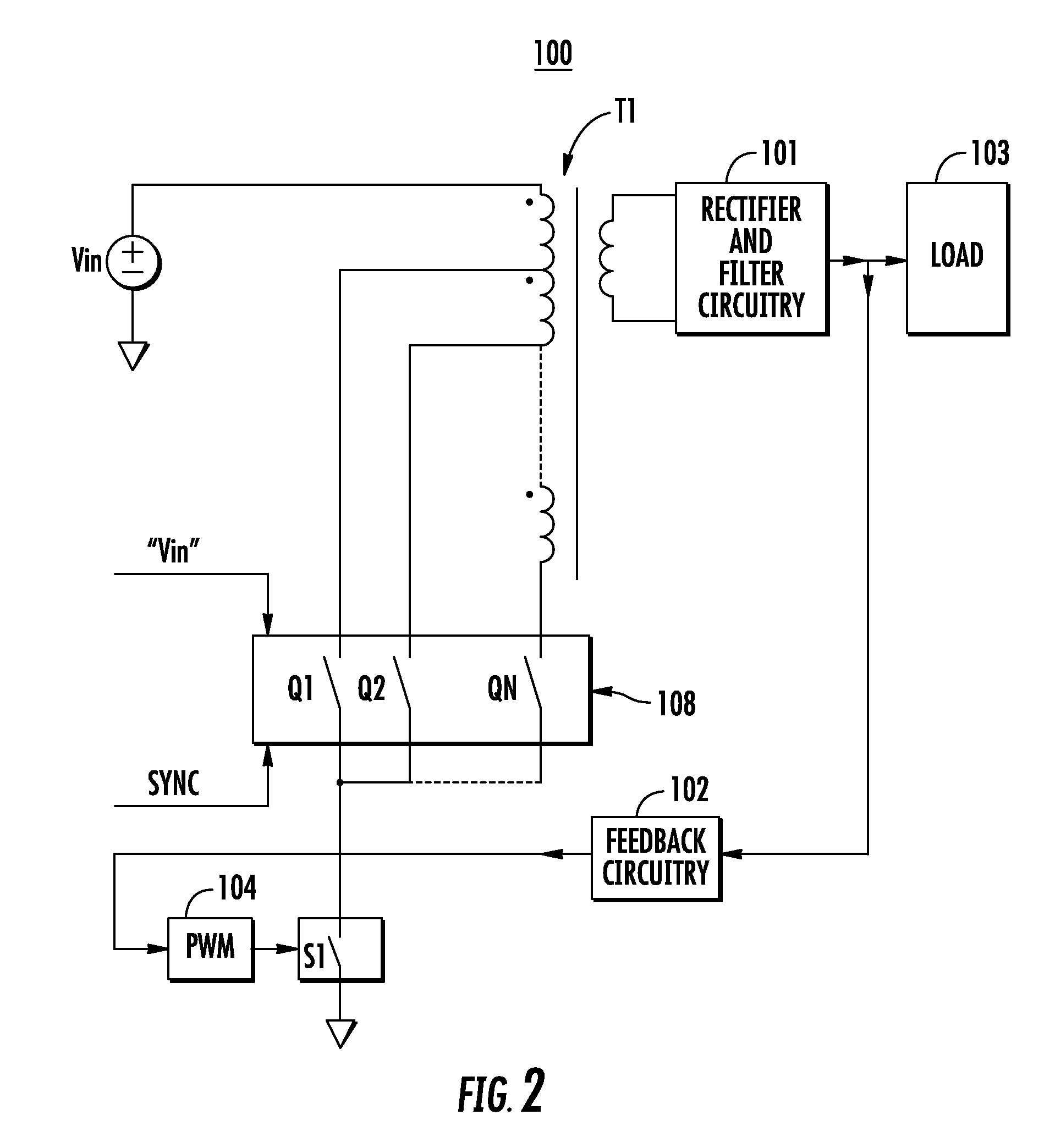

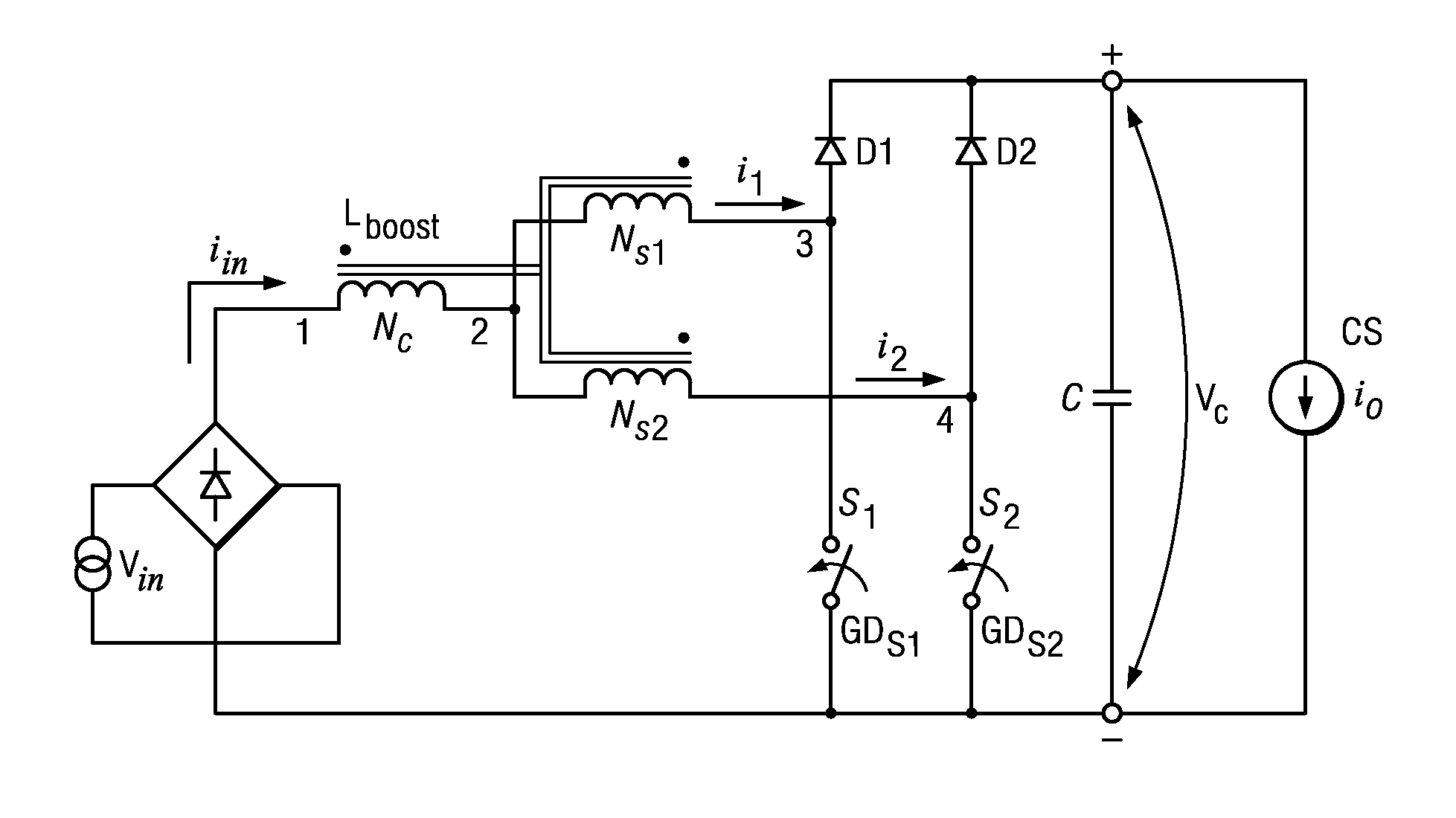

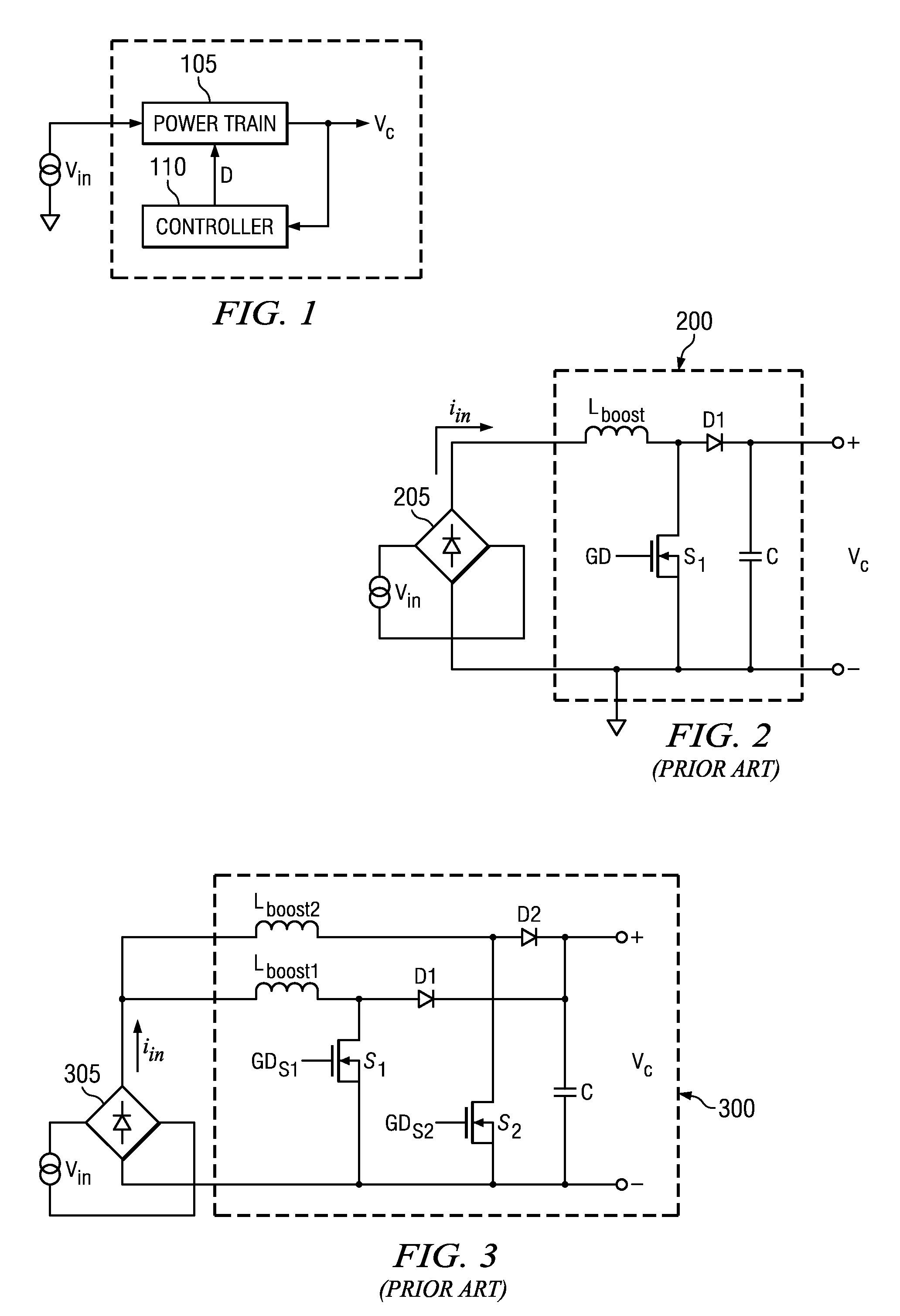

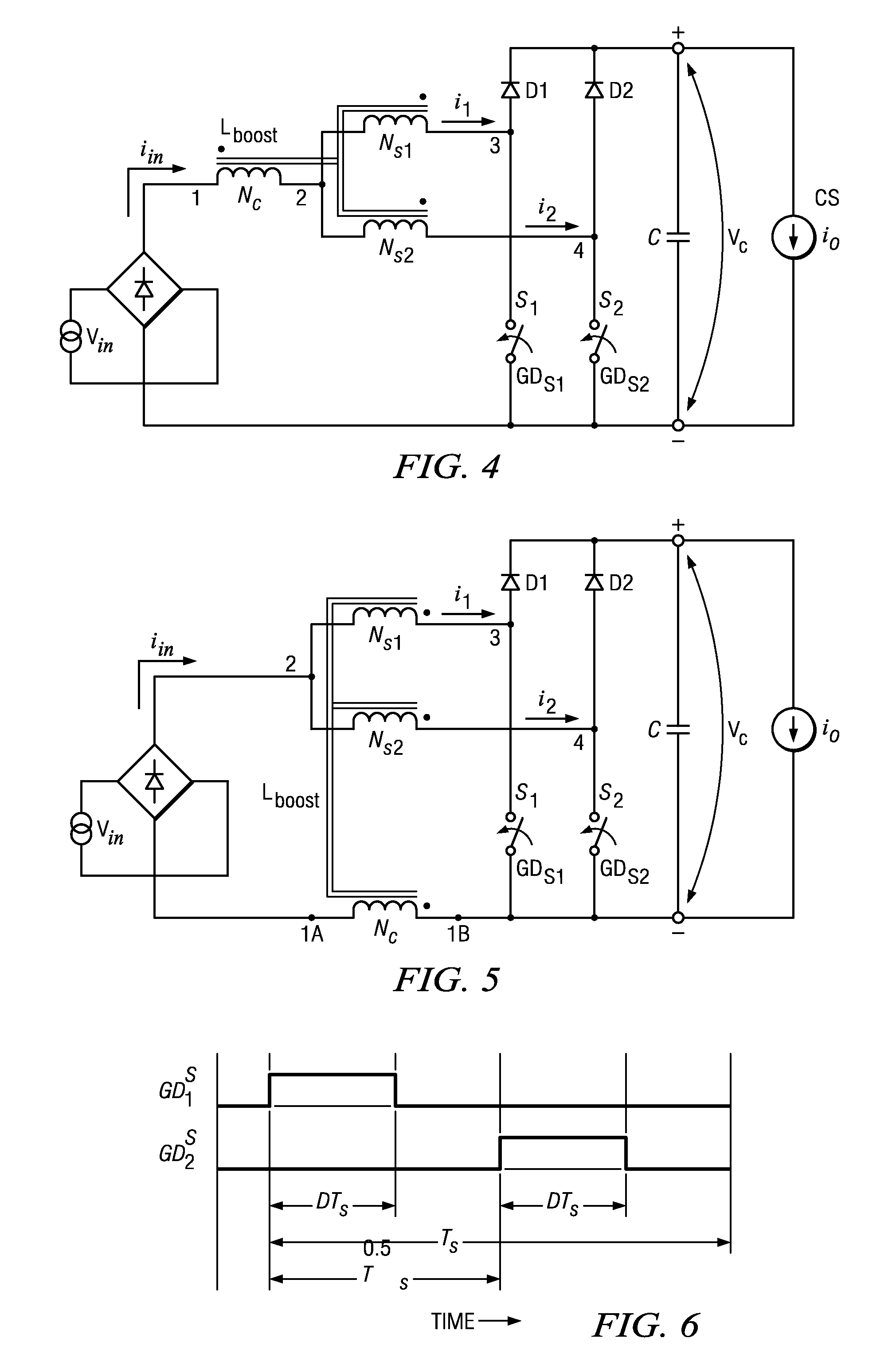

Method and apparatus for power conversion with wide input voltage range

A power conversion system includes an input terminal that is arranged to be connected to a voltage source; a transformer having a first winding connected to the input terminal and a second winding connected to an output terminal of the power conversion system, either the first winding or the second winding is provided with at least three taps that are arranged to divide the first winding or the second winding into at least two sub-windings; at least one tap switch connected to the at least two sub-windings; a control circuit connected to the at least one tap switch; and at least one switch connected to the at least one tap switch. The control circuit is arranged to control the at least one tap switch to control the turn ratio of the transformer.

Owner:MURATA POWER SOLUTIONS

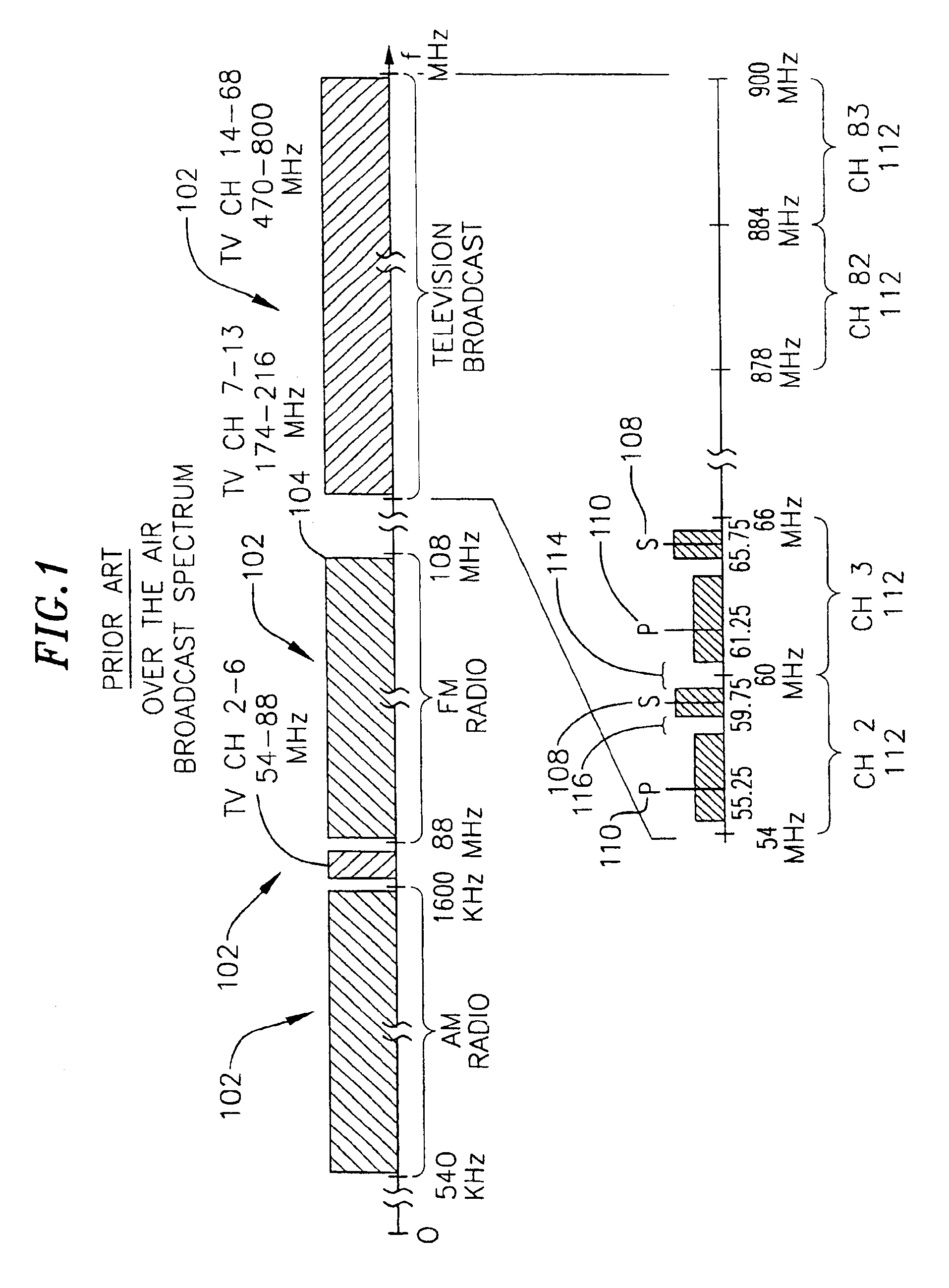

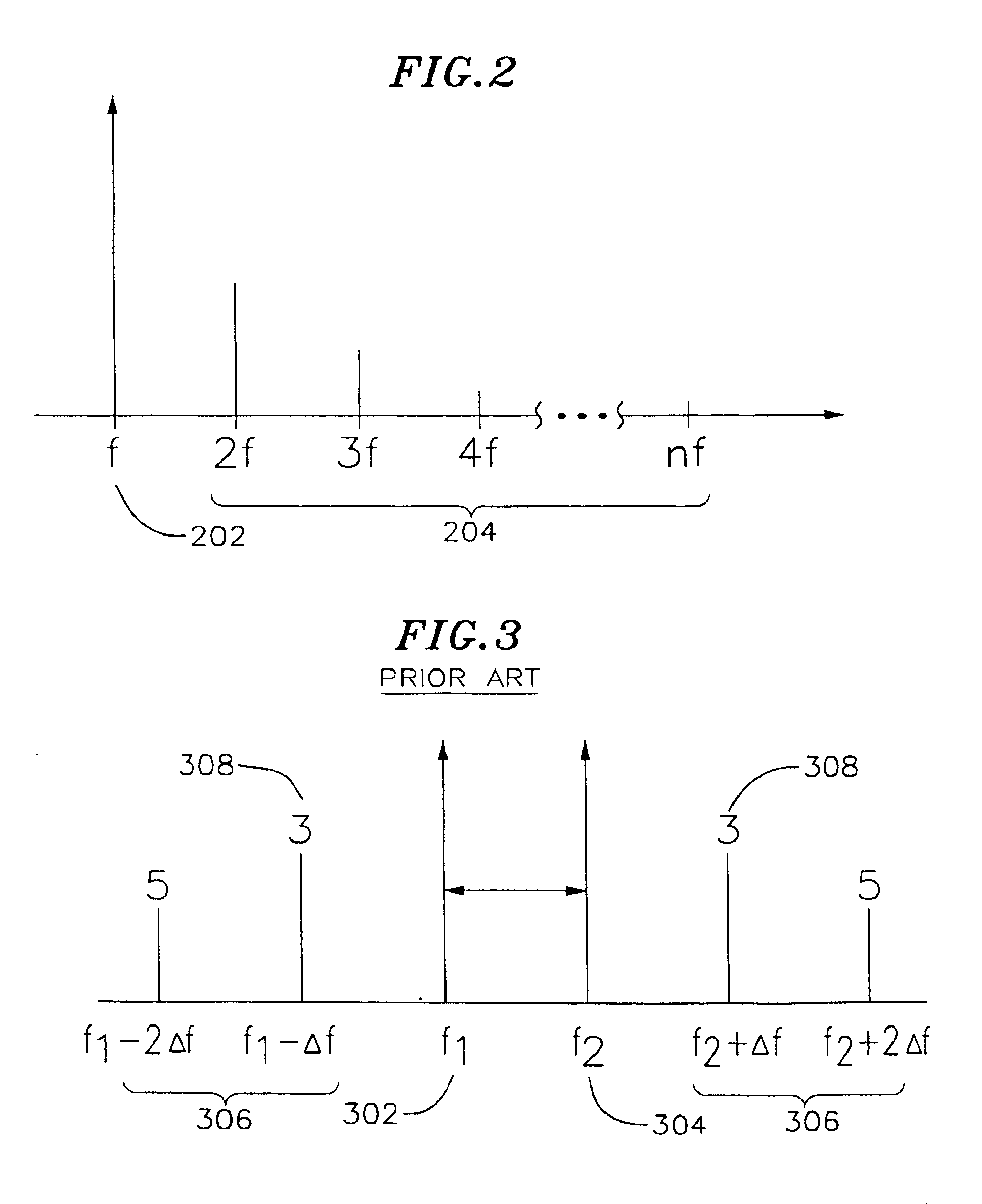

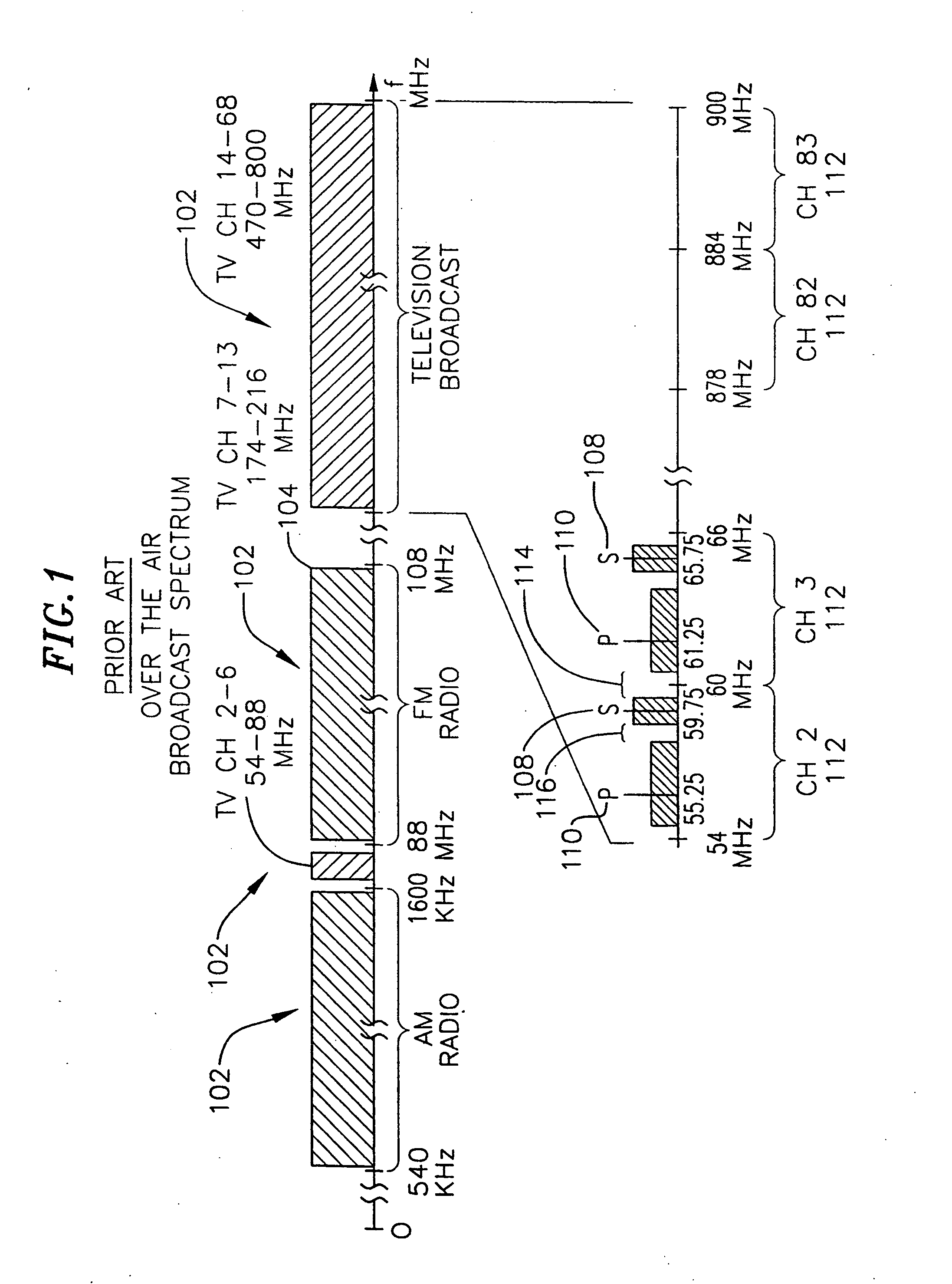

Integrated spiral inductor

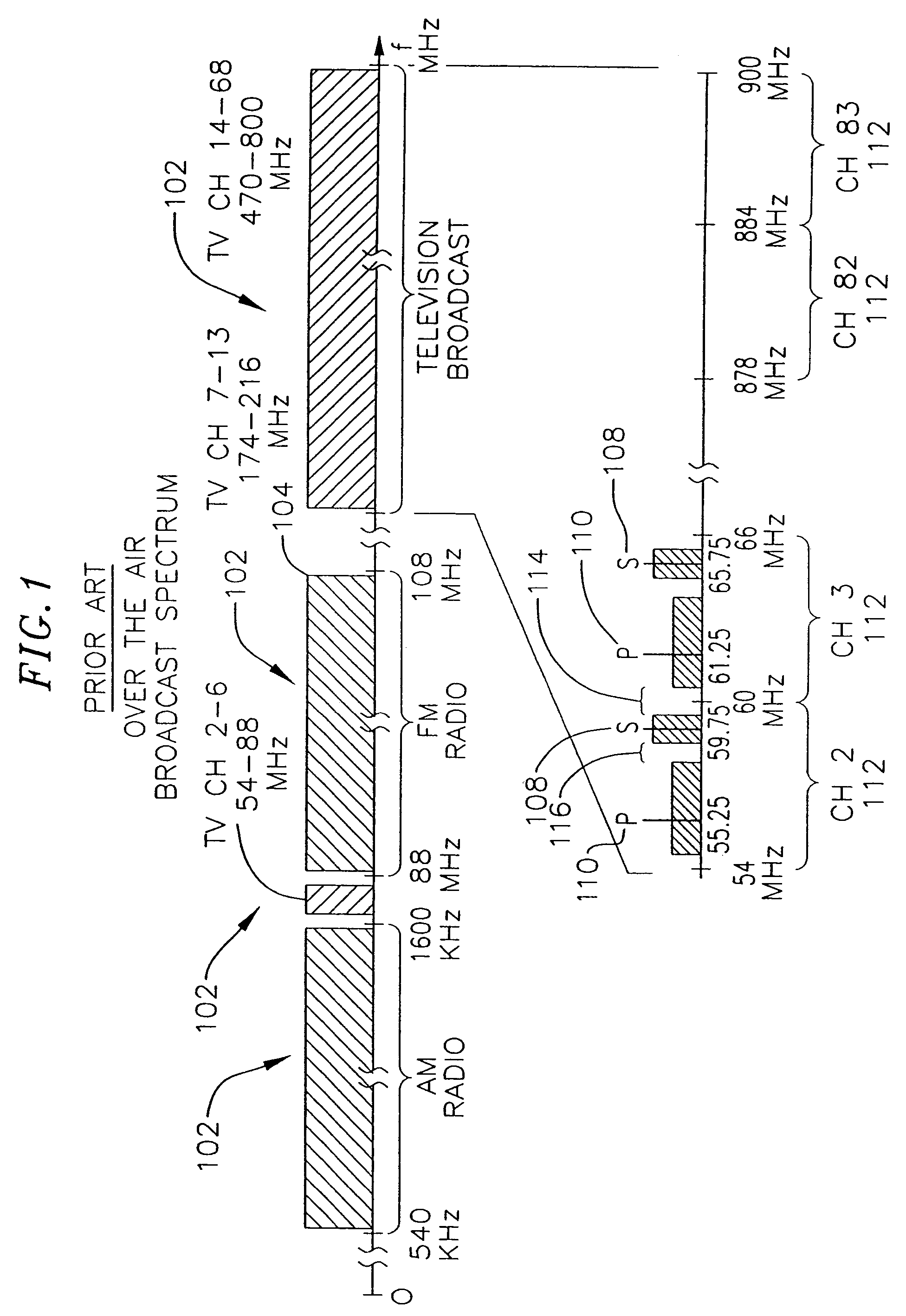

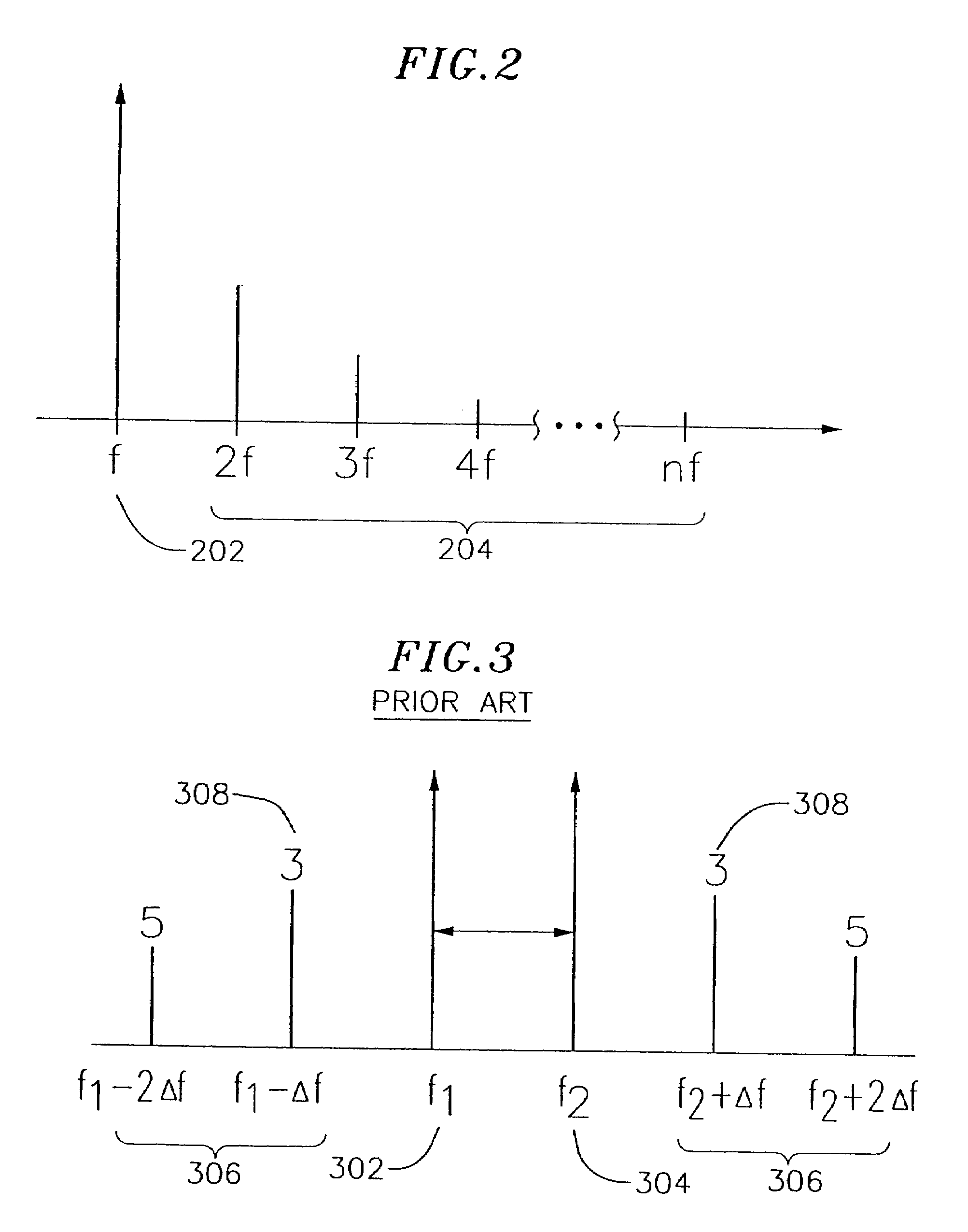

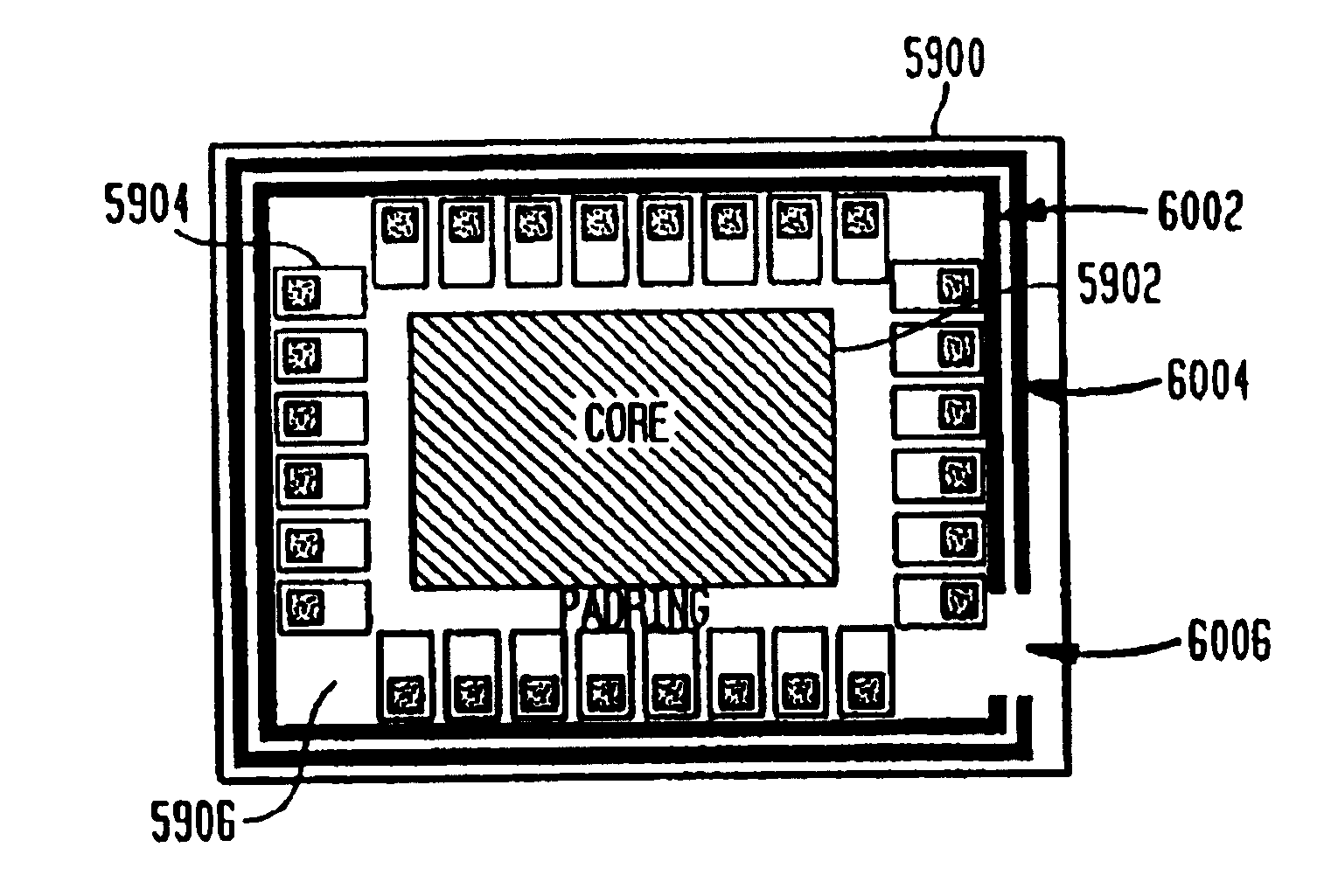

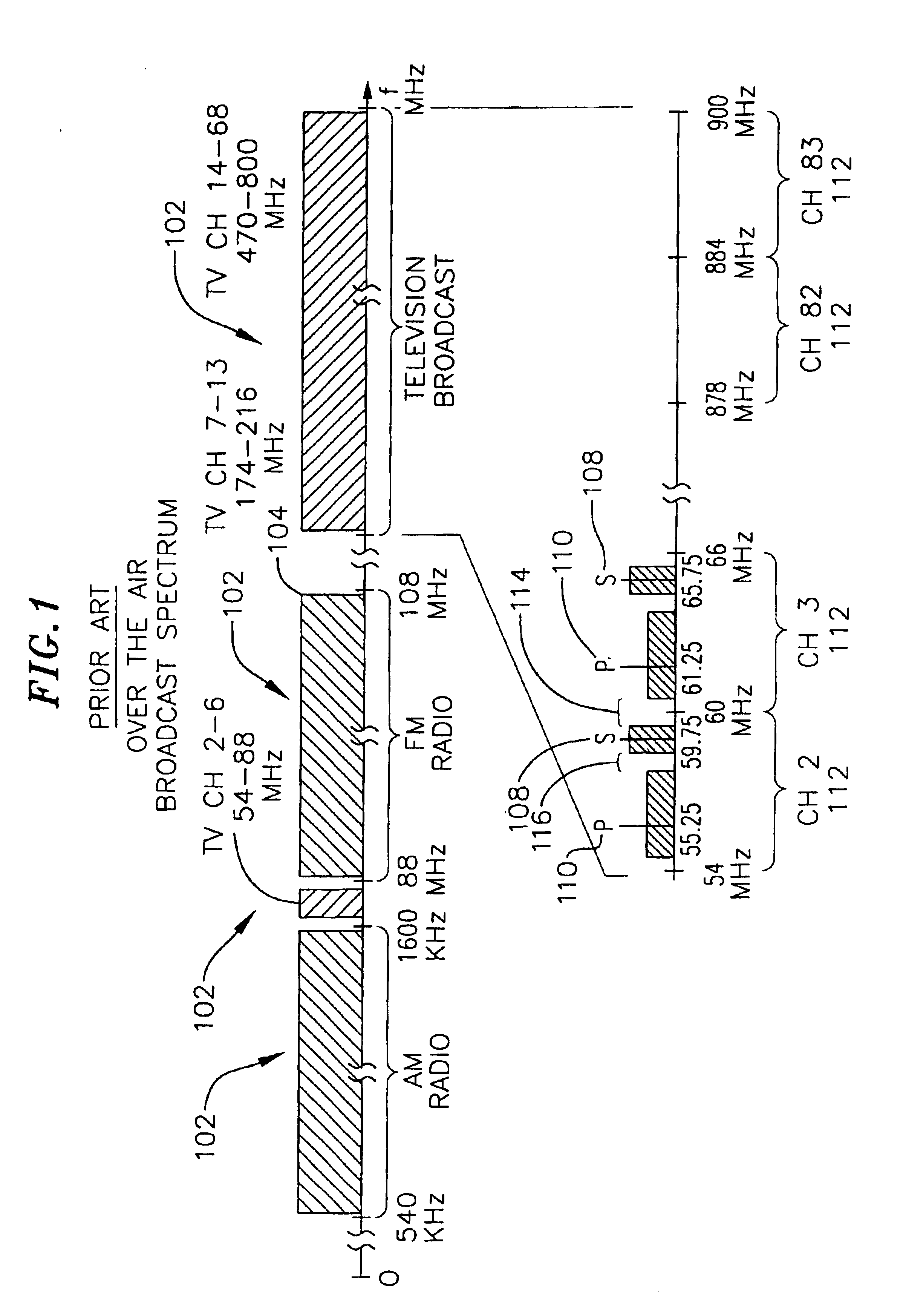

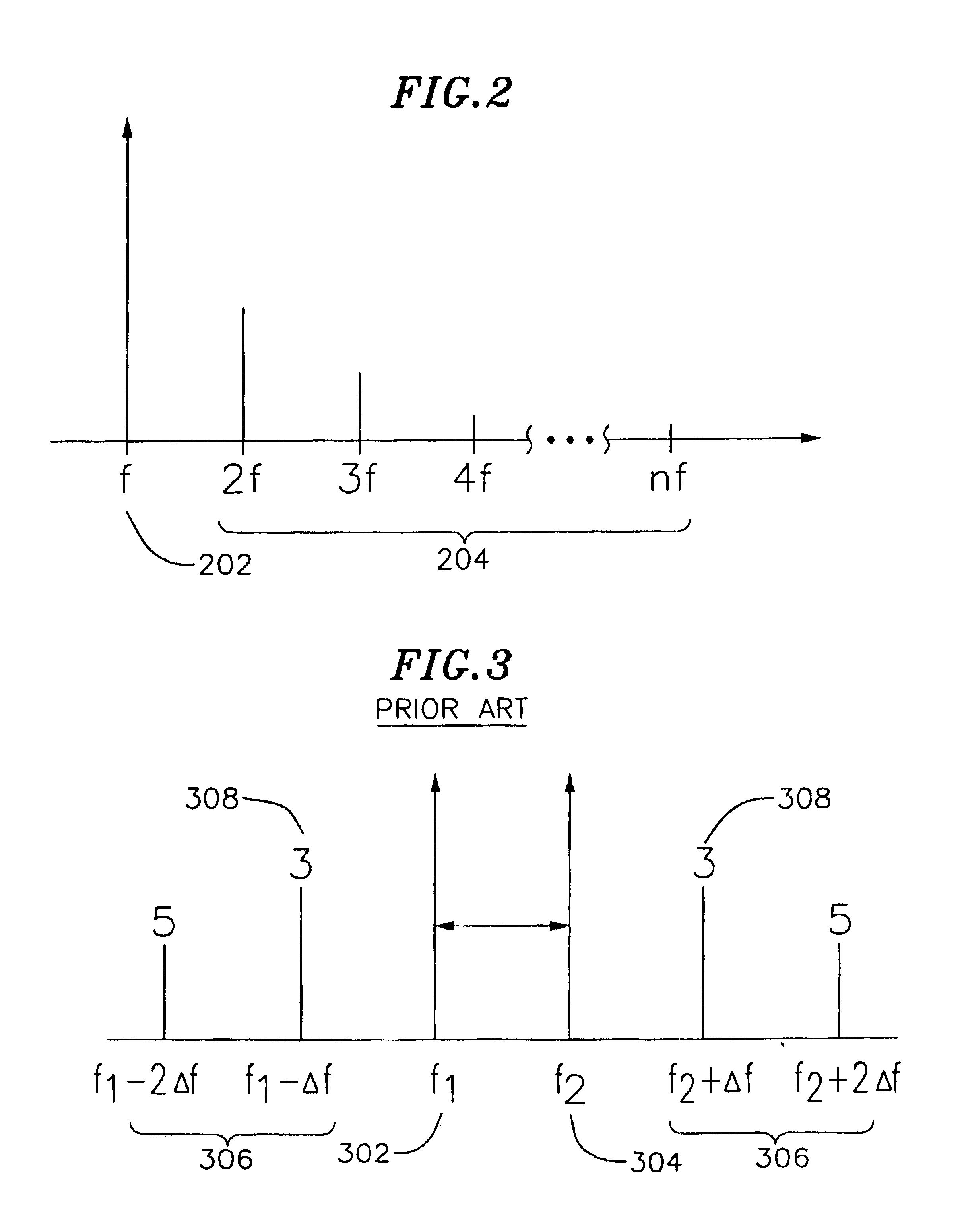

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

Integrated transformer with stack structure

ActiveUS20060077028A1Precise positioningReduced insertion lossTransformers/inductances coils/windings/connectionsSolid-state devicesTransformerEngineering

An integrated transformer with a stack structure comprises a middle dielectric layer, a bottom dielectric layer, a first winding and a second winding. A portion of the first winding is disposed over a surface of the middle dielectric layer and the remaining portion of the first winding is disposed over a surface of the bottom dielectric layer. A portion of the second winding is disposed over the surface of the middle dielectric layer and the remaining portion of the second winding is disposed over the surface of the bottom dielectric layer. The second winding doesn't intersect with the first winding. The portions of the first and second windings over the surface of the middle dielectric layer connect with the remaining portions of the first and second windings over the surface of the bottom dielectric through via plugs.

Owner:WINBOND ELECTRONICS CORP

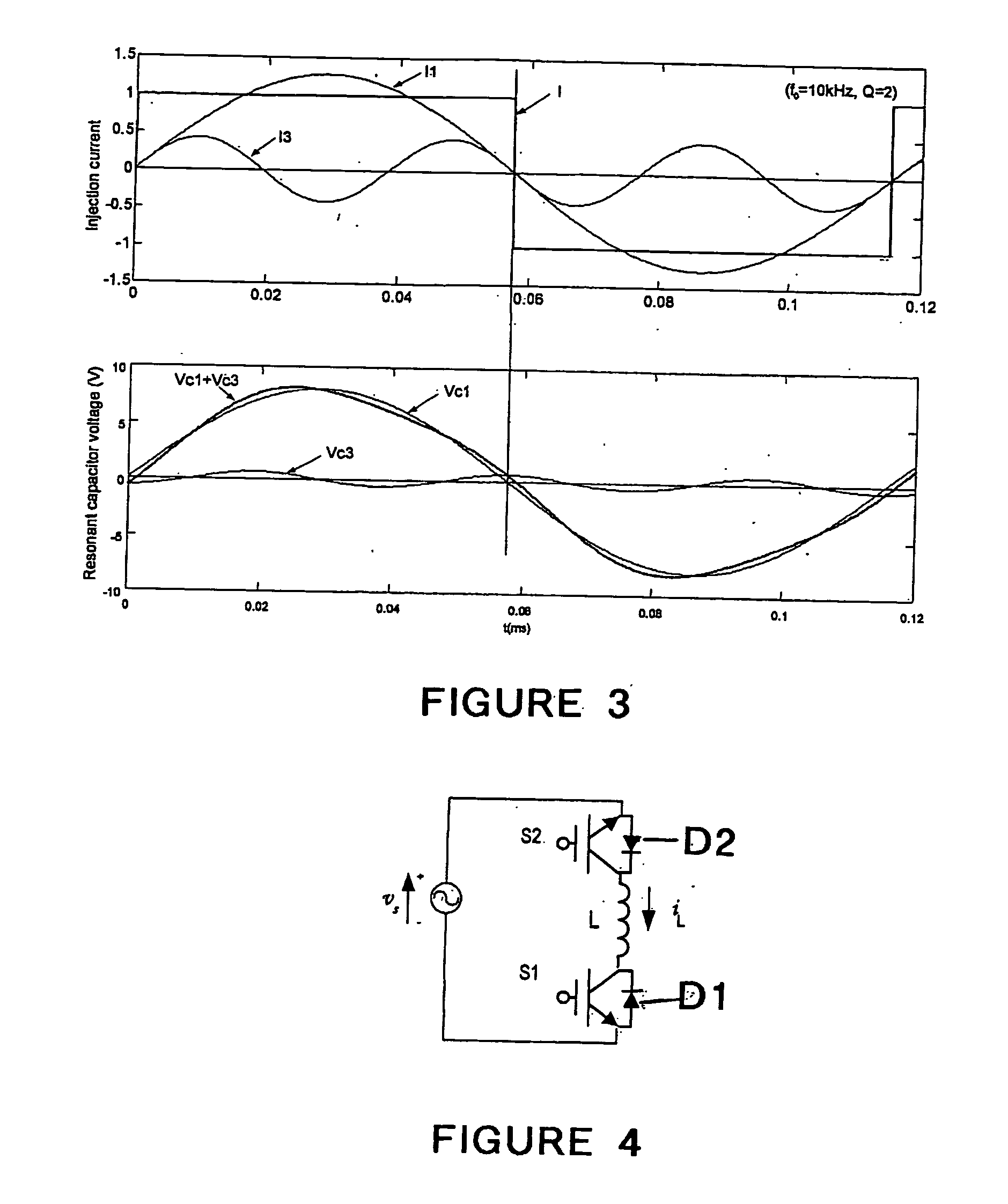

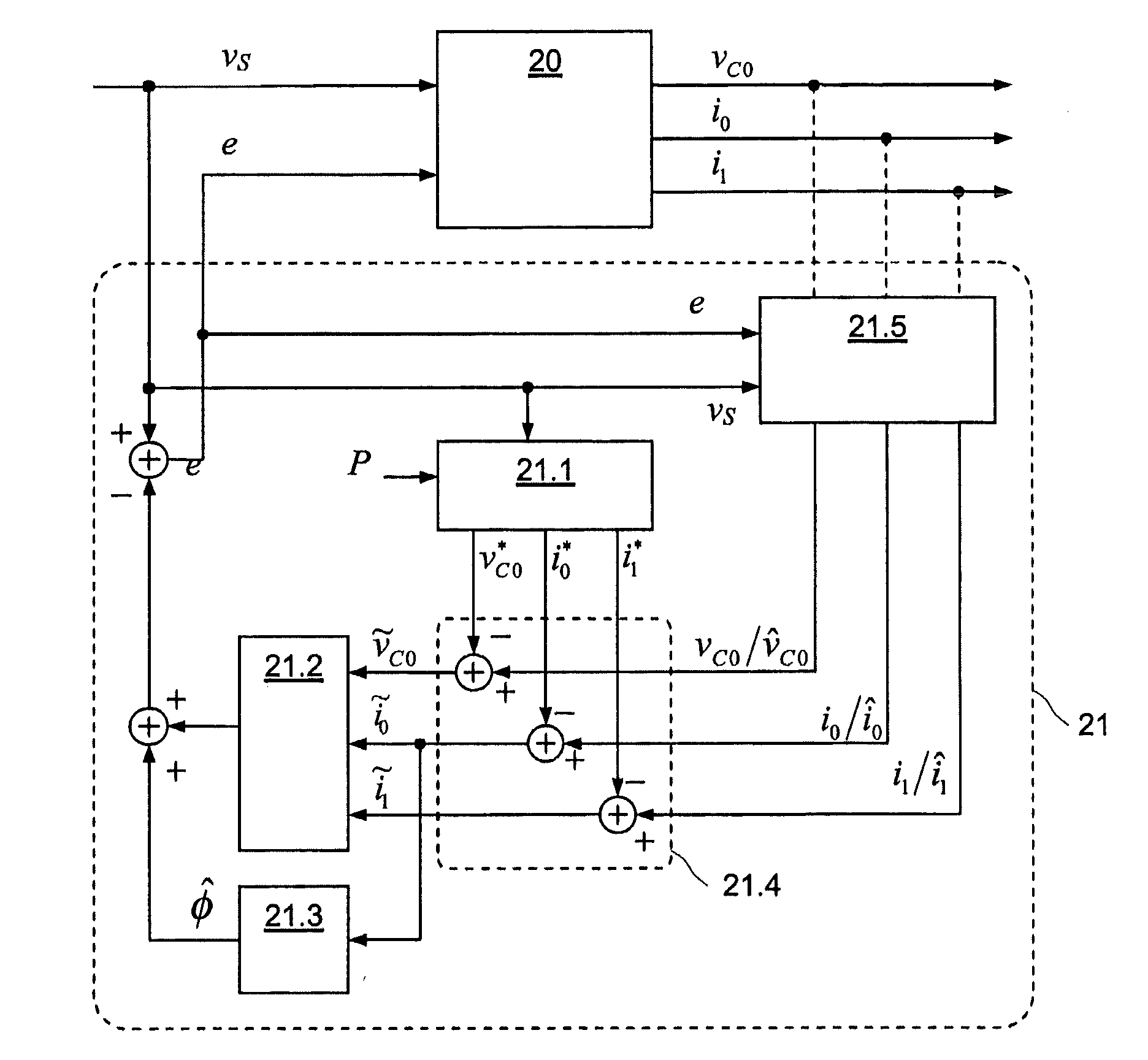

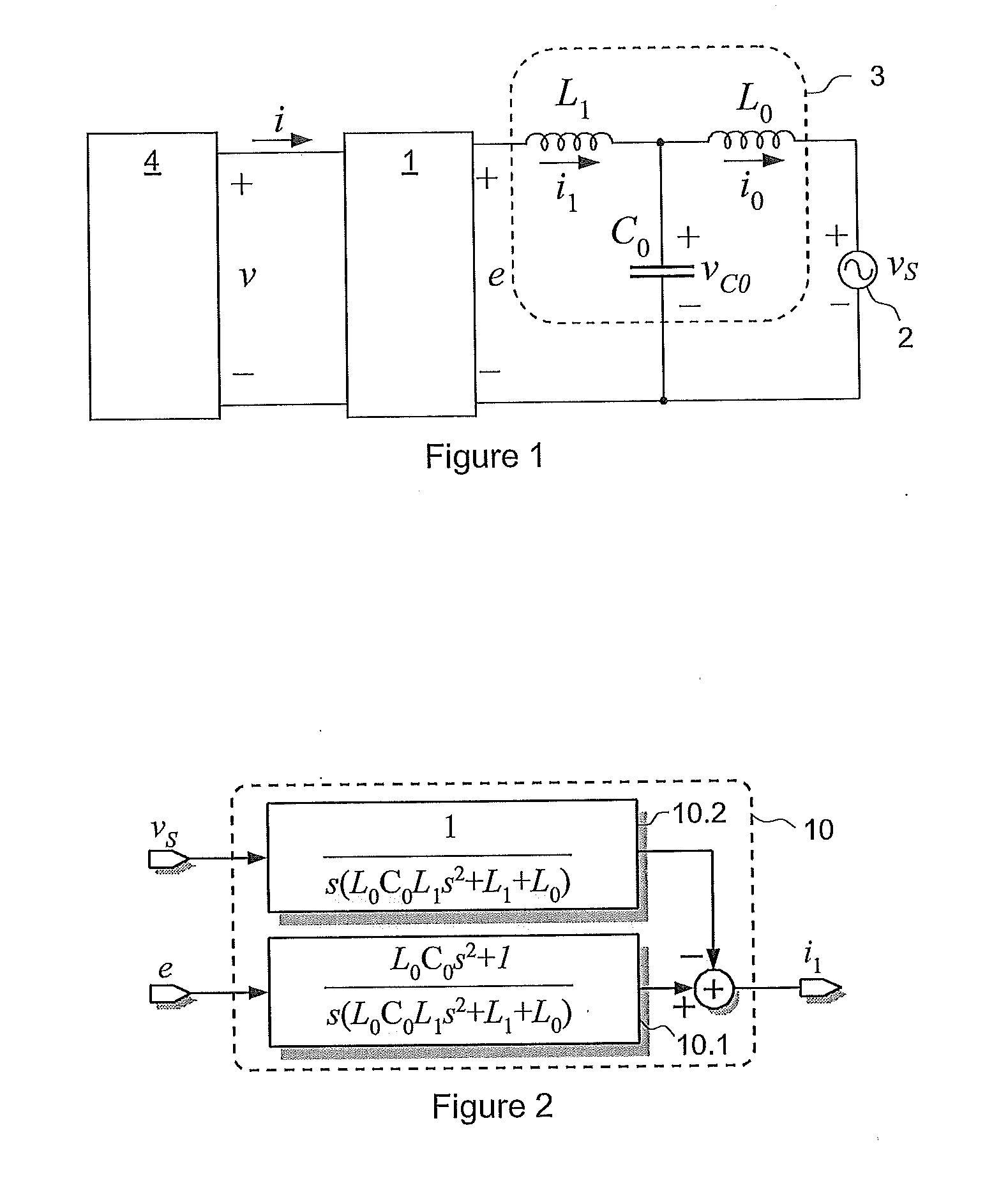

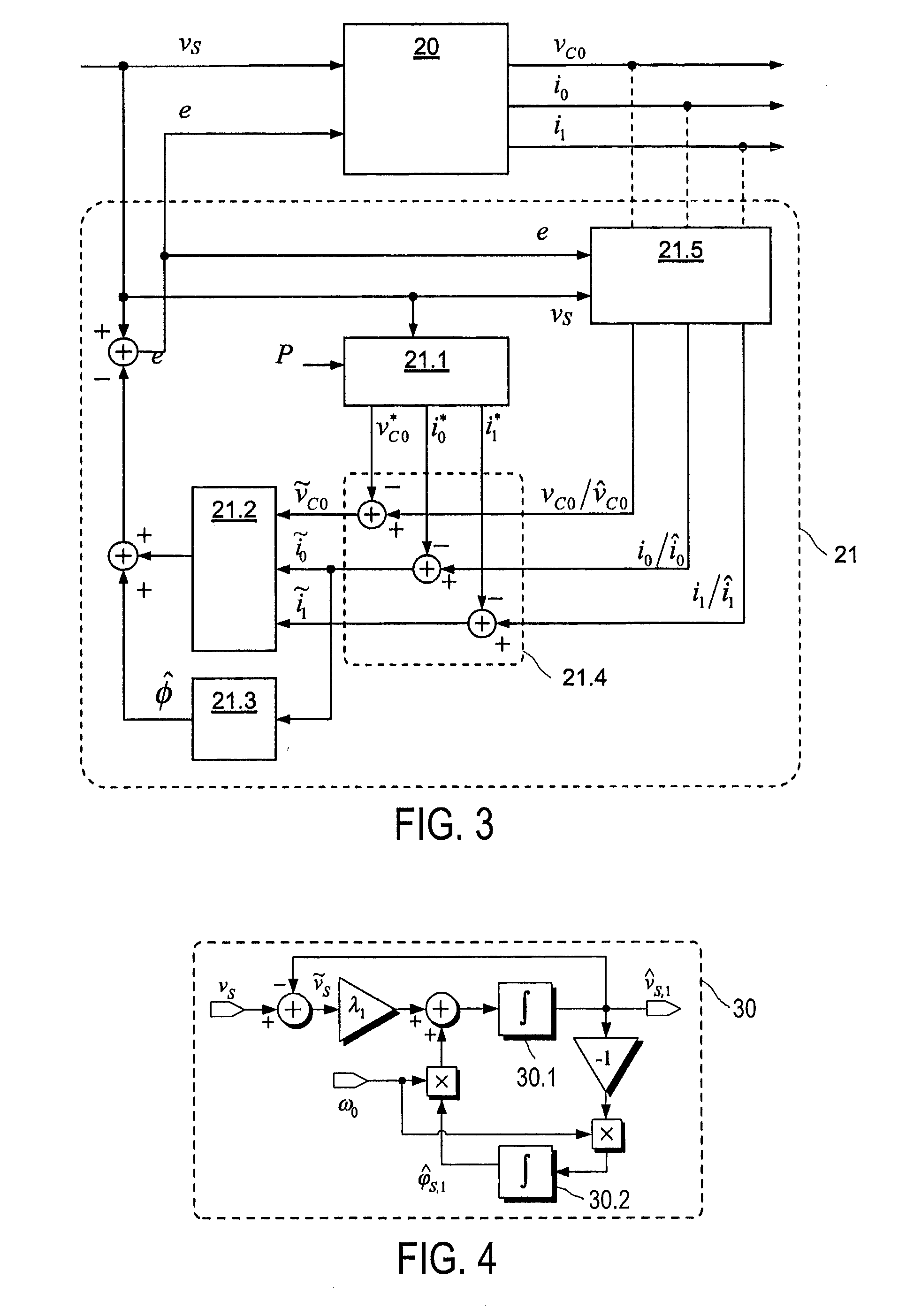

Control method for single-phase grid-connected lcl inverter

ActiveUS20110221420A1Improve performanceReduce resonanceVariable inductancesFixed transformers or mutual inductancesResonanceCapacitor voltage

A method of controlling the grid-side current of a single-phase grid-connected converter having an LCL filter connected between the output of the converter and the grid. The method includes measuring a grid voltage (vS) and at least one signal in a group of signals consisting of a grid-side current (i0), a converter-side current (i1) and a capacitor voltage (vC0). The method includes estimating the fundamental component (vS,1) of the grid voltage (vS), forming a grid-side current reference (i0*), a converter-side current reference (i1*) and a capacitor voltage reference (vC0*) for the grid-side current of the LCL filter using the fundamental component of the grid voltage (vS,1), forming estimates for the non-measured signals in said group of signals, forming a grid-side current difference term (ĩ0), a converter-side current difference term (ĩ1) and a capacitor voltage difference term ({tilde over (v)}C0) from the differences between the references and measured / estimated values of said signals, forming an injection term for damping the resonance of the LCL filter by using an active damping injection mechanism (ADI), in which the grid-side current difference term (ĩ0), the converter-side current difference term (ĩ1) and the capacitor voltage difference term ({tilde over (v)}C0) are used, forming an estimate of harmonic distortion term ({circumflex over (φ)}) using the grid-side current difference term (ĩ0), and controlling the output voltage (e) of the converter on the basis of the grid voltage, formed injection term and formed estimate of the harmonic distortion term ({circumflex over (φ)}) to produce a grid side (i0) current corresponding to the current reference.

Owner:MARICI HLDG THE NETHERLANDS BV

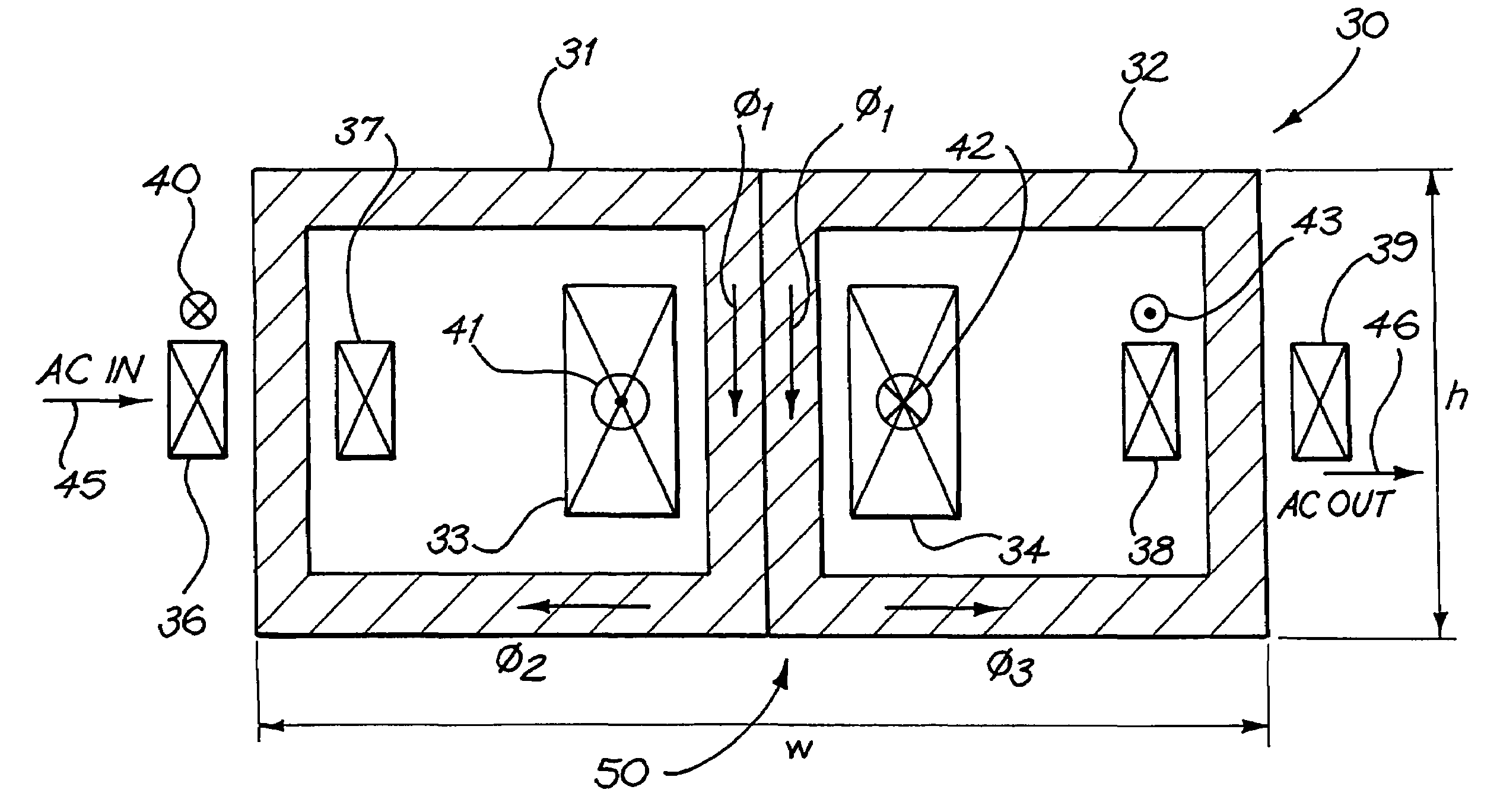

Superconducting fault current limiter

InactiveUS7193825B2Superconductors/hyperconductorsTransformersCurrent limitingSuperconducting fault current limiters

Owner:ZENERGY POWER

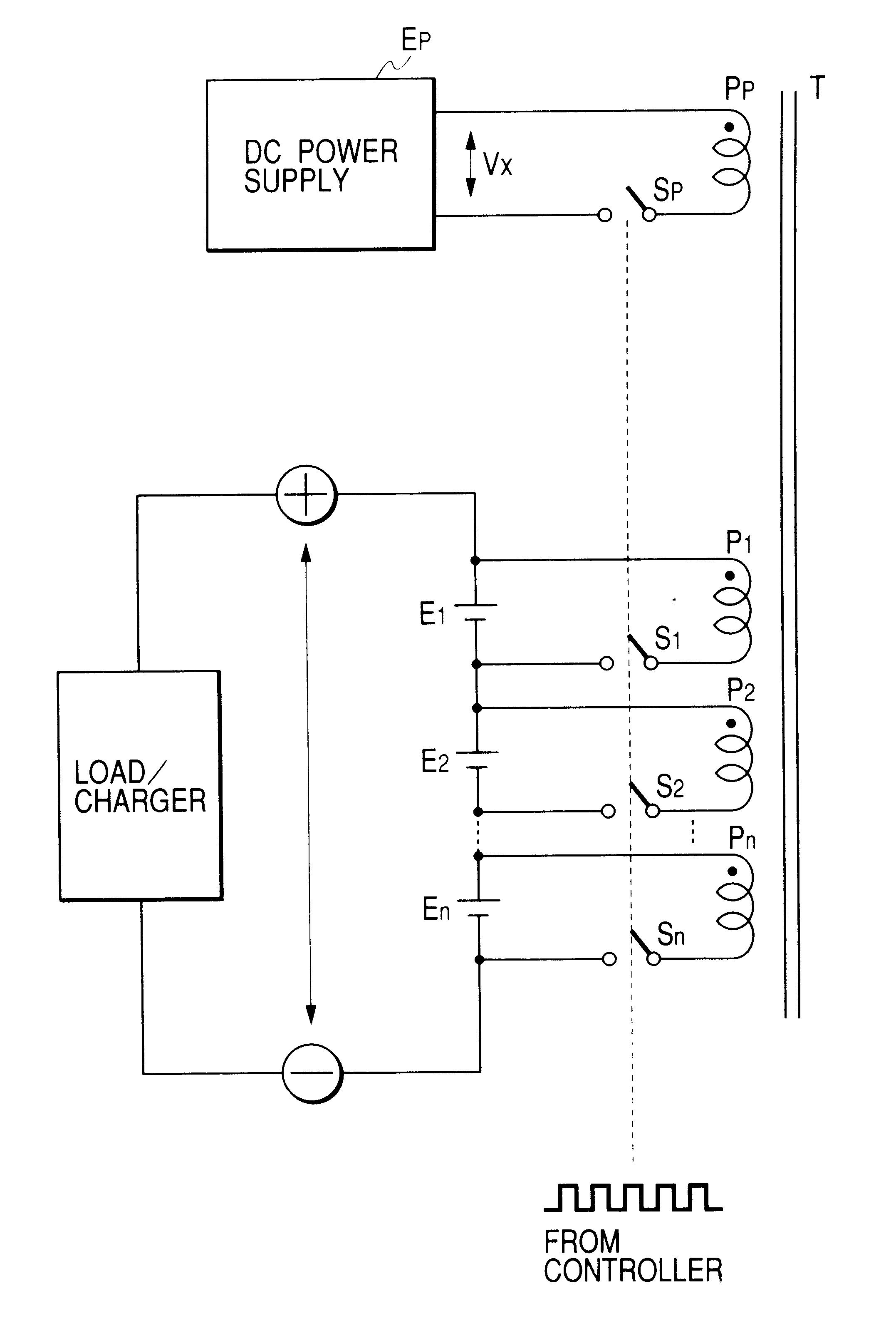

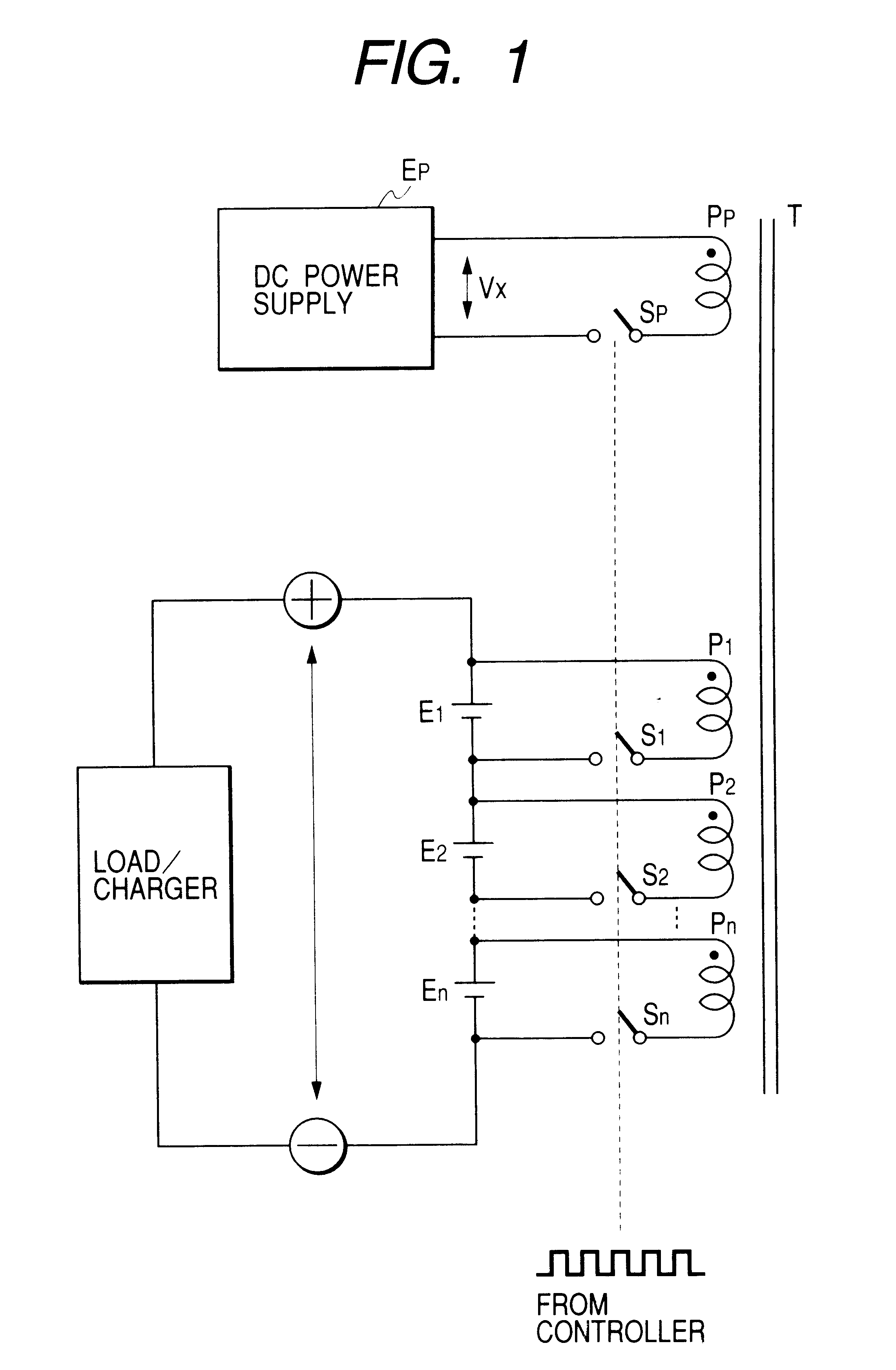

Voltage equalizer apparatus and method thereof

InactiveUS6586910B2Dc network circuit arrangementsCharge equalisation circuitElectromagnetic couplingConductor Coil

In such a voltage equalizer circuit in which each of plural windings P1 to Pn electromagnetically coupled to each other, each of plural storage elements E1 to En series-connected to each other, and each of plural first switching elements S1 to Sn are connected to each other in a series connecting manner so as to constitute a plurality of closed circuits, this voltage equalizer apparatus is featured by that a reference voltage winding Pp electromagnetically coupled to the plurality of windings is provided; both a DC power supply Ep and a second switching element Sp are series-connected to the second winding; and all of the plural first switching elements and the second switching element are turned ON / OFF in a synchronous manner.

Owner:SUBARU CORP +1

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

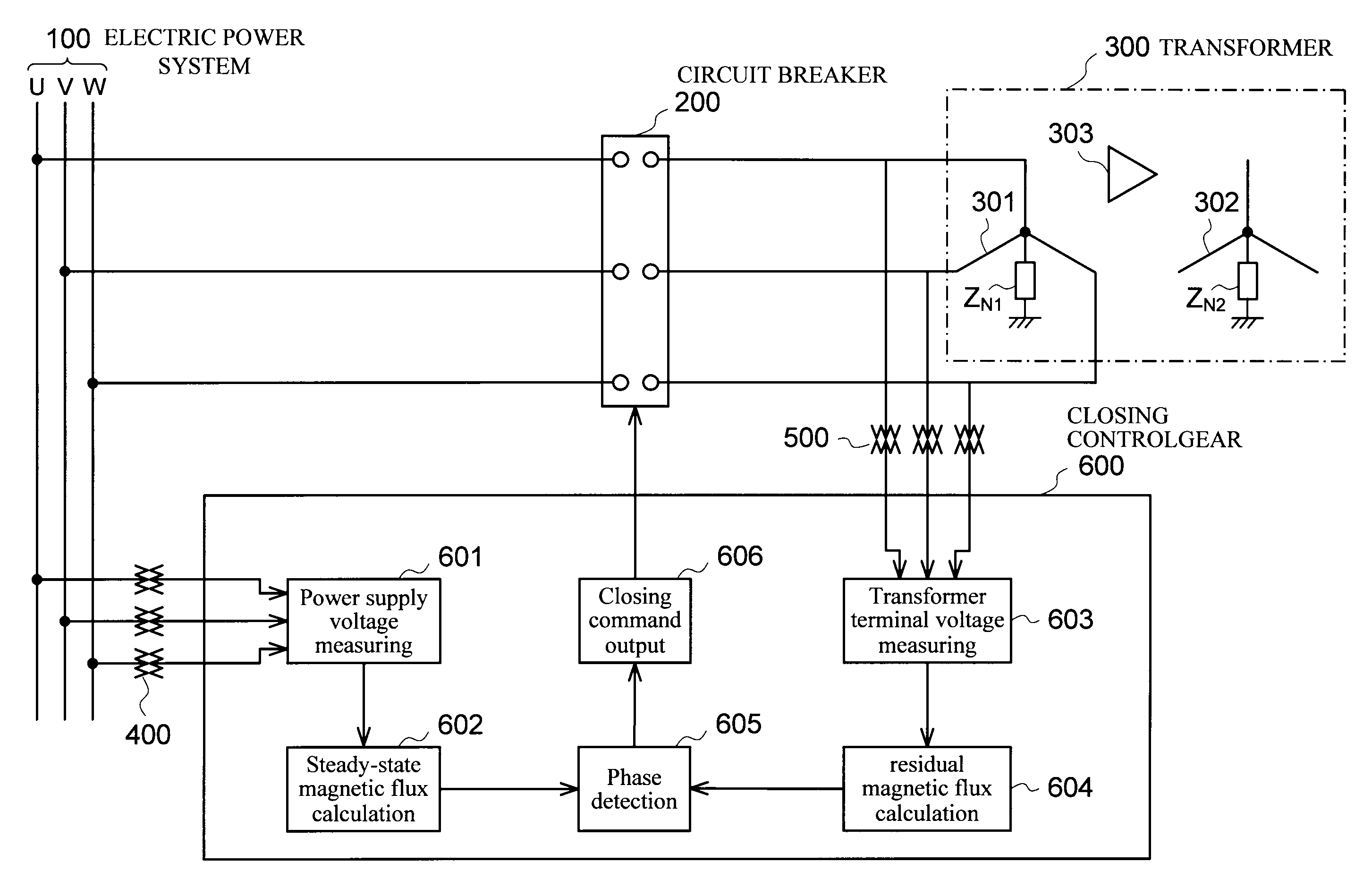

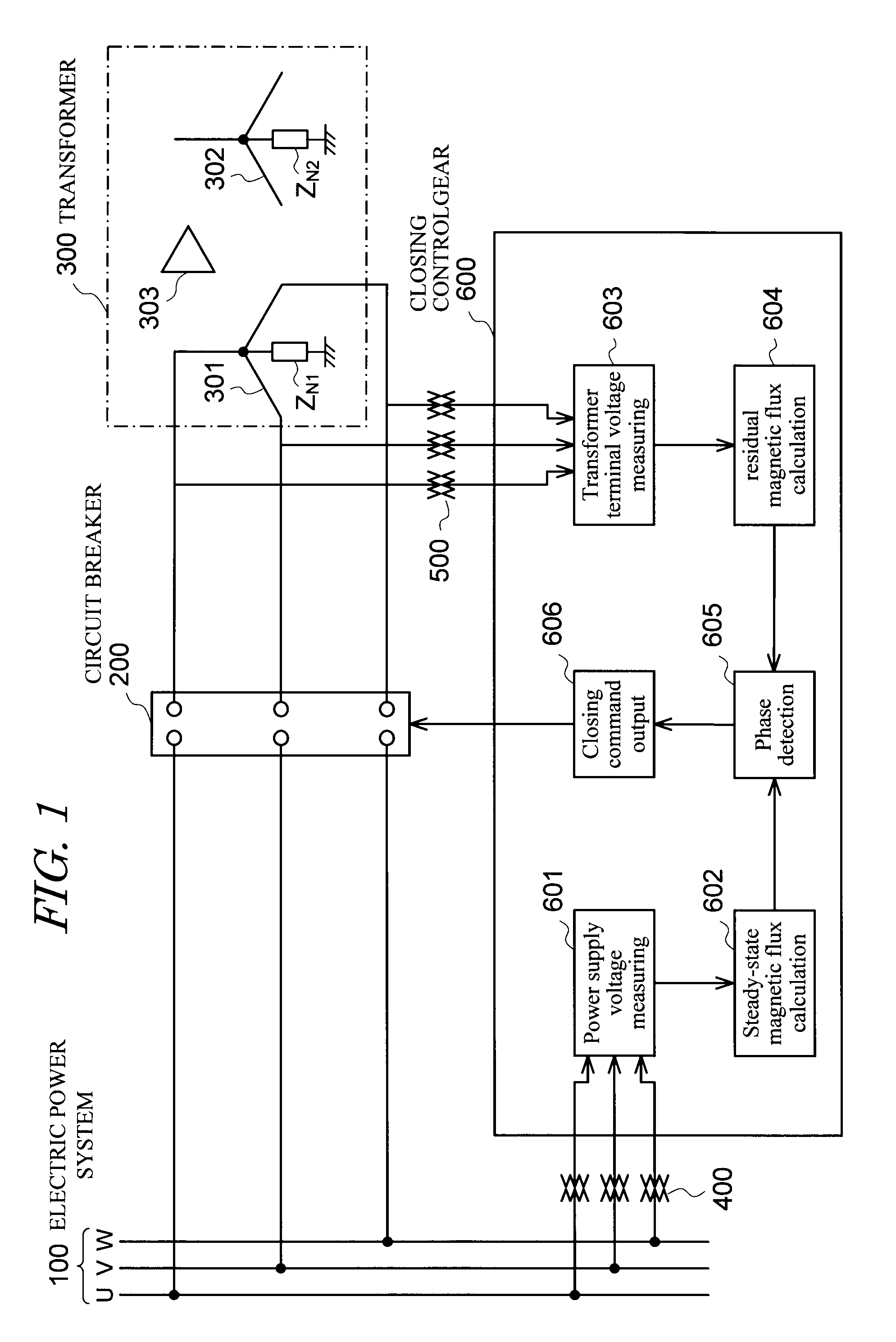

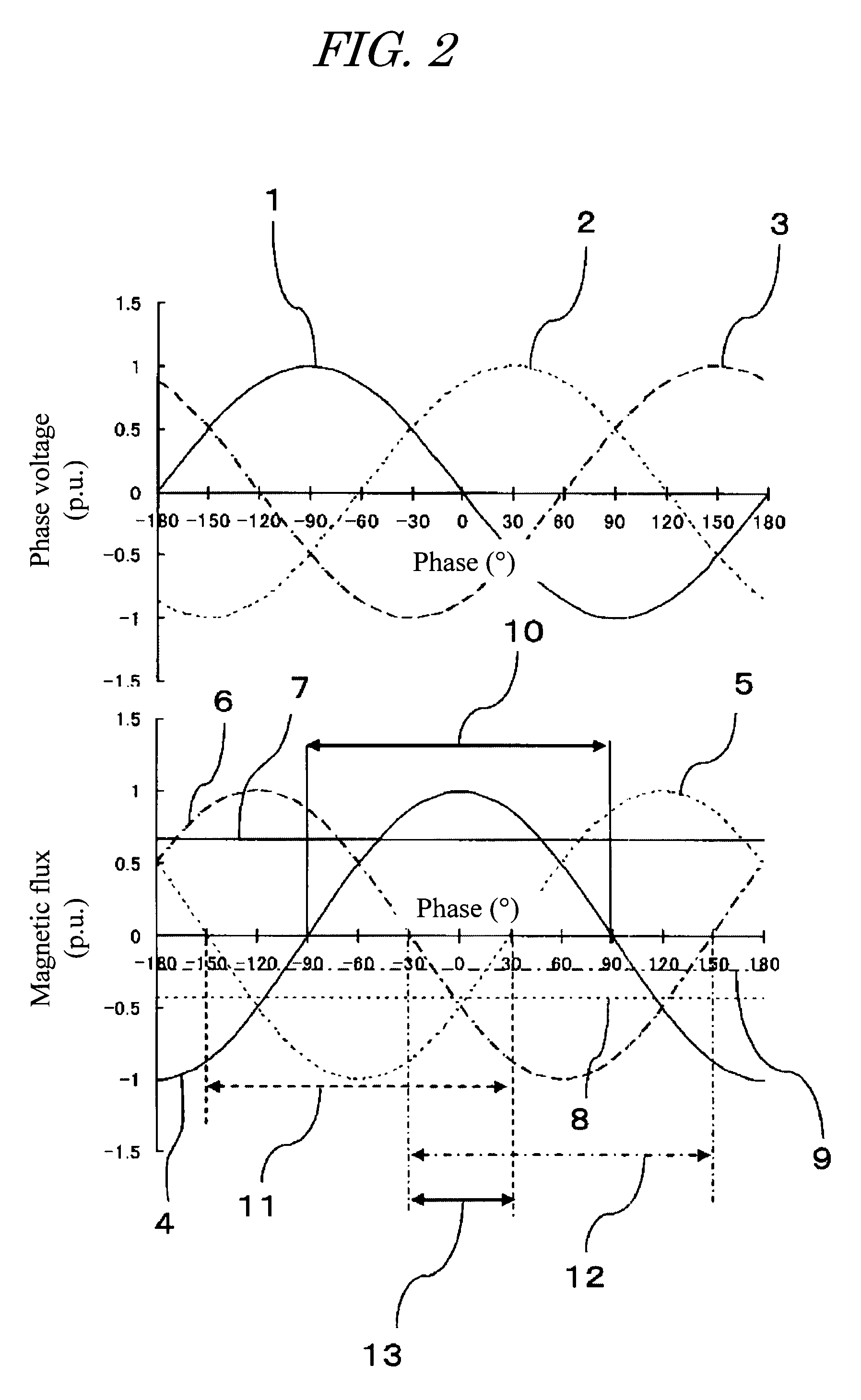

Magnetizing inrush current suppression device and method for transformer

ActiveUS20100141235A1Accurate calculationBatteries circuit arrangementsVariable inductances/transformersEngineeringInrush current

To suppress the magnetizing inrush current occurring when supplying power of three phases of the transformer are performed simultaneously using three single-phase circuit breakers or a non-phase segregated operation-type circuit breaker, without providing a circuit breaker with a resistor or other equipment. A magnetizing inrush current suppression method for transformer suppresses a magnetizing inrush current occurring at the start of energizing of a three-phase transformer 300, when a three-phase power supply 100 is input to a terminal of each phase by means of a three-phase circuit breaker 200. In the method, by integrating phase voltages or line-to-line voltages on the primary side or the secondary side or the tertiary side when three-phase AC voltages are applied in a steady state to the transformer 300, steady-state magnetic flux 4, 5, 6 for each phase of the transformer is calculated, and the polarity and magnitude of the residual magnetic flux 7, 8, 9 of each phase of the transformer after the circuit breaker 200 shuts off the transformer are calculated, and the three-phase circuit breaker is caused to close simultaneously in a region 13 in which three phases overlap, each of the three phases having the polarity of the steady-state magnetic flux 4, 5, 6 equal to the polarity of the residual magnetic flux 7, 8, 9 for each phase of the transformer.

Owner:KK TOSHIBA

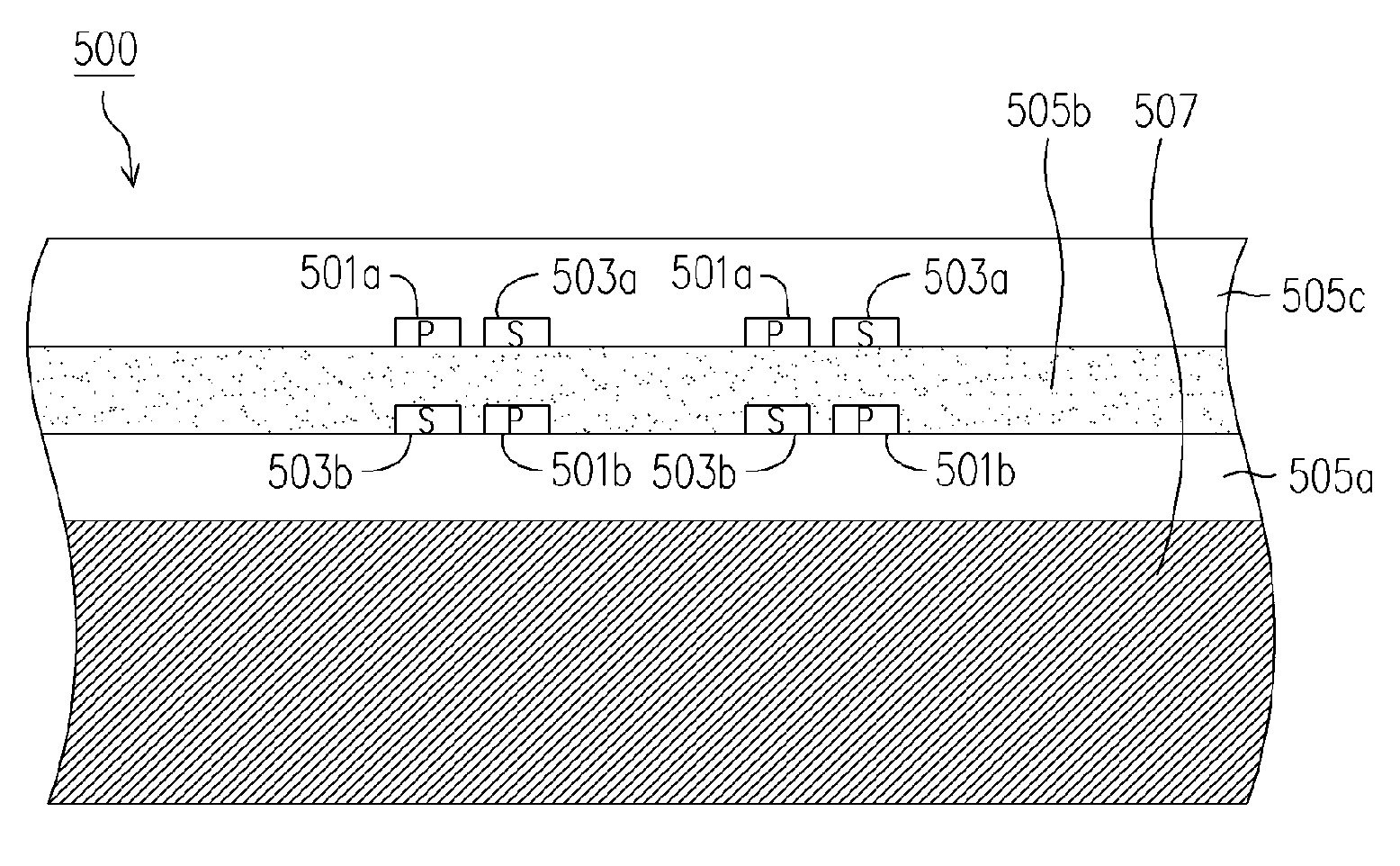

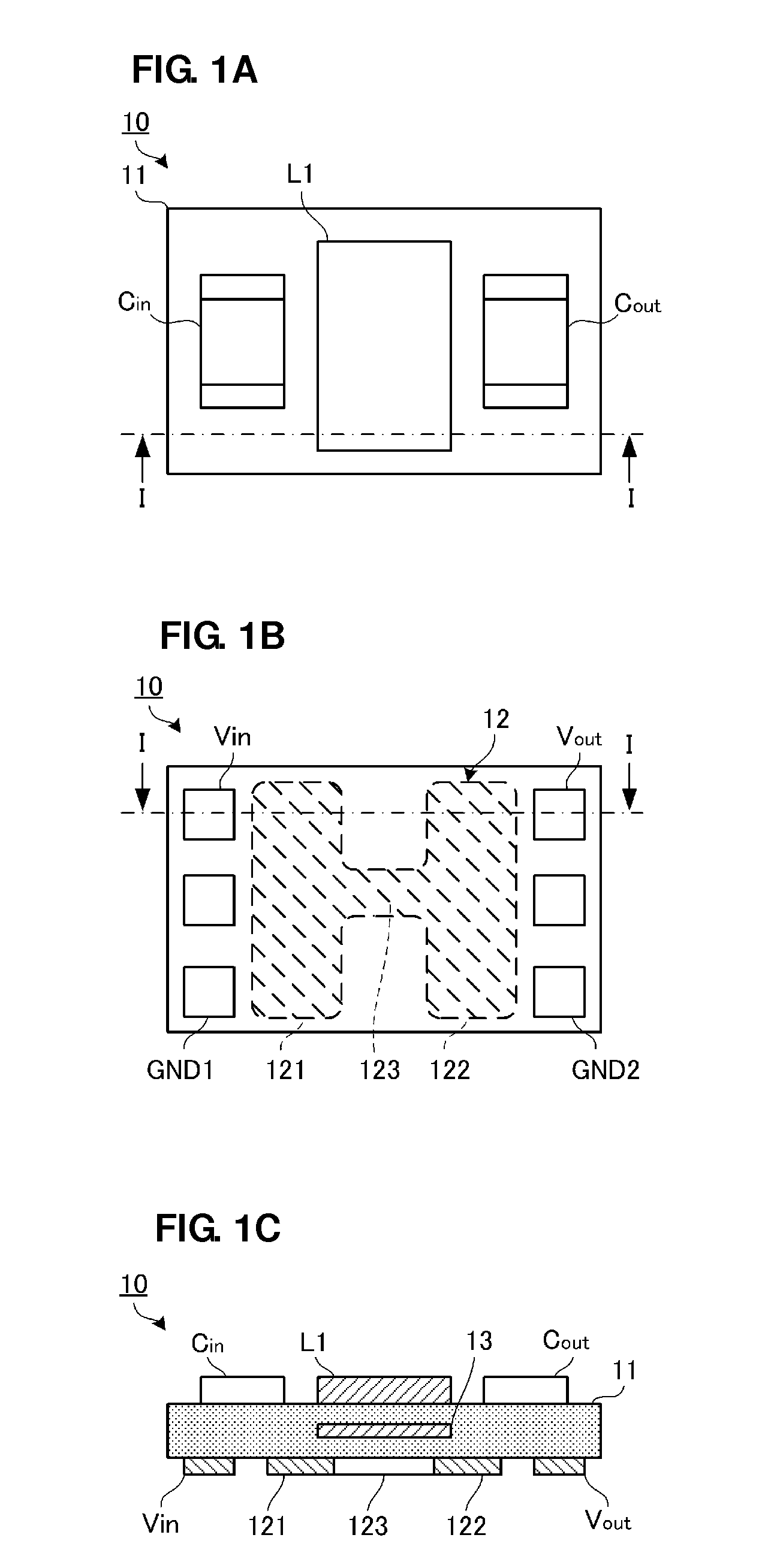

Chip scale power converter package having an inductor substrate

ActiveUS20080238599A1Improve efficiencySemiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsPlanar spiral inductorsInductor

A chip scale power converter package having an inductor substrate and a power integrated circuit flipped onto the inductor substrate is disclosed. The inductor substrate includes a high resistivity substrate having a planar spiral inductor formed thereon.

Owner:ALPHA & OMEGA SEMICON INC

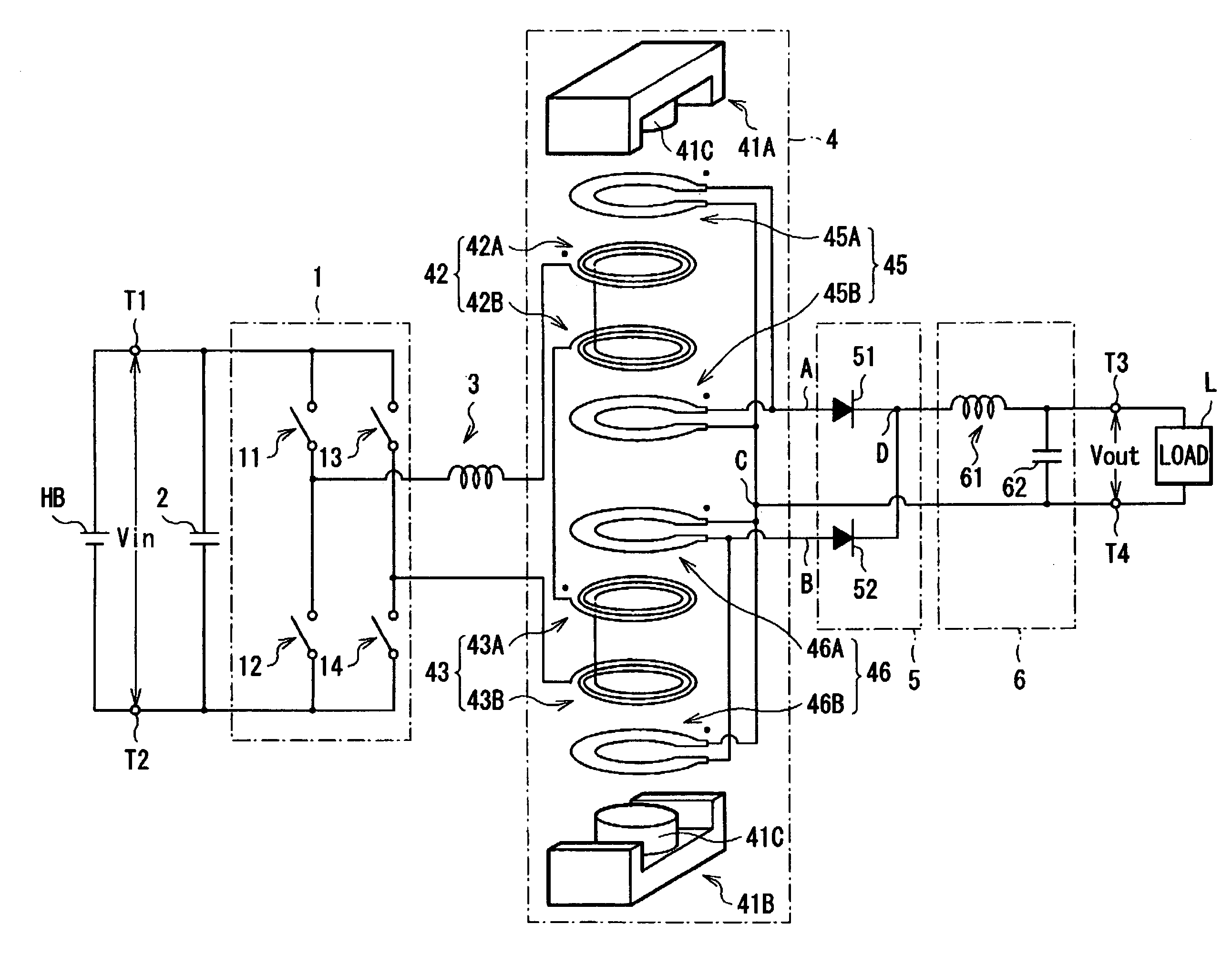

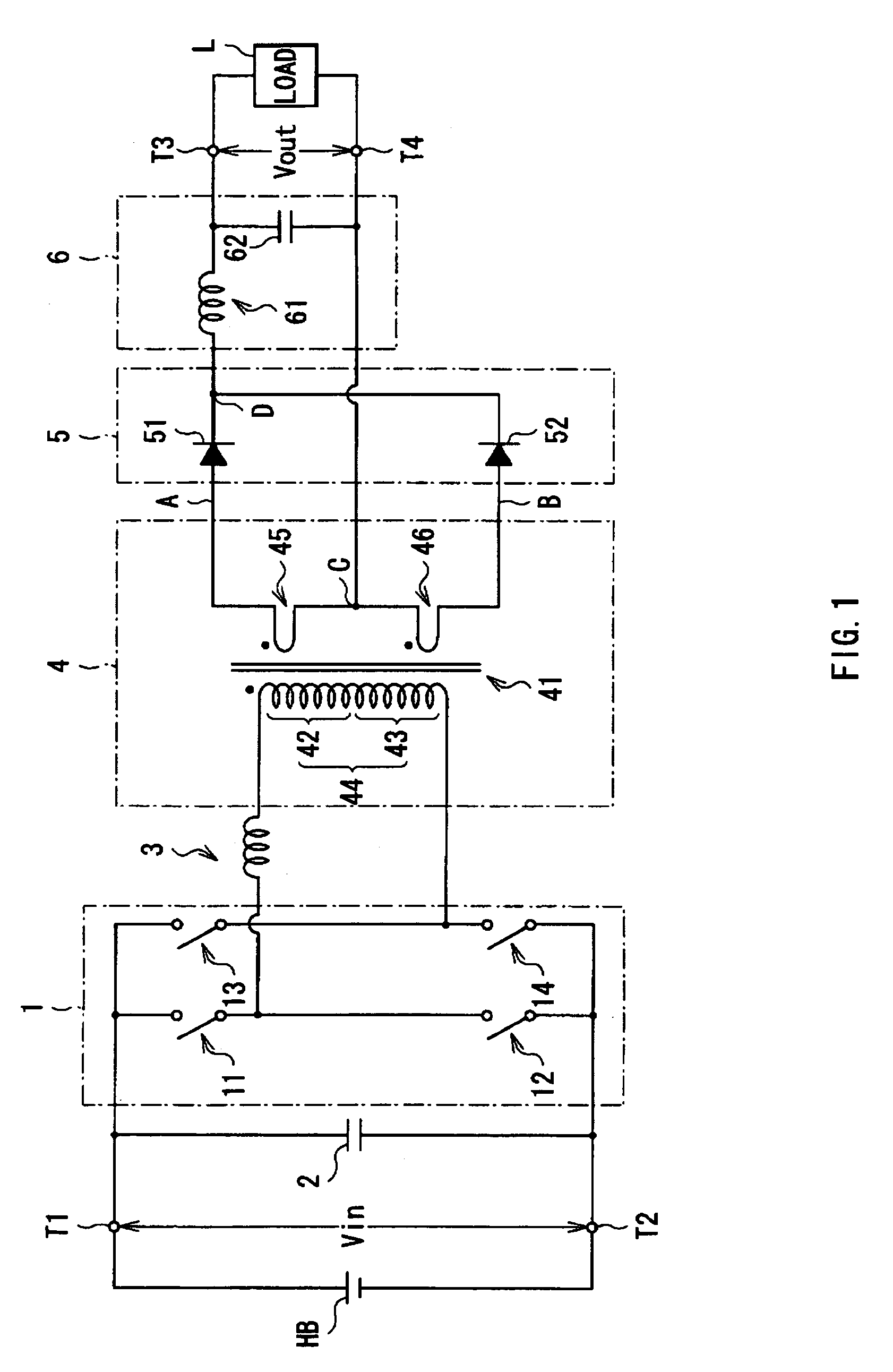

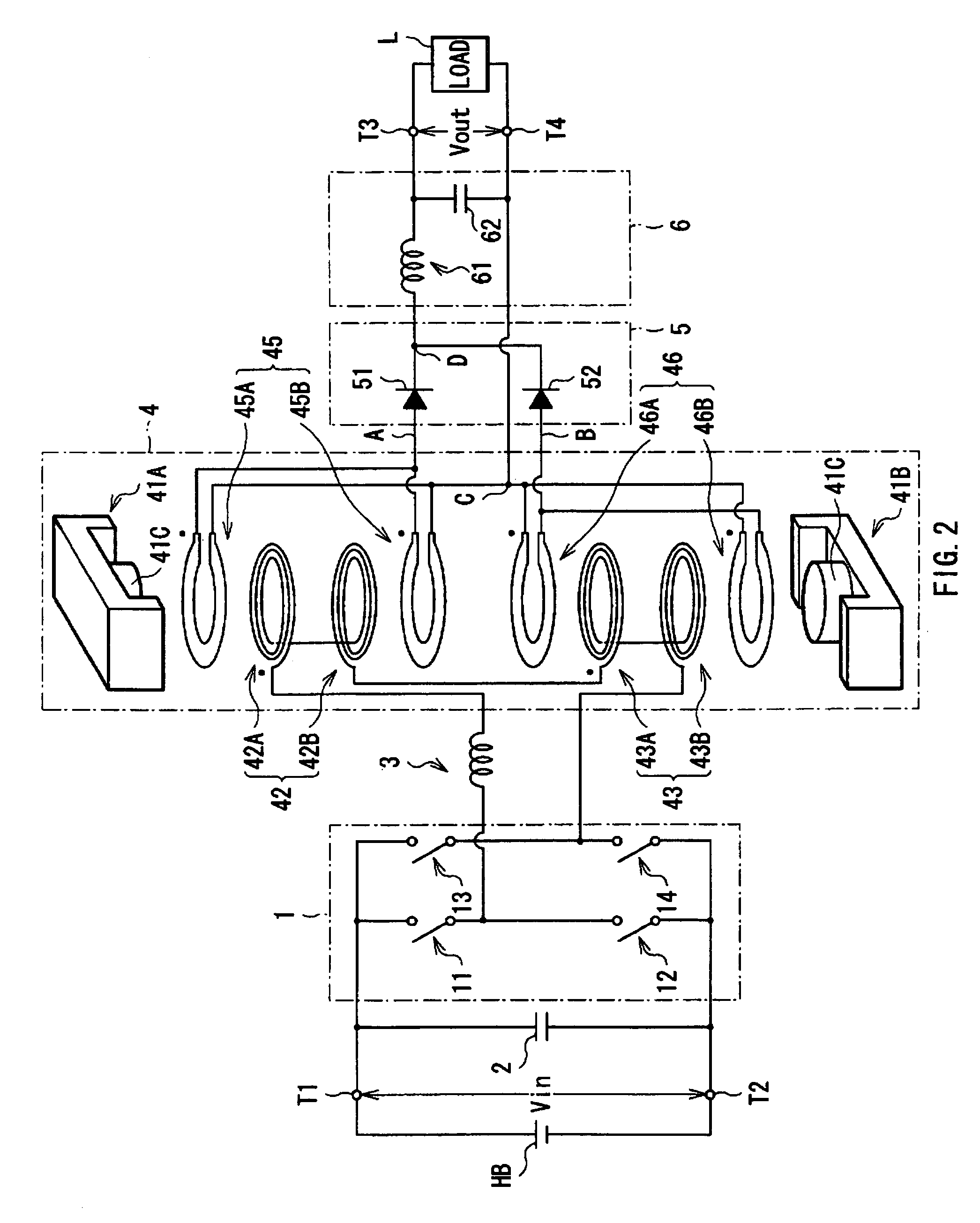

Switching power supply unit

ActiveUS7199569B1Line capacitanceLow efficiencyConversion constructional detailsTransformers/inductances coils/windings/connectionsPower inverterEngineering

A switching power supply unit is provided, in which core loss in a transformer or a level of heating due to AC resistance of the transformer can be reduced. A switching power supply unit has a transformer, an inverter circuit and a rectifier circuit. In a secondary side of the transformer, secondary wirings are connected to each other. In a primary side of the transformer, primary wirings are connected in series to each other, and connected to the inverter circuit to allow them to be driven in a time-divisional manner in phases opposite to each other in response to operation of the inverter circuit. The rectifier circuit has diodes connected to the secondary wirings to allow the secondary wirings to be driven in a time-divisional manner in phases opposite to each other in response to operation of the inverter circuit.

Owner:TDK CORPARATION

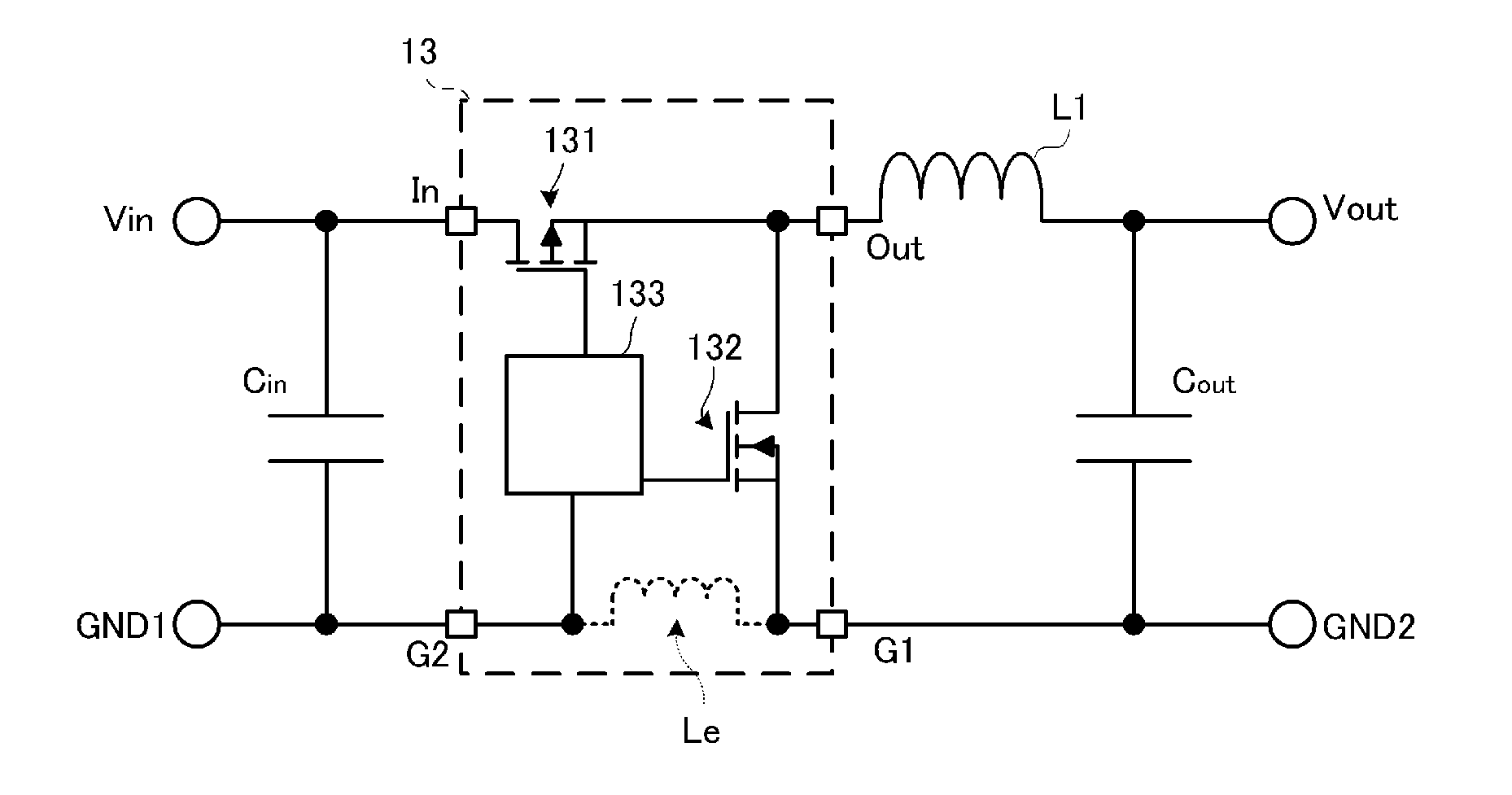

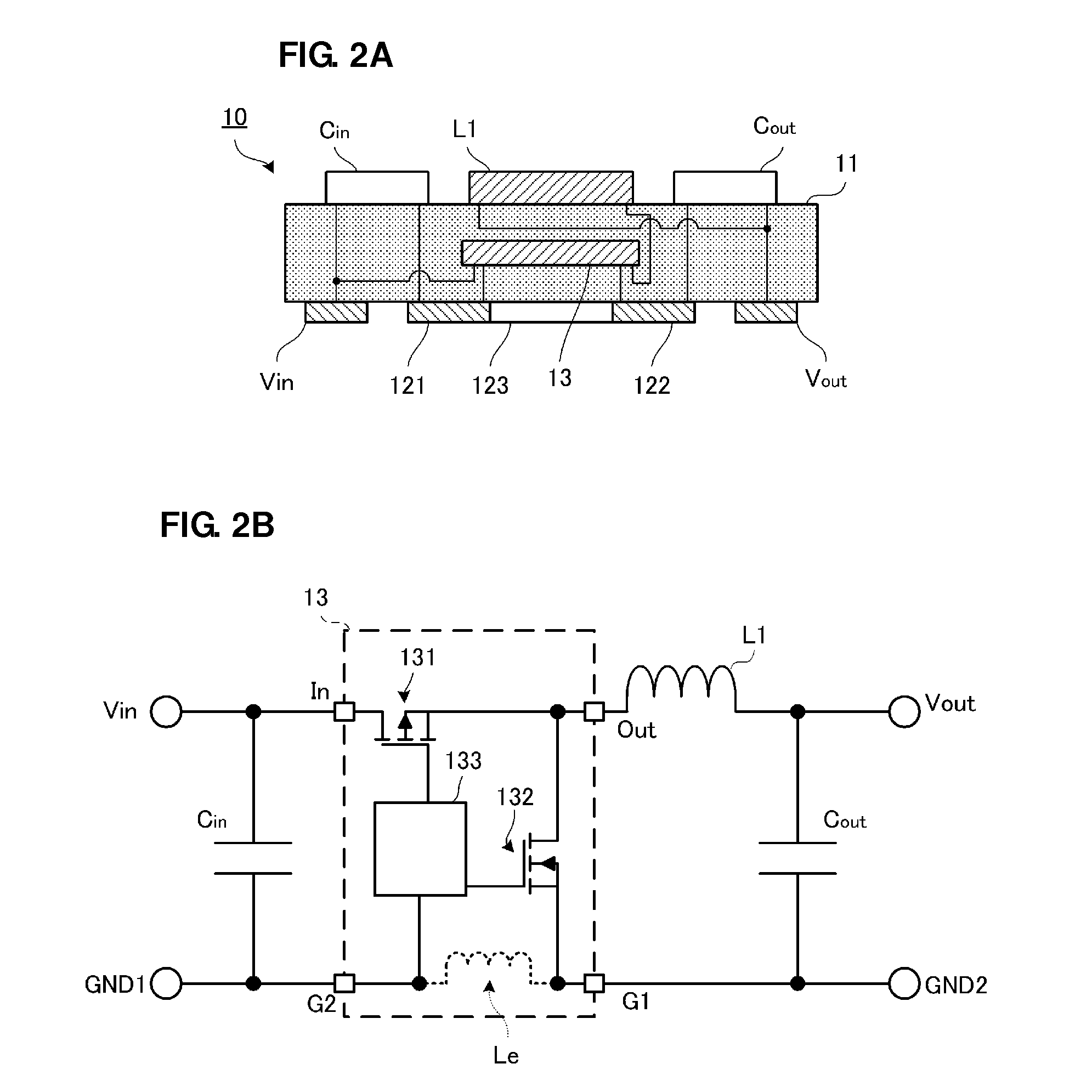

Dc-dc converter

ActiveUS20130049730A1Avoid switchingNoise current is significantly reduced and preventedEfficient power electronics conversionSemiconductor/solid-state device detailsDc dc converterBridge pattern

Owner:MURATA MFG CO LTD

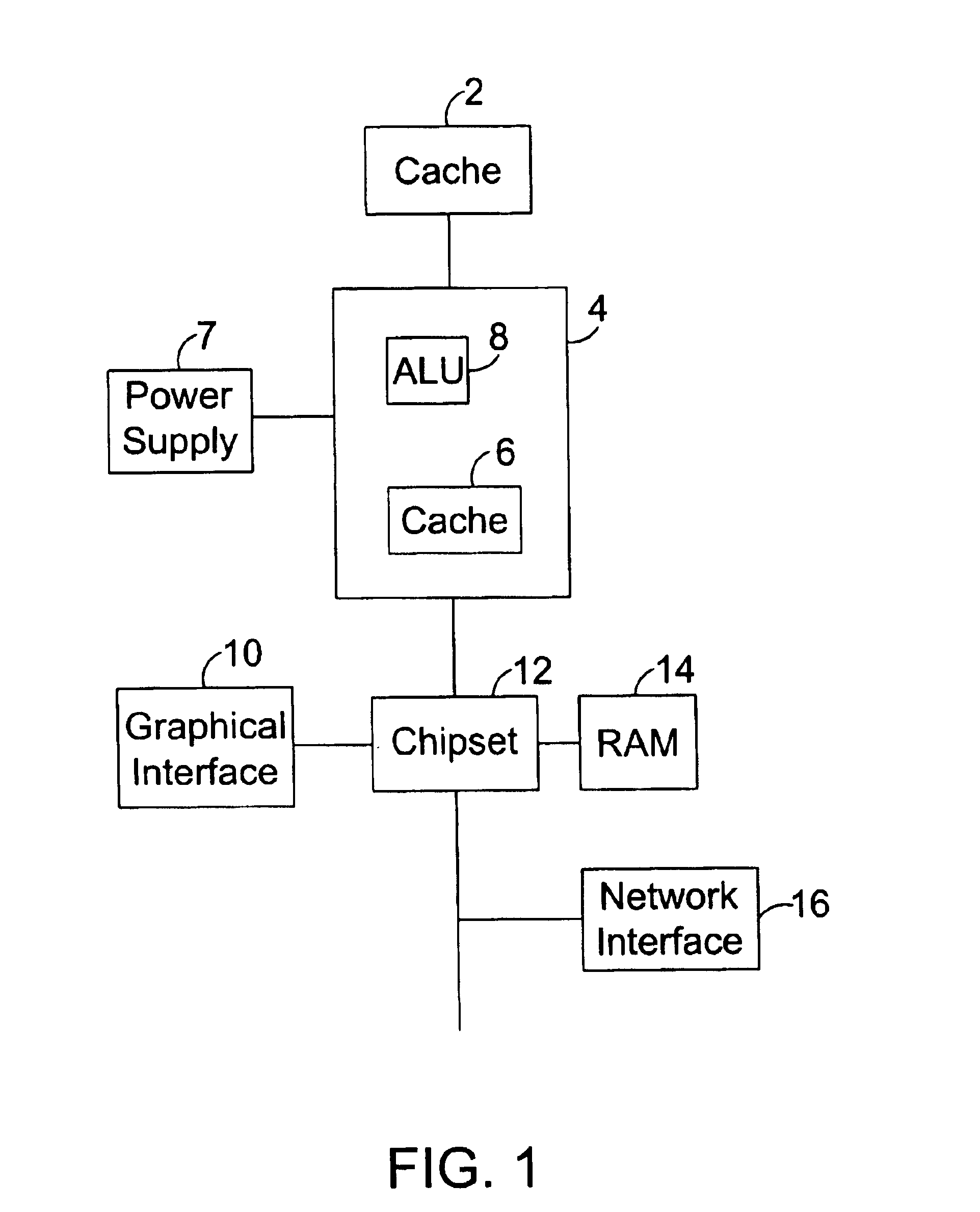

Power converter employing regulators with a coupled inductor

A power converter includes a power train with a coupled inductor and a plurality of regulators, and method of forming and operating the same. In one embodiment, the power train includes a coupled inductor including a magnetic core with a common leg, a first leg and a second leg. The coupled inductor also includes a common winding formed around the common leg, and first and second windings. The first winding is formed around the first leg, and is electrically and magnetically coupled to the common winding. The second winding is formed around the second leg, and is electrically and magnetically coupled to the common winding. The power train also includes a first regulator including a first main switch coupled to the first winding and a second regulator including a second main switch coupled to the second winding.

Owner:MYPAQ HLDG LTD

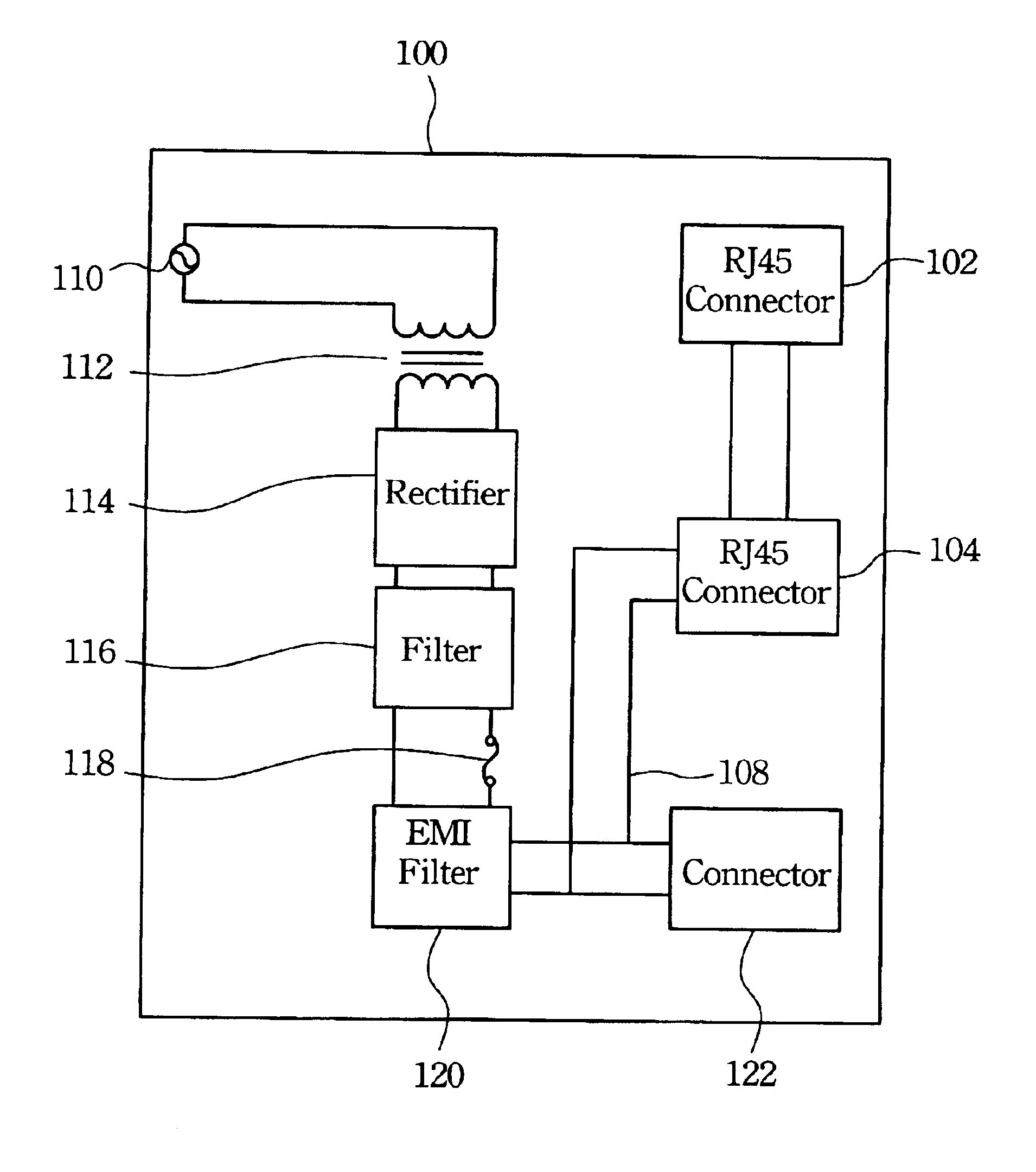

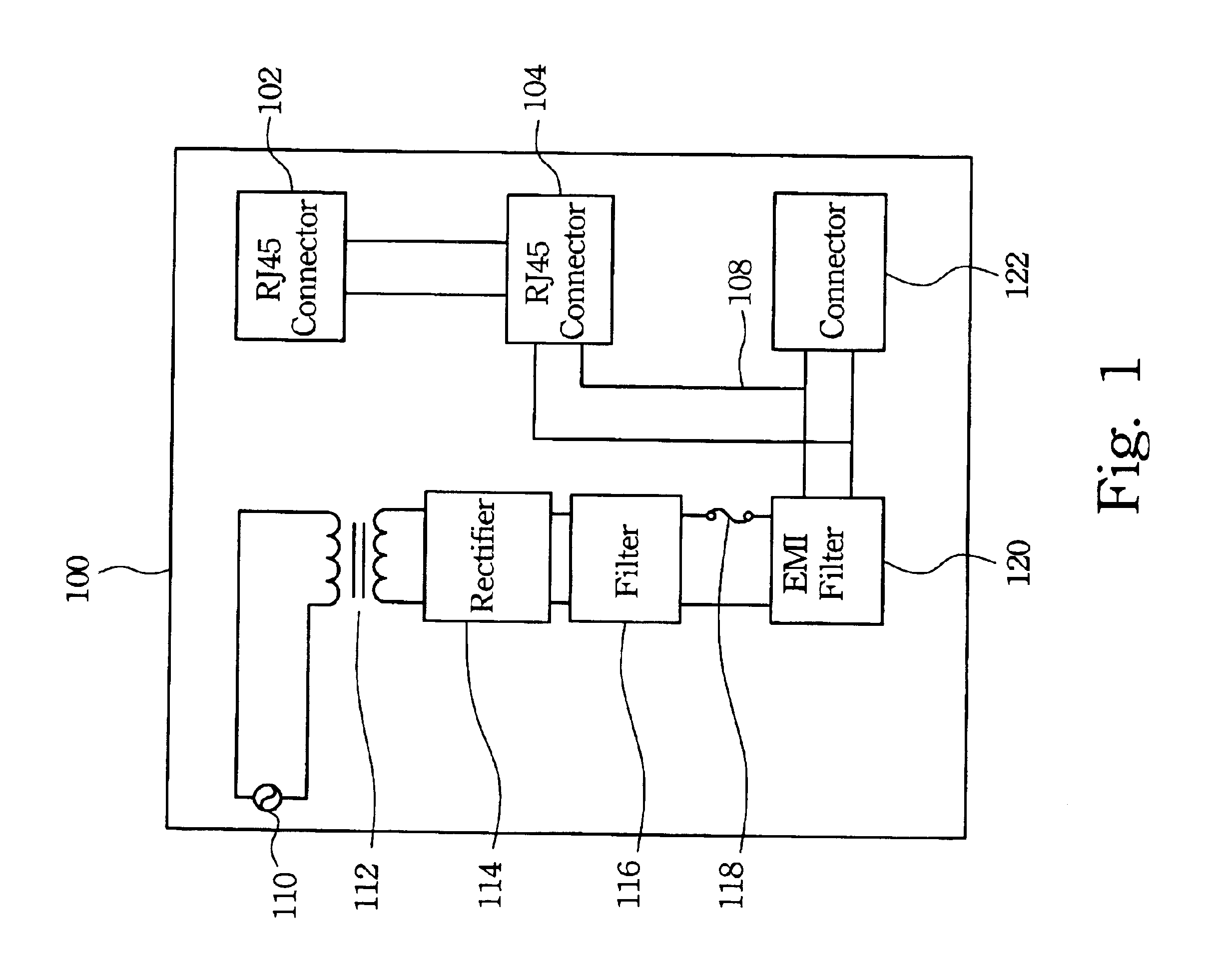

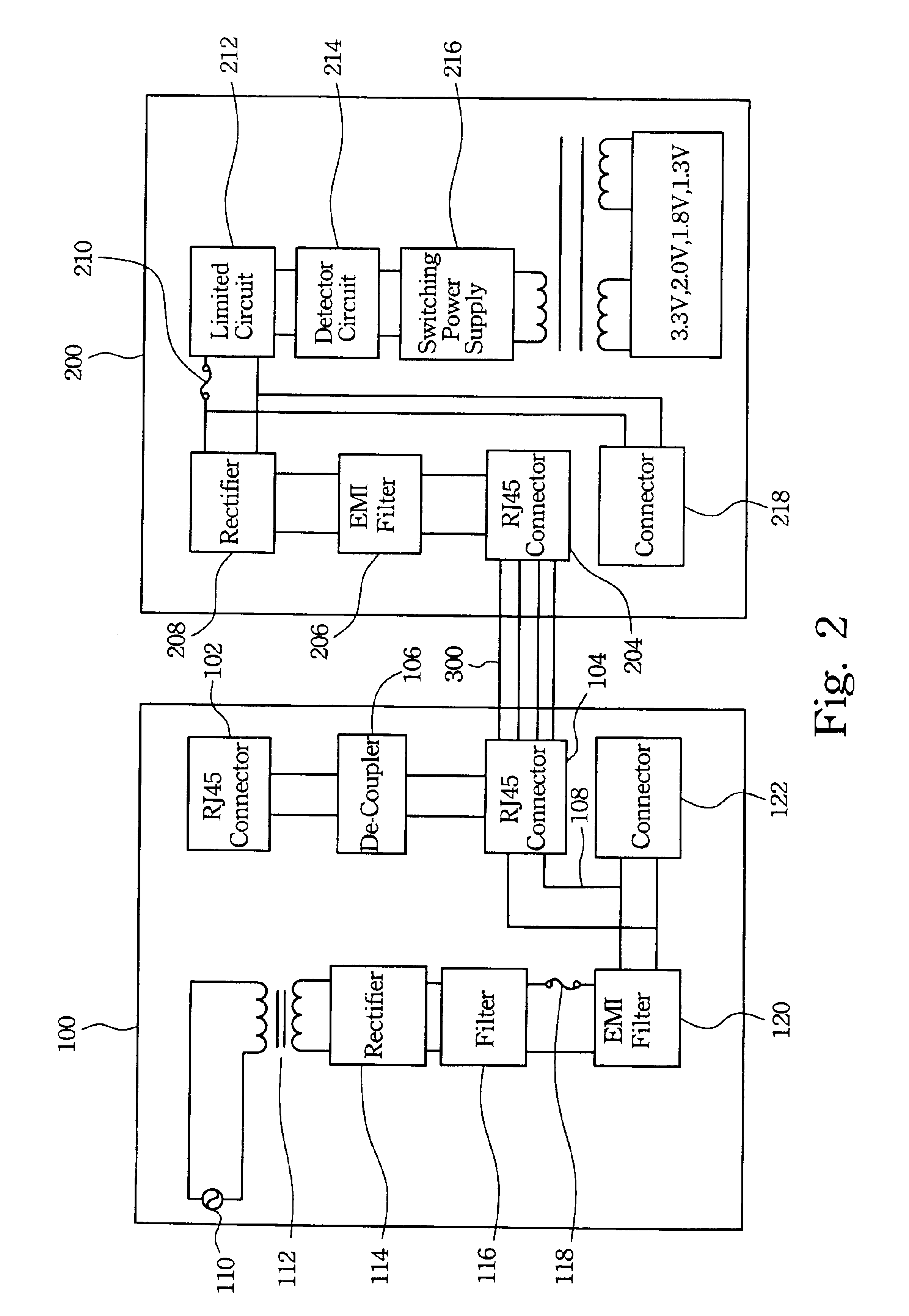

Power injector apparatus

The present invention provides a power injector apparatus that can supply two power sources, one from the Ethernet and the other from AC power. The Internet device can select the AC power as a power source when the Internet device requires power exceeding the Hub or the Switch can supply. Moreover, the Internet device can select the Ethernet as the power source when the supplied power is sufficient.

Owner:ACCTON TECHNOLOGY CORPORATION

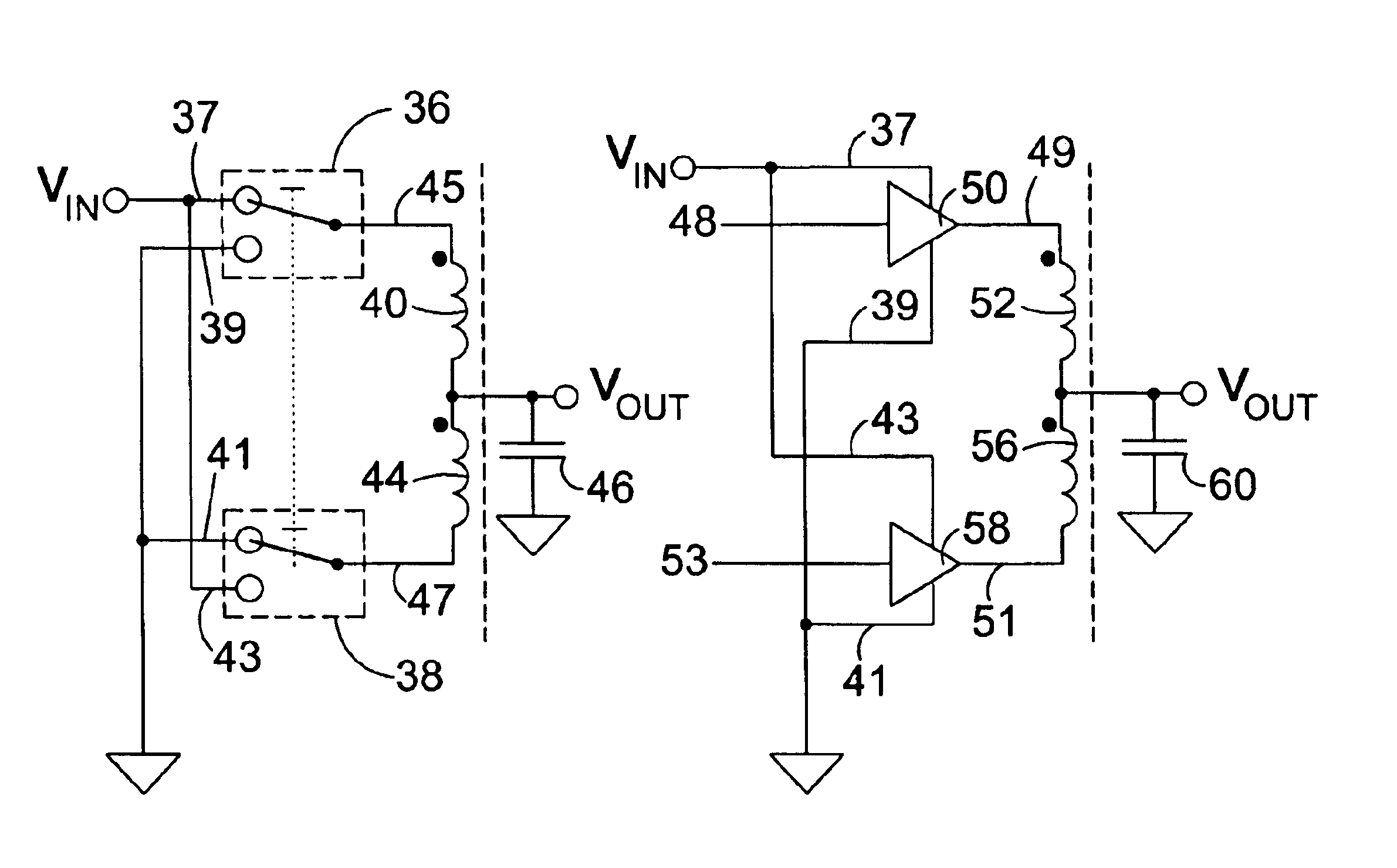

Voltage converter utilizing independently switched inductors

Embodiments of the present invention relate to independently switched inductors in a voltage converter. Each voltage transforming inductor of a voltage converter may be deignated a switch or bridge at each opposing terminal. The function of these switches is to periodically reverse the polarity of voltage across the inductors. By configuring independently switched inductors in series, the frustration of voltage tolerance limitations of the switches is mitigated.

Owner:INTEL CORP