Patents

Literature

35results about How to "Improve random access performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

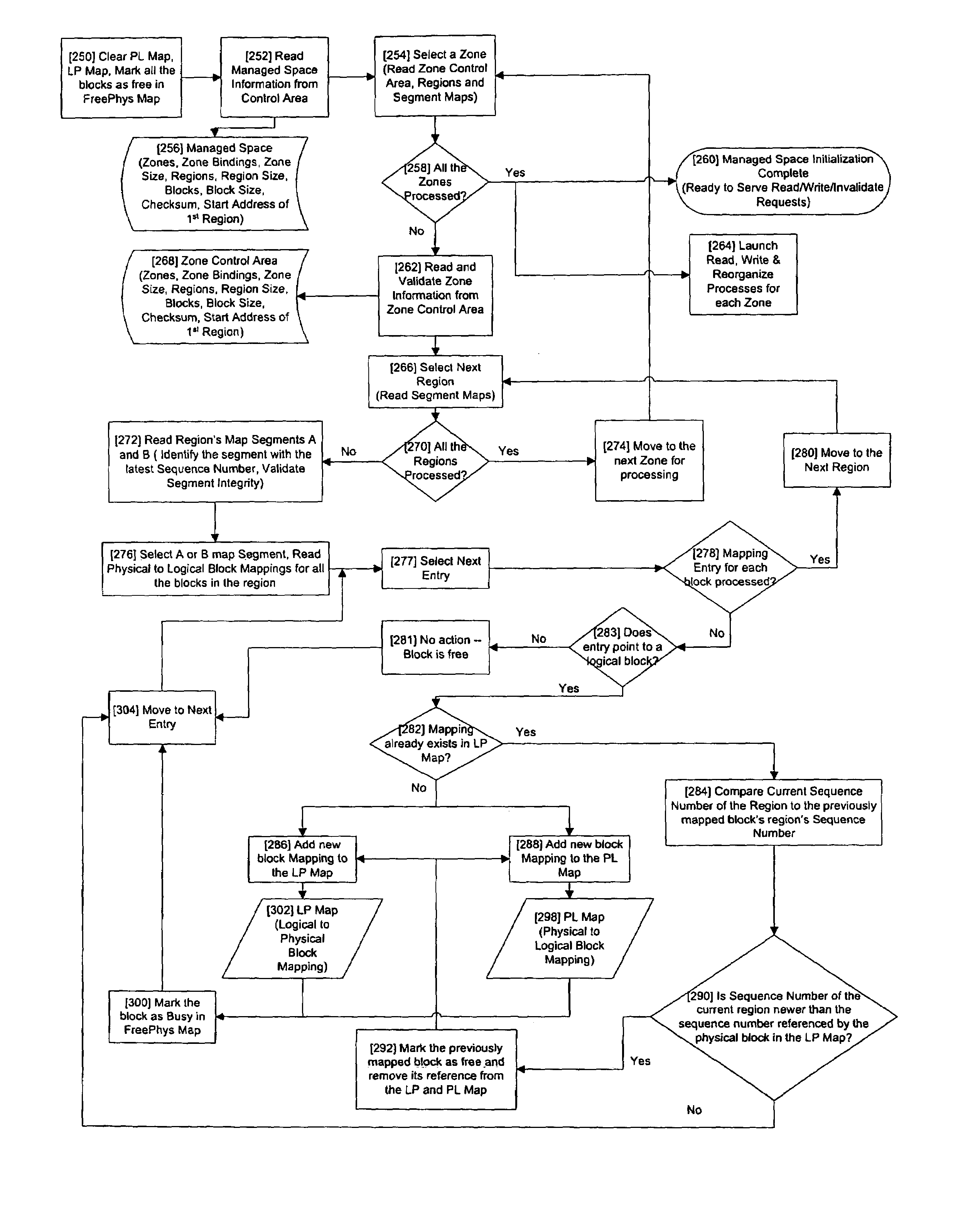

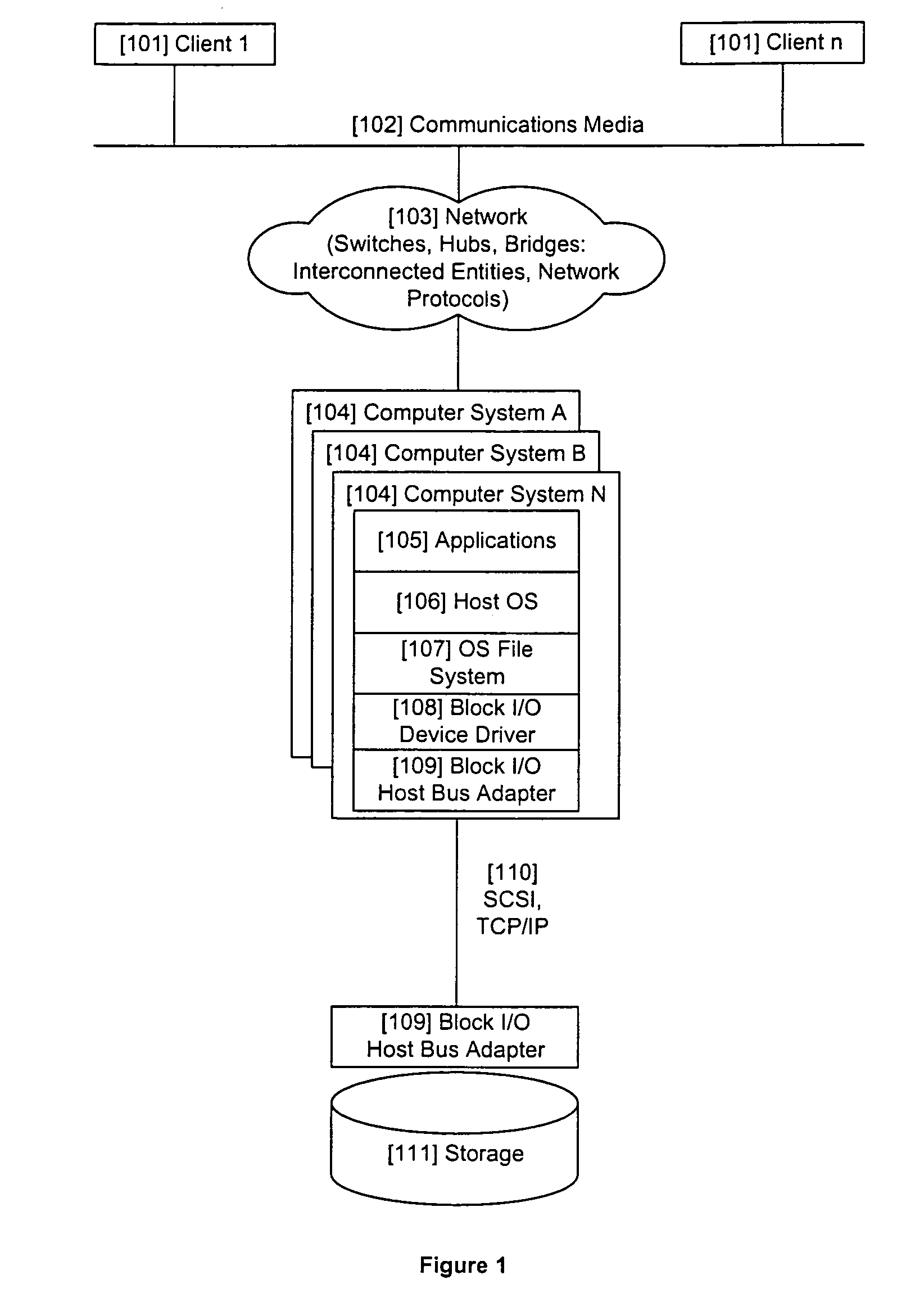

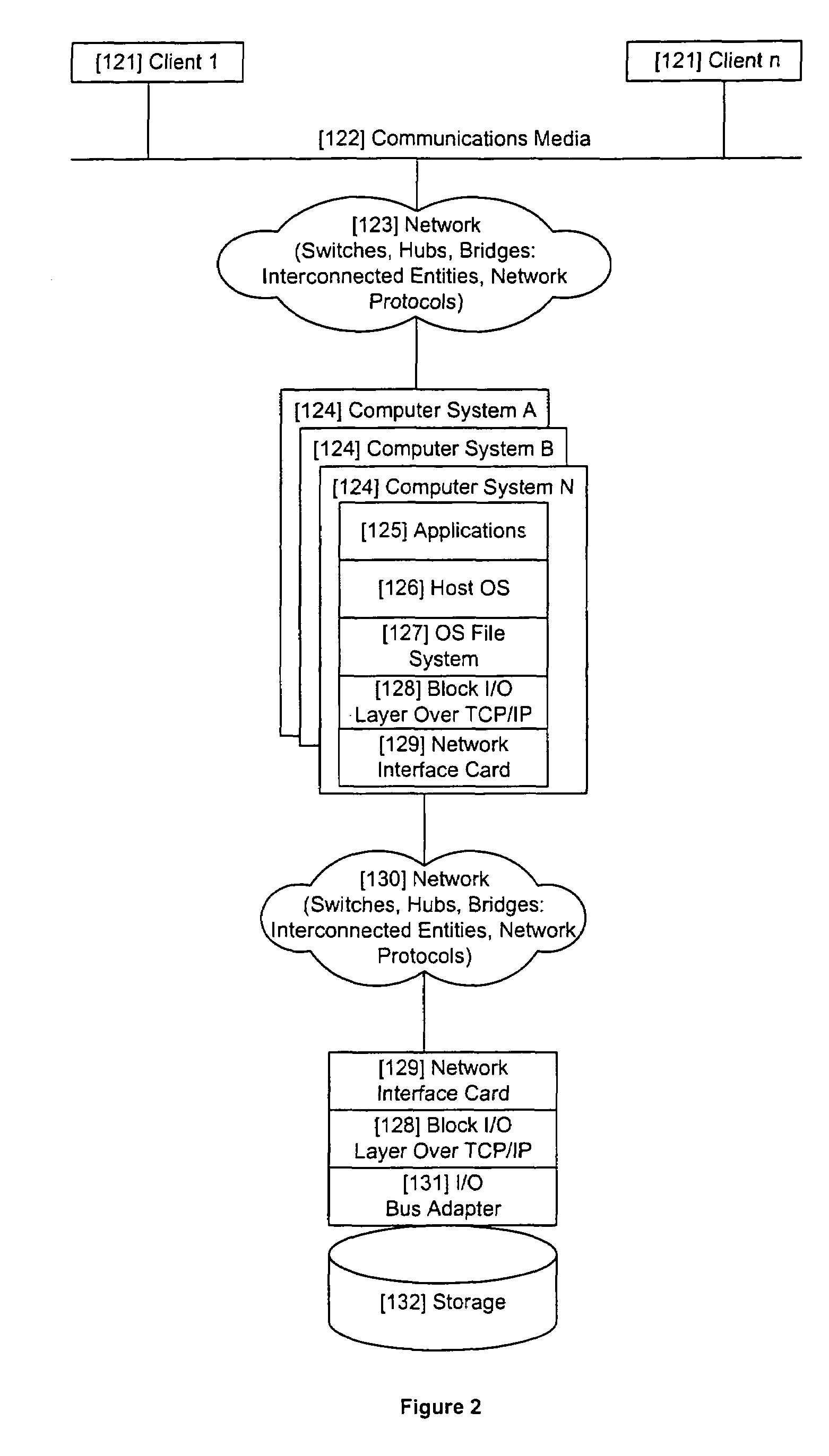

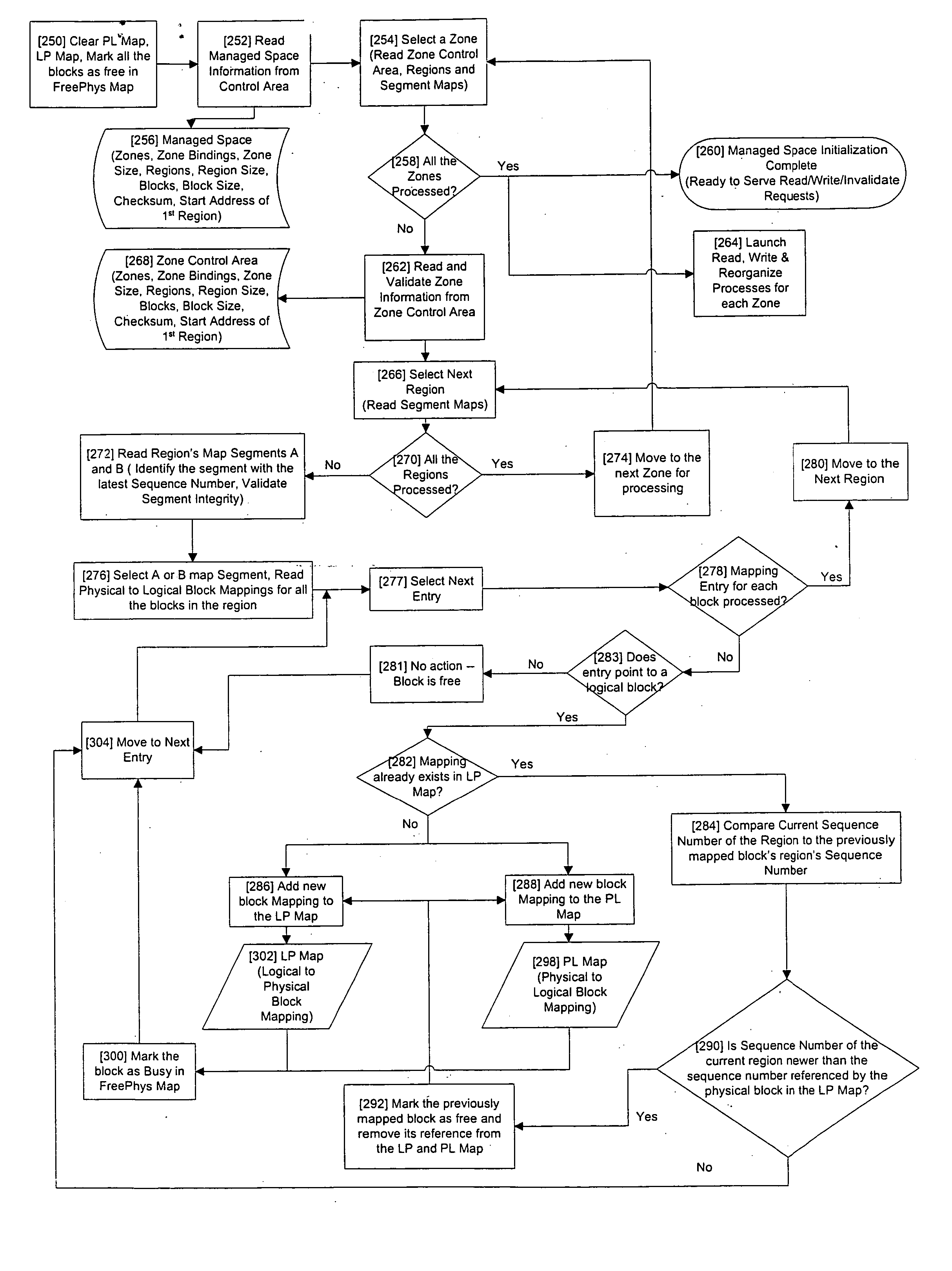

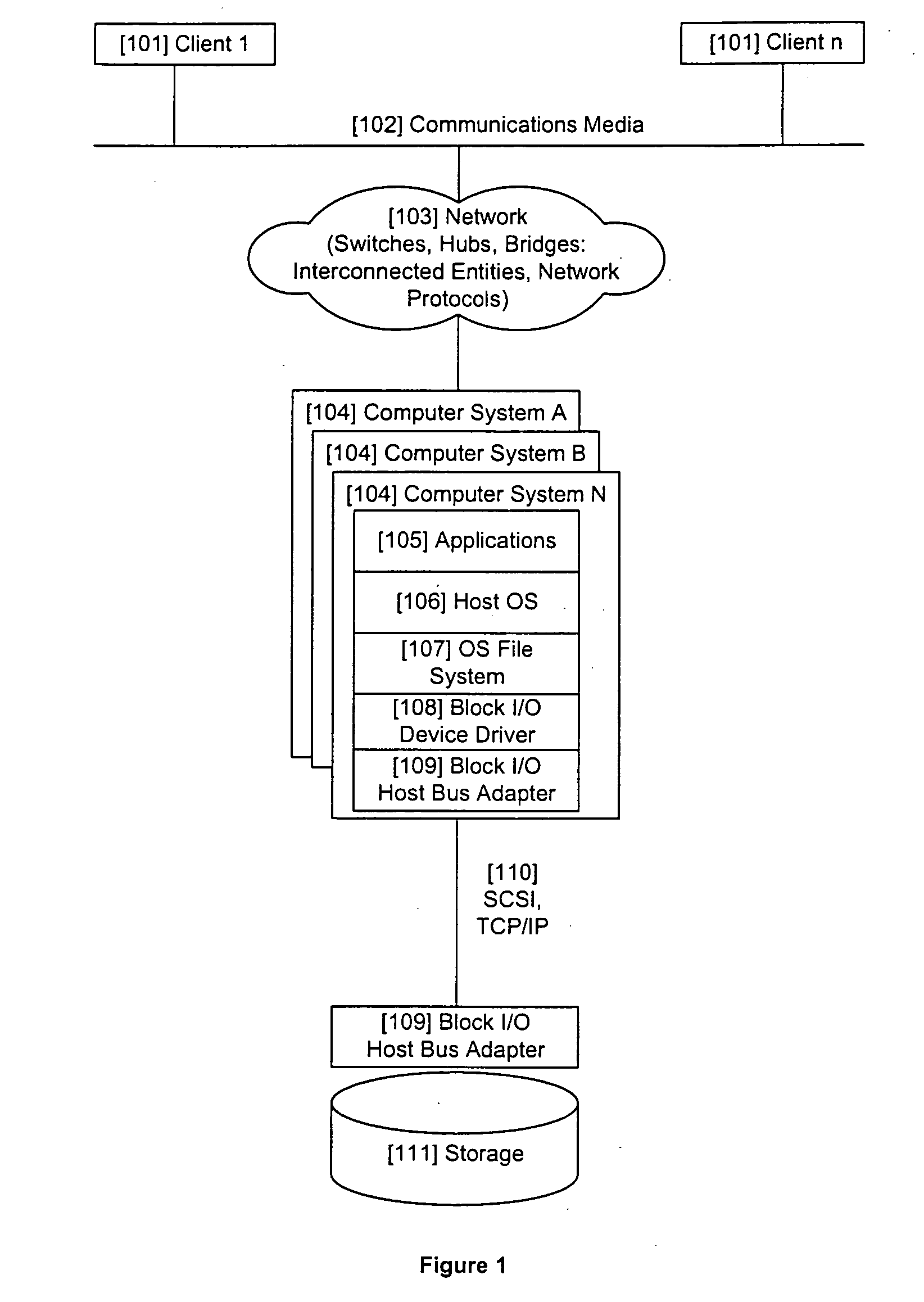

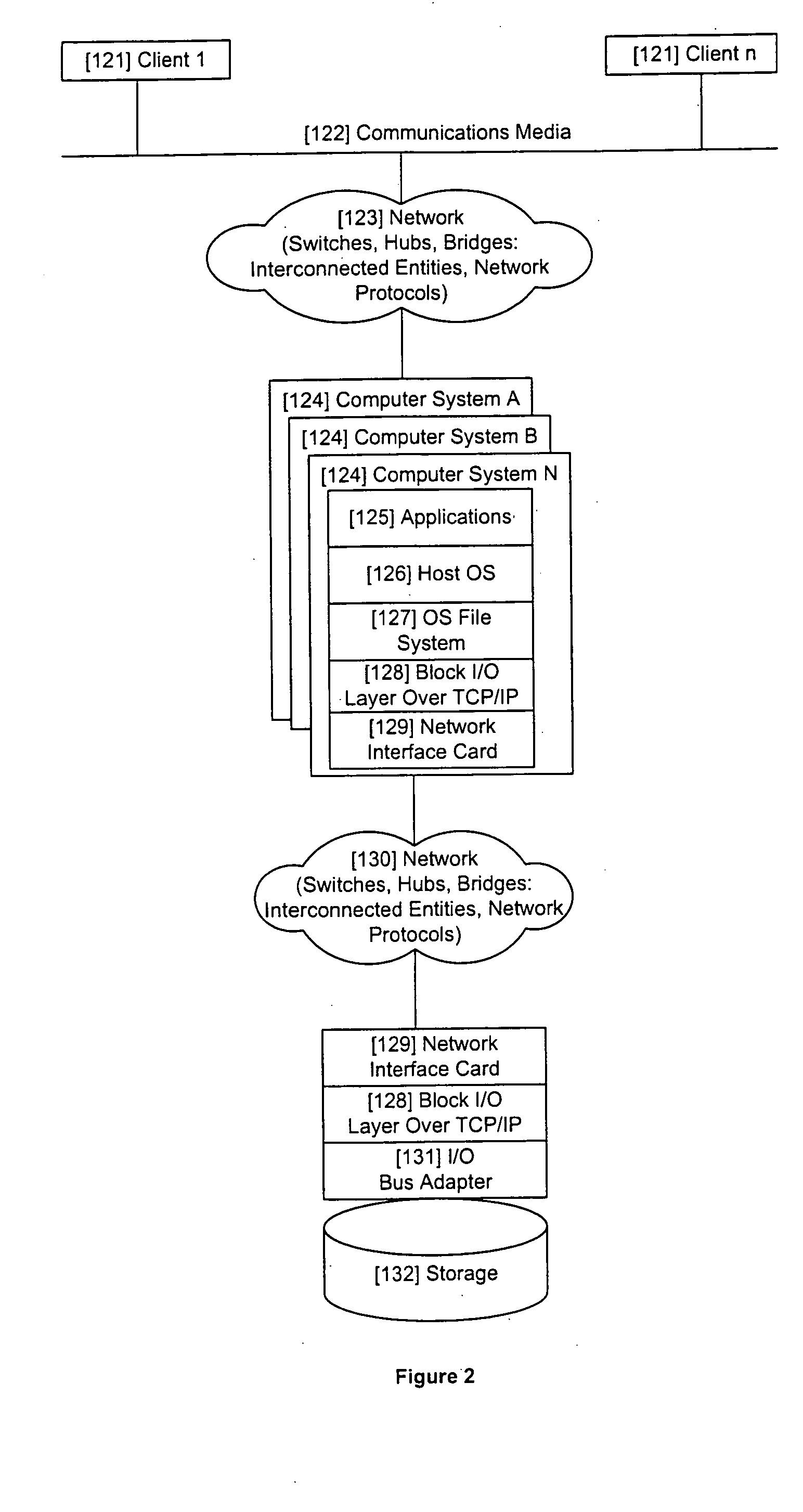

Method and apparatus for improving update performance of non-uniform access time persistent storage media

InactiveUS7328307B2Improve performanceImprove random access performanceInput/output to record carriersMemory adressing/allocation/relocationRAIDAccess time

A high volume storage system is described which continuously remaps where data is stored. The remapping is designed so that writing occurs on an optimum speed basis tuned to the storage system being utilized, e.g., the writes occur in substantially sequential disk storage locations to the extent possible. By remapping data on a substantially continuous basis writes advantageously occur nearer the sequential performance limits of the particular drive or devices being utilized. A methodology is described which improves the external performance of a random access storage system, such as a RAID array. The illustrative embodiments introduce a continuous, optimized dynamic reorganization of the storage media that converts concurrent updates from one or more logical volumes to one or more sequential streams, as appropriate to the number of physical devices and channels over which the updates can be dispersed and thereby minimize the number of seek operations necessary on each physical device.

Owner:UNIFIED PATENTS

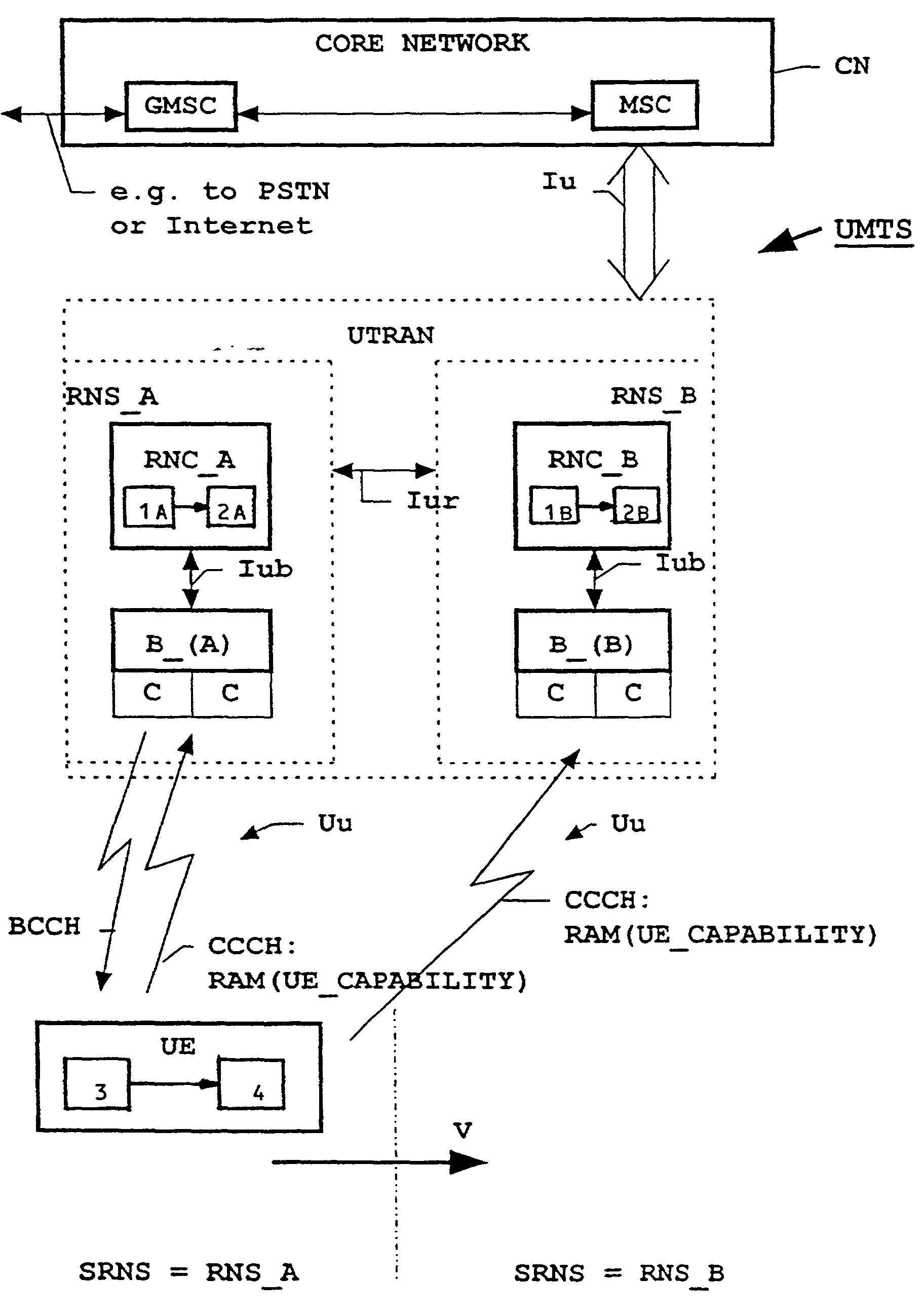

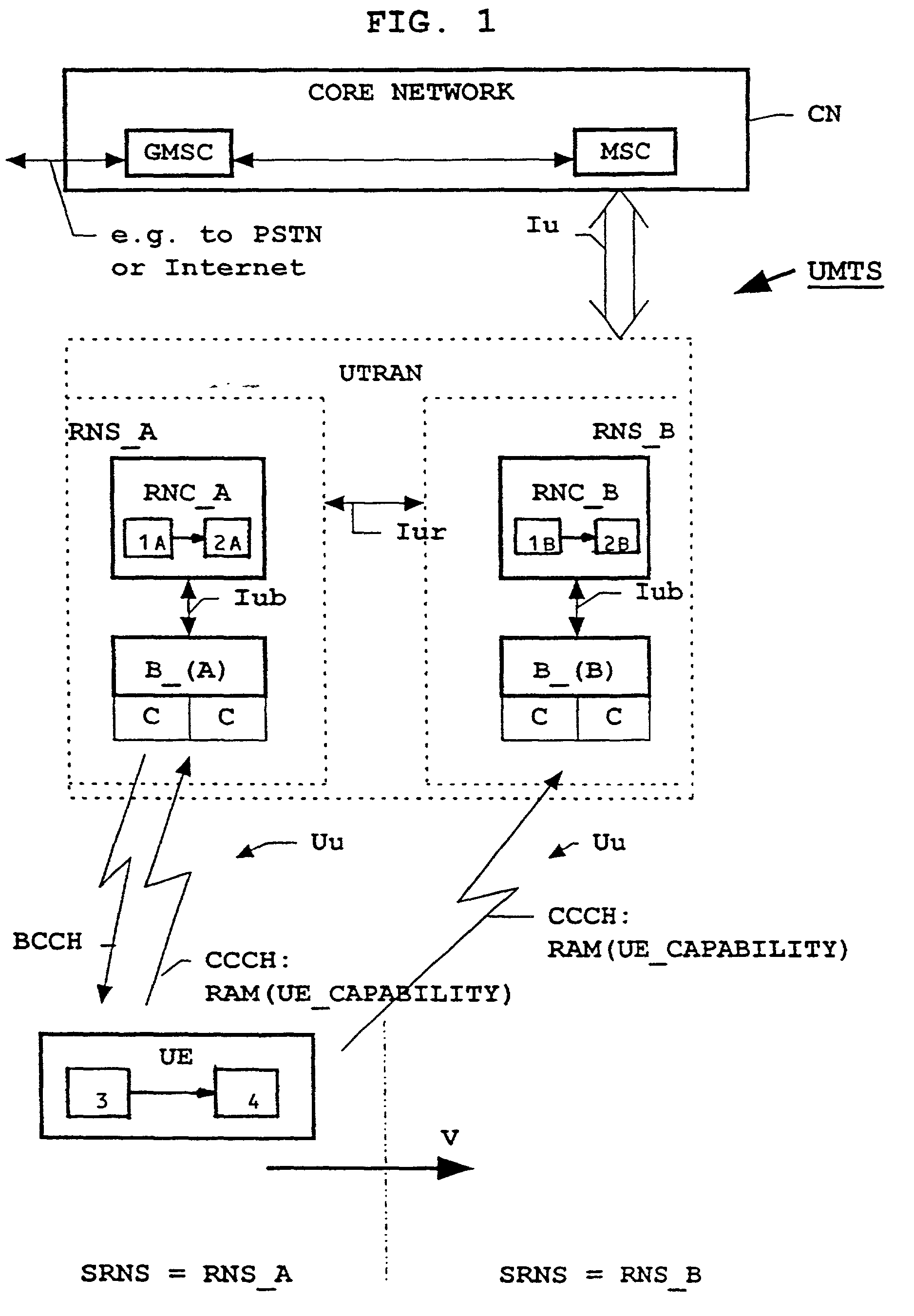

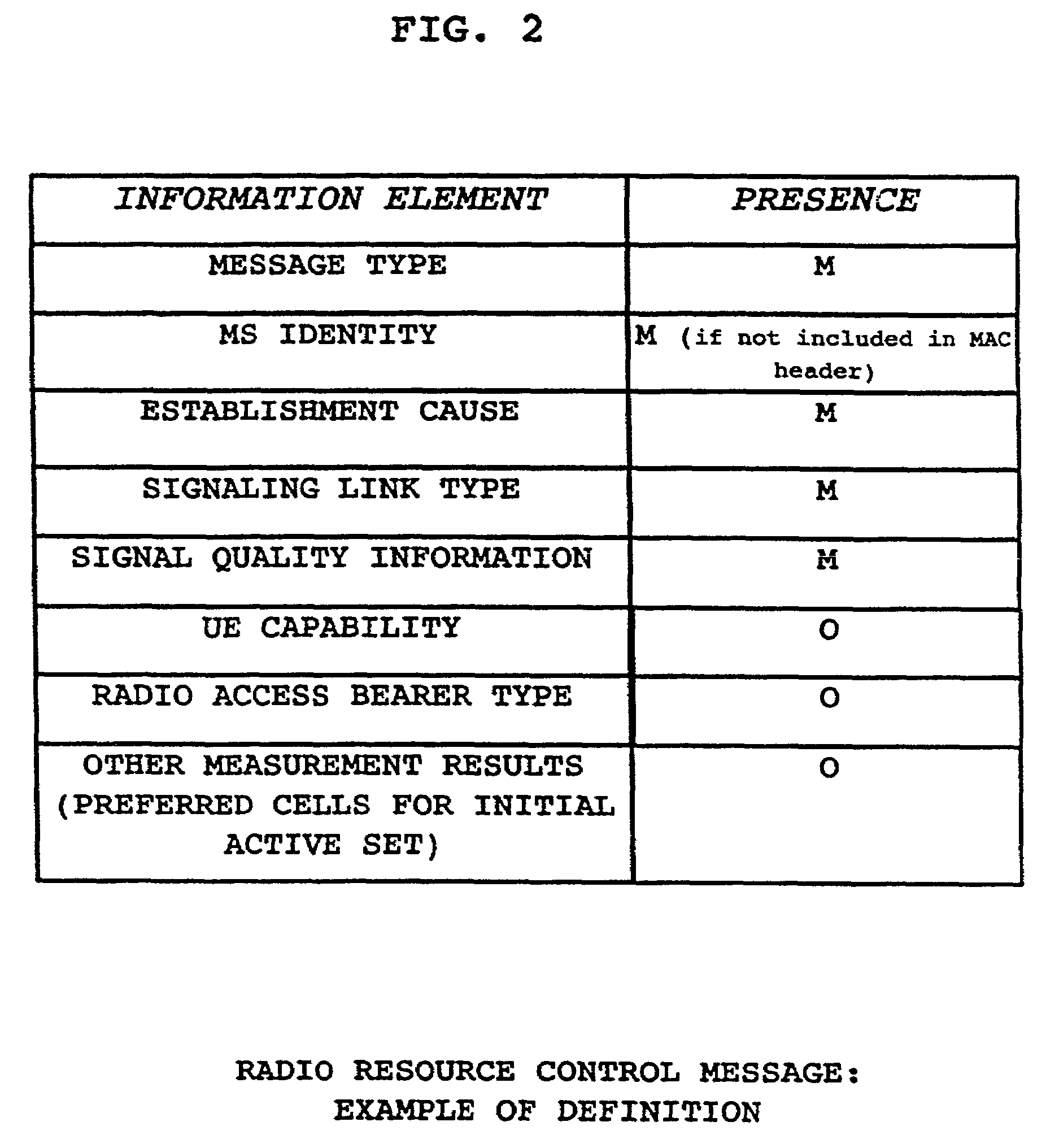

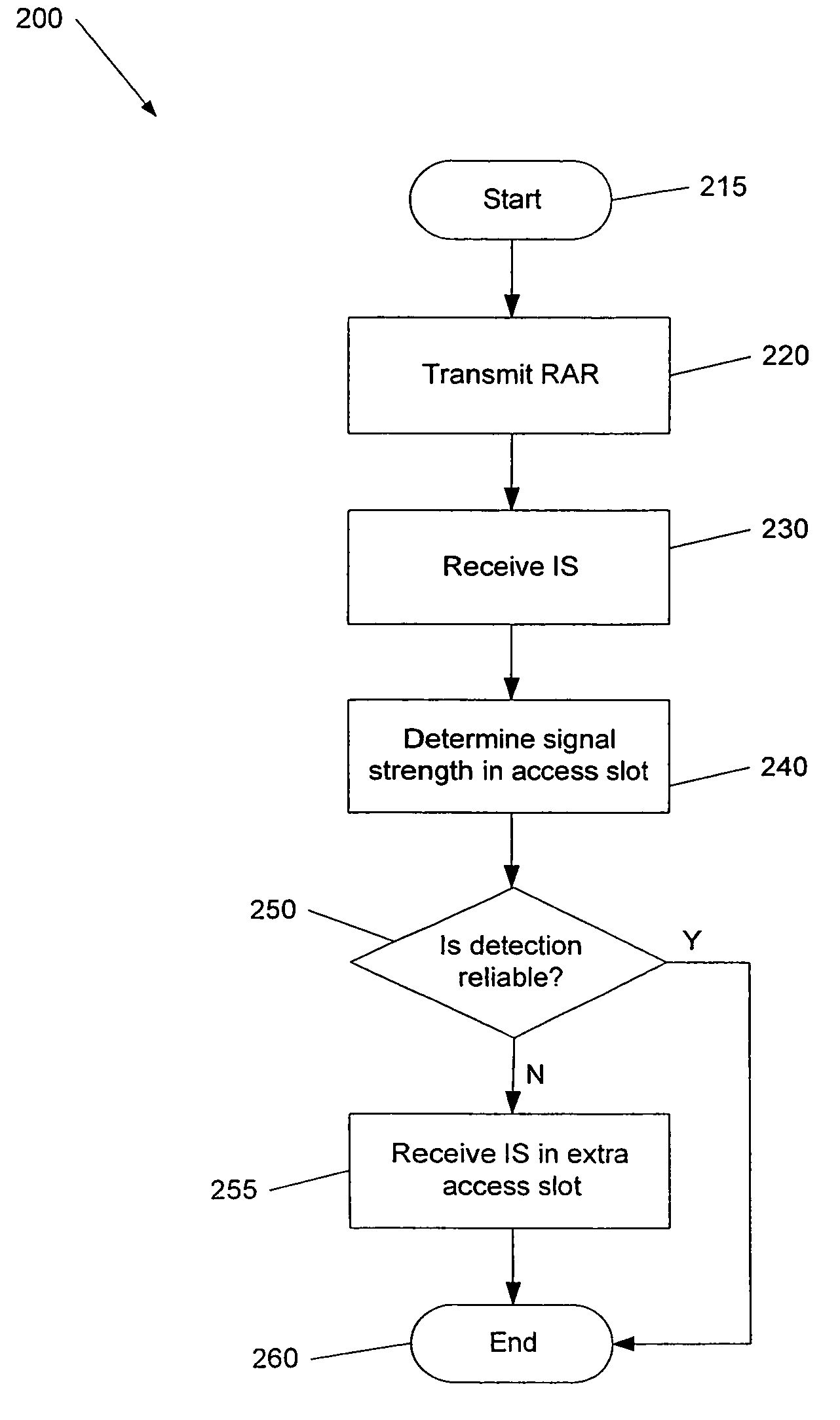

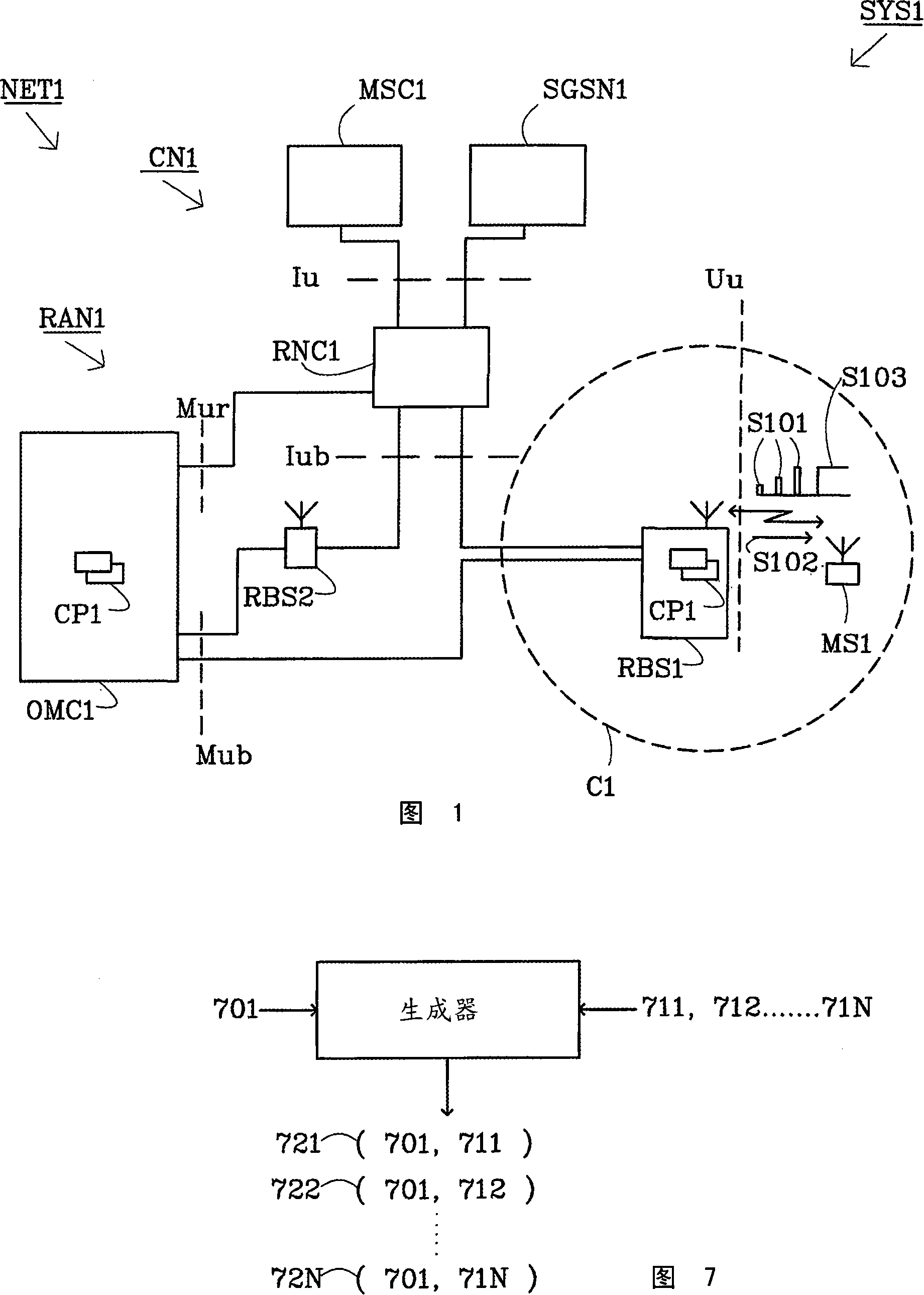

Method for establishing a communication link between a user equipment and a radio network

InactiveUS7433334B2Improve random access performanceFunction increaseTime-division multiplexRadio/inductive link selection arrangementsTelecommunications linkRadio networks

A method for improving the performance of random access when establishing a communication link between a user equipment (UE) and a radio network (UTRAN) the method includes transmitting a random access message (RAM) from the user equipment (UE) to the radio network (UTRAN), wherein the radio random access message (RAM) contains information describing a functional capability (UB_CAPABILITY) of the user equipment (UE). Thereby, the network knows the capabilities of the terminal as early as possible and can thus optimize all functions performed by the network to be in conformity with the terminal capabilities.

Owner:WSOU INVESTMENTS LLC

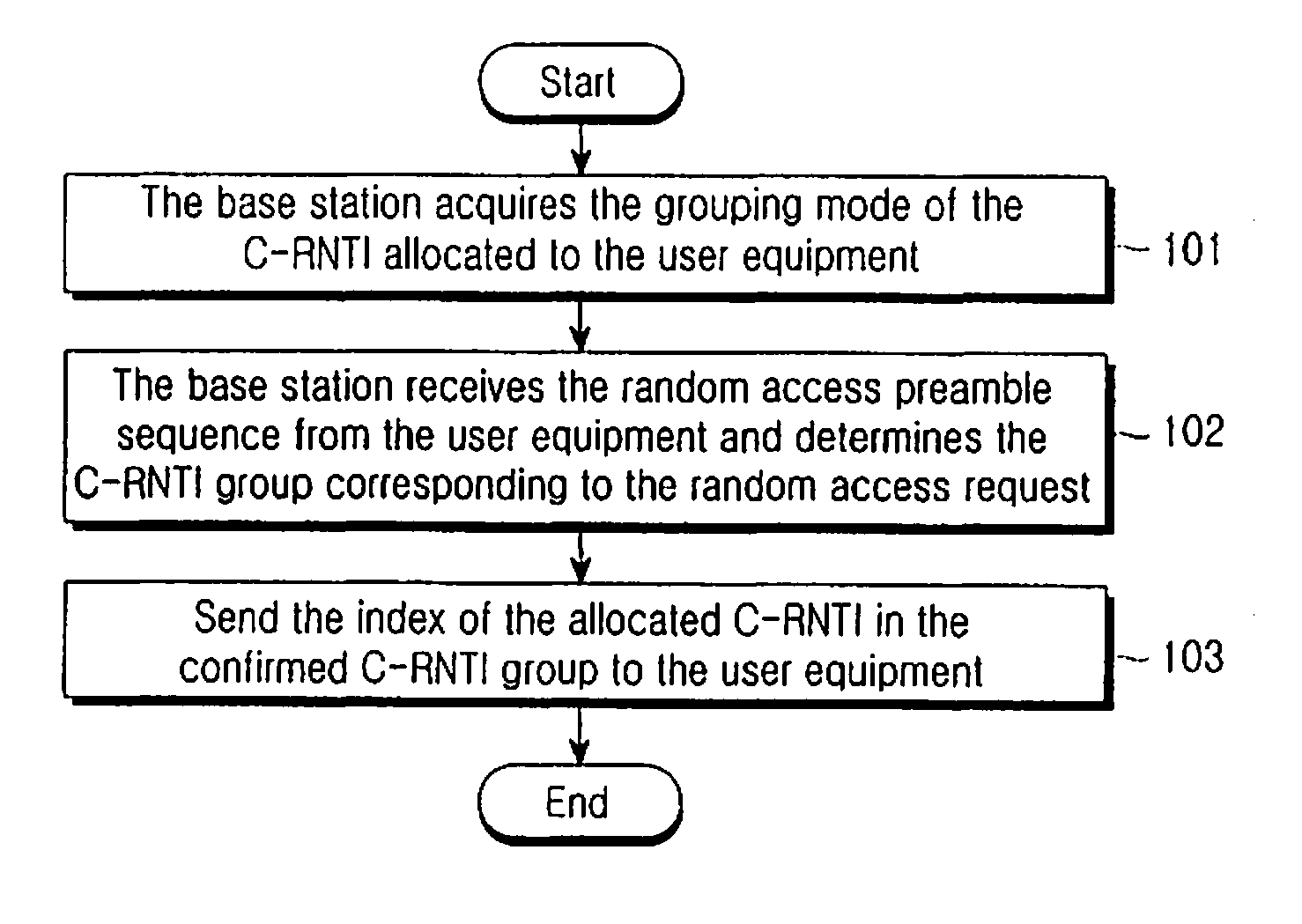

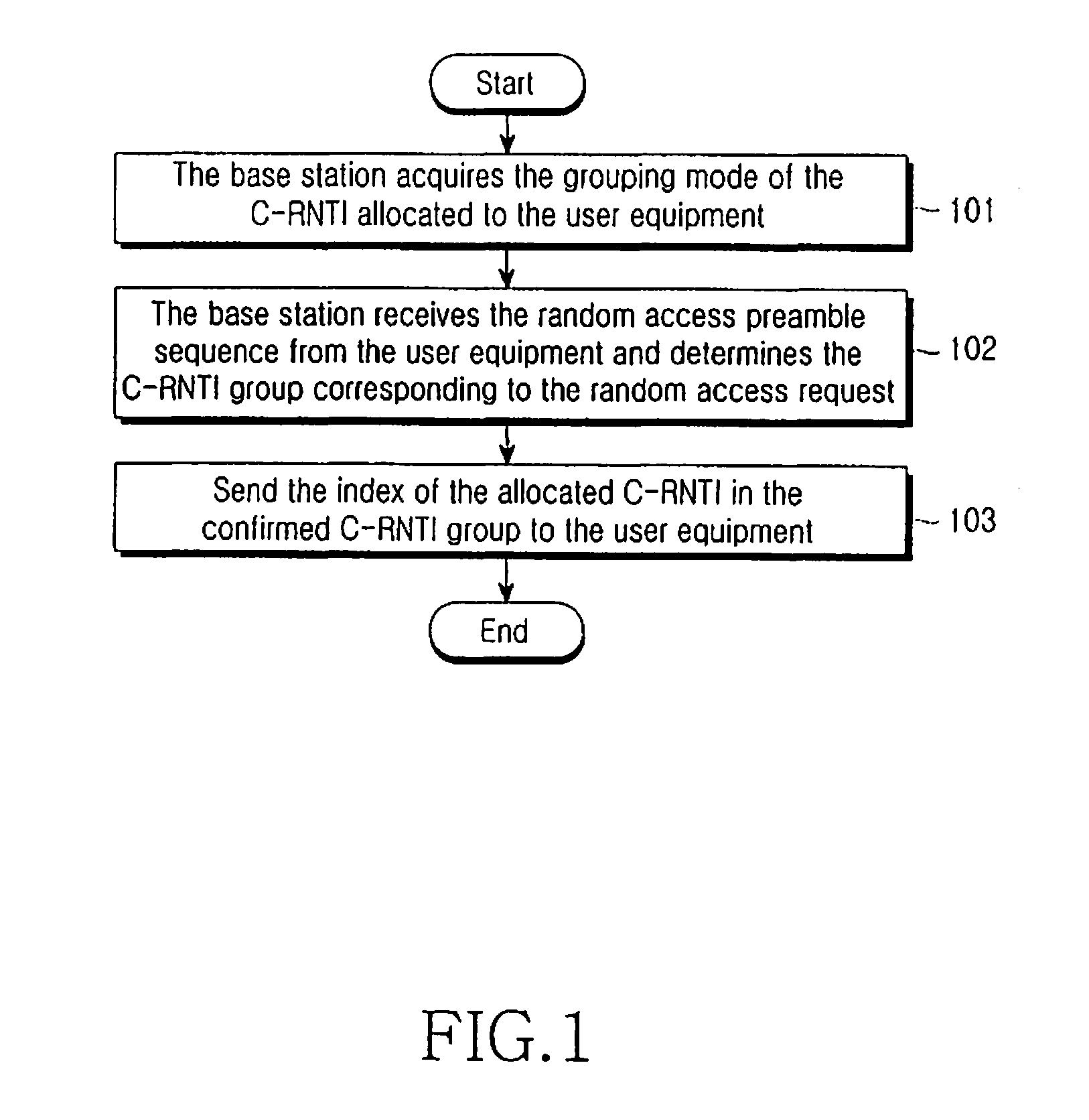

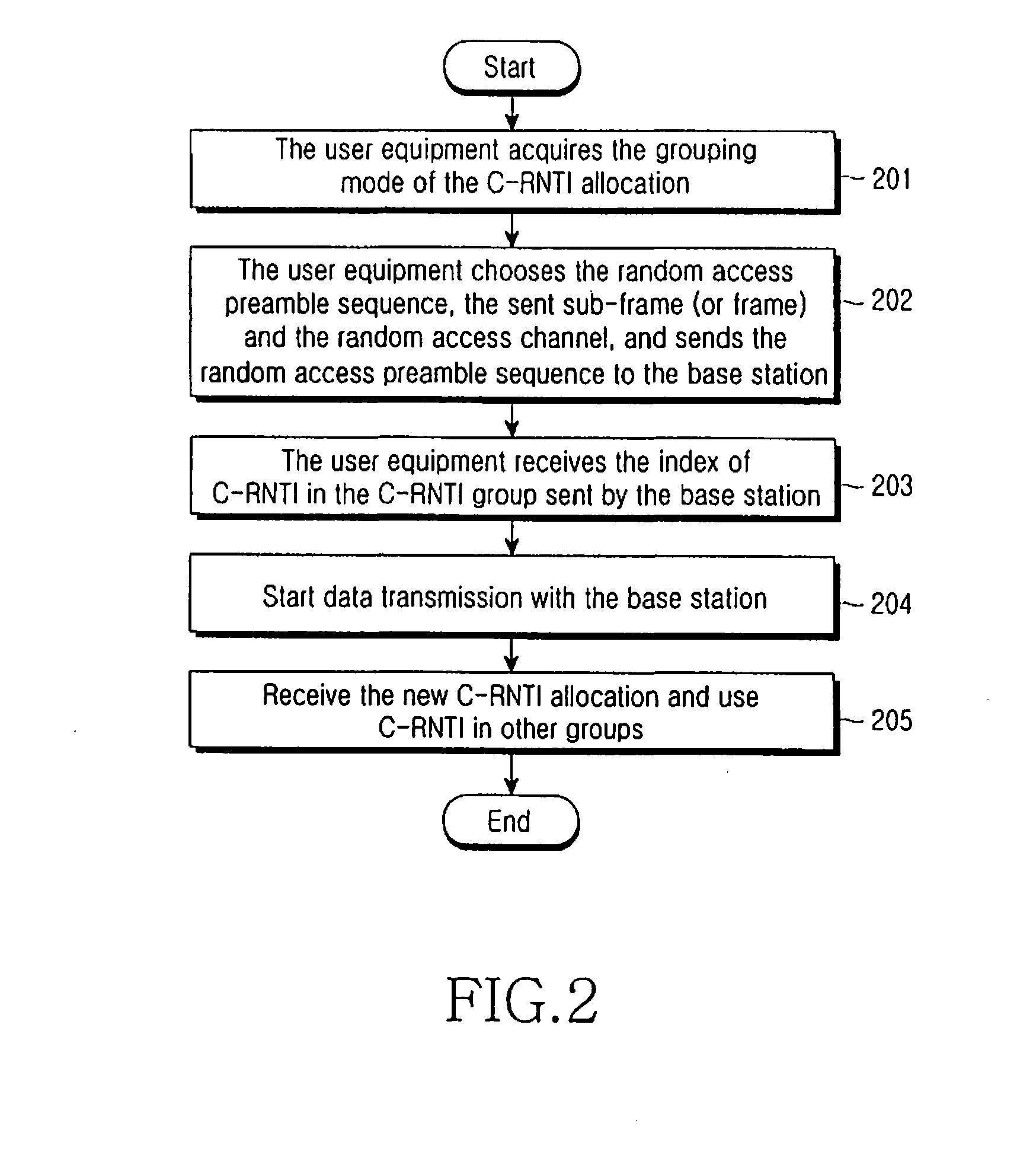

Methods and apparatus for allocating cell radio network temporary identity

InactiveUS20080139214A1Reduce needSimple processRadio/inductive link selection arrangementsWireless communicationRadio networksRandom-access channel

The present invention describes that the C-RNTIs are grouped based on the random access preamble sequence, the transmission sub-frame and the transmission random access channel information used for the user equipment and detected by the base station. In such a way, the indicating information bits needed by C-RNTI allocation are decreased and the signaling overhead needed by C-RNTI allocation is also decreased. In addition, the random access process is optimized and the random access performance is improved.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Method and apparatus for improving update performance of non-uniform access time persistent storage media

InactiveUS20050210218A1Improve performanceImprove random access performanceInput/output to record carriersMemory adressing/allocation/relocationRAIDAccess time

A high volume storage system is described which continuously remaps where data is stored. The remapping is designed so that writing occurs on an optimum speed basis tuned to the storage system being utilized, e.g., the writes occur in substantially sequential disk storage locations to the extent possible. By remapping data on a substantially continuous basis writes advantageously occur nearer the sequential performance limits of the particular drive or devices being utilized. A methodology is described which improves the external performance of a random access storage system, such as a RAID array. The illustrative embodiments introduce a continuous, optimized dynamic reorganization of the storage media that converts concurrent updates from one or more logical volumes to one or more sequential streams, as appropriate to the number of physical devices and channels over which the updates can be dispersed and thereby minimize the number of seek operations necessary on each physical device.

Owner:UNIFIED PATENTS

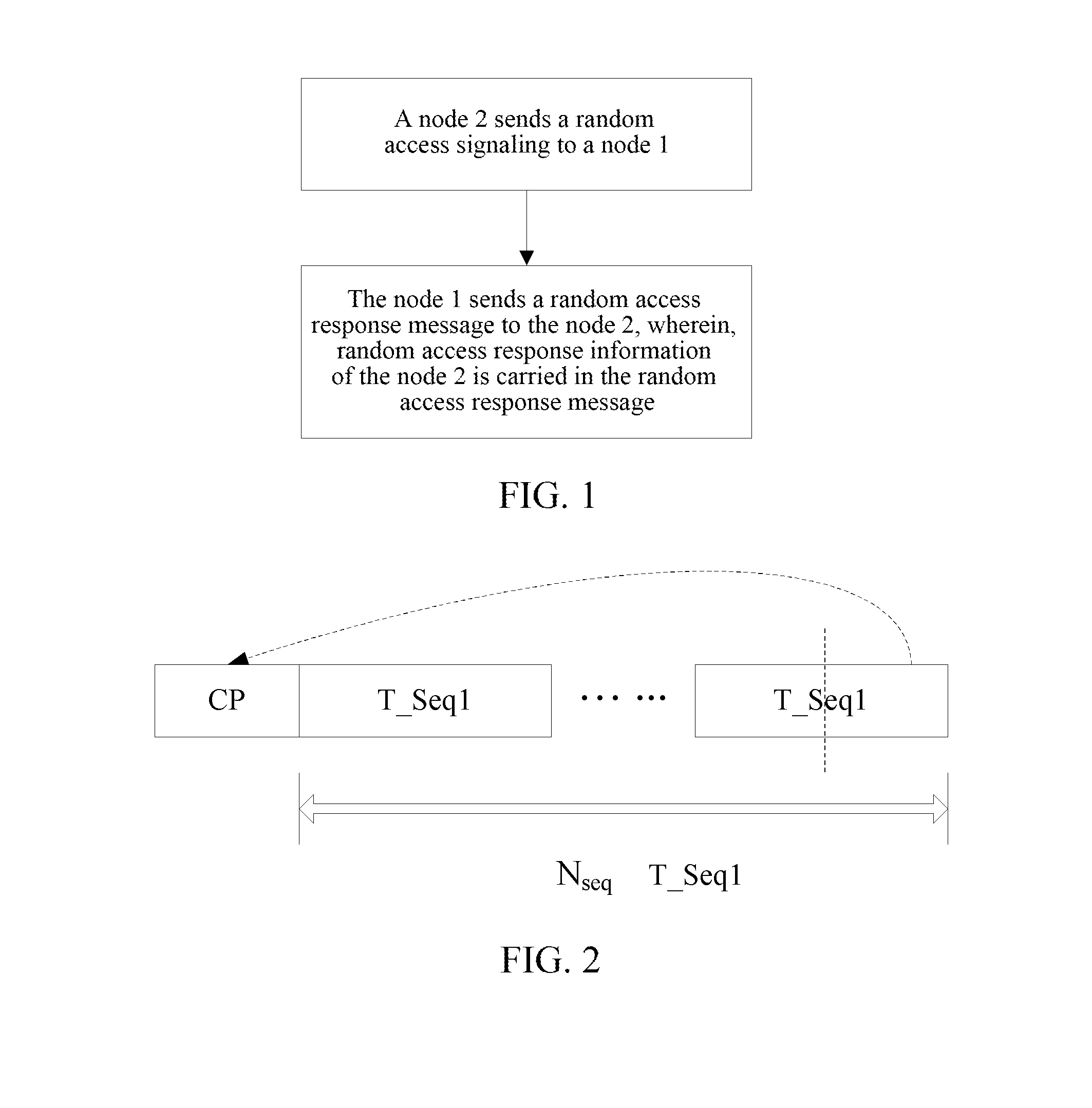

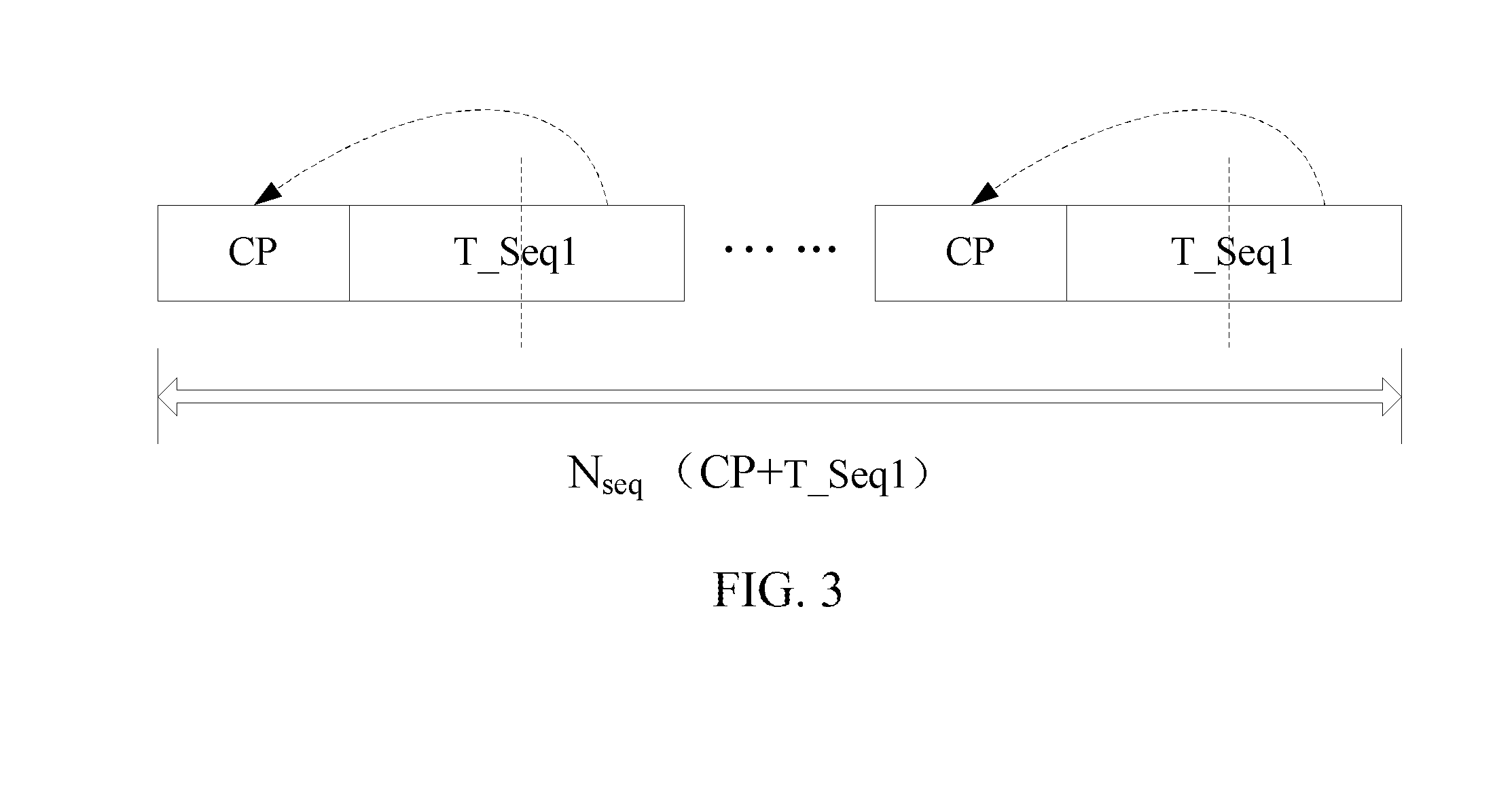

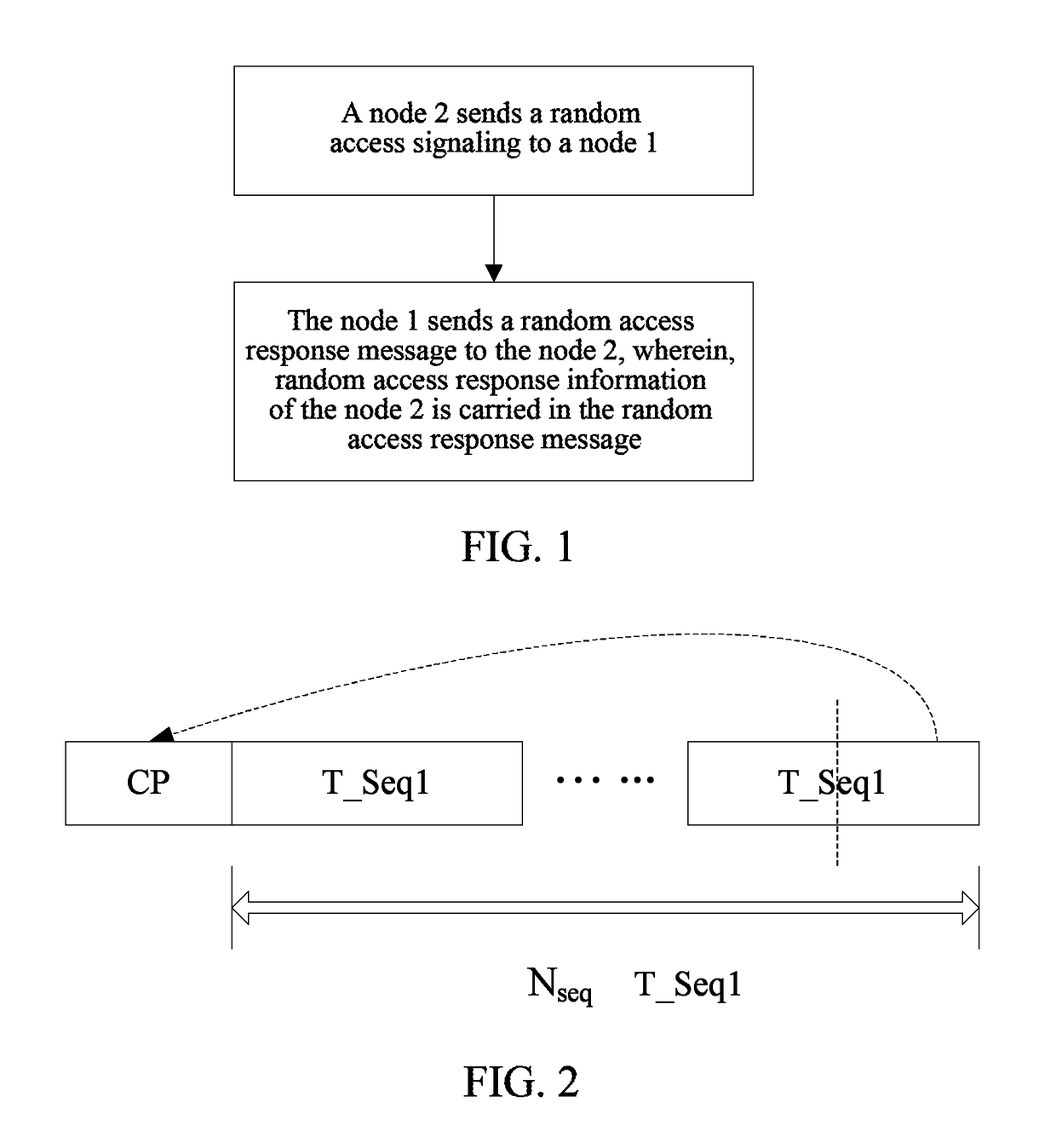

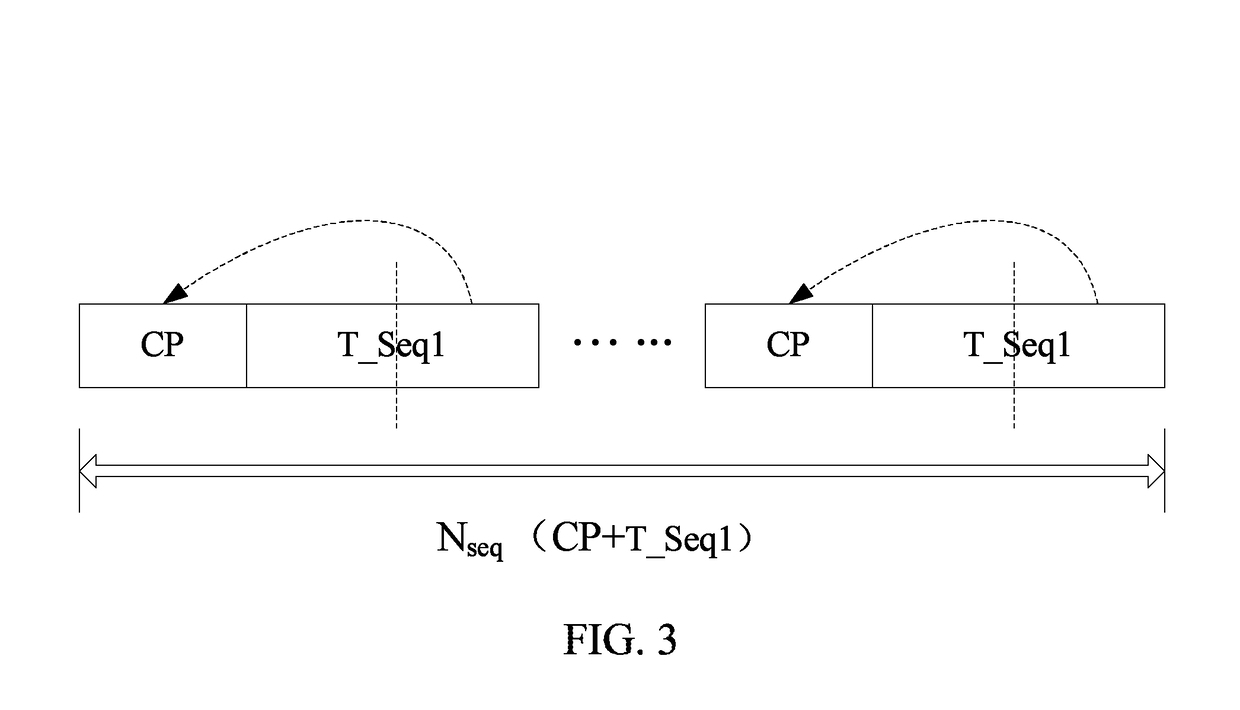

Random access sequence transmission method and device

ActiveCN104184548AImprove random access performanceError preventionWireless communicationRandom-access channelEmbedded system

The invention provides a random access sequence transmission method and device, relates to the communication field, and helps to solve the problem that random access signaling sent by MTC UE in a hostile environment can be guaranteed be correctly detected by eNB. The method comprises a first node sends a random access channel configuration message, wherein the random access channel configuration message at least comprises random access channel resource configuration information of a third node. According to the technical scheme provided in the invention, the random access sequence transmission method and device are suitable for M2M services in an LTE system, and higher MTC UE random access performance is realized.

Owner:ZTE CORP

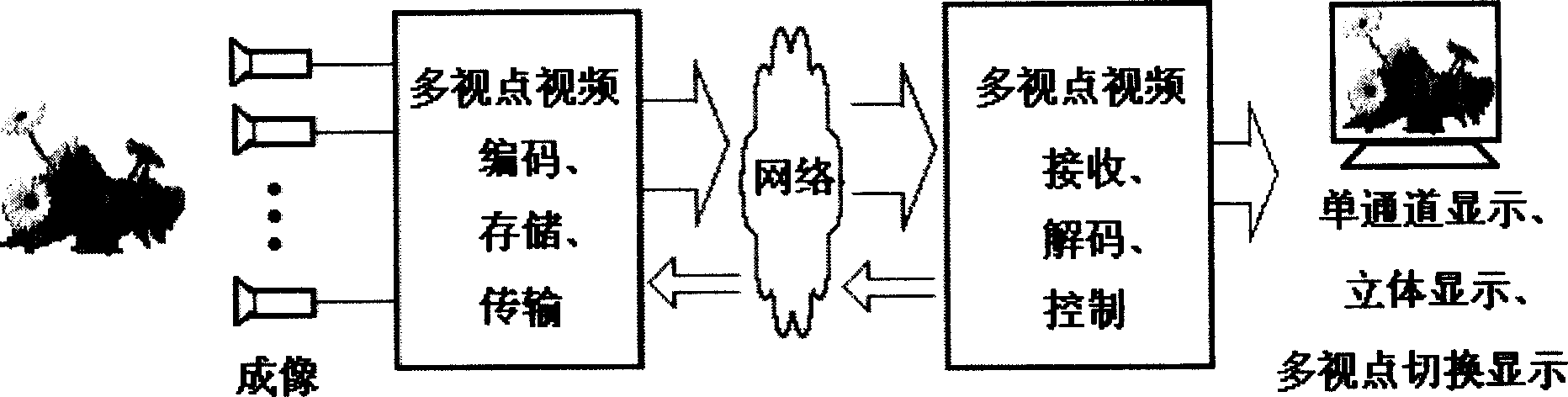

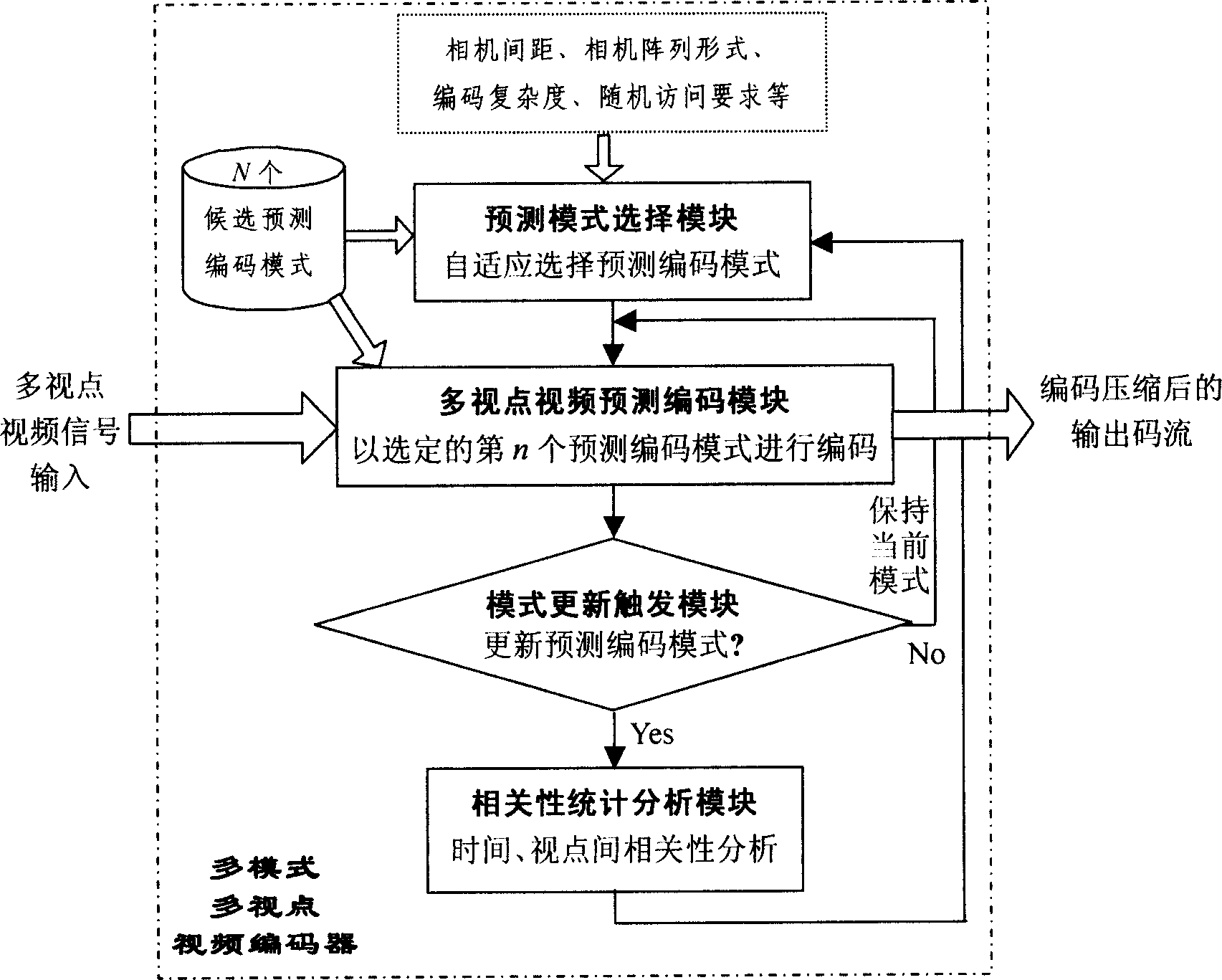

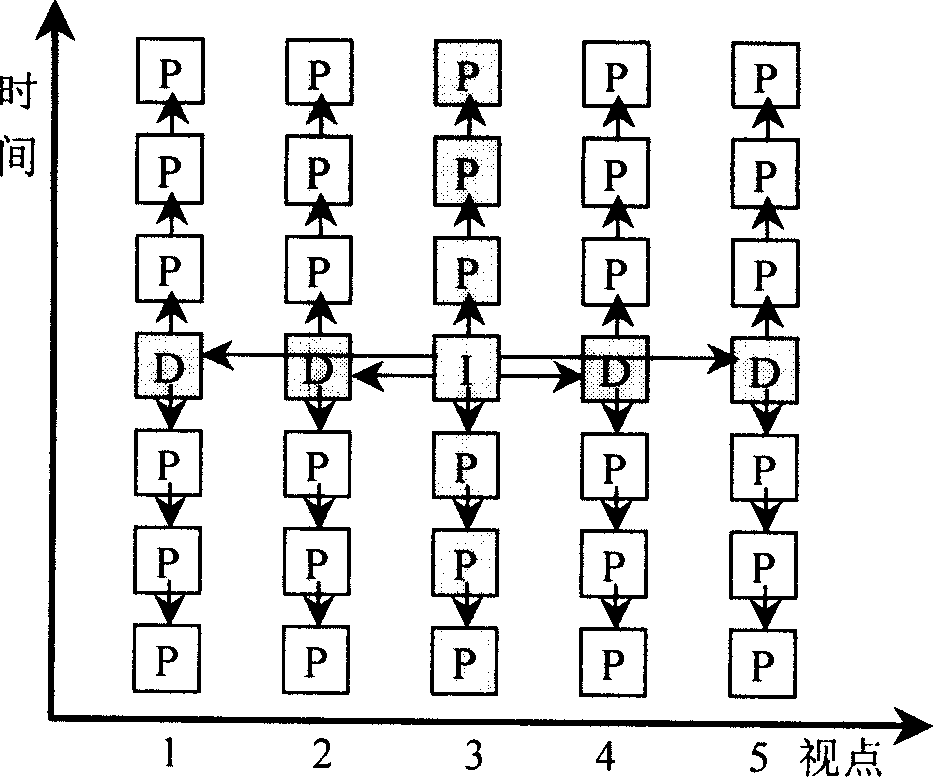

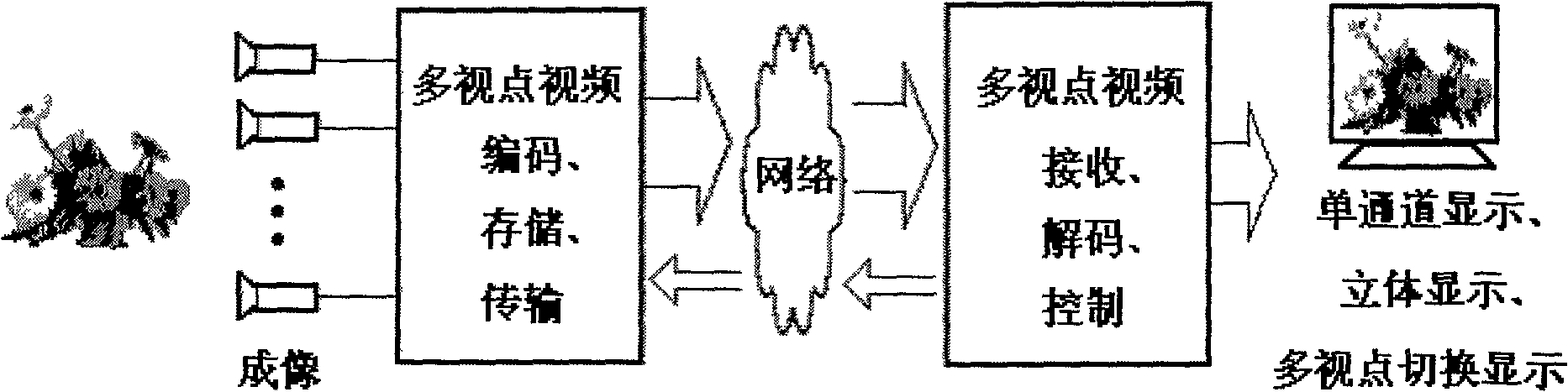

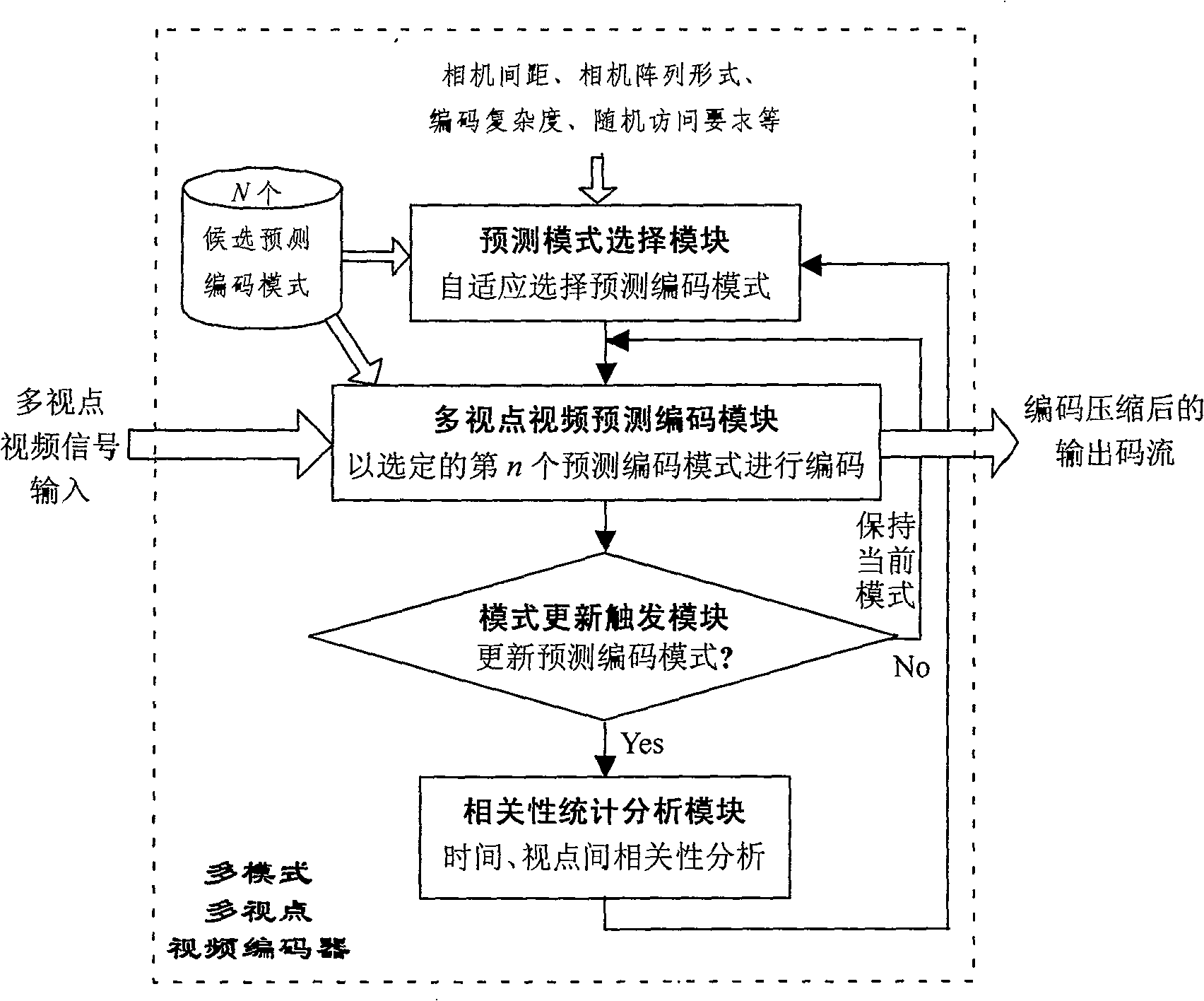

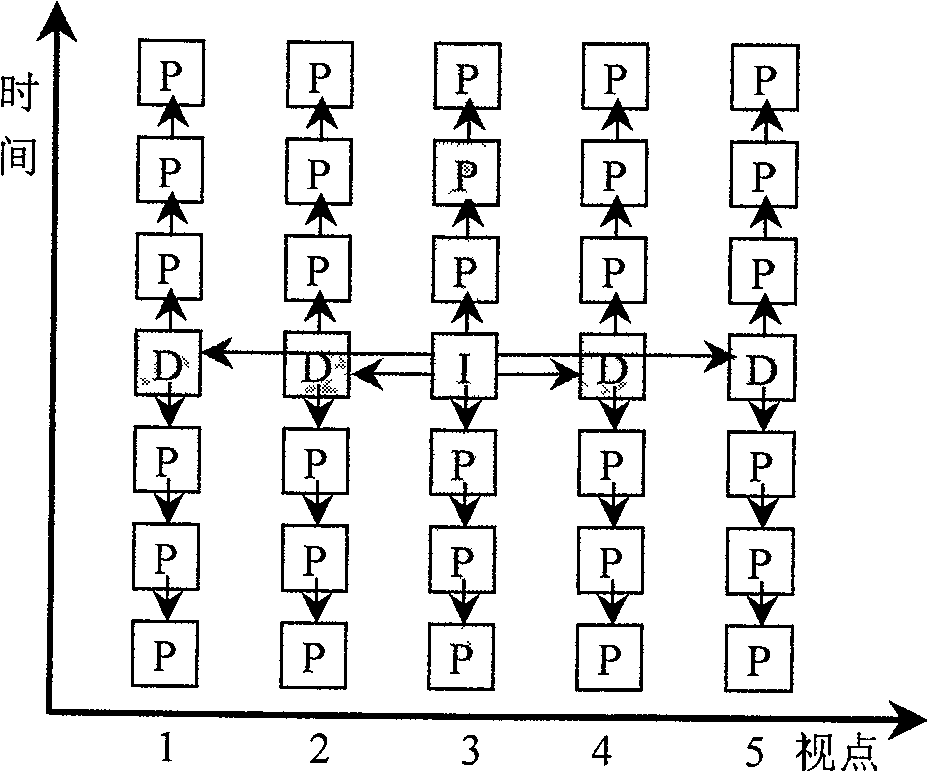

Multi-mode multi-viewpoint video signal code compression method

InactiveCN1913640AImprove random access performanceReduce computational complexityTelevision systemsDigital video signal modificationViewpointsComputation complexity

The invention discloses a video encoding method with multi-mode and multi-view. According to the analysis of the time correlation for the multi-view video signals and view correlation , as well as the comprehensive characters such as the compressing efficiency, complexity of encoding, random access performance and coding delay demanded by the system, the method adaptively dynamic-chooses the predictive coding mode which meets the features and the comprehensive encoding requirements of the current signals to encode them, in order to replace the method with single mode and complex calculation that forecasts by the union of time and space, and decrease the calculation complexity of compressing the signal coding.

Owner:上海斯派克斯科技有限公司

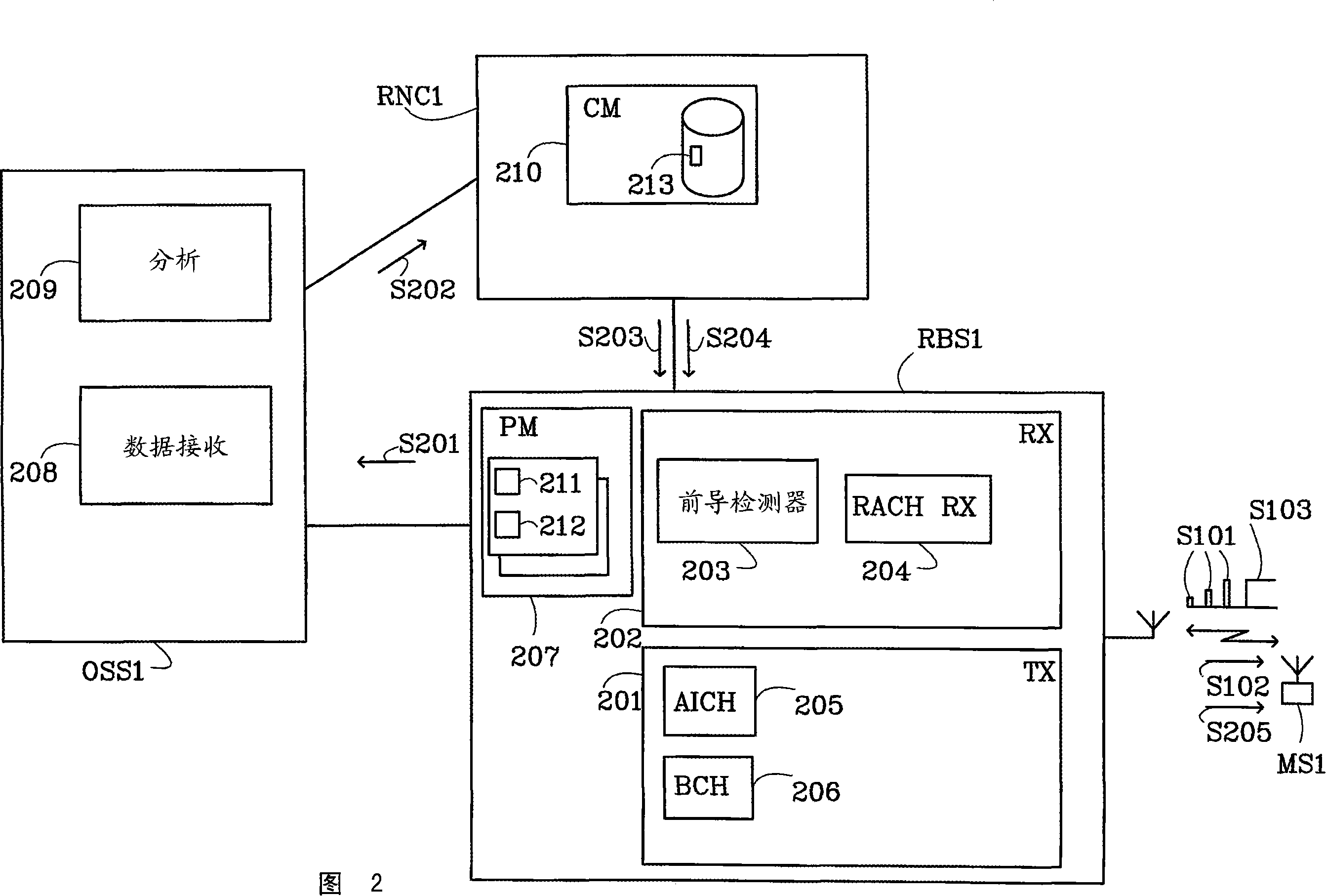

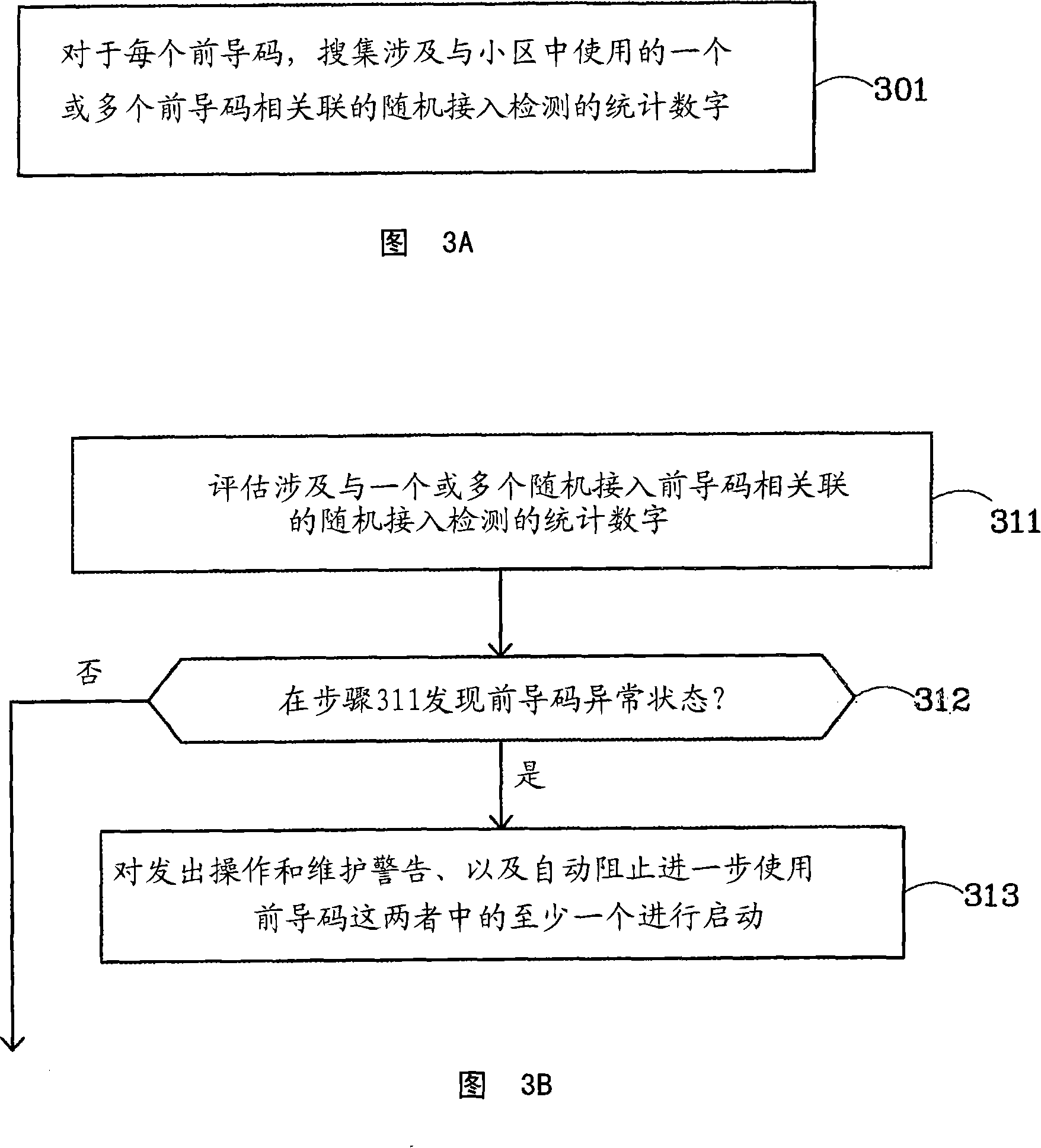

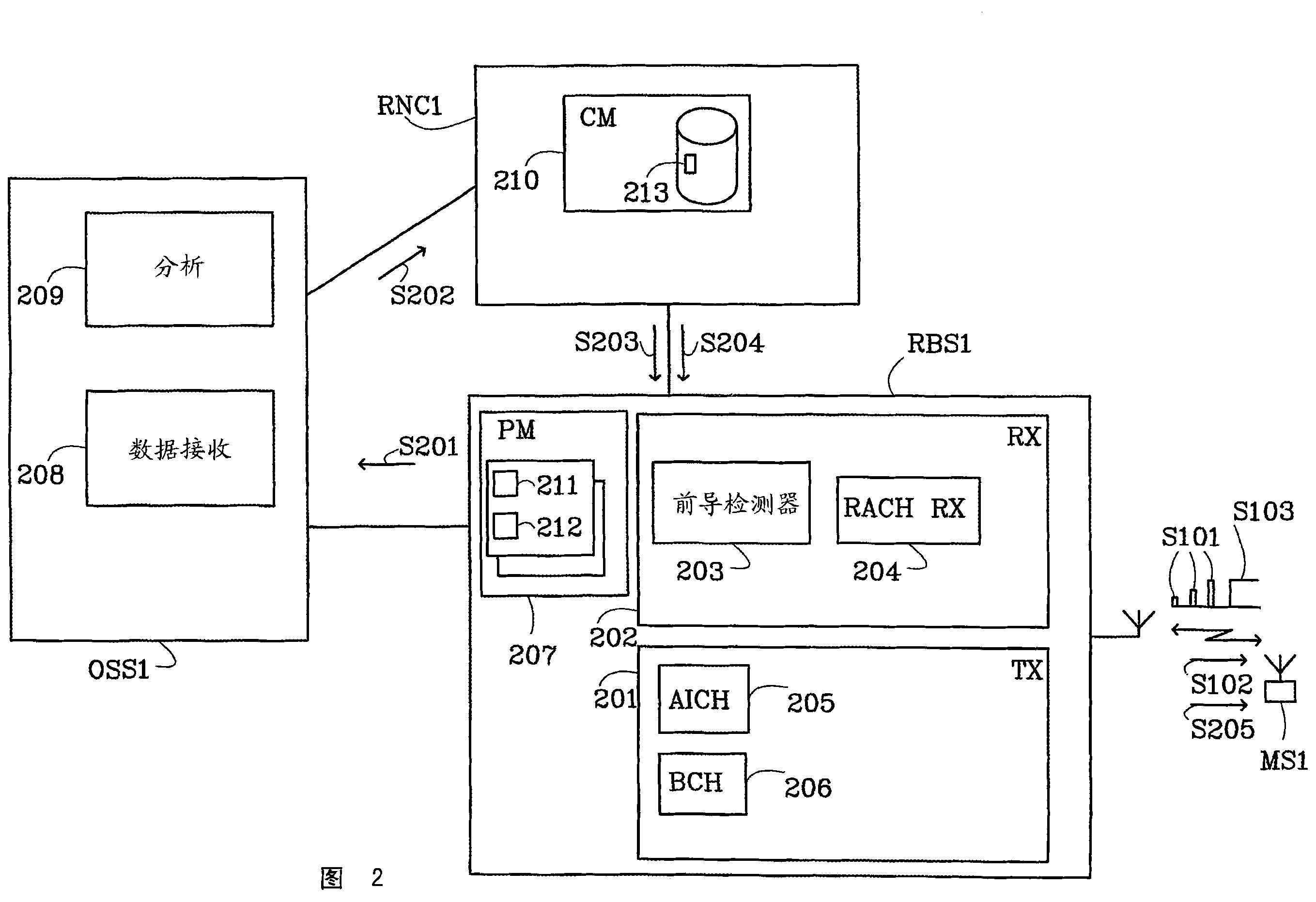

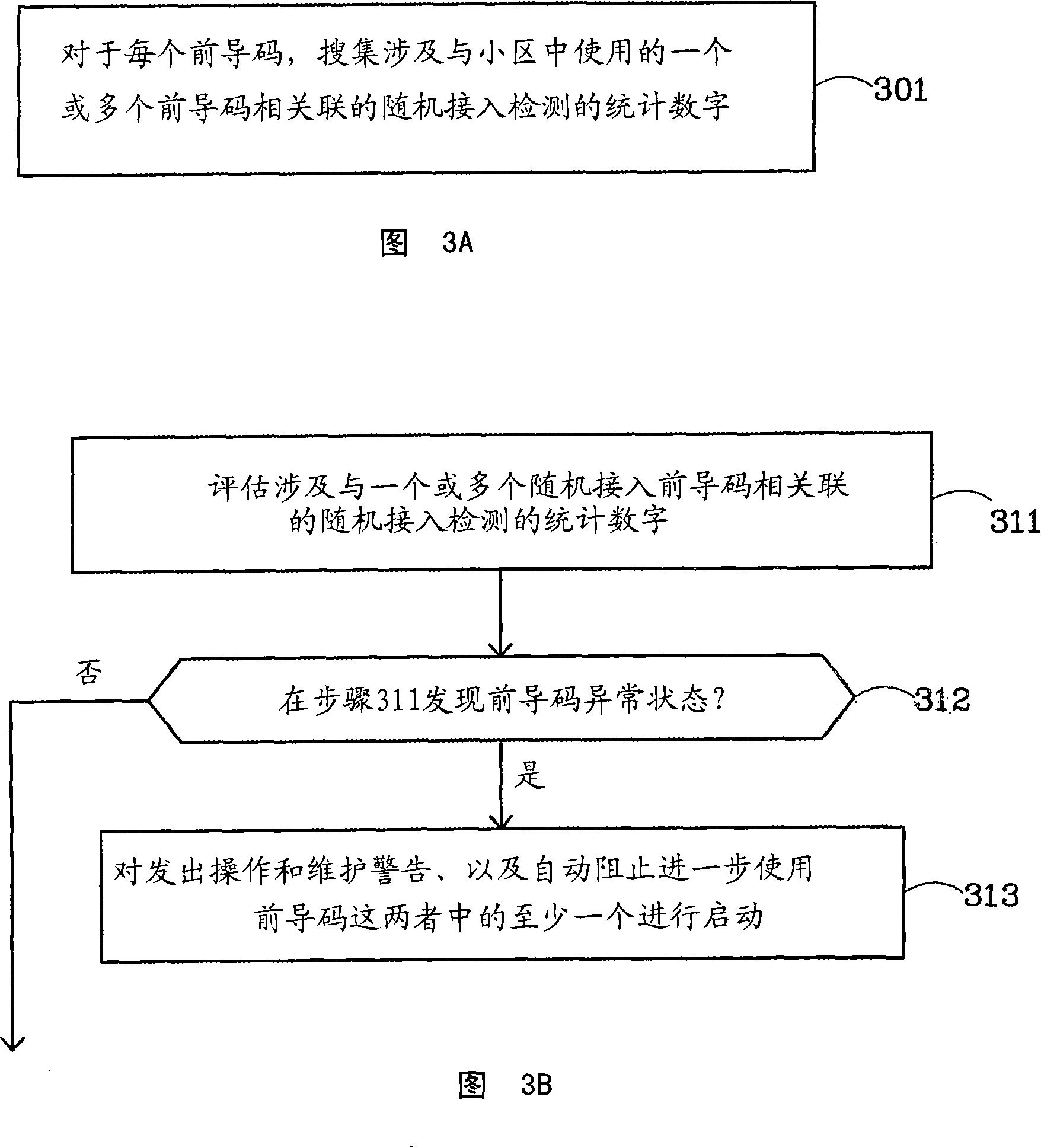

Evaluation of random access lead code

InactiveCN101208977AImprove random access performanceImprove random access operationRadio/inductive link selection arrangementsMultiplex code allocationCellular radioTheoretical computer science

The invention relates to a method and arrangement for collecting statistics relating to random access operations and managing these random access operations in cells of a cellular radio communication network. For each random access preamble, statistics are collected (301) relating to random access detections associated with one or more random access preambles used at the cell. Based on these collected statistics, the random access operation in the cell can be managed by evaluating (311) the collected statistics, and based on determining (312) the random access detection performance associated with a particular random access preamble activating at least one of signaling a corresponding operation and maintenance warning, and automatically preventing further use of said particular random access preamble in the cell, 313).

Owner:TELEFON AB LM ERICSSON (PUBL)

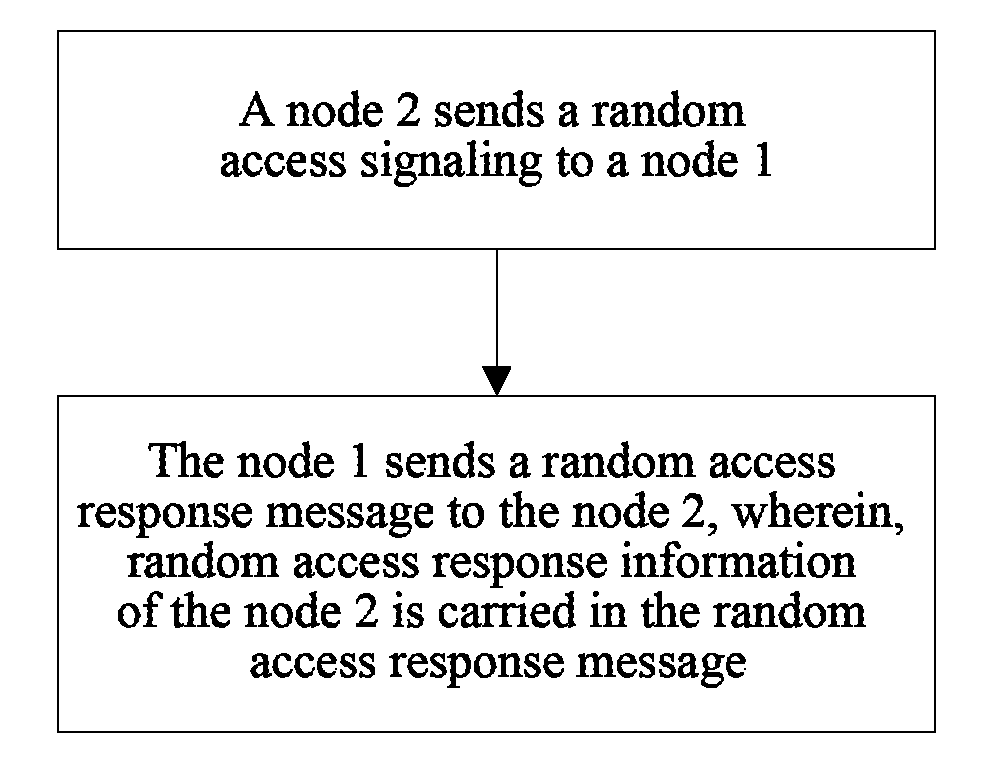

Random Access Method and System

ActiveUS20160088660A1Decrease probability of collisionReduce access delayError prevention/detection by using return channelTransmission systemsRandom accessReal-time computing

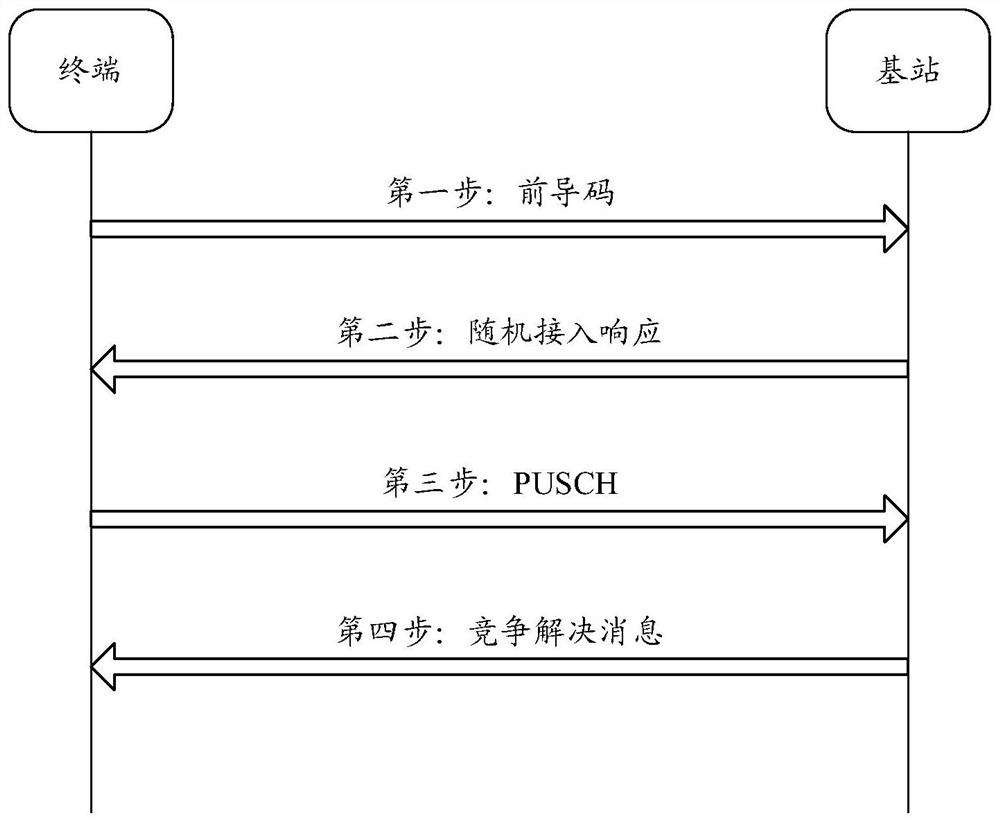

A random access method and system are disclosed. The method includes: a second node sending a random access signaling to a first node; and the first node replying a random access response message to the second node, wherein random access response information of the second node is carried in the random access response message.

Owner:ZTE CORP

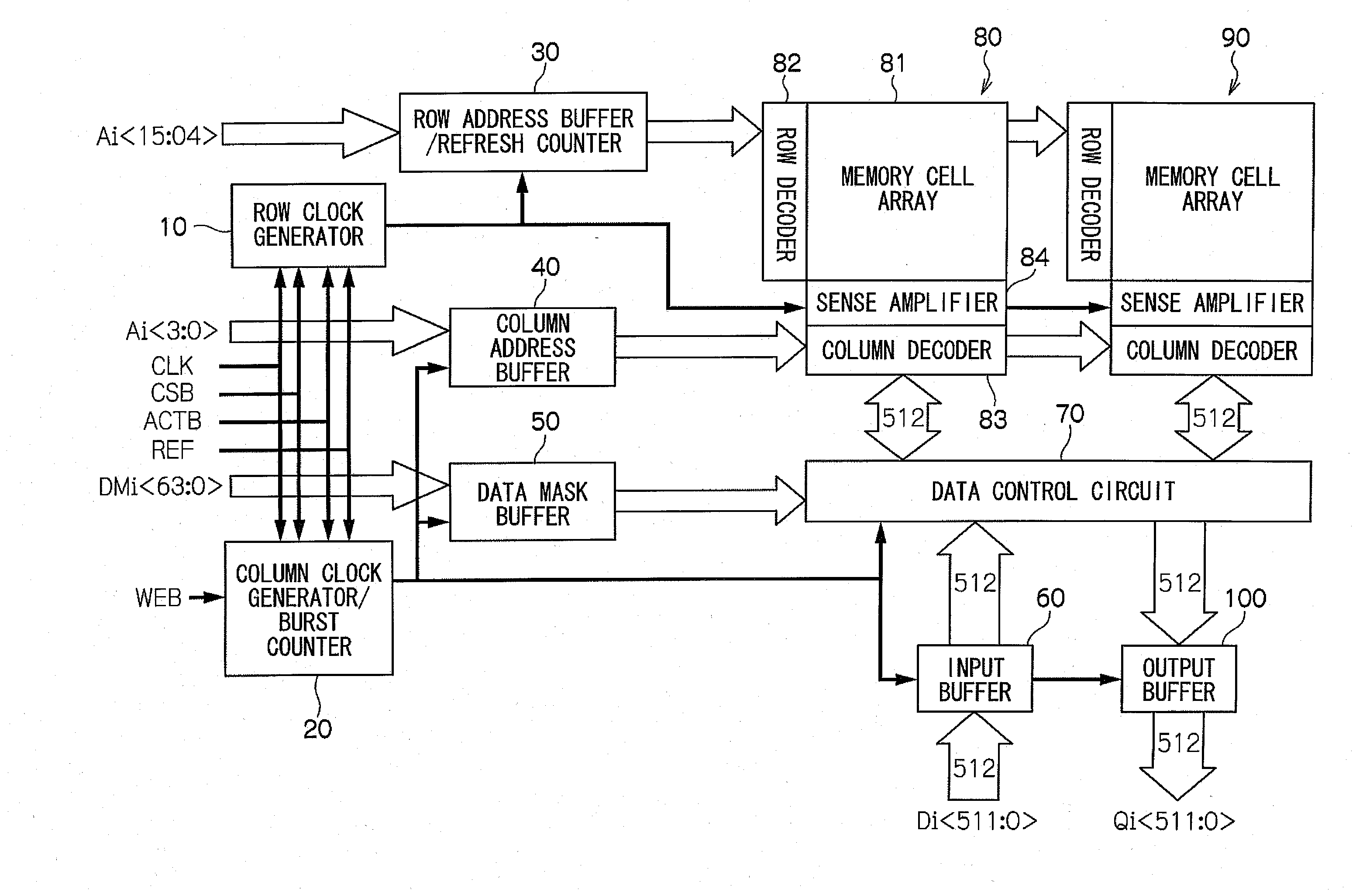

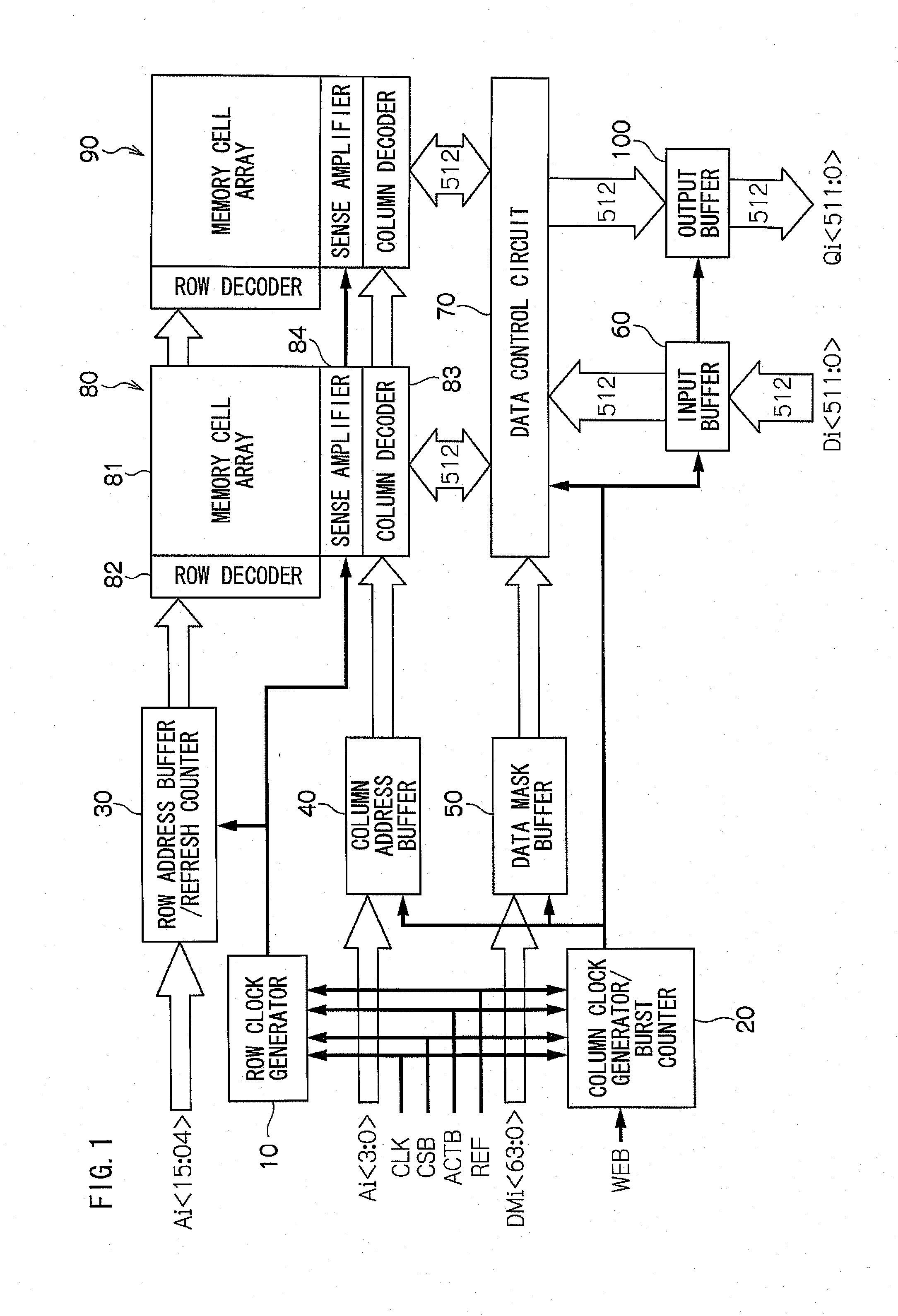

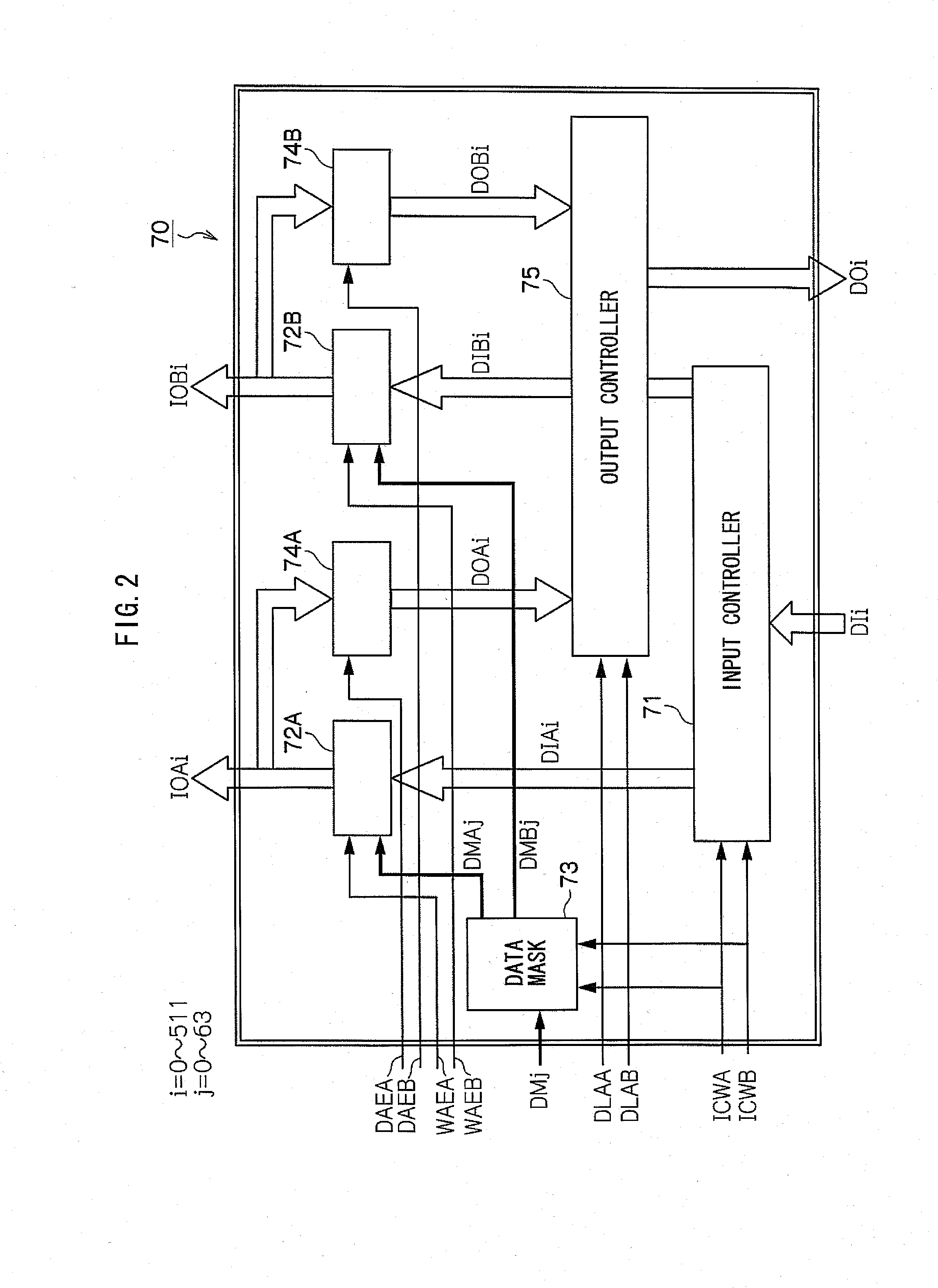

Semiconductor memory device

InactiveUS20100110747A1Enhances random accessHigh-speed writingDigital storageMemory bankHemt circuits

The semiconductor memory device proposed in the present invention comprises memory cells disposed in the row direction and the column direction, a plurality of first lines by which supply voltages are supplied in order to select memory cells disposed in the row direction among the plurality of cells, a plurality of second lines by which supply voltages are supplied in order to select memory cells disposed in the column direction among the plurality of cells, the data lines which input and output the data to the selected memory cells, the first power voltage supply circuit which supplies the predetermined supply voltages to the first lines corresponding with the externally input row address synchronizing with an act command, and the second power voltage supply circuit which supplies the predetermined supply voltages to the second lines corresponding with the externally input column address synchronizing with an act command. It also comprises m pieces of memory banks (m is a natural number larger than 2) which write or read the data into or from the memory cells which are selected one after another in the row or column directions, data input circuits in which multiple bits of serial data which is larger than 512 bits to be written in the m pieces of memory banks, data output circuits which reads the data from the m pieces of memory banks and output in a form of multiple bits of serial data which is larger than 512 bits, and data conversion circuits which convert the serial data input in the data input circuits to parallel data so that it can be written in each memory bank or to convert each parallel data read from each memory bank to serial data so that such data are supplied to the data output circuits.

Owner:RAMBUS INC

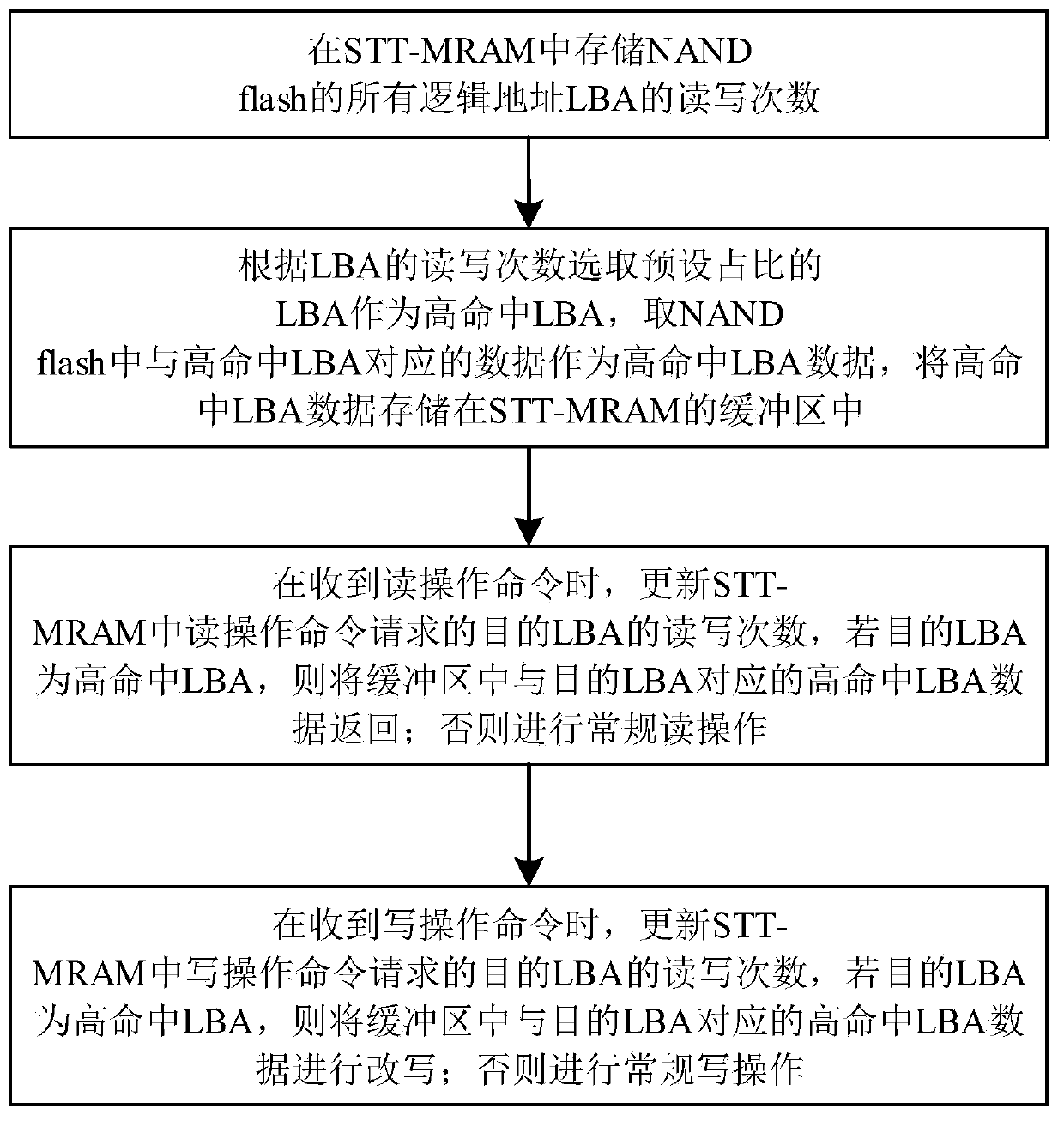

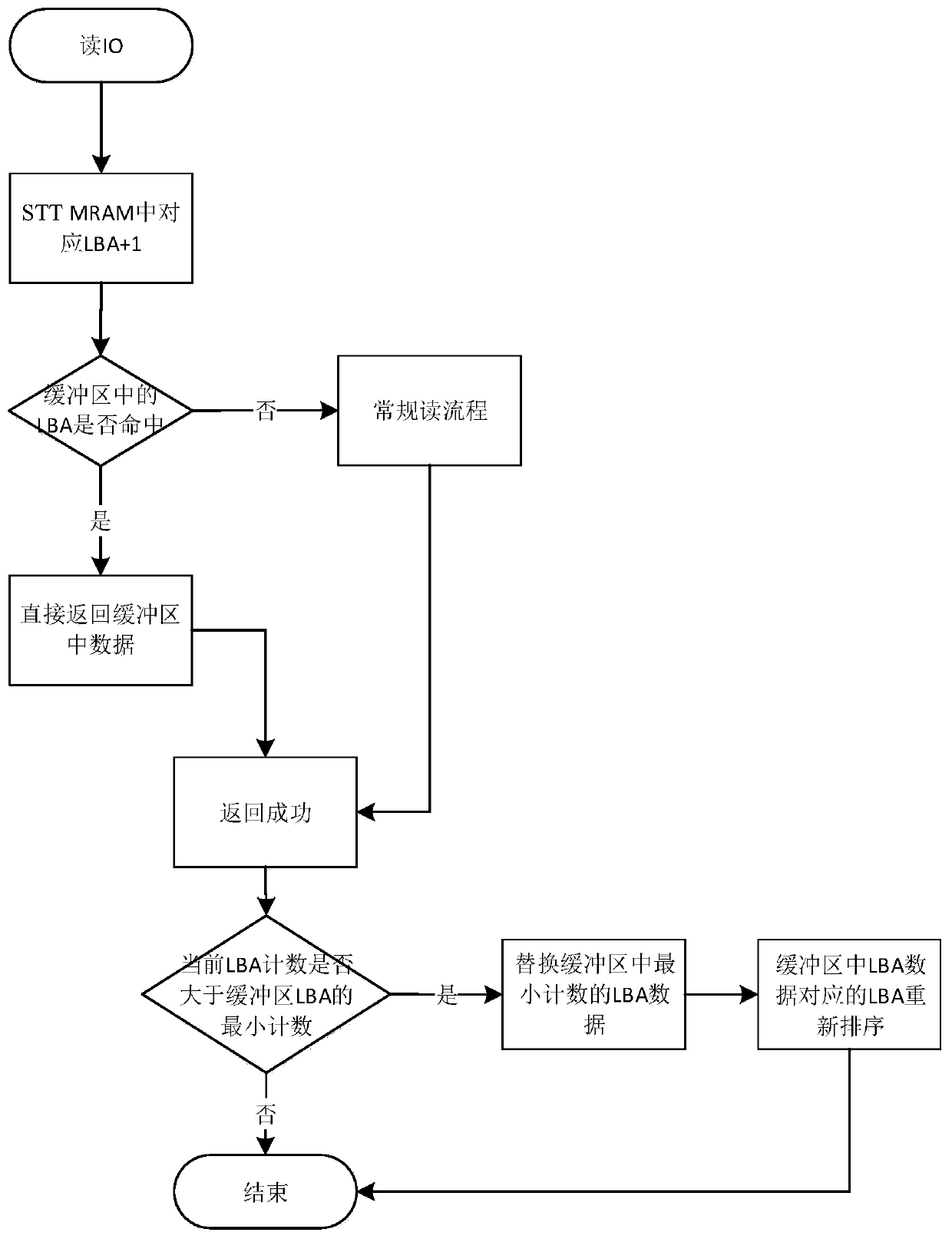

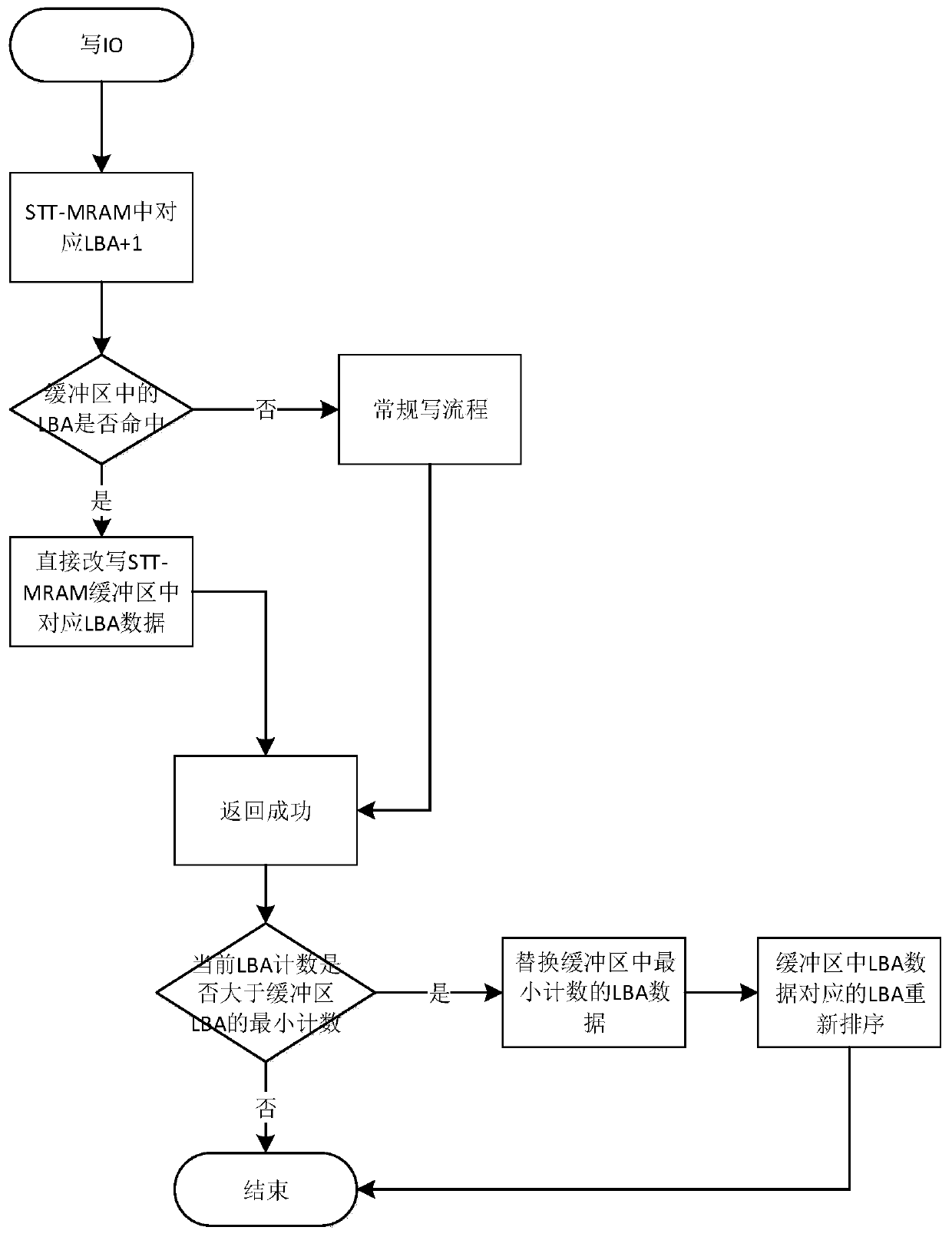

Solid-state memory device random access performance improving method based on STT-MRAM

ActiveCN110275678ASimplify the response pathImprove random access performanceInput/output to record carriersEnergy efficient computingElectricitySolid-state storage

The invention discloses a solid-state memory device random access performance improving method based on STT-MRAM. The solid-state storage device comprises a magnetic random access memory STT-MRAM and a storage medium NAND flash. The high-speed read-write performance and the power-down nonvolatile performance of the STT-MRAM are utilized. The STT-MRAM is adopted as the high-hit LBA data cache in the solid-state storage device controller, the response path of the high-hit LBA is simplified, and the random access performance of the system is enhanced. And when GC occurs, the high-hit LBA data is uniformly put into the target BLOCK by utilizing the LBA read-write frequency data in the STT-MRAM, so that the high-hit LBA data can be read into the STT-MRAM for buffering at one time when the data in the buffer area of the STT-MRAM is lost or damaged, and the response time is shortened.

Owner:CETHIK GRP

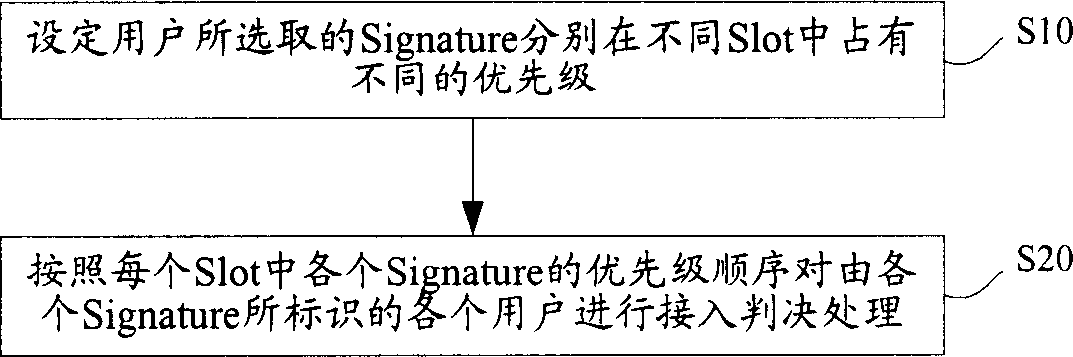

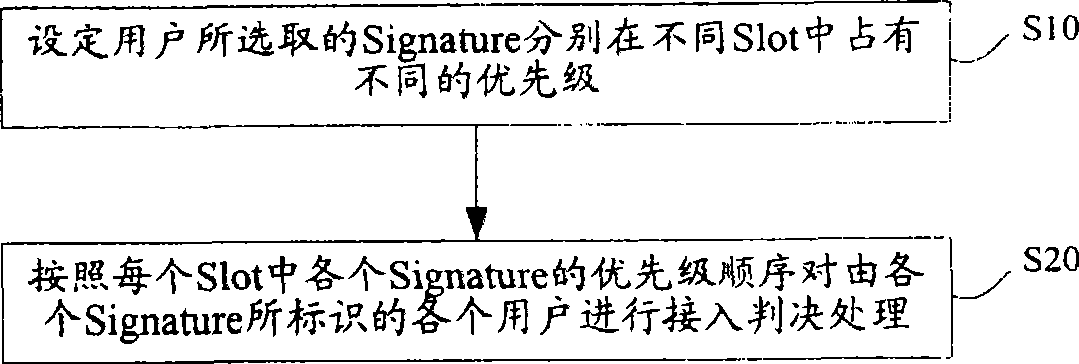

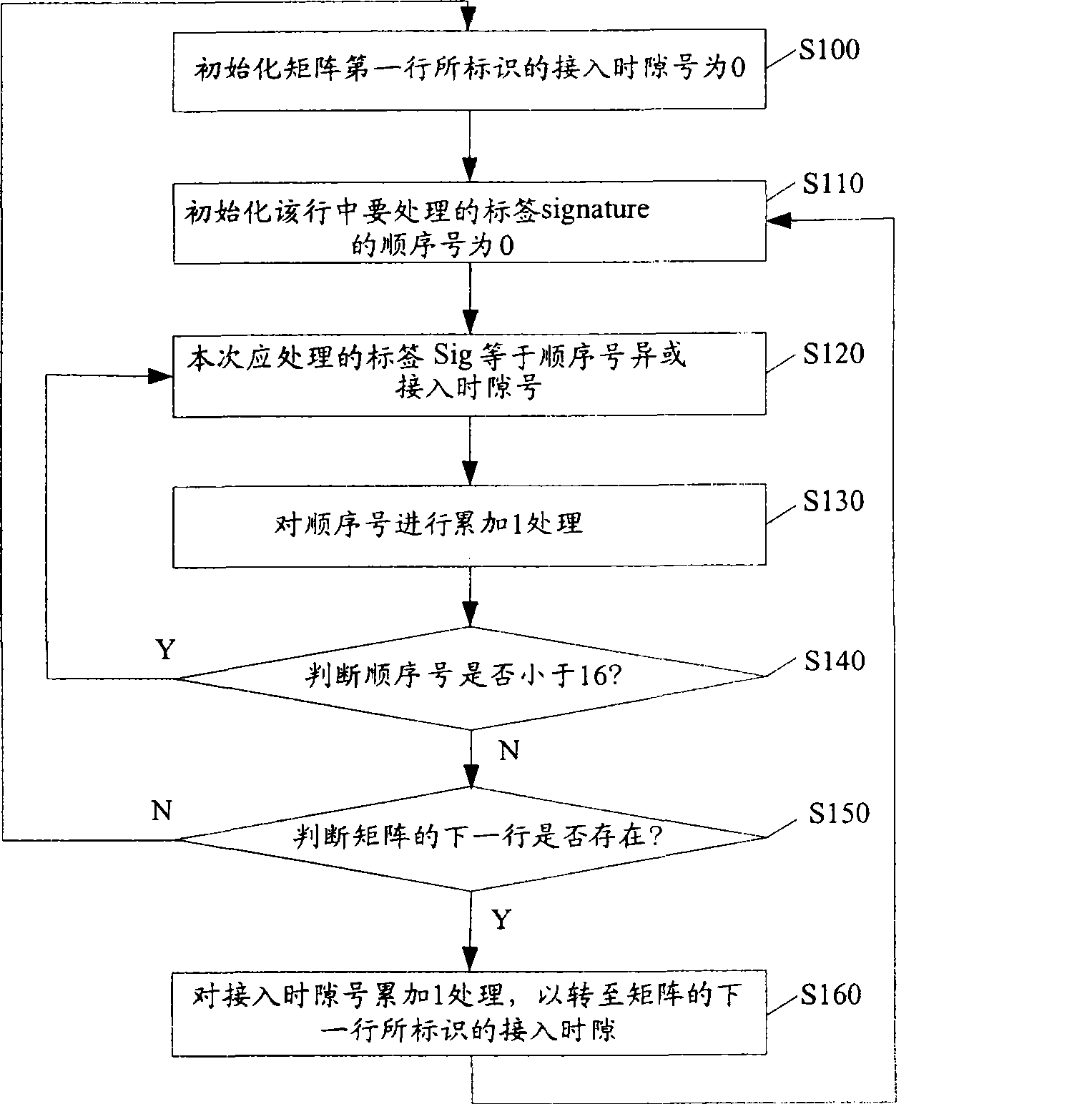

Method of implementing random access

ActiveCN1809004ALow management complexityReduce overheadData switching by path configurationCode division multiplexNetwork managementDistributed computing

This invention discloses one random interfacing realization method, which comprises the following steps: setting user selected signature with different priority to different interface and processing each user by each signature according to each signal priority order of each interface gap. This invention method can make each user reduce network management complexity and materials spending on base of even opportunity to interface to network.

Owner:HUAWEI TECH CO LTD

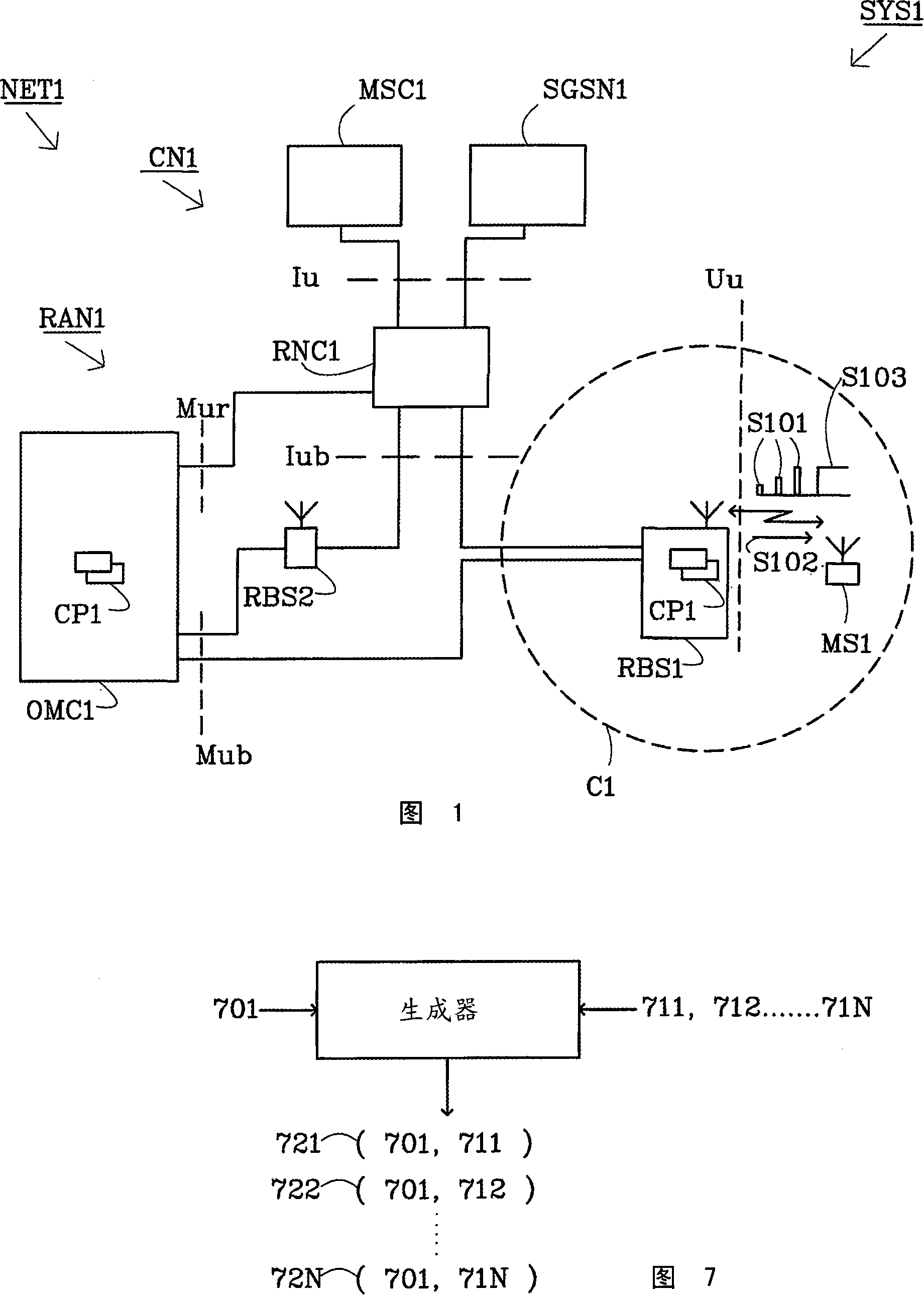

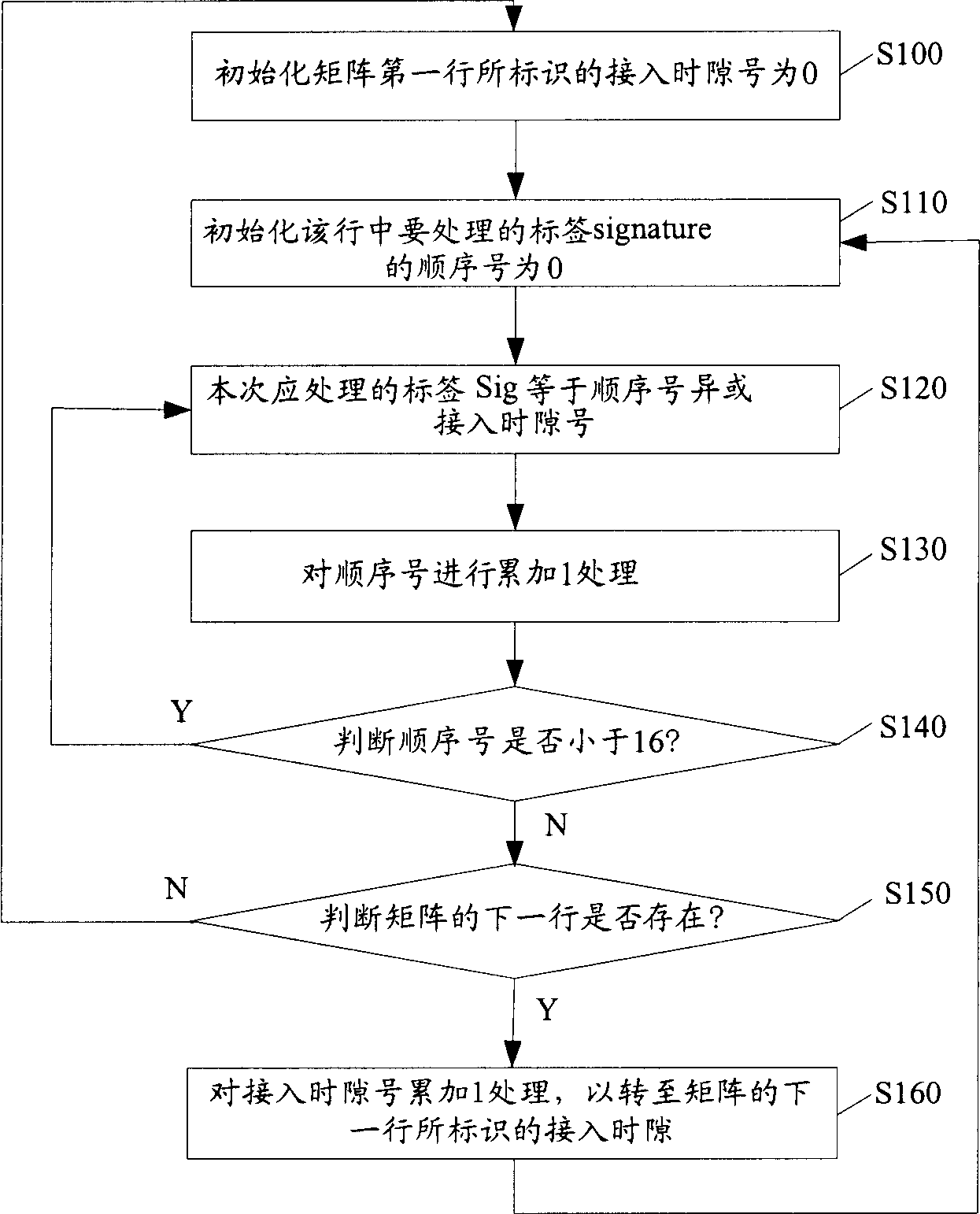

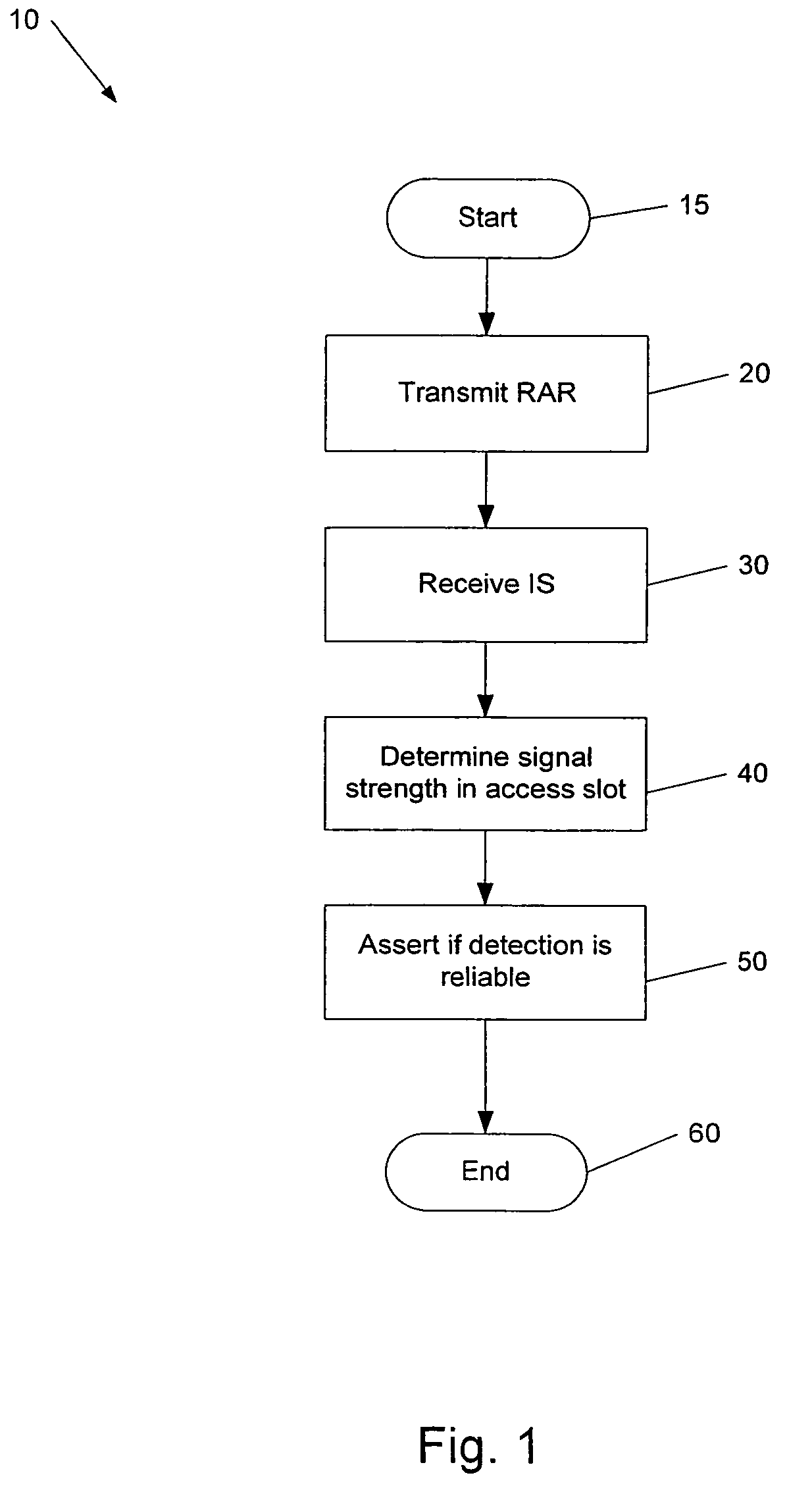

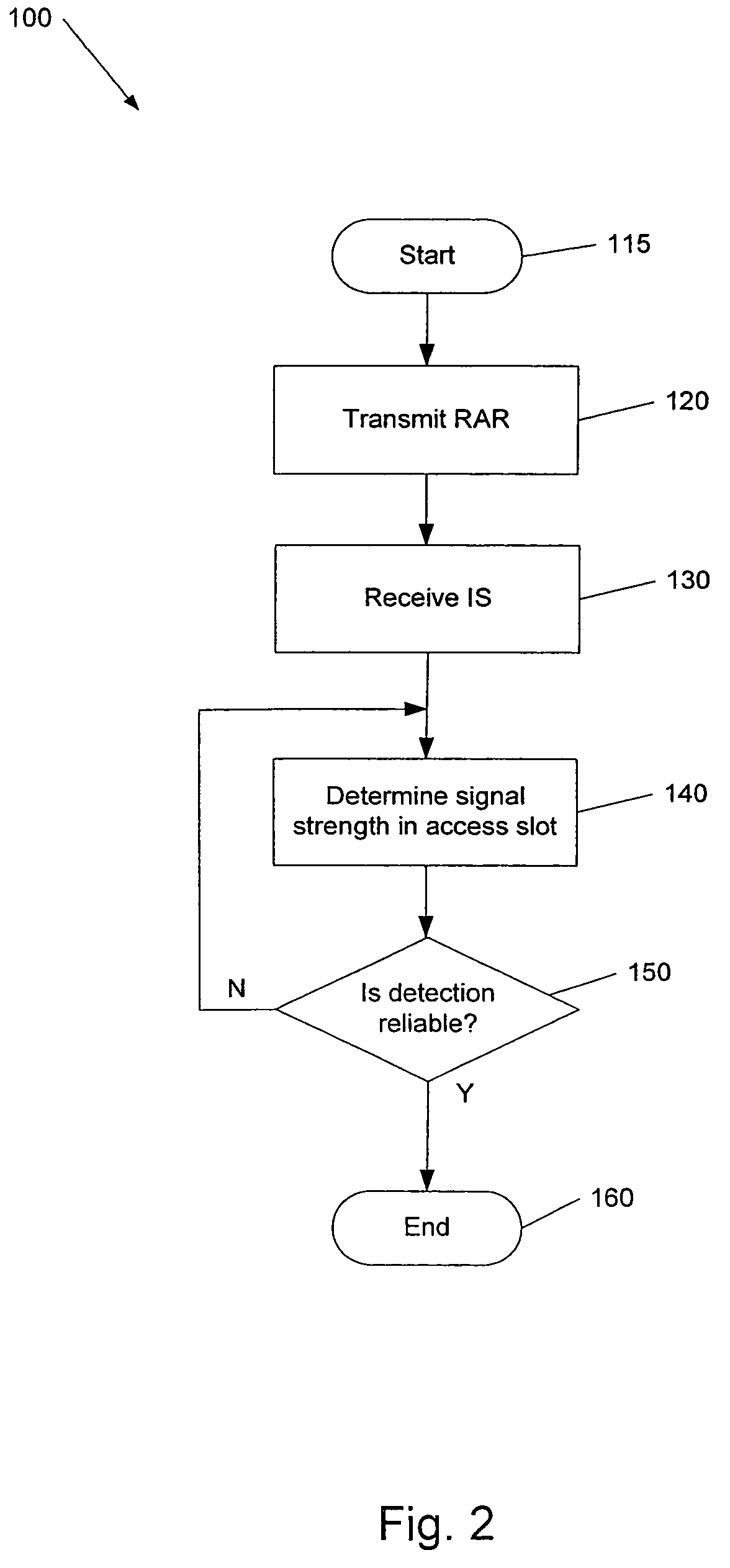

Performance in mobile communications systems

ActiveUS7852824B2Improve random access performanceWeaken influenceNetwork traffic/resource managementRadio transmissionMobile communication systemsMobile station

In third generation mobile communications networks, e.g. CDMA systems, a mobile station intending to access a base station transmits a request for access to a base station and waits for a response in the form of an indicator signal. Both detecting a signal as an acknowledgement message without one being sent from the base station and failing to detect such an acknowledgement message can give rise to noise and interference in the whole cell. The invention provides a method and a user equipment for determining the received signal strength in an access slot in a downlink channel and for asserting whether detection of an indicator signal from the base station in the access slot in the downlink channel is reliable. Hereby, a more secure reception of indicator signals can be obtained, which leads to reduced interference and noise in the whole cell.

Owner:TELEFON AB LM ERICSSON (PUBL)

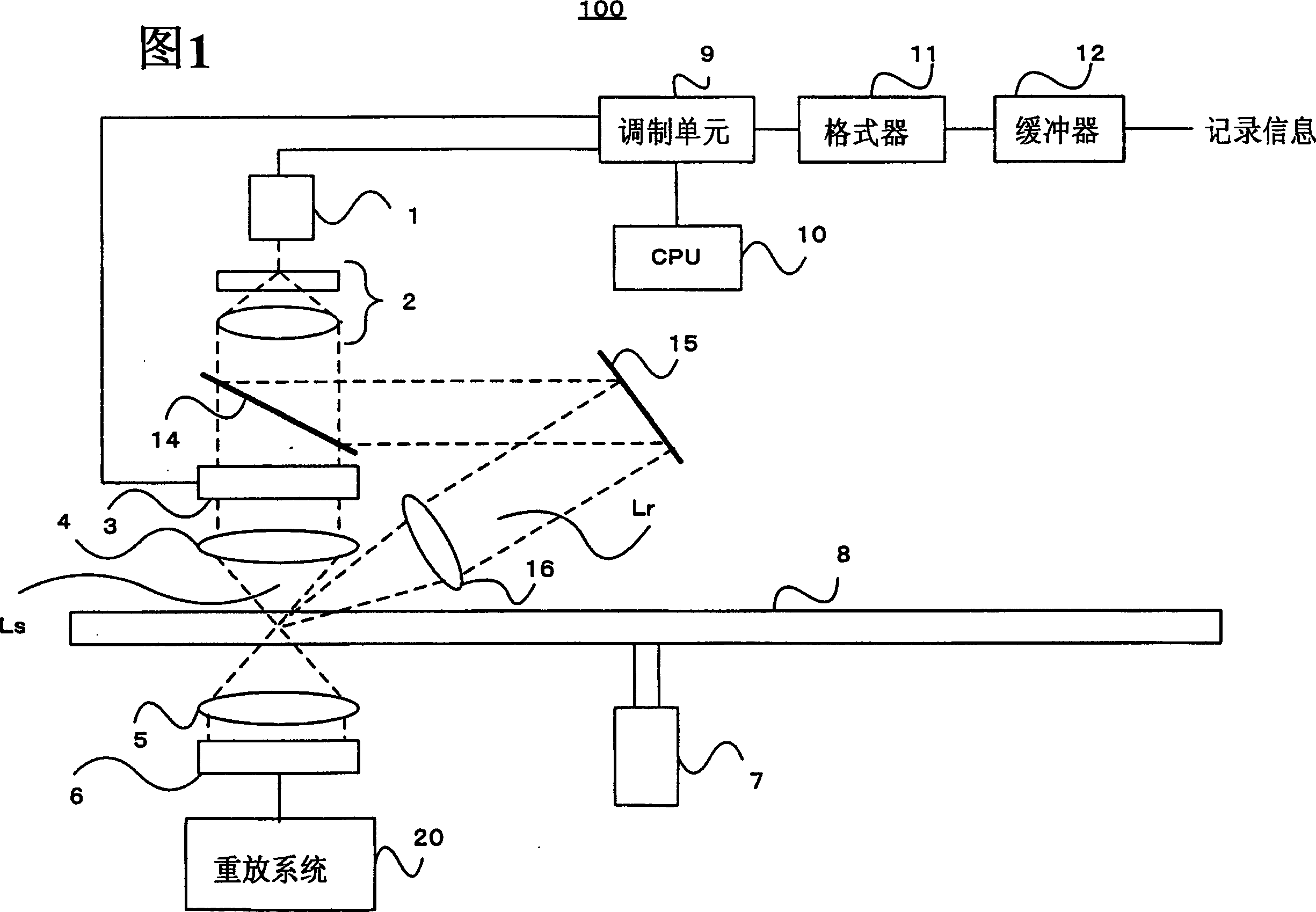

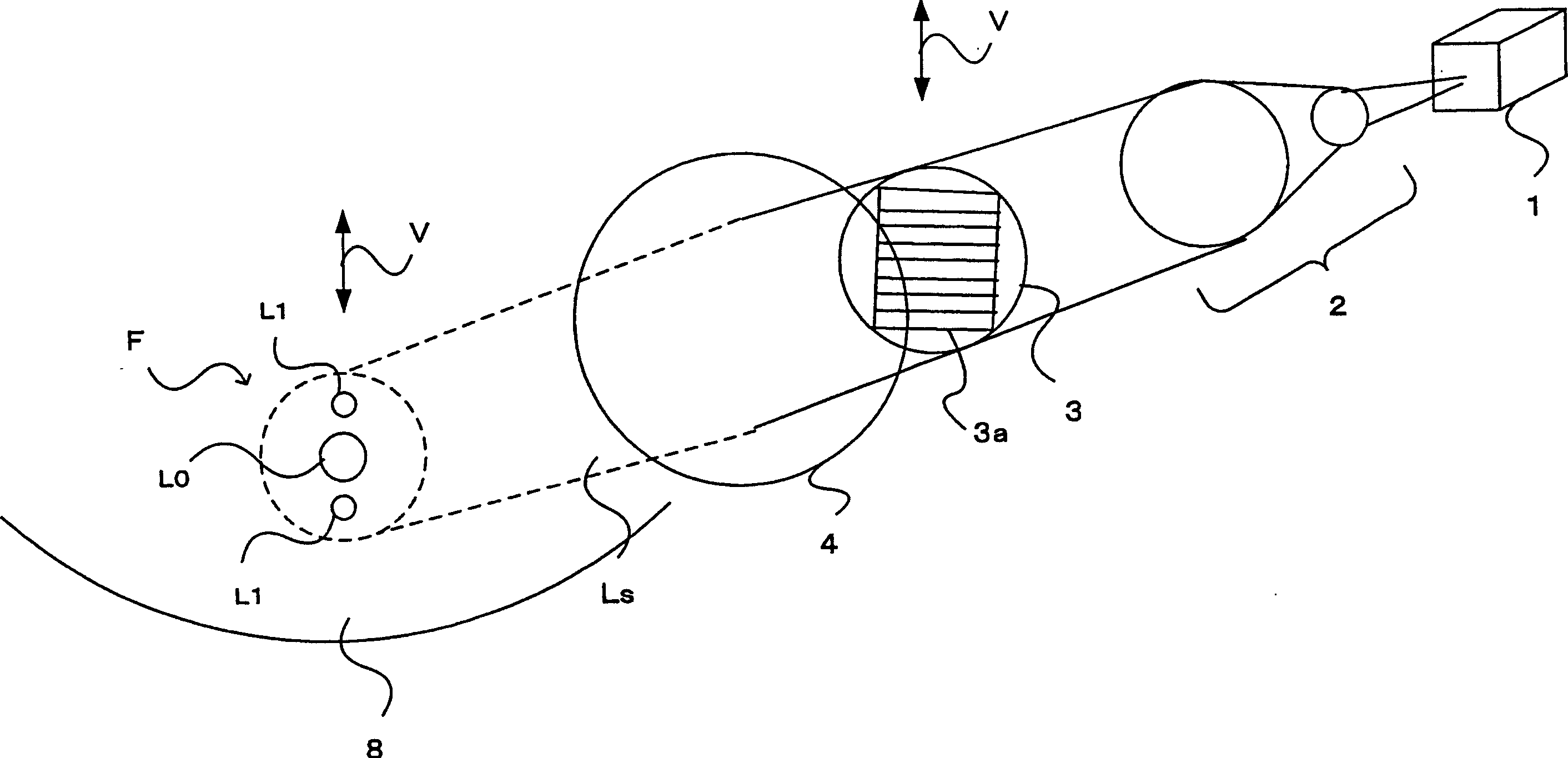

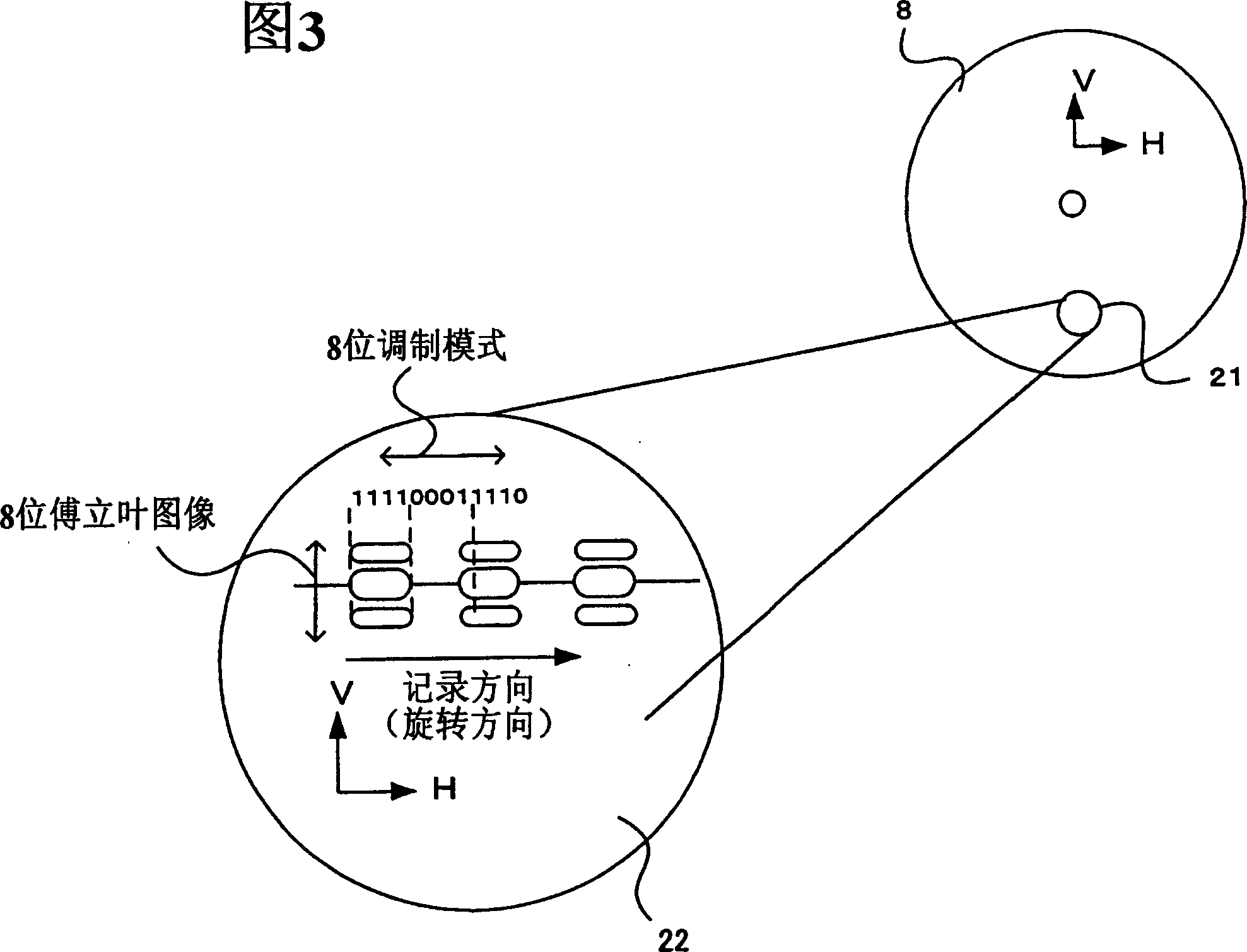

Information recording equipment, information replay equipment, recording method and replay method, and information recording medium

InactiveCN1536561AImprove random access performanceOptical beam sourcesRecord information storageSignal lightLaser light

The information recording apparatus (100) generates the signal light (Ls) and the reference light (Lr) from one laser light, and irradiates the signal light and the reference light on the recording medium (8) to record the information by utilizing the interference fringes. Namely, the information recording apparatus executes a so-called hologram recording. Though the signal light is generated by spatial-modulating the laser light by the recording information, the one-dimensional spatial modulation is performed in the present invention. By performing the one-dimensional spatial modulation, recording the information is possible even if the recording medium is moving in a direction perpendicular or nearly perpendicular to the direction of the spatial modulation. Thereby, even if the irradiation position of the signal light and the reference light is moving relatively to the recording medium, e.g., while a disc-type recording medium is rotating, the hologram recording is possible. Thus, the random access performance to the recorded information can be improved and a configuration of the apparatus can be simplified.

Owner:PIONEER CORP

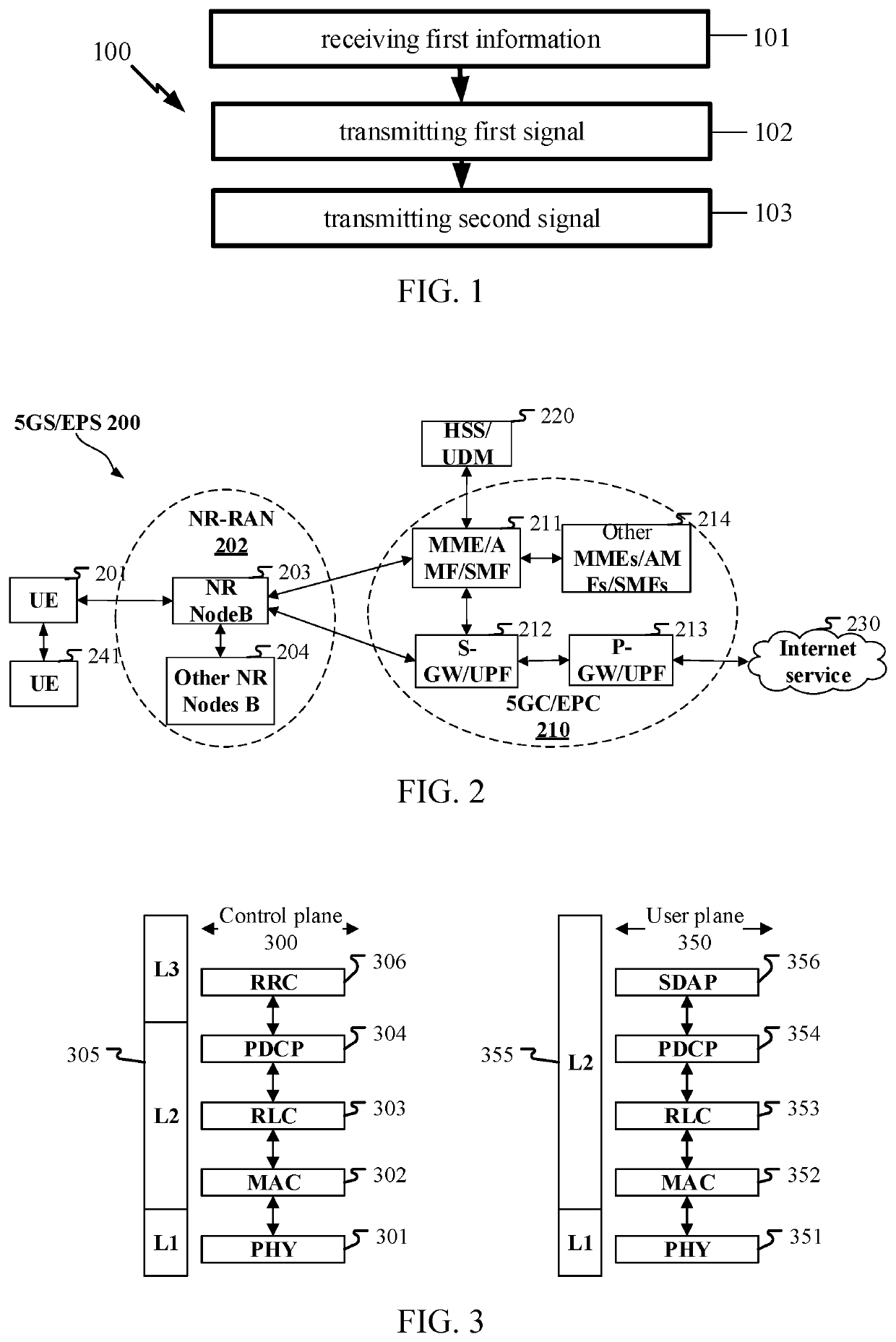

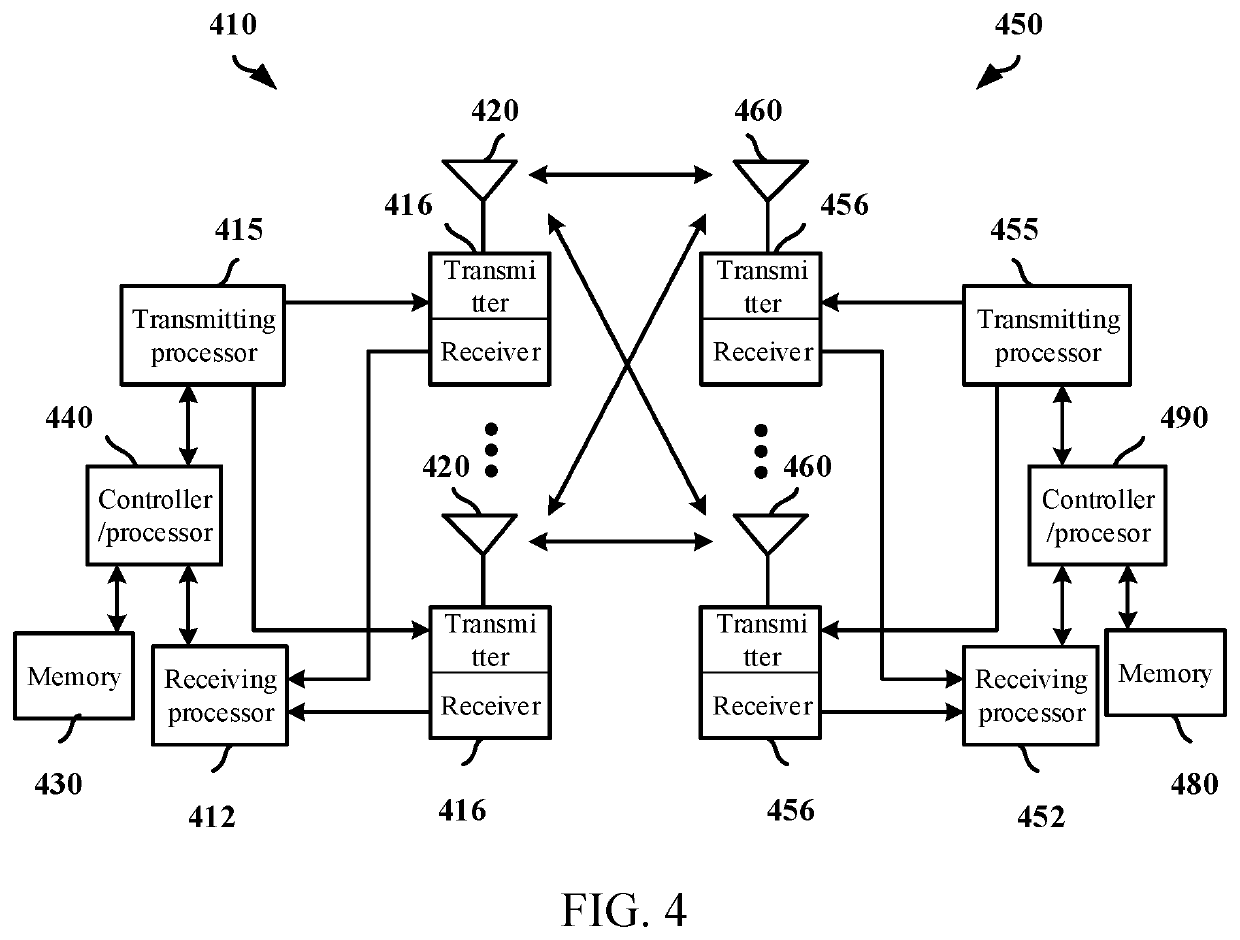

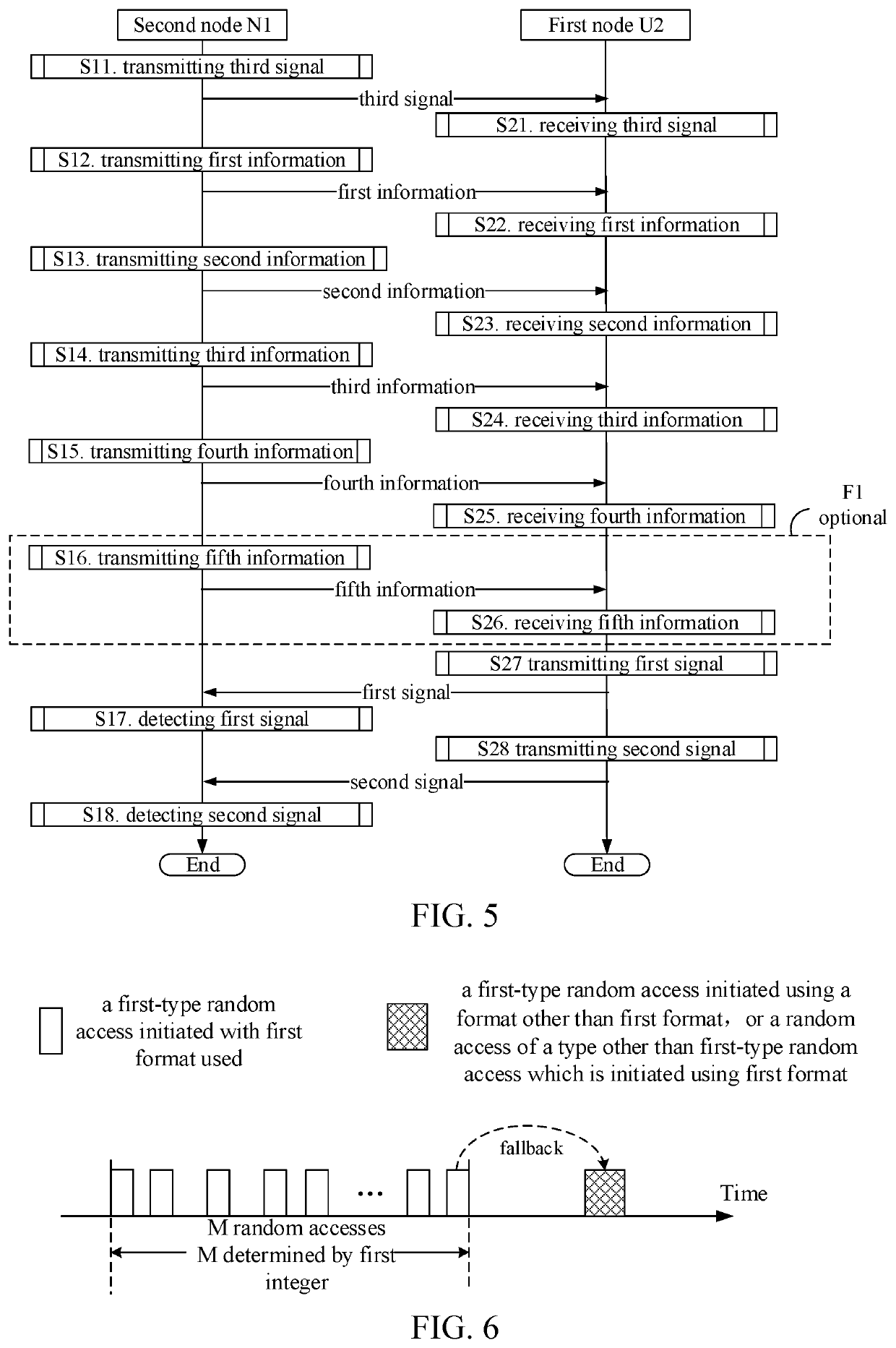

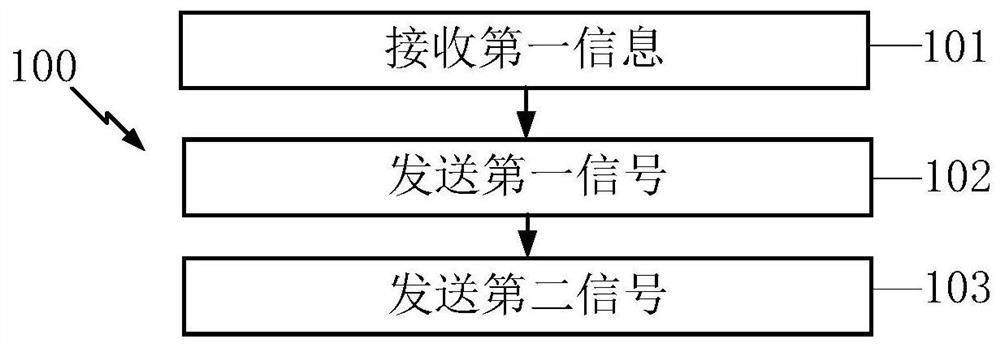

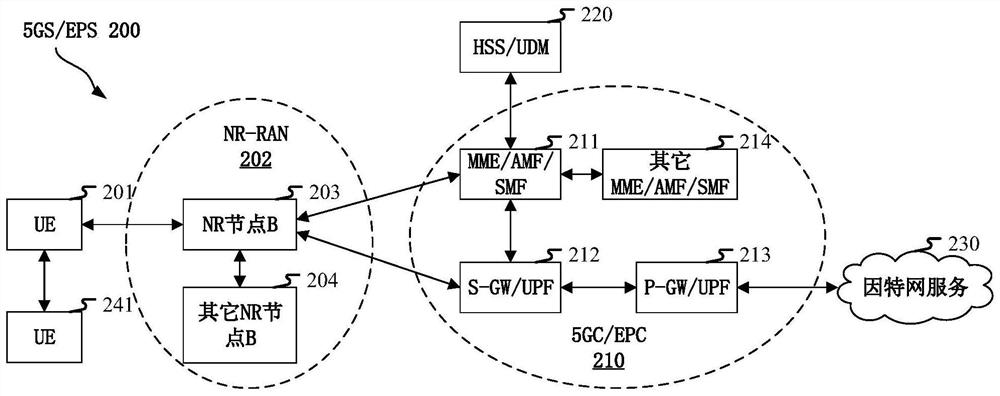

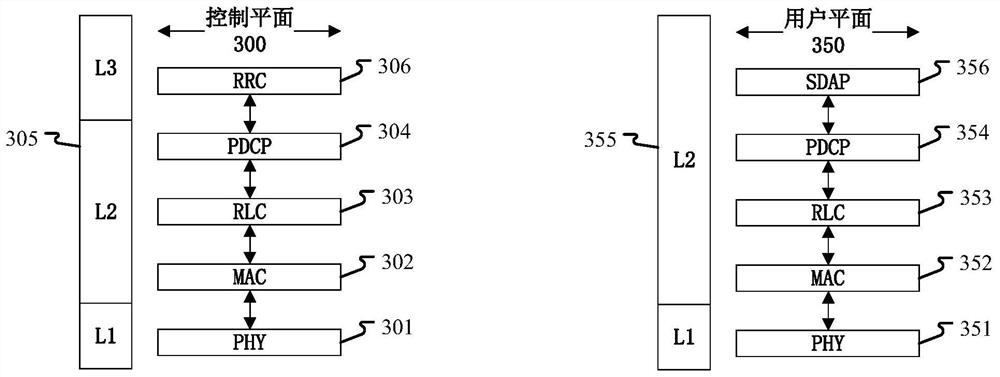

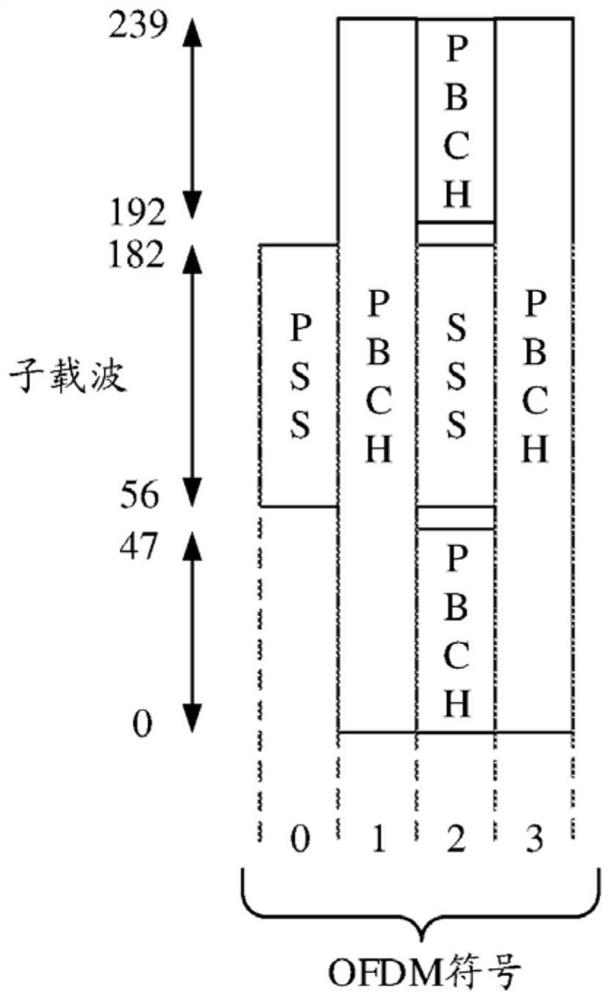

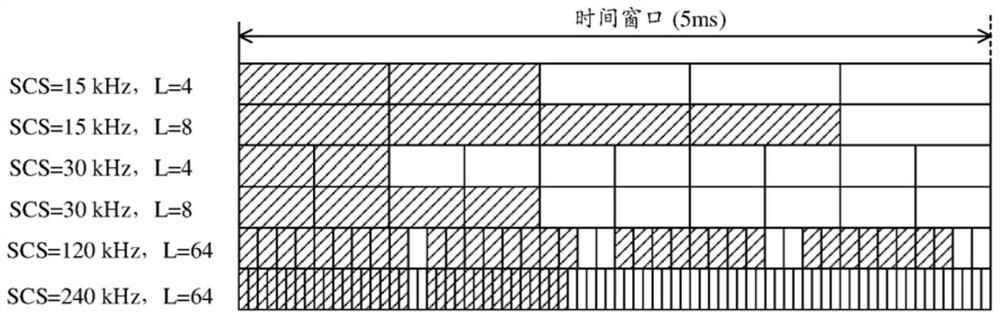

Method and device in nodes used for wireless communication

PendingUS20220304077A1Reduce complexityLow costPower managementSynchronisation arrangementElectrical and Electronics engineeringReal-time computing

Method and device in nodes used for wireless communications. A node receives first information, the first information being used to determine X candidate formats; transmits a first signal, the first signal using a first format; and transmits a second signal, the second signal using a second format; the first format is one of the X candidate formats, and the second format is also one of the X candidate formats; a first timing offset value is used to determine a transmission timing for the first signal, while a second timing offset value is used to determine a transmission timing for the second signal, where the first timing offset value is unequal to the second timing offset value; the first format relates to the first timing offset value while the second format relates to the second timing offset value. The present disclosure improves the random access performance.

Owner:SHANGHAI LANGBO COMM TECH CO LTD

Random access method and system

ActiveUS10021723B2Improve random access performanceReduce the probability of collisionError prevention/detection by using return channelTransmission path divisionAccess methodRandom access memory

Owner:ZTE CORP

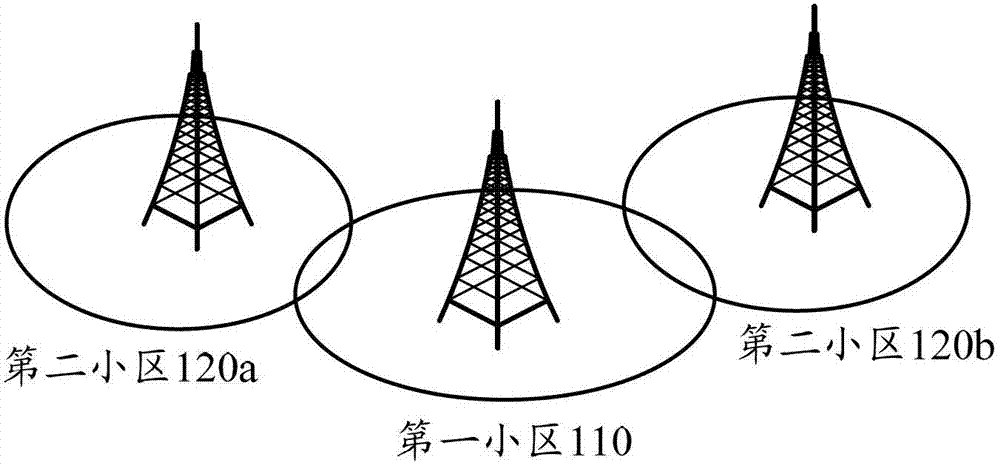

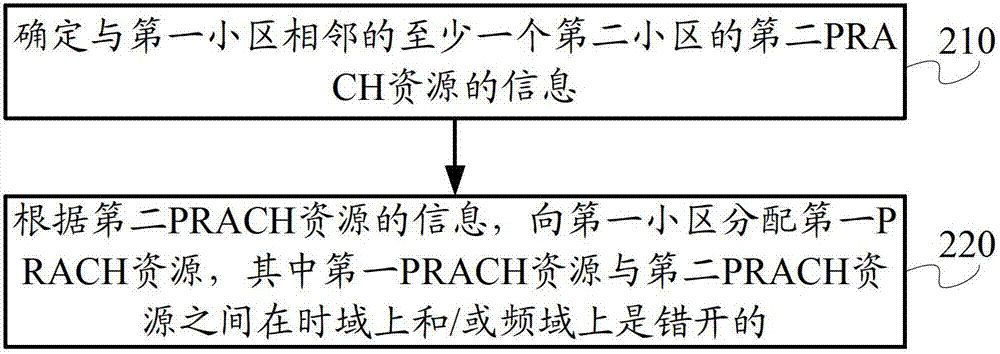

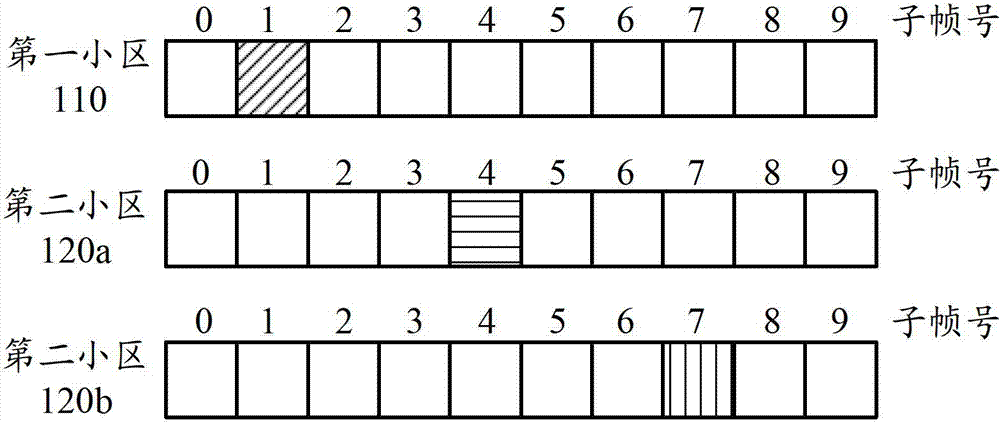

Method and device for allocating resource

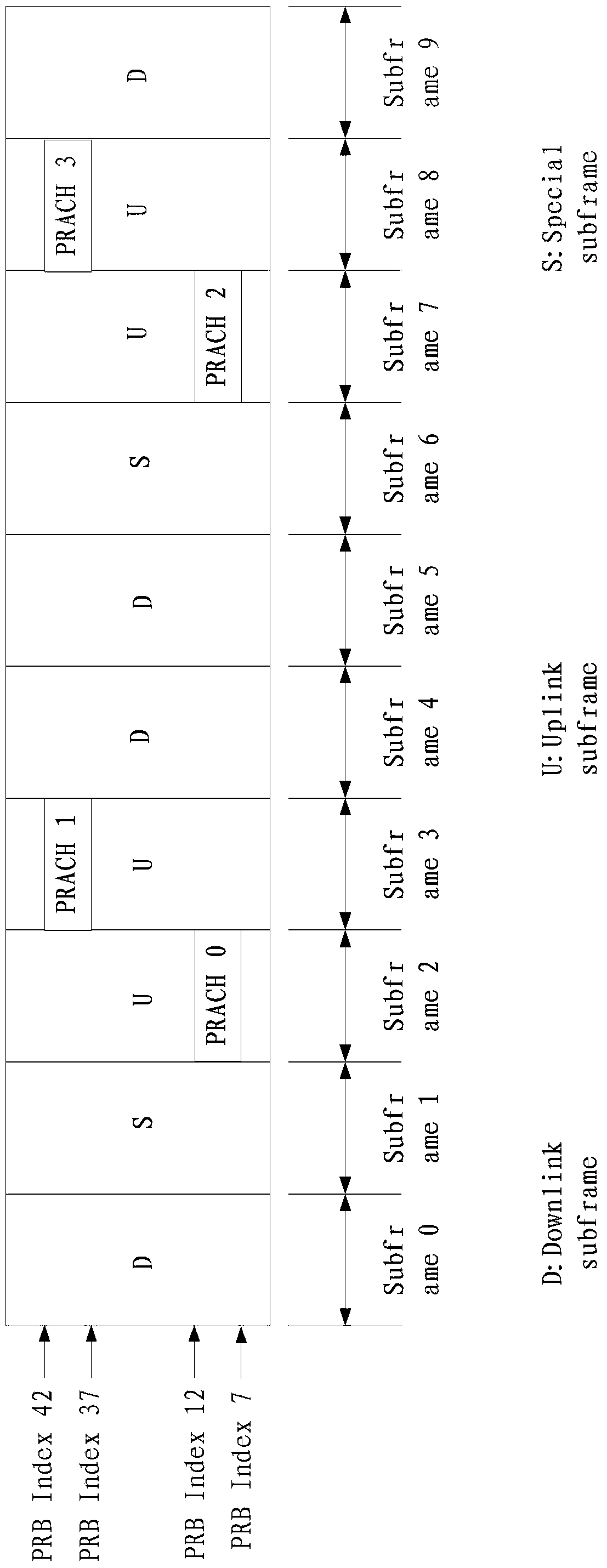

ActiveCN102695278BReduce co-channel interferenceReduce false alarm rateWireless communicationTime domainRandom-access channel

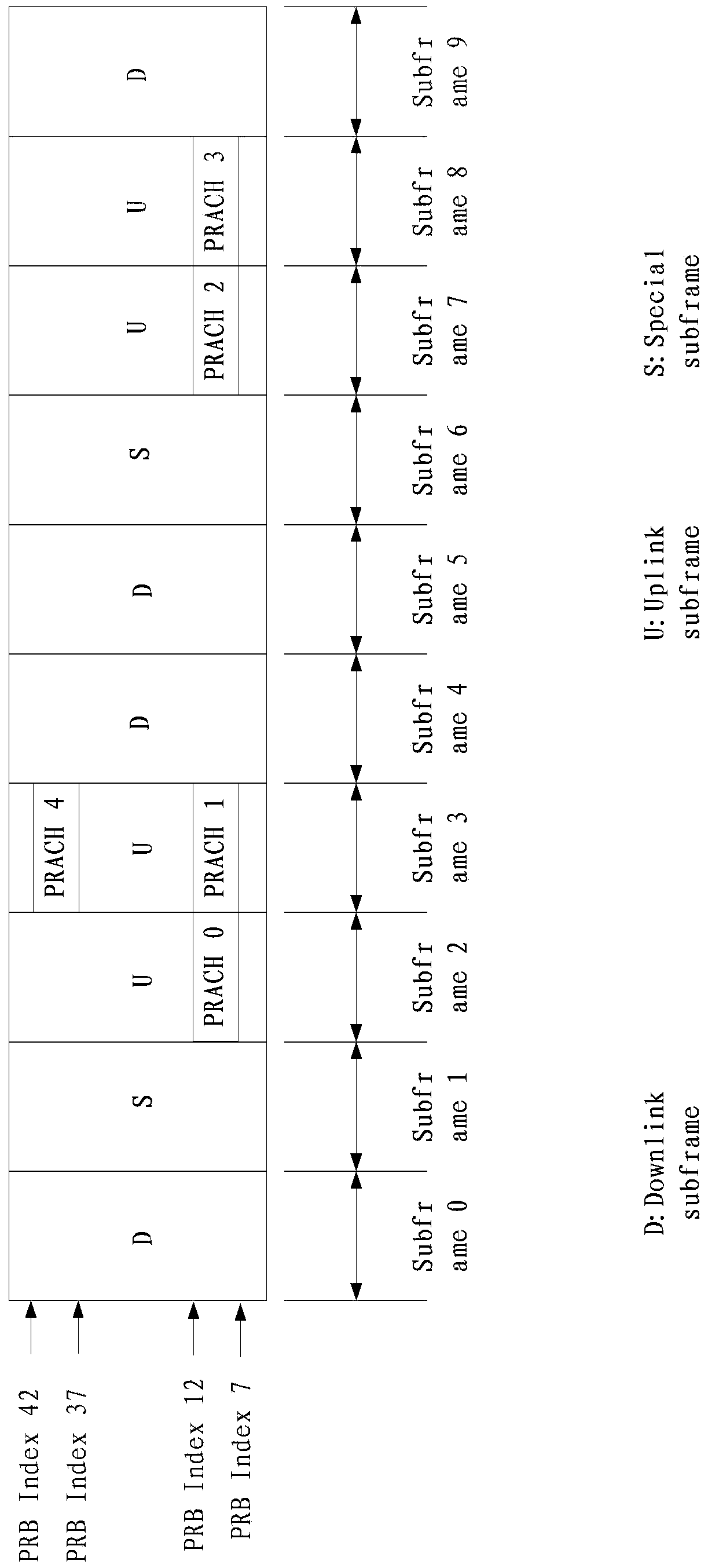

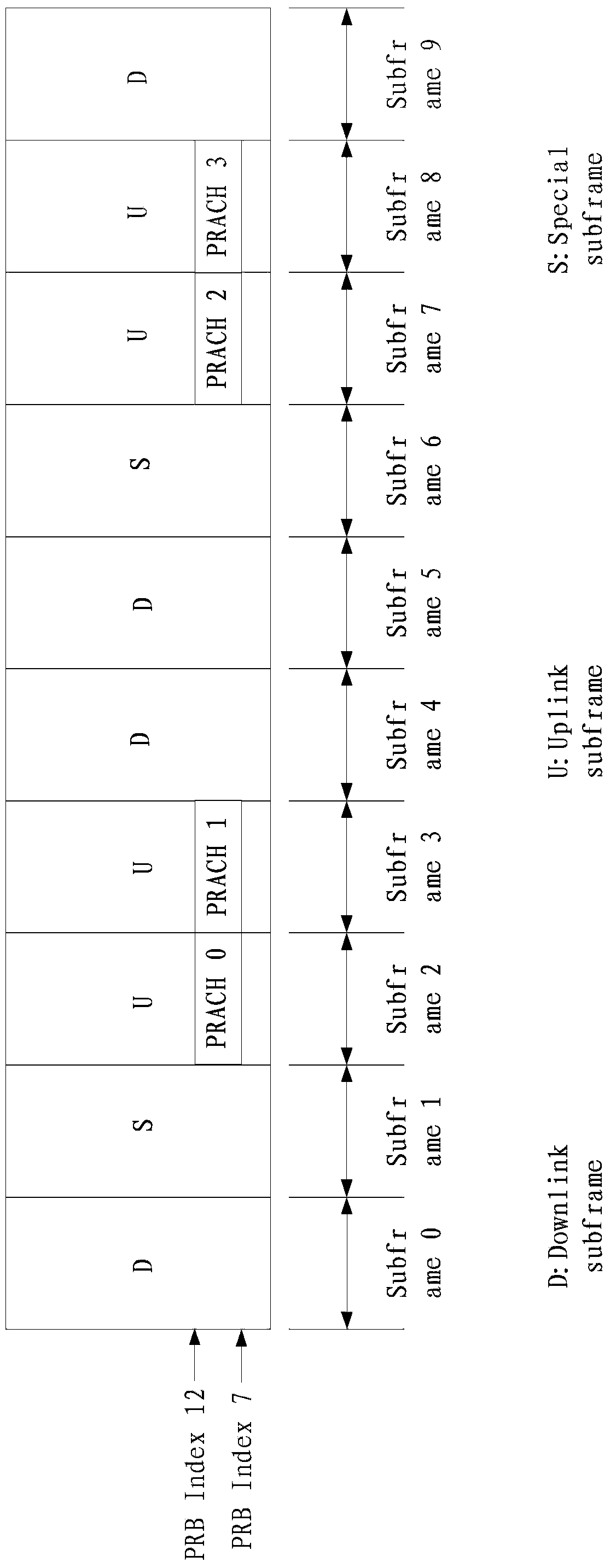

The present invention provides a method and a device for allocating resource. The method comprises: determining information of a second Physical Random Access Channel (PRACH) resource of at least one second cell adjacent to a first cell; and allocating a first PRACH resource for the first cell according to the information of the second PRACH resource, wherein the first PRACH resource and the second PRACH resource are staggered on time domain and / or frequency domain. According to the embodiment of the present invention, since the first PRACH resource allocated for the first cell and the second PRACH resource of the adjacent second cell are staggered on time domain and / or frequency domain, the same frequency interference on the first PRACH resource by the second PRACH resource can be reduced, the false alarm probability caused by the same frequency interference can be reduced, and thus the random access performance and the access success rate can be increased.

Owner:HUAWEI TECH CO LTD

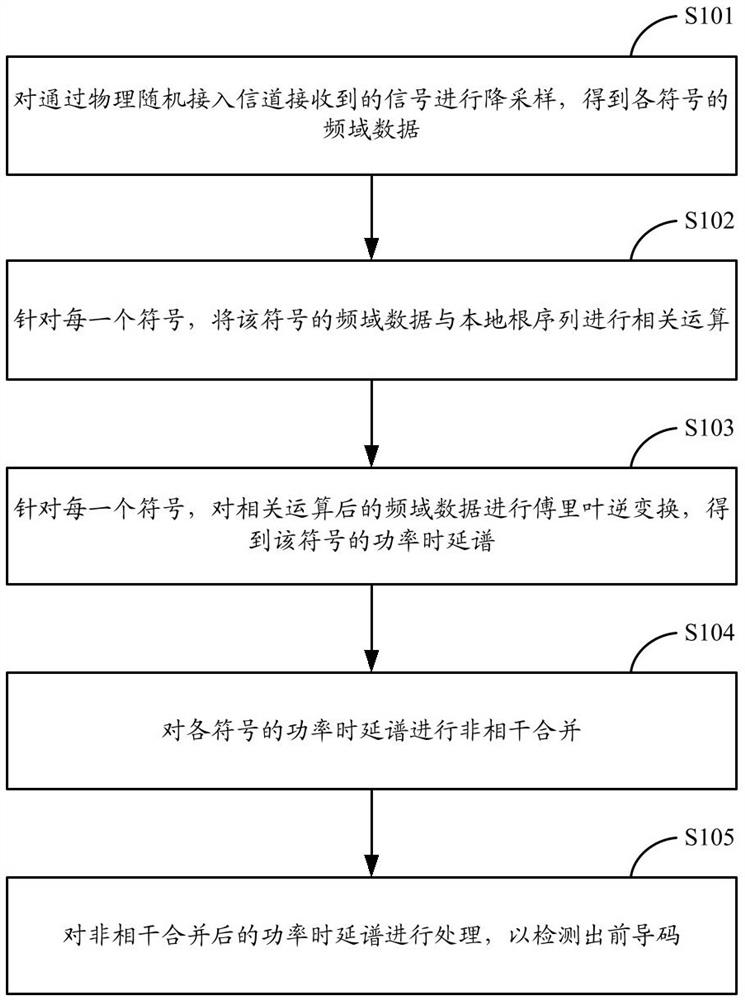

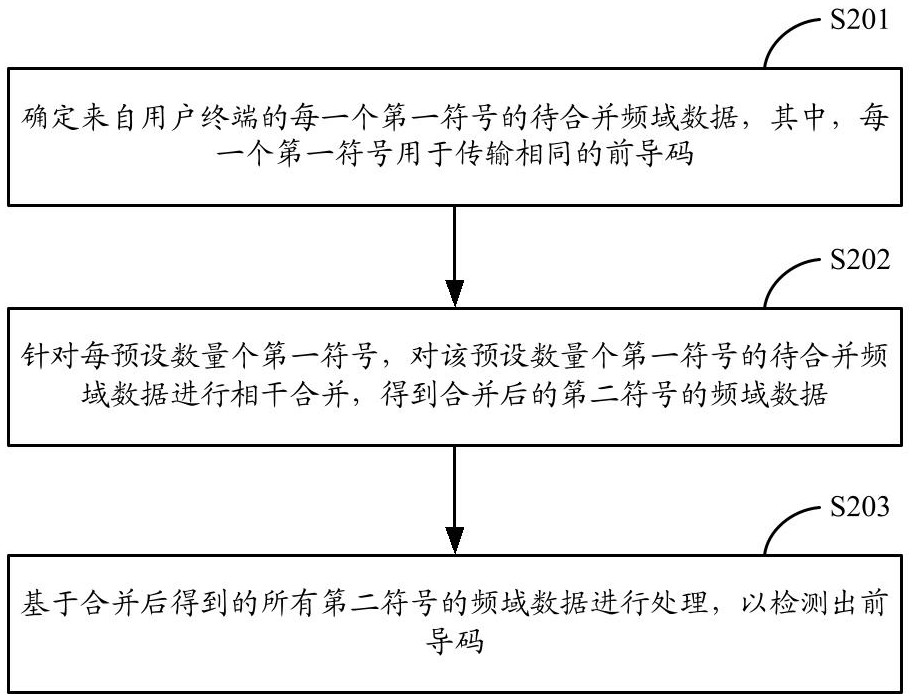

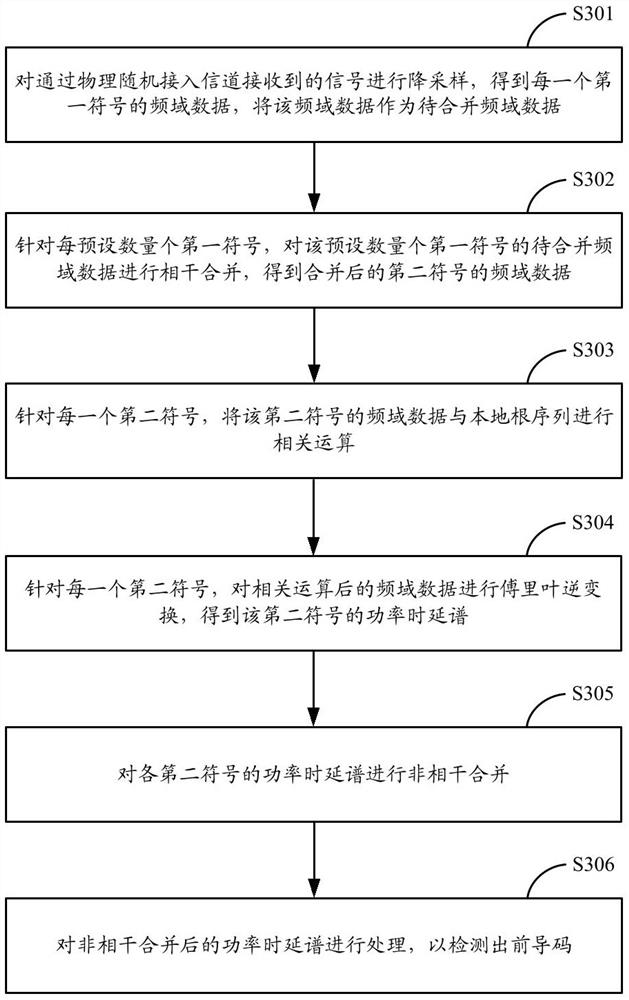

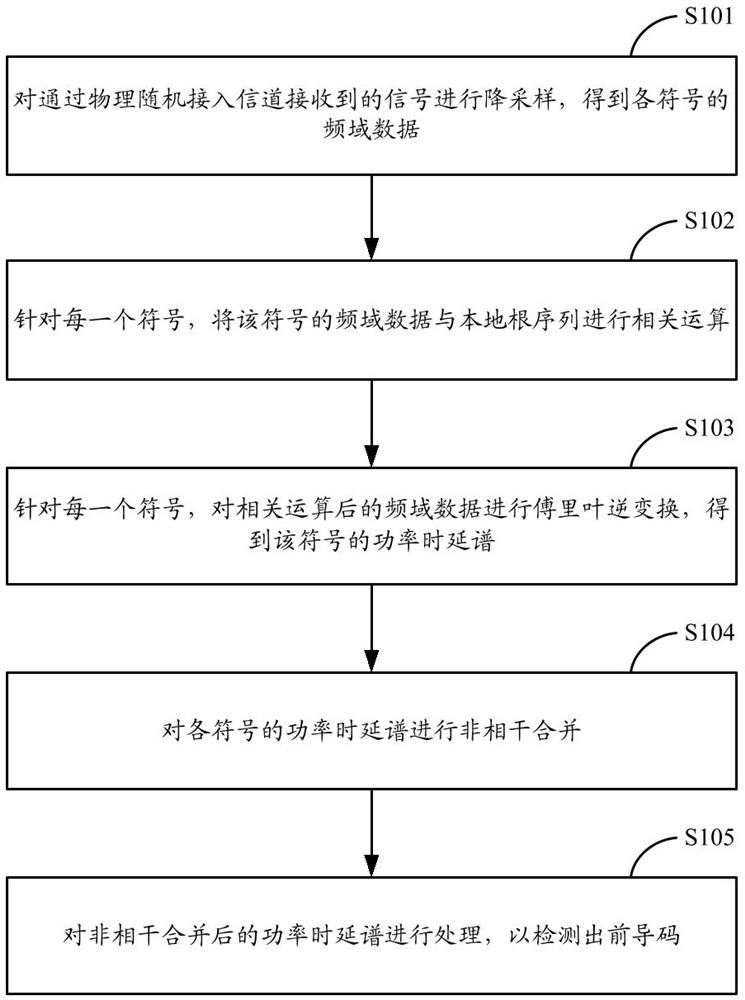

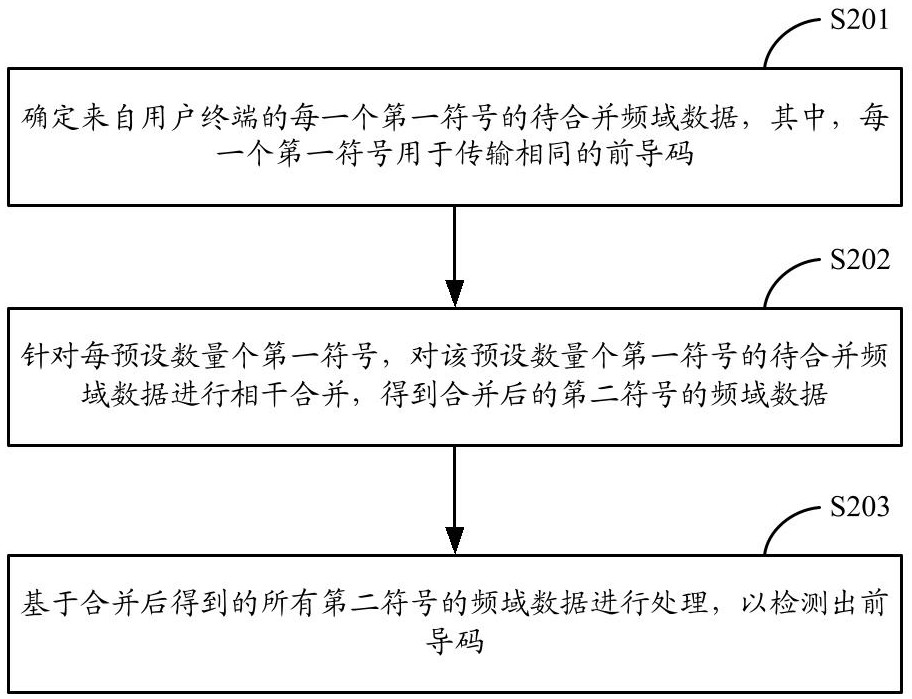

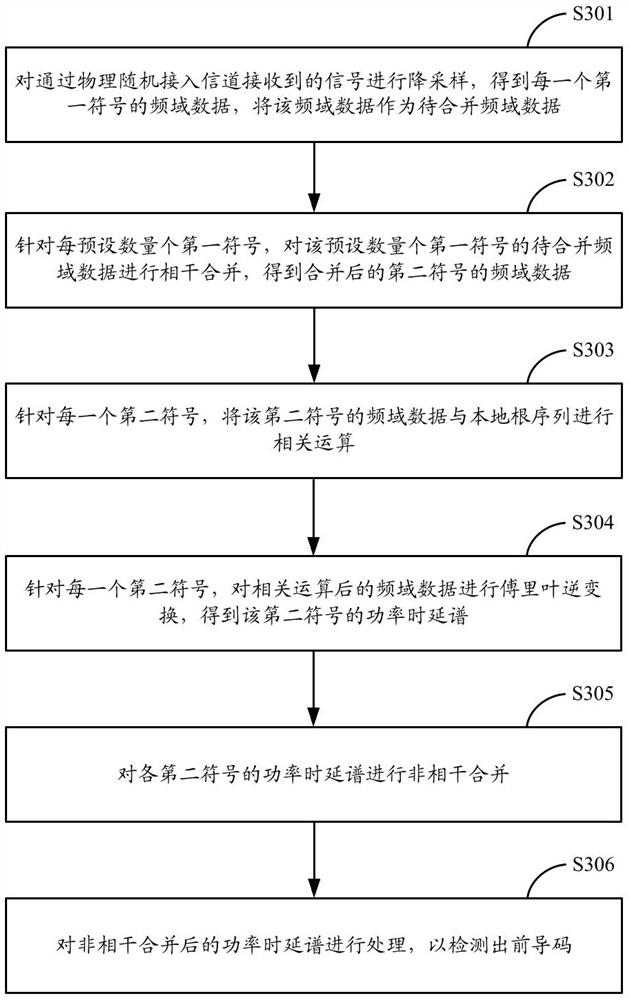

Preamble detection method and device

ActiveCN114423092BImprove the detection rateImprove detection efficiencyWireless communicationElectrical and Electronics engineeringReal-time computing

The present application provides a method and device for detecting a preamble. In this method, the base station determines the frequency domain data to be combined for each first symbol from the user terminal, wherein each first symbol is used to transmit the same preamble; for every preset number of first symbols, the preamble Suppose that the frequency domain data of a number of first symbols to be combined are coherently combined to obtain the frequency domain data of the combined second symbol; and perform processing based on the frequency domain data of all the second symbols obtained after the combination to detect the preamble code. The present application can effectively improve the random access performance of the system.

Owner:NEW H3C TECH CO LTD

Method of implementing random access

ActiveCN100495999CLow management complexityReduce overheadData switching by path configurationCode division multiplexNetwork managementDistributed computing

This invention discloses one random interfacing realization method, which comprises the following steps: setting user selected signature with different priority to different interface and processing each user by each signature according to each signal priority order of each interface gap. This invention method can make each user reduce network management complexity and materials spending on base of even opportunity to interface to network.

Owner:HUAWEI TECH CO LTD

Preamble detection method and device

ActiveCN114423092AImprove the detection rateImprove detection efficiencyWireless communicationAlgorithmComputer engineering

The invention provides a lead code detection method and device. In the method, a base station determines to-be-merged frequency domain data of each first symbol from a user terminal, each first symbol being used for transmitting the same lead code; for each preset number of first symbols, performing coherent combination on the to-be-combined frequency domain data of the preset number of first symbols to obtain combined frequency domain data of second symbols; and processing based on the frequency domain data of all the second symbols obtained after combination to detect the lead code. According to the invention, the random access performance of the system can be effectively improved.

Owner:NEW H3C TECH CO LTD

Evaluation of random access lead code

InactiveCN101208977BImprove random access performanceImprove random access operationMultiplex code allocationTransmissionCellular radioTheoretical computer science

The present invention relates to methods and arrangements for gathering statistics relating to random access operation in a cell of a cellular radio communication network and supervising such random access operation. Statistics are gathered (301), per random access preamble code, relating to random access detections associated with one or more random access preamble codes used in the cell. Based on such gathered statistics, random access operation in the cell may be supervised by evaluating (311) the gathered statistics and, upon determining (312) that the random access detections associated with a specific random access preamble code exhibit an abnormal behaviour likely to be caused by false random access preamble detections, initiating (313) at least one of issuing a corresponding operation and maintenance alarm signal and automatically blocking further use of said specific random access preamble code in the cell.

Owner:TELEFON AB LM ERICSSON (PUBL)

Method and apparatus in node for wireless communication

ActiveCN112996135AImplementation supportGuaranteed successPower managementSynchronisation arrangementTelecommunicationsElectrical and Electronics engineering

The invention discloses a method and an apparatus in a node for wireless communication. The method comprises the steps of: enabling a node to receive first information, wherein the first information is used for determining X alternative formats; sending a first signal, wherein the first signal adopts a first format; sending a second signal, wherein the second signal adopts a second format, wherein the first format is one alternative format in the X alternative formats, and the second format is one alternative format in the X alternative formats, a first timing offset value is used for determining the sending timing of the first signal, a second timing offset value is used for determining the sending timing of the second signal, the first timing offset value and the second timing offset value are not equal, the first format is related to the first timing offset value, the second format is related to the second timing offset value, and the first signal and the second signal are both used for random access. The random access performance is improved.

Owner:SHANGHAI LANGBO COMM TECH CO LTD

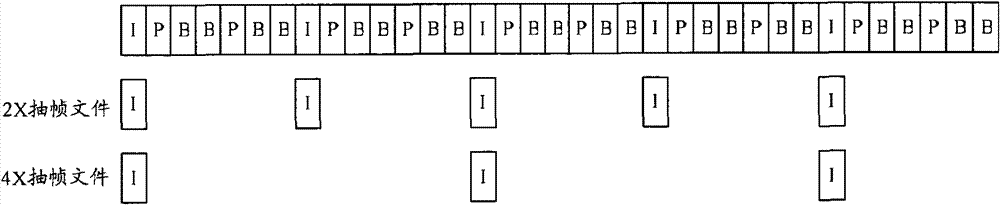

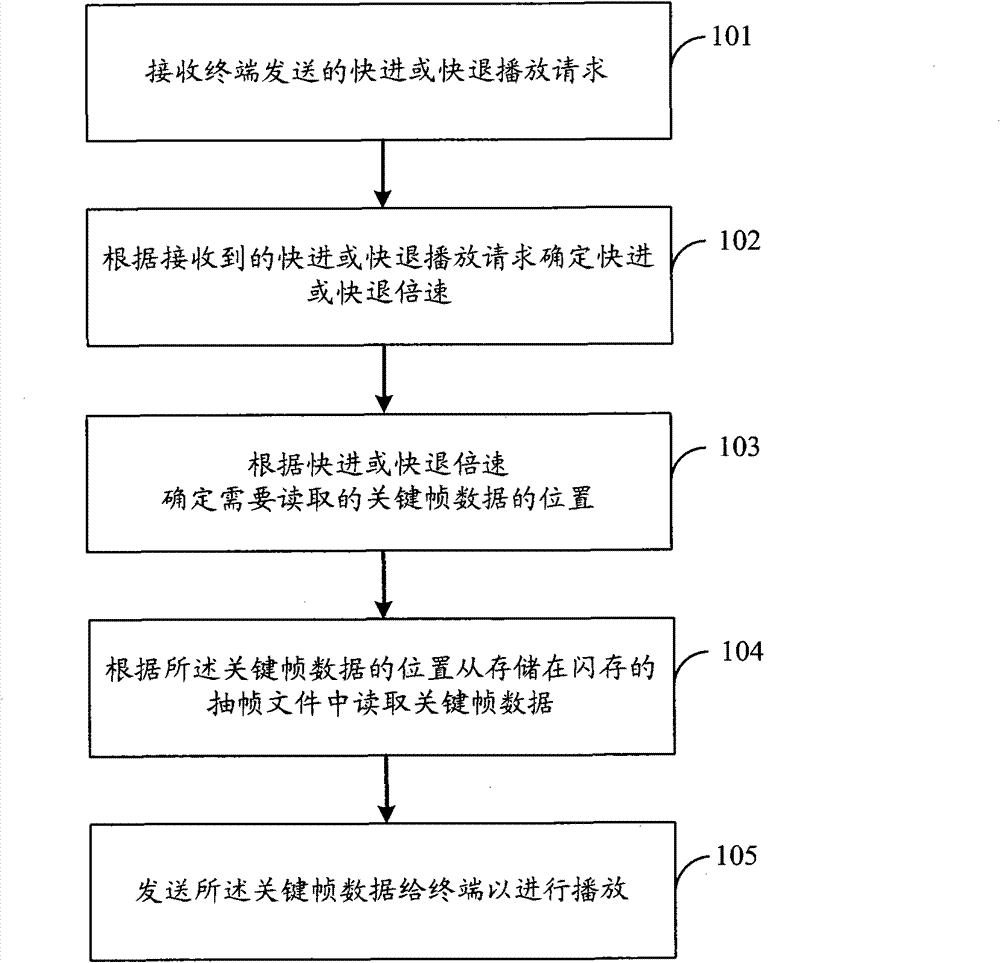

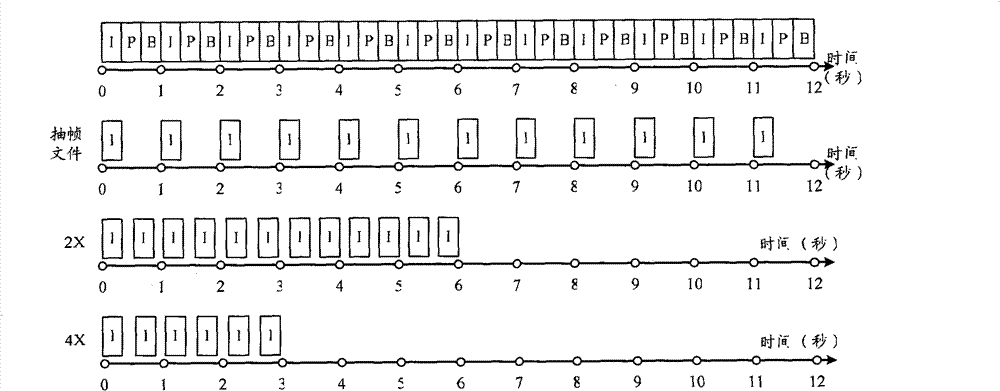

Processing method, device and system for fast forward and fast backward playing of network stream media

ActiveCN102025956BImprove performanceImprove random access performanceTelevision system detailsRecord information storageCommunications systemComputer terminal

Owner:HUAWEI TECH CO LTD

Random access method and equipment

ActiveCN114340014AImprove random access performanceRandom access increaseSynchronisation arrangementTerminal equipmentReal-time computing

Provided are a random access method and device, which can improve the performance of random access of a terminal device on an unlicensed frequency band. The method comprises: a terminal device receiving a PDCCH, the PDCCH comprising PRACH resource indication information, the PRACH resource indication information being used for indicating a public PRACH resource scheduled by a network device, the PRACH resource indication information comprises at least one of the following information: information of the PRACH resource, information of a synchronization signal block (SSB) associated with the PRACH resource, and information of a PRACH lead code transmitted on the PRACH resource; and the terminal equipment uses the PRACH resource to send the PRACH according to the PRACH resource indication information.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

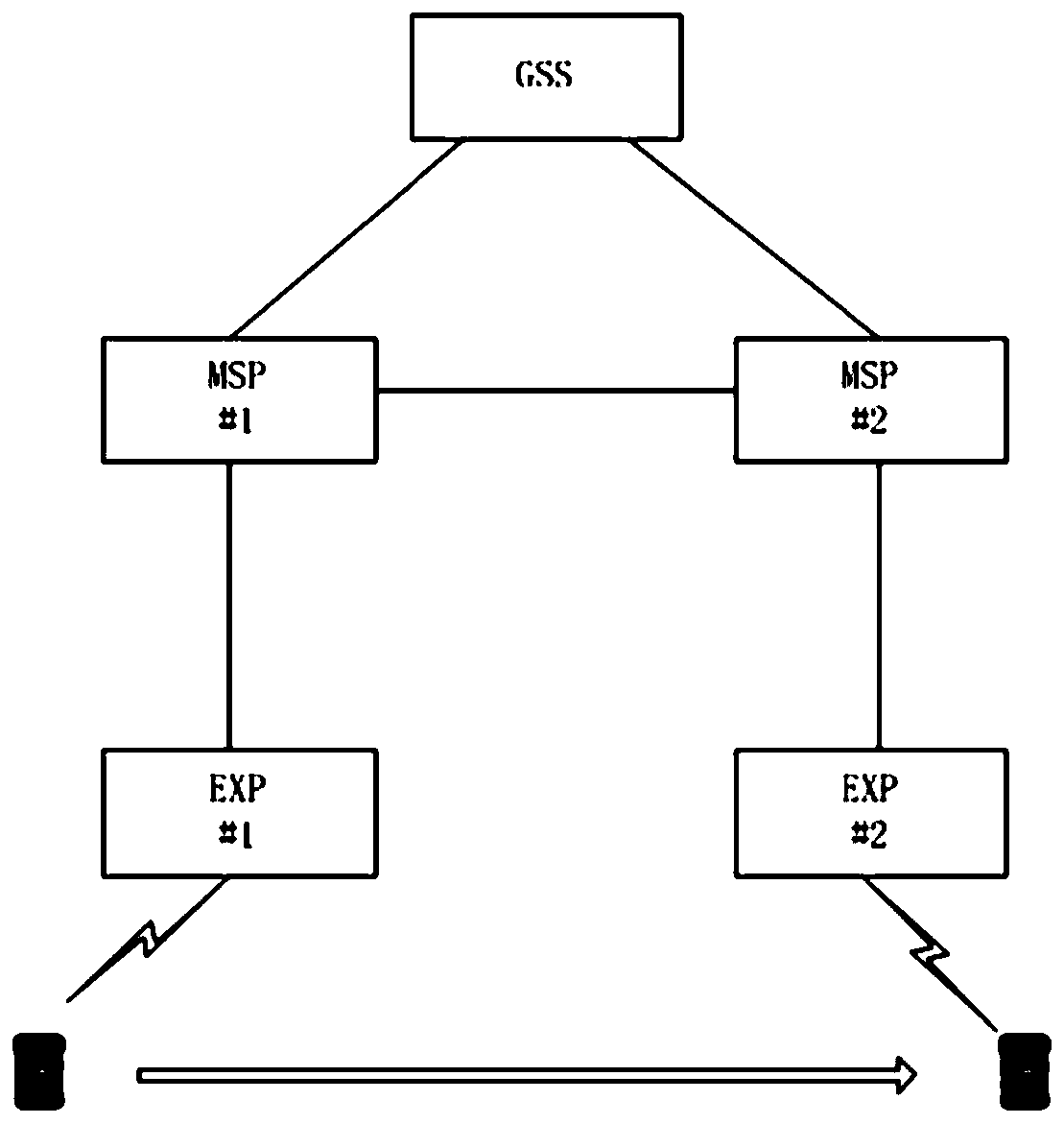

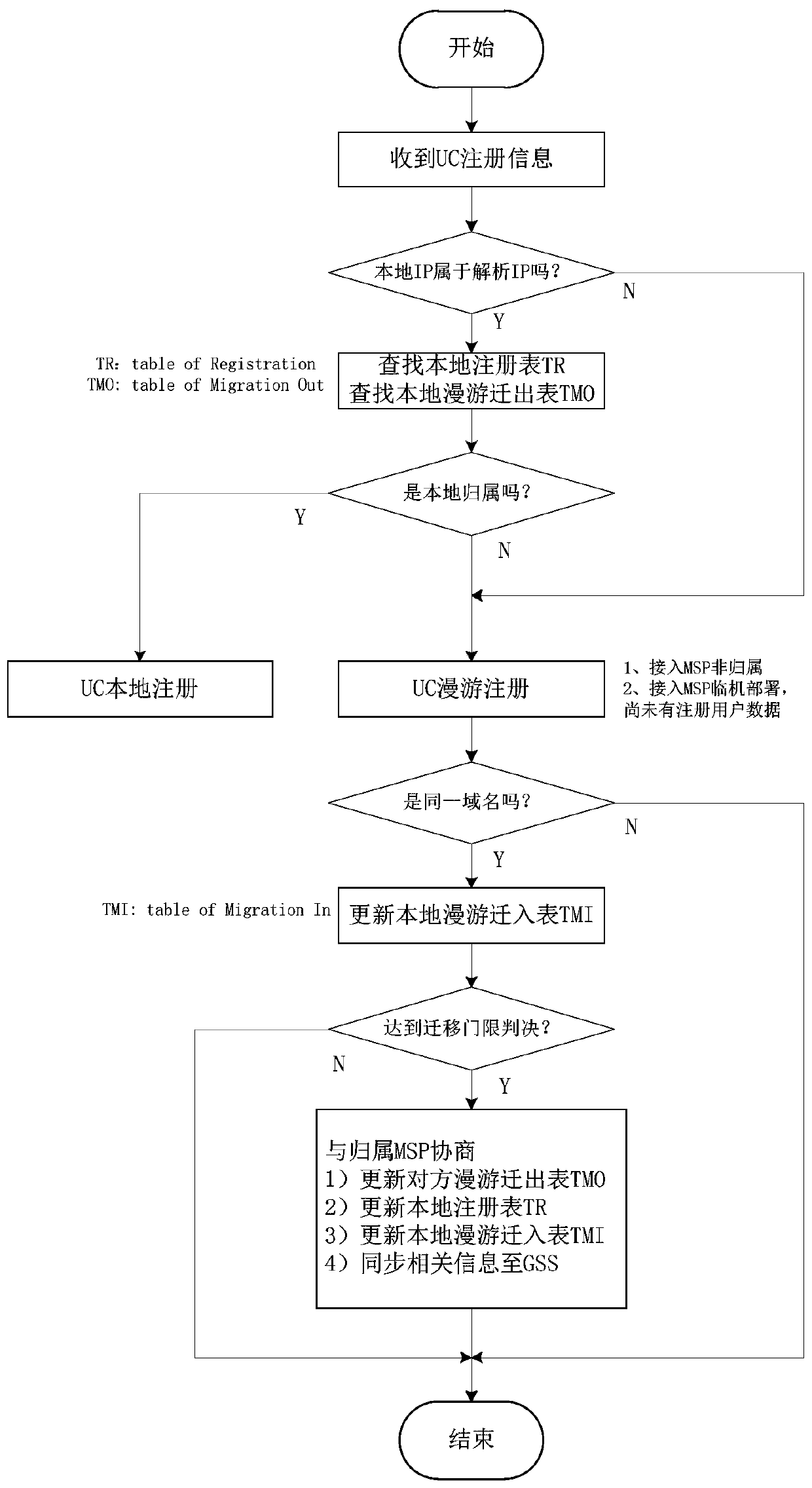

Converged communication attribution transfer and registration method suitable for narrowband network

ActiveCN110839230AReduce the number of roaming usersGuaranteed uptimeNetwork data managementCommunications systemIndustrial Internet

The invention provides a converged communication attribution transfer and registration method suitable for a narrowband network. The converged communication attribution transfer and registration method comprises the following steps: step 1, designing a local registry TR, a local roaming immigration table TMI and a local roaming emigration table TMO; step 2, establishing an attribution adaptive evolution method, and performing attribution migration; step 3, carrying out prefix splitting and merging to realize nearby local registration access; and step 4, completing registration by roaming users. Attribution dynamic adjustment is made so that the large number of roaming registered users are adjusted into local registered users; therefore, the bandwidth requirement and the link quality requirement on the communication network are greatly reduced; the method can support the quick deployment of the converged communication system in communication environments with narrow-band and weak-connection link characteristics, such as industrial Internet of Things, battlefield communication, narrow-band ad hoc networks and cluster communication networks, supports the random access and roaming switching of terminals, and can improve the robustness of the converged communication system.

Owner:THE 28TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

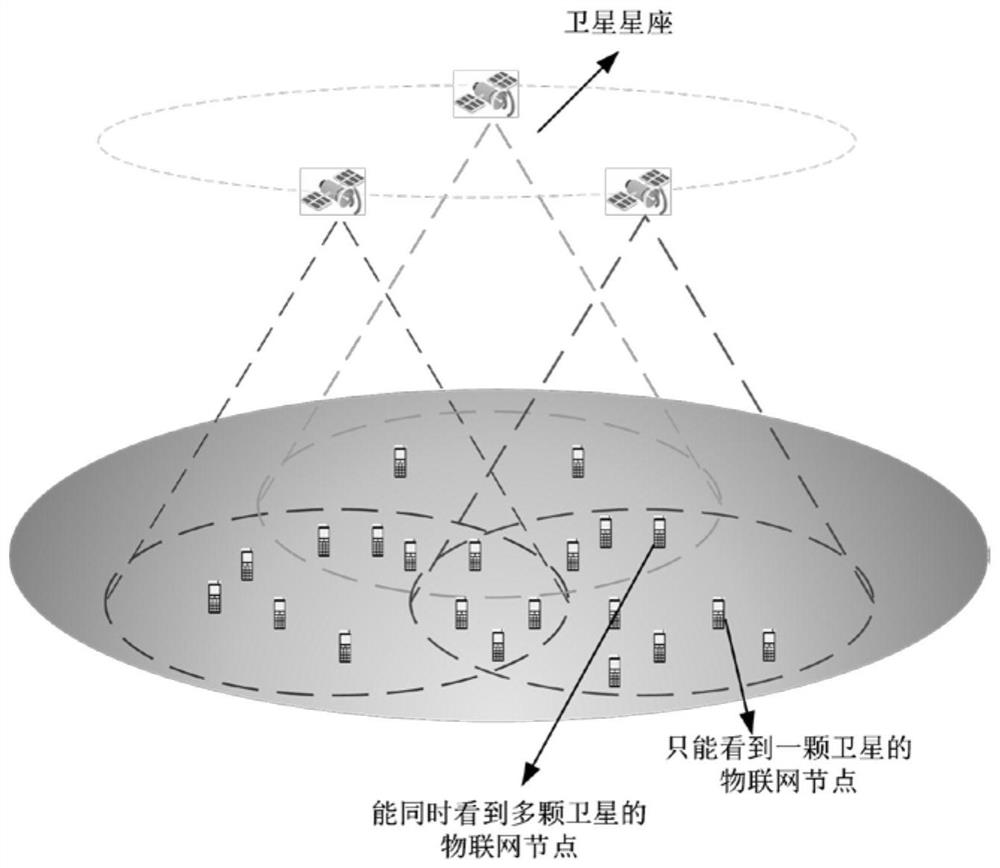

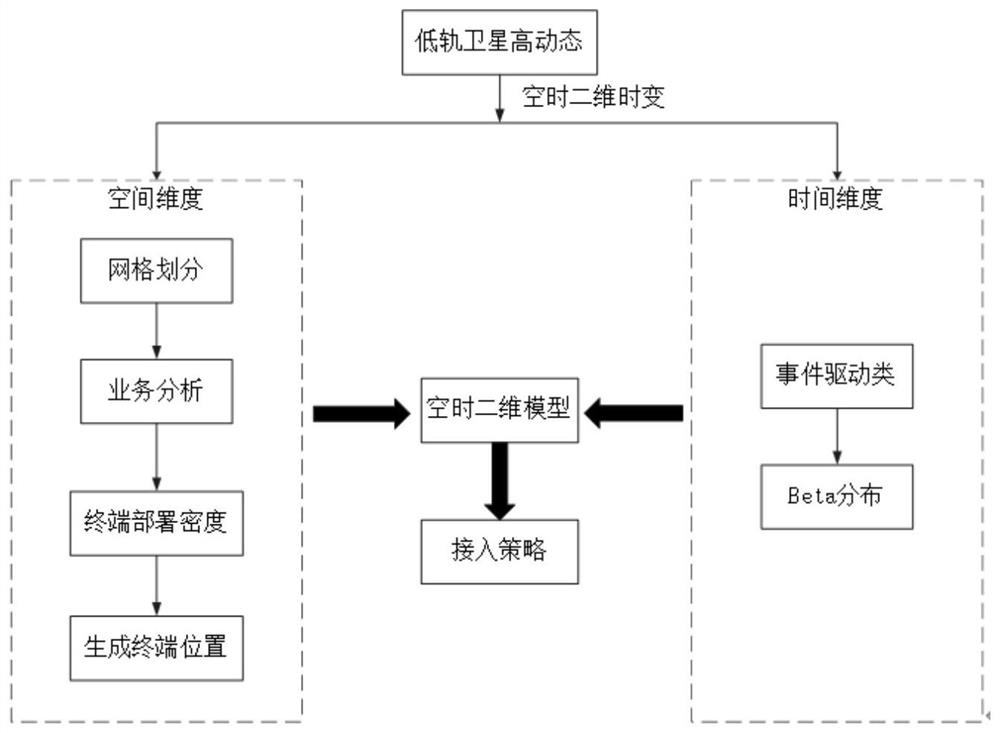

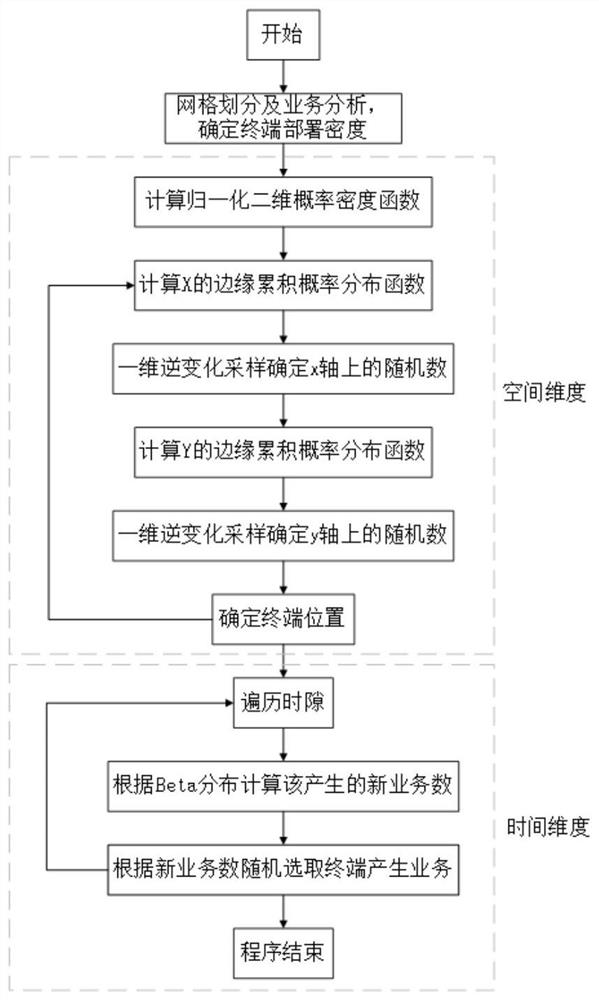

Low earth orbit satellite Internet of Things service model based on attractor selection algorithm and multi-satellite load balancing algorithm

ActiveCN113037358AExhibits spatiotemporal inhomogeneityContribute to researchNetwork traffic/resource managementBiomolecular computersNetwork activityThe Internet

The invention discloses a low earth orbit satellite Internet of Things service model based on an attractor selection algorithm and a multi-satellite load balancing algorithm. according to the business model, a method for determining terminal deployment density by grid division is adopted in the spatial dimension, a random position generation method is adopted, and specific coordinates of a terminal are determined by constructing a terminal deployment density matrix, utilizing the characteristics of an edge cumulative probability distribution function pair and using mathematical methods such as one-dimensional inverse change sampling and affine transformation; and in the time dimension, event-driven services are researched, and burst traffic characteristics in a short time range are accurately captured. In the multi-satellite load balancing algorithm, the network activity and the network state of each satellite are calculated in real time to guide the Internet of Things terminal to carry out dynamic self-adaptive satellite decision. Therefore, the method is more suitable for high-dynamic scenes such as the satellite Internet of Things, and can enable the terminal to make adaptive decision adjustment and improve the random access performance when the external access scale changes.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

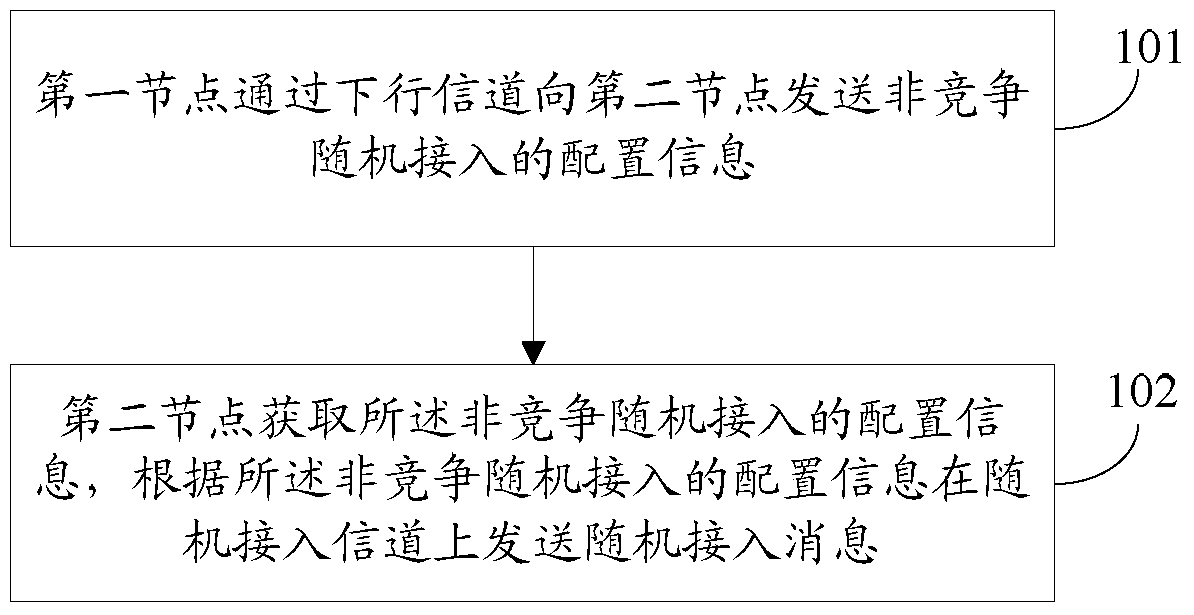

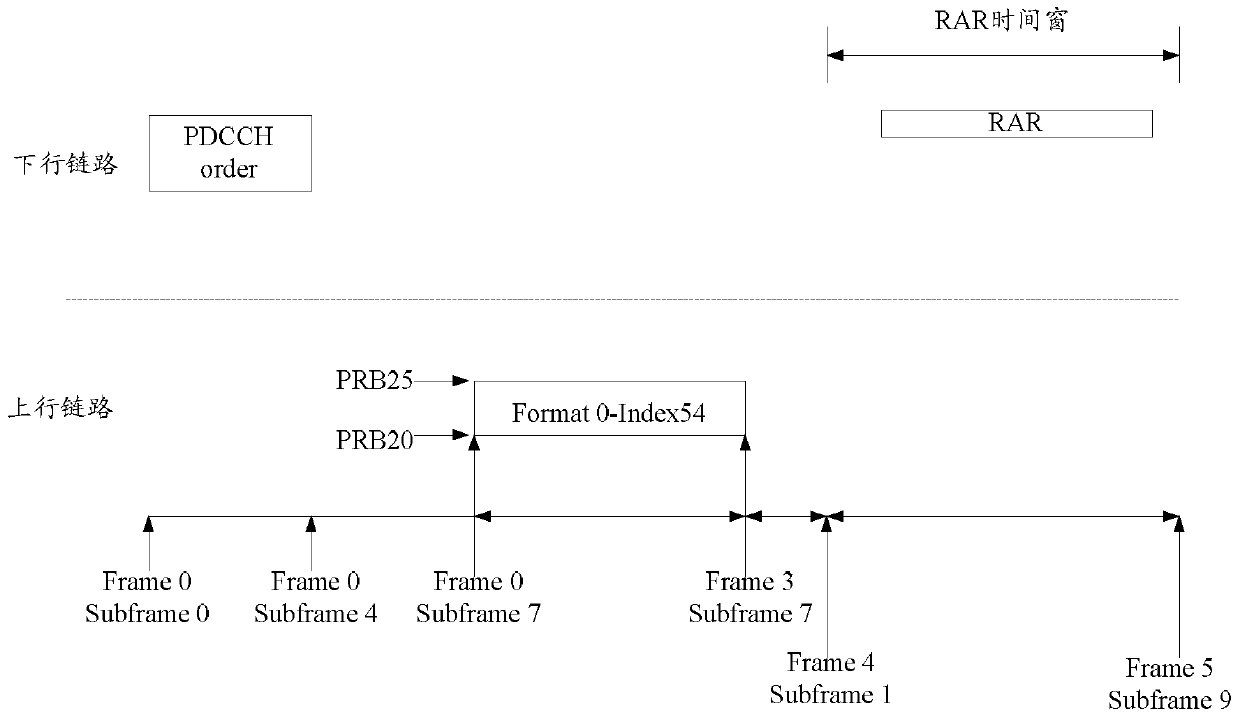

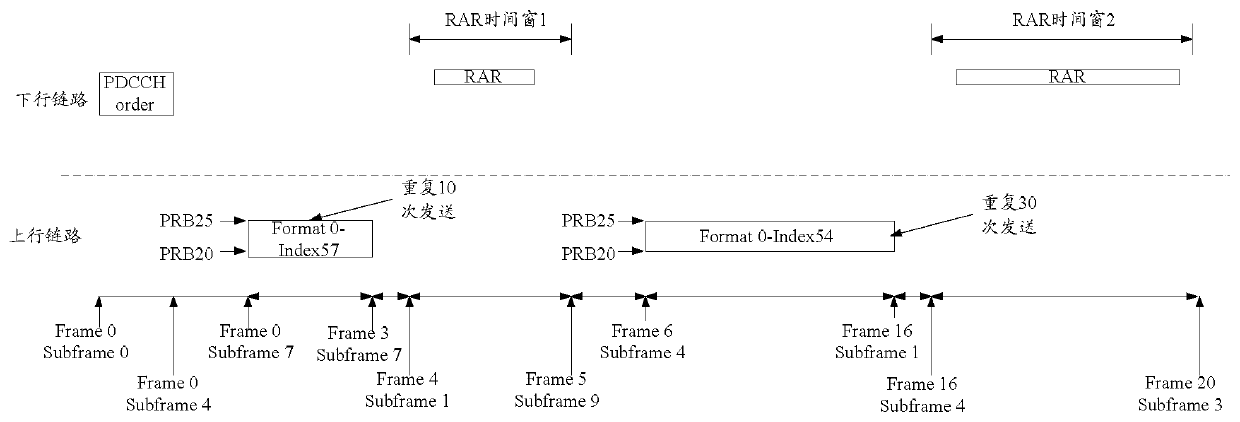

A non-contention random access method, node device and system

ActiveCN104780617BImprove random access performanceReduce access delayNetwork traffic/resource managementComputer hardwareRandom-access channel

Examples of the present invention disclose a non -competitive random access method, node equipment and systems; of which, the non -competitive random access method includes: the first node sends a non -competitive random access configuration to the second node through the downward channel.Information; the second node obtains the configuration information of non -competitive random access, and sends random access messages on the random access channel based on the configuration information.

Owner:ZTE CORP

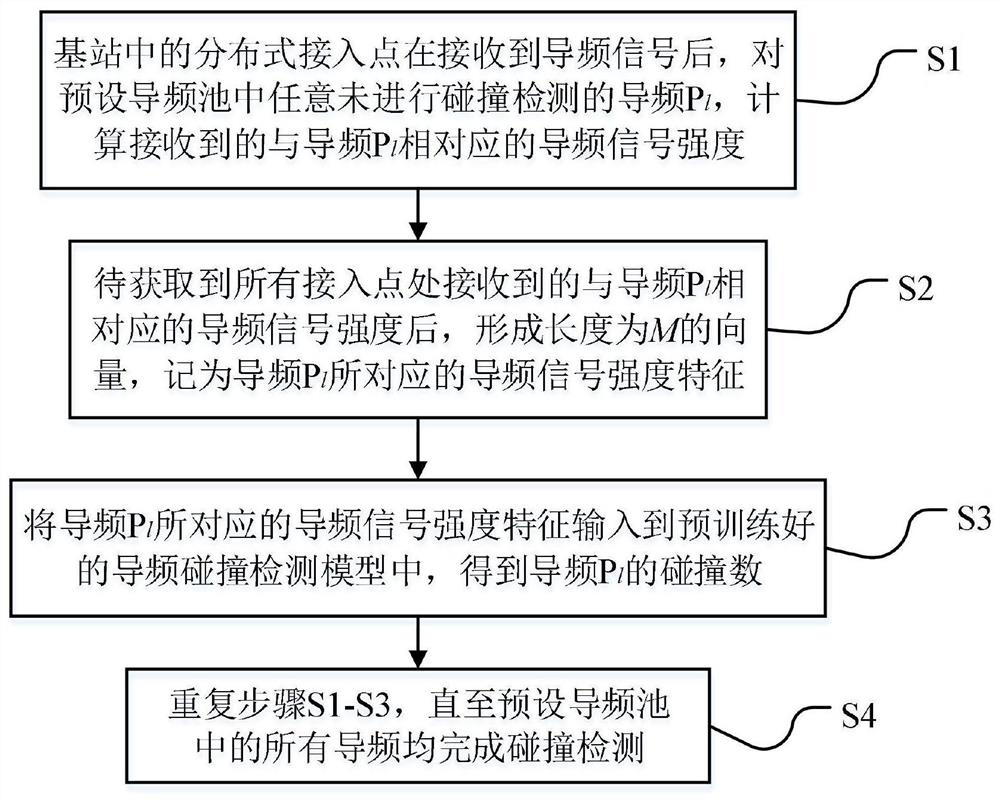

Pilot collision detection method, device and system

ActiveCN112512075AImprove random access performanceReduce energy consumptionMulti-frequency code systemsHigh level techniquesResource assignmentCollision detection

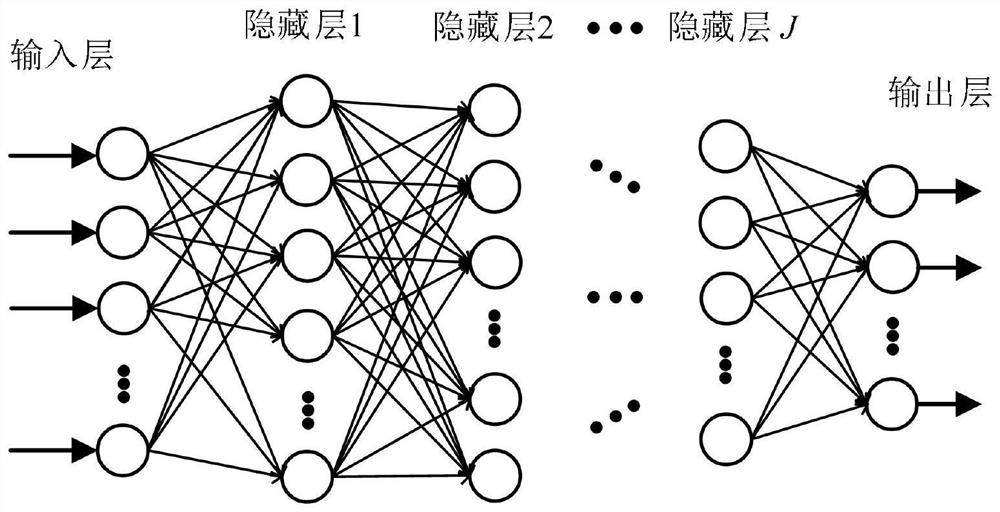

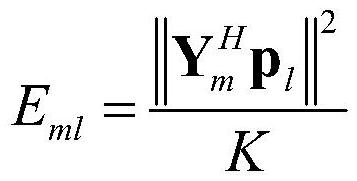

The invention discloses a pilot collision detection method, device and system, and the method comprises the steps: S1, calculating the intensity of a received pilot signal corresponding to any undetected pilot pl in a preset pilot pool after a distributed access point in a base station receives the pilot signal; S2, after pilot signal intensities corresponding to the pilot pl and received at all access points are obtained, forming a vector; S3, inputting the obtained vector into a pre-trained pilot collision detection model to obtain a collision number of the pilot p1, and repeating the step S1S3 until all pilots in the preset pilot pool complete collision detection. When MTC massive terminals are randomly accessed, pilot collision and the number of conflicting terminals can be rapidly detected only according to received pilot signals, so extra wireless resources and time expenditure in random access are avoided, and energy consumption and time delay of access terminals in random access are reduced, so that the base station can carry out timely and effective resource allocation conveniently, and the random access performance of the terminal is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

Random access sequence transmission method and device

ActiveCN104184548BImprove random access performanceError preventionWireless communicationRandom-access channelComputer science

The invention provides a random access sequence transmission method and device. The invention relates to the field of communication; and solves the problem that the random access signaling transmitted by the MTC UE in a harsh environment can be correctly detected by the eNB. The method includes: the first node sends a random access channel configuration message, wherein the random access channel configuration message includes at least a random access channel resource configuration information of the third node. The technical solution provided by the present invention is applicable to the M2M service in the LTE system, and achieves a higher random access performance of the MTC UE.

Owner:ZTE CORP

Random access method and device, and terminal

PendingCN114222373AImprove random access performanceWireless communicationError prevention/detection by transmission repeatTelecommunicationsRandom-access channel

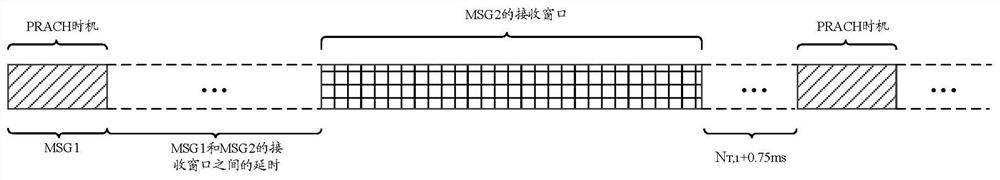

The embodiment of the invention provides a random access method and device and a terminal, and the method comprises the steps: preparing to retransmit a first uplink data channel in a third time interval after a first downlink data channel under the condition that the terminal determines to retransmit the first uplink data channel in a first message, the first message comprises a first random access channel and a first uplink data channel; wherein the first downlink data channel is used for bearing a second message, and the second message is a response message of the first message.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Multi-mode multi-viewpoint video signal code compression method

InactiveCN100415002CImprove random access performanceReduce computational complexityTelevision systemsDigital video signal modificationViewpointsComputation complexity

The invention discloses a video encoding method with multi-mode and multi-view. According to the analysis of the time correlation for the multi-view video signals and view correlation , as well as the comprehensive characters such as the compressing efficiency, complexity of encoding, random access performance and coding delay demanded by the system, the method adaptively dynamic-chooses the predictive coding mode which meets the features and the comprehensive encoding requirements of the current signals to encode them, in order to replace the method with single mode and complex calculation that forecasts by the union of time and space, and decrease the calculation complexity of compressing the signal coding.

Owner:上海斯派克斯科技有限公司