RapidIO network switching method for VPX switching board

A technology of network switching and switching boards, which is applied in the field of rapidIO network switching of VPX switching boards, can solve problems such as waste of resources, dead links, inconvenient management of rapidIO nodes, etc., and achieve the effect of saving resources and boards

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention mainly implements rapidIO network enumeration, hot plugging and bandwidth allocation functions on the FPGA of the switch board, and integrates the rapidIO-FC optical fiber switching module. The specific implementation method is as follows:

[0014] 1) Construction of SOPC hardware system based on MicroBlaze:

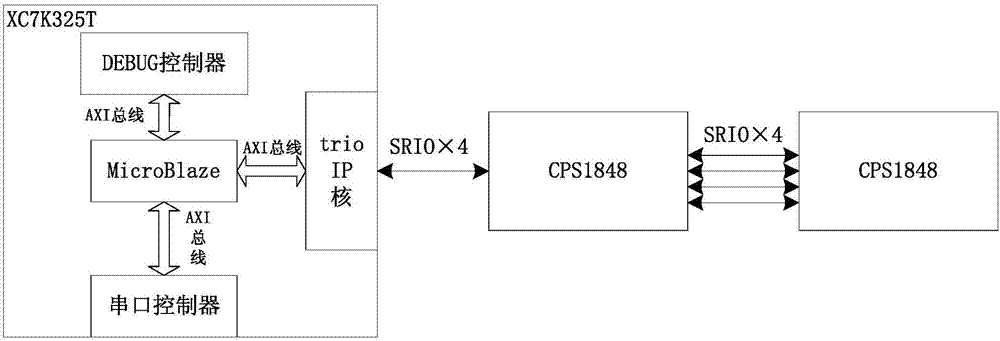

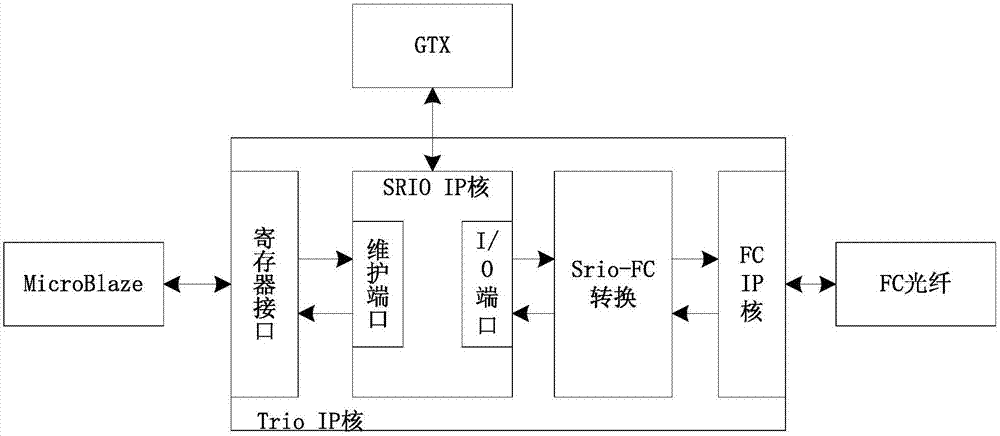

[0015] Using Xilinx's vivado suite, the SOPC system-on-chip hardware framework is built by combining MicroBlaze soft core, AXI Connect core, UART, and custom rapidIO switching IP core. The IP core of the peripheral device is connected through the AXI bus, and the devices interact with each other through the AXI bus protocol. The block diagram of the SOPC-based RapidIO switch board is as follows: figure 1 As shown, the logical design block diagram of the rapidIO switching IP core is shown in figure 2 shown.

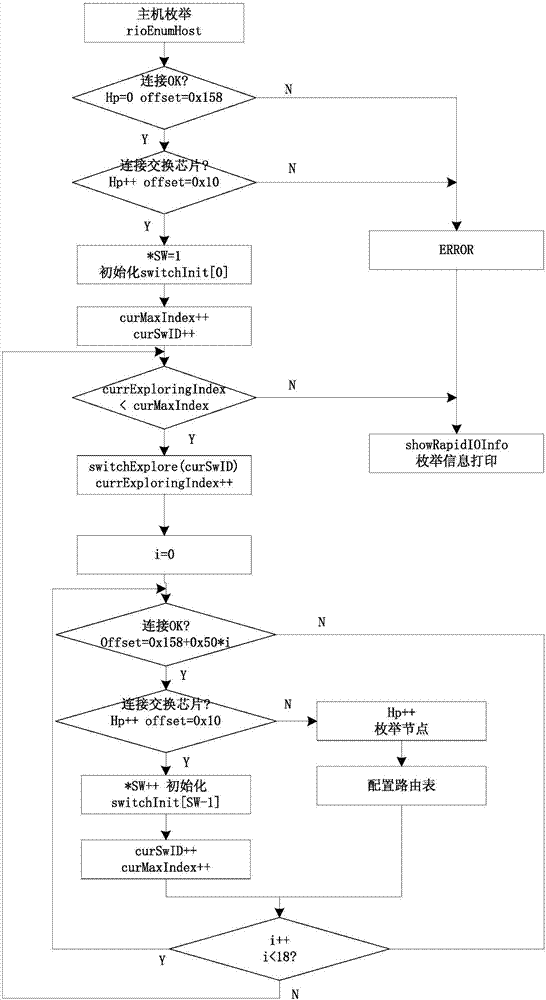

[0016] 2) RapidIO network enumeration and bandwidth allocation implementation:

[0017] Under the hardware framework, using the SDK...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More