Interconnection method among cores of multi-core processor

A multi-core processor and core technology, applied in a variety of digital computer combinations, electrical components, digital transmission systems, etc., can solve the problems of difficult integration, inapplicability to the chip level, and difficulty in implementation, and achieve the effect of convenient implementation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

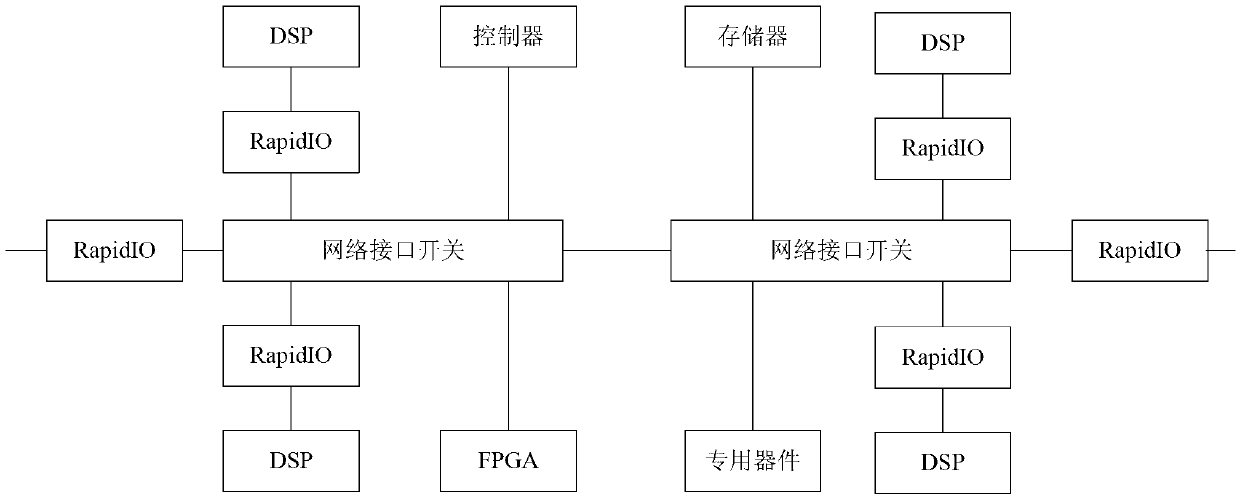

[0025] Embodiment one: see attached figure 1 shown.

[0026] A multi-core processor refers to a chip containing two or more "execution cores". Compared with single-core processors, multi-core processors face more challenges when conducting technical research on architecture, such as inter-core communication, memory system, low power consumption, and software and hardware coordination. How to realize mutual cooperation and communication between multi-core cores, to ensure the improvement of processing speed and chip processor performance is the main content of the research on inter-core communication structure, and it is also the focus of academic circles.

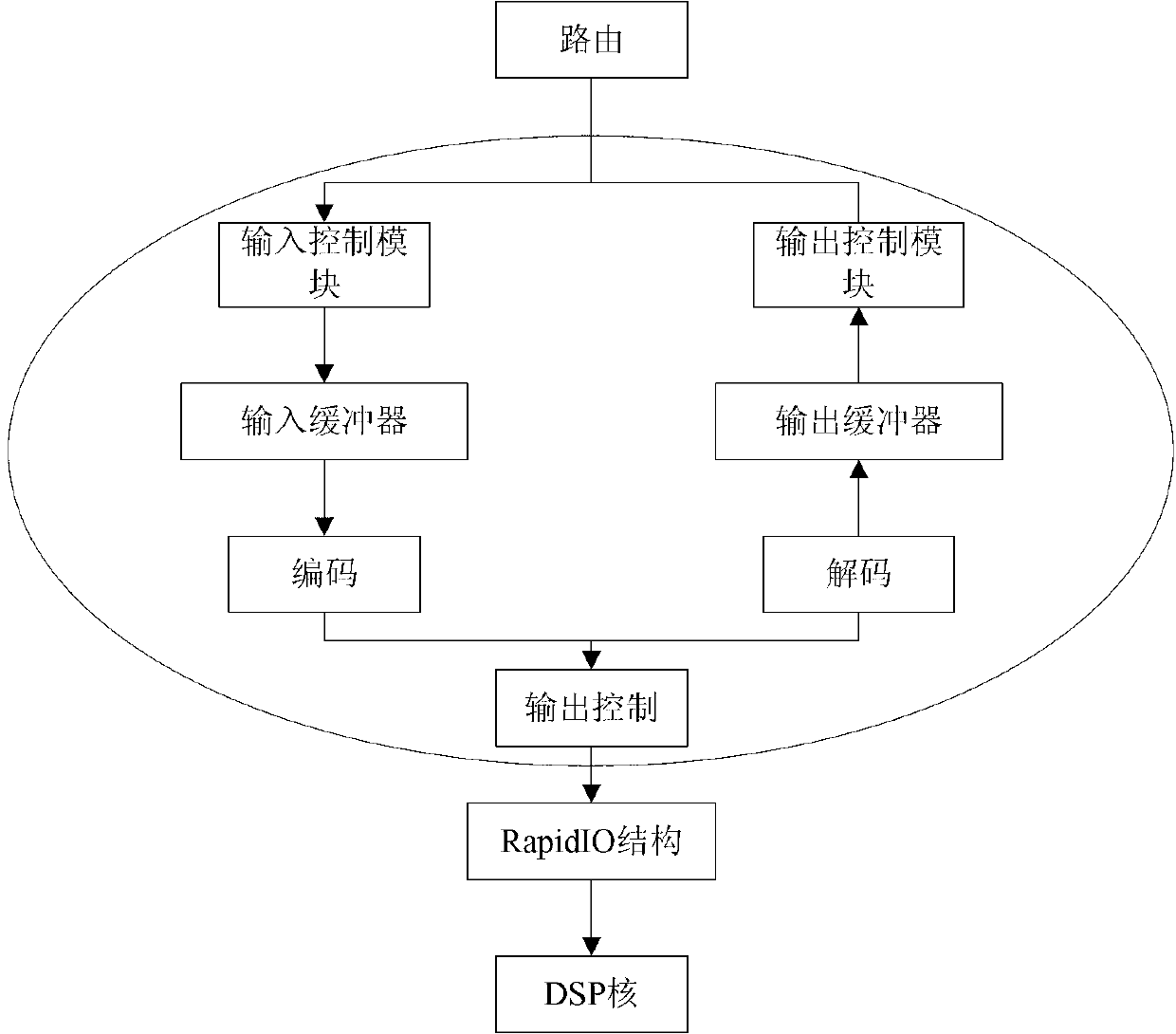

[0027] The emergence of NoC (Network on-Chip) has brought continuous development momentum to deep submicron SoC. NoC is a higher-level, larger-scale system on a chip, and a network system on a chip. The core idea of NoC technology is to transplant computer network technology into chip design and completely solve the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More