Patents

Literature

241 results about "High-Speed Serial Interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The High-Speed Serial Interface (HSSI) is a differential ECL serial interface standard developed by Cisco Systems and T3plus Networking primarily for use in WAN router connections. It is capable of speeds up to 52 Mbit/s with cables up to 50 feet (15 m) in length.

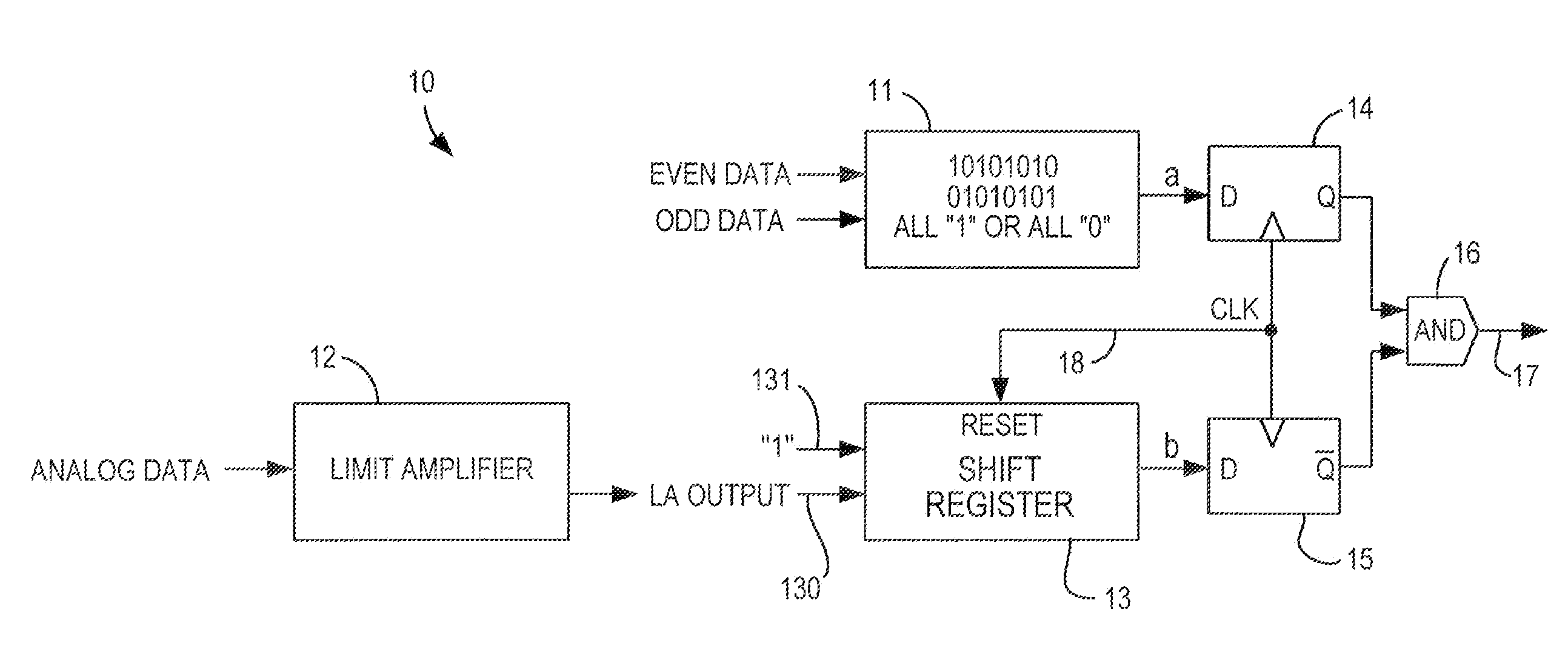

Signal loss detector for high-speed serial interface of a programmable logic device

InactiveUS7996749B2Multiple-port networksData representation error detection/correctionPattern matchingProgrammable logic device

Owner:ALTERA CORP

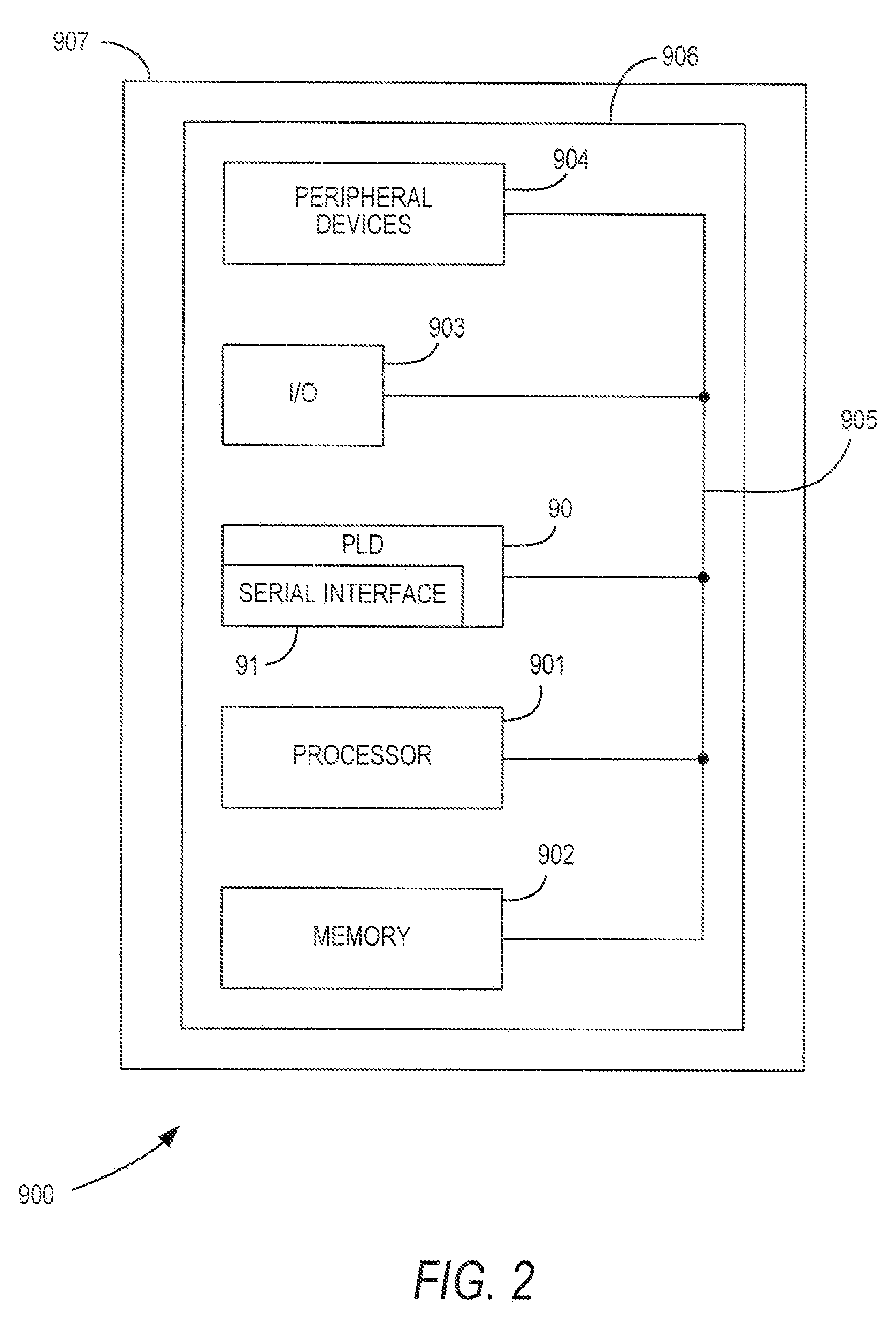

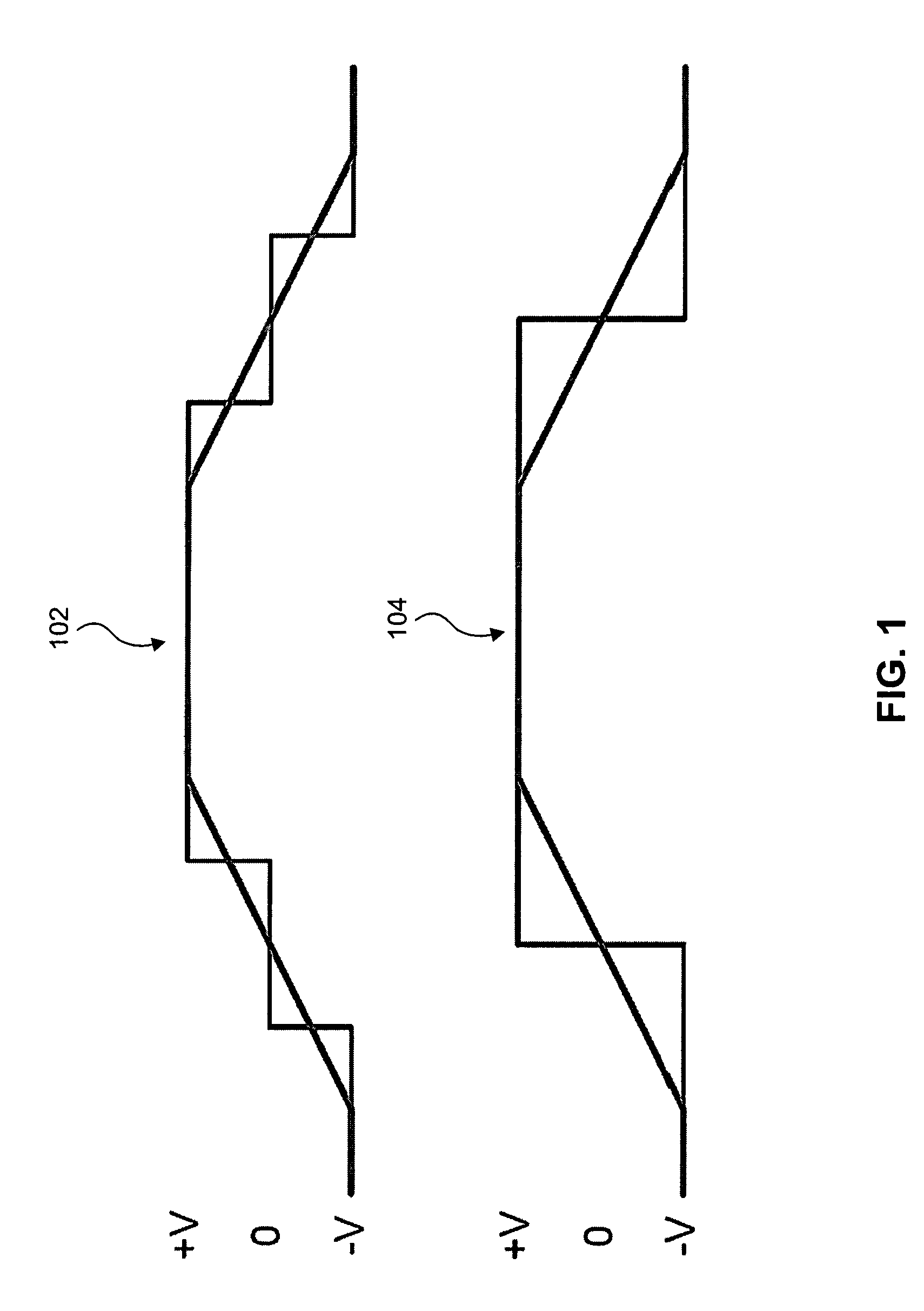

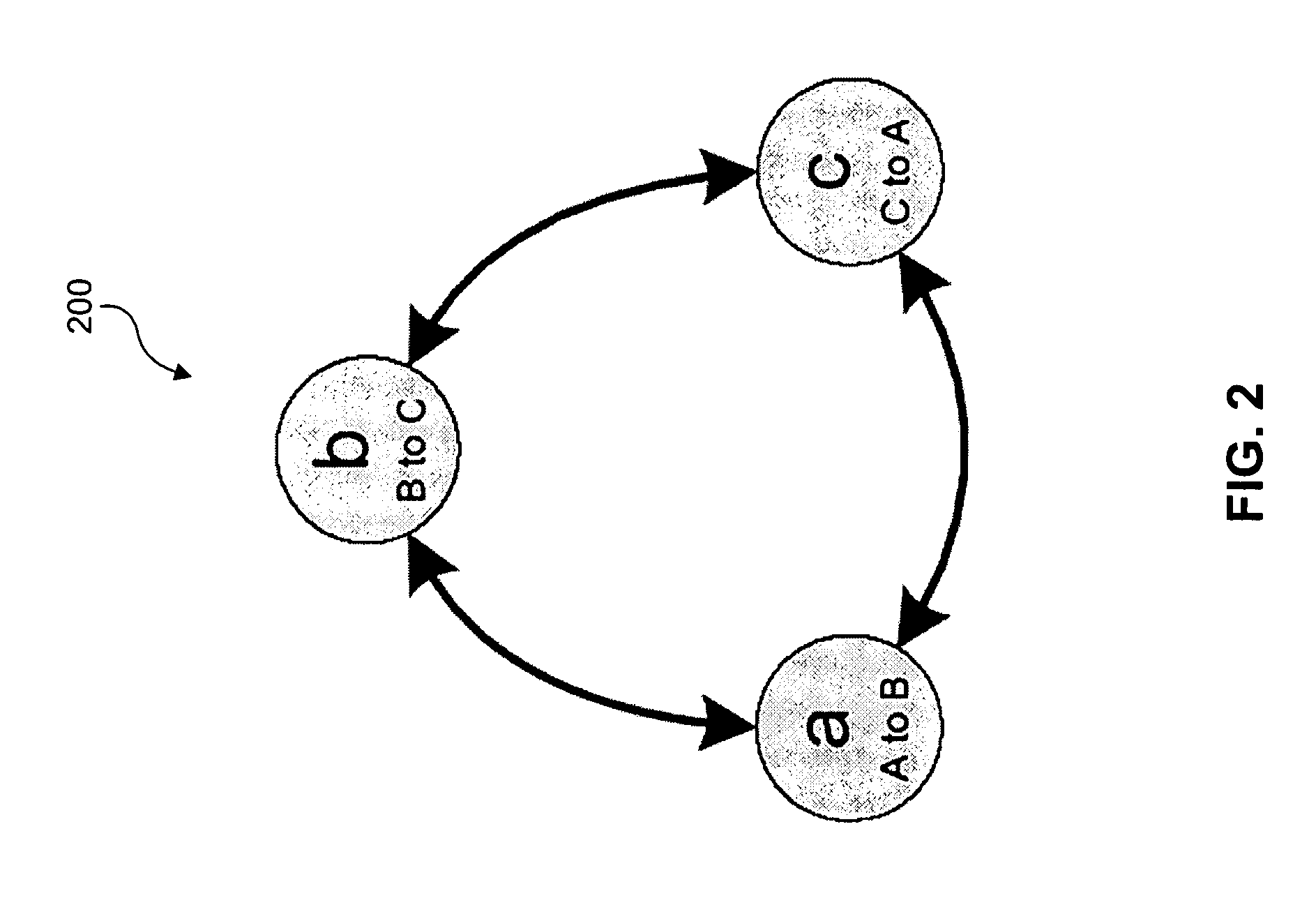

Three phase and polarity encoded serial interface

ActiveUS8064535B2Shorten the timeImprove efficiencyIndividual digits conversionPhase-modulated carrier systemsSerial digital interfaceElectrical conductor

A high speed serial interface is provided. In one aspect, the high speed serial interface uses three phase modulation for jointly encoding data and clock information. Accordingly, the need for de-skewing circuitry at the receiving end of the interface is eliminated, resulting in reduced link start-up time and improved link efficiency and power consumption. In one embodiment, the high speed serial interface uses fewer signal conductors than conventional systems having separate conductors for data and clock information. In another embodiment, the serial interface allows for data to be transmitted at any speed without the receiving end having prior knowledge of the transmission data rate. In another aspect, the high speed serial interface uses polarity encoded three phase modulation for jointly encoding data and clock information. This further increases the link capacity of the serial interface by allowing for more than one bit to be transmitted in any single baud interval.

Owner:QUALCOMM INC

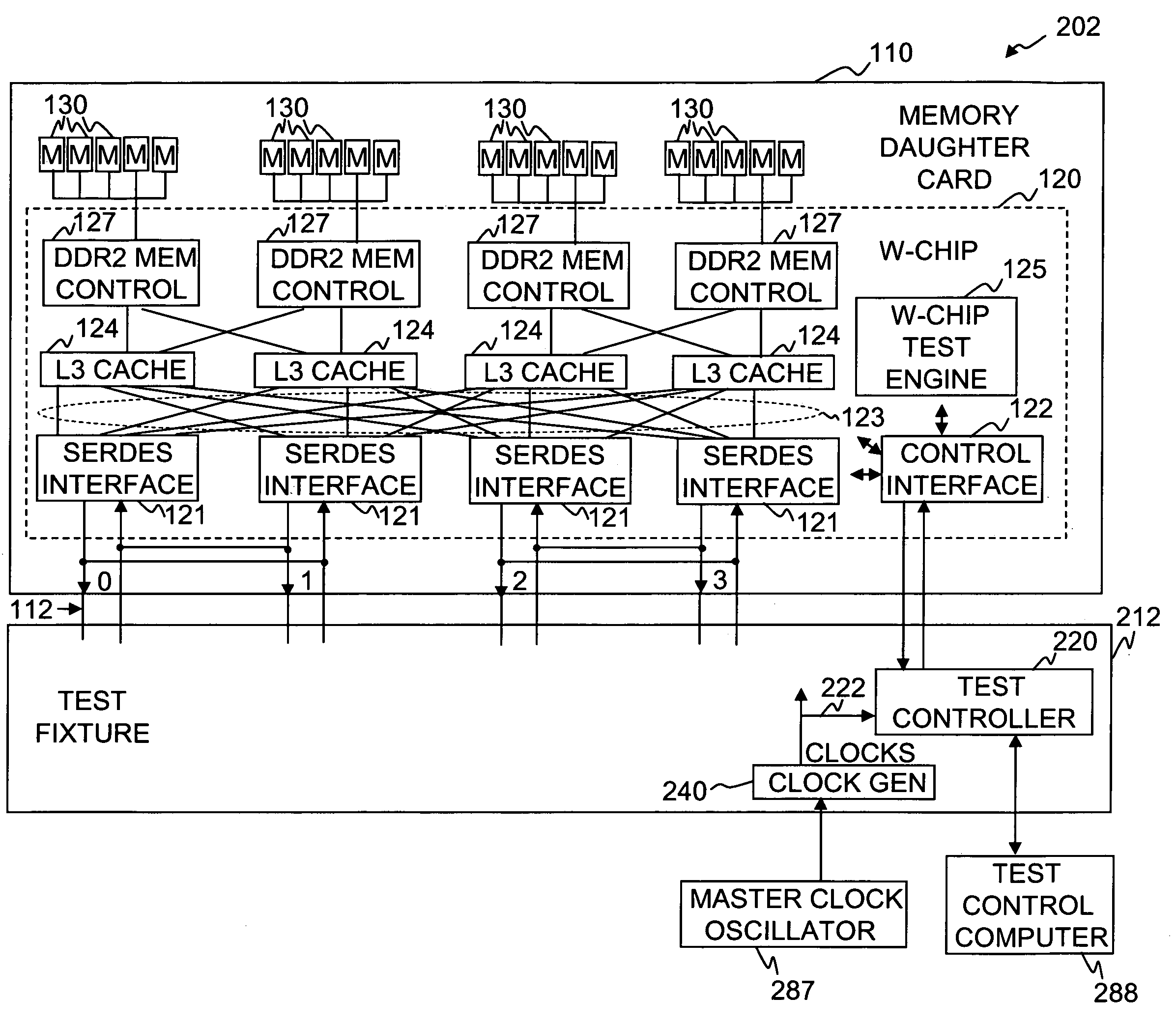

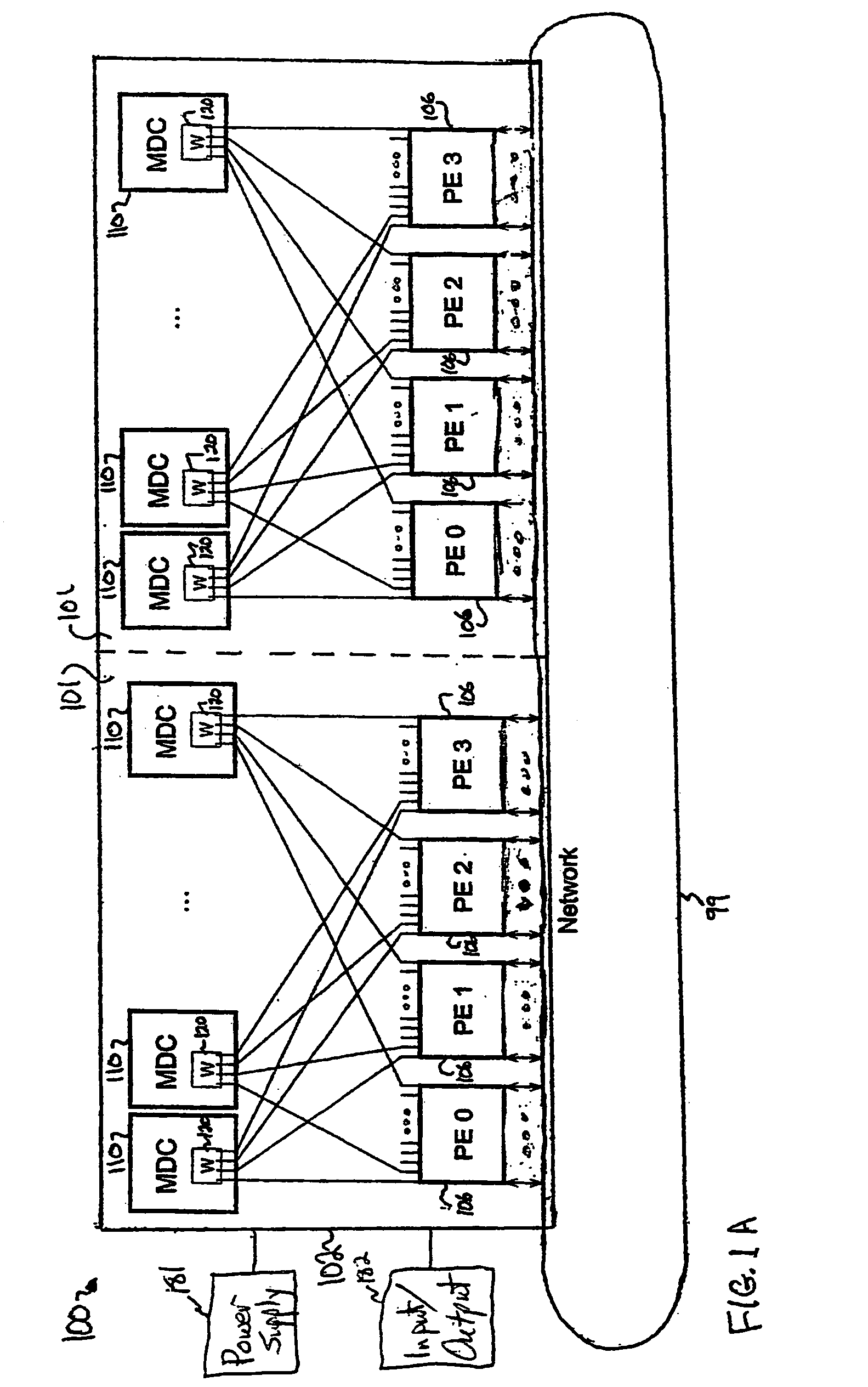

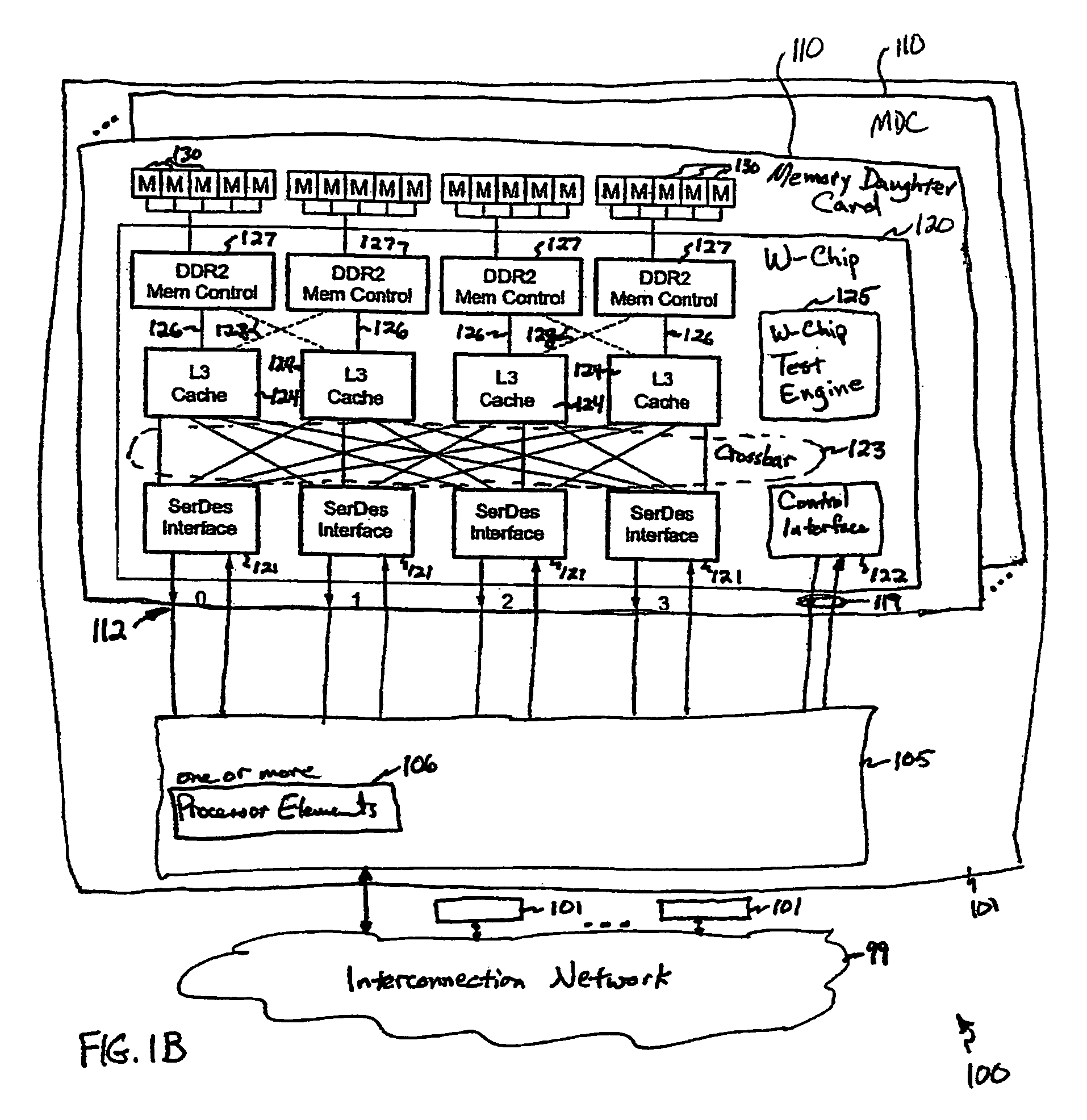

Apparatus and method for testing memory cards

A memory daughter card (MDC) is described, having a very high-speed serial interface and an on-card MDC test engine that allows one MDC to be directly connected to another MDC for testing purposes. In some embodiments, a control interface allows the test engine to be programmed and controlled by a test controller on a test fixture that allows simultaneous testing of a single MDC or one or more pairs of MDCs, one MDC in a pair (e.g., the “golden” MDC) testing the other MDC of that pair. Other methods are also described, wherein one MDC executes a series of reads and writes and other commands to another MDC to test at least some of the other card's functions, or wherein one port executes a series of test commands to another port on the same MDC to test at least some of the card's functions.

Owner:CRAY

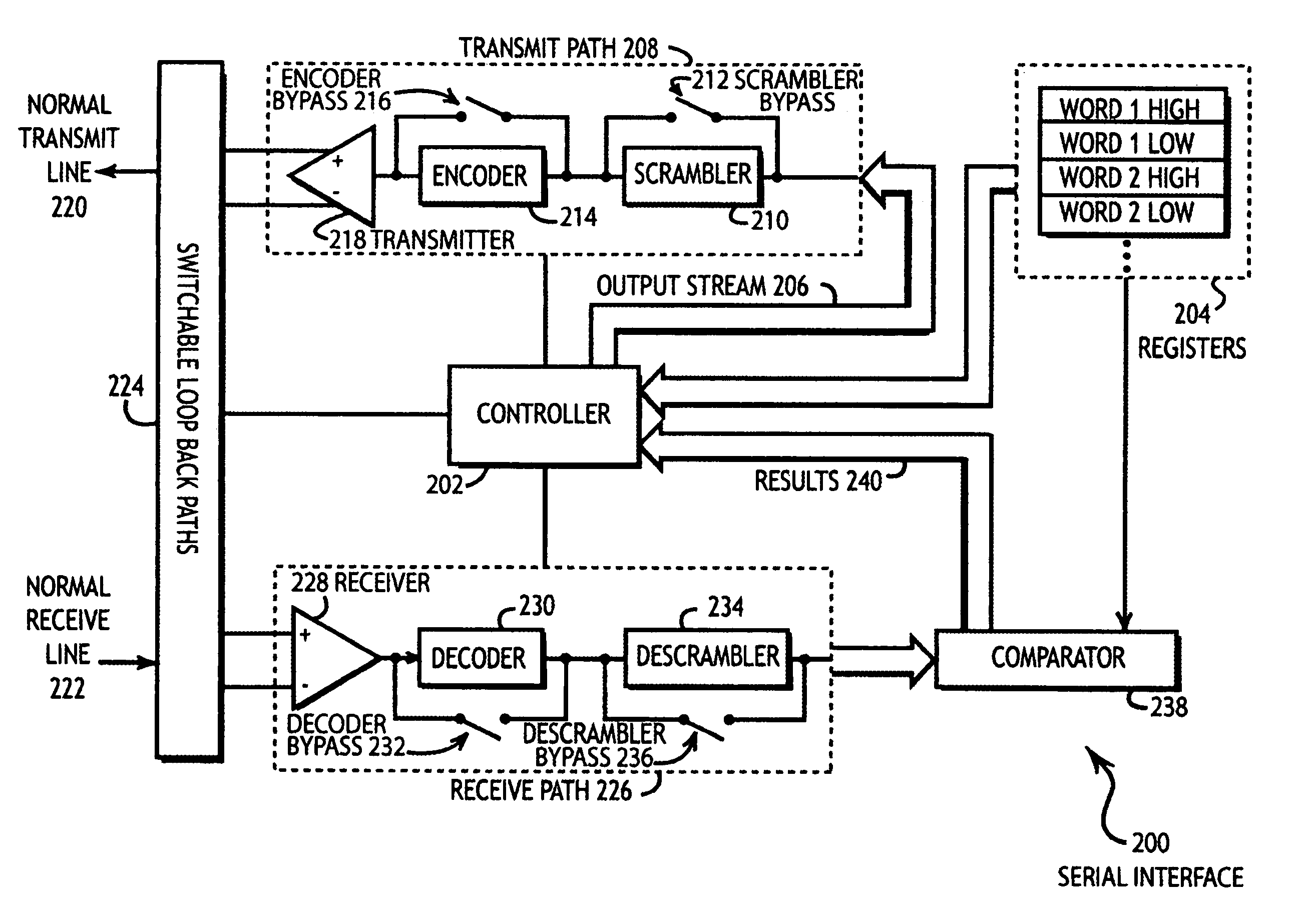

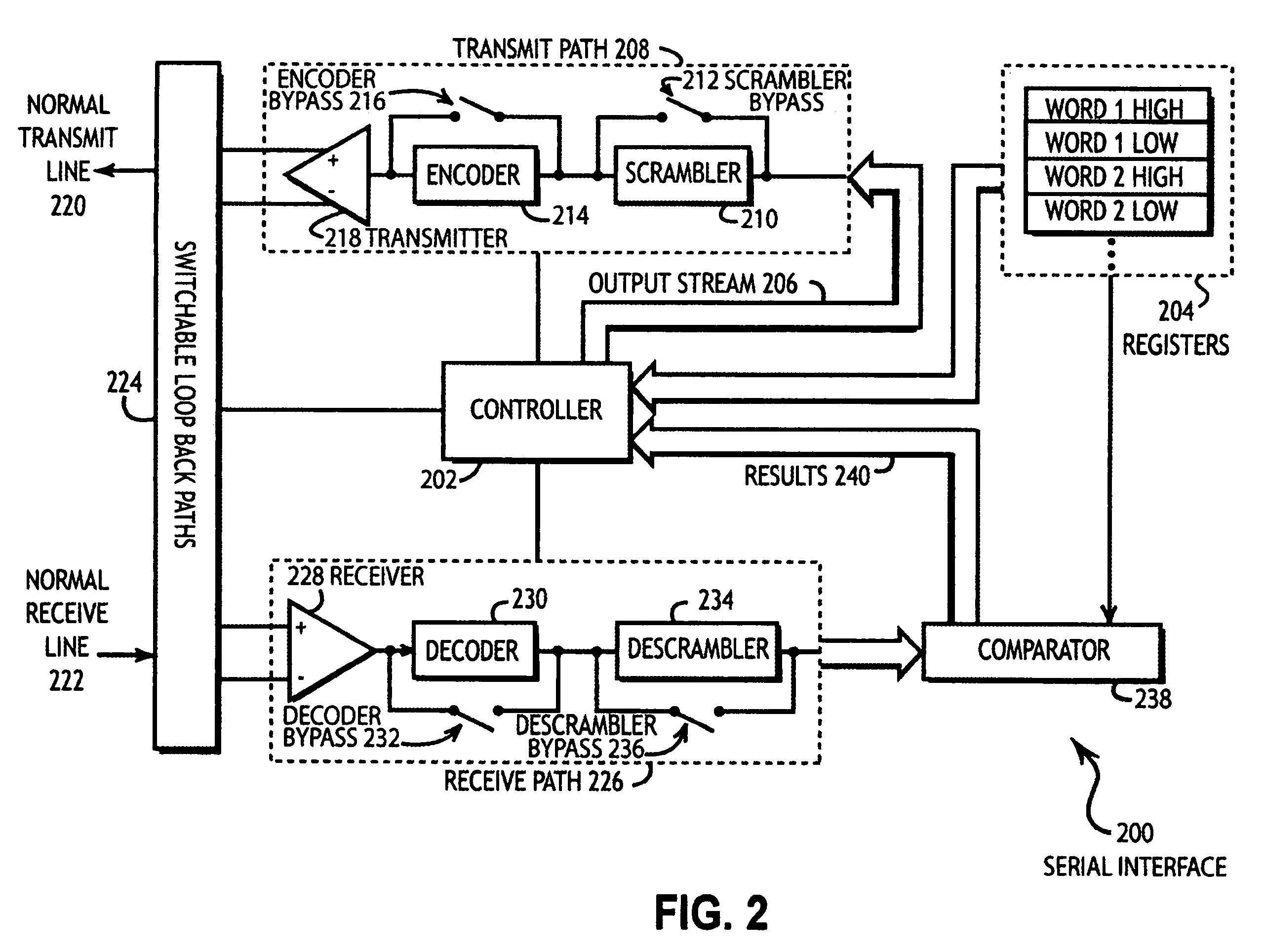

High speed serial interface test

InactiveUS7082557B2Facilitate debugging and testingIncrease speedError preventionTransmission systemsTest equipmentHigh-Speed Serial Interface

A high speed, two-way serial interface with a scrambler and de-scrambler may be tested by sending a single word repeatedly through the scrambler to create a pseudo-random sequence. The pseudo-random sequence is then passed through the transmitter and looped back through the receiver of the serial interface. The pseudo-random sequence is then descrambled and compared to the input word. Since the input sequence is only a single word rather than a series of words, the comparison is very simple and capable of being performed within the serial interface itself without the need for external test equipment.

Owner:NETWORK APPLIANCE INC

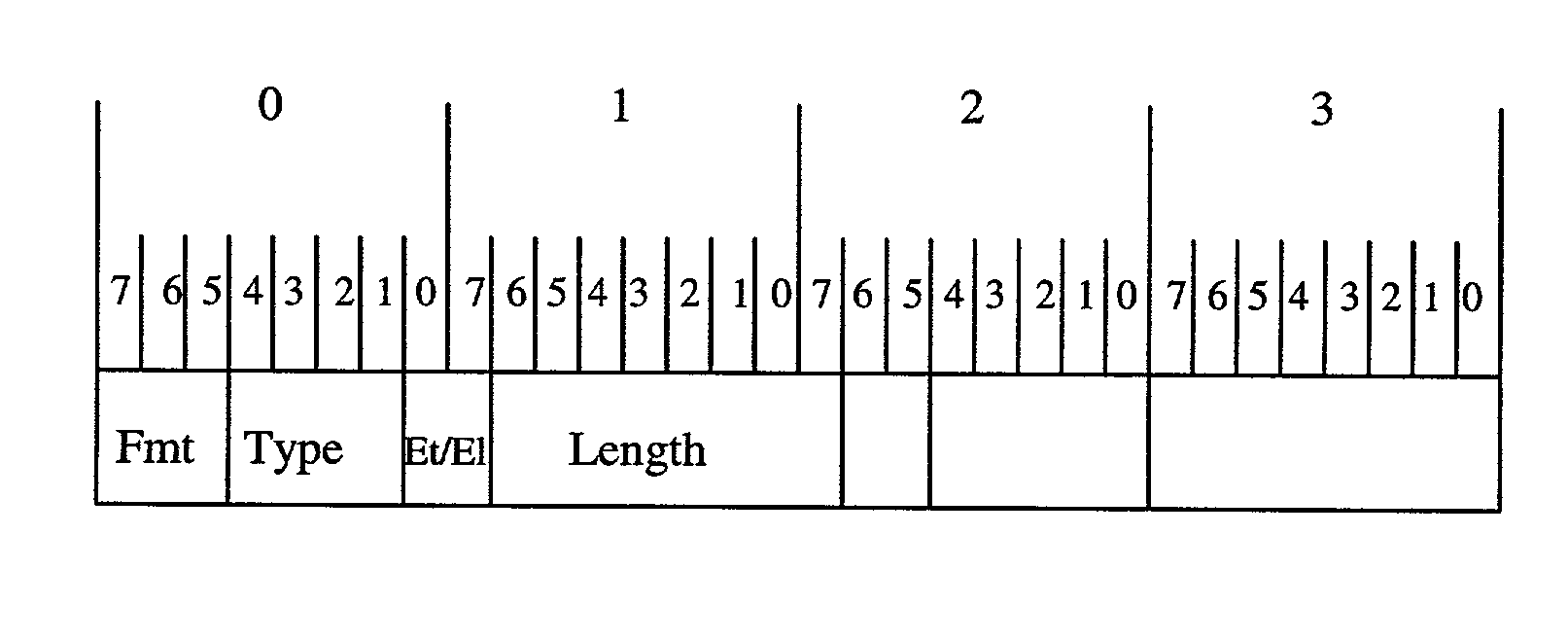

Communicating transaction types between agents in a computer system using packet headers including an extended type/extended length field

InactiveUS6944617B2Data processing applicationsMultiple digital computer combinationsComputerized systemComputer science

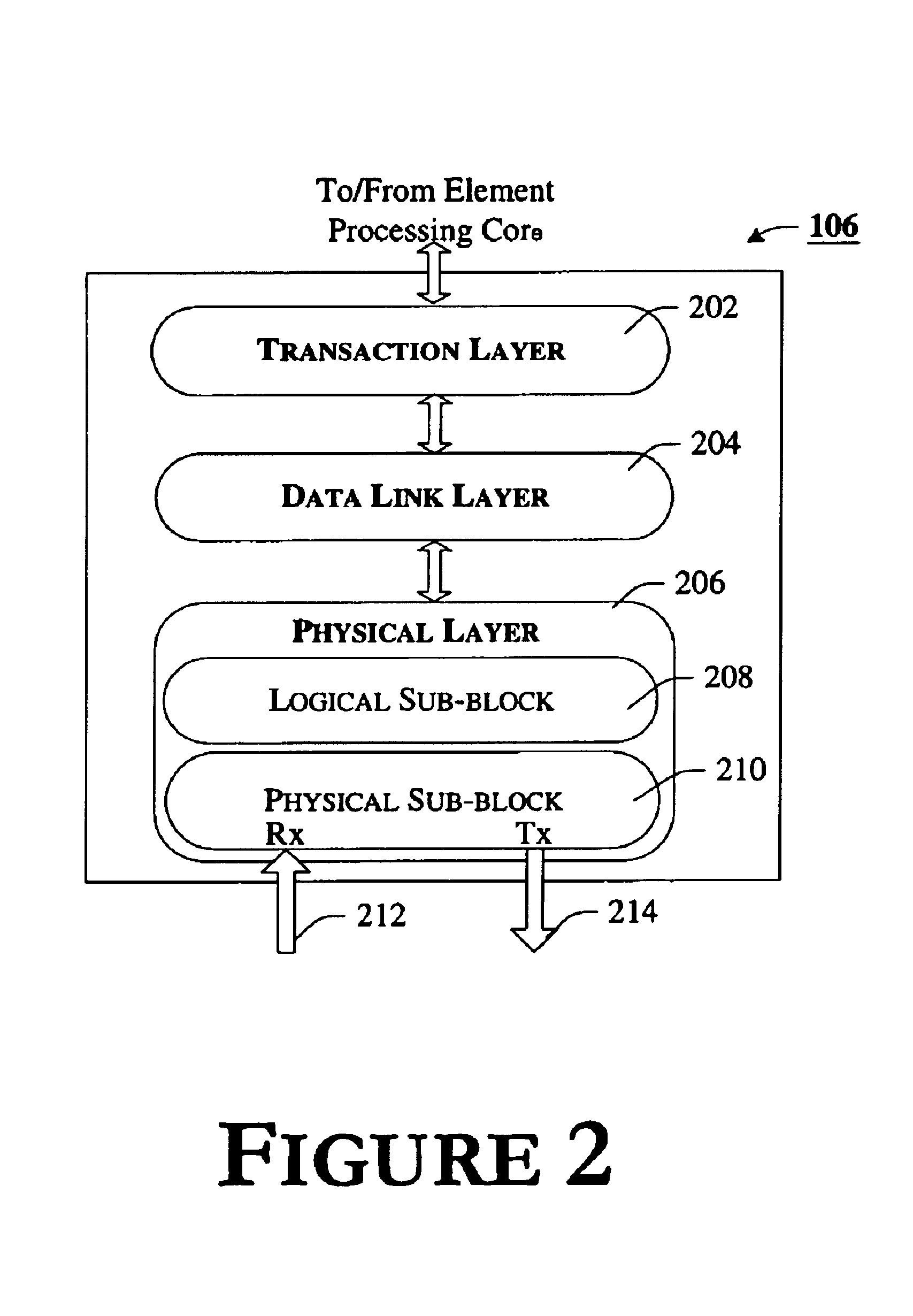

A transmitting device and a receiving device are coupled via a high-speed serial interface within a computer system. The transmitting device transmits a packet that includes an extended type / extended length field that extends either a type field or a length field depending on the value of the type field. The extended type / extended length field extends the length field when the type field indicates a memory read request transaction.

Owner:INTEL CORP

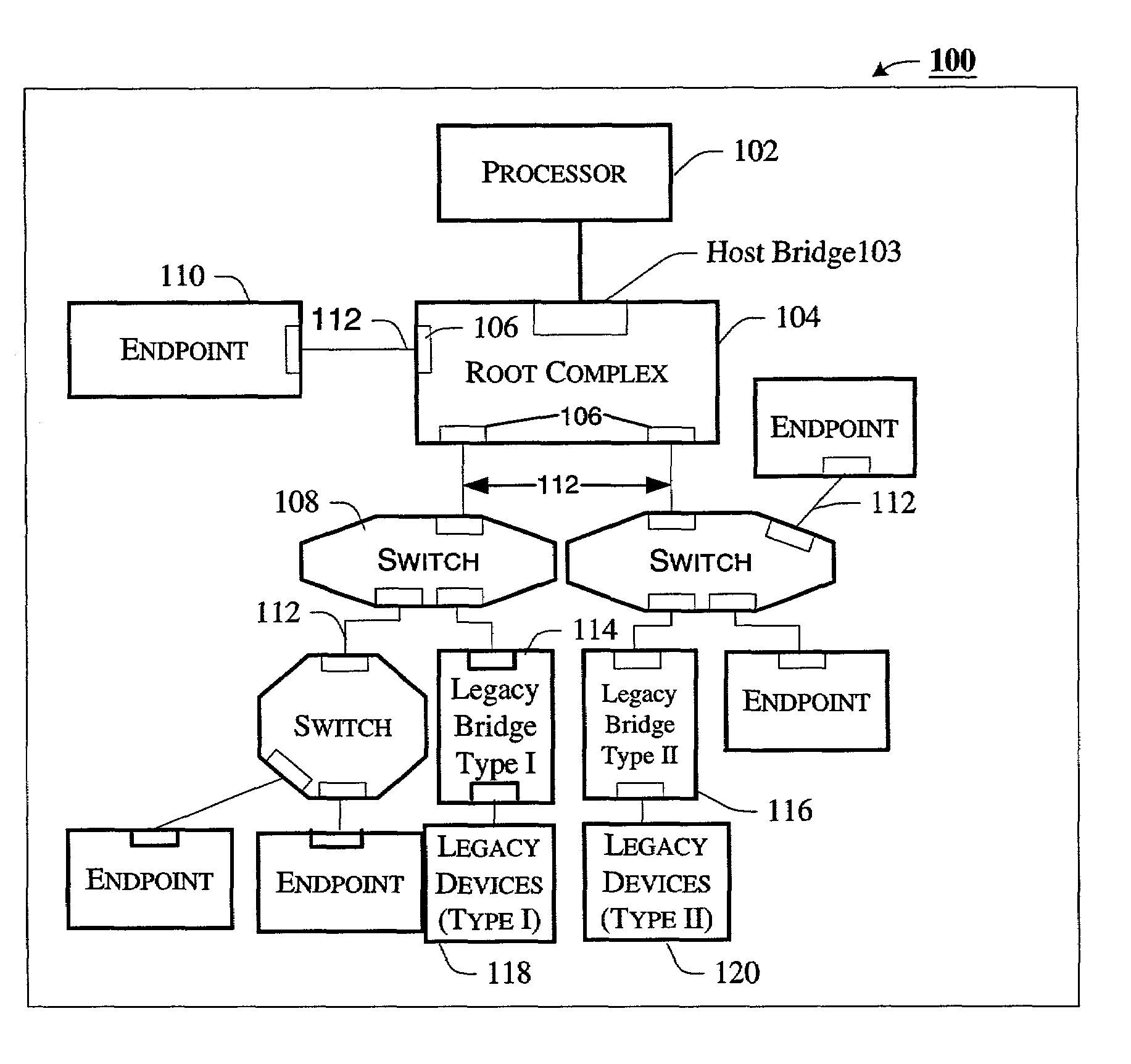

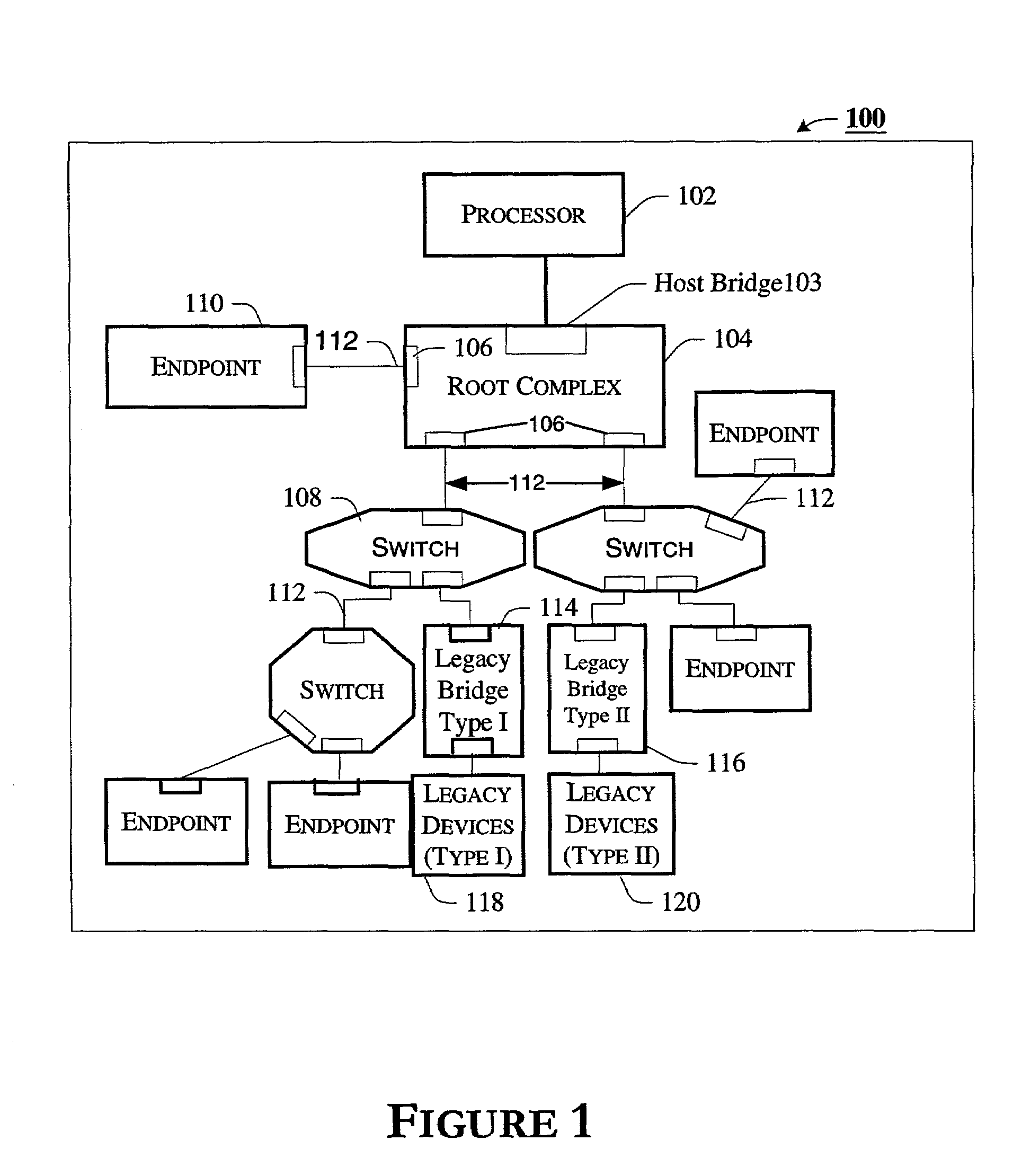

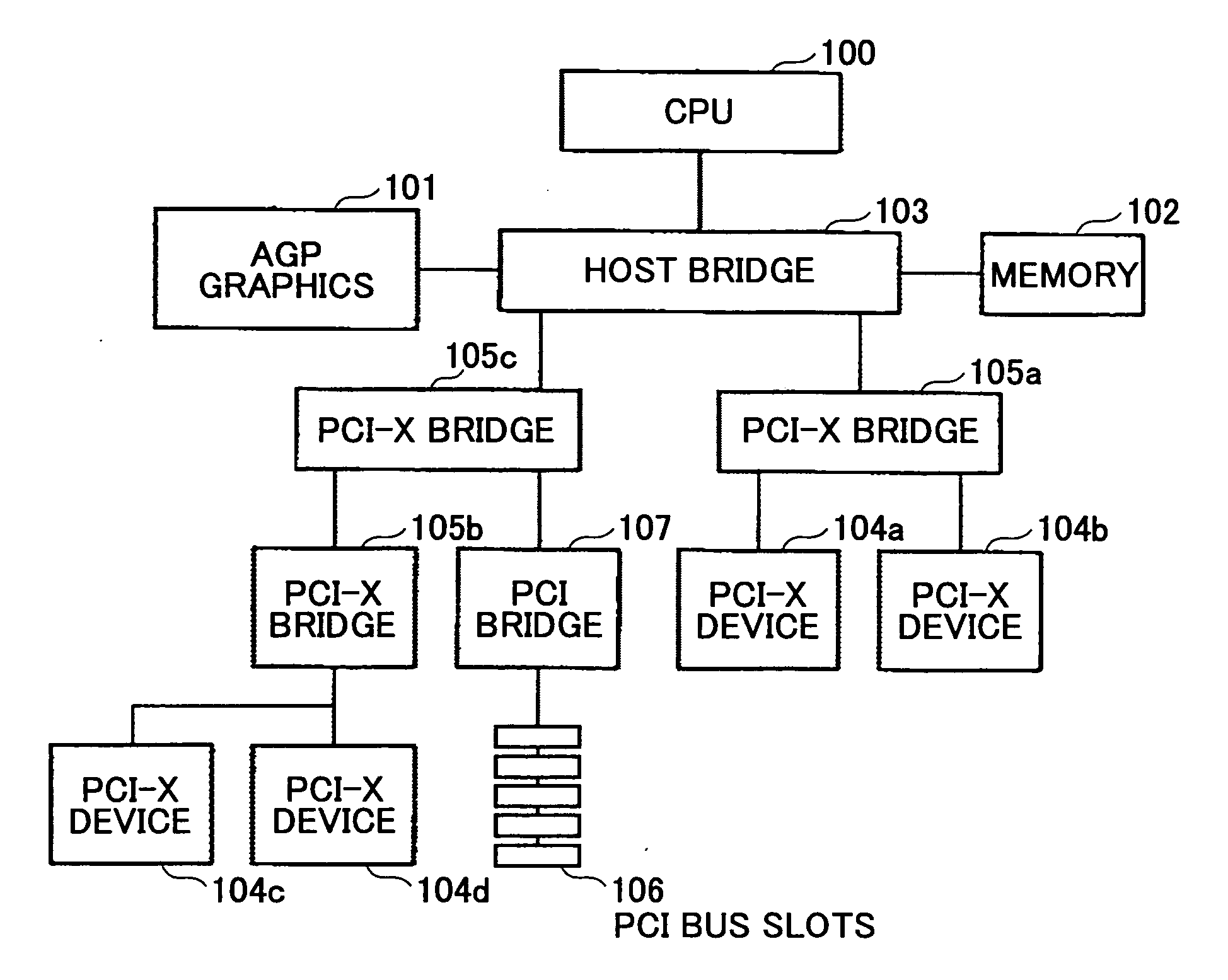

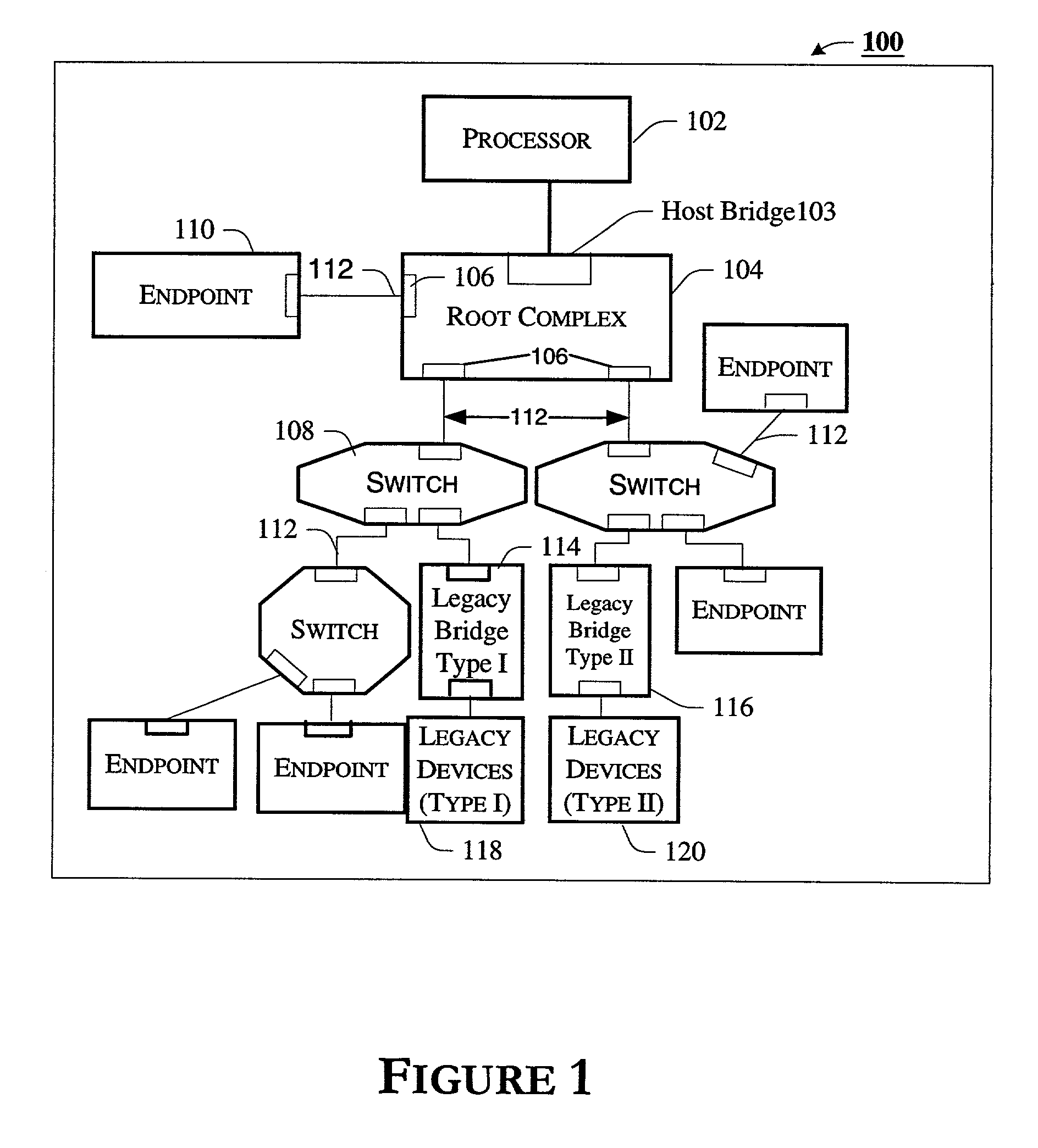

Data transfer system, data transfer method, and image apparatus system

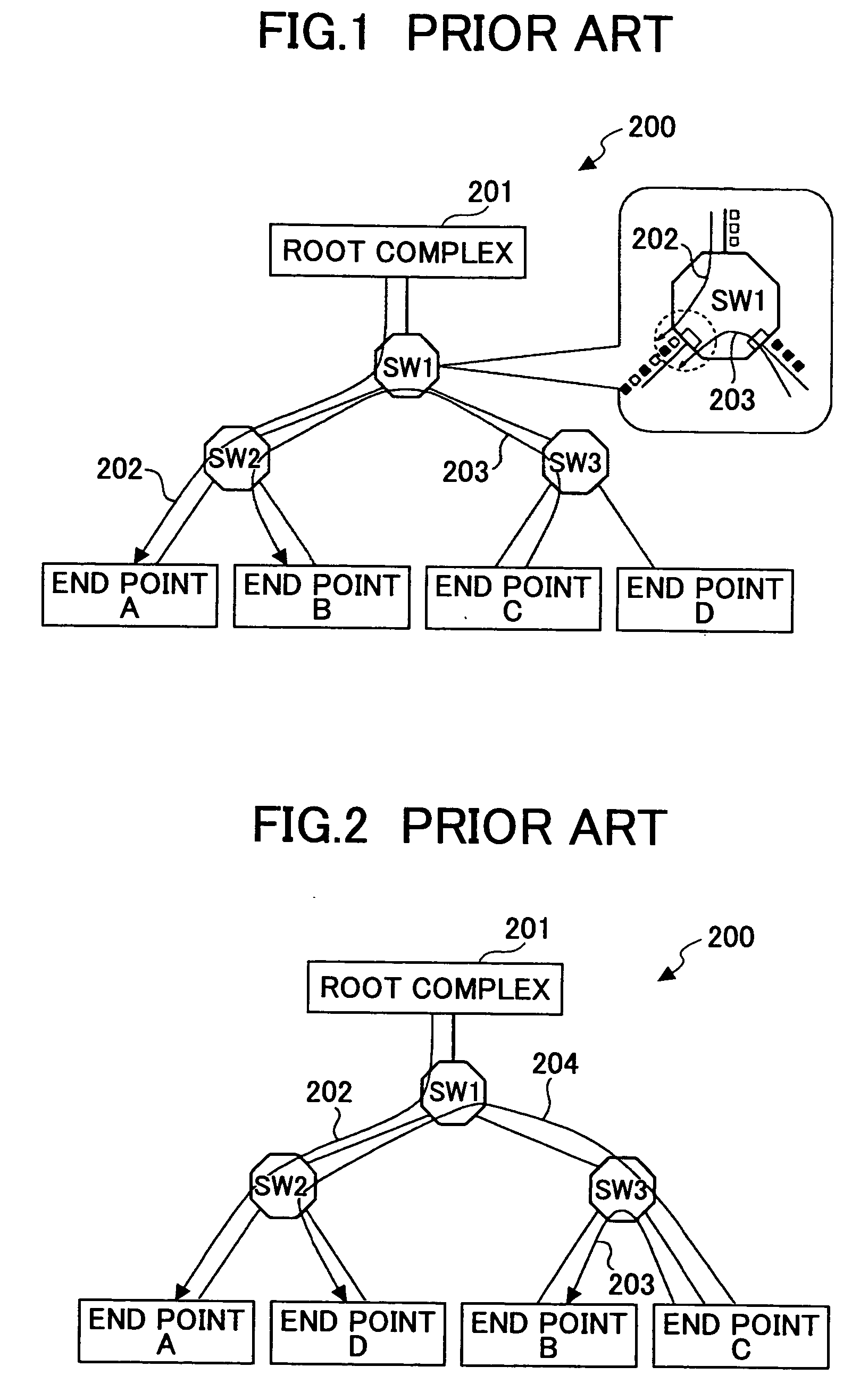

InactiveUS20060114918A1Improve data transfer efficiencyAvoid contentionData switching by path configurationTransfer systemOperation mode

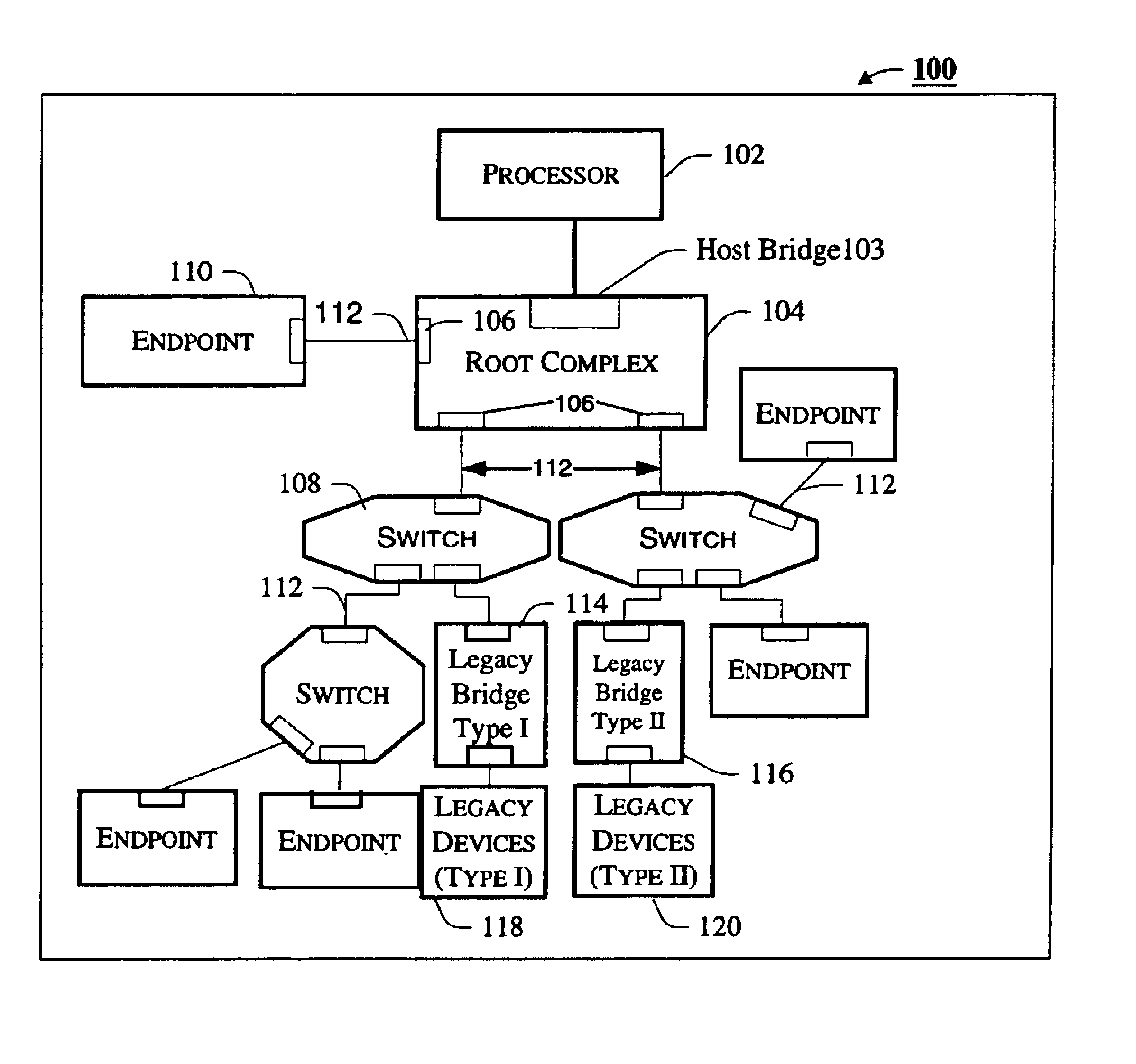

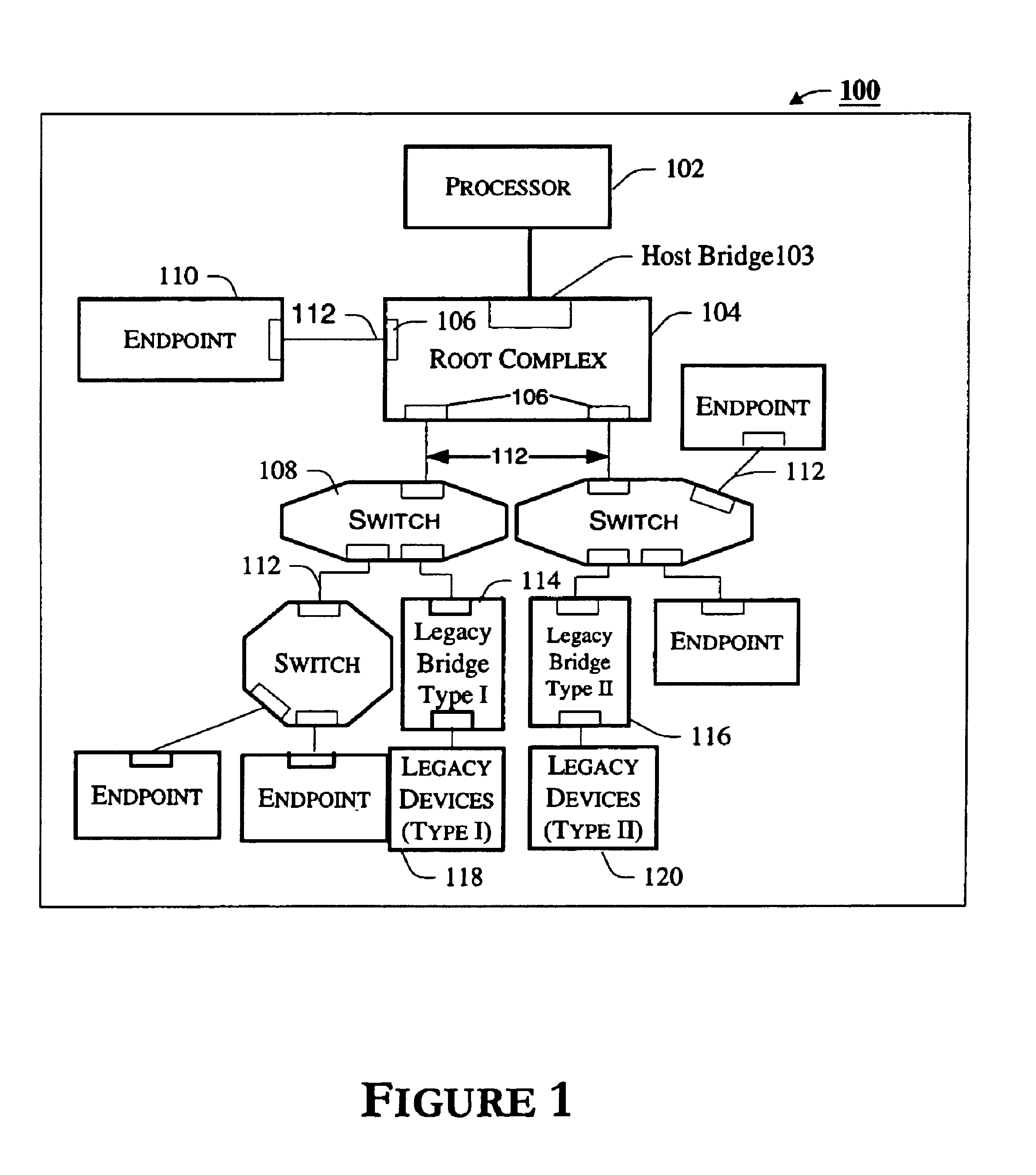

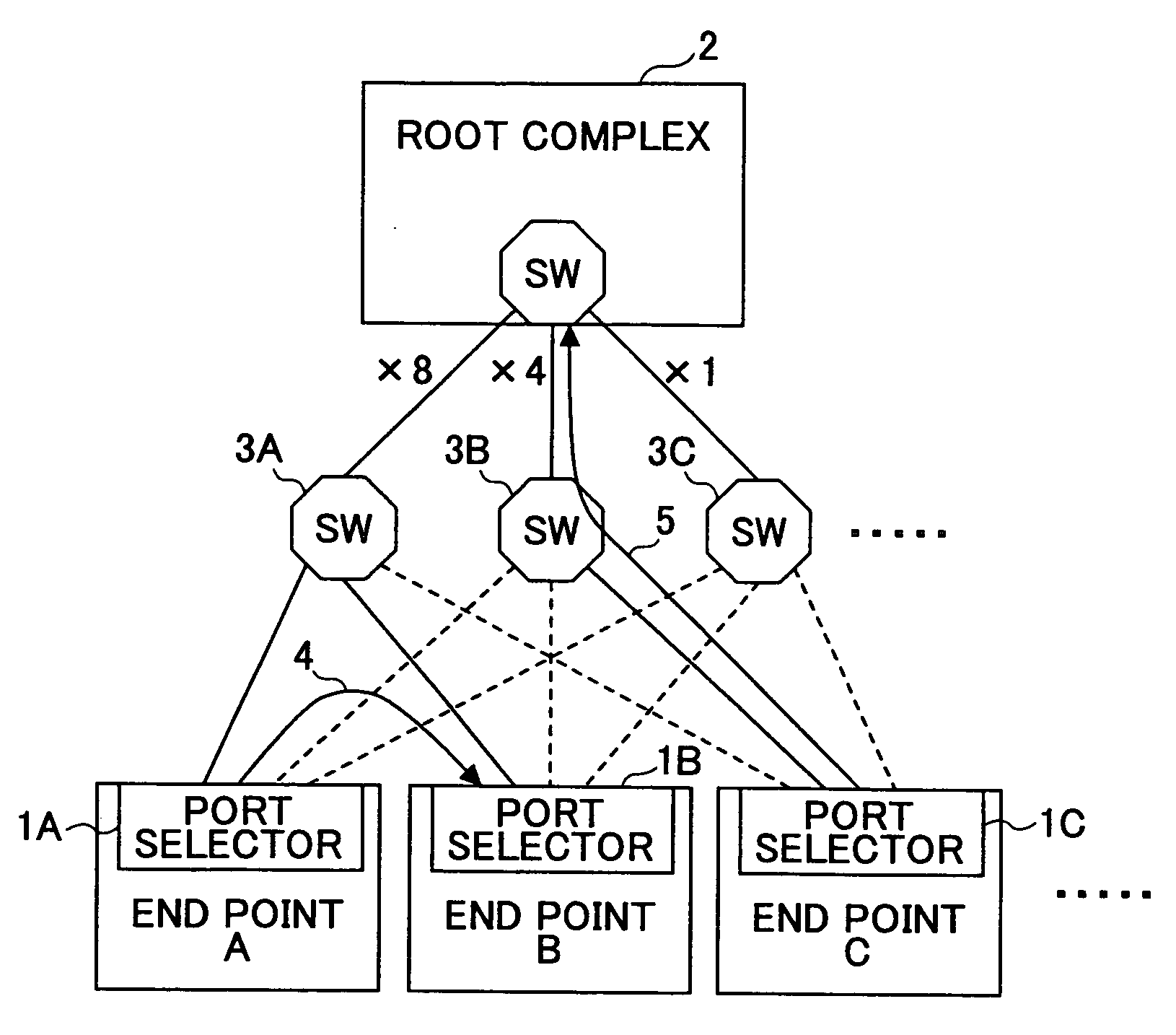

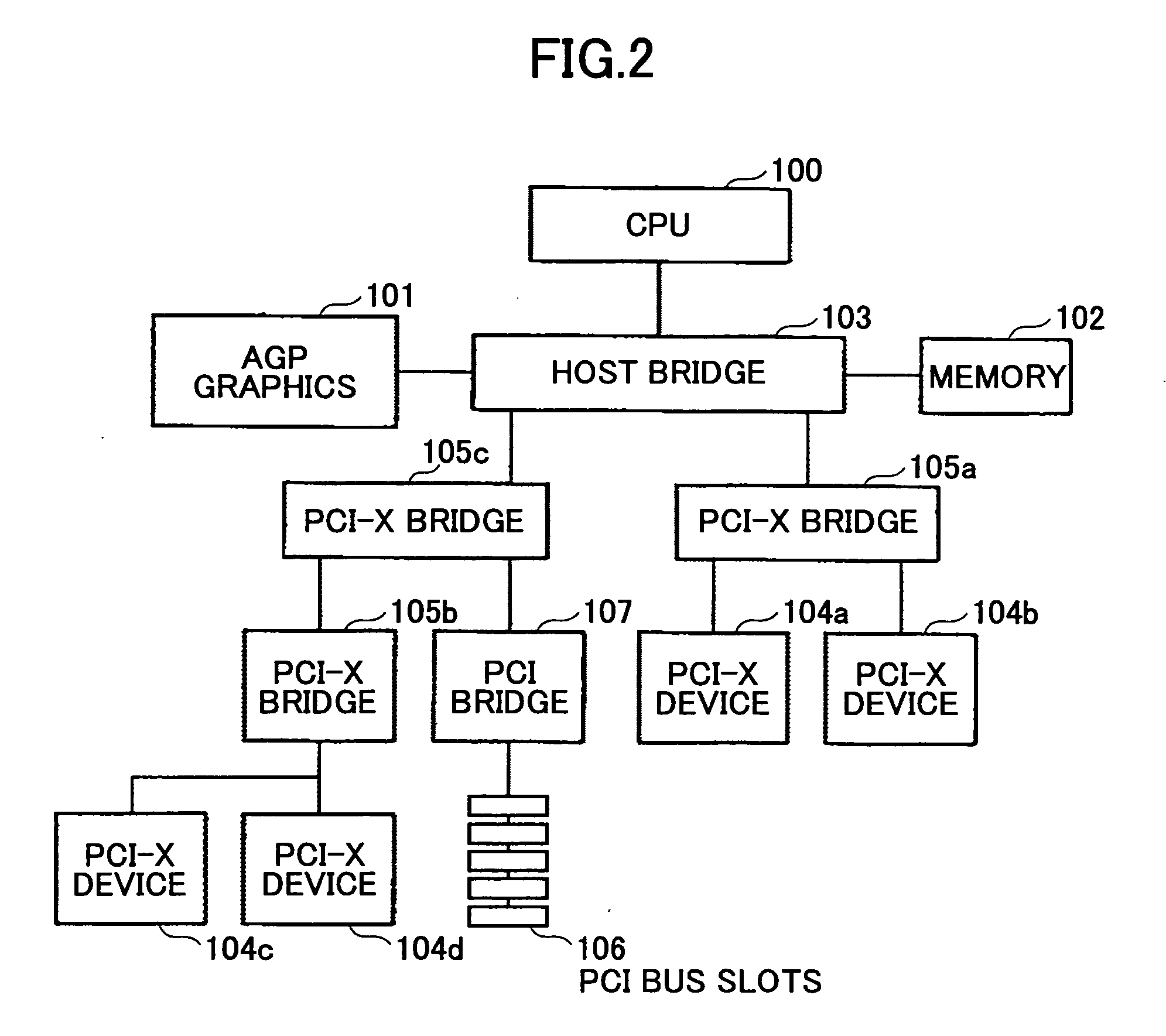

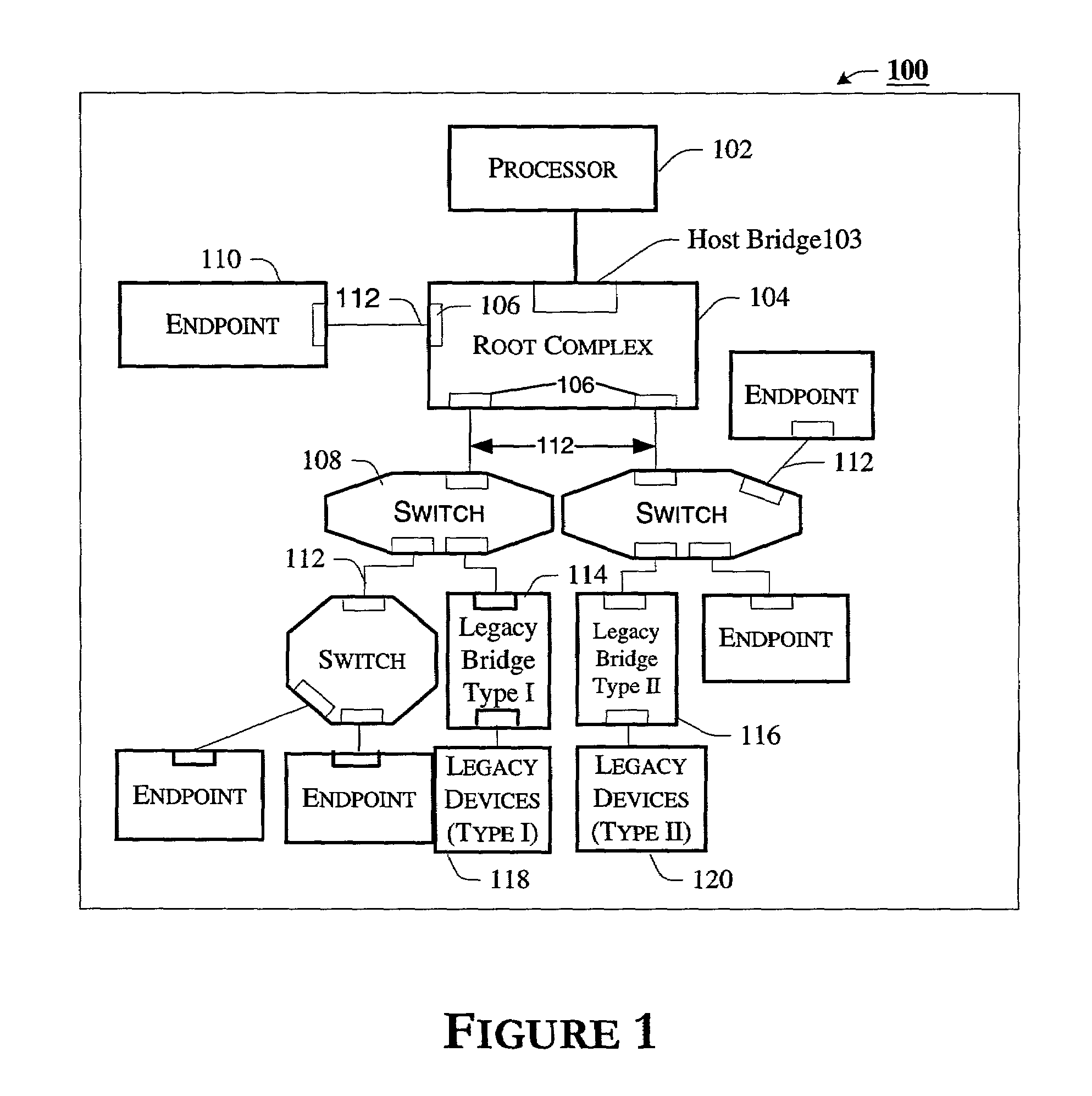

A data transfer system using a high-speed serial interface system that forms a tree structure in which point-to-point communication channels are established for data sending and data receiving independently is provided. The data transfer system includes plural end points each having plural upper ports each of which is connected to a switch of an upper side, wherein each end point includes a port selecting part for selecting a port to be used according to an operation mode of the data transfer system so as to dynamically change the tree structure.

Owner:RICOH KK

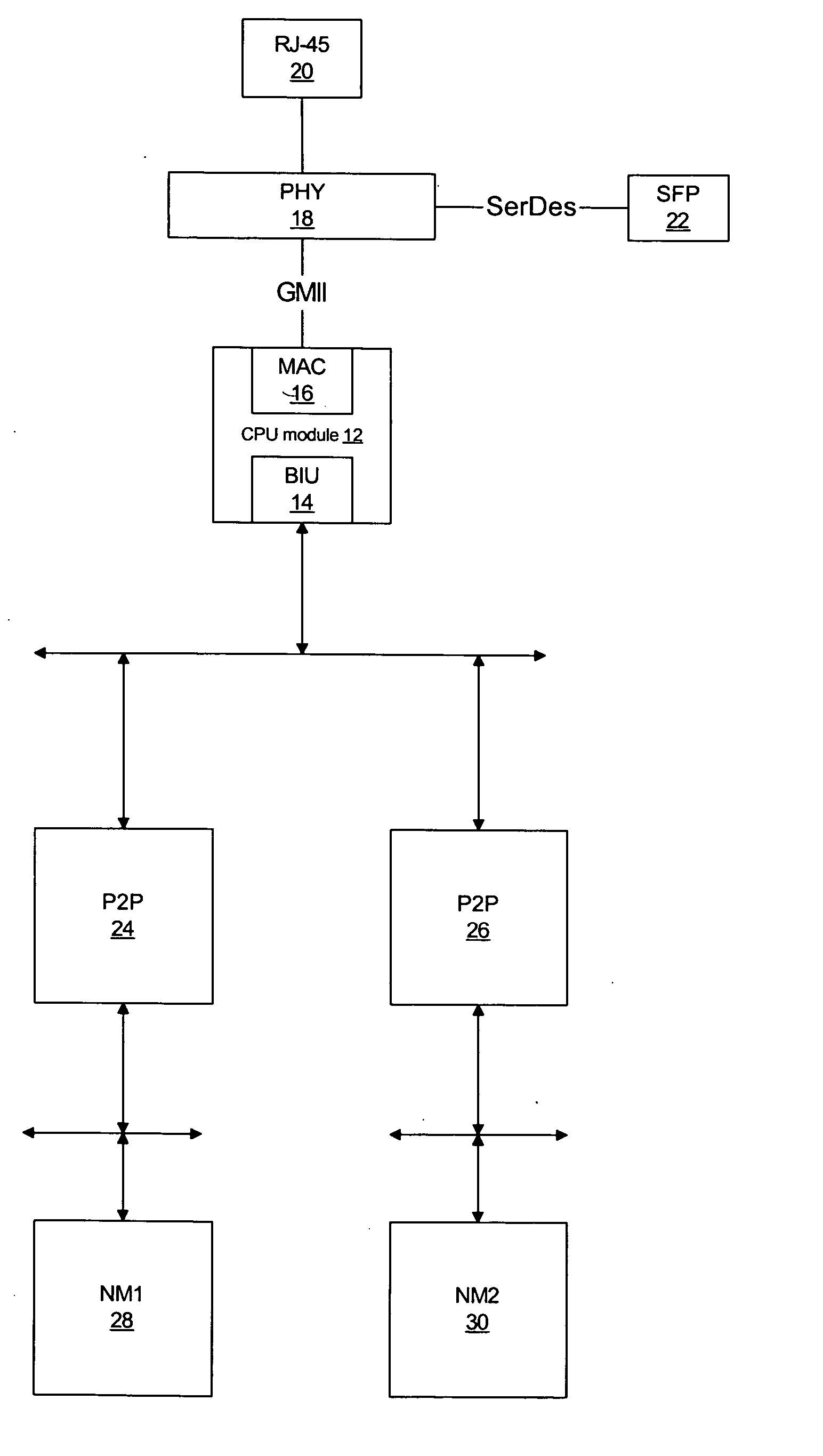

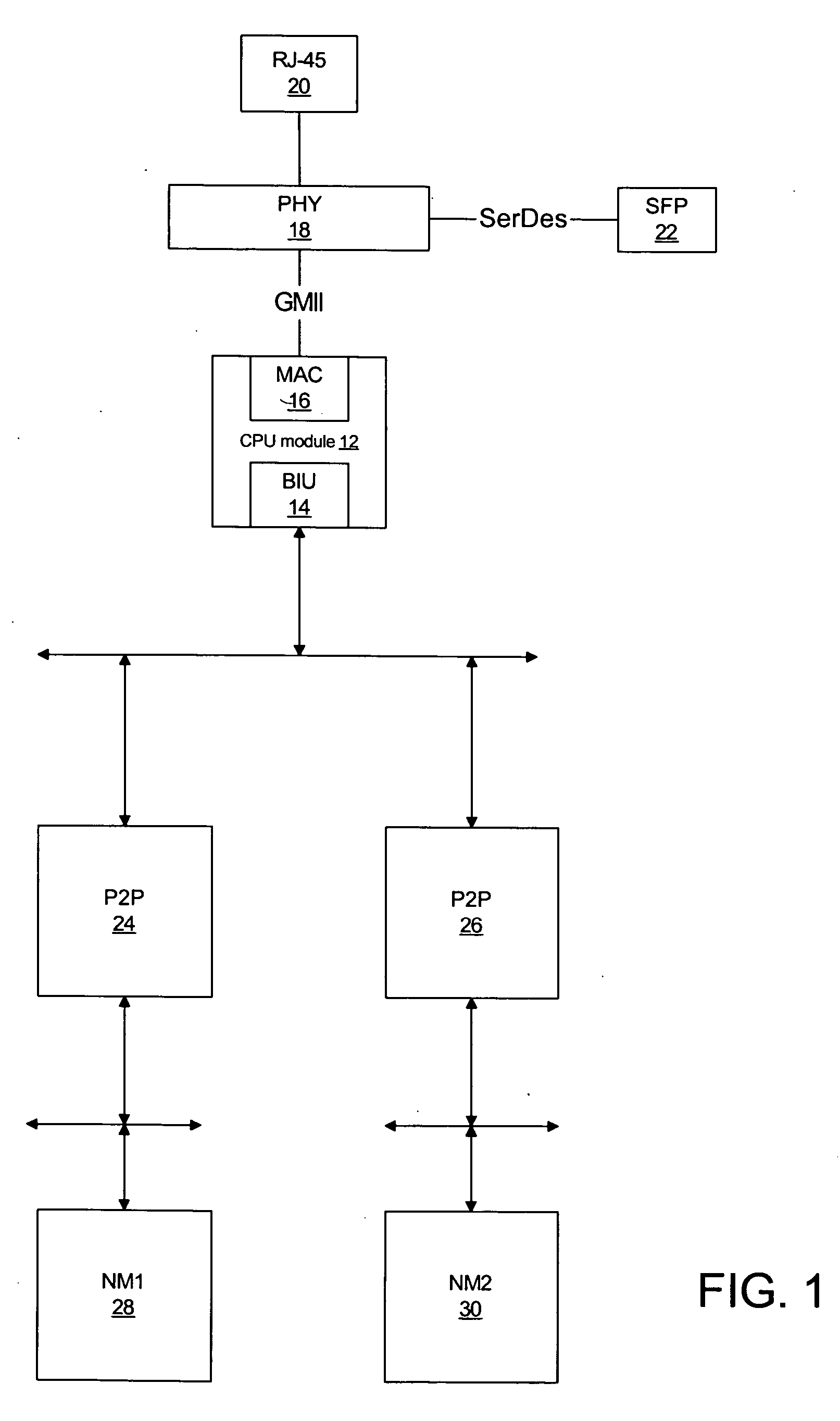

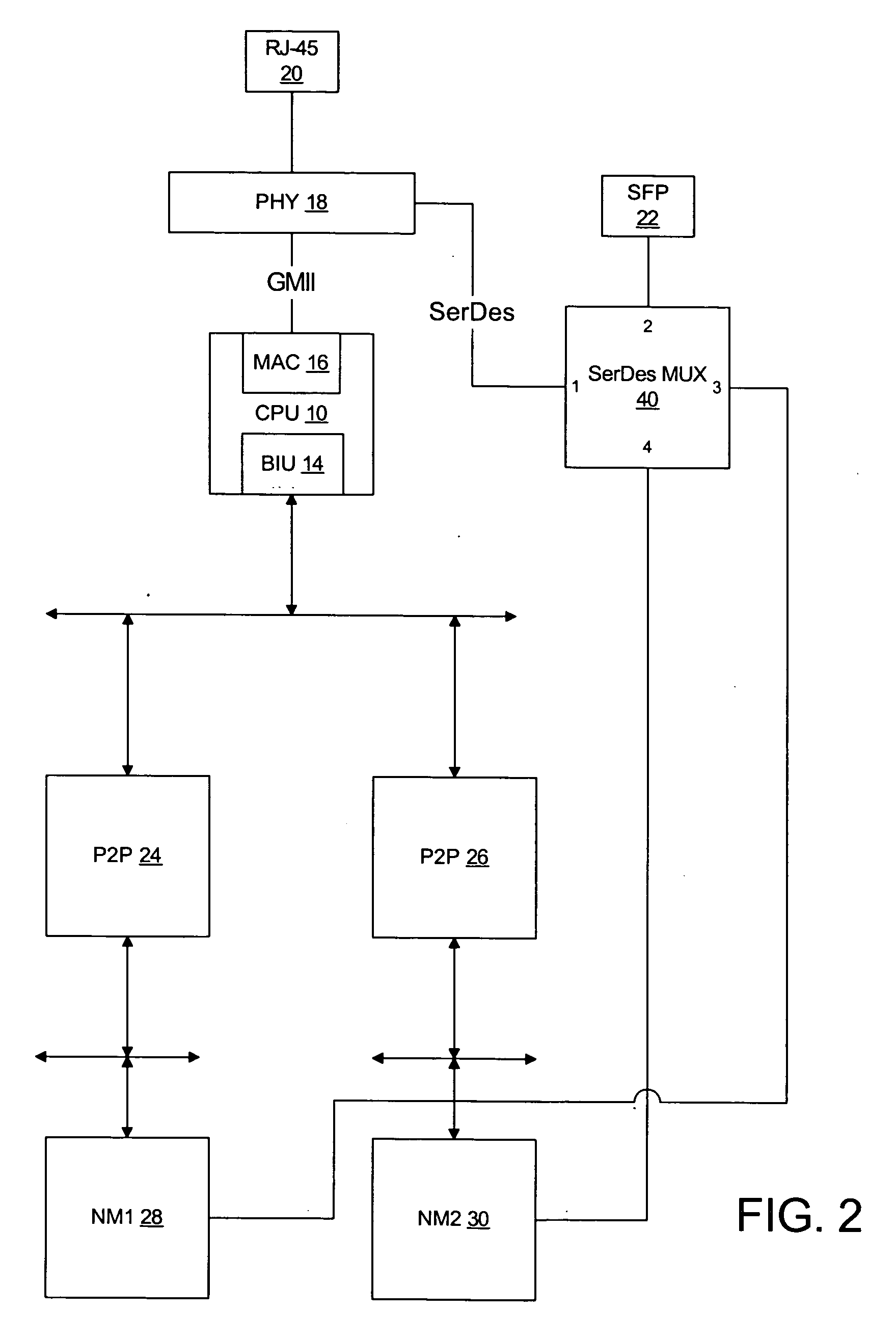

Method and system for configuring high-speed serial links between components of a network device

ActiveUS20060075175A1Low-latency communicationMultiplex system selection arrangementsData switching by path configurationMultiplexingLatency (engineering)

A system for selectively forming high-speed serial connections between various components of a network device that includes a multiplexing switch coupled a GE slot and to the high speed serial interfaces of a PHY and at least two network devices. The switch can be programmed to connect the serial interfaces of the two network modules to provide a high-speed, low-latency serial link between the two network modules. Alternatively, the serial interface of a network module can be connected to the GE slot to provide a high-speed, low-latency serial link between the network module and the GE slot.

Owner:CISCO TECH INC

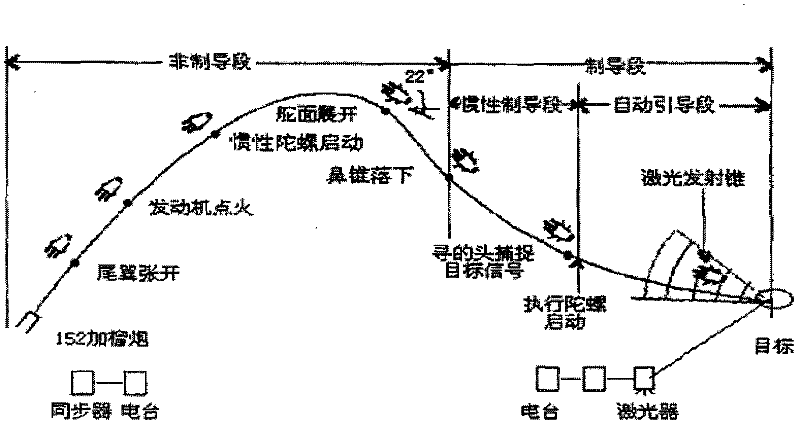

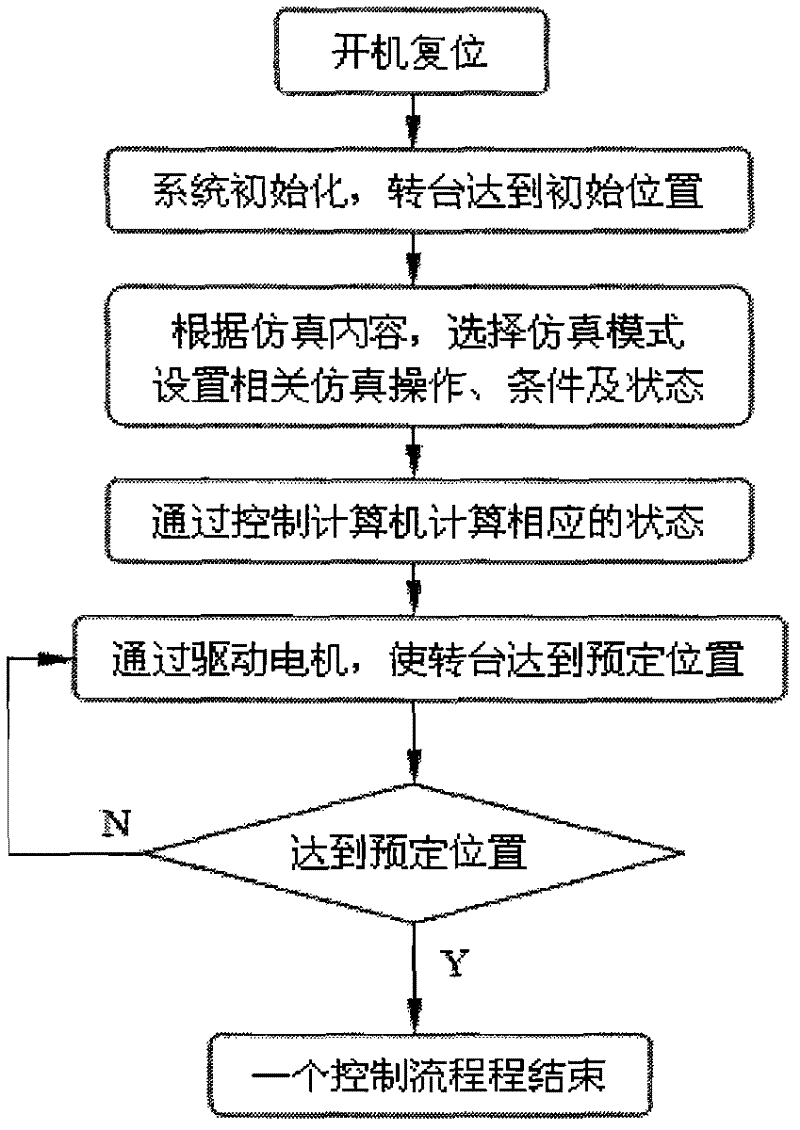

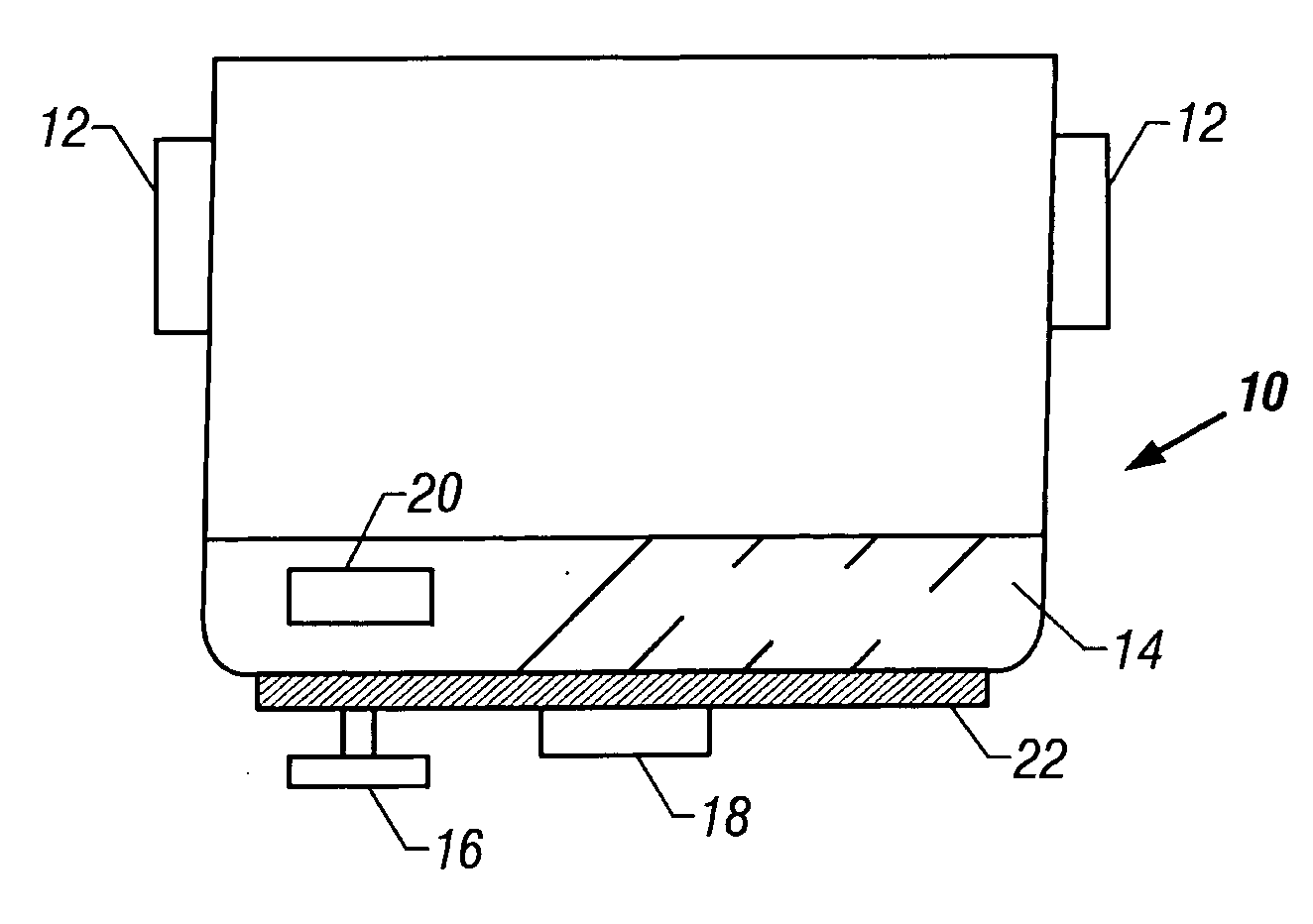

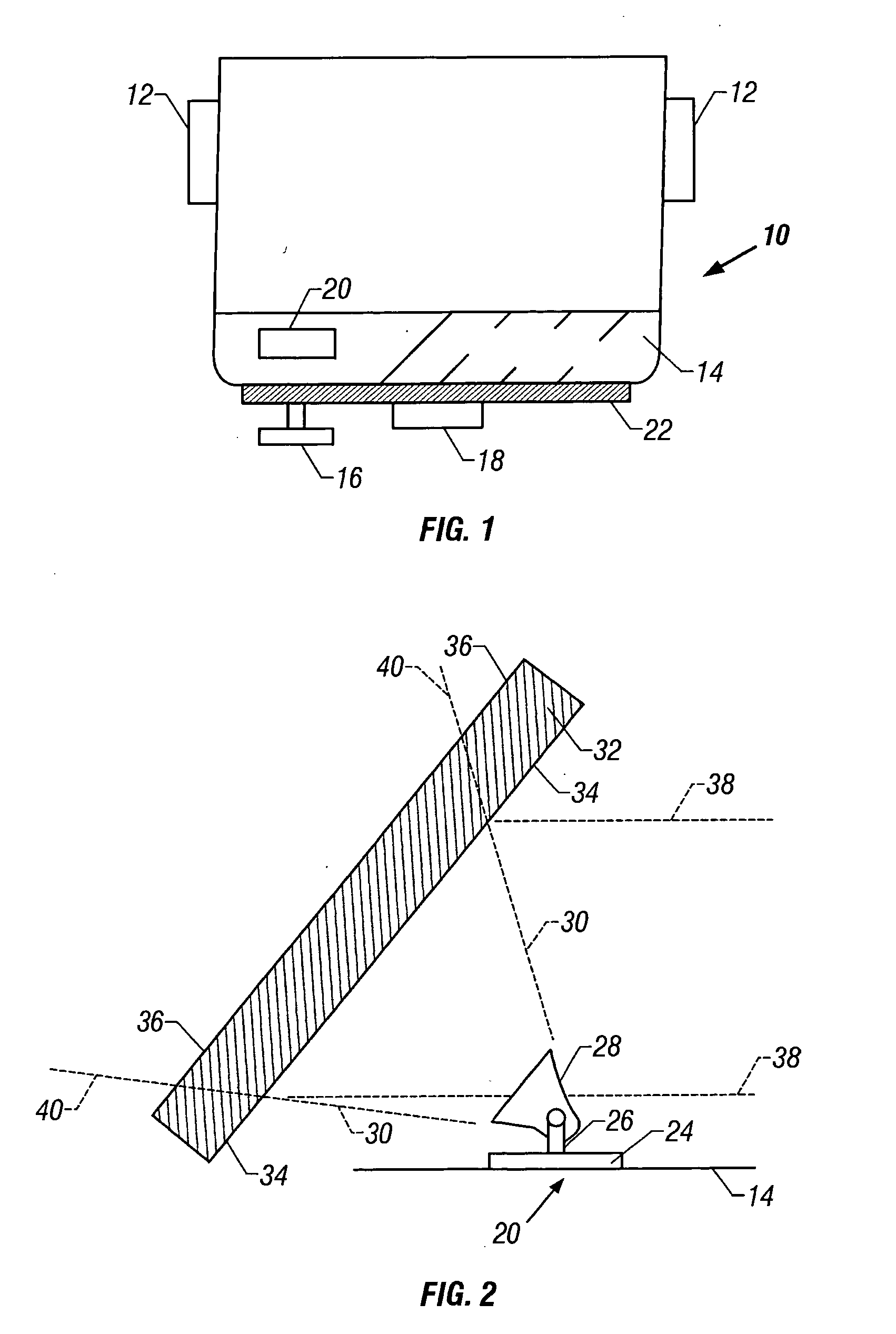

Turntable for semi-physical simulation of laser terminally guided projectile

InactiveCN102410785AMeet the speedSatisfy position accuracyAiming meansHuman–machine interfaceMan machine

The invention relates to a laser terminally guided projectile and particularly discloses a turntable for the semi-physical simulation of the laser terminally guided projectile. The turntable comprises a table body and a control cabinet, wherein the table body is used for simulating a projectile body attitude motion characteristic or a projectile body-target relative motion characteristic, can be used for load mounting and is provided with an angle measurement element so as to supply a corner signal to serve as position feedback and speed feedback; the control cabinet is used for realizing the control over the table body; the control cabinet comprises an upper computer and a lower computer; the upper computer can interact with an operator through a human-machine interface so as to realize control instruction input, configuration data correction, safety protection, system state monitoring, and data receiving and processing for the turntable; and the lower computer can be connected with the upper computer through a high-speed serial interface and connected with the table body through a cable so as to complete the real-time control over the table body.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

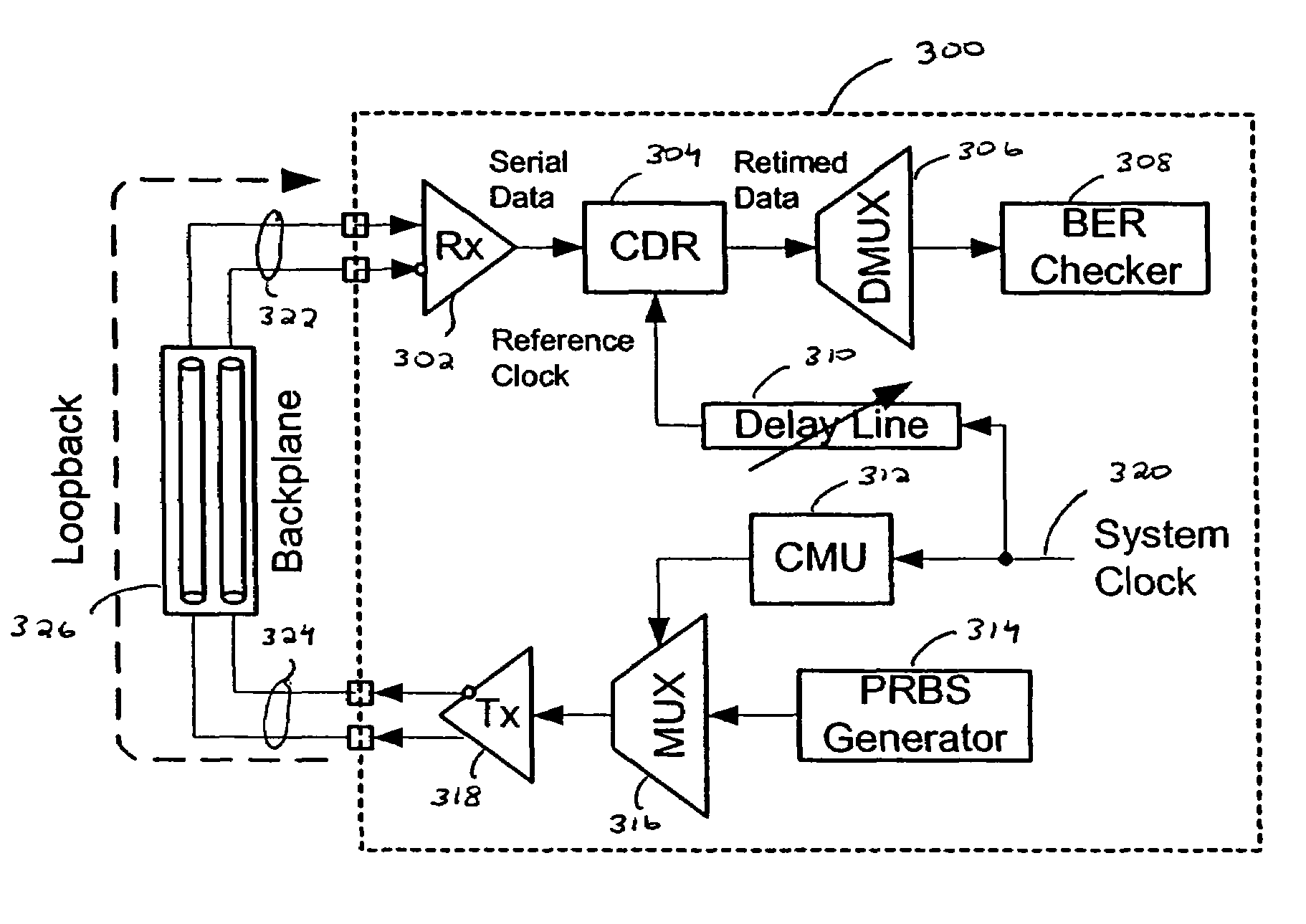

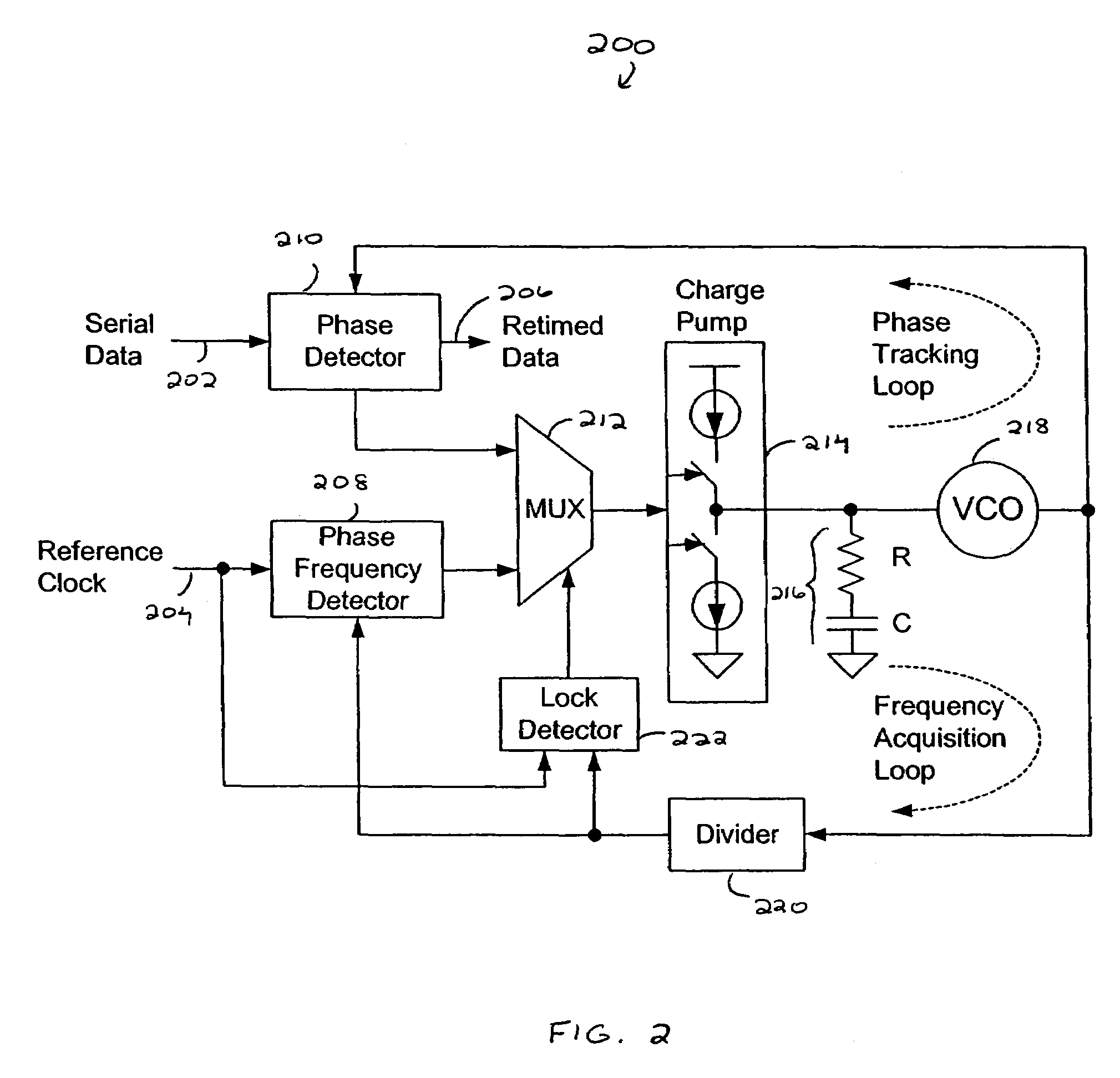

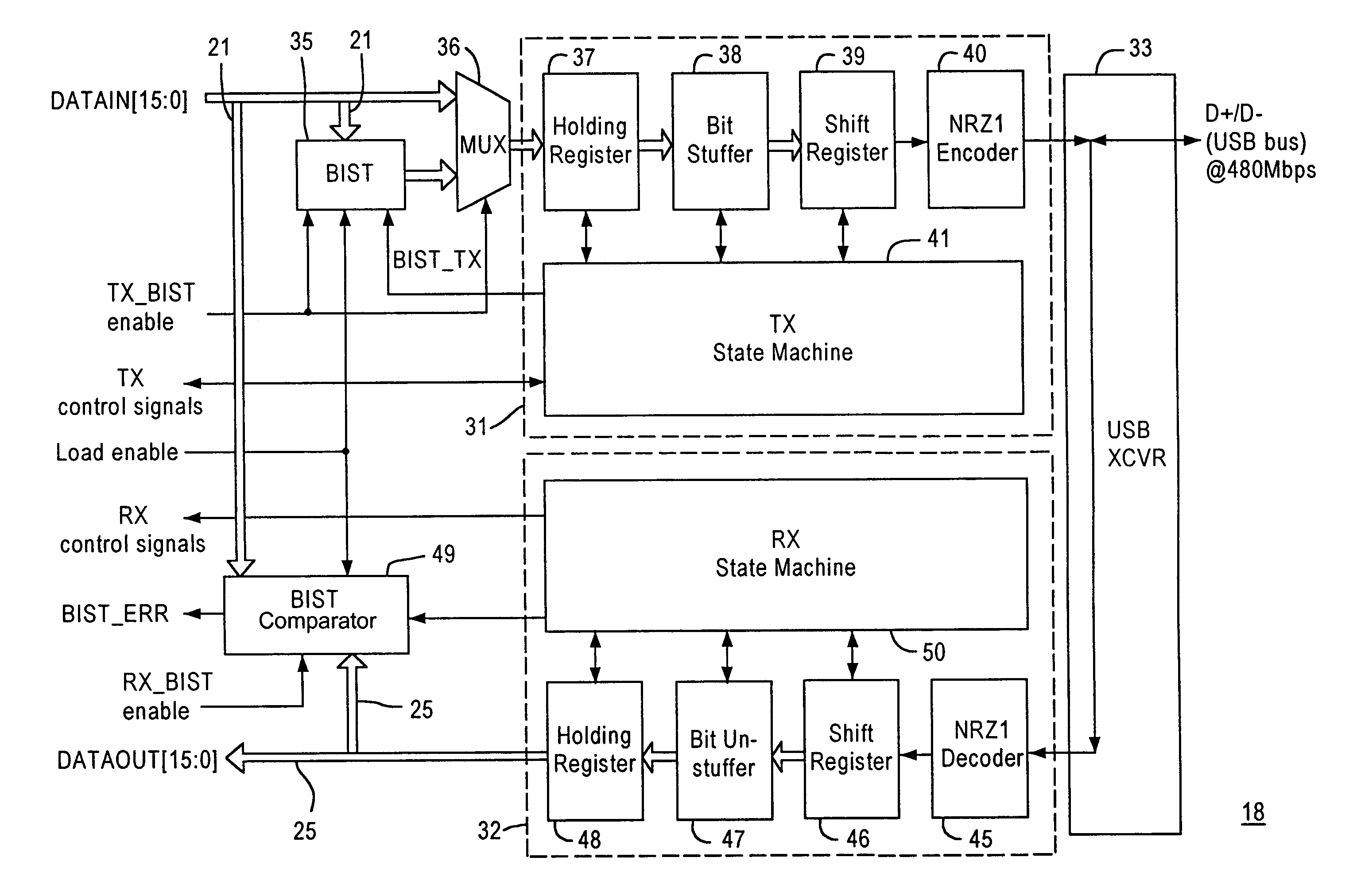

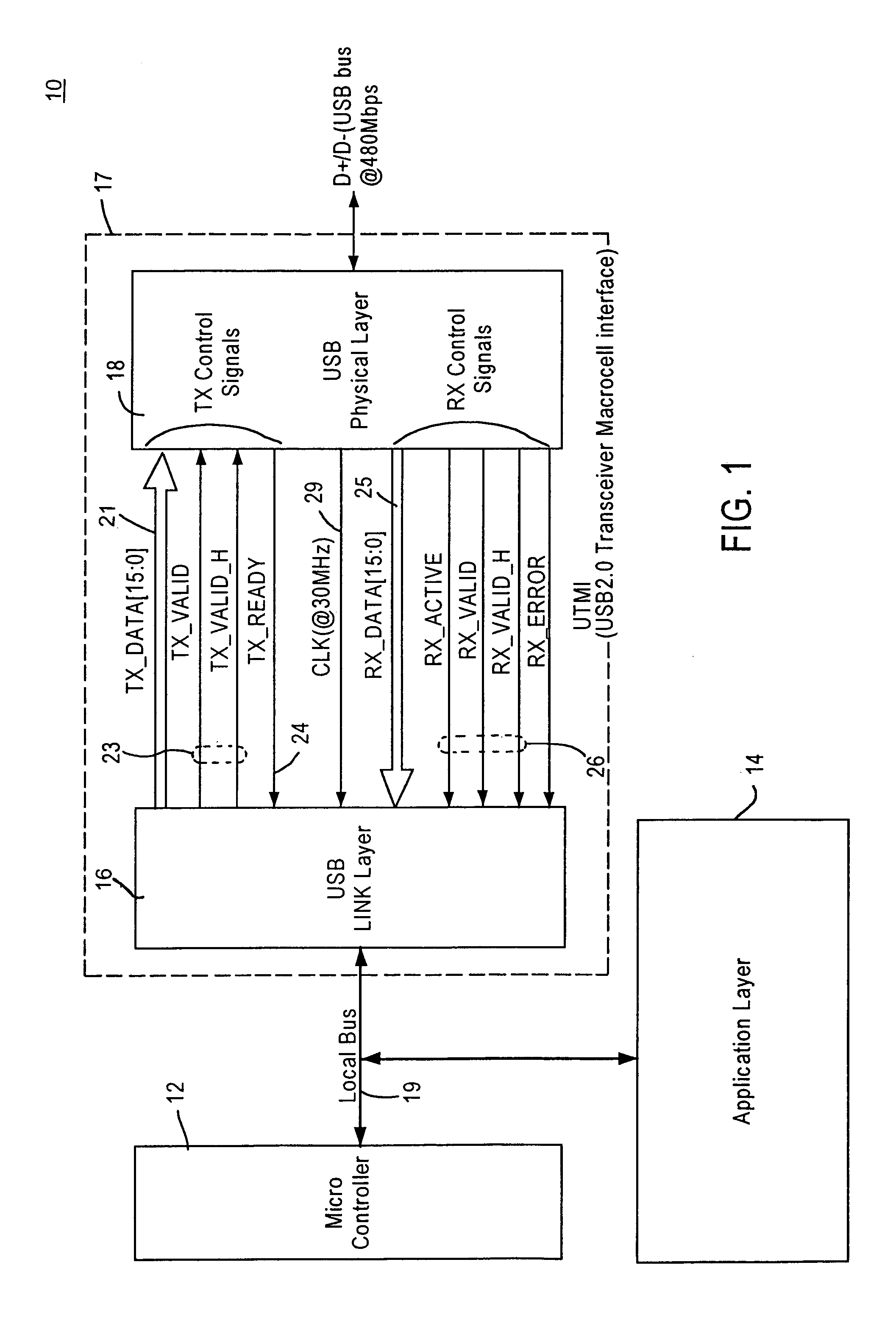

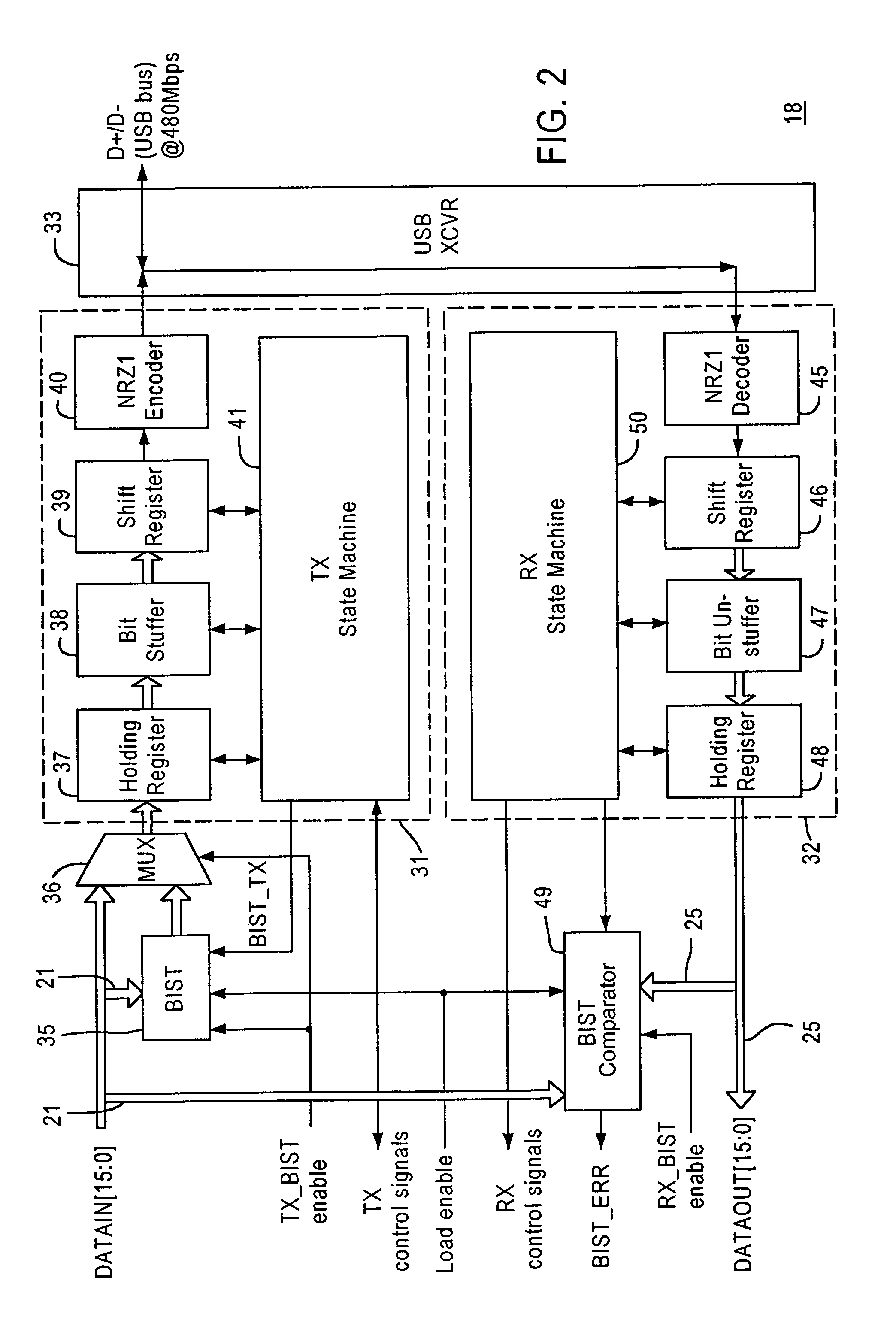

Built-in at-speed bit error ratio tester

InactiveUS7743288B1Low-cost solutionEfficient testingError preventionTransmission systemsEqualizationBuilt-in self-test

A built-in, at-speed BERT is provided that may be part of high-speed serial interface circuitry implemented on an integrated circuit. The built-in, at-speed BERT takes advantage of an existing clock data recovery (CDR) dual-loop architecture and built-in self test (BIST) circuitry. The built-in, at-speed BERT provides a low-cost solution for production testing of high-speed serial links, facilitating jitter analysis and evaluation of pre-emphasis and equalization performance. This further allows adaptation of pre-emphasis and equalization.

Owner:ALTERA CORP

Communicating message request transaction types between agents in a computer system using multiple message groups

A transmitting device and a receiving device are coupled via a high-speed serial interface within a computer system. The transmitting device transmits a packet header for a message request transaction that include a message group sub-field that indicates one of a plurality of message groups. The packet header also includes a format field that indicates whether the message request packet includes data. The packet header further includes a message code field to indicate a specific message type.

Owner:INTEL CORP

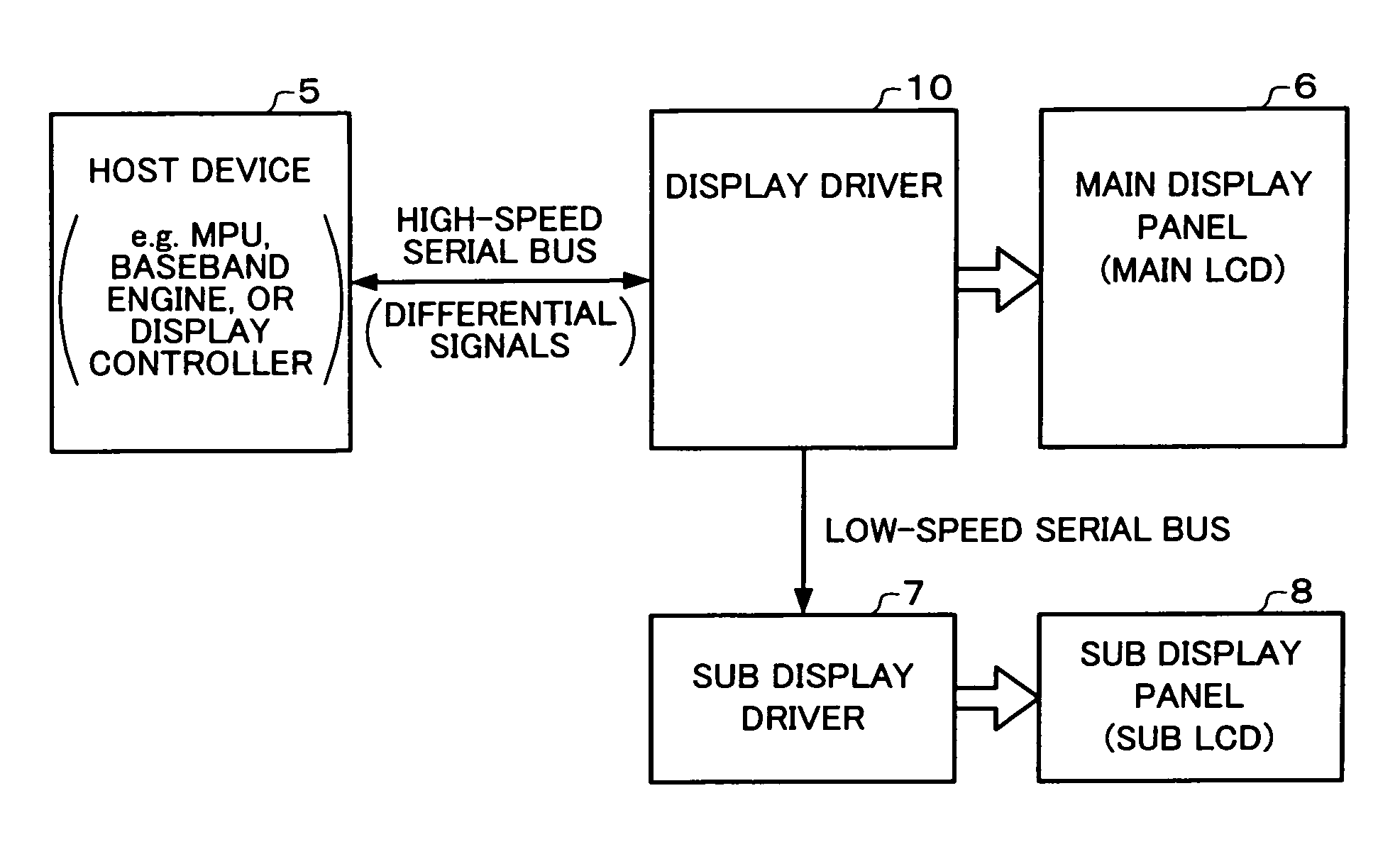

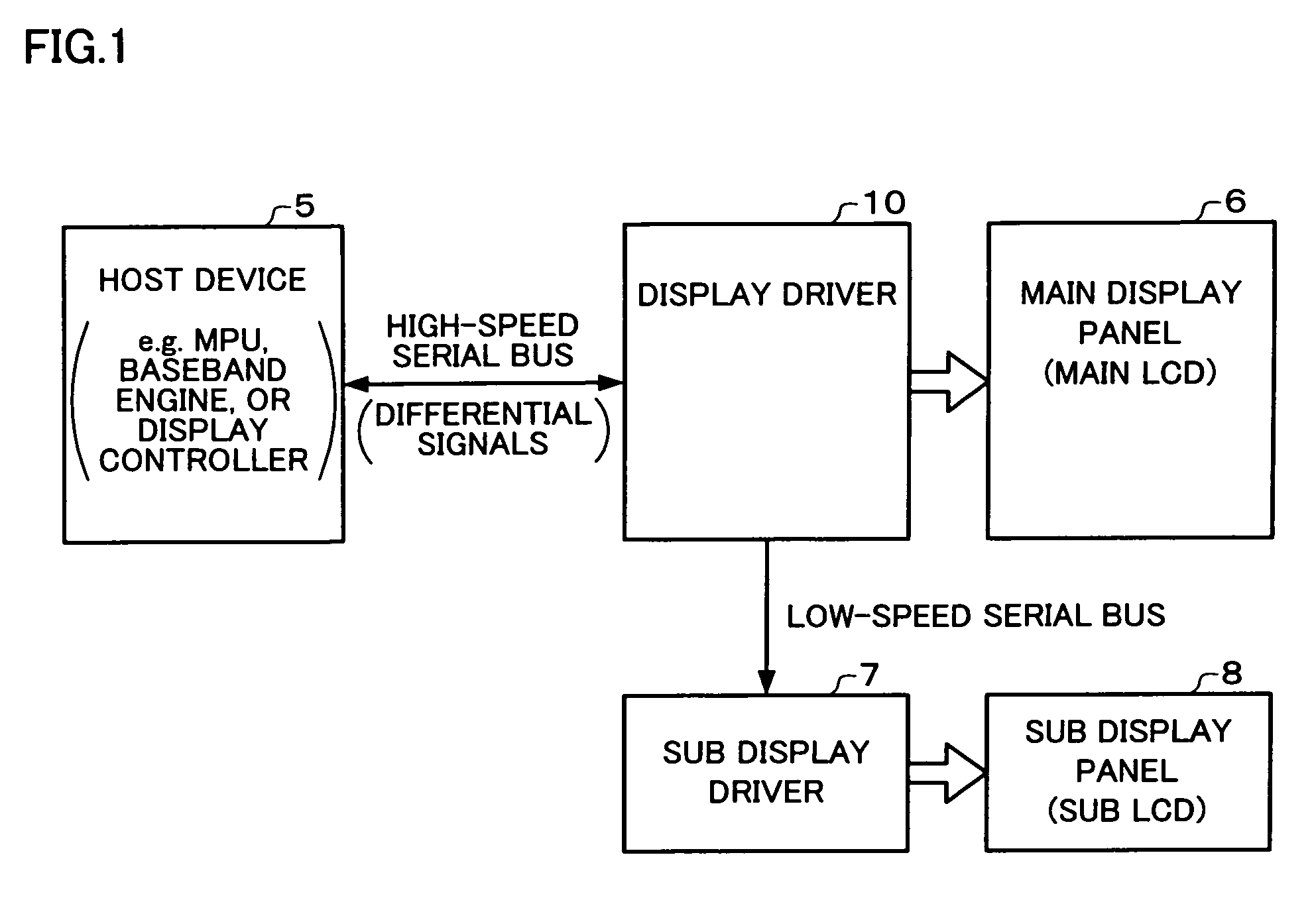

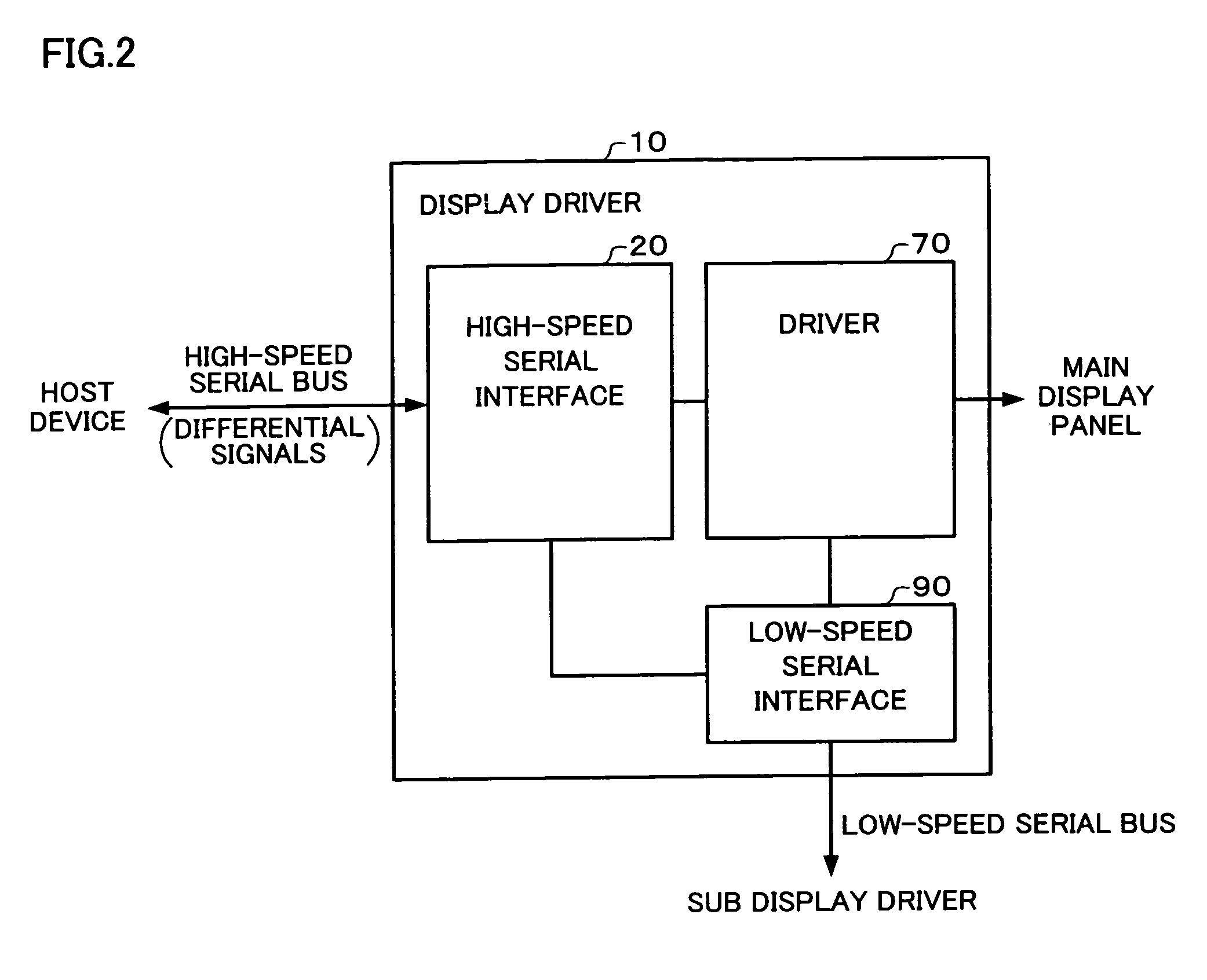

Display driver and electronic instrument

InactiveUS8031130B2Effective controlElectric/magnetic signal storageCathode-ray tube indicatorsDriver circuitLow speed

A display driver comprising: a high-speed serial interface circuit which receives a packet from a host device through a high-speed serial bus using differential signals, and outputs a command or data included in the received packet; a driver circuit which drives a main display panel based on the output command or data; and a low-speed serial interface circuit which outputs a command or data to a sub display driver through a low-speed serial bus when the packet received from the host device includes the sub display driver command or data. And the display driver inserts dummy data to the packet to adjust the difference of the transfer rate by inserting a dummy the dummy data. And the display driver adjust the difference of the transfer rate.

Owner:SEIKO EPSON CORP

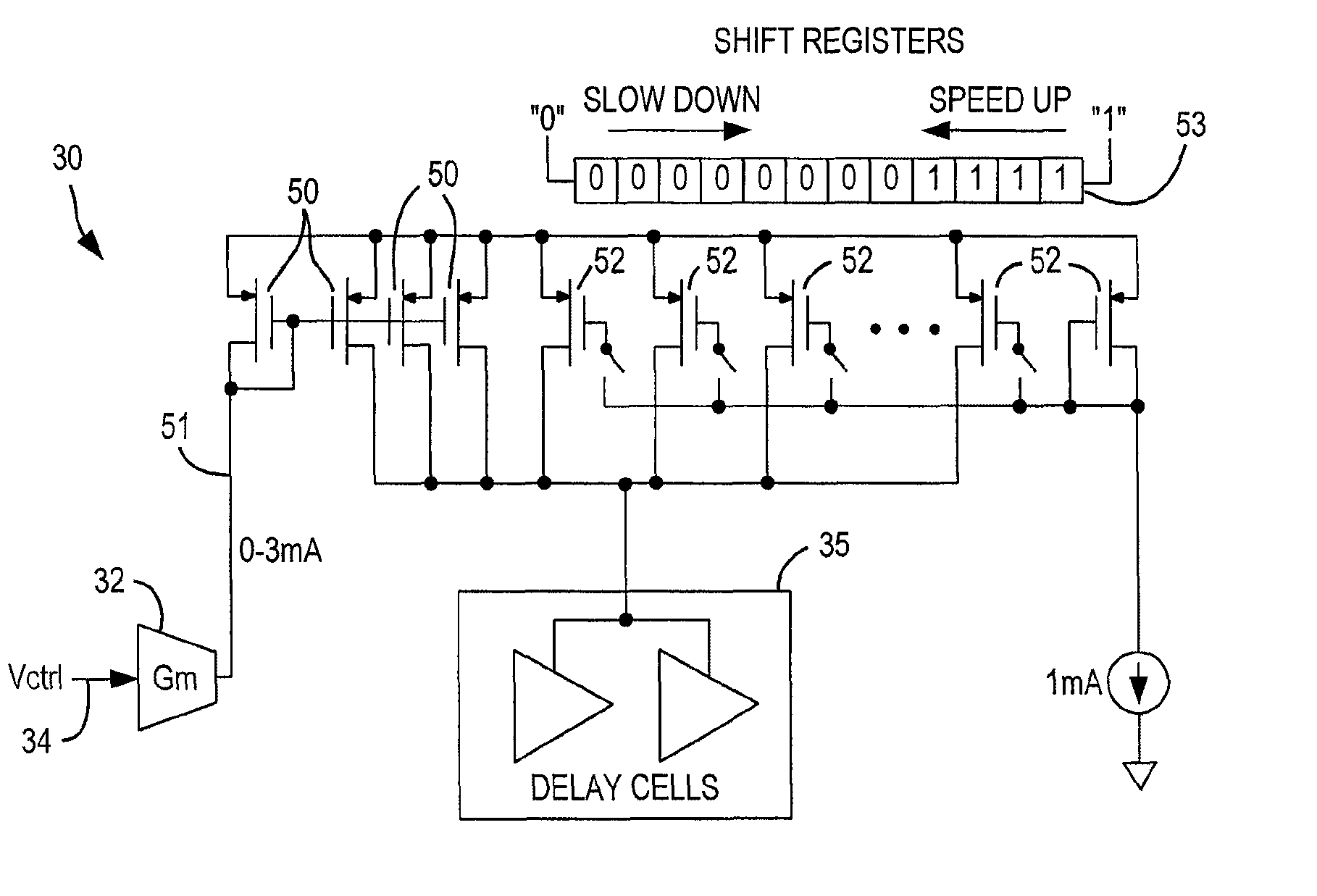

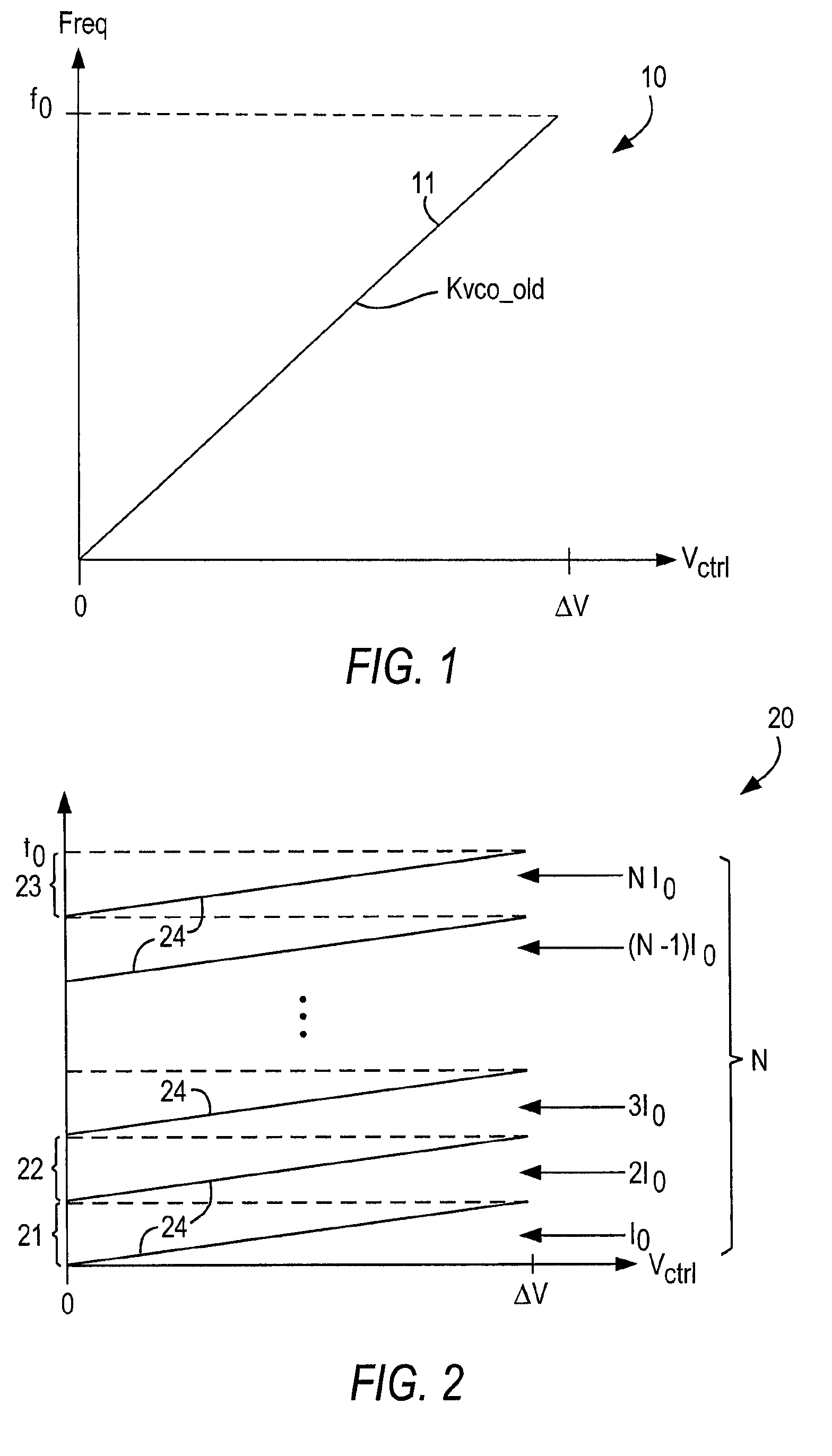

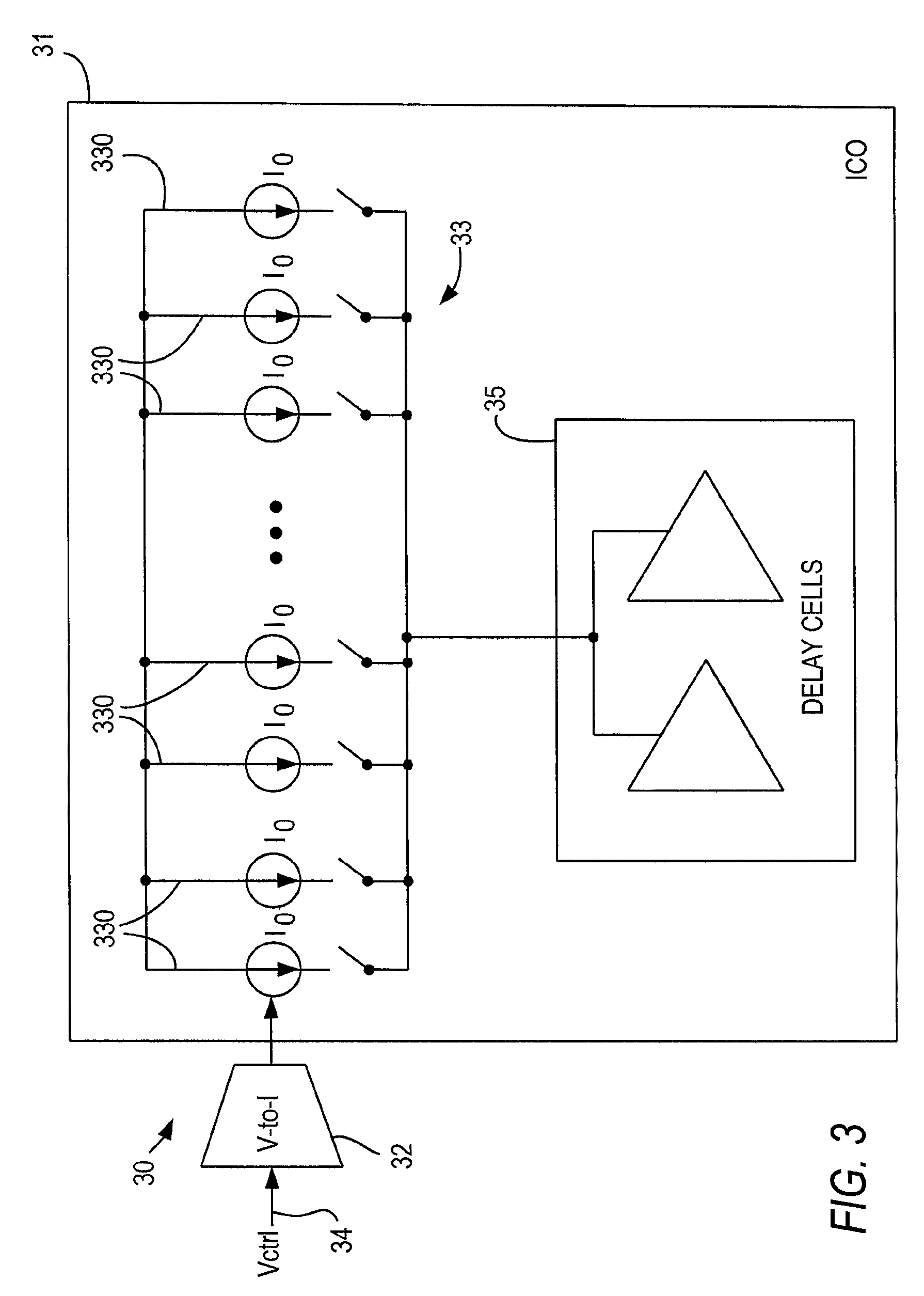

High-frequency low-gain ring VCO for clock-data recovery in high-speed serial interface of a programmable logic device

ActiveUS7956695B1Angle modulation by variable impedencePulse automatic controlControl signalProgrammable logic device

A voltage-controlled oscillator operates at high frequency without high gain by dividing the frequency range into a plurality of subranges, which preferably are substantially equal in size. Within any subrange, the full extent of variation in the control signal changes the frequency only by the extent of the subrange. The gain is thus substantially equal to the gain one would expect for the full frequency range, divided by the number of subranges. The subrange may be selected manually, or by an initial calibration process. In one embodiment, the oscillator includes a voltage-to-current converter and a current-controlled oscillator, with a current mirror arrangement. In that embodiment, selection of the subrange may be controlled by turning on the correct number of current legs.

Owner:ALTERA CORP

Imaging system and image processing apparatus

InactiveUS20050248584A1Flexible processVersatile and flexible image processing unitCathode-ray tube indicatorsElectric digital data processingSimplex communicationImaging processing

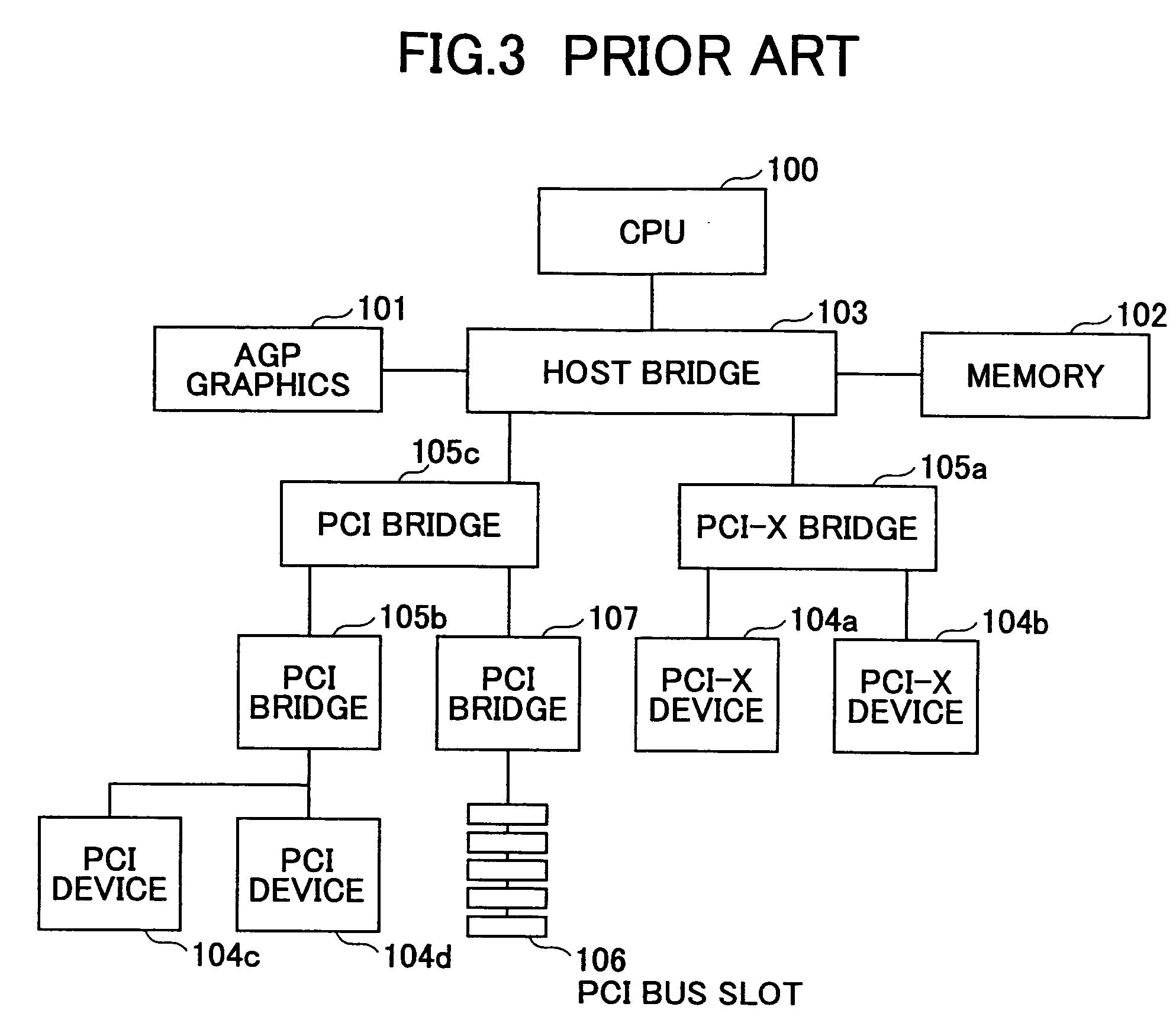

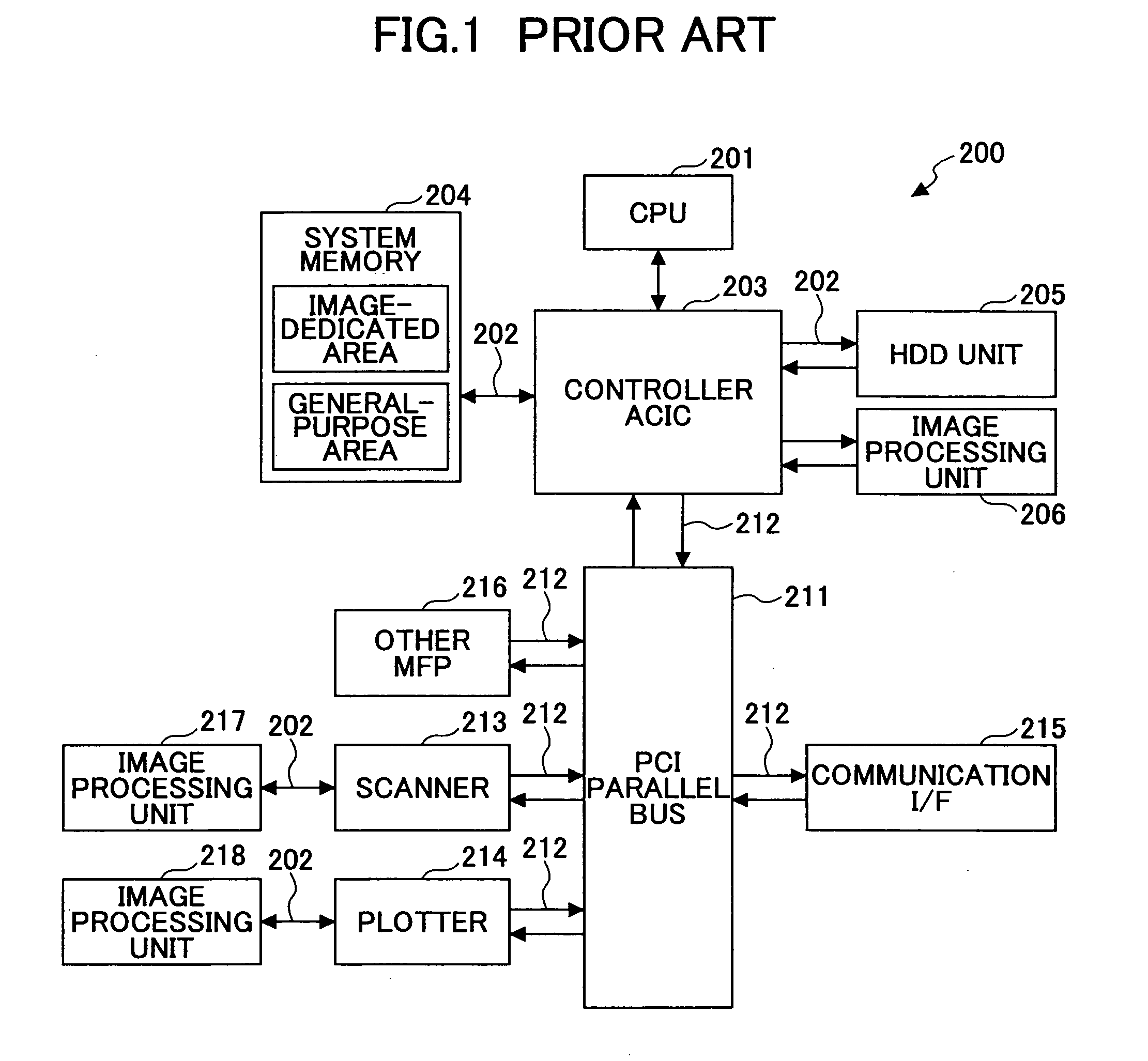

An imaging system that implements a PCI Express high-speed serial interface system is disclosed in which a plurality of point-to-point simplex communication channels are established to realize a data communication network having a tree structure. The imaging system includes a PCI Express high-speed serial interface, and plural independent image processing units as end point devices of the tree structure that are connected by the PCI Express high-speed serial interface.

Owner:RICOH KK

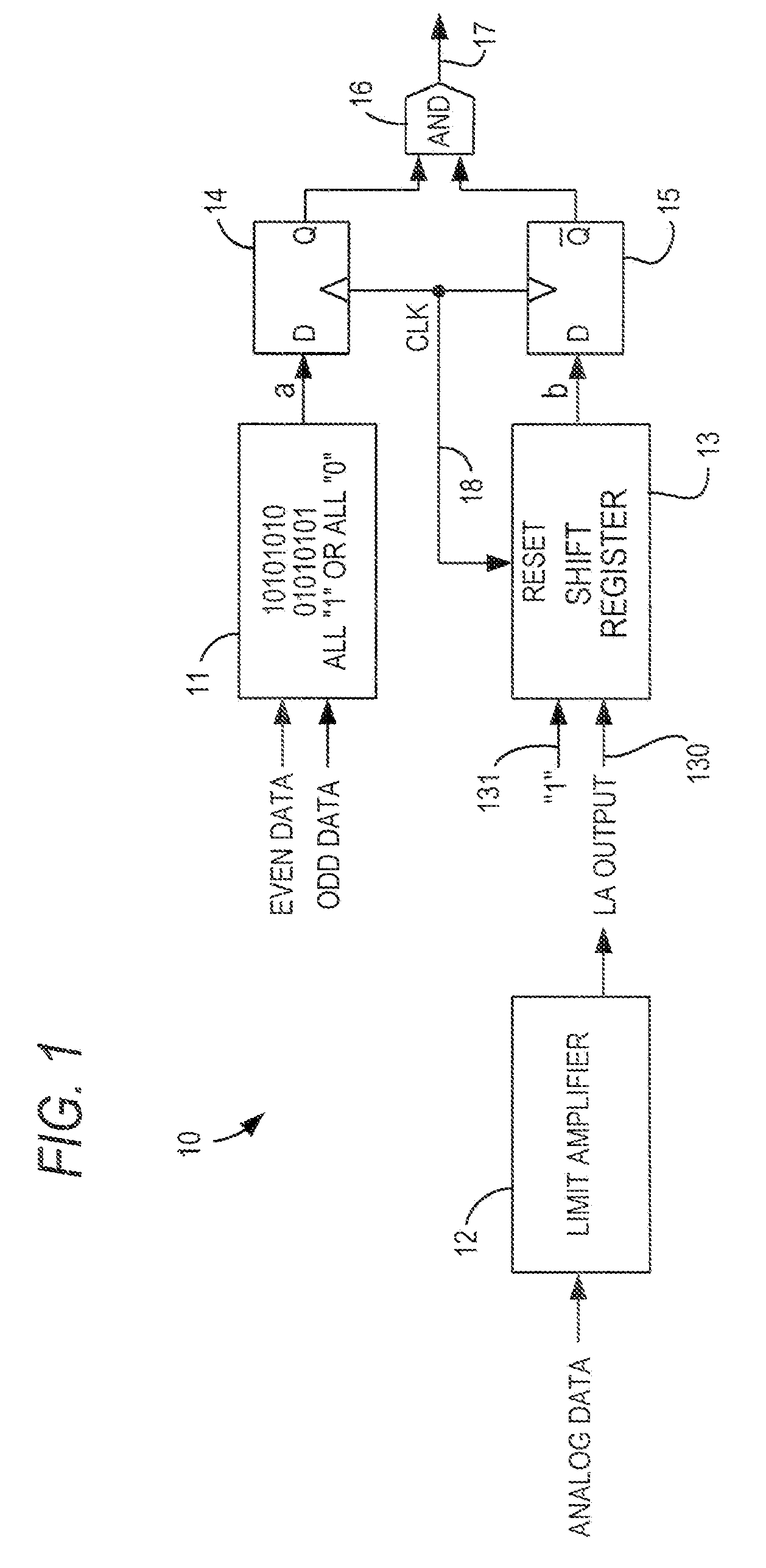

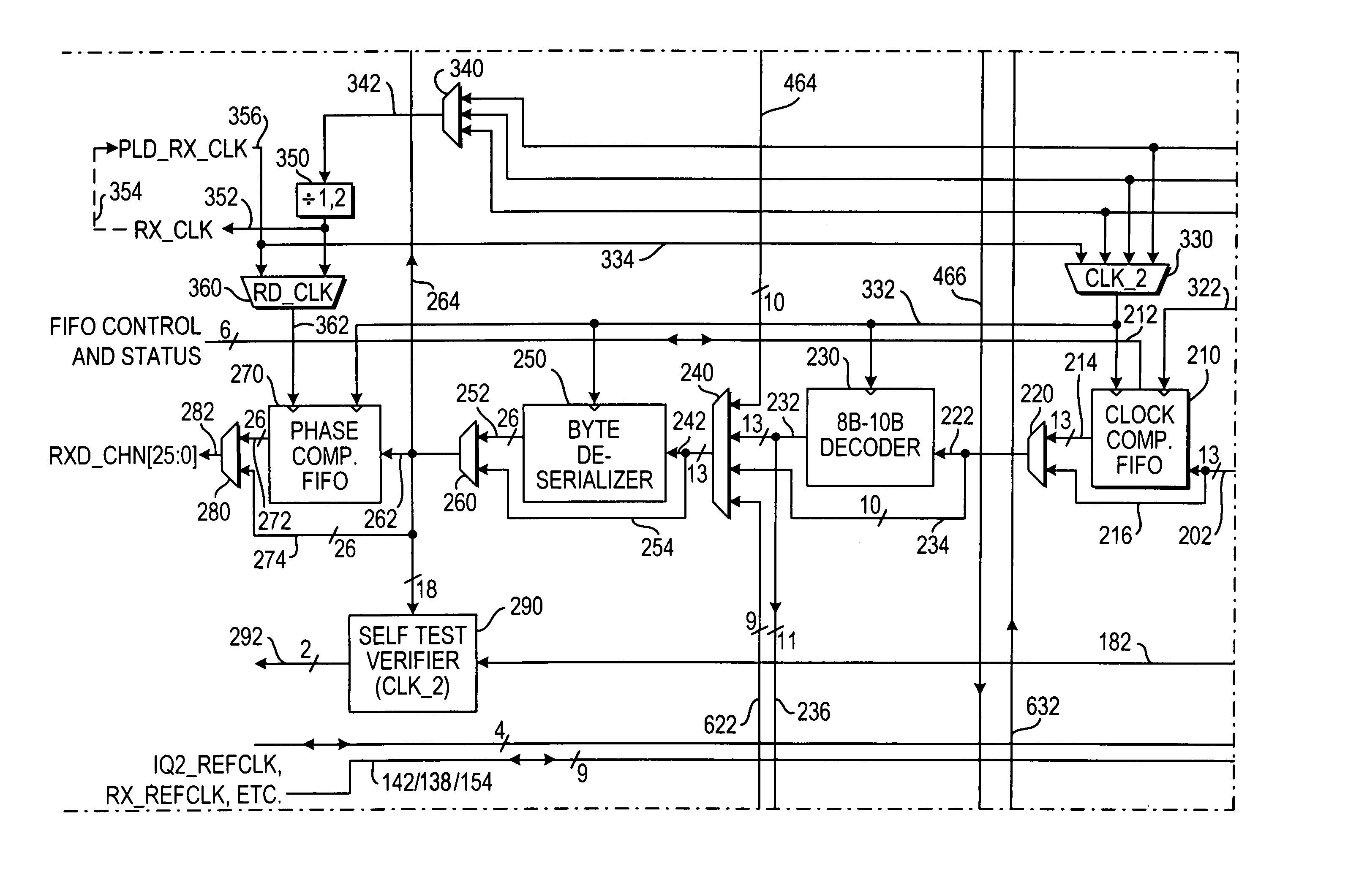

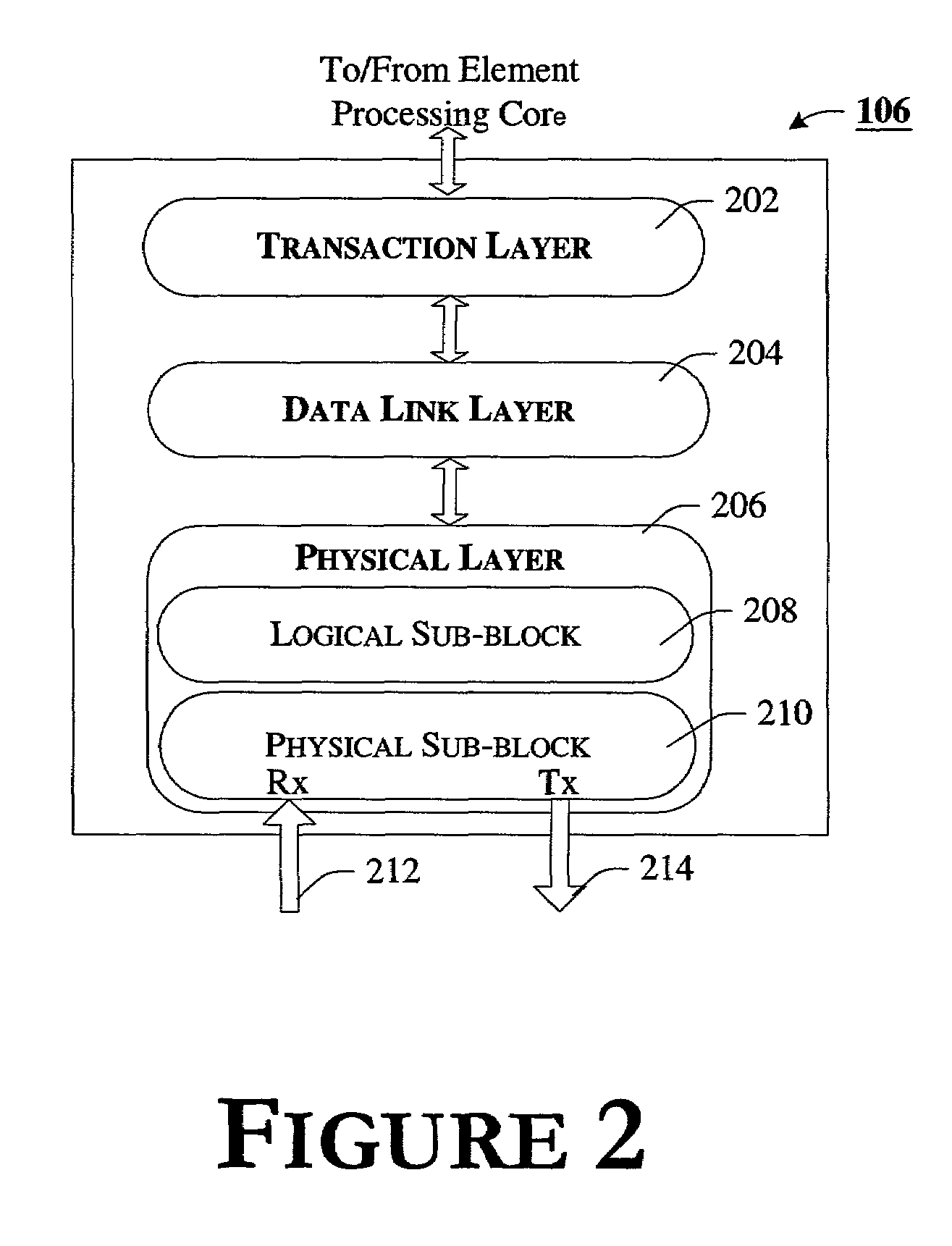

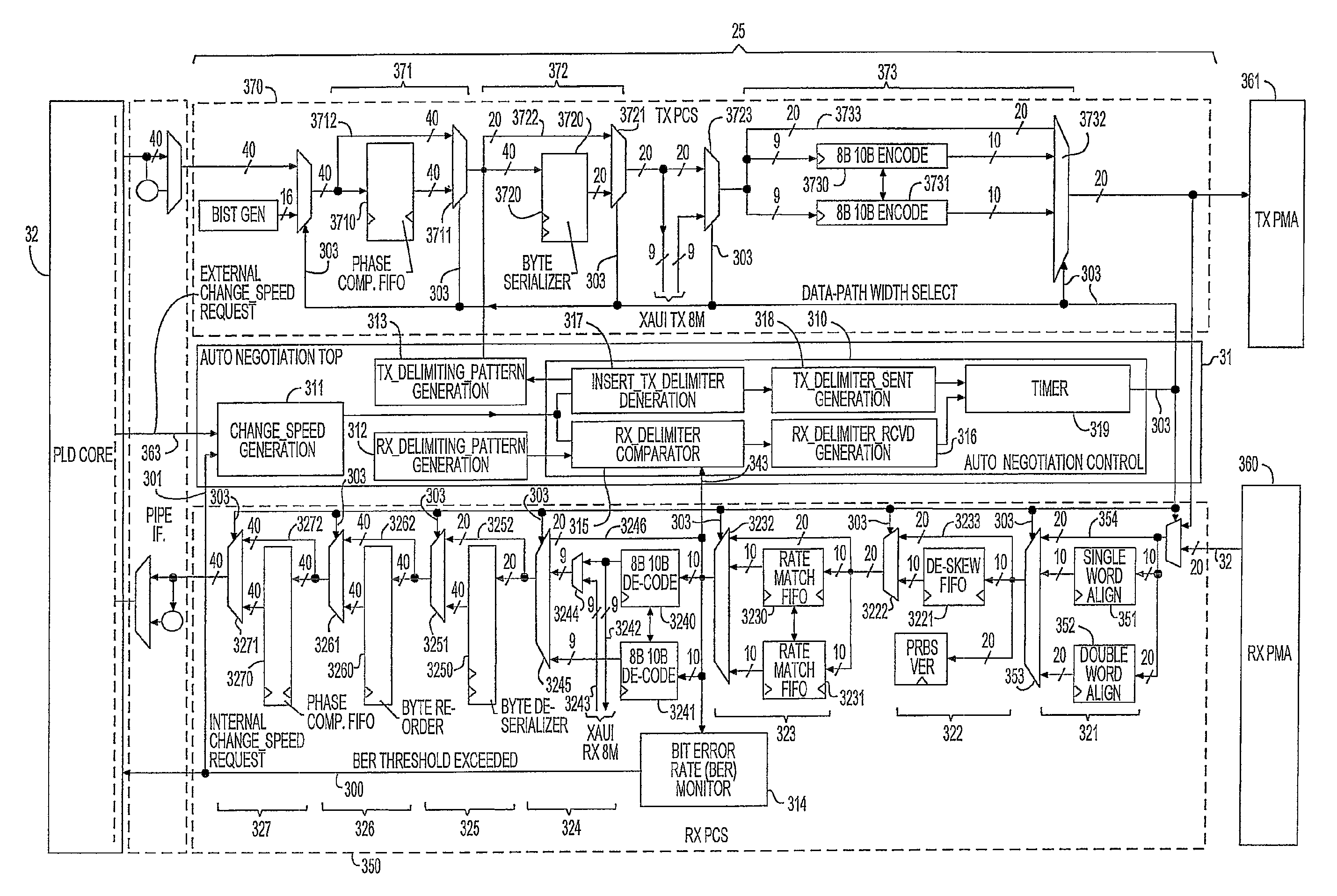

Clock signal circuitry for multi-protocol high-speed serial interface circuitry

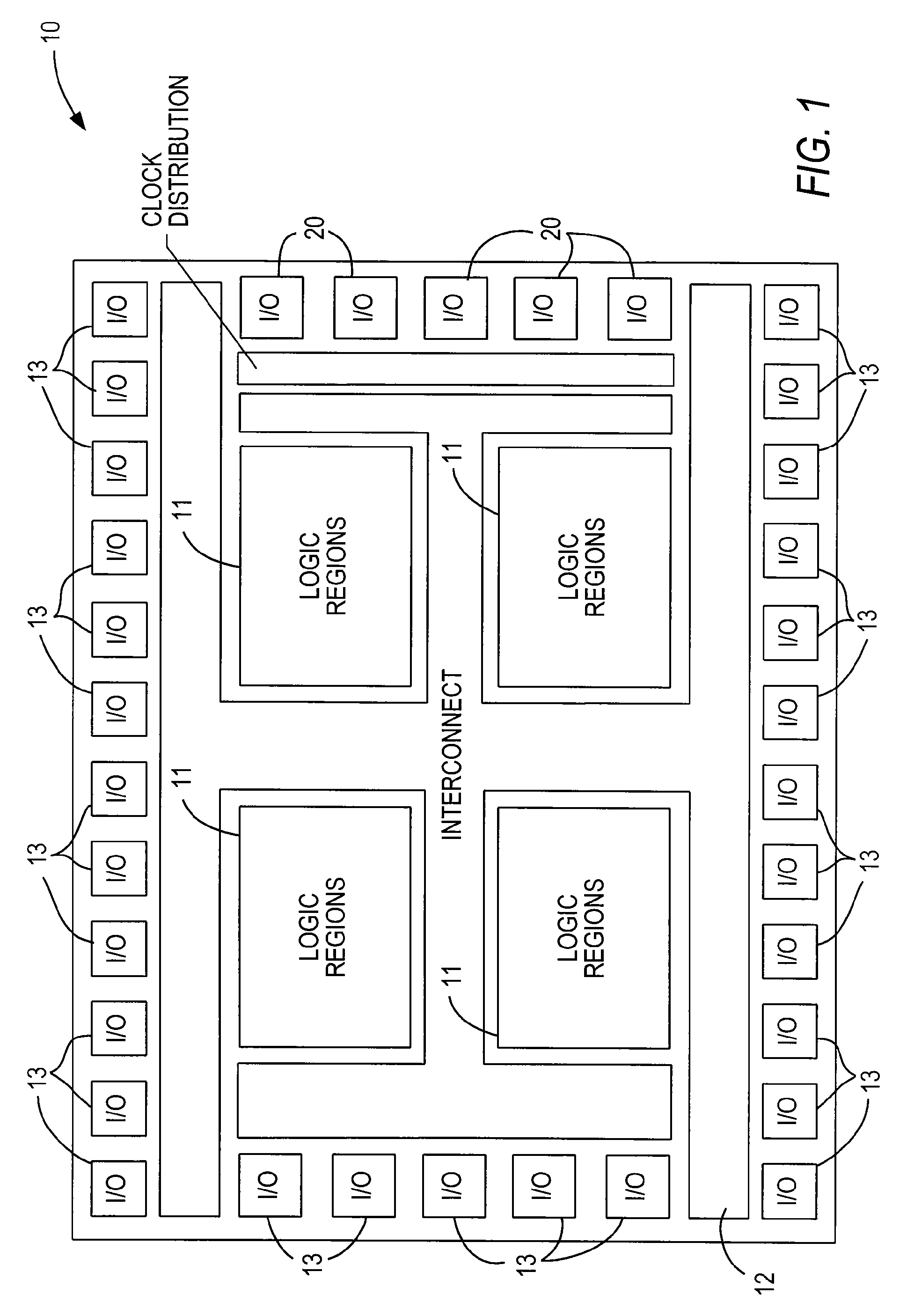

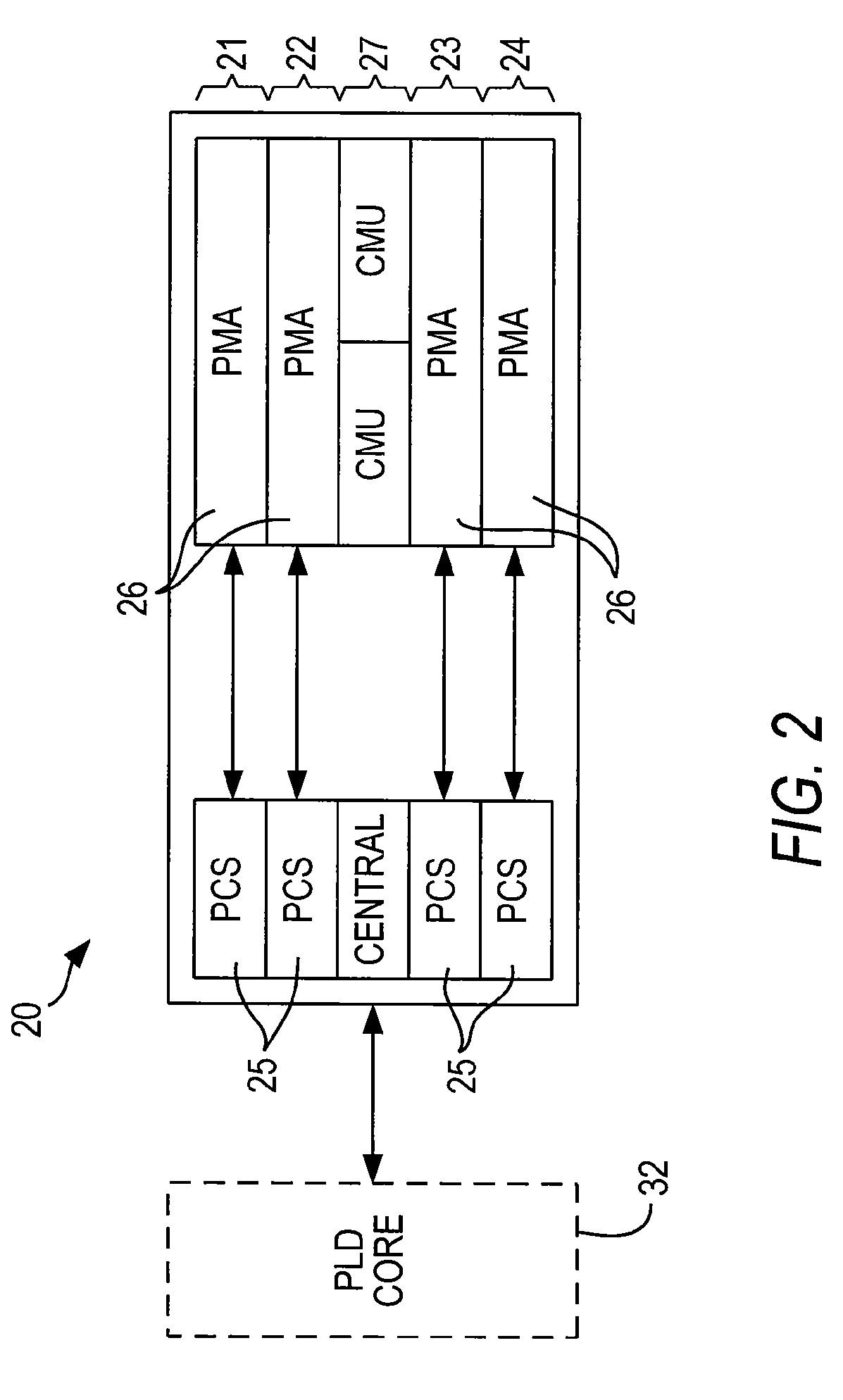

ActiveUS7180972B1Generating/distributing signalsSynchronising arrangementPhase differenceProgrammable logic device

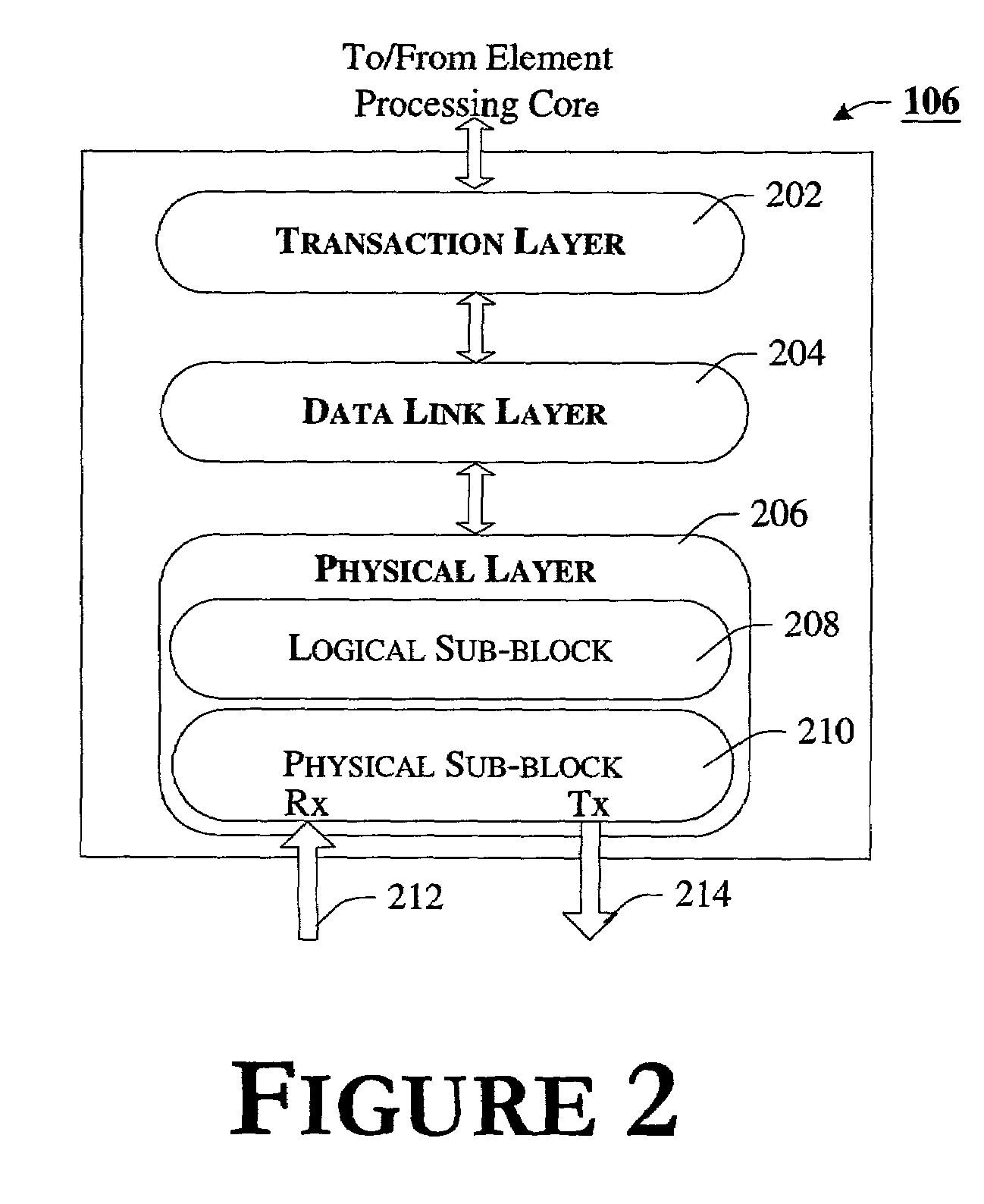

A programmable logic device (“PLD”) includes high-speed serial interface (“HSSI”) circuitry. The HSSI circuitry includes clock signal circuitry that allows various components of the HSSI circuitry to be clocked in different ways to facilitate use of the HSSI circuitry to support a number of different communication protocols. Some of the HSSI clock signals may be routed through the clock distribution network of the associated PLD logic circuitry. The HSSI circuitry may include phase compensation buffer circuitry to compensate for possible phase differences across the interface between the HSSI circuitry and the associated PLD logic circuitry.

Owner:TAHOE RES LTD

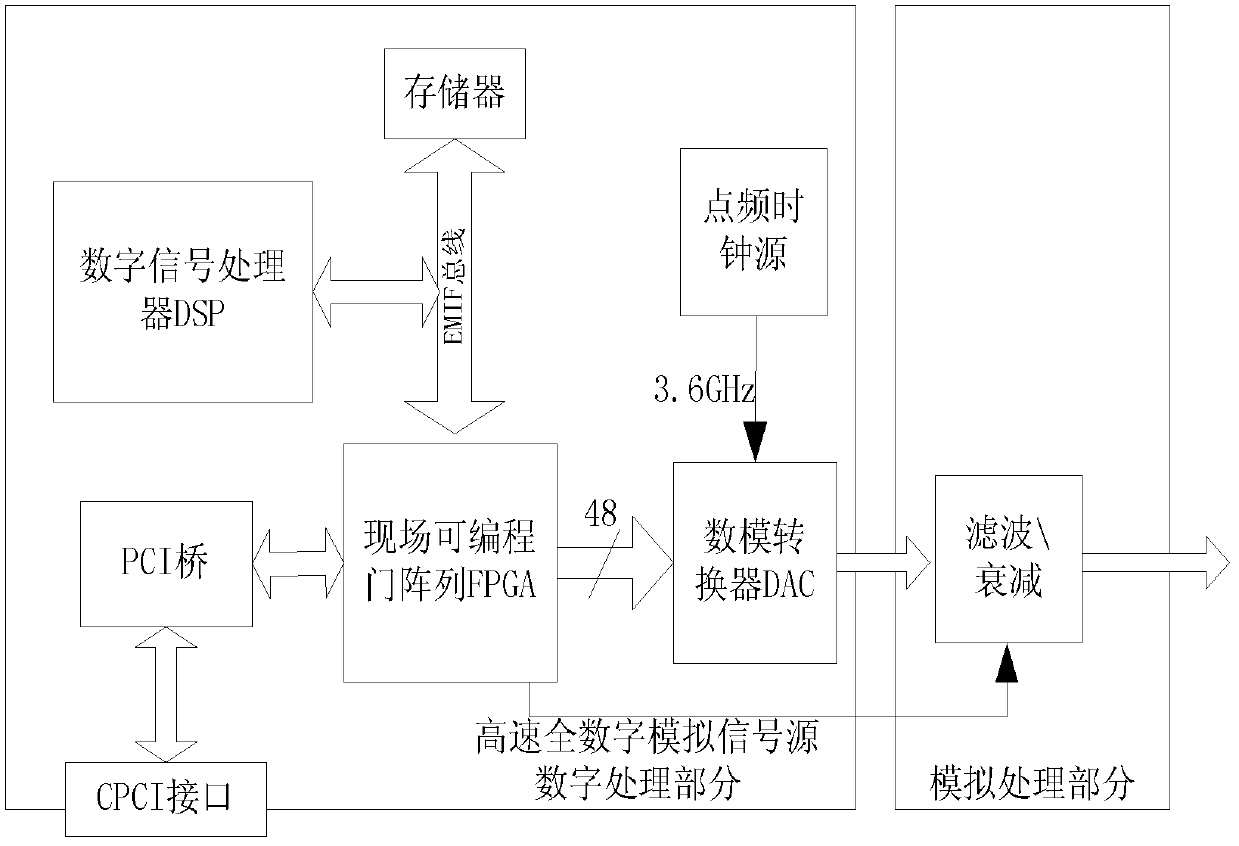

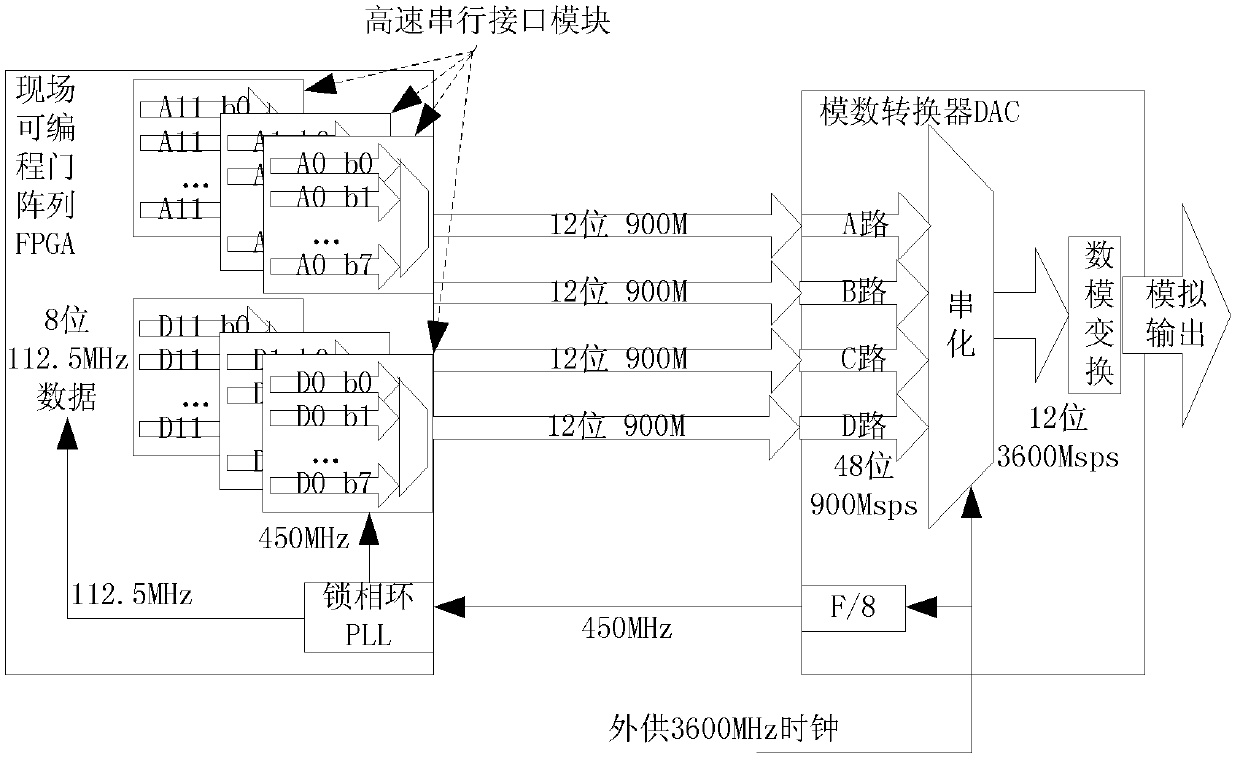

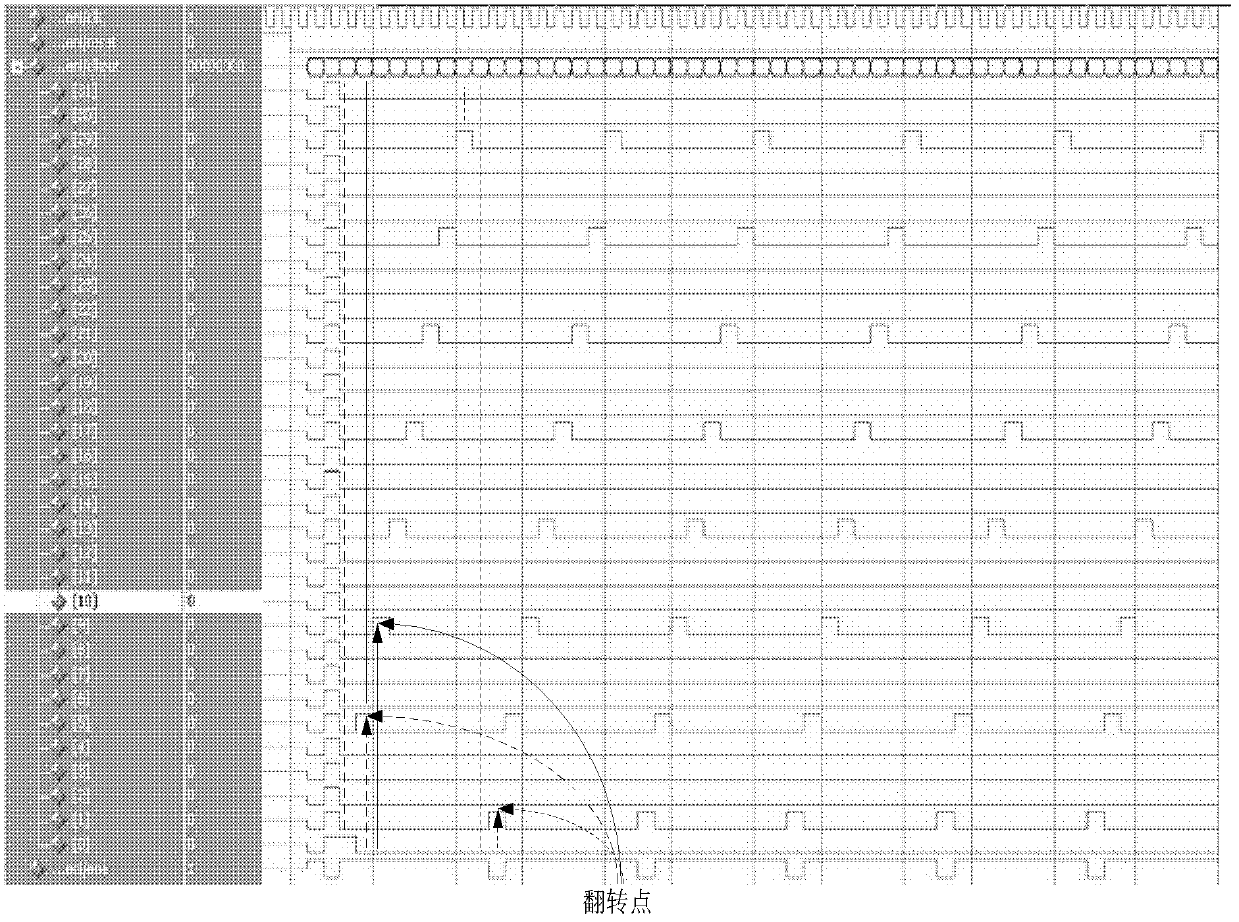

All-digital satellite signal simulated source

InactiveCN102710316AIntegrity guaranteedFlexible configurationRadio transmissionSymbol rateHigh-Speed Serial Interface

The invention provides an all-digital satellite signal simulated source. The all-digital satellite signal simulated source comprises a double-port storage, the double-port storage is a FPGA which provides interfaces for various rate conversions between coding and modulation, is connected with a digital to analog converter through a high-speed serial interface to form a core hardware framework of the satellite signal simulated source, and is connected with a broadband filter directly through a simulation output end to produce multimode high and moderate frequency broadband satellite signal simulated signals with code rates which can vary continuously, a digital signal processor serves as a main control device of the simulated source and performs analysis of various parameters issued by a monitor and parameter configuration of the FPGA, a 32-channel parallel modulation system is arranged inside the FPGA, for example, a 32-channel direct digital synthesizer (DDS) performs parallel output and composition of the central frequency, the FPGA determines the overturn of the carrier phase according to a symbol rate and a main frequency of parallel calculation, IQ two-channel signals, signal coding, code conversion and quadrature modulation are produced through a logical algorithm, a Q channel uniformization coefficient is calculated according to an IQ unbalanced parameter, Q channel uniformization coefficient and the Q channel signal amplitude are subjected to multiply-add arithmetic to calculate the Q channel amplitude, IQ is added, and a unbalanced quadrature phase shift keying (UQPSK) modulation method is simulated.

Owner:10TH RES INST OF CETC

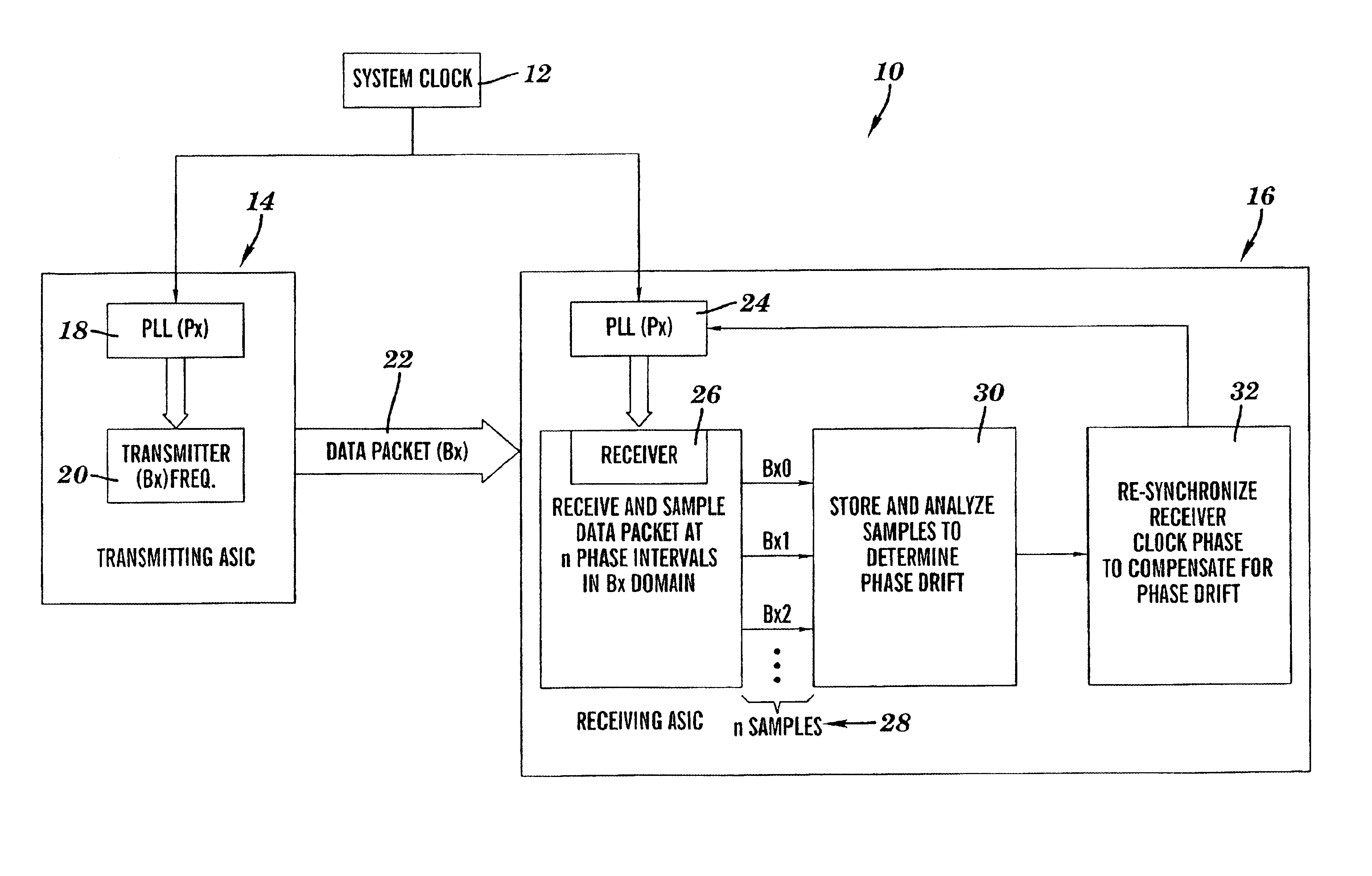

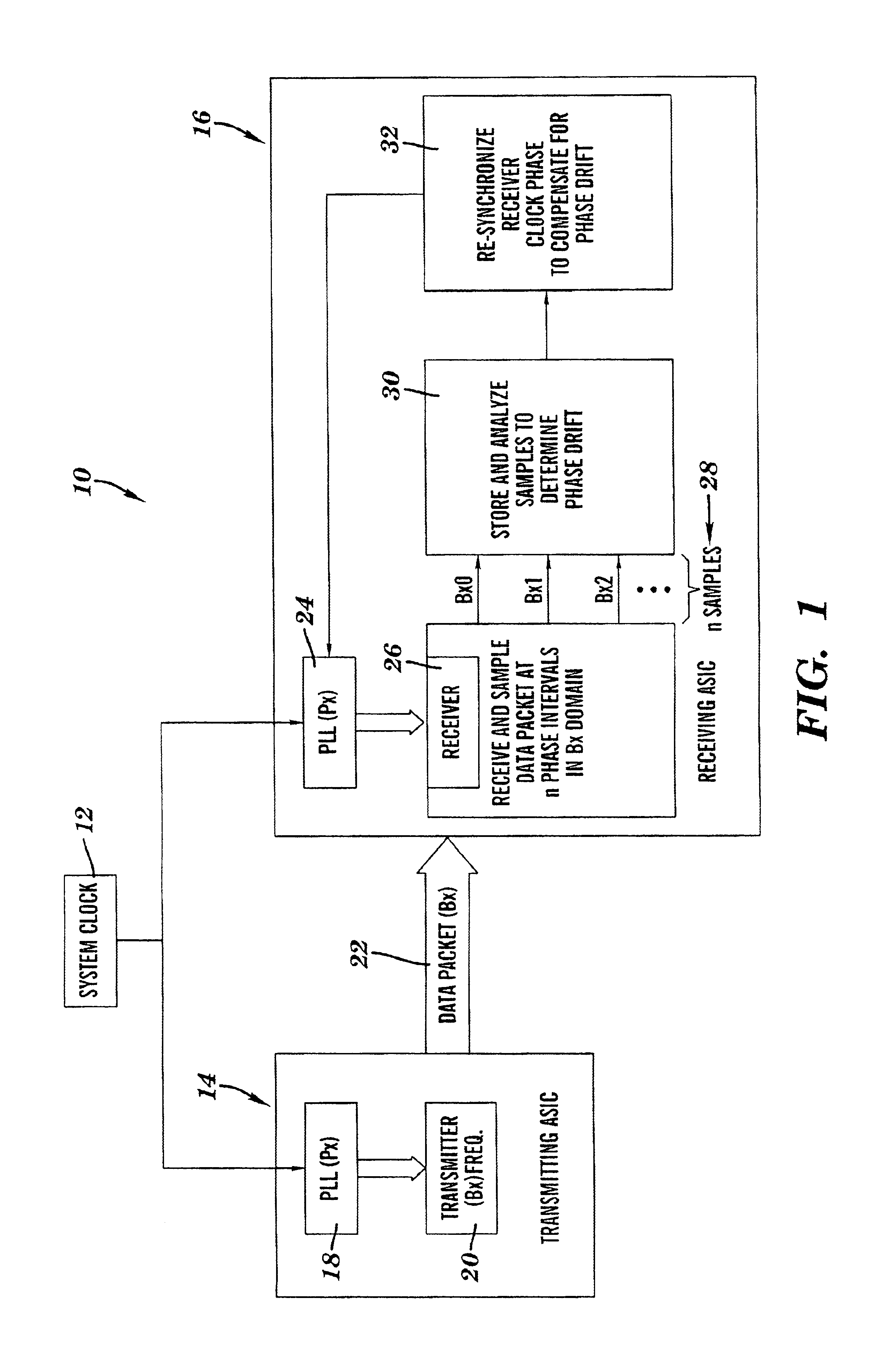

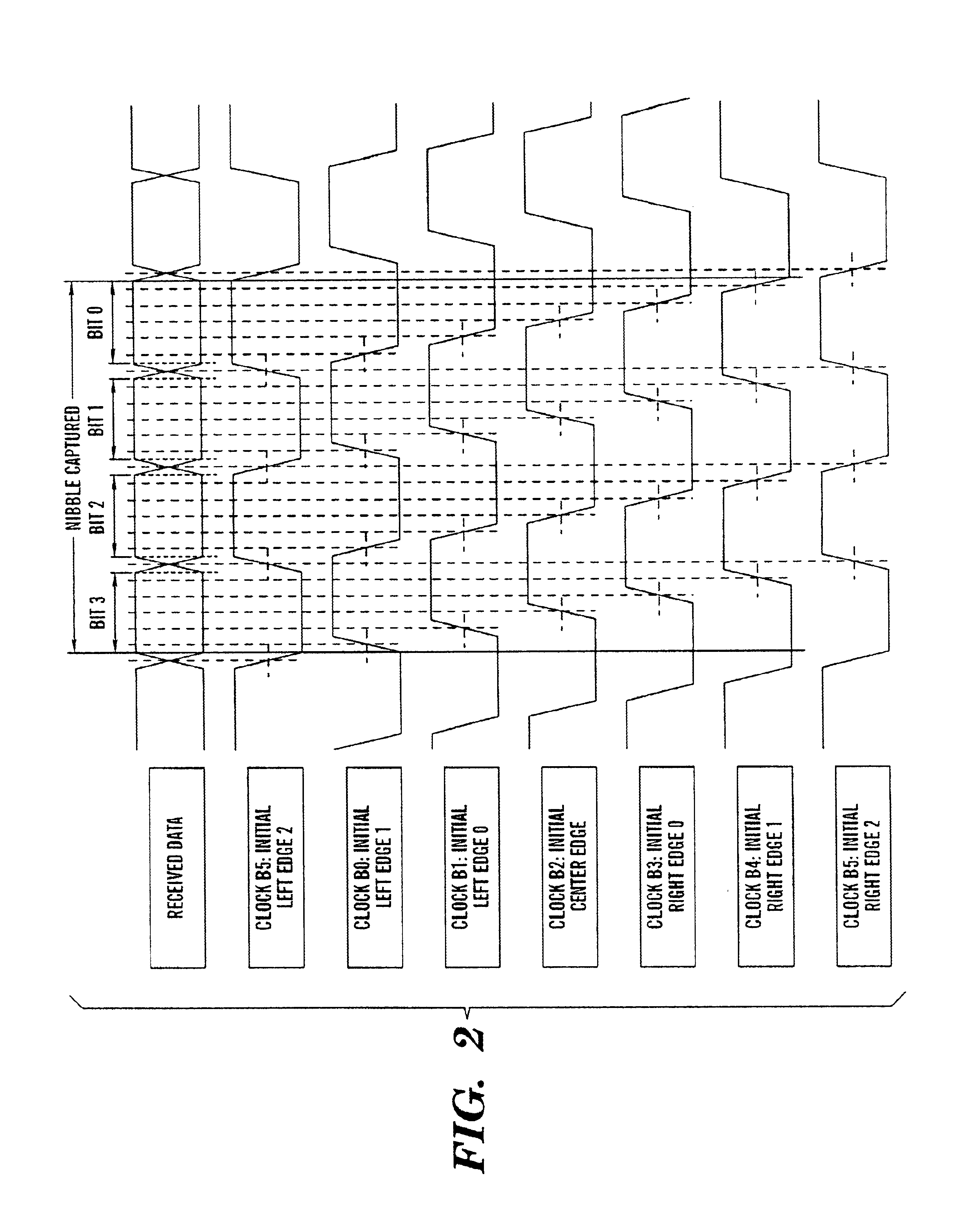

High speed serial interface

InactiveUS6895062B1Accurate frequency and phase lockingIncrease speedModulated-carrier systemsSynchronisation signal speed/phase controlNetwork packetComputer science

A high speed serial interface system that compensates for phase drift by over sampling received data packets. The system utilizes a transmitter and receiver that operate within the same clock domain to achieve a frequency lock between the two devices. The receiver receives and samples each data packet at n phase intervals, stores and analyzes the samples to determine phase drift, and resynchronizes the receiver clock to compensate for phase drift on an ongoing basis.

Owner:MEDIATEK INC

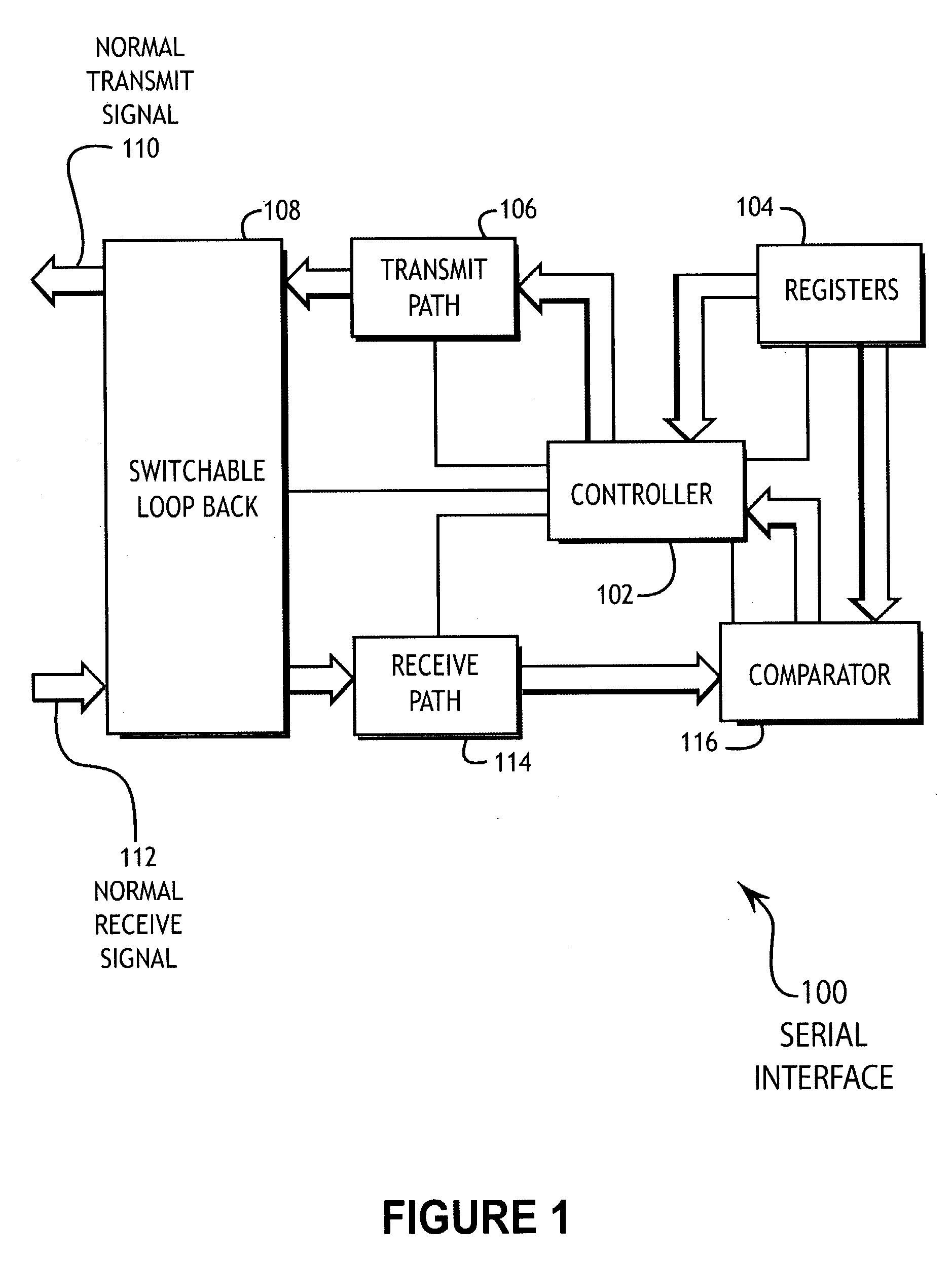

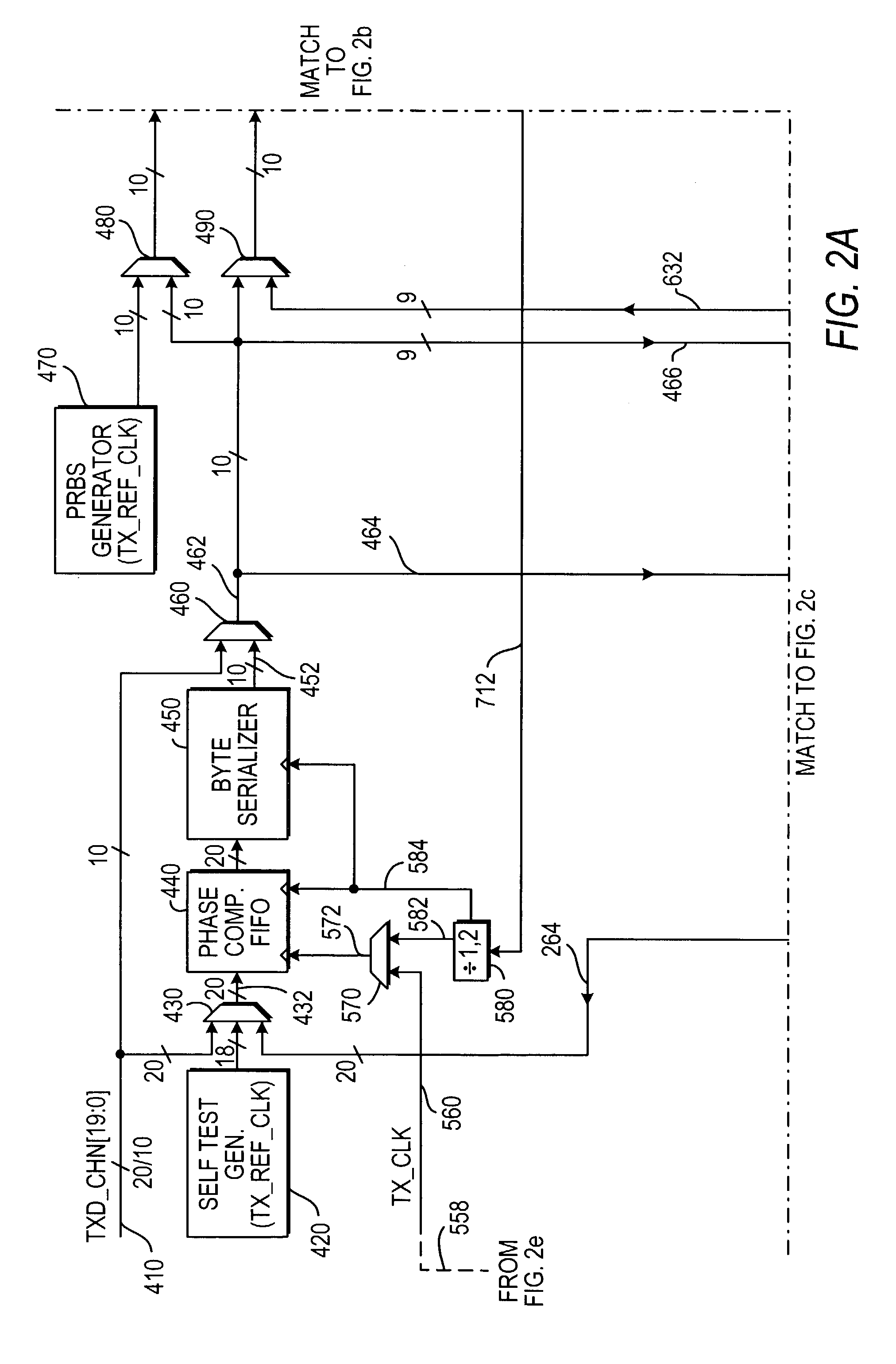

Self test circuit for evaluating a high-speed serial interface

InactiveUS6977960B2Detecting errorEasy to testCorrect operation testingElectronic circuit testingTransceiverNumber generator

A data transceiver including a self-test data generator for generating test data, which includes a first pseudo-random number generator programmable so as to allow the operator to input the test data values. The data transceiver further includes a transmitter section coupled to the self-test data generator, a receiver section coupled to the transmitter section, and a test data analyzer coupled to the receiver section, wherein the test data analyzer includes a second pseudo-random number generator, which allows the operator to input the data value via a data bus coupled to the test data analyzer. Both the self-test data generator and the test data analyzer are independently controllable.

Owner:PANASONIC CORP

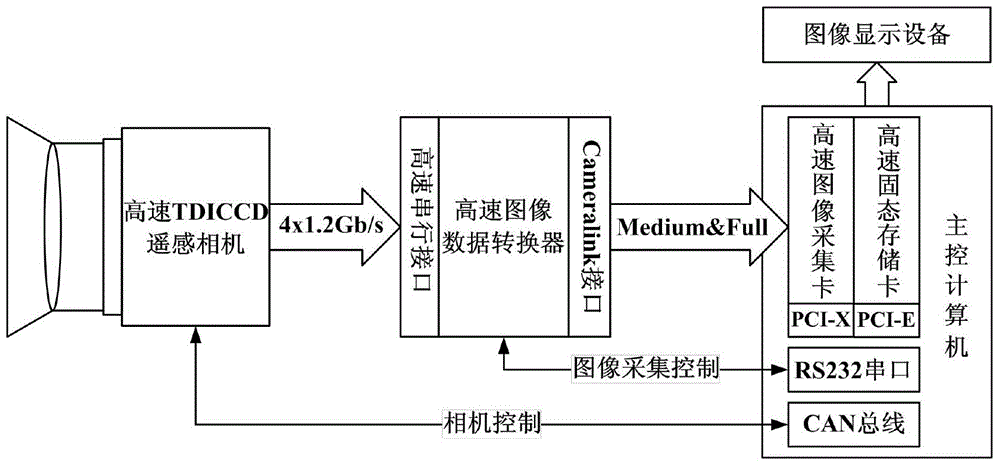

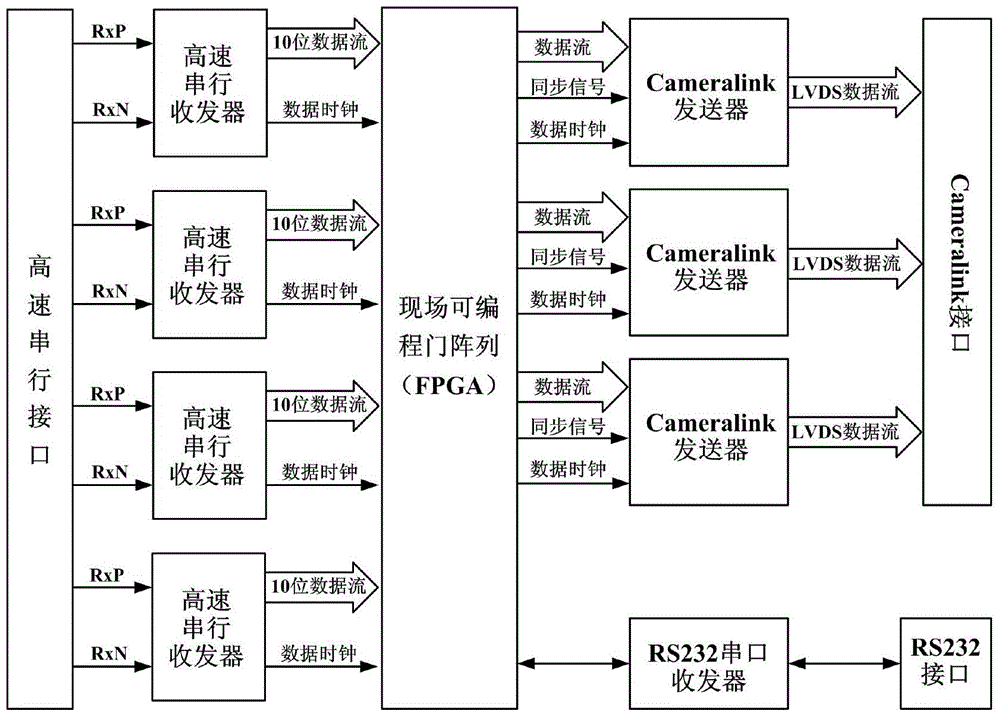

Image collecting and displaying device of high-speed TDICCD remote sensing camera

InactiveCN103986869AEfficient receptionEasy to implementTelevision system detailsColor television detailsTransceiverFpga implementations

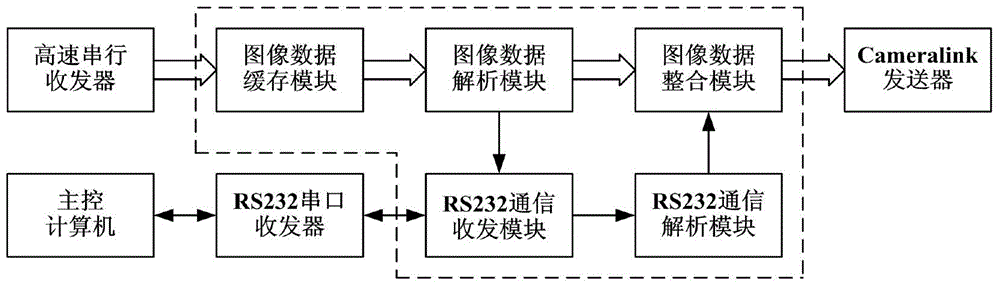

The invention provides an image collecting and displaying device of a high-speed TDICCD remote sensing camera and relates to the field of space high-speed TDICCD camera electronic system researching. The device comprises a high-speed serial interface, a high-speed serial transceiver, an FPGA, a Cameralink transmitter, a Cameralink interface, an RS 232 serial transceiver, an RS 232 serial port, a high-speed image capture card, a high-speed solid storage card, a main control computer and an image display device. According to the image collecting and displaying device of the high-speed TDICCD remote sensing camera, CCD original image data of all passages of the high-speed TDICCD remote sensing camera can be effectively received and stored, processed and displayed in real time, conversion and output of the high-speed image data of multiple passages are achieved by means of the FPGA, hardware is easy to achieve, the device is flexible to control, hardware cost is little, integration is high, and a ground test system which is stable in performance and portable is provided for researching of the high-speed TDICCD remote sensing camera.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Embedded Linux system firmware downloading method and device

InactiveCN101216773AImprove download speedEasy to operateProgram loading/initiatingGNU/LinuxPersonal computer

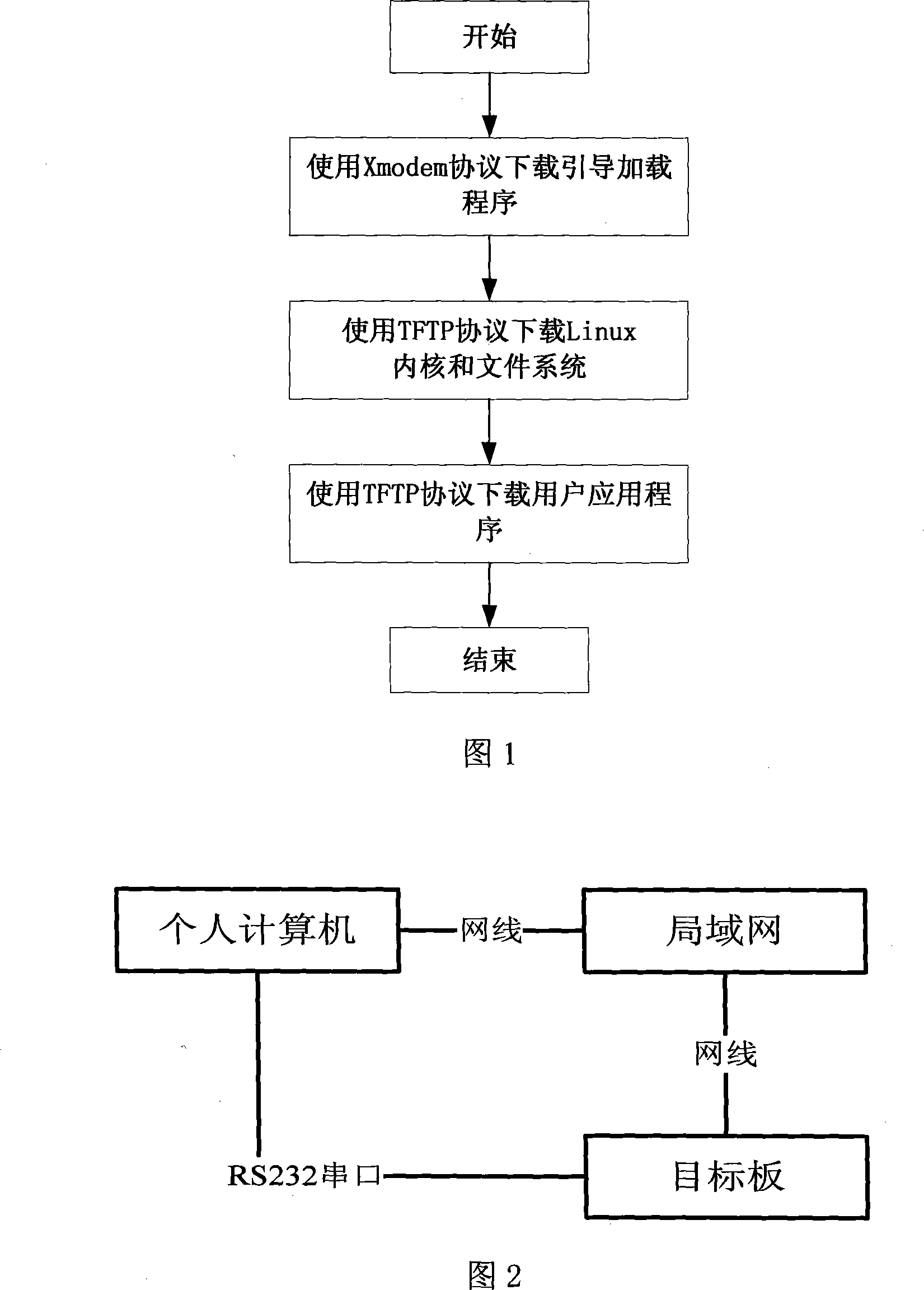

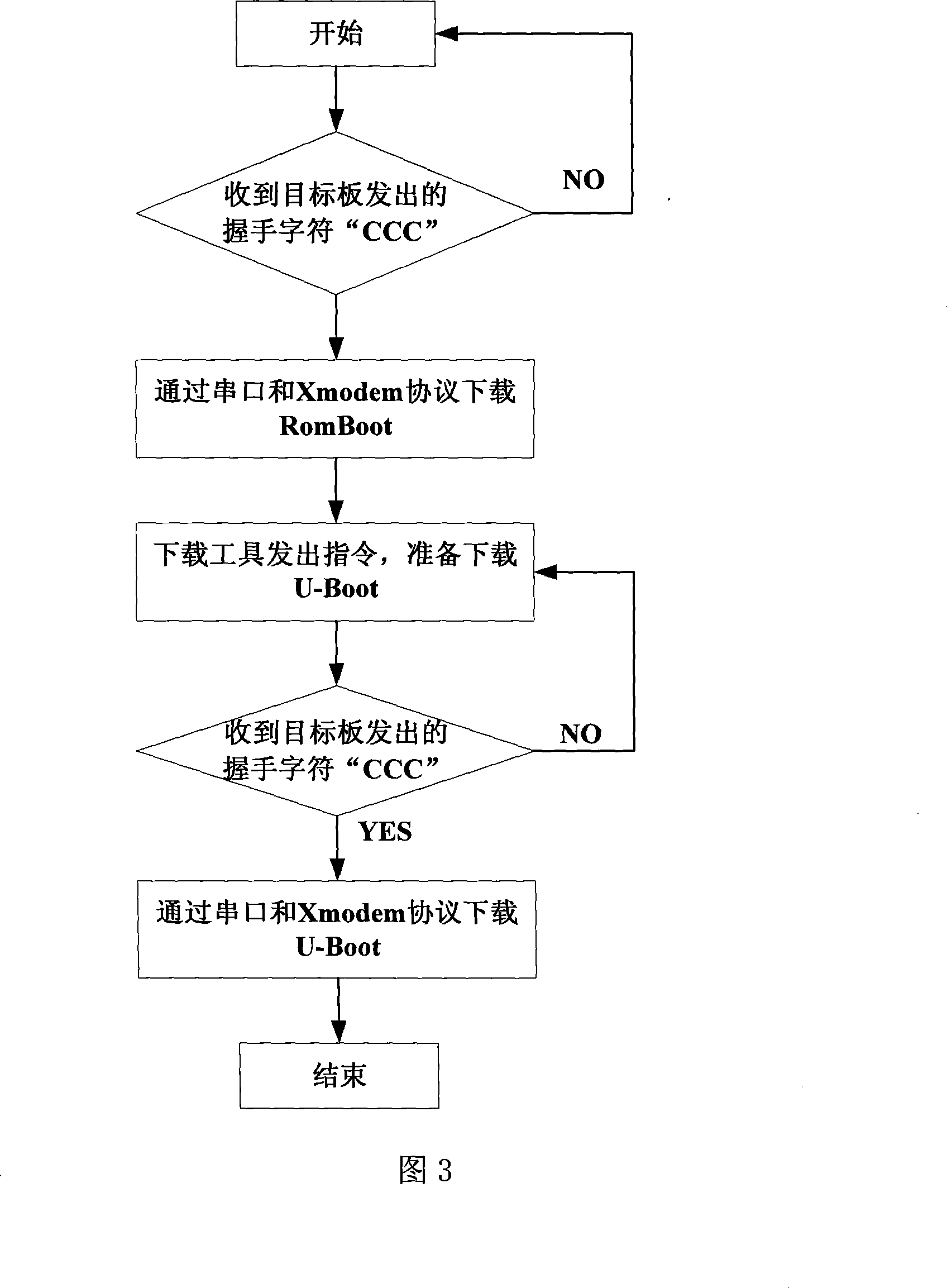

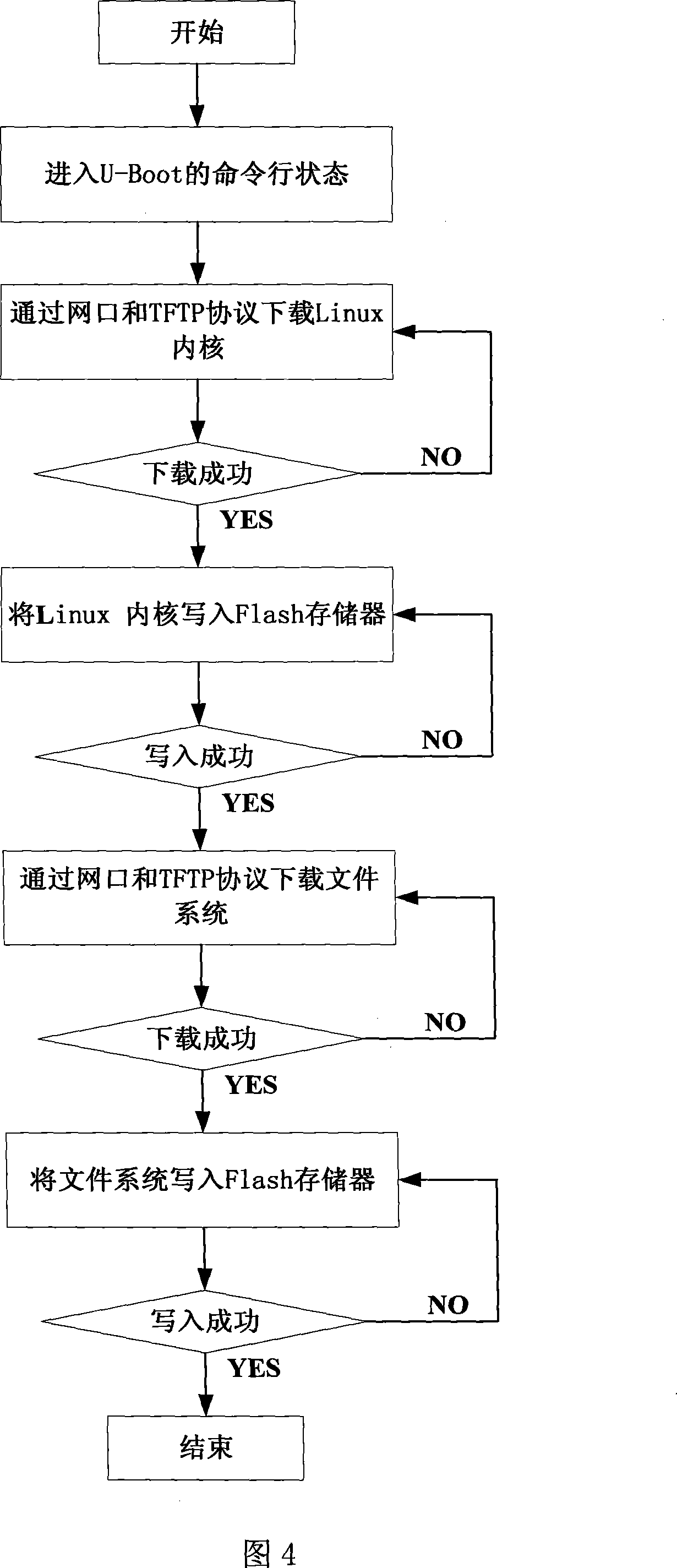

The invention discloses a device and a method for downloading firmware of an embedded Linux system. According to the principle of downloading from the simple to the complex, the most fundamental and simplest part is downloaded through a serial port, then the more complex part is downloaded, and finally, a user application program is downloaded. By adopting the device and the method provided by the invention, the firmware downloading for the embedded Linux system can be completed by a PC, thus a Flash memory is programmed through serial port and a high-speed serial interface, and the disposition of the whole system is completed. Compared with prior art, the invention has the advantages of high downloading speed, simple operation, low cost, and suitability for both R&D stage and mass production stage.

Owner:SHENZHEN GRENTECH CO LTD

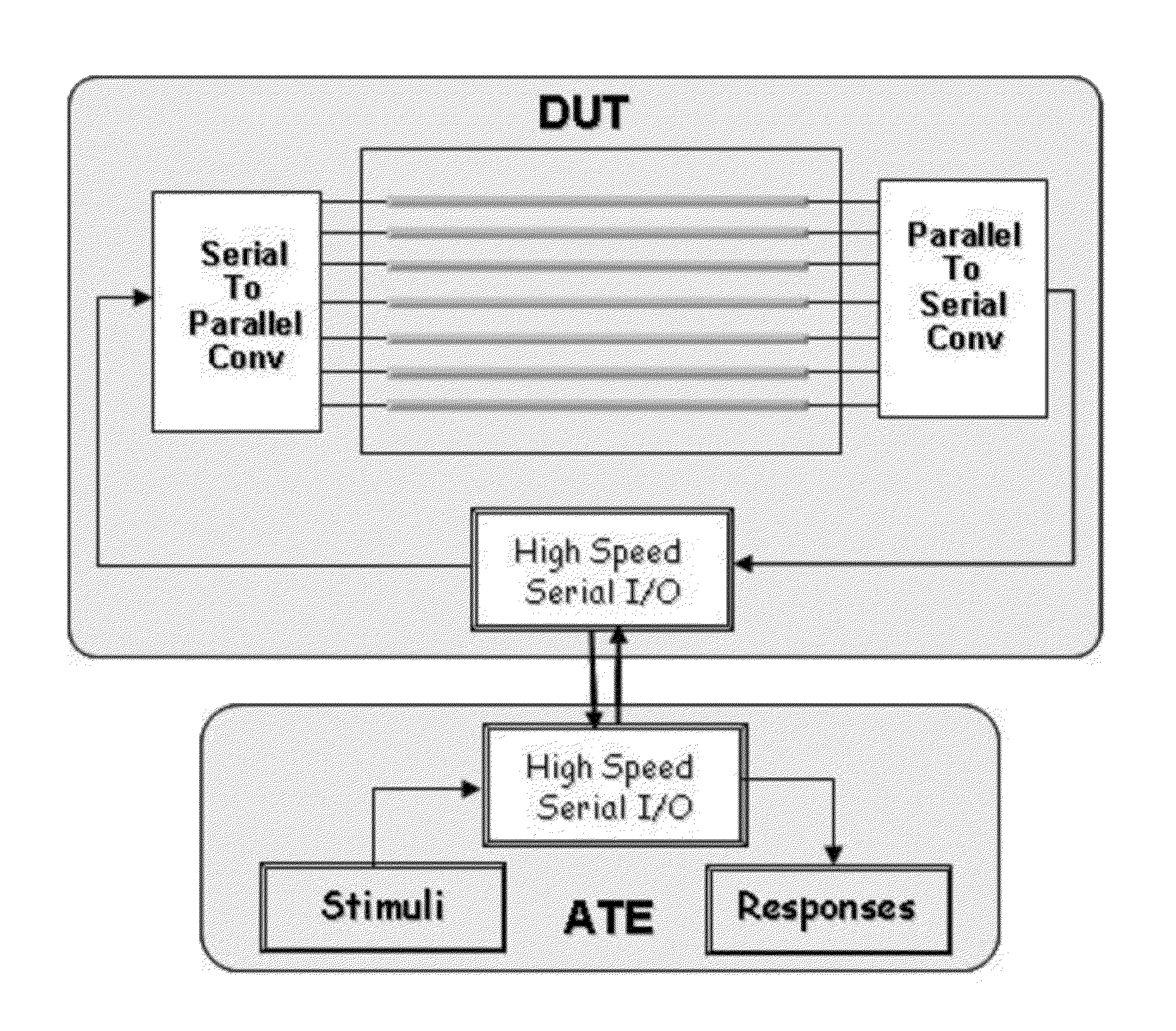

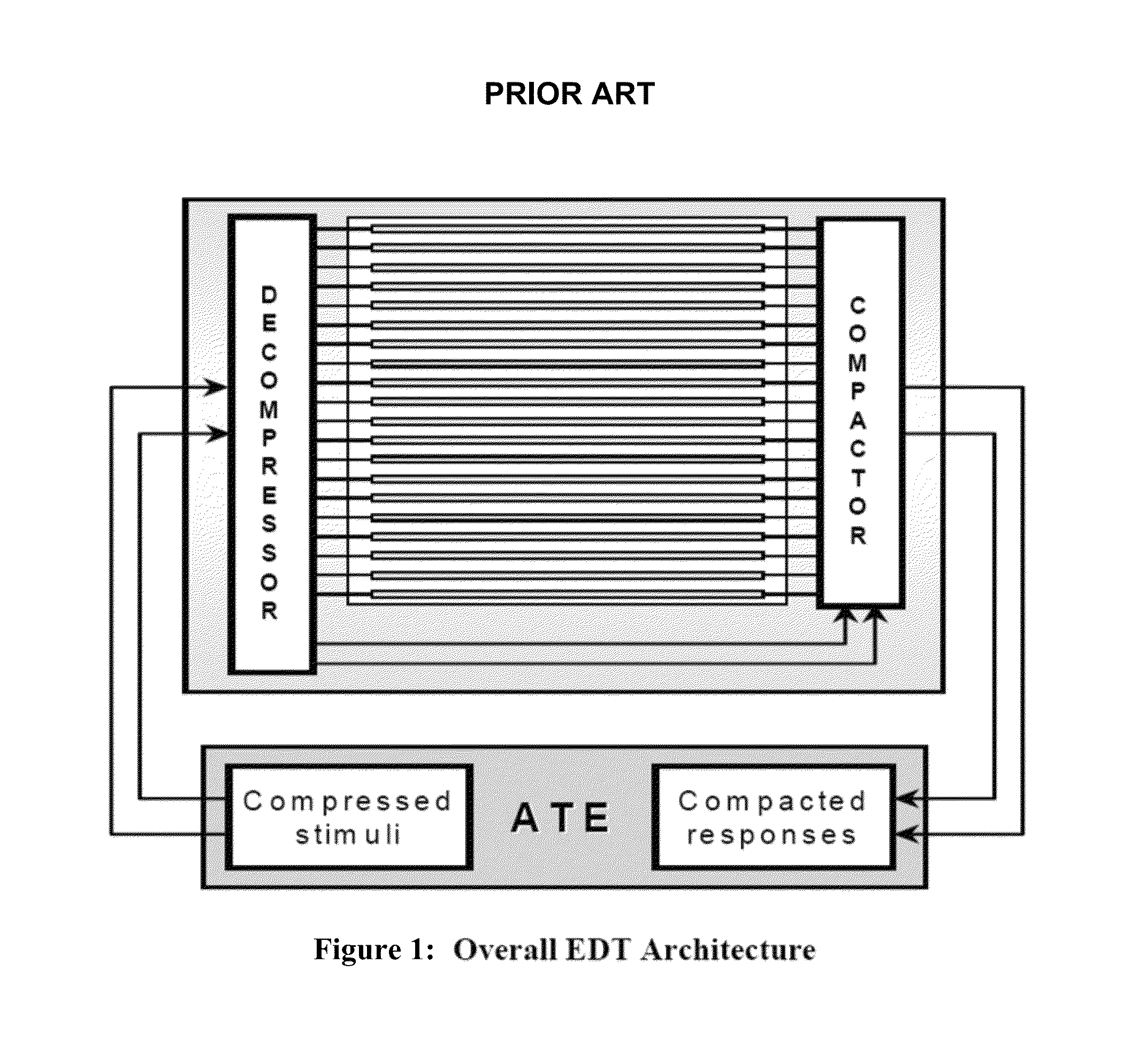

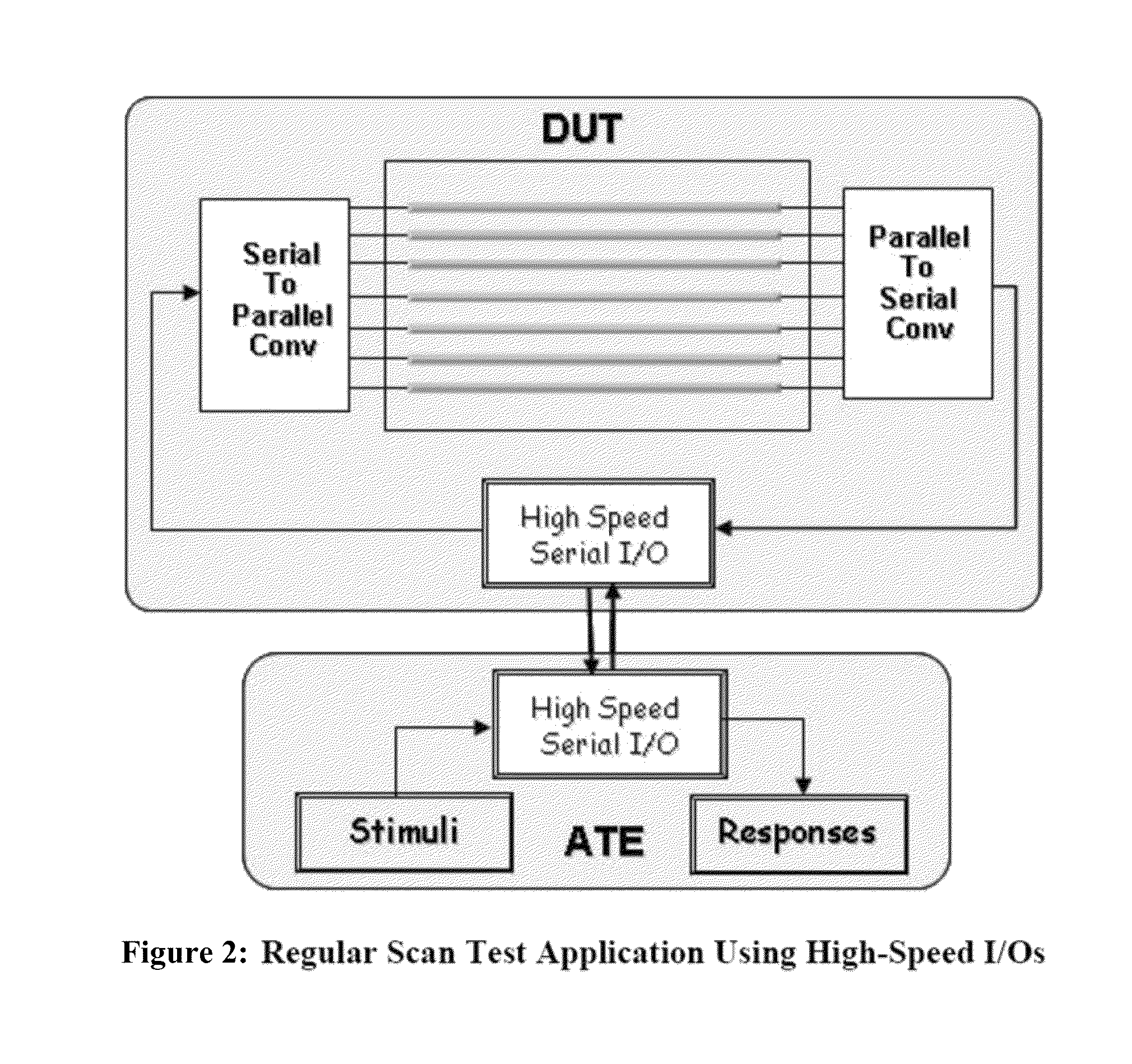

Scan test application through high-speed serial input/outputs

ActiveUS8726112B2Reduce test data volumeMinimize timeElectronic circuit testingData compressionAsynchronous operation

Methods and devices for using high-speed serial links for scan testing are disclosed. The methods can work with any scheme of scan data compression or with uncompressed scan testing. The protocol and hardware to support high speed data transfer reside on both the tester and the device under test. Control data may be transferred along with scan data or be partially generated on chip. Clock signals for testing may be generated on chip as well. In various implementations, the SerDes (Serializer / Deserializer) may be shared with other applications. The Aurora Protocol may be used to transport industry standard protocols. To compensate for effects of asynchronous operation of a conventional high-speed serial link, buffers may be used. The high-speed serial interface may use a data conversion block to drive test cores.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

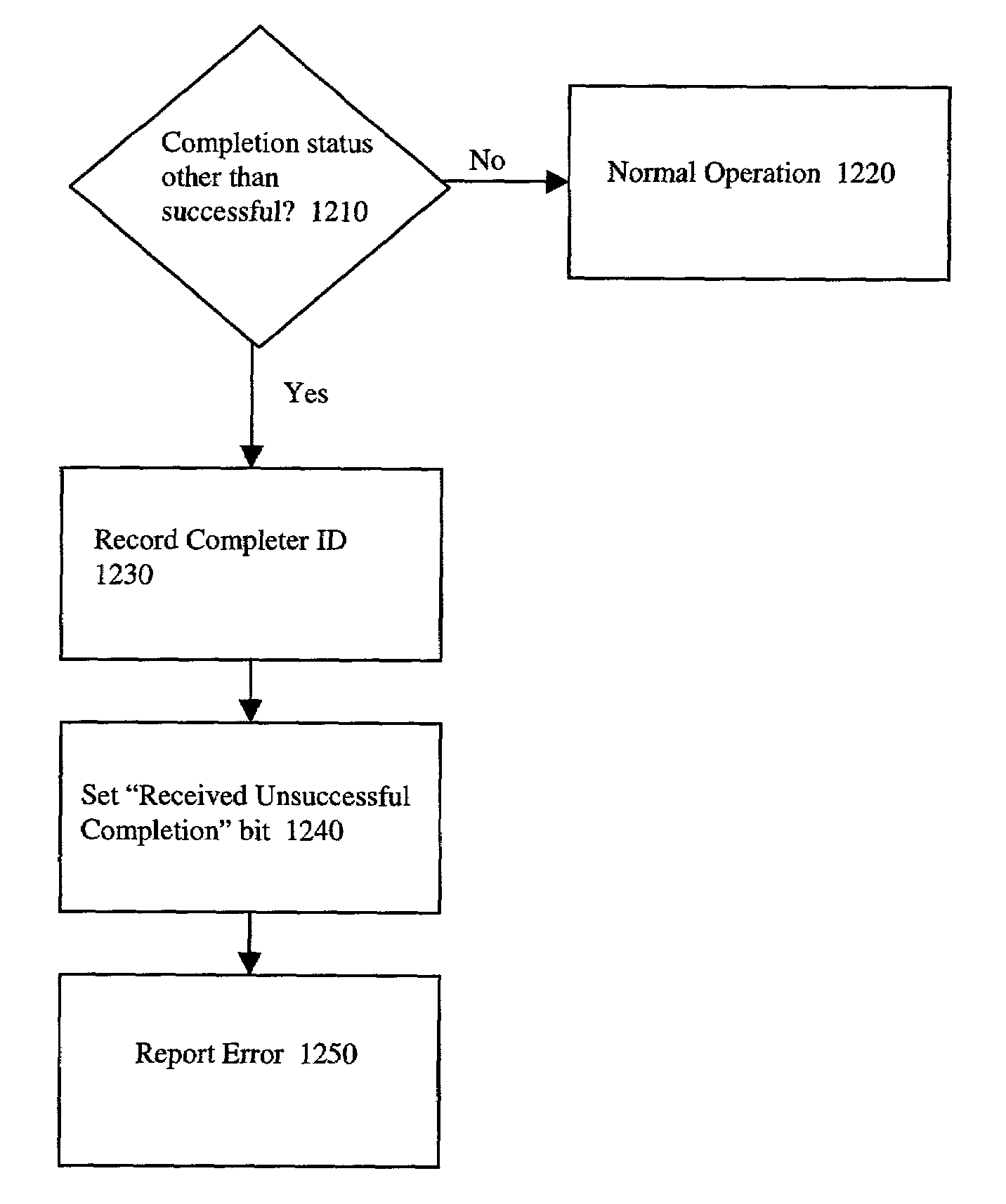

Method for handling completion packets with a non-successful completion status

A requesting device and a completer device are coupled via a high-speed serial interface within a computer system. The requesting device transmits a packet for a request transaction to a completer device. The completer device checks for error conditions in the course of servicing the request. If an error condition is found then the completer device transmits a completion packet with a completion status of something other than successful. The completion packet includes a completer identification field. The requesting device records the completer identification value and indicates in a register that a completion packet has been received with a non-successful completion status.

Owner:INTEL CORP

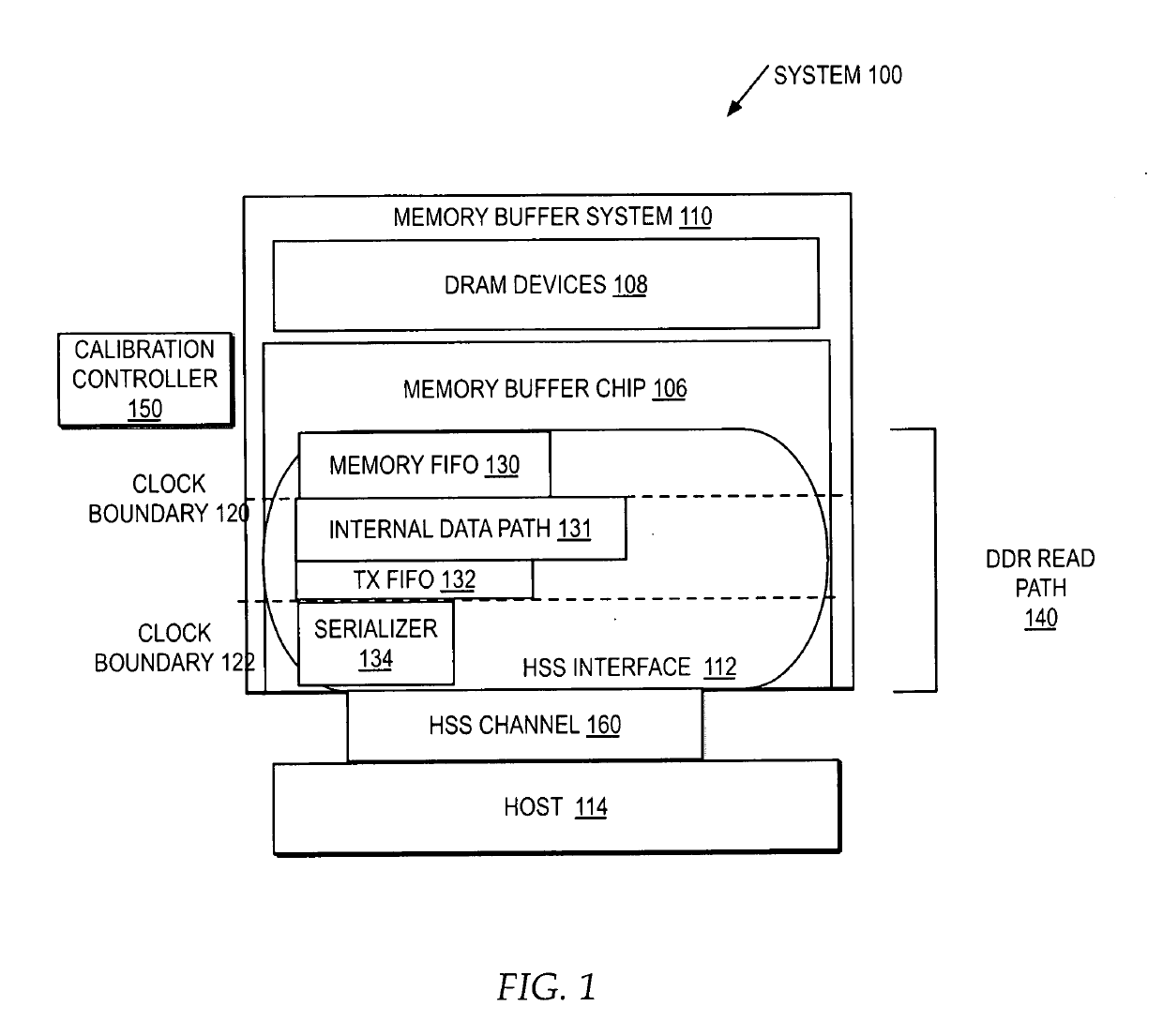

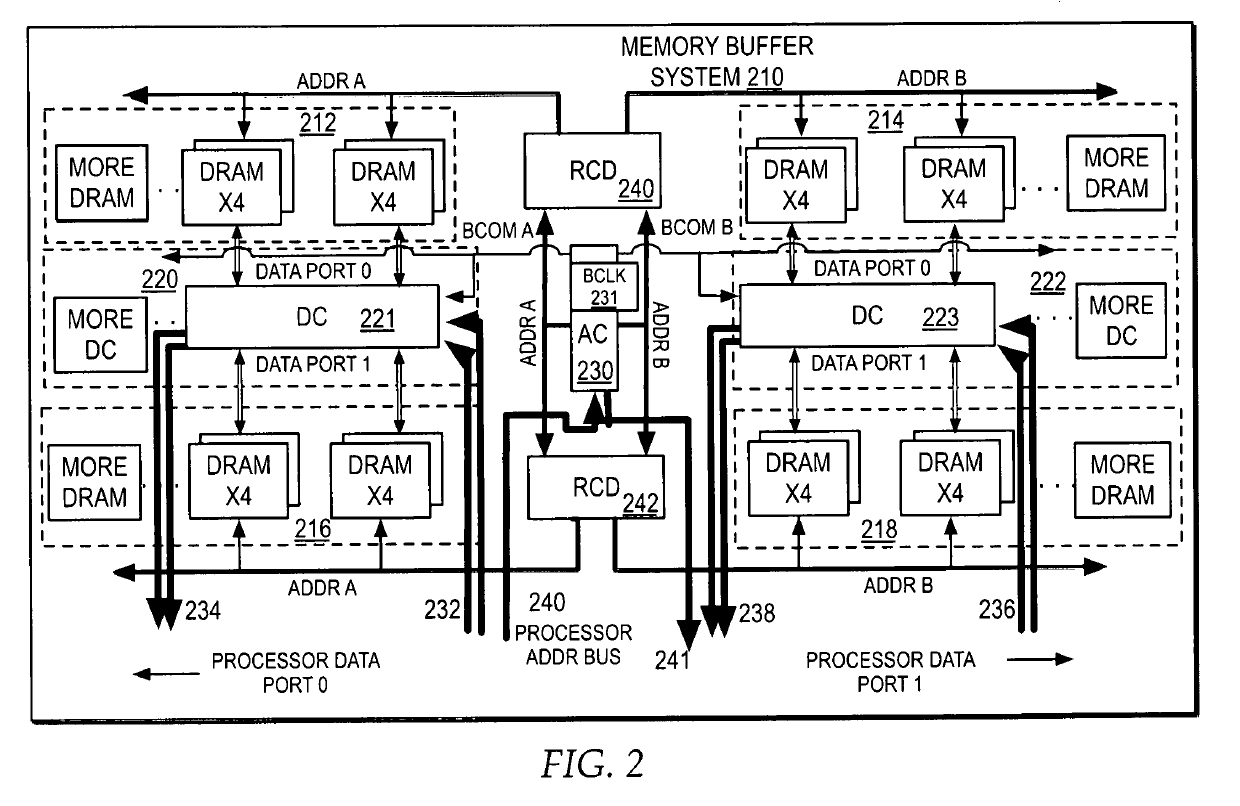

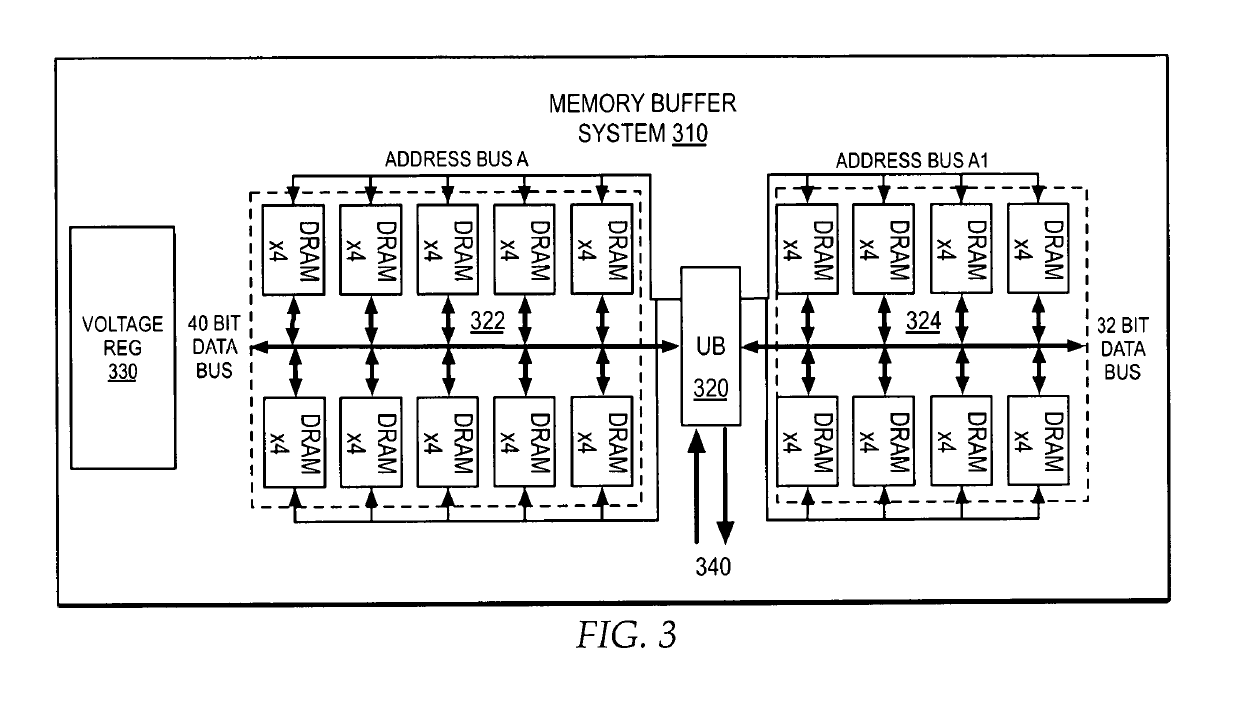

Reducing latency of memory read operations returning data on a read data path across multiple clock boundaries, to a host implementing a high speed serial interface

A calibration controller determines a latest arriving data strobe at a first data buffer in a read data path between at least one memory chip and a host on a high speed interface. The calibration controller aligns a chip clock distributed to a second data buffer in the read data path with the latest arriving data strobe, wherein data crosses a first clock boundary from the first data buffer to the second data buffer, to minimize a latency in the read data path across the first clock boundary. The calibration controller aligns the chip clock with a high speed clock for controlling an unload pointer to unload data from the second data buffer to a serializer in the read data path, wherein data crosses a second clock boundary from the second data buffer to the serializer, to minimize a latency in the read data path across a second clock boundary.

Owner:IBM CORP

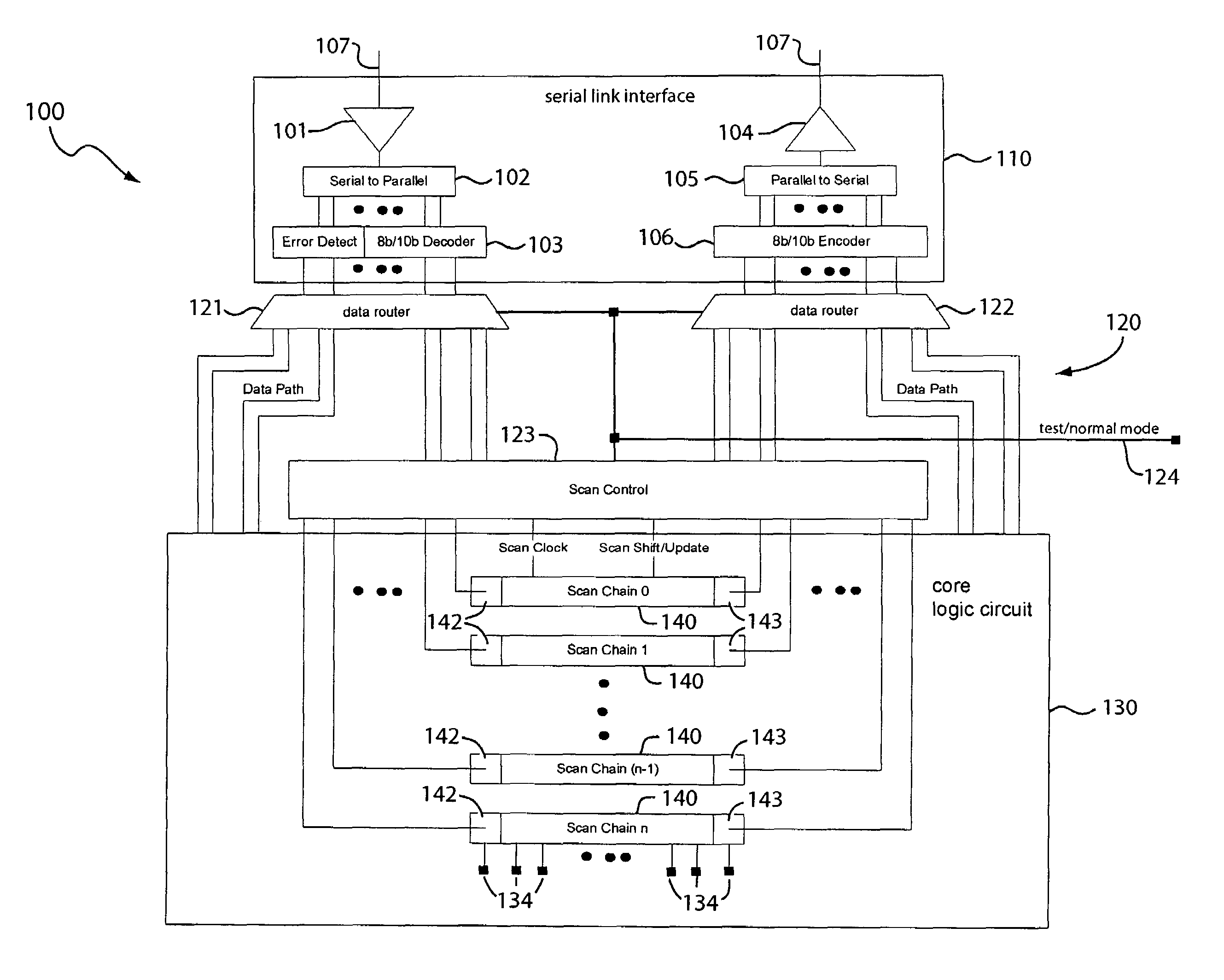

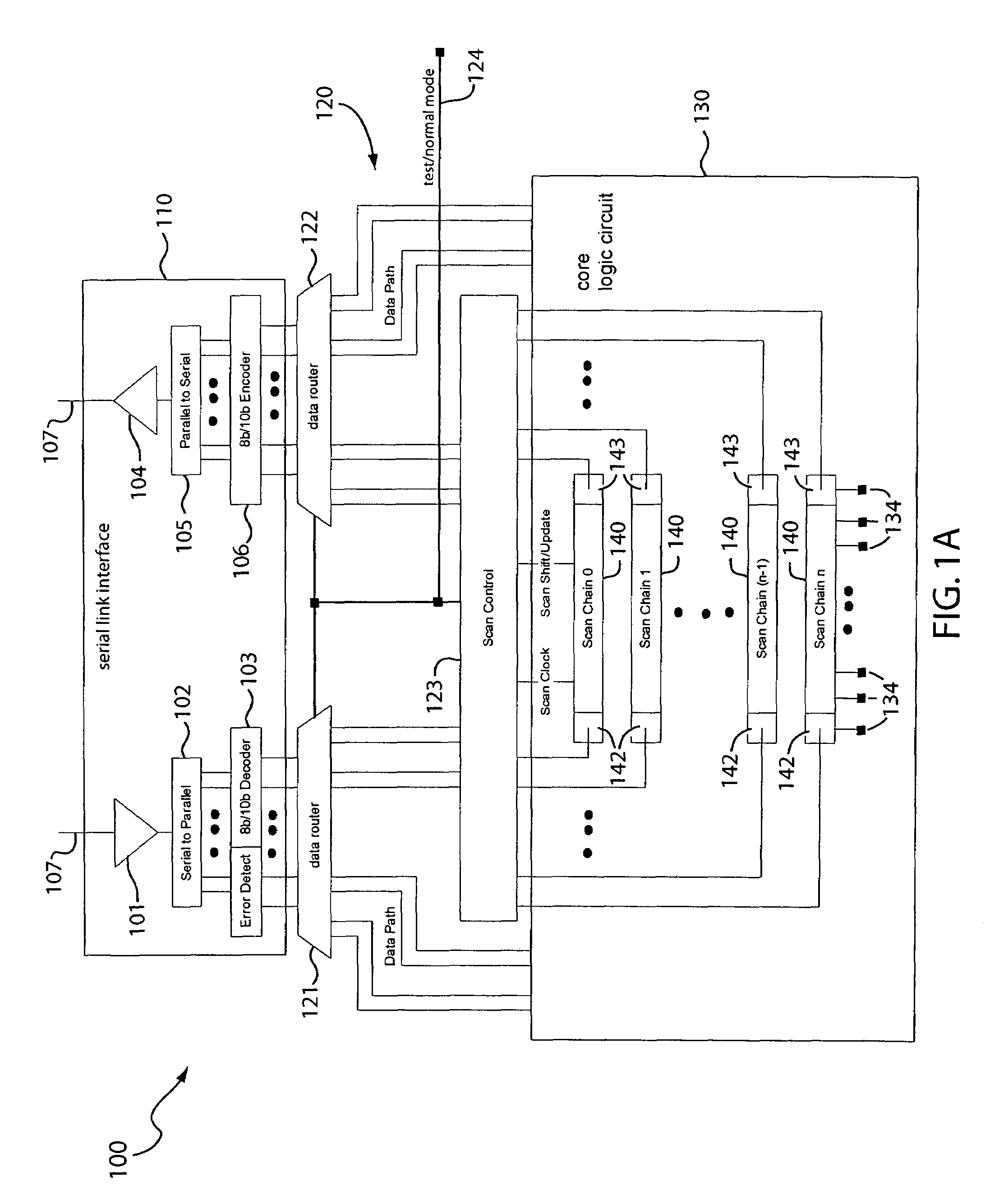

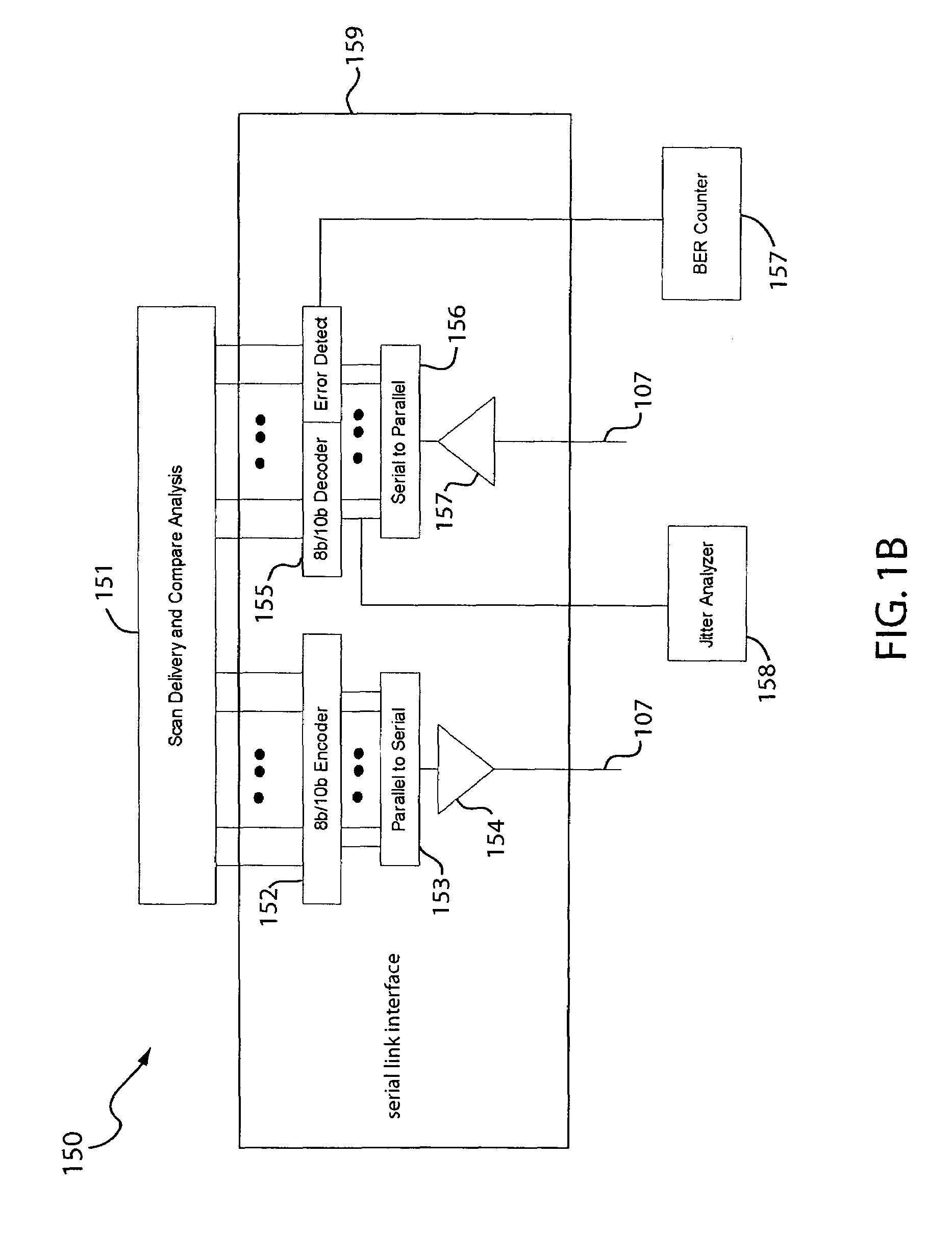

Scan testing of integrated circuits with high-speed serial interface

In one embodiment, an integrated circuit includes a serial link interface configured to send and receive data over a serial bus both during normal operation and during scan tests. The integrated circuit may include data routing circuitry for transferring data between the serial link interface and a scan chain during a scan test, and for transferring data between the serial link interface and a core logic circuit of the integrated circuit, without going through the scan chain, during normal operation. Scan data may be generated and analyzed by a tester integrated circuit coupled to the integrated circuit over the serial bus.

Owner:MONTEREY RES LLC

Communicating transaction types between agents in a computer system using packet headers including format and type fields

InactiveUS7581026B2Multiple digital computer combinationsInput/output processes for data processingComputer hardwareComputerized system

A transmitting device and a receiving device are coupled via a high-speed serial interface within a computer system. The transmitting device transmits a packet that includes a format field to partially specify the packet header format and a type field to specify a transaction type. The format field and the type field together specify the packet header format and the format field indicates the size of the packet header.

Owner:INTEL CORP

Multi-protocol low latency automatic speed negotiation architecture for an embedded high speed serial interface in a programmable logic device

ActiveUS7684477B1Transmission monitoringLine-transmission monitoring/testingDelayed periodsControl signal

A serial interface for a programmable logic device includes receiver and transmitter portions, and an automatic speed negotiation module to adjust the data rates of both portions. The speed adjustment may be accomplished by adjusting the widths of the data paths in both portions. The speed adjustment occurs on receipt of a control signal generated elsewhere on the programmable logic device, or generated by the module. One reason for generating the control signal is the detection of data errors in the received data, or the detection of a delimiter pattern in the received data signifying that a remote device is about to change its data rate.Similarly, before changing its data rate, the module may insert a delimiter in the data in the transmitter portion. After receipt or transmission of a delimiter pattern, the module may wait for a predetermined delay period to elapse before changing the data rate.

Owner:ALTERA CORP

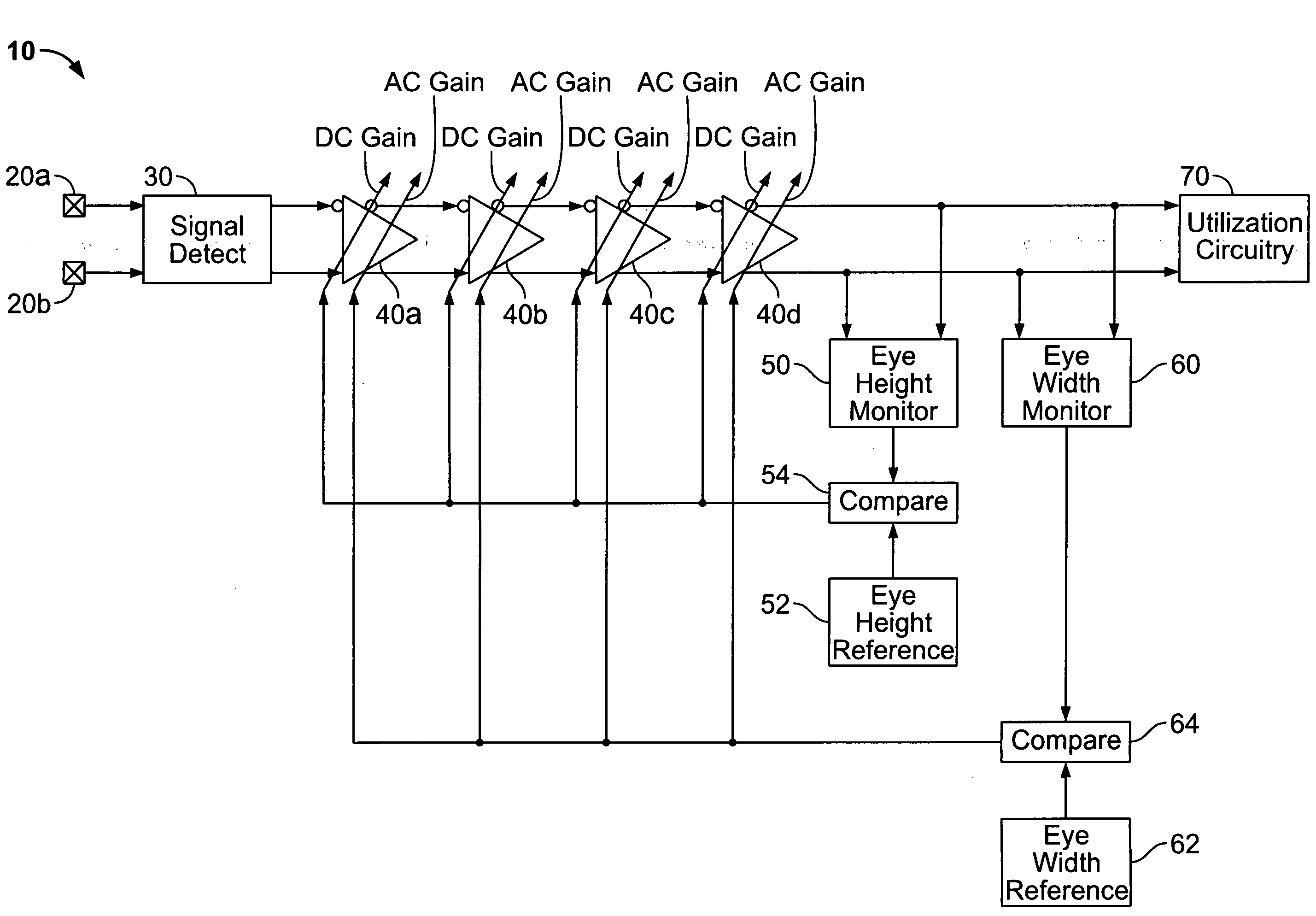

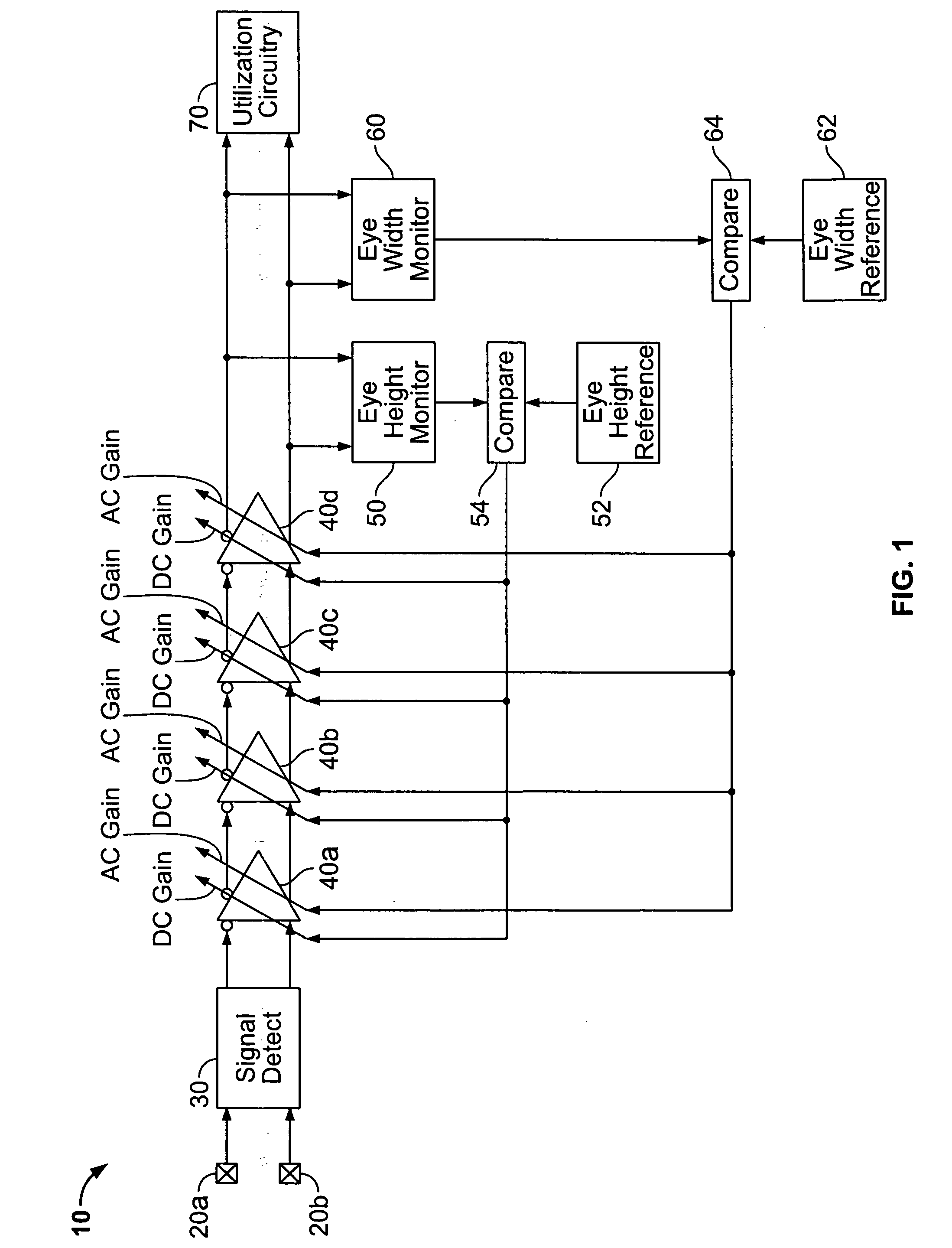

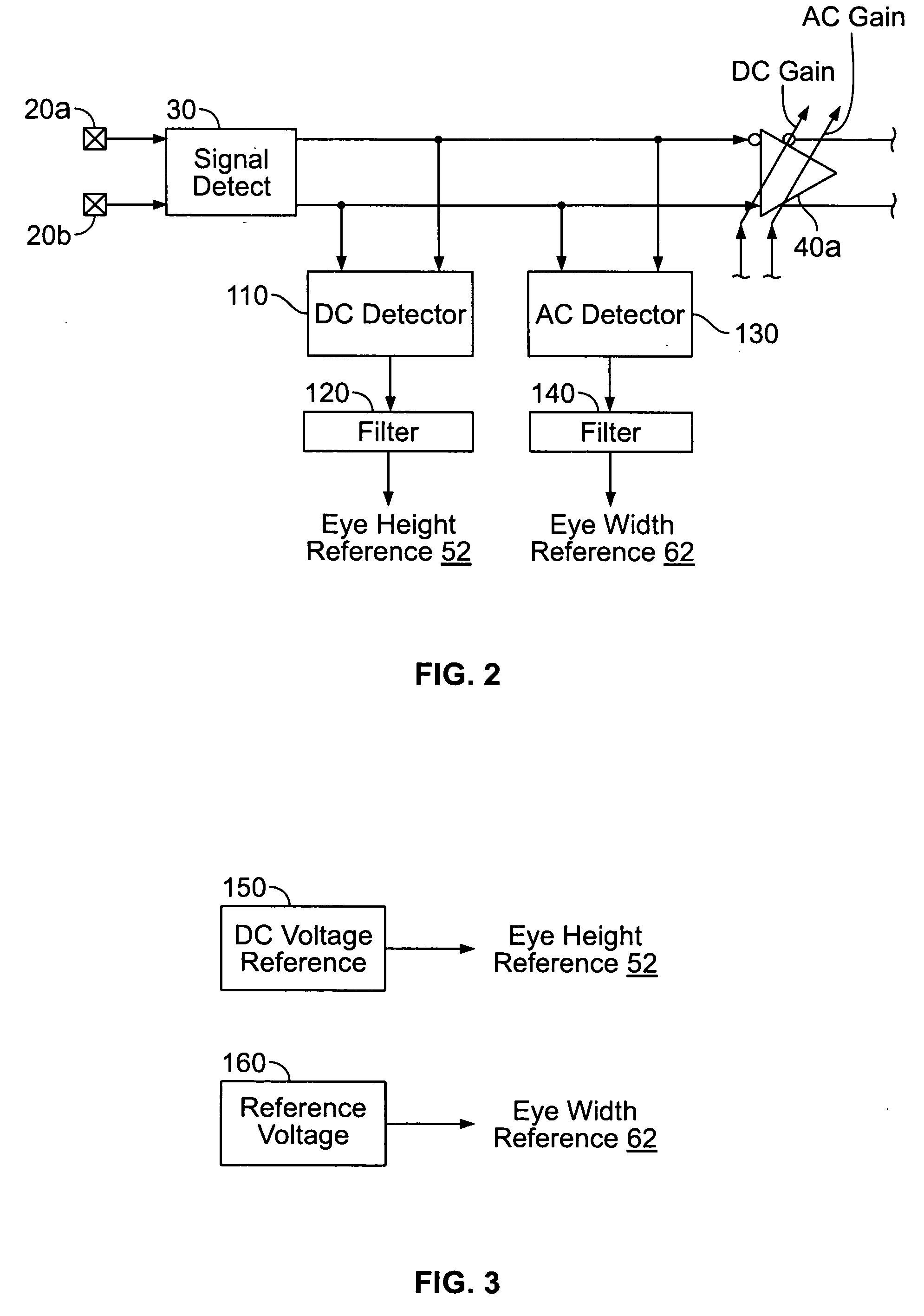

Automatic calibration in high-speed serial interface receiver circuitry

Circuitry for receiving a serial data signal (e.g., a high-speed serial data signal) includes adjustable equalizer circuitry for producing an equalized version of the serial data signal. The equalizer circuitry may include controllably variable DC gain and controllably variable AC gain. The circuitry may further include eye height and eye width monitor circuitry for respectively producing first and second output signals indicative of the height and width of the eye of the equalized version. The first output signal may be used in control of the DC gain of the equalizer circuitry, and the second output signal may be used in control of the AC gain of the equalizer circuitry.

Owner:ALTERA CORP

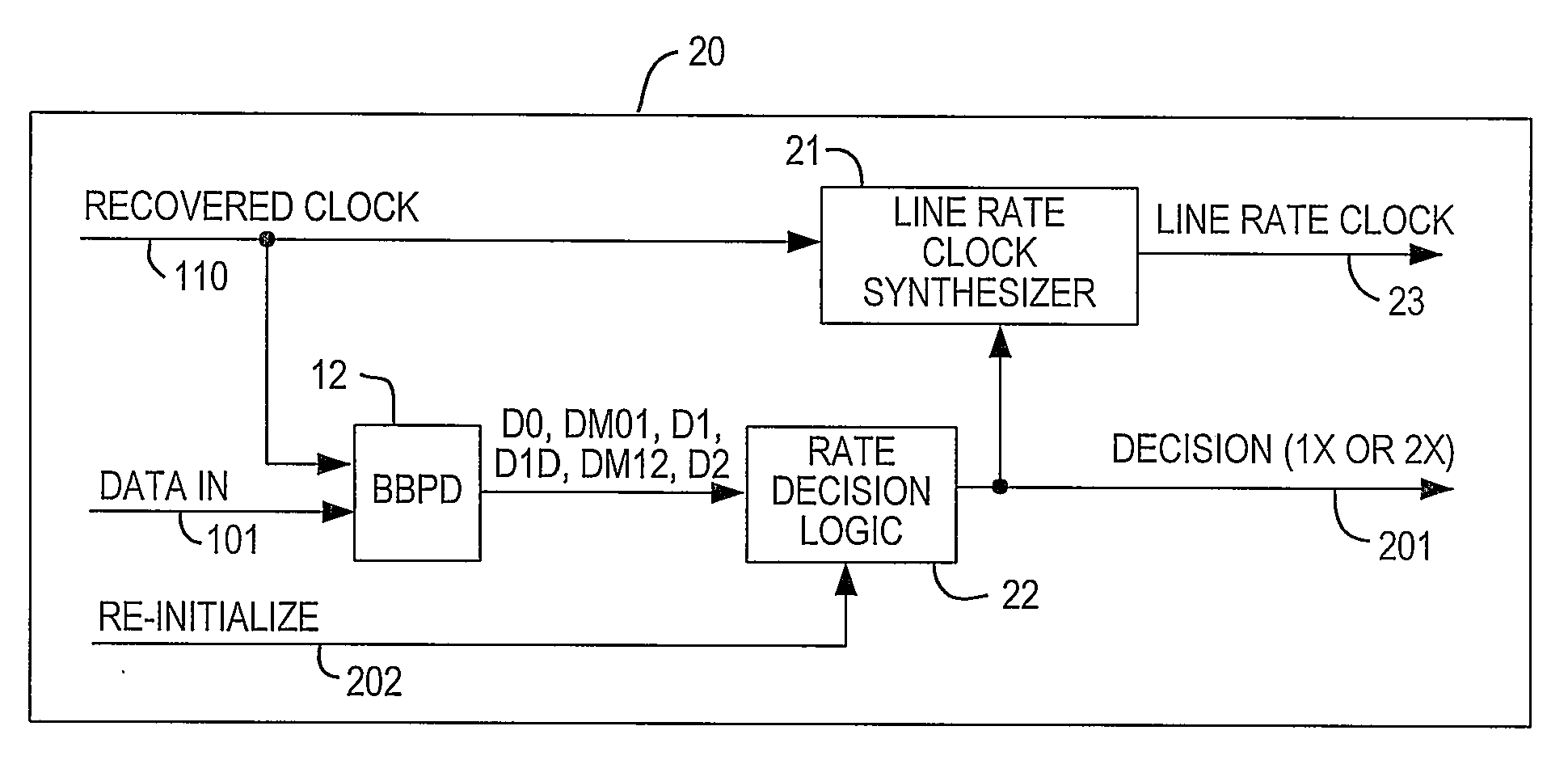

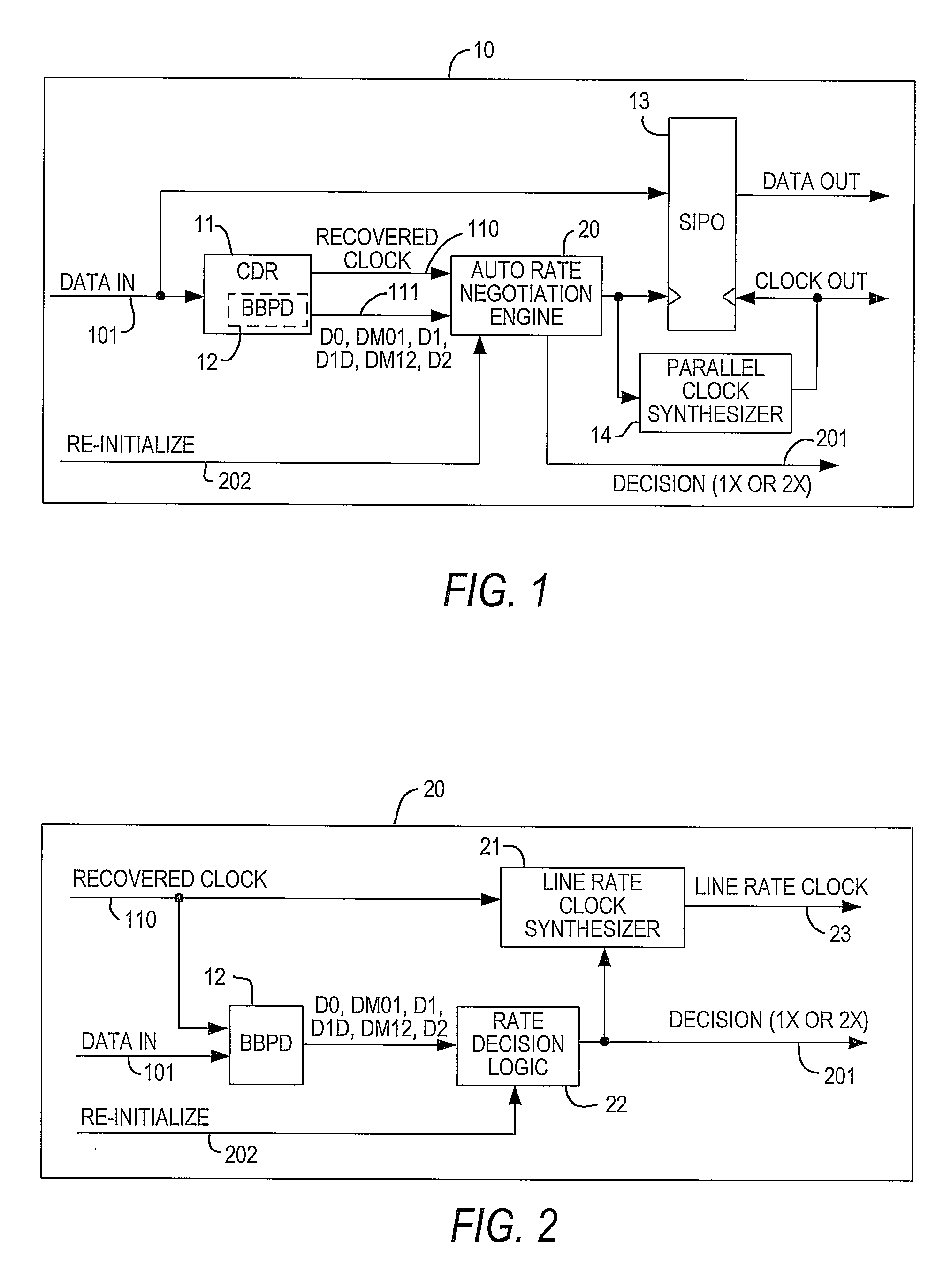

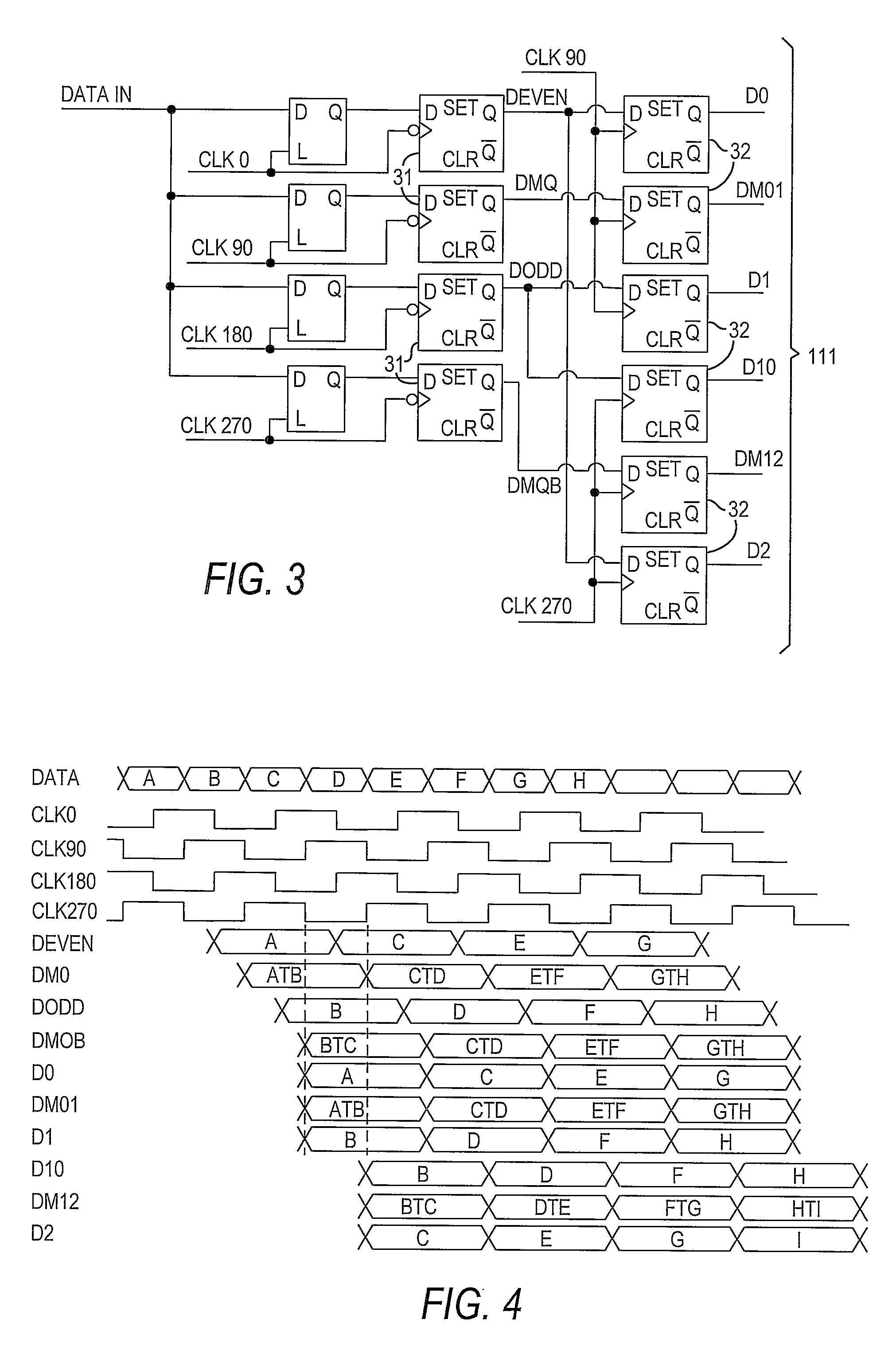

Protocol-agnostic automatic rate negotiation for high-speed serial interface in a programmable logic device

ActiveUS20080225933A1Transmission monitoringLine-transmission monitoring/testingProgrammable logic deviceBang bang phase detector

Automatic rate negotiation logic for a high speed serial interface in a programmable logic device determines whether multiple occurrences of a single-bit transition (i.e., a data transition from “0” to “1” to “0” or from “1” to “0” to “1”) occur within a predetermined time interval on a data channel of a high-speed serial interface. The interval preferably is selected such that multiple occurrences of a single-bit transition mean that the data channel is operating in full-rate mode. The rate negotiation logic may share a phase detector with clock data recovery circuitry in the interface. The phase detector may be a bang-bang phase detector specially adapted to detect single-bit transitions.

Owner:ALTERA CORP

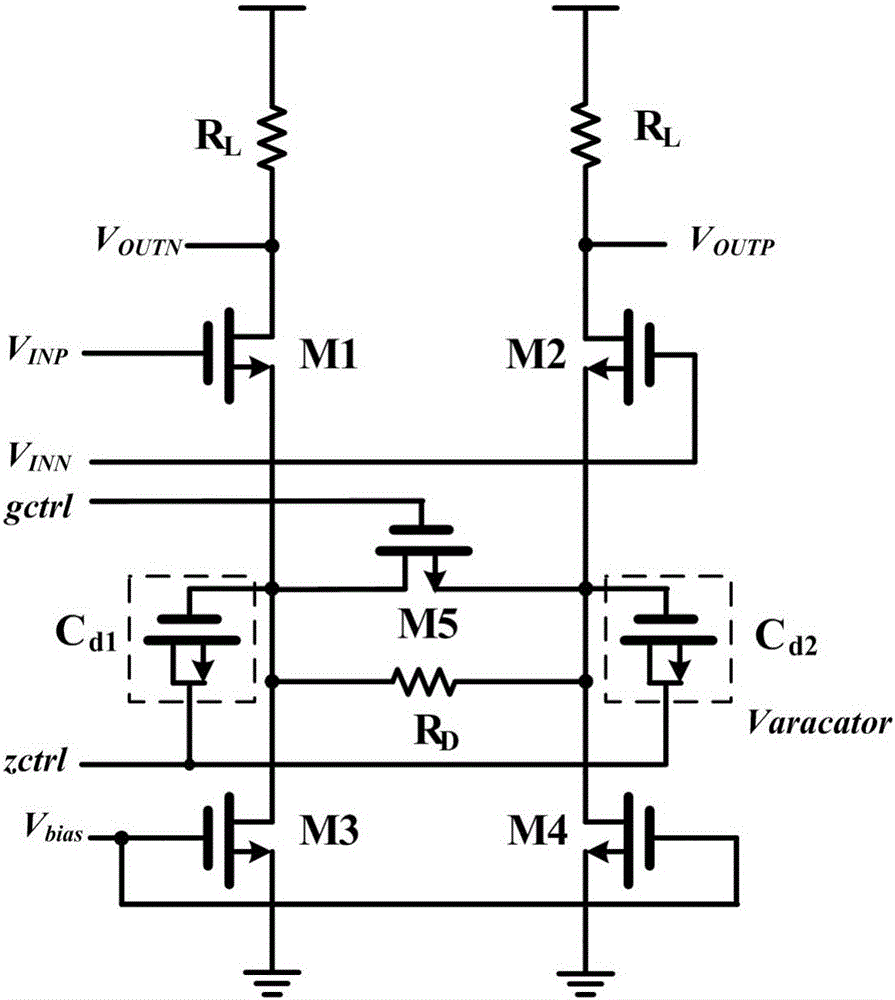

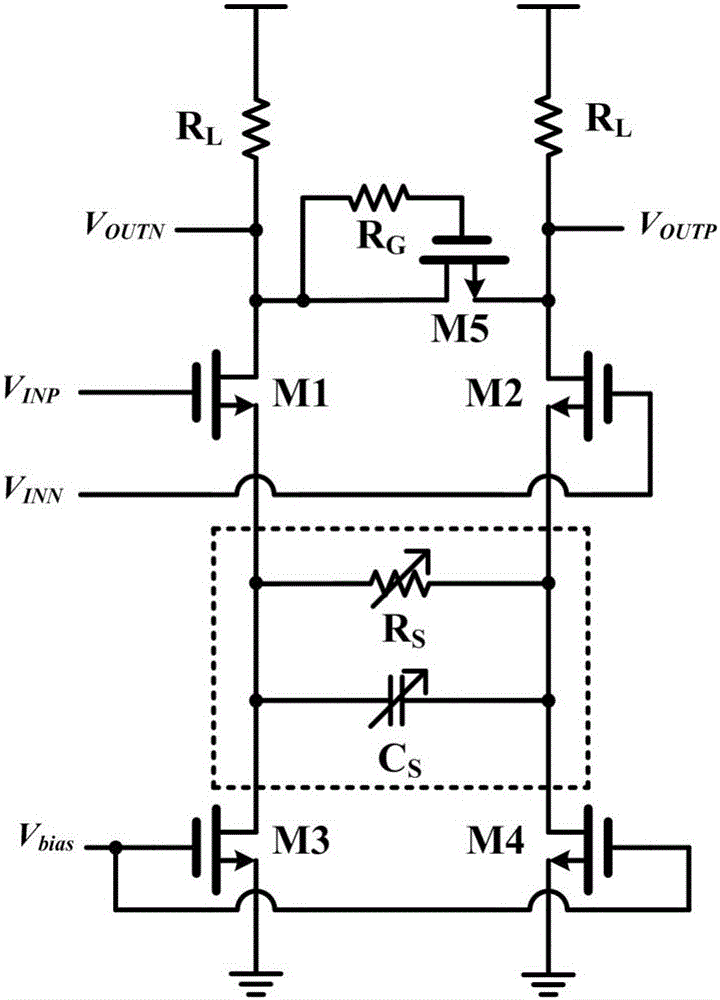

Linear equalizer applicable to high-speed serial interface

ActiveCN106209709AIncrease the frequency valueHigh bandwidthTransmitter/receiver shaping networksCapacitanceEngineering

The present invention relates to a linear equalizer applicable to a high-speed serial interface, comprising a differential input pair transistor consisting of a first NMOS transistor M1 and a second NMOS transistor M2, a bias current source consisting of a third NMOS transistor M3 and a fourth NMOS transistor M4, a pair of differential input signals VINP and VINN, and a pair of differential output signals VOUTP and VOUTN. The linear equalizer further comprises a capacitance-resistance negative feedback equalizer circuit consisting of a variable resistor RS and a variable capacitor CS and an active inductor consisting of a resistor RG and a fifth NMOS transistor M5, which form an output load together with two load resistors RL. According to the linear equalizer applicable to a high-speed serial interface, an active inductor can generate a null point higher than channel bandwidth, and provide broader bandwidth and a greater high-frequency gain in a high-speed serial data transmission process, so that equalizer performance is improved, and a chip area of an integrated circuit chip is effectively reduced, thereby reducing power consumption.

Owner:58TH RES INST OF CETC

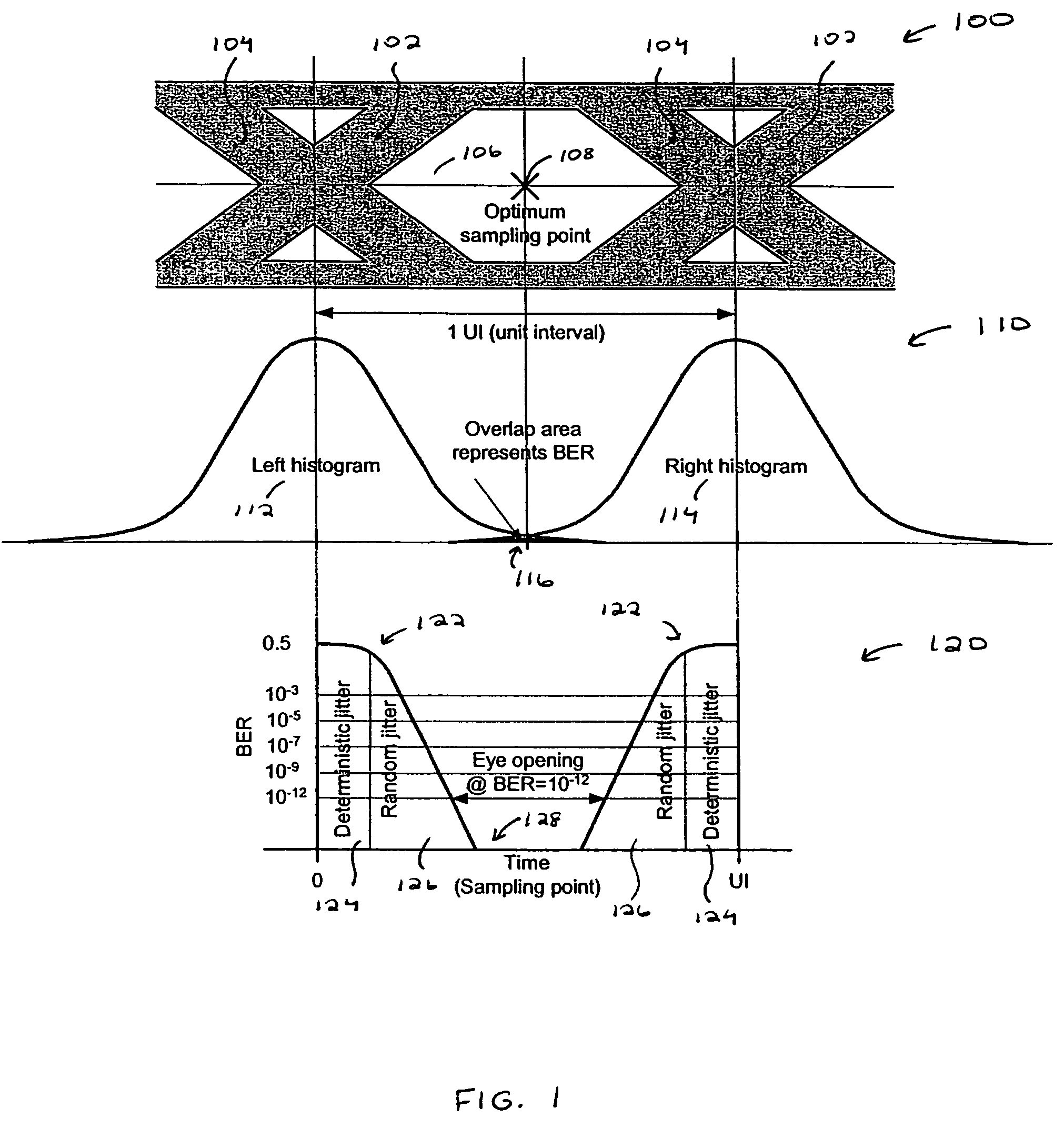

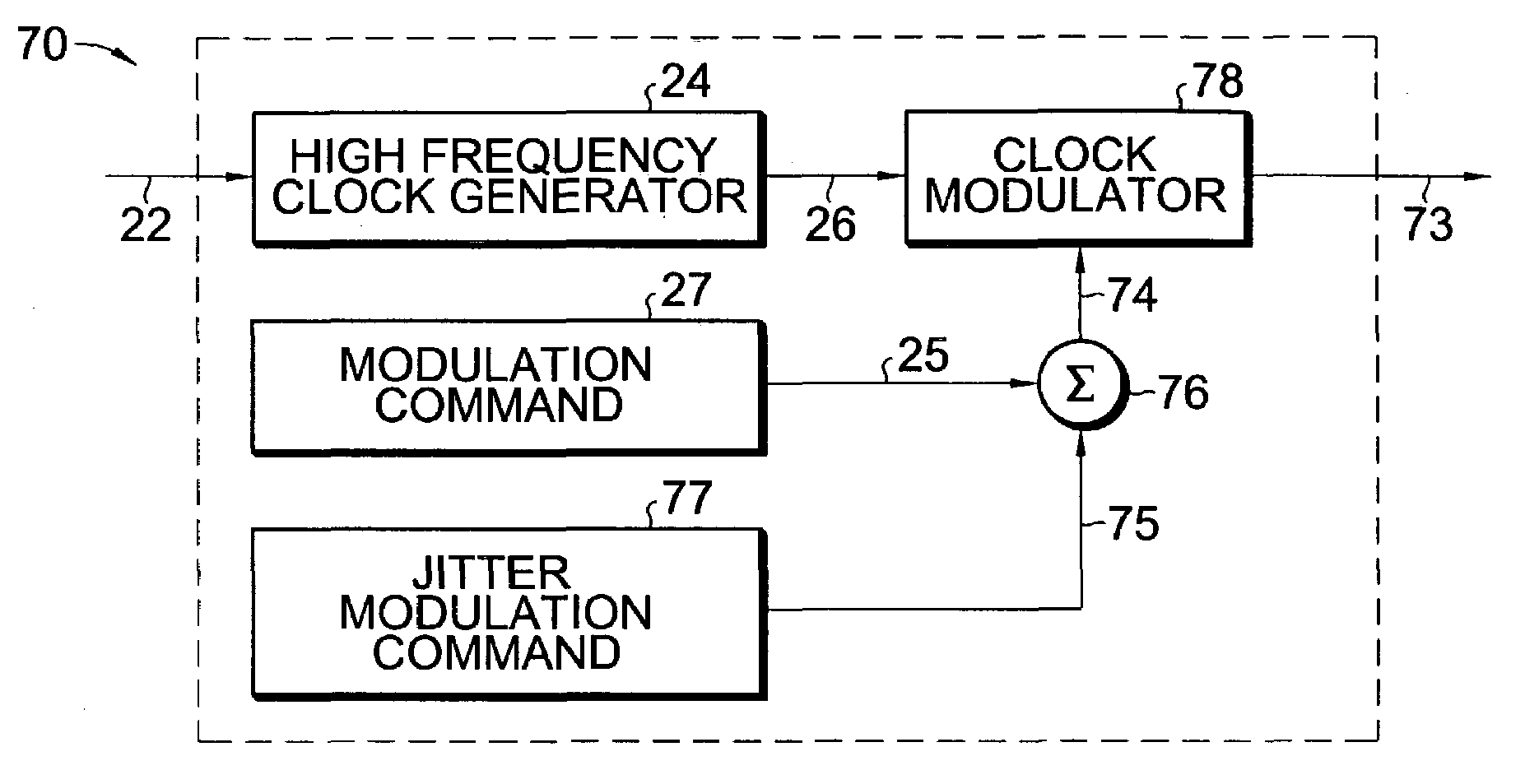

Integrated data jitter generator for the testing of high-speed serial interfaces

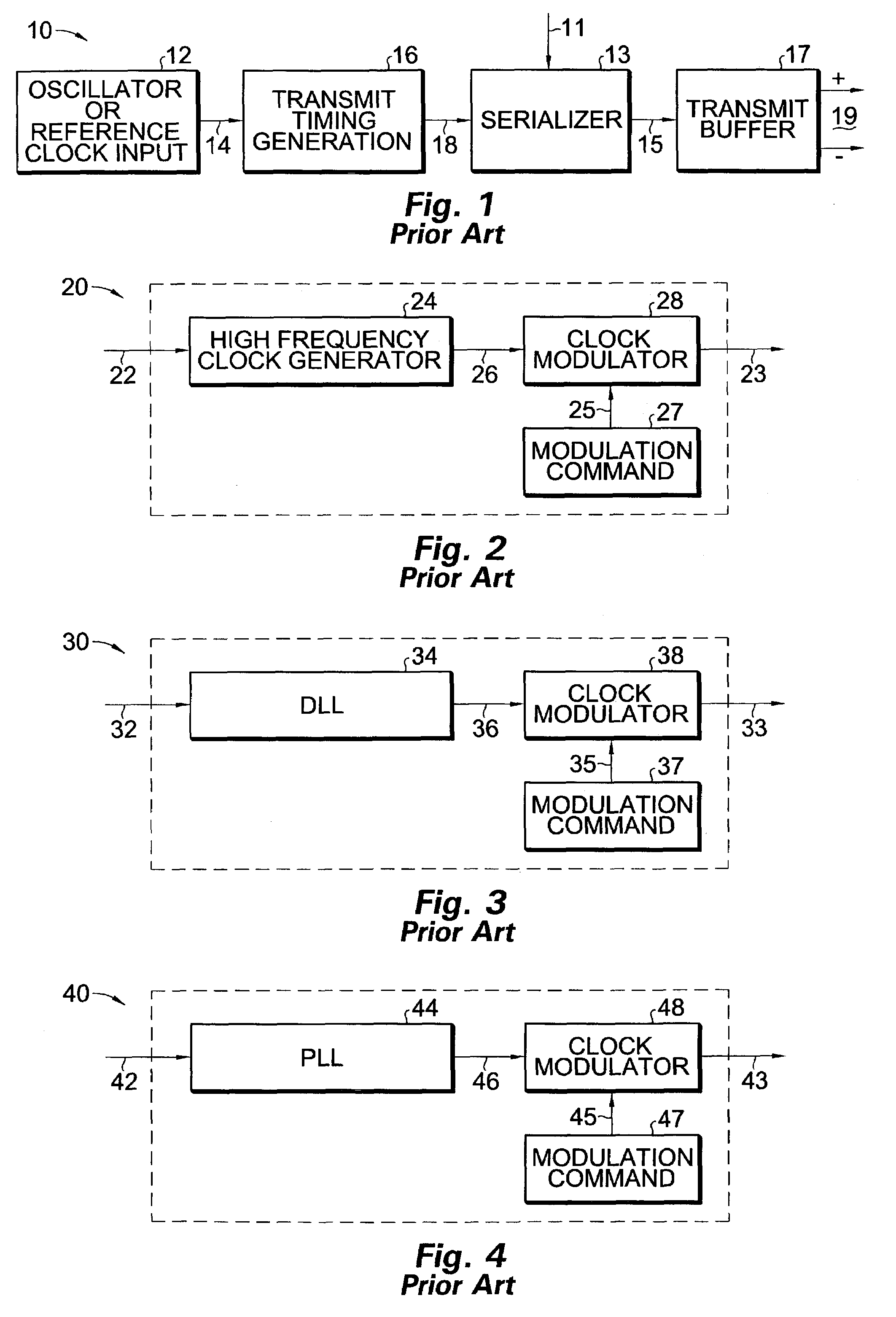

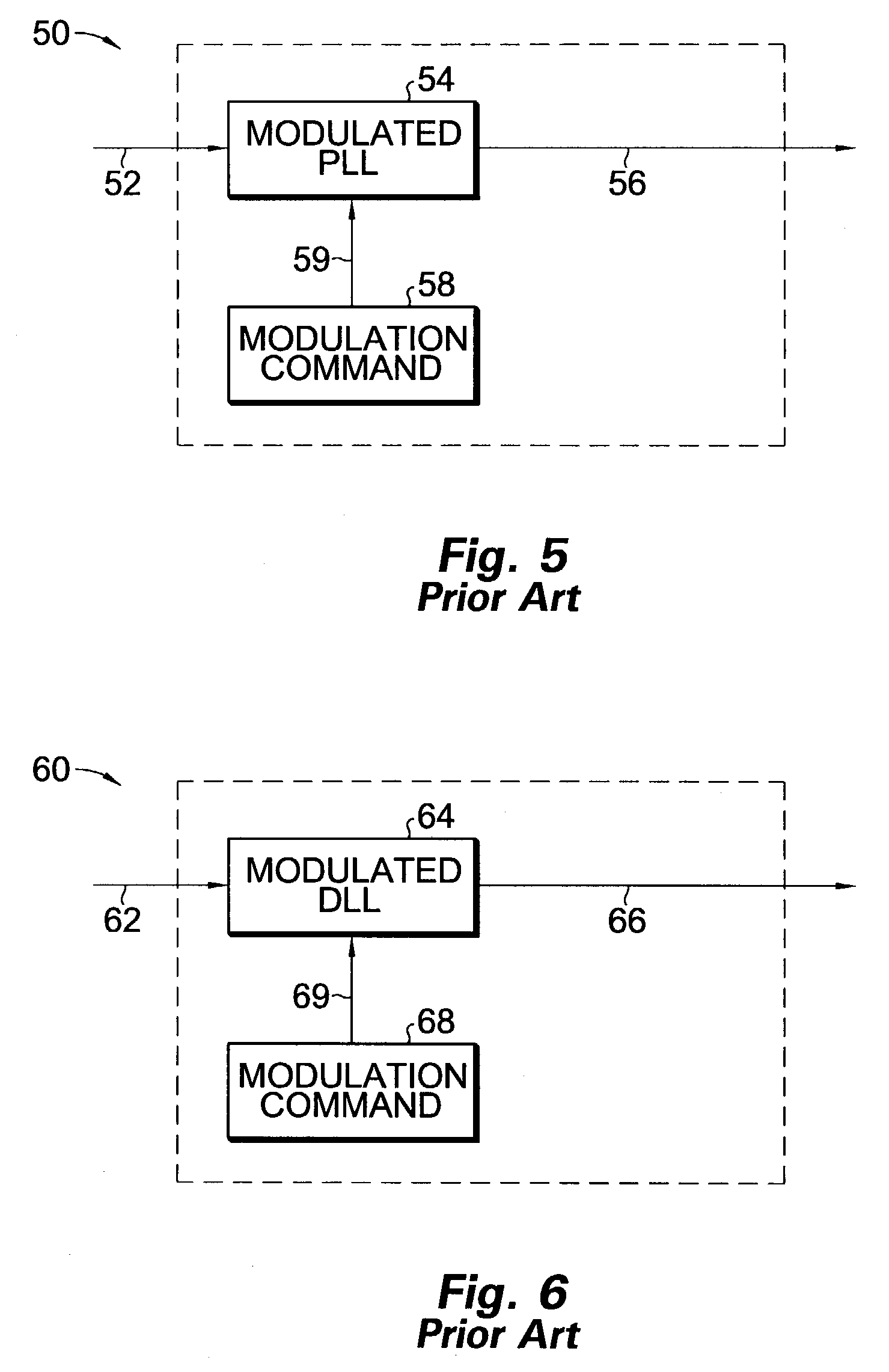

ActiveUS7230981B2Convenient jitter testing abilityMinimal cost impactAmplitude modulation detailsError detection/prevention using signal quality detectorDelay-locked loopDatapath

An integrated data jitter generator for the testing of high speed serial interfaces is provided. A transmit timing generator for use in a transmit data path includes a high frequency clock generator such as a phase-locked loop or a delay-locked loop having an input for receiving an oscillator or reference clock input. A clock modulator receives both an existing low frequency modulation signal and a high frequency modulation signal. A high-speed modulated clock signal is generated to enable jitter testing by a downstream-coupled receiver. Fixed frequencies such as 3, 6, 125, 150, 250, 300, 750, or 1500 MHz are used for the high-speed modulation signal, but any high-speed modulation frequency can be used to generate the desired amount of jitter. Likewise, the amplitude of the high frequency modulation signal can also be varied as desired.

Owner:STMICROELECTRONICS SRL

Navigation system utilizing portable and adjustable heads up display

InactiveUS20070146235A1Minimal distractionCathode-ray tube indicatorsNavigation instrumentsMicrocontrollerHead-up display

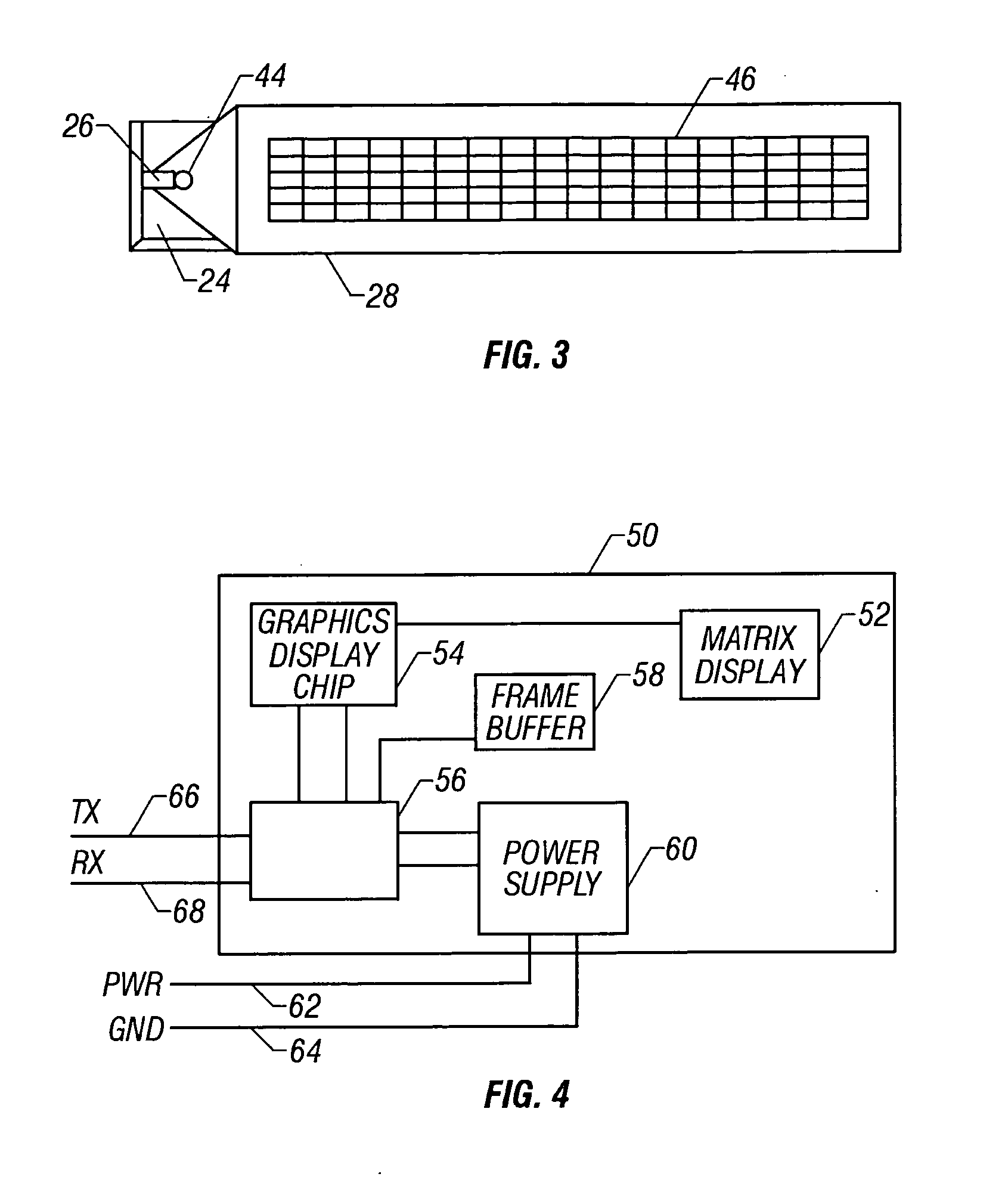

A navigation system with a portable heads up display (HUD). The HUD comprises a housing rotably mounted on a stand. The housing holds a device for generating an image that can be projected onto a vehicle windshield, for example a vacuum fluorescent display (VFD) module. Preferably, the navigation system is a NavMate® Navigation System from Visteon Technologies LLC, and the HUD is operatively connected to the navigation system by a high speed serial interface, for example an RS232 interface. An exemplary HUD includes a microcontroller, frame buffer, and a graphic display module. A preferred image generator is a Futaba GP1045A02A graphic display module.

Owner:TOMTOM INT BV