Patents

Literature

555 results about "Dummy data" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In Informatics, dummy data is benign information that does not contain any useful data, but serves to reserve space where real data is nominally present. Dummy data can be used as a placeholder for both testing and operational purposes. For testing, dummy data can also be used as stubs or pad to avoid software testing issues by ensuring that all variables and data fields are occupied. In operational use, dummy data may be transmitted for OPSEC purposes. Dummy data must be rigorously evaluated and documented to ensure that it does not cause unintended effects.

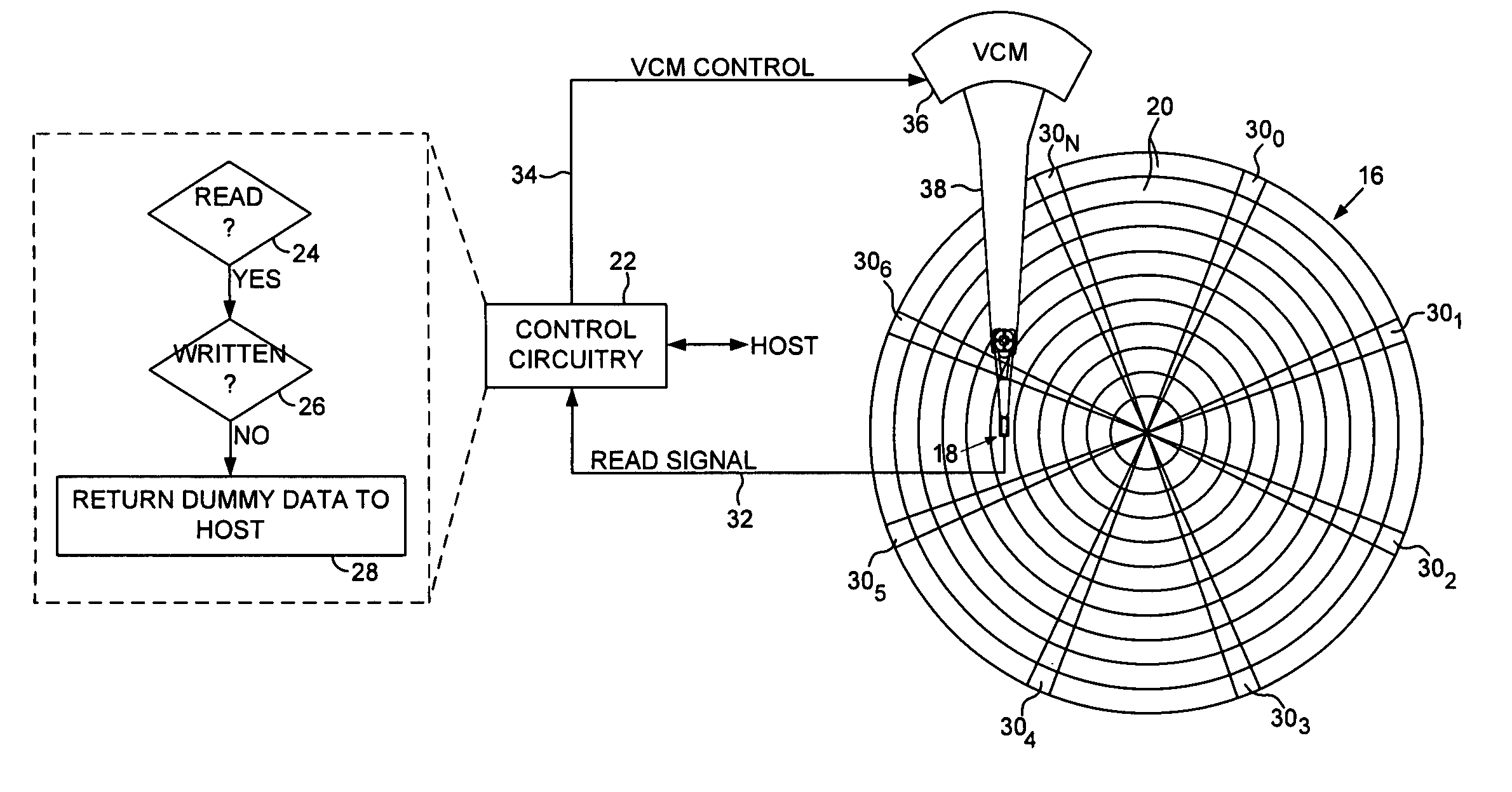

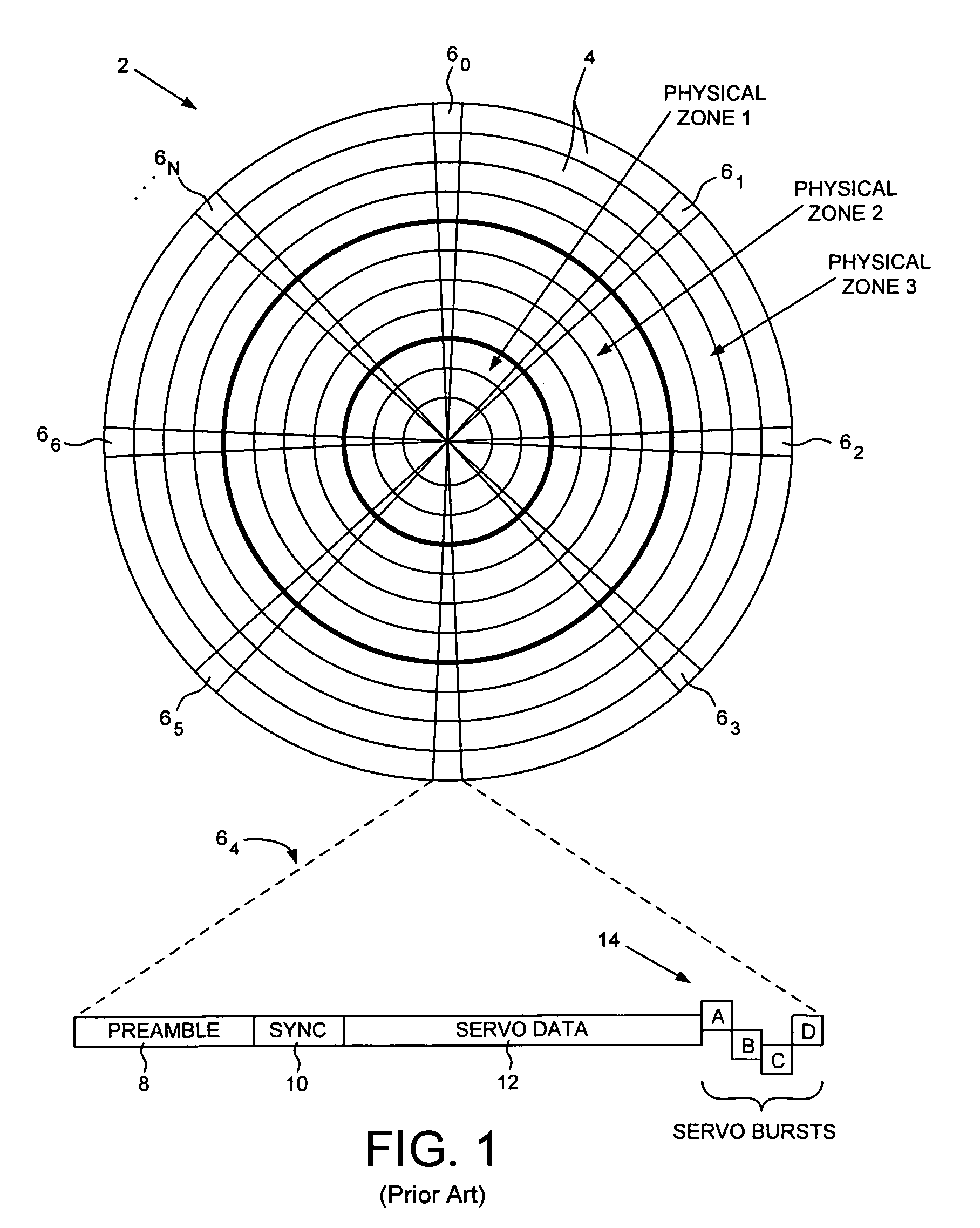

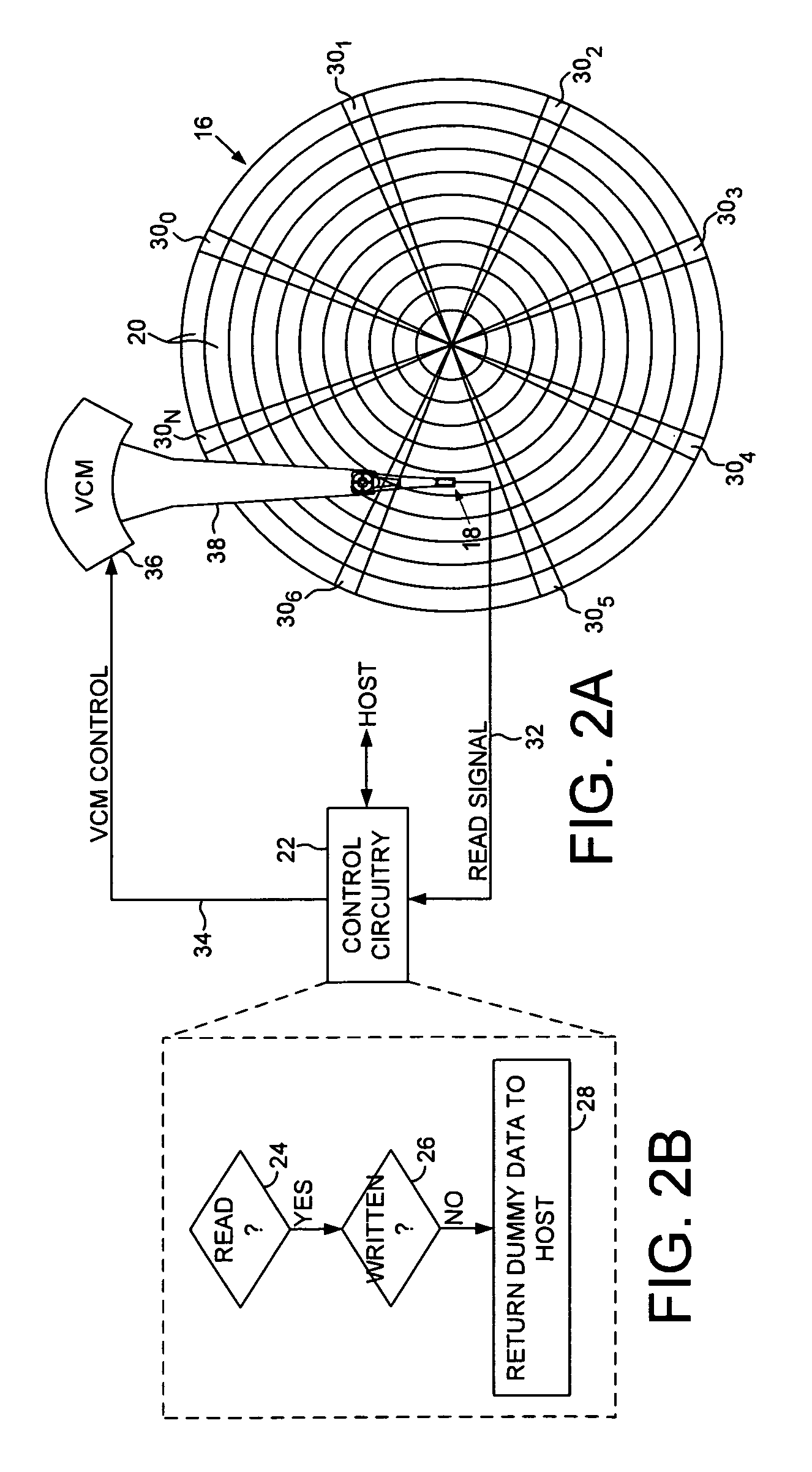

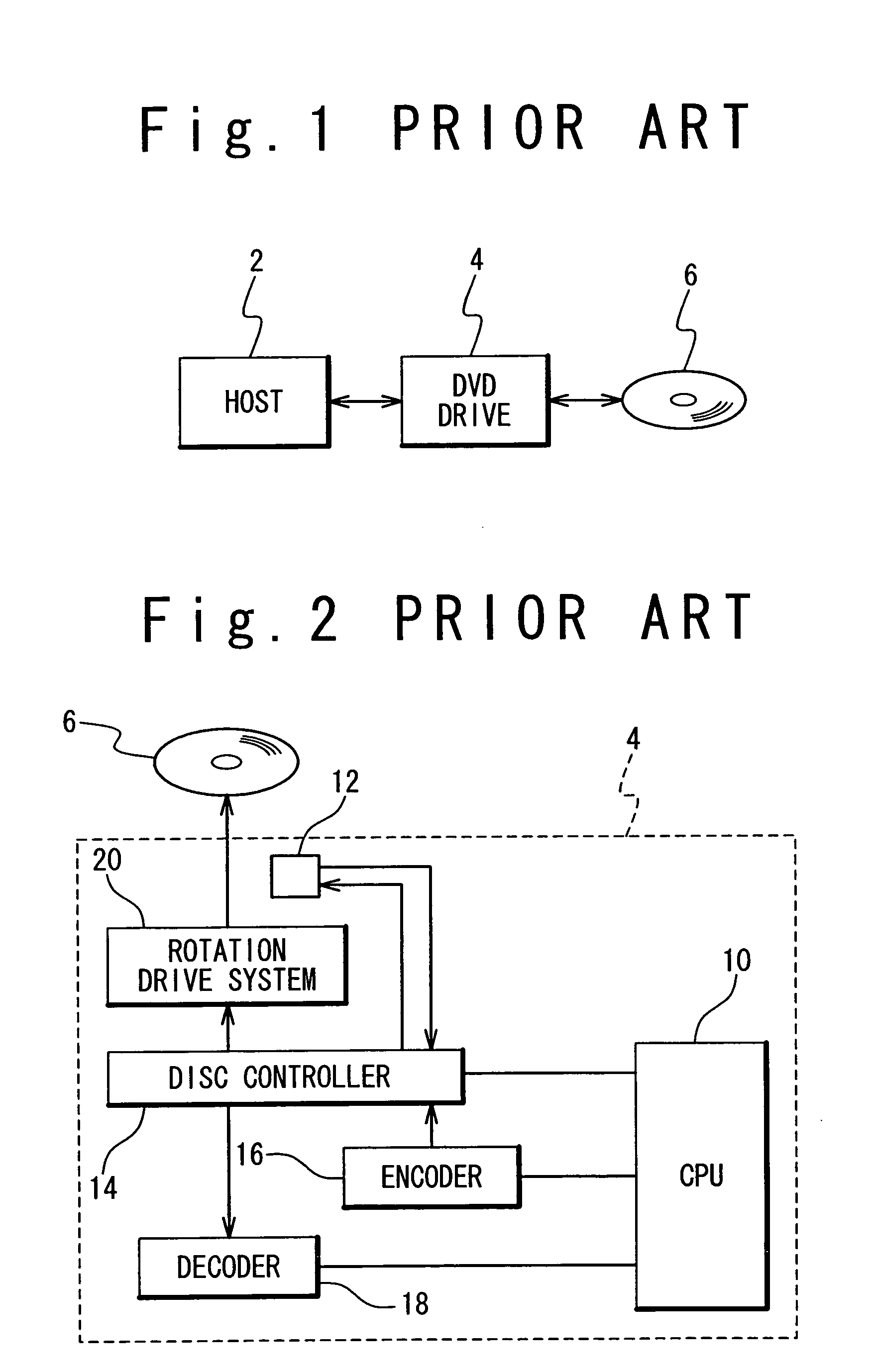

Disk drive returning dummy data to a host when reading an unwritten data sector

InactiveUS7852596B2Disc-shaped record carriersDriving/moving recording headsDummy dataOperating system

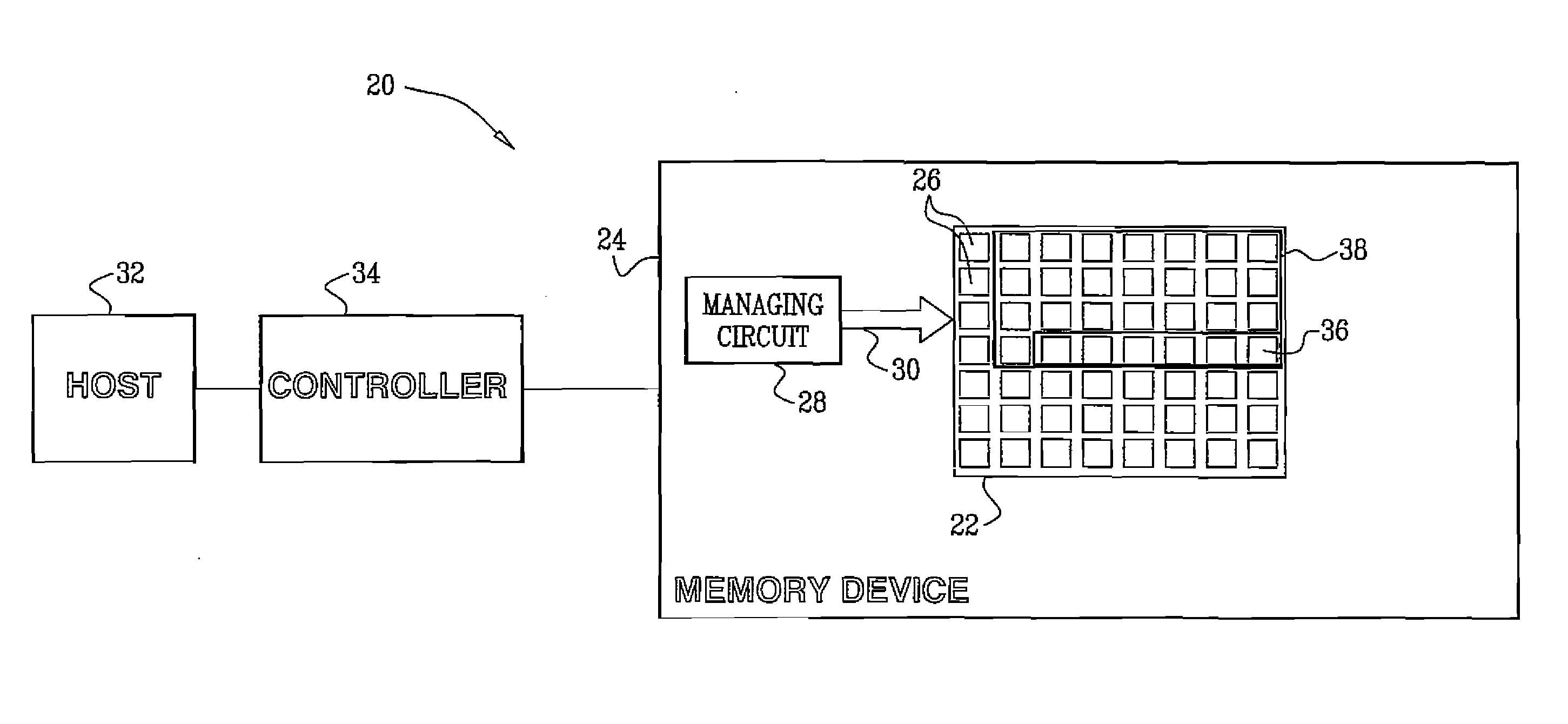

A disk drive is disclosed comprising a disk and a head actuated over the disk. The disk comprises a plurality of tracks, wherein each track comprises a plurality of data sectors. A read command is received from a host to read data from a target data sector. When it is determined that the target data sector has not been written by the host, dummy data is returned to the host.

Owner:WESTERN DIGITAL TECH INC

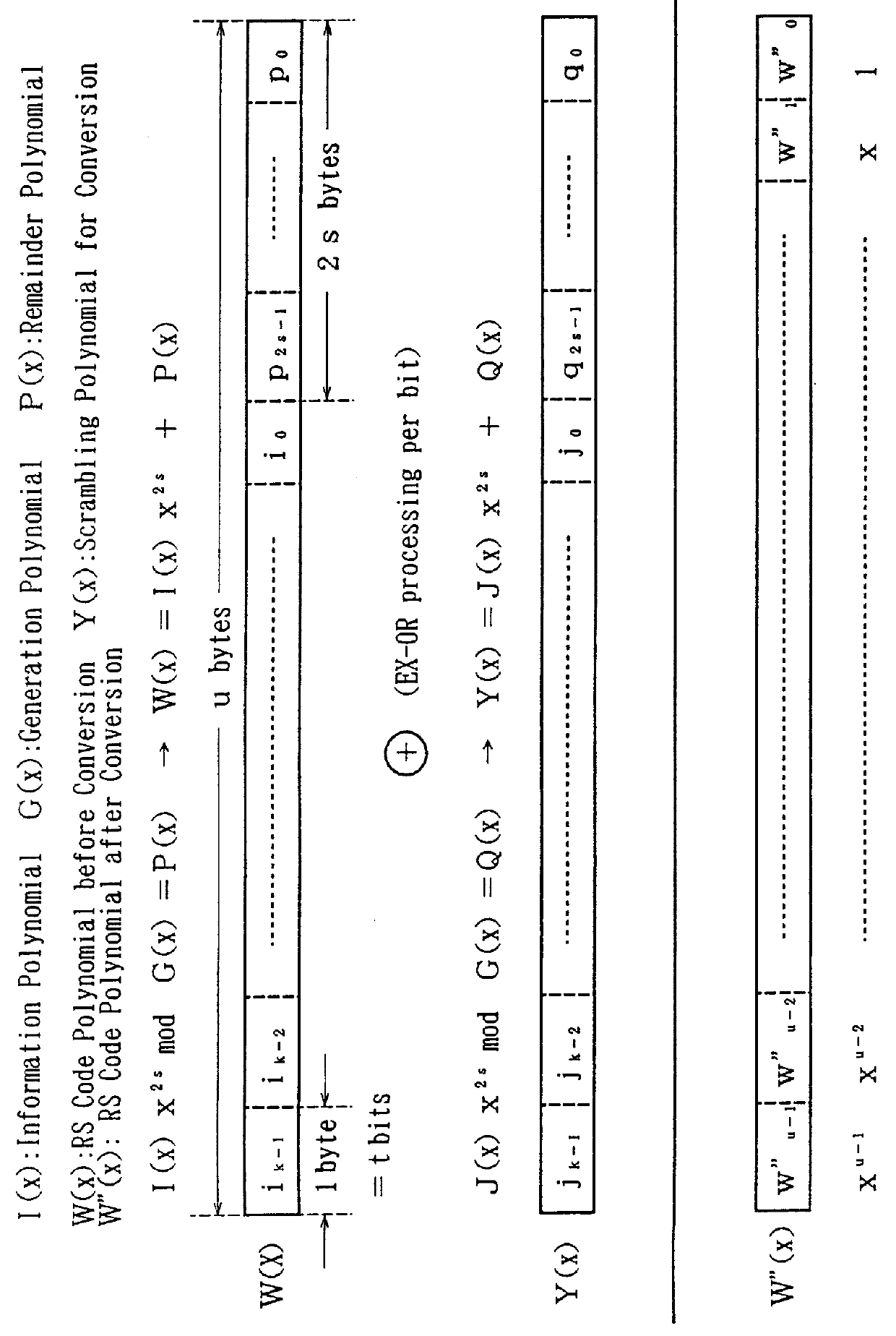

Digital modulation and demodulation

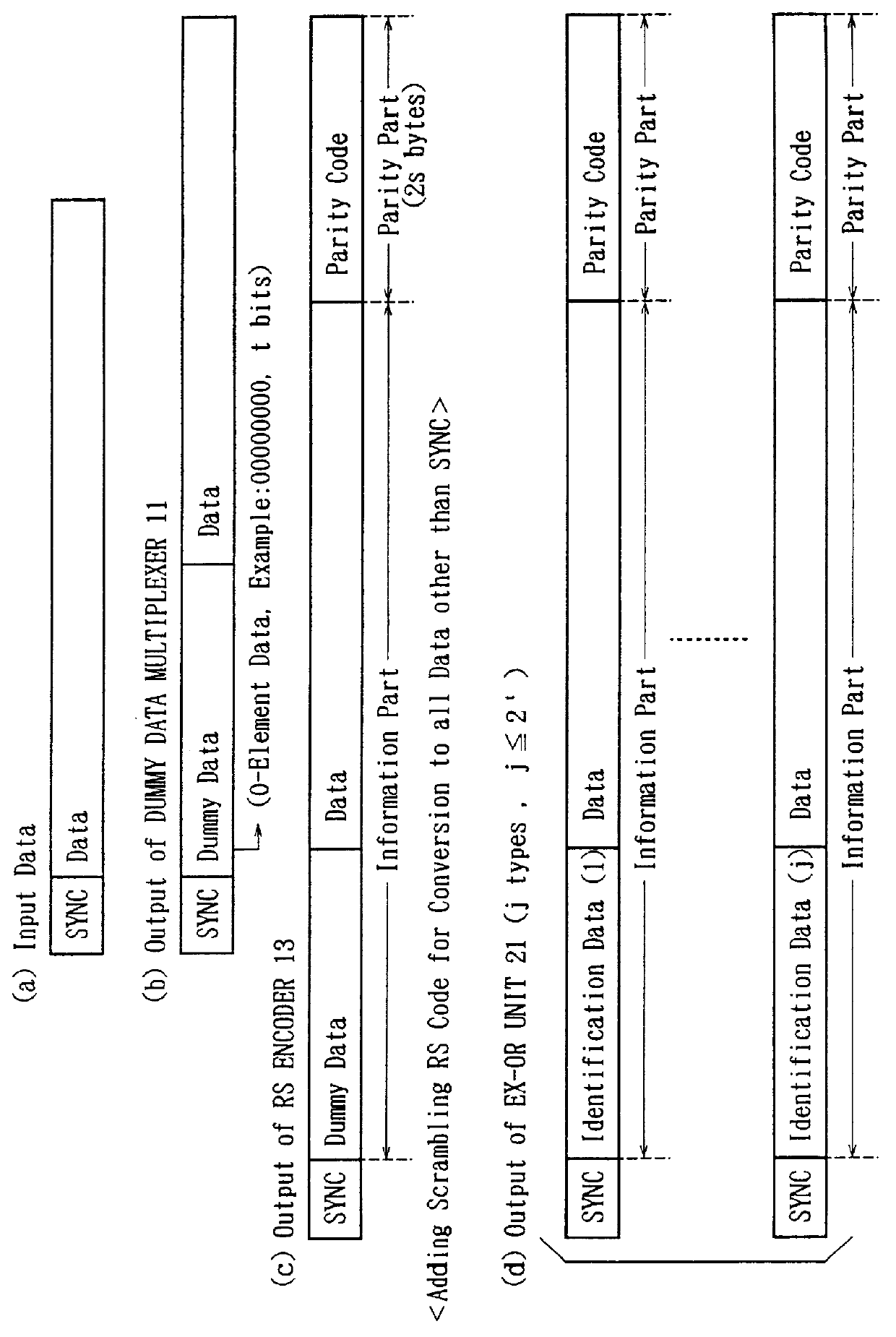

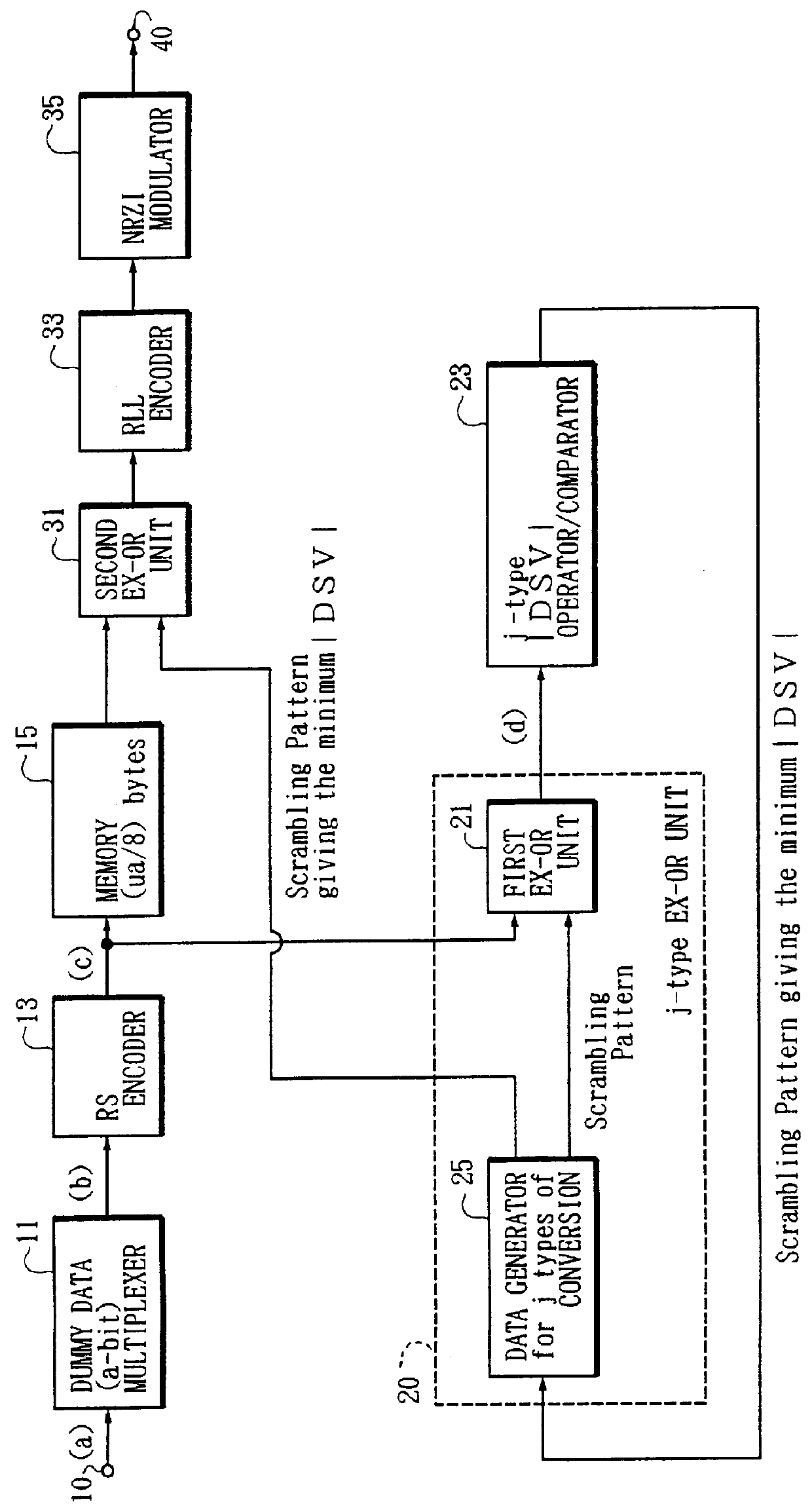

A digital modulator which inputs a data stream to convert to a channel bit stream. The multiplexed data block is generated by multiplexing dummy data to any position within each data block cut out of the data stream one by one. The first Reed-Solomon code is generated by Reed-Solomon-encoding the multiplexed data block as an information part. A plurality of second Reed-Solomon codes are generated by adding a plurality of Reed-Solomon codes for scrambling each of which has identification data showing its scrambling pattern in the same position as that of the dummy data, and the code length of information part and parity part is the same as the first Reed-Solomon code. The second Reed-Solomon code in which the characteristics becomes desirable after modulation among the plurality of the second Reed-Solomon codes is set for output.

Owner:SANYO ELCETRIC CO LTD +1

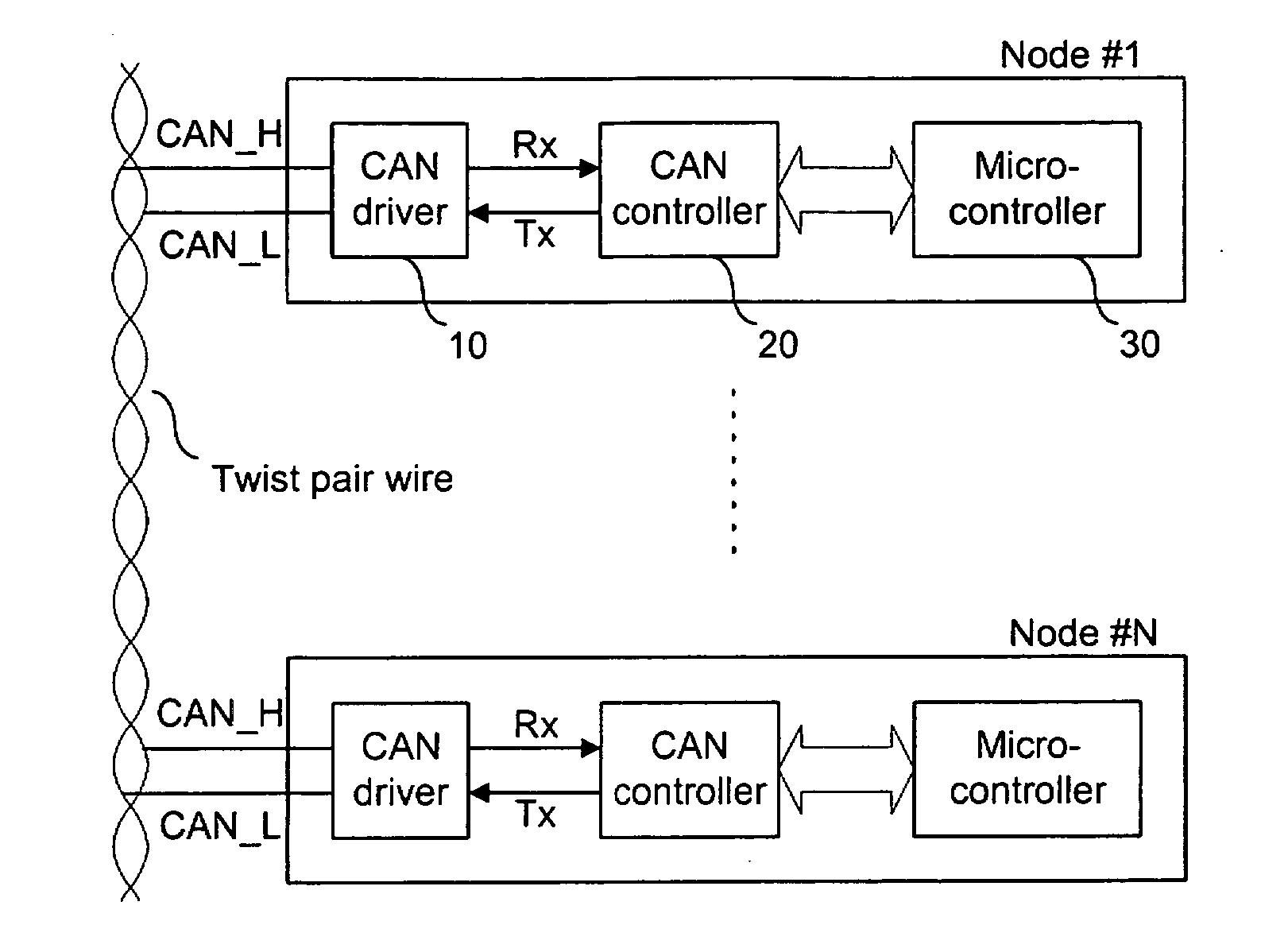

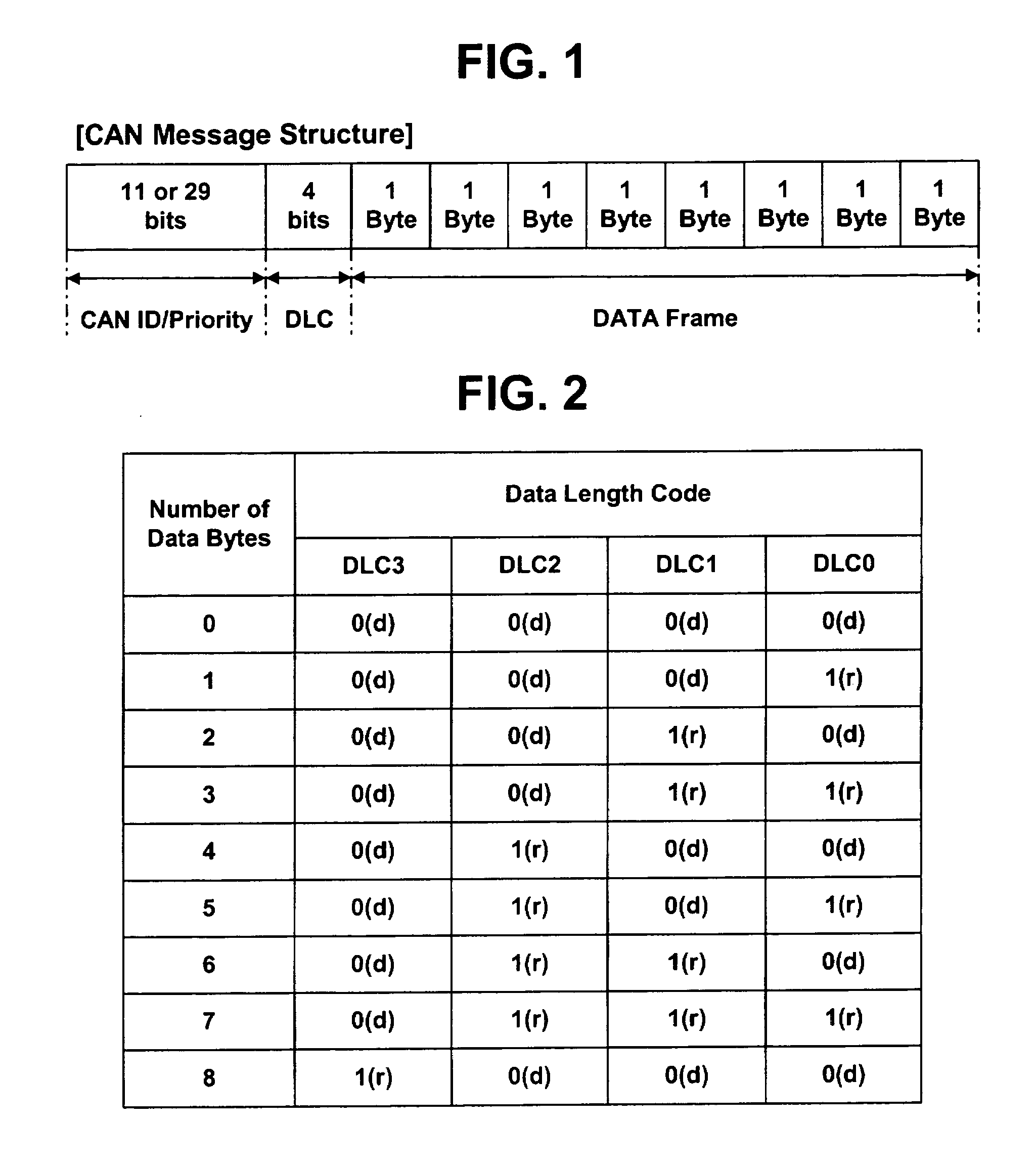

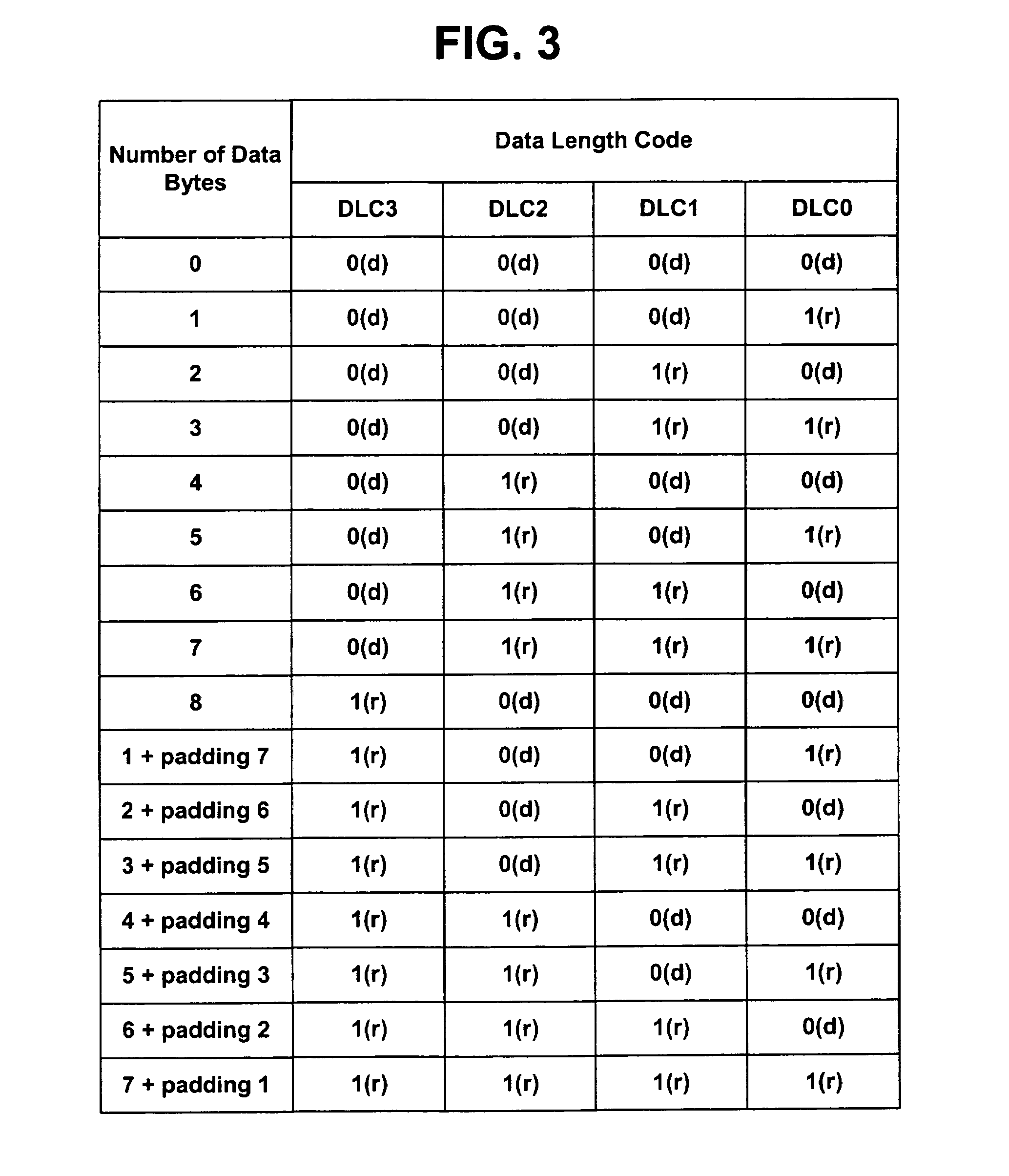

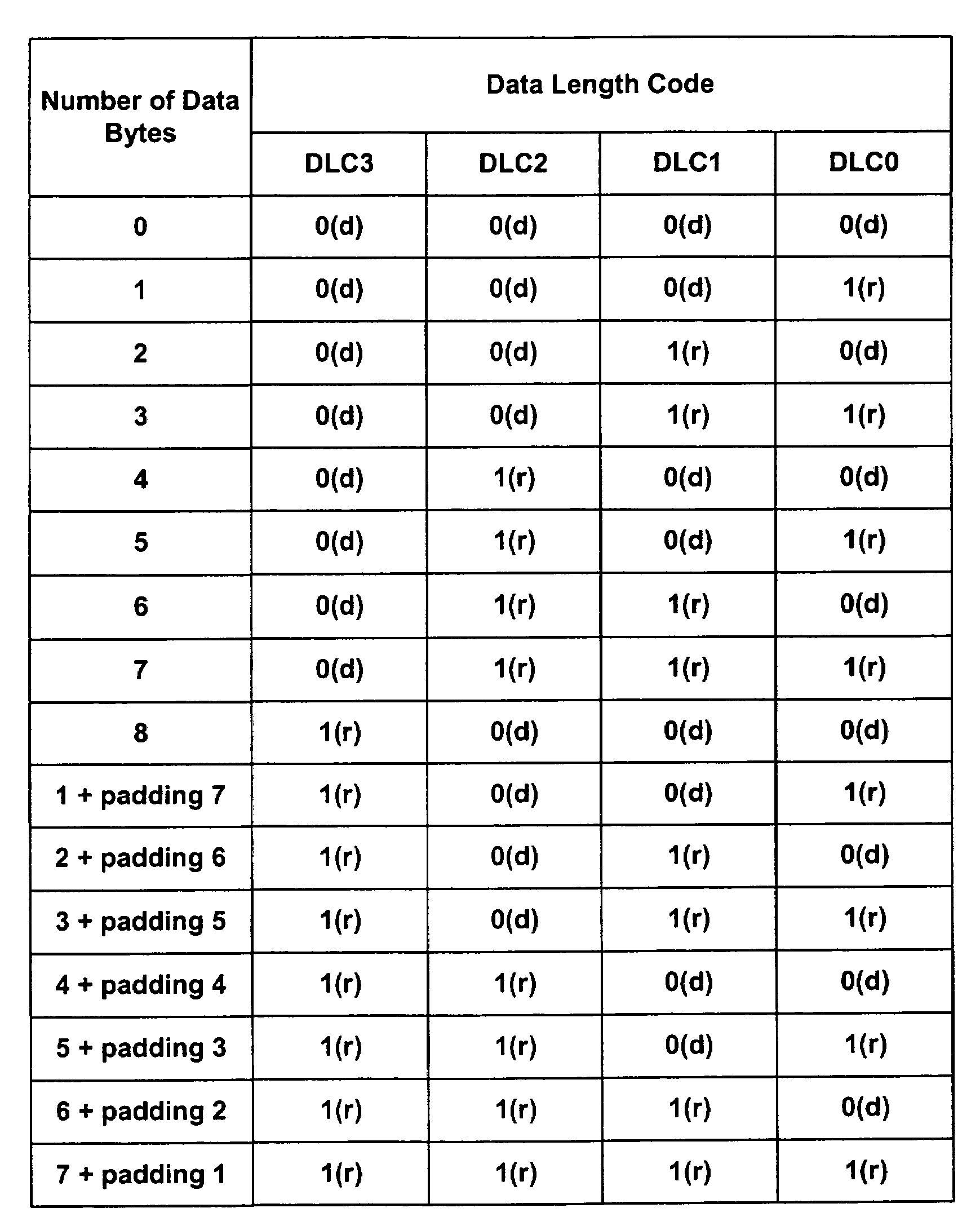

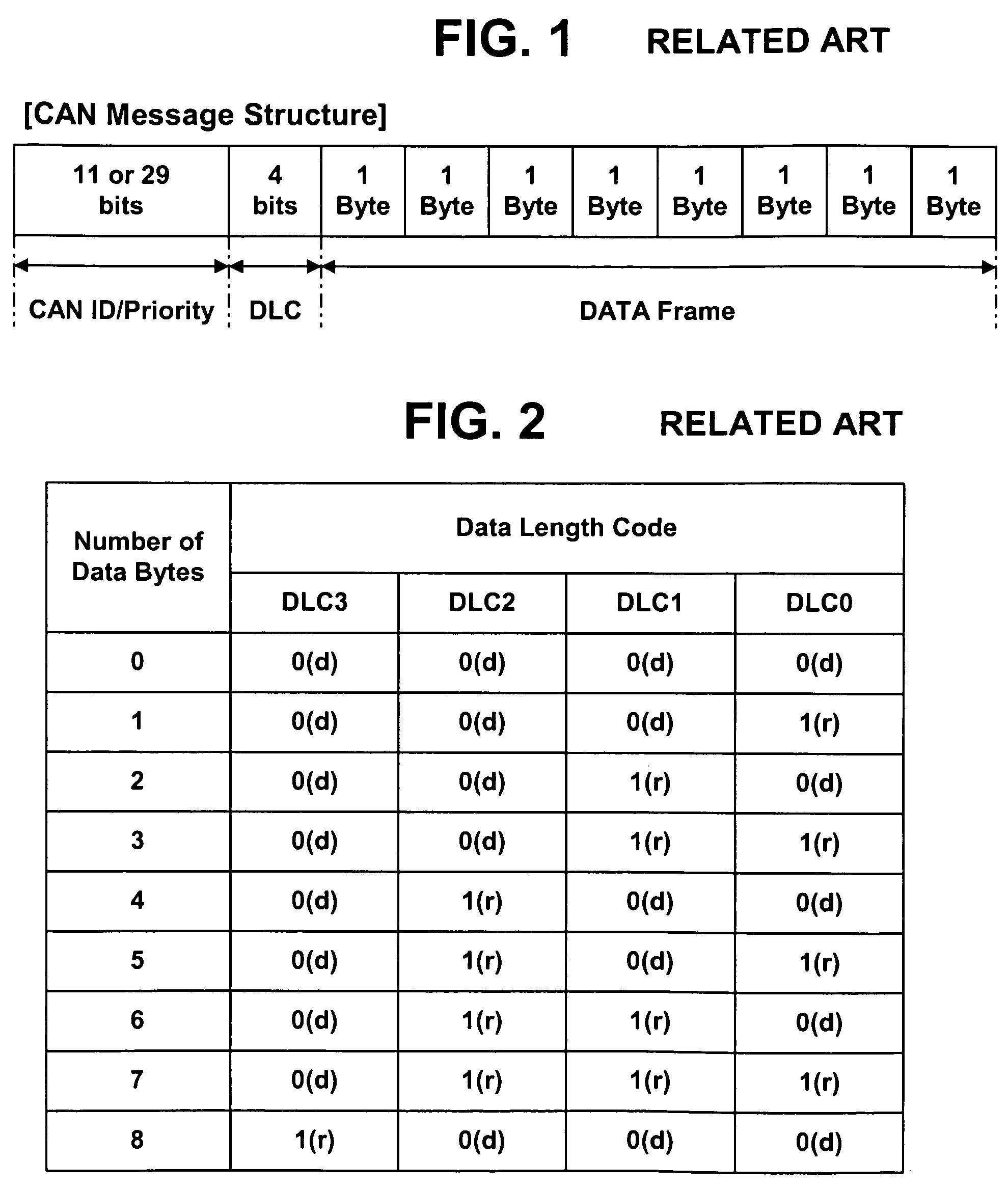

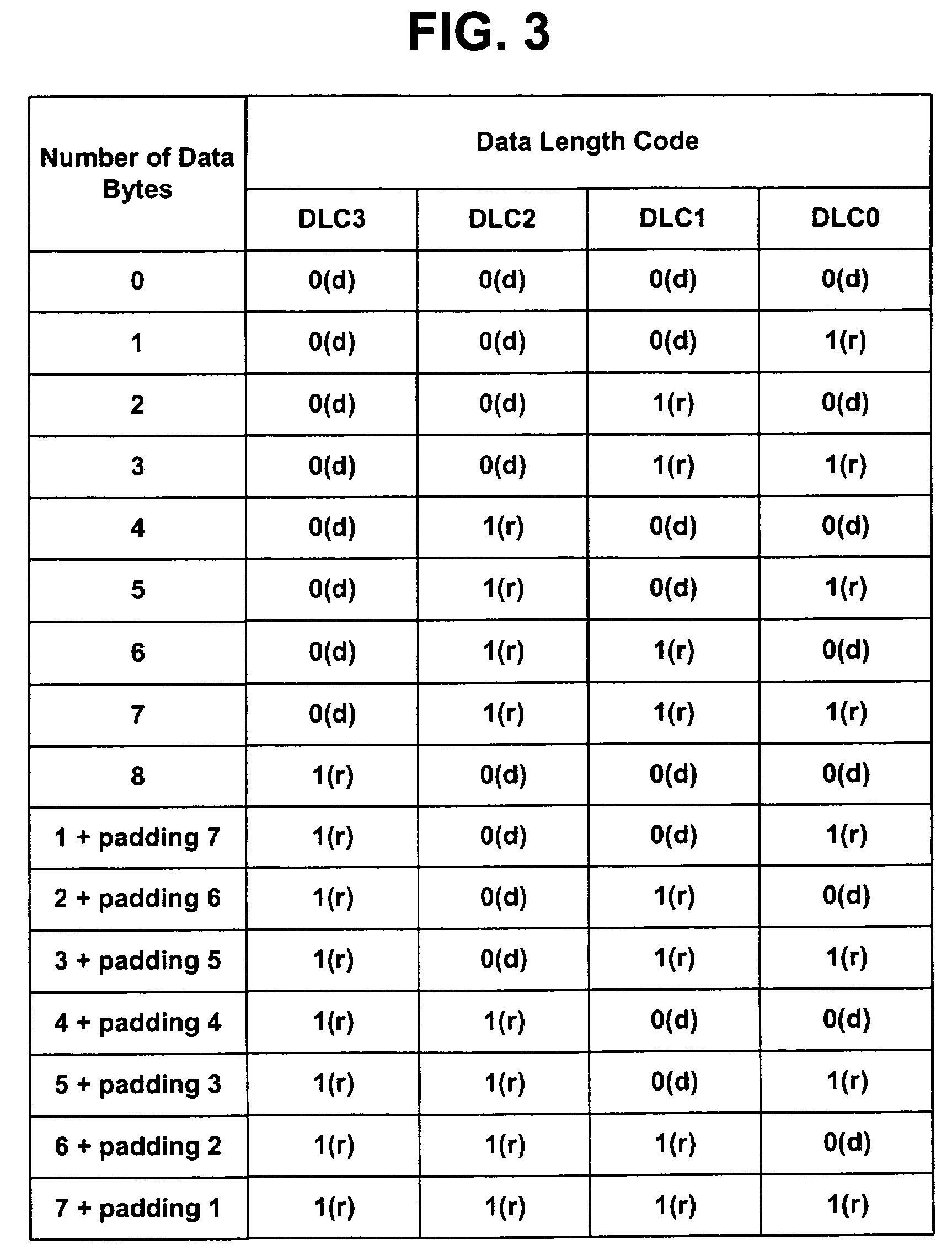

Method and apparatus for processing data in controller area network

InactiveUS20070091932A1Improve data processing efficiencyError preventionTime-division multiplexArea networkDummy data

A method and apparatus for processing data in a Controller Area Network (CAN) are discussed. In an embodiment of this invention, dummy data is added to data to be transmitted via a CAN message, and information indicating that the dummy data is added is transmitted via the CAN message. A length of the dummy data is determined such that data to be transmitted via the CAN message becomes a predetermined length, and data in which five or more successive bits do not have a same value is added as the dummy data. The information is included in a field indicating a length of data to be transmitted via the CAN message, and is indicated by a value within a reserved range of the field. Accordingly, data processing efficiency can be improved, and flexible CAN communication can be performed via the CAN message.

Owner:LG ELECTRONICS INC

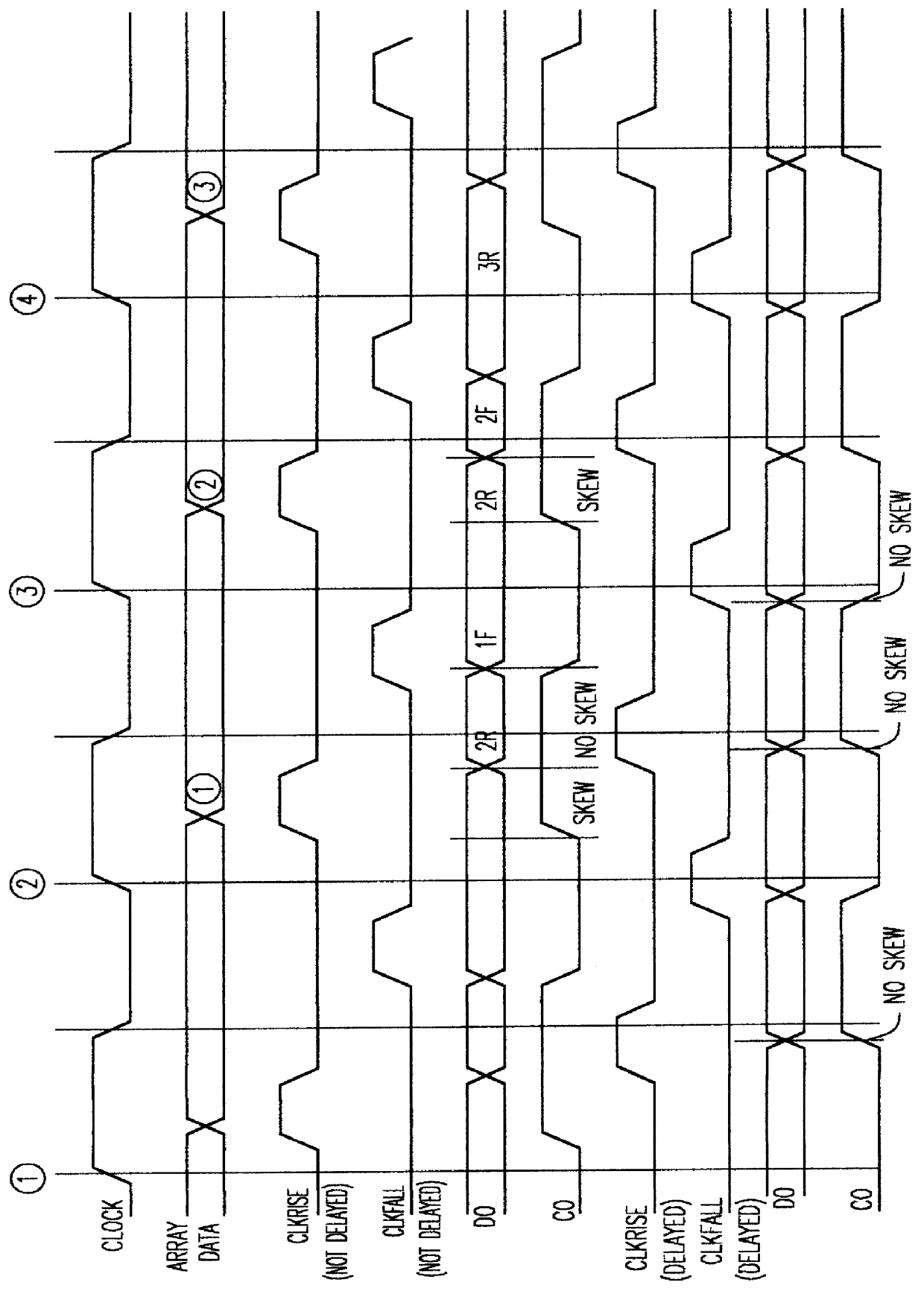

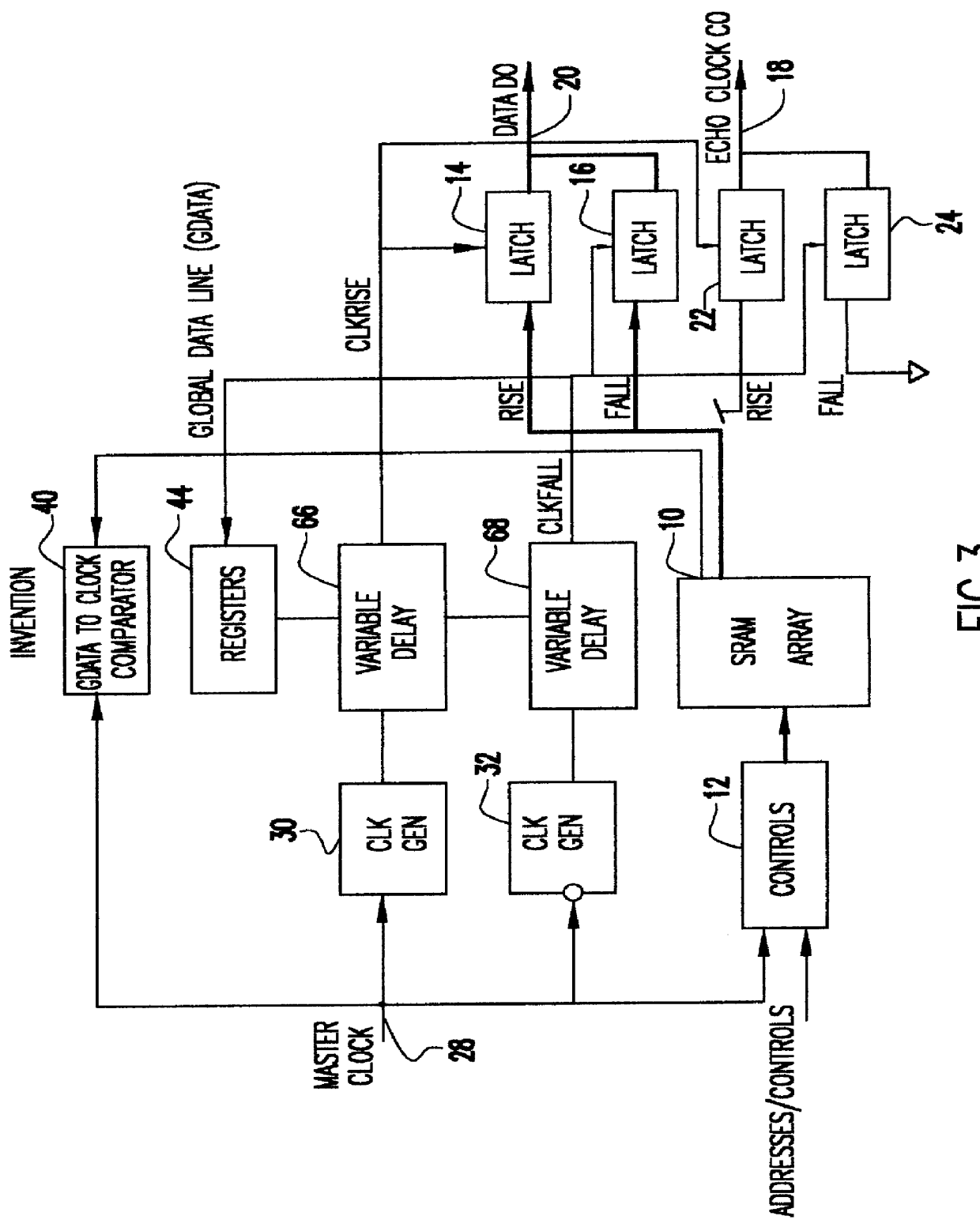

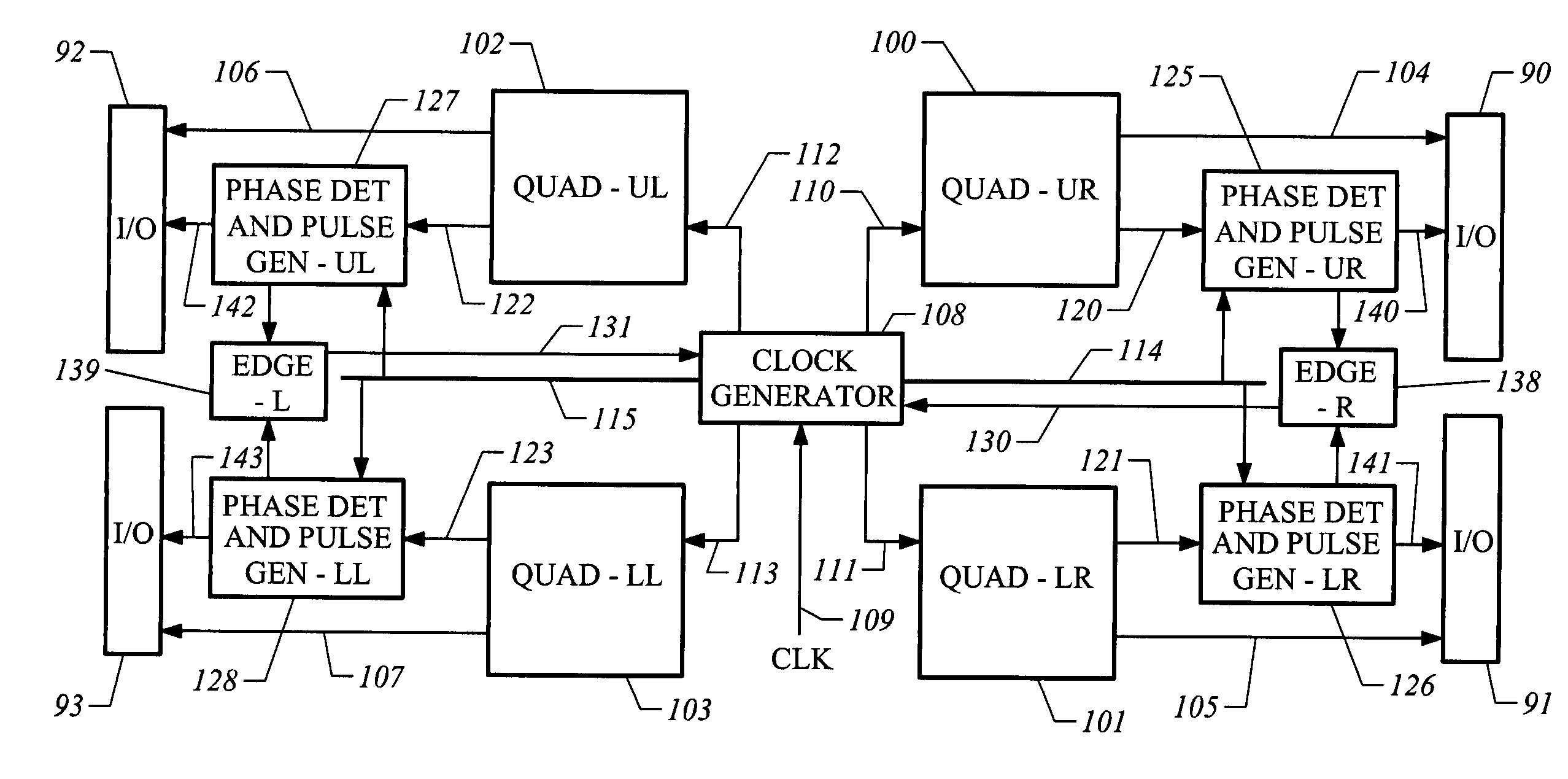

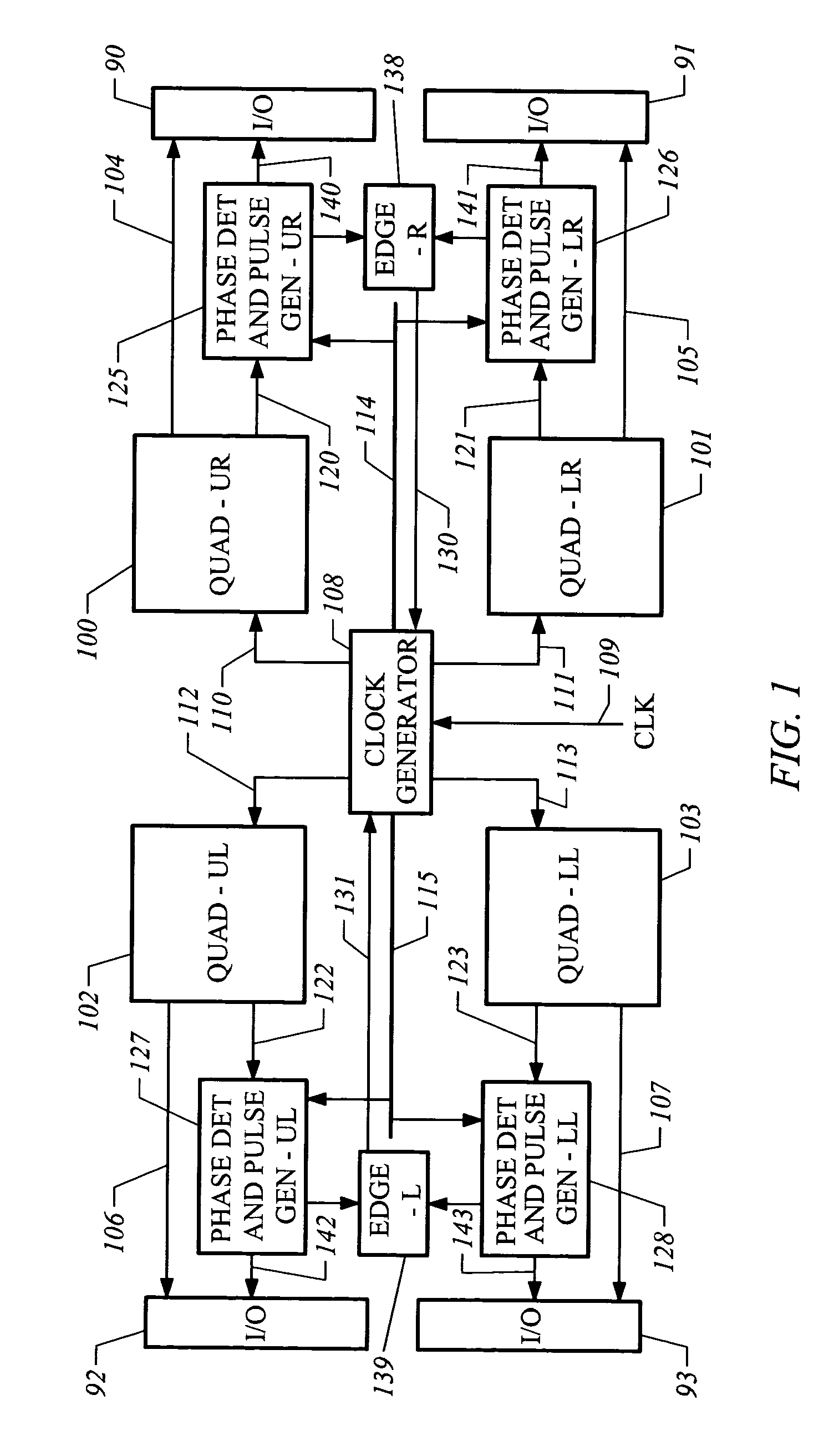

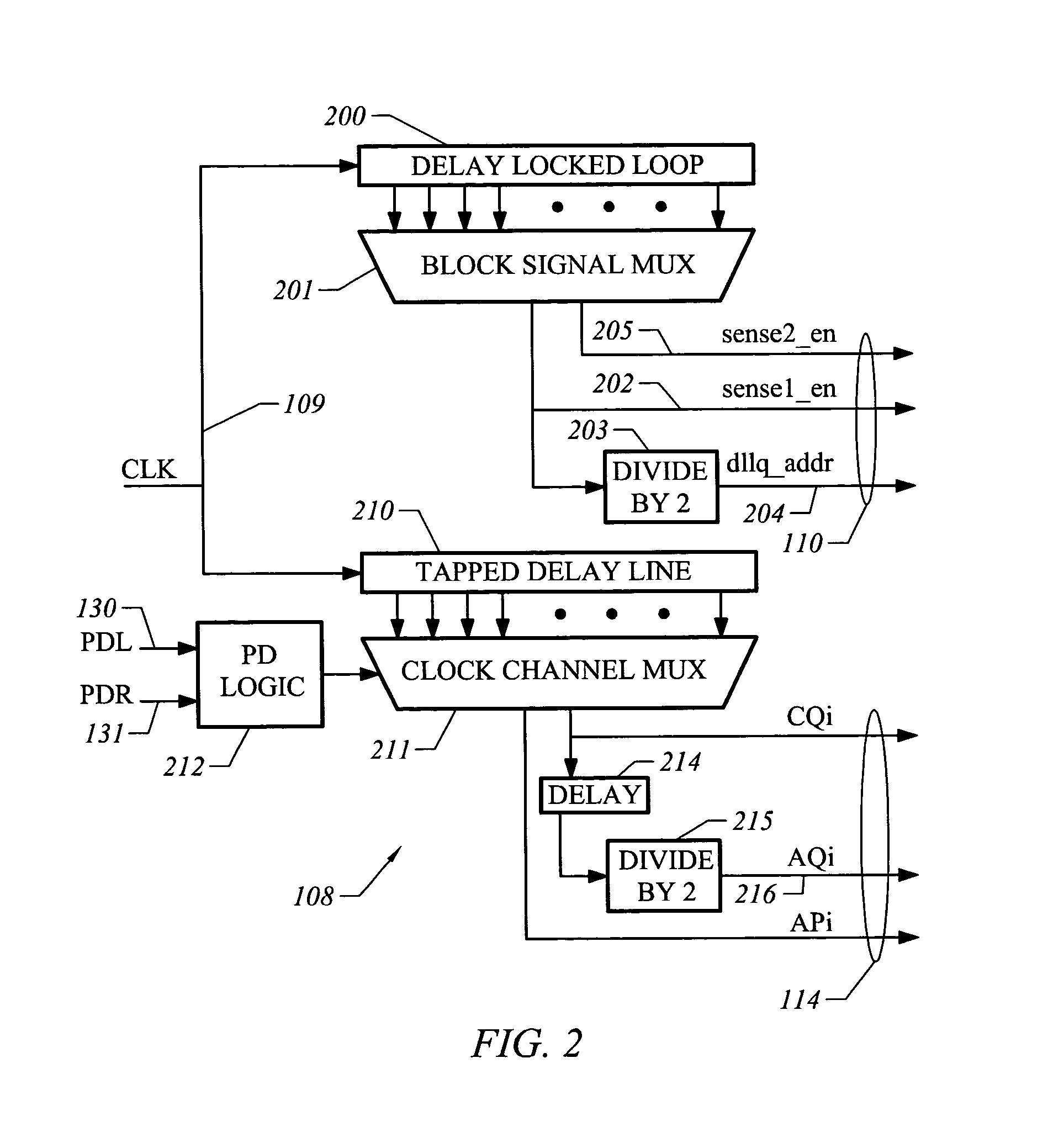

Cycle independent data to echo clock tracking circuit

InactiveUS6134182AAvoid dataDigital storageGenerating/distributing signalsDouble data rateData signal

A comparator and variable delay circuit are provided to maintain the tracking between data and echo clocks in a double data rate (DDR)RAM device. This is accomplished by providing a global data signal (dummy data signal) that tracks with the actual memory array data. This global data signal is compared to the timing of the RAM clock (CLOCK) to determine a delay time between the two by which the pipeline clocks (CLKRISE / CLKFALL) must be delayed. As a result, the pipeline clocks are pushed out as needed so that they always transition after the array data arrives at the output latch. Therefore, as cycle time decreases, both echo clocks and data are pushed out identically and maintain their required tracking.

Owner:IBM CORP

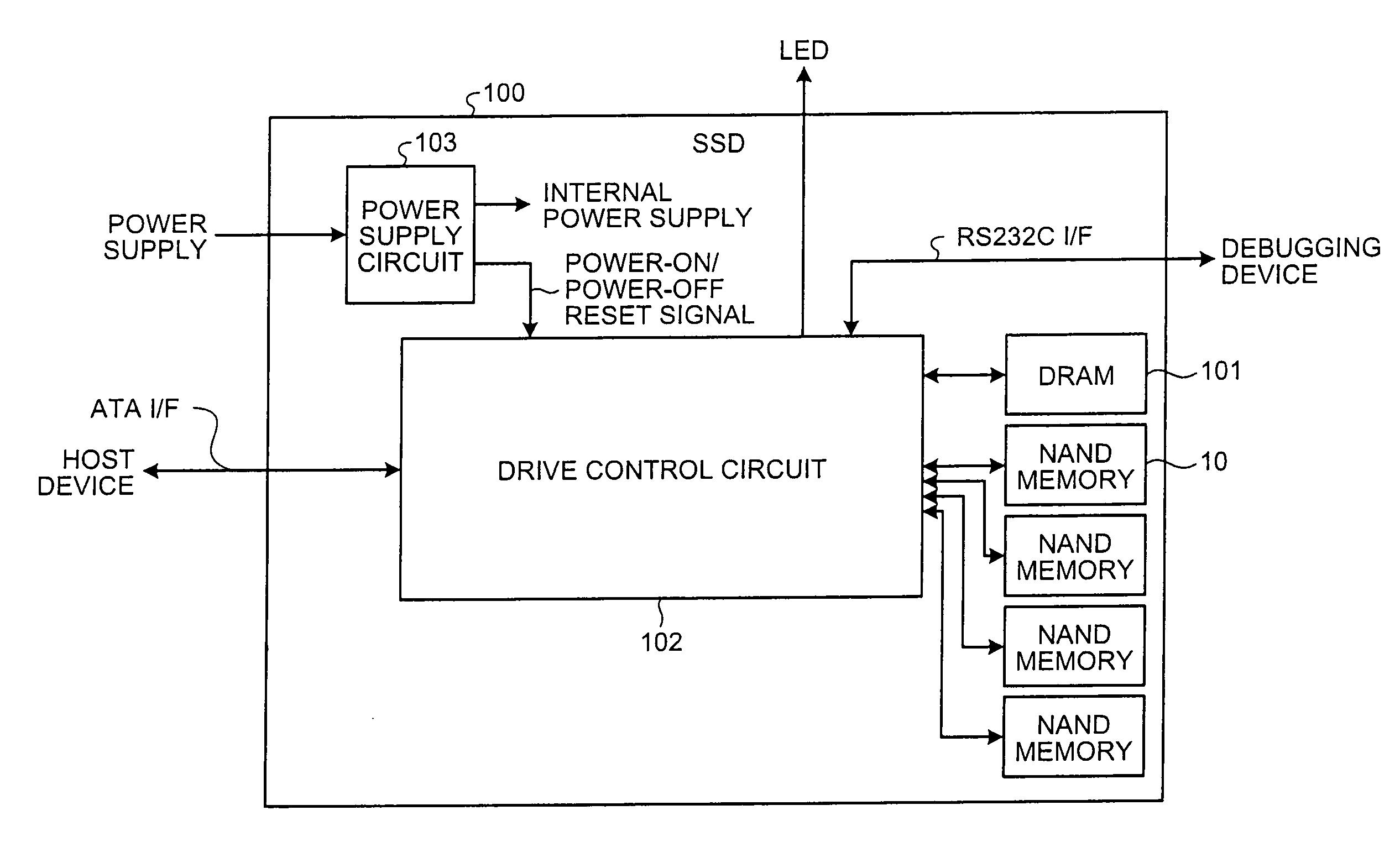

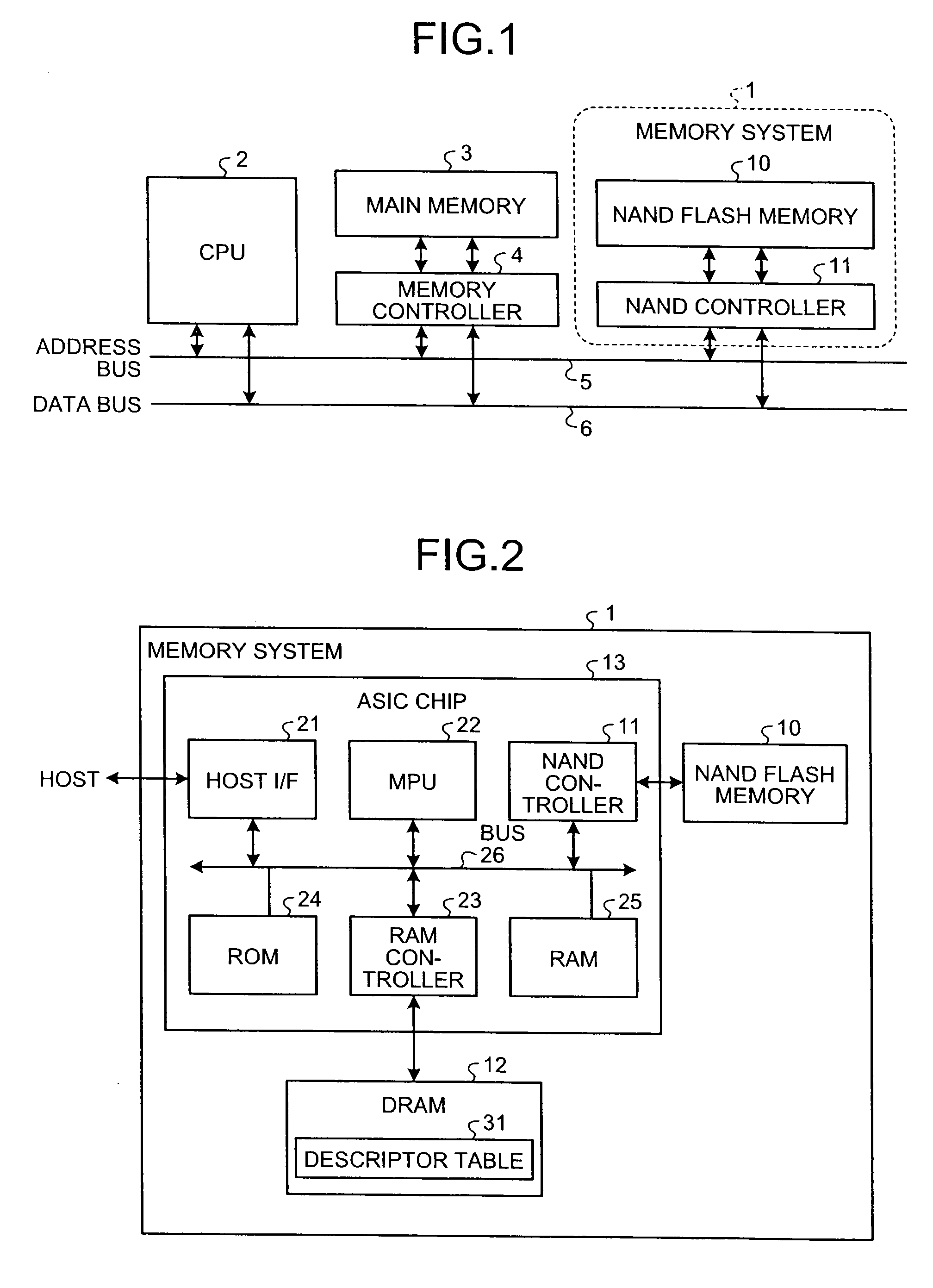

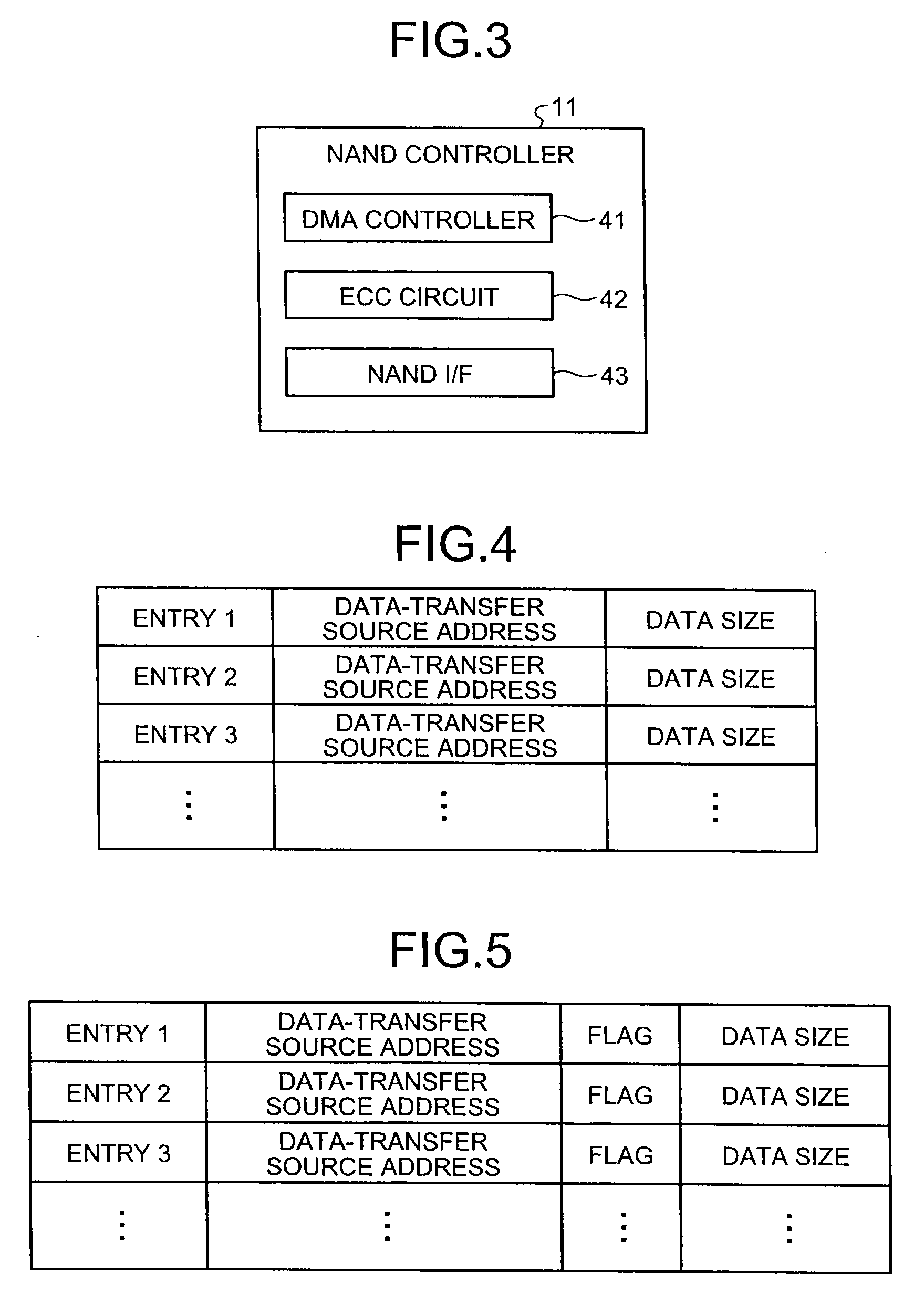

Memory controller, memory system, and access control method of flash memory

InactiveUS20090216937A1Memory architecture accessing/allocationEnergy efficient ICTDummy dataMemory controller

A memory controller adds dummy data to write data by referring to instruction information about a descriptor transfer of the write data if a size of the write data to be written according to a data-write request information does not match a page size unit, thereby adjusting the size of the write data to the page size unit and then outputs the write data.

Owner:KK TOSHIBA

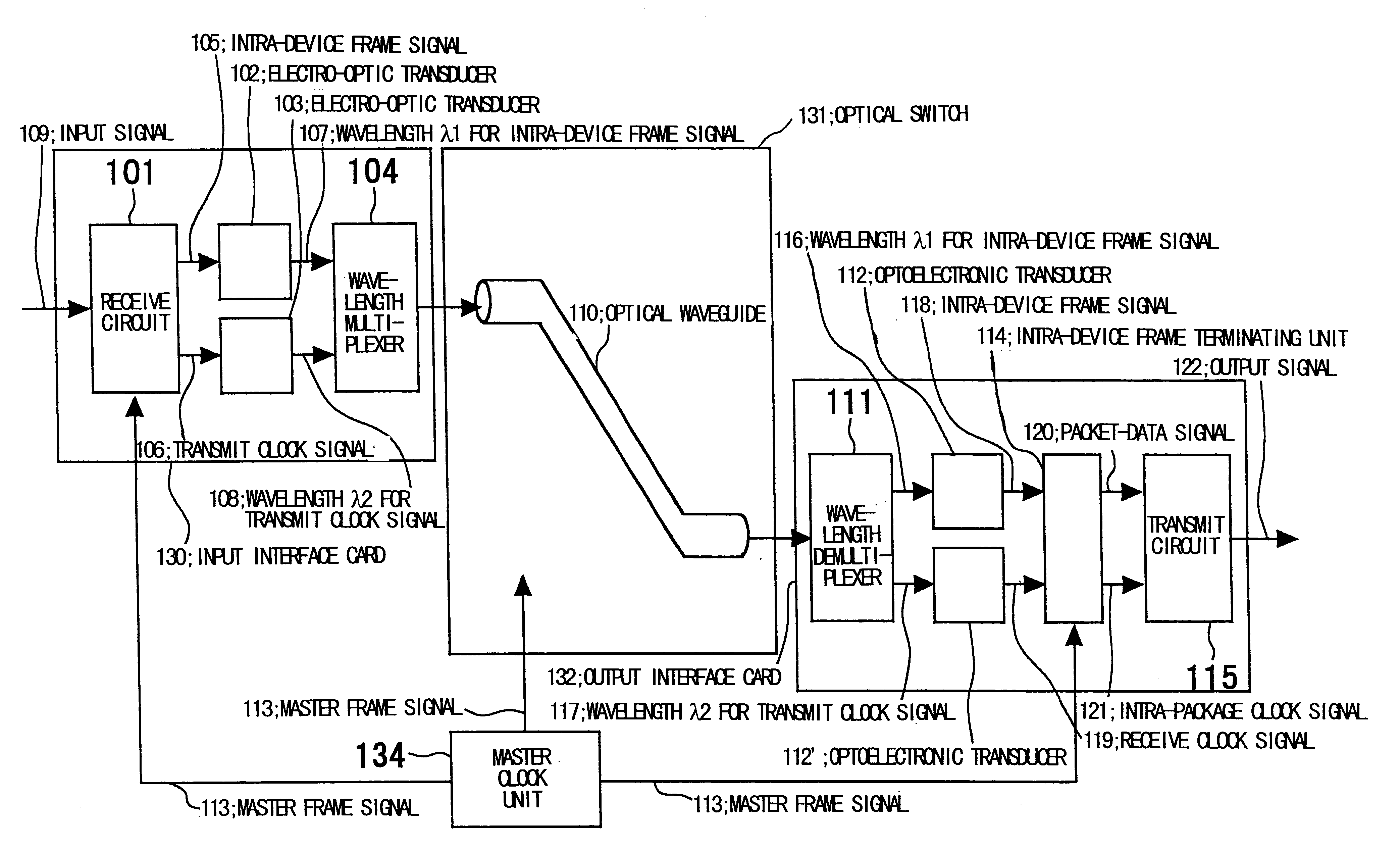

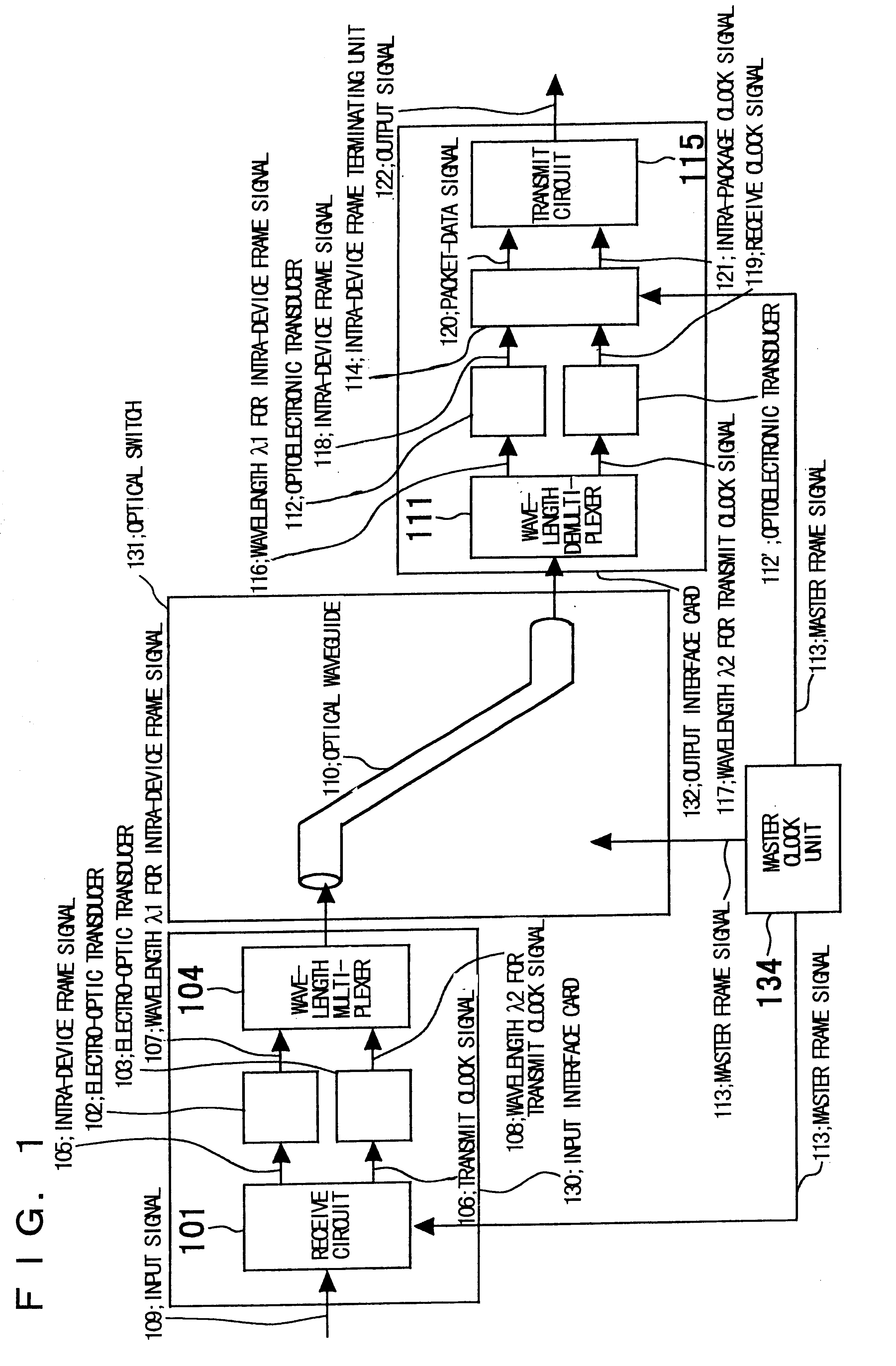

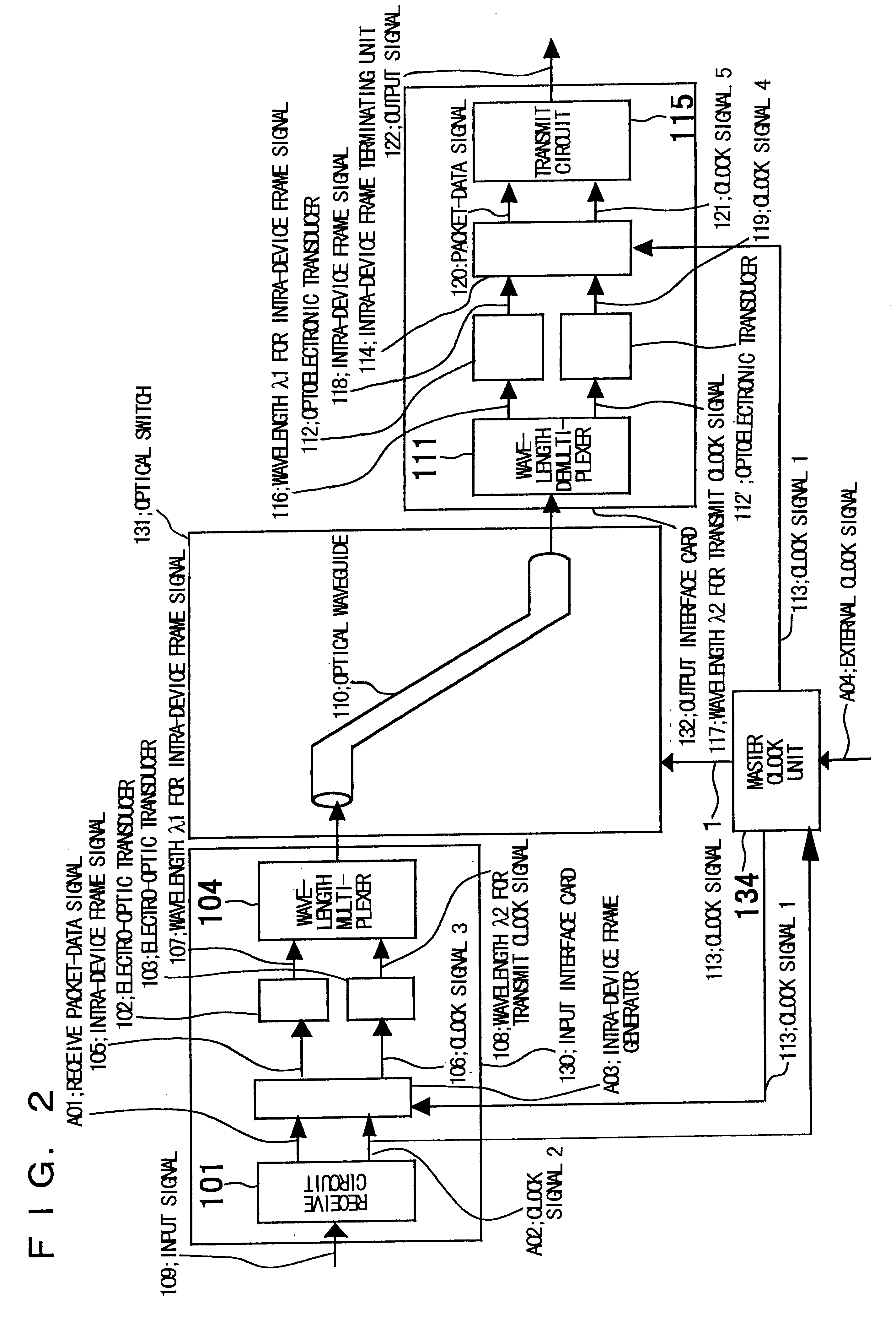

Optical packet switch

InactiveUS6512616B1Increase in sizeDevice is bulkyMultiplex system selection arrangementsTime-division optical multiplex systemsOptical packetData field

An optical packet switch uses electric circuits to implement input and output sections of an optical switch that performs packet switching. Retiming of packet data in the output section is facilitated to reduce the scale of the circuitry. In the input section a packet-data signal and a clock signal for retiming the packet data are wavelength multiplexed by a wavelength multiplexer and transferred over the same optical waveguide of the optical switch. In the output section the packet-data signal and the clock signal, which have been transferred from the same optical waveguide in the packet switch, are demultiplexed by a wavelength demultiplexer, and retiming of the packet-data signal is performed by an intra-device frame terminating unit. A frame format comprises, in addition to a flag pattern and a data field, a preamble and dummy data at the beginning and end thereof, respectively, for accommodating skew caused by transfer through the optical switch as well as a period of signal instability produced by switching of the optical switch. The packet data is transferred upon being placed in the data field of the frame format.

Owner:NEC CORP

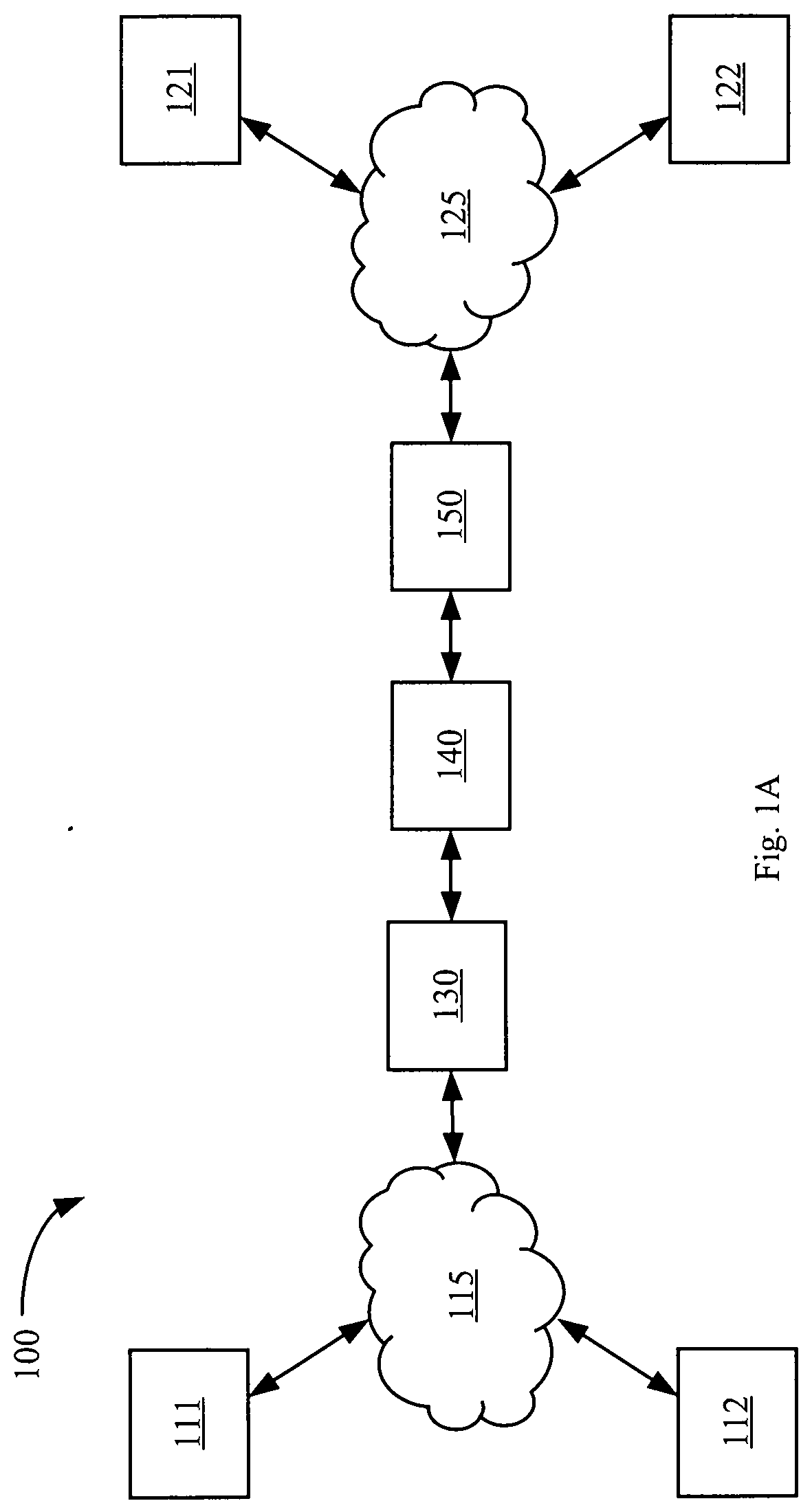

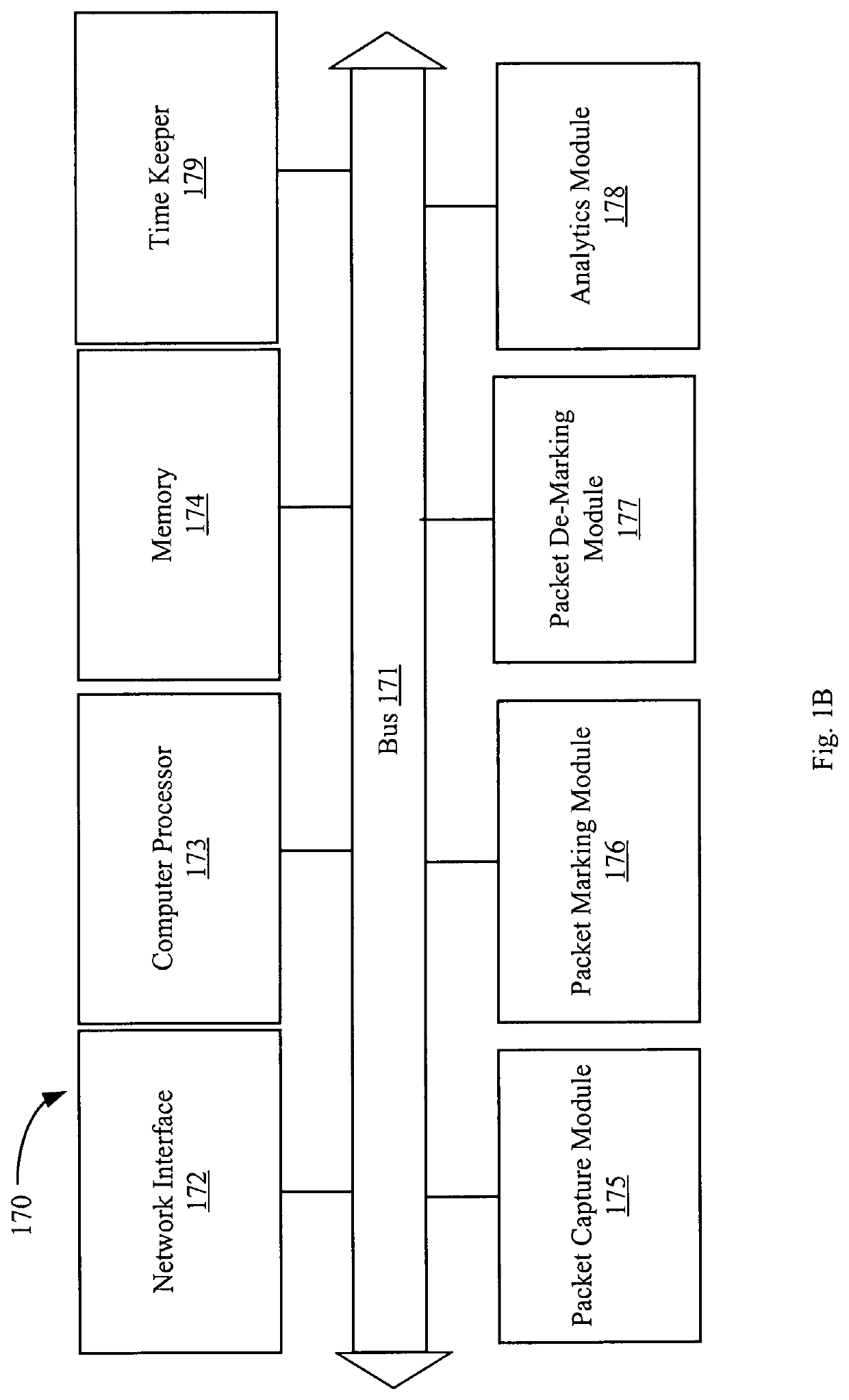

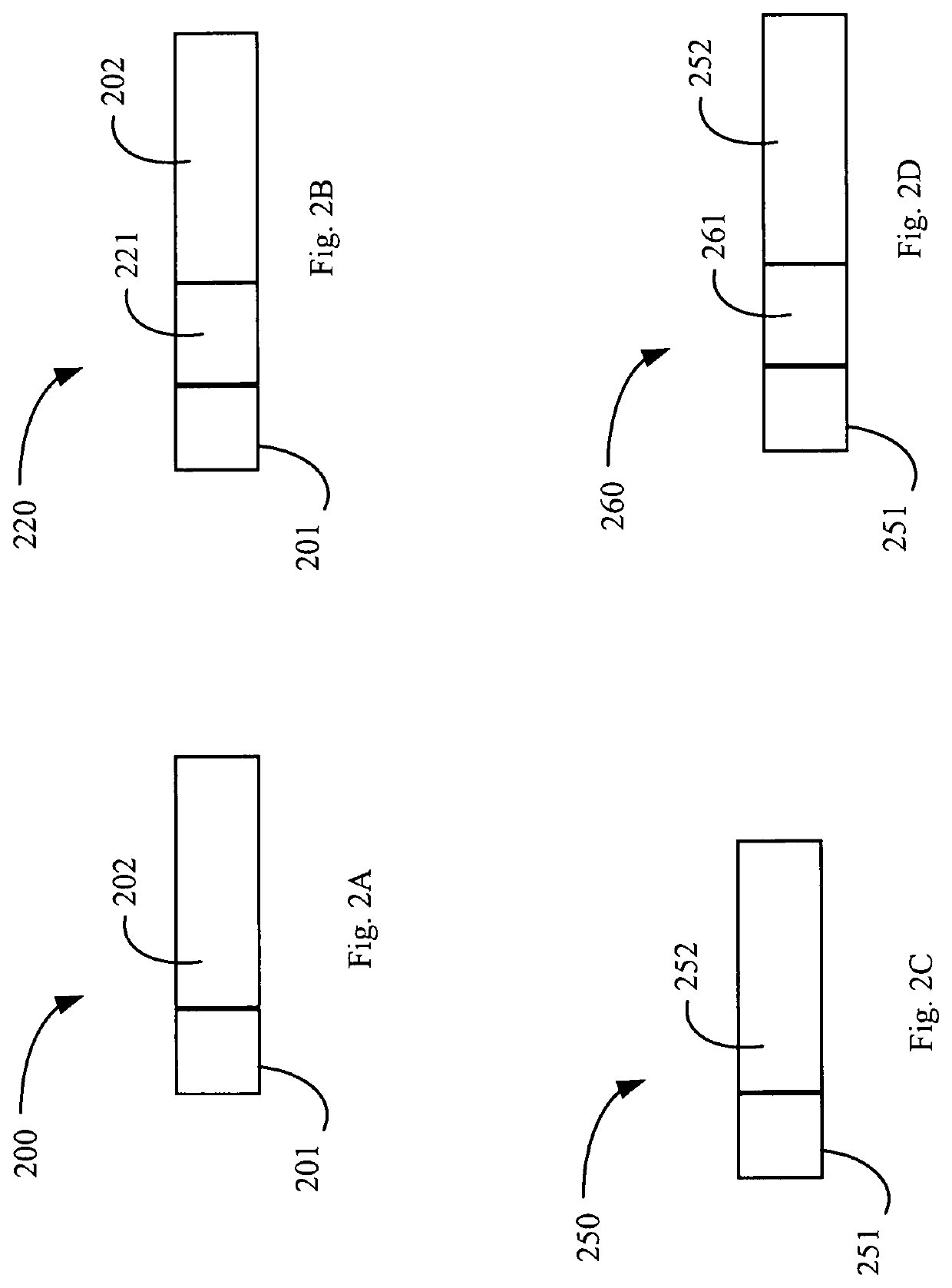

In-line performance monitoring

One function of a communications network, or of nodes in such a network, is to gather data that is useful in assessing network performance, and quantifying metrics of node and / or network performance. Various embodiments disclosed herein improve the ability of nodes and networks to gather such data, and quantify metrics of node and / or network performance by selectively marking existing network traffic, and in preferred embodiments without having to dilute network traffic by generating and transmitting dummy data packets.

Owner:128 TECH

Apparatus and method for producing dummy data and output clock generator using same

InactiveUS7464282B1Improve performanceAvoid failurePulse automatic controlDigital storageDummy dataDatapath

An apparatus and method for producing dummy data is based on timing paths co-located with the address / data paths of the memory. An output clock generator uses the dummy data. The technique for producing dummy data is particularly important for memory systems in which the output of memory cells do not normally provide large voltage swings, making them less practical for self timing approaches to dummy data generation.

Owner:T RAM ASSIGNMENT FOR THE BENEFIT OF CREDITORS LLC +1

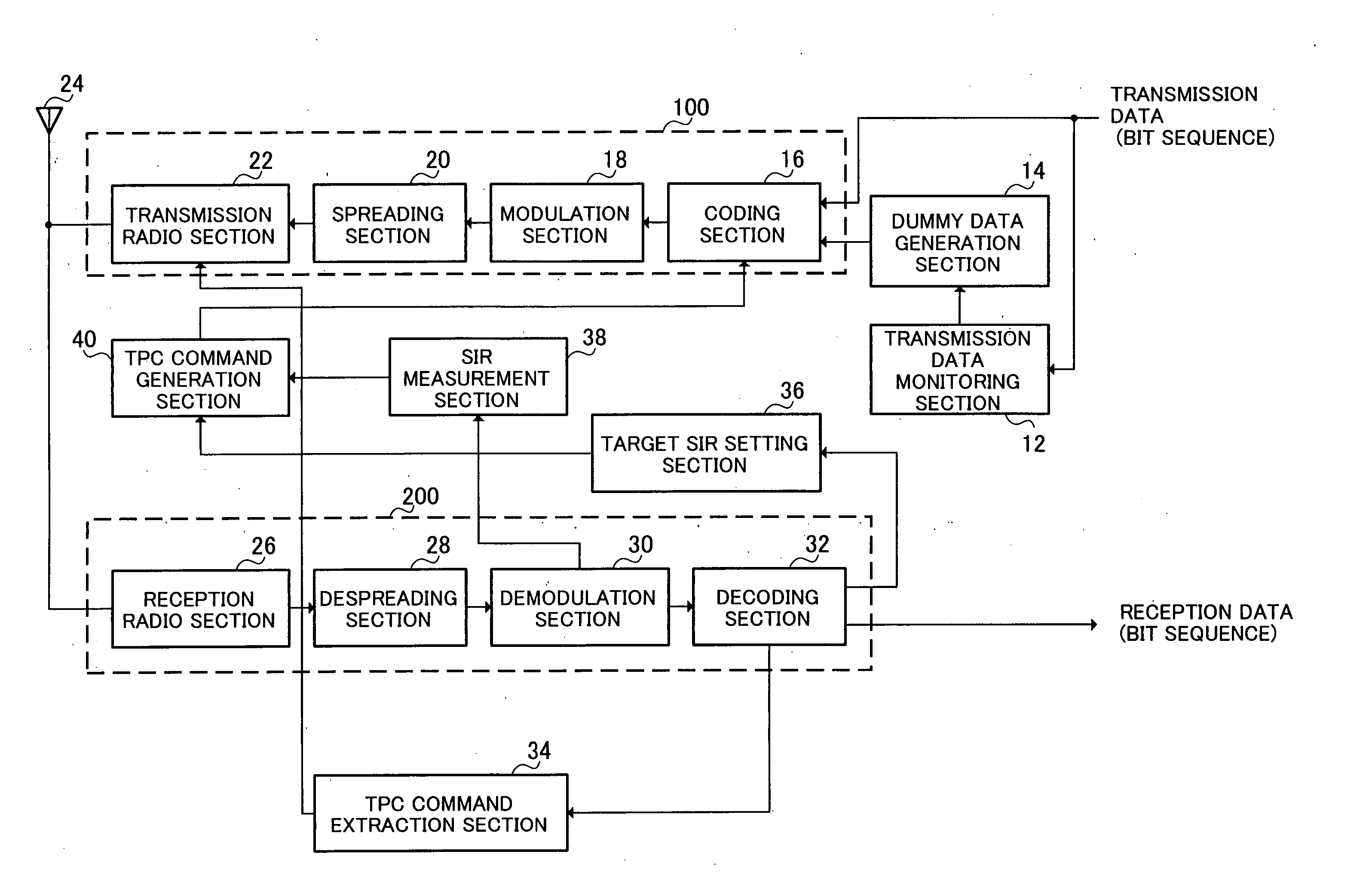

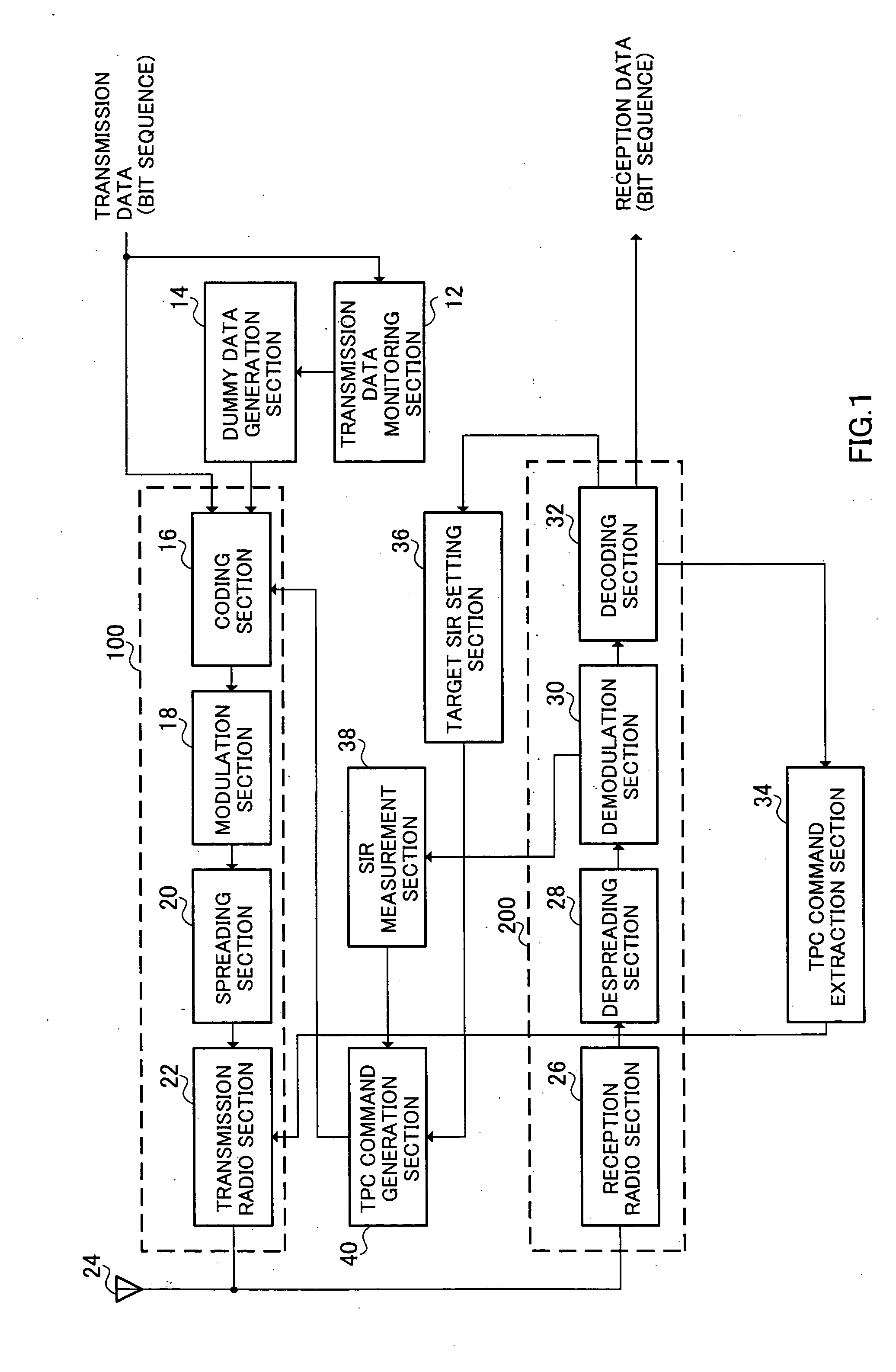

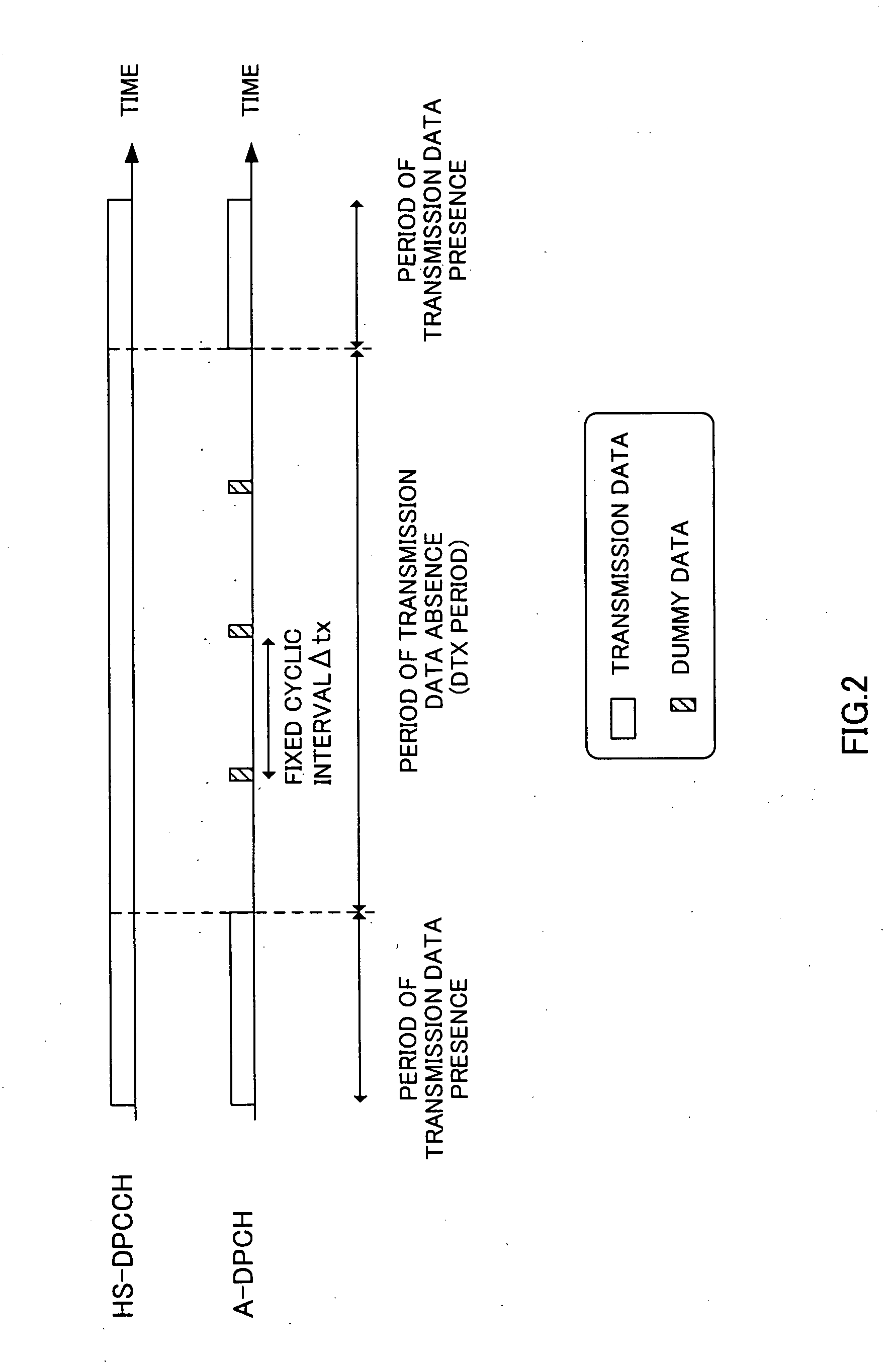

Outer loop transmission power control method and radio communication device

InactiveUS20050186981A1Power managementTransmission control/equalisingCommunications systemDummy data

In a wireless communication system in which A-DPCH (Associated-Dedicated Physical CHannel) and HS-DPCCH (High Speed-Dedicated Physical Control CHannel) exist, for the purpose of performing an appropriate outer loop transmission power control for HS-DPCCH even during an A-DPCH DTX (Discontinuous Transmission) period, transmission data monitoring section 12 monitors whether a bit sequence transmitted via A-DPCH is present or not, and dummy data generation section 14 generates a random sequence used for outer loop transmission power control of HS-DPCCH during a DTX period in which a bit sequence is absent, and coding section 16 performs CRC coding on the generated random sequence, and transmission radio section 22 then transmits the CRC-coded random sequence via A-DPCH.

Owner:PANASONIC CORP

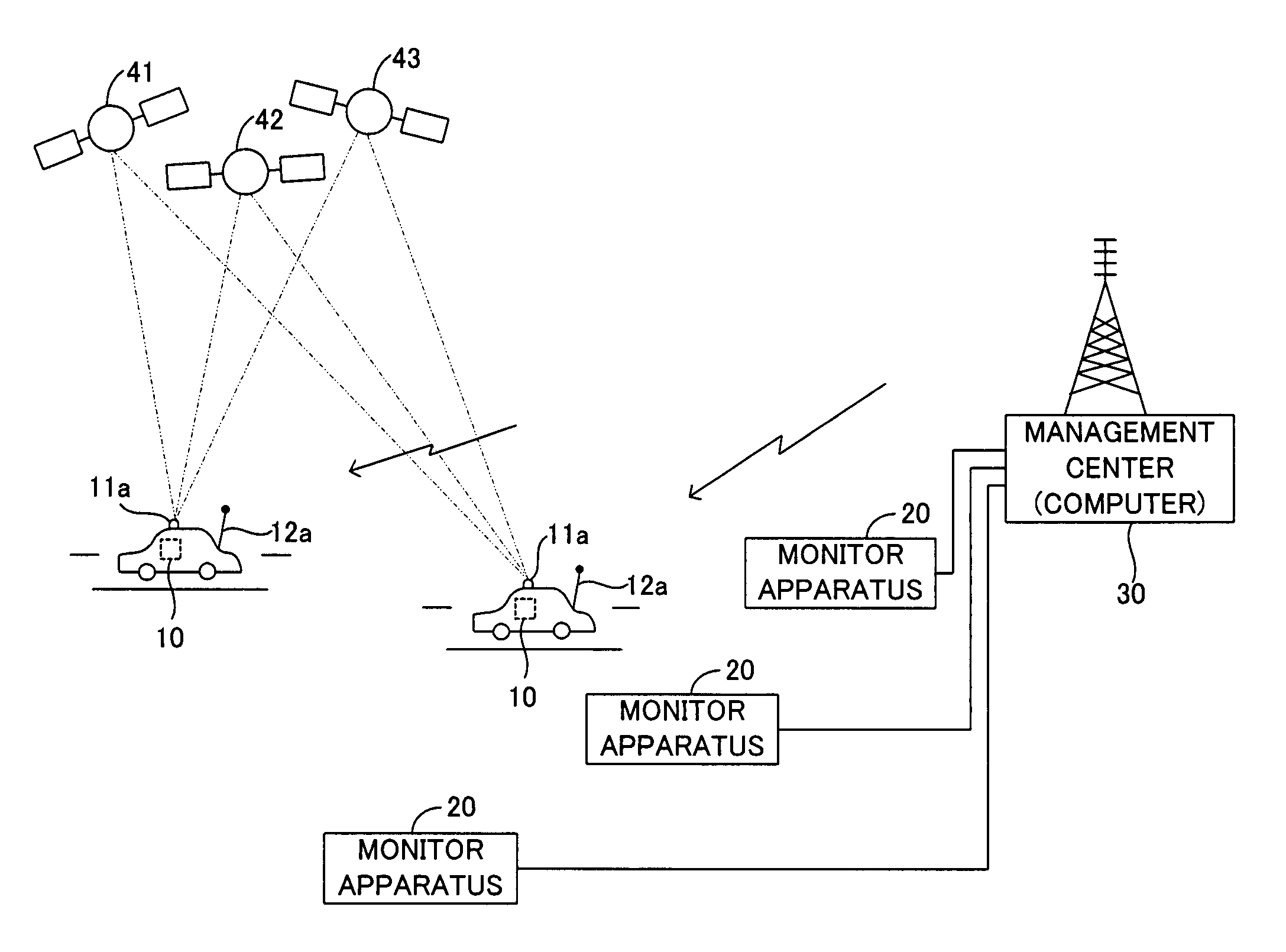

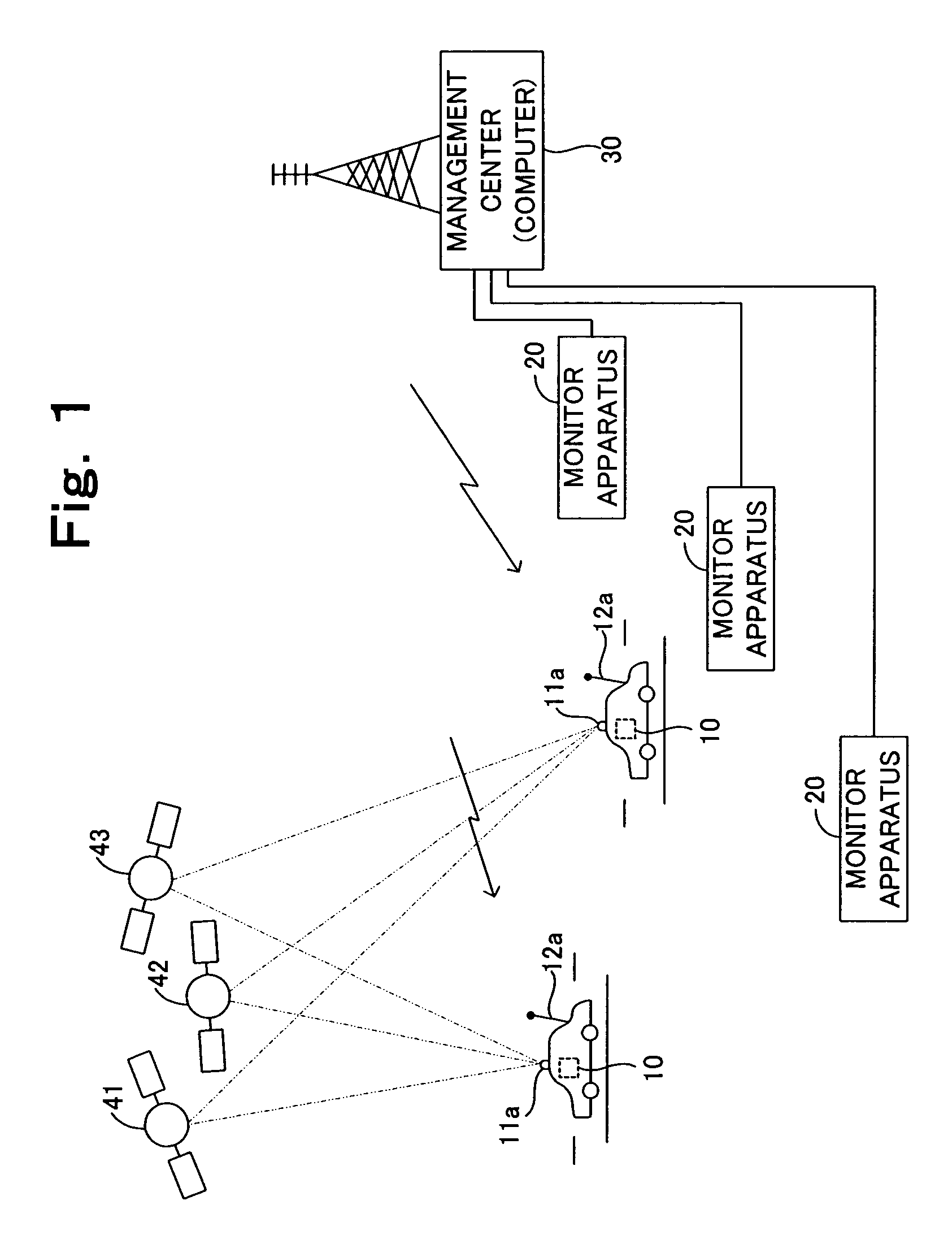

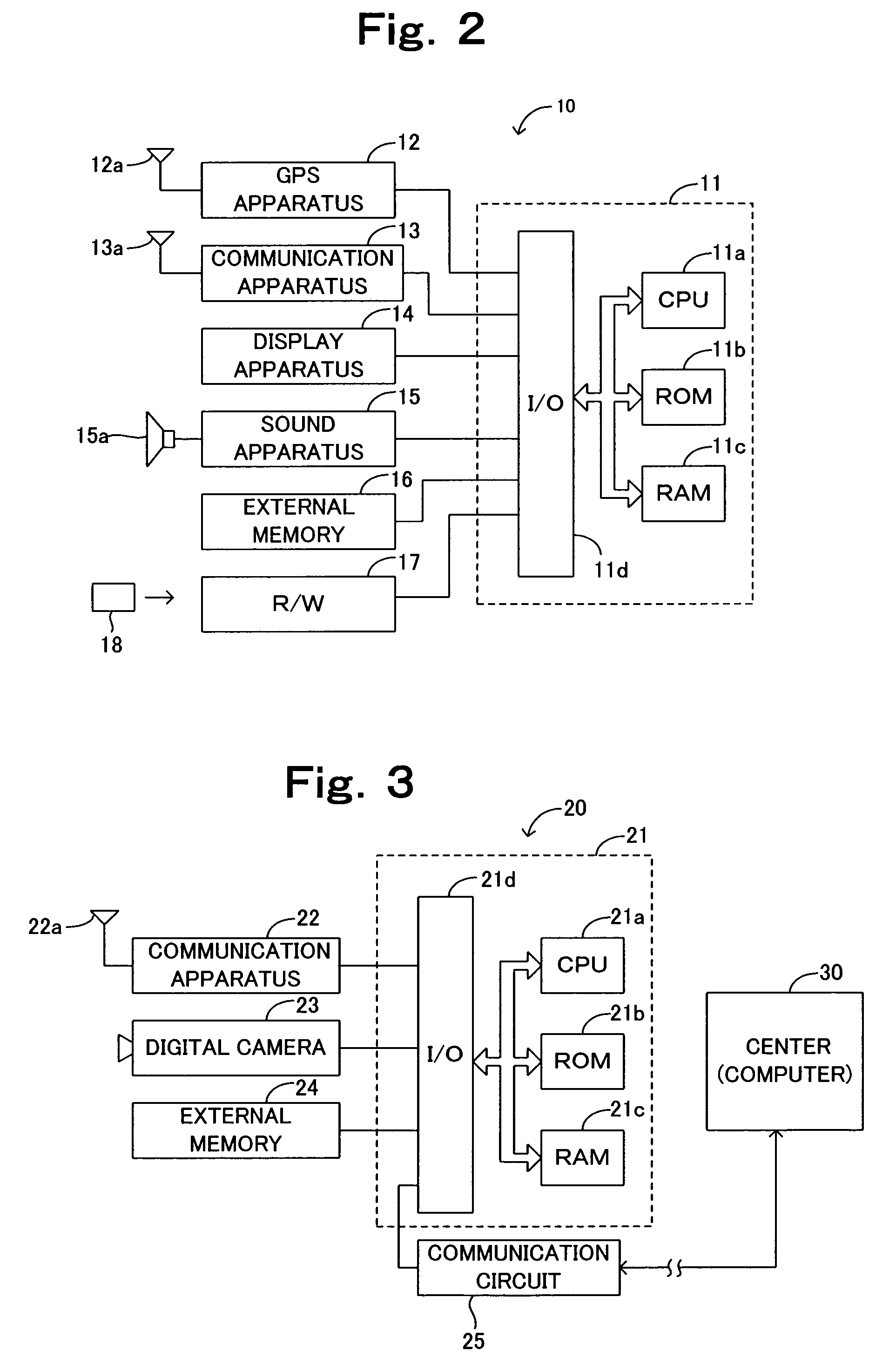

Monitoring system for automatic charging apparatus for vehicle

InactiveUS7053792B2Centralized managementLong calculation timeAcutation objectsTicket-issuing apparatusDummy dataMonitoring system

When a monitor apparatus judges that a vehicle has stopped at a predetermined position (step 705), the monitor apparatus transmits pseudo position information of the vehicle (dummy data) to an automatic charging apparatus (step 725). The automatic charging apparatus calculates a charge amount on the basis of the dummy data, and transmits the result of the calculation to the monitor apparatus. The monitor apparatus receives the result (step 735) and judges on the basis of the result whether the automatic charging apparatus is in an anomalous state (step 740). Since the above-described successive operations are performed only when the vehicle stays, the status of another automatic charging apparatus not monitored is not misidentified as the status of an automatic charging apparatus to be monitored.

Owner:AISIN SEIKI KK +1

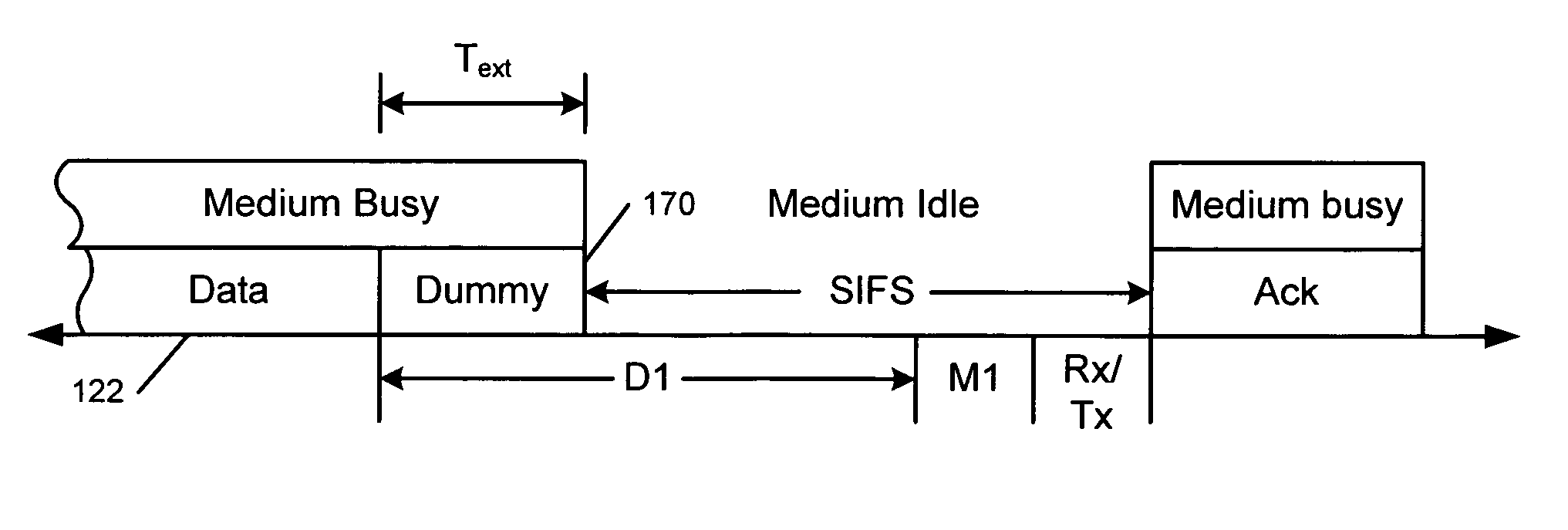

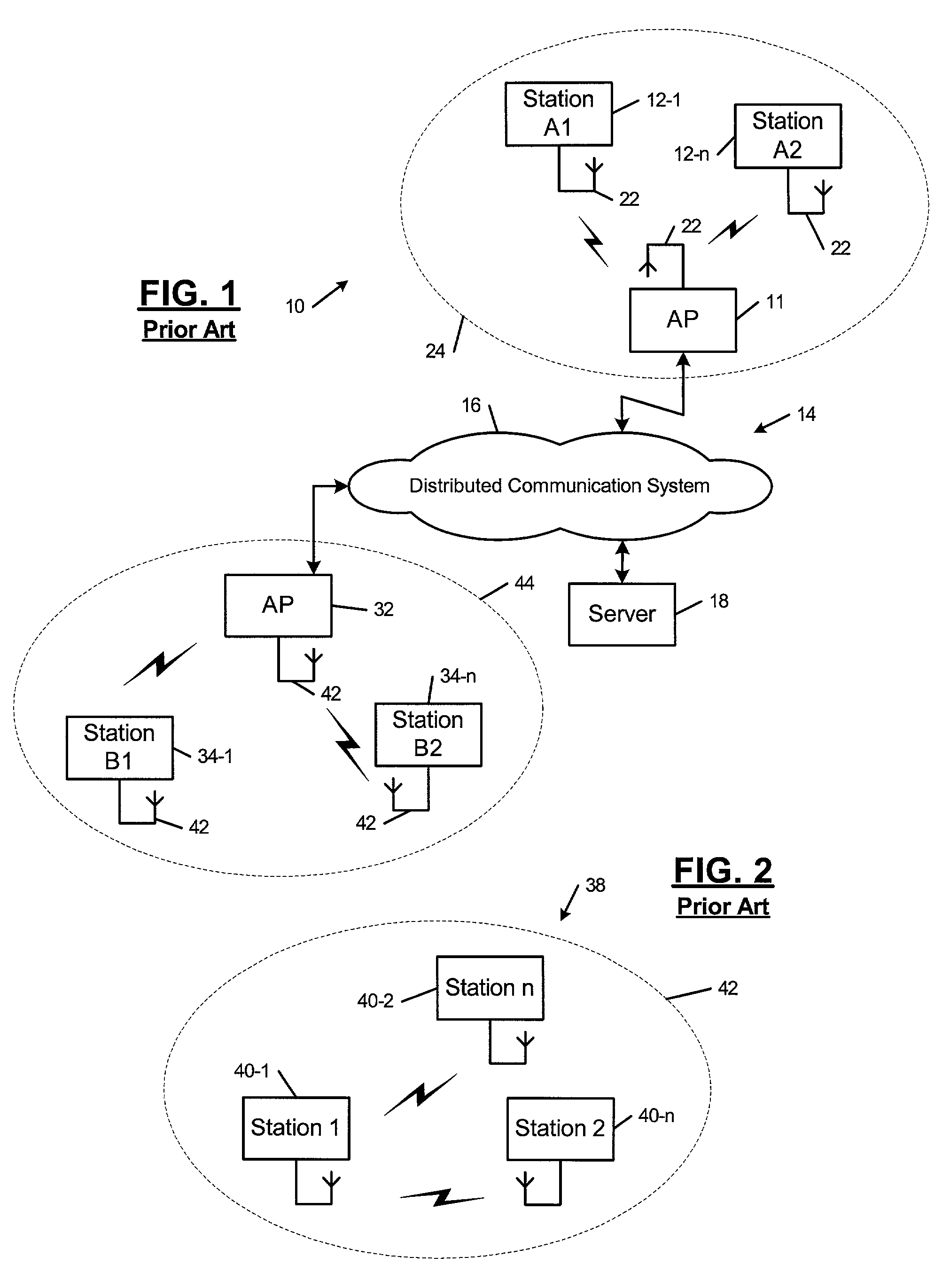

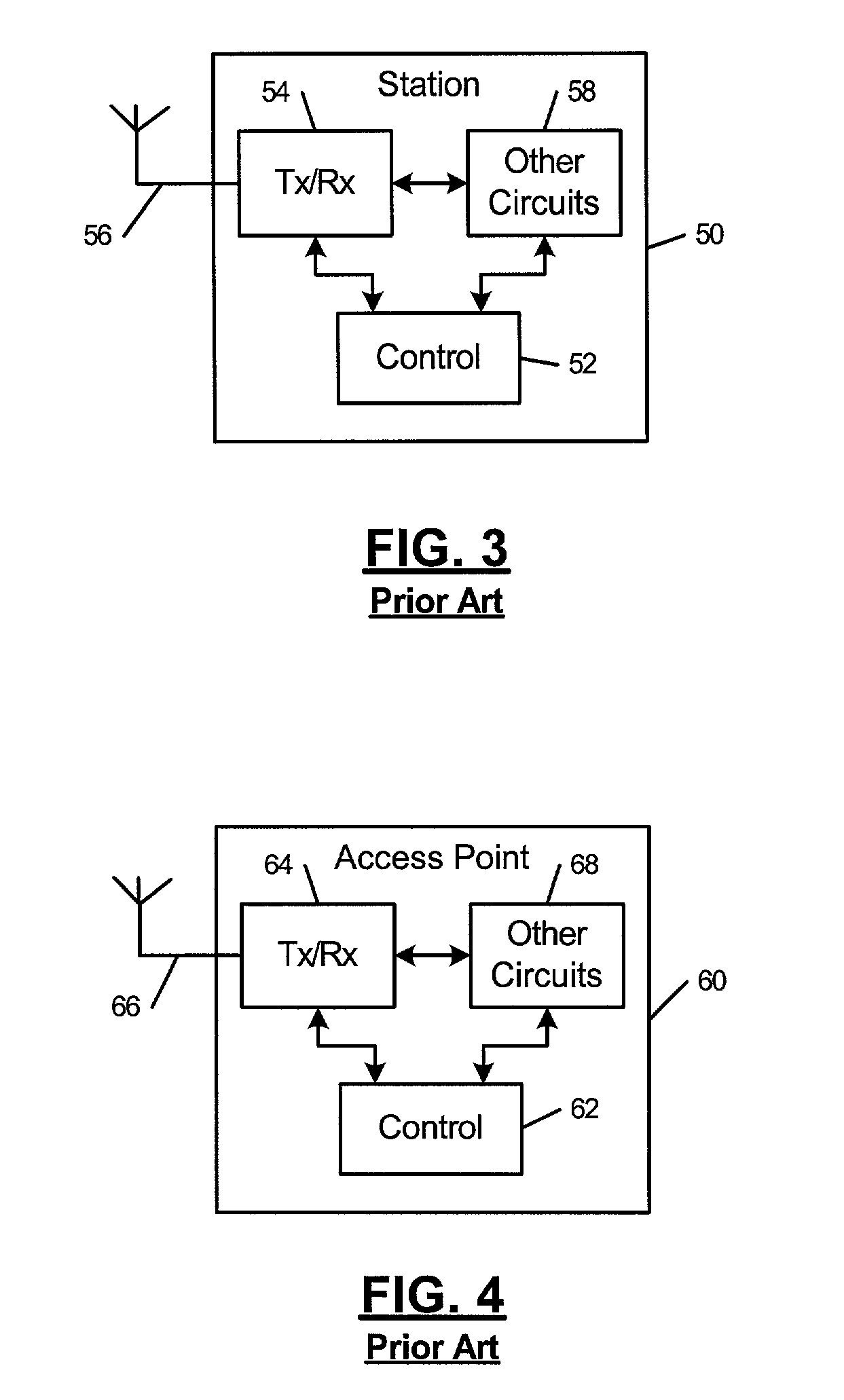

Extension mode for wireless lans complying with short interframe space requirement

A method and apparatus enables advanced signal processing in a wireless local area network (WLAN). First and second WLAN transceivers are provided with advanced signal processing capabilities. A maximum interframe period between data and an acknowledgement is required by the WLAN for compatibility. A duration of the interframe period is shorter than a duration that is required to perform the advanced signal processing. The first WLAN transceiver transmits a header and data. A first data field in the header is specified that enables the advanced signal processing. A second data field is specified that defines a data time period and an extension time period. The first WLAN transceiver transmits data during the data time period and dummy data during the extension time period. The second WLAN transceiver receives the header and initiates receiver processing during the extension time period.

Owner:MARVELL ASIA PTE LTD

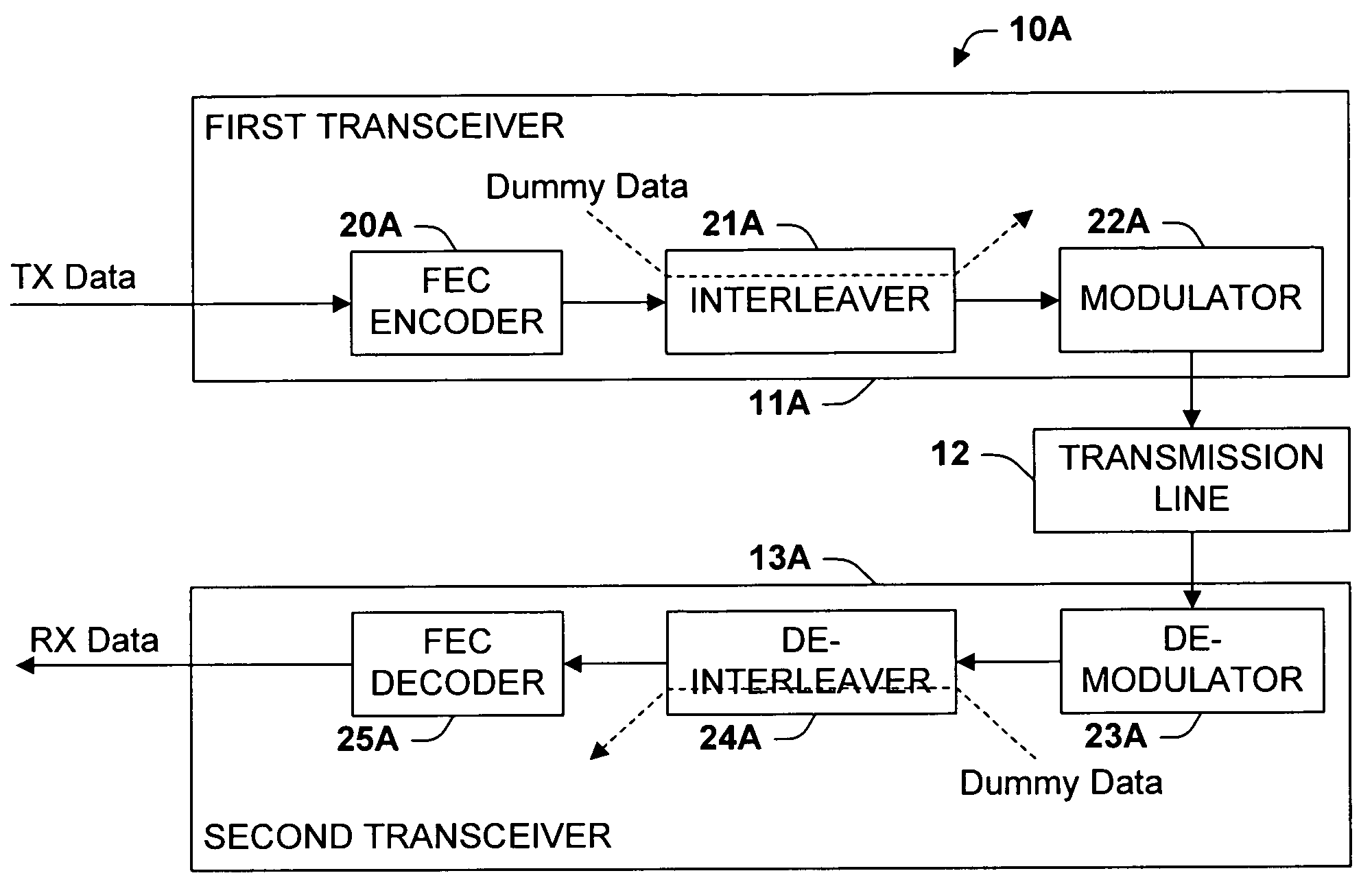

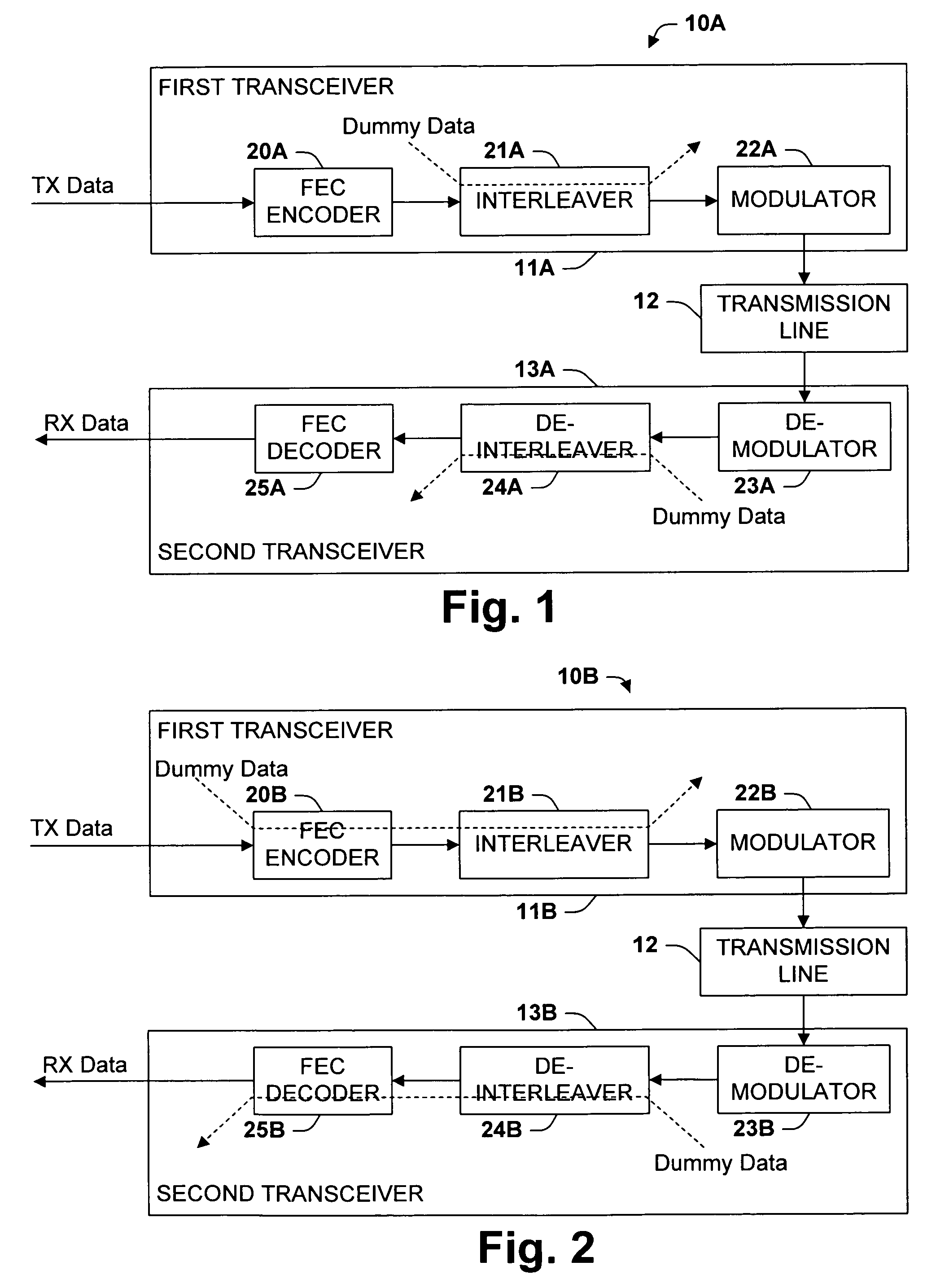

Method for seamless bit rate adaptation for multicarrier DSL

ActiveUS7519124B2Improve protectionReduce variationTransmission path divisionCriteria allocationData streamCarrier signal

Owner:INTEL GERMANY GMBH & CO KG

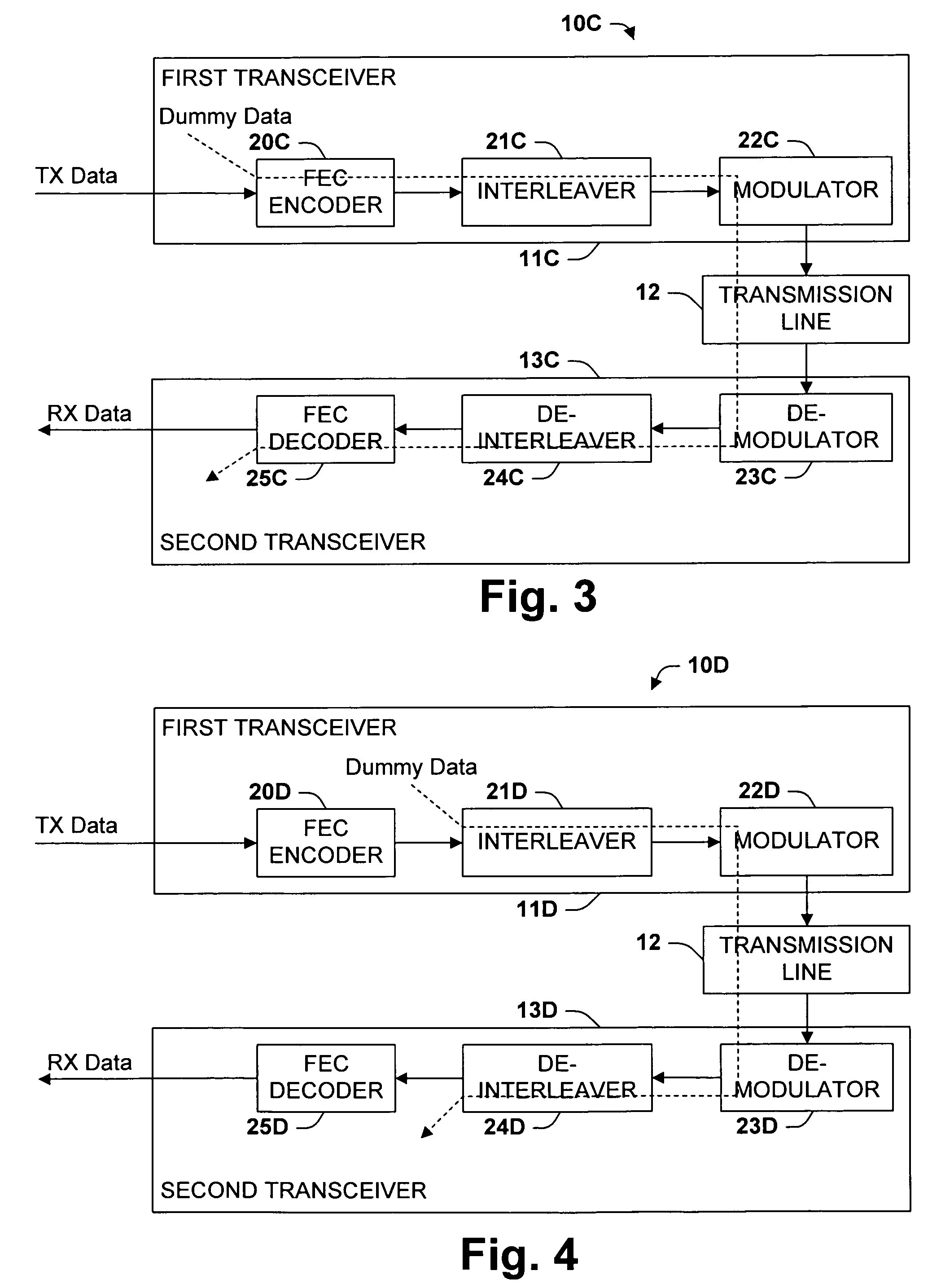

Packet relay apparatus and control method for data relay apparatus

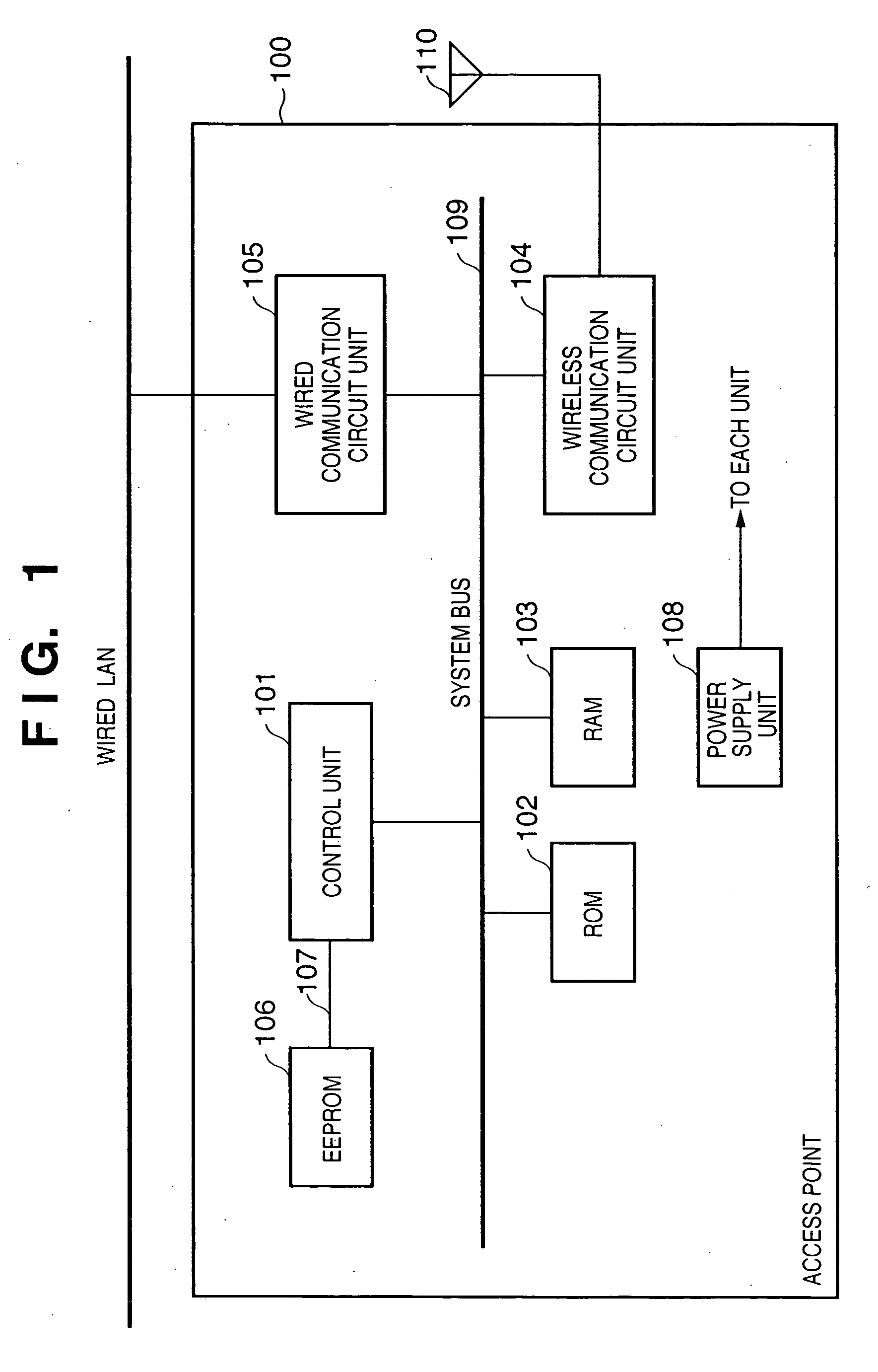

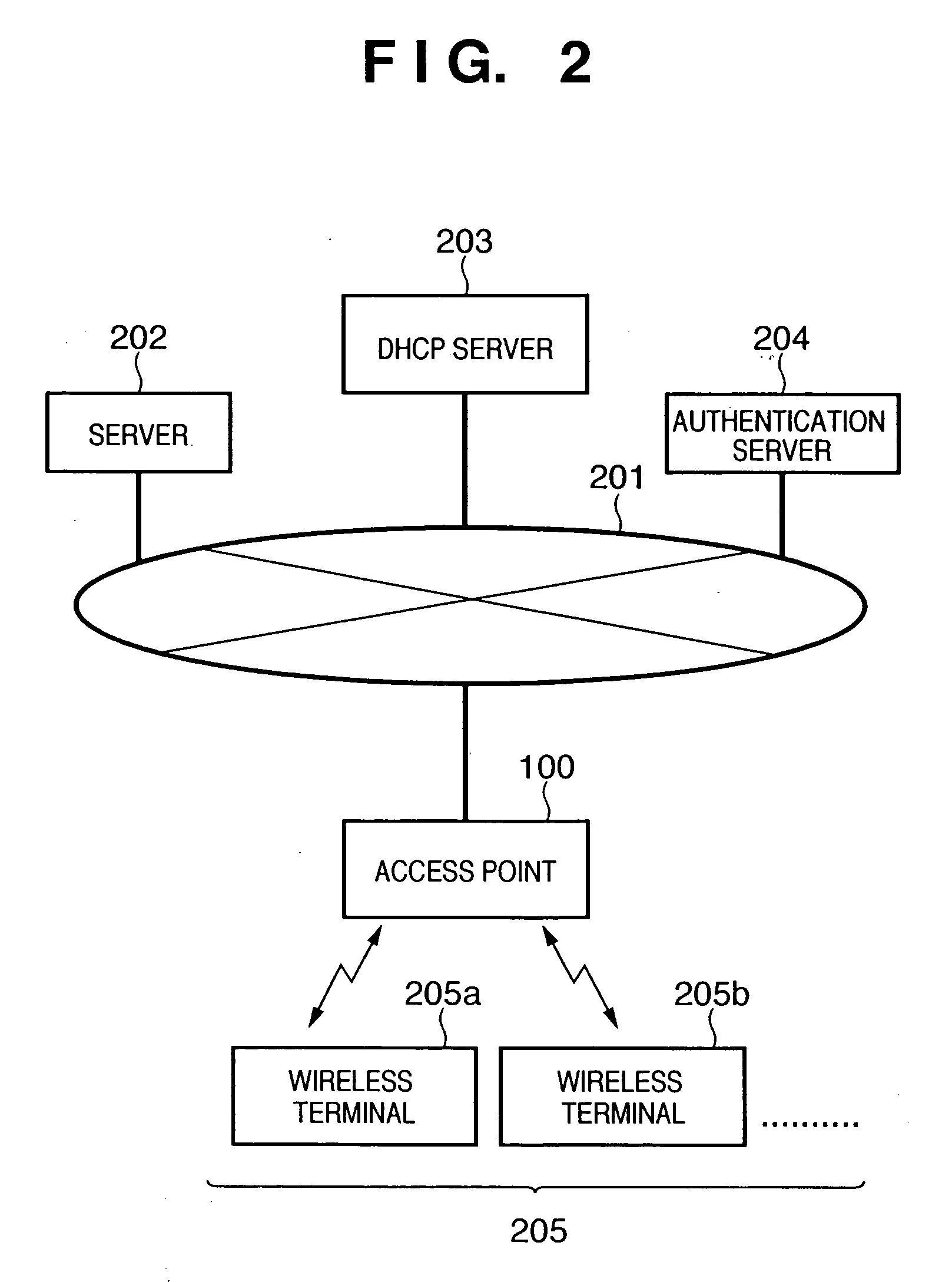

A data relay apparatus (access point) connects to a network having a DHCP server and authentication server. The data relay apparatus stores the MAC address of a communication device which is permitted to connect. When a communication device starts to connect to the data relay apparatus, it is determined whether or not the MAC address of the communication device is stored. Assume that the address is stored. In this case, even if, for example, the communication device is not authenticated by authentication processing performed by the authentication server, dummy data indicating that authentication is successful is transmitted to the communication device to notify the communication device that the authentication is successful. Subsequently, since the communication device requests the DHCP server to assign an IP address, the address assignment request from the communication device is transferred to the DHCP server so as to assign the IP address to the communication device. In addition, different security levels at the time of network access are set for a communication device which has failed in authentication by the authentication server but is assigned an IP address and a communication device which is successful in authentication.

Owner:CANON KK

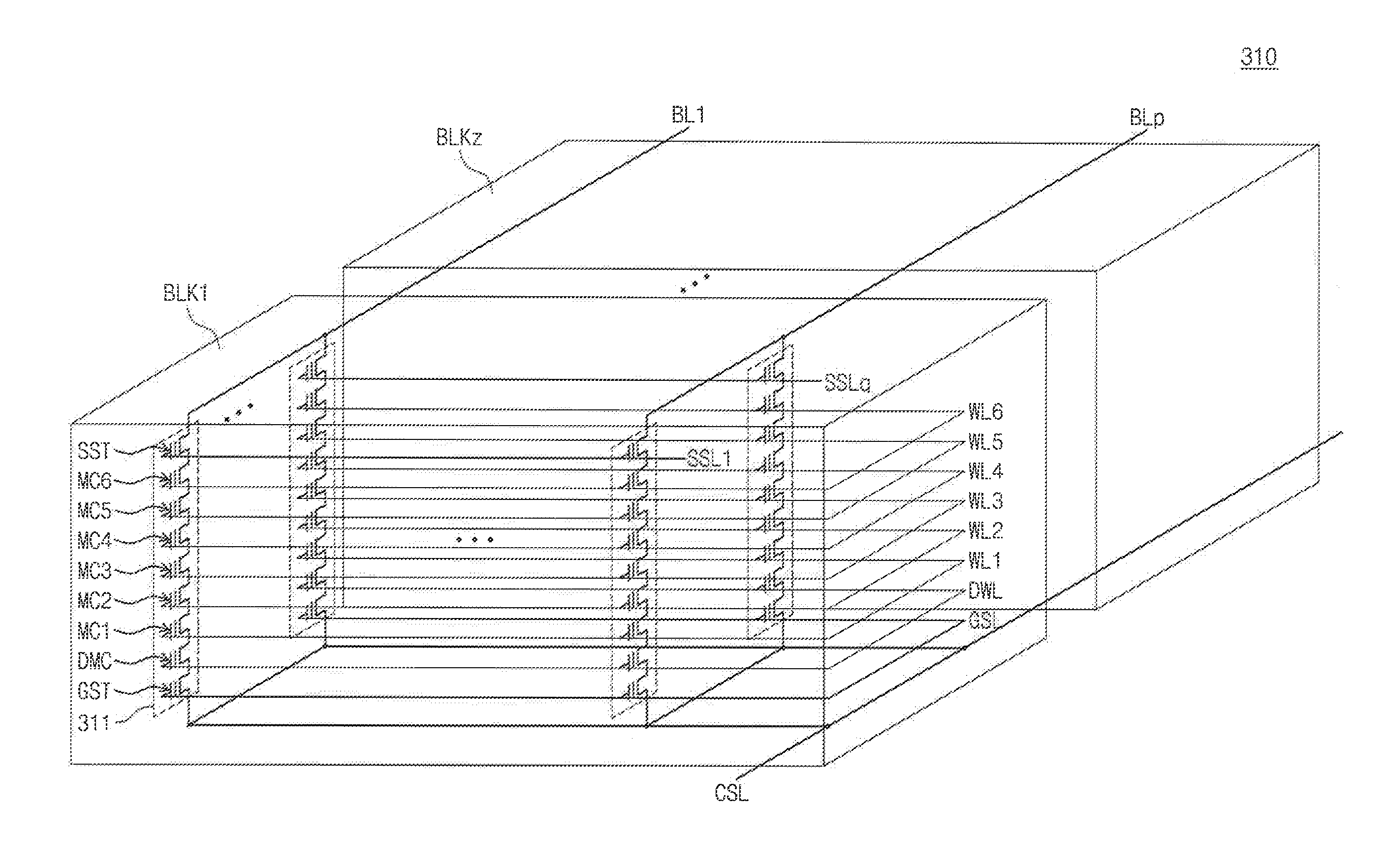

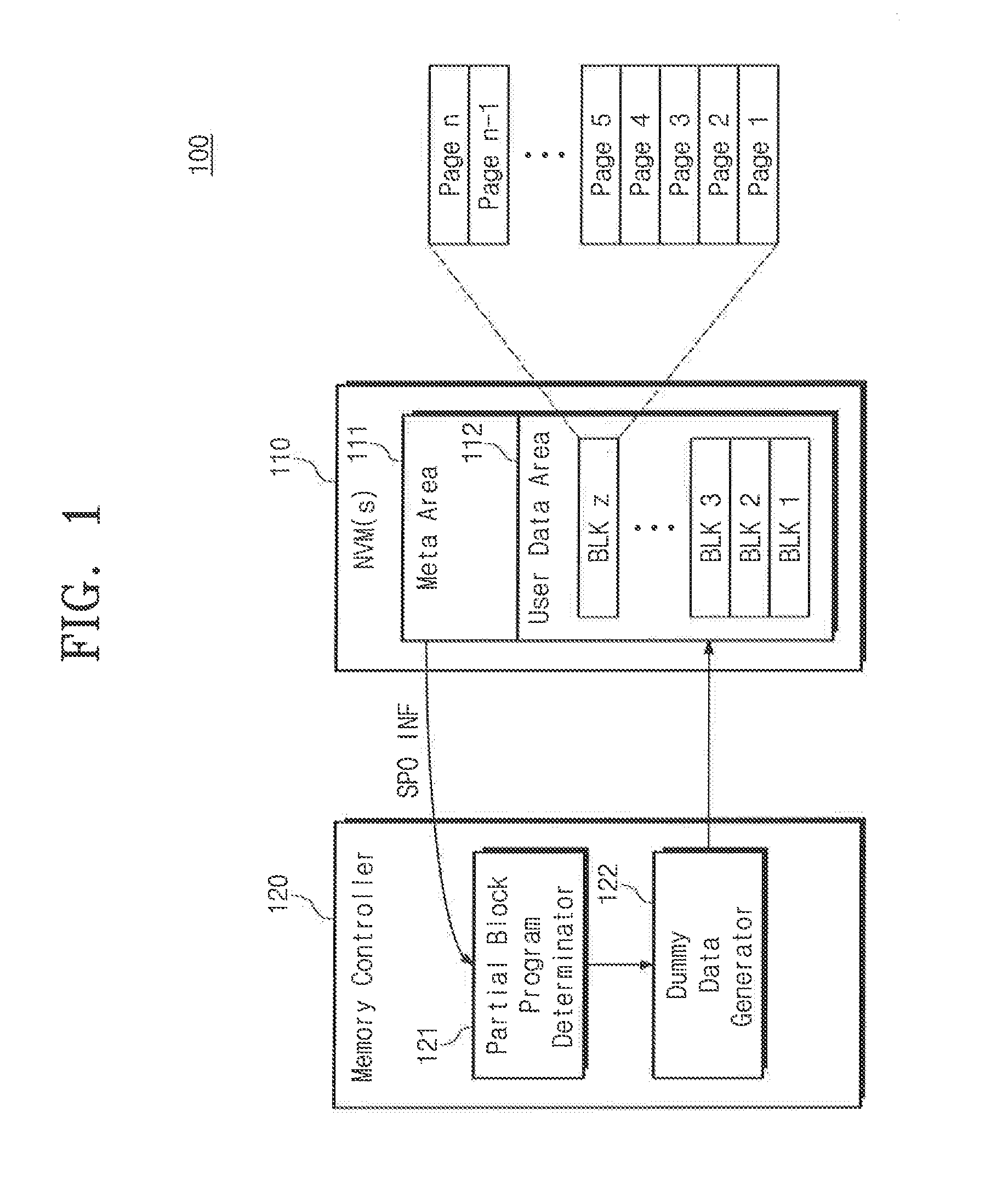

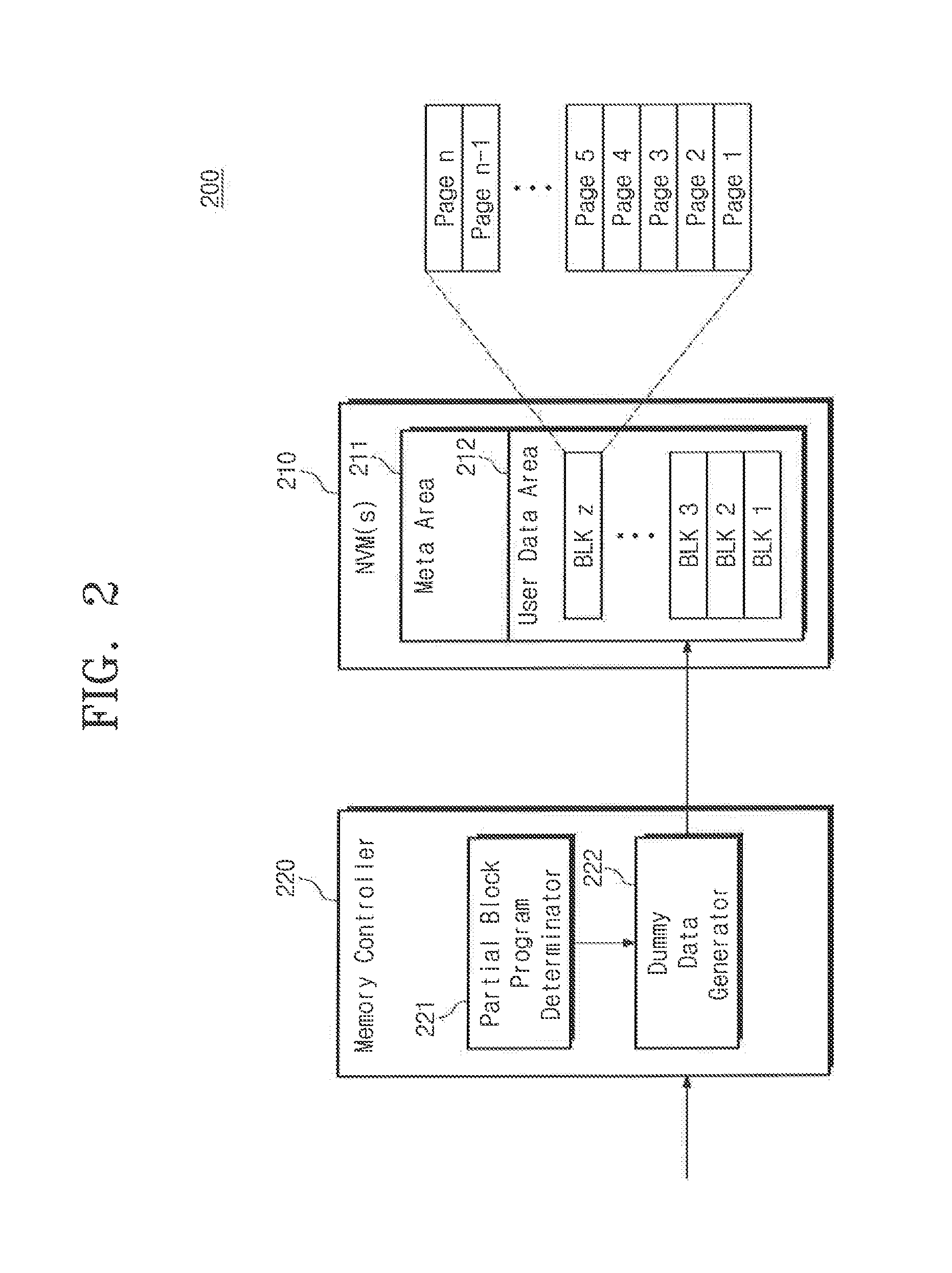

Nonvolatile memory device, storage device including the nonvolatile memory device, and operating method of the storage device

A storage device includes a nonvolatile memory device and a memory controller is provided. The nonvolatile memory device includes a plurality of blocks. The memory controller is configured to detect, upon receiving a power-on signal, a partial block among the plurality of blocks. The partial block includes a first page incompletely programmed due to sudden power-off occurred to the storage device. The memory controller determines whether or not to perform a dummy program operation on the partial block, and programs a second page of the partial bock with dummy data. The first page is different from the second page.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and apparatus for processing data in controller area network

InactiveUS7738462B2Improve data processing efficiencyError preventionTime-division multiplexArea networkDummy data

A method and apparatus for processing data in a Controller Area Network (CAN) are discussed. In an embodiment of this invention, dummy data is added to data to be transmitted via a CAN message, and information indicating that the dummy data is added is transmitted via the CAN message. A length of the dummy data is determined such that data to be transmitted via the CAN message becomes a predetermined length, and data in which five or more successive bits do not have a same value is added as the dummy data. The information is included in a field indicating a length of data to be transmitted via the CAN message, and is indicated by a value within a reserved range of the field. Accordingly, data processing efficiency can be improved, and flexible CAN communication can be performed via the CAN message.

Owner:LG ELECTRONICS INC

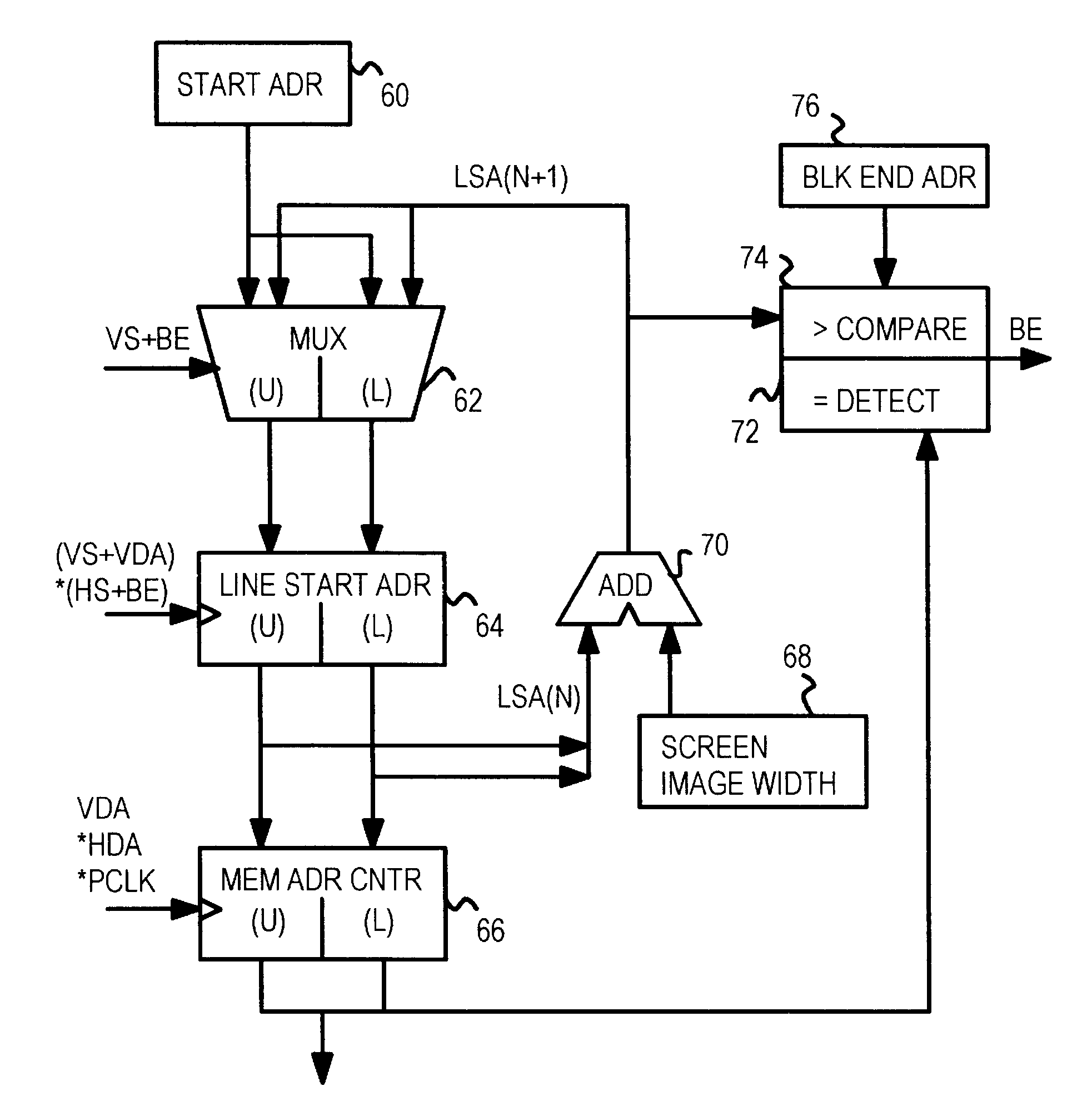

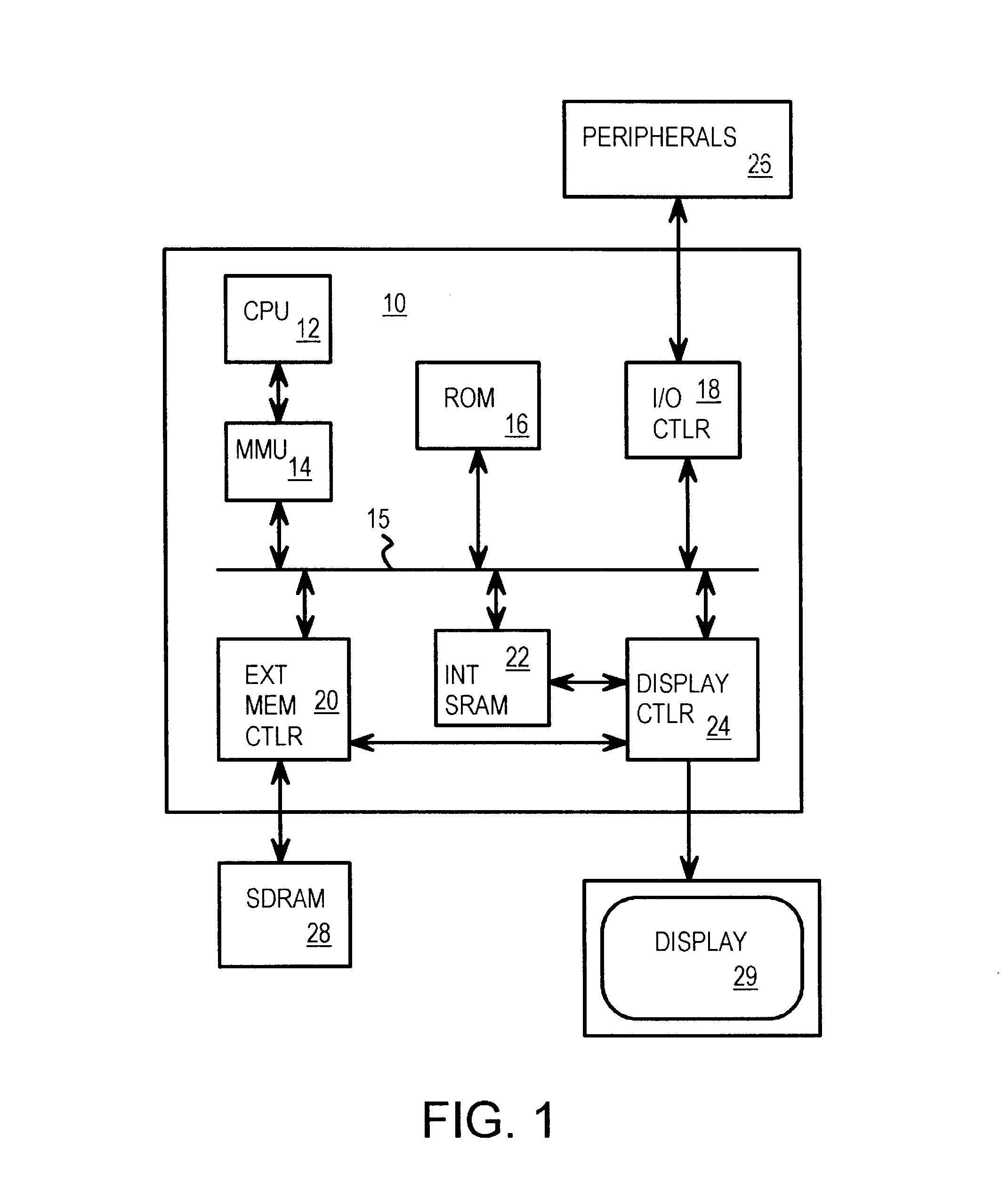

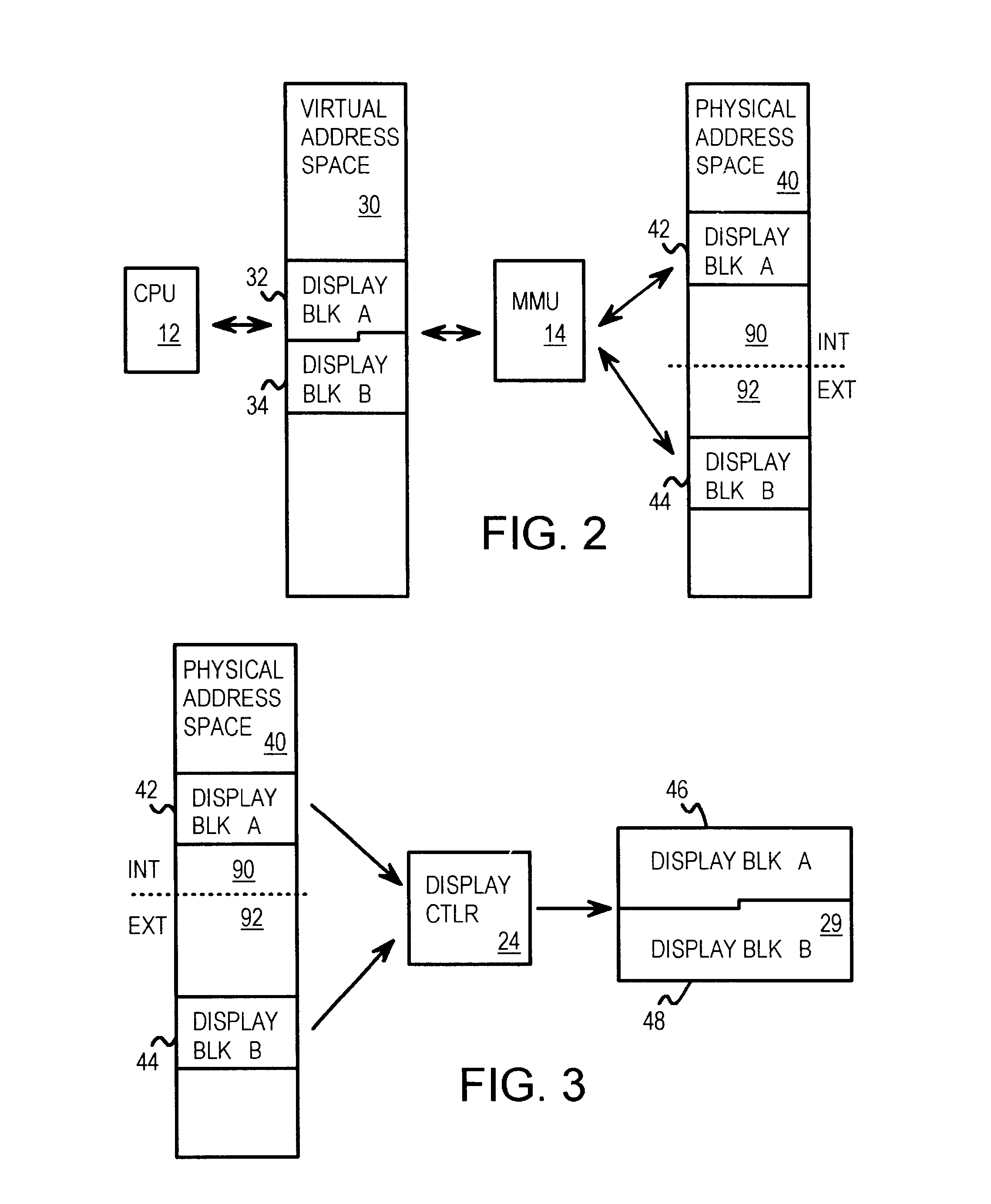

Single-block virtual frame buffer translated to multiple physical blocks for multi-block display refresh generator

InactiveUS6680738B1Memory adressing/allocation/relocationCathode-ray tube indicatorsPower modeExternal storage

A graphics controller for a System-On-a-Chip (SOC) used with a battery-powered device allows for reduced-power display modes. The microprocessor writes to a frame buffer that is a single, contiguous address block in virtual memory. A memory management unit (MMU) translates frame-buffer address to multiple physical blocks. The graphics controller fetches pixels from the multiple physical blocks, including a block in an on-chip memory and a block in an external memory. In a low-power mode, pixels are only fetched from the lower-power on-chip memory and not the higher-power external memory. A smaller display window is defined and pixels outside the window are replaced by dummy data,.eliminating external-memory fetches. The smaller display window falls within the first block in the on-chip memory. Status and other information can be displayed in the smaller display window during stand-by modes, while a full-screen of data is displayed for full-power modes.

Owner:MIND FUSION LLC +1

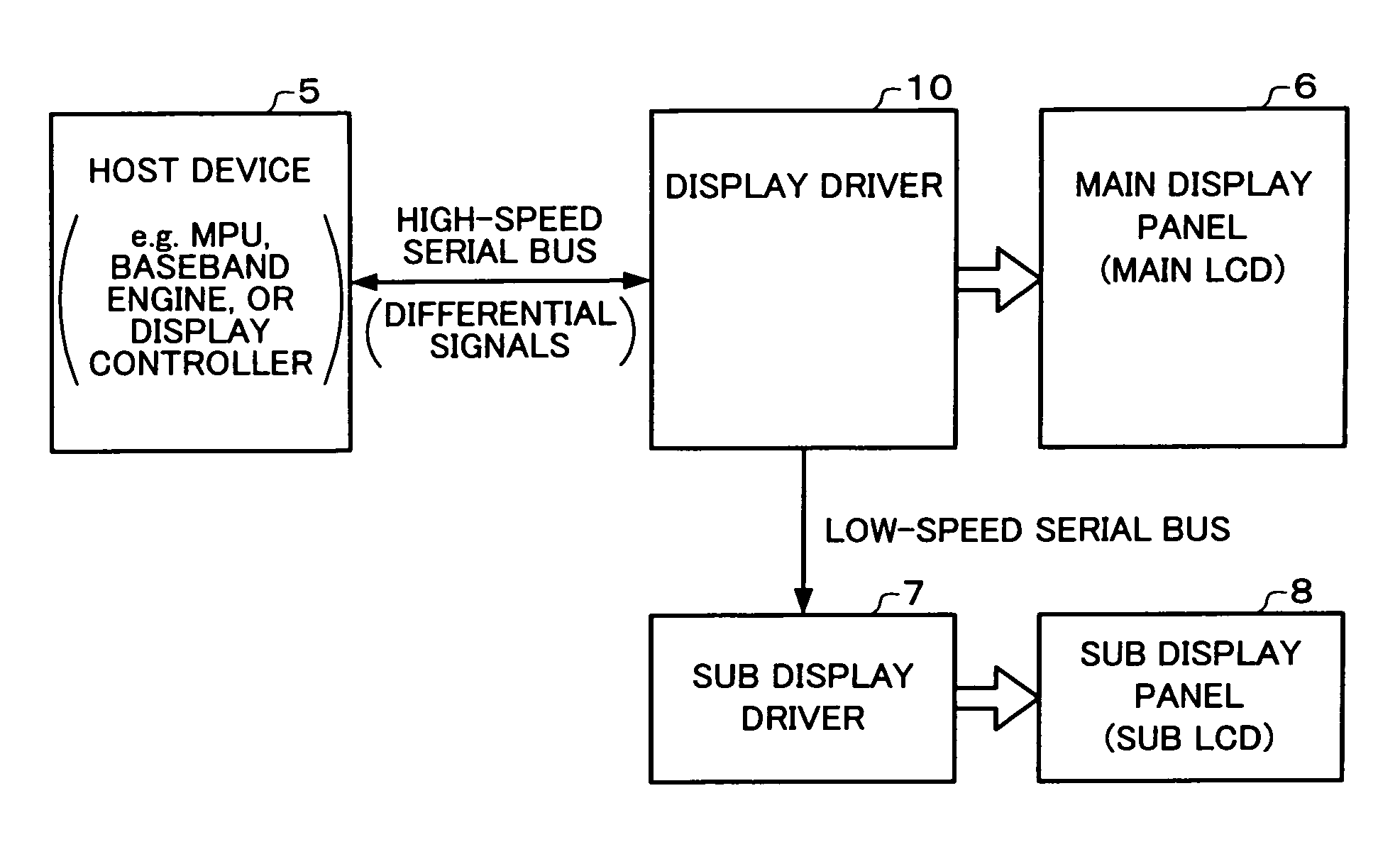

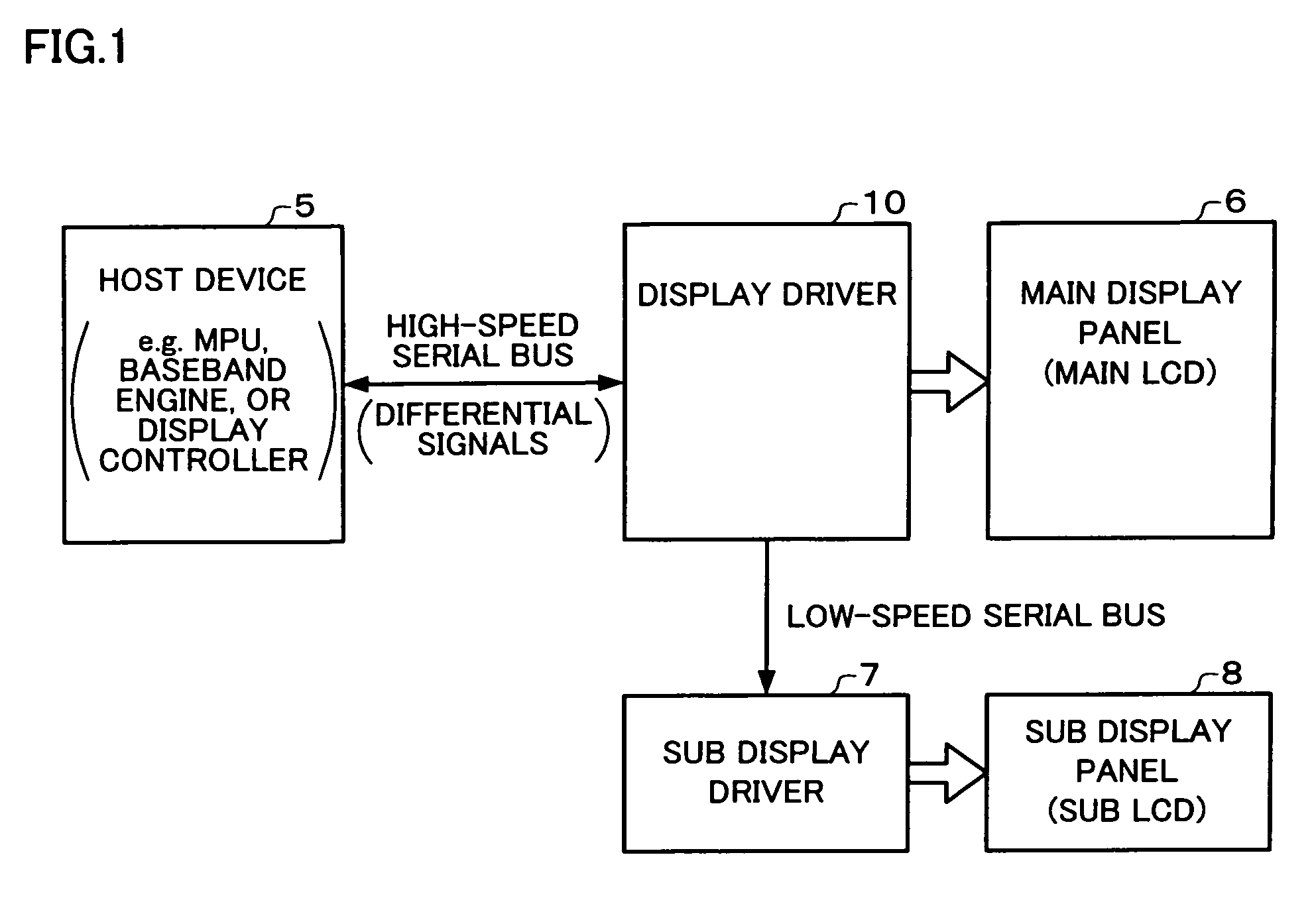

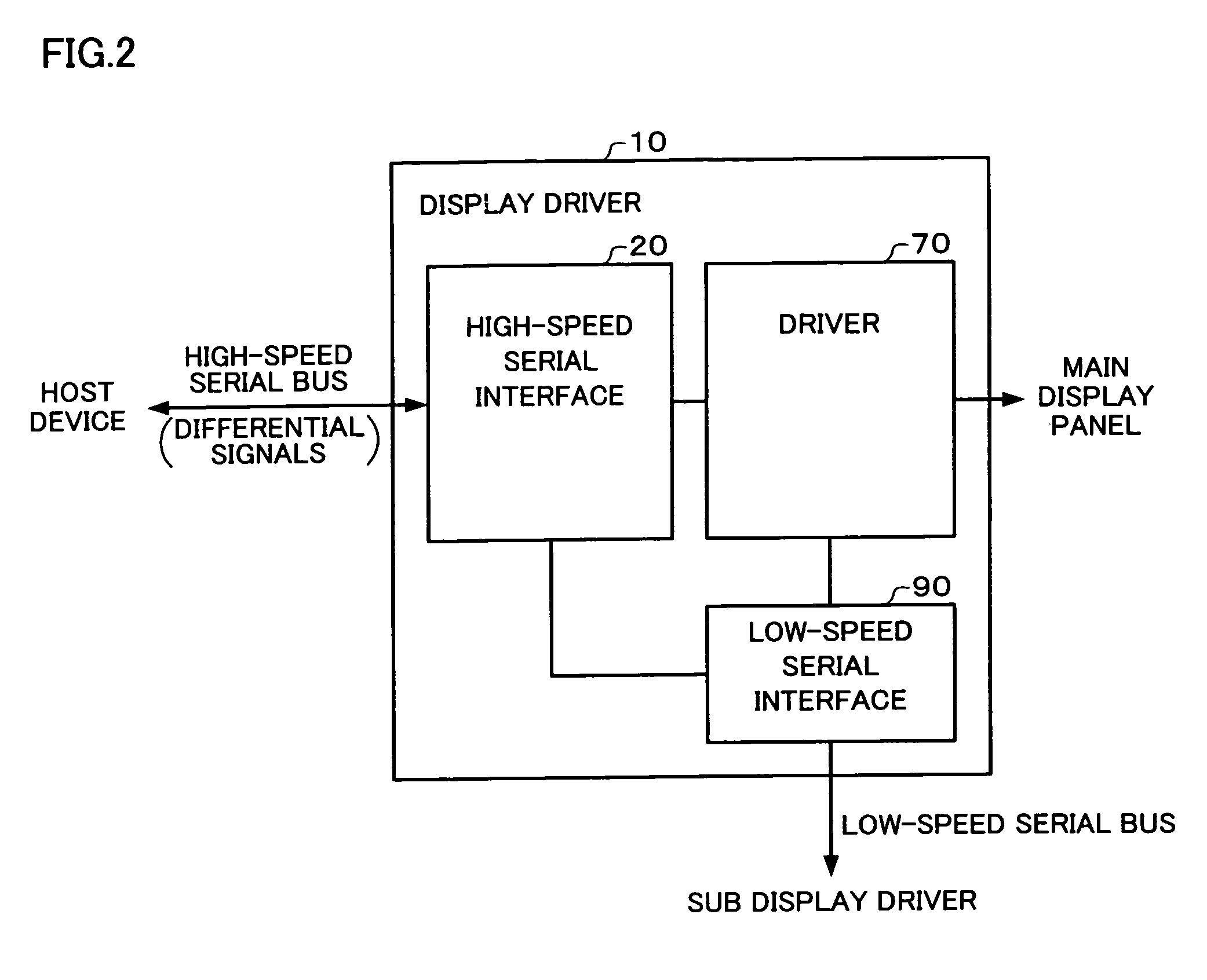

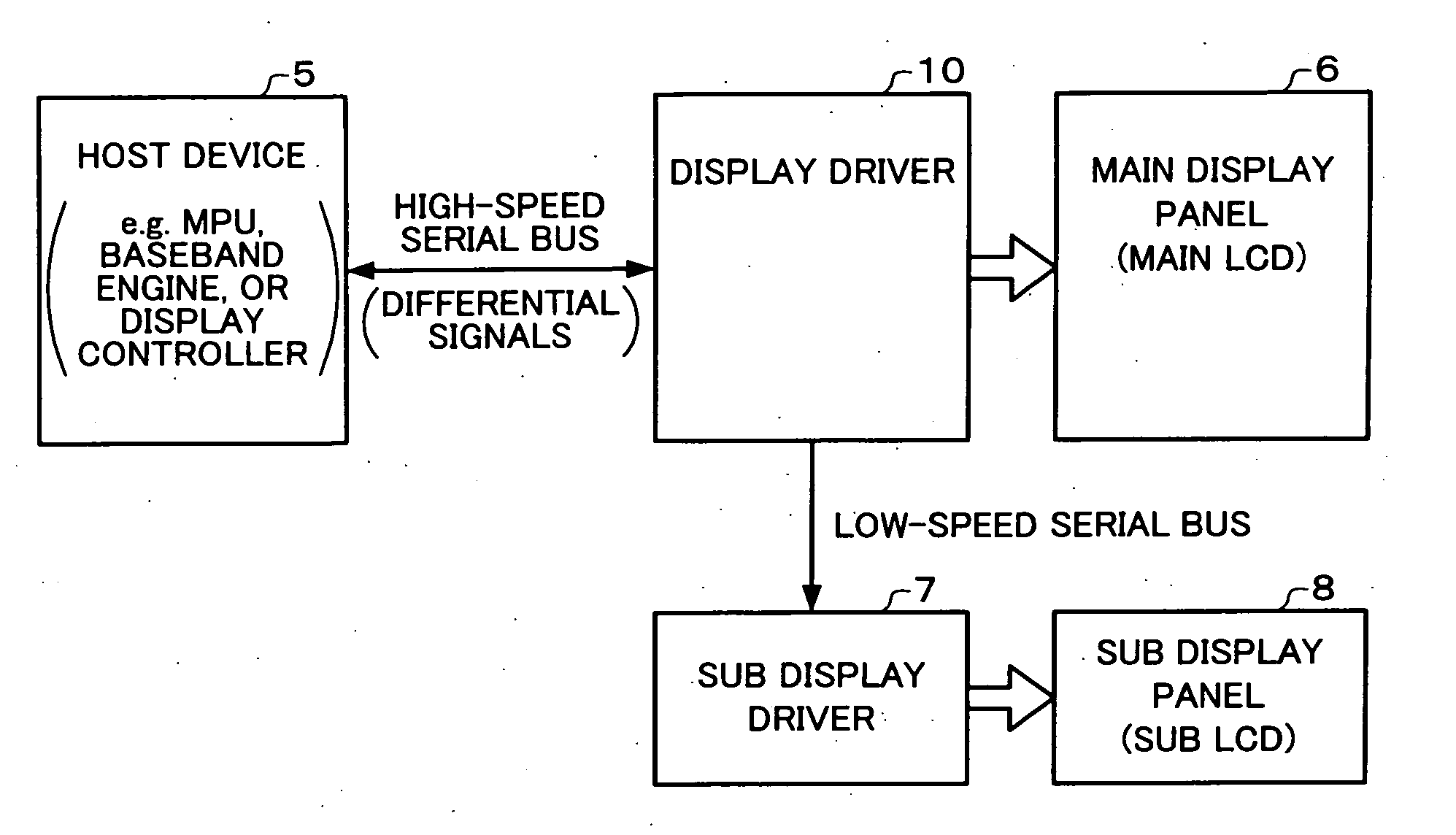

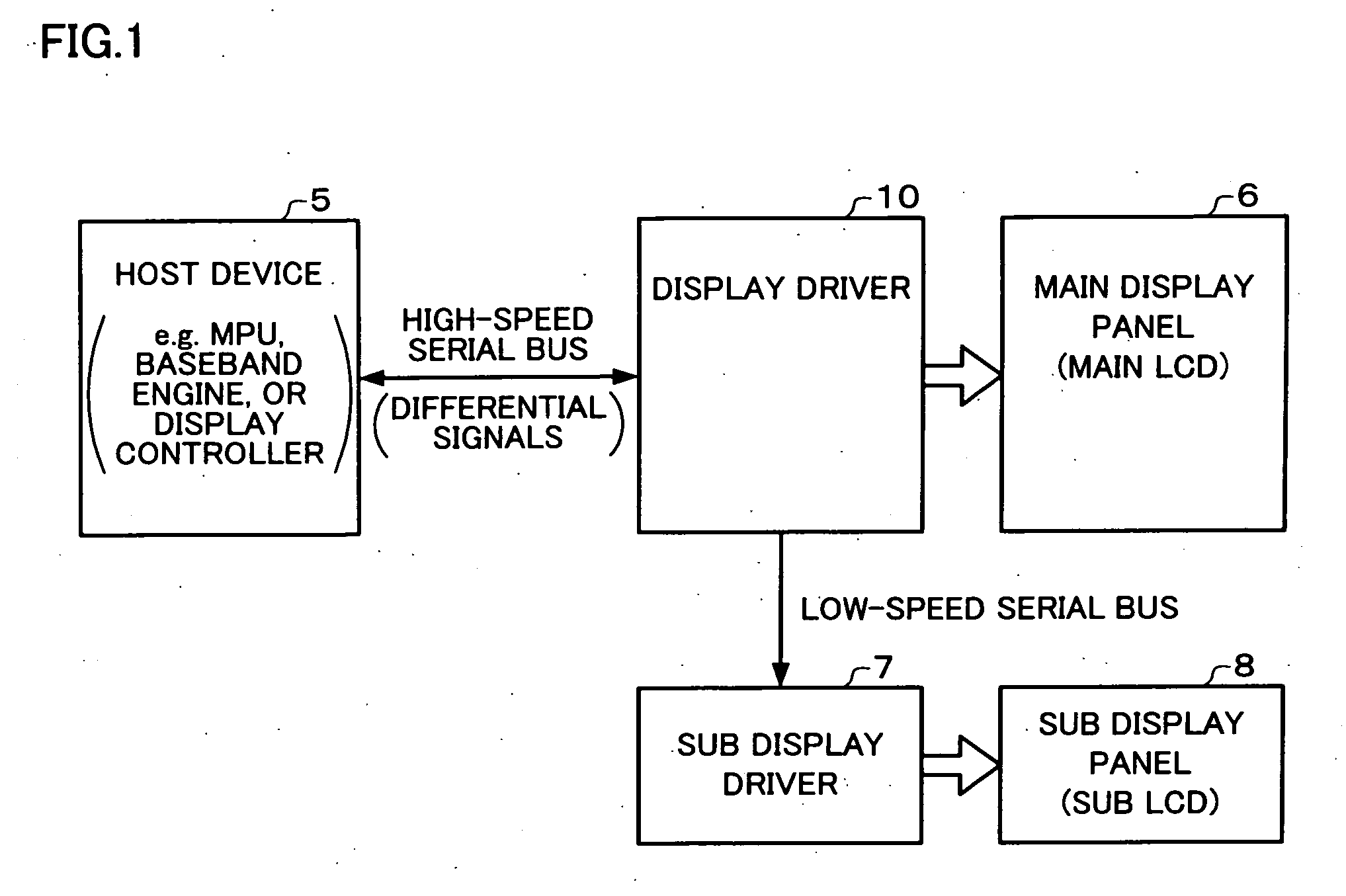

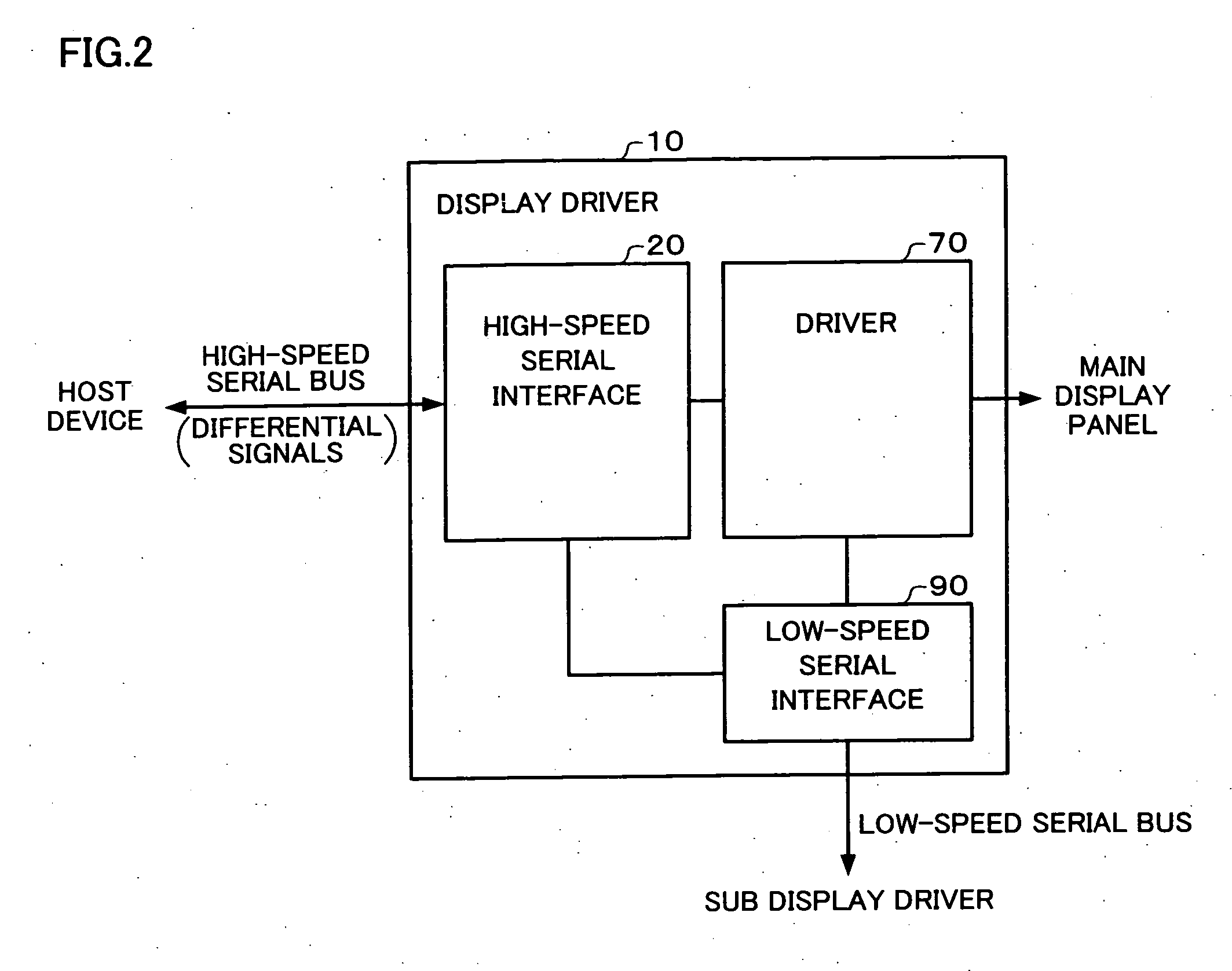

Display driver and electronic instrument

InactiveUS8031130B2Effective controlElectric/magnetic signal storageCathode-ray tube indicatorsDriver circuitLow speed

A display driver comprising: a high-speed serial interface circuit which receives a packet from a host device through a high-speed serial bus using differential signals, and outputs a command or data included in the received packet; a driver circuit which drives a main display panel based on the output command or data; and a low-speed serial interface circuit which outputs a command or data to a sub display driver through a low-speed serial bus when the packet received from the host device includes the sub display driver command or data. And the display driver inserts dummy data to the packet to adjust the difference of the transfer rate by inserting a dummy the dummy data. And the display driver adjust the difference of the transfer rate.

Owner:SEIKO EPSON CORP

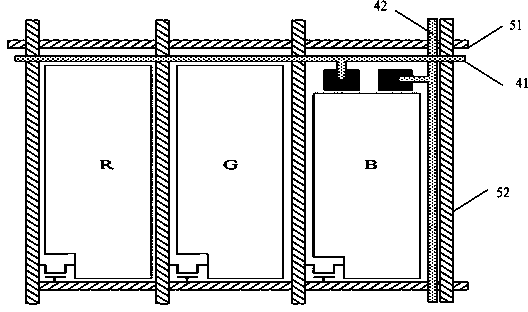

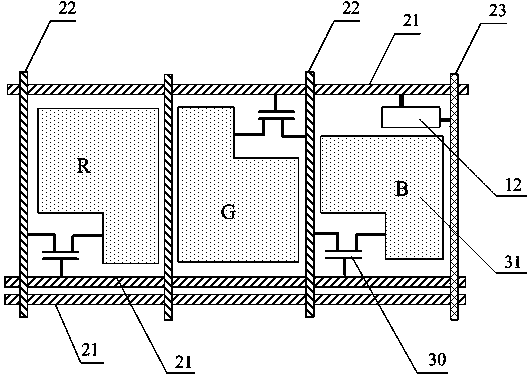

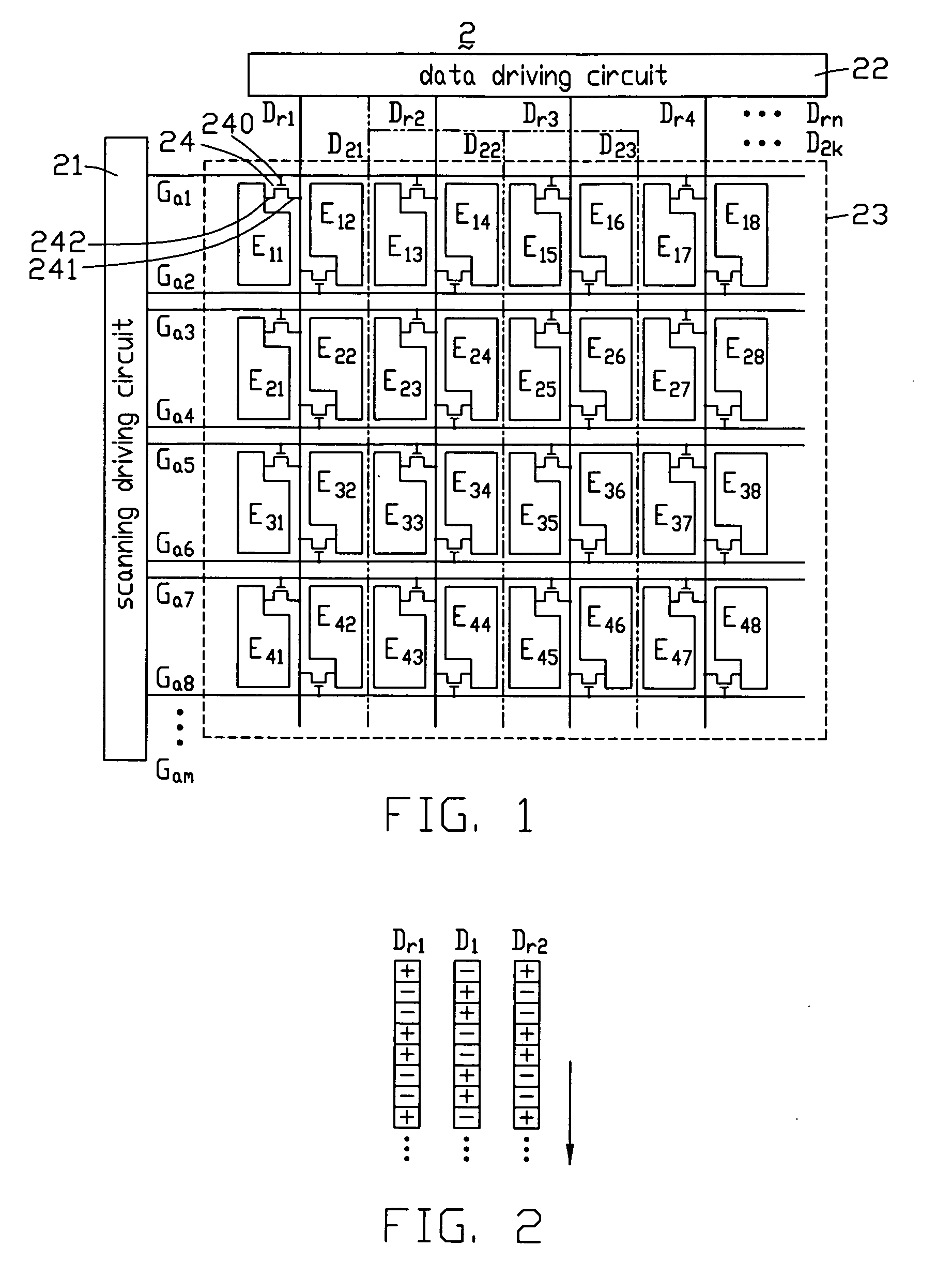

Touch liquid crystal display and array substrate thereof

InactiveCN103728762AReduce layout densityReduce the number of timesNon-linear opticsInput/output processes for data processingLiquid-crystal displayTouch Senses

Embodiments of the invention disclose a touch liquid crystal display array substrate comprising a plurality of pixel units defined by gate lines and data lines. A thin-film transistor and a pixel electrode are formed in each pixel unit. The array substrate further comprises touch circuit units used for touch positioning. Each touch circuit unit comprises a touch emitting line, a touch sensing line, and a photosensitive unit; the touch emitting line and the touch sensing line interest with each other; the photosensitive unit disposed at an intersection is connected with both the touch emitting line and the touch sensing line; the touch emitting line is one gate line; the touch sensing line is one dummy data line arranged on the array substrate; the dummy data line and one adjacent data line are spaced by at least one pixel electrode. The embodiments correspondingly disclose a touch liquid crystal display. Through the application of the embodiments, pixel aperture ratio can be increased, touch positioning sensitivity is improved, and product yield is increased.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

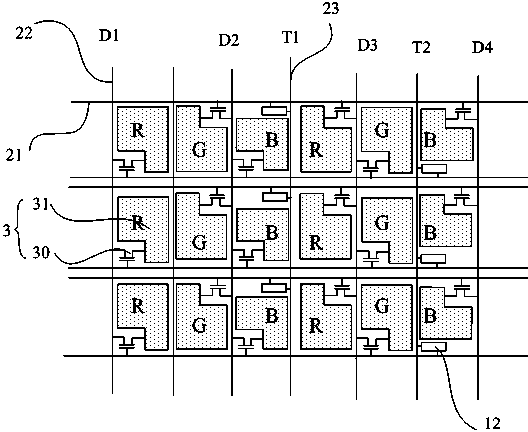

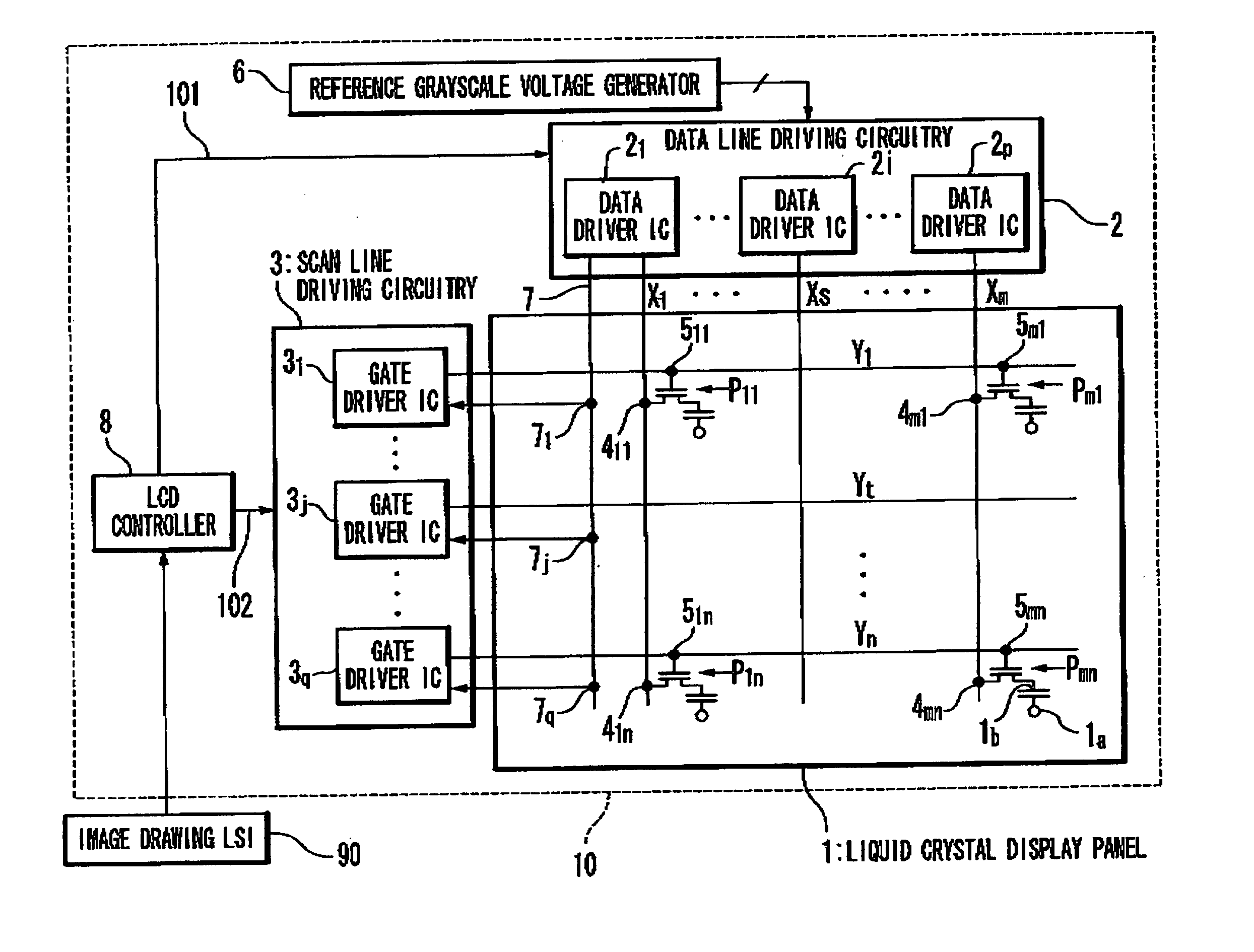

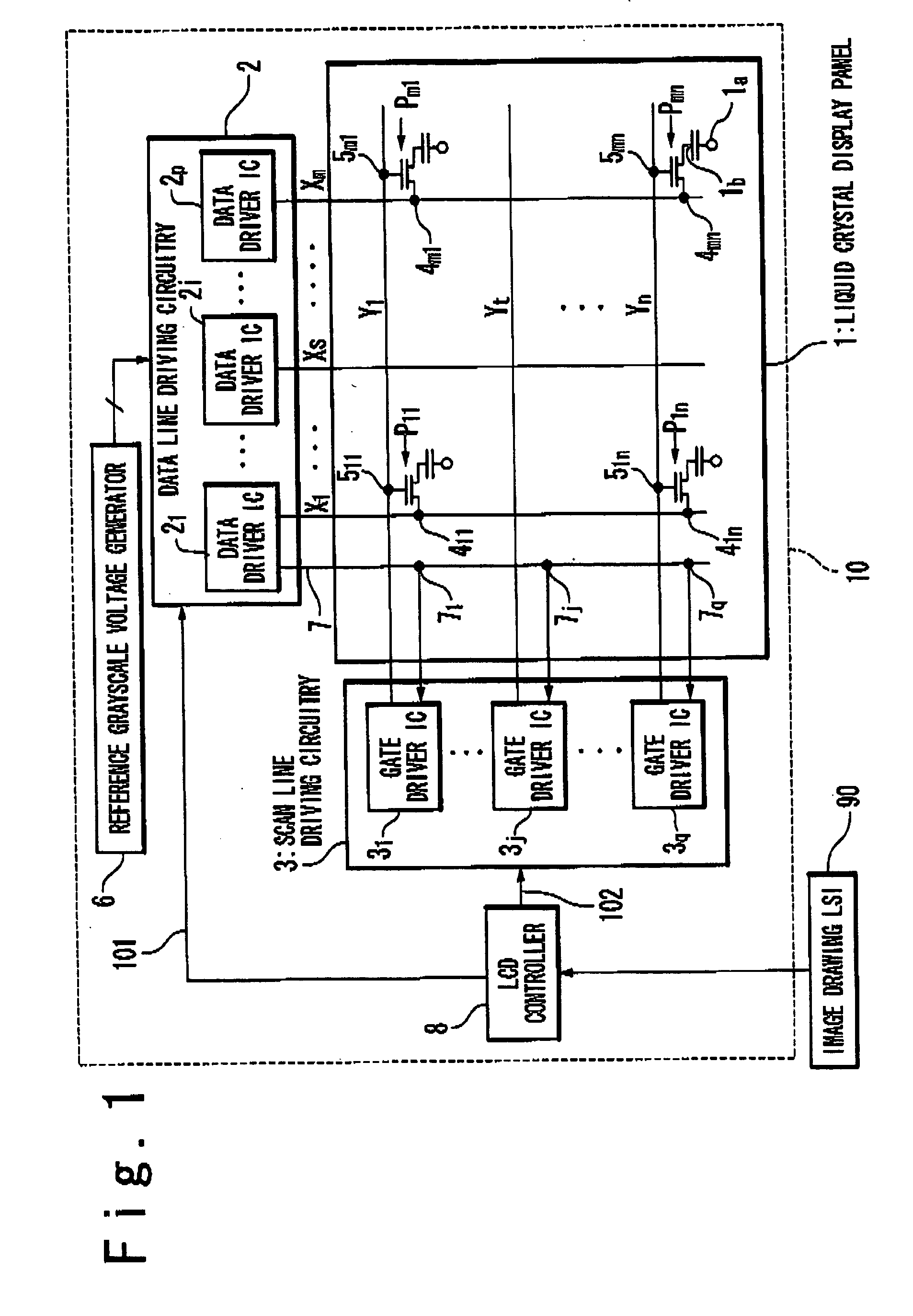

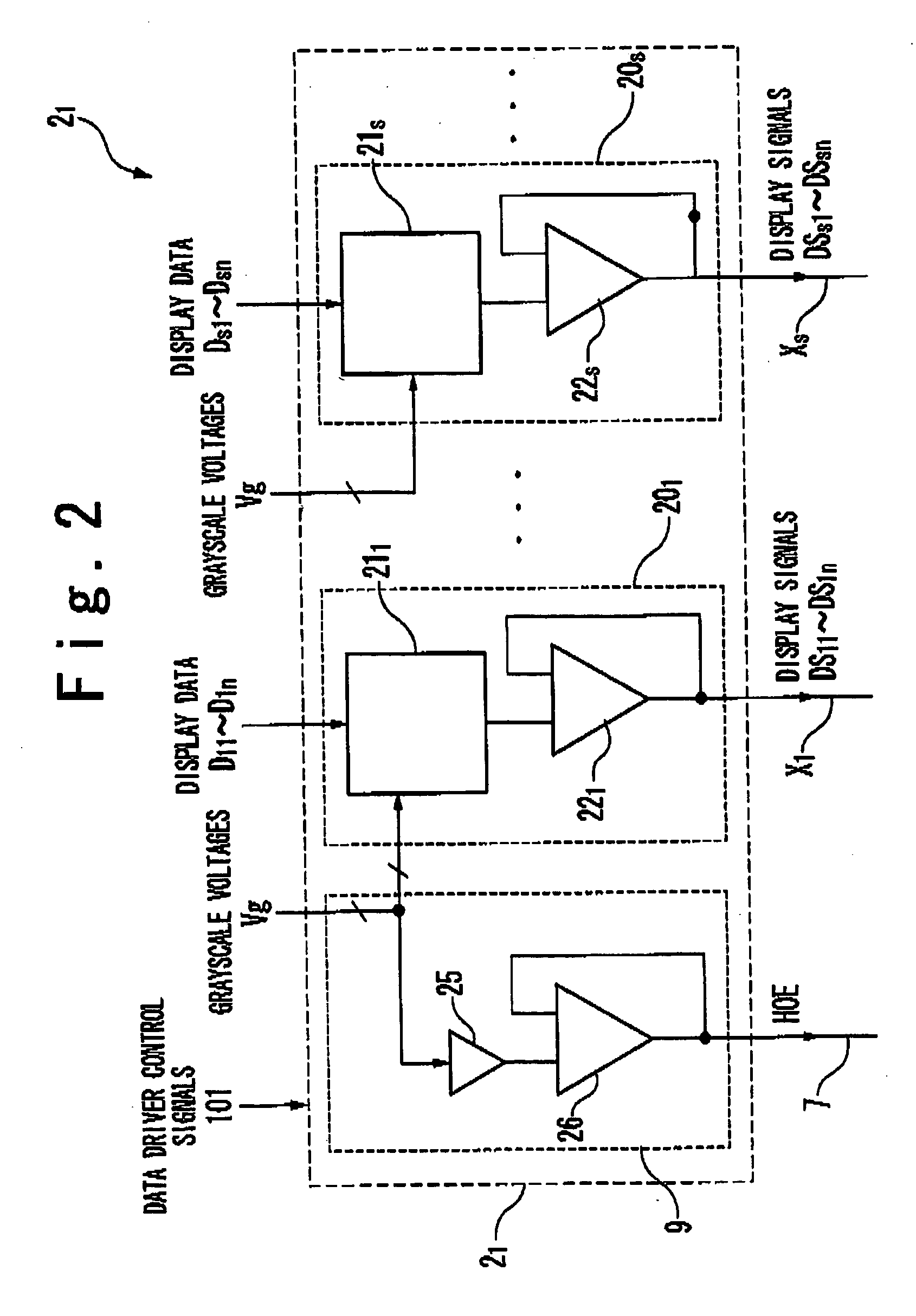

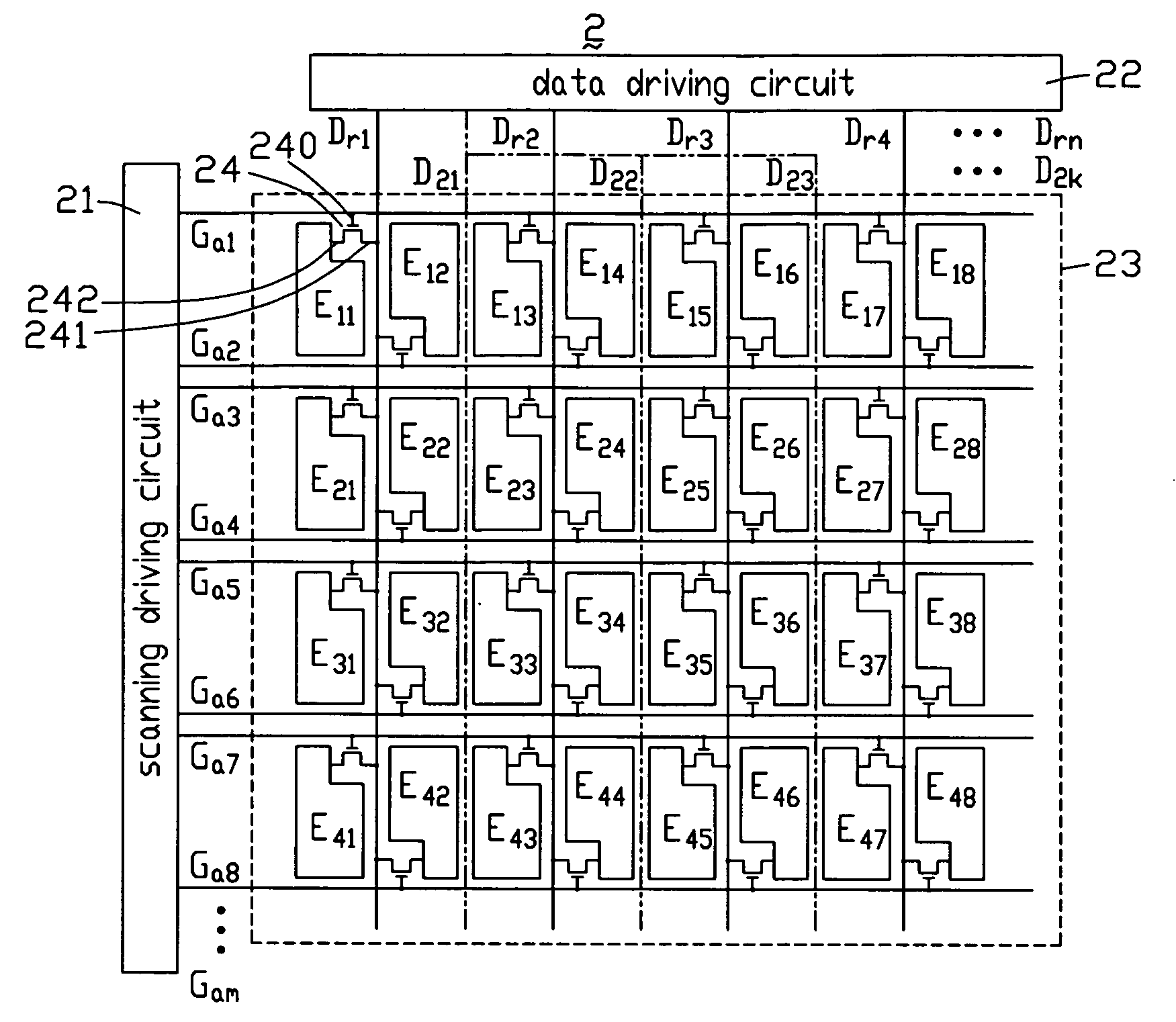

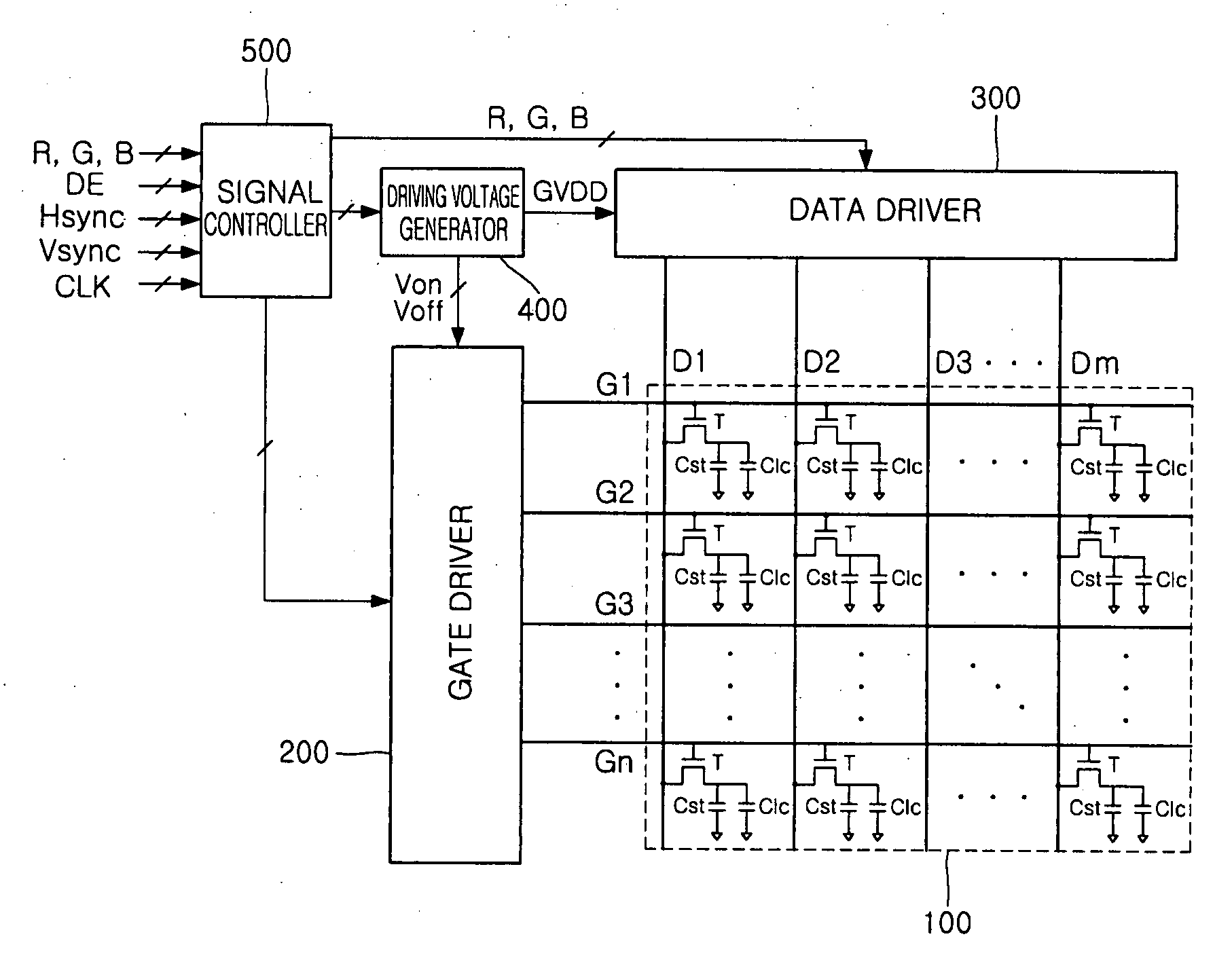

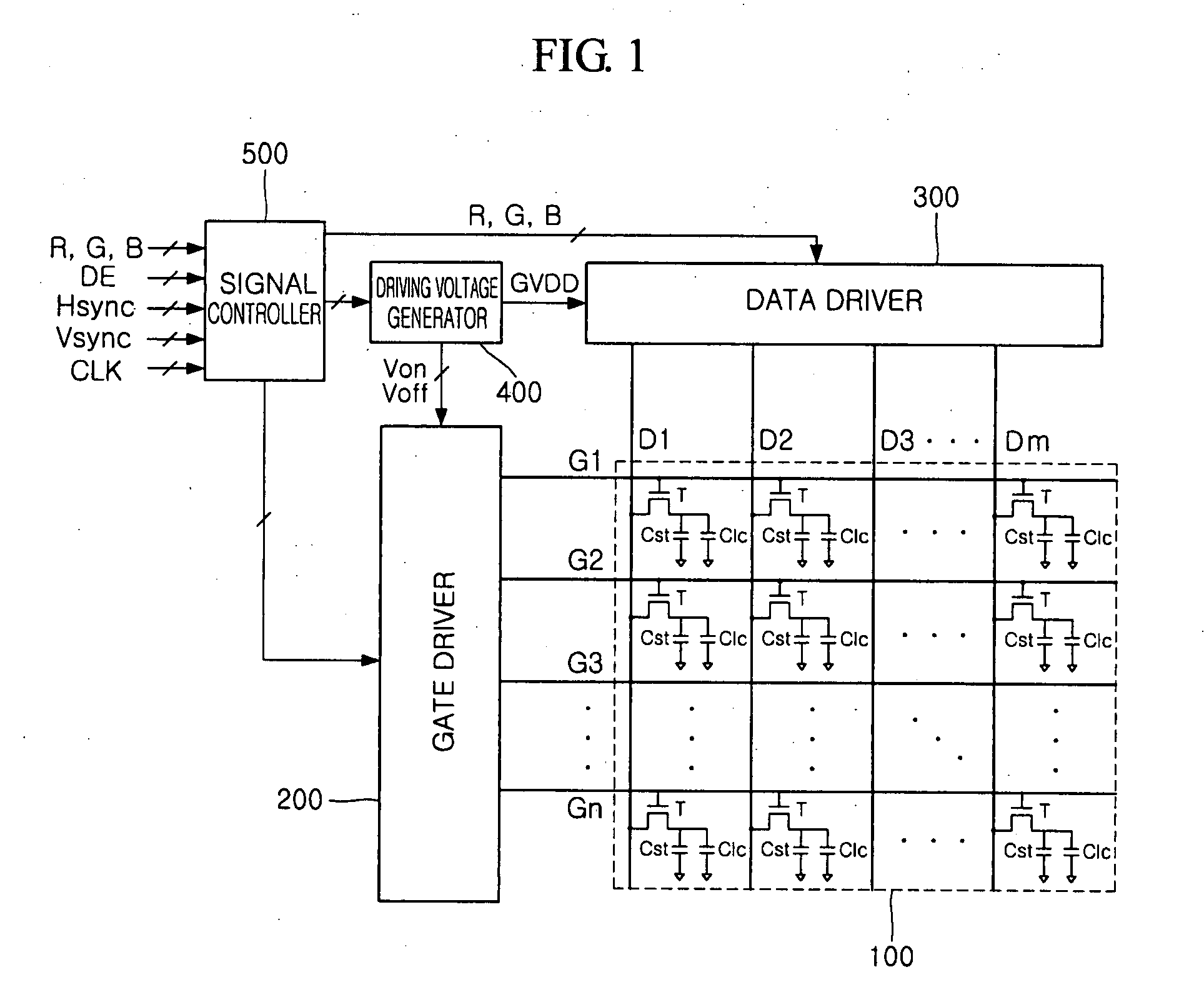

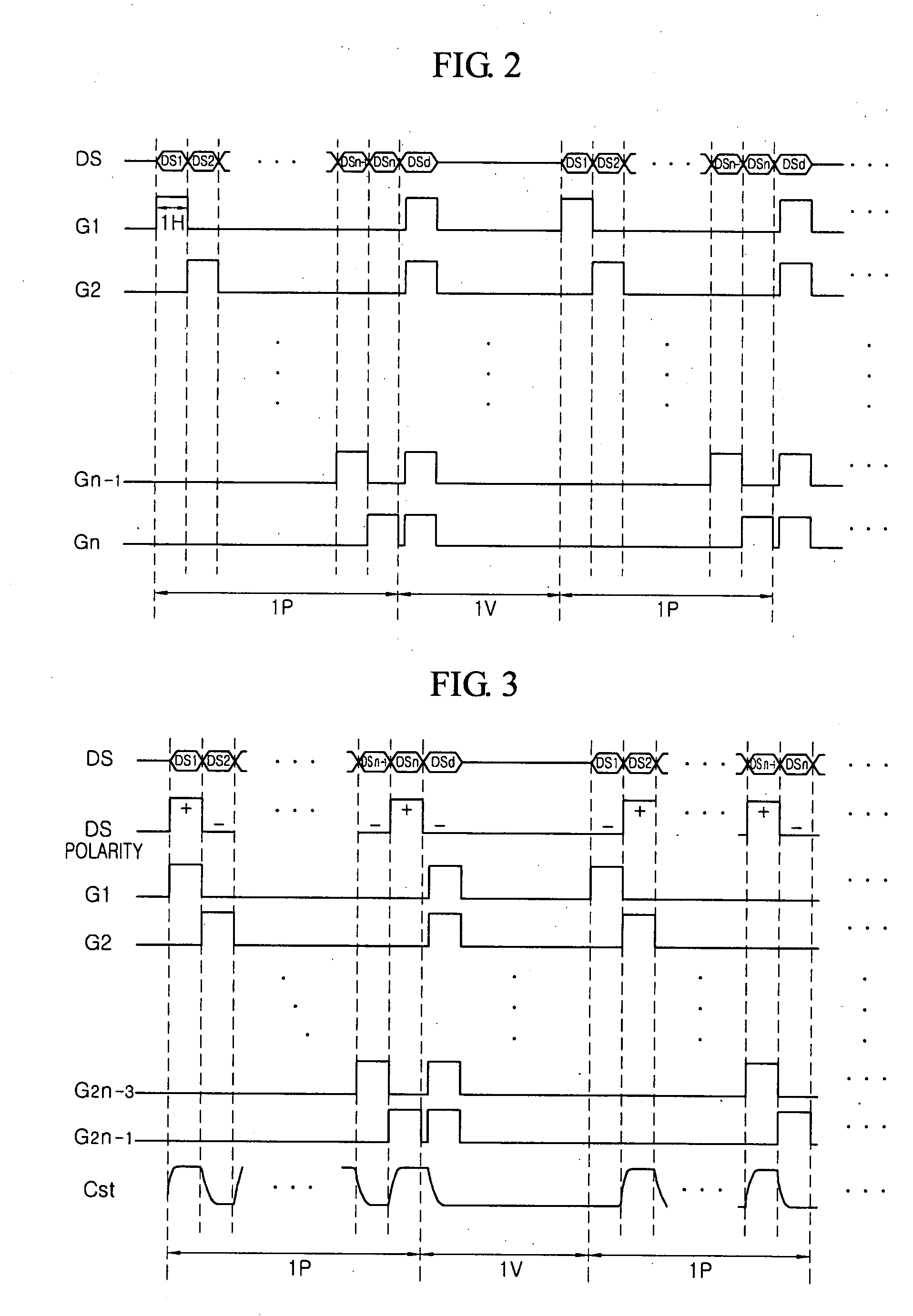

Device and method for driving large-sized and high-resolution display panel

InactiveUS20070085798A1Improved control of scanEasy to controlStatic indicating devicesScan lineDisplay device

A display device is provided with a display panel, a data line driving circuitry, and a scan line driving circuitry. The display panel includes: a plurality of data lines extending in a column direction; a plurality of scan lines extending in a row direction; a plurality of pixels disposed at respective intersections of the plurality of data lines and the plurality of scan lines, and a dummy data line arranged in parallel to the plurality of data lines. The data line driving circuitry drives the plurality of data lines and the dummy data line. The scan line driving circuitry drives the plurality of scan lines. The data line driving circuitry feeds a dummy signal to the scan line driving circuitry through the dummy data line. The scan line driving circuitry drives the scan lines in response to the dummy signal.

Owner:RENESAS ELECTRONICS CORP

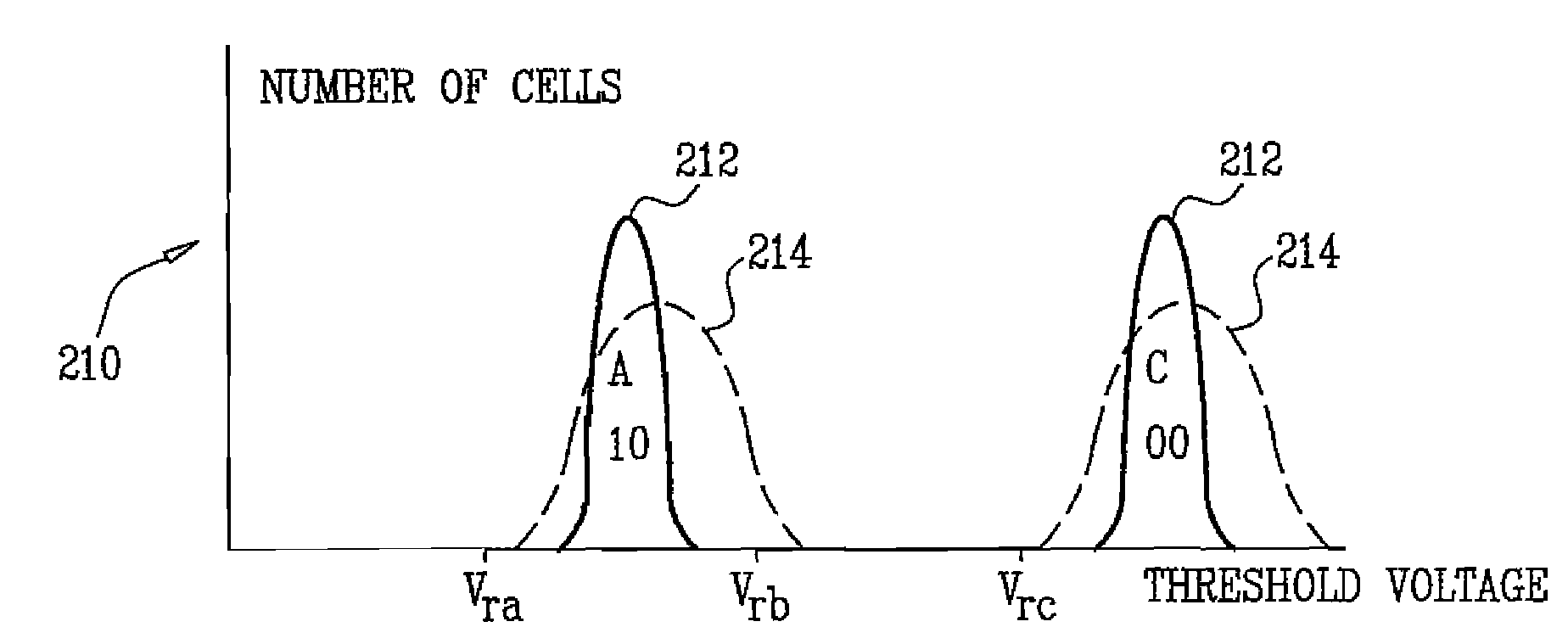

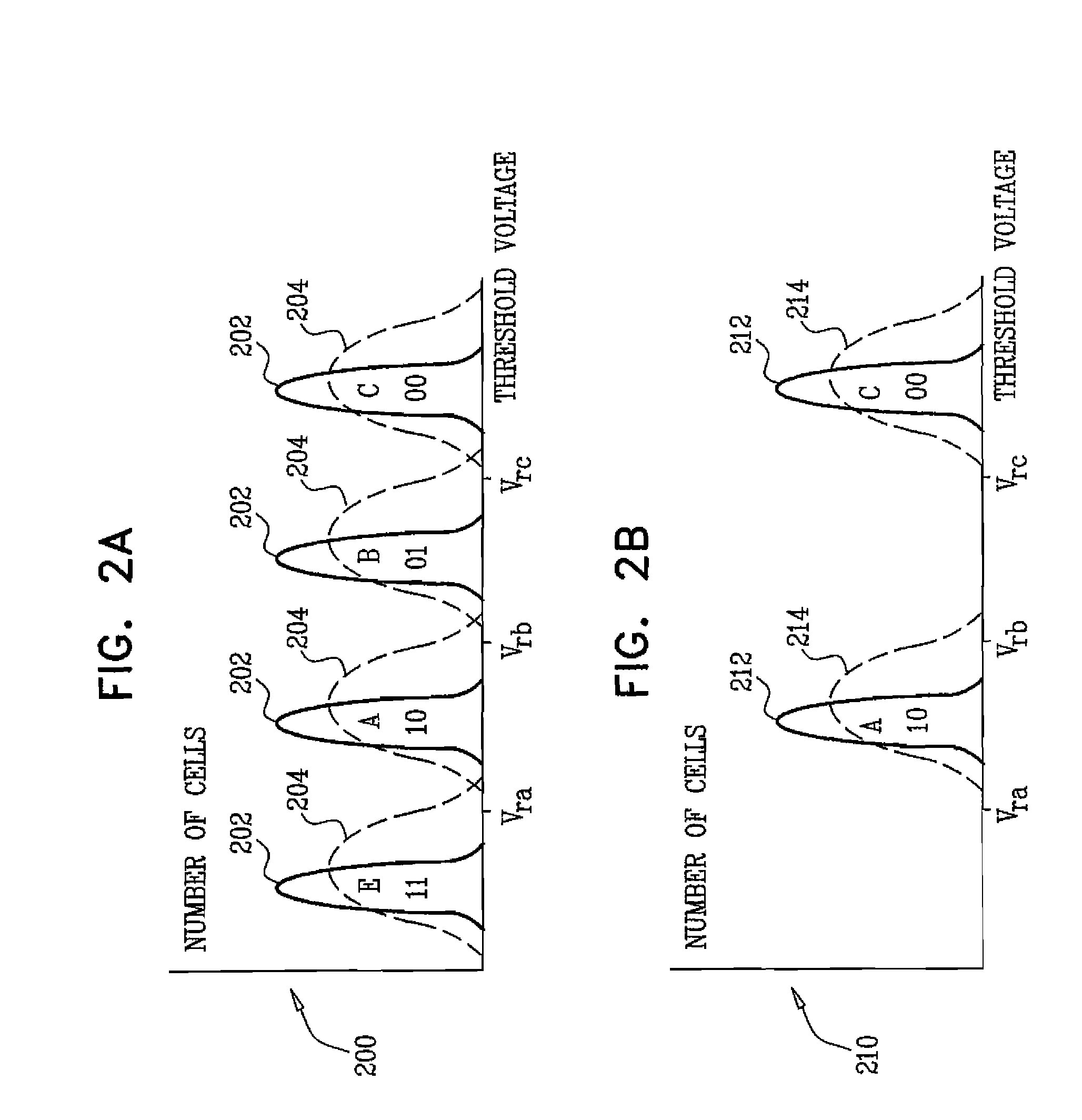

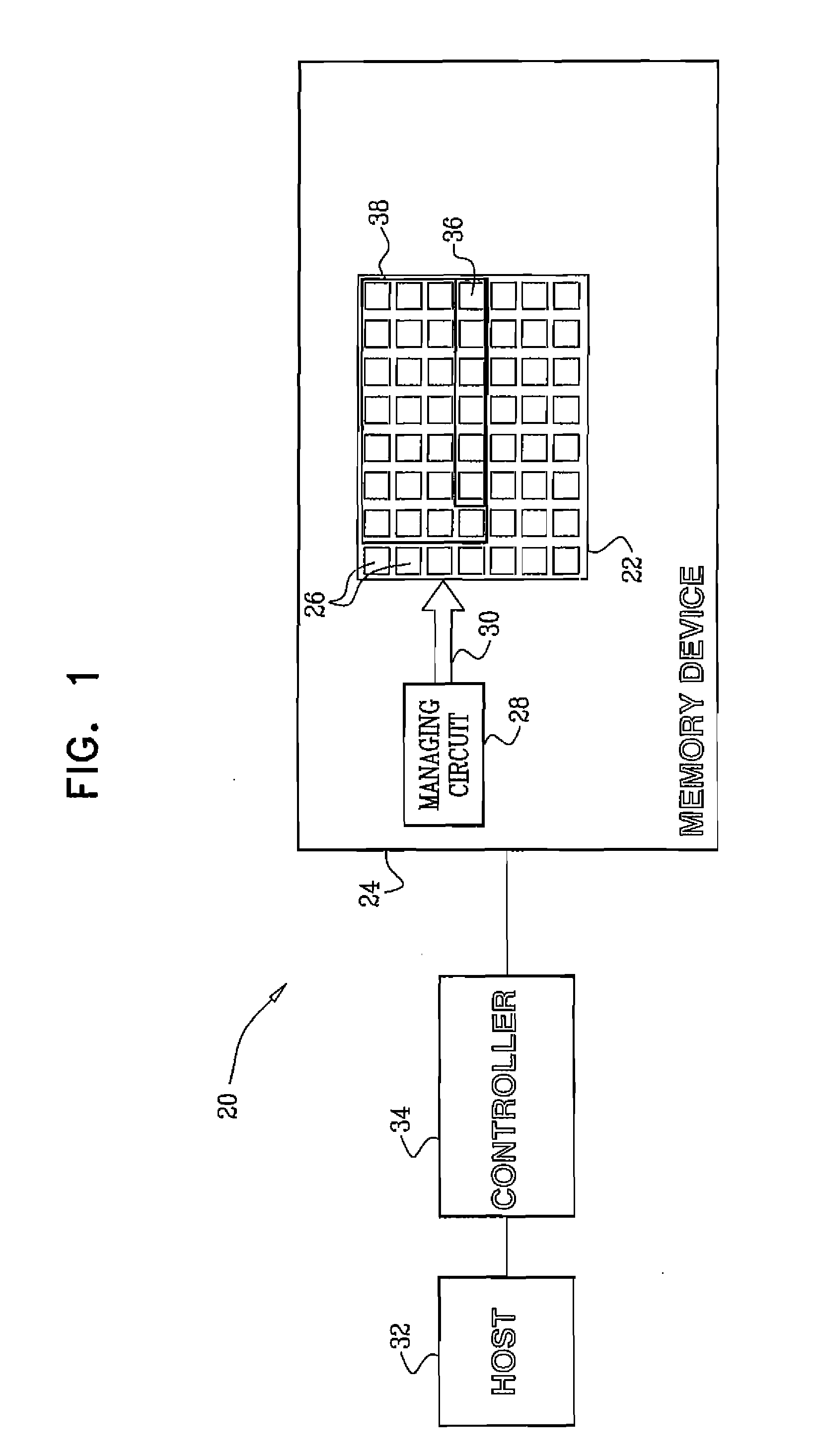

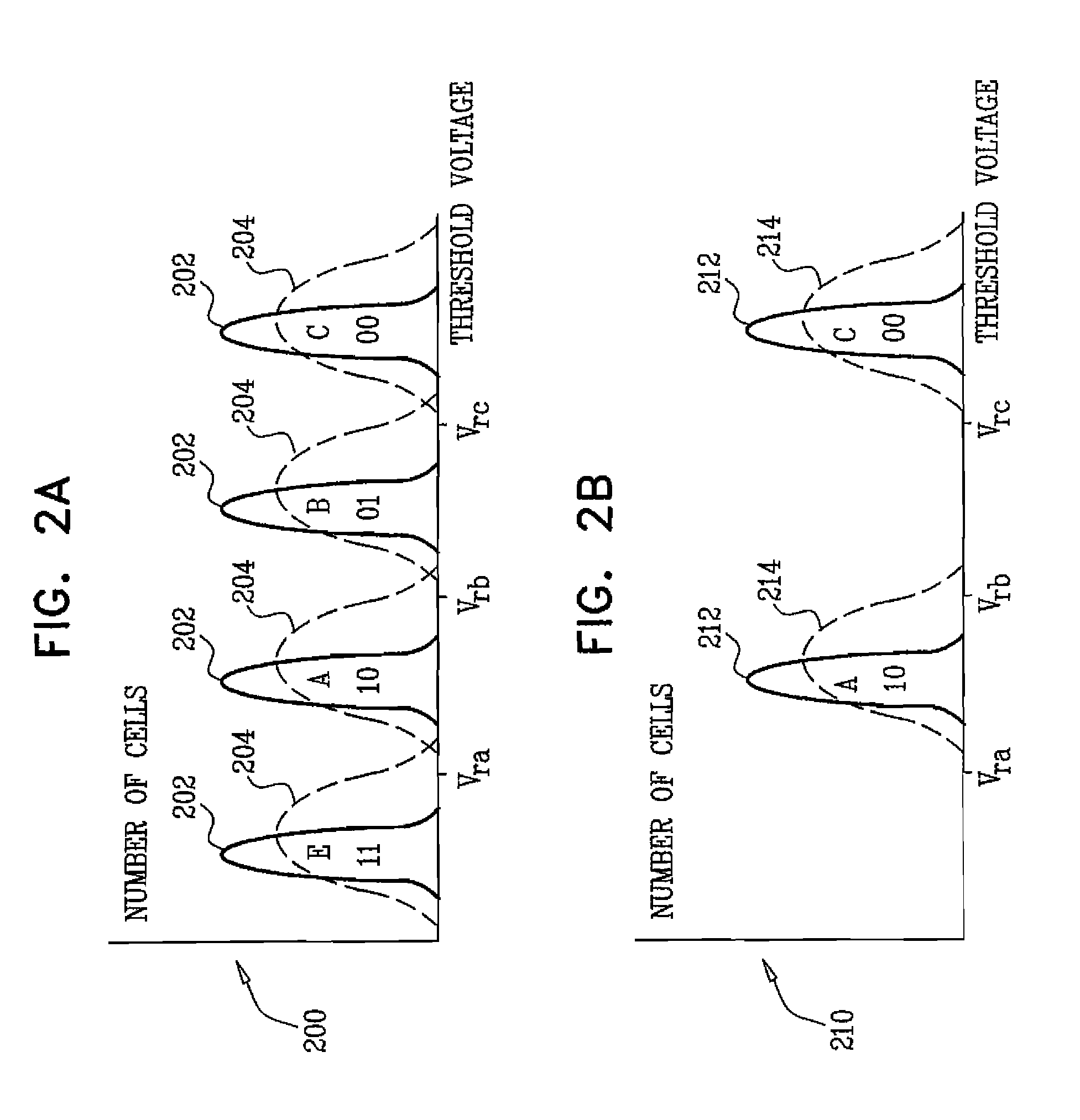

Using MLC flash as SLC by writing dummy data

ActiveUS7545673B2Improve reliabilityLow densityRead-only memoriesDigital storageParallel computingDummy data

A method for storing data includes designating, in a memory array including cells configured for writing a first number of bits per cell, a group of the cells to which input data are to be written at a second number of bits per cell, smaller than the first number. Dummy data that are independent of the input data are stored in a first set of one or more bits of the cells in the group. The input data are written to a second set of at least one other bit of the cells in the group.

Owner:WESTERN DIGITAL ISRAEL LTD

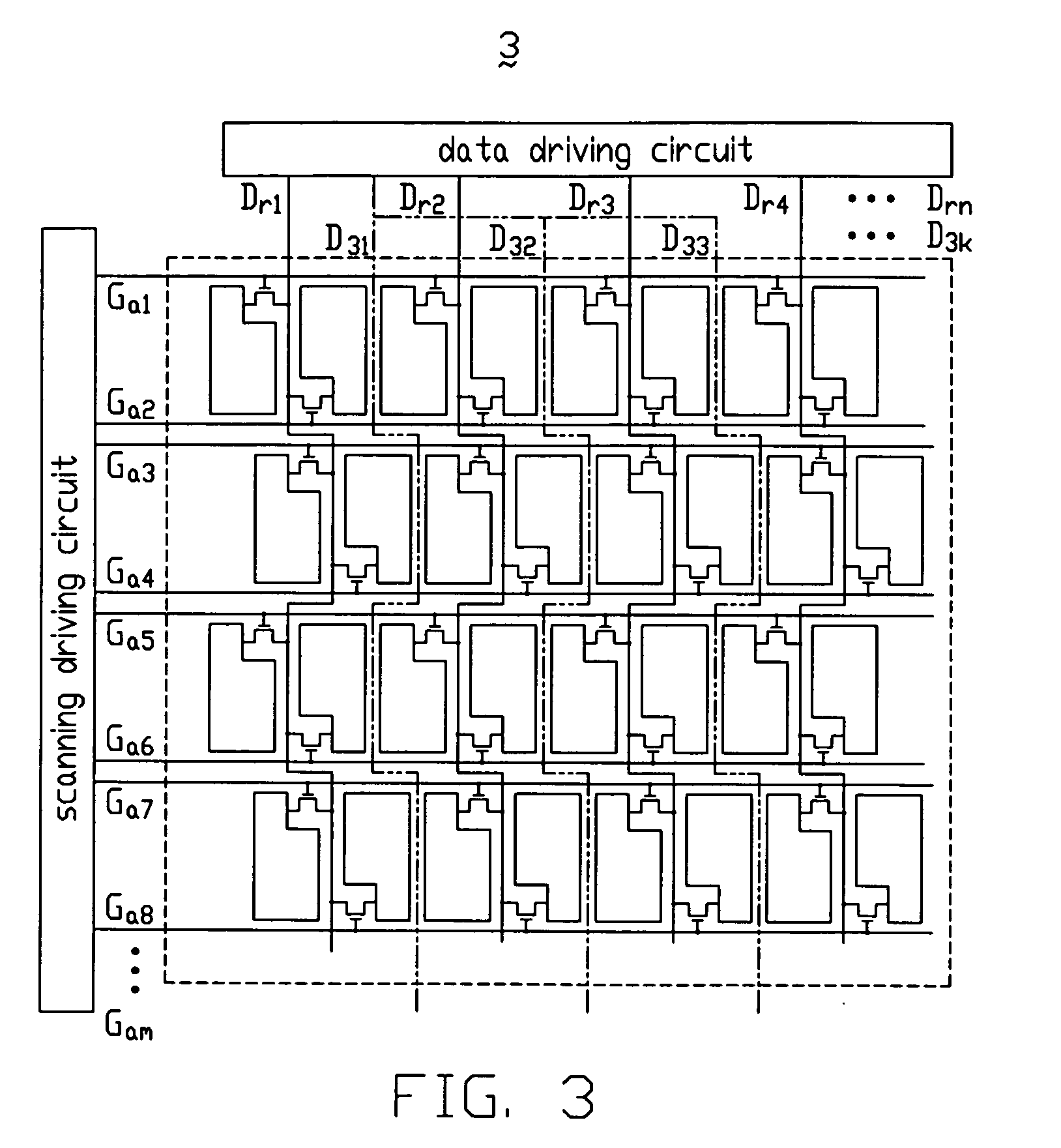

Active matrix display device with dummy data lines

ActiveUS20090262054A1Cathode-ray tube indicatorsInput/output processes for data processingCapacitanceActive matrix

An exemplary active matrix display device includes a display panel comprising a plurality of scanning lines extending along a horizontal axis, a plurality of data lines extending along a vertical axis, and a plurality of dummy data lines. Two scanning lines and two data lines define two display pixels; each of the plurality of data lines is connected to at least two adjacent display pixels along the horizontal axis, and the at least two adjacent display pixels are driven by the two scanning lines, respectively. Each of the plurality of dummy data lines is disposed between two random adjacent data lines and is provided with gray scale voltage signals by a driving circuit of the display panel, thereby forming coupling capacitances between each of the plurality of dummy data lines and two pixel electrodes of the two display pixels.

Owner:INNOLUX CORP

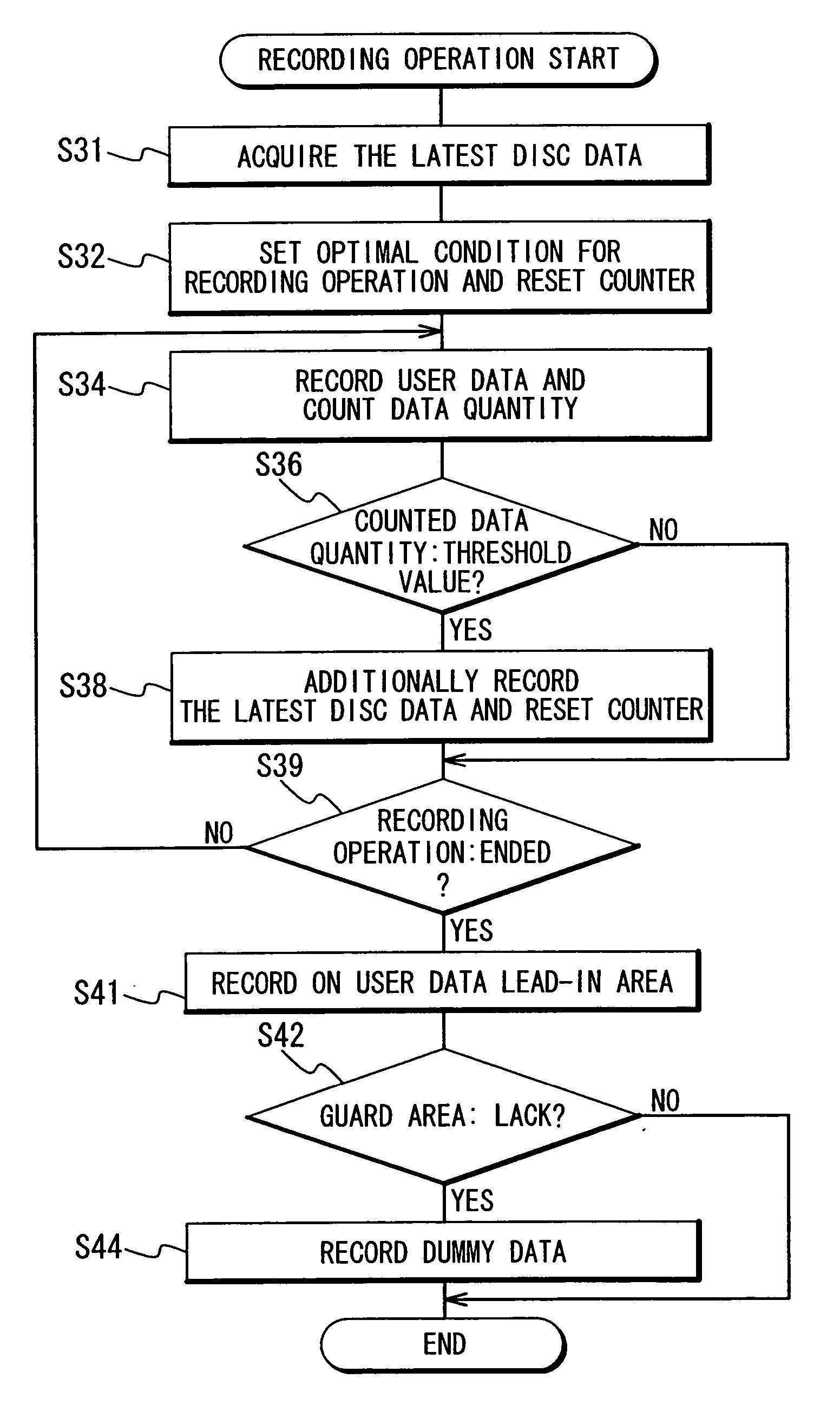

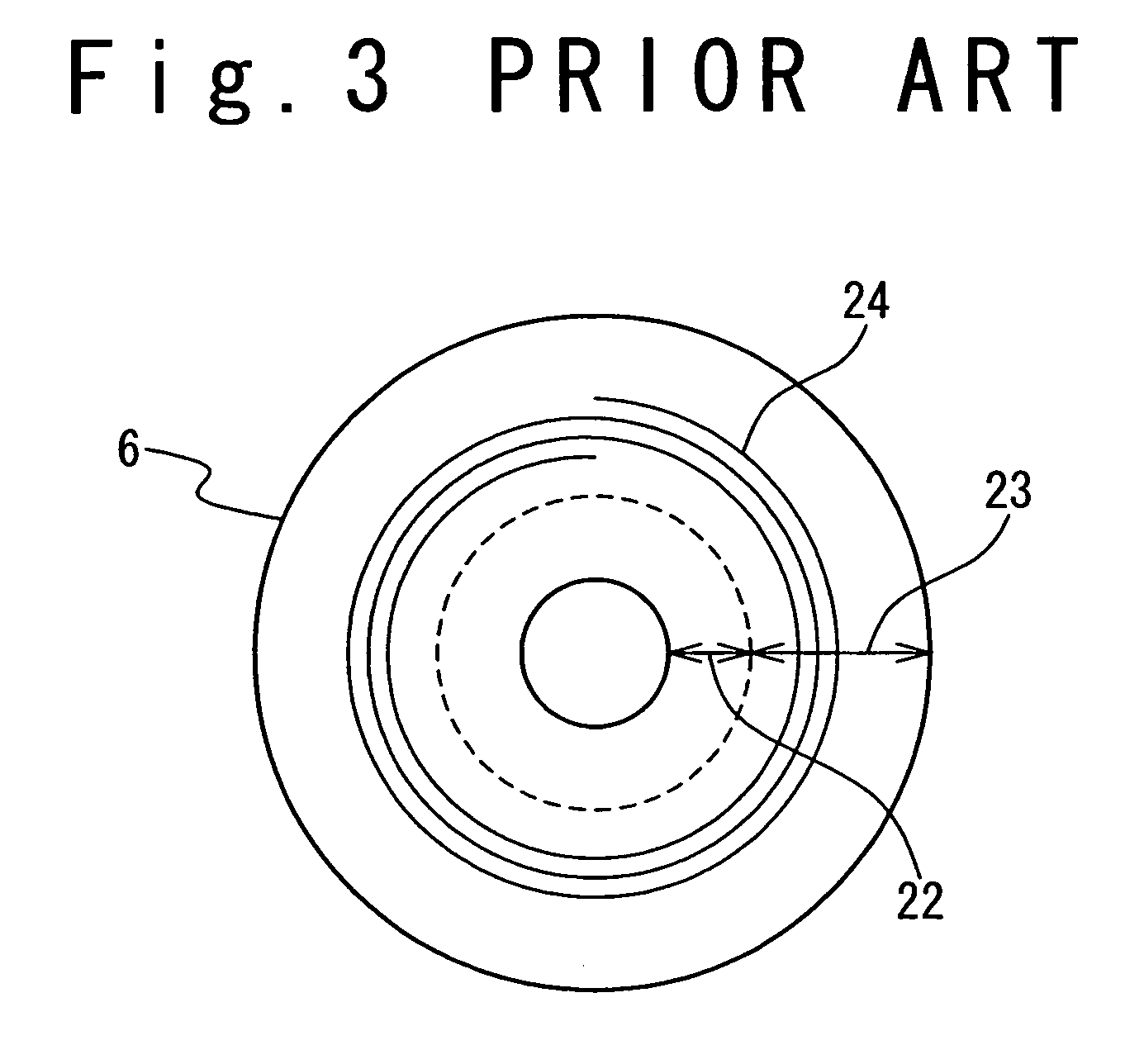

Optical disc medium, and apparatus and method for recording data on the same

InactiveUS20050141377A1Recordable capacity can be increasedIncrease capacityOptical beam sourcesRecord information storageDummy dataControl data

An optical disc medium includes a system area and a data area. The system area includes a recording operation test area to which a trial recording operation is carried out to determine an optimal record condition when data is recorded in the data area; a record control data area where data necessary to record user data on the data area is recorded; and a user data lead-in area necessary to reproduce the user data from the optical disc medium. Dummy data are recorded to a portion of the record control data area on a side of the user data lead-in area to prevent a track-out when the data area is accessed.

Owner:NEC CORP

Display driver and electronic instrument

InactiveUS20060214902A1Effective controlElectric/magnetic signal storageCathode-ray tube indicatorsInterface circuitsDummy data

A display driver comprising: a high-speed serial interface circuit which receives a packet from a host device through a high-speed serial bus using differential signals, and outputs a command or data included in the received packet; a driver circuit which drives a main display panel based on the output command or data; and a low-speed serial interface circuit which outputs a command or data to a sub display driver through a low-speed serial bus when the packet received from the host device includes the sub display driver command or data. And the display driver inserts dummy data to the packet to adjust the difference of the transfer rate by inserting a dummy the dummy data. And the display driver adjust the difference of the transfer rate

Owner:SEIKO EPSON CORP

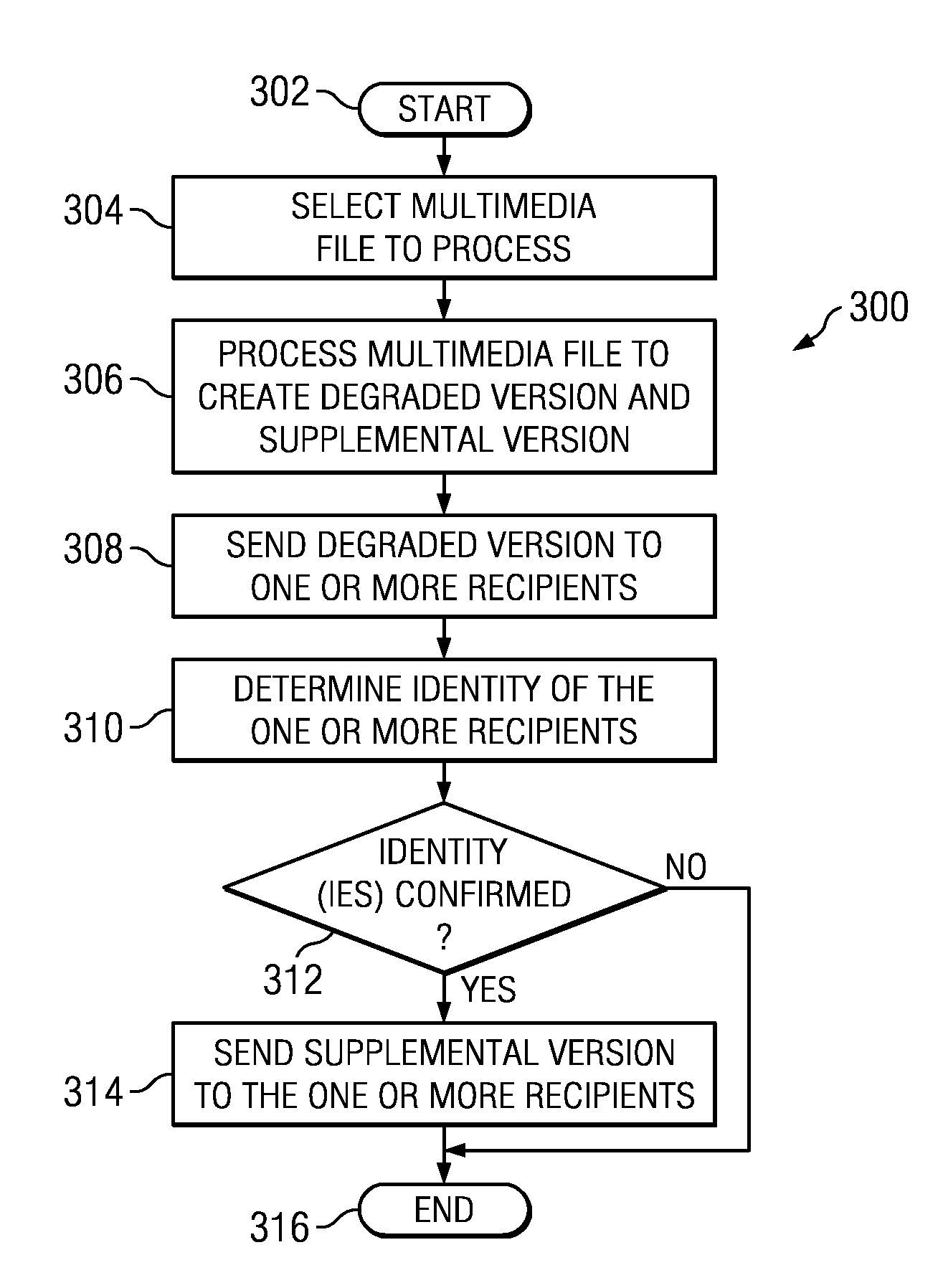

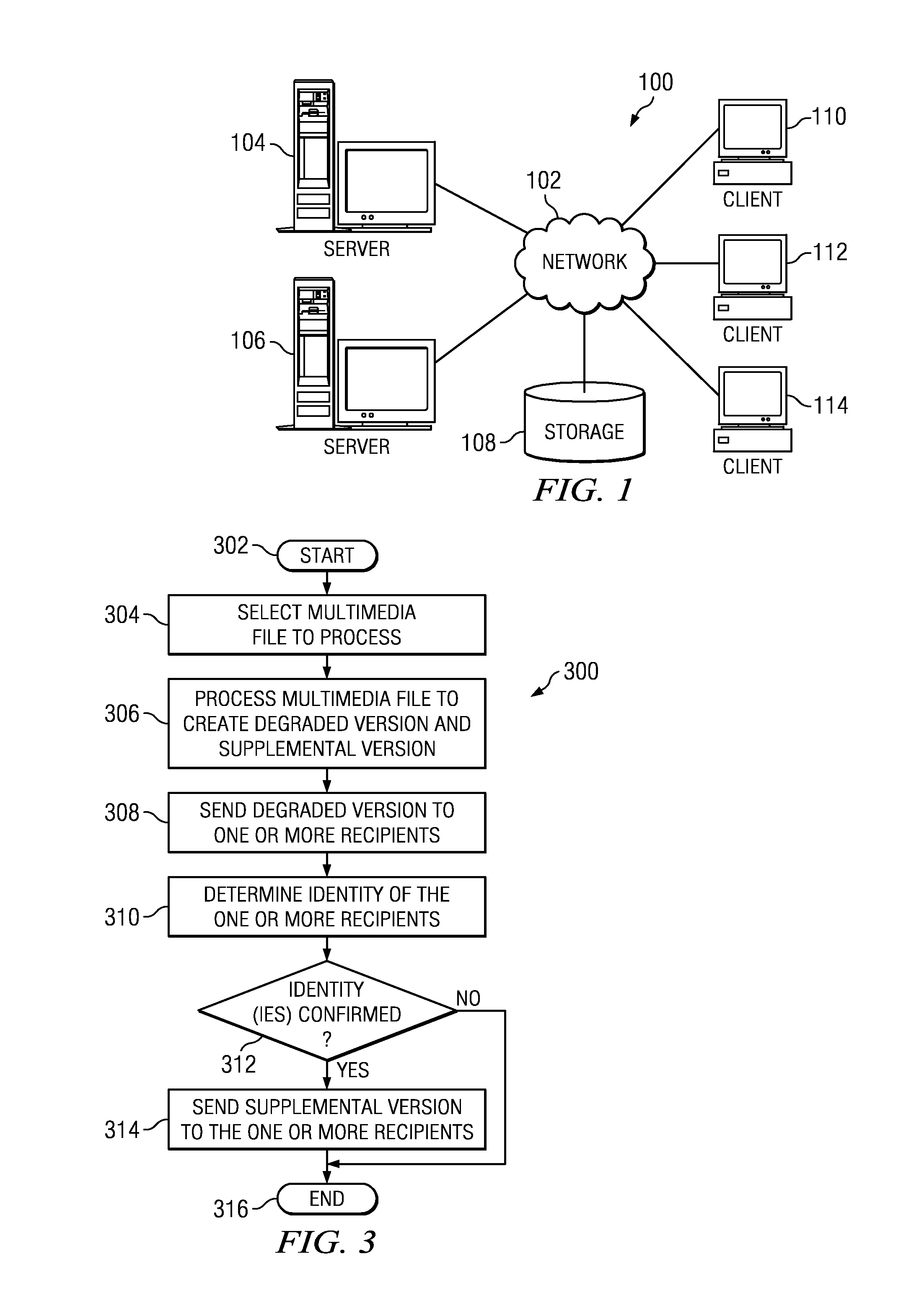

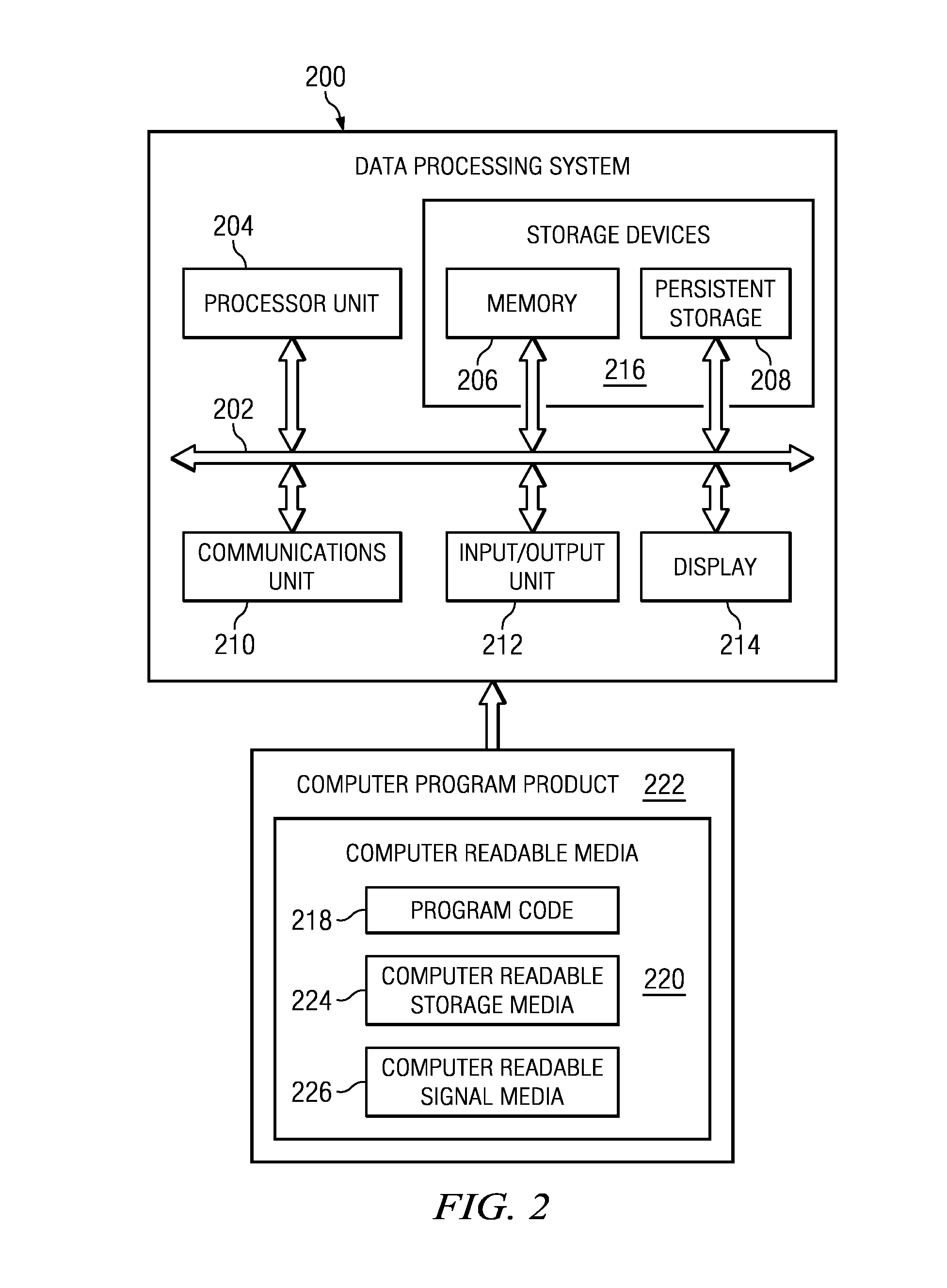

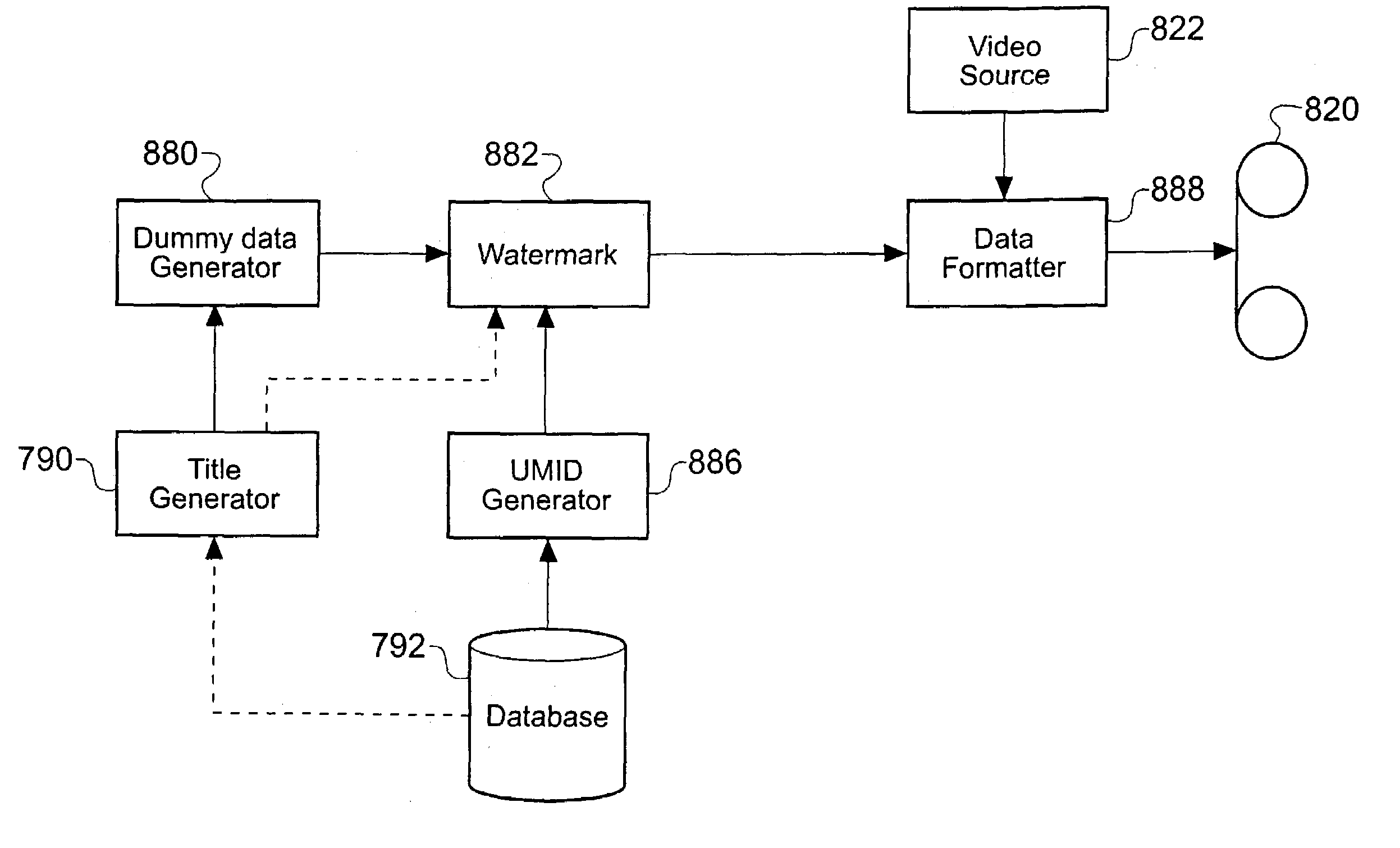

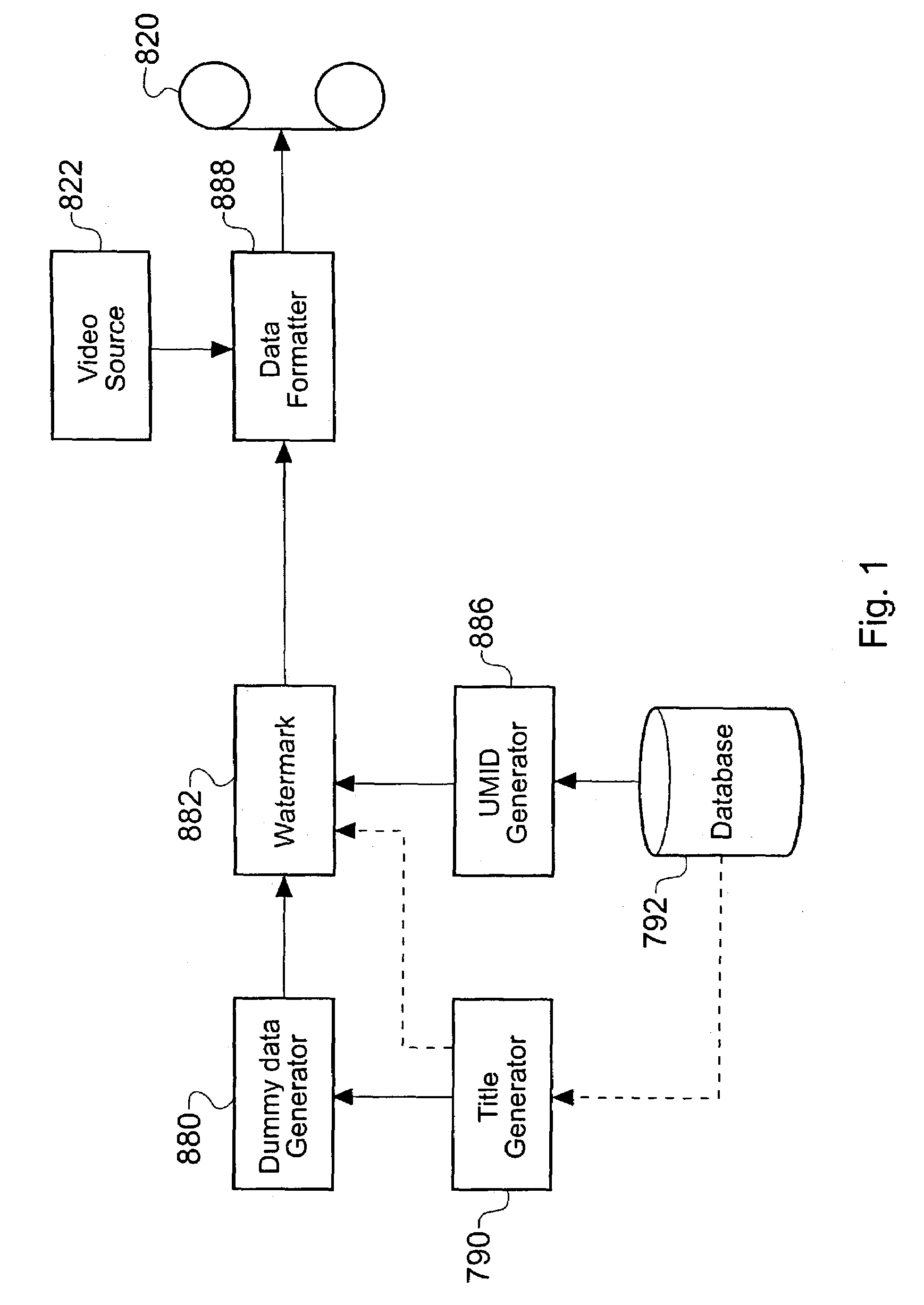

Apparatus and Method for Secure Distribution of Media Data

InactiveUS20120117659A1Mitigates/eliminates piracyQuality improvementTelevision conference systemsDigital data processing detailsData processing systemDummy data

A technique for distributing media data in a secured fashion that mitigates unwanted or illegal copying / distribution of such data. An initial, degraded version of the media data is sent to one or more recipient(s). After confirming identity of a recipient at a receiving system, a supplemental version of the media data is sent to the receiving system which augments the degraded version such that it can then be played by the recipient(s). The degraded version of the media data has a reduced quality that is obtained by removing portions of the data and filling in the removed portions with dummy data. During a subsequent rebuilding of the media data, a supplemental version of the media data is sent to the receiving data processing system where it is merged / combined with the degraded version to form a copy that corresponds to the original, high-quality version of the media data.

Owner:IBM CORP

LCD driving methods

InactiveUS20080143659A1Avoid it happening againStatic indicating devicesNon-linear opticsDisplay deviceDummy data

A method for driving a display device includes sequentially applying a gate turn-on voltage to respective gate lines of the device during successive image display periods thereof, applying a respective one of a plurality of successive data signals, each corresponding to a respective one of the gate lines, to a plurality of data lines of the device while the gate turn-on voltage is being applied to the corresponding gate line, applying the gate turn-on voltage to all of the of gate lines of the device during successive vertical blanking periods of the device that alternate with the image display periods, and applying a dummy data signal to the data lines while the turn-on voltage is being applied to the gate lines. The dummy data signal forcibly discharges any residual charges in the pixel storage capacitors to prevent the occurrence of residual images in the display.

Owner:SAMSUNG ELECTRONICS CO LTD

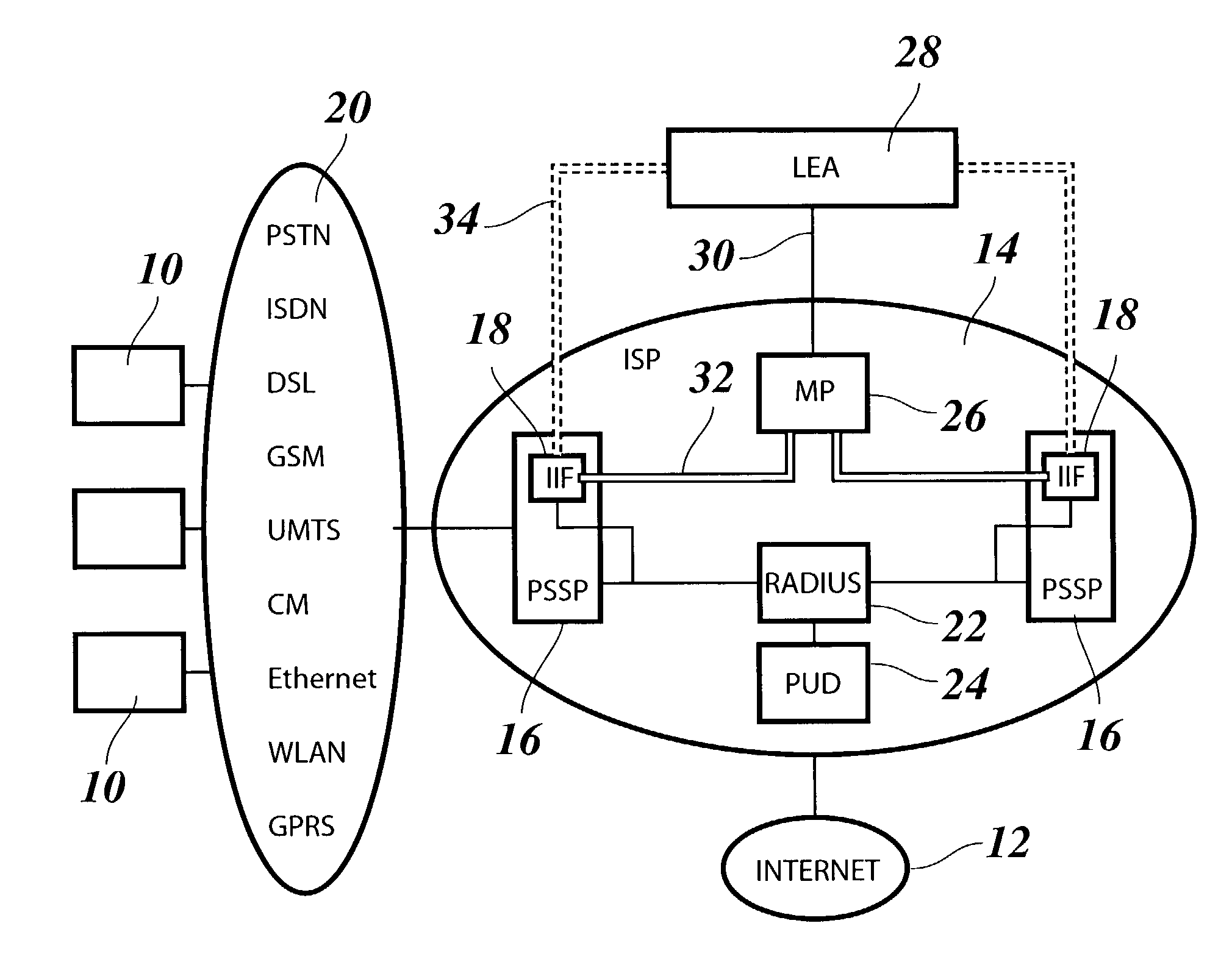

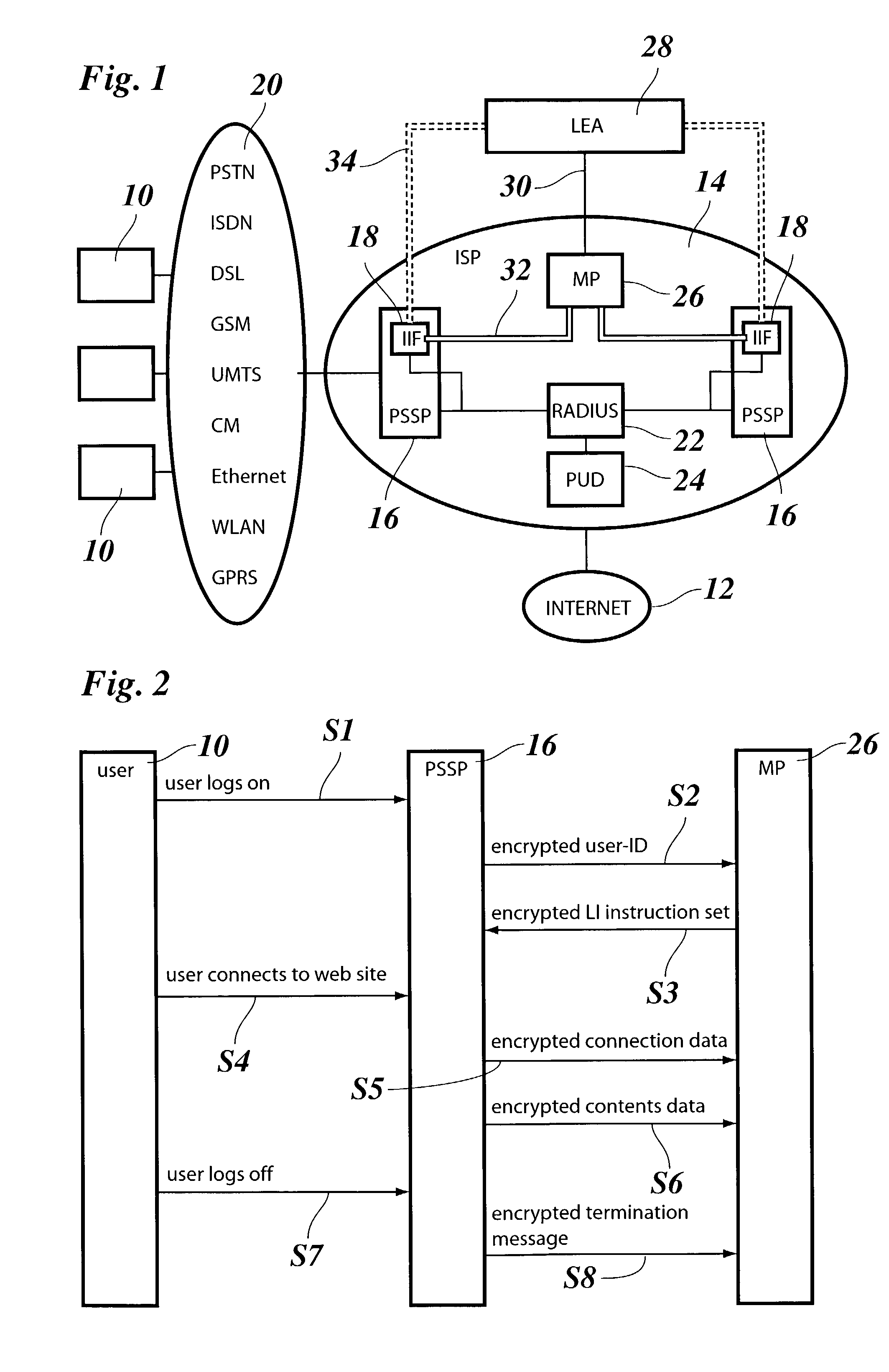

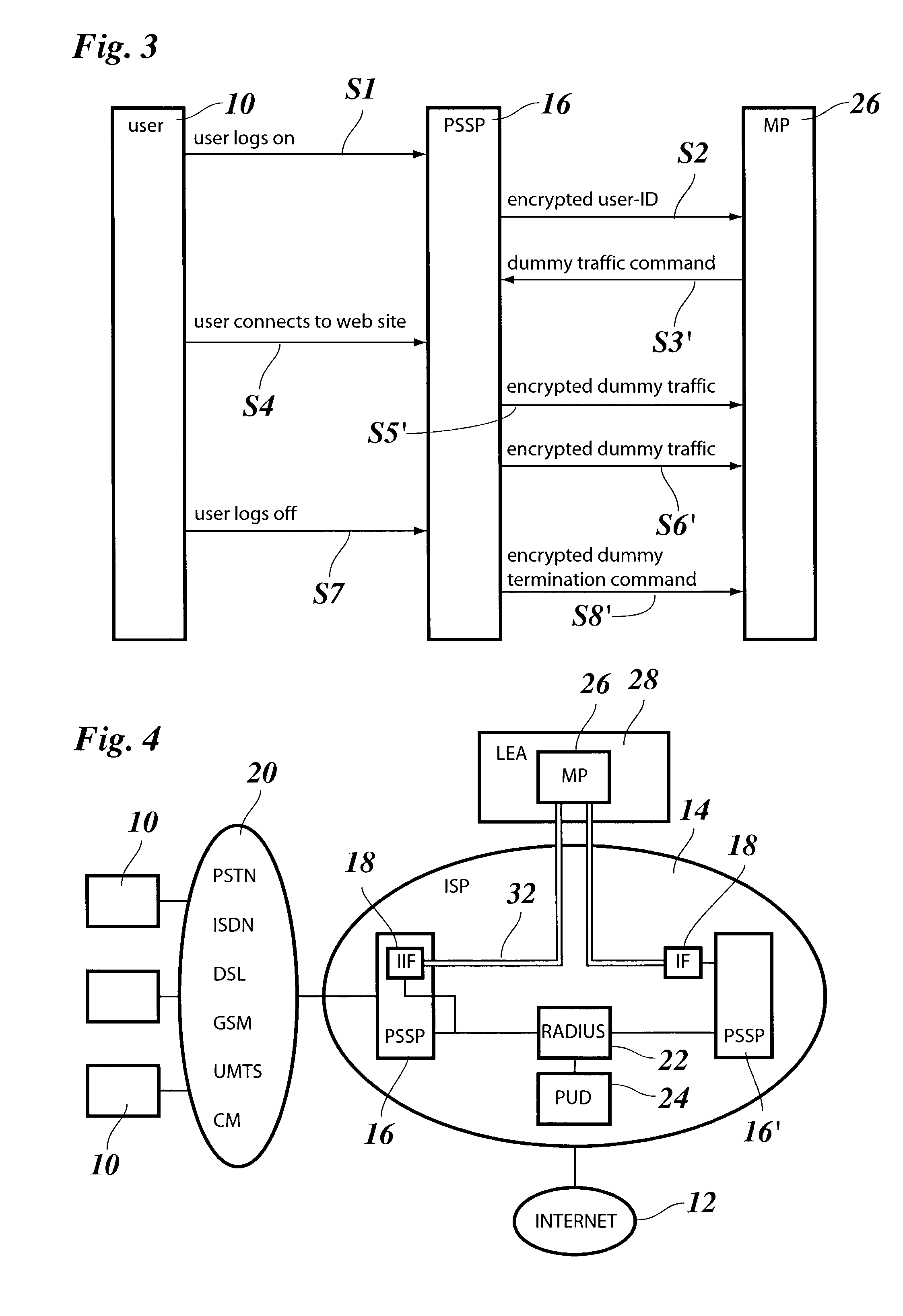

Method and system for lawful interception of packet switched network services

InactiveUS7447909B2Low costImprove securityMemory loss protectionDigital data processing detailsLawful interceptionTraffic capacity

A method for lawful interception of packet switched network services, comprising the steps of:when a user accesses the network and is identified by a target-ID at a primary interception point of the network, sending the target-ID to an interception management center,checking at the interception management center whether the user is a lawful interception target and sending an encrypted interception instruction set to a secondary interception point,decrypting said interception instruction set at the secondary interception point and performing an interception process in accordance with the interception instruction set, said interception process including the transmission of encrypted interception and dummy data to a mediation device, wherein said dummy data are added for obscuring true interception traffic between the secondary interception point and the mediation device.

Owner:RPX CLEARINGHOUSE

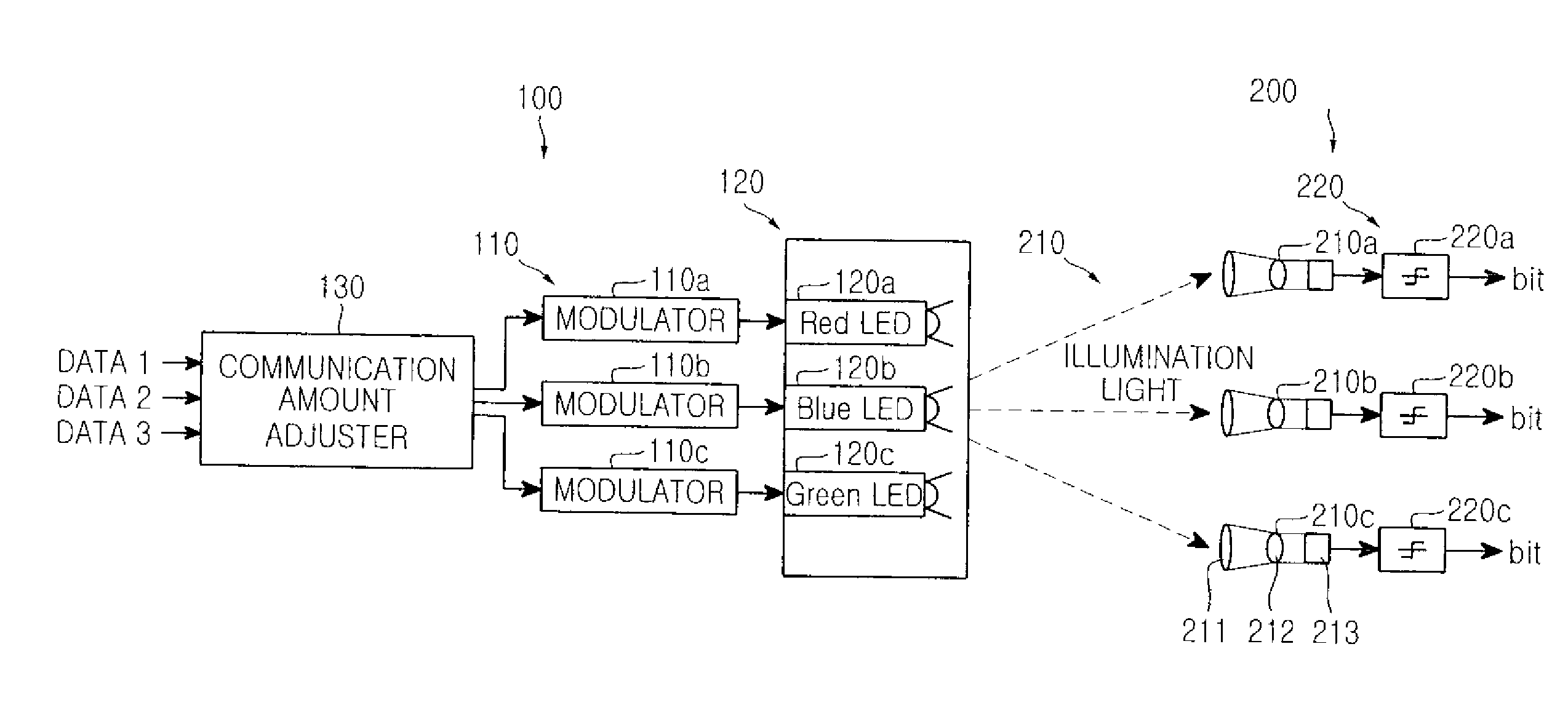

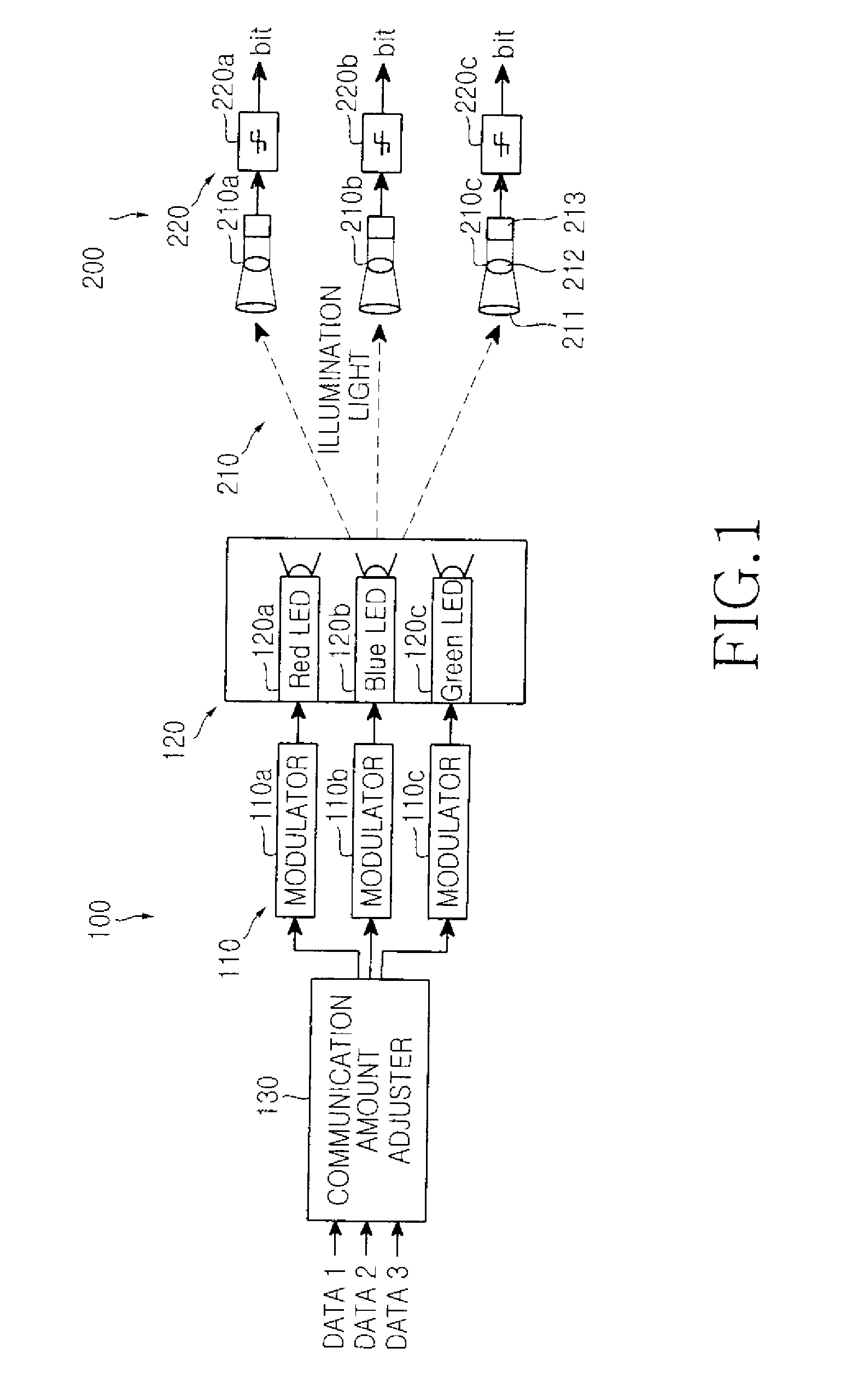

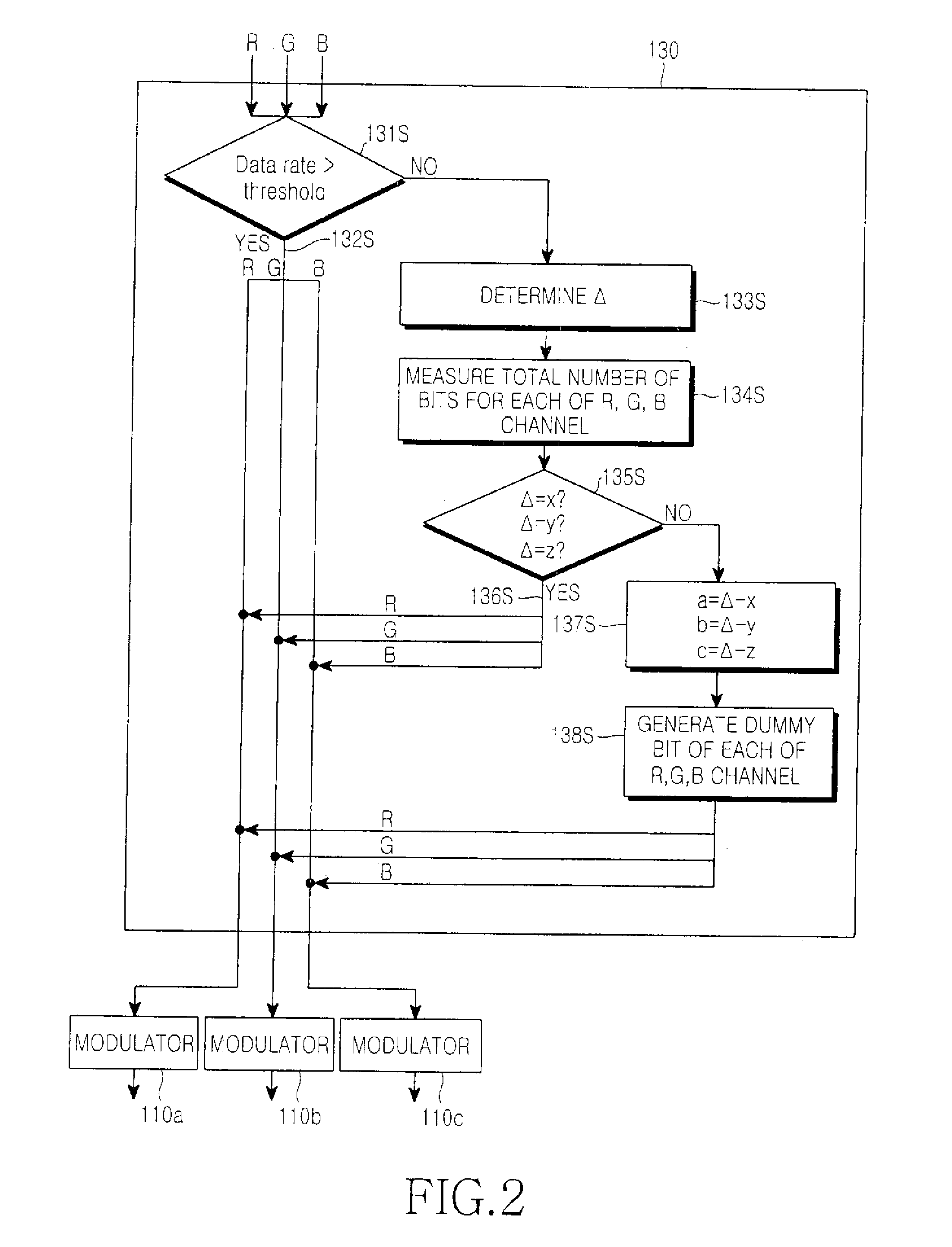

Apparatus and method for visible light communication

Disclosed are an apparatus and a method for visible light communication, which apparatus uses an illuminator equipped with a plurality of light sources, so that the apparatus can be used for illumination, as well as for visible light communication. The visible light communication apparatus includes an illuminator for generation of the illumination light, the illuminator including a plurality of light sources with luminescence center wavelengths on mutually different visible regions; a communication amount adjuster for receipt of the plurality of communication data signals, and generation of each dummy data so that data to be transmitted through each of the plurality of LEDs has an equal communication amount; and a modulator for receipt of the plurality of communication data signals and their corresponding dummy data, and modulation of the received communication data signals and their corresponding received dummy data into driving signals for a plurality of LEDs configured as a light source.

Owner:SAMSUNG ELECTRONICS CO LTD

Using mlc flash as slc by writing dummy data

ActiveUS20090080247A1Improve reliabilityLow densityRead-only memoriesDigital storageParallel computingDummy data

A method for storing data includes designating, in a memory array including cells configured for writing a first number of bits per cell, a group of the cells to which input data are to be written at a second number of bits per cell, smaller than the first number. Dummy data that are independent of the input data are stored in a first set of one or more bits of the cells in the group. The input data are written to a second set of at least one other bit of the cells in the group.

Owner:WESTERN DIGITAL ISRAEL LTD

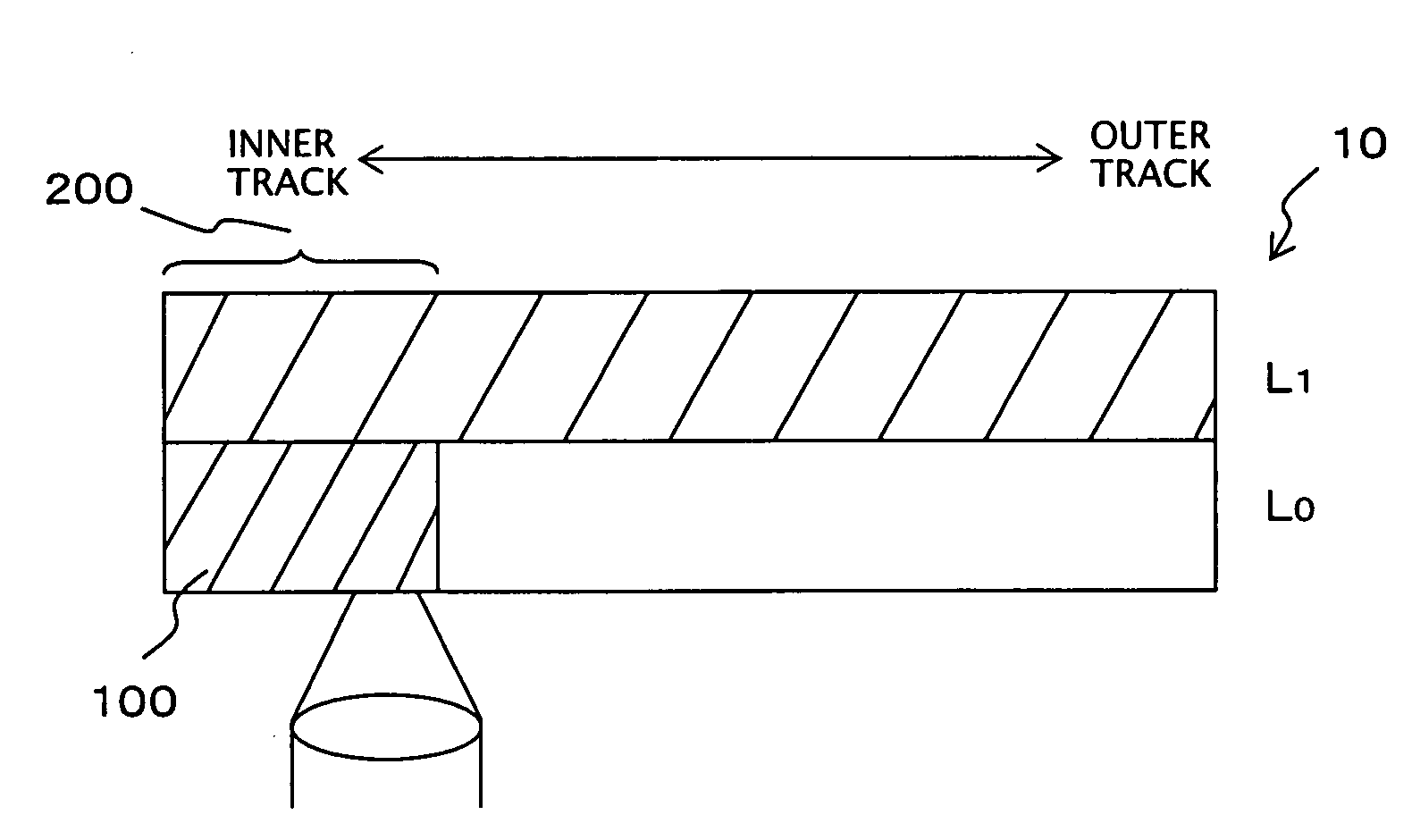

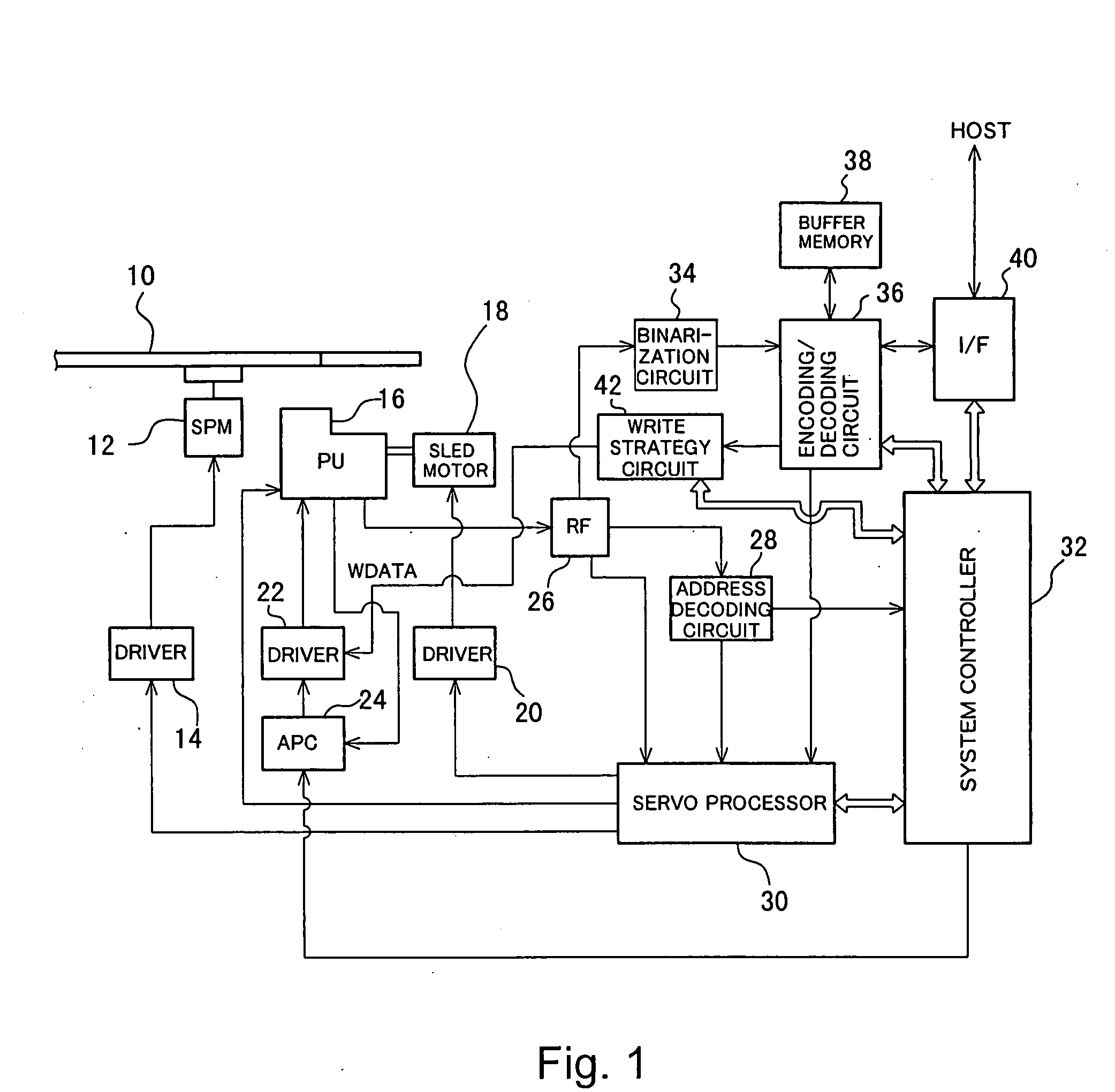

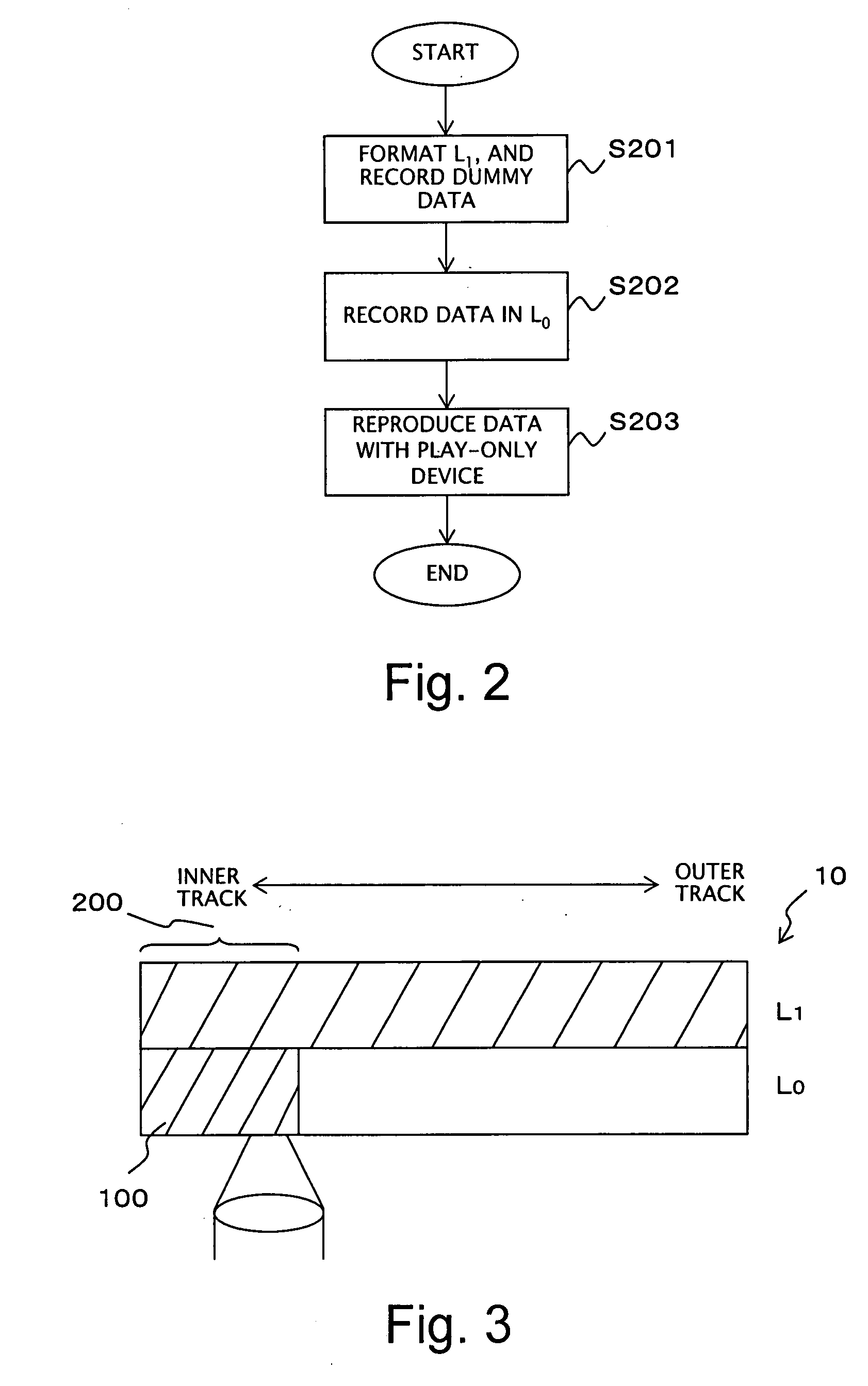

Optical disk drive and method for recording data

InactiveUS20070253307A1Reduce processing timeMechanical record carriersRecord information storageDummy dataData recording

Recording of data into a multilayer optical disk and reliable reproduction of the data are enabled. When user data are recorded on a multilayer optical disk having a first layer L0 and a second layer L1, the second layer L1 is formatted beforehand, to thus record dummy data. Subsequently, the user data are recorded into the first layer L0. Even after completion of recording of the user data at some point in the first layer L0, an area of the second layer L1 located immediately above or below a recorded area of the first layer L0 remains in a recorded state at all times. Compatibility with a play-only disk is maintained, and the play-only drive can reproduce the user data immediately after recording of the data.

Owner:TEAC CORP

Material display

InactiveUS7043638B2High data payloadAvoid damageTelevision system detailsColor television signals processingDummy dataData store

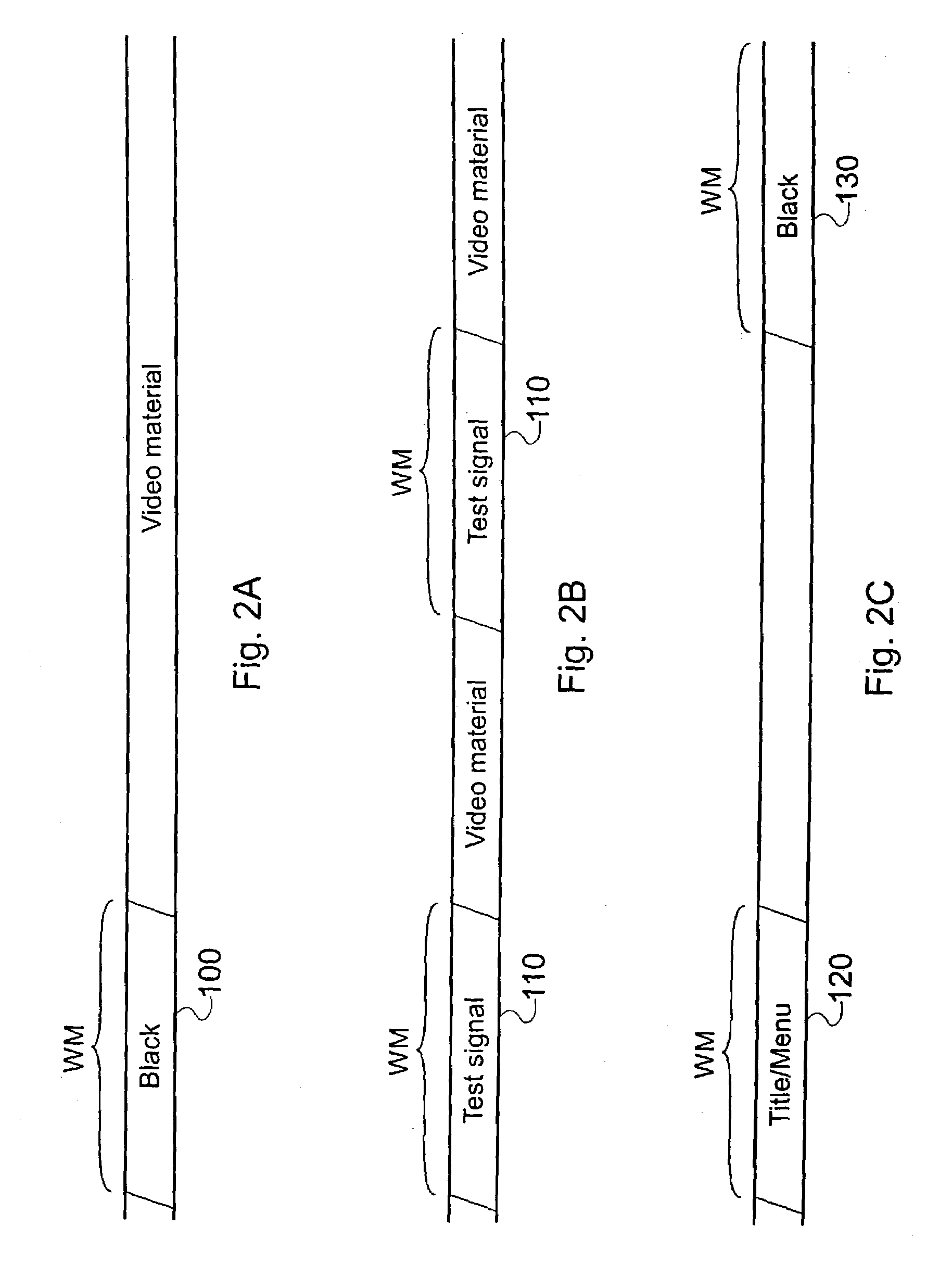

The invention relates to a data storage medium storing data material having a data replay order, the stored data material being associated with dummy data material stored on the medium at a different position in the data replay order, in which metadata identifying the data material is encoded as a watermark in the dummy data material.

Owner:SONY UK LTD