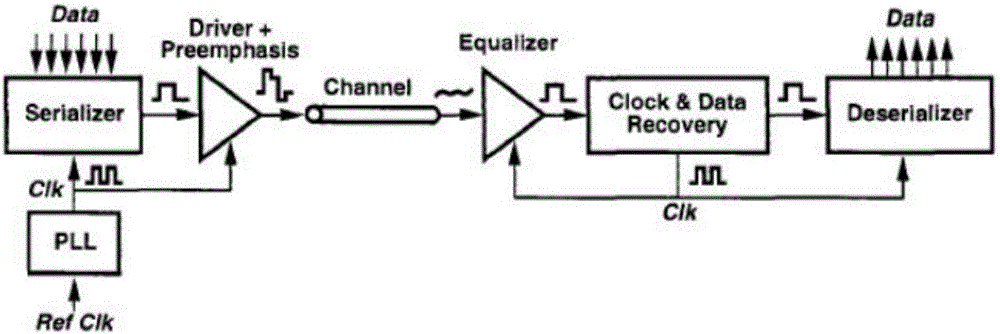

Linear equalizer applicable to high-speed serial interface

A high-speed serial interface, linear equalizer technology, applied in the direction of shaping network, baseband system, digital transmission system, etc. The effect of reducing the layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

[0028] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

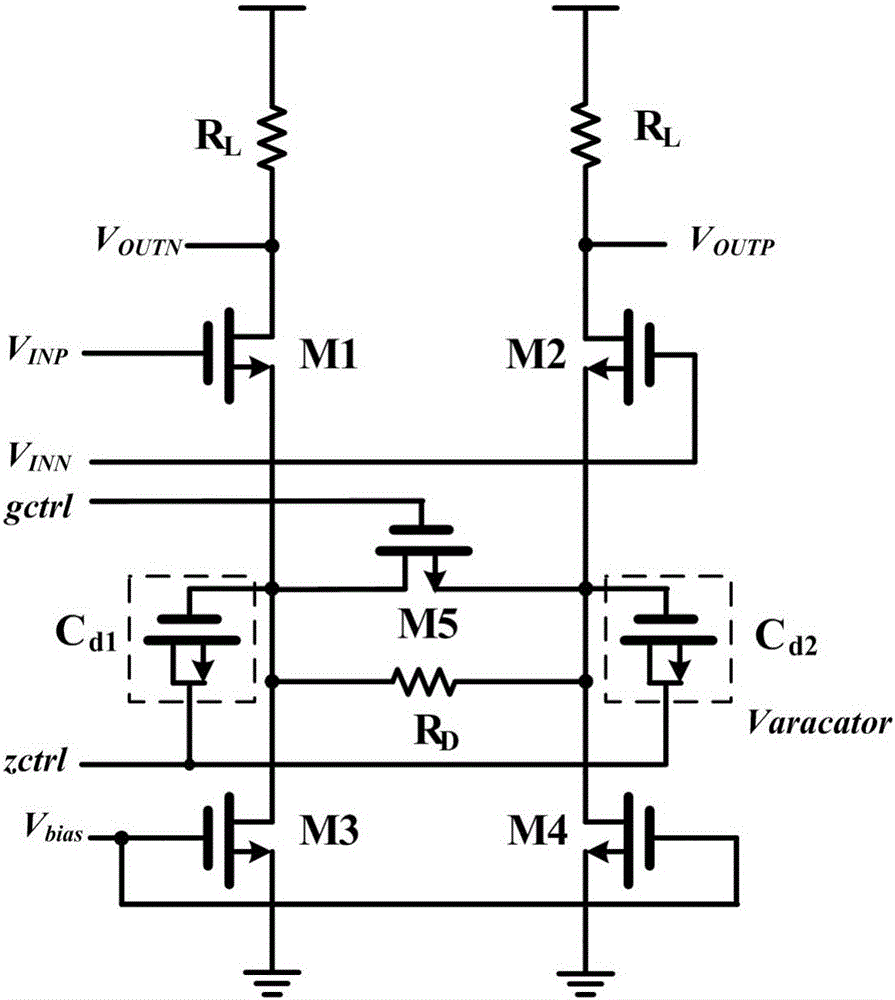

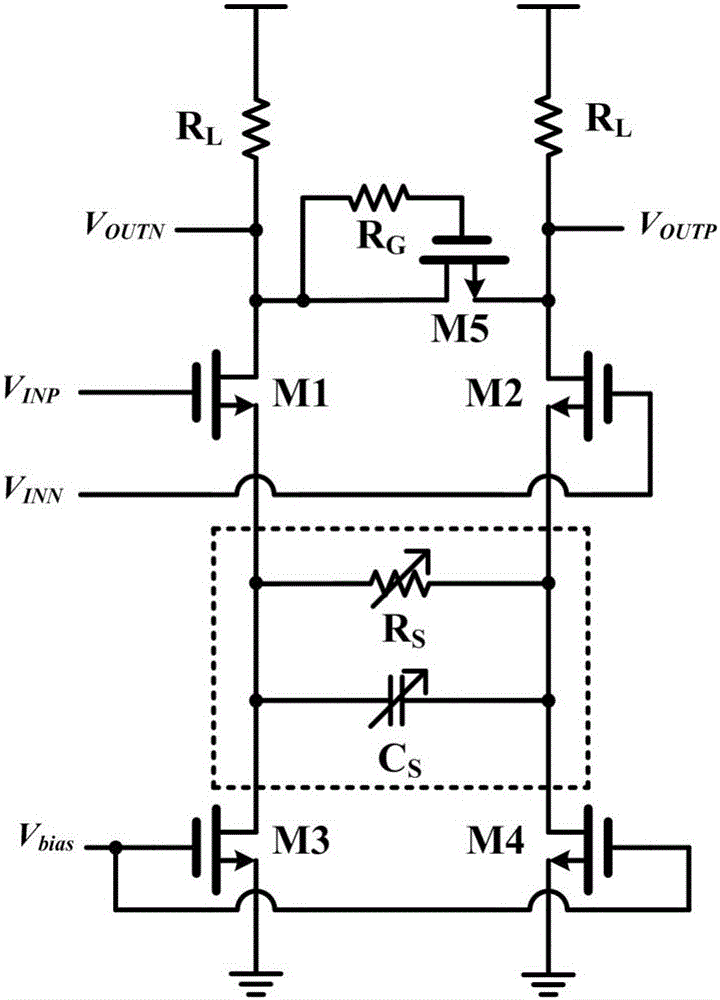

[0029] The invention introduces the inductance peaking technology, utilizes the resonance between the inductance and the output node capacitance, and further expands the bandwidth. image 3 It is a linear equalizer suitable for a high-speed serial interface of the present invention, including a differential input pair consisting of a first NMOS transistor M1 and a second NMOS transistor M2; Bias current...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More