Mapping method and device for simulating single physical network port into multiple logical network ports

A technology of a logical network port and a mapping device, which is applied in the field of network interfaces and can solve problems such as network processor performance bottlenecks, core processor performance bottlenecks, and coprocessor performance bottlenecks.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

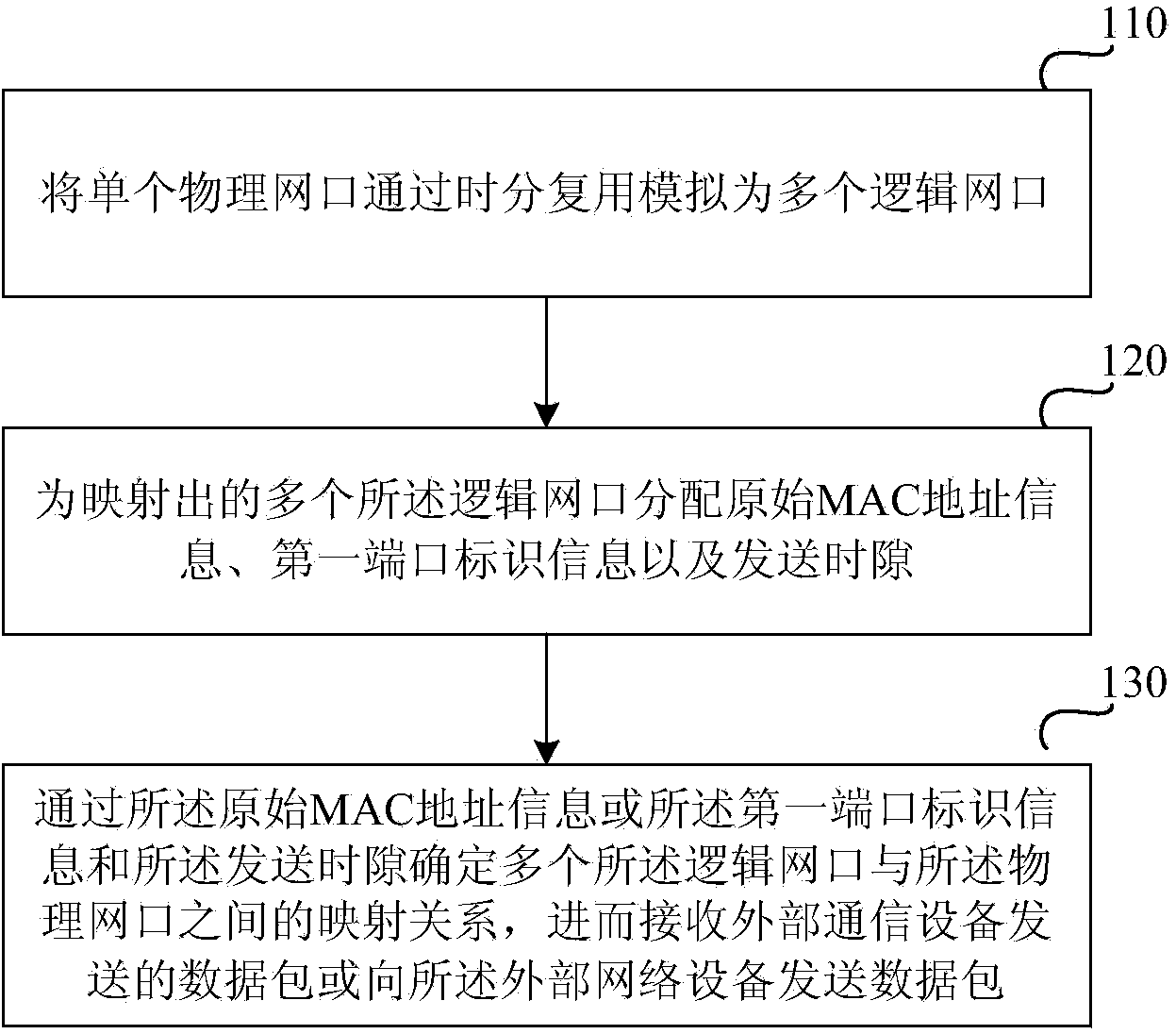

[0059] Below to figure 1 As an example, describe in detail the mapping method in which a single physical network port is simulated as multiple logical network ports provided by Embodiment 1 of the present invention. figure 1 The flow chart of the mapping method for simulating a single physical network port into multiple logical network ports is provided in Embodiment 1 of the present invention. In the embodiment of the present invention, the implementer who performs the following steps may be a network server, but it is not limited thereto , and the following takes the network server as the implementation subject to describe in detail. Such as figure 1 As shown, this embodiment specifically includes the following steps:

[0060] Step 110, simulating a single physical network port into multiple logical network ports through time division multiplexing.

[0061] Specifically, the network server includes a single physical network port, and the physical network port is used to r...

Embodiment 2

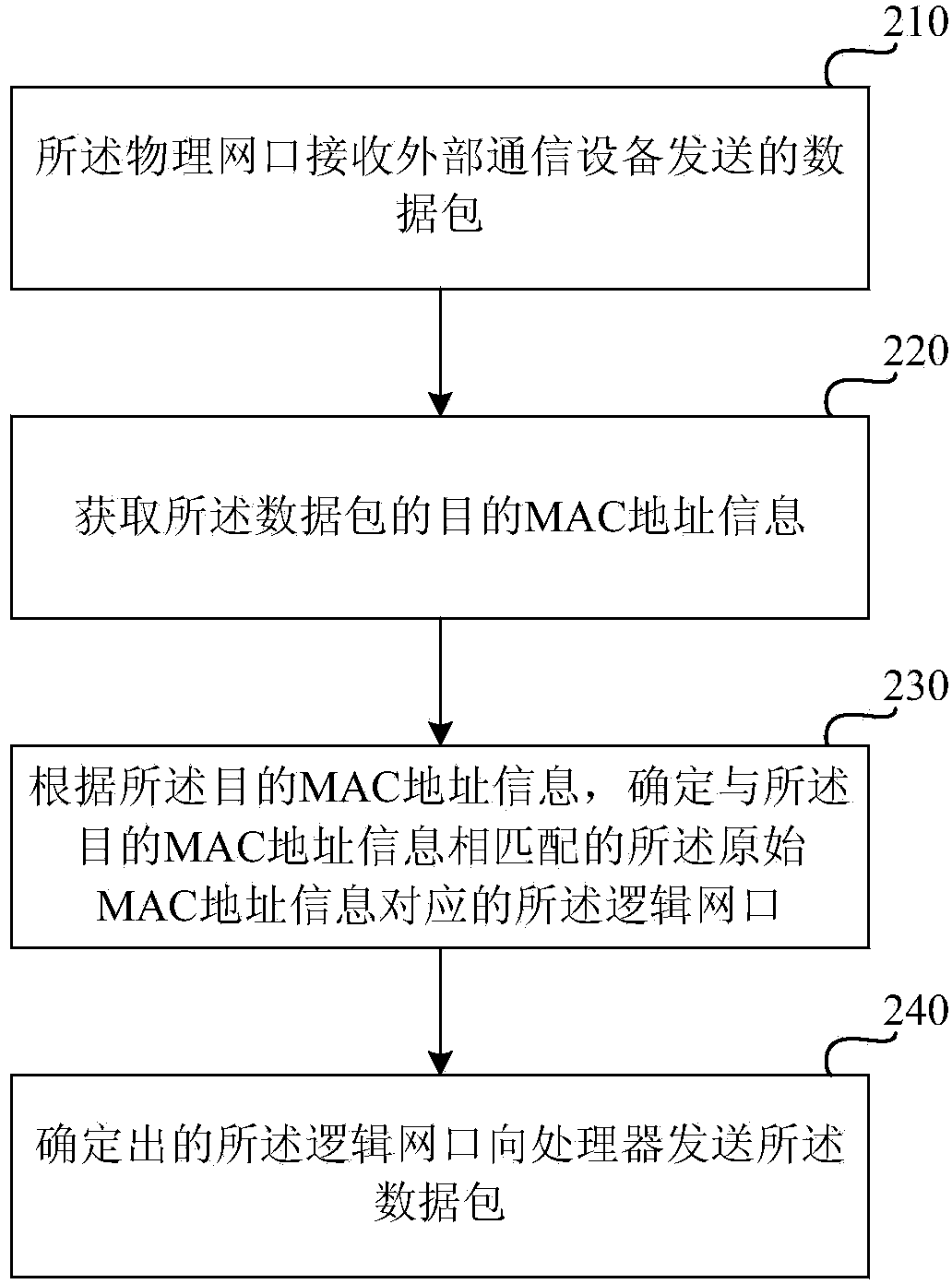

[0073] In the foregoing embodiments, it is briefly described that the network server can determine the mapping relationship between multiple logical network ports and physical network ports through the original MAC address information, and then receive the data packets sent by the external communication device. In order to facilitate real-time understanding of the present invention, the following will further explain and illustrate with specific embodiments in conjunction with the accompanying drawings, and the embodiments do not constitute a limitation to the embodiments of the present invention.

[0074] Below to figure 2 As an example to describe in detail the working process of the network server receiving data packets provided by the second embodiment of the present invention, figure 2 The flow chart of receiving data packets provided by Embodiment 2 of the present invention. In the embodiment of the present invention, the implementer who executes the following steps ma...

Embodiment 3

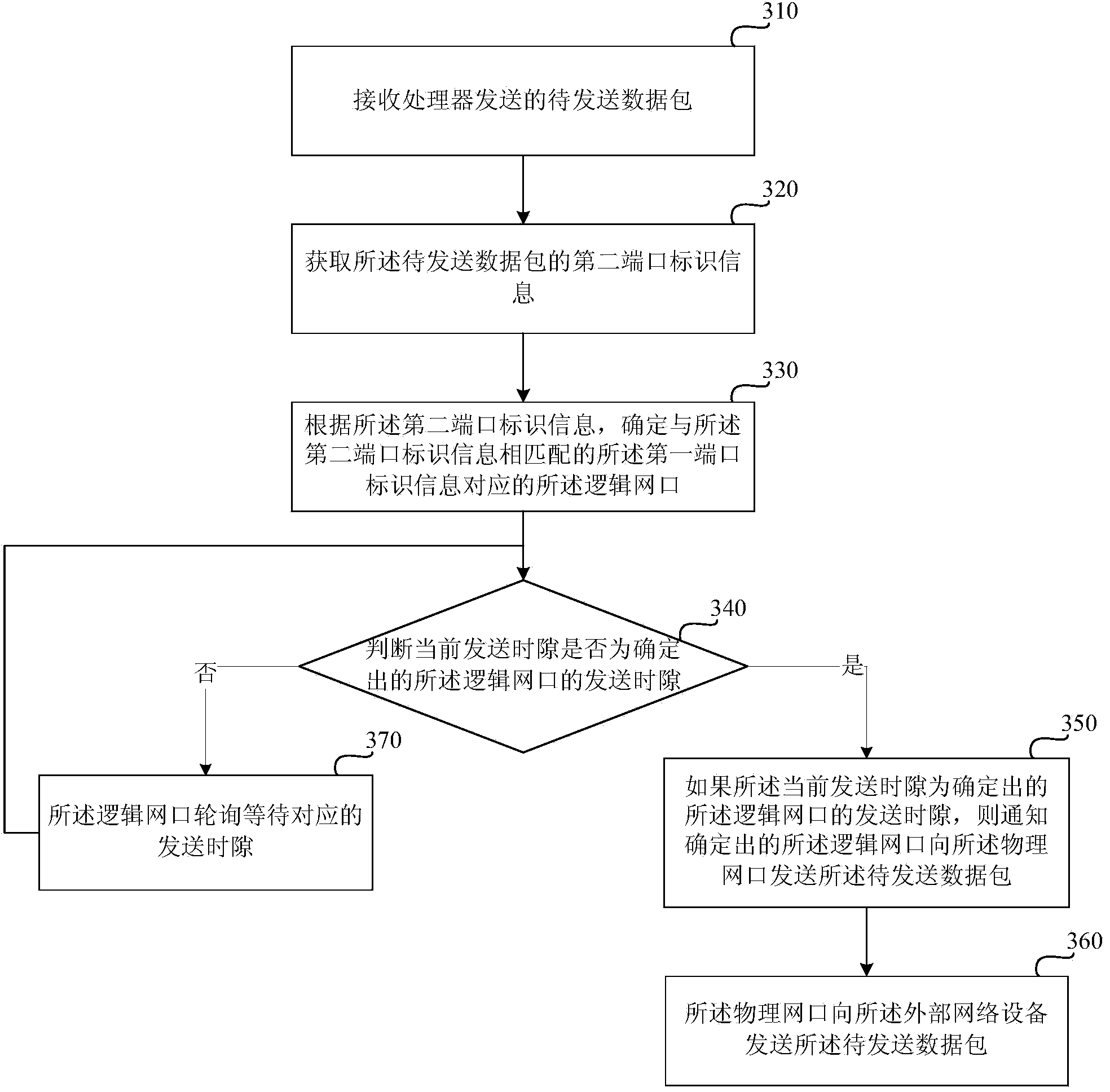

[0087] In the foregoing embodiments, it is briefly described that the network server can determine the mapping relationship between multiple logical network ports and physical network ports through the first port identification information and the sending time slot, and then send data packets to external network devices. In order to facilitate real-time understanding of the present invention, the following will further explain and illustrate with specific embodiments in conjunction with the accompanying drawings, and the embodiments do not constitute a limitation to the embodiments of the present invention.

[0088] Below to image 3 As an example, the working process of sending data packets by the network server provided by the third embodiment of the present invention is described in detail. image 3 The flow chart of sending data packets provided by Embodiment 3 of the present invention. In the embodiment of the present invention, the implementer who executes the following ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More